Patents

Literature

130 results about "Physical Coding Sublayer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

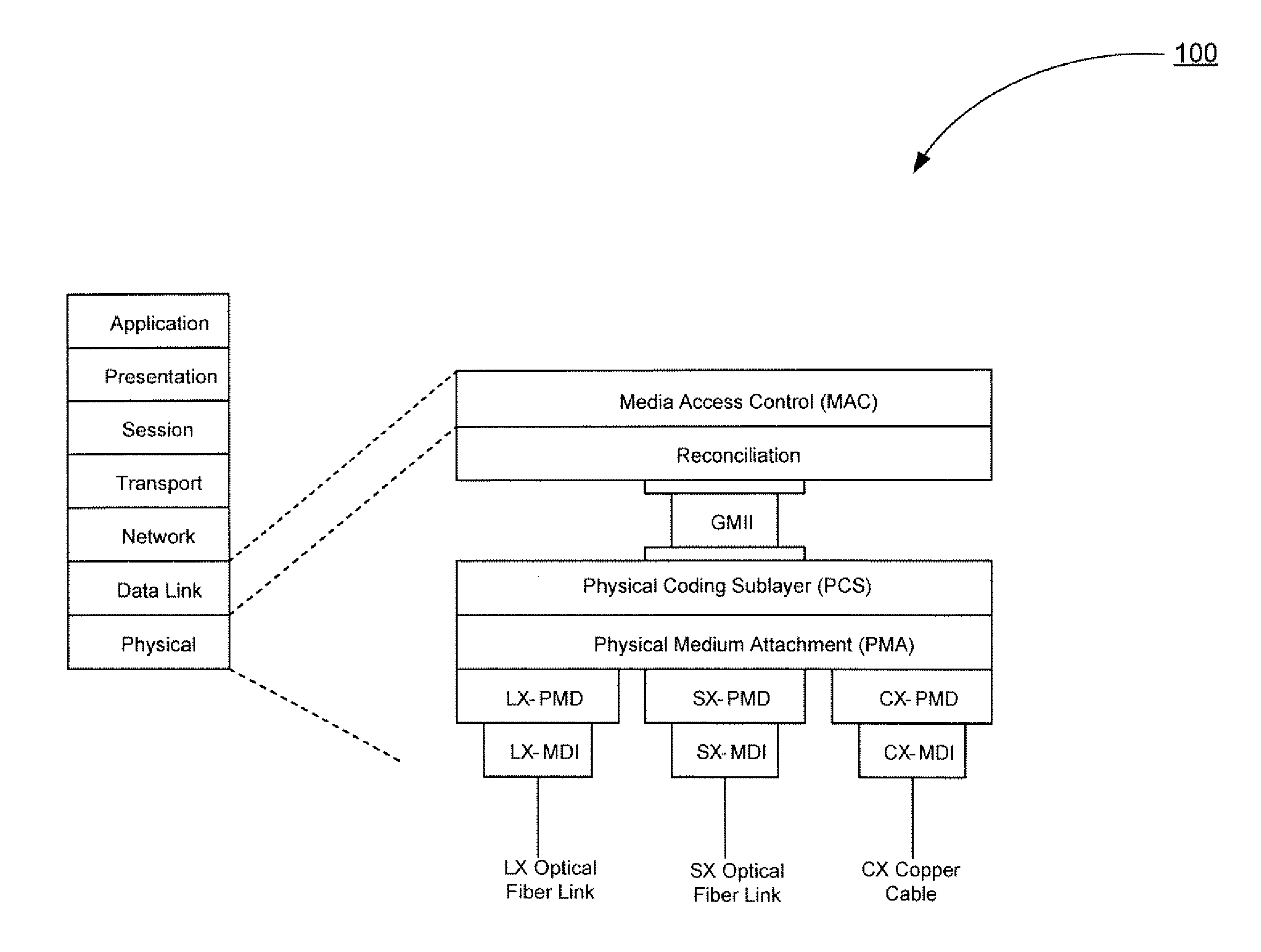

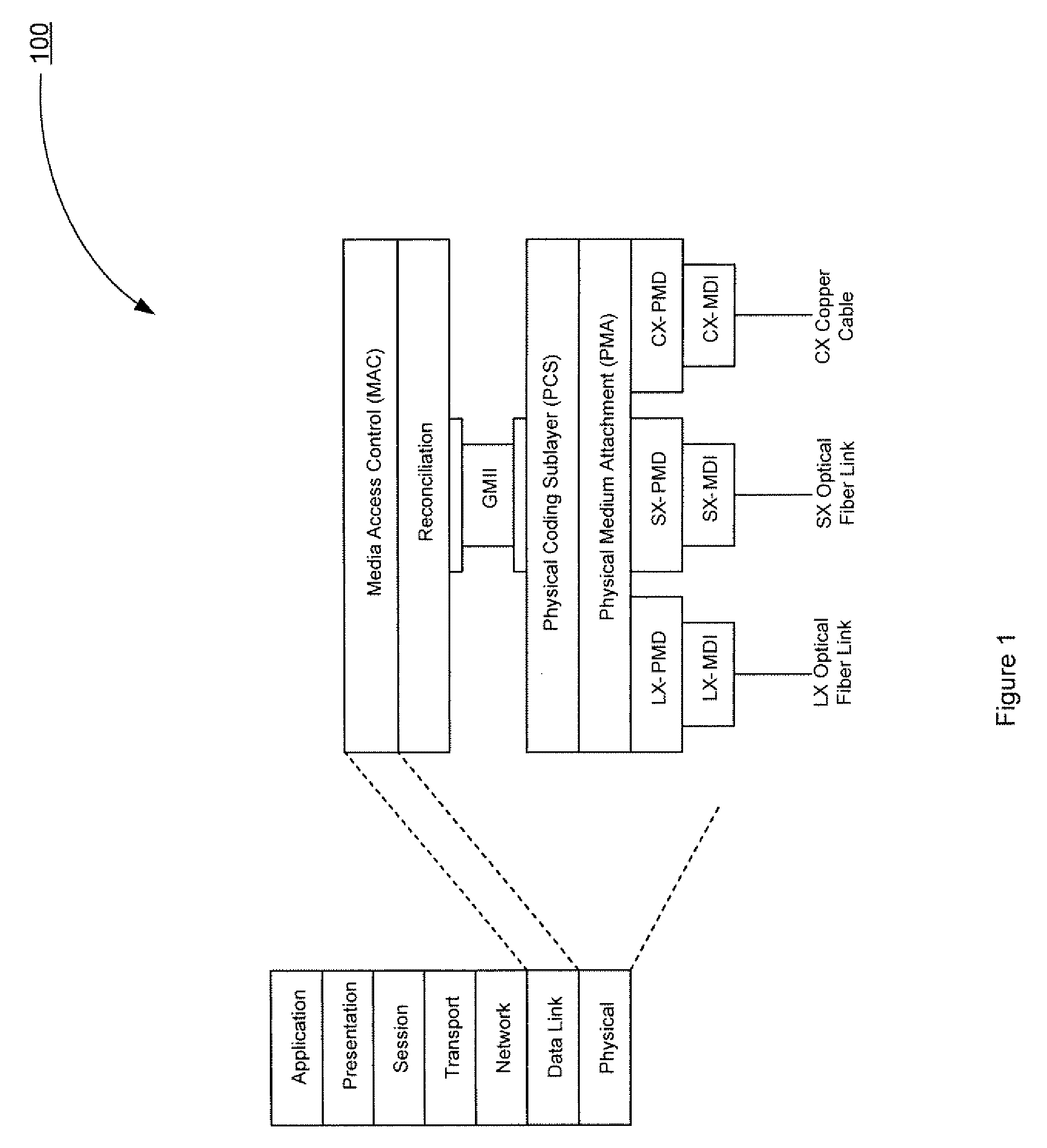

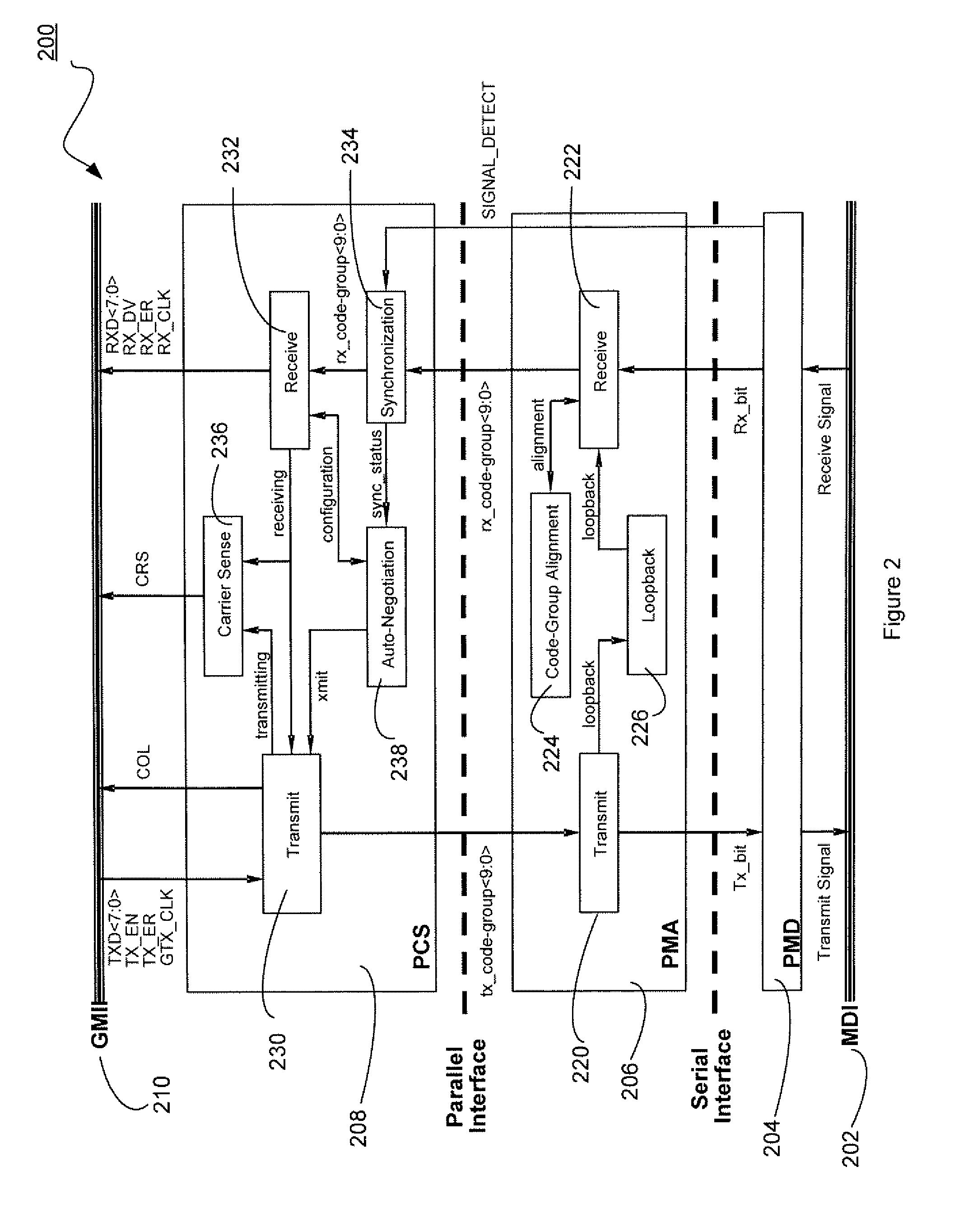

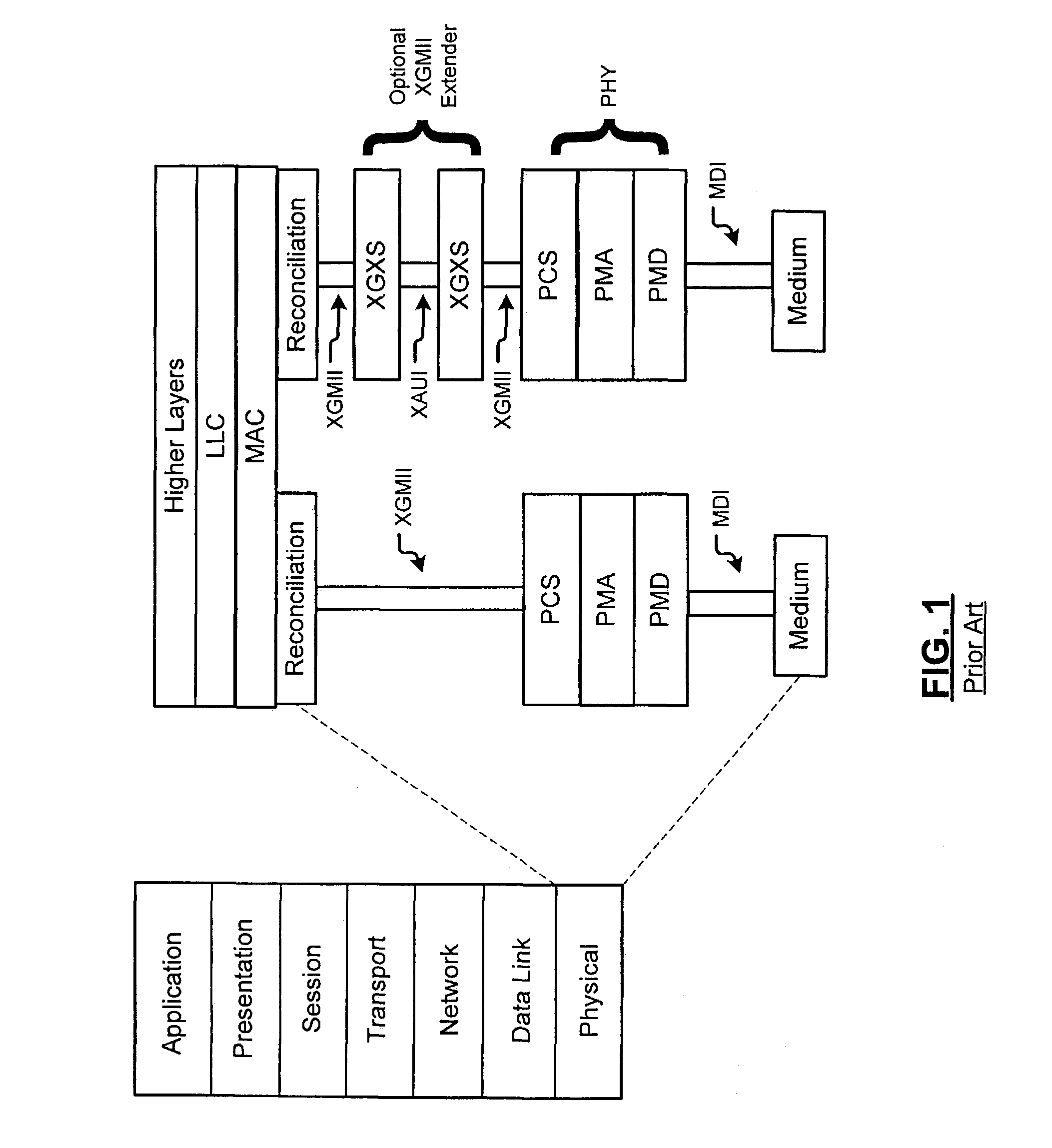

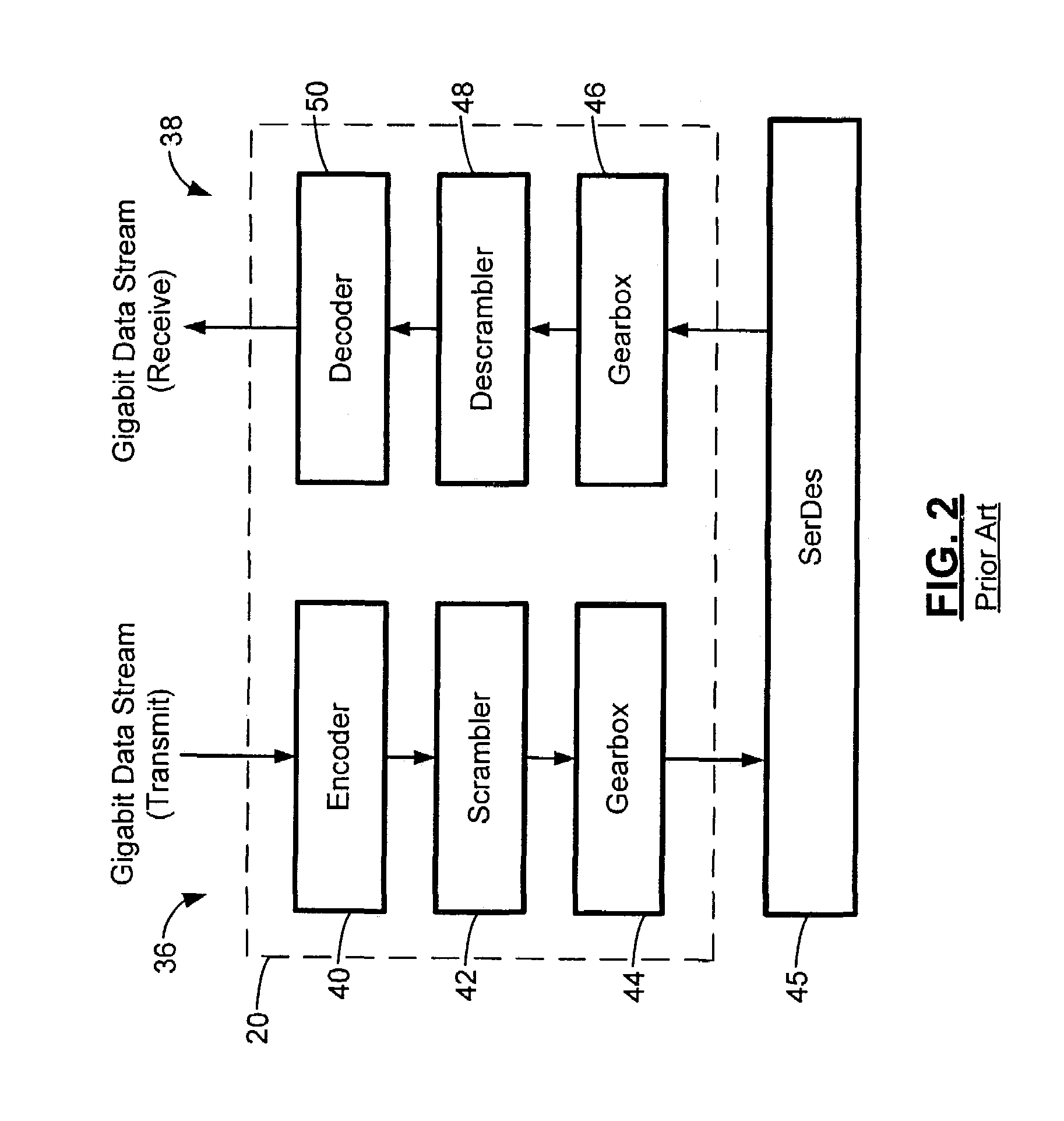

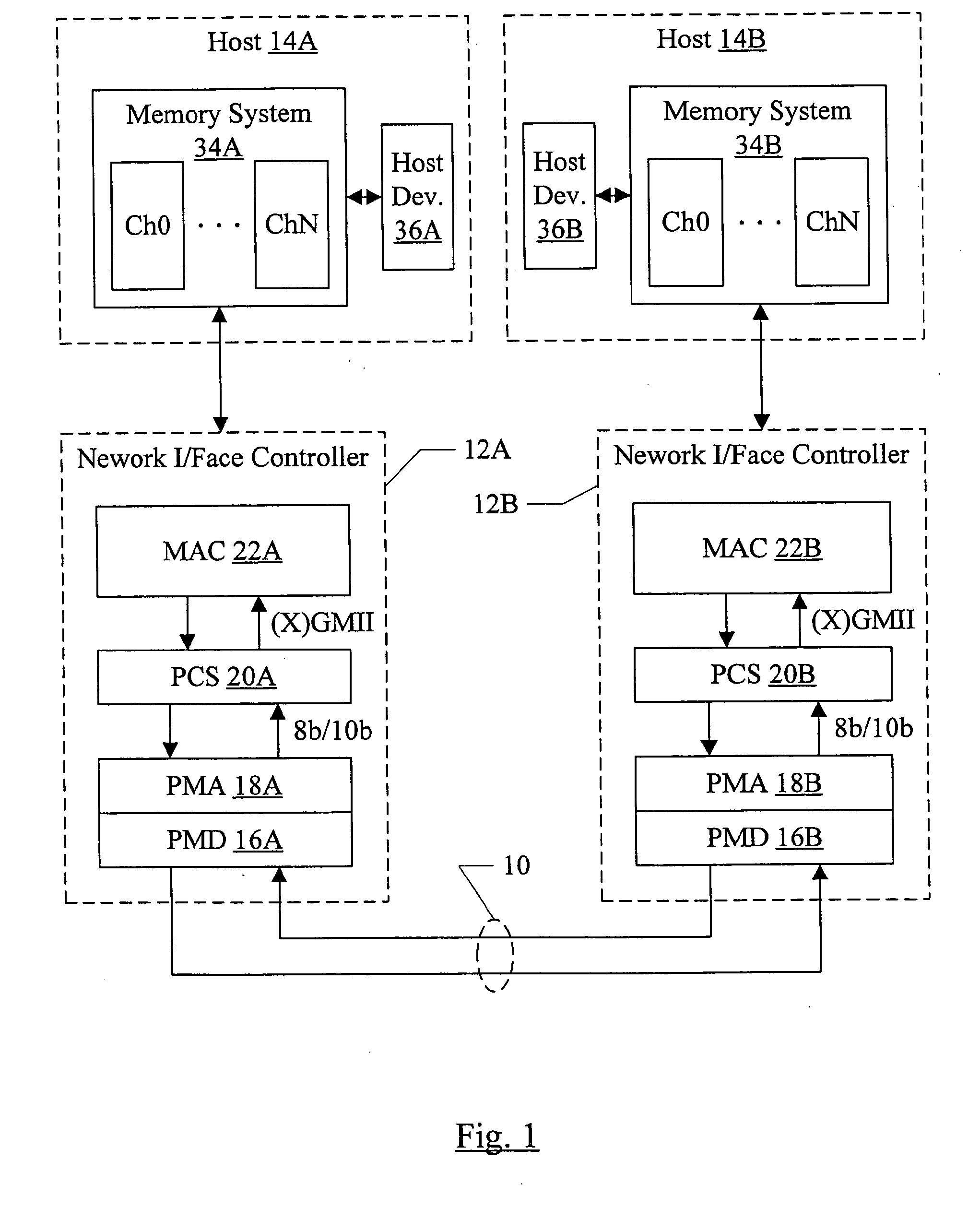

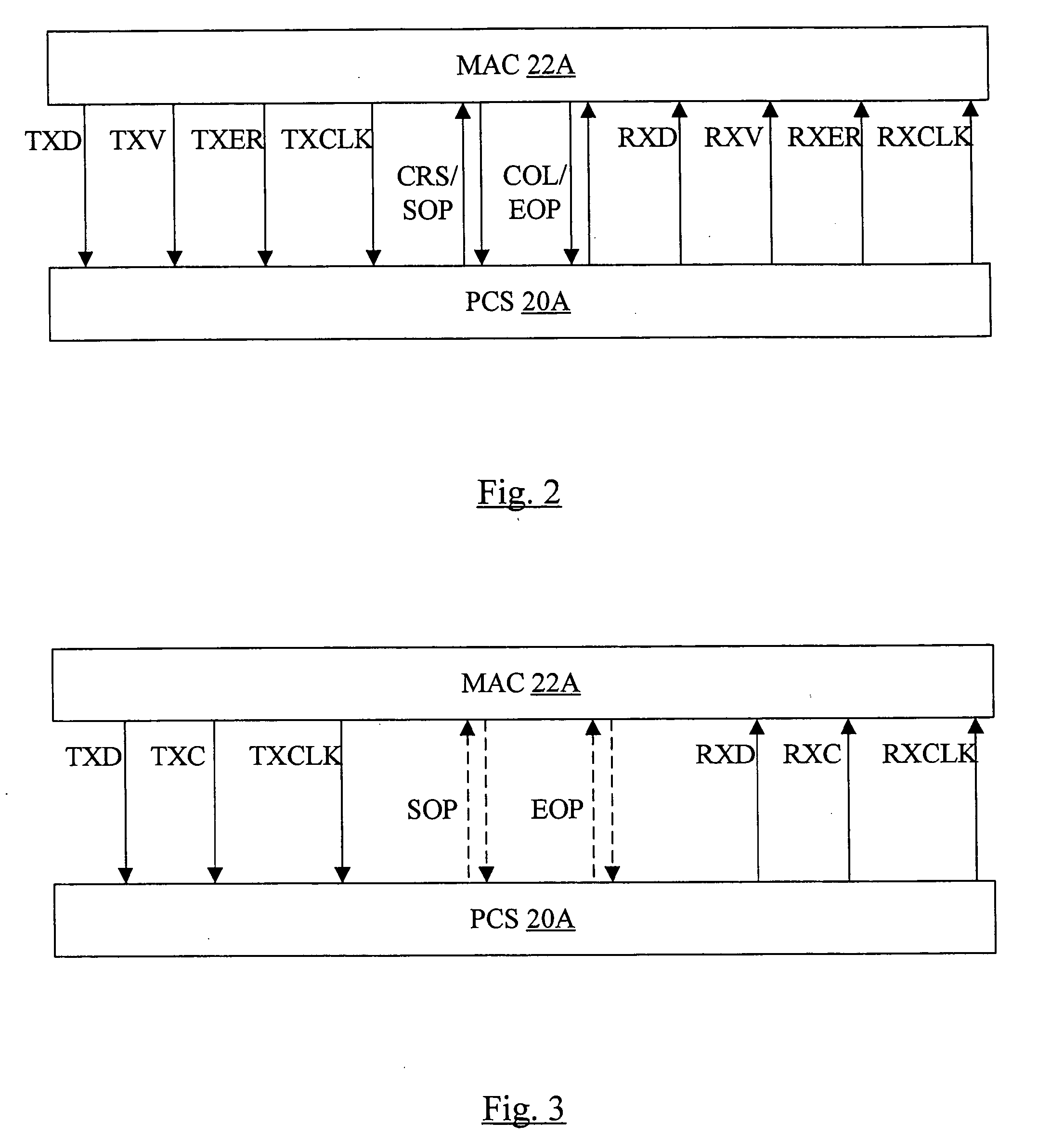

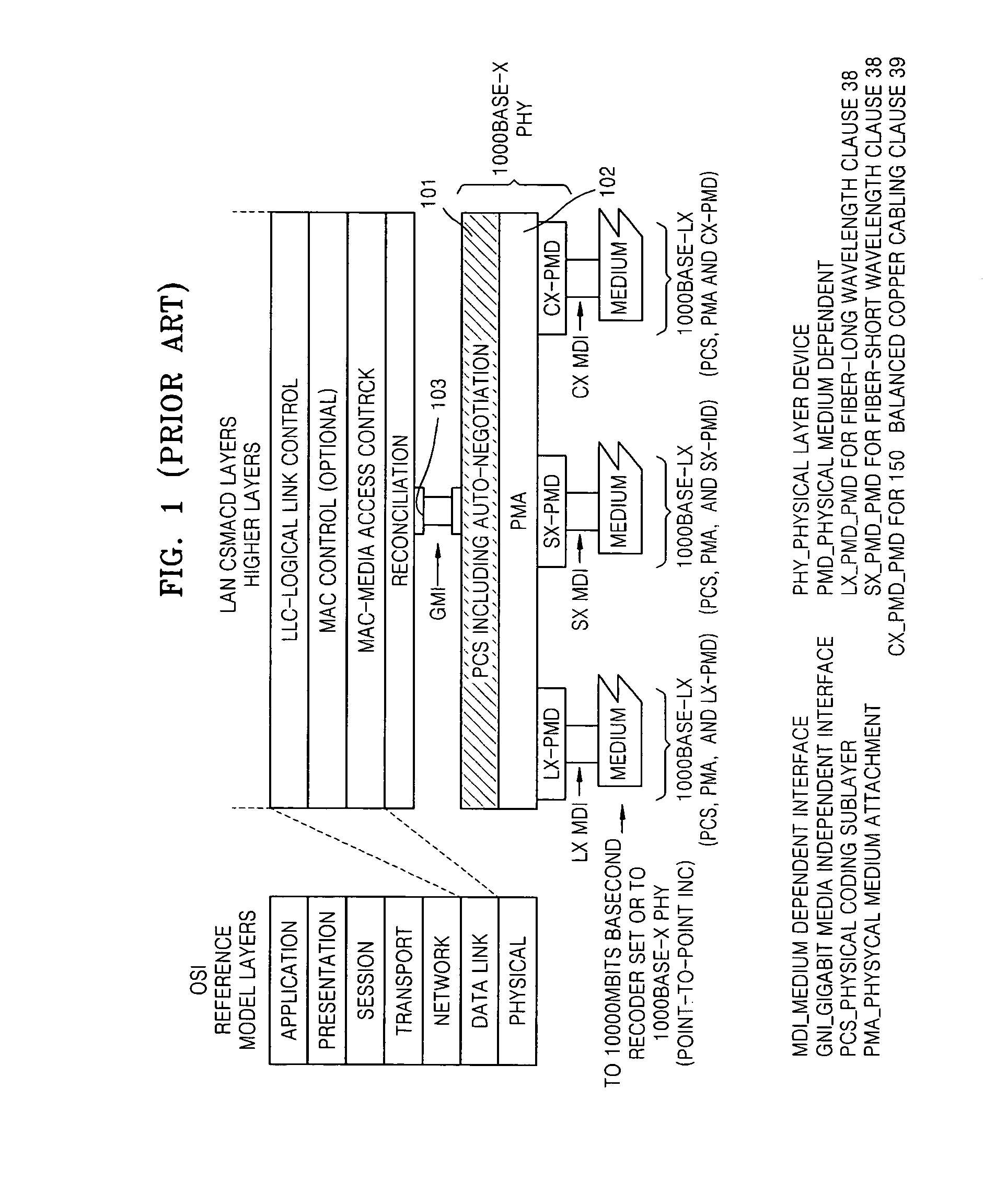

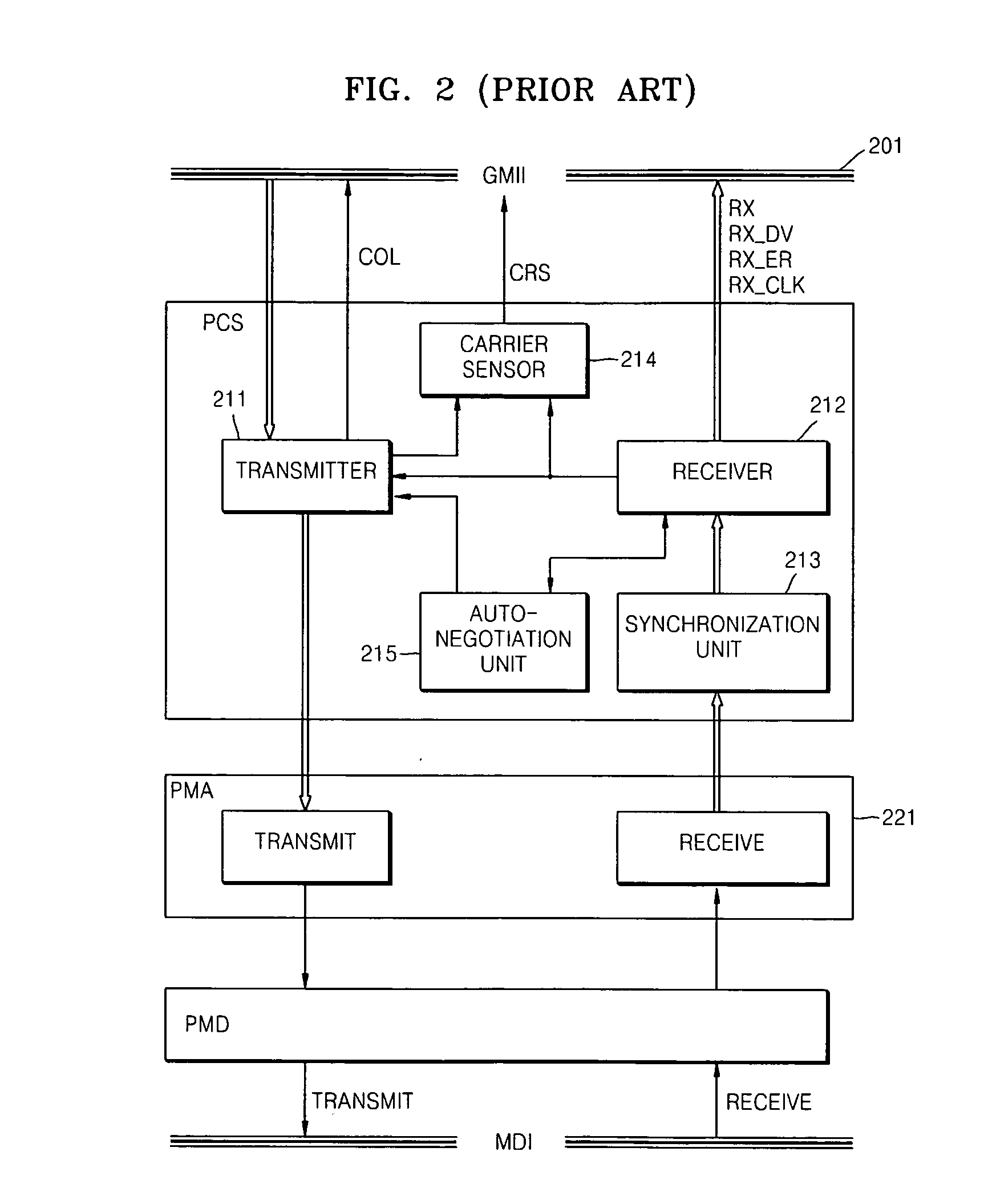

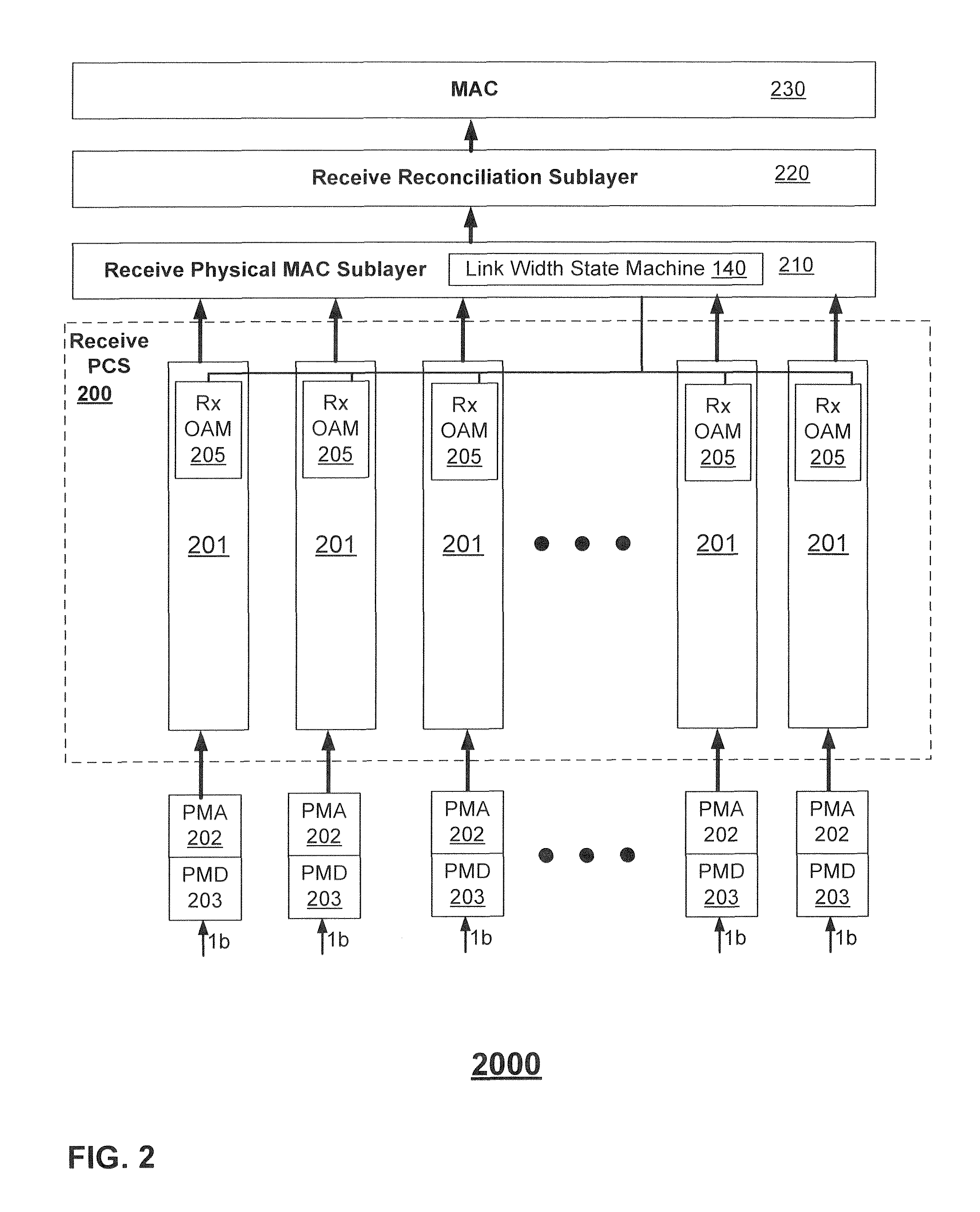

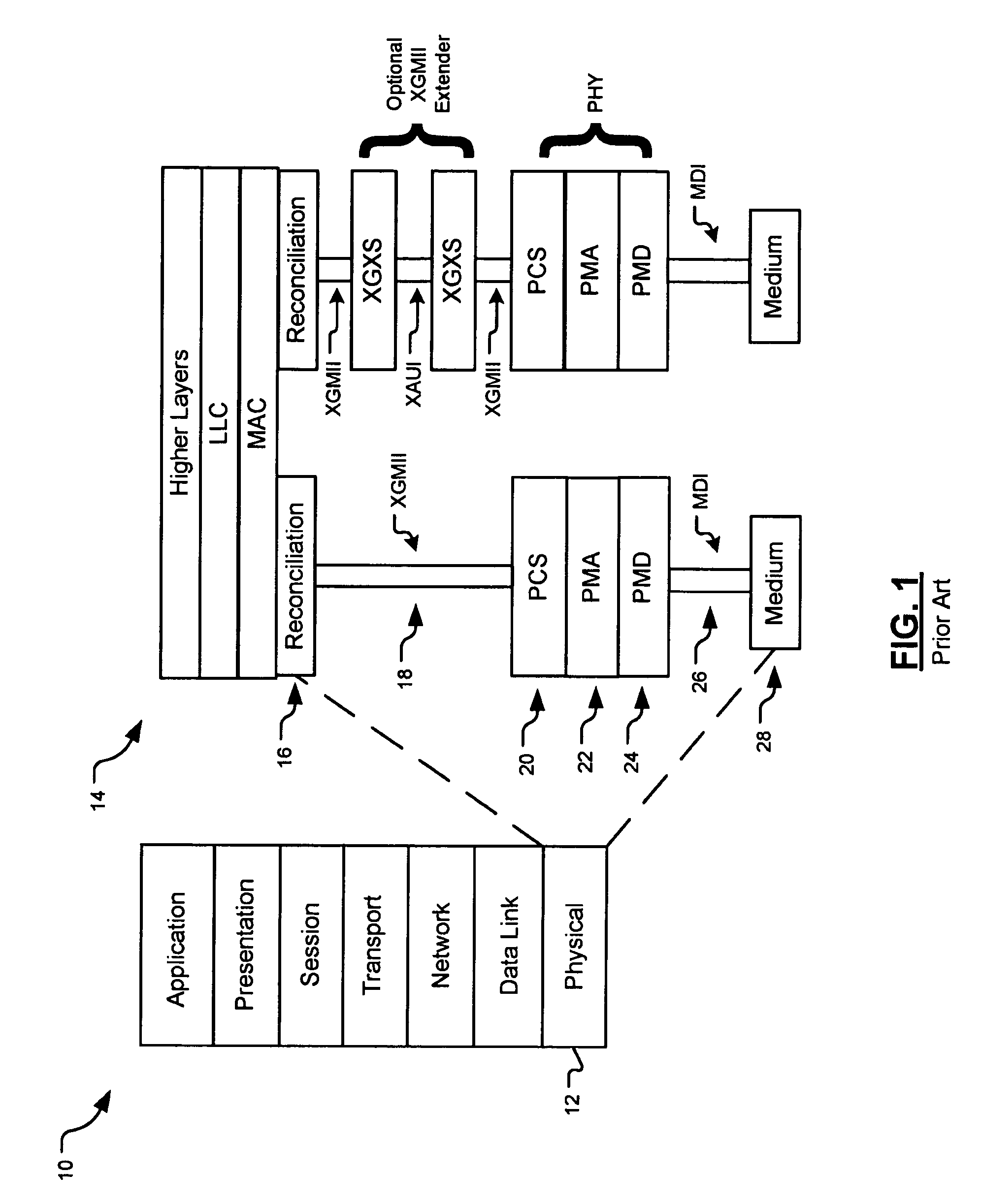

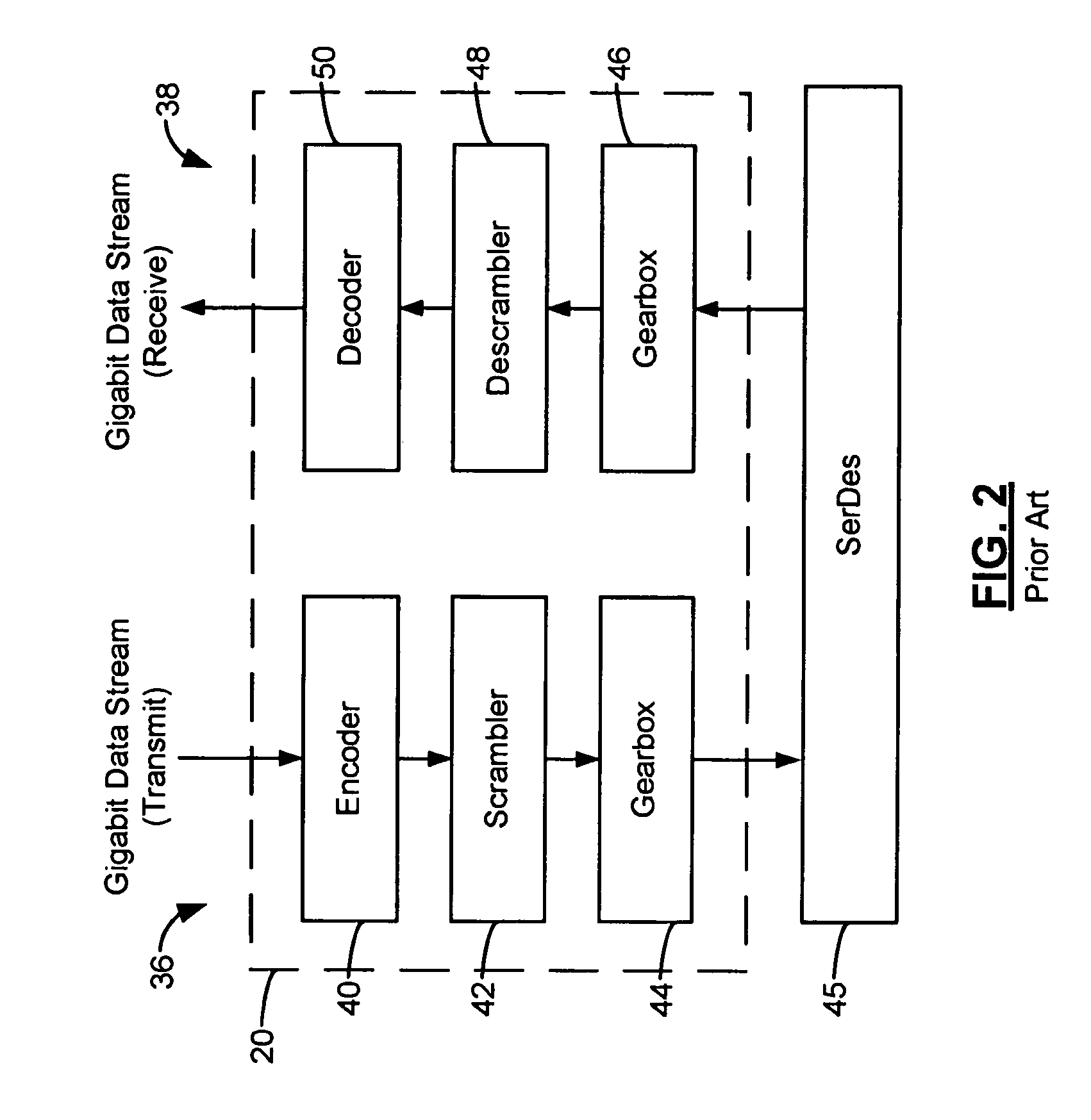

The Physical Coding Sublayer (PCS) is a networking protocol sublayer in the Fast Ethernet, Gigabit Ethernet, and 10 Gigabit Ethernet standards. It resides at the top of the physical layer (PHY), and provides an interface between the Physical Medium Attachment (PMA) sublayer and the Media Independent Interface (MII). It is responsible for data encoding and decoding, scrambling and descrambling, alignment marker insertion and removal, block and symbol redistribution, and lane block synchronization and deskew.

Method for data transmission, transmitter and receiver

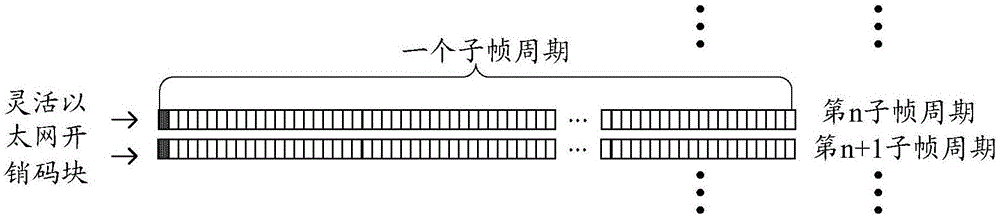

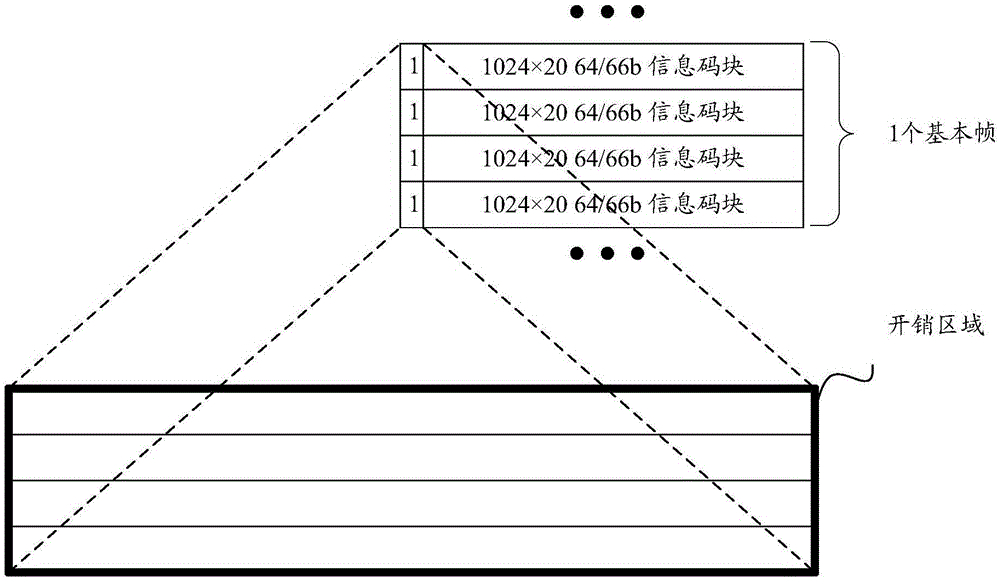

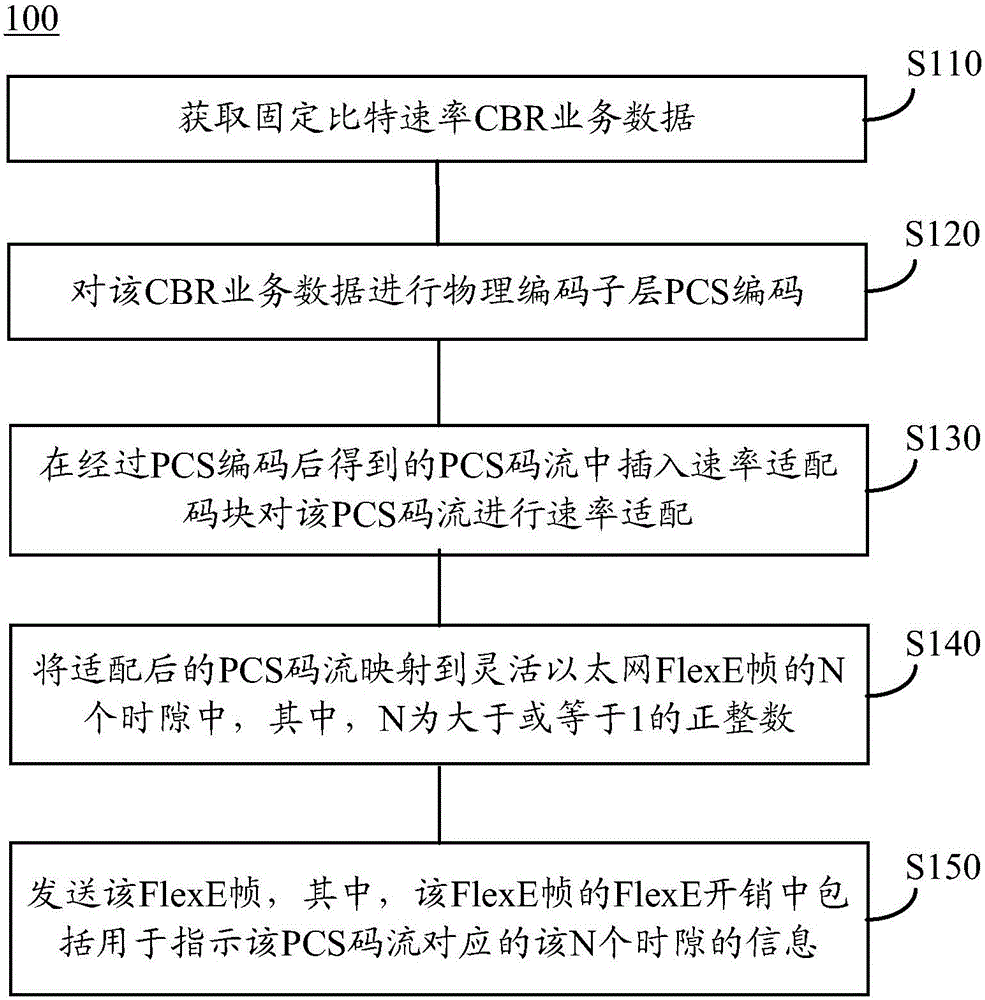

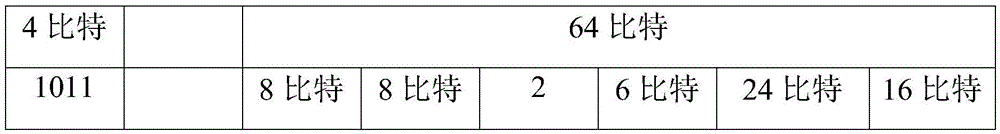

ActiveCN106411454AFlexible mappingImprove carrying capacityTime-division multiplexSignalling characterisationCoding blockRate adaptation

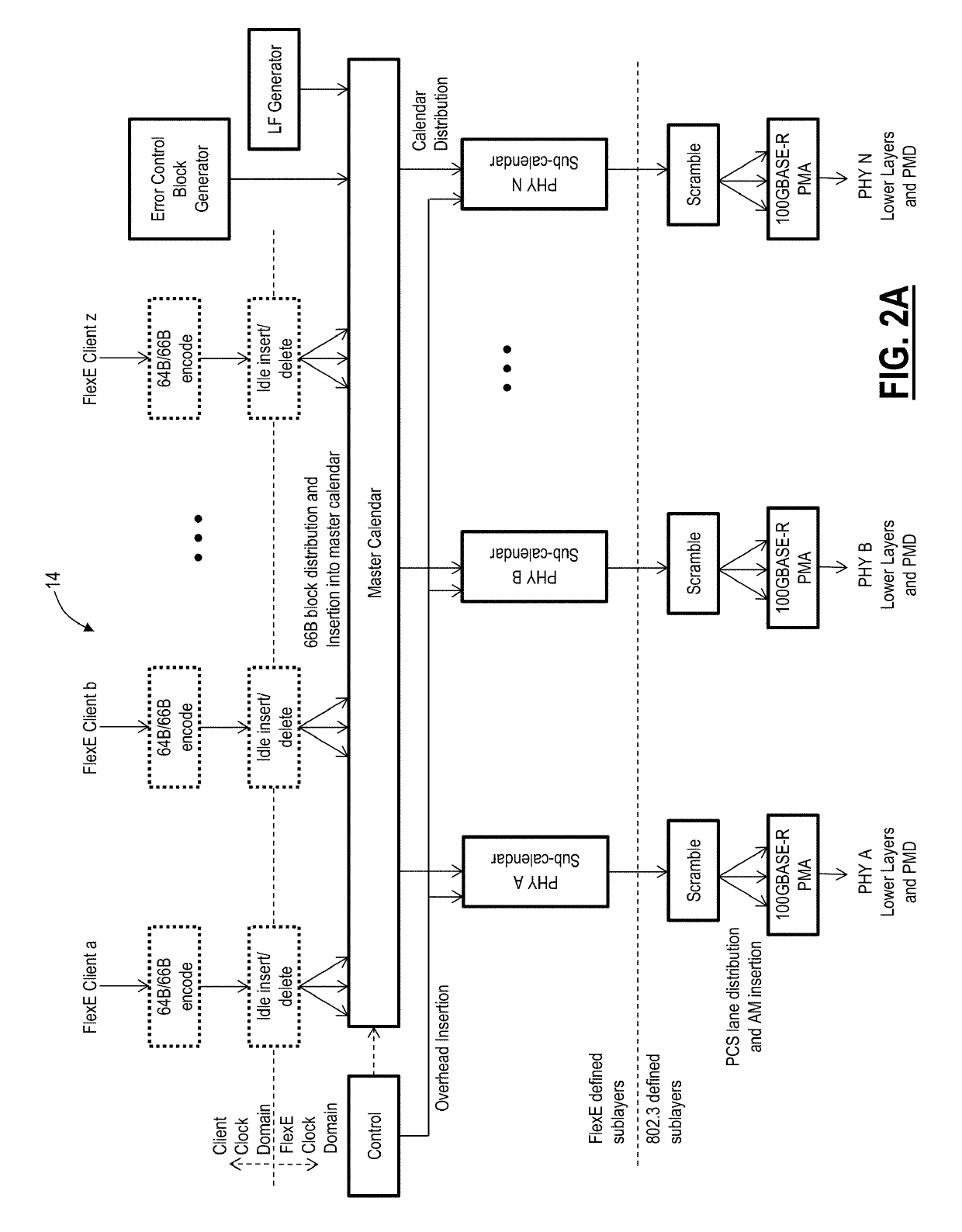

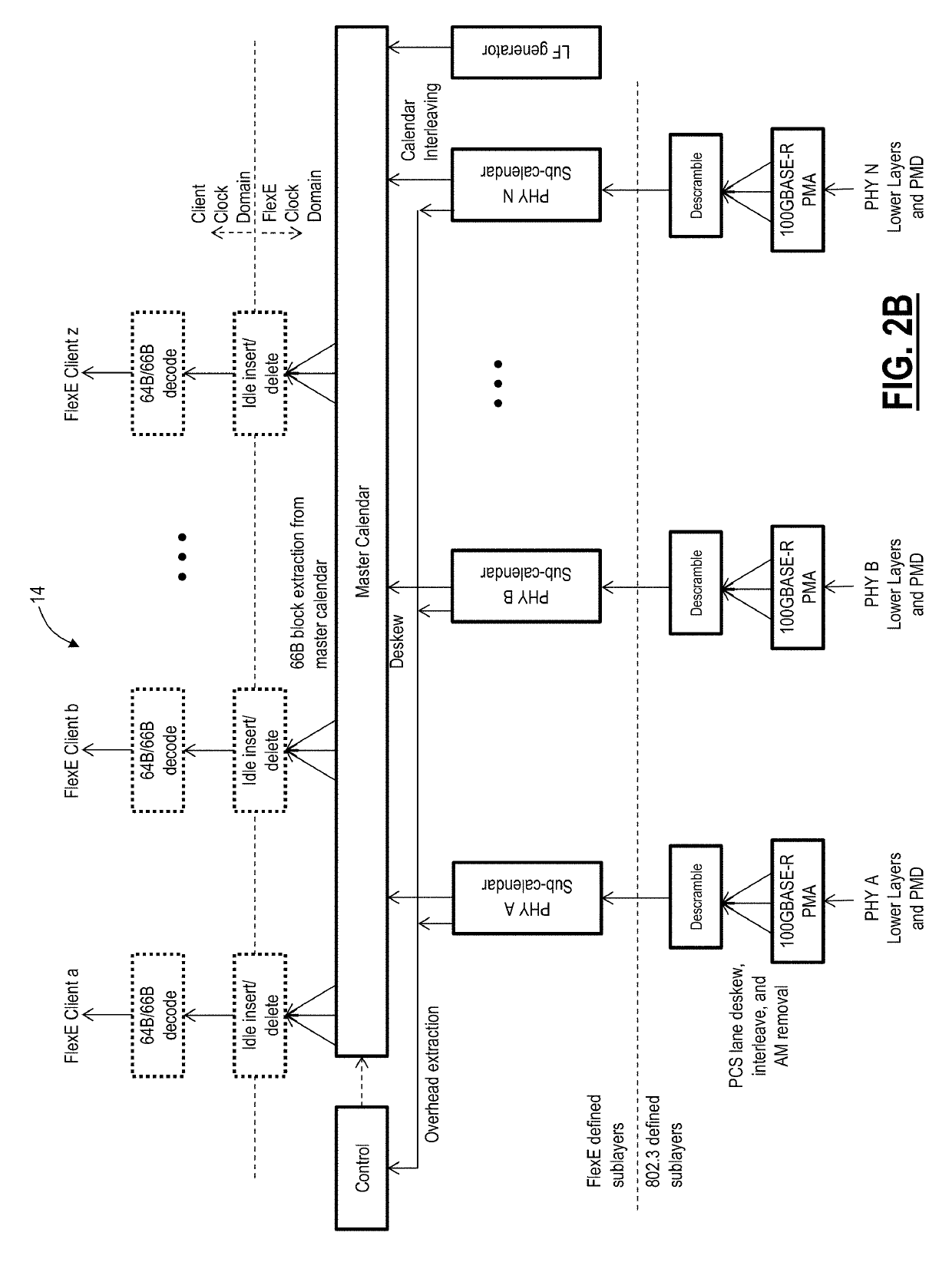

The invention discloses a method for data transmission, a transmitter and a receiver. The method comprises the steps of obtaining constant bit rate (CBR) service data; performing physical coding sublayer (PCS) coding on the CBR service data; inserting a rate adaptation code block into a PCS code stream obtained by the PCS coding for rate adaptation of the PCS code stream; mapping the the PCS rate stream after adaptation into N time slots of a flexible Ethernet (FlexE) frame, where N is a positive integer greater than or equal to 1; and transmitting the FlexE frame, wherein the FlexE overhead of the FlexE frame includes information indicating the N time slots corresponding to the PCS code stream. The method for the data transmission, the transmitter and the receiver according to the embodiment of the invention can realize flexible Ethernet mapping of the CBR service data and enhance the carrying capacity of the flexible Ethernet.

Owner:HUAWEI TECH CO LTD

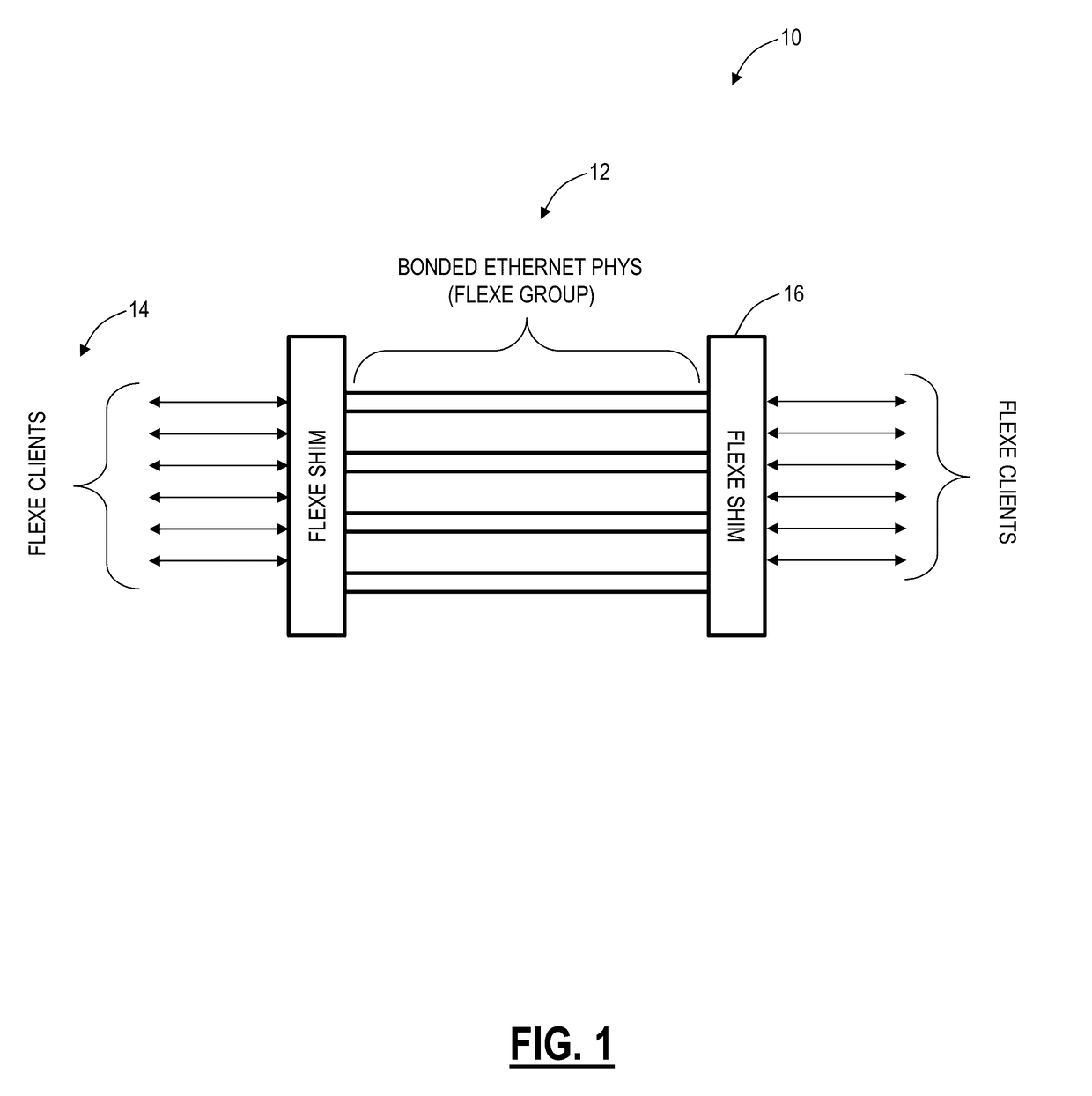

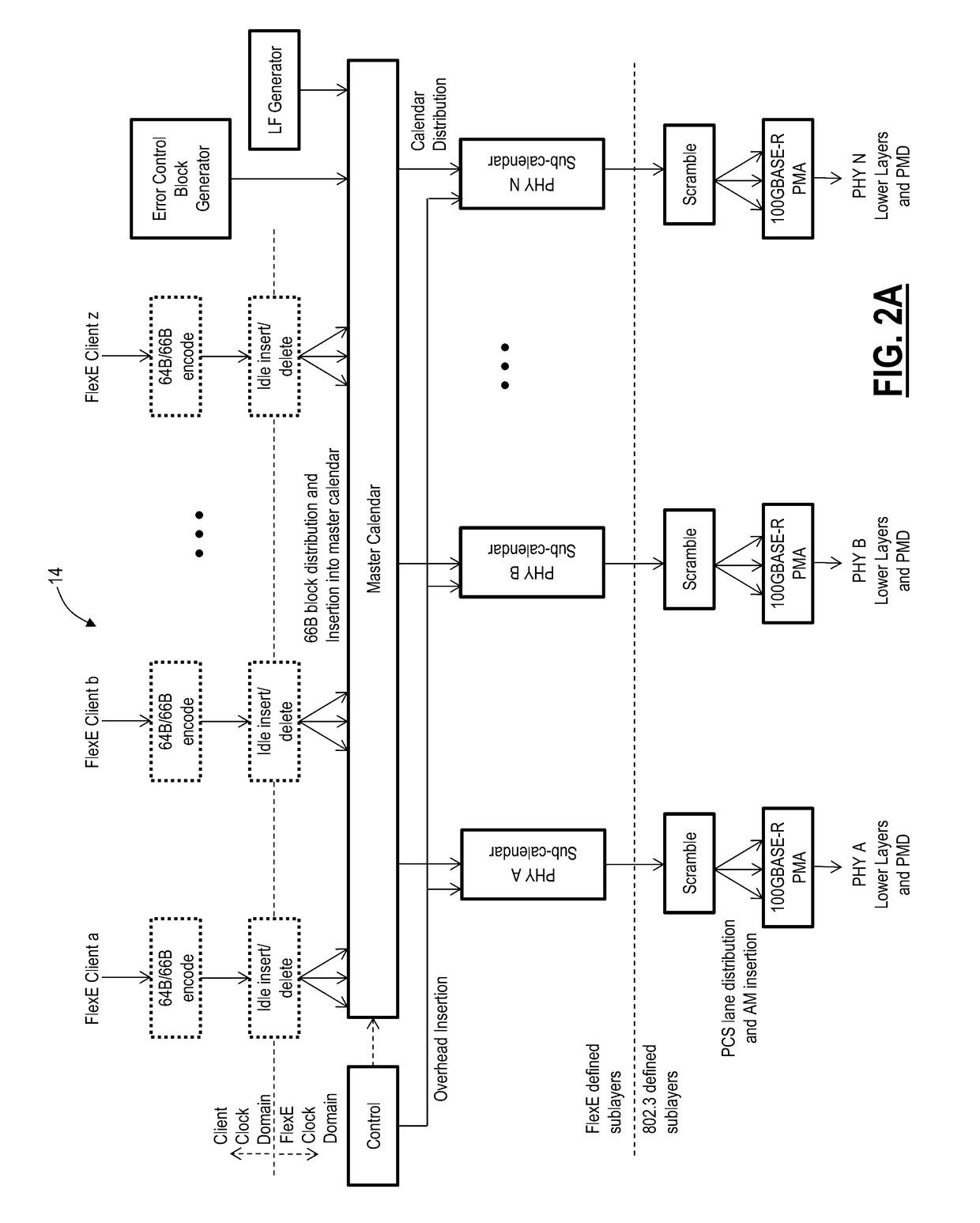

Flexible Ethernet lane management method and apparatus

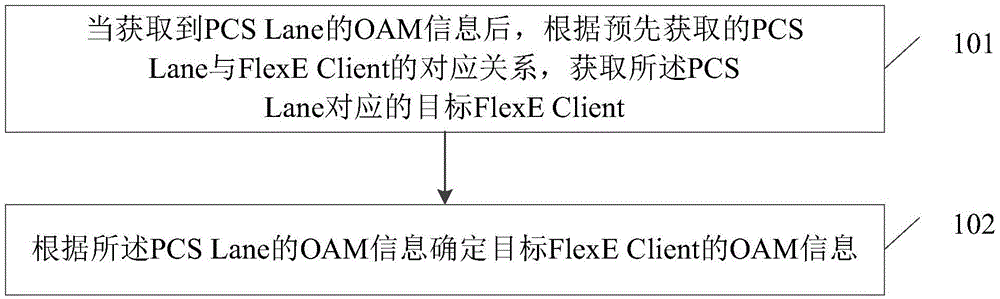

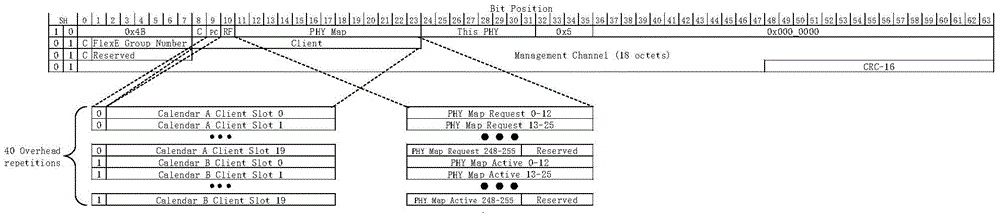

InactiveCN106612220ARealize managementDoes not cause paralysisData switching by path configurationEthernetPhysical Coding Sublayer

The present invention provides a flexible Ethernet lane management method and apparatus. The method comprises the steps of when OAM information of a PCS Lane is acquired, acquiring a target FlexE Client corresponding to the PCS Lane according to a pre-acquired correspondence between the PCS Lane and the FlexE Client; and determining OAM information of the target FlexE Client according to the OAM information of the PCS Lane.

Owner:ZTE CORP

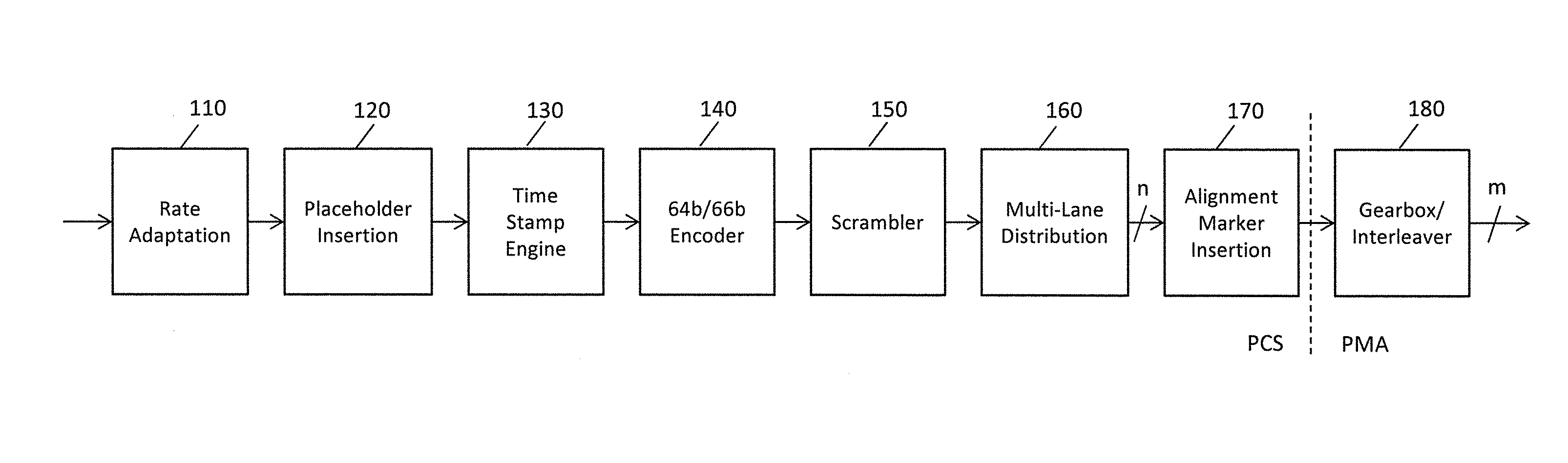

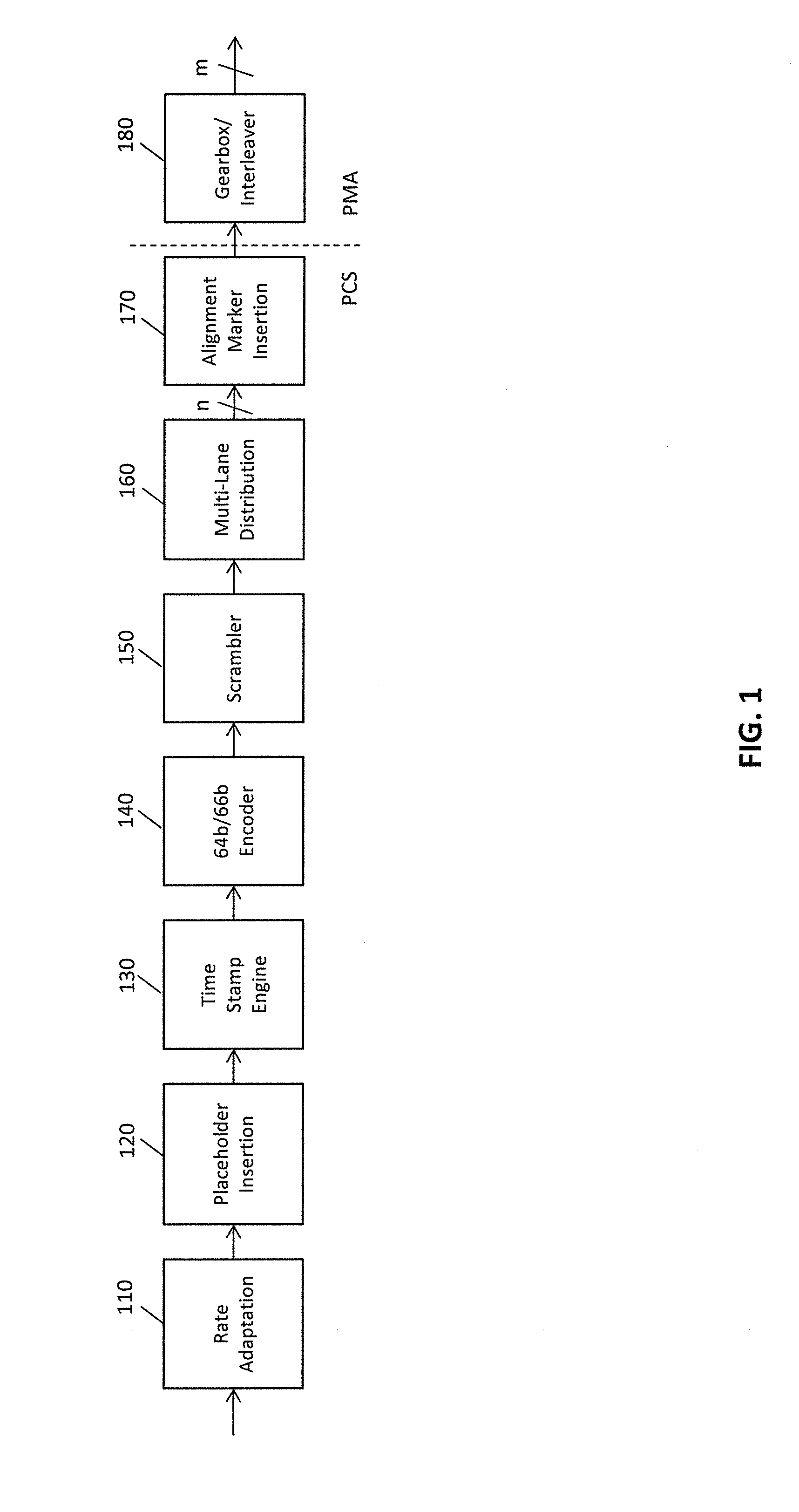

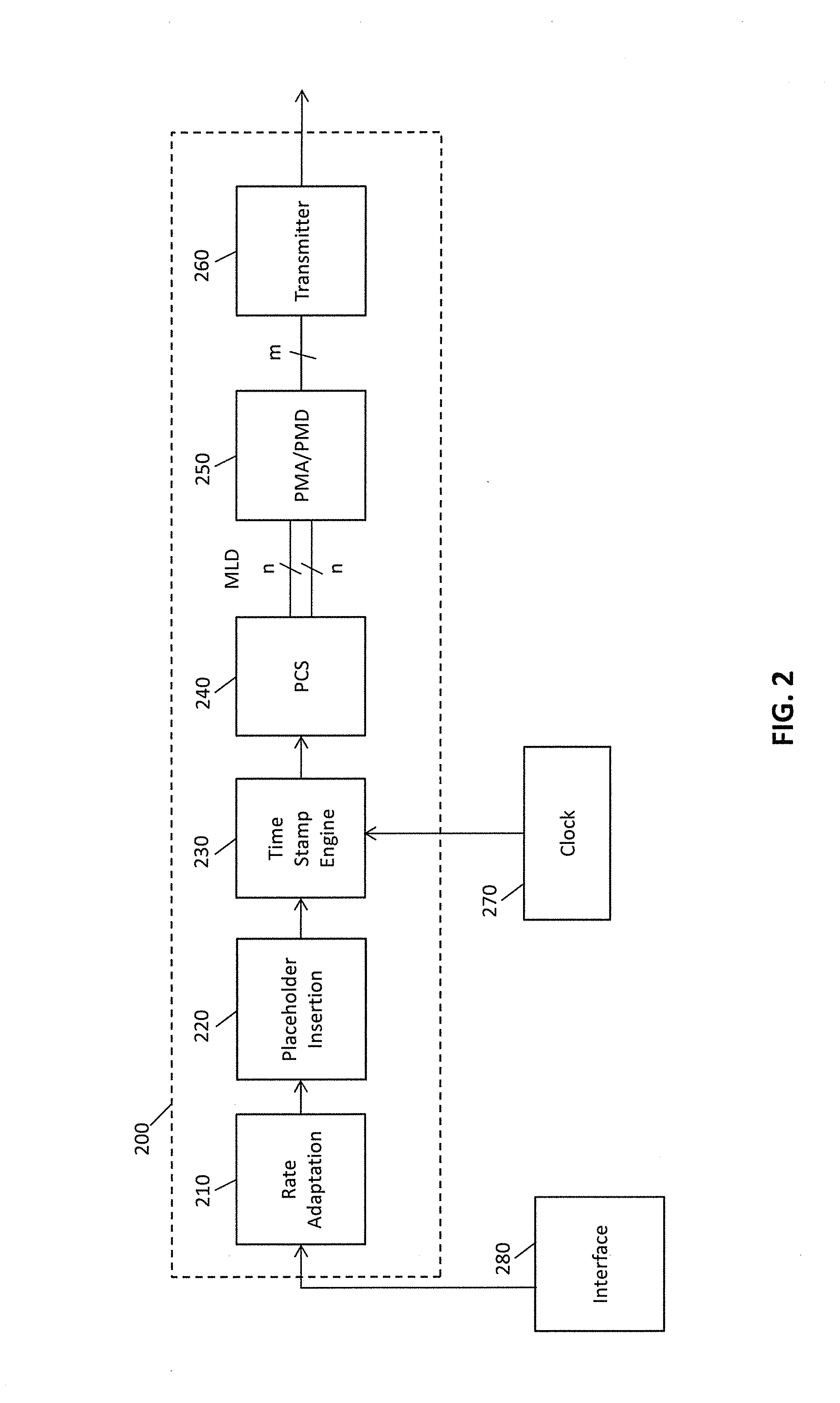

High accuracy 1588 timestamping over high speed multi lane distribution physical code sublayers

ActiveUS20140092918A1Fully comprehendedChannel dividing arrangementsError preventionTight frameReal-time computing

A physical layer device provides for synchronization of clocks in a communication network. A place holder for an alignment marker is inserted into a frame to be transmitted. Once the placeholder alignment marker is inserted into the frame, no additional data is added to the frame. Transmission of the frame including the placeholder alignment marker may also be delayed to allow data processing in subsequent blocks within a transmit block to complete prior to further processing of the frame including the placeholder alignment marker (e.g., timestamping, MACSec, etc.) to improve timing accuracy with a multi lane distribution environment.

Owner:MICROSEMI STORAGE SOLUTIONS

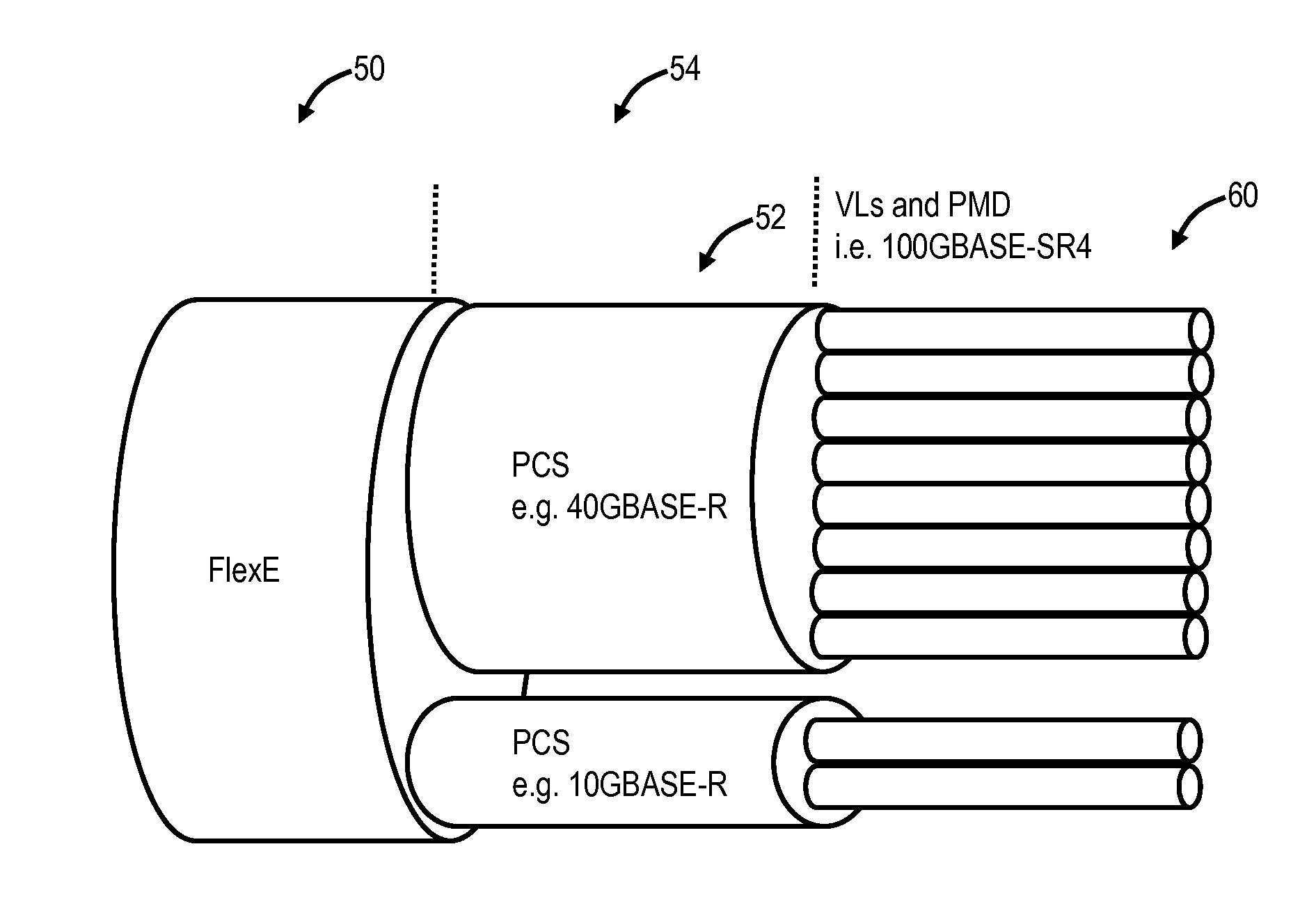

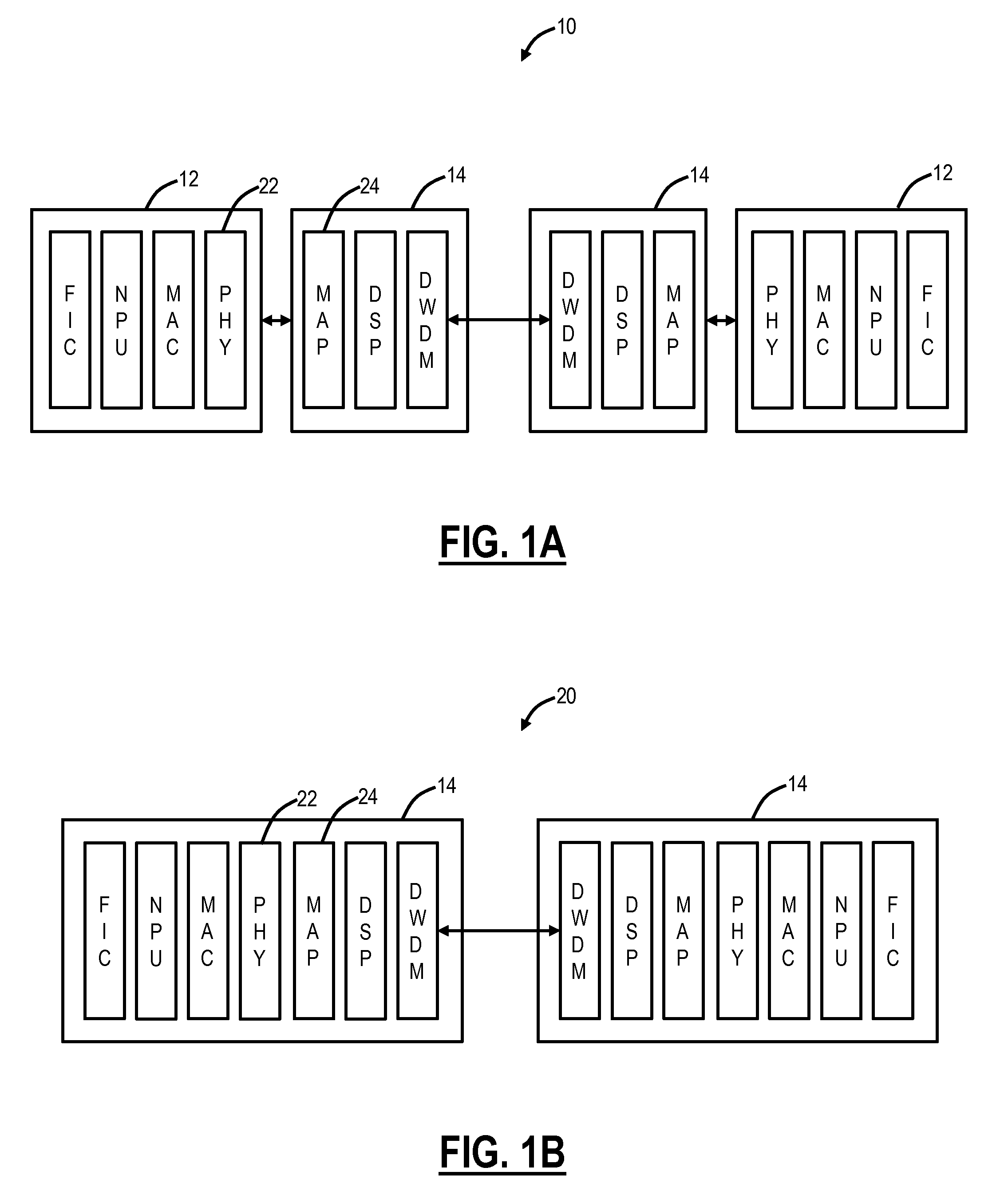

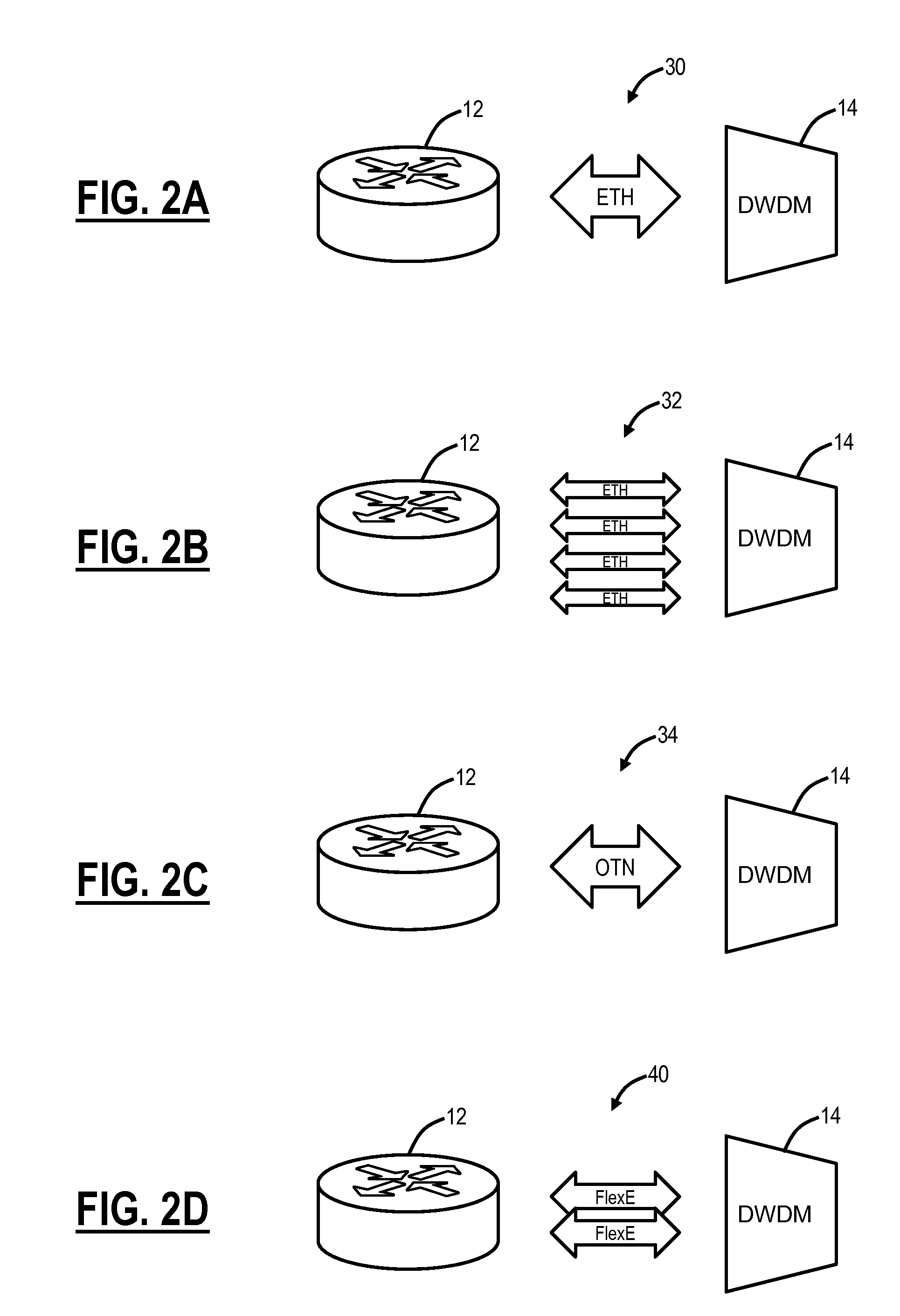

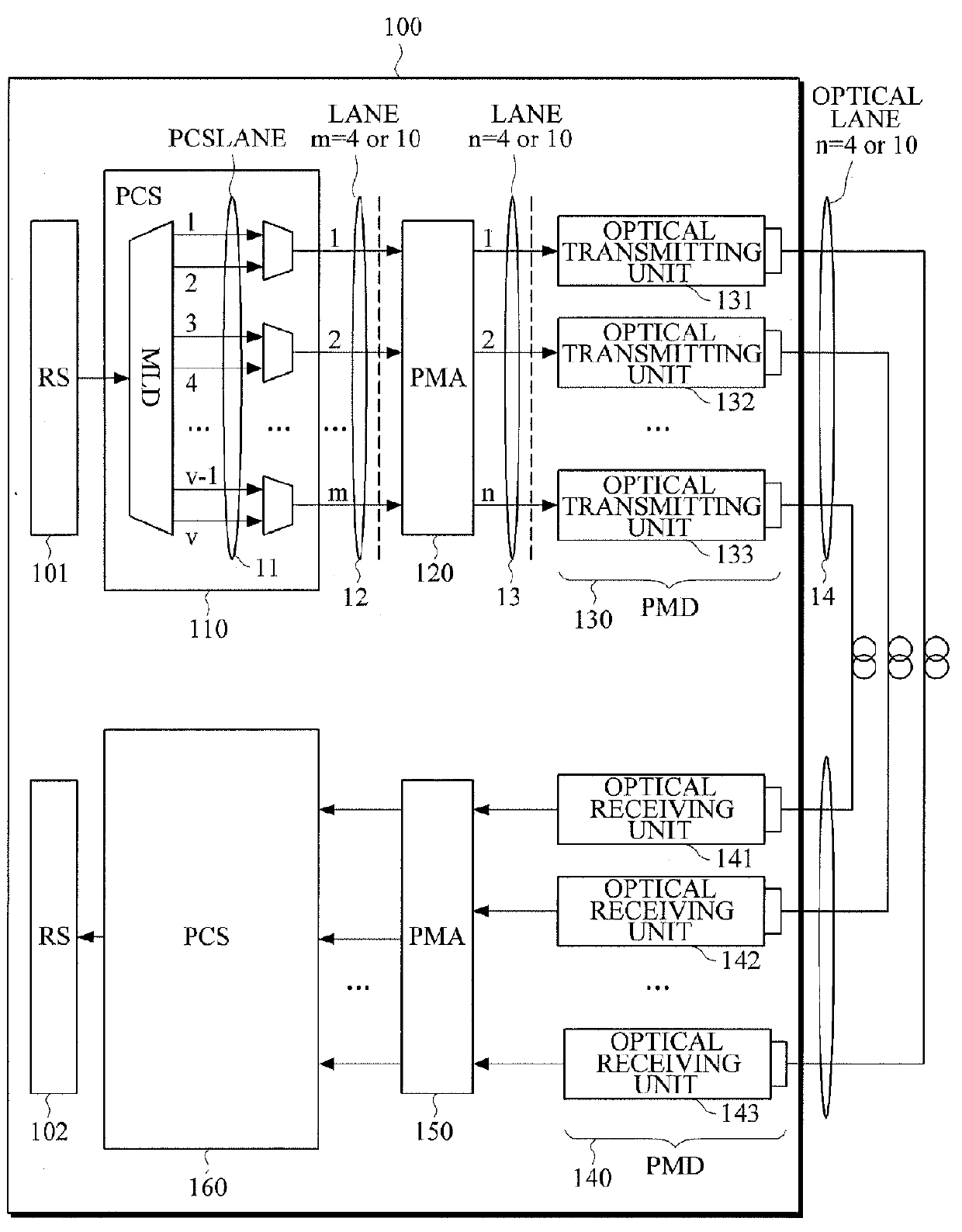

Flexible ethernet and multi link gearbox mapping procedure to optical transport network

ActiveUS20160119075A1Wavelength-division multiplex systemsTime-division multiplexTransport systemMulti link

A flexible mapping method to map a Physical Coding Sublayer (PCS) structure from Flexible Ethernet and / or Multi Link Gearbox (MLG) to Optical Transport Network (OTN), includes receiving one or more Virtual Lanes; and mapping each of the one or more Virtual Lanes into a Tributary Slot, wherein a rate and number of the Tributary Slot(s) in OTN is set based on a rate and number of the one or more Virtual Lanes. A transport system and a flexible de-mapping method are also described. The systems and methods map the generalized MLG-style group of lanes (virtual PHYs / PMDs) into an OPUflex Tributary Slot (TS) structure, keeping PCS structures intact, and creates a single ODUflex container with a matching rate of FlexE for end-to-end flow.

Owner:CIENA

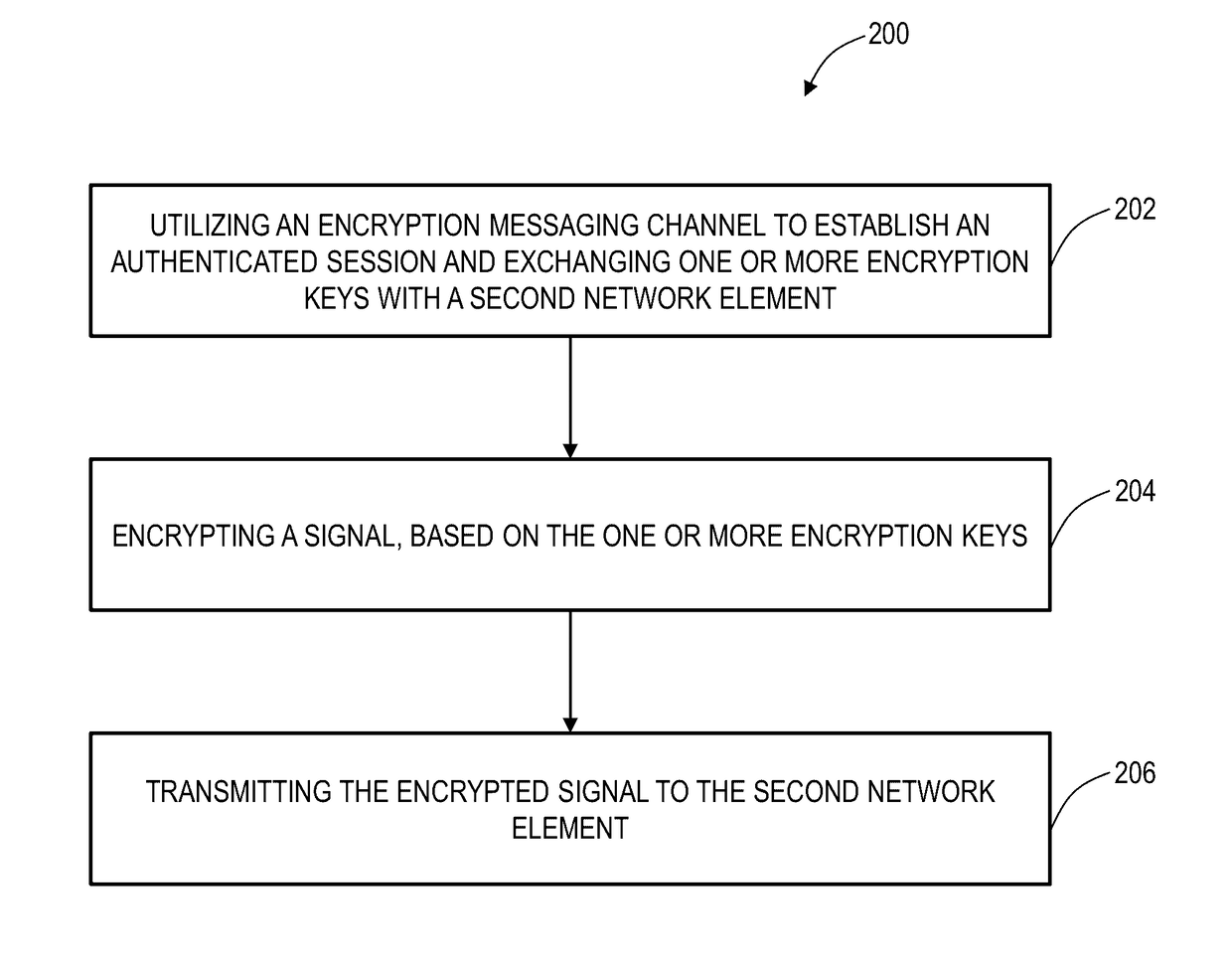

Flexible ethernet encryption systems and methods

Systems and methods for Physical Coding Sublayer (PCS) encryption implemented by a first network element communicatively coupled to a second network element include utilizing an encryption messaging channel to establish an authenticated session and exchanging one or more encryption keys with a second network element; encrypting a signal, based on the one or more encryption keys; and transmitting the encrypted signal to the second network element.

Owner:CIENA

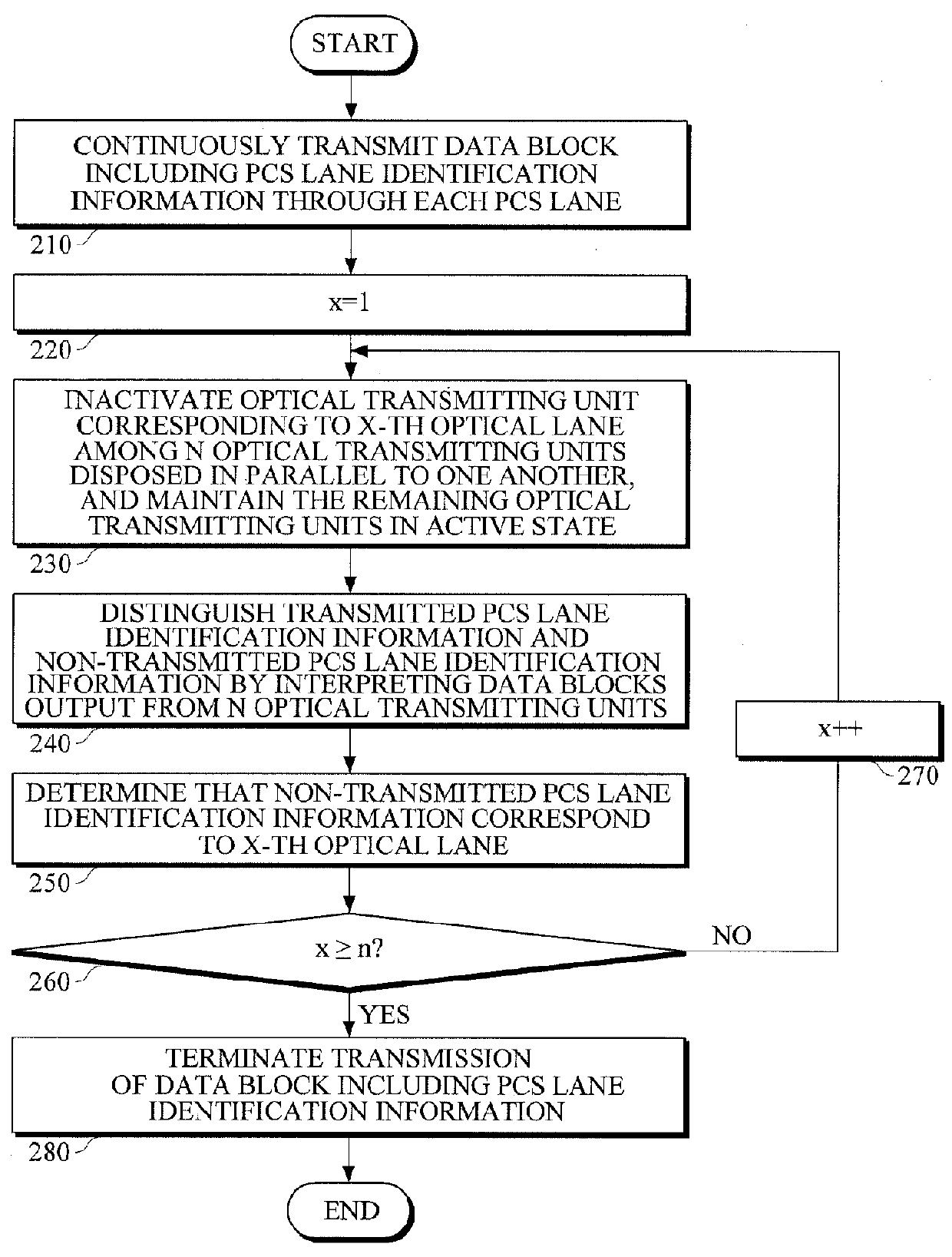

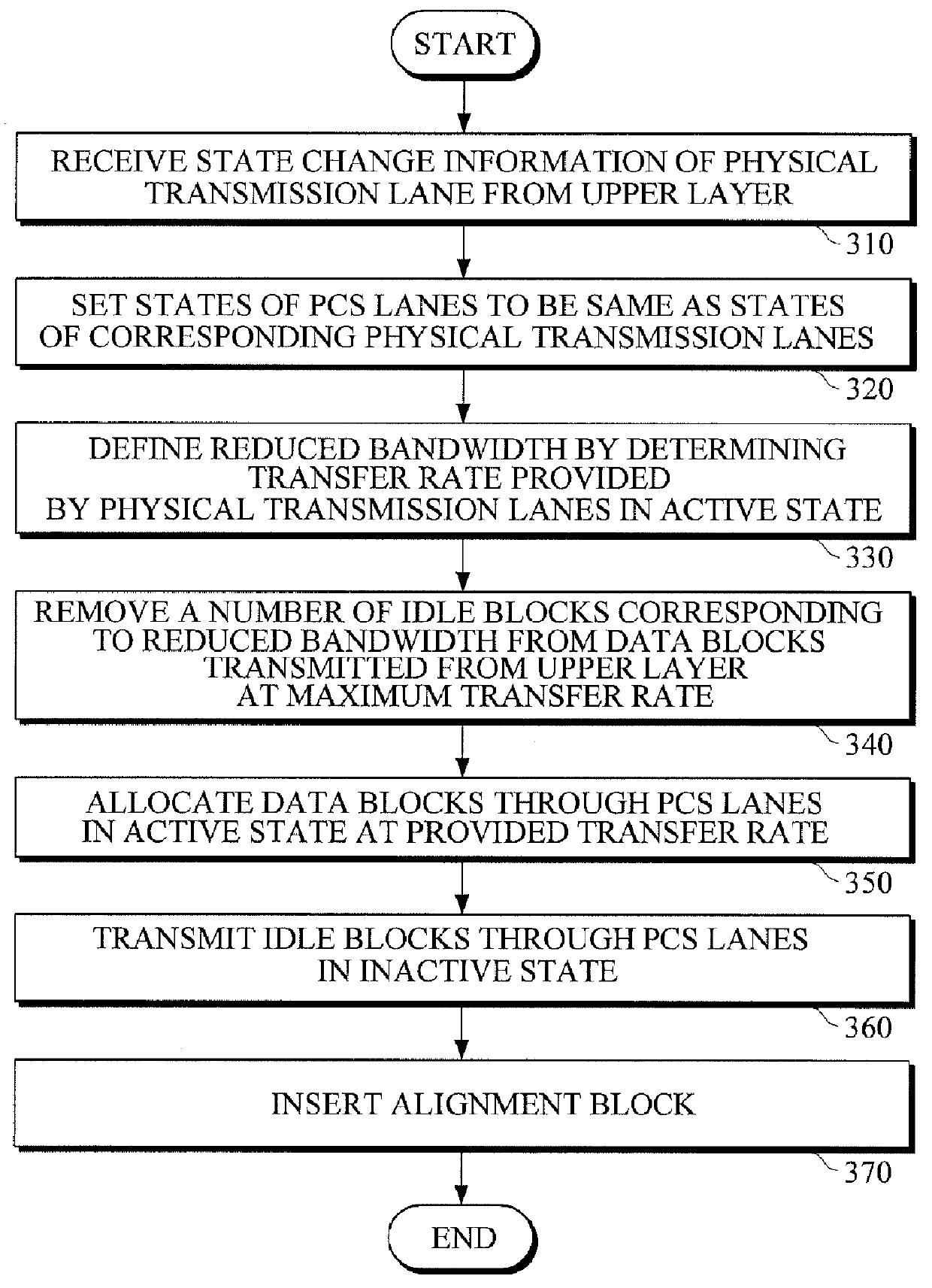

Ethernet apparatus and method for selectively operating multiple lanes

InactiveUS20120155486A1Time-division multiplexTransmission path multiple useData transmissionEthernet

A high-speed Ethernet apparatus having a multiple lane configuration and method for selectively operating the multiple lanes to allow lanes to participate or not in data transmission and reception. The Ethernet apparatus includes: a transfer rate control unit to set a state of each of multiple physical coding sub-layer (PCS) lanes inside to be the same as a state of corresponding each of multiple physical transmission lanes based on state change information that indicates whether the each physical transmission lane is activated or not, and to remove idle blocks from data blocks which are received at a transfer rate of a physical transmission lane in active state among the multiple physical transmission lanes; and a block allocating unit to allocate the data blocks from which the idle blocks have been removed through PCS lanes in active state that correspond to the physical transmission lanes in active state.

Owner:ELECTRONICS & TELECOMM RES INST

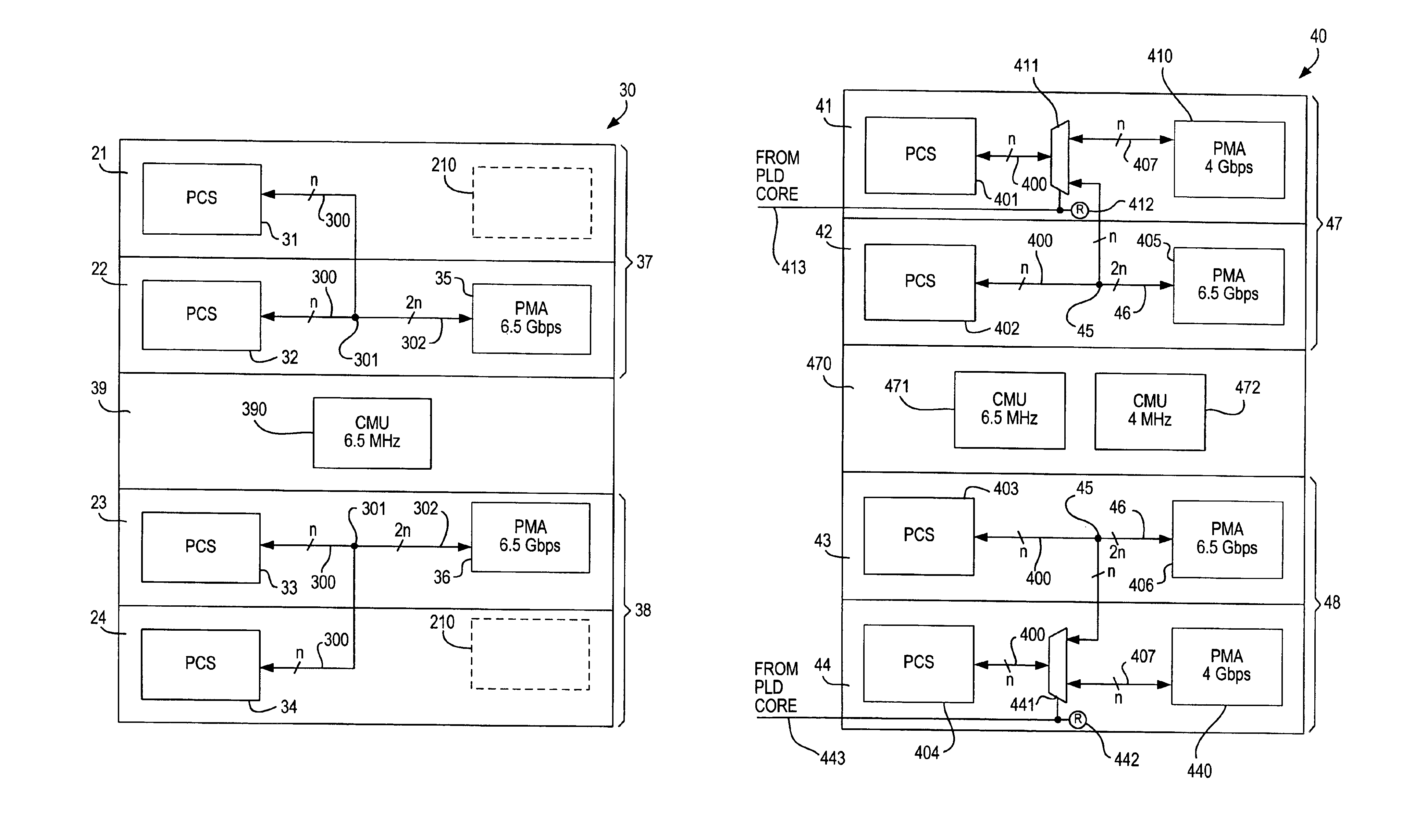

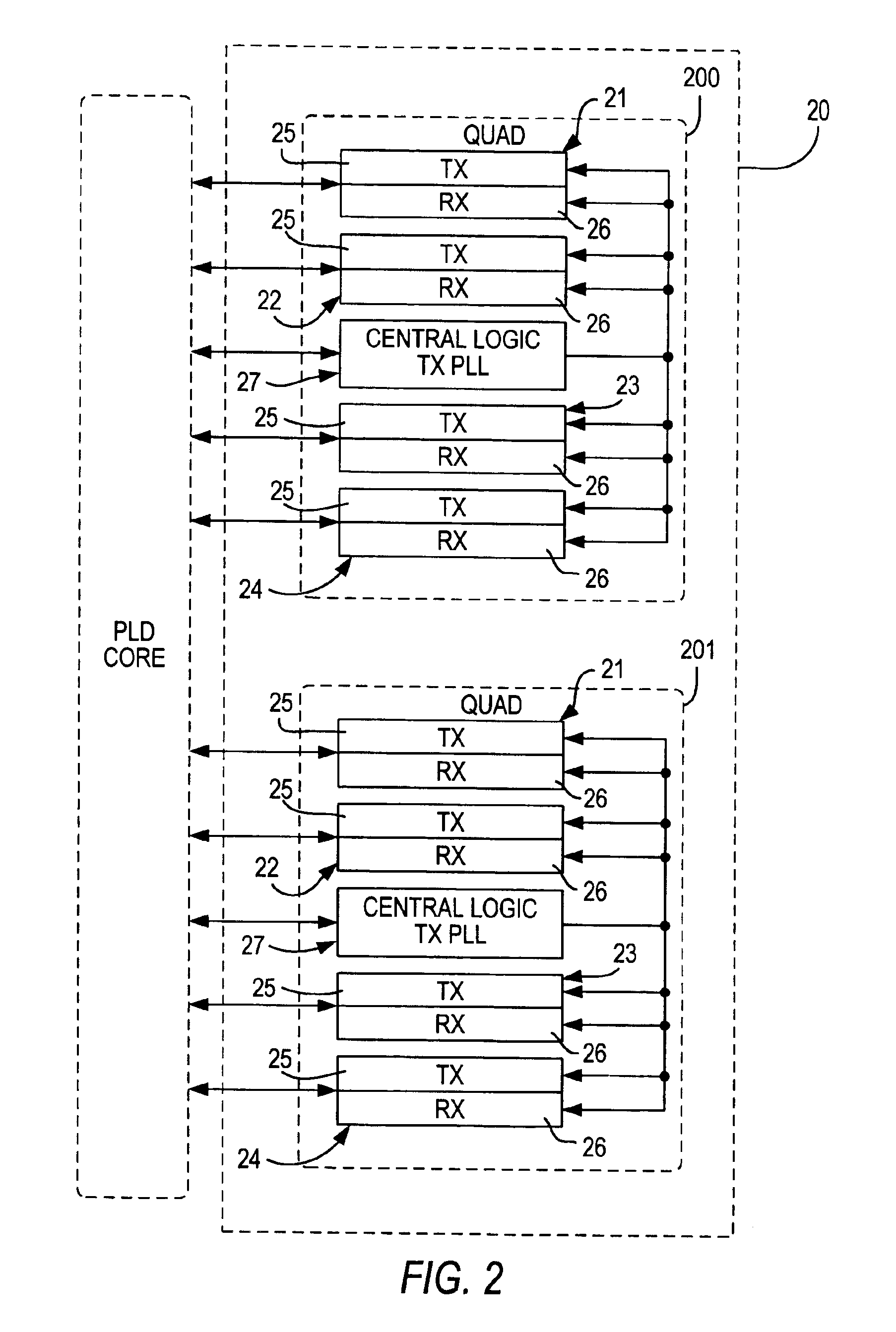

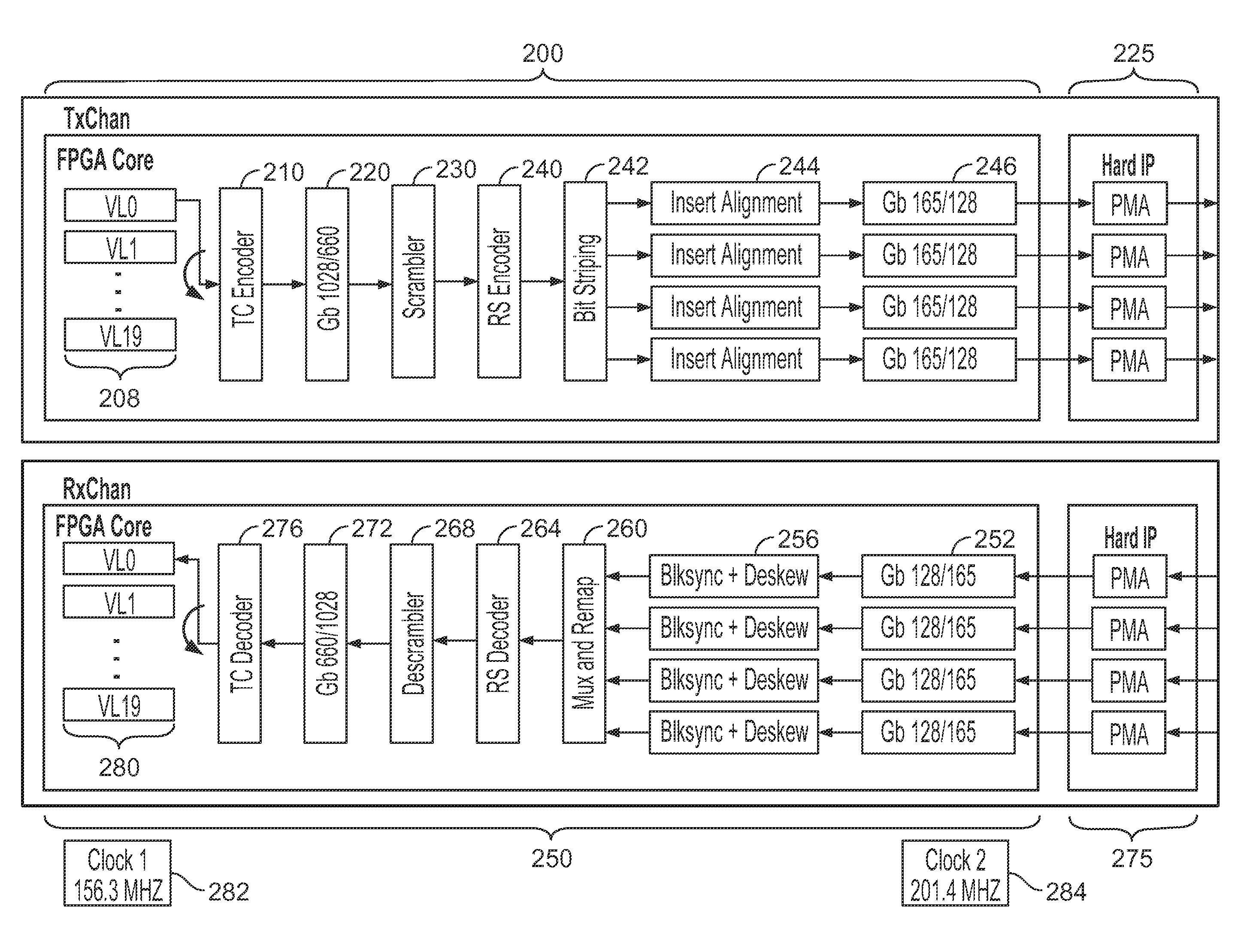

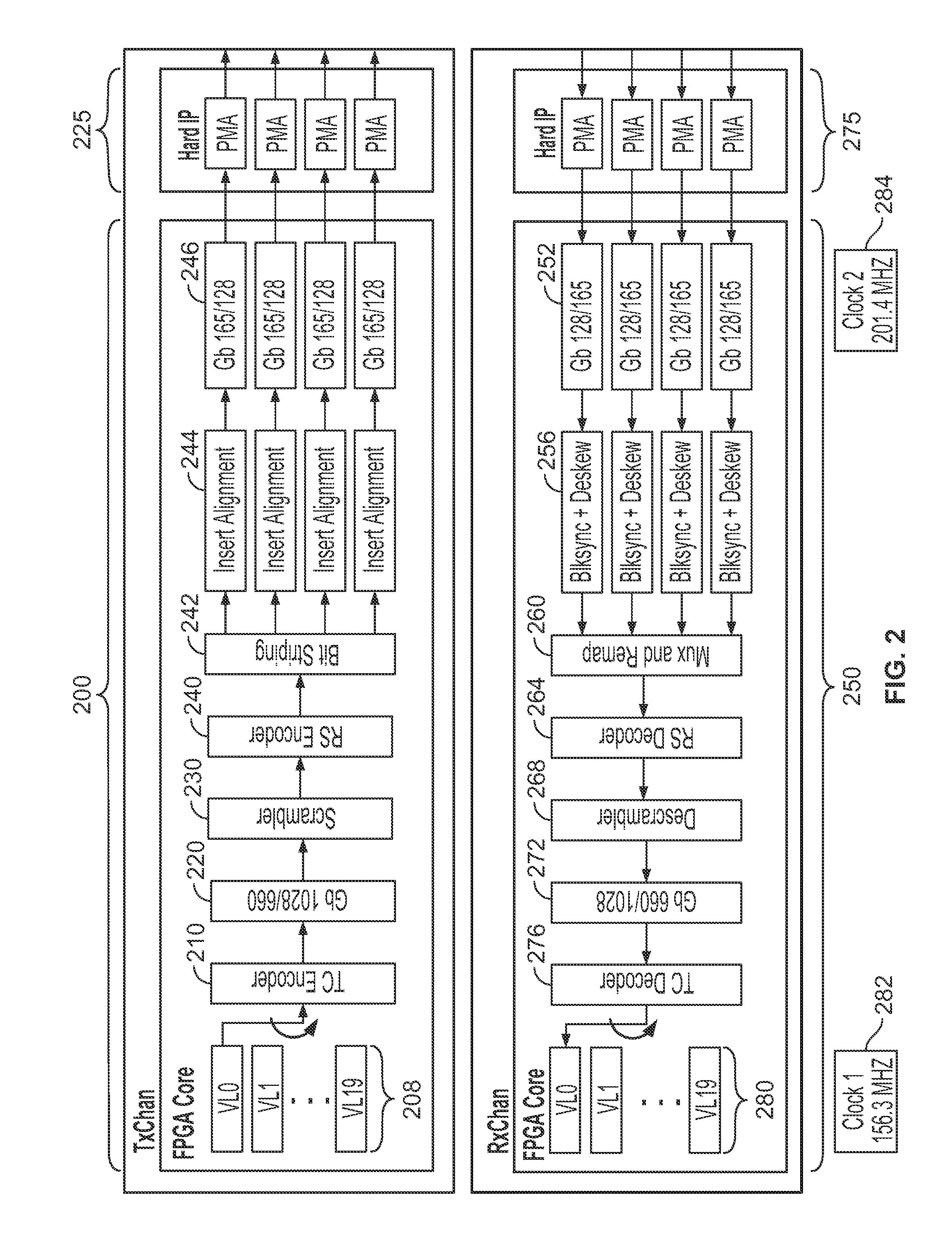

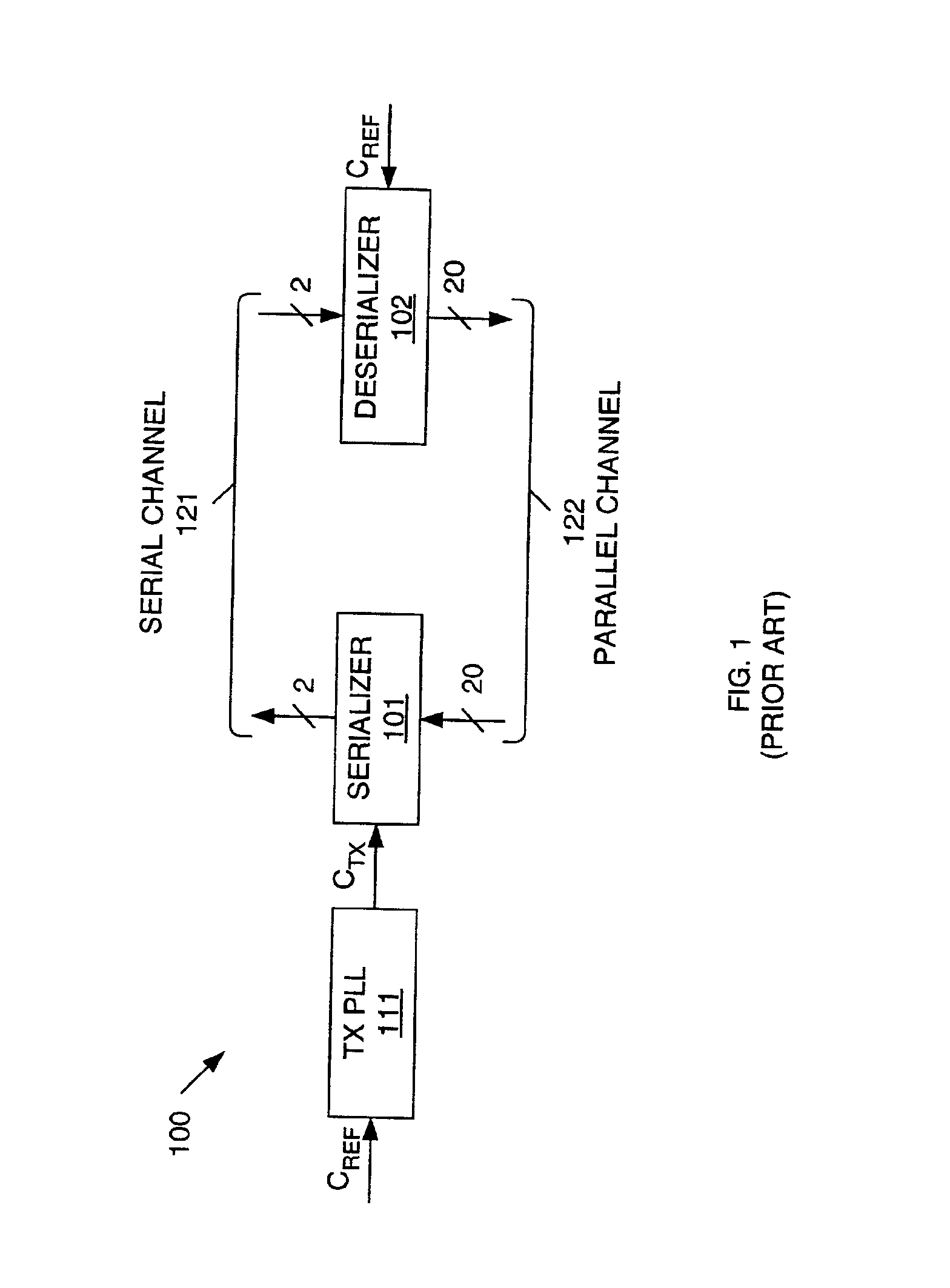

Multiple data rates in programmable logic device serial interface

A serial interface for a programmable logic device supports a higher physical medium attachment (“PMA”) data rate than the available physical coding sublayer (“PCS”) data rate by using multiple PCS modules, operating in parallel, to support one PMA module. In a channel-based structure, the PMA module is supported by a PCS module in its own channel and at least one PCS module from a second channel. The second channel may include its own PMA module which, if provided, may operate at a lower rate, supportable by the PCS module in that channel. Optionally, two modes are provided. In one mode, two PCS modules in two channels support one higher-speed PMA module in one of the channels. In a second mode, each PCS module supports a PMA module in its own channel, with the higher-speed PMA module constrained to operate at the lower data rate of the PCS module.

Owner:ALTERA CORP

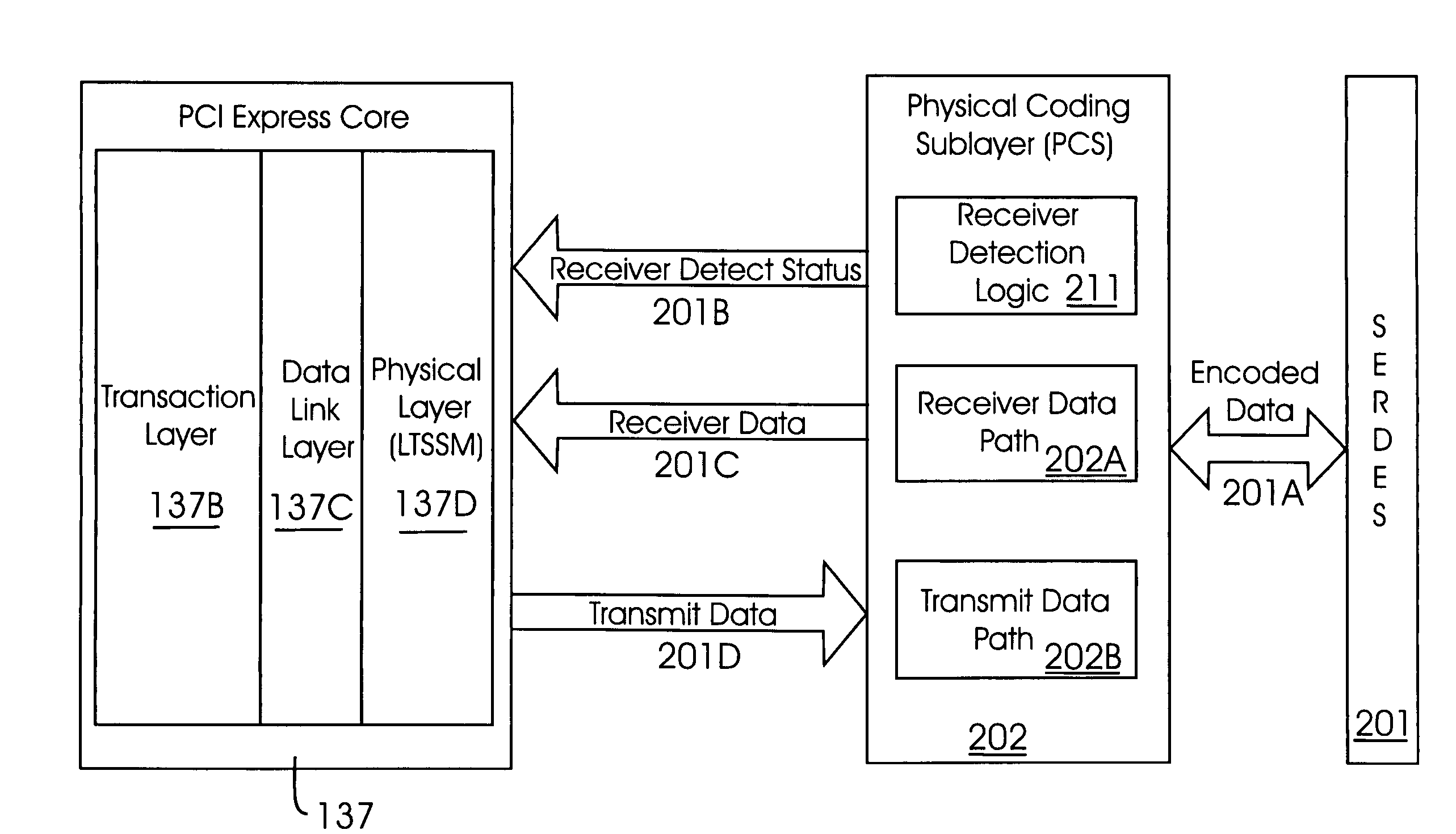

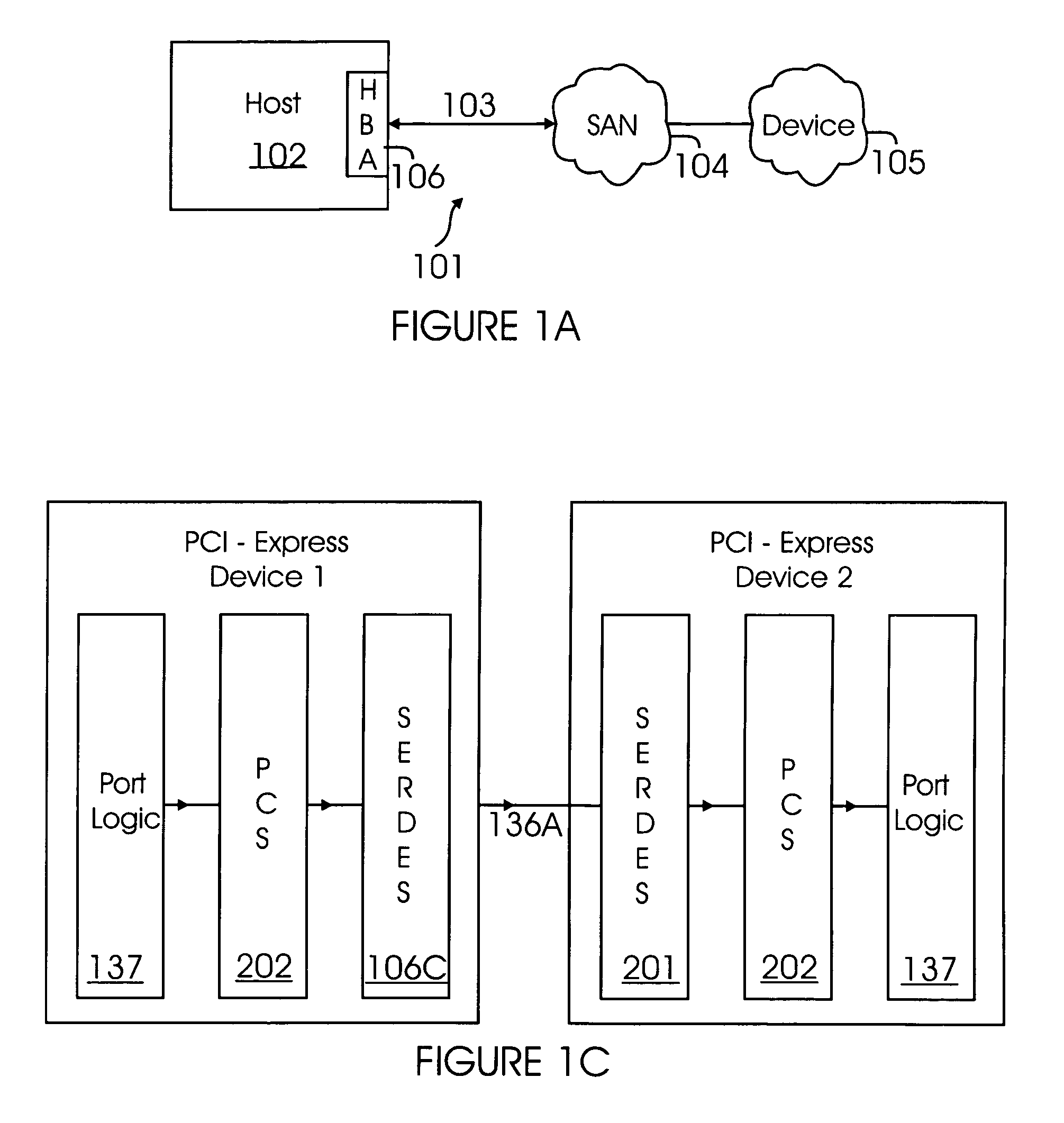

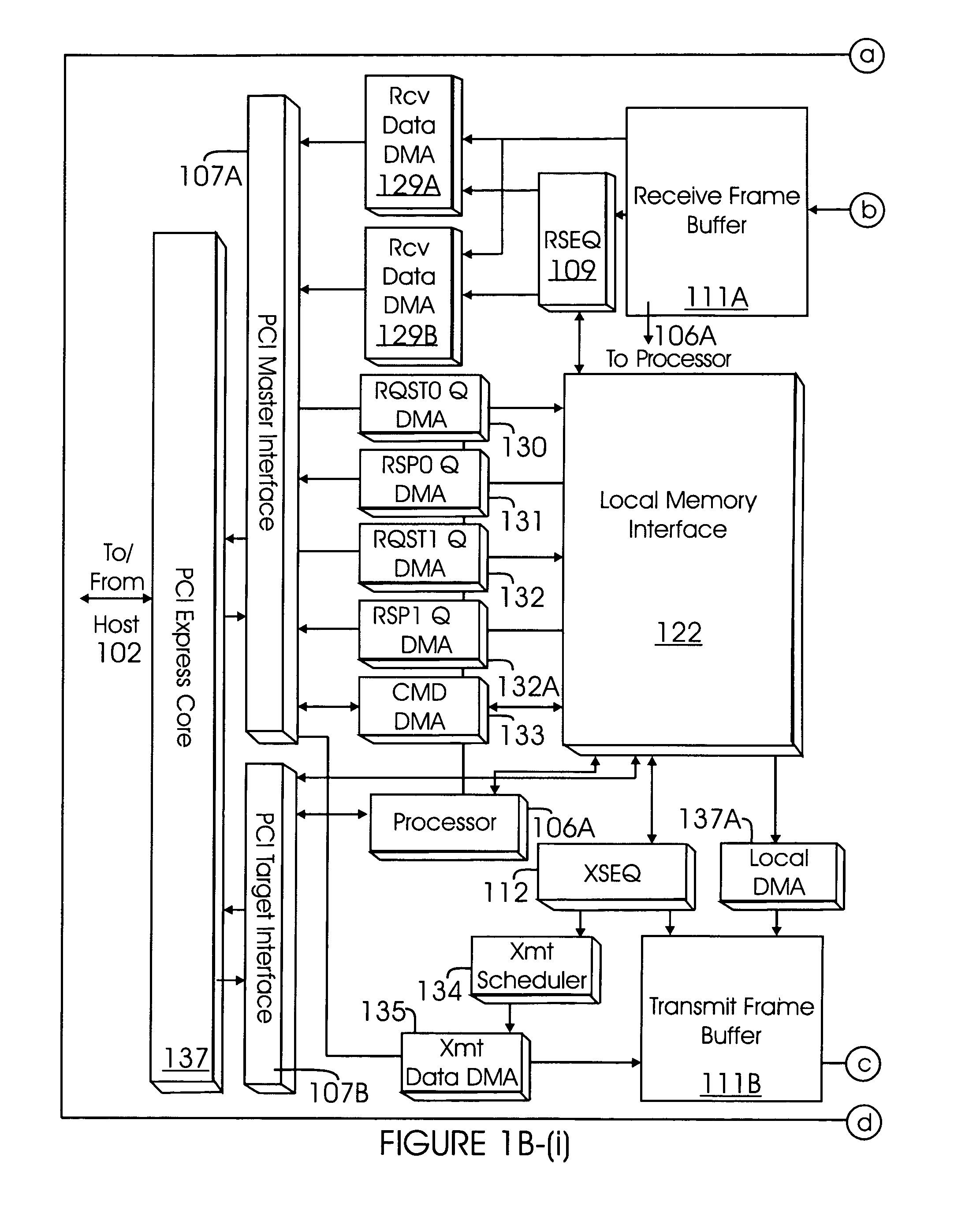

Method and system for dynamically adjusting data transfer rates in PCI-express devices

Method and system for configuring a PCI-Express device is provided. The method includes determining if a number of lanes supported by the PCI-Express device is equal to or greater than a number X, after a receiver is detected by the PCI-Express device; and setting a transfer rate depending on the number X. The PCI-Express Device includes PCI-Express core logic that receives information from a Physical Coding Sub-layer indicating if a number of lanes supported by the PCI-Express device is equal to or greater than a number X, after a receiver is detected; and a transfer rate is set depending on the number X. The value of X depends on the PCI-Express device's throughput capability and a data transfer rate.

Owner:MARVELL ASIA PTE LTD

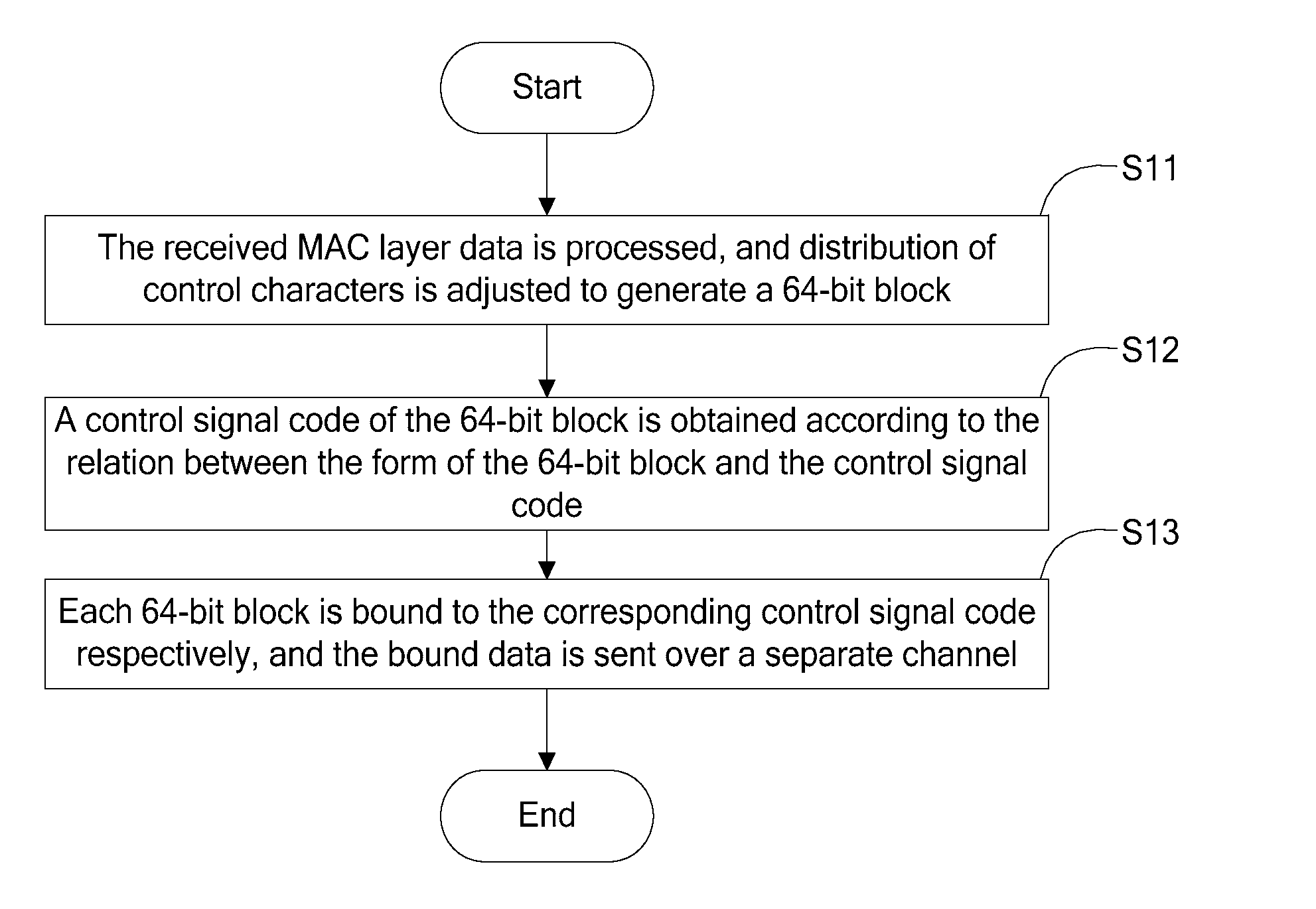

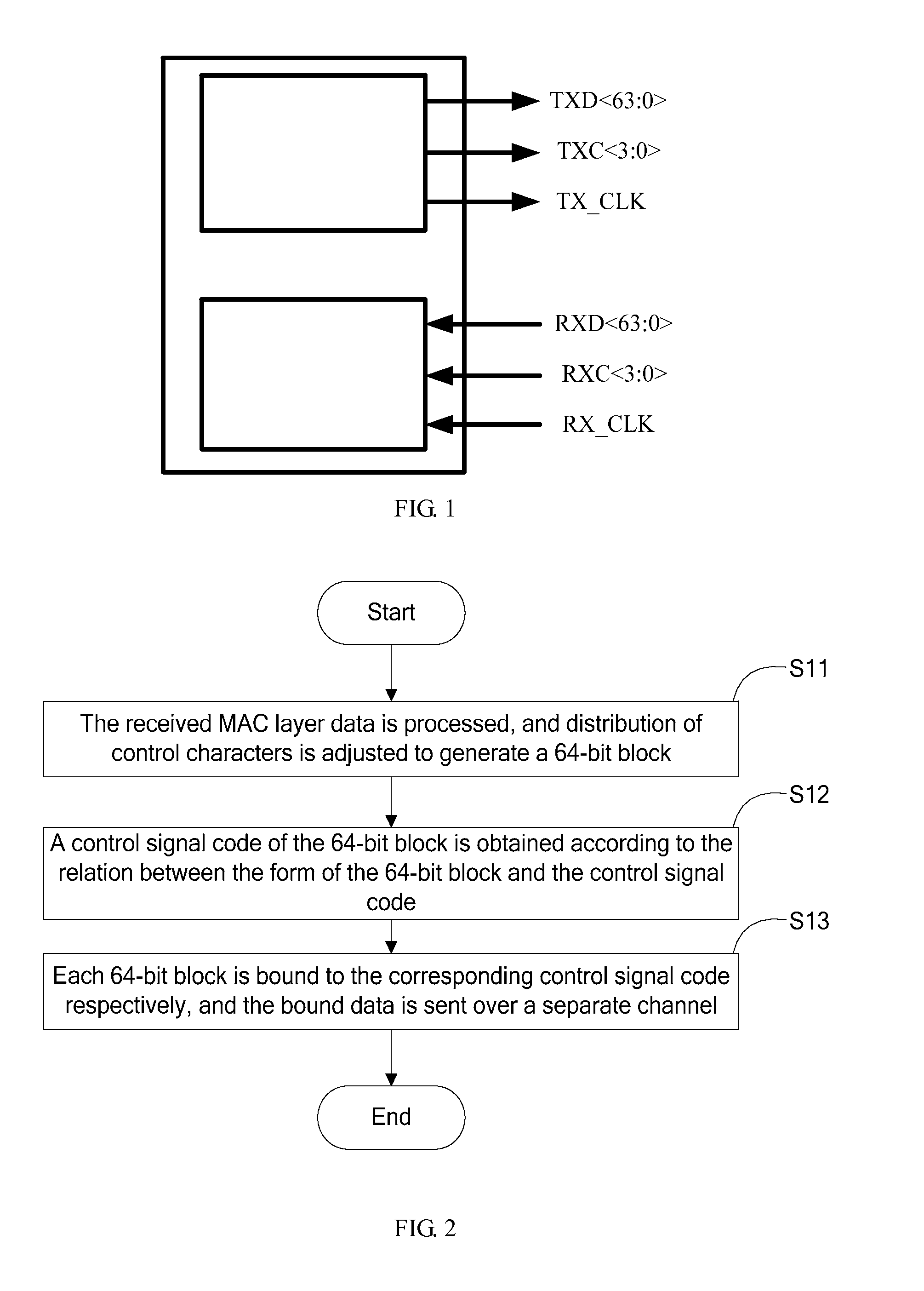

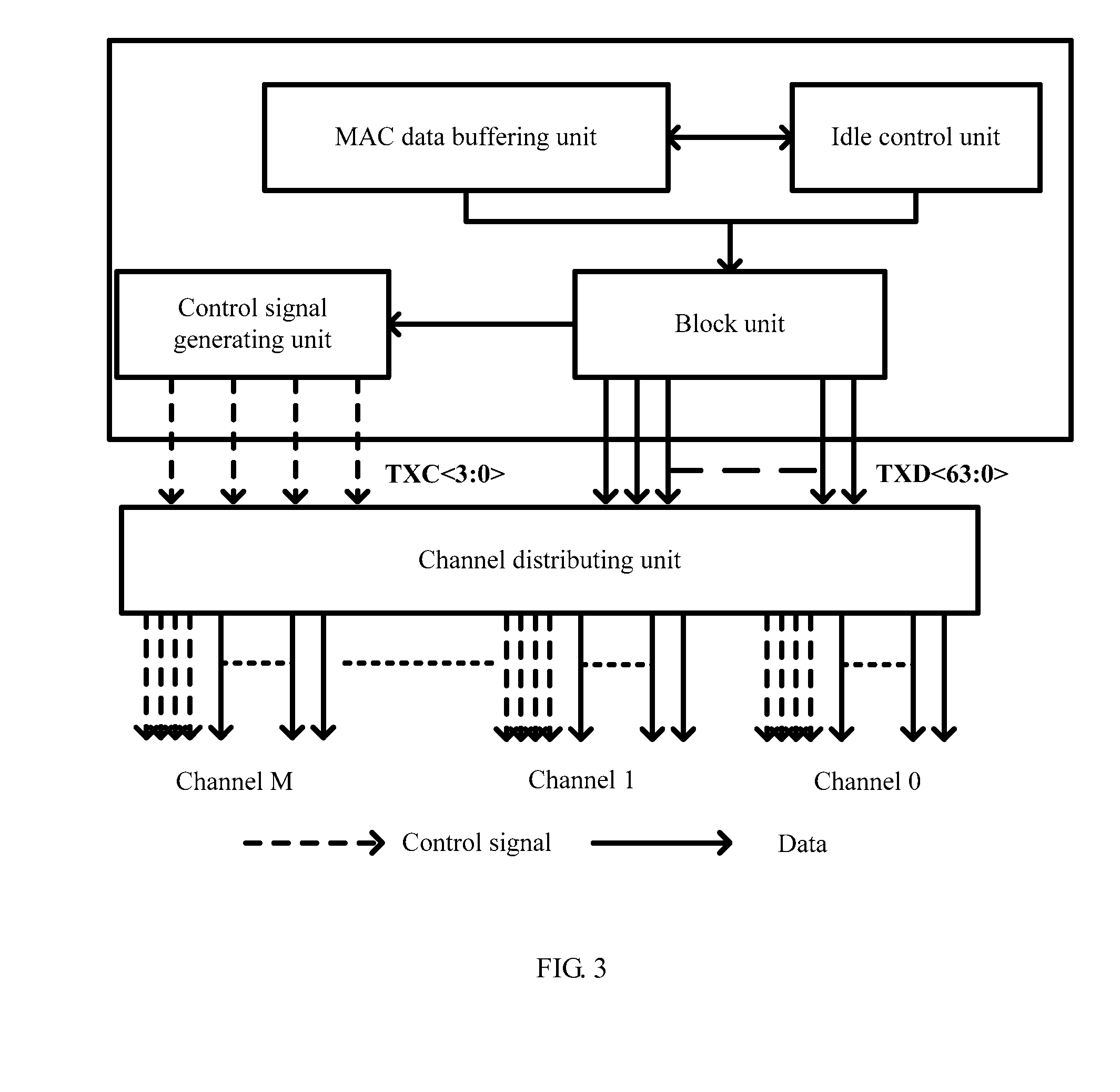

Method and apparatus for distributing and receiving high-speed ethernet media independent interface blocks

ActiveUS20090274172A1Increase bit widthControl information effectivelyError preventionTime-division multiplexControl signalControl character

A method and apparatus for distributing and receiving high-speed Ethernet Media Independent Interface (MII) blocks are provided to moderate the increase of control lines with the increase of the bit width and to simplify the block types in the coding process of the Physical Coding Sublayer (PCS). The technical solution disclosed herein includes: processing received Media Access Control (MAC) layer data, and adjusting distribution of control characters to generate a 64-bit block; obtaining a control signal code of the 64-bit block according to the relation between the form of the 64-bit block and the control signal code; and binding each 64-bit block to the corresponding control signal code respectively, and sending bound data over a separate channel.

Owner:HUAWEI TECH CO LTD

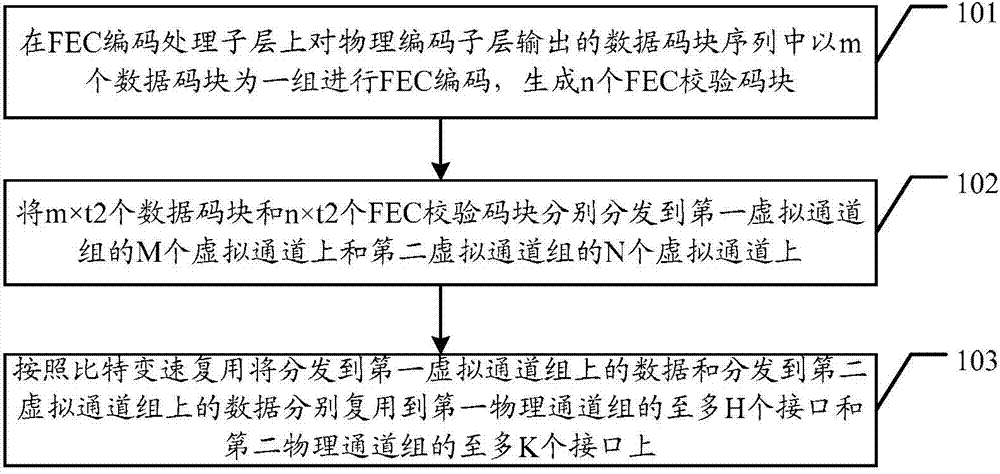

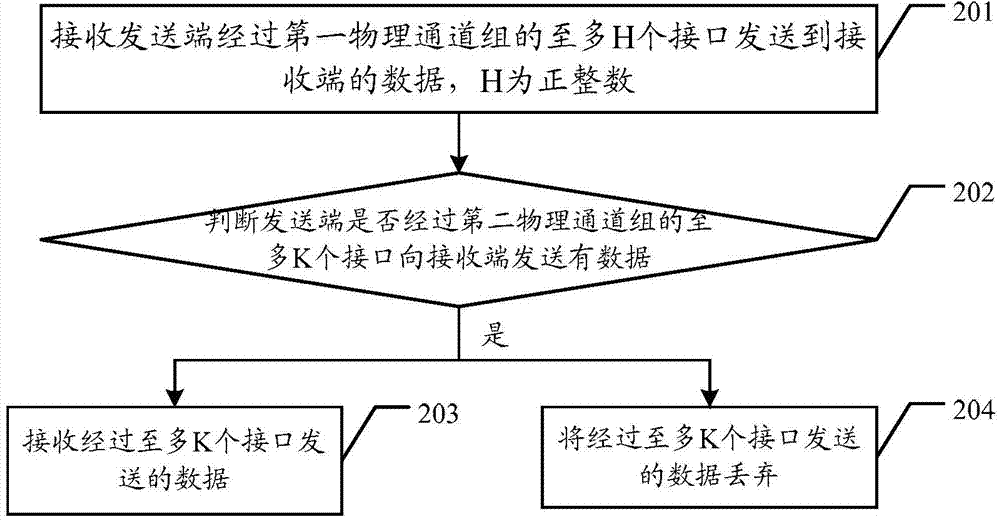

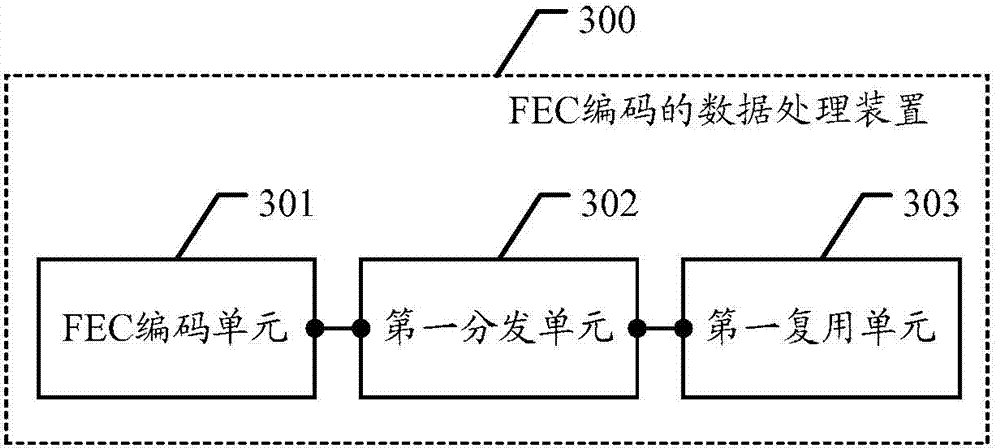

Data processing method coded and decoded by FEC, and relative device

ActiveCN103534971ADoes not reduce data transfer bandwidthGuaranteed interoperabilityRedundant data error correctionTransmission link error control systemComputer hardwareMultiplexing

The invention provides a data processing method coded and decoded by FEC, and a relative device. The method comprises: carrying out FEC coding on a FEC code processing sub-layer for a data code block sequence which is output by a physical code sub-layer and uses m data code blocks as a group, to generate n FEC check code blocks; respecitively distributing m*t2 data code blocks and n*t2 FEC check code blocks to M virtual channels of a first virtual channel group and N virtual channels of a second virtual channel group, wherein m*t2 is less than or equal to m_max, m_max is t1 times of M, n is less than or equal to n_max, n_max is t1 times of N, and m, n, t1 and t2 are positive integers; and respectively multiplexing data distributed to the first virtual channel group and the second virtual channel group onto at most H interfaces of a fisrt physical channel group and at most K interfaces of a second physical channel group according to bit speed-changing multiplexing, wherein M is integral multiple times of H, and N is integral multiple times of K.

Owner:HUAWEI TECH CO LTD

Techniques for time transfer via signal encoding

InactiveUS20100080248A1Synchronisation arrangementTime-division multiplexComputer hardwareTime transfer

Techniques for time transfer via signal encoding are disclosed. In one particular exemplary embodiment, the techniques may be realized as a method for time transfer via signal encoding comprising generating a time service ordered-set for inclusion in a physical coding sublayer frame of a physical layer device, generating time service data for inclusion in the physical coding sublayer frame of the physical layer device, and transmitting the physical coding sublayer frame.

Owner:RPX CLEARINGHOUSE

Low overhead coding with arbitrary control symbol placement

ActiveUS7251699B1Multiple digital computer combinationsData switching networksMultiplexingData stream

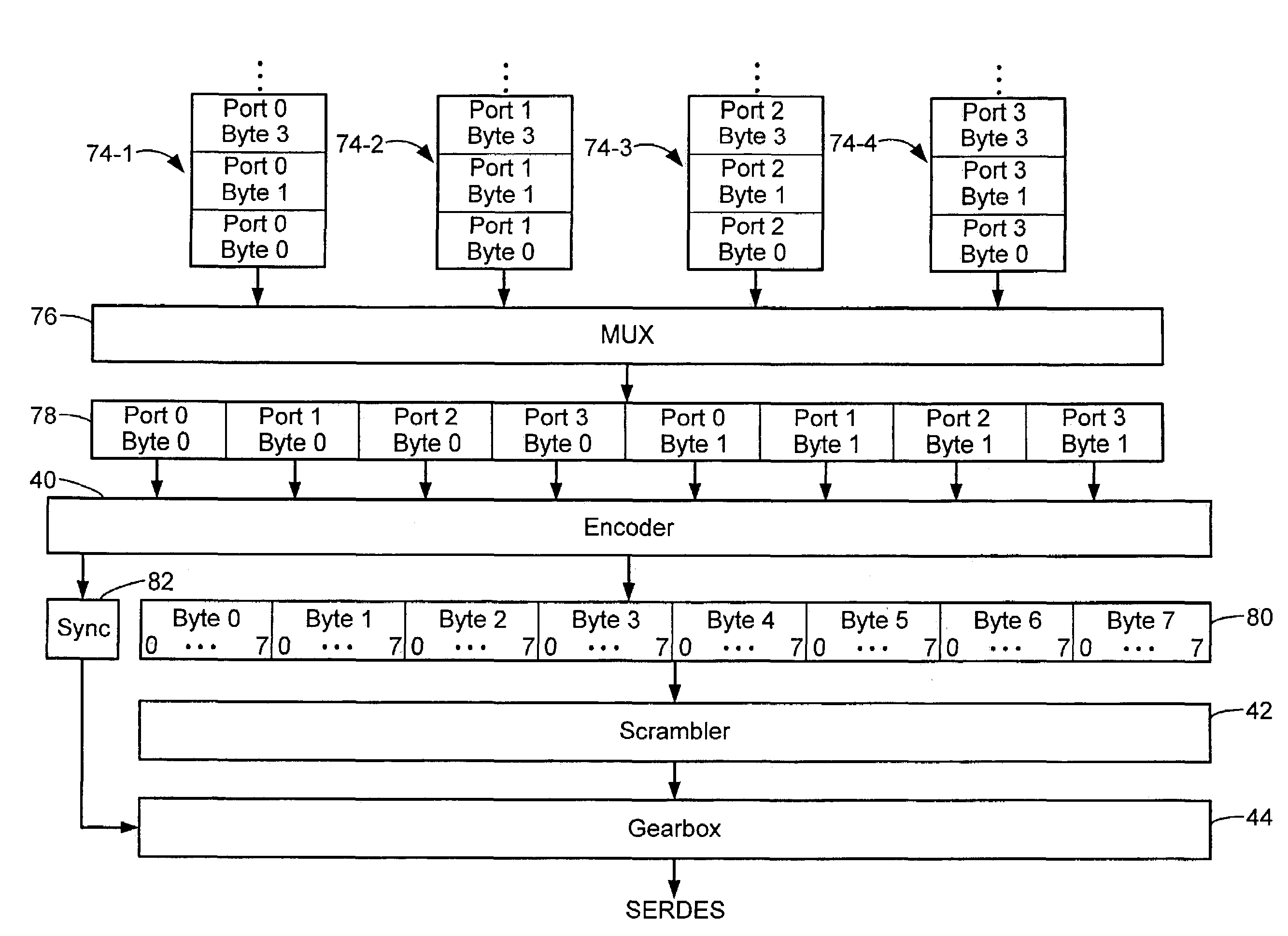

A physical coding sublayer (PCS) device in a physical layer device of an Ethernet network device includes a multiplexer that aggregates data, which includes at least one of data portions and control portions, from a plurality of data streams into a multiplexed data block. An encoder encodes the multiplexed data block to produce an encoded data block that includes n data blocks. Each of the n data blocks includes at least one of data portions, pointer portions, and control code portions. The control code portions can be located within any of the n data blocks.

Owner:MARVELL ASIA PTE LTD

Flexible high speed forward error correction (FEC) physical medium attachment (PMA) and physical coding sublayer (PCS) connection system

Systems, methods, apparatus, and techniques relating to a transmitter interface are disclosed. A soft-IP transmitter interface includes a Reed-Solomon encoder operating according to any one of multiple bus width and bandwidth parameter pairs, and a gearbox module that includes multiple gearboxes. The multiple gearboxes receive input data at a bus width and clock rate parameter pair specified by the soft-IP transmitter interface and convert the input data into output data according to a number of physical lanes and bandwidth parameter pair specified by a physical medium attachment (PMA) standard.

Owner:ALTERA CORP

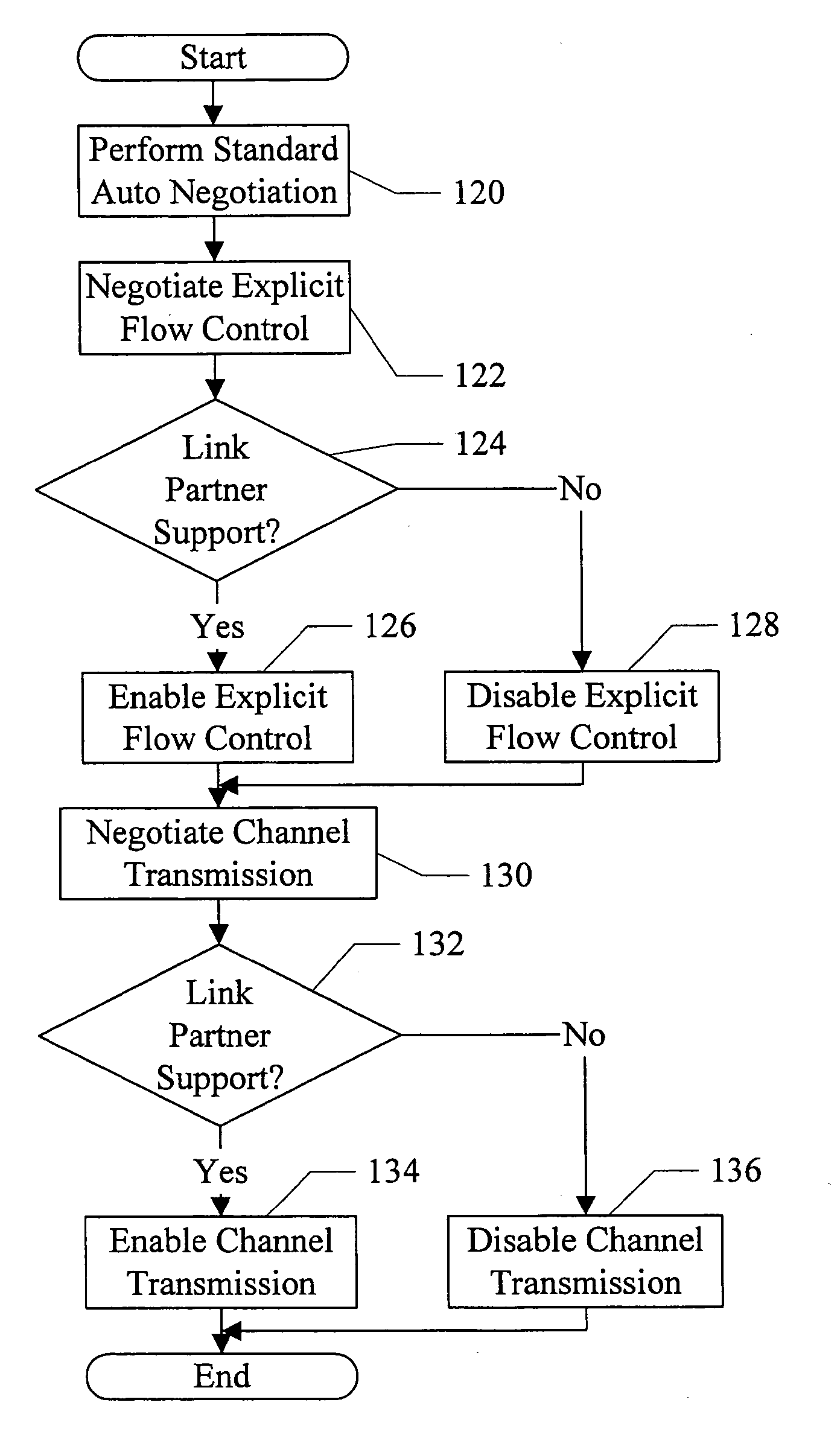

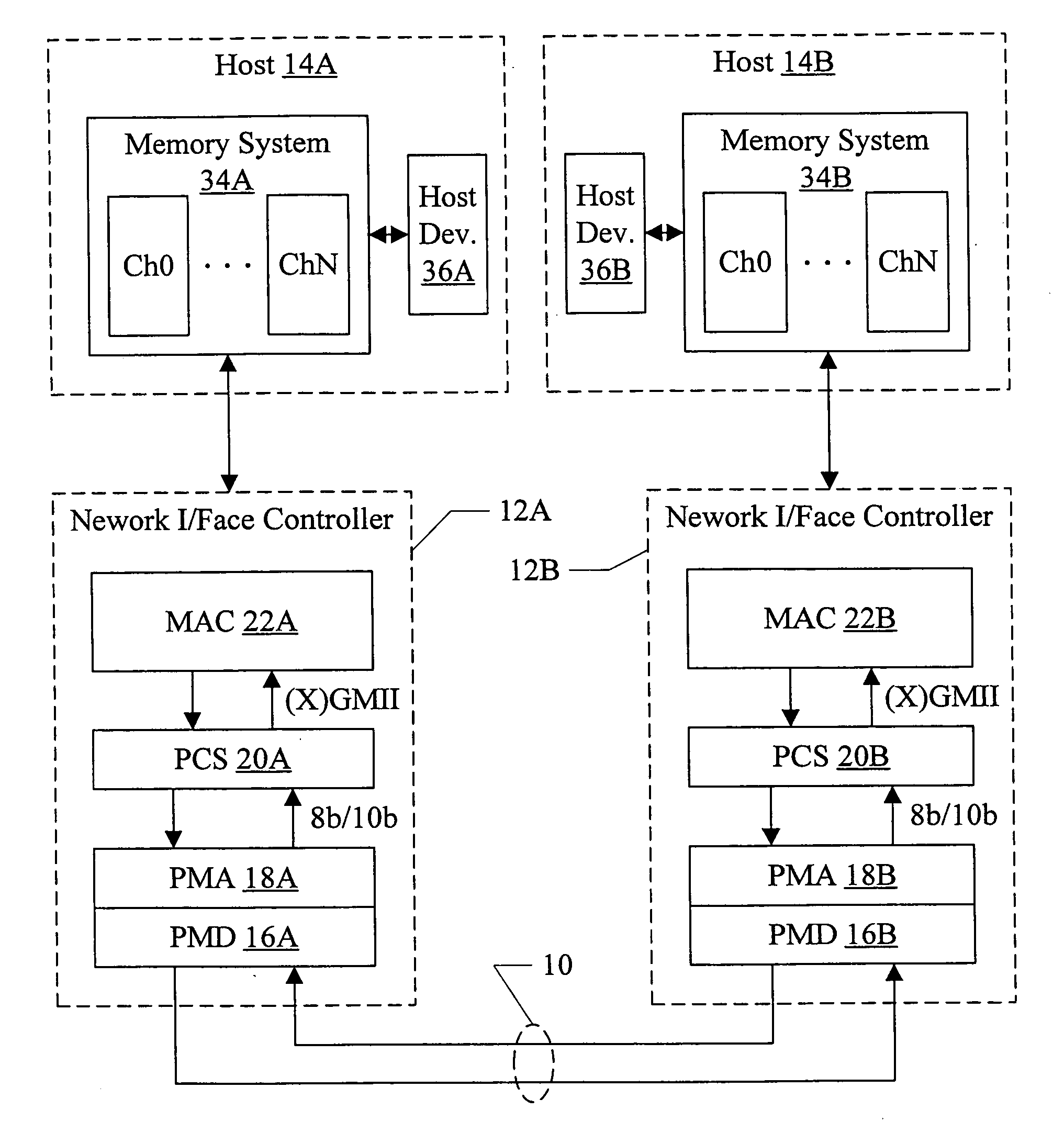

Explicit Flow Control in a Gigabit/10 Gigabit Ethernet System

InactiveUS20100188980A1Error preventionFrequency-division multiplex detailsTraffic capacity10 Gigabit Ethernet

In one embodiment, a system comprises a communication medium; a first controller coupled to the communication medium; and a second controller coupled to the communication medium. The first controller is configured to interrupt transmission of a packet on the communication medium to the second controller subsequent to transmission of a first portion of the packet. The first controller is configured to transmit at least one control symbol on the communication medium in response to interrupting transmission of the packet, and wherein the first controller is configured to continue transmission of the packet with a second portion of the packet. The controller(s) may include, in some embodiments, a media access controller and a physical coding sublayer.

Owner:DESAI SHAILENDRA S +1

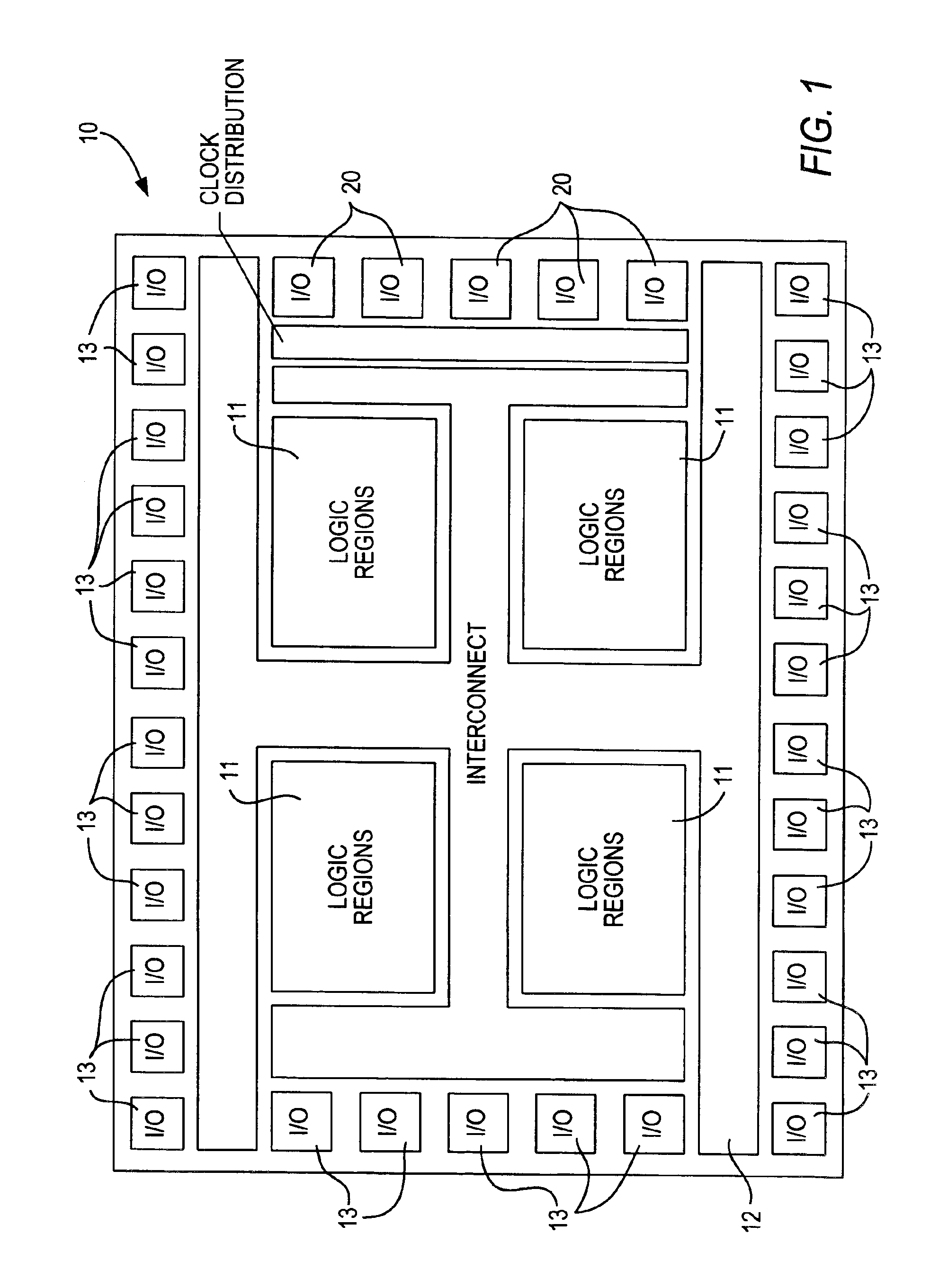

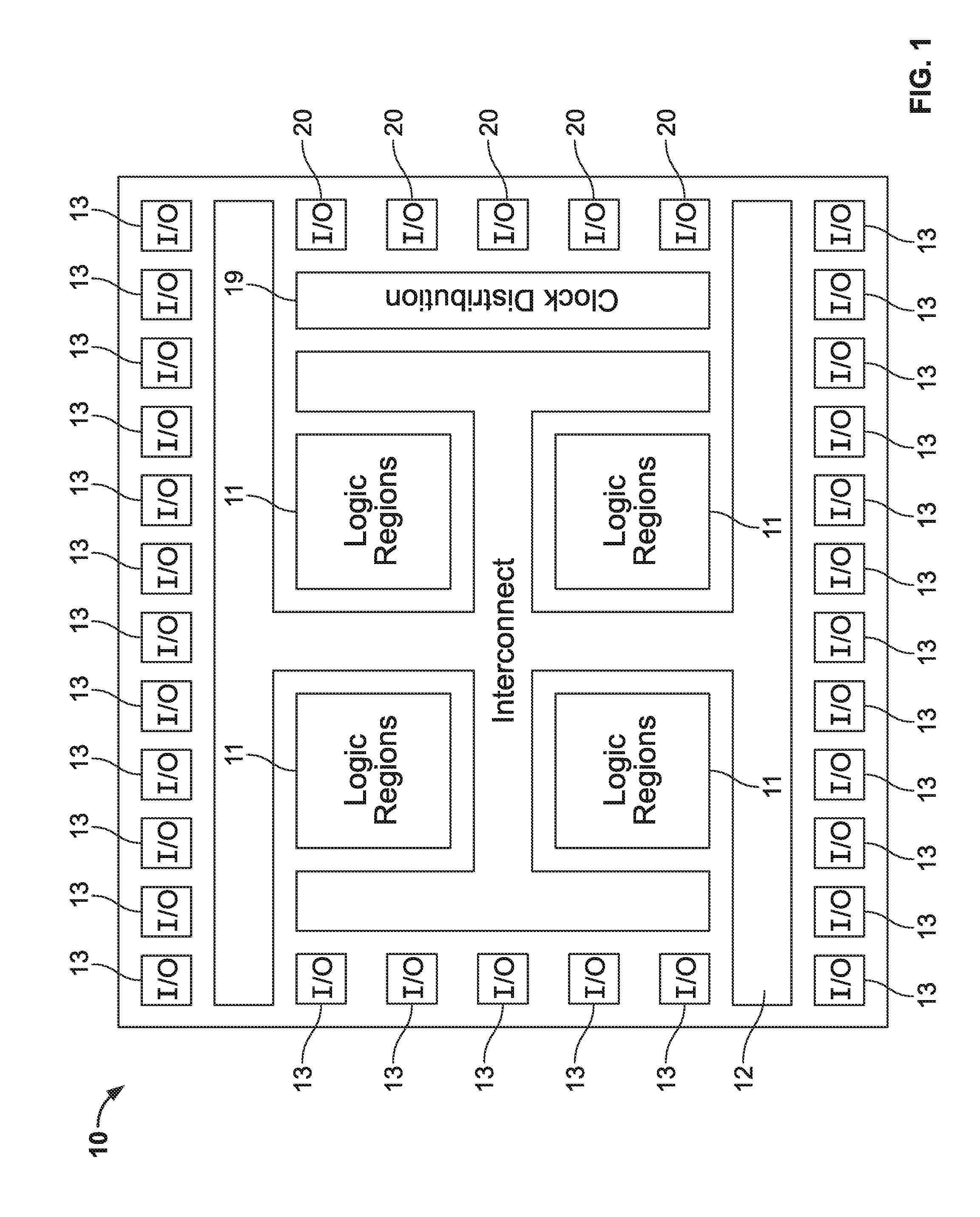

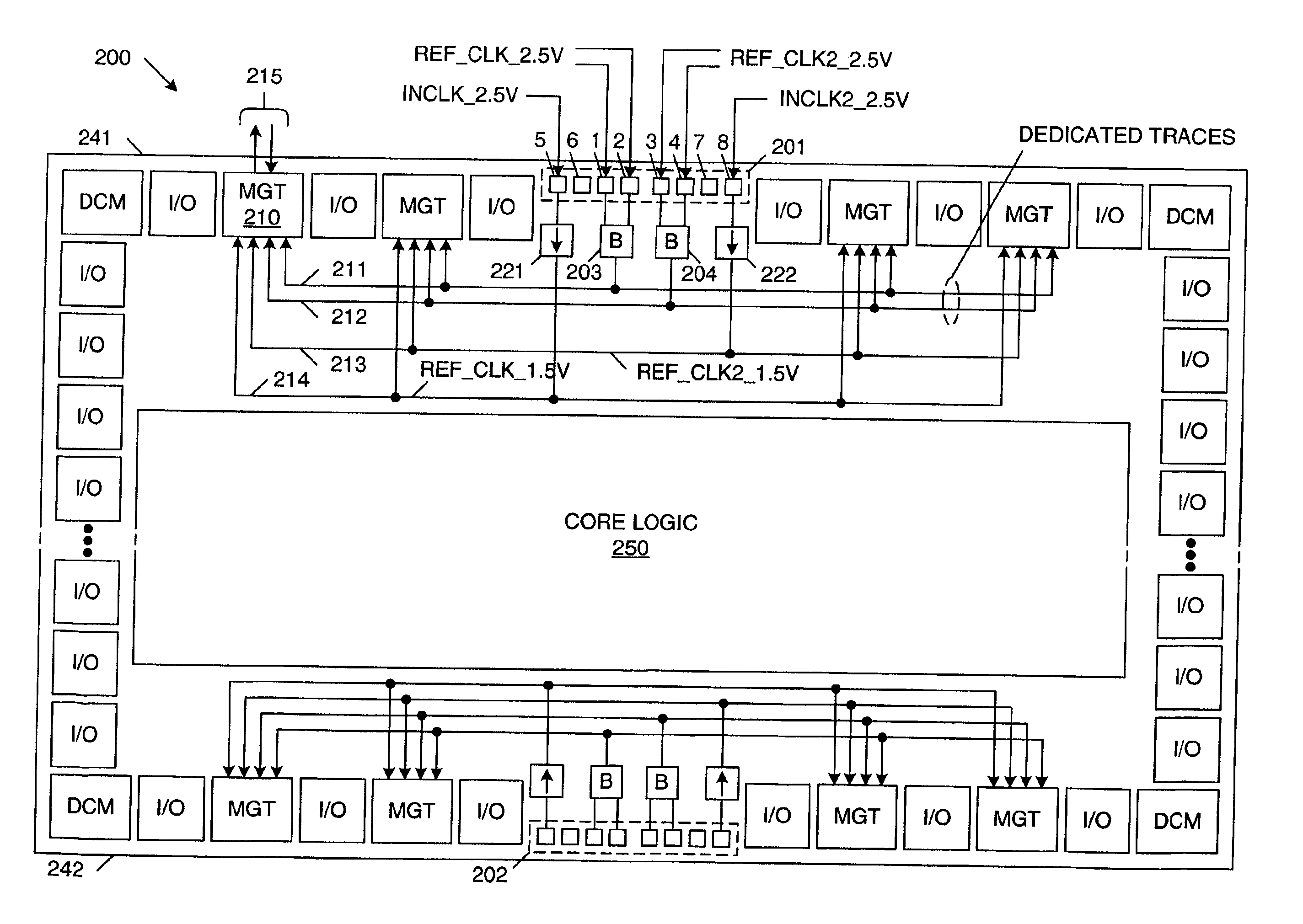

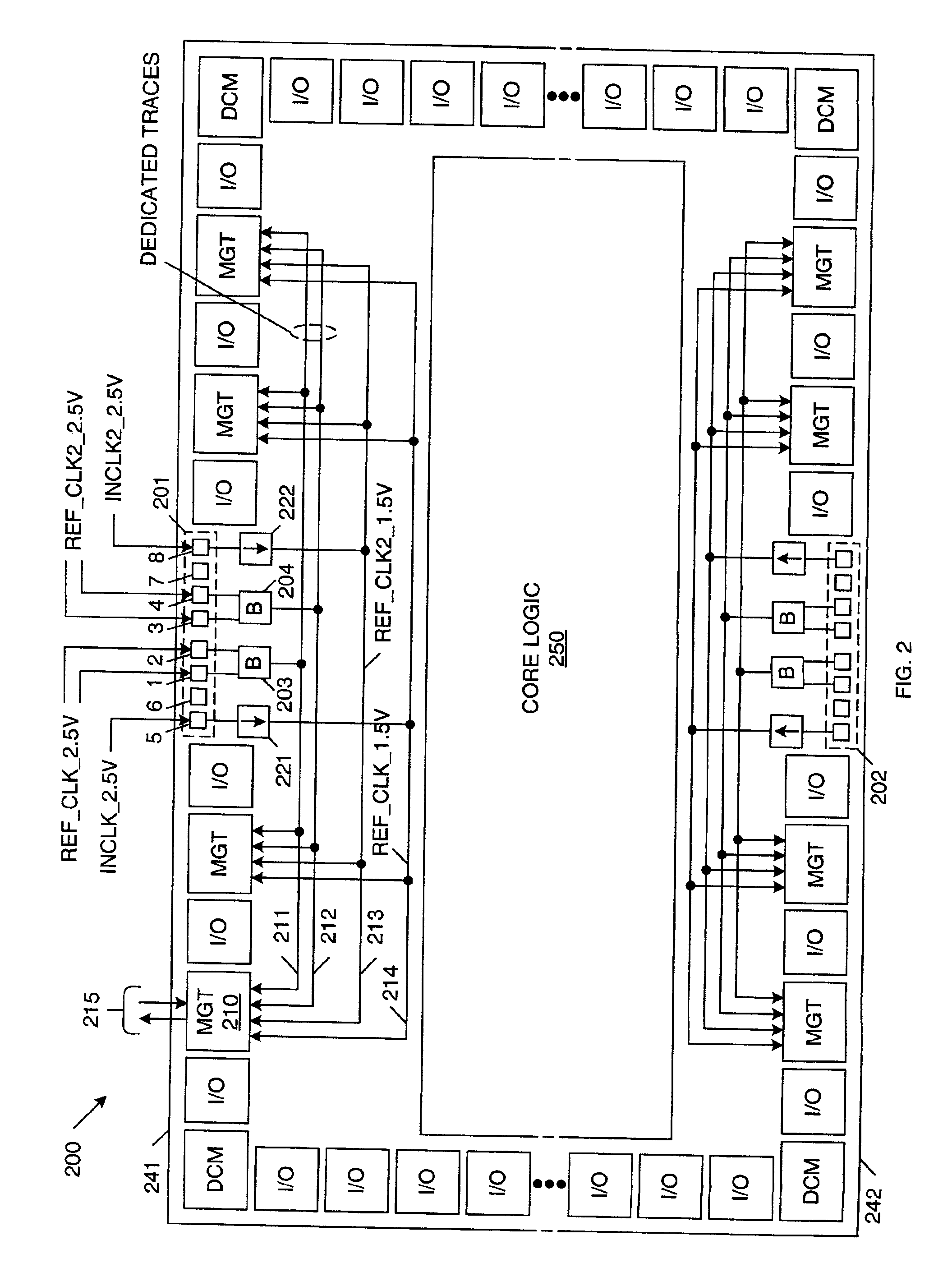

Low jitter clock for a physical media access sublayer on a field programmable gate array

InactiveUS6911842B1Increase flexibilityIncrease jitterSolid-state devicesElectronic switchingGeneral purposeProgrammable logic device

A programmable logic device (PLD) is provided that supports multi-gigabit transceivers (MGTs). The PLD includes one or more pairs of shared clock pads for receiving one or more high-quality differential clock signals. Dedicated clock traces couple each pair of shared clock pads to one or more MGTs on the PLD. Each MGT includes a clock multiplexer circuit, which allows one of the high-quality differential clock signals to be routed as a reference clock signal for the MGT. The clock multiplexer circuits are designed such that no significant jitter is added to the high-quality clock signals. The clock multiplexer circuits can also route general-purpose clock signals received by the PLD as lower quality reference clock signals for the MGTs. The reference clock signal routed by the clock multiplexer circuit can be stepped down to provide a reference clock for a physical coding sublayer of the MGT.

Owner:XILINX INC

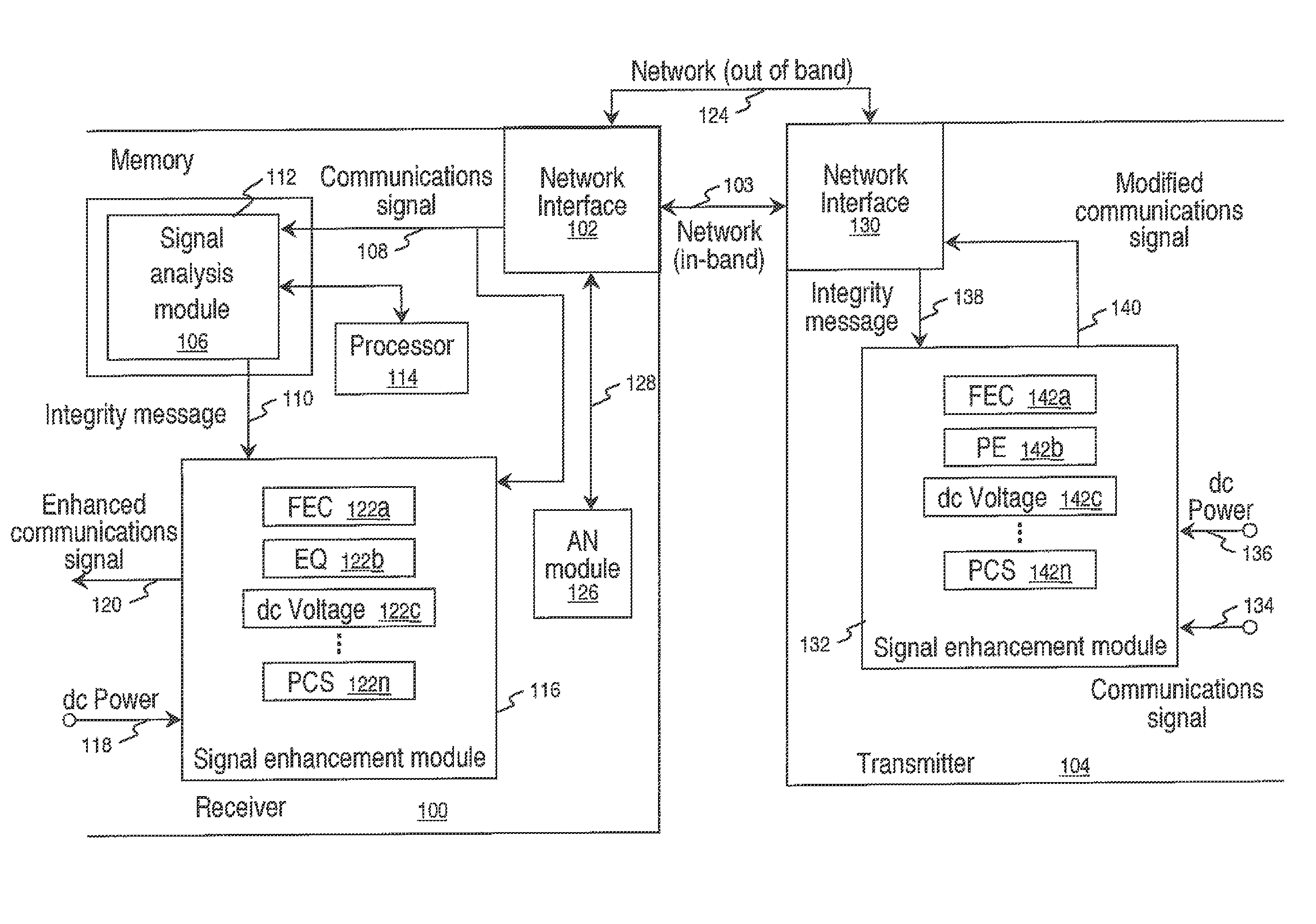

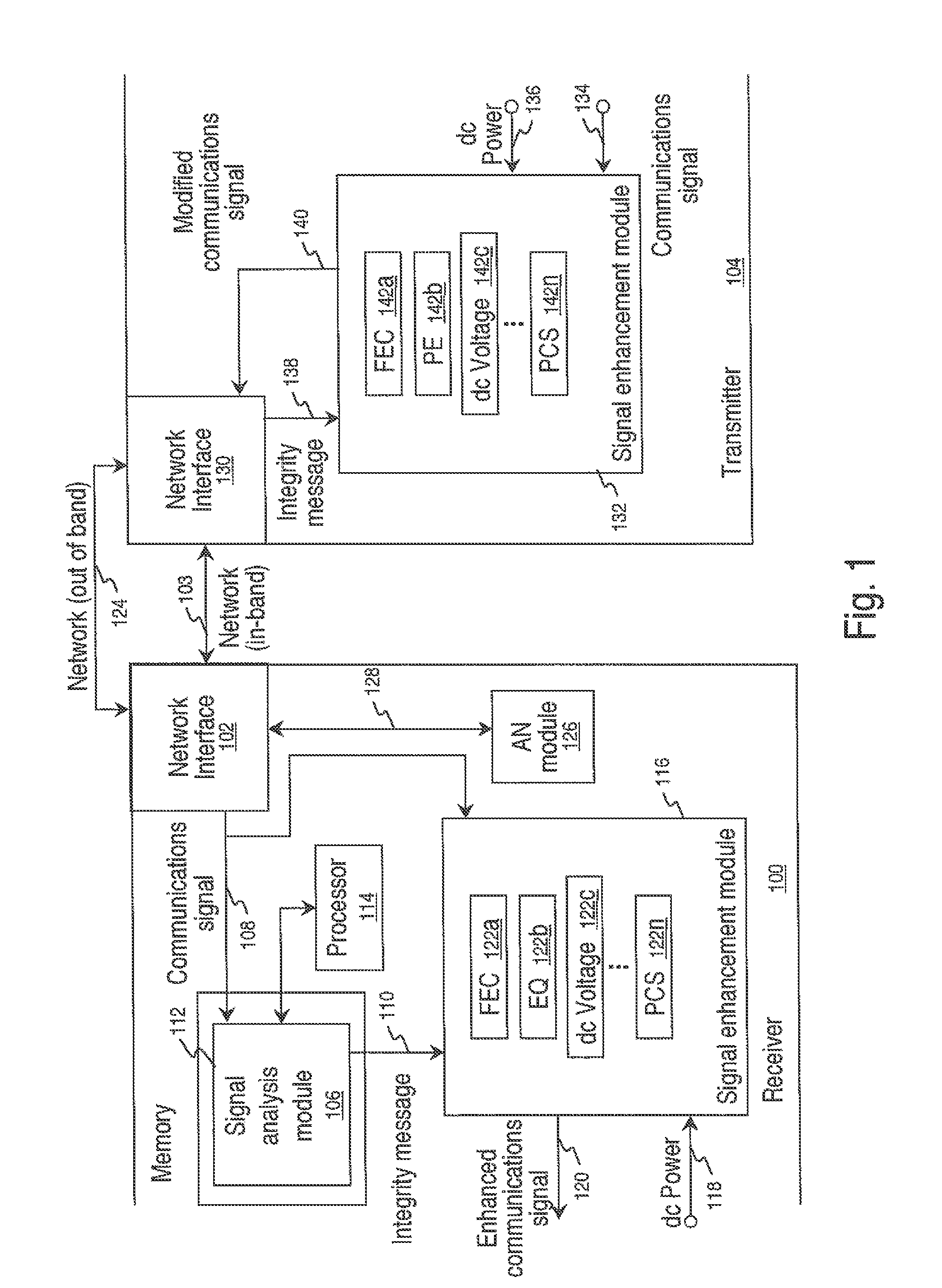

System and method for closed-loop optical network power backoff

ActiveUS8649686B1Reduce power consumptionReduce the required powerReceiver specific arrangementsFibre transmissionClosed loopEngineering

In a communication device using a plurality of signal enhancement mechanisms, a system and method are provided for managing signal processing power consumption. A receiver accepts a communications signal and analyzes signal integrity. In response to analyzing the signal integrity, a signal enhancement mechanism is changed, and device power consumption is modified in response to changing the signal enhancement mechanism. In one aspect, the receiver changes a receiver signal enhancement mechanism, and modifies its power consumption. For example, one or more of the following receiver signal enhancement mechanisms may be selected: forward error correction (FEC), equalization, dc voltage level, and physical coding sublayer (PCS).

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

Packet Network Interface Apparatus and Method

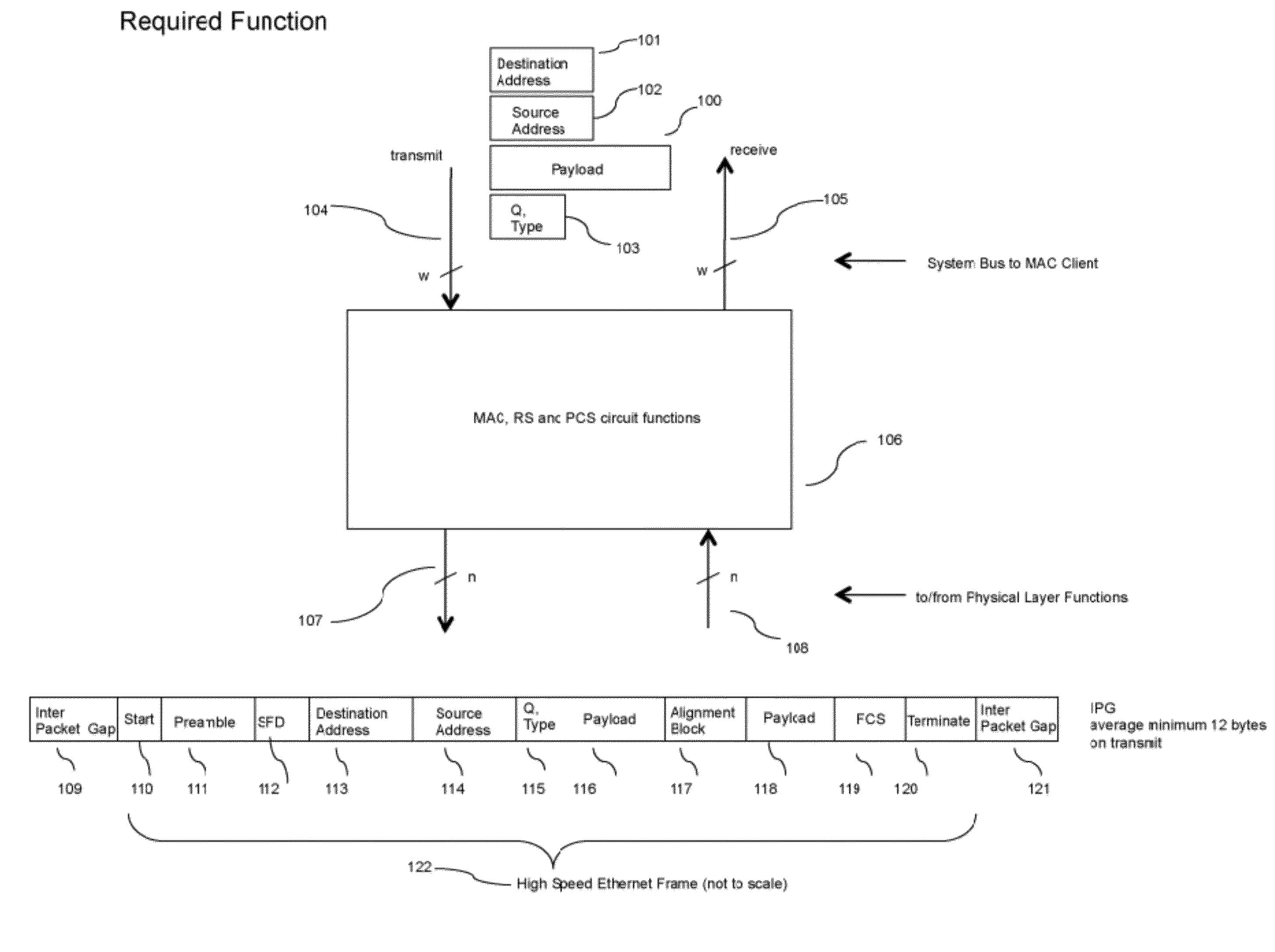

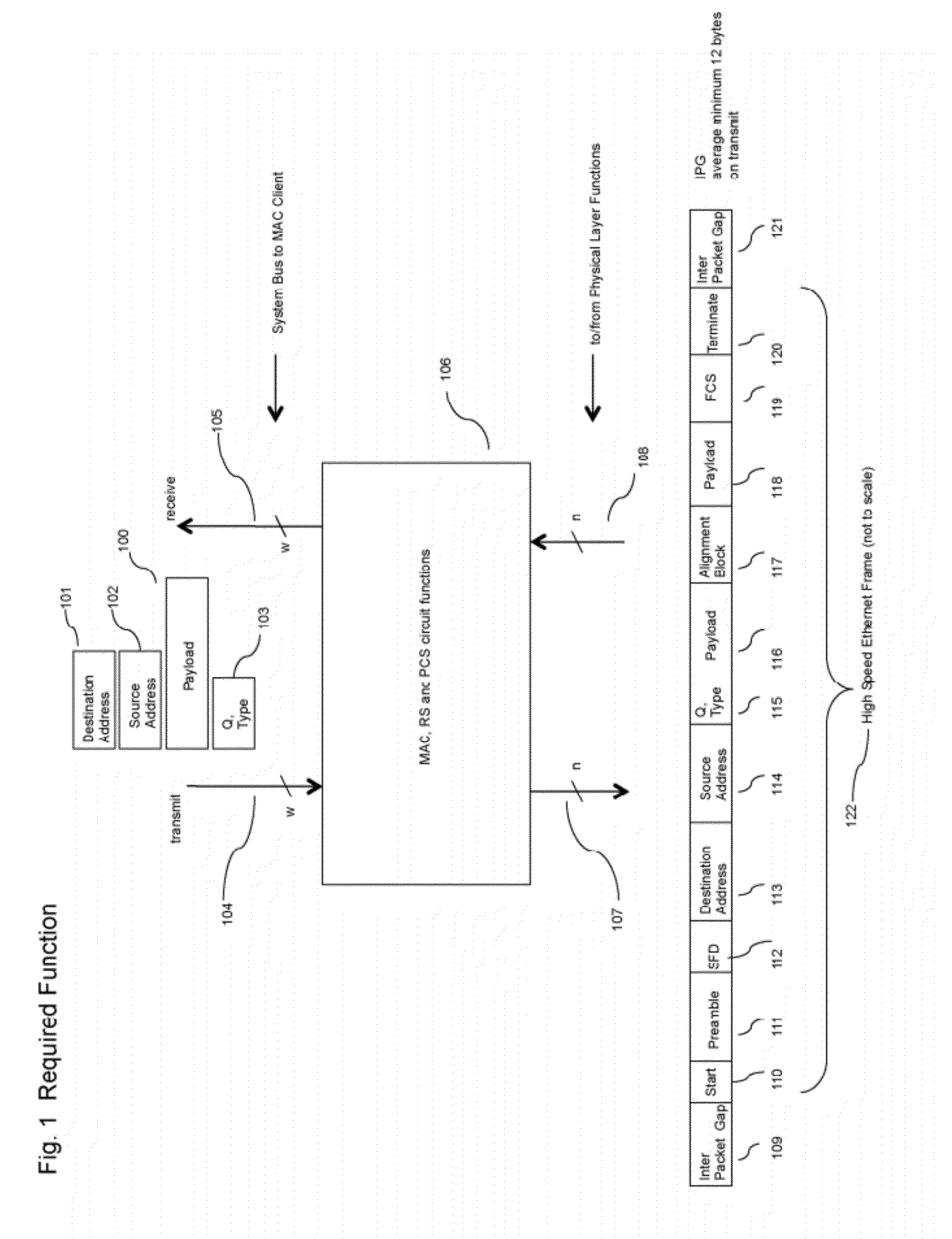

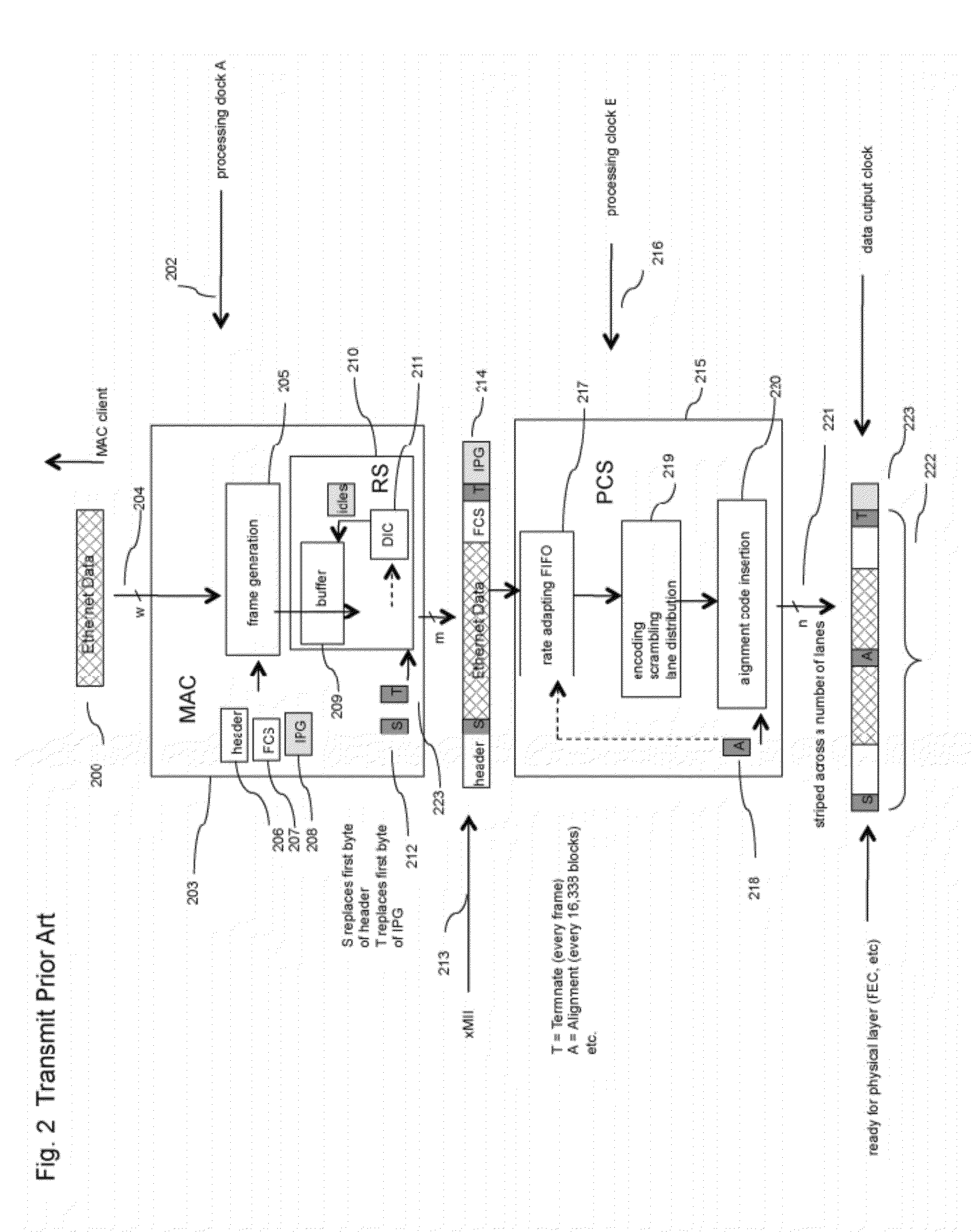

ActiveUS20120236878A1Small circuitReduce circuitTime-division multiplexTransmissionTime domainNetwork interface device

A packet network interface apparatus includes a media access control (MAC) module for constructing a packet for transmission over a packet network and a physical coding sublayer (PCS) module for encoding the packet for transmission over a physical interface. An inter packet gap module located between the MAC module and the PCS module directly transfers data to the PCS module while maintaining a certain inter packet gap by deleting or inserting idle characters. The inter packet gap module has at least one memory module for temporary storage of packet data. The modules preferably operate in a common time domain.

Owner:XILINX INC

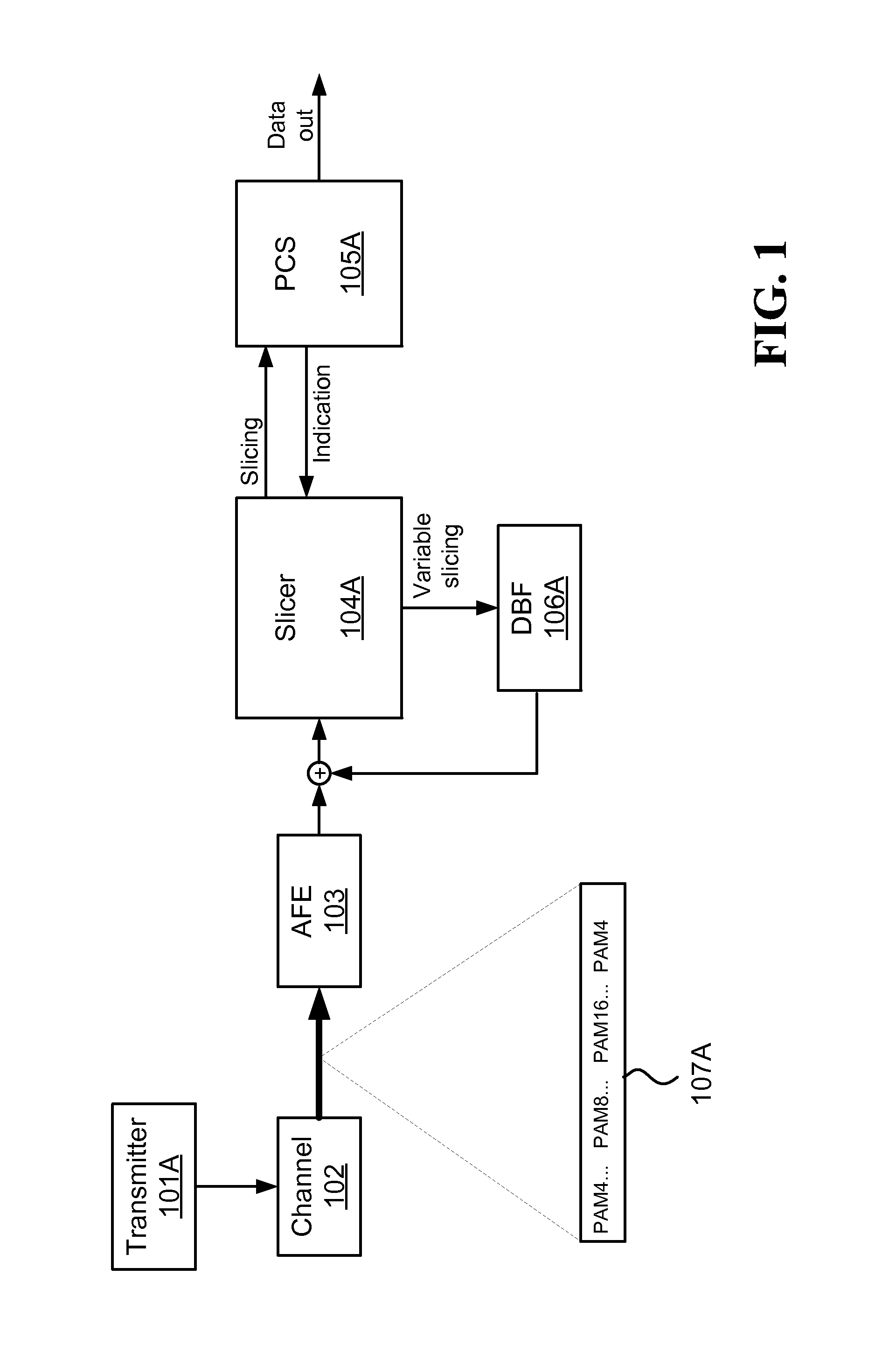

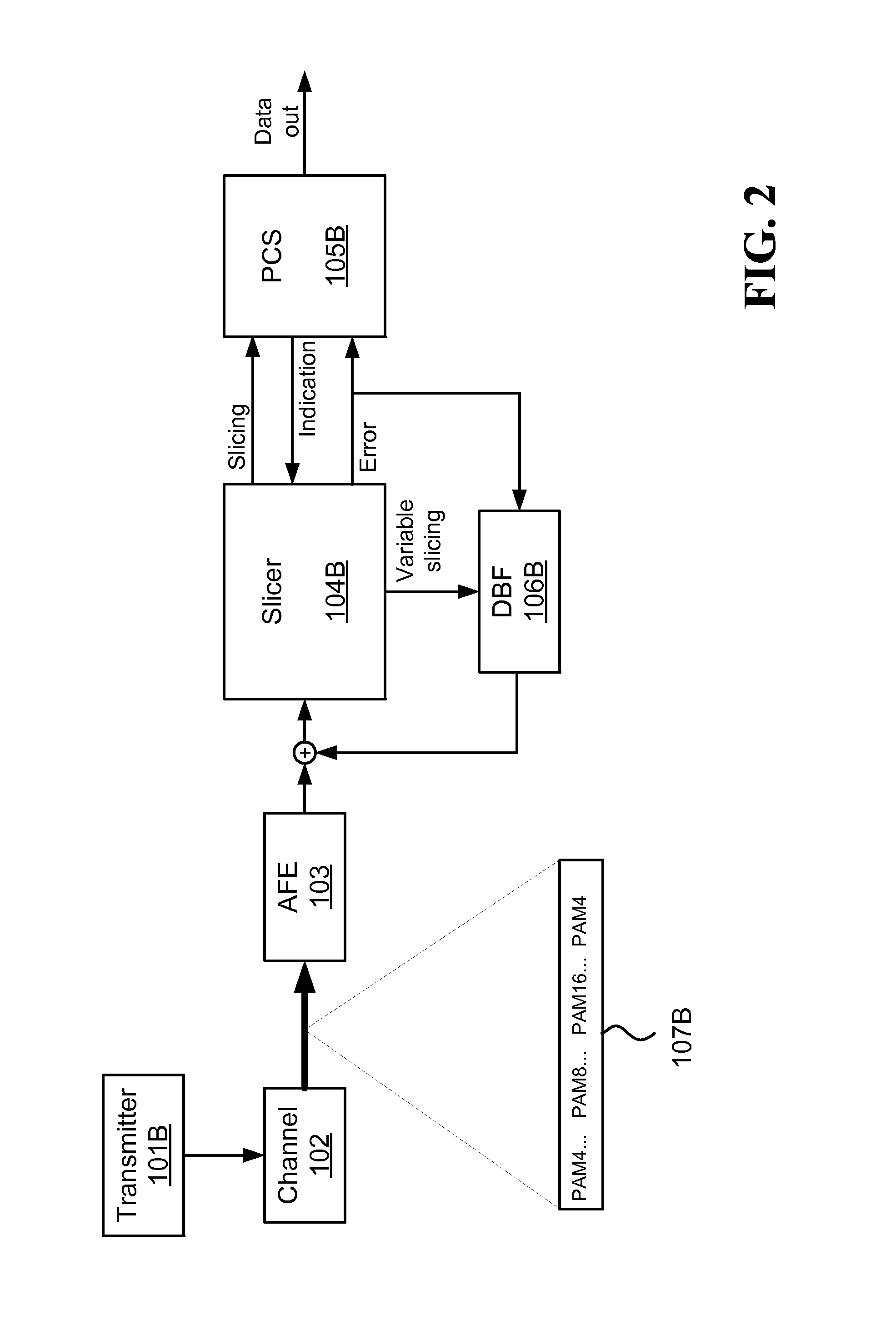

Methods for slicing dynamically modulated symbols

ActiveUS8930795B1Improve data transfer rateReduce probabilityMultiple modulation transmitter/receiver arrangementsTransmission path divisionModulation orderComputer science

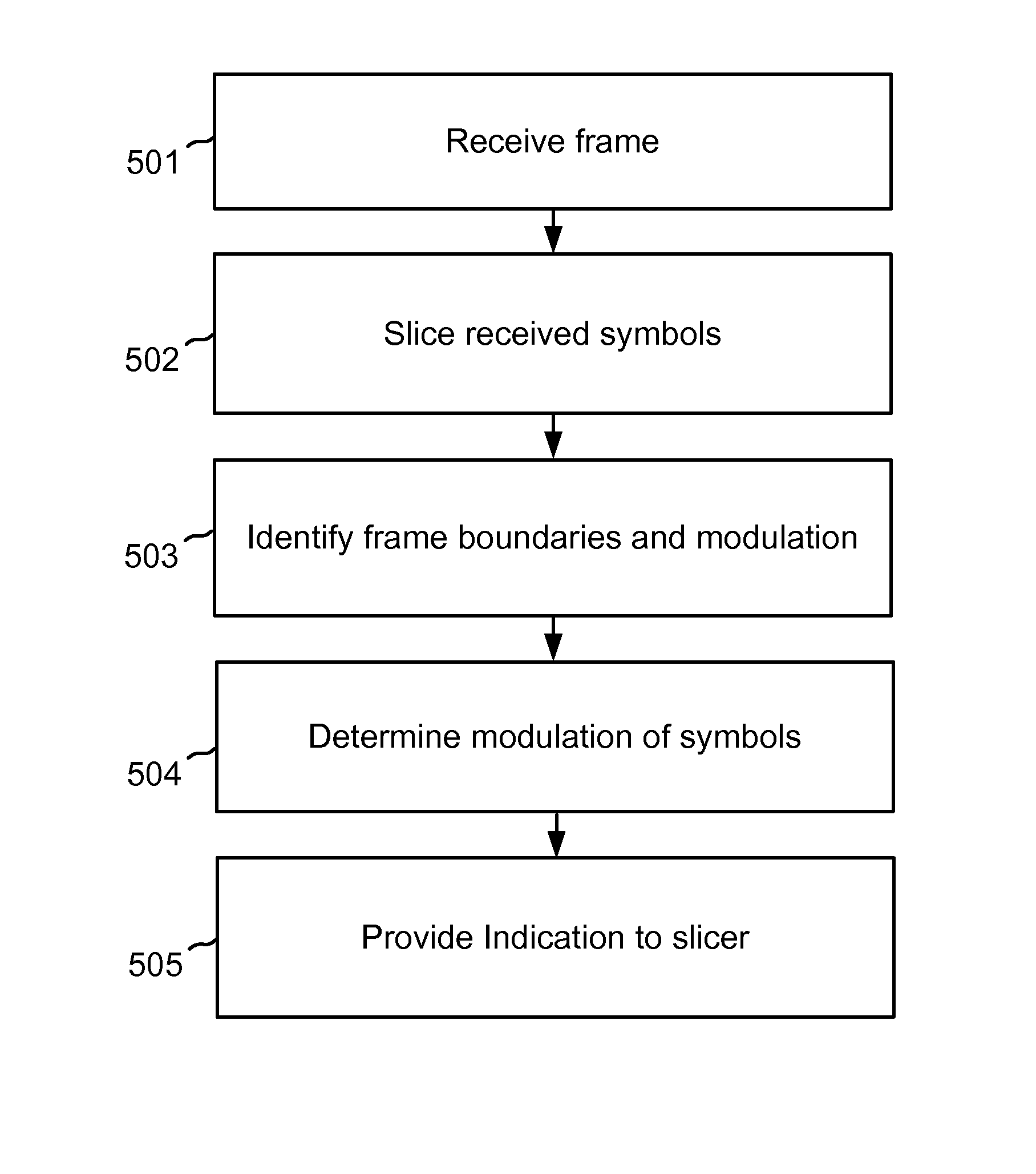

Reducing decision based filter error propagation by feedback from a physical coding sublayer (PCS) to a slicer. One method includes: receiving a frame comprising symbols of at least two different modulation orders that use subsets of a symbol superset; slicing the received symbols according to the highest modulation order by a slicer having slicing functions suitable for the different modulations; identifying frame boundaries and modulation information, which are modulated according to a predetermined modulation order; using the identified modulation information for determining the modulation of a nonempty set of dynamically modulated symbols in the received frame; and providing the slicer with an indication of which slicer function output to use for feeding a decision based filter.

Owner:VALENS SEMICON

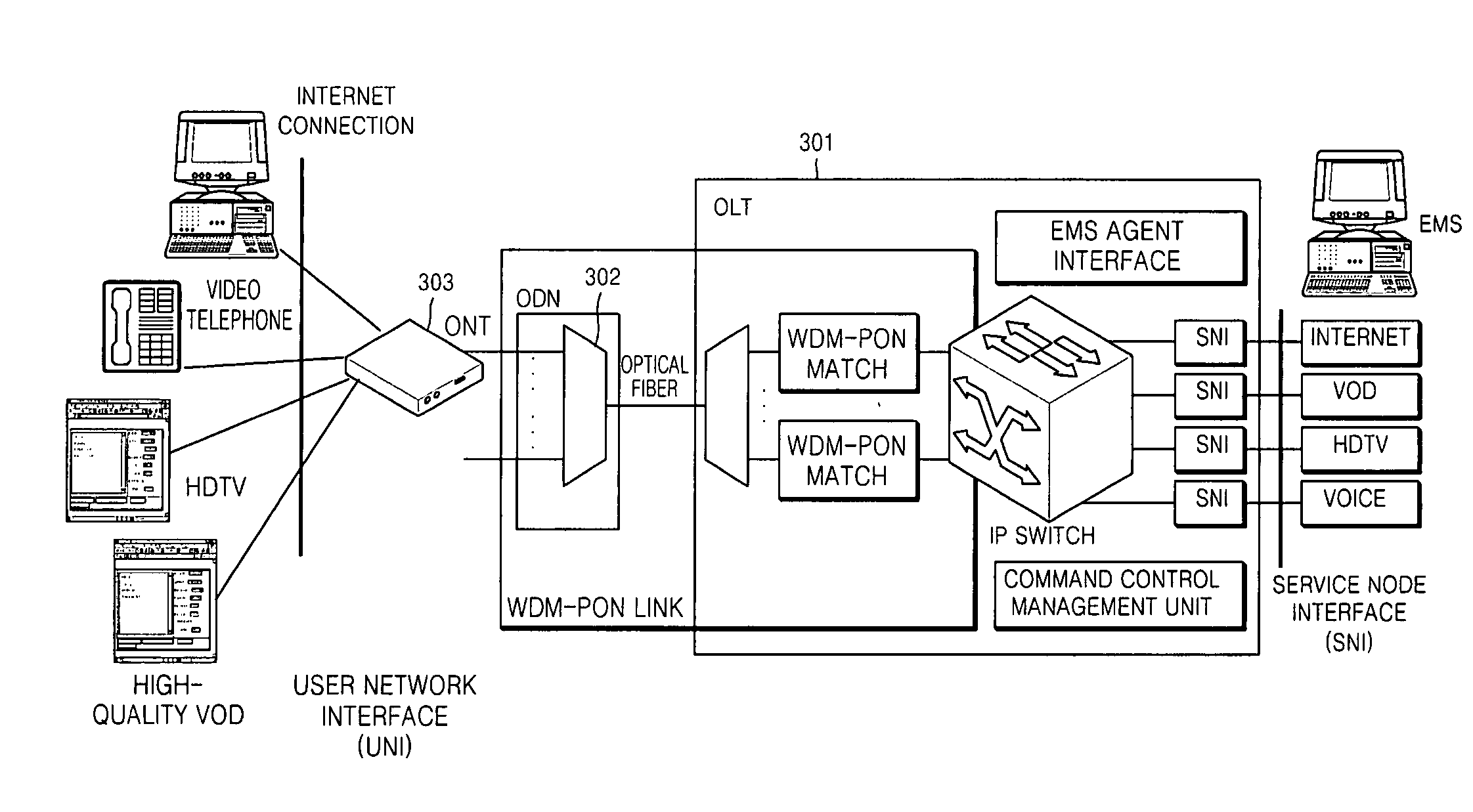

Physical coding sublayer apparatus and Ethernet layer architecture for network-based tunable wavelength passive optical network system

InactiveUS20070133986A1Multiplex system selection arrangementsOptical multiplexOptical line terminationLength wave

Provided are a physical coding sublayer (PCS) apparatus and an Ethernet layer architecture for a network-based tunable-wavelength passive optical network (T-PON) system employing an Ethernet communications technology, and more particularly, to a PCS apparatus and an Ethernet layer architecture for supporting a series of initialization function of allocating wavelengths between an optical line terminal (OLT) and an optical network terminal (ONT) and arranging the allocated wavelengths. A PCS layer transmits and allocates wavelength information such that wavelengths for setting a link between an OLT and an ONT are allocated, optical wavelengths within the ONT are observed while a system operates to allow continuous control so that operating of the system can be stably maintained.

Owner:ELECTRONICS & TELECOMM RES INST

Flexible ethernet encryption systems and methods

ActiveUS20190173856A1Key distribution for secure communicationEncryption apparatus with shift registers/memoriesEthernetPhysical Coding Sublayer

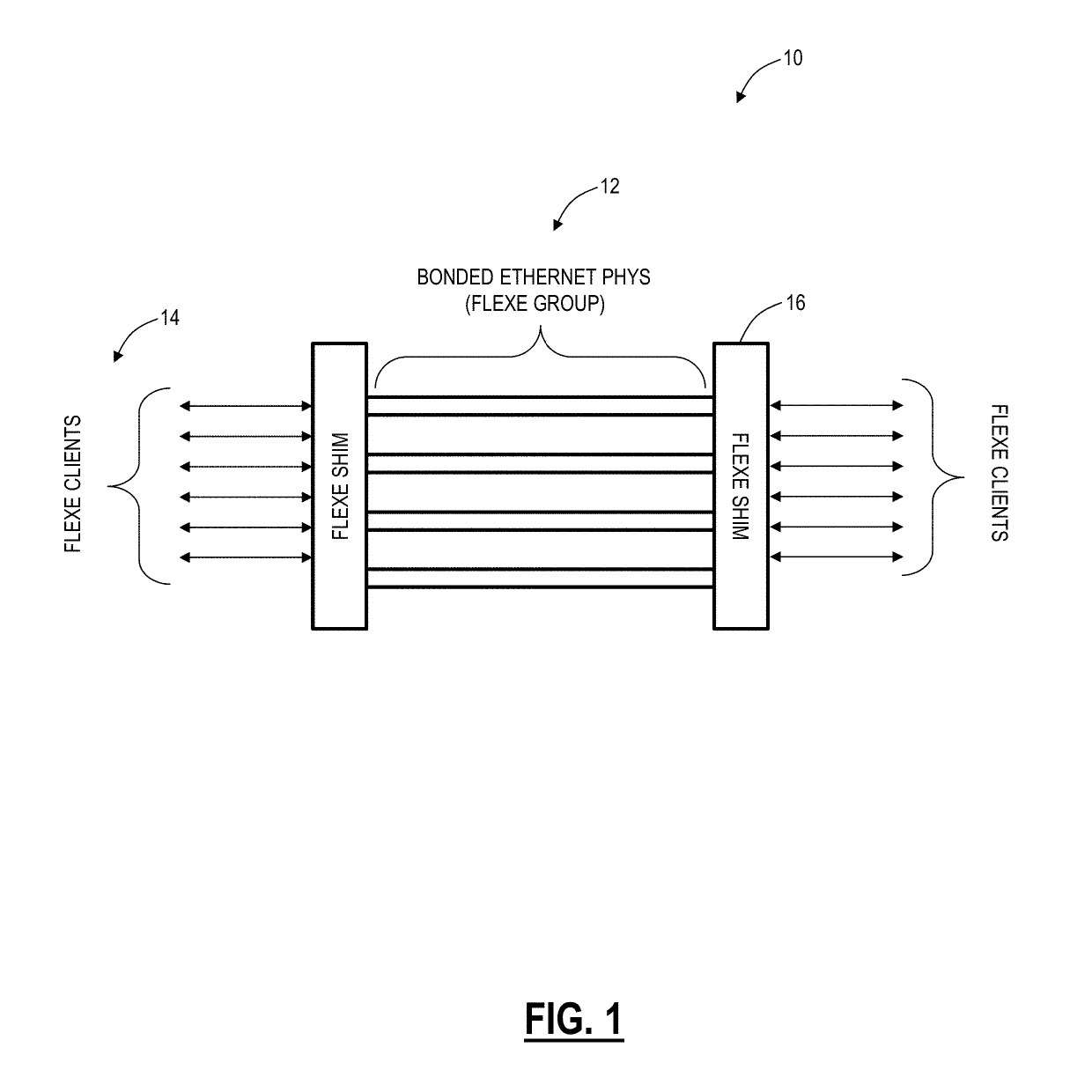

Systems and methods for Physical Coding Sublayer (PCS) encryption implemented by a first network element communicatively coupled to a second network element include encrypting a Flexible Ethernet (FlexE) signal based on a first encryption key with encryption applied to a 64b / 66b bit stream associated with the FlexE signal at one or more of a FlexE client layer and a FlexE shim layer; switching to a second encryption key at a predetermined point in the FlexE signal; and encrypting the FlexE signal with the second encryption key subsequent to the switching.

Owner:CIENA

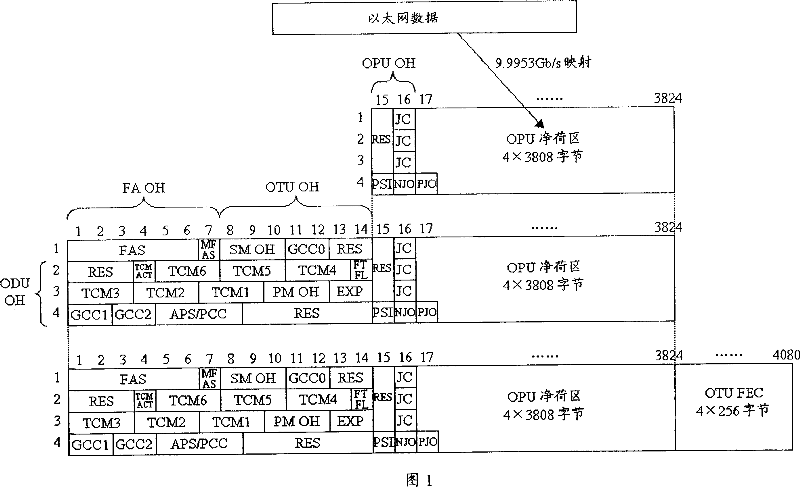

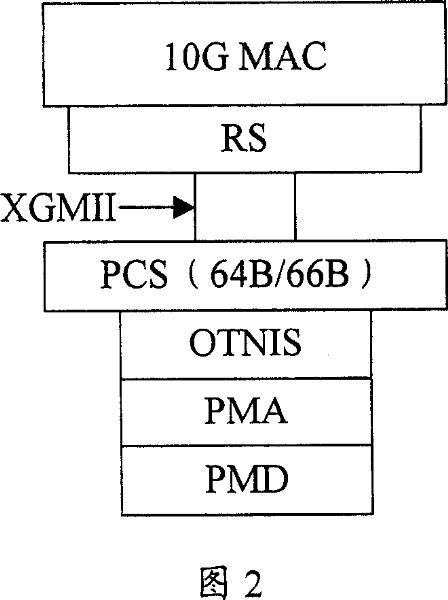

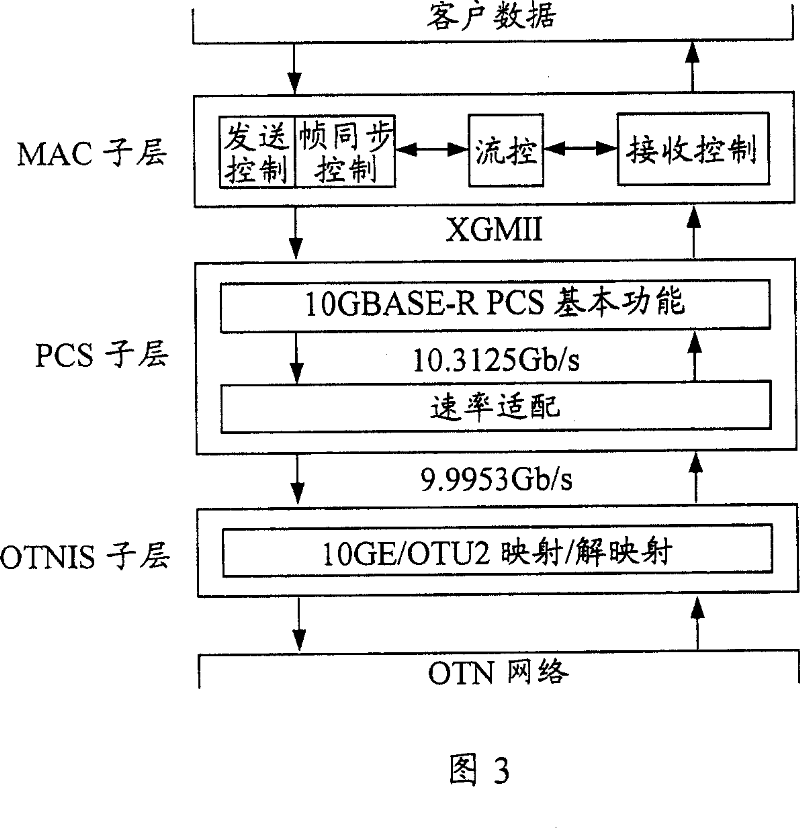

Data transmission method from high speed Ethernet to optical transmission network and related interface and equipment

InactiveCN101039245AGuaranteed efficiencyQuality assuranceTime-division multiplexNetworks interconnectionStructure of Management InformationInternet business

Owner:HUAWEI TECH CO LTD

Explicit flow control in Gigabit/10 Gigabit Ethernet system

In one embodiment, a system comprises a communication medium; a first controller coupled to the communication medium; and a second controller coupled to the communication medium. The first controller is configured to interrupt transmission of a packet on the communication medium to the second controller subsequent to transmission of a first portion of the packet. The first controller is configured to transmit at least one control symbol on the communication medium in response to interrupting transmission of the packet, and wherein the first controller is configured to continue transmission of the packet with a second portion of the packet. The controller(s) may include, in some embodiments, a media access controller and a physical coding sublayer.

Owner:APPLE INC

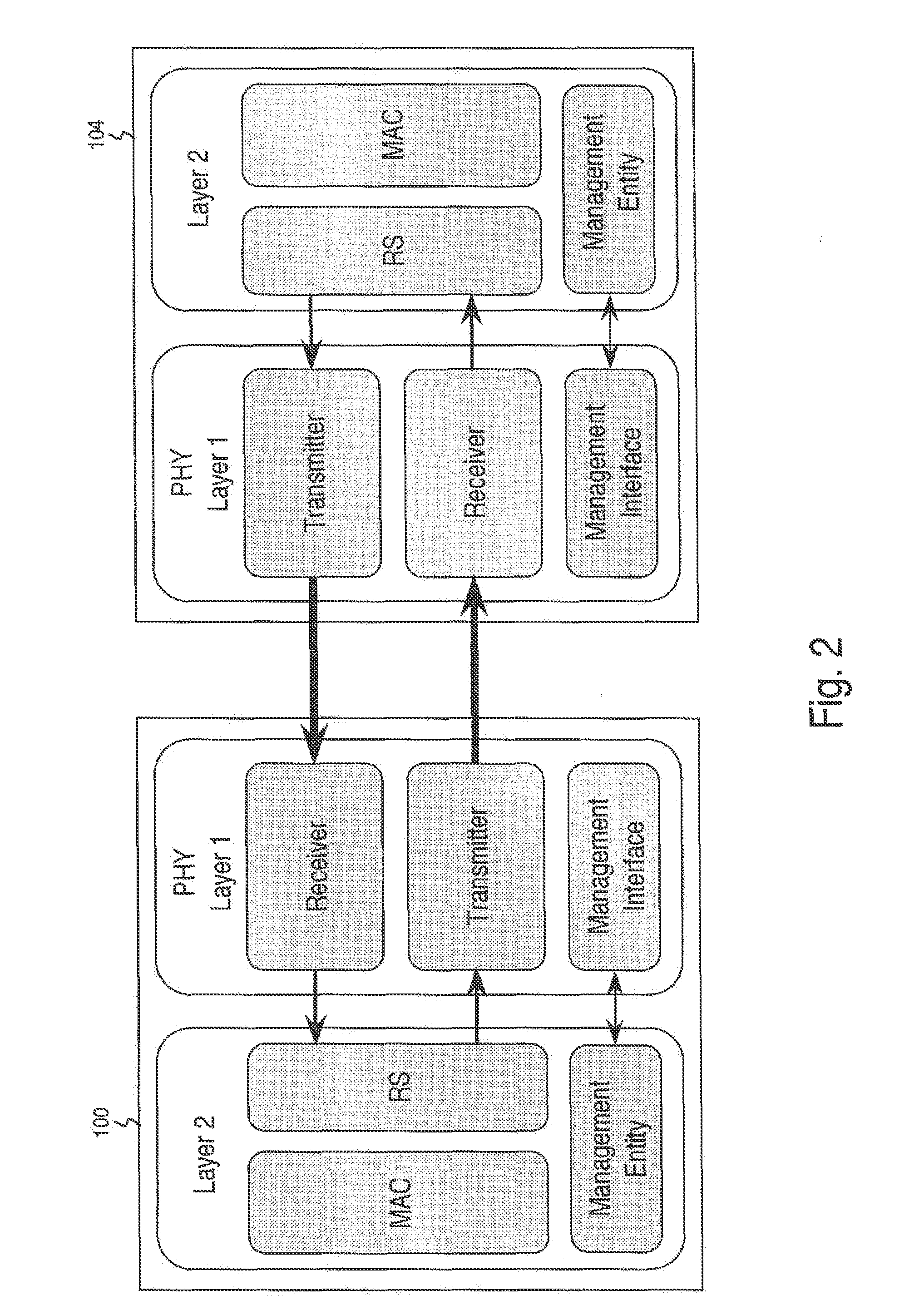

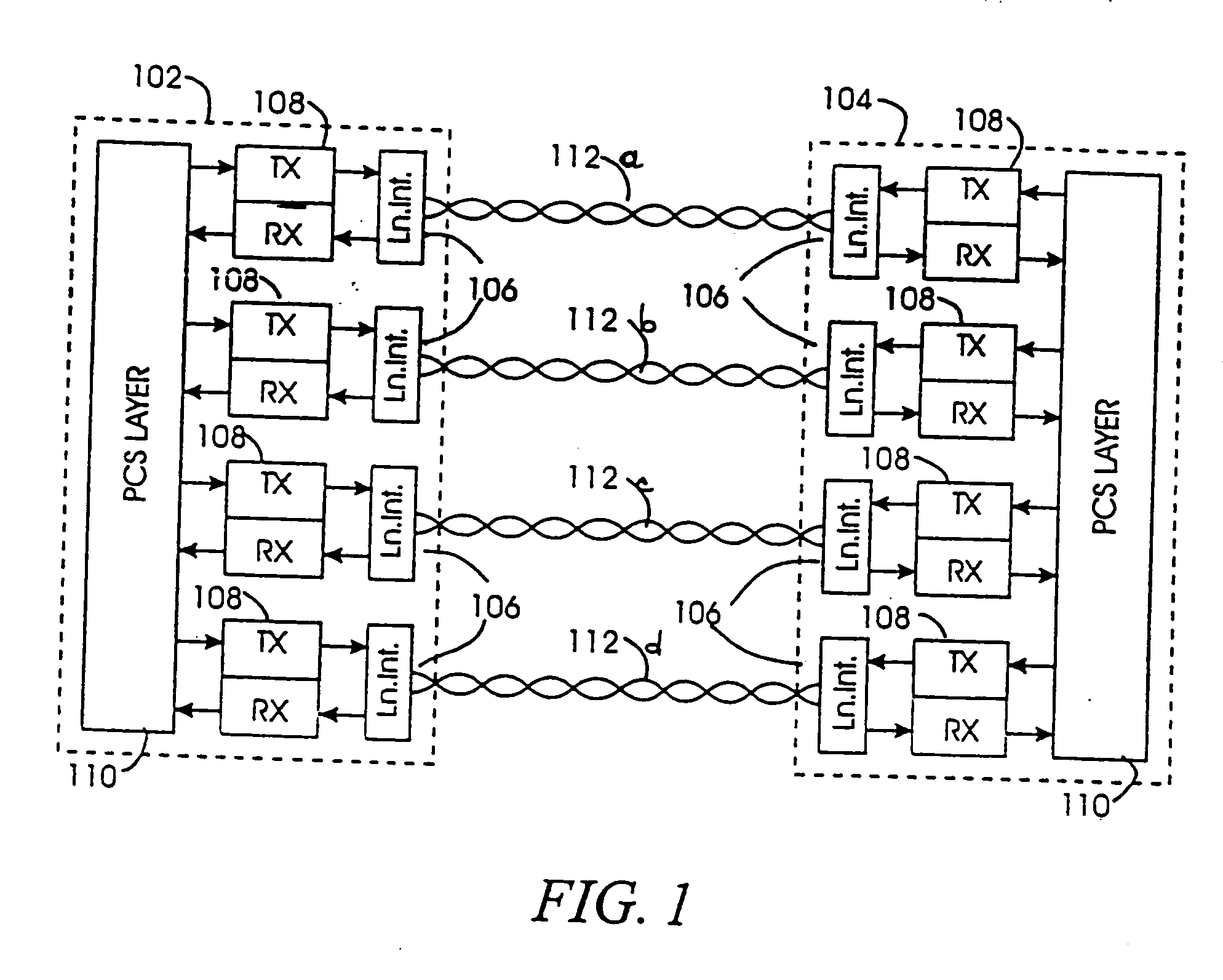

Multi-protocol configurable transceiver with independent channel-based PCS in an integrated circuit

Structures and methods are disclosed relating to a multi-protocol transceiver including lane-based Physical Coding Sublayer (“PCS”) circuitry that is configurable to adapt to one of a plurality of communication protocols. Particular embodiments of the present invention include lane based configurable data paths through PCS transmit and receive circuitry.

Owner:ALTERA CORP

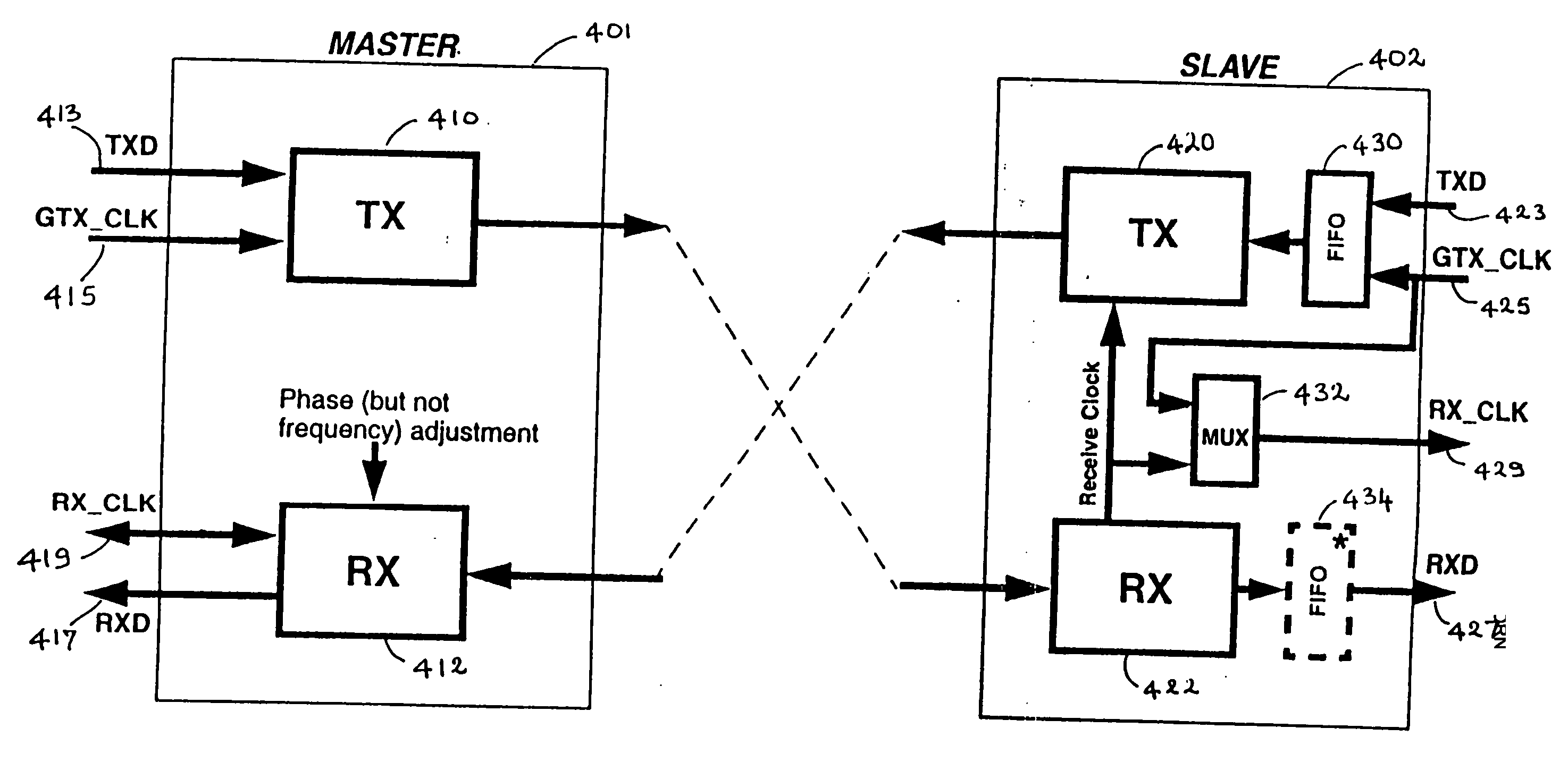

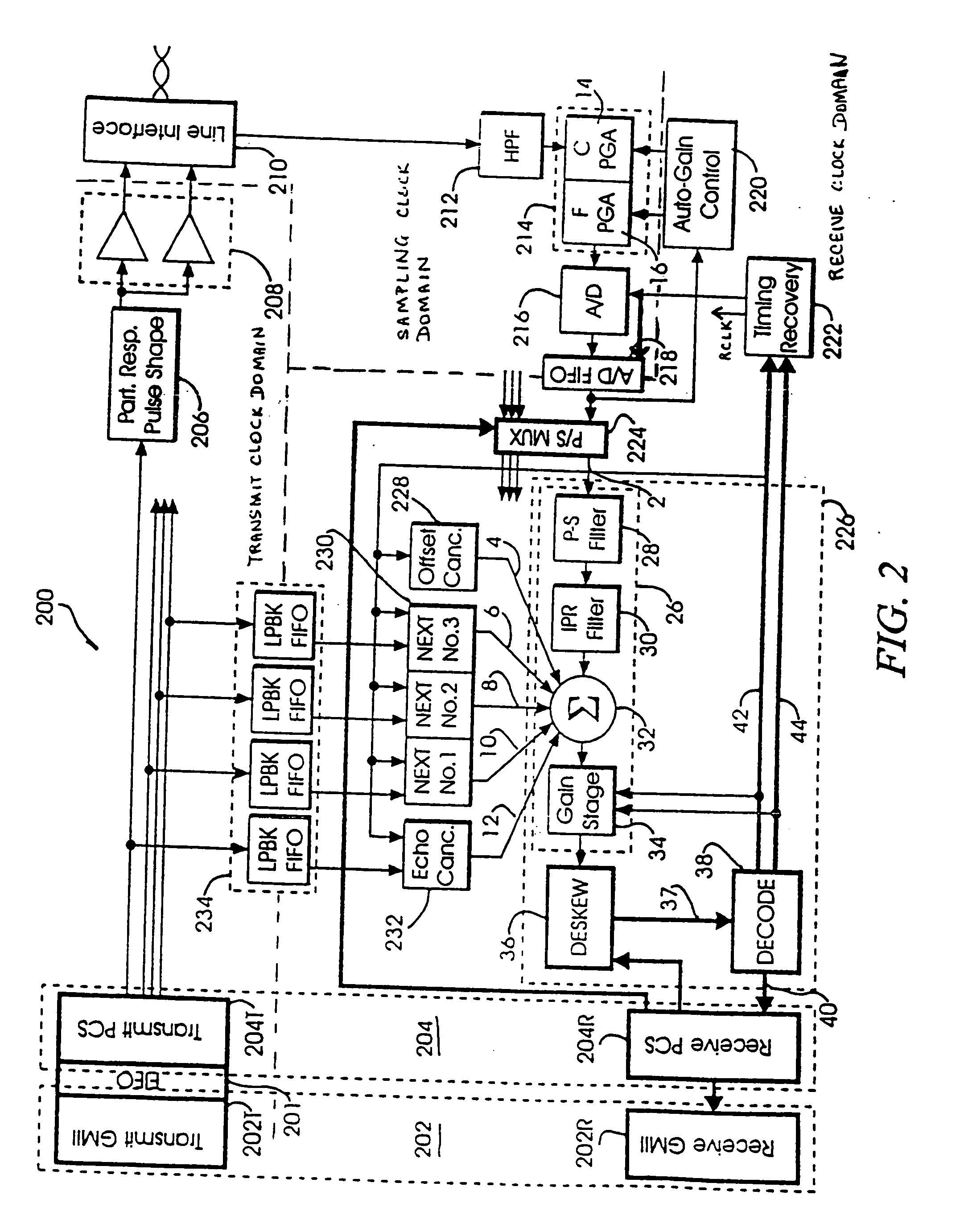

PHY control module for a multi-pair gigabit transceiver

InactiveUS20050041727A1Multiple-port networksChannel dividing arrangementsDigital signal processingSignal response

A method for controlling operation of a multi-pair gigabit transceiver. The multi-pair gigabit transceiver comprises a Physical Layer Control module (PHY Control), a Physical Coding Sublayer module (PCS) and a Digital Signal Processing module (DSP). The PHY Control receives user-defined inputs from the Serial Management module and status signals and diagnostics signals from the DSP and the PCS and generates control signals, responsive to the user-defined inputs, the status signals and diagnostics signals, to the DSP and the PCS.

Owner:AVAGO TECH INT SALES PTE LTD

64/66 encoder

A physical layer device for a network interface includes a reconciliation device that includes a first interface that outputs data. A physical coding sublayer (PCS) device communicates with the first interface and includes an encoder that encodes the data to produce an encoded data block including an offset portion and n data blocks, each including at least one of data portions and control code portions. The encoder is capable of locating the control code portions within any of the n data blocks based on the offset portion.

Owner:MARVELL ASIA PTE LTD

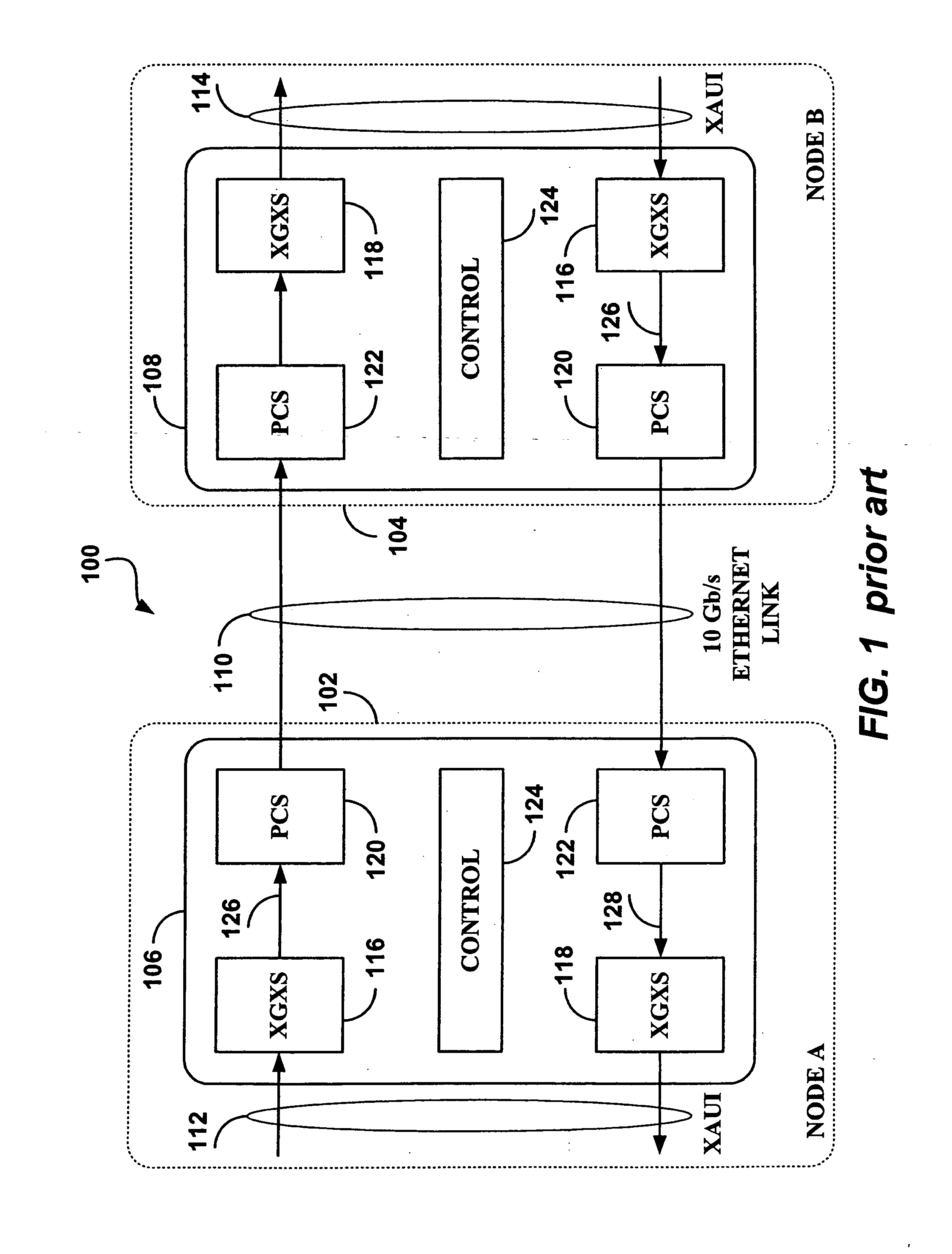

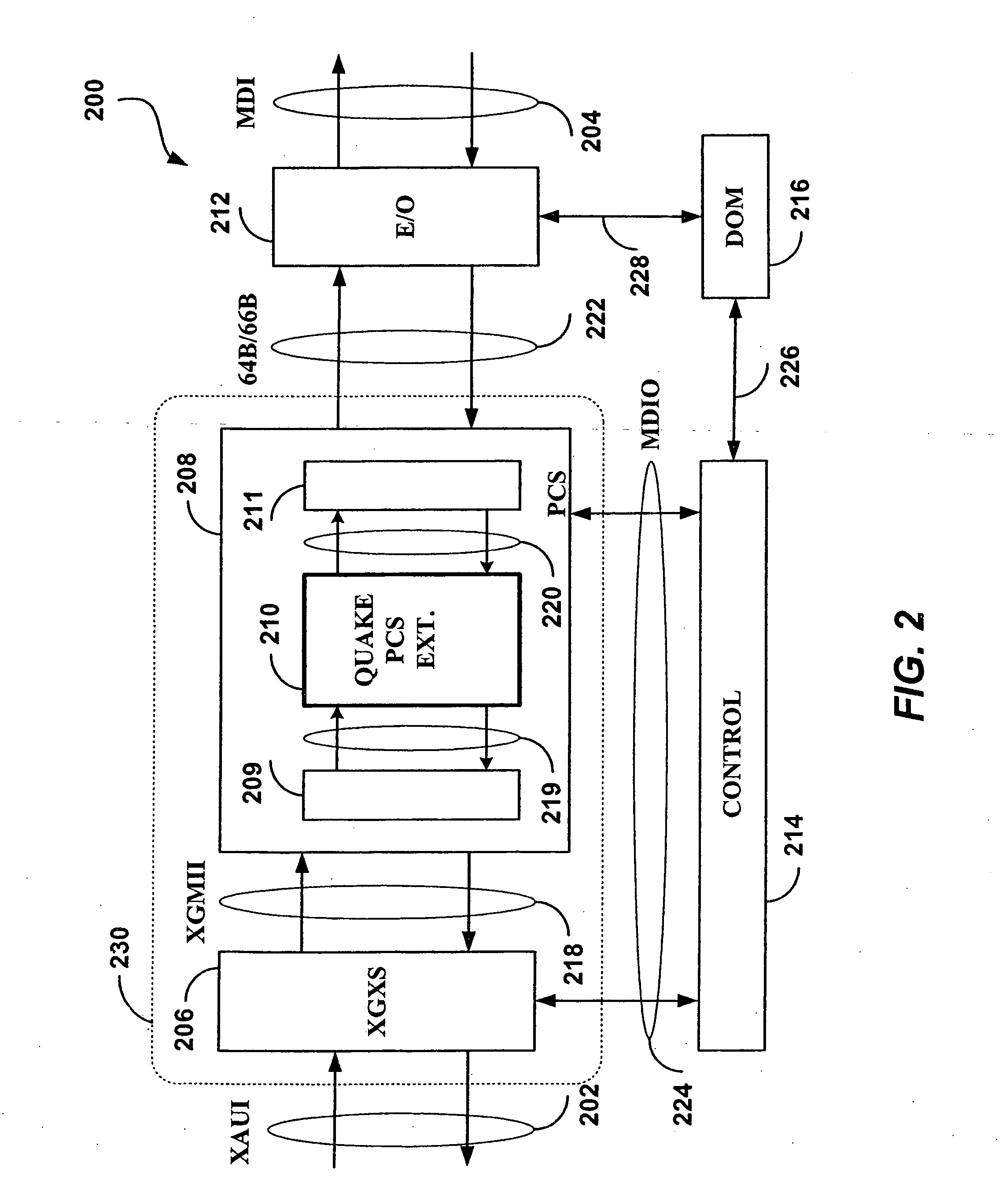

Ethernet Link Monitoring Channel

InactiveUS20080228941A1Digital computer detailsData switching networksTransceiverMedia access control

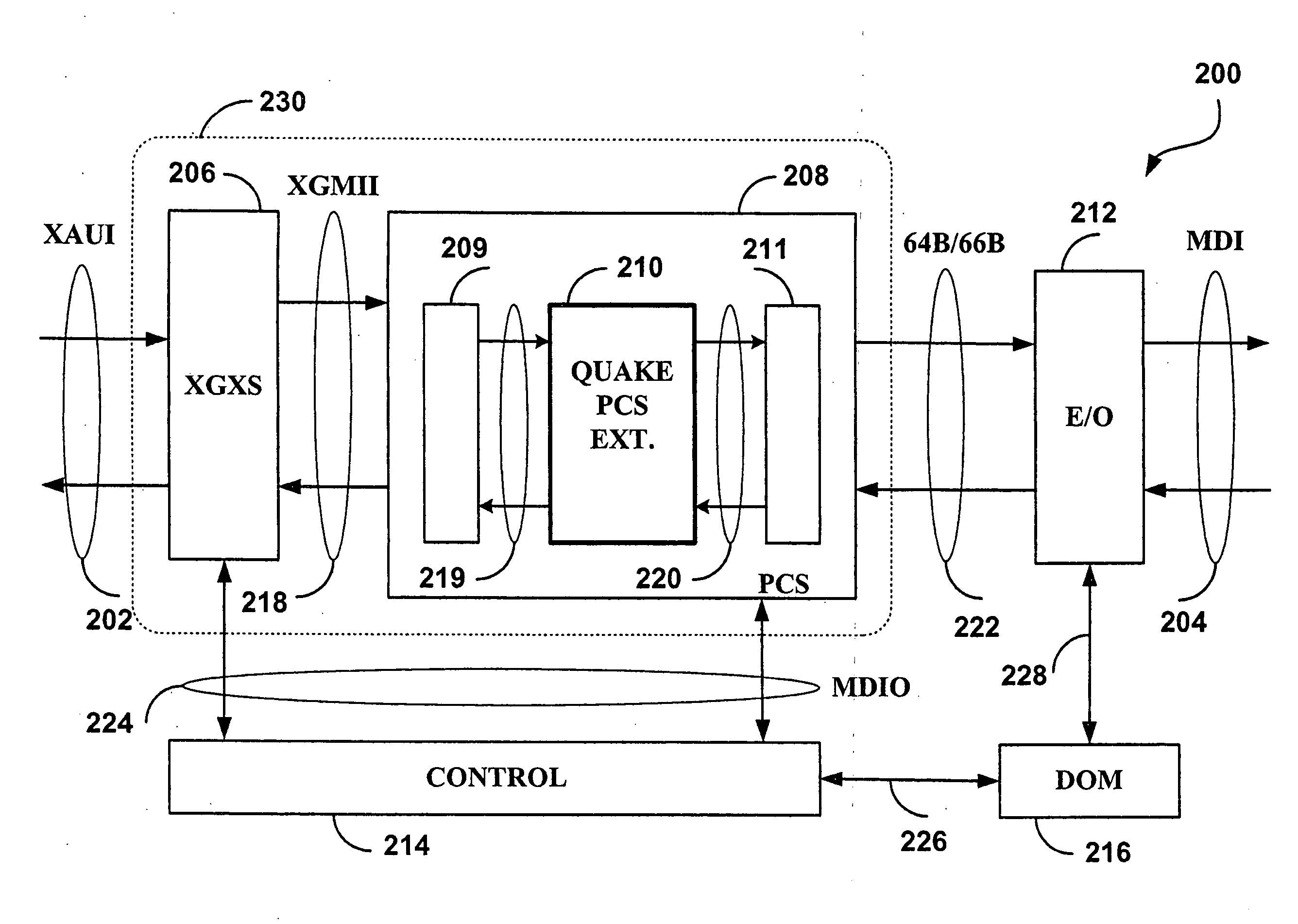

The invention provides a method for utilizing the Inter Packet Gaps (IPGs) to create an Extended Link Monitoring Channel in a physical layer transceiver for a 10 Gb / s Ethernet link for communicating link related information, thus providing an extensive link maintenance capability. A corresponding transceiver between an Ethernet media access control (MAC) layer device and a 10 Gb / s Ethernet link, comprising a physical coding sublayer (PCS) extension circuit for implementing the Extended Link Monitoring Channel is also provided.

Owner:QUALCOMM INC

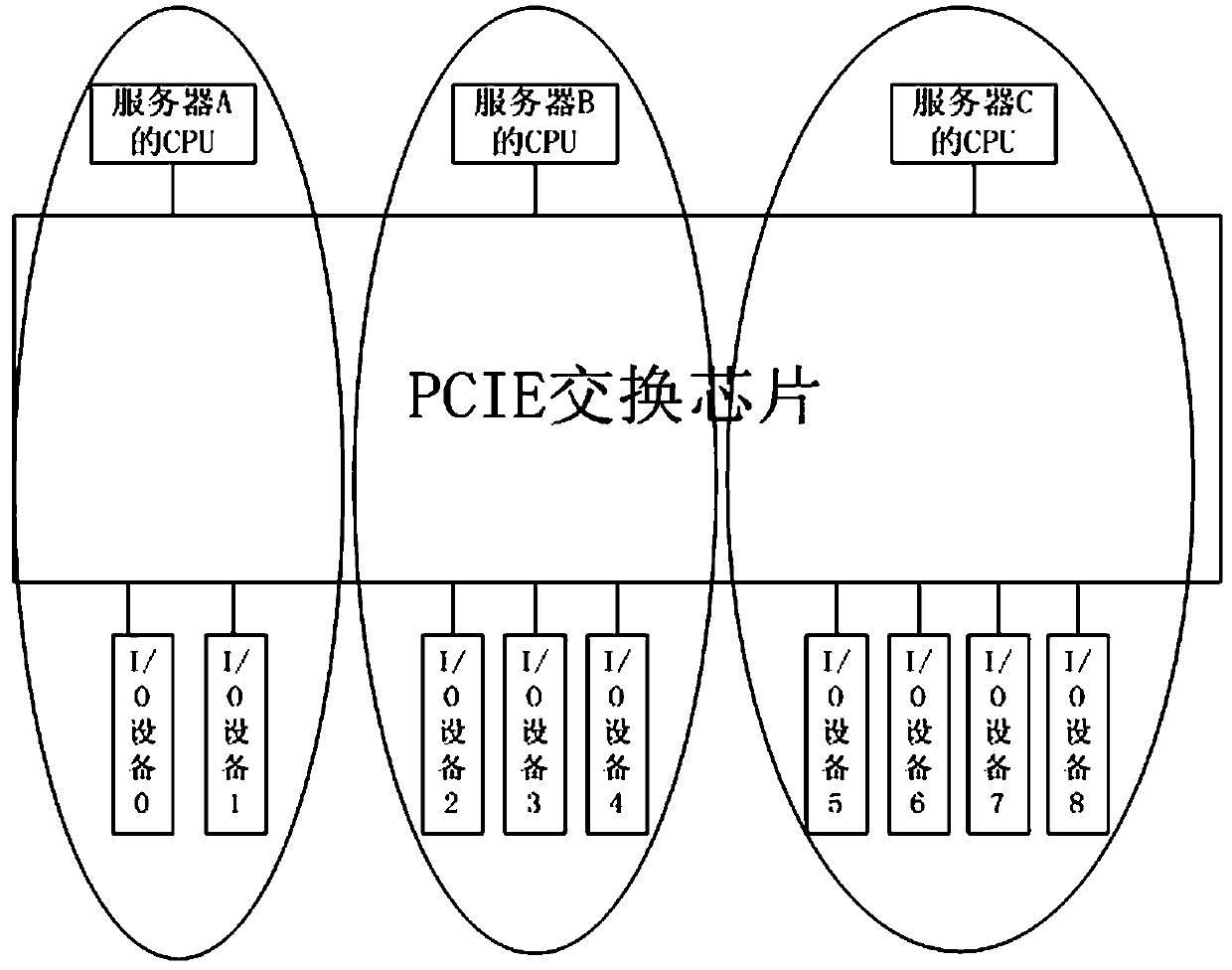

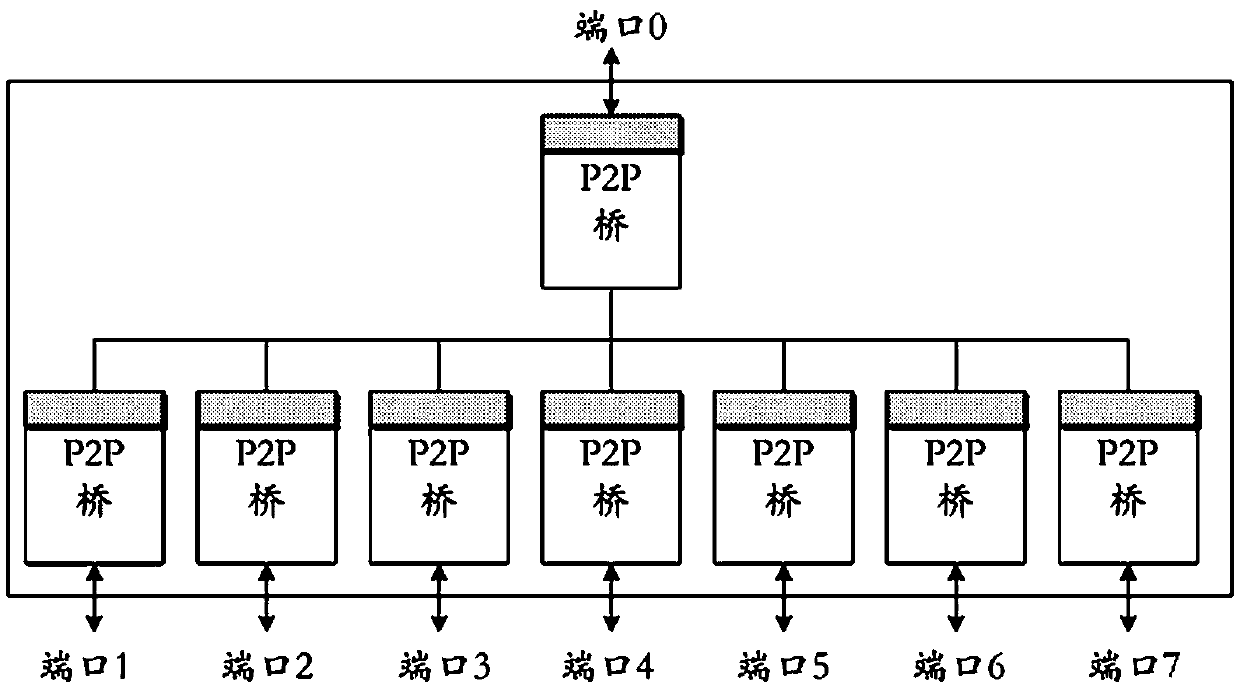

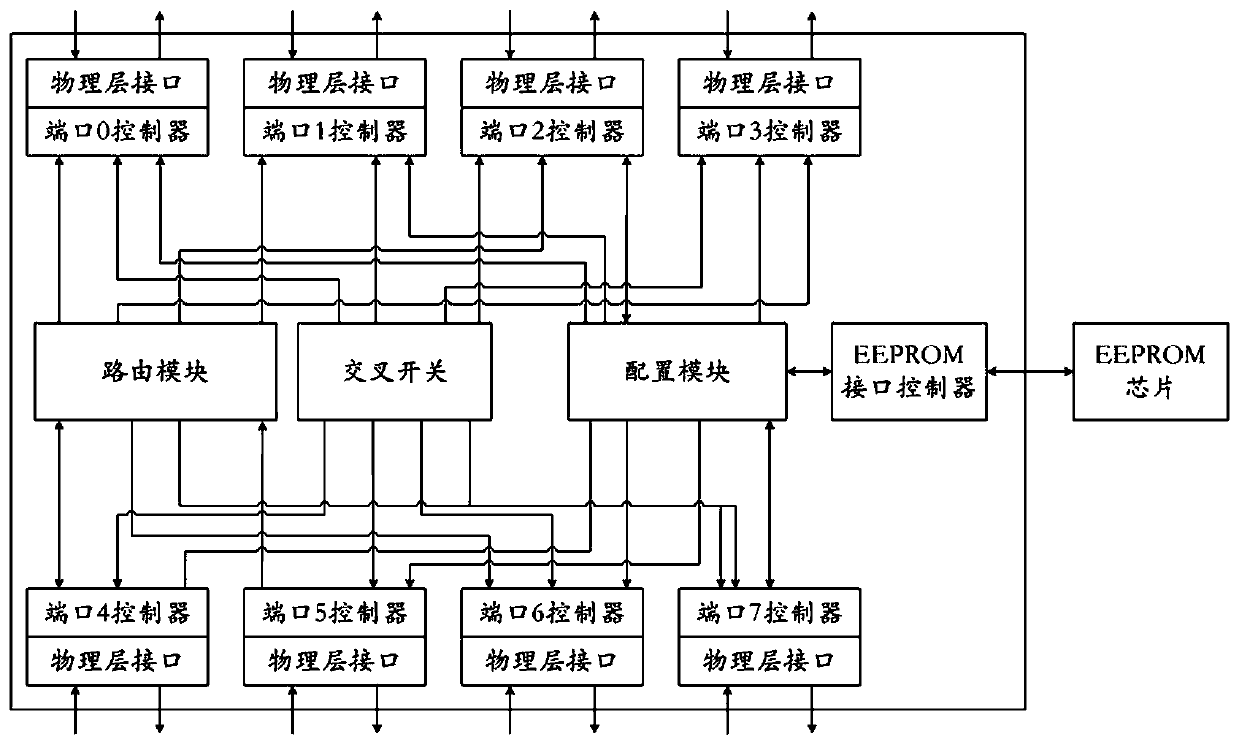

PCIE exchange chip port configuration system and method supporting virtual exchange

ActiveCN111092773AAccurate configurationSimple structureData switching networksElectric digital data processingCrossbar switchData pack

The invention discloses a PCIE exchange chip port configuration system and method supporting virtual exchange, and the system comprises: a port controller which is used for realizing the functions ofa medium access control layer, a data link layer and a transaction layer of a physical layer; a physical layer interface for realizing the functions of a physical medium adaptation layer and a physical coding sub-layer of a PCIE physical layer; a routing module which is used for receiving routing information from the port controller, carrying out routing lookup according to the routing informationand acquiring a processing mode and a transceiving port number of the data packet; an EEPROM interface controller for reading configuration information of an external EEPROM and sending the configuration information to the configuration module; a configuration module which is used for receiving configuration information, configuring the ports, configuring the ports as upstream ports or downstreamports, dividing a virtual switching area in the chip, and controlling each port to be enabled; and a crossbar switch for forwarding the data packet passing through the PCIE switching chip. The port configuration can be quickly completed, and the time limit requirement of PCIE switching chip initialization is met.

Owner:成都华大九天科技有限公司

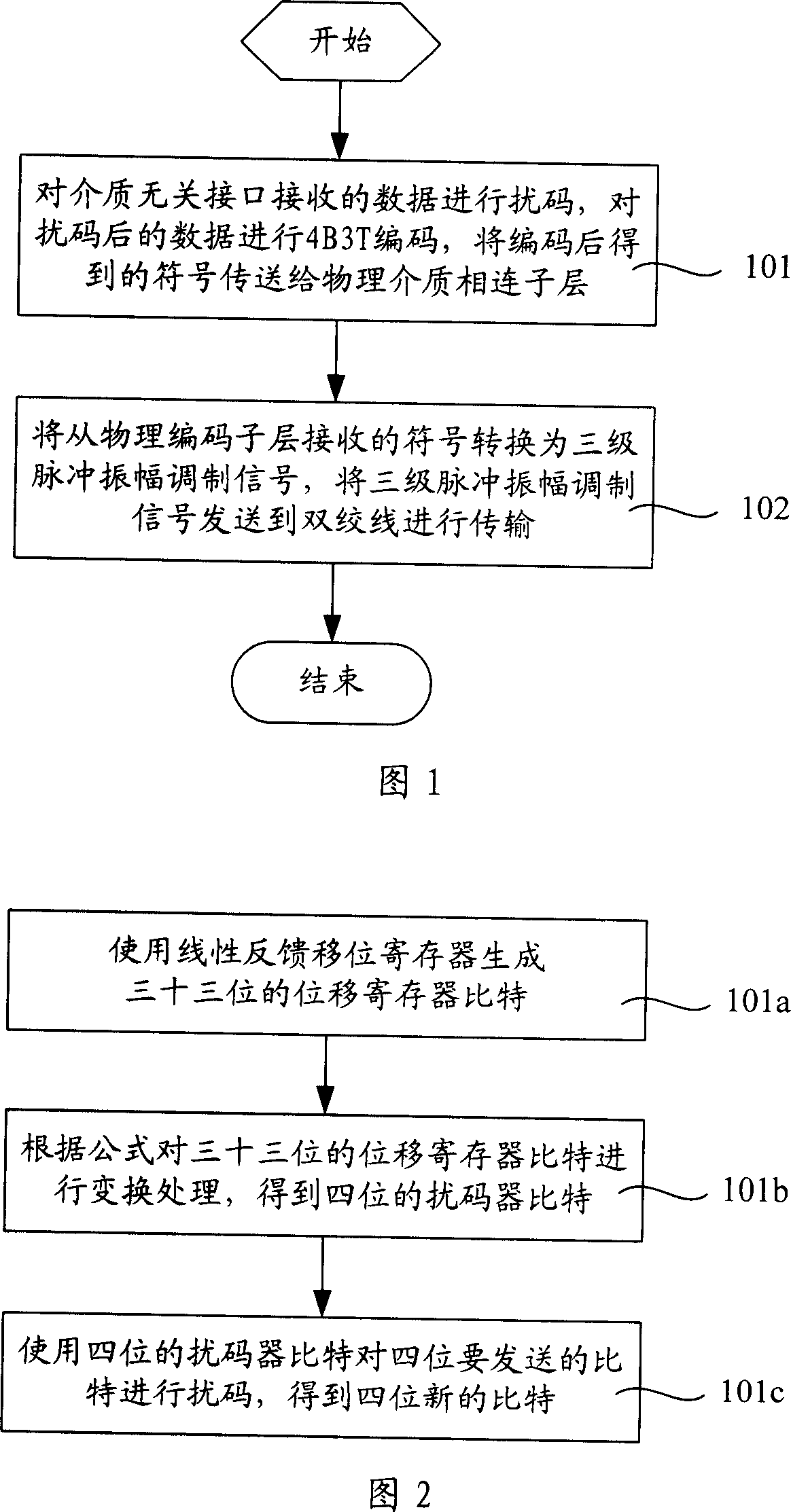

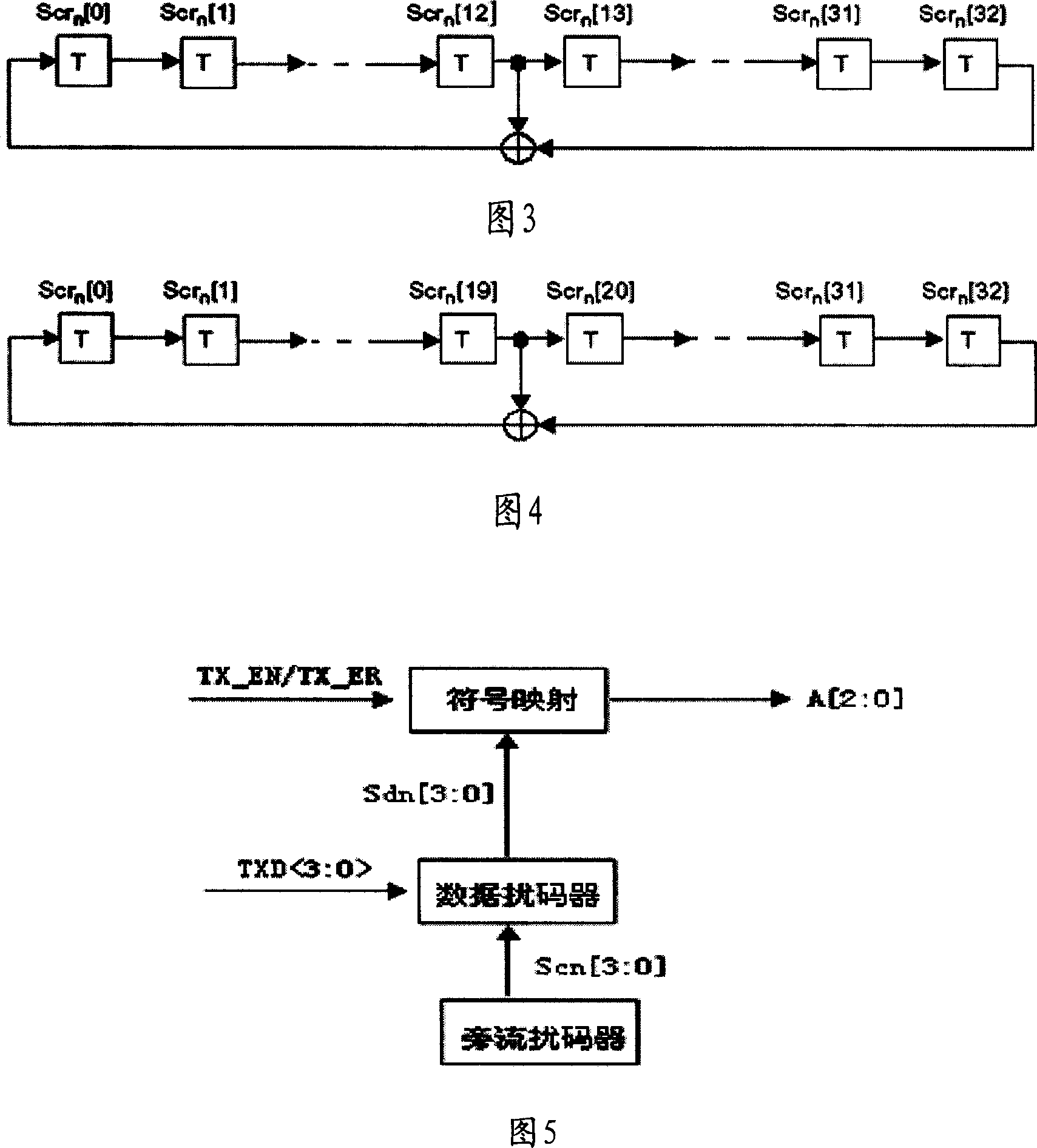

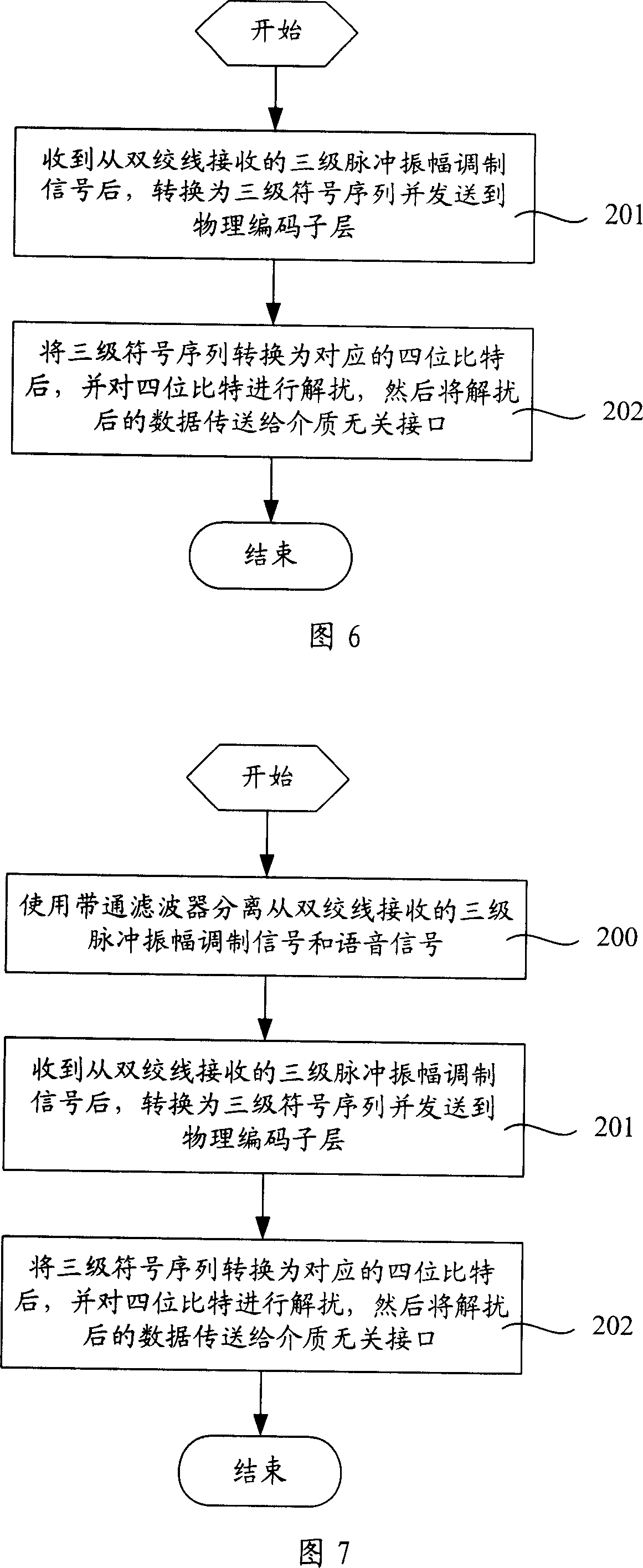

Physical layer data transmitting method and receiving method and physical layer chip

ActiveCN101026523AHigh bandwidthImprove reliabilityError preventionData switching by path configurationHigh bandwidthInterference resistance

The method includes steps: physical coding sub layer (PCSL) carries out code scrambling for data received from medium not related interface, and carrying out 4B3T encoding operation for scrambled data; transmitting encoded symbol sequence in three stage to sub layer connected to physical medium; the sub layer connected to physical medium converts symbol sequence in three stage received PCSL to pulse amplitude modulation signal (PAMS) in tree stage; through medium related interface and interface in use for interacting twisted-pair. The PAMS in tree stage is sent to twisted-pair for transmission. The invention also discloses method for receiving data in physical layer, and a physical chip. Through phone line, the invention realizes Ethernet connection. Advantages are: high bandwidth, reliability, and easy of maintenance of Ethernet, lowered installation cost, complexity, raised decoding and error detecting capability, and suitable to crosstalk under large number of pair of cables.

Owner:NEW H3C TECH CO LTD

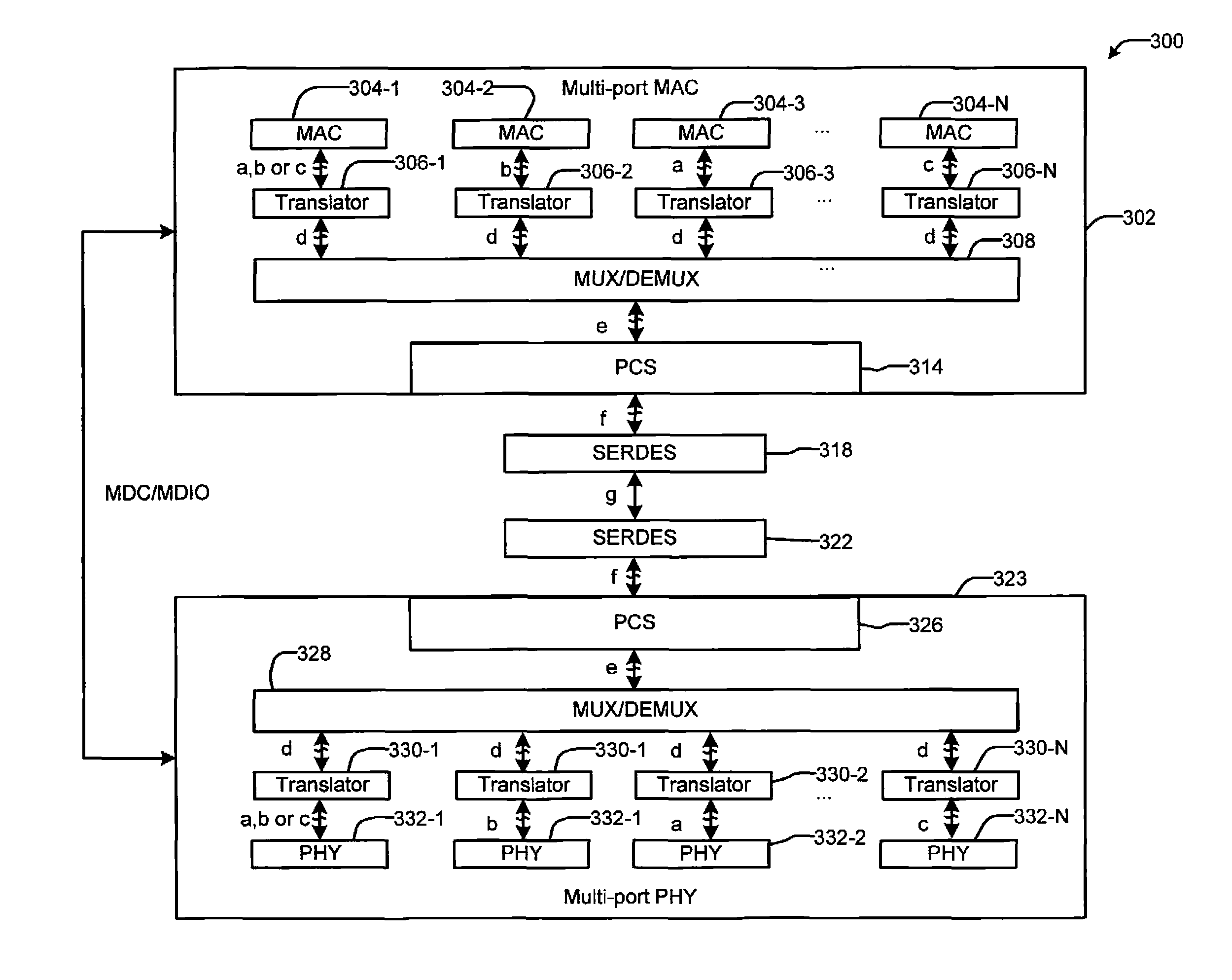

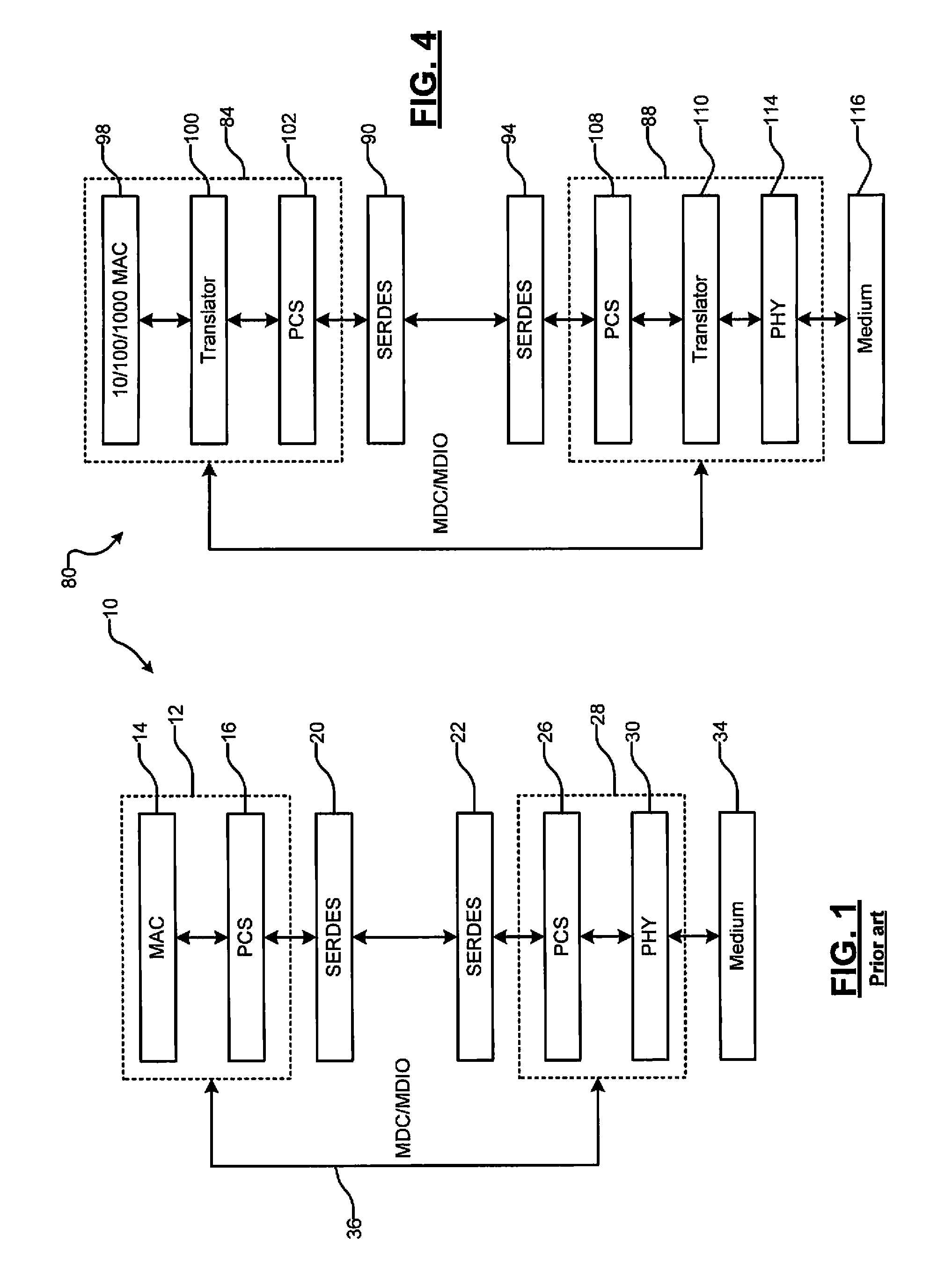

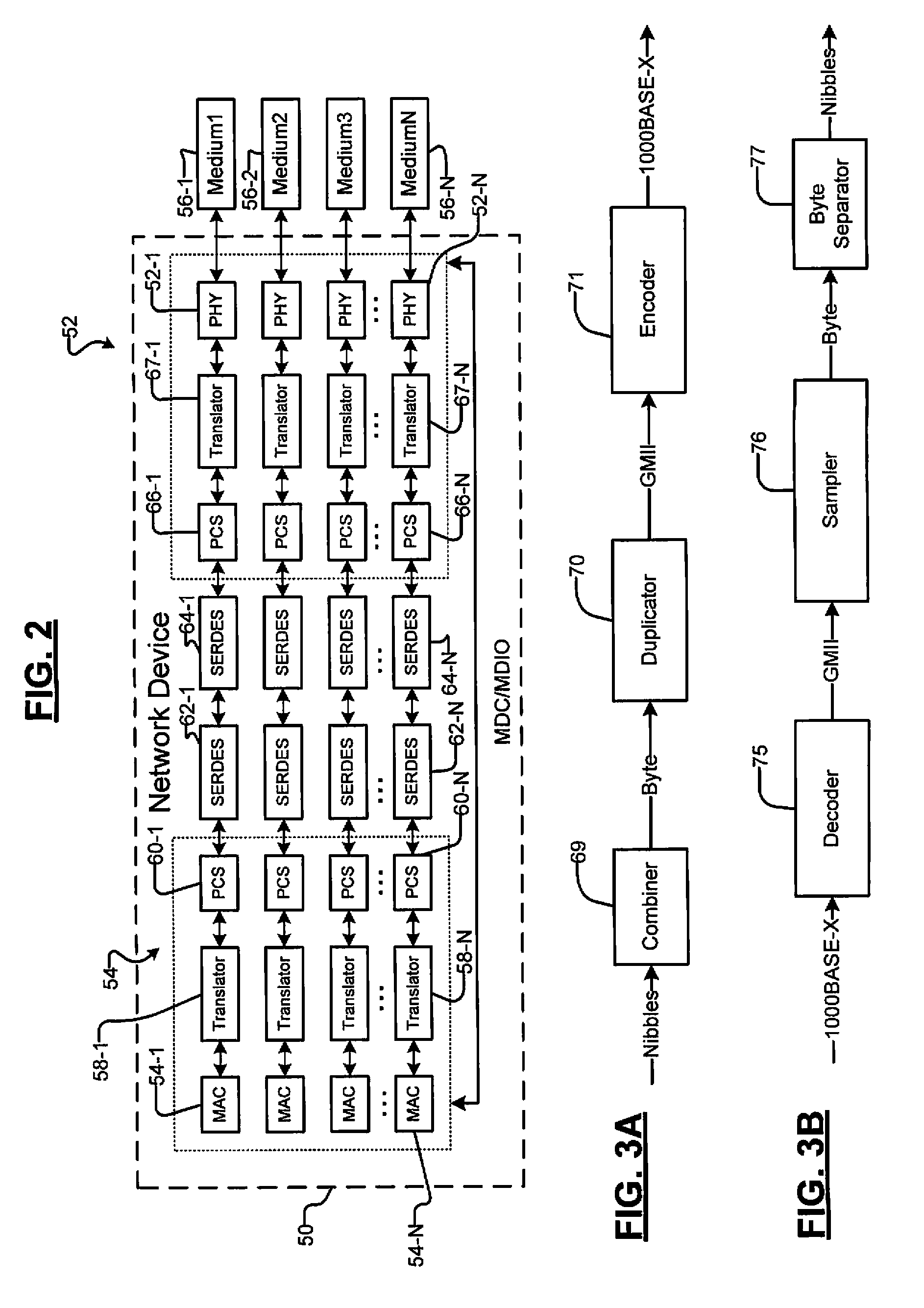

Network device with multiple MAC/PHY ports

ActiveUS8018924B1Multiplex system selection arrangementsCircuit switching systemsSerial transferMultiplexing

A network device includes a multi-port media access controller (MAC) device that comprises a plurality of MAC devices. Some of the MAC devices output respective data streams at different speeds. A plurality of speed translators translates the speeds of the respective data streams to be greater than or equal to a highest output speed of the plurality of MAC devices and generates parallel speed translated data streams. A multiplexer multiplexes the parallel speed translated data streams to generate a multiplexed data stream corresponding to one of the plurality of MAC devices with the highest output speed defined by the parallel speed translated data streams. A first serializer and deserializer receives the multiplexed data stream that is encoded at a physical coding sublayer and serially transmits the multiplexed data stream to a multi-port physical layer device.

Owner:MARVELL ISRAEL MISL

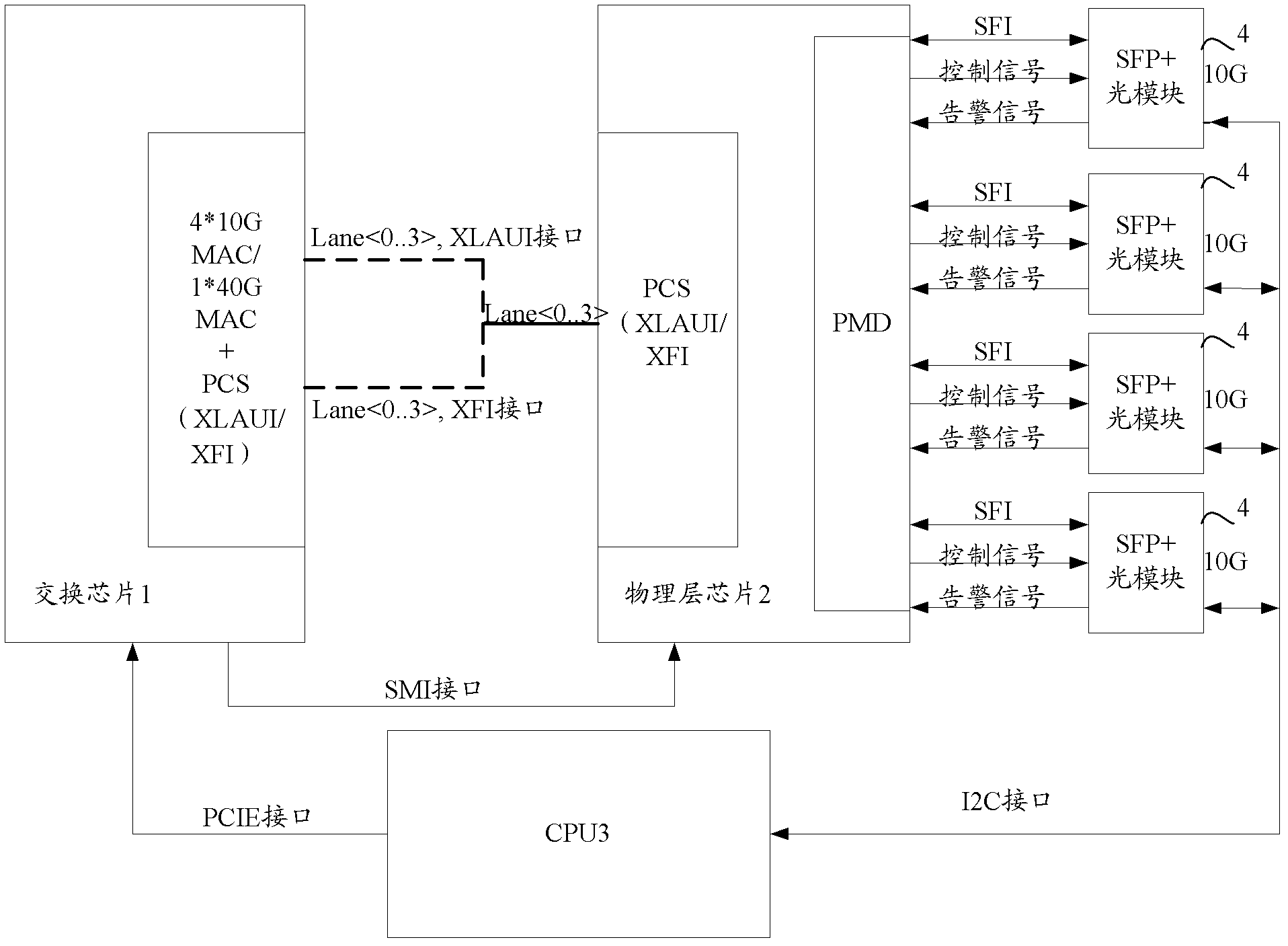

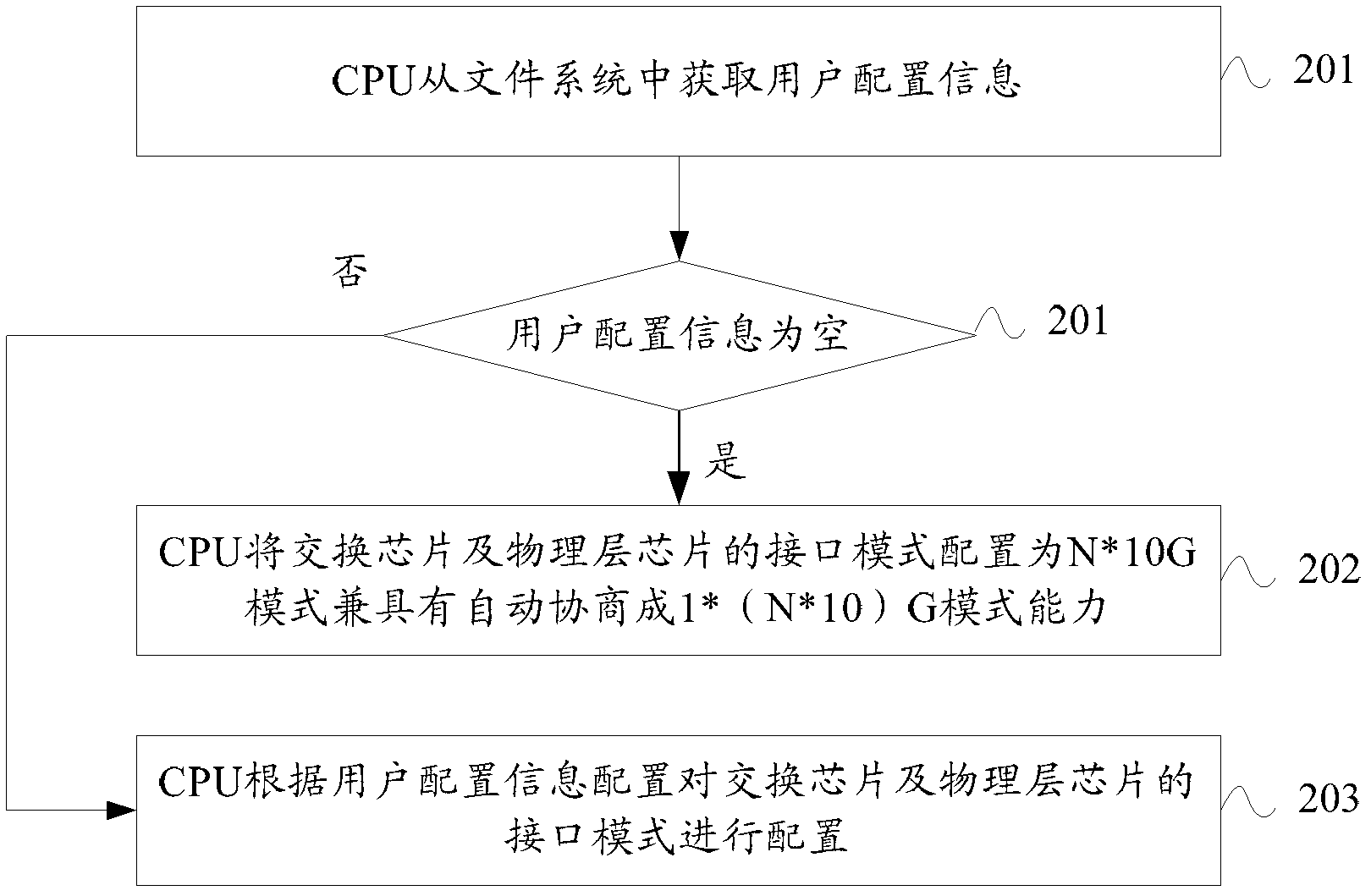

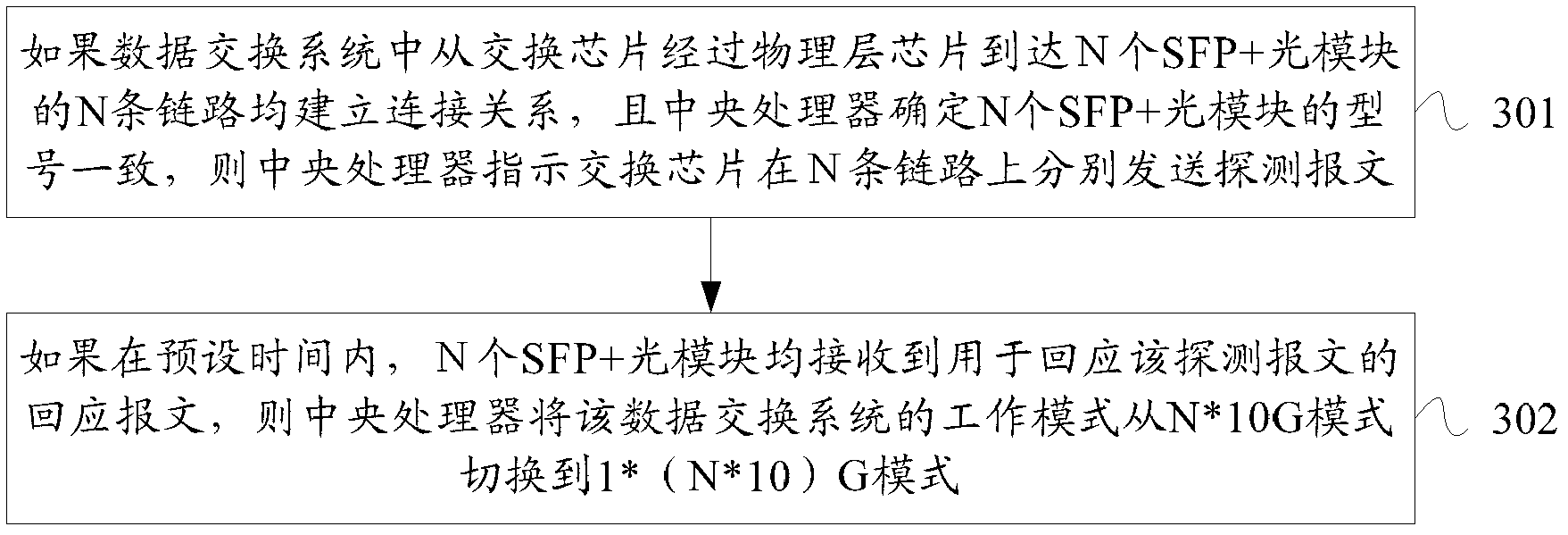

Data exchange system and operating mode self-negotiation method thereof

ActiveCN102595260AHigh speed transmissionMultiplex system selection arrangementsElectromagnetic transmissionTransceiverOptical Module

The invention provides a data exchange system and an operating mode self-negotiation method thereof. The system comprises an exchange chip, a physical layer chip, a central processing unit (CPU) and N small form-factor pluggable (SFP+) optical modules, wherein the exchange chip is connected with a physical coding sublayer of the physical layer chip through N lane interfaces, so that the physical coding sublayer is operated in an (N*10) G mode; a physical medium dependent sublayer of the physical layer chip is operated in a 10G SFP+ mode, and the N SFP+ optical modules are respectively connected with the physical medium dependent sublayer of the physical layer chip through N SERDES framer interfaces (SFIs); and the CPU is connected with the N SFP+ optical modules through an inter-integrated circuit (I2C) interface and connected with the exchange chip through a peripheral component interconnect express (PCIE) interface, wherein N is a positive integer more than or equal to one. By the technical scheme provided by the invention, a transceiver module can support transmission of long distance (more than forty kilometers).

Owner:RUIJIE NETWORKS CO LTD