Patents

Literature

30results about How to "Small circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

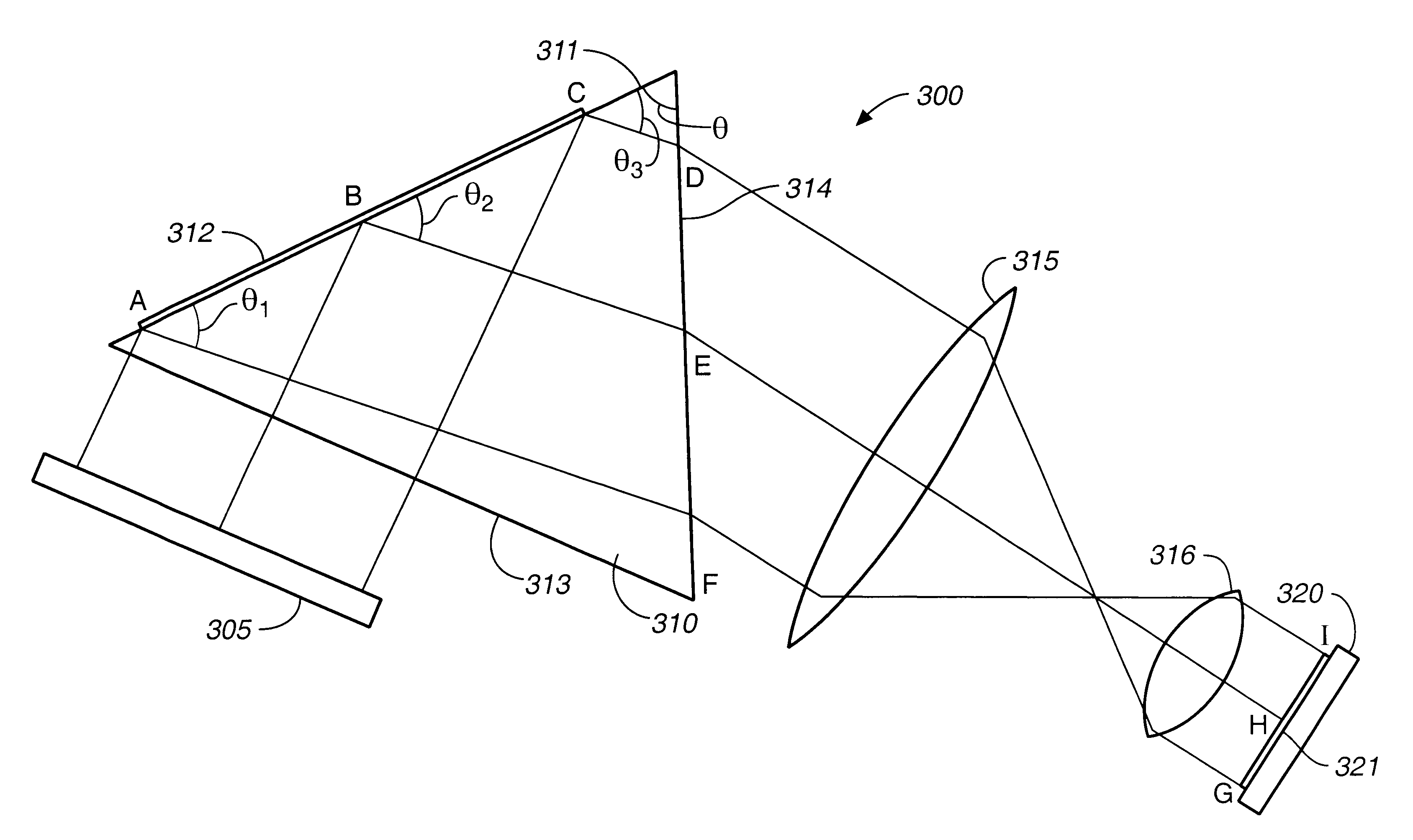

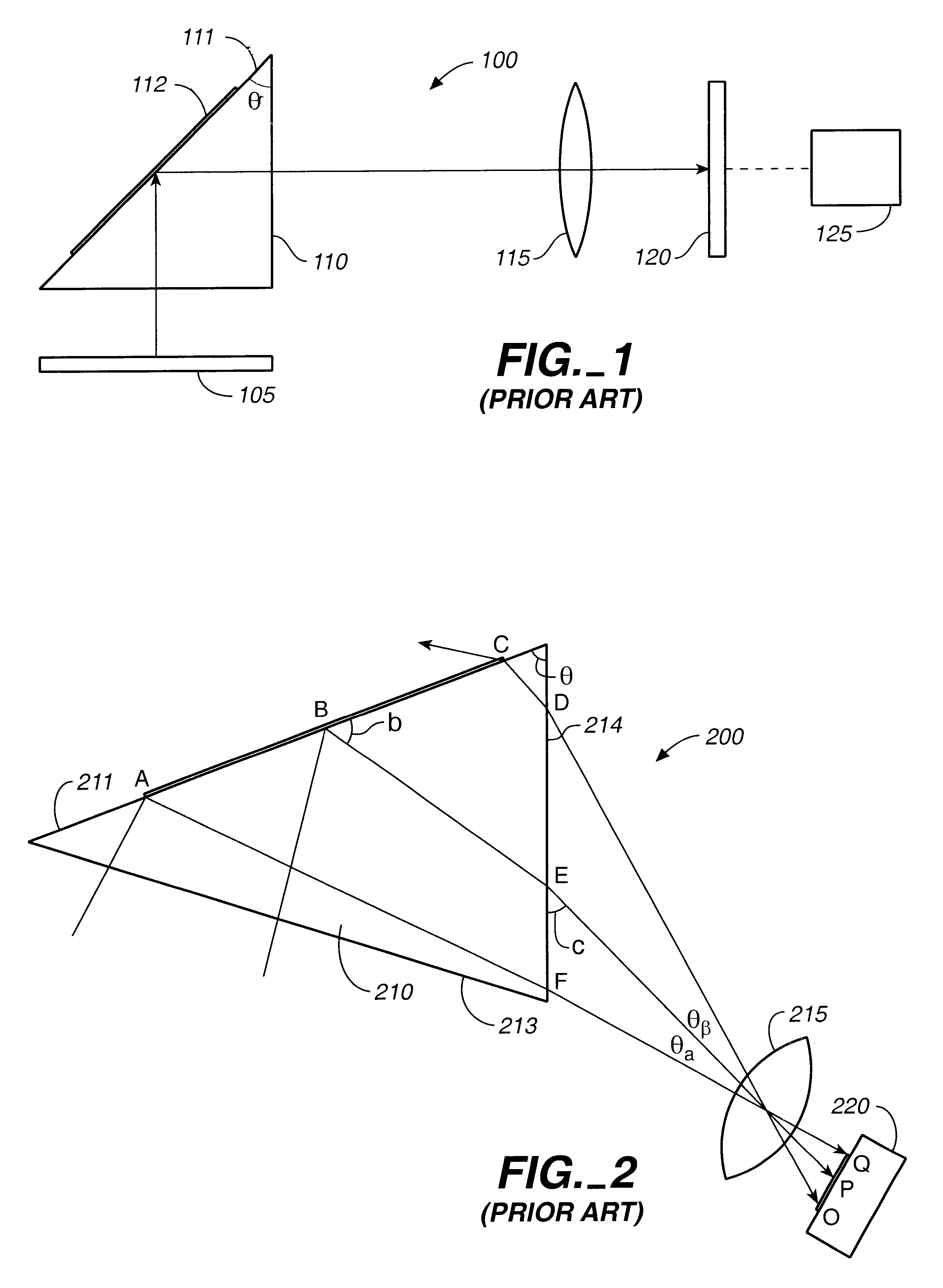

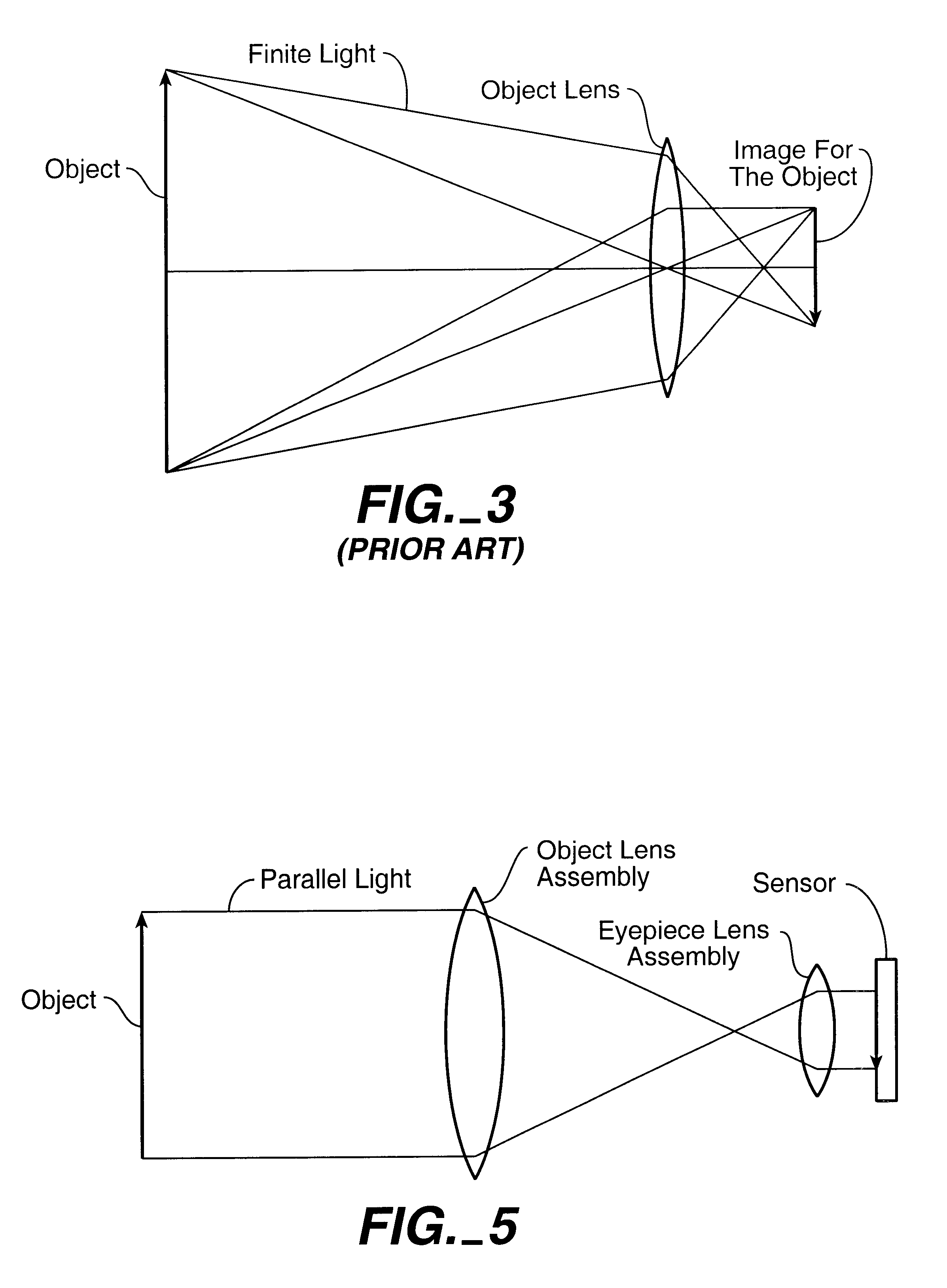

Compact optical fingerprint capturing and recognition system

InactiveUS6870946B1Solve bulkyImprove simplicityCharacter and pattern recognitionUsing optical meansRecognition systemFingerprint

An apparatus and method for acquiring an image of a patterned object such as a fingerprint including a light refracting device, a focusing lens, a light source, and a biometric circuit for detecting the presence of a patterned object such as a fingerprint at the light refracting device. Incident light from the light source is projected through a light receiving surface of the light refracting device and is directly reflected off an imaging surface. The resulting image is projected through the focusing lens. The focusing lens has a diameter which is larger than the projection of the patterned object through the light refracting device.

Owner:SECUGEN CORP

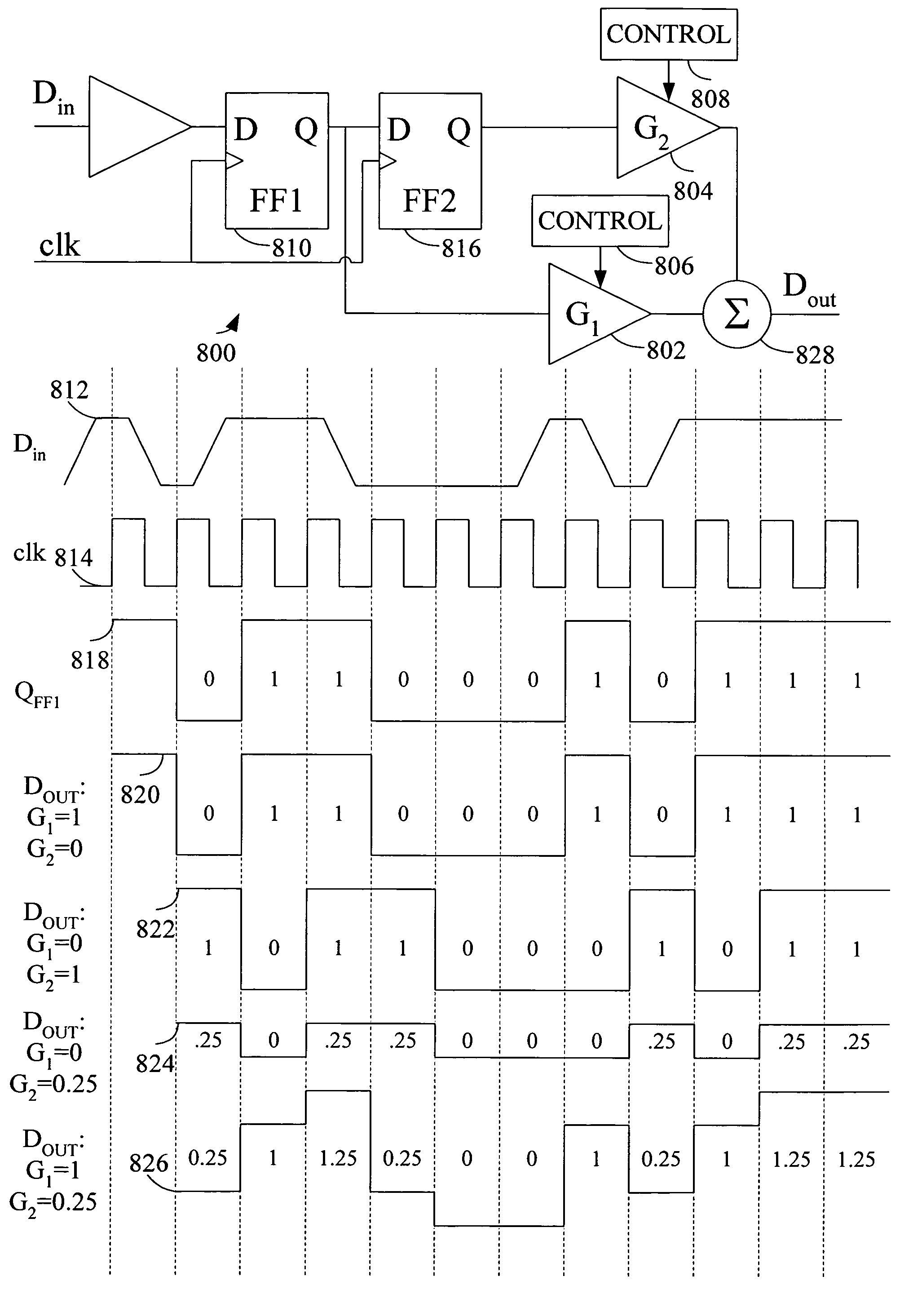

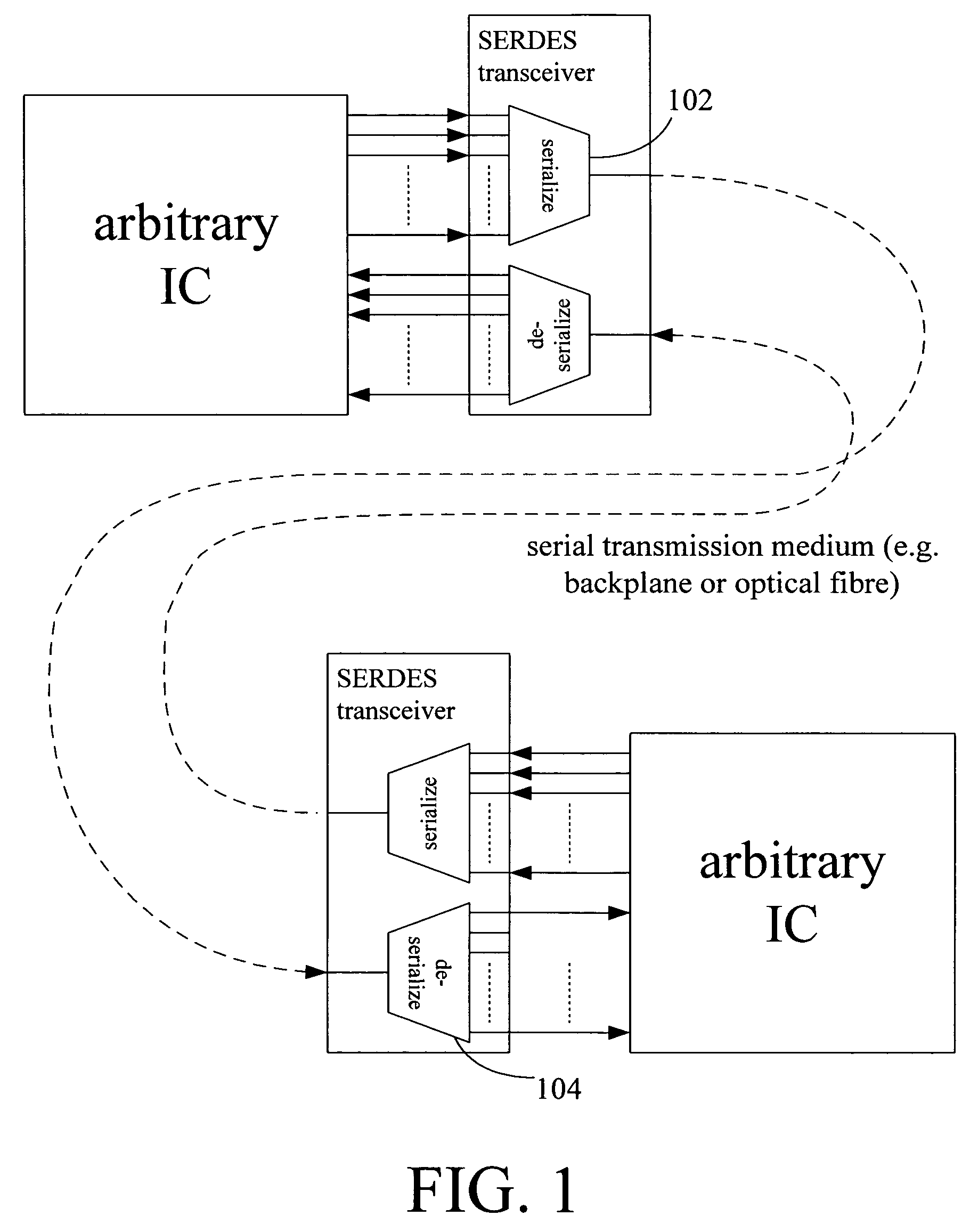

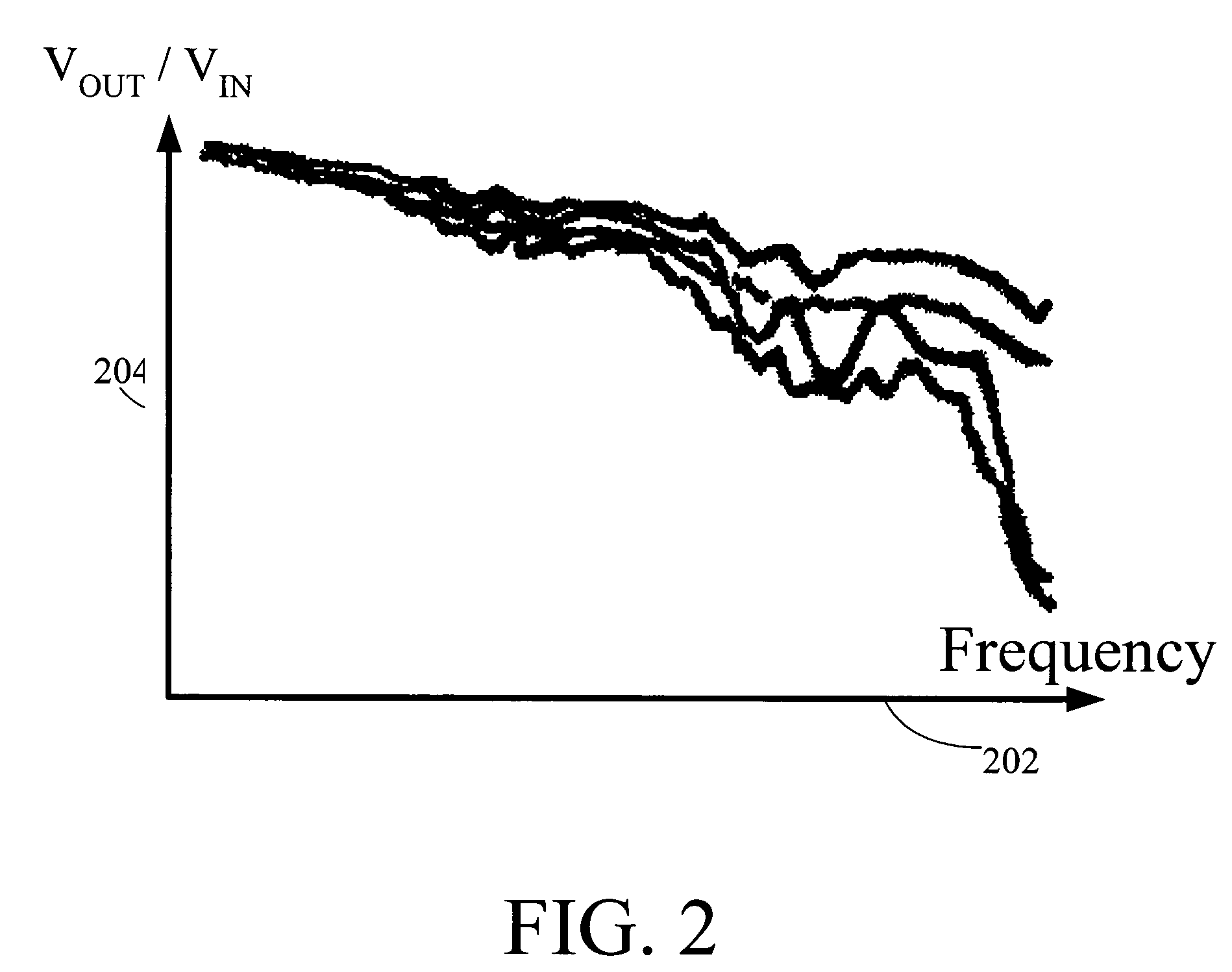

Built in self test (BIST) for high-speed serial transceivers

InactiveUS7756197B1Advantageously highly scaleableIncrease data rateCorrect operation testingTransmission monitoringFinite impulse responseTransceiver

A relatively high-speed serial data transmitter incorporates built in self test (BIST). The BIST circuit advantageously provides tests modes to obviate the need to build expensive test equipment for high-speed serial data devices, such as a serializer / deserializer (SerDes) or other transceivers. Multiple data paths in a finite impulse response (FIR) filter of transmitter of the SerDes or a transceiver can be independently tested. The transmitter output can also be selectively degraded to test a receiver of a transceiver. An attenuated output signal can be provided to test receiver sensitivity. A low-pass filter can be invoked to emulate a backplane, while a loopback circuit can provide the emulated backplane attenuation to the receiver to permit testing of the equalization circuitry of a receiver without requiring the presence of an actual backplane for testing.

Owner:MICROSEMI STORAGE SOLUTIONS

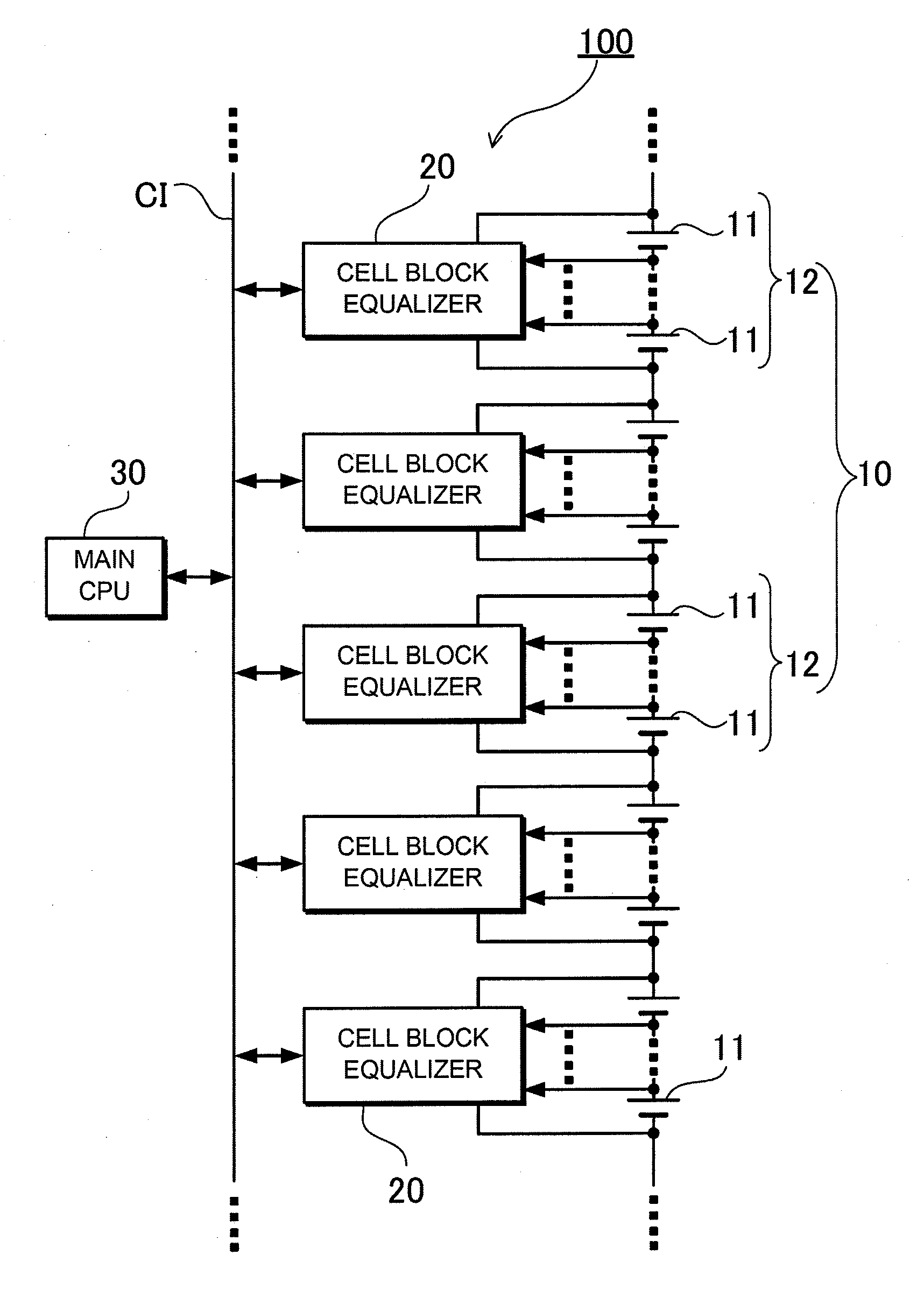

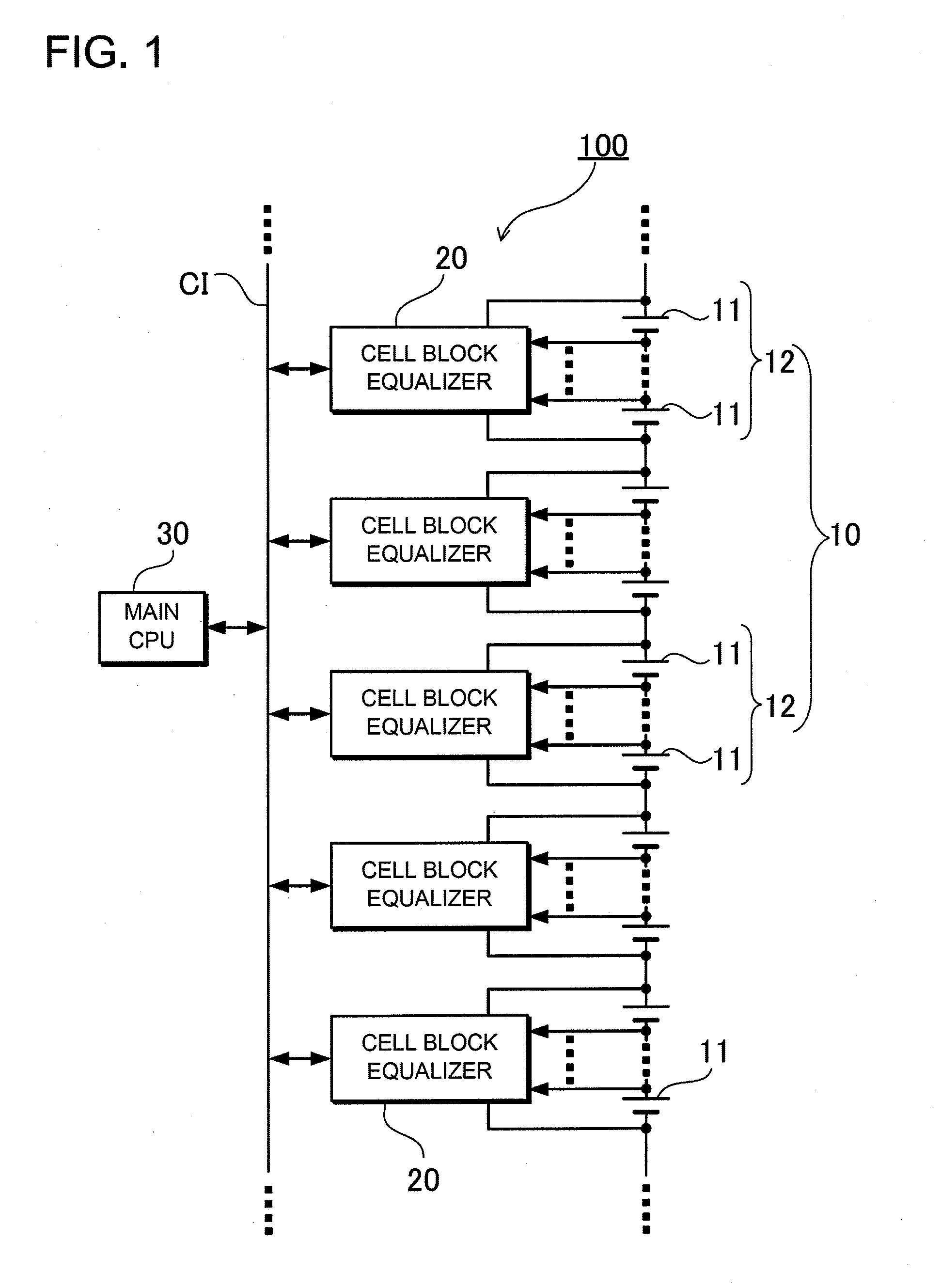

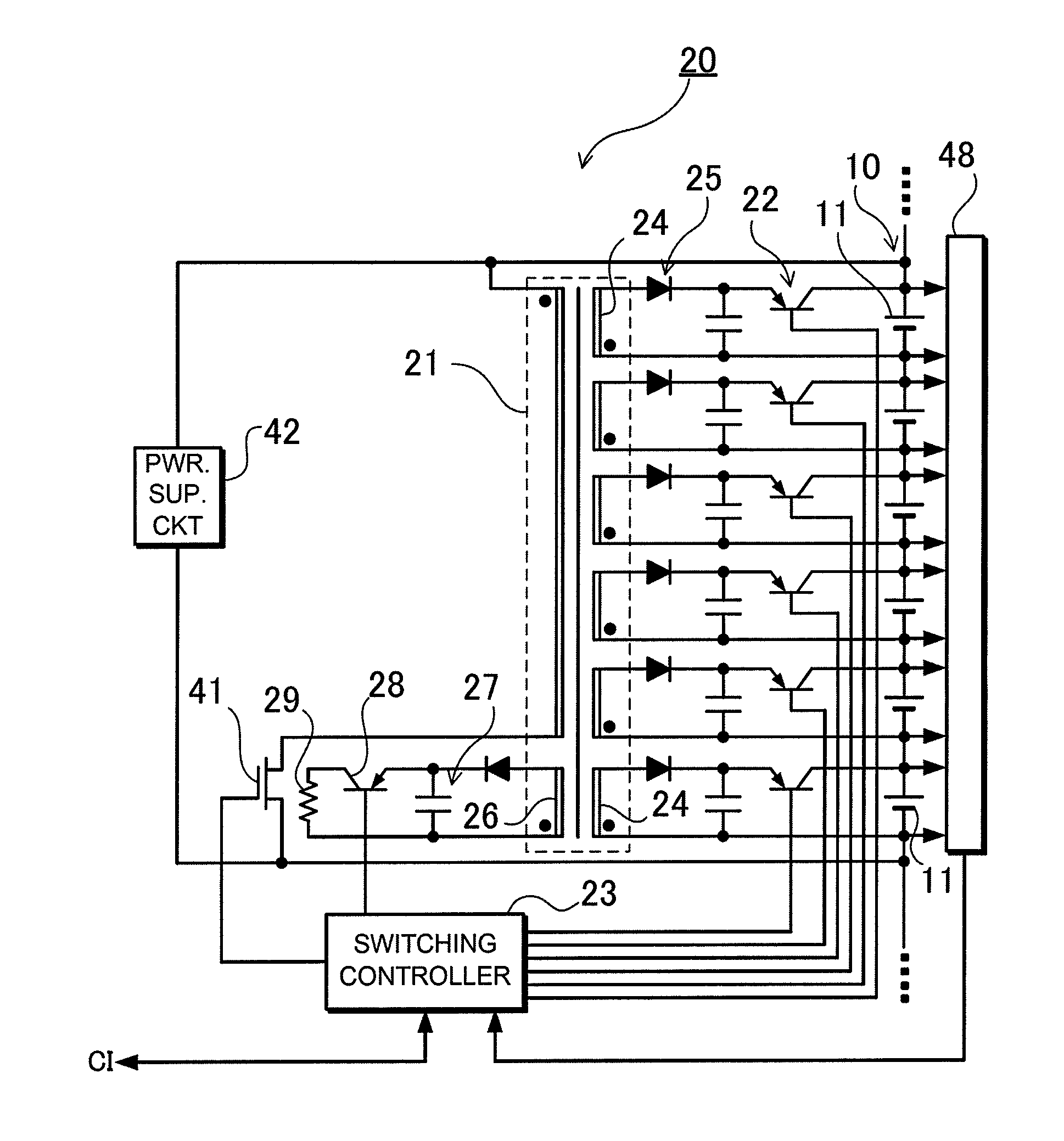

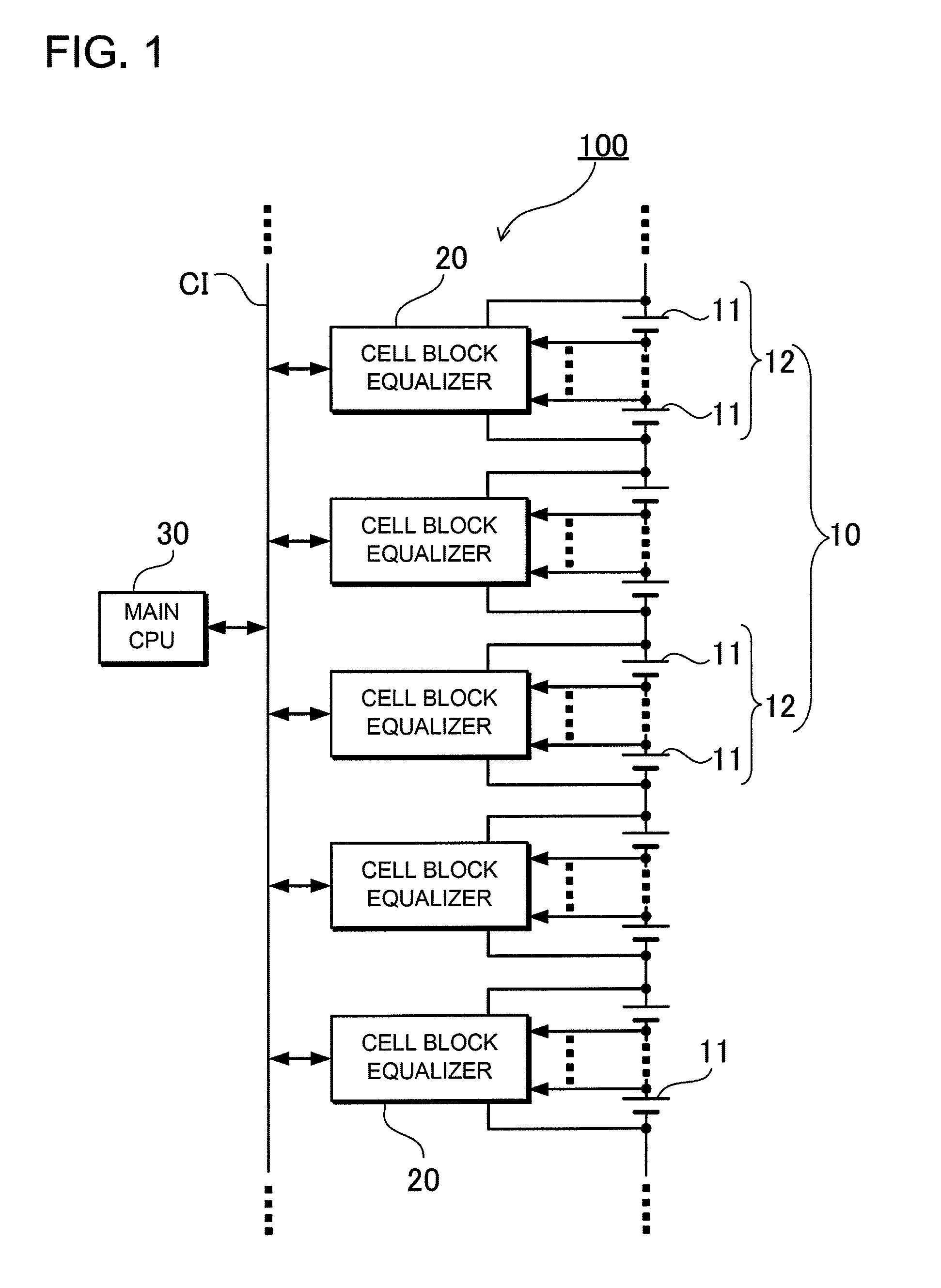

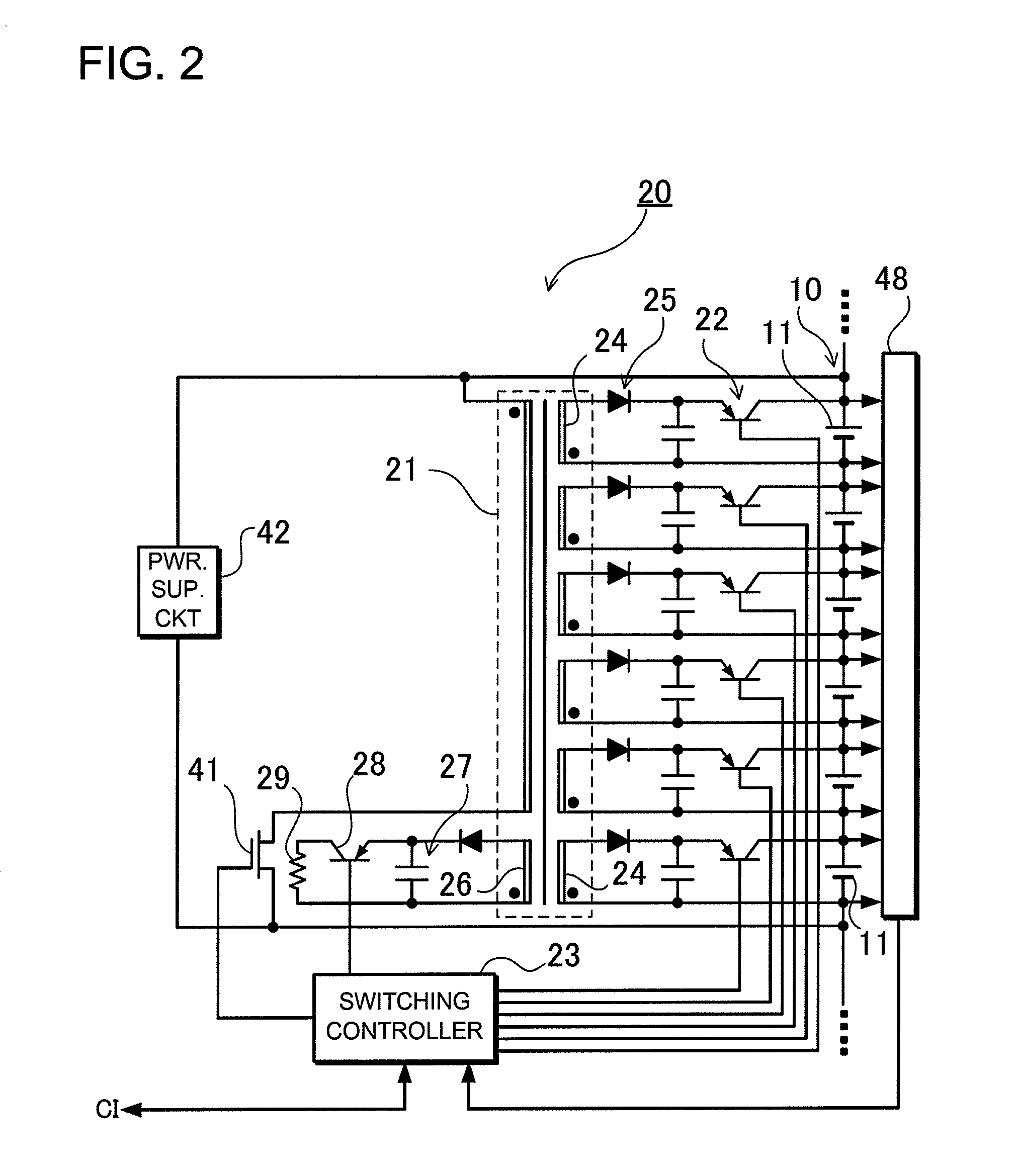

Power supply device capable of equalizing electrical properties of batteries

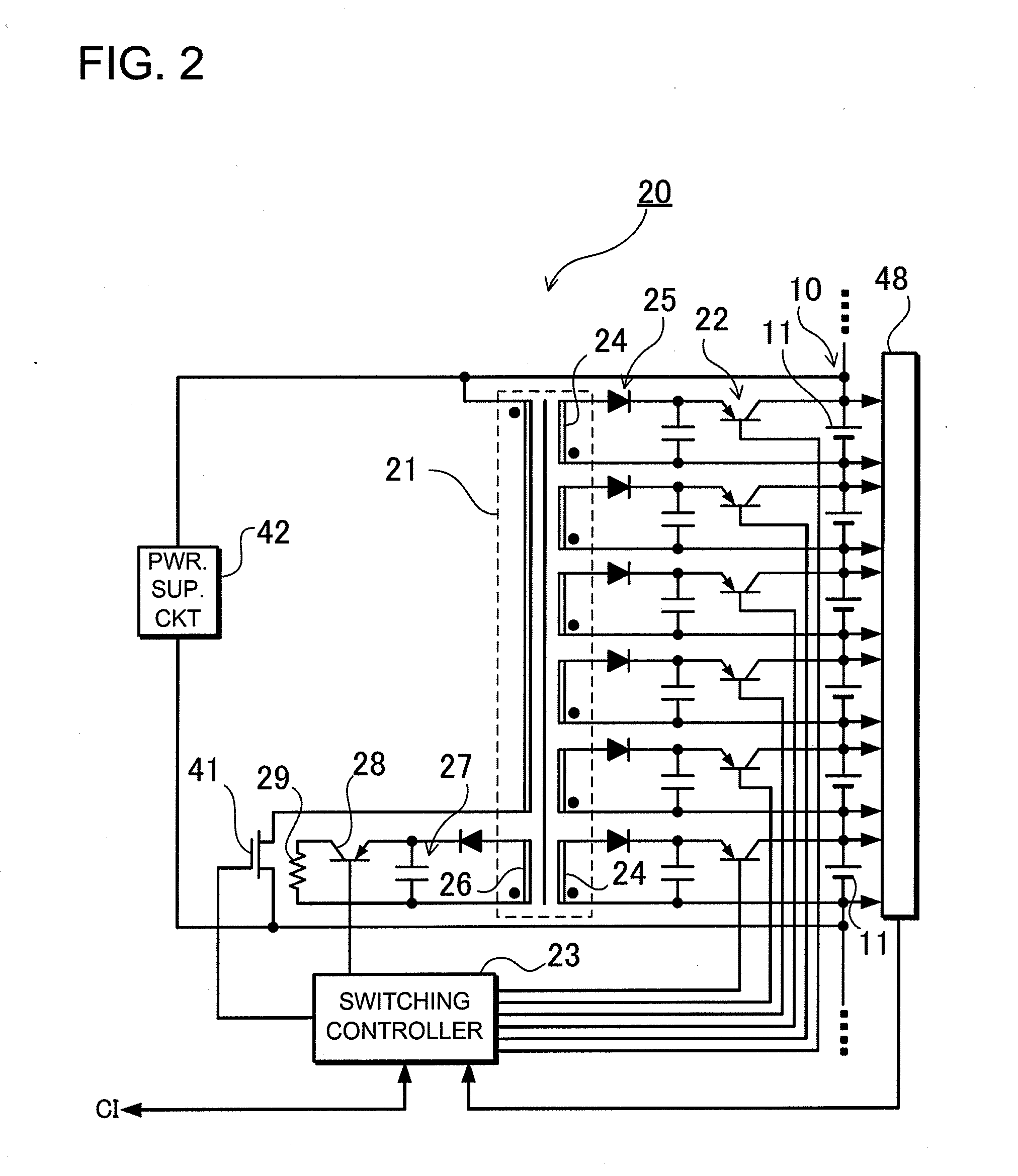

ActiveUS20110234164A1Maintain balanceReduce the amount requiredCharge equalisation circuitSecondary cellsEngineeringControl switch

A transformer 21 includes charging secondary winding lines 24 that can charge batteries 11 composing a corresponding cell block, and a discharging secondary winding line 26 that can discharge the corresponding cell block. Each of the charging secondary winding lines 24 is connected to corresponding one of the batteries 11 through corresponding one of secondary-side rectification output circuits 25 and corresponding one of output control switches 22. The discharging secondary winding line 26 is connected to a block discharging circuit through a block discharging switch 28. A switching control circuit 23 controls the block discharging switch 28. The switching control circuit 23 controls the output control switches 22 so that the electrical properties of the batteries 11 in the cell block are equalized. In addition, the switching control circuits 23 control the block discharging switches 28 so that the electrical properties of the batteries among the cell blocks are equalized.

Owner:SANYO ELECTRIC CO LTD

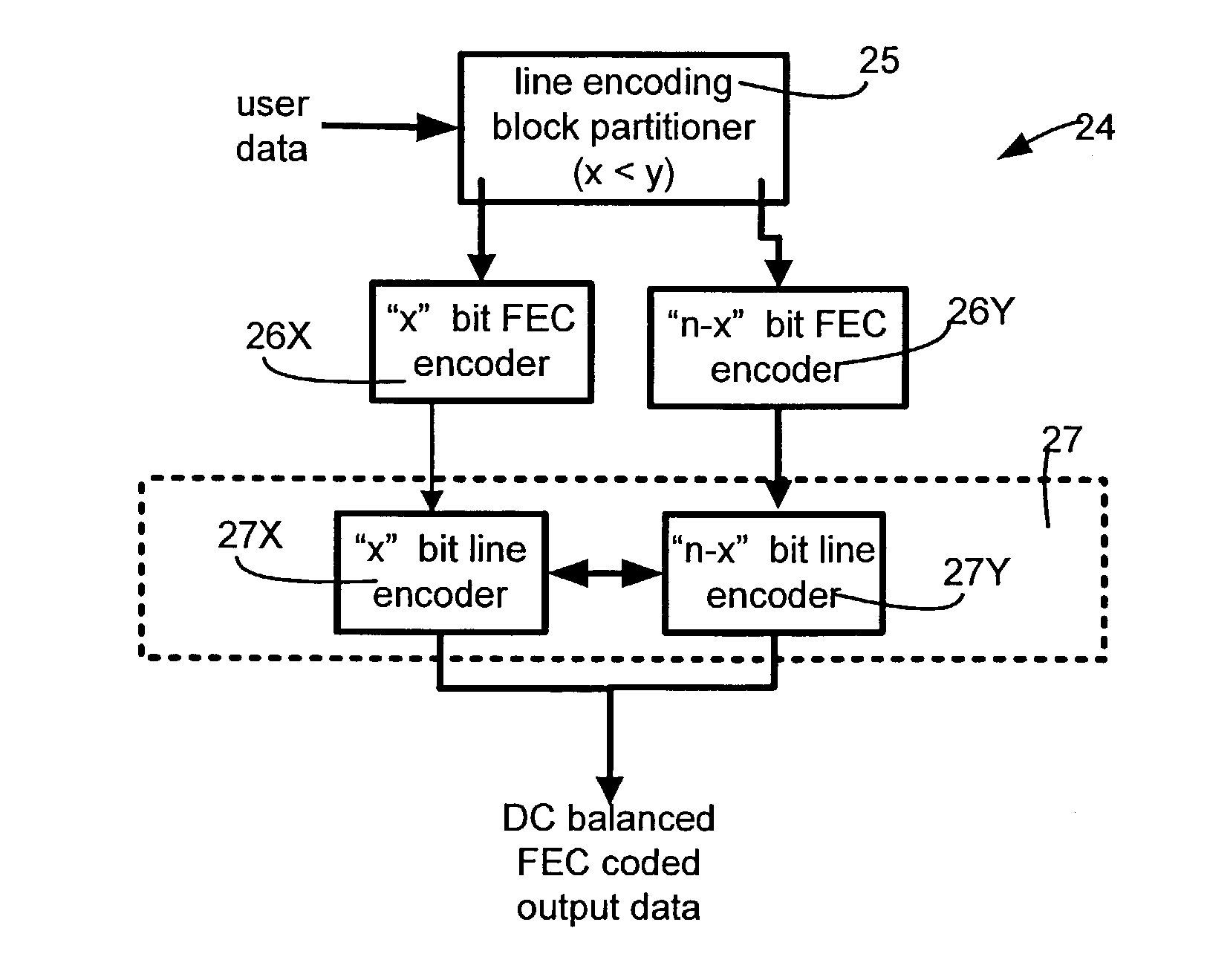

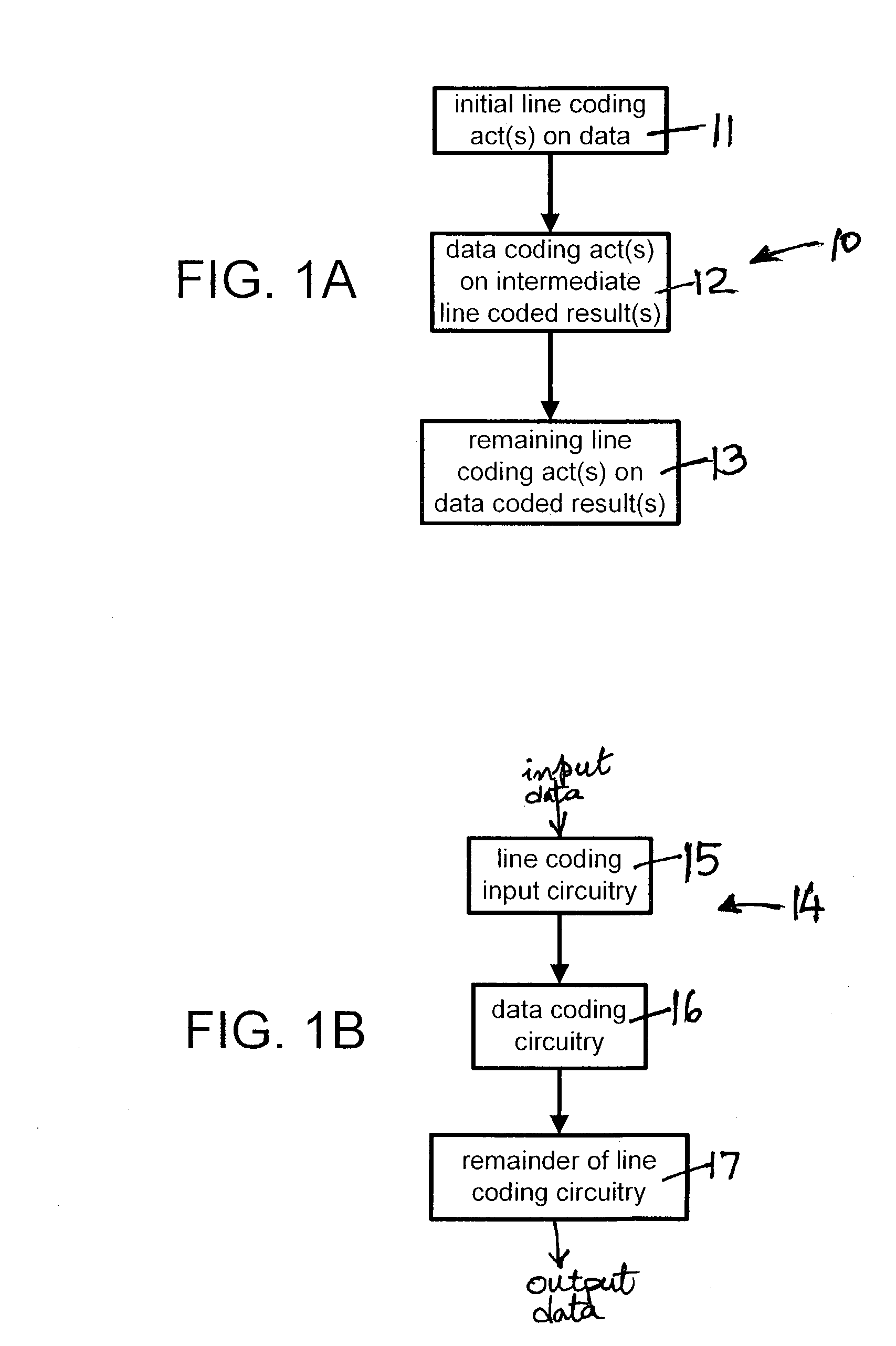

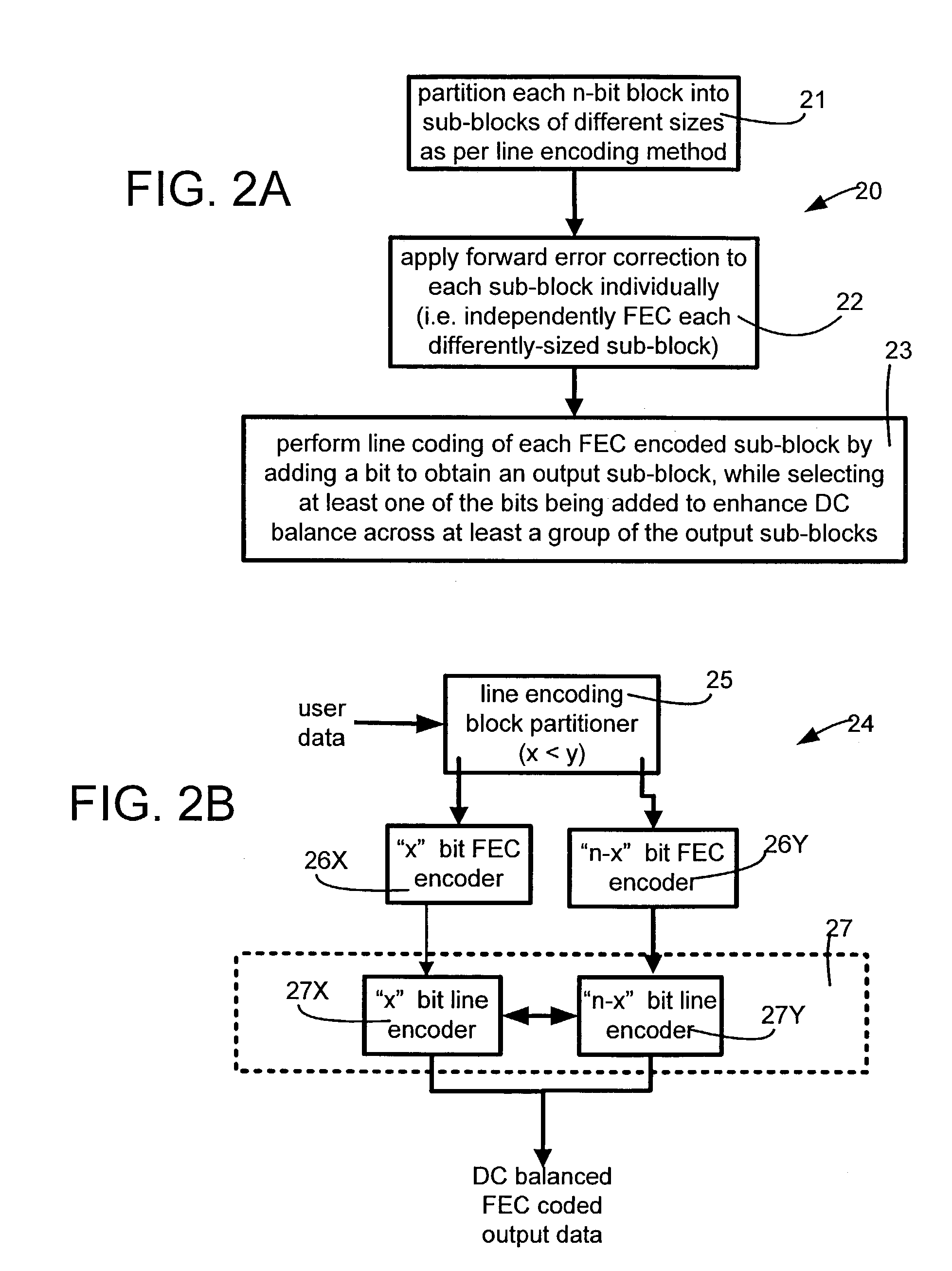

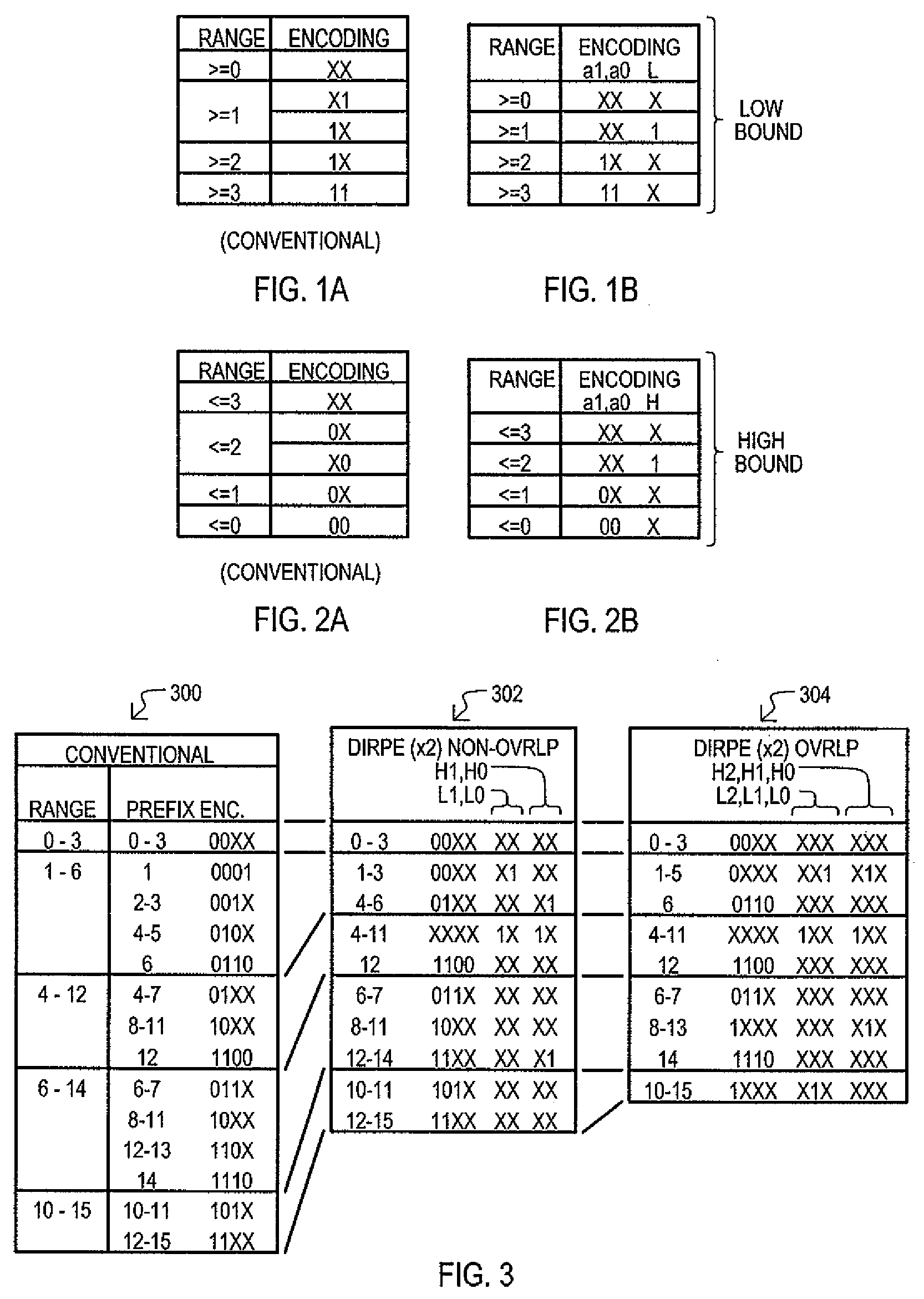

DC balanced error correction coding

ActiveUS7103830B1Simple processSmall circuitIndividual digits conversionError detection only8b/10b encodingData encoding

Two types of codings are integrated, instead of performing each coding independently. The two codings may be integrated by interleaving one or more acts of one coding method (e.g. data coding) between two or more acts of the other coding method (e.g. line coding). In some embodiments, partitioning of a block of data (e.g. a byte) for line coding (e.g. DC balance coding) is done prior to data coding (e.g. error correction coding). In such embodiments, the remaining acts of line coding may be performed after the data coding is completed. In one particular embodiment, an 8 bit byte is not directly used in error correction coding and instead, the 8 bit byte is initially partitioned into two sub-blocks (of 3 bits and 5 bits) as required by 8B / 10B encoding (which is an example of line coding). After partitioning, the 8B / 10B encoding is not continued, and instead Reed Solomon coding (which is an example of data coding) is then performed (to completion) on the individual sub-blocks (of 3 bits and 5 bits). The error correction coded sub-blocks (of 3 bits and 5 bits) are then used for the remainder of 8B / 10B encoding.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

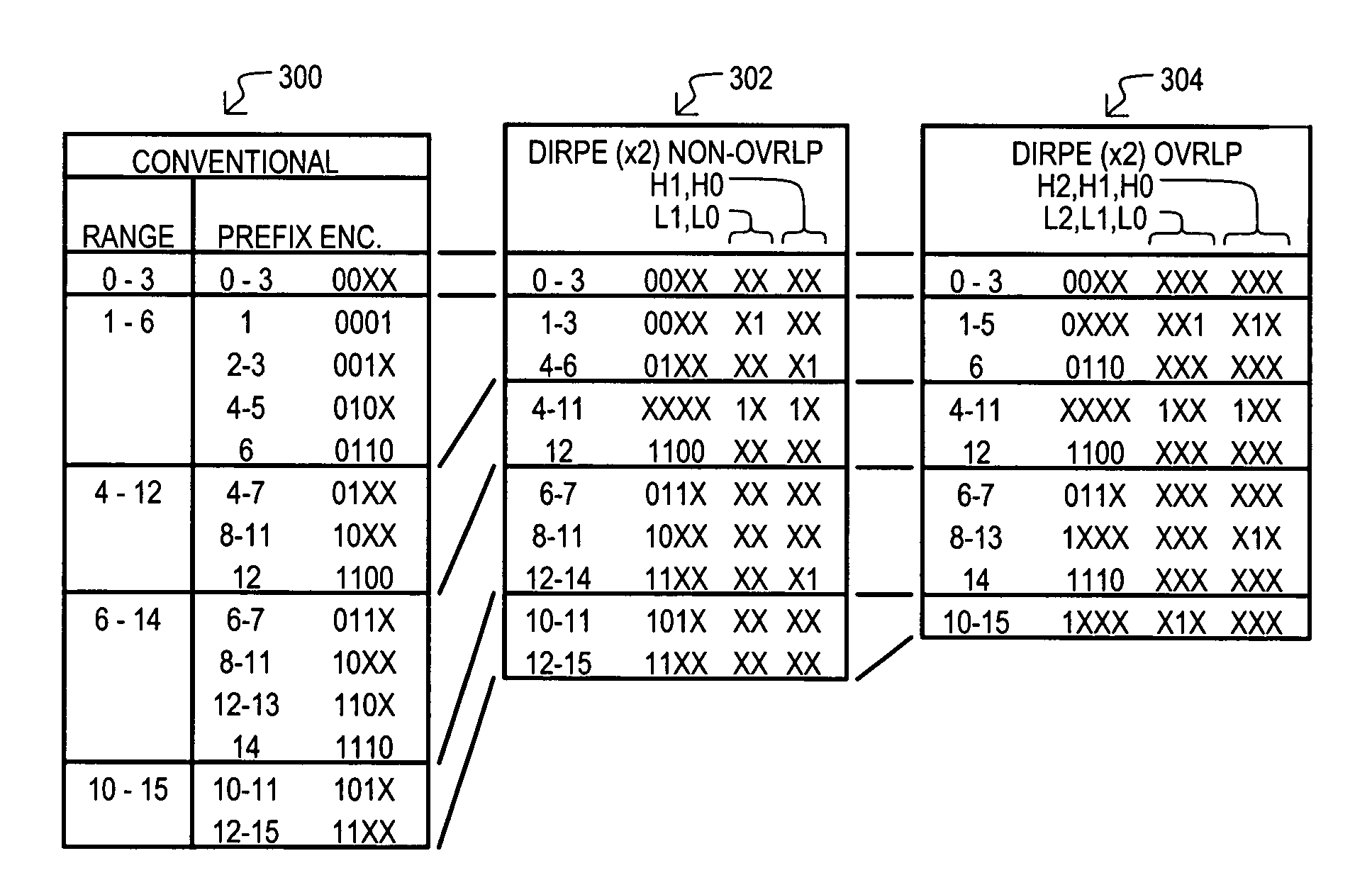

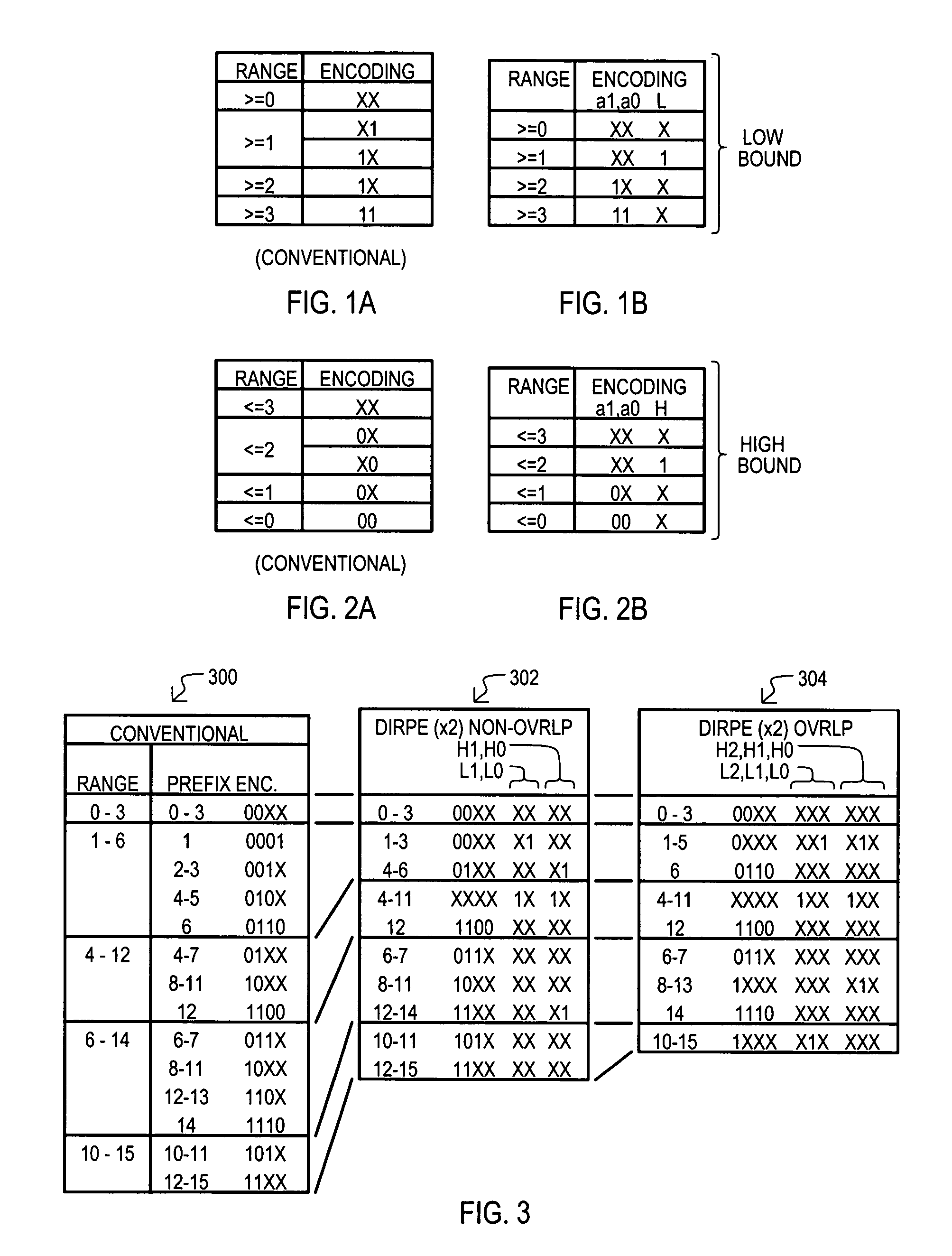

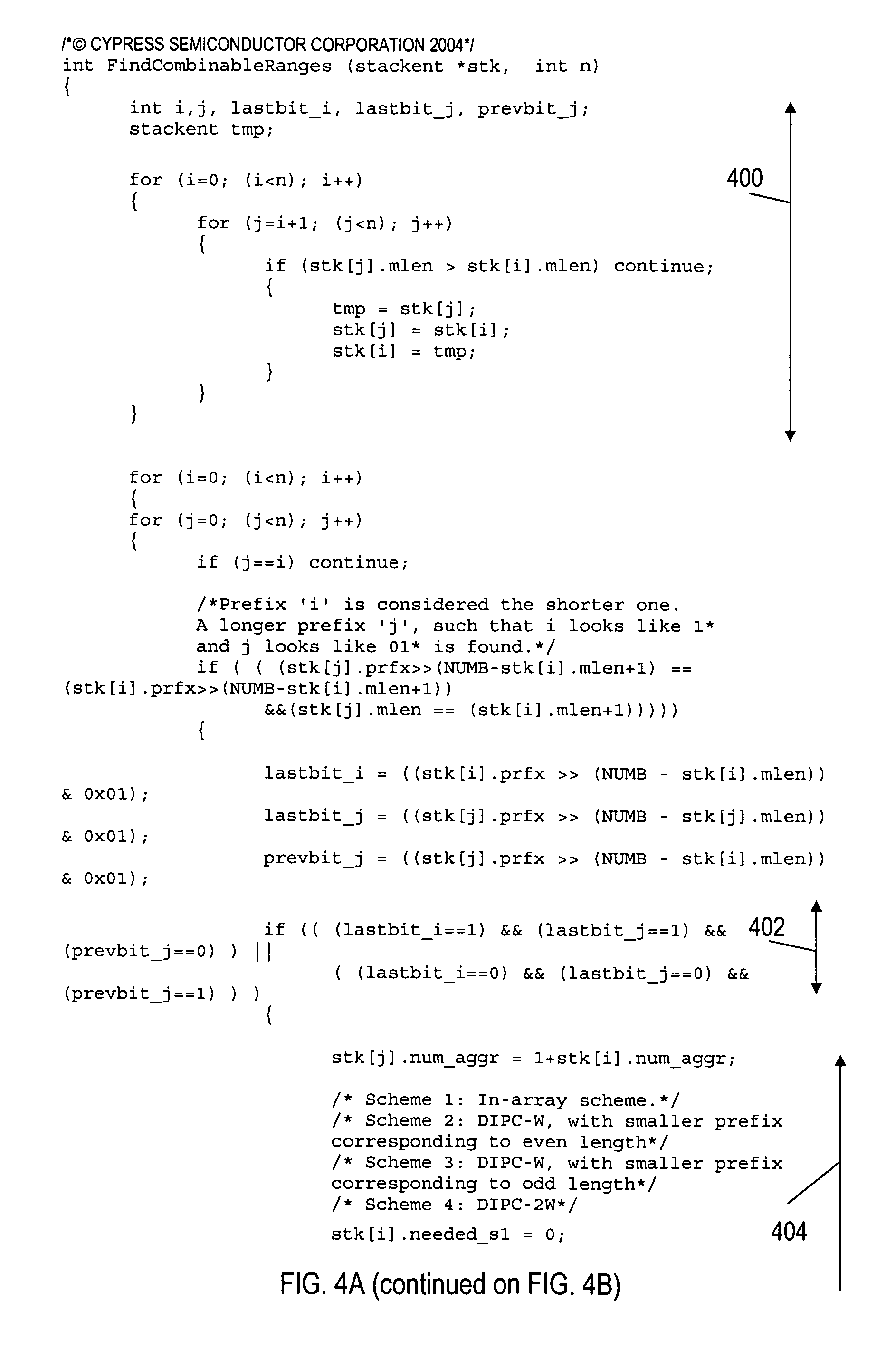

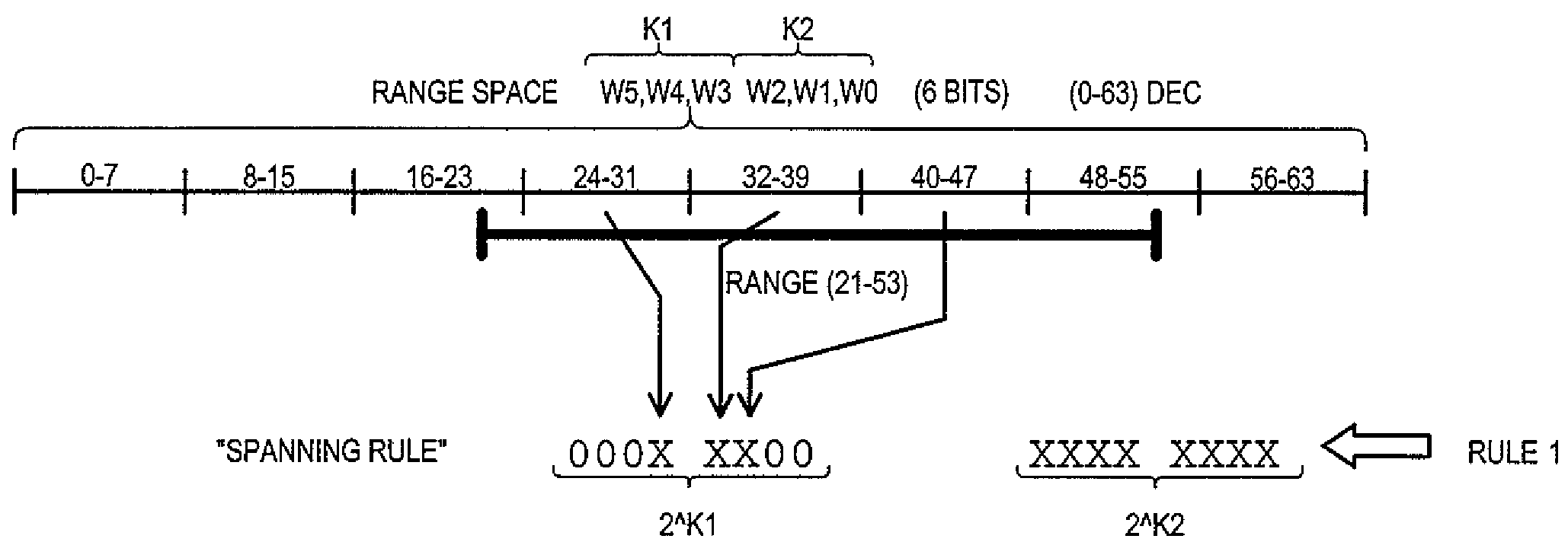

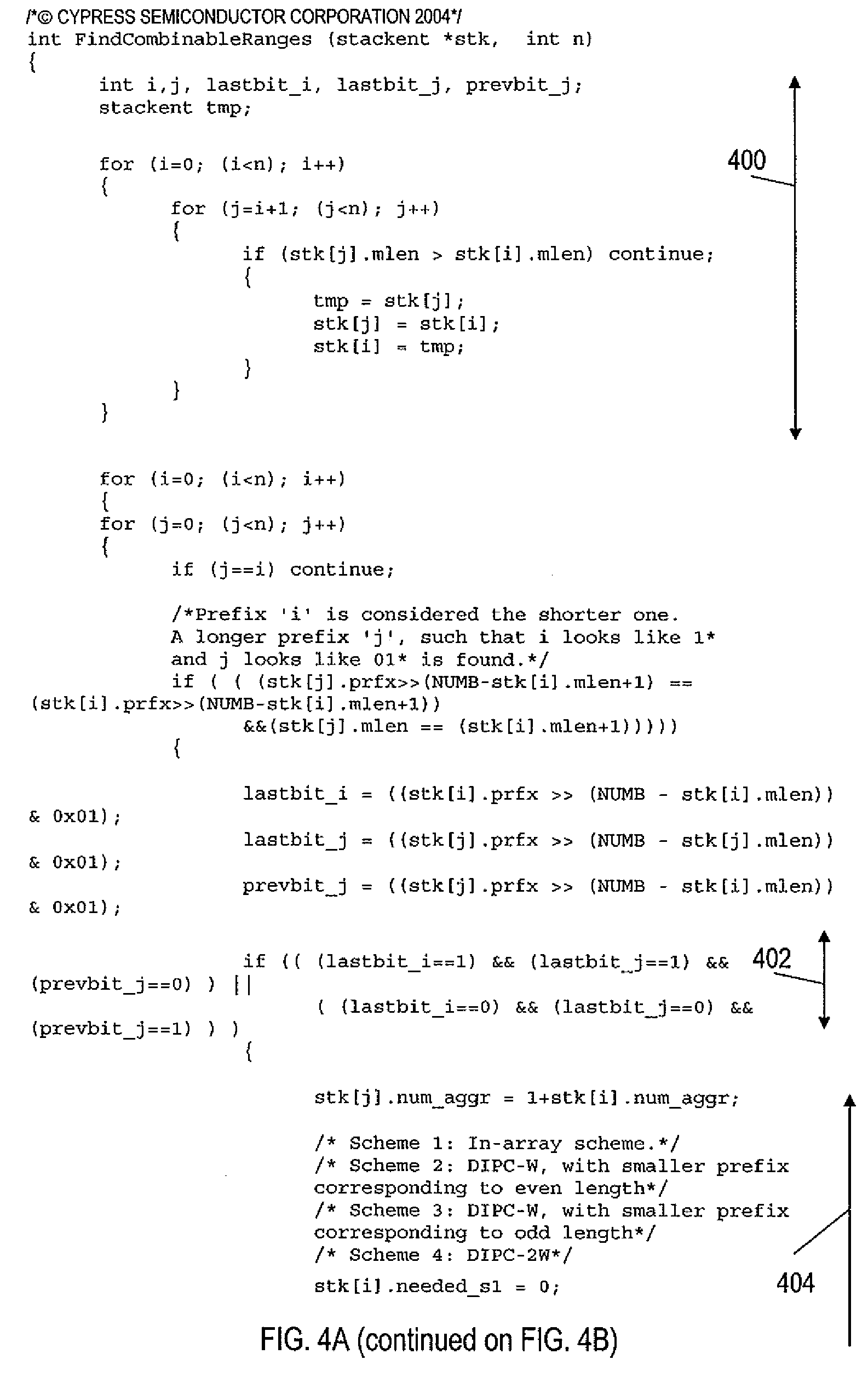

Range code compression method and apparatus for ternary content addressable memory (CAM) devices

InactiveUS7711893B1Reduce in quantityIncrease in sizeDigital storageMemory systemsPartial representationOne-hot

A content addressable memory (CAM) device, method, and method of generating entries for range matching are disclosed. A CAM device (800) according to one embodiment can include a pre-encoder (806) that encodes range bit values W into additional bits E. Additional bits E can indicate compression of range rules according to particular bit pairs. A CAM array (802) can include entries that store compressed range code values (RANGE) with corresponding additional bit values (ENC). Alternate embodiments can include pre-encoders that encode portions of range values (K1 to Ki) in a “one-hot” fashion. Corresponding CAM entries can include encoded value having sections that each represent increasingly finer divisions of a range space.

Owner:AVAGO TECH INT SALES PTE LTD

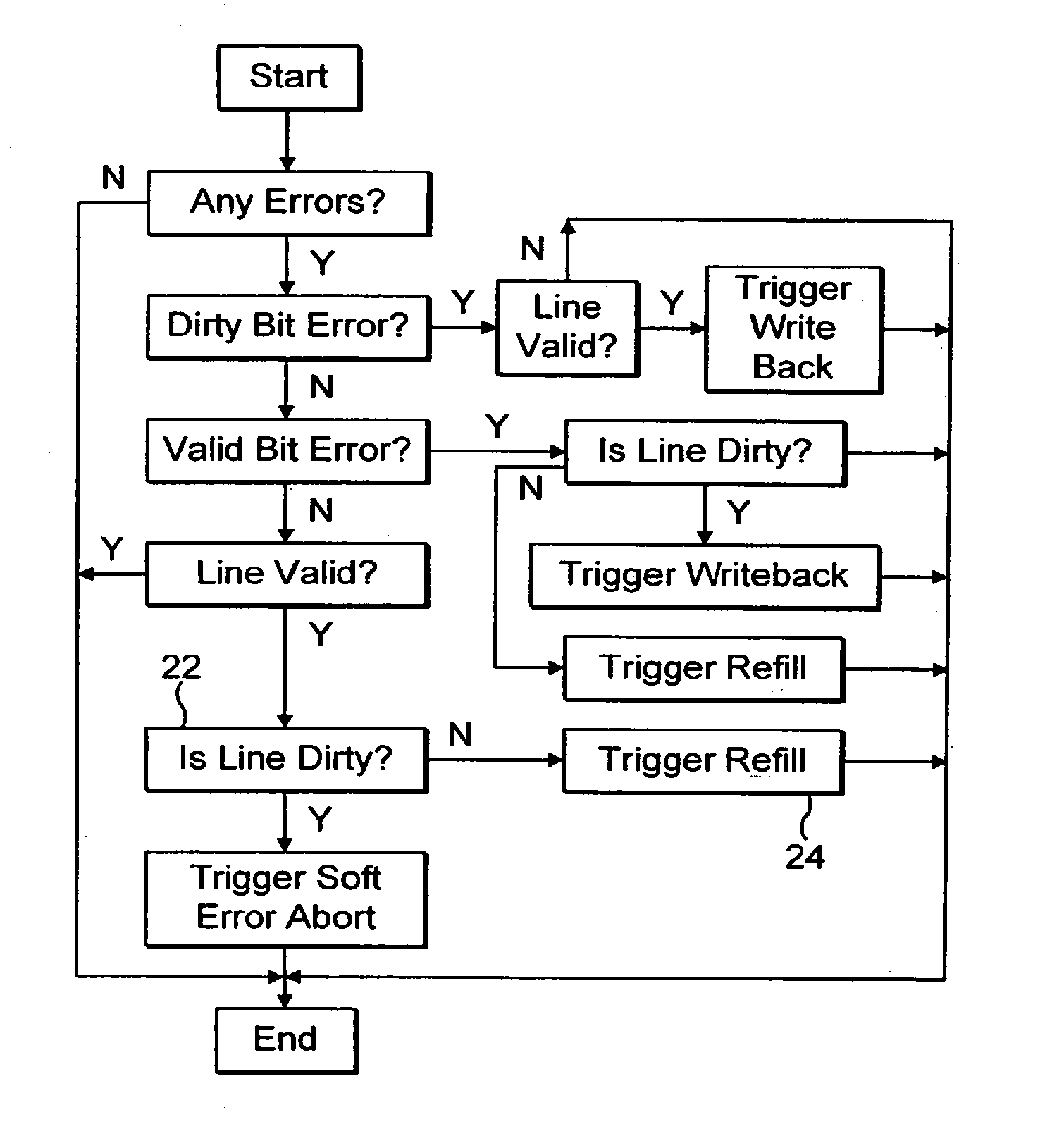

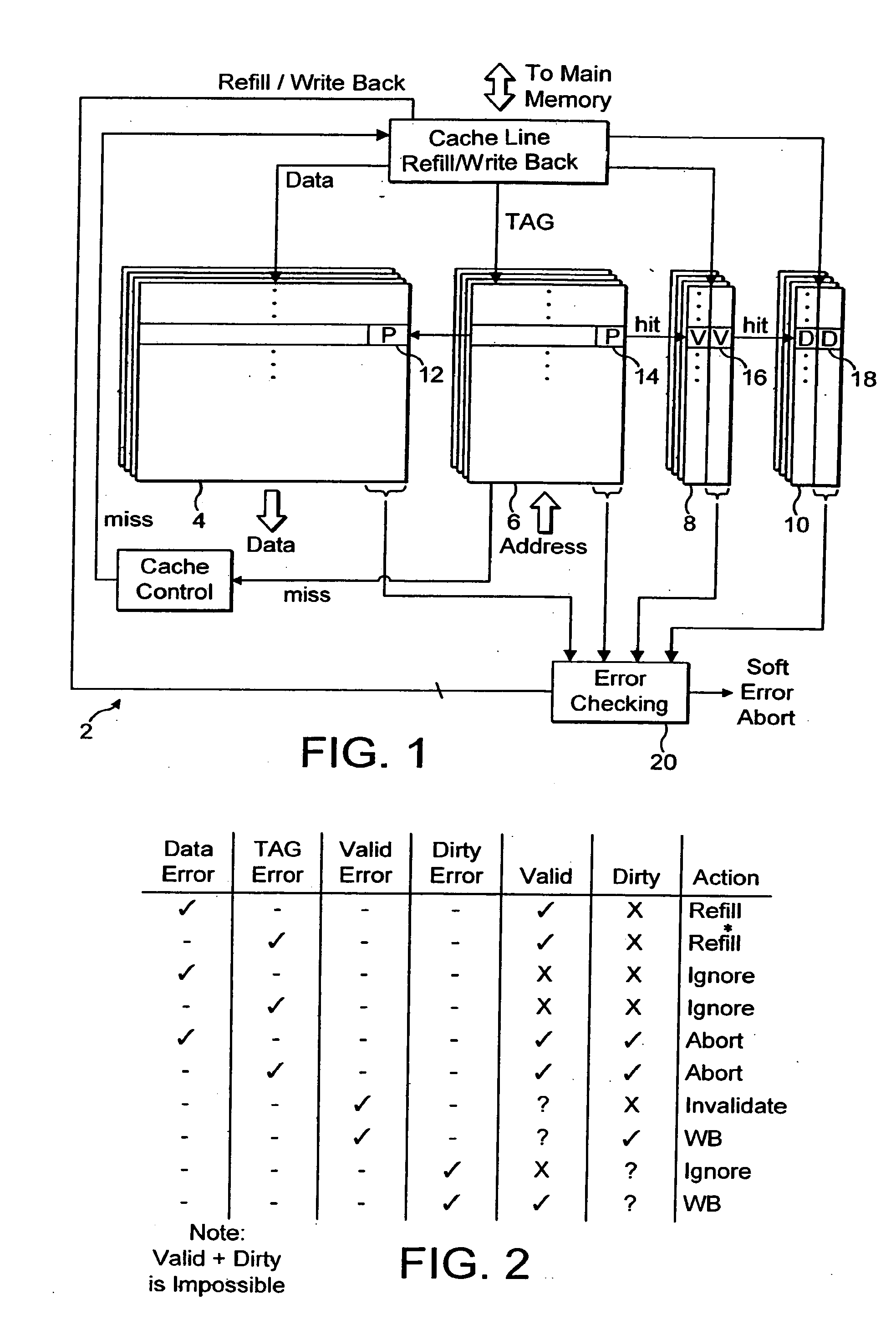

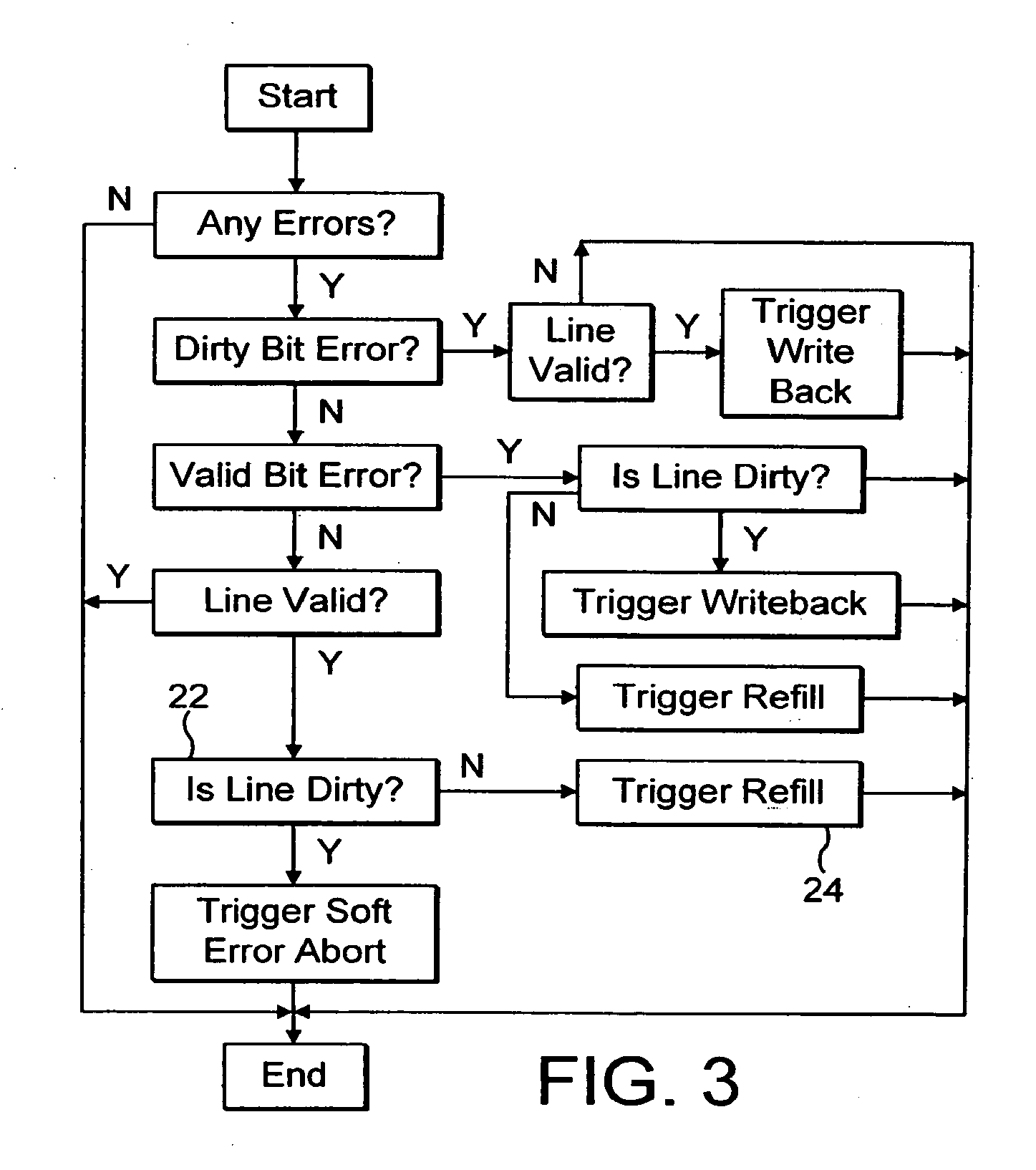

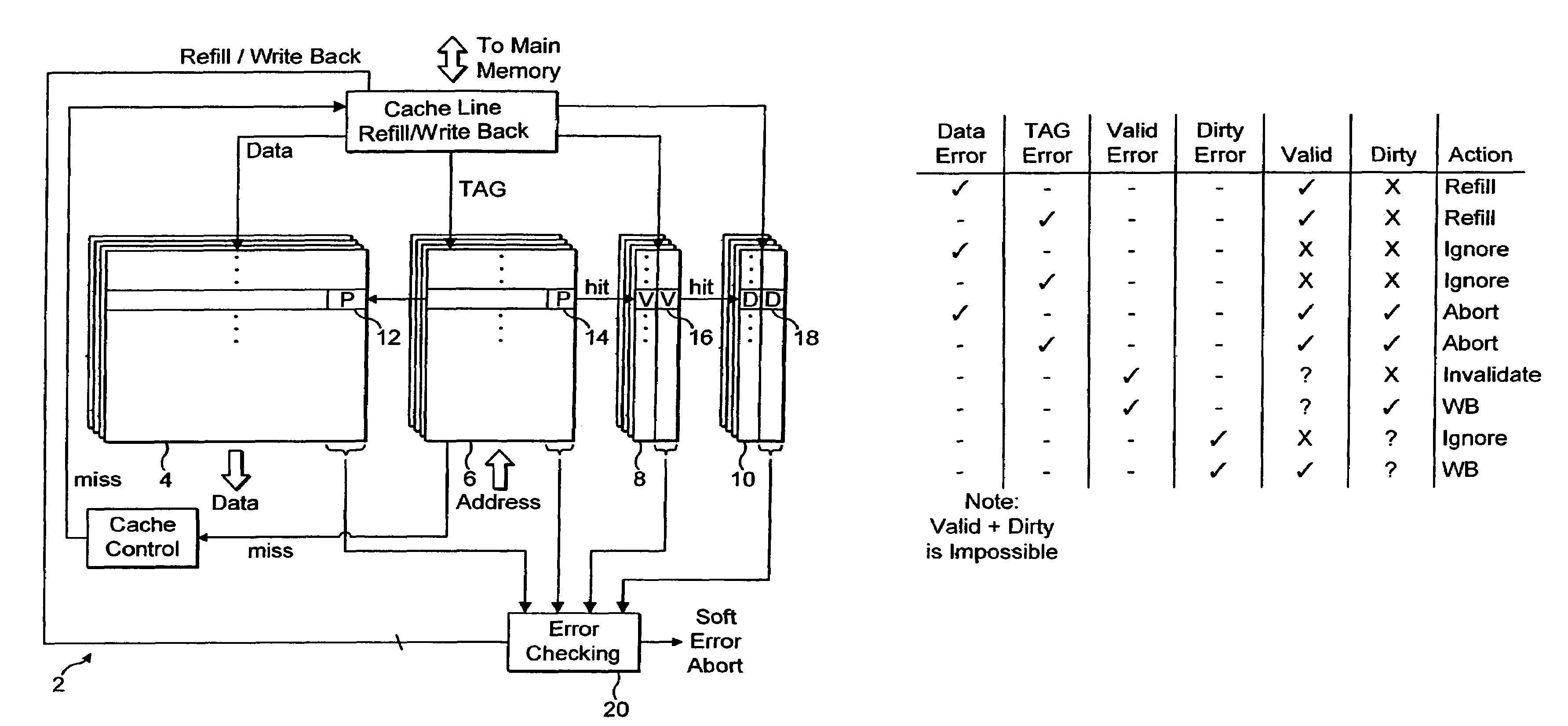

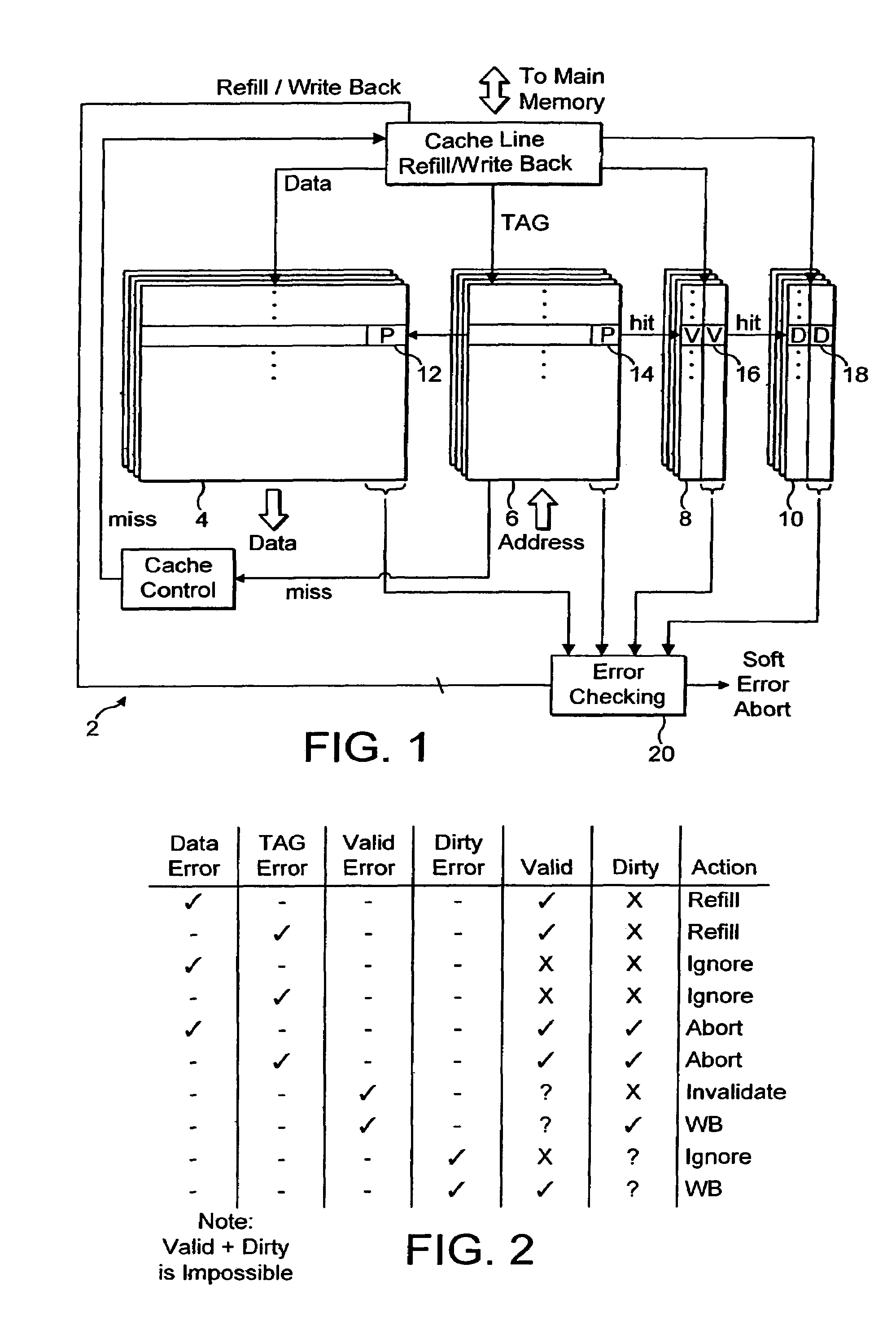

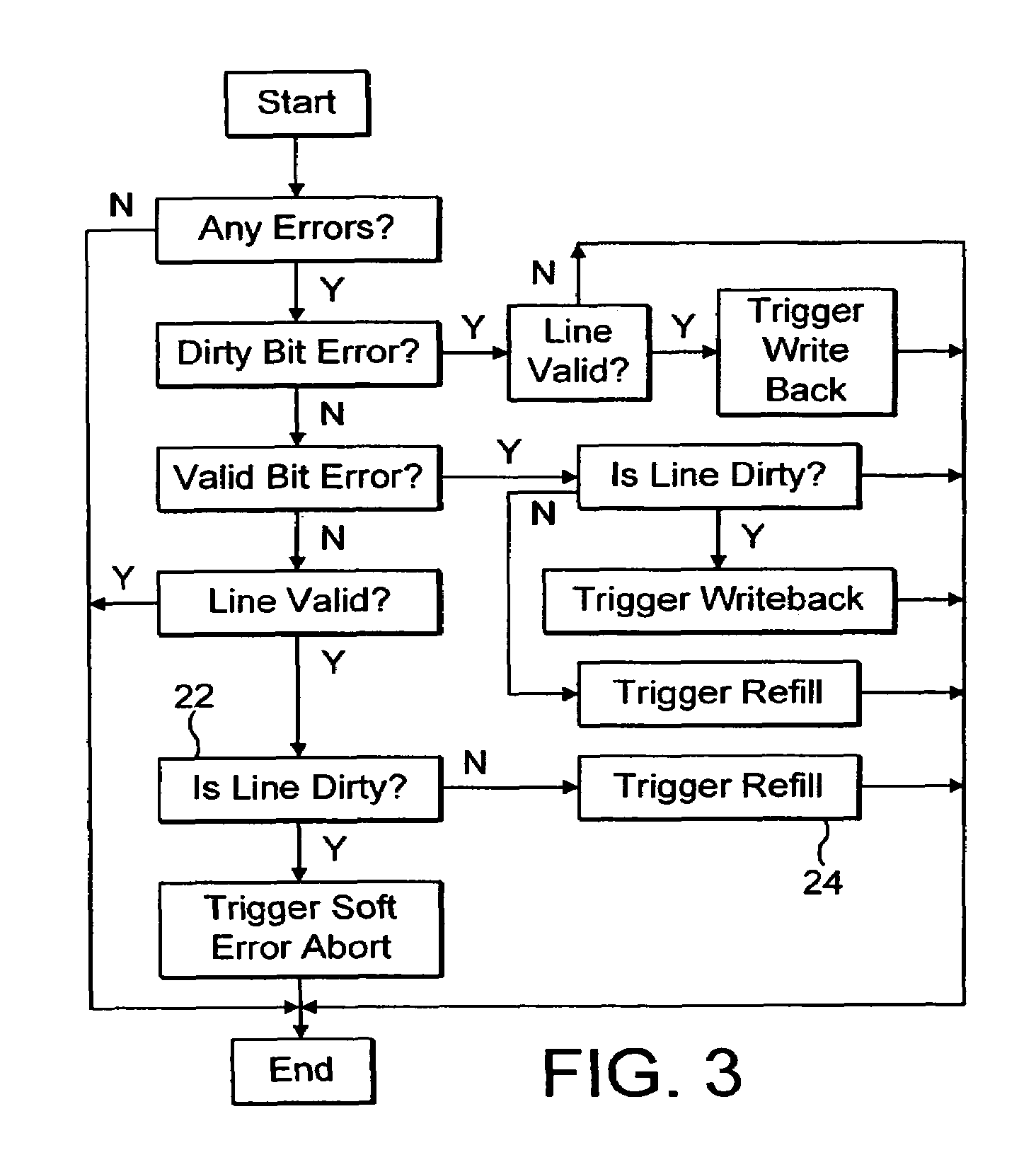

Error correction within a cache memory

ActiveUS20050188249A1Easy refillEfficient repairMemory loss protectionMemory adressing/allocation/relocationComputer hardwareSoft error

A cache memory 2 includes error bits corresponding to each line of data. An error detecting circuit uses these error bits 12, 14, 16, 18 to detect if a soft error has occurred within the data of a cache line. If such an error has occurred, then the line may be refilled from the main memory or some other action taken, such as a write back or generation of a soft error abort signal.

Owner:ARM LTD

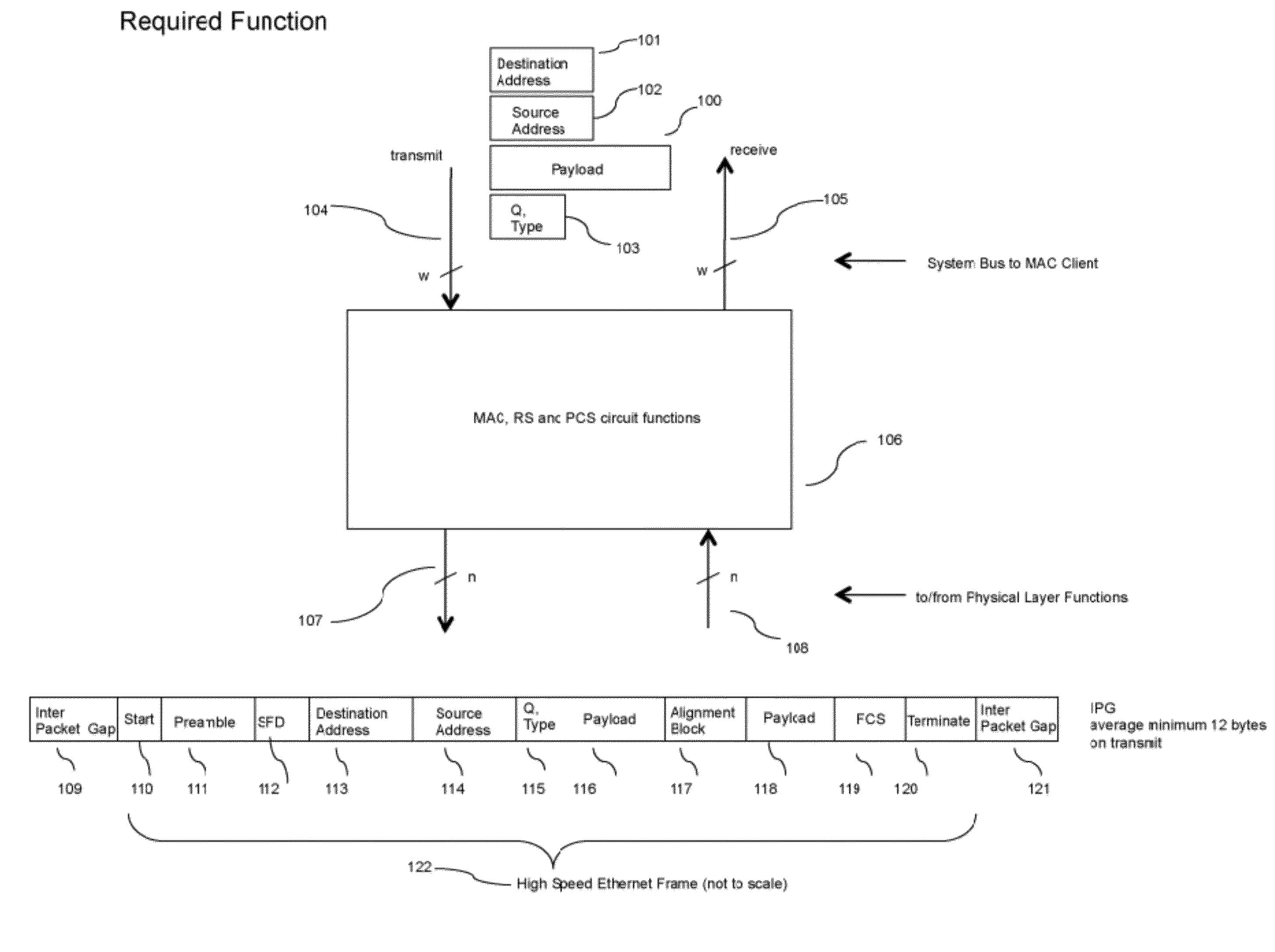

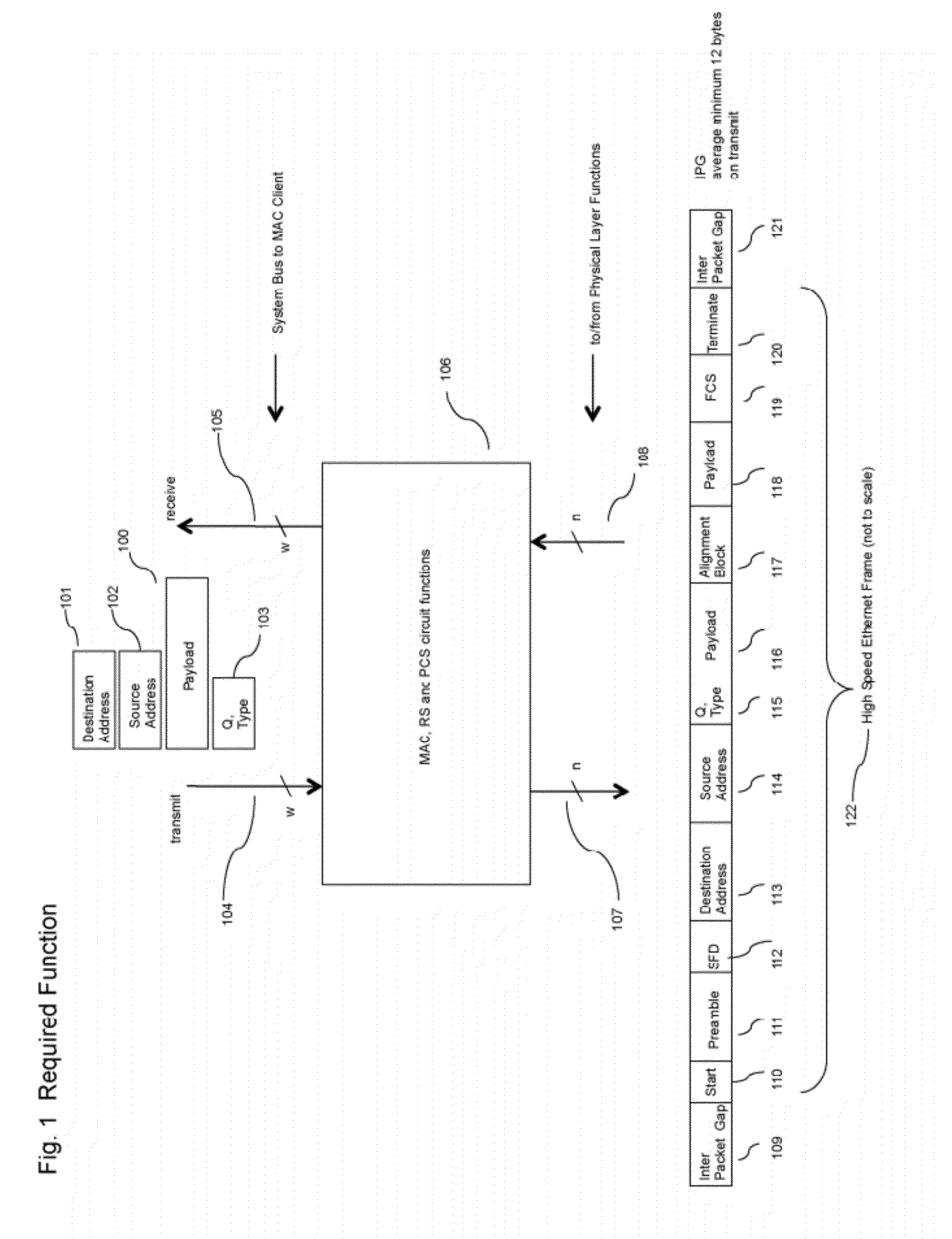

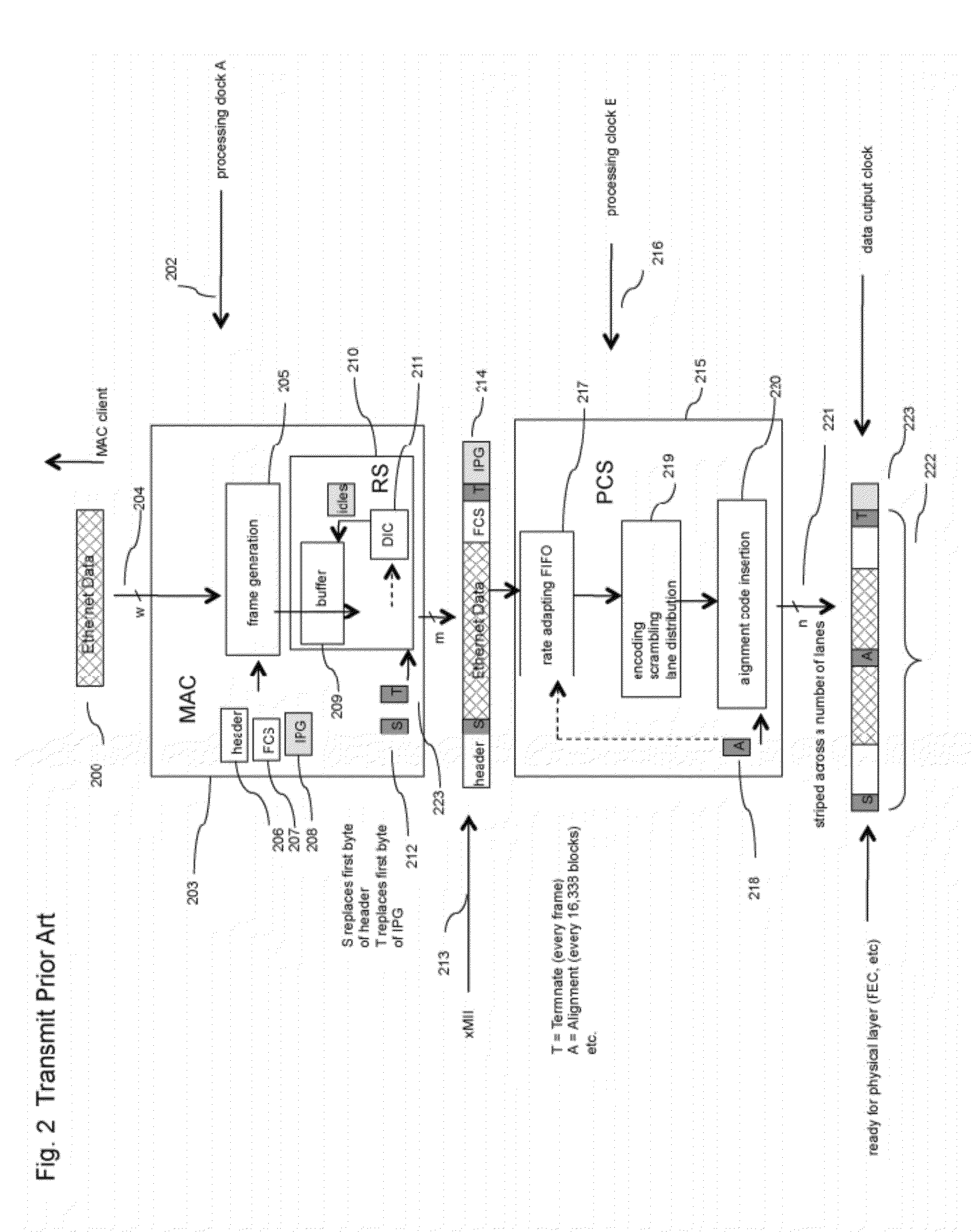

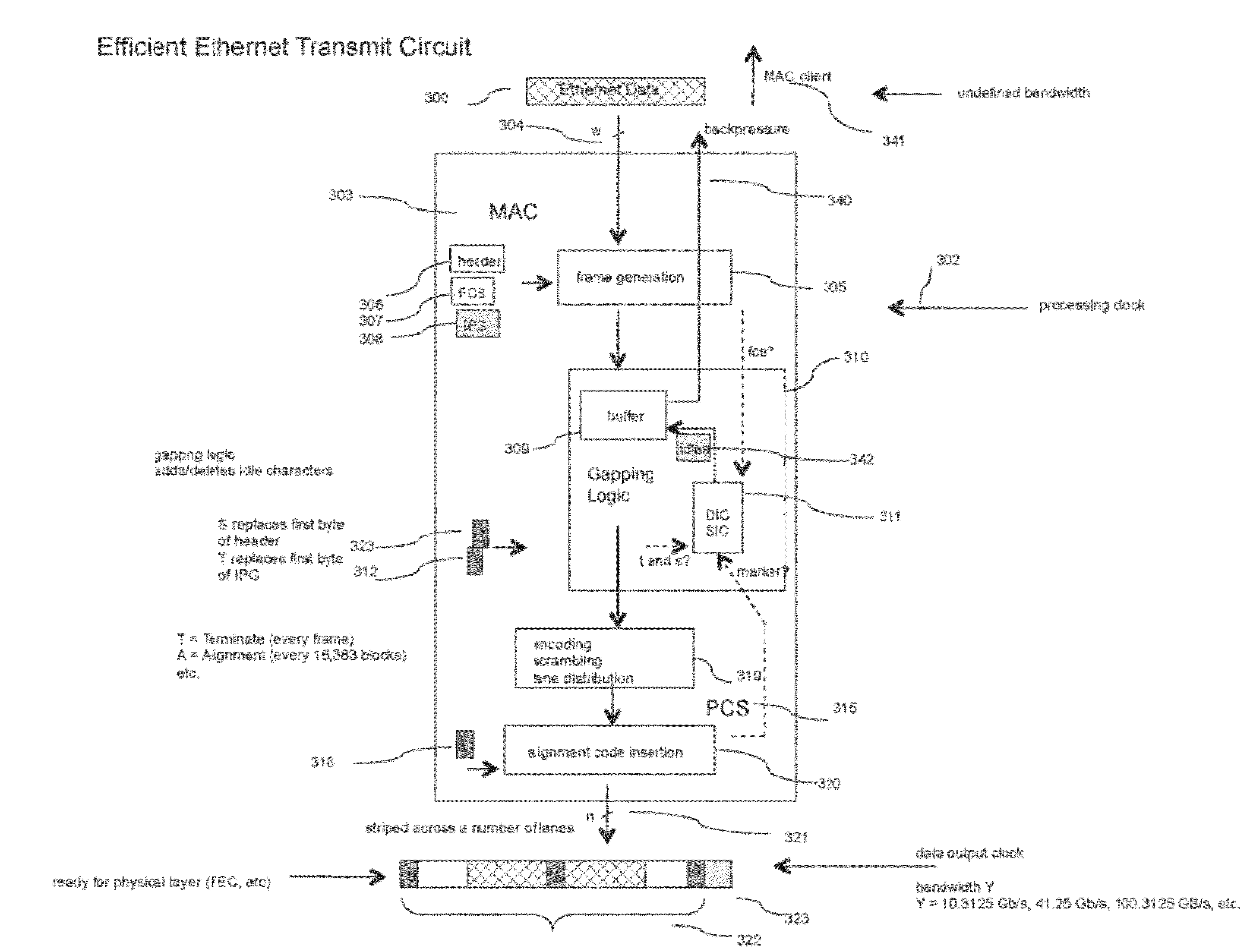

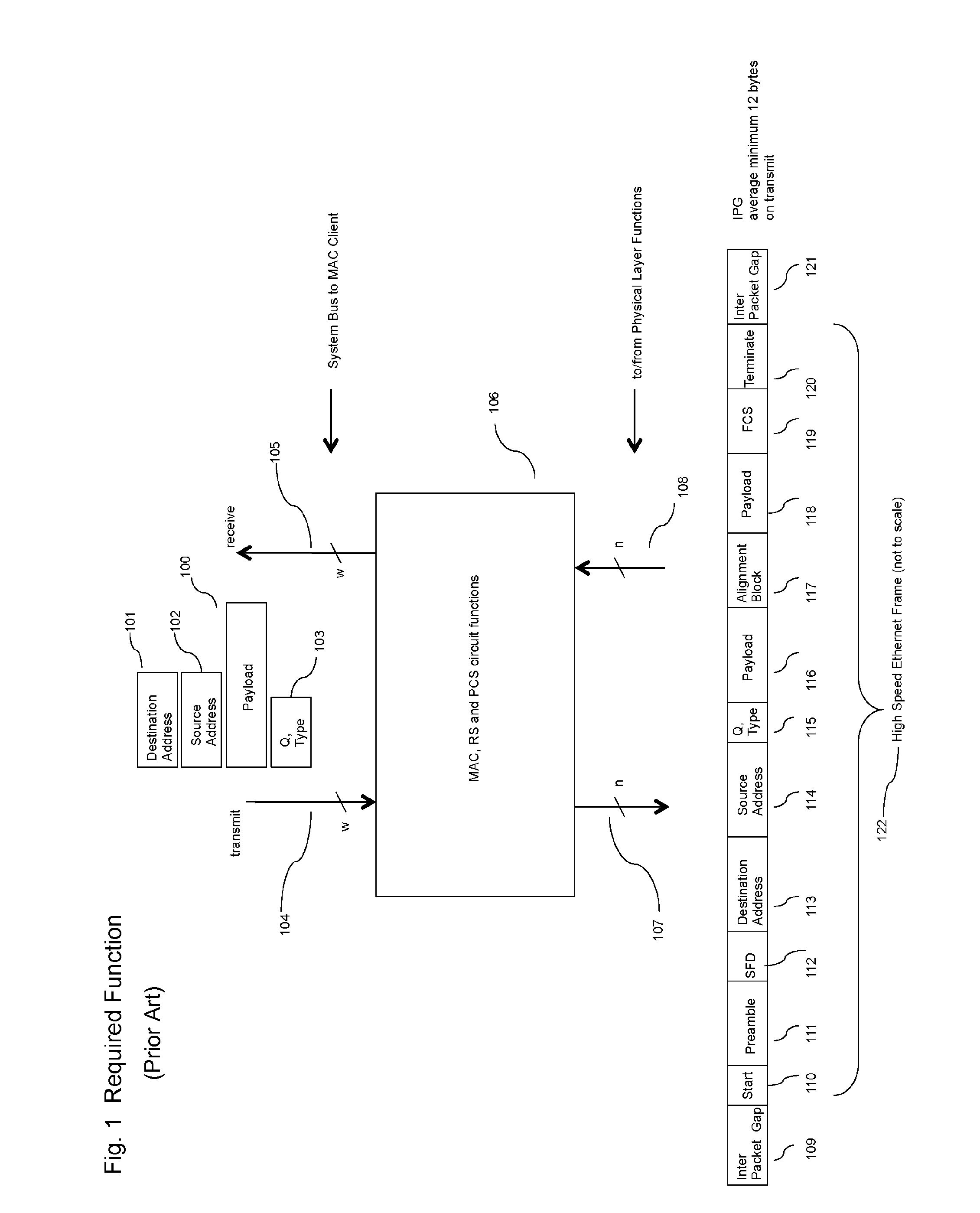

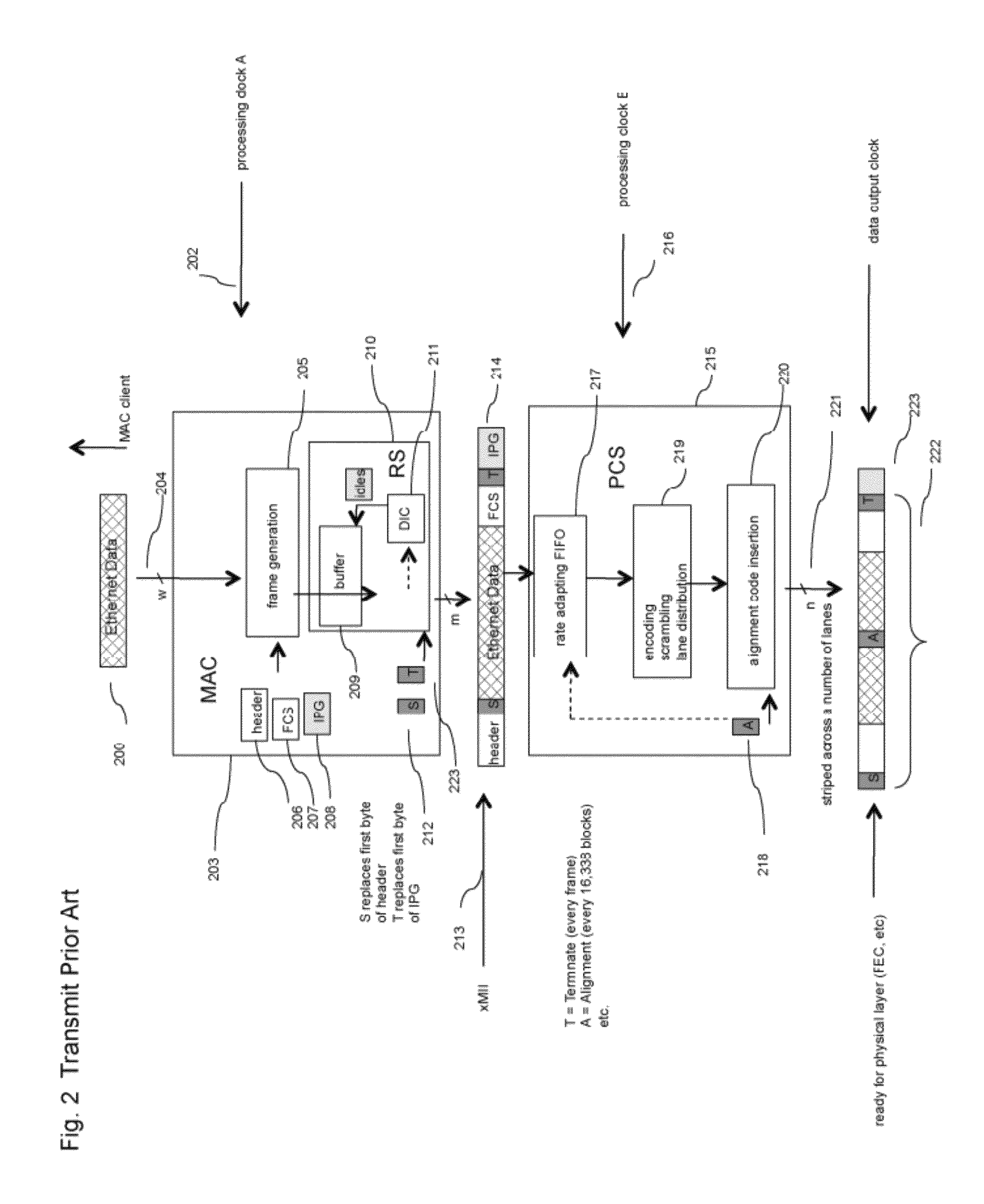

Packet Network Interface Apparatus and Method

ActiveUS20120236878A1Small circuitReduce circuitTime-division multiplexTransmissionTime domainNetwork interface device

A packet network interface apparatus includes a media access control (MAC) module for constructing a packet for transmission over a packet network and a physical coding sublayer (PCS) module for encoding the packet for transmission over a physical interface. An inter packet gap module located between the MAC module and the PCS module directly transfers data to the PCS module while maintaining a certain inter packet gap by deleting or inserting idle characters. The inter packet gap module has at least one memory module for temporary storage of packet data. The modules preferably operate in a common time domain.

Owner:XILINX INC

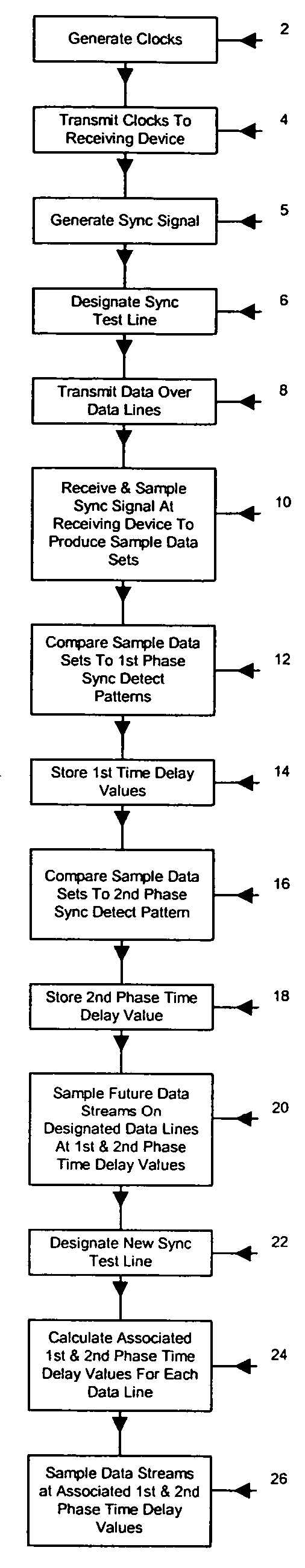

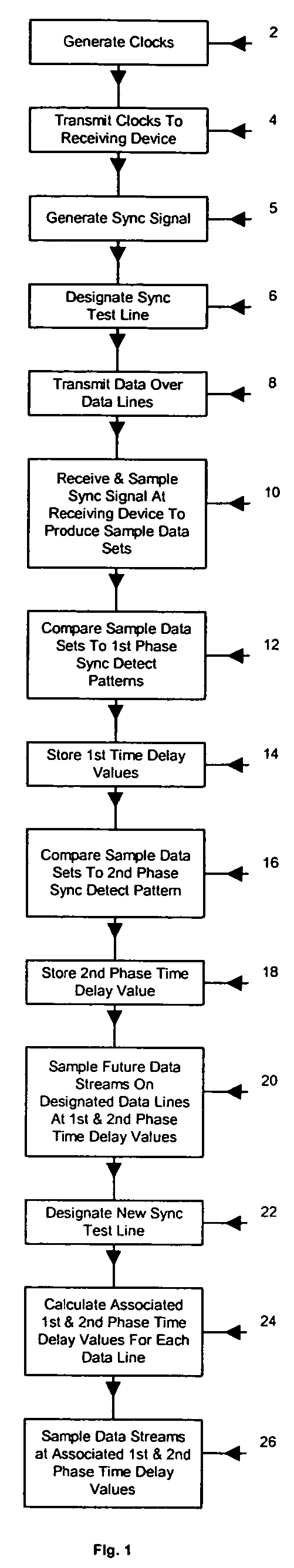

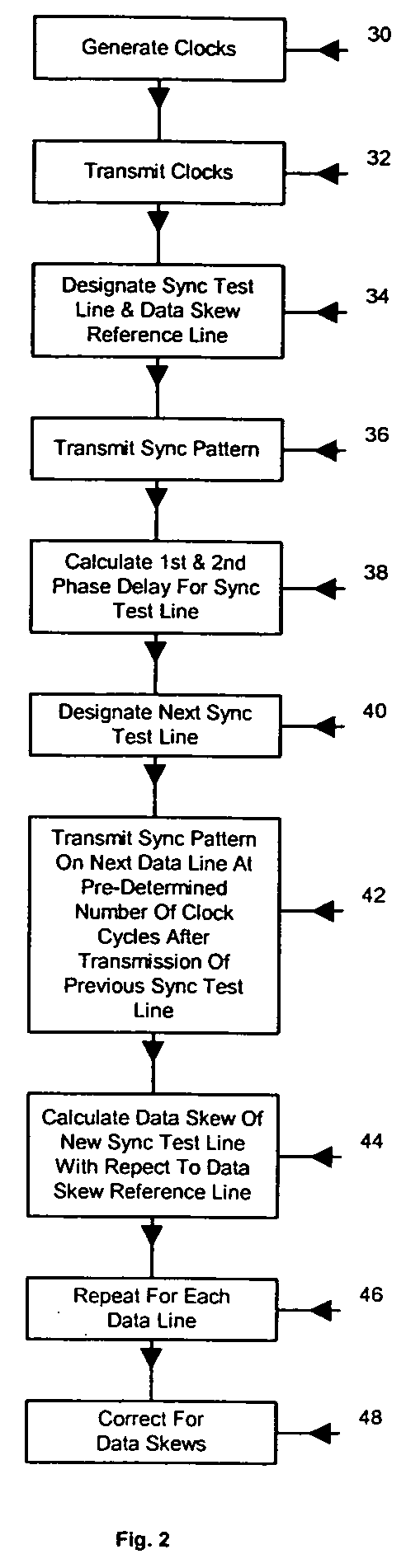

Coherent expandable high speed interface

InactiveUS20050069041A1Implemented cost-effectivelyEffective phase delayChannel dividing arrangementsSynchronisation signal speed/phase controlData streamImproved method

A method and apparatus is provided for passing an N bit wide data stream between two physical devices at high speed while maintaining the coherency of the data streams during the transfer. The N bit wide data stream is transmitted in N parallel data streams on N of N+1 differential data lines. A predetermined serial sync detect pattern is transferred on the remaining differential data line, which is designated as the sync line. A sub interval clock phase is then determined for the sync line that will successfully extract the transmitted sync detect pattern during each half cycle of the clock. This sub interval clock phase compensates for differing delays in the data streams across the physical interface. All of the N+1 differential data lines are in turn designated as the sync line to determine a sub interval clock phase for each of the respective differential data lines. Data is then extracted from the N data streams by sampling at the sub interval clock phase determined for each particular data line. The number of clock cycles that pass between reception of the sync detect pattern on the sync line and reception of the sync detect pattern on the next data line designated as the sync line is counted. The counted number of clock cycles is then compared to a predetermined number of clock cycles that pass between transmission of the sync detect pattern on the respective lines to determine if any data skew of multiple clock cycles is present between the respective lines. Any detected data skew is corrected. Thus, the present invention provides an improved method and apparatus for transmitting continuous parallel data streams while the bits in the data streams maintain their relative positions when received.

Owner:LINCOLN DANIEL J

Error correction within a cache memory

ActiveUS7328391B2Easy refillEfficient repairMemory loss protectionMemory adressing/allocation/relocationComputer hardwareForward error correction

A cache memory includes error bits corresponding to each line of data. An error detecting circuit uses these error bits to detect if a soft error has occurred within the data of a cache line. If such an error has occurred, then the line may be refilled from the main memory or some other action taken, such as a write back or generation of a soft error abort signal.

Owner:ARM LTD

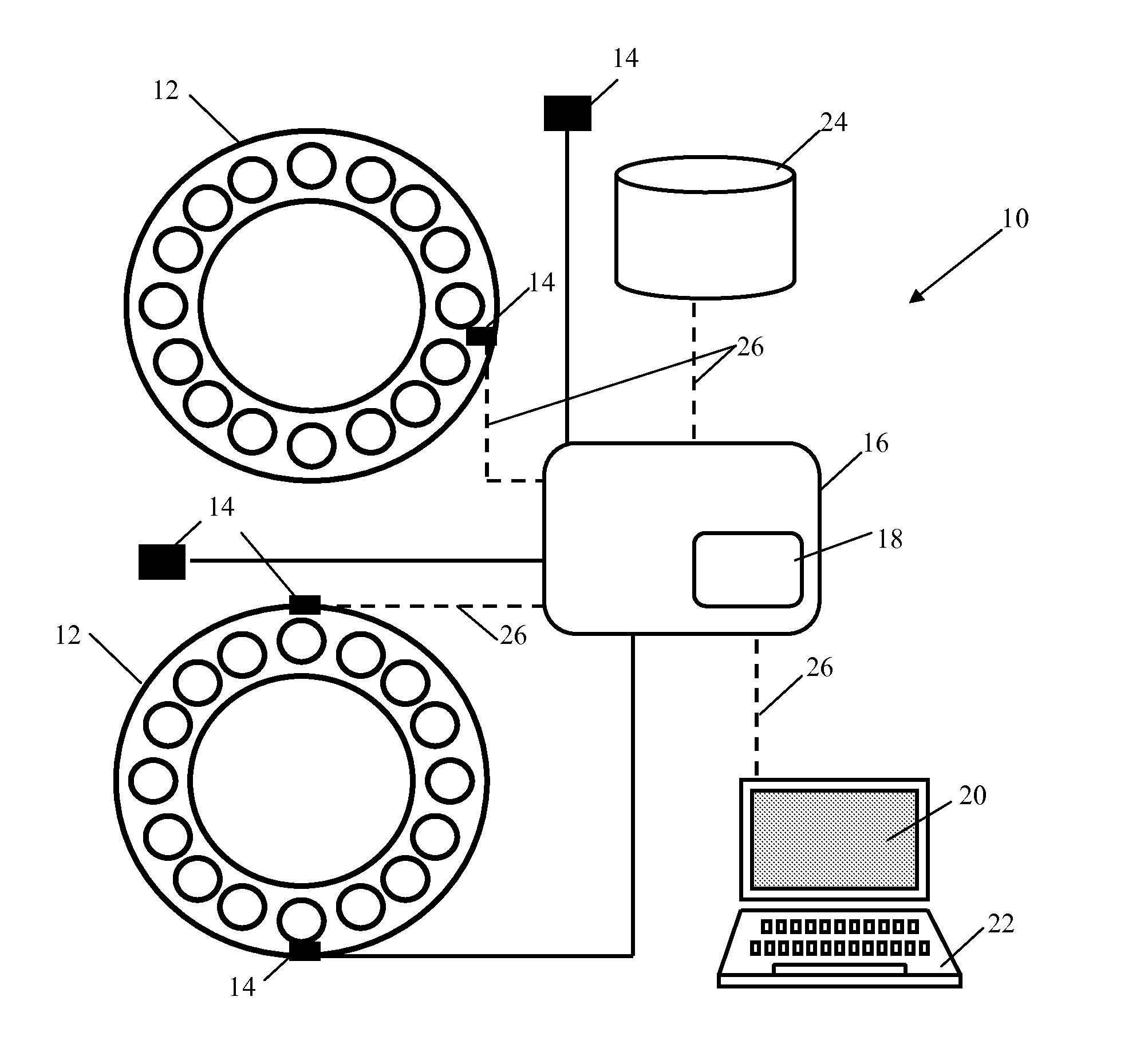

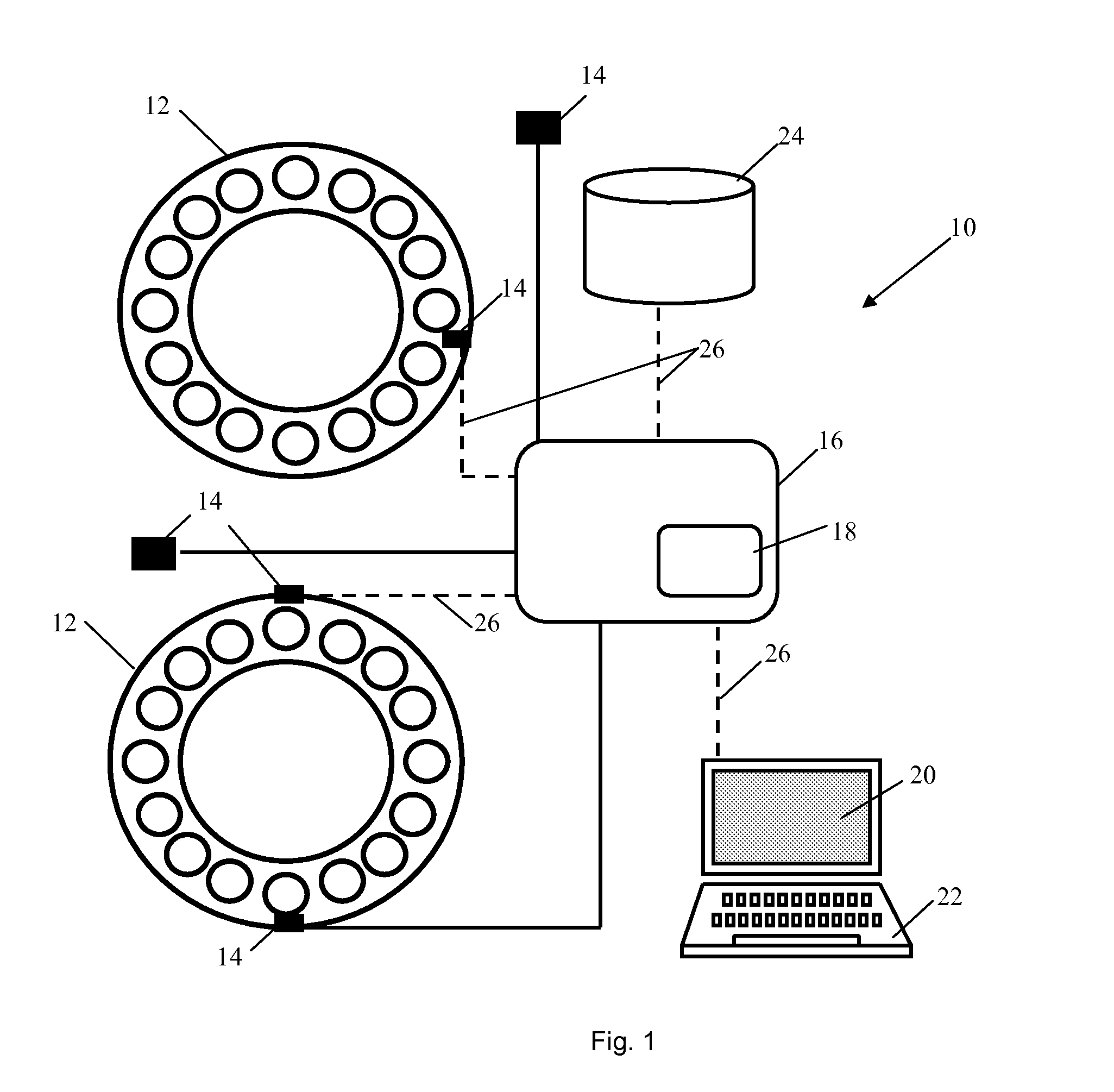

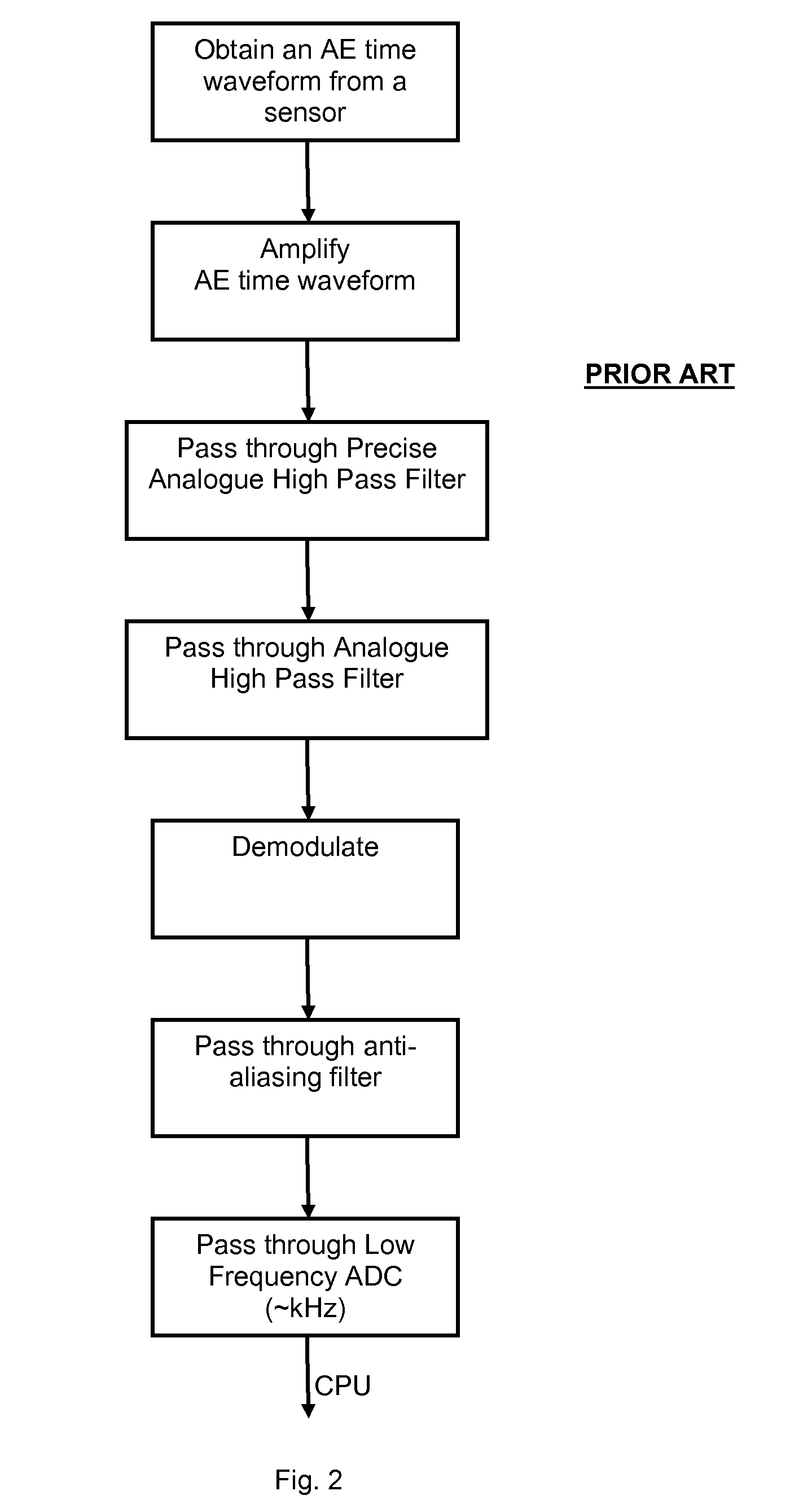

Method, computer program product & system

InactiveUS20160047717A1Improve circuit performanceLower average currentVibration measurement in solidsMaterial analysis using acoustic emission techniquesCondition monitoringAcoustic emission

A method for processing data obtained from a condition monitoring system, the method including steps of (a) obtaining an Acoustic Emission time waveform from at least one sensor and (b) digitally demodulating the Acoustic Emission time waveform.

Owner:AB SKF

Power supply device capable of equalizing electrical properties of batteries

ActiveUS8330418B2Maintain balanceReduce the amount requiredCharge equalisation circuitSecondary cellsControl switchConductor Coil

A transformer 21 includes charging secondary winding lines 24 that can charge batteries 11 composing a corresponding cell block, and a discharging secondary winding line 26 that can discharge the corresponding cell block. Each of the charging secondary winding lines 24 is connected to corresponding one of the batteries 11 through corresponding one of secondary-side rectification output circuits 25 and corresponding one of output control switches 22. The discharging secondary winding line 26 is connected to a block discharging circuit through a block discharging switch 28. A switching control circuit 23 controls the block discharging switch 28. The switching control circuit 23 controls the output control switches 22 so that the electrical properties of the batteries 11 in the cell block are equalized. In addition, the switching control circuits 23 control the block discharging switches 28 so that the electrical properties of the batteries among the cell blocks are equalized.

Owner:SANYO ELECTRIC CO LTD

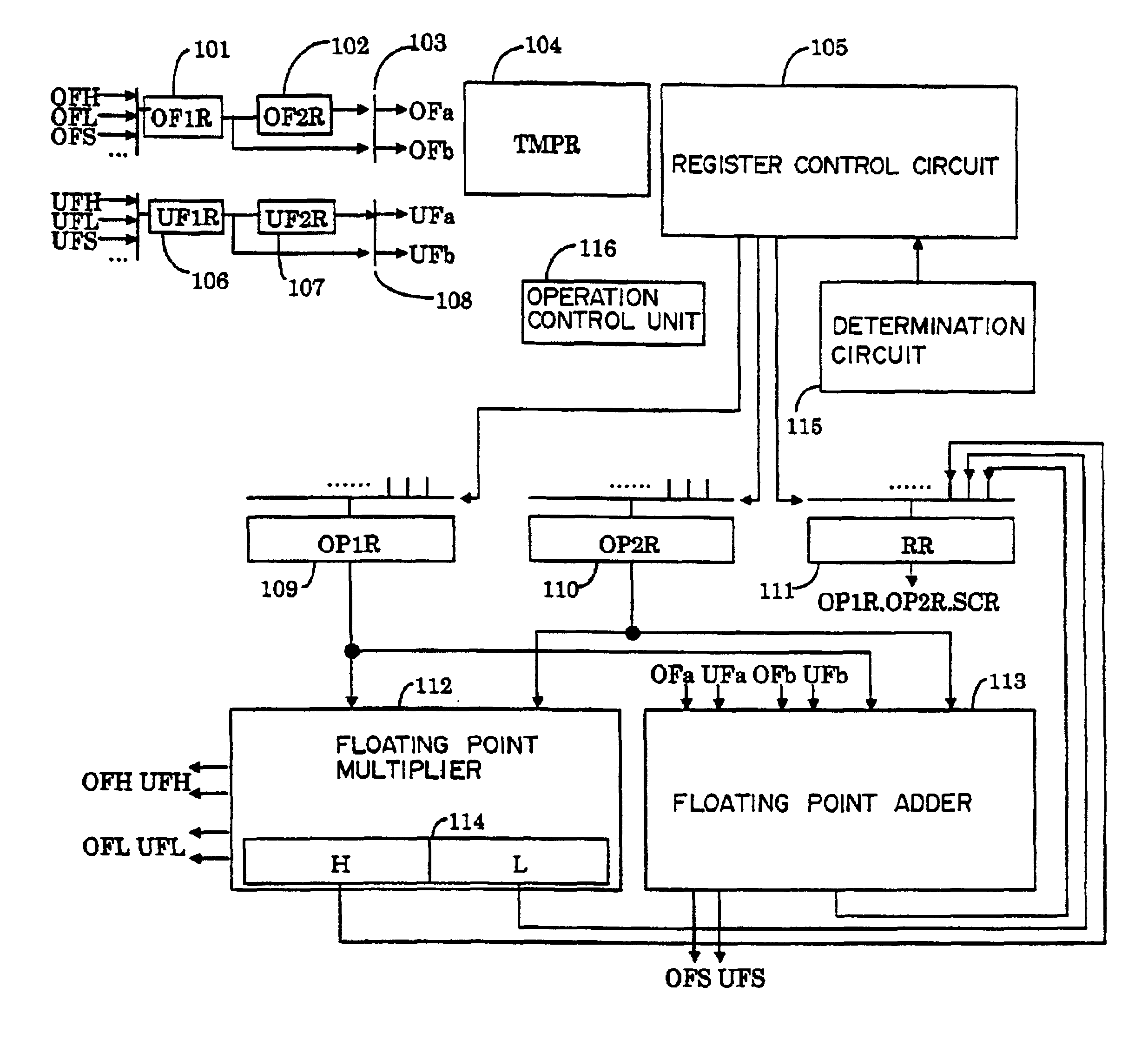

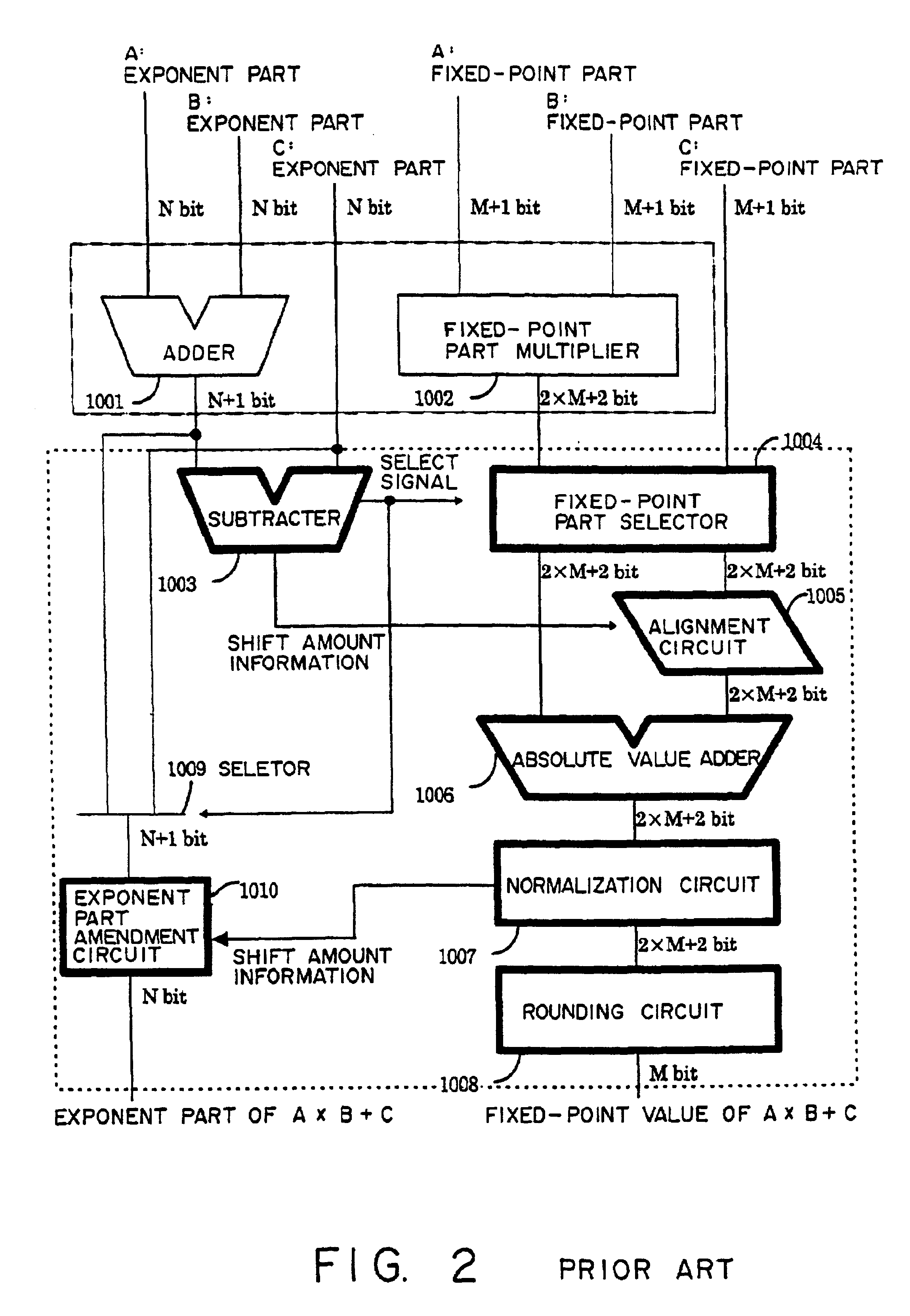

Apparatus and method of performing product-sum operation

InactiveUS6895423B2Reduce circuit sizeSmall circuitComputation using non-contact making devicesComplex mathematical operationsTheoretical computer scienceFloating point multiplier

To perform a product-sum operation by adding third data to a product of first data and second data, a floating point multiplier first multiplies the first data by the second data, and a bit string representing a fixed-point part in the multiplication result is divided into a portion representing more significant digits in the fixed-point part and a portion representing less significant digits in the fixed-point part. Then, a floating point adder first adds less significant multiplication result data having a bit string representing the less significant digits as a fixed-point part to the third data, and then adds the addition result to more significant multiplication result data having a bit string representing the more significant digits as a fixed-point part. A rounding process is performed on the two addition results to obtain a result of the product-sum operation.

Owner:FUJITSU LTD

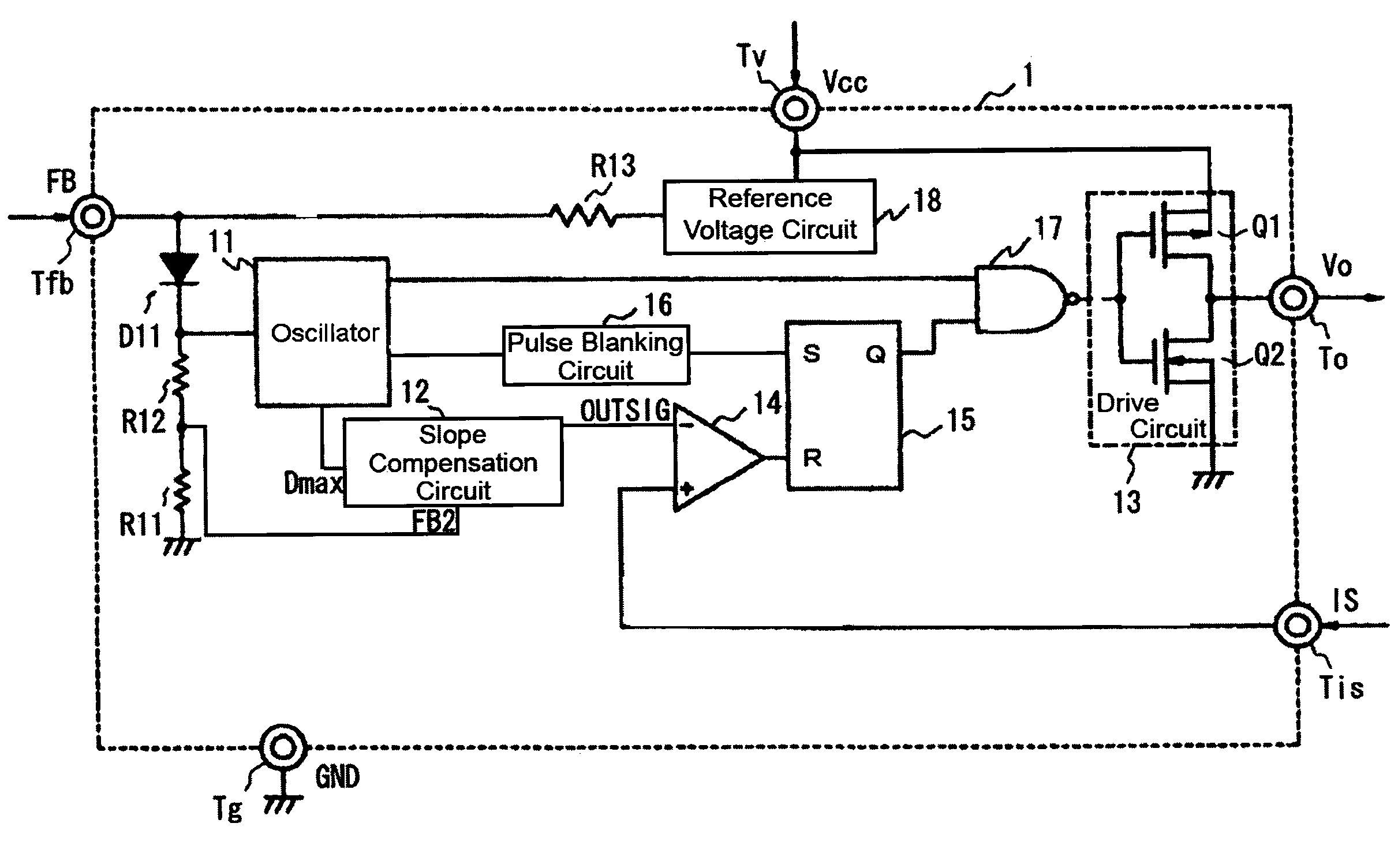

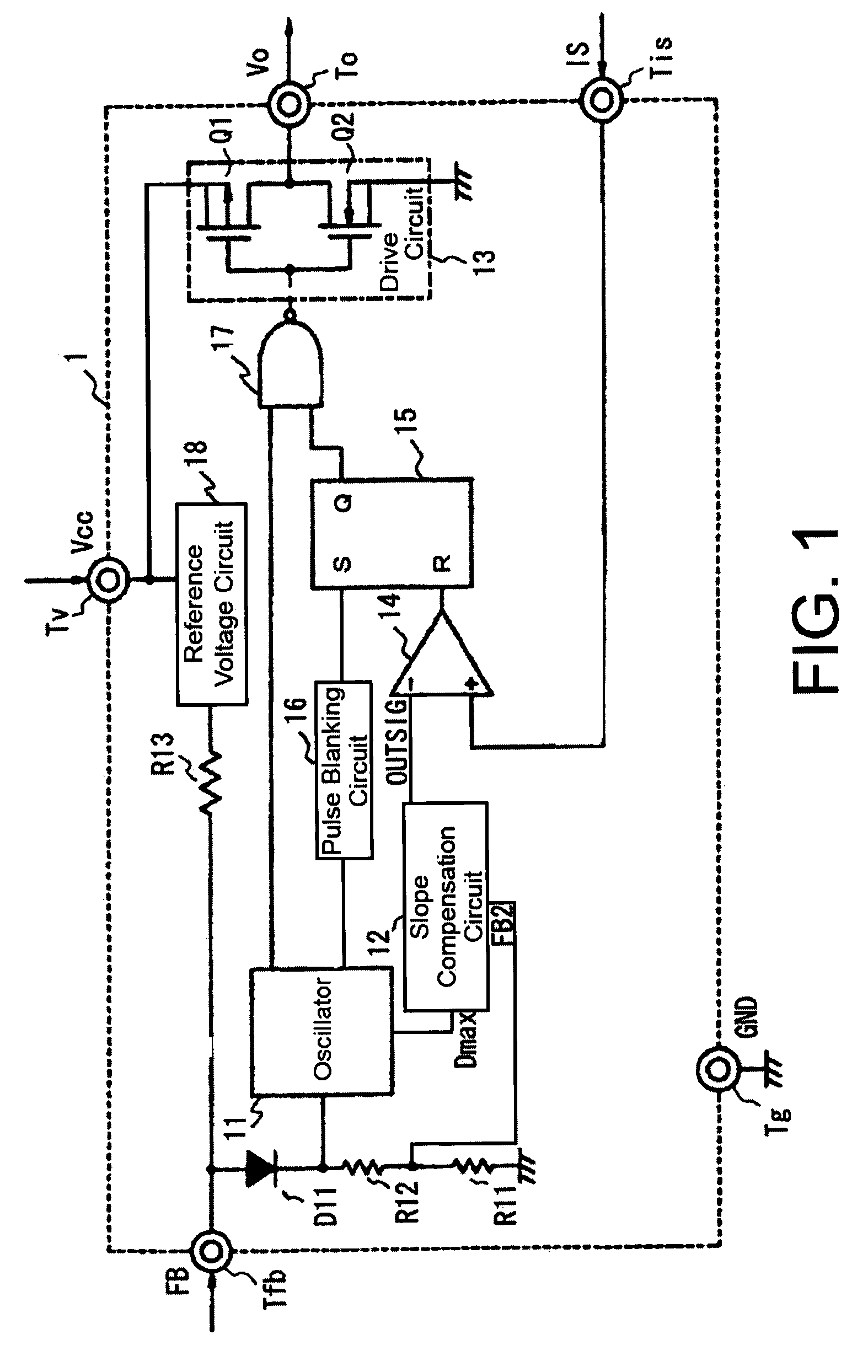

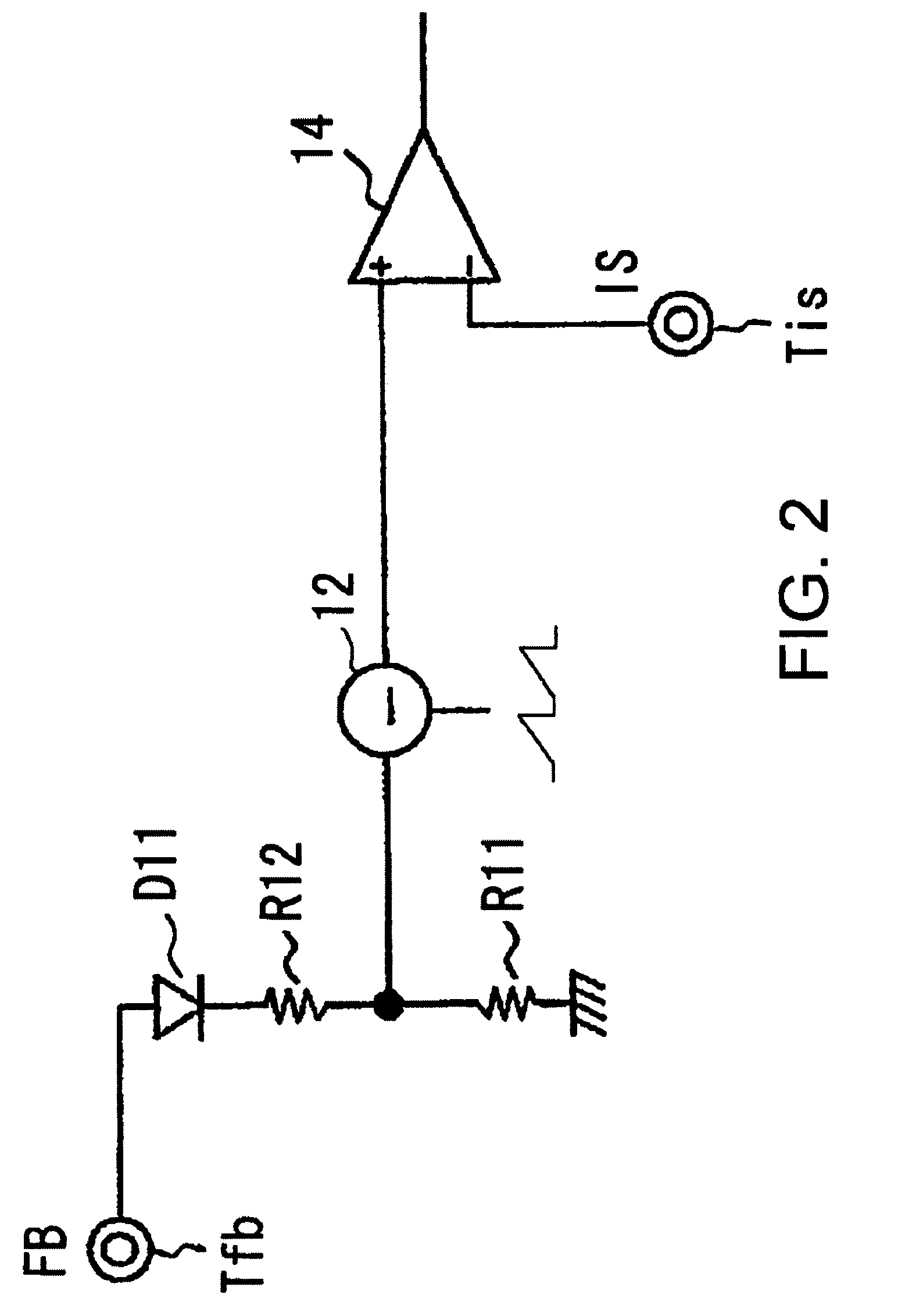

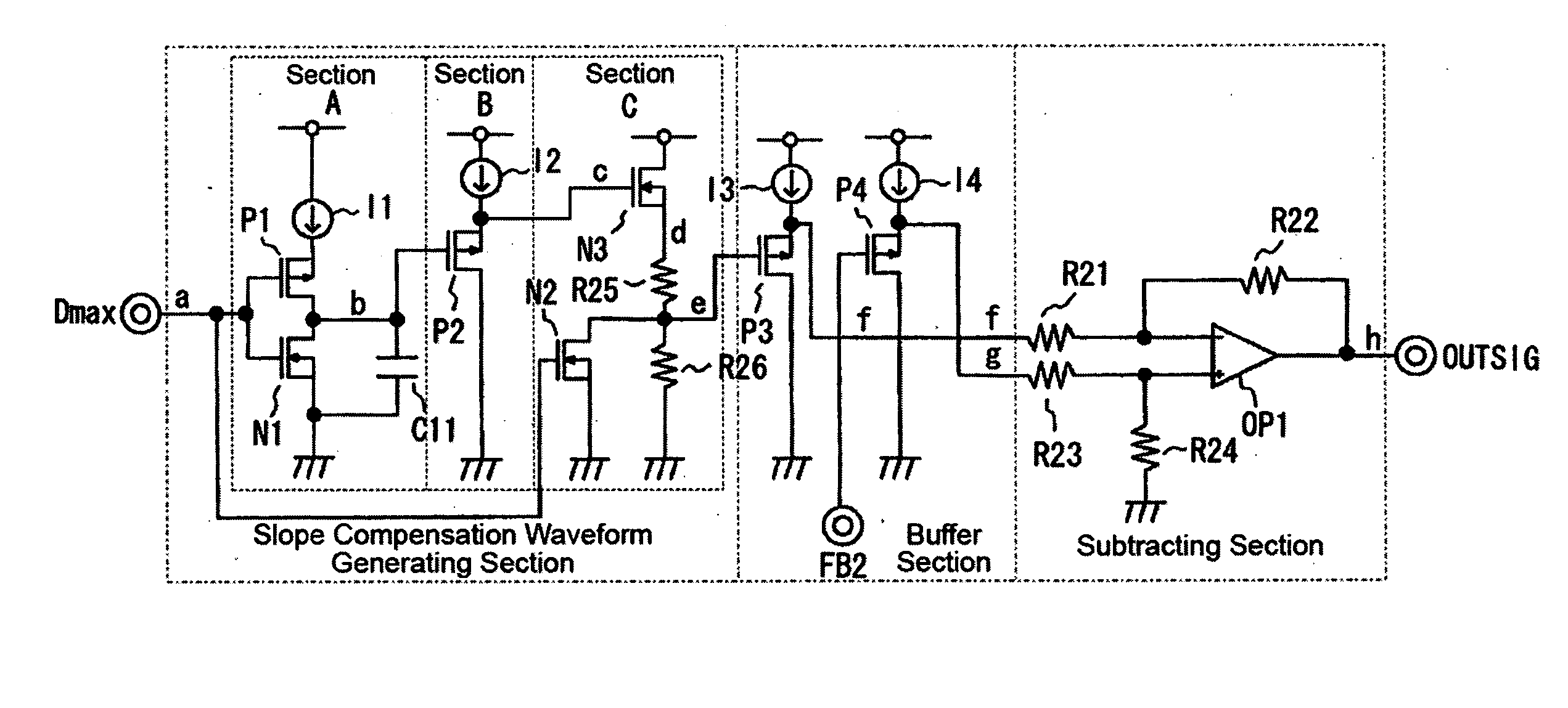

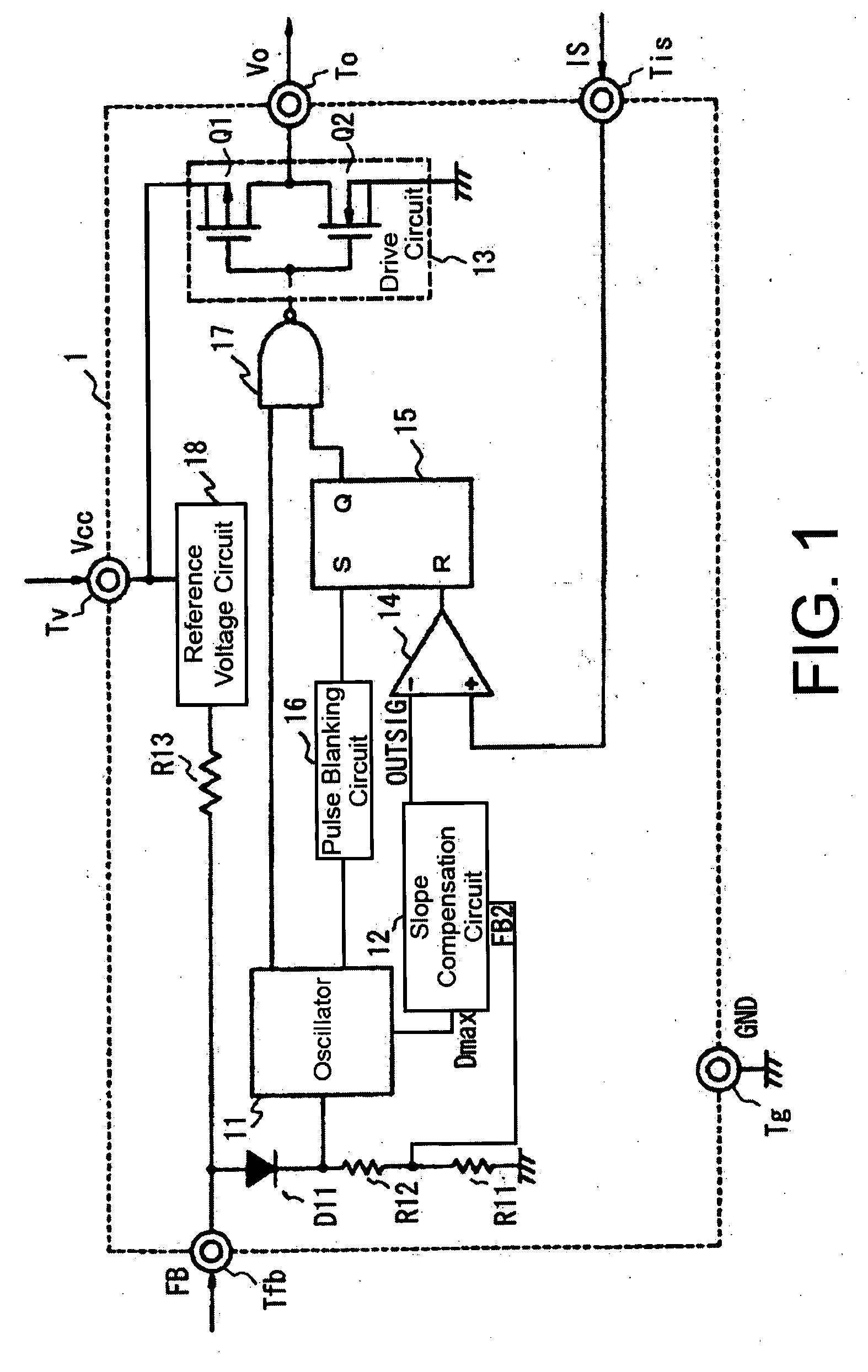

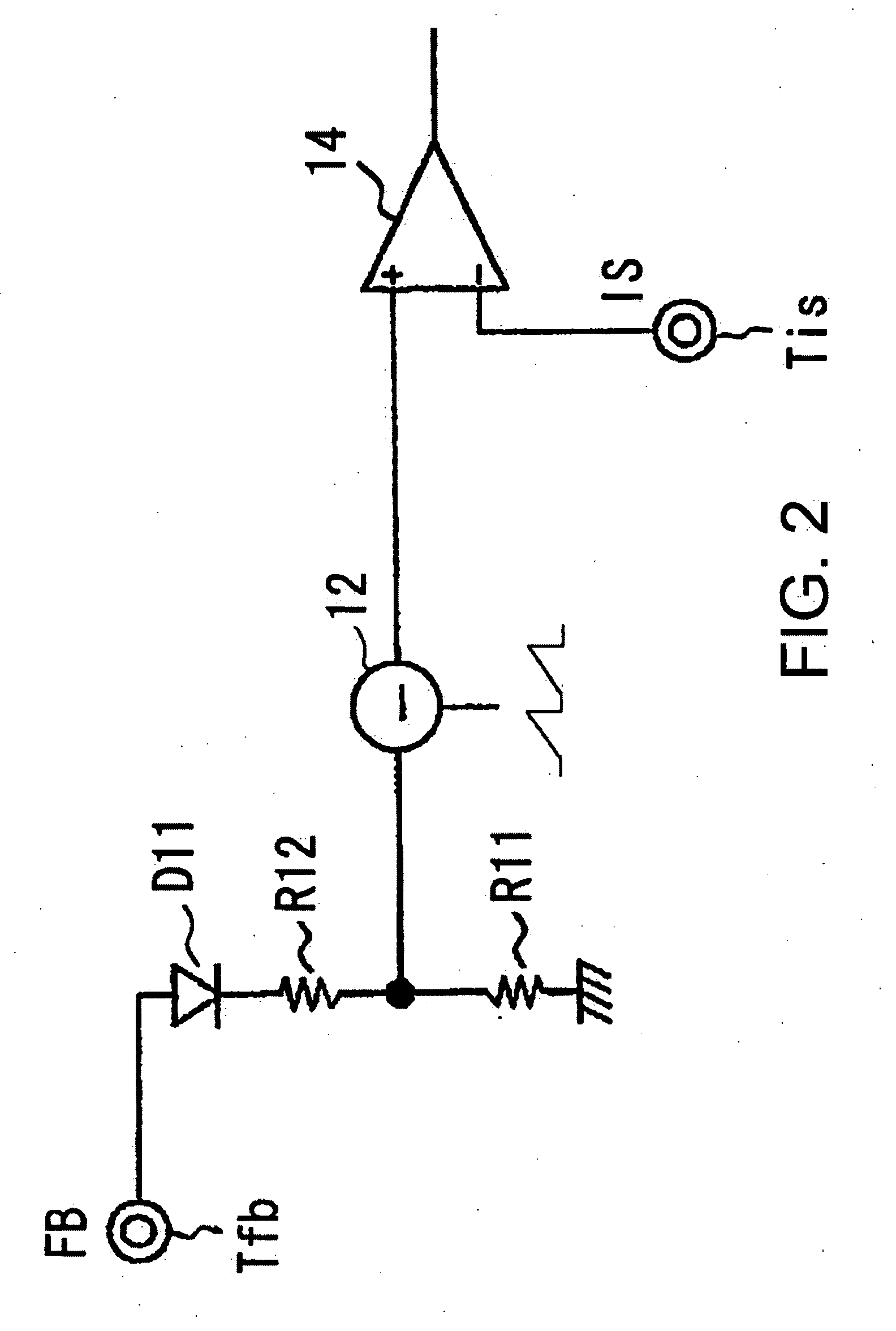

Switching power supply

InactiveUS7515441B2Easy to controlSimple circuit configurationConversion with intermediate conversion to dcDc-dc conversionOutput transformerEngineering

Owner:FUJI ELECTRIC CO LTD

Switching power supply

InactiveUS20080007975A1Easy to controlSimple circuit configurationConversion with intermediate conversion to dcDc-dc conversionOutput transformerEngineering

A switching power supply, in which a switching element turns on and off electric current flowing on the primary side of an output transformer so as to rectify and output a pulsating flow generated on the secondary side of the output transformer, includes a voltage detecting section that detects an output voltage, a current detecting section that detects electric current flowing through a power transistor as the switching element, a controller that compares a voltage detection signal from the voltage detecting section and a current detection signal from the current detecting section to control the duty of the power transistor during an ON time, and a slope compensation circuit that compensates the rate of change of the voltage detection signal using a slope compensation signal. The slope compensation circuit subtracts the slope compensation signal from the voltage detection signal and outputs the resulting signal to a PWM comparator.

Owner:FUJI ELECTRIC CO LTD

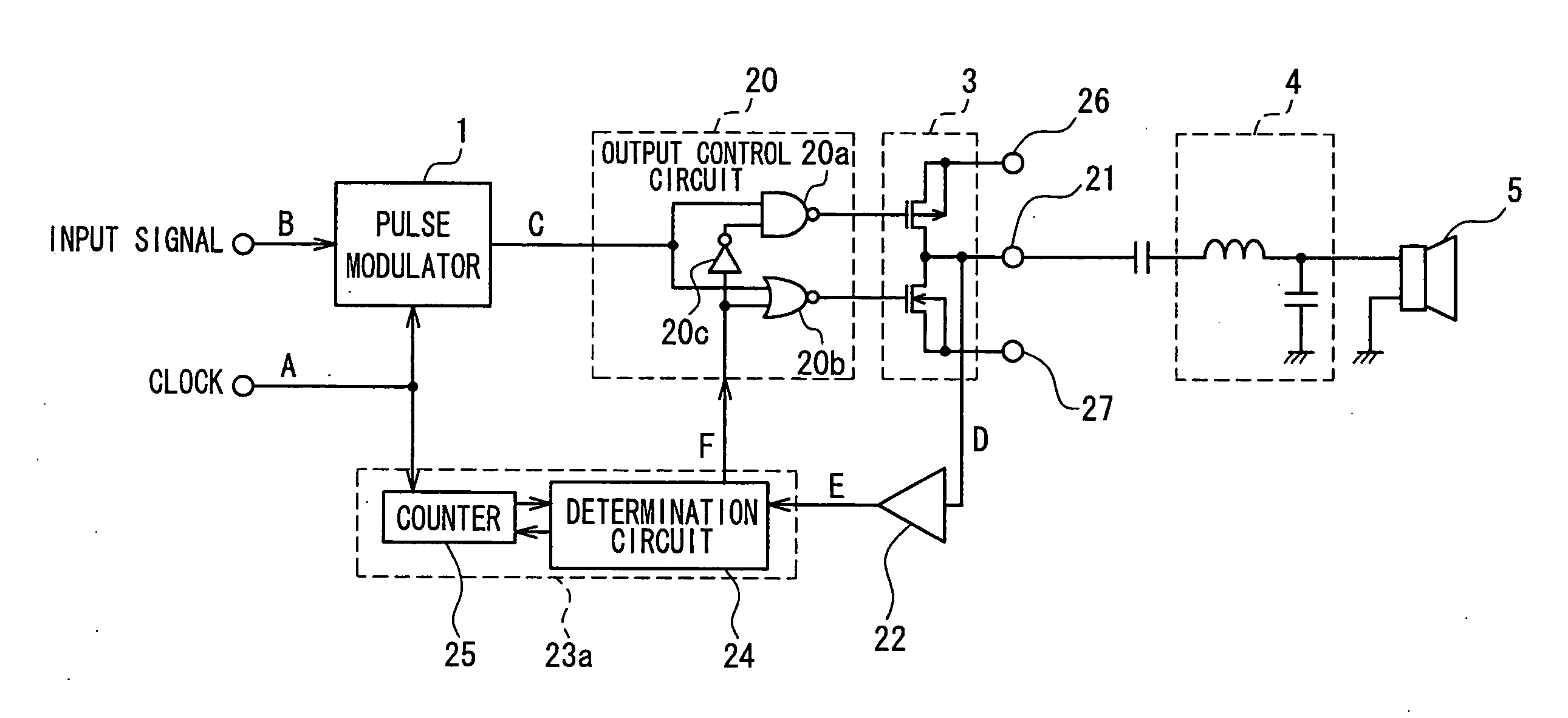

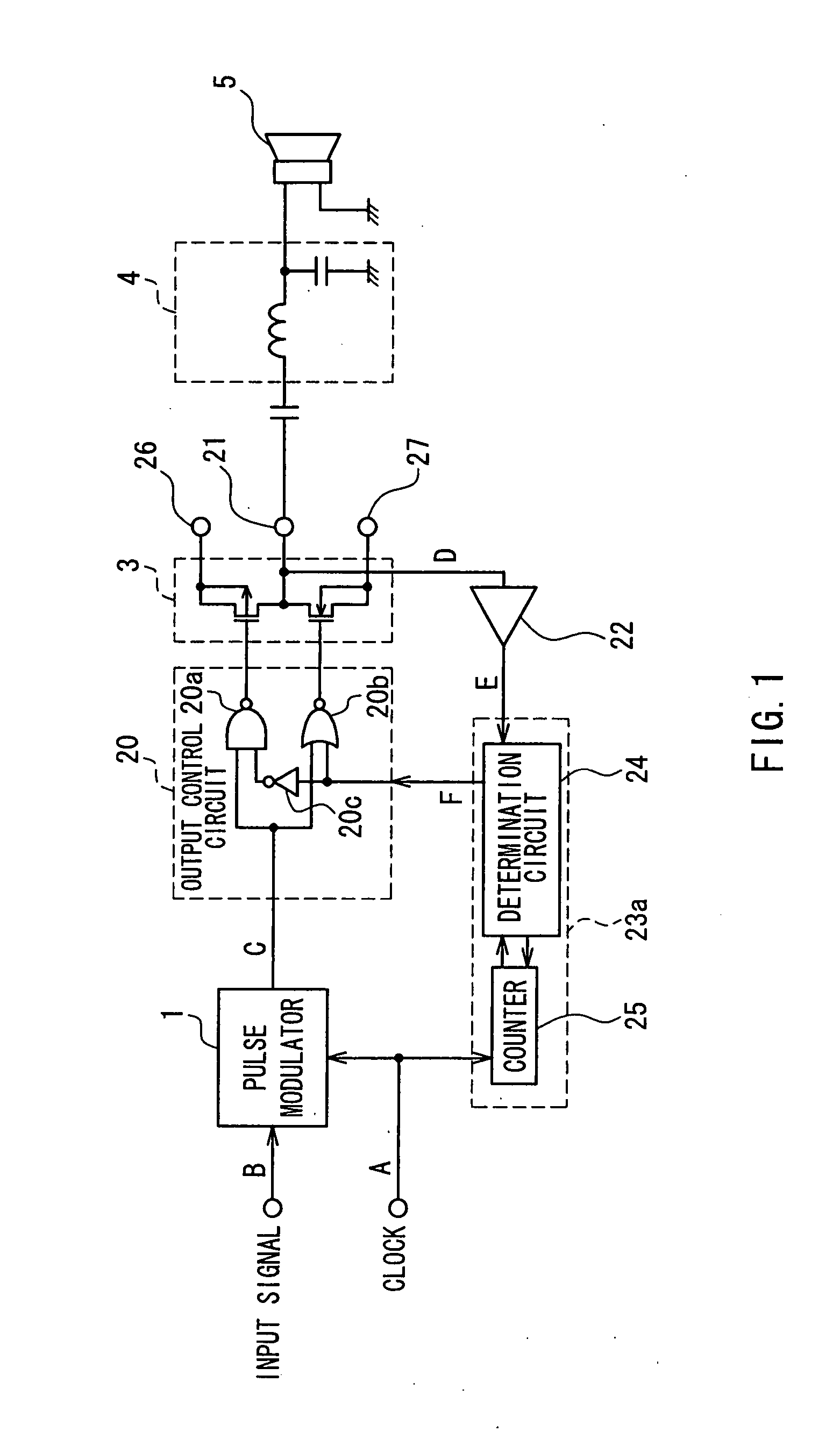

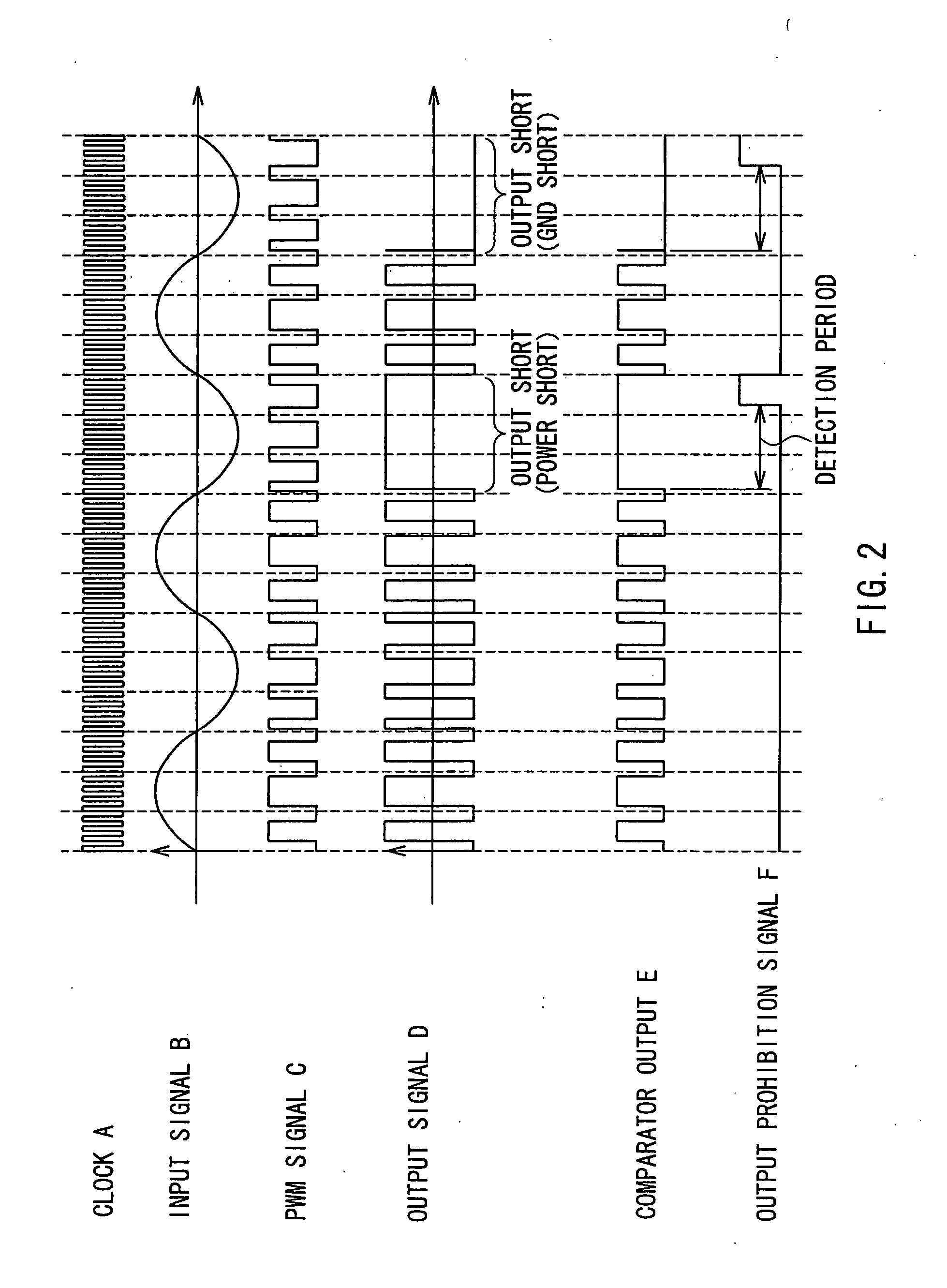

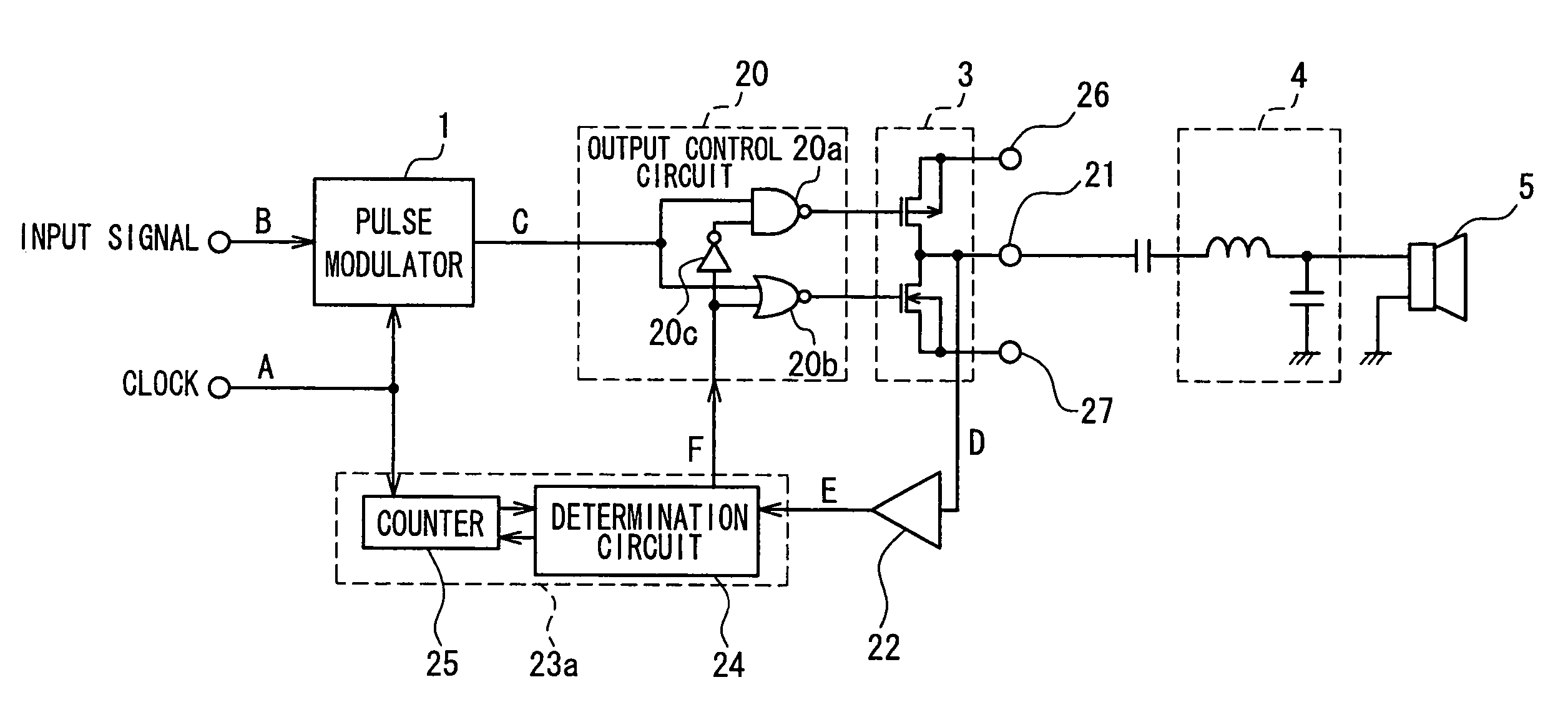

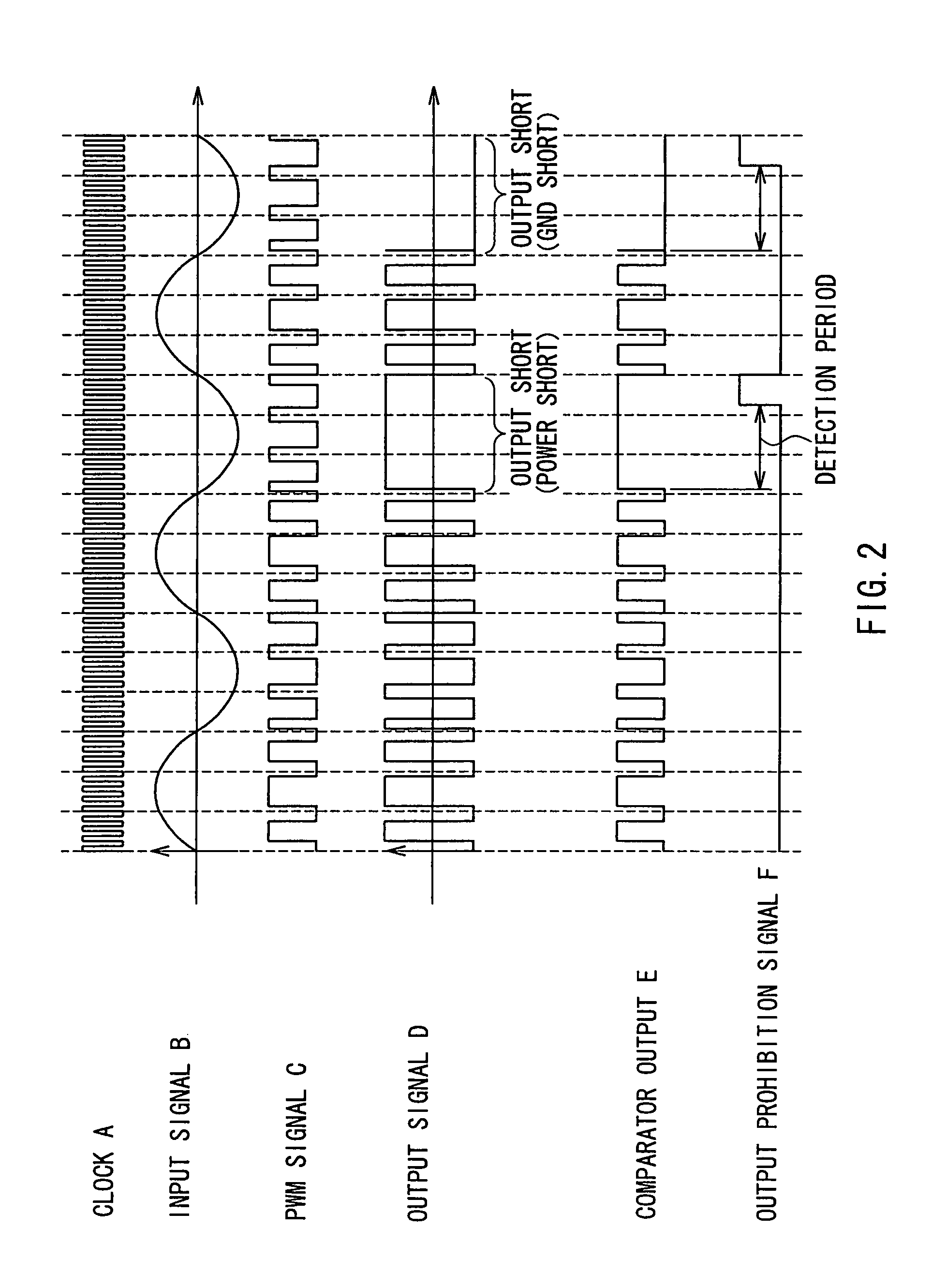

Pulse modulation type electric power amplifier

InactiveUS20070236286A1Reduce areaReduce power consumptionEmergency protective circuit arrangementsAmplifier protection circuit arrangementsAudio power amplifierTerminal voltage

A pulse modulation type electric power amplifier includes a pulse modulator that receives as input a clock and an input signal, and converts the input signal to a pulse train, an output control circuit that receives as input the pulse train output by the pulse modulator, and controls output of the pulse train, an output circuit that performs switching according to the pulse train output by the output control circuit, a comparator that converts an output terminal voltage of the output circuit to a high or a low digital value, and a short-circuit determination circuit that determines whether an output short circuit has occurred based on a state of an output signal of the comparator, and outputs an output prohibition signal to the output control circuit when an output short circuit is detected. The output control circuit controls output of the pulse train when the output prohibition signal is input, so that the output circuit stops the switching operation. An output short-circuit protection circuit can thereby be configured simply with little circuitry, and is thus small, low power, and integrated easily.

Owner:PANASONIC CORP

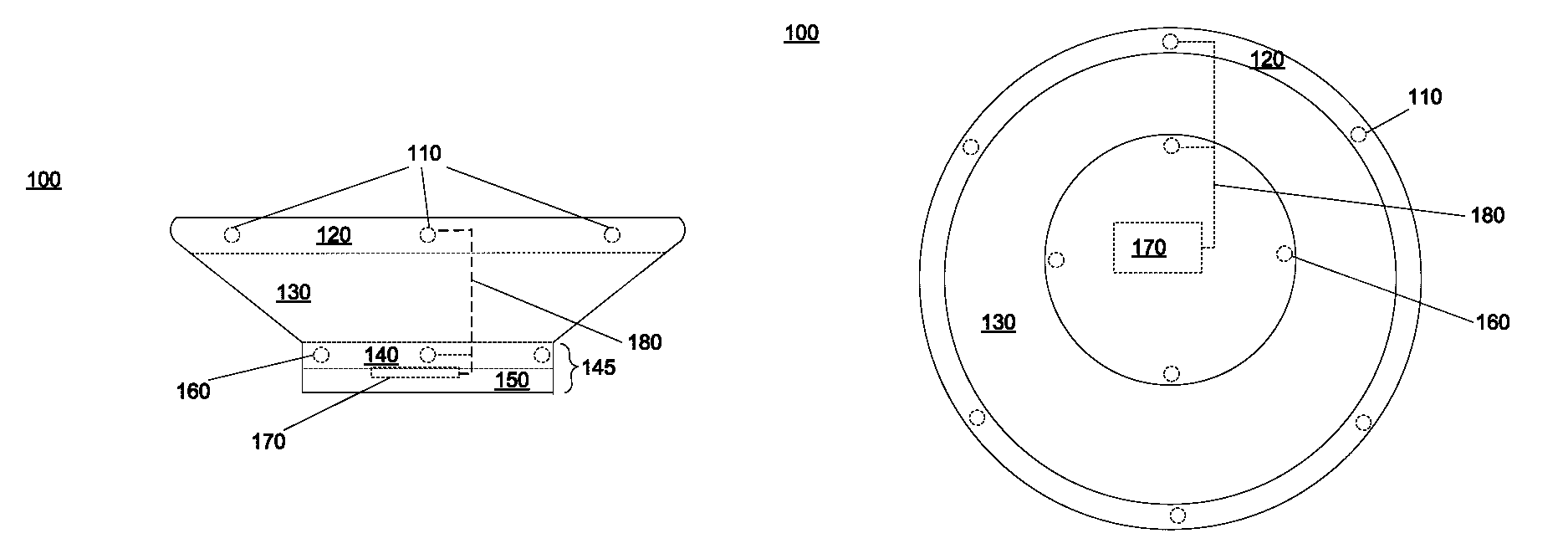

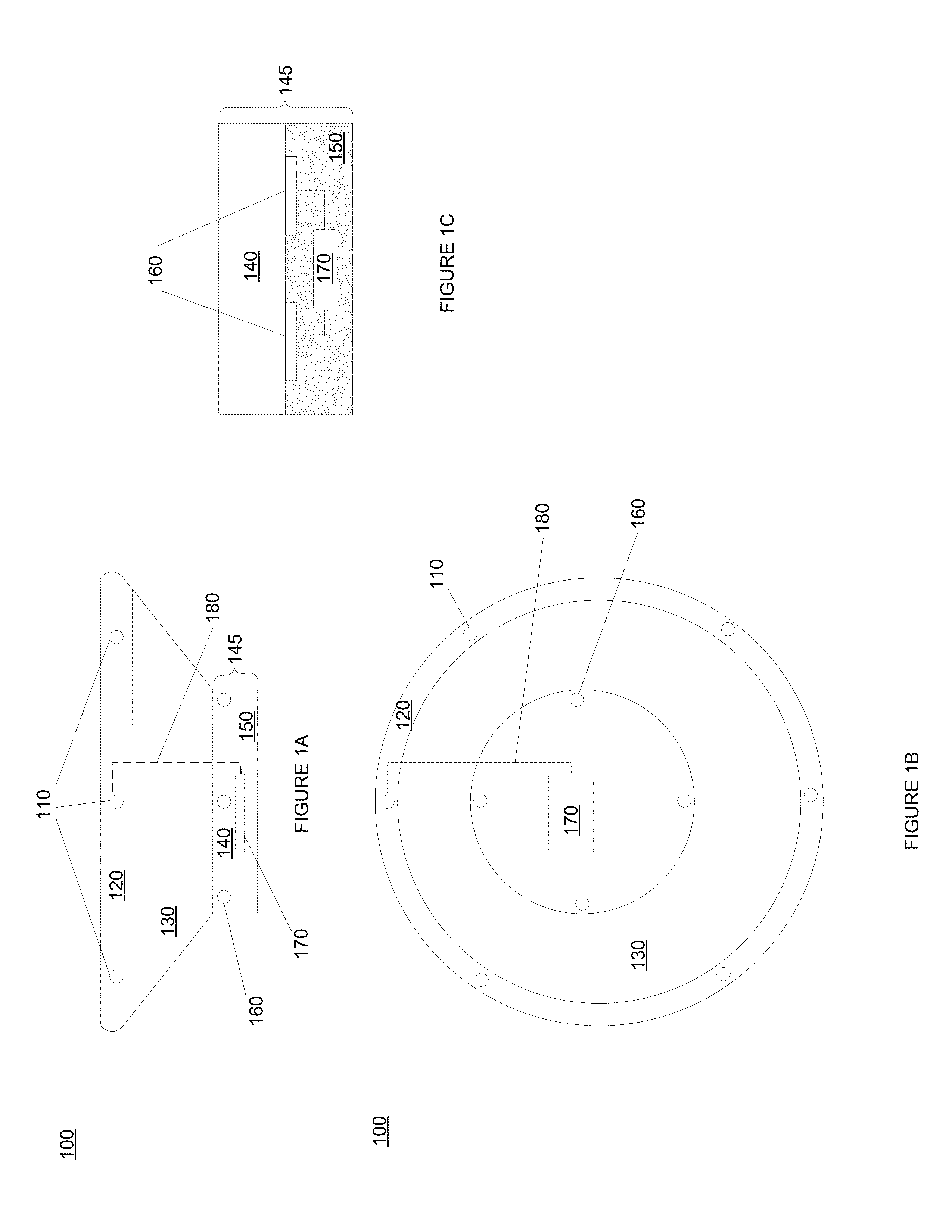

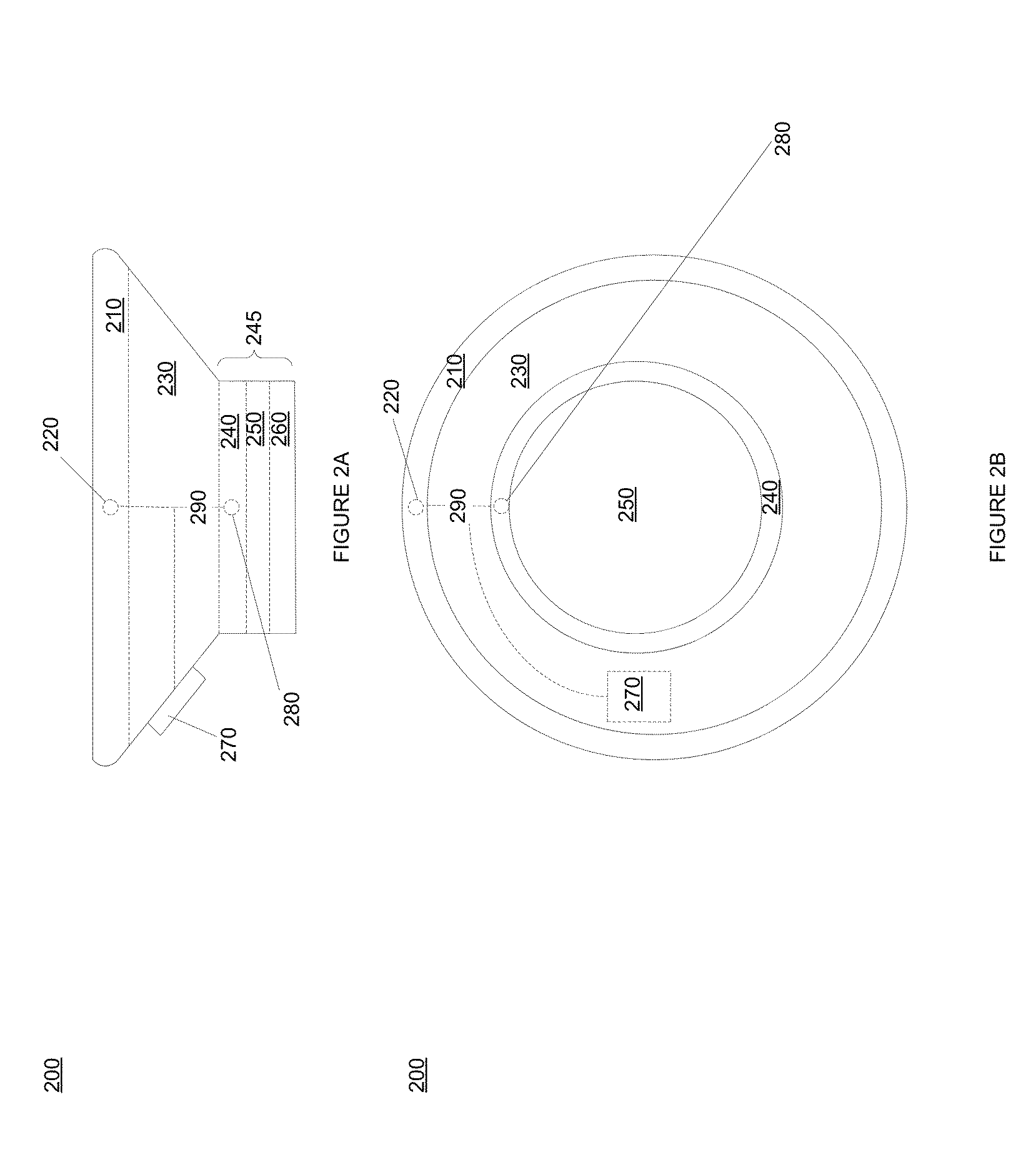

Charger plate having illuminated members

InactiveUS8444288B1Easy to hideSmall circuitLighting support devicesPoint-like light sourceLight pipeEngineering

A charger plate having illuminated members. The charger plate includes a base, a raised portion, a rim and a circuit. The base is positioned substantially at a center of the charger plate and includes a first plurality of light emitting sources (LES) that outputs light from the base. The raised portion is substantially opaque and circumferentially surrounds the base. The rim circumferentially surrounds the raised portion and includes a second plurality of LES that outputs light from the rim. The circuit may independently control color and brightness associated with the first plurality of LES and the second plurality of LES. The base may include a reflective portion operable to reflect light from the first plurality of LES. The base and the rim may include a light pipe each for distributing the light emitted from their respective LES. The circuit may be powered via power inductive magnets instead of a battery.

Owner:LEAL MARGO

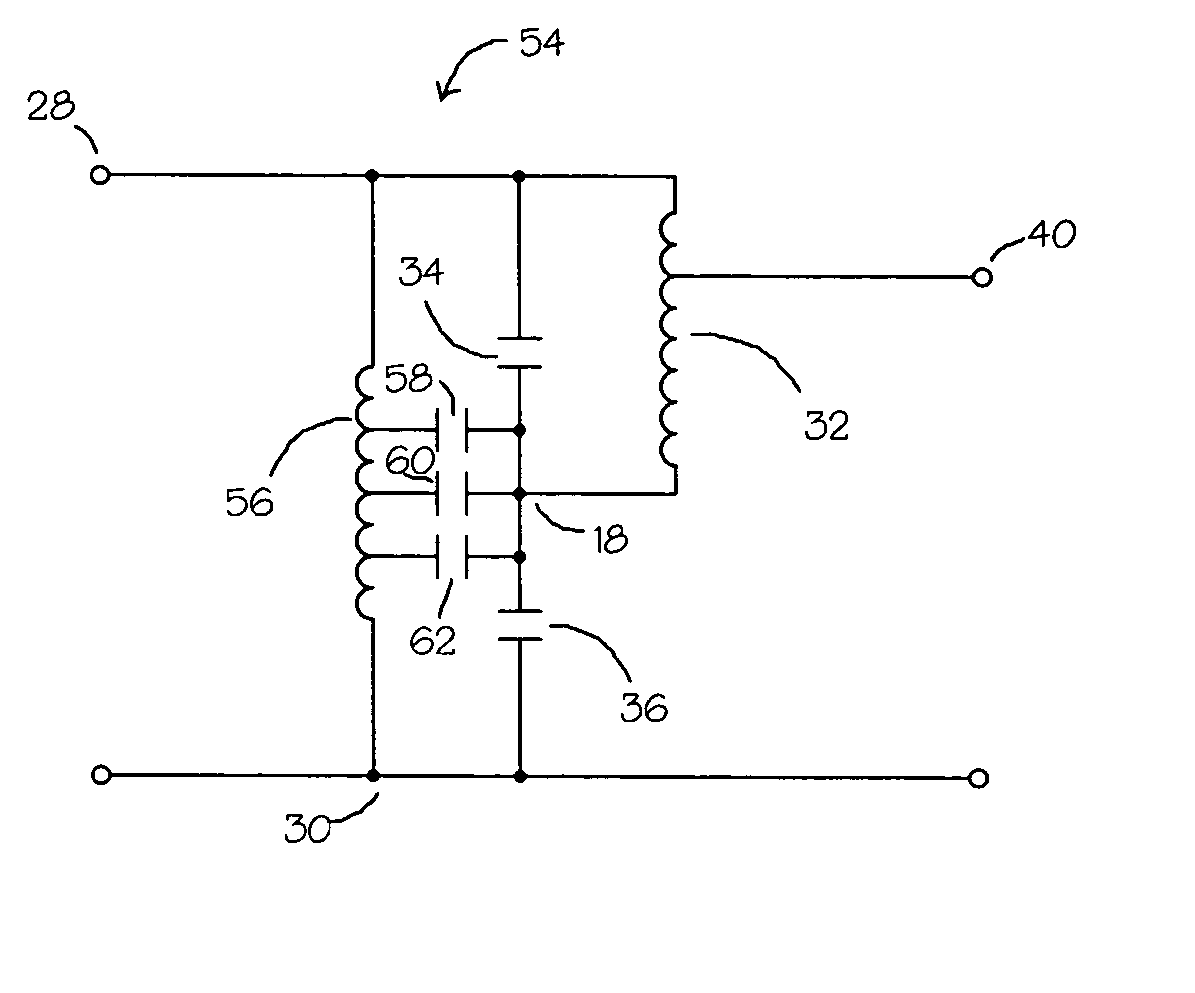

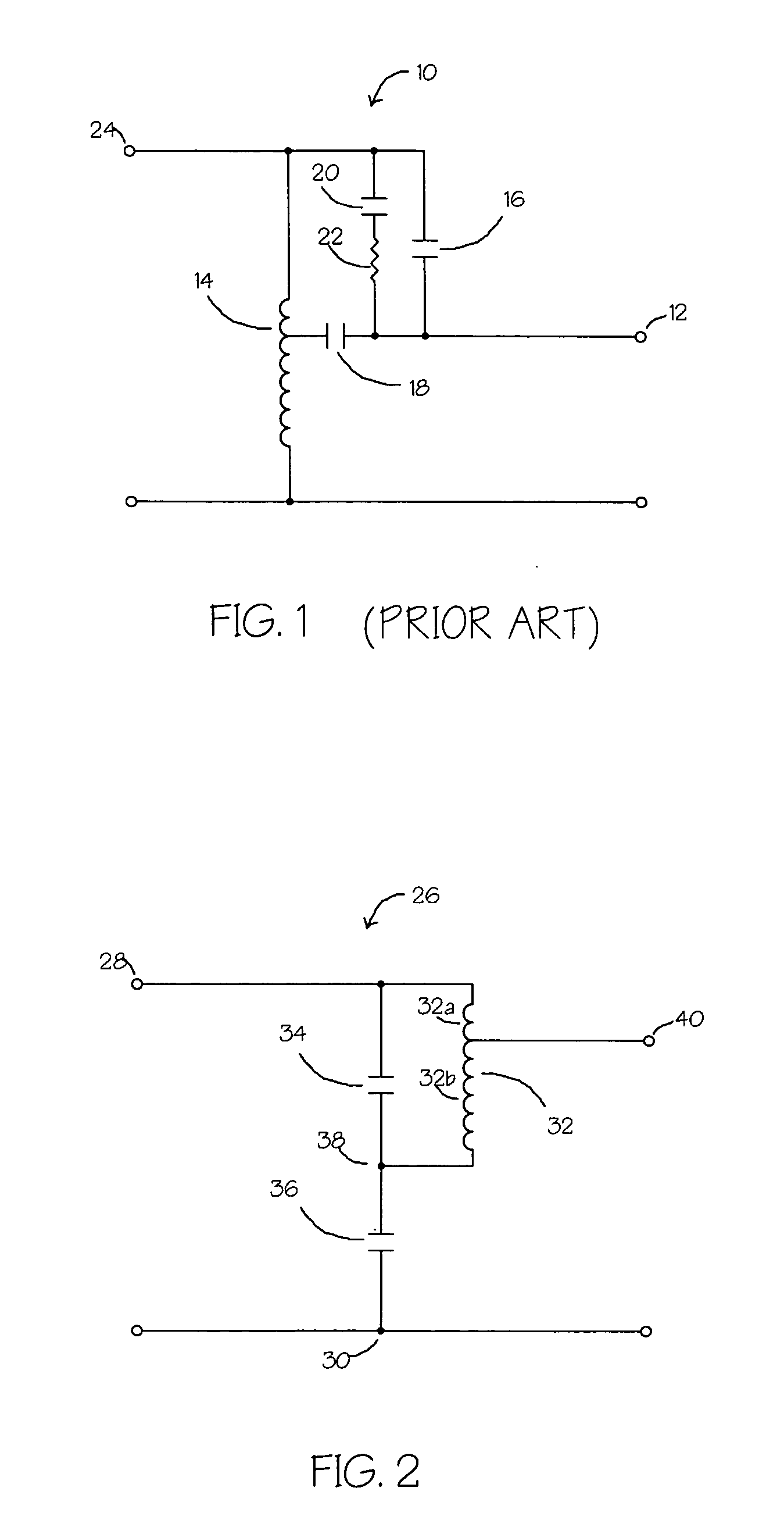

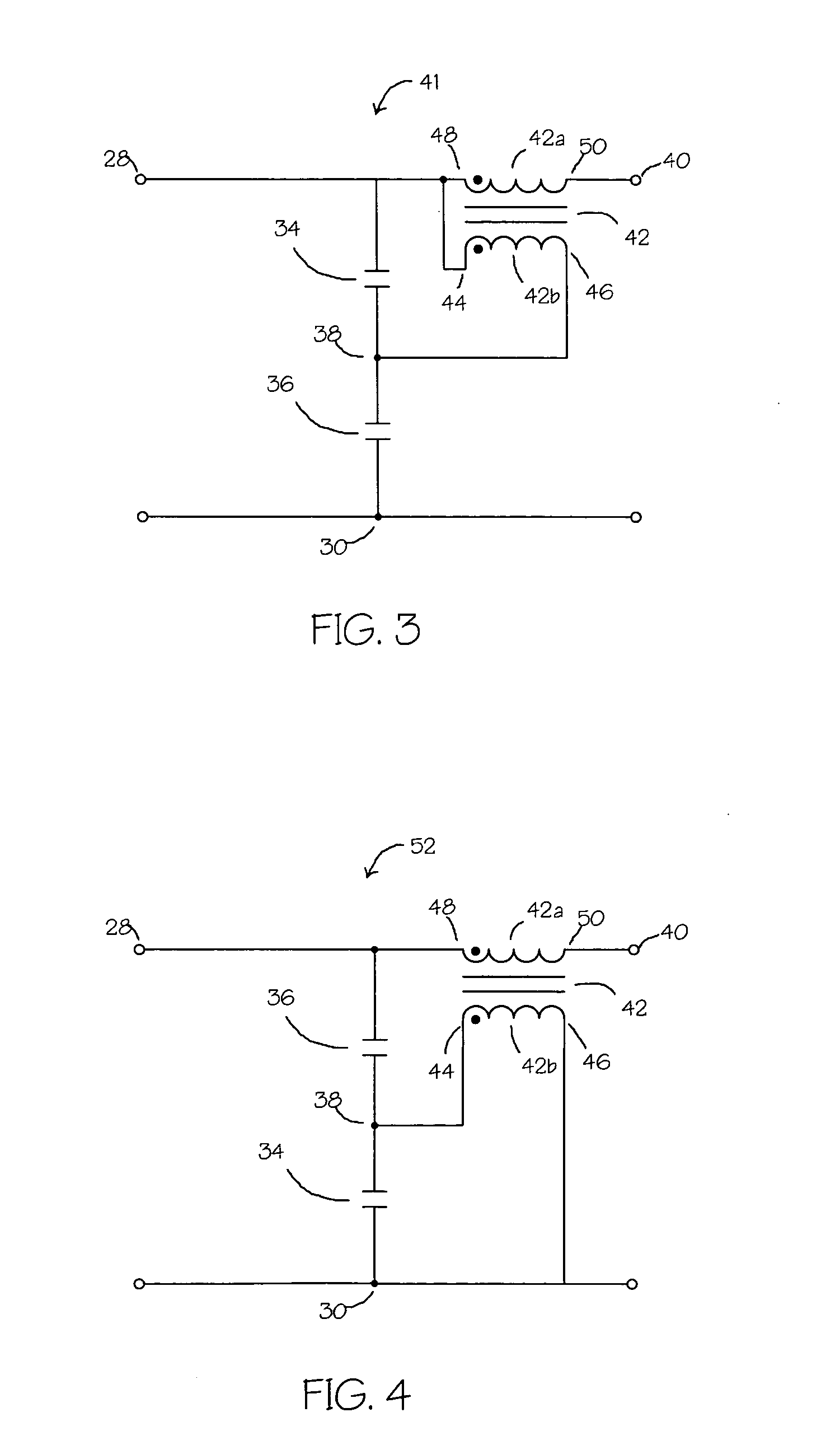

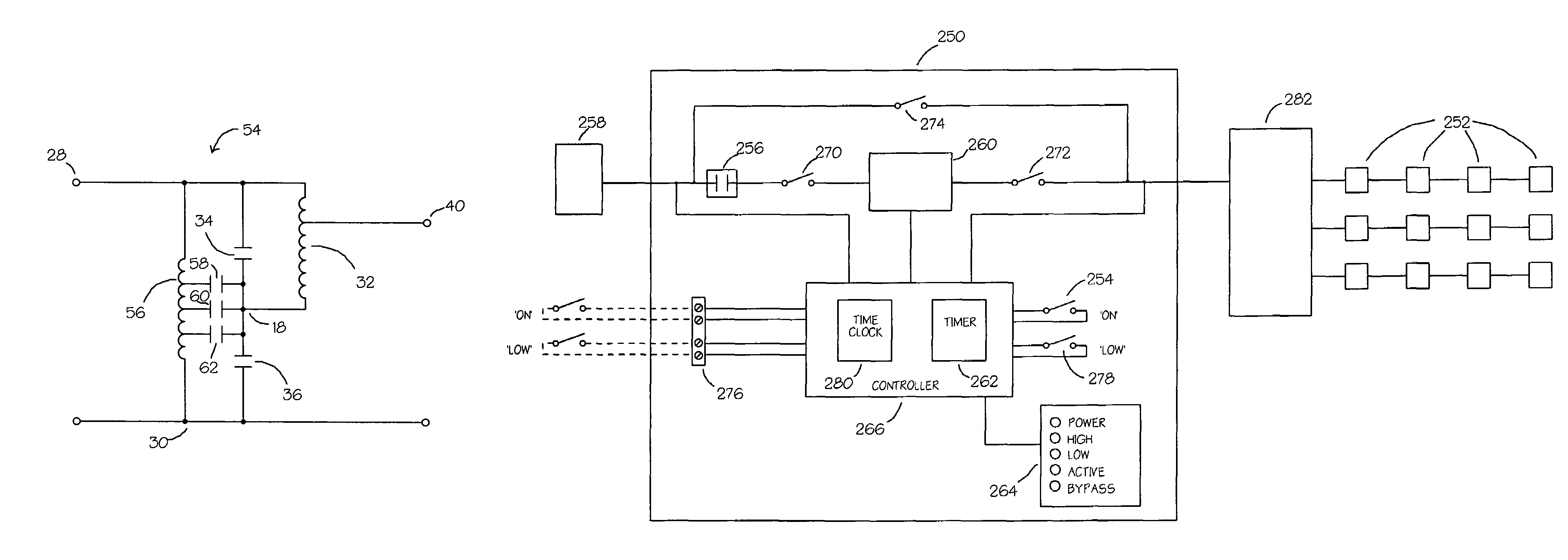

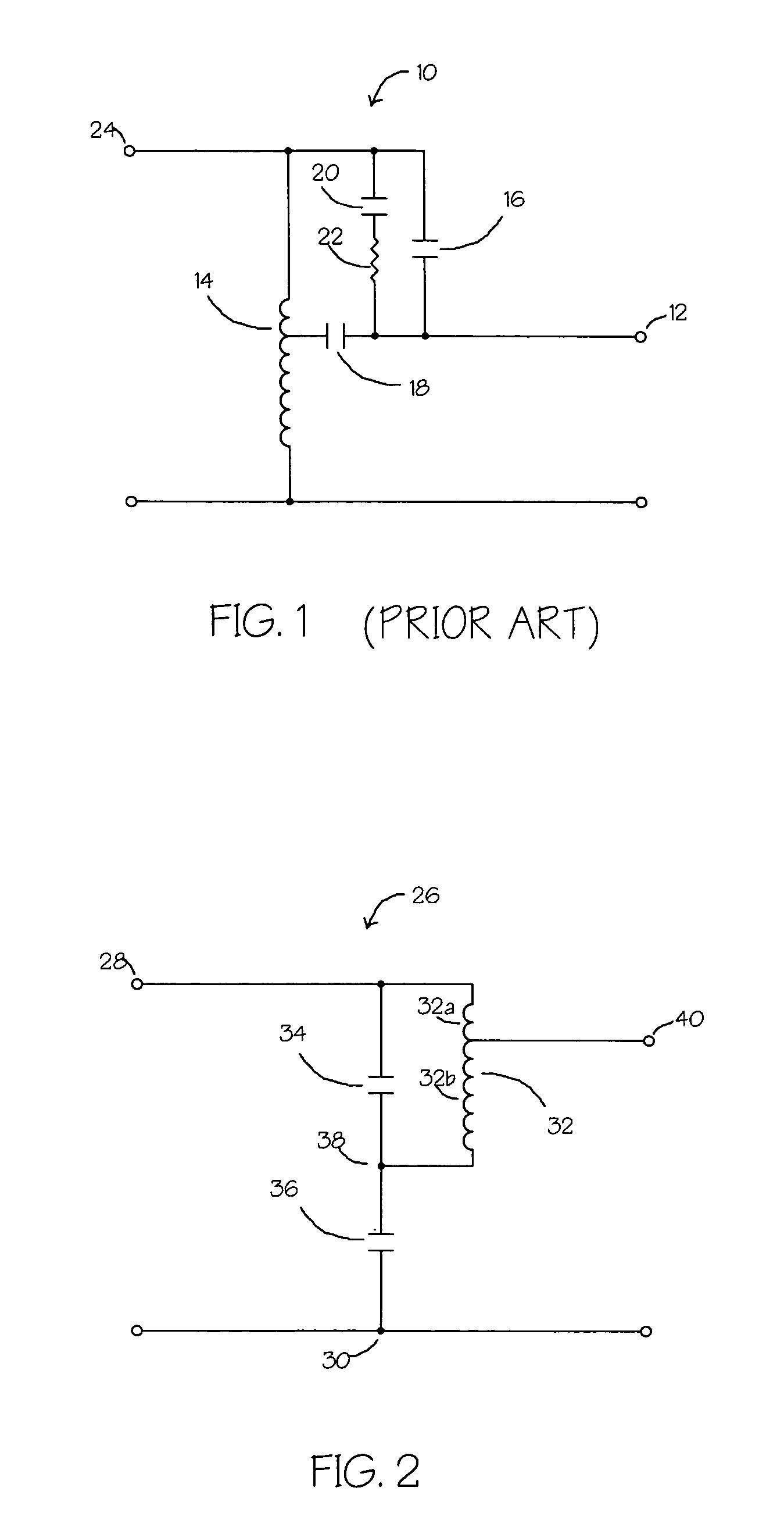

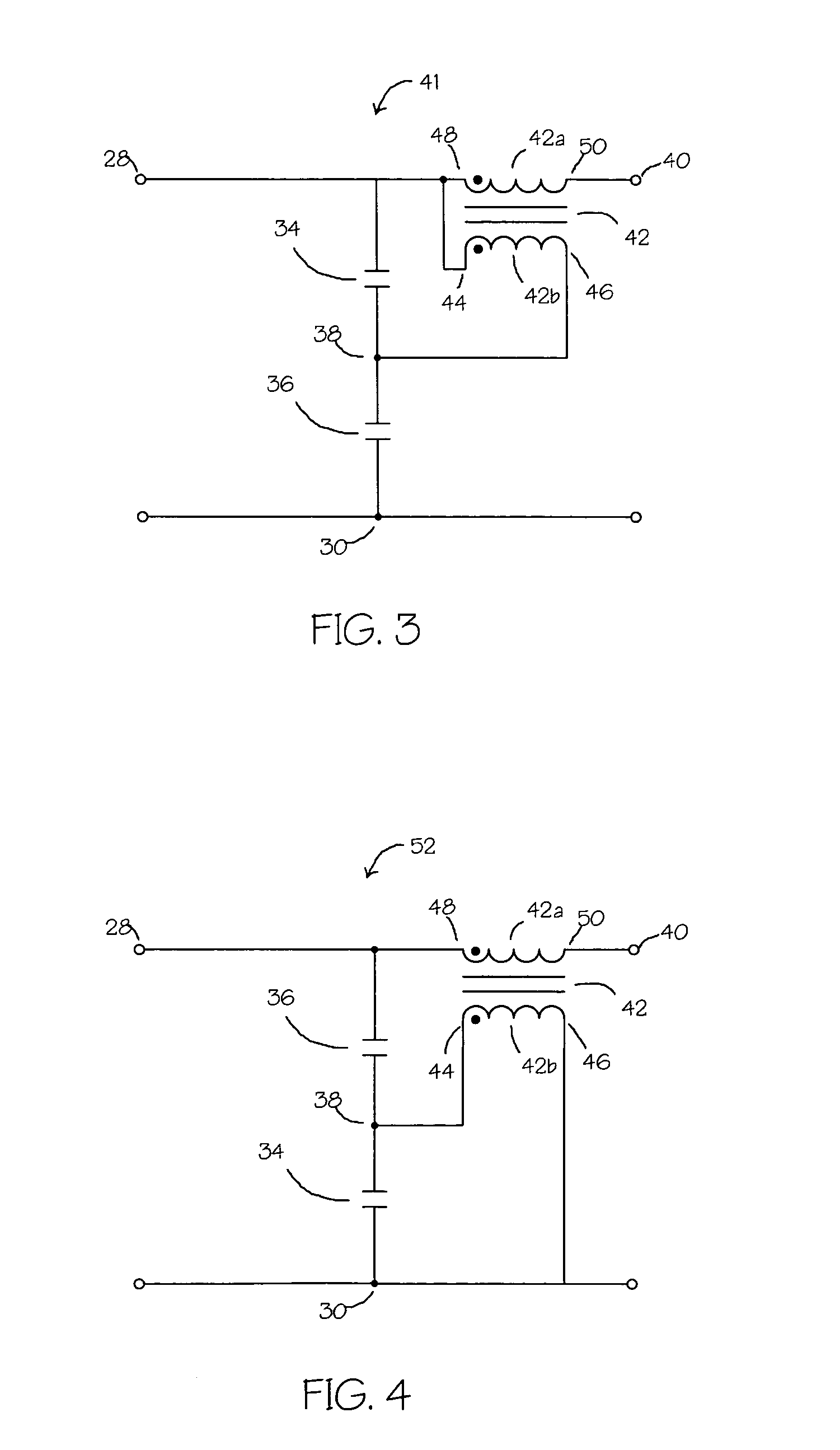

Voltage control system

InactiveUS20050024027A1Small circuitReduces complexity (and cost)Conversion with intermediate conversion to dcElectric lighting sourcesControl systemEngineering

The present invention is directed at circuit for controlling a voltage applied to an output voltage terminal from a first voltage level supplied by an input voltage terminal comprising a first switch and a second switch connected in series between said input voltage terminal and a common terminal; a transformer, having a primary side and a second side, connected with said first switch on the primary side and to said output terminalon the secondary side; wherein when said first switch is closed and said second switch open, said first voltage level is supplied to said output voltage terminal; and wherein when said first switch is open and said second switch is closed, a second voltage level is supplied to said output voltage terminal.

Owner:748038 ONTARIO INC

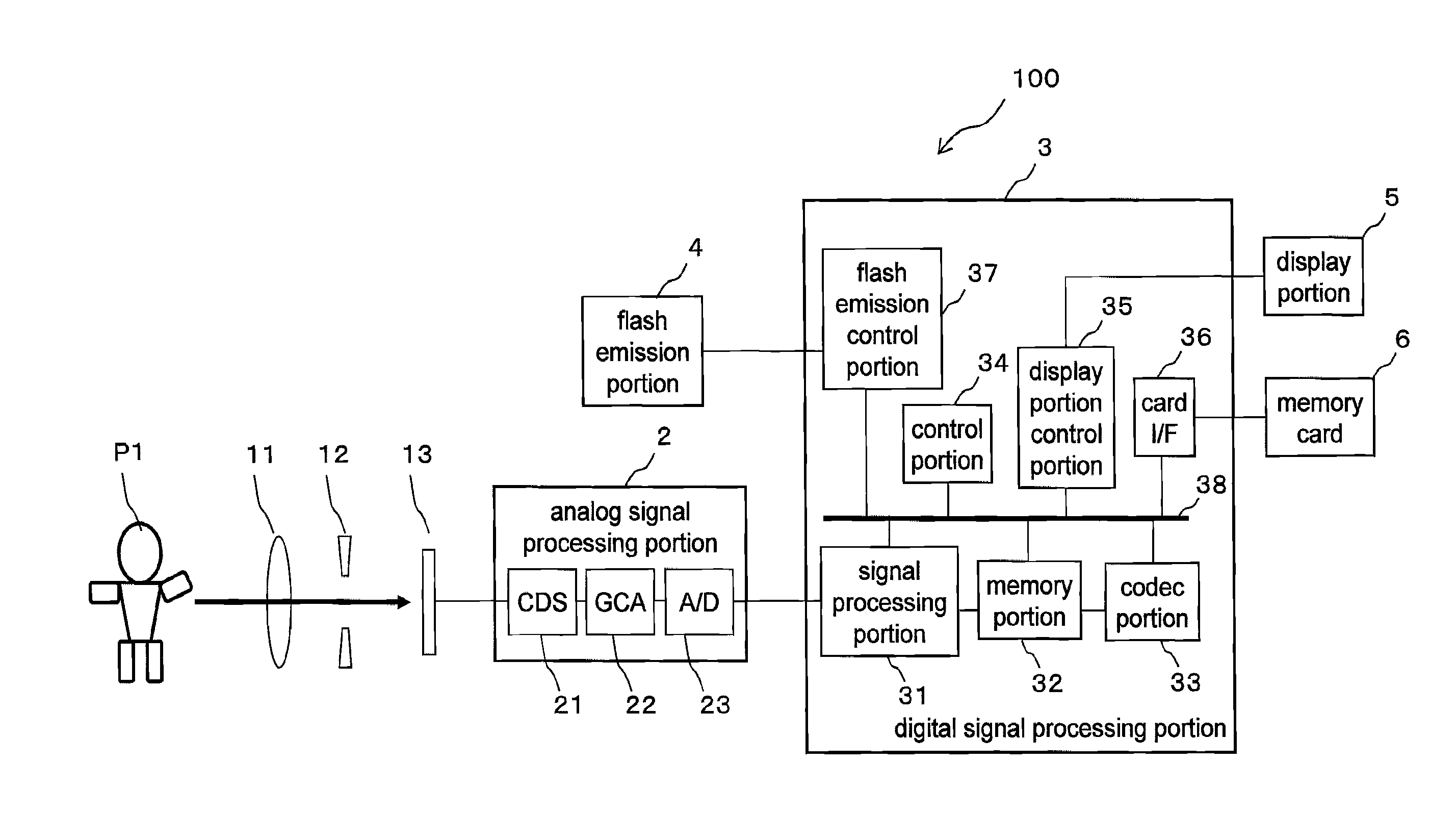

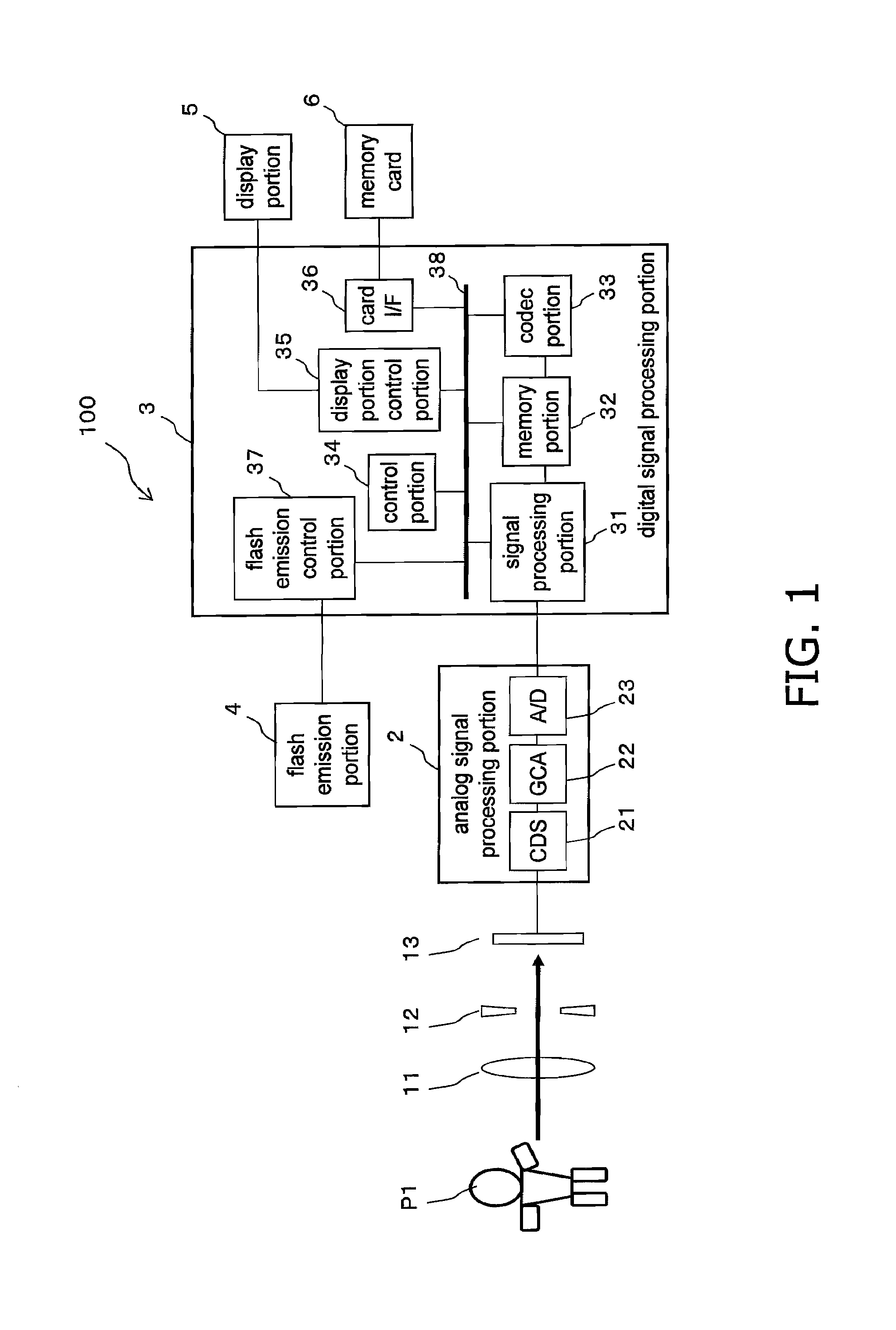

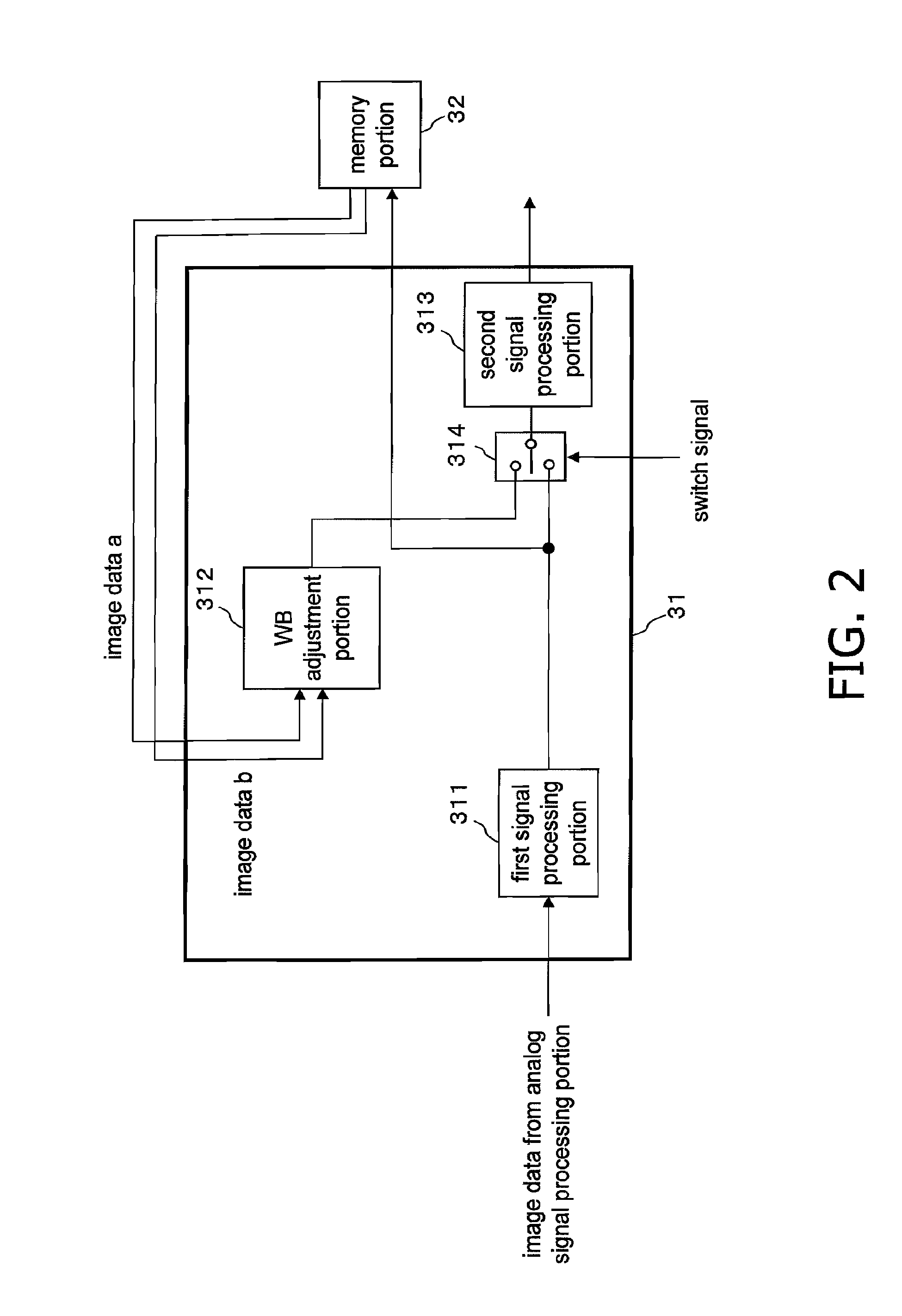

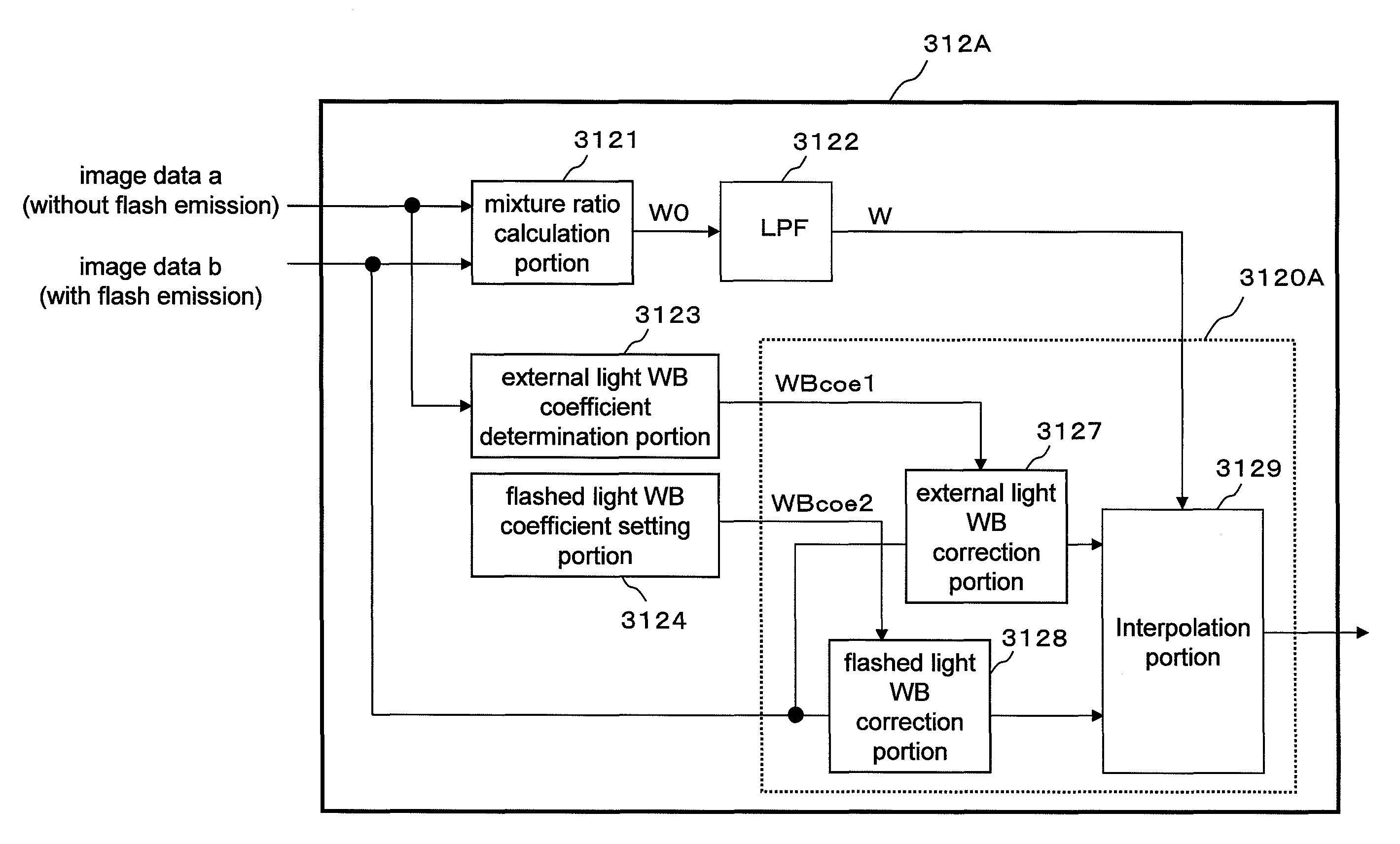

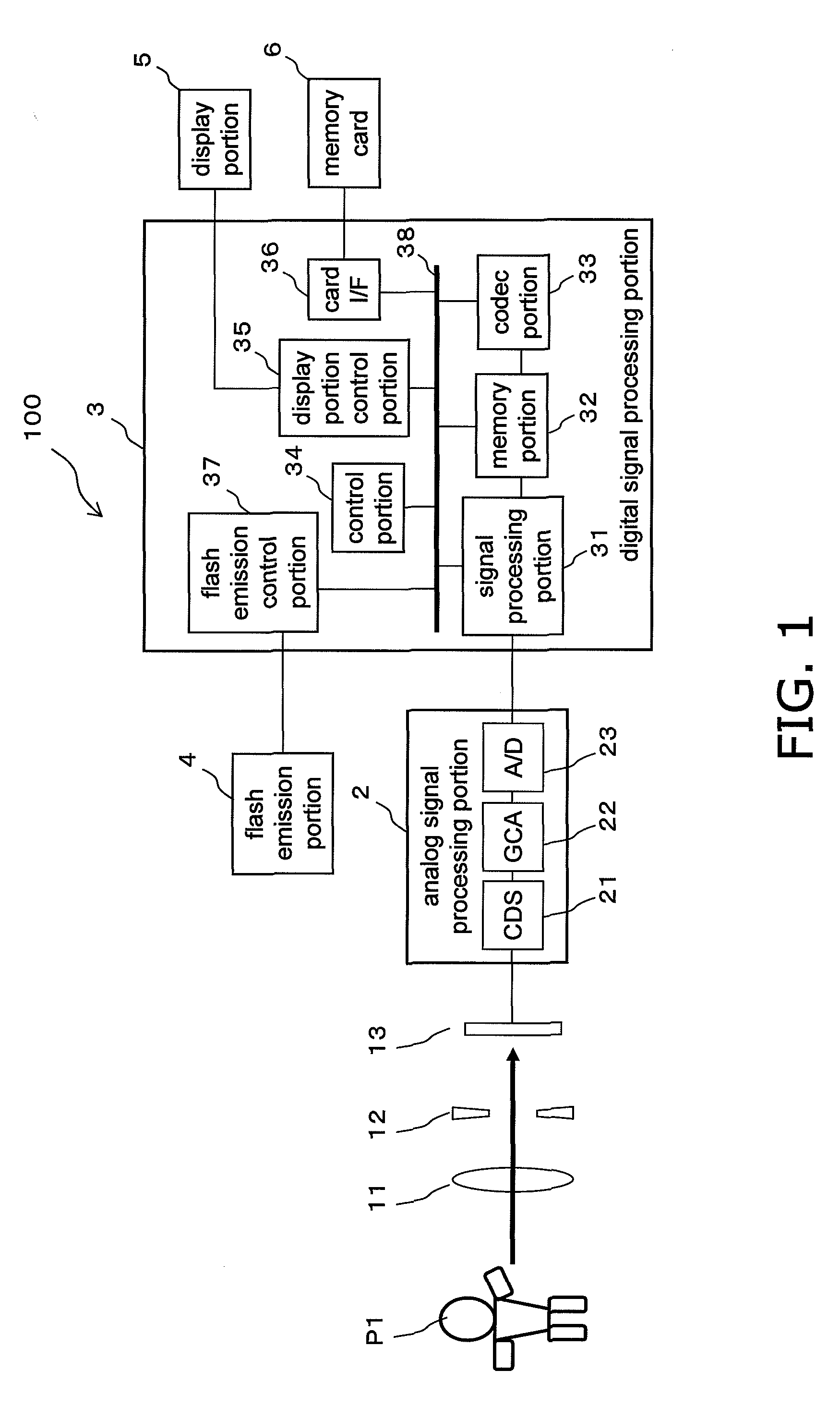

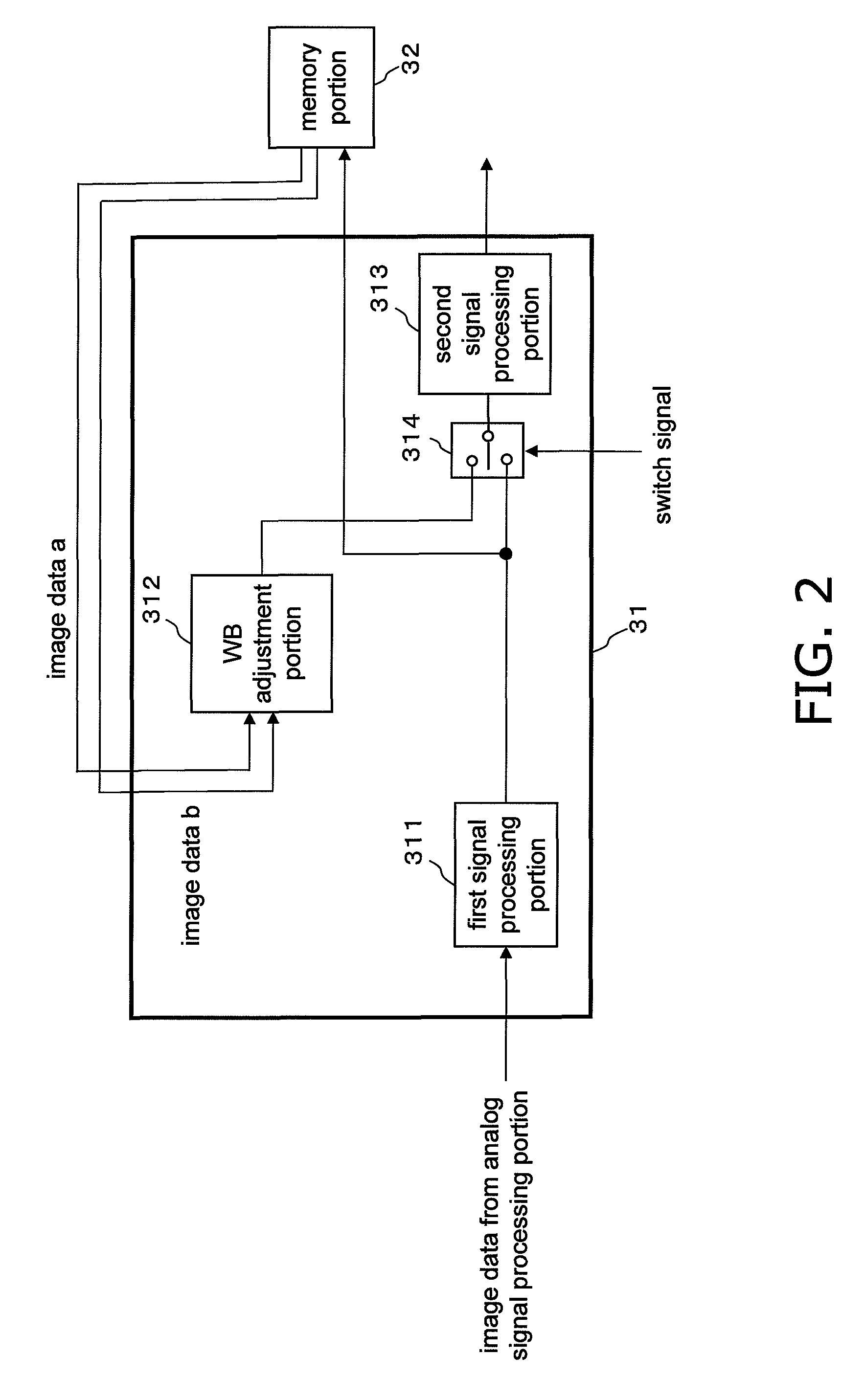

White balance adjustment device, image capture device, white balance adjustment method, storage medium, and integrated circuit

InactiveUS20120008009A1Easy to adjustReduce colorColor signal processing circuitsFlash lightImage signal

A natural white balance is achieved in images that are captured while emitting a flash. The white balance of an image is adjusted using a WB adjustment portion and a mixture ratio calculation portion estimating a mixture ratio of an external light component and a flashed light component that are present in an image captured with emitting a flash, from the image obtained that is captured while emitting a flash and an image signal that is obtained without emitting a flash. Further, an external light WB coefficient determination portion determines an WB coefficient for the external light, a flashed light WB coefficient setting portion sets a WB coefficient for the flashed light, and a WB processing portion that continuously performs WB processing on the image captured while emitting a flash by using the mixture ratio as an interpolation ratio.

Owner:PANASONIC CORP

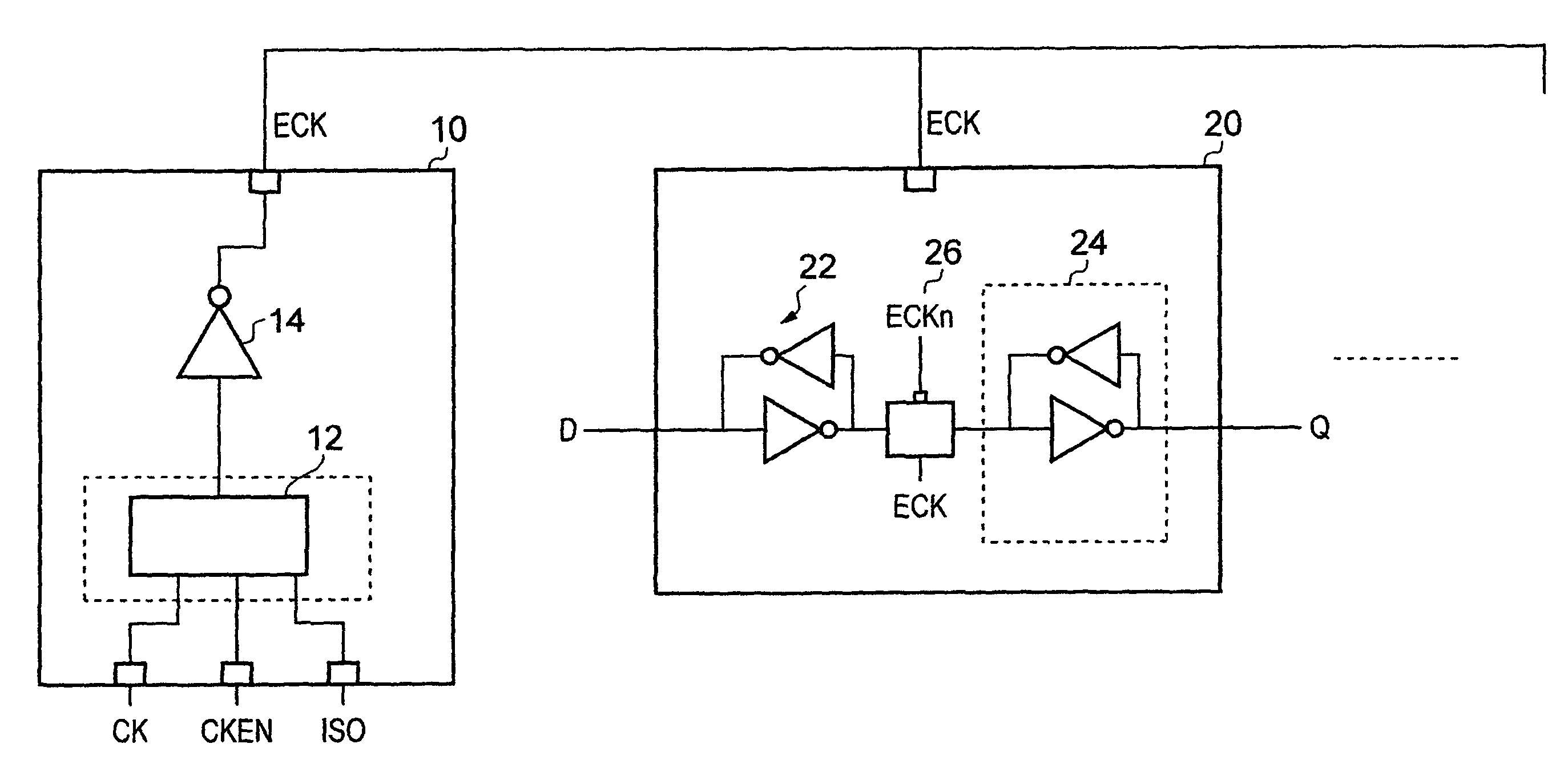

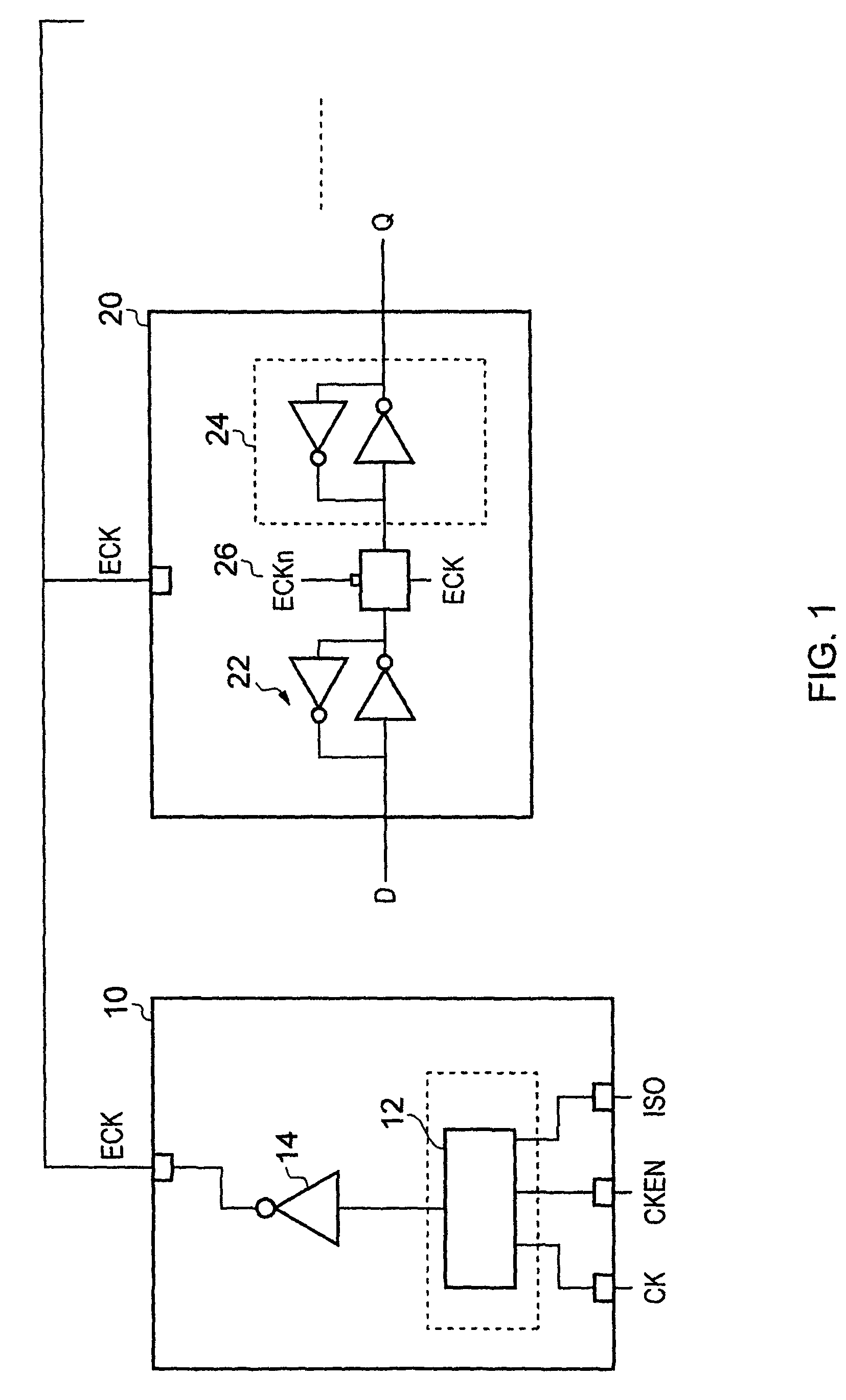

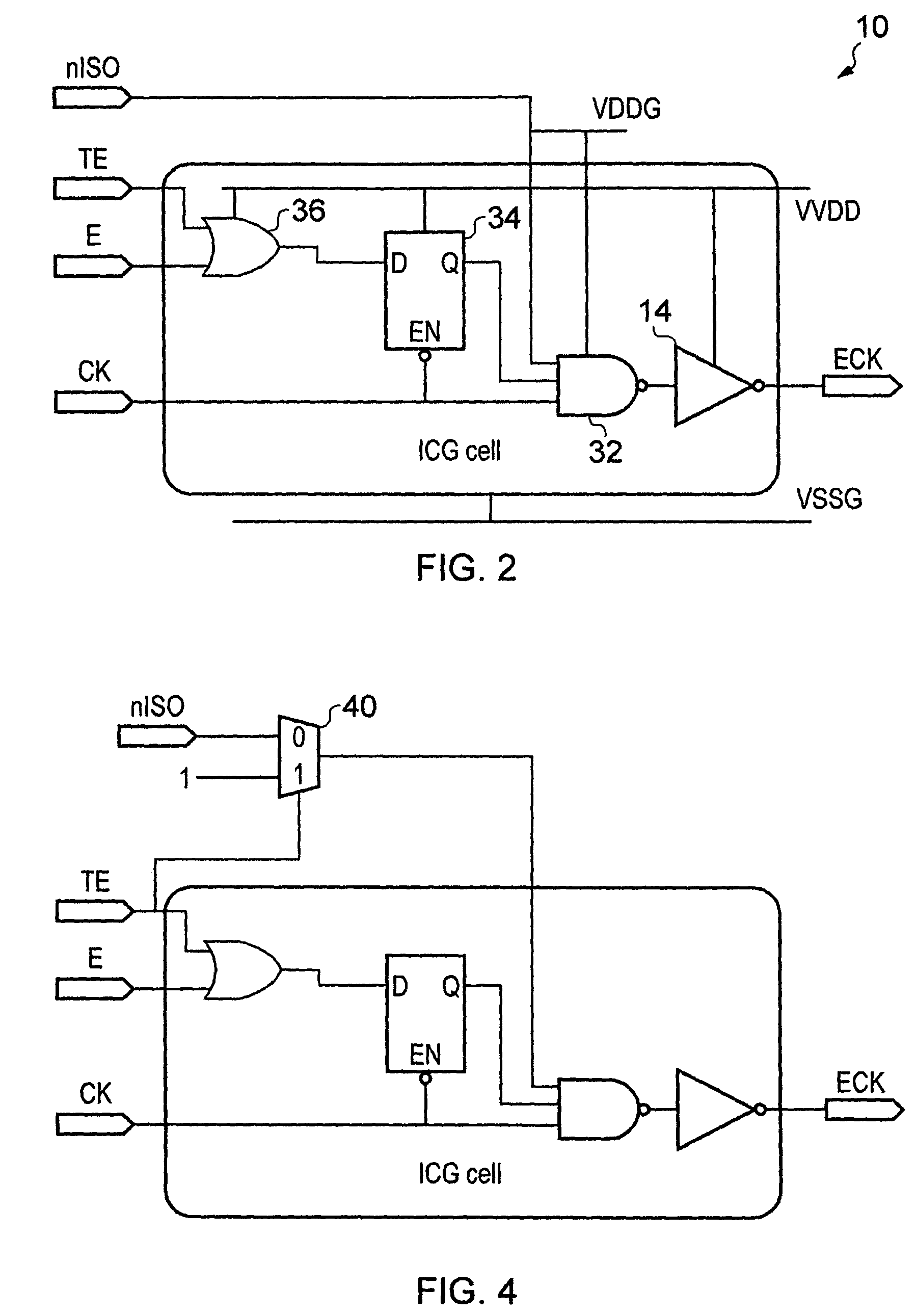

Supplying a clock signal and a gated clock signal to synchronous elements

ActiveUS8390328B2Secure retentionReduce areaPower reduction in field effect transistorsPower reduction by control/clock signalPower modeLogic circuitry

A clock gating circuitry is configured to receive a clock signal and to output an output signal comprising either the clock signal or the predetermined gated value. The circuitry receives a clock signal, a clock enable signal having either an enable value or a disable value, and a power mode signal having either a low power value (indicating entry to a low power mode in which at least a portion of the plurality of synchronous elements are powered to retain data and are not clocked and at least a further portion of the plurality of synchronous elements are powered down), or a functional mode value (indicating the plurality of synchronous elements are to be powered). A clock gating unit has logic circuitry that is configured to output the clock signal or the predetermined gated value depending upon the low power value and the functional mode value.

Owner:ARM LTD

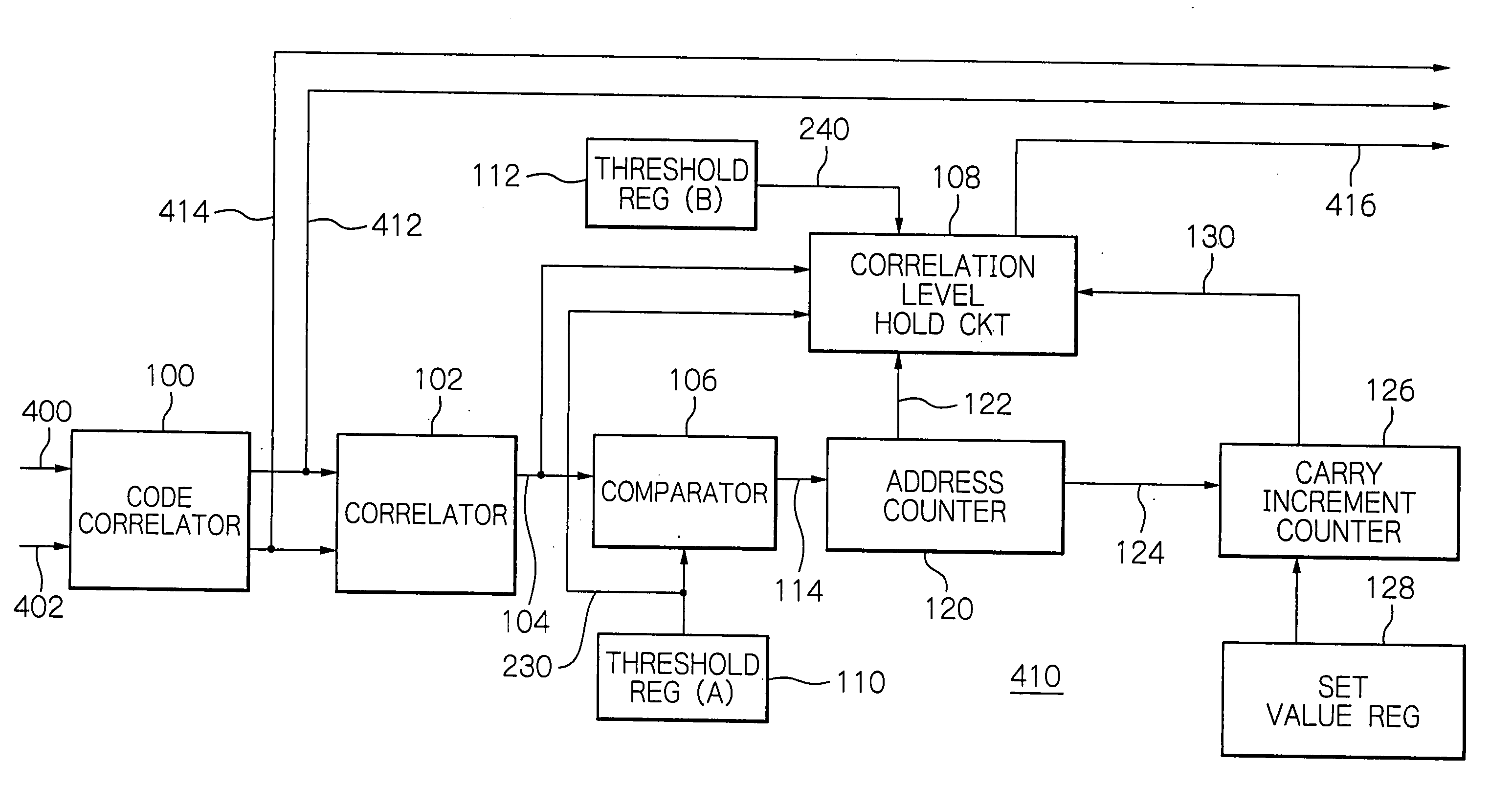

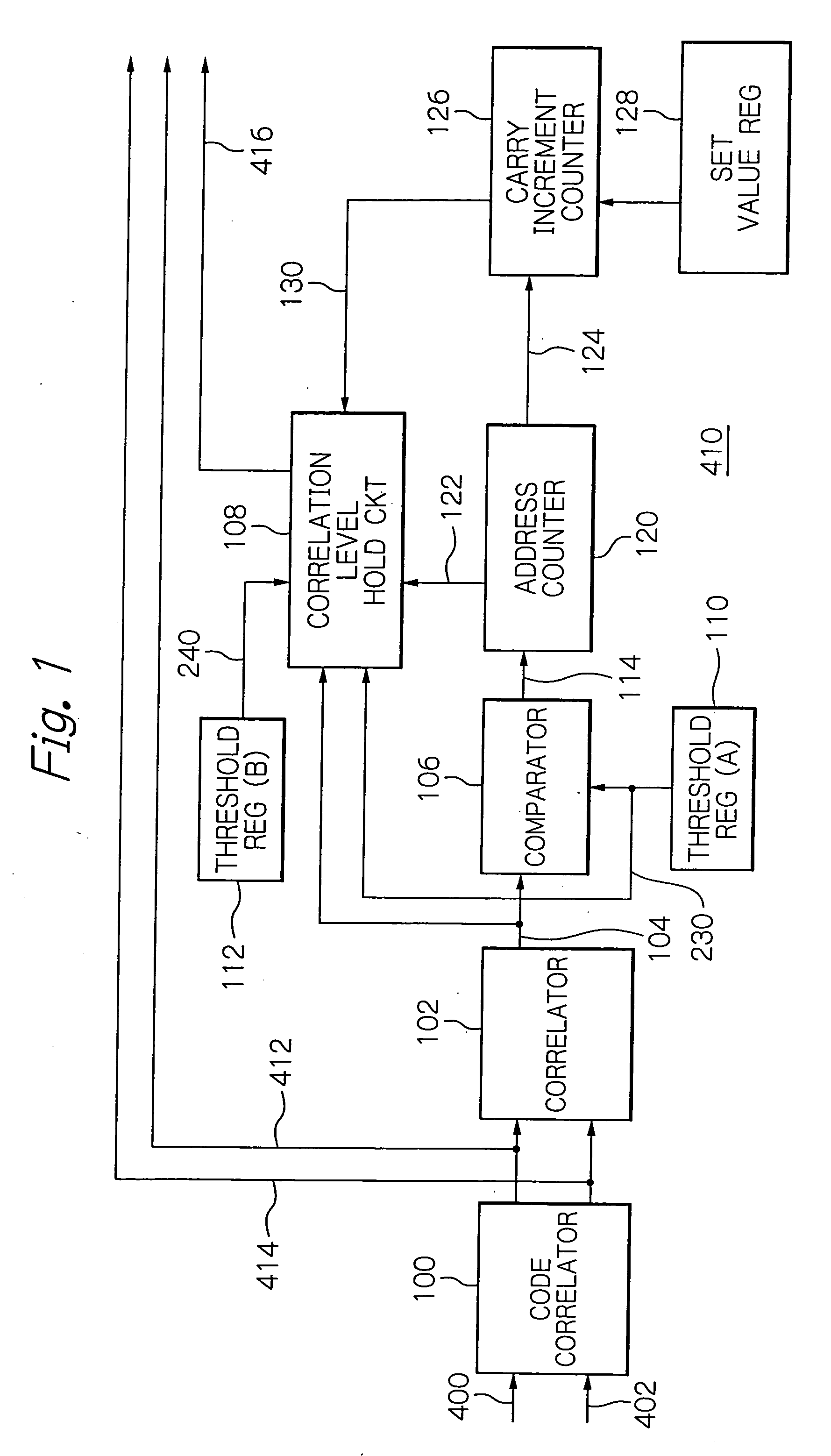

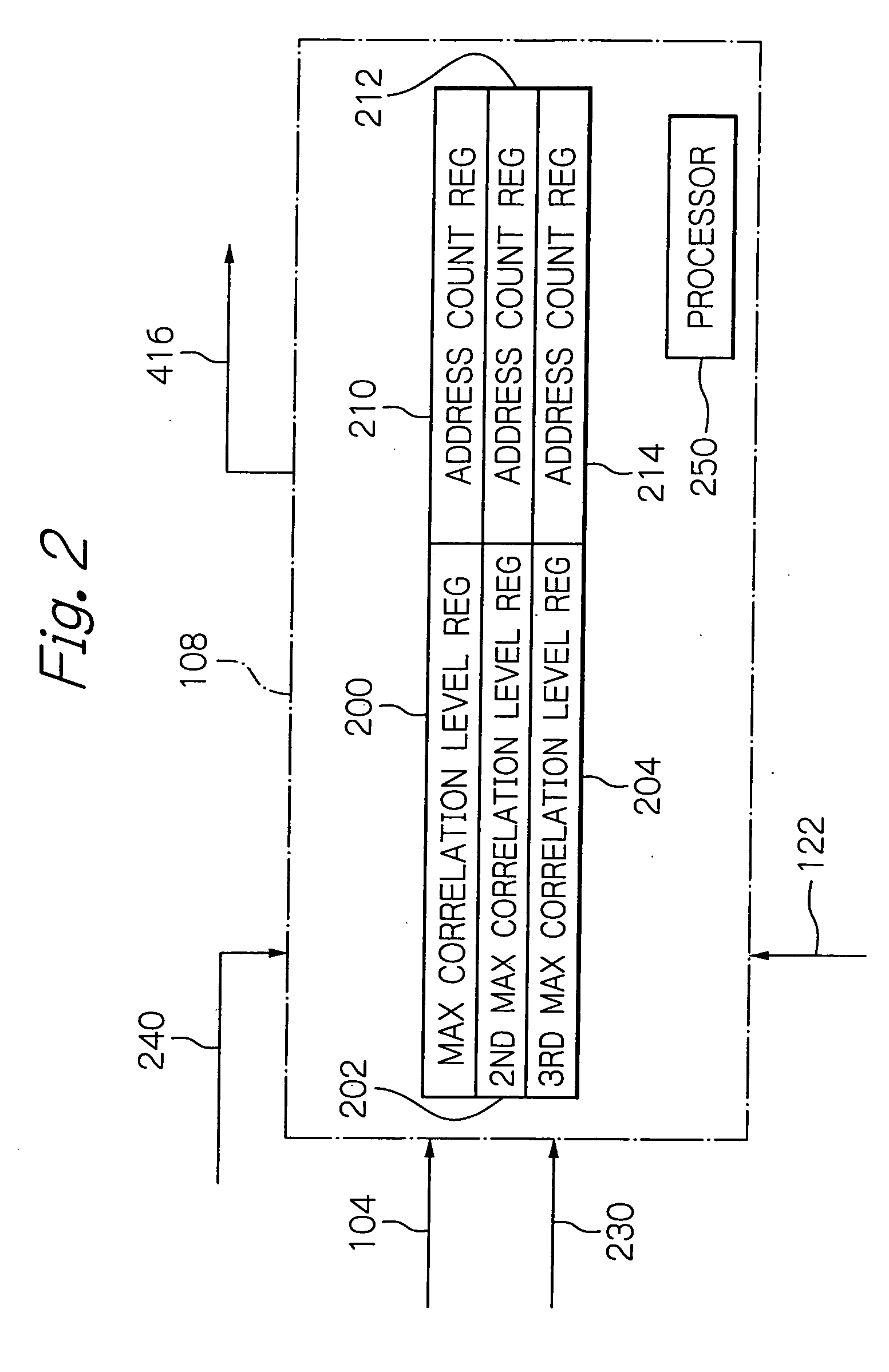

Synchronous control apparatus for initial synchronization when receiving a wireless signal

InactiveUS20070047630A1Small circuitImprove receive snrSynchronisation arrangementAmplitude-modulated carrier systemsPacket communicationWireless signal

A synchronous control apparatus for reception control in wireless packet communication suppresses detection errors during controlling synchronization to detect codes for improved signal reception. An initial synchronizer includes a code correlator for receiving delayed waves on plural paths. The code correlator outputs a correlation level value through another correlator. The correlation level value is compared with a threshold value from a threshold value register, with the result inputted into an address counter. The correlation level value is also inputted into a correlation level hold circuit. The hold circuit sums the correlation level values obtained in the correlator for a portion of the paths corresponding to a count in the address counter. The hold circuit compares the summed correlation level values with another threshold value from another threshold value register, and uses the result as a basis to set a top timing for receiving delayed waves.

Owner:LAPIS SEMICON CO LTD

Range code compression method and apparatus for ternary content addressable memory (CAM) devices

InactiveUS7904643B1Reduce in quantityIncrease in sizeDigital storageMemory systemsPartial representationOne-hot

A content addressable memory (CAM) device, method, and method of generating entries for range matching are disclosed. A CAM device (800) according to one embodiment can include a pre-encoder (806) that encodes range bit values W into additional bits E. Additional bits E can indicate compression of range rules according to particular bit pairs. A CAM array (802) can include entries that store compressed range code values (RANGE) with corresponding additional bit values (ENC). Alternate embodiments can include pre-encoders that encode portions of range values (K1 to Ki) in a “one-hot” fashion. Corresponding CAM entries can include encoded value having sections that each represent increasingly finer divisions of a range space.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Packet network interface apparatus and method

ActiveUS8649398B2Elimination of rate adaptingSmall circuitTime-division multiplexMultiple digital computer combinationsTime domainNetwork interface device

A packet network interface apparatus includes a media access control (MAC) module for constructing a packet for transmission over a packet network and a physical coding sublayer (PCS) module for encoding the packet for transmission over a physical interface. An inter packet gap module located between the MAC module and the PCS module directly transfers data to the PCS module while maintaining a certain inter packet gap by deleting or inserting idle characters. The inter packet gap module has at least one memory module for temporary storage of packet data. The modules preferably operate in a common time domain.

Owner:XILINX INC

Pulse modulation type electric power amplifier

InactiveUS7586369B2Reduce areaReduce power consumptionNegative-feedback-circuit arrangementsGain controlTerminal voltageShort circuit protection

A pulse modulation type electric power amplifier includes a pulse modulator that receives as input a clock and an input signal, and converts the input signal to a pulse train, an output control circuit that receives as input the pulse train output by the pulse modulator, and controls output of the pulse train, an output circuit that performs switching according to the pulse train output by the output control circuit, a comparator that converts an output terminal voltage of the output circuit to a high or a low digital value, and a short-circuit determination circuit that determines whether an output short circuit has occurred based on a state of an output signal of the comparator, and outputs an output prohibition signal to the output control circuit when an output short circuit is detected. The output control circuit controls output of the pulse train when the output prohibition signal is input, so that the output circuit stops the switching operation. An output short-circuit protection circuit can thereby be configured simply with little circuitry, and is thus small, low power, and integrated easily.

Owner:PANASONIC CORP

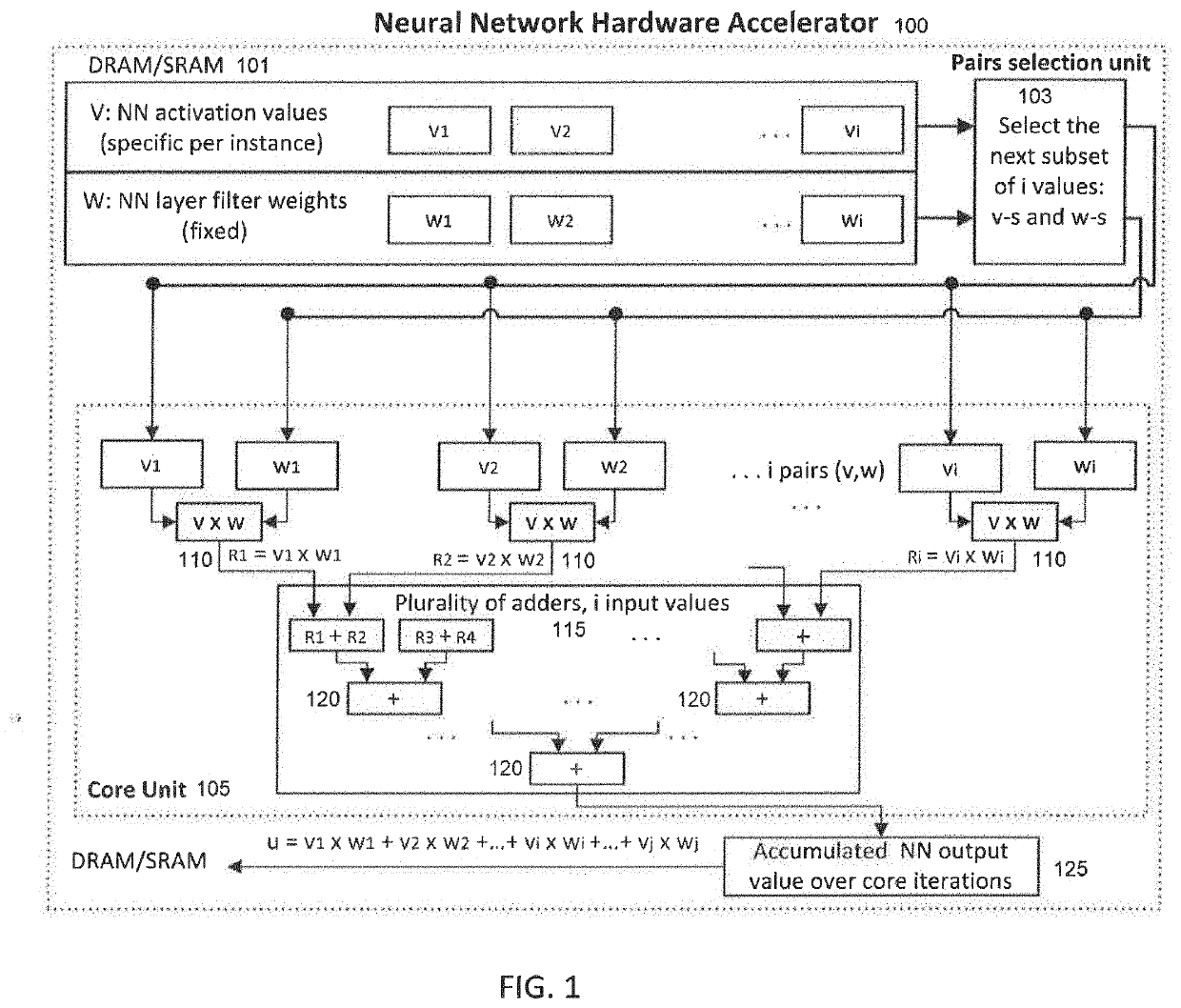

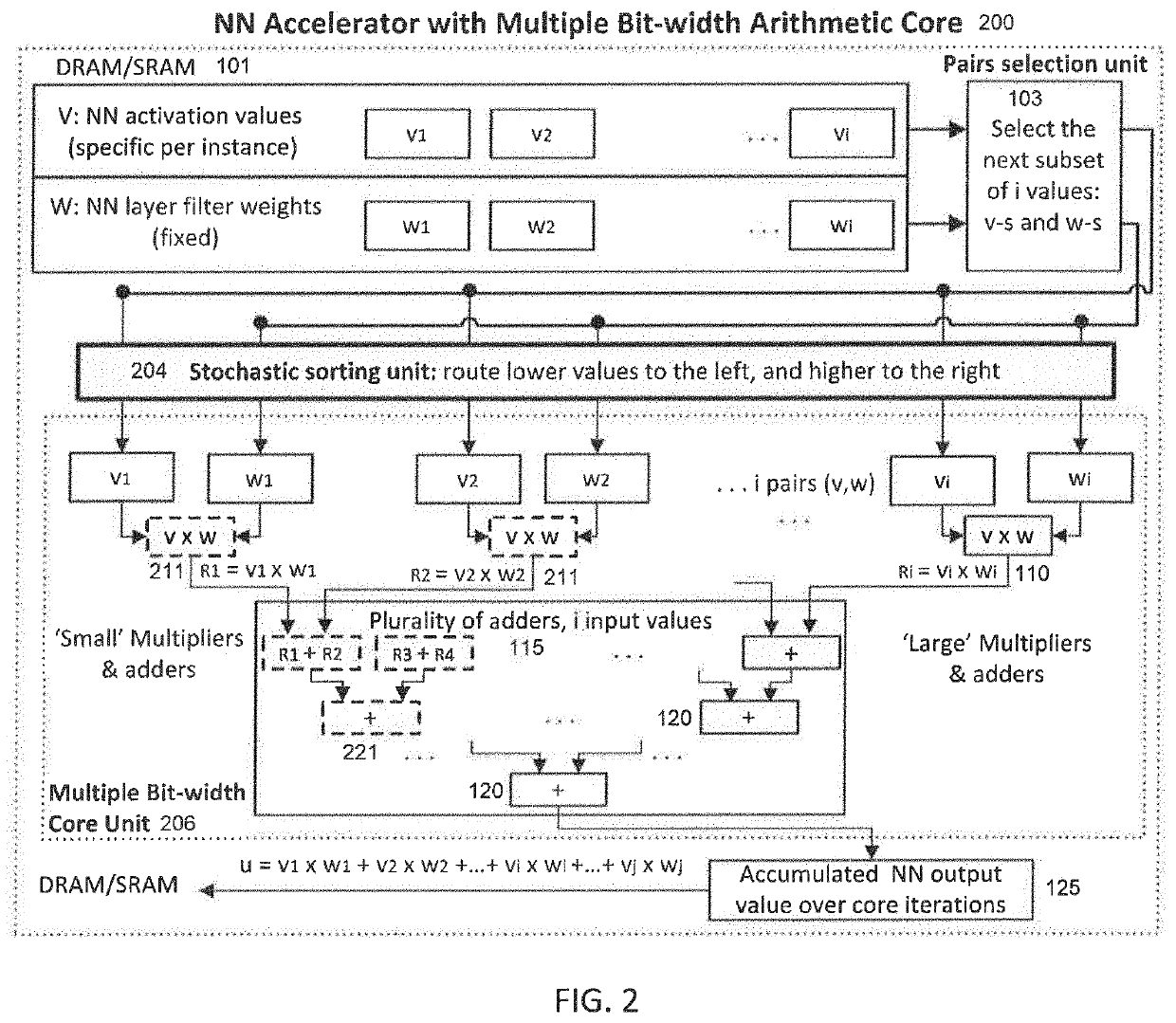

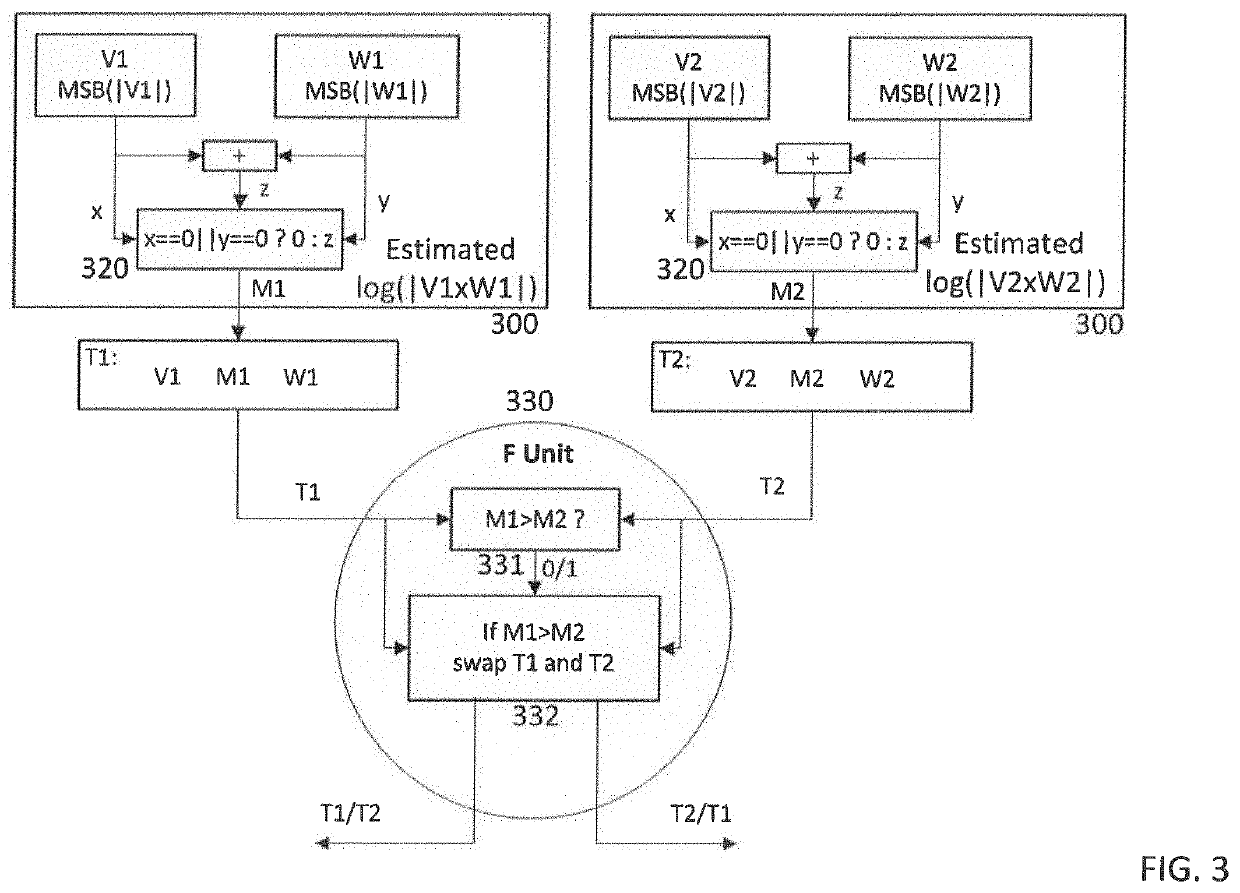

Neural network hardware acceleration with stochastic adaptive resource allocation

ActiveUS20190378001A1Accurate multiplicationConsuming less powerDigital data processing detailsProgram controlBinary multiplierAlgorithm

A digital circuit for accelerating computations of an artificial neural network model includes a pairs selection unit that selects different subsets of pairs of input vector values and corresponding weight vector values to be processed simultaneously at each time step; a sorting unit that simultaneously processes a vector of input-weight pairs wherein pair values whose estimated product is small are routed with a high probability to small multipliers, and pair values whose estimated product is greater are routed with a high probability to large multipliers that support larger input and output values; and a core unit that includes a plurality of multiplier units and a plurality of adder units that accumulate output results of the plurality of multiplier units into one or more output values that are stored back into the memory, where the plurality of multiplier units include the small multipliers and the large multipliers.

Owner:SAMSUNG ELECTRONICS CO LTD

Voltage control system

InactiveUS7250743B2Reduces complexity (and cost)Easy transitionElectrical apparatusElectric lighting sourcesControl systemVoltage control

The present invention is directed at circuit for controlling a voltage applied to an output voltage terminal from a first voltage level supplied by an input voltage terminal comprising a first switch and a second switch connected in series between said input voltage terminal and a common terminal; a transformer, having a primary side and a second side, connected with said first switch on the primary side and to said output terminal on the secondary side; wherein when said first switch is closed and said second switch open, said first voltage level is supplied to said output voltage terminal; and wherein when said first switch is open and said second switch is closed, a second voltage level is supplied to said output voltage terminal.

Owner:748038 ONTARIO INC

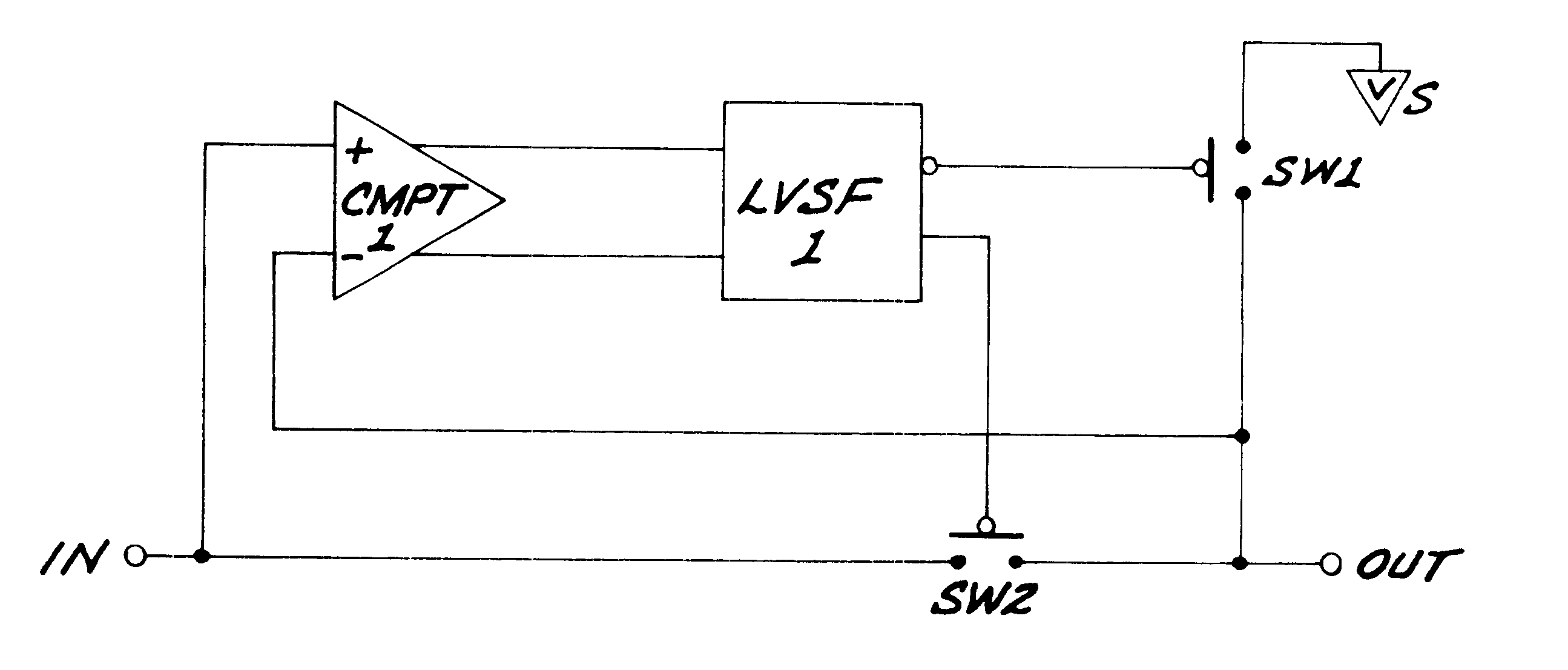

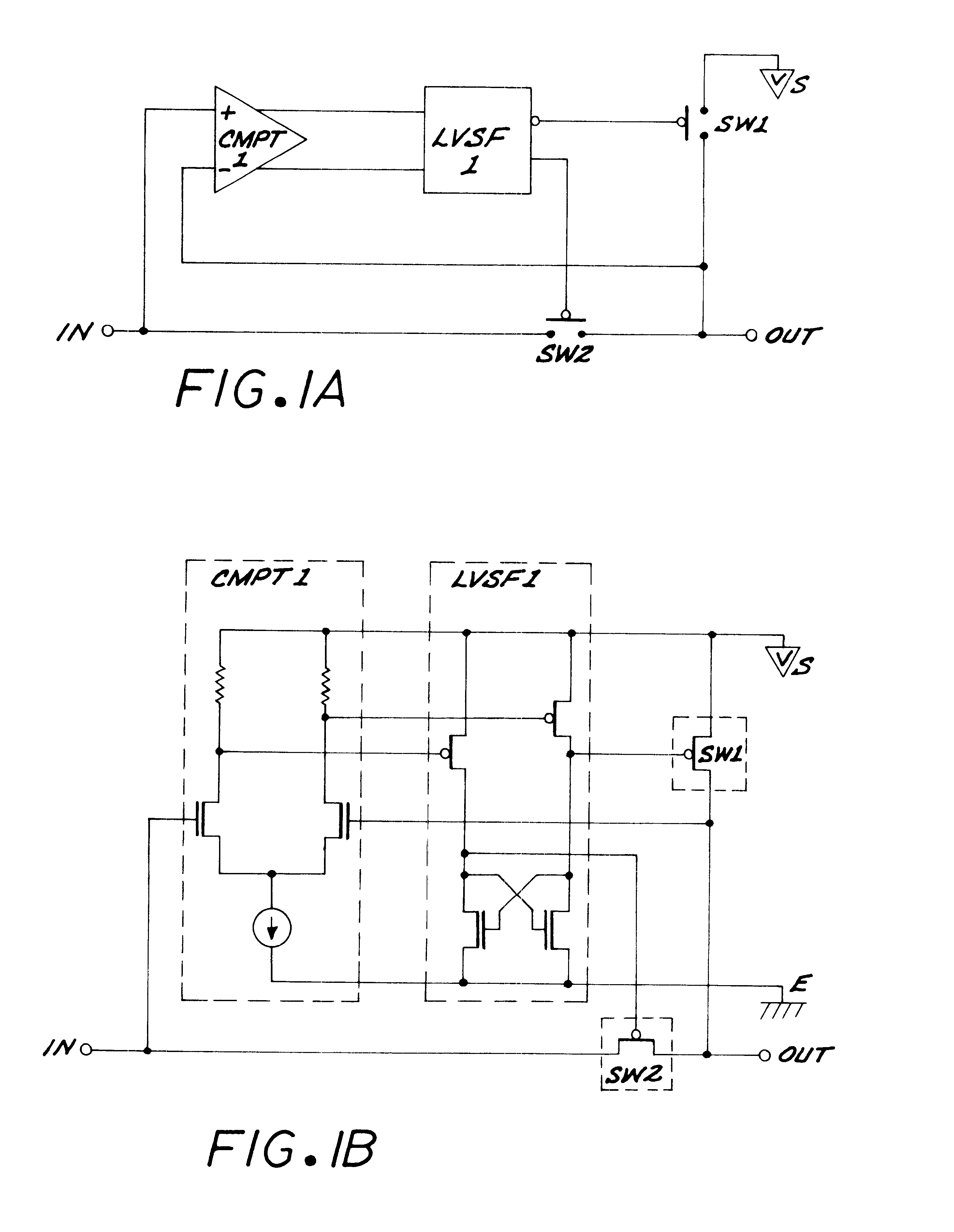

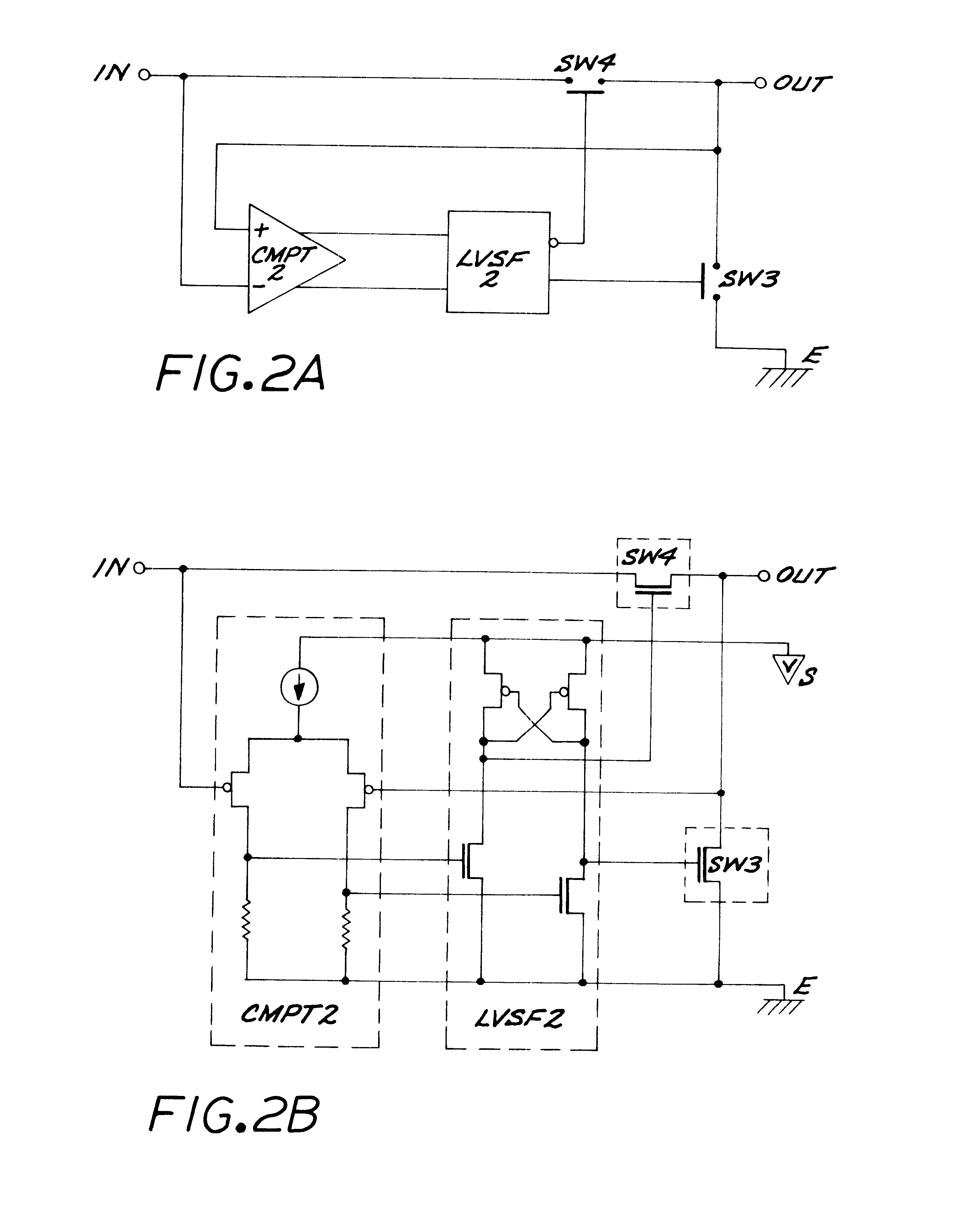

Digitally-operated analog buffer amplifiers

InactiveUS6459332B2Increase speedReduce power consumptionPulse automatic controlComputing operations for optimisationAudio power amplifierHigh velocity

Digitally-operated analog buffer amplifiers which are characterized by small circuits, no offset voltage, high speed and low power consumption. Circuit means are provided so that when the value of the output voltage of the buffer amplifier nears the approximate value (set voltage value) of the input voltage value, the input terminal and output terminal short-circuit so that the output voltage and the input voltage are made equal, thereby preventing the generation of offset voltage. Power consumption is reduced because the circuit completes the operation in a digital operation state.

Owner:UCHIDA YASUHISA

White balance adjustment device, image capture device, white balance adjustment method, storage medium, and integrated circuit

InactiveUS8040391B2Easy to adjustReduce colorColor signal processing circuitsImage signalComputer science

Owner:PANASONIC CORP

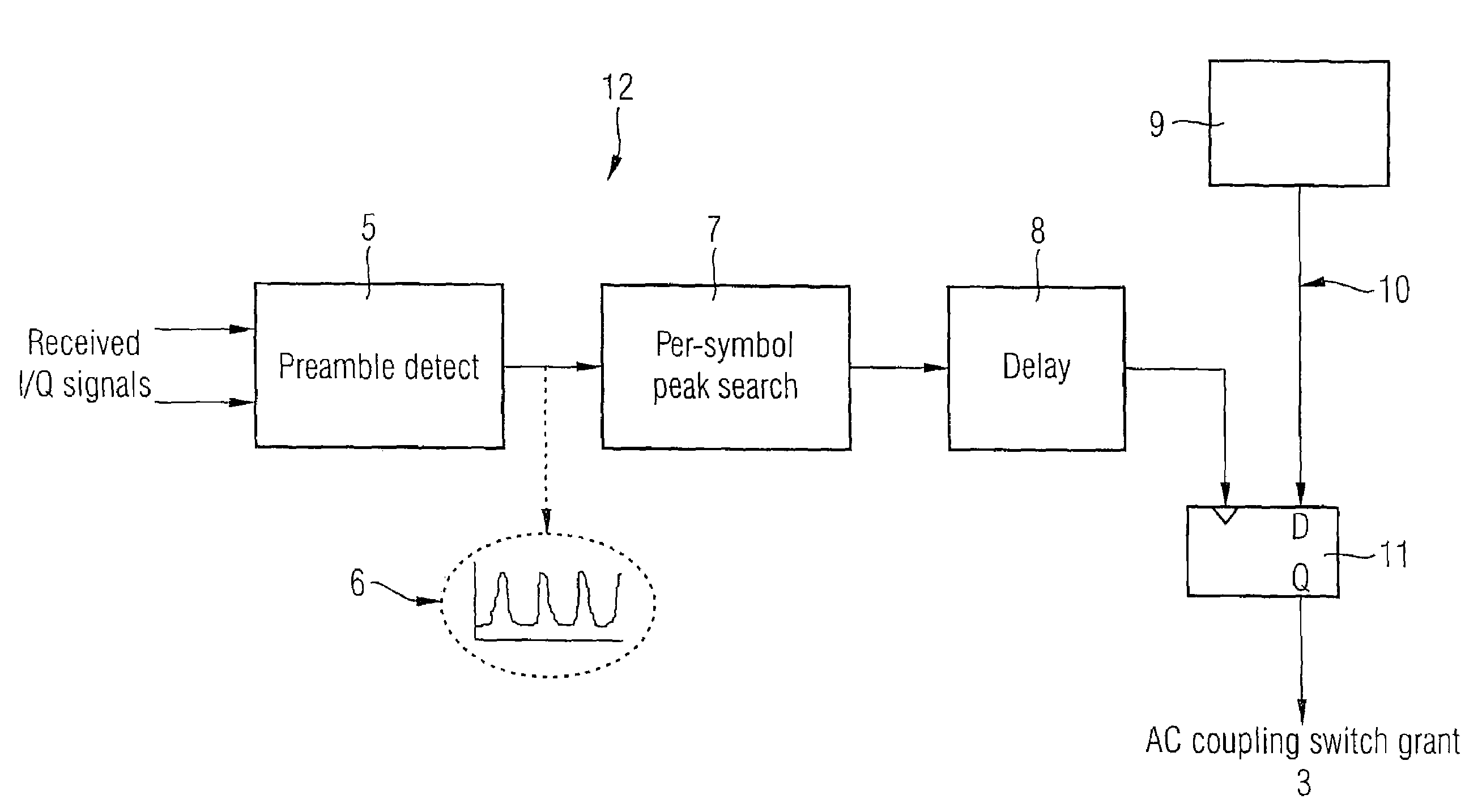

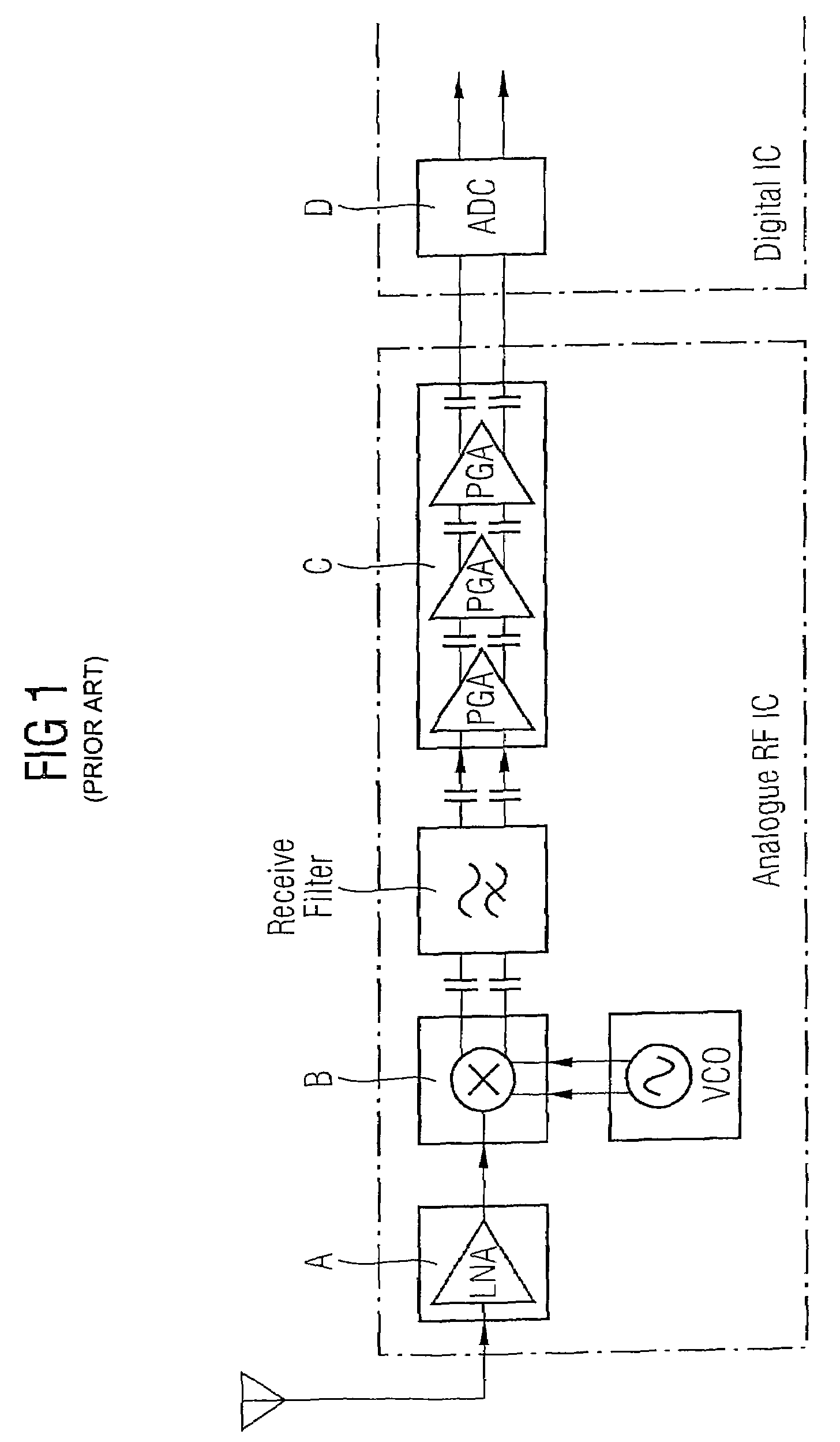

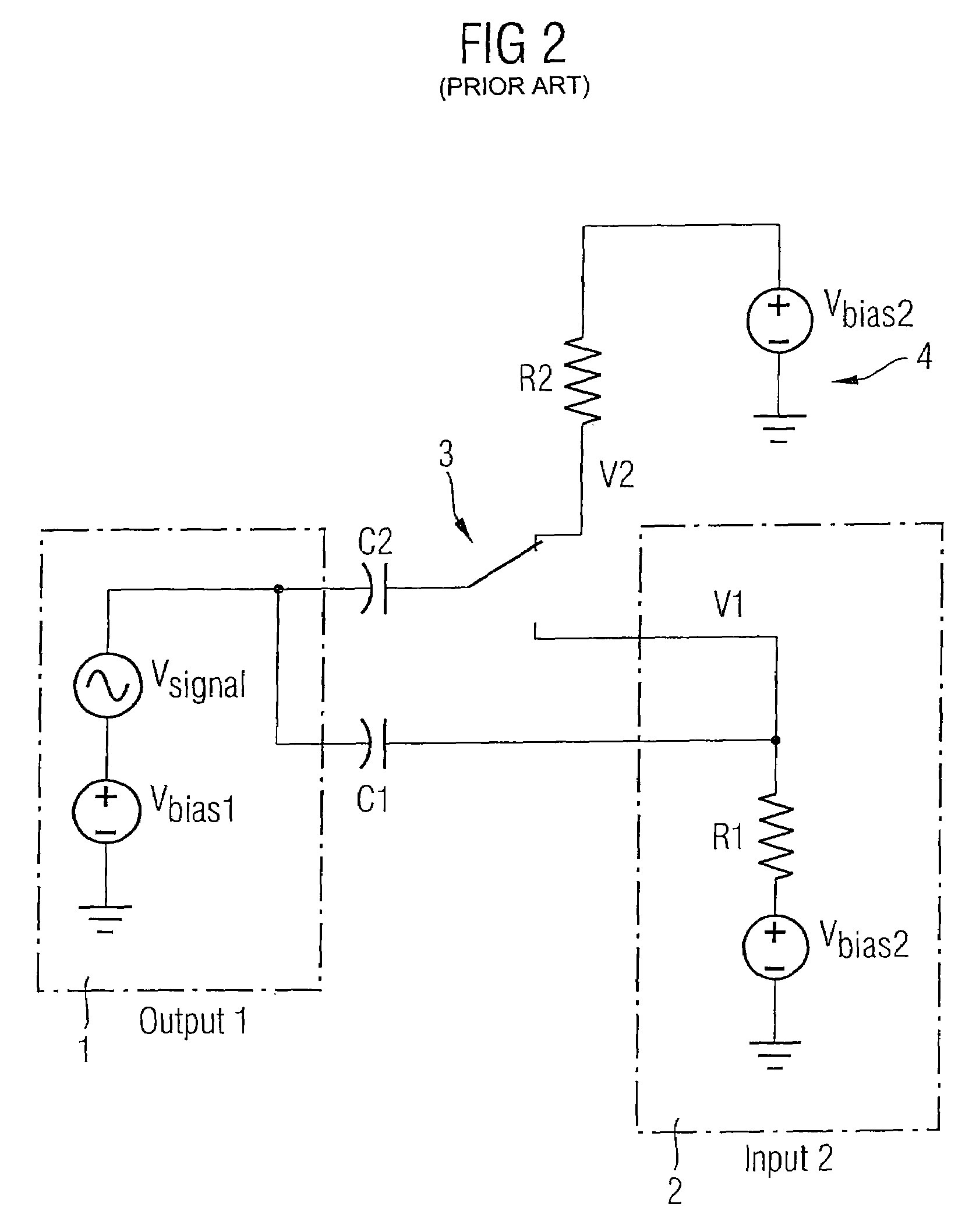

AC coupling bandwidth switch

InactiveUS7643575B2Significant reductionSmall circuitError preventionDc level restoring means or bias distort correctionCouplingEngineering

The present invention relates to receiver equipment with AC-coupled receiver circuits and AC coupling filters. A switch connected between a first stage and a second stage among the receiver circuits is adapted to switch from a high coupling corner frequency, for rapid settling of a signal during preparation of data reception, to a low corner frequency, for low signal distortion during data reception. The receiver circuits are adapted to use known properties in the signal to perform the switch at a time when the short term DC-components of the signal are as low as possible.

Owner:INTEL CORP

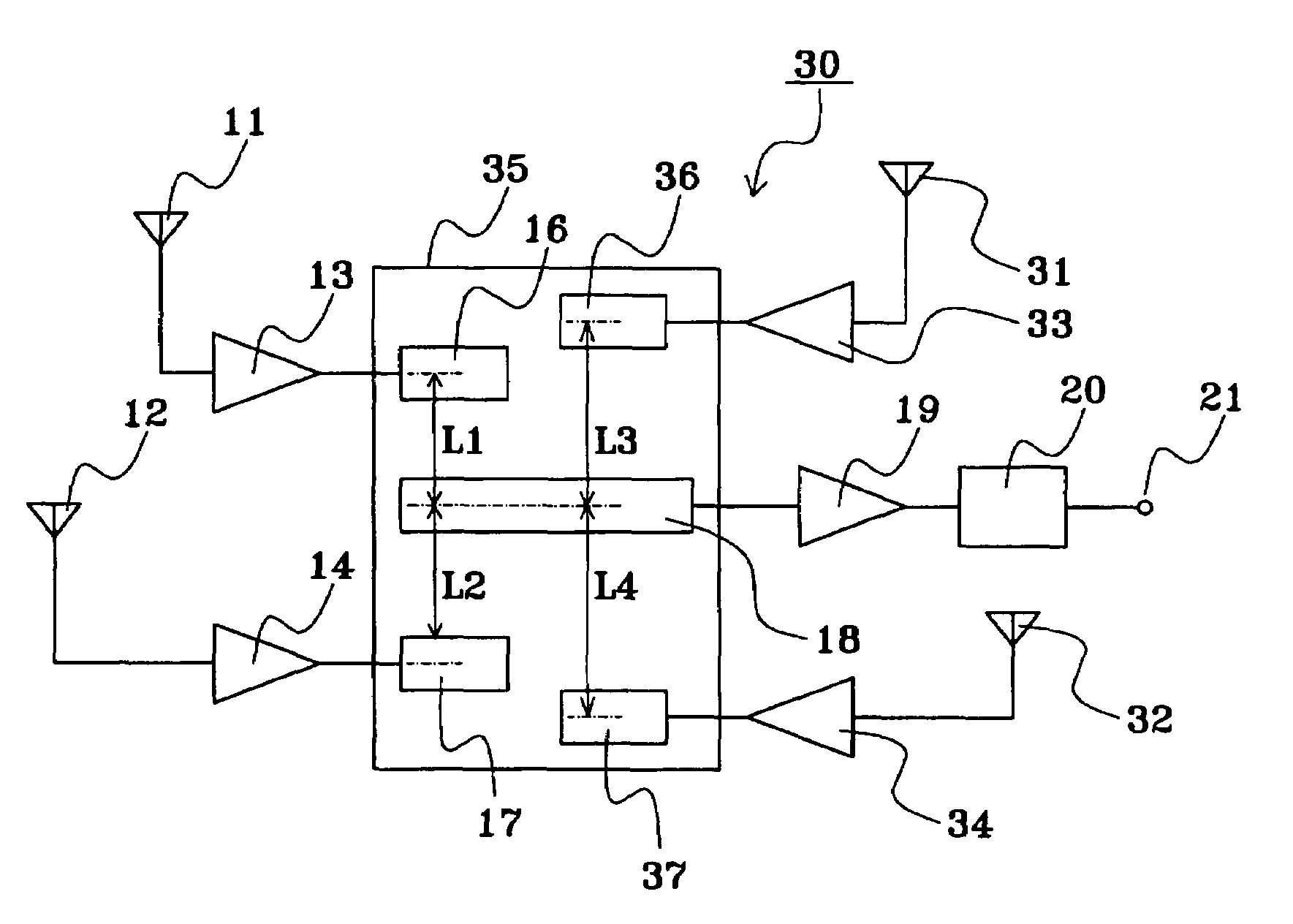

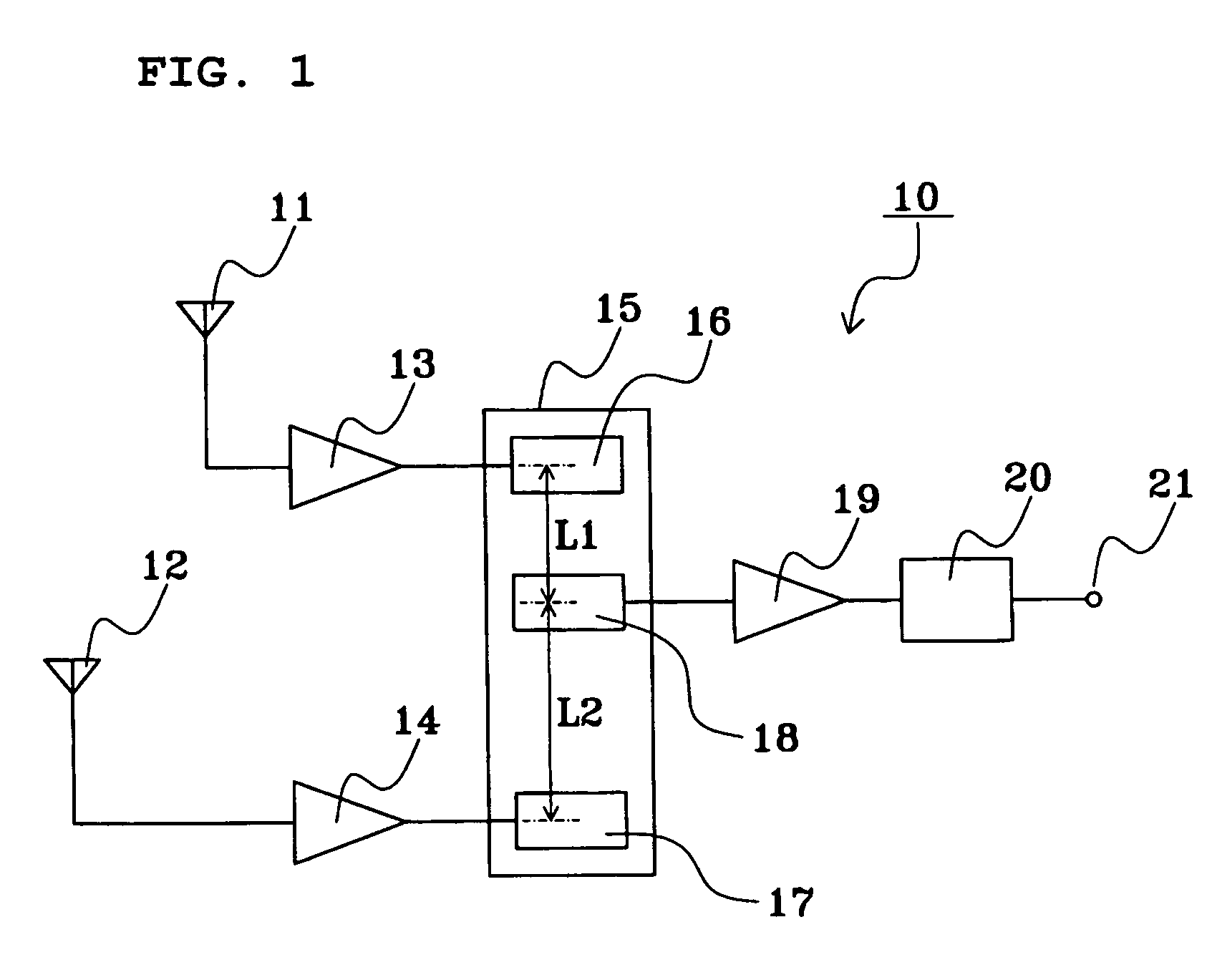

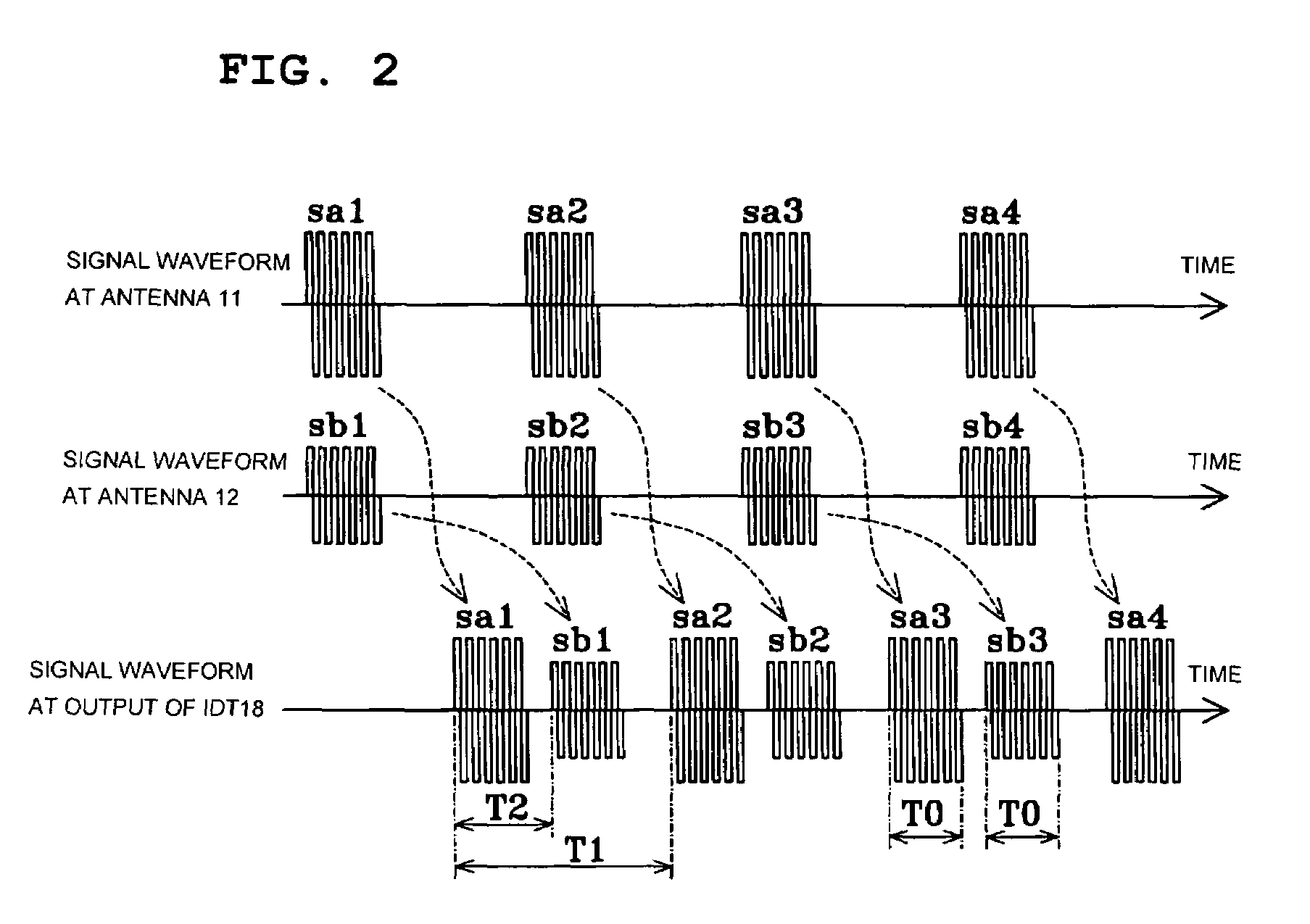

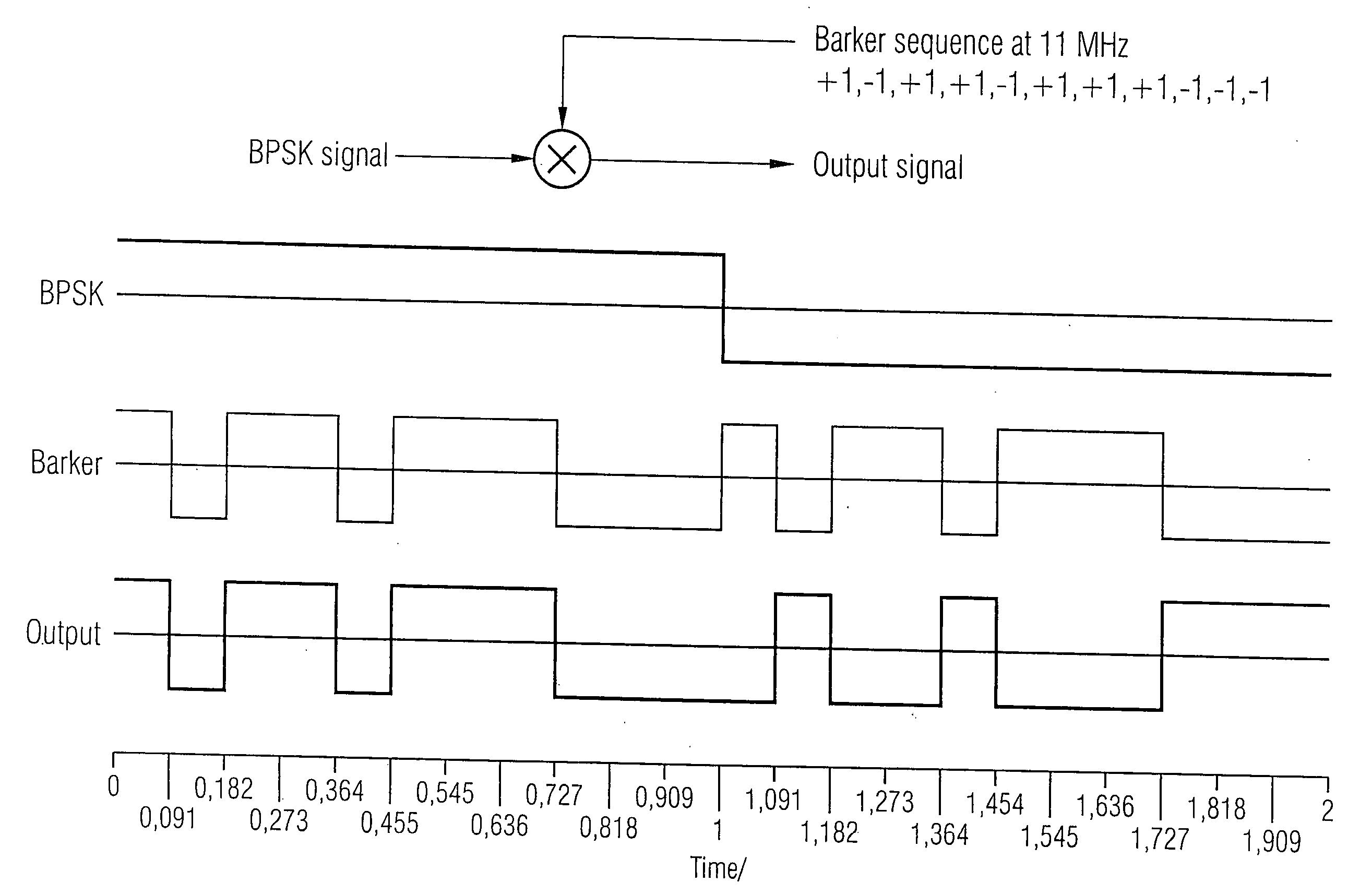

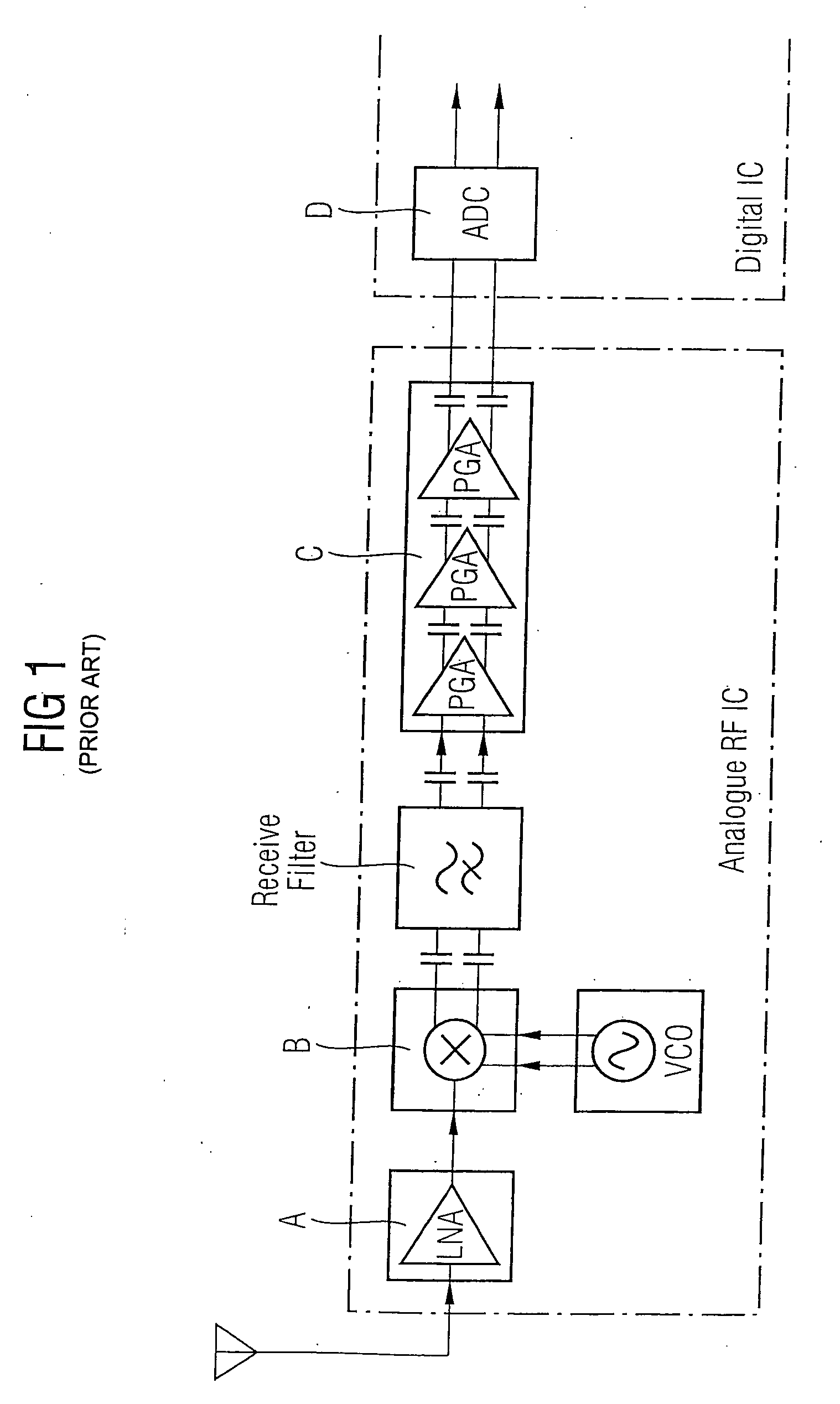

Radio receiving apparatus

InactiveUS7522894B2Simple and small circuitSmall circuitSpatial transmit diversityPiezoelectric/electrostriction/magnetostriction machinesAudio power amplifierDetector circuits

A radio receiving apparatus includes two receiving antennas, two upstream RF amplifiers, a SAW filter having two input IDTs and an output IDT, a downstream RF amplifier, and a detector circuit. The antennas are connected to the respective input IDTs via the respective upstream RF amplifiers. The detector circuit is connected via the downstream RF amplifier to the output IDT, which receives a signal from each of the two input IDTs. The distances from the center of the output IDT to the centers of the input IDTs differ from one another. The SAW filter functions as two band-pass filters, two delay circuits connected to the respective band-pass filters, and a combiner circuit for combining the outputs from the delay circuits.

Owner:MURATA MFG CO LTD

AC coupling bandwidth switch

InactiveUS20070071144A1Significant reductionSmall circuitError preventionDc level restoring means or bias distort correctionCouplingShort terms

The present invention relates to receiver equipment with AC-coupled receiver circuits and AC coupling filters. A switch connected between a first stage and a second stage among the receiver circuits is adapted to switch from a high coupling corner frequency, for rapid settling of a signal during preparation of data reception, to a low corner frequency, for low signal distortion during data reception. The receiver circuits are adapted to use known properties in the signal to perform the switch at a time when the short term DC-components of the signal are as low as possible.

Owner:INTEL CORP