Patents

Literature

38 results about "Floating point multiplier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Floating point multiplier is done using VHDL .Implementation in VHDL (VHSIC Hardware Description Language) is used because it allow direct implementation on the hardware while in other language we have to convert them into HDL then only can be implemented on the hardware.

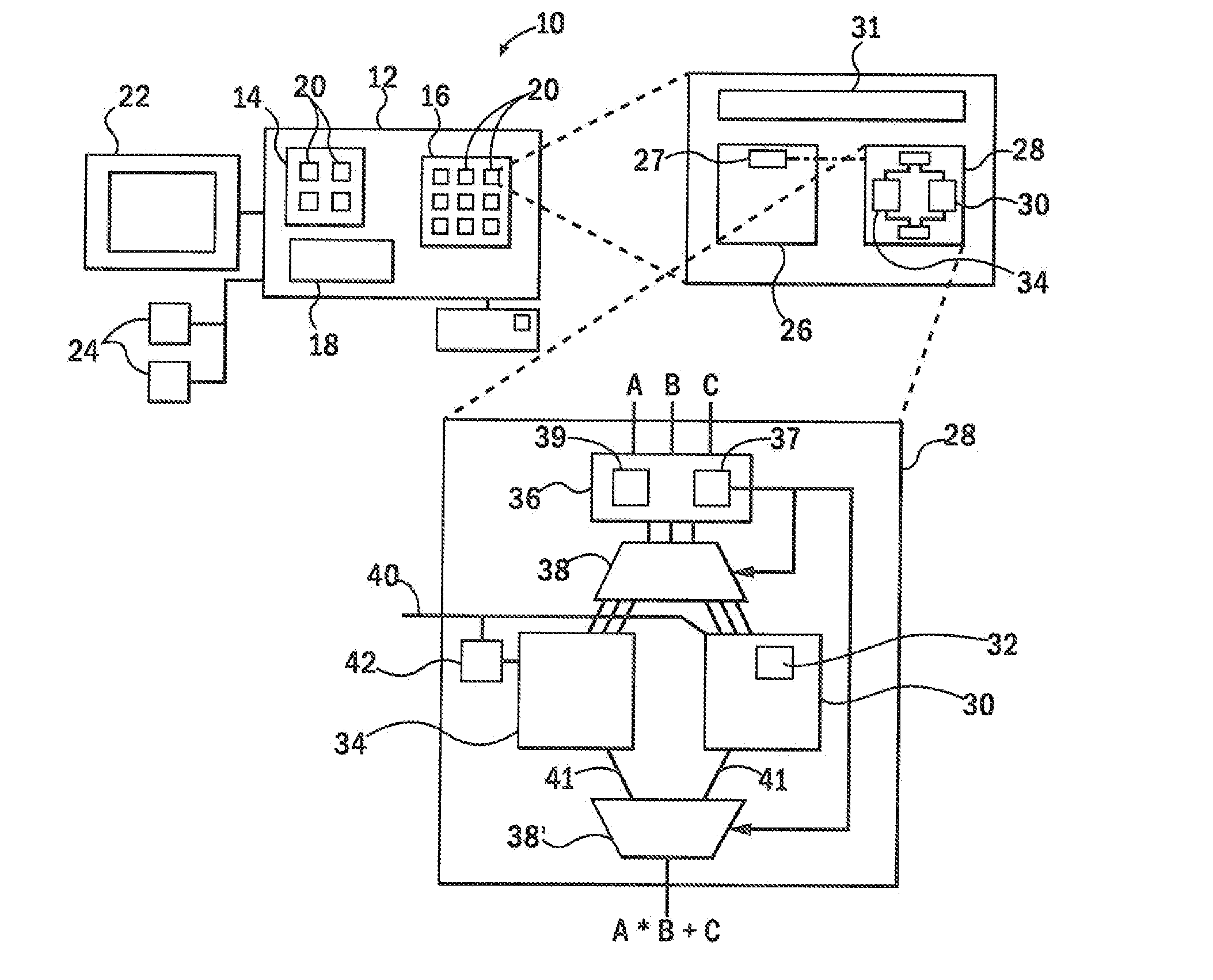

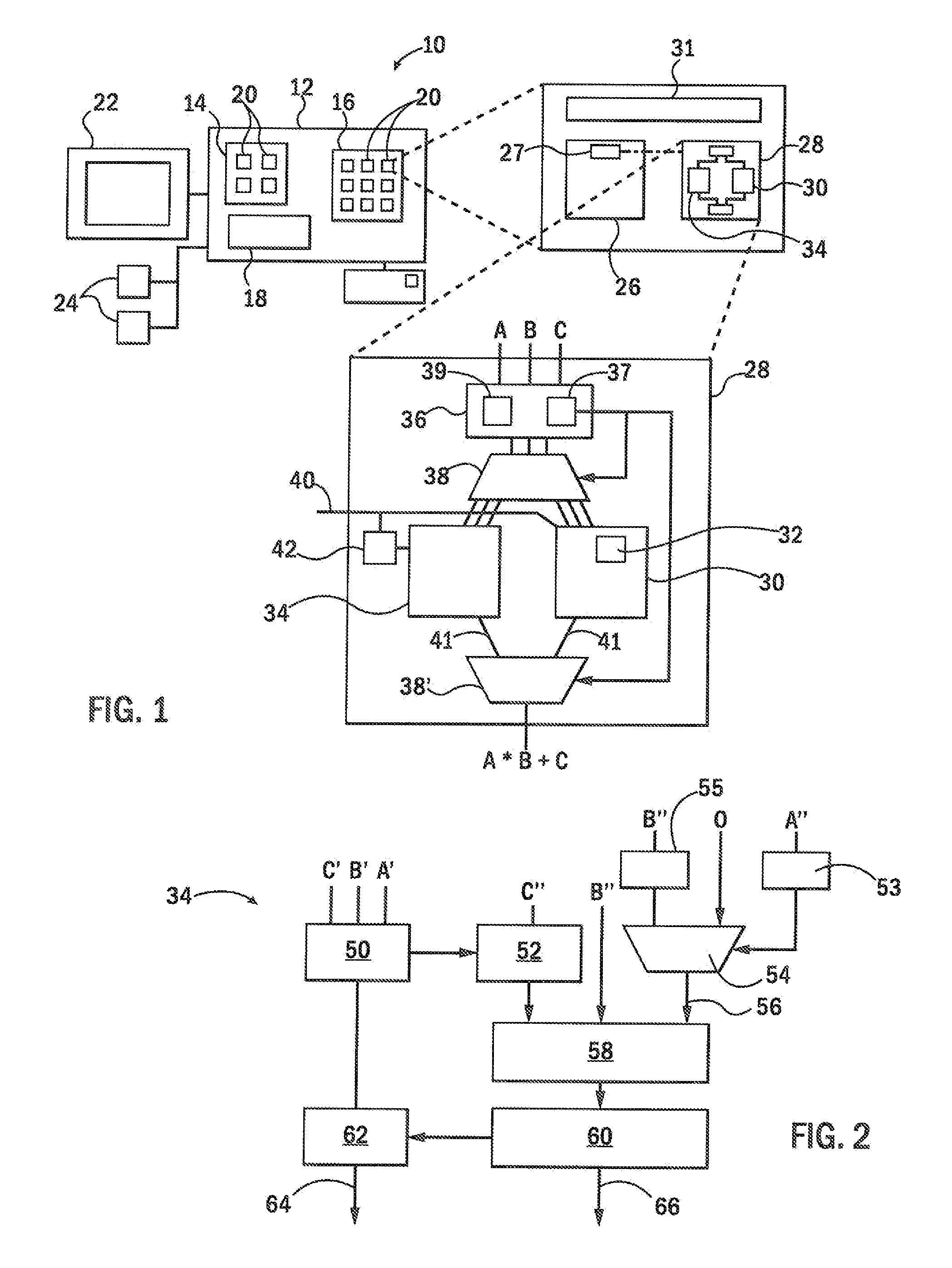

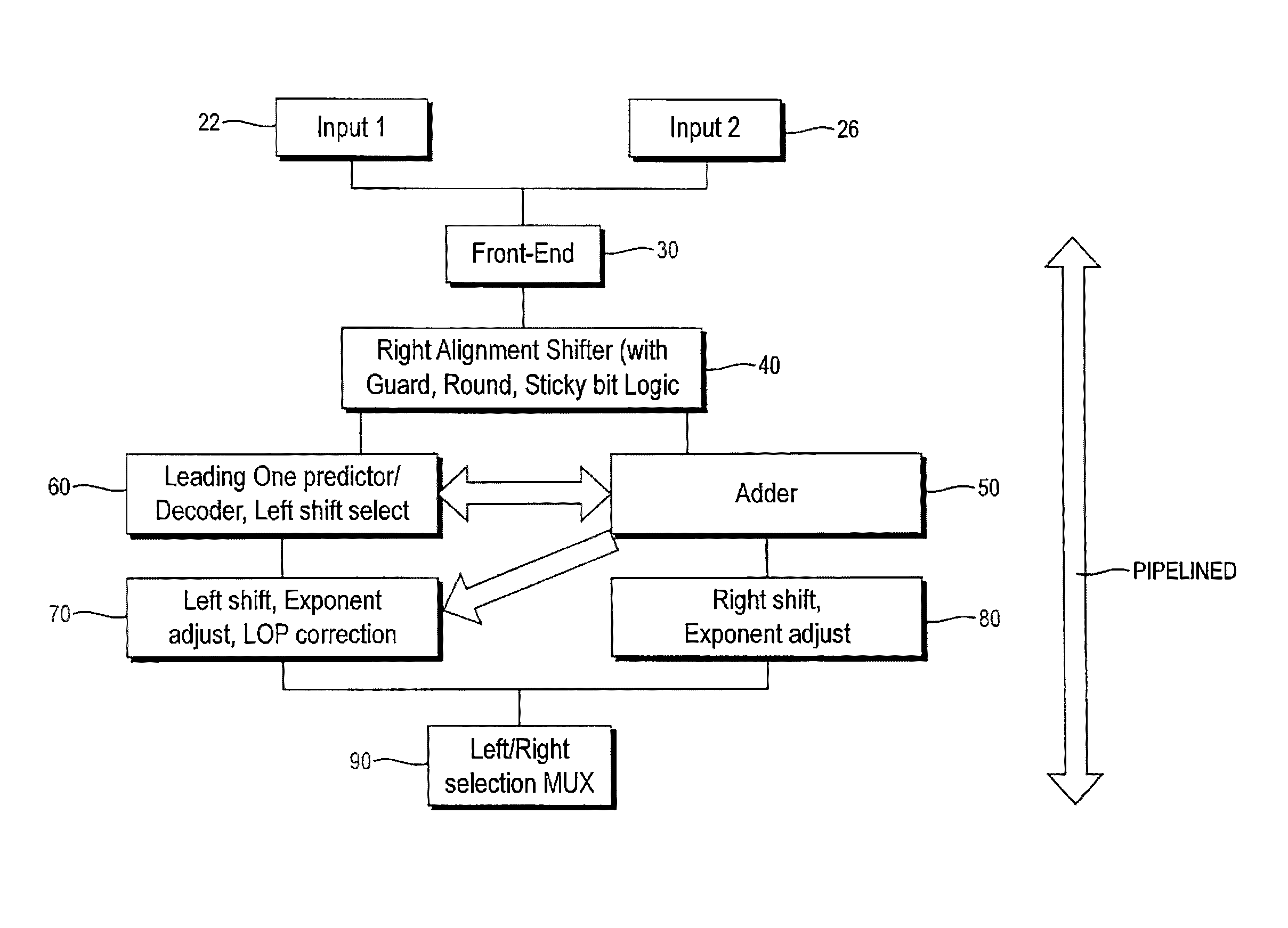

Floating point multiplier/accumulator with reduced latency and method thereof

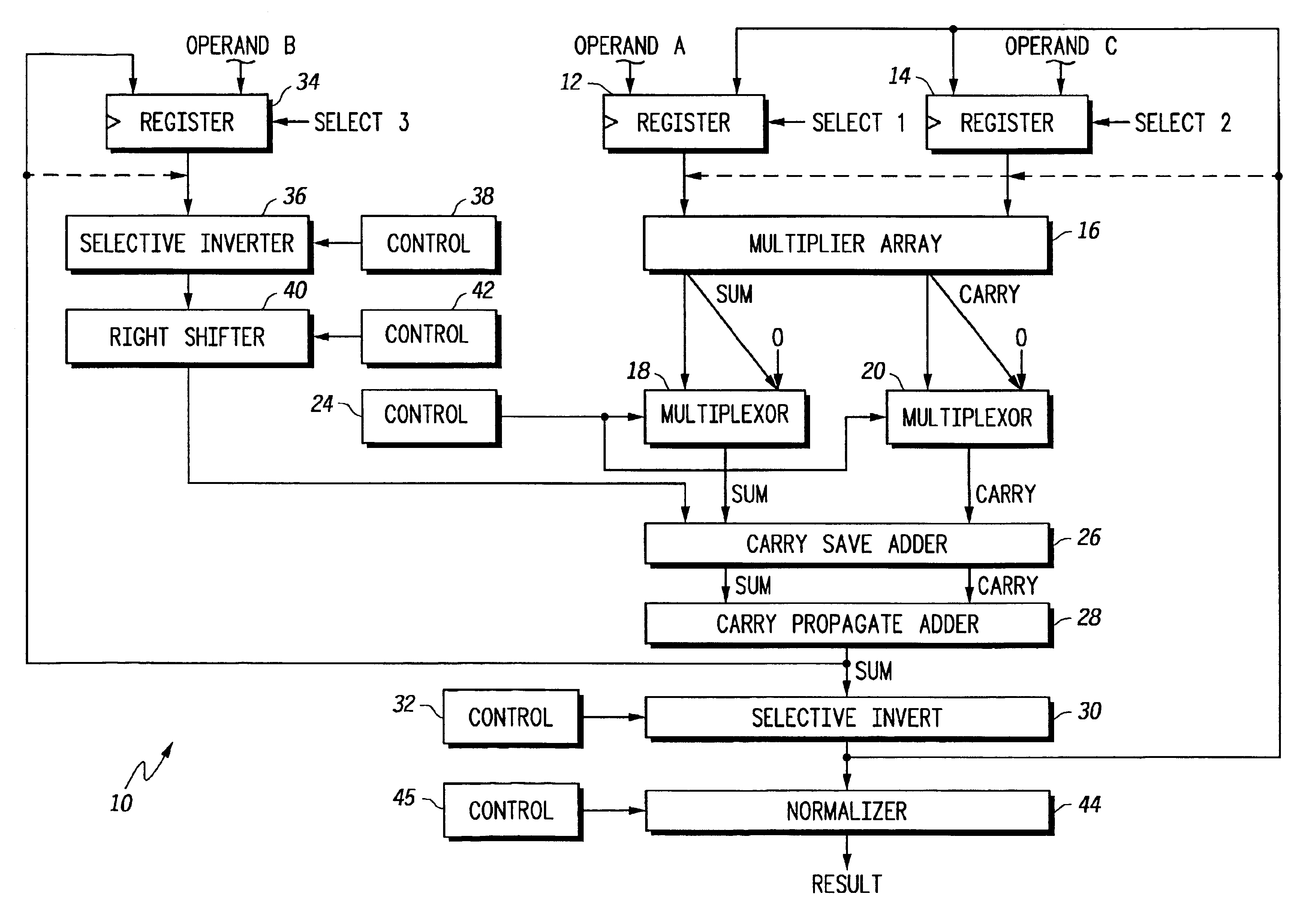

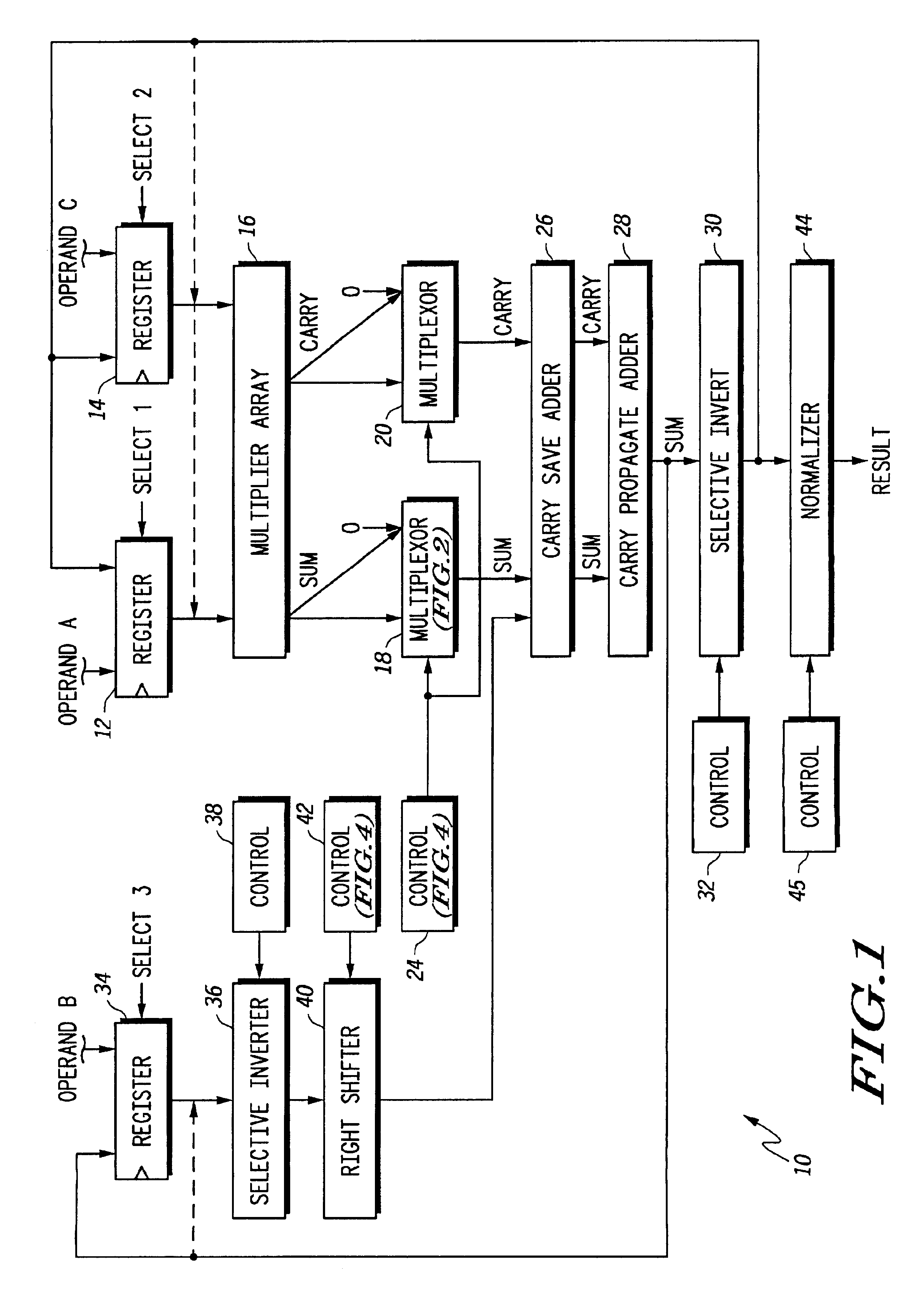

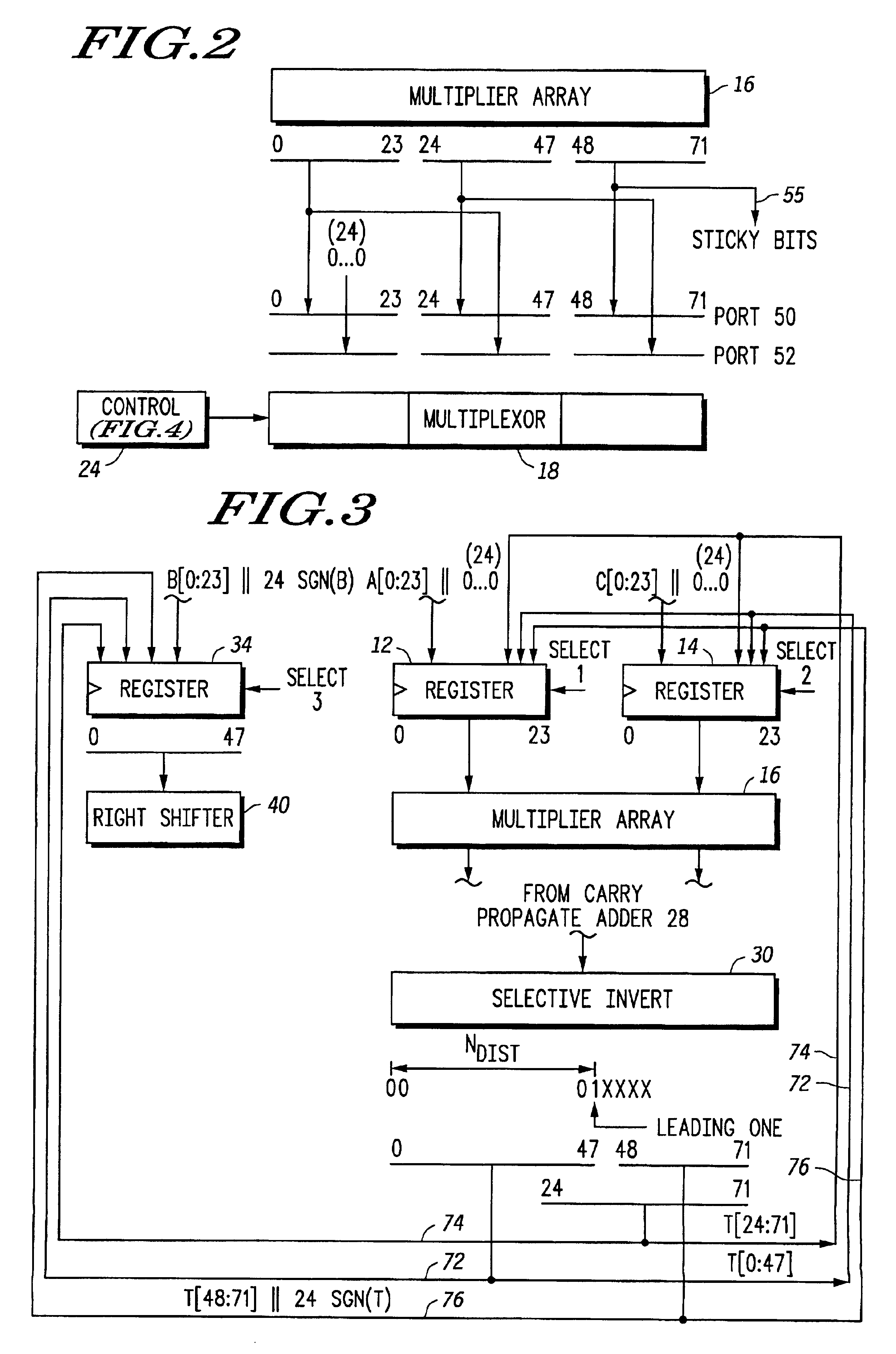

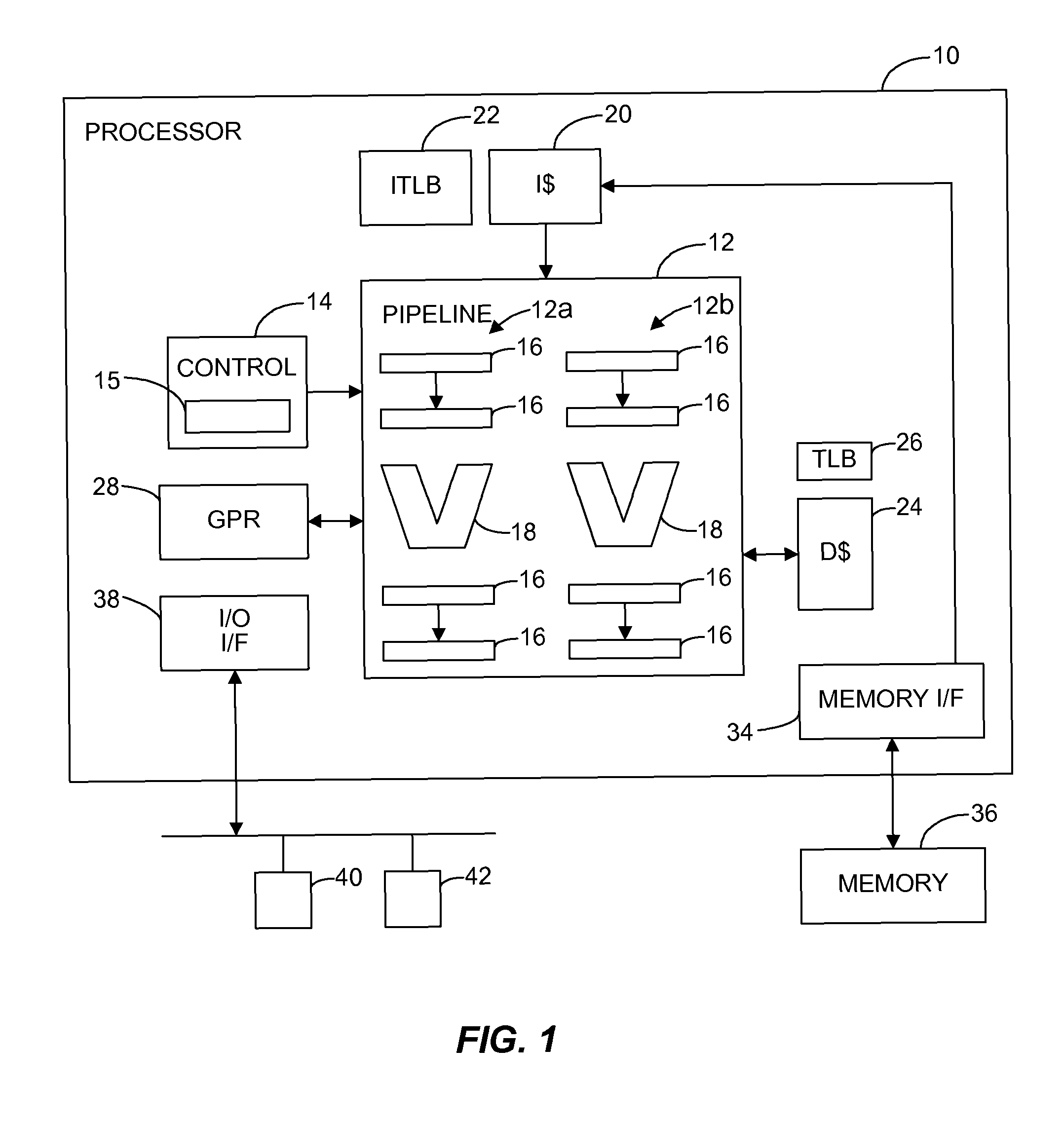

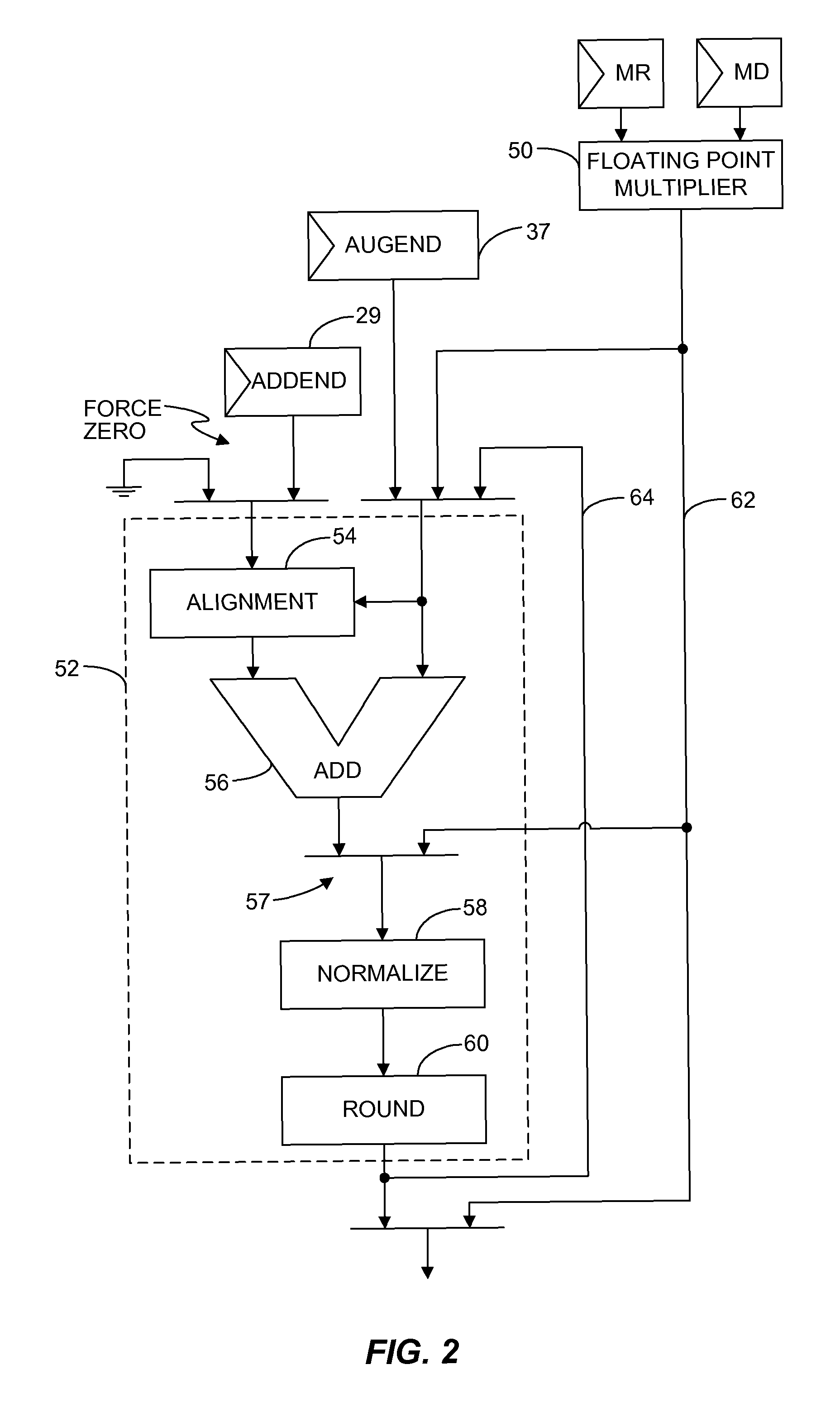

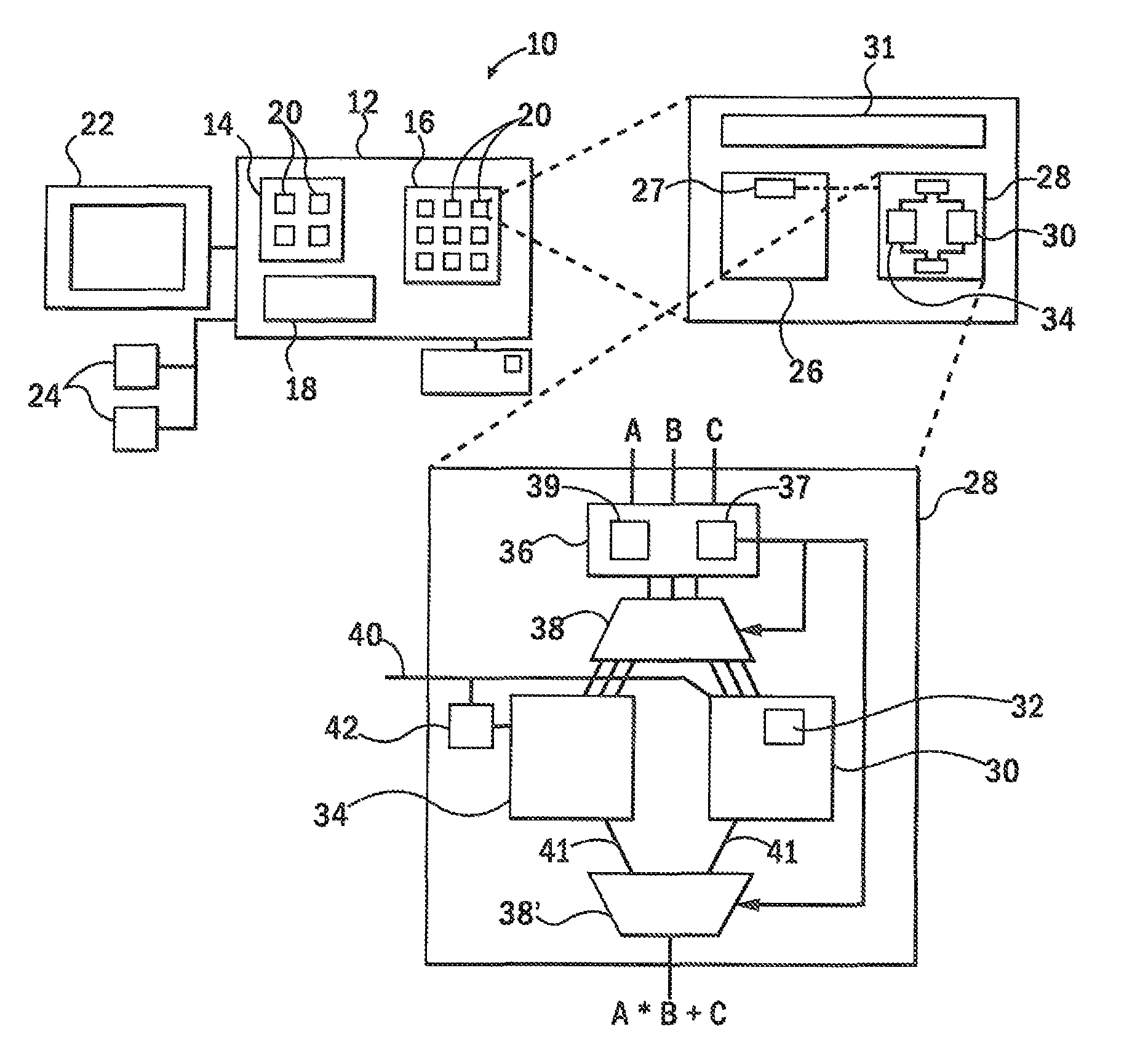

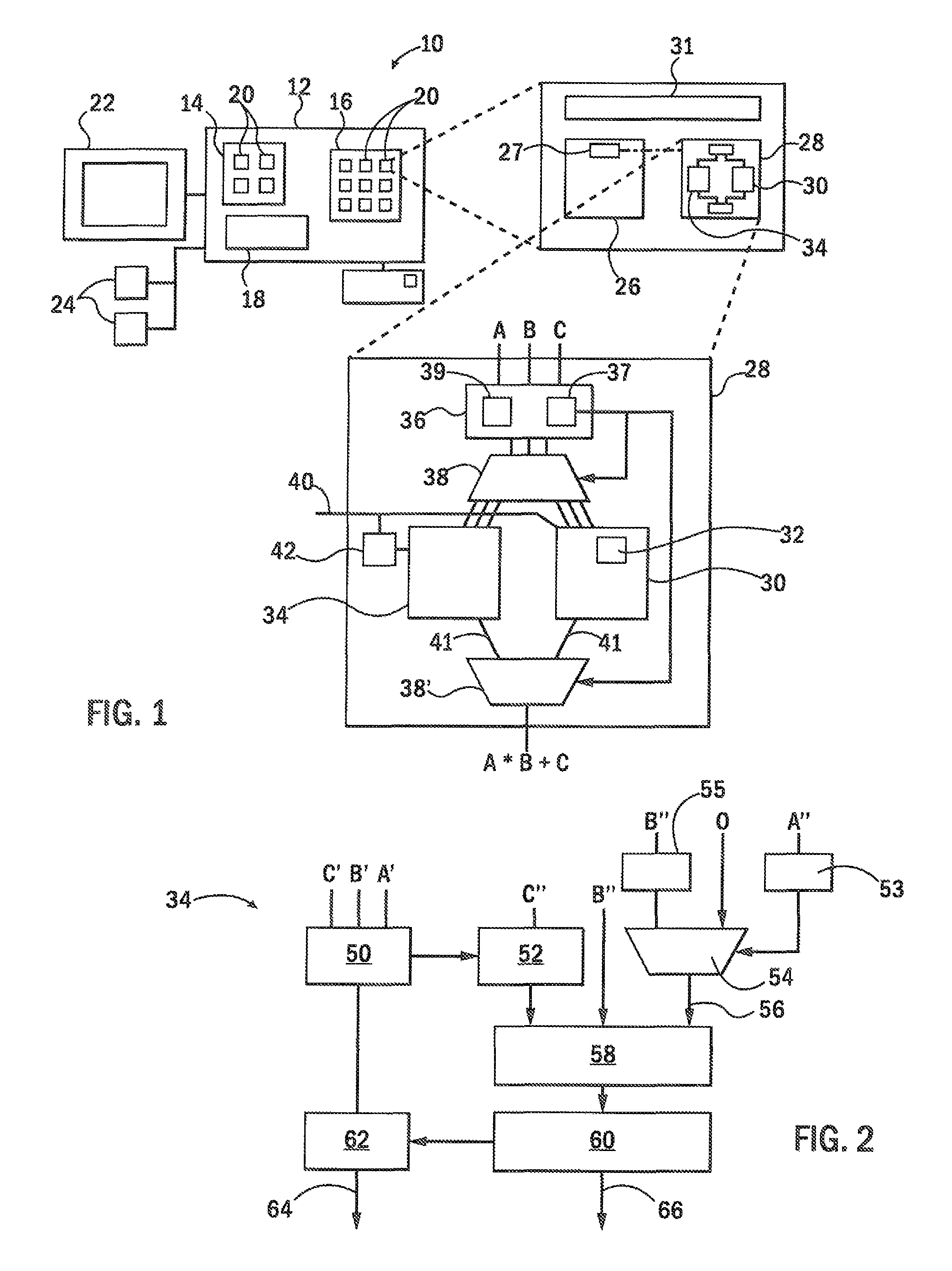

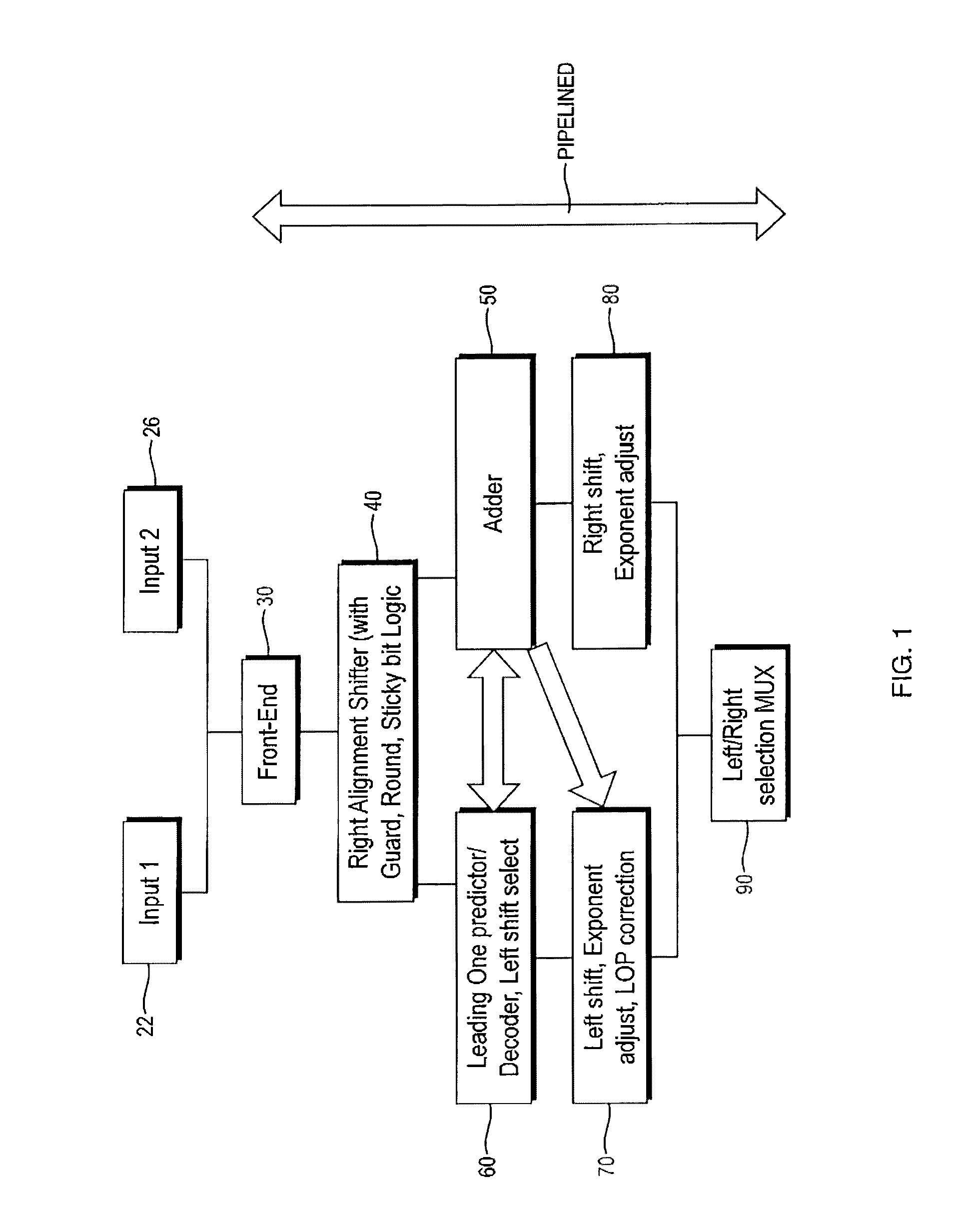

A circuit (10) for multiplying two floating point operands (A and C) while adding or subtracting a third floating point operand (B) removes latency associated with normalization and rounding from a critical speed path for dependent calculations. An intermediate representation of a product and a third operand are selectively shifted to facilitate use of prior unnormalized dependent resultants. Logic circuitry (24, 42) implements a truth table for determining when and how much shifting should be made to intermediate values based upon a resultant of a previous calculation, upon exponents of current operands and an exponent of a previous resultant operand. Normalization and rounding may be subsequently implemented, but at a time when a new cycle operation is not dependent on such operations even if data dependencies exist.

Owner:NORTH STAR INNOVATIONS

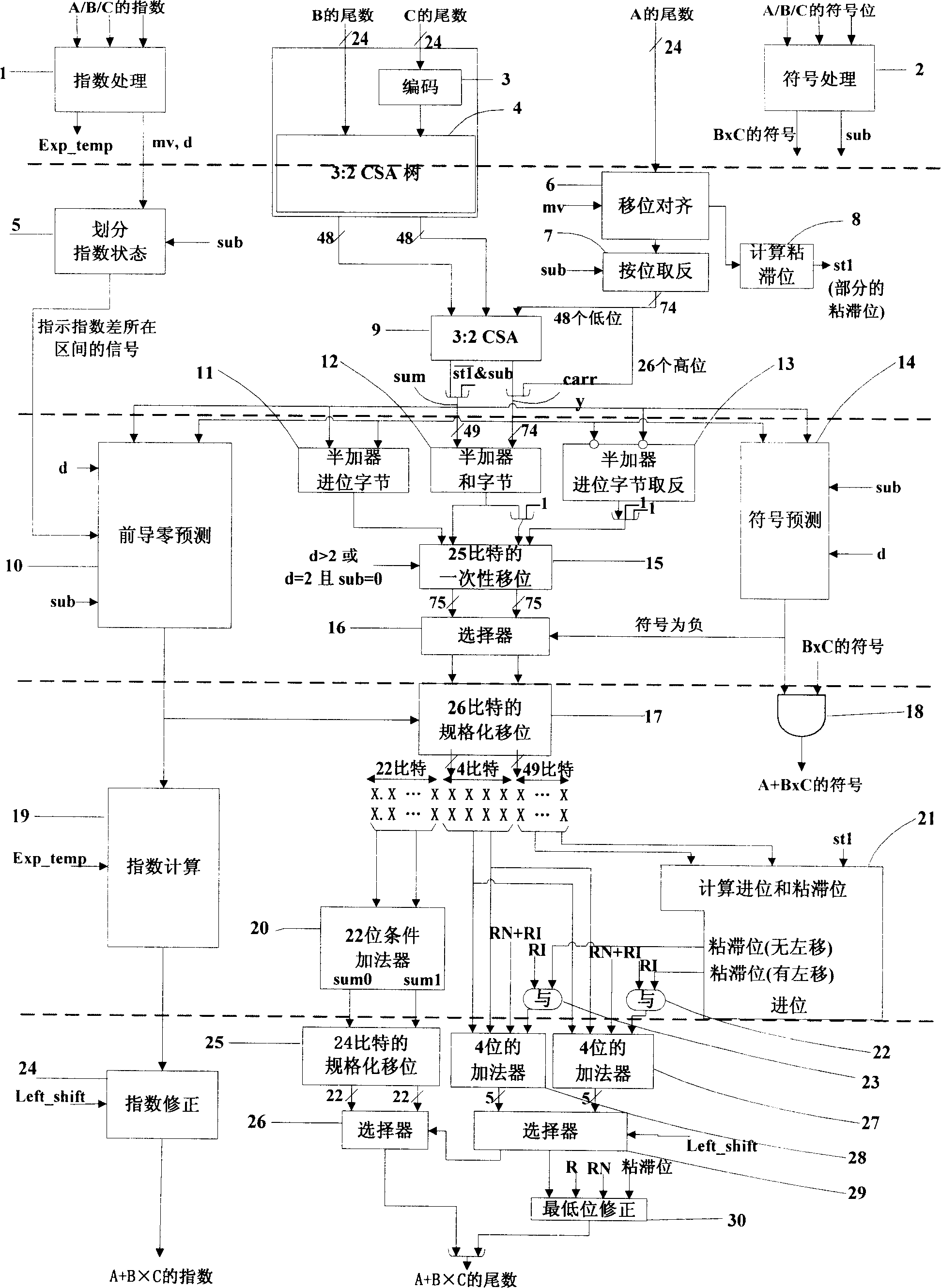

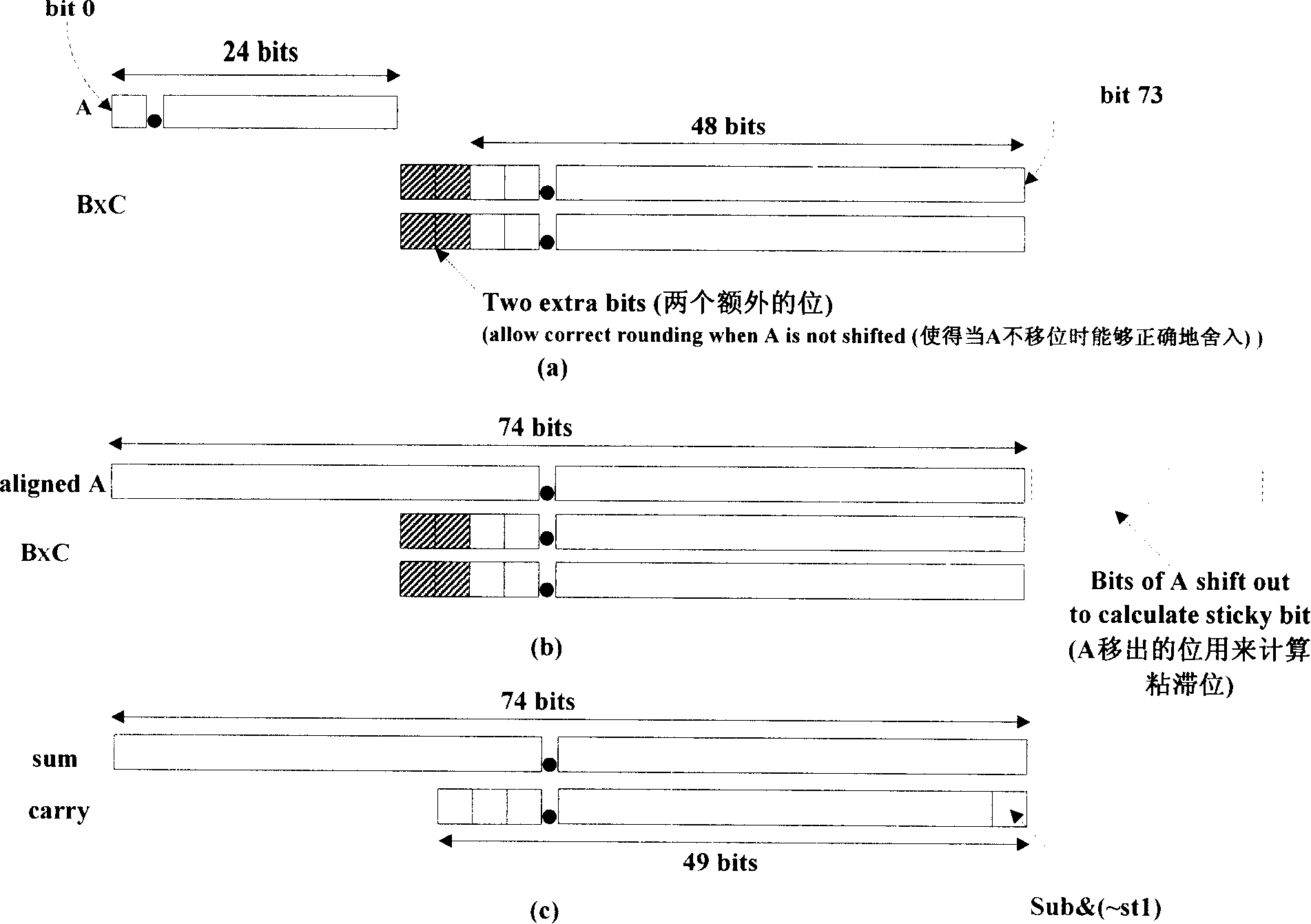

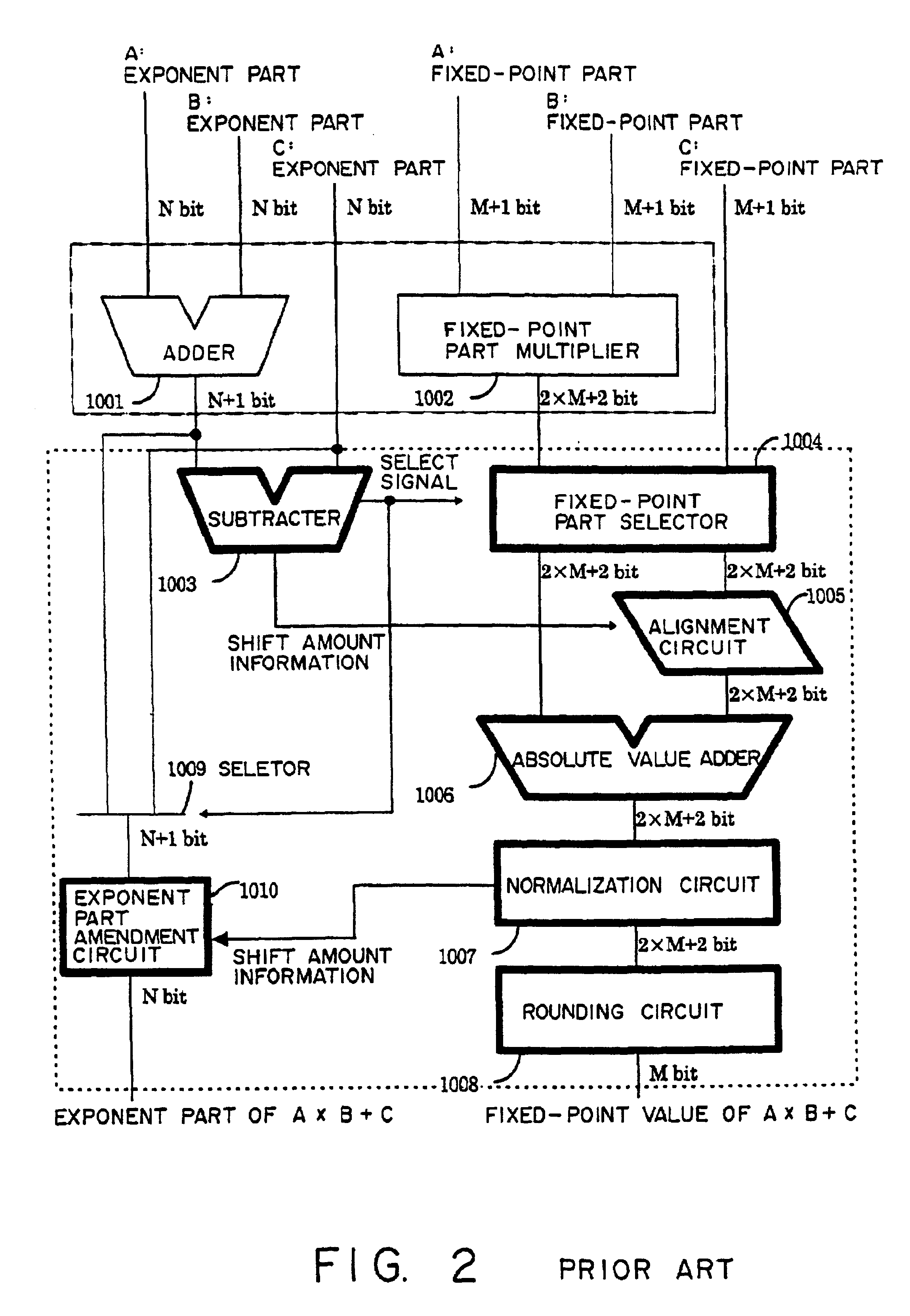

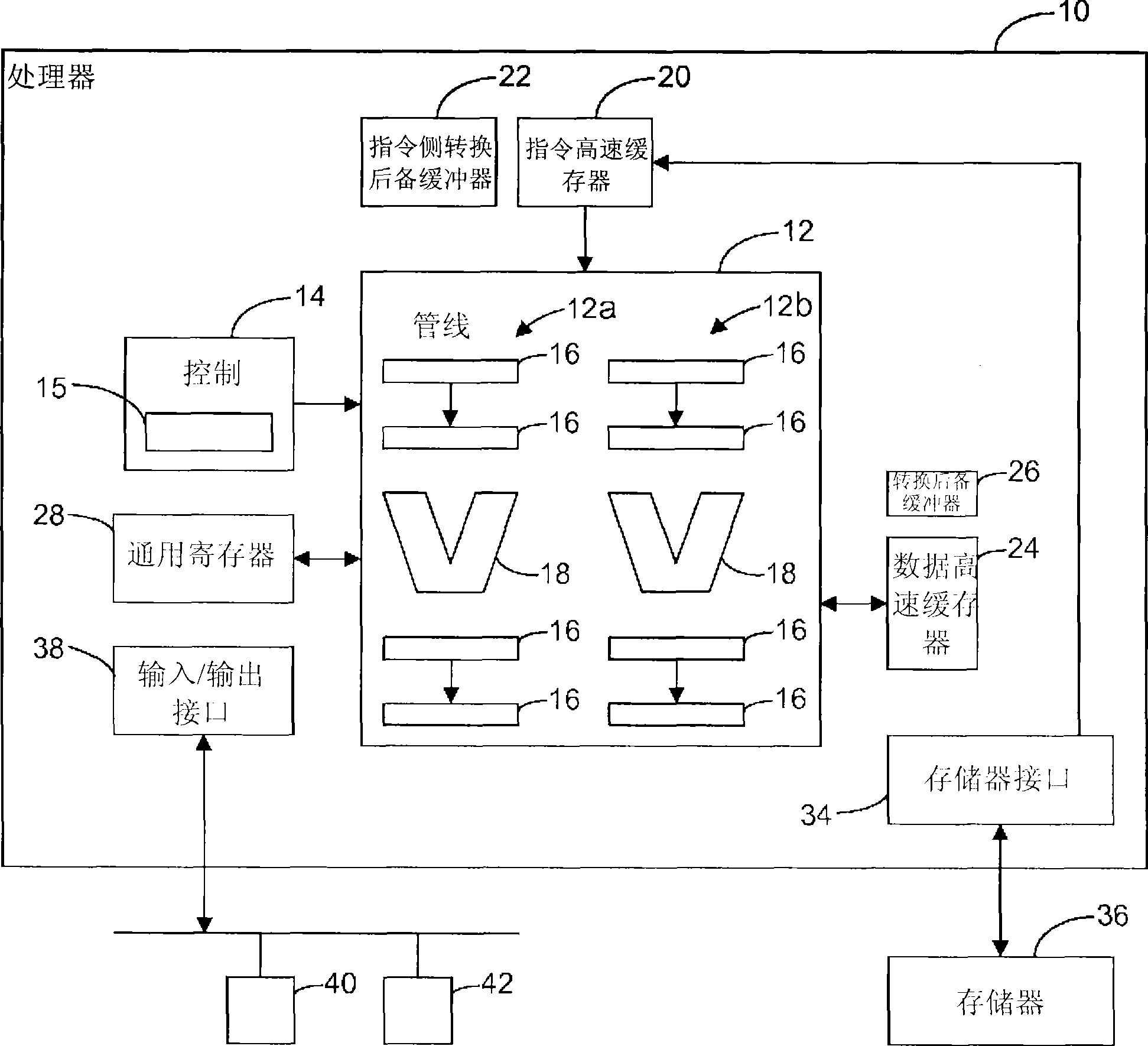

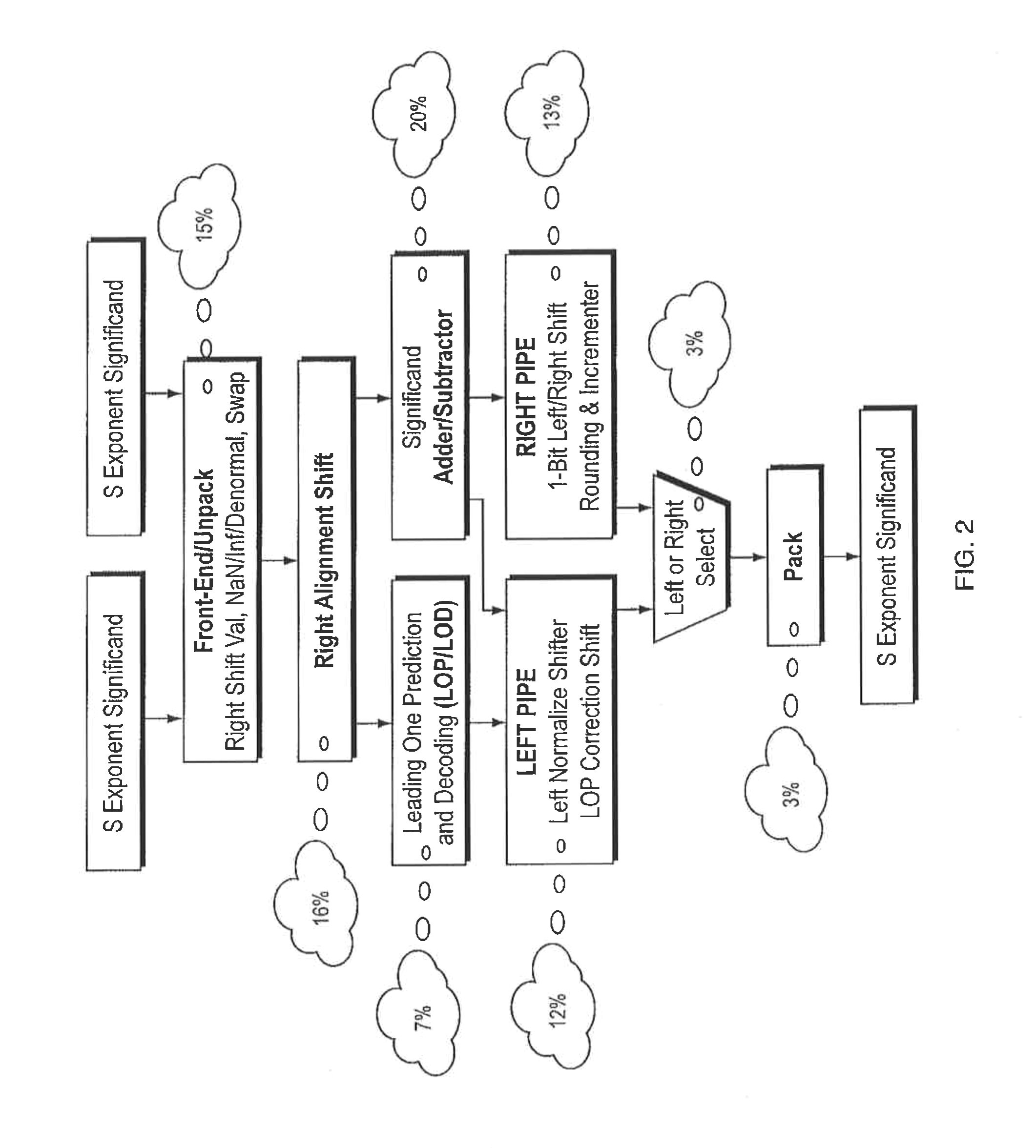

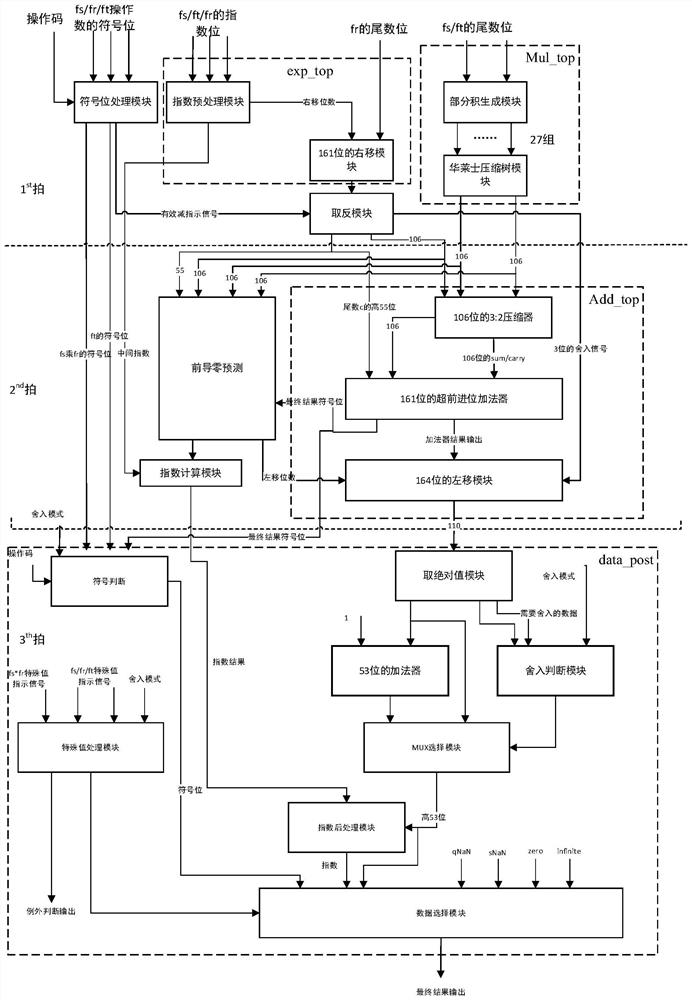

5-grade stream line structure of floating point multiplier adder integrated unit

ActiveCN101174200AHigh precisionDigital data processing detailsSymbol of a differential operatorLeading zero

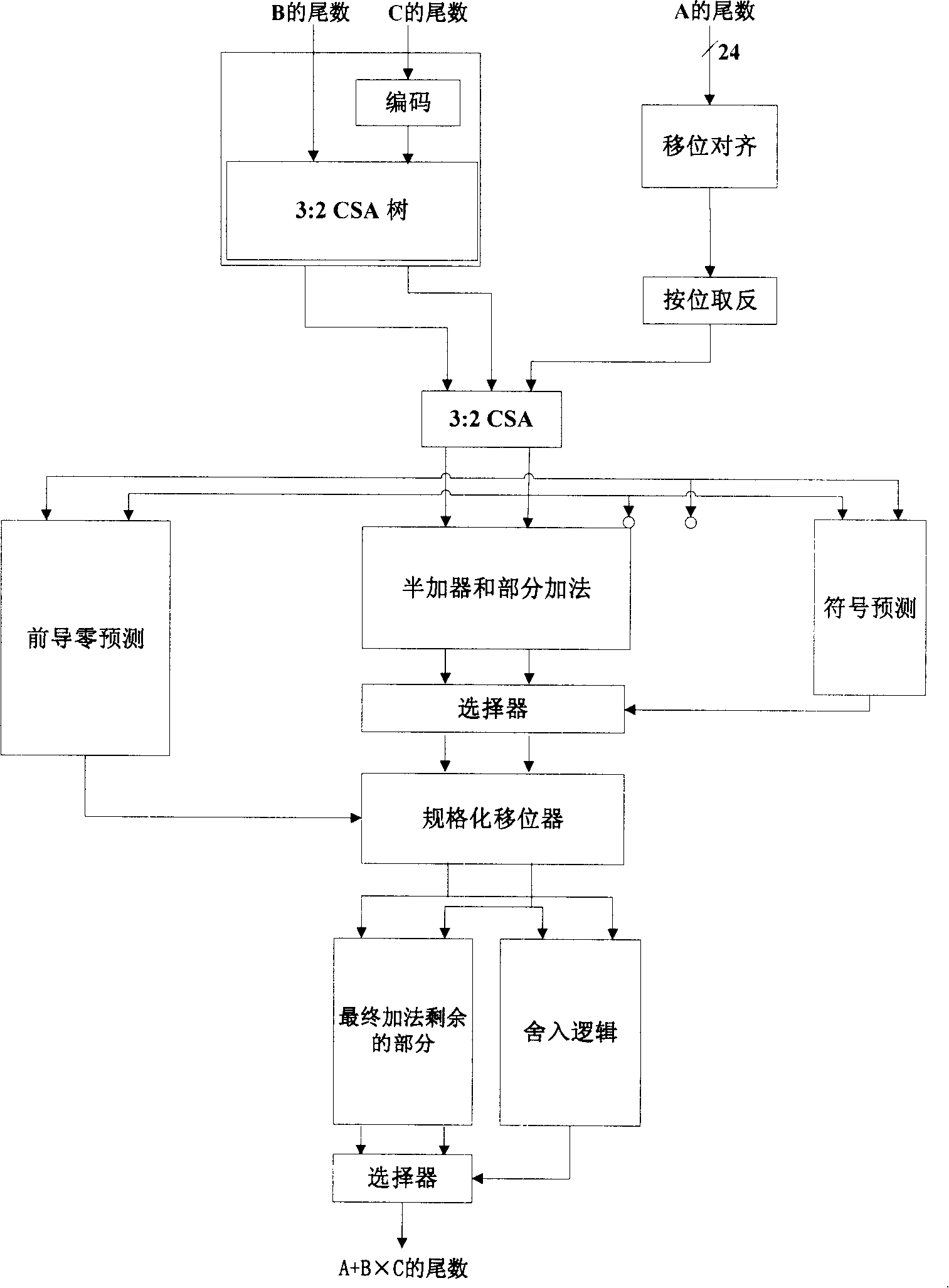

The invention discloses a design of a full pipeline of a single precision floating point multiplication-add fused unit, which realizes multiplication-add operation in the form of A+B x C. the multiplication-add operation is realized in the following five pipelines: in the first stage pipeline, exponential difference is calculated and a part of the multiplication is completed; in the second stage pipeline, A and B x C are aligned according to the exponential difference, effective subtraction and complement are performed, the rest multiplication is completed, simultaneously, the exponent is divided into six states, and the calculation method of normalized shift amount in different states are different; in the third stage pipeline, the number of leading zero is pre-estimated, simultaneously the sign of the final result is synchronously pre-estimated, and finally first stage normalized shift is performed; in the fourth stage pipeline, second normalized shift is performed first, and then addition and a part of half adjust are performed; in the last stage pipeline, addition and half adjust are completed, exponential terms are amended, and third stage normalized shift is completed in the spacing of the half adjust. The invention has the advantages that high performance and high precision are realized in the condition of low hardware cost.

Owner:TSINGHUA UNIV

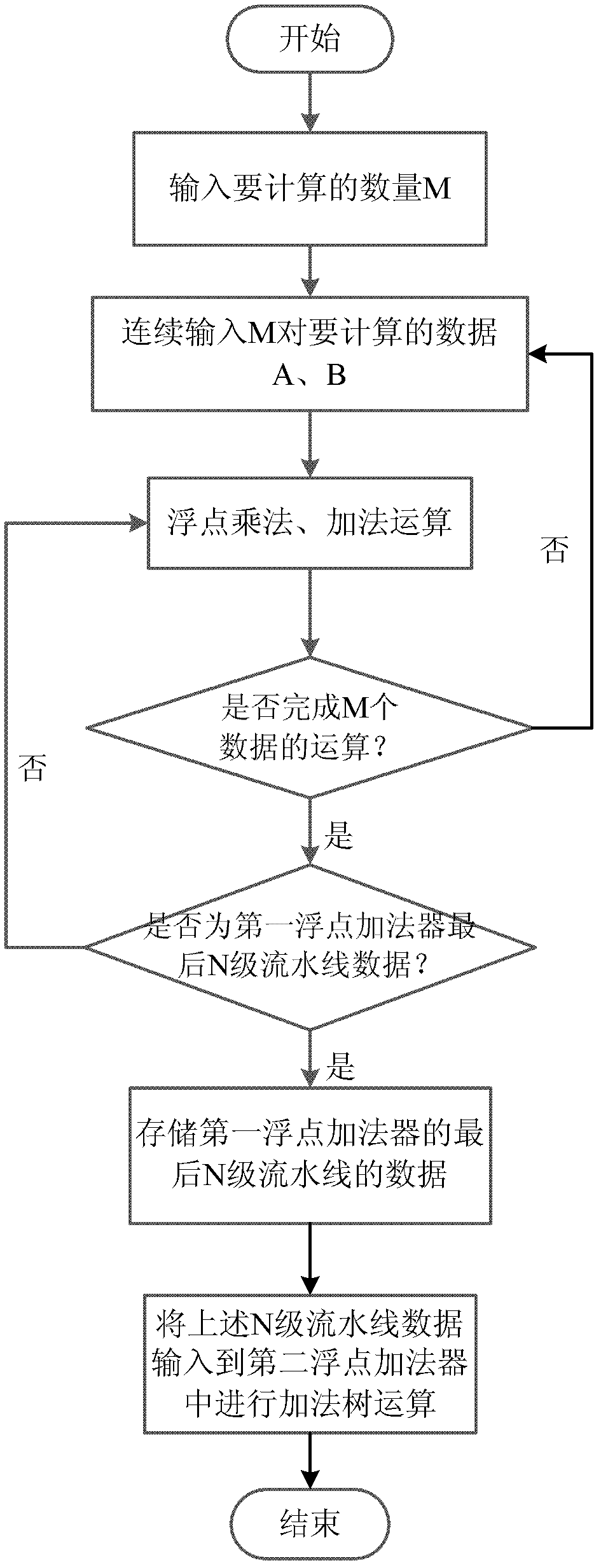

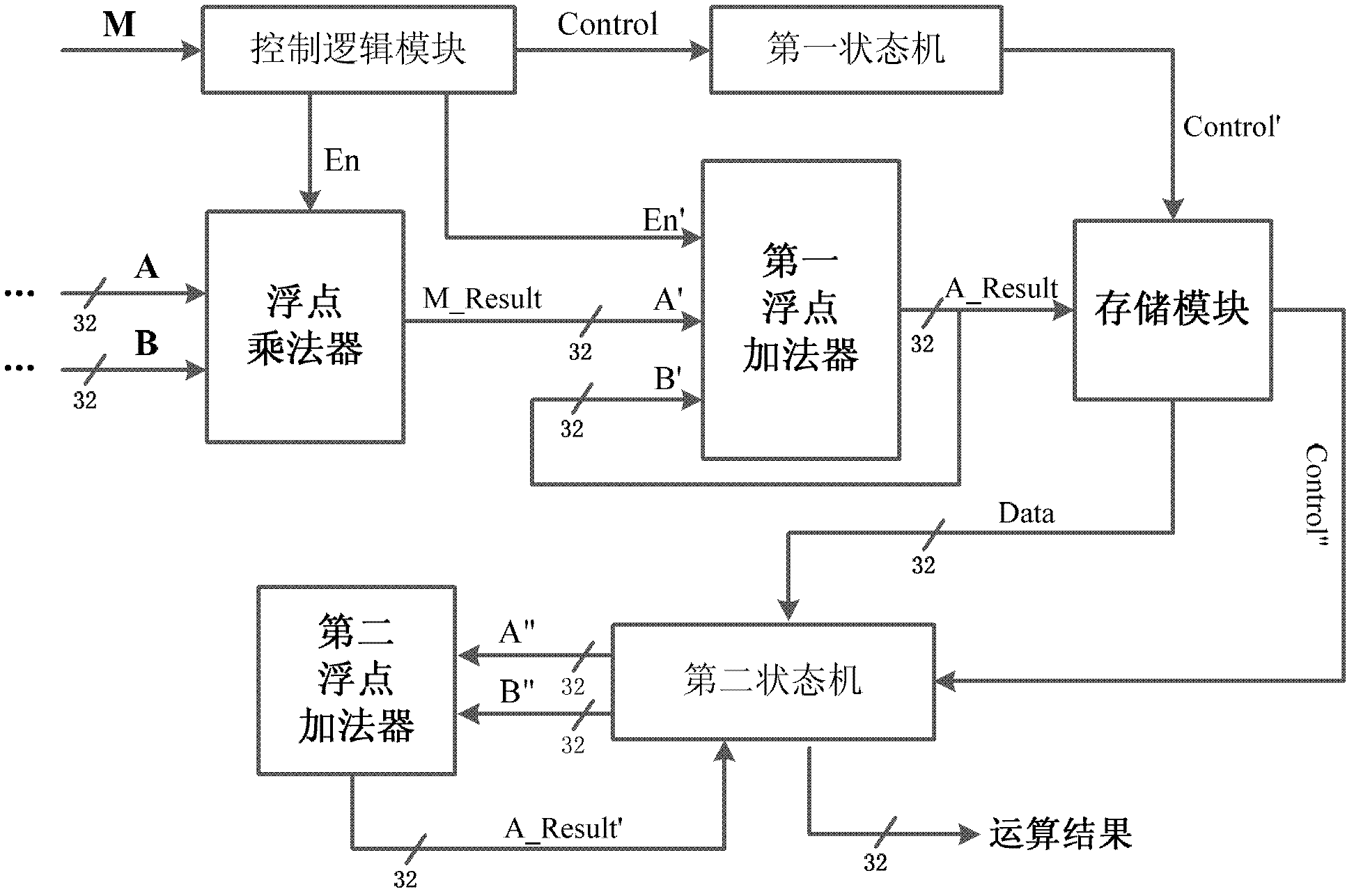

Water floating point multiply-accumulate method based on FPGA

InactiveCN102629189AEasy to implementRun fastComputation using non-contact making devicesConcurrent instruction executionComputer scienceOperating speed

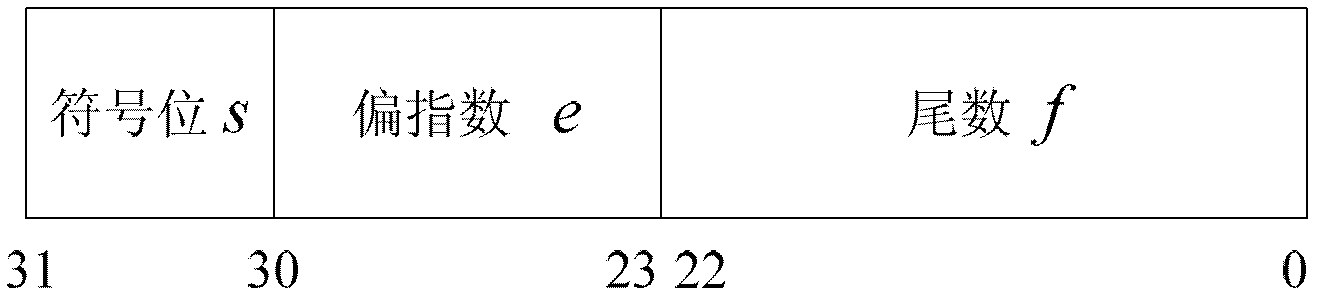

The invention discloses a water floating point multiply-accumulate method based on FPGA. The method comprises the following steps: firstly inputting a number M to undergo multiply-accumulate calculation, secondly, sequentially inputting M 32-bit binary floating point numbers A and B which are required to be calculated into floating-point multiplier to undergo multiplication till the operation of M data is accomplished, and simultaneously and continuously inputting the product result of the floating-point multiplier and the addition result of a first floating-point adder to the first floating-point adder to accomplish a part of summation operation to obtain a summation result, and thirdly, inputting data of the last N stage pipeline in the summation result obtained in step two into a second floating-point adder to be calculated to obtain the result of the whole multiply-accumulate process. The method has the advantages that the principle is simple, the universality is good, the operating speed can be improved, and the like.

Owner:HUNAN UNIV

Floating point multiplier with partial product shifting circuitry for result alignment

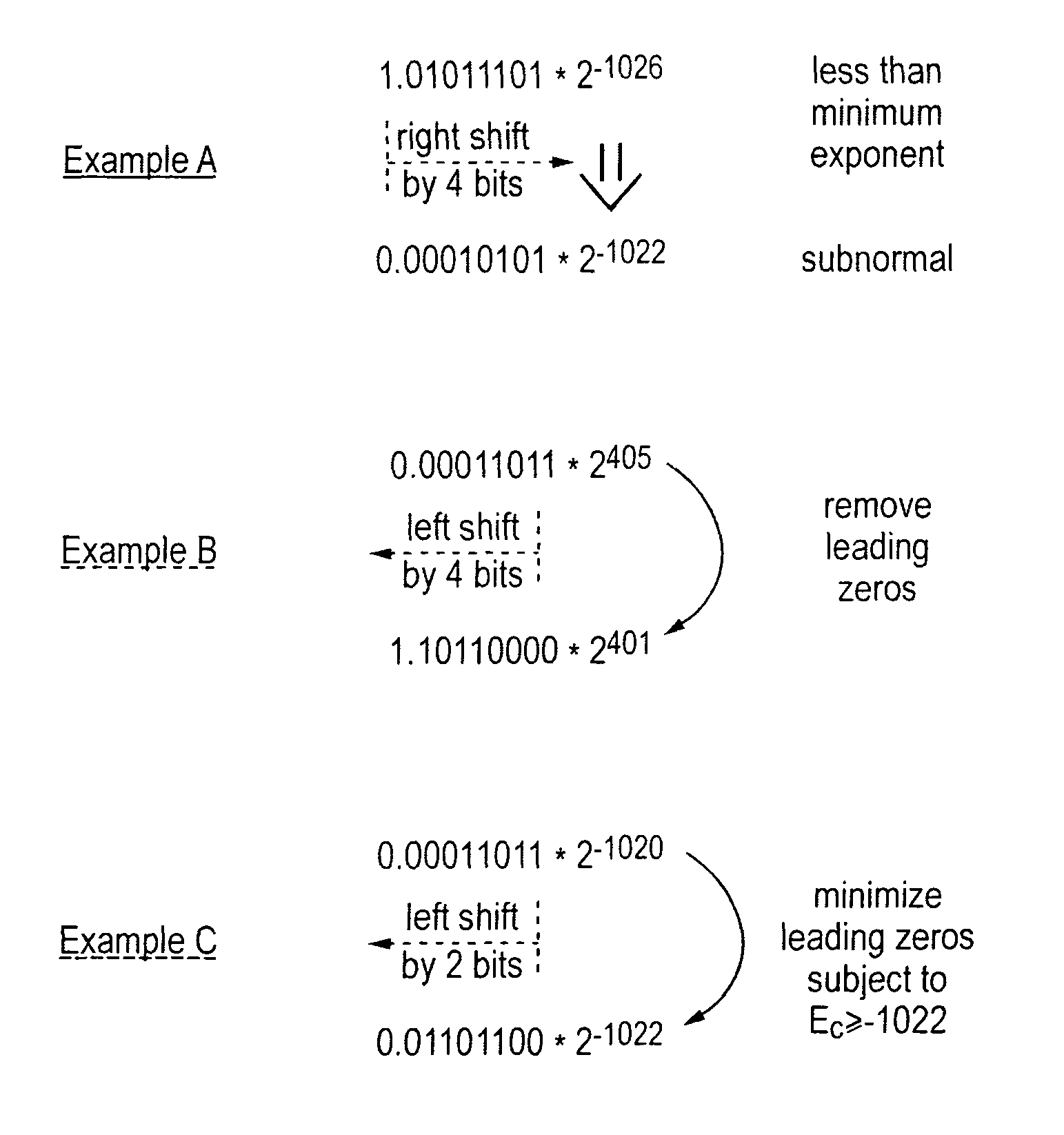

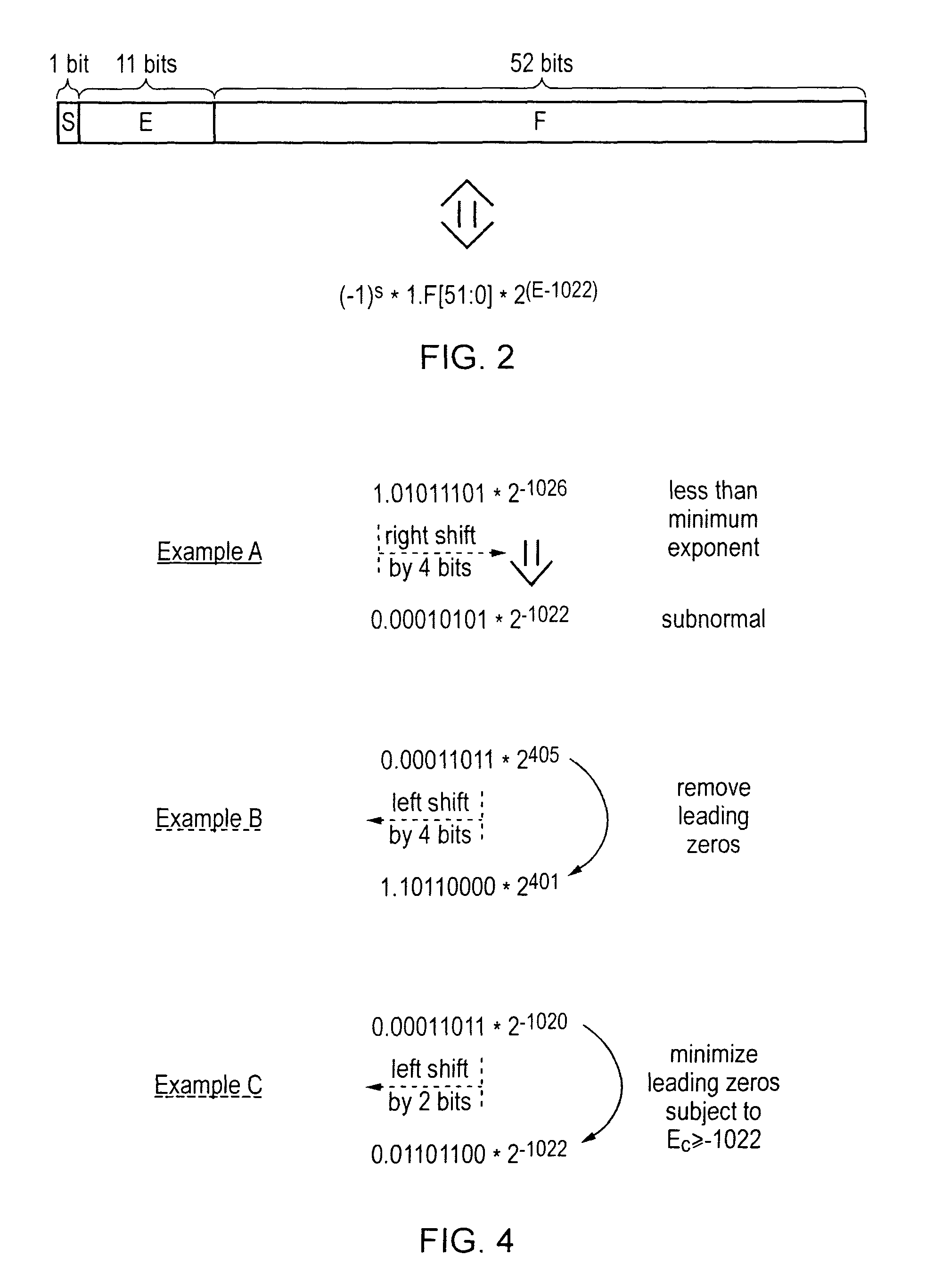

ActiveUS20110106868A1Minimize the numberReduce delaysDigital computer detailsData conversionRight shiftOperand

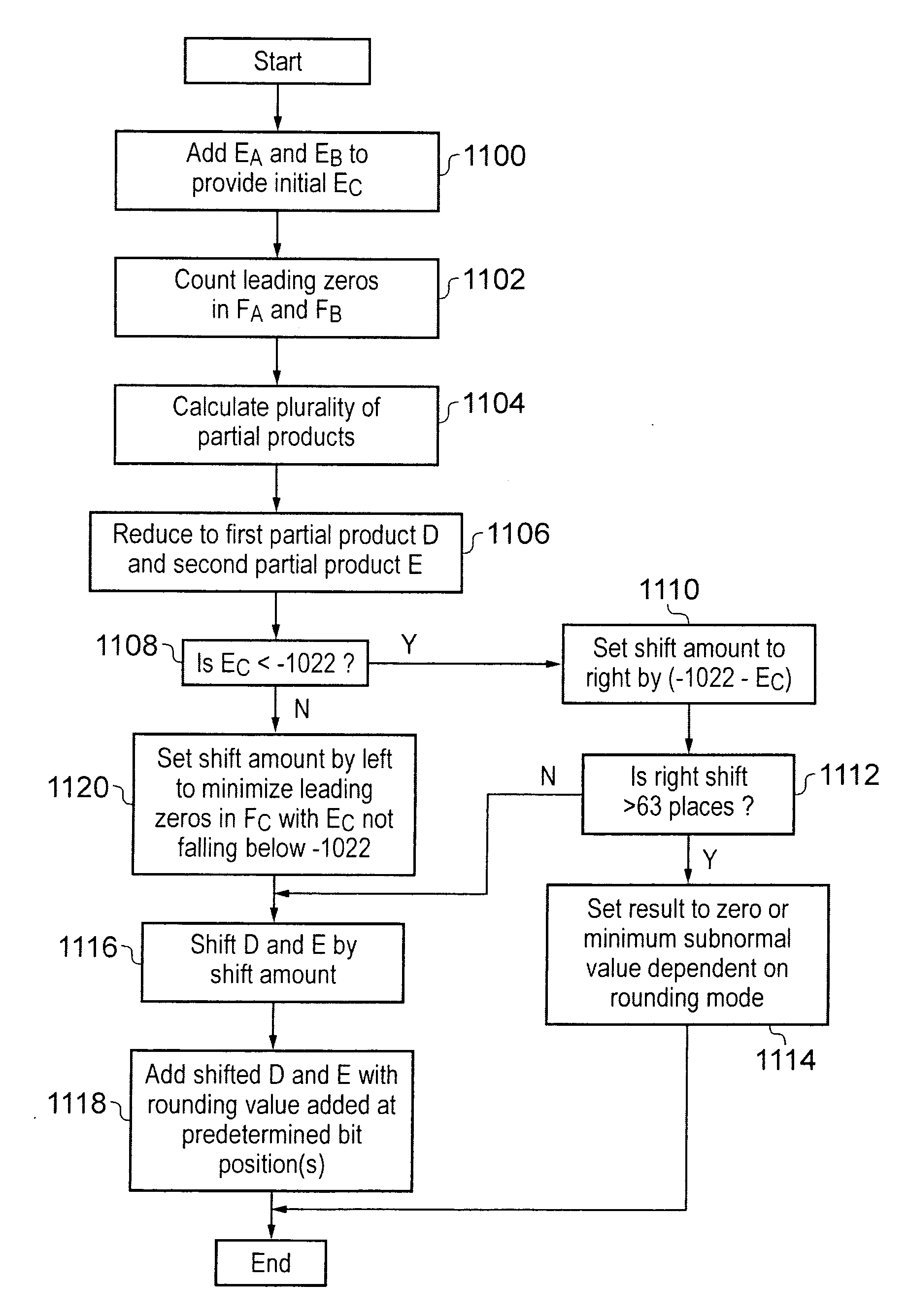

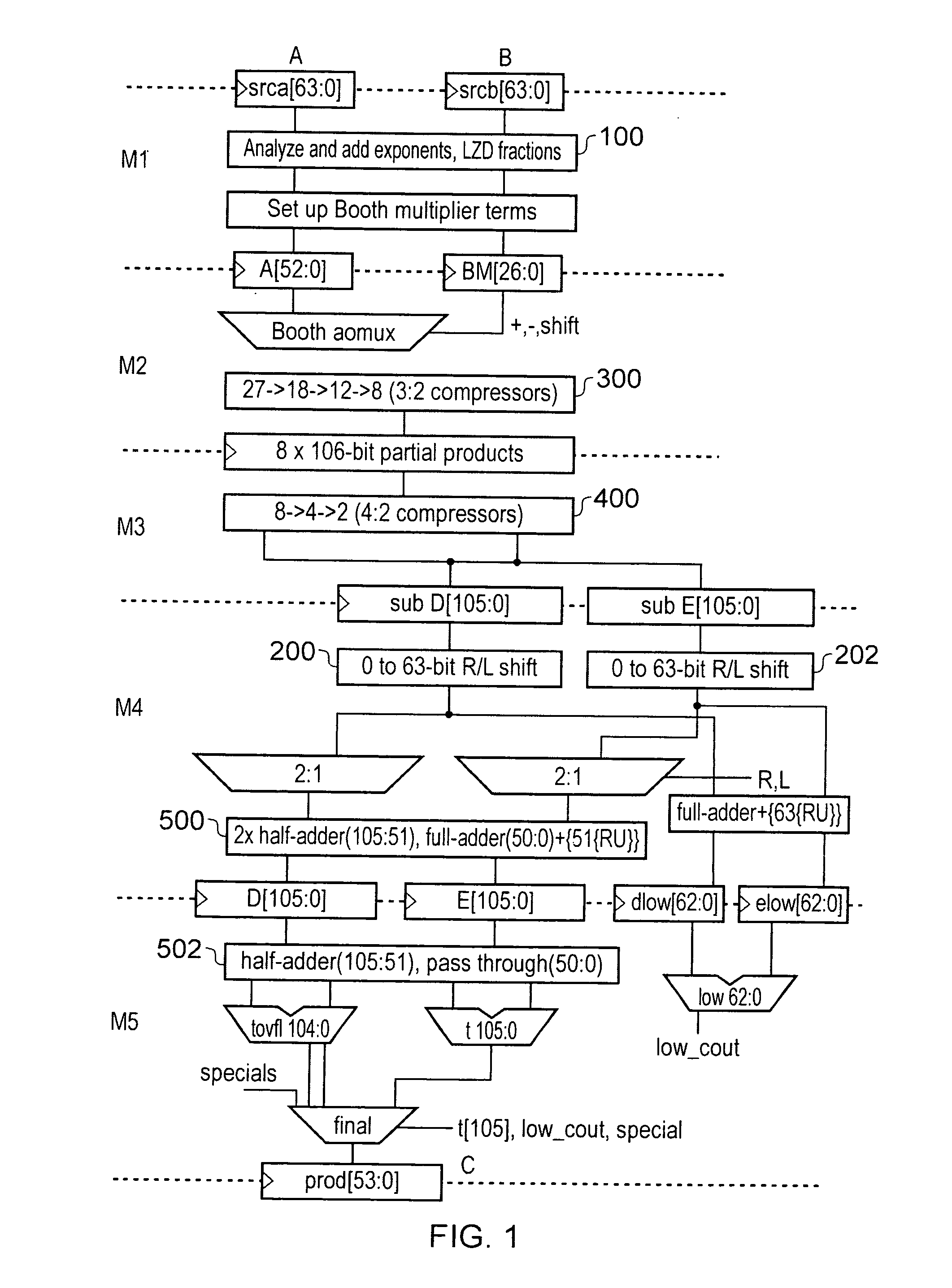

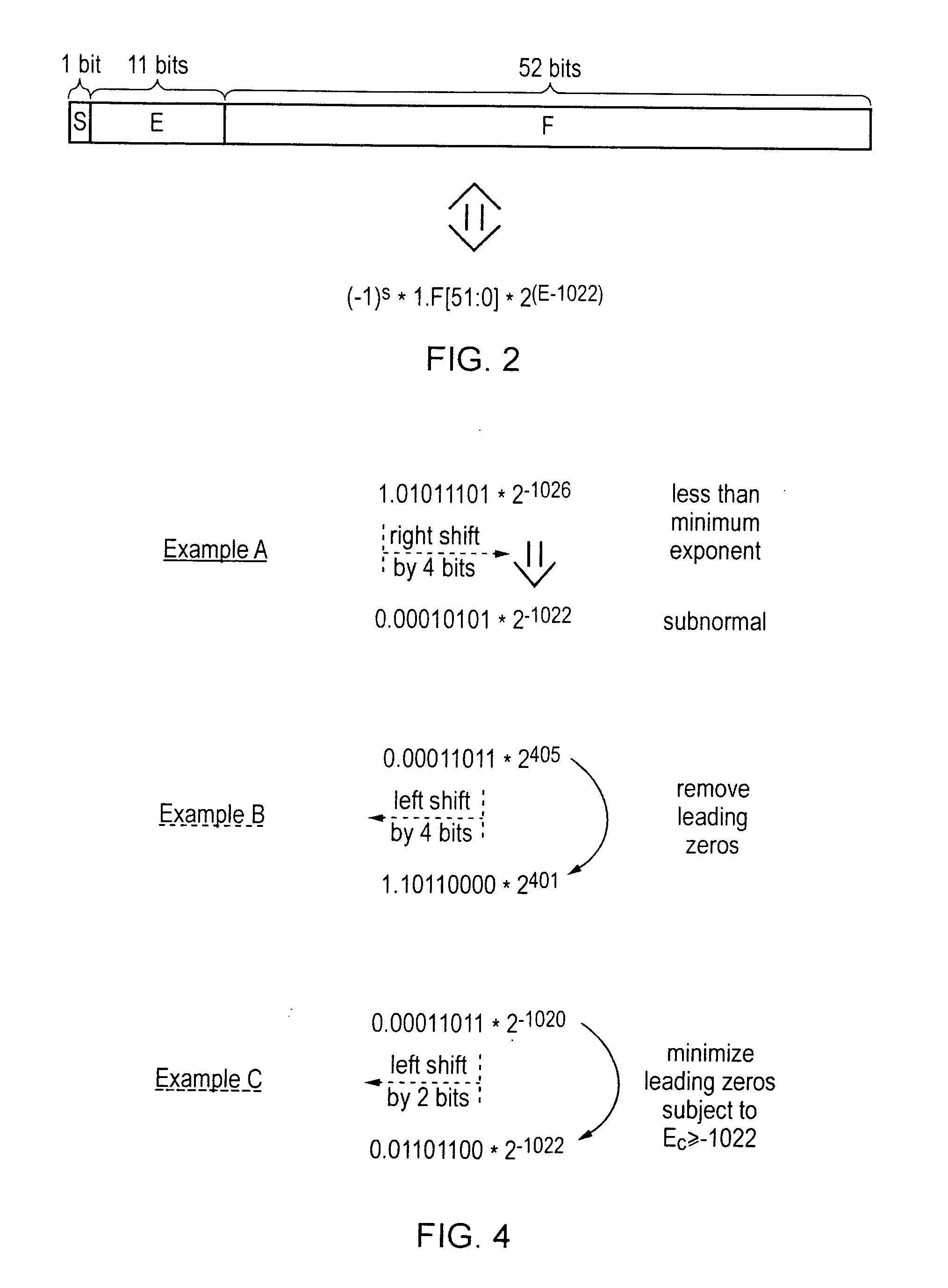

A floating point multiplier includes a data path in which a plurality of partial products are calculated and then reduced to a first partial product and a second partial product. Shift amount determining circuitry 100 analyses the exponents of the input operands A and B as well as counting the leading zeros in the fractional portions of these operands to determine an amount of left shift or right shift to be applied by shifting circuitry 200, 202 within the multiplier data path. This shift amount is applied so as to align the partial products so that when they are added they will produce the result C without requiring this to be further shifted. Furthermore, shifting the partial products to the correct alignment in this way in advance of adding these partial products permits injection rounding combined with the adding of the partial products to be employed for cases including subnormal values.

Owner:ARM LTD

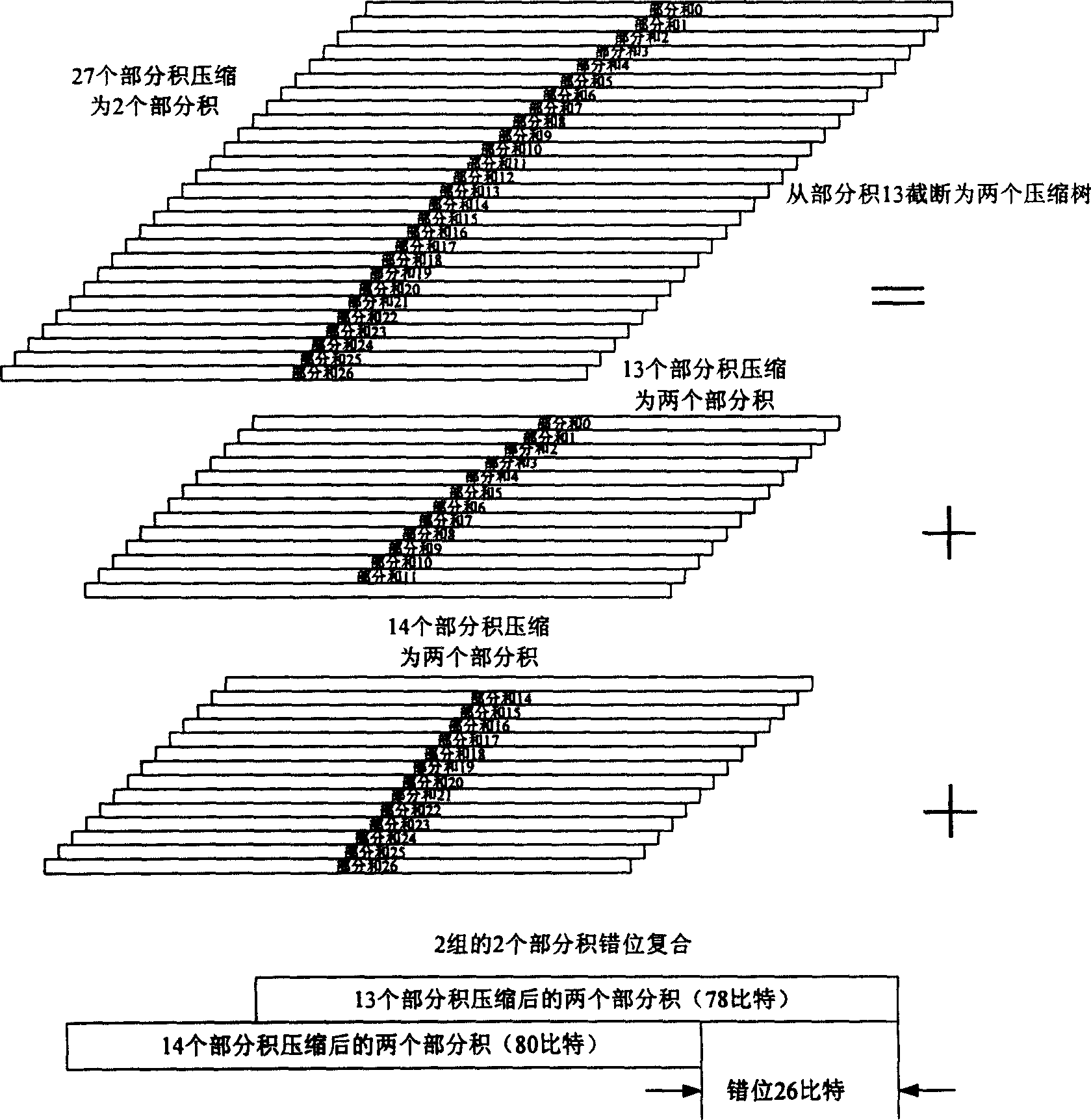

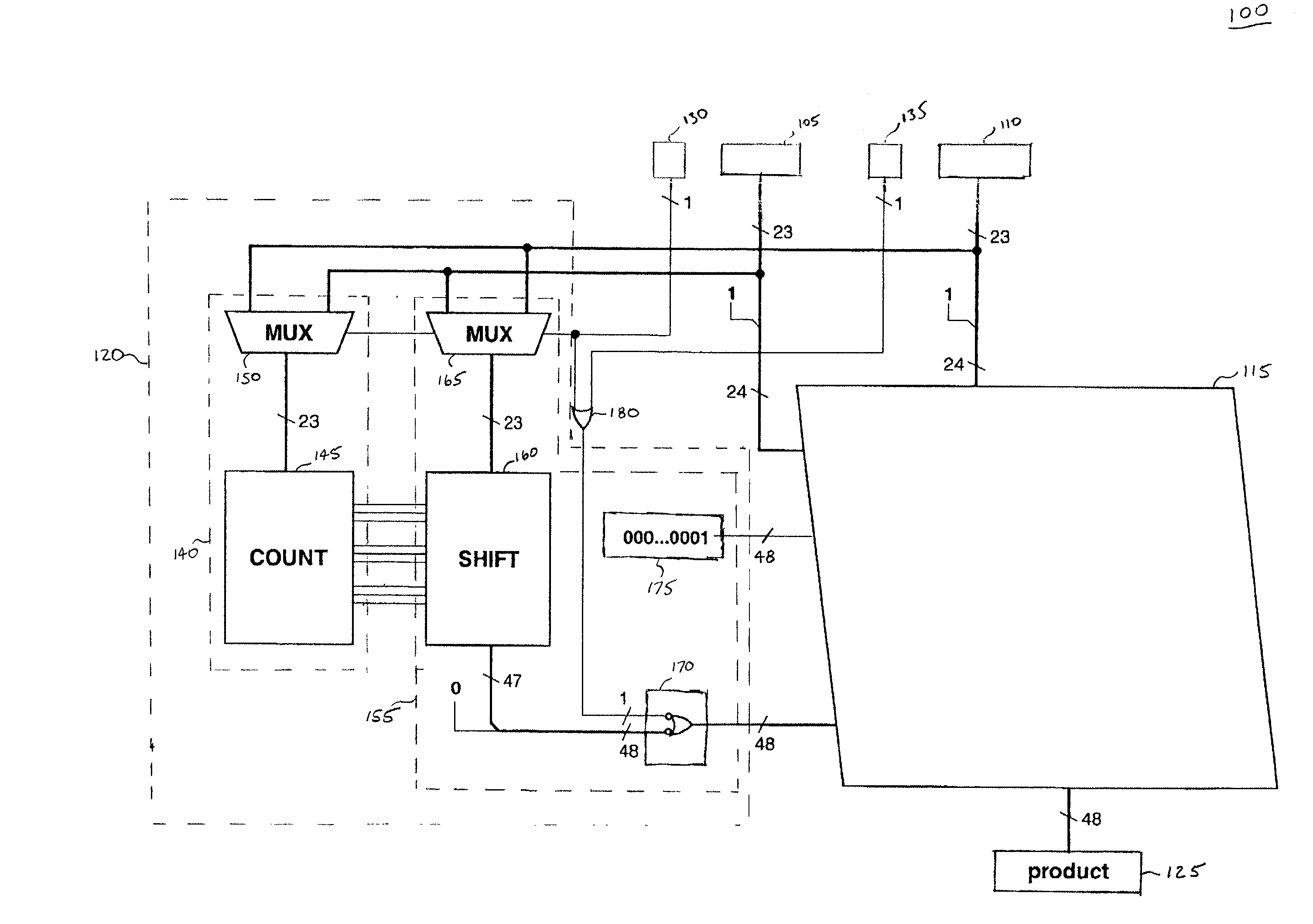

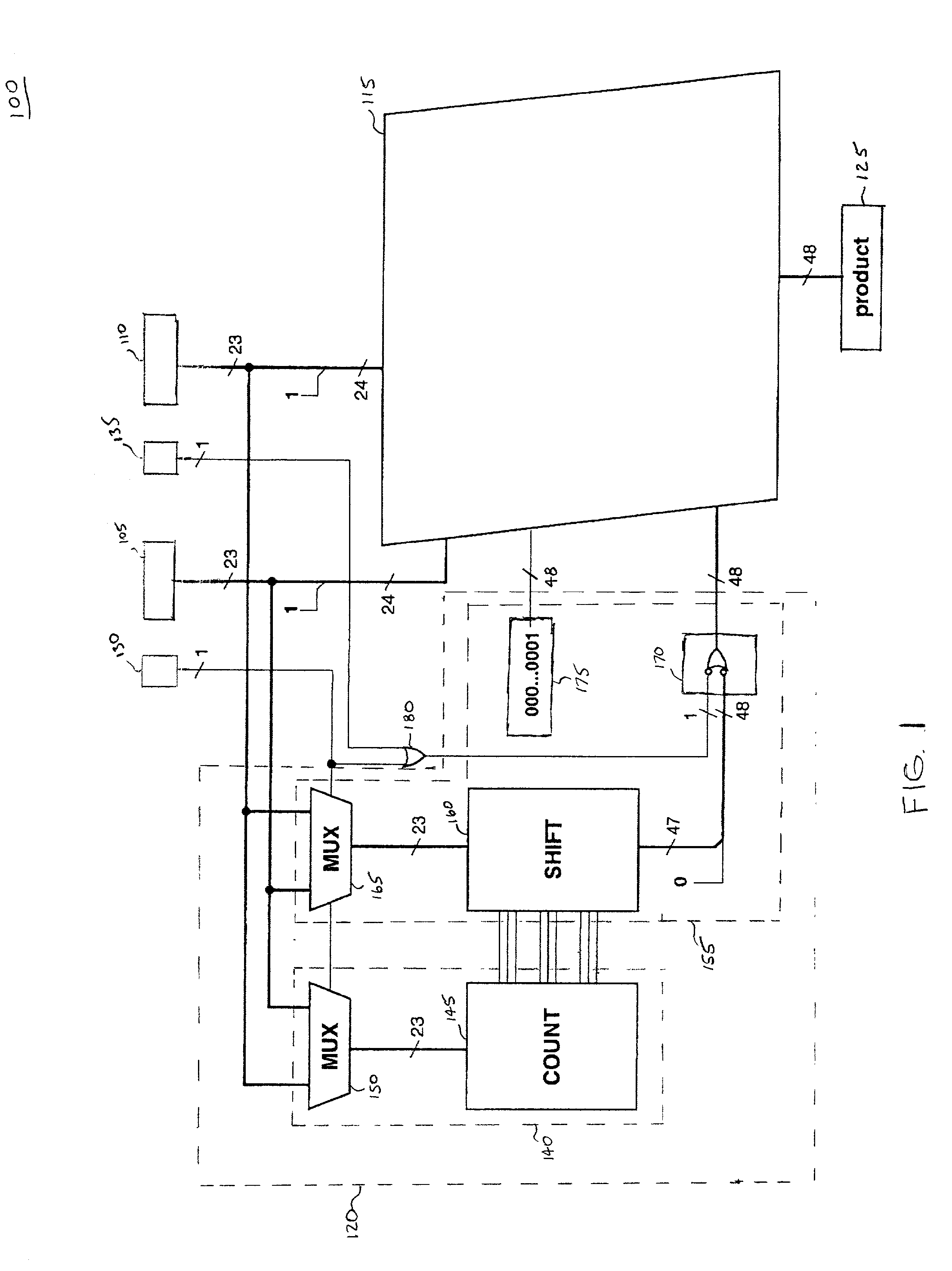

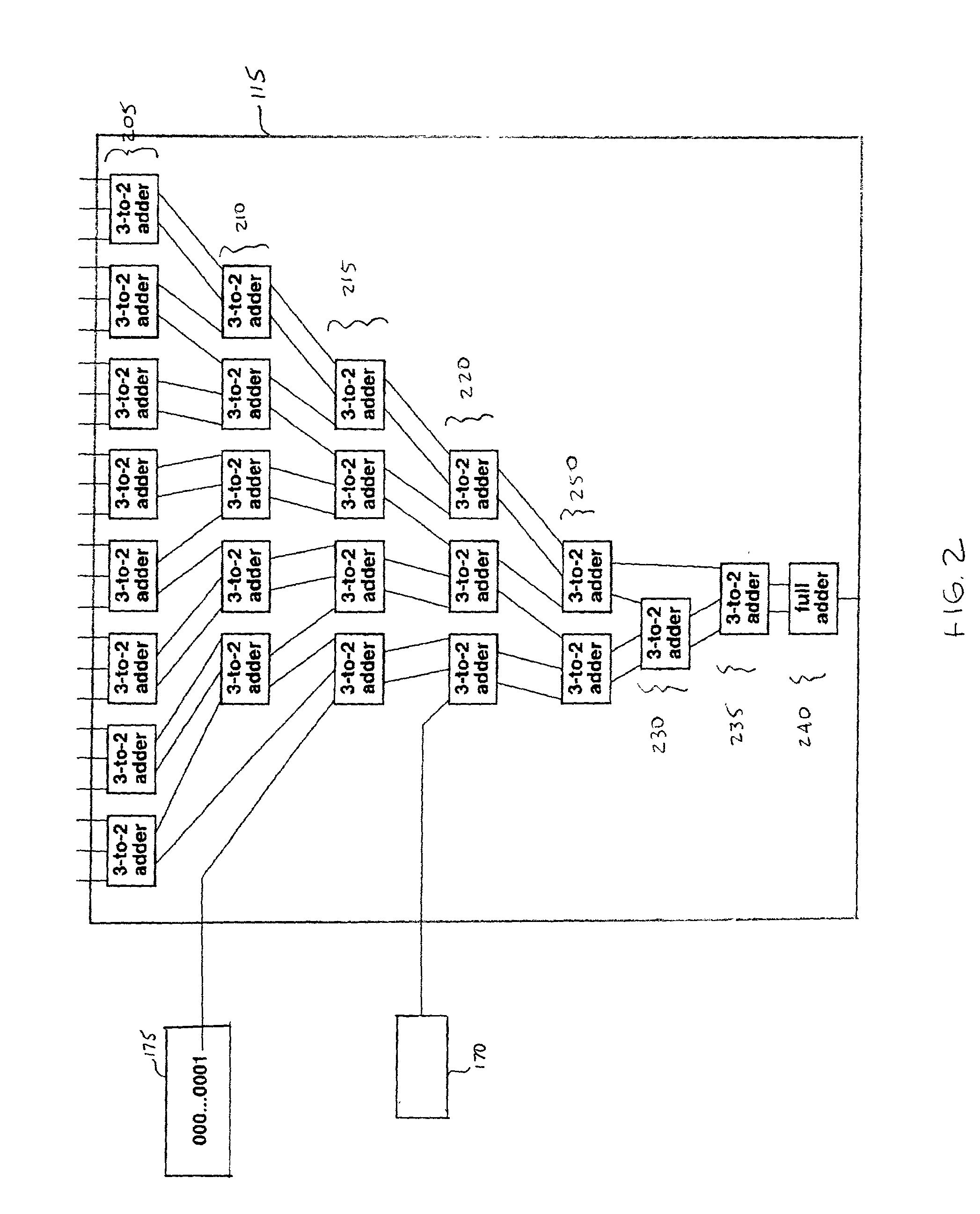

Apparatus and method for multiple pass extended precision floating point multiplication

InactiveUS8019805B1Computations using contact-making devicesComputation using non-contact making devicesComputational scienceCarry-save adder

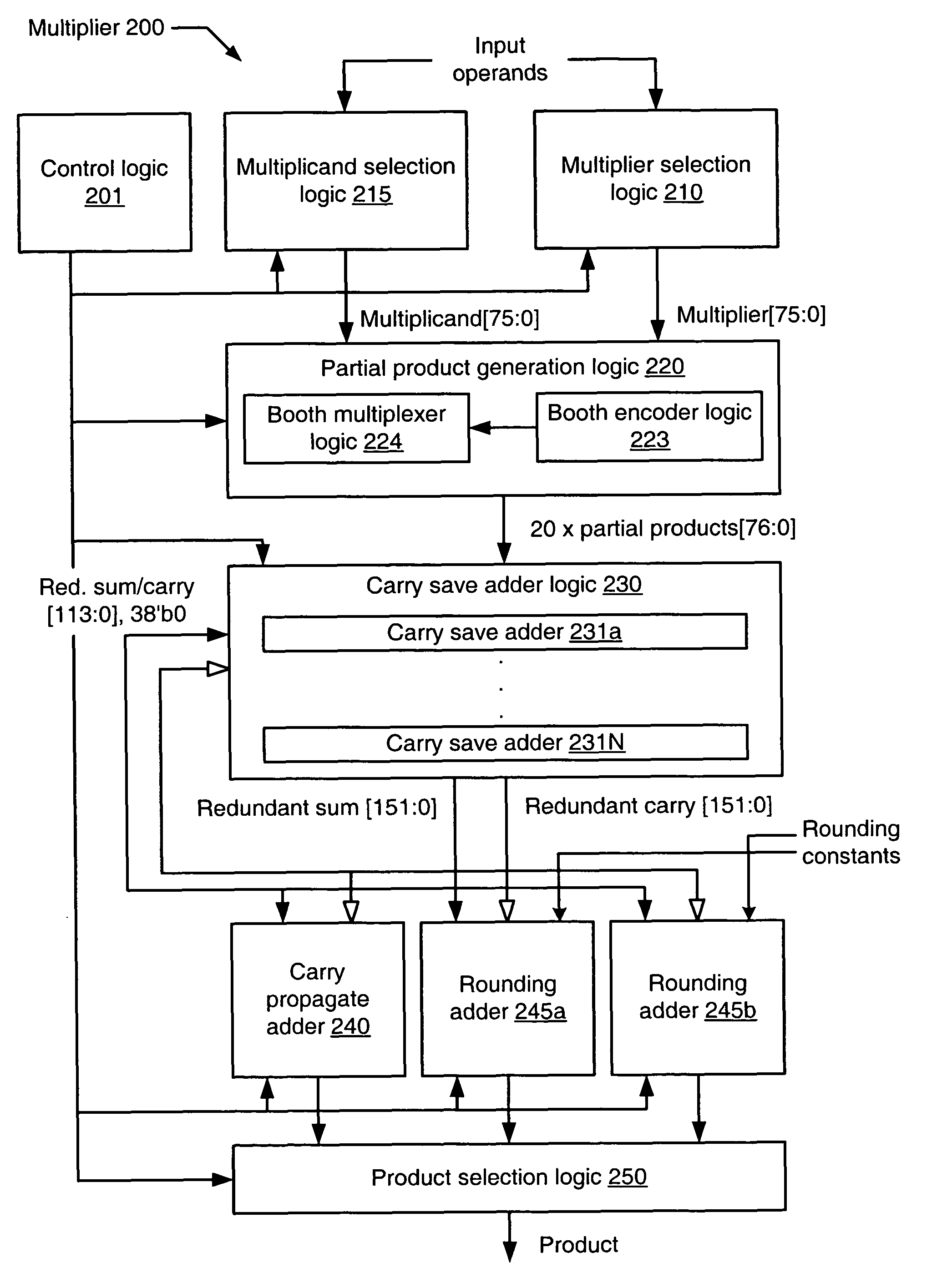

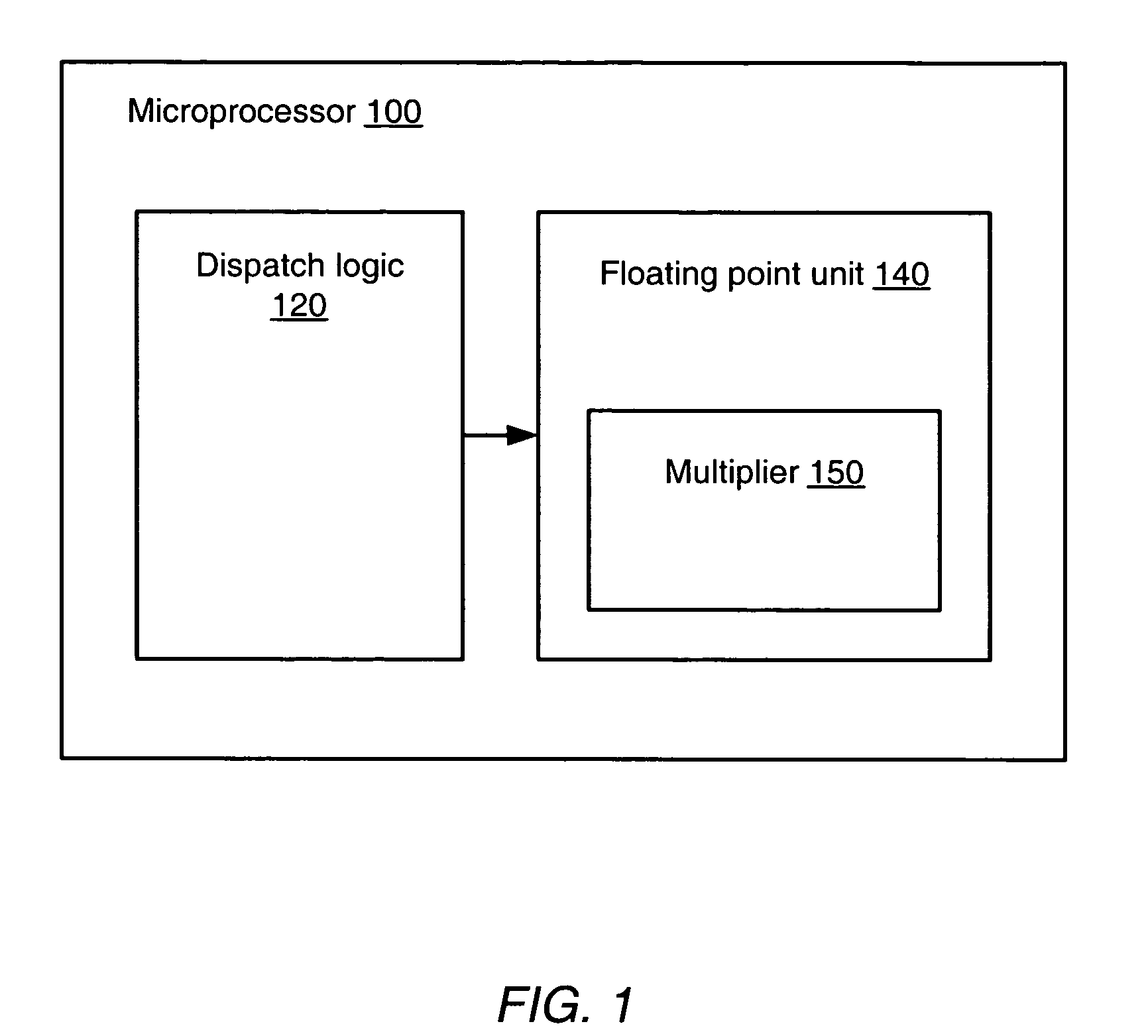

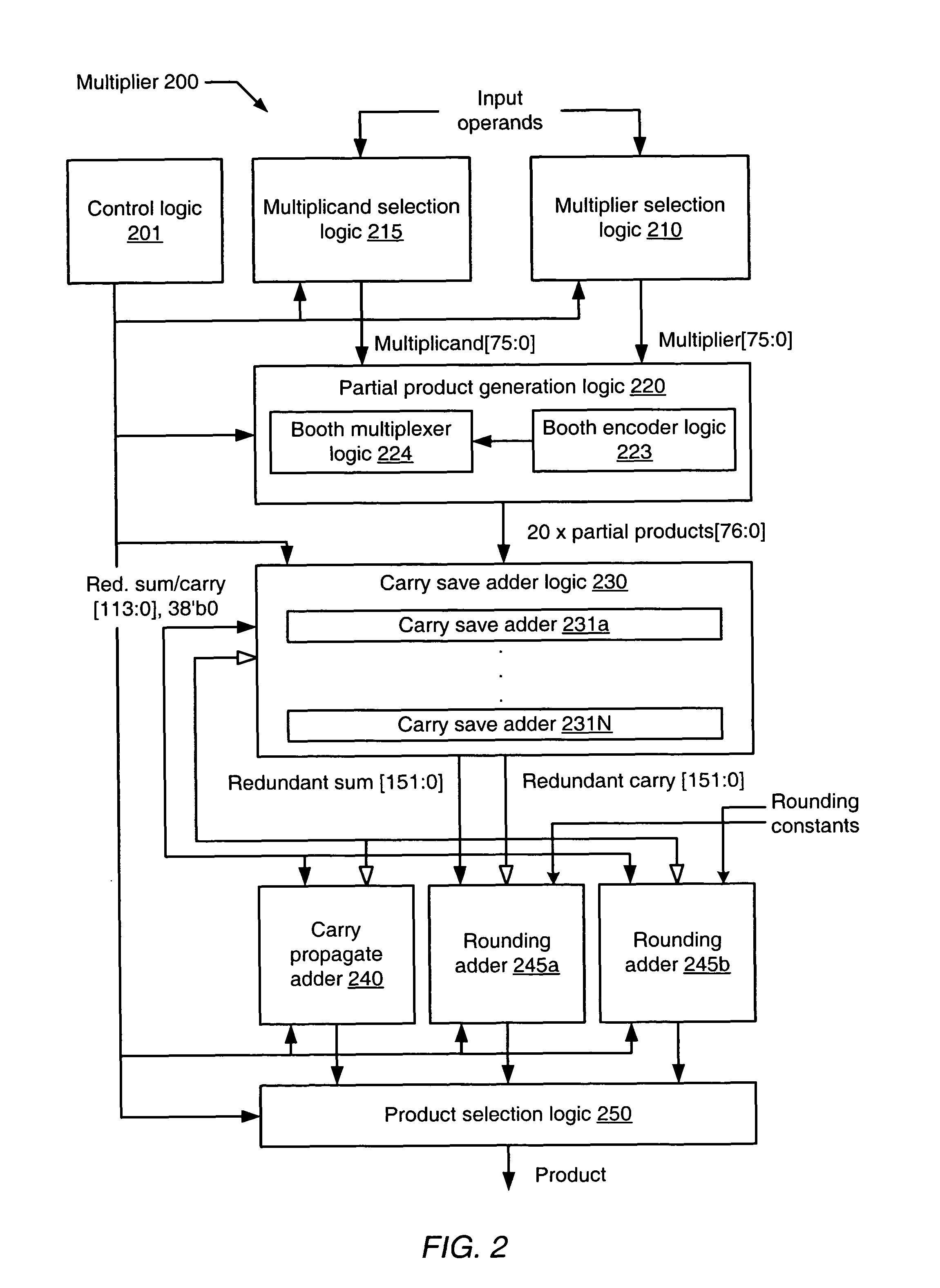

A floating point multiplier circuit includes partial product generation logic configured to generate a plurality of partial products from multiplicand and multiplier values. The plurality of partial products corresponds to a first and second portion of the multiplier value during respective first and second partial product execution phases. The multiplier also includes a plurality of carry save adders configured to accumulate the plurality of partial products generated during the first and second partial product execution phases into a redundant product during respective first and second carry save adder execution phases. The multiplier further includes a first carry propagate adder coupled to the plurality of carry save adders and configured to reduce a first and second portion of the redundant product to a multiplicative product during respective first and second carry propagate adder phases. The first carry propagate adder phase begins after the second carry save adder execution phase completes.

Owner:GLOBALFOUNDRIES INC

Approximate floating-point multiplier for neural network processor and floating-point multiplication

ActiveCN107273090AImprove work efficiencyImprove performanceDigital data processing detailsPhysical realisationOperandApproximate computing

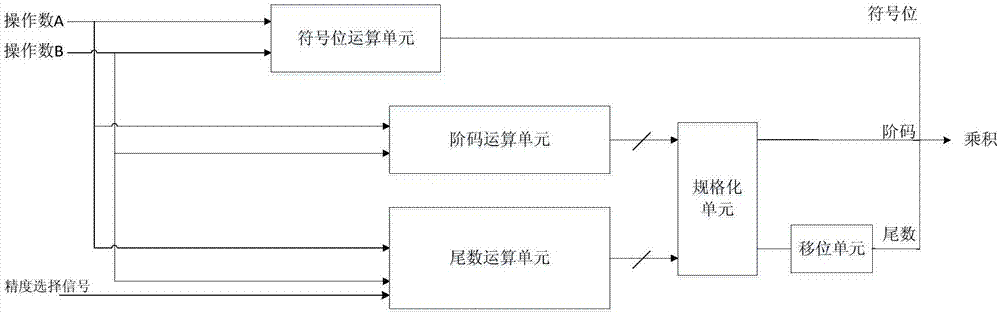

The invention discloses an approximate floating-point multiplier for a neural network processor and a floating-point multiplication. When the approximate floating-point multiplier executes fractional part multiplying operation on an operand, part bits are intercepted from all high bits of a fractional part of the operand according to designated precision, and 1 is supplemented to the front and the back of the intercepted part bits to obtain two new fractional parts; multiplying operation is performed on the two new fractional parts to obtain an approximate fractional part of a product; and zero is supplemented to a low bit of the normalized approximate fractional part so that the bits of the approximate fractional part are consistent with the bits of the fractional part of the operand, and therefore the fractional part of the product is obtained. According to the approximate floating-point multiplier, an approximate calculation mode is adopted, different bits of the fractional part are intercepted according to a precision demand for corresponding multiplying operation, energy loss of multiplying operation is lowered, multiplying operation speed is increased, and therefore the performance of a neural network processing system is more efficient.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

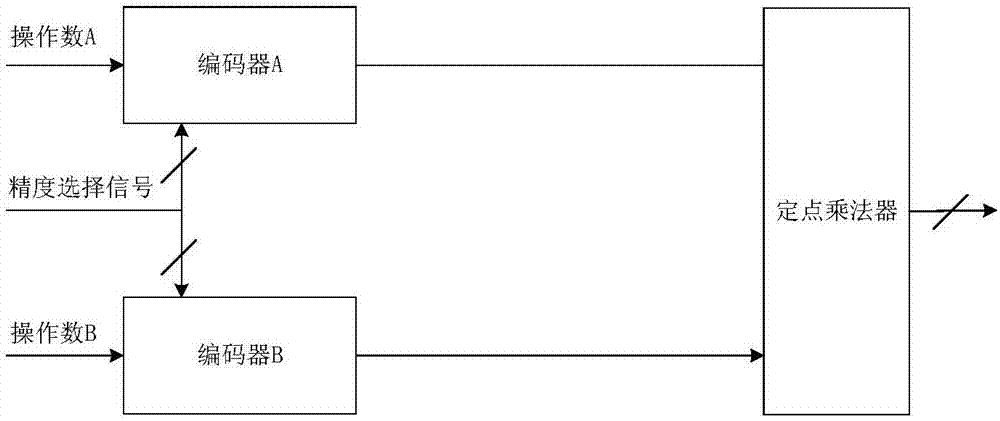

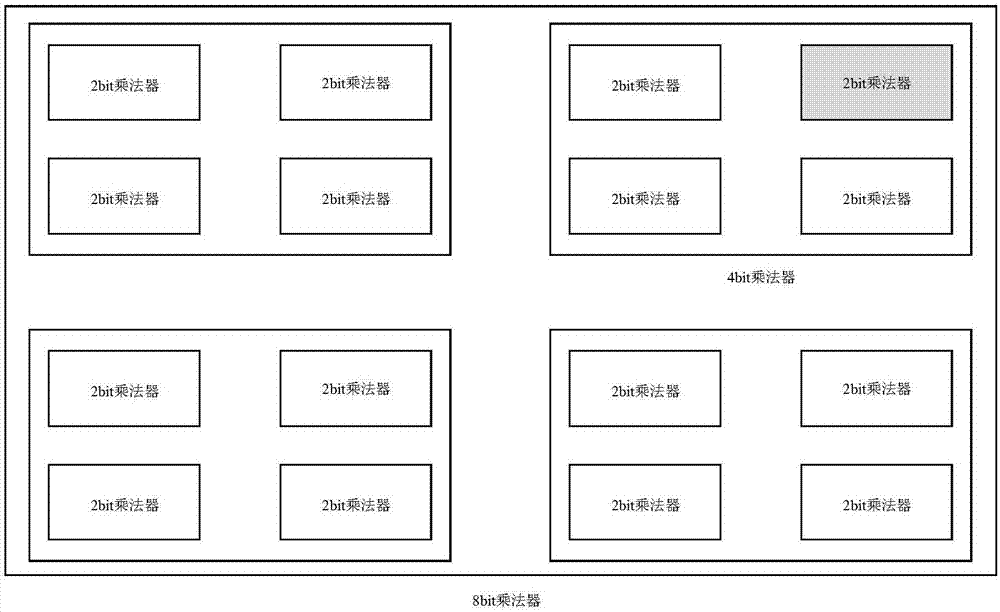

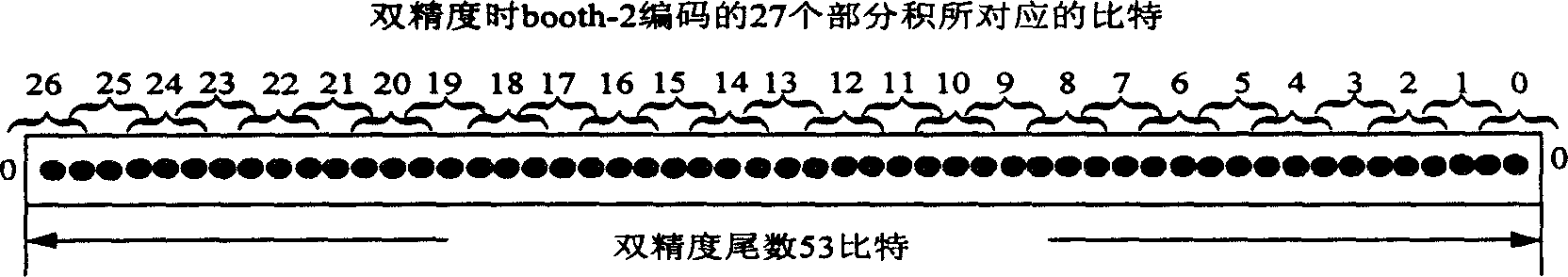

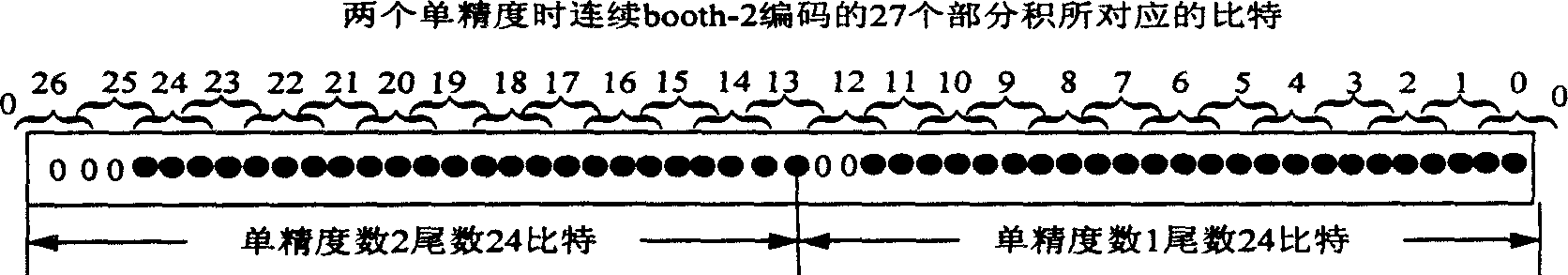

Floating-point multiplicator and method of compatible double-prepcision and double-single precision computing

ActiveCN1831753ATake advantage ofNo wasteComputation using non-contact making devices48-bitFloating point multiplier

A floating-point multiplier consists of single accuracy continuous coding - packing unit, the first selector, base 2 Pots coder, 13 : 2 compression tree, 14 : 2 compression tree, 48 bit adder, 4 : 2 compression composite tree, the second selector, 106 bit adder, 48 bit single accuracy round - off and normalization unit, 106 bit double accuracy round - off and normalization unit, double accuracy and double accuracy index processing unit . The said floating-point multiplier can multiplex double accuracy data channel for carrying out calculation to obtain two single accuracy multiplication results of floating-point at each beat.

Owner:LOONGSON TECH CORP

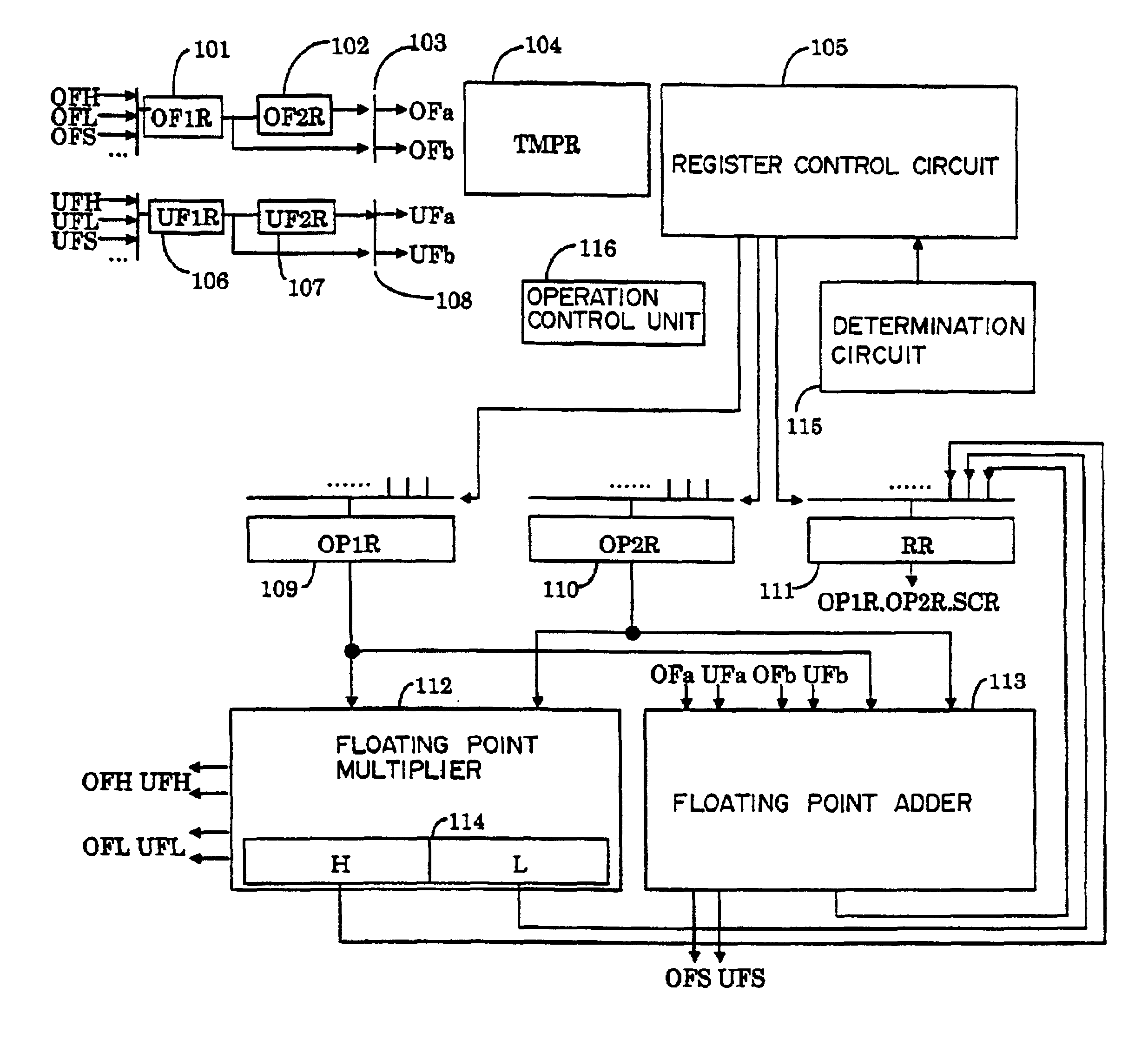

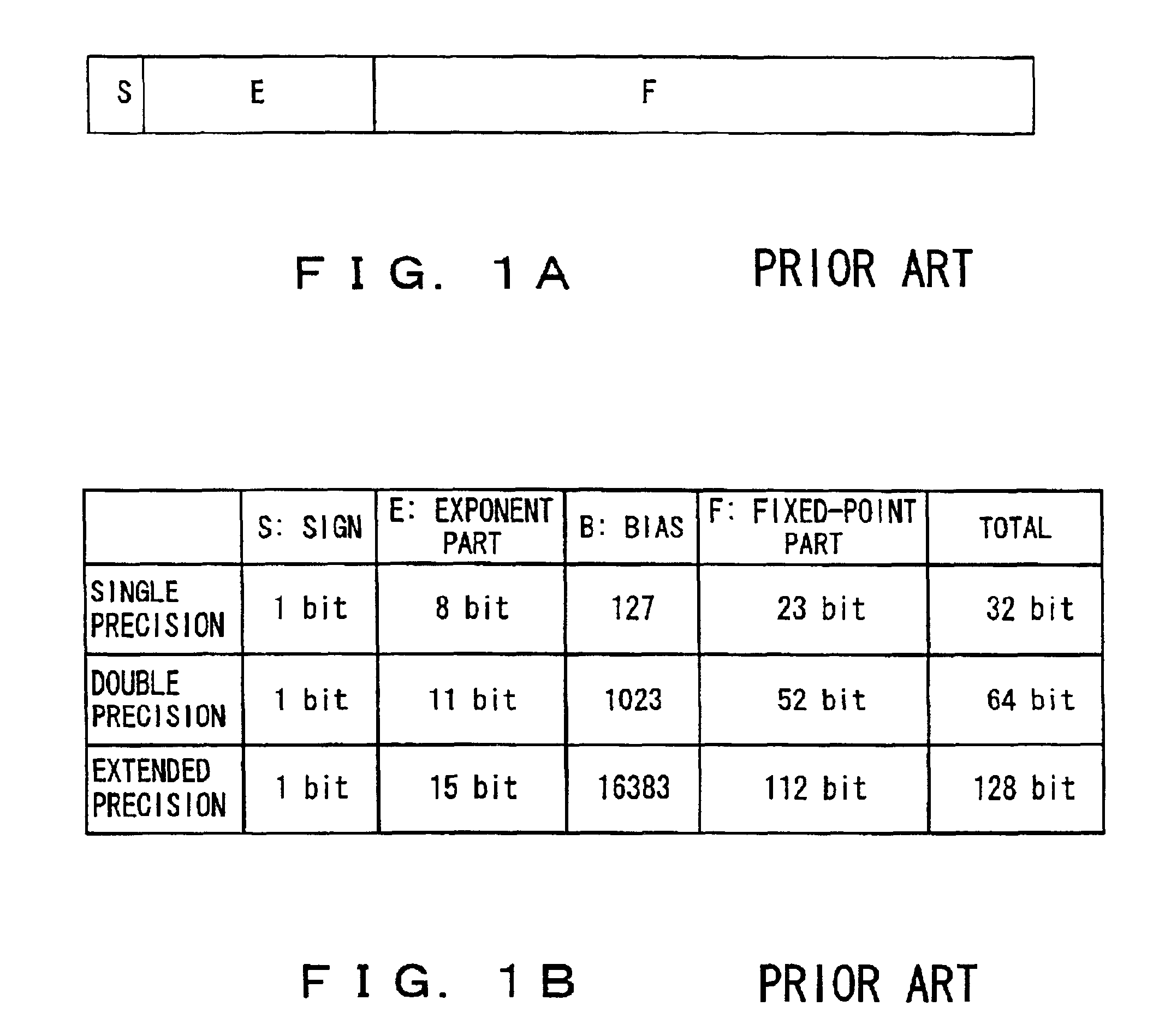

Apparatus and method of performing product-sum operation

InactiveUS6895423B2Reduce circuit sizeSmall circuitComputation using non-contact making devicesComplex mathematical operationsTheoretical computer scienceFloating point multiplier

To perform a product-sum operation by adding third data to a product of first data and second data, a floating point multiplier first multiplies the first data by the second data, and a bit string representing a fixed-point part in the multiplication result is divided into a portion representing more significant digits in the fixed-point part and a portion representing less significant digits in the fixed-point part. Then, a floating point adder first adds less significant multiplication result data having a bit string representing the less significant digits as a fixed-point part to the third data, and then adds the addition result to more significant multiplication result data having a bit string representing the more significant digits as a fixed-point part. A rounding process is performed on the two addition results to obtain a result of the product-sum operation.

Owner:FUJITSU LTD

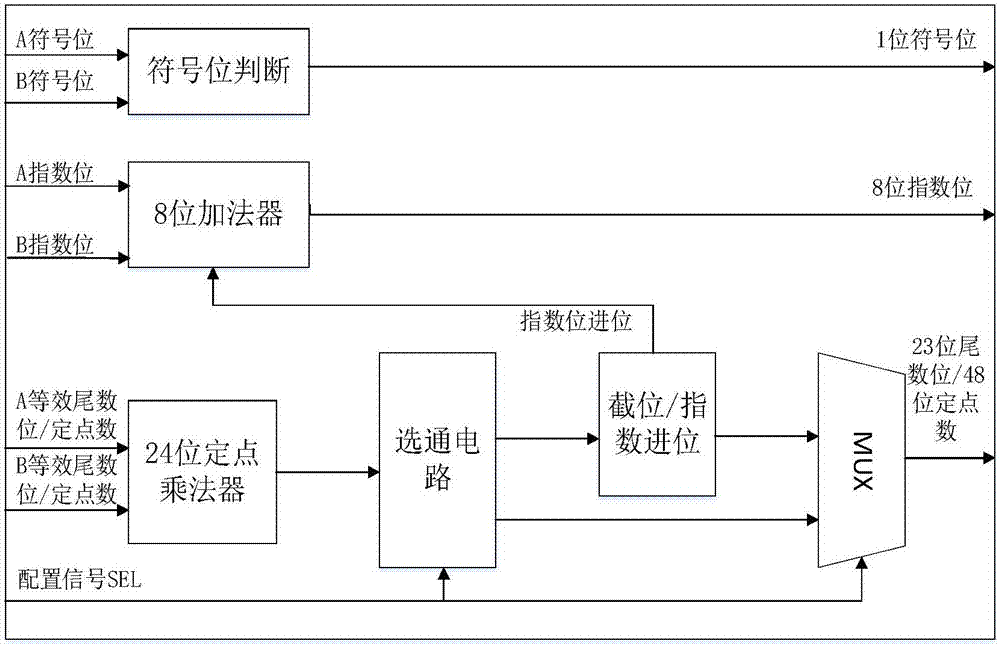

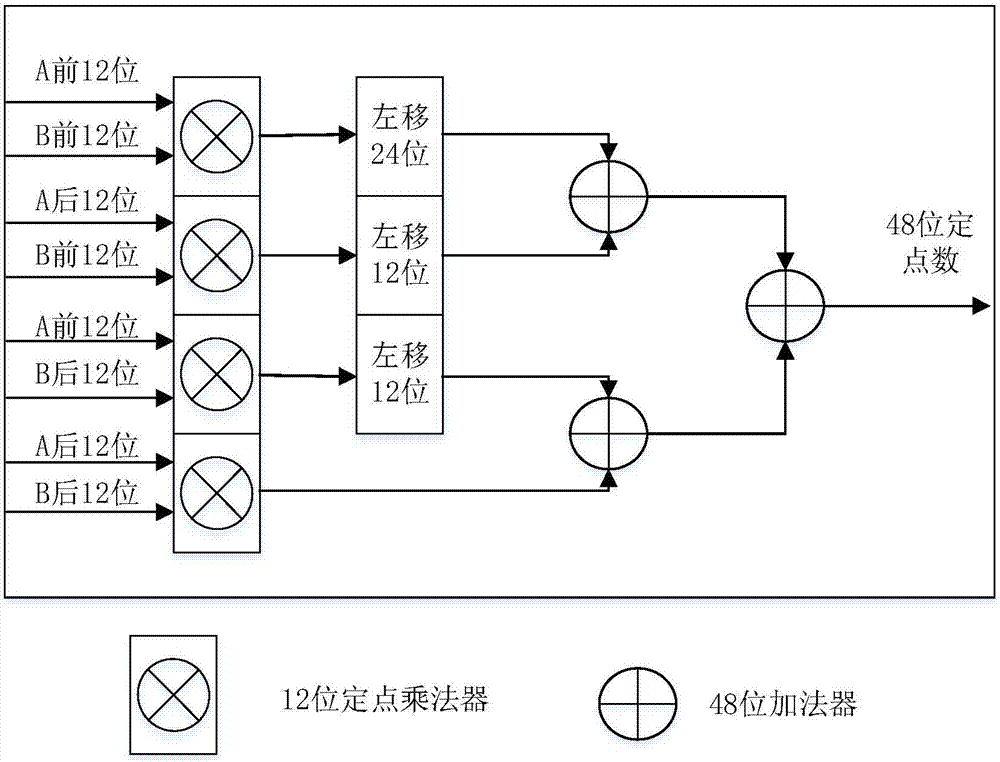

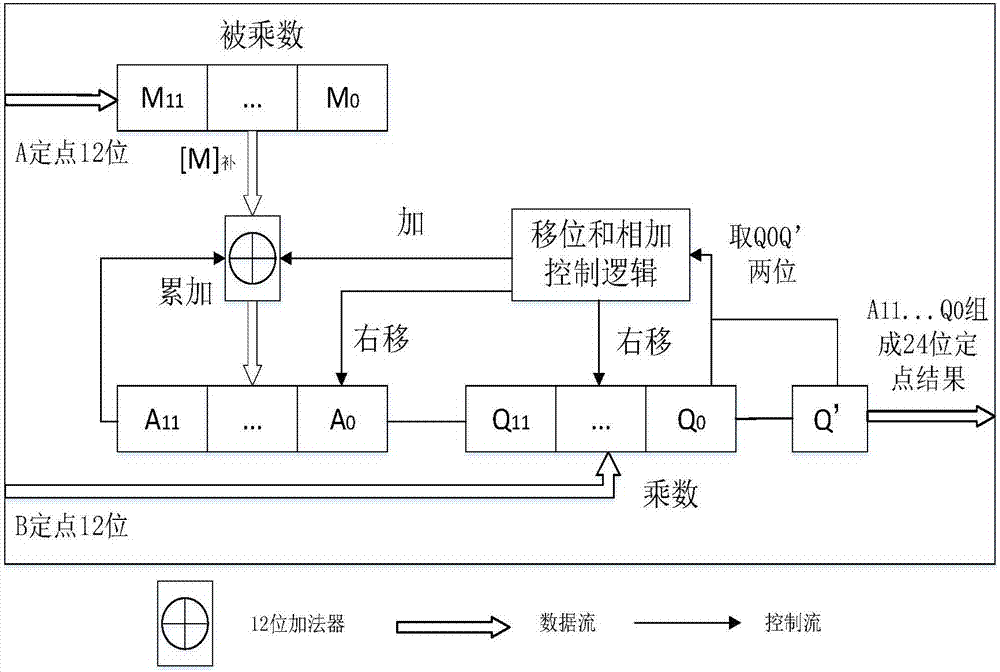

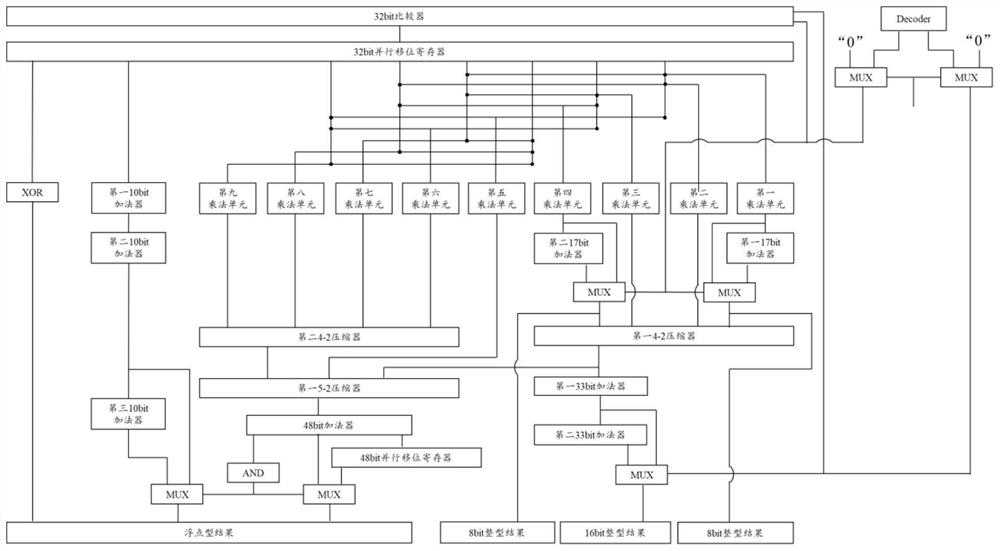

Reconfigurable universal fixed floating-point multiplier

ActiveCN106951211AImprove versatilityImprove computing efficiencyDigital data processing detailsBinary multiplierFloating point multiplication

The invention provides a universal fixed floating-point multiplier, which can realize not only 24-bit fixed-point multiplication operation but also 32-bit single-precision floating-point multiplication operation. According to the multiplier, a fixed-point multiplier is separated from a main body structure, and the 24-bit fixed-point multiplier is reconfigured as a single-precision floating-point multiplier. The 24-bit fixed-point multiplier consists of four 12-bit multipliers, wherein each 12-bit multiplier adopts a BOOTH algorithm, and operation is finished through a contracted structure of multiplication accumulation, so that the multiplication operation efficiency is effectively improved and the operation resource overhead is reduced. The multiplier except the 24-bit fixed-point multiplier does not additionally occupy excessive resources, so that the universality of the multiplier is effectively improved under the condition of ensuring operation precision and data throughput.

Owner:NANJING UNIV

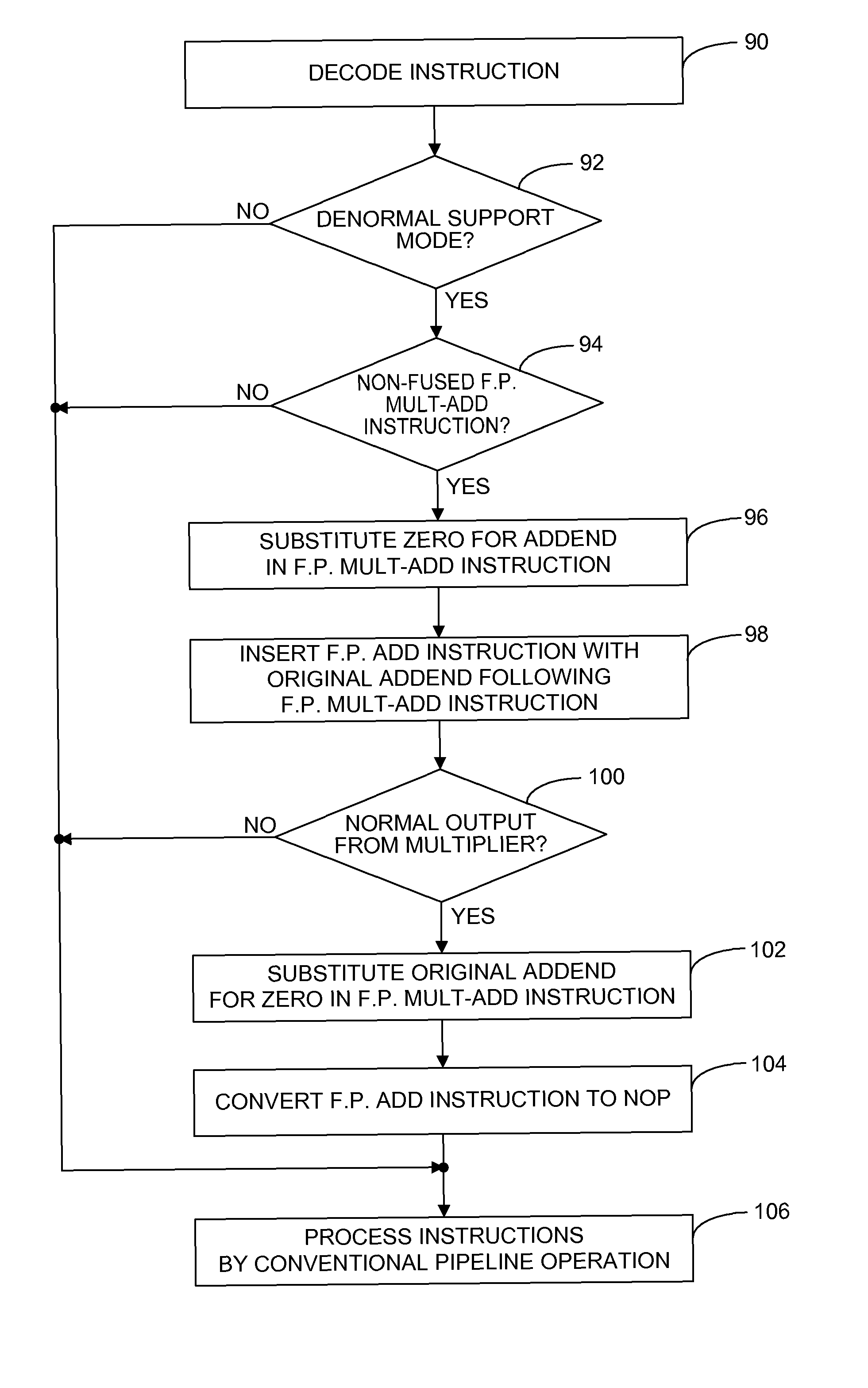

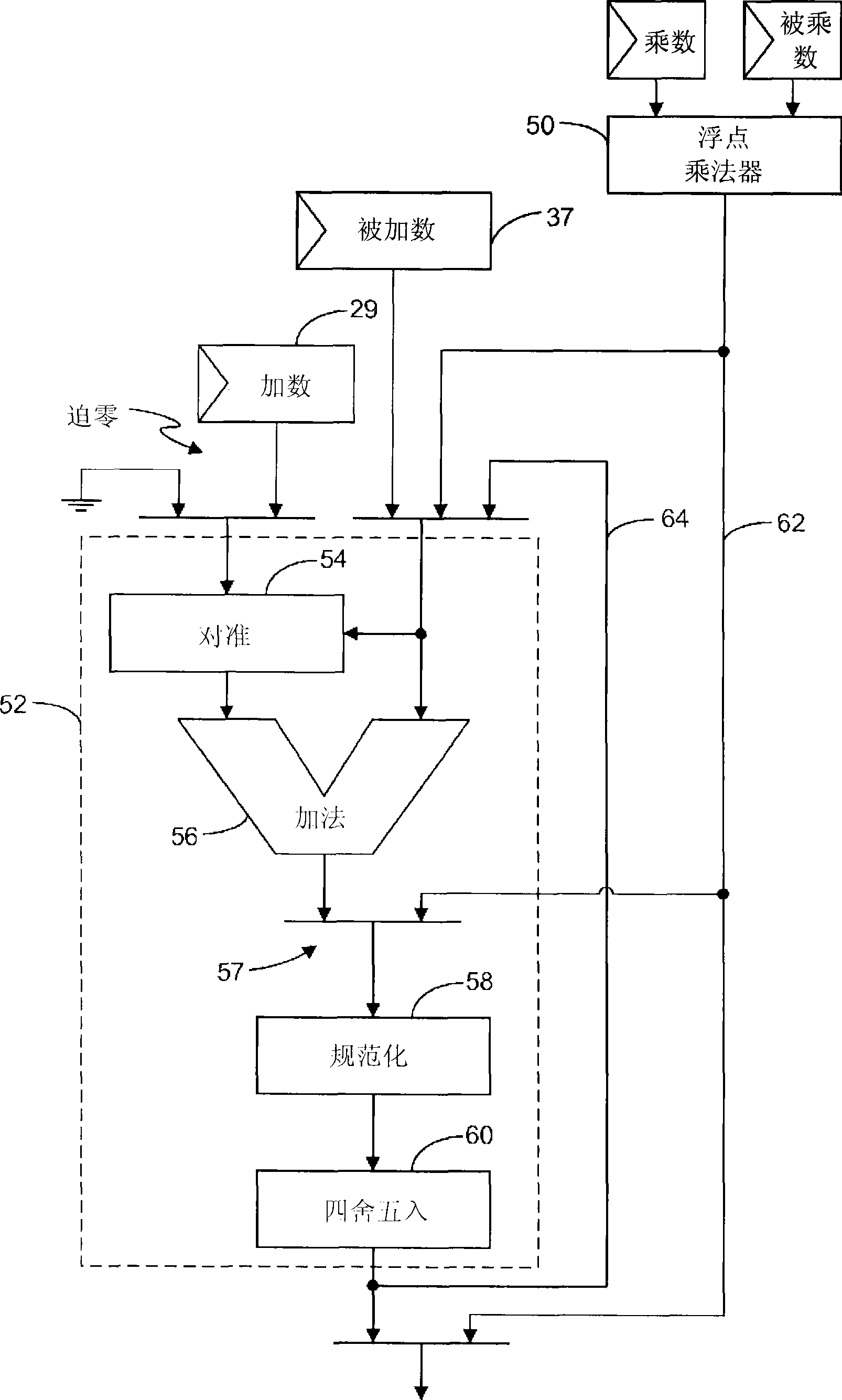

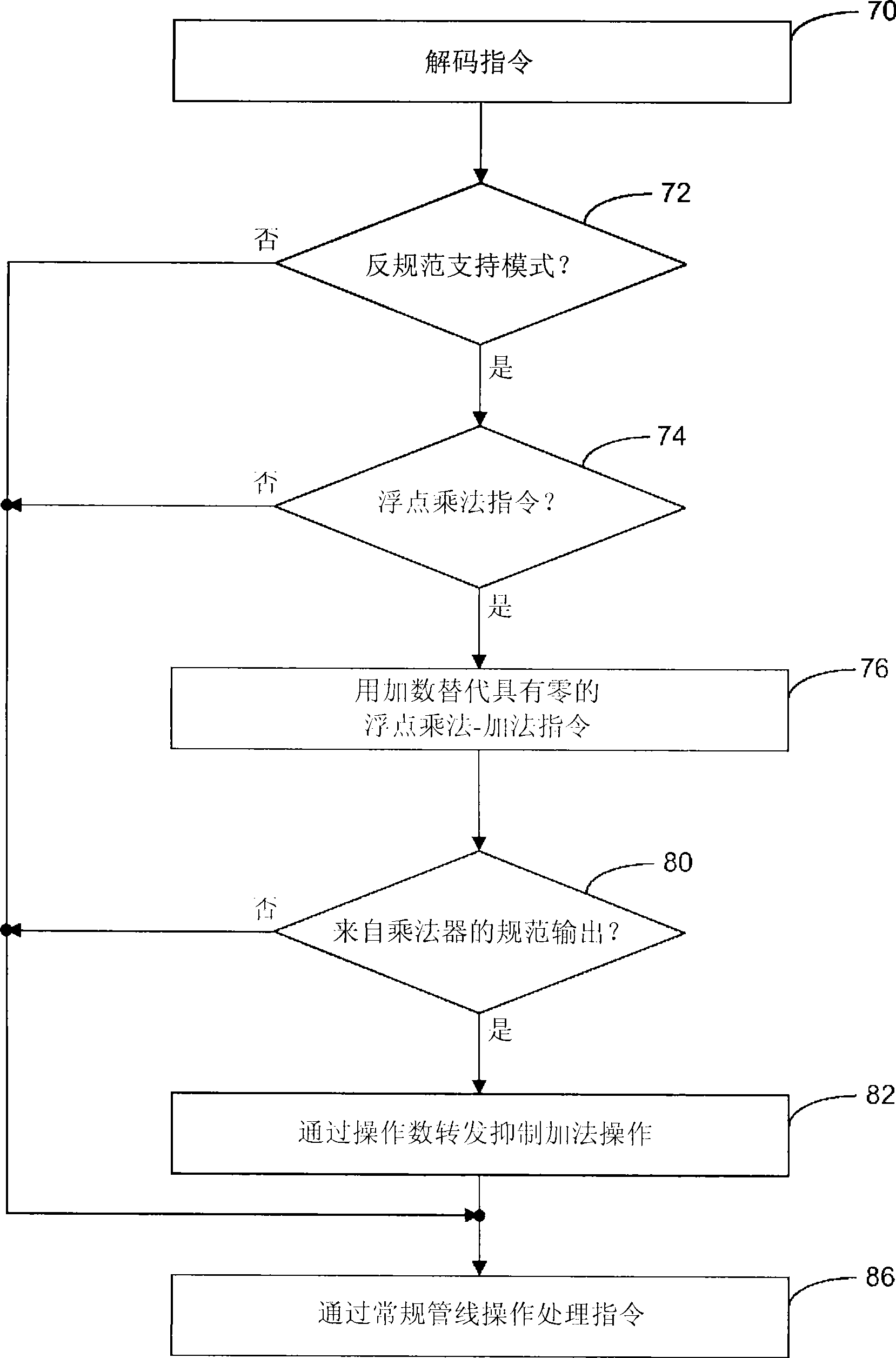

Mode-based multiply-add recoding for denormal operands

ActiveUS7912887B2Computations using contact-making devicesFloating point multiplierInstruction stream

In a denormal support mode, the normalization circuit of a floating-point adder is used to normalize or denormalized the output of a floating-point multiplier. Each floating-point multiply instruction is speculatively converted to a multiply-add instruction, with the addend forced to zero. This preserves the value of the product, while normalizing or denormalizing the product using the floating-point adder's normalization circuit. When the operands to the multiply operation are available, they are inspected. If the operands will not generate an unnormal intermediate product or a denormal final product, the add operation is suppressed, such as by operand-forwarding. Additionally, each non-fused floating-point multiply-add instruction is replaced with a multiply-add instruction having a zero addend, and a floating-point add instruction having the addend of the original multiply-add instruction is inserted into the instruction stream. Upon inspection of the operands, if an unnormal intermediate result or a denormal final result will not occur, the addend may be restored to the multiply-add instruction and the add instruction converted to a NOP.

Owner:QUALCOMM INC

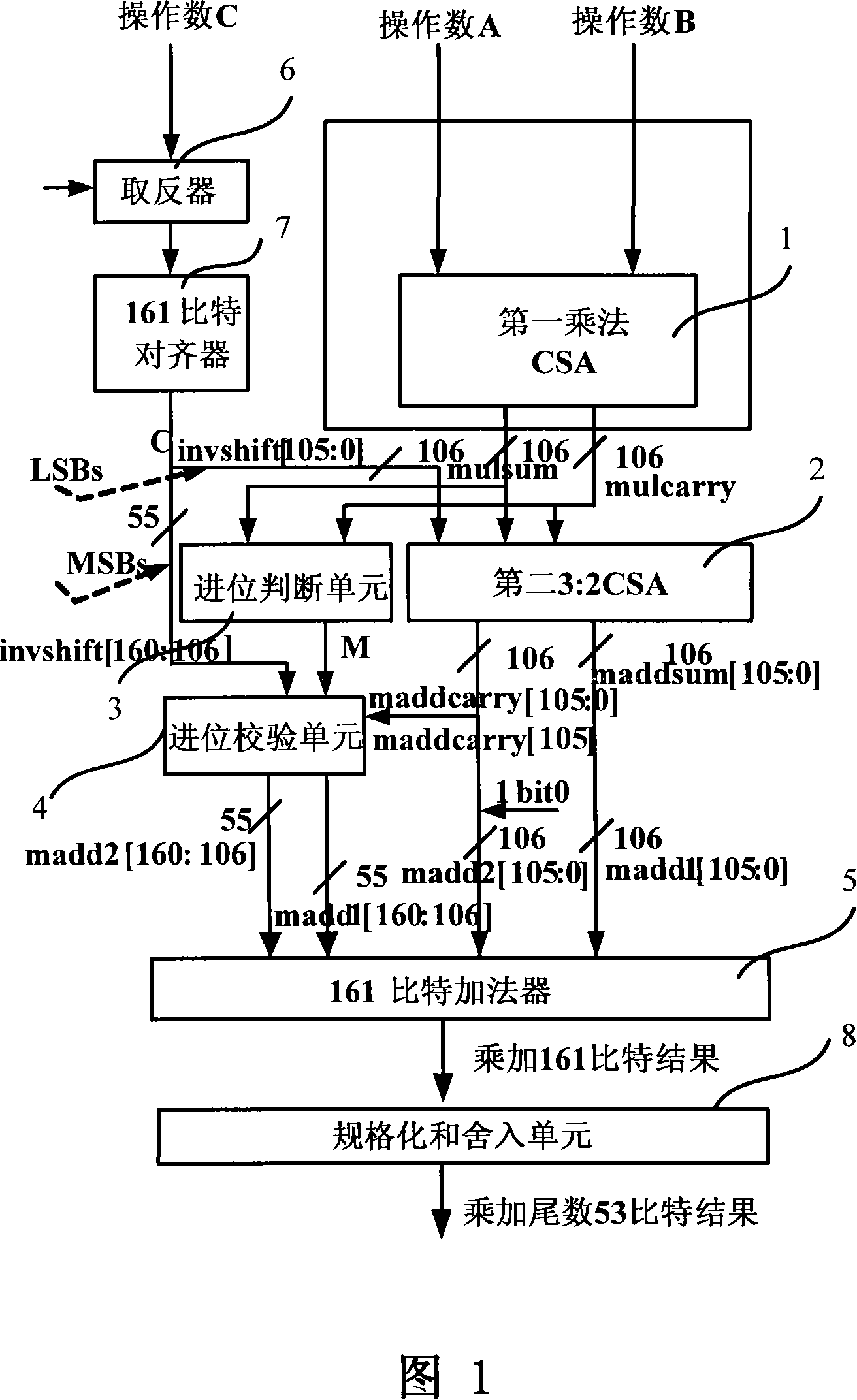

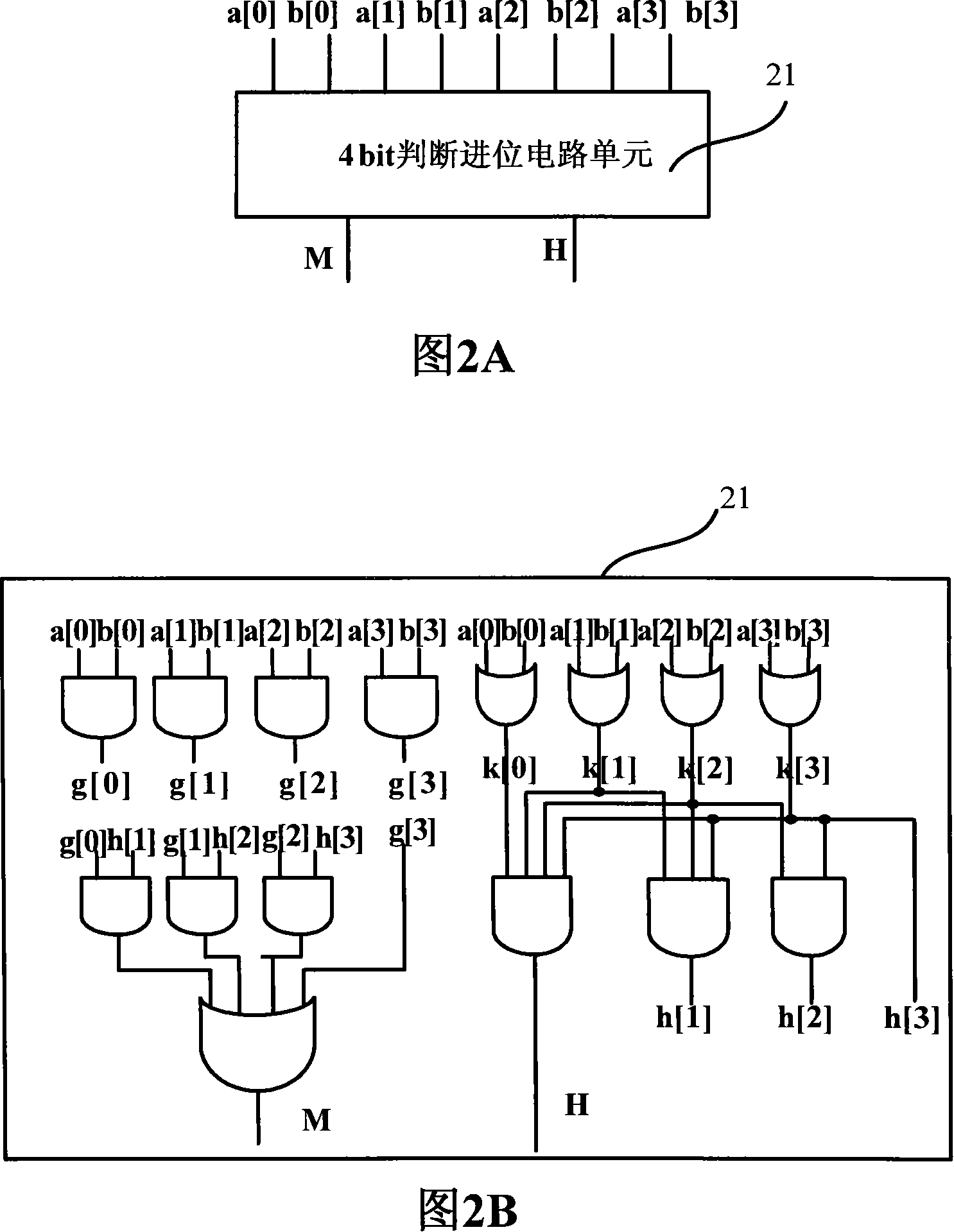

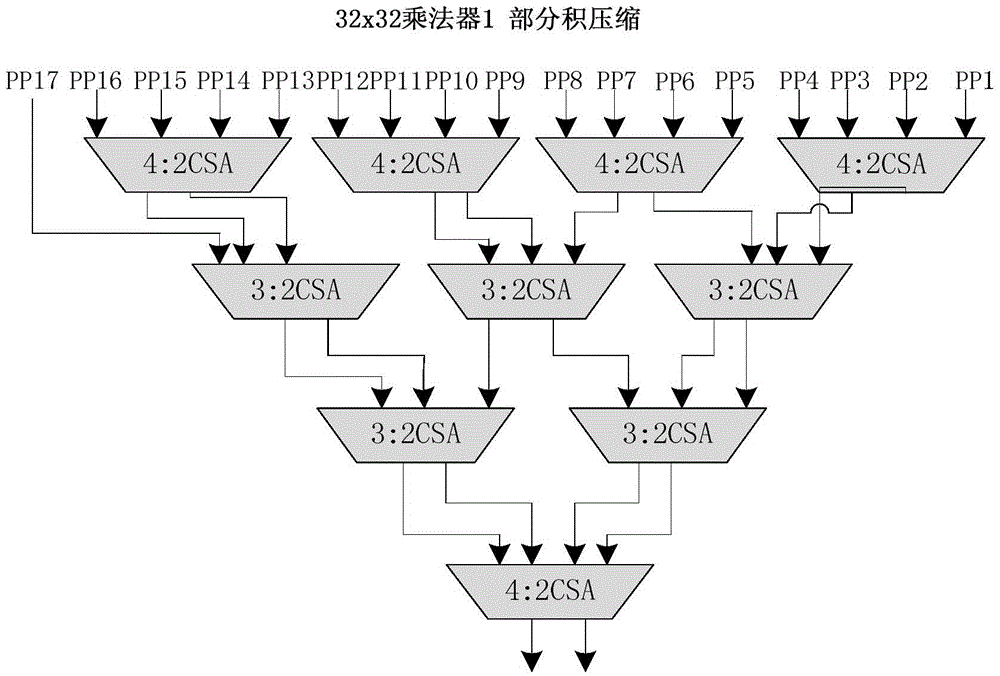

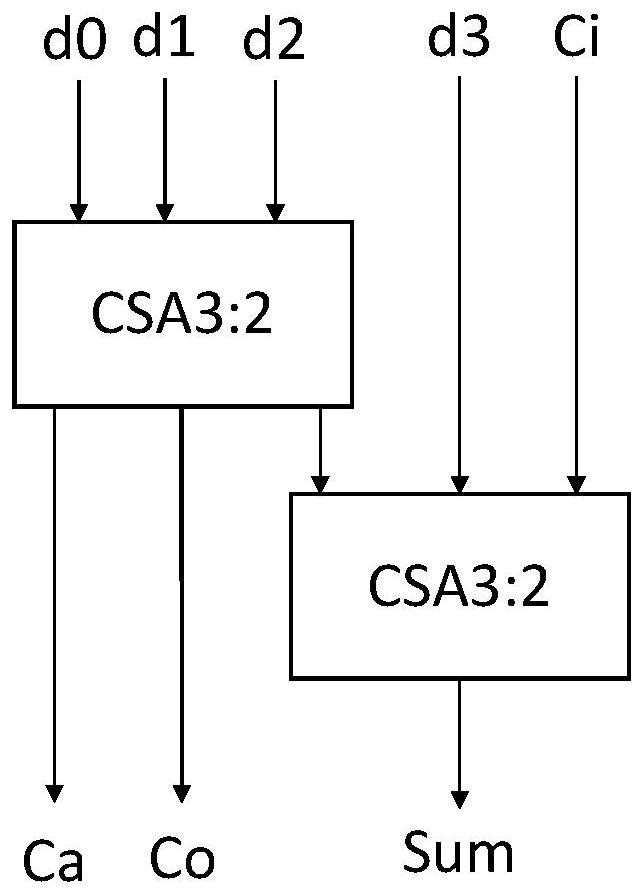

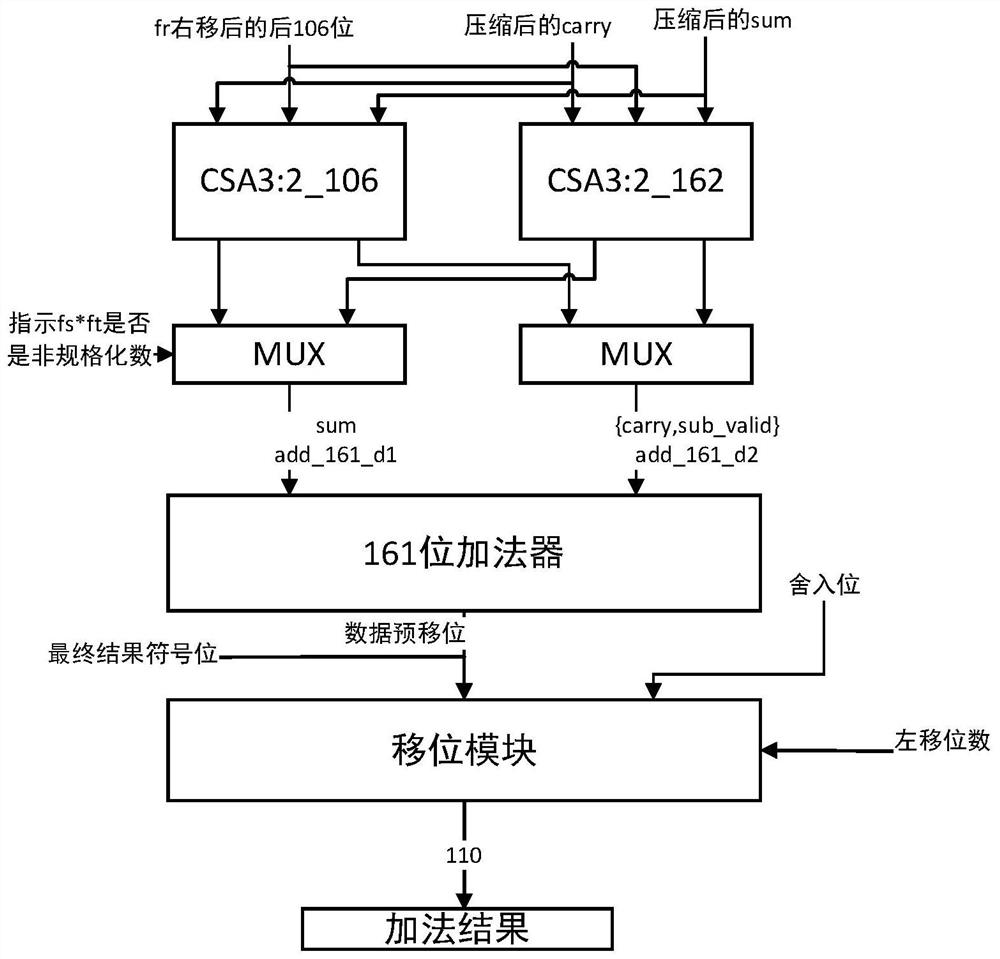

Carry verification device of floating point unit for multiply and summation, and multiplication CSA compression tree

A floating point multiplier-adder is prepared for using carry-over judgment unit to judge whether added result is carried-over or not by utilizing data of compression carry-over unit and compression sum unit as input value, outputting carry-over calibration bit M according to carry-over state, using carry-over calibration unit to operate high 55 bit and highest bit for making carry-over correction and outputting two sets of 55 bit values into high 55 bit in two set of data on 161 bit adder.

Owner:LOONGSON TECH CORP

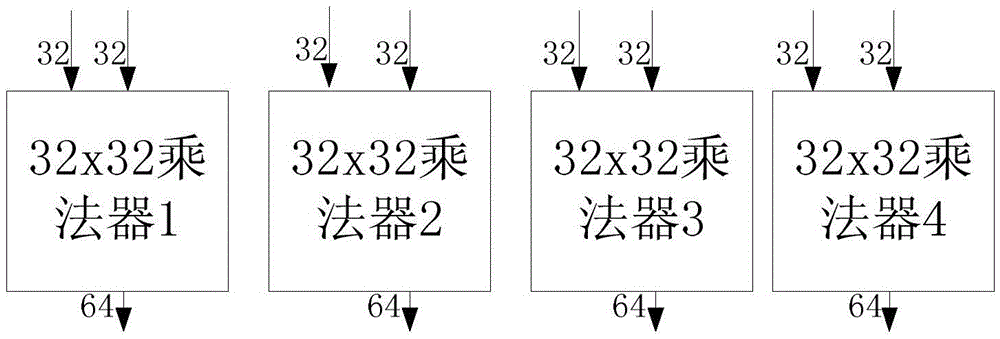

64-bit fixed and floating point multiplier unit supporting complex operation and subword parallelism

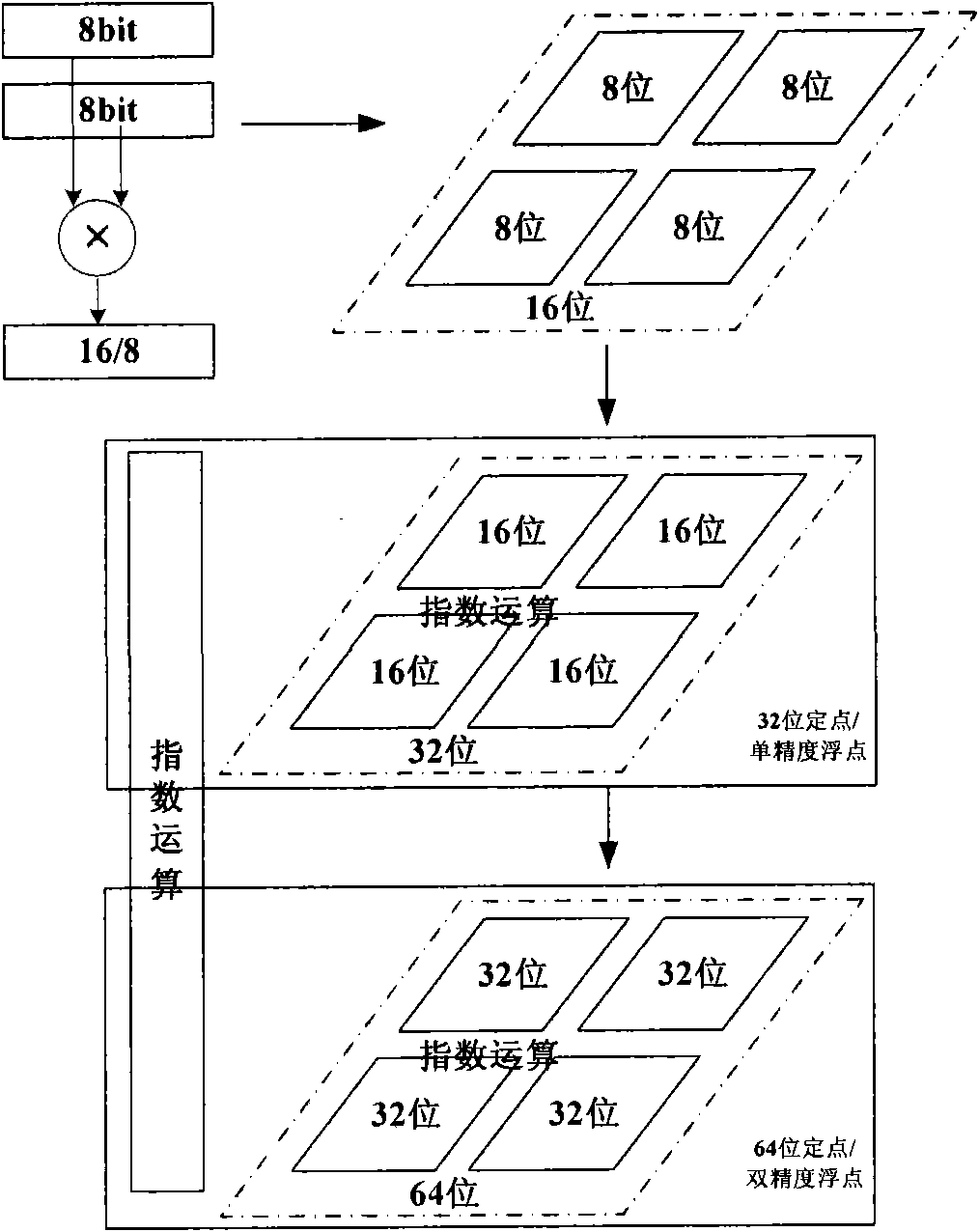

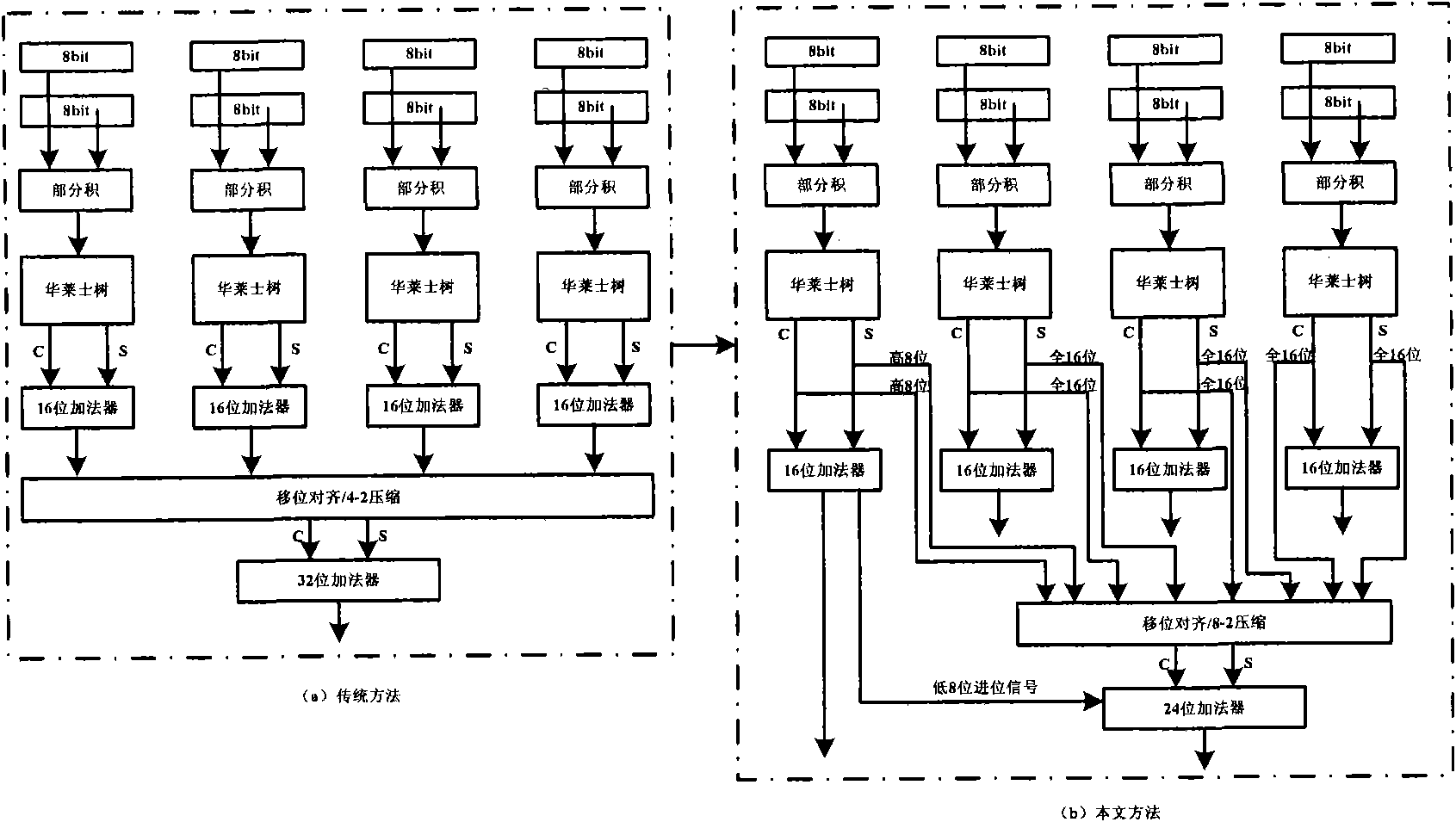

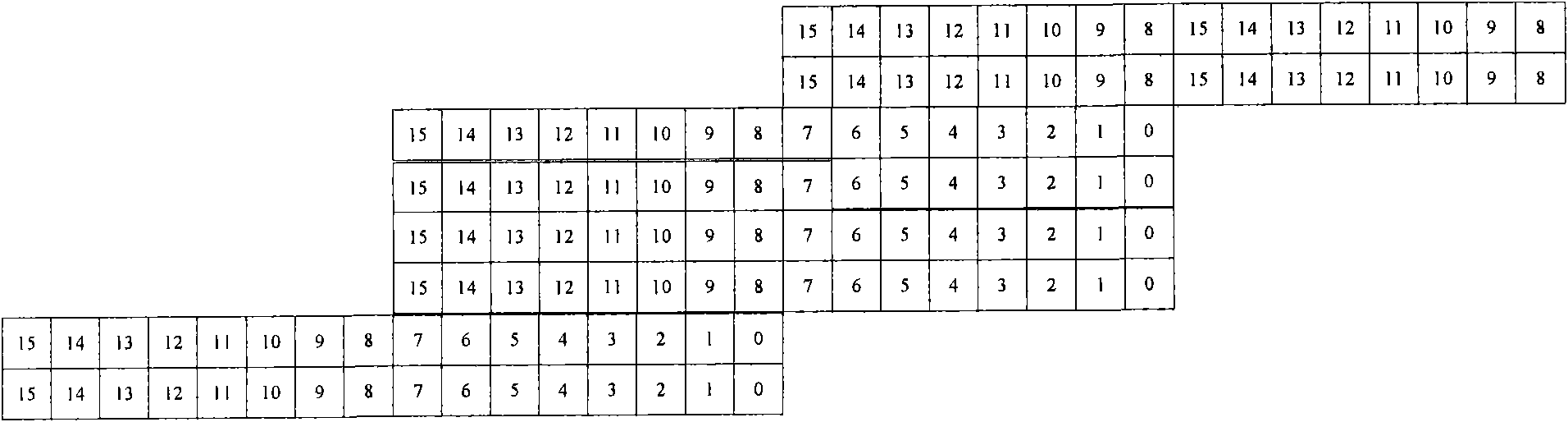

ActiveCN101840324ALower latencyReduce overheadDigital data processing detailsBinary multiplierTheoretical computer science

The invention discloses a 64-bit fixed and floating point multiplier unit supporting complex operation and subword parallelism. The multiplier unit is formed by combining four 32-bit multiplier units, wherein each 32-bit multiplier unit contains a 'carry' string used as output and an 'And' string used as output; the four 32-bit multiplier units contain four 'carry' strings and four 'And' strings; and the four 'carry' strings and the four 'And' strings are compressed by a 8-2 compressor to obtain a new 'carry' string and a new 'And' string for summation, so that the sum is used as the output of the multiplier unit. The 64-bit fixed and floating point multiplier unit reduces the time delay of key paths and the expense of operation resources.

Owner:BEIJING SMART LOGIC TECH CO LTD

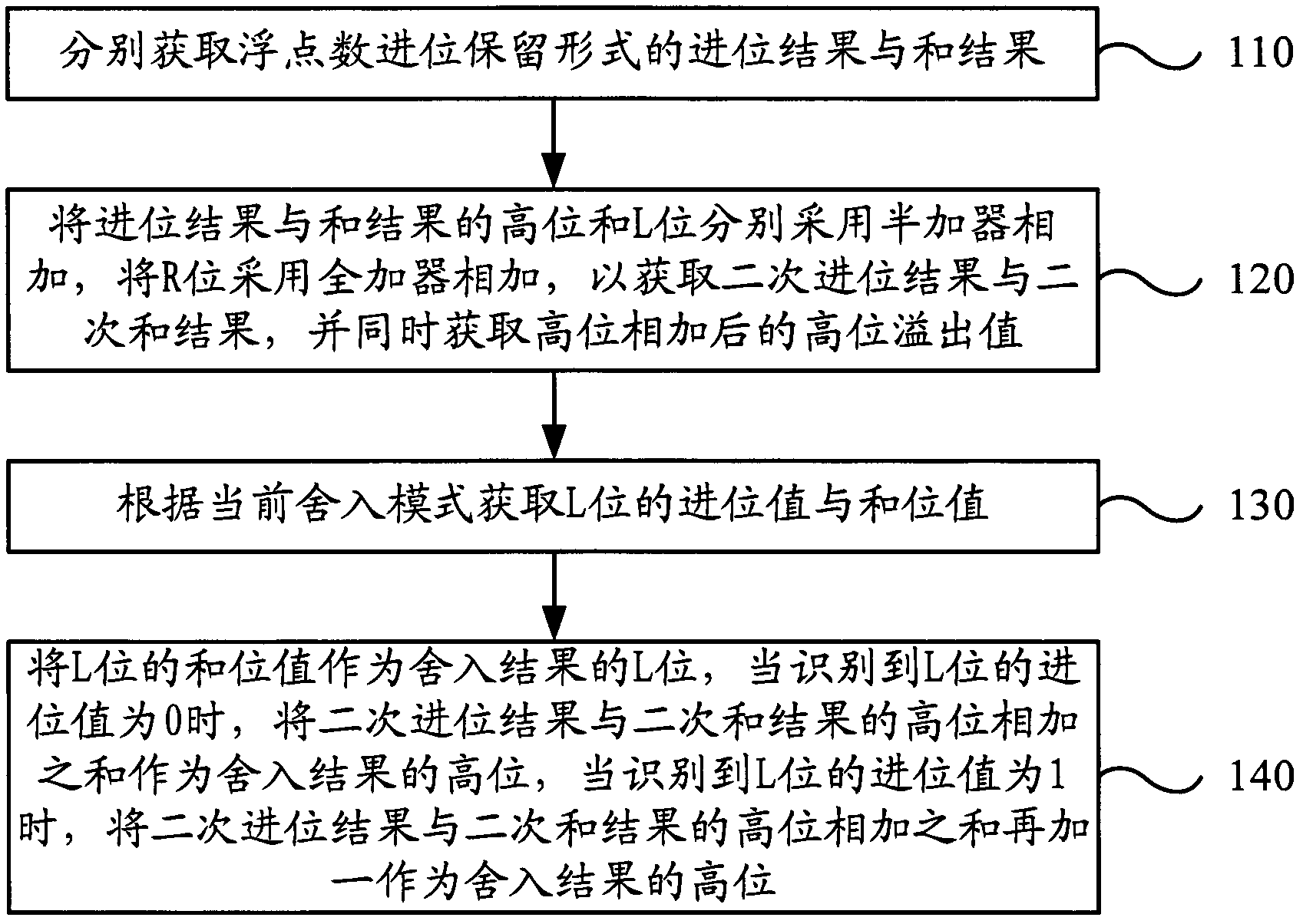

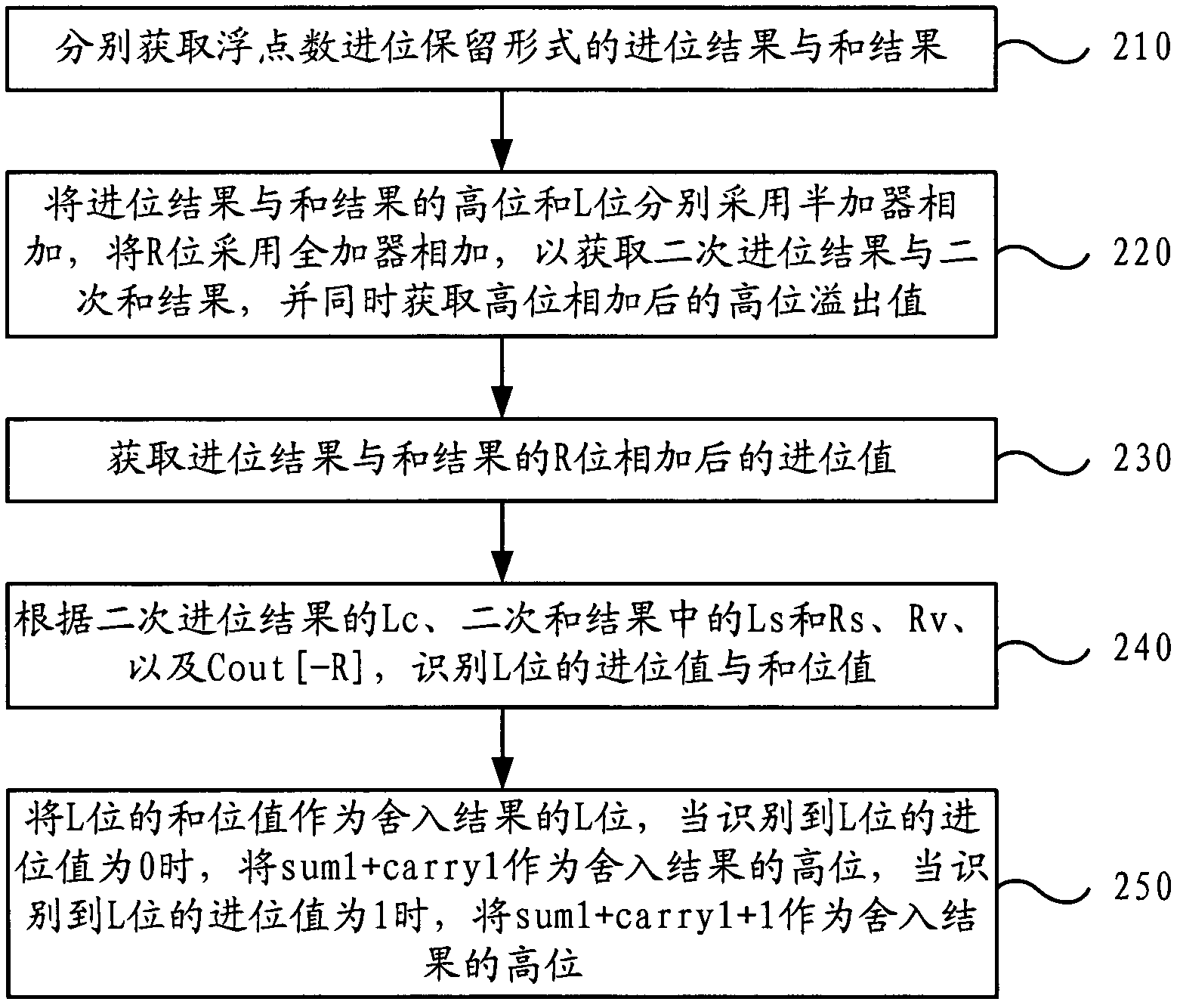

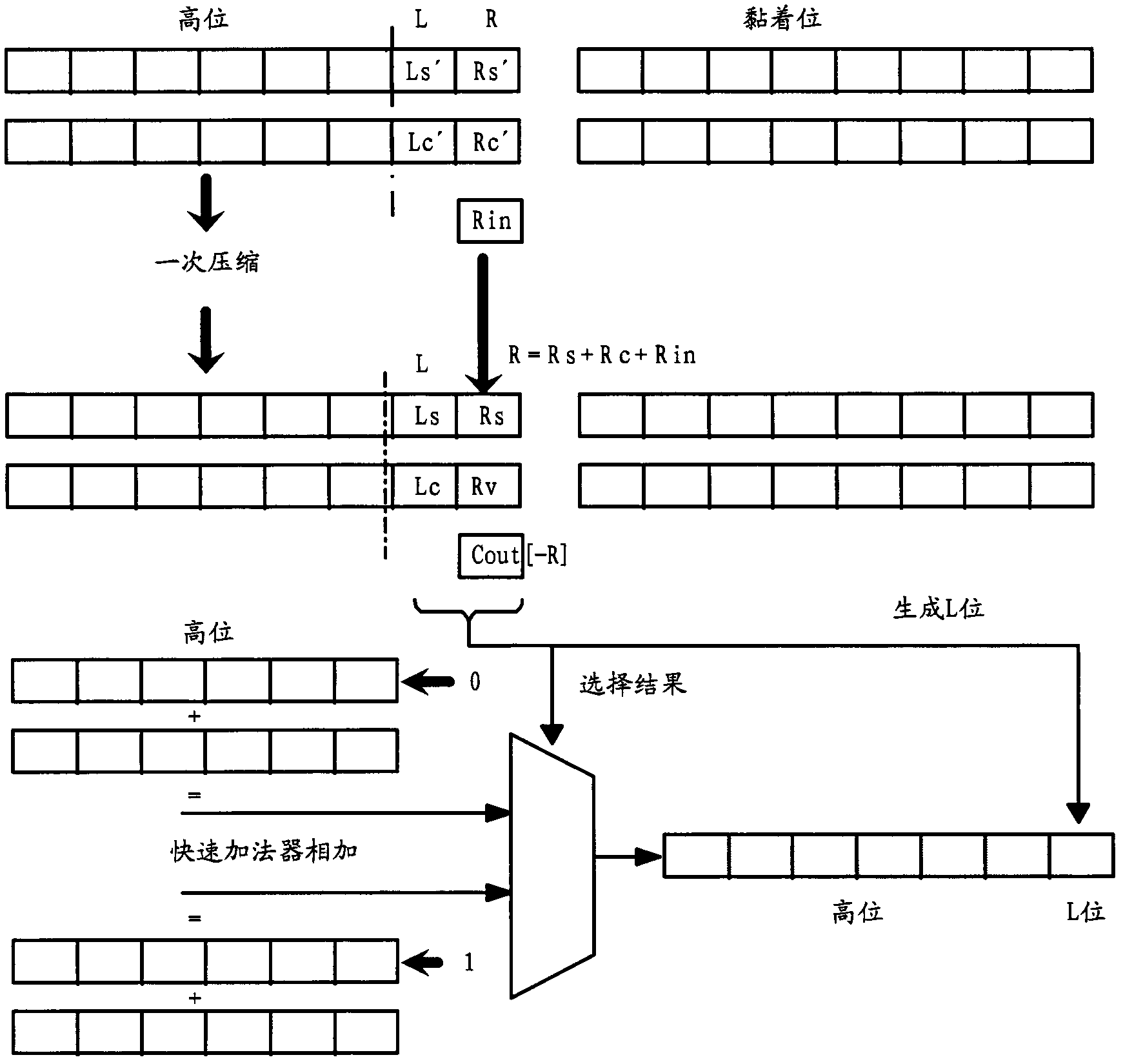

Multiplication rounding implementation method and device

InactiveCN102004627AImprove performanceImprove execution efficiencyDigital data processing detailsFloating point multiplierComputer engineering

The invention discloses a multiplication rounding implementation method and a device. The method comprises the following steps: respectively obtaining carry result and sum result in the floating point number carry save form; adopting a half-adder to respectively add the high bit and the L bit of the carry result and the sum result, adopting a full adder to add the R bit to obtain secondary carry result and secondary sum result, and simultaneously obtaining high bit overflow value after high bit adding; obtaining carry value and sum value of the L bit in the current rounding mode; taking the sum value of the L bit as the L bit of rounding result, taking the sum of the high bit of the secondary carry result and the high bit of the secondary sum result as the high bit of the rounding result when the carry value of the L bit is identified to be 0, and taking the sum of the high bit of the secondary carry result and the high bit of the secondary sum result plus 1 as the high bit of the rounding result when the carry value of the L bit is identified to be 1. The method and the device can improve the execution efficiency of the rounding operation of a floating-point multiplier and improve the performances of a floating-point processing unit.

Owner:HISILICON TECH

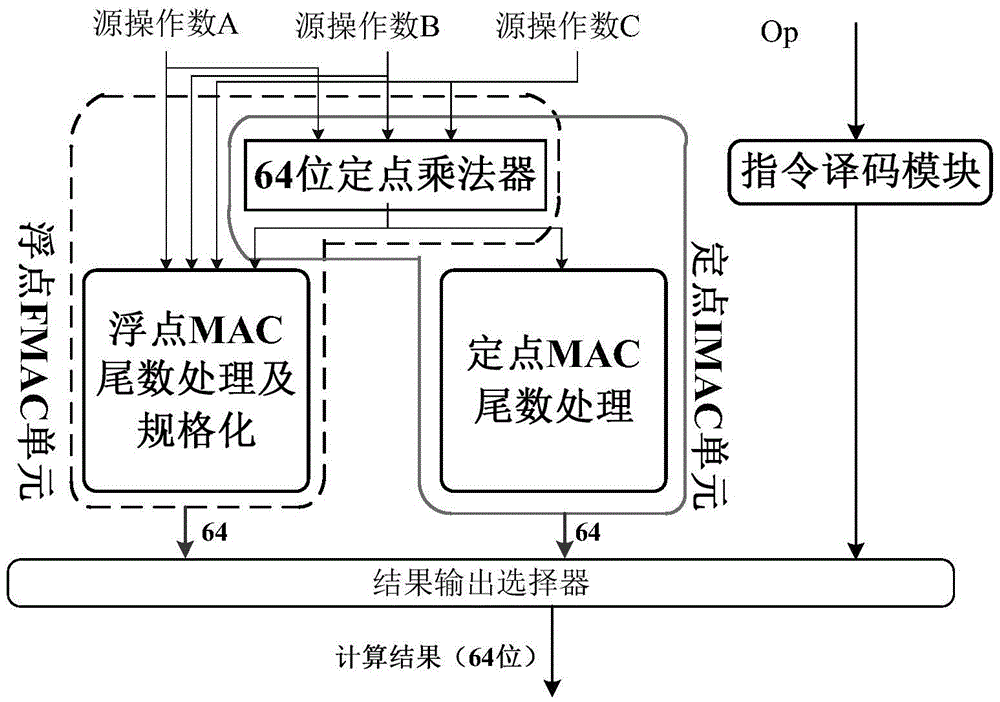

Fixed-point and floating-point operation part with shared multiplier structure in GPDSP

InactiveCN105607889AReduce areaImprove resource utilizationComputation using non-contact making devicesGeneral purposeBinary multiplier

The invention discloses a fixed-point and floating-point operation part with a shared multiplier structure in a GPDSP (General-Purpose Digital Signal Processor). The fixed-point and floating-point operation part comprises a floating-point multiplier-adder unit, a fixed-point multiplier-adder unit and a 64-bit fixed-point multiplier, wherein the floating-point multiplier-adder unit is used for supporting double-precision floating-point operation and double / single-precision floating point multiplication, multiplication-addition, multiplication-subtraction and complex multiplication operations of an SIMD structure; the fixed-point multiplier-adder unit is used for supporting 64-bit signed or unsigned fixed-point multiplication operation and double 32-bit signed or unsigned fixed-point multiplication operation of the SIMD structure; and the 64-bit fixed-point multiplier performs operation by regarding floating-point mantissa multiplication as unsigned fixed-point multiplication by multiplexing the structure of the same multiplier. The fixed-point and floating-point operation part has the advantages of capabilities of increasing the hardware utilization rate and reducing the chip area, and the like.

Owner:NAT UNIV OF DEFENSE TECH

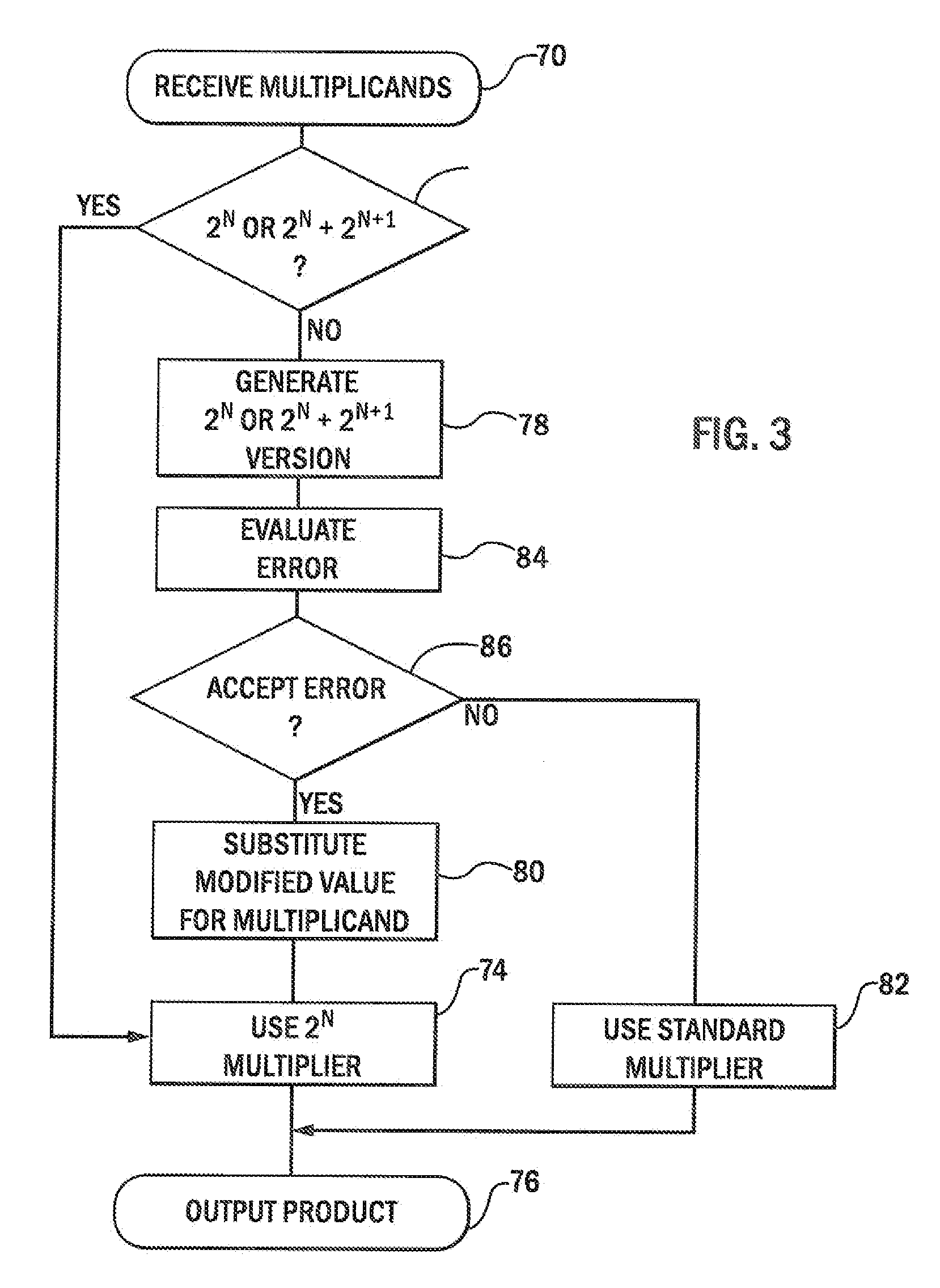

High Efficiency Computer Floating Point Multiplier Unit

ActiveUS20150370537A1Reduce the required powerSignificant power savingComputations using contact-making devicesOperandFloating point multiplication

Owner:WISCONSIN ALUMNI RES FOUND

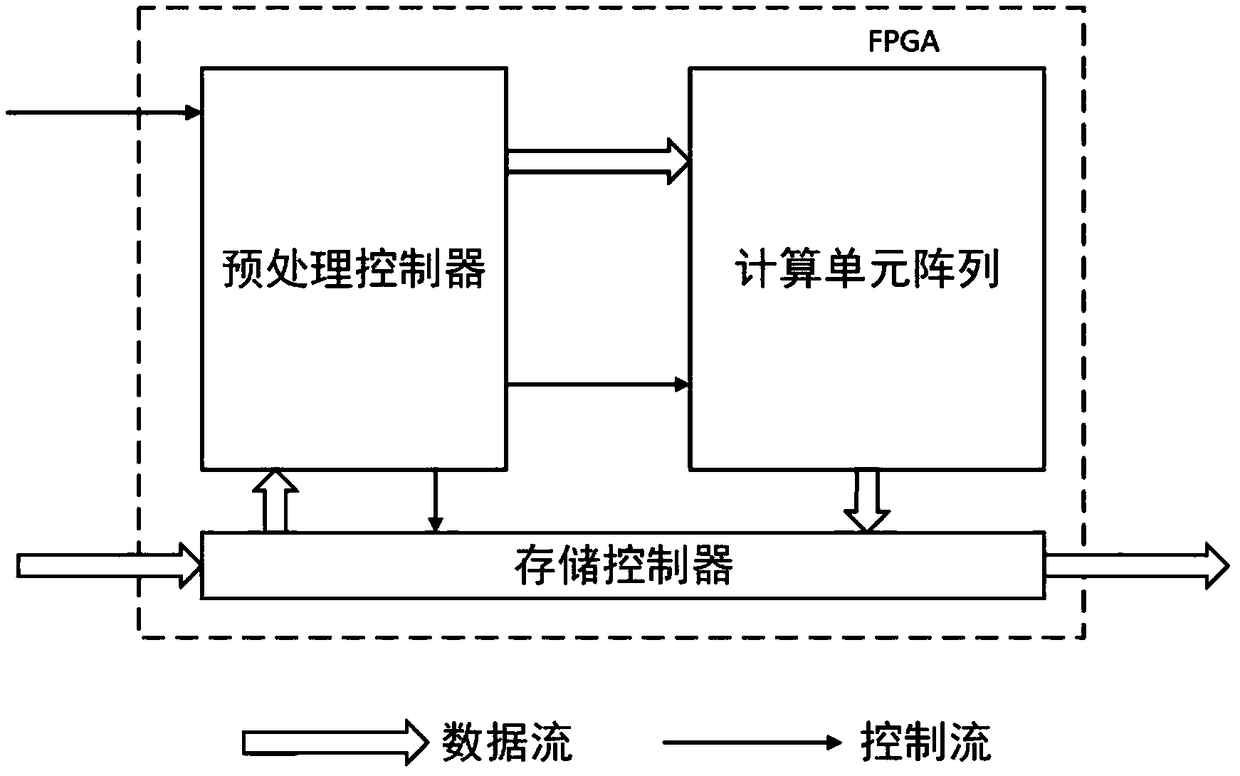

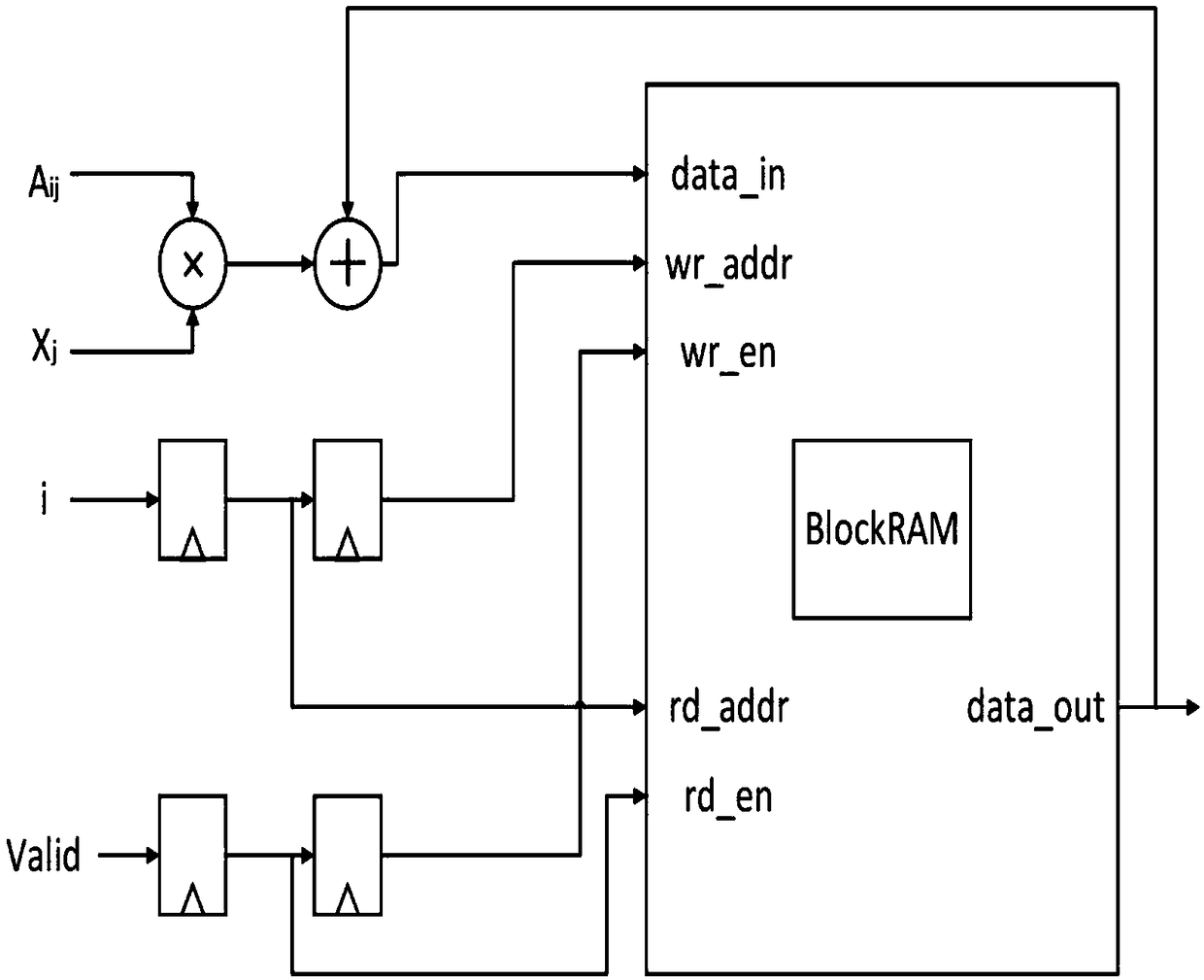

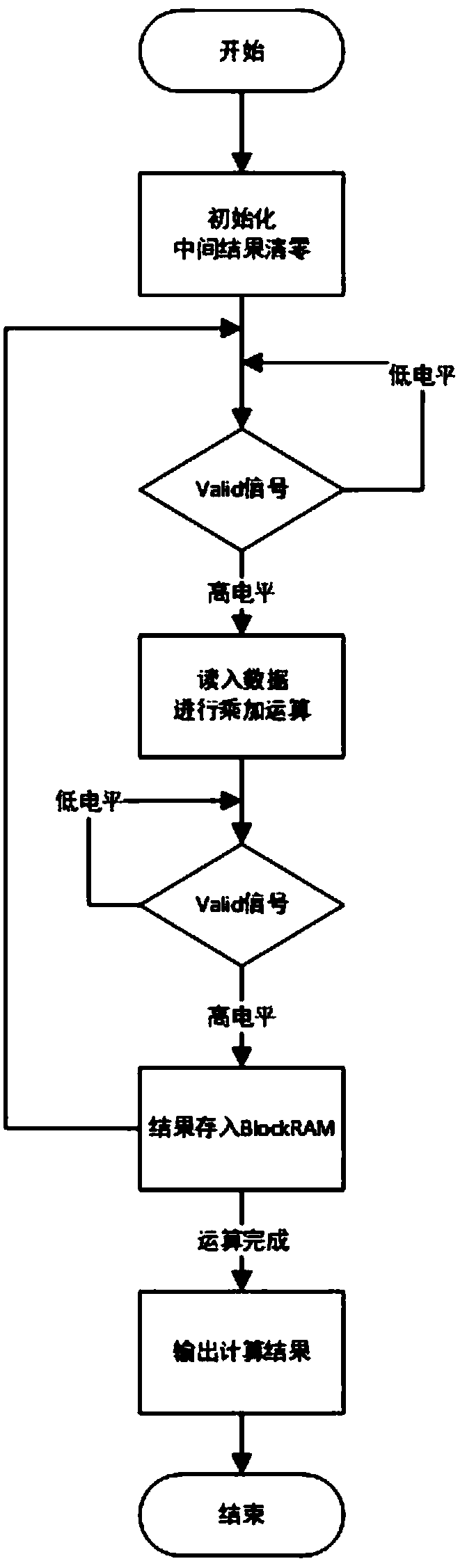

FPGA-based expandable sparse matrix vector multiplication processor

PendingCN108710505AEasy to operateImprove data throughputMachine execution arrangementsSparse matrix vectorControl store

Owner:NANJING UNIV

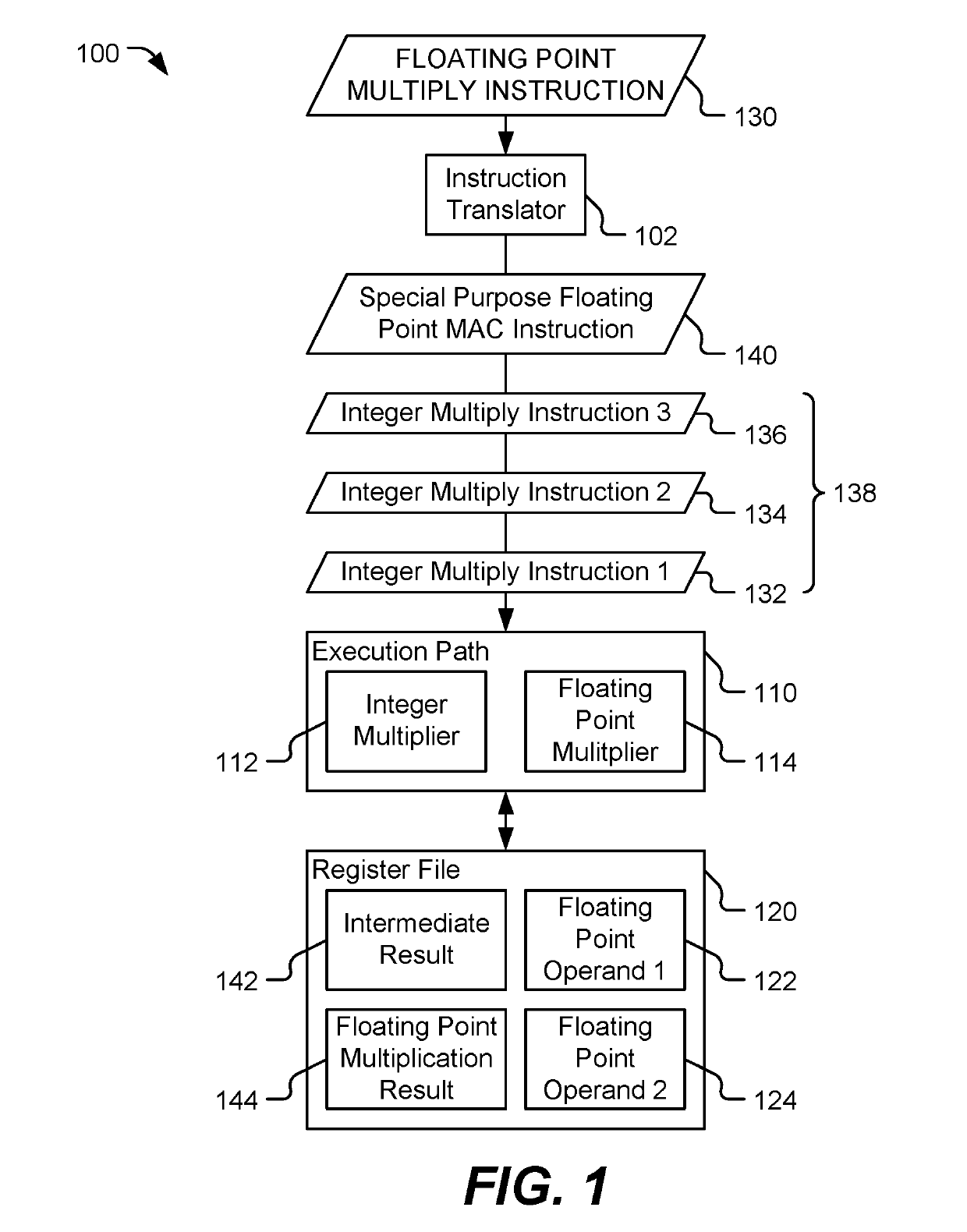

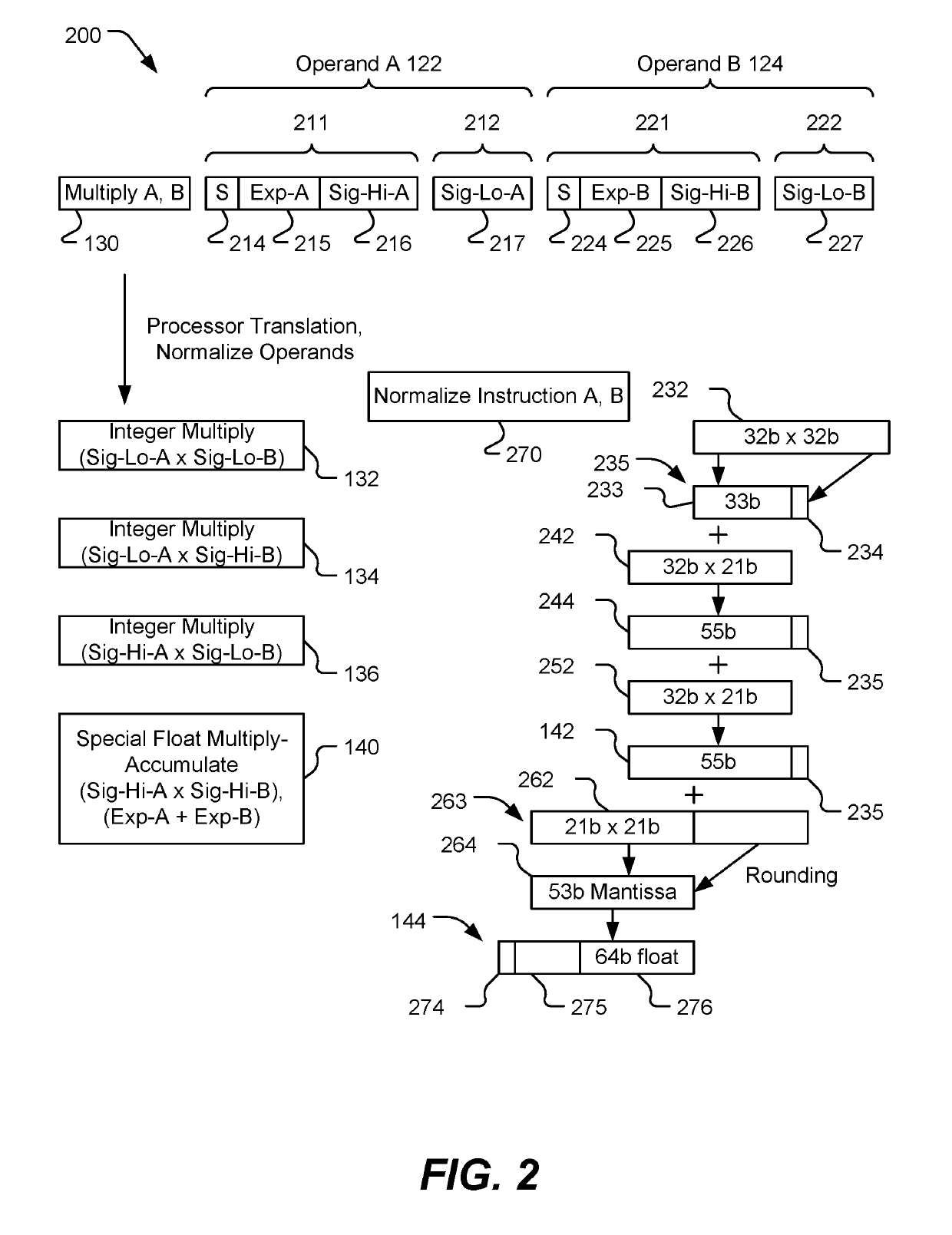

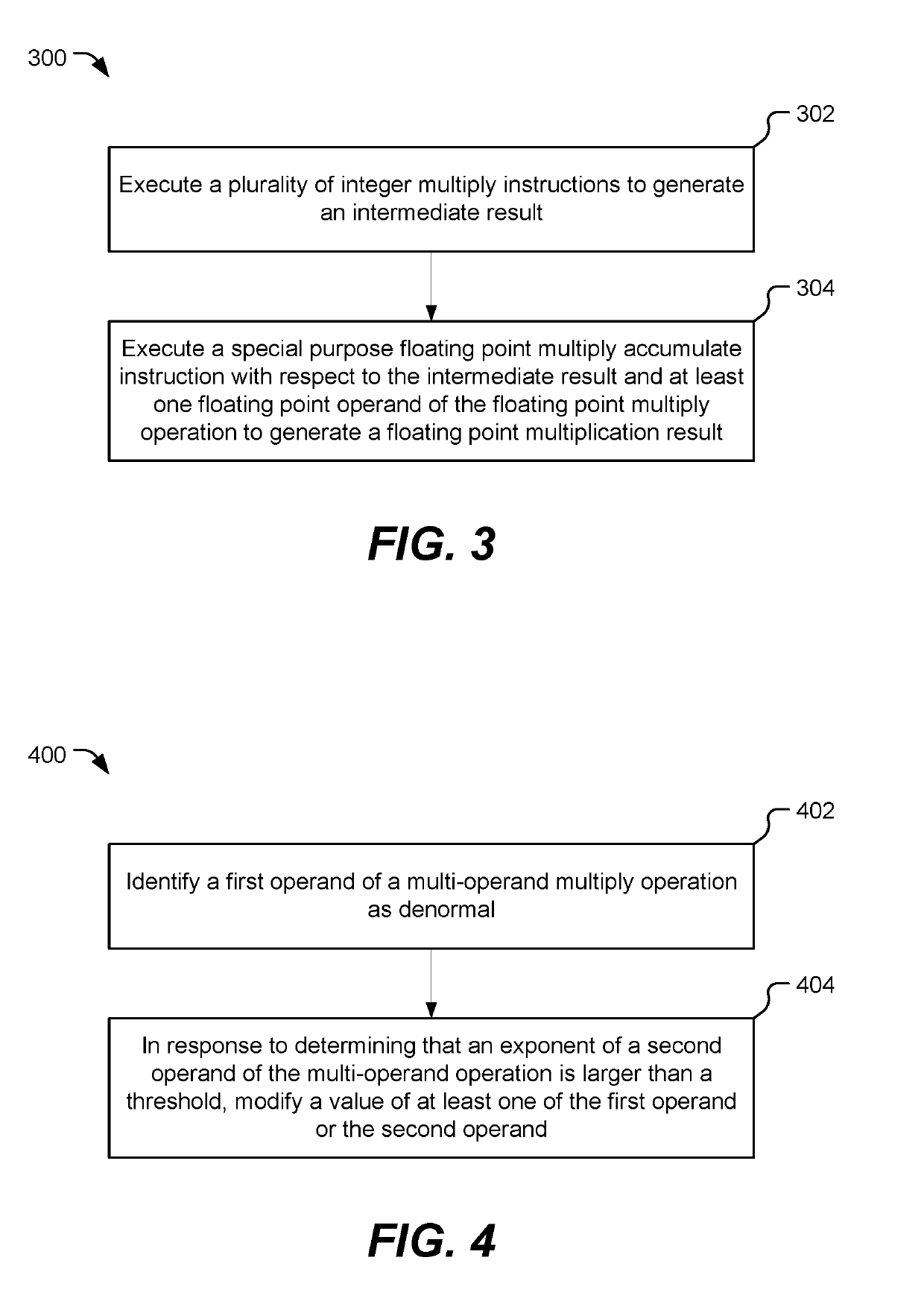

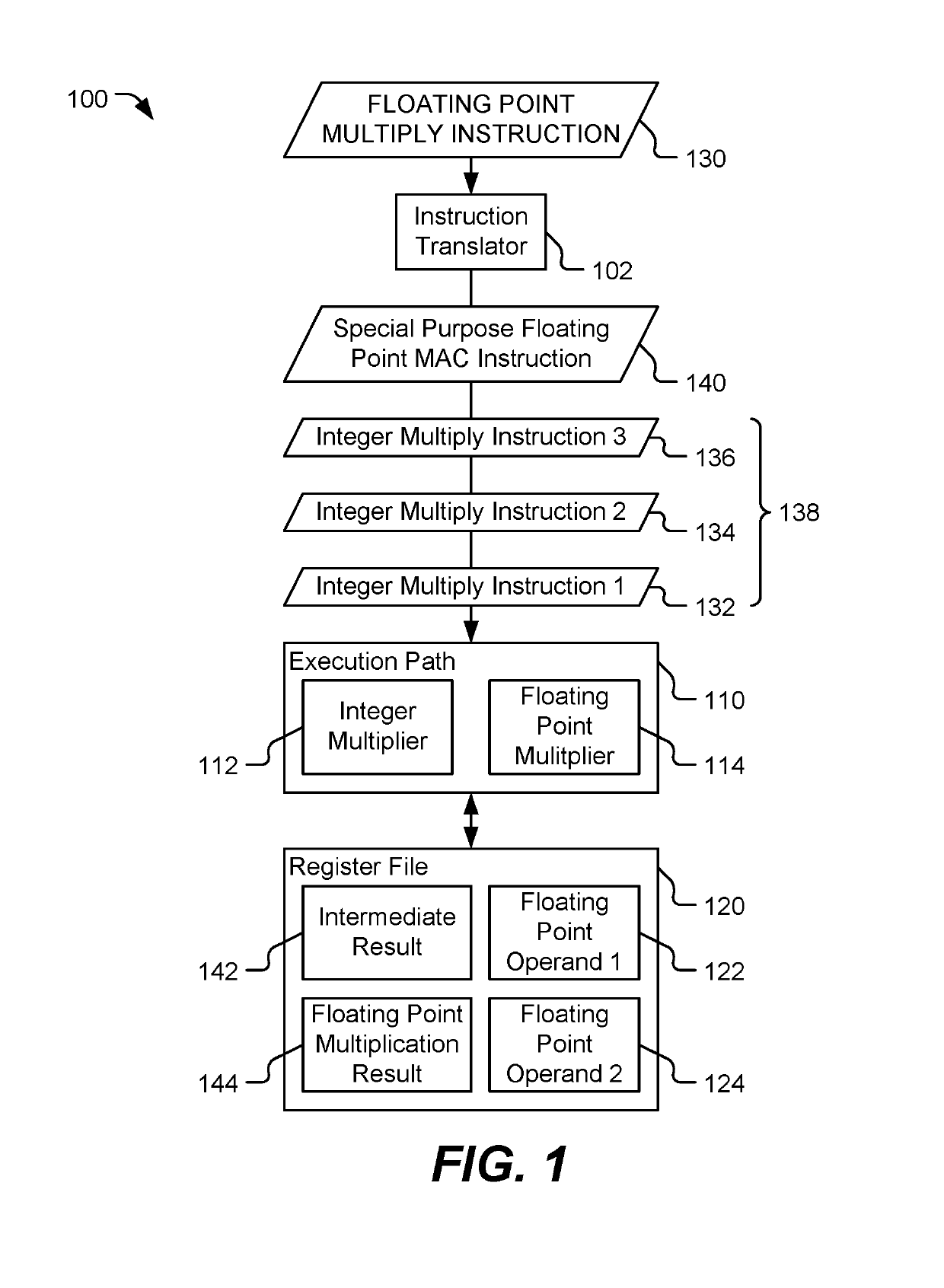

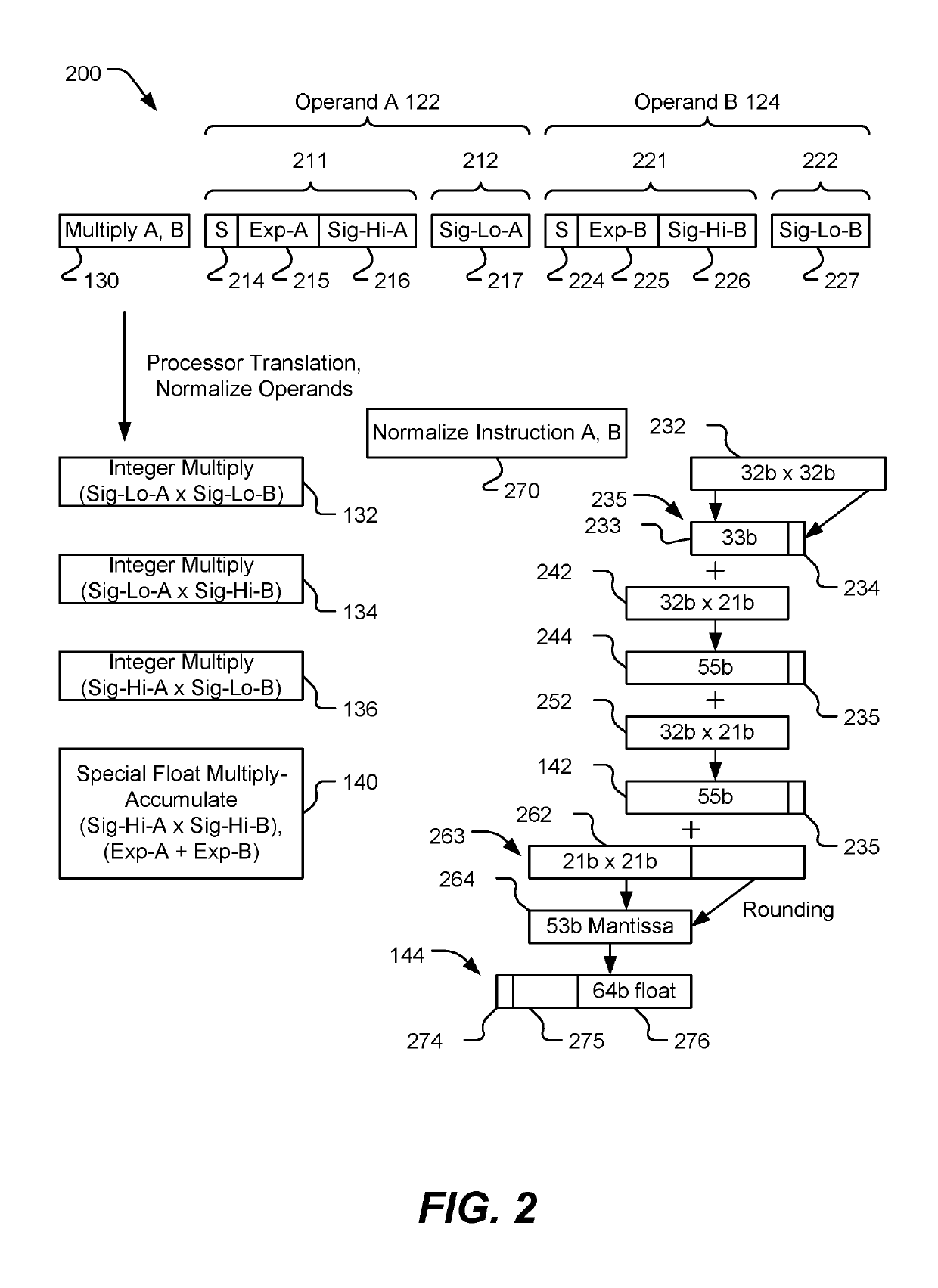

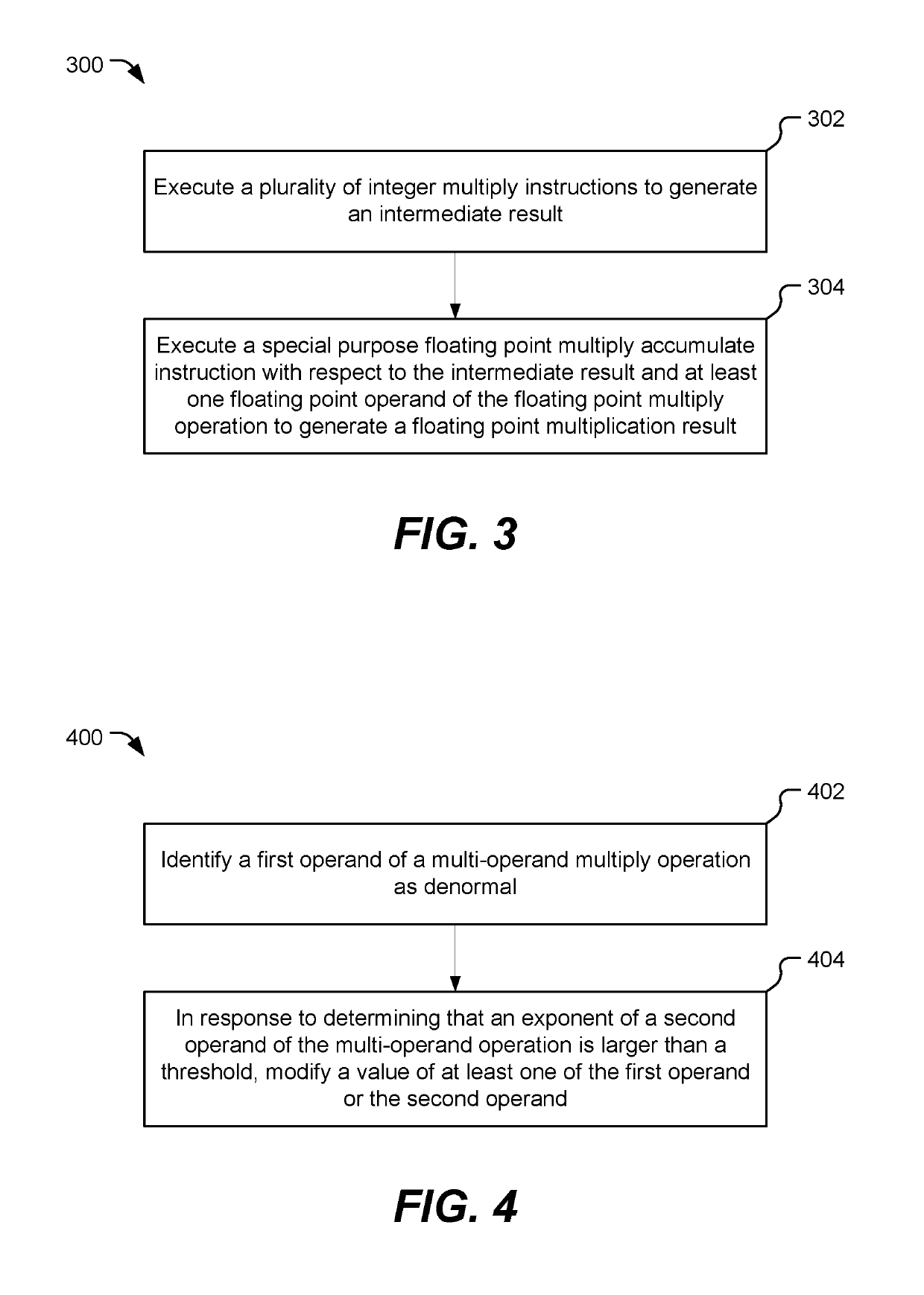

System and method of floating point multiply operation processing

ActiveCN111492343ALow costReduce areaComputation using non-contact making devicesComputer architectureBinary multiplier

A processor includes an integer multiplier configured to execute an integer multiply instruction to multiply significand bits of at least one floating point operand of a floating point multiply operation. The processor also includes a floating point multiplier configured to execute a special purpose floating point multiply accumulate instruction with respect to an intermediate result of the floating point multiply operation and the at least one floating point operand to generate a final floating point multiplication result.

Owner:QUALCOMM INC

Floating point multiplier with first and second partial product shifting circuitry for result alignment

ActiveUS8463834B2Reduce delaysLittle hardware overheadDigital computer detailsData conversionRight shiftOperand

A floating point multiplier includes a data path in which a plurality of partial products are calculated and then reduced to a first partial product and a second partial product. Shift amount determining circuitry 100 analyzes the exponents of the input operands A and B as well as counting the leading zeros in the fractional portions of these operands to determine an amount of left shift or right shift to be applied by shifting circuitry 200, 202 within the multiplier data path. This shift amount is applied so as to align the partial products so that when they are added they will produce the result C without requiring this to be further shifted. Furthermore, shifting the partial products to the correct alignment in this way in advance of adding these partial products permits injection rounding combined with the adding of the partial products to be employed for cases including subnormal values.

Owner:ARM LTD

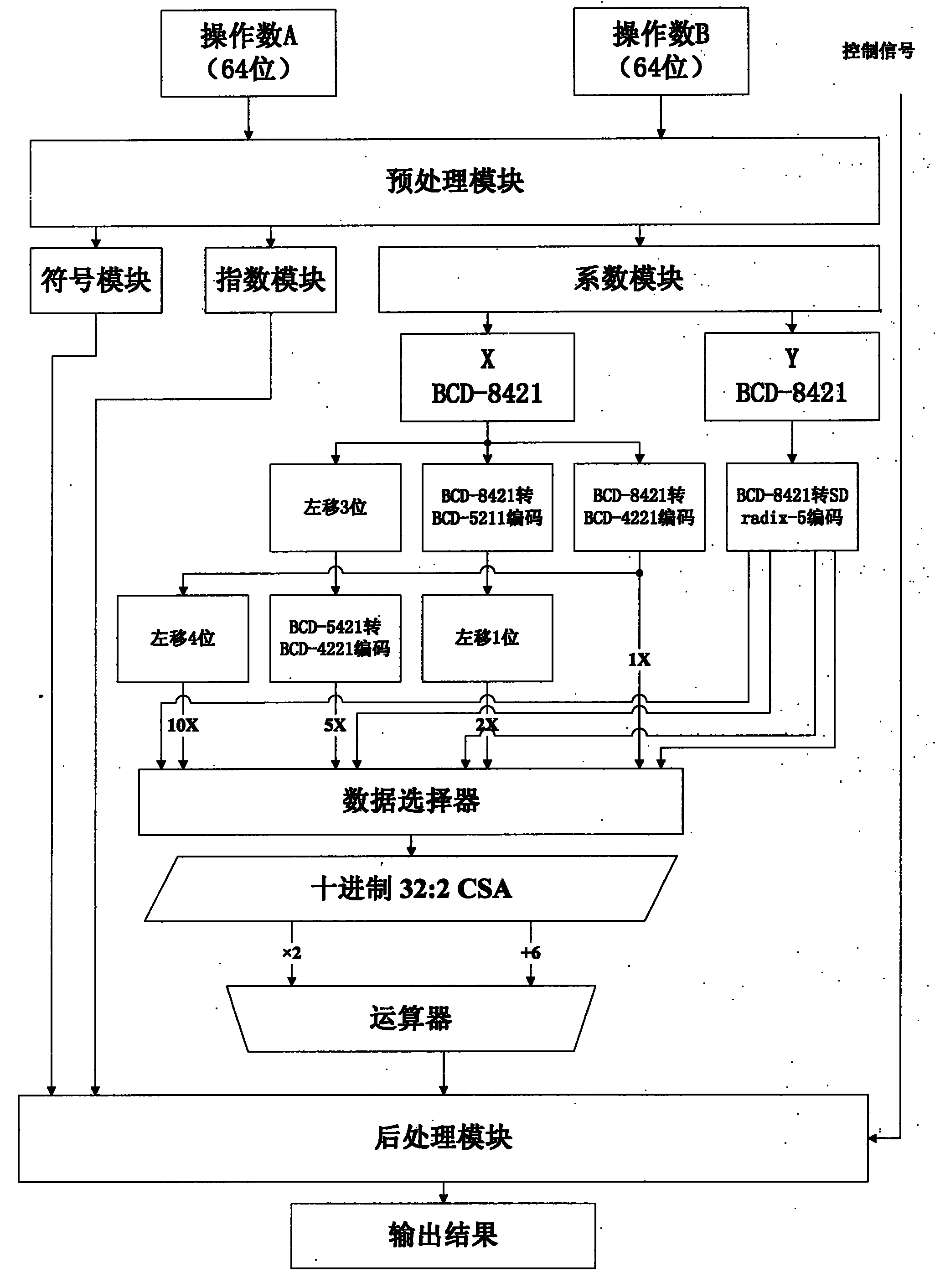

Field programmable gata array (FPGA)-based metric floating-point multiplier design

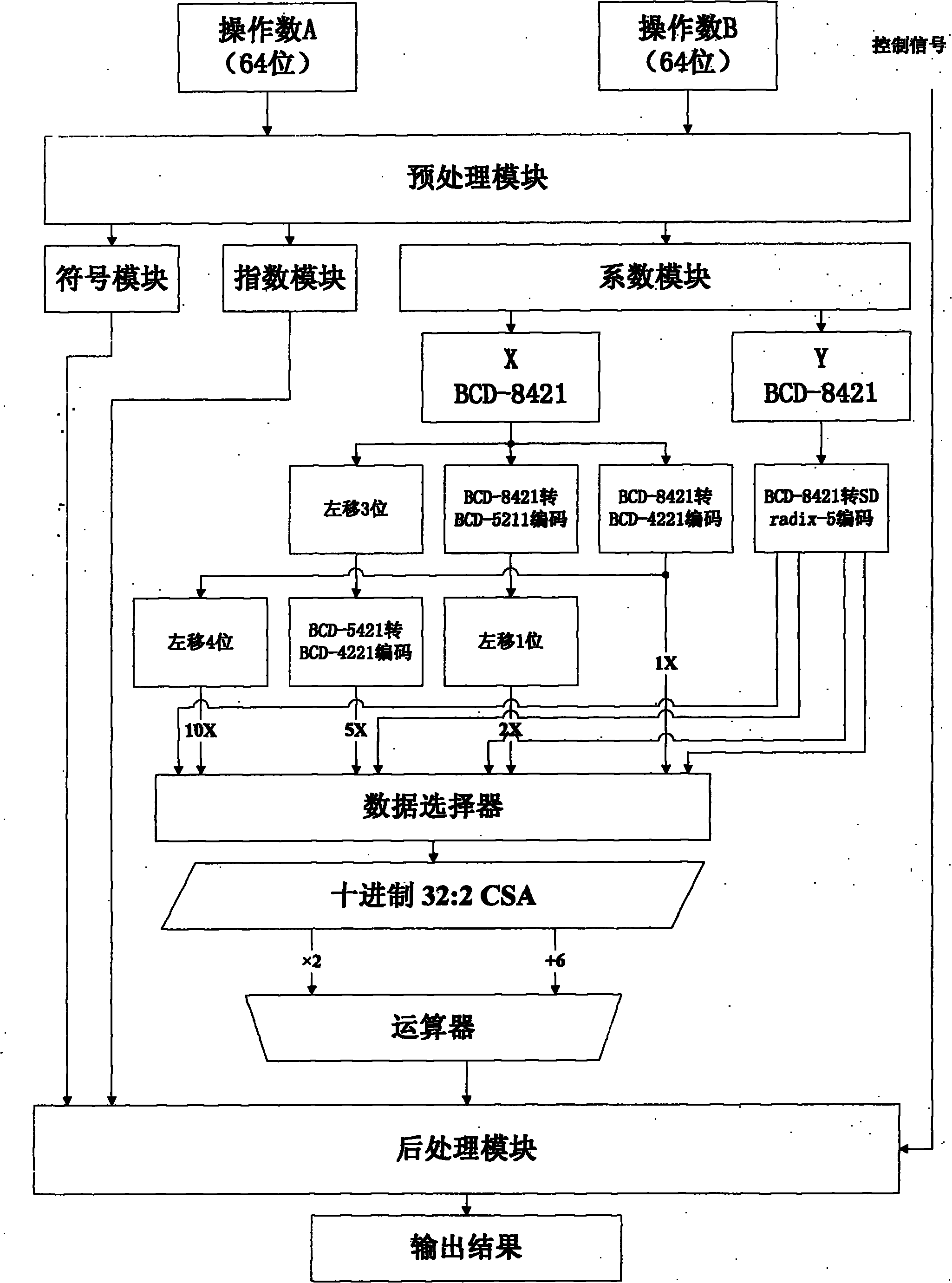

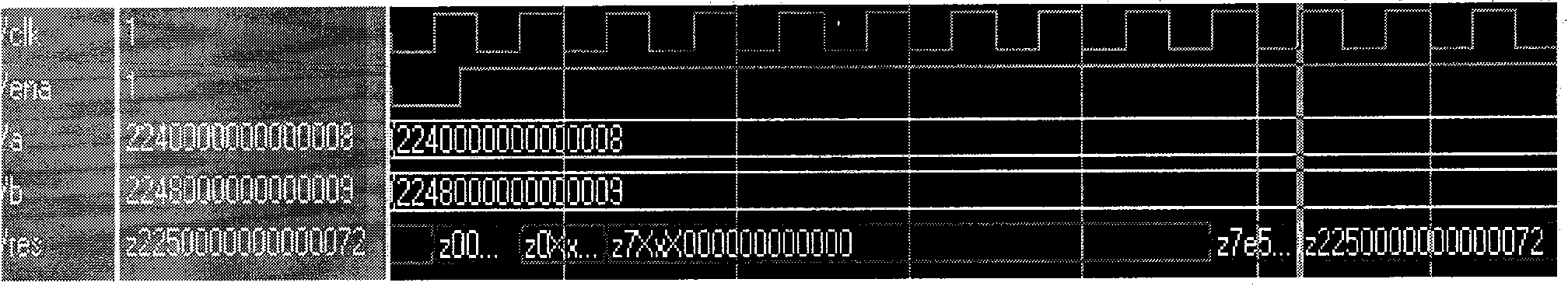

InactiveCN102073473ASave resourcesFix conversion precision issuesDigital data processing detailsImaging processingDensely packed decimal

The invention discloses a field programmable gata array (FPGA)-based metric floating-point multiplier design. The design adopts advanced and quick algorithms such as densely-packed decimal (DPD) coding, novel binary-coded decimal (BCD) coding, signed-digit radix-5, decimal 32:2 carry-save adder (CSA) and the like, is realized by programming through a Verilog hardware description language and can perform multiplication of 64-digit decimal floating-point numbers in accordance with the Institute of Electrical and Electronic Engineers (IEEE) 754-2008 new standard. The design effectively solves the problem of conversion accuracy existing in binary / decimal operation on the conventional hardware platform and the time problem of the realization of decimal floating-point multiplication by using software, consumes a small number of hardware resources and has high operation speed and a simple structure; moreover, according to the performance and characteristic of the FPGA, a system can be developed repeatedly, and a decimal floating-point unit which is accordant with the IEEE 754-2008 standard specification can be further developed and designed. The design is mainly applied to industries such as bank finance, image processing, medical treatment and the like.

Owner:YUNNAN UNIV

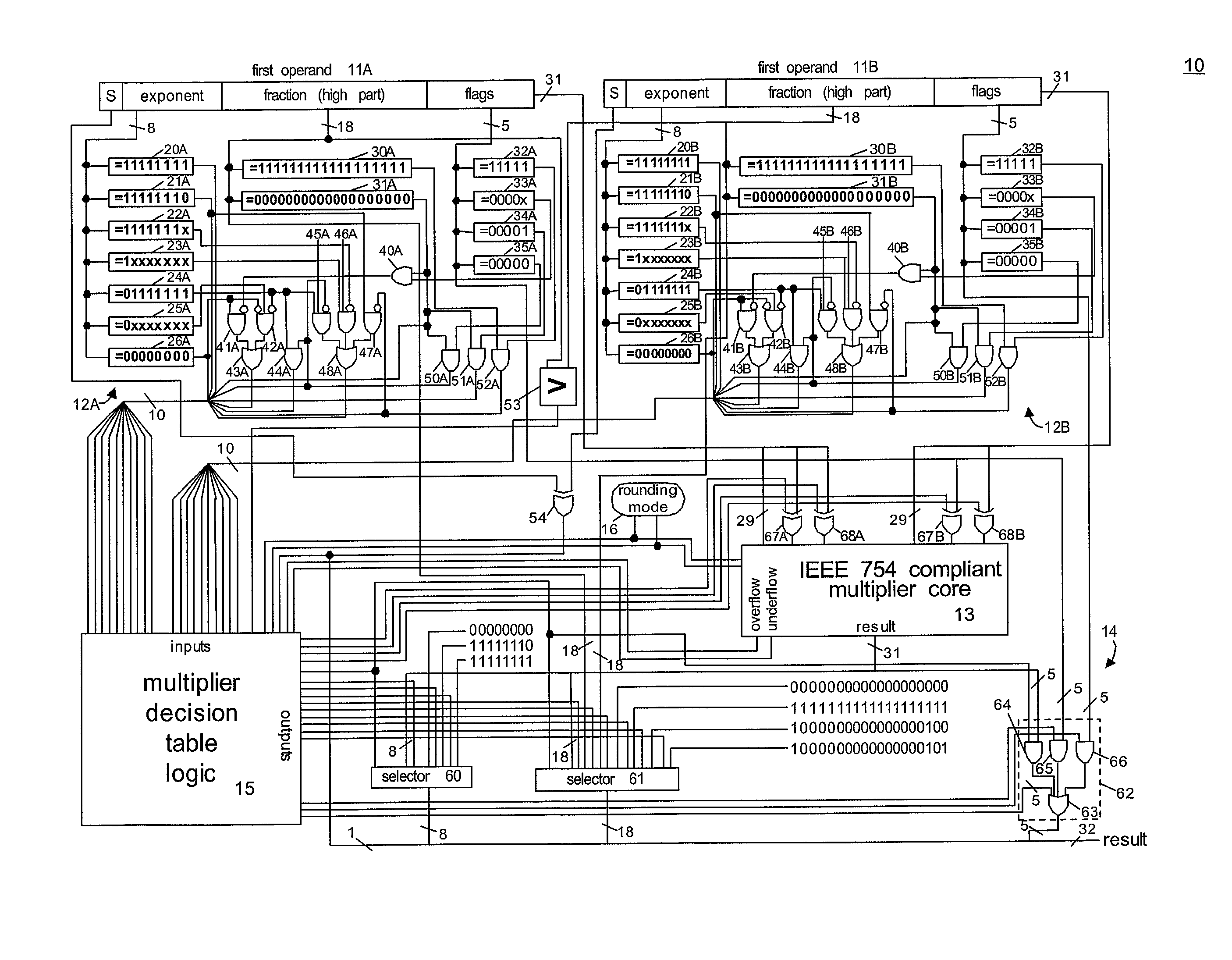

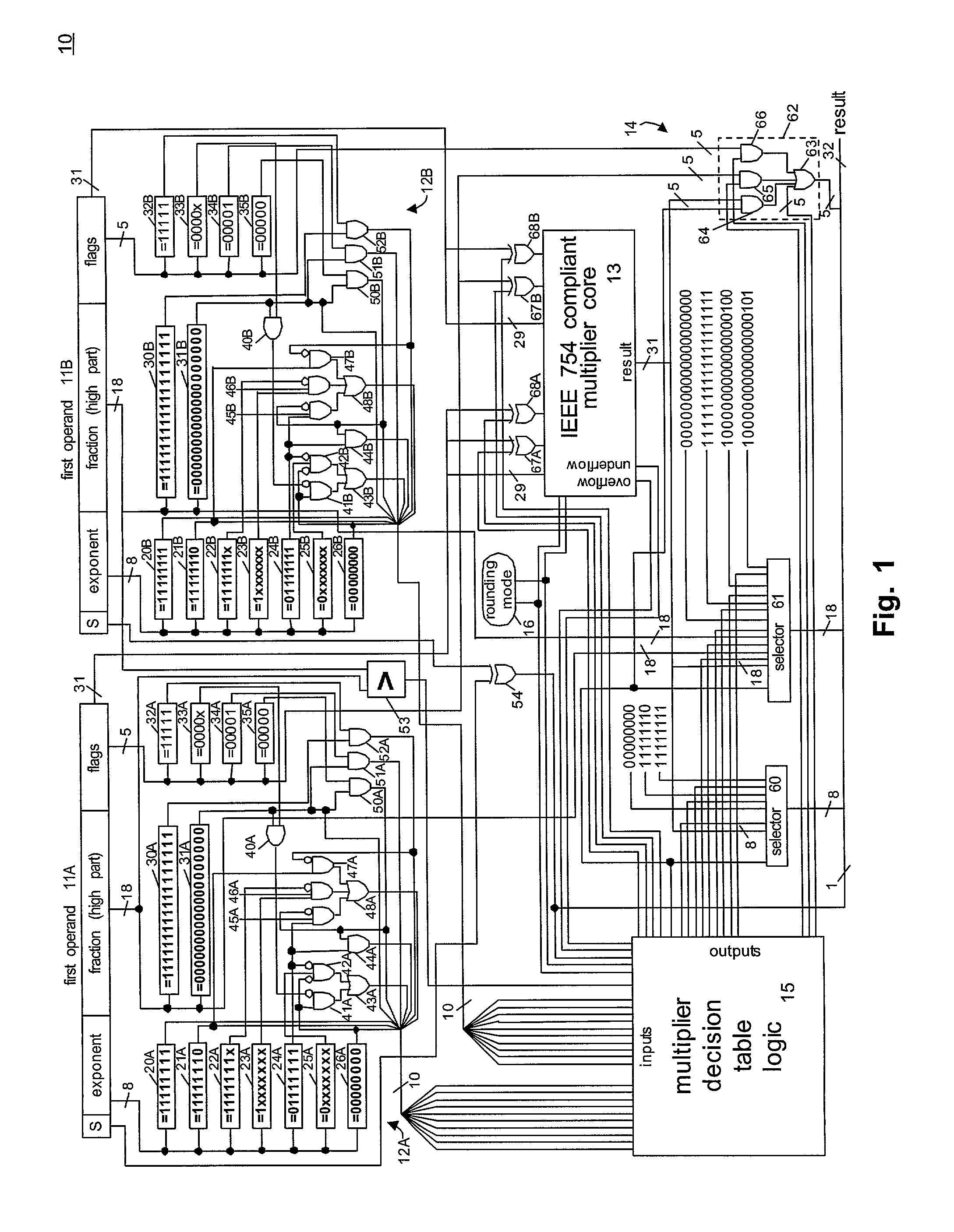

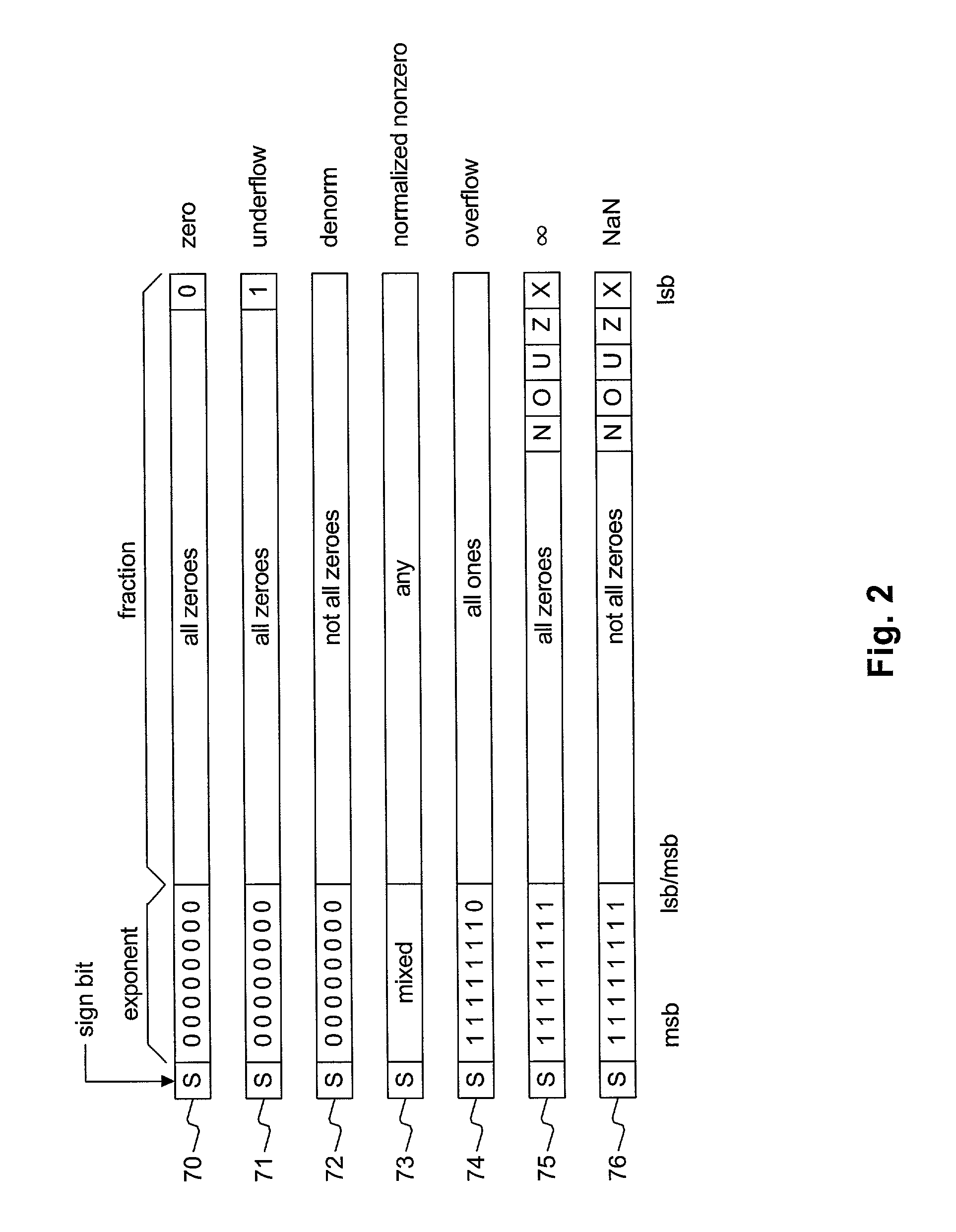

Floating point multiplier with embedded status information

InactiveUS7831652B2Conditional code generationComputations using contact-making devicesOperandFloating point multiplier

A system for providing a floating point product comprises an analyzer circuit configured to determine a first status of a first floating point operand and a second status of a second floating point operand based upon data within the first floating point operand and data within the second floating point operand respectively. In addition, the system comprises a results circuit coupled to the analyzer circuit. The results circuit is configured to assert a resulting floating point operand containing the product of the first floating point operand and the second floating point operand. Additionally, the results circuit provides a resulting status embedded within the resulting floating point operand.

Owner:ORACLE INT CORP

System and method of floating point multiply operation processing

ActiveUS20190196785A1Sufficient bit widthIncrease widthDigital data processing detailsOperandFloating point multiplication

A processor includes an integer multiplier configured to execute an integer multiply instruction to multiply significand bits of at least one floating point operand of a floating point multiply operation. The processor also includes a floating point multiplier configured to execute a special purpose floating point multiply accumulate instruction with respect to an intermediate result of the floating point multiply operation and the at least one floating point operand to generate a final floating point multiplication result.

Owner:QUALCOMM INC

Mode-based multiply-add processor for denormal operands

InactiveCN101438233AComputation using denominational number representationDenormalizationFloating point multiplier

Owner:QUALCOMM INC

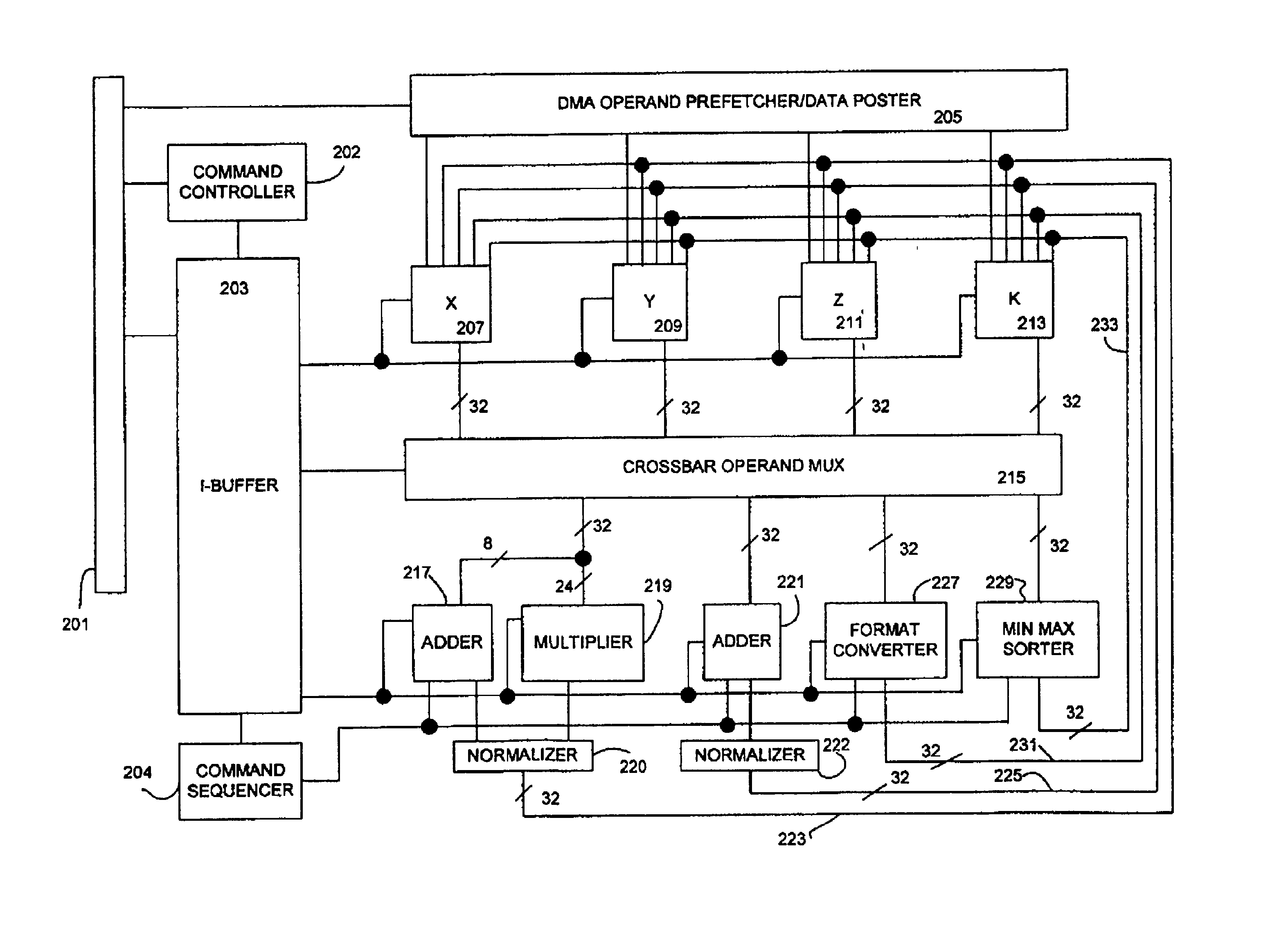

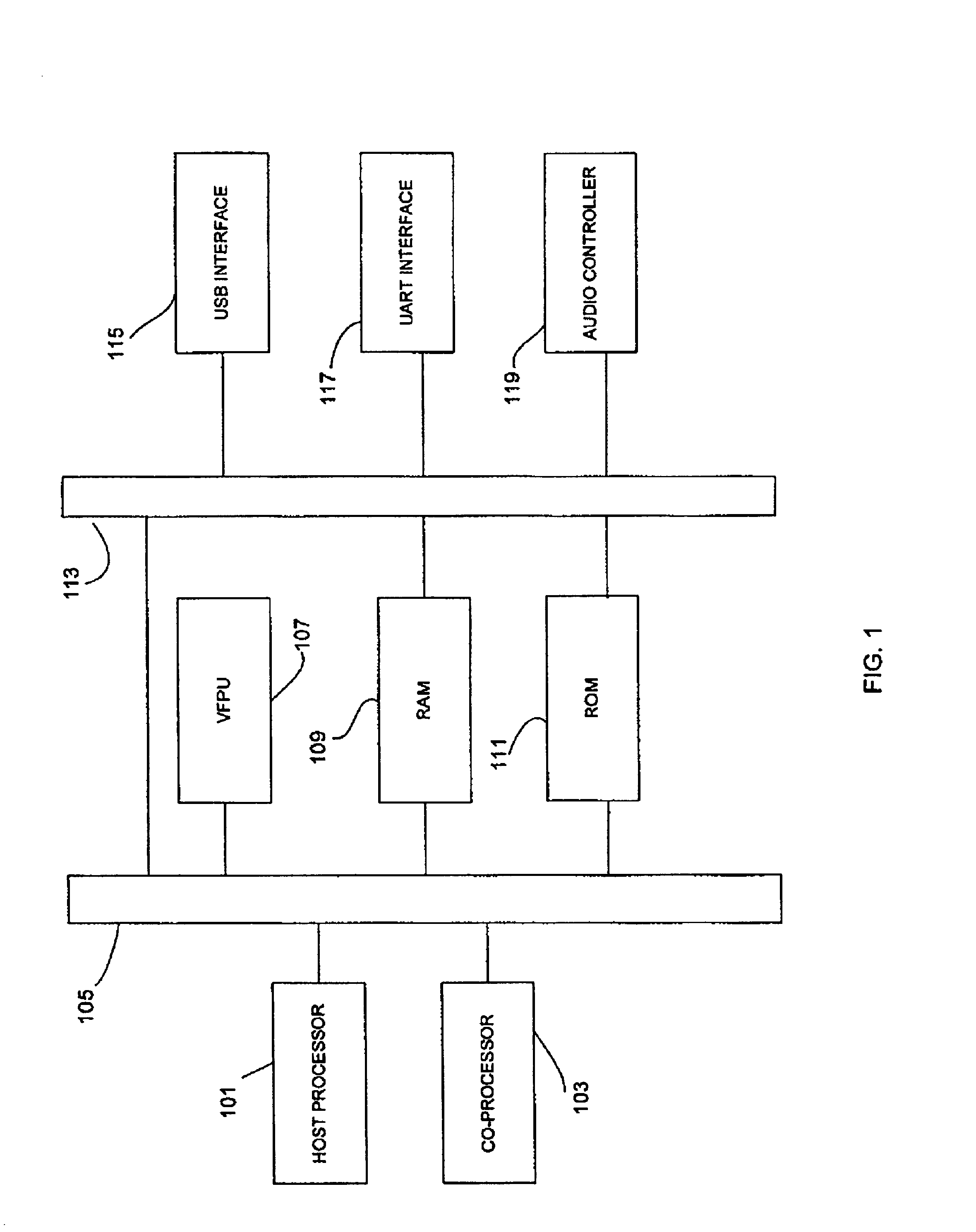

Vector floating point unit

InactiveUS6922771B2Quick configurationFine-tune performanceInstruction analysisGeneral purpose stored program computerProcessor registerFloating-point unit

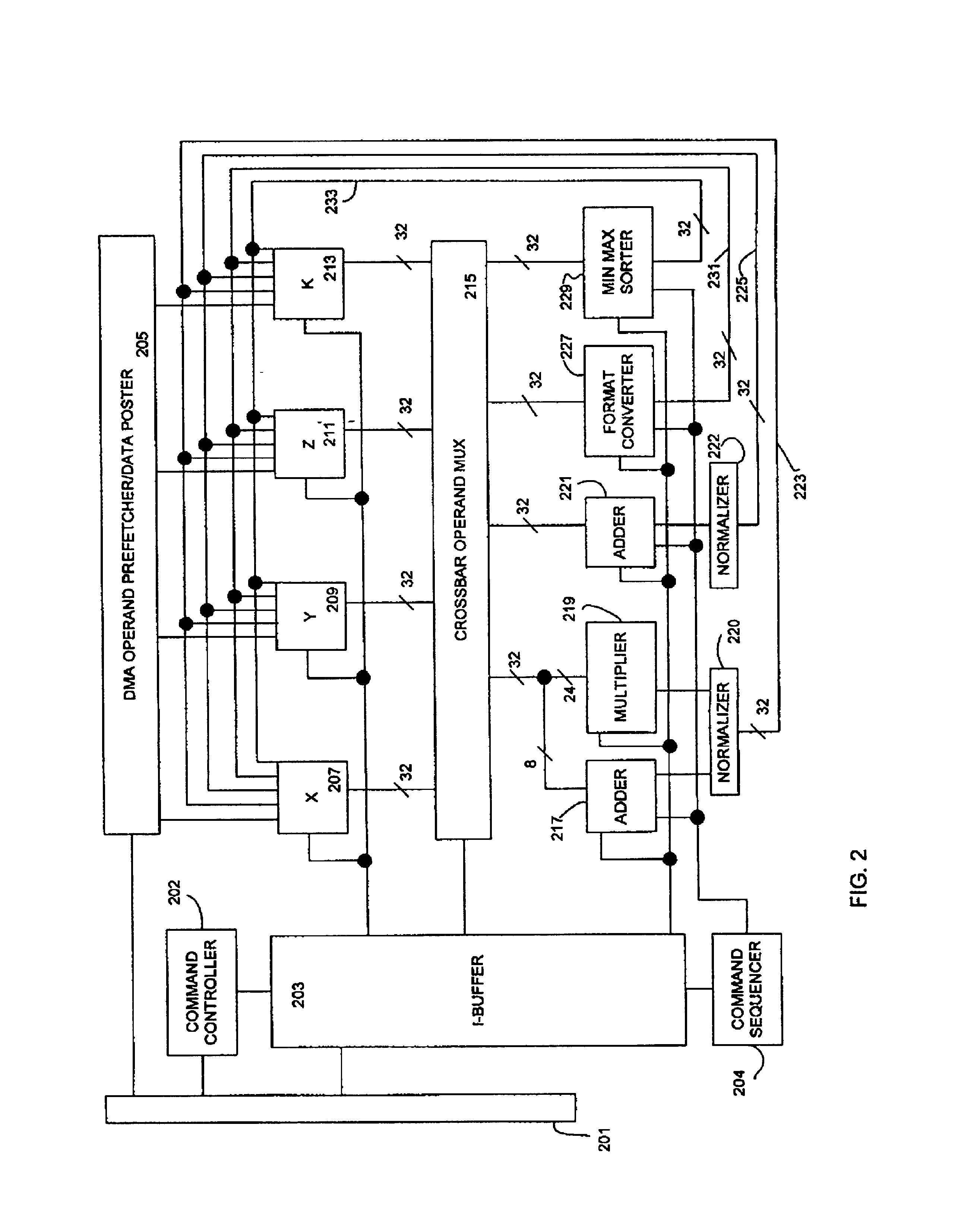

The present invention provides a vector floating point unit (FPU) comprising a product-terms bus, a summation bus, a plurality of FIFO (first in first out) registers, a crossbar operand multiplexor coupled, a floating point multiplier, and a floating point adder. The floating point multiplier and the floating point adder are disposed between the crossbar operand multiplexor and the product-terms and summation buses, and are in parallel to each other. The invention also provides the configuration register and the command register in order to provide flexible architecture and the capability to fine-tune the performance to a particular application. The invention performs the multiplication operation and the addition operation in a pipelined fashion. Once the pipeline is filled, the invention outputs one multiplication output and one addition output at each clock cycle. The invention reduces the latency of the pipelined operation and improves the overall system performance by separating the floating point multiplier from the floating point adder so that the multiplication operation can be executed separately and independently of the addition operation.

Owner:NVIDIA CORP

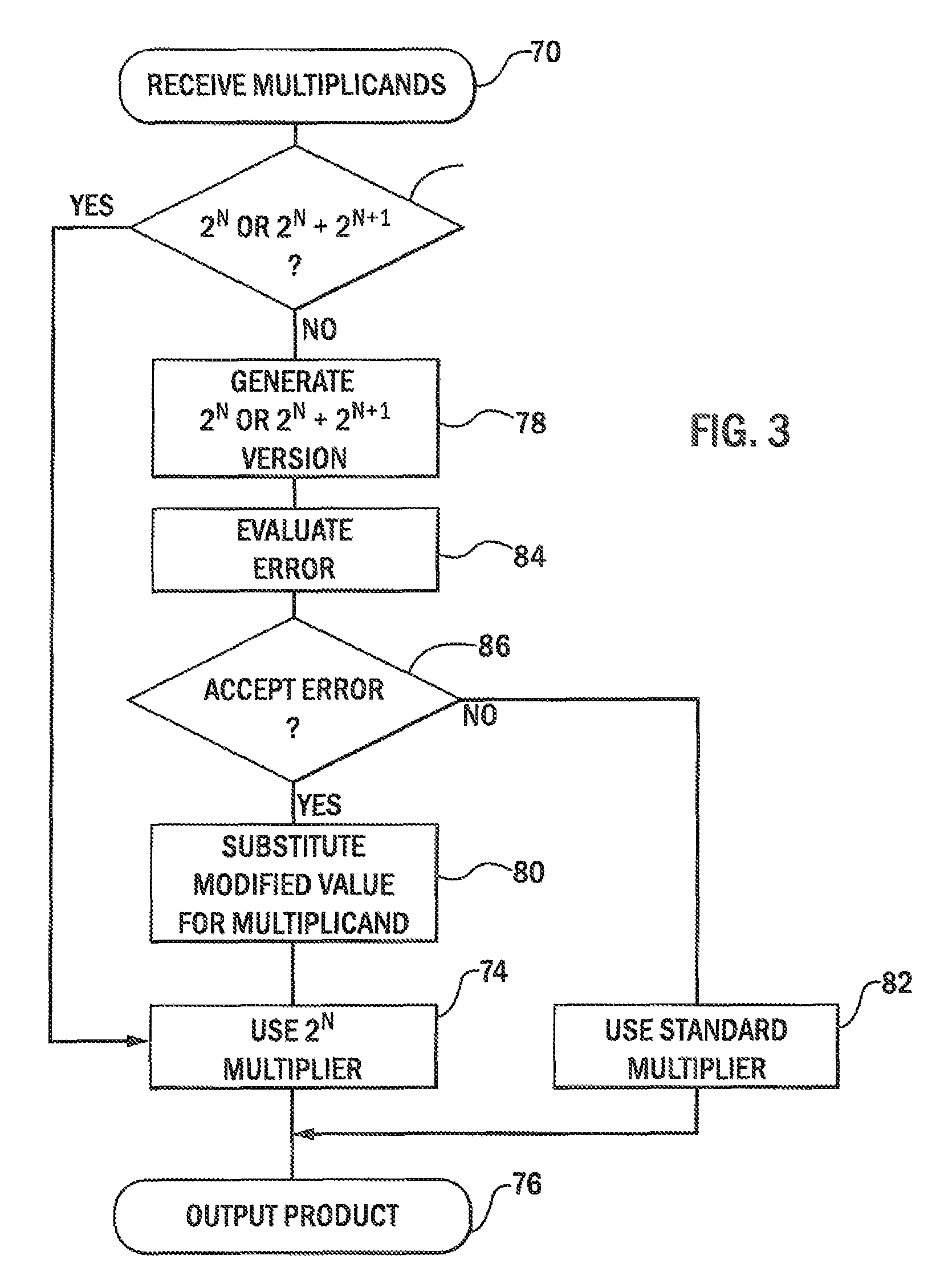

High efficiency computer floating point multiplier unit

ActiveUS9519459B2Significant power savingSpeed advantageDigital data processing detailsOperandFloating point multiplication

Owner:WISCONSIN ALUMNI RES FOUND

System and method of floating point multiply operation processing

ActiveUS10346133B1Sufficient bit widthIncrease widthDigital data processing detailsOperandFloating point multiplication

A processor includes an integer multiplier configured to execute an integer multiply instruction to multiply significand bits of at least one floating point operand of a floating point multiply operation. The processor also includes a floating point multiplier configured to execute a special purpose floating point multiply accumulate instruction with respect to an intermediate result of the floating point multiply operation and the at least one floating point operand to generate a final floating point multiplication result.

Owner:QUALCOMM INC

Operand-optimized asynchronous floating-point units and method of use thereof

ActiveUS9524270B2Complex mathematical operationsComputation using denominational number representationFloating-point unitOperand

Asynchronous arithmetic units including an asynchronous IEEE 754 compliant floating-point adder and an asynchronous floating point multiplier component. Arithmetic units optimized for lower power consumption and methods for optimization are disclosed.

Owner:CORNELL UNIVERSITY

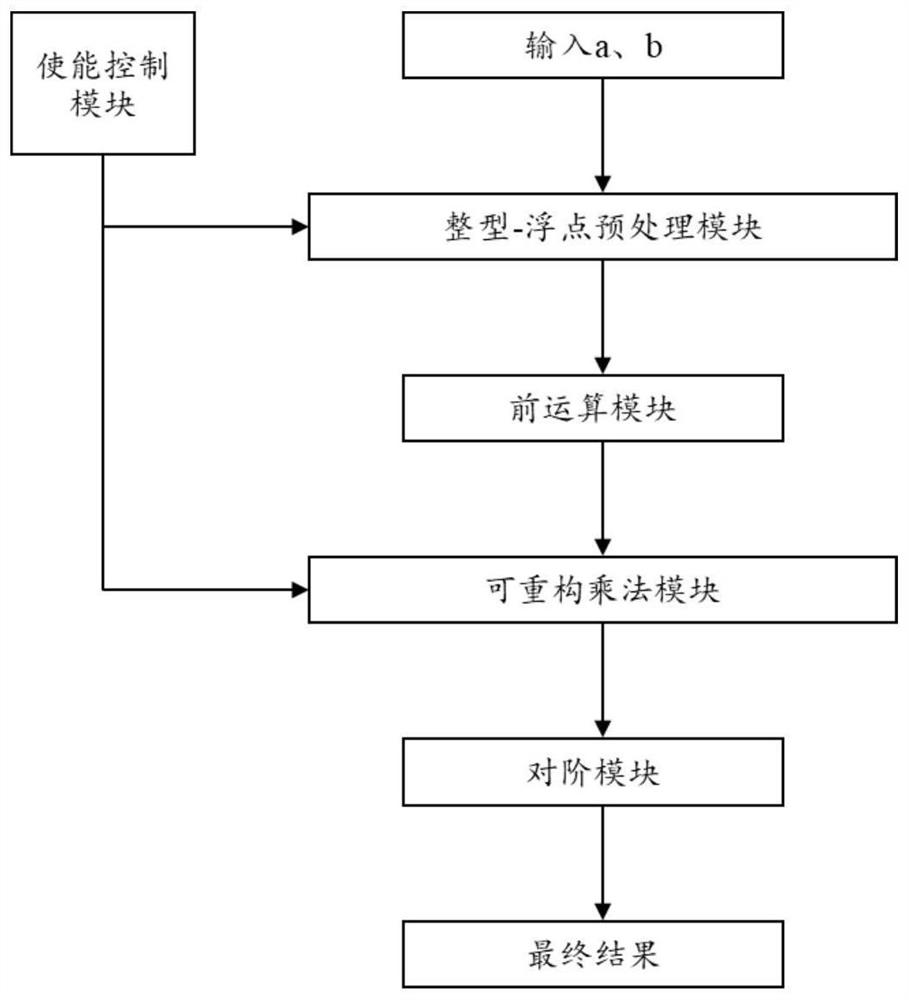

Reconfigurable integer-floating point multiplier

ActiveCN113157247AMeet needsImprove resource utilizationDigital data processing detailsDigital signal processingBinary multiplier

The invention belongs to the field of digital signal processing, and discloses a reconfigurable integer-floating point multiplier which comprises an enabling control module, an integer-floating point preprocessing module, a pre-operation module, a reconfigurable multiplication module and an order matching module. The enabling control module generates a first control signal and a second control signal; the integer-floating point preprocessing module obtains first floating point type data and second floating point type data to obtain a first expansion mantissa and a second expansion mantissa; the front operation module obtains a sign bit of the floating point result and a temporary order code of the floating point result; the reconfigurable multiplication module obtains a temporary mantissa of an integer result or a floating point result; the order matching module obtains the mantissa and the order code of the floating point result. According to the method, floating point multiplication operation can be achieved, integer multiplication operation can be achieved under the condition that extra resources are not increased, the requirements of a current artificial intelligence chip can be fully met, data operation modes can be flexibly selected when different requirements are met, and the method has the better resource utilization rate, functionality and universality.

Owner:XI AN JIAOTONG UNIV

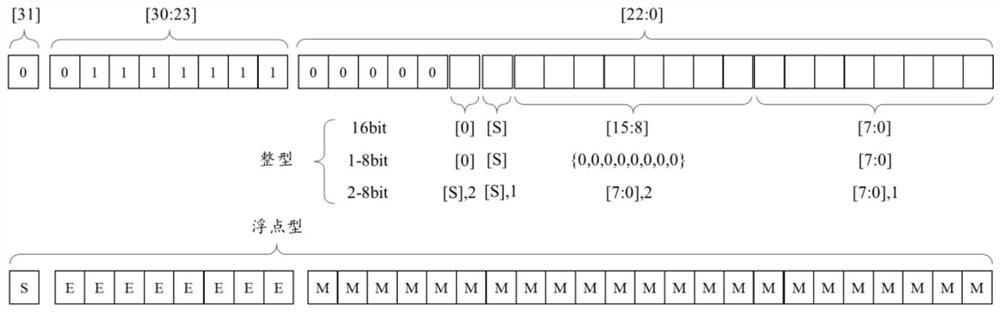

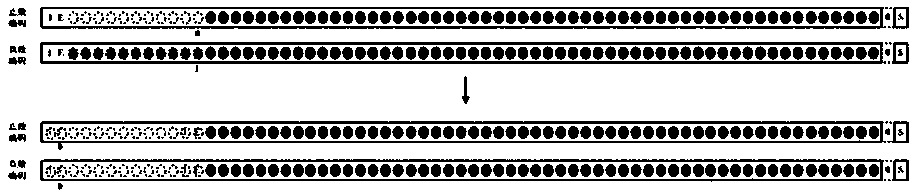

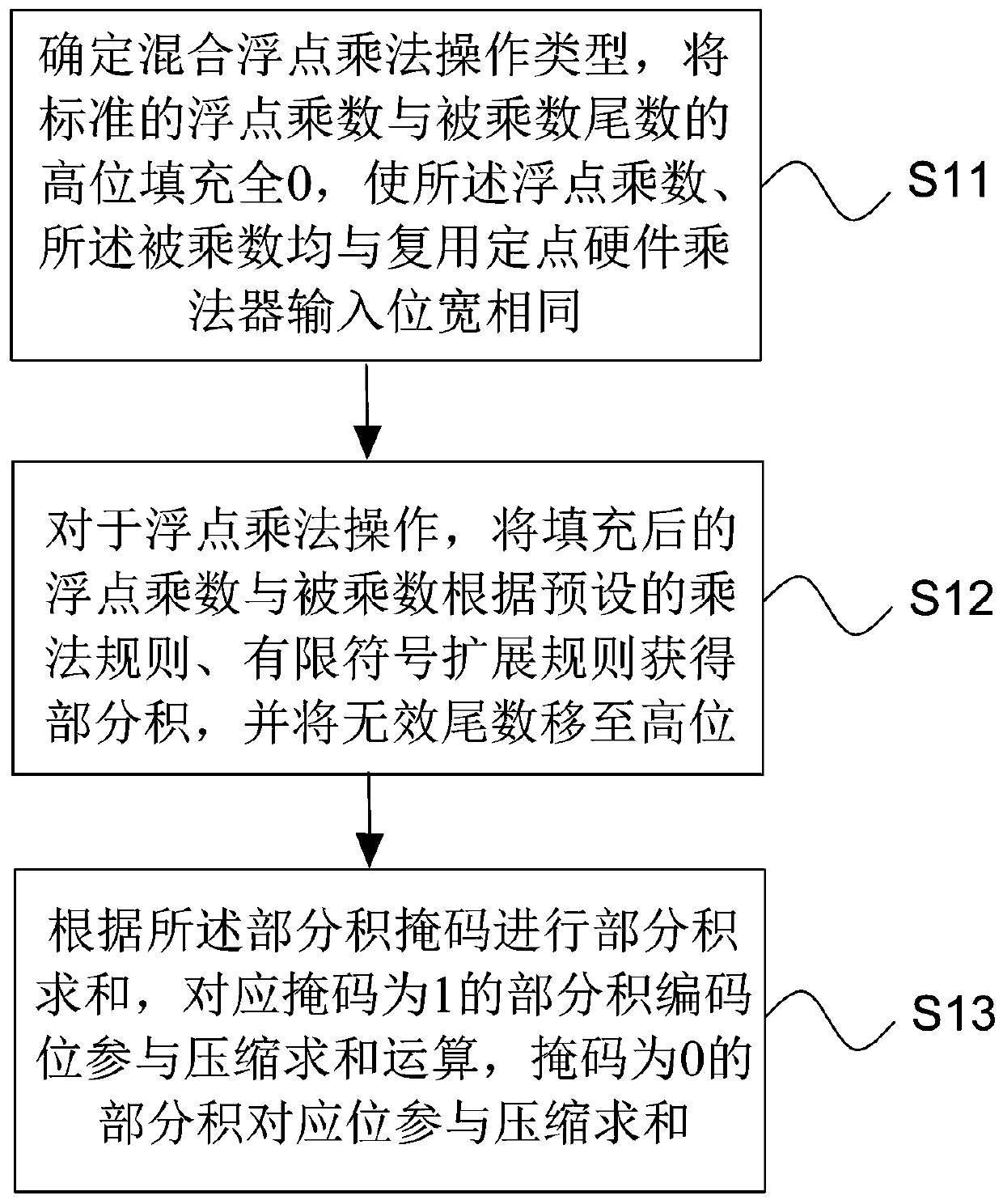

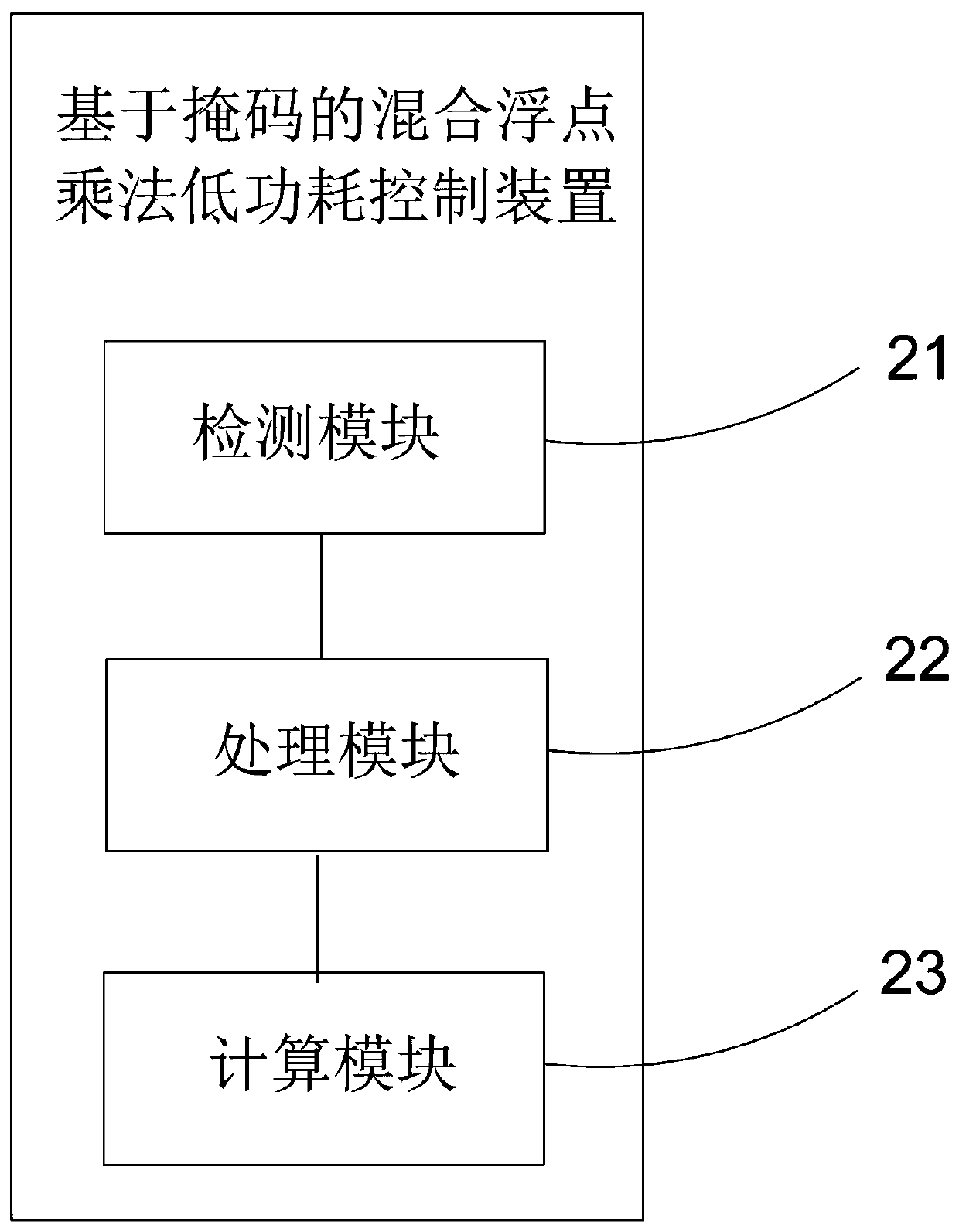

Mask-based hybrid floating-point multiplication low-power-consumption control method and device

ActiveCN110727412AReduce overheadSimple implementation logicDigital data processing detailsMultiplexingBinary multiplier

Owner:JIANGNAN INST OF COMPUTING TECH

Floating point multiplier for delimited operands

InactiveUS7003540B2Avoid problemsConditional code generationComputations using contact-making devicesIntermediate stageOperand

A method for providing a floating point product consistent with the present invention includes multiplying a subprecise operand and a non-subprecise operand using a plurality of intermediate stages. The method further includes correcting an error introduced by the subprecise operand by performing an operation in conjunction with a one of the plurality of intermediate stages utilizing a compensating summand.

Owner:ORACLE INT CORP

Floating point multiplier-adder

PendingCN114741049AImplement multiplication and addition operationsMeet computing needsDigital data processing detailsStructural engineeringAssembly line

The invention discloses a floating-point multiply-add device, which realizes floating-point multiply-add operation in a form of A * B + C. The floating-point multiply-add device adopts a three-stage pipeline mode to realize the floating-point multiply-add operation, completes floating-point multiplication in a first pipeline beat, completes addition in a second pipeline beat and completes rounding operation and exception judgment in a third pipeline beat, and outputs a final result. The floating-point multiply-add device has the advantages that single-double-precision floating-point number multiply-add operation is achieved, and a three-level assembly line framework of non-normalized numbers is supported.

Owner:江苏华创微系统有限公司 +1