Water floating point multiply-accumulate method based on FPGA

A floating-point multiplier and floating-point multiplication technology, which is applied to calculations using number system representation, calculations using non-contact manufacturing equipment, concurrent instruction execution, etc., can solve problems such as designing and optimizing multiplication accumulators, and achieve versatility Good, improved running speed, and strong portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

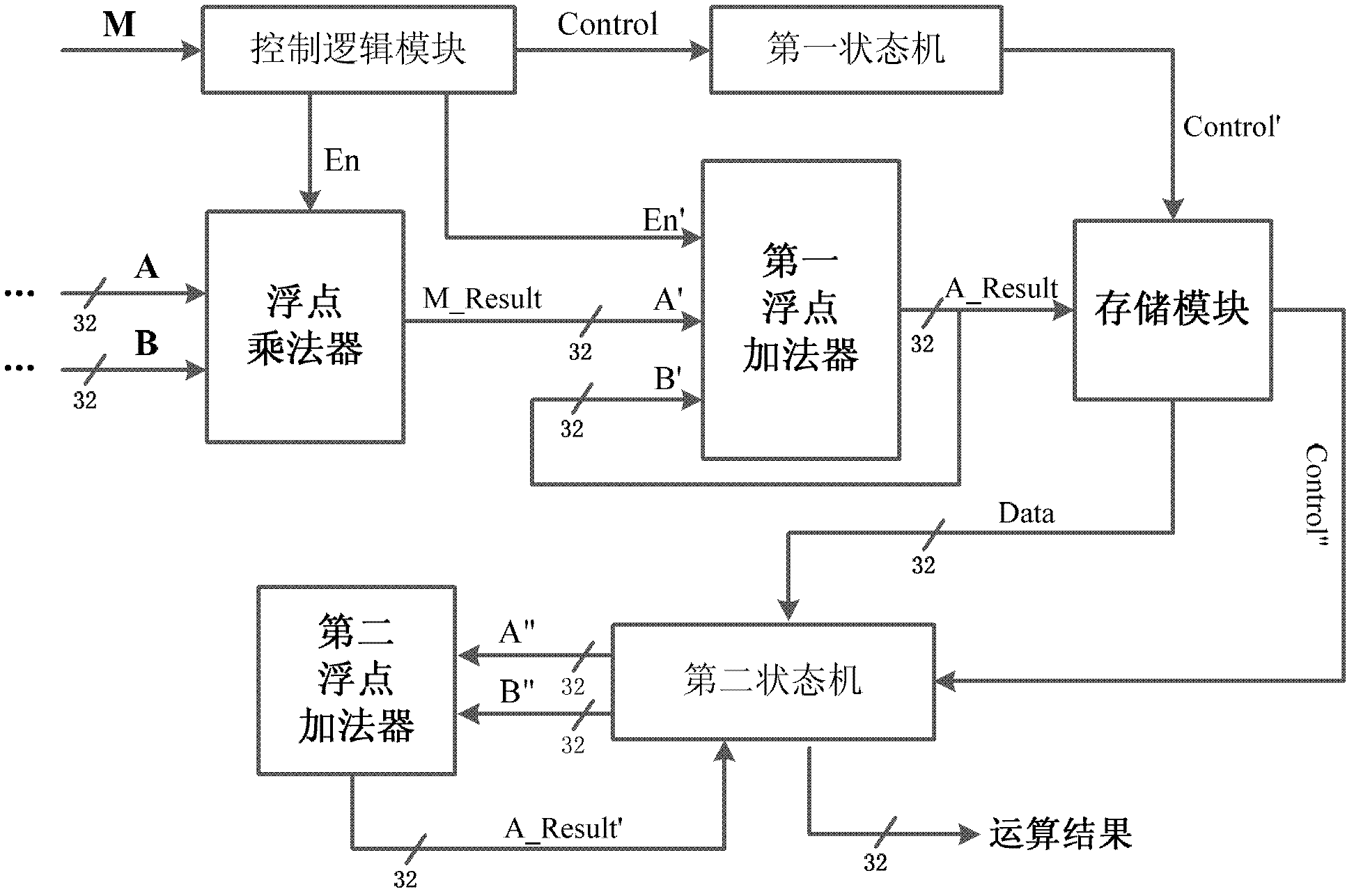

[0031] The present invention will be further described in detail below with reference to the drawings and specific embodiments of the specification.

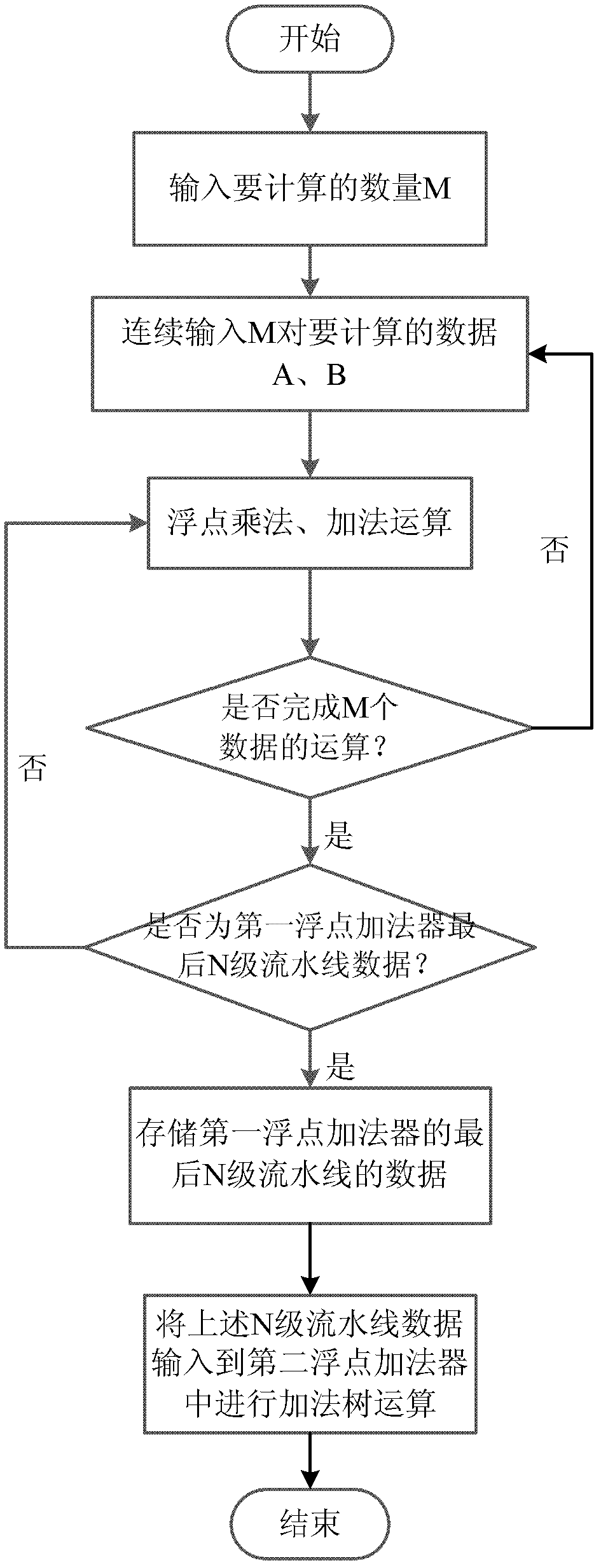

[0032] Such as figure 1 As shown, the FPGA-based floating-point multiply-accumulator method of the present invention has the following flow:

[0033] (1) Input the number M that needs to be multiplied and accumulated through the external module; the whole calculation process will drive the floating-point multiplier, floating-point adder and the enable signal of each calculation module according to the value of M;

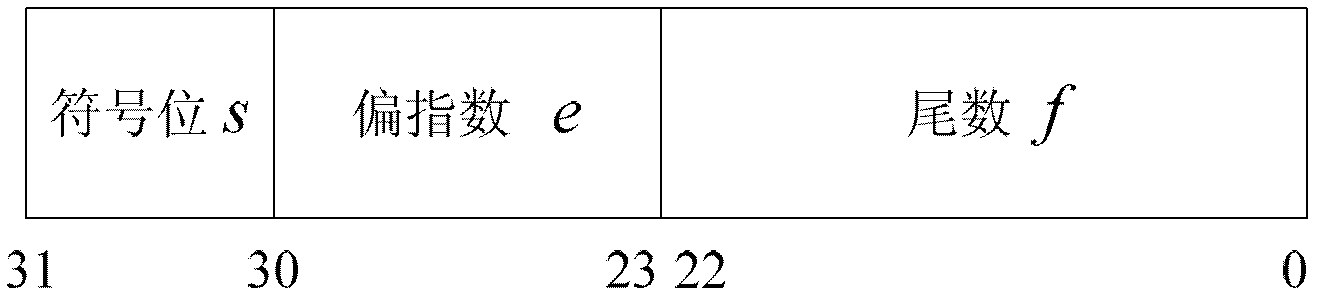

[0034] (2) According to the calculation rules of the multiply accumulator and the pipeline characteristics of the floating-point multiplier and the adder IP core, the M that needs to be calculated is input into the floating-point multiplier for the multiplication of the 32-bit binary floating-point numbers A and B at the same time. A set of inputs for A and B until all M operations on data are completed; at the same time, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More