Patents

Literature

53 results about "Floating point adder" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

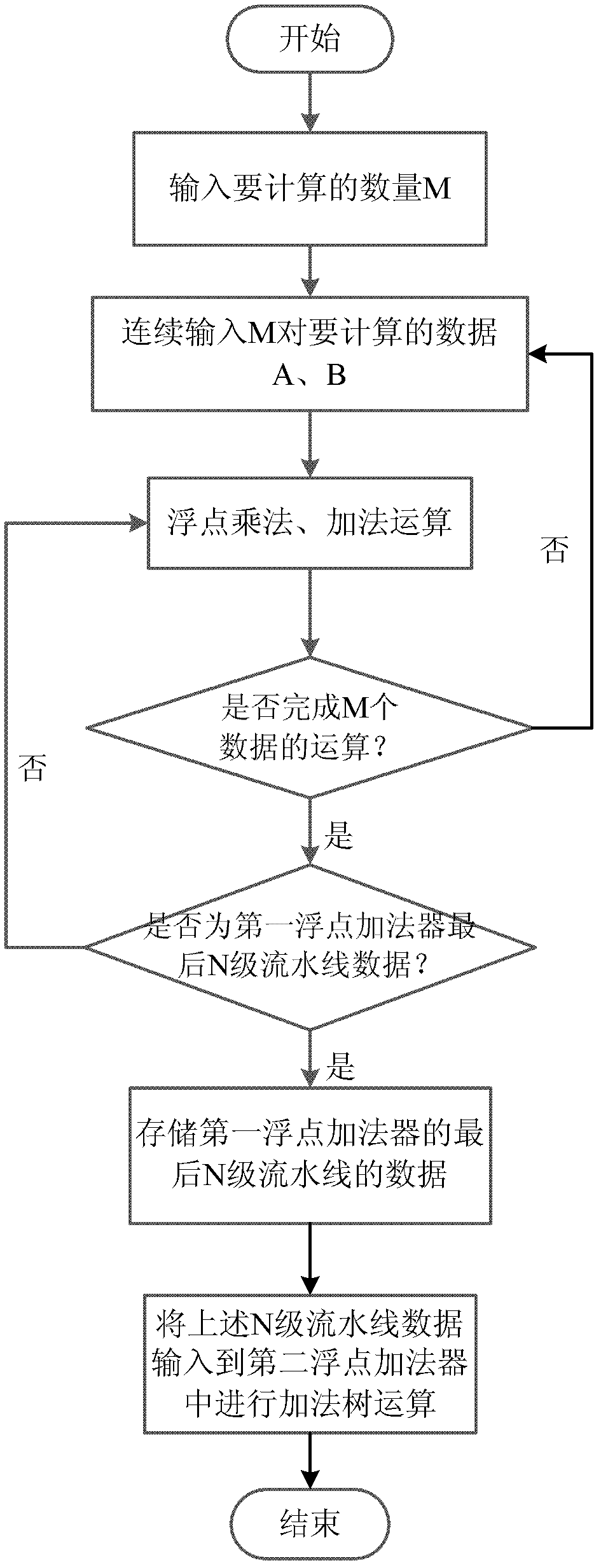

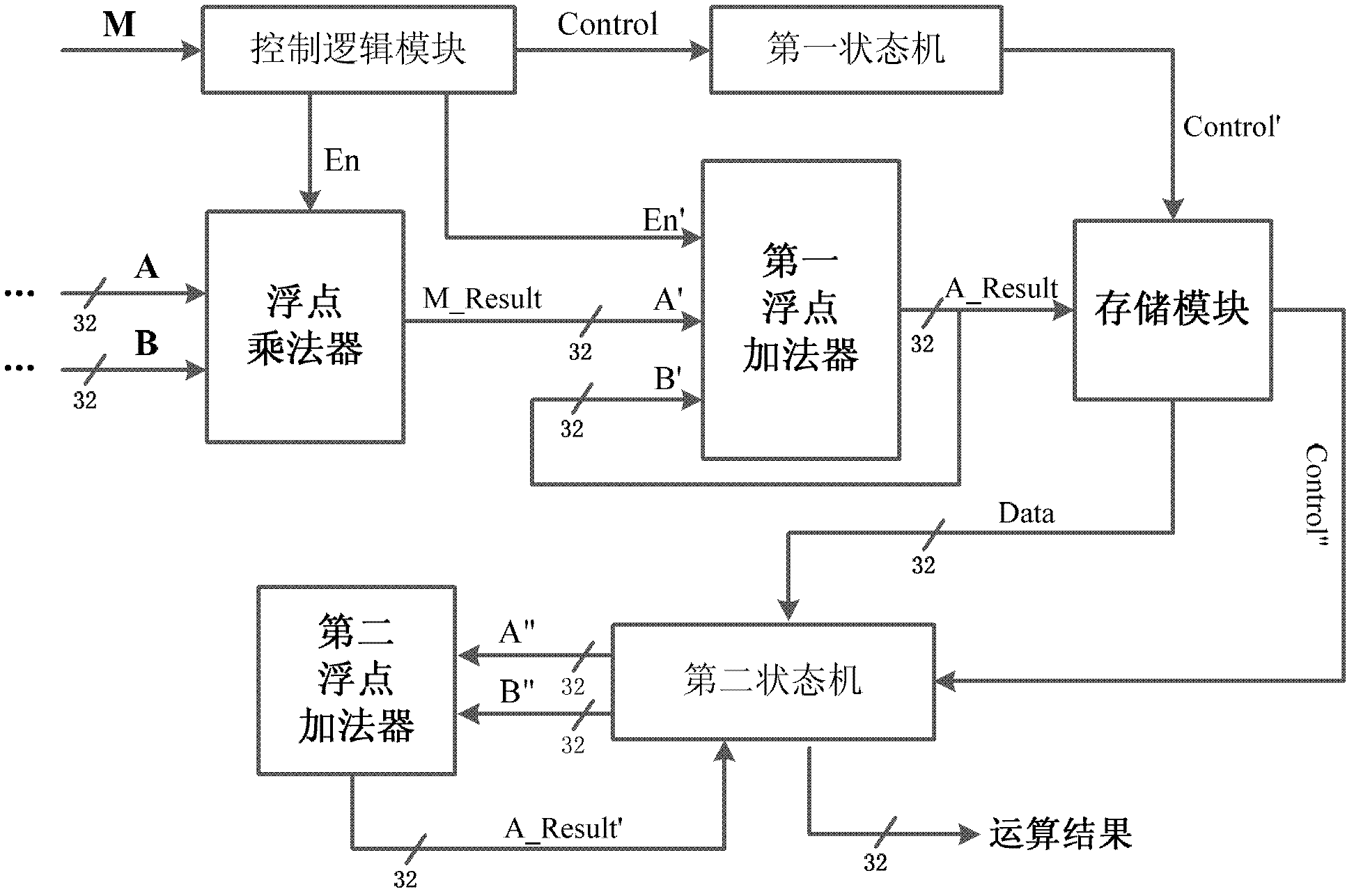

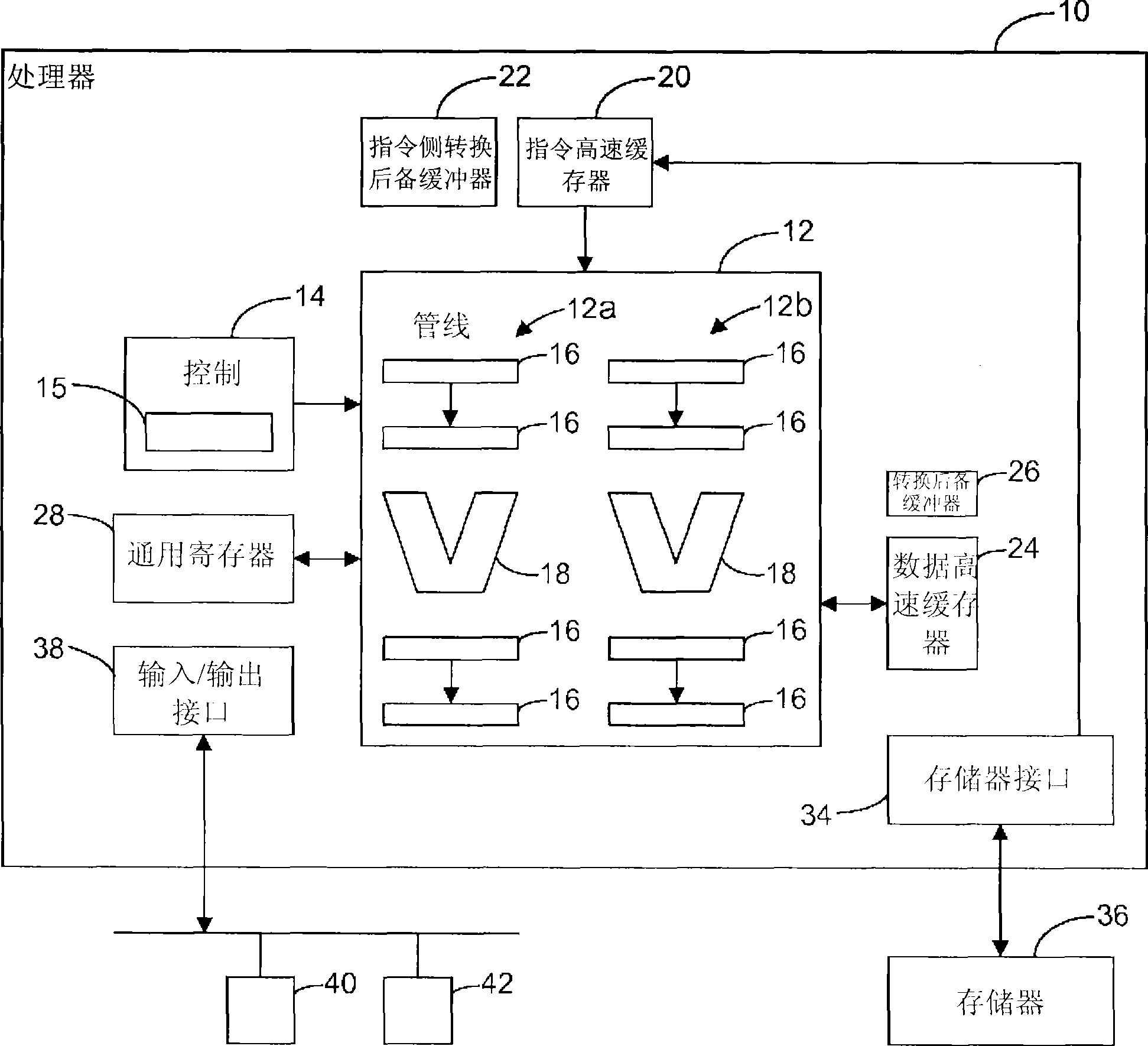

Water floating point multiply-accumulate method based on FPGA

InactiveCN102629189AEasy to implementRun fastComputation using non-contact making devicesConcurrent instruction executionComputer scienceOperating speed

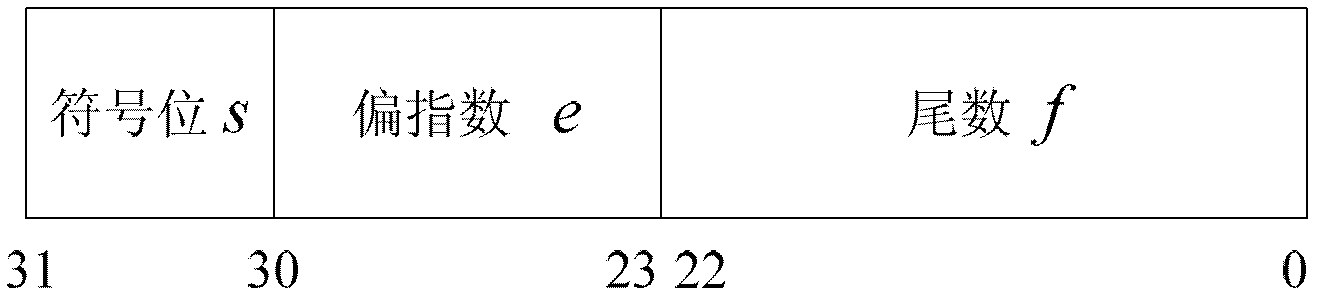

The invention discloses a water floating point multiply-accumulate method based on FPGA. The method comprises the following steps: firstly inputting a number M to undergo multiply-accumulate calculation, secondly, sequentially inputting M 32-bit binary floating point numbers A and B which are required to be calculated into floating-point multiplier to undergo multiplication till the operation of M data is accomplished, and simultaneously and continuously inputting the product result of the floating-point multiplier and the addition result of a first floating-point adder to the first floating-point adder to accomplish a part of summation operation to obtain a summation result, and thirdly, inputting data of the last N stage pipeline in the summation result obtained in step two into a second floating-point adder to be calculated to obtain the result of the whole multiply-accumulate process. The method has the advantages that the principle is simple, the universality is good, the operating speed can be improved, and the like.

Owner:HUNAN UNIV

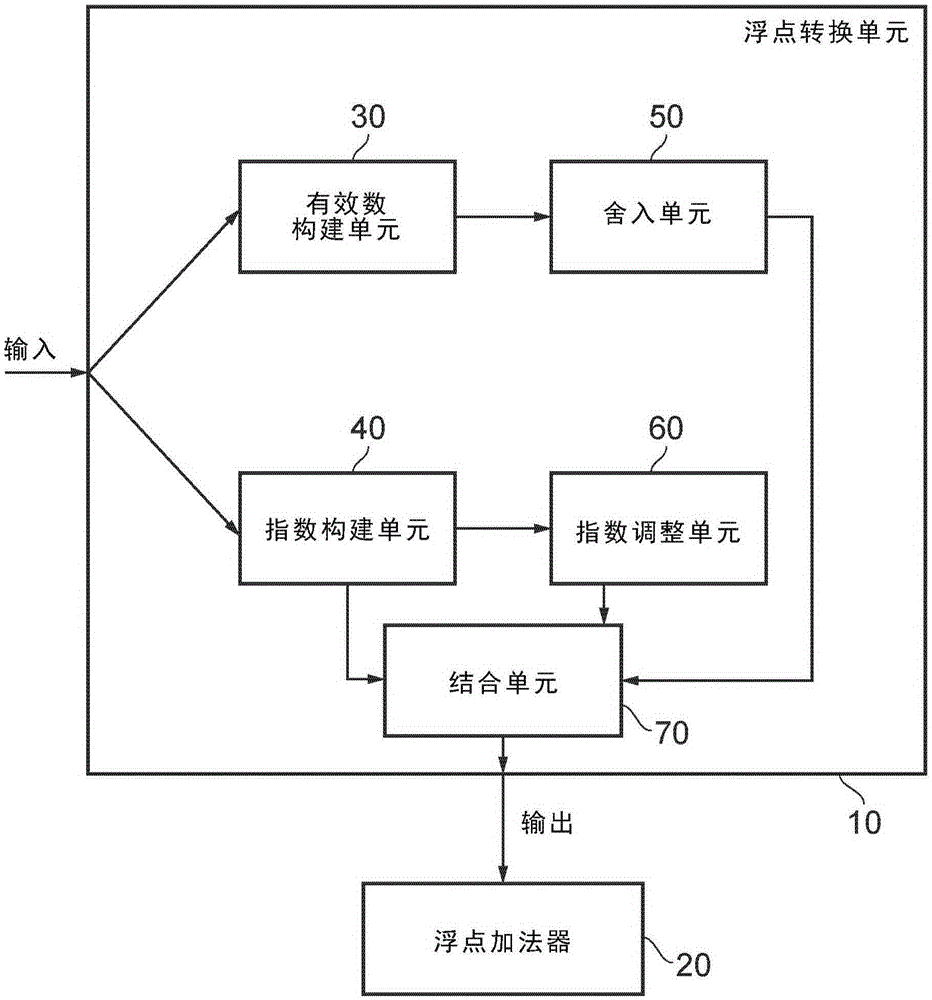

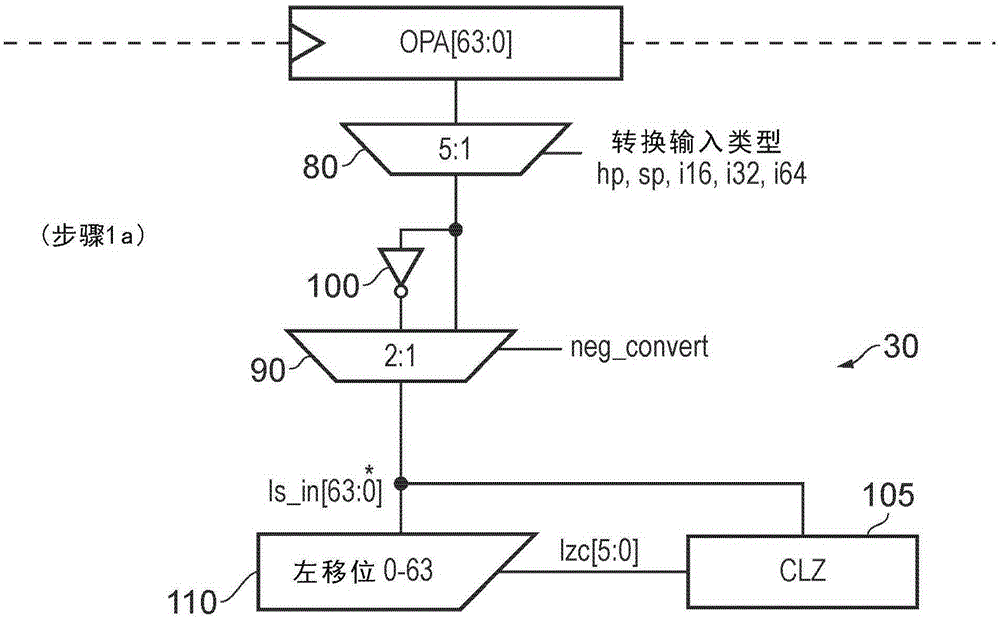

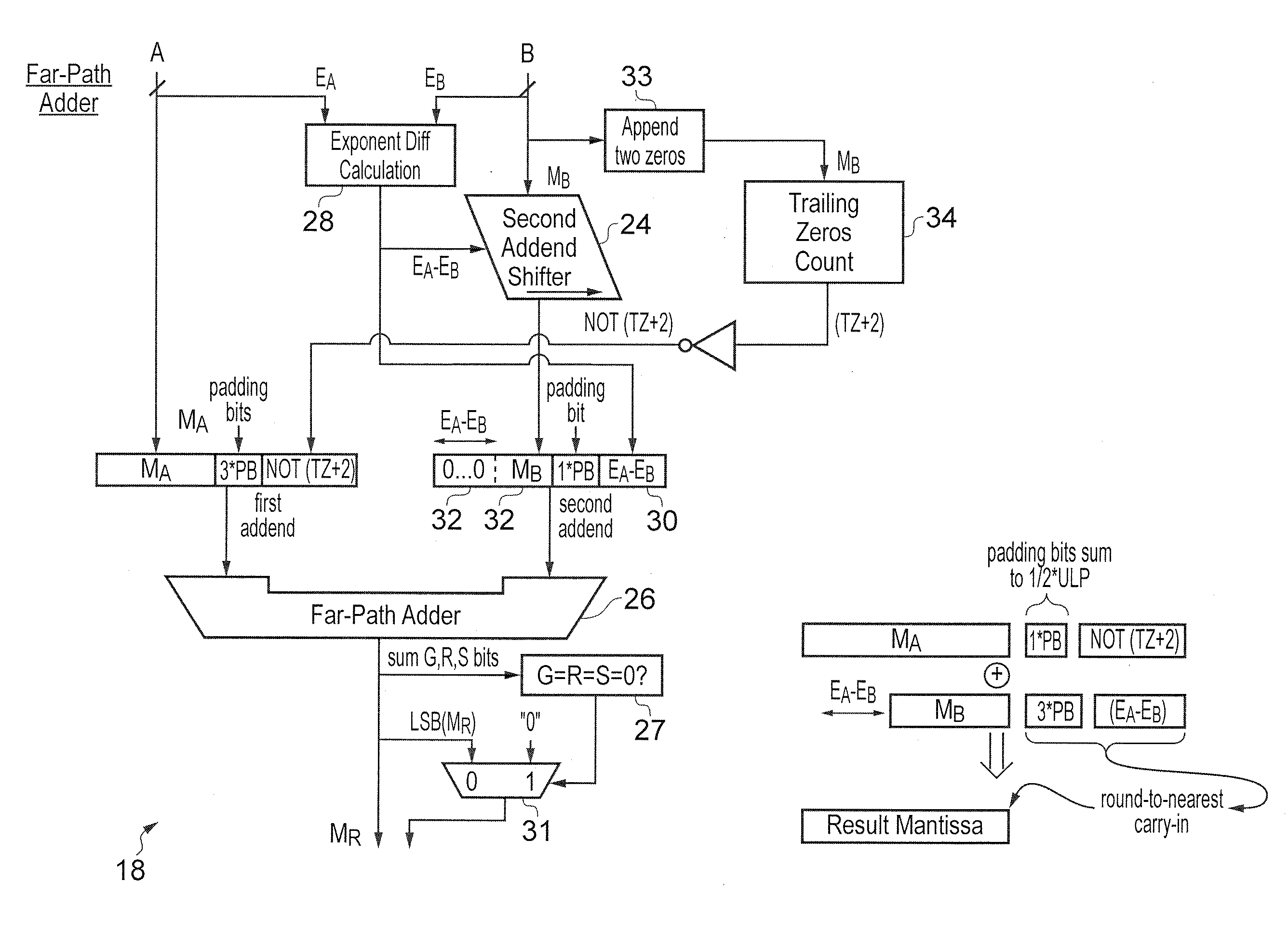

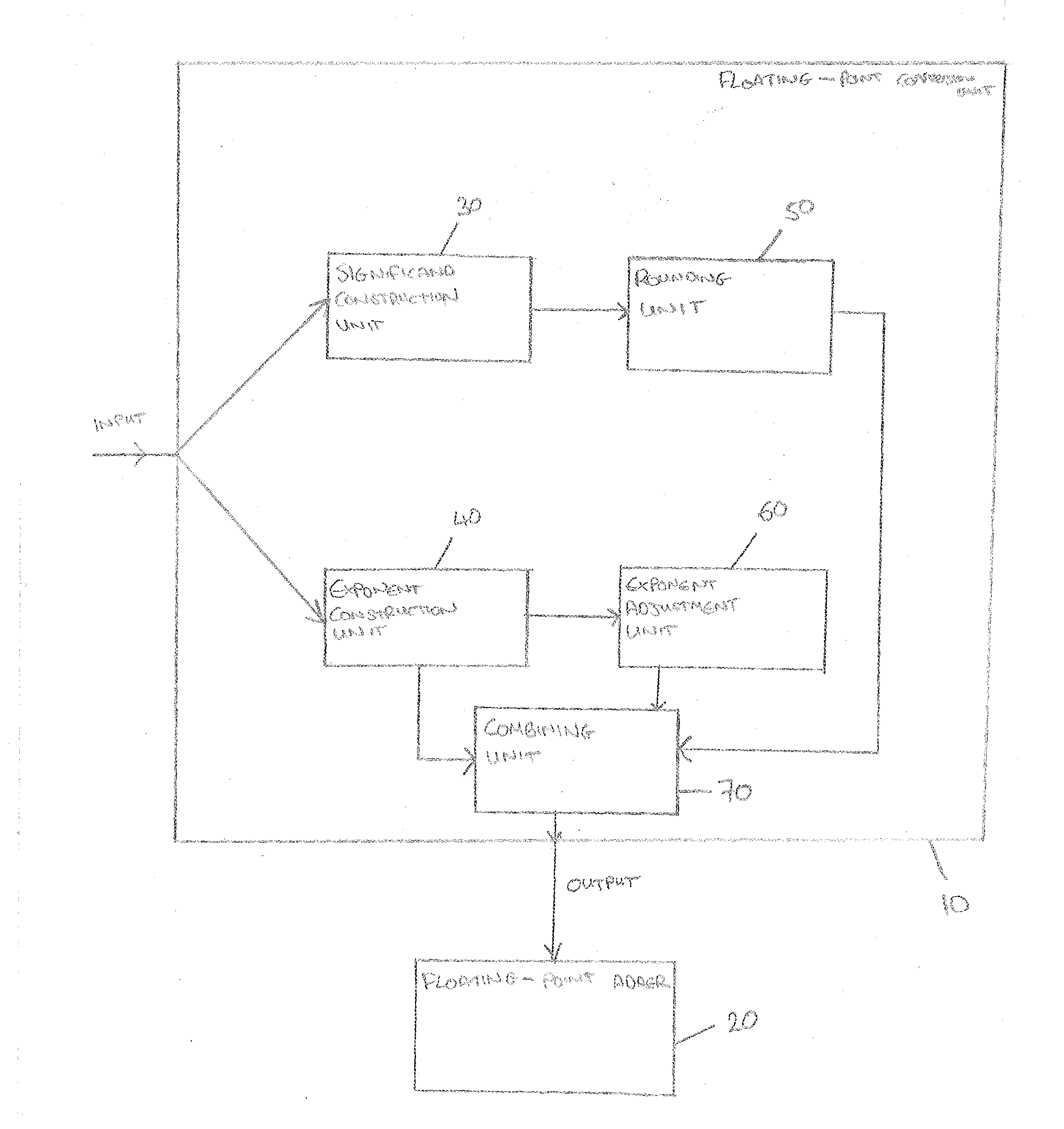

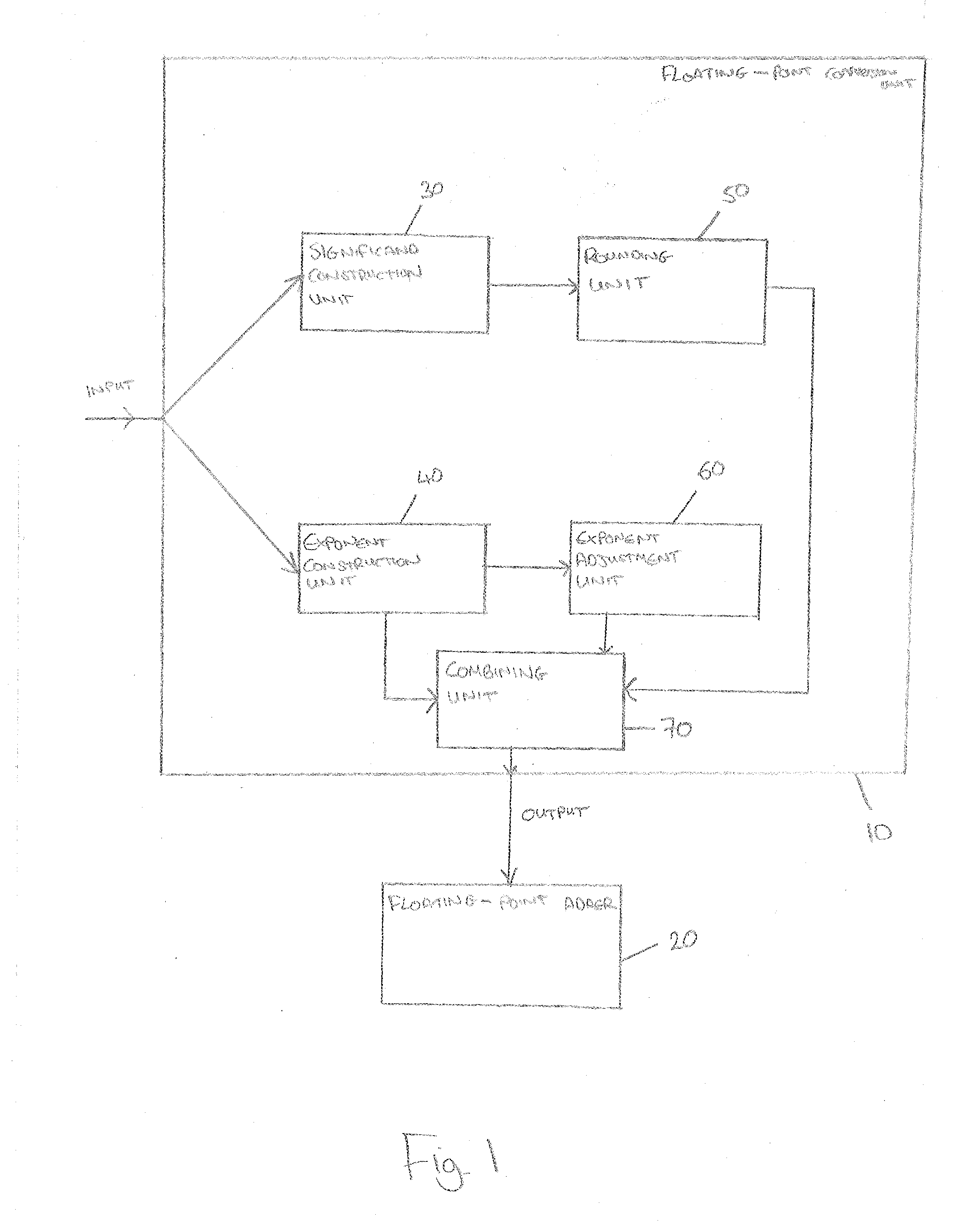

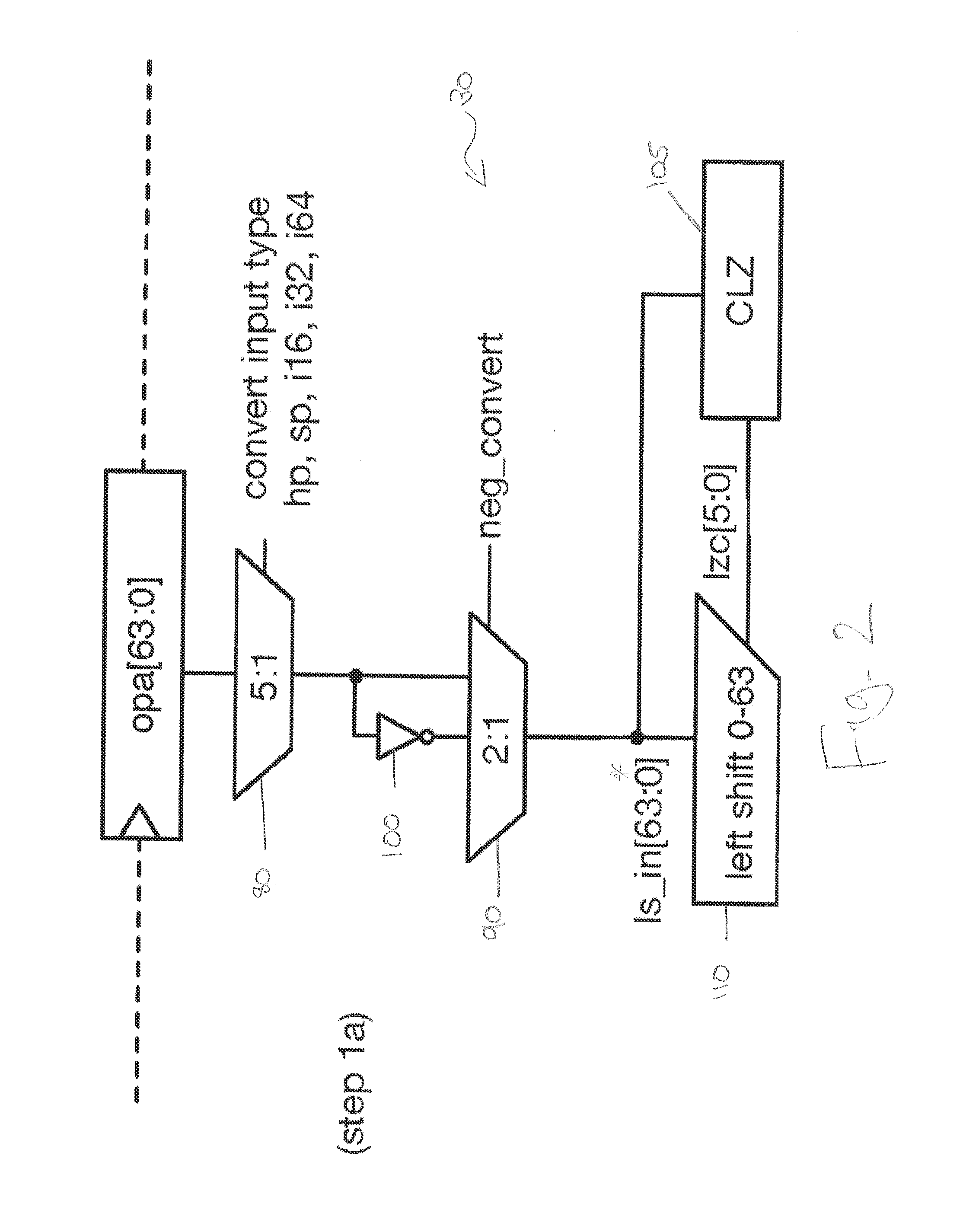

Standalone floating-point conversion unit

The invention relates to a standalone floating-point conversion unit. A data processing apparatus includes floating-point adder circuitry and floating-point conversion circuitry that generates a floating-point number as an output by performing a conversion on any input having a format from a list of formats including: an integer number, a fixed-point number, and a floating-point number having a format smaller than the output floating-point number. The floating-point conversion circuitry is physically distinct from the floating-point adder circuitry.

Owner:ARM LTD

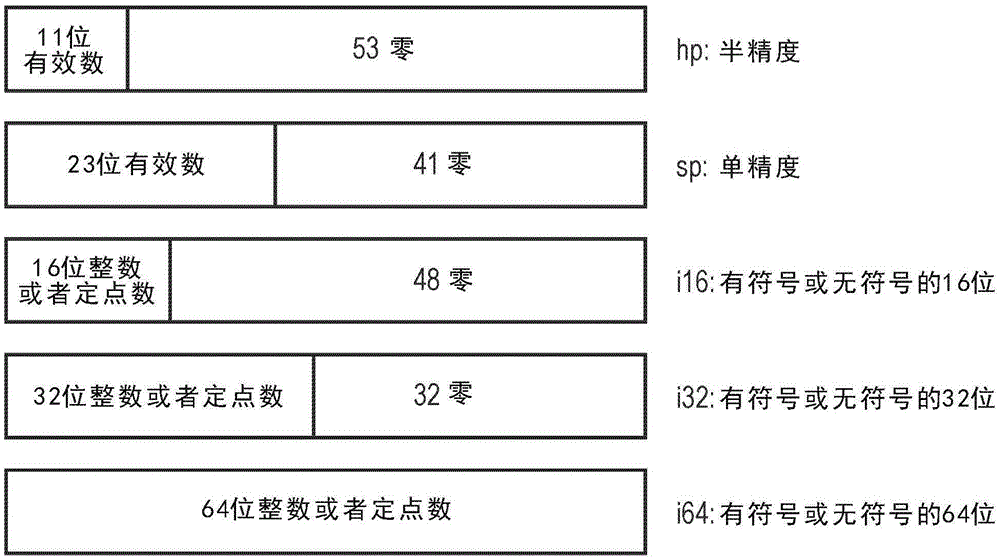

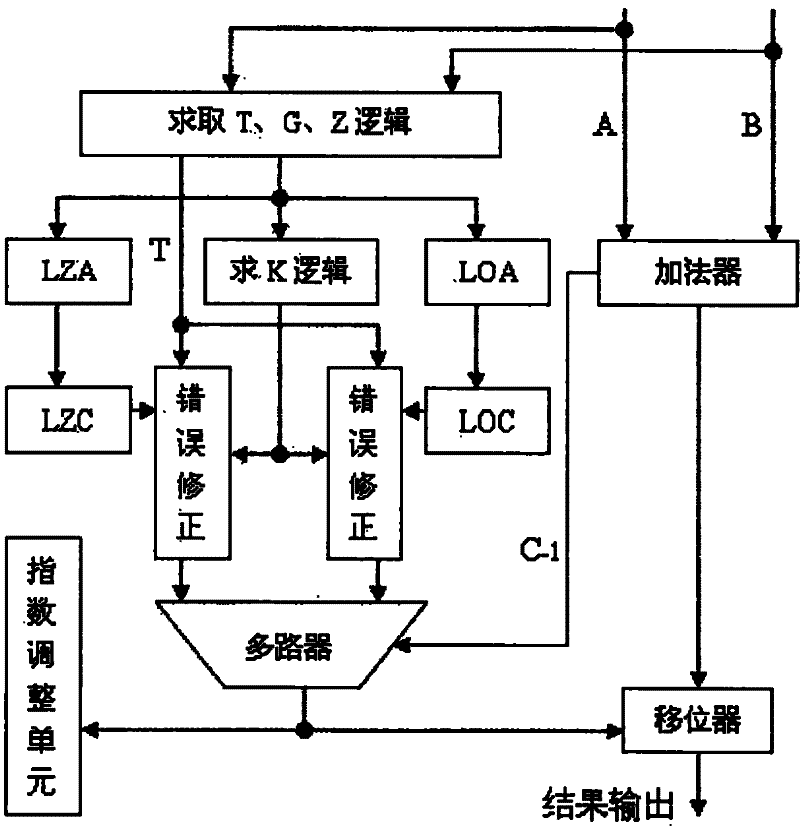

Floating-point adder

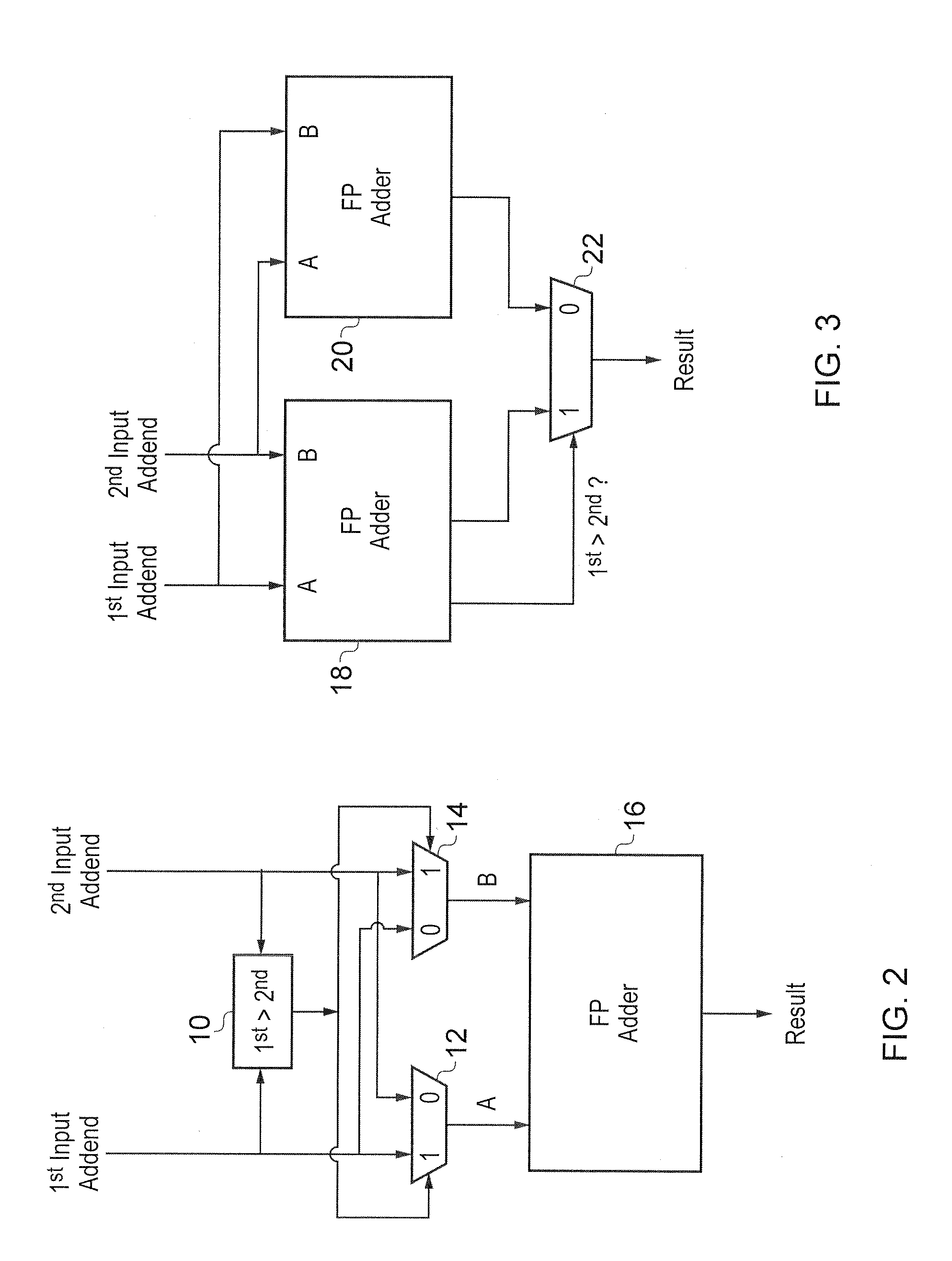

ActiveUS20130007084A1Lower latencyMaintain balanceComputations using contact-making devicesComputer architectureOperand

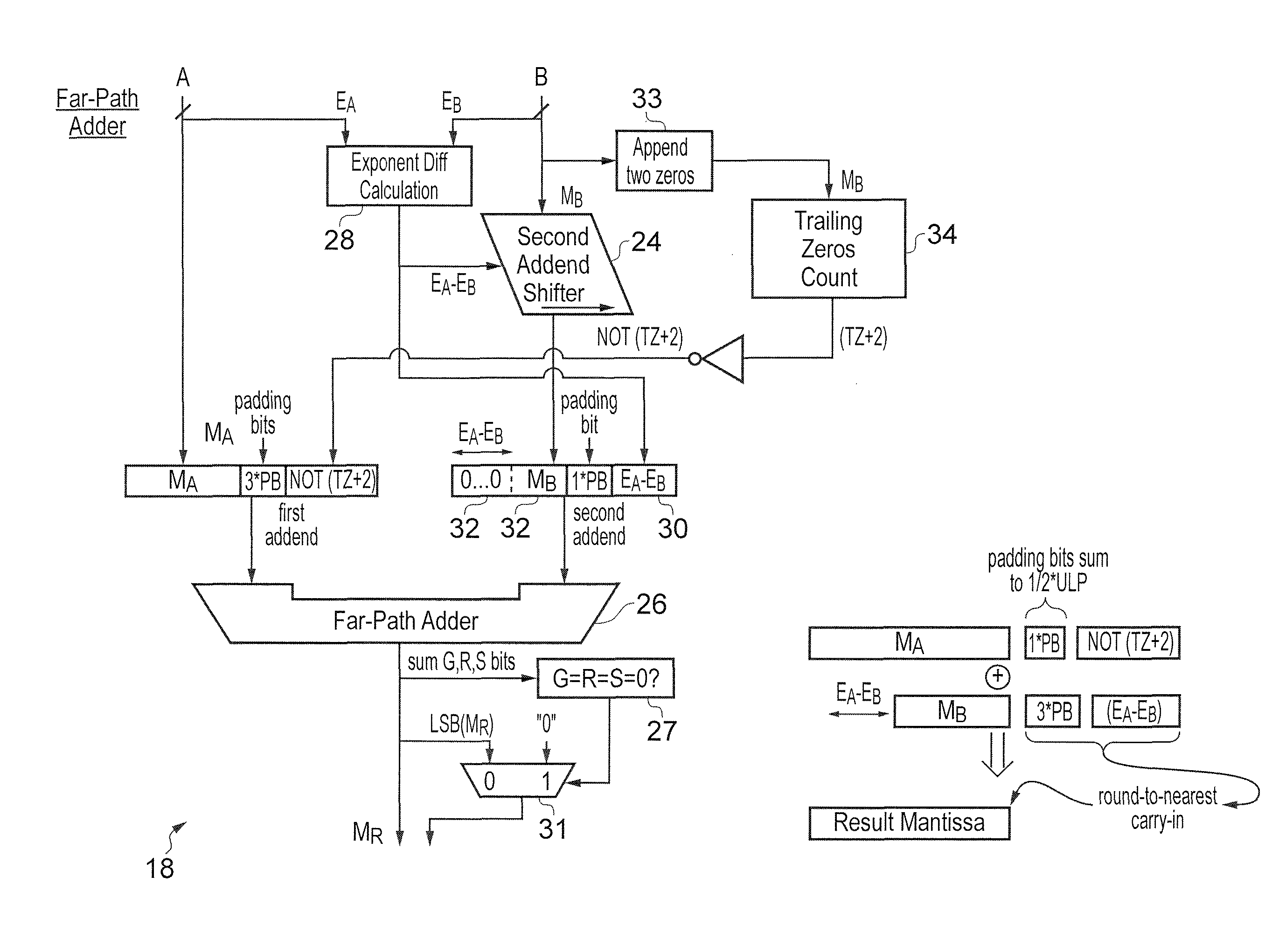

Floating point adder circuitry 16, 18, 20 is provided with far-path circuitry 18 and near-path circuitry 20. The far-path circuitry utilises a count of trailing zeros TZ and a difference in the input operand exponents to form respective suffix values which are concatenated with the mantissas of the input addends and serve when summed to generate a carry out taking the place of a conventionally calculated sticky bit. Within the near-path, minimum value circuitry 46 is used to calculate the lower of a leading zeros count of the intermediate mantissa produced in a subtraction and the larger of the input operand exponent values such that a left shift applied to the intermediate mantissa value is not able to produce a invalid floating point result due to applying a left shift to remove leading zeros that is too larger and accordingly corresponds to an exponent which cannot be validly represented.

Owner:ARM LTD

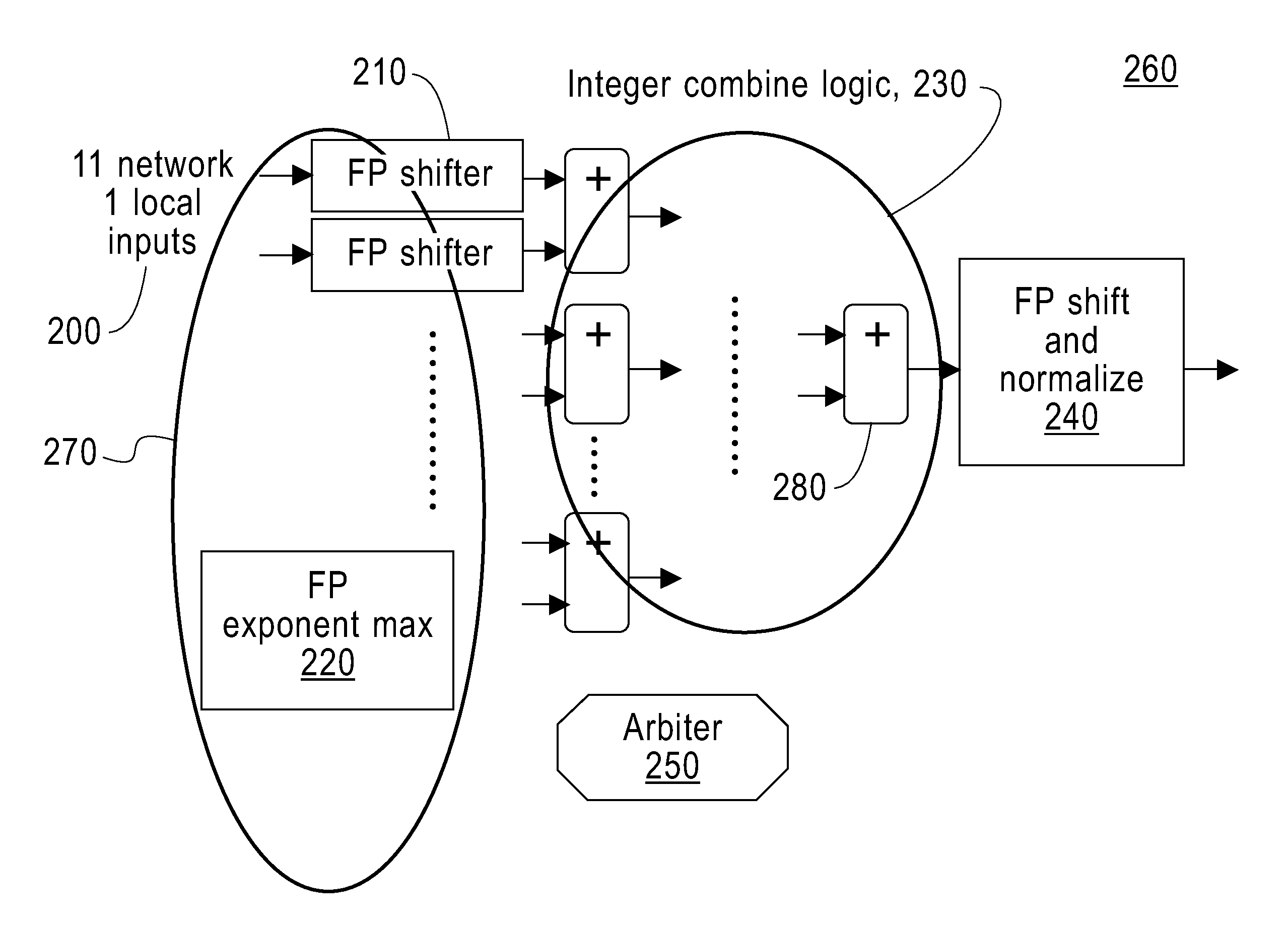

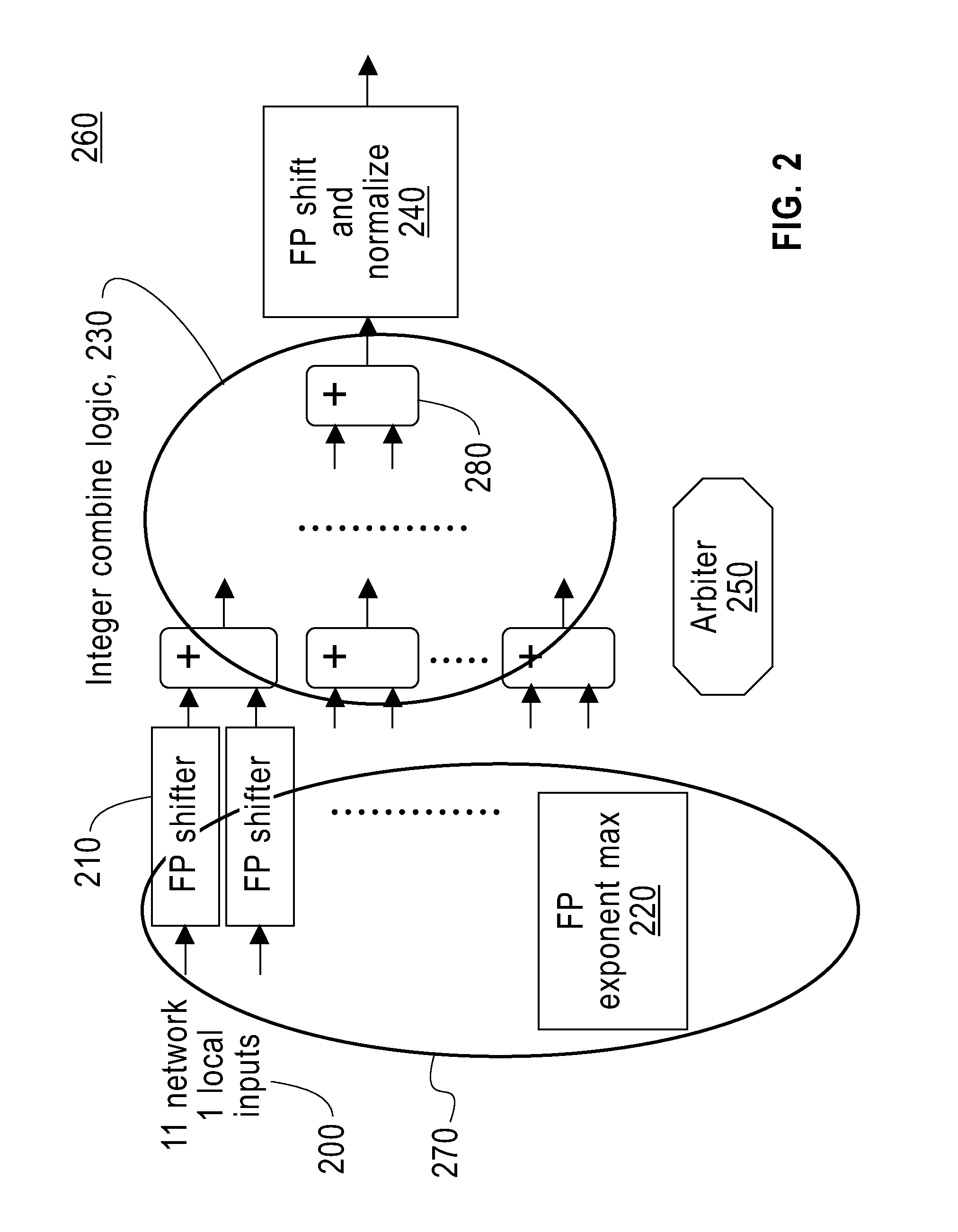

Multi-input and binary reproducible, high bandwidth floating point adder in a collective network

ActiveUS20110173421A1Digital computer detailsSpecific program execution arrangementsMulti inputConcurrent computation

To add floating point numbers in a parallel computing system, a collective logic device receives the floating point numbers from computing nodes. The collective logic devices converts the floating point numbers to integer numbers. The collective logic device adds the integer numbers and generating a summation of the integer numbers. The collective logic device converts the summation to a floating point number. The collective logic device performs the receiving, the converting the floating point numbers, the adding, the generating and the converting the summation in one pass. One pass indicates that the computing nodes send inputs only once to the collective logic device and receive outputs only once from the collective logic device.

Owner:IBM CORP

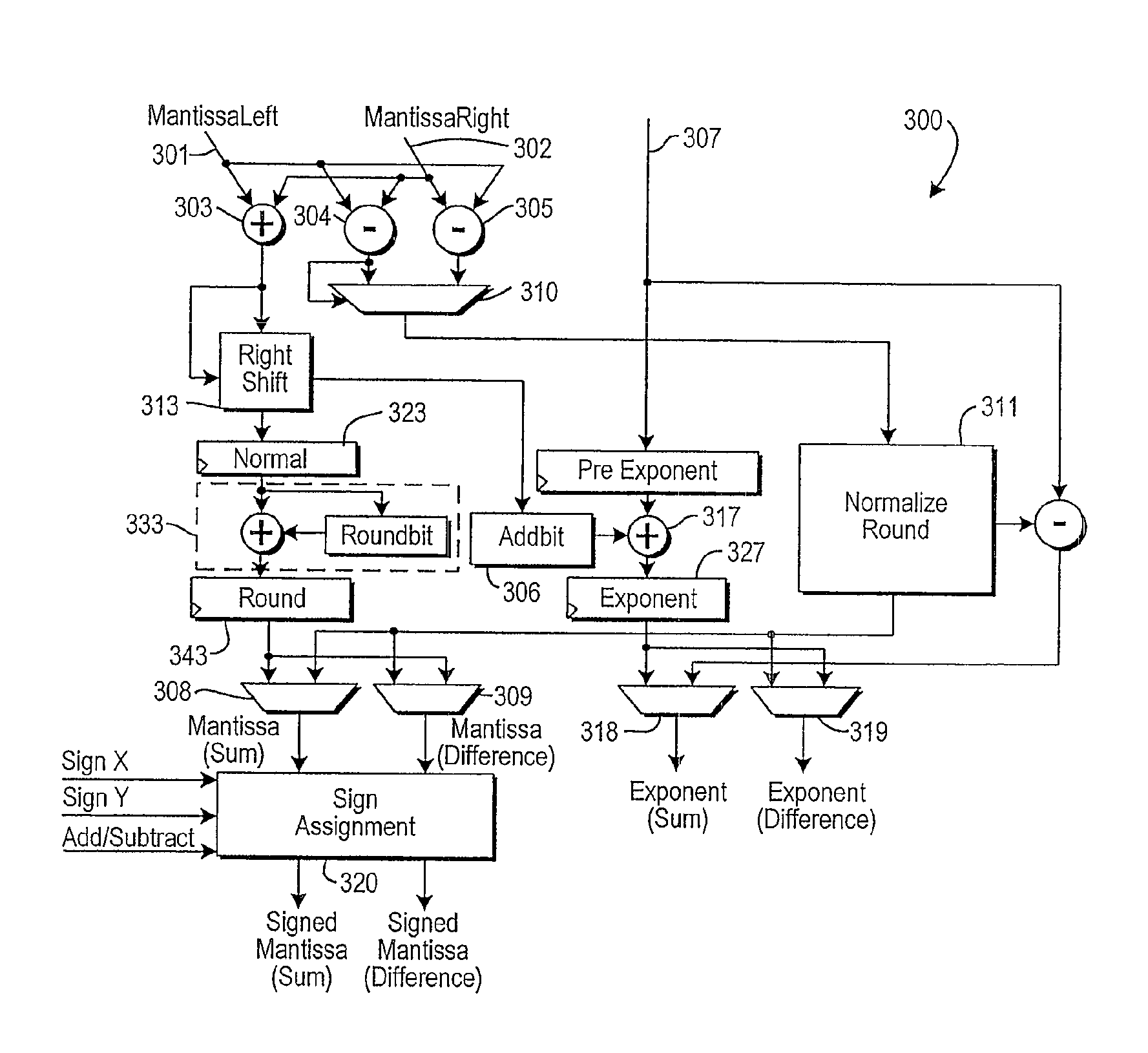

Combined floating point adder and subtractor

InactiveUS8645449B1Reduced resourceComputations using contact-making devicesFloating pointComputer science

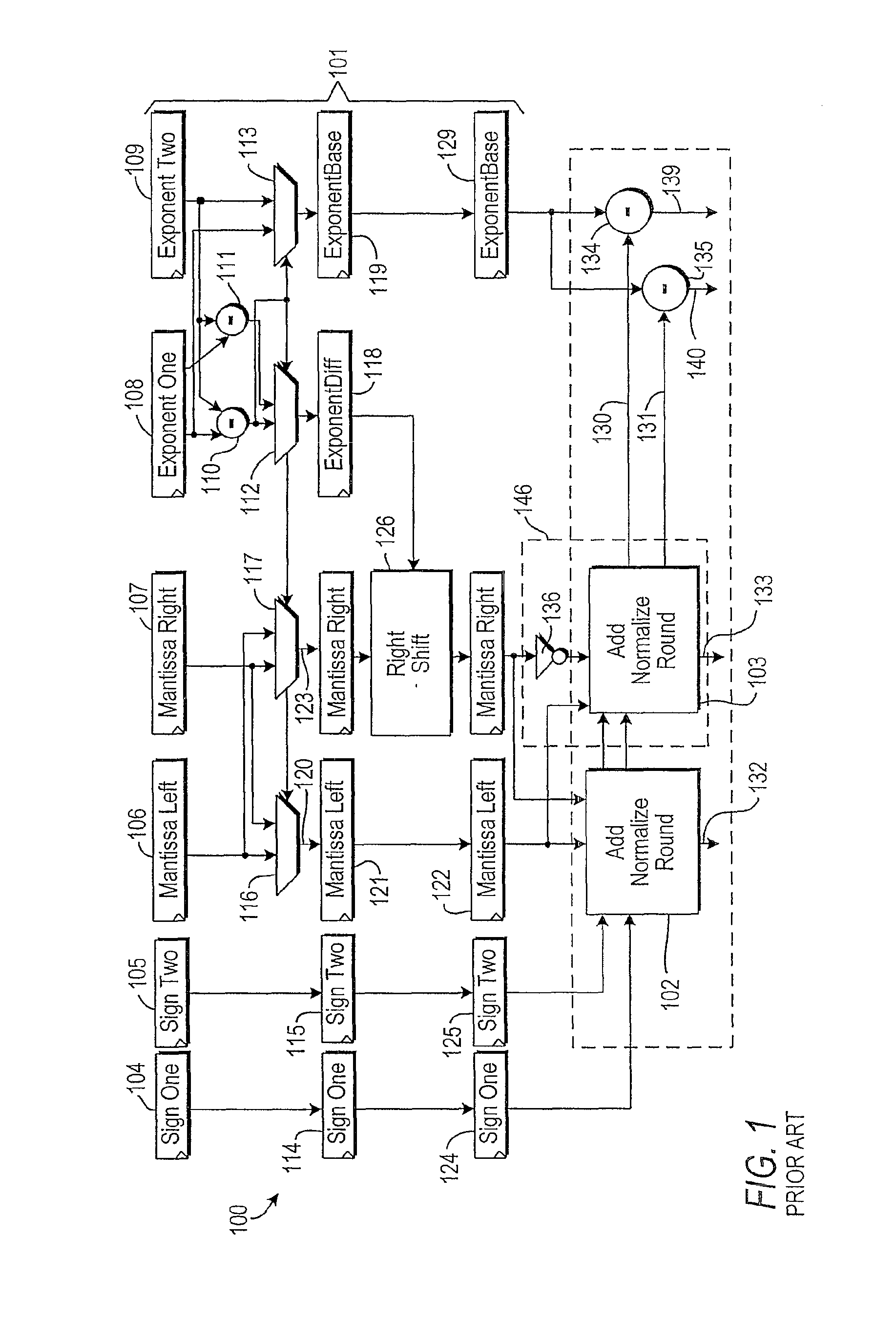

Circuitry (fixed or configured in a programmable device) for performing floating point addition and subtraction uses approximately the same resources as required for either operation separately. The circuitry is based on a recognition that when adding or subtracting two numbers, the two resulting mantissa values will be two out of three possibilities, and will involve either a one-bit shifting operation, or a shifting operation involving a large number of bits. Therefore, one mantissa path—a subtraction path—can be provided with full add / normalize / round circuitry, while a second mantissa path—an addition path—can be provided with a simple one-bit shifter and simplified rounding circuitry. Because the input numbers are signed, the “addition path,” which only adds the mantissas, may provide the mantissa for the subtraction result, depending on the signs of the input numbers. Similarly, the “subtraction path” may provide the mantissa for the addition result.

Owner:ALTERA CORP

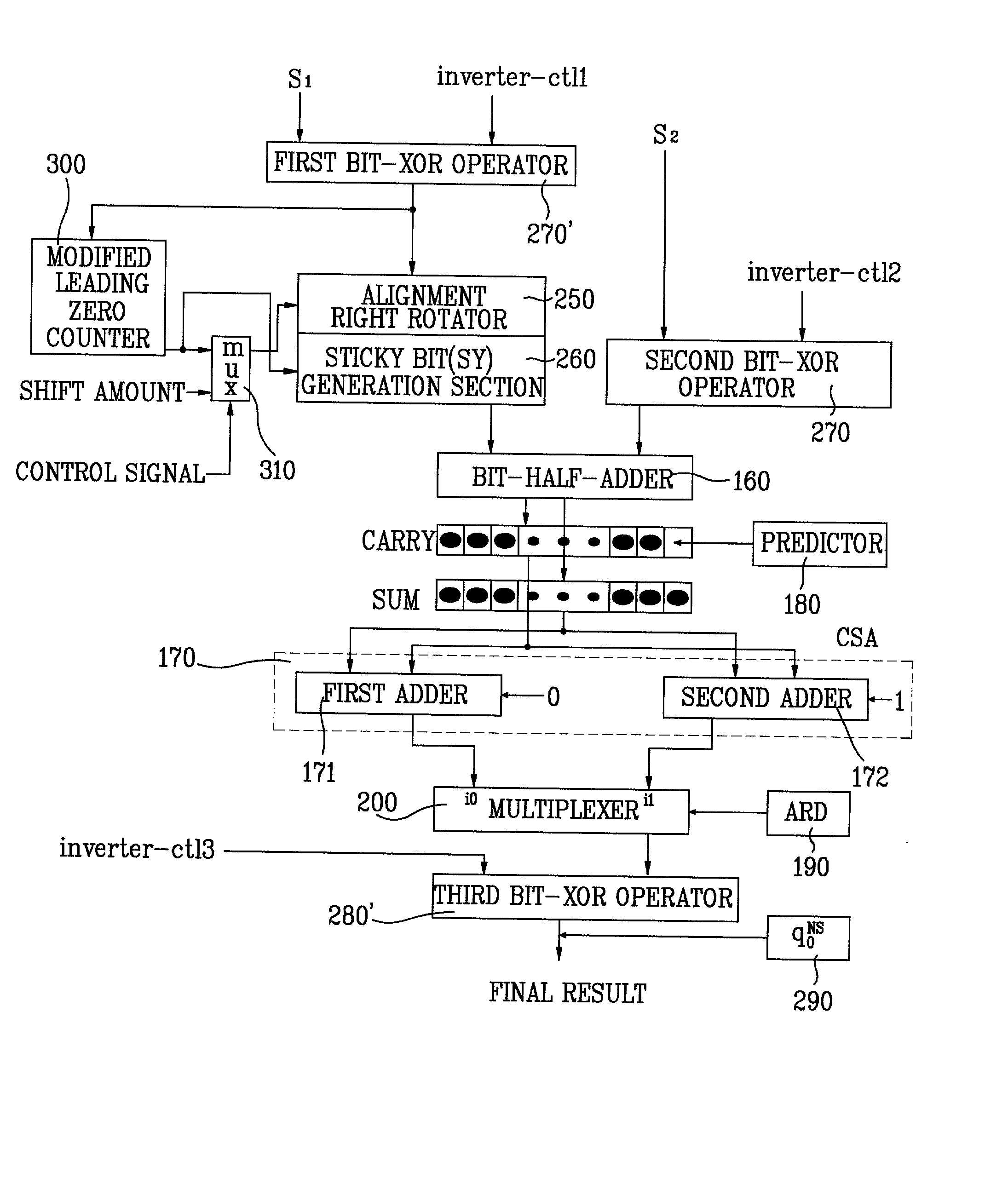

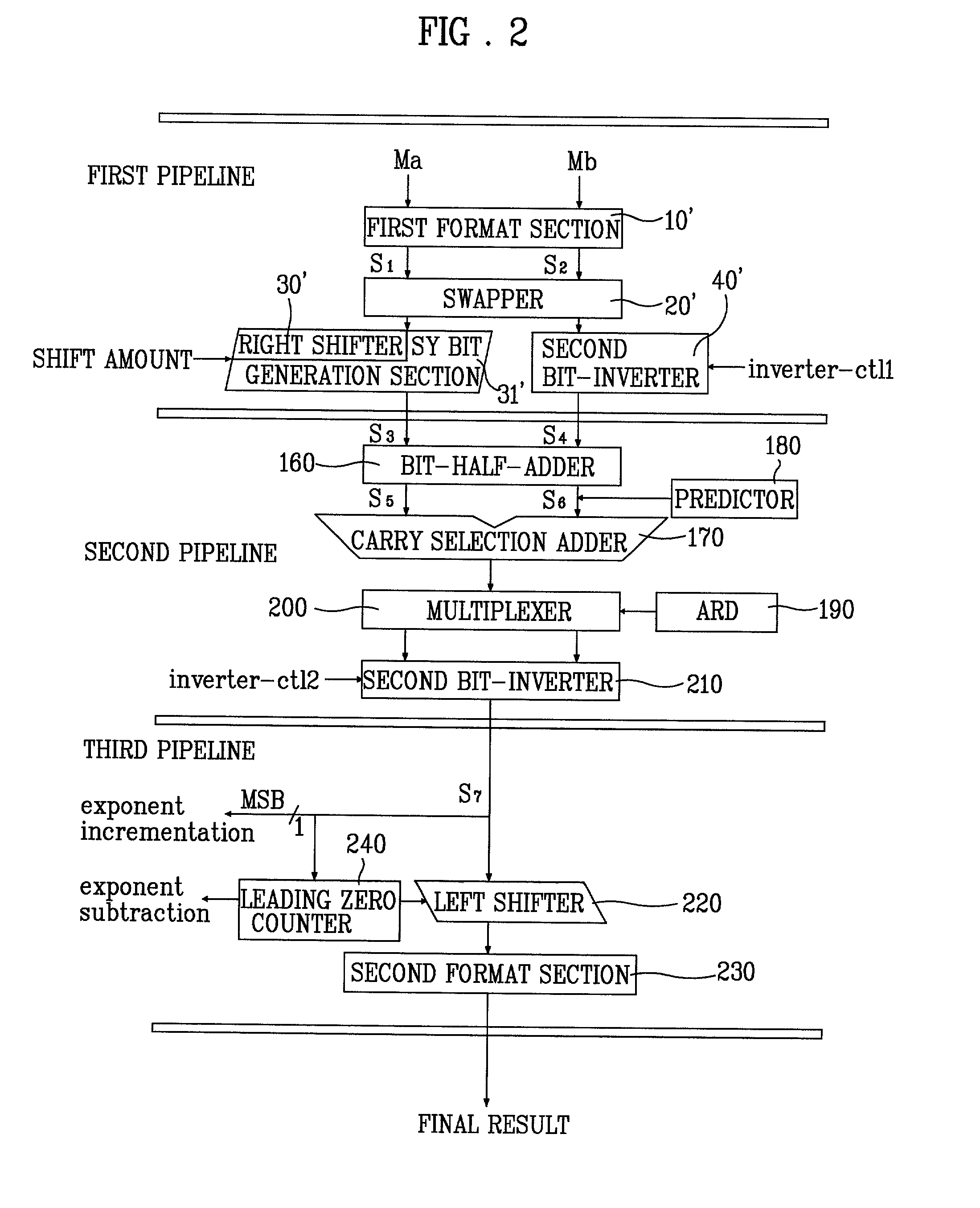

Apparatus and method of performing addition and rounding operation in parallel for floating-point arithmetic logical unit

InactiveUS20020129075A1Computations using contact-making devicesComputation using non-contact making devicesArithmetic logic unitRight shift

A floating-point ALU that performs an IEEE rounding and an addition in parallel in a simultaneous rounding method (SRM) type floating-point adder. The floating-point ALU includes an alignment / normalization section for bypassing or inverting a first fraction part and a second fraction part, performing an alignment by performing a right shift as much as a value obtained from an exponent part or performing a normalization through a left shift by calculating a leading zero with respect to the first fraction part, and obtaining a guard bit (G), round bit (R), and sticky bit (Sy); and an addition and rounding operation section for performing a addition and rounding with respect to the first fraction part and second fraction part outputted through the alignment / normalization section. According to the floating-point ALU, the processing time and the hardware size can be reduced, and the hardware of the SRM can be used as it is.

Owner:YONSEI UNIVERSITY

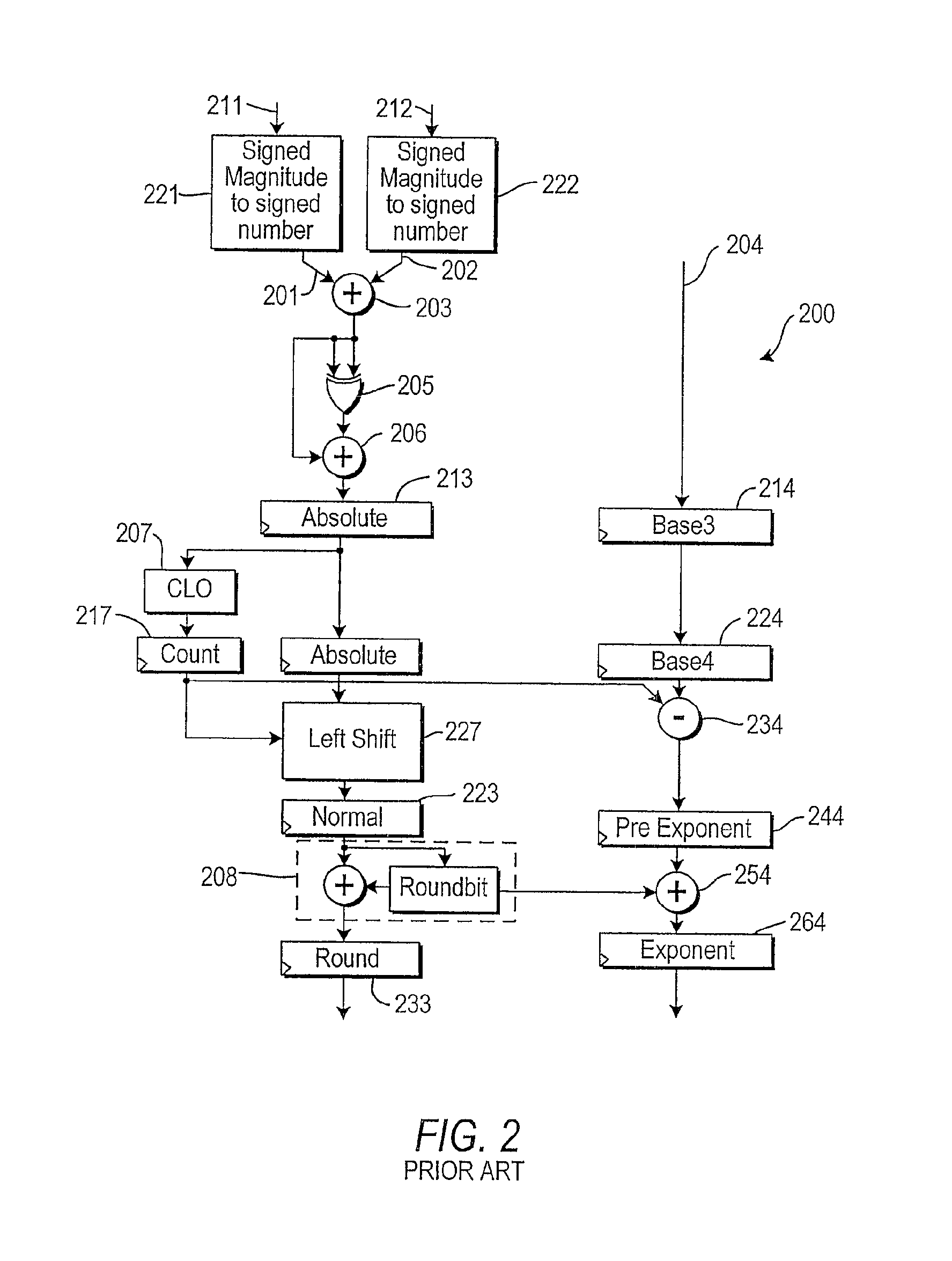

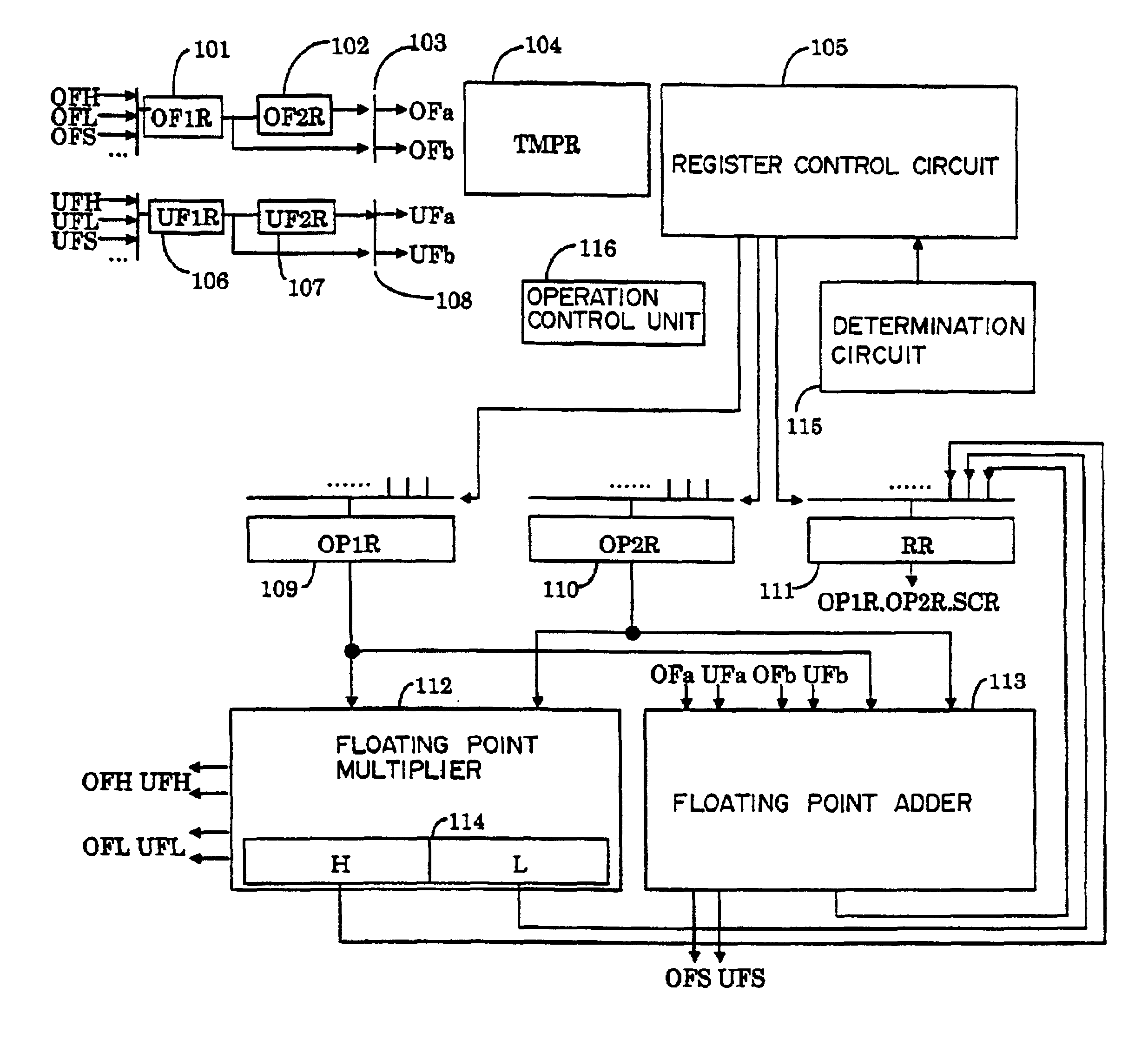

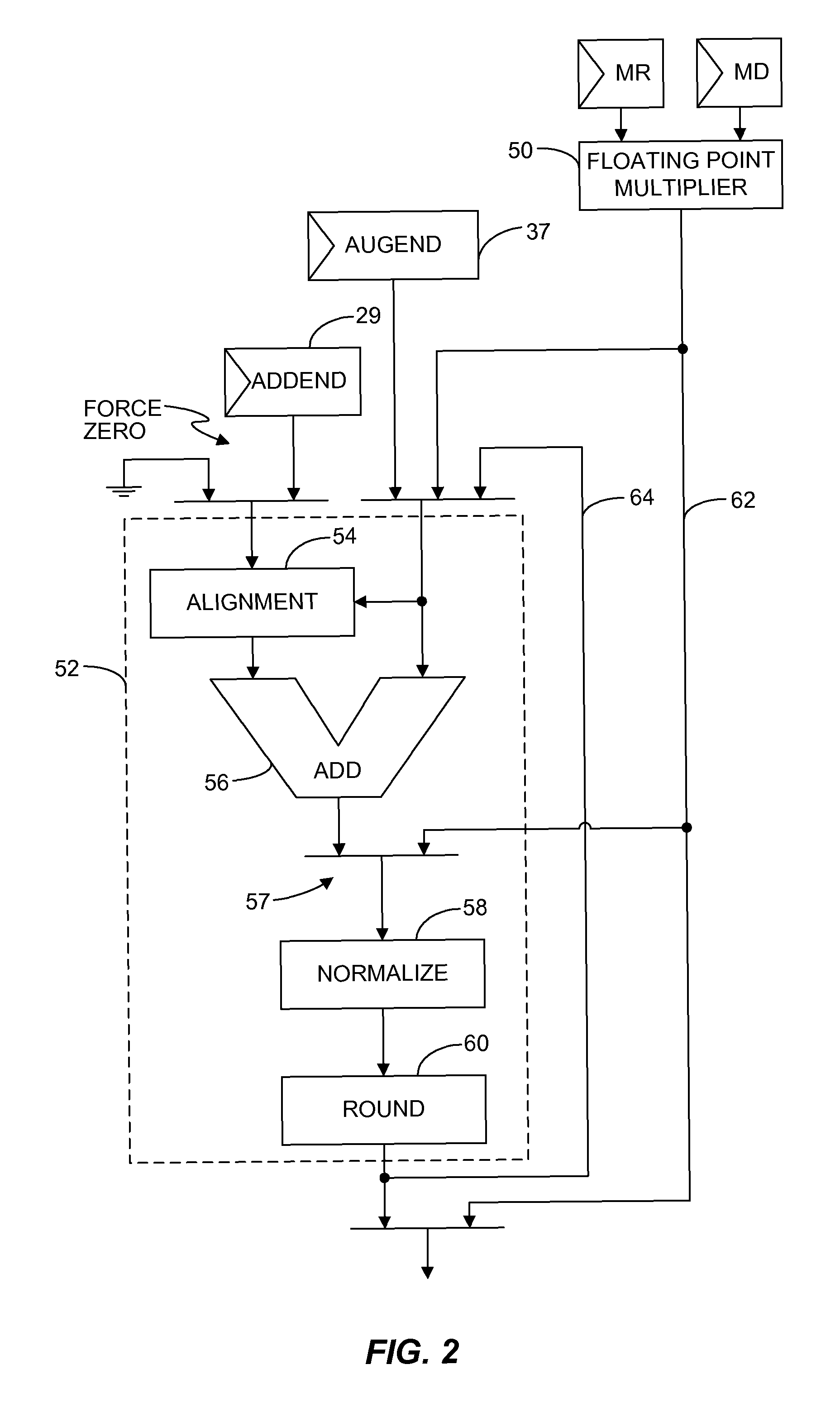

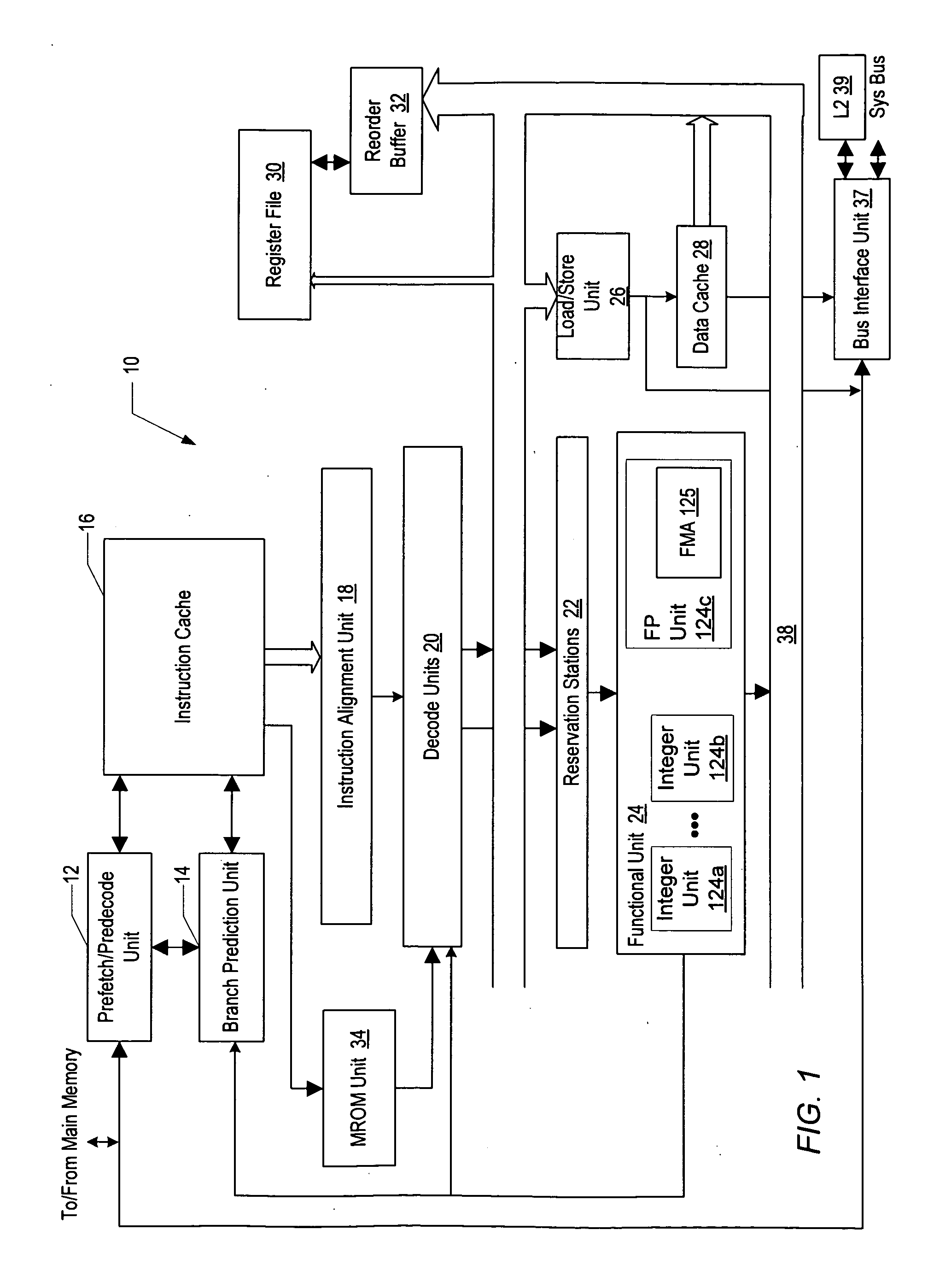

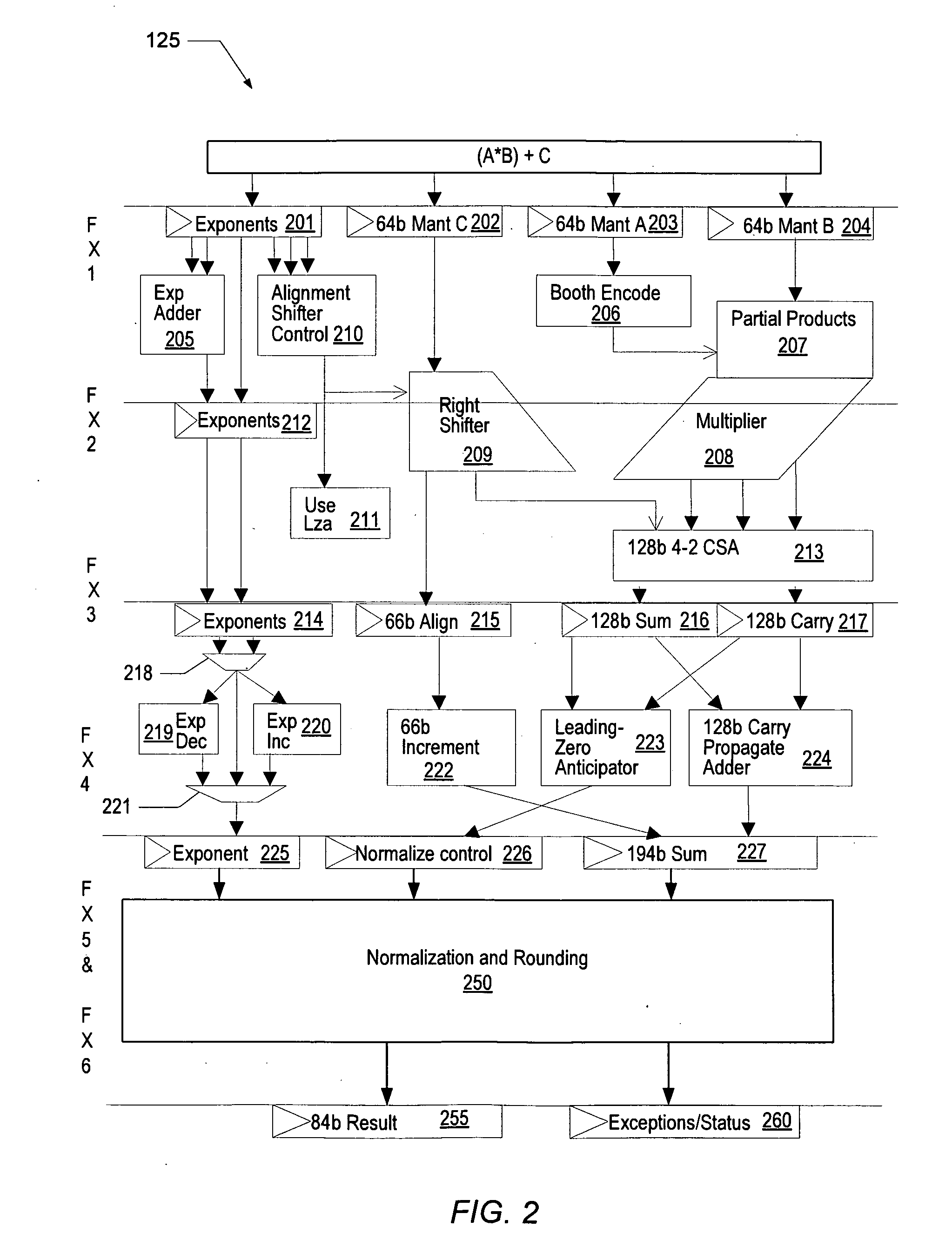

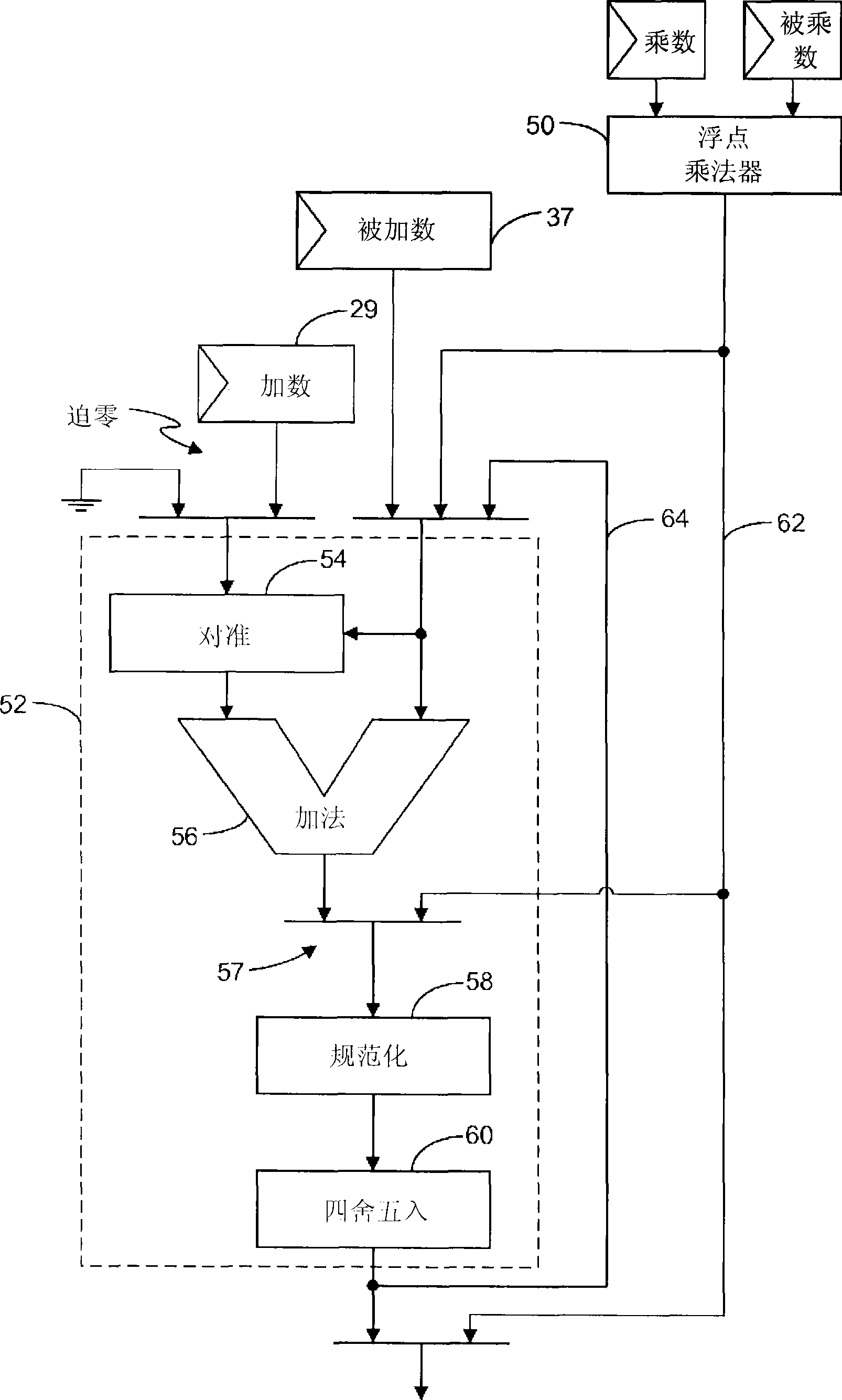

Apparatus and method of performing product-sum operation

InactiveUS6895423B2Reduce circuit sizeSmall circuitComputation using non-contact making devicesComplex mathematical operationsTheoretical computer scienceFloating point multiplier

To perform a product-sum operation by adding third data to a product of first data and second data, a floating point multiplier first multiplies the first data by the second data, and a bit string representing a fixed-point part in the multiplication result is divided into a portion representing more significant digits in the fixed-point part and a portion representing less significant digits in the fixed-point part. Then, a floating point adder first adds less significant multiplication result data having a bit string representing the less significant digits as a fixed-point part to the third data, and then adds the addition result to more significant multiplication result data having a bit string representing the more significant digits as a fixed-point part. A rounding process is performed on the two addition results to obtain a result of the product-sum operation.

Owner:FUJITSU LTD

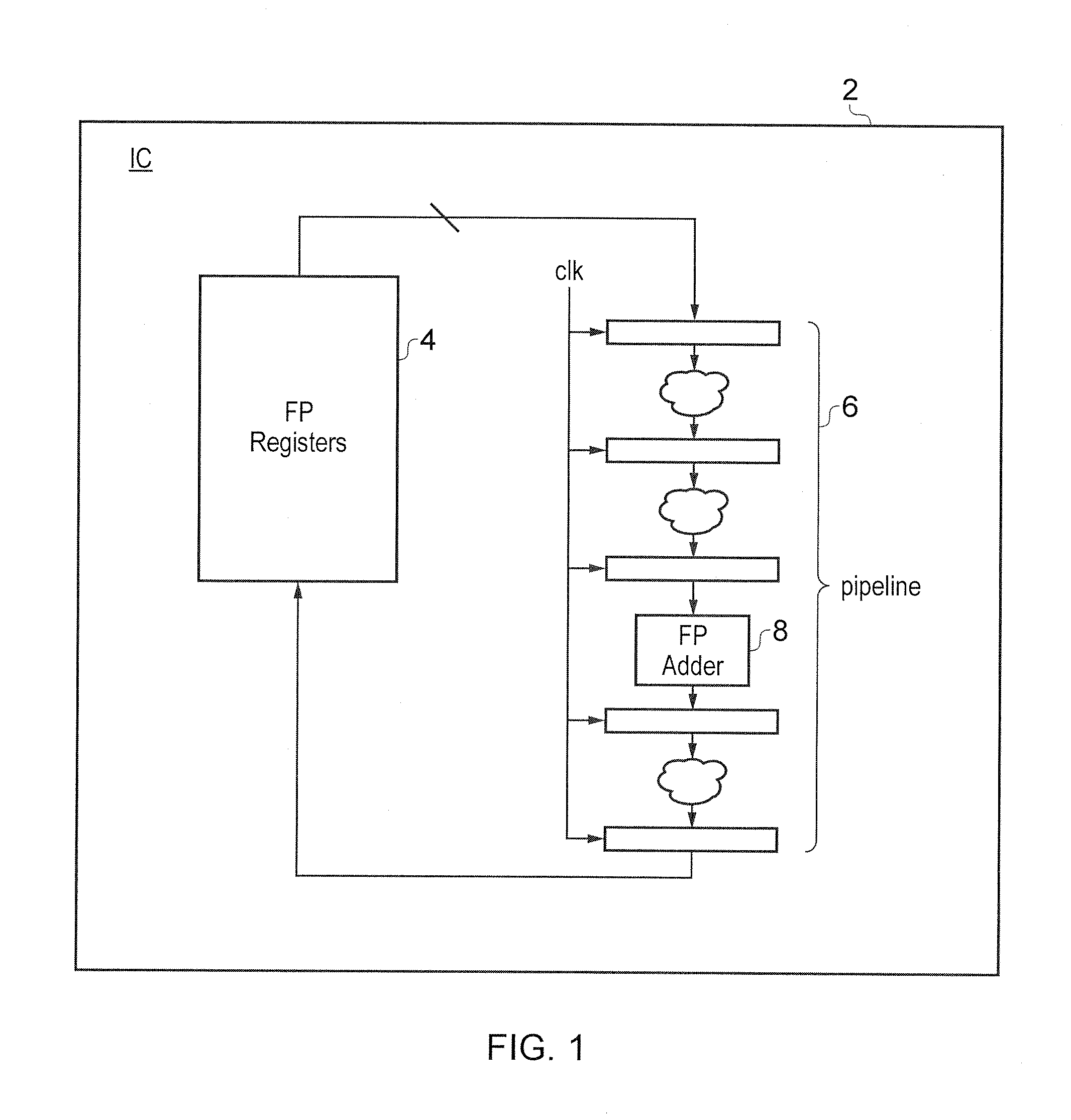

Floating-point adder circuitry

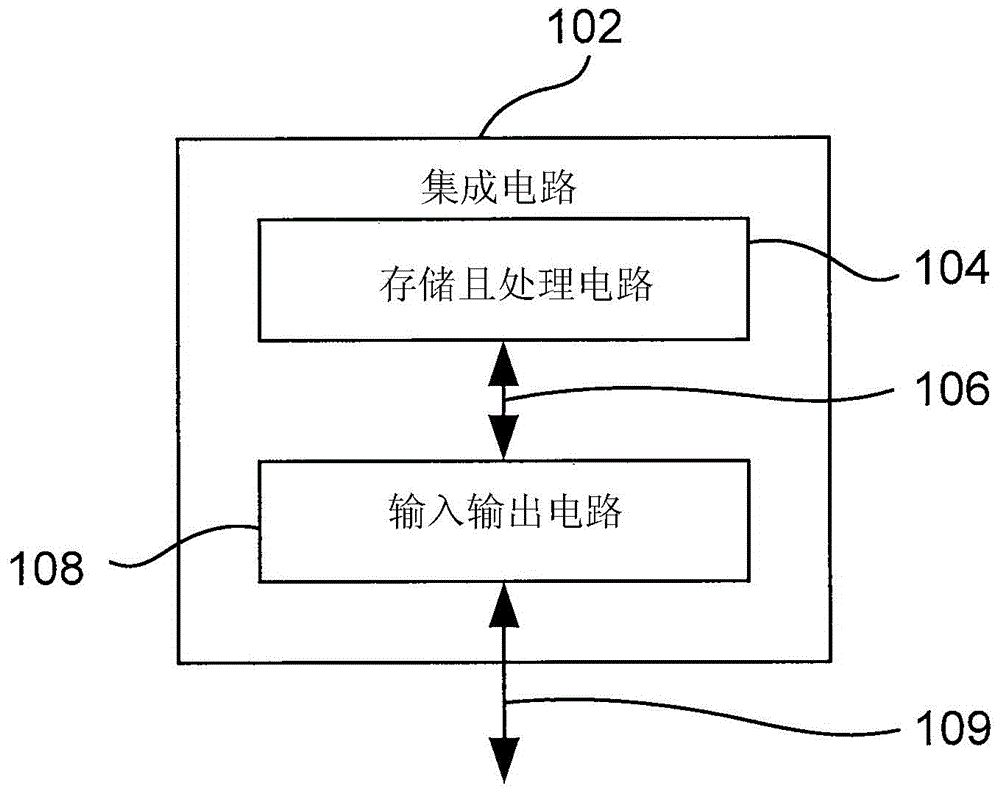

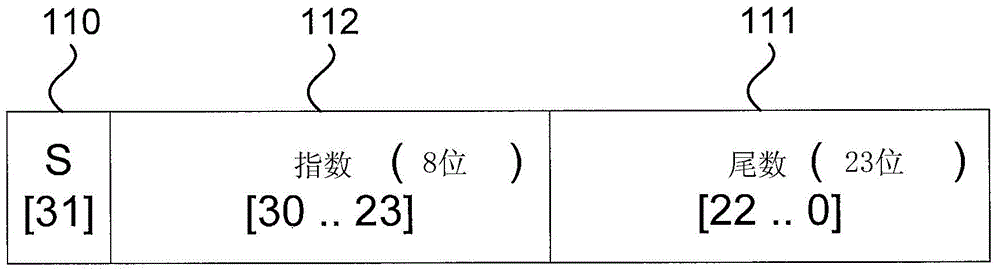

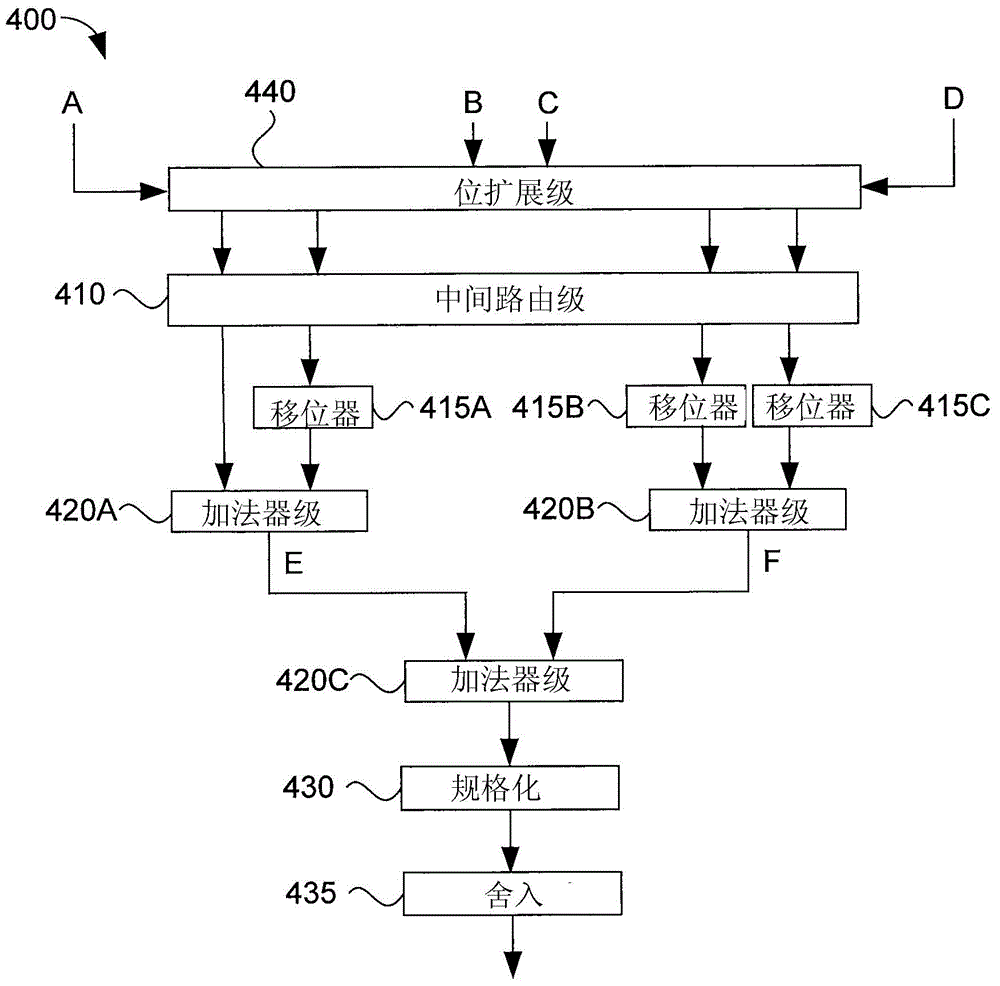

ActiveCN104423926ADigital data processing detailsComplex mathematical operationsComputer hardwareHemt circuits

An integrated circuit is provided that performs floating-point addition or subtraction operations involving at least three floating-point numbers. The floating-point numbers are pre-processed by dynamically extending the number of mantissa bits, determining the floating-point number with the biggest exponent, and shifting the mantissa of the other floating-point numbers to the right. Each extended mantissa has at least twice the number of bits of the mantissa entering the floating-point operation. The exact bit extension is dependent on the number of floating-point numbers to be added. The mantissas of all floating-point numbers with an exponent smaller than the biggest exponent are shifted to the right. The number of right shift bits is dependent on the difference between the biggest exponent and the respective floating-point exponent.

Owner:ALTERA CORP

Floating-point adder

ActiveUS9009208B2Lower latencyLittle countComputations using contact-making devicesComputer architectureOperand

Floating point adder circuitry 16, 18, 20 is provided with far-path circuitry 18 and near-path circuitry 20. The far-path circuitry utilises a count of trailing zeros TZ and a difference in the input operand exponents to form respective suffix values which are concatenated with the mantissas of the input addends and serve when summed to generate a carry out taking the place of a conventionally calculated sticky bit. Within the near-path, minimum value circuitry 46 is used to calculate the lower of a leading zeros count of the intermediate mantissa produced in a subtraction and the larger of the input operand exponent values such that a left shift applied to the intermediate mantissa value is not able to produce a invalid floating point result due to applying a left shift to remove leading zeros that is too larger and accordingly corresponds to an exponent which cannot be validly represented.

Owner:ARM LTD

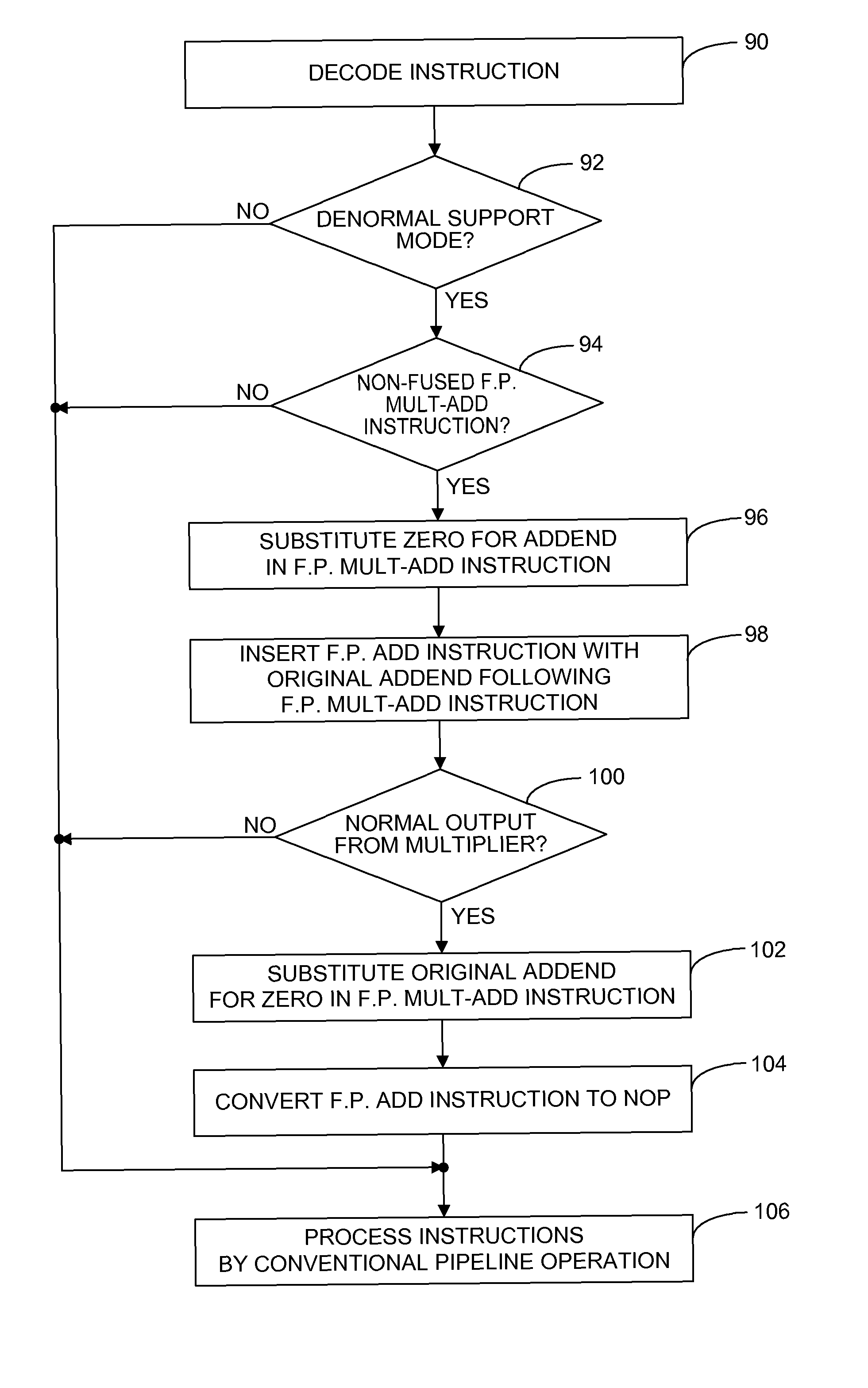

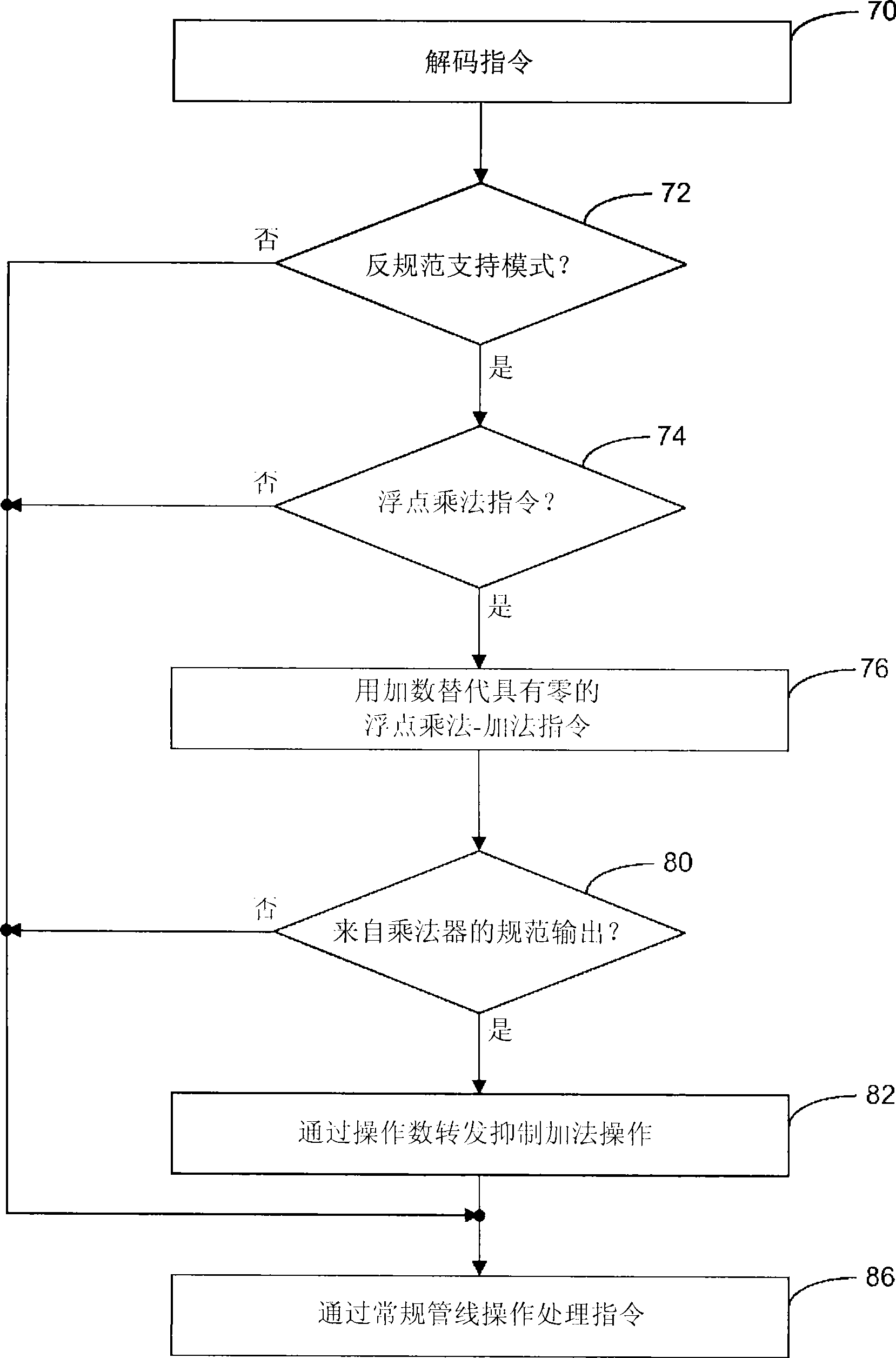

Mode-based multiply-add recoding for denormal operands

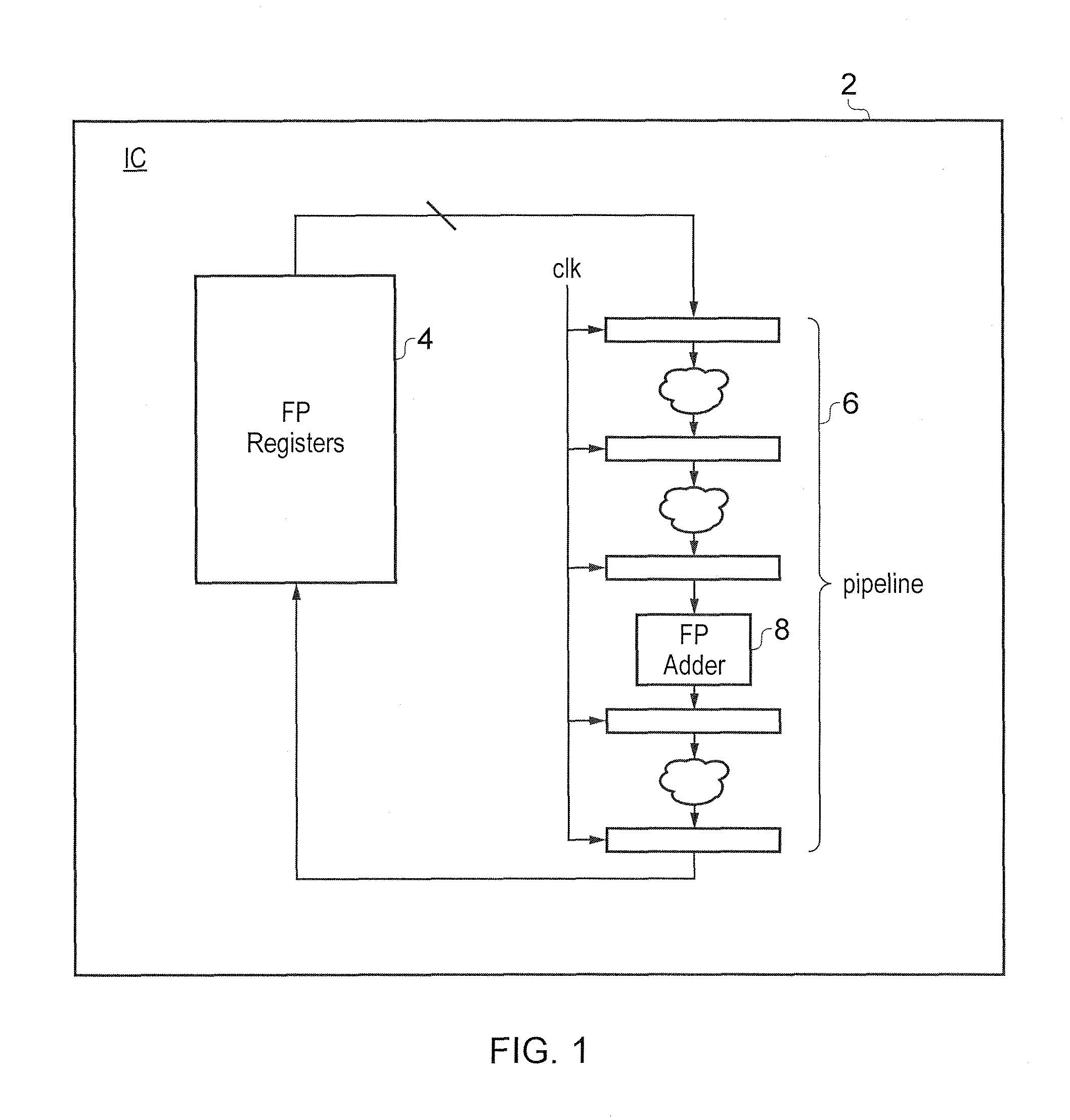

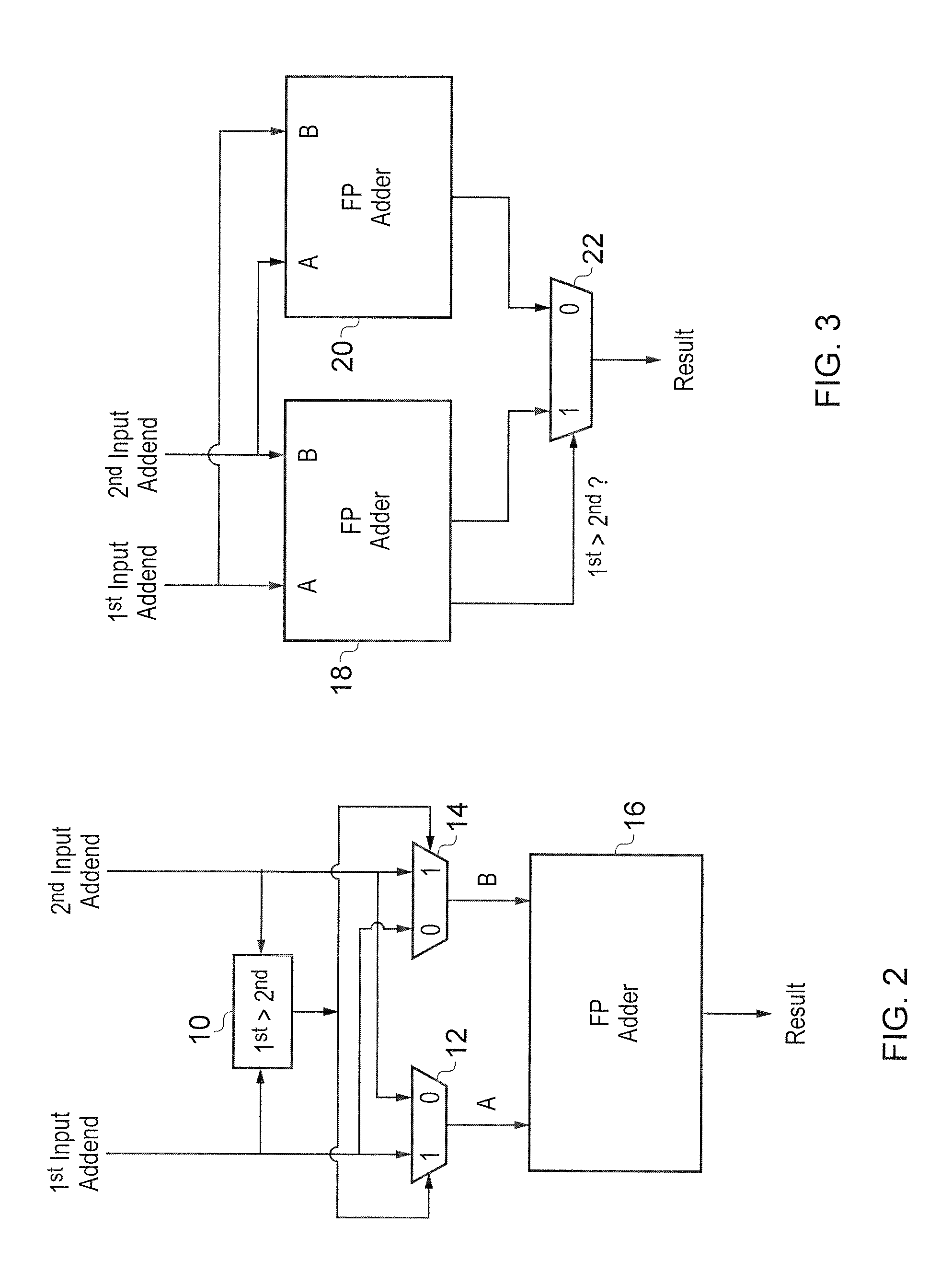

ActiveUS7912887B2Computations using contact-making devicesFloating point multiplierInstruction stream

In a denormal support mode, the normalization circuit of a floating-point adder is used to normalize or denormalized the output of a floating-point multiplier. Each floating-point multiply instruction is speculatively converted to a multiply-add instruction, with the addend forced to zero. This preserves the value of the product, while normalizing or denormalizing the product using the floating-point adder's normalization circuit. When the operands to the multiply operation are available, they are inspected. If the operands will not generate an unnormal intermediate product or a denormal final product, the add operation is suppressed, such as by operand-forwarding. Additionally, each non-fused floating-point multiply-add instruction is replaced with a multiply-add instruction having a zero addend, and a floating-point add instruction having the addend of the original multiply-add instruction is inserted into the instruction stream. Upon inspection of the operands, if an unnormal intermediate result or a denormal final result will not occur, the addend may be restored to the multiply-add instruction and the add instruction converted to a NOP.

Owner:QUALCOMM INC

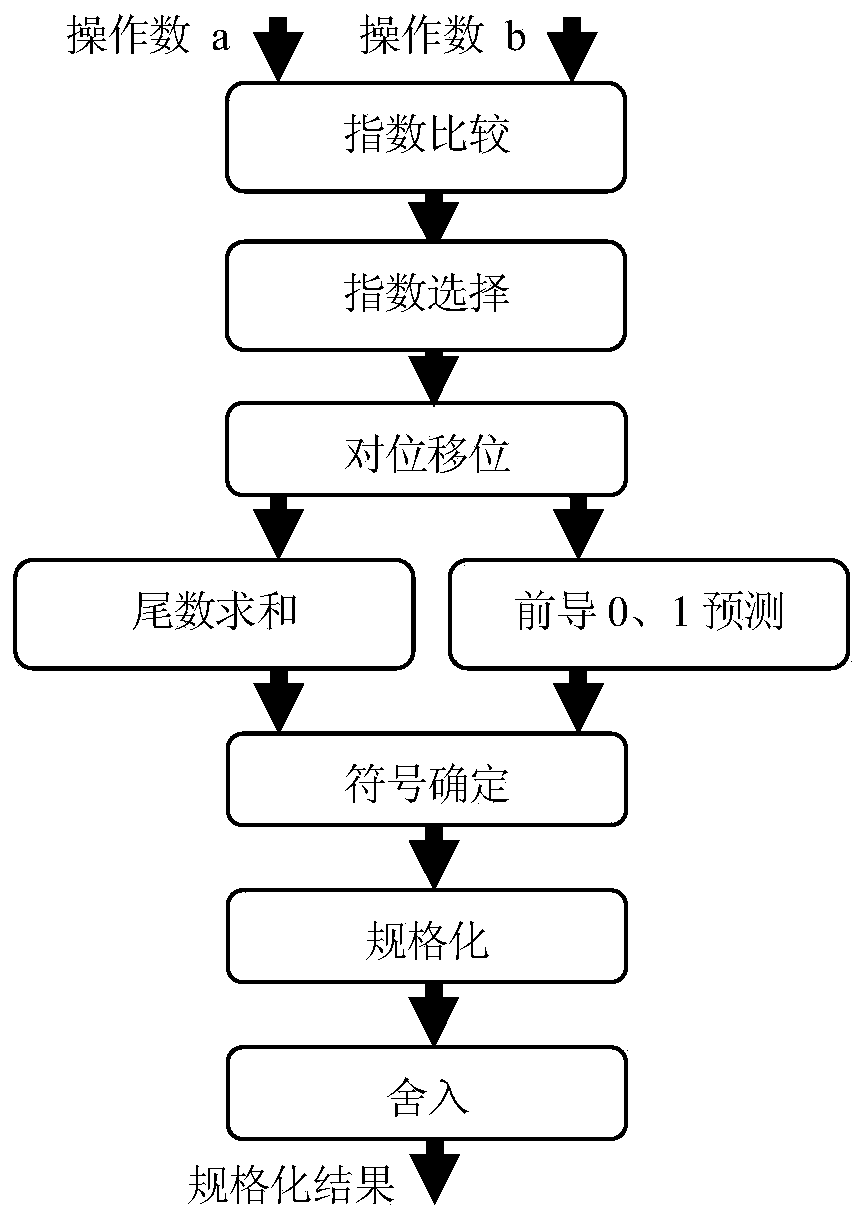

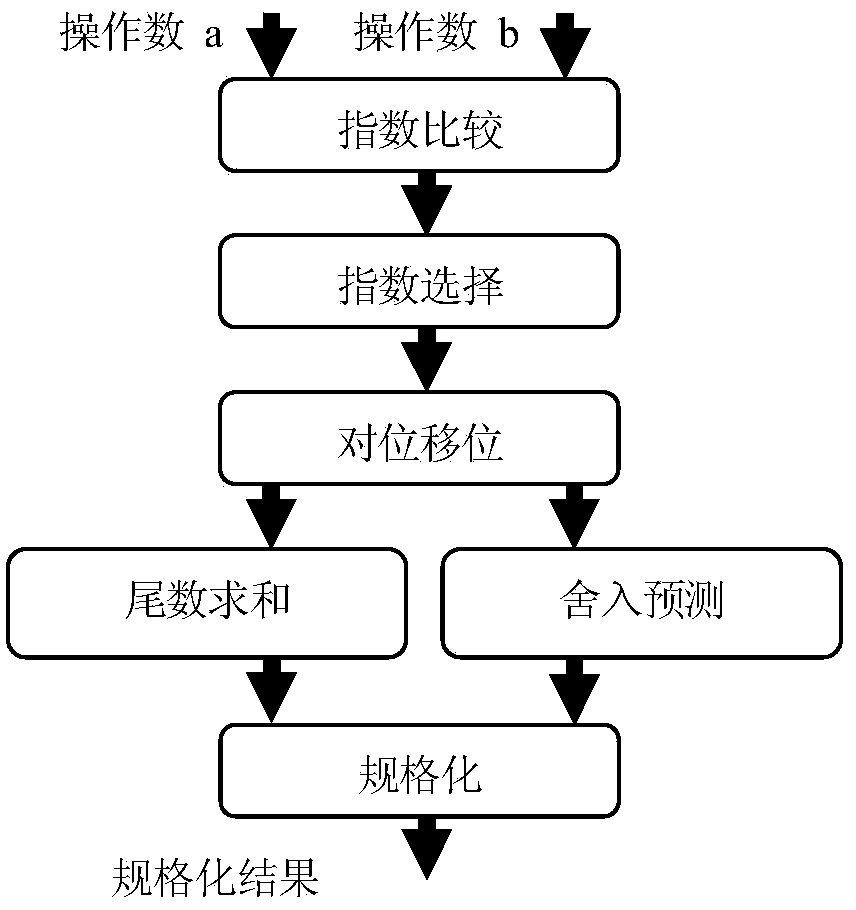

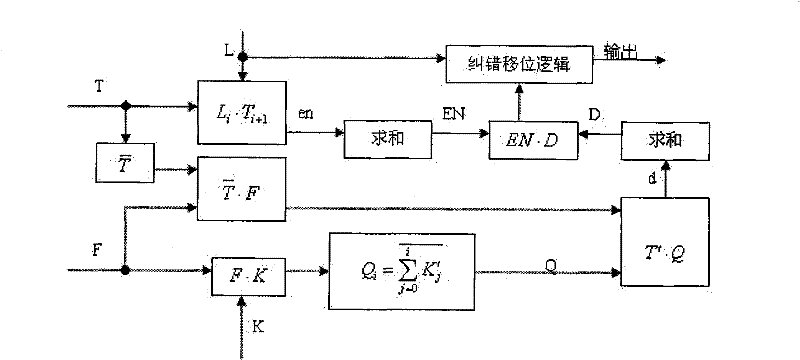

Rounding prediction method for floating point adder

InactiveCN103455305AReduce stepsDigital data processing detailsVery large scale integrated circuitsPredictive methods

The invention discloses a rounding prediction method for a floating point adder. The performance of the adder can be improved. A rounding prediction unit realized by using the method works in parallel with a mantissa adder of the adder to generate a normalized displacement control signal and a mantissa adjustment control signal including rounding information. A mantissa and an index are adjusted by a post-order unit by using the normalized displacement control signal, so that a normalized result including round-up information can be obtained; the displaced mantissa is then adjusted by using the mantissa adjustment control signal, so that a final result of the adder can be obtained. Thus, according to the adder using the prediction unit, symbol confirmation and rounding operations are successfully fallen into the normalization operation, and the operation of two-stage consumption time in the adder is reduced. The area and the critical path delay of the unit are not increased with the increase in precision of the operation processed by the unit, so that the method is particularly suitable for a high-precision adder and is realized through a super-large-scale integrated circuit.

Owner:XI AN JIAOTONG UNIV

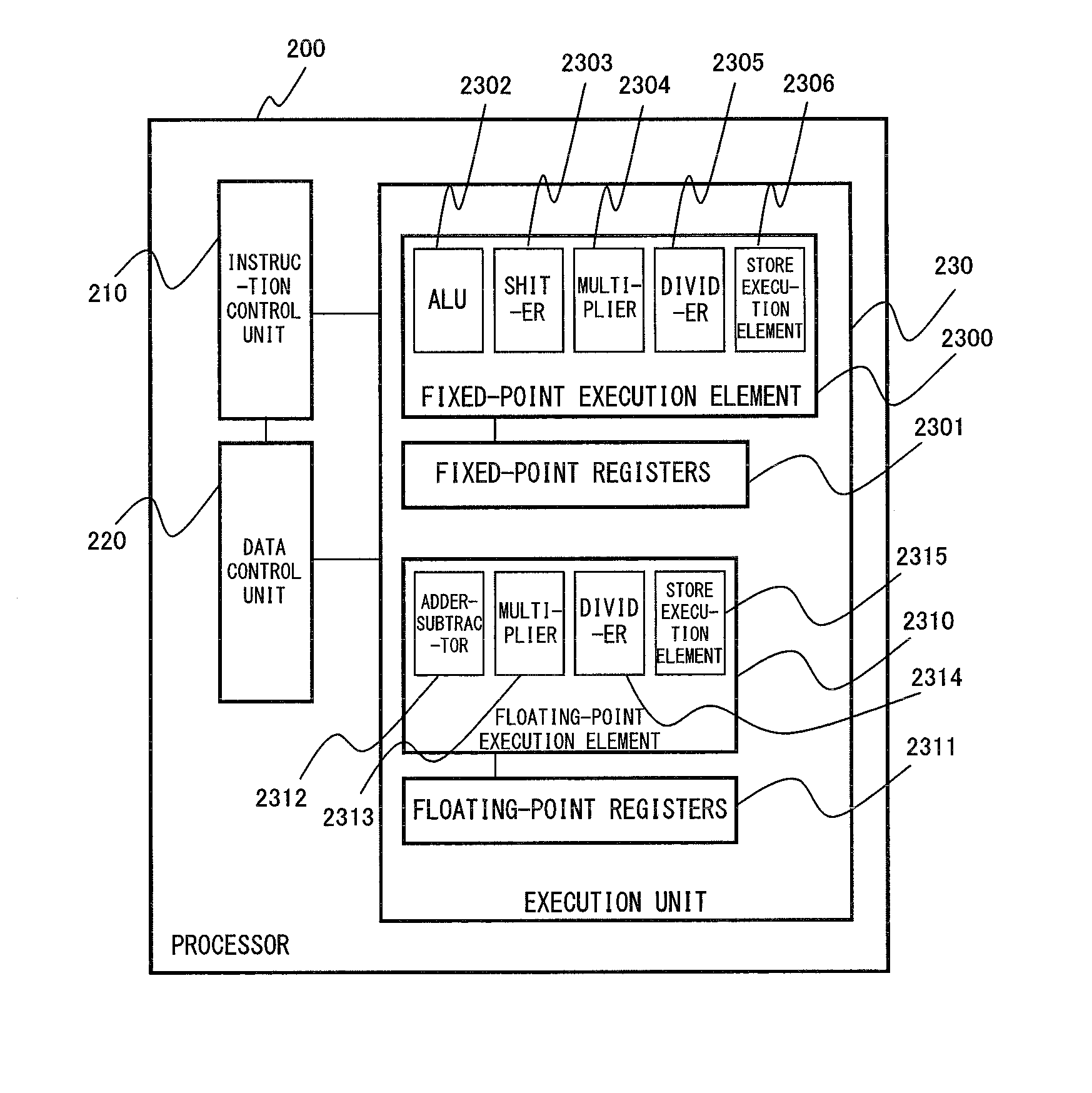

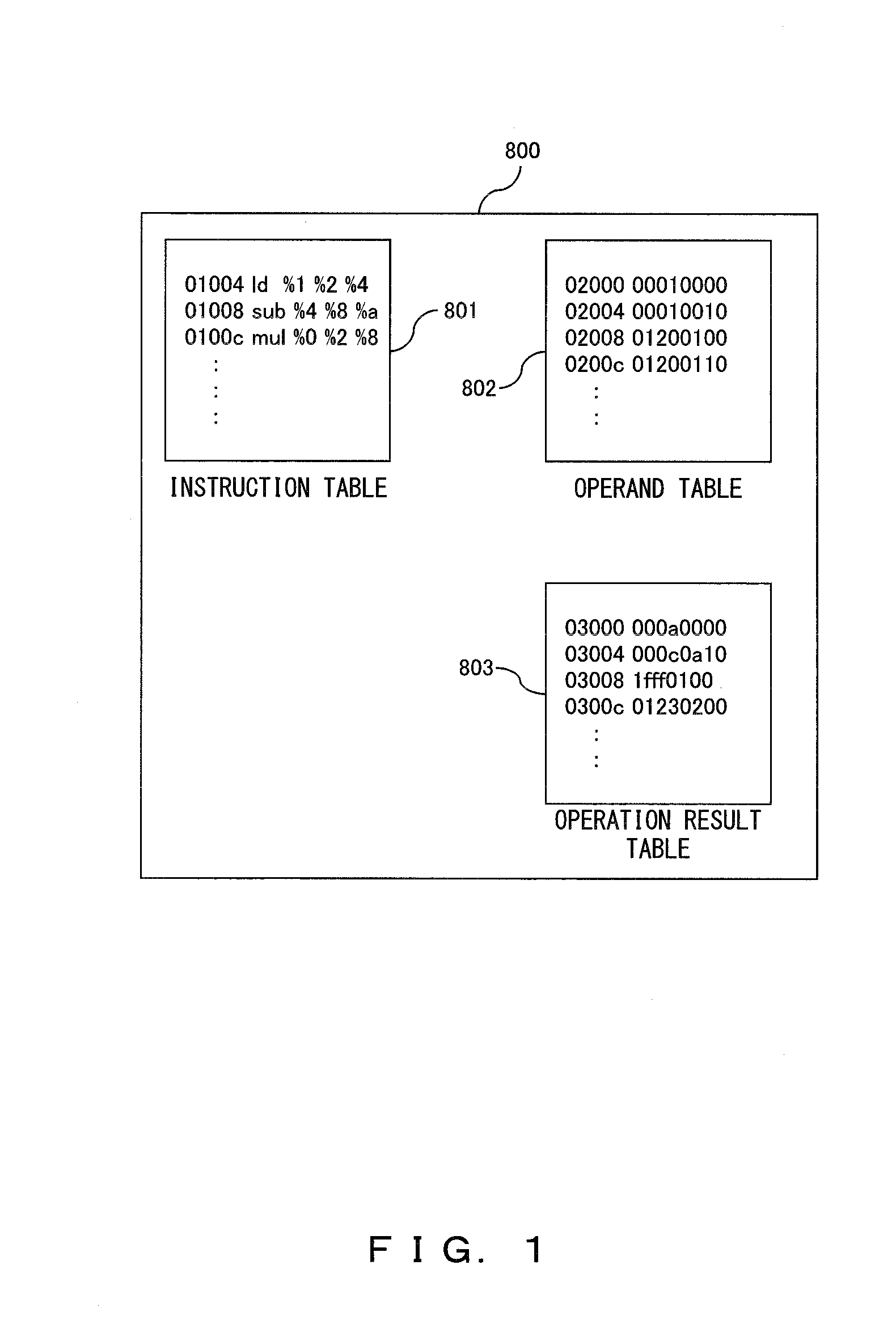

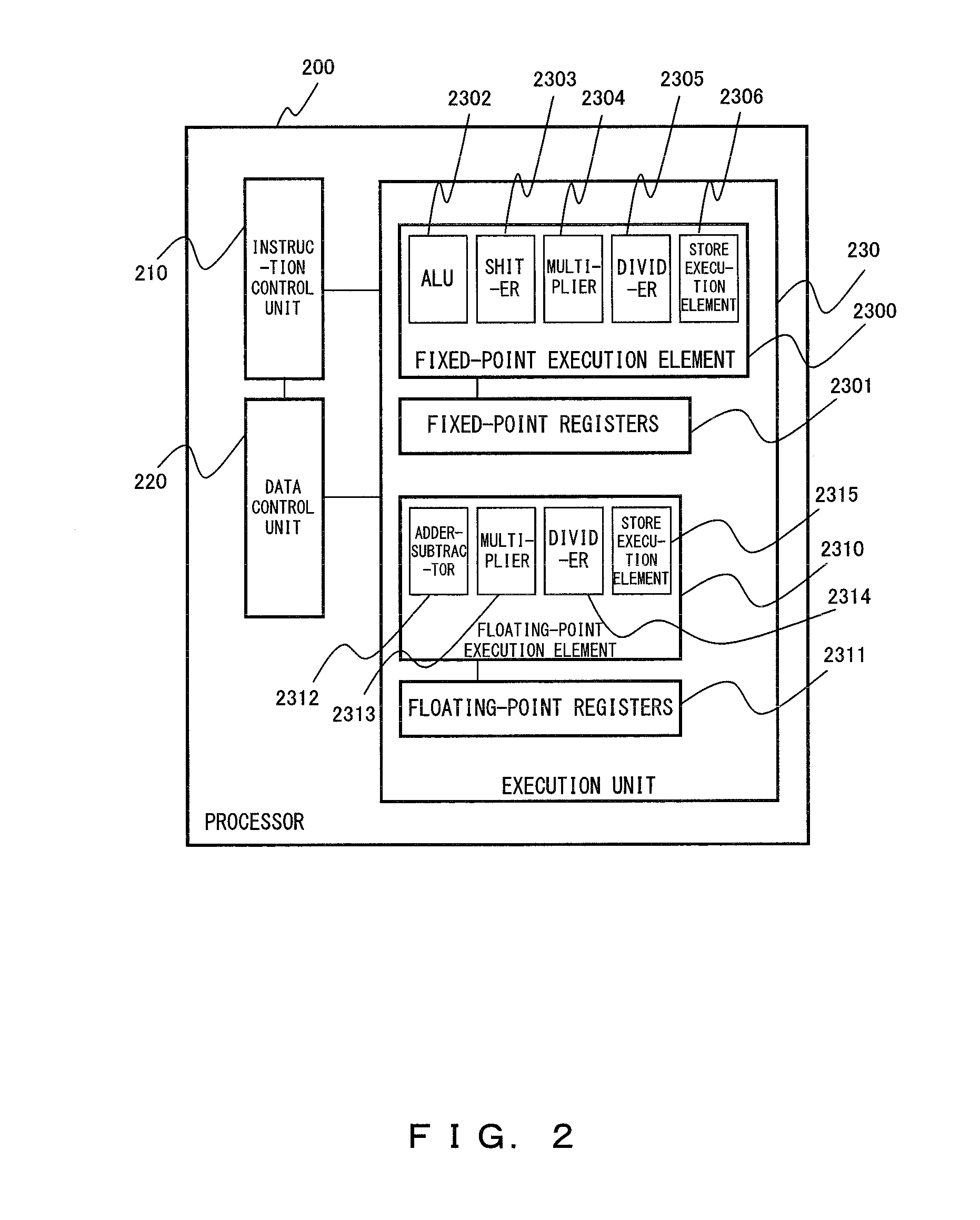

Operation verification method for verifying operations of a processor

InactiveUS20080172551A1Electronic circuit testingError detection/correctionValidation methodsFloating point

To verify an addition-function of a floating-point adder-subtractor in a processor, parameters such as the number of verification patterns of a verification program are set, a floating-point addition instruction to be verified is created, and operands used for this addition are created at random. The floating-point addition instruction thus created is emulated only by a fixed-point instruction and processed only by using the fixed-point execution element, thereby creating an expectation value. The floating-point addition instruction is computed by using the floating-point adder-subtractor to be verified, and the created expectation value is compared with the operation result. If they do not correspond to each other, the set number of operation patterns is checked. If the number has reached a prescribed value, the operation verification is terminated in the normal manner.

Owner:FUJITSU LTD

Standalone floating-point conversion unit

ActiveUS20160092169A1Digital data processing detailsDigital computer detailsFloating point adderComputer hardware

A data processing apparatus includes floating-point adder circuitry and floating-point conversion circuitry that generates a floating-point number as an output by performing a conversion on any input having a format from a list of formats including: an integer number, a fixed-point number, and a floating-point number having a format smaller than the output floating-point number. The floating-point conversion circuitry is physically distinct from the floating-point adder circuitry.

Owner:ARM LTD

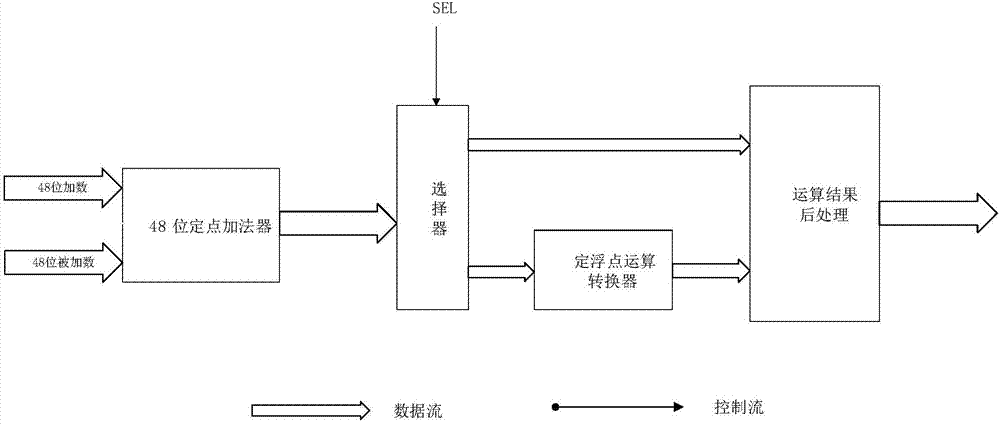

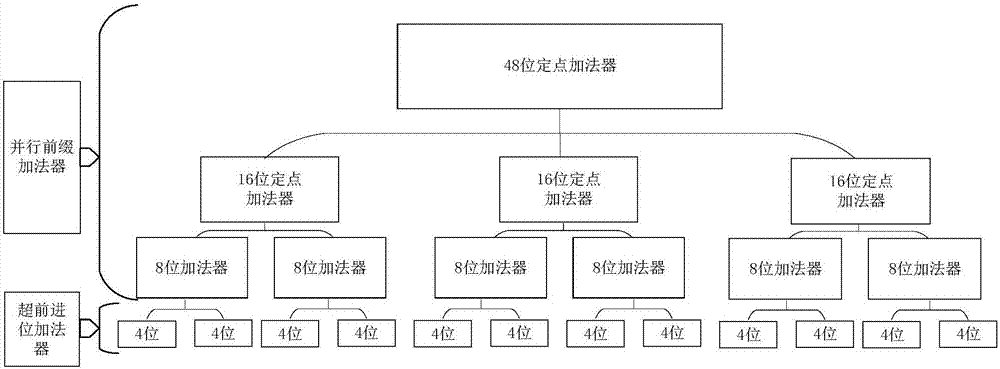

Reconfigurable fixed/floating point general adder

InactiveCN106970775AImprove versatilityImprove data throughputDigital data processing details48-bitFloating point

The invention provides a reconfigurable fixed / floating point general adder. The general adder comprises a 48-bit fixed point adder, a selector and a fixed / floating point operation converter, wherein the 48-bit fixed point adder performs fixed point additive operation and can be reconfigured into a single-precision floating point adder; the selector selects a corresponding fixed point or floating point additive operation passage according to top configuration information and performs output control; and the fixed / floating point operation converter converts the 48-bit fixed point adder into a 32-bit single-precision floating point adder. The general adder has the advantages that a full running structure is adopted, the fixed point adder is correspondingly optimized based on a parallel prefix adder, and on the basis of guaranteeing the operation performance of the fixed point adder, operation delay of the fixed point adder is shortened, and a gate circuit area is reduced. Through the overall structure of the fixed / floating point general adder, the universality of the adder is effectively improved under the condition that precision and data throughput are guaranteed.

Owner:NANJING UNIV

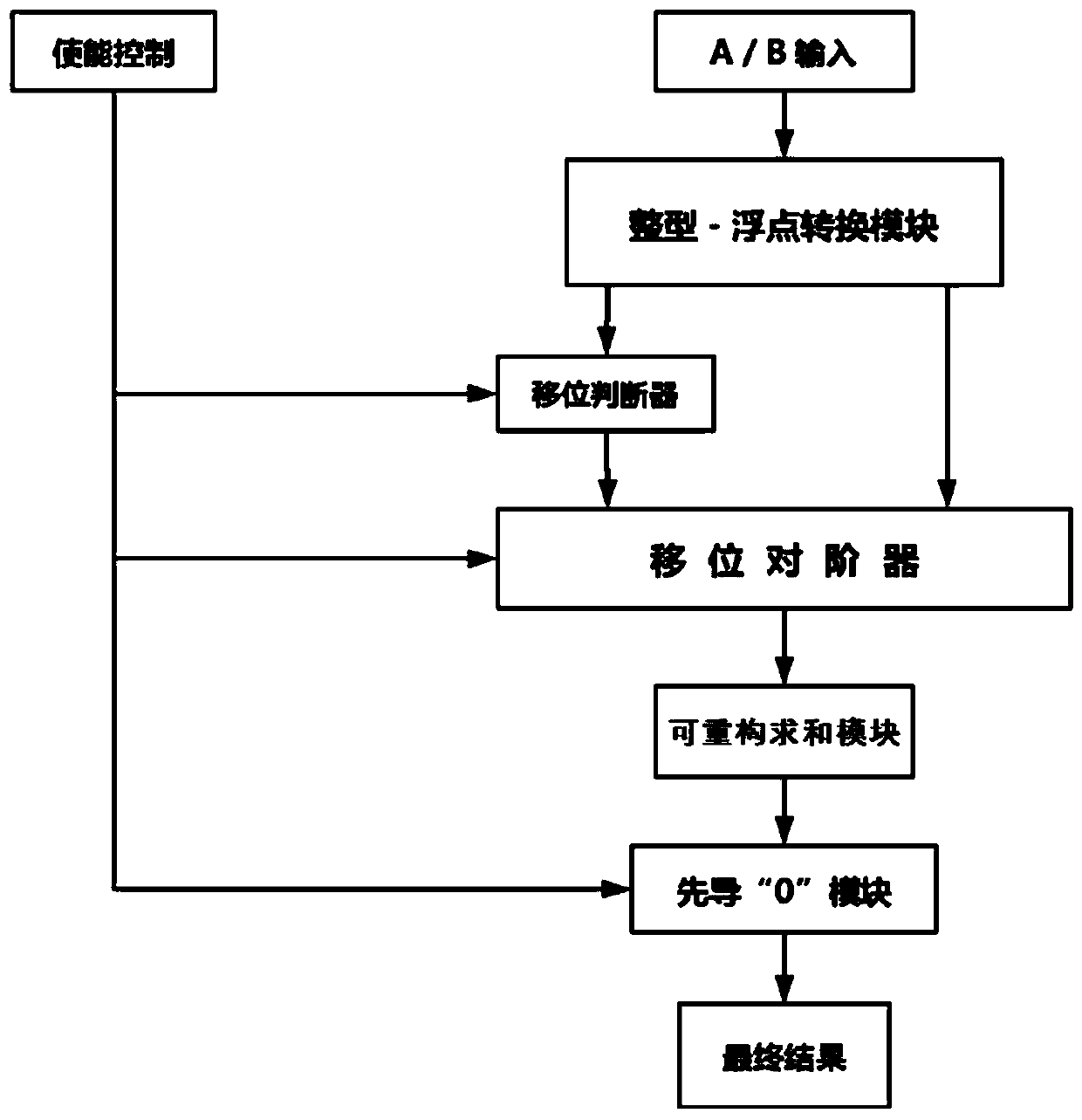

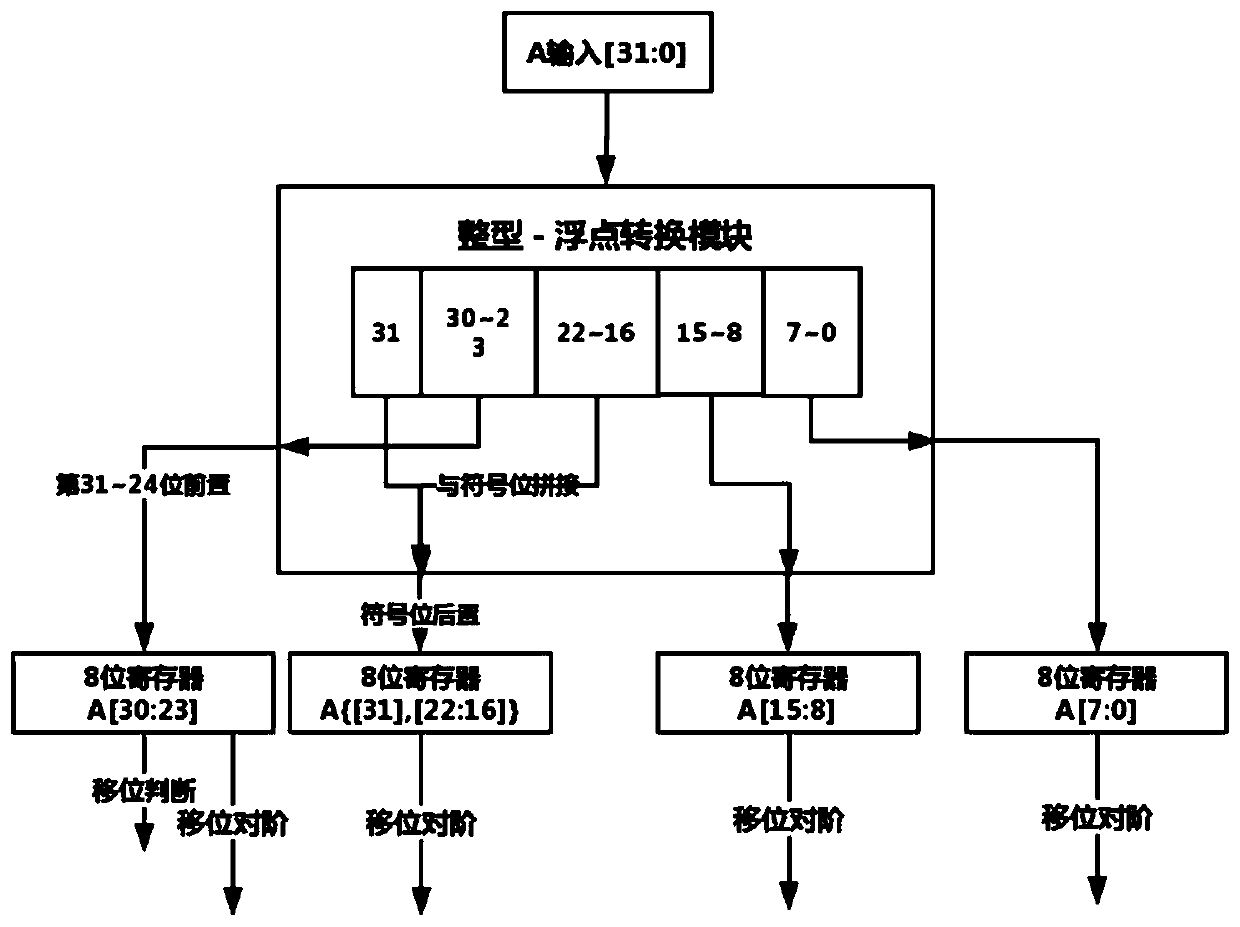

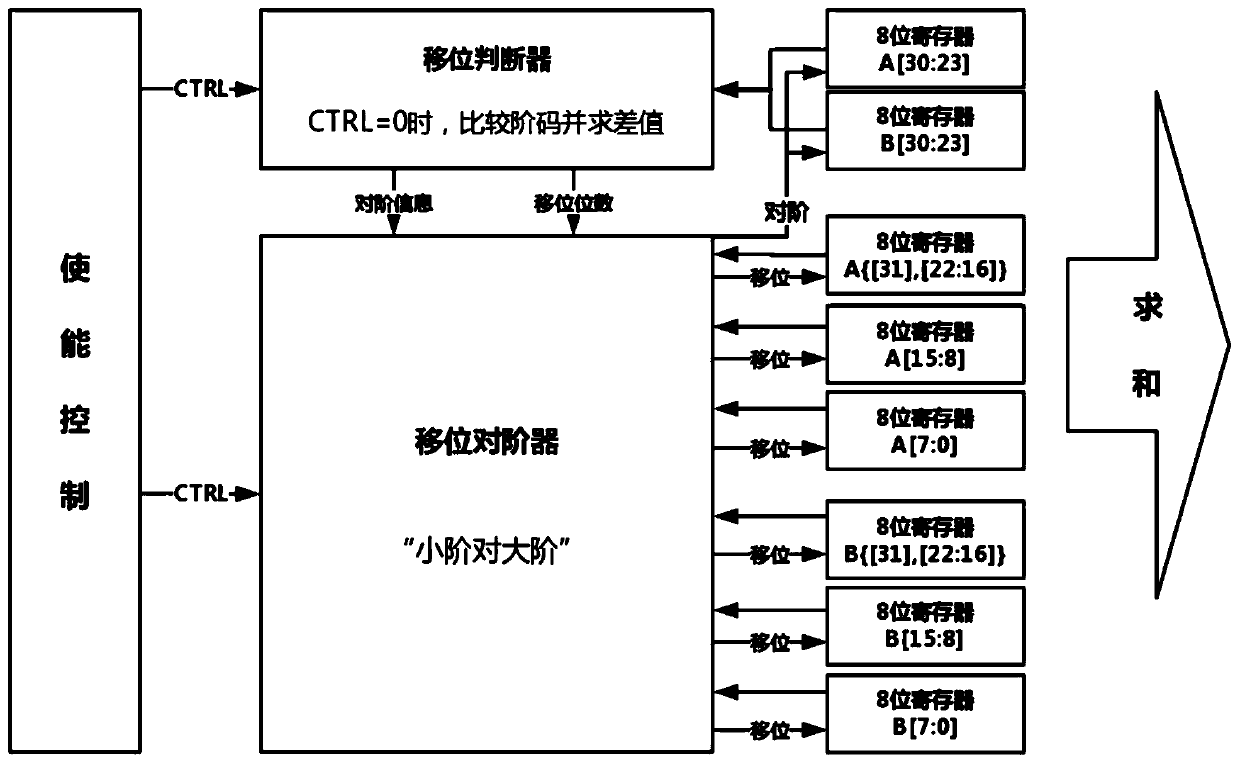

Reconfigurable integer-floating point adder

InactiveCN110688086AIncrease flexibilityLow costDigital data processing detailsControl engineeringFloating point

The invention discloses a reconfigurable integer-floating point adder, and the adder comprises an enabling control module which is used for controlling and switching an operation mode of the reconfigurable integer-floating point adder: an integer mode or a floating point mode; an integer-floating point conversion module which is used for carrying out homogenization pretreatment on the input integer data or floating point data; a shift order matching module which is used for performing shift judgment and shift order matching operation on the data preprocessed by the integer-floating point conversion module in a floating point operation mode; a reconfigurable summation module which is used for completing summation operation of the processed integer or floating point data to obtain a preliminary summation result; and a pilot '0' counting shifter which is used for performing normalization processing on the preliminary summation result of summation in the floating point operation mode and outputting a final result. The method has better universality when meeting the operation requirement of simultaneously processing various types of data, and meanwhile, the flexibility of hardware distribution is improved, so that the layout area is reduced, the power consumption is reduced, and the hardware cost is reduced.

Owner:XI AN JIAOTONG UNIV

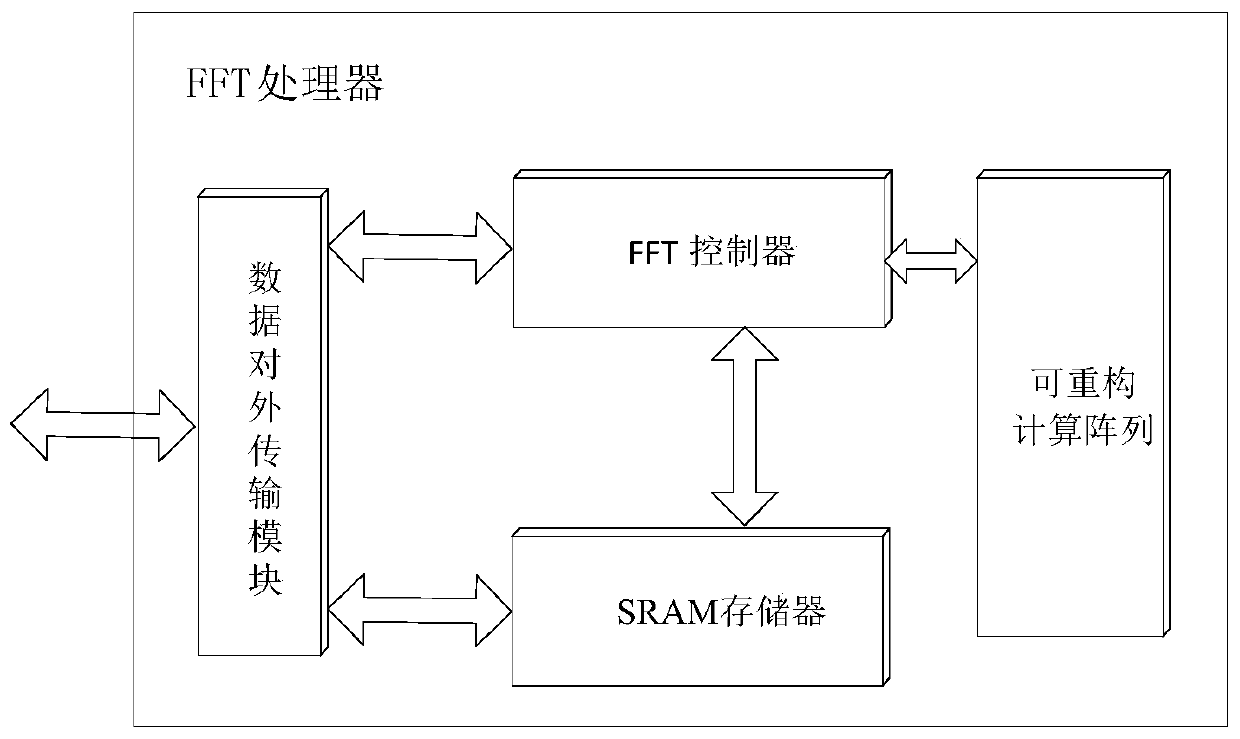

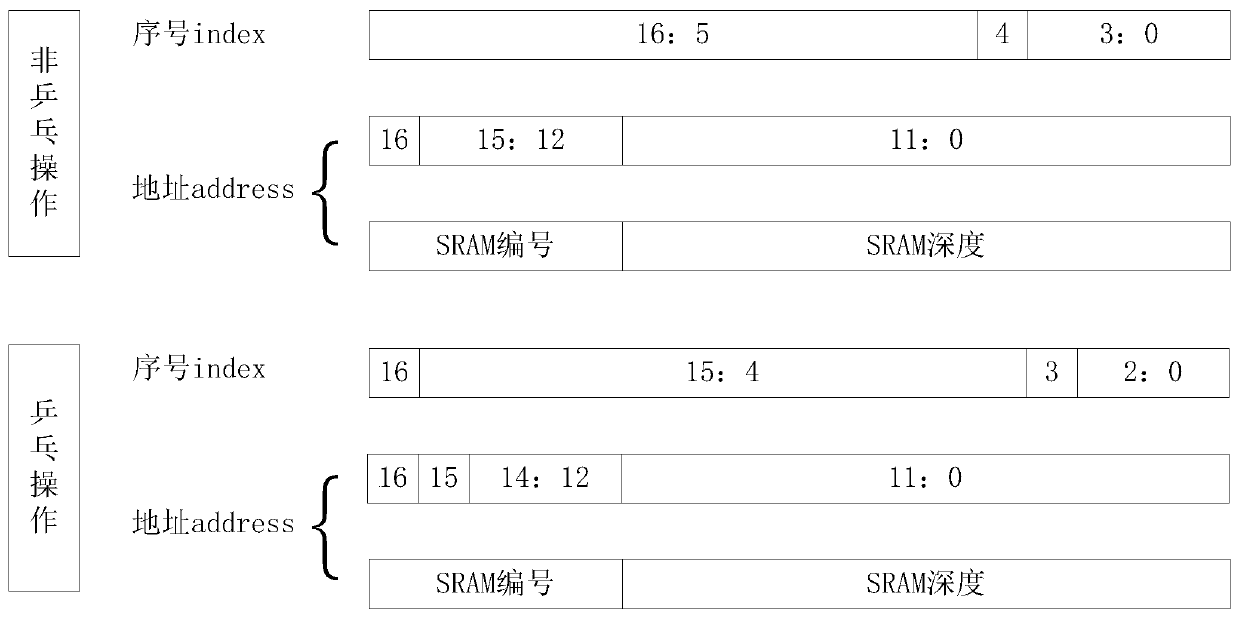

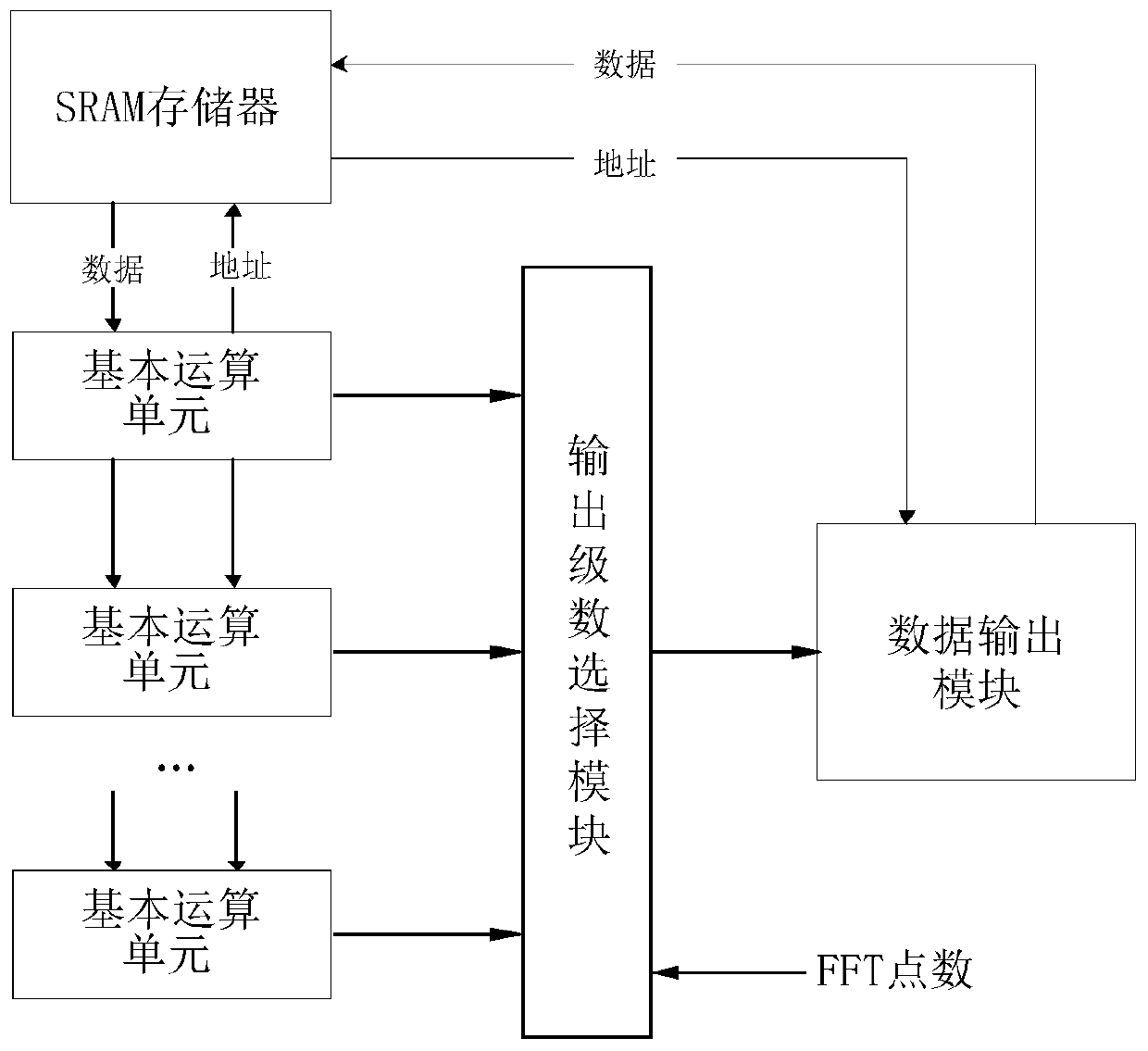

A reconfigurable FFT processor supporting multi-mode configuration

ActiveCN109977347AImprove resource utilizationImprove operation accuracyDigital data processing detailsEnergy efficient computingResource utilizationFft processor

A reconfigurable FFT processor supporting multi-mode configuration comprises an on-chip SRAM memory which communicates with an off-chip memory through a data external transmission module; a reconfigurable computing array which comprises a plurality of single-precision floating point adders based on the IEEE-754 standard, the subtracters and the floating point multipliers; an FFT controller which is used for controlling the whole flow of the FFT operation; and the data external transmission module which is used for controlling the data transmission between the processor and the off-chip memory.The beneficial effects are that the processor has the high operation precision, obvious acceleration effect and high utilization rate of hardware resources.

Owner:NANJING UNIV

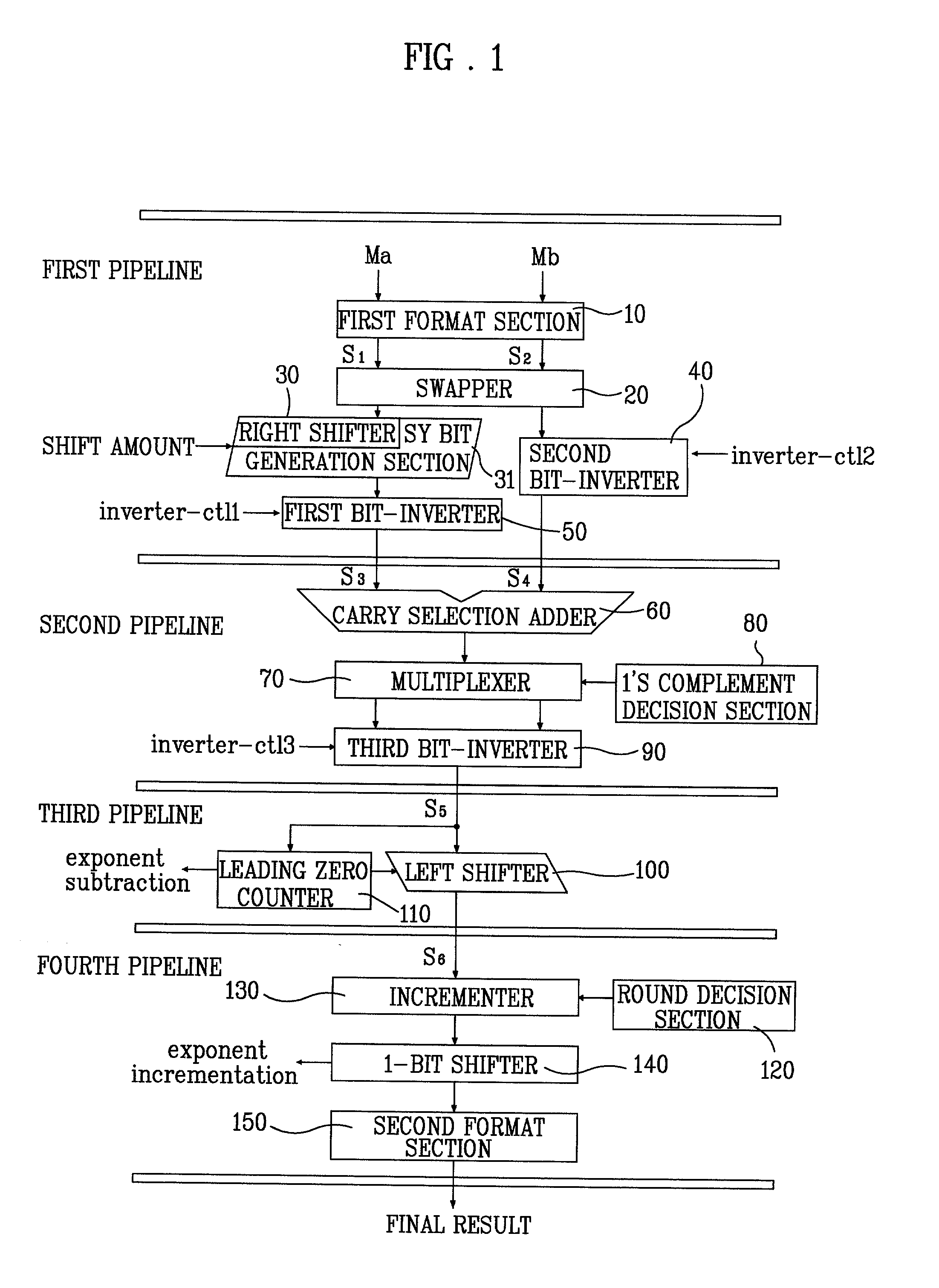

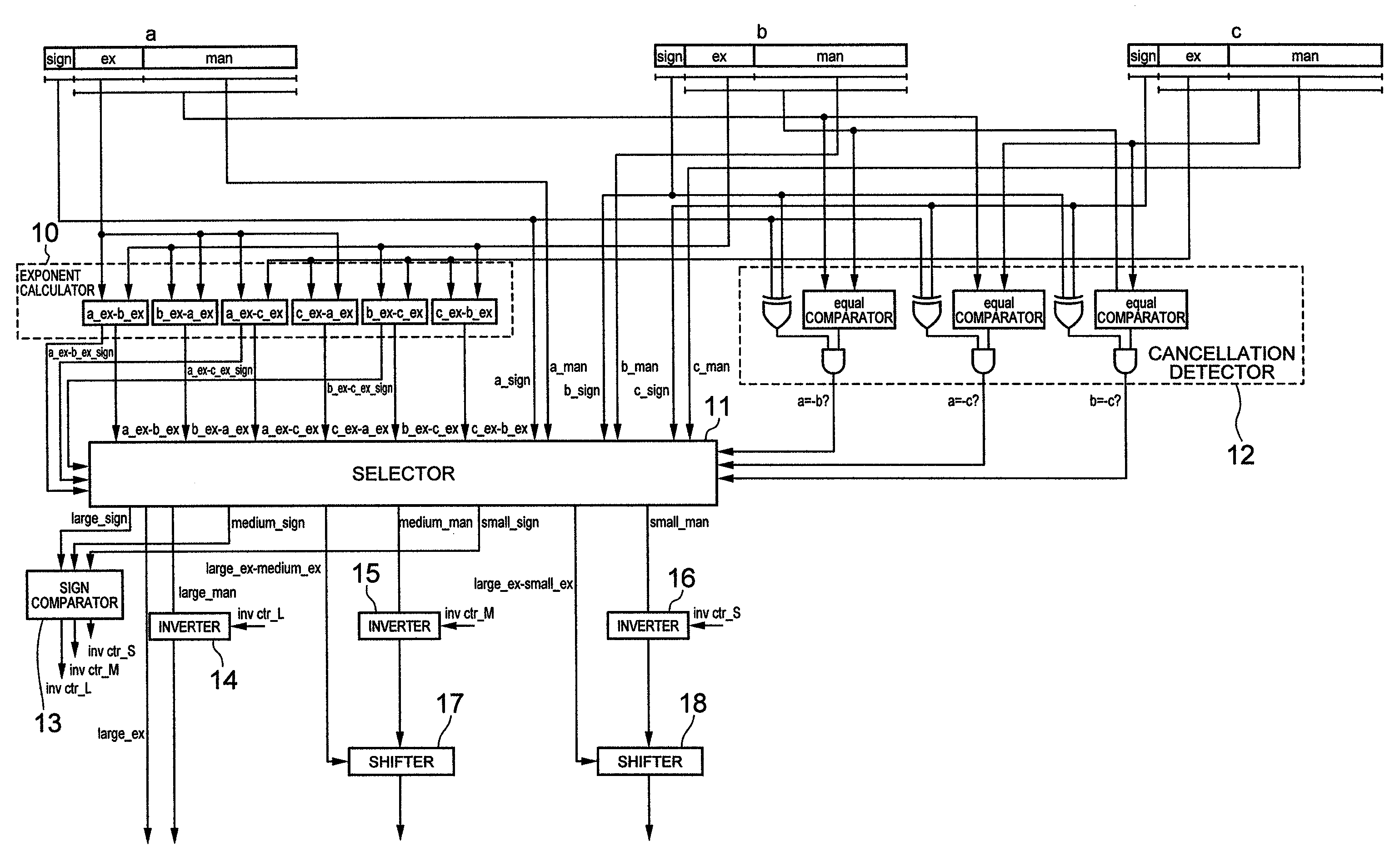

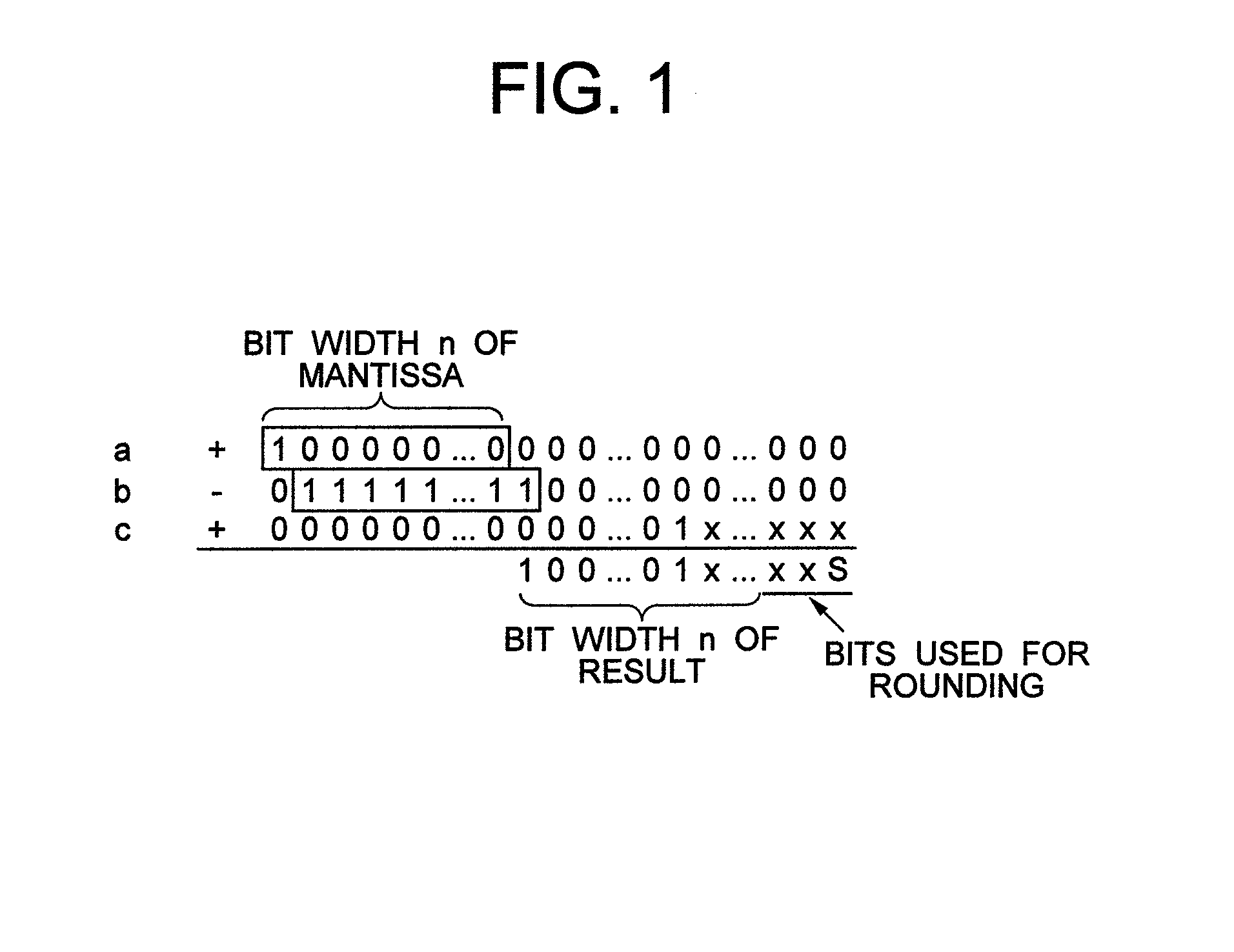

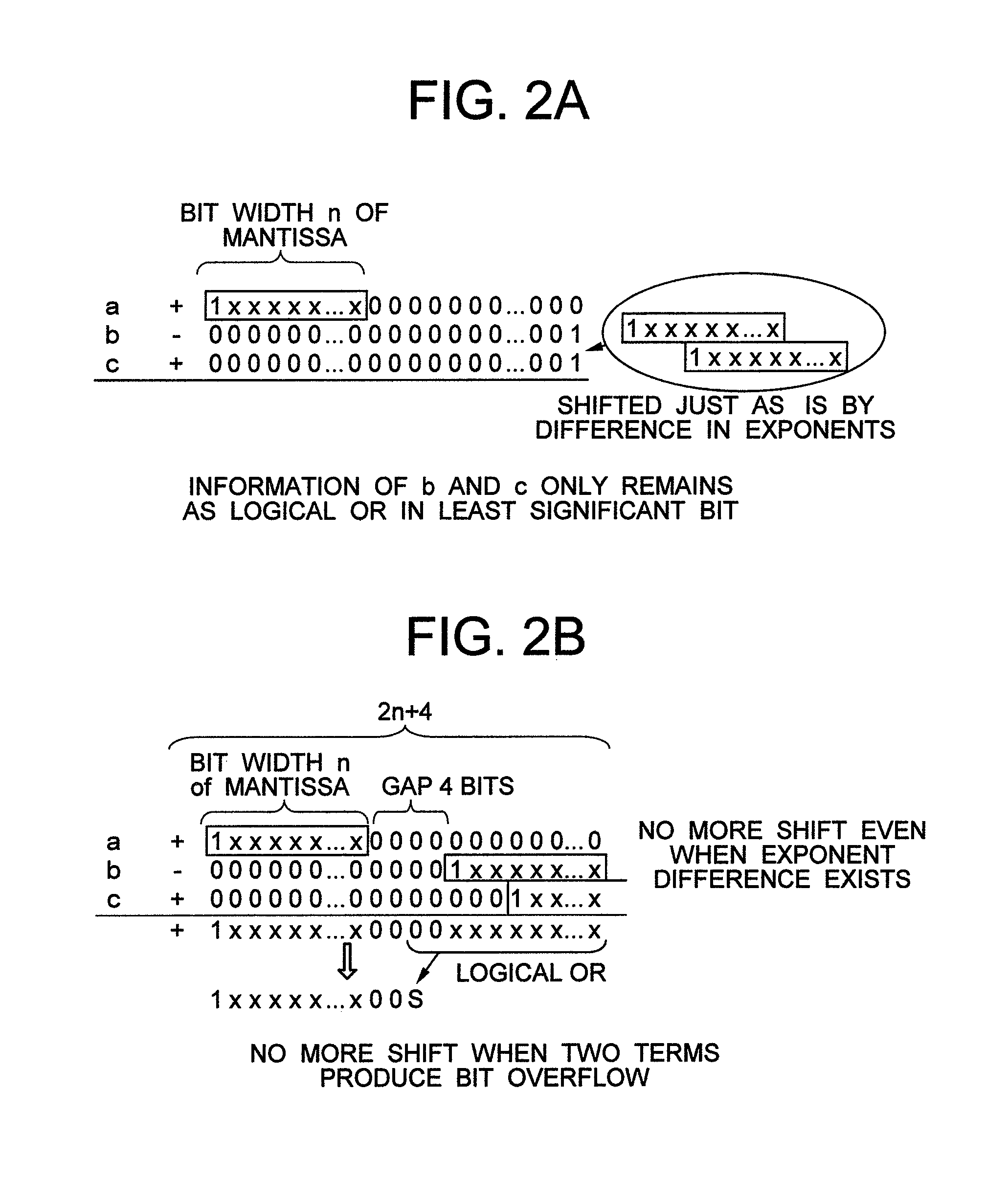

Three-term input floating-point adder-subtractor

InactiveUS8185570B2Computations using contact-making devicesError detection/correctionAdder–subtractorRight shift

The adder-subtractor includes a pre-processing circuit which divides three inputted terms into a mantissa having an exponent of maximum value, mantissa having an exponent of intermediate value and mantissa having an exponent of minimum magnitude and outputting a mantissa obtained by right-shifting the mantissa having the exponent of intermediate value and the mantissa having the minimum exponent of 2n+3 bits and adjusting digits and the mantissa having the maximum exponent, which reduces the mantissas from three to two terms, which carries out addition on the mantissas of the two terms, a normalization circuit which makes left shift so that the most significant bit becomes 1, a rounding circuit which uses an (n+3)th bit from the most significant bit as a new sticky bit, takes logical OR with the lower bits and performs rounding and an exponent operation unit which outputs a final exponent.

Owner:HITACHI LTD

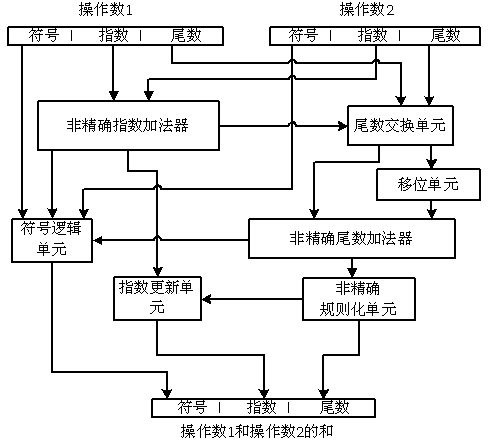

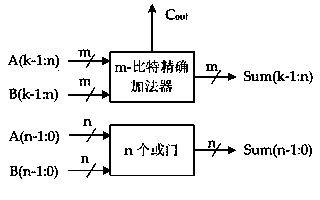

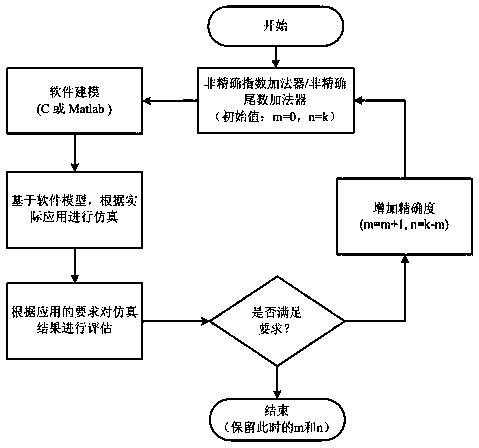

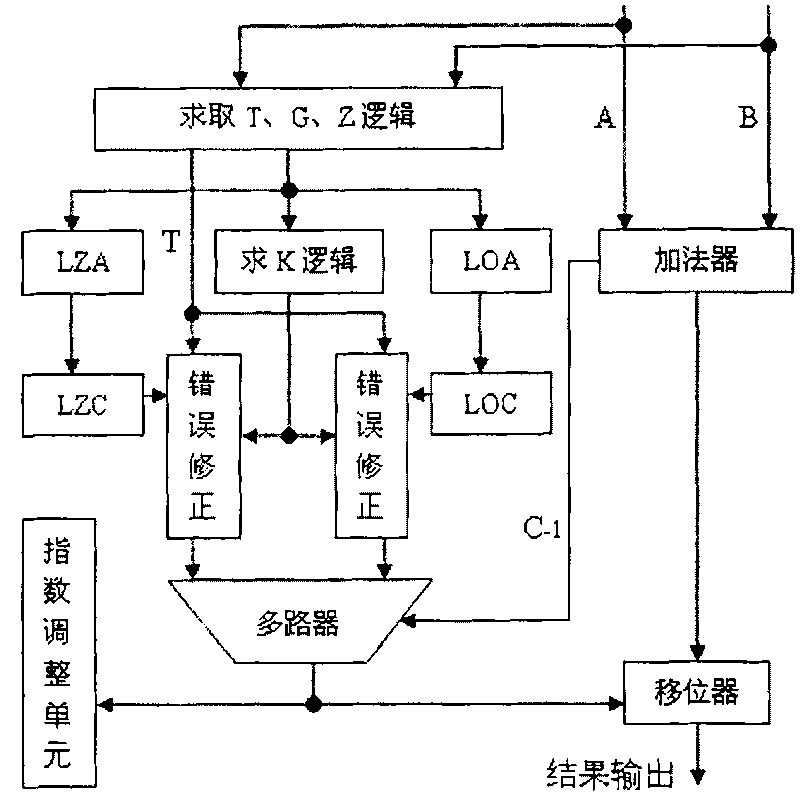

High-performance imprecise floating point adder and application method thereof

InactiveCN104238992ASave hardware resourcesReduce power consumptionDigital data processing detailsParallel computingFloating point

The invention discloses a high-performance imprecise floating point adder and an application method thereof. The imprecise floating point adder consists of an imprecise index adder, a mantissa exchanging unit, a shifting unit, an imprecise mantissa adder, a symbolic logic unit, an index updating unit and an imprecise regularization unit, wherein high m bits of the imprecise index adder and the imprecise mantissa adder are provided with precise pointing adders, and lower n bits of the imprecise index adder and the imprecise mantissa adder are provided with imprecise pointing adders. When the high-performance imprecise floating point adder is applied, the bit numbers of the precise pointing adders in the imprecise index adder and the mantissa adder and the bit numbers of the imprecise pointing adders need to be determined by virtue of a software simulation method. The high-performance imprecise floating point adder is capable of adapting to floating point numbers with various precision, which conform to the IEEE754 protocol, is a novel, high-speed and small-area floating point adder with lower energy consumption and has extensive application prospect in the field of digital signal processors.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

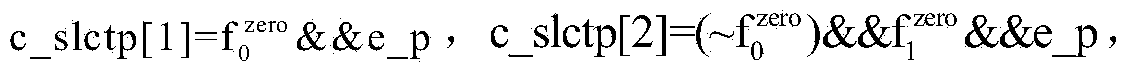

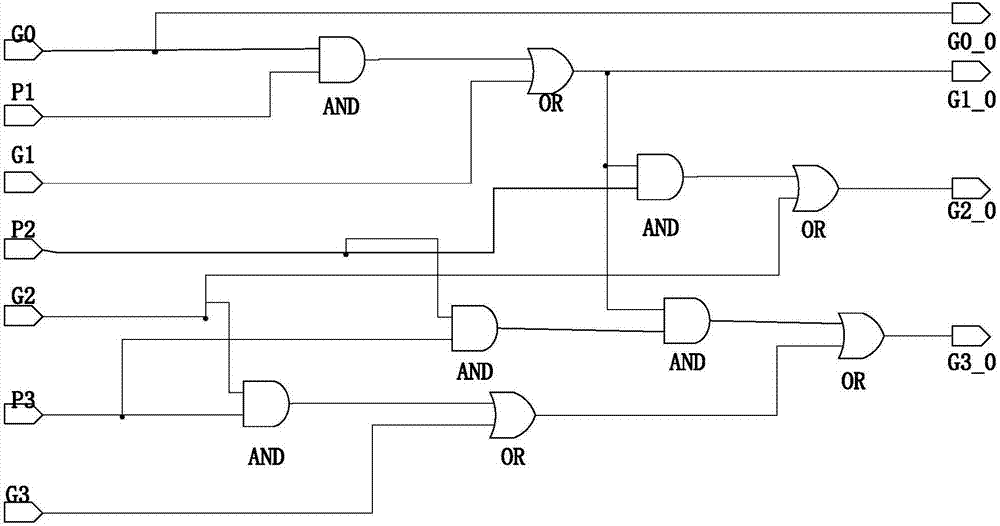

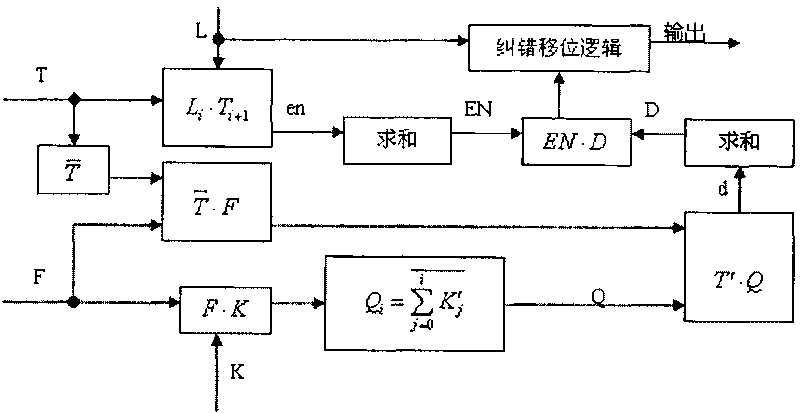

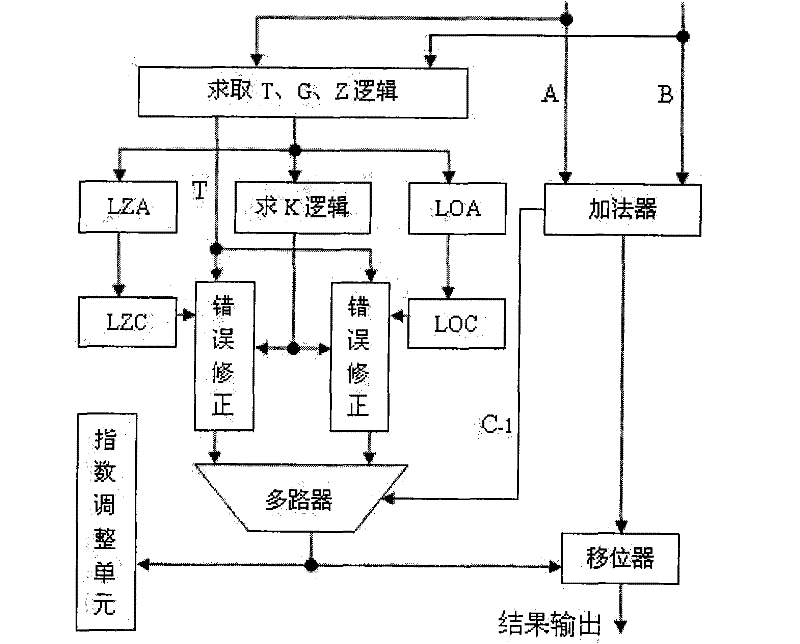

Self-correction precursor 0/1 predicting unit for floating-point adder

InactiveCN101699390ADoes not affect the lengthDigital data processing detailsPath lengthFloating point

The invention relates to a self-correction precursor 0 / 1 predicting method for a floating-point adder, which adopts the combination method of a multiple-input logical gate and parallel computation to realize an output result as a final correct result, and the output result has no need to be corrected by depending on an adder; the parallel computation is adopted, for example, the operand bit wide is increased, and the critical path length can not be influenced. When the floating-point add is computed, the displacement time and index regulating information needed by the normalization of a computation result is synchronously predicted, a predicting result is not output by the adder but is generated by the predicting unit and is a corrected value which has no need to be further corrected, and the critical path of the predicting unit can not be lengthened along with lengthening the bit wide of an operand.

Owner:XI AN JIAOTONG UNIV

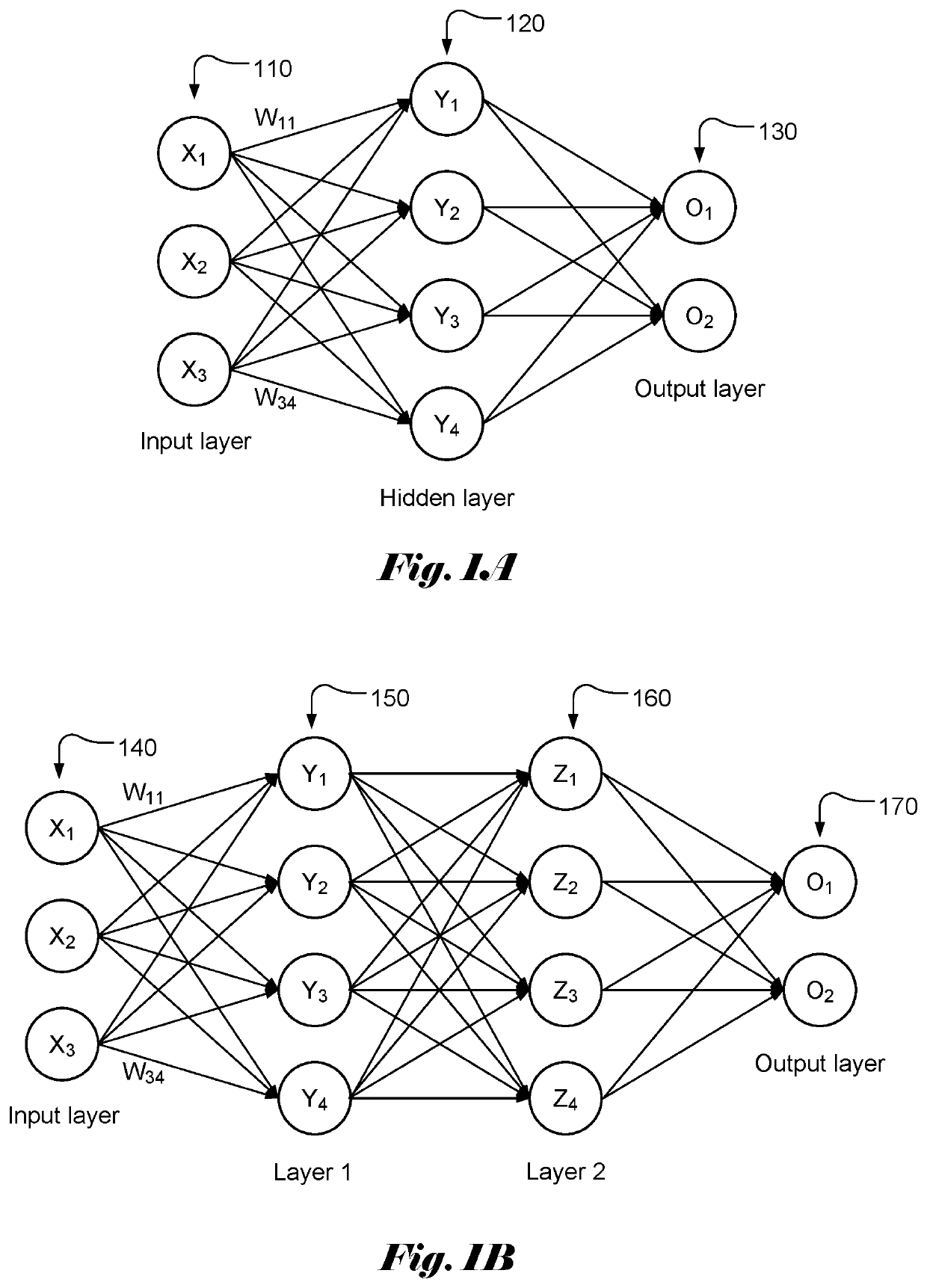

Apparatus and Method of Fast Floating-Point Adder Tree for Neural Networks

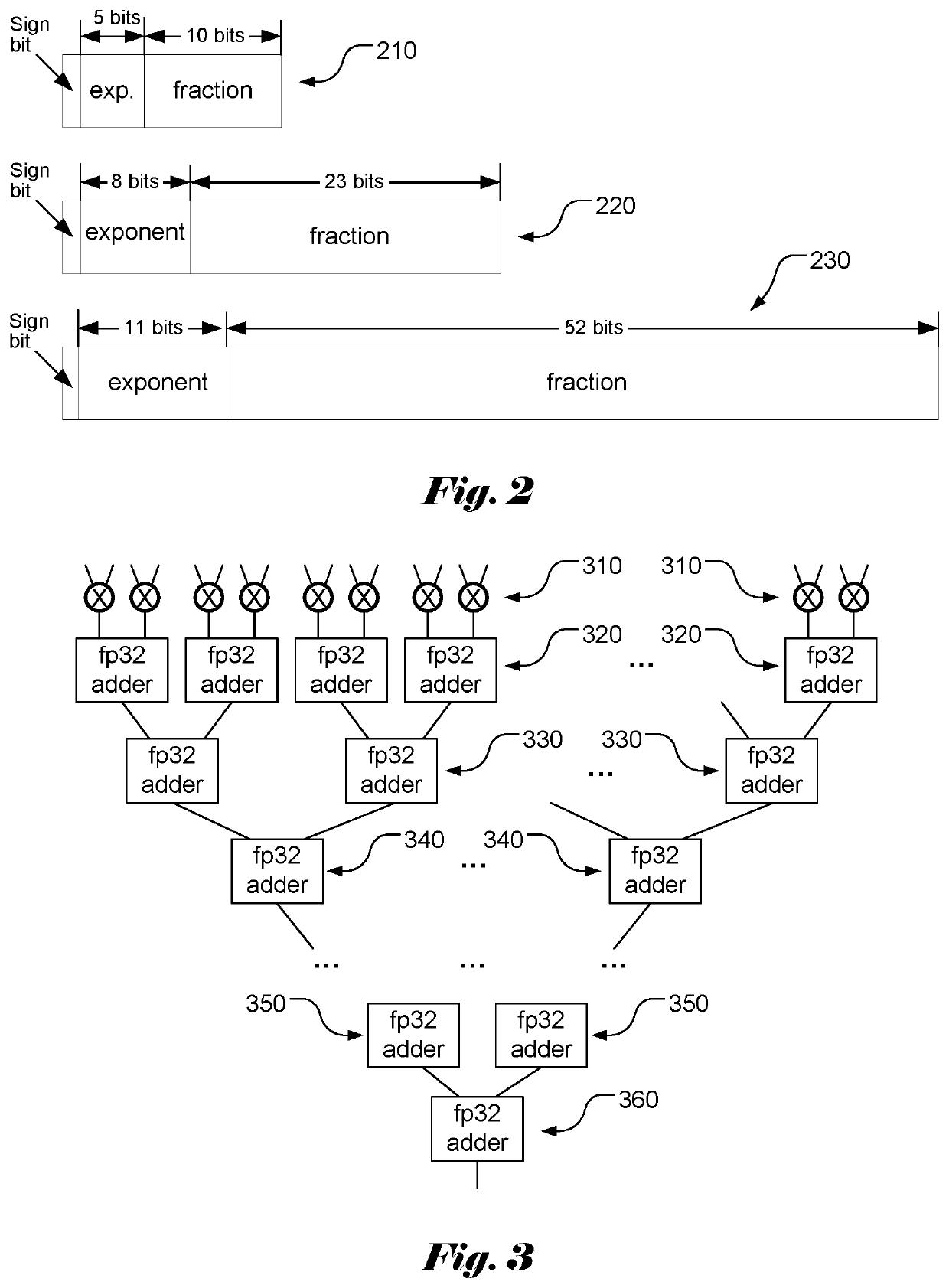

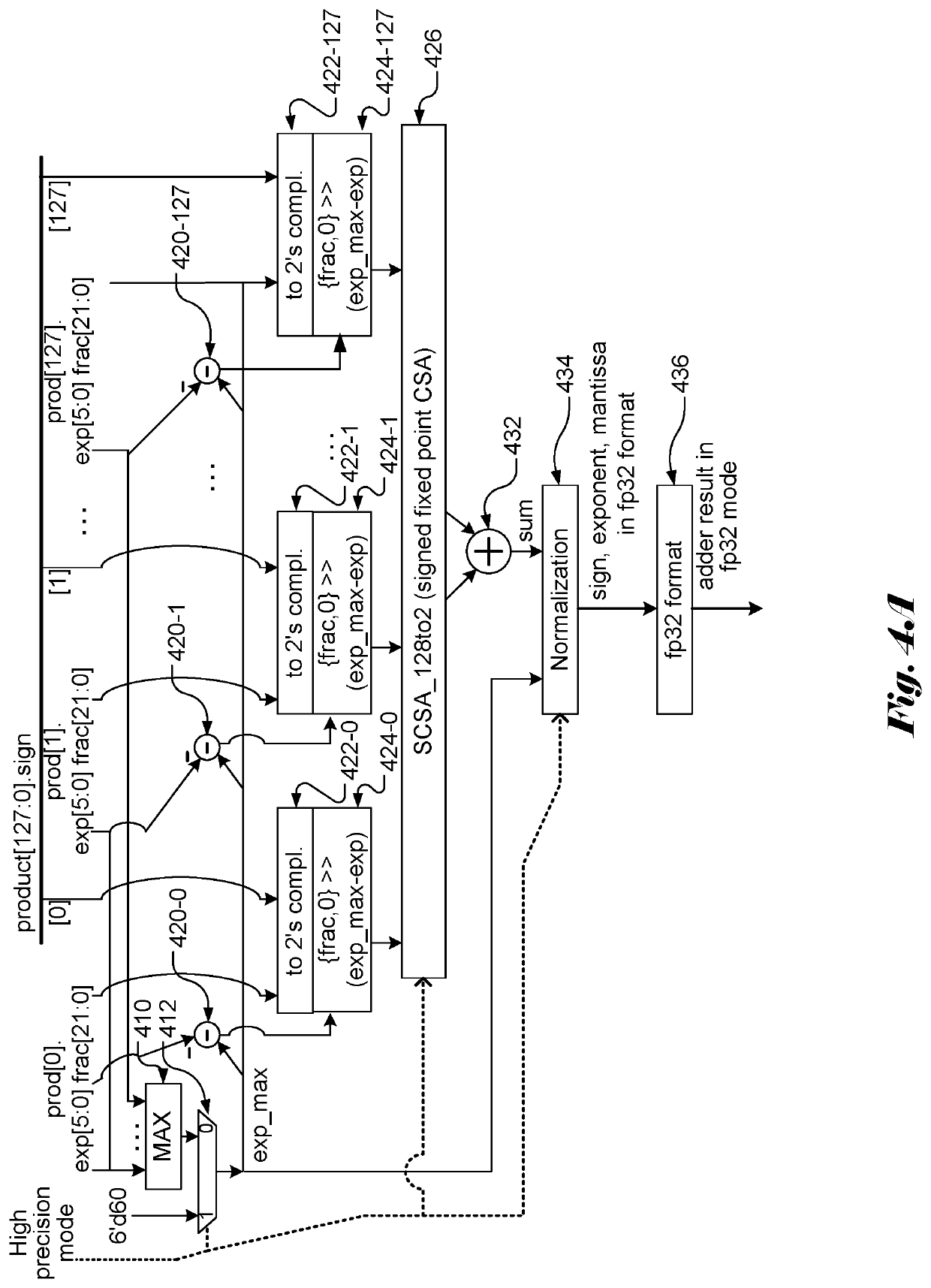

ActiveUS20200272417A1Computation using non-contact making devicesPhysical realisationData packSign bit

A computing device to implement fast floating-point adder tree for the neural network applications is disclosed. The fast float-point adder tree comprises a data preparation module, a fast fixed-point Carry-Save Adder (CSA) tree, and a normalization module. The floating-point input data comprises a sign bit, exponent part and fraction part. The data preparation module aligns the fraction part of the input data and prepares the input data for subsequent processing. The fast adder uses a signed fixed-point CSA tree to quickly add a large number of fixed-point data into 2 output values and then uses a normal adder to add the 2 output values into one output value. The fast adder uses for a large number of operands is based on multiple levels of fast adders for a small number of operands. The output from the signed fixed-point Carry-Save Adder tree is converted to a selected floating-point format.

Owner:DINOPLUSAI HLDG LTD

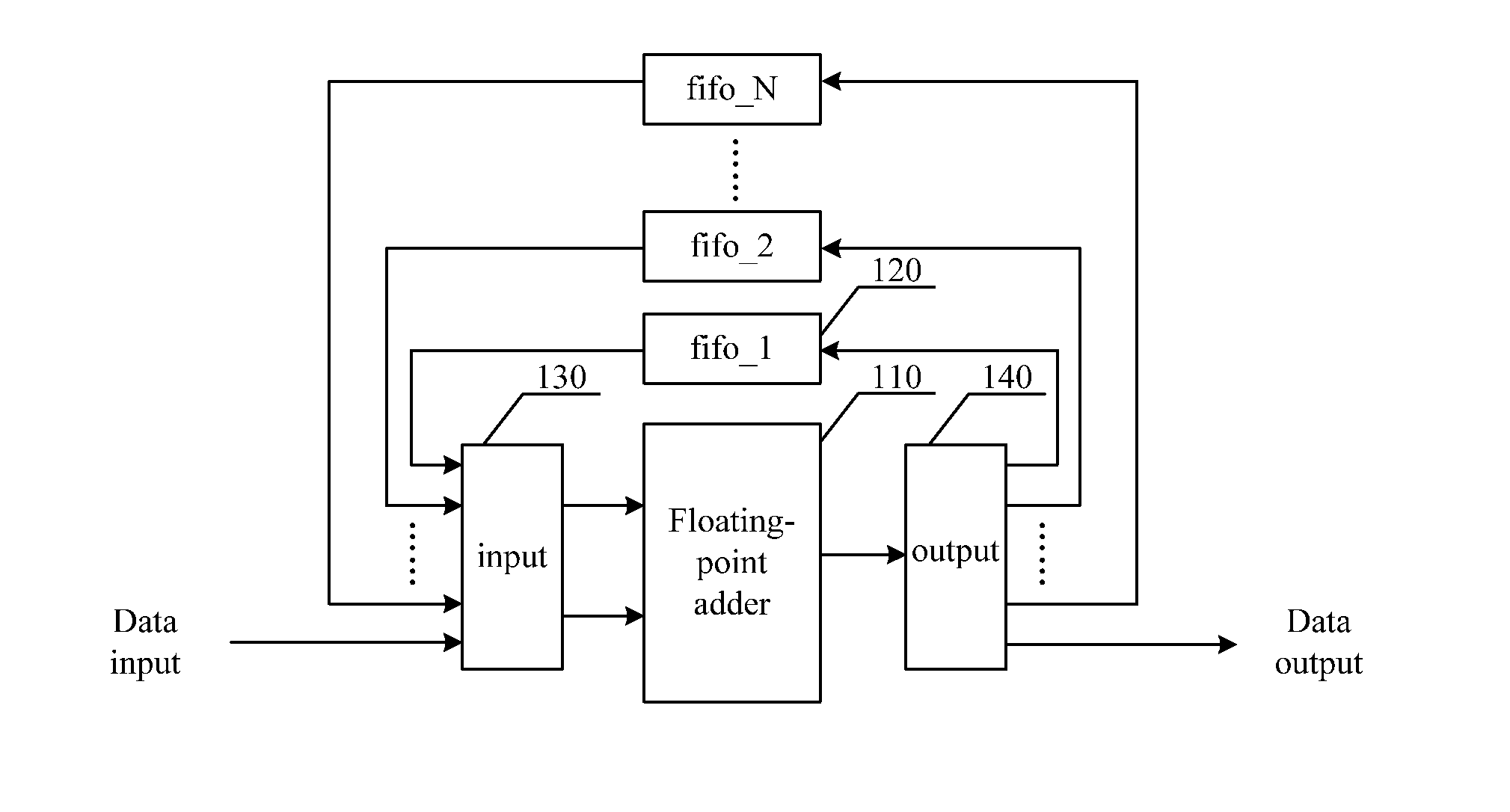

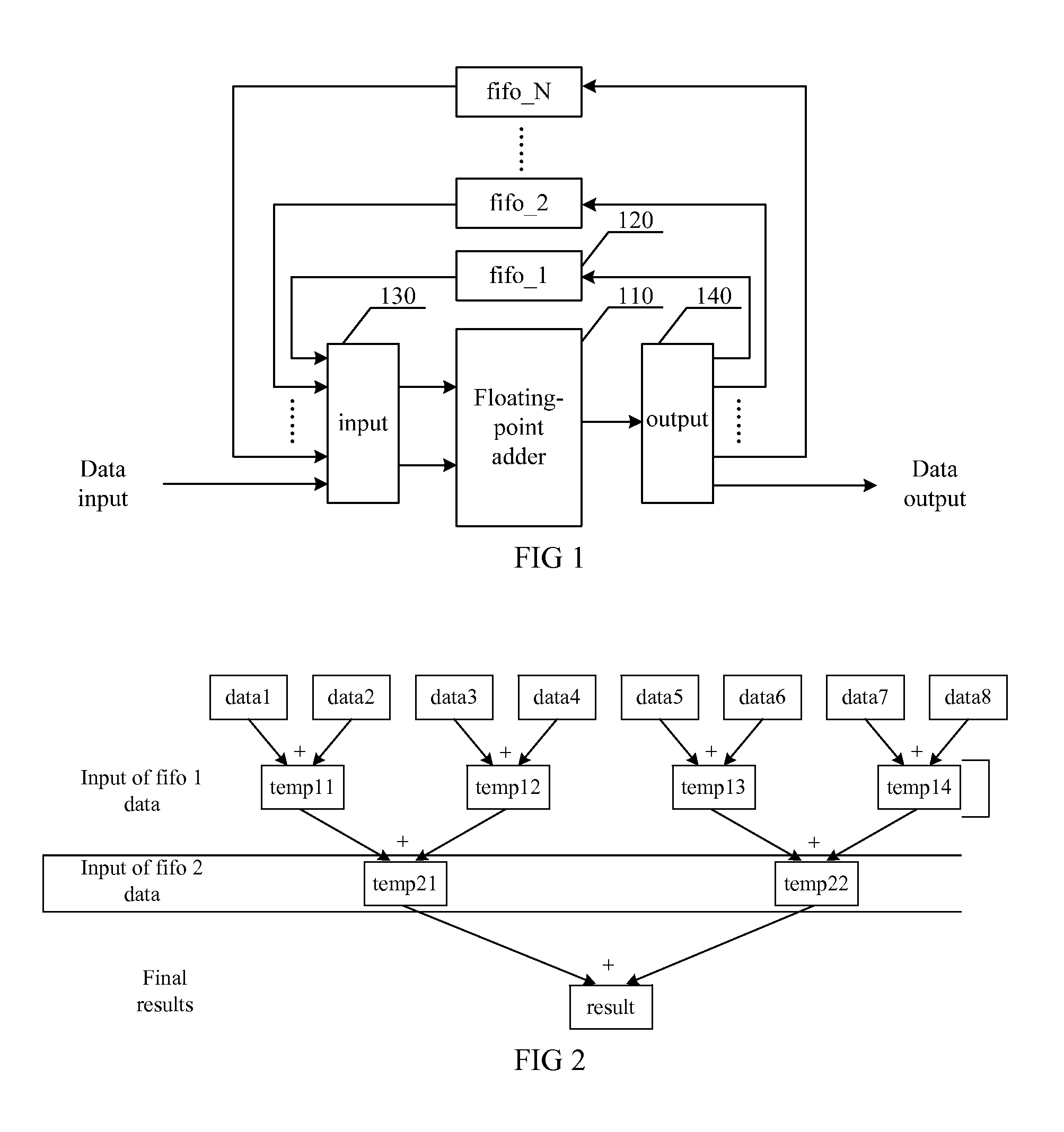

FPGA-based high-speed low-latency floating point accumulator and implementation method therefor

ActiveUS20130297666A1Reduce consumptionImprove utilization efficiencyComputations using contact-making devicesLatency (engineering)Input control

This invention discloses a FPGA based high-speed low-latency floating-point accumulation and its implementation method. Floating accumulation of this invention comprises a floating-point adder unit, numerous intermediate result buffers, an input control unit and an output control unit. The floating-point accumulation implementation method of this invention is used for gradation of the whole accumulation calculation process to ensure cross execution of accumulation calculation processes and graded storage of intermediate results of accumulation calculation at different levels; meanwhile, the operation in the mode of pure flow line can significantly improve utilization rate of internal floating-point adder, and maintain relatively low latency to output of final results of floating-point accumulation calculation. This invention is expected to improve utilization rate of floating-point adder through dynamic allocation of input data in internal floating-point adder unit, and thereby maintains higher arithmetic speed and relatively low latency while ensuring minimized consumption of logic or DSP resources as required.

Owner:ZHEJIANG UNIV

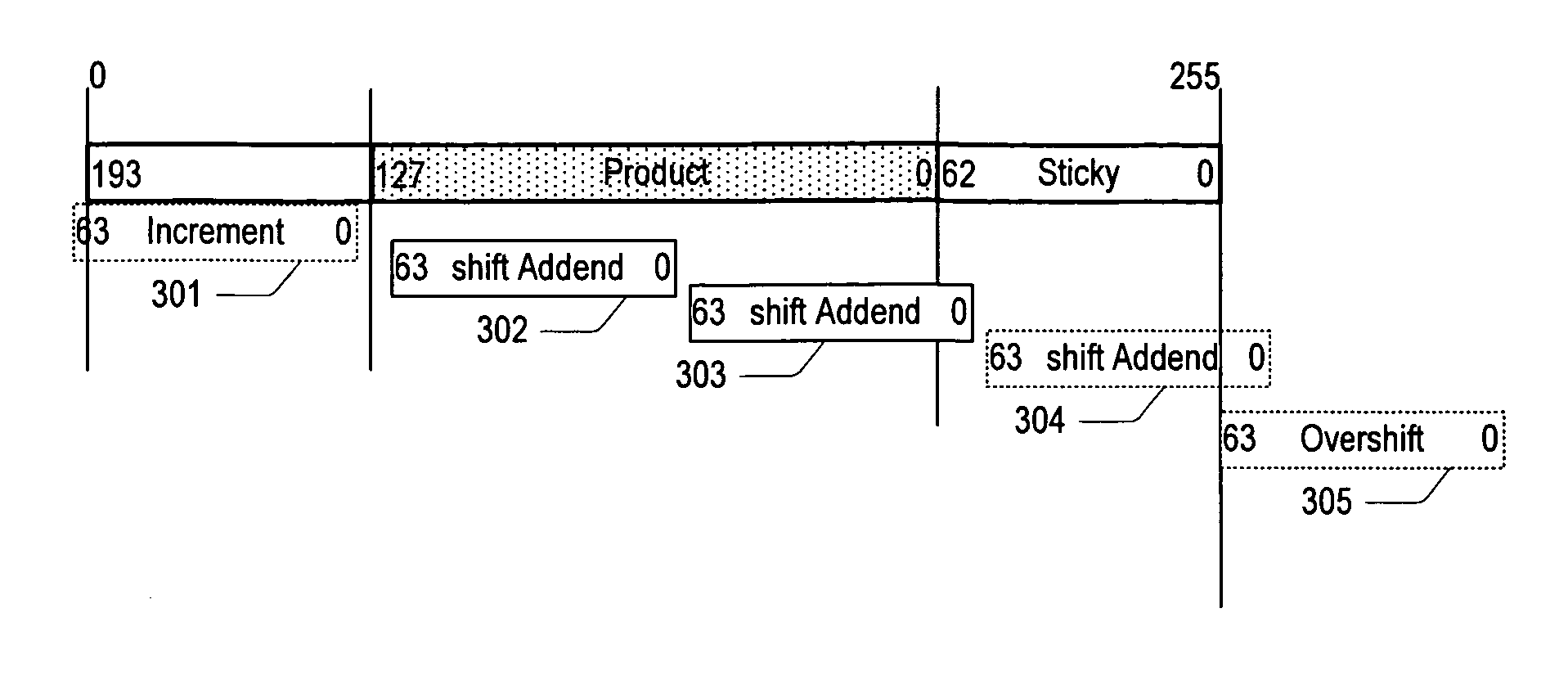

Mechanism for fast detection of overshift in a floating point unit of a processing device

ActiveUS20100235416A1Computations using contact-making devicesDigital computer detailsLeast significant bitFloating-point unit

A floating point unit includes a floating point adder to perform a floating point addition operation between first and second floating point numbers each having an exponent and a mantissa. The floating point unit also includes an alignment shifter that may calculate a shift value corresponding to a number of bit positions to shift the second mantissa such that the second exponent value is the same as the first exponent value. The alignment shifter may detect an overshift condition, in which the shift value is greater than or equal to a selected overshift threshold value. The selected overshift threshold value comprises a base 2 number in a range of overshift values including a minimum overshift threshold value and a maximum overshift threshold value, and which has a largest number of a consecutive of bits that are zero beginning at a least significant bit.

Owner:ADVANCED MICRO DEVICES INC

Mode-based multiply-add processor for denormal operands

InactiveCN101438233AComputation using denominational number representationDenormalizationFloating point multiplier

Owner:QUALCOMM INC

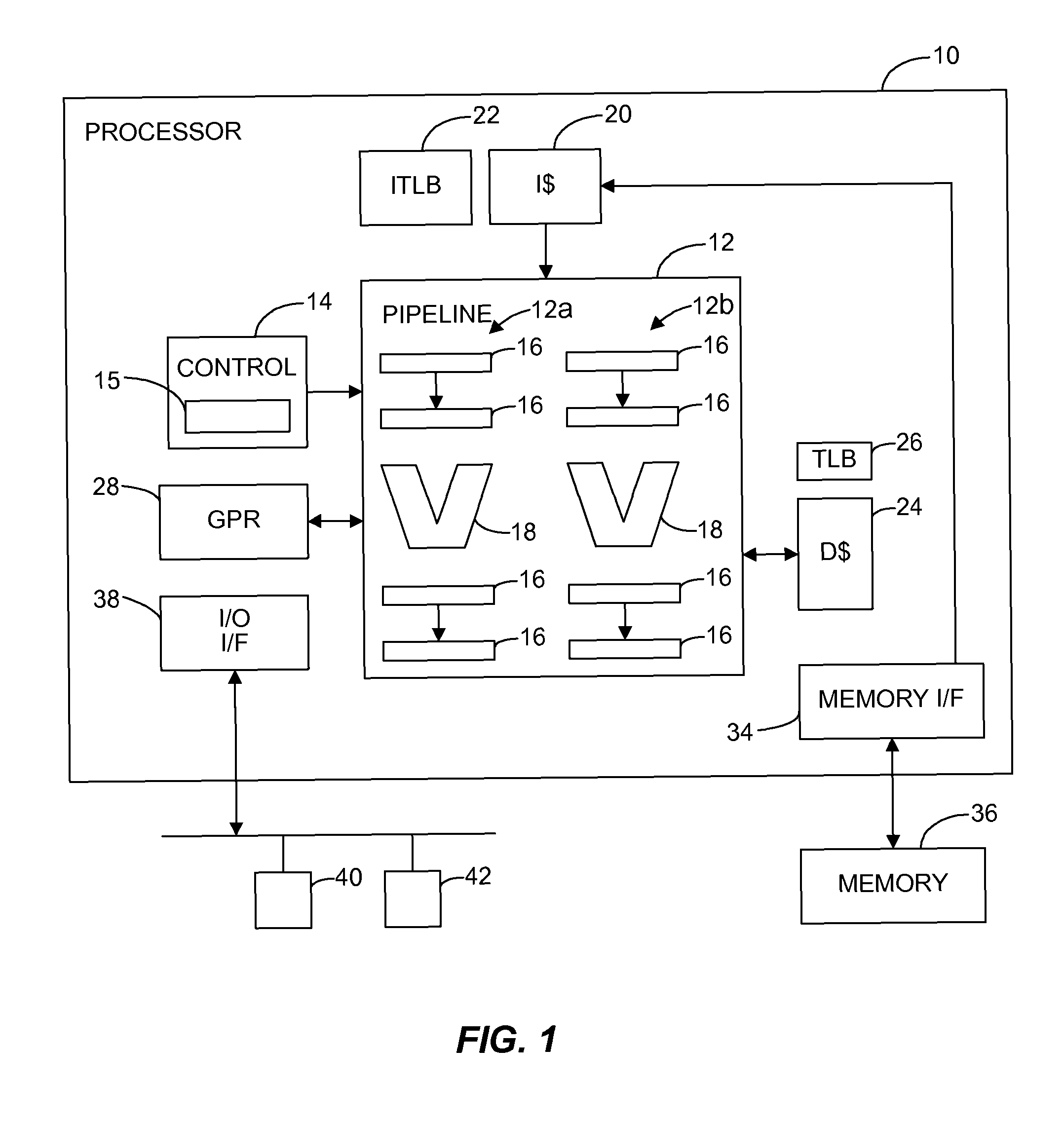

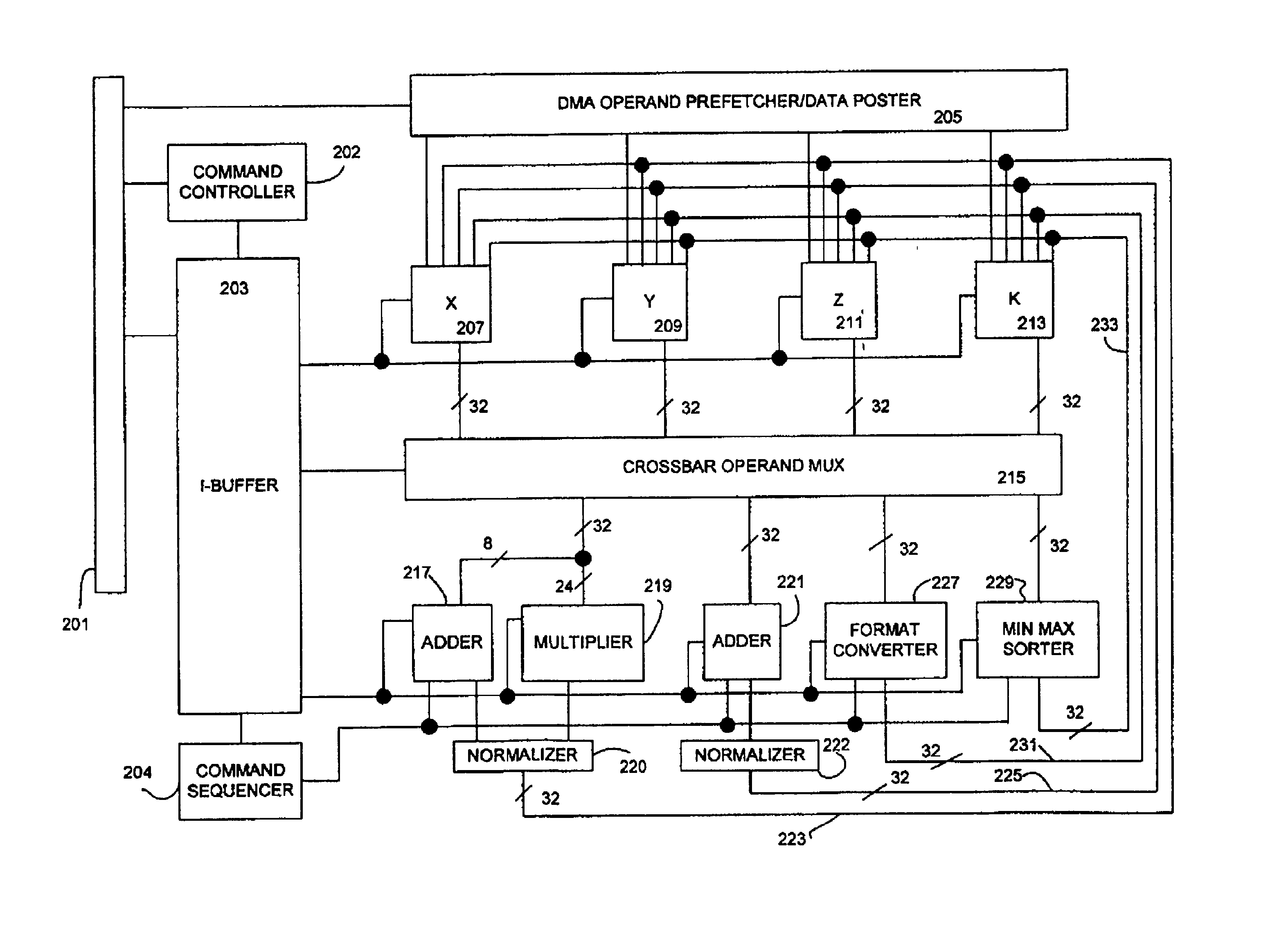

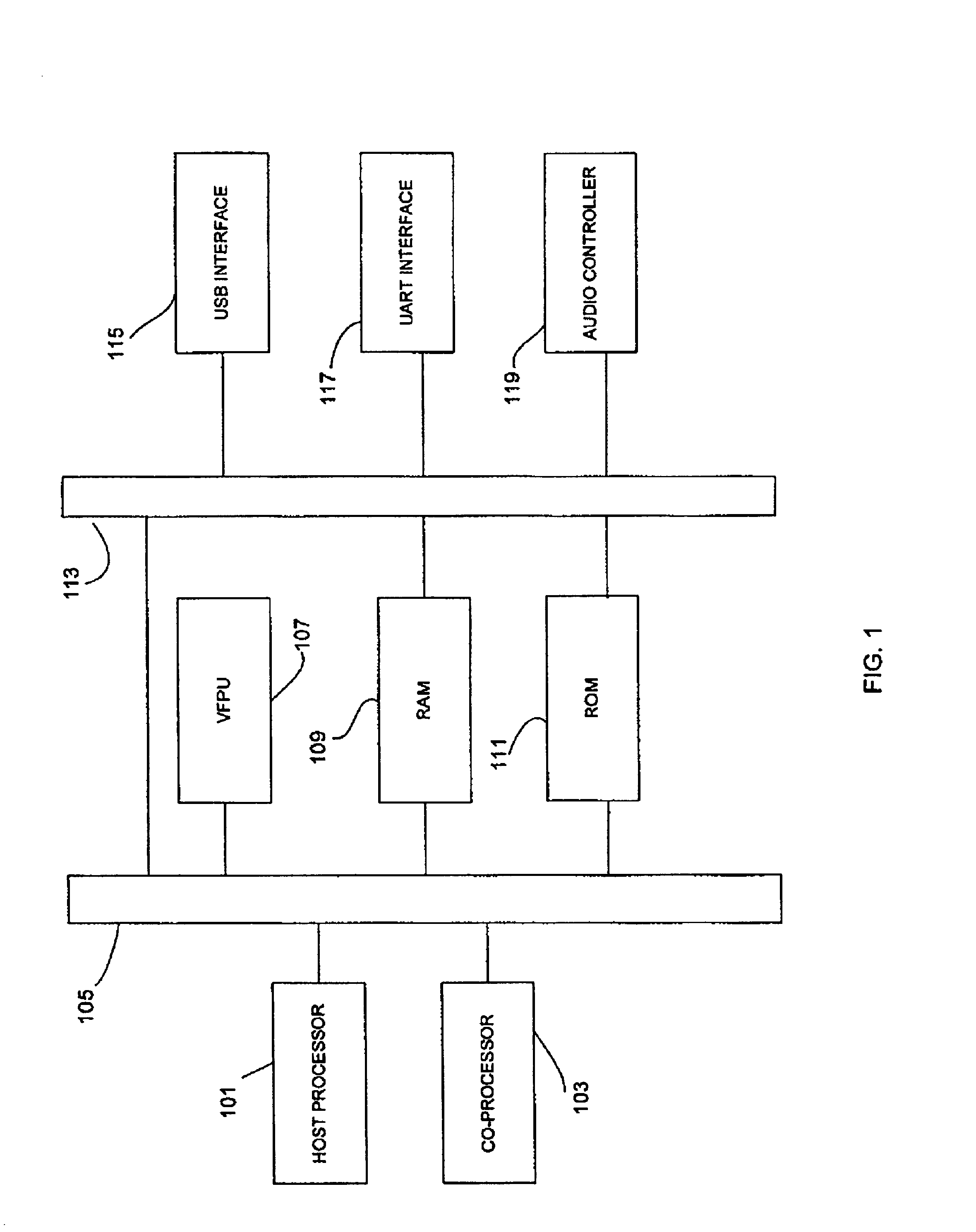

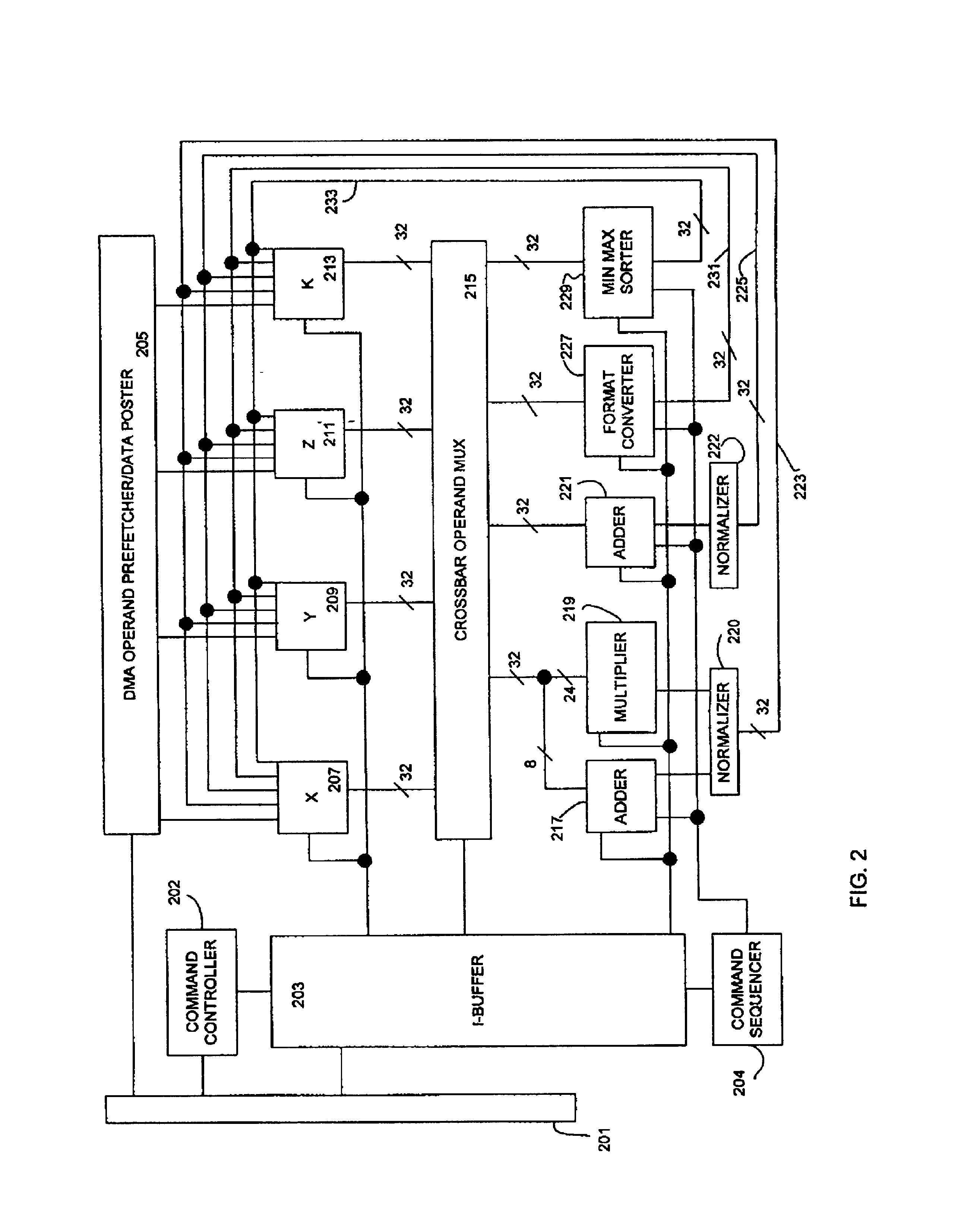

Vector floating point unit

InactiveUS6922771B2Quick configurationFine-tune performanceInstruction analysisGeneral purpose stored program computerProcessor registerFloating-point unit

The present invention provides a vector floating point unit (FPU) comprising a product-terms bus, a summation bus, a plurality of FIFO (first in first out) registers, a crossbar operand multiplexor coupled, a floating point multiplier, and a floating point adder. The floating point multiplier and the floating point adder are disposed between the crossbar operand multiplexor and the product-terms and summation buses, and are in parallel to each other. The invention also provides the configuration register and the command register in order to provide flexible architecture and the capability to fine-tune the performance to a particular application. The invention performs the multiplication operation and the addition operation in a pipelined fashion. Once the pipeline is filled, the invention outputs one multiplication output and one addition output at each clock cycle. The invention reduces the latency of the pipelined operation and improves the overall system performance by separating the floating point multiplier from the floating point adder so that the multiplication operation can be executed separately and independently of the addition operation.

Owner:NVIDIA CORP

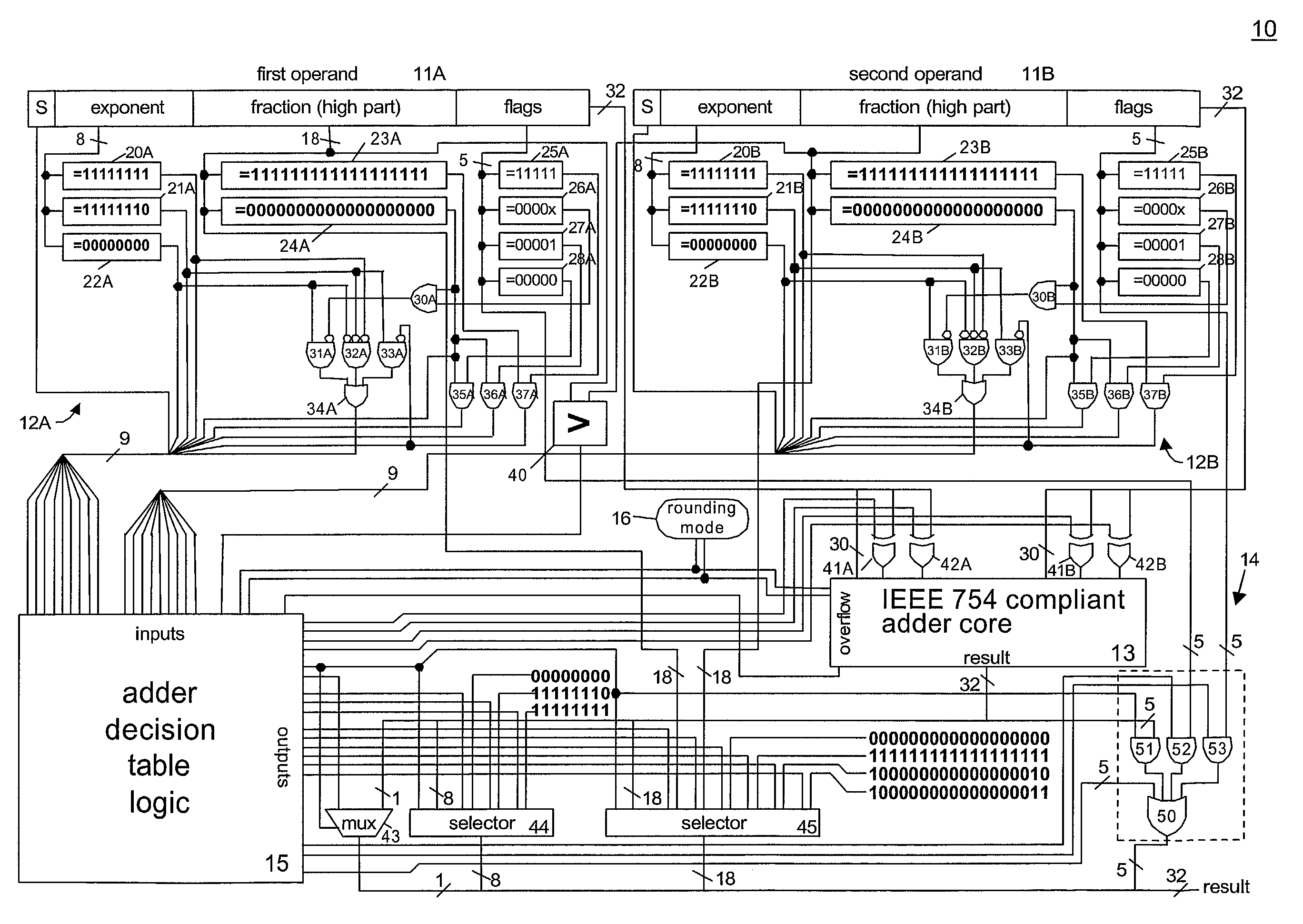

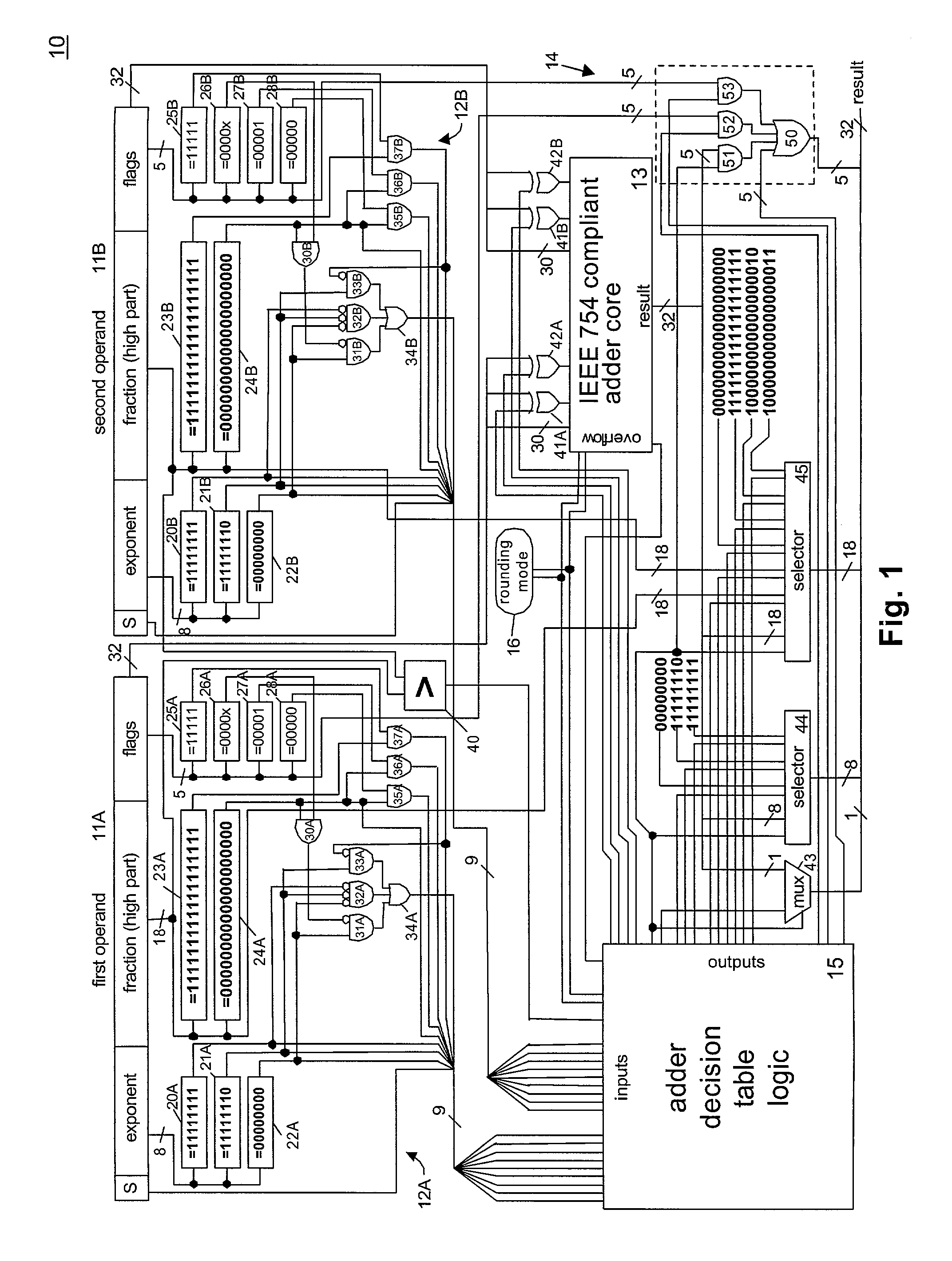

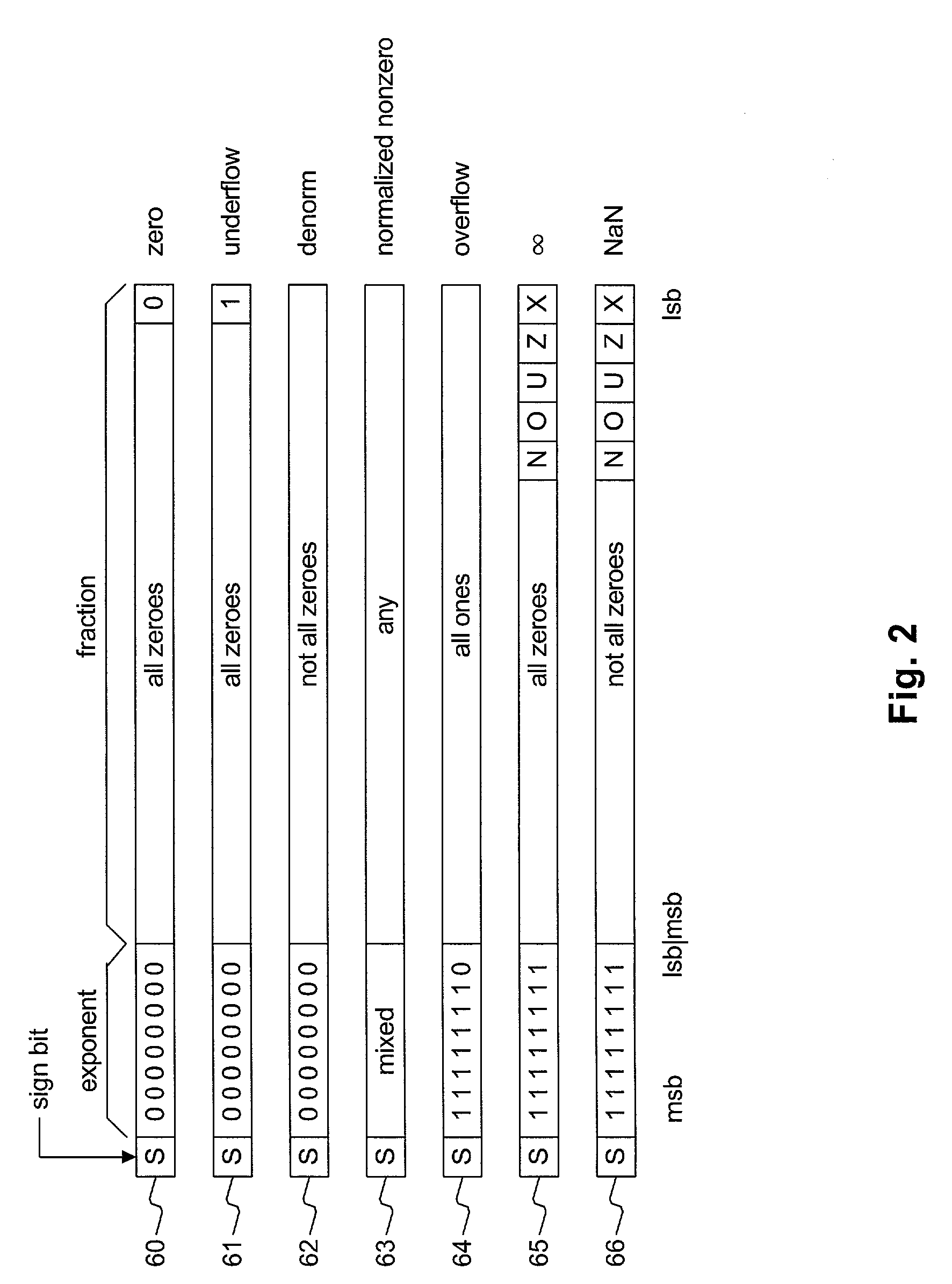

Floating point adder with embedded status information

ActiveUS7366749B2Avoid problemsConditional code generationComputations using contact-making devicesOperandFloating point

A system for providing a floating point sum includes an analyzer circuit configured to determine a first status of a first floating point operand and a second status of a second floating point operand based upon data within the first floating point operand and data with the second floating point operand respectively. In addition, the system includes a results circuit coupled to the analyzer circuit. The results circuit is configured to assert a resulting floating point operand containing the sum of the first floating point operand and the second floating point operand and a resulting status embedded within the resulting floating point operand.

Owner:ORACLE INT CORP

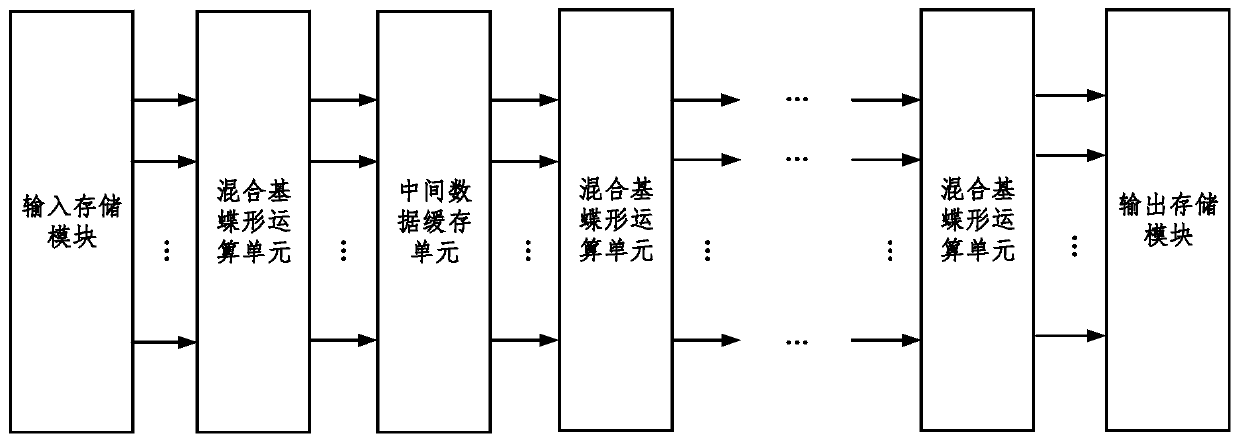

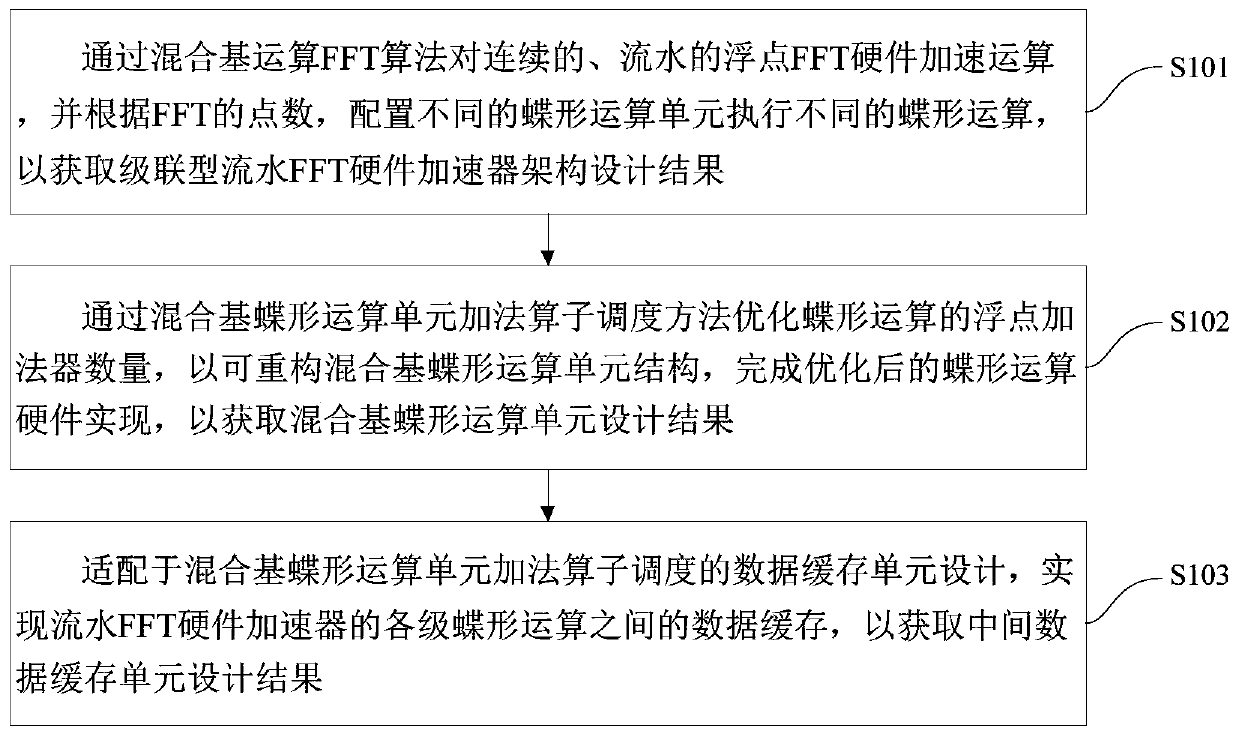

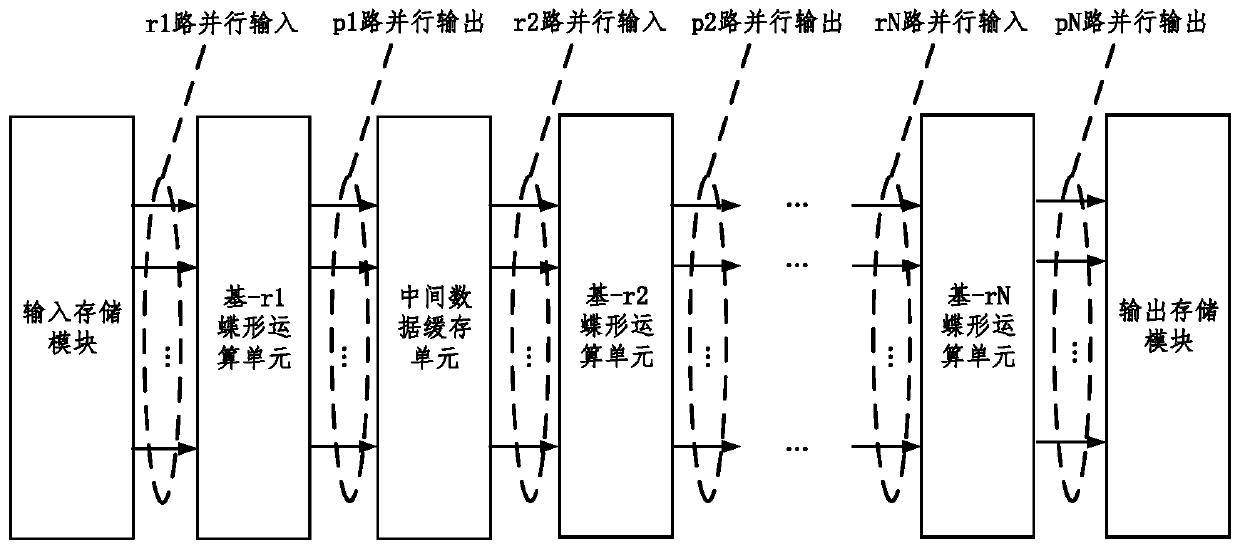

A high-efficiency floating-point FFT hardware accelerator design method based on mixed base operation

InactiveCN109815438AHigh precisionGuaranteed floating-point arithmetic precisionComplex mathematical operationsOperator schedulingParallel computing

The invention discloses a high-efficiency floating point FFT hardware accelerator design method based on mixed base operation. The method comprises the following steps of carrying out floating point FFT hardware acceleration operation through a mixed base operation FFT algorithm, configuring different butterfly operation units to execute different butterfly operations according to the point numberof FFT, and obtaining a cascade type pipeline FFT hardware accelerator architecture design result; optimizing the number of floating point adders for butterfly operation through a hybrid-base butterfly operation unit addition operator scheduling method, completing the implementation of optimized butterfly operation hardware, and obtaining a hybrid-base butterfly operation unit design result; andadopting the data caching unit to the design of a data caching unit scheduled by an addition operator of the hybrid butterfly operation unit, so that data caching among all stages of butterfly operations of the pipeline FFT hardware accelerator is realized, and a design result of an intermediate data caching unit is obtained. The method has the advantages of being high in calculation precision anddynamic range, fast in processing speed, lower in hardware cost and power consumption, flexible in configuration and the like.

Owner:TSINGHUA UNIV

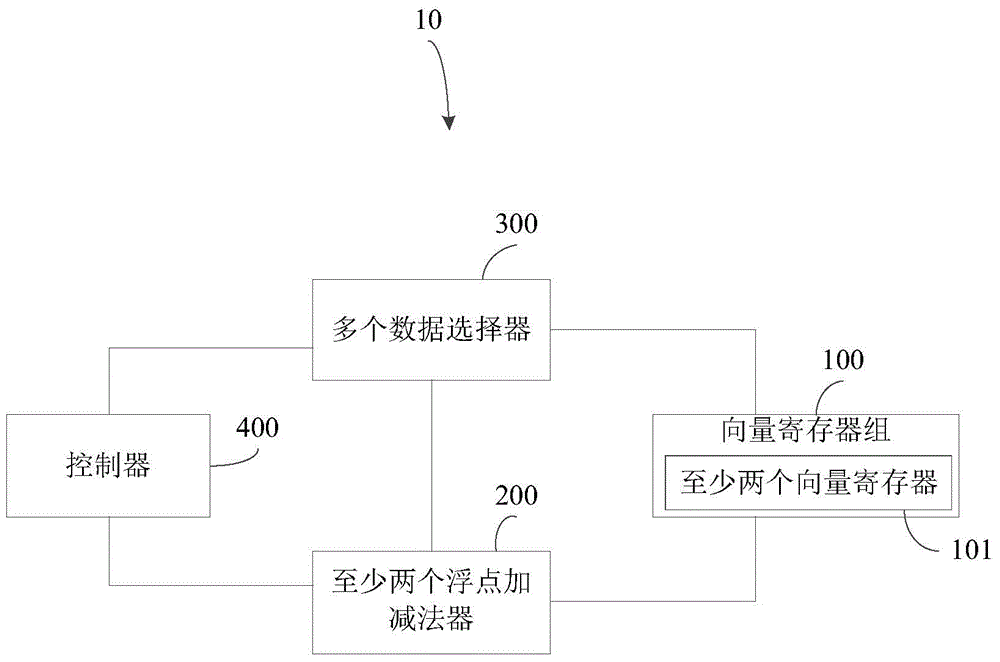

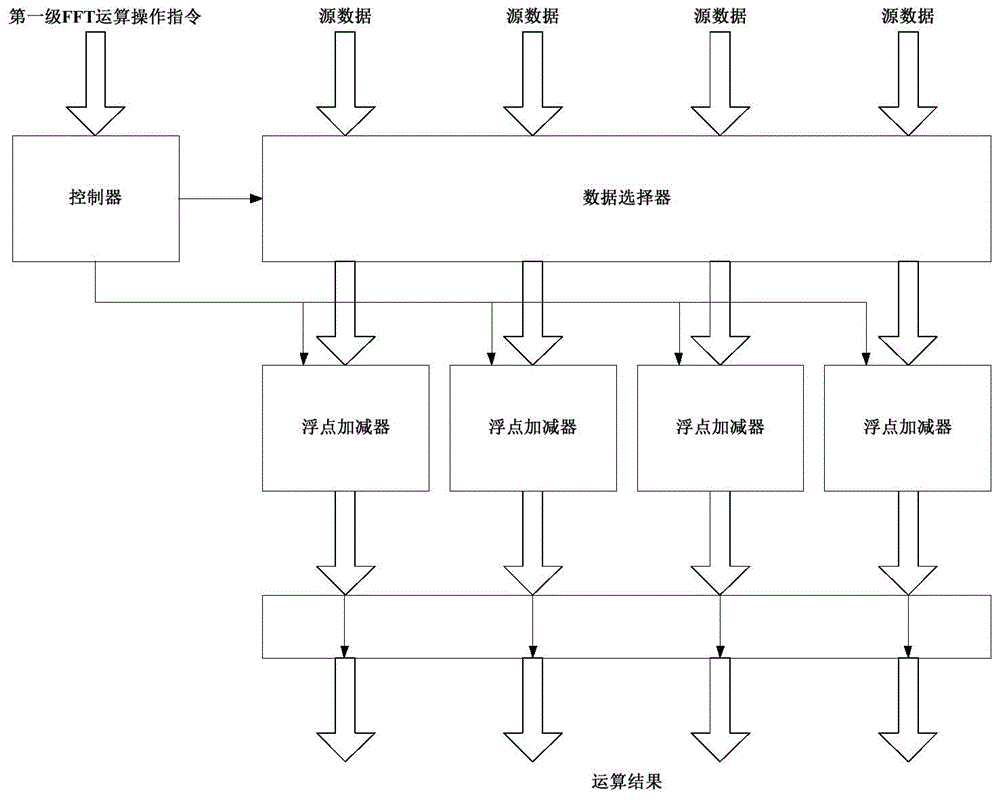

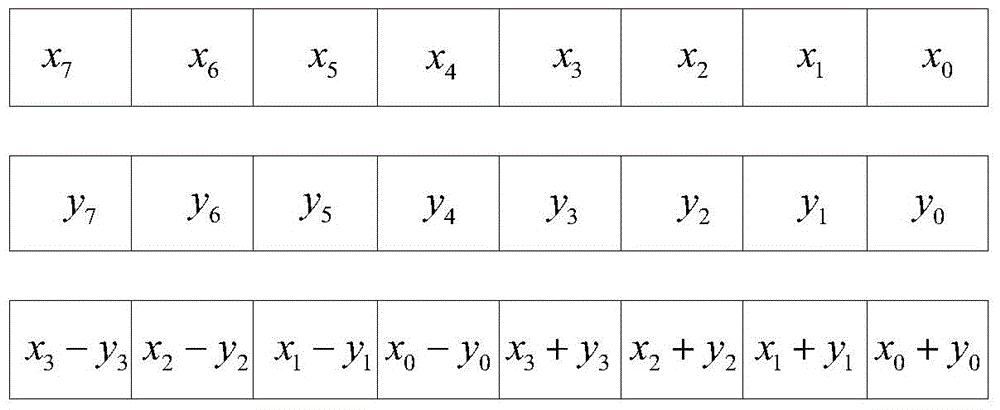

Floating point complex number vector first-level FFT computing method and system

InactiveCN105302772ASave resourcesImprove execution efficiencyComplex mathematical operationsFast Fourier transformTwo-vector

The invention provides a floating point complex number vector first-level FFT (Fast Fourier Transform) computing system. The floating point complex number vector first-level FFT computing system comprises a vector register group, at least two floating point adder-subtractors, multiple data selectors and a controller. The vector register group comprises at least two vector registers; each vector register is used for storing multiple floating point complex numbers; each floating point adder-subtractor is used for performing addition and subtraction for the floating point complex numbers; each data selector is used for obtaining the floating point complex numbers from the vector register and delivering the floating point complex numbers to each floating point adder-subtractor; the controller is used for receiving a first-level FFT computation operational instruction, controlling each data selector to obtain two groups of the floating point complex numbers from the vector register group based on the instruction and controlling each floating point adder-subtractor to perform addition and subtraction for the two groups of the floating point complex numbers so as to obtain a floating point complex number vector; and the floating point complex number vectors are combined to generate a final operating result, and the operating result is stored in each vector register. The floating point complex number vector first-level FFT computing system is high in computing efficiency and low in cost.

Owner:北京国睿中数科技股份有限公司 +1

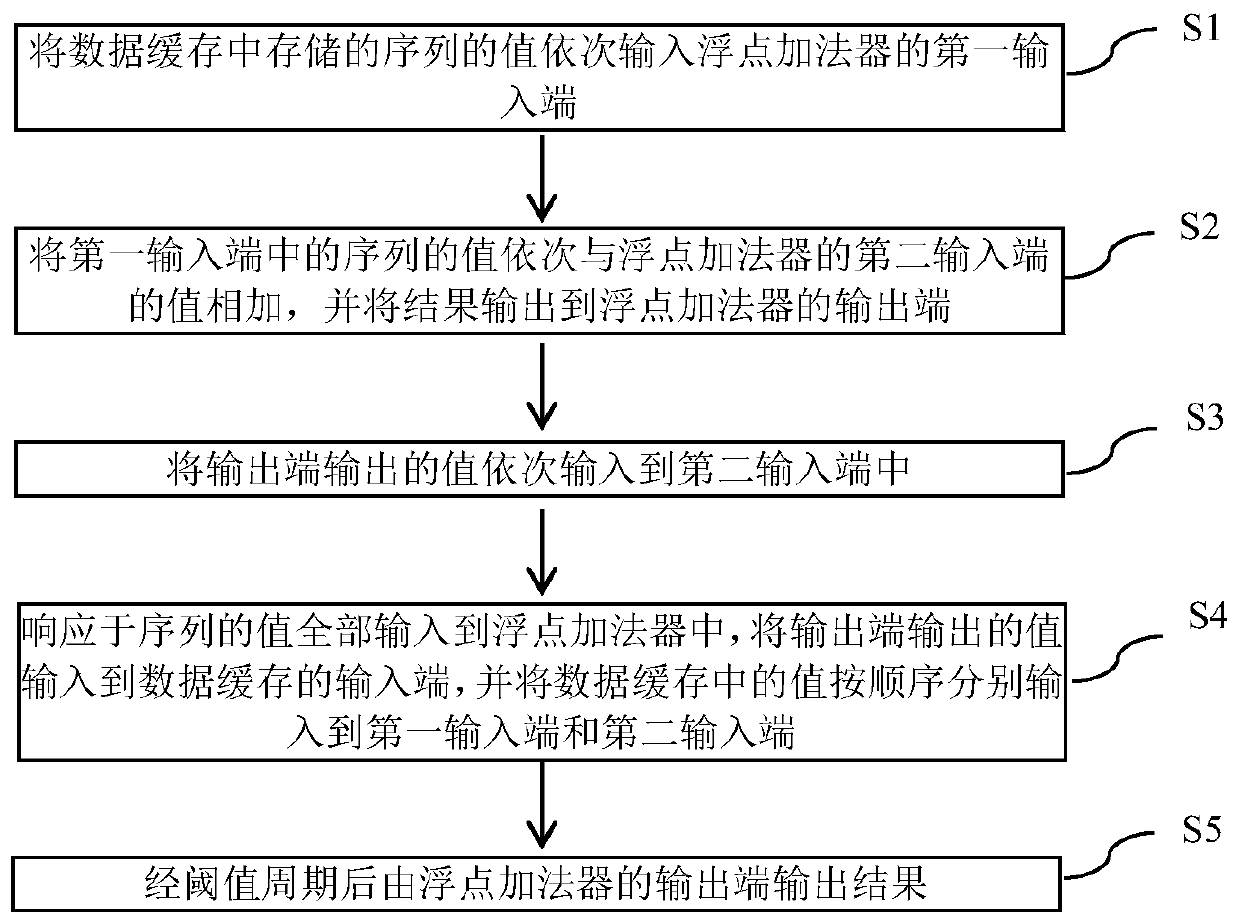

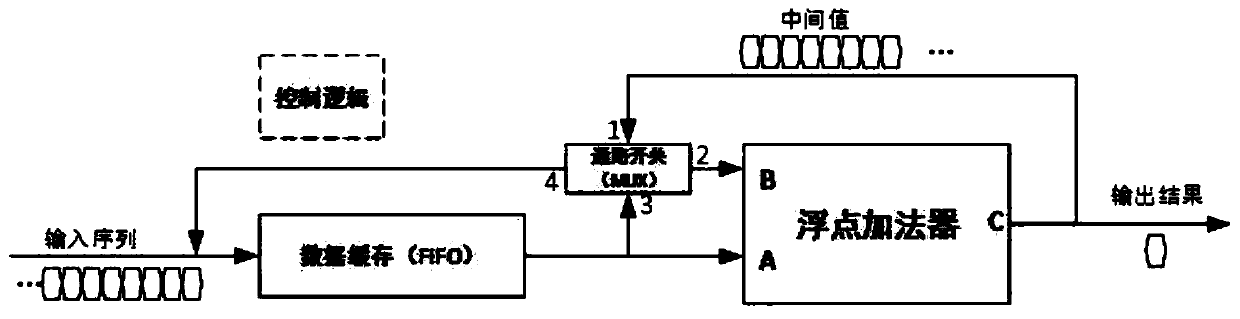

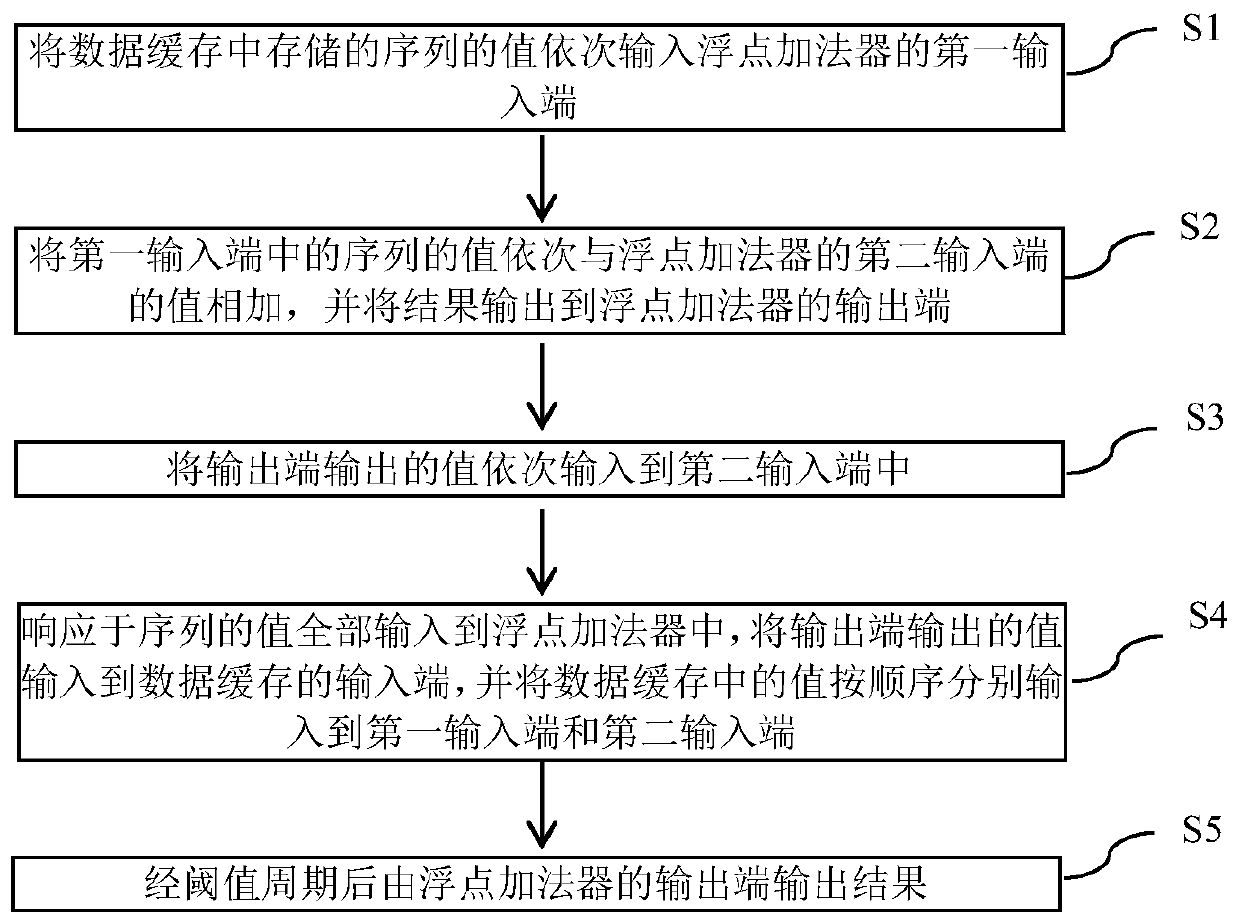

Operation method and device of sequence accumulator

ActiveCN111124358AReduce waiting periodShort operation cycleDigital data processing detailsComputer hardwareEngineering

The invention provides an operation method and device of a sequence accumulator. The method comprises the following steps of: sequentially inputting value of sequences stored in a data cache into a first input end of a floating point adder; sequentially adding the value of the sequence in the first input end to the value of the second input end of the floating point adder, and outputting a resultto the output end of the floating point adder; sequentially inputting the value output by the output end into a second input end; in response to the fact that all the values of the sequence are inputinto the floating point adder, inputting the value output by the output end into the input end of the data cache, and the value in the data cache into the first input end and the second input end in sequence; and outputting a result by the output end of the floating point adder after a threshold period. The assembly line waiting period caused by the delay of the adder can be effectively reduced, and the invention has the advantages of short operation period, high resource utilization rate, small assembly line interval, small cache occupation and the like, and can be flexibly applied to different scenes.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Self-correction precursor 0/1 predicting unit for floating-point adder

InactiveCN101699390BDoes not affect the lengthDigital data processing detailsPath lengthFloating point

The invention relates to a self-correction precursor 0 / 1 predicting method for a floating-point adder, which adopts the combination method of a multiple-input logical gate and parallel computation to realize an output result as a final correct result, and the output result has no need to be corrected by depending on an adder; the parallel computation is adopted, for example, the operand bit wide is increased, and the critical path length can not be influenced. When the floating-point add is computed, the displacement time and index regulating information needed by the normalization of a computation result is synchronously predicted, a predicting result is not output by the adder but is generated by the predicting unit and is a corrected value which has no need to be further corrected, andthe critical path of the predicting unit can not be lengthened along with lengthening the bit wide of an operand.

Owner:XI AN JIAOTONG UNIV

Mechanism for fast detection of overshift in a floating point unit of a processing device

ActiveUS8402075B2Computations using contact-making devicesDigital computer detailsLeast significant bitFloating-point unit

A floating point unit includes a floating point adder to perform a floating point addition operation between first and second floating point numbers each having an exponent and a mantissa. The floating point unit also includes an alignment shifter that may calculate a shift value corresponding to a number of bit positions to shift the second mantissa such that the second exponent value is the same as the first exponent value. The alignment shifter may detect an overshift condition, in which the shift value is greater than or equal to a selected overshift threshold value. The selected overshift threshold value comprises a base 2 number in a range of overshift values including a minimum overshift threshold value and a maximum overshift threshold value, and which has a largest number of a consecutive of bits that are zero beginning at a least significant bit.

Owner:ADVANCED MICRO DEVICES INC