High-performance imprecise floating point adder and application method thereof

A fixed-point adder, non-accurate technology, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., to achieve the effect of less hardware resources, wide application, and high speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Below in conjunction with accompanying drawing, technical scheme of the present invention is described in further detail:

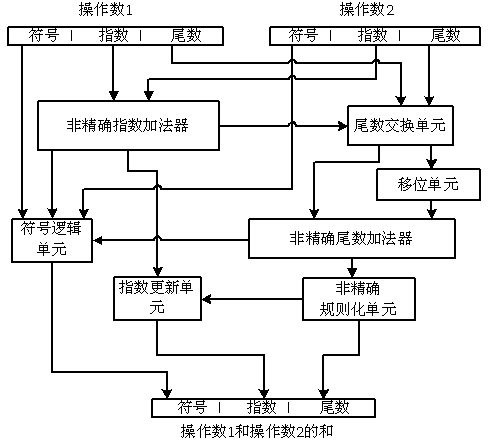

[0031] Such as figure 1 As shown, the present invention discloses a high-performance non-precise floating-point adder, including a non-precise exponent adder, a mantissa exchange unit, a shift unit, a non-precise mantissa adder, a symbol logic unit, an exponent update unit and an non-precise rule chemical unit;

[0032] The inaccurate exponent adder is used to compare the exponent parts of the two operands, and deliver the result of the exponent comparison to the mantissa exchange unit, the sign logic unit and the exponent update unit;

[0033] The mantissa exchange unit is used to exchange the mantissa parts of the two operands according to the result of the exponent comparison, so as to ensure that the mantissa that needs to be shifted is in the correct position, and at the same time, the mantissa that needs to be shifted is passed to the shift ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More