Patents

Literature

57 results about "Adder–subtractor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

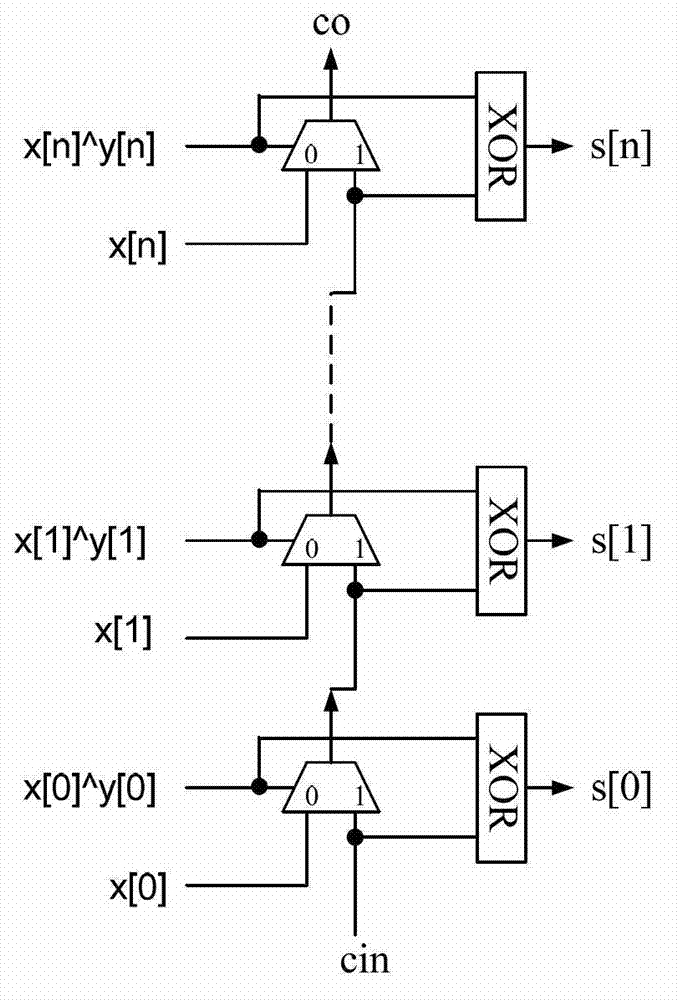

In digital circuits, an adder–subtractor is a circuit that is capable of adding or subtracting numbers (in particular, binary). Below is a circuit that does adding or subtracting depending on a control signal. It is also possible to construct a circuit that performs both addition and subtraction at the same time.

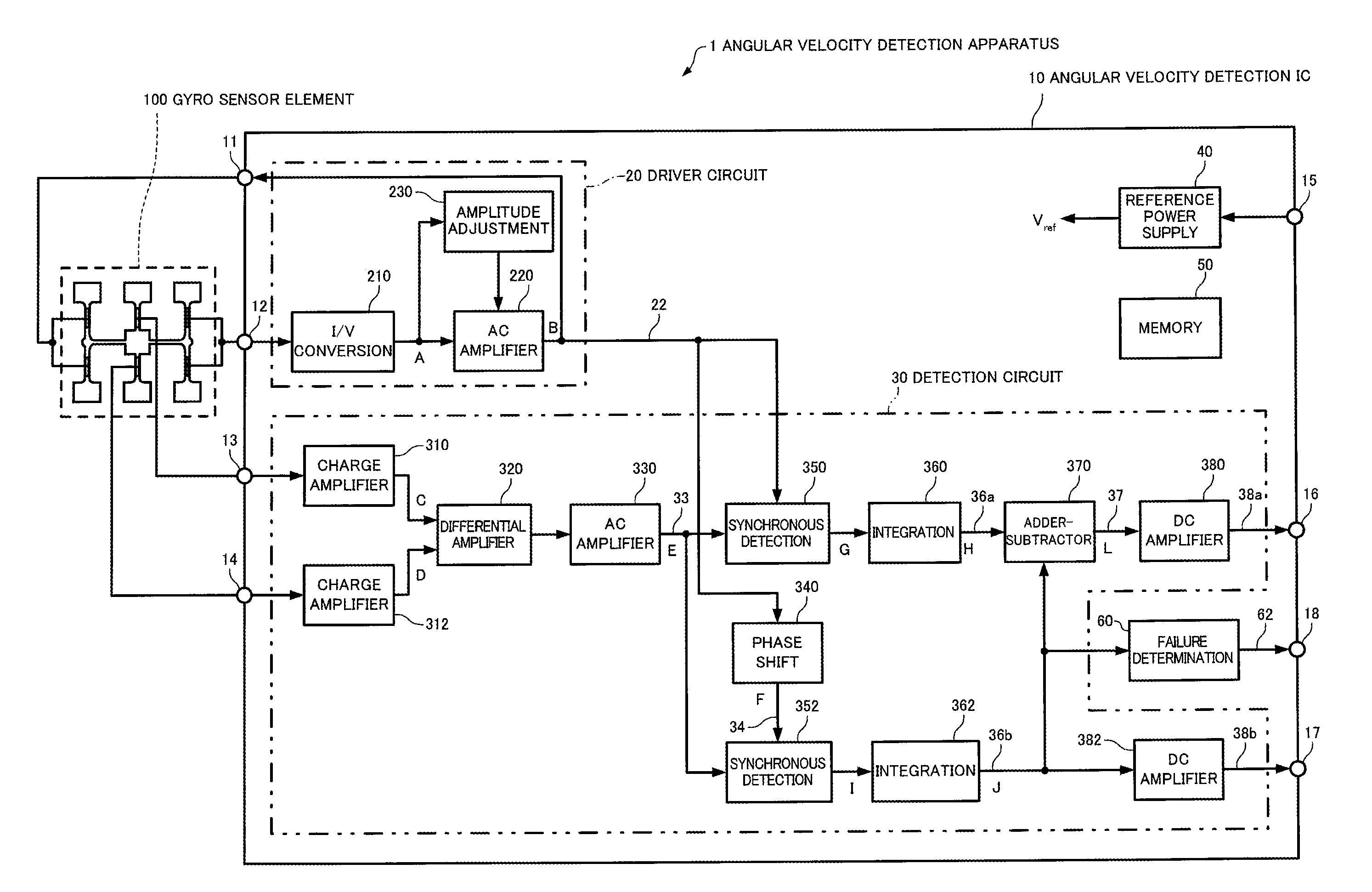

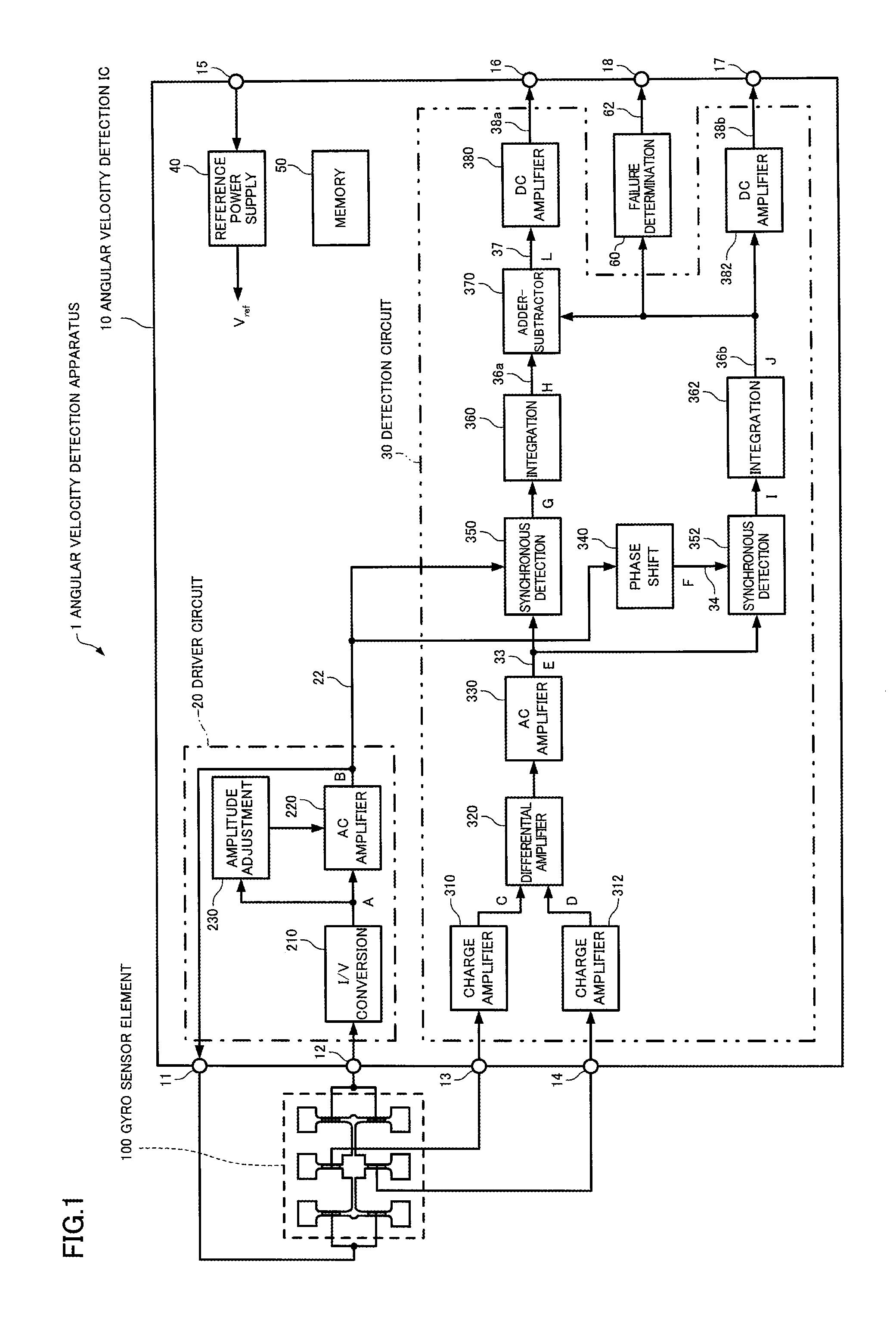

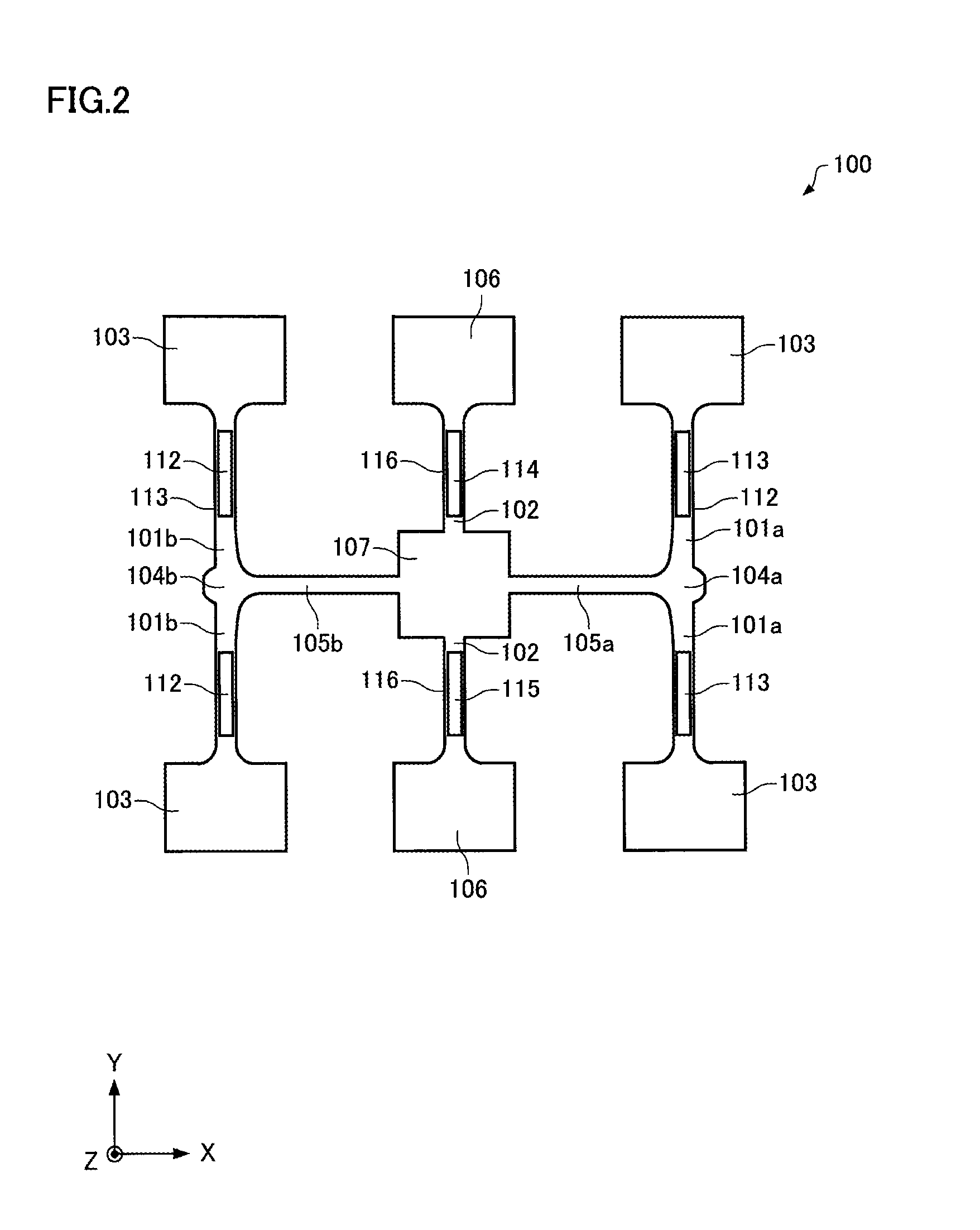

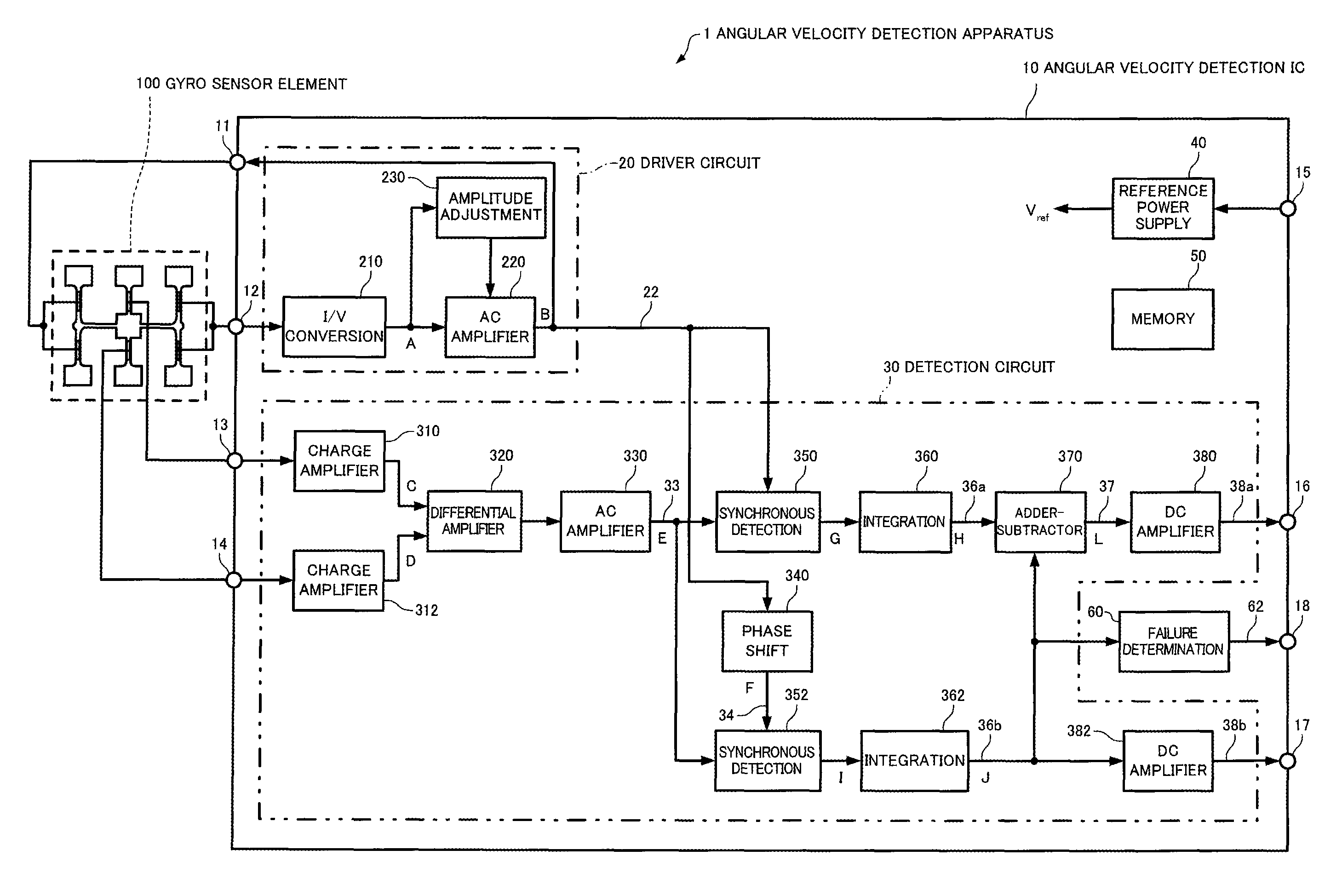

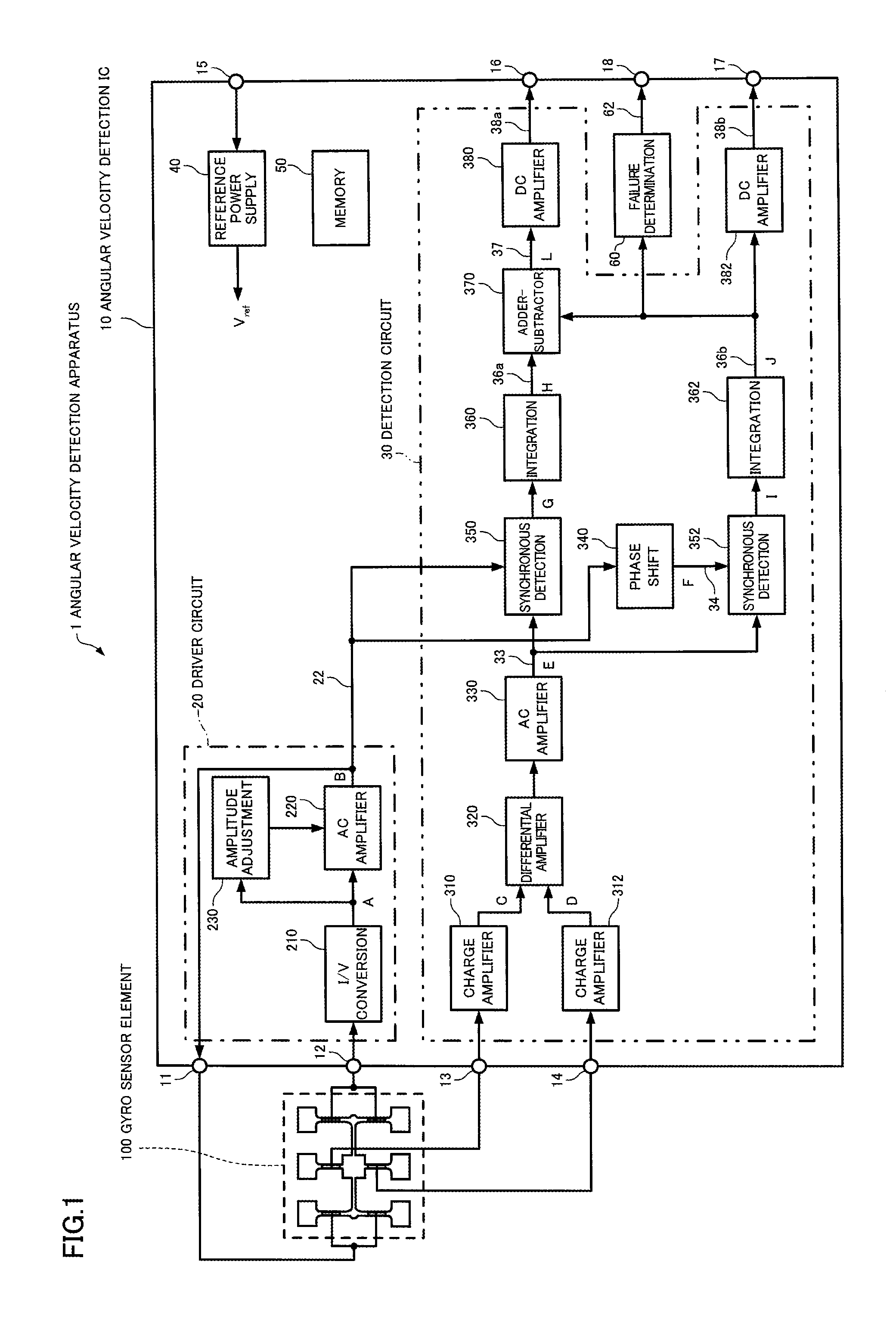

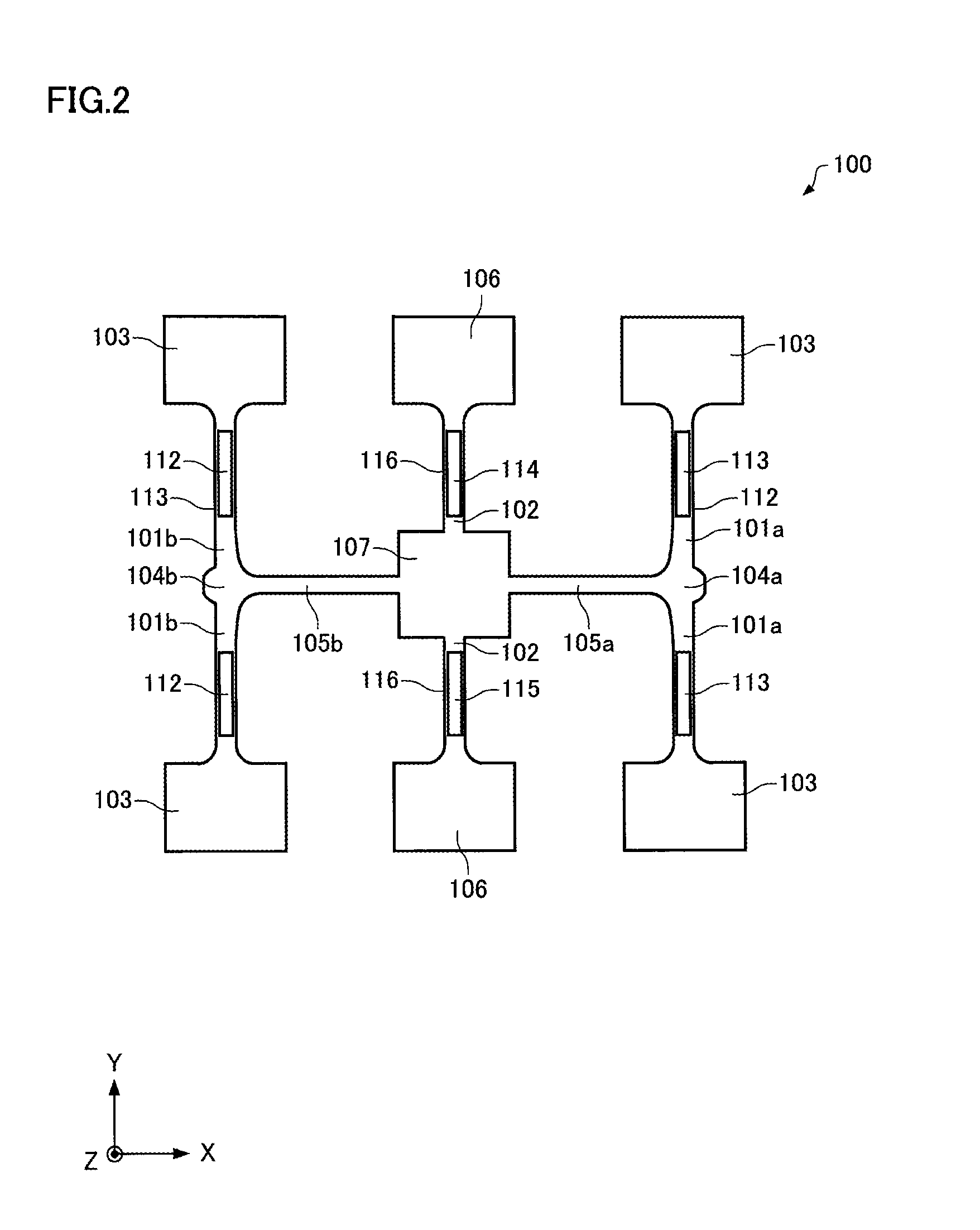

Angular velocity detection apparatus and electronic instrument

ActiveUS20120055230A1Linear/angular speed measurementTesting/calibration of speed/acceleration/shock measurement devicesAdder–subtractorAngular velocity

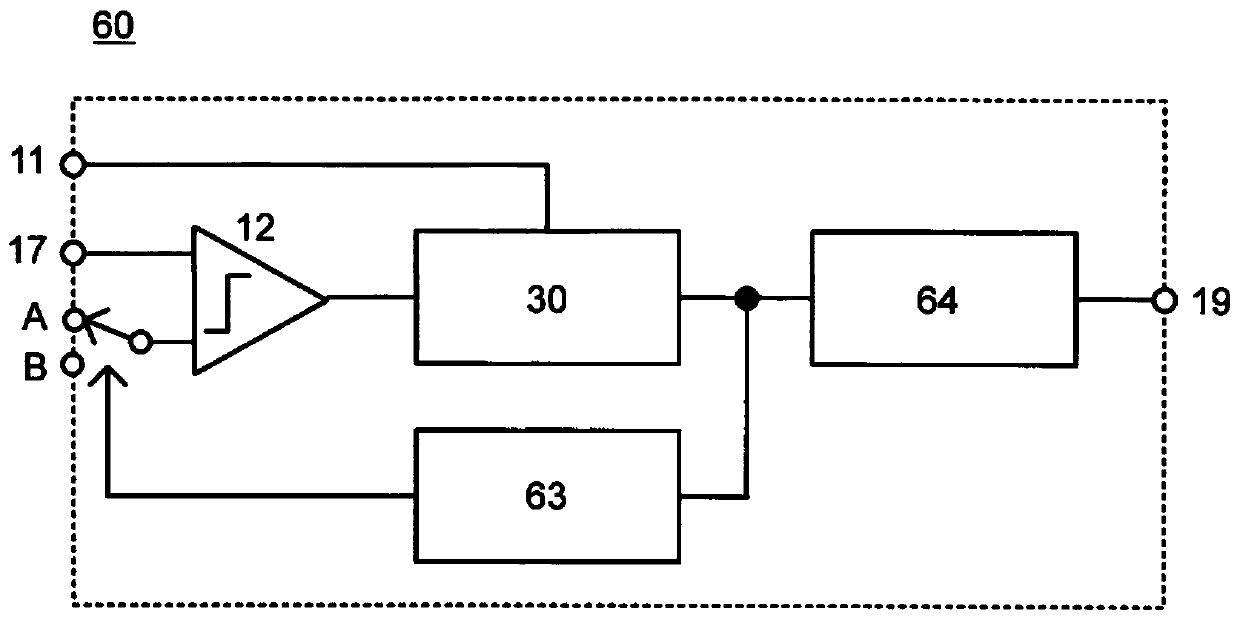

An angular velocity detection apparatus includes a vibrator that generates a signal that includes an angular velocity component and a vibration leakage component, a driver section that generates the drive signal, and supplies the drive signal to the vibrator, an angular velocity signal generation section that extracts the angular velocity component from the signal generated by the vibrator, and generates an angular velocity signal corresponding to the magnitude of the angular velocity component, a vibration leakage signal generation section that extracts the vibration leakage component from the signal generated by the vibrator, and generates a vibration leakage signal corresponding to the magnitude of the vibration leakage component, and an adder-subtractor section that adds the vibration leakage signal to the angular velocity signal, or subtracts the vibration leakage signal from the angular velocity signal, in a given ratio to correct temperature characteristics of the angular velocity signal.

Owner:SEIKO EPSON CORP

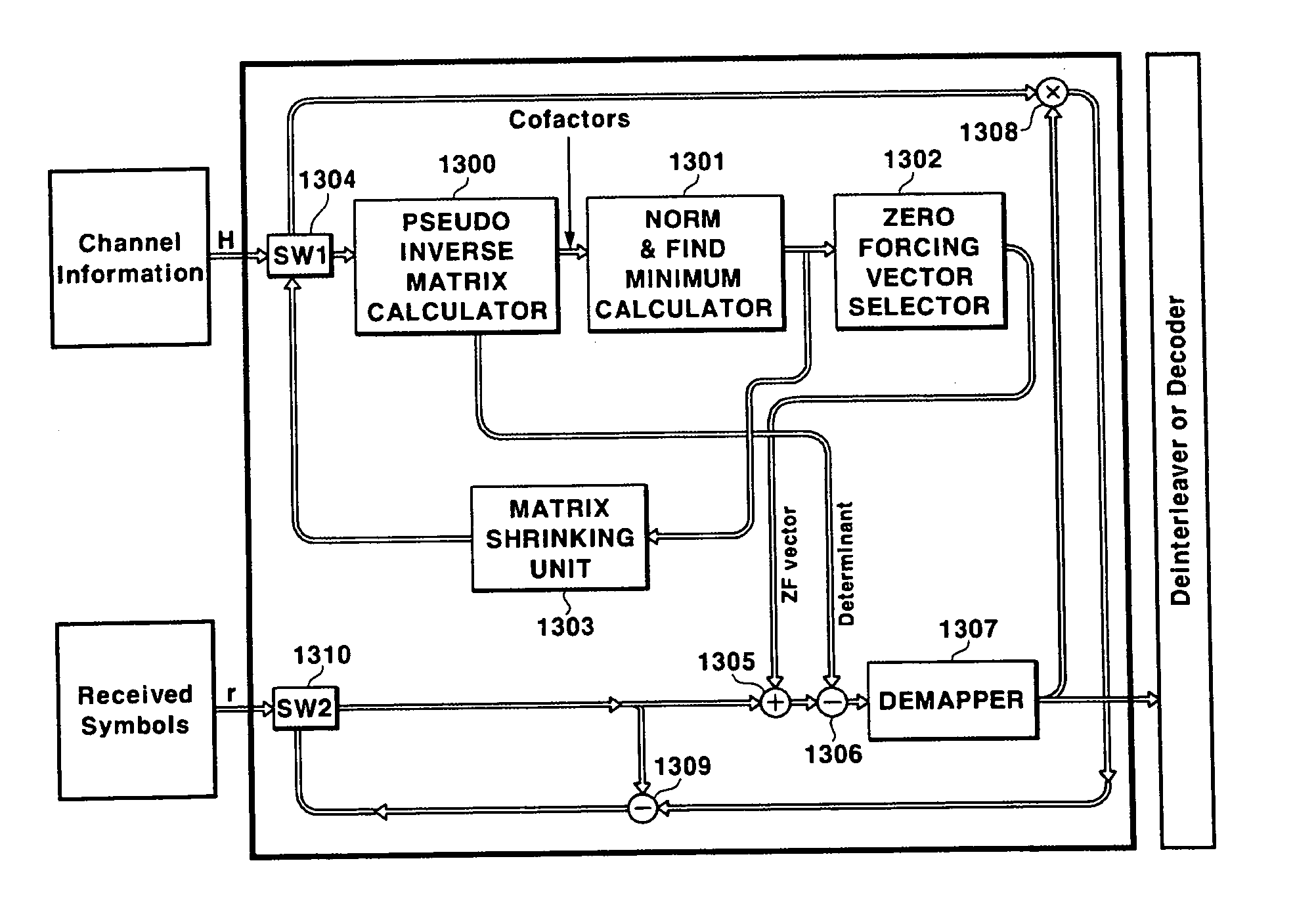

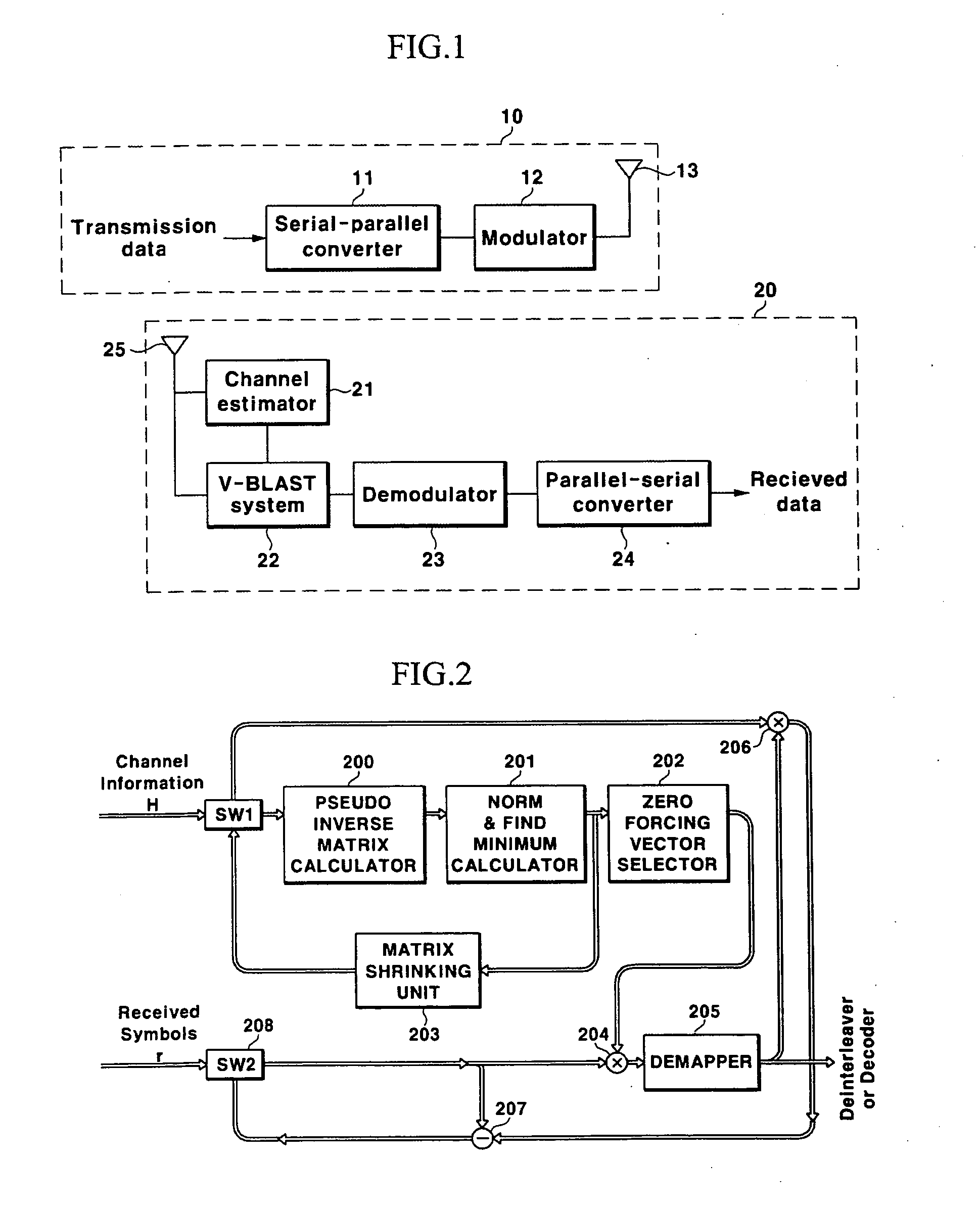

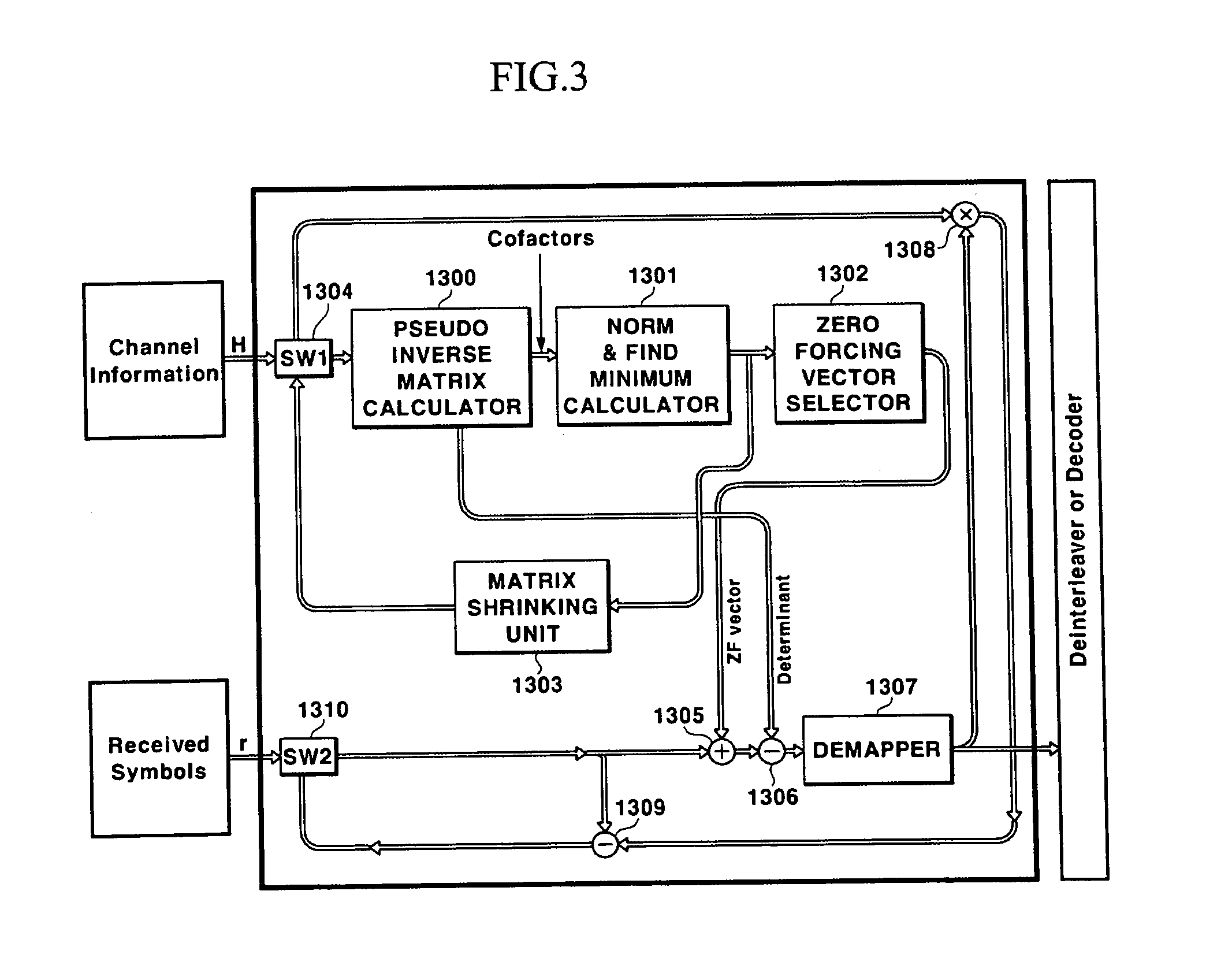

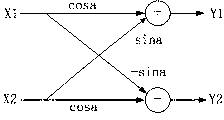

Processing device for a pseudo inverse matrix and V-BLAST system

InactiveUS20050149596A1Effective functionEfficient processingBaseband system detailsComputation using non-contact making devicesTransfer function matrixCommunications system

Disclosed is a V-BLAST system for a MIMO communication system. In the V-BLAST system for a MIMO communication system, a pseudo inverse matrix calculator receives a channel transfer function matrix including channel information and produces a cofactor matrix and a determinant for a pseudo inverse matrix. A norm & minimum calculator calculates a minimum index for the cofactor matrix outputted from the pseudo inverse matrix calculator, a weight vector selector selects a row vector having the minimum index and calculates a transposed matrix for the row vector; an adder adds the transposed matrix to a received input symbol, and a subtractor subtracts the determinant to the output. A demapper performs a determined function operation to the output and produces estimated information.

Owner:ELECTRONICS & TELECOMM RES INST

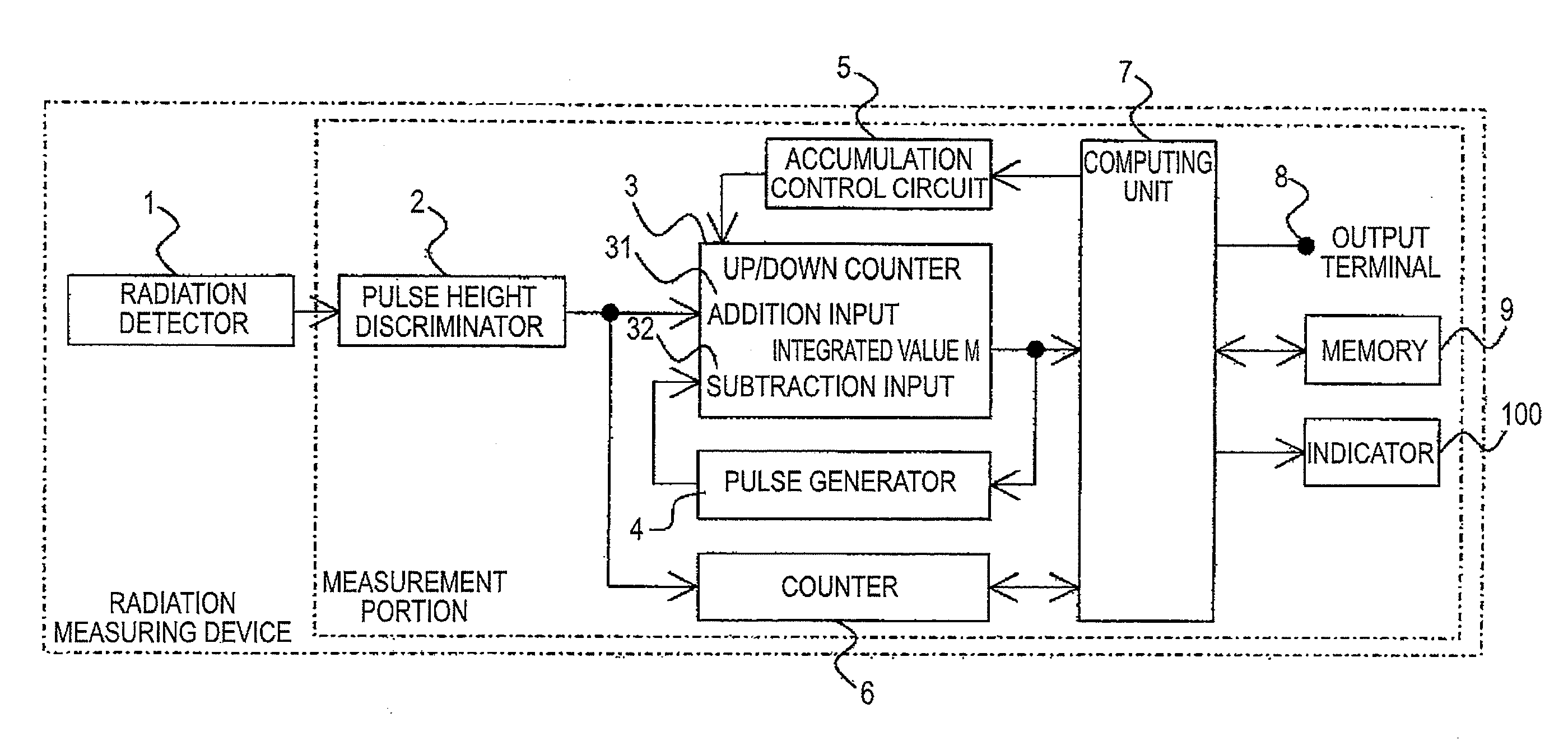

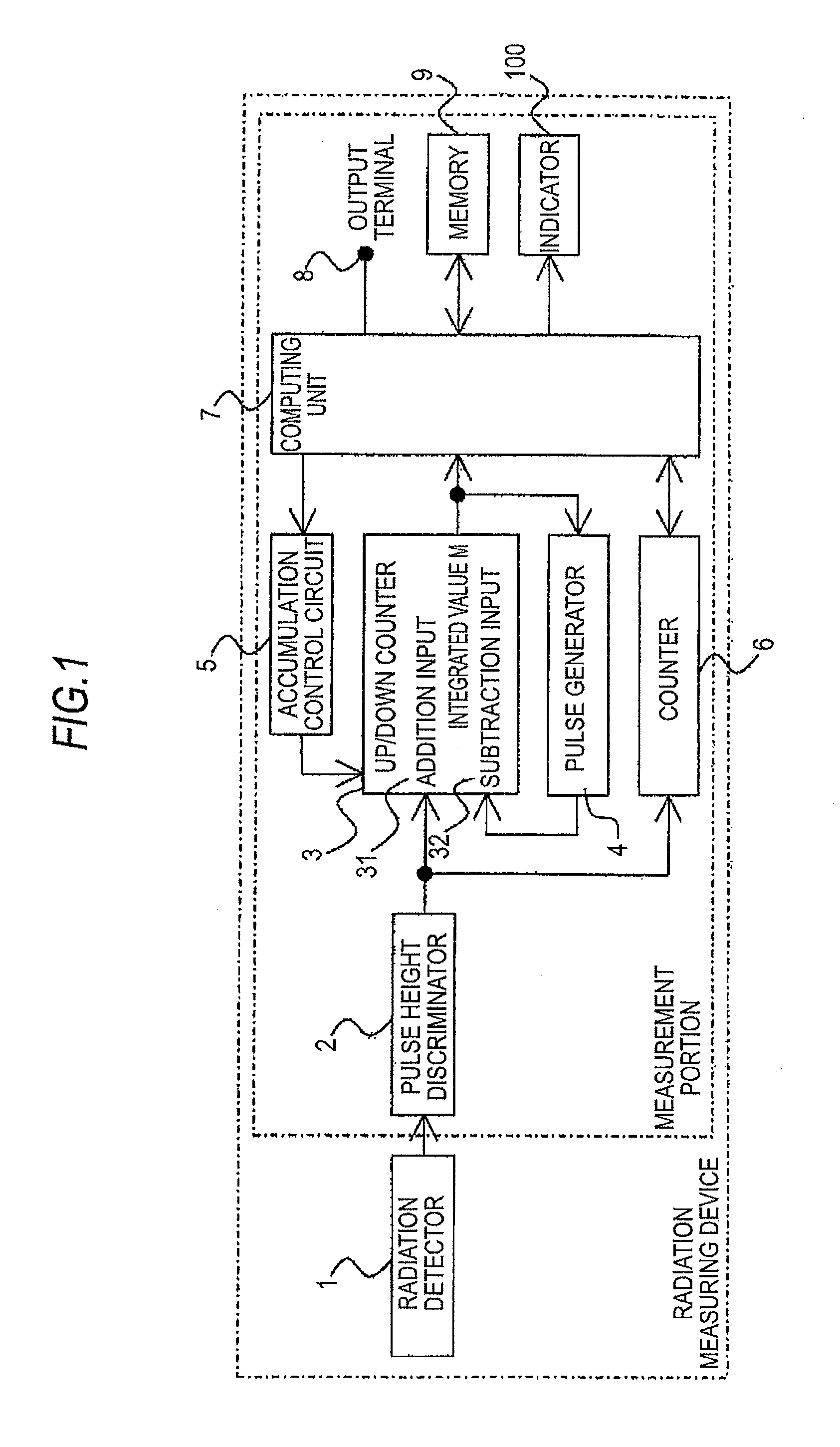

Radiation measuring device and diagnostic method thereof

ActiveUS20110144945A1Simple configurationImprove reliabilityAmplifier modifications to reduce noise influencePhotometryDiscriminatorCounting rate

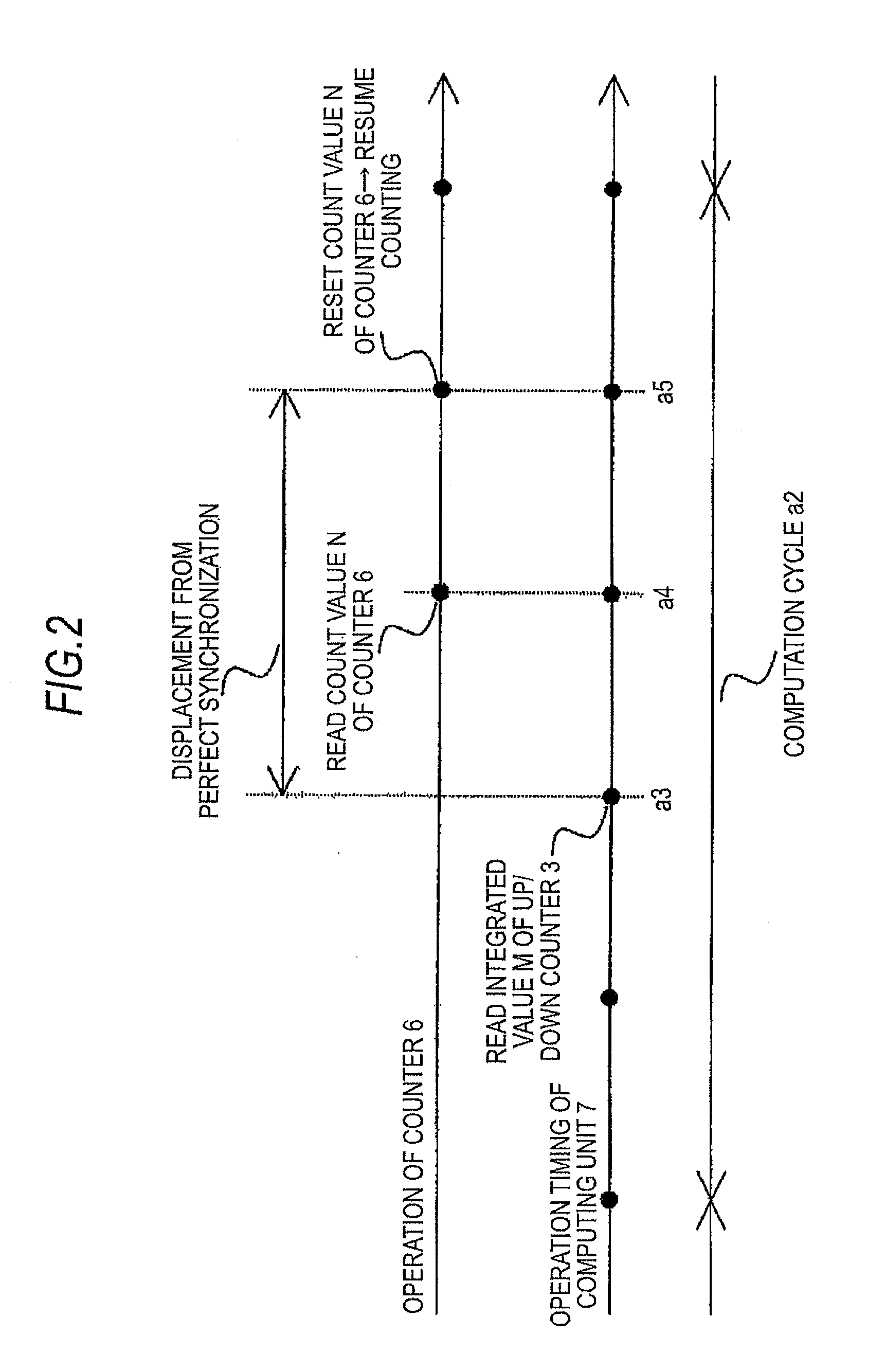

A radiation measuring device includes a computing unit that receives an input of a count value of a count portion configured to receive an input of a digital pulse from a pulse height discriminator and count the digital pulse in a fixed cycle and an integrated value of an adder-subtractor accumulation portion configured to add the digital pulse and subtract a feedback pulse and finds a first current rate on the basis of the count value and the integrated value and a second count rate on the basis of the integrated value, so that soundness of the adder-subtractor accumulation portion is diagnosed and outputted by comparing the first count rate with the second count rate. A radiation measuring device of a simple configuration and a diagnosis method thereof enabling a high-accurate self-diagnosis online on the count rate measurement that is the keystone of the radiation measurement can be thus obtained.

Owner:MITSUBISHI ELECTRIC CORP

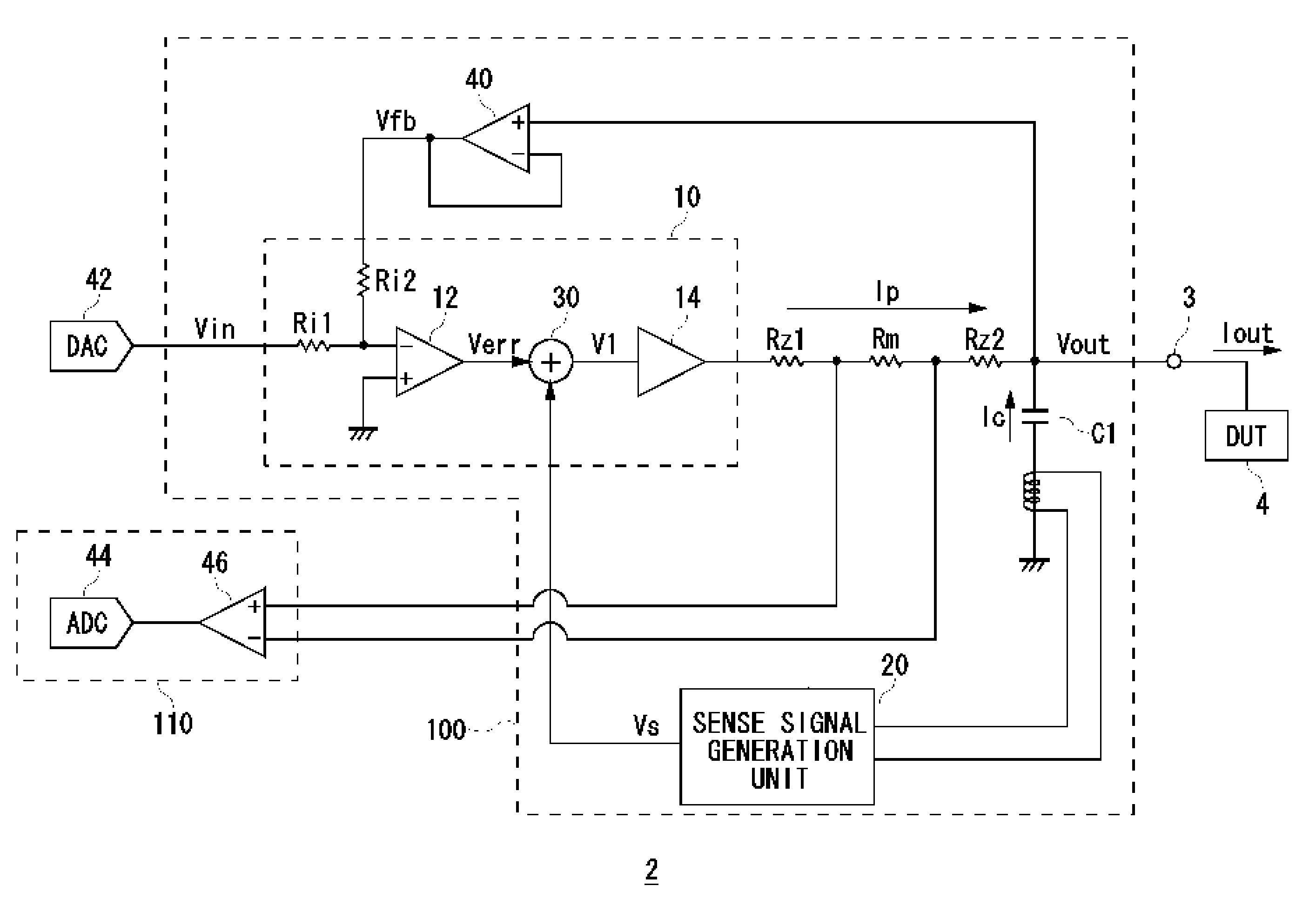

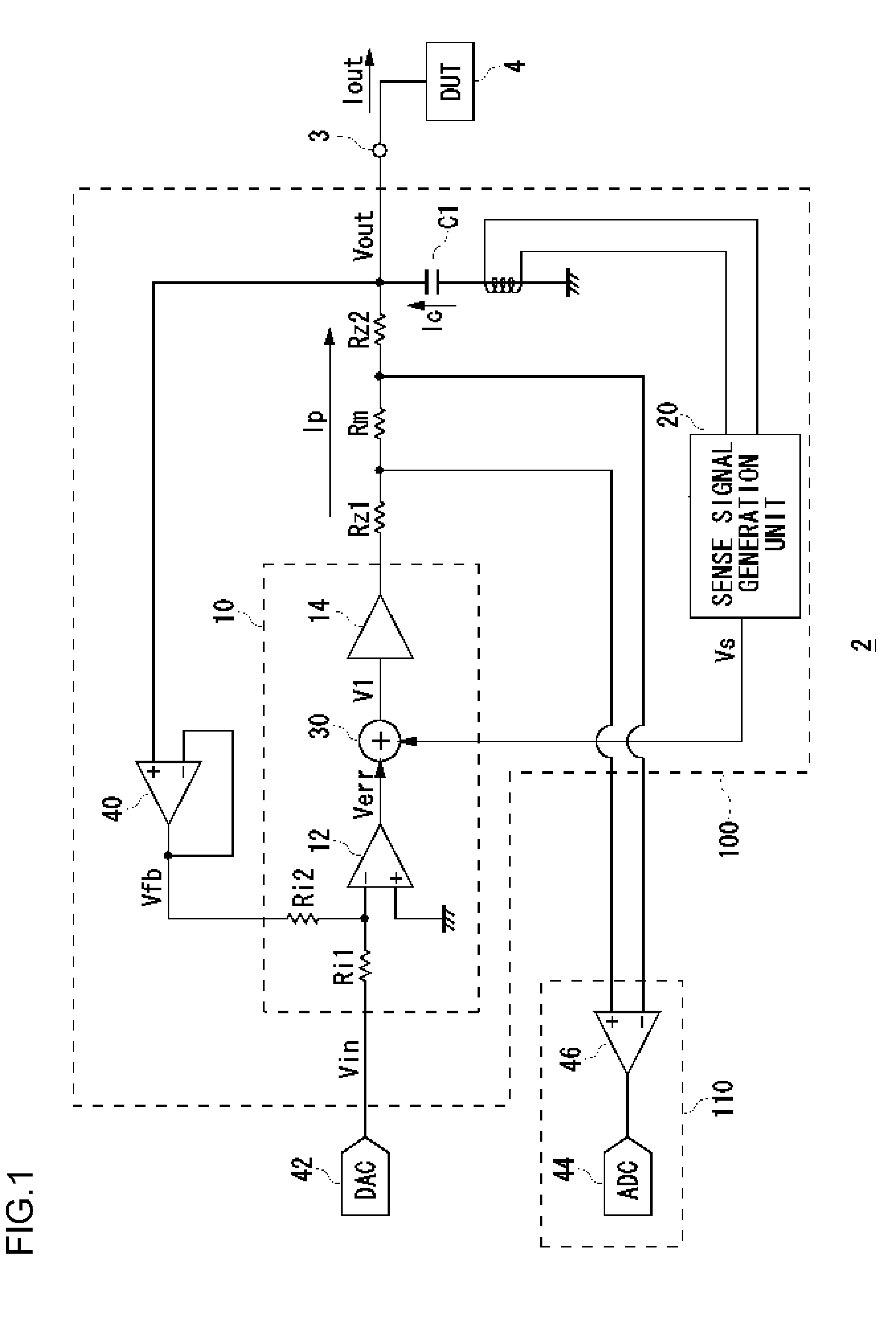

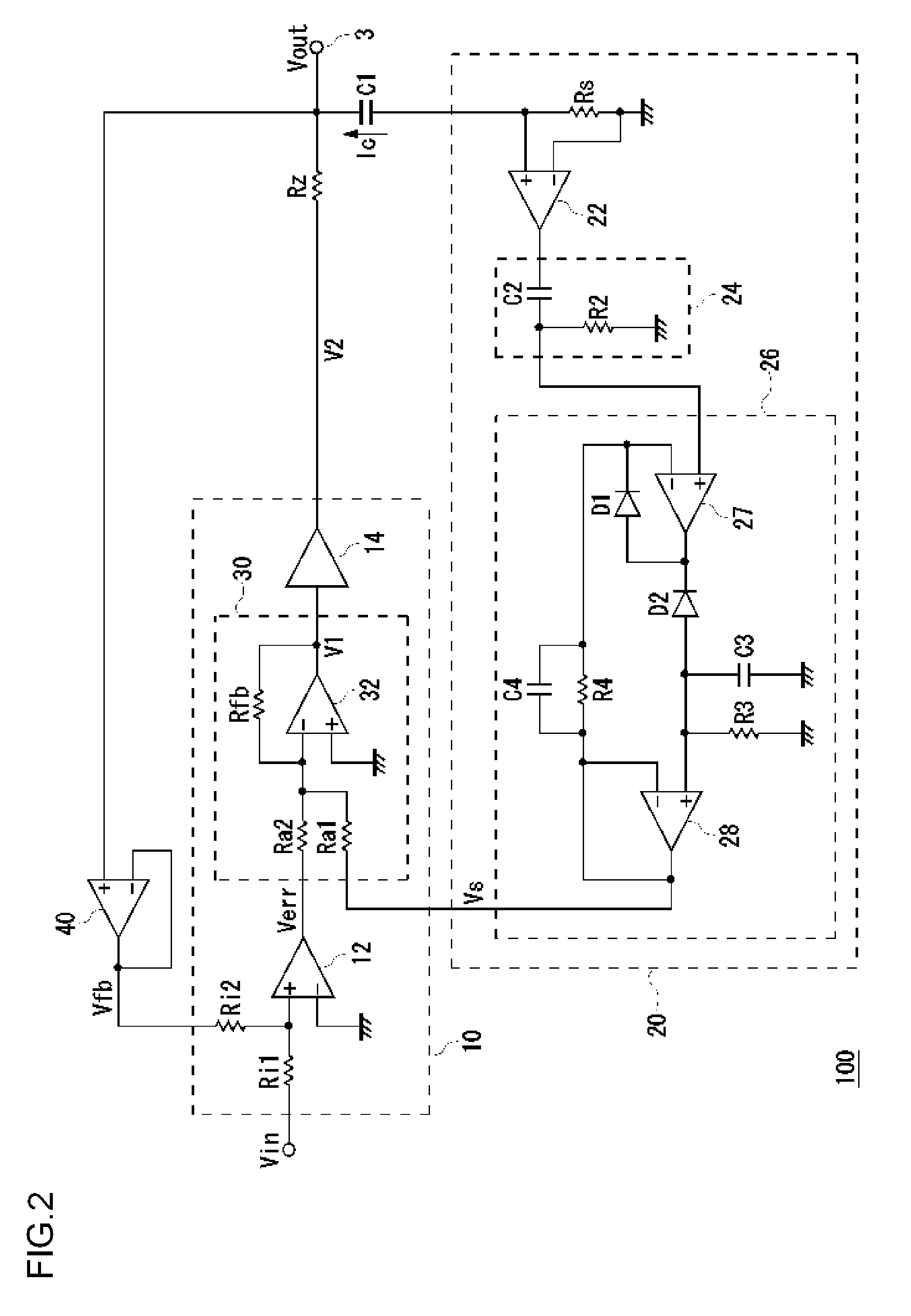

Voltage generating apparatus

InactiveUS20090015221A1Improve load characteristicsElectrical testingElectric variable regulationVoltage generatorAudio power amplifier

A voltage generating apparatus generates an output voltage based on an input voltage. A voltage generator includes a first operational amplifier operative to receive the input voltage and a feedback voltage proportional to the output voltage. The voltage generator regulates the output voltage so that a virtual short circuit is produced in the first operational amplifier. An output capacitor smoothes the output voltage generated by the voltage generating apparatus. A sense signal generator detects a current flowing in the output capacitor and generates a sense signal proportional to the current detected. An adder-subtractor circuit superimposes the sense signal on at least one of the input and the output of the first operational amplifier.

Owner:ADVANTEST CORP

Digital loop for regulating DC/DC converter using segmented switching

InactiveCN1906833ASmall pulsationApparatus without intermediate ac conversionElectric variable regulationSoftware engineeringMechanical engineering

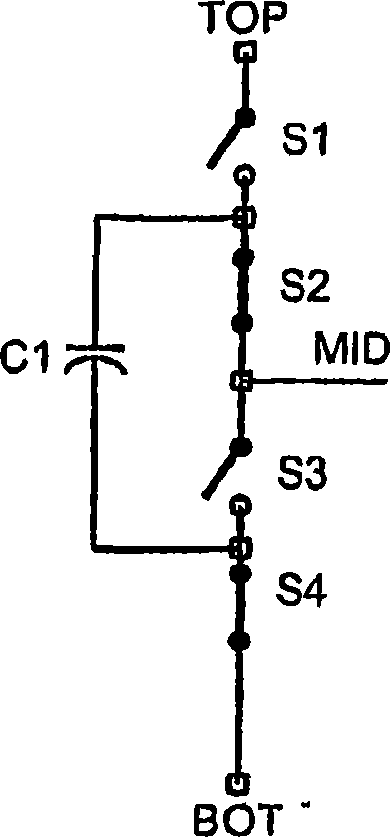

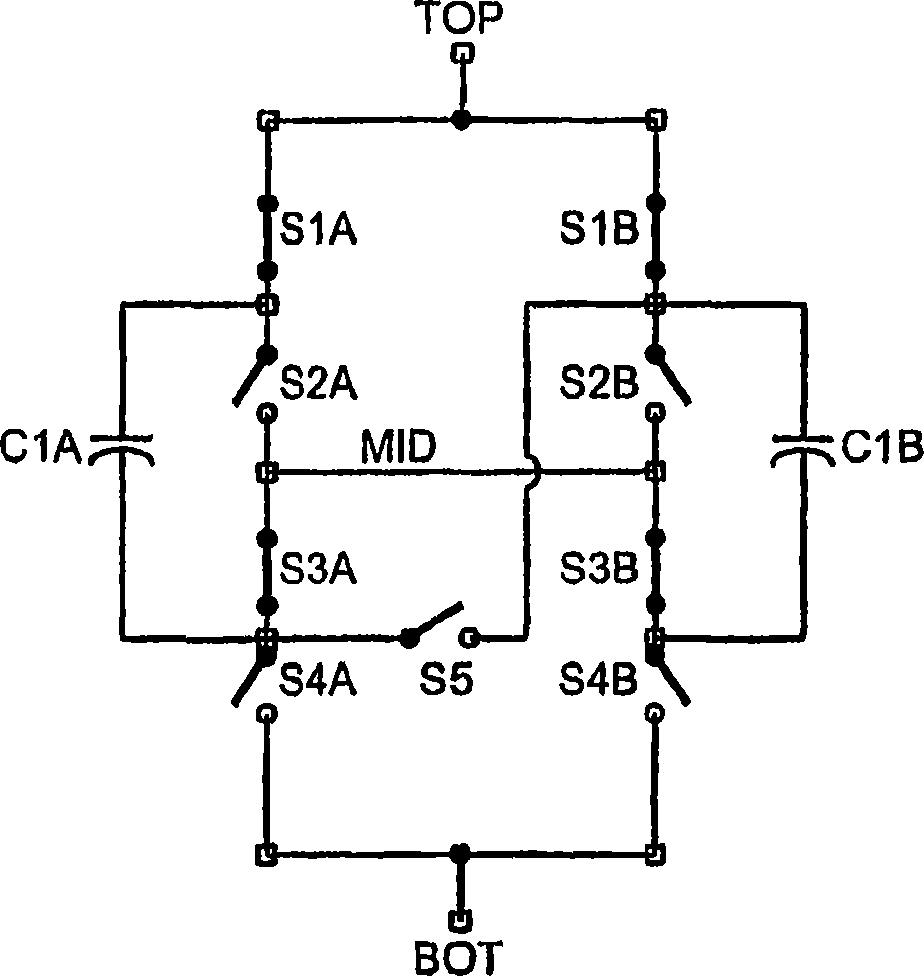

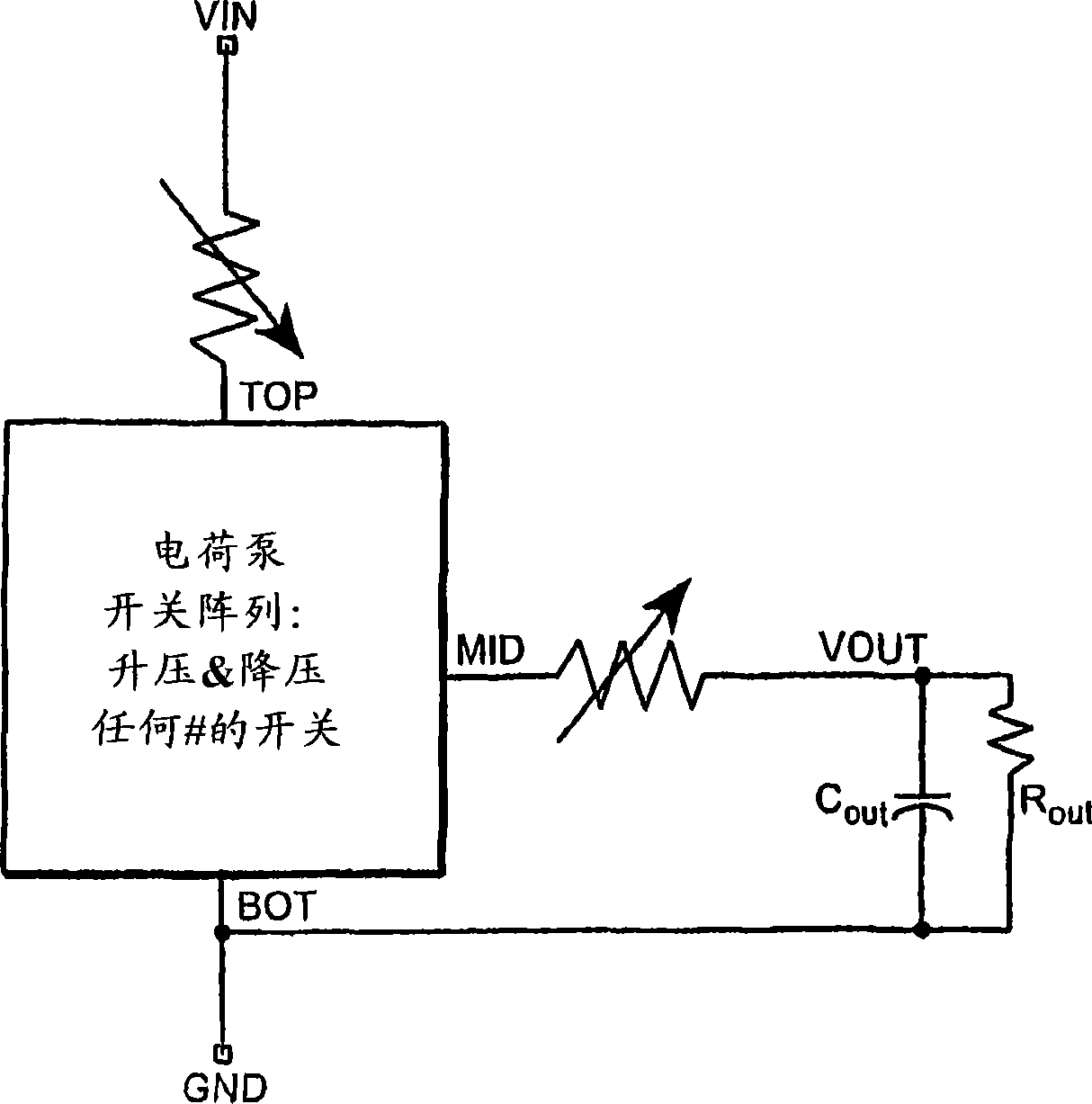

A power control circuit is provided containing a switch array, which includes segmented switches, a flying capacitor, an output voltage terminal, a feedback loop, and a digital voltage regulator block. The digital voltage regulator block includes an A / D converter, an encoder, an add-subtractor, and a gate logic. These power control circuits do not include pass transistors. A method is also provided, where the charge pumps of the power control circuit are operated in two-phase cycles including a charging phase and a pumping phase. The power control circuit is controlled in both of these phases, thereby reducing the ripple of the output voltage.

Owner:FAIRCHILD SEMICON CORP

Angular velocity detection apparatus and electronic instrument

ActiveUS8701487B2Acceleration measurement using interia forcesSpeed measurement using gyroscopic effectsAdder–subtractorAngular velocity

Owner:SEIKO EPSON CORP

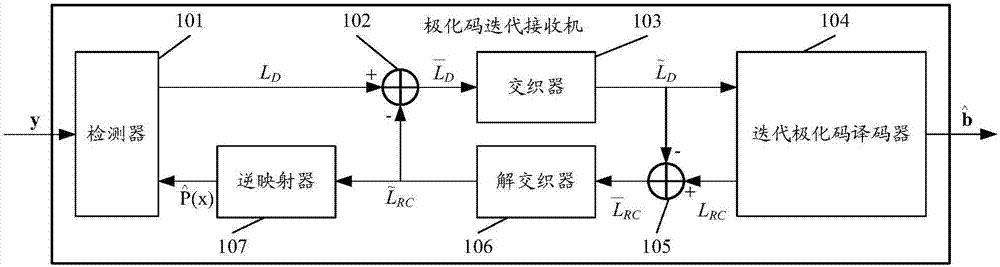

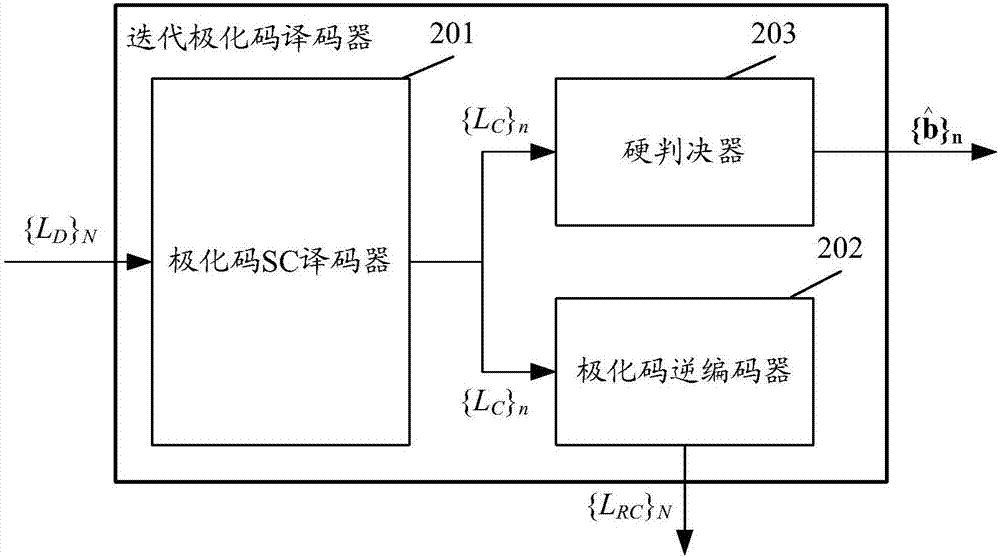

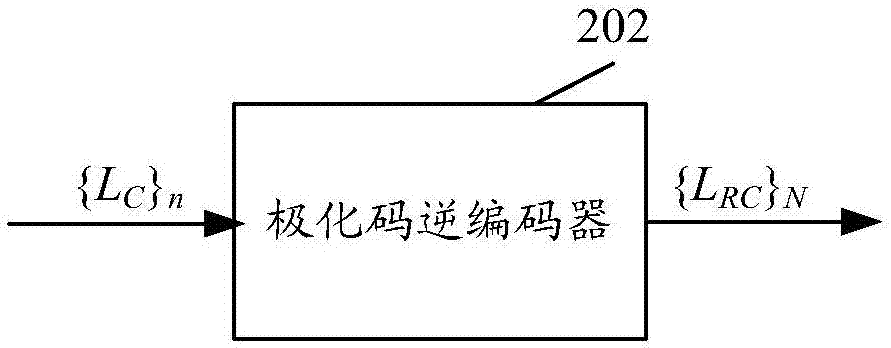

Iterative polarization code receiver, system and iterative polarization code decoding method

ActiveCN107231158ARetain gainReduce decoding complexityError correction/detection using linear codesComputer hardwareCommunications system

The invention discloses an iterative polarization code receiver and an iterative polarization code decoding method. The iterative polarization code receiver comprises a detector, a first adder-subtractor, a deinterleaver, an iterative polarization decoder, a second adder-subtractor, a second interleaver and an inverse mapper. According to the iterative polarization code receiver and the iterative polarization code decoding method, the bit error rate and block error rate performances of a wireless communication system can be improved on the condition of not improving the decoding complexity while coding gain is kept, and therefore the user experience is improved.

Owner:SOUTHWEST JIAOTONG UNIV

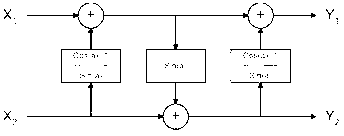

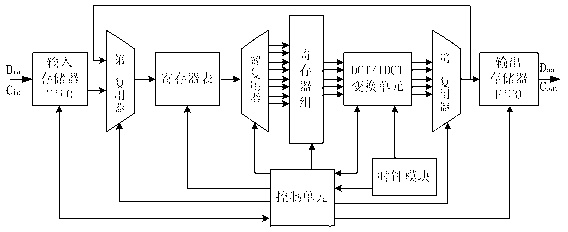

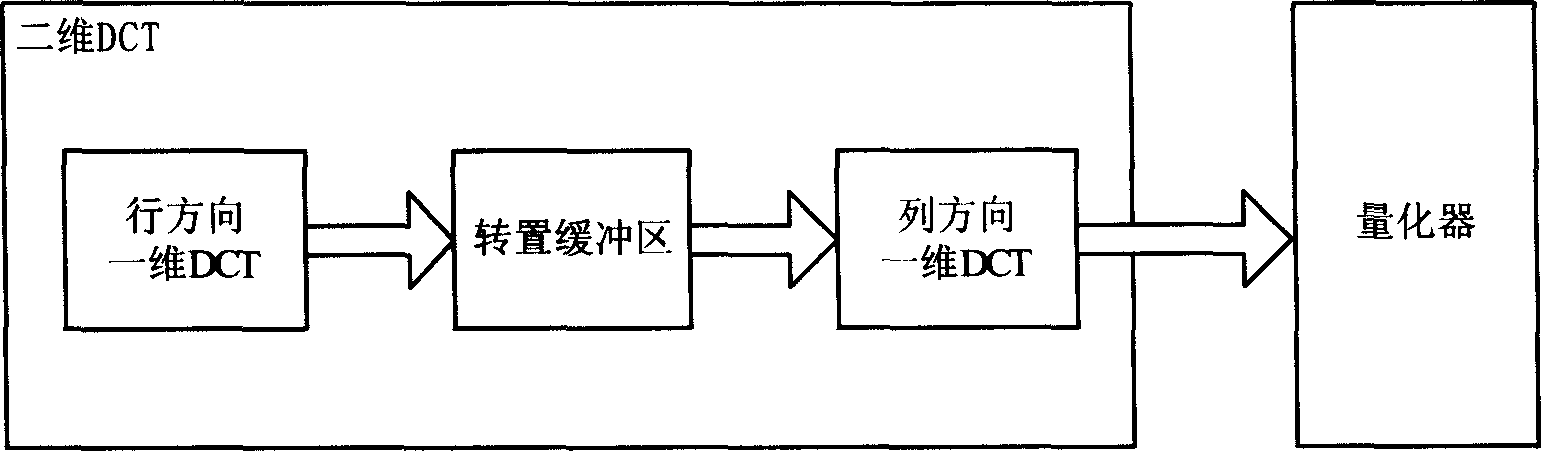

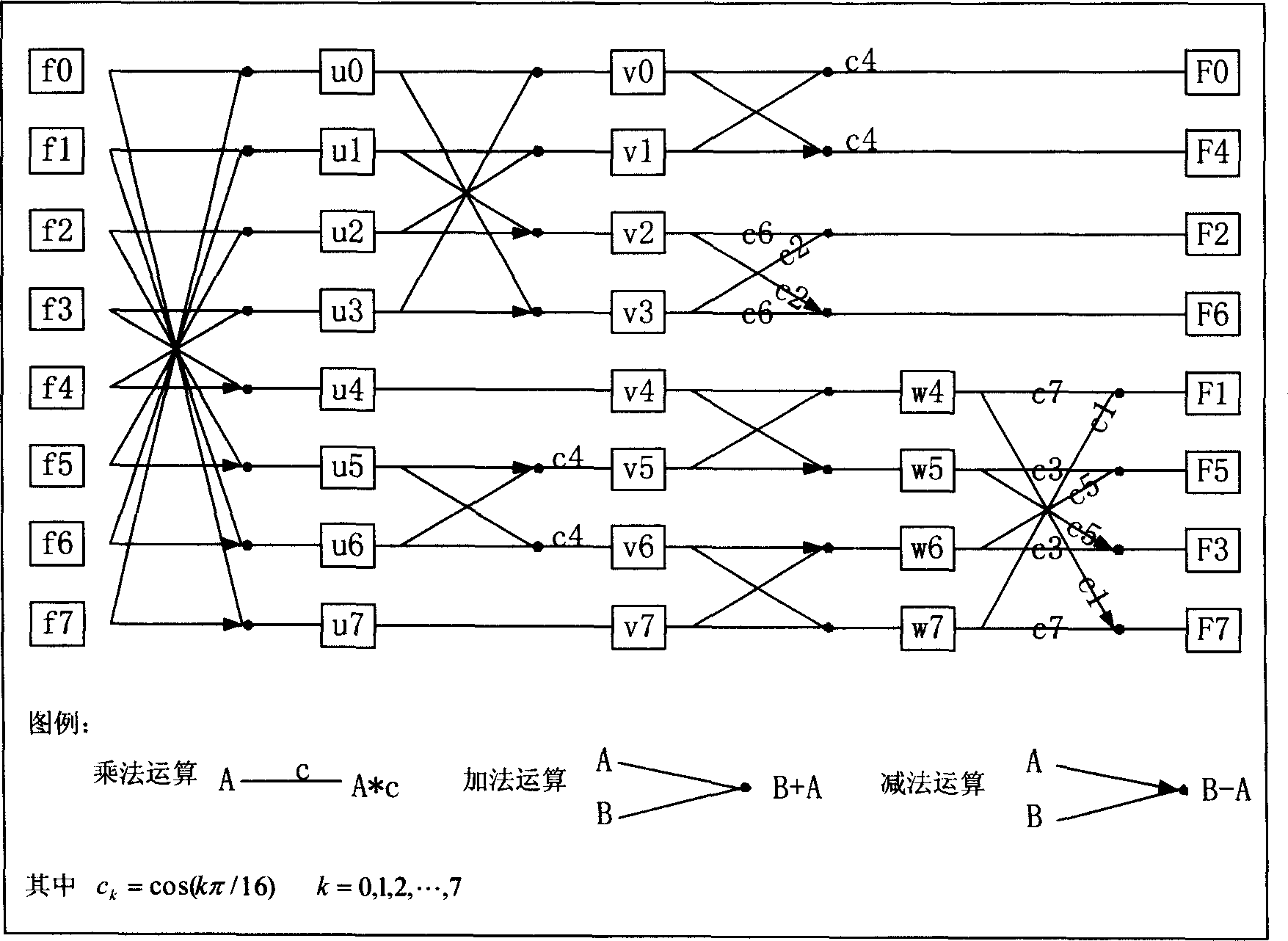

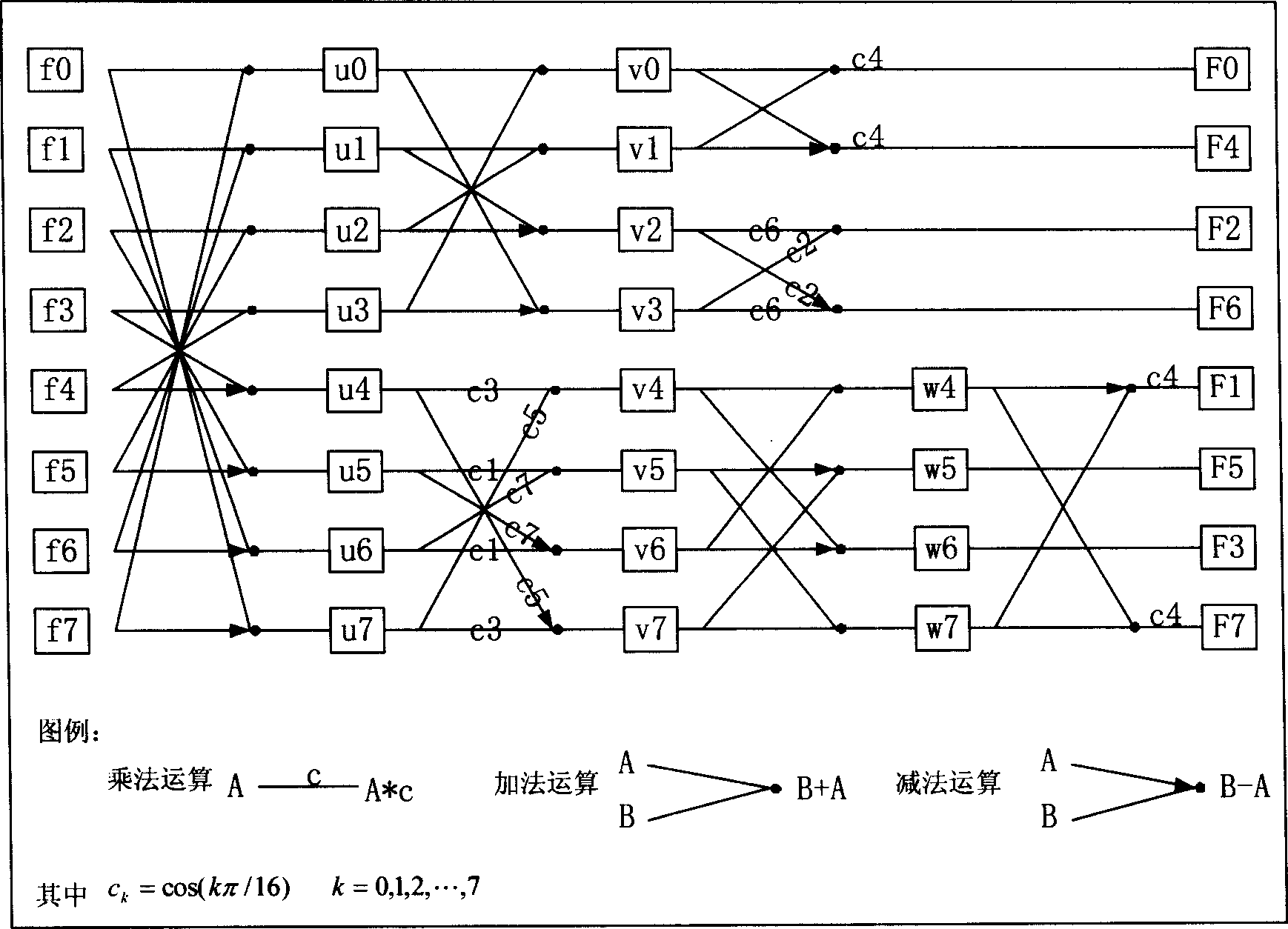

Two-dimensional discrete cosine transformation (DCT)/inverse DCT circuit and method

InactiveCN103237219AEfficient multiplier-less DCT transformImprove parallelismTelevision systemsDigital video signal modificationBinary multiplierMultiplexer

The invention relates to a two-dimensional discrete cosine transformation (DCT) / inverse DCT circuit and method. The circuit comprises an input memory, a first multiplexer, a register list, a demultiplexer, a DCT / inverse DCT unit, a second multiplexer and an output memory, wherein the input memory, the first multiplexer, the register list, the demultiplexer, the DCT / inverse DCT unit, the second multiplexer and the output memory are sequentially connected, the DCT / inverse DCT unit comprises a register, a first sum-and-difference operation unit and a second sum-and-difference operation unit, the first sum-and-difference operation unit is used for carrying out sum-and-difference operation on the data in the register for once, the second sum-and-difference operation unit is used for carrying out two sum-and-difference operations on the shifted data in the register, the input ends and output ends of the first sum-and-difference operation unit and the second sum-and-difference operation unit are respectively connected with the register, the register is also connected with the demultiplexer and the second multiplexer. The circuit and the method have the advantage that an adder-subtractor and two shifters are used for replacing a multiplier, the particular coefficients are selected, and then the multiplier with more wasted resources and lower speed is not used in the hardware circuit, so a calculation unit of the hardware can be repetitively used.

Owner:NANJING LONGYUAN MICROELECTRONICS TECH CO LTD

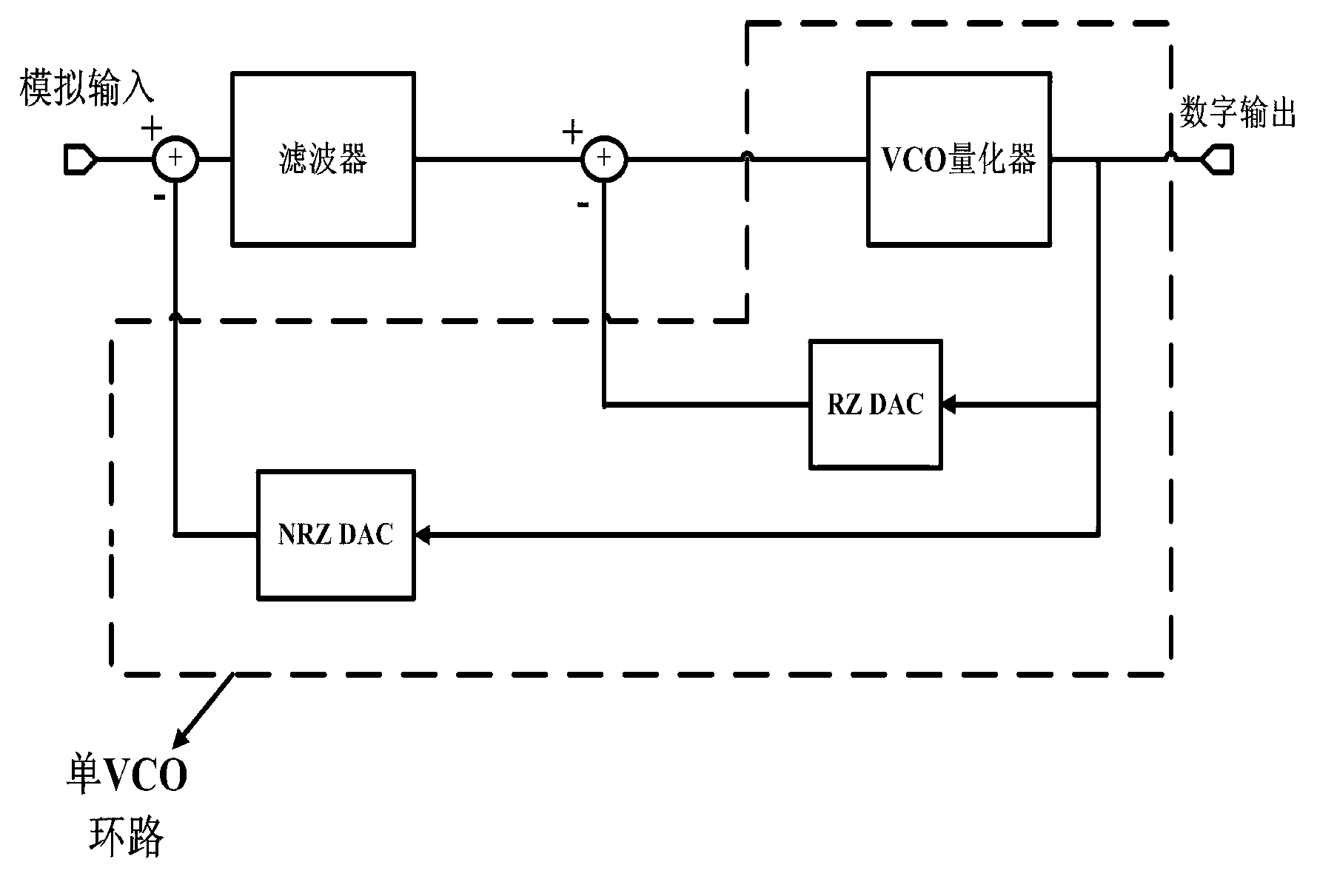

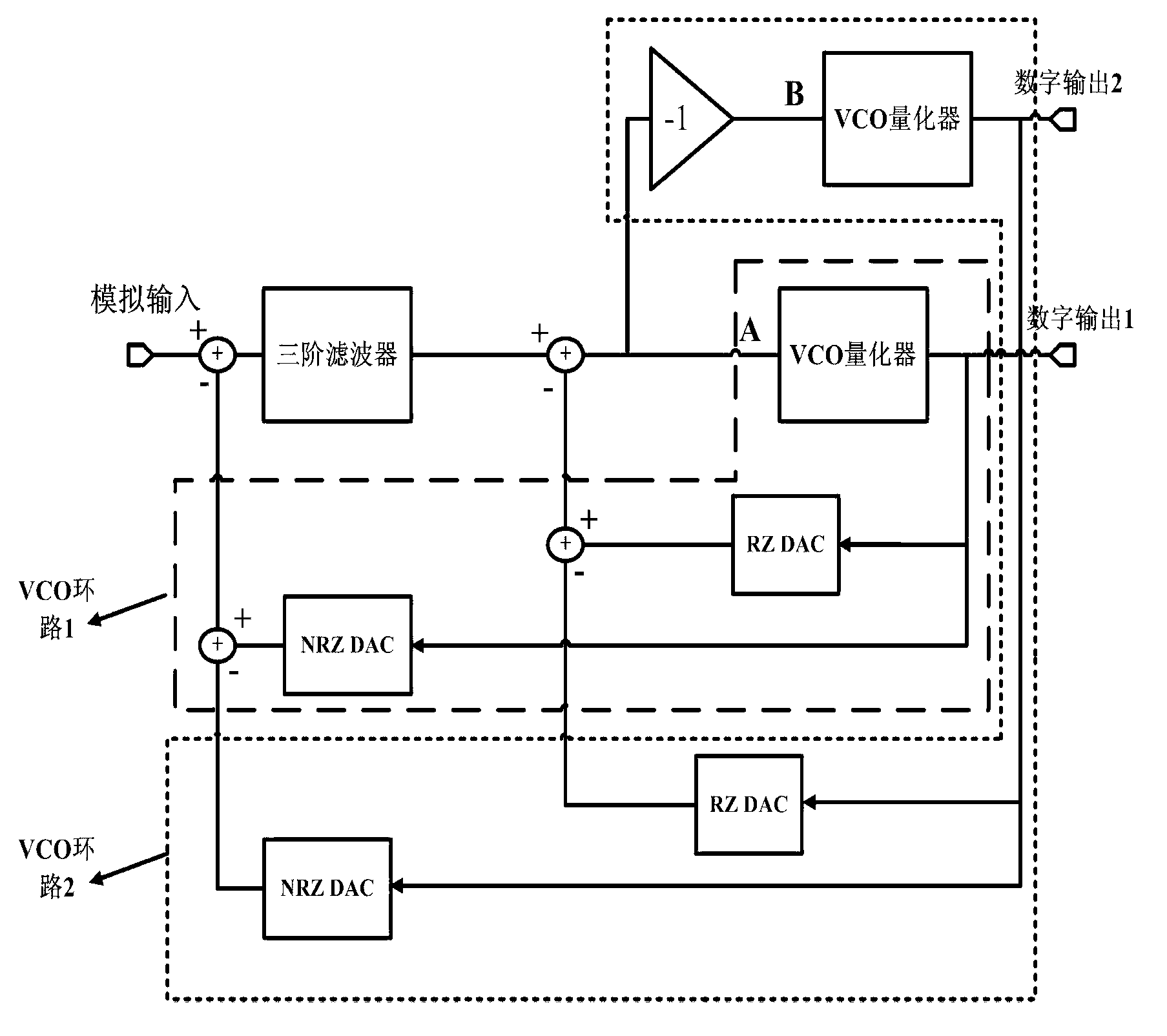

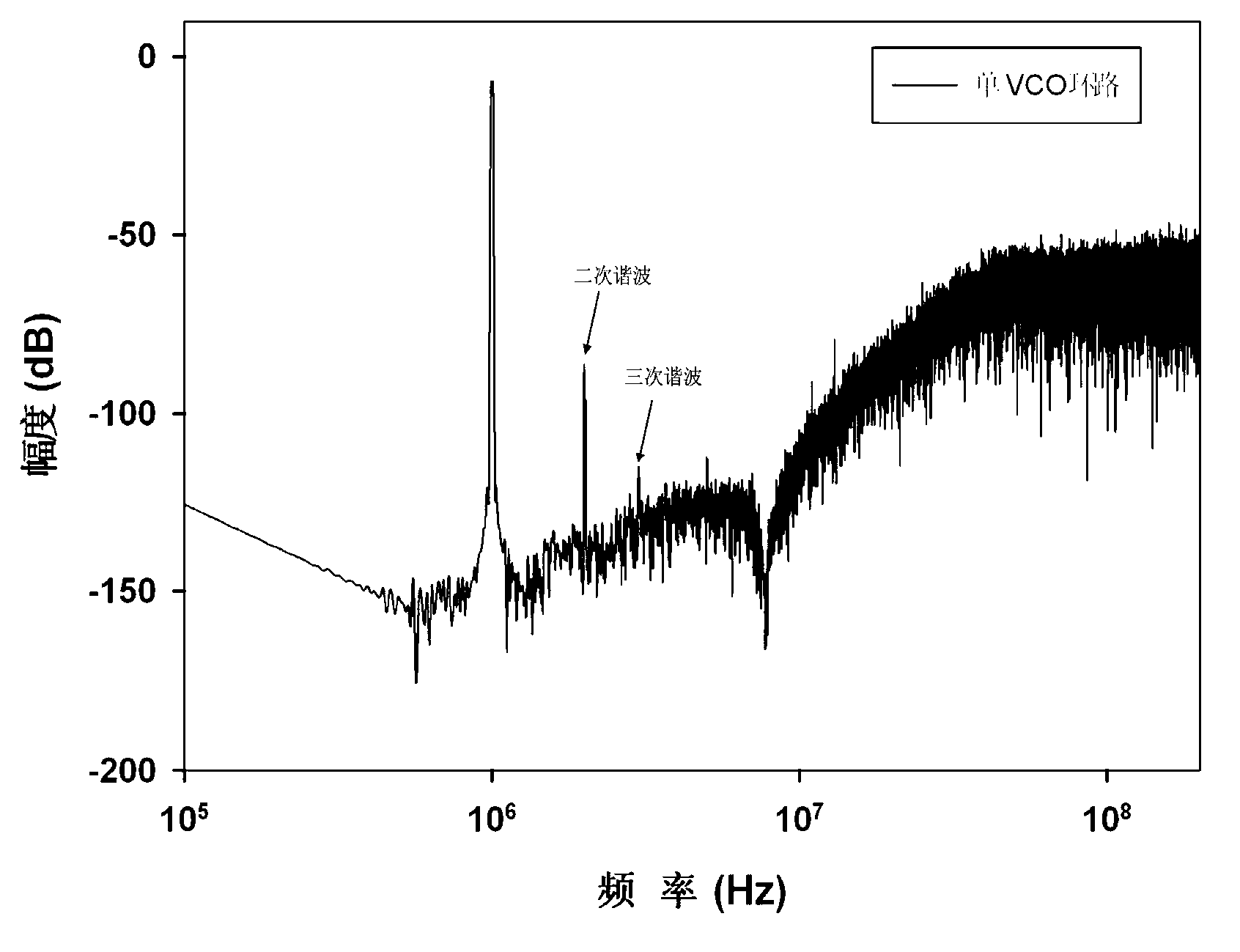

Dual-voltage-controlled oscillator loop-based Sigma-Delta analog to digital converter

ActiveCN102801425ASuppress nonlinear distortionReduce nonlinear distortionAnalogue conversionAnalogue-digital convertersNonlinear distortionLow-pass filter

The invention discloses a dual-voltage-controlled oscillator (VCO) loop-based Sigma-Delta analog to digital converter which belongs to the technical field of analog integrated circuits, in particular relates to a Sigma-Delta analog to digital converter comprising two VCO loops and a three-order filter. The Sigma-Delta analog to digital converter comprises a three-order low-flux filter with two feedforward branches and a feedback branch, two VCO quantizers, an NRZ DAC (Non Return To Zero Digital to Analog Converter) and an RZ DAC, and an adder-subtractor device. According to the VCO loop-based Sigma-Delta analog to digital converter, through the dual VCO loops, the even harmonics of the VCO are eliminated, the nonlinear distortion is reduced, and the adopted three-order low-flux filter comprising the two feedforward branches and the feedback branch, on the premise of ensuring system stability, the nonlinear distortion and the quantizing noise of the VCO quantizers can be further reduced. The Sigma-Delta analog to digital converter can be suitable for being applied at high speed, higher precision and low power consumption when working at a low power supply voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

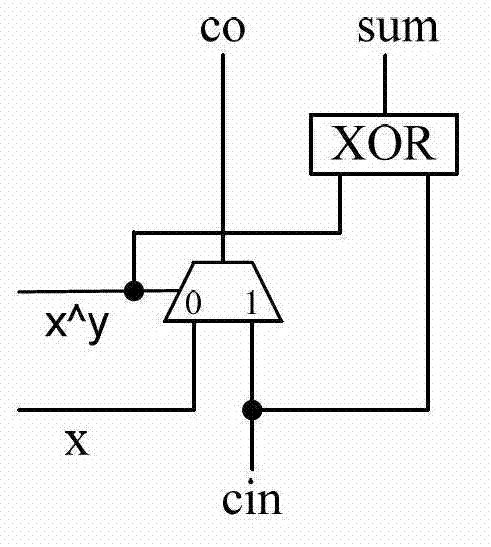

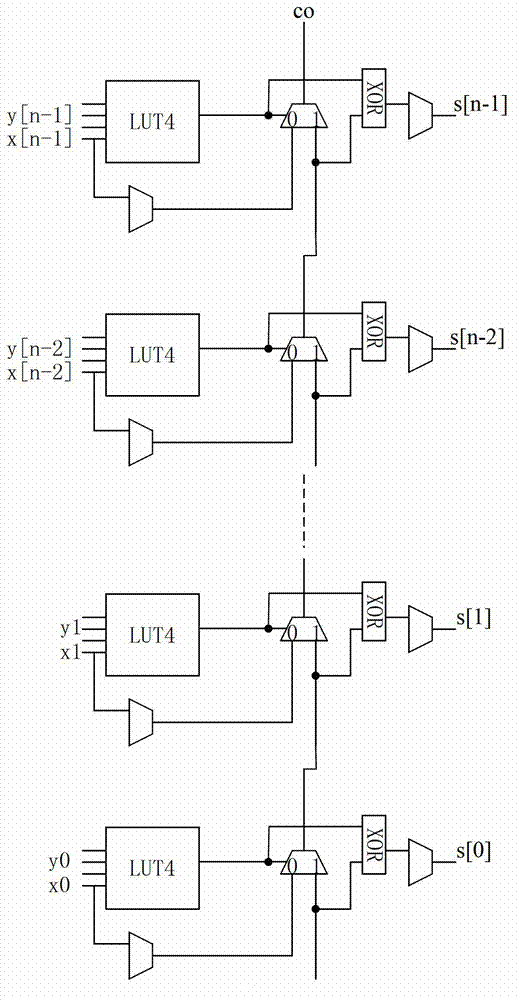

Binary system adder-subtractor based on enhancement-type LUT (look up table) 5 structure

ActiveCN103176766AImprove area utilizationScalableComputation using non-contact making devicesControl signalResource utilization

The invention relates to a binary system adder-subtractor, and discloses a binary system adder-subtractor based on an enhancement-type LUT (look up table) 5 structure. According to the invention, the binary system adder-subtractor comprises an enhancement-type 5 input LUT structure, a carry chain structure and a standard xor structure; addition and subtraction logic of two digits is realized for the LUT5 structure by utilizing a LUT 4 with two 3 input share; the port resource utilization ratio achieves 4 / 5; when controllable addition and subtraction logic (with addition and subtraction control signal input) is realized, the port resource utilization ratio even achieves 5 / 5=100%; compared with the existing individual 4 input LUT, one digit addition and subtraction is realized, the port utilization ratio is increased by 30%, and the area utilization ratio is improved greatly. Additionally, the carry chain structure comprises two carry look ahead structures; two carry chain logic delays are lowered from two traditional selectors to delay time of a tristate phase inverter; the digit transmission delay is reduced; and the working frequency of the adder-subtractor is improved.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

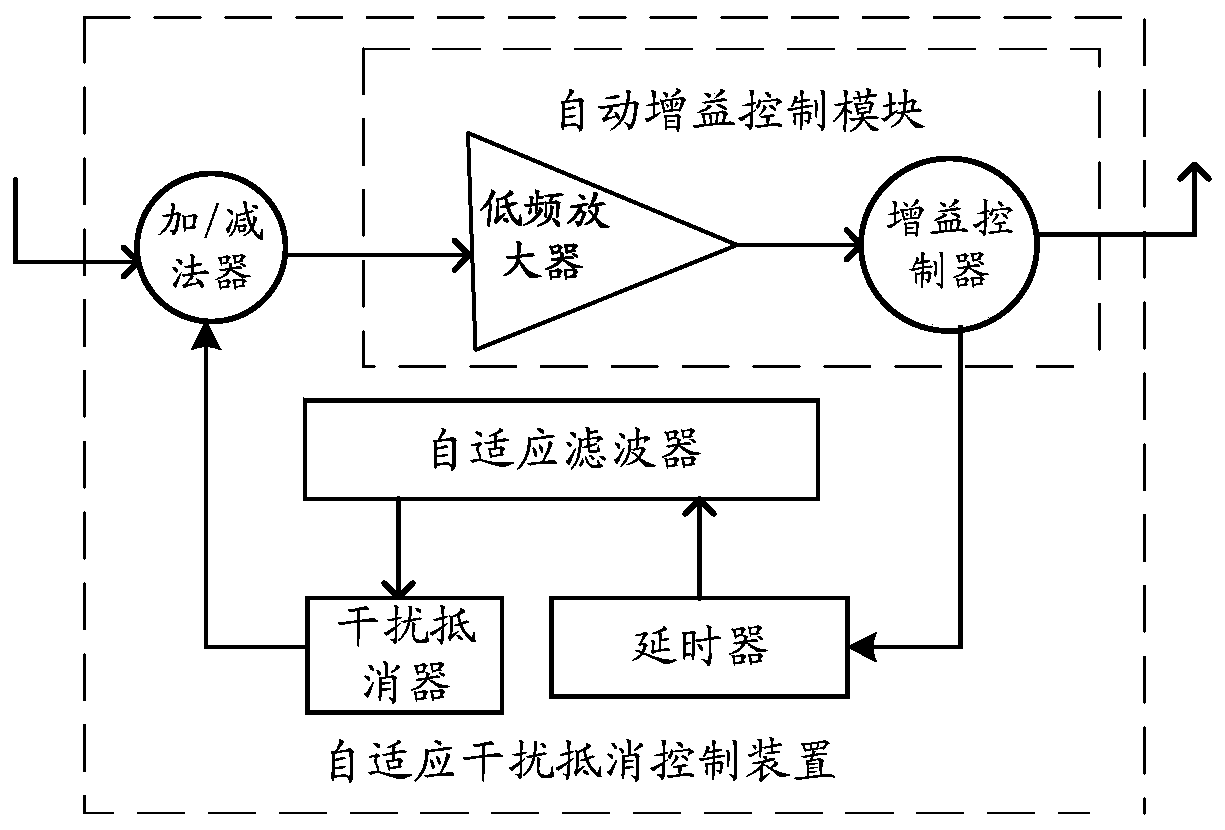

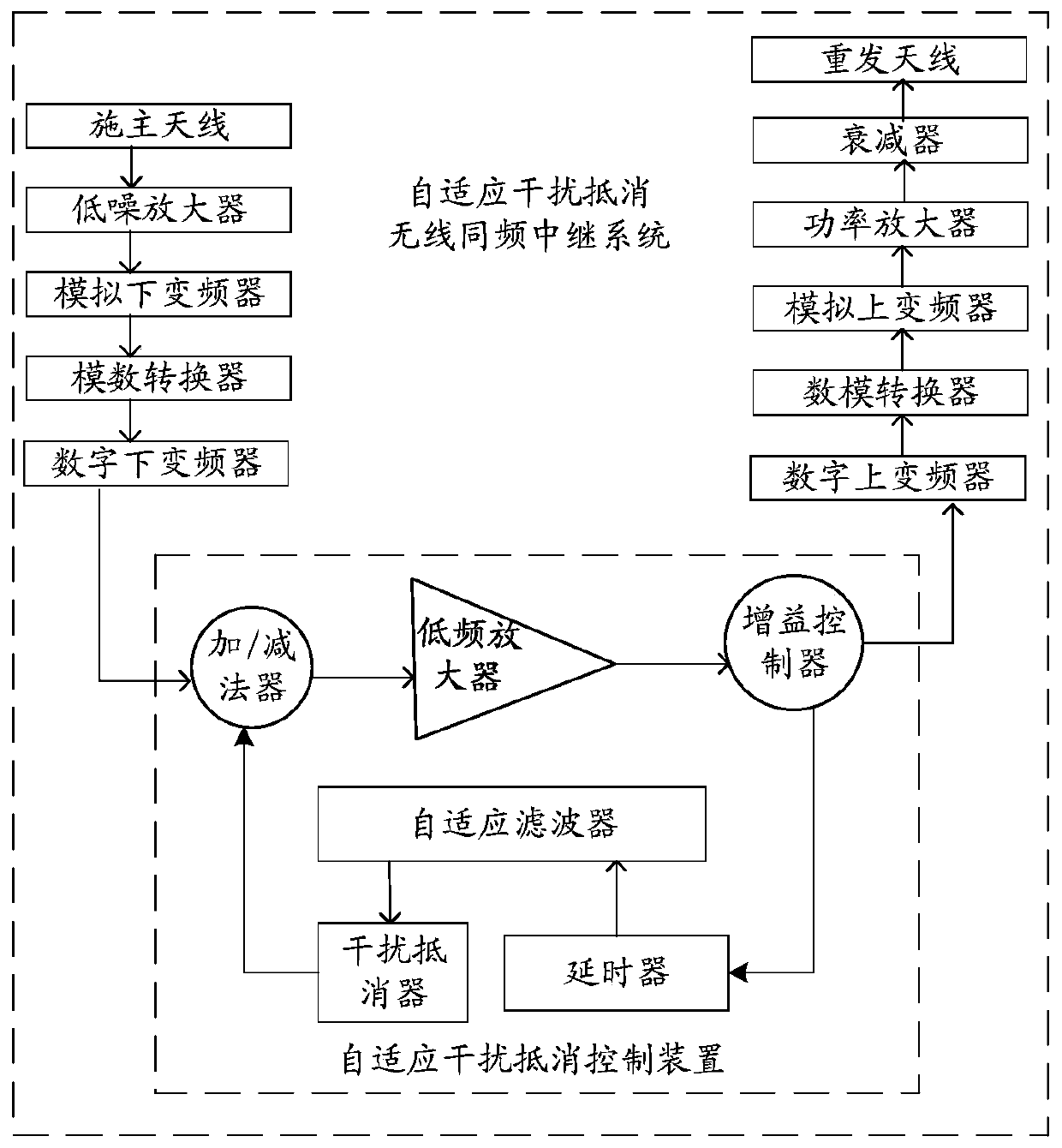

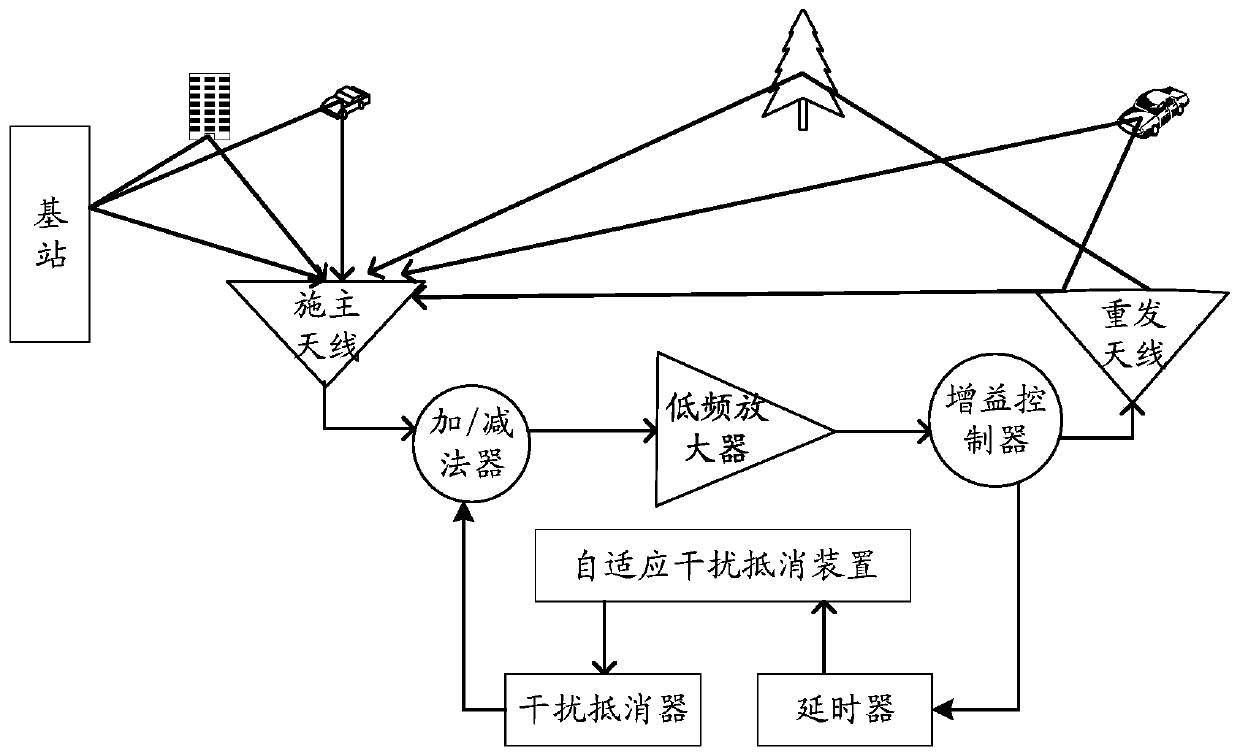

Self-adaptive interference cancellation control device, system and method

PendingCN110868235ASolve the problem of insufficient isolationEliminate some issues caused by feedback noiseRadio transmissionInterference cancellerAdaptive filter

The invention provides a self-adaptive interference cancellation control device which is used in wireless same-frequency relay equipment. The self-adaptive interference cancellation control device comprises an adder / subtractor, an automatic gain control module, an adaptive filter, an interference canceller and a delayer. One input end of the adder / subtracter is connected with a digital down converter in the wireless same-frequency relay equipment; the output end of the adaptive filter is connected with the other input end of the adder / subtracter through the interference canceller; the output end of the adder / subtractor is connected with the input end of the automatic gain control module, one output end of the automatic gain control module is connected with the input end of the self-adaptive filter through the delayer, and the other output end of the automatic gain control module is connected with a digital up-converter in the wireless same-frequency relay device. The invention furtherprovides a self-adaptive interference cancellation wireless same-frequency relay system and a self-adaptive interference cancellation control method, and the self-excitation problem of the wireless same-frequency relay equipment can be effectively solved.

Owner:福州智程信息科技有限公司

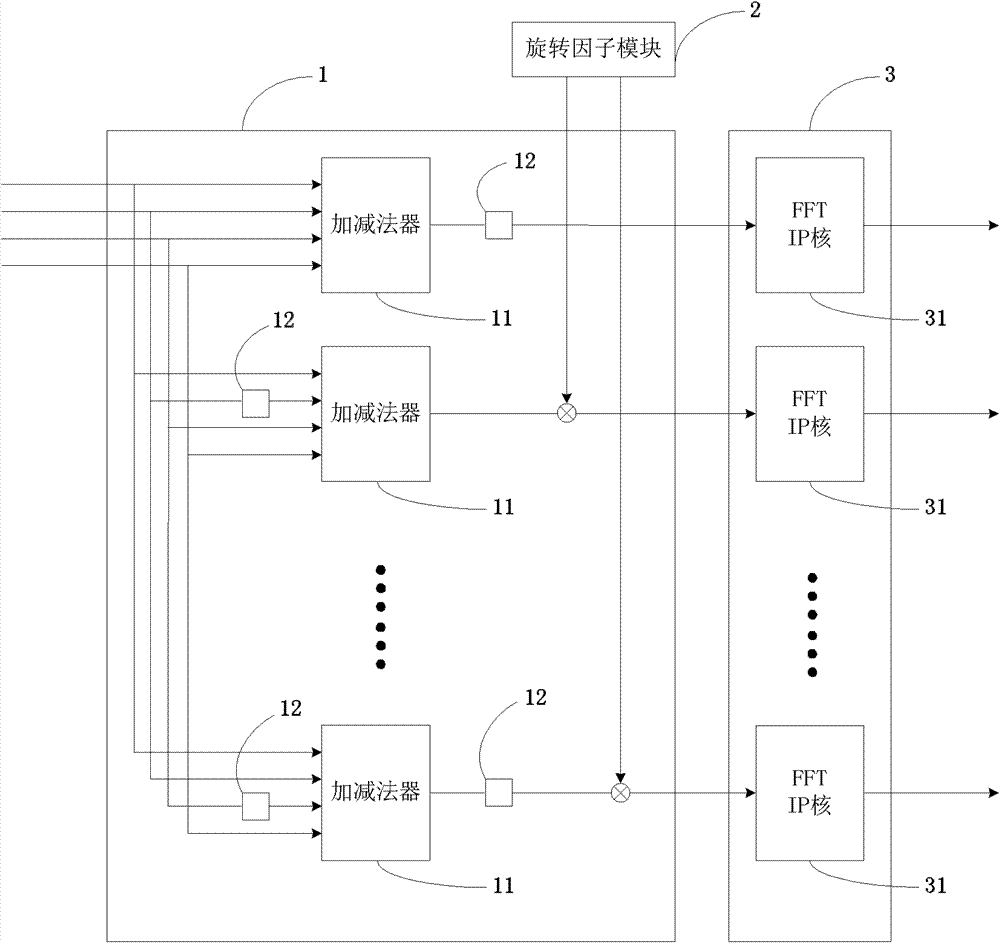

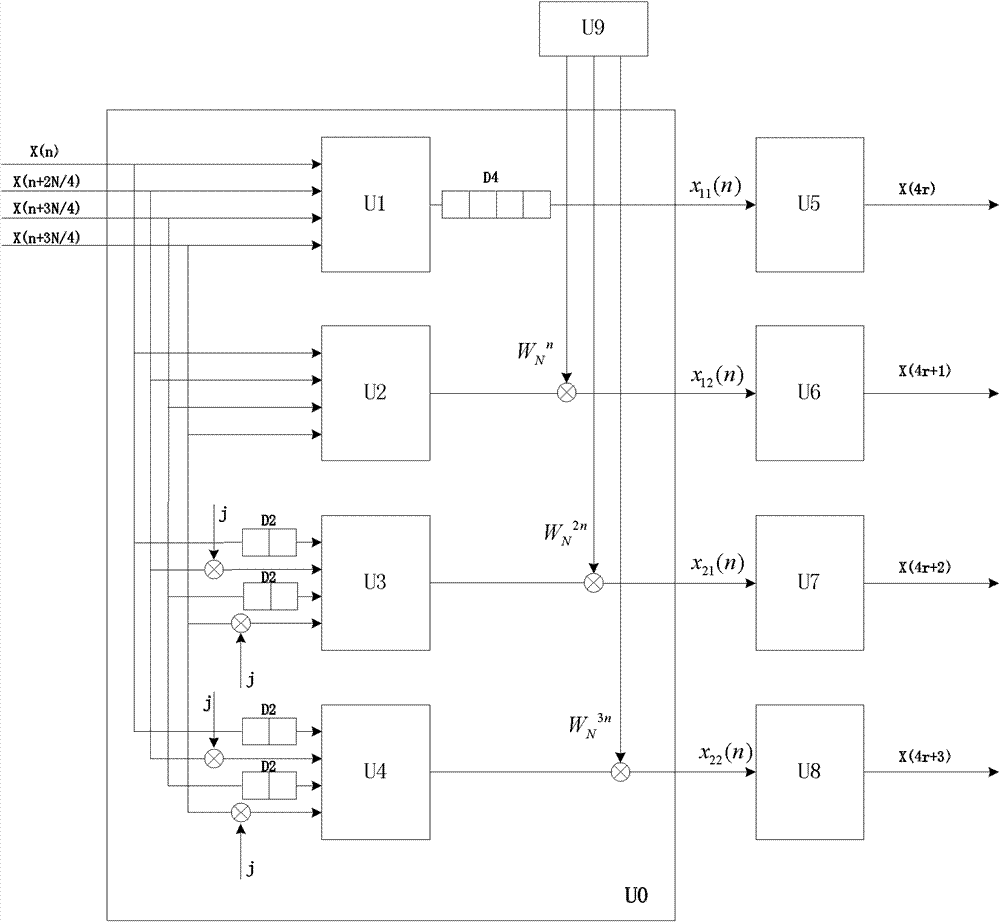

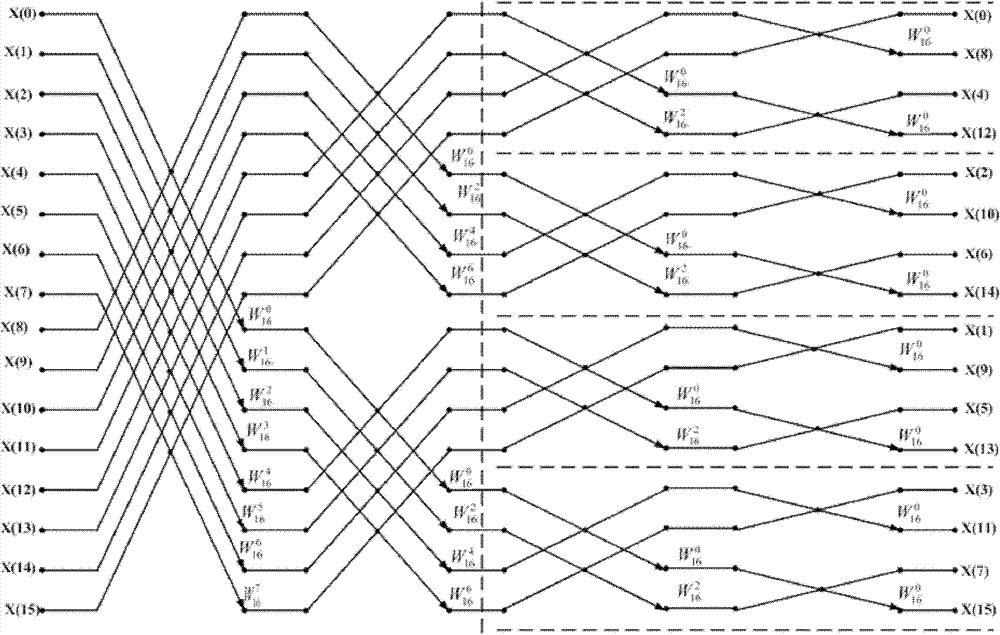

Base-2 parallel FFT (fast Fourier transformation) processor based on DIF (decimation in frequency) and processing method thereof

InactiveCN102955760AImprove processing speedImprove system throughputComplex mathematical operationsFast Fourier transformIntellectual property

The invention discloses a base-2 parallel FFT (fast Fourier transformation) processor based on DIF (decimation in frequency) and a processing method thereof. The processor comprises a parallel FFT input arithmetic unit, a twiddle factor module and an FFT processor. The parallel FFT input arithmetic unit comprises 2M parallel adder--subtractors and delay units for achieving time synchronization, wherein M is a nonnegative integer. The FFT processor comprises 2M parallel FFTIP (fast Fourier transform intellectual property) cores. The 2M parallel adder-subtractors are in one-to-one correspondence connection with the 2M parallel FFTIP cores. An output sequence of each adder-subtractor multiplies a corresponding twiddle factor in the twiddle factor module and is input to one FFTIP core in one-to-one correspondence connection with the adder-subtractor. The delay units are disposed at input ends or / and output ends of the adder-subtractors in the FFT input arithmetic unit. The base-2 parallel FFT processor based on DIF splits long sequences into short sequences, FFT of the short sequences is achieved by the FFTIP cores, and accordingly processing speed and system throughput are increased linearly.

Owner:SHANGHAI BOOM FIBER SENSING TECH

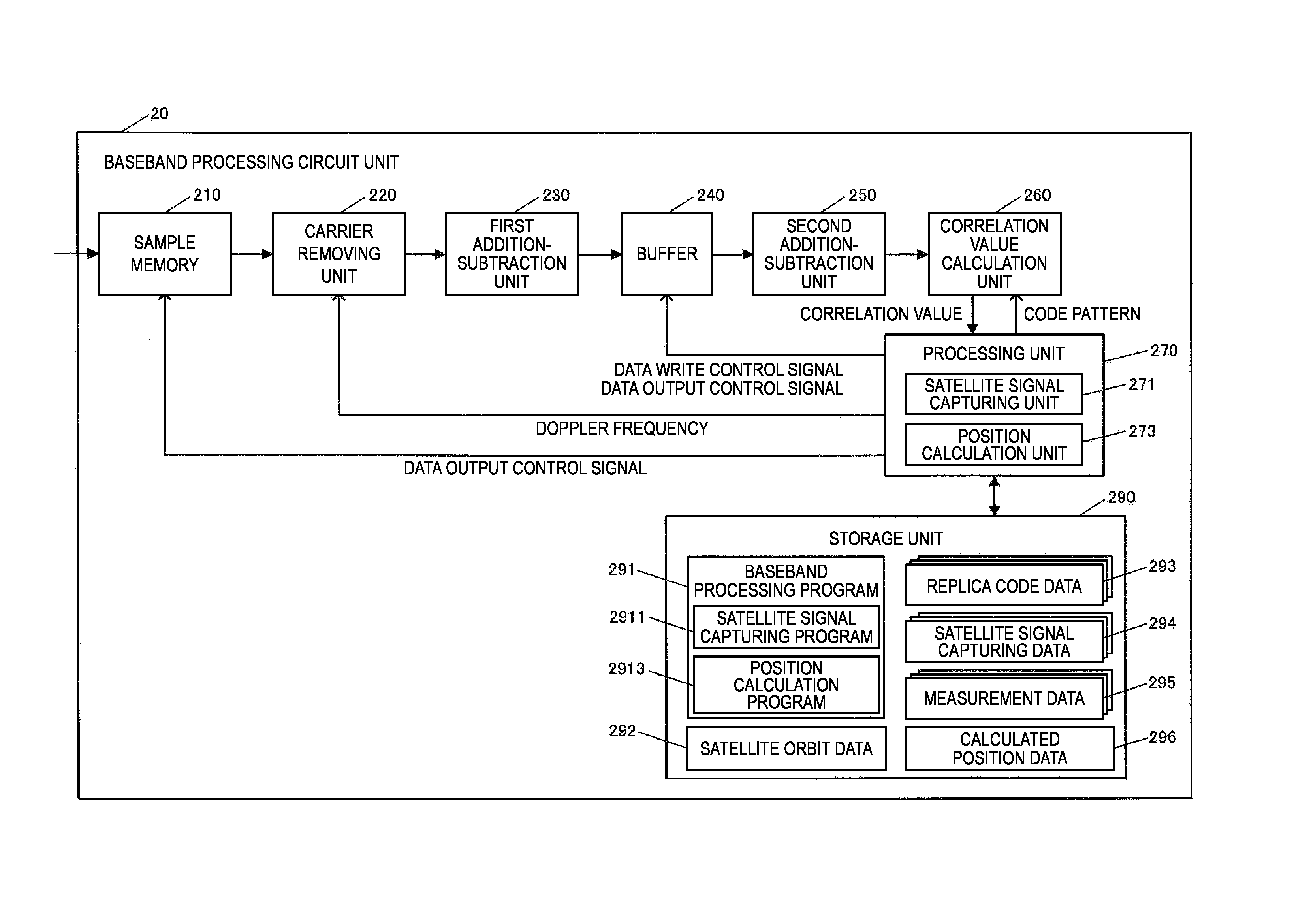

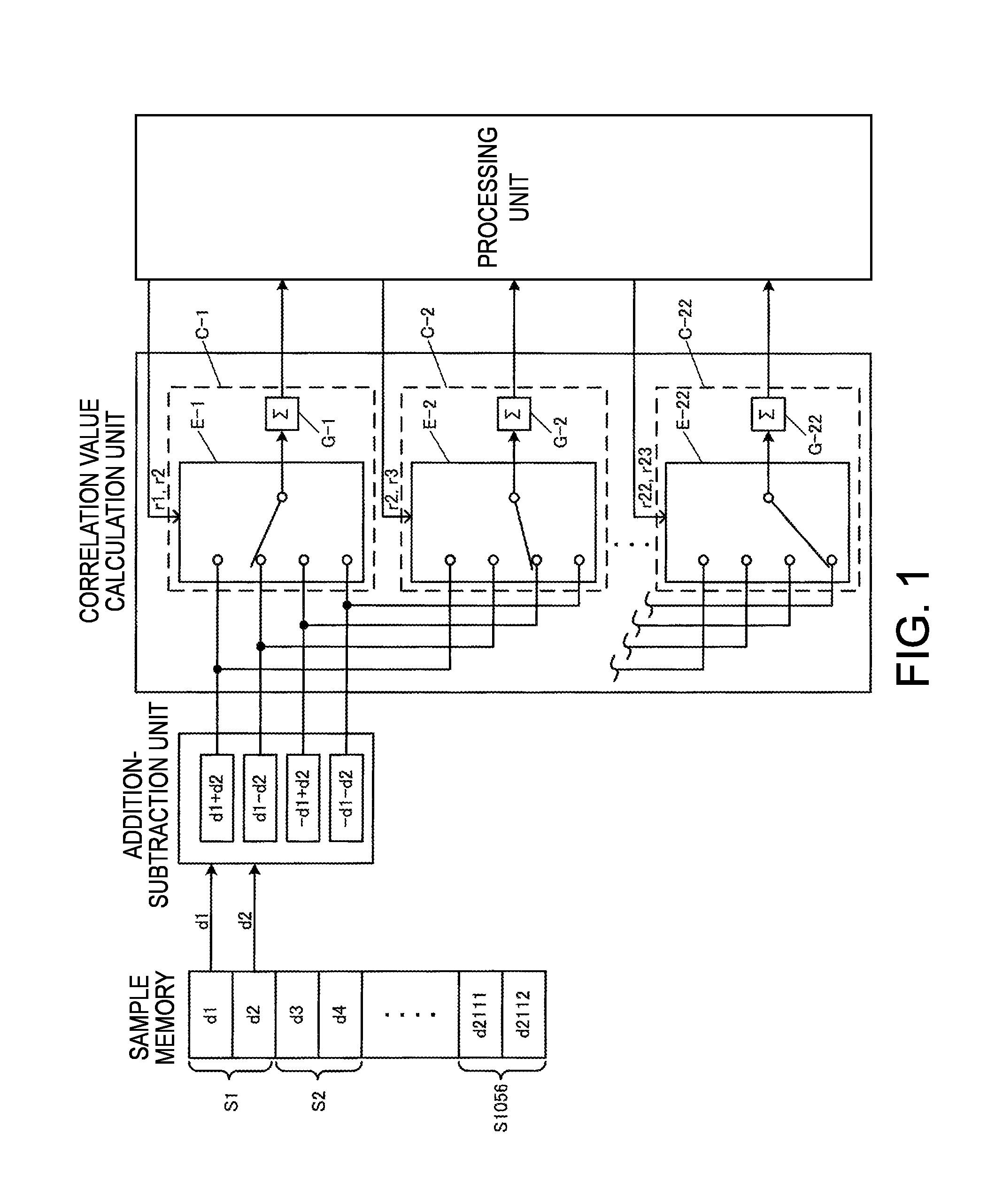

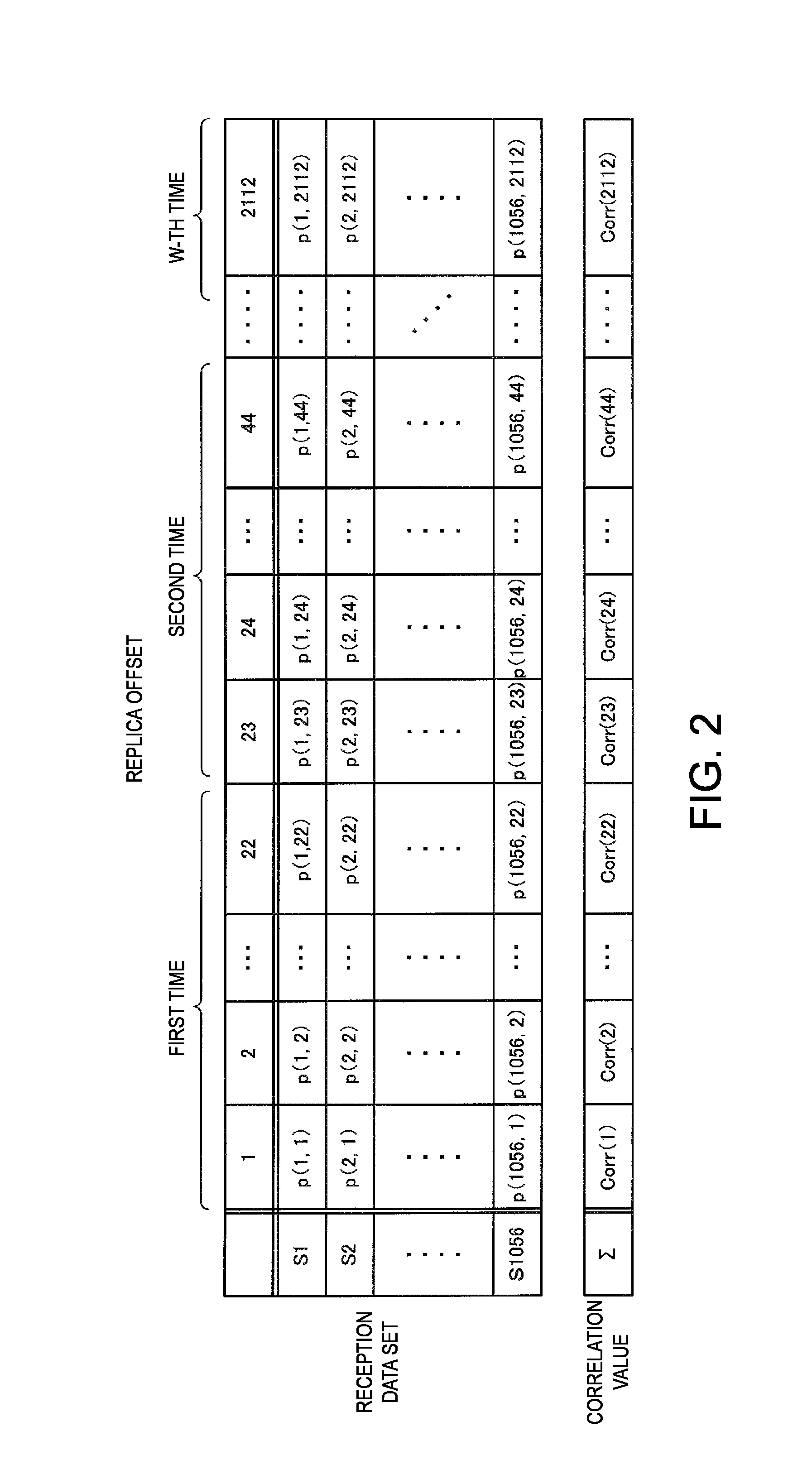

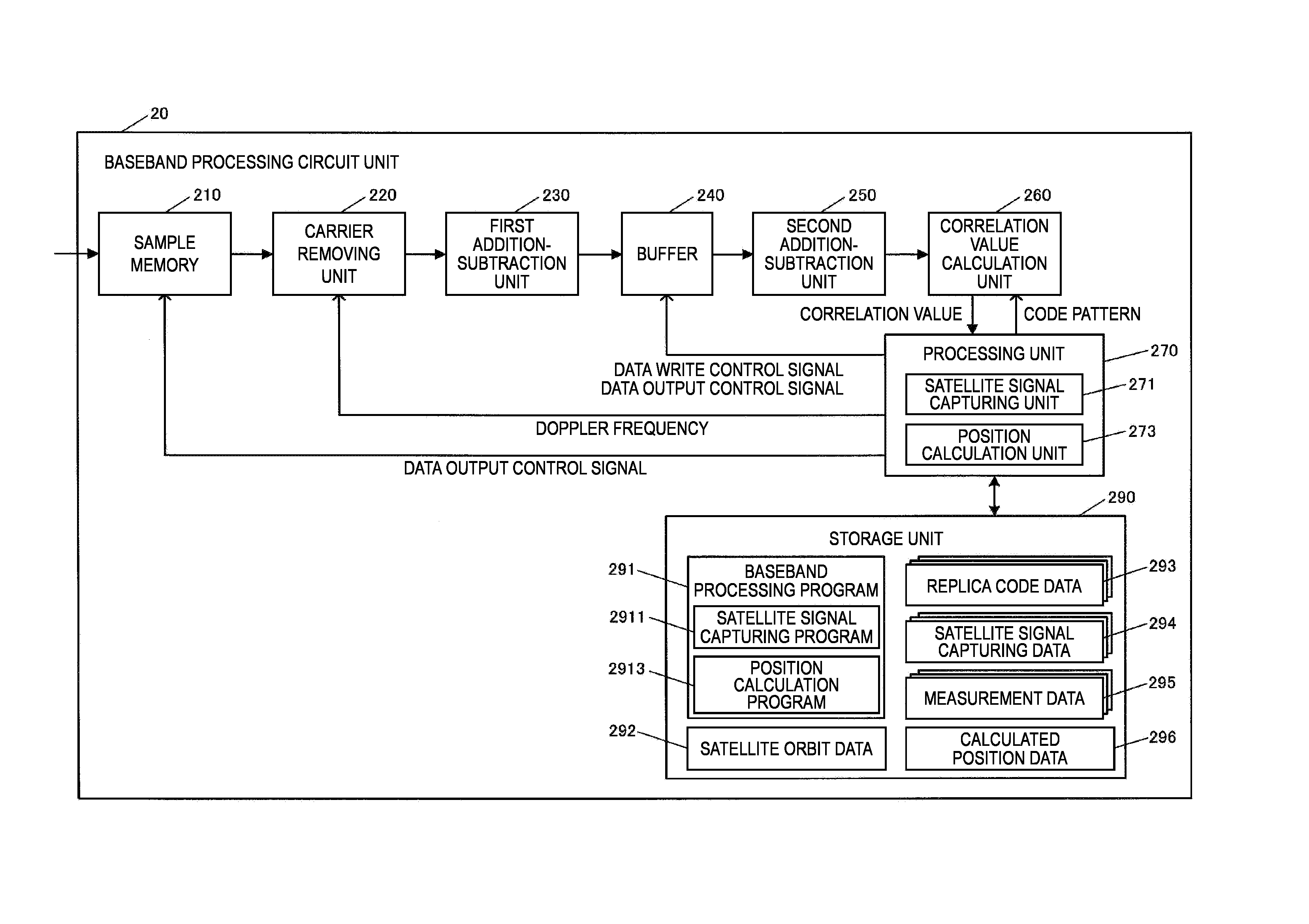

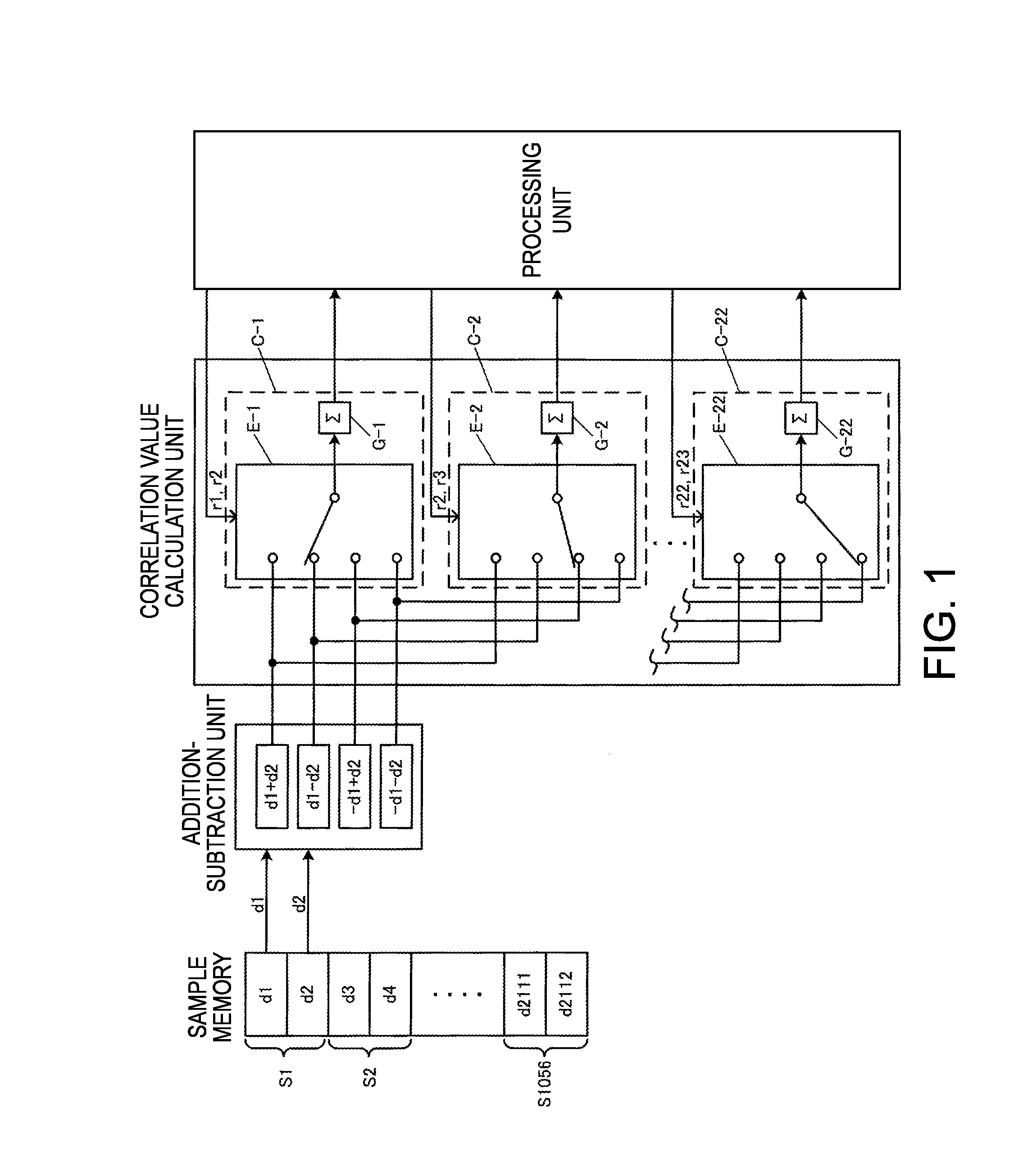

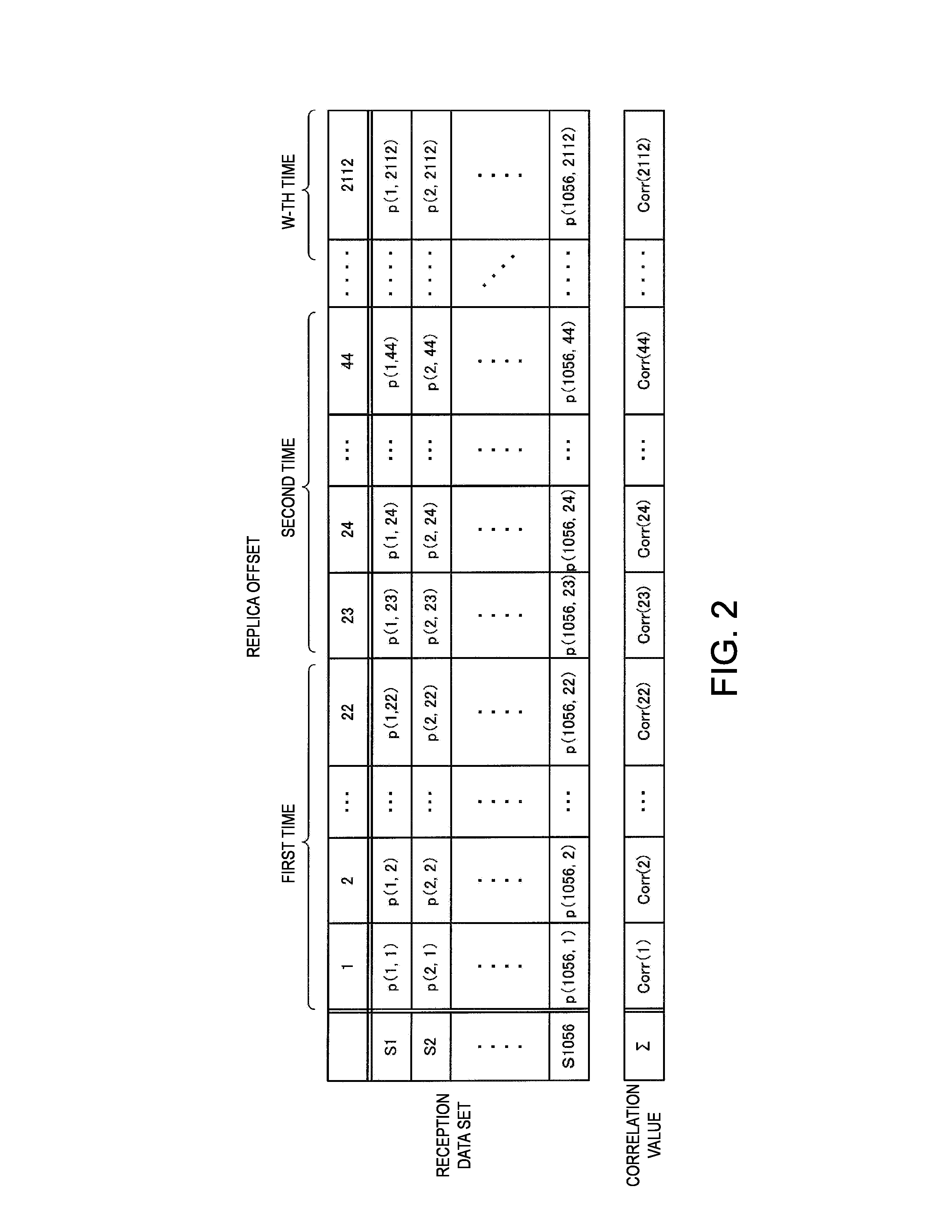

Method of capturing satellite signal and device for capturing satellite signal

InactiveUS8855173B2Reduce power consumptionSimple circuit configurationSatellite radio beaconingTransmissionAdder–subtractorVIT signals

A method of acquiring a satellite signal includes calculating a correlation result of a reception signal from a GPS satellite and a replica code using an output value of one adder-subtractor for a combination of addition and subtraction corresponding to time-series change in code values of the replica code from among a plurality of adder-subtractors for addition-subtraction of sampling values obtained by sampling the reception signal in a time series with different combinations of addition and subtraction, and acquiring the satellite signal of the GPS satellite using the correlation result.

Owner:SEIKO EPSON CORP

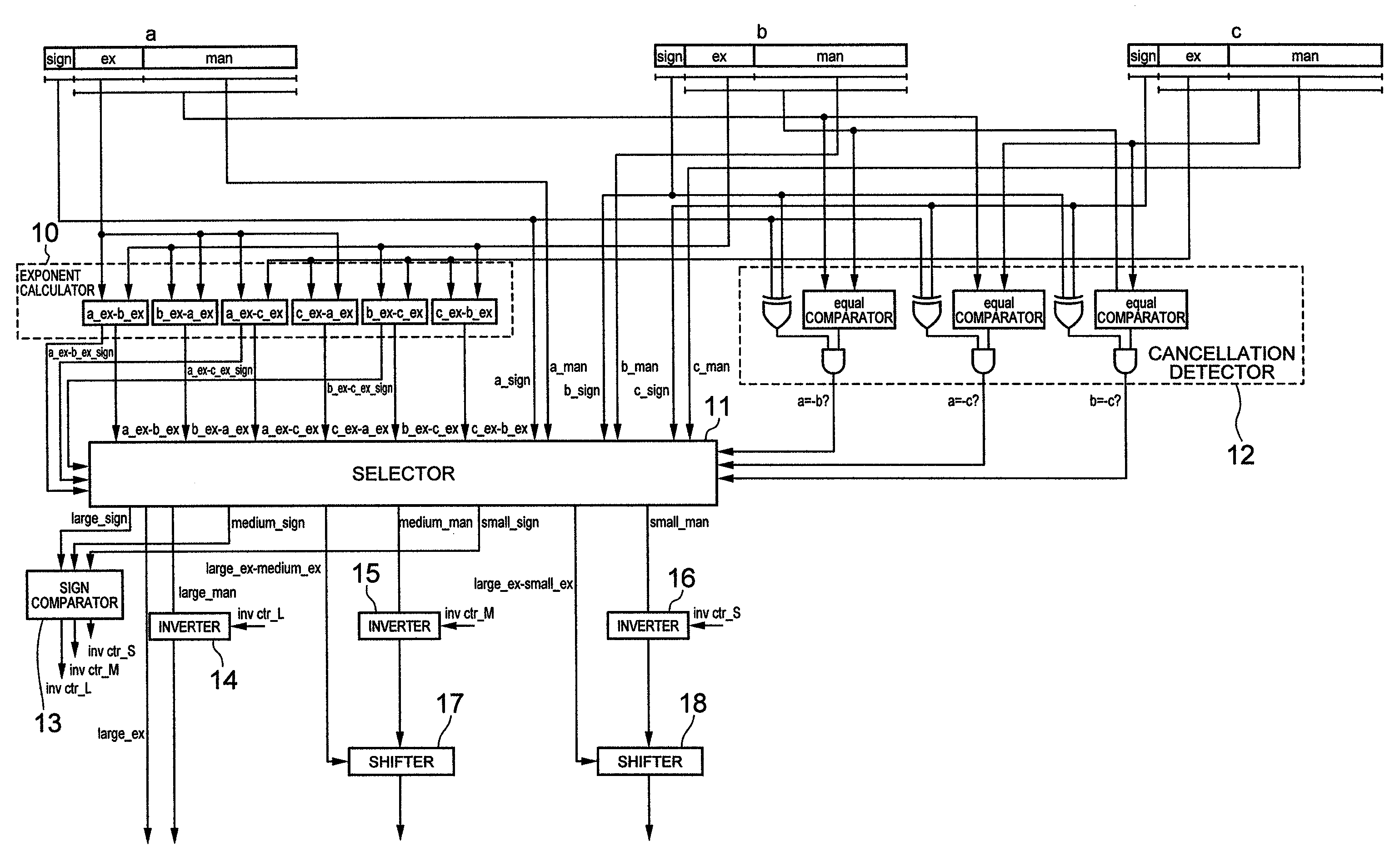

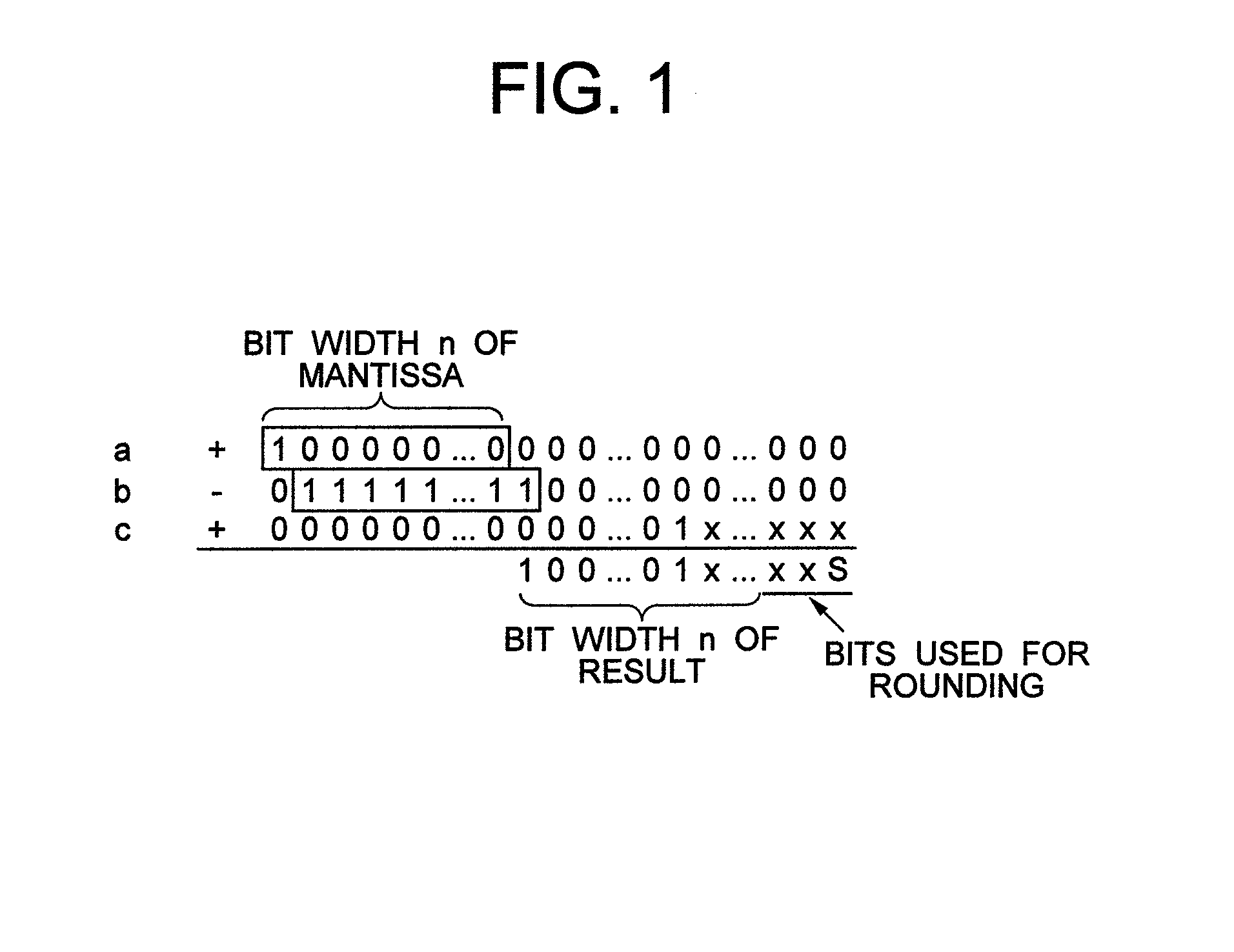

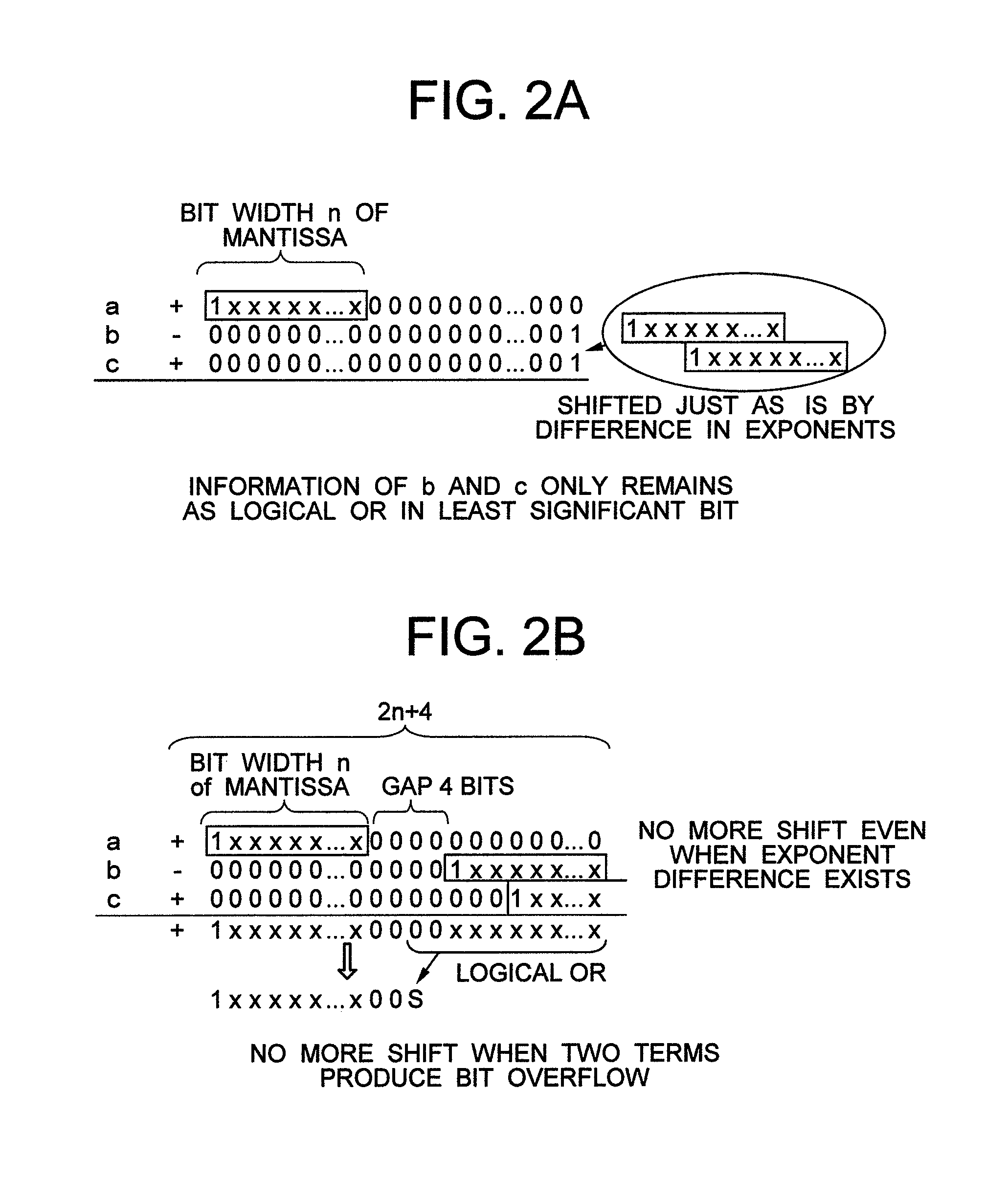

Three-term input floating-point adder-subtractor

InactiveUS8185570B2Computations using contact-making devicesError detection/correctionAdder–subtractorRight shift

The adder-subtractor includes a pre-processing circuit which divides three inputted terms into a mantissa having an exponent of maximum value, mantissa having an exponent of intermediate value and mantissa having an exponent of minimum magnitude and outputting a mantissa obtained by right-shifting the mantissa having the exponent of intermediate value and the mantissa having the minimum exponent of 2n+3 bits and adjusting digits and the mantissa having the maximum exponent, which reduces the mantissas from three to two terms, which carries out addition on the mantissas of the two terms, a normalization circuit which makes left shift so that the most significant bit becomes 1, a rounding circuit which uses an (n+3)th bit from the most significant bit as a new sticky bit, takes logical OR with the lower bits and performs rounding and an exponent operation unit which outputs a final exponent.

Owner:HITACHI LTD

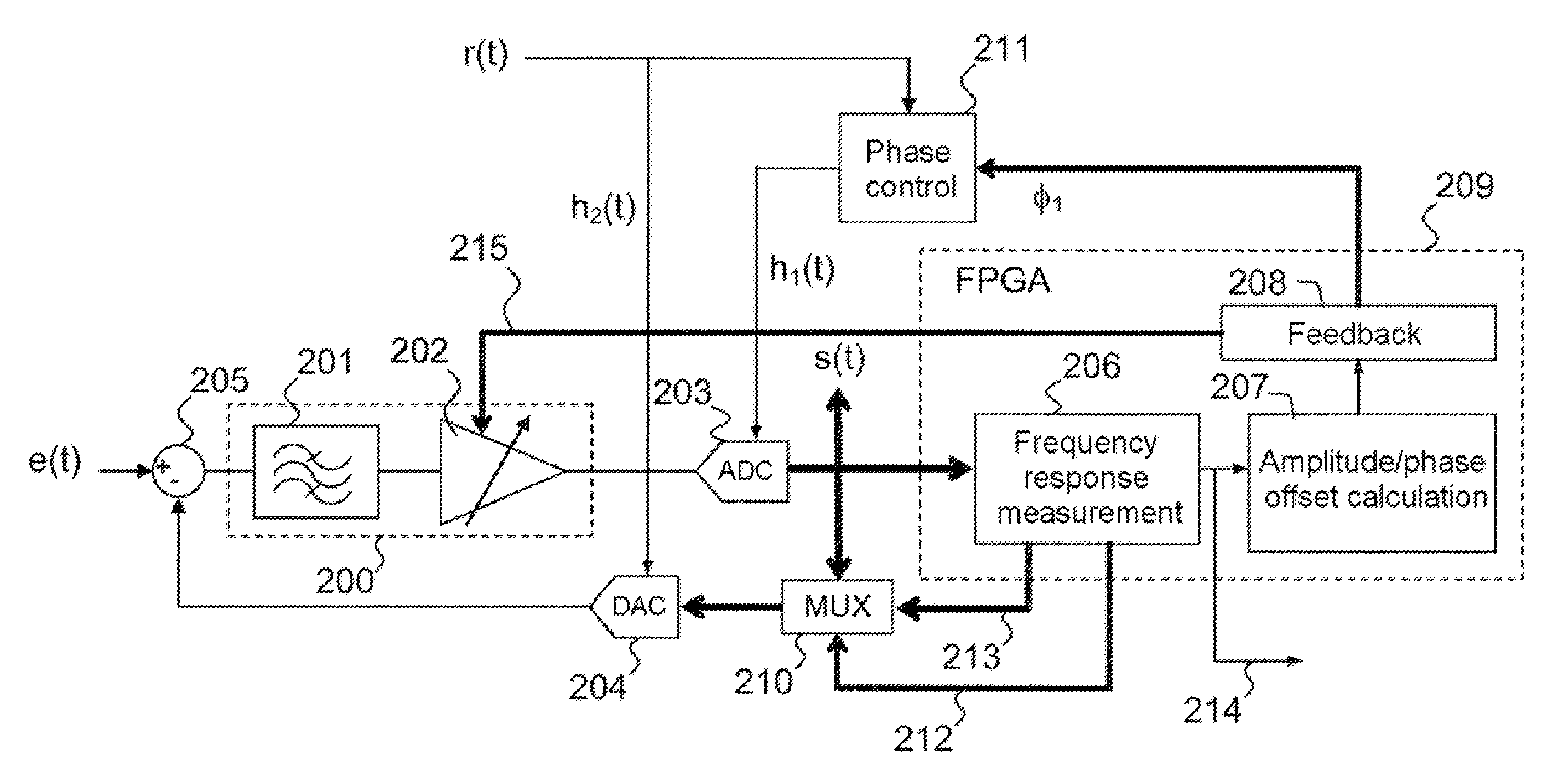

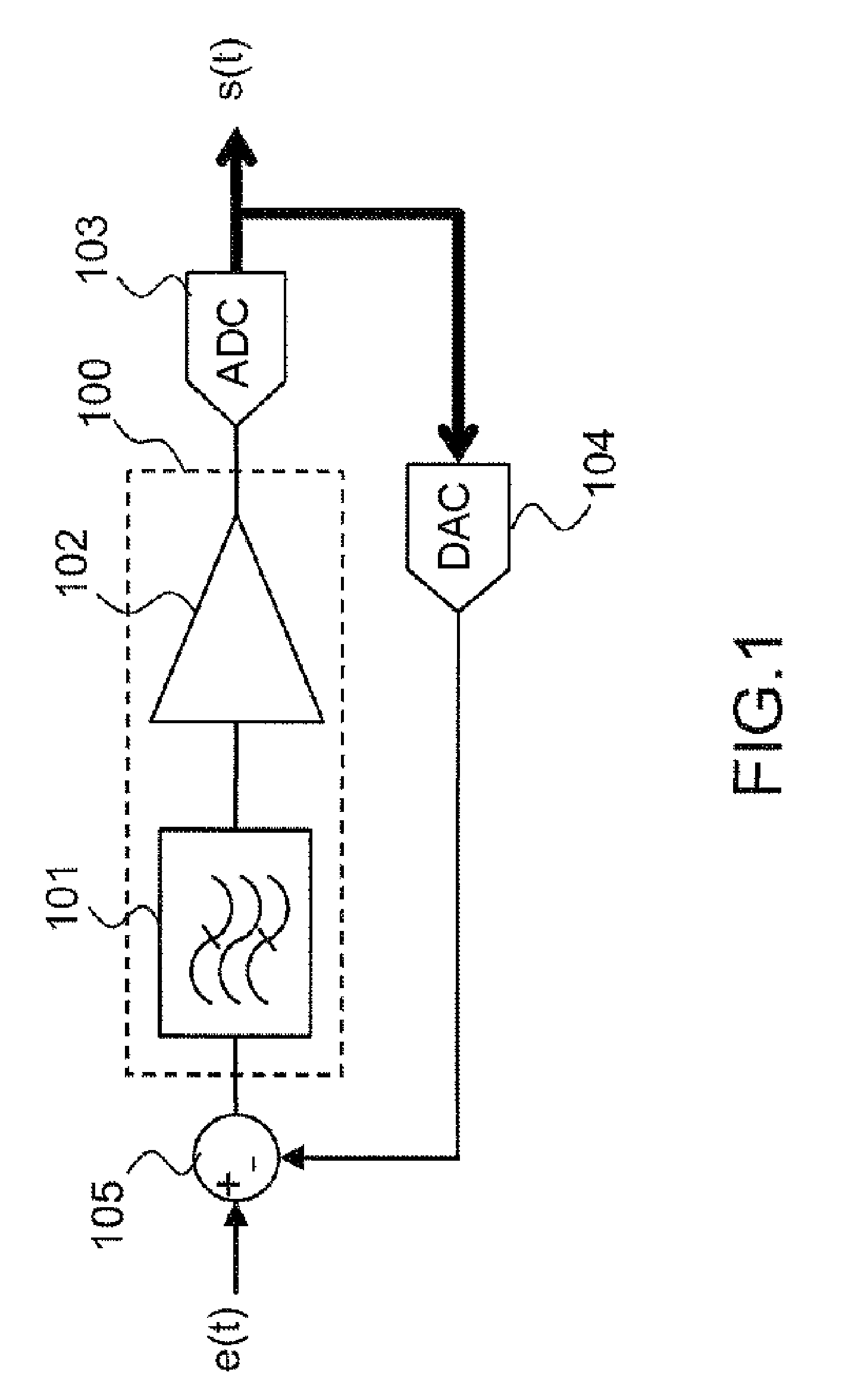

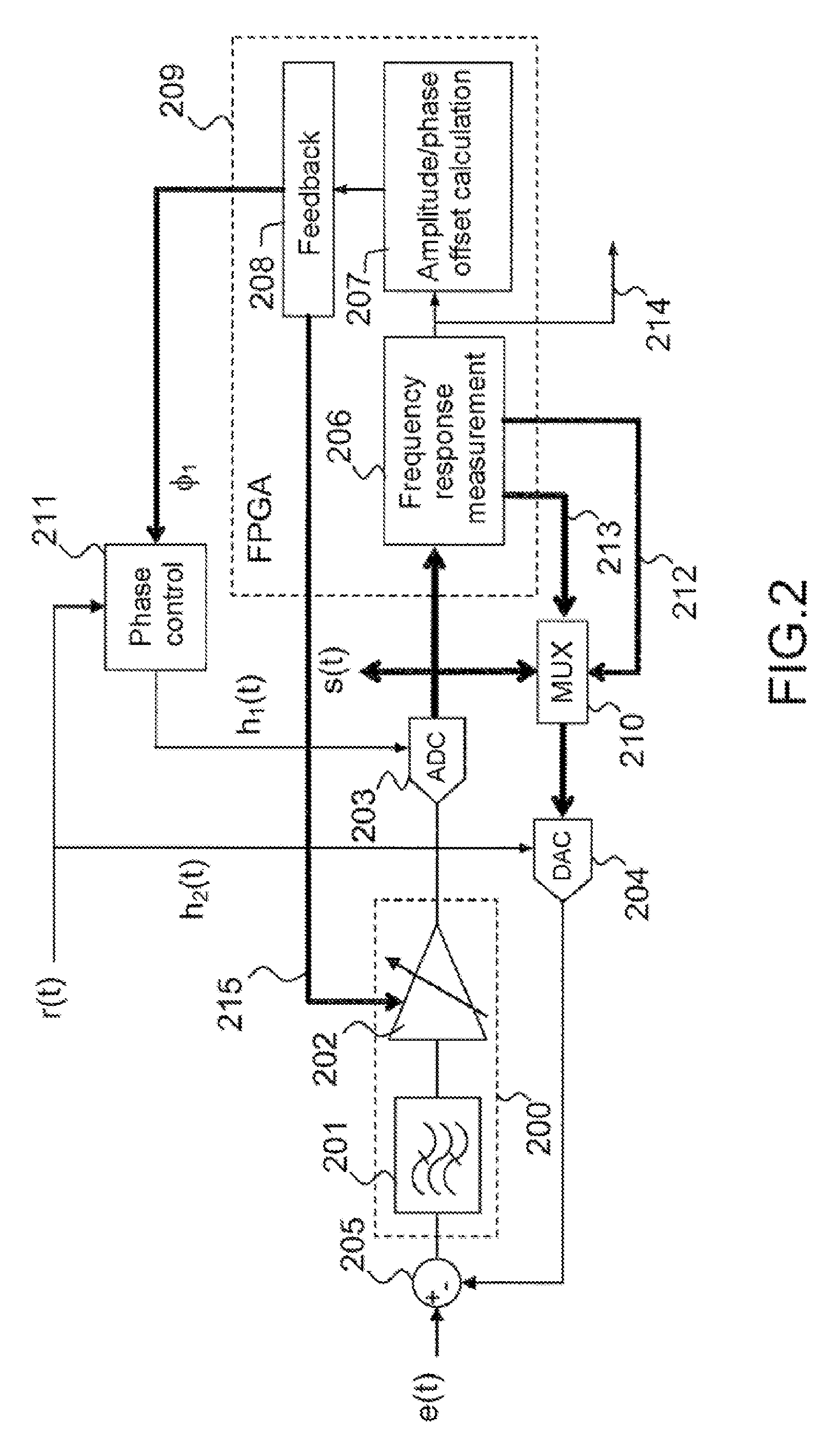

Method for correcting amplitude and phase offsets in a sigma-delta modulator and sigma-delta modulator implementing said method

InactiveUS8614635B2High precisionError minimizationElectric signal transmission systemsAnalogue conversionIntegratorPhase response

In a method for correcting amplitude and phase offsets in a sigma-delta modulator having a loop including an integrator with a filter and an amplifier, an analog-to-digital converter, a digital-to-analog converter, and an adder-subtractor, an open-loop amplitude / phase frequency response of the modulator is estimated digitally. A phase offset value and an amplitude offset value are calculated by comparing the estimated open-loop amplitude / phase response with a reference amplitude / phase frequency response. The phase and gain offsets of the loop are then compensated for according to the estimated offset values. A sigma-delta modulator implements the method.

Owner:THALES SA

Method of capturing satellite signal and device for capturing satellite signal

InactiveUS20130177046A1Reduce power consumptionSimple circuit configurationSatellite radio beaconingTransmissionAdder–subtractorVIT signals

A method of acquiring a satellite signal includes calculating a correlation result of a reception signal from a GPS satellite and a replica code using an output value of one adder-subtractor for a combination of addition and subtraction corresponding to time-series change in code values of the replica code from among a plurality of adder-subtractors for addition-subtraction of sampling values obtained by sampling the reception signal in a time series with different combinations of addition and subtraction, and acquiring the satellite signal of the GPS satellite using the correlation result.

Owner:SEIKO EPSON CORP

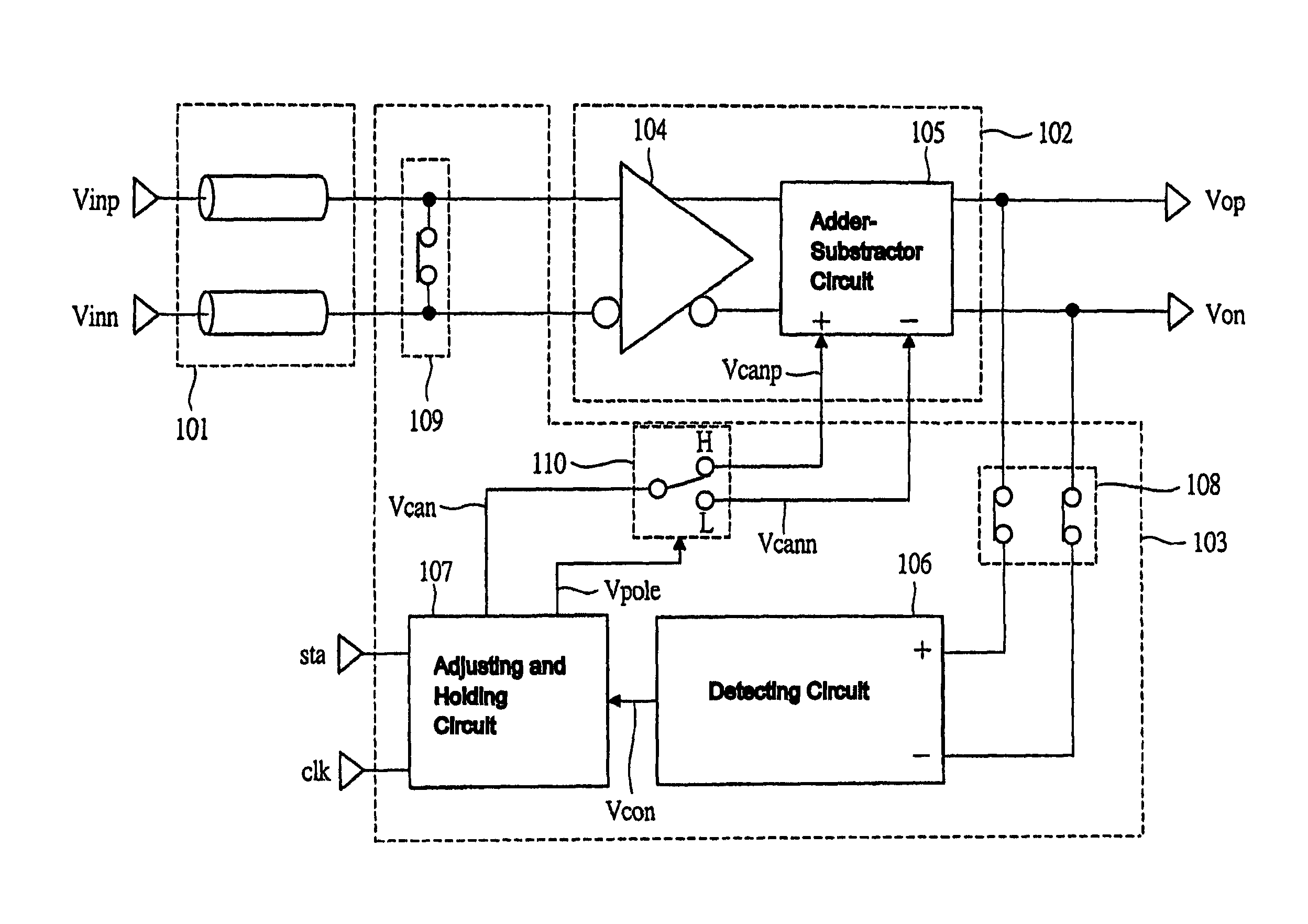

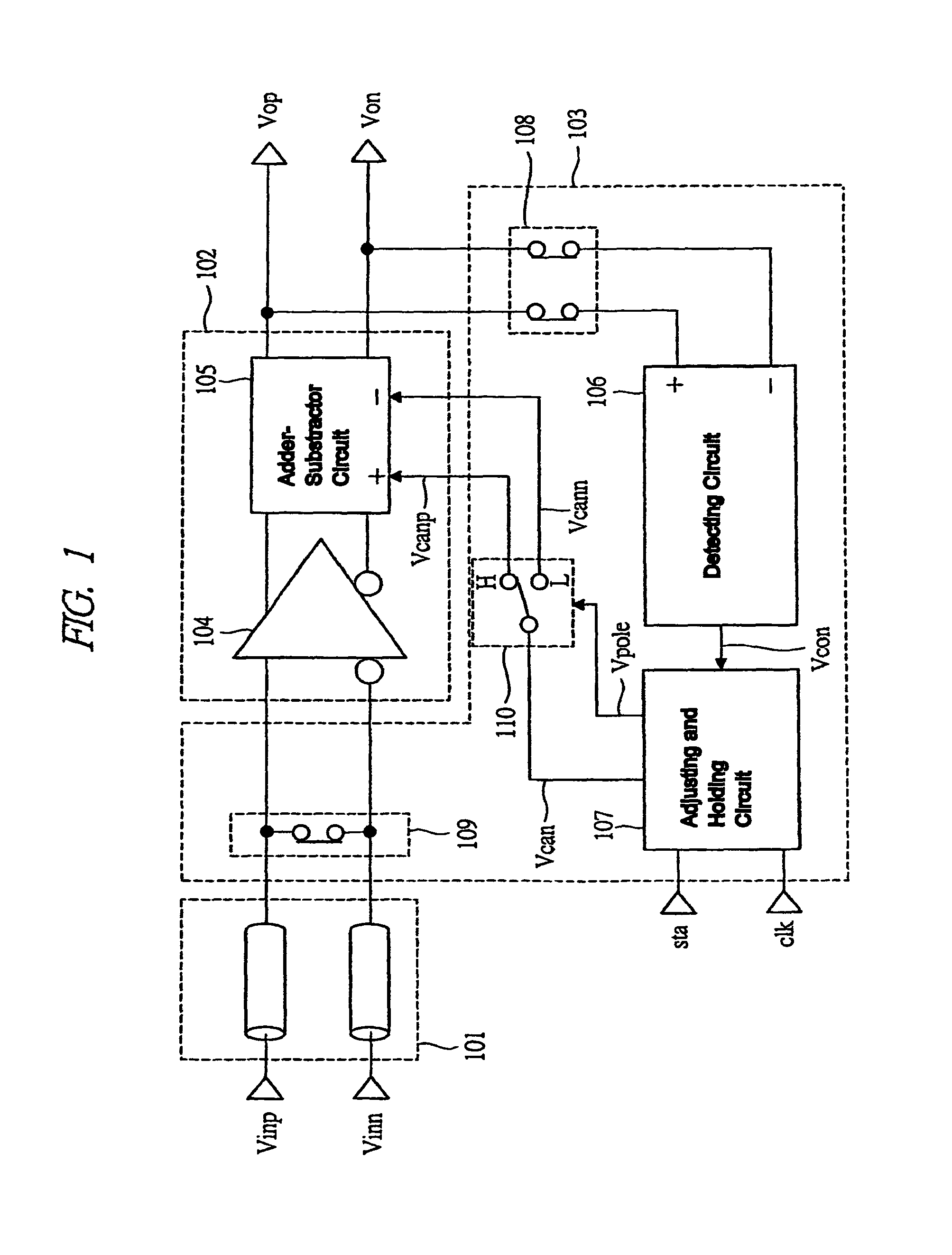

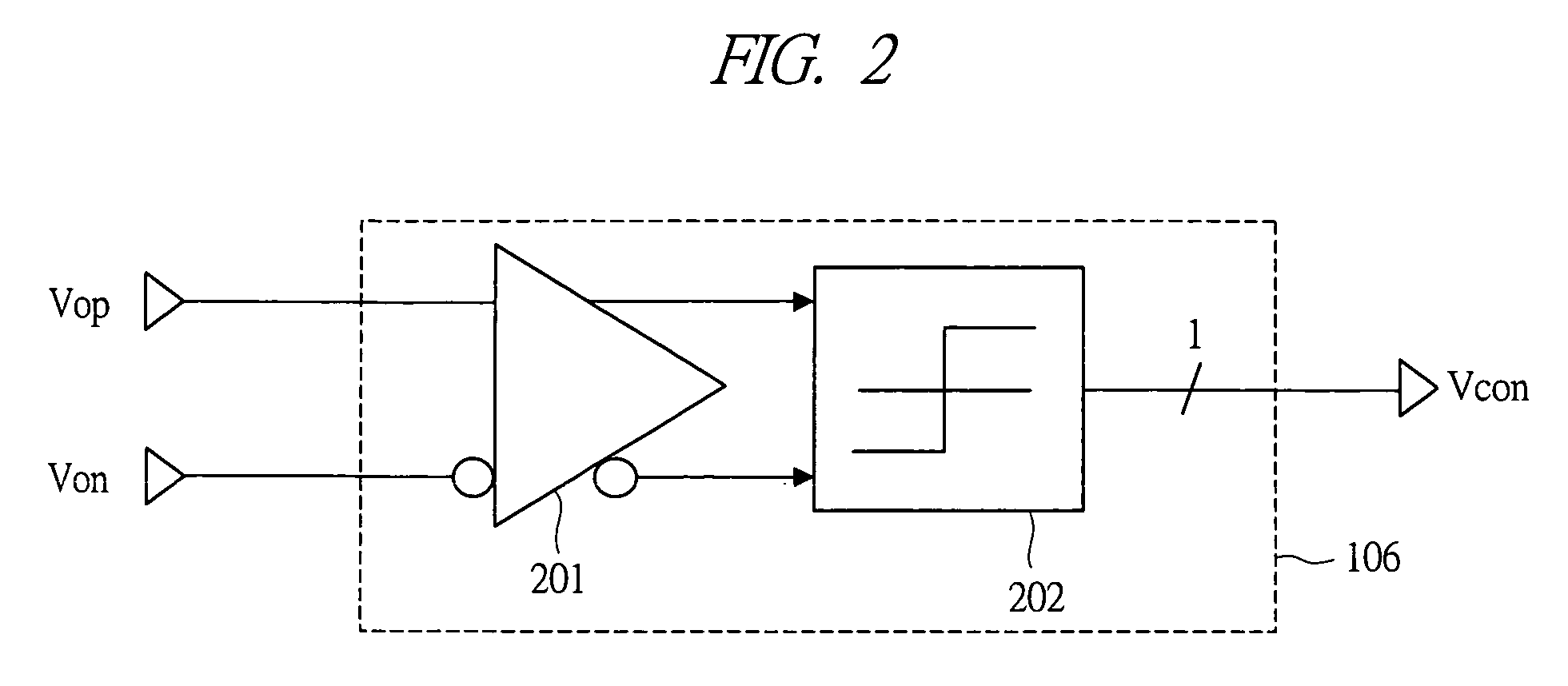

Low offset input circuit and transmission system with the input circuit

InactiveUS8358708B2Lower Offset VoltageAdjustable voltagePower amplifiersLine-transmissionNegative feedbackAdder–subtractor

A low offset input circuit and a signal transmission system which can accommodate a high-speed interface and achieve reduction of an offset voltage are provided. An offset voltage compensating circuit block 103 having an input circuit block 108 including an input circuit 104 and an adder-subtractor circuit block 105, switches 108, 109, a detecting circuit block 106, and an adjusting and holding circuit block 107 is provided. To compensate for an offset voltage of the input circuit block 102, an offset voltage of the input circuit block 102 is detected at the detecting circuit block 106 by turning on the switches 108, 109, and the detected offset voltage is held in the adjusting and holding circuit block 107, and negative feedback of the held offset voltage to the adder-subtractor circuit block 105 is performed. Thereby, signals Vop, Von having compensated offset voltages are outputted from the input circuit block 102.

Owner:HITACHI LTD

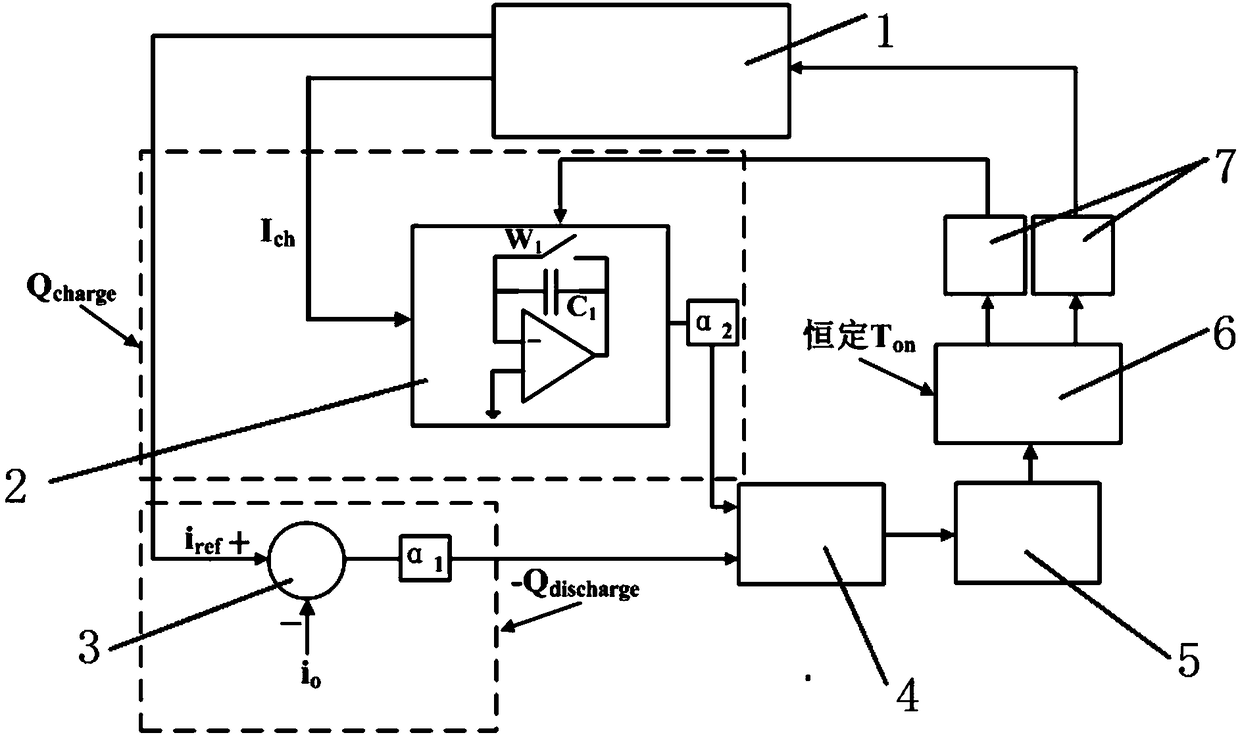

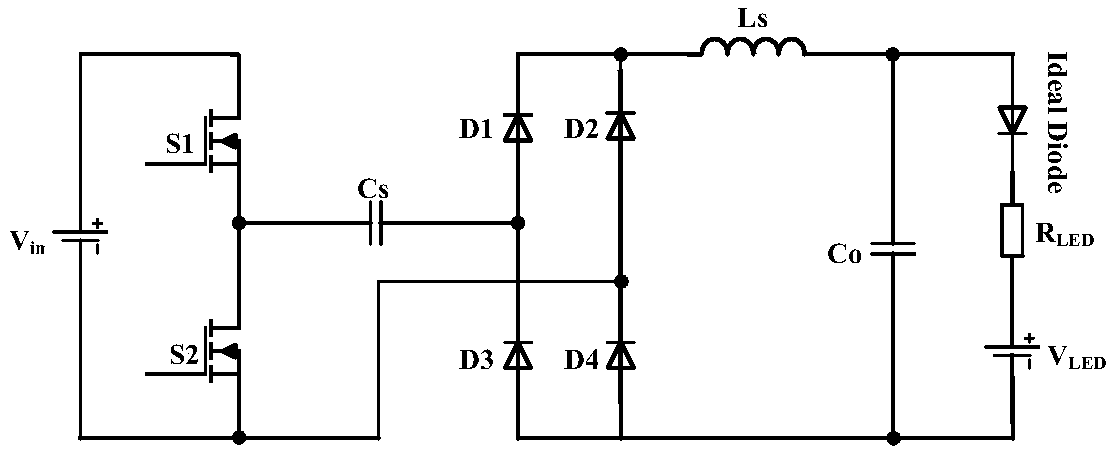

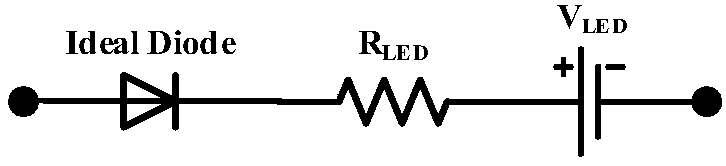

Variable frequency constant-current control method for LED drive system based on switched capacitor converter

ActiveCN108391344ASuppress interferenceRealize brightness adjustmentElectroluminescent light sourcesApparatus without intermediate ac conversionCapacitanceIntegrator

The invention discloses a variable frequency constant-current control method for an LED drive system based on a switched capacitor converter, and the method comprises the steps: taking a current Ich of a capacitor CS of the LED drive system based on the switched capacitor converter in a charging circuit as an integration input quantity, and inputting the integration input quantity into a resettable integrator; feeding back a given output current reference quantity Iref of the LED drive system based on the switched capacitor converter in the charging circuit and the whole output current Io of the LED drive system based on the switched capacitor converter to an adder-subtractor for difference solving; enabling an output signal of the adder-subtractor and an output signal of the resettable integrator to be transmitted to a comparator for comparison, and then transmitting the output signals to a D trigger, and then to a monostable multi-harmonic oscillator; enabling a signal outputted by the monostable multi-harmonic oscillator to pass through an output drive signal amplification circuit for driving a switching tube S1 and a switching tube S2 to operate, thereby achieving the constant-current output purpose and increasing the dynamic response speed of the LED drive system based on the switched capacitor converter.

Owner:XIAN UNIV OF TECH

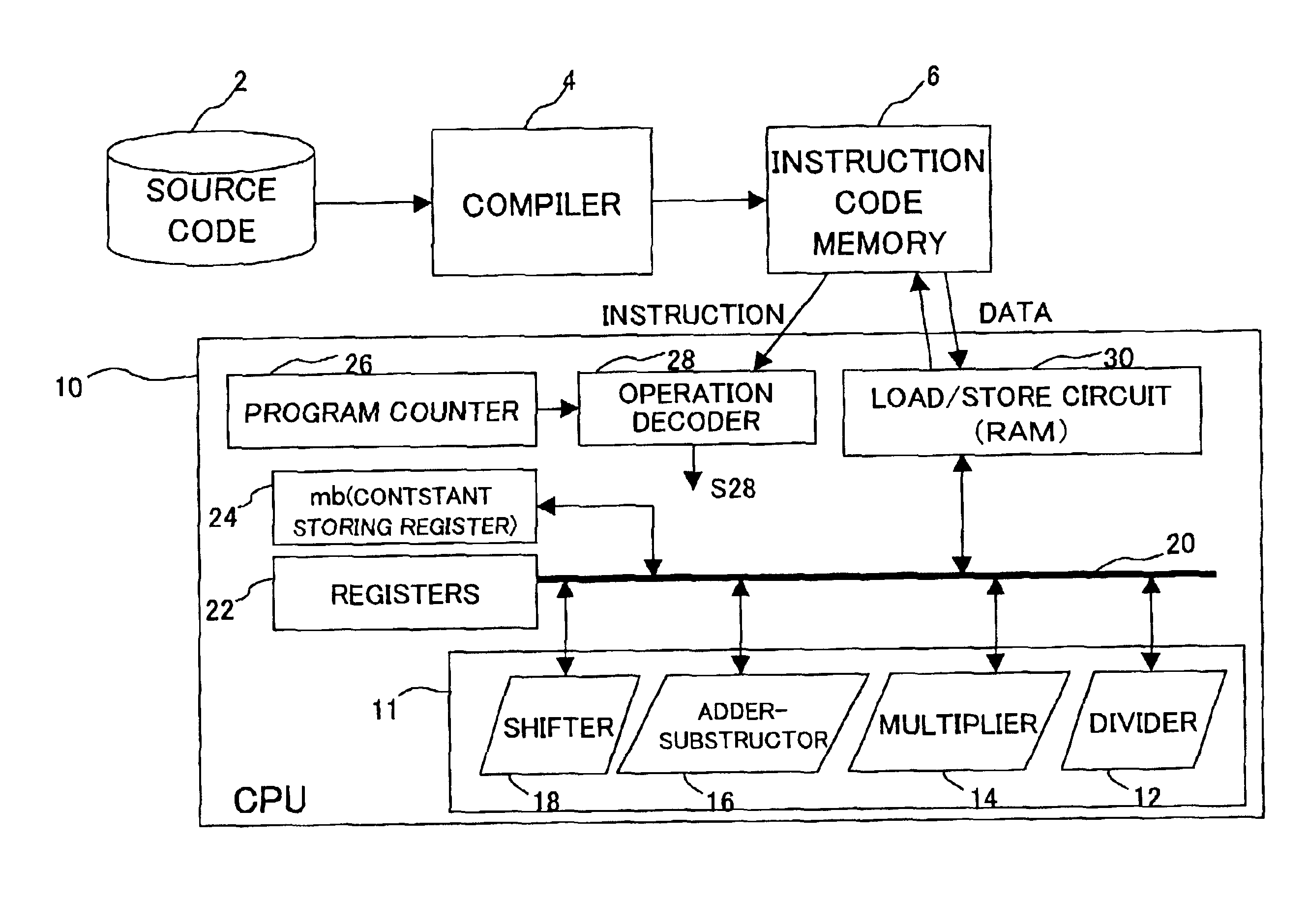

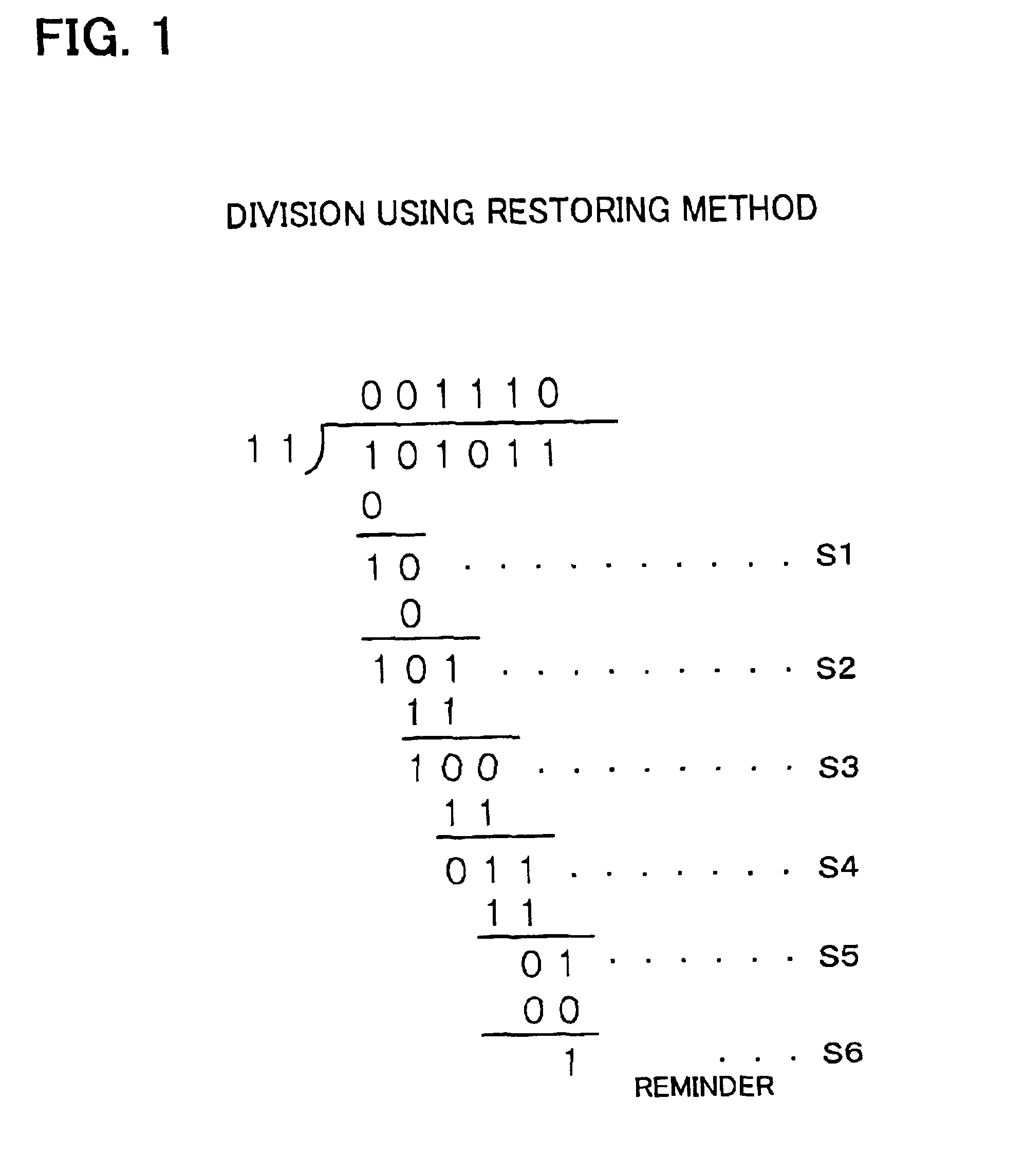

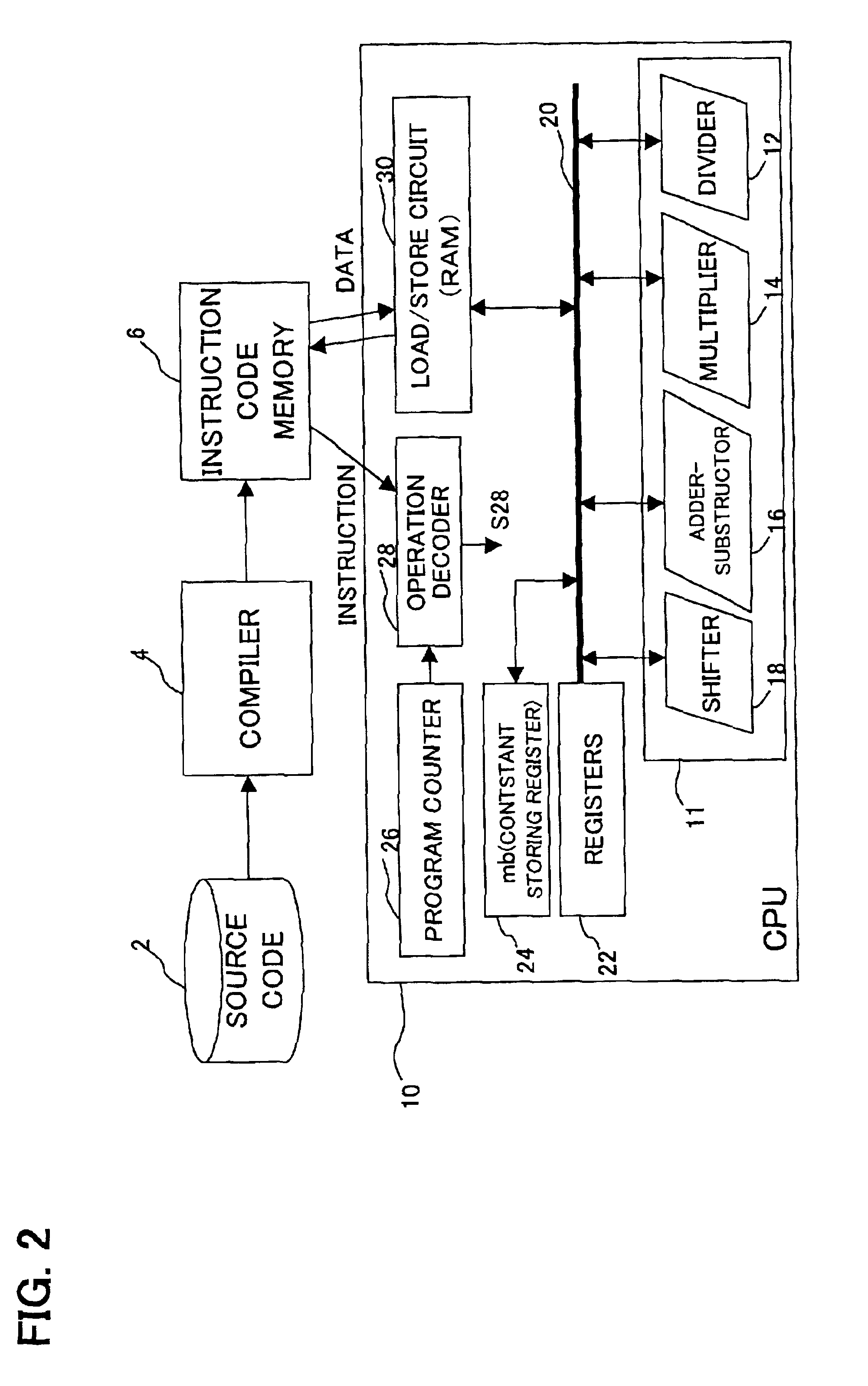

Development system of microprocessor for application program including integer division or integer remainder operations

InactiveUS6907442B2Reduce microprocessor execution timeReduce in quantityComputation using non-contact making devicesProgram controlAdder–subtractorObject code

A microprocessor (10) comprises a compiler (4), which, for a source program including an integer division q=int(a÷b)(int( ) is a function discarding figures below decimal point in parentheses) for dividing integer a, expressed in N bits, by integer constant b, causes a computer to execute a first process for calculating mb=int(m÷b) (where m=2N), and a second process for generating an object code, which stores the mb in a first register (24), calculates qx=int(a×mb÷m), calculates rx=a−qx×b, set a quotient q to q=qx when rx<b, or q=qx+1 when rx>=b;[0001]and a microprocessor having an arithmetic circuit (11), which comprises the first register, a multiplier (14), and an adder-subtractor (16), and which executes the object code generated by the compiler.

Owner:SOCIONEXT INC

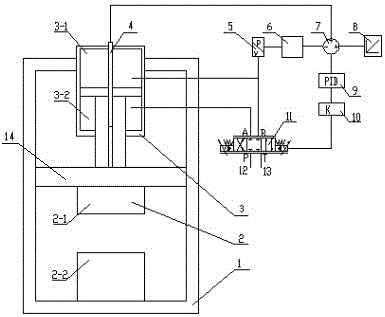

High precision control system and method for forging oil press

ActiveCN105834338AHigh control precisionQuick responseForging press drivesPetroleum engineeringInput device

The invention provides a high precision control system and method for a forging oil press. The high precision control system comprises a press frame and a movable transverse beam moving on the press frame, a mold anvil is installed on the lower surface of the movable transverse beam, a main cylinder is connected to the upper surface of the movable transverse beam through a plunger piston, and a position sensor is arranged on the main cylinder and electrically connected with an adder-subtractor; the adder-subtractor is electrically connected with an input device, the main cylinder is connected with a proportional direction valve through a pipe, and the proportional direction valve, an amplifier, a PID controller and the adder-subtractor are sequentially and electrically connected; and the pipe for connecting the main cylinder with the proportional direction valve is provided with a pressure sensor, and the pressure sensor, a frame deformation convertor and the adder-subtractor are sequentially and electrically connected. By means of the high precision control system and method for the forging oil press, the pressure of the main cylinder is monitored through the pressure sensor, the pressure of the main cylinder is converted into frame deformation Uk, the influences of the frame deformation Uk of the press on Ue are singly considered in the control process, and the control accuracy is higher; and when the pressure changes are larger, the system response speed is higher than that in the prior art.

Owner:CHINA NAT HEAVY MACHINERY RES INSTCO

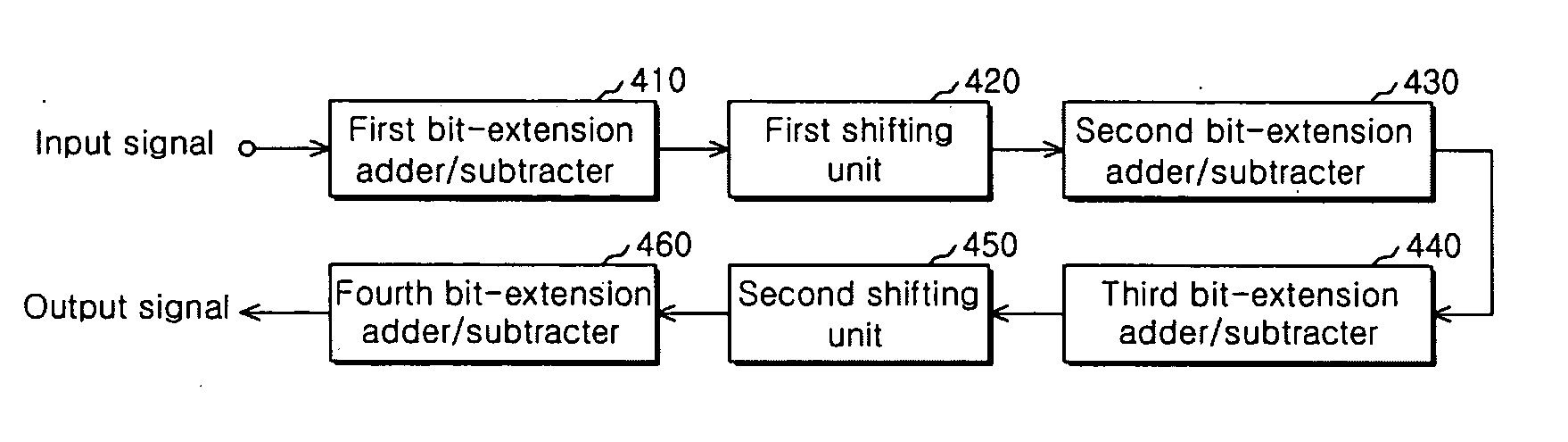

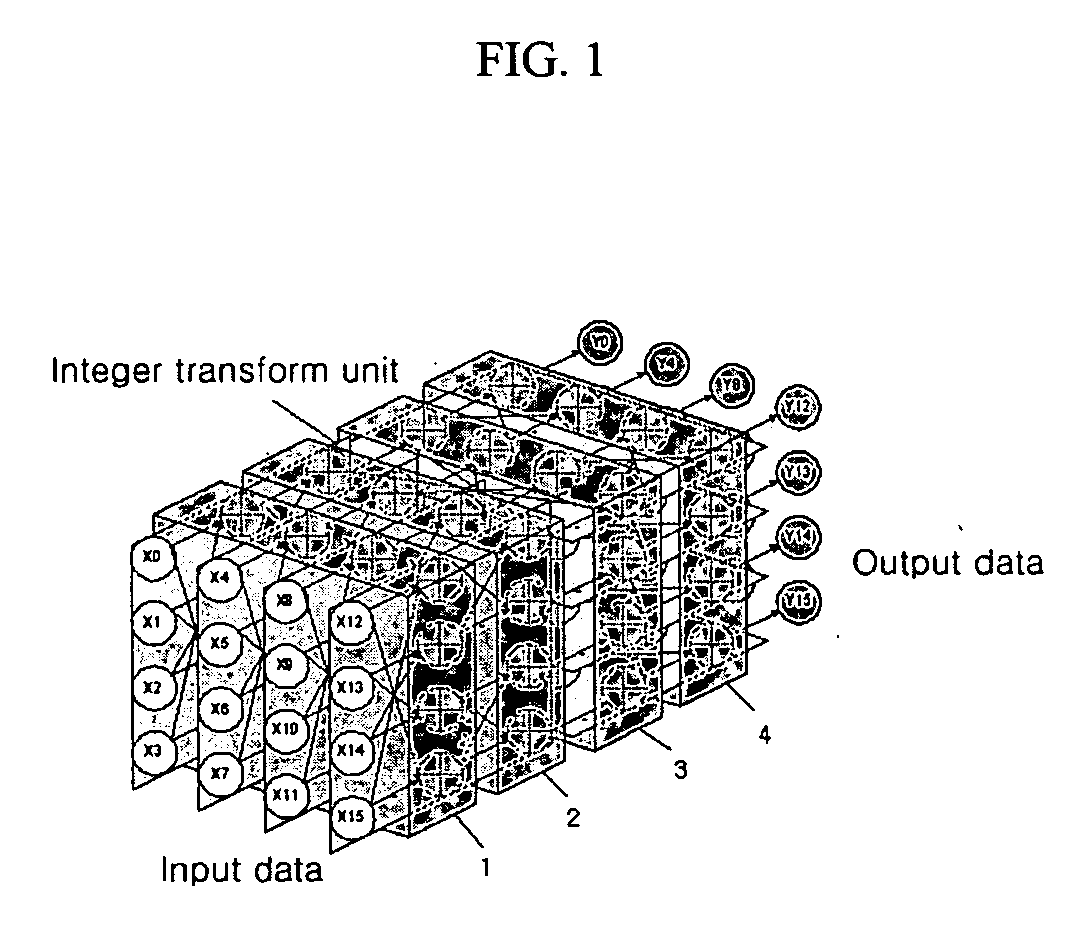

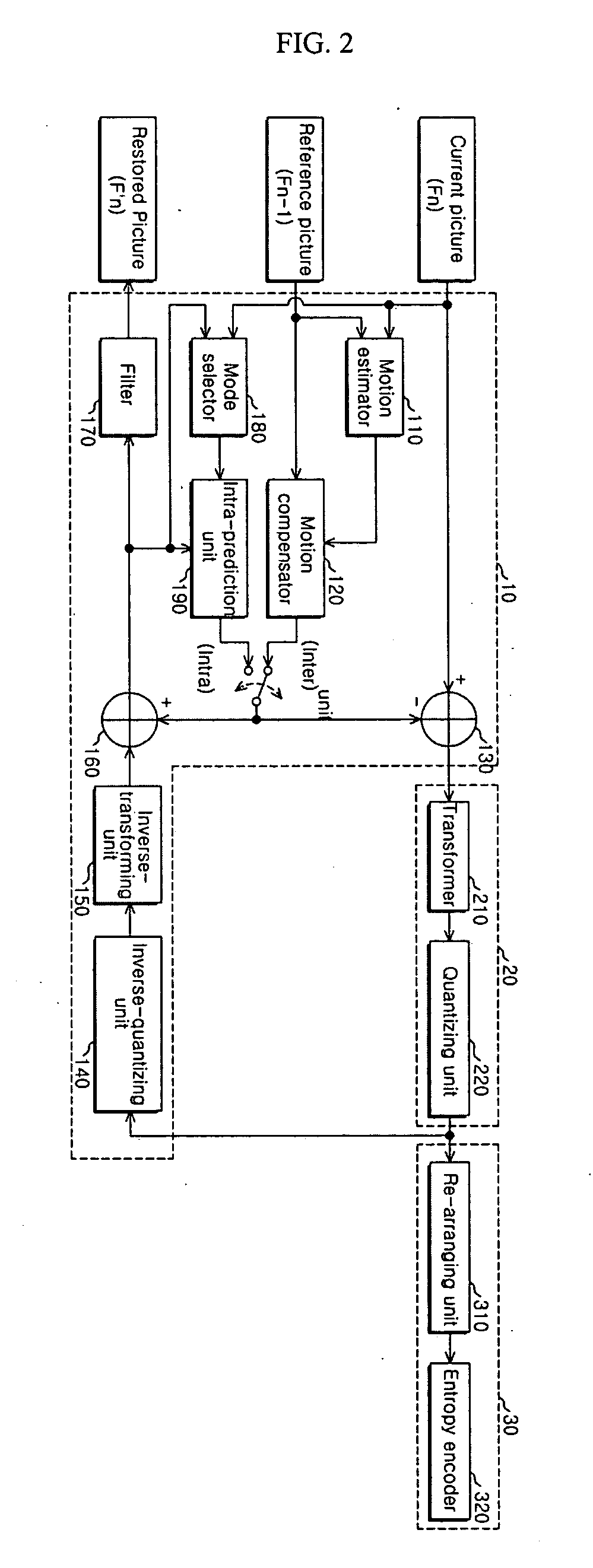

Integer transforming device for moving-picture encoder

InactiveUS20060259536A1Computation using non-contact making devicesDigital video signal modificationAdder–subtractorComputer science

An integer transforming device for a moving-picture compression encoder, associated with the H.264 standard, comprising: a first adding / subtracting stage including pluralities of adders / subtracters to execute addition and subtraction for input data, generating data extended by a predetermined bit number; a second adding / subtracting stage including pluralities of adders / subtracters to execute addition and subtraction for a shifted result of output data of the first adding / subtracting stage, generating data extended by a predetermined bit number; a third adding / subtracting stage including pluralities of adders / subtracters to execute addition and subtraction for an operation result of the second adding / subtracting stage, generating data extended by a predetermined bit number; and a fourth adding / subtracting stage including pluralities of adders / subtracters to execute addition and subtraction for a shifted result of the third adding / subtracting stage, generating data extended by a predetermined bit number.

Owner:GWANGJU INST OF SCI & TECH

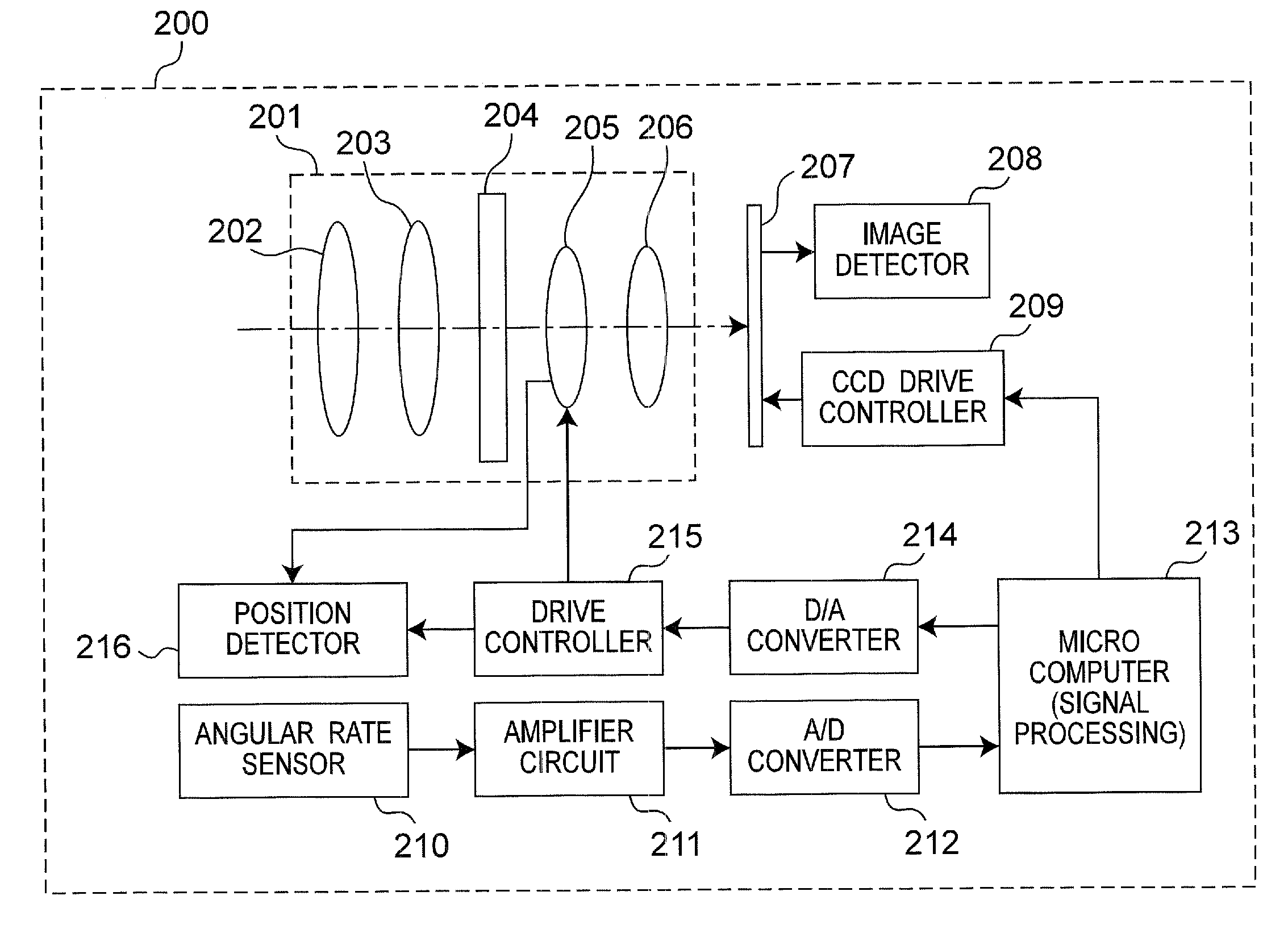

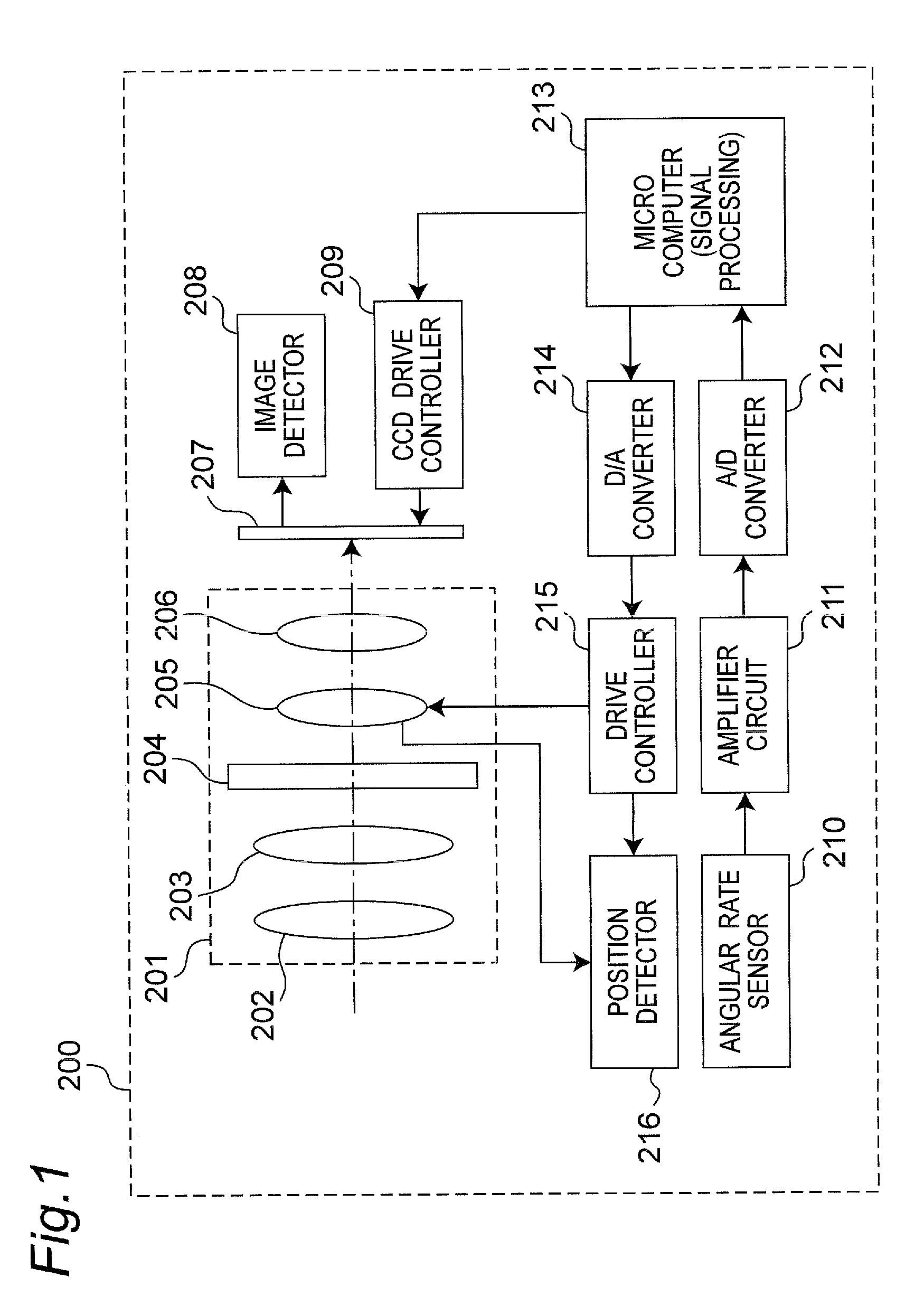

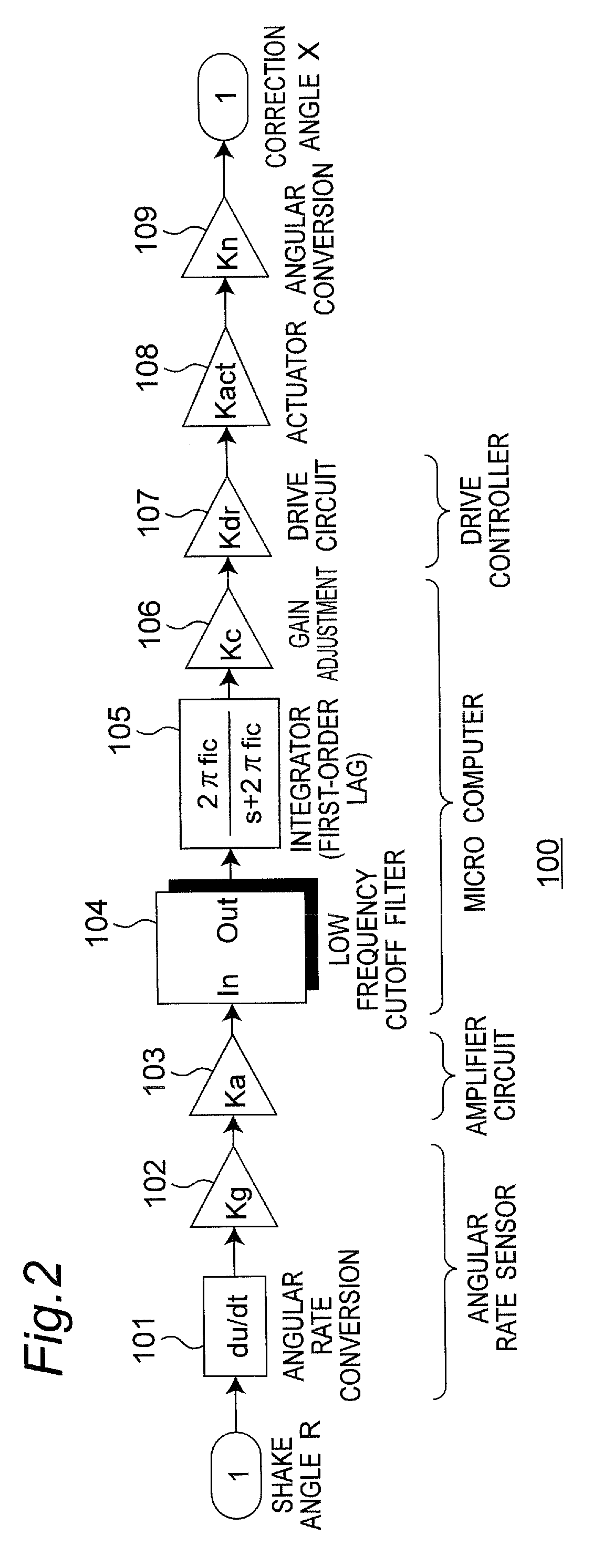

Composite low frequency cutoff filter and imaging apparatus using the same

ActiveUS20100302386A1Excellent camera shake correction performanceImprove featuresTelevision system detailsPrintersAdder–subtractorImaging equipment

An imaging apparatus includes a composite low frequency cutoff filter. The composite low frequency cutoff filter includes a first low frequency cutoff filter, a second low frequency cutoff filter, and an adder-subtractor. The second low frequency cutoff filter receives an output of the first low frequency cutoff filter. The adder-subtractor subtracts an output of the second low frequency cutoff filter from an input to the composite low frequency cutoff filter, and outputs a result of the subtraction to the first low frequency cutoff filter. An output of the first low frequency cutoff filter is outputted as an output of the composite low frequency cutoff filter.

Owner:PANASONIC CORP

Time domain a/d converter group and sensor device using same

ActiveCN111201715AReduce noiseHigh resolutionPower saving provisionsElectric signal transmission systemsTime domainConverters

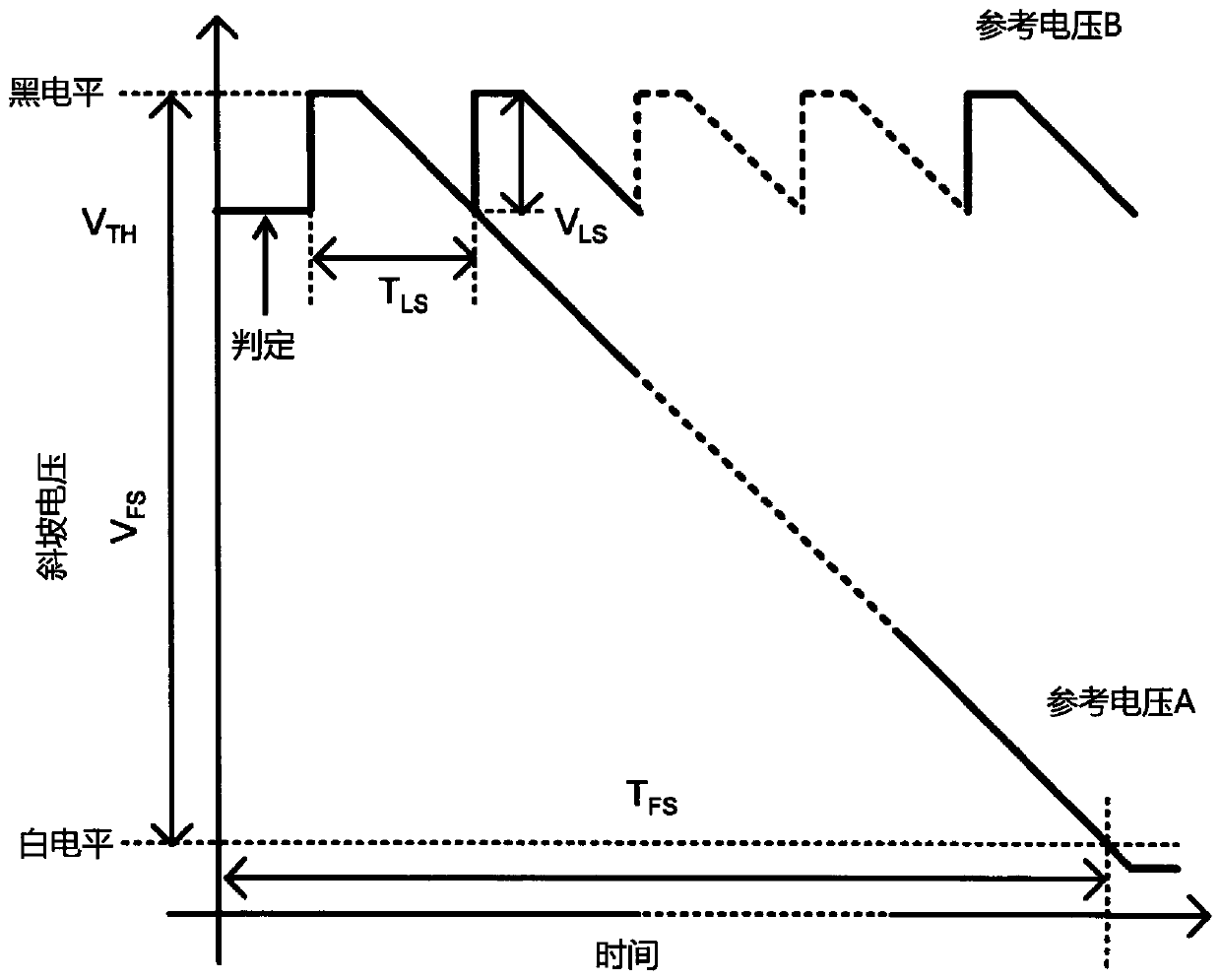

Individual A / D converters constituting a time domain A / D converter group according to an embodiment of the present invention each comprises: a reference voltage selection circuit that is connected toa reference signal generation circuit for generating a first reference signal to sweep a full-scale range and a second reference signal to periodically sweep a limited voltage range a plurality of times and that switches between the first and second reference signals that are outputs of the reference signal generation circuit; a comparator that compares the first or second reference signal selected by the reference voltage selection circuit with an input signal; an internal A / D converter that implements an A / D conversion by use of a comparison output signal from the comparator; and a cumulative adder-subtracter that, if the second reference signal has been selected, outputs a signal obtained by averaging A / D conversion values obtained from the A / D conversion.

Owner:TECH IDEA CO LTD

High-precision number cosine converting circuit without multiplier and its conversion

ActiveCN1855149AImprove parallelismImprove consistencyImage codingDigital video signal modificationBinary multiplierAdder–subtractor

Owner:XIAMEN UNISOC TECH CO LTD

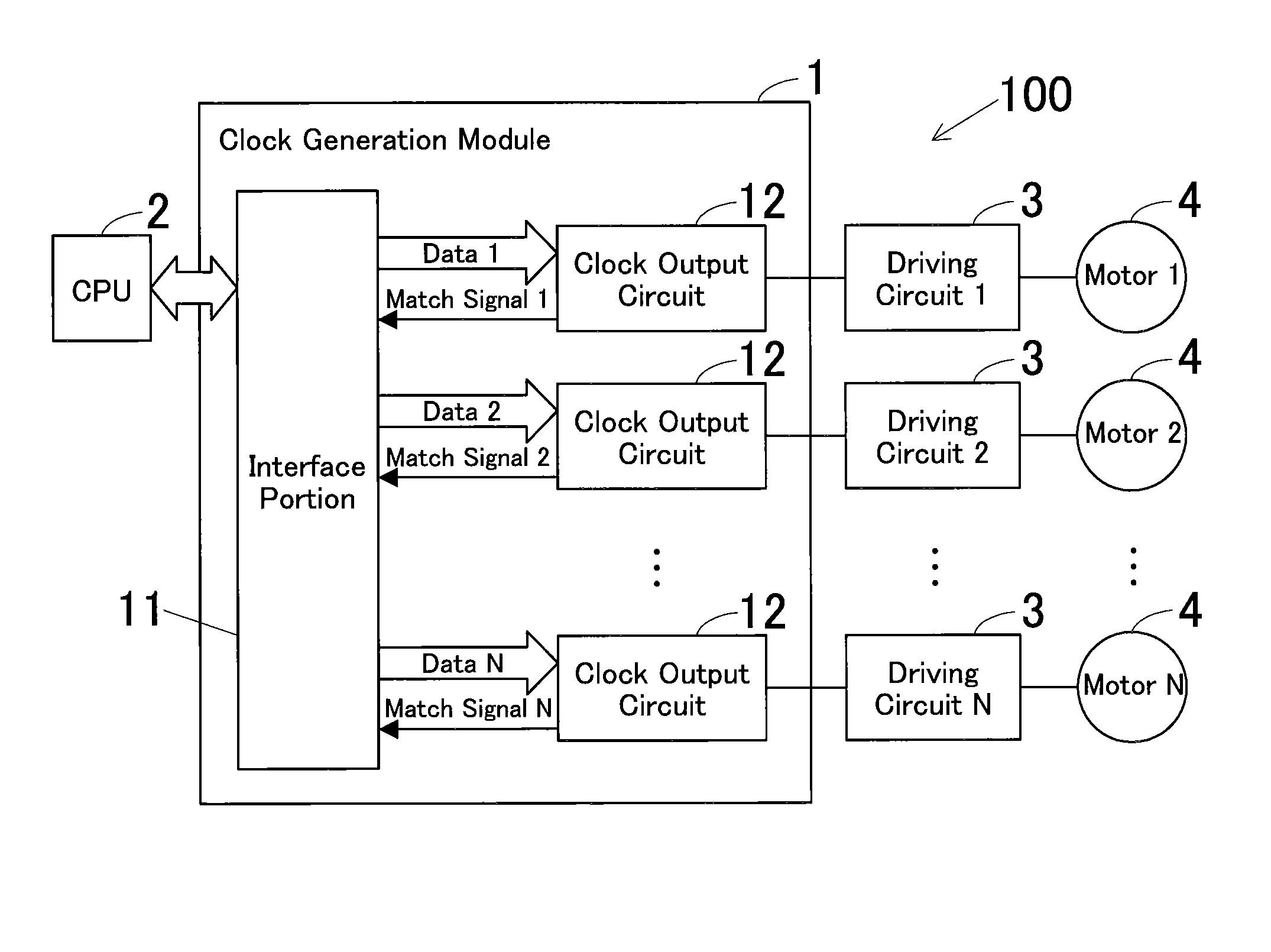

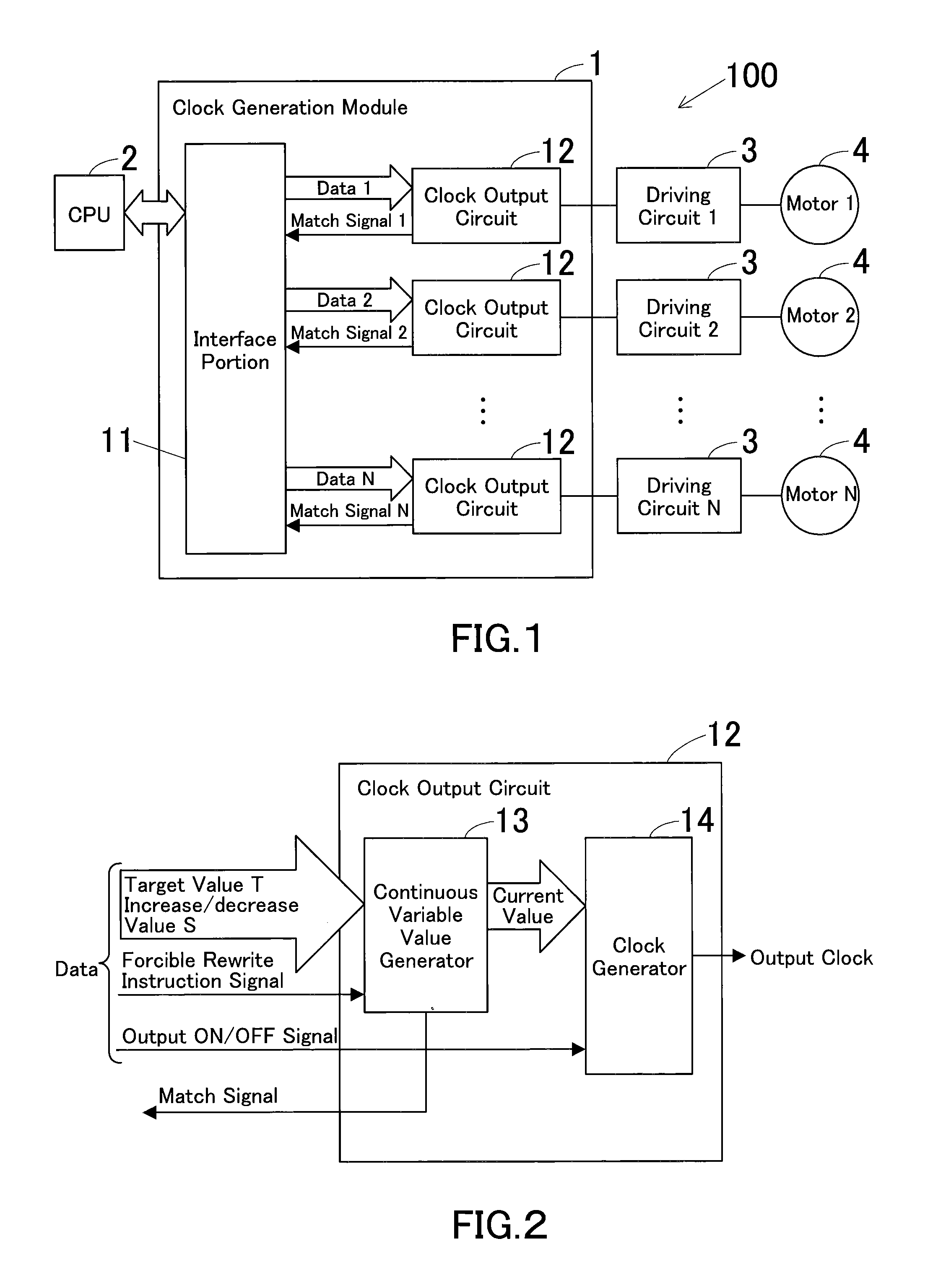

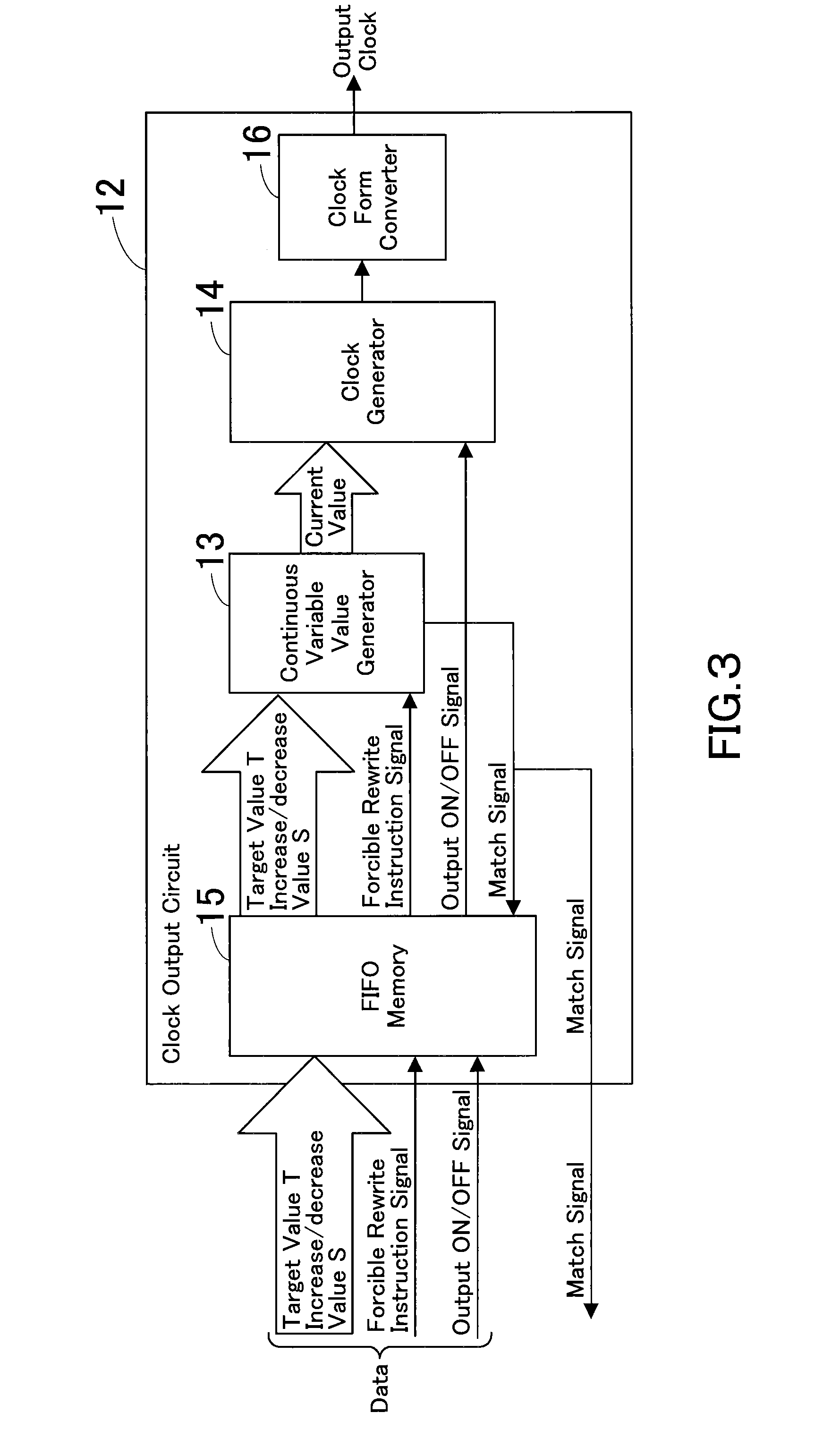

Variable frequency clock output circuit and apparatus, motor driving apparatus, and image forming apparatus

ActiveUS20080122514A1Simple structureImprove versatilityProgramme controlDynamo-electric converter controlMotor driveAdder–subtractor

A variable frequency clock output circuit, comprising: a target value register which stores a target value corresponding to an arbitrarily set target frequency; an increase / decrease value register which stores an arbitrarily set increase / decrease value; an adder-subtractor which has an input portion into which a current output value is inputted and outputs a calculation result obtained by adding / subtracting the increase / decrease value stored in the increase / decrease value register to / from the current output value inputted into the input portion based on an addition / subtraction instruction signal; a comparator which compares an output value of the adder-subtractor to the target value stored in the target value register, and outputs an addition / subtraction instruction signal to the adder-subtractor until the output value of the adder-subtractor and the target value coincide; and a clock generator which outputs a clock signal having a frequency proportional to the output value of the adder-subtractor.

Owner:KONICA MINOLTA BUSINESS TECH INC

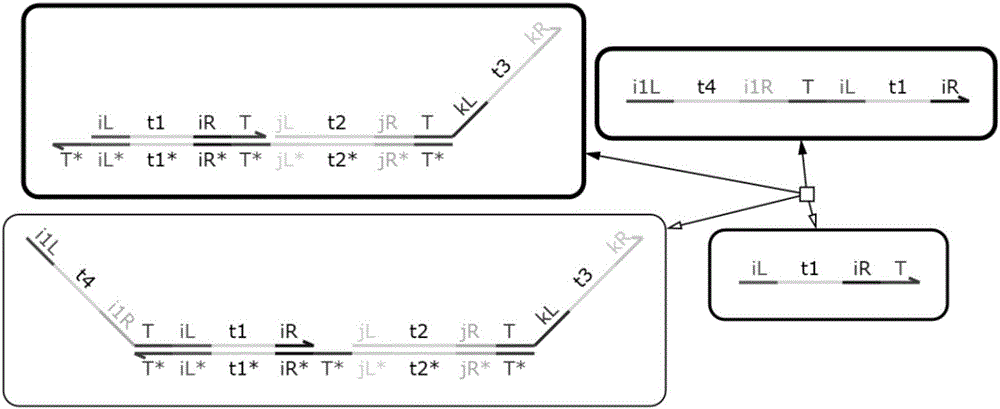

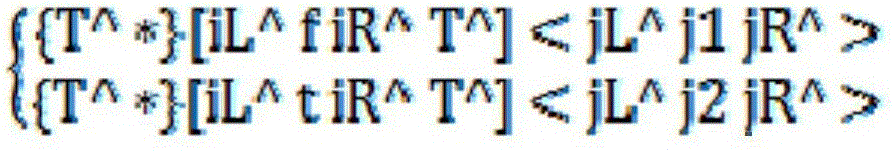

Mapping module-based 16-bit adder-subtractor design method

ActiveCN106126191AImprove certaintyAvoid instabilityComputation using non-contact making devicesLeft halfAdder–subtractor

The invention relates to a method for designing a 16-bit adder-subtractor by utilizing mapping modules, and belongs to the technical field of computer application. The method comprises the following steps of 1: marking a DNA strand by utilizing a domain t and a domain f that represent logic 1 and logic 0 respectively, and establishing a domain-marked DNA signal strand that achieves a medium effect of transferring a signal in a DNA strand displacement reaction, wherein an input / output strand is the DNA signal strand, the DNA signal strand is symmetric in structure, the left half side of the DNA signal strand and a corresponding module of an upstream part can be subjected to the DNA strand displacement reaction, and the right half side of the DNA signal chain and a corresponding module of a downstream part can be subjected to the DNA strand displacement reaction; 2: establishing domain-marked 1 input-mapping modules; and 3: establishing domain-marked 2 input-mapping modules. The logic 1 and the logic 0 are represented through the domain t and the domain f respectively, so that the certainty of the reaction is enhanced and the instability caused by the fact that logic values are represented by concentration is avoided.

Owner:DALIAN UNIVERSITY

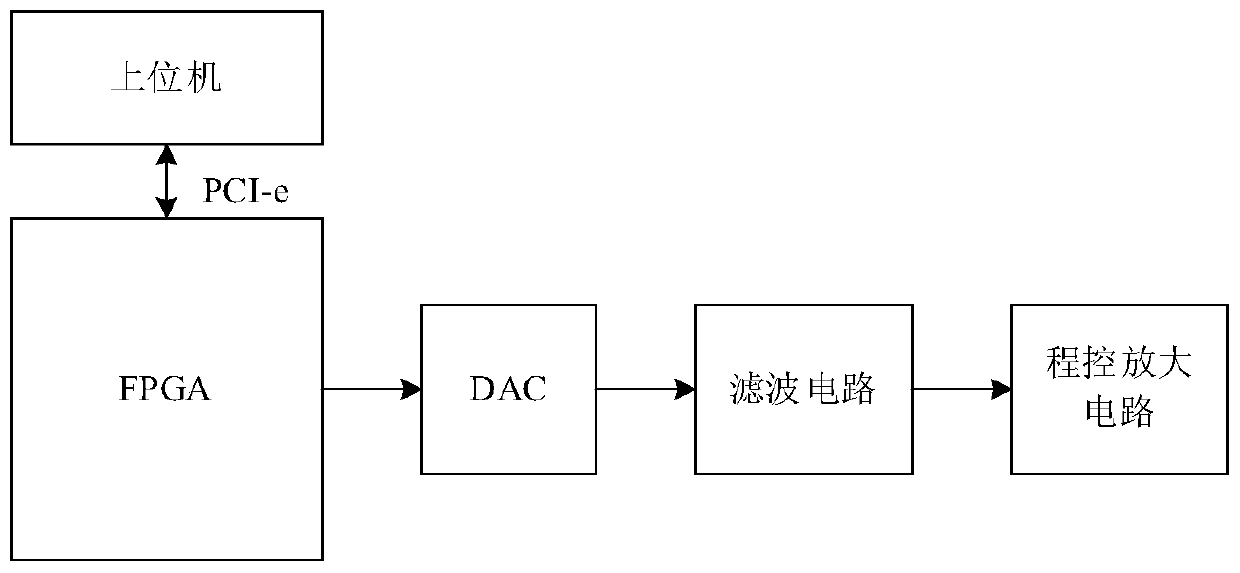

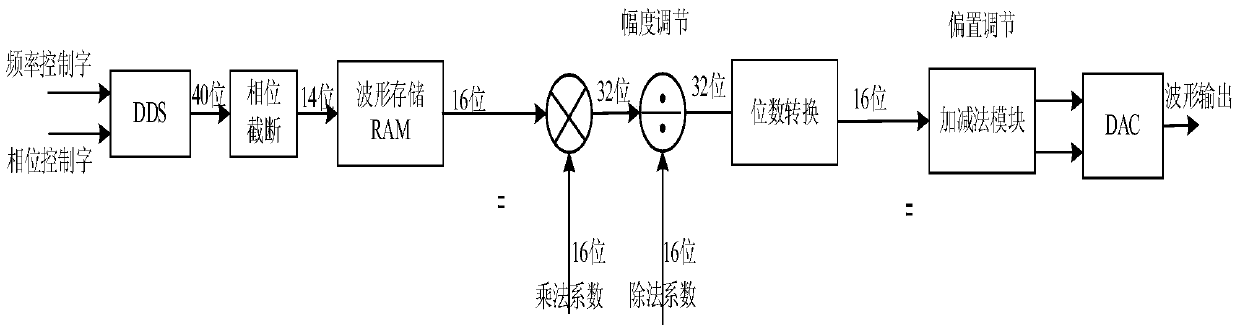

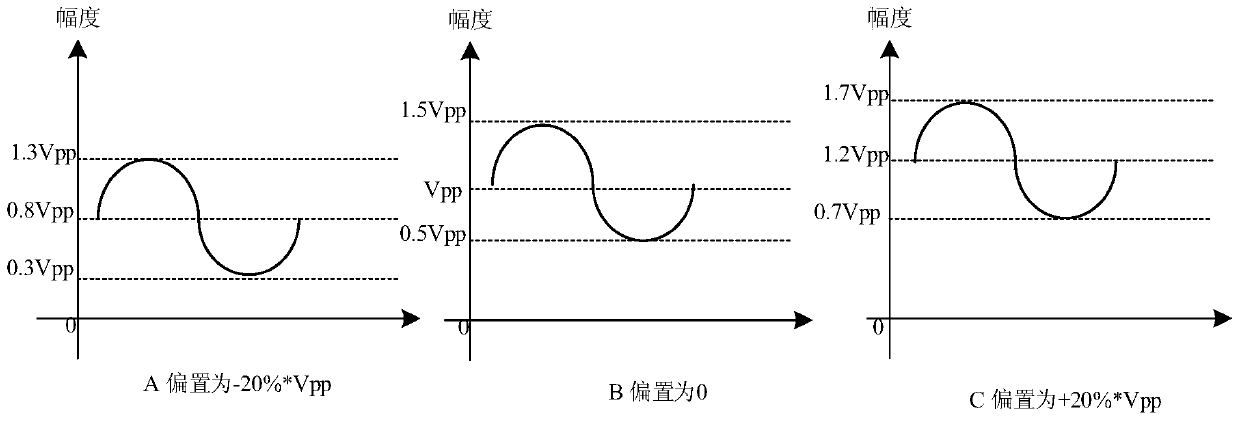

A waveform generation circuit and method based on fpga with adjustable amplitude offset

ActiveCN104316737BHigh precisionImprove adaptabilityProgramme controlComputer controlAutomatic controlAdder–subtractor

An FPGA-based waveform generation circuit and method with adjustable amplitude bias are widely used in the fields of electronic circuits, automatic control, scientific experiments and the like. The circuit is composed of FPGA, DAC, filter circuit and program-controlled amplifier circuit. The method includes determining a waveform data width and a waveform data range. The upper computer generates a cycle of waveform data and corresponding control words according to the set waveform generation parameters. The host computer transmits the waveform data to the FPGA, and the FPGA stores the obtained waveform data in the waveform RAM. FPGA uses DDS and waveform storage RAM to generate waveforms according to the obtained frequency control word and phase control word. The waveform generated by DDS is controlled by the amplitude adjustment module. Set the offset, and adjust the offset by passing the amplitude-adjusted waveform digital quantity through the adder and subtractor. According to the actual test, the loss of waveform amplitude caused by the frequency effect is determined, and the relationship between the waveform amplitude and frequency is determined, so as to control the program-controlled amplification to compensate the waveform amplitude according to this relationship, so as to ensure the accuracy of the amplitude.

Owner:内蒙古远致科技有限公司

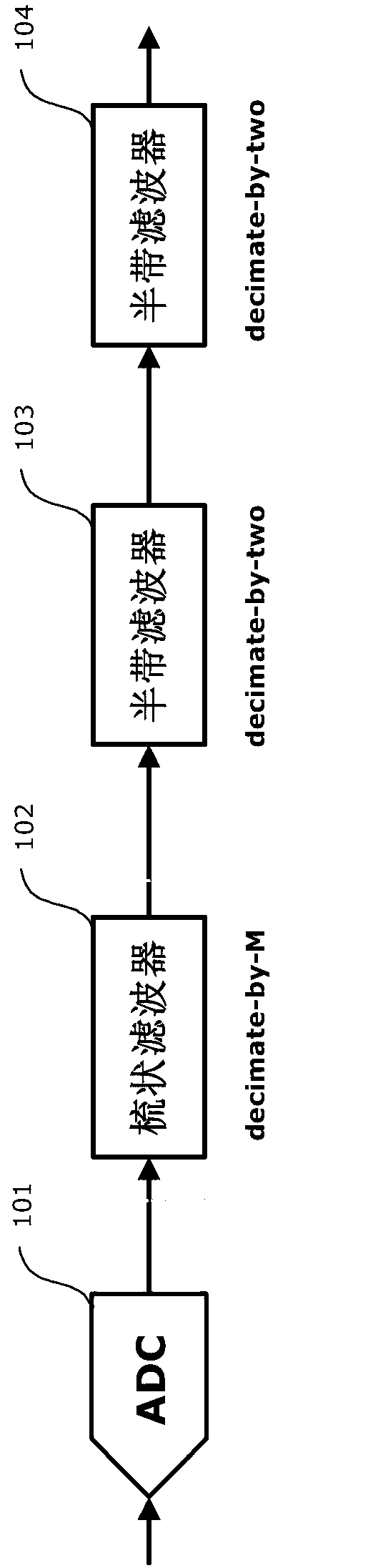

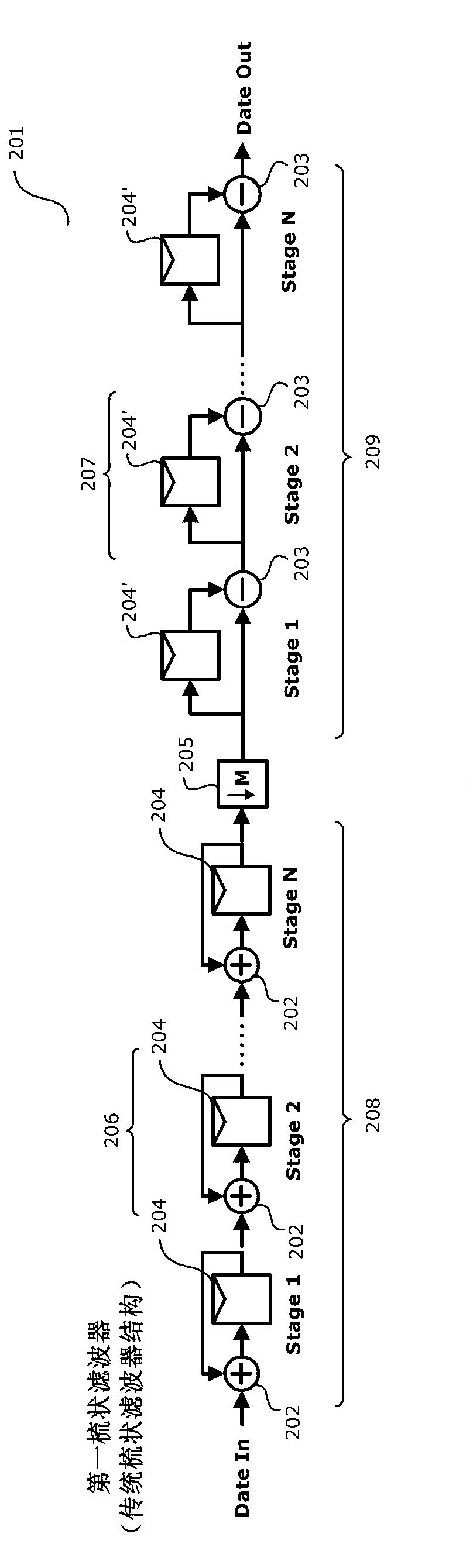

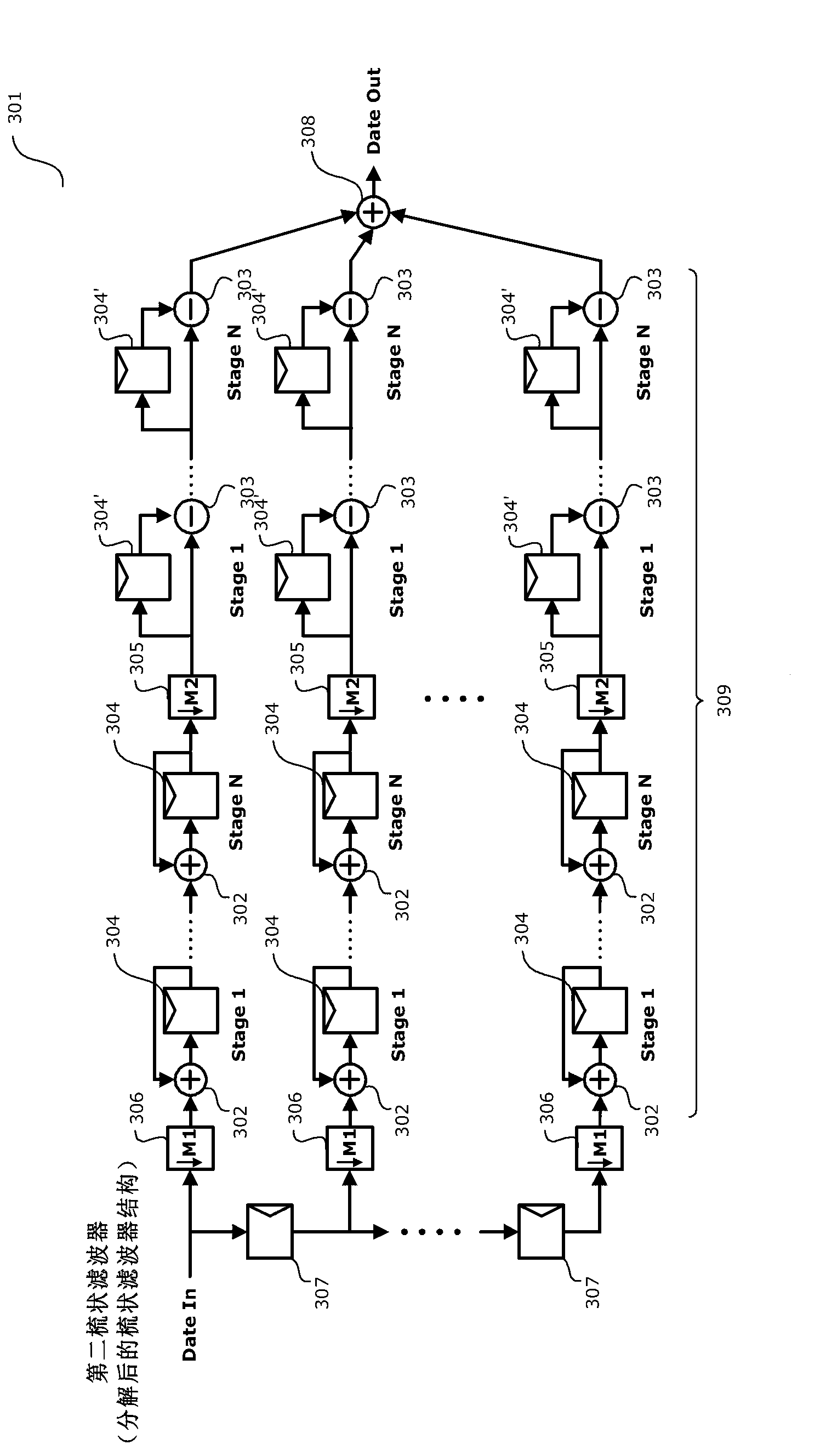

Multi-channel comb filter

ActiveCN103066949AOptimize architectureReduce consumptionDigital technique networkShift registerIntegrator

The invention discloses a multi-channel comb filter. By decomposition of comb filter transfer function, architecture of the comb filter is optimized. The comb filter is decomposed as a comb filter which is in a multi-phase parallel structure, and by utilization of a shifting register and a random access memory (RAM), a complex comb filter shares an integrator, a comb-shaped device and an adder-subtractor with the multi-channel comb filter. Therefore, on the basis that an area and complexity are not increased, the high-speed multi-channel comb filter is achieved, hardware resource consumption is reduced, cost is saved, working frequency is reduced before the operation of addition and subtraction, and thus the whole working frequency of the comb filter is improved and the multi-channel comb filter is suitable for a next mobile communication system.

Owner:SHANGHAI BEILING

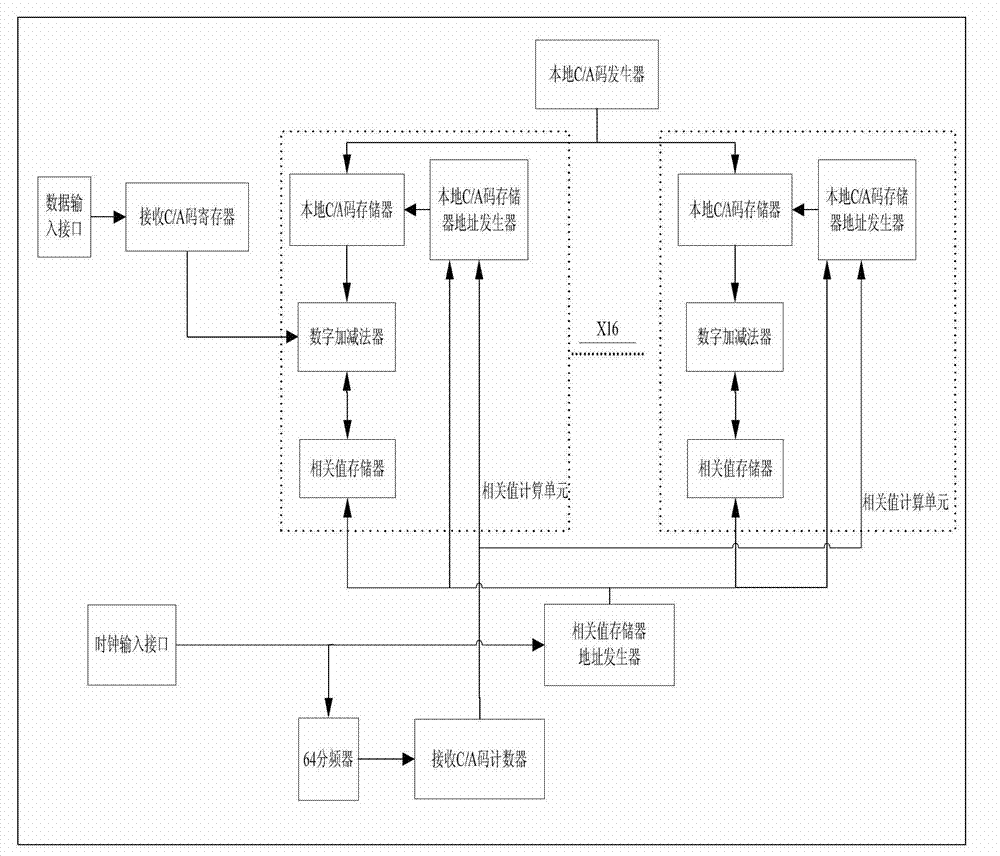

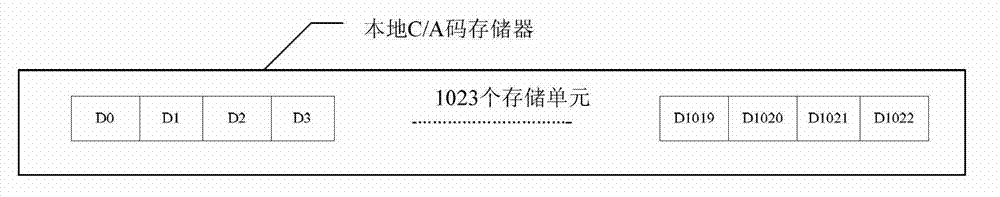

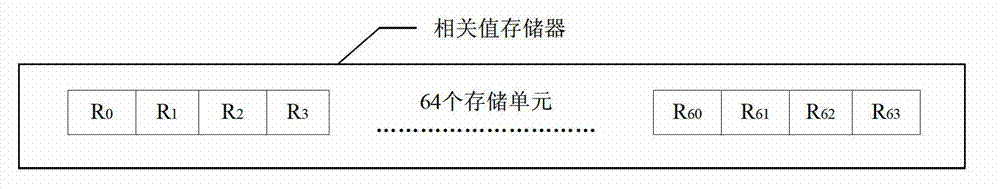

GPS (Global Position System) signal digital correlator

InactiveCN103018753ASimplify complexitySearch capture is fast and accurateSatellite radio beaconingAdder–subtractorResource consumption

The invention discloses a GPS (Global Position System) signal digital correlator, comprising a local C / A code generator, a data input interface, a C / A code receiving register, 16 correlation value computing units, correlation value storage address generator, a clock input interface, a 64 frequency divider and a C / A code receiving counter; each correlation value computing unit comprises a local C / A code storage address generator, a local C / A code storage, a digital adder-subtractor and a correlation value storage connected orderly; the local C / A code generator is connected with each local C / A code storage; the C / A code receiving register is connected with the data input interface and each digital adder-subtractor; and the correlation value storage address generator is respectively connected with the correlation value storage and the local C / A code storage address generator. By using the structure, the effects of less resource consumption, short capture time and accurate capture result in a signal capture process can be achieved.

Owner:JIANGSU UNIV OF SCI & TECH

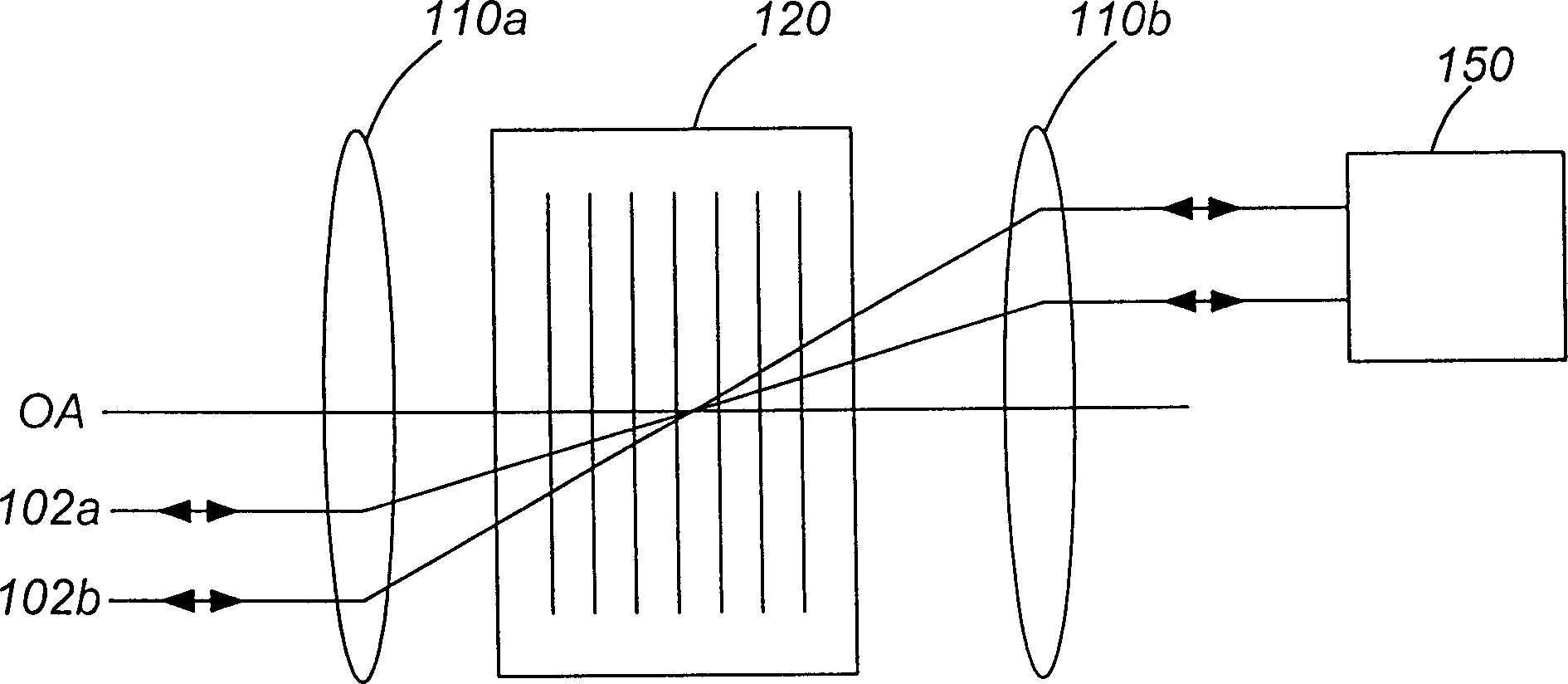

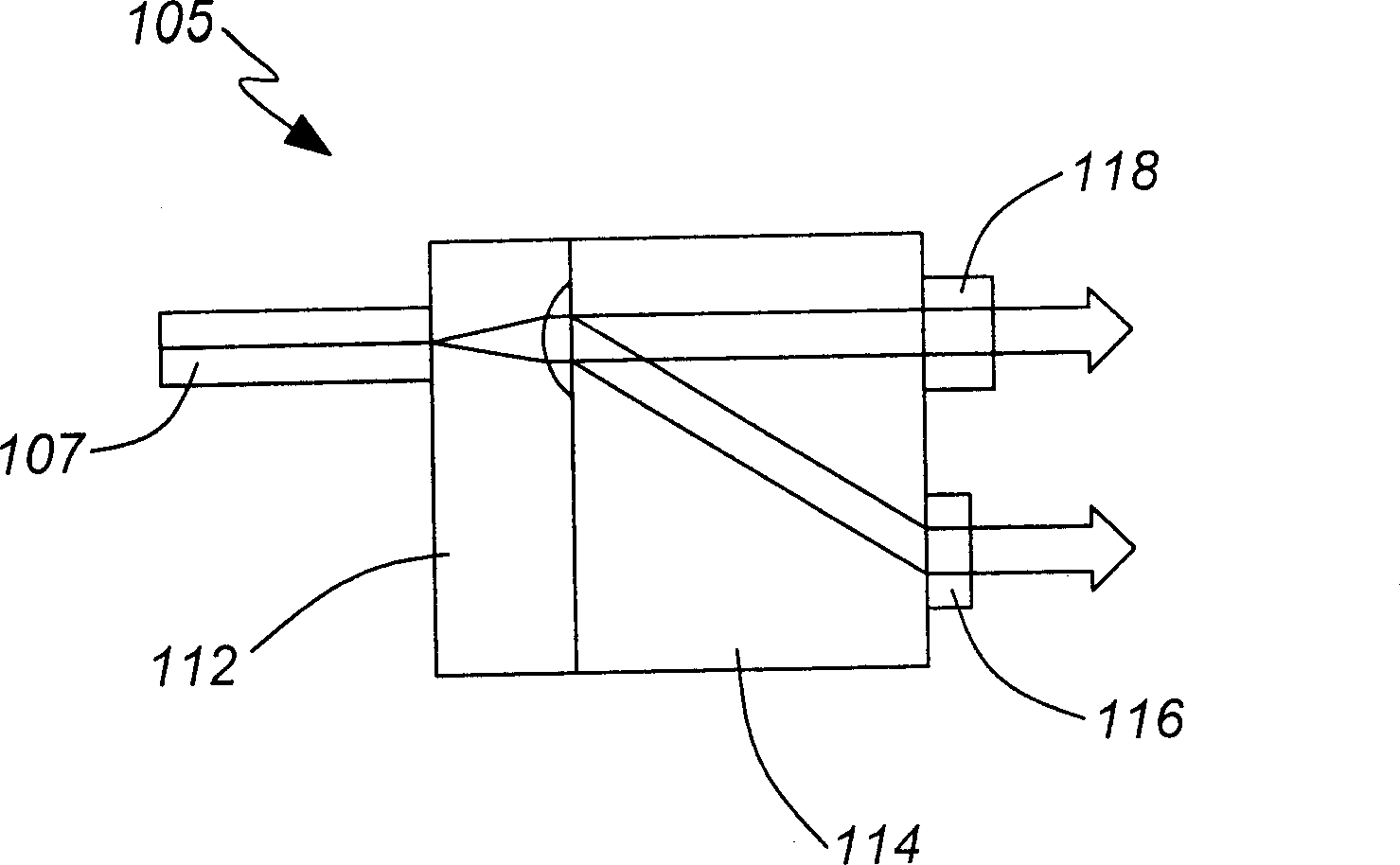

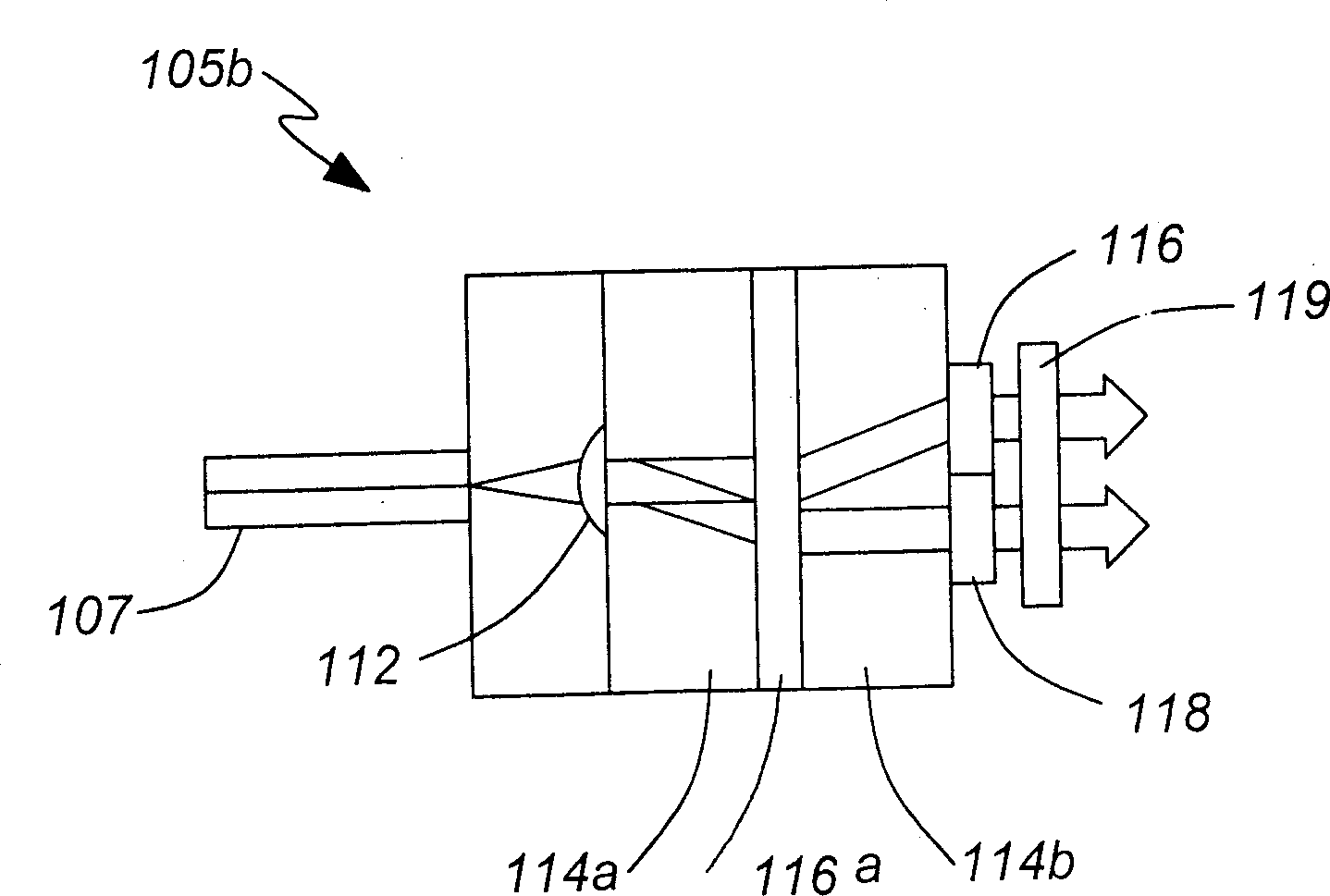

Optical allocation for dynamic gain balancer and adder-subtractor

InactiveCN1156715CCompact structureWavelength-division multiplex systemsCoupling light guidesAdder–subtractorOptical power

An optical device for rerouting and modifying an optical signal is disclosed. The optical design includes a front-end unit for providing a collimated beam of light, an element having optical power for providing collimating / focusing effects, a diffraction element for providing spatial dispersion, and modifying means which in a preferred embodiment includes one of a MEMS array and a liquid crystal array for reflecting and modifying at least a portion of a beam of light. The modifying means functions as an attenuator when the optical device operates as a DGE and as a switching array when the optical device operates as a COADM.

Owner:LUMENTUM OPERATIONS LLC