Binary system adder-subtractor based on enhancement-type LUT (look up table) 5 structure

An addition and subtraction device, an enhanced technology, applied in the field of binary addition and subtraction devices, can solve the problems of large bit-width addition and subtraction logic delay, cost increase, and multiple lookup table structures, and achieve the effect of improving area utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In the following description, many technical details are proposed in order to enable readers to better understand the application. However, those skilled in the art can understand that without these technical details and various changes and modifications based on the following implementation modes, the technical solution claimed in each claim of the present application can be realized.

[0044] In order to make the purpose, technical solution and advantages of the present invention clearer, the following will further describe the implementation of the present invention in detail in conjunction with the accompanying drawings.

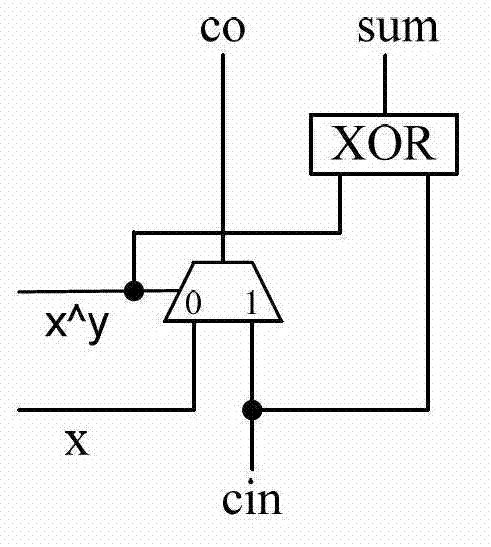

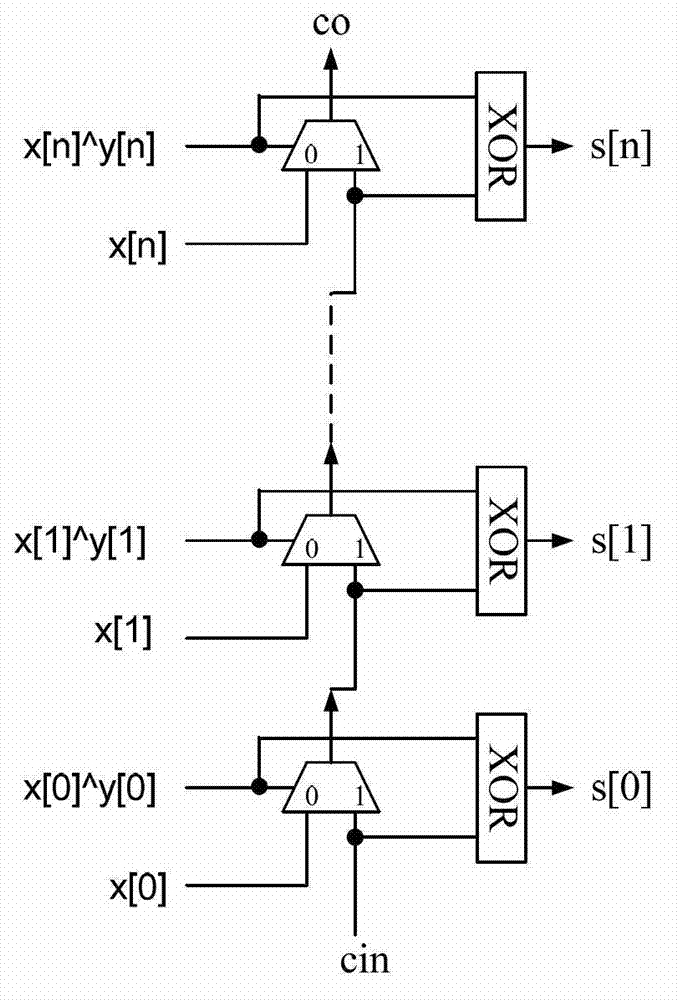

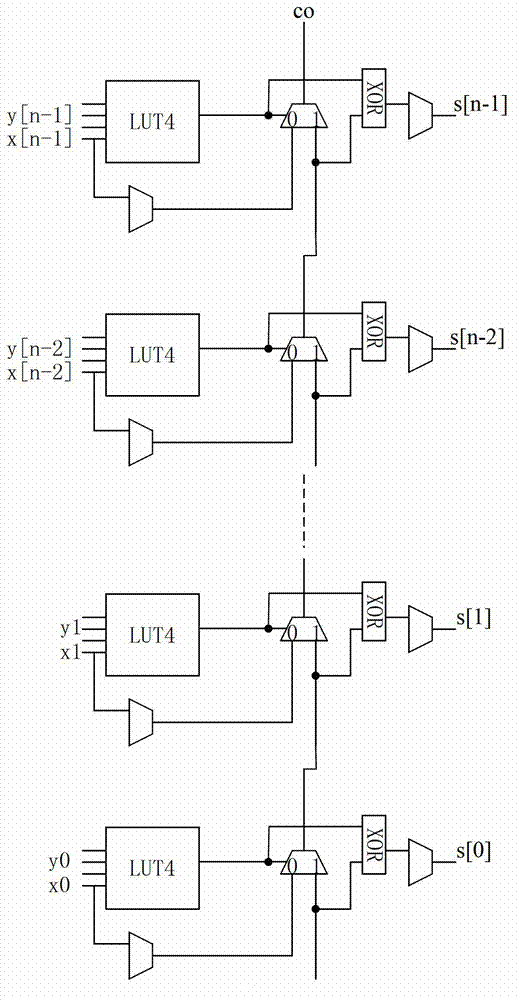

[0045] The first embodiment of the present invention relates to a binary adder-subtractor based on an enhanced LUT5 structure. The enhanced LUT5 structure refers to adding a 2-to-1 selector at the input end of the ordinary LUT5 structure to generate two LUT4 structures with 3 inputs shared, such as Figure 5 As shown, A, B, and C are the three shar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More