Base-2 parallel FFT (fast Fourier transformation) processor based on DIF (decimation in frequency) and processing method thereof

A processing method and processor technology, applied in the direction of complex mathematical operations, etc., can solve problems such as insufficient flexibility, and achieve the effect of improving processing speed and system throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

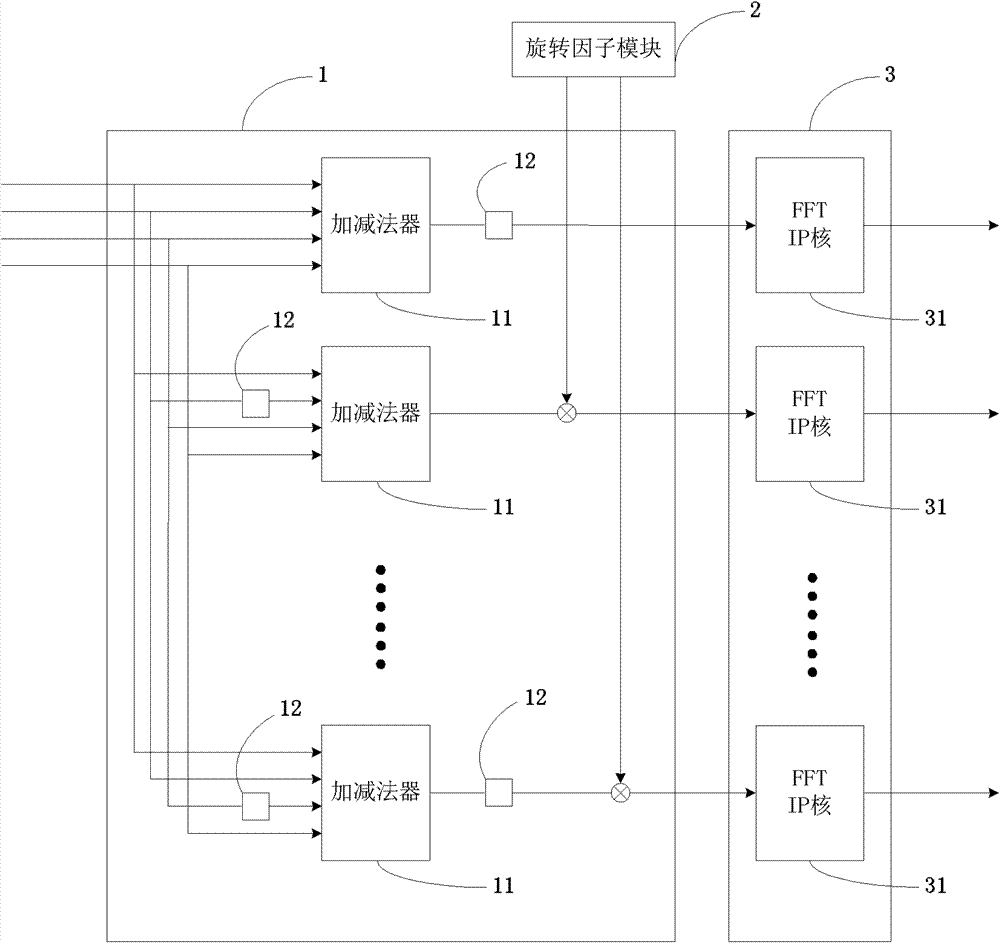

[0027] This embodiment provides a DIF-based radix-2 parallel FFT processor, such as figure 1 As shown, it includes a parallel FFT input operator 1, a twiddle factor module 2 and an FFT processor 3; the parallel FFT input operator 1 includes 2 M Road parallel adder and subtractor 11 and delay unit 12, wherein M is a non-negative integer; the FFT IP core 3 includes 2 M Parallel FFT IP core 31; 2 M Parallel adder and subtractor 11 and 2 M The parallel FFT IP cores 31 are connected one by one; the output sequence of each adder-subtractor 11 is multiplied by the corresponding twiddle factor in the twiddle factor module 2 and input to the corresponding FFT IP core 31 connected to itself.

[0028] The input sequence length of the DIF-based radix-2 parallel FFT processor is K·2 M , where K is a positive integer, and the length of the sequence processed by the FFTIP core 31 is K. The twiddle factor lookup table is stored in the twiddle factor module 2 . The input terminal and / or o...

Embodiment 2

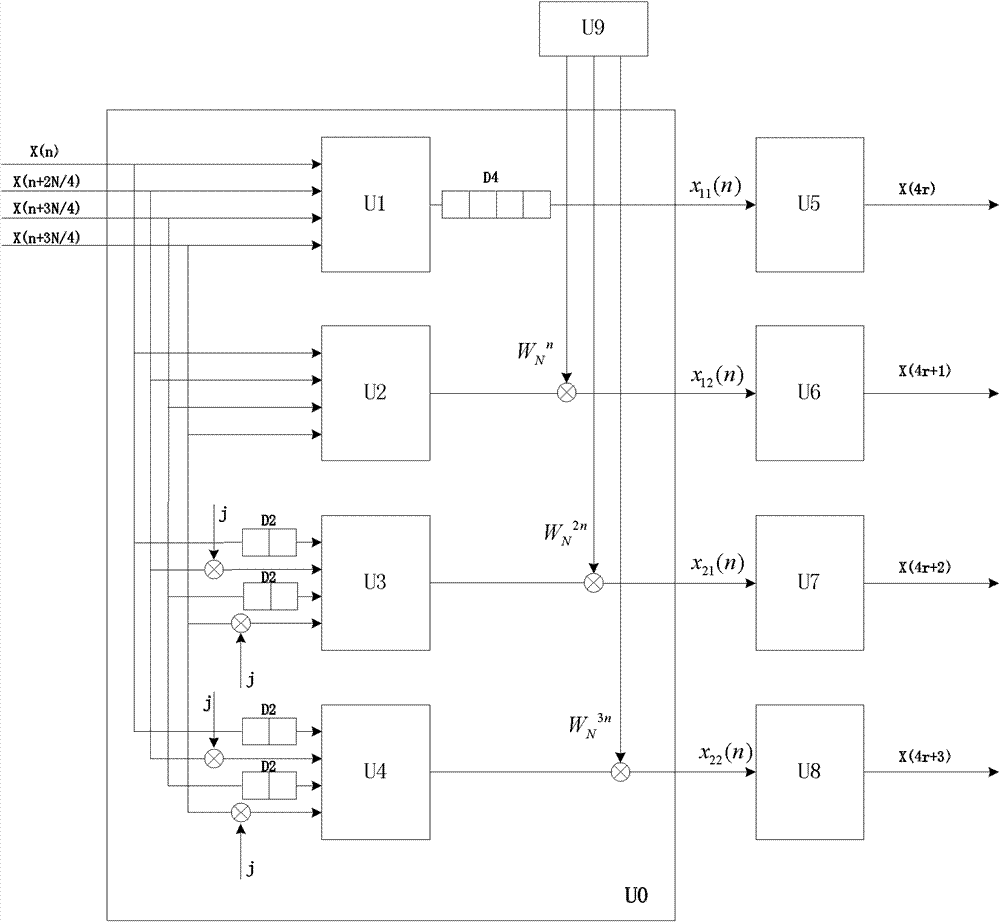

[0035] This embodiment provides a base-2 parallel FFT processor based on DIF, such as figure 2 As shown, the difference between it and Embodiment 1 is: the parallel FFT input operator includes 4-way parallel adder and subtractor, and the FFT processor includes 4-way parallel FFT IP cores; the base-2 parallel FFT processor based on DIF The input sequence is of length N.

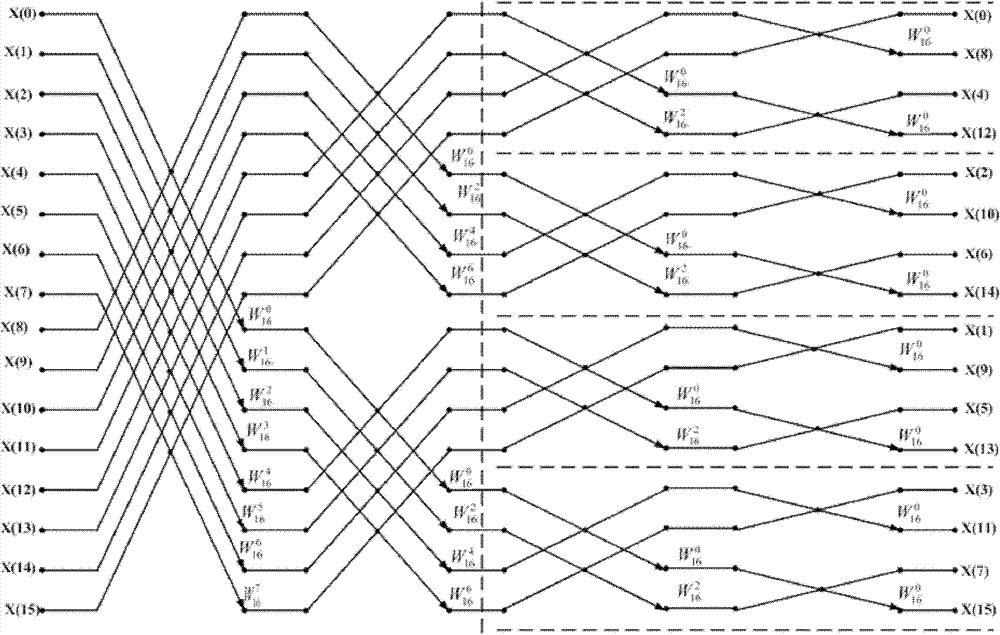

[0036] image 3 Shows a standard N=16-point FFT operation flowchart of the decimation by frequency method (DIF), wherein the data flow after the first two stages is clearly divided into four independent units horizontally (such as image 3 Shown by the dotted line in the middle), each unit implements N / 4-point FFT independently, thus forming a four-way parallel structure. Therefore, four N / 4-point FFT units can be used to calculate N-point FFT in parallel, that is, the so-called parallel structure FFT. Then design a specific structure of the arithmetic circuit to handle the first two stages.

[0037] The ...

Embodiment 3

[0087] In this embodiment, in the case of single-way, double-way and four-way parallel, the resources (Resources) consumed by the FFT processor, the clock frequency (Maximum Speed) that can be achieved, the waiting time (Latency), the conversion time ( TransformTime) and system throughput (Throughput) etc., further prove the beneficial effect of the parallel FFT processor proposed by the present invention and its processing method.

[0088] The radix-2 parallel FFT processor based on DIF described in the present invention has been verified on the experimental board DASQ_USB_V1 with Virtex-II serial FPGA XC2V3000. The real sequence with a length of 2048 points is split into four input FPGAs, and the four parallel FFT units use the free FFT IP core that comes with the Xilinx FPGA development tool ISE10.1, which can realize pipeline input and output. An FFT verification result with an input sequence length of N=2048 is shown in Table 1. The input and output data in the table are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More