Patents

Literature

240 results about "Twiddle factor" patented technology

Efficacy Topic

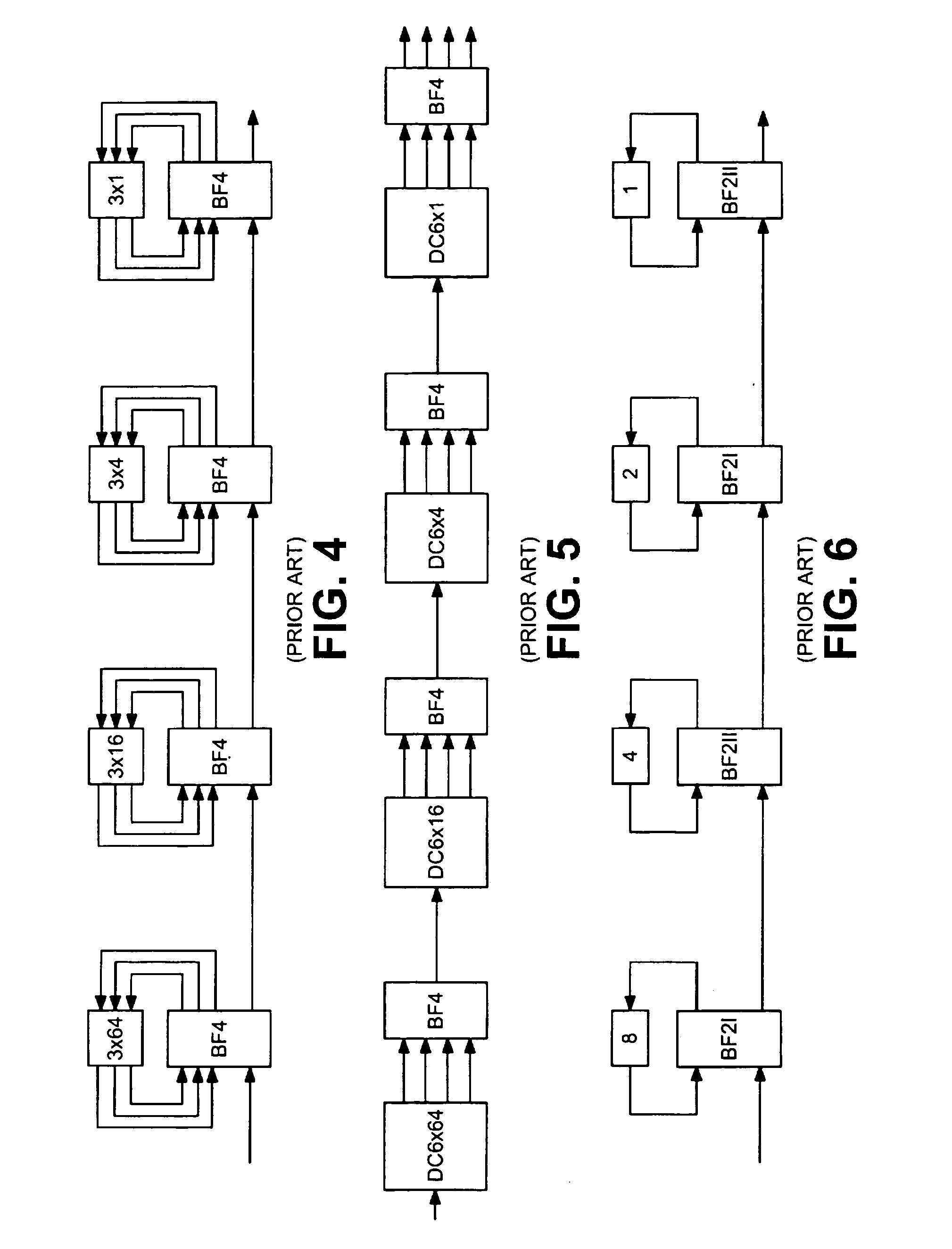

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

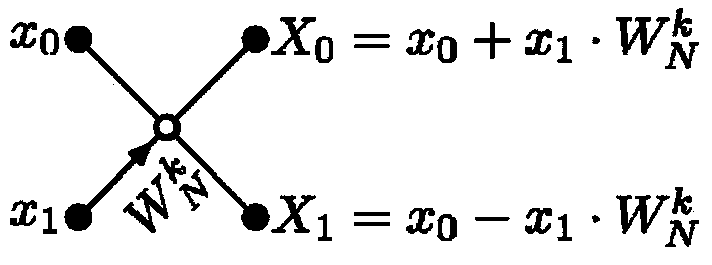

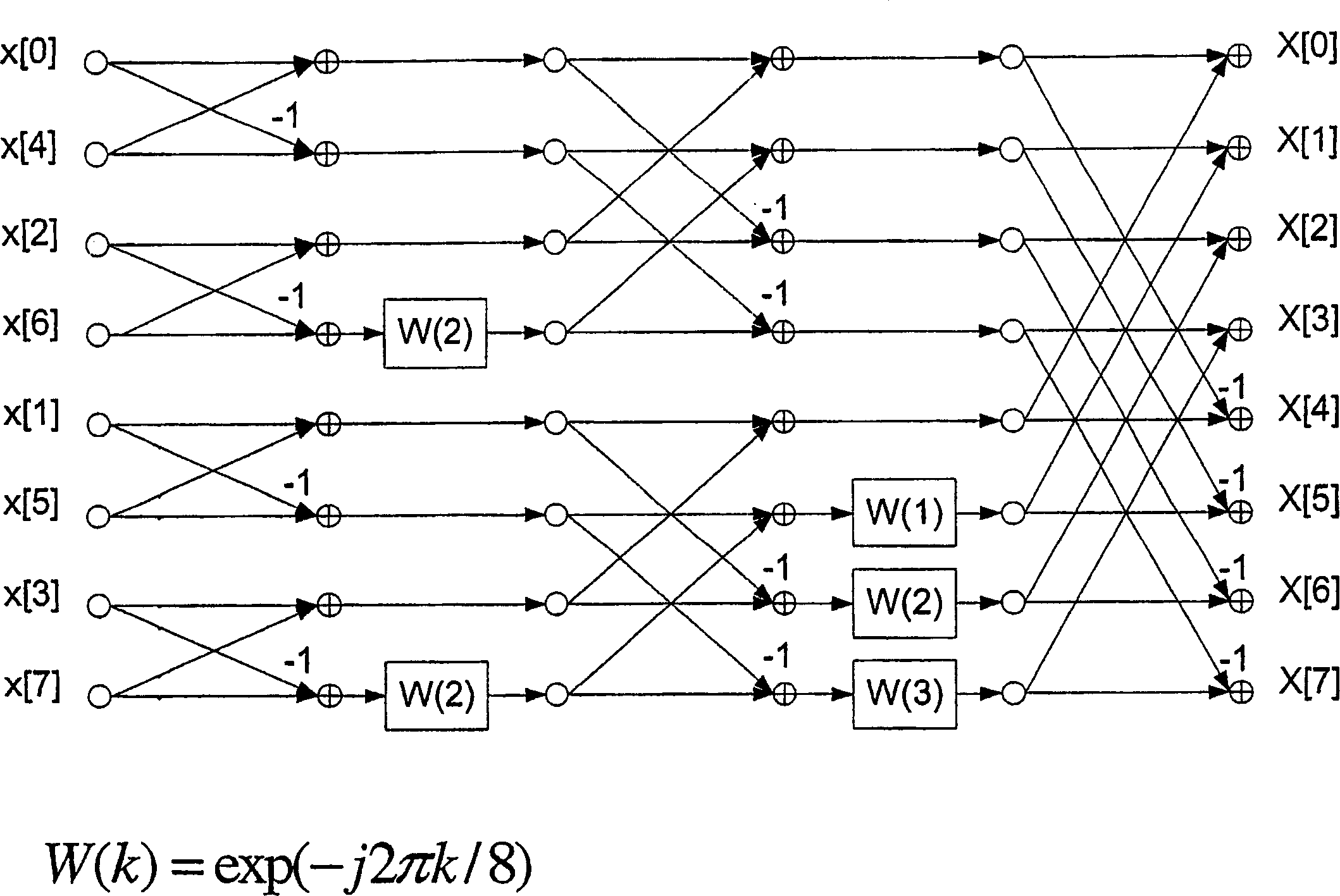

A twiddle factor, in fast Fourier transform (FFT) algorithms, is any of the trigonometric constant coefficients that are multiplied by the data in the course of the algorithm. This term was apparently coined by Gentleman & Sande in 1966, and has since become widespread in thousands of papers of the FFT literature.

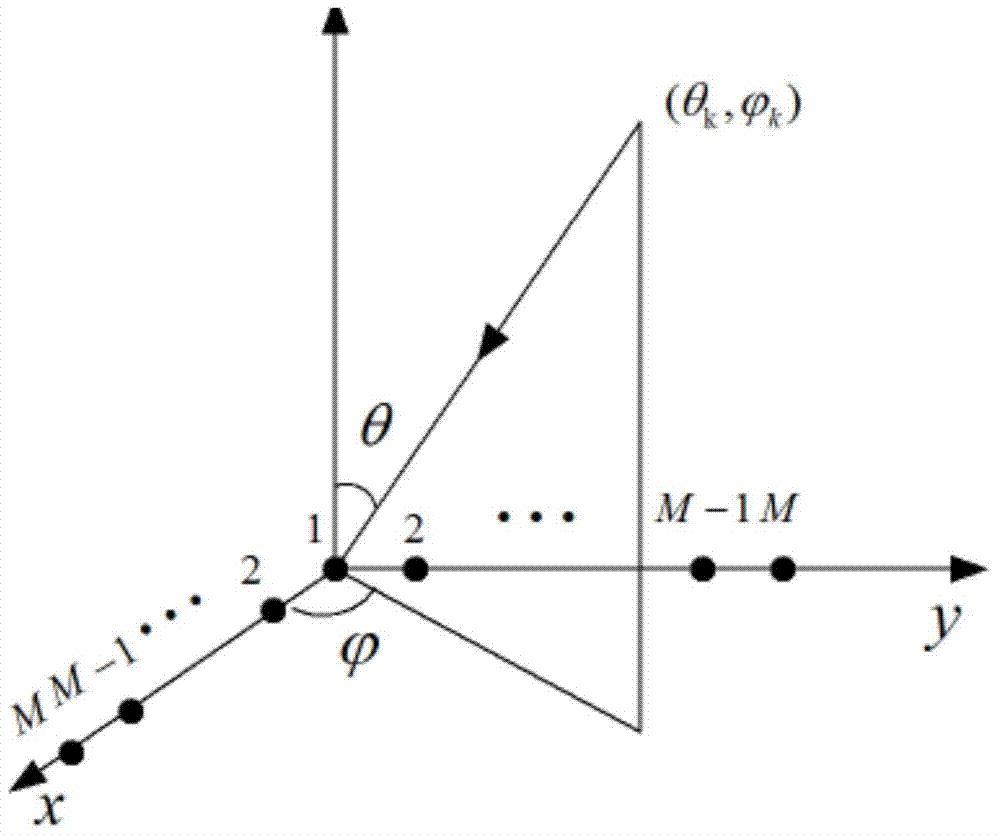

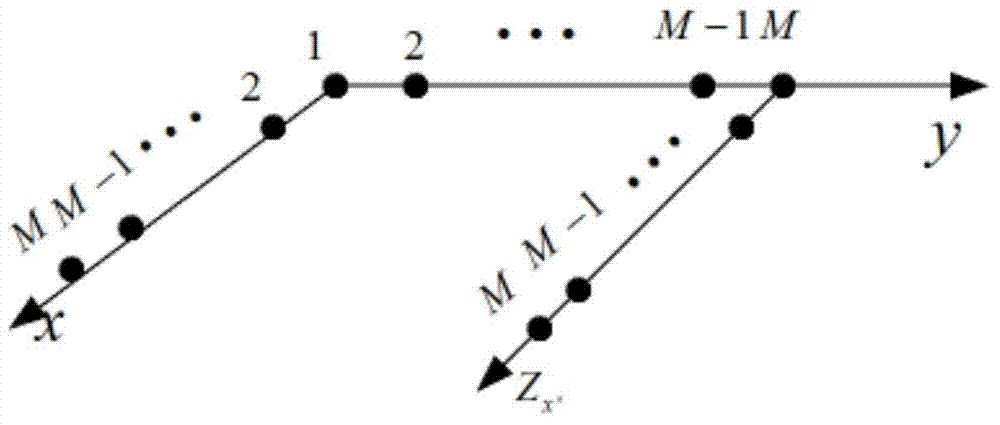

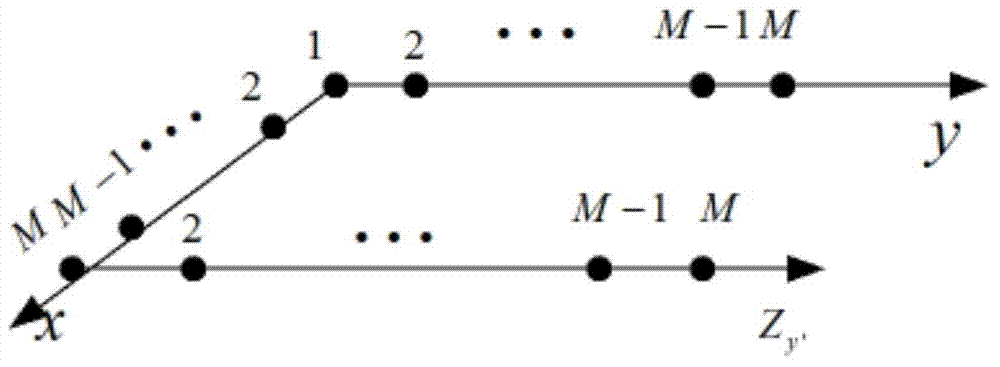

Virtual array DOA estimation method based on L type array

InactiveCN104730491AReduce complexityLarge apertureDirection/deviation determination systemsDecompositionSignal subspace

The invention discloses a virtual array DOA estimation method based on an L type array. The method comprises the steps that 1, based on the shift invariant property, a subarray Zx and a subarray Zy of the L type array horizontally shift to obtain a virtual array Zx' and a virtual array Zy', rotation invariance of two sub signals is formed due to the shift invariant property of the subarrays, and the virtual subarray signals are equal to the L type subarray Zx and L type subarray Zy input signals multiplied by a twiddle factor respectively; 2, the output of the four subarrays are combined to form a virtual array output signal Z (t); 3, the signal subspace and the noise subspace can be described by decomposing the features of covariance matrixes output by the array, mutual correlation processing is carried out on the array output signal Z(t) to obtain Rzz, and eigenvalue decomposition is carried out to obtain signal subspaces; 4, the twiddle factor is solved through linear operation, and the signal wave arrival direction can be obtained through the diagonal element of the twiddle factor. According to the virtual array DOA estimation method, no spectral function needs to be calculated, the phenomenon that the wave arrival direction is indirectly calculated without searching for the peak value is avoided, the complexity is lowered, the equipment complexity and cost are reduced, and the positioning precision is high.

Owner:CHINA JILIANG UNIV

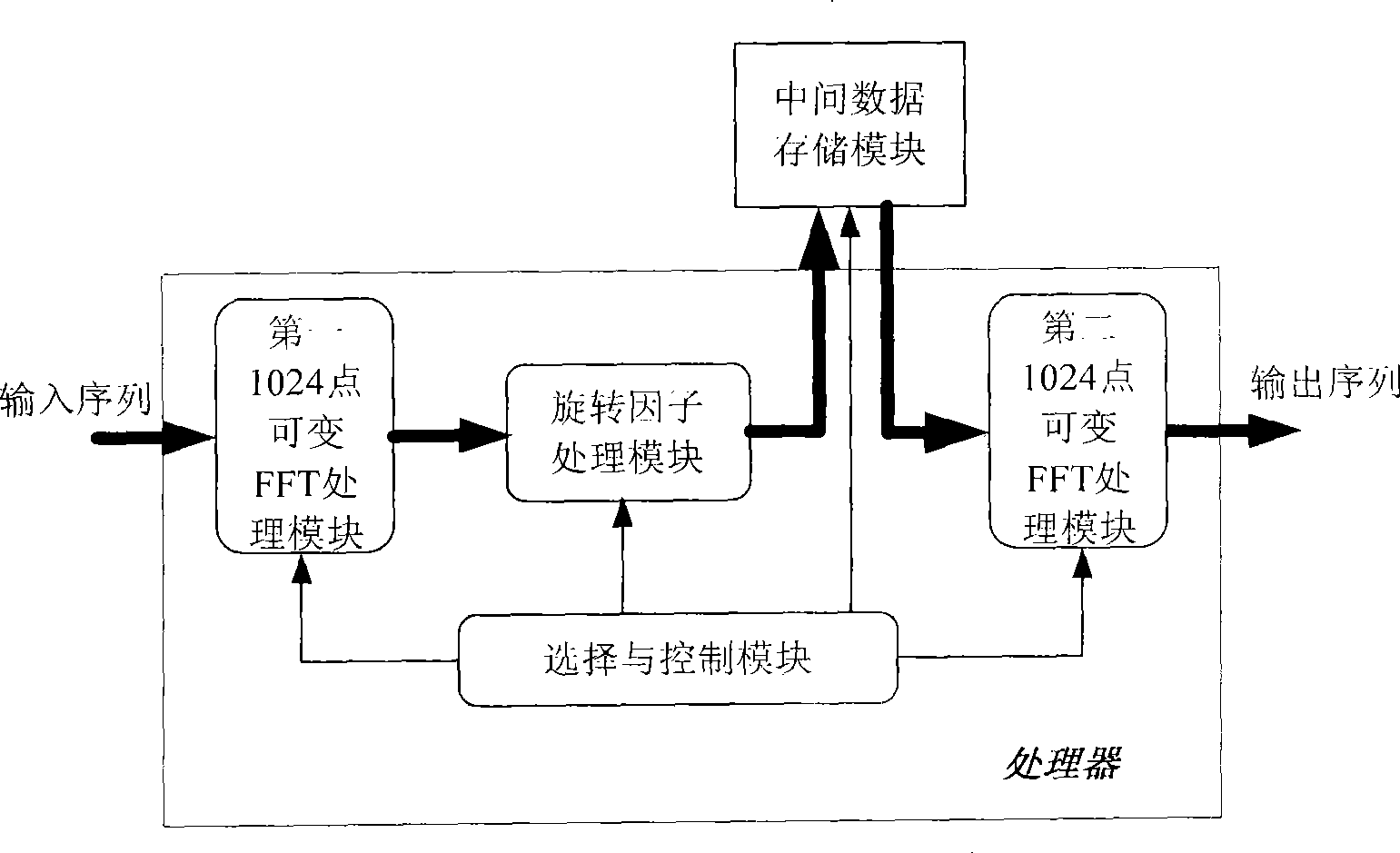

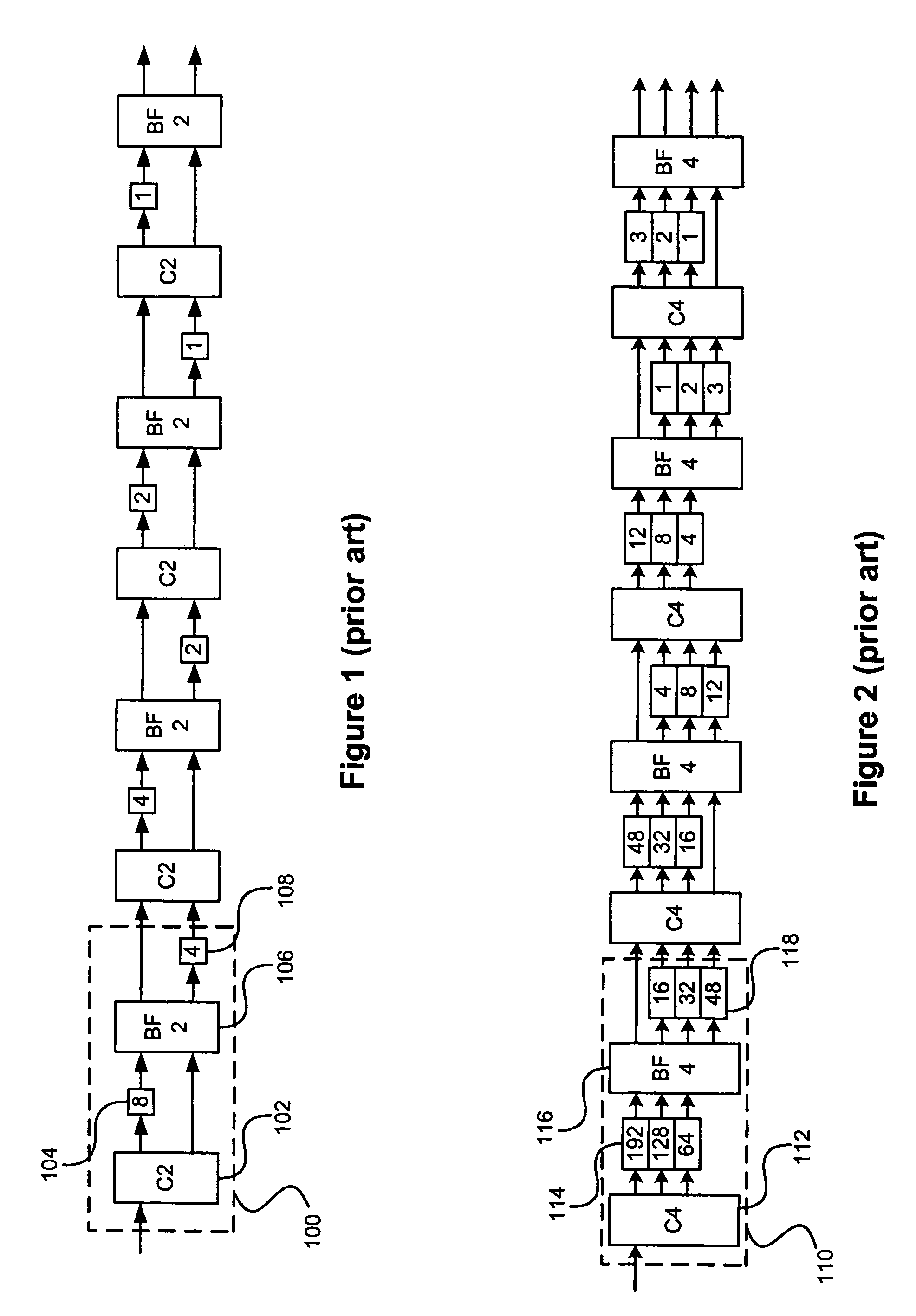

Point-variable assembly line FFT processor

InactiveCN101504638AReal-time processingUpdate output data in real timeComplex mathematical operationsFft processorParallel computing

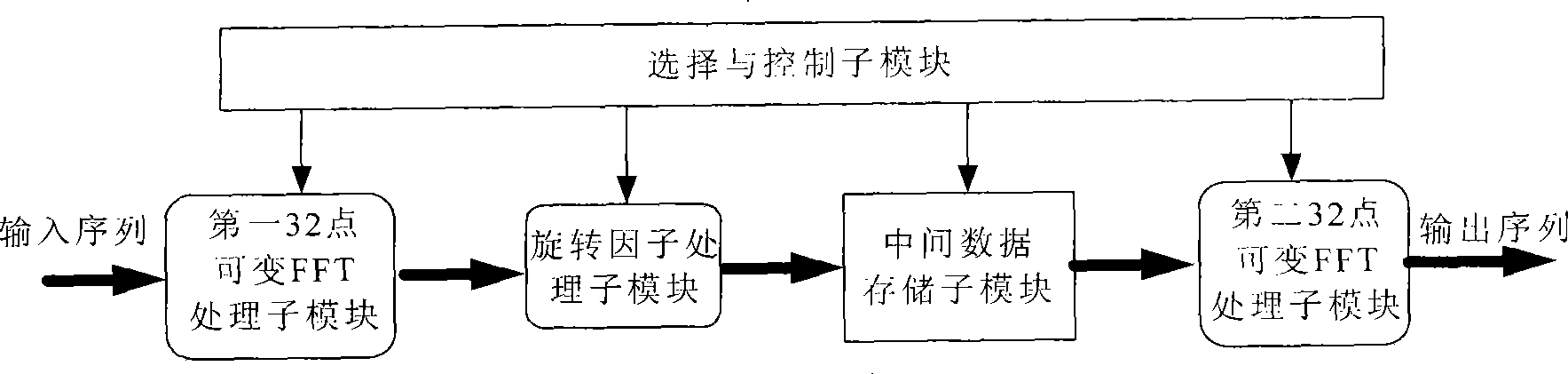

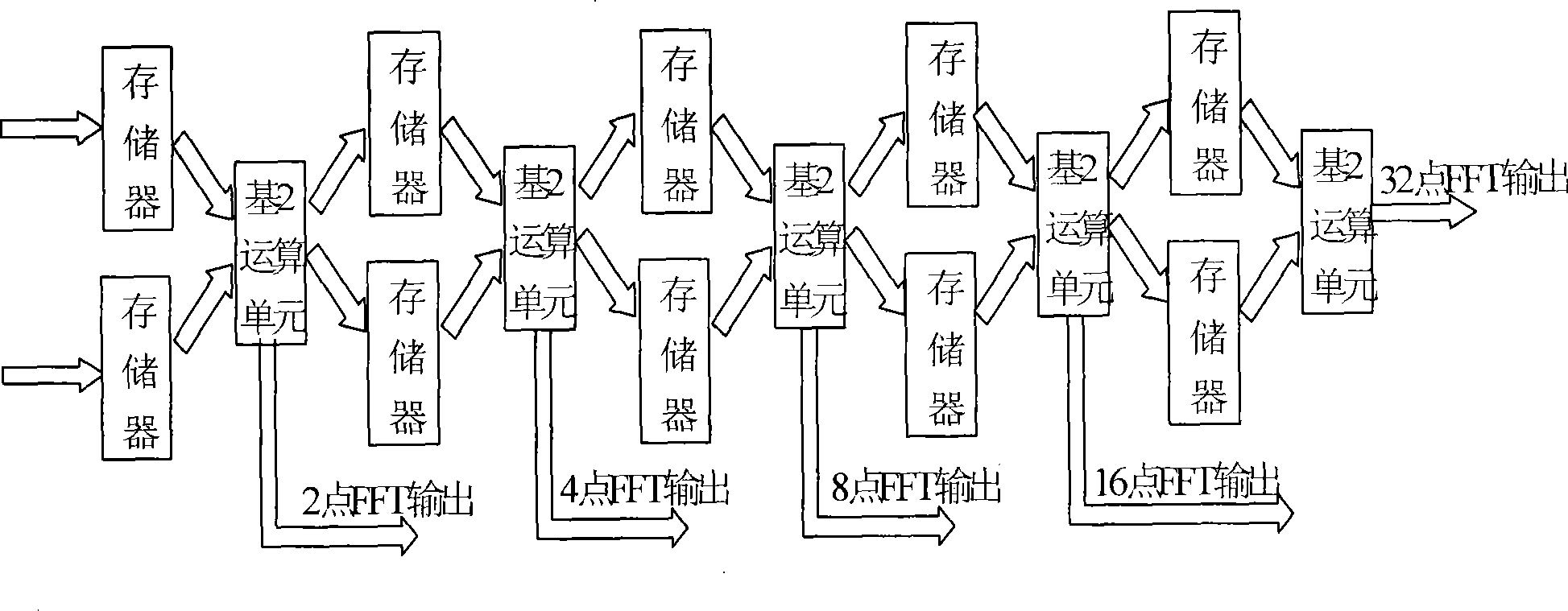

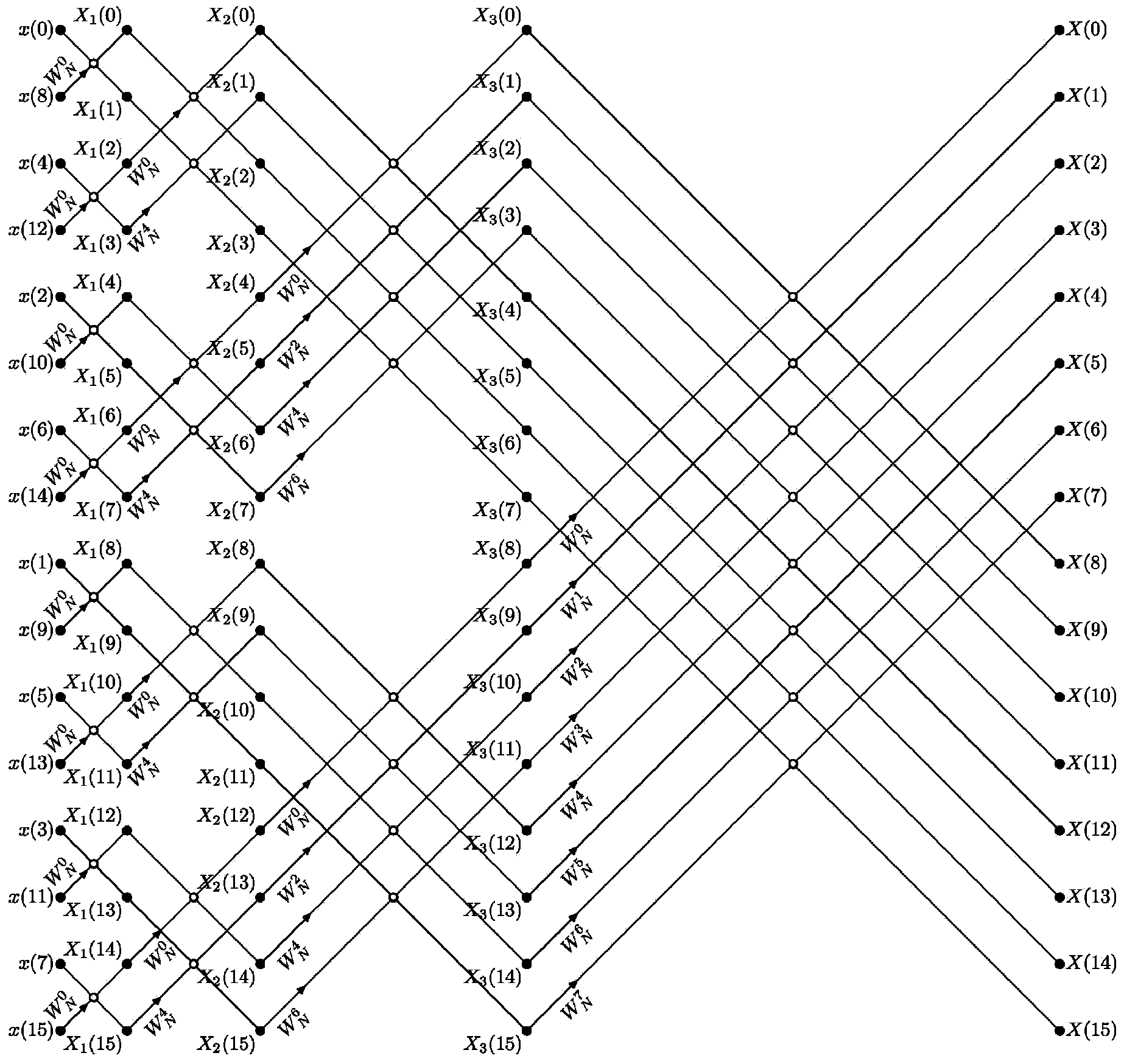

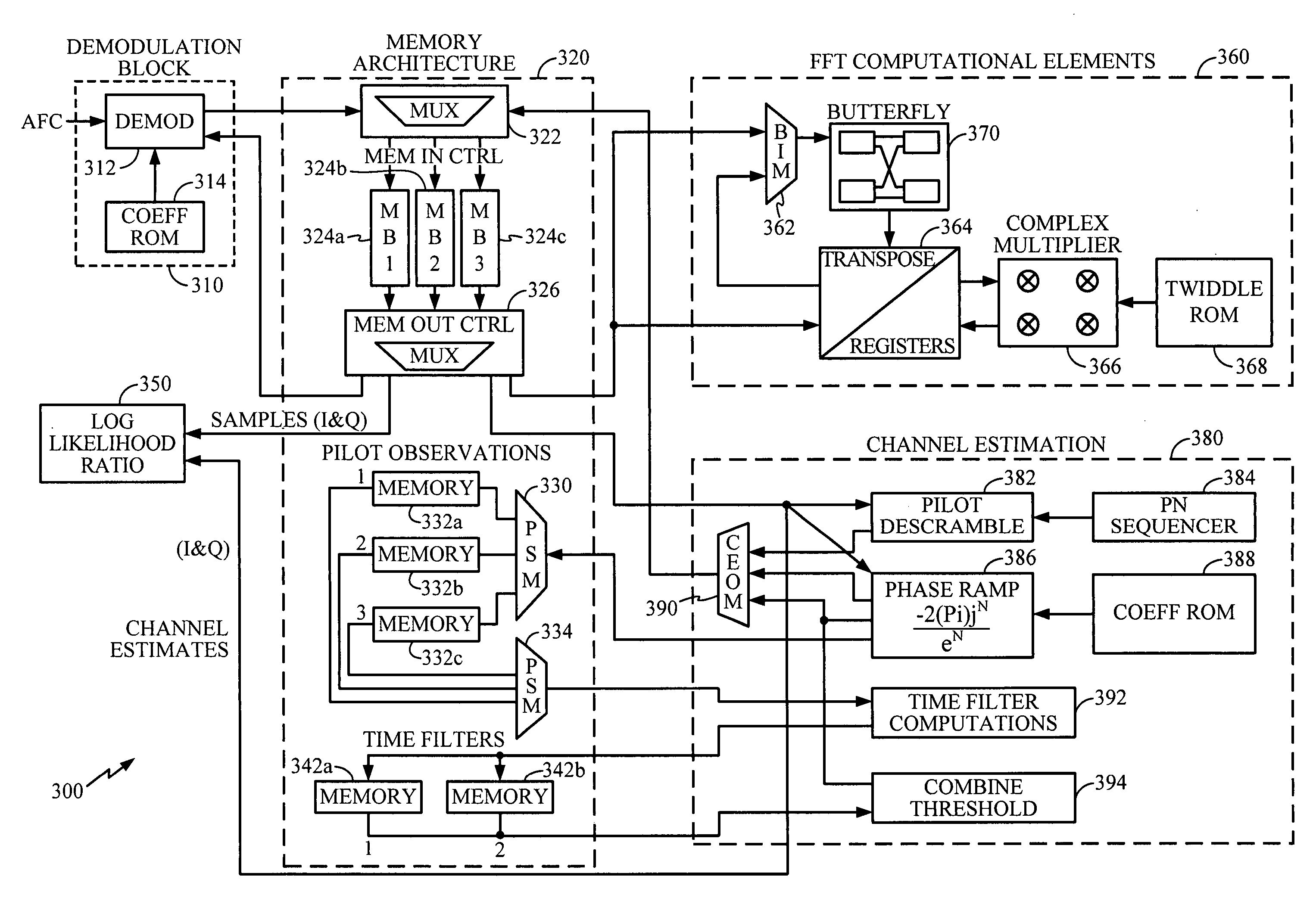

The invention provides a pipeline FFT processor variable in the number of points, which comprises a first 1024-point variable FFT processing module, a twiddle-factor processing module, a second 1024-point variable FFT processing module and a selection-control module, wherein the four modules and an intermediate data storage module outside the processor jointly complete FFT two-dimensional processing large in the number of points; each 1024-point variable FFT processing module comprises a first 32-point variable FFT processing sub-module, a second 32-point variable FFT processing sub-module, a twiddle-factor processing sub-module, an intermediate data storage sub-module and a selection-control sub-module; variable-point FFT operation is implemented through the 32-point variable FFT processing sub-modules; the twiddle-factor processing module generates and multiplies intermediate twiddle factors by the result of FFT operation; and the selection-control module realizes control over a whole chip. The processor is suitable to be realized in single-chip FPGA or ASIC, and can simultaneously obtain high speed, low power consumption, high precision and other characteristics.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

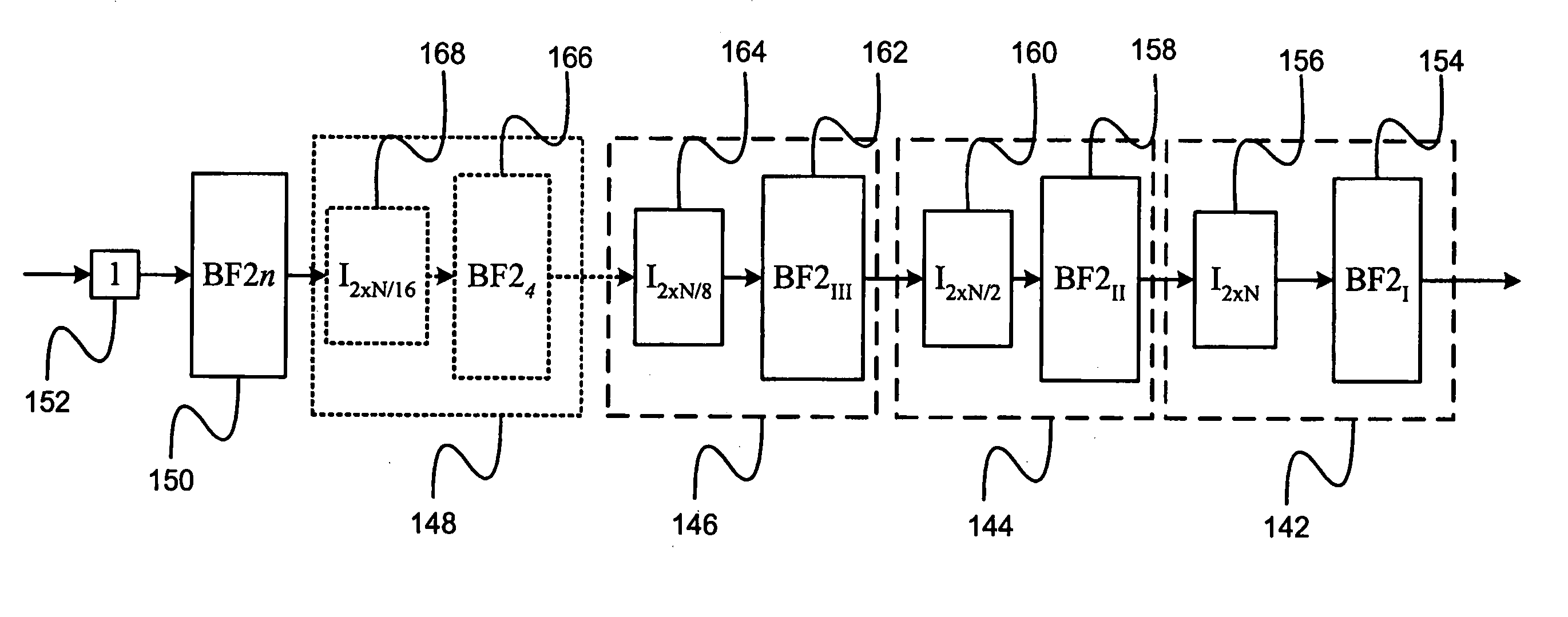

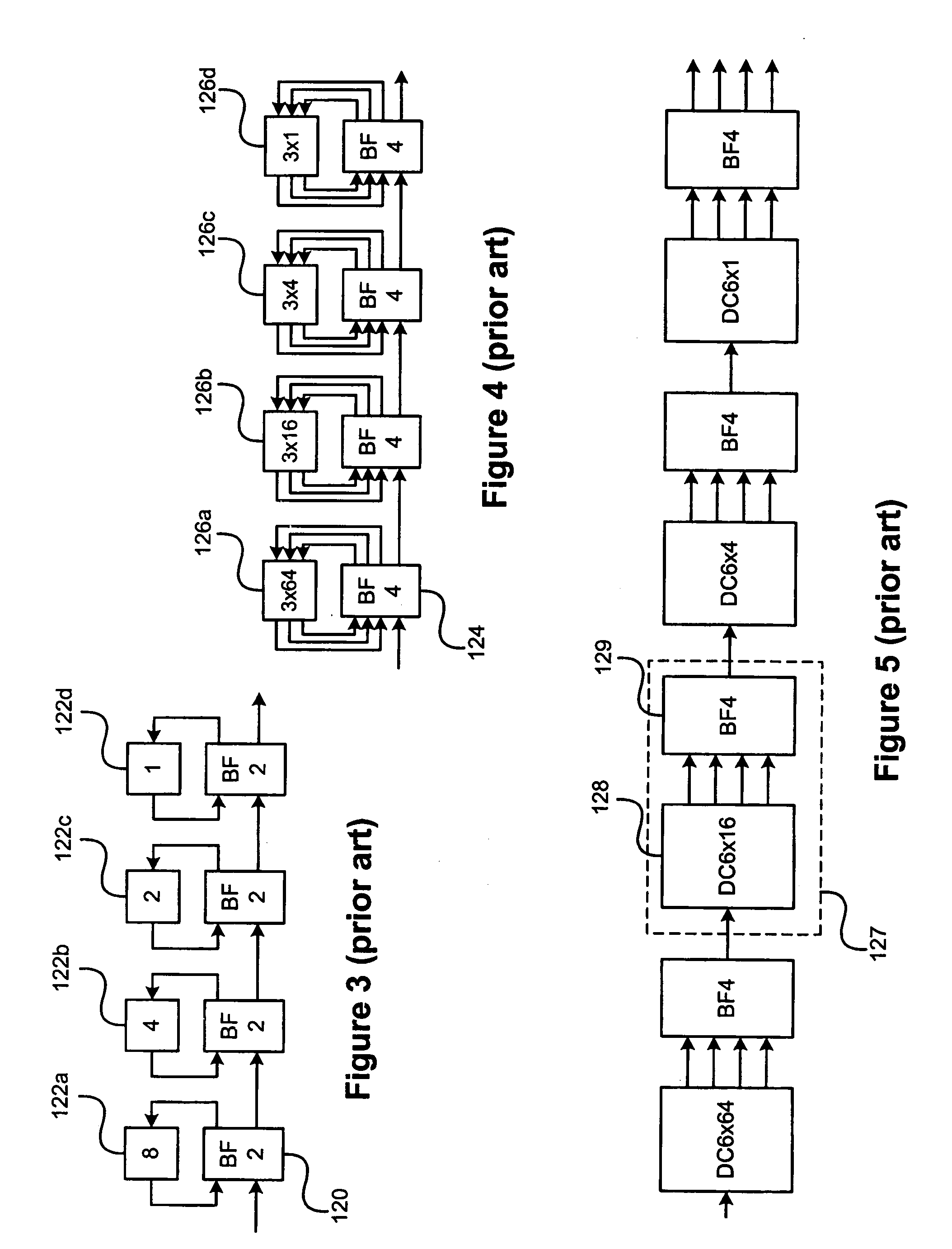

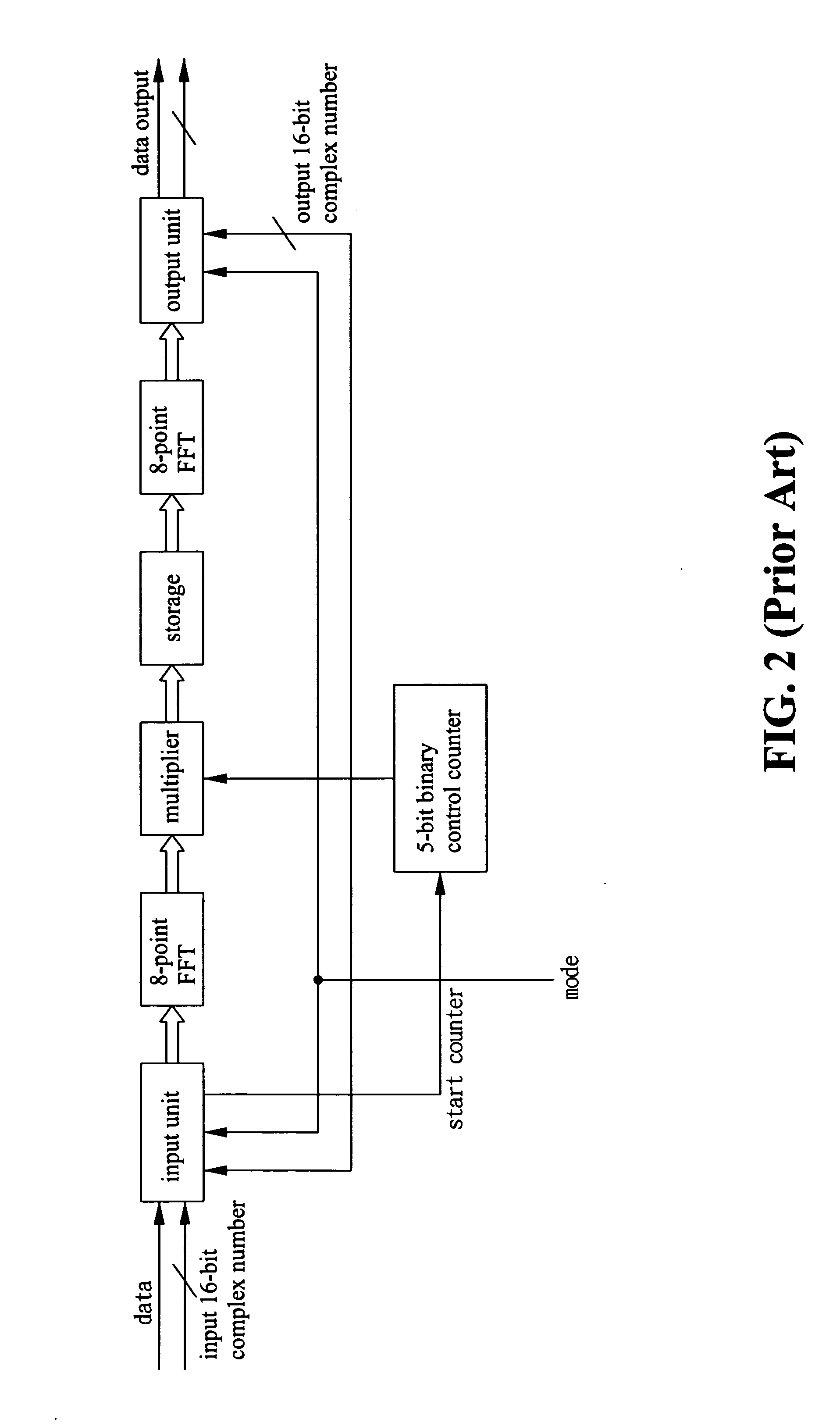

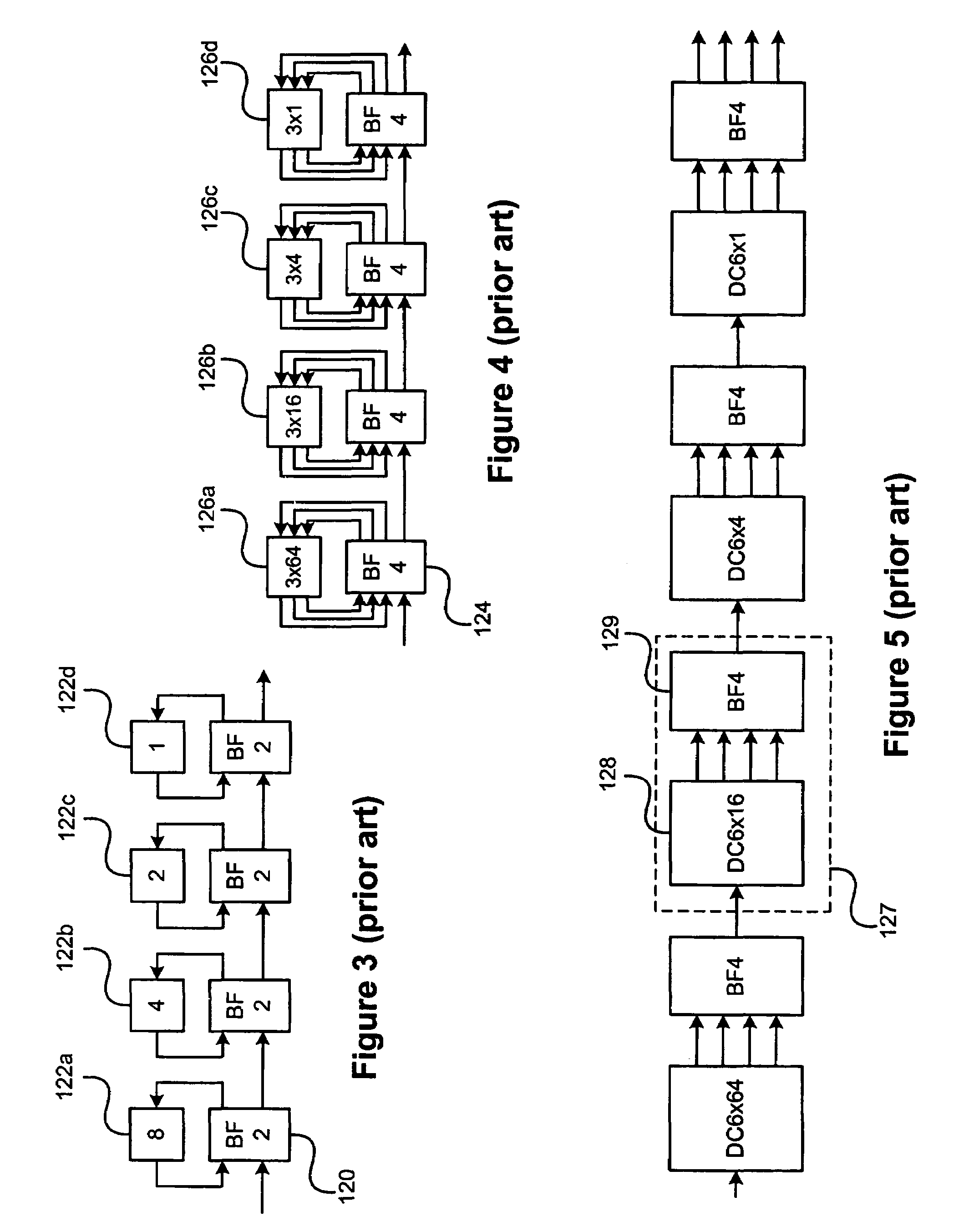

Recoded radix-2 pipeline FFT processor

InactiveUS20050015420A1Digital computer detailsComplex mathematical operationsComputational scienceRotation factor

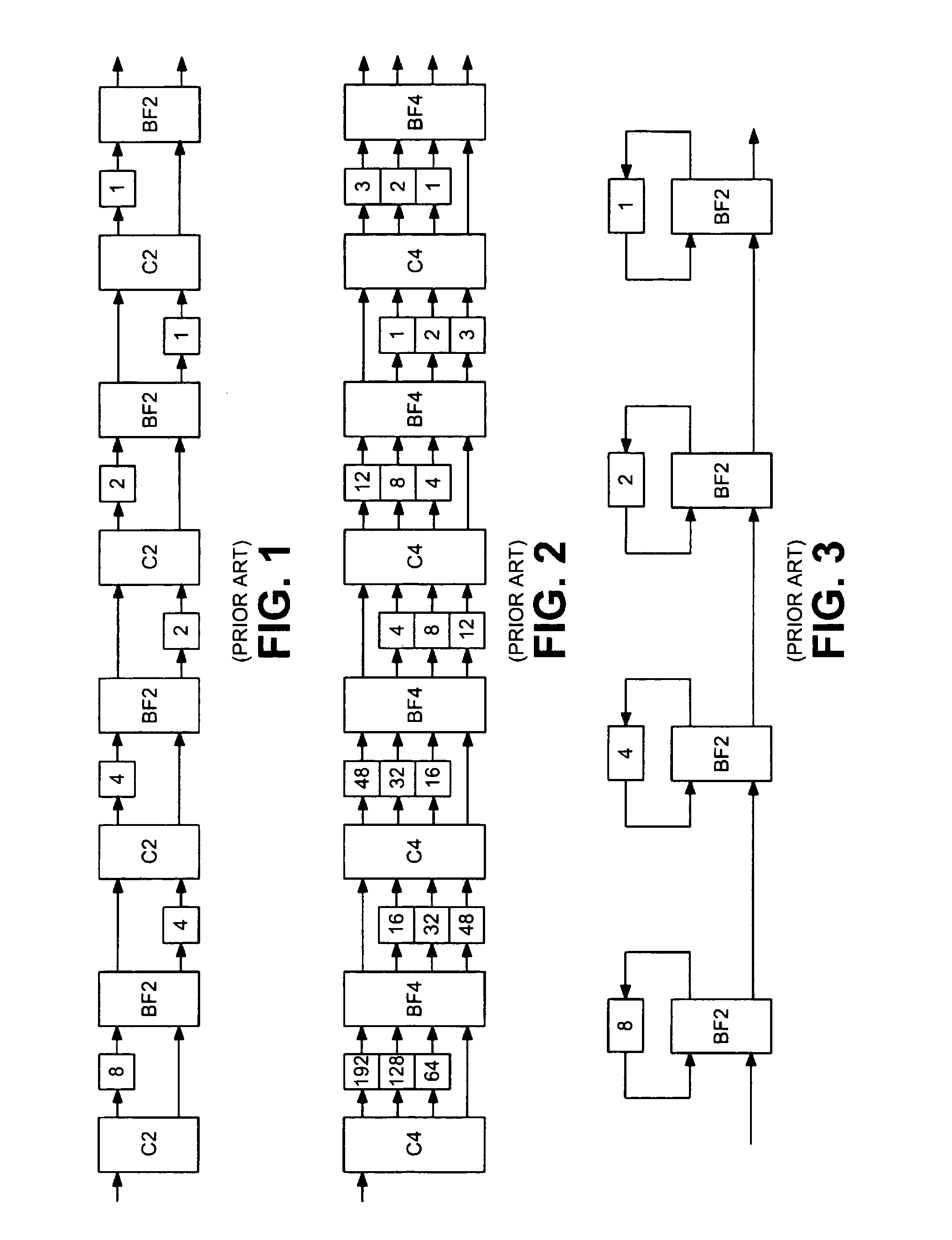

A single-path delay feedback pipelined fast Fourier transform processor comprising at least one set of triplet FFT stage means: a first FFT stage means comprising a radix-2 butterfly, a feedback memory, and a multiplication by unity; a second FFT stage means comprising a trivial coefficient pre-multiplication, a radix-2 butterfly, a feedback memory, and a multiplication by selectable unity or WNN / 8; and a third FFT stage means comprising a trivial coefficient pre-multiplication, a butterfly, a feedback memory, and a complex twiddle coefficient multiplication with coefficients determined using a twiddle factor decomposition technique.

Owner:CYGNUS COMM CANADA CO

Fast fourier transform on a single-instruction-stream, multiple-data-stream processor

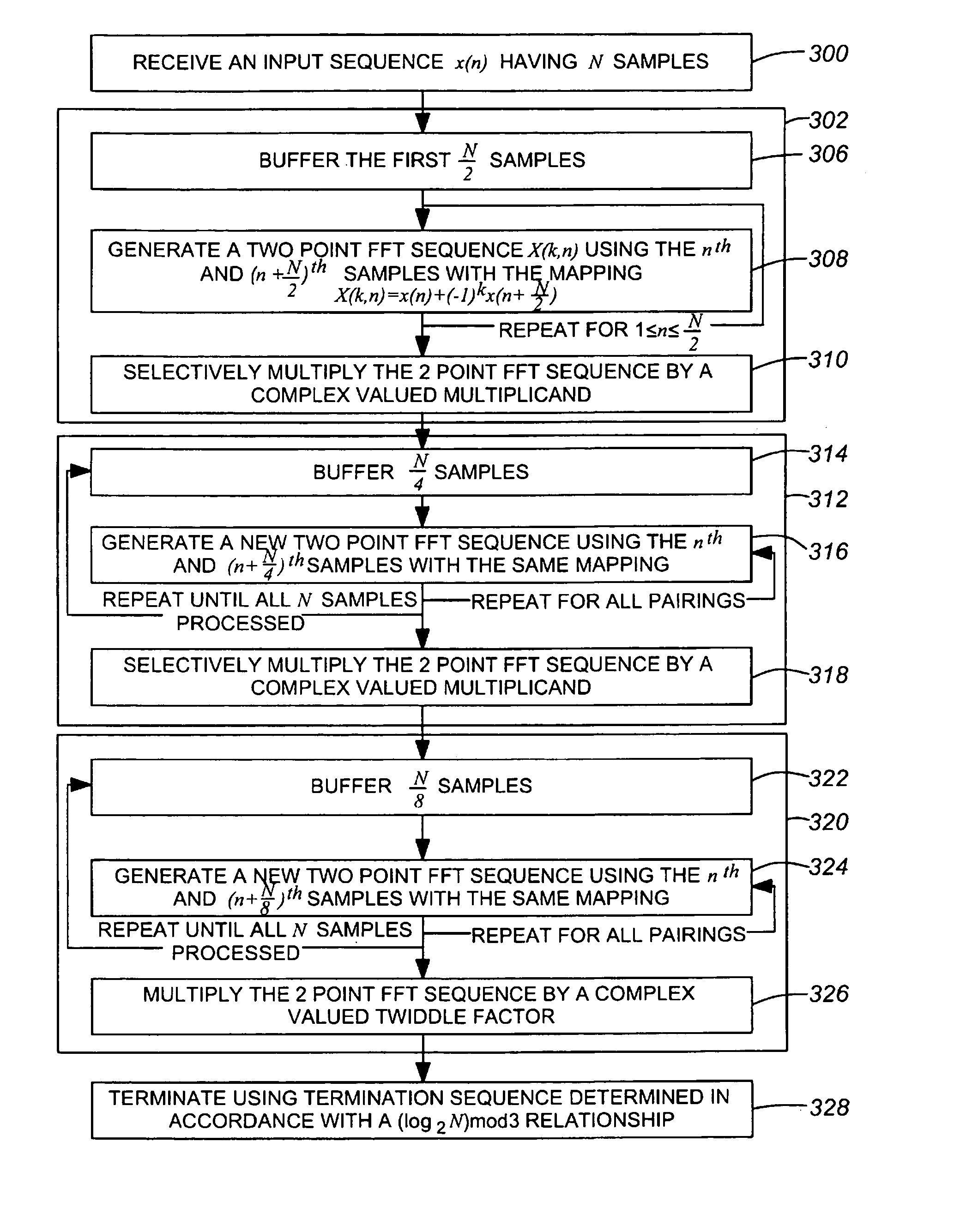

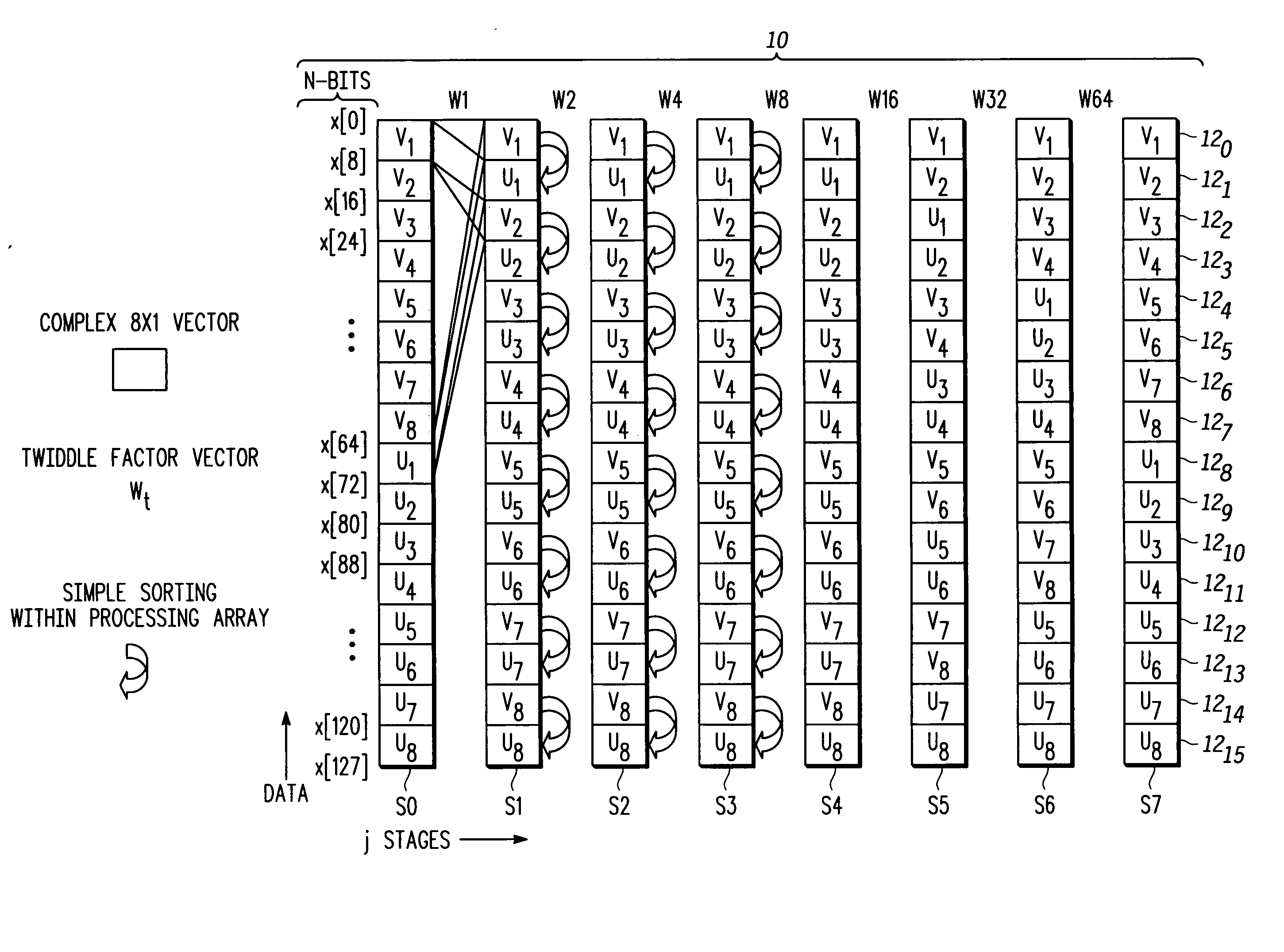

A method of performing a fast Fourier transform (FFT) in a single-instruction-stream, multiple-data-stream (SIMD) processor includes providing n-bits of input data, and implementing j number of stages of operations. The n-bits of input data are grouped into groups of x-bits to form i number of vectors so that i=n / x. The method includes parallel butterflies operations on vector [i] with vector [i+(n / 2)] using a twiddle factor vector Wt. Data sorting is performed within a processing array if a present stage j is less than y, where y is an integer less than a maximum value of j. The parallel butterflies operations and data sorting are repeated i times, then the process increments to the next stage j. The parallel butterflies operations, data sorting and incrementing are repeated (j−1) times to generate a transformed result and then the transformed result is output.

Owner:FREESCALE SEMICON INC

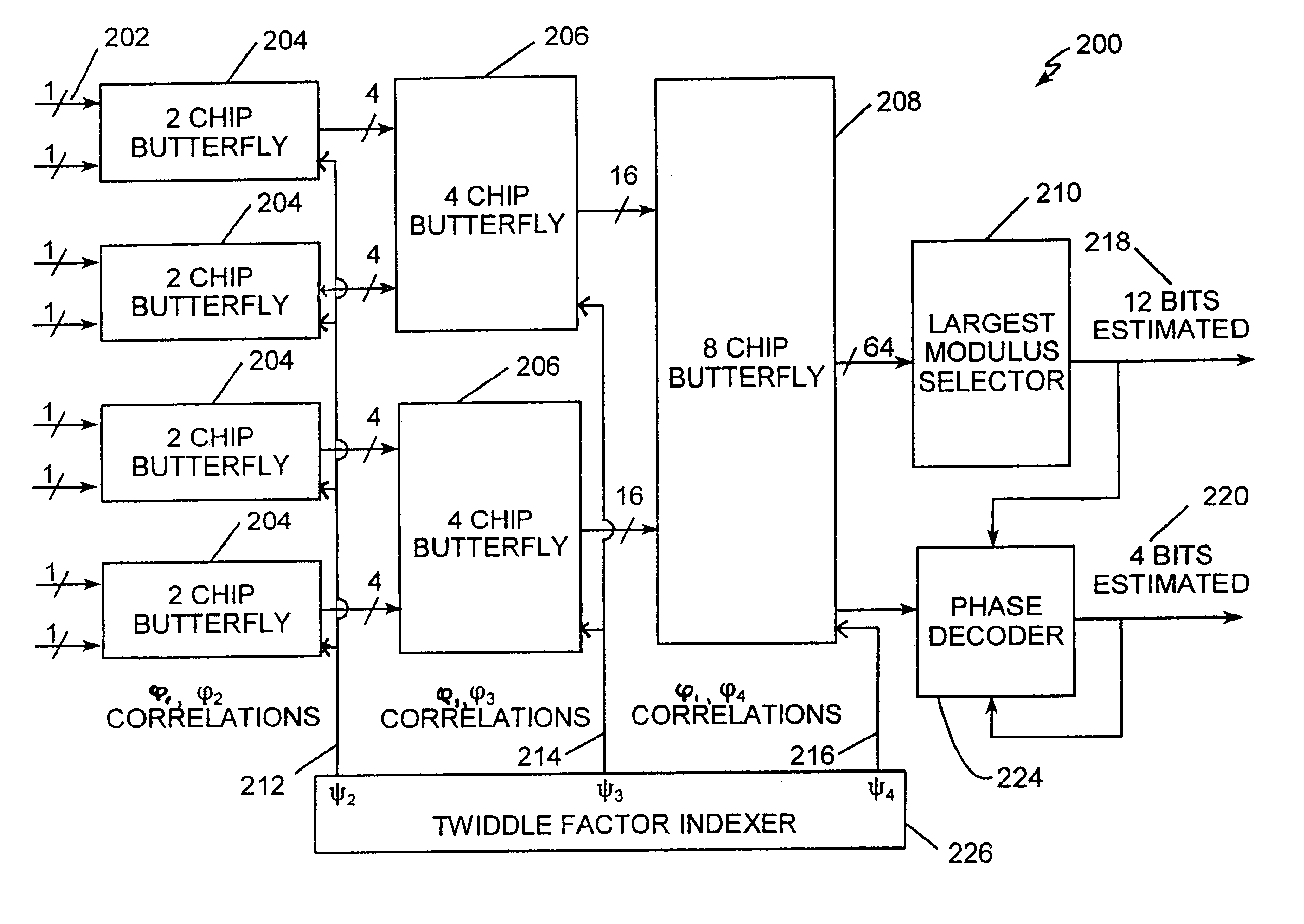

Fast transform system for an extended data rate WLAN system

In a direct sequence spread spectrum receiver an “as received” signal is decoded by correlation. Phase shift key, complementary code key modulated signals are correlated by transforming samples of the signal in a series of butterfly transform processors producing a number of correlations equal to the number of possible transmitted codewords. The largest correlation is selected as the transmitted signal. To reduce the number of processors required to transform a multi-level phase shift key signal, a correlation method and apparatus are disclosed wherein the butterfly transforms are modified with additional twiddle factors selected from a set of twiddle factors. In the alternative, the inputs to the butterfly processors of a correlator can be weighted as a function the additional twiddle factors. A set of signal samples is correlated for each combination of the set of additional twiddle factors and the largest correlation selected as the signal.

Owner:SHARP LAB OF AMERICA INC

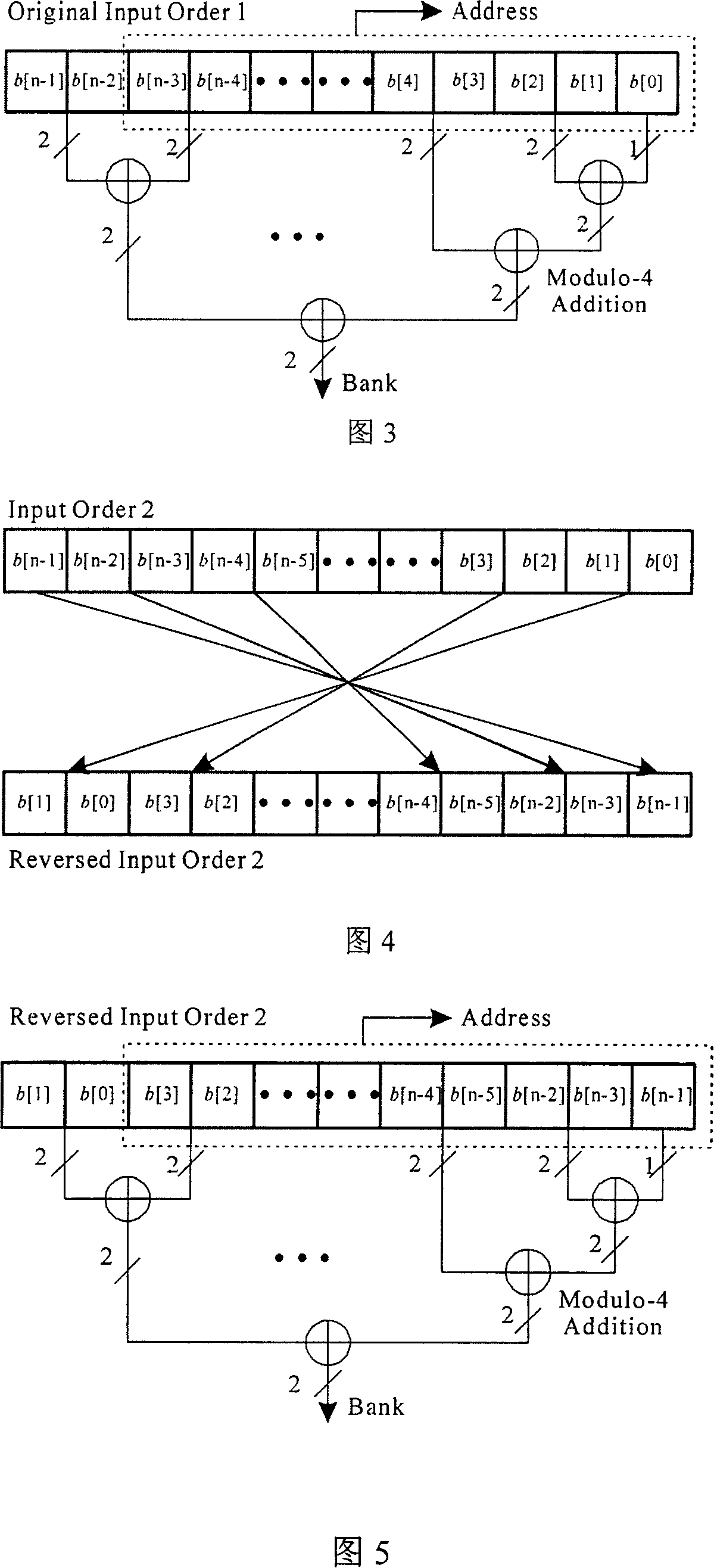

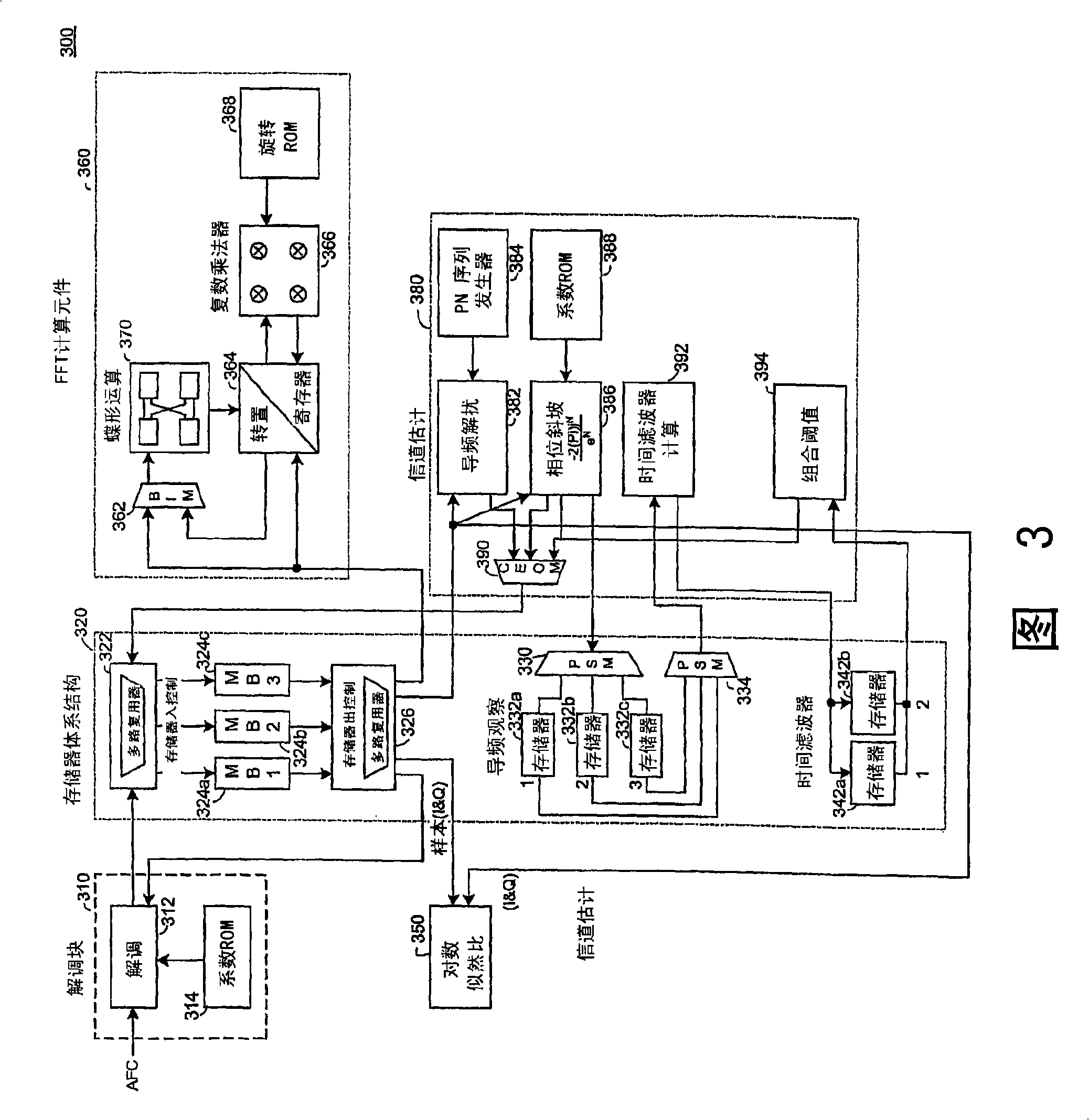

FFT processor data storage system and method

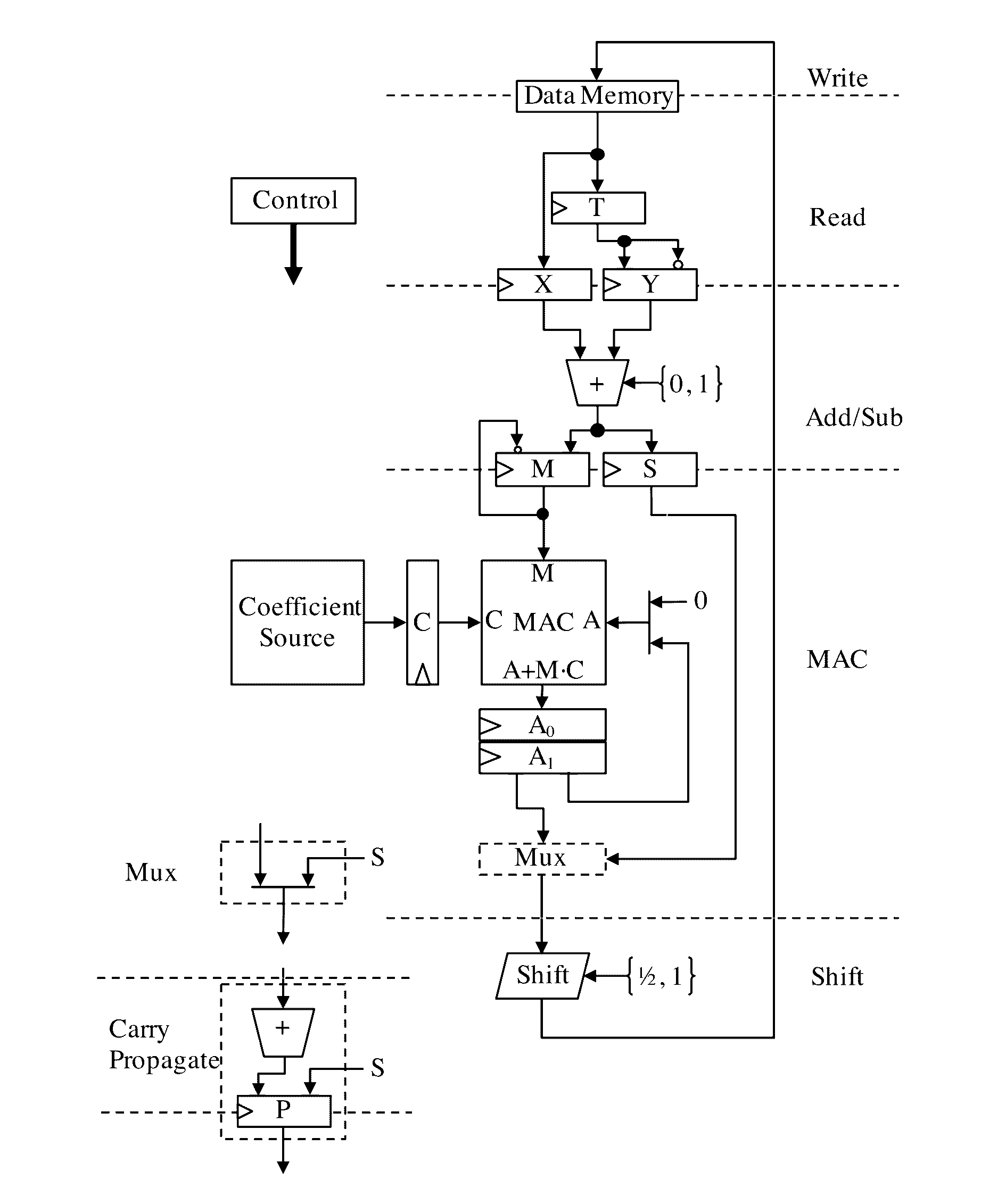

ActiveCN101290613AIncrease profitReduce areaComplex mathematical operationsFft processorTwiddle factor

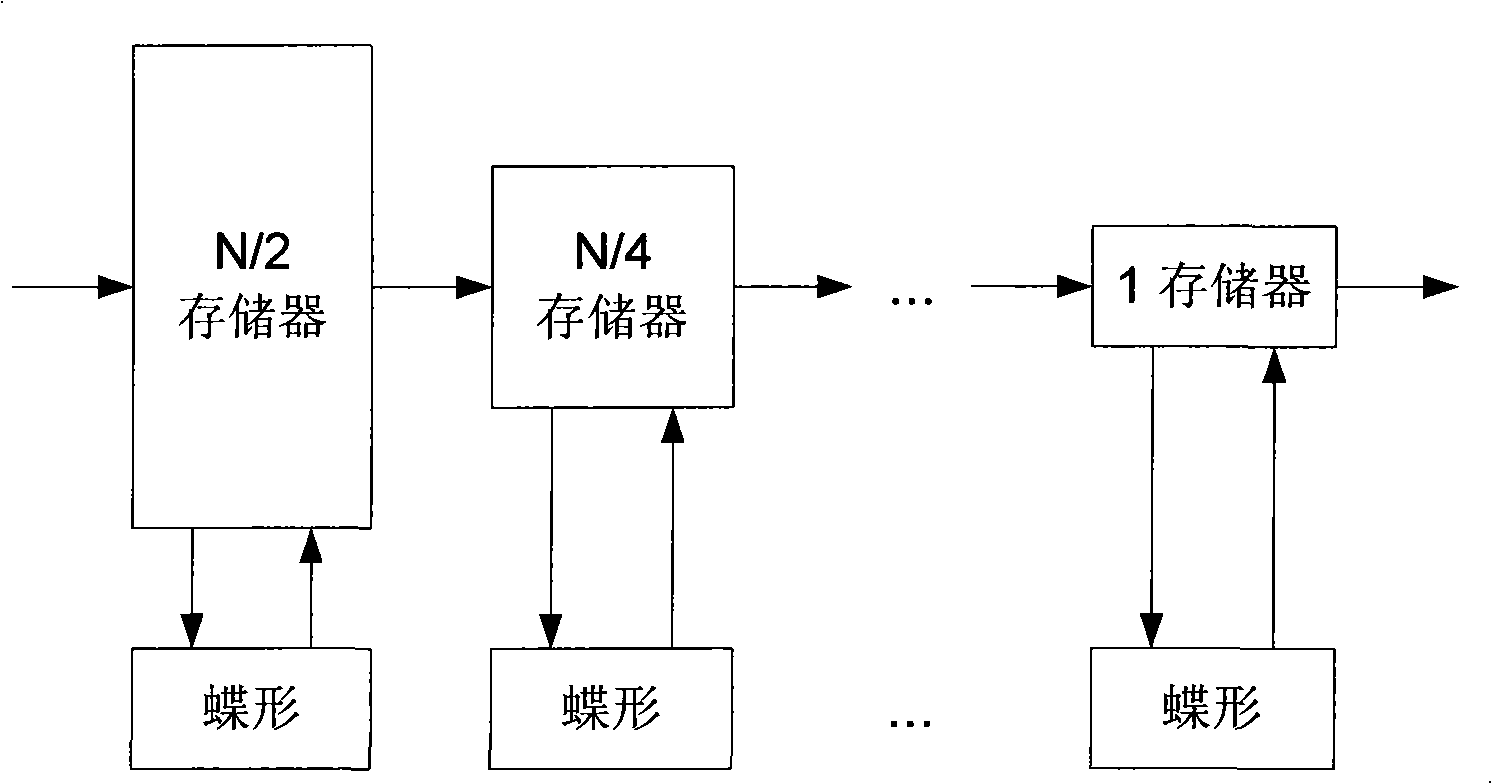

The invention discloses a system and a method for data storage of an FFT processor. The data storage system comprises a controller, a storage, a papilionaceous operation unit and a twiddle factor form; the storage is used for storing data; the twiddle factor form stores a twiddle factor needed for each papilionaceous operation according to the sequence; the papilionaceous operation unit is used for the papilionaceous operation; the controller comprises a papilionaceous operation counter, a series counter, an index number generator, an address mapping device, a delay unit and a twiddle factor serial number generator; the data storage method comprises the following steps that: according to the input sequence, input data is recorded as dindex, wherein, the index is equal to 0, 1, ..., N-1; the index is represented by a binary digit and needs m bits, wherein, the m is equal to log 2N, that is, recorded as index[m-1:0]; and the input data is stored in the storage. The system and the method for data storage of the FFT processor use a single-port storage to realize the conflict-free read-write access; and the utilization rate of the papilionaceous operation unit is nearly 100 percent, thereby effectively improving the utilization efficiency of hardware resource.

Owner:MAXSCEND MICROELECTRONICS CO LTD

Uplink ranging system and method in OFDMA system

ActiveUS20050141474A1Effectively carrying out timing synchronizationTime-division multiplexFrequency-division multiplexBinary multiplierTwiddle factor

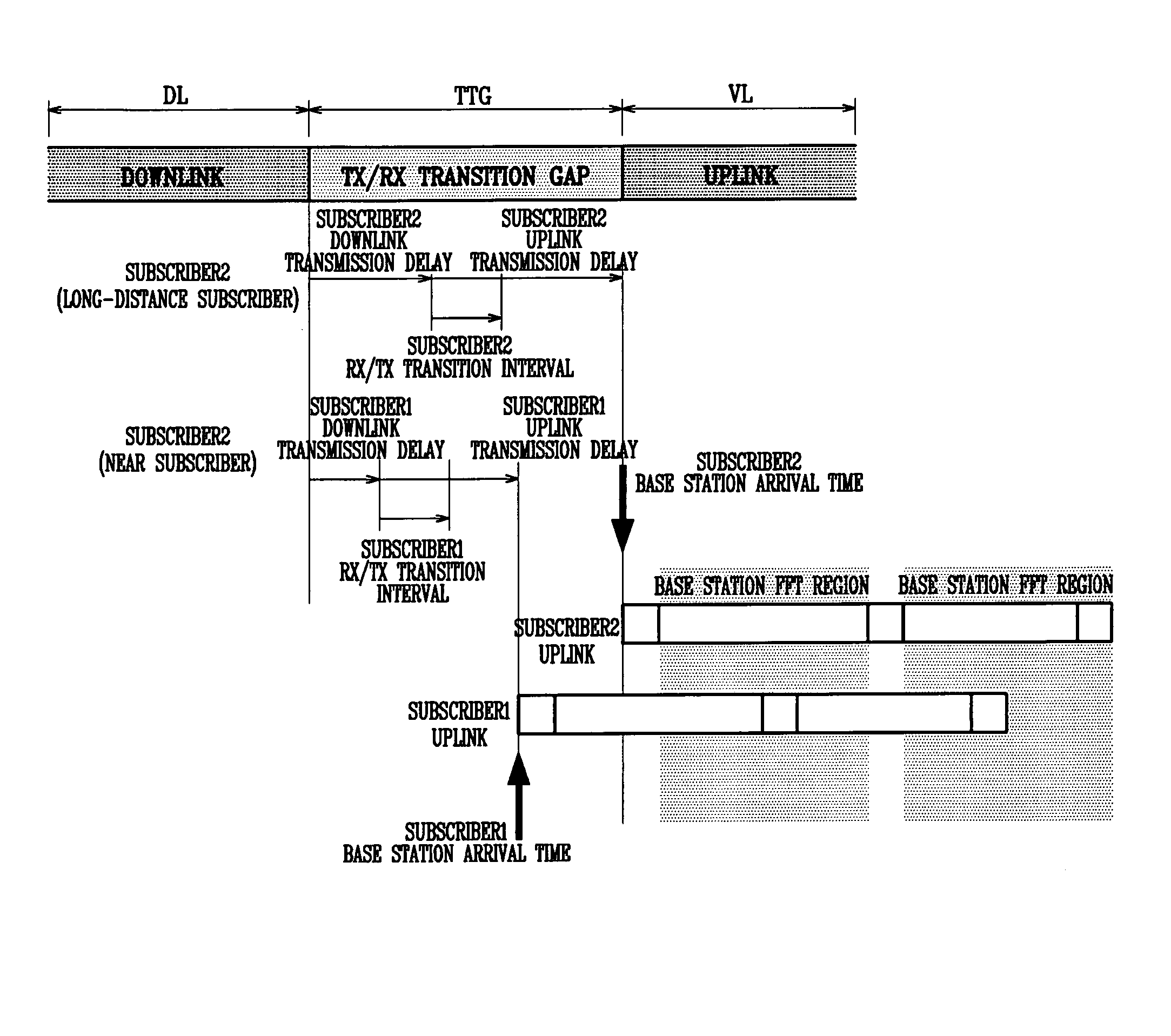

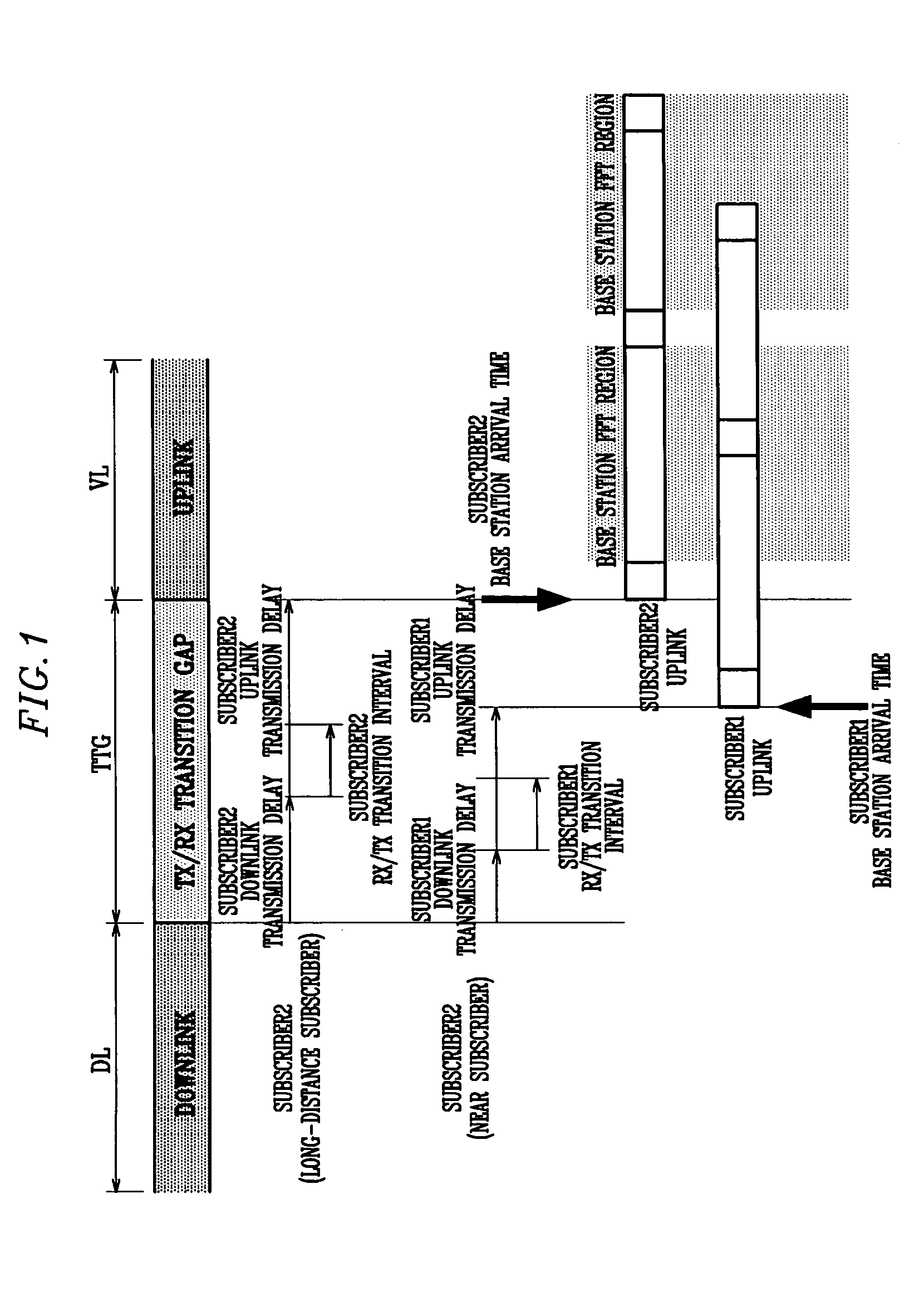

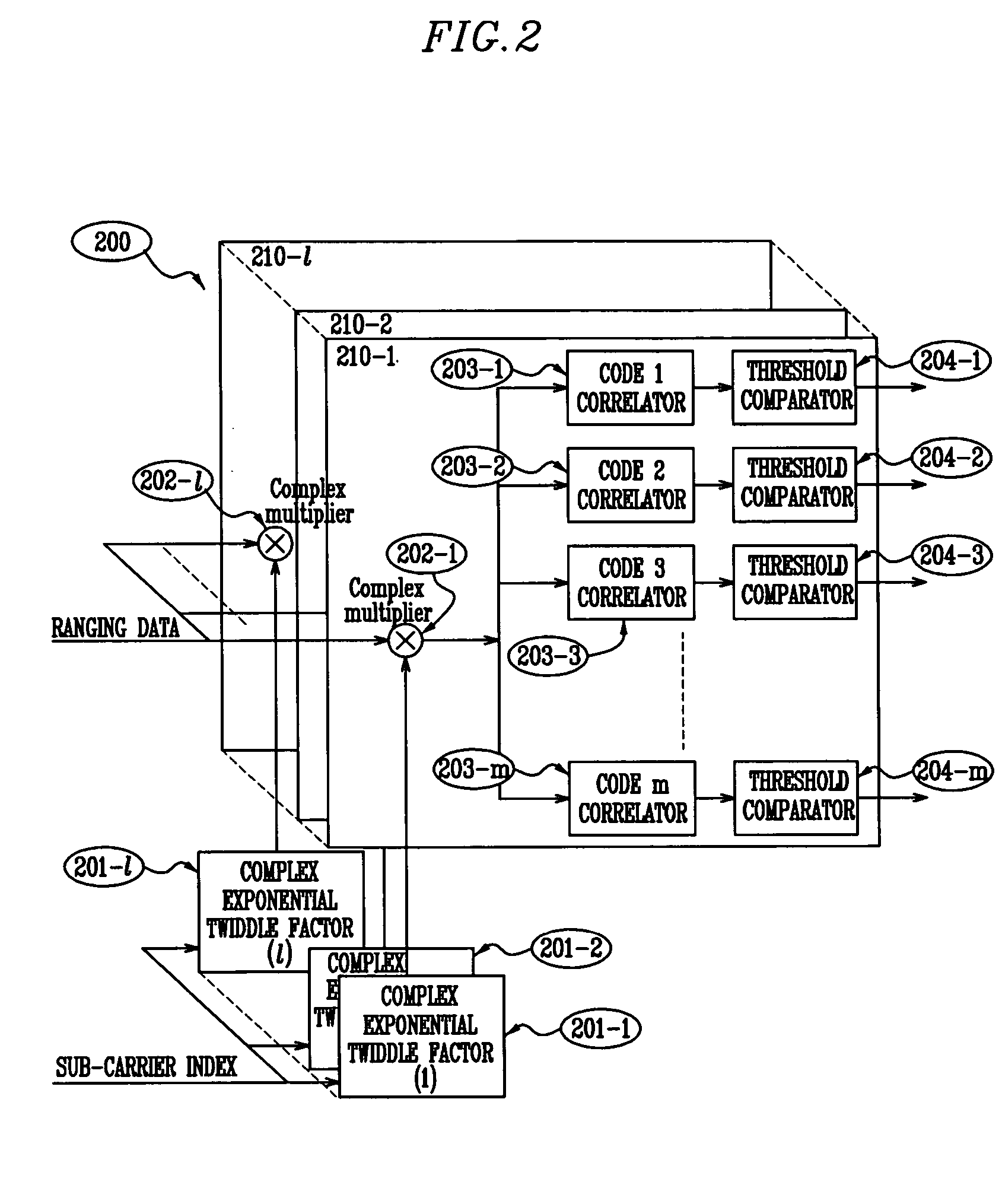

Disclosed is a ranging system and method in an OFDMA system. The ranging system includes complex exponential twiddle storage units for respectively storing complex exponential twiddle factors corresponding to a timing error, complex multipliers for respectively complex-multiplying the complex exponential twiddle factors by received uplink ranging data, code correlators for respectively correlating the outputs of the complex multipliers and ranging codes, and threshold comparators for respectively comparing the outputs of the code correlators with a threshold.

Owner:KT CORP +4

Fourier transform implementation method based on reconfigurable technology

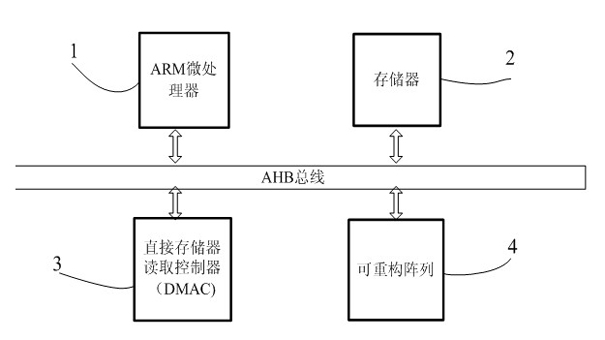

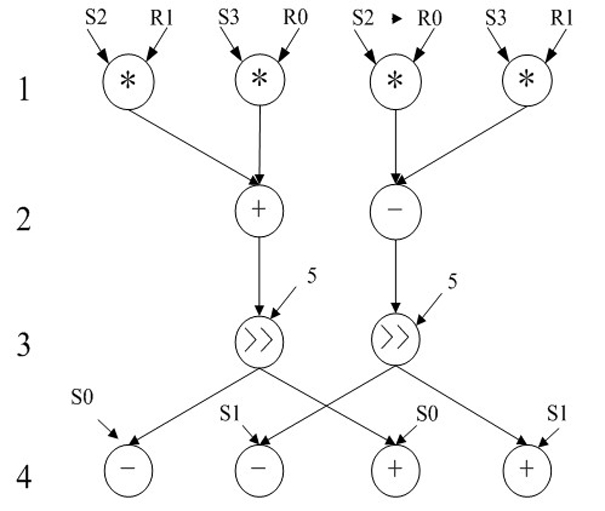

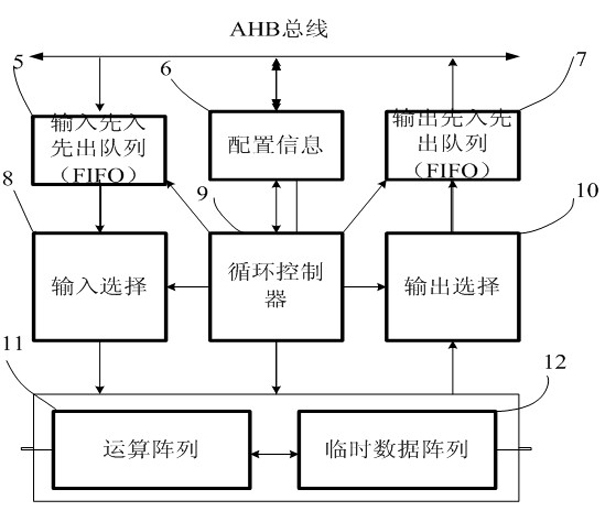

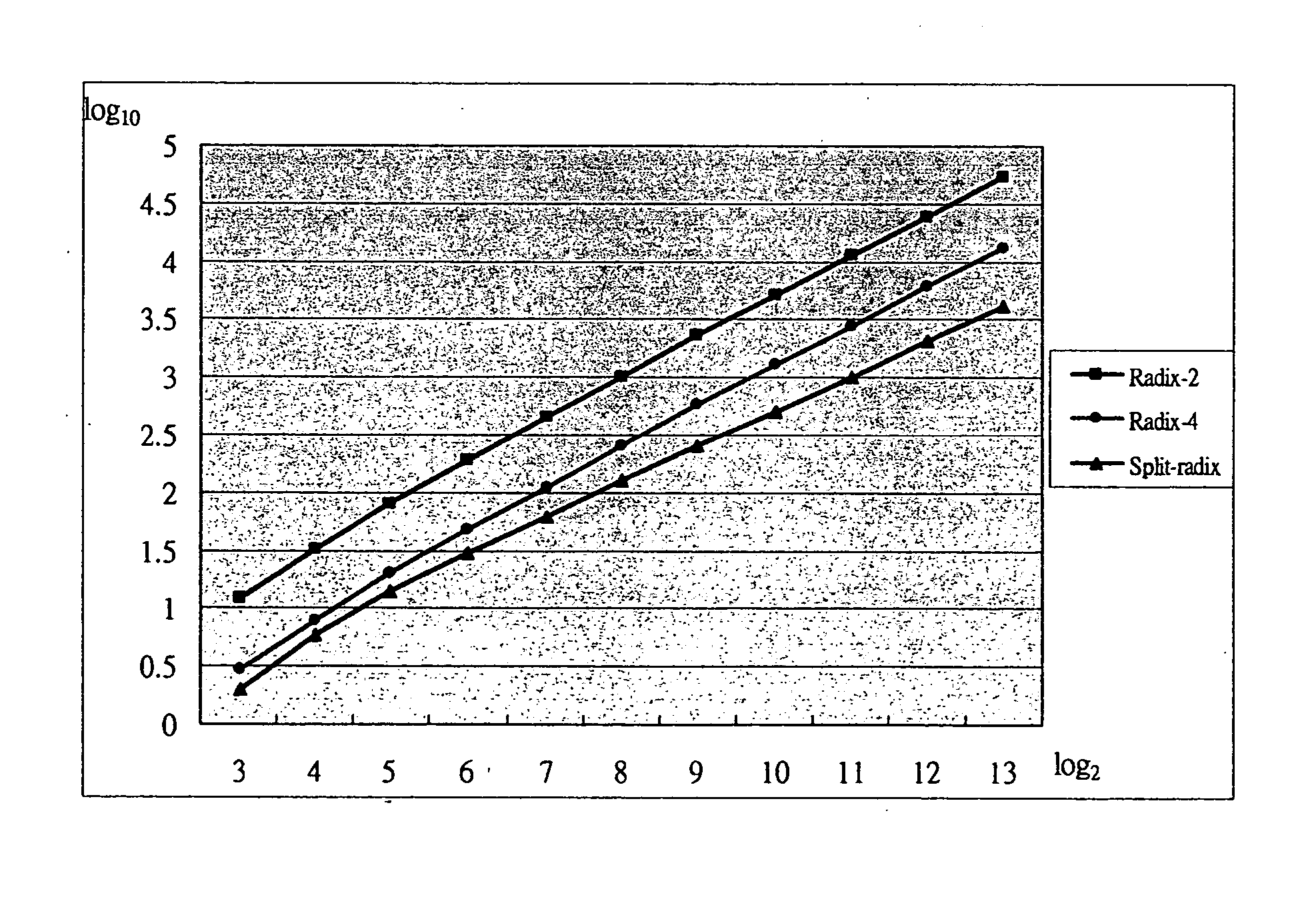

InactiveCN102043761AImprove computing efficiencyIncrease flexibilityComplex mathematical operationsDirect memory accessFourier transform on finite groups

The invention relates to a Fourier transform implementation method based on a reconfigurable technology. In the method, aiming at the common point-based discrete Fourier transform algorithm, the point-based fast Fourier transform computing is decomposed into M exponent arithmetic processes, each exponent arithmetic is composed of N / 2 butterfly arithmetics, and each butterfly arithmetic utilizes one twiddle factor, wherein M is any positive integer, and N is the length of a sequence needing to be subject to Fourier transform, namely a corresponding value. The method can be applied to an embedded system which comprises a bus, an embedded microprocessor, a memory, a reconfigurable array and a direct memory access (DMA) controller, wherein the embedded microprocessor, the memory, the reconfigurable array and the DMA controller respectively communicate with the bus. By utilizing the method, the computing efficiency is improved.

Owner:SOUTHEAST UNIV

Split-radix FFT/IFFT processor

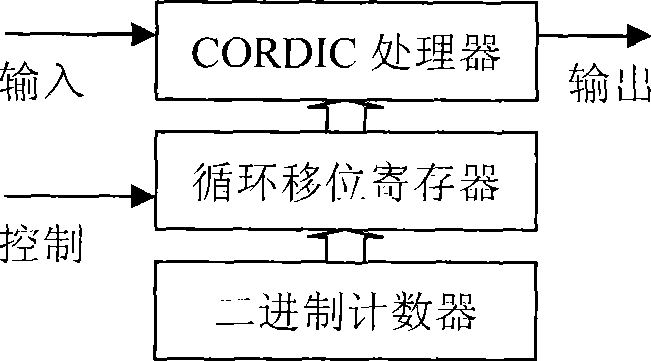

InactiveUS20070266070A1Easy to useDigital computer detailsComplex mathematical operationsFast Fourier transformControl signal

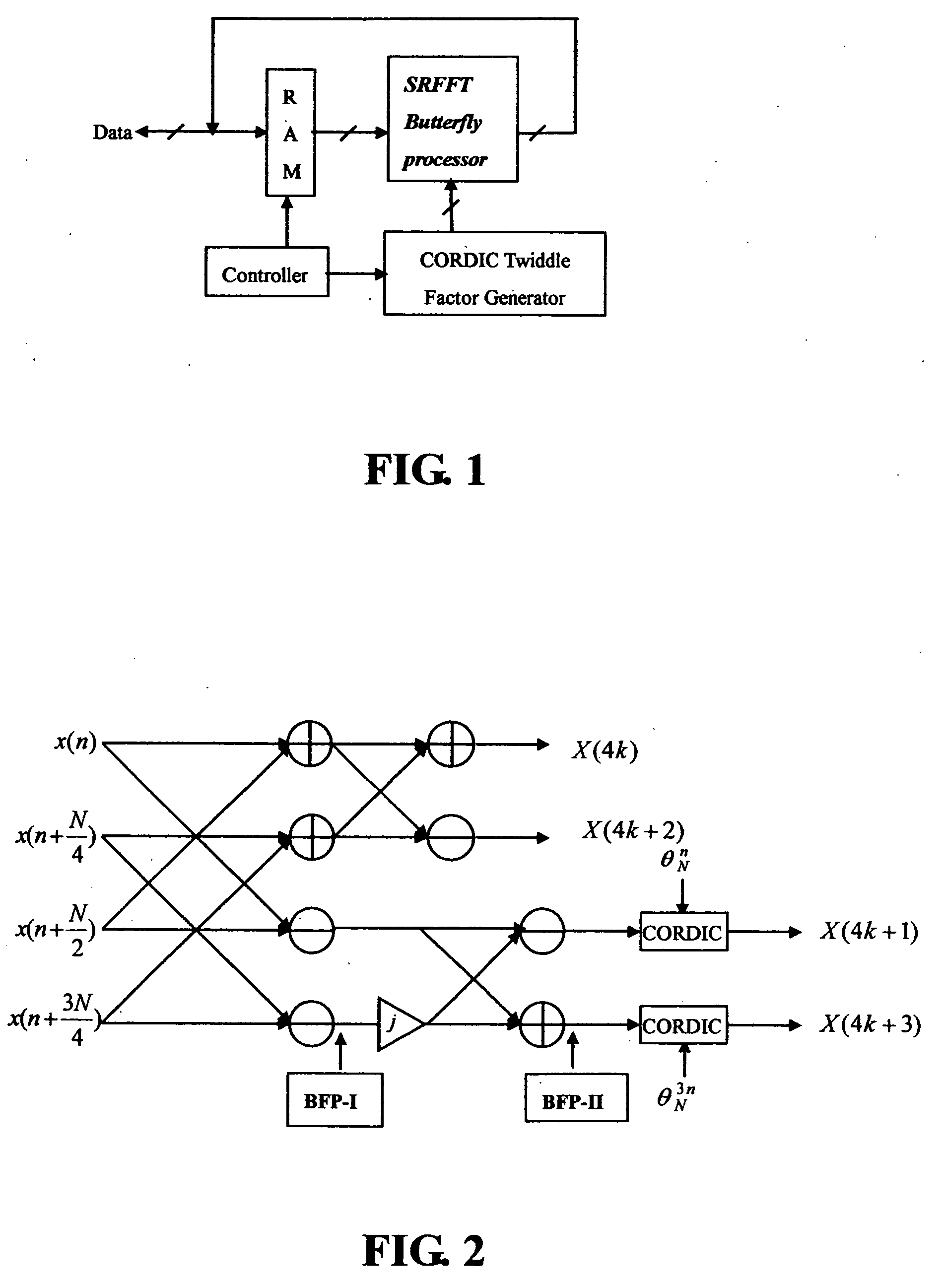

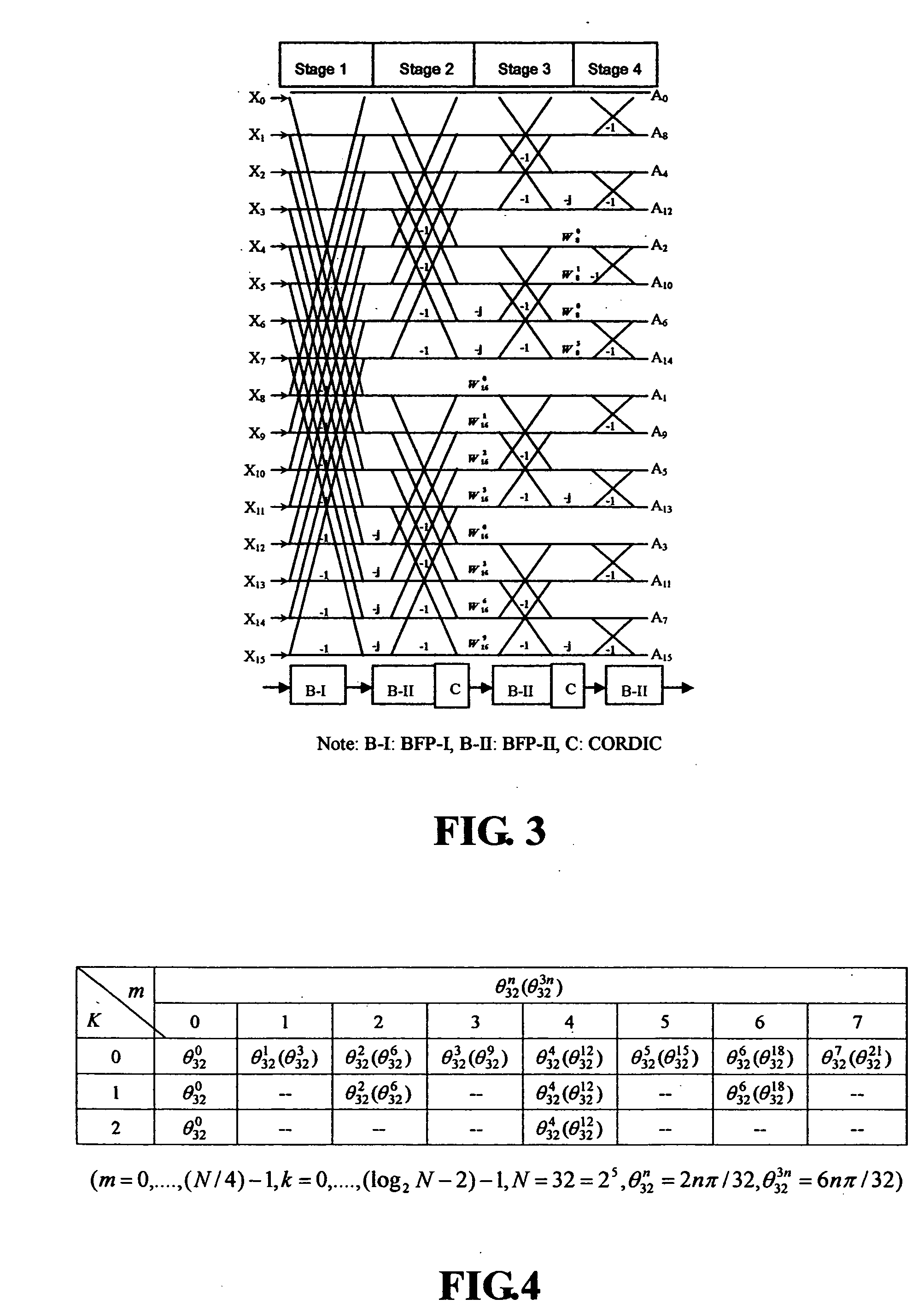

This invention presents a CORDIC-based split-radix FFT / IFFT (Fast Fourier Transform / Inverse Fast Fourier Transform) processor dedicated to the computation of 2048 / 4096 / 8192-point DFT (Discrete Fourier Transform). The arithmetic unit of butterfly processor and twiddle factor generator are based on CORDIC (Coordinate Rotation Digital Computer) algorithm. An efficient implementation of CORDIC-based split-radix FFT algorithm is demonstrated. All control signals are generated internally on-chip. The modified-pipelining CORDIC arithmetic unit is employed for the complex multiplication. A CORDIC twiddle factor generator is proposed and implemented for saving the size of ROM (Read Only Memory) required for storing the twiddle factors. Compared with conventional FFT implementations, the power consumption is reduced by 25%.

Owner:CHUNG HUA UNIVERSITY

Quick Fourier transformation implementation device and method

InactiveCN103970718AImprove performanceReduce usageComplex mathematical operationsShift registerFast Fourier transform

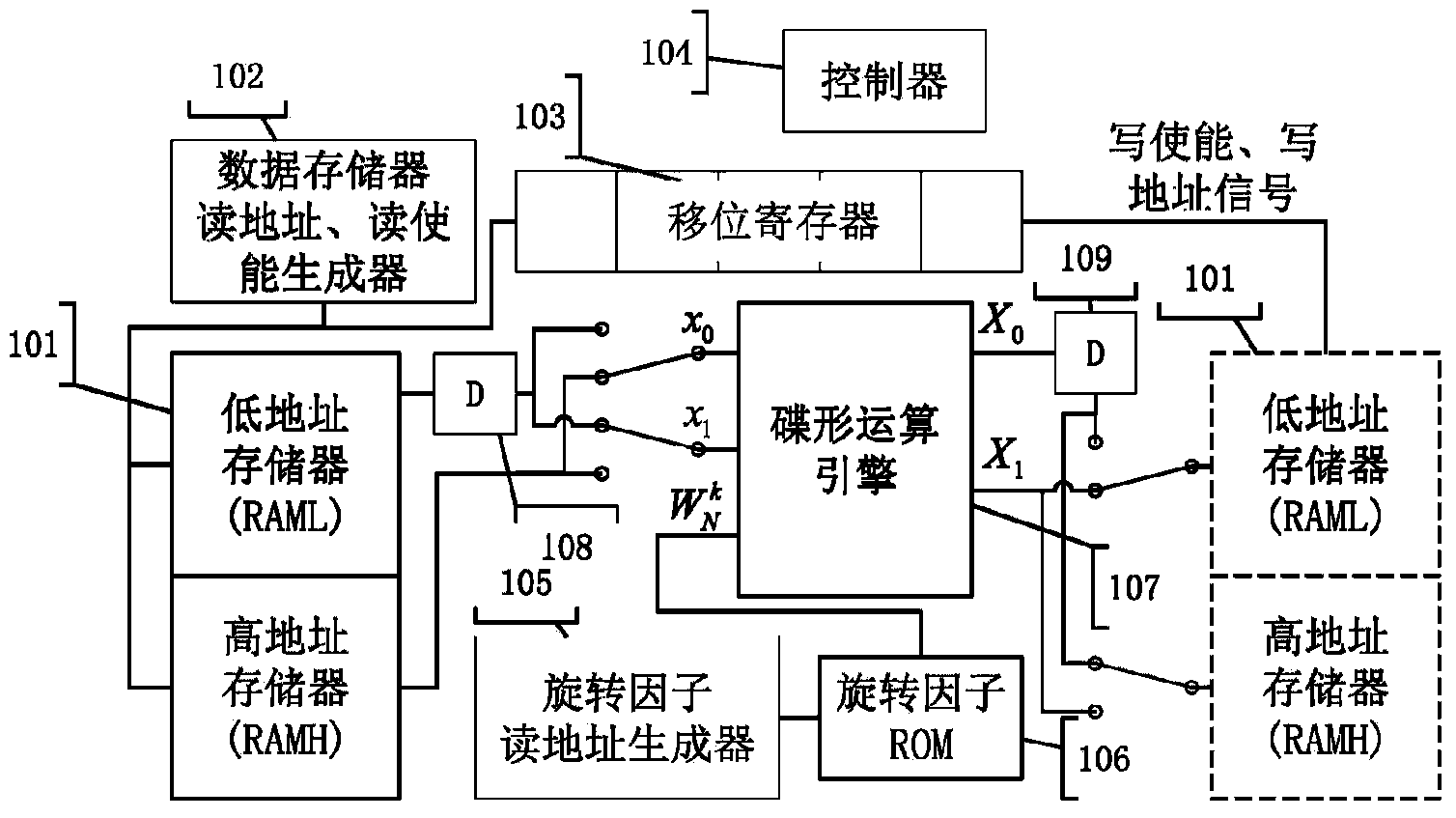

The invention relates to a quick Fourier transformation implementation device and method. The method comprises the steps that input data are stored to two data storage units divided into high addresses and low addresses, two complex numbers are read out from a read address generator, low address data are input into a register by delaying one period; according to a controller signal, the low address data and high address data are input into two input branches of a butterfly computation engine through a selector; at the same time, a twiddle factor is read out from a twiddle factor storage unit according to the address given by a twiddle factor address generator and input to the butterfly computation engine; in the output process, it is guaranteed that the address is written back to the data storage unit according to the delay address of a displacement register and the selector. In the address generator, a simple base value and a deviation value are used for obtaining a read address, and meanwhile the data of the two storage units are read for operation in turn. Compared with the prior art, the operation cycle is shortened, the highest operation frequency is increased, meanwhile, the twiddle factor storage unit is only 1 / 4 space of the needed twiddle factor, and thus design resources are saved.

Owner:COMMUNICATION UNIVERSITY OF CHINA

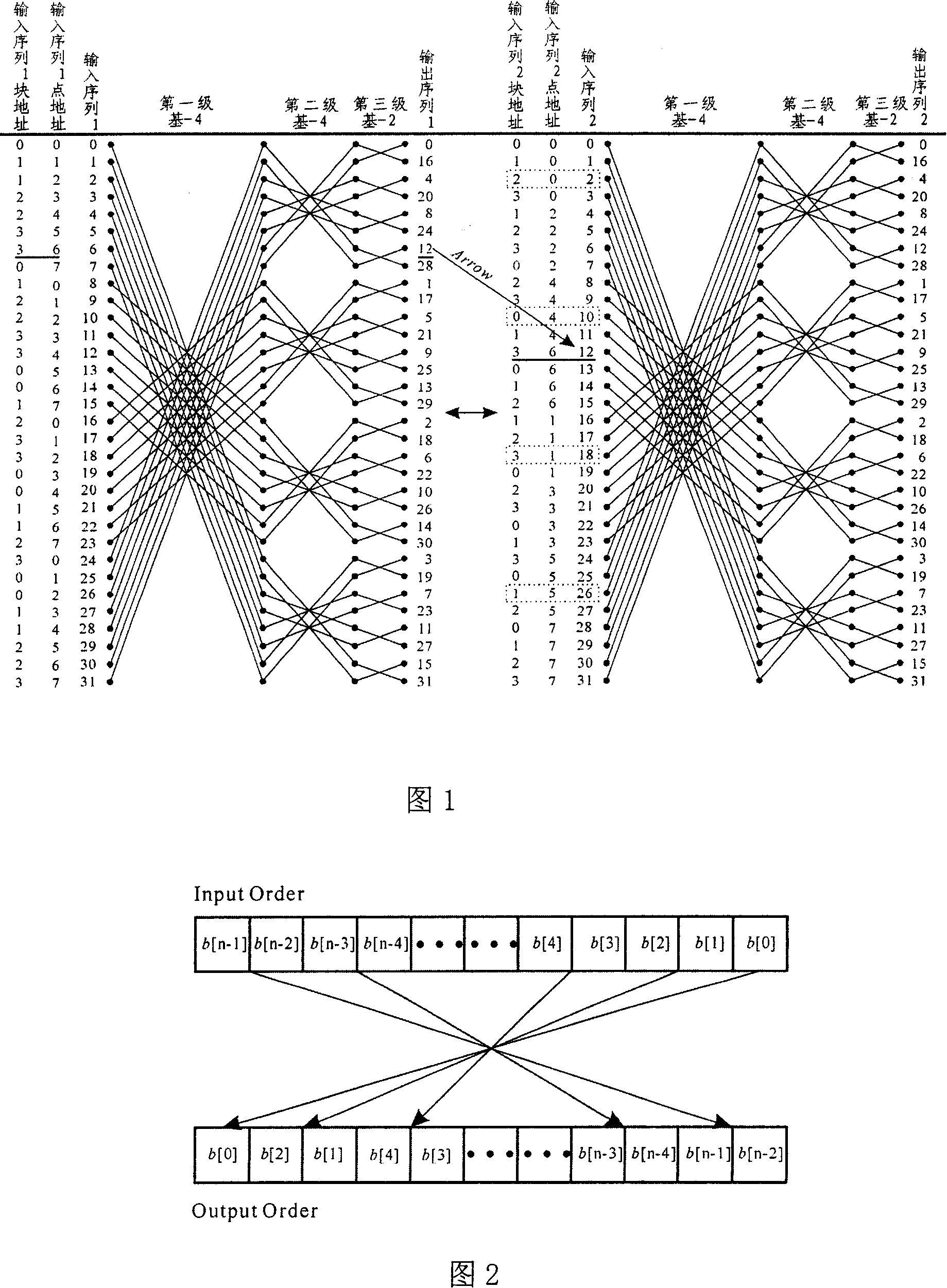

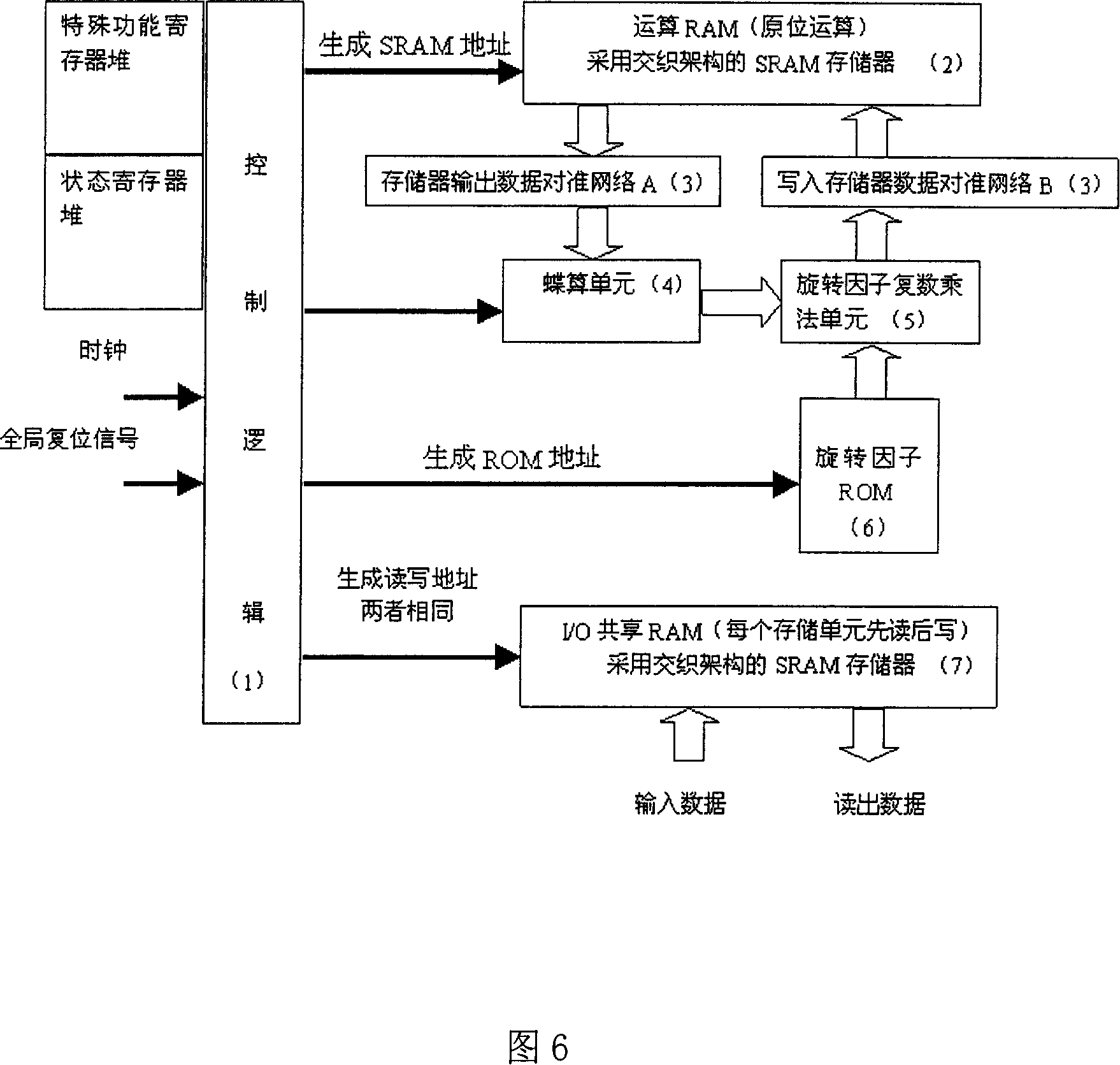

Low memory spending hybrid base FFT processor and its method

InactiveCN101083643AMulti-frequency code systemsComplex mathematical operationsComputer architectureFft processor

Being related to area of wireless communication technique, especially the invention is related to general operand conflict free created mixed base FFT processor with low spending memory. The FFT processor is composed of control logic unit, operation RAM, network, butterfly operation unit, complex multiplication unit of twiddle factor (CMUTF), twiddle factor ROM, and I / O shared RAM. The control logic unit controls the operation RAM, the butterfly operation unit, twiddle factor ROM, and I / O shared RAM. Through network, the operation RAM is connected to the butterfly operation unit, and CMUTF. CMUTF is connected to the twiddle factor ROM.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Fast fourier transform twiddle multiplication

InactiveUS20060248135A1Effectively pipelinedModulated-carrier systemsTransmission path divisionBinary multiplierTheoretical computer science

An FFT engine implementing a cycle count method of applying twiddle multiplications in multi-stages. When implementing a multistage FFT, the intermediate values need to be multiplied by various twiddle factors. The FFT engine utilizes a minimal number of multipliers to perform the twiddle multiplications in an efficient pipeline. Optimizing a number of complex multipliers based on an FFT radix and a number of values in each row of memory allows the FFT function to be performed using a reasonable amount of area and in a minimal number of cycles. Strategic ordering and grouping of the values allows the FFT operation to be performed in a fewer number of cycles.

Owner:QUALCOMM INC

Point-variable real-time FFT processing chip

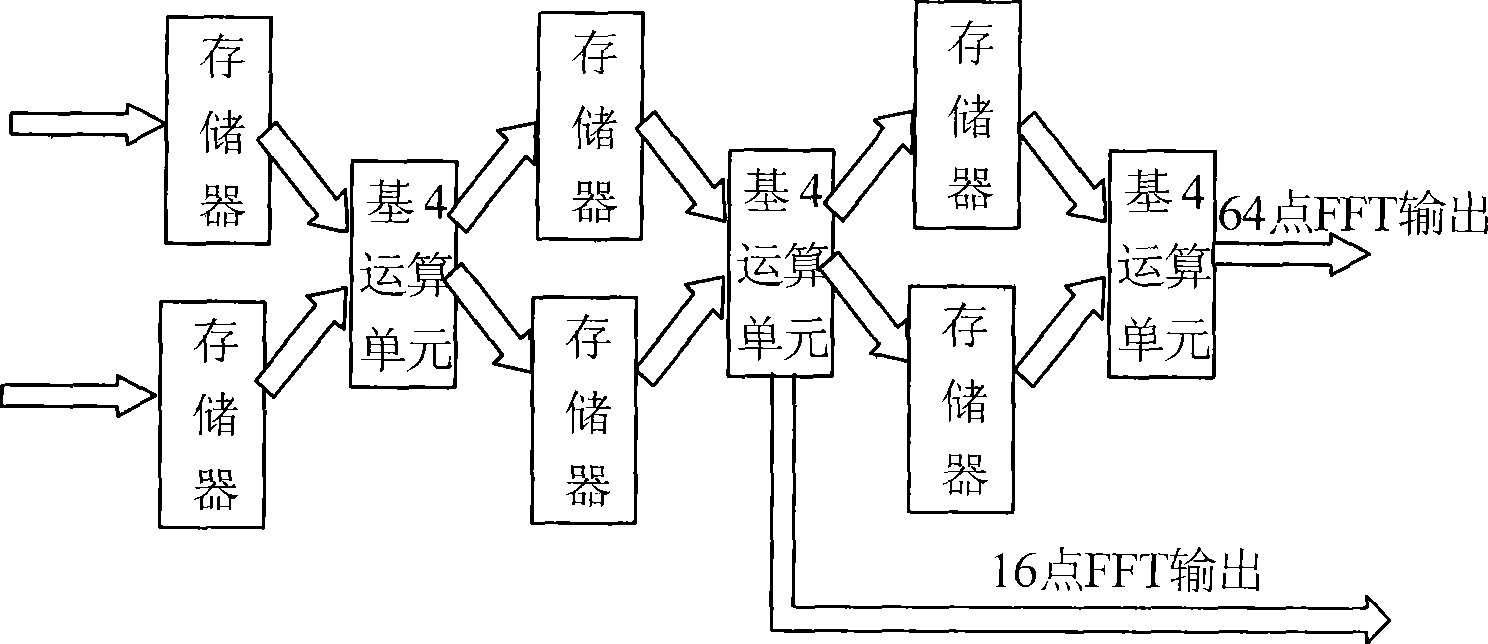

InactiveCN101504637AReal-time processingUpdate output data in real timeComplex mathematical operationsTwiddle factorComputer science

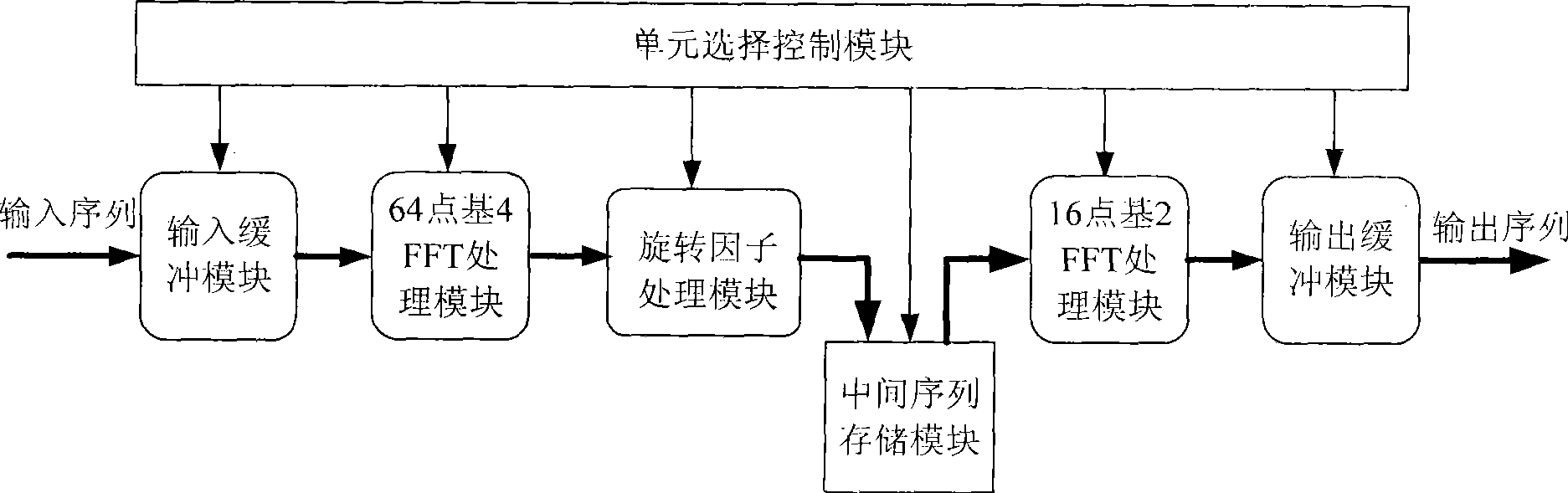

The invention provides a real-time FFT processing chip variable in the number of points, which comprises an input buffer module, a 64-point FFT pipeline processing module, a twiddle-factor processing module, an intermediate sequence storage module, a 16-point FFT pipeline processing module, a unit selection-control module and an output buffer module. The seven modules complete FFT two-dimensional processing together, wherein the 64-point FFT pipeline processing module implements 16-point or 64-point variable FFT operation; the 16-point FFT pipeline processing module implements 2-point, 4-point, 8-point or 16-point variable FFT operation; the twiddle-factor processing module is based on CORDIC algorithm; and the selection-control module realizes control over the whole chip. The chip can realize 2-point variable FFT operation, is small in area occupied in a tube core, has the characteristics of real-time high-speed processing, low power consumption, high precision and the like, and is suitable to be realized in ASIC.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

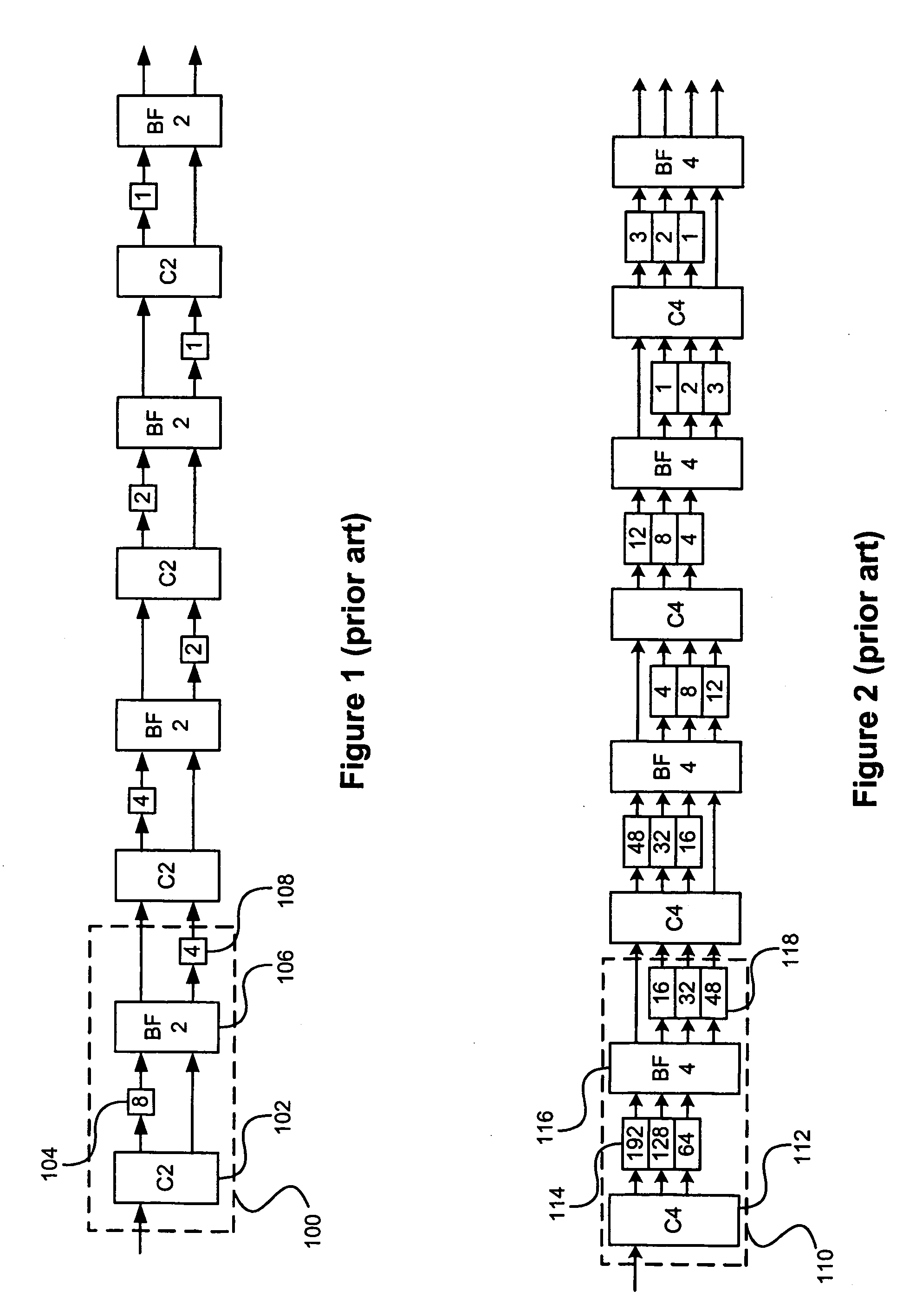

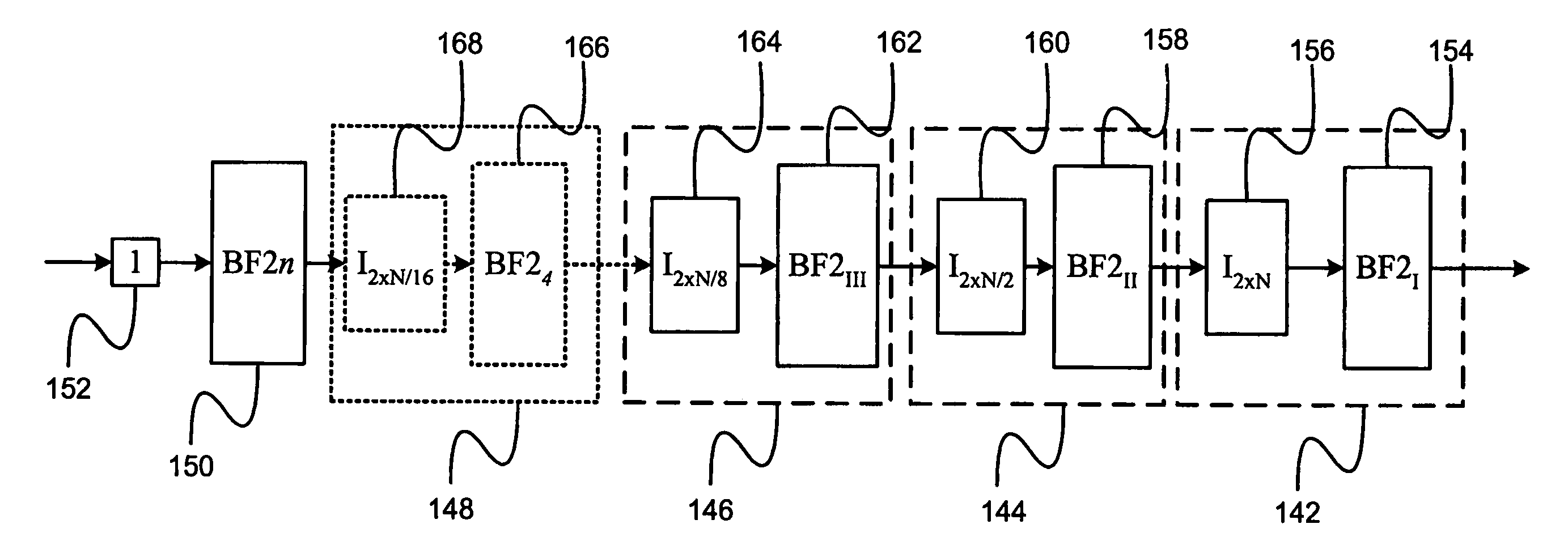

Pipelined FFT processor with memory address interleaving

InactiveUS20050114420A1Avoid overwritingReduce areaDigital computer detailsComplex mathematical operationsMemory addressParallel computing

An FFT processor using a single delay path and a permuter provides a reduction in the implementation area and a related reduction in power consumption through efficiencies obtained by the modification of a butterfly unit and the use of a novel interleaver. The modified butterfly unit is obtained by removal of complex variable multipliers, which is possible due to the simplification of twiddle factors in the stages that correspond to the modified butterfly unit.

Owner:MICROSEMI SOLUTIONS (US) INC

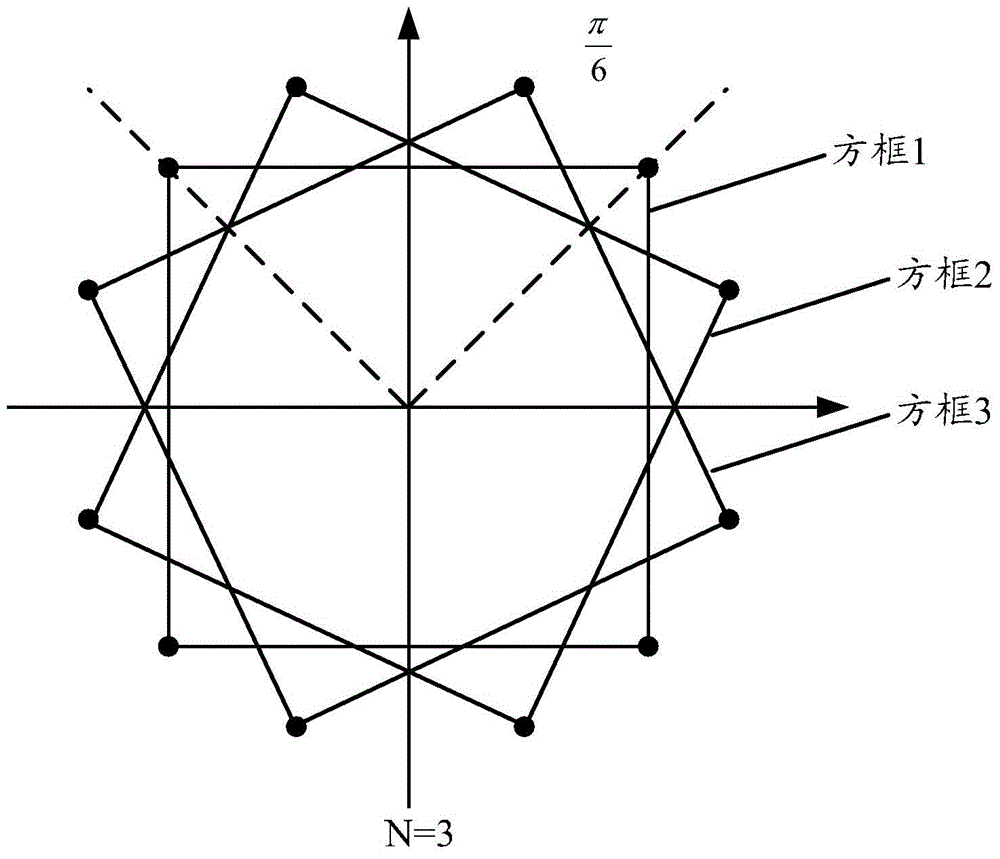

Data transmission method, receiving signal detection method and device, and data transmission sending device

ActiveCN106160971AImprove performanceTransmission path divisionAmplitude-modulated carrier systemsData streamTwiddle factor

The embodiment of the invention relates to the technical field of wireless communication, and especially relates to a data transmission method, a receiving signal detection method and device, and a data transmission sending device. The methods and the devices are used for solving the problem that in the prior art, under a scene that each column of a coding matrix of PDMA (Pattern Division Multiple Access) corresponds to a layer of data streams, overlap occurs in multiple layers of data modulation symbols when detection is carried out at a receiving end, so that signal detection is influenced is solved. According to the embodiment of the method and the device, each layer of data modulation symbols obtained by modulating original modulation constellation graphs are adjusted according to modulation constellation twiddle factors corresponding to each layer of data modulation symbols, so that the modulation constellation graphs corresponding to each layer of data modulation symbols are not overlapped; the problem that under the scene that each column of the coding matrix of PDMA (Pattern Division Multiple Access) corresponds to one layer of data streams, overlap occurs in multiple layers of data modulation symbols, so that signal detection is influenced is avoided; and the system performance is further improved.

Owner:DATANG MOBILE COMM EQUIP CO LTD

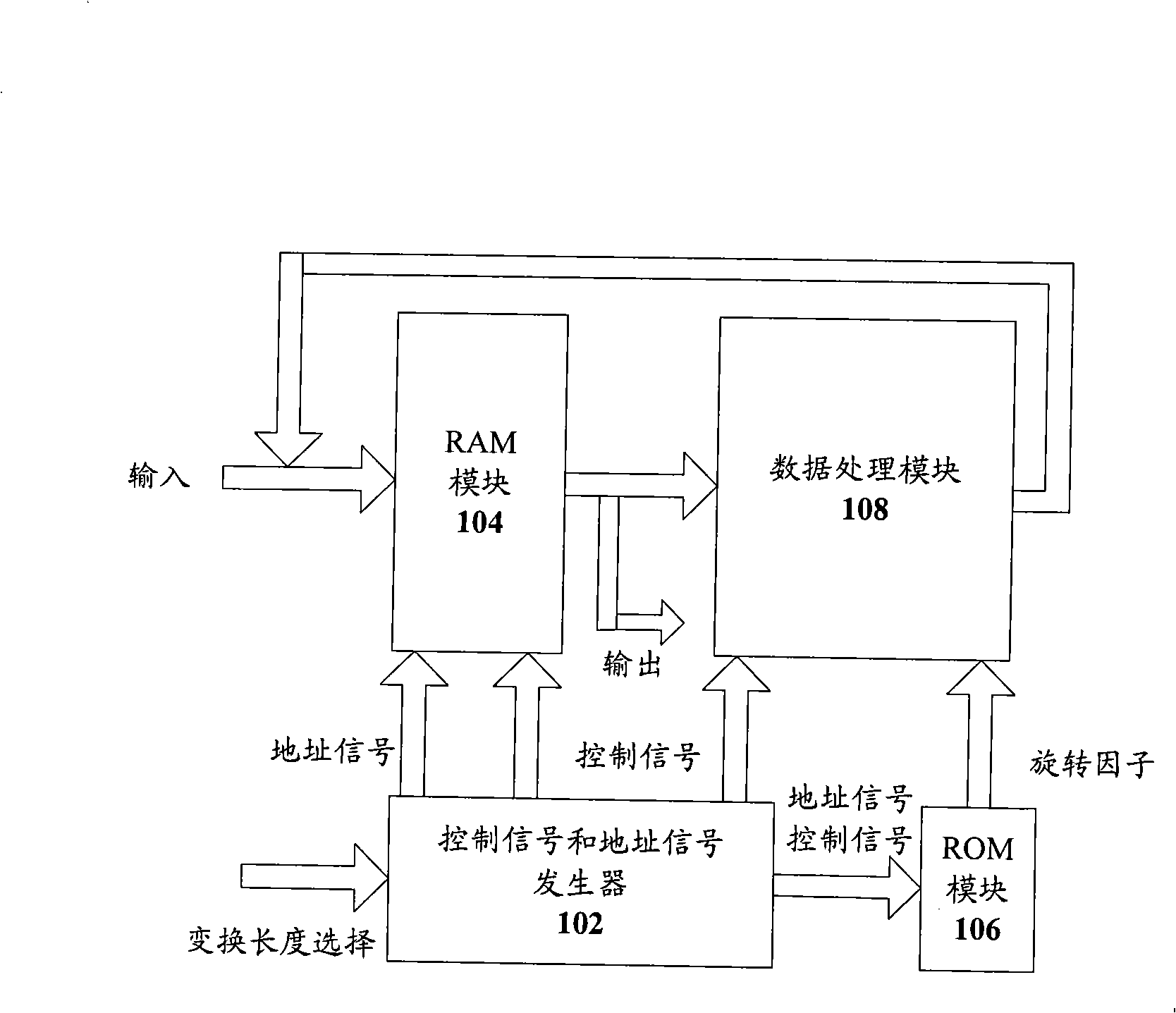

Processor for FFT / IFFT as well as processing method thereof

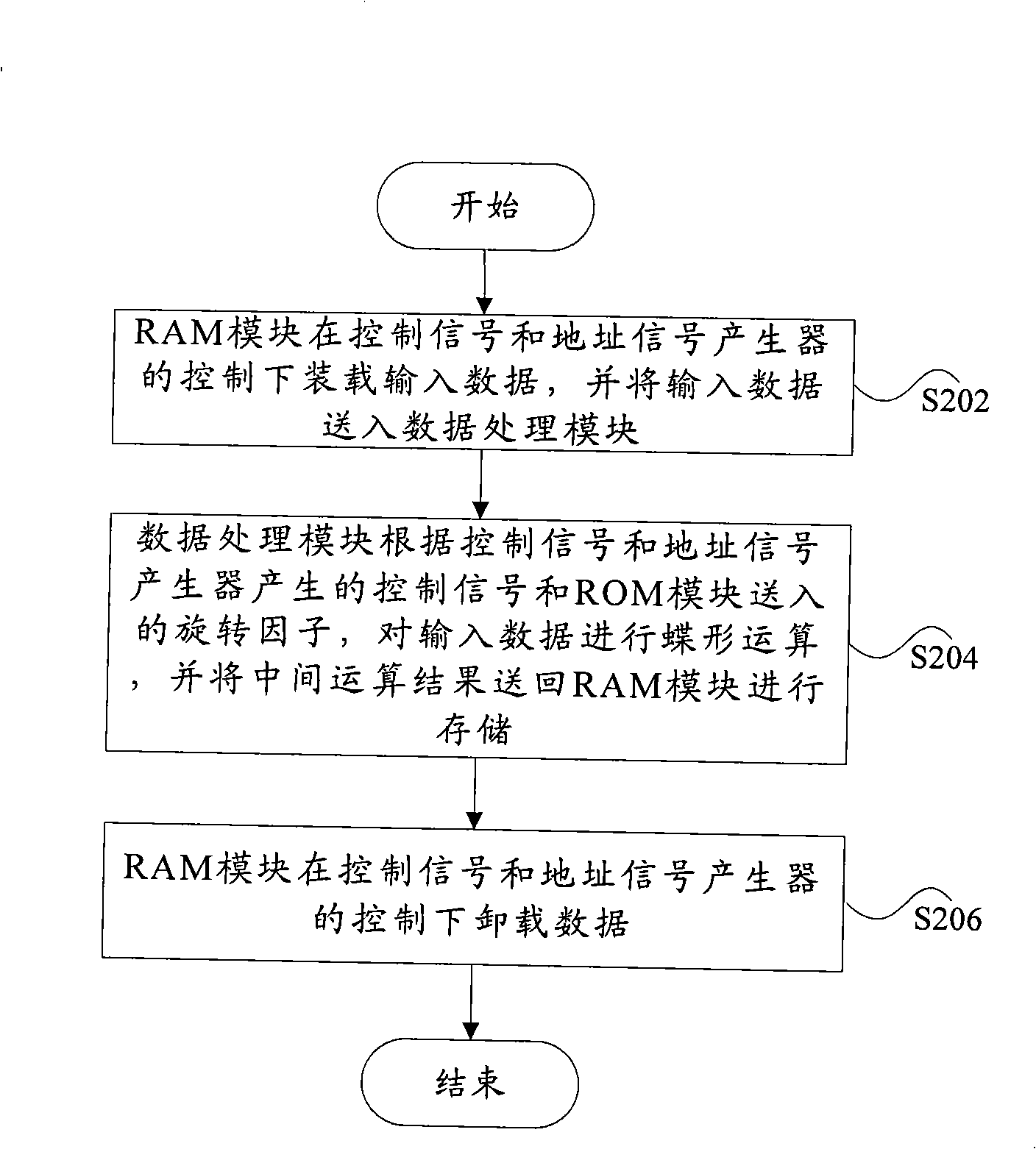

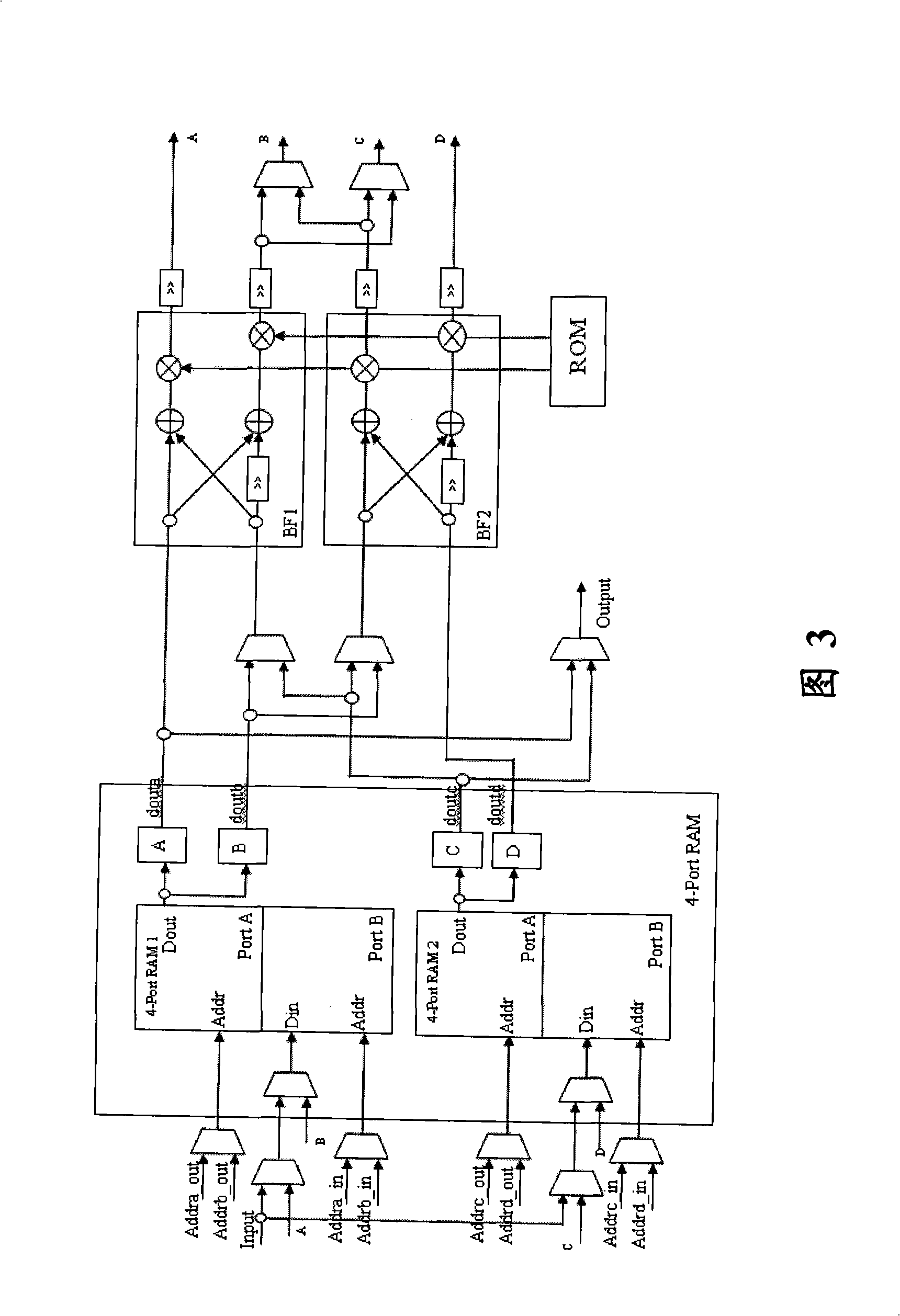

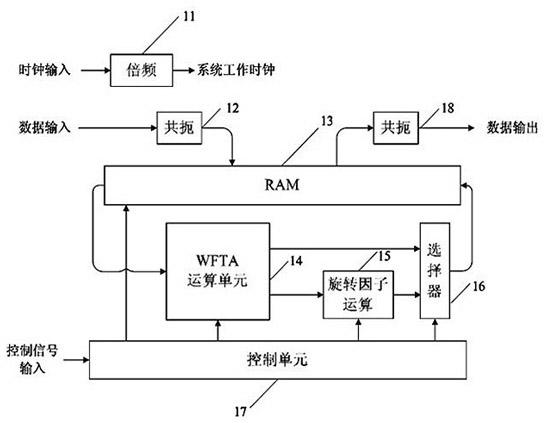

InactiveCN101330489ASolve lengthSolving FFTs for multiple modesMulti-frequency code systemsSpecial data processing applicationsControl signalRandom access memory

The invention discloses a fast Fournier transform / fast inverse Fourier transform processor and a processing method thereof. The processor comprises a control signal and address signal generator used for generating control signals and address signals; a random access memory module used for storing input data and interim calculation results; a read only memory used for storing twiddle factors; and a data processing module used for performing butterfly calculation to the input data according to the control signals and the address signals and sending the interim calculation results back to the random access memory module for storage. The processor and the processing method can realize the purpose that the IFFT / FFT transformation of any even point with length more than or equal to 4 is compatible.

Owner:ZTE CORP

Method and Apparatus for Decimation in Frequency FFT Butterfly

Owner:TEMPO SEMICON

Polyphase filter with stack shift capability

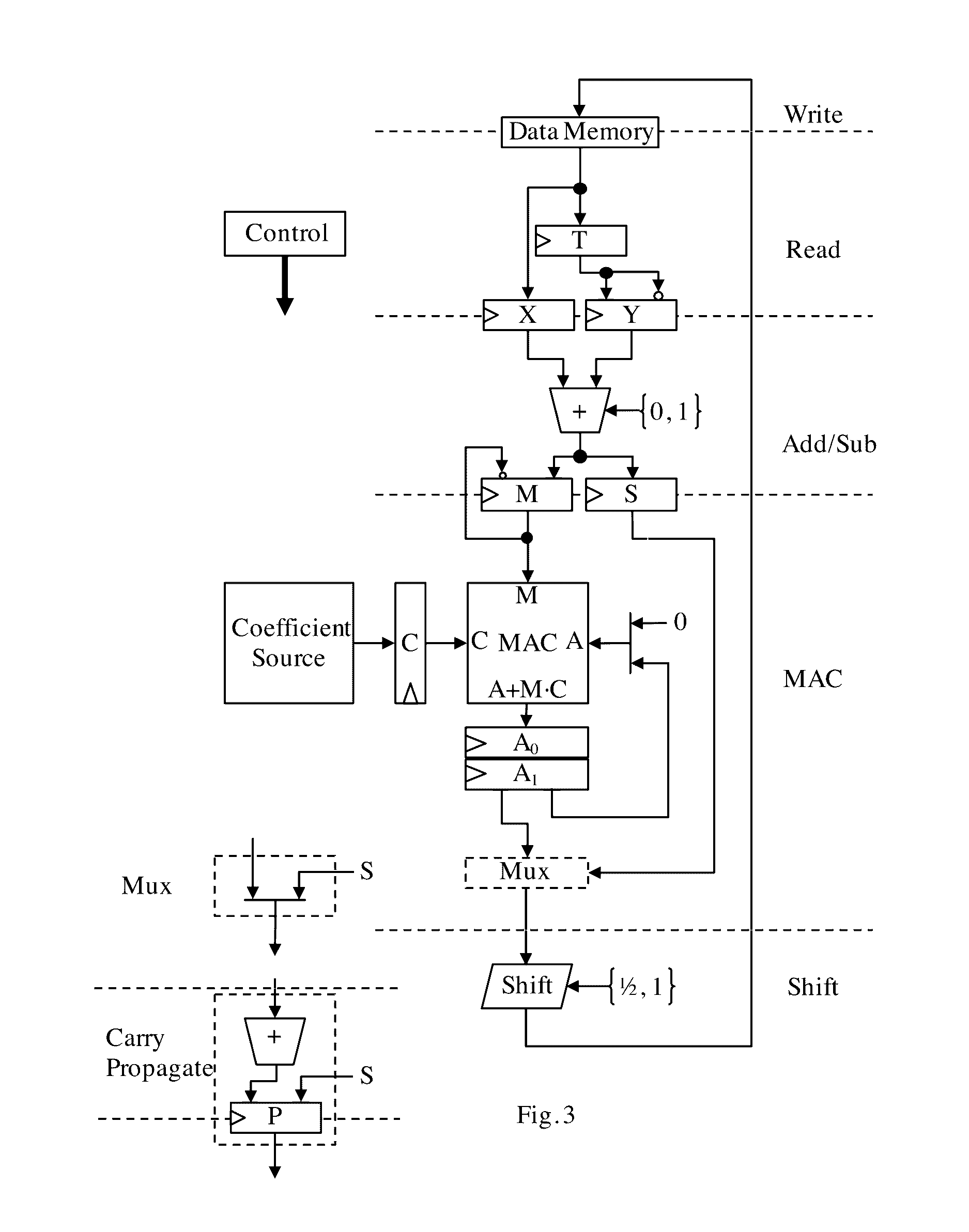

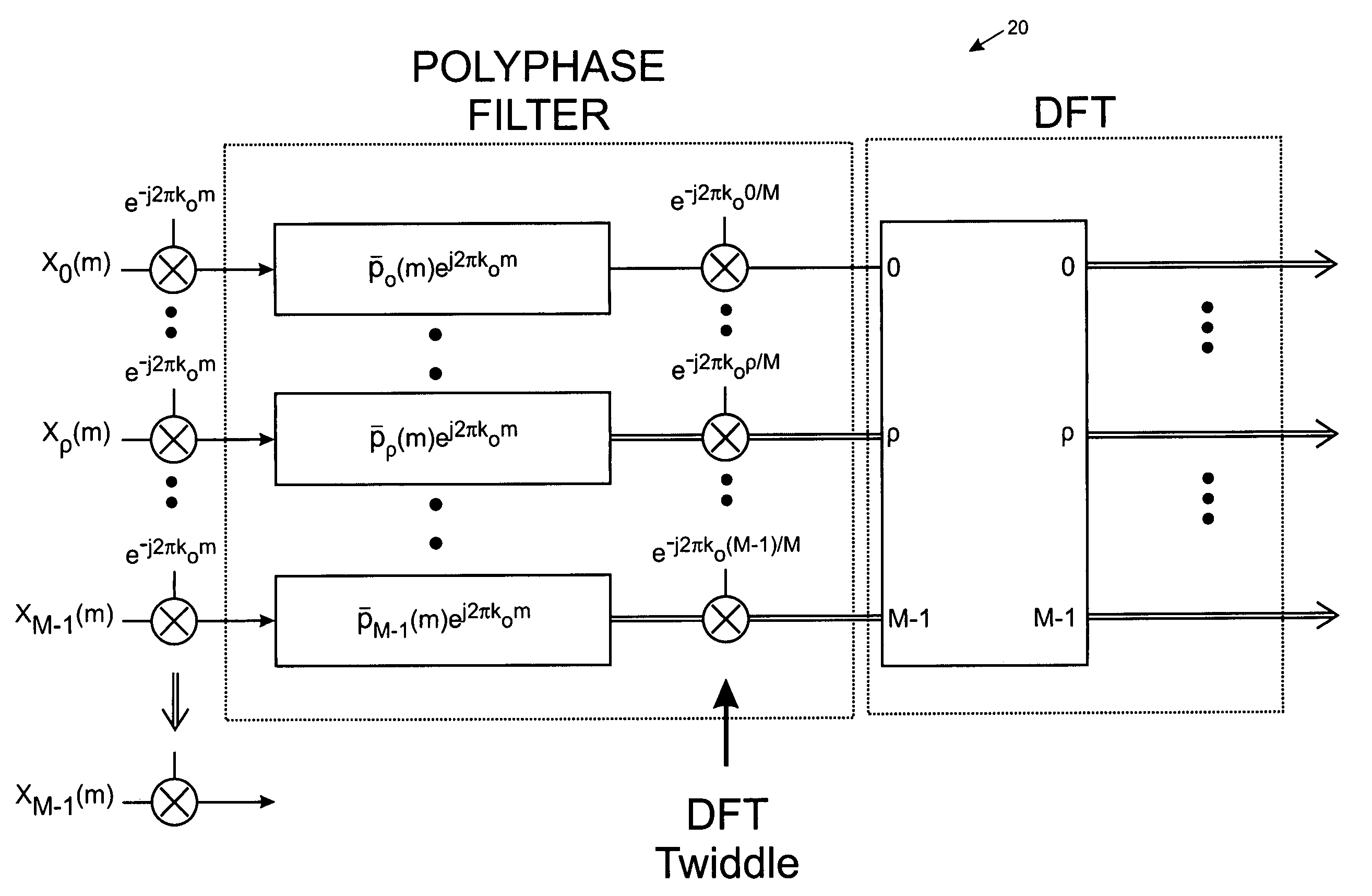

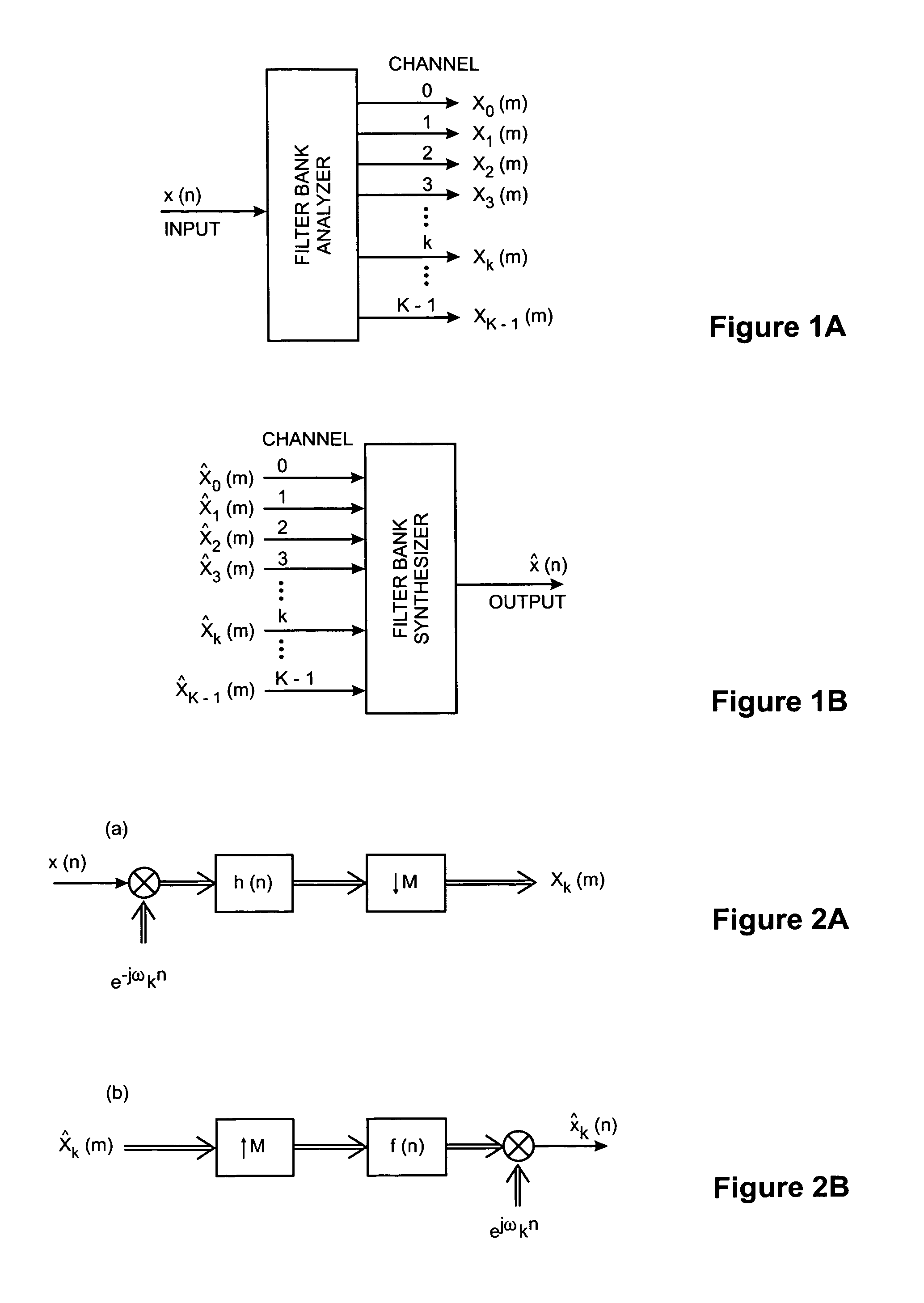

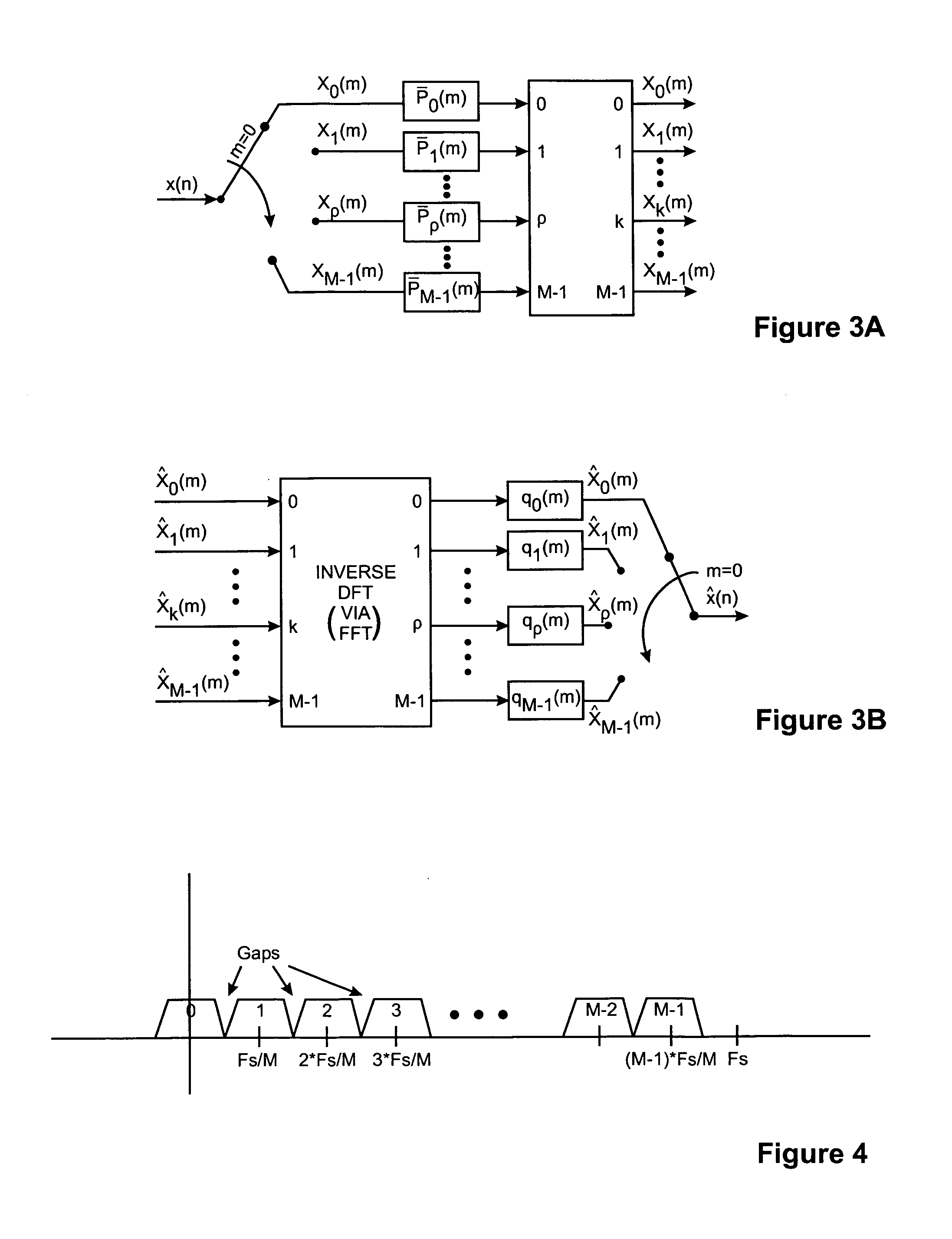

InactiveUS7095781B1Hardware to be reduced significantlyDigital technique networkAmplitude-modulated carrier systemsFourier transform on finite groupsEngineering

A discrete Fourier transform (DFT) filter bank with stack shift capability, configured, for example, as an analyzer, but equally applicable to a synthesizer, and implemented as a polyphase filter. The DFT filter bank includes a complex modulator for multiplying the input signals x0(m), x1(m) . . . xM−1(m) by a complex modulator e−2πk<sub2>o< / sub2>(m). In order to keep the coefficients for the polyphase filter real, the coefficients are modulated by a DFT twiddle factor e−2πk<sub2>o< / sub2>ρ / M. The use of the DFT twiddle factor enables the hardware to be reduced significantly. For example, for an 8 phase 203 tap filter, only 8 selectable negators are required as opposed to 211 for known DFT filter banks.

Owner:NORTHROP GRUMMAN SYST CORP

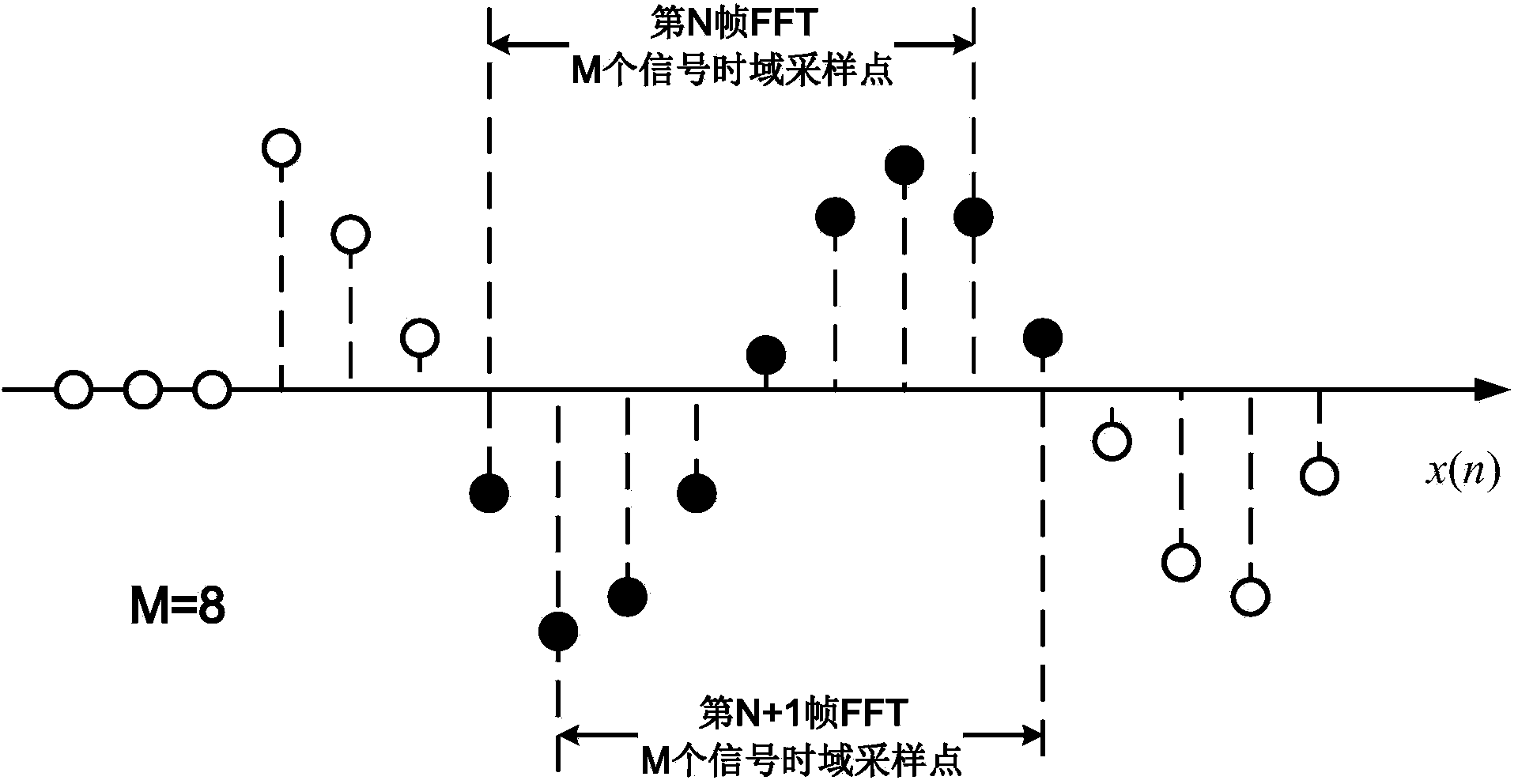

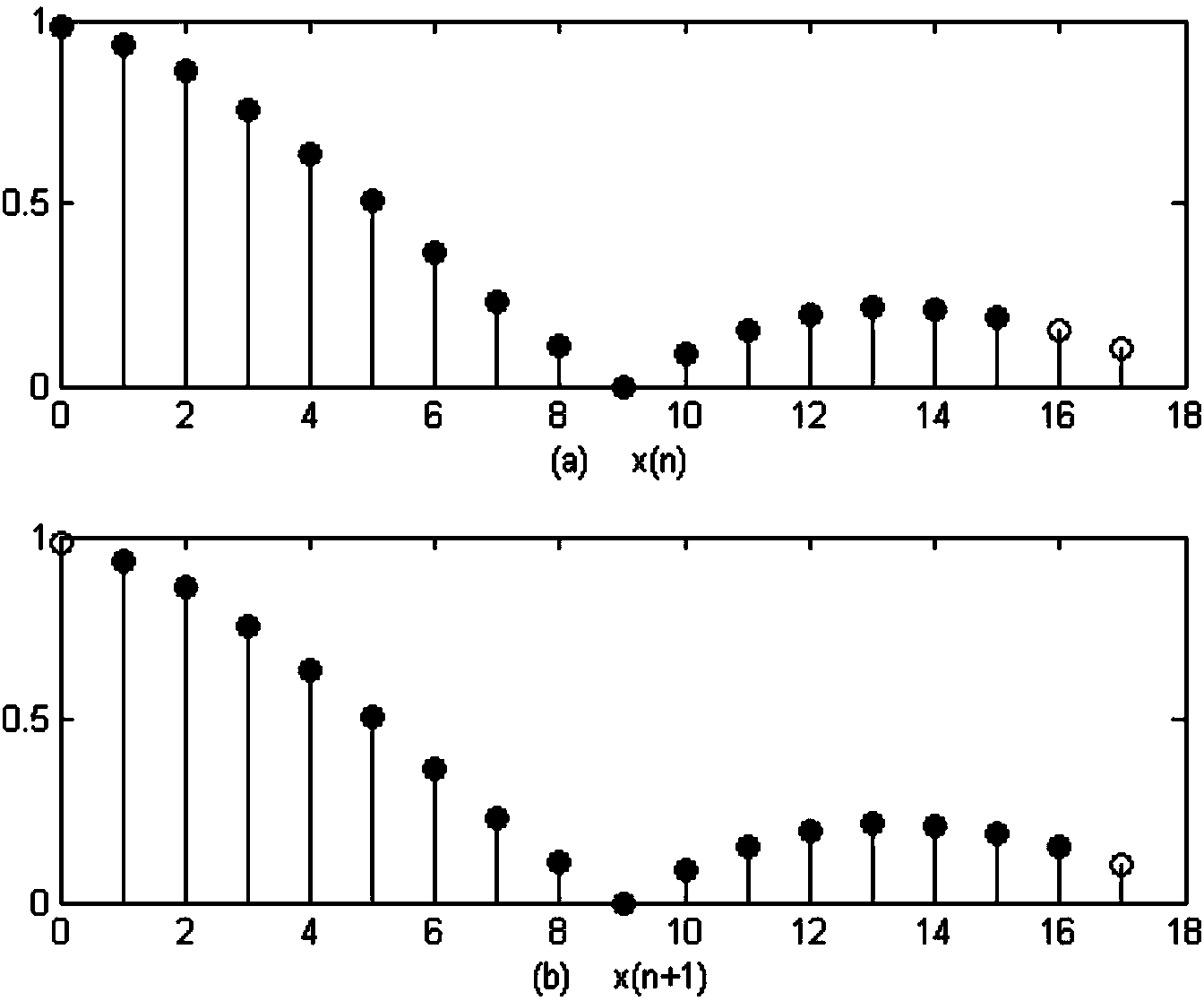

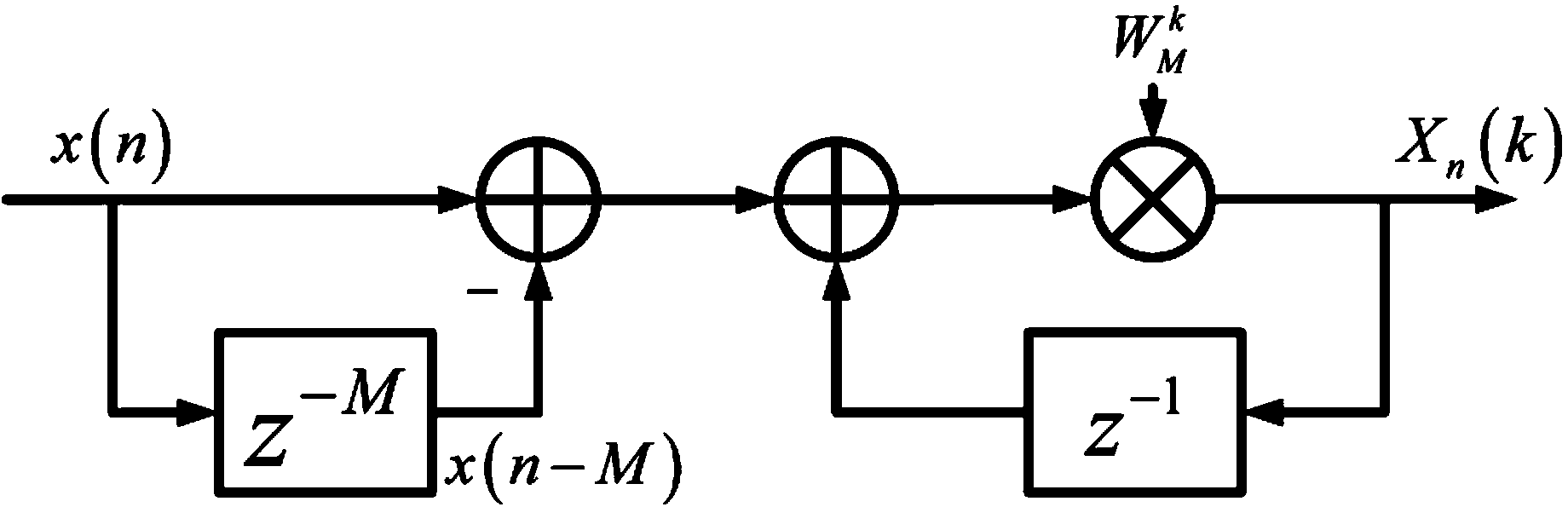

Discrete digital signal hopping sliding discrete Fourier transform method

InactiveCN104268123AEfficient removalGuaranteed smooth progressComplex mathematical operationsSliding discrete fourier transformS transform

The invention provides a digital discrete signal hopping sliding discrete Fourier transform method, namely an SDFT (Modulated Hopping DFT, mHDFT) transform method for solving the problem of potential instability and accumulated errors of HDFT transform of an HDFT (hexagon discrete Fourier transform) transform method in practical engineering application. The method utilizes DFT circulating frequency domain shifting characteristics and modified UVT transform for effectively removing twiddle factors in a feedback loop of an HDFT resonator, accurately fixing HDFT poles on a unit circle and obtaining a DFT transform result of a frequency point k at n time, thereby effectively reducing the cumulative errors as well as ensuring the constant stability of the HDFT.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

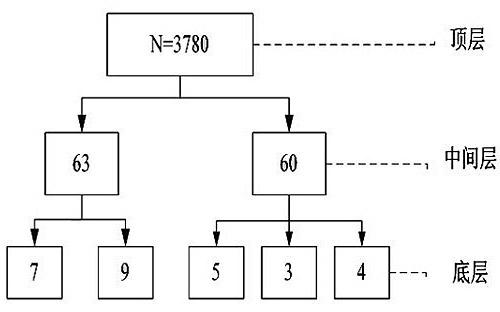

Method for realizing 3780-point fast Fourier transform/inverse fast Fourier transform (FFT/IFFT) and processor thereof

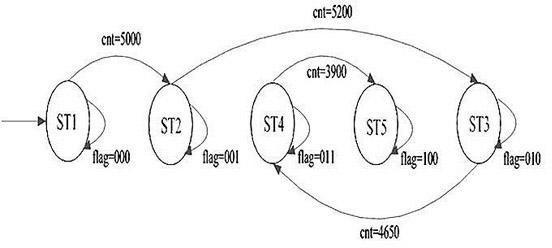

InactiveCN102214159AGuaranteed real-timeSave storage resourcesComplex mathematical operationsRotation factorFast Fourier transform

The invention relates to a method for realizing 3780-point fast Fourier transform / inverse fast Fourier transform (FFT / IFFT) and a processor thereof. The processor consists of a top layer, an intermediate layer and a bottom layer, wherein the top layer resolves 3780-point by using a mixed based number algorithm, the intermediate layer resolves 63-point and 60-point FFT by using a prime factor algorithm, and the bottom layer complete 7-point, 9-point, 3-point, 4-point and 5-point FFT calculation by using a winograd fourier transform algorithm (WFTA) algorithm. The method realizes 3780-point FFT by combining the mixed base number algorithm, the prime factor algorithm and the WFTA algorithm, avoids errors caused by calculating 4096-point by using an interpolation method, and reduces rotation factors and a chaotic unit in the mixed base number algorithm. Furthermore, an index structure completed by a multiplex memory in the design has a simple circuit, is easy to realize, and can save chip resources.

Owner:FUZHOU UNIV

Fast fourier transform processor

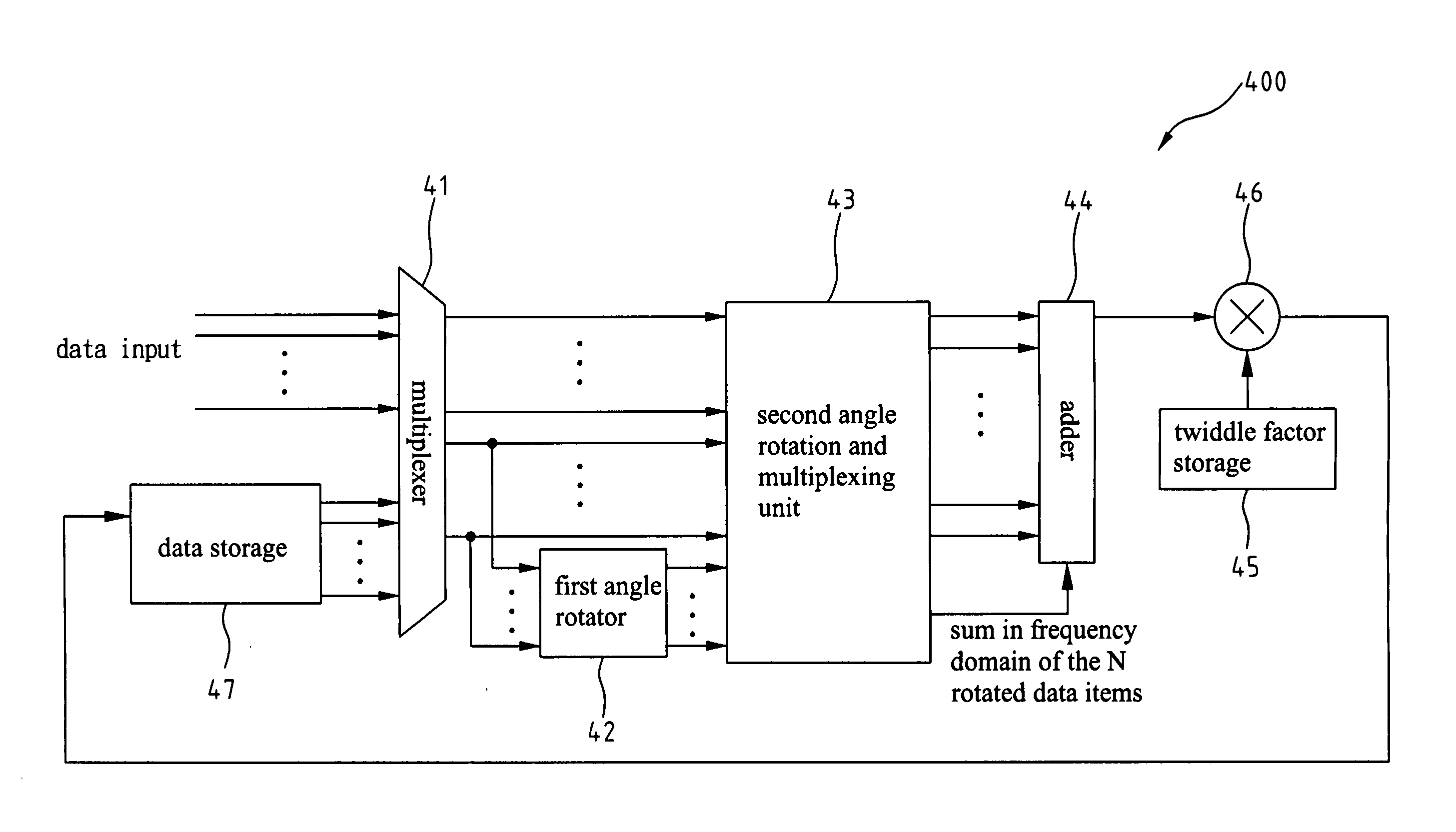

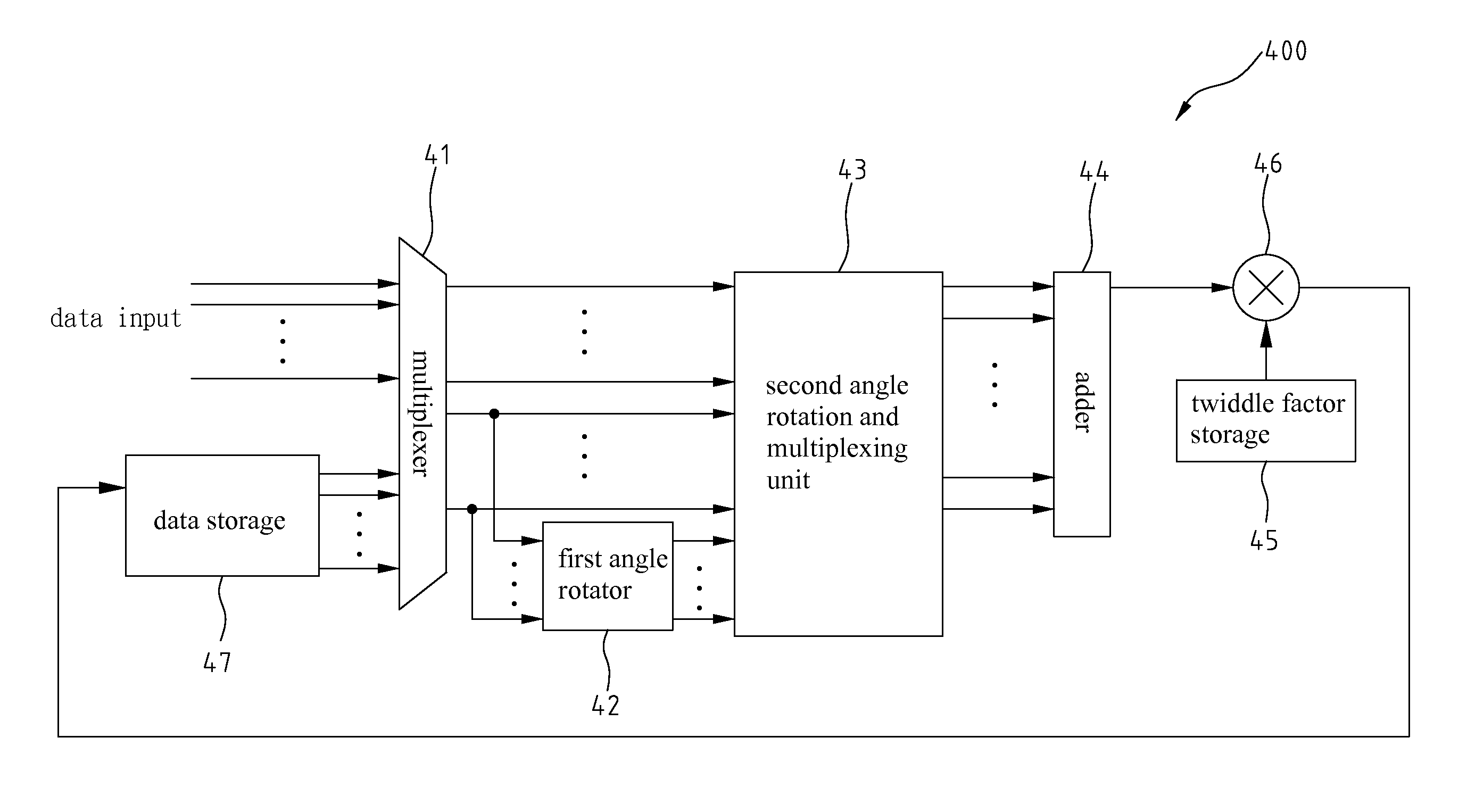

InactiveUS20060143258A1Reduces hardware circuitry areaLow costDigital computer detailsComplex mathematical operationsFast Fourier transformMultiplexing

A Fast Fourier Transform (FFT) processor is provided. It comprises a multiplexer, a first angle rotator, a second angle rotation and multiplexing unit, an adder, a twiddle factor storage, a multiplier, and a data storage. The FFT processor analyzes the input / output order of the Fast Fourier Transformation, separates the portions requiring complex computations, simplifies the hardware thereof, and adjusts the output order. It not only effectively saves the hardware area, but also reduces the computations and memory access count. Thereby, the power consumption is reduced.

Owner:IND TECH RES INST

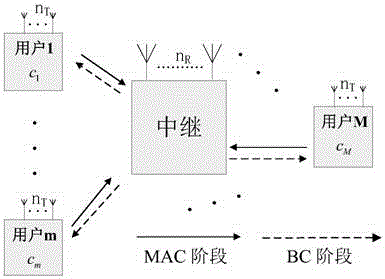

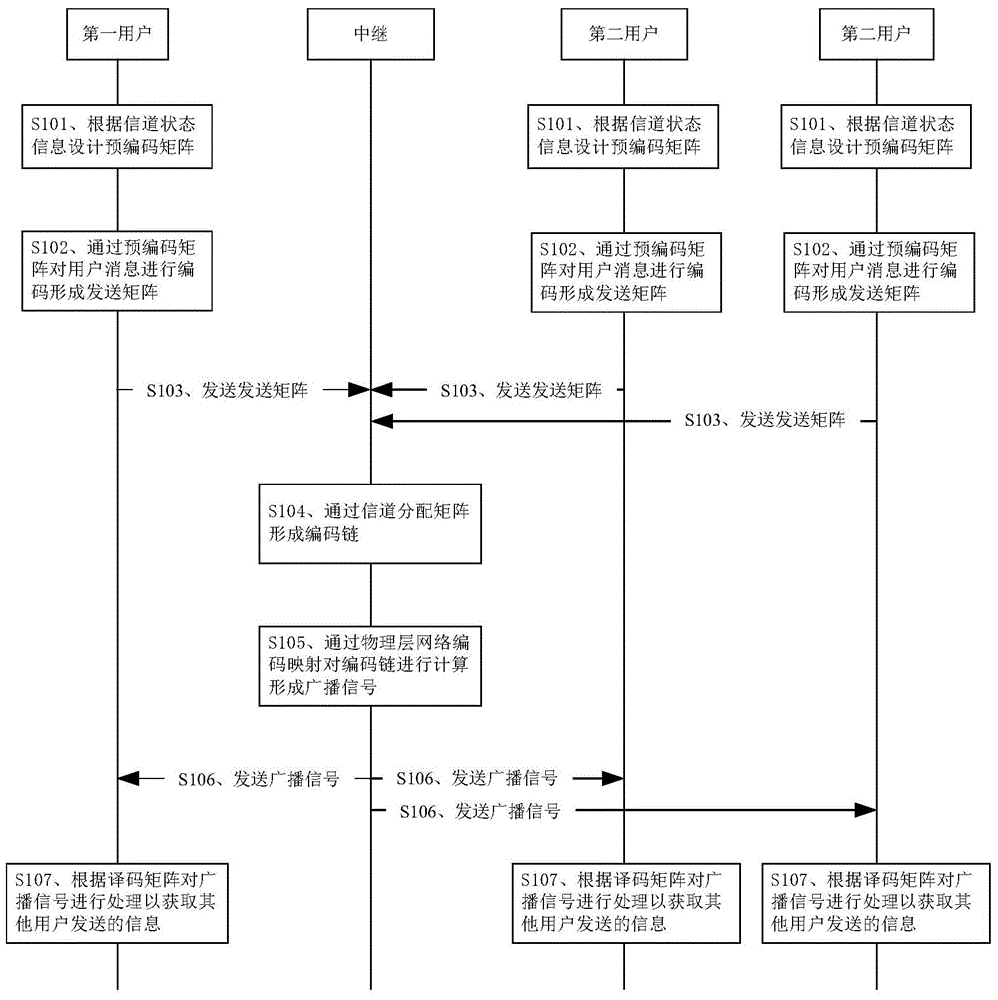

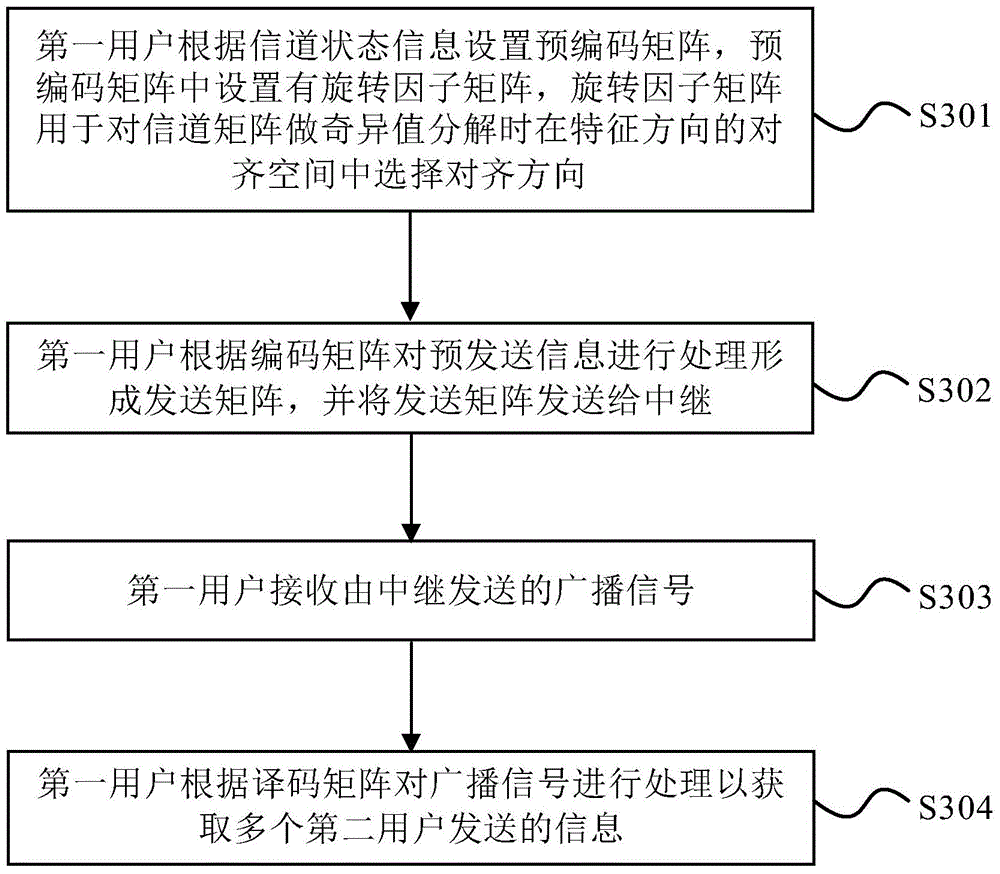

Information transmission method for multi-user MIMO relay system

ActiveCN105007141AImprove decoding performanceWith secure transmission featuresSpatial transmit diversityActive radio relay systemsSingular value decompositionInformation transmission

The invention relates to an information transmission method for a multi-user MIMO relay system. The information transmission method comprises that: a first user sets a precoding matrix K according to CSI, wherein the precoding matrix K is provided with a twiddle factor matrix K used for selecting the alignment direction in the alignment space of an eigen direction when performing singular value decomposition (SCD) on a channel matrix; the first user processes pre-sending information according to the precoding matrix in order to form a sending matrix and sends the sending matrix to a relay; the first user receives a broadcast signal transmitted from the relay; and the first user processes the broadcast signal according to the precoding matrix in order to obtain information transmitted from multiple second users. The information transmission method designs the eigen direction alignment precoding and the twiddle factor matrix by means of the SVD, performs decoding by means of a simple ZF decoding algorithm so as to effectively improve decoding performance when good transmission channel relevance is provided, and has a physical layer safe transmission characteristic.

Owner:XIDIAN UNIV

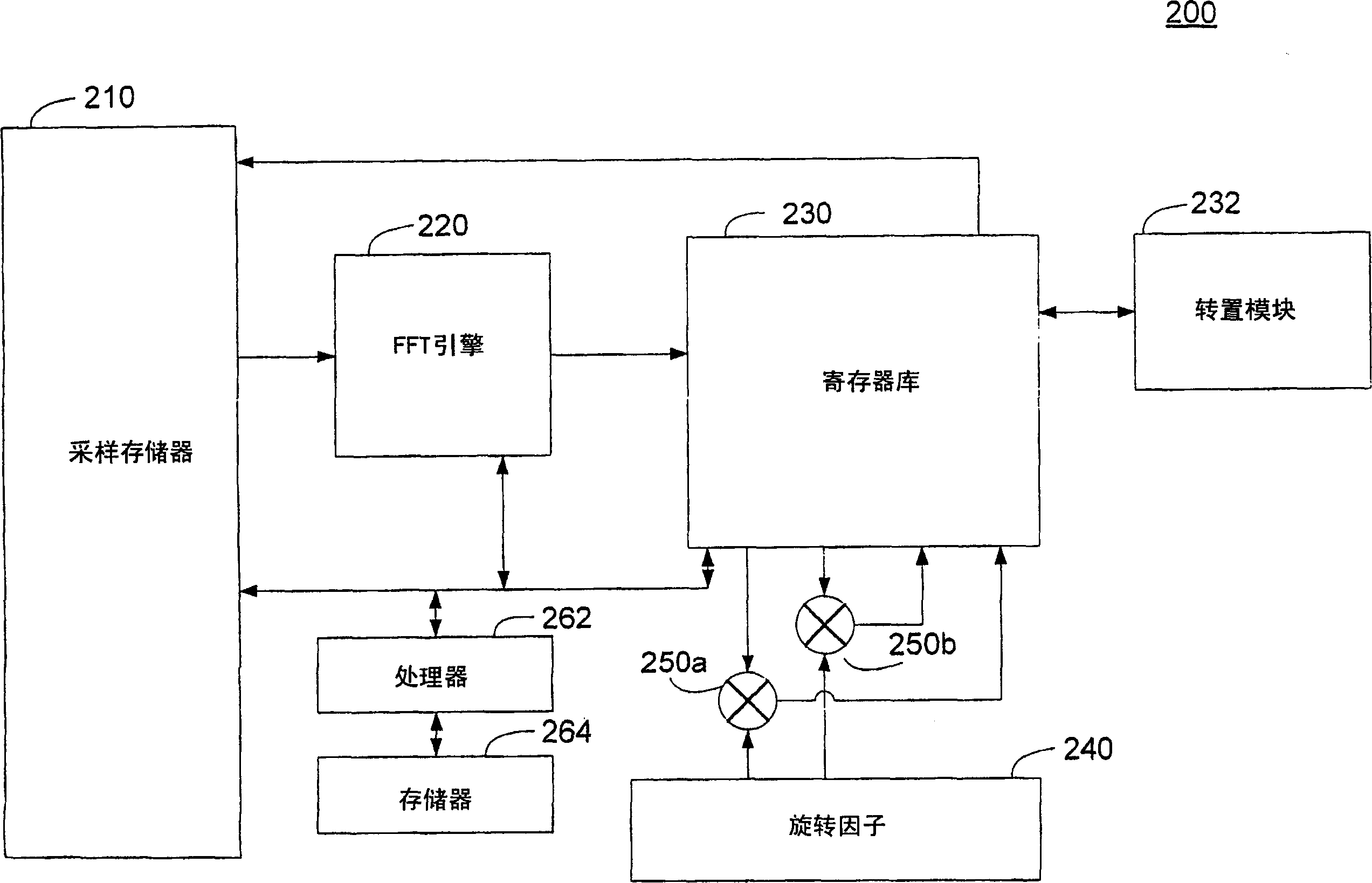

FFT architecture and method

InactiveCN1914607ADigital computer detailsMulti-frequency code systemsComputer architectureTrademark

A Fast Fourier Transform(FFT) hardware implementation and method provides efficient FFT processing while minimizing the die area needed in an Integrated Circuit(IC). The FFT hardware can implement an N point FFT, where N = rn is a function of a radix(r). The hardware implementation includes a sample memory having N / r rows, each storing r samples. A twiddle factor memory can store k twiddle factors per row, where 0 < k G06F 17 / 14 8 18 8 2004 / 12 / 3 1914607 2007 / 2 / 14 000000000 Qualcomm Inc. United Krishnamoorthi Raghuraman Ganapathy Chinnappa K. wang yang 72002 NTD Patent & Trademark Agency Ltd. Units 1805-6, 18th Floor, Greenfield Tower, Concordia Plaza, No.1 Science Museum Road, Tsimshatsui, east, Kowloon, Hong Kong 100045 United 2003 / 12 / 5 60 / 527,196 2006 / 8 / 4 PCT / US2004 / 040498 2004 / 12 / 3 WO2005 / 057423 2005 / 6 / 23 English

Owner:QUALCOMM INC

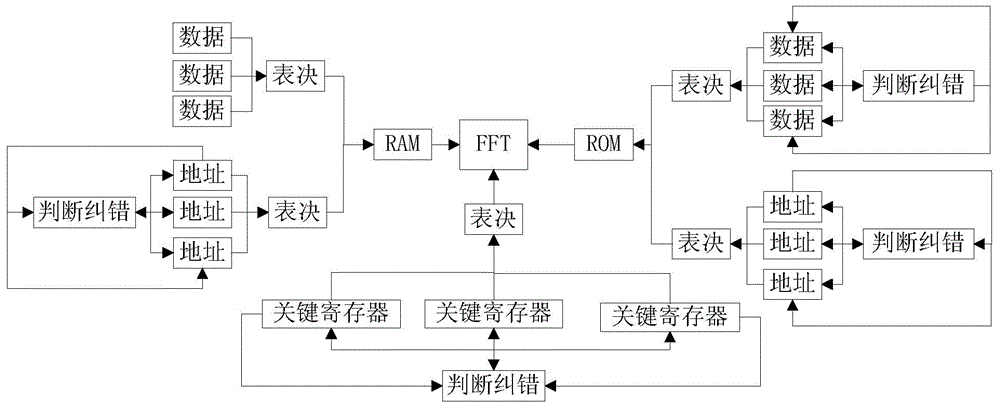

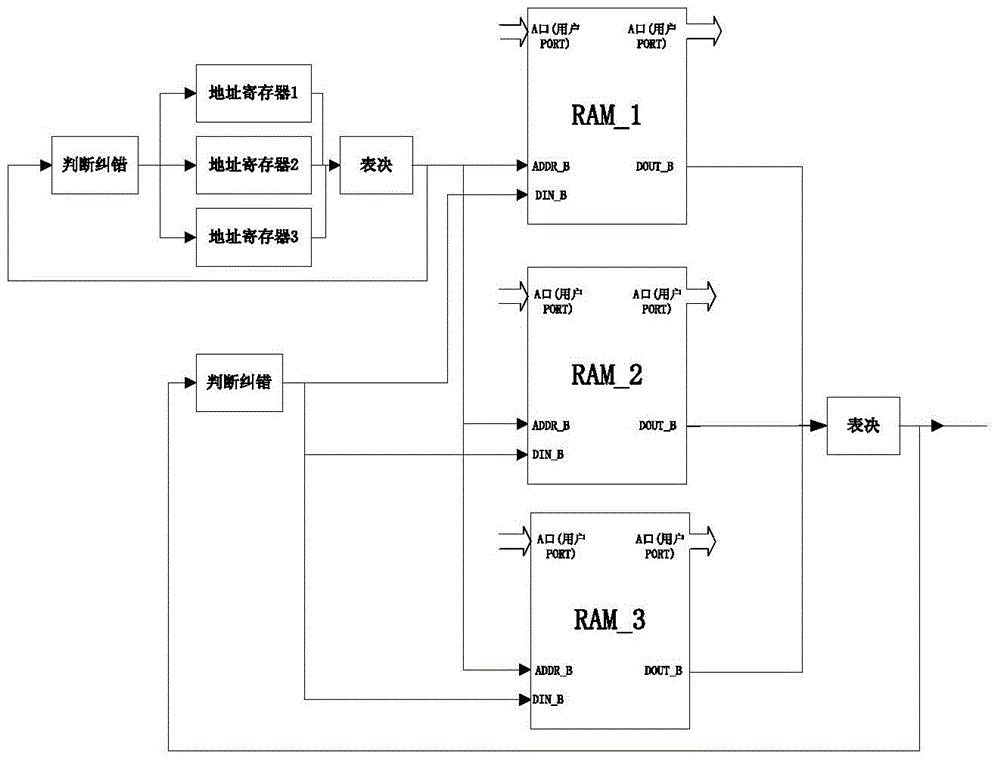

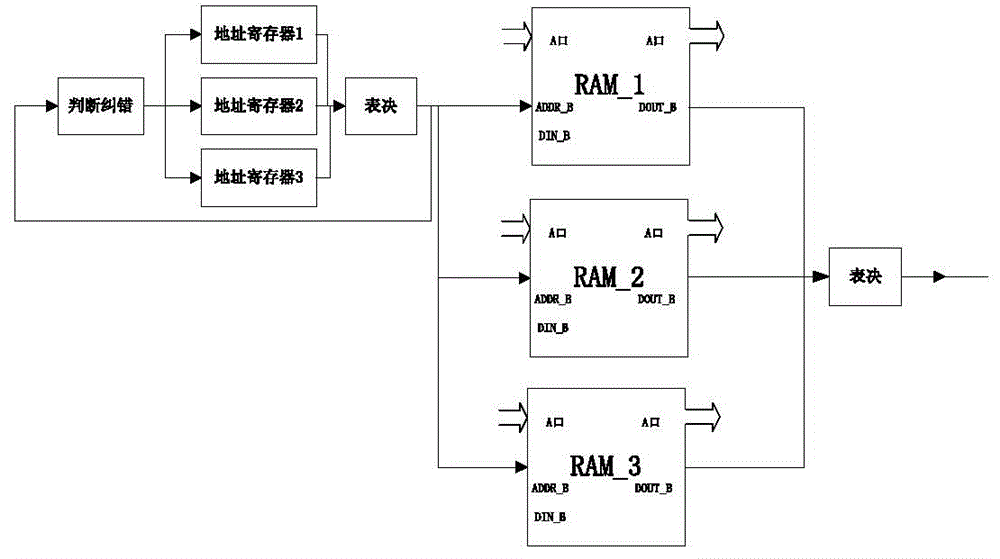

FFT (fast Fourier transform) reinforcing design method with single event upset-resistant capability

ActiveCN103955448ASave space resourcesSave space costComplex mathematical operationsFast Fourier transformSpace environment

The invention relates to an FFT (fast Fourier transform) reinforcing design method with single event upset-resistant capability. The method comprises the following steps of analyzing an FFT algorithm and a circuit structure, adopting an RAM (random access memory) structure for the required ROM (read only memory) which is used for storing twiddle factors in a circuit, and carrying out feedback type triple modular redundancy reinforcing on the data and addresses of the RAM; reinforcing the RAM which is used for storing the final results and has bit-reversed order in the circuit, respectively reinforcing the data and addresses of RAM, and respectively carrying out feedback type triple modular redundancy and triple modular redundancy on an address register and data; carrying out the feedback type triple modular redundancy on a key register which is used for finding the twiddle factors in the ROM. The method has the advantages that the reliability of the FFT circuit in the space environment is improved, the single event upset-resistant capability of the FFT circuit is improved, the certain flexibility in the reinforcing design is realized, the design of FFT circuit with higher single event upset-resistant capability is provided for equipment, and the method can be quickly applied to the research and development of satellite processing equipment.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

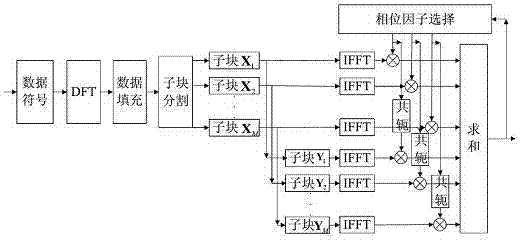

Low-complexity peak-to-average ratio restraining method for optical communication DCO-OFDM (direct current-biased optical-orthogonal frequency division multiplexing) system

InactiveCN104753848ALower peak-to-average ratioReduce correlationMultiplex system selection arrangementsFibre transmissionConjugate symmetryFast Fourier transform

The invention discloses a low-complexity peak-to-average ratio restraining method for an optical communication DCO-OFDM (direct current-biased optical-orthogonal frequency division multiplexing) system. The low-complexity peak-to-average ratio restraining method comprises the following steps of firstly, performing precoding DFT (discrete Fourier transform) on inputted digital modulation signs so as to reduce correlation between the signs; secondly, performing subblock division and conjugate symmetry on a precoded data sequence; and finally, selecting a suboptimal phase twiddle factor for each subblock so as to reduce a peak-to-average ratio. Because IFFT (inverse fast Fourier transform) and suboptimal iterative loop phase factor selection are carried out sequentially, the implementing complexity of the system can be reduced while the peak-to-average ratio is restrained.

Owner:LINYI UNIVERSITY

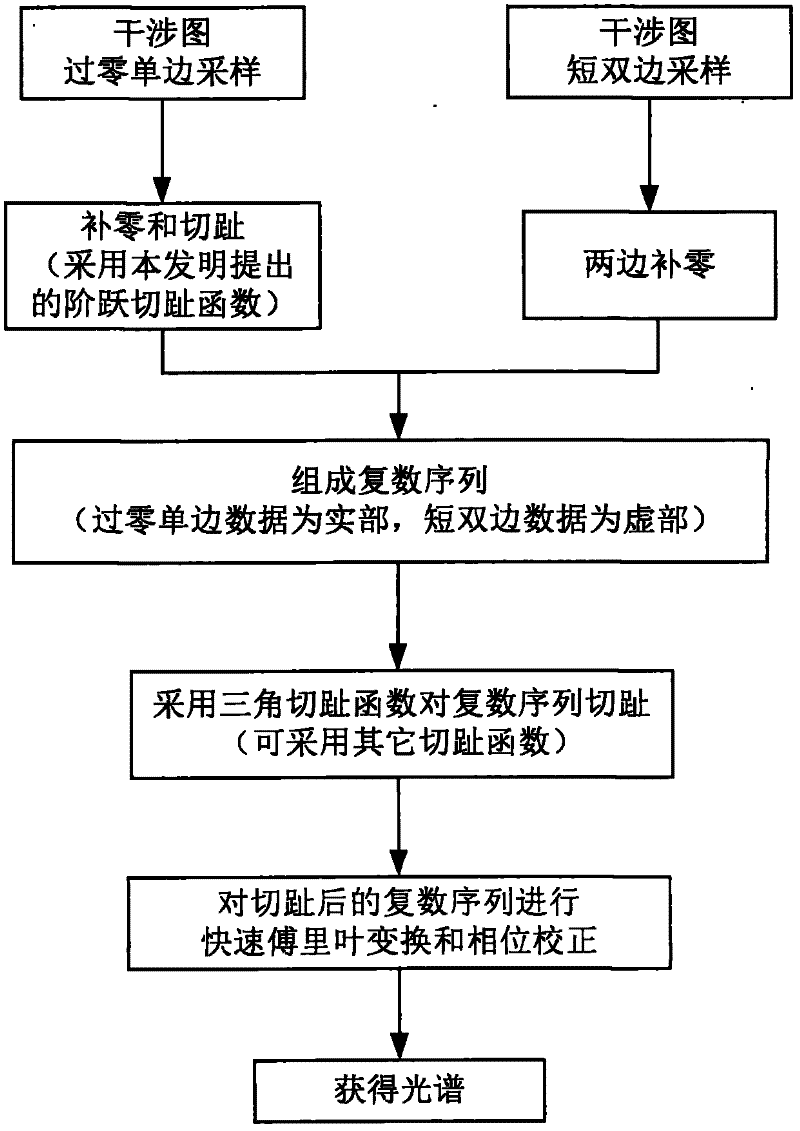

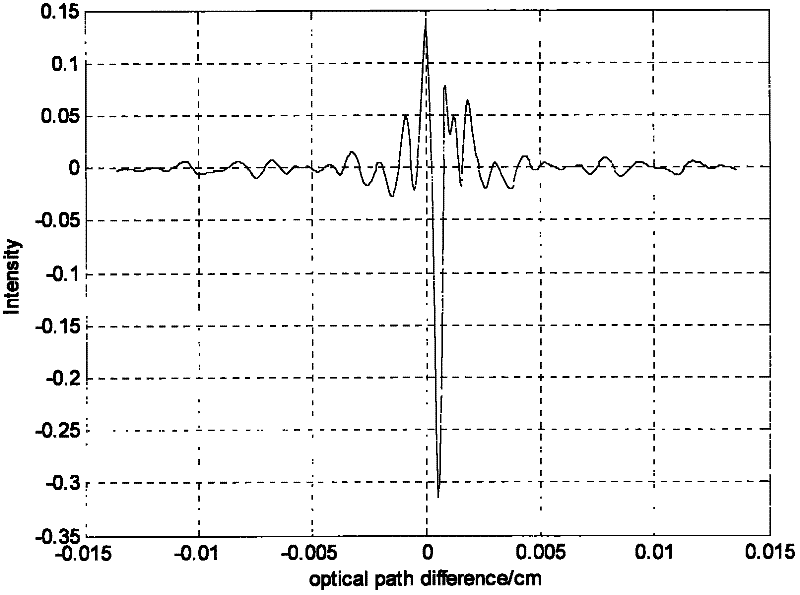

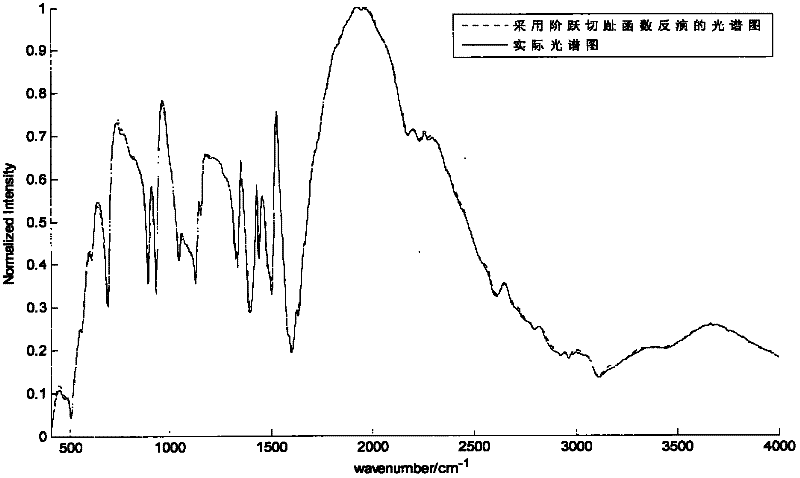

Phase correction apodization method for Fourier transform spectrometer

The invention relates to a phase correction apodization method for a Fourier transform spectrometer. In the method, by weighting a zero-crossing single-sided interferogram, the errors caused by utilizing data near a zero optical path difference point in the calculation process twice are reduced. The method has better weighting effects than an apodization method provided by Mertz, the accuracy of a recovery spectrum can be ensured, and the calculation complexity is effectively reduced simultaneously. After the zero-crossing single-sided interferogram is weighted by the apodization method provided by the invention, the sum of products of light intensity of two corresponding points with the same optical path difference in a short double side of the zero-crossing single-sided interferogram and respective corresponding twiddle factors is an average value of the sum of the products of the light intensity of the two corresponding points and respective corresponding twiddle factors before weighting. Thus the calculation errors brought by asymmetry of the interferogram are reduced, and a more precise recovery spectrum is obtained.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

Pipelined FFT processor with memory address interleaving

InactiveUS7428564B2Avoid overwritingReduce areaDigital computer detailsComplex mathematical operationsFast Fourier transformMemory address

A fast Fourier transform processor using a single delay path and a permuter provides a reduction in the implementation area and a related reduction in power consumption through efficiencies obtained by the modification of a butterfly unit and the use of a novel interleaver. The modified butterfly unit is obtained by the removal of complex variable multipliers, which is possible due to the simplification of twiddle factors in the stages that correspond to the modified butterfly unit.

Owner:MICROSEMI SOLUTIONS (US) INC

Fast fourier transform processor

InactiveUS7577698B2Reduces hardware circuitry area and cost and technical complexityOvercomes drawbackDigital computer detailsComplex mathematical operationsMultiplexingMultiplexer

A Fast Fourier Transform (FFT) processor is provided. It comprises a multiplexer, a first angle rotator, a second angle rotation and multiplexing unit, an adder, a twiddle factor storage, a multiplier, and a data storage. The FFT processor analyzes the input / output order of the Fast Fourier Transformation, separates the portions requiring complex computations, simplifies the hardware thereof, and adjusts the output order. It not only effectively saves the hardware area, but also reduces the computations and memory access count. Thereby, the power consumption is reduced.

Owner:IND TECH RES INST

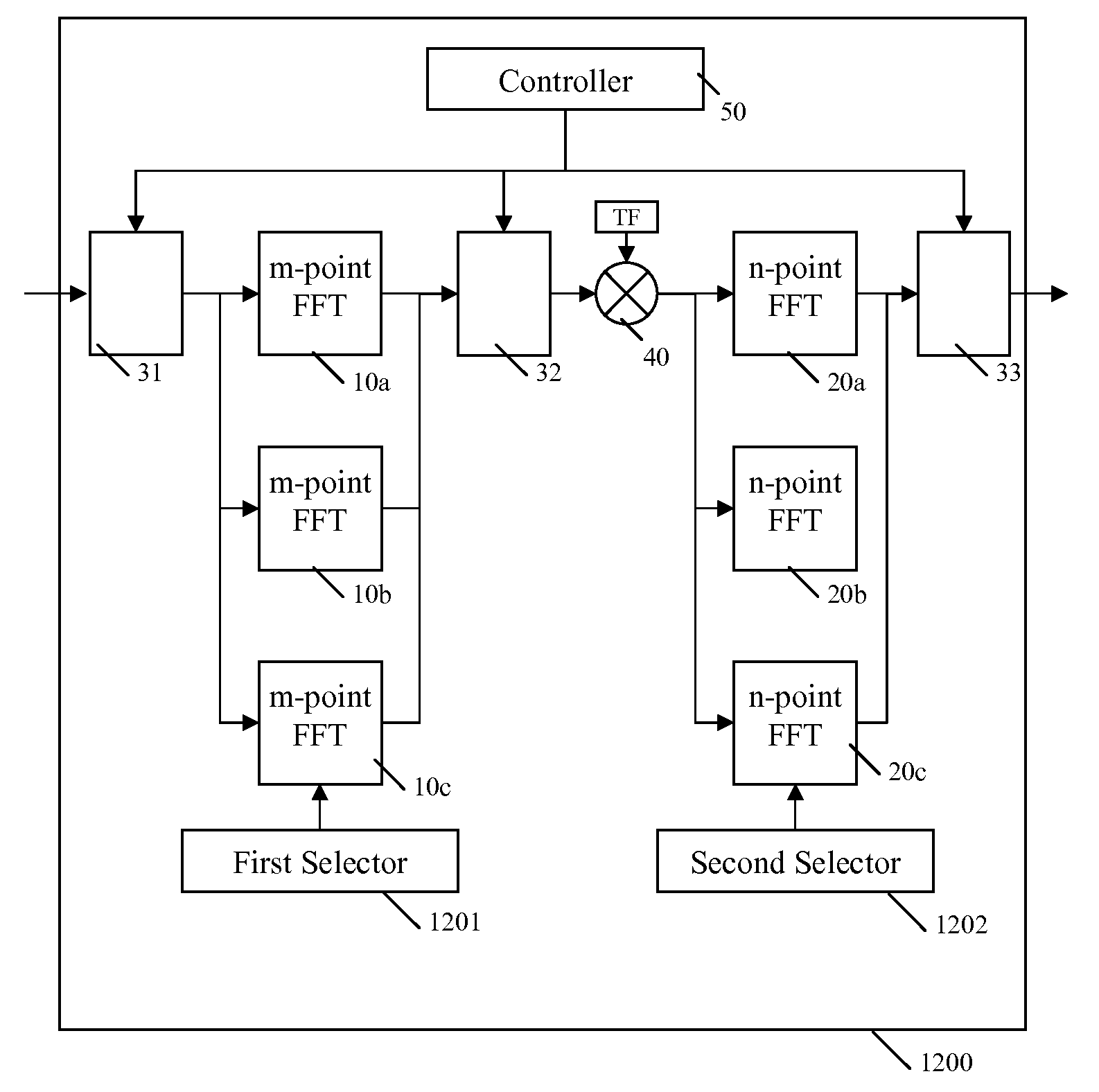

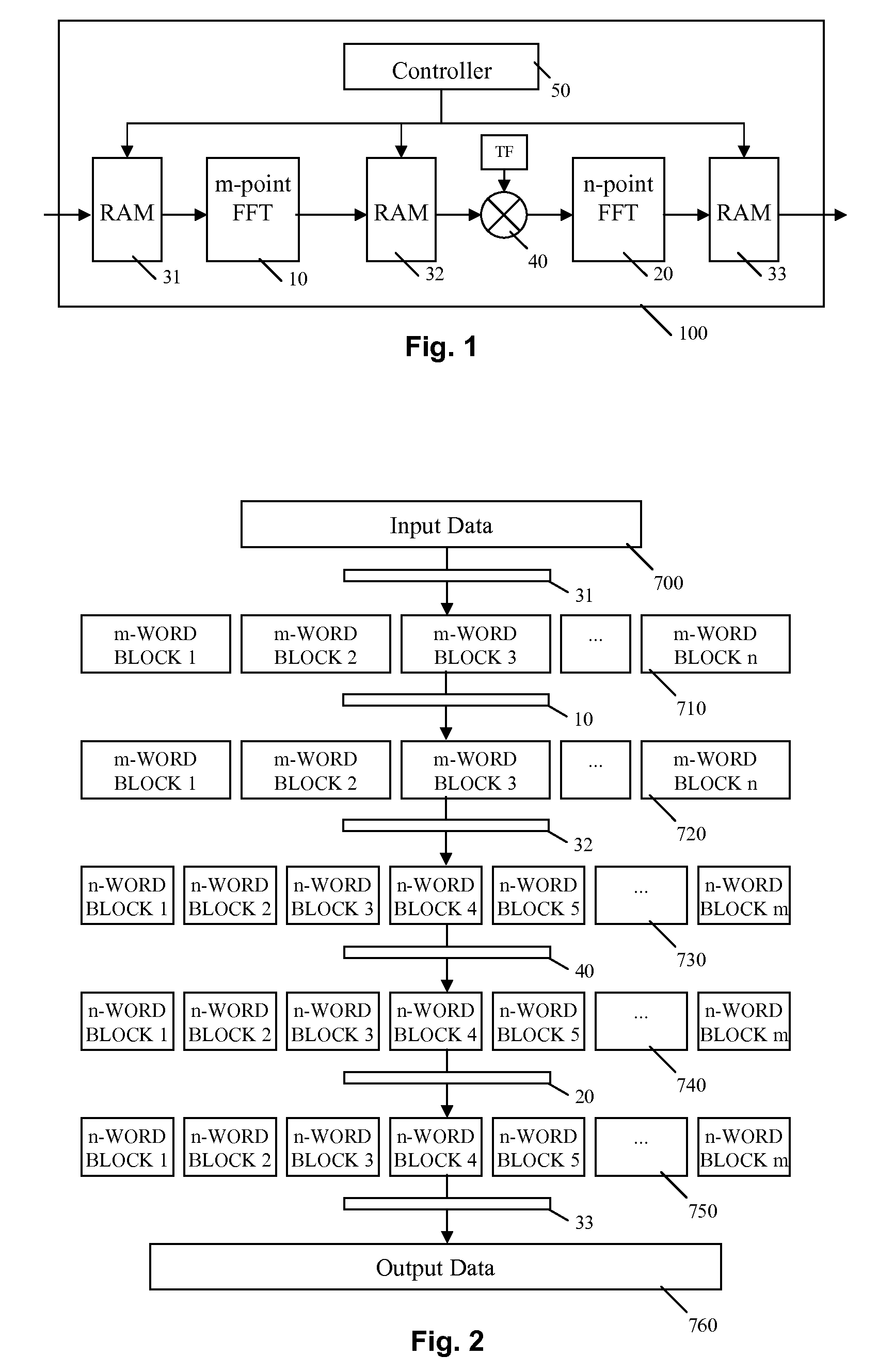

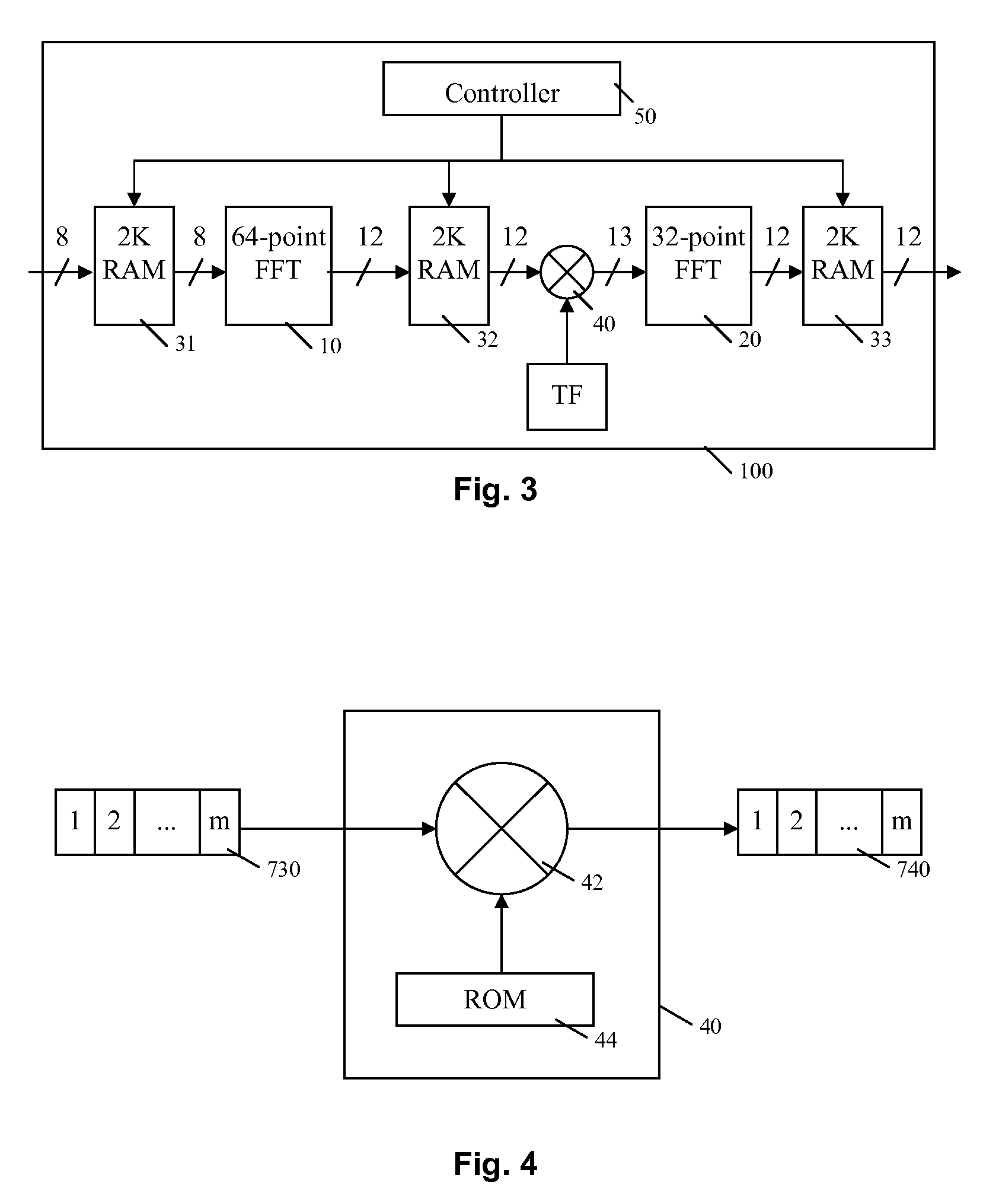

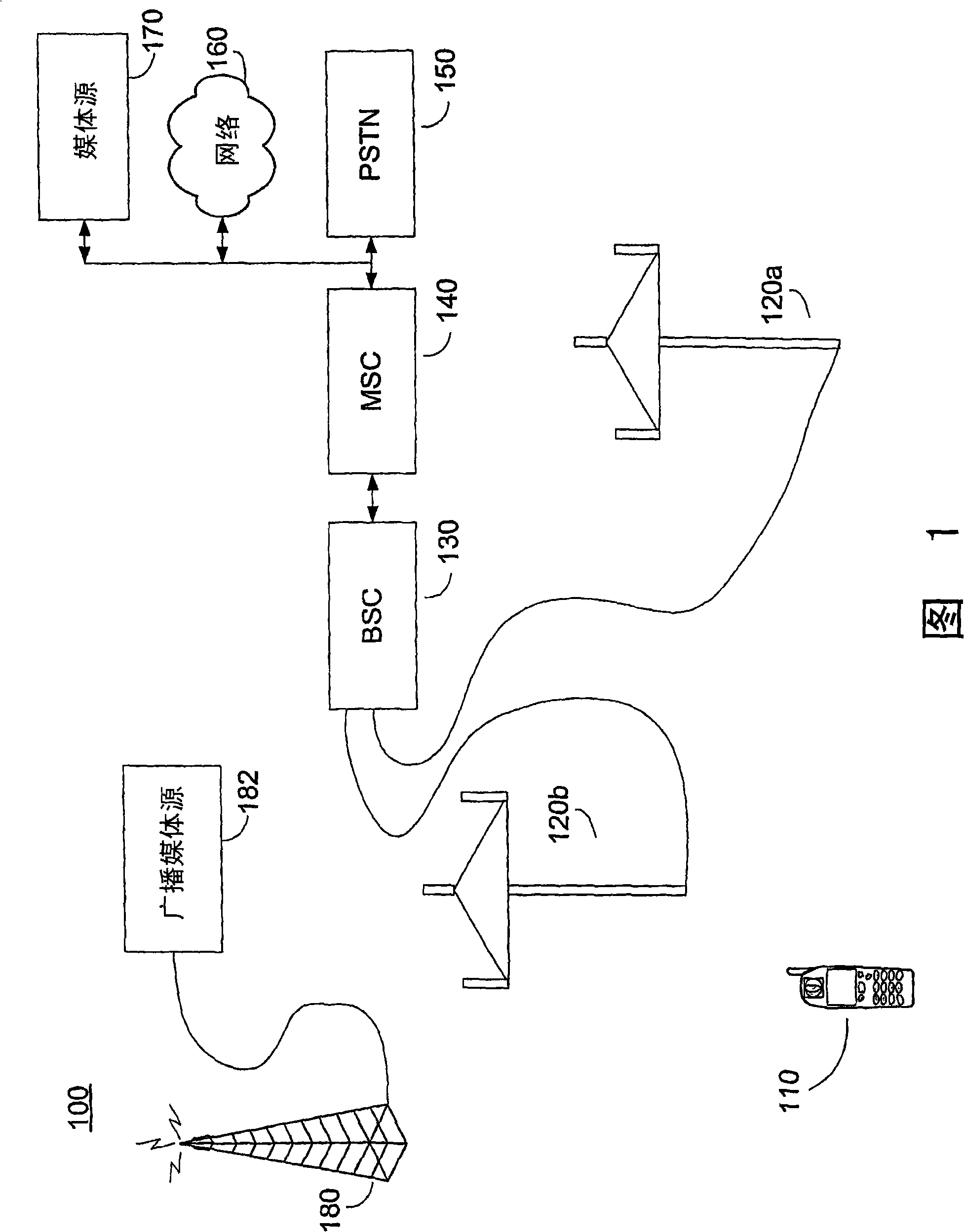

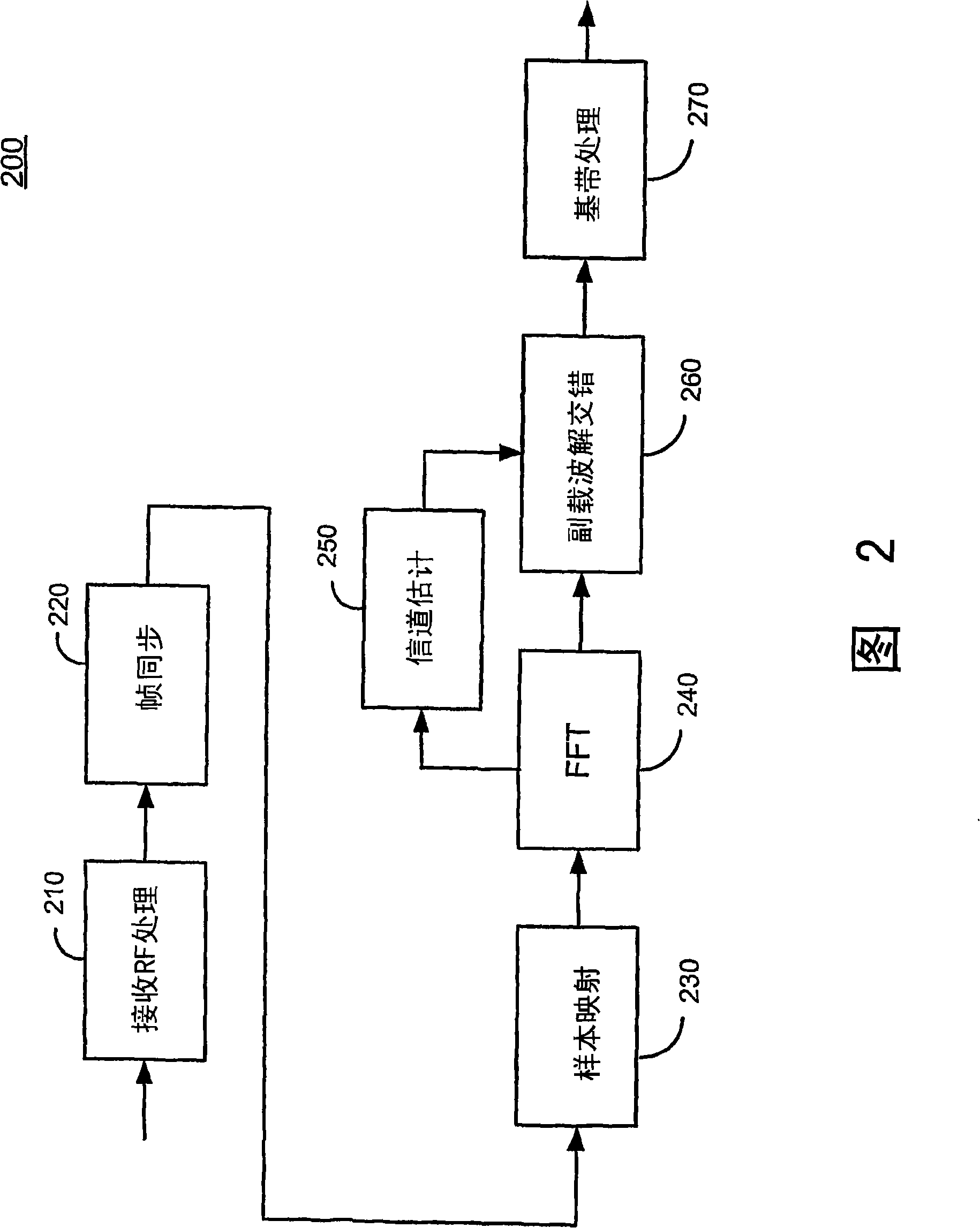

Fft processor

InactiveUS20100128818A1Improve throughputEasy to adaptModulated-carrier systemsDigital computer detailsDigital signal processingParallel computing

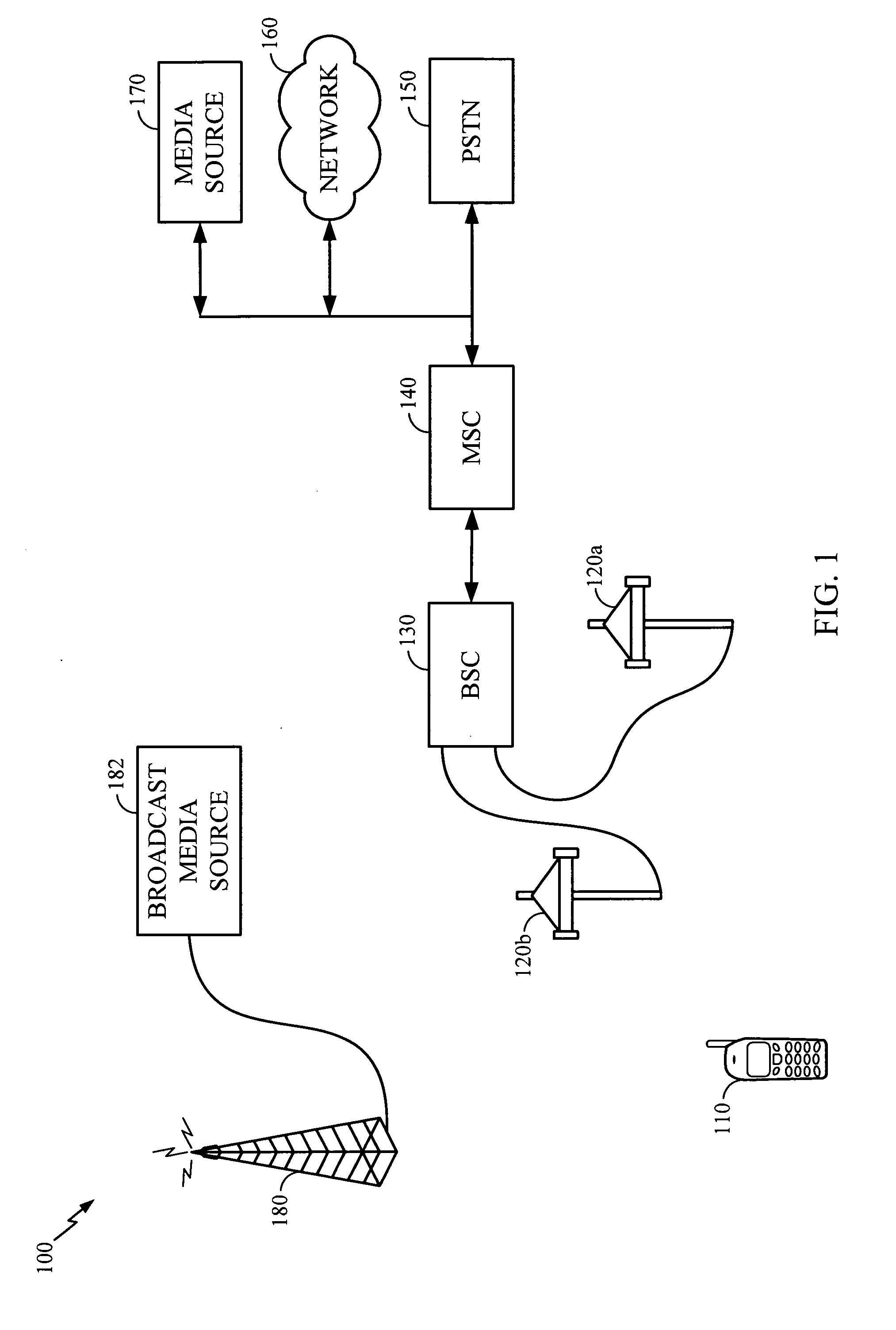

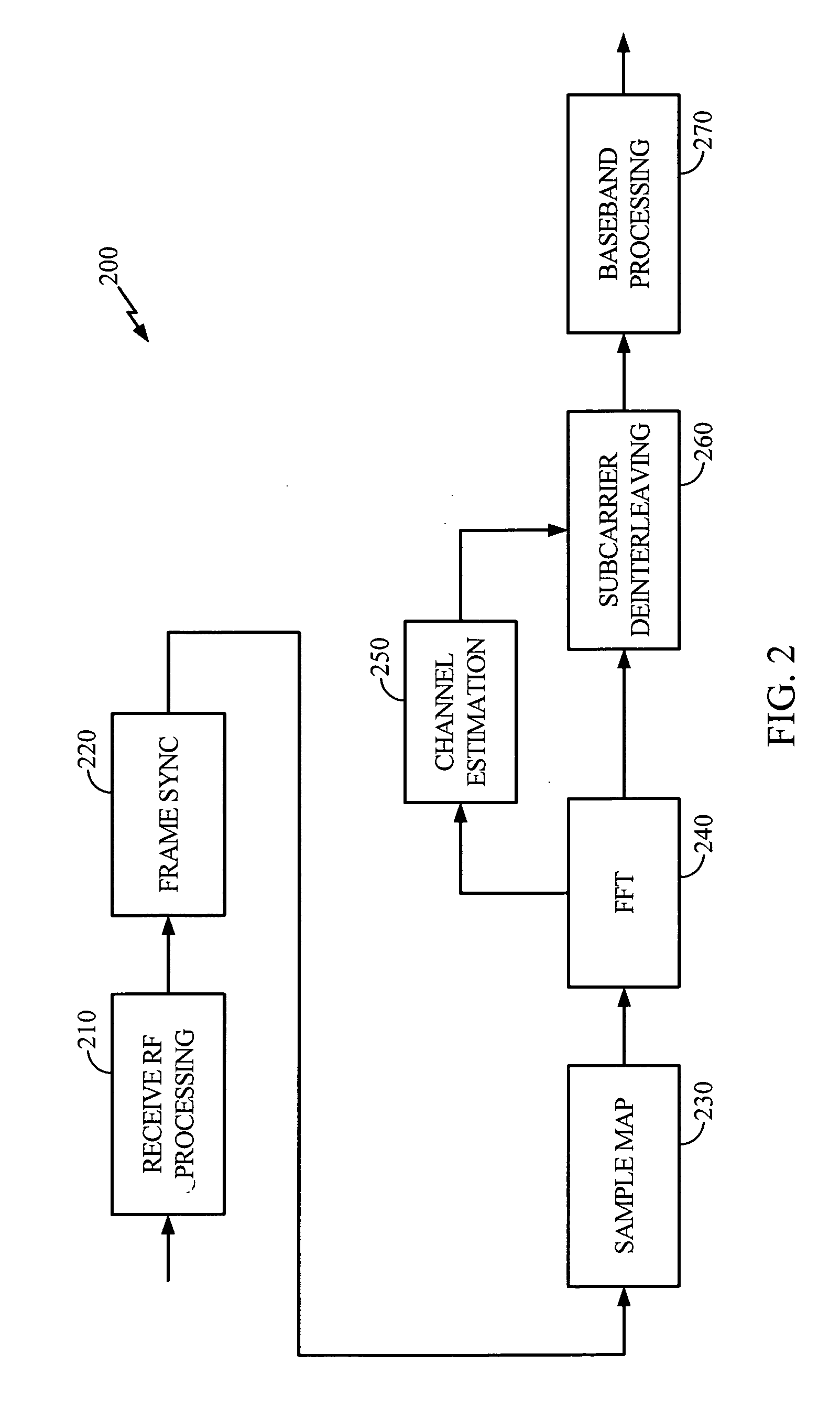

An N-point FFT processor 100 suitable for large data inputs (e.g. 2 k or 8 k-point input data) is formed from a m-point FFT processor unit 10 and a n-point FFT processor unit 20 in combination, where N=m×n and m and n are any positive integers. First, second and third permutation units 31, 32&33 perform global permutations on the data passing through the FFT processor. A twiddle factor unit 40 applies twiddle factors. A digital signal processing apparatus 1100 (FIG. 11) comprising the FFT processor 100 is also described. Further, a testing apparatus 1200 (FIG. 12) is described for testing an N-point FFT processor 100 by selecting amongst a plurality of m-point FFT processor units 10-10c and a plurality of n-point FFT processor units 20a-2c.

Owner:UNIVERSITY OF BRADFORD

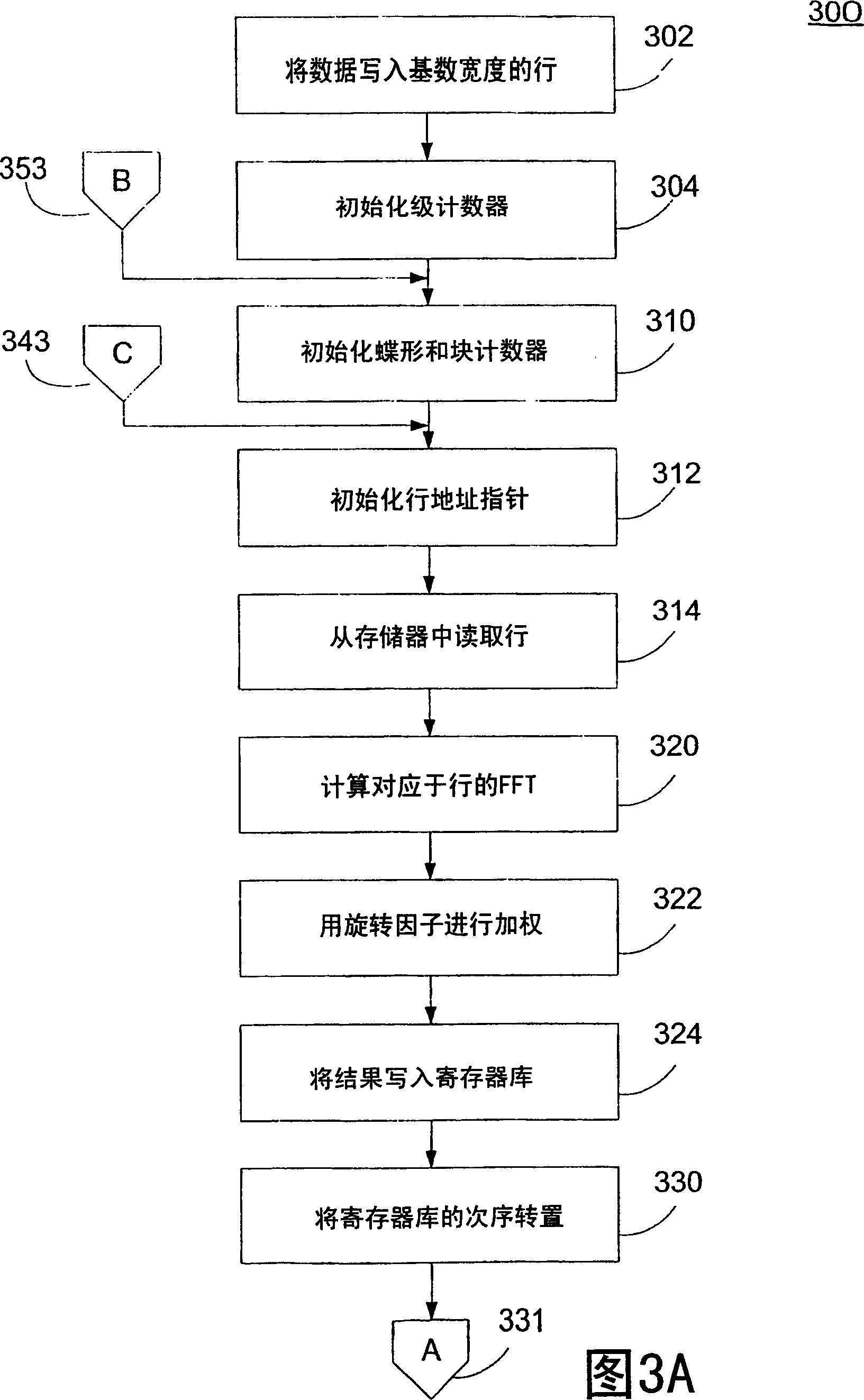

Fast fourier transform twiddle multiplication

InactiveCN101300572AMulti-frequency code systemsComplex mathematical operationsFast Fourier transformTwiddle factor

An FFI engine is used for achieving a cycle count method applying twiddle multiplication in multilevel. When achieving the multilevel FFT, the immediate numerical value needs multiplying a variety of twiddle factors. In a high efficient streamline, the FFI engine uses fewest multipliers to perform the twiddle multiplication. The amount of plural multipliers is optimized on the basis of the amount of numerical values in every line of FFT cardinal numbers and a memory, in such a way, rational storage space amount and cycle of fewest numbers are permitted to perform an FFT function. The strategic ordering and grouping of the numerical values permit to perform the FFT operation by fewest cycles.

Owner:QUALCOMM INC