Low memory spending hybrid base FFT processor and its method

A technology with low memory and memory, applied in the field of wireless communication and digital signal processing, can solve the problems of inability to handle 32-point, 128-point, 512-point, 2048-point FFT, many operation stages, and unfavorable low-power design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

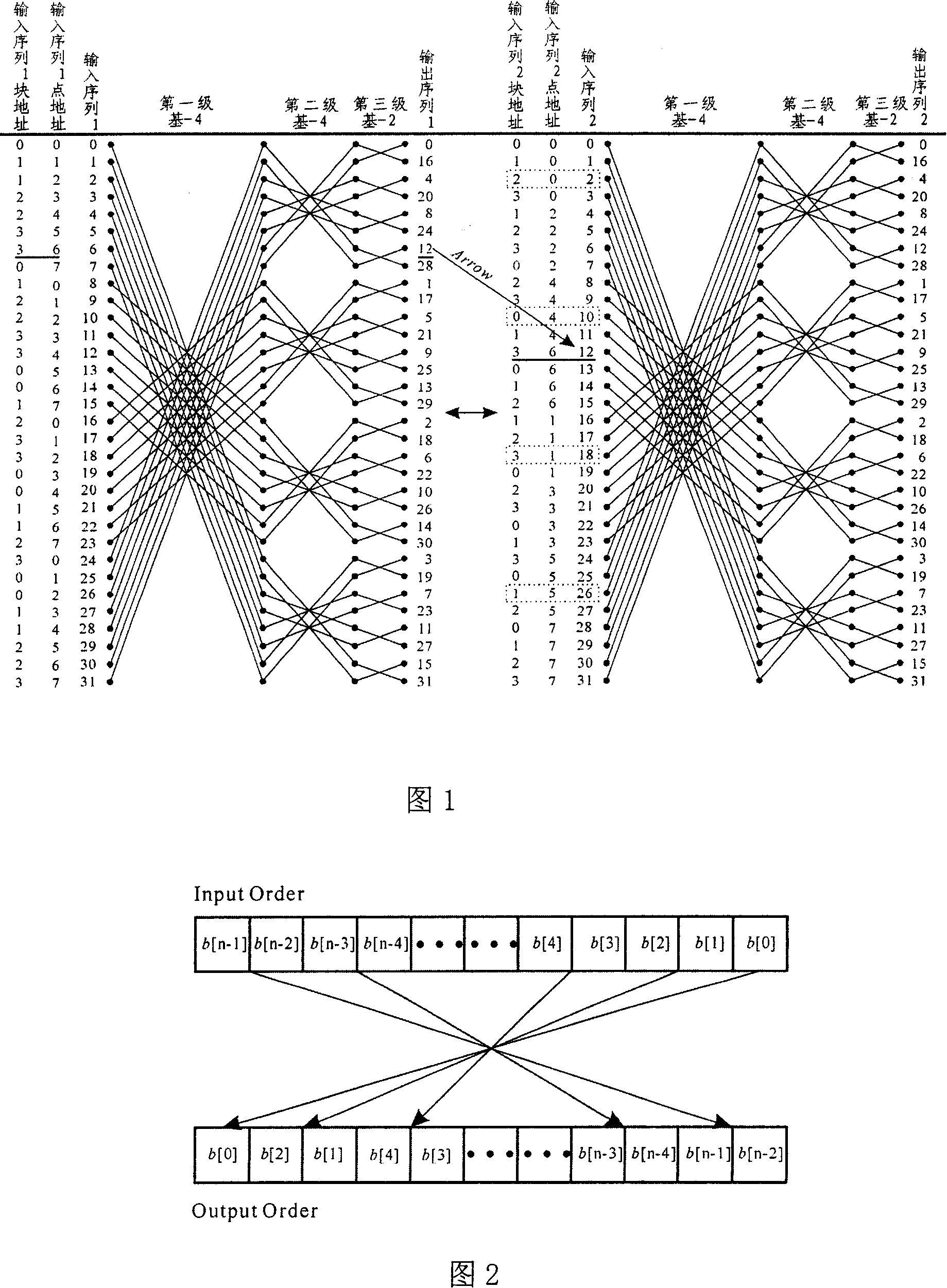

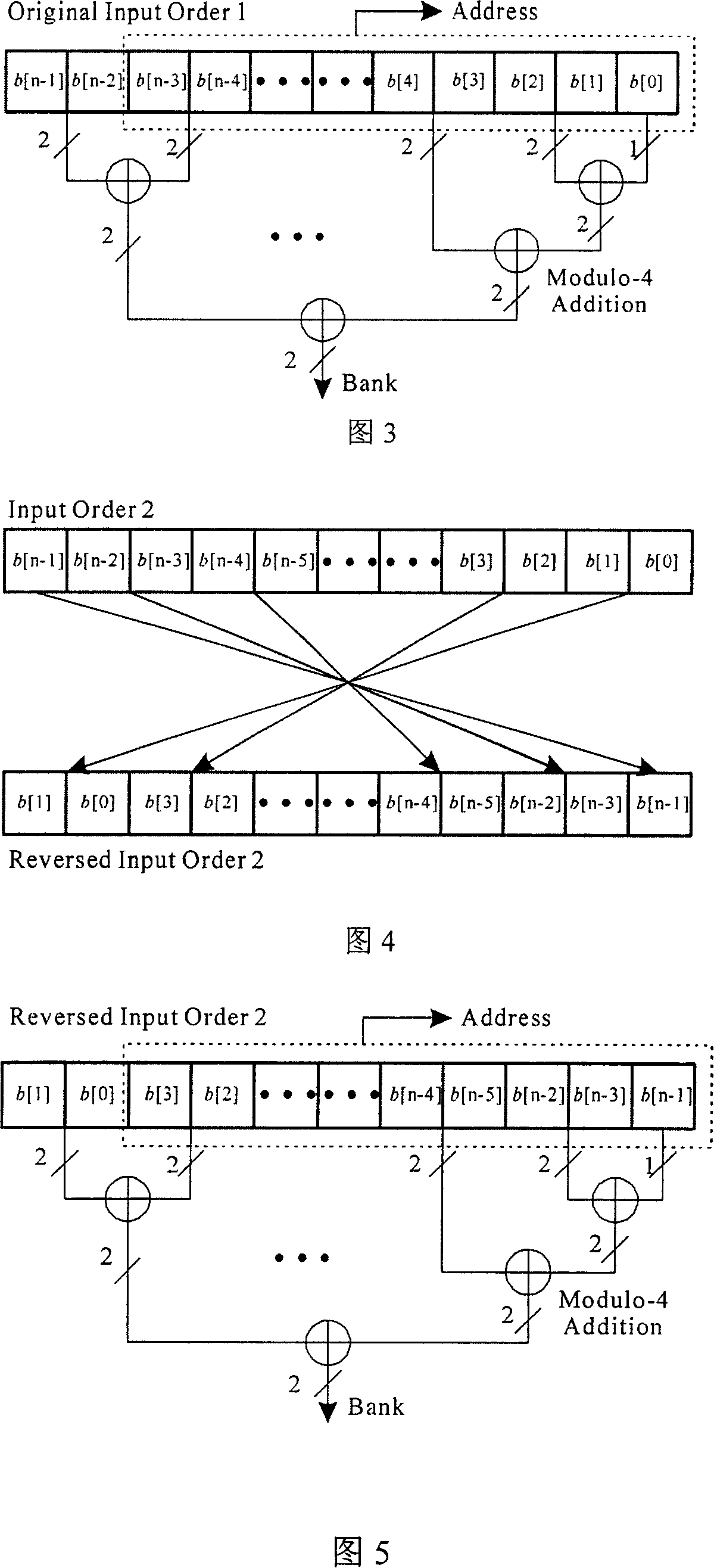

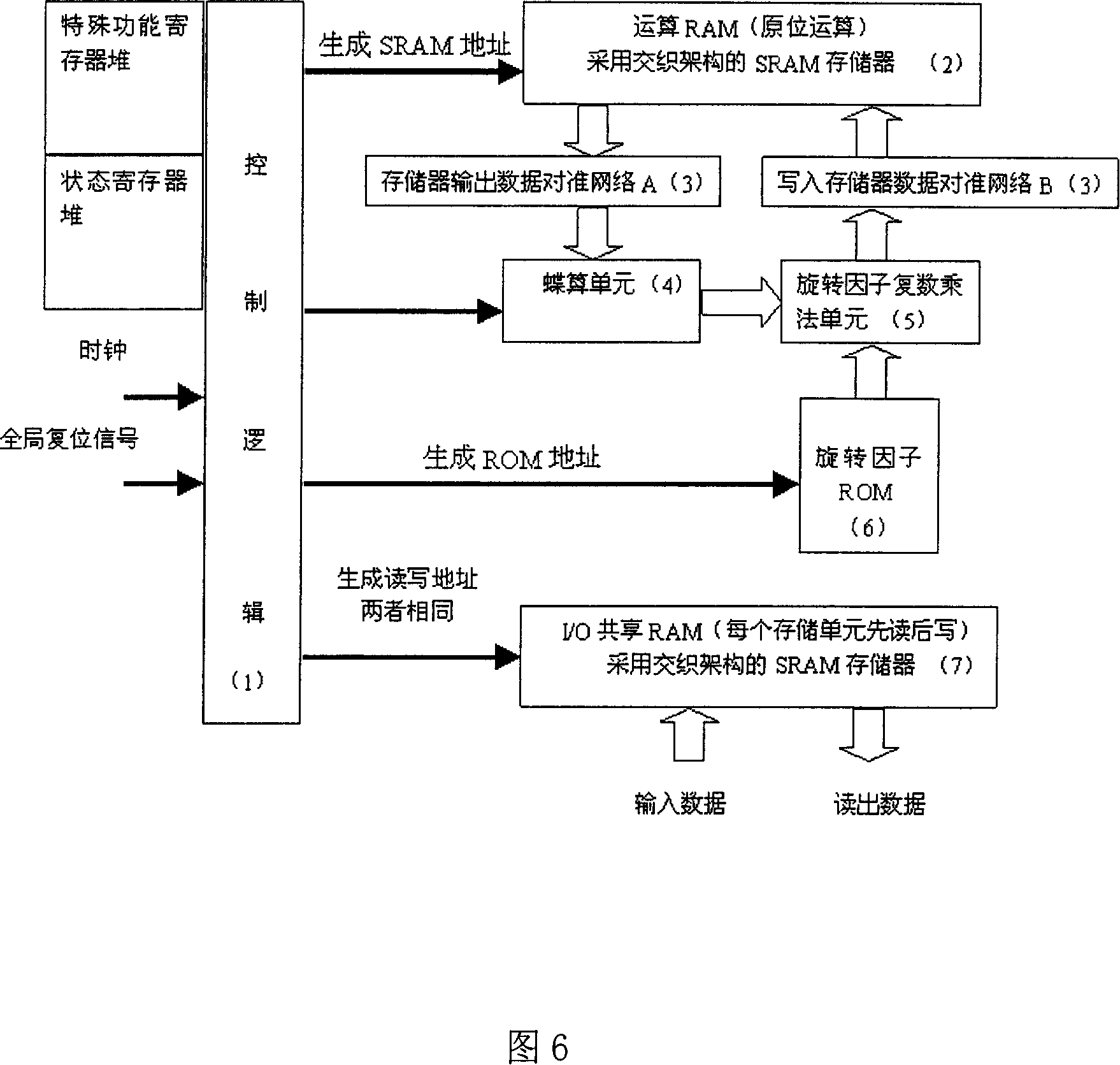

[0019] Here, the radix-4 / 2 mixed radix 32-point FFT data flow diagram is used to illustrate the specific implementation, and the algorithm derivation and hardware mapping here are also suitable for other mixed radix high-point FFT algorithms. The corresponding hardware architecture adopts two blocks of RAM, which are I / O memory and operation memory. Output sequence 1 and input sequence 2 share the same I / O memory, and each input sequence is defined as a frame. Without loss of generality, input sequence 1 represents odd frames and input sequence 2 represents even frames. I / O memory and operation memory are rotated by frame, and FFT operation is carried out continuously. The order of frequency domain points of output sequence 1 and output sequence 2 are generated by the original Input Order register, and both are exactly the same. Original Input Order1, Input Order1, Input Order 2, and Reversed Input Order2 are cumulative counting registers with a bit length of n bits, where n ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More