Point-variable assembly line FFT processor

A processor and pipeline technology, applied in the field of signal processing, can solve the problems of large circuit scale, high memory resource occupation, and limited computing power.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

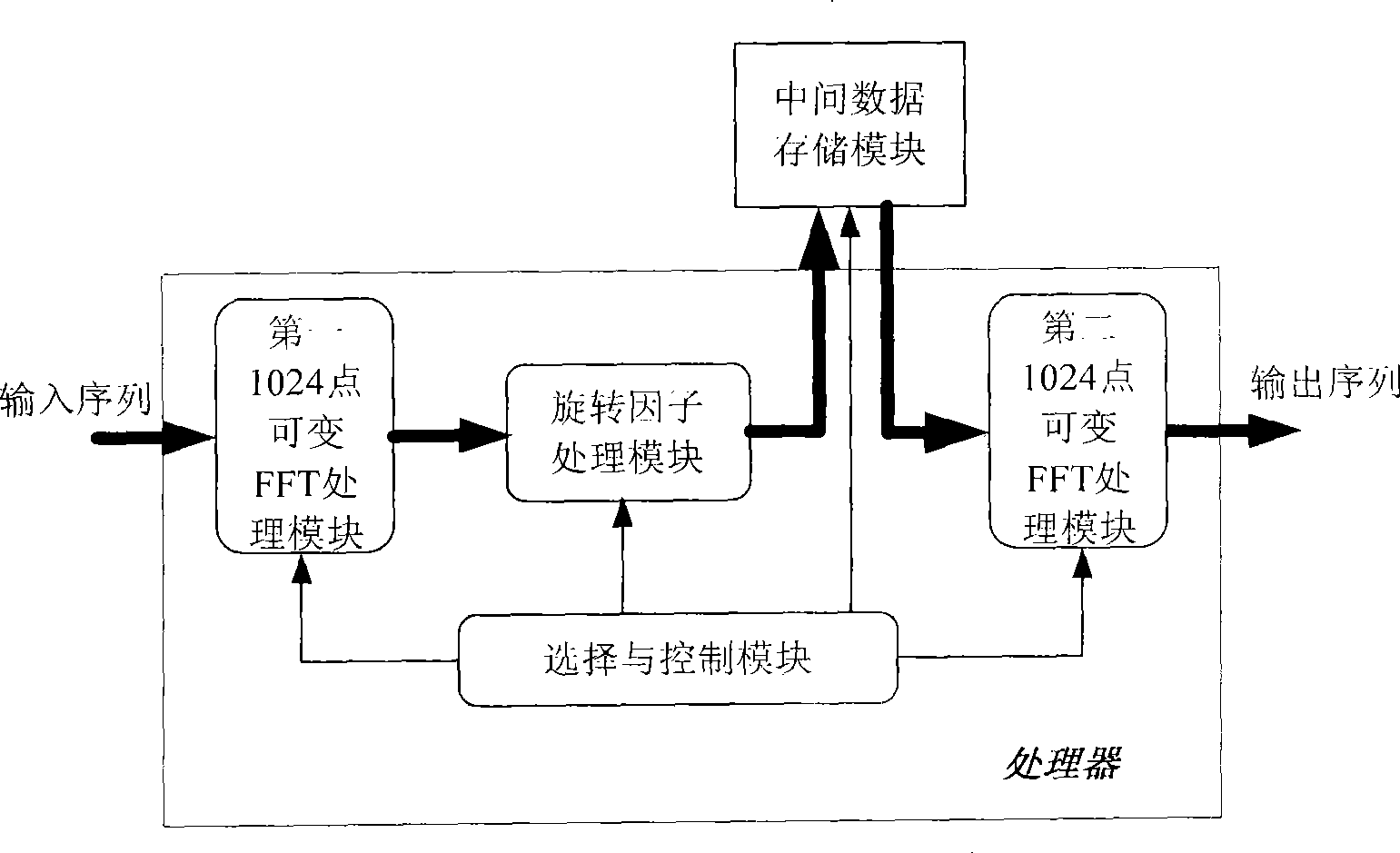

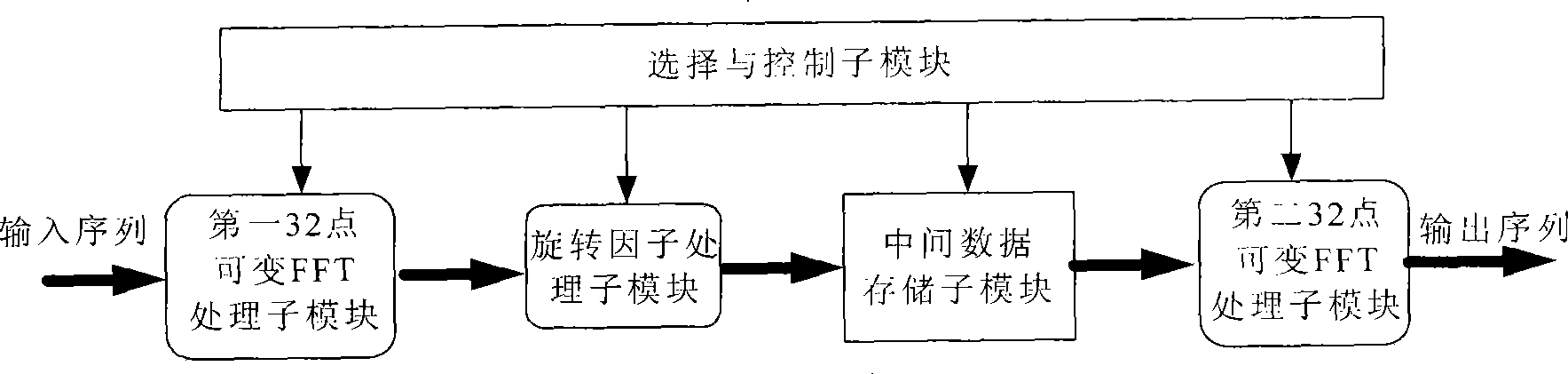

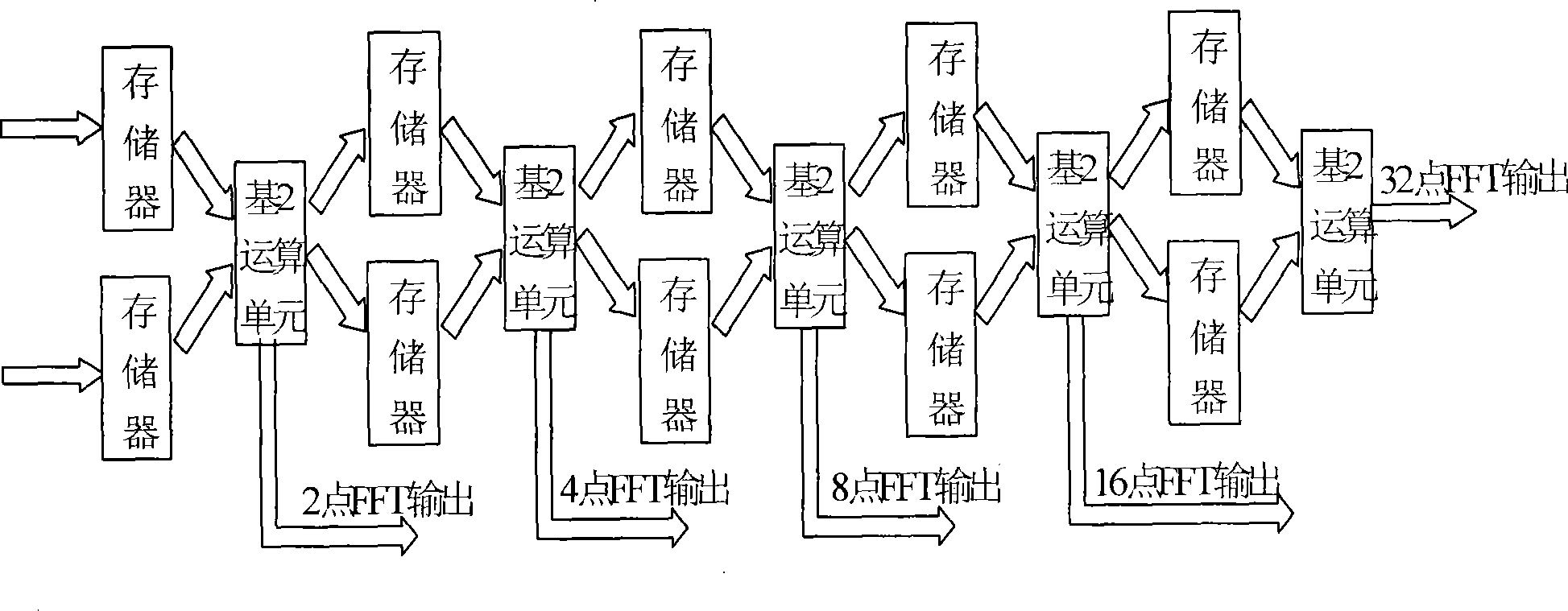

[0100] When realizing the FFT of ultra-long points, the corresponding module will be activated according to the selection and control module. For example, when realizing the FFT of 512K points, it is decomposed according to N=M×L=1024×512, and the first 1024 points are variable In the FFT processing module, 512 times of 1024-point FFT processing are completed, and the twiddle factor generation and multiplication are completed through the twiddle factor processing module, and then the data is sent to the external intermediate data storage module of the processor for caching, and then in the second 1024-point variable FFT processing module Complete 1024 times of 512-point FFT processing in the process to form an output sequence. Take the 512-point FFT processing in the second 1024-point variable FFT processing module as an example, first decompose according to N=M×L=32×16, and the data first completes 16 points in the first 32-point variable FFT processing sub-module The second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More