Fourier transform implementation method based on reconfigurable technology

A technology of Fourier transform and implementation method, applied in complex mathematical operations and other directions, can solve problems such as poor flexibility and defective performance, and achieve the effect of high flexibility and high computing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

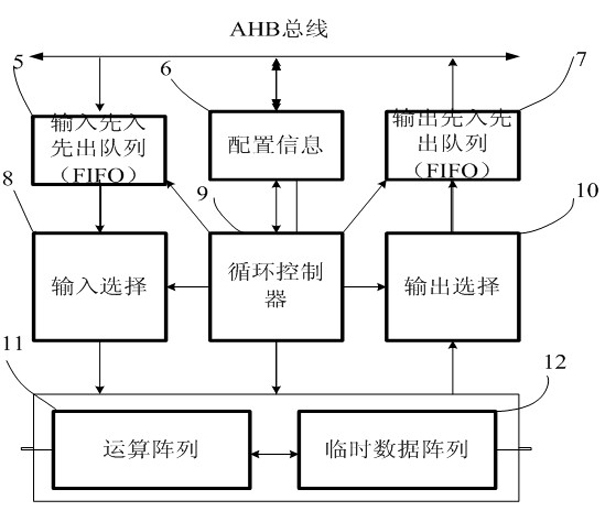

[0027] The present invention will be further described below in conjunction with the accompanying drawings.

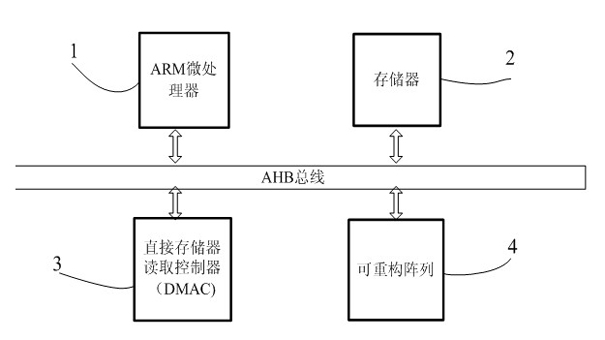

[0028]Explanation 1: The English words used below represent the meanings: Discrete Fourier Transform (DFT), Reconfigurable Array (Reconfigurable Array, RCA), ARM (the name of a microprocessor), AHB (a system bus Name), direct memory access controller (DMAC), arithmetic unit (PE), master (master), slave (slave), arithmetic logic unit (Arithmetic Logic Unit, ALU), Fast Fourier Transform (Fast Fourier Transform, FFT ), embedded reconfigurable array system on chip (system on chip, SoC), discrete Fourier transform (Discrete FourierTransform, DFT).

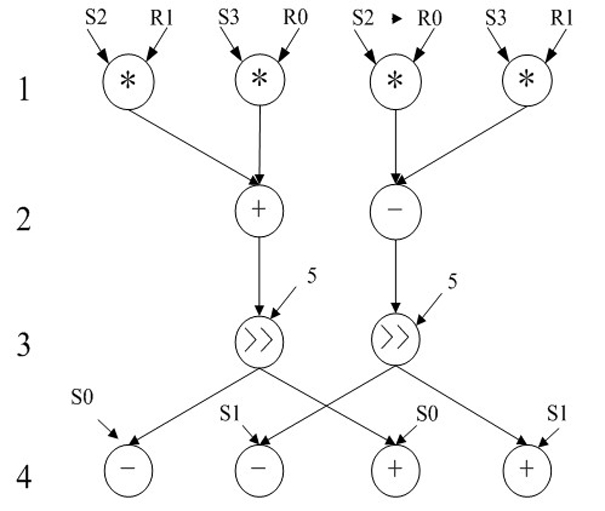

[0029] Table 1 is a description of the reconfigurable array internal registers involved in the FFT algorithm implementation method based on reconfigurable technology of the present invention;

[0030] Table 2 shows configuration information for configuring a reconfigurable array in a 2048-point FFT algorithm implementation meth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More