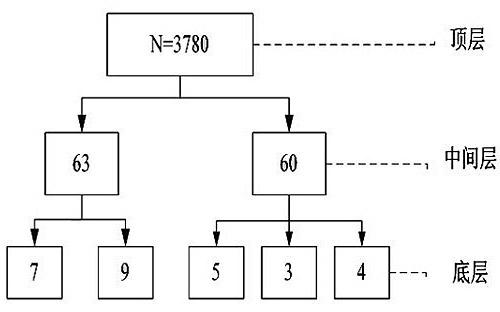

Method for realizing 3780-point fast Fourier transform/inverse fast Fourier transform (FFT/IFFT) and processor thereof

A processor and algorithm technology, applied in the field of fast Fourier transform processors, can solve problems such as increasing the amount and complexity of algorithm calculations, consuming more resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solution involved in the present invention will be described below with a specific implementation example in conjunction with the accompanying drawings.

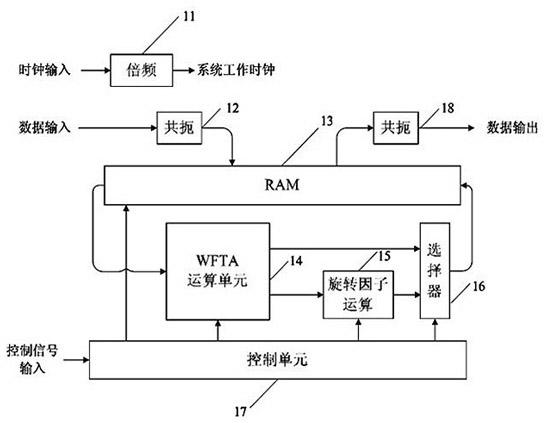

[0027] The hardware architecture of this FFT / IFFT processor based on the FPGA platform is as follows: figure 2 shown.

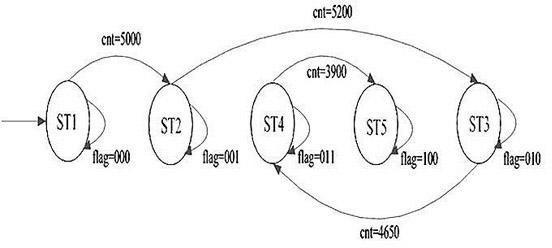

[0028] figure 2 It is a hardware system block diagram of the FFT / IFFT processor of the present invention. In this example, a group of data with a length of 3780 points enters the input conjugation module 12 under the synchronous effect of the clock, and is stored in the RAM unit 13 in a cycle according to the real part and the imaginary part. Under the control of the control unit 17, the data is transferred from Read out from the RAM unit 13, enter the WFTA operation unit 14 to perform n-point WFTA calculations, and store them in the corresponding address of the RAM unit 13 after calculation to realize the original address operation. After the 9-point WFTA operation is performed, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More