FFT processor data storage system and method

A data storage system and processor technology, applied in the field of digital mobile communication, can solve the problem of increasing the area of hardware resources, and achieve the effect of small area and high utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

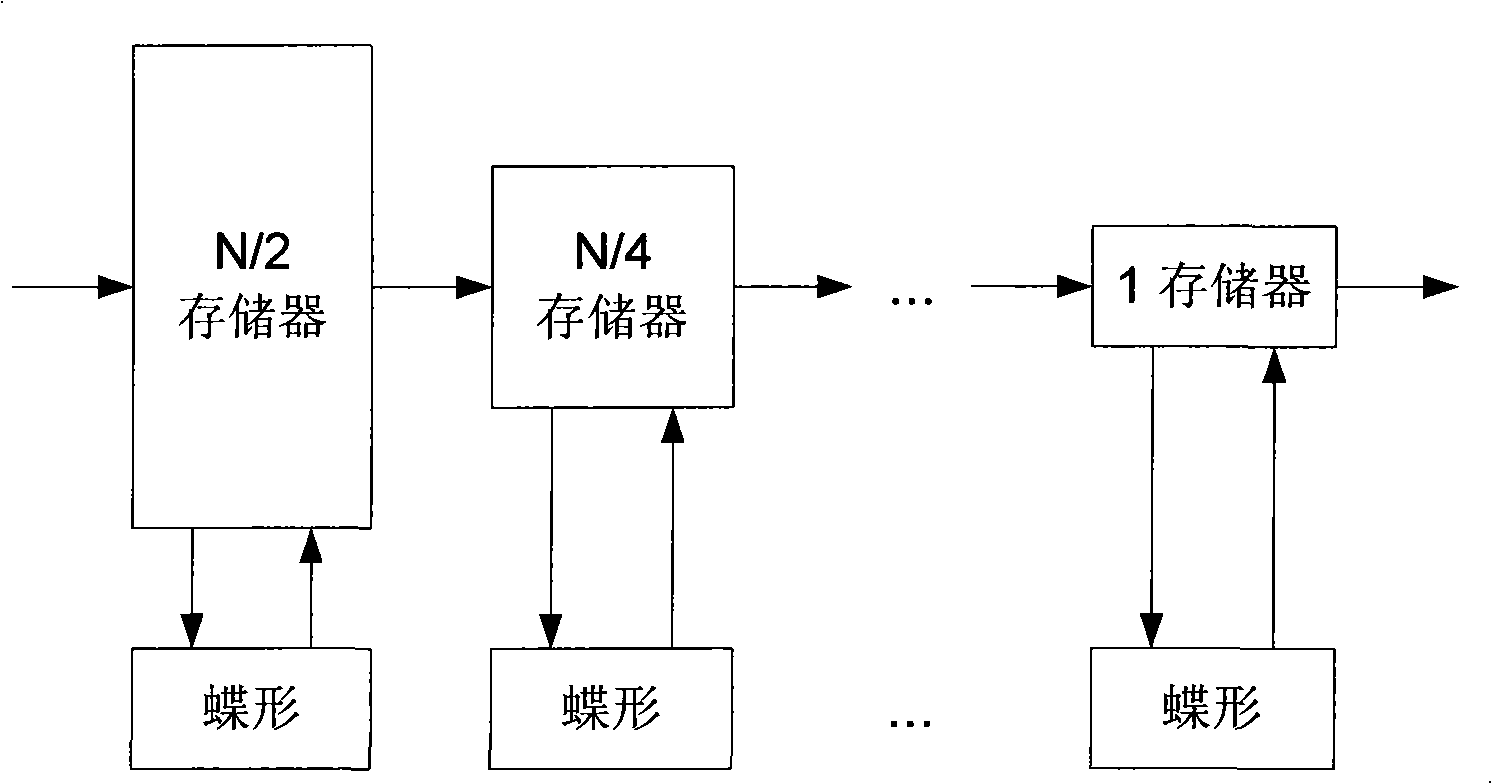

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] An example of a radix-2FFT processor at N points is given below. In the radix-2FFT operation, there are log 2 N levels, the number of butterfly operations per level is N / 2.

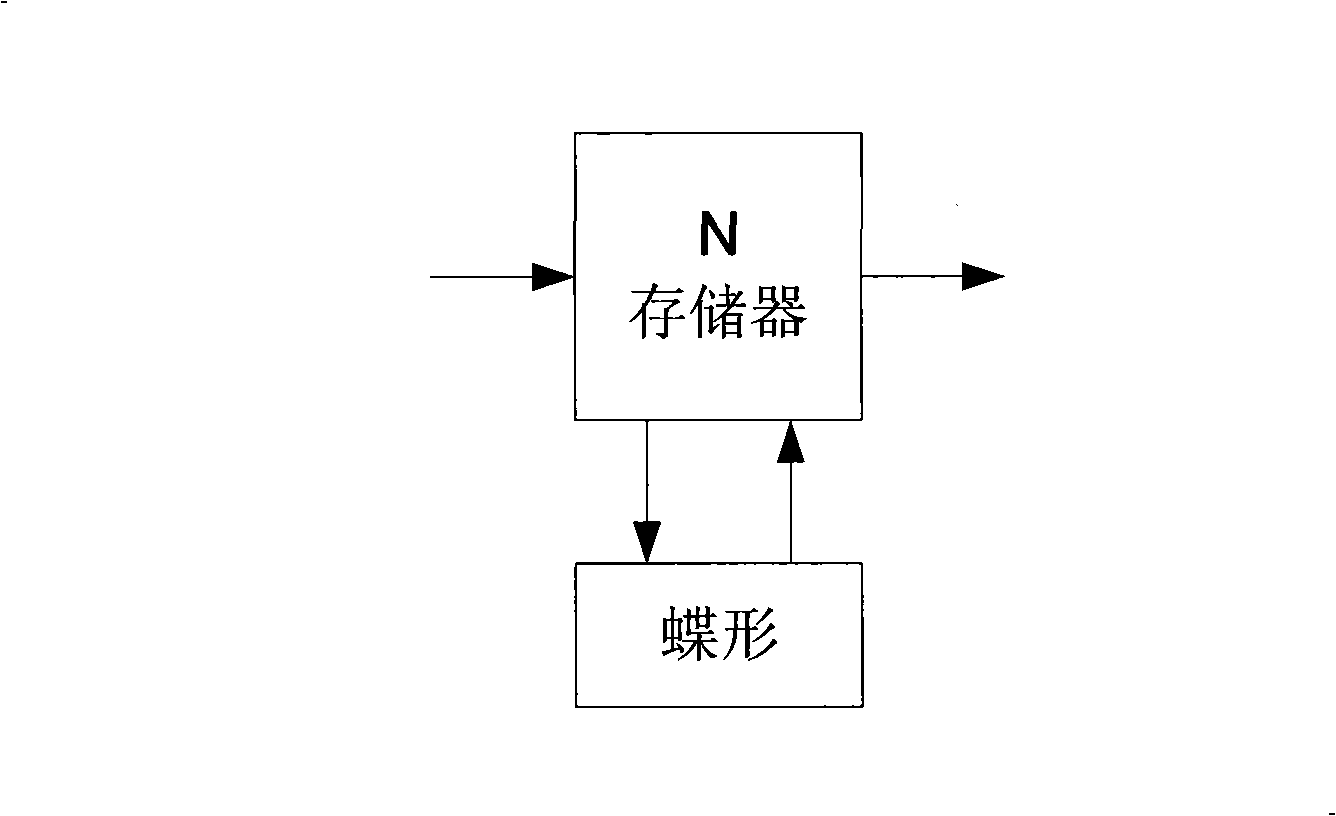

[0020] Such as image 3 As shown, the data storage system of the FFT processor of the present invention includes a controller, a butterfly operation unit, a data memory, and a twiddle factor table. The controller includes a butterfly operation counter, a stage counter, an index number generator, an address mapper, a delay unit, and a twiddle factor sequence number generator.

[0021] The butterfly operation counter indicates the serial number of the butterfly operation in each stage, the counting range is from 0 to N / 2-1, the butterfly operation counter is incremented by one every clock cycle, and restarts from 0 after counting to N / 2-1 . Counting in binary, the butterfly operation counter needs m-1 bits, where m=log 2 N, the counting result is recorded as count[m-2:0].

[0022] The series cou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More