Patents

Literature

581 results about "Level structure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

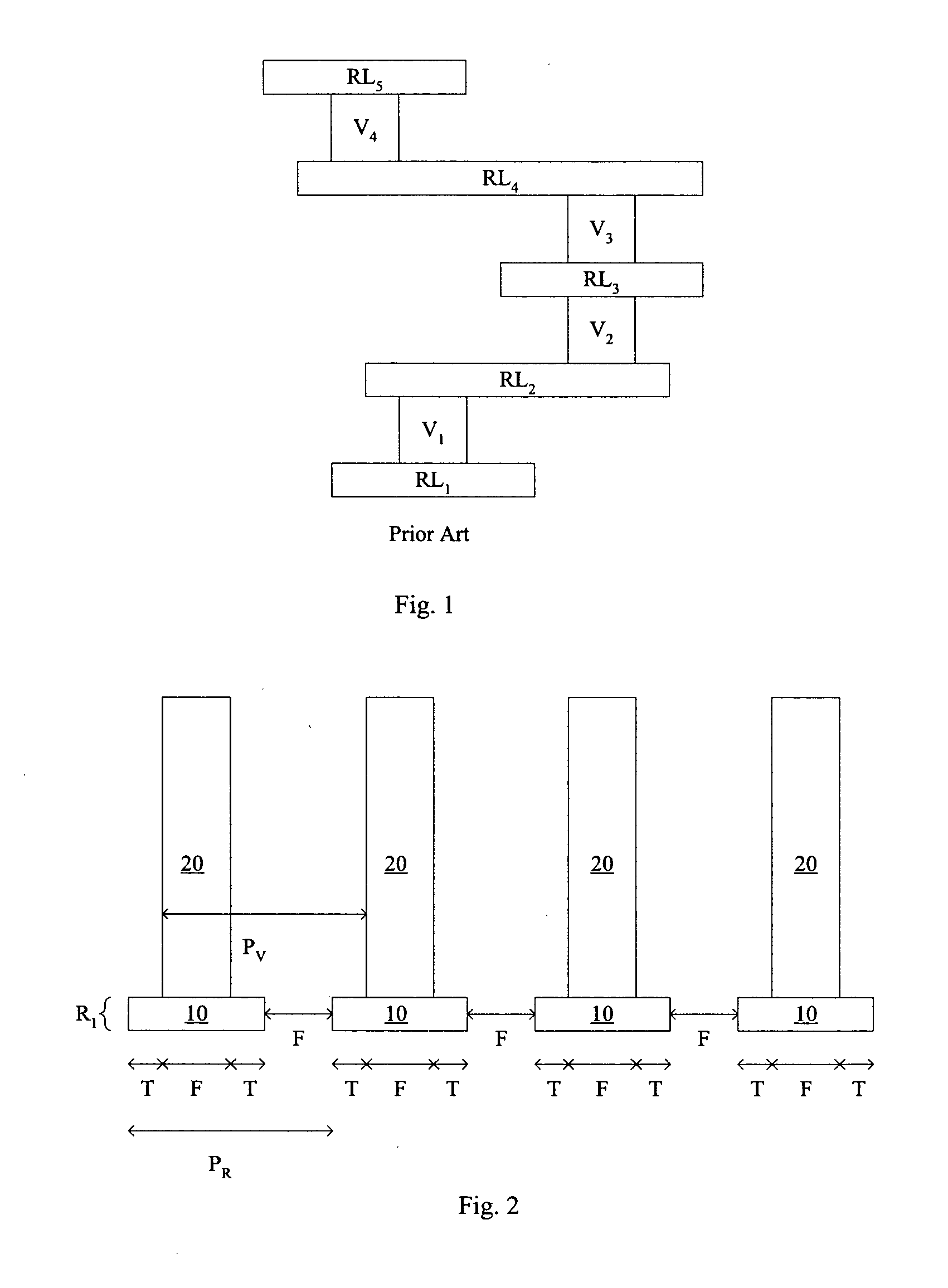

In the mathematical subfield of graph theory a level structure of an undirected graph is a partition of the vertices into subsets that have the same distance from a given root vertex.

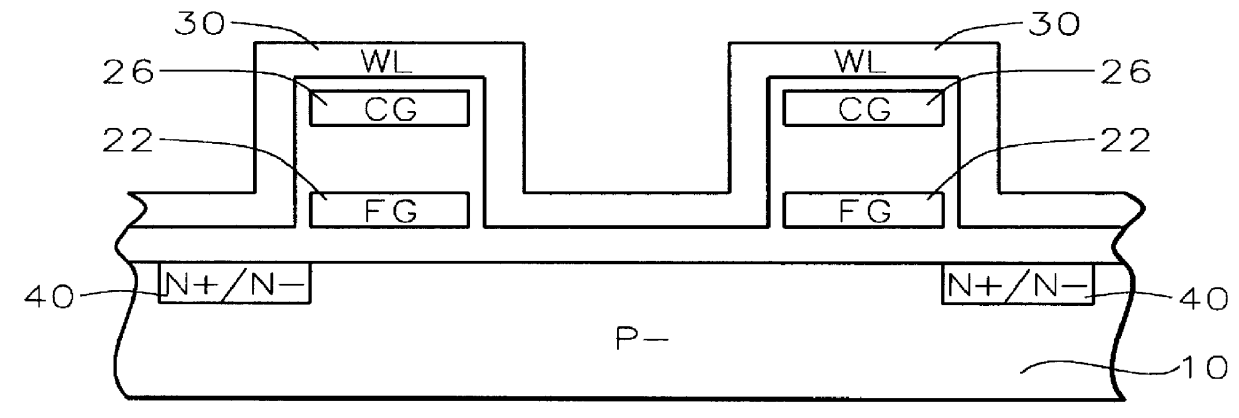

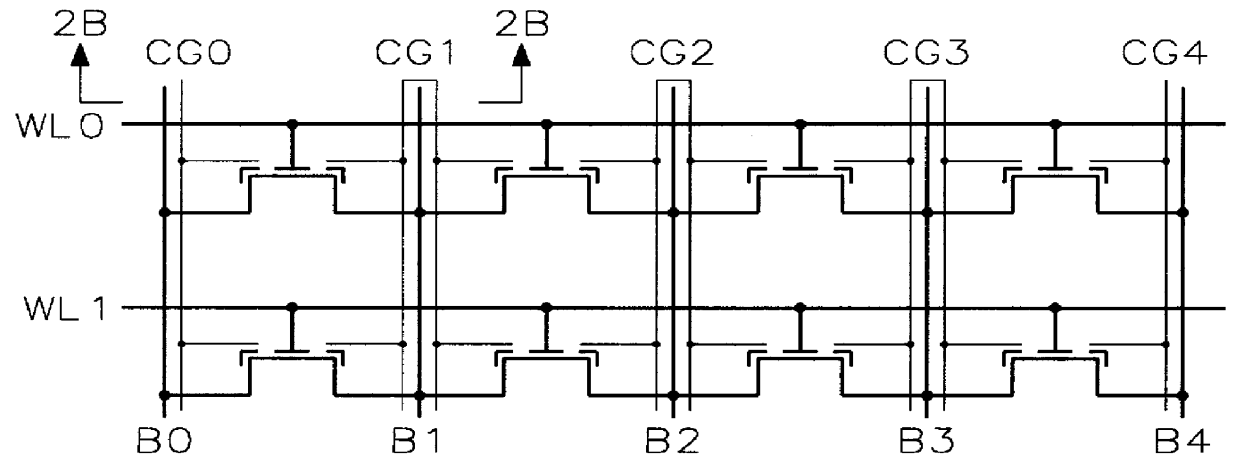

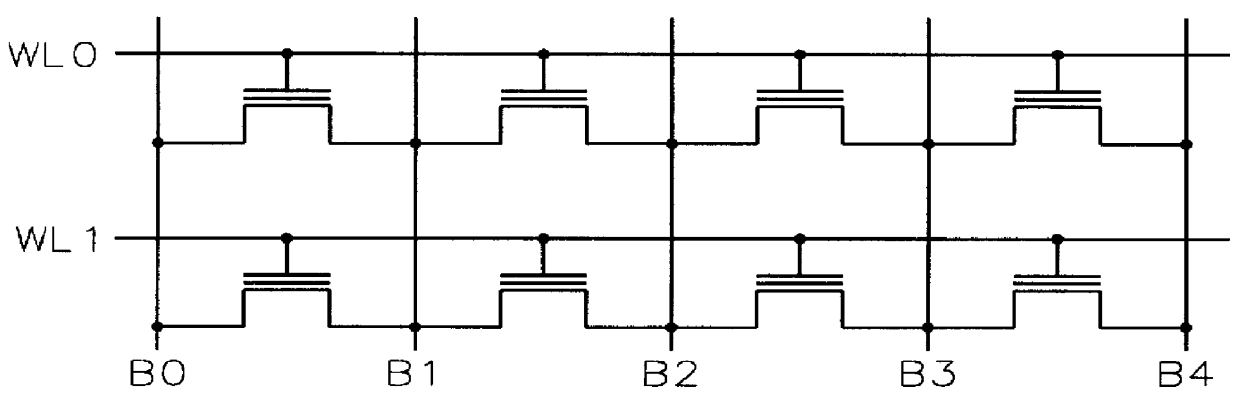

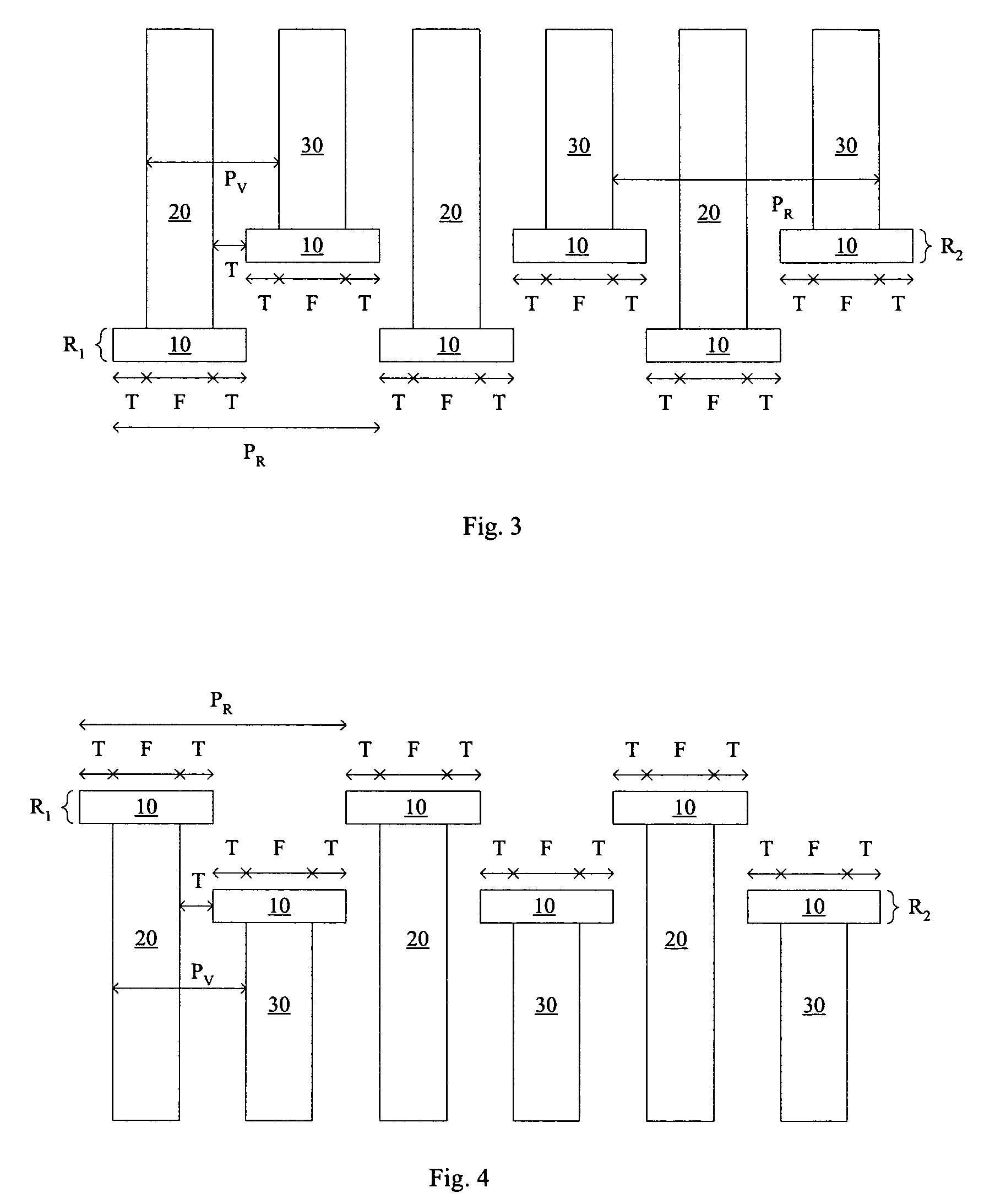

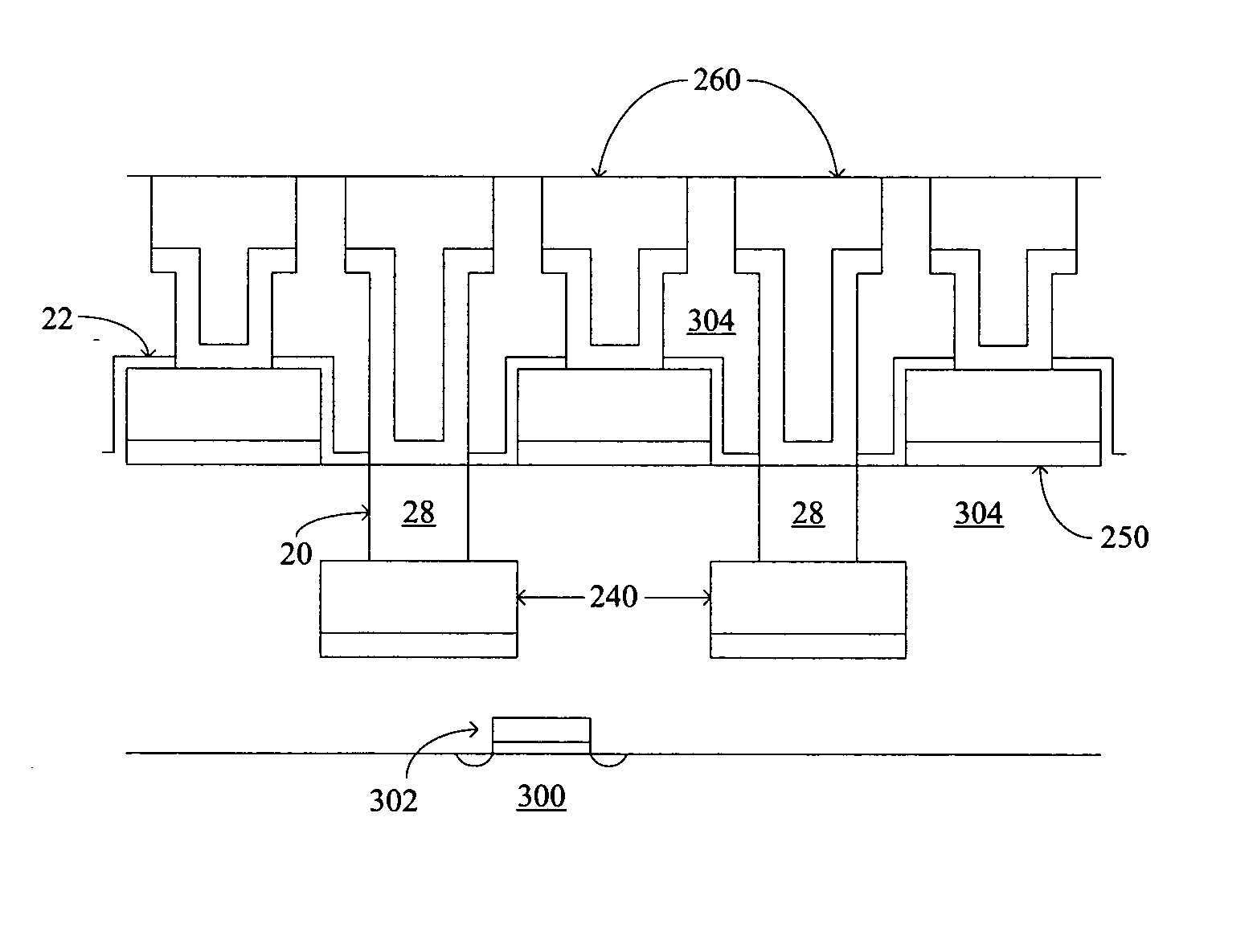

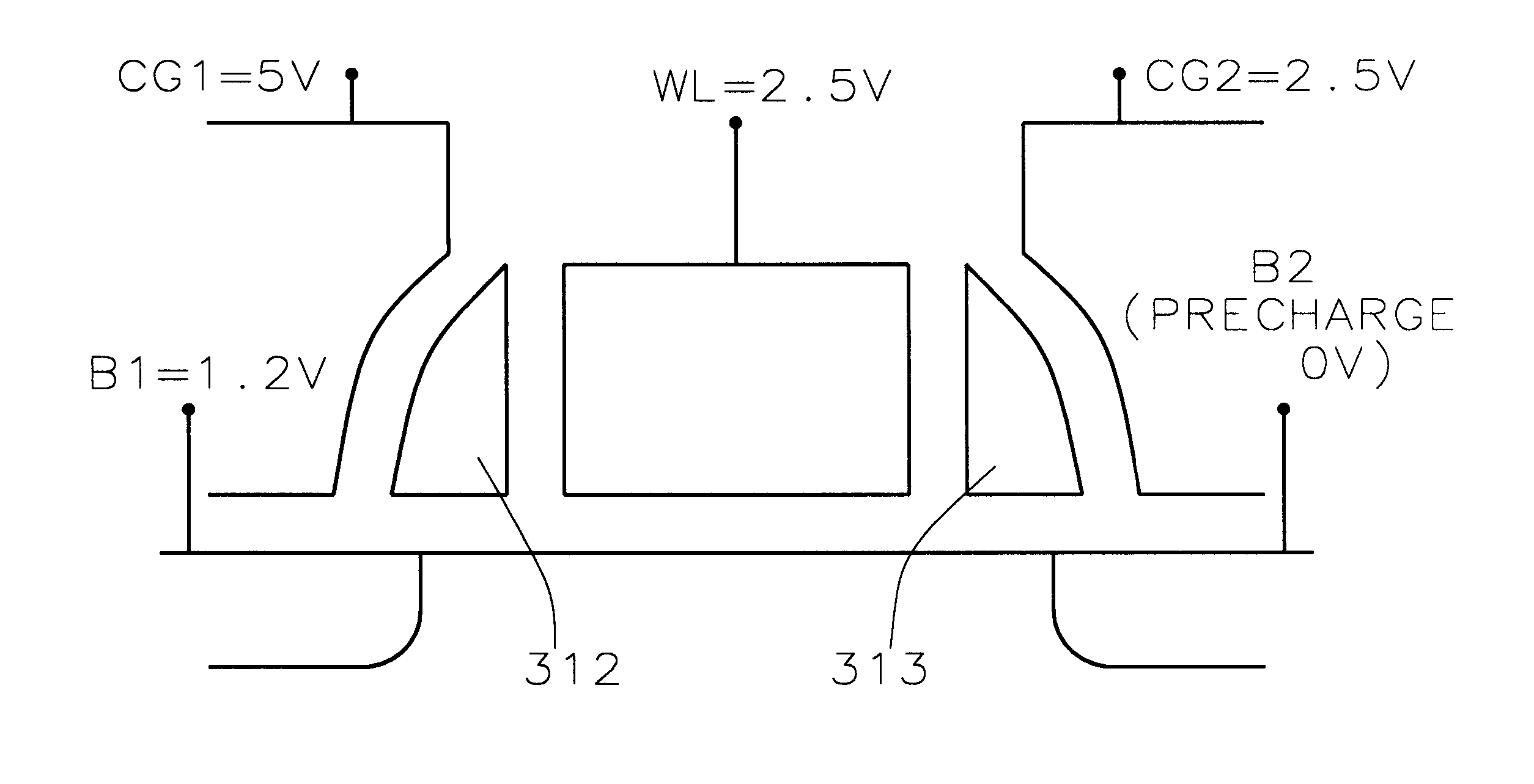

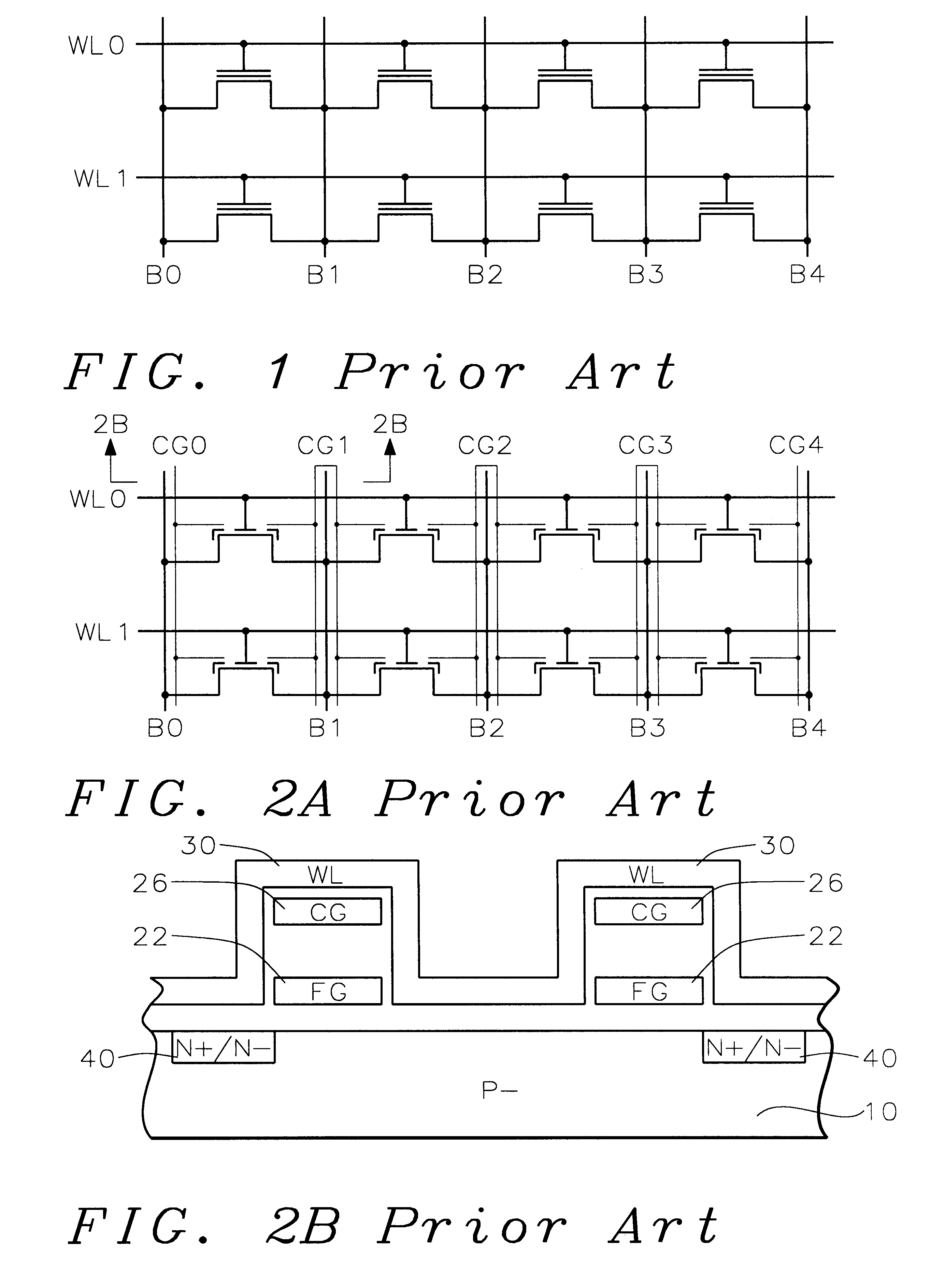

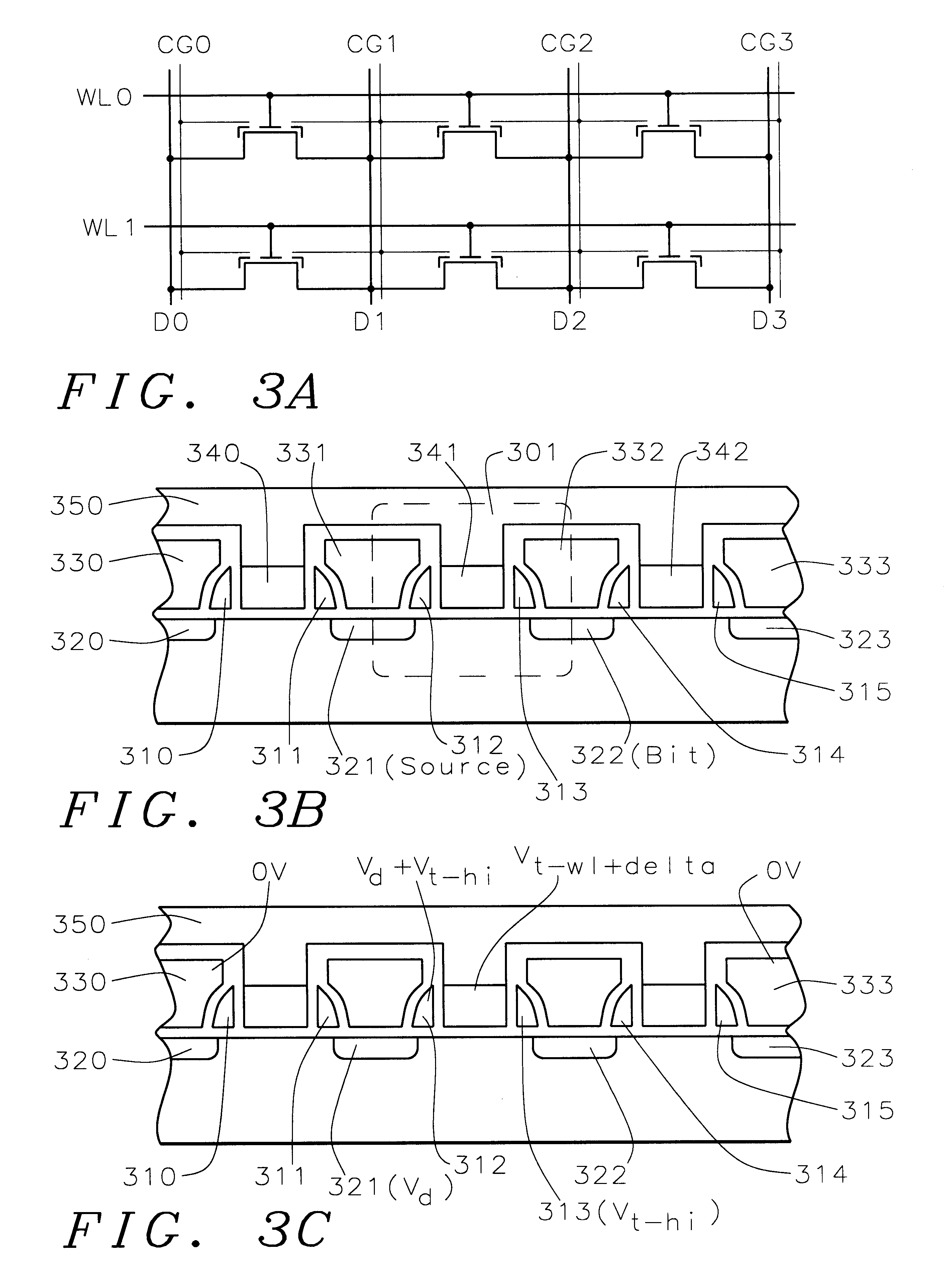

Process for making and programming and operating a dual-bit multi-level ballistic flash memory

An fast program, ultra-high density, dual-bit, multi-level flash memory process, which can be applied to a ballistic step split gate side wall transistor, or to a ballistic planar split gate side wall transistor, which enables program operation by low voltage requirement on the floating gate during program is described. Two side wall floating gates are paired with a single word line select gate, and word lines are arranged to be perpendicular both the bit lines and control gate lines. Two adjacent memory cells on the same word line do not require an isolation region. Also, the isolation region between adjacent memory cells sharing the same bitline is defined by the minimum lithography feature, utilizing a self align fill technique. Adjacent memory cells on the same word line share bitline diffusion as well as a third poly control gate. Control gates allow program and read access to the individual floating gate. In addition to the dual-bit nature of the cell, density can be even further improved by multi-level storage. In one embodiment, the dual multi-level structure is applied to the ballistic step split gate side wall transistor. In a second embodiment, the dual multi-level structure is applied to the ballistic planar split gate side wall transistor. Both types of ballistic transistors provide fast, low voltage programming. The control gates are used to override or suppress the various threshold voltages on associated floating gates, in order to program to and read from individual floating gates. The targets for this non-volatile memory array are to provide the capabilities of high speed, low voltage programming (band width) and high density storage.

Owner:HALO LSI DESIGN & DEVICE TECH

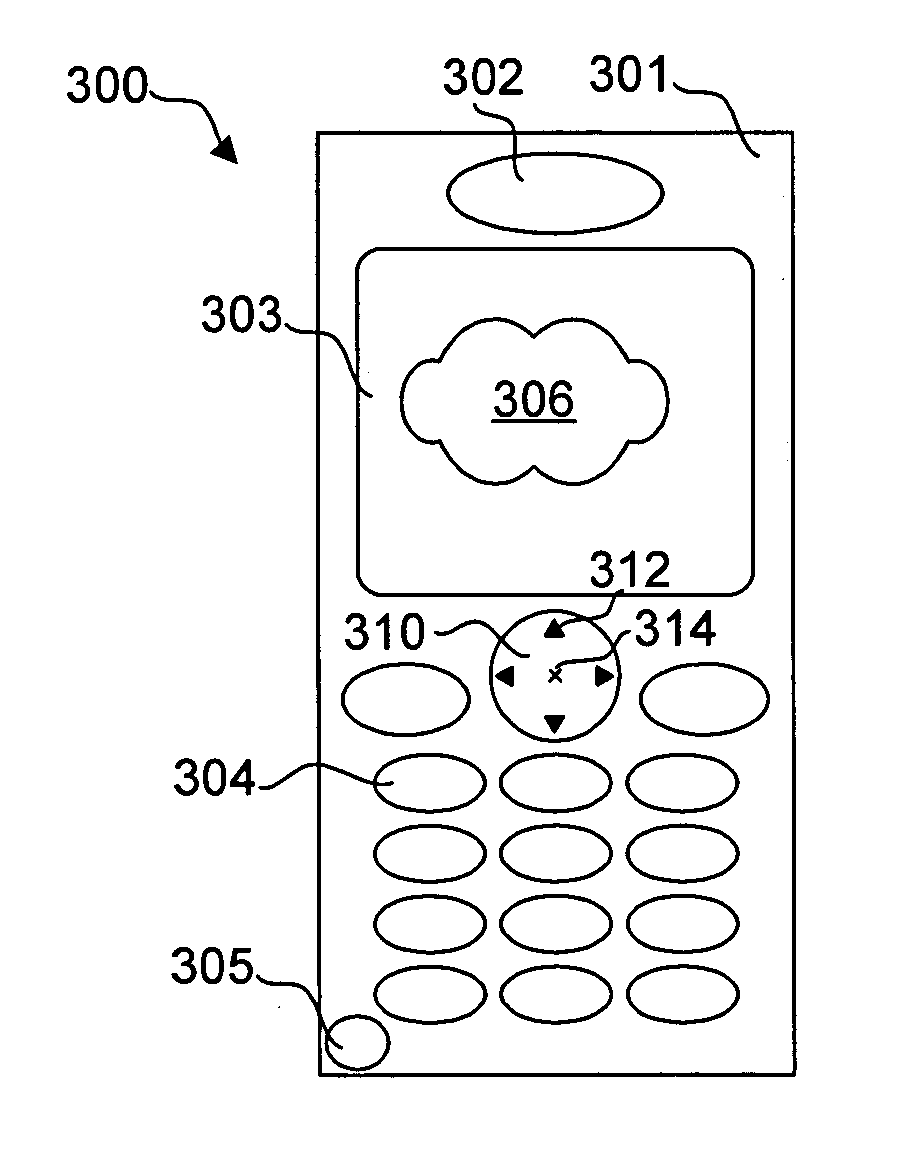

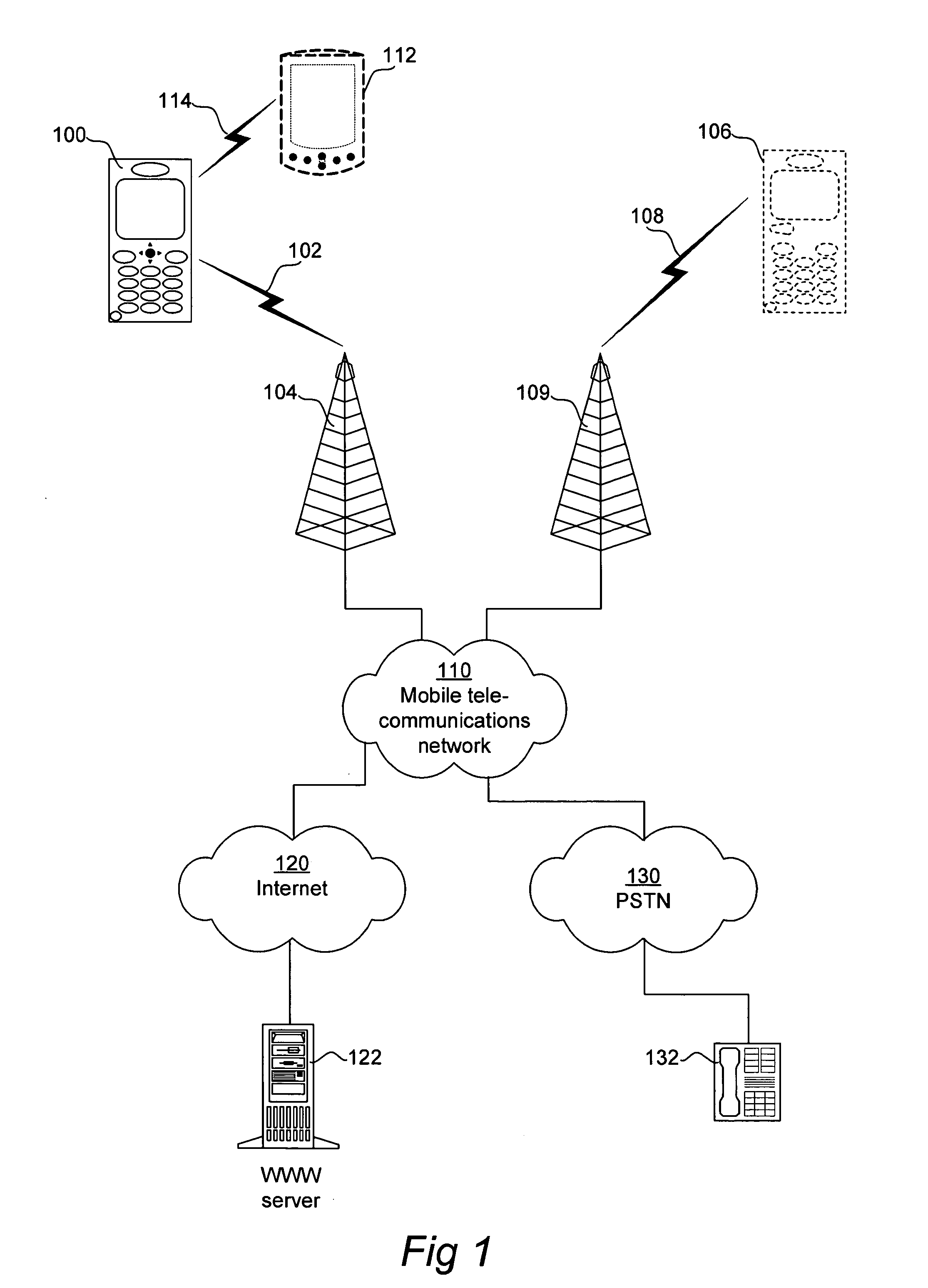

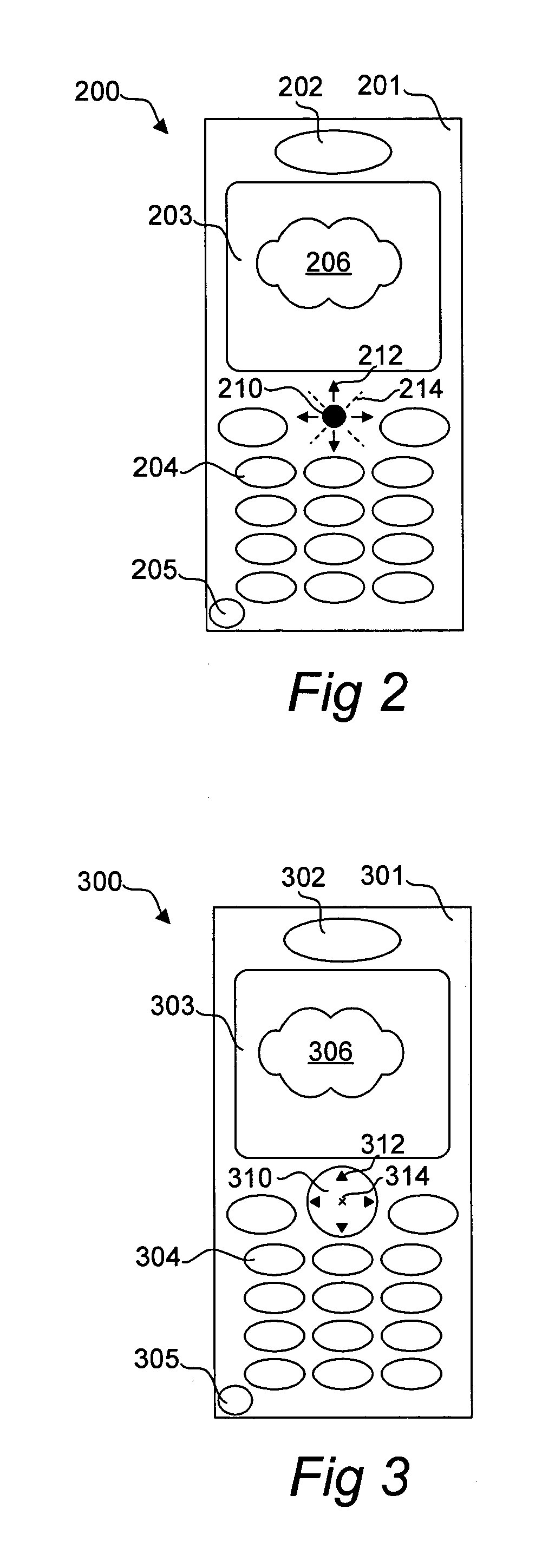

Mobile communications terminal and method therefore

InactiveUS20060271867A1Easy to navigateLess tiredSubstation equipmentProgram controlGraphicsLevel structure

A graphical user interface for an electronic apparatus such as a mobile terminal is presented. The graphical user interface gives a user access to a multi-level structure of selectable user interface items. The graphical user interface involves, on a display of the electronic apparatus, a focused region, an unfocused region and a descriptor region. The focused region presents a first plurality of user interface items belonging to a current level in said multi-level structure. The focused region has a focus area for focusing on a desired user interface item in response to user input on an input device of the electronic apparatus. The unfocused region presents a second plurality of user interface items belonging to at least one level superior to the current level in the multi-level structure. The descriptor region presents descriptive information about a currently focused user interface item in the focus area.

Owner:NOKIA CORP

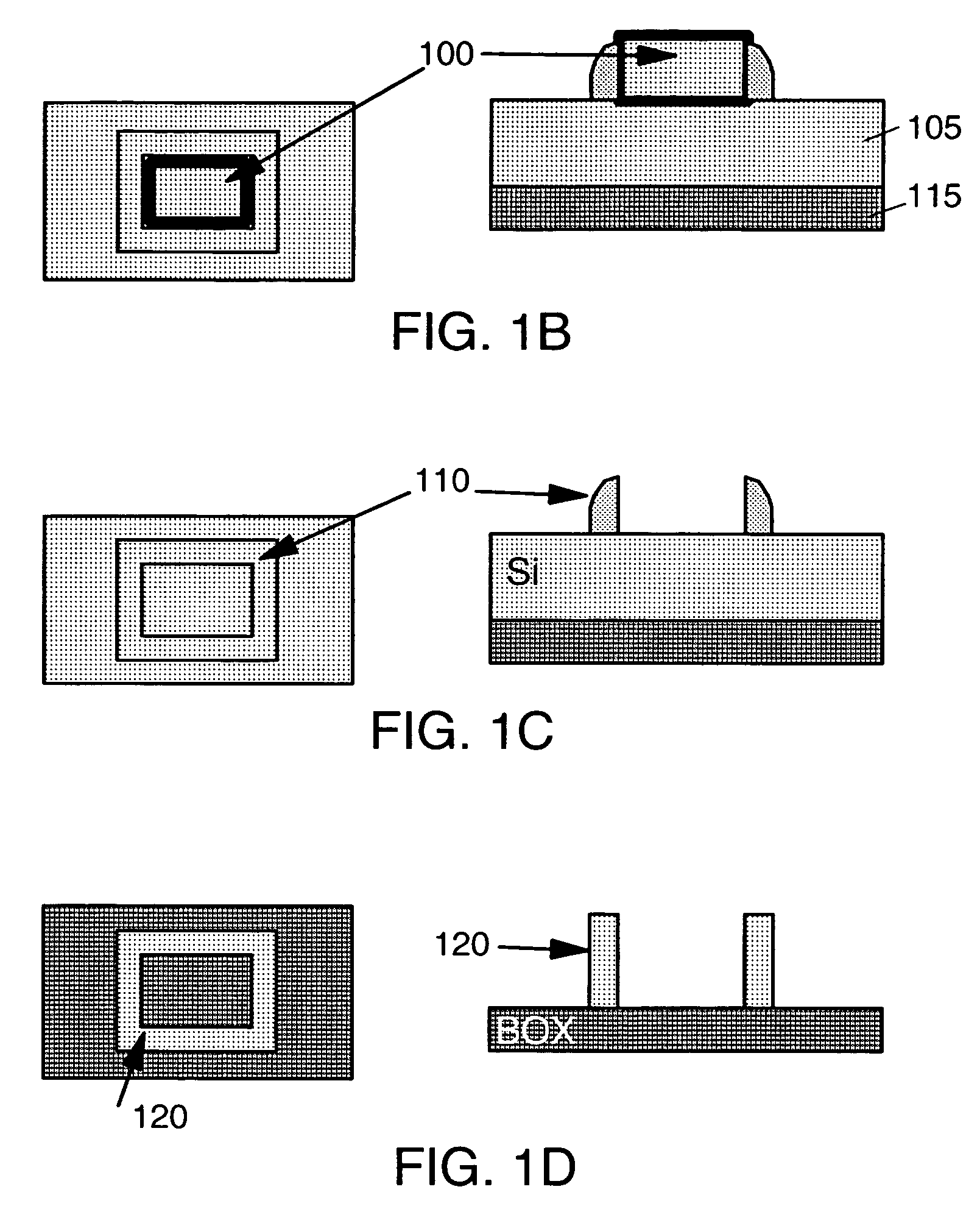

High density contact to relaxed geometry layers

ActiveUS7474000B2Semiconductor/solid-state device detailsSolid-state devicesLevel structureHigh density

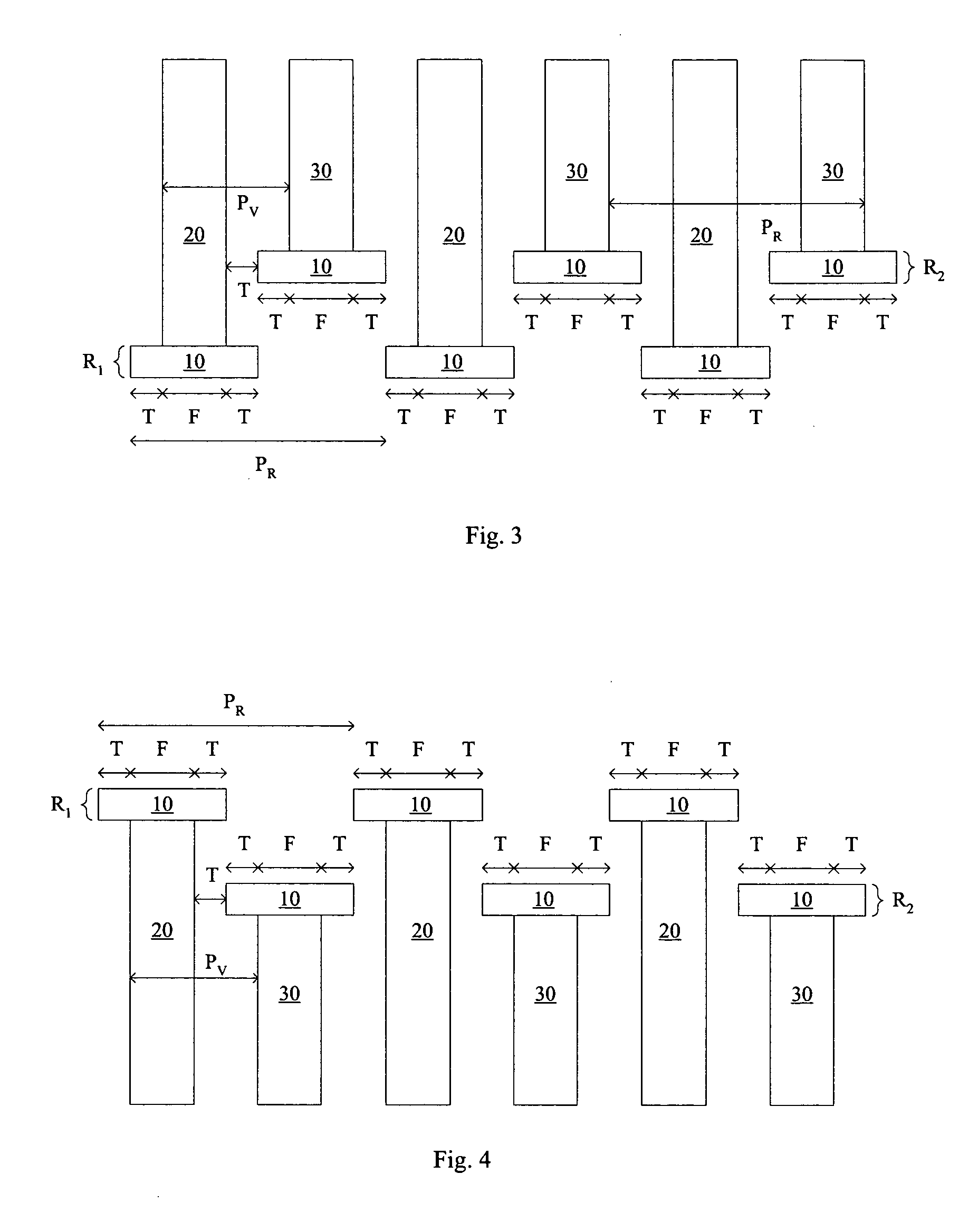

The present invention provides for a via and staggered routing level structure. Vertically overlapping vias connect to two or more routing levels formed at different heights. The routing levels are either both formed above or both formed below the vias, and all are formed above a semiconductor substrate wafer. In this way vias can be formed having a pitch smaller than the pitch of either the first routing level or the second routing level, saving space.

Owner:SANDISK TECH LLC

Detecting long latency pipeline stalls for thread switching

InactiveUS6016542AGeneral purpose stored program computerConcurrent instruction executionLong latencyLevel structure

An apparatus is provided that operates in conjunction with a processor having registers and associated caches and a memory. A load management module monitors loads that return data to the registers, including bus requests generated in response to loads that miss in one or more of the caches. A cache miss register includes entries, each of which is associated with one of the registers. A mapping module maps a bus request to a register and sets a bit in a cache miss register entry associated with the register when the bus request is directed to a higher level structure in the memory system.

Owner:INTEL CORP

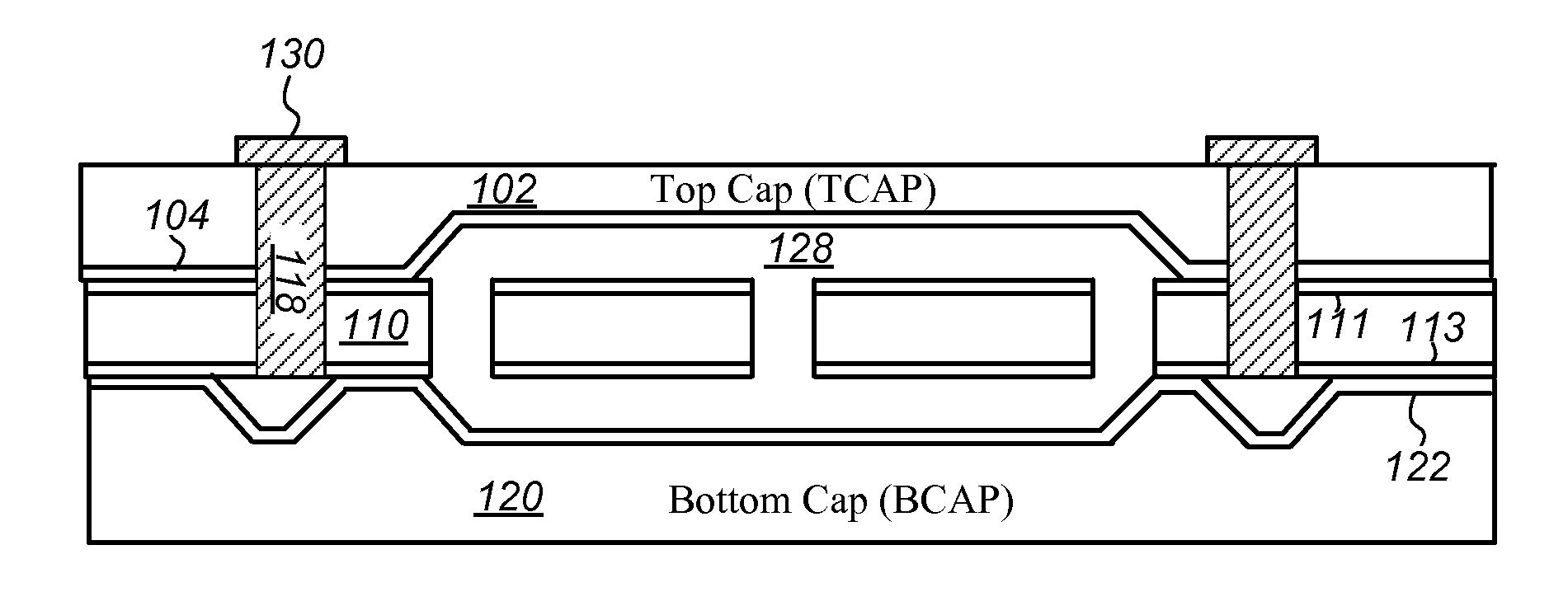

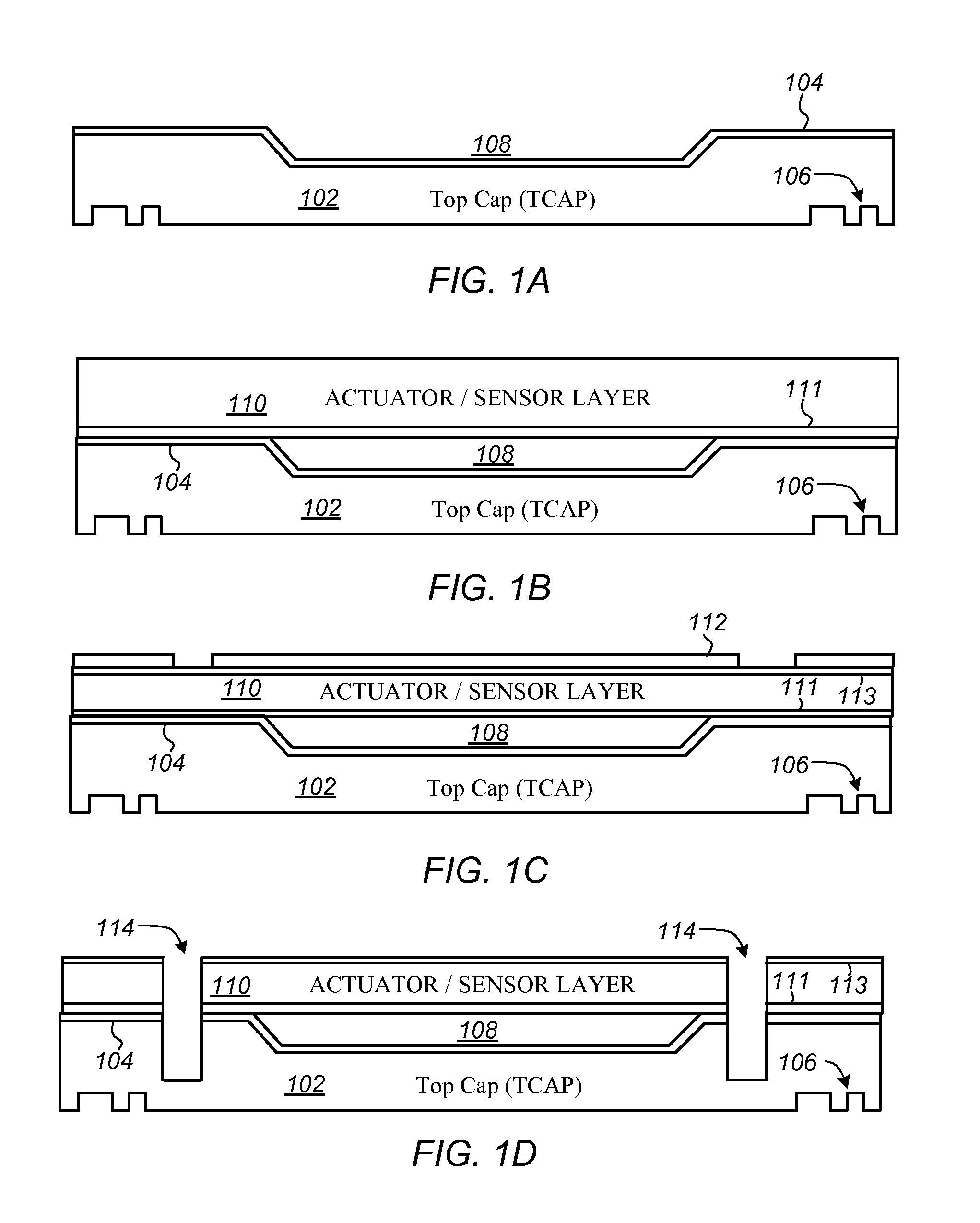

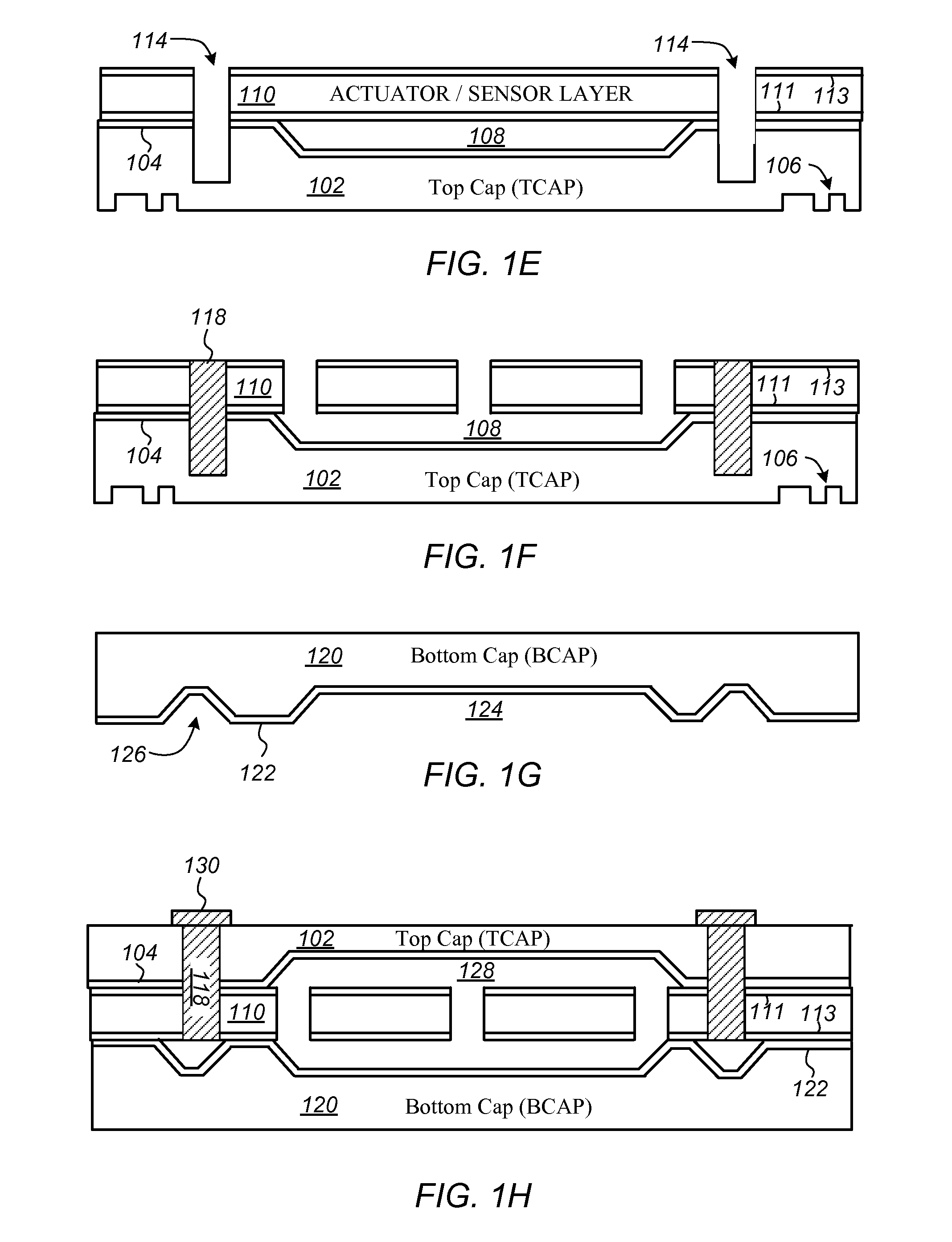

Wafer Level Structures and Methods for Fabricating and Packaging MEMS

ActiveUS20120142144A1Solid-state devicesSemiconductor/solid-state device manufacturingLevel structureHermetic seal

Methods of fabricating a Micro-Electromechanical System (MEMS) in a hermetically sealed cavity formed at a substrate level are provided. Generally, the method comprises: (i) forming a number of first open cavities in a surface of a first substrate and a number of second open cavities in a surface of a second substrate corresponding to the first open cavities; (ii) forming an actuator / sensor layer including a number of MEMS devices with electrically conductive regions therein; (iii) bonding the first substrate and the second substrate to the actuator / sensor layer so that at least one of the number of the first and second open cavities align with at least one of the number of MEMS devices to form a sealed cavity around the MEMS; and (iv) electrically connecting the electrically conductive regions of the MEMS device to a pad outside of the sealed cavity through an electrical interconnect. Other embodiments are also described.

Owner:INTEGRATED BIOSENSING TECH

Multistack 3-dimensional high density semiconductor device and method for fabrication

InactiveUS6291858B1Function increaseHigh densitySemiconductor/solid-state device detailsSolid-state devicesLevel structureHigh density

A multistack 3-D semiconductor structure comprising a first level structure comprising a first semiconductor substrate and first active devices; and a second level structure comprising a SOI semiconductor structure bonded to the first level structure and further comprising second active devices; and wherein the first active devices are more heat tolerant than the second active devices is provided along with a method for its fabrication.

Owner:IBM CORP

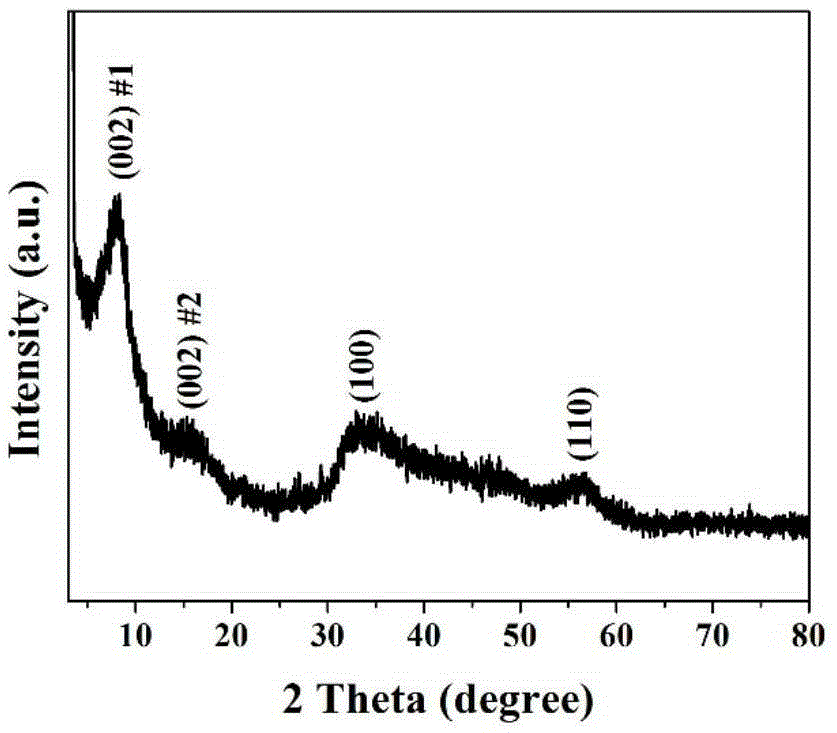

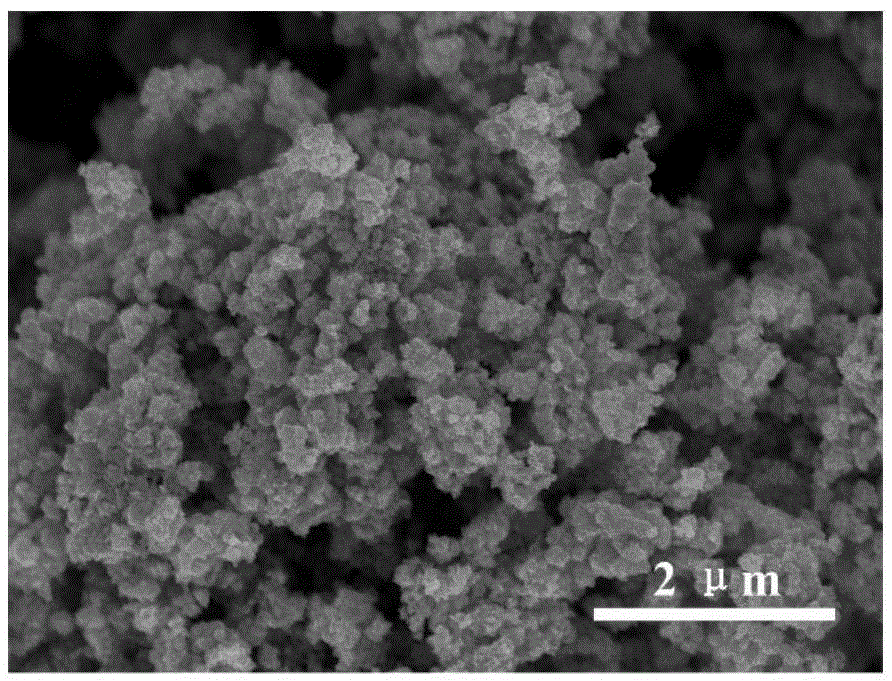

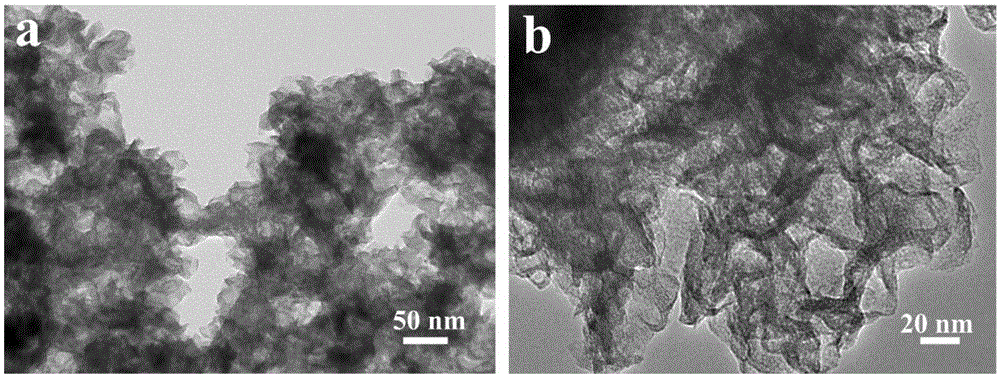

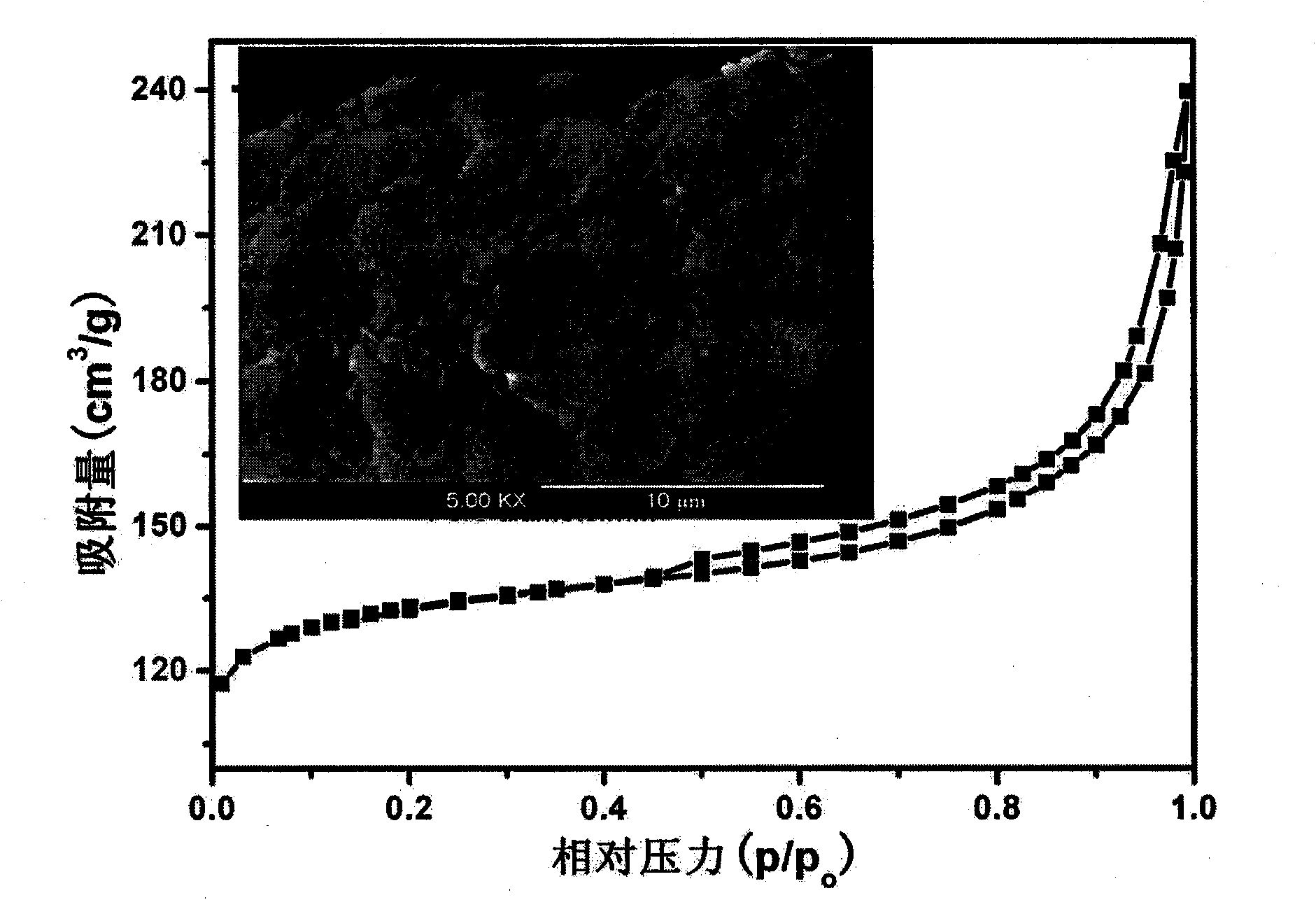

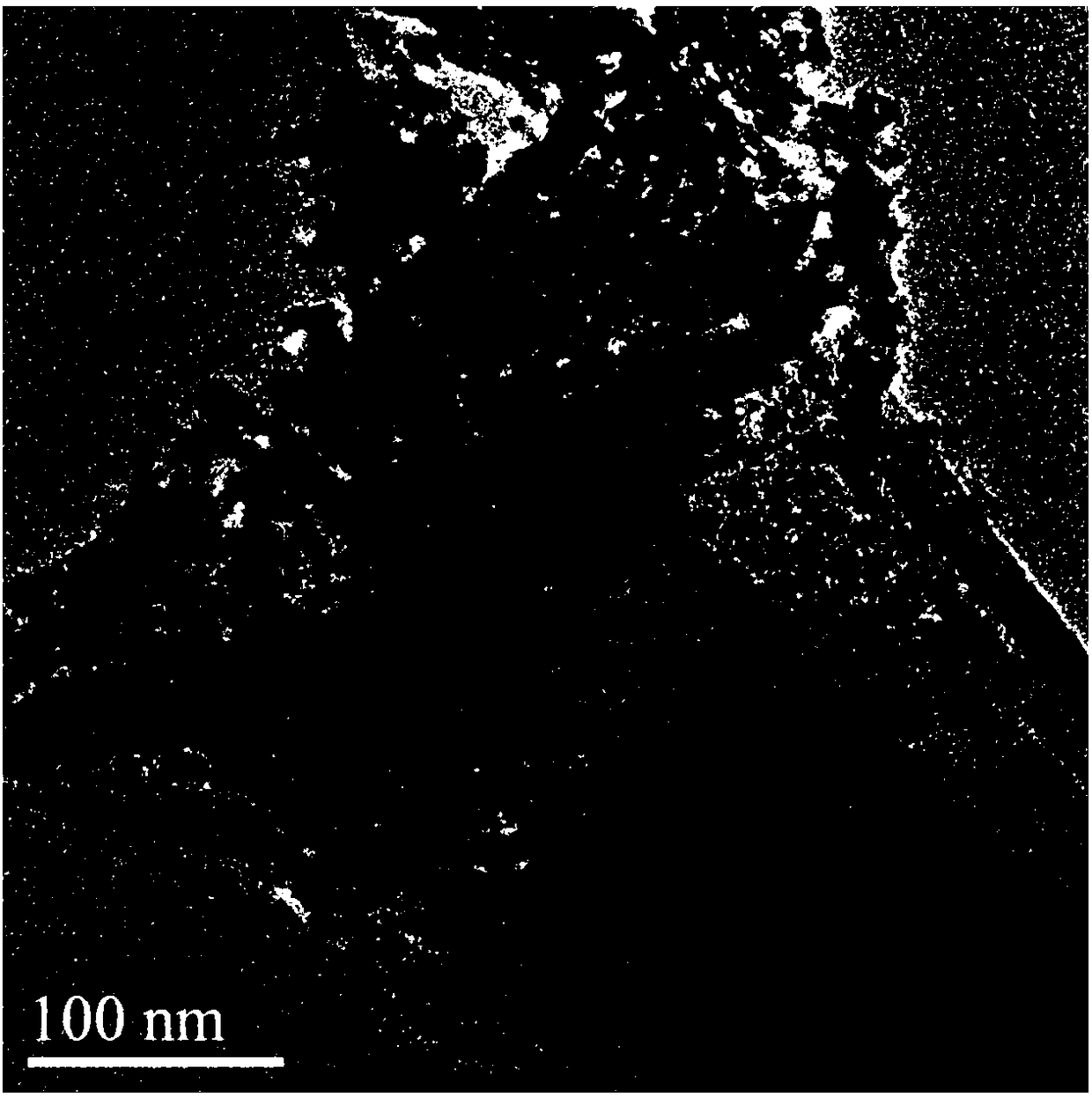

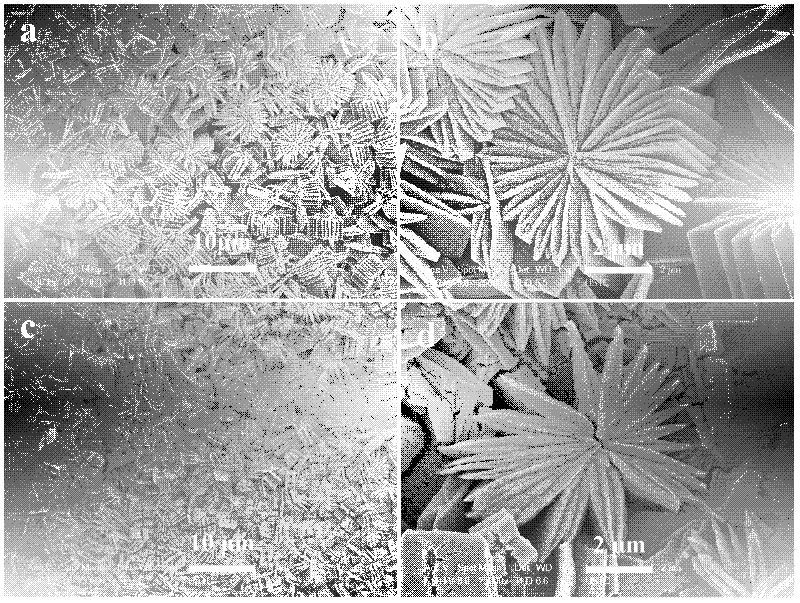

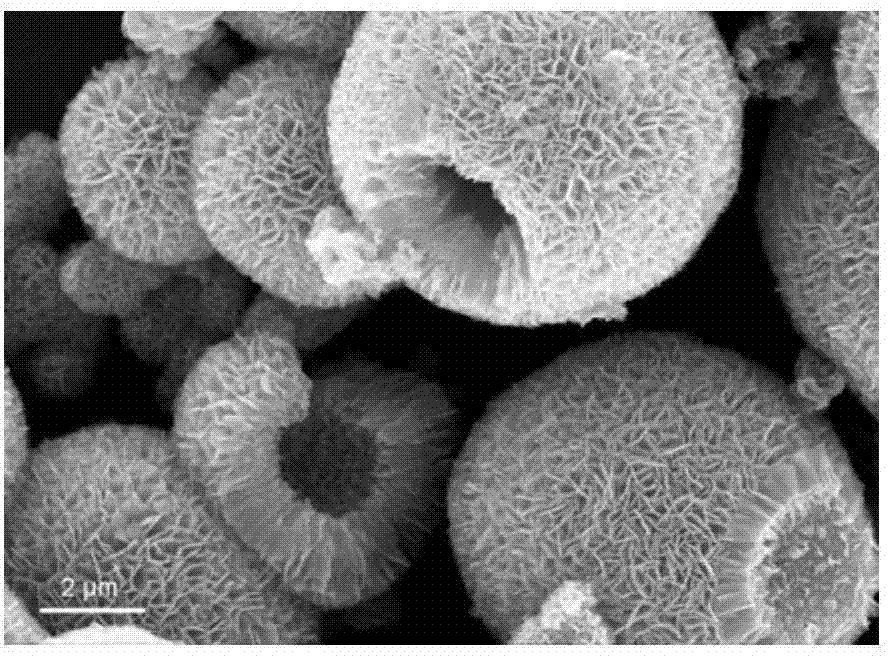

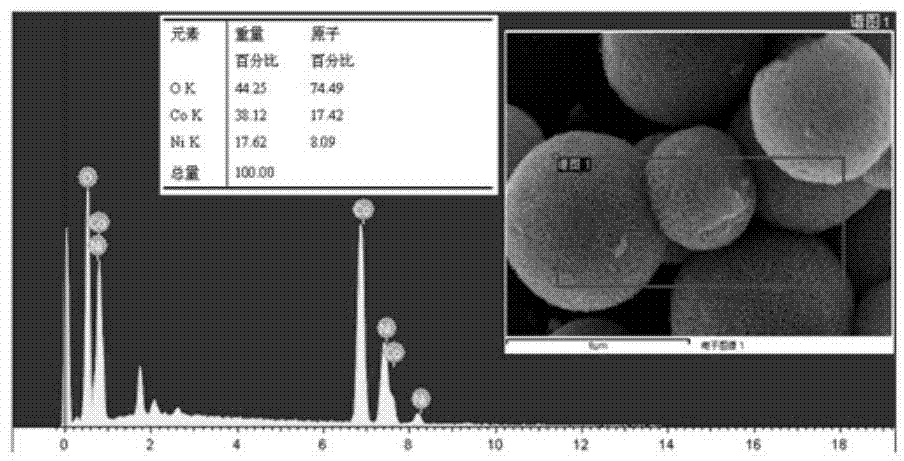

Cobalt-intercalated molybdenum sulfide secondary battery material and preparation method and application thereof

InactiveCN106611837AAvoid reunionAvoid stackingMaterial nanotechnologyHybrid capacitor electrodesLevel structureChemical solution

The invention relates to a cobalt-intercalated molybdenum sulfide secondary battery material and a preparation method and an application thereof. A three-dimensional cobalt-intercalated molybdenum sulfide multi-level structure is prepared by adopting a chemical solution method; firstly, a cobalt salt, a molybdenum salt and a sulfur source are dispersed into a solvent to prepare a reaction liquid; and then the prepared reaction liquid is subjected to solvent thermal treatment to obtain the three-dimensional cobalt-uniformly-intercalated molybdenum sulfide multi-level structure which is self-assembled by graphene-like ultra-thin nanosheets, wherein the size of the multi-level structure is about 100nm. The invention also discloses a preparation method for the multi-level structure. The secondary battery material prepared by the method is stable in nanomaterial performance, and long in cycle life when the secondary battery material is used as a negative electrode material of a lithium ion battery and an electrode material of a supercapacitor.

Owner:SHANGHAI JIAO TONG UNIV

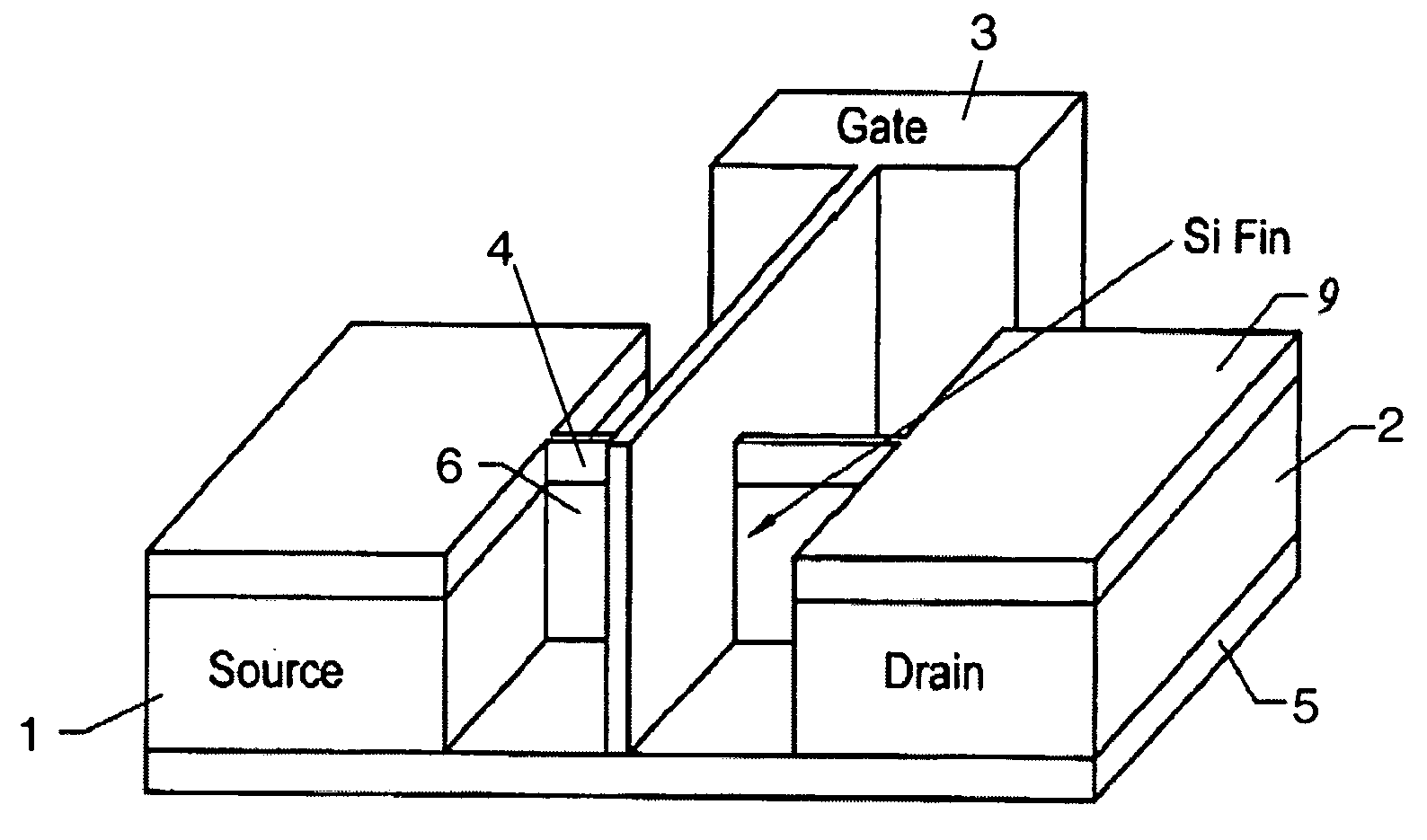

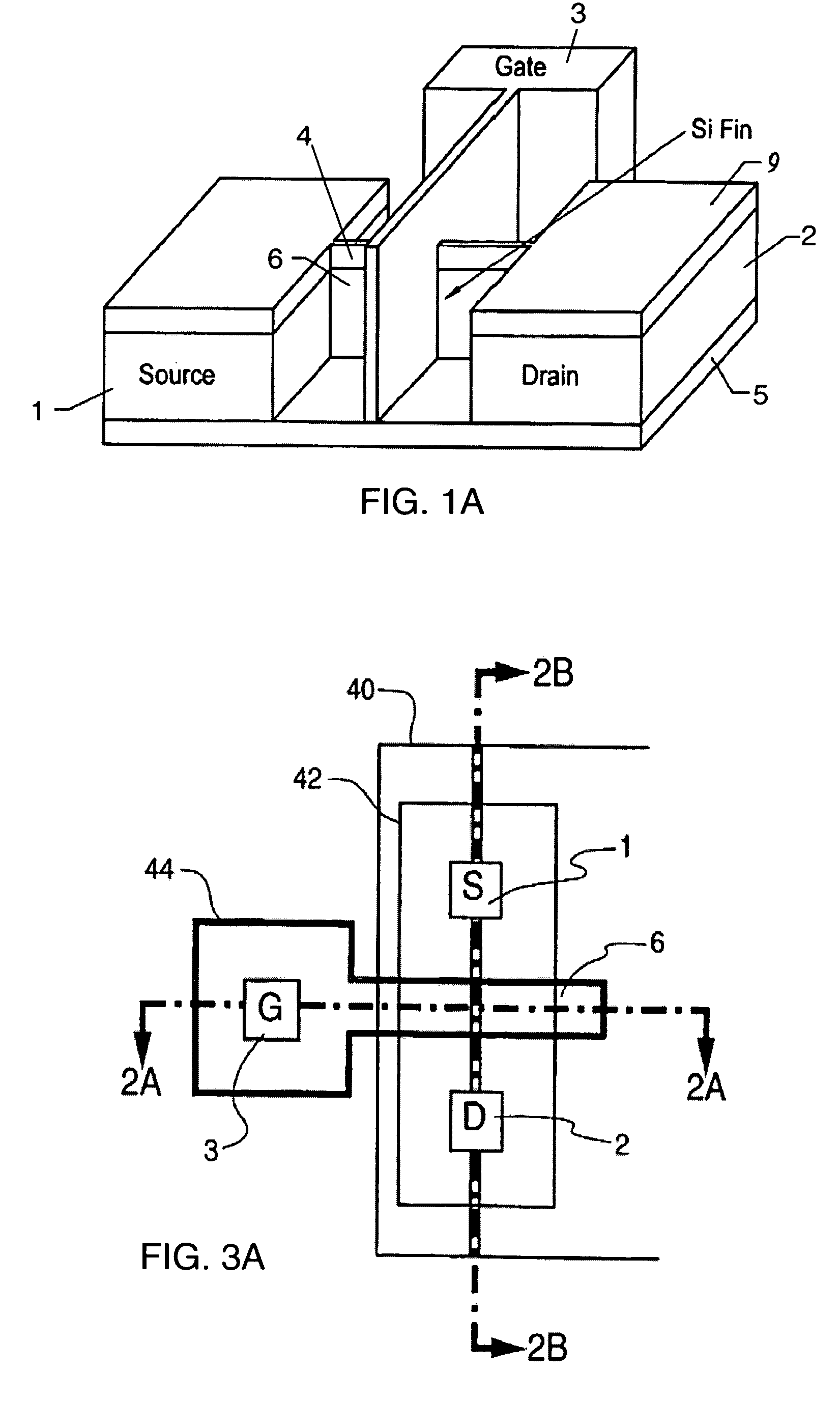

Method and device for automated layer generation for double-gate FinFET designs

InactiveUS20050136582A1Reduce effortEnhance layeringTransistorSolid-state devicesLevel structureEngineering

In a FinFET integrated circuit design, a combined cell structure contains two single cell structures at a first design hierarchy having fin shapes, the cell structures are placed adjacent to each other. The combined fin shapes of the two single cell structures at the first design hierarchy lead to a violation of a design rule related to fin topology in the overlapping region. A fin generation tool thus decides not to place the fins in the first design hierarchy. The fin generation is delegated another design hierarchy resulting in the generation of a single combined fin for both single cells.

Owner:IBM CORP

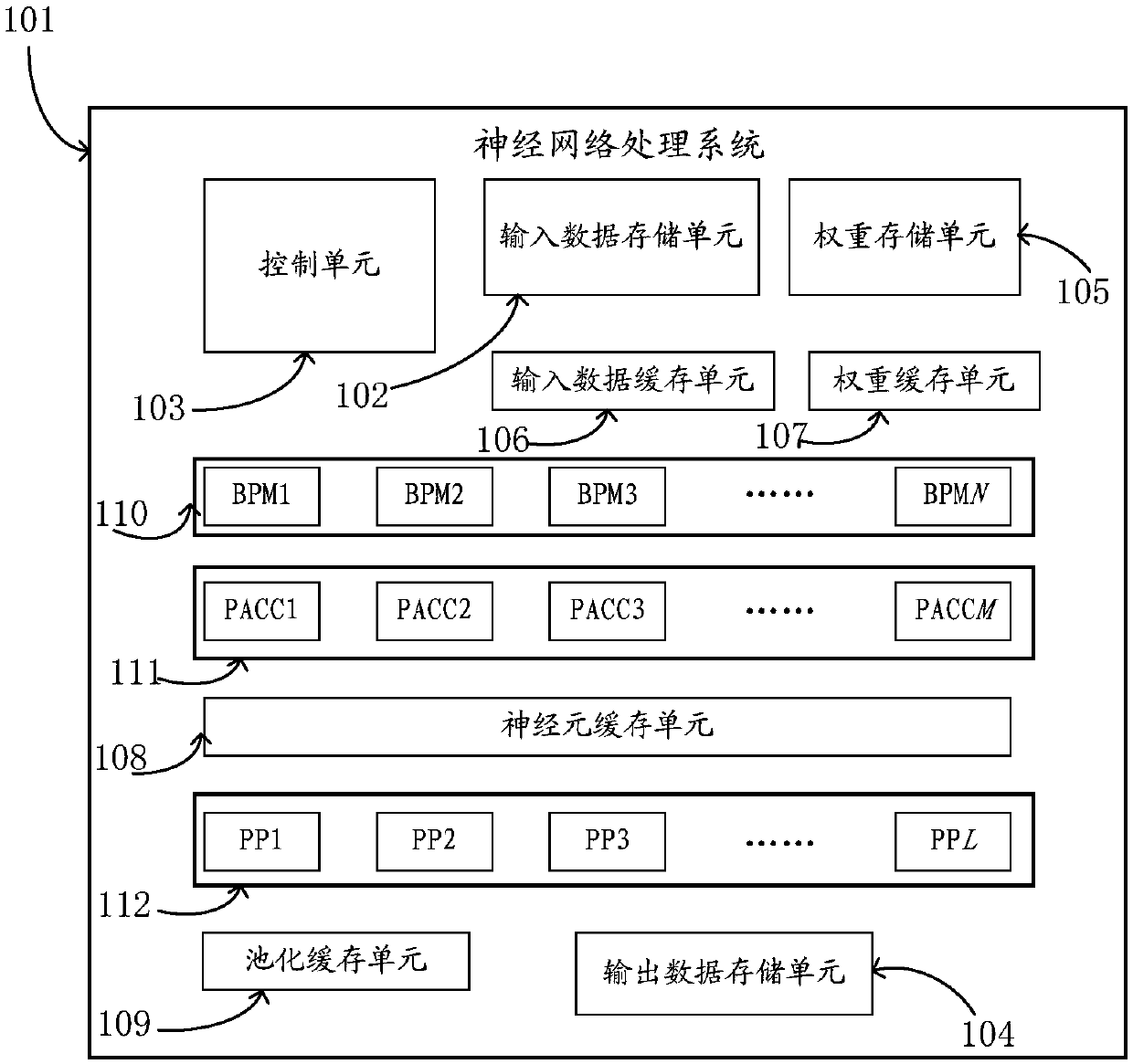

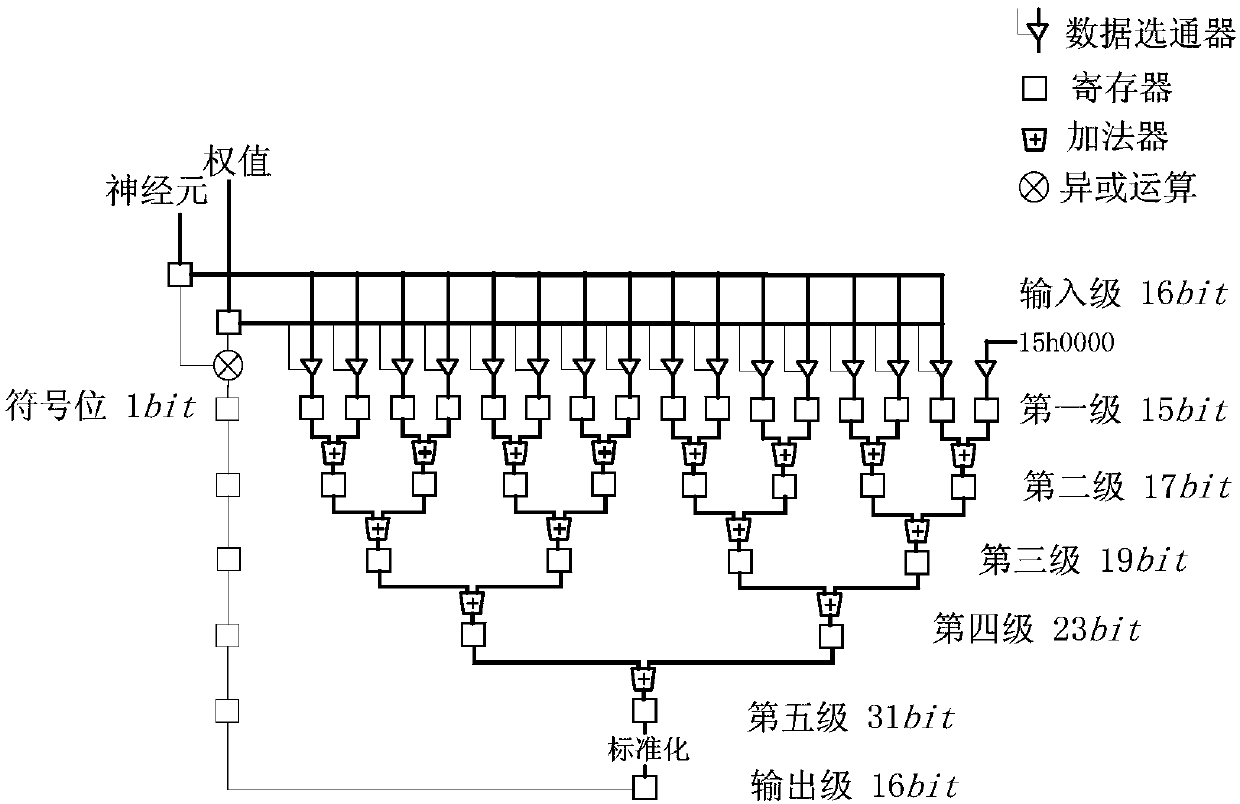

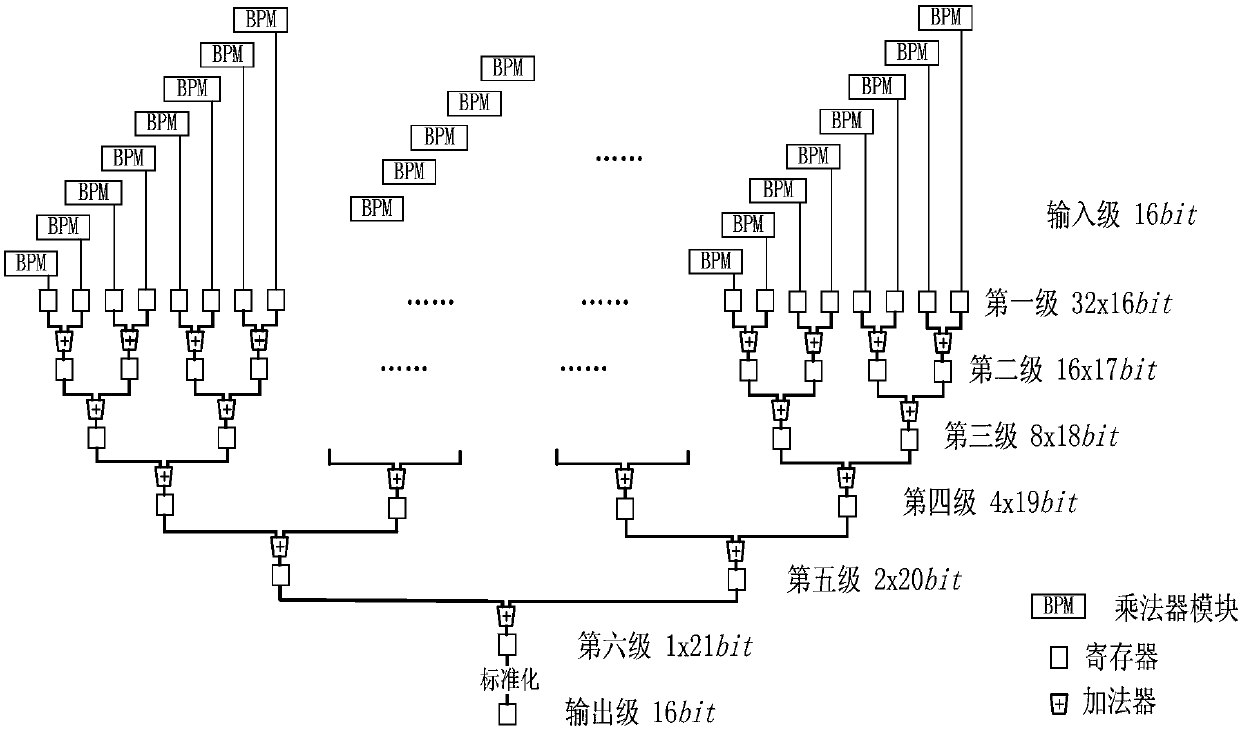

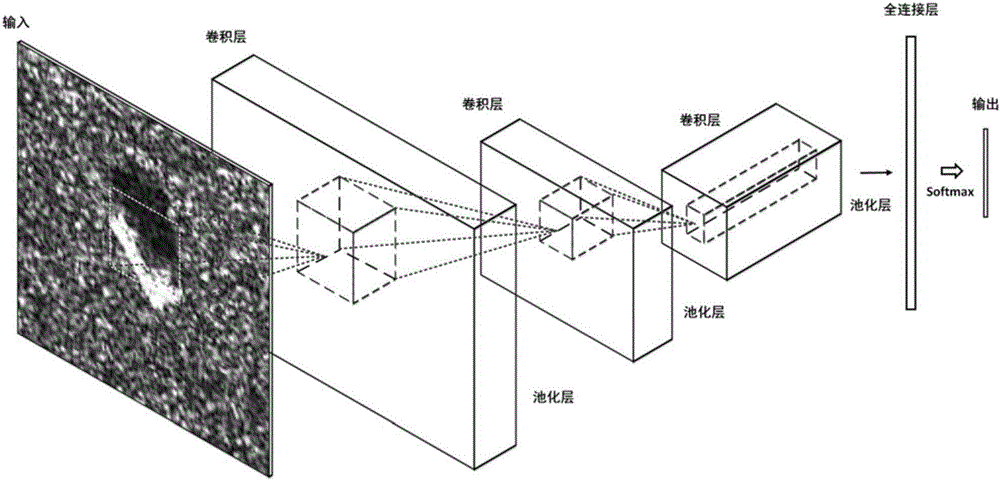

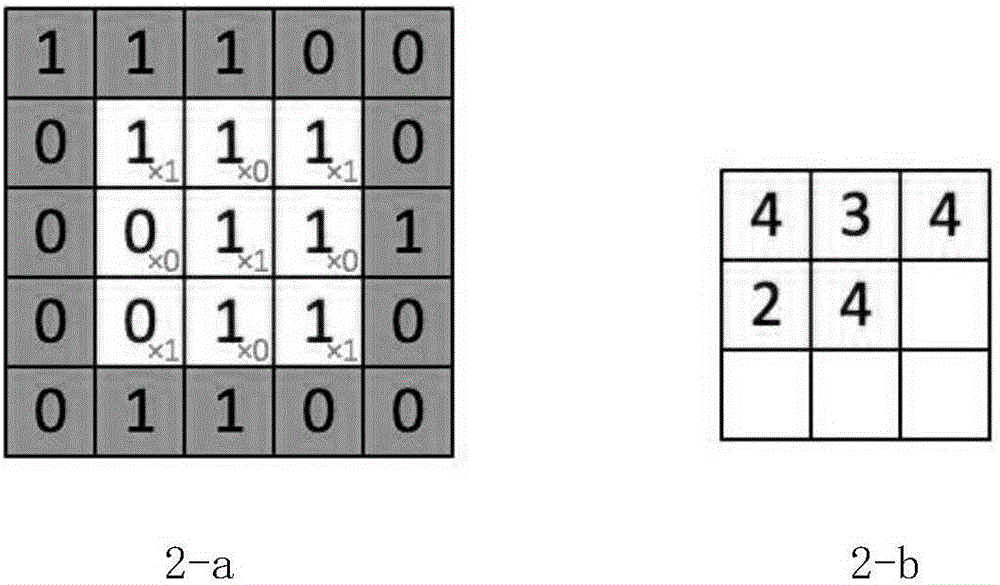

Pipeline-based neural network processing system and processing method

ActiveCN107862374AProcessing speedImprove computing efficiencyNeural architecturesLevel structureResource utilization

The present invention provides a neural network processing system. The processing system comprises a multiplier module, wherein the multiplier module contains a multi-level structure constituting a pipeline, and is configured to perform a multiplication operation of to-be-calculated neurons and weights in a neural network, and each level structure of the multiplier module completes the sub-operation of the multiplication of the neuron and the weight; an accumulator module, wherein the accumulator module comprises a multi-level structure constituting the pipeline, and is configured to perform an accumulation operation on the multiplication result of the multiplier module to obtain the output neurons of the convolutional layer in the neural network, and each level structure of the accumulator module completes the sub-operations of the accumulation operation; a pooling unit, wherein the pooling unit is configured to perform the pooling processing on the output neurons of the convolutionallayer; and a control unit, wherein the control unit is configured to control the transfer of data in the neural network processing system. By using the neural network processing system of the presentinvention, resource utilization and the data processing speed can be improved.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

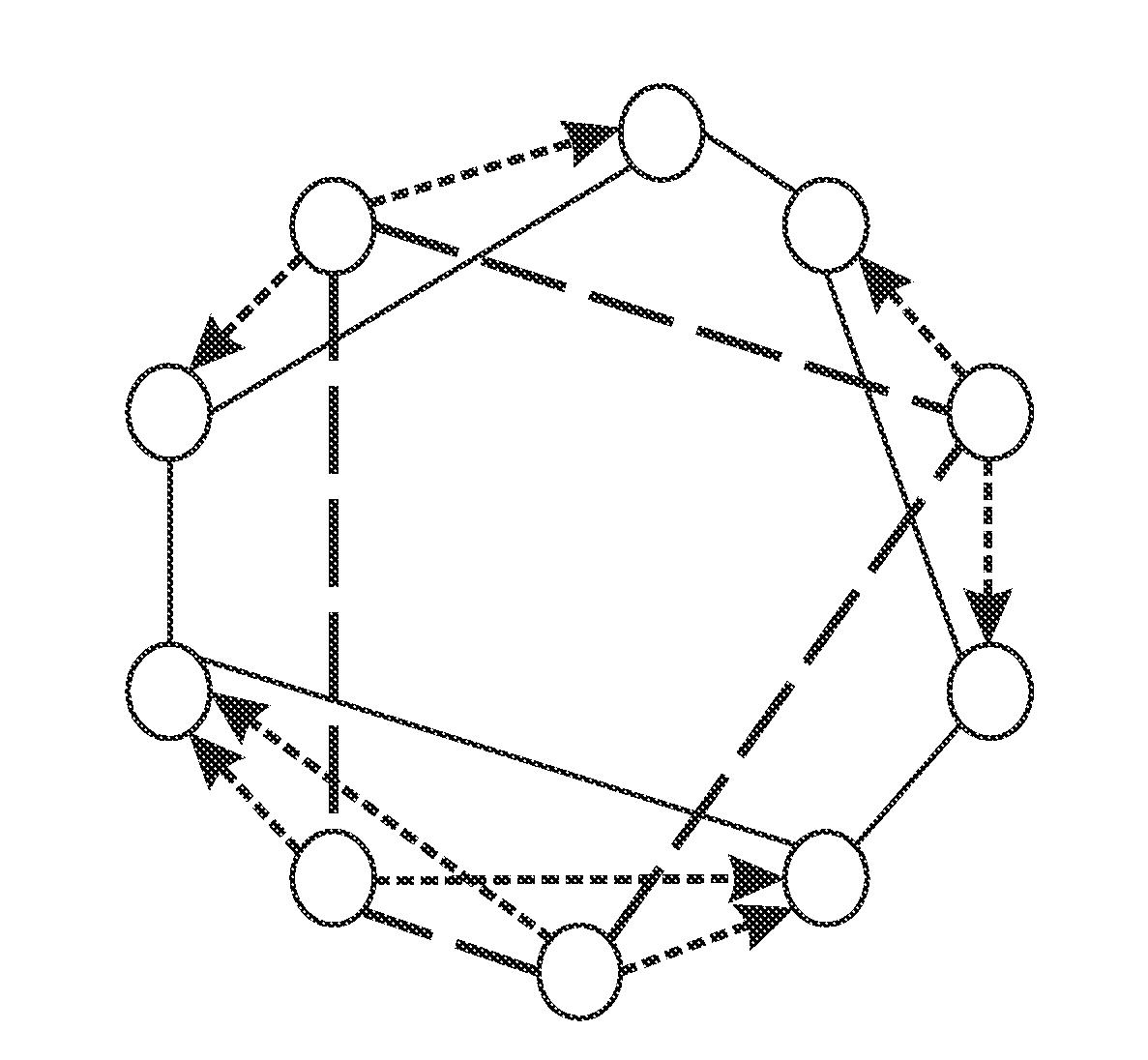

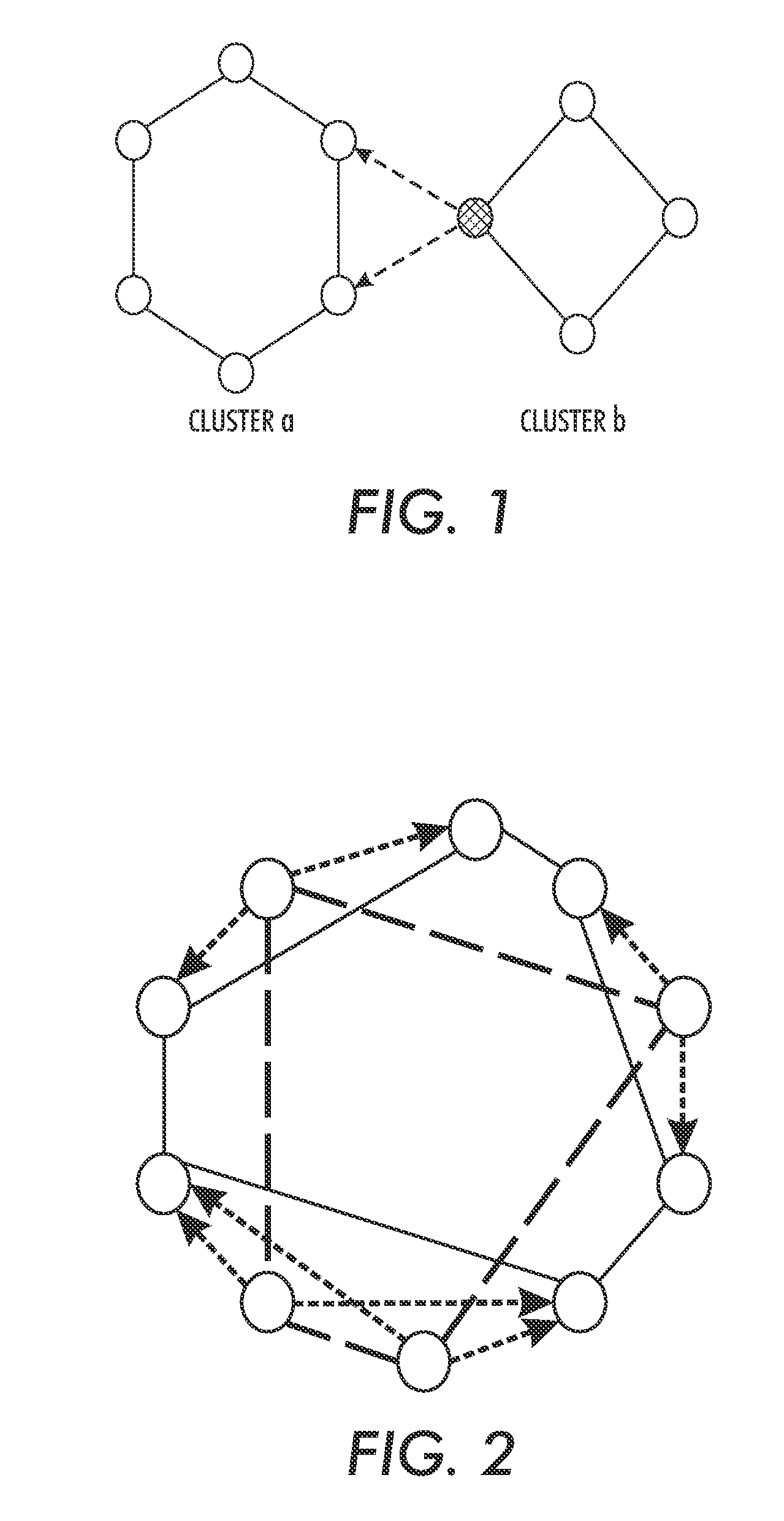

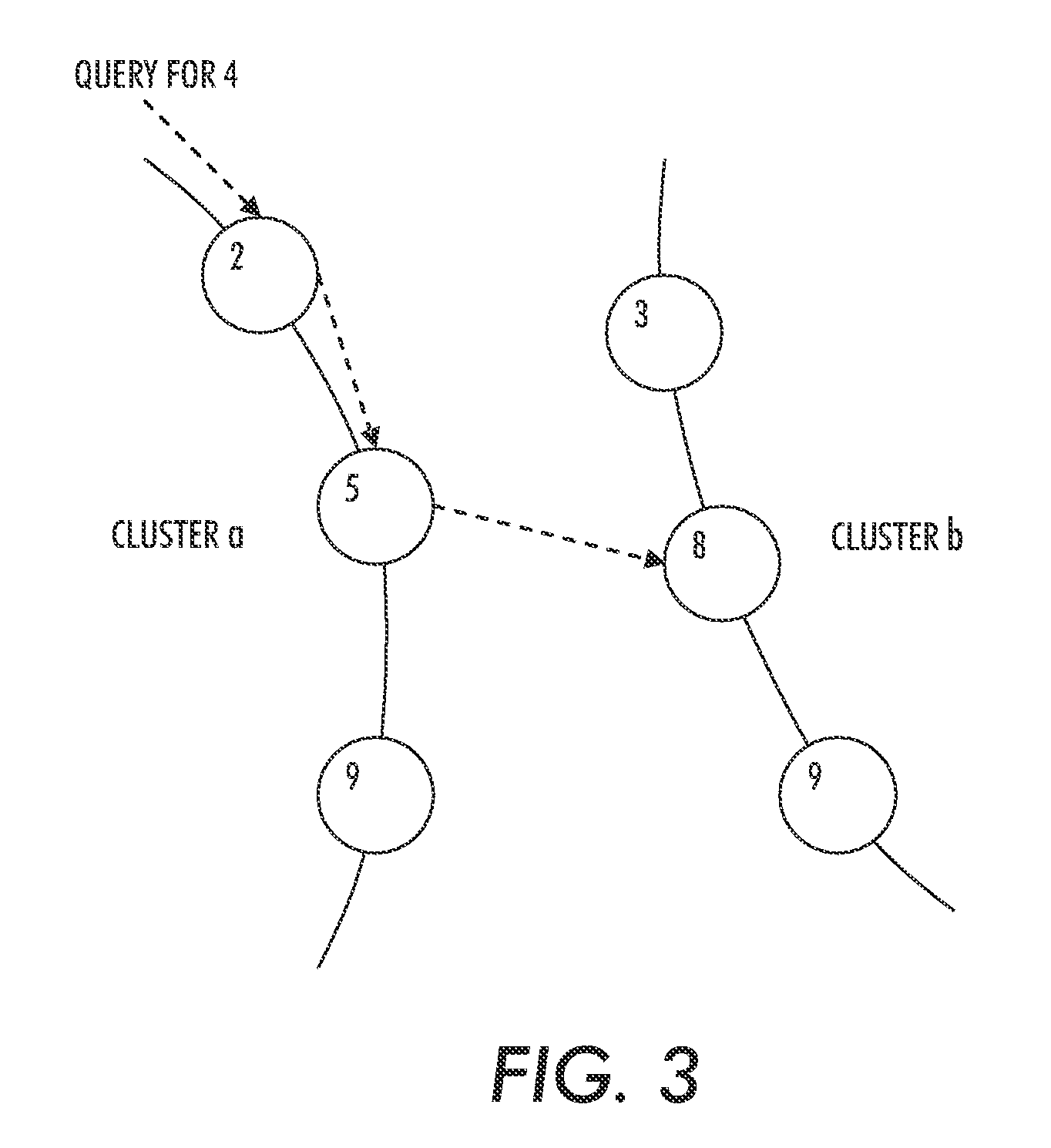

Two-level structured overlay design for cluster management in a peer-to-peer network

InactiveUS20080177767A1Multiple digital computer combinationsData switching networksFile replicationLevel structure

A method and system for designing file replication schemes in file sharing systems consider node storage constraints and node up / down statistics, file storage costs, and file transfer costs among the nodes, user request rates for the files, and user specified file availability requirements. Based on these considerations, a systematic method for designing file replication schemes can be implemented. The method first determines the number of copies of the files to be stored in the system to achieve the desired goal (e.g., to satisfy file availability requirements, or to maximize the system hit rate), and then selects the nodes at which to store the file copies to minimize the total expected cost. The file replication scheme for a peer-to-peer file sharing system in a distributed and adaptive manner can scale to a large number of nodes and files and can handle changes in the user request pattern over time.

Owner:XEROX CORP

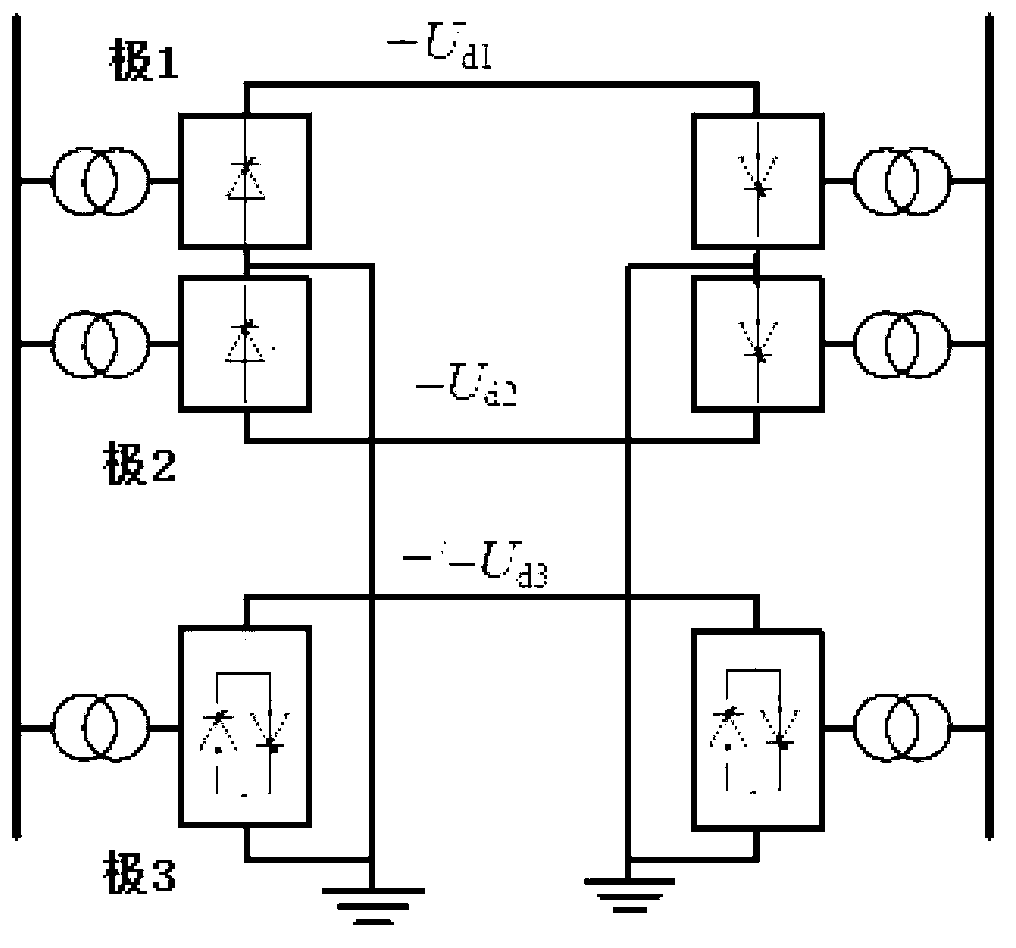

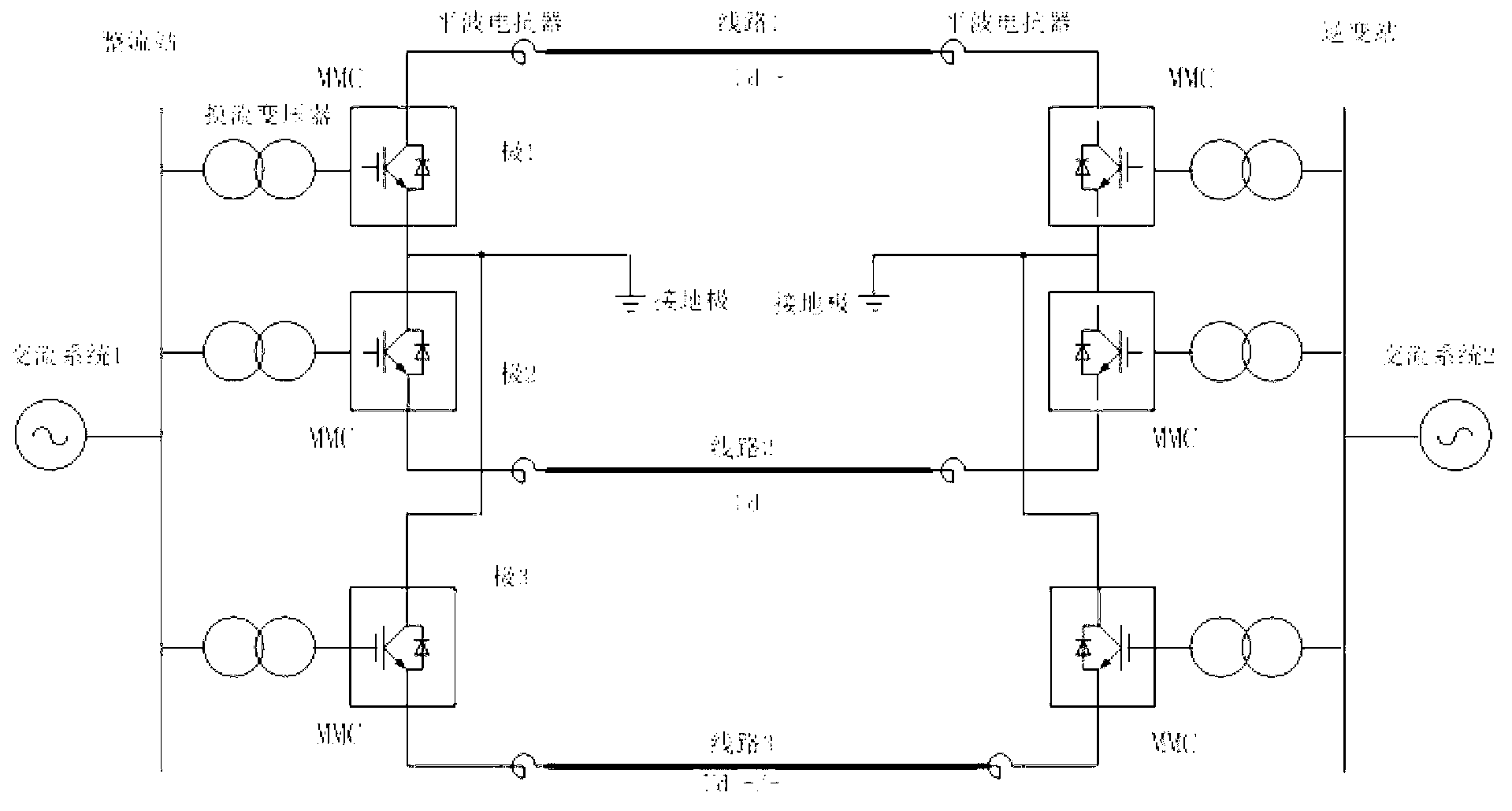

Tri-pole direct current transmission system topology structure based on modular multi-level converter (MMC)

ActiveCN103311947AMeet the needs of transformation into DC linesStable voltageElectric power transfer ac networkLevel structureTransformer

The invention discloses a tri-pole direct current transmission system topology structure based on an MMC. The tri-pole direct current transmission system topology structure is characterized in that direct current transmission is performed in a tri-pole connecting mode, and each pole comprises a rectification-side converter transformer, a rectification-side converter, a rectification-side smoothing reactor, a direct current transmission line, an inversion-side smoothing reactor, an inversion-side converter and an inversion-side converter transformer group. The rectification-side converters and the inversion-side converters are in modular multi-level structures, sub-modules of different amounts are connected in series and in parallel to be adapted to requirements for different voltage classes and currents, and three transmission lines used in a tri-pole direct current system are cables or overhead lines. The tri-pole direct current transmission system topology structure is high in reliability and capable of meeting the requirement for changing alternating current lines into direct current lines, phase change failures on the inversion side can be avoided under the condition that an alternating current system breaks down, voltages on two sides of the alternating current system can be stabilized, a alternating current filtering and reactive compensation device is not needed, and good application values are provided.

Owner:NR ELECTRIC CO LTD +1

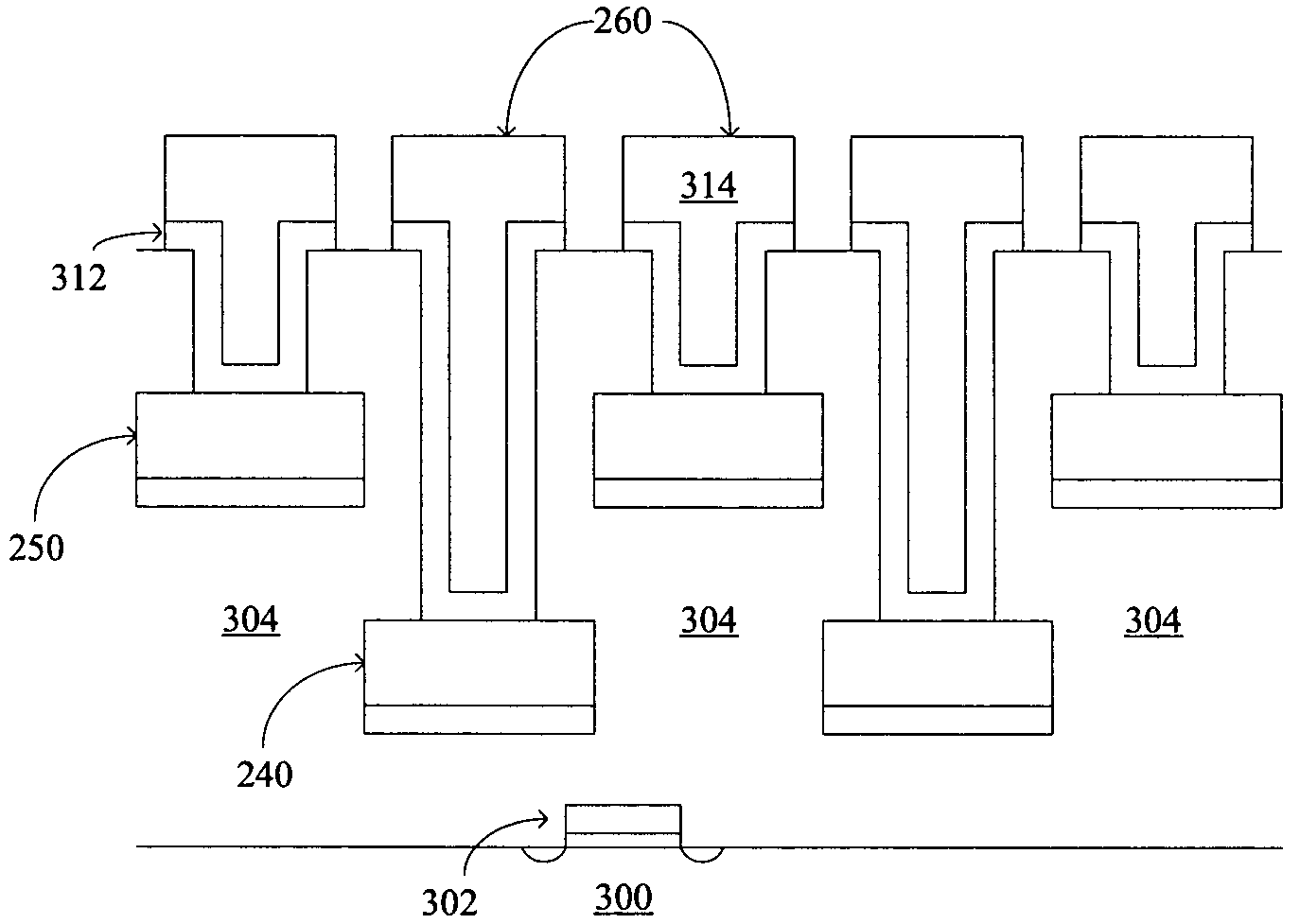

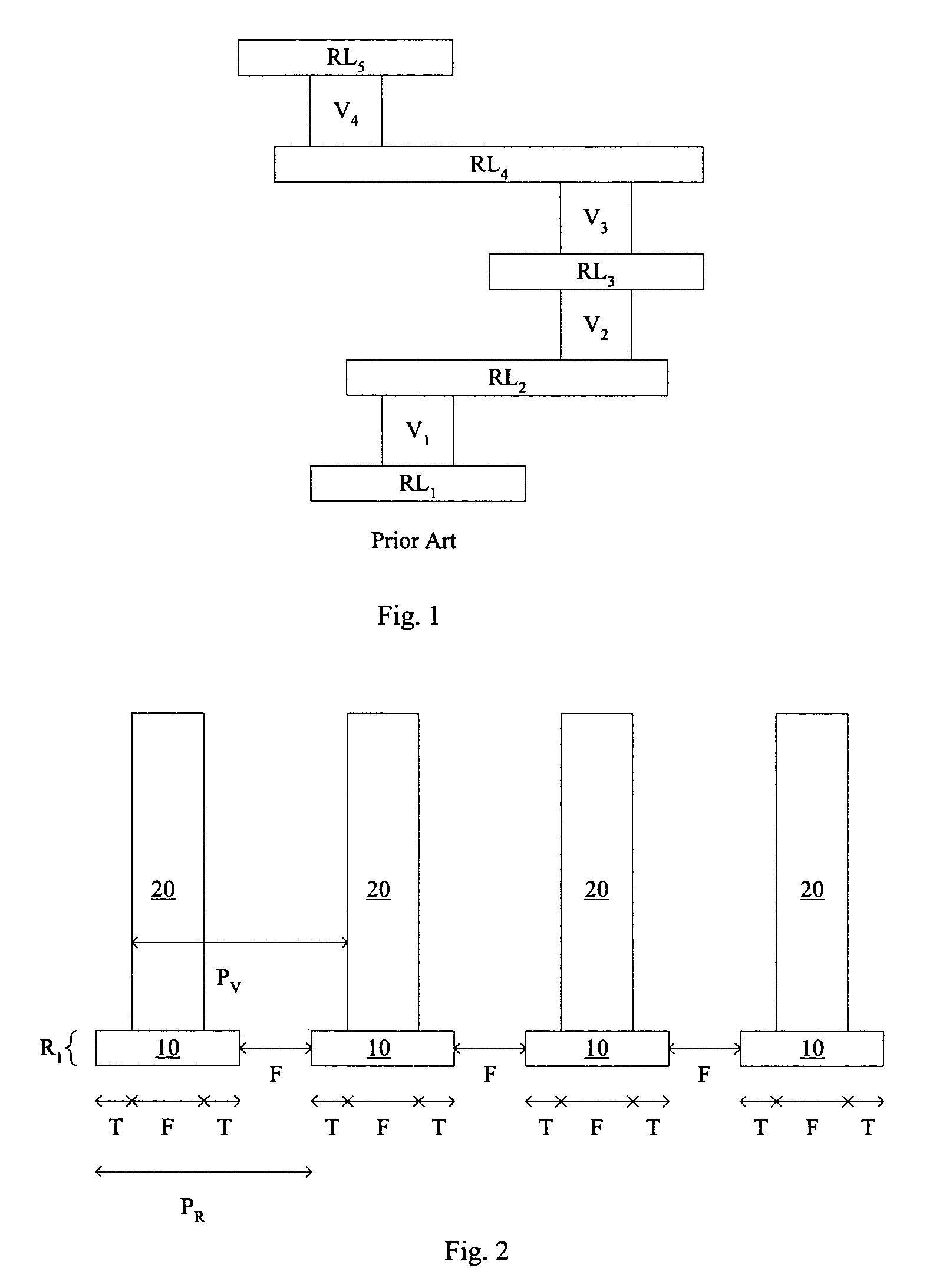

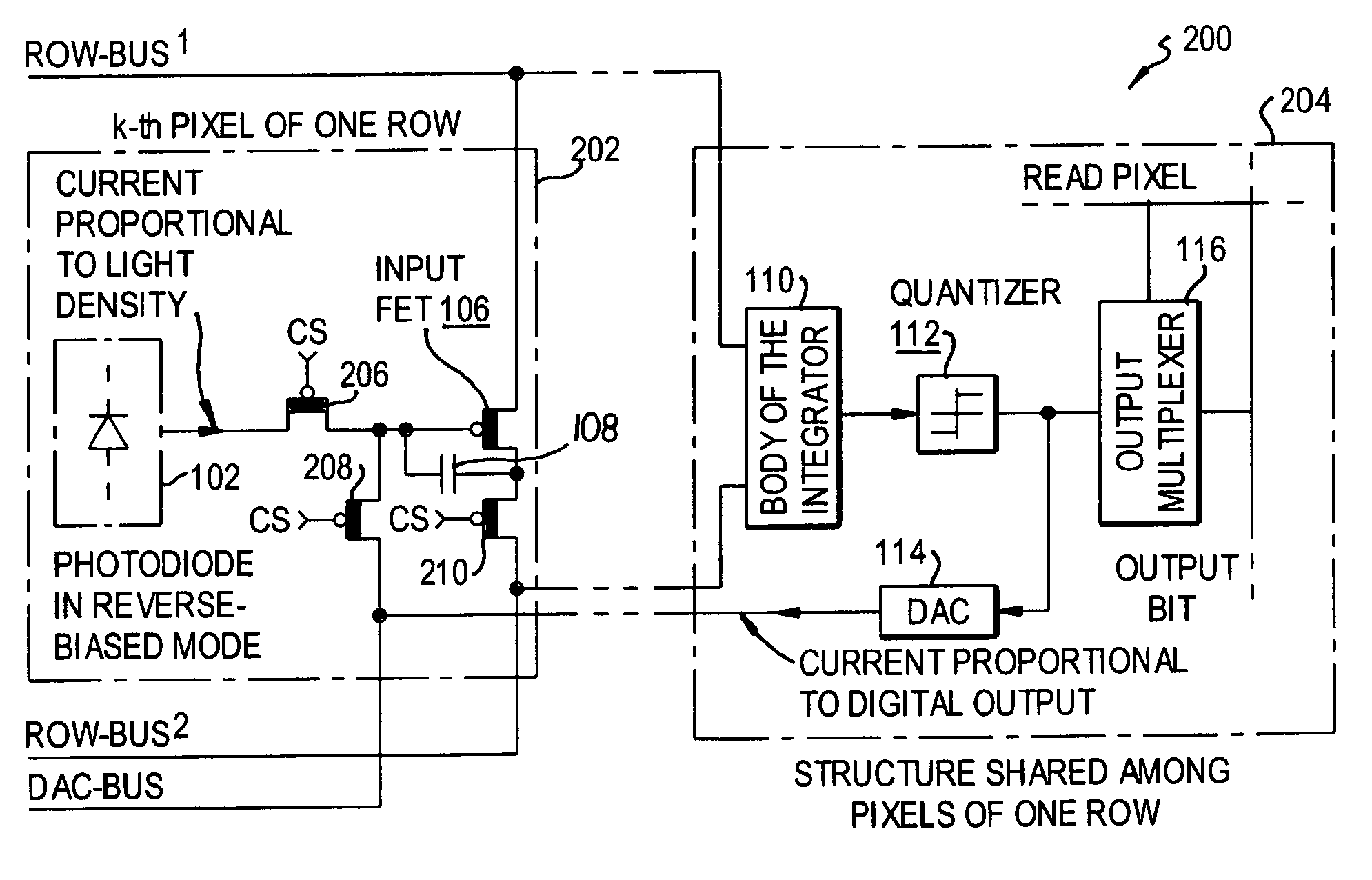

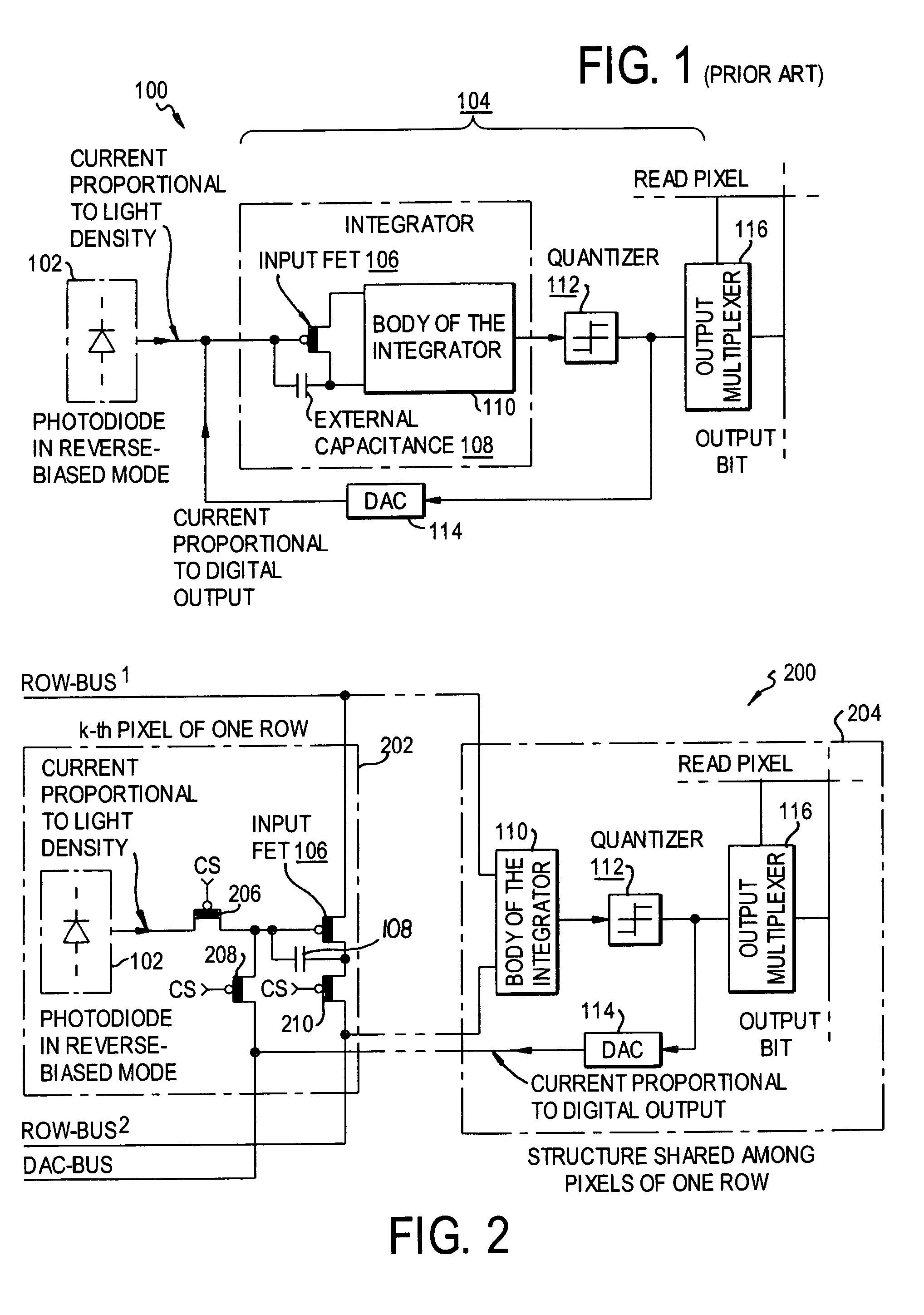

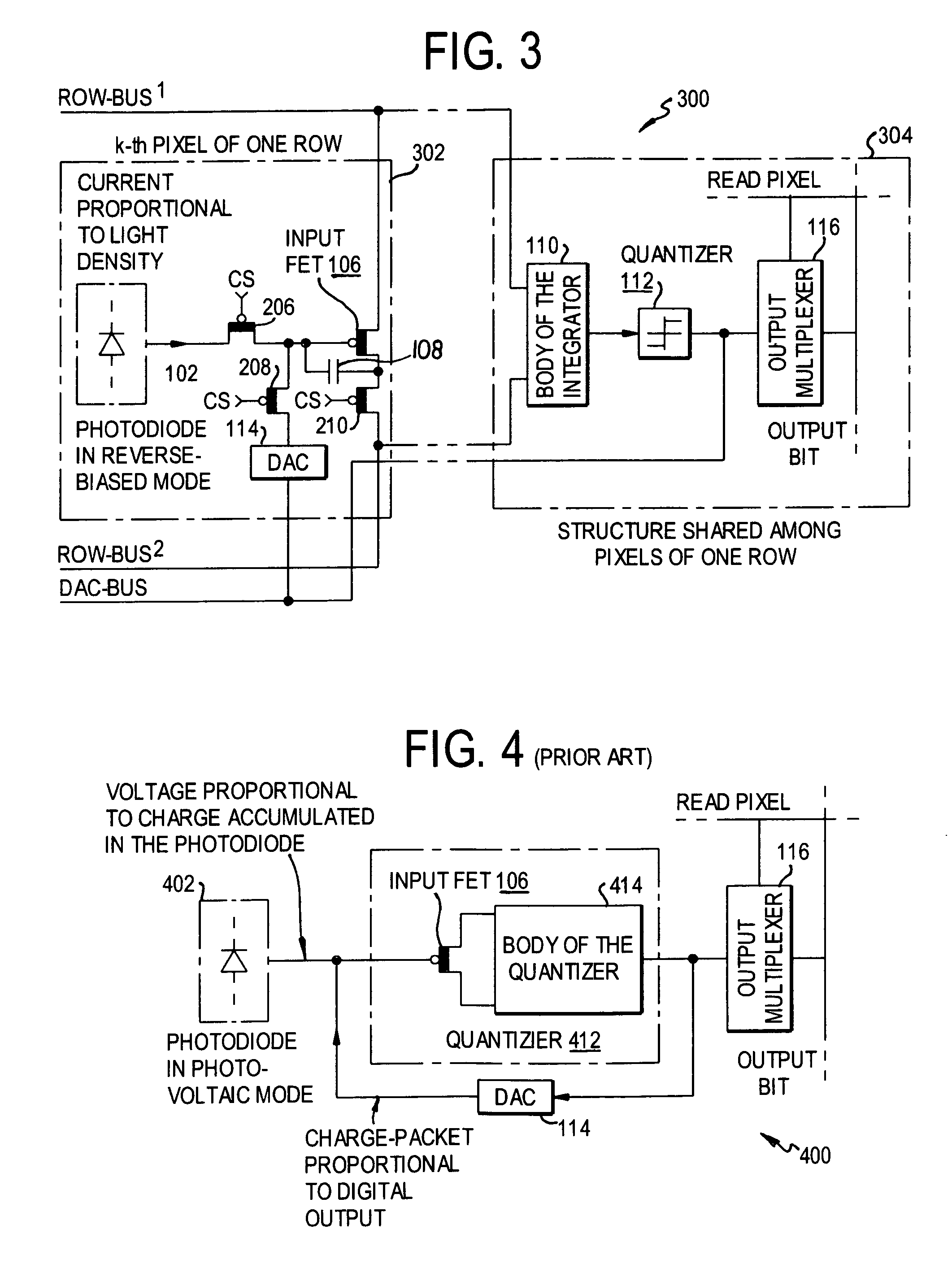

Multiplexed-input-separated sigma-delta analog-to-digital converter design for pixel-level analog-to-digital conversion

InactiveUS7023369B2Improve linearityReduce power consumptionTelevision system detailsElectric signal transmission systemsMultiplexingIntegrator

An image-sensing element has an array of photodiodes or other photodetecting elements and performs sigma-delta analog-to-digital conversion on the outputs of the photodetecting elements. The sigma-delta analog-to-digital converters have components divided between pixel-level and row-level structures, with each row-level structure connected to its pixel-level structures to define a multiplexed-input-separated sigma-delta analog-to-digital converter. The converter can include an integrator or can rely on an integration effect of the photodetecting element. The feedback required for sigma-delta analog-to-digital conversion can involve digital-to-analog converters located at each row-level structure or at each pixel-level structure.

Owner:UNIVERSITY OF ROCHESTER

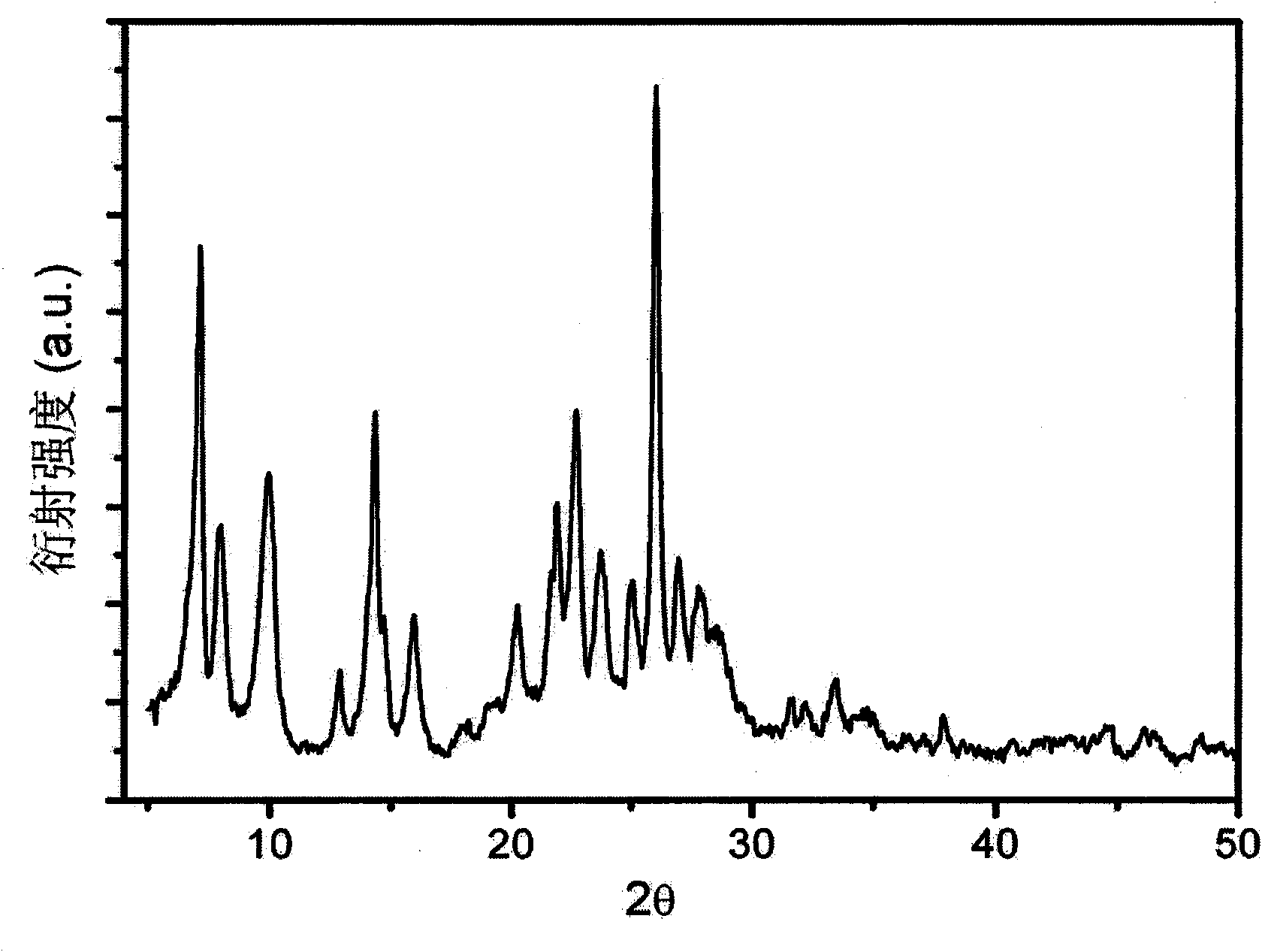

Method for improving catalytic property of methane aromatization catalyst

InactiveCN101618337AImprove catalytic performanceImprove bindingMolecular sieve catalystsHydrocarbonsLevel structureActive component

The invention relates to a method for improving the catalytic property of methane aromatization catalyst, belonging to the technical field of molecular sieve catalysis. The invention is characterized in that on the condition of no-second template, the crystal growth of zeolite molecular sieve is controlled by reasonablely controlling zeolite molecular sieve synthesis conditions such as synthesis formulation, charging sequence, ageing time, crystallization temperature, crystallization time and the like, small molecular sieve crystal is used for assembly and intergrowth to form MCM-22 and ZSM-5 molecular sieve assembly with multi-stage pore path structure, Mo or Re used can be adopted as active component to perform loading and modification to the prepared molecular sieve assembly, and the invention provides Mo-based MCM-22 and ZSM-5 molecular sieve assembly catalysts and an application thereof in methane non-oxidative aromatization reaction. The effects and the benefits of the invention is that the operation is simple, the cost is low and in methane non-oxidative aromatization reaction, the multi level structure assembly catalyst prepared by the method of the invention has better catalytic performance compared with the traditional catalyst.

Owner:DALIAN UNIV OF TECH

High density contact to relaxed geometry layers

ActiveUS20050127519A1Semiconductor/solid-state device detailsSolid-state devicesHigh densityLevel structure

The present invention provides for a via and staggered routing level structure. Vertically overlapping vias connect to two or more routing levels formed at different heights. The routing levels are either both formed above or both formed below the vias, and all are formed above a semiconductor substrate wafer. In this way vias can be formed having a pitch smaller than the pitch of either the first routing level or the second routing level, saving space.

Owner:SANDISK TECH LLC

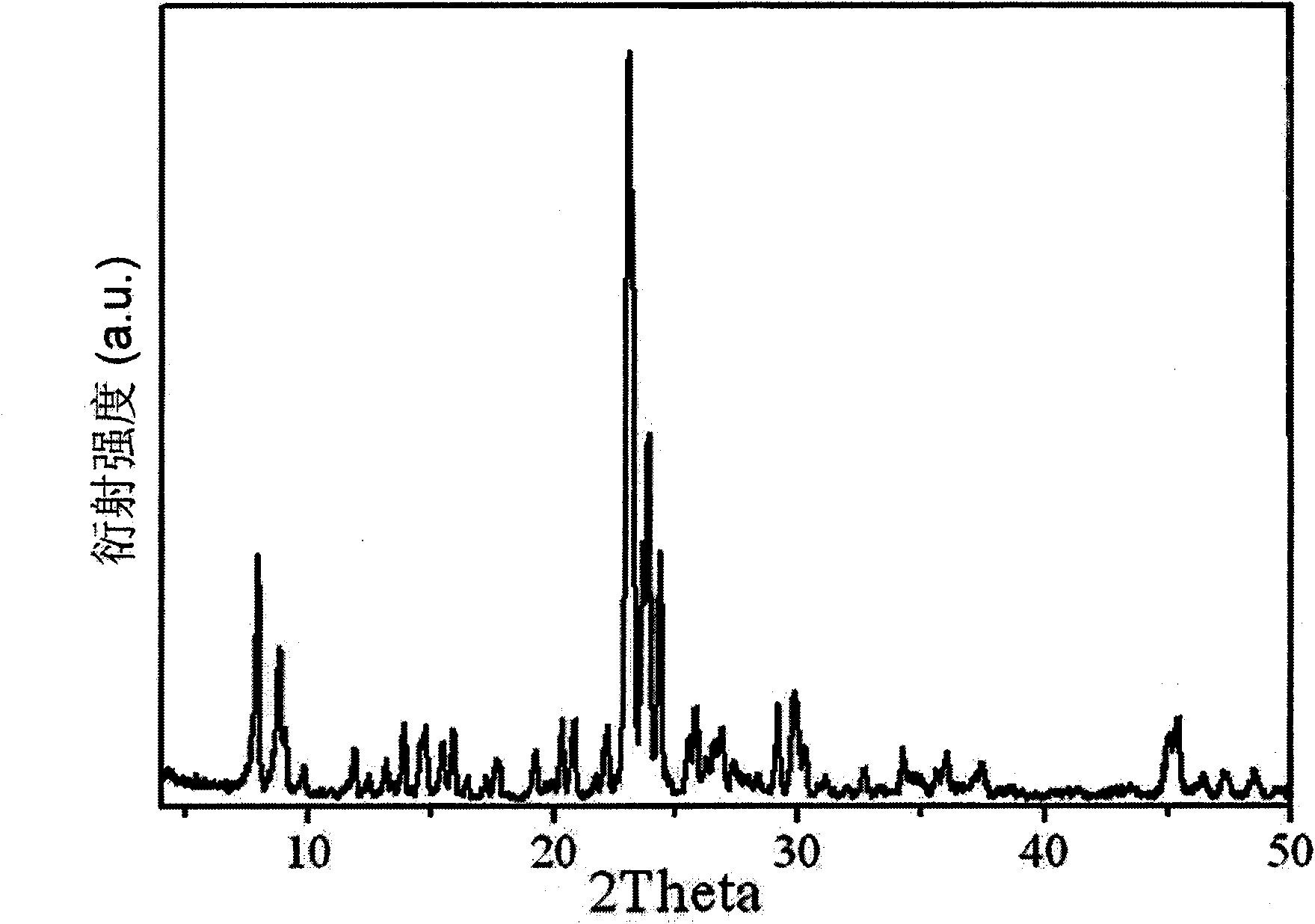

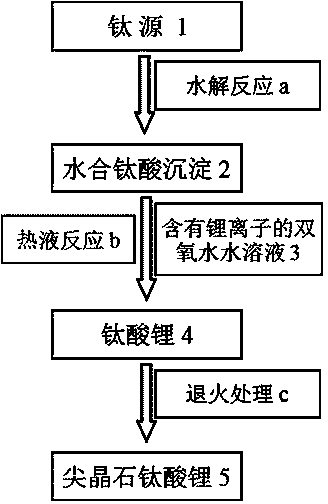

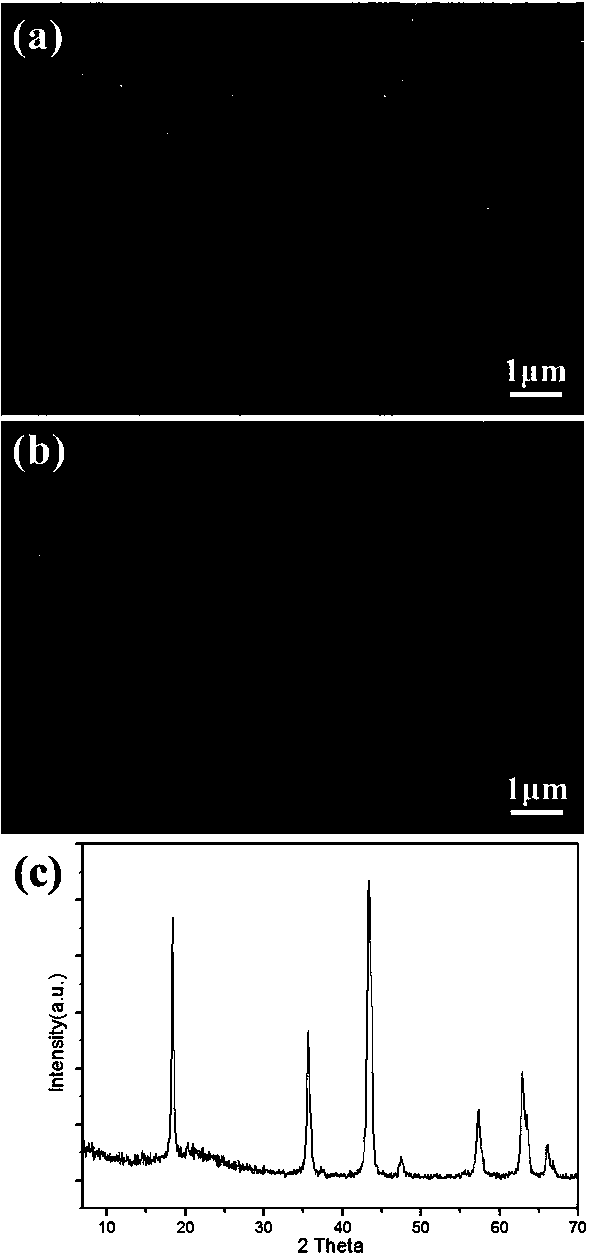

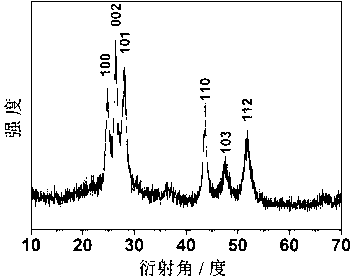

Method for preparing spinel lithium titanate

InactiveCN104201364AOvercome conductivityLow priceMaterial nanotechnologyAlkali titanatesLithiumNanowire

The invention discloses a method for preparing spinel lithium titanate. The method is characterized by comprising the steps of S1, performing hydrolysis reaction on a titanium source to obtain hydrated titanium acid sediments; S2, dispersing the hydrated titanium acid sediments into lithium ion-containing hydrogen peroxide aqueous solution to obtain a mixture; S3, performing hydrothermal reaction on the mixture to obtain nanowire type lithium titanate and / or lithium titanate with a nano differential level structure; S4, annealing the nanowire type lithium titanate and / or the lithium titanate with the nano differential level structure to obtain nanowire type spinel lithium titanate and / or the spinel lithium titanate with the nano differential level structure. According to the method, both spinel lithium titanate nanowires and the spinel lithium titanate with the nano differential level structure can be prepared.

Owner:李建明

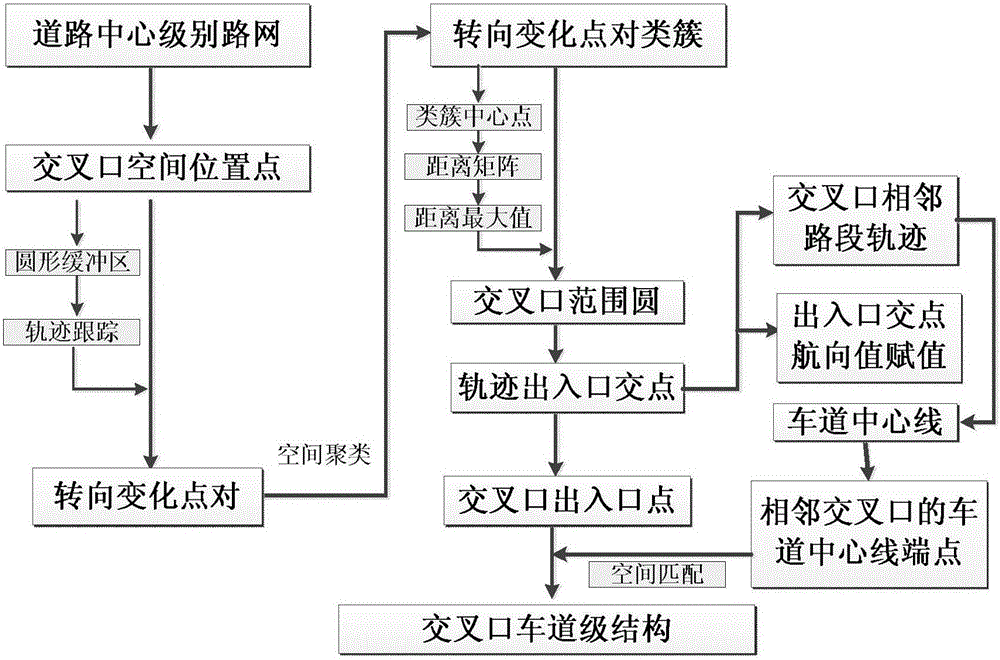

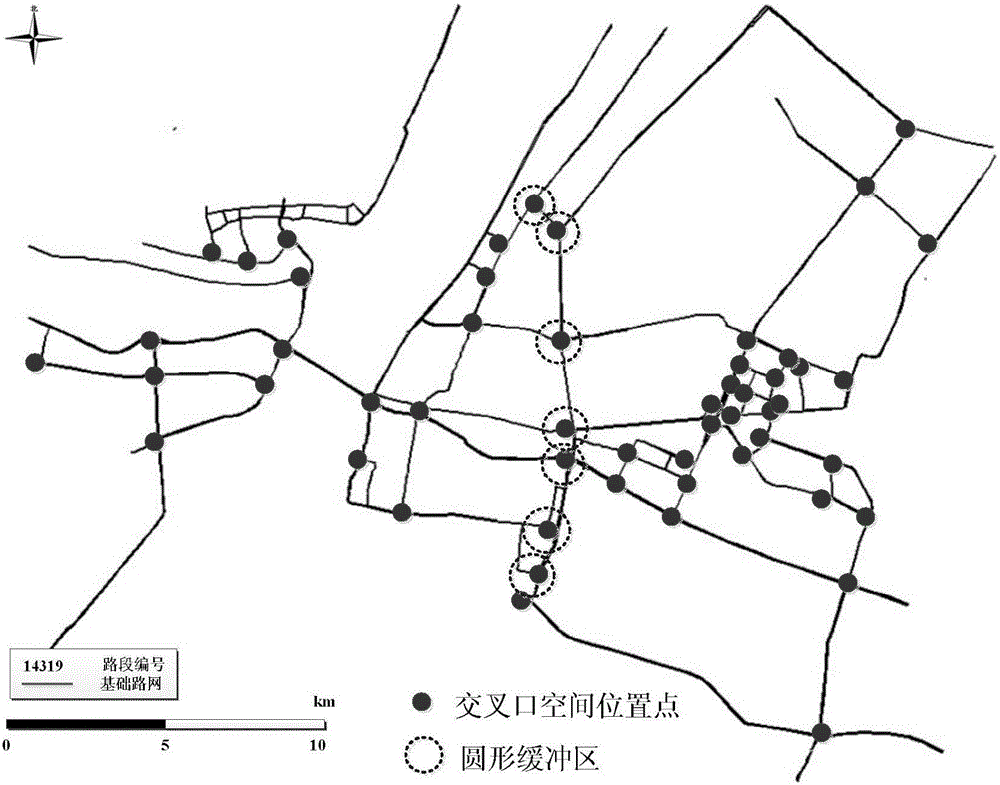

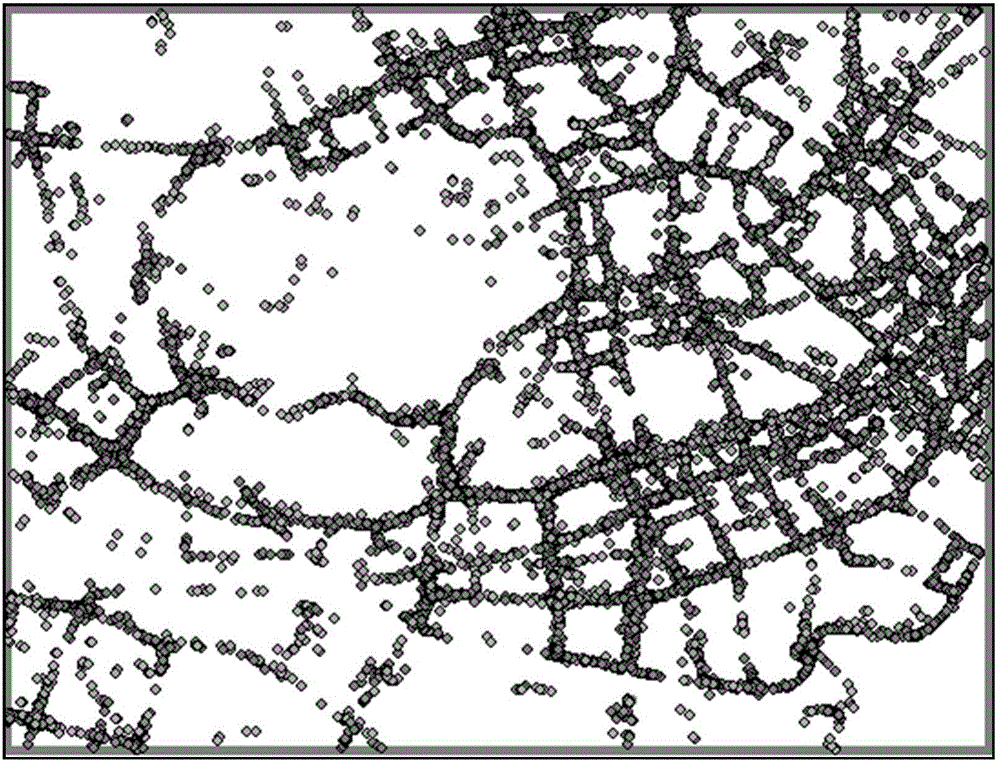

Urban intersection lane-level structure extraction method based on time-space trajectory big data

ActiveCN105788274ALow costThe detection method is simpleDetection of traffic movementLevel structureRoad networks

The invention provides an urban intersection lane-level structure extraction method based on time-space trajectory big data, which reduces the cost for obtaining urban intersection structure, has simple detection method and is easy to realize. The method comprises following steps: first, obtaining position points of urban intersections according to an existing road axis-level road network graph, and then setting up a circular buffer area; extracting trajectory points whose course angle variation exceeds 45 degrees in trajectory data as turning changing points by means of a trajectory tracking method; secondary, performing clustering to the turning changing points by means of a density clustering method, and establishing an intersection range circle by extracting cluster centers and the spatial distance among them; finally, calculating the intersection points of the trajectory passing through the intersection range circle by means of the trajectory tracking method again, extracting turning entrance points and exit points of the intersection, and matching the turning entrance points and exit points of the intersection with lane axis of adjacent roads by means of spatial matching method to complete the extraction of urban intersection lane-level structure. The accuracy of intersection entrance point and exit point plane structure graph obtained by means of the method is 94.3%.

Owner:WUHAN UNIV

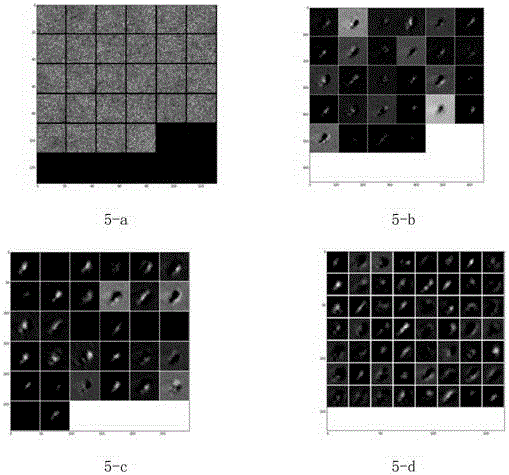

Synthetic aperture radar image target identification method based on depth model

ActiveCN106407986AReduce overheadTarget recognition facilitatesCharacter and pattern recognitionFeature extractionLevel structure

The invention discloses a synthetic aperture radar image target identification method based on a depth model. The method comprises steps of image cutting; depth model level structure design, characteristic extraction filter design, parameter quantity control and overfitting prevention, function activation and non-linear lifting, identification classification and autonomous parameter correction update; depth model training; target identification. The method is advantaged in that filter parameters can realize autonomous iteration update in a training process, characteristic selection and extraction cost is greatly reduced, moreover, target different-level characteristics can be extracted through the depth model, the characteristics can be acquired through high-degree matching and training, so high-degree target representation can be realized, and target identification accuracy of SAR images is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

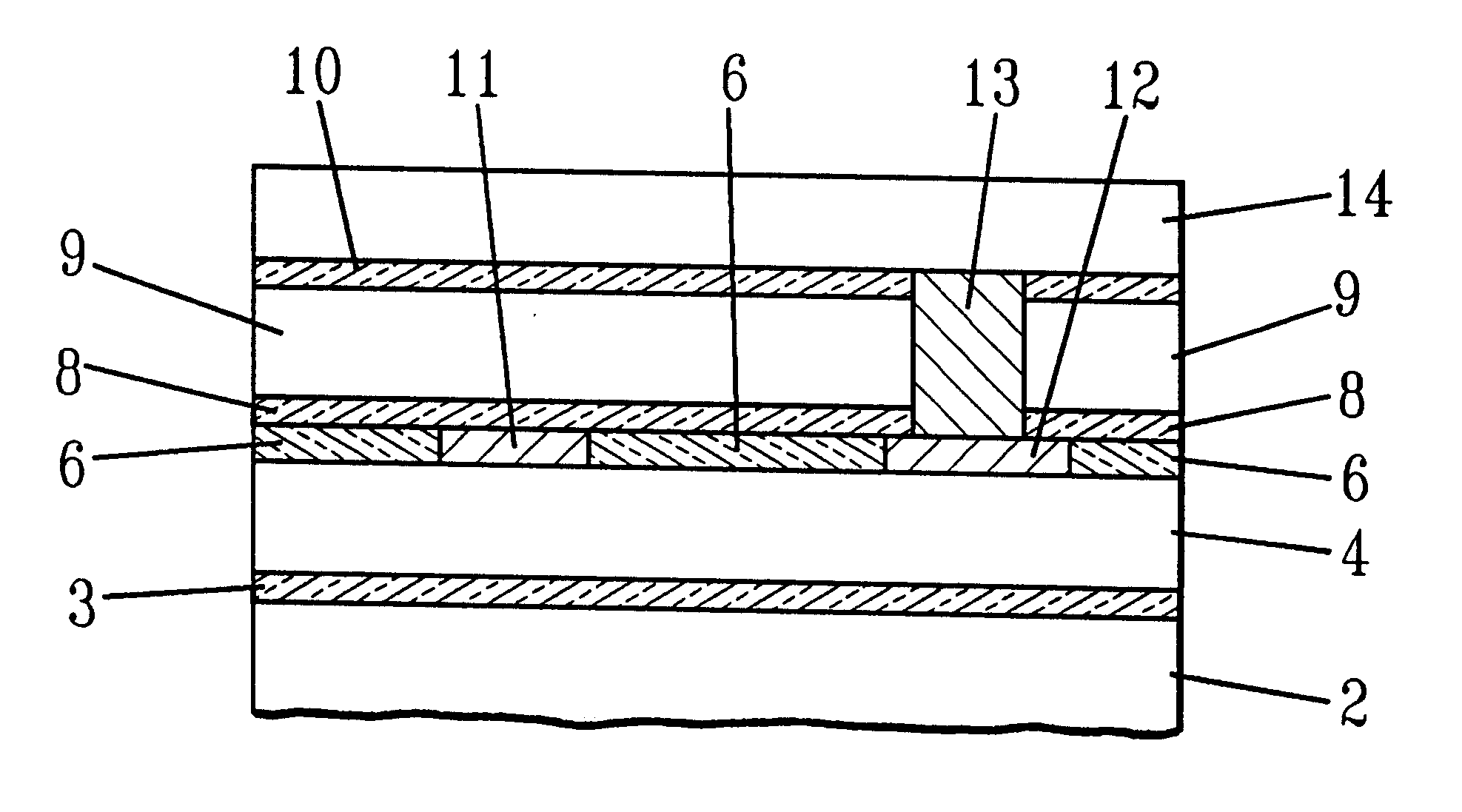

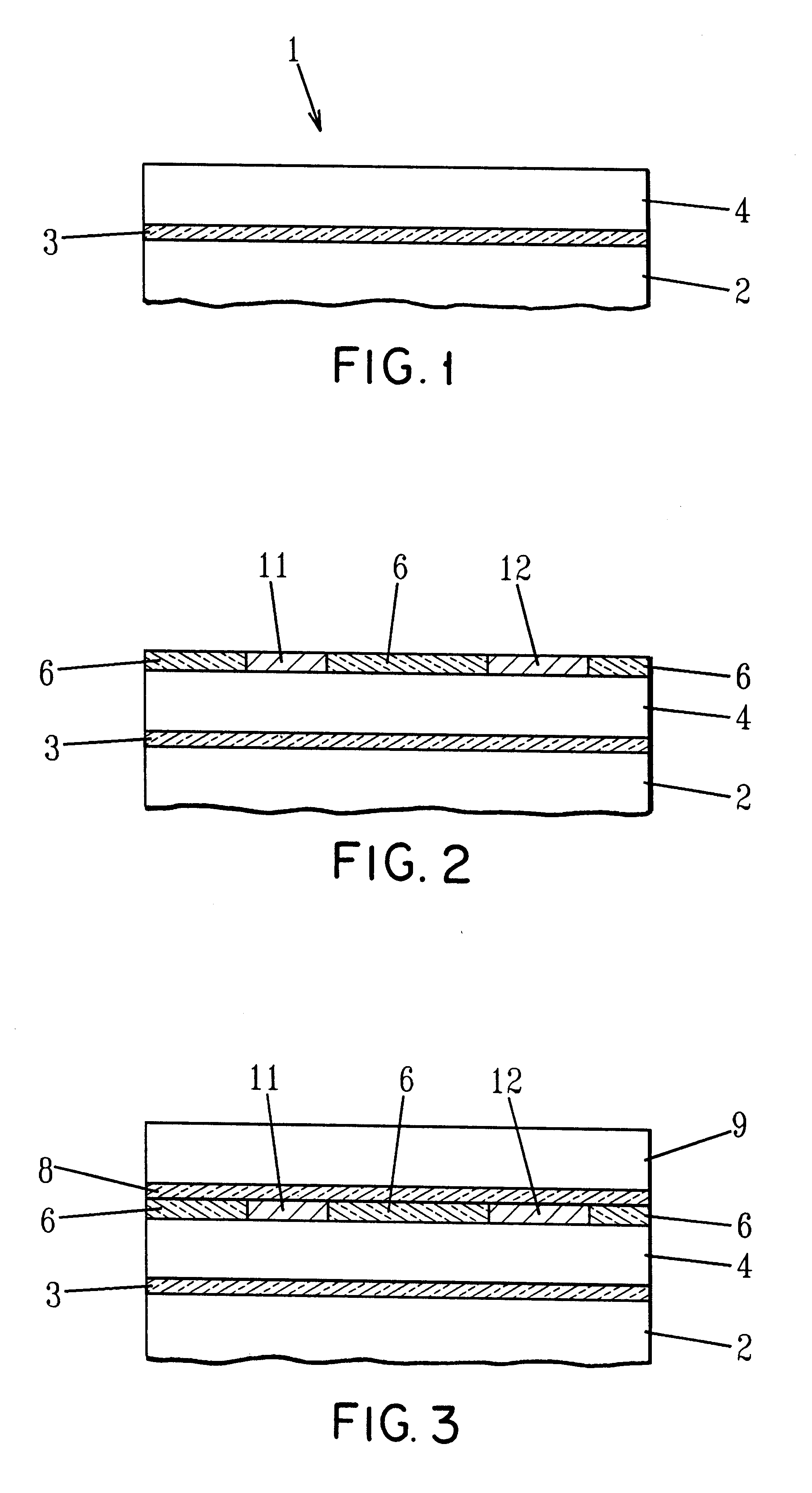

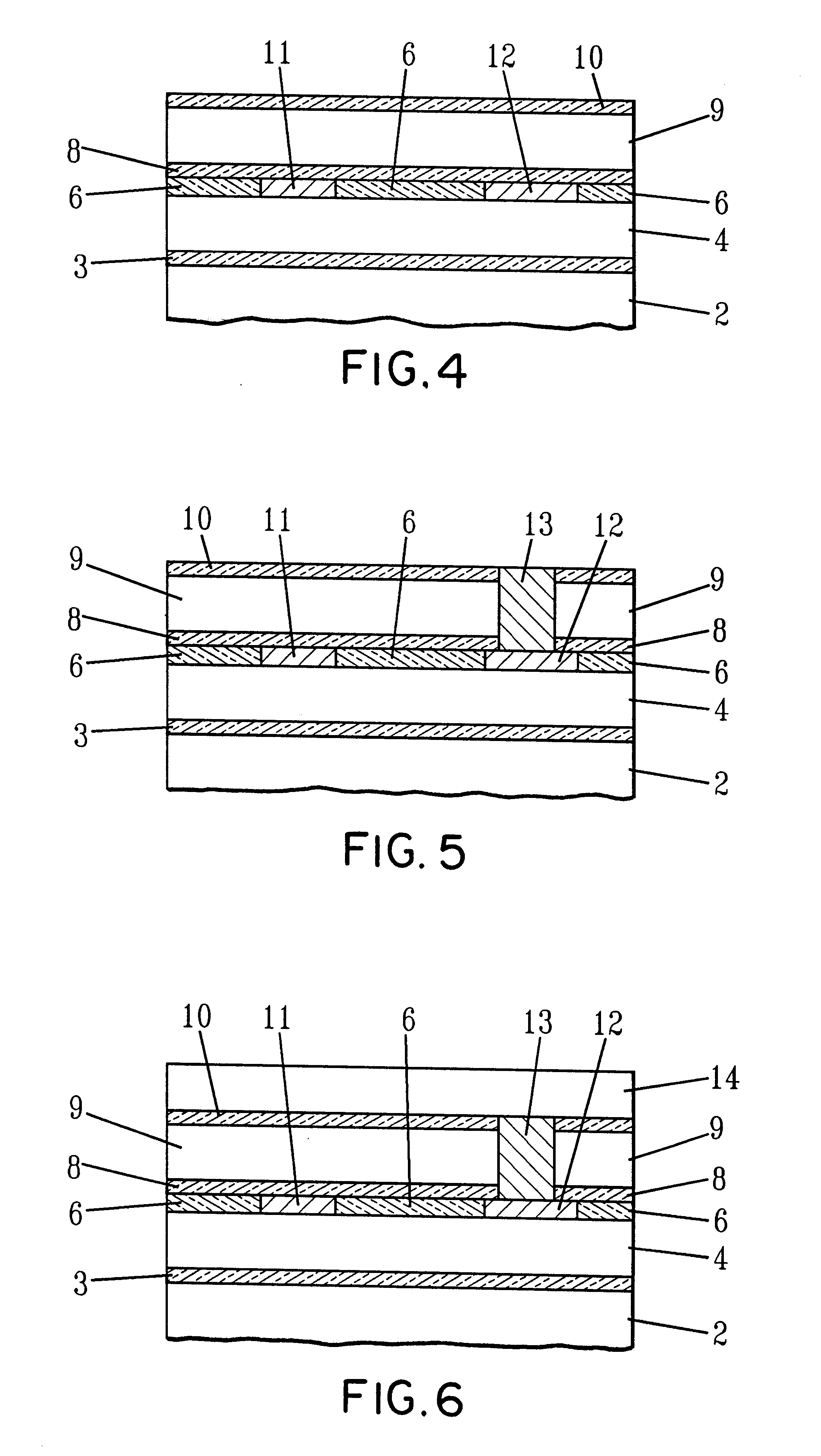

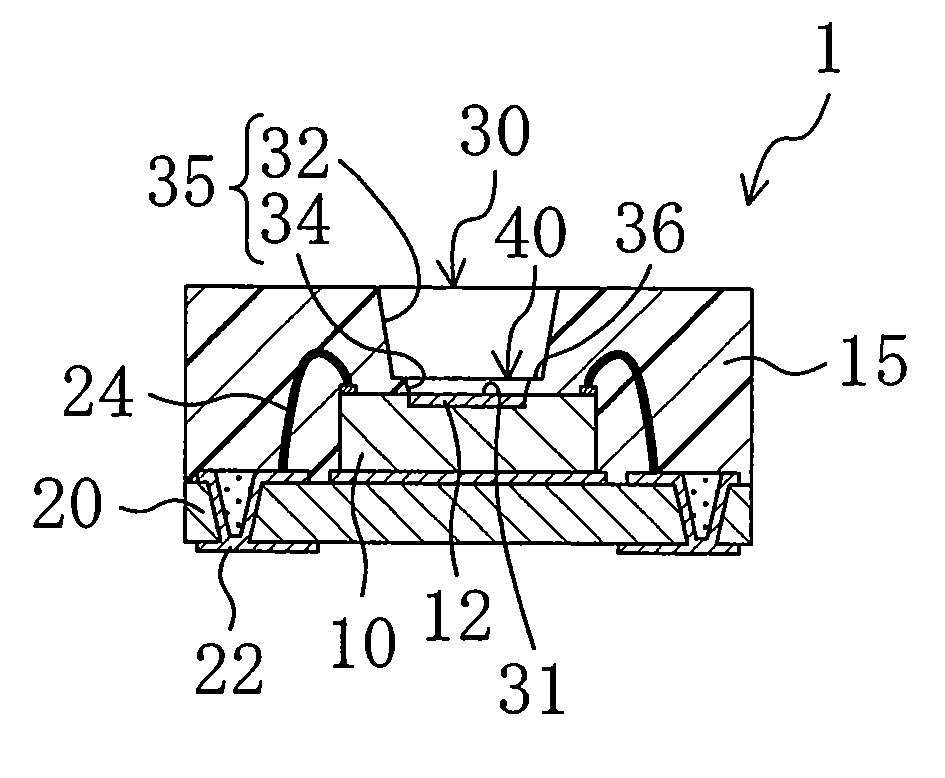

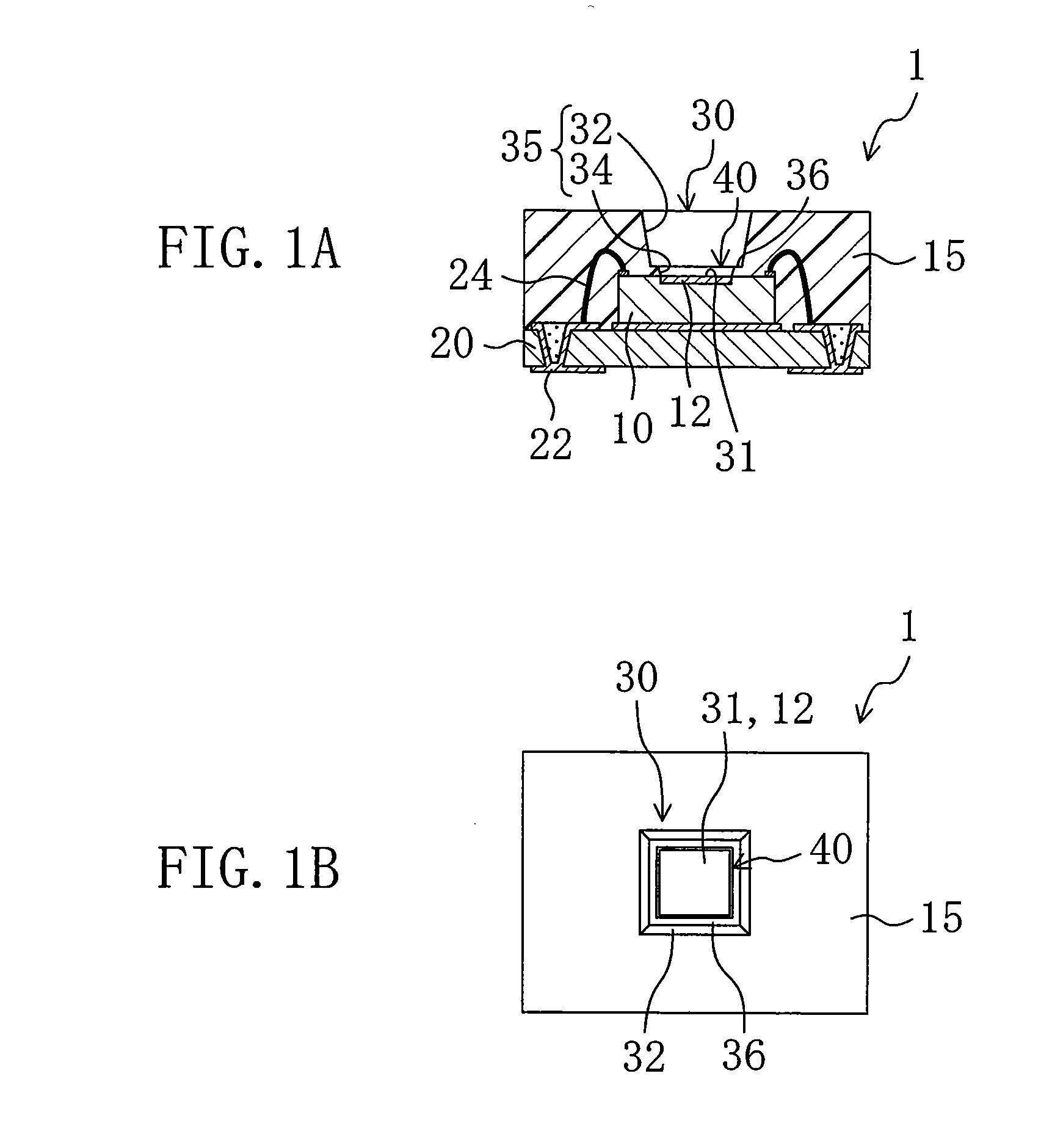

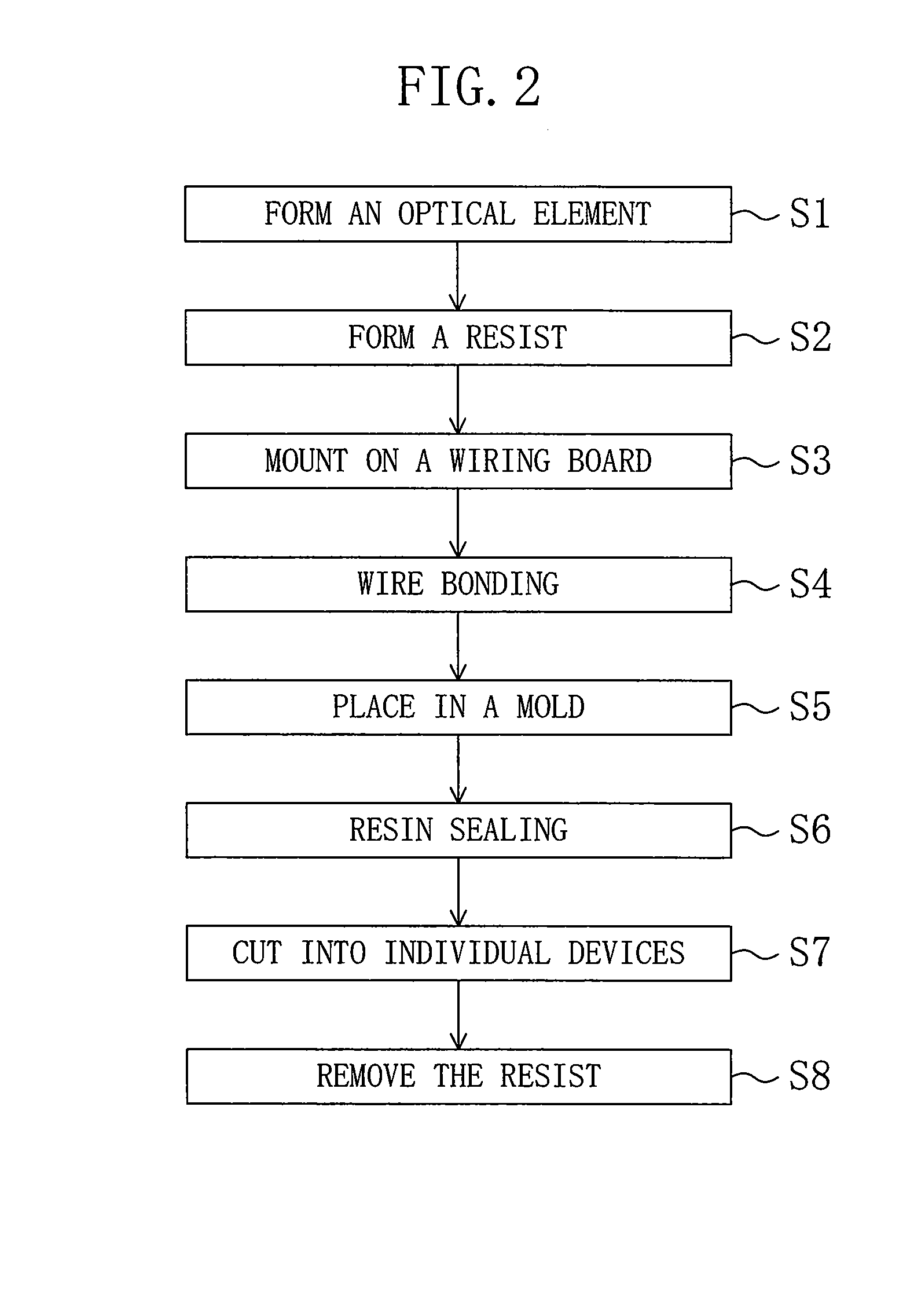

Optical device and manufacturing method thereof

InactiveUS20090086449A1Reduce the opening areaSimple and low-cost methodSolid-state devicesOptical articlesLevel structureEngineering

An optical element mounted on a wiring board is sealed by a sealing resin except an optical function region. Wires connecting the wiring board with the optical element are also sealed by the sealing resin. The optical function region is exposed as a bottom surface of a recess whose side surface is formed by the sealing resin. The recess has a two-level structure of a bottom recess and a portion located over the bottom recess. A stepped portion extends from an upper end of a first side surface of the bottom recess to a lower end of a second side surface of the bottom recess.

Owner:PANASONIC CORP

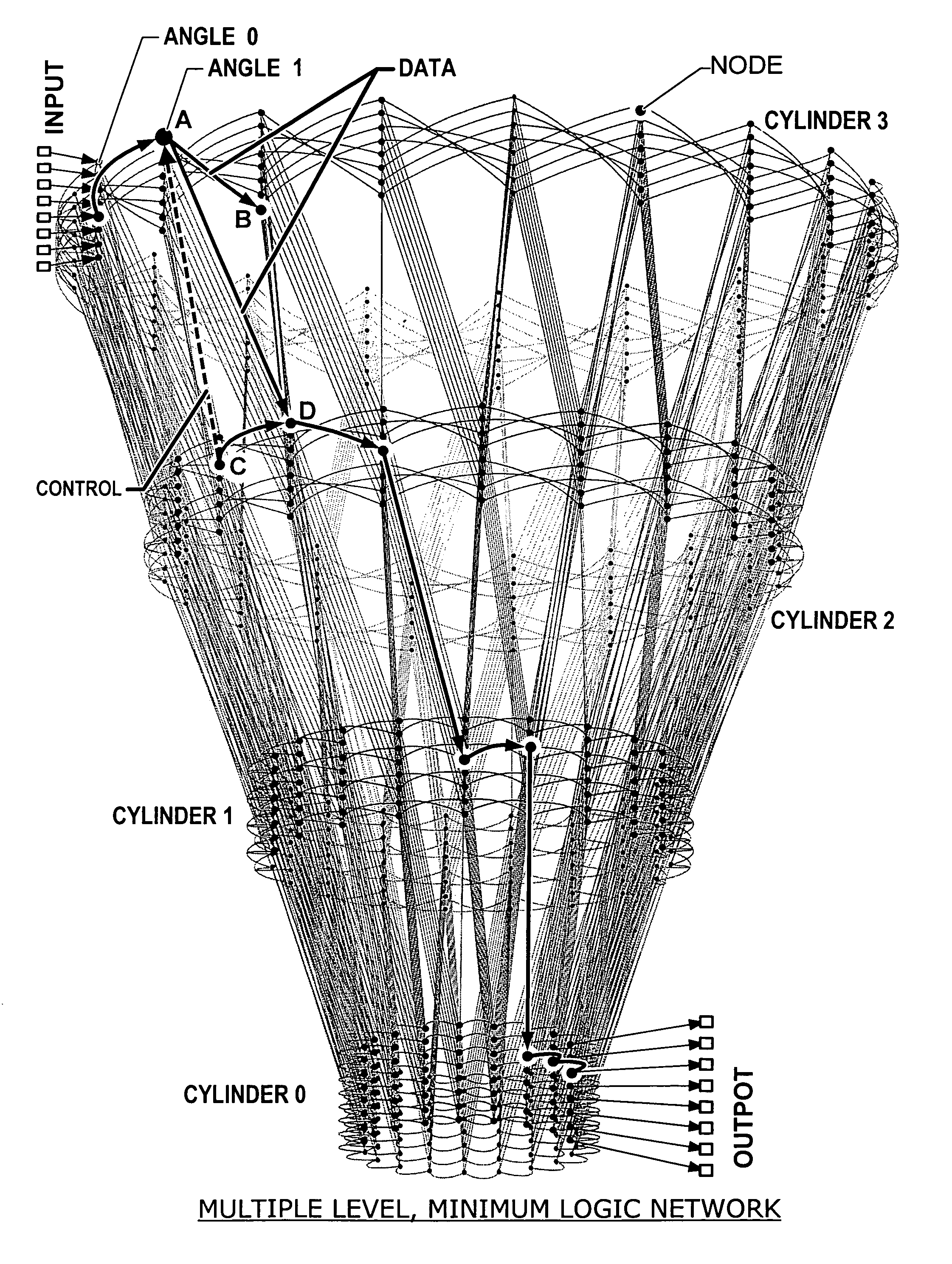

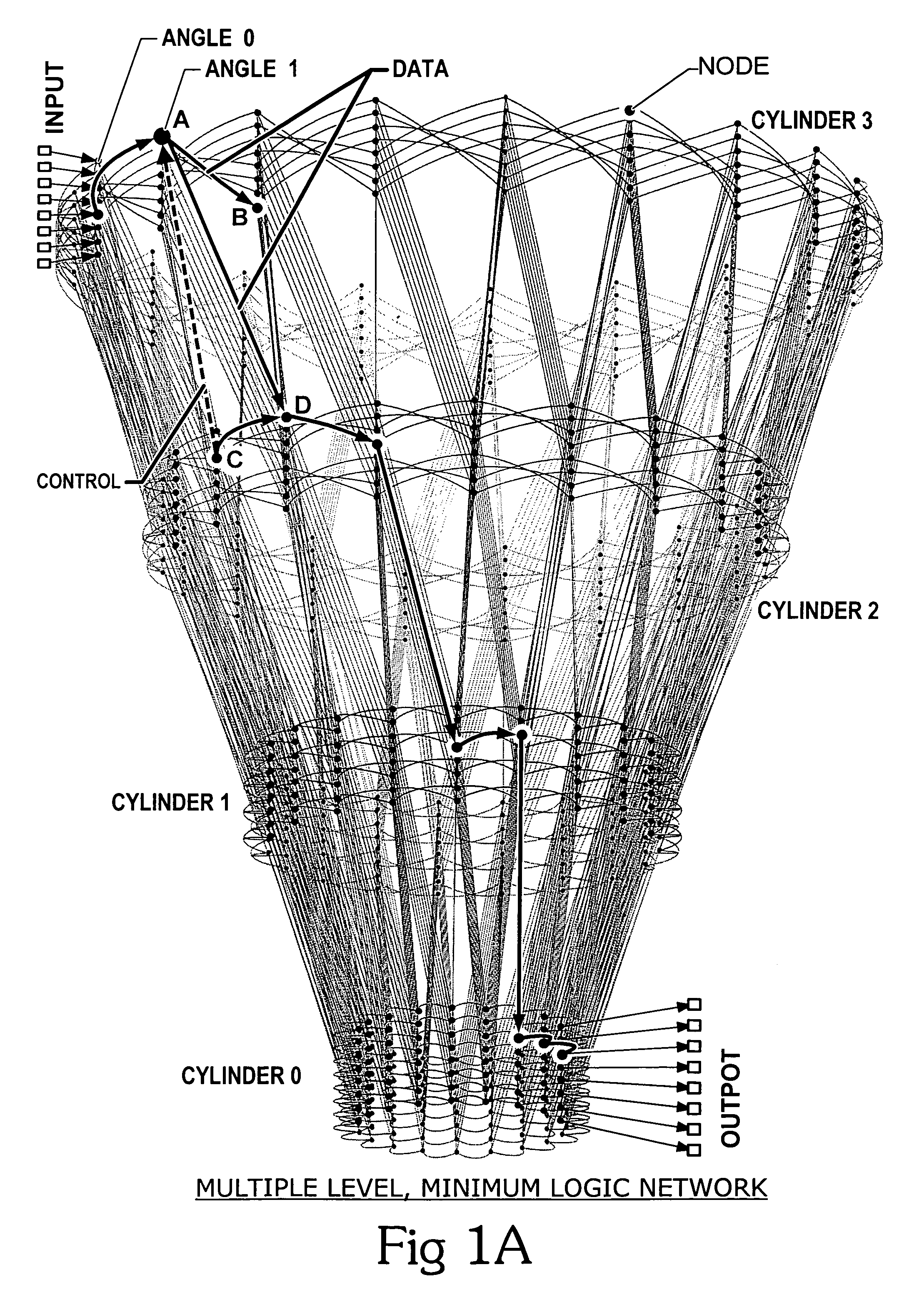

Scaleable interconnect structure utilizing quality-of-service handling

InactiveUS7016363B1Quality improvementData switching by path configurationTime-division multiplexing selectionQuality of serviceLevel structure

An interconnect structure and method of communicating messages on the interconnect structure assists high priority messages to travel through the interconnect structure at a faster rate than normal or low priority messages. An interconnect structure includes a plurality of nodes with a plurality of interconnect lines selectively coupling the nodes in a hierarchical multiple-level structure. Data moves from an uppermost source level to a lowermost destination level. Nodes in the structure are arranged in columns and levels. Data wormholes through the structure and, in a given time-step, data always moves from one column to an adjacent column and while remaining on the same level or moving down to a lower level. When data moves down a level, an additional bit of the target output is fixed so data exiting from the bottom of the structure arrives at the proper target output port.

Owner:INTERACTIC HLDG LLC

Development method for integrated circuits, program storage medium for storing the development method for integrated circuits, and concurrent development system, development program, and development method of ASIC and programmable logic device

InactiveUS20050071787A1Keep in touchAvoid repetitionSemiconductor/solid-state device manufacturingCAD circuit designComputer architectureLevel structure

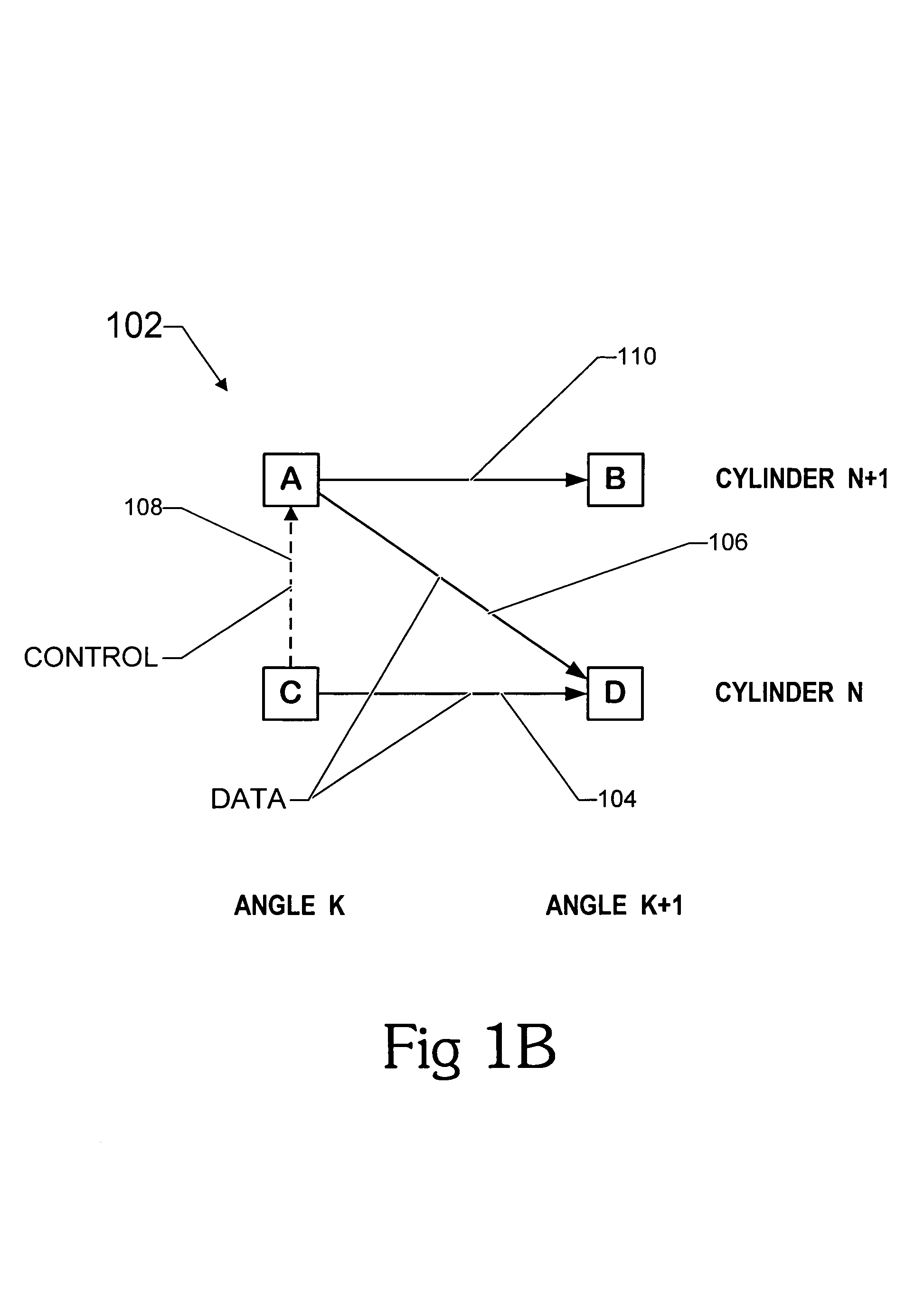

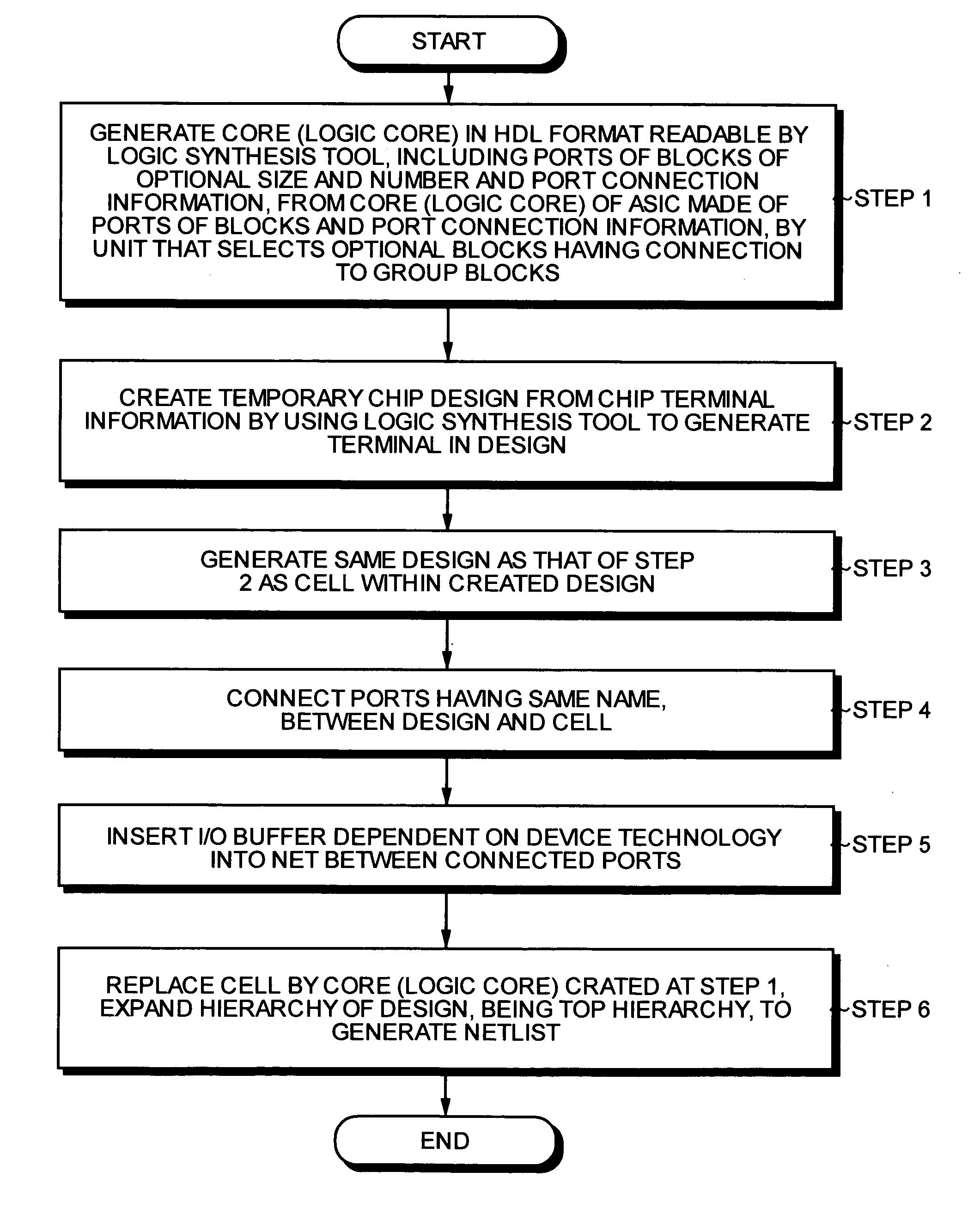

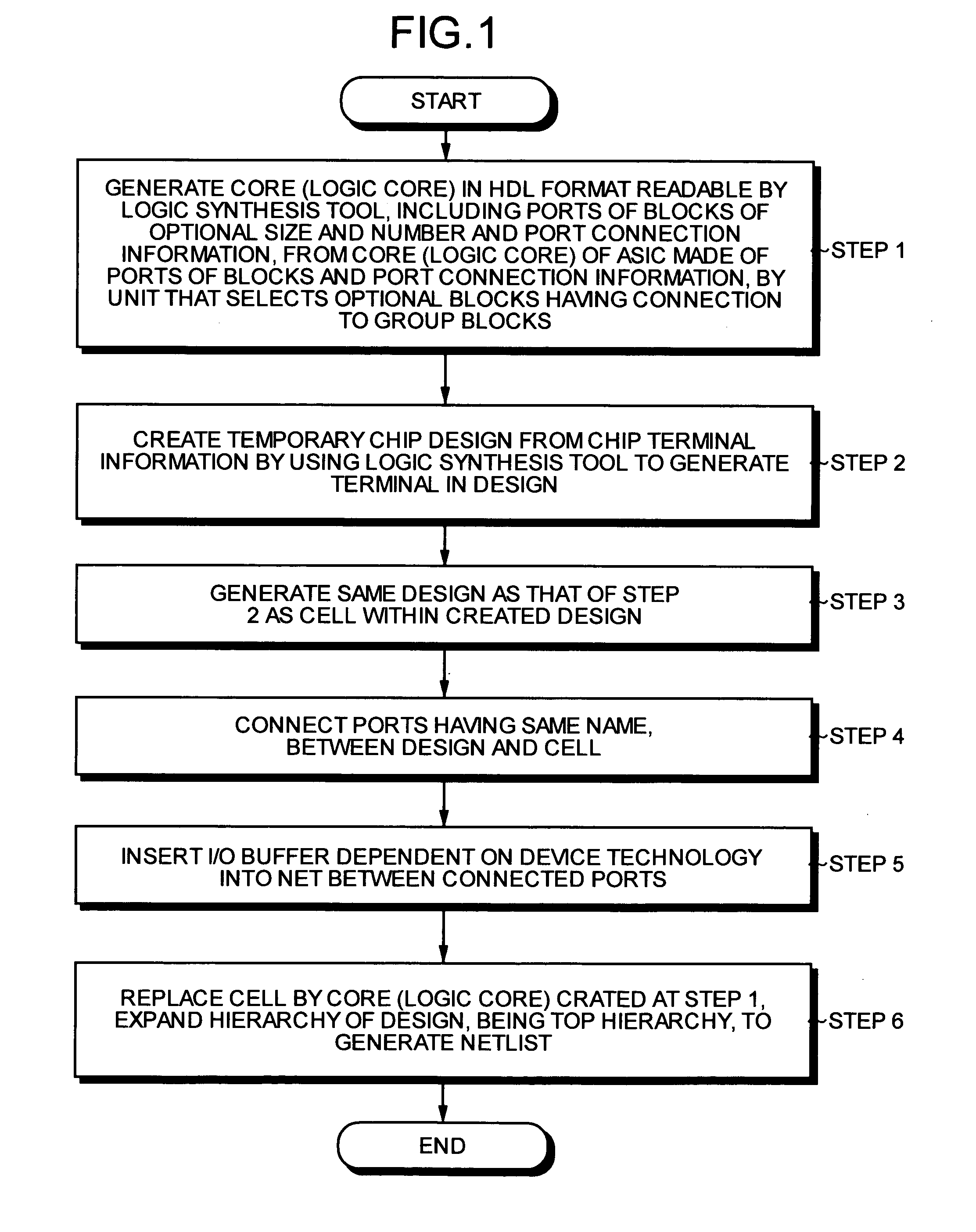

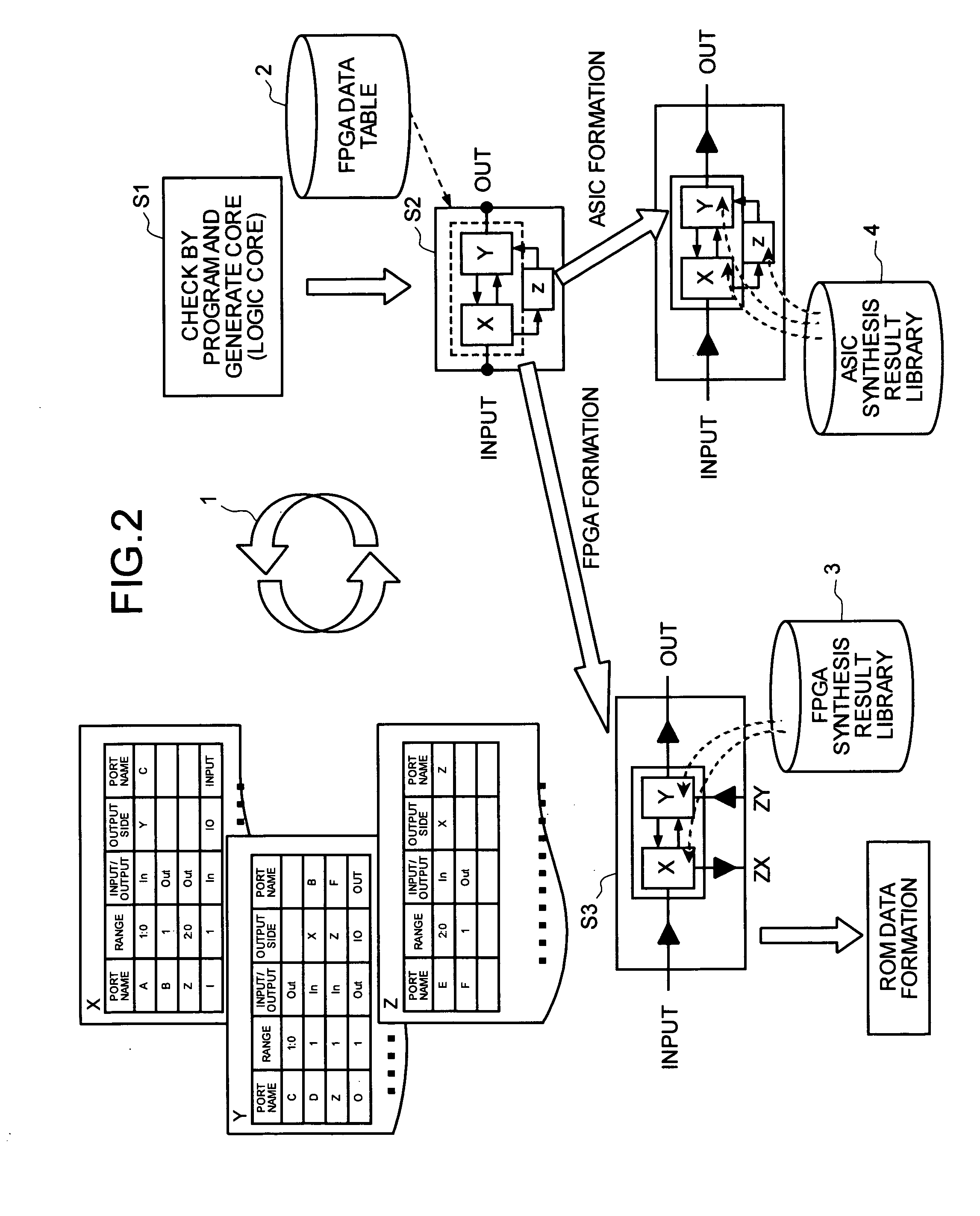

A method for developing integrated circuits includes generating a core (logic core) in an HDL format readable by a logic synthesis tool, from an ASIC core (logic core) made of ports of blocks and port connection information, creating a temporary chip design from chip terminal information to generate a terminal in the temporary chip design, generating a design identical to that created, as a cell within the design created, connecting a design port with a cell port, wherein a name of the design port is identical to a name of the cell port, inserting an I / O buffer, depending on the device technology, into a net between the ports connected, replacing the cell by the core (logic core) created to gerate a netlist, and expanding a hierarchy of the design, being the top hierarchy.

Owner:FUJITSU LTD

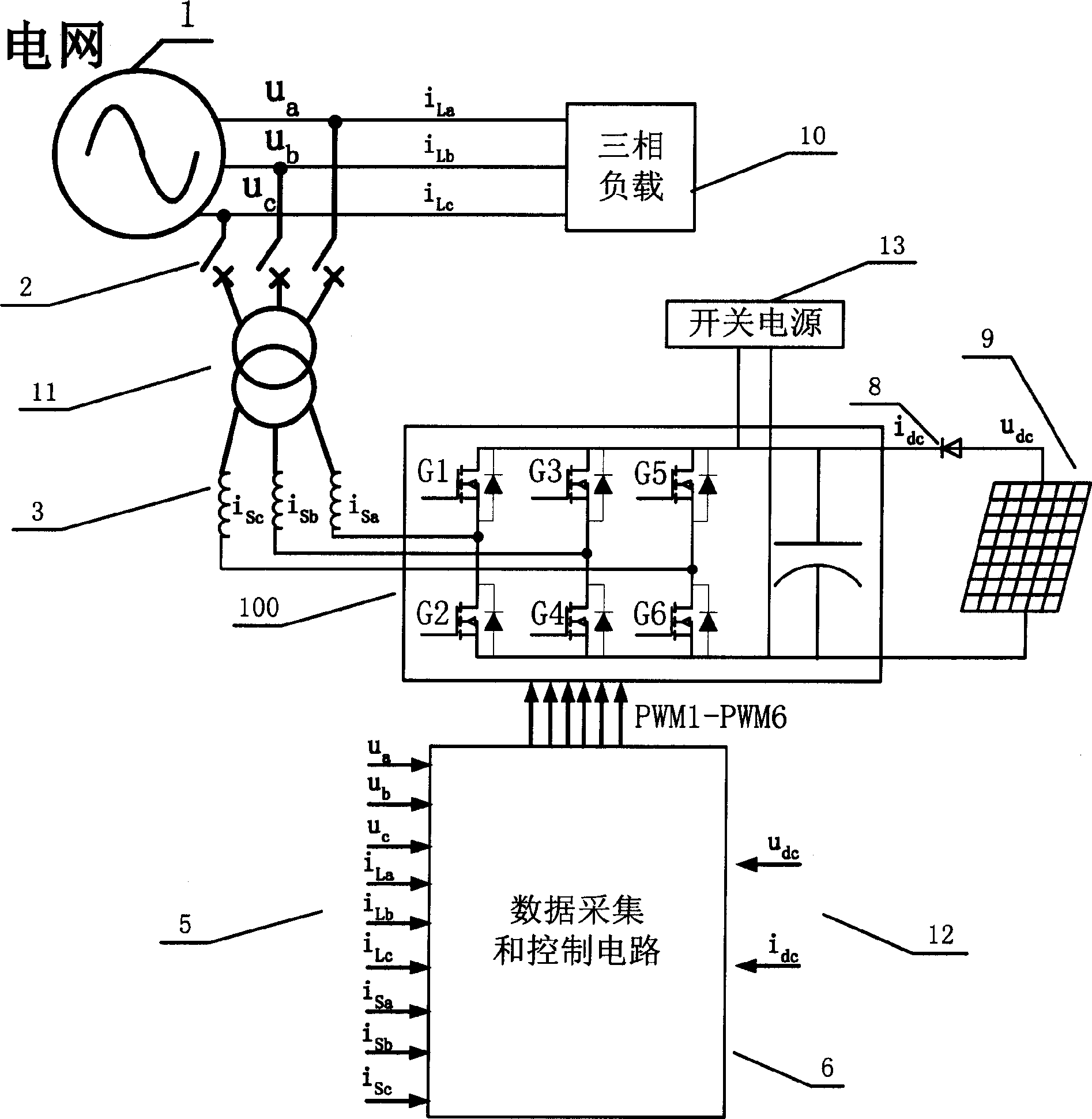

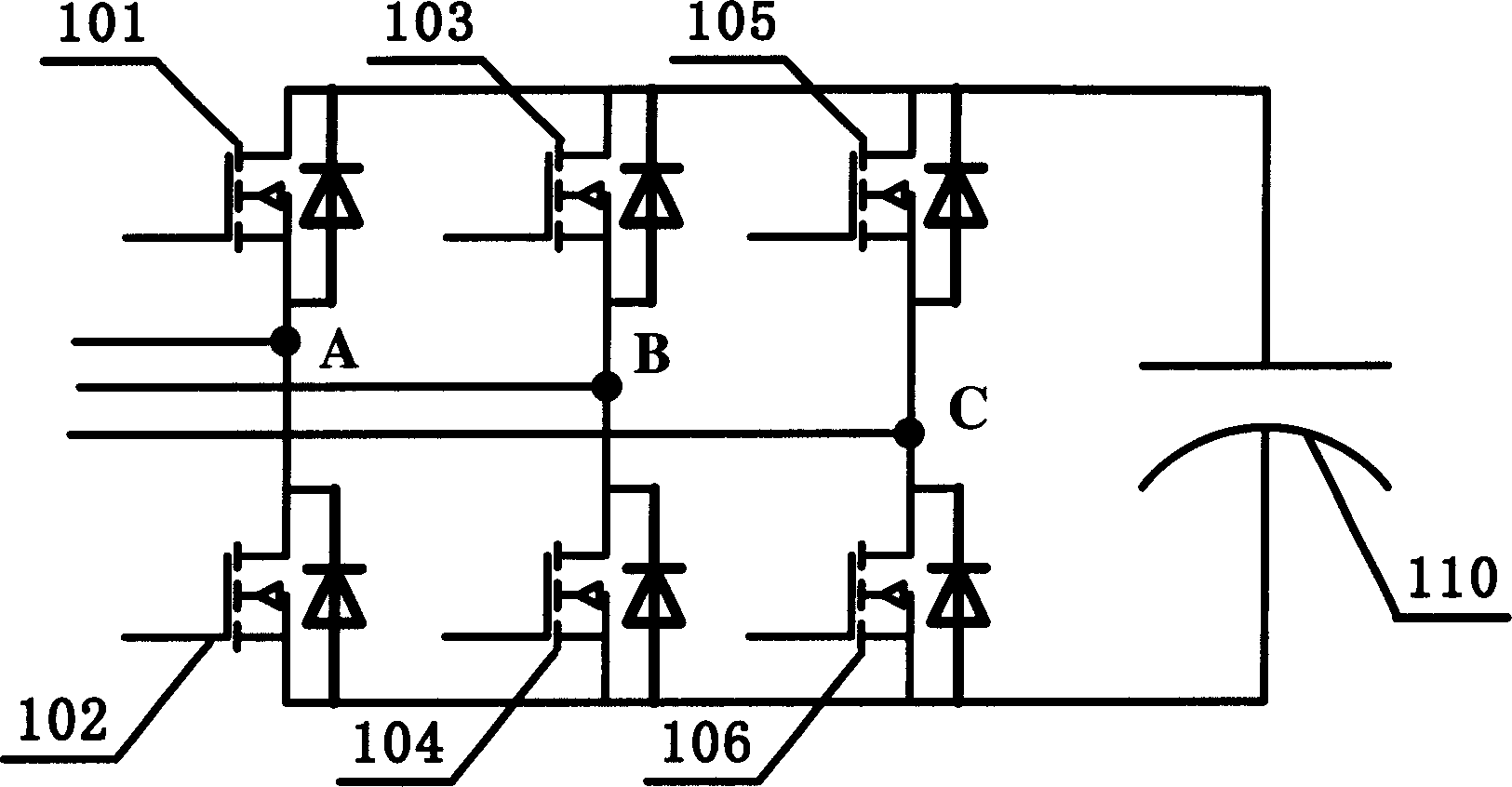

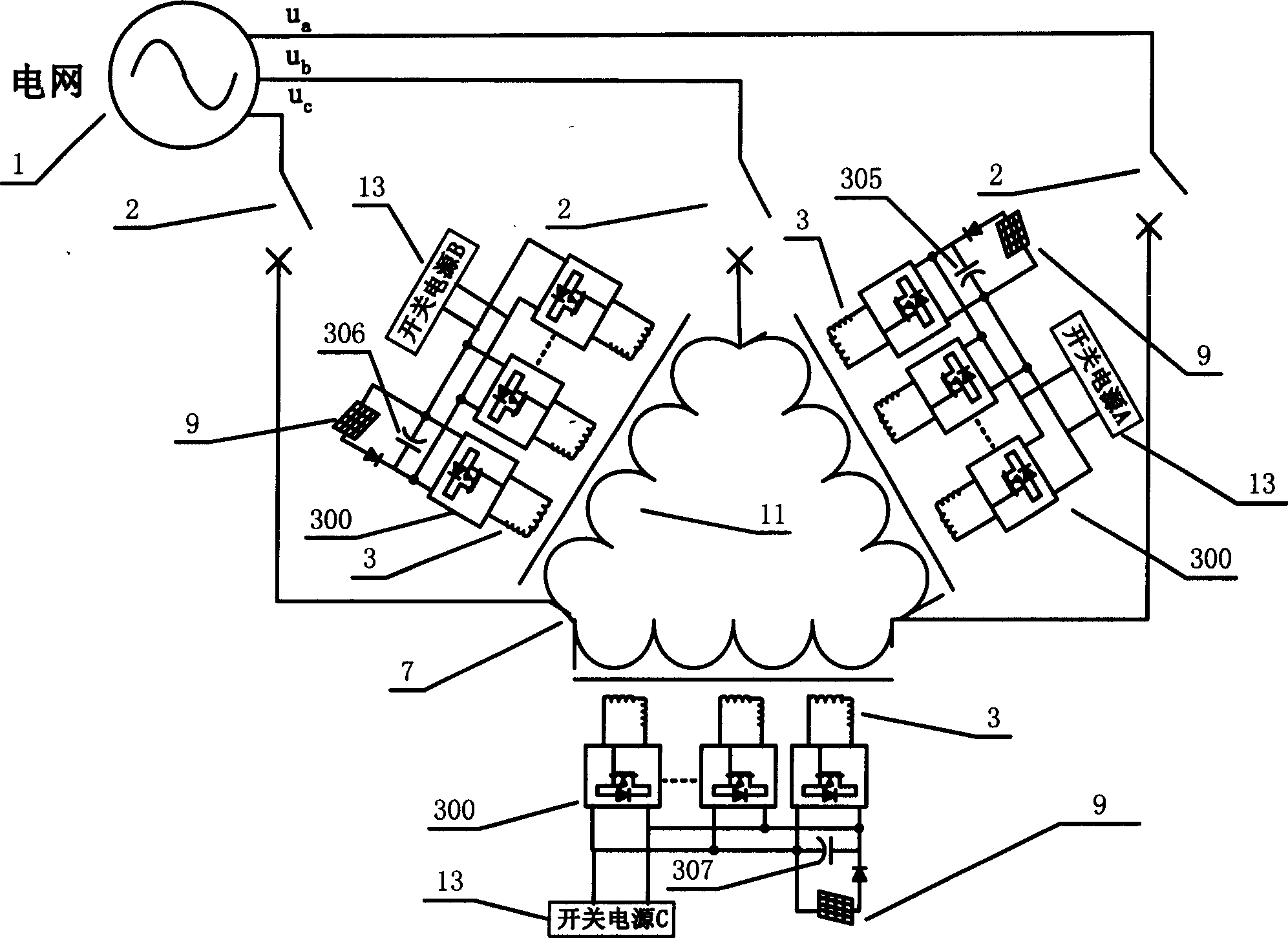

Photovoltaic parallel network device having reactive and harmonic compensation function

InactiveCN1658465APhotovoltaic energy generationDc-ac conversion without reversalCapacitanceThree level

A three-phase photovoltaic interconnected device having both reaction and harmonic compensation function, and belongs to the field of multi-functional photovoltaic interconnected device technology. The characteristic is: the main power circuit of this device is composed of the photovoltaic array, the interconnected inverter and interconnected filter sensor. The structure of the inverter has many kinds of patterns, such as the two level structure, the three level structure, the three-phase generatrix capacitance separated chain structure with transformation, the three-phase union capacitance chain structure with transformation and the chain structure without transformation. This device can emit the power to the electric net, and can in time compensate the reaction and harmonic wave of the current in the net. This invention increases the utilization ratio of the solar battery board of photovoltaic electricity generation, and meanwhile it solves the problem of the working method of the photovoltaic system in the bad lighting conditions, that is, the system will not be left unused and compensate the harmonic wave and reaction of the electric net.

Owner:TSINGHUA UNIV

Process for making and programming and operating a dual-bit multi-level ballistic flash memory

An fast program, ultra-high density, dual-bit, multi-level flash memory process, which can be applied to a ballistic step split gate side wall transistor, or to a ballistic planar split gate side wall transistor, which enables program operation by low voltage requirement on the floating gate during program is described. Two side wall floating gates are paired with a single word line select gate, and word lines are arranged to be perpendicular both the bit lines and control gate lines. Two adjacent memory cells on the same word line do not require an isolation region. Also, the isolation region between adjacent memory cells sharing the same bitline is defined by the minimum lithography feature, utilizing a self align fill technique. Adjacent memory cells on the same word line share bitline diffusion as well as a third poly control gate. Control gates allow program and read access to the individual floating gate. In addition to the dual-bit nature of the cell, density can be even further improved by multi-level storage. In one embodiment, the dual multi-level structure is applied to the ballistic step split gate side wall transistor. In a second embodiment, the dual multi-level structure is applied to the ballistic planar split gate side wall transistor. Both types of ballistic transistors provide fast, low voltage programming. The control gates are used to override or suppress the various threshold voltages on associated floating gates, in order to program to and read from individual floating gates. The targets for this non-volatile memory array are to provide the capabilities of high speed, low voltage programming (band width) and high density storage.

Owner:HALO LSI DESIGN & DEVICE TECH

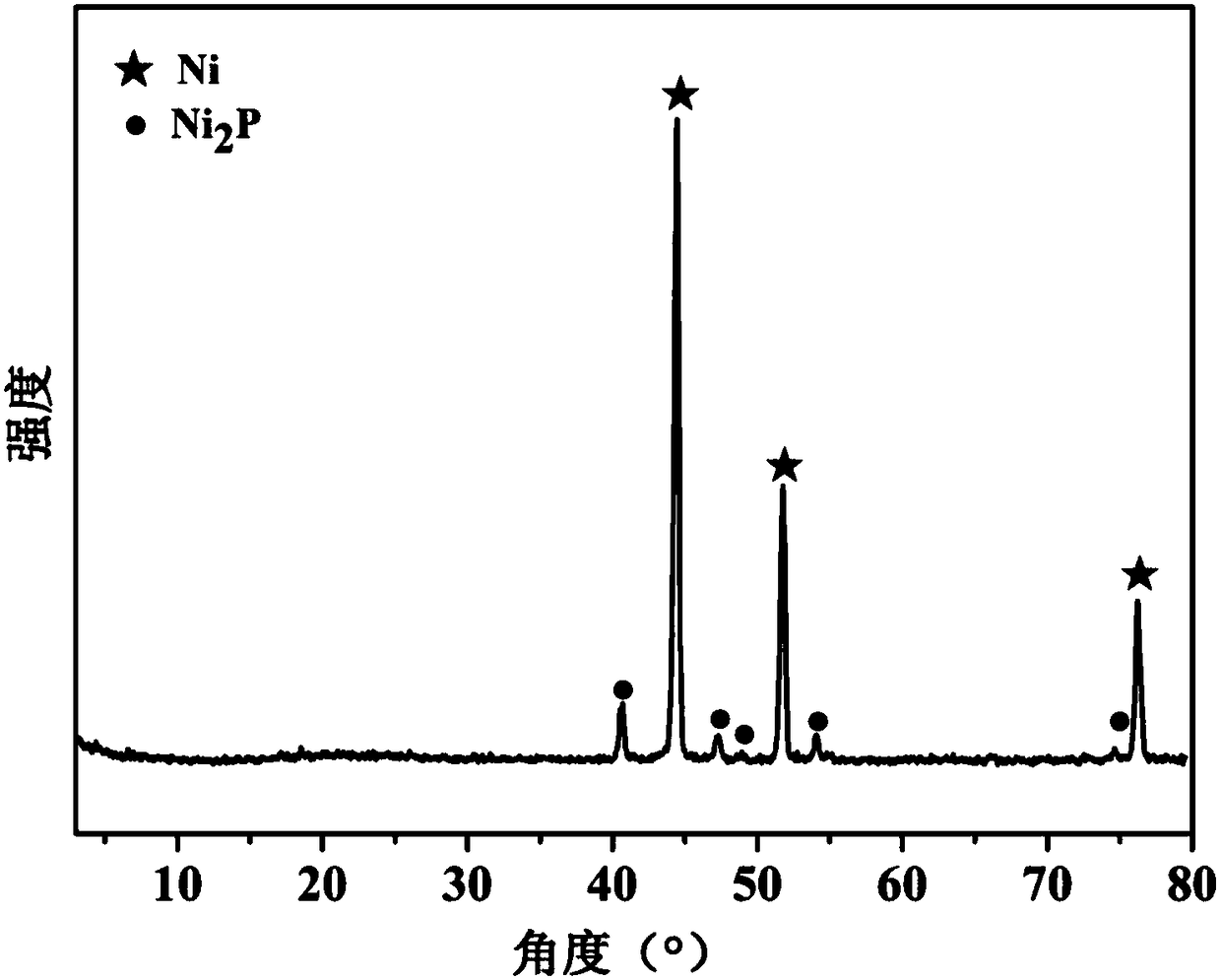

Three-dimensional multi-level structure type high-dispersion nickel-based electro-catalytic material and preparation method thereof

ActiveCN108554413AAffects catalytic performanceUnique structural featuresCatalyst activation/preparationElectrolytic organic productionLevel structureIon exchange

The invention provides a three-dimensional multi-level structure type high-dispersion nickel-based electro-catalytic material and a preparation method thereof. The method takes foam nickel as a conducting matrix and a nickel source needed by reaction is provided; urea is used as a precipitating agent, ammonium fluoride is used as an etching agent and an NiAl-LDH / / NF precursor grows on the surfaceof a foam nickel framework structure in situ; negative ions including H2PO4<-> and B(OH)4<-> are introduced into hydrotalcite layers through an ion exchanging method; a hydrotalcite intermediate containing the negative ions is reduced at high temperature to obtain the three-dimensional multi-level structure type high-dispersion nickel-based electro-catalytic material; a chemical formula is NiY-Al2O3 / NF, wherein Y is one of P or B. The material is used for electro-catalytic oxygen evolution reaction under an alkaline condition; when the current density reaches 10mA.cm<-2>, the overpotential ofthe oxygen evolution reaction is 270 to 190mV. When the material is used for carrying out selective electro-catalytic oxidization reaction on 5-hydroxymethylfurfural under the alkaline condition, theconversion rate and the selectively reach 92 to 100 percent and 95 to 100 percent respectively, and the invention proves that the material is suitable for being used as the electro-catalytic material.

Owner:BEIJING UNIV OF CHEM TECH

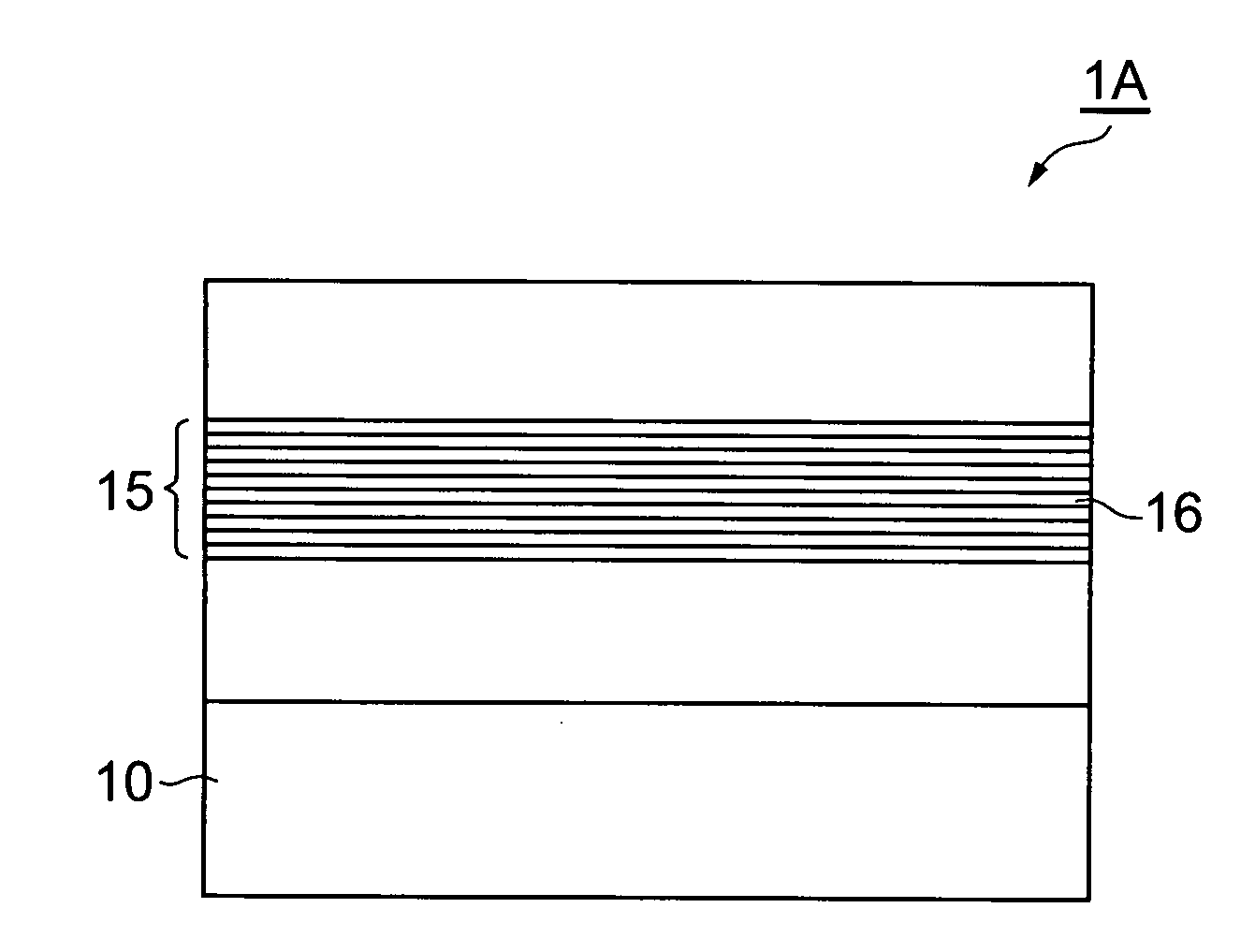

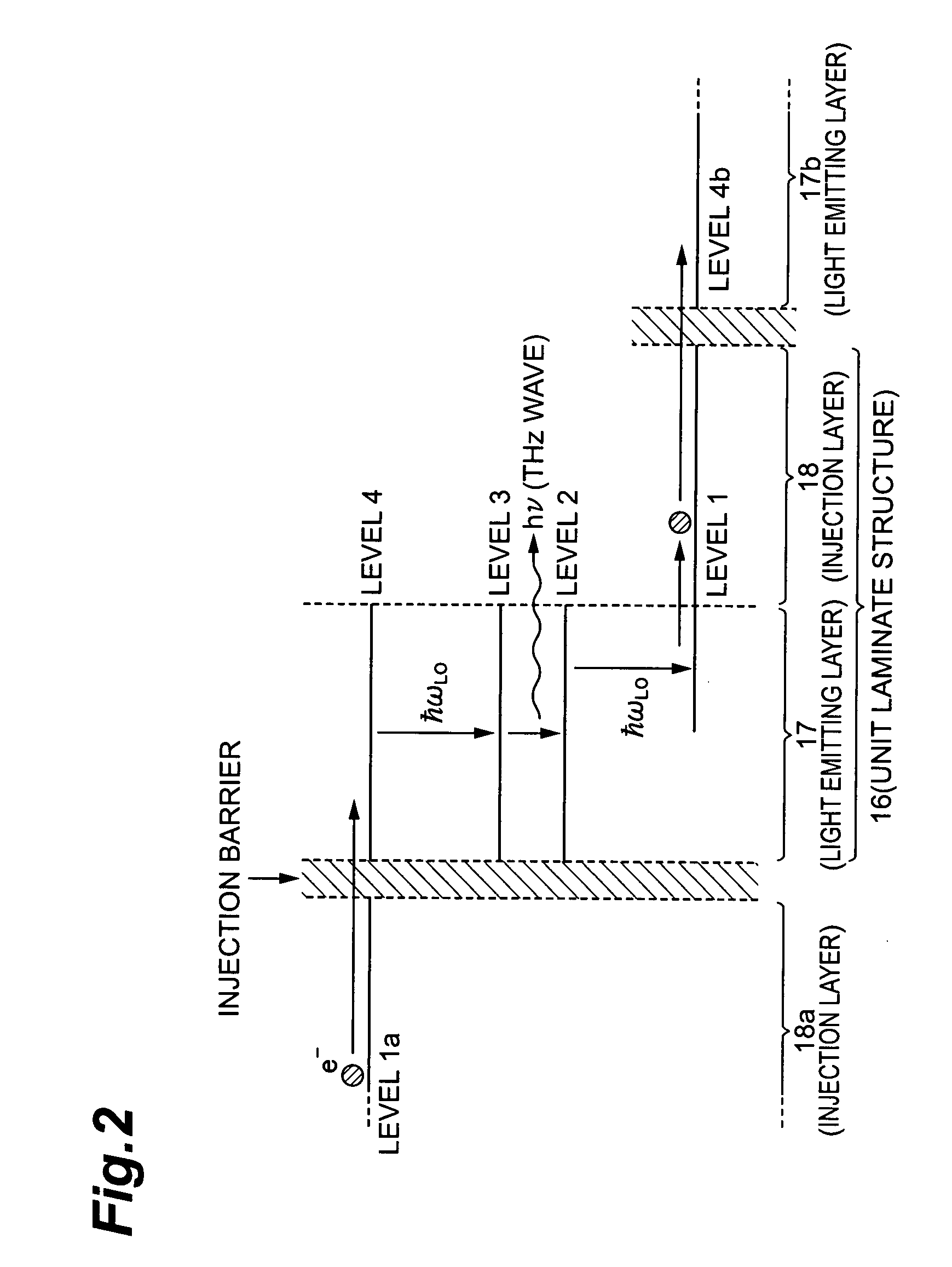

Quantum cascade laser

ActiveUS20080219308A1Increase supplyIncrease productionOptical wave guidanceLaser detailsLevel structureQuantum well

A quantum cascade laser is composed of a semiconductor substrate, and an active layer provided on the semiconductor substrate and having a cascade structure formed by multistage-laminating unit laminate structures 16 each of which includes a quantum well light emitting layer 17 and an injection layer 18. The unit laminate structure 16 has, in its subband level structure, an emission upper level 3, an emission lower level 2, and an injection level 4 as an energy level higher than the emission upper level 3, and light hν is generated by means of intersubband transition of electrons from the level 3 to the level 2 in the light emitting layer 17, and electrons through the intersubband transition are injected into the injection level in a unit laminate structure of the subsequent stage via the injection layer 18, and from this injection level, electrons are supplied to the emission upper level. Thereby, a quantum cascade laser which realizes operation with a high output at a high temperature is realized.

Owner:HAMAMATSU PHOTONICS KK

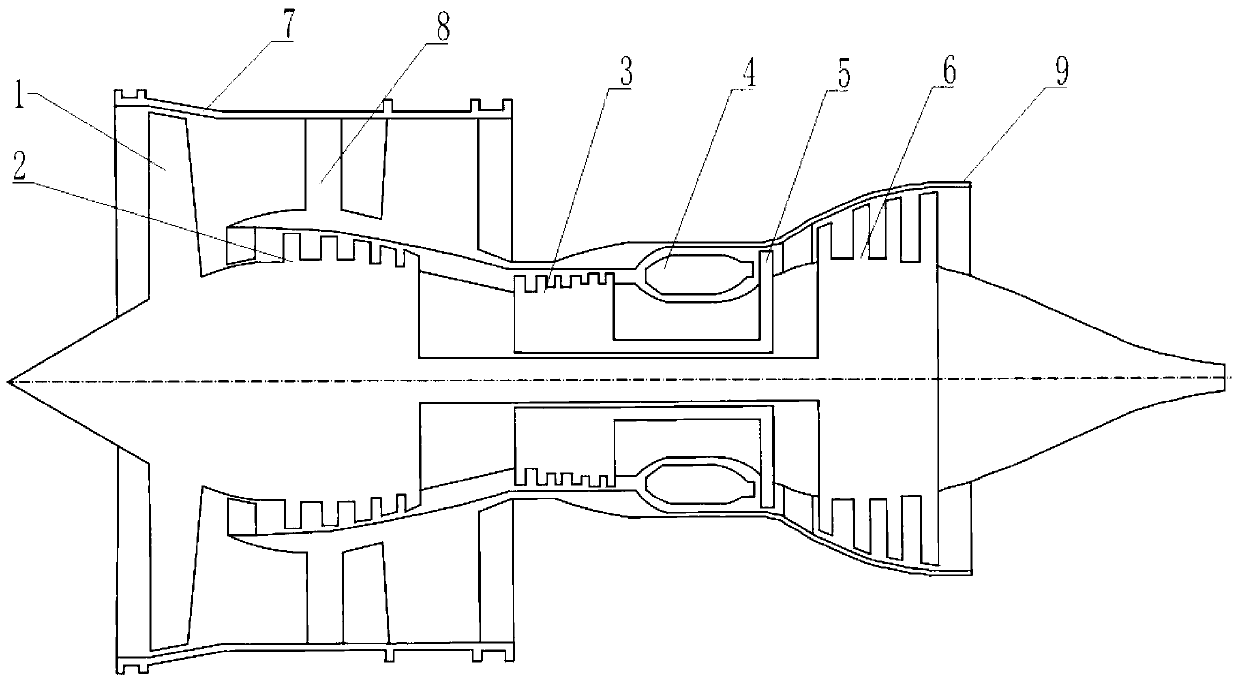

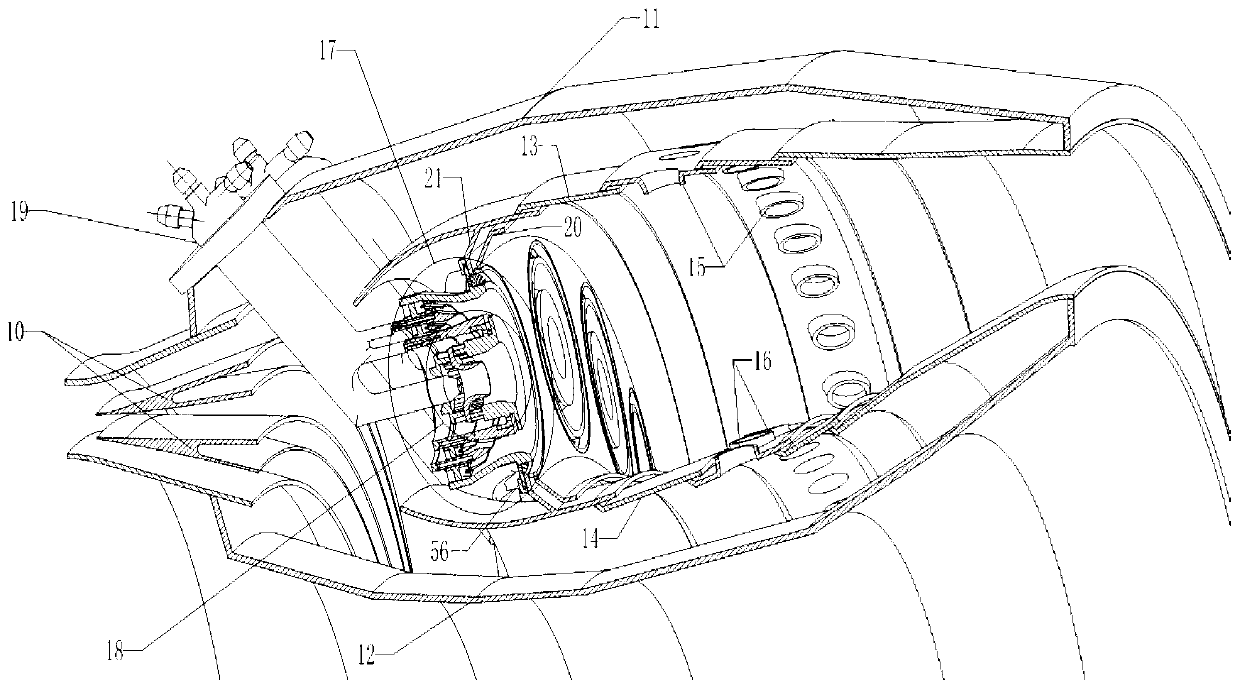

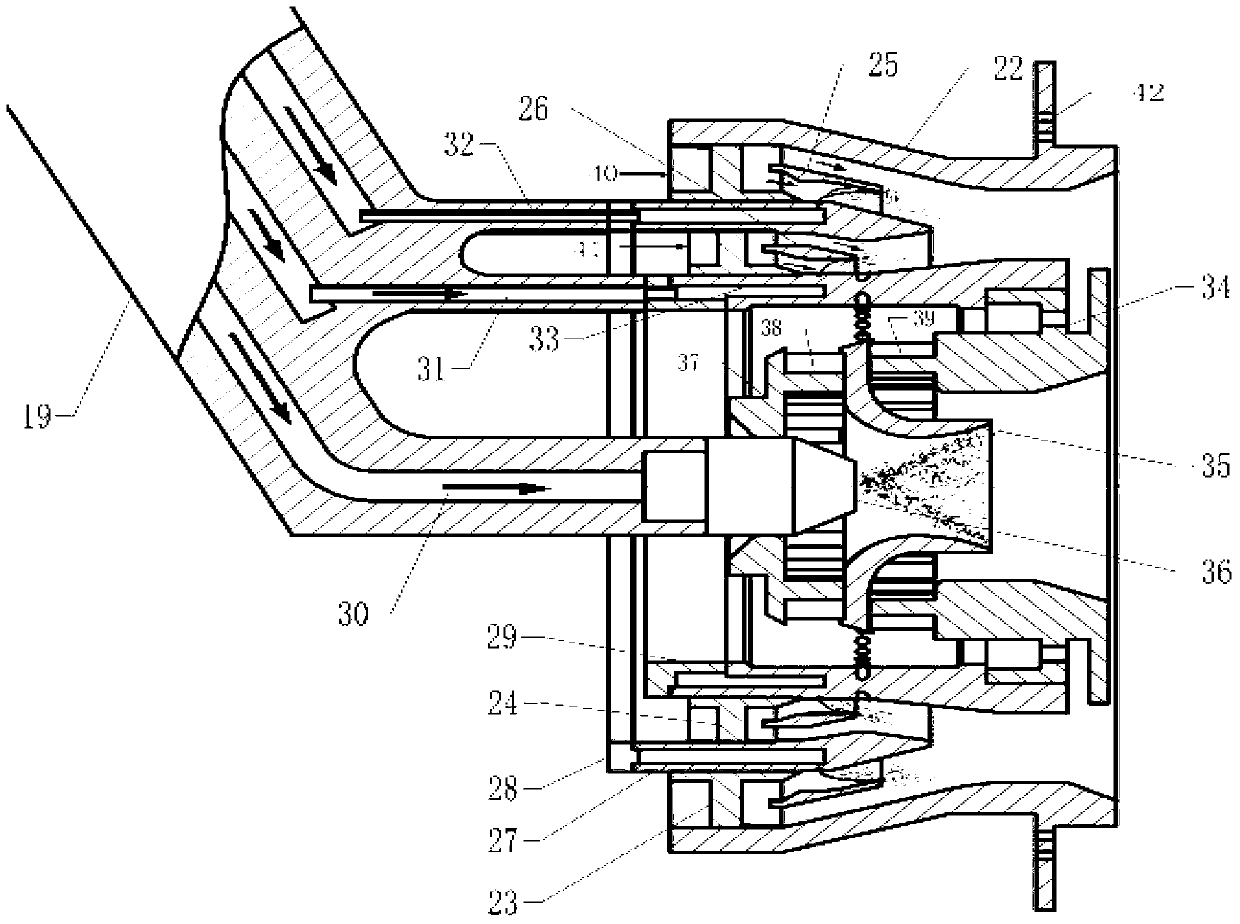

Double-pre-film pneumatic nebulization low pollution combustor head structure

The invention discloses a double-pre-film pneumatic nebulization low pollution combustor head structure. Combustion is organized in a combustor head in a center classification mode. The combustor head structure is divided into a main combustion level and a pre-combustion level. The pre-combustion level is of a double-level swirl cup structure, combustion is organized in a partially premixing mode, and the requirements for combustion stability and pollutant discharge of small working conditions are met. The main combustion level is of an axial swirler double-pre-film structure, combustion is conducted in a combustor in a premixing mode, and combustion pollutants can be effectively reduced through premixing combustion. The double-pre-film type main combustion level structure comprises two stages of independent oil collecting rings, two stages of axial swirlers and two stages of pre-film plate structures. Each stage of independent oil collecting ring is provided with a plurality of beveled fuel injection holes. Each stage of fuel is injected out through the fuel injection holes and then strikes the pre-film plates to be expanded into oil films. The structure is beneficial for fuel classification of the whole combustor under different working conditions, ensures reasonable oil-gas distribution, and further reduces the pollutant discharge level in the whole cycle of landing and taking off of the combustor of an aero-engine.

Owner:BEIHANG UNIV +1

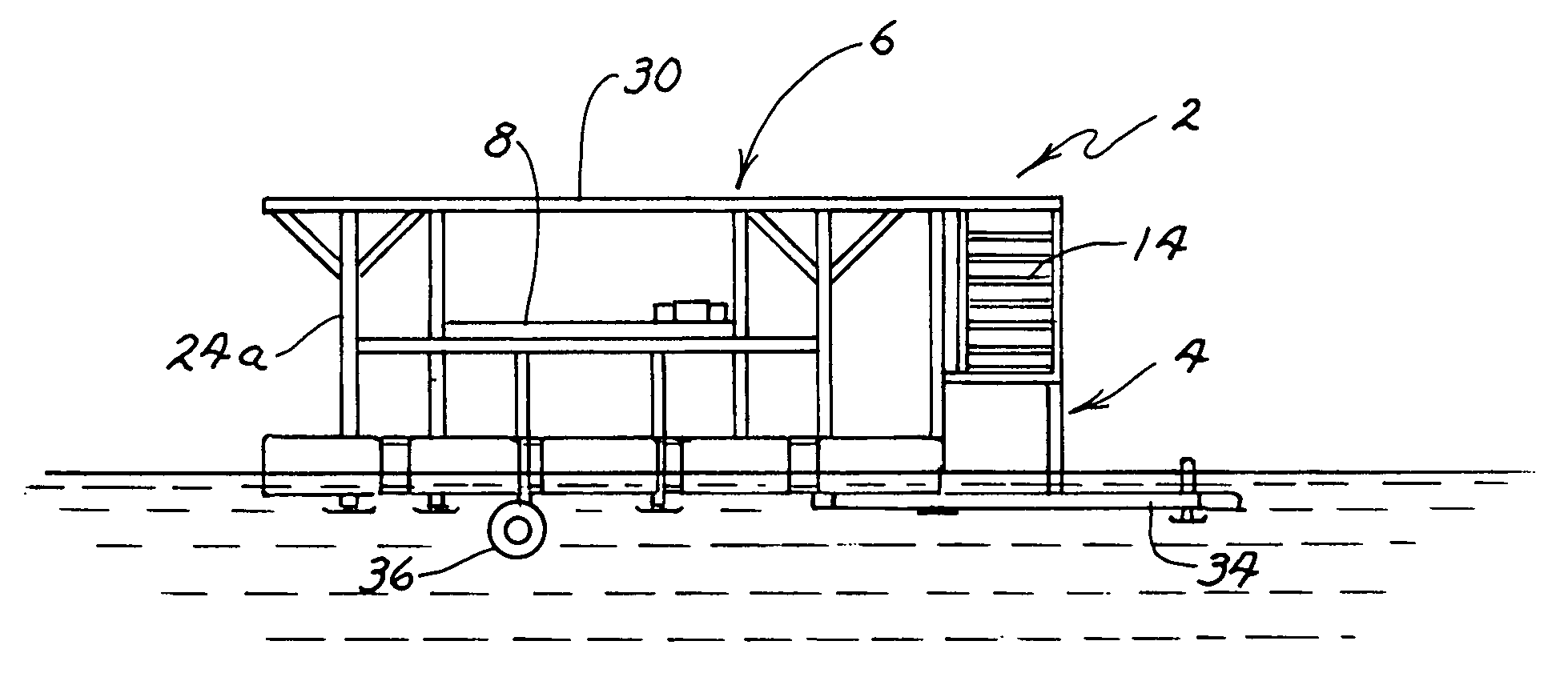

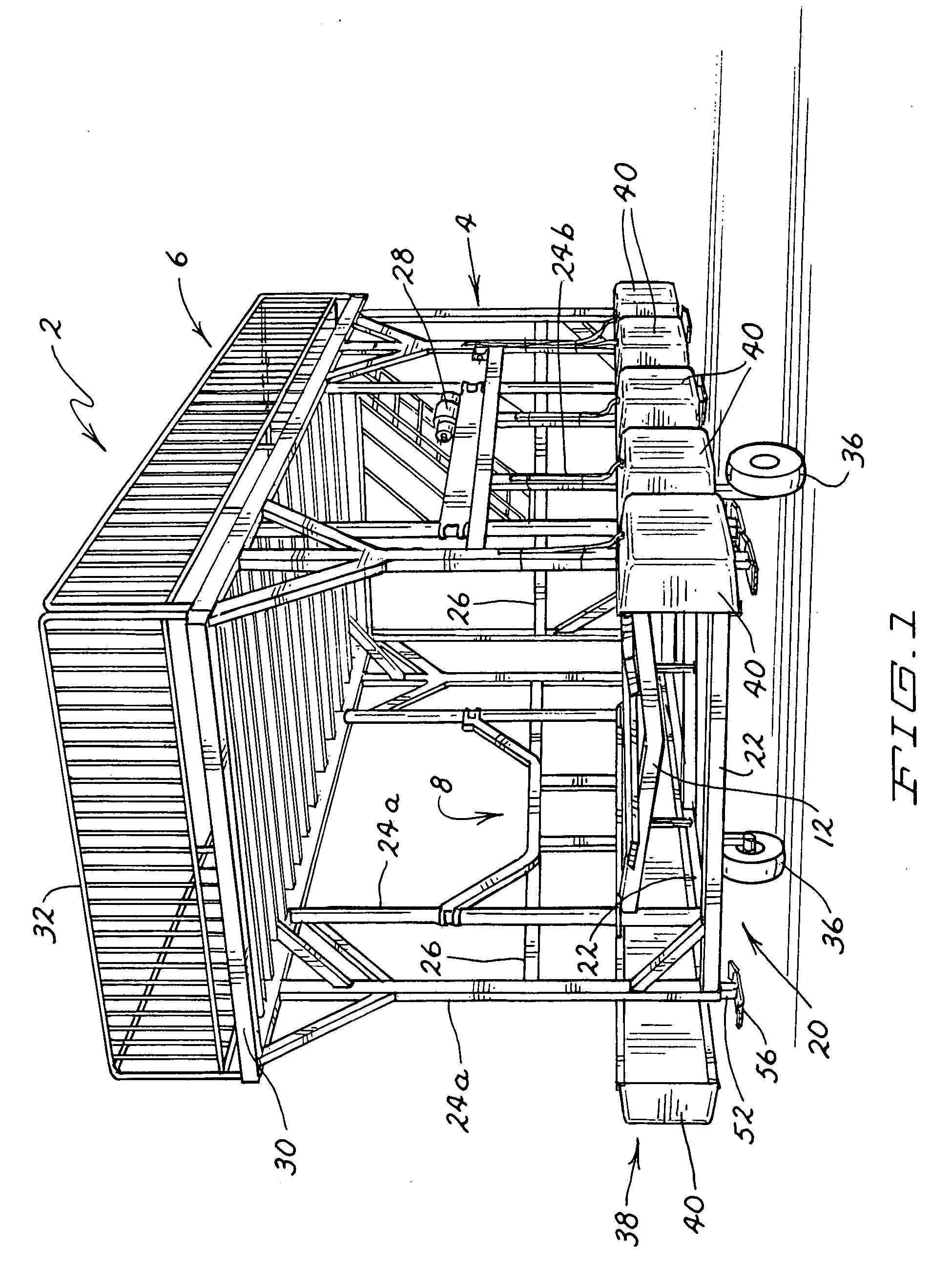

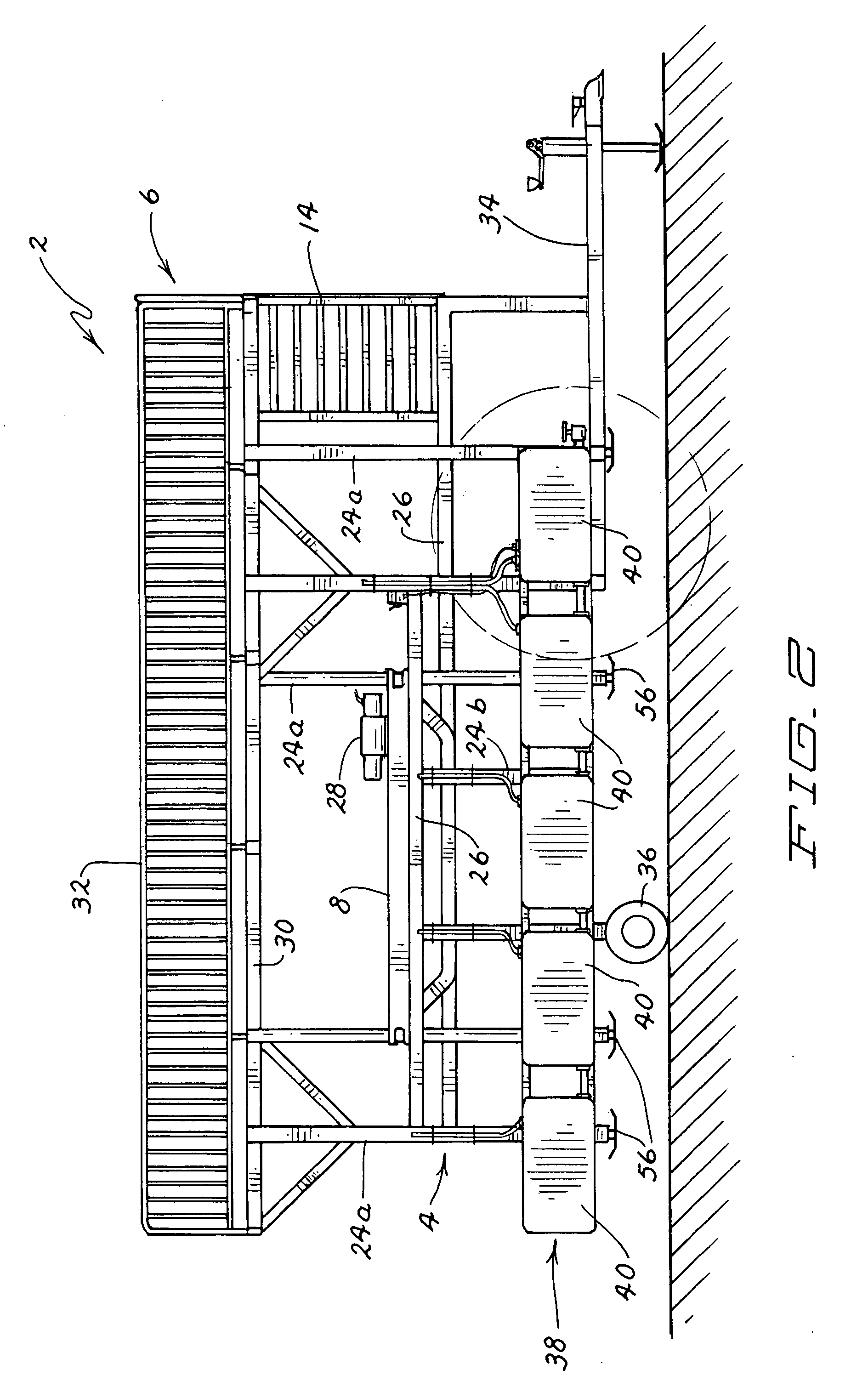

Seasonal, multi-use, multi-level structure transportable both by ground and water for use in a body of water

ActiveUS20060278154A1Towing/pushing equipmentItem transportation vehiclesLevel structureAtmospheric air

A multi-use, multi-level structure can be installed in and removed from a body of water in a seasonal fashion. The structure has a lower level that includes a boat lift and an upper level that provides an entertainment area. The structure carries a buoyancy system for selectively floating the structure on the body of water or sinking the structure in the water. The buoyancy system preferably comprises a ballast system that includes an array of hydraulically interconnected ballast tanks that are vented to the atmosphere. A valve may be opened to admit water to the ballast tanks to flood the tanks. A pump is used to pump water out of the ballast tanks when desired.

Owner:POWERBLOCK HLDG

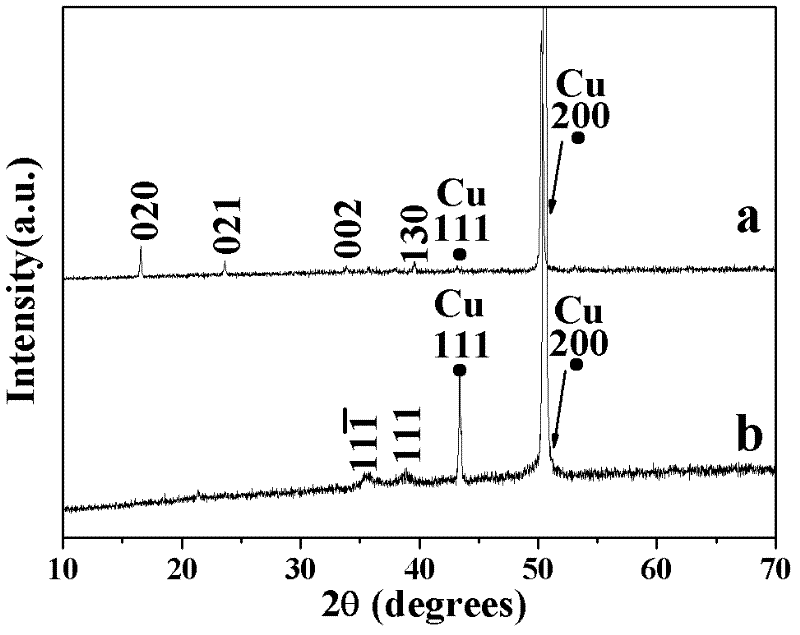

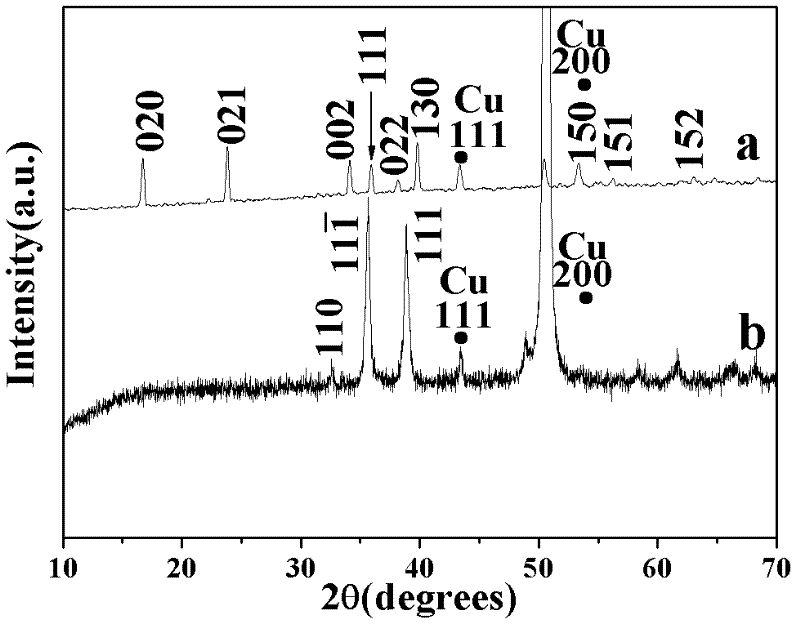

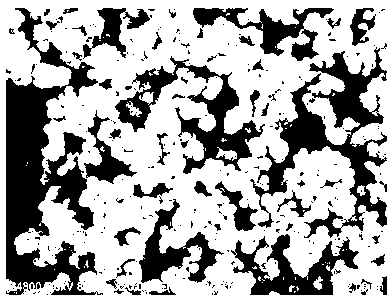

Method for preparing electrode material CuO (cupric oxide) film of lithium ion battery on copper substrate

InactiveCN102231435AUniform shapeThe synthesis method is simple and controllableCell electrodesMicro nanoLevel structure

The invention provides a method for preparing electrode material CuO (cupric oxide) film of a lithium ion battery on a copper substrate. The method comprises the following steps of: reacting a pretreated copper substrate with a microemulsion for 2-96 hours at room temperature or reacting the pretreated copper substrate with an alkaline aqueoussolution for 40-90 minutes at room temperature; takingout the copper substrate, and washing and drying the copper substrate to obtain a Cu(OH)2 micro-nano multi-level structure film or Cu(OH)2 nano-rod array film; and processing the dried film in an inert atmosphere fro 4-6 hours at a temperature of 150-200 DEG C to obtain a CuO micro-nano multi-level structure film or CuO nano-rod array film with the similar shape. The film is uniform in shape and stable in structure and can be used as an electrode of a lithium ion battery directly; in addition, by using the film, the preparing processes of the electrode can be simplified, the initial dischargespecific capacity of the battery can be improved obviously, the initial irreversible capacity loss can be reduced and the cycle performance and the multiplying power performance can be improved further.

Owner:HEFEI UNIV OF TECH

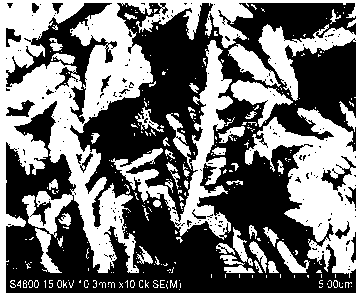

Complexing-agent-assisted preparation method of cadmium sulfide multi-level-structured nano-grade material

InactiveCN103073049AEasy to controlImprove protectionCadmium sulfidesNanotechnologyVacuum pumpingChemical reaction

The invention relates to a complexing-agent-assisted preparation method of a cadmium sulfide multi-level-structured nano-grade material. The method is characterized in comprising the steps that: a, a chemical reaction liquid is prepared, wherein 1 part of cadmium salt by weight and 0-50 parts of organic small-molecular compound by weight are dissolved in 100 parts of water or water / ethanol mixture by weight; under a temperature of 30-80 DEG C, stirring is sufficiently carried out, such that a reaction liquid is prepared; b, the cadmium sulfide multi-level-structured nano-grade material is synthesized, wherein the reaction liquid prepared in the step a is delivered into an autoclave with a polytetrafluoroethylene liner; a sulfur source is added, and a reaction is carried out; after the reaction, the autoclave is naturally cooled to 60 DEG C; methanol with a volume of 20-30% of that of the total volume of the reaction liquid is added; a product is filtered, and is washed multiple times by using anhydrous ethanol; and the product is dried by vacuum pumping, such that the cadmium sulfide nano-grade material with different crystal forms and morphologies is obtained. The method provided by the invention has the advantages of simple process, low cost, and high operability. With the method, requirements of production and application can be satisfied by one step.

Owner:SHANGHAI NAT ENG RES CENT FORNANOTECH

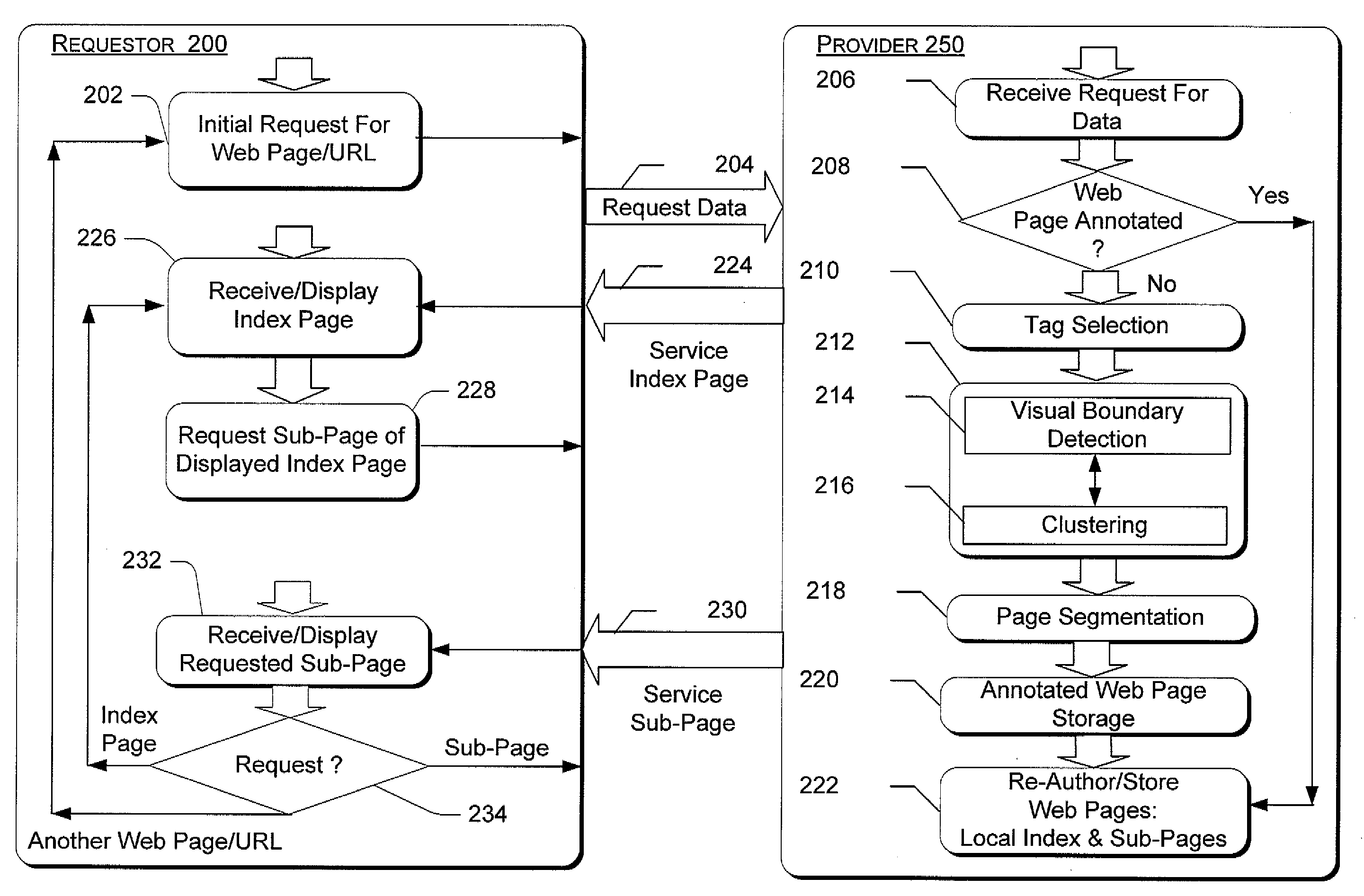

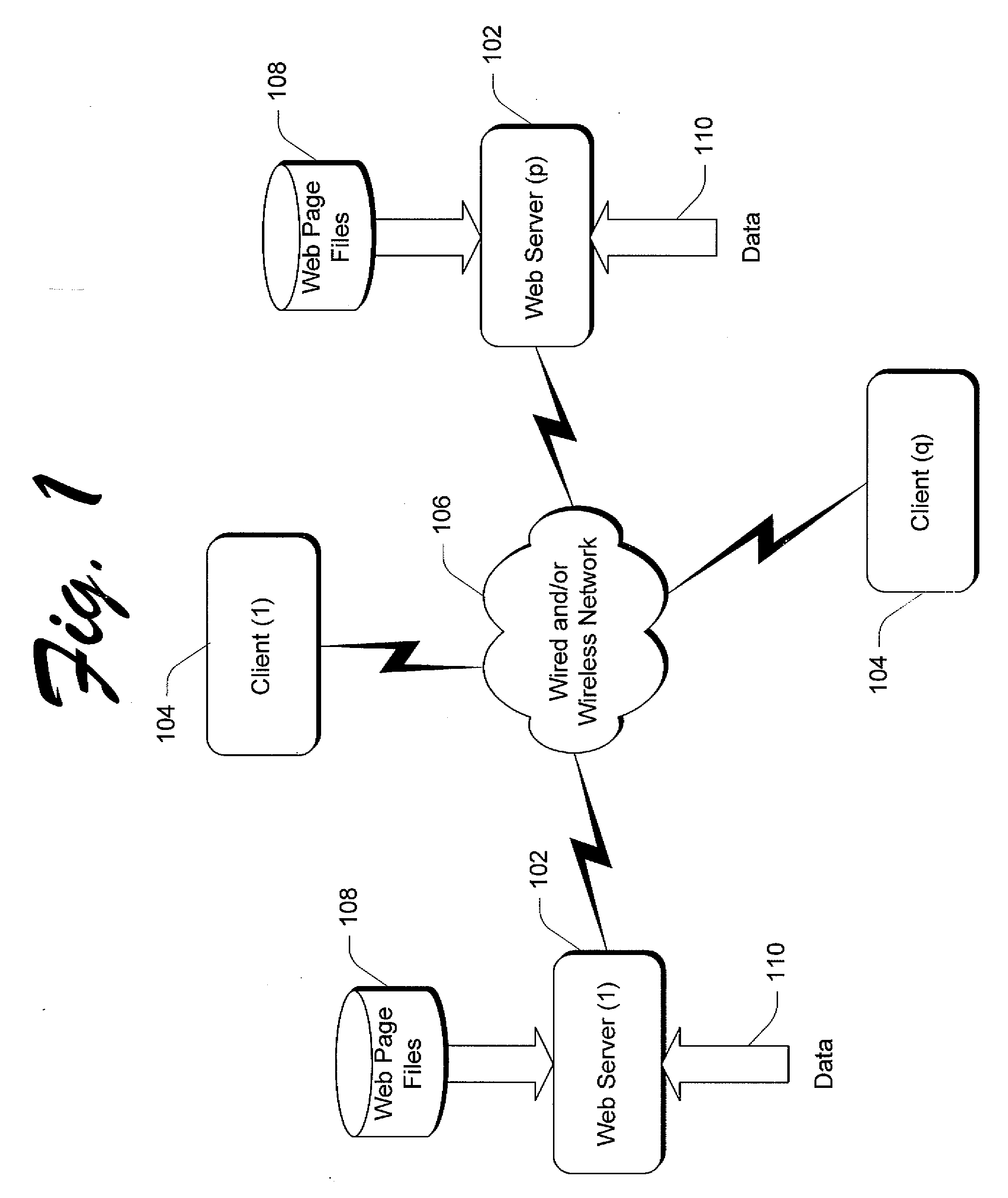

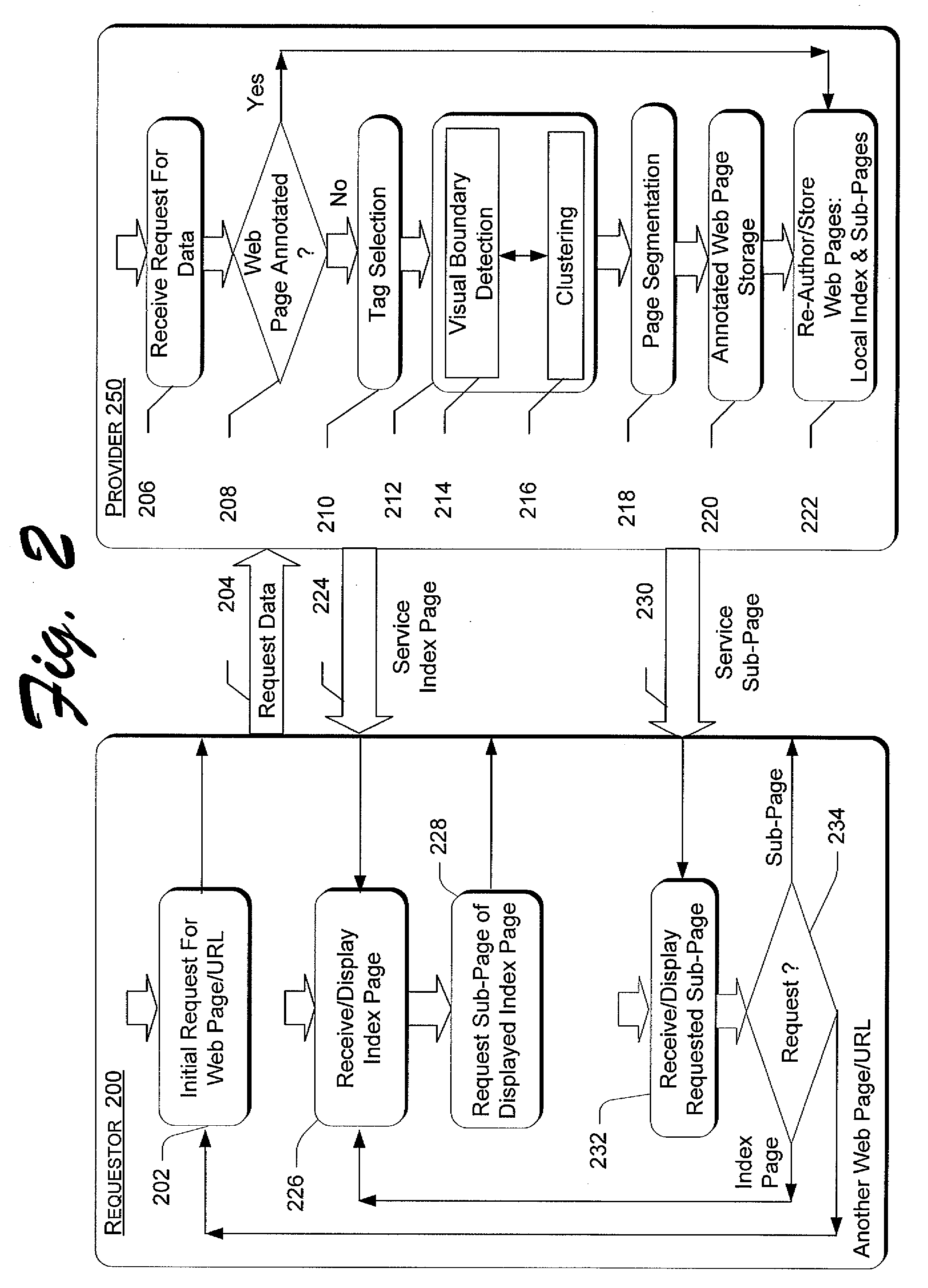

Small Form Factor Web Browsing

InactiveUS20060282444A1Digital data information retrievalDigital data processing detailsLevel structureSmall form factor

A large web page is analyzed and partitioned into smaller sub-pages so that a user can navigate the web page on a small form factor device. The user can browse the sub-pages to find and read information in the content of the large web page. The partitioning can be performed at a web server, an edge server, at the small form factor device, or can be distributed across one or more such devices. The analysis leverages design habits of a web page author to extract a representation structure of an authored web page. The extracted representation structure includes high level structure using several markup language tag selection rules and low level structure using visual boundary detection in which visual units of the low level structure are provided by clustering markup language tags. User viewing habits can be learned to display favorite parts of a web page.

Owner:MICROSOFT TECH LICENSING LLC

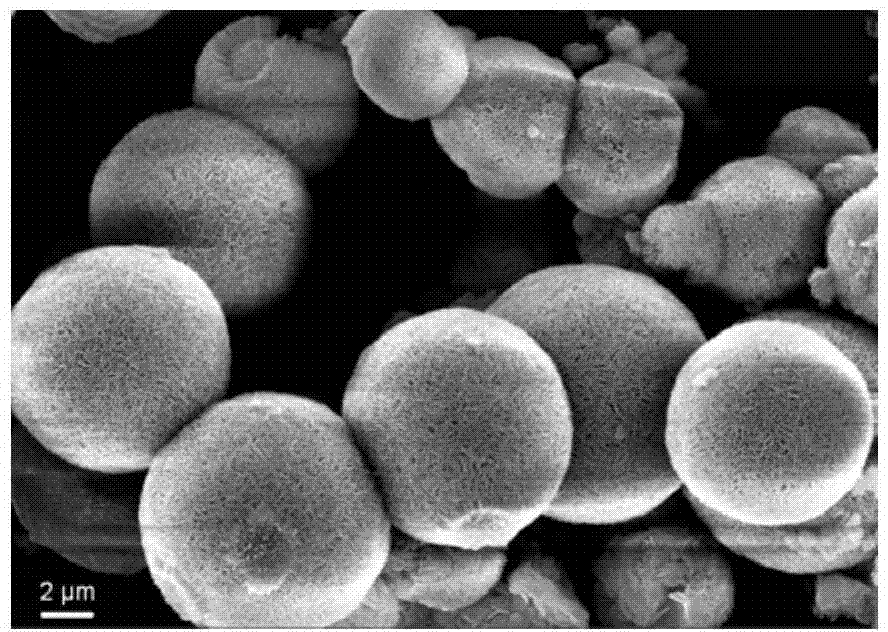

Preparation method of three-dimensional flower-shaped nickel cobaltate nano-sheet mesoporous microspheres

InactiveCN104773764AEasy to operateGood experimental reproducibilityMaterial nanotechnologyNickel compoundsAir atmosphereNano catalyst

The invention relates to a preparation method of three-dimensional flower-shaped nickel cobaltate nano-sheet mesoporous microspheres, and relates to the technical field of multi-level structured nano-grade catalyst materials. First, nickel nitrate hexahydrate and cobalt nitrate hexahydrate are adopted as a nickel source and a cobalt source, a deionized water-isopropanol mixed phase with a proper proportion is adopted as a solvent, methanol is adopted as a reactant, and no additional base precipitating agent is adopted; a three-dimensional flower-shaped nano-sheet microsphere precursor is prepared in a Ni<2+>-Co<2+>-NH3-NH4<+>-SG<n->-H2O-IPA-CH3OH system (SG<n-> is CO3<2-> or HCOO<->); the temperature is increased to 300-400 DEG C in an air atmosphere with a speed of 1 DEG C / min, and the precursor is calcined for 2-3h, such that the three-dimensional flower-shaped nickel cobaltate nano-sheet mesoporous microspheres are obtained. According to the invention, co-precipitation of the formulated cobalt and nickel in the raw materials is realized. The prepared three-dimensional flower-shaped nickel cobaltate nano-sheet mesoporous microspheres are spinel cubic phases with high purity, and are formed by ultrathin nano-sheet self-assembly. The microspheres comprise rich mesopores, and have a large specific surface area. The method has the advantages of simple operation, appropriate conditions and easy control.

Owner:BEIJING UNIV OF CHEM TECH