FFT architecture and method

A multiplier and memory technology, applied in the field of signal processing, can solve the problems of reducing processing power and insufficient processing power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

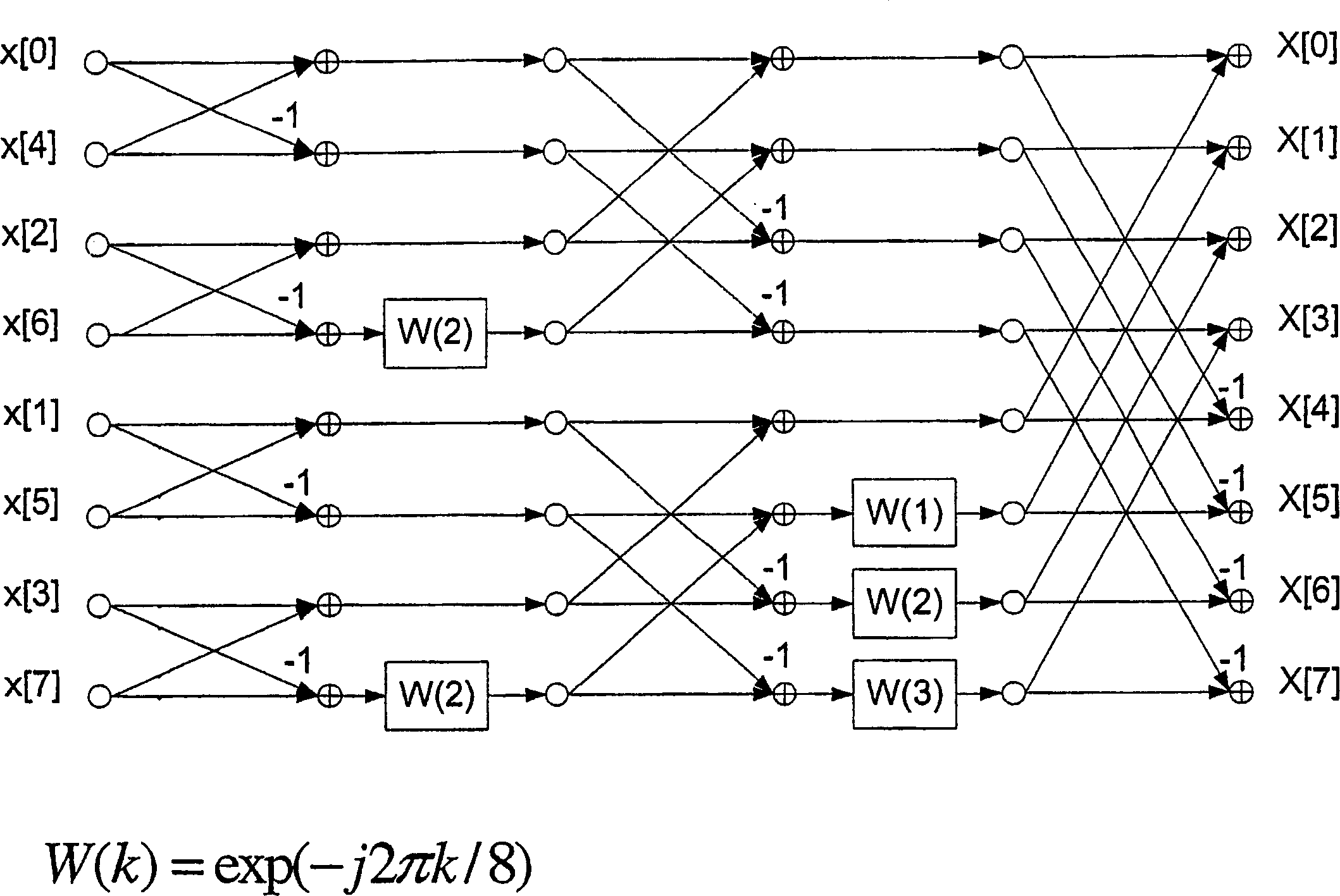

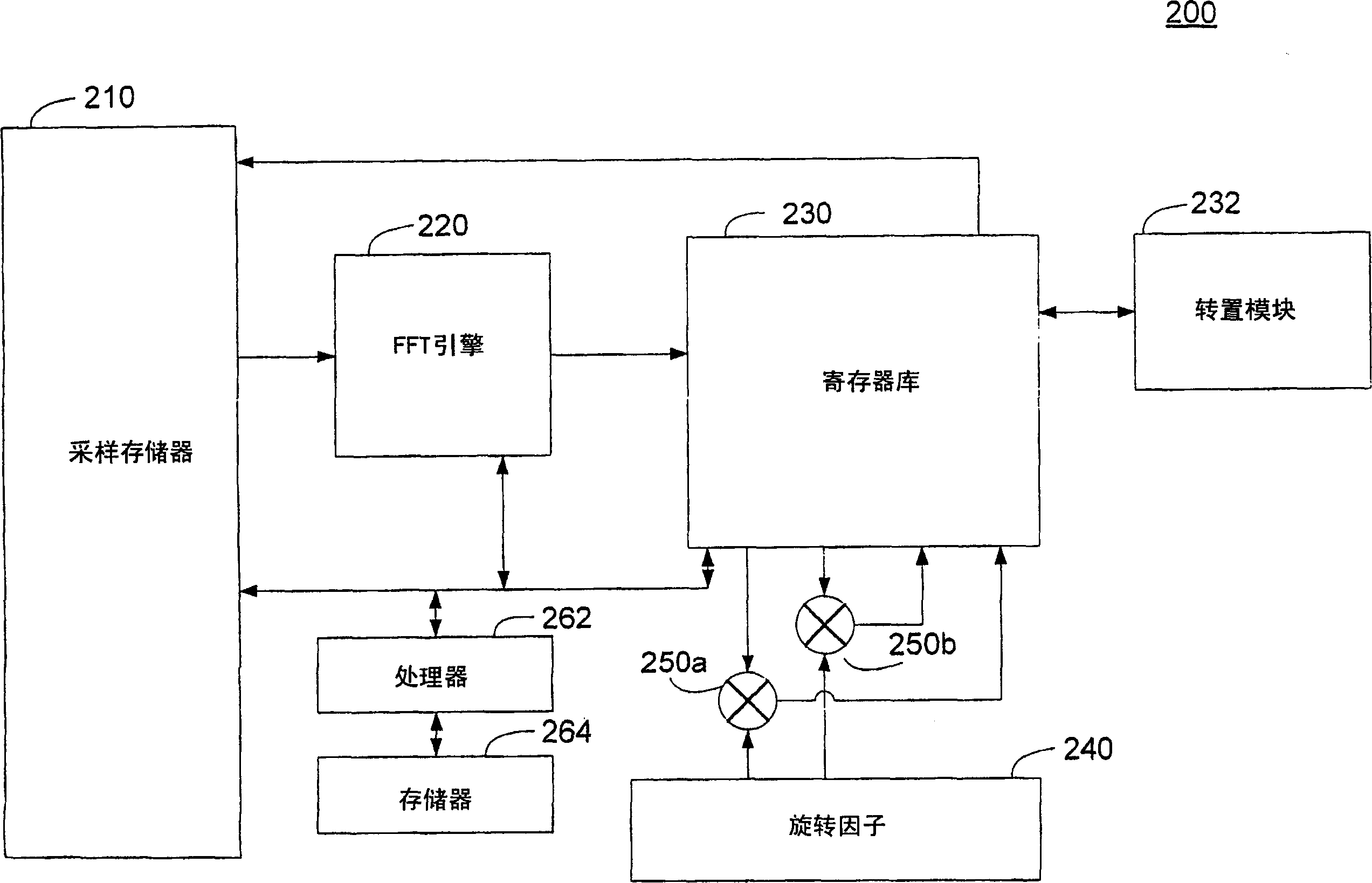

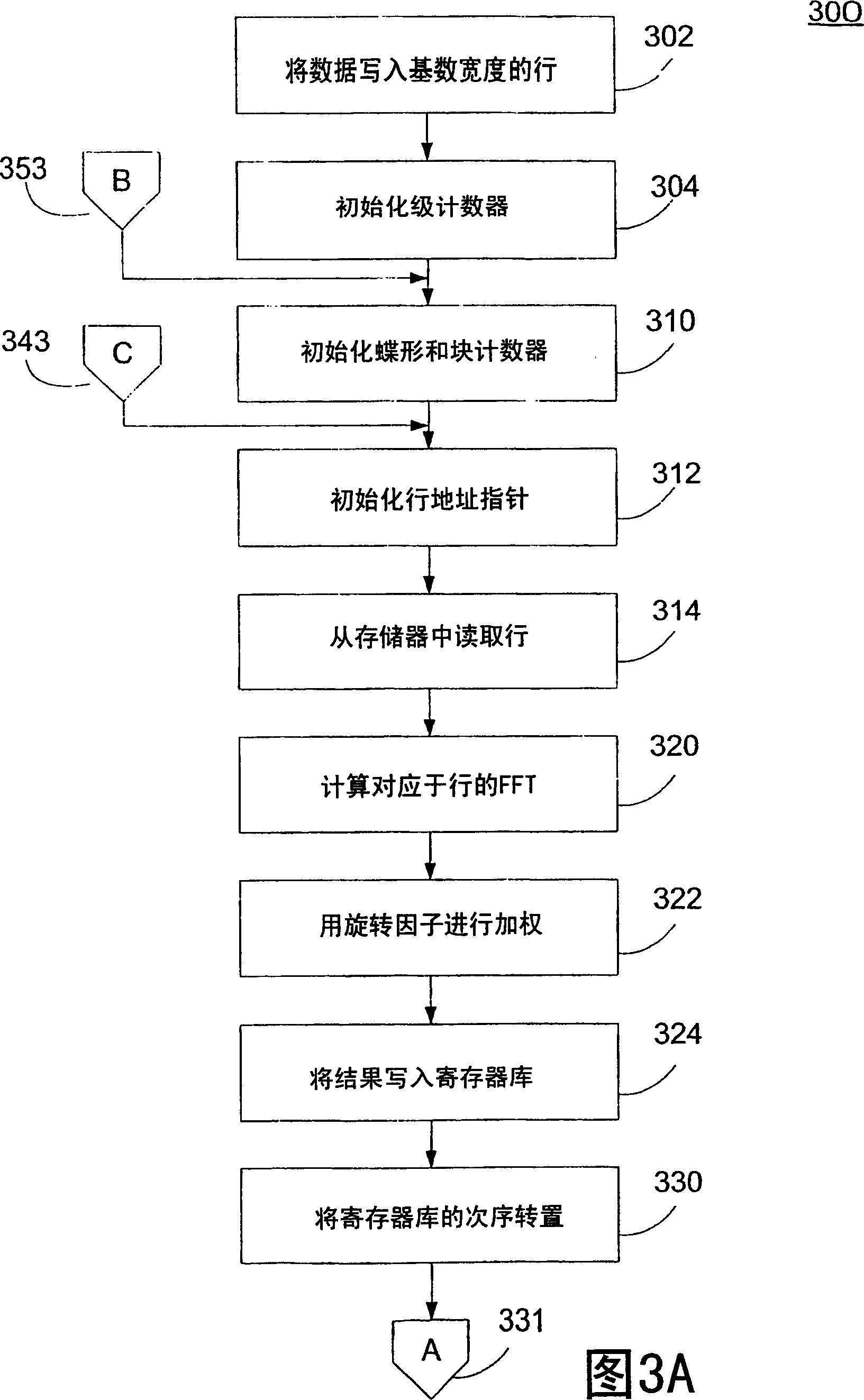

[0020] The present application discloses a hardware structure suitable for FFT or inverse FFT (IFFT), a device integrating the FFT module, and a method for performing FFT or IFFT. The FFT structure is generic so that any radix FFT can be implemented. This FFT structure minimizes the number of cycles used to perform the FFT while keeping the chip area small. Specifically, the FFT architecture configures memory and register space to facilitate optimization of memory accesses when performing in place FFTs. This FFT structure provides additional implementation flexibility, allowing for different numbers of radix and complex multipliers depending on specific design constraints. In speed-sensitive implementations that are less sensitive to die area, the FFT structure can be implemented with additional complex multipliers and higher radix. In implementations that are more sensitive to die area, the number of radix and complex multipliers can be reduced.

[0021] The FFT structure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More