FFT (fast Fourier transform) reinforcing design method with single event upset-resistant capability

A design method and anti-single event technology, applied in the direction of complex mathematical operations, etc., can solve the problems of unseen reinforcement methods, low space resource utilization, resource waste, etc., to improve anti-single event flipping ability, save space resources and costs , to ensure the effect of reliability and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Further illustrate working principle and working process of the present invention below in conjunction with accompanying drawing:

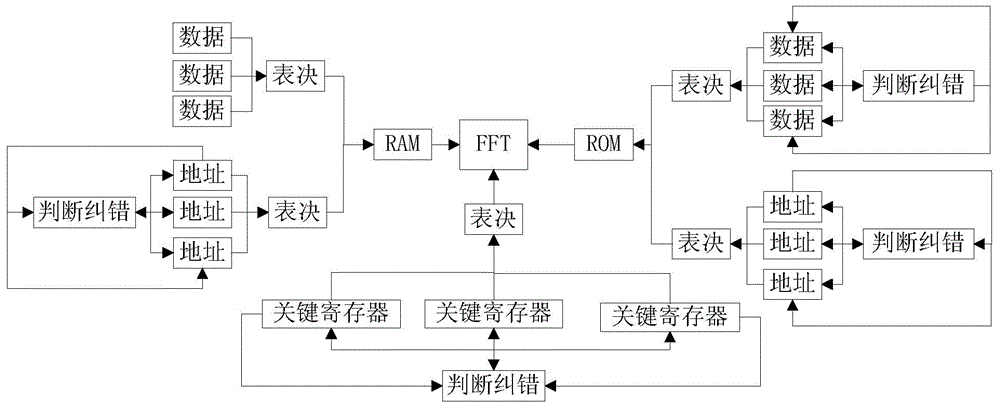

[0019] Such as figure 1 As shown, the present invention provides an anti-single event reversal FFT reinforcement design method, and the implementation method is as follows:

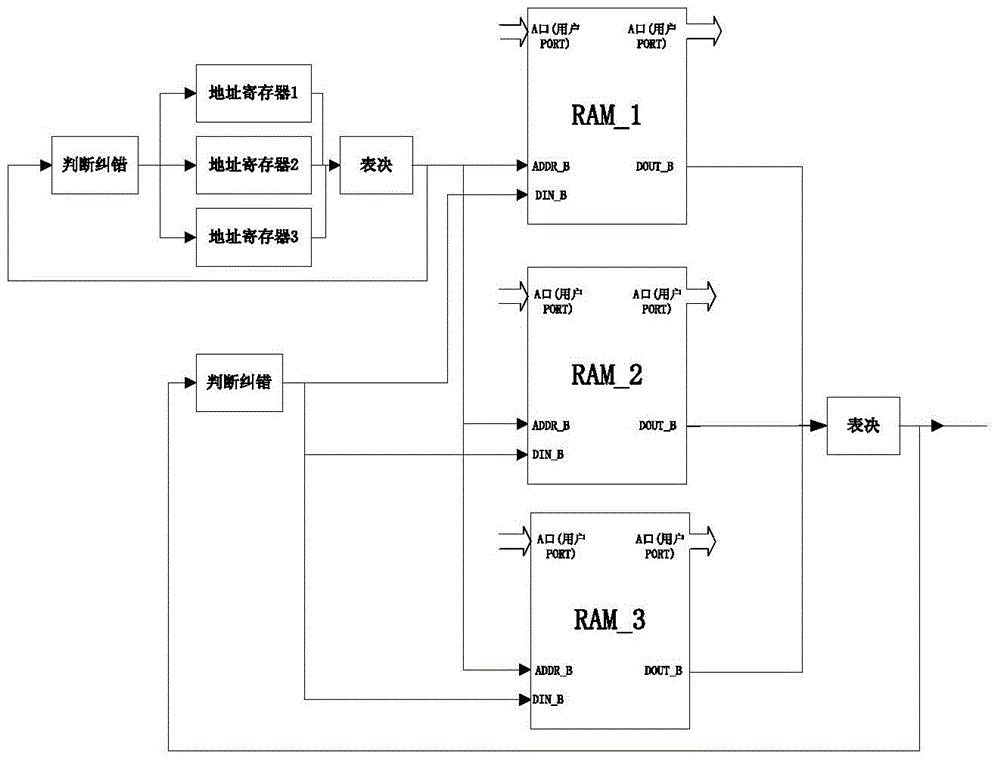

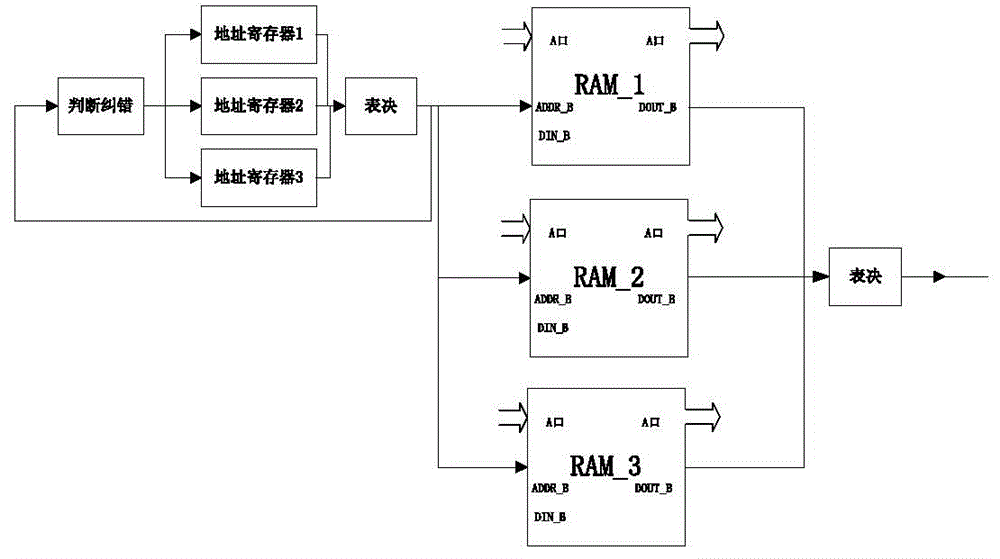

[0020] (1) Analyze the structure of the FFT algorithm, find out the ROM that stores the twiddle factors when the FFT circuit is realized, the RAM that stores the final data and realizes the inversion order, and the key registers that look for the twiddle factors; after the key registers are affected by the single event effect, Registers where errors can occur and affect subsequent calculations.

[0021] Through the specific analysis of the implementation structure of the radix-2FFT, radix-4FFT and split-radix FFT algorithms, the present invention finds that although different FFT algorithms are slightly different at the algorithm level, the basic operation structure i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More