Patents

Literature

15852results about How to "High control precision" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

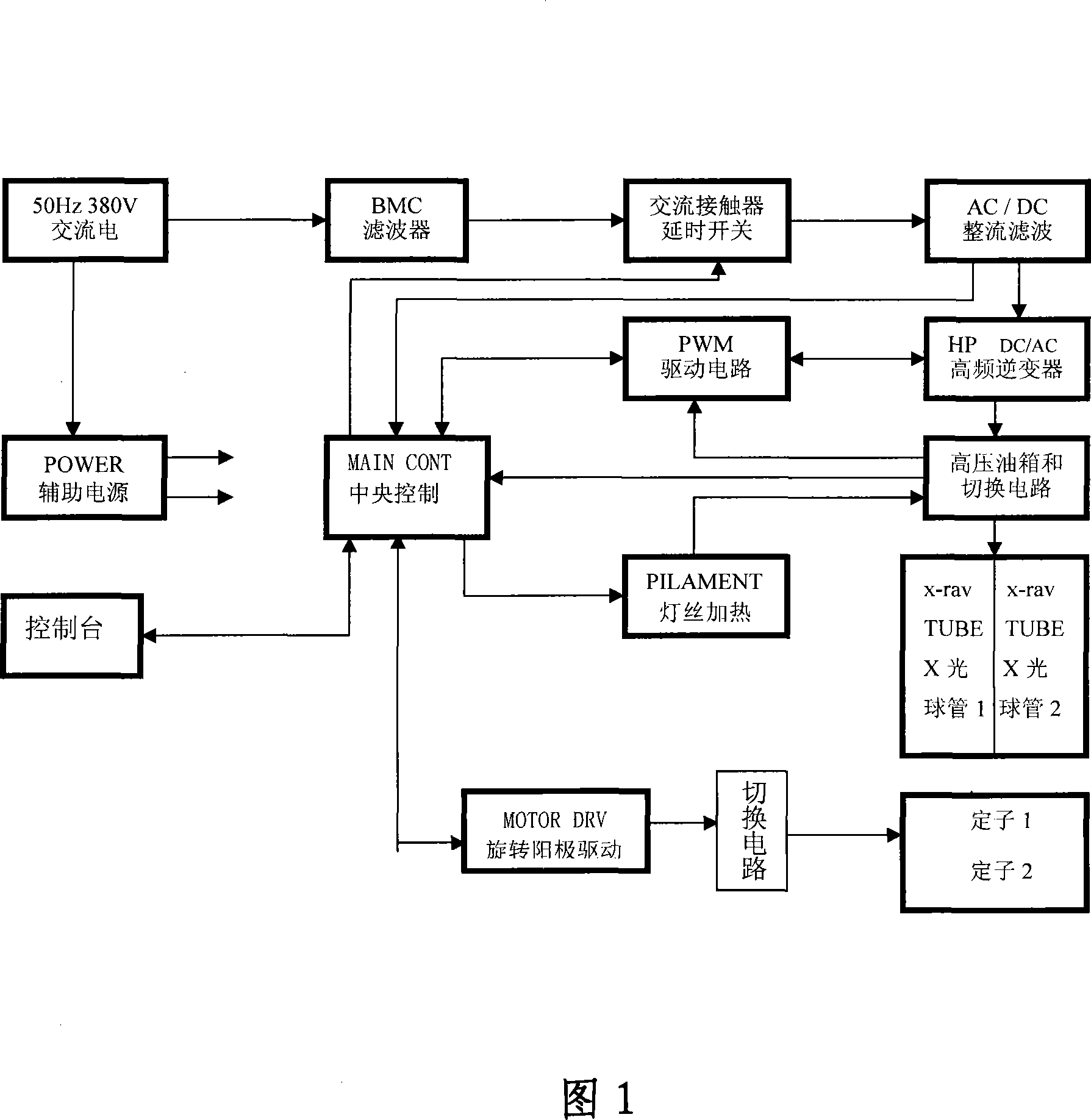

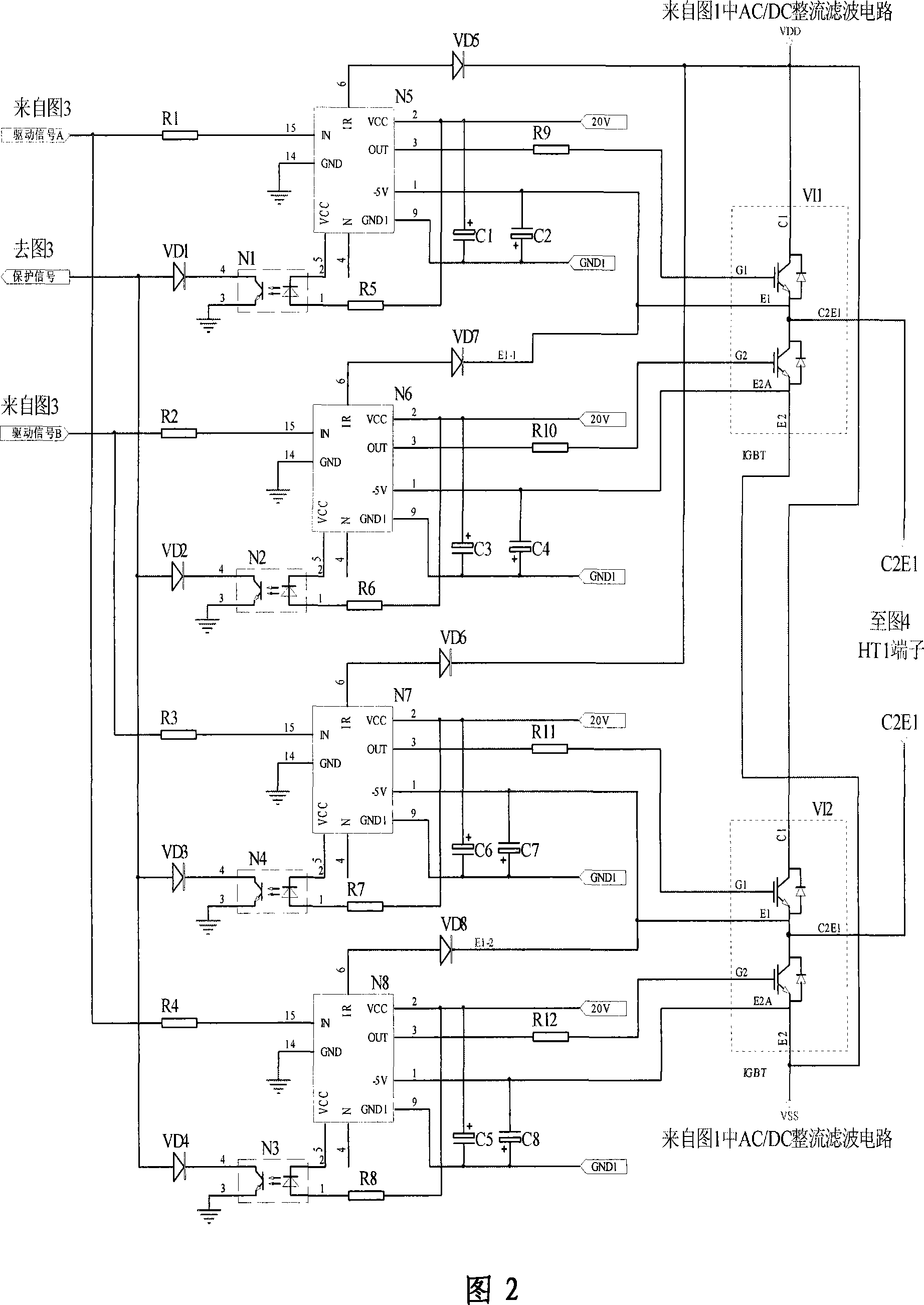

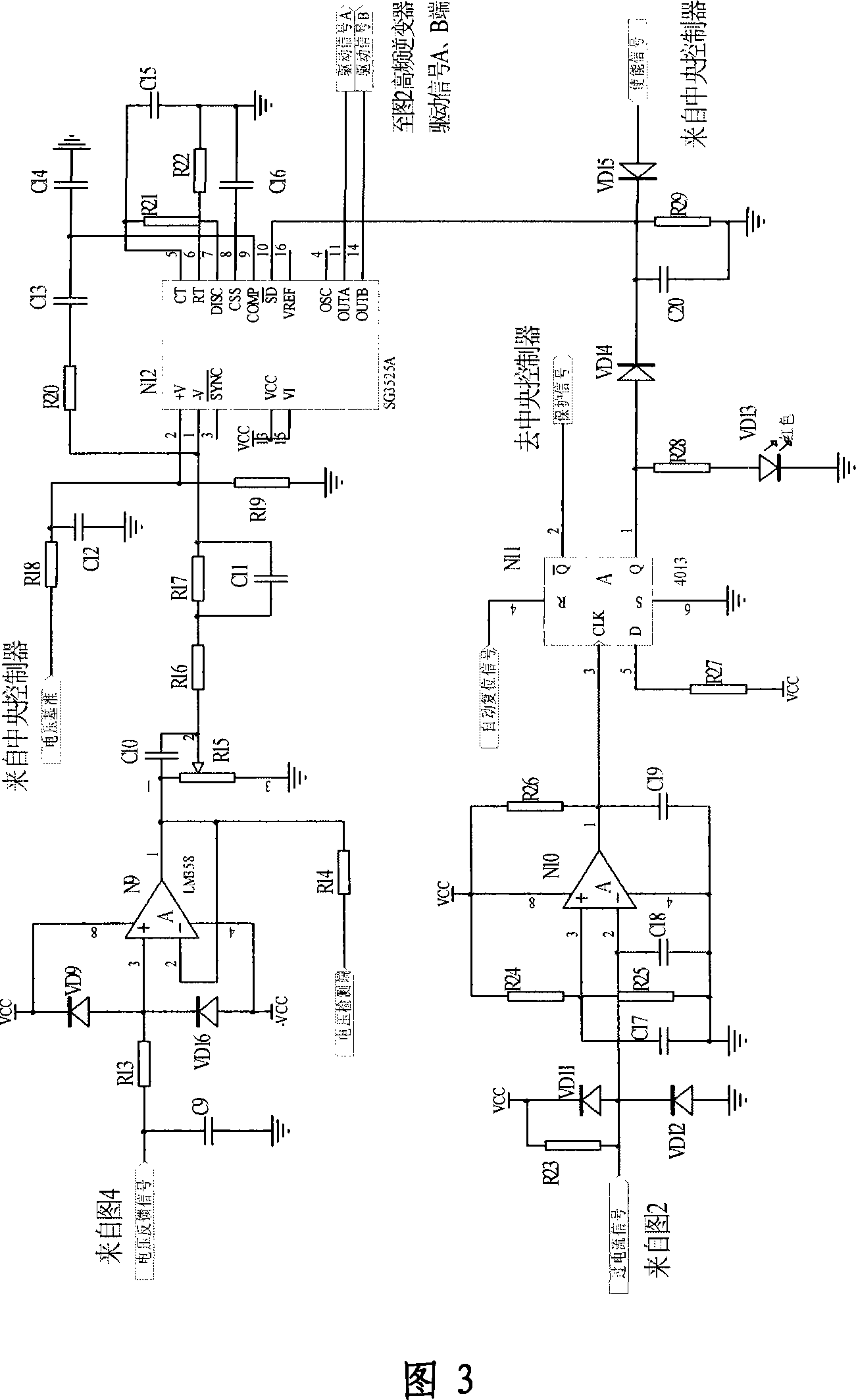

Medical diagnosis X radial high-frequency and high-voltage generator based on dual-bed and dual-tube

ActiveCN101188900ASolve the problem of shift workImprove clarityAc-dc conversionX-ray apparatusX-rayEngineering

The invention discloses a two-bed duplex tube medical diagnosis X-ray high frequency high voltage generator, which comprises a power supply and a central control unit, and also comprises a high frequency inverter circuit, a pulse-width modulation drive circuit and a high voltage commutation circuit. The generator converts the industrial power supply into two way high frequency high voltage, and then obtains positive end DC high voltage and negative end DC high voltage after the rectification and the filter to supply an X-ray pipet for working. Because the frequency is high and the high voltage ripple after the rectification and the filter is minimum, causing the X-ray pipet of a radiographic table and the X-ray pipet of an electric perspective table to work in turn under the condition of arranging only one set of high voltage supply. The equipment investment is saved, and the work of using the X-ray diagnosis for the medical staff is convenient. Being served as the high voltage supply, the invention is also suitable for the safety detection fields such as the industrial fault detection, the civil aviation, the station, the custom, etc., and supplies the stable high quality high voltage for the equipment.

Owner:广西道纪医疗设备有限公司

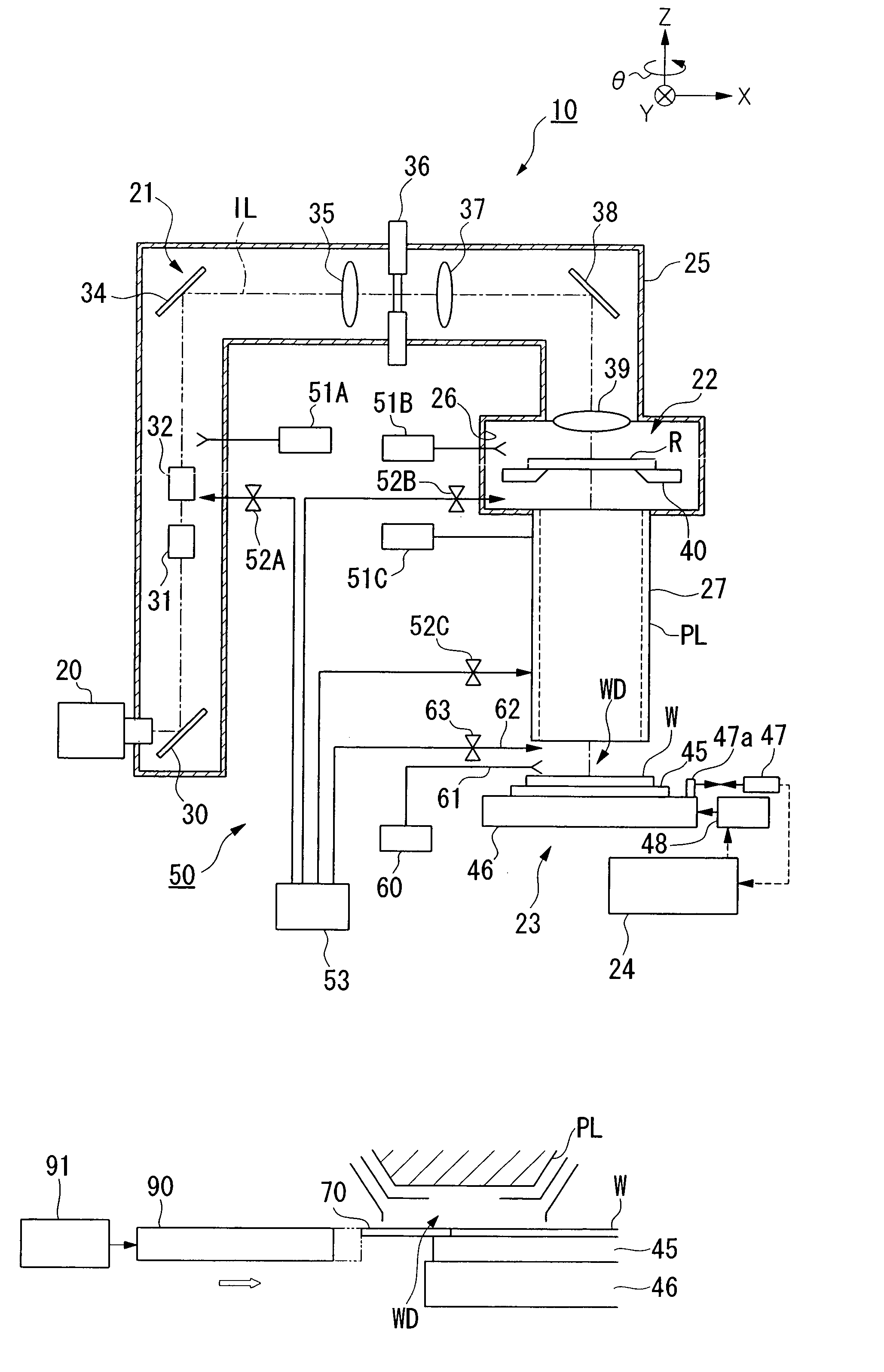

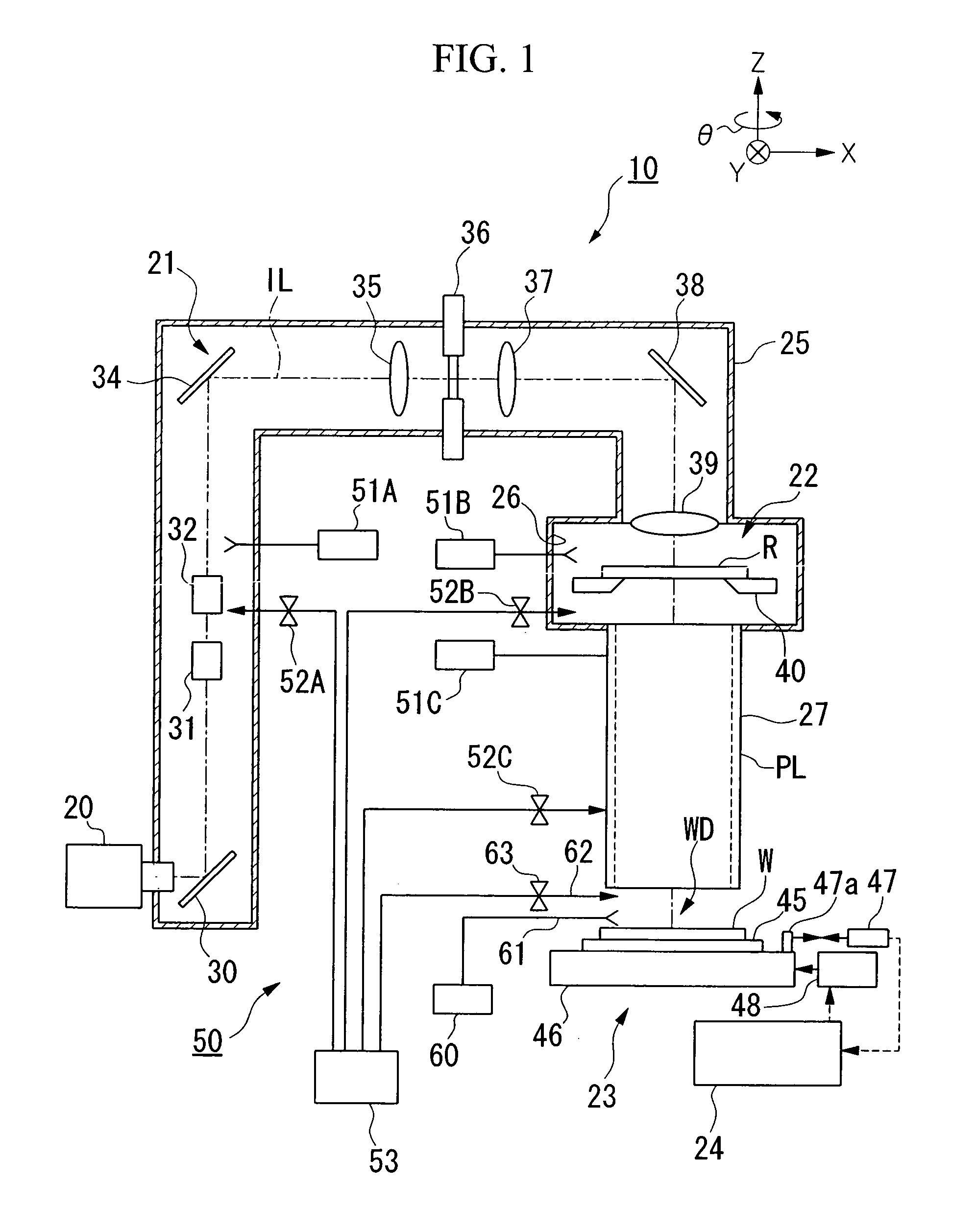

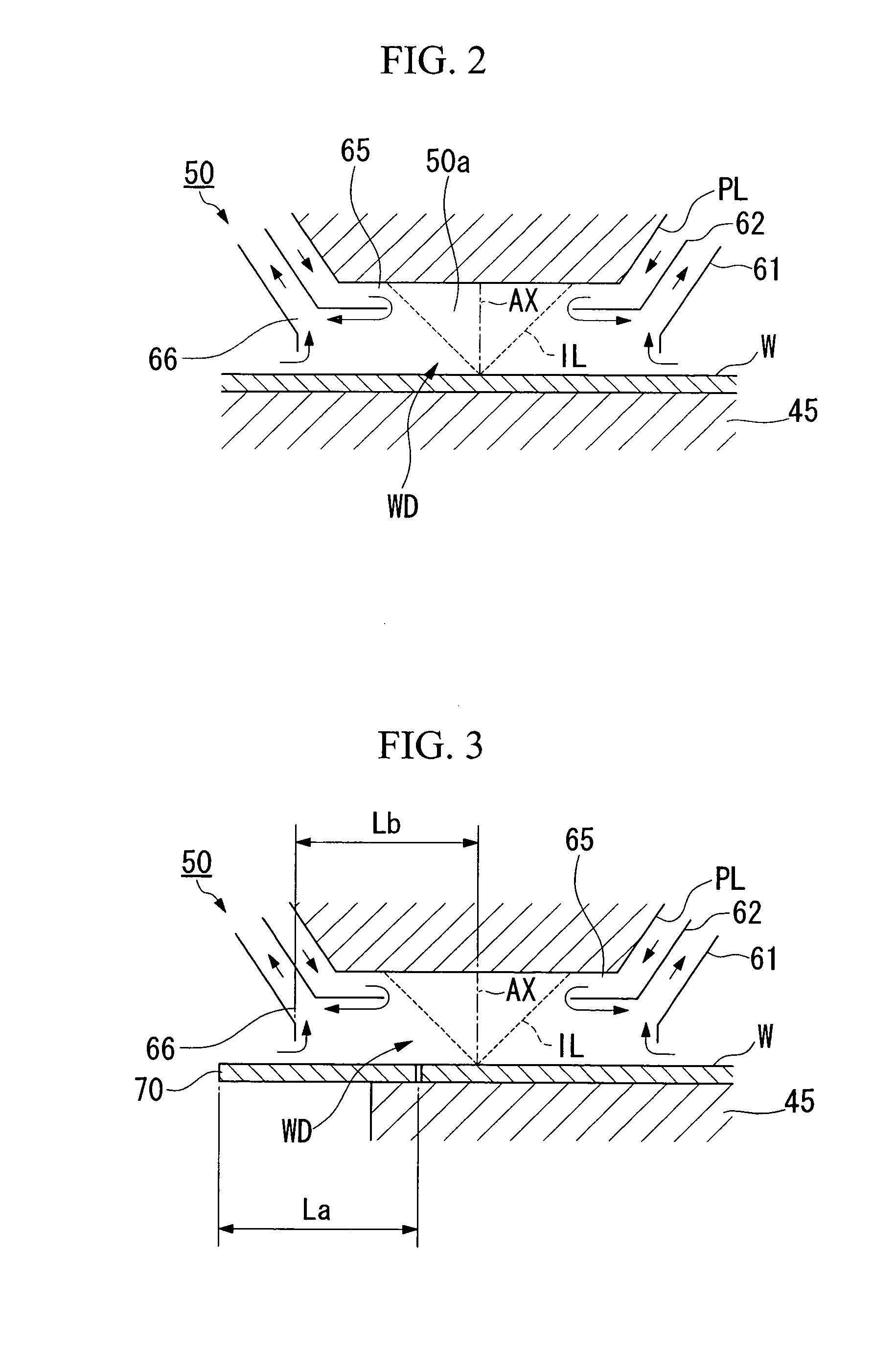

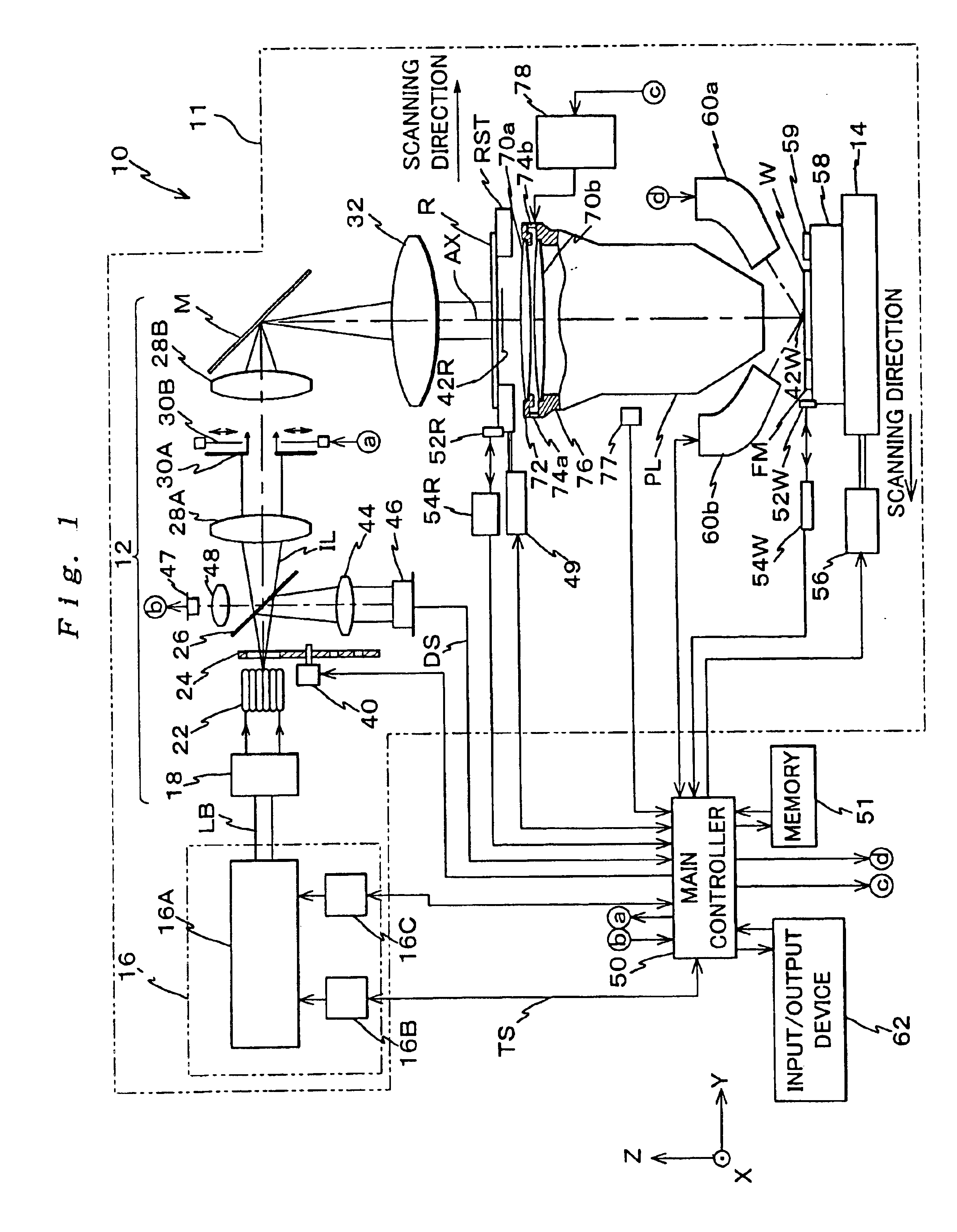

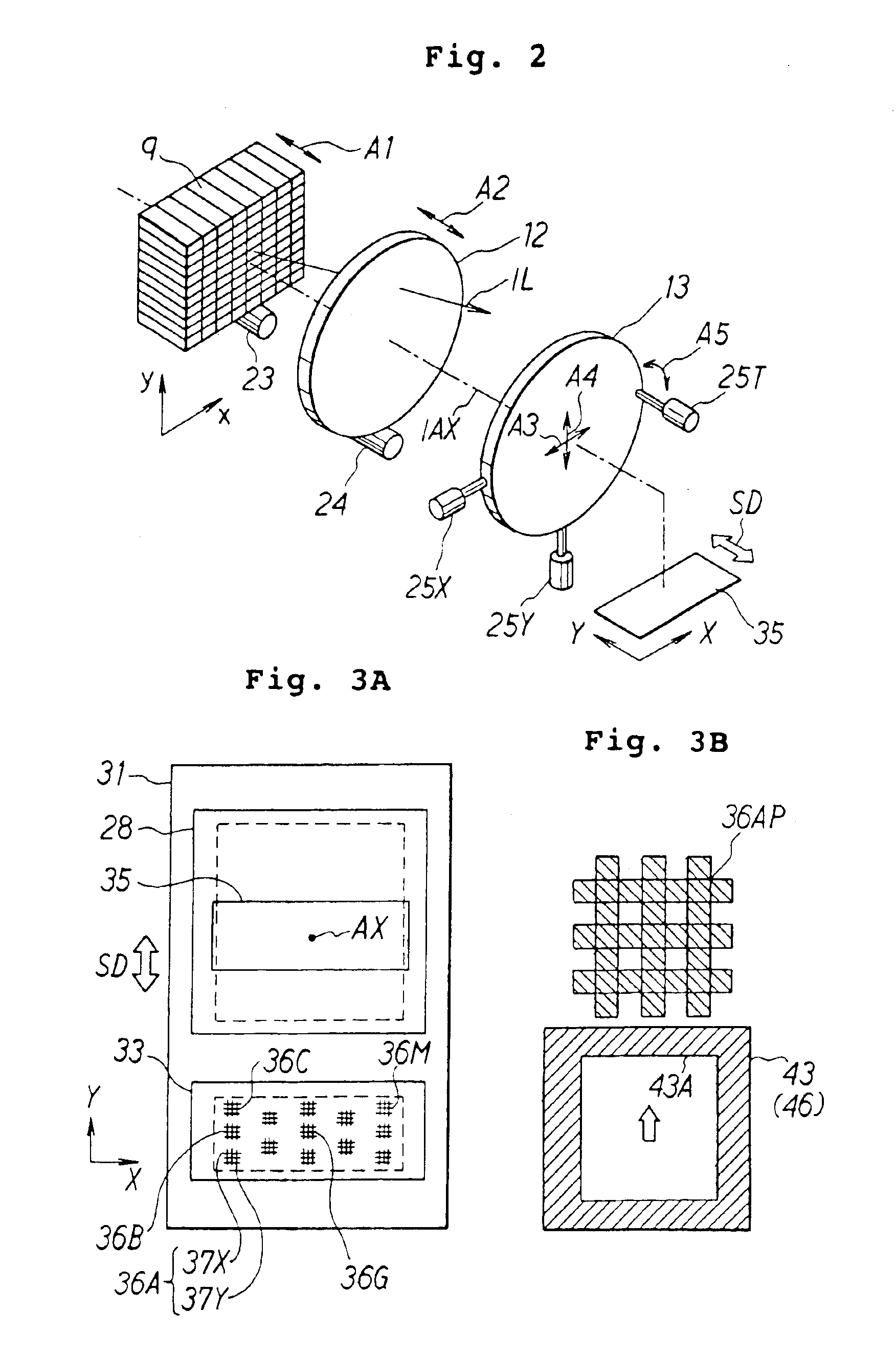

Exposure method, exposure apparatus, and method for manufacturing device

InactiveUS7098991B2Containment leakHigh control precisionPhotomechanical exposure apparatusMicrolithography exposure apparatusOptoelectronics

According to one embodiment of the invention, a pattern of a mask is transferred onto a substrate via a projection optical system using an energy beam by placing a substrate on side of an energy beam emitting end portion of projection optical system, when the substrate is exposed, and placing an object on the side of the energy beam emitting end portion of the projection optical system in place of the substrate when the substrate is exchanged. This can adequately remove a light absorptive substance from the region near an output end of the projection optical system and can maintain the gas state even at a time of moving or replacing the substrate.

Owner:NIKON CORP

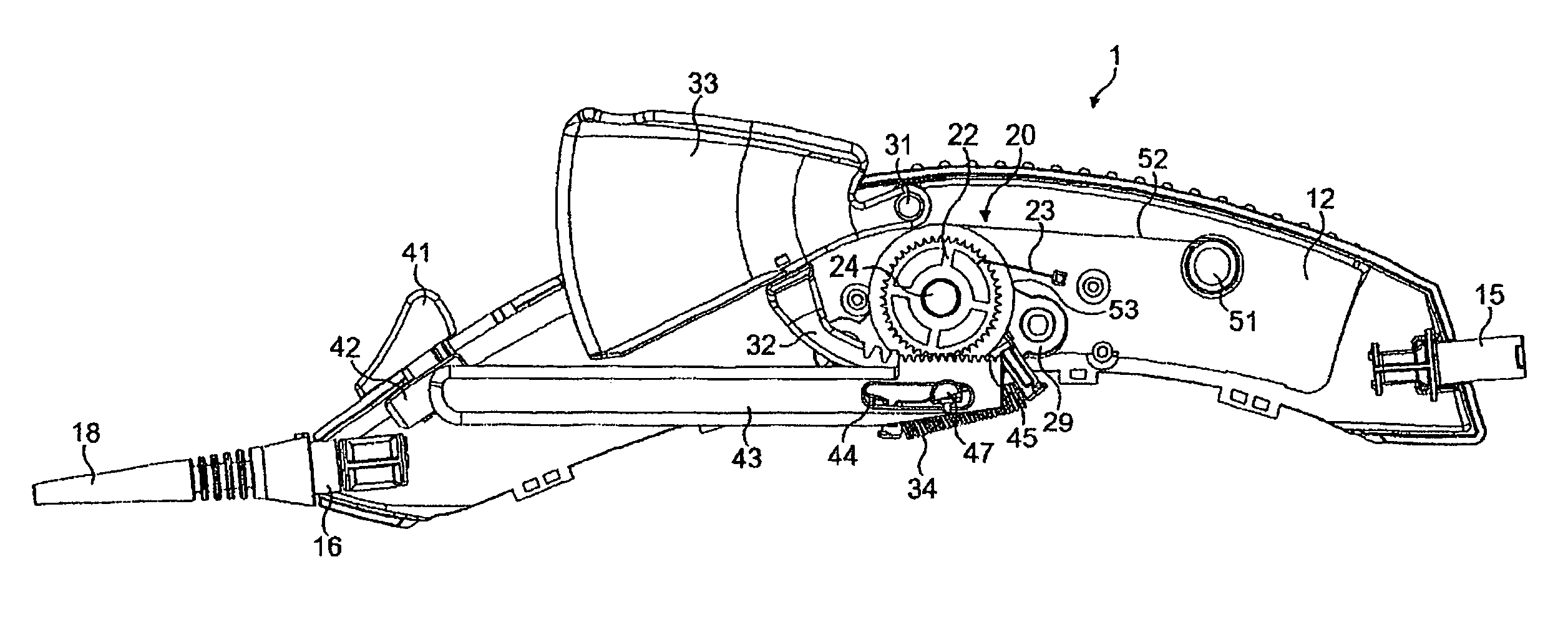

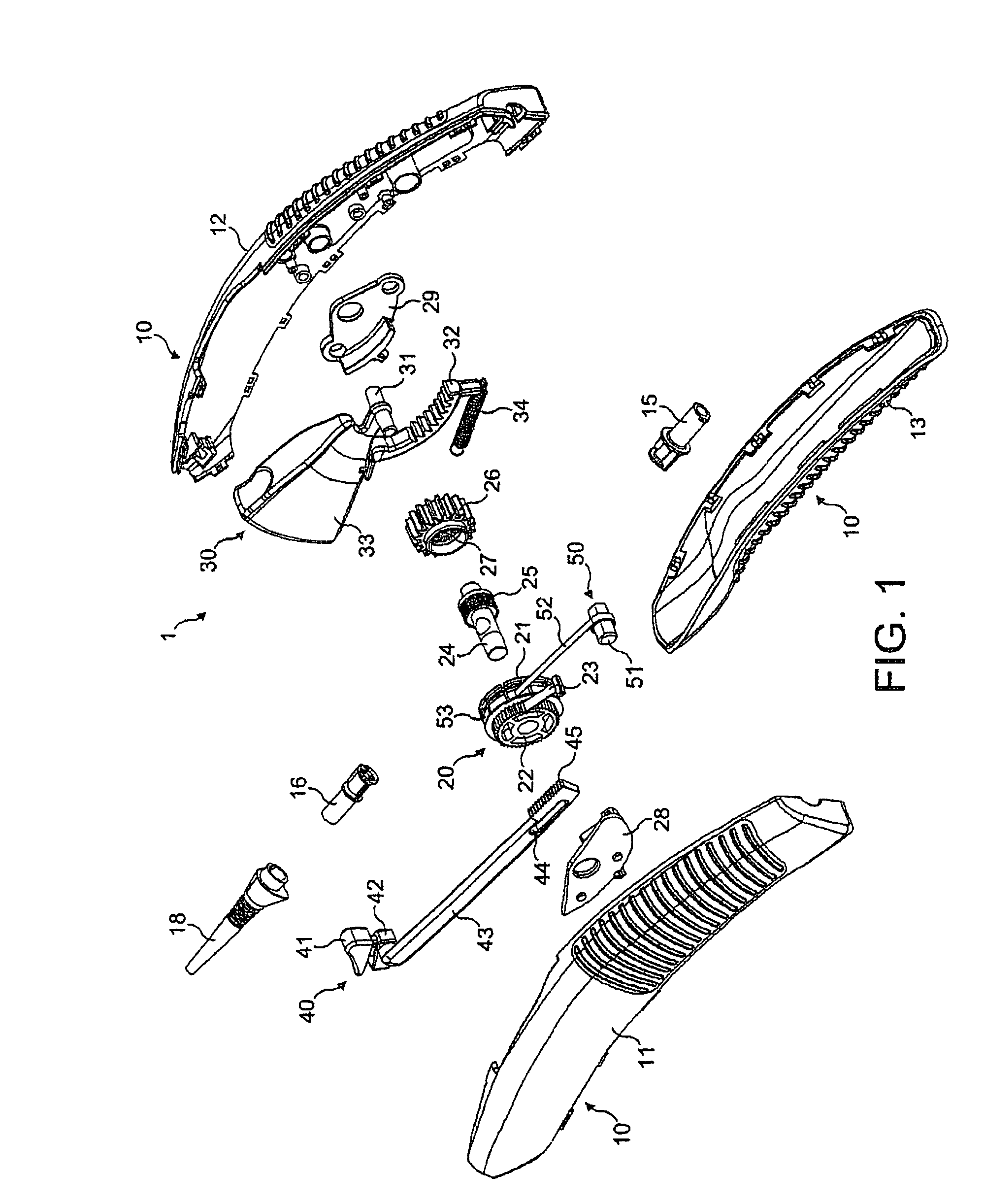

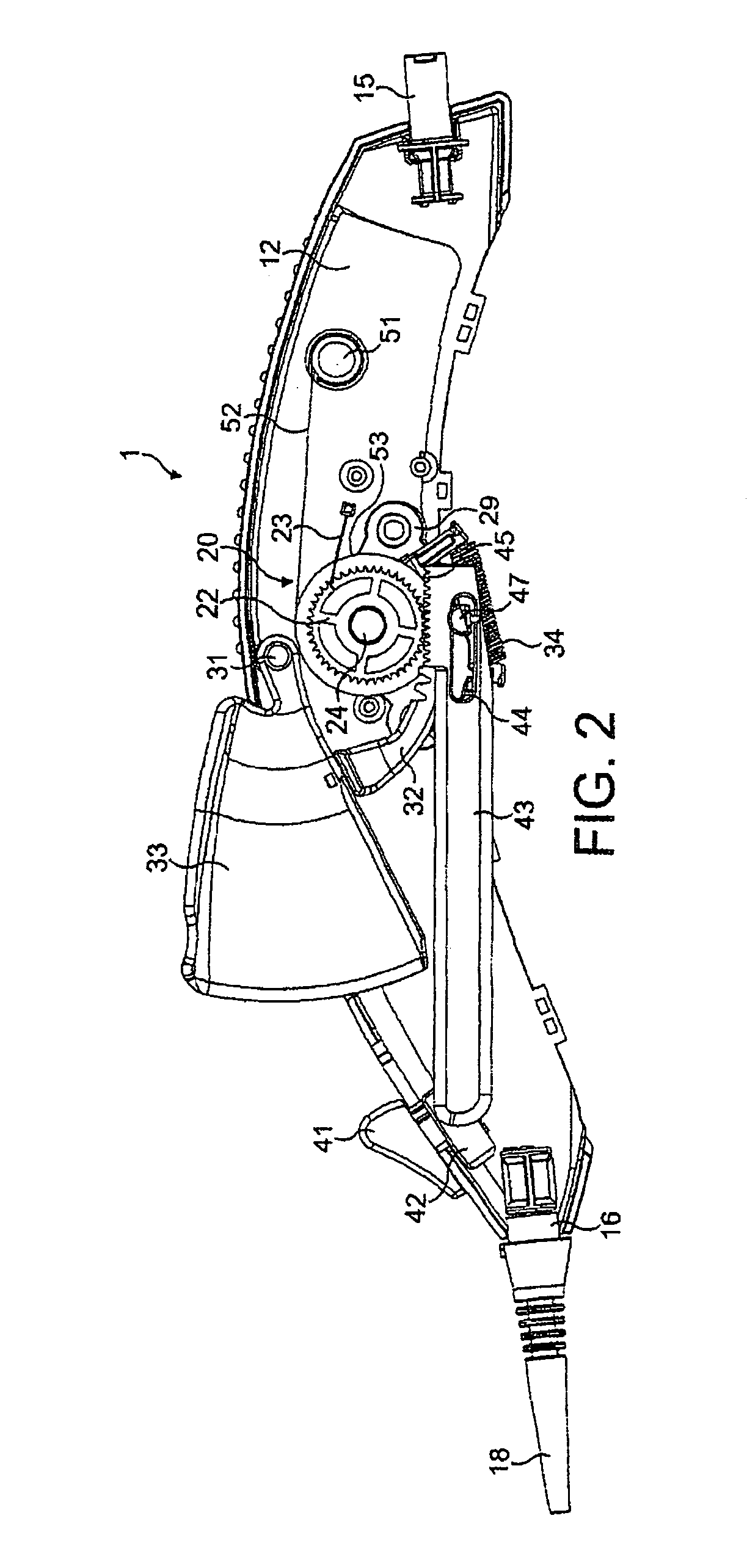

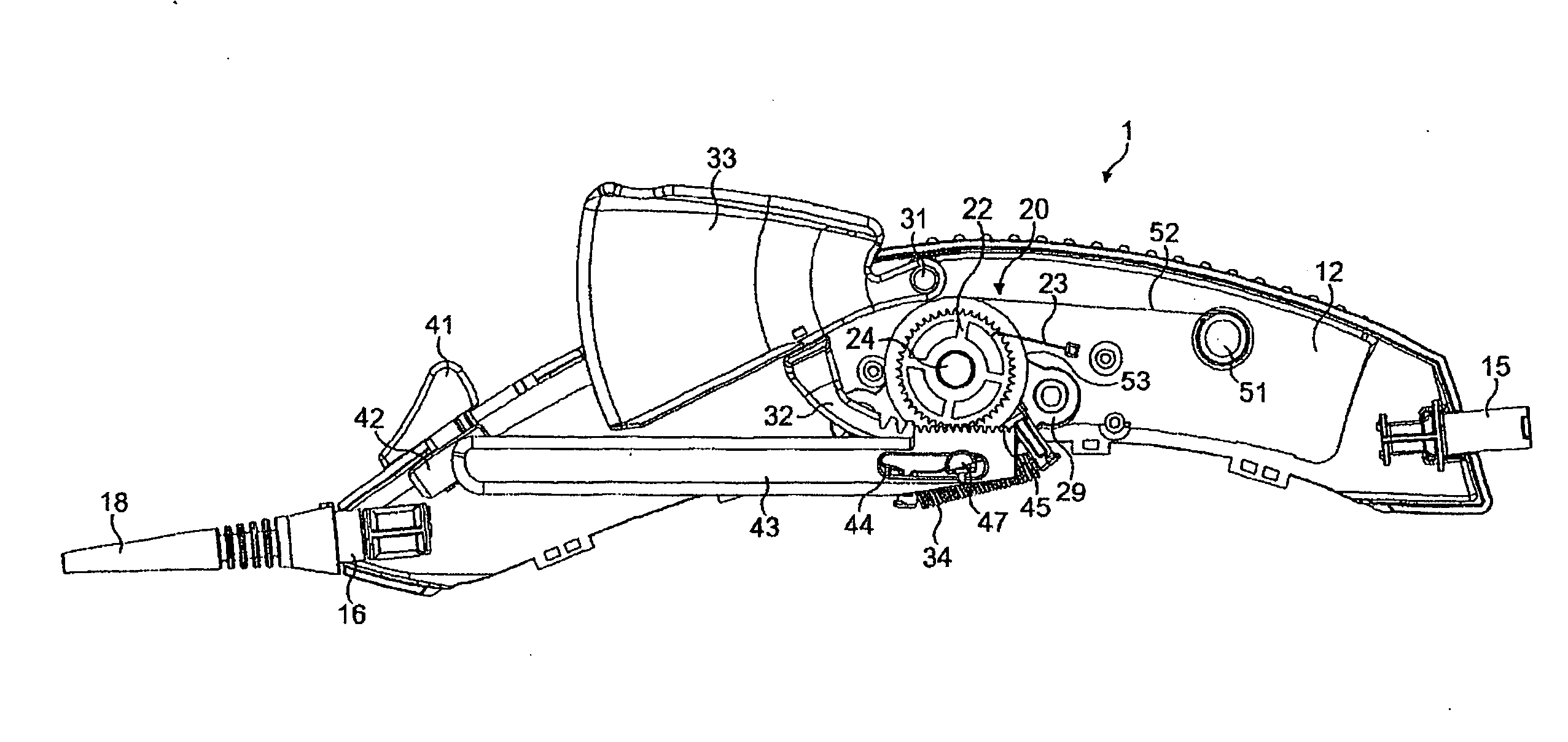

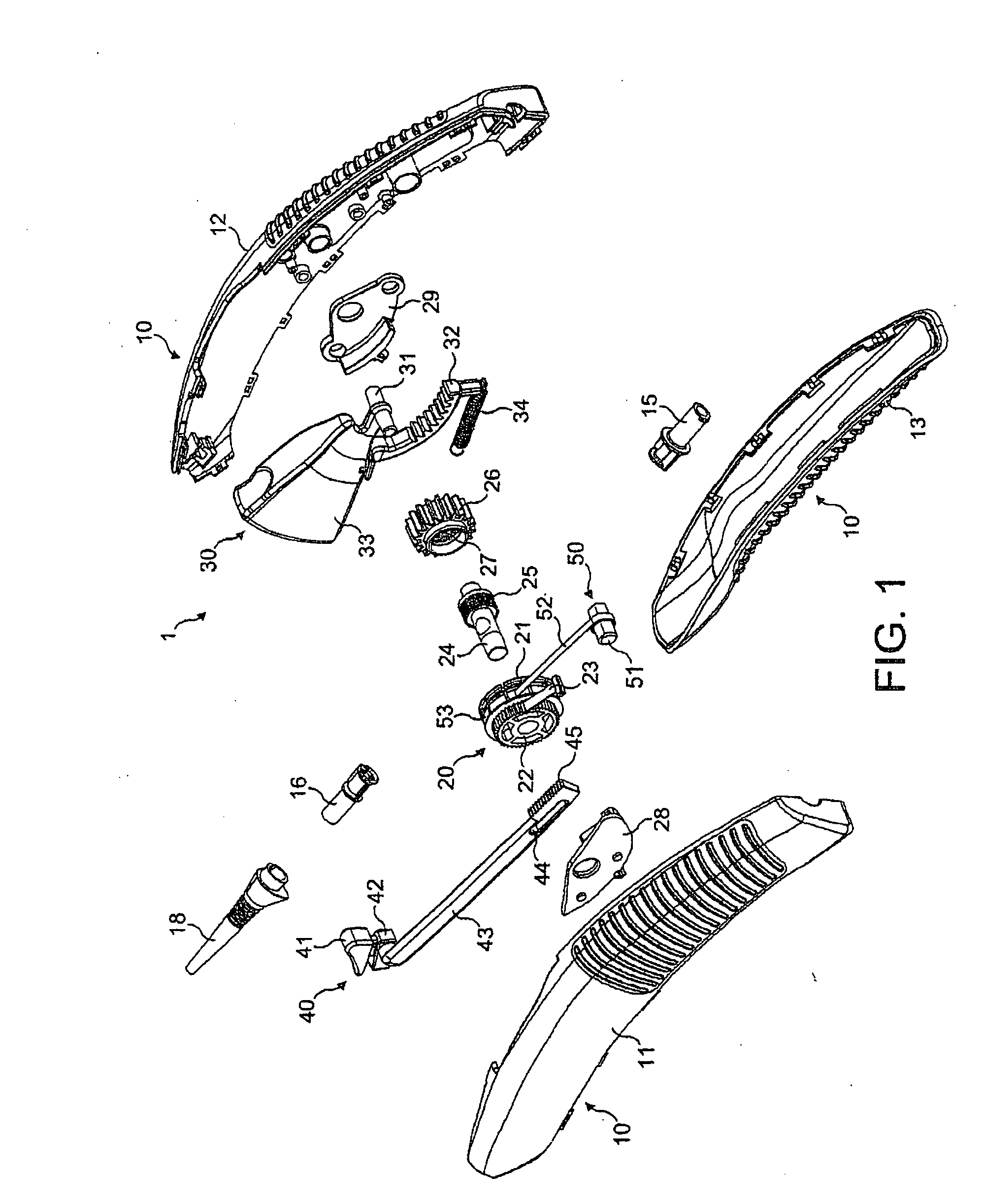

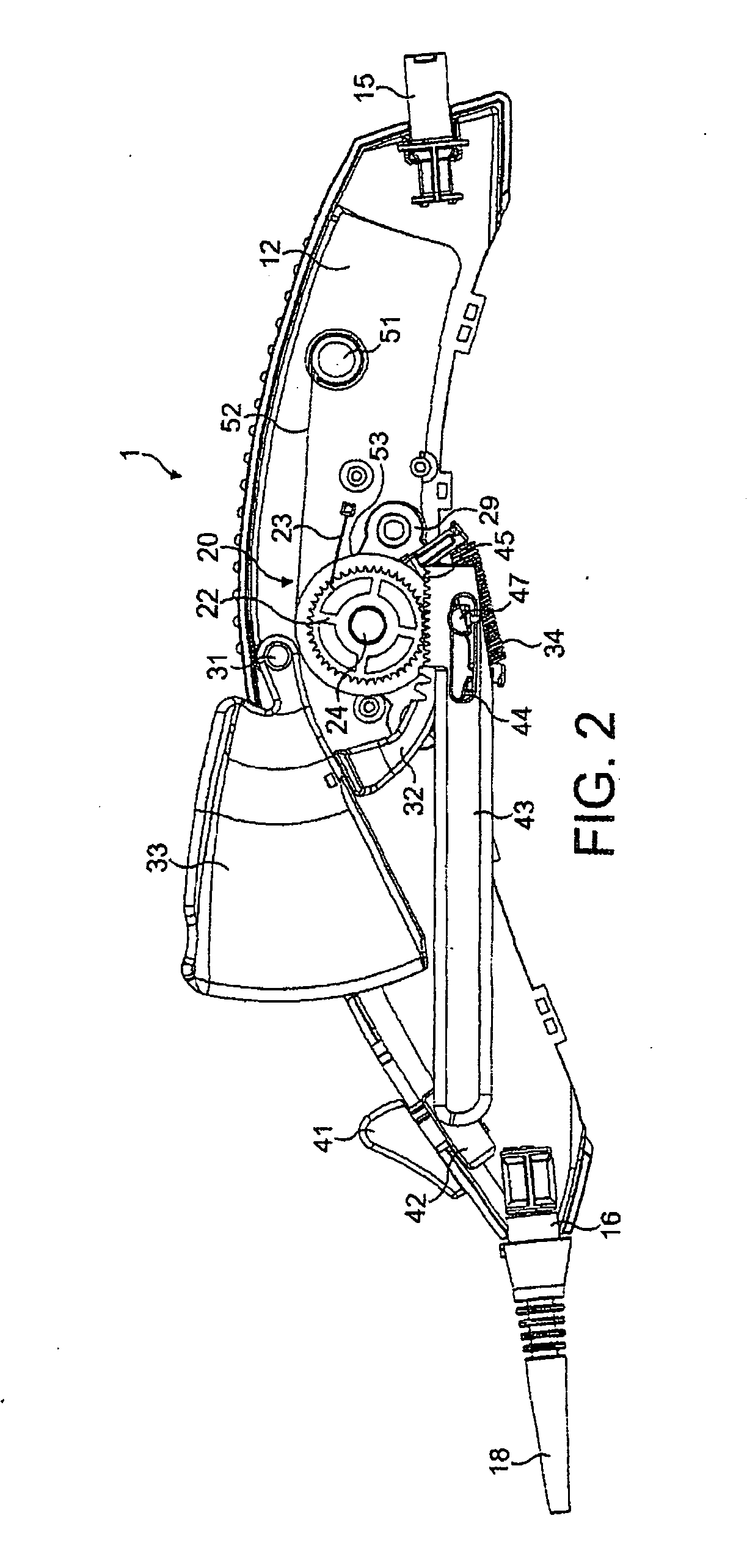

Device for catheter sheath retraction

Owner:CR BARD INC

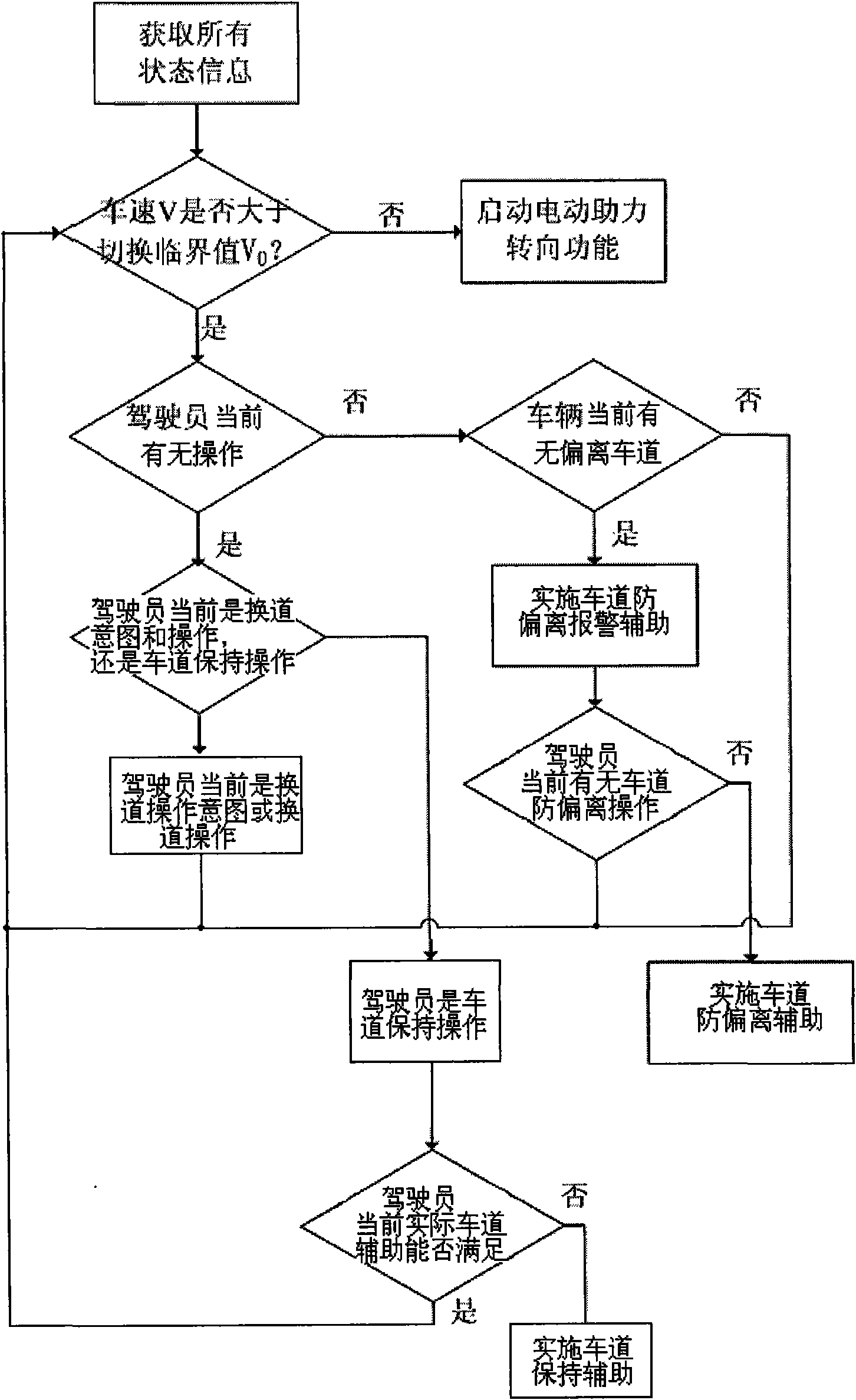

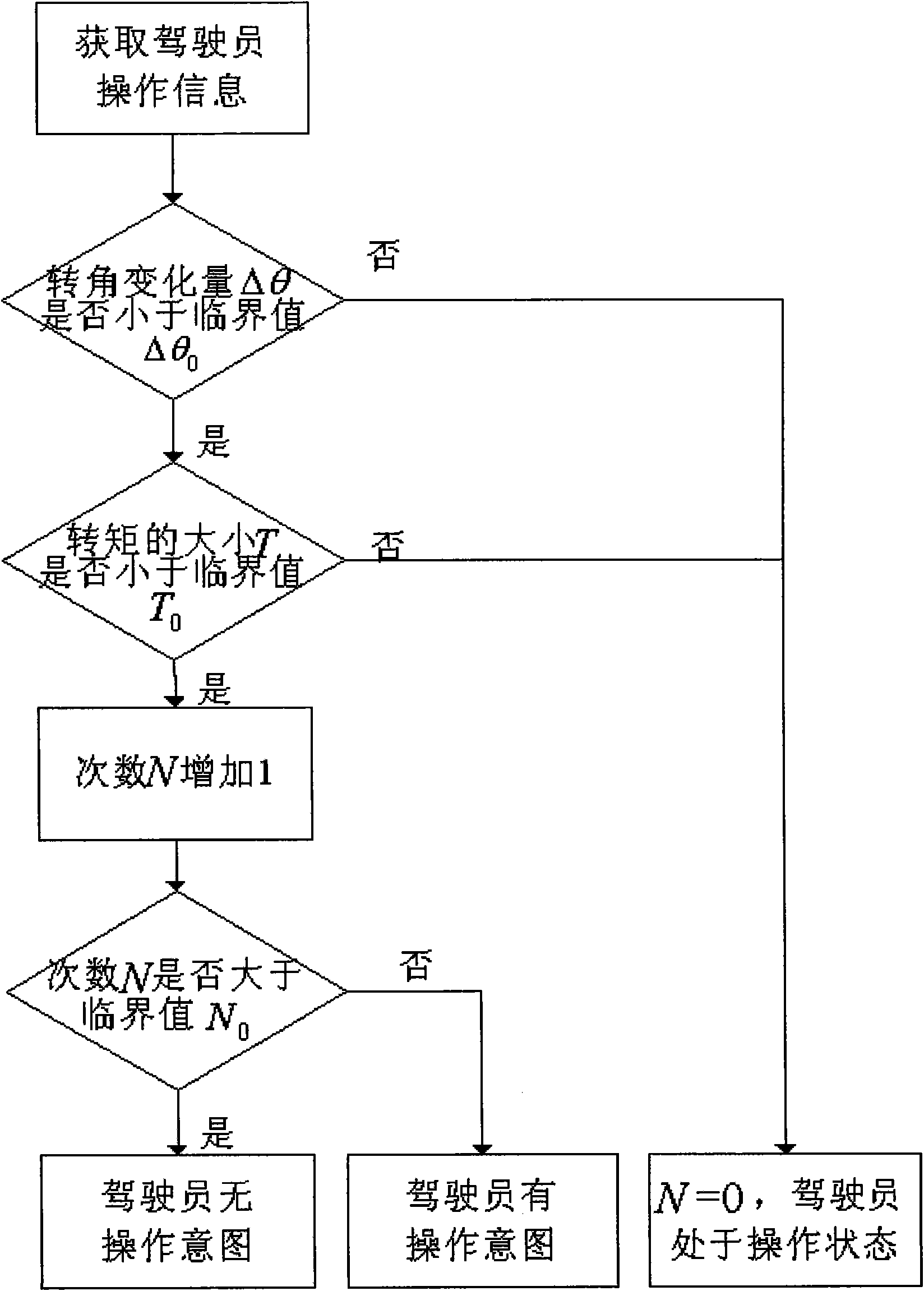

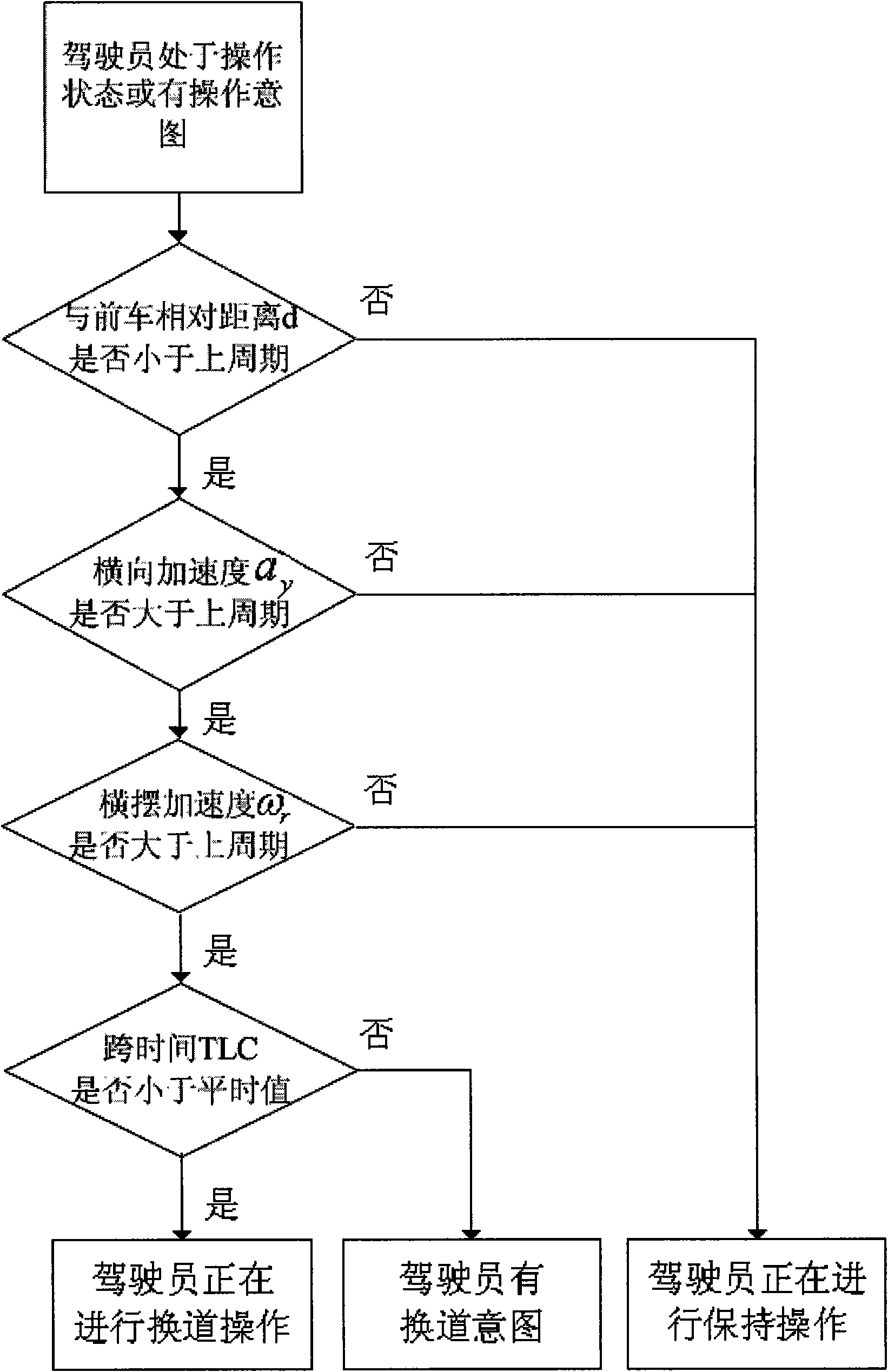

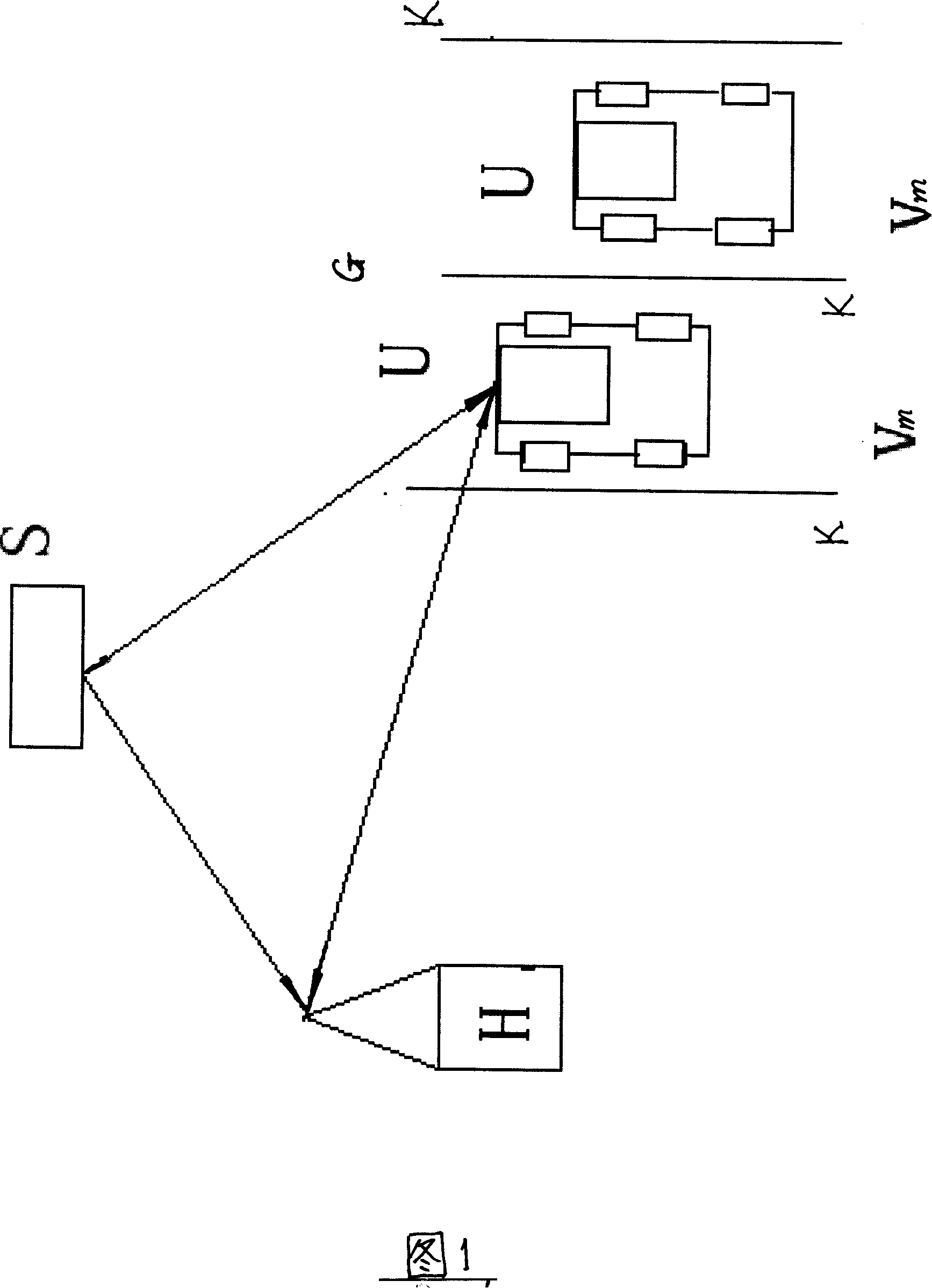

Assisting method for transverse driving of multipurpose automobile and assisting system therefor

InactiveCN101596903AVersatileSafe drivingSteering linkagesAutomatic steering controlDriver/operatorEngineering

The invention relates to an assisting method for transverse driving of a multipurpose automobile and an assisting system therefor, comprising the steps as follows: 1. setting a transverse driving assisting system of the multipurpose automobile; 2. judging whether the current vehicle velocity V is larger than V0 according to obtained driver operation information and the self running state information of the vehicle, if yes, entering step 3, otherwise starting electric assisting reversing function; 3. judging whether the driver operates or not, if no, entering step 4, otherwise judging that the driver at present has operation intention of changing the lane or is in the operation of changing the lane or operation of maintaining the lane; 4. judging whether the vehicle deviates from the lane or not, if yes, entering step 5, otherwise returning to step 2; and 5. implementing lane deviation proof alarm assistance, and judging whether the driver executes lane deviation proof operation or not, if yes, returning to step 2, otherwise implementing lane deviation proof assistance. The invention is complete in functions, high in control accuracy and easy to be accepted by drivers.

Owner:TSINGHUA UNIV

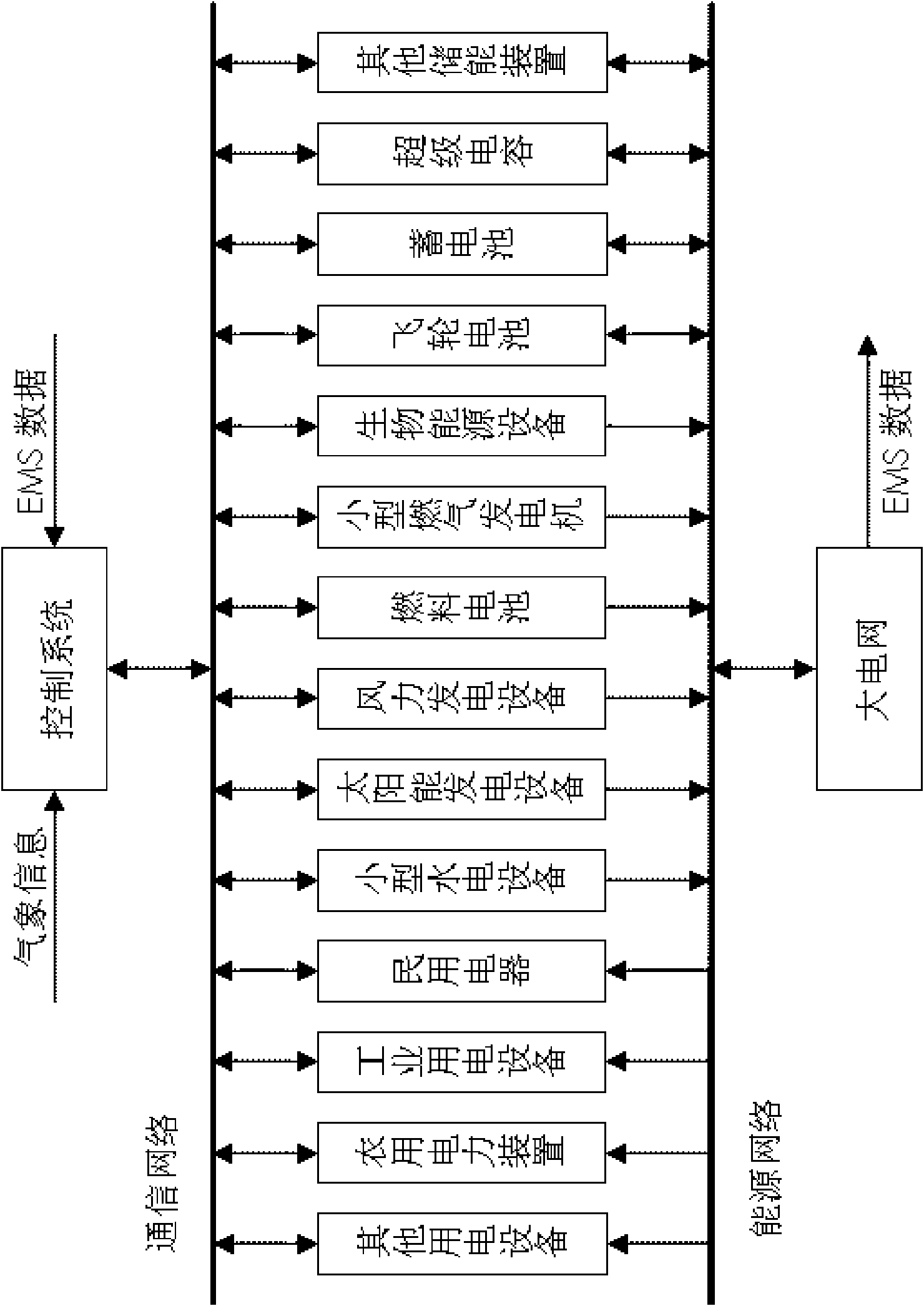

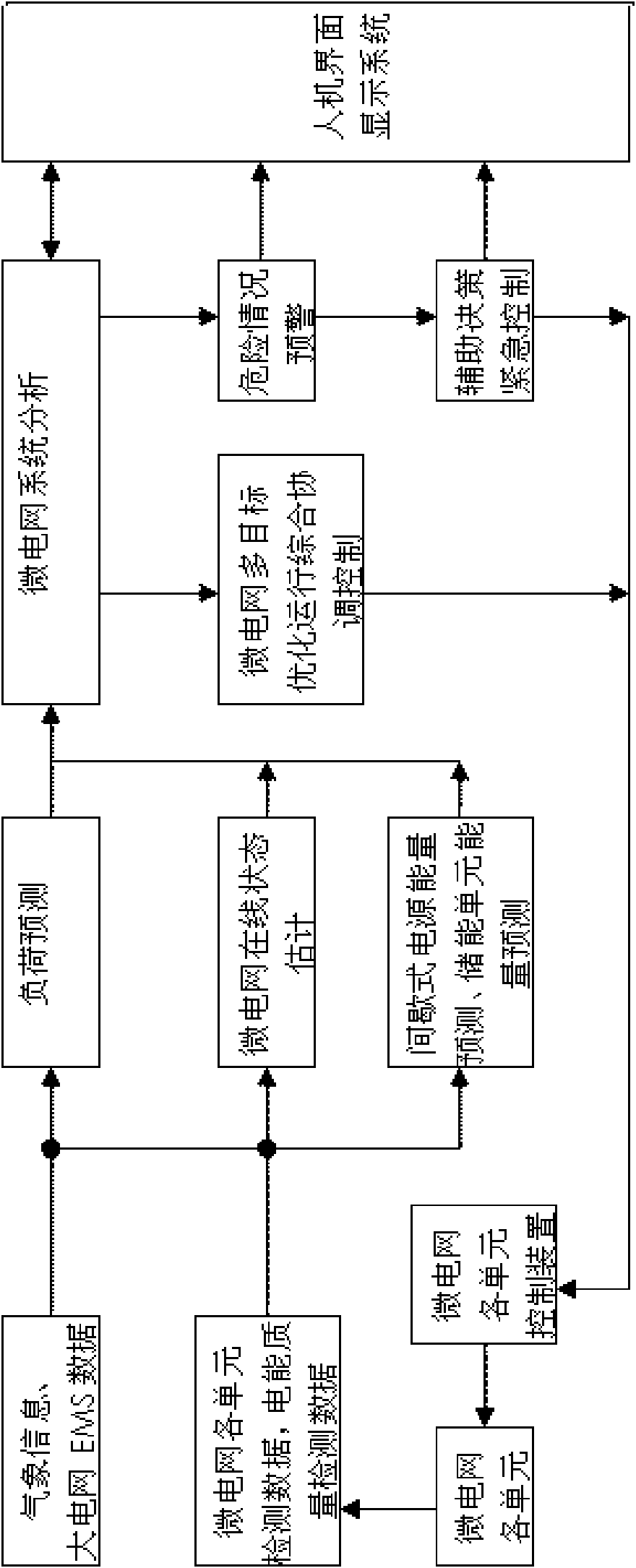

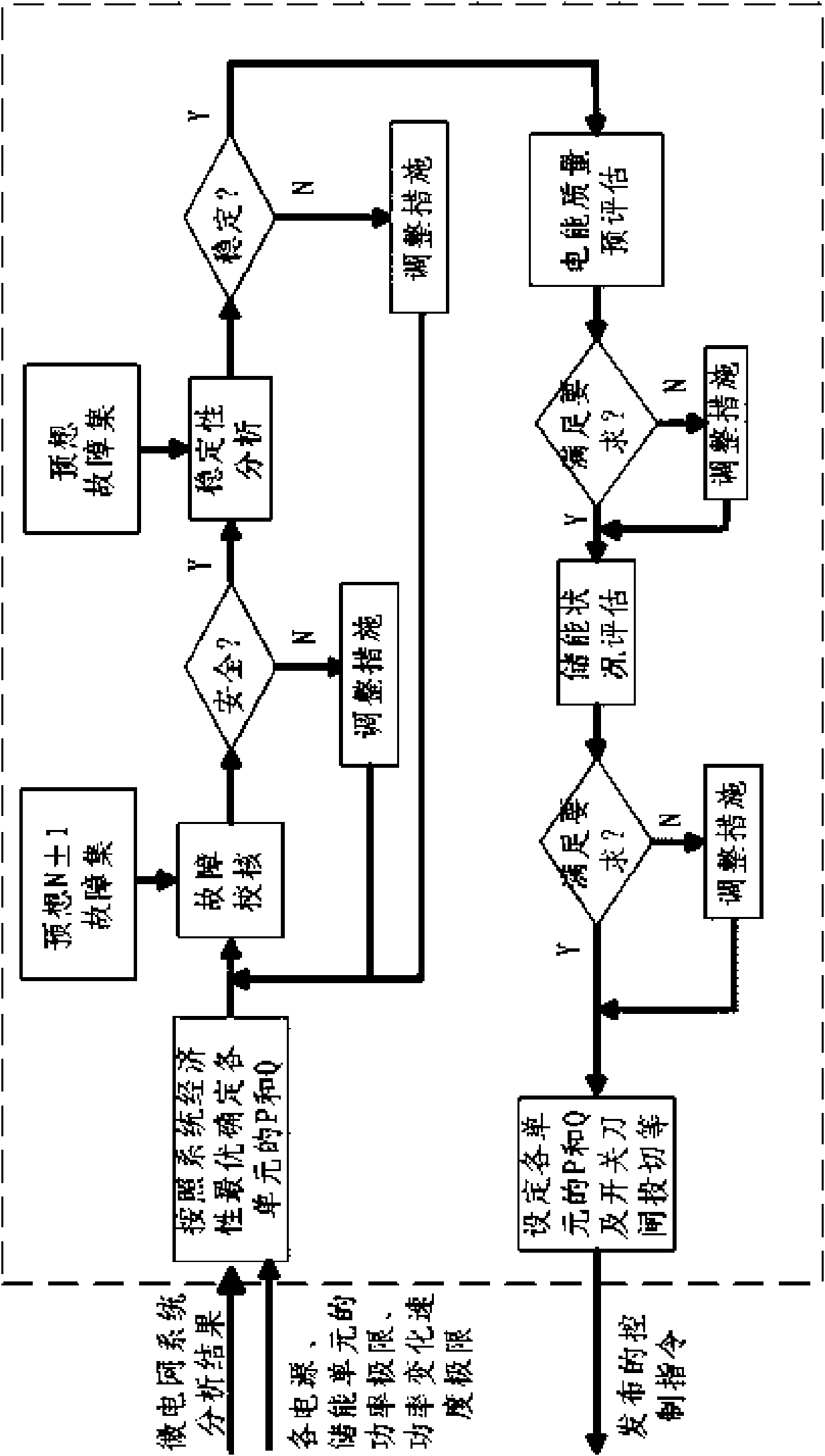

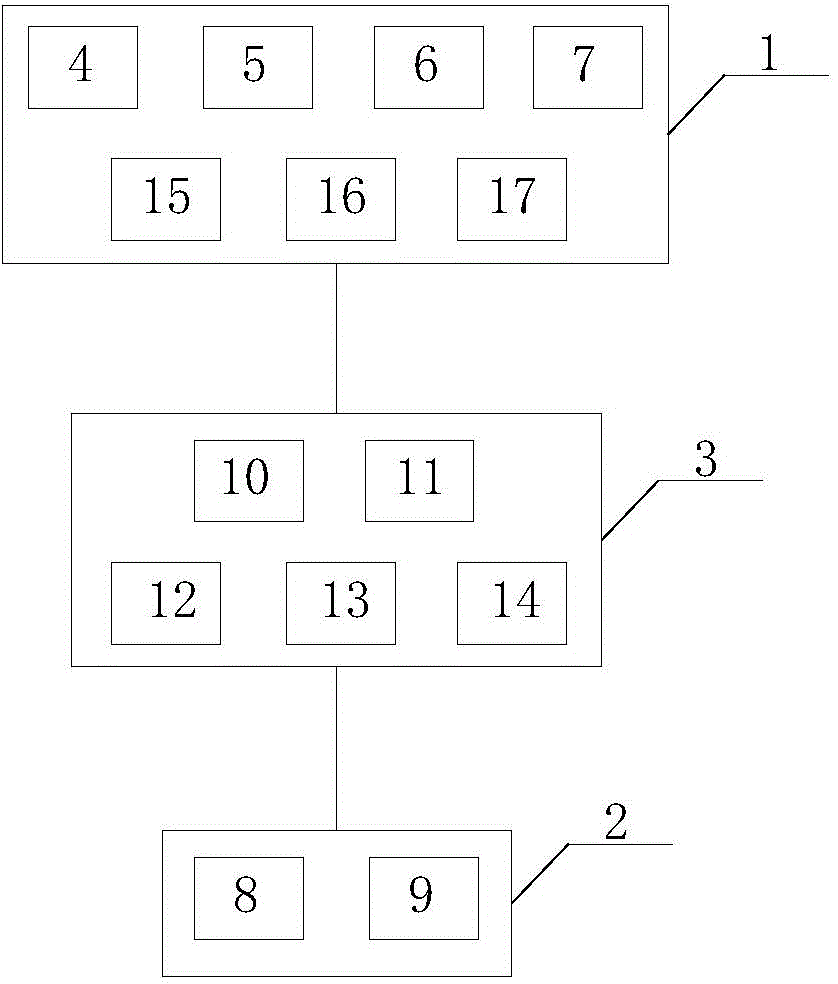

Intelligent control system for microgrid energy

InactiveCN101630840ARich control functionsHigh control precisionTotal factory controlProgramme total factory controlMicrogridEnergy control

The invention relates to a miniature power supplying system containing a plurality of distributed power supplies, and discloses an intelligent energy control system capable of controlling a microgrid by using forecast information. The intelligent control system for microgrid energy comprises a microgrid system and a control system, wherein the microgrid system comprises a power supply unit, an energy storage unit and a load unit, and the control system comprises an information collecting system and a central processing unit. The central processing unit comprises a load forecasting module, a microgrid online status estimating module, an energy forecasting module of an intermittent power supply energy forecasting and storing unit, a microgrid system analyzing module and a microgrid multiobjective optimization operation and comprehensive coordination control module. The intelligent control system for microgrid energy can control the microgrid according to the forecast information and accomplish the intelligent operation of the microgrid.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

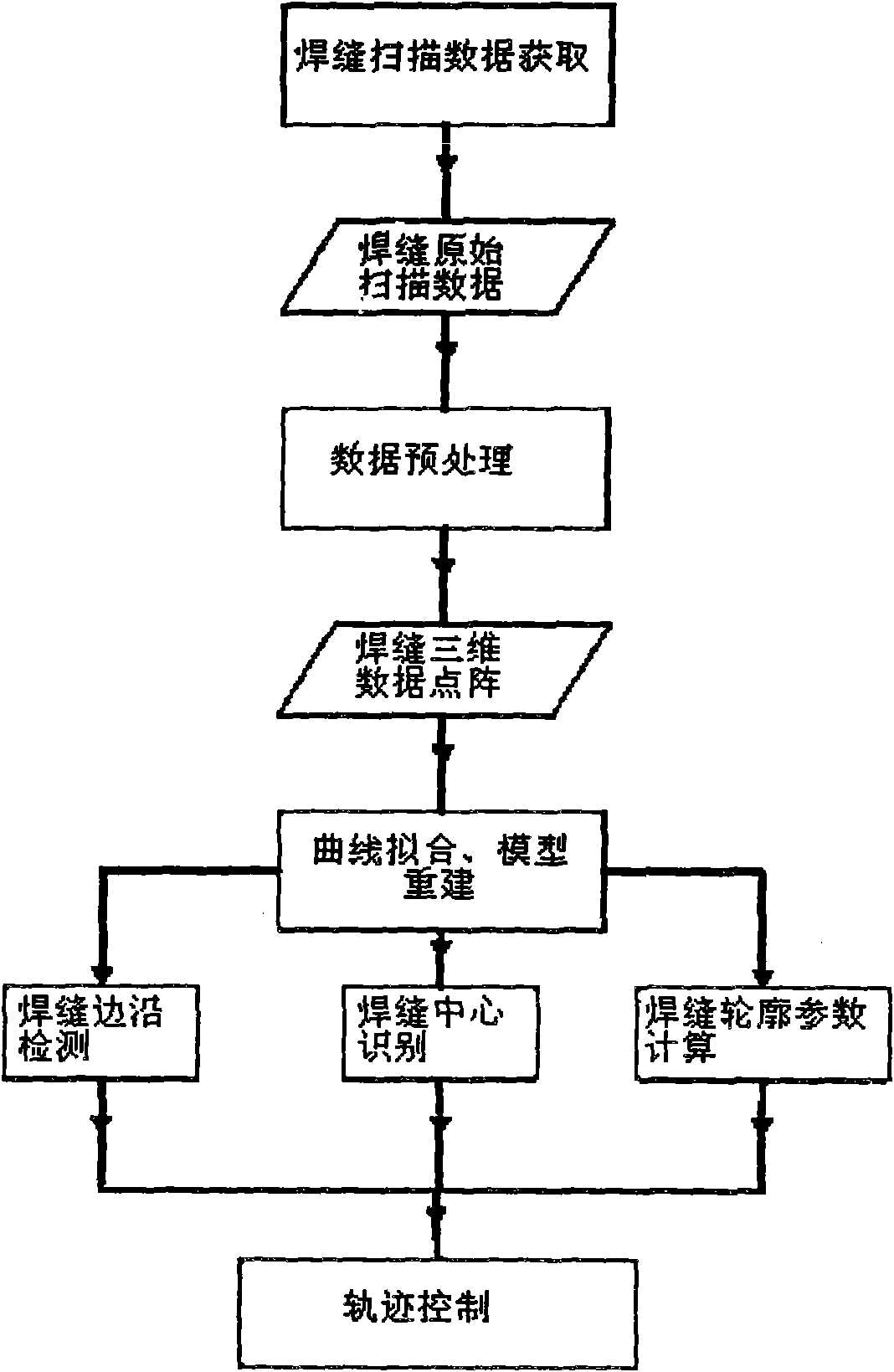

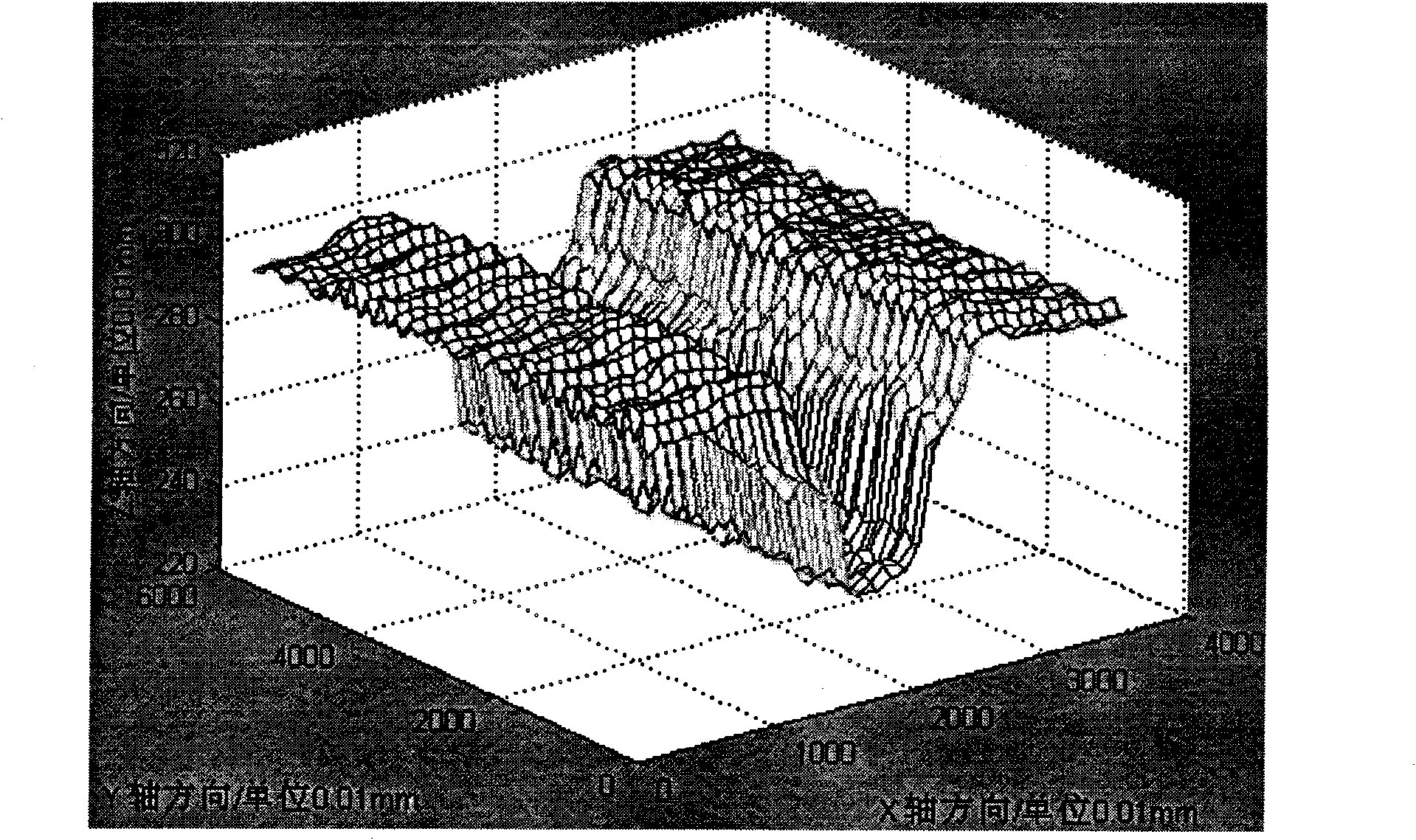

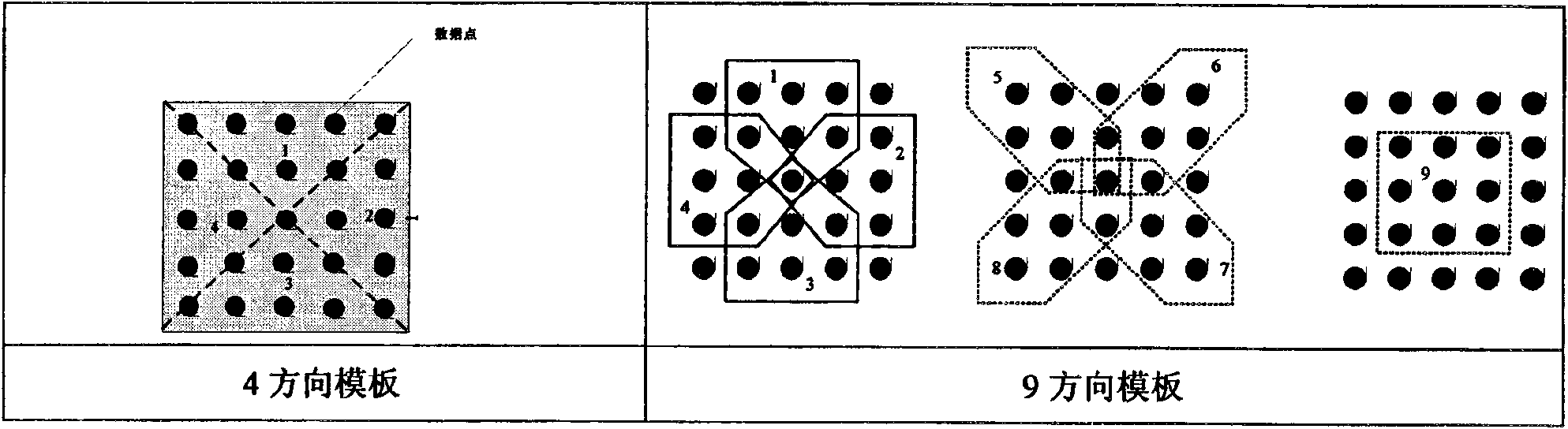

Welding track detection and control method of plate butt weld based on laser ranging

InactiveCN101559512ATo achieve the purpose of seam trackingTo achieve the purpose of trackingArc welding apparatusNumerical controlLaser rangingField tests

The invention relates to a welding track detection and control method of plate butt weld based on laser ranging, including the following steps: A. track detection is carried out; B. track identification and extraction are carried out; C. track control is carried out; D. the relative position relation between a welding gun and a welding seam is adjusted at last by performing mechanism actions. In the invention, the information of welding seam profile is obtained by transverse scanning of a laser sensor, and welding seam is rebuilt after effective wave filtering treatment to realize three-dimensional detection of the welding seam; simultaneously, the welding track curve is obtained by fit while detecting welding seam by using dynamic B spline fit algorithm, and the track control is carried out in combination with constant speed B spline track interpolation algorithm, thereby fundamentally solving the problem of track detection and control in automatic welding of plate butt weld. By using the method in the invention, the field test welding has welding profile identification precision of 0.15mm and welding track identification precision of 0.2mm, and the welding speed is more than four times of common manual welding.

Owner:SHANDONG UNIV

Device for catheter sheath retraction

Owner:CR BARD INC

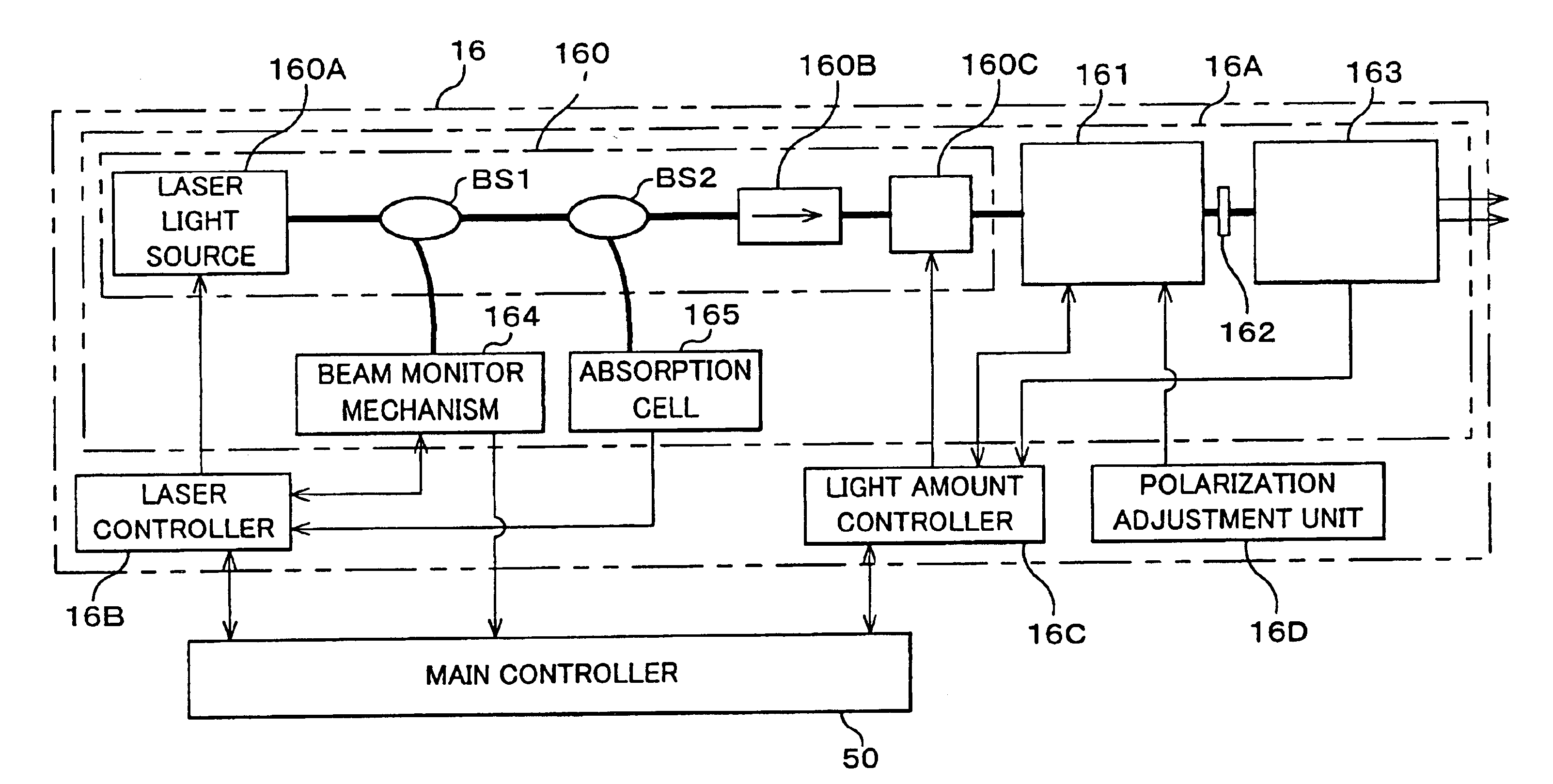

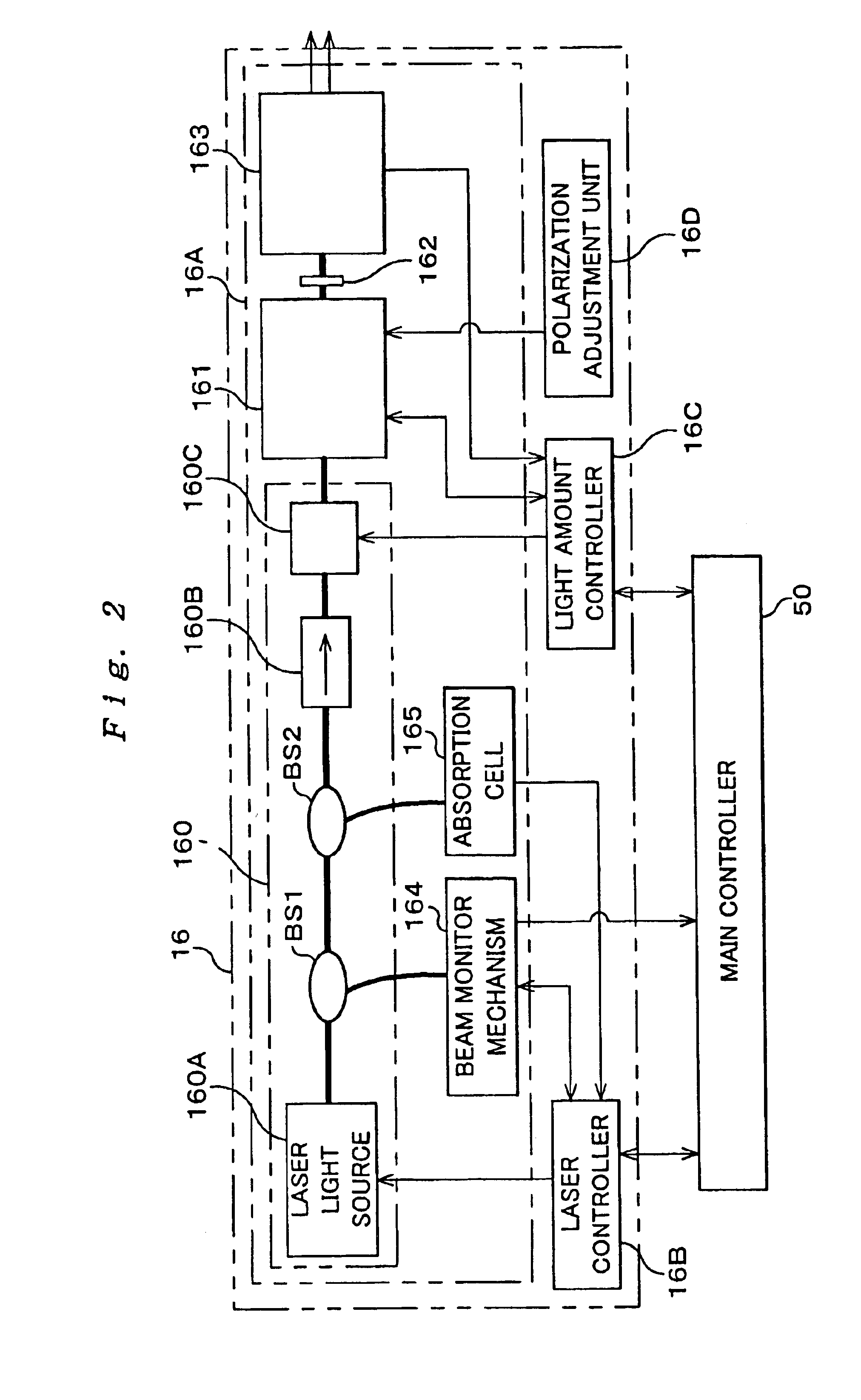

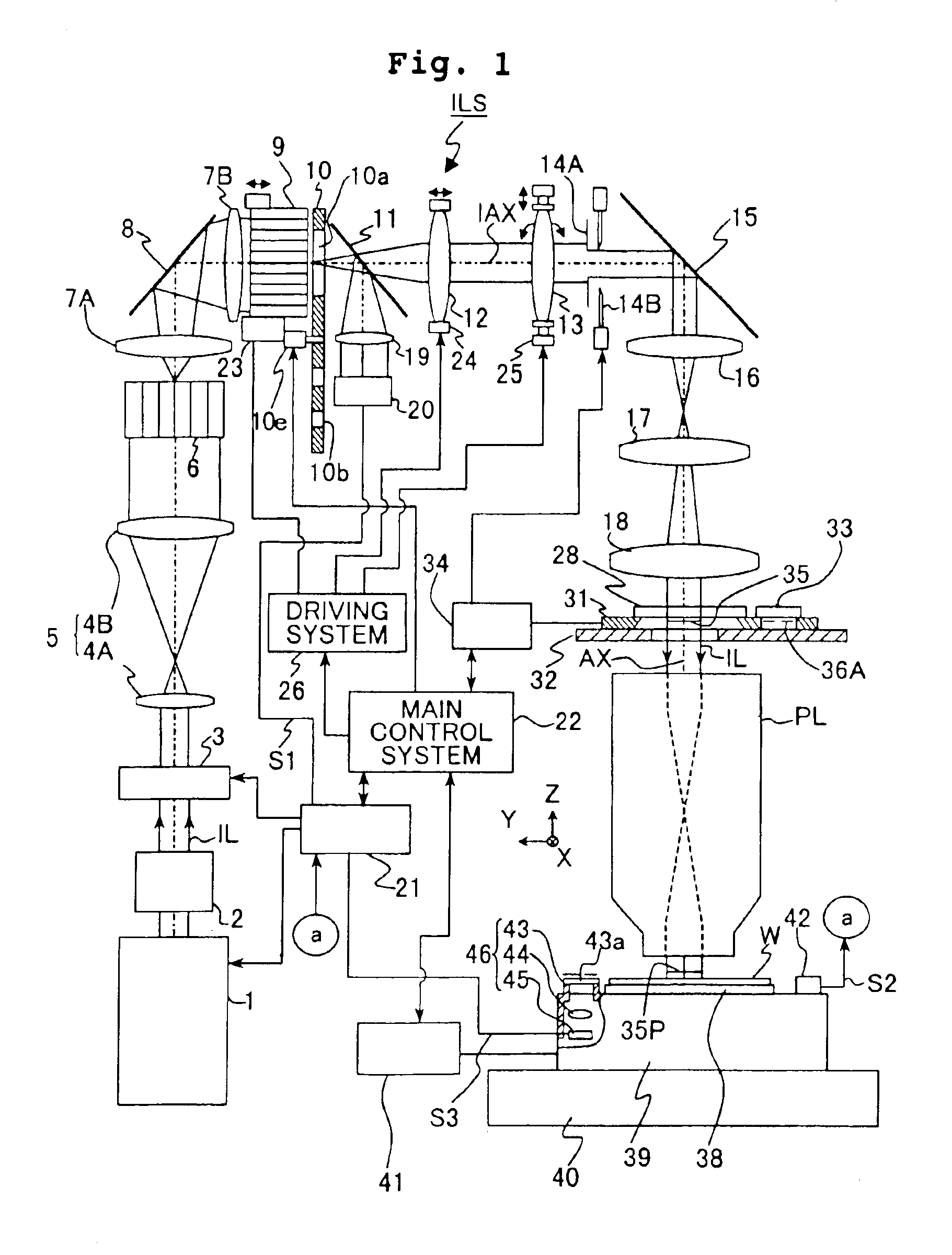

Light source unit and wavelength stabilizing control method, exposure apparatus and exposure method, method of making exposure apparatus, and device manufacturing method and device

InactiveUS7098992B2Accurate and reliable light amount controlDegree of linearityLaser arrangementsPhotomechanical exposure apparatusFiberPeak value

The light source unit includes a single wavelength oscillation light source, a light generating portion which has an optical modulator converting and emitting light from the light source into a pulse light, a light amplifying portion made up of an optical fiber group in which each fiber has a fiber amplifier to amplify the pulse light from the optical modulator, and a light amount controller. The light amount controller performs a step-by-step light amount control by individually turning on / off the light output of each fiber making up the optical fiber group, and a light amount control of controlling at least either of the frequency or the peak power of the emitted pulse light of the optical modulator. Accordingly, in addition to the step-by-step light amount control, fine adjustment of the light amount in between the steps becomes possible due to the control of at least either the frequency or the peak power of the pulse light, and if the set light amount is within a predetermined range, the light amount can be made to coincide with the set light amount.

Owner:NIKON CORP

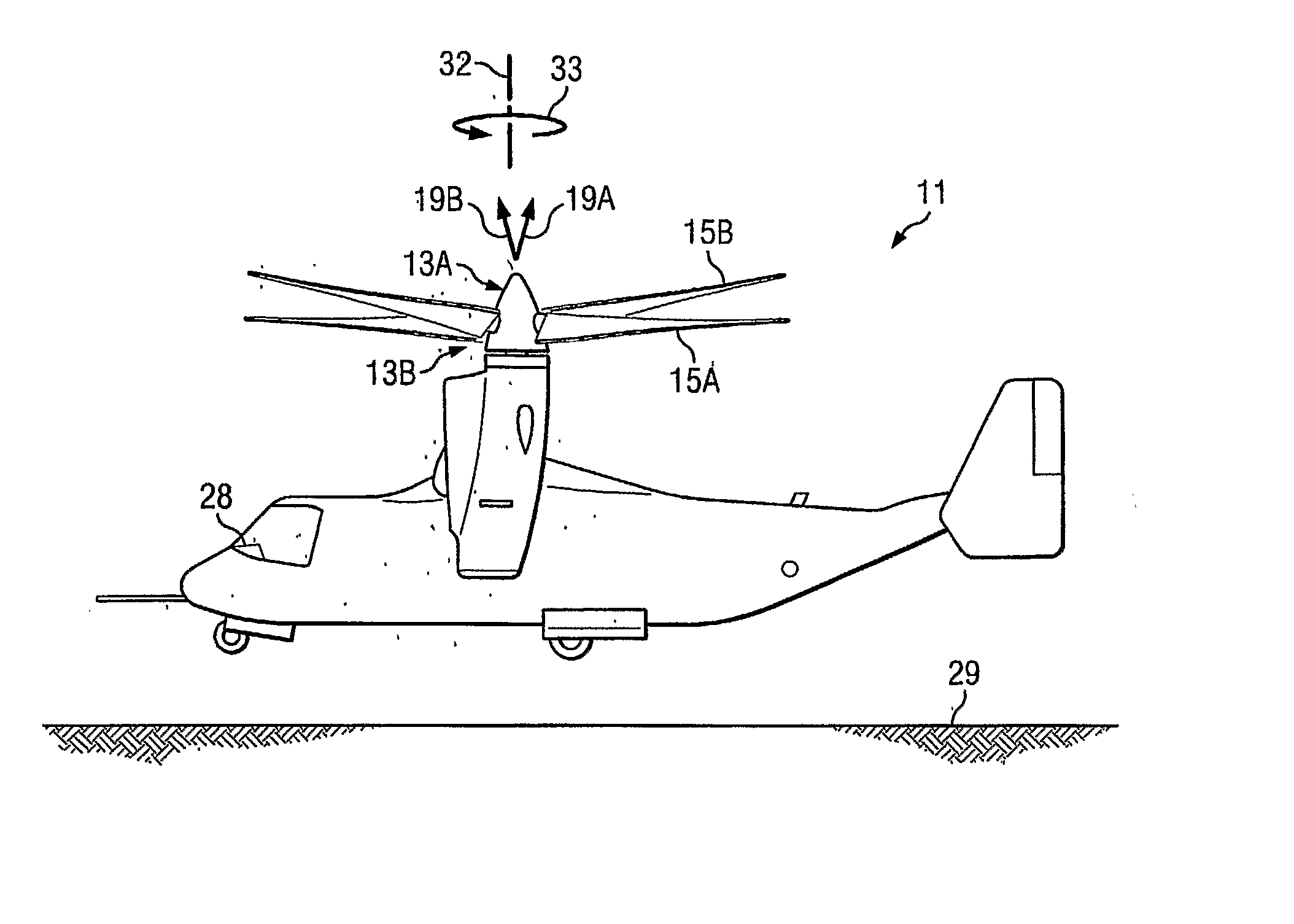

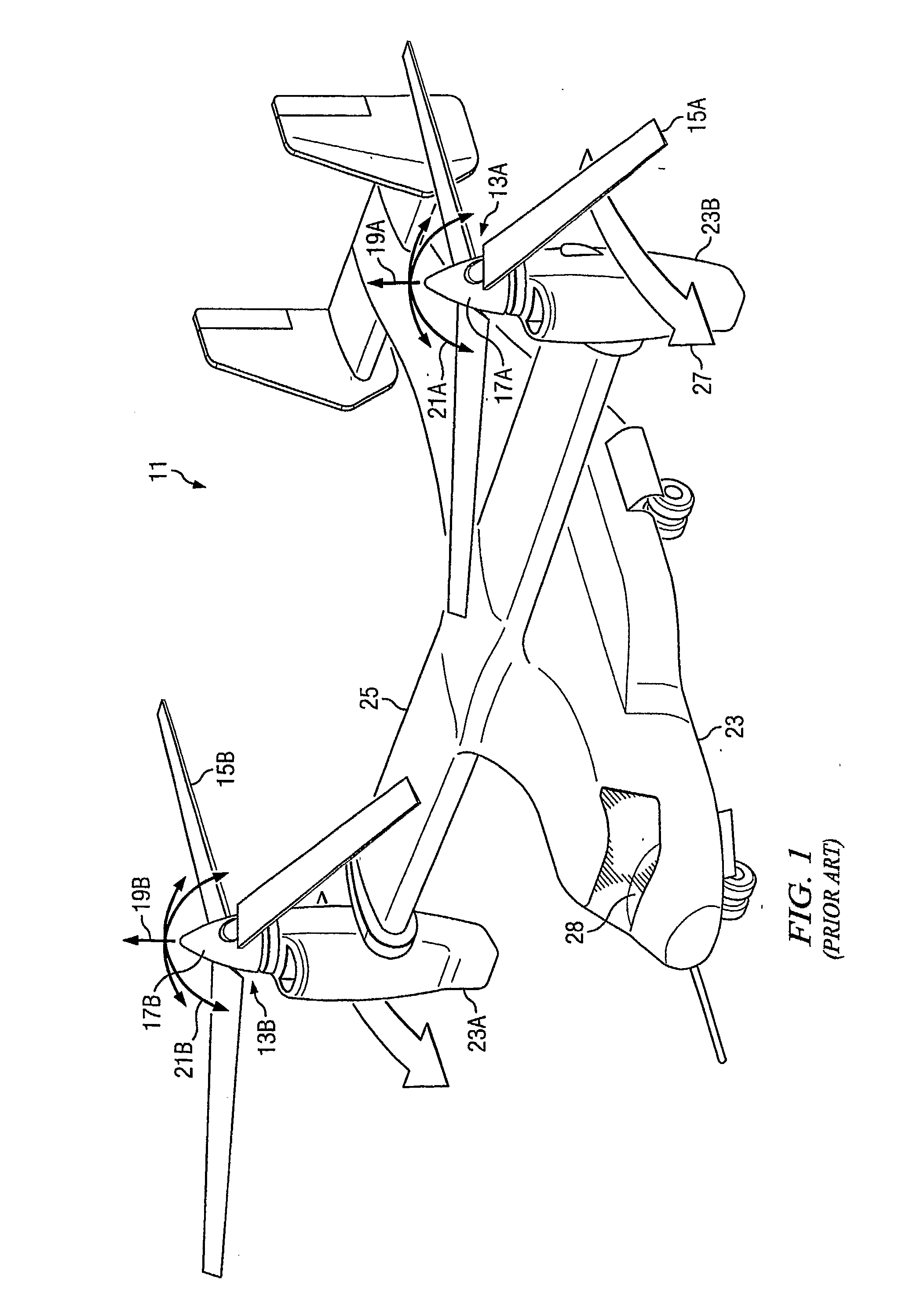

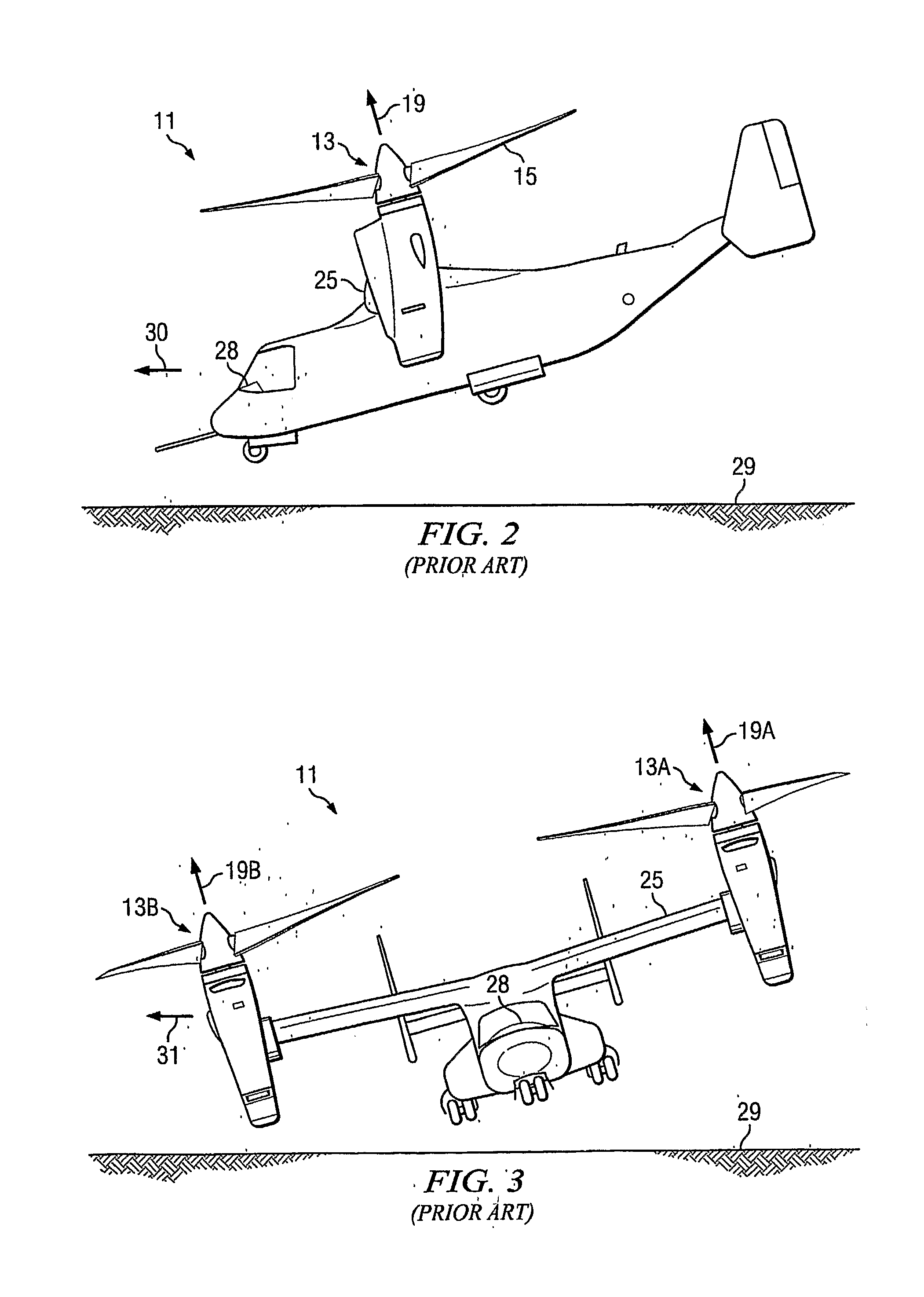

Method and Apparatus for Flight Control of Tiltrotor Aircraft

ActiveUS20070221780A1Short response timeImprove accuracyVehicle position/course/altitude controlVertical landing/take-off aircraftsAutomatic controlNacelle

A method and apparatus provide for automatically controlling the flight of a tiltrotor aircraft while the aircraft is in flight that is at least partially rotor-borne. The method and apparatus provide for automatically tilting nacelles in response to a longitudinal-velocity control signal so as to produce a longitudinal thrust-vector component for controlling longitudinal velocity of the aircraft. Simultaneously, cyclic swashplate controls are automatically actuated so as to maintain the fuselage in a desired pitch attitude. The method and apparatus also provide for automatically actuating the cyclic swashplate controls for each rotor in response to a lateral-velocity control signal so as to produce a lateral thrust-vector component for controlling lateral velocity of the aircraft. Simultaneously, collective swashplate controls for each rotor are automatically actuated so as to maintain the fuselage in a desired roll attitude. The method and apparatus provide for yaw control through differential longitudinal thrust produced by tilting the nacelles.

Owner:TEXTRON INNOVATIONS

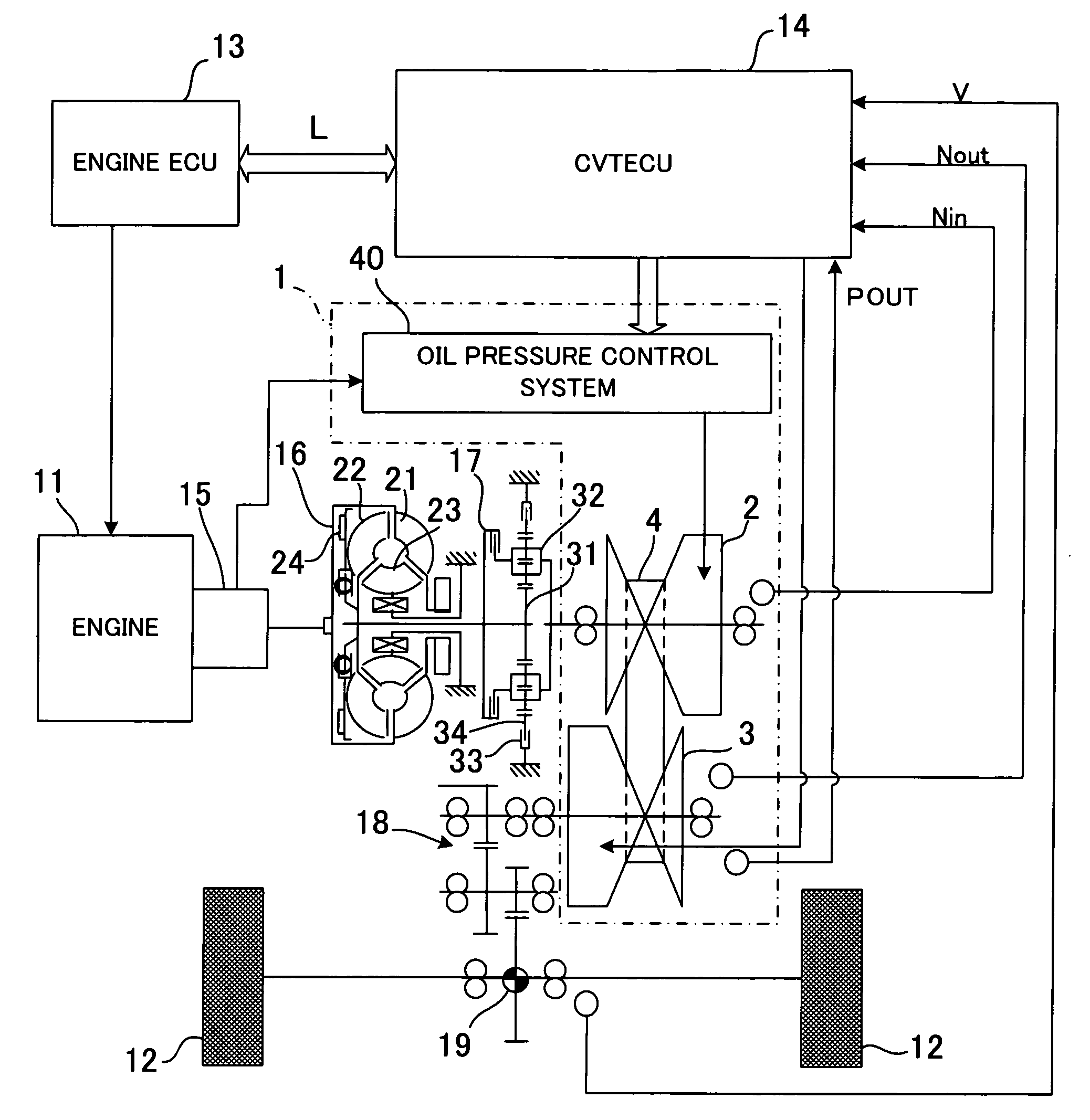

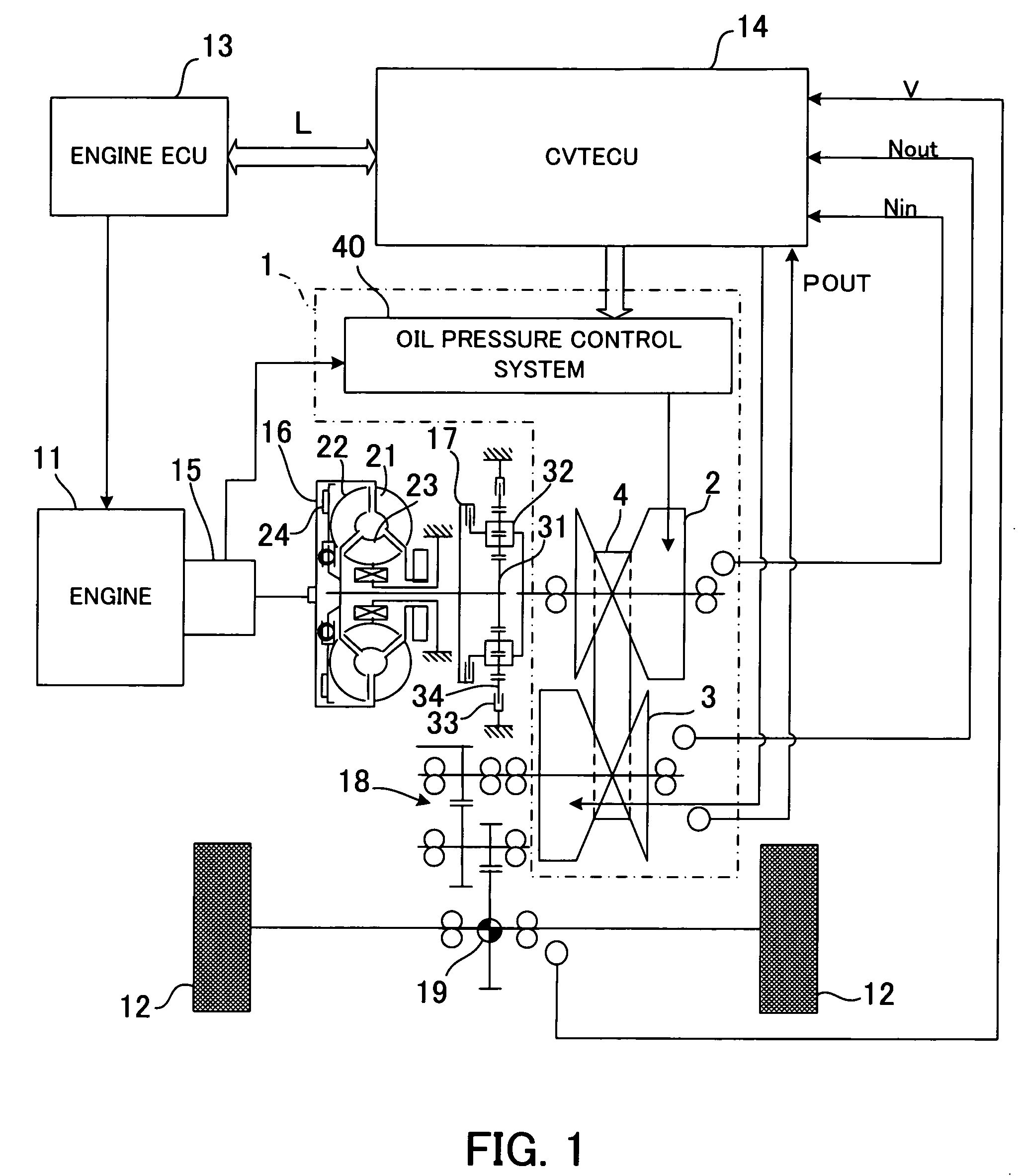

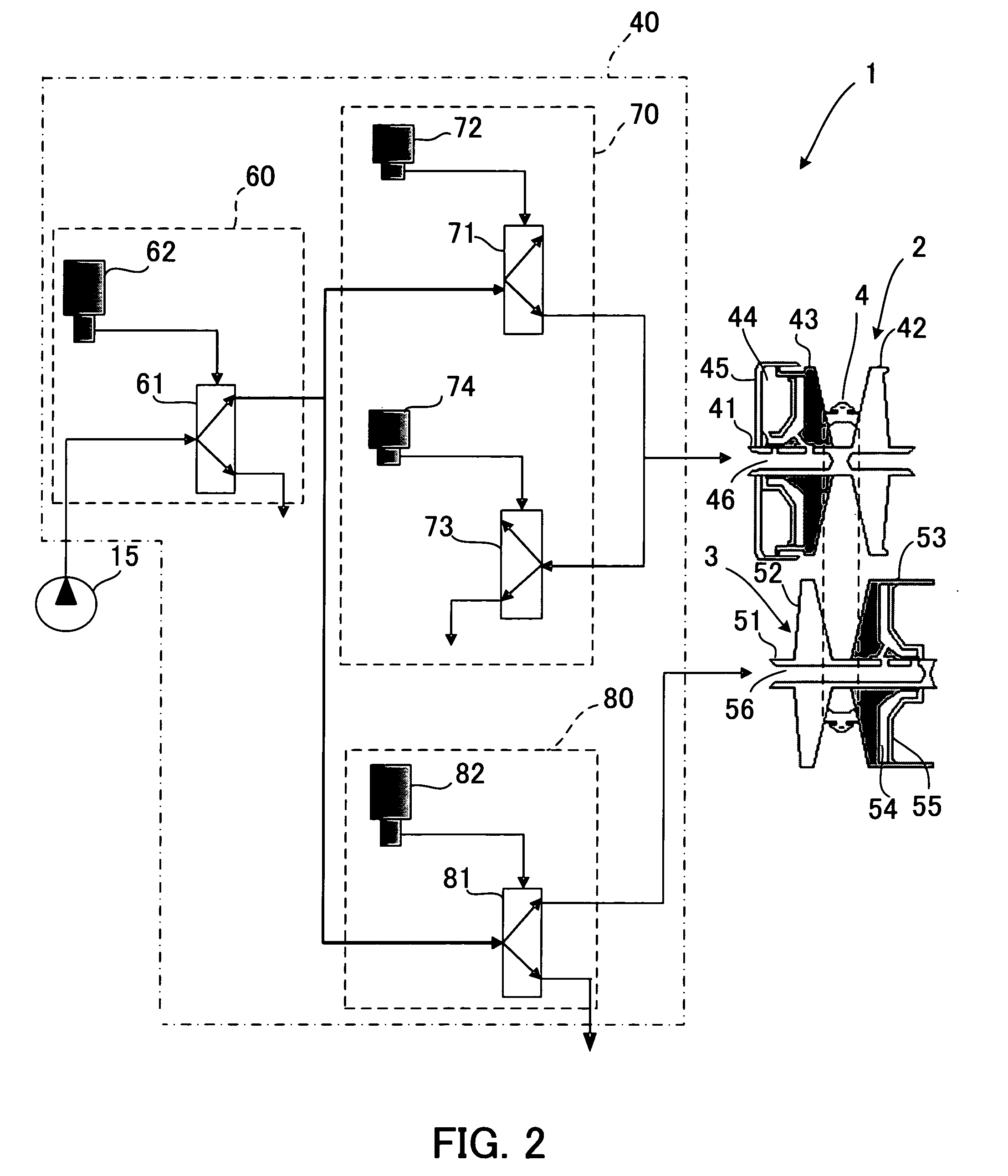

Method of controlling continuously variable transmission and control system

An oil pressure-learning method which enables an oil pressure control system that controls line pressure and belt clamping pressure by oil pressure actuators independently of each other, to accurately control both the line pressure and the belt clamping pressure. The oil pressure-learning method is applied to an oil pressure control system provided with a line pressure control solenoid for controlling a line pressure control valve, and a belt clamping pressure control solenoid for controlling a belt clamping pressure control valve. A belt clamping pressure command value that is outputted to the belt clamping pressure control solenoid as a control command value of belt clamping pressure, and a line pressure command value that is outputted to the line pressure control solenoid as a control command value of line pressure are learned in advance. This enables the oil pressure control system to control both the line pressure and the belt clamping pressure with accuracy.

Owner:FUJITSU GENERAL LTD

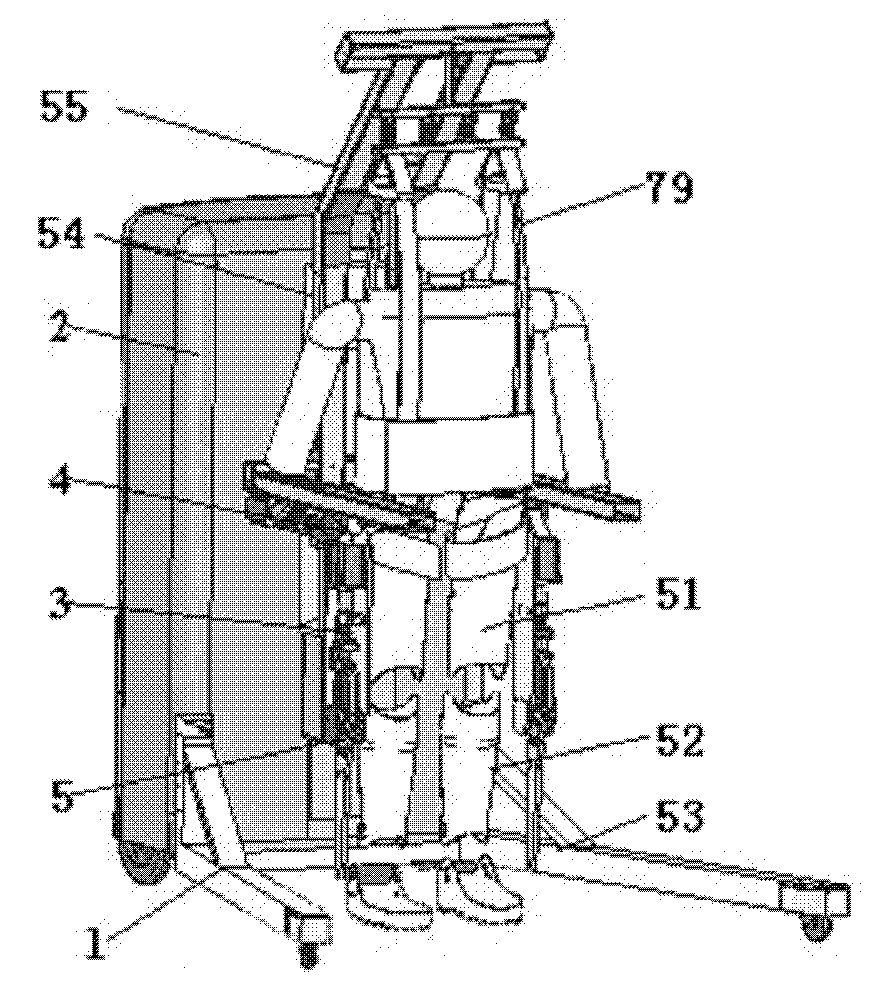

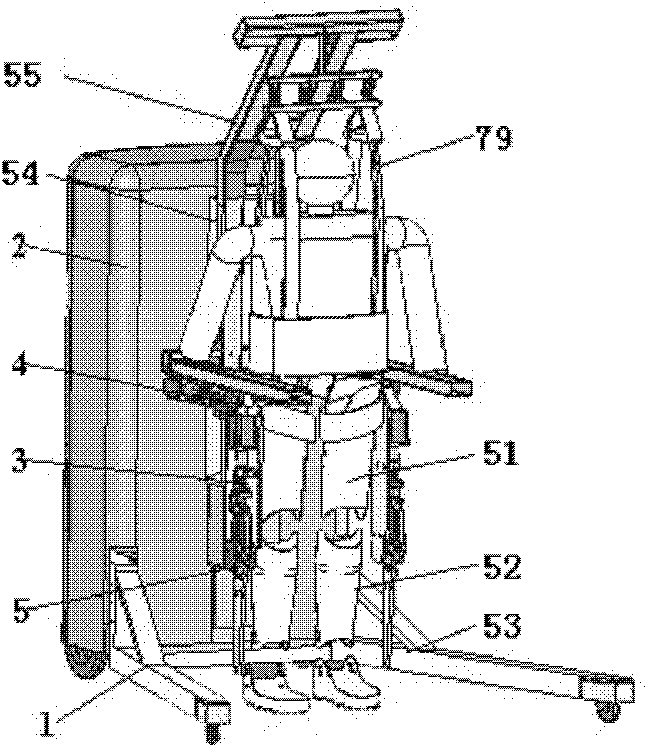

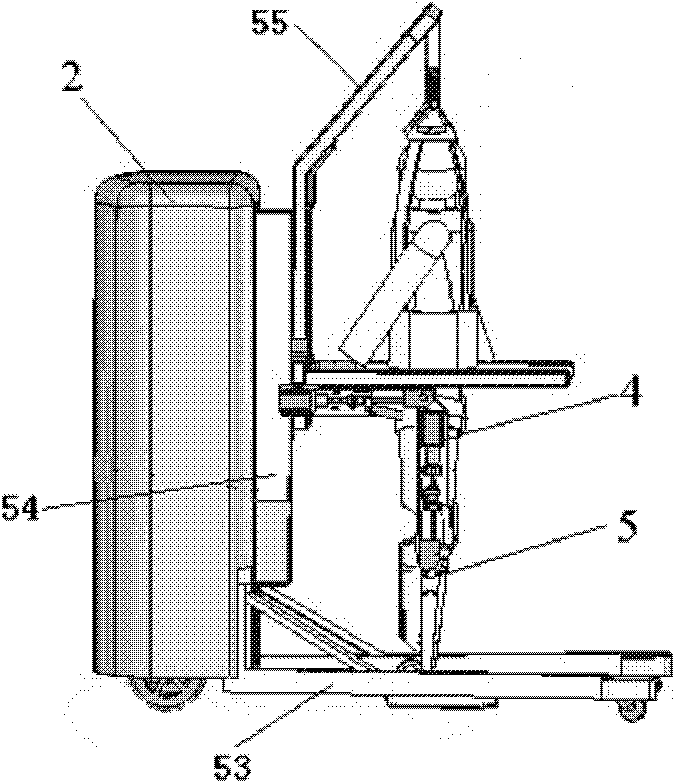

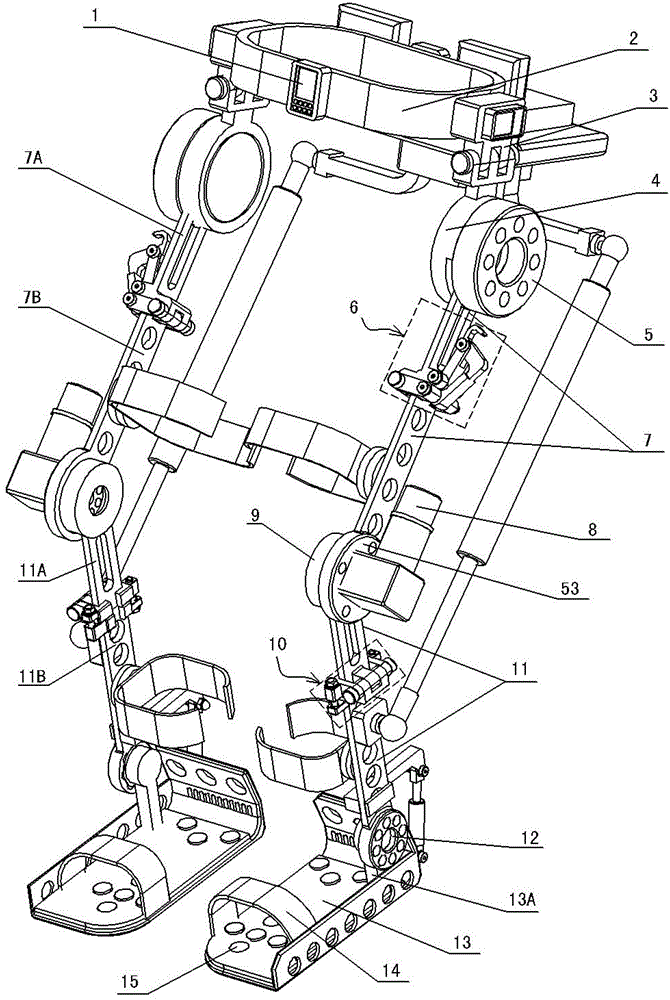

Walking aid exoskeleton rehabilitation robot

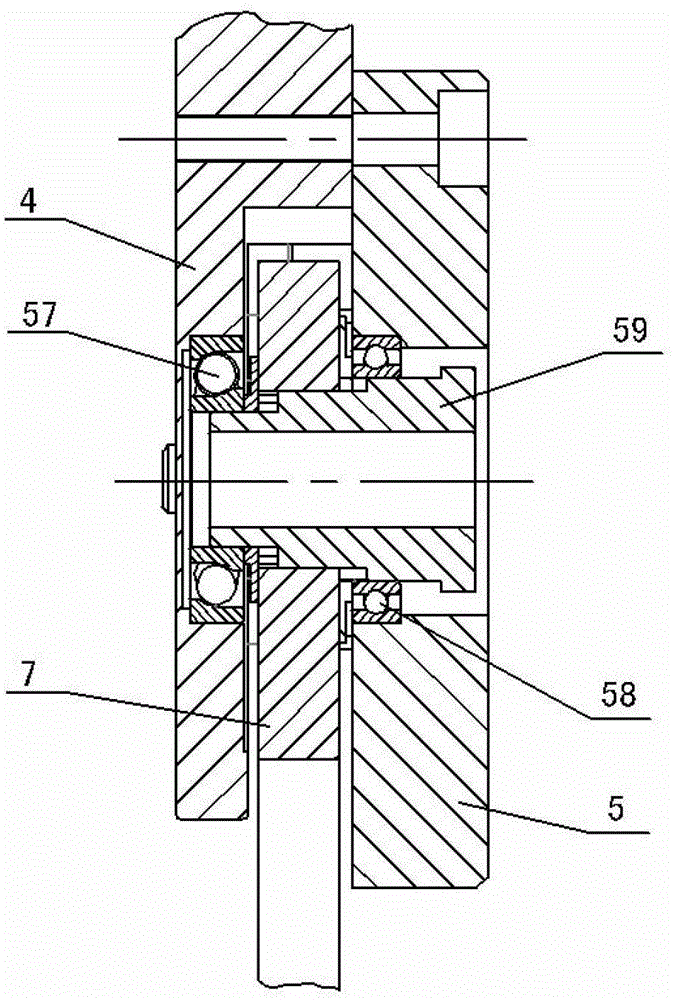

InactiveCN101810533ACompact designLarge range of joint rotationChiropractic devicesWalking aidsHuman bodyRehabilitation engineering

The invention discloses a walking aid exoskeleton rehabilitation robot in the technical field of rehabilitation engineering, which comprises a mobile auxiliary mechanism, a control mechanism and an exoskeleton prosthesis mechanism, wherein the mobile auxiliary mechanism is connected with the exoskeleton prosthesis mechanism, and the control mechanism is connected with the mobile auxiliary mechanism and the exoskeleton prosthesis mechanism respectively. The exoskeleton prosthesis mechanism has compact design structure and large rotation range of each joint, and can meet the requirement on actual motion of a human body. By adopting a servo motor to drive, the control precision is high, and the output torque is large; and the mobile auxiliary mechanism rotates under the driving of the servo motor, can freely move, and has higher climbing capacity and movement speed. The height of the mobile auxiliary mechanism is adjusted to be applied to people with different heights. When the patient undergoes gait rehabilitation training, the human gravity center is actively adjusted to accord with the characteristics that the human body is fluctuated along with alternative gait. The mobile auxiliary mechanism also can support the human body, prevent people from tumbling in walking, and guarantee the whole stability.

Owner:SHANGHAI JIAO TONG UNIV

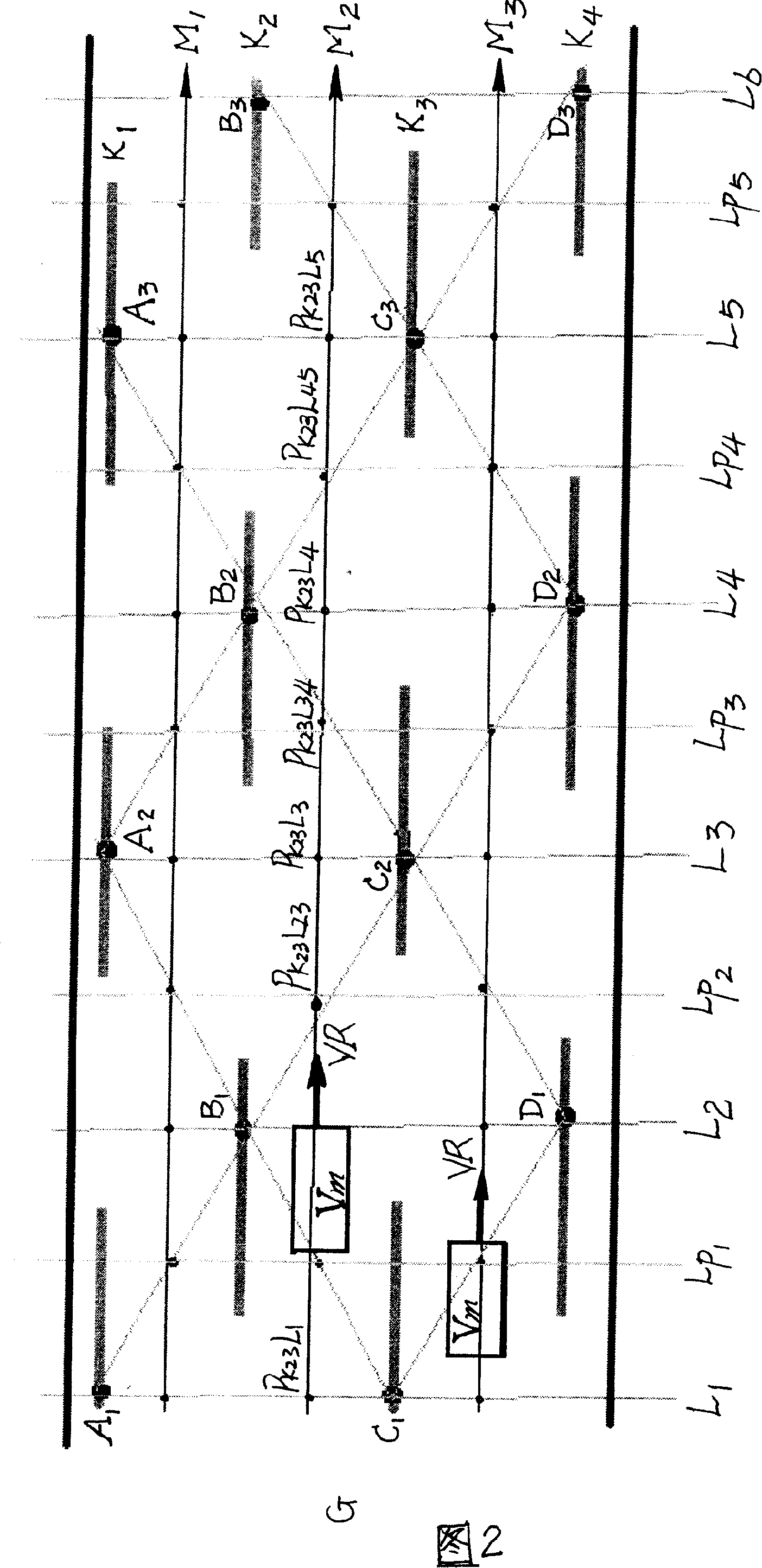

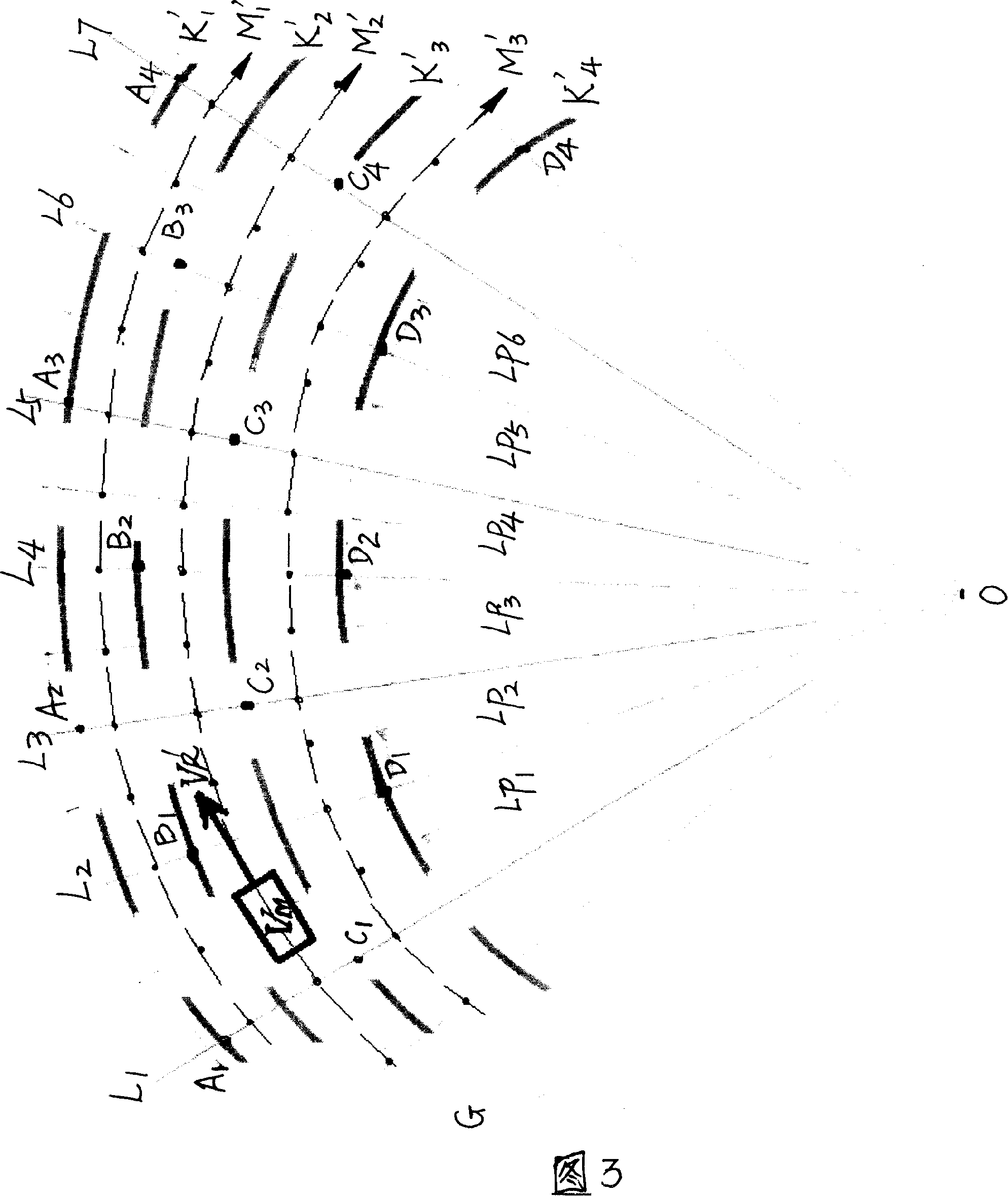

Automatic pilot system for road vehicle

InactiveCN101131588ARealize autonomous drivingPracticalPosition/course control in two dimensionsPilot systemAutomatic control

This invention relates to an automatic driving system of a road vehicle, especially to a system which providing automatic driving information indication for traveling vehicles and realizing vehicle automatic driving through the vehicle automatic control system, which is characterized by comprising: fixing markers at interval along a road travelling line, receiving information feedback by the fixed markers through a set relay information station and forming the vehicle and road information on the road, and constantly supplying the road and vehicle information of the road where the vehicle is to a vehicle automatic receiving processor after the received GPS(Global Position System) information and the vehicle and road information on the road are overall treated, installing an automatic driving software in a vehicle-mounted computer which can receive and treat relevant information of the relay information station at any time, constantly sending operation instructions to a vehicle automatic controller so as to keep the vehicle travelling information direction line consistent with the vehicle driving speed direction line, and sending instructions to the vehicle automatic controller according to the selected mode by a driver so as to realize vehicle automatic driving.

Owner:吴体福

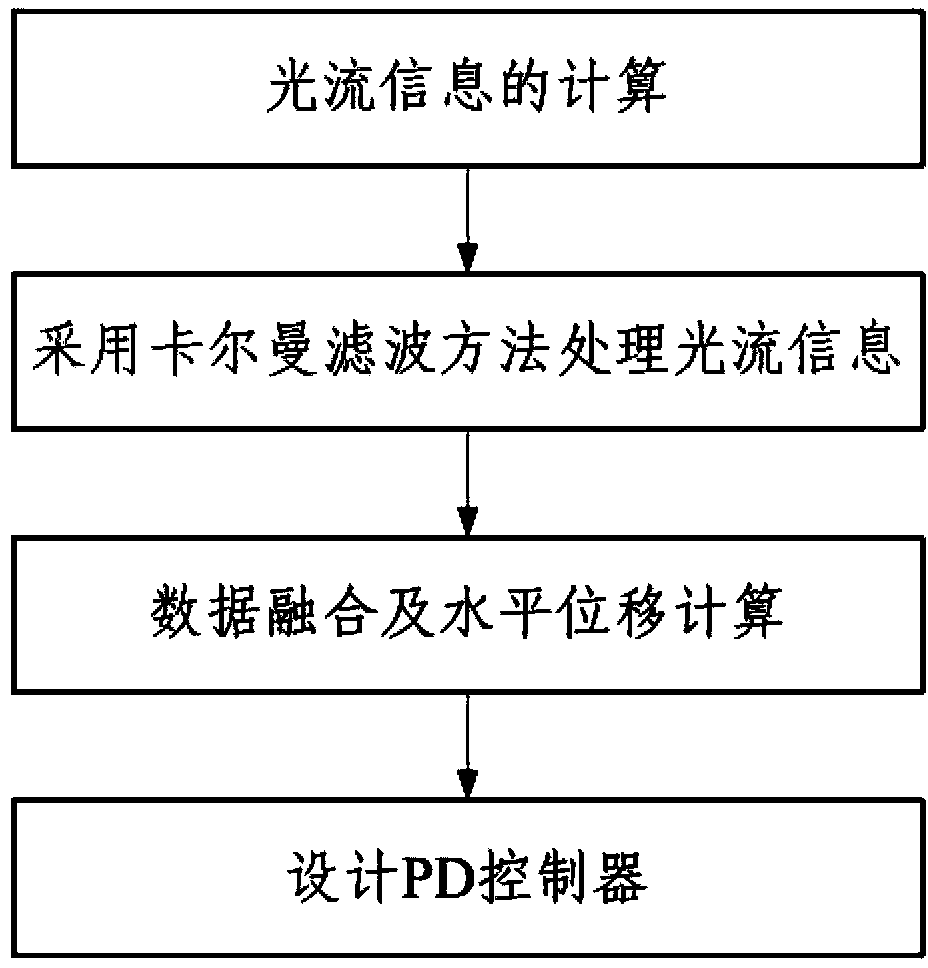

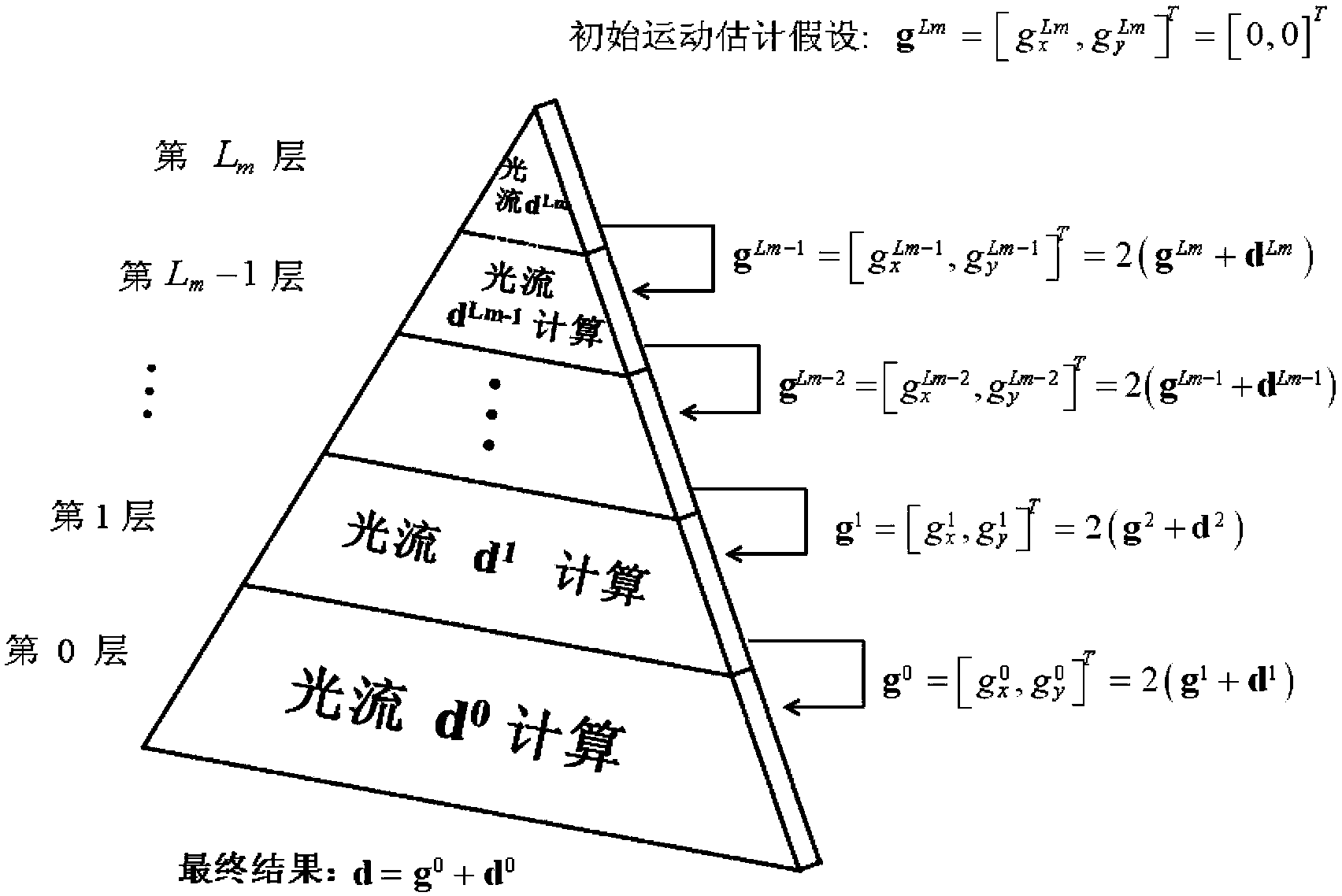

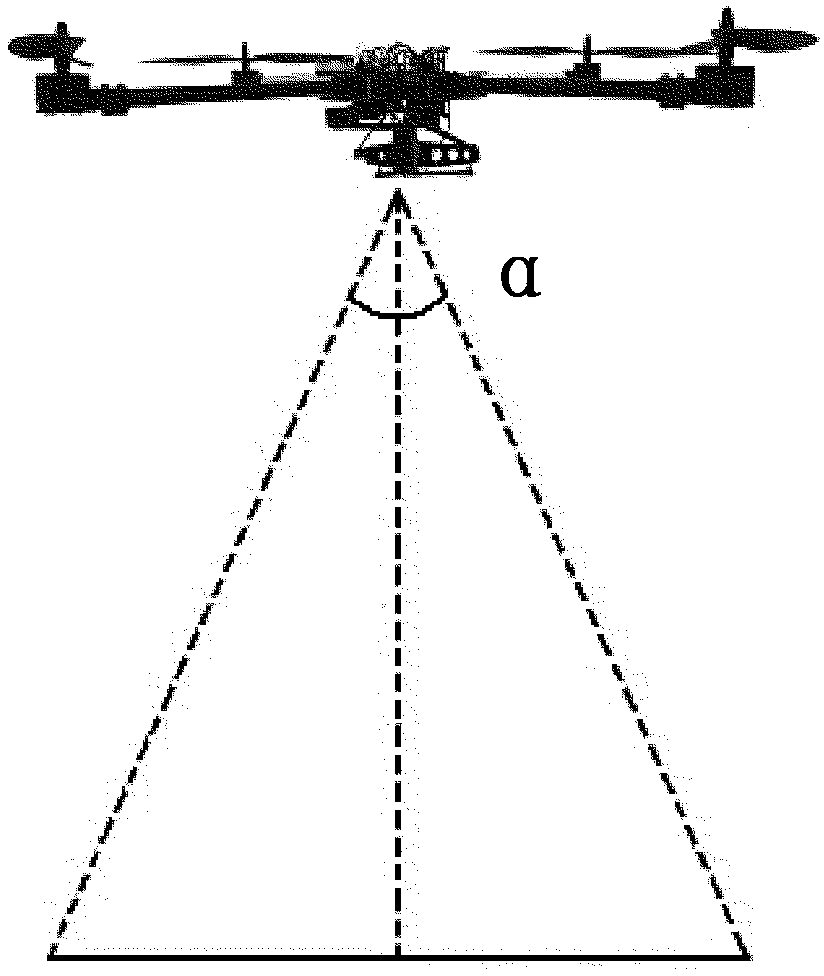

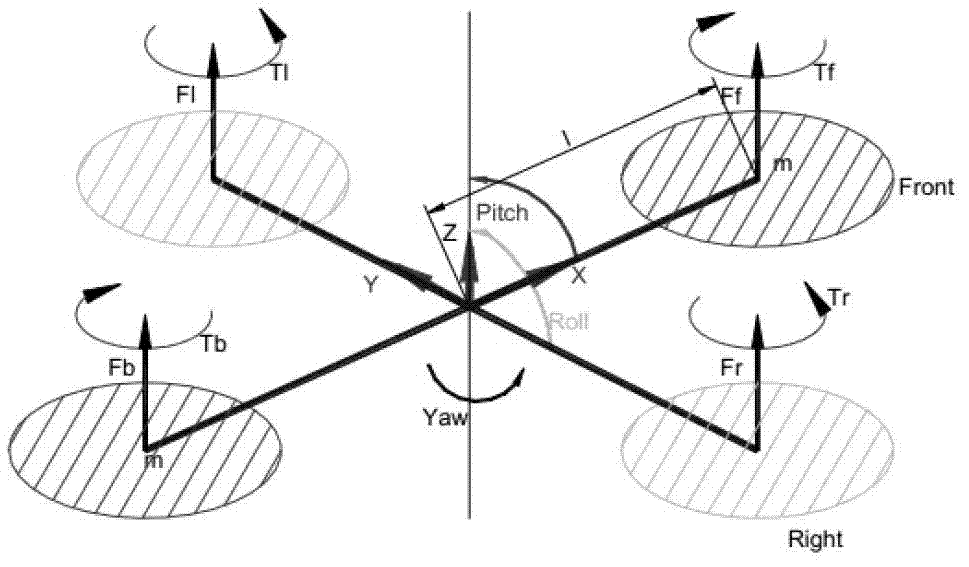

Optical flow-based four-rotor unmanned aerial vehicle flight control method

ActiveCN103365297AReduce volumeReduce weightPosition/course control in three dimensionsVehicle dynamicsProportional differential

The invention discloses an optical flow-based four-rotor unmanned aerial vehicle flight control method. The method comprises the following steps: calculating optical flow information by utilizing an image pyramid-based Lucas. Canard method; processing the optical flow information by adopting a Kalman filtering method; performing data fusion on an optical flow and an attitude angle, and calculating the horizontal displacement of an unmanned aerial vehicle; and designing a proportional-differential controller, including determining a four-rotor unmanned aerial vehicle dynamic model and designing a control algorithm. By the optical flow-based four-rotor unmanned aerial vehicle flight control method disclosed by the invention, the horizontal position information of the unmanned aerial vehicle is calculated by fusing the image information and the attitude angle information acquired by utilizing an airborne camera; and the position of a small unmanned aerial vehicle is controlled by taking the unmanned aerial vehicle horizontal position information as the feedback information of an outer ring PD (proportional-differential).

Owner:TIANJIN UNIV

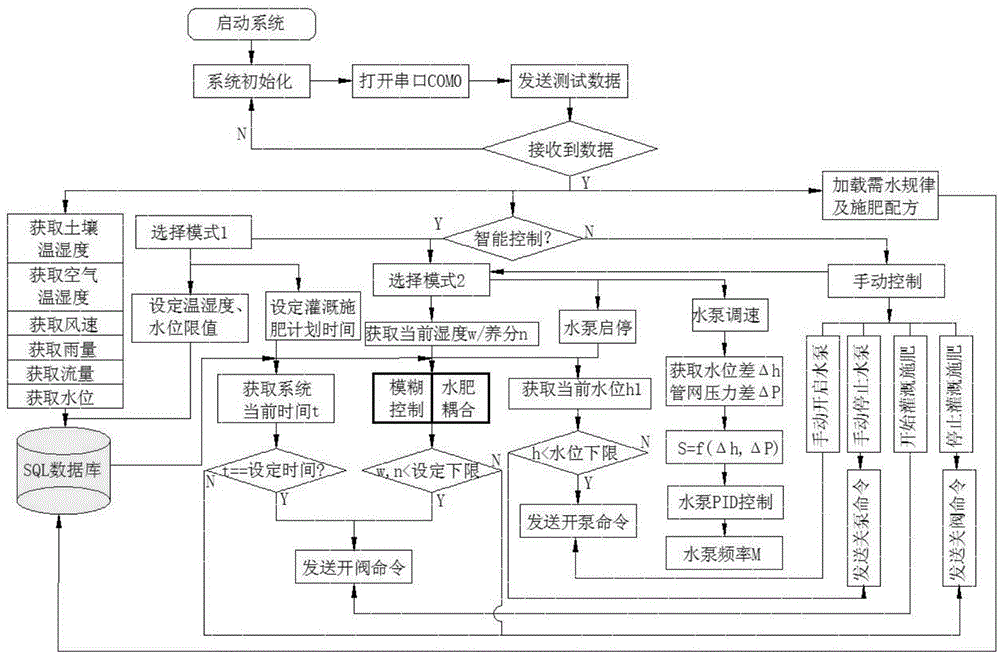

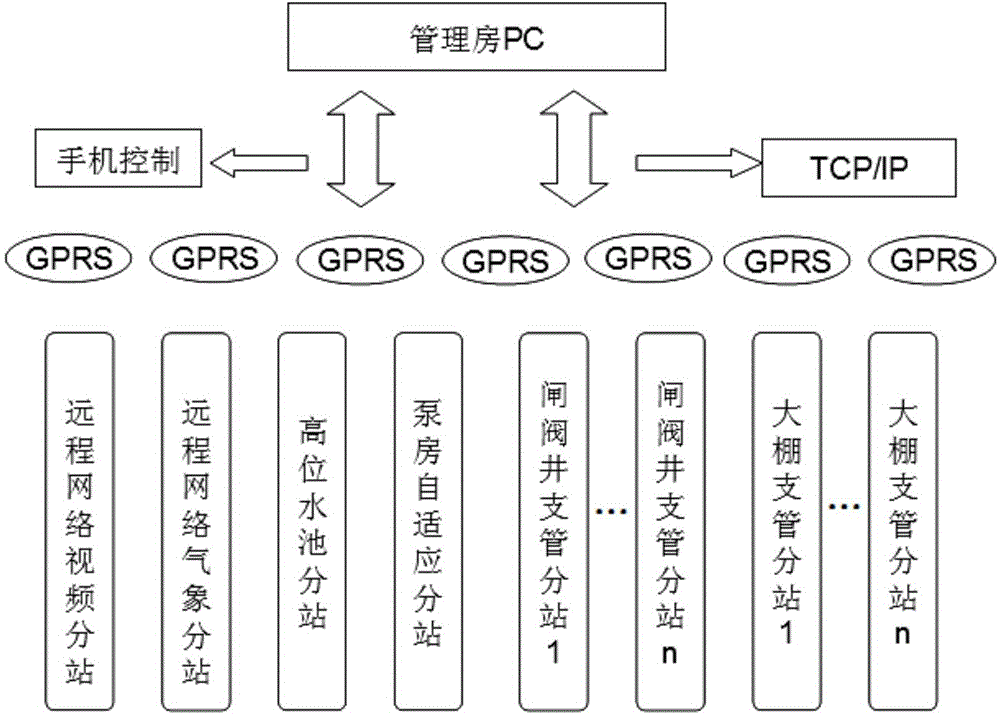

Fuzzy-control-based internet of things intelligent irrigation and fertilization control method and system

ActiveCN104460582AReduce pollutionHigh control precisionProgramme total factory controlData acquisitionLimit value

The invention discloses a fuzzy-control-based internet of things intelligent irrigation and fertilization control method and system. The method comprises the first step of data collection and processing, wherein limiting values of the soil humidity, nutrients and pond water level and the irrigation and fertilization planning time are set and stored in a database according to the water demand regulation and a fertilization formula of crops, and collected soil temperature and humidity, soil nutrients, air temperature and humidity, air speed, rainfall, flow, pond water level and pipe network pressure data; the second step of intelligent control, wherein corresponding data are read from the database and an irrigation valve and a fertilization valve are intelligently controlled by the adoption of the fuzzy control algorithm and a water and fertilizer coupling mode, by comparing the current pond water level with the set limiting value of the pond water level, starting and stopping of a water pump are intelligently controlled, and the speed of the water pump is adjusted and controlled by a PID algorithm. The fuzzy-control-based internet of things intelligent irrigation and fertilization control method and system have the advantages of being good in performance, complete in function, high in expansibility, easy to operate and manage and the like, and intelligent management and control are achieved by the adoption of fuzzy control.

Owner:贵州省水利科学研究院 +1

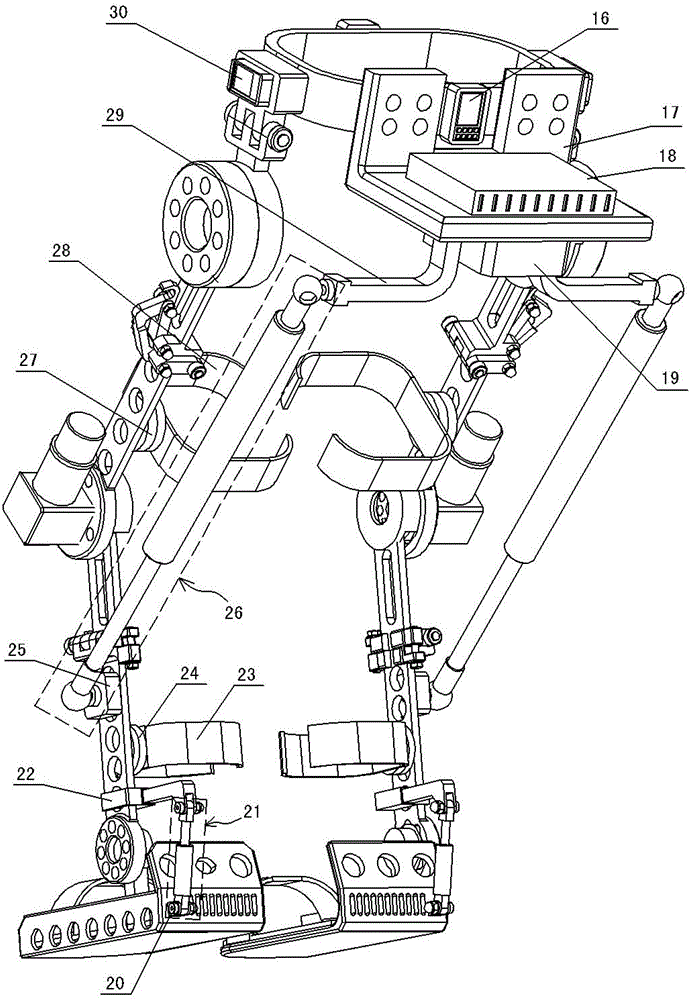

Wear type lower limb assistant robot, folding method thereof and hand luggage for carrying

ActiveCN103330635ASafe, Reliable and Reasonable BehaviorTimely and accurate judgmentWalking aidsLuggageMan machineEngineering

The invention discloses a wear type lower limb assistant robot, a folding method thereof and a hand luggage for carrying. The robot is characterized by comprising a lower limb assistant mechanical device and a servocontrol system, wherein the lower limb assistant mechanical device is provided with wearable assistant mechanical legs which are symmetrically arranged on the two sides of a wearable waistband. The wearing load on human bodies can be effectively relieved, and the robot has the characteristics of high safety performance, simple man-machine coordination control, good following assist effect, high cost performance and the like; the robot can be changed into a portable body which is compact in structure through the folding method, and a user can conveniently carry and store the robot in various manners through matching with the hand luggage for carrying, so that the nursing requirements of the middle-aged and the aged people on daily activities such as walking and walking up and down stairs can be better satisfied.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

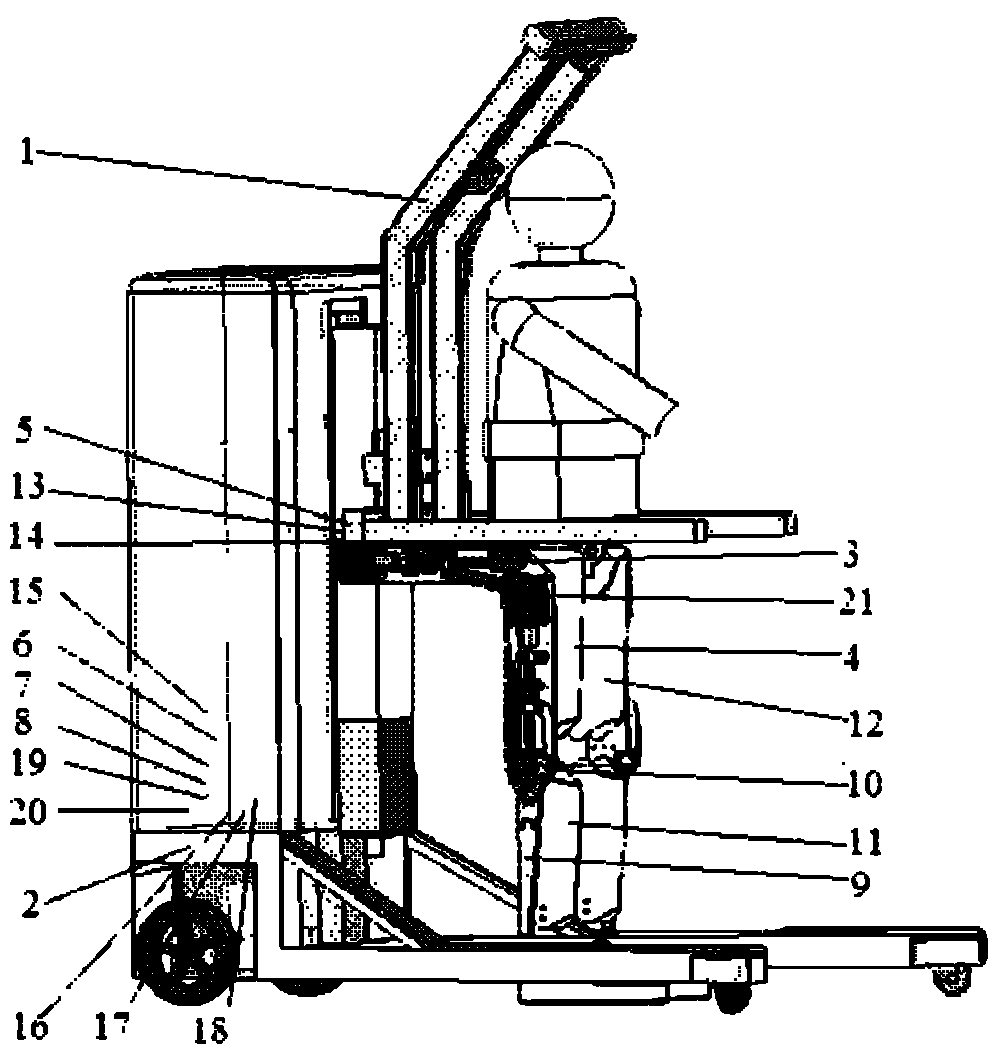

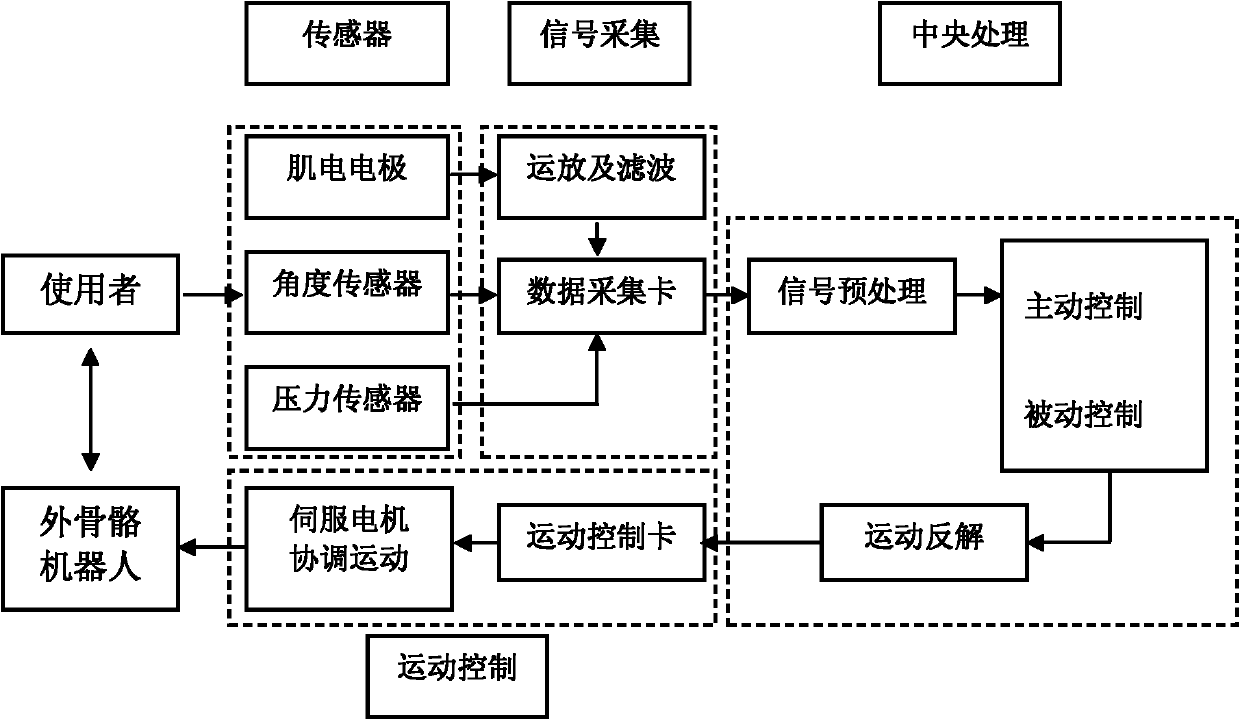

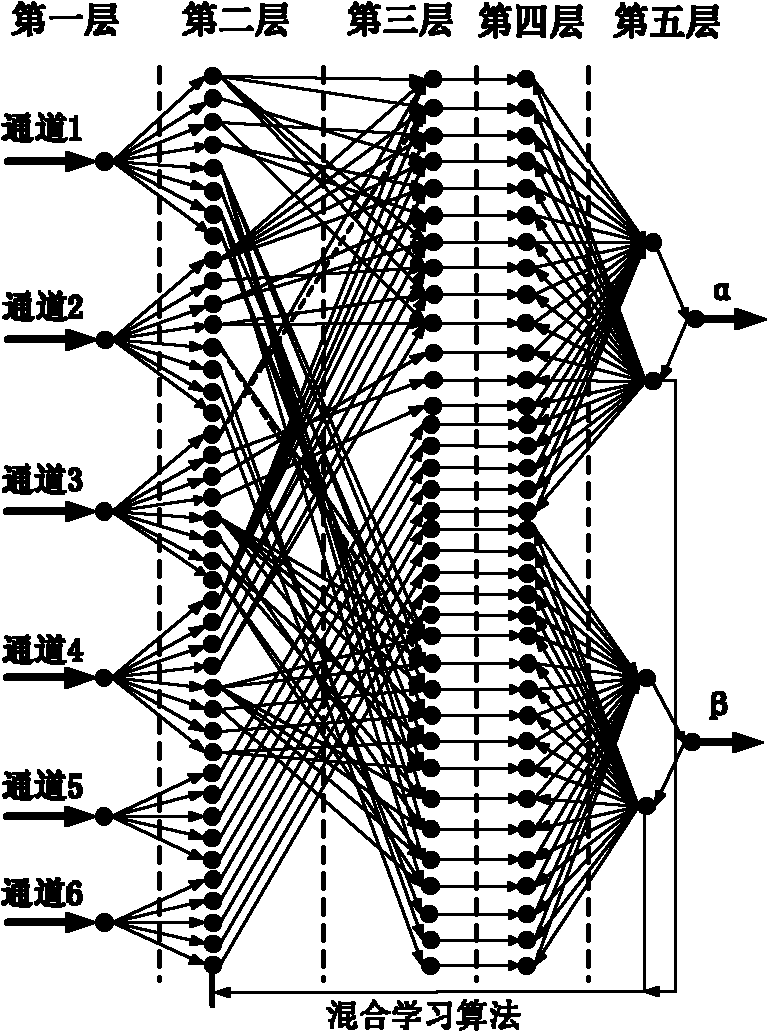

Walk-aiding exoskeleton robot system and control method

InactiveCN101791255ACompact designMeet the actual sports requirementsWalking aidsArtificial legsHuman bodyExoskeleton robot

The invention relates to a walk-aiding exoskeleton robot system and a control method, which belong to the technical field of rehabilitation engineering. The system comprises a hanging support, a moving platform, joints, protecting sleeves, a sensor module, a signal acquisition module, a central processing module and a motion control module, wherein the hanging support is fixed on the moving platform, the joints are connected with the hanging support to form an exoskeleton robot, the sensor module, the signal acquisition module, the central processing module and the motion control module are sequentially connected, the sensor module is used for acquiring joint angles, the interacting force of the exoskeleton robot and the human being and the myoelectric signals of the muscles of the human body, the signal acquisition module carries out signal conditioning and digital-to-analog conversion, the central processing module carries out action generation and the reverse solution of motion, and transmits an action command to the motion control module, and the motion control module is connected with the exoskeleton robot and generates a pulse signal to control the coordinated motion of the exoskeleton robot. The invention realizes the synchronous motion of the exoskeleton robot and the human body and real-time active control.

Owner:SHANGHAI JIAO TONG UNIV

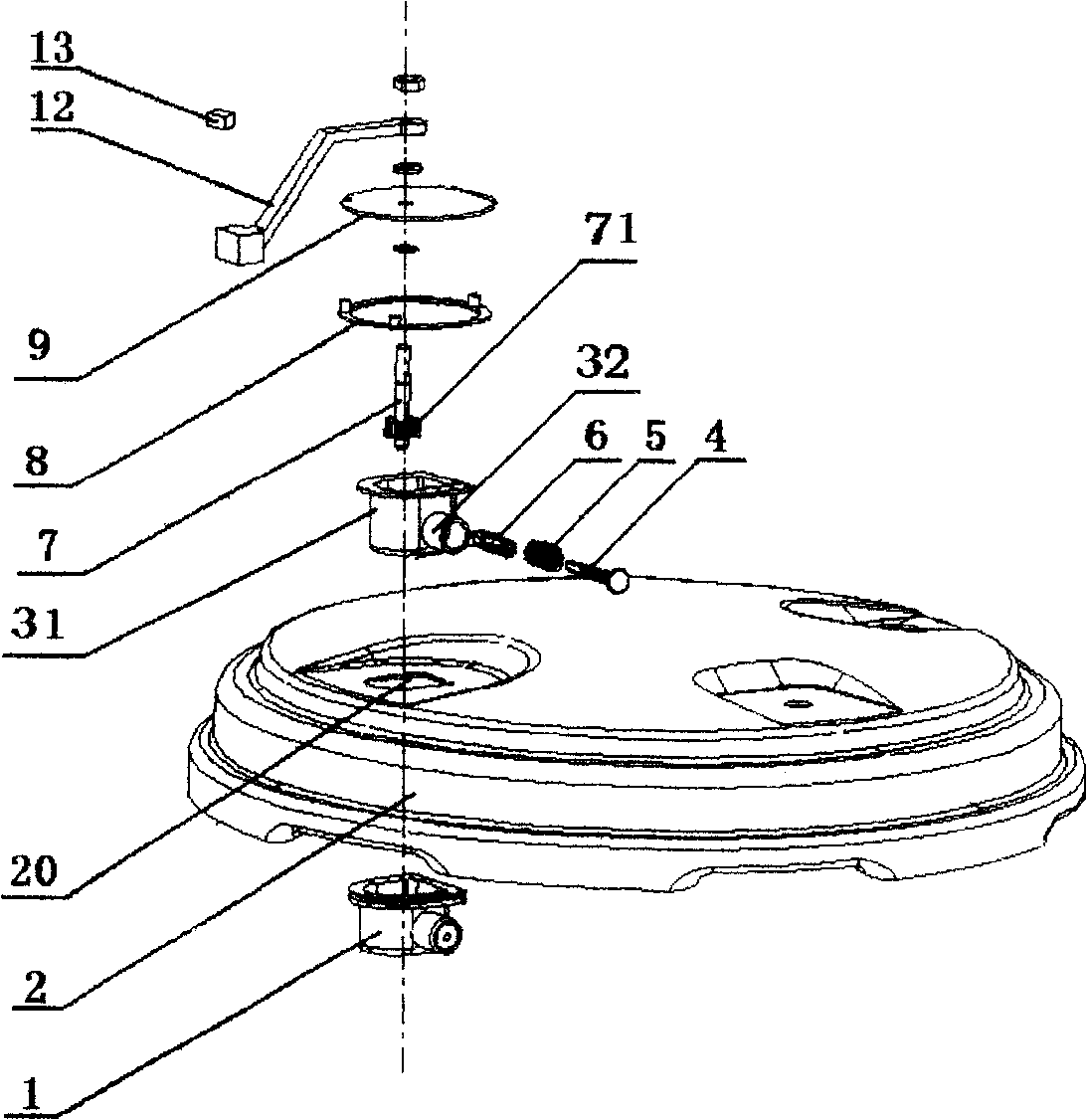

Enzyme-linked immune analysis method and fully-automatic enzyme-linked immune analyzer

ActiveCN102116771AUnique structural shapeNo wasteMaterial analysis by optical meansBiological testingTemperature controlControl system

The invention relates to an enzyme-linked immune analysis method and a fully-automatic enzyme-linked immune analyzer. The analyzer comprises a rack component, a washing component, a sample adding / reagent adding component, a heating and temperature control component, a fluid path system, an input and output device, an optical measurement component and a control system, wherein the rack component comprises a rack soleplate; a pillar is arranged on the rack soleplate; a lower fixed plate and an upper fixed plate are arranged on the pillar from bottom to top in sequence; a circular reaction plate is arranged between the lower fixed plate and the upper fixed plate; the circular reaction plate is connected with the upper fixed plate and the lower fixed plate through a central shaft; a first motor is fixedly arranged at the lower part of the lower fixed plate; and the first motor is used for driving the circular reaction plate to rotate through a first transmission mechanism. When in use, the enzyme-linked immune analysis method and the fully-automatic enzyme-linked immune analyzer can carry out the detection of corresponding projects without wasting reagent through only one sample; and detection reagents need not to be respectively contained in different reagent bottles, so that the operation is very convenient, and the operation error is not easily caused, thereby ensuring the accuracy of the detection results.

Owner:SHENZHEN YHLO BIOTECH

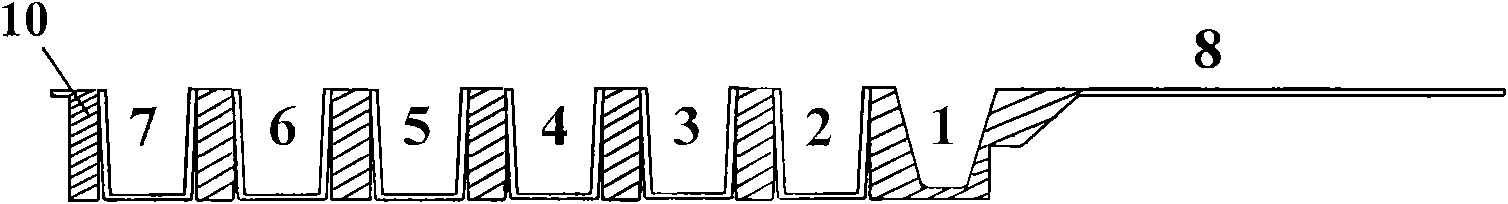

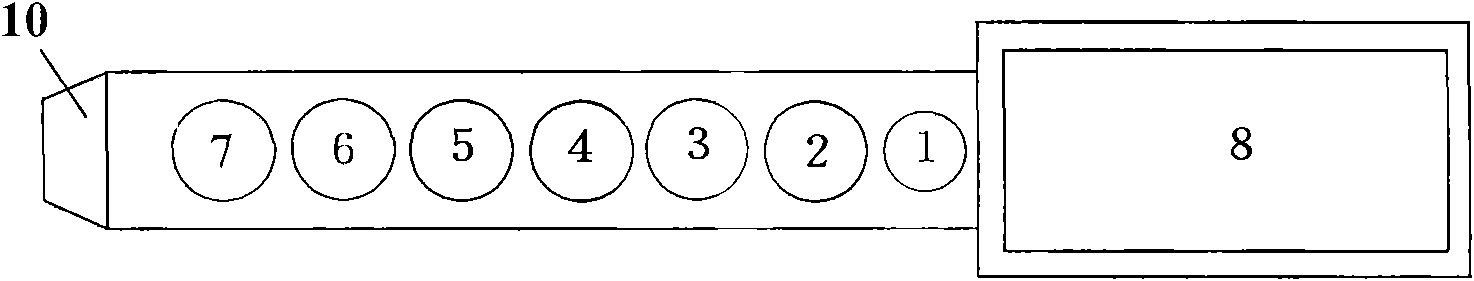

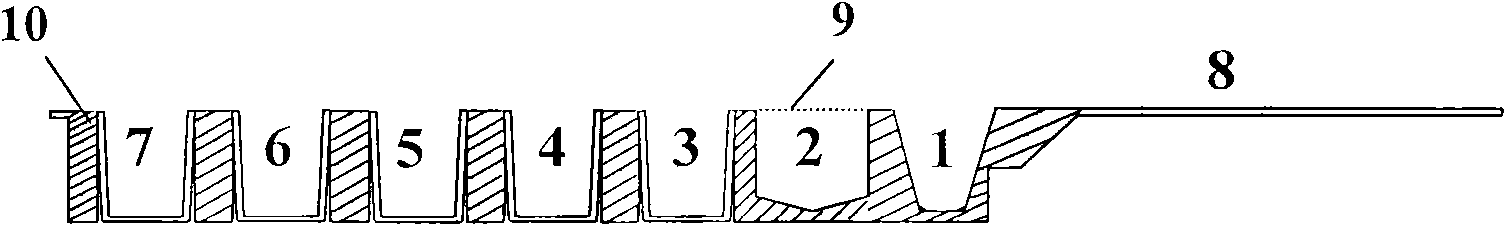

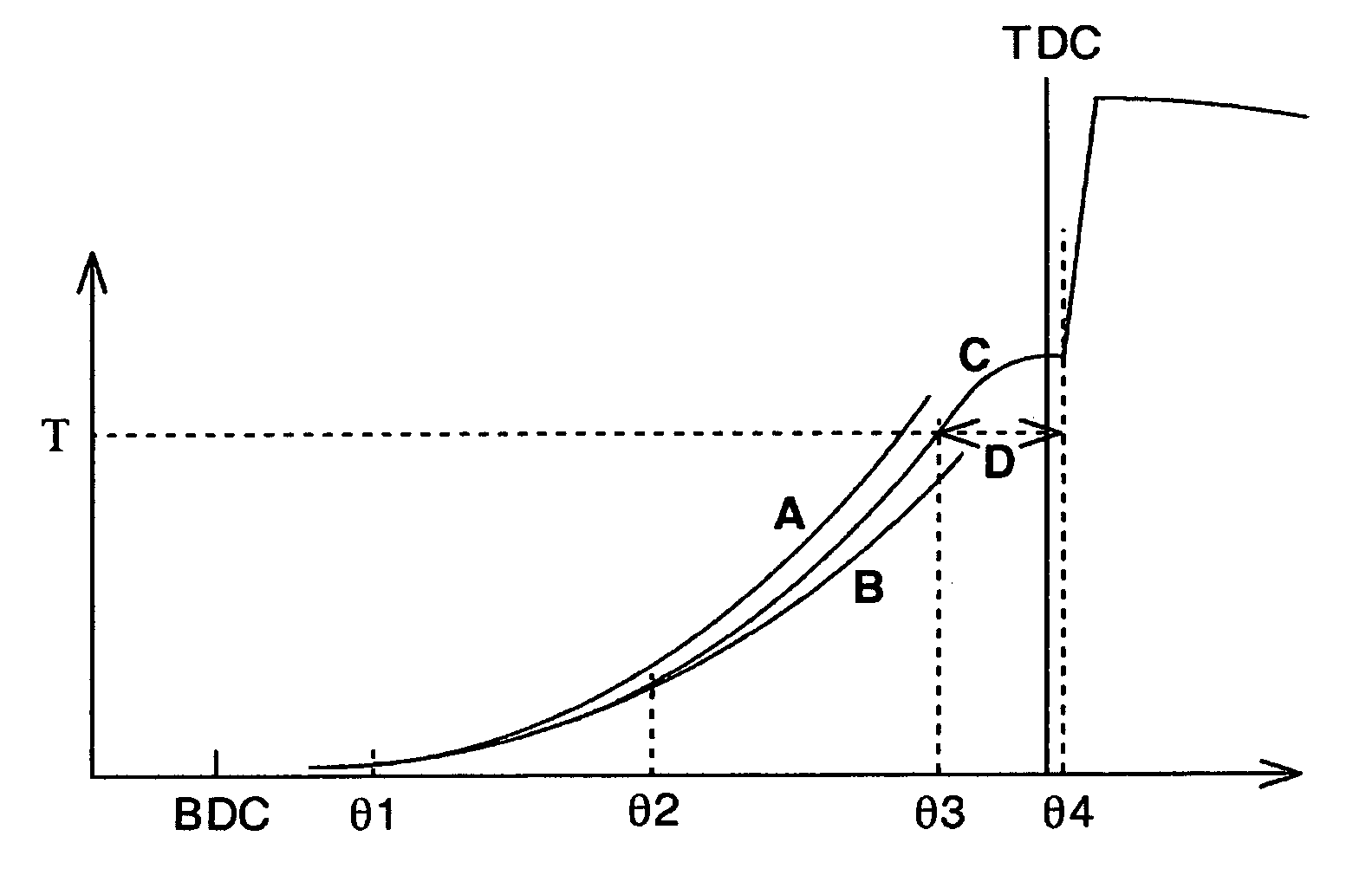

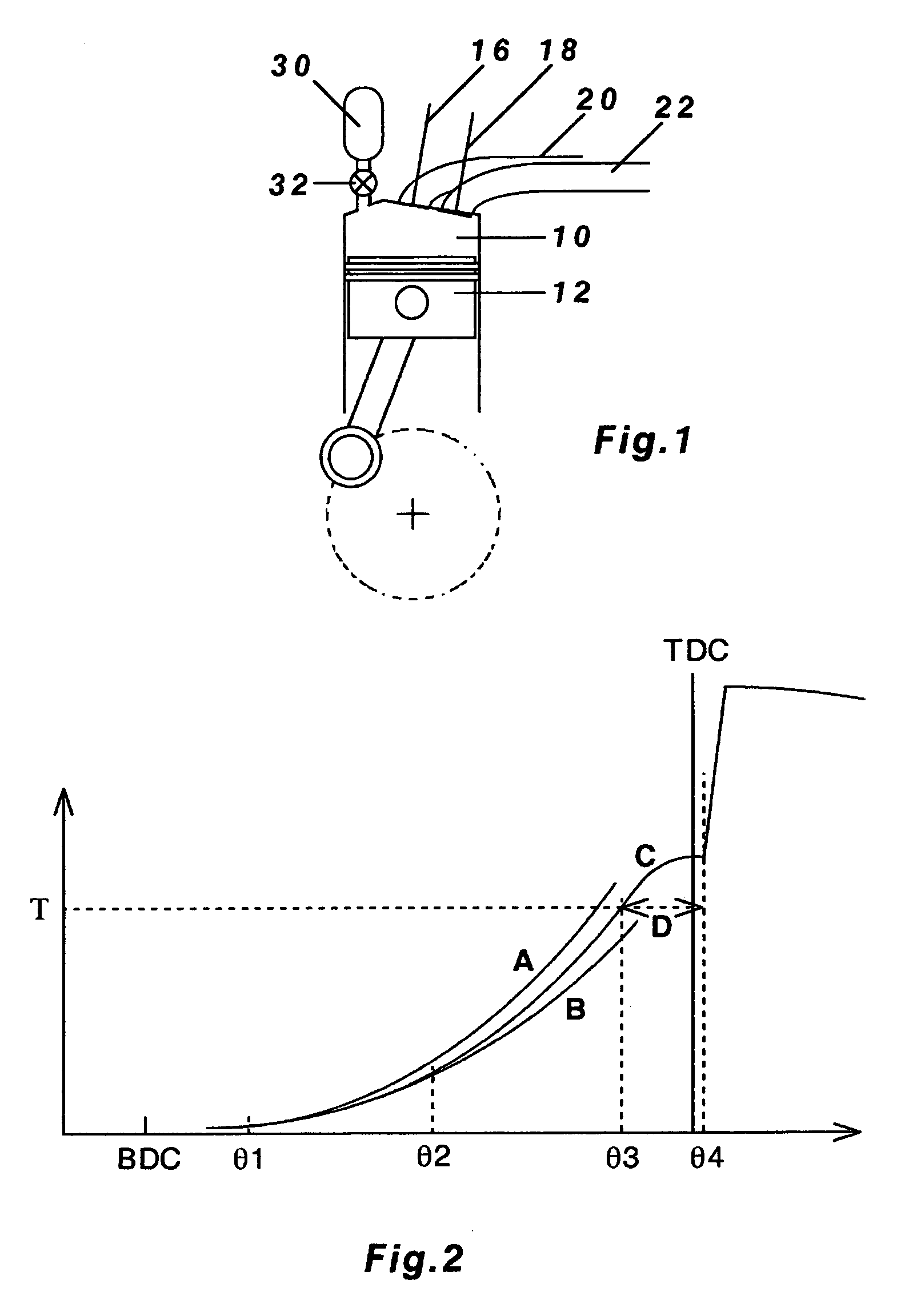

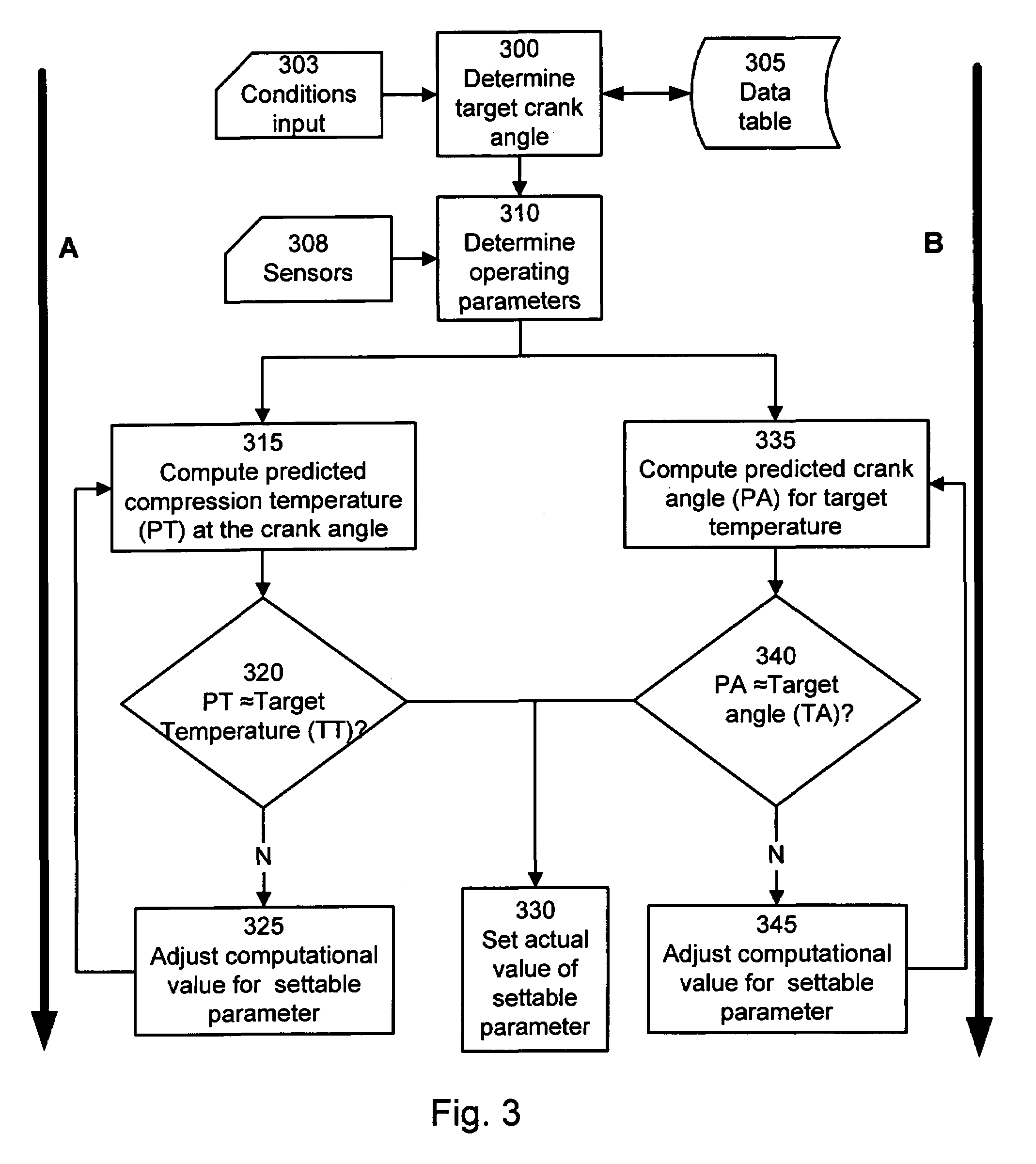

Auto-ignition timing control and calibration method

InactiveUS7076360B1Reduce Calibration ComplexityLess calibration workElectrical controlInternal combustion piston enginesEngineeringAuto ignition

An auto-ignition timing control and calibration method for use in an internal combustion engine having more than one ignition modes including the mode of compression ignition of a premixed fuel / air mixture (CAI / HCCI), wherein when the engine is operating in the CAI / HCCI mode, in order to determine a prescribed setting or combination of settings of engine operating parameters necessary to achieve a target auto-ignition timing according to a predetermined auto-ignition timing map, the associated compression temperature trajectory of the cylinder charge with time, calculated in dependence on the initial and boundary conditions of the said charge subjected to the said prescribed setting or combination of settings of the said engine operating parameters, and further in dependence on the interim heat exchange processes affecting the said charge, is used for testing and verifying that the said trajectory reaches a target temperature at a target reference timing relative to TDC of the engine, and wherein the said target temperature and timing are predetermined by calibration.

Owner:MA THOMAS TSOI HEI

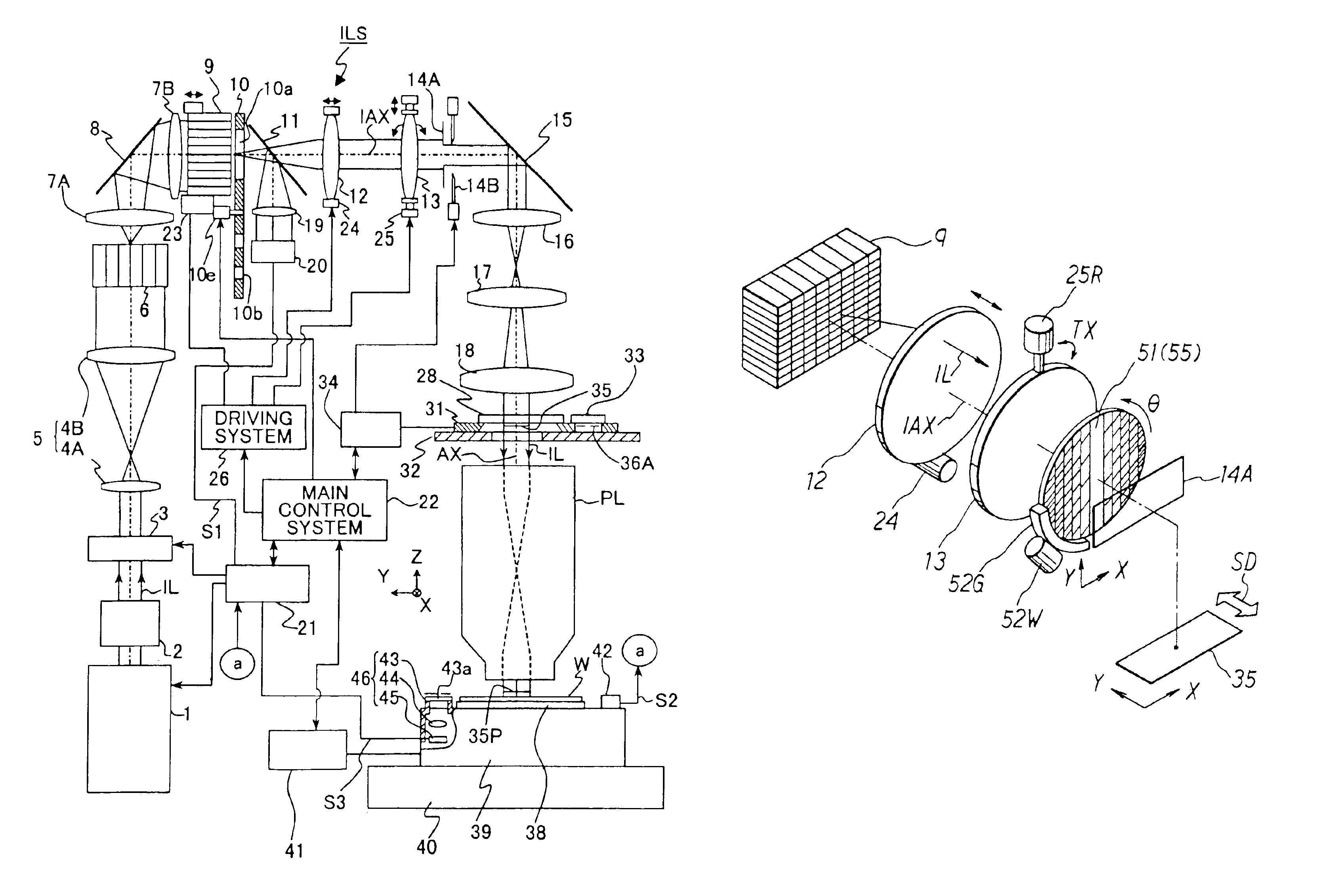

Exposure apparatus and exposure method capable of controlling illumination distribution

InactiveUS6927836B2Highly functionalHigh control accuracySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusIntegratorTransmittance

An exposure apparatus which expose a photosensitive layer on an object with light via a mask having a pattern to be transferred onto the photosensitive layer, includes an illumination optical system having plural optical elements provided along an optical axis substantially perpendicular to a plane on which the pattern is placed, and which include an optical integrator from which the mask is illuminated with the light through a part of the plural optical elements. The apparatus also includes a filter device having a rotatable filter element provided between the optical integrator and the plane, and having a transmittance distribution in a predetermined area. Light from the optical integrator passes through a portion in the predetermined area. Light from the filter element has a variable intensity distribution different from that of the light incident on the filter element from the optical integrator, and made variable by rotating the filter element.

Owner:NIKON CORP

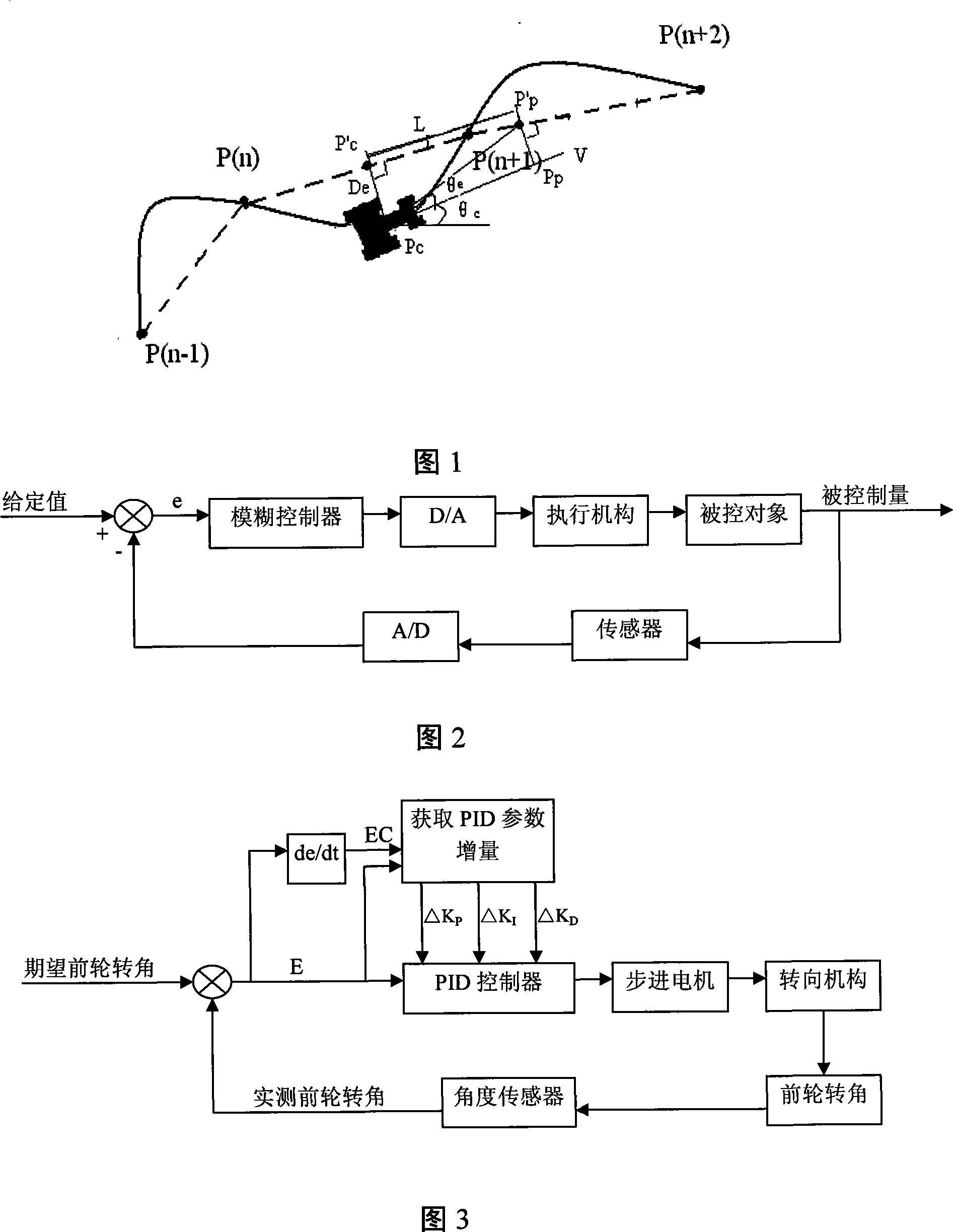

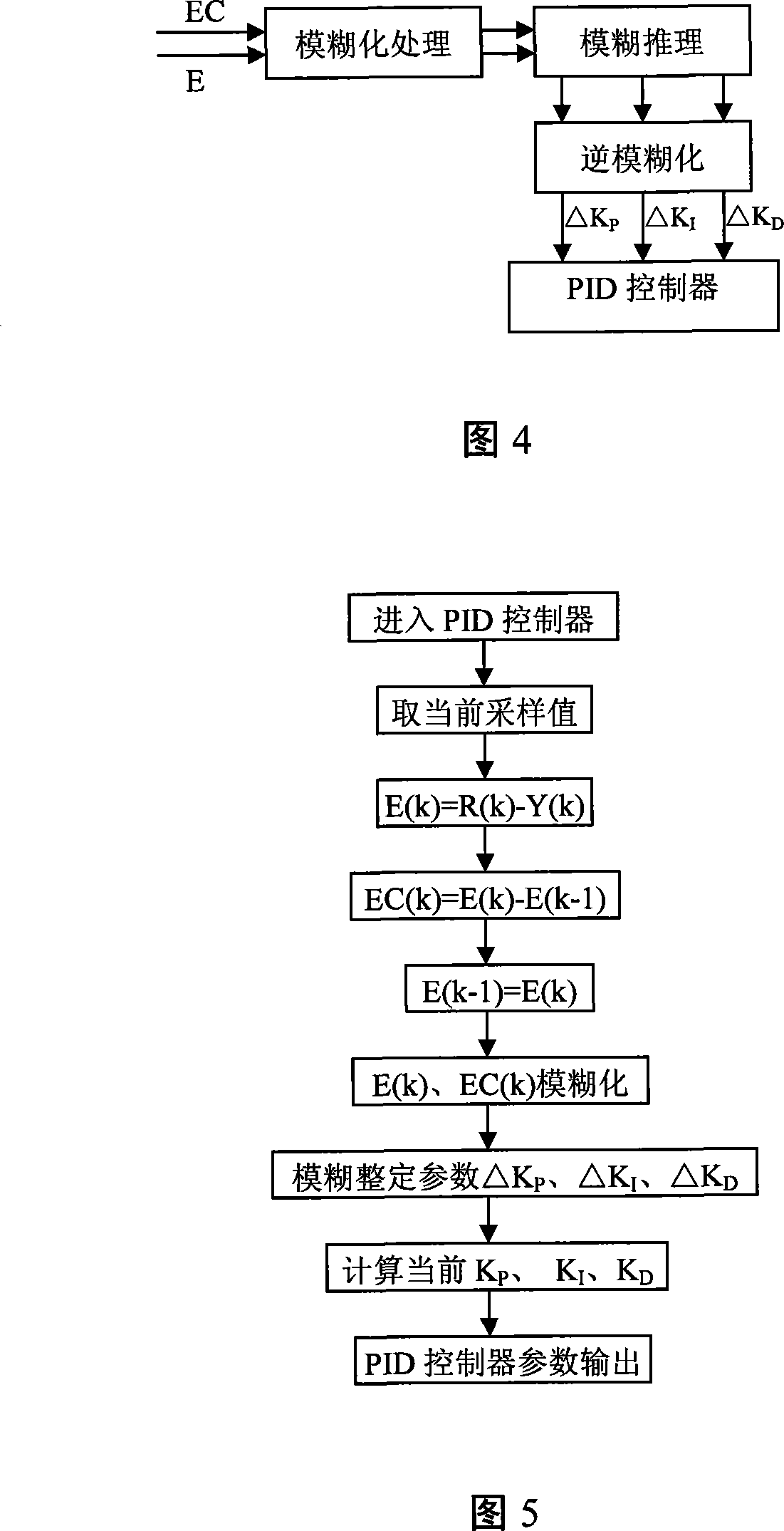

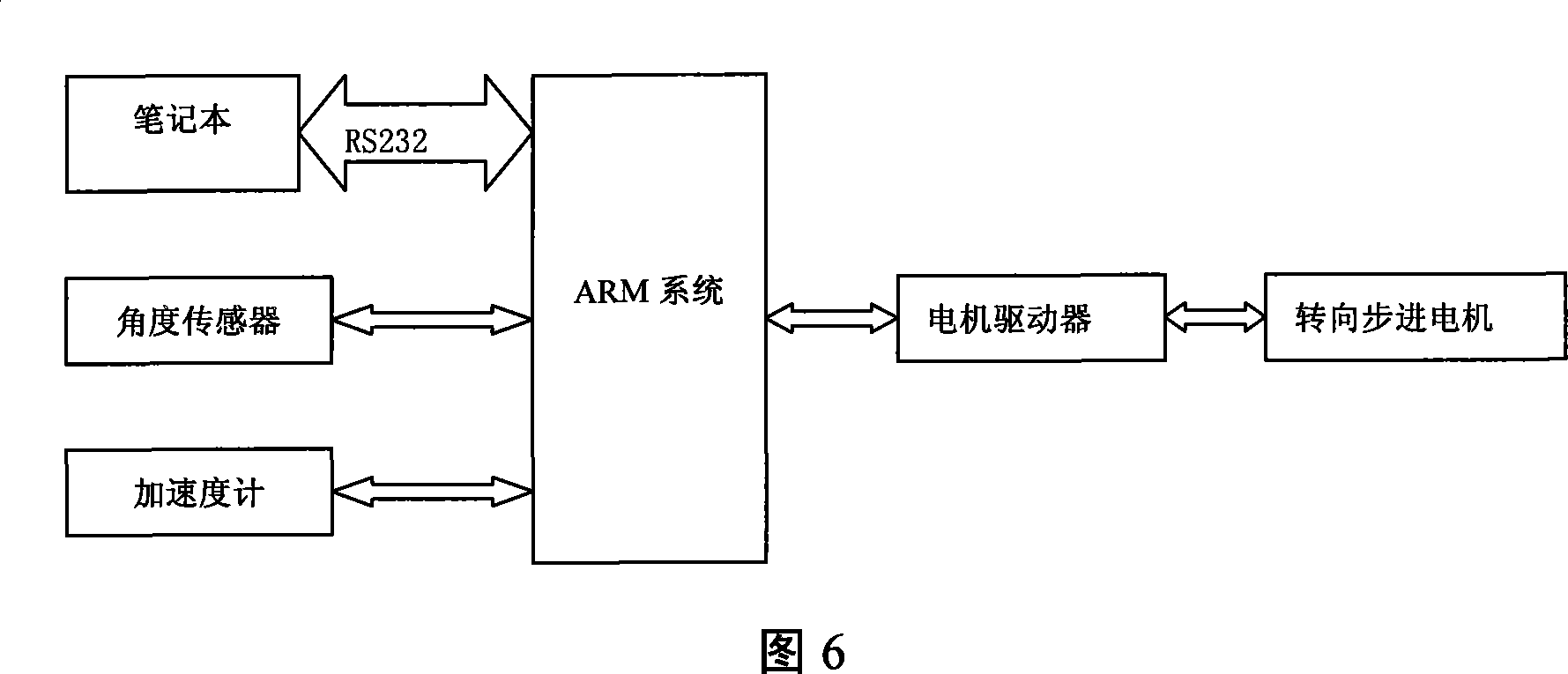

Mechanical automatic steering control method

InactiveCN101221447AHigh control precisionFlexibleGuiding agricultural machinesTarget-seeking controlAutomatic steeringPid control algorithm

The invention relates to a machinery automatic steering control method which comprises the following steps that: positional deviation and course deviation are determined; according to the variance in the practical front wheel rotating angle of an agricultural machine, online setting of PID parameter is completed by means of parameter self-setting PID control algorithm; moreover, the expected front wheel rotating angle of the next moment is calculated, thereby realizing automatic steering control of the agricultural machine. Based on conventional PID navigation control method, the invention makes full use of the fuzzy control method; according to the variance in the practical front wheel rotating angle of an agricultural machine, the invention meets the different requirements of the machine on PID control parameter under different errors and error change rate, thereby realizing online setting of PID parameter. The invention not only has the advantages of fuzzy control such as flexibility and adaptability, but also has the characteristics of higher precision of PID control; therefore, the invention can increase the stability and precision of agricultural machine automatic steering control and the robustness of a control system.

Owner:CHINA AGRI UNIV

Variable-frequency air-conditioner control method and control device thereof

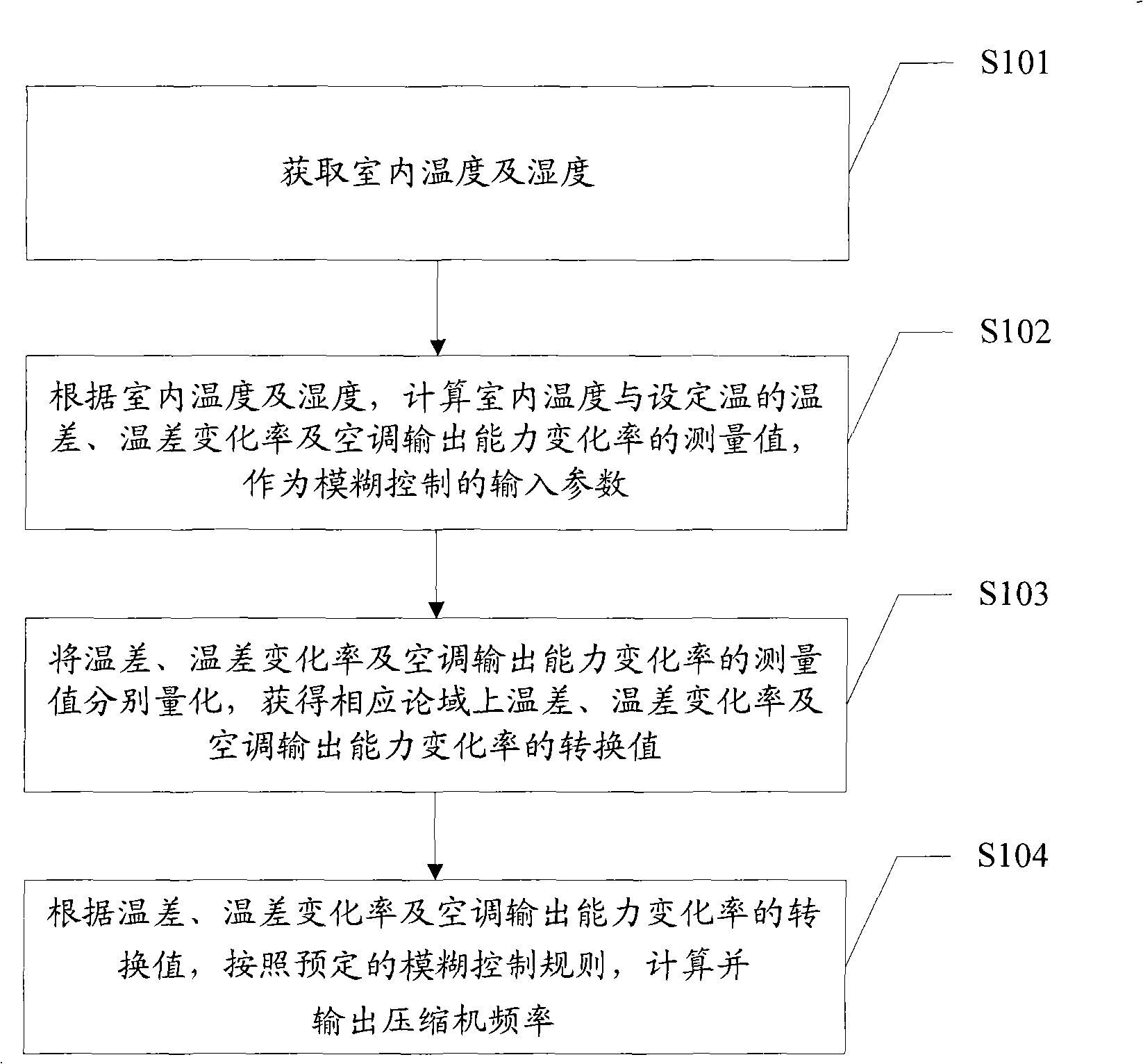

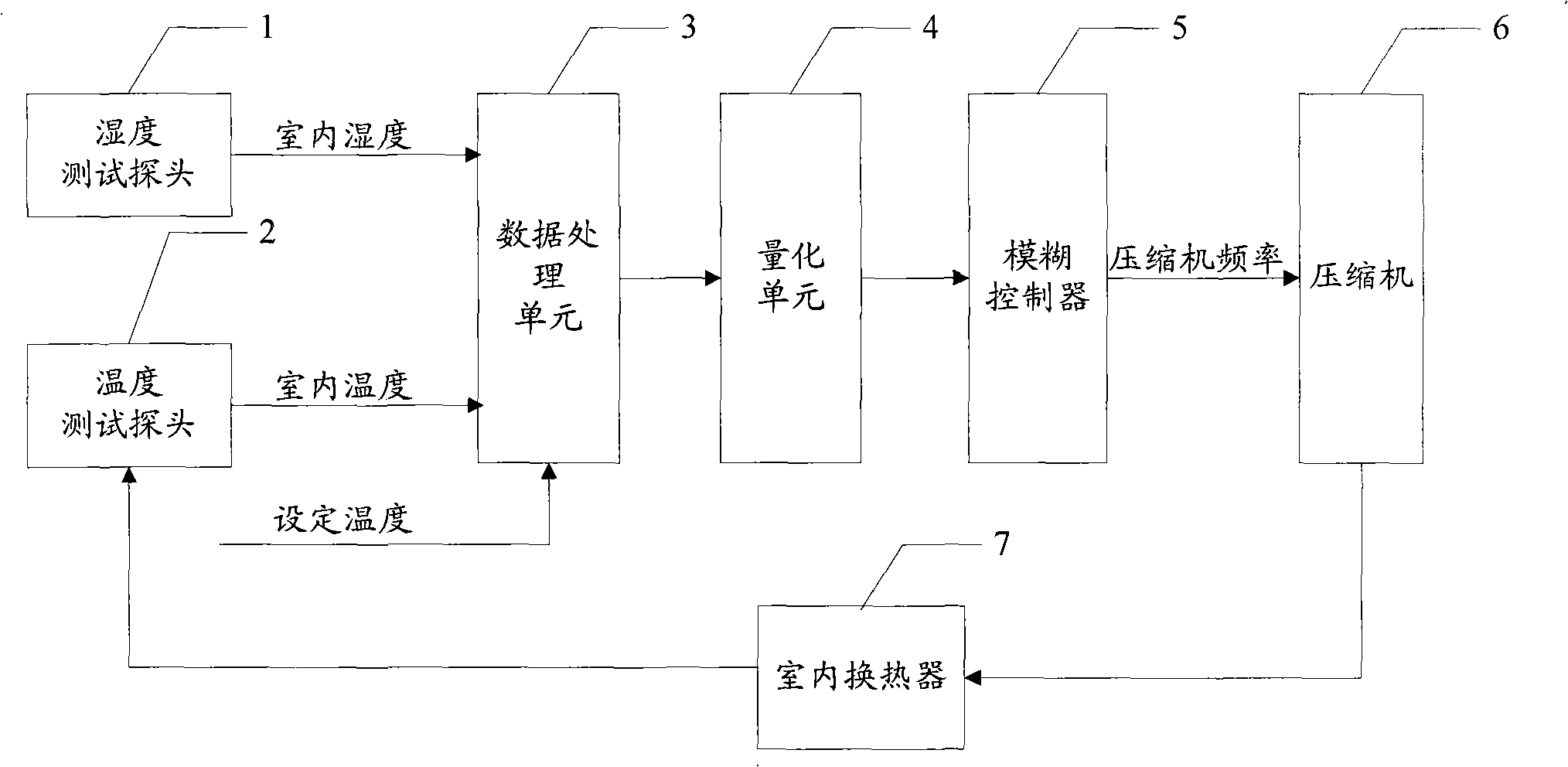

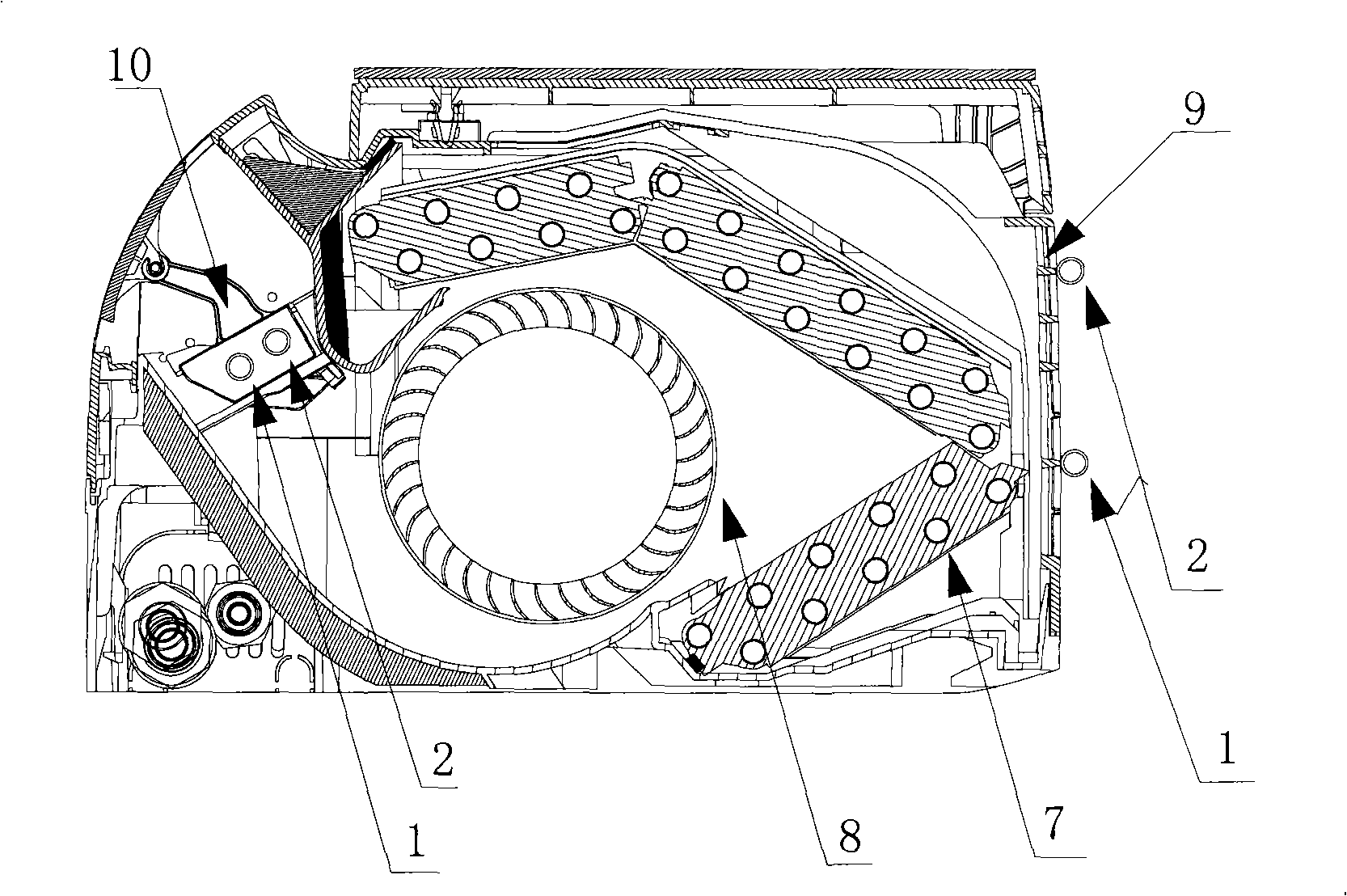

ActiveCN101526260AImprove robustnessHigh control precisionSpace heating and ventilation safety systemsLighting and heating apparatusFuzzy control systemRoom temperature

The invention discloses a variable-frequency air-conditioner control method. The method includes: acquiring room temperature and humidity; according to room temperature and humidity, calculating the difference between room temperature and set temperature and the measured values of temperature difference change rate and air-conditioning output capacity change rate as the input parameters of fuzzy control; respectively quantifying the temperature difference and the measured values of temperature difference change rate and air-conditioning output capacity change rate so as to acquire the converting values of the temperature difference, the temperature difference change rate and the air-conditioning output capacity change rate in the corresponding universe of discourse; according to the converting values of the temperature difference, the temperature difference change rate and the air-conditioning output capacity change rate, calculating and outputting compressor frequency by preset fuzzy control regulations. The invention with the characteristics of accurate control, quick response and small overshooting can satisfy the requirements of high control accuracy, excellent transition process and high comfort, which is conducive to reducing the tear and wear of the compressor and saving the energy. Correspondingly, the invention also discloses a variable-frequency air-conditioner control device thereof.

Owner:GUANGDONG CHIGO AIR CONDITIONING

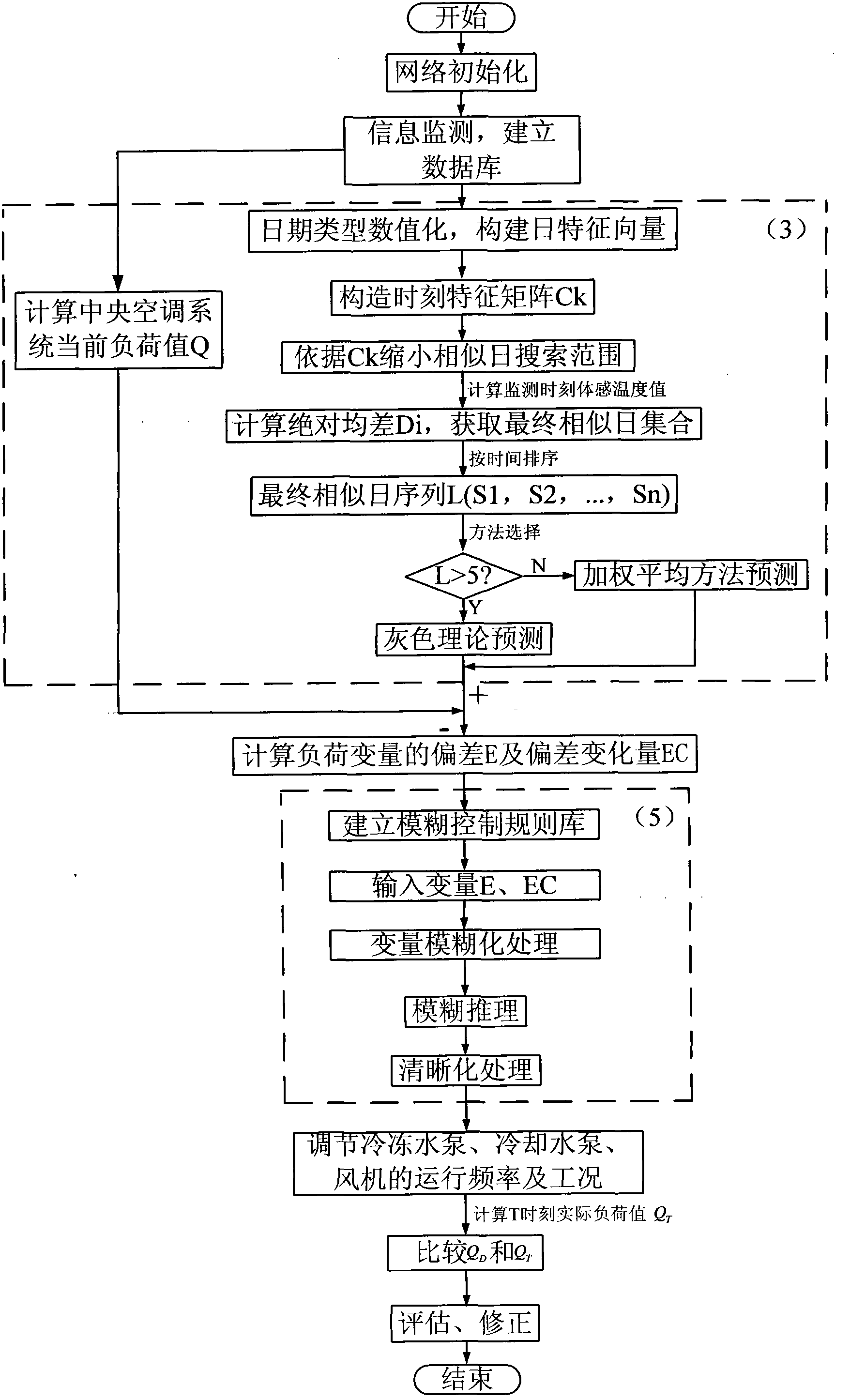

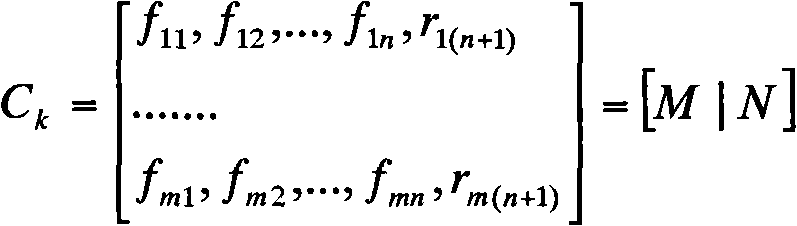

Central air conditioner intelligent control system based on wireless sensor network and method

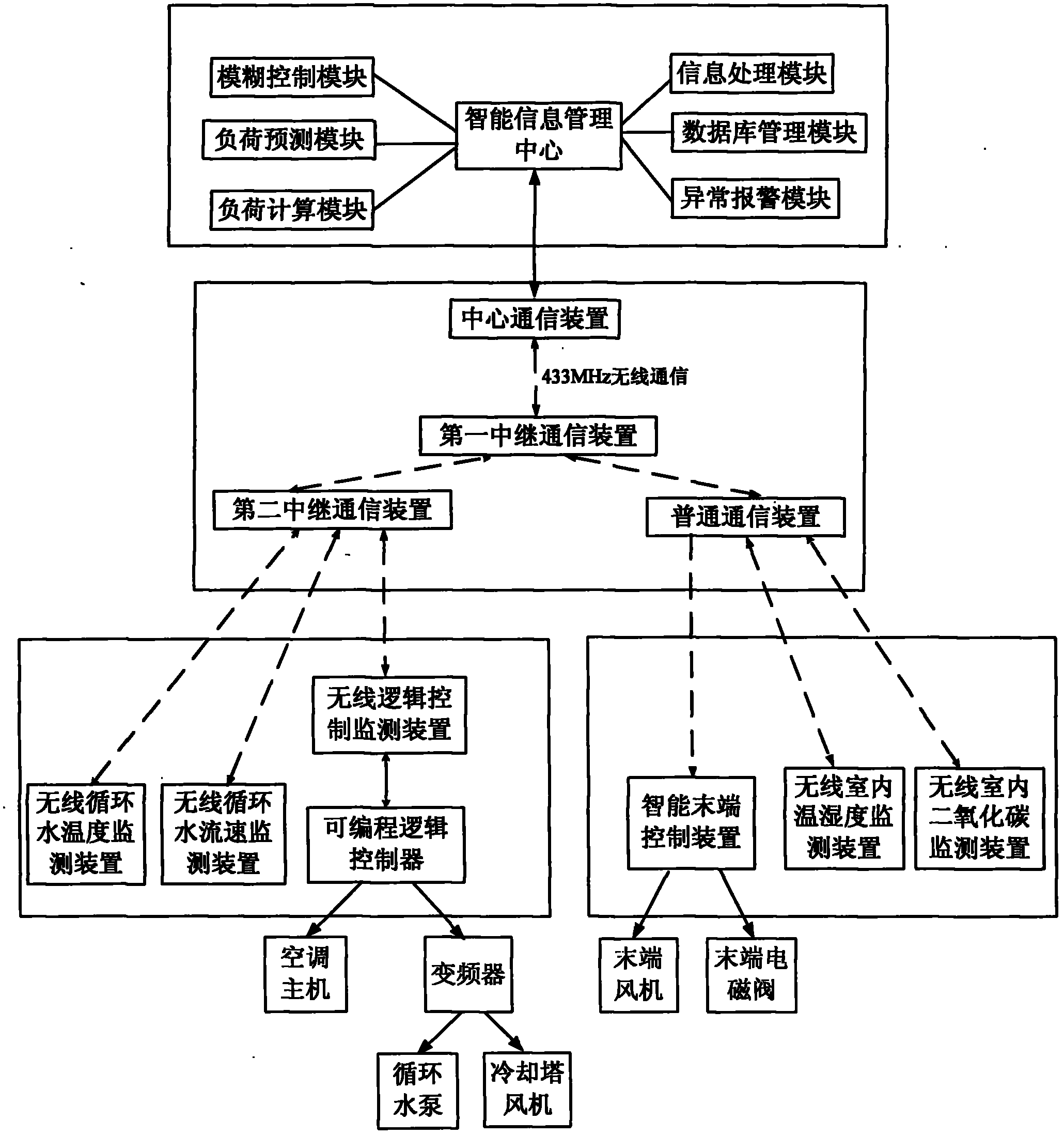

InactiveCN102052739AStrong obstacle avoidance abilityImplement extensionsSpace heating and ventilation safety systemsLighting and heating apparatusShort termsCommunication device

The invention discloses a central air conditioner intelligent control system based on a wireless sensor network and a method, and belongs to the technical field of central air conditioner control. The central air conditioner intelligent control system comprises an intelligent information management center, wireless communication devices, a central air conditioner information monitoring and control module, a room information monitoring and control module and the like. The invention adopts the method that the central air conditioner intelligent control system is used to monitor information, build a data base, calculate current load of the system, and realize advance, accurate and optimized control of a central air conditioner system by combining a short-term loading forecasting method based on similar dates and fuzzy control technology, as well as taking the temperature variation of supply / return chilled / cooling water of a central air conditioner as the manipulated variable. The central air conditioner intelligent control system has the characteristics of great communication capacity, guaranteed communication quality, powerful network functions, wide monitoring range and extensive control quantity of the central air conditioner system, optimized control, high control accuracy, good energy saving effect and the like, and can be widely used in energy-saving optimizing control of various buildings, and is particularly suitable for energy-saving optimizing control of central air conditioners of intelligent buildings.

Owner:CHONGQING UNIV

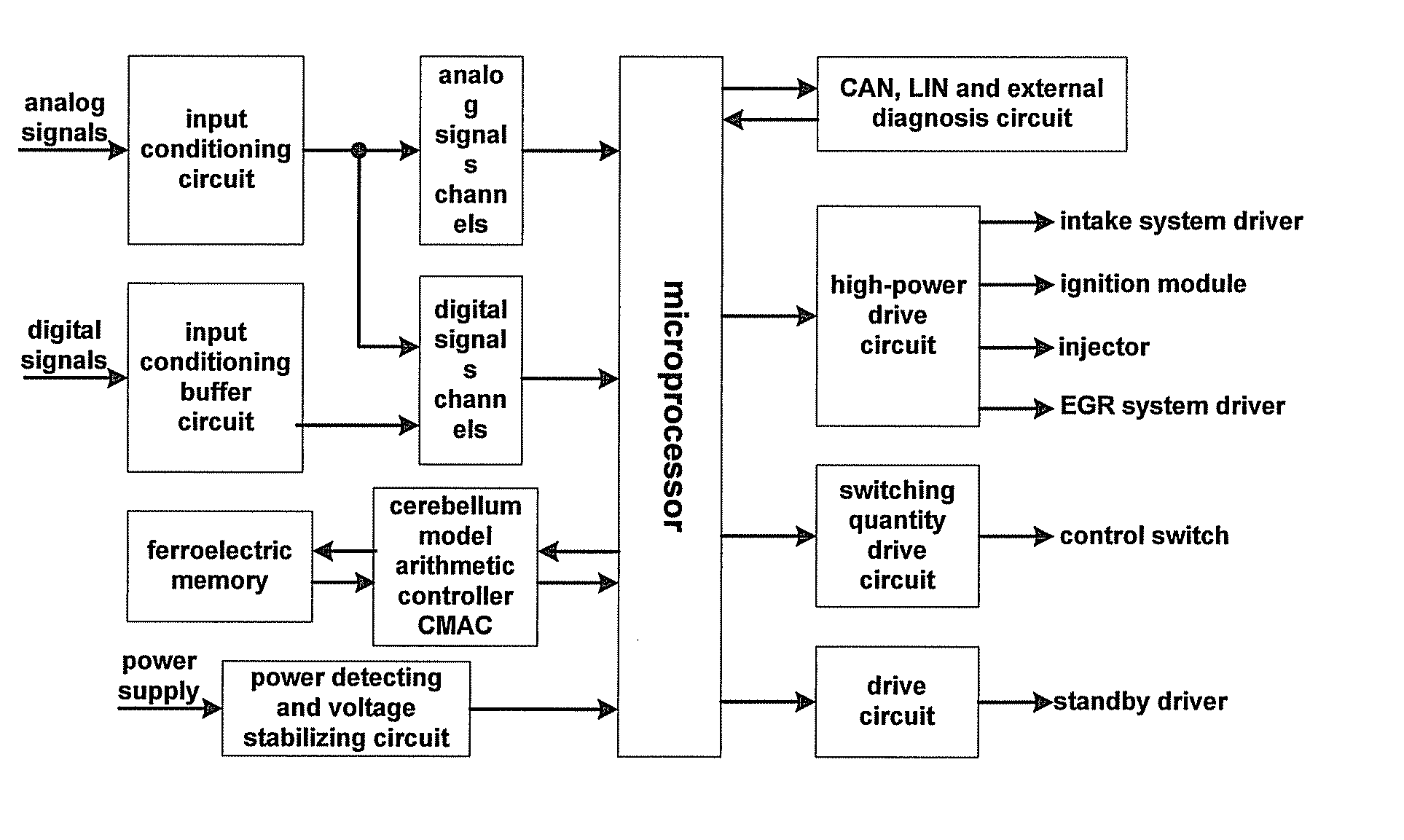

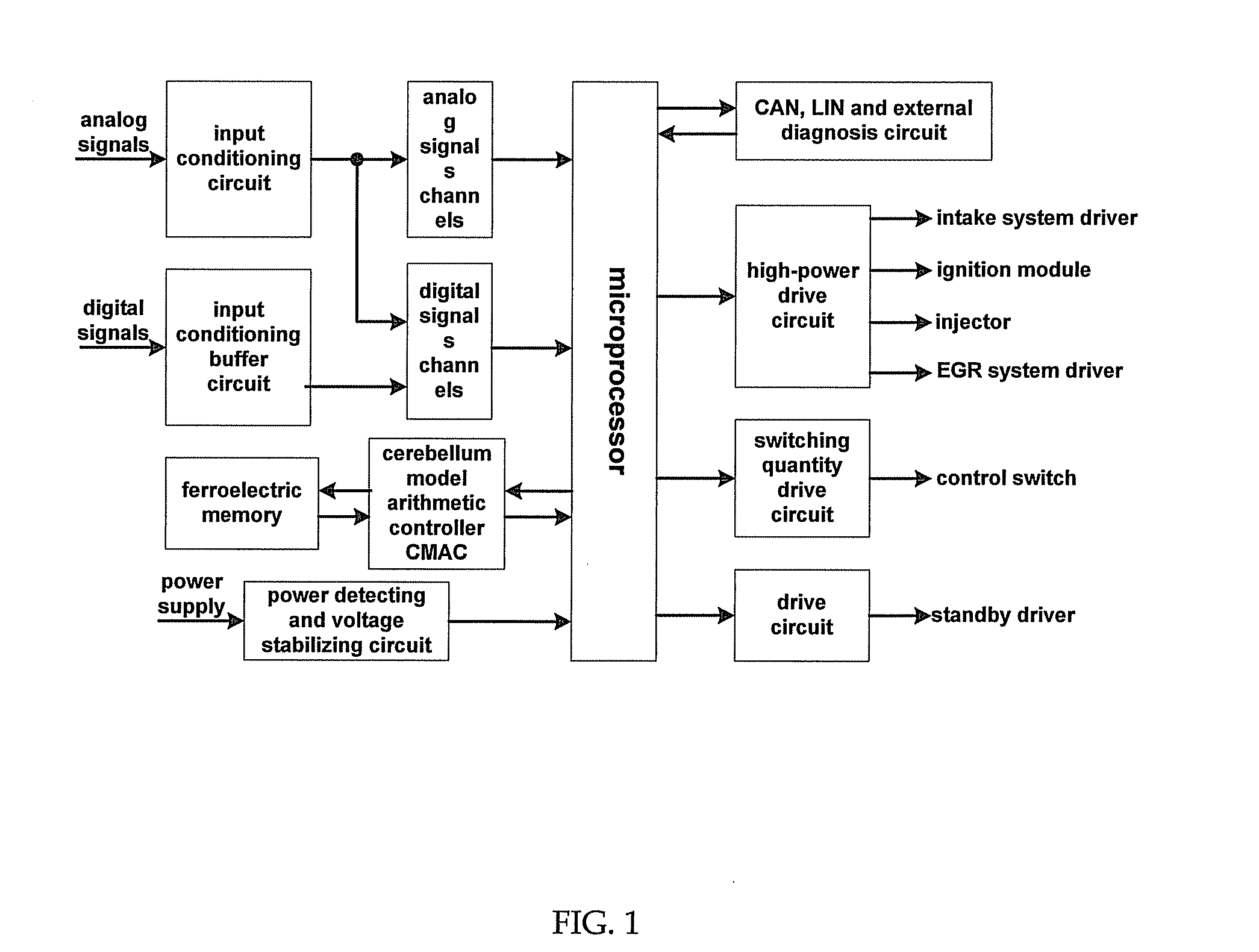

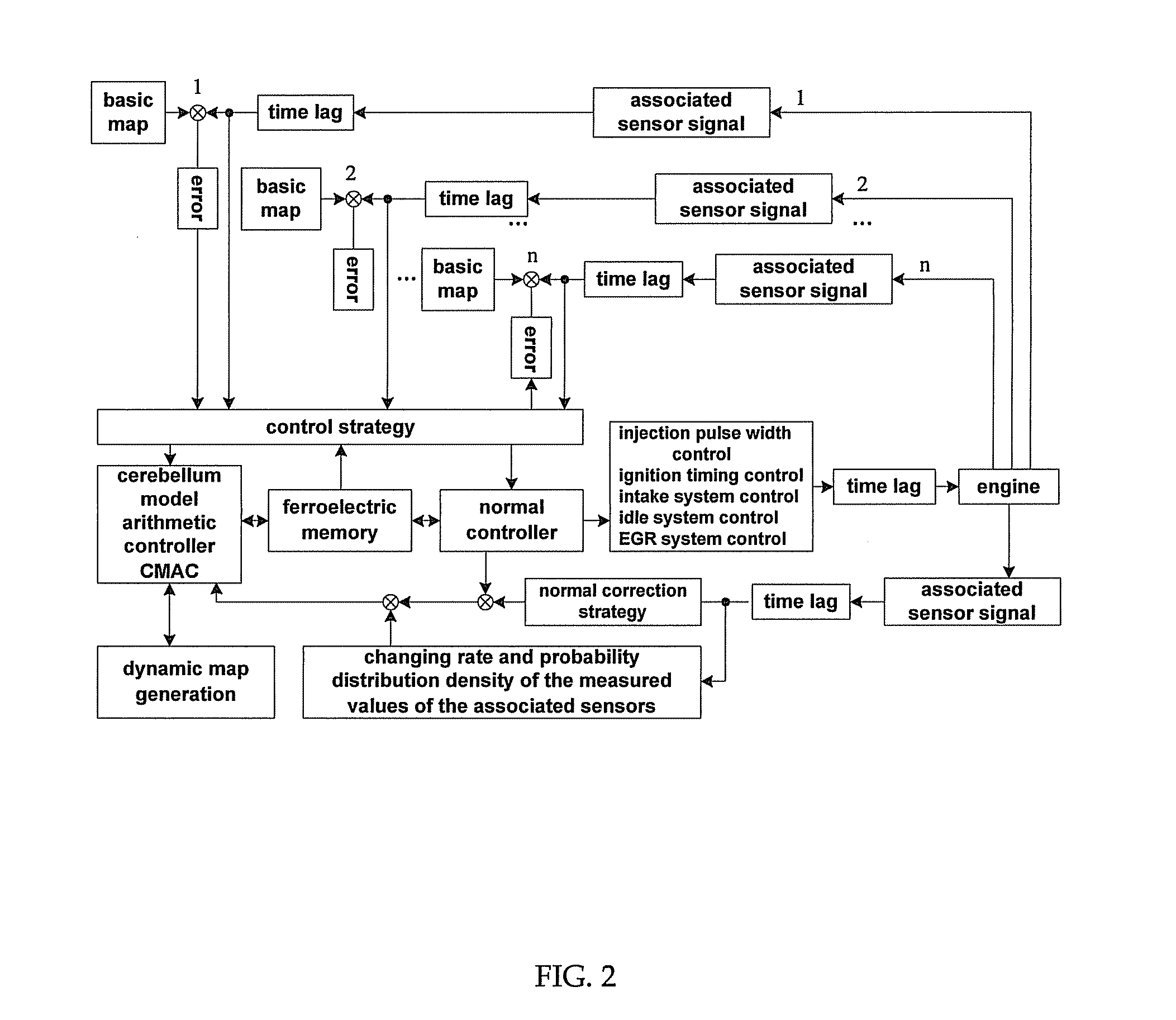

Control Method and Device For Engine

InactiveUS20100168989A1Reduce and eliminate errorHigh control precisionProgramme controlAnalogue computers for vehiclesSelf adaptiveEngineering

A control method and a control device of an engine are introduced. During the process of the engine controlling, the control unit does the adaptive learning for the actual target value of the feedback of different aims, and following the dynamic spectrogram generation strategy optimizing compares the adaptively learning parameter of the same working status and the same time with the basic spectrogram parameter. If the compared result doesn't meet the condition, then keep the basic spectrogram parameter. And if it meets the condition, then the engine generates the dynamic spectrogram parameter. Based on the dynamic spectrogram combination strategy, the engine combines the basic spectrogram parameter and the dynamic spectrogram parameter generated to the combined spectrogram parameter instead of the basic spectrogram parameter.

Owner:SHANDONG SHENPU TRAFFIC TECHNOLOGY CO LTD

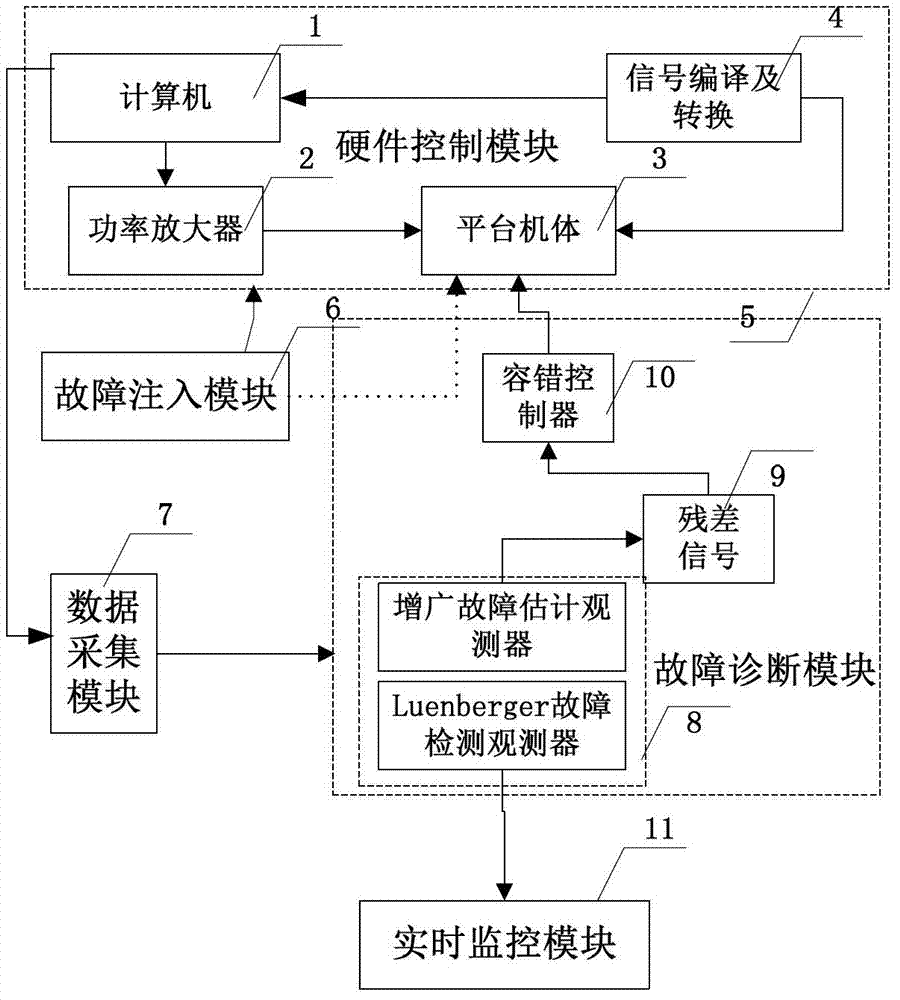

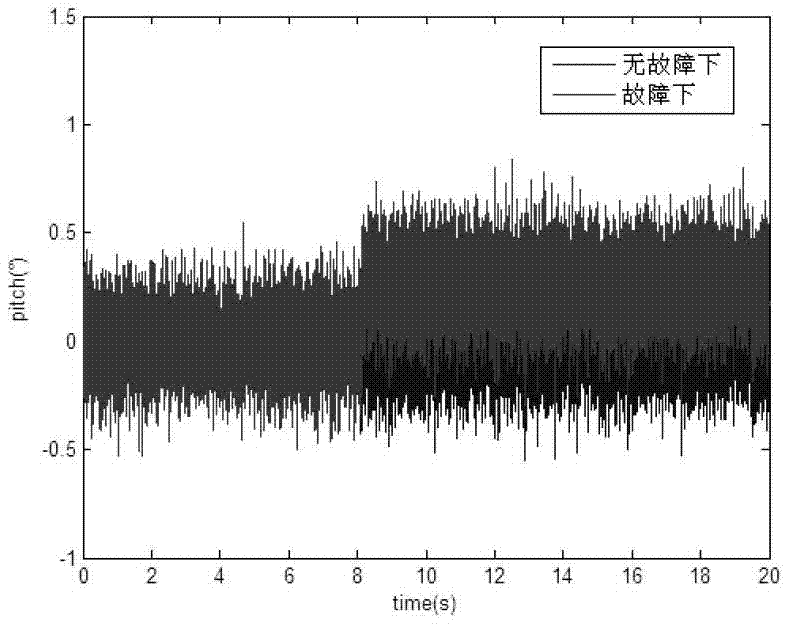

A plurality of united observer based fault diagnosis and fault-tolerant control device and method

ActiveCN102854874AAvoid serious coupling problemsAvoid errorsElectric testing/monitoringAviationDiagnosis methods

The invention discloses a plurality of united observer based fault diagnosis and fault-tolerant control device and a method and belongs to the field of aerospace. The plurality of united observer based fault diagnosis and fault-tolerant control device comprises following modules of a fault injection module, a fault diagnosis module, a real time monitoring module and a hardware control module. According to the method, the problem that traditional observer based fault diagnosis methods are limited by conditions is mainly solved, the operation is simple, the implementability is high, and the method can be used for diagnosing faults of actuating mechanisms of a four rotor wing helicopter and verifying feasibility of state monitoring.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

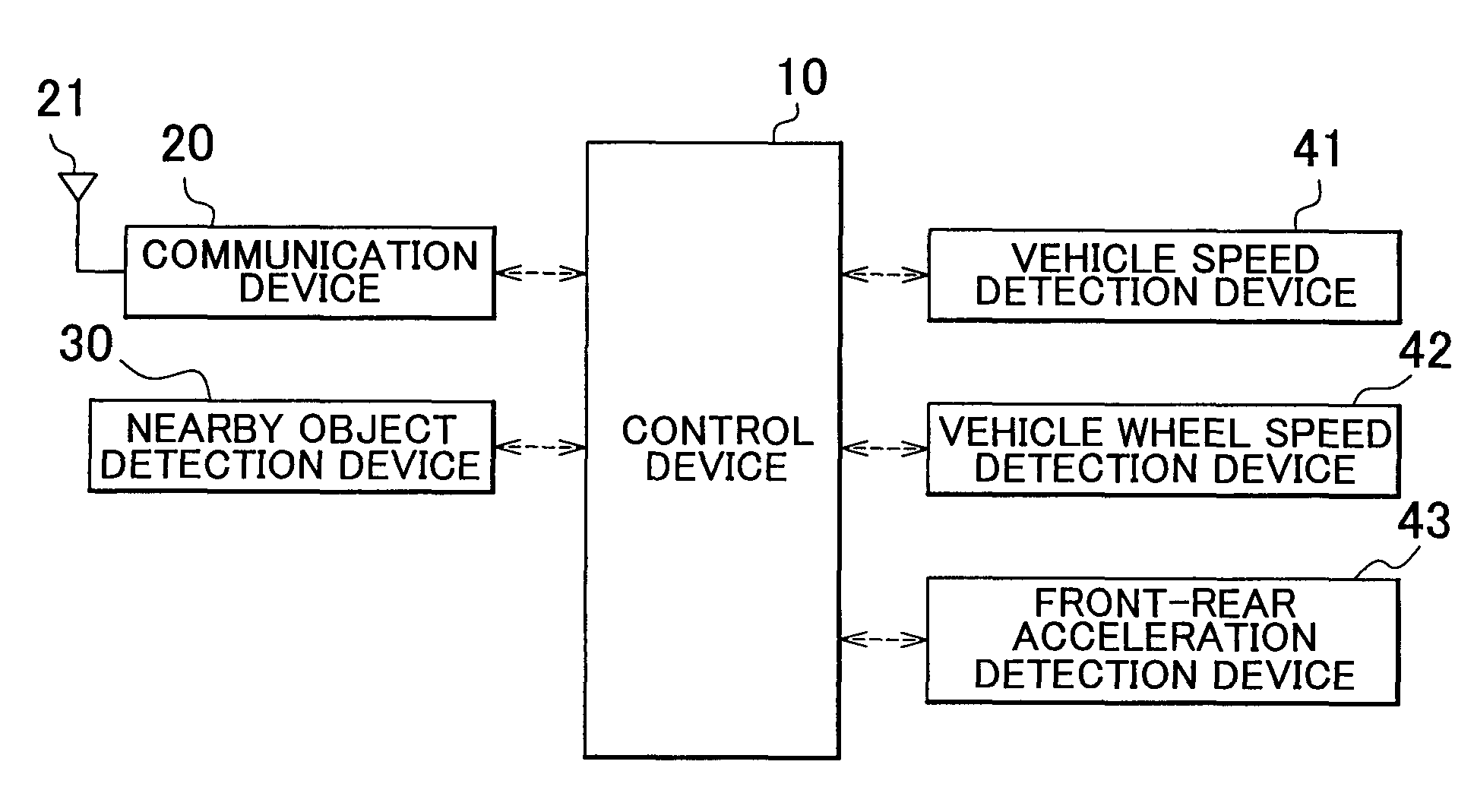

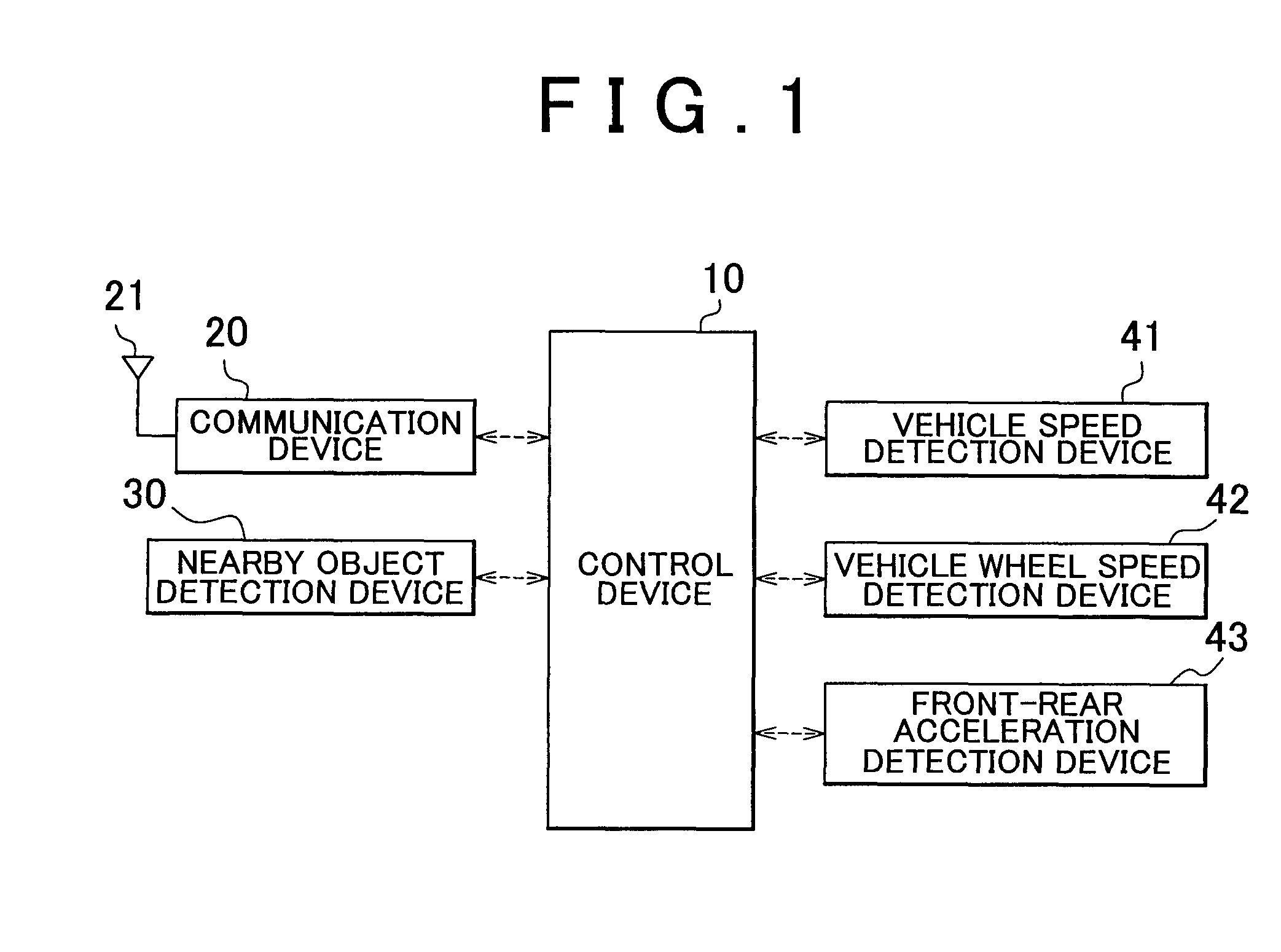

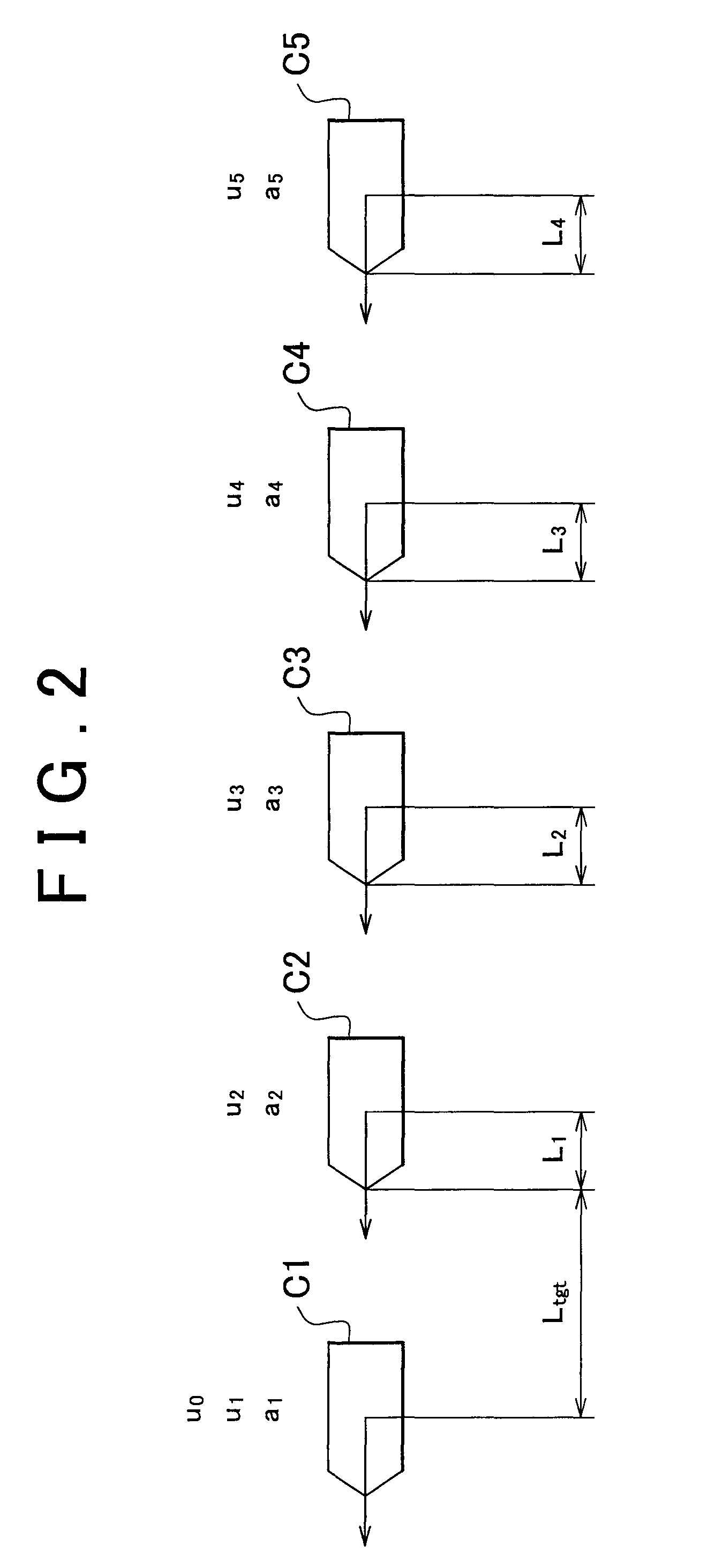

Vehicle control system

ActiveUS20130116861A1High control precisionHigh precisionVehicle fittingsDigital data processing detailsControl systemEngineering

A vehicle control system includes: a communication device provided in a vehicle to receive information relating to another vehicle from outside the vehicle; and a control device that performs travel control on the vehicle on the basis of information pertaining to a transfer function for a control target value used during travel control of the other vehicle and the control target value of the other vehicle, which is obtained via the communication device of the vehicle. Further, a vehicle control system includes: a communication device provided in a vehicle; and a control device that performs travel control using information relating to another vehicle, which is received from outside the vehicle via the communication device, wherein the communication device transmits information pertaining to a transfer function for a control target value used during the travel control.

Owner:TOYOTA JIDOSHA KK

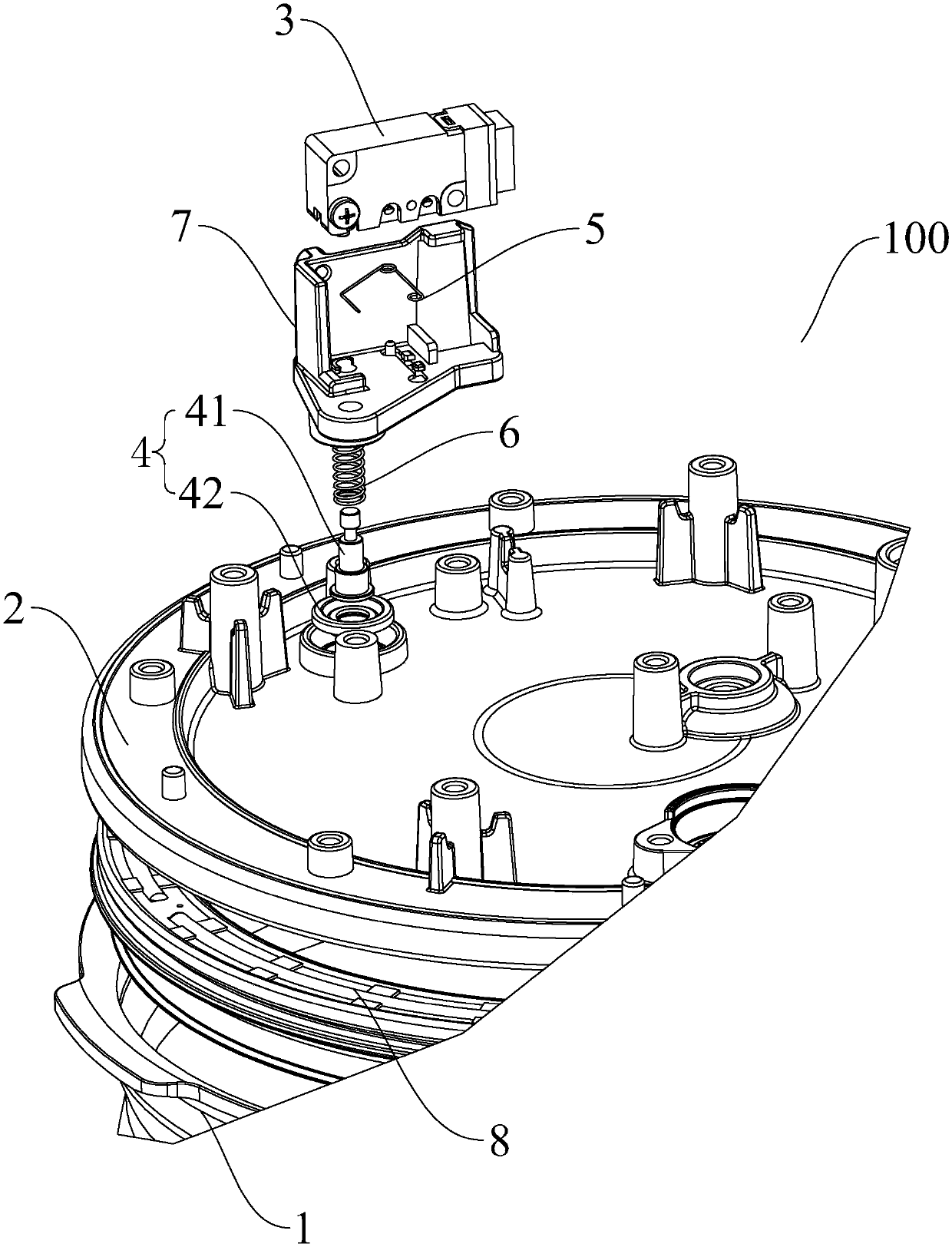

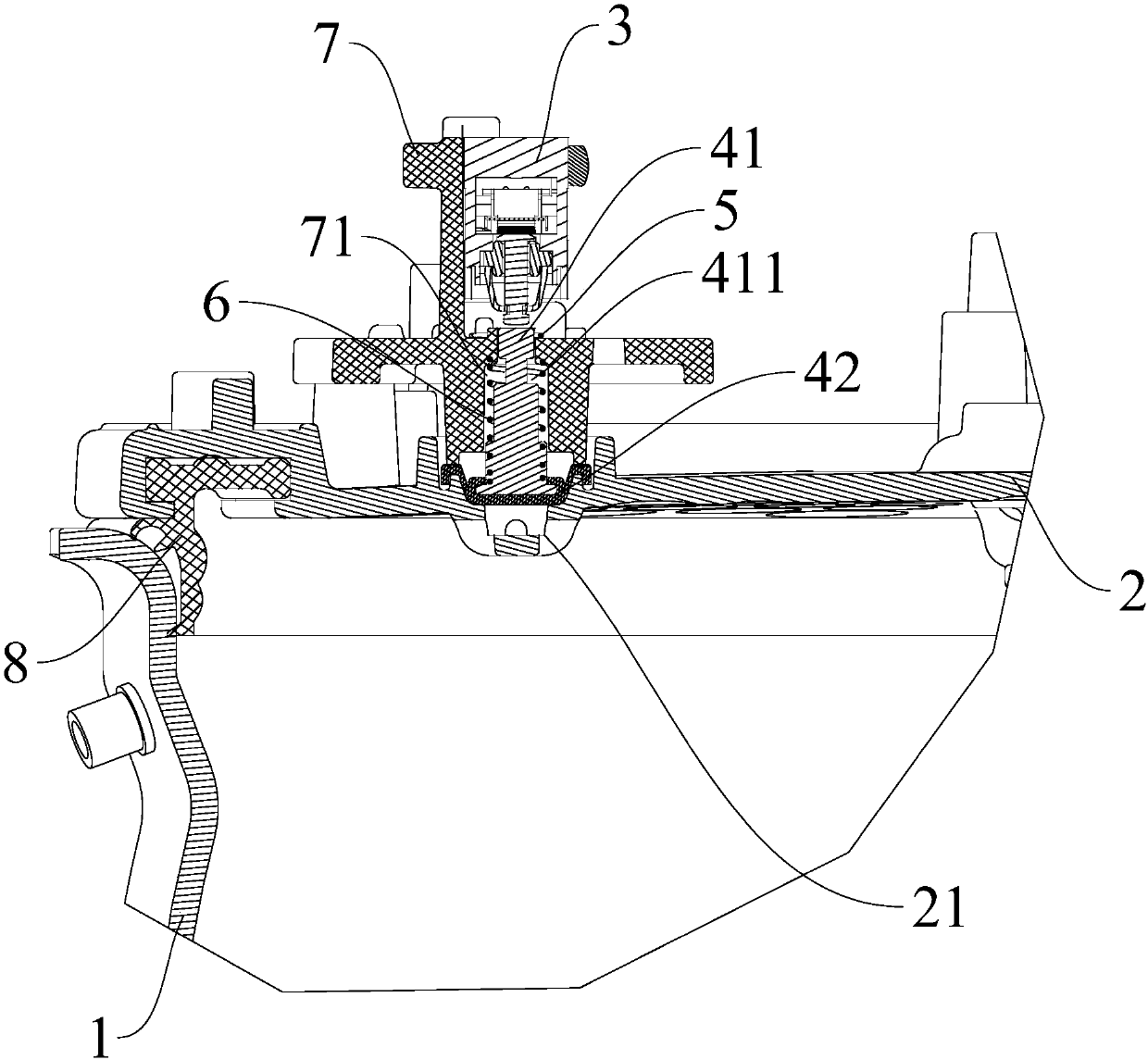

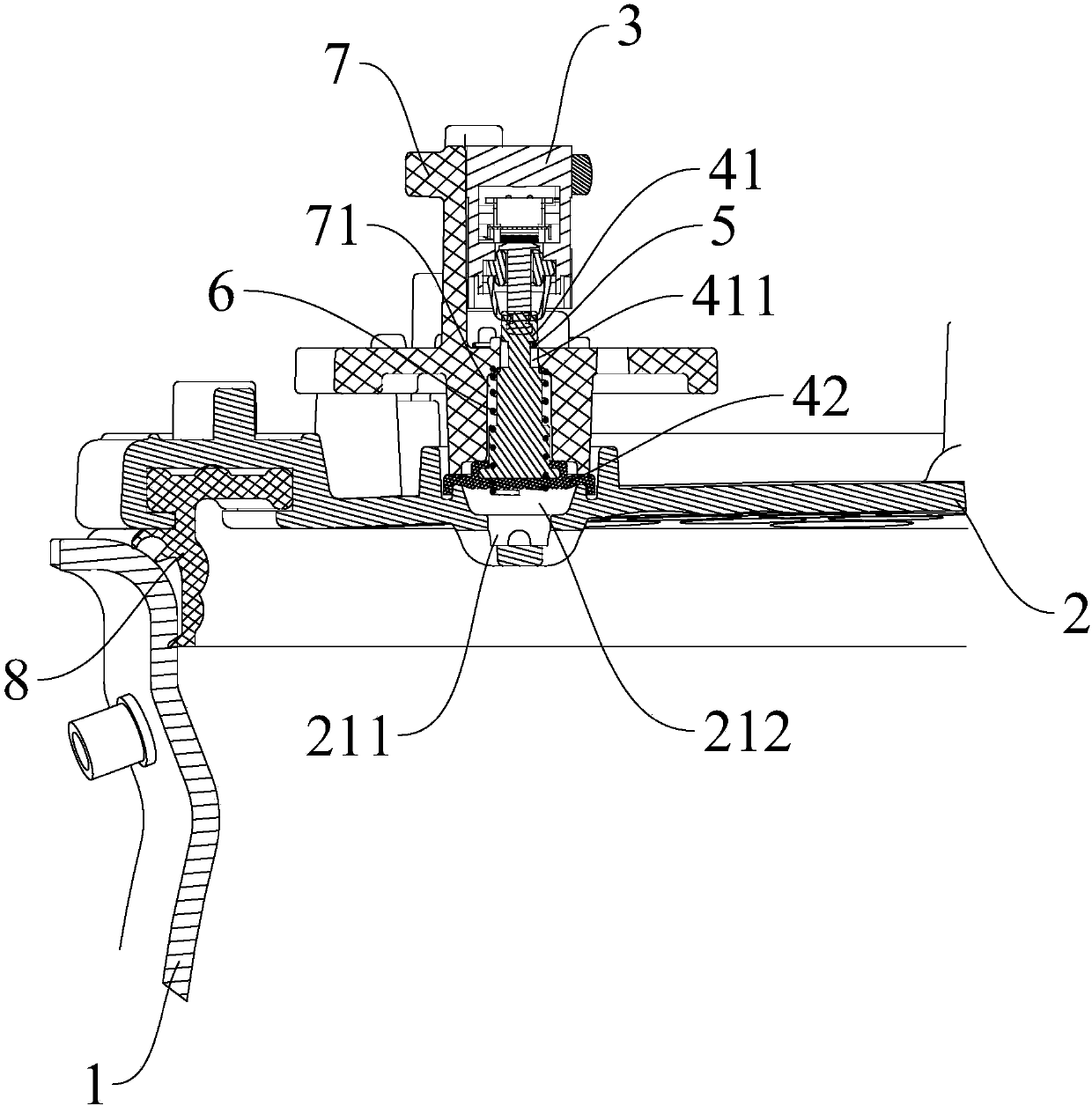

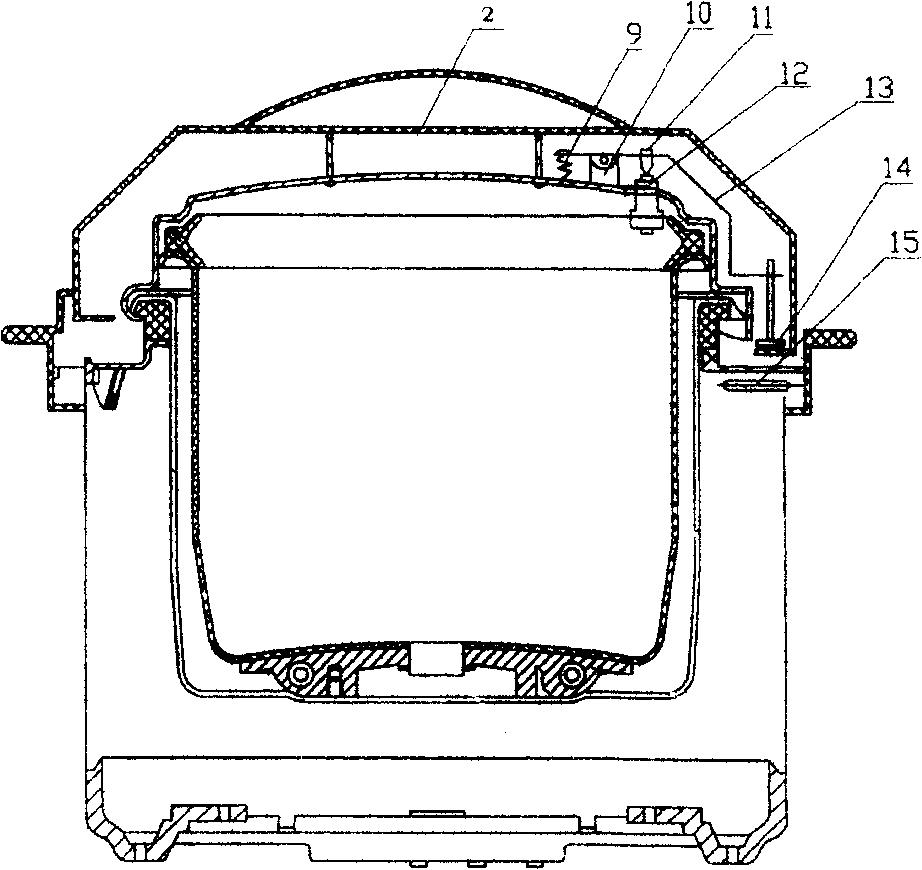

Pressure device

ActiveCN107647777AGuarantee the safety of useEnsure safetyPressure-cookersEngineeringPressure vessel

The invention discloses a pressure device comprises a pressure device, a cover board, an over-pressure outage switch and a trigger device; the cover board is installed on the pressure device; a pressure space is defined between the cover board and the pressure device; a penetrating through hole is formed in the cover board; the over-pressure outage switch is installed on the cover board and is positioned at the through hole; the trigger device is installed between the cover board and the over-pressure outage switch; the trigger device comprises a push rod and an elastic sealing member; the push rod is movably installed between the cover board and the over-pressure outage switch; a first end of the push rod is adapted to trigger the over-pressure outage switch so that the over-pressure outage switch is cut off; the elastic sealing member is installed at the through hole; the elastic sealing member is connected with a second end of the push rod; when the pressure in the pressure space reaches a preset pressure, the pressure in the pressure space is directly applied on the elastic sealing member to drive the push rod to move to trigger the over-pressure outage switch so that the over-pressure outage switch is cut off and the pressure device is powered off. According to the pressure device of the invention, the use safety of the pressure device is effectively guaranteed.

Owner:FOSHAN SHUNDE MIDEA ELECTRICAL HEATING APPLIANCES MFG CO LTD

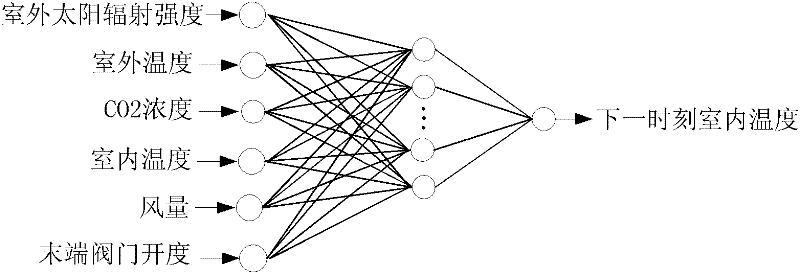

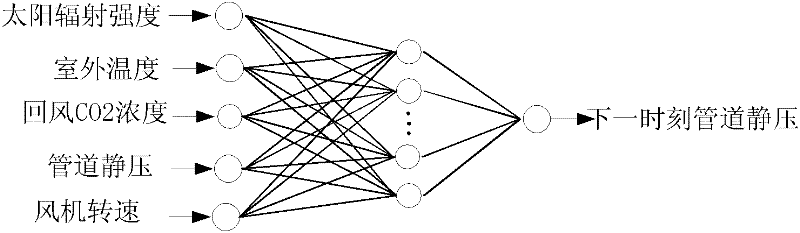

Control method of VAV (variable air volume) air-conditioning system

InactiveCN102353119ASolve the problem of on-site parameter settingAdaptableSpace heating and ventilation safety systemsLighting and heating apparatusAir volumeControl parameters

The invention provides a control scheme of a VAV (variable air volume) air-conditioning system. A neural network predictive control method is used for a tail end VAV-BOX and an air-conditioning unit, thus the hysteresis characteristic of a VAV system can be overcome, the control accuracy is improved, the resonance phenomena of an actuating mechanism can be greatly reduced, the energy-saving effect is improved by above 13%, and the control parameter tuning problem in the project is solved. A pressure independent cascade stage predictive control method is used for the tail end VAV-BOX, thus thecontrol accuracy can also be improved. The air-conditioning unit is provided with four control loops and can automatically select a static pressure control or total air volume control policy with adjustable setting static pressure by using an all-condition integrated control technology, thus the predictive control on a fan can be realized; the primary air volume of all the tail end VAV-BOXes can be detected and the air supply temperature can be adjusted according to the operation condition, thus the problem of too low temperature in partial air-conditioning area in the lowest fresh air operation is solved; the cascade stage predictive control method is adopted for a fresh air ratio control loop, thus the accurate control on the fresh air ratio can be realized and the energy-saving level can be further improved.

Owner:BEIJING UNIVERSITY OF CIVIL ENGINEERING AND ARCHITECTURE +1

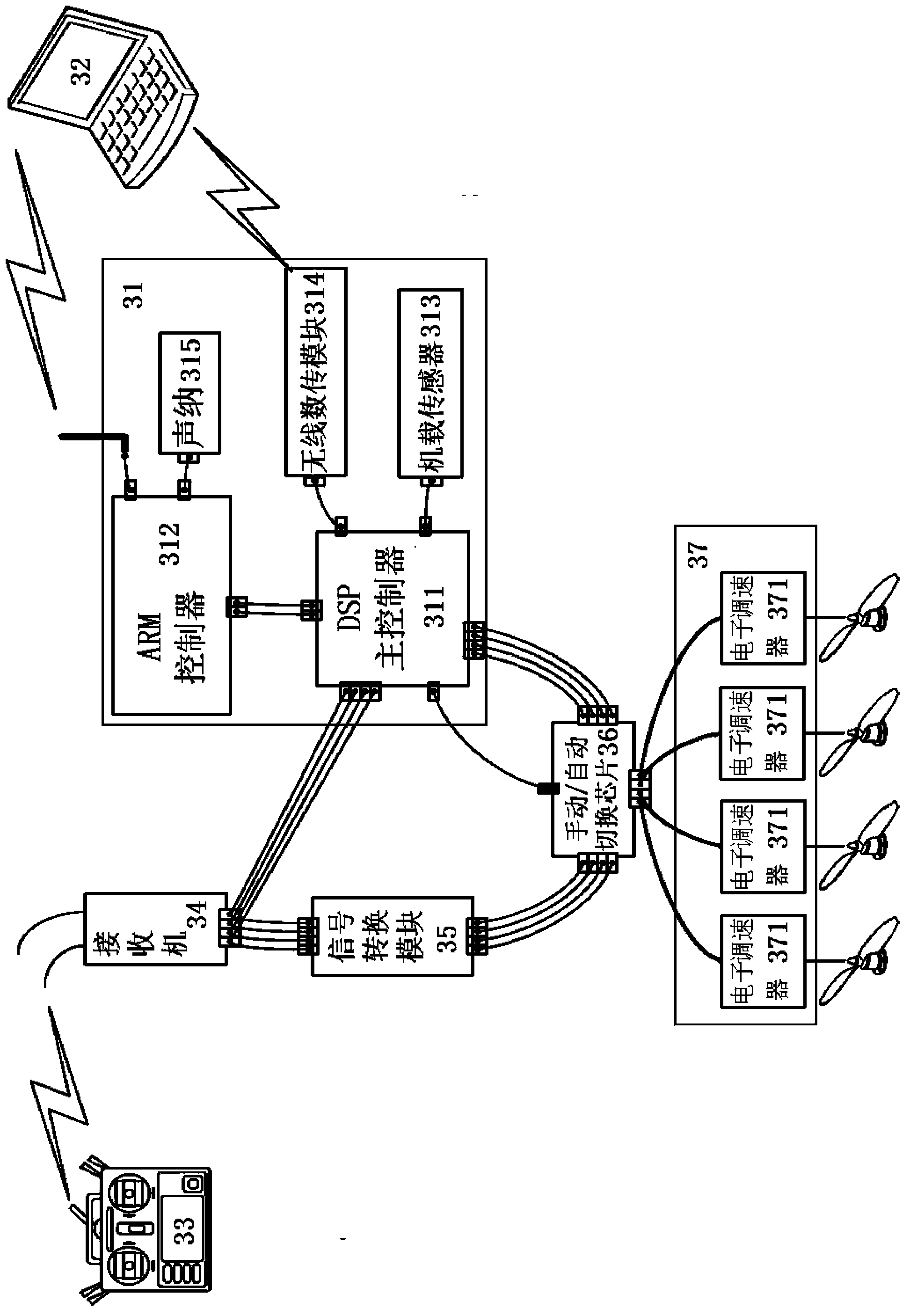

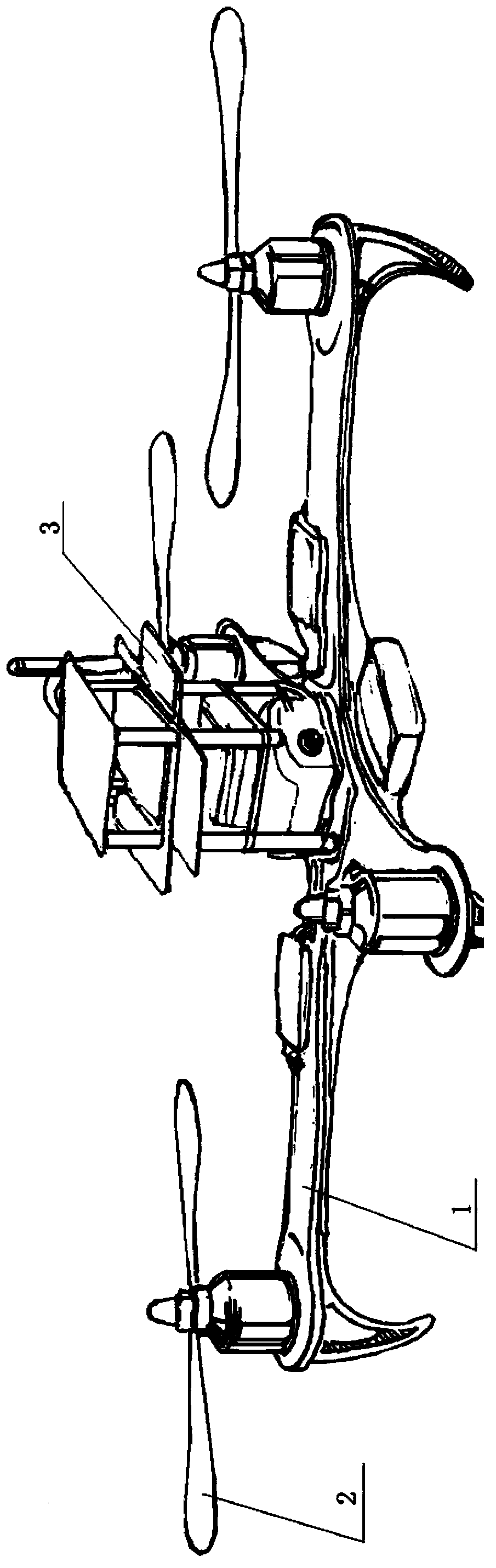

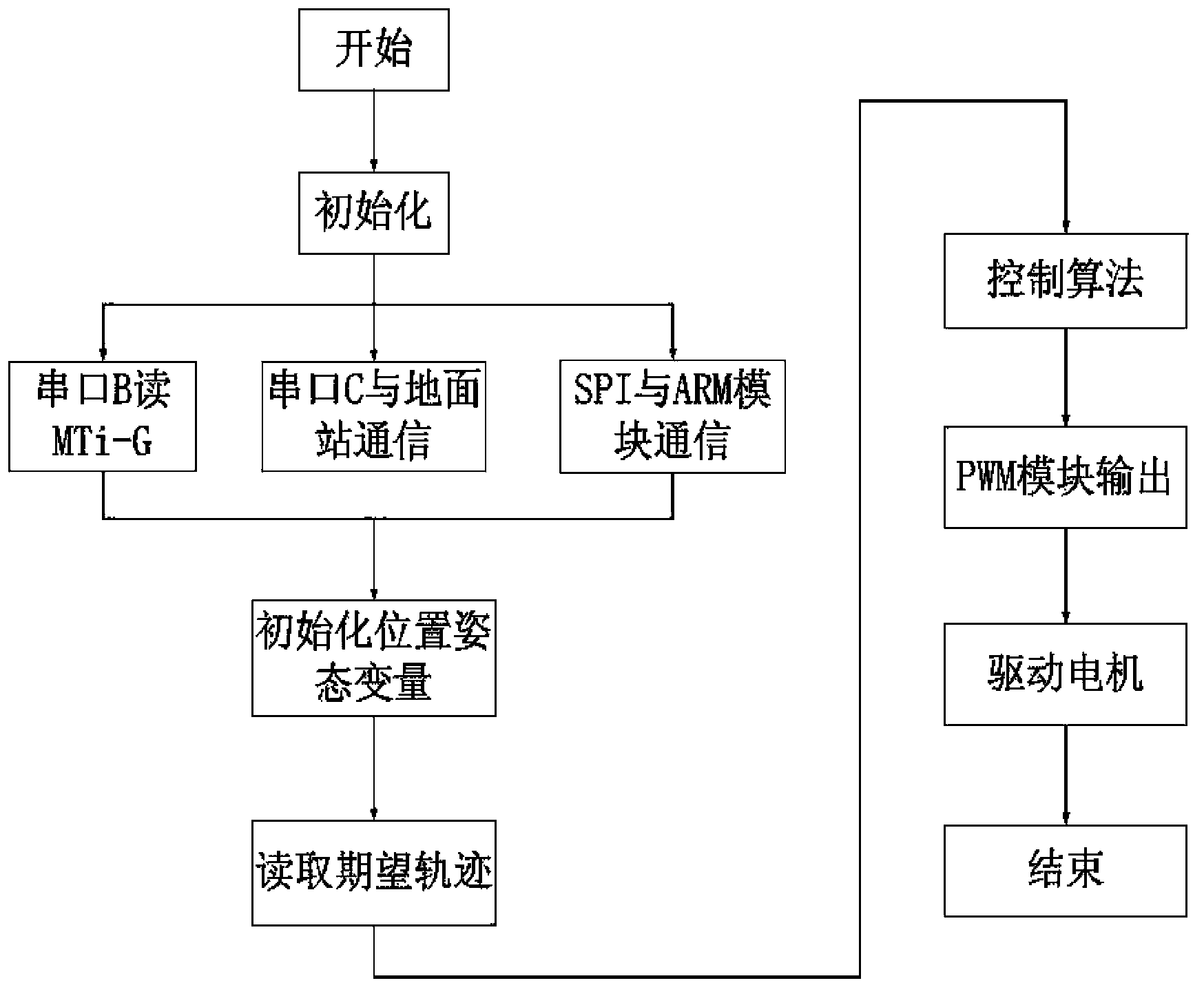

DSP (Digital Signal Processor)-based quad-rotor unmanned aerial vehicle autonomous hover control system and method

ActiveCN103365295ALow costEasy to replacePosition/course control in three dimensionsBrushless motorsQuad rotor

The invention discloses a DSP (Digital Signal Processor)-based quad-rotor unmanned aerial vehicle autonomous hover control system and method. The control system is provided with four screw propellers and control units which are arranged on four airfoils respectively; and each control unit is that a master control unit is connected to a ground computer through a wireless network, and a receiver is connected with a signal conversion module and a manual / automatic switching chip in sequence, transmits a received signal transmitted by a remote controller into the manual / automatic switching chip through the signal conversion module, is also connected with the manual / automatic switching chip through the master control unit and is used for transmitting the received signal to the manual / automatic switching chip through the master control unit for controlling driving units to drive direct current brushless motors on the four screw propellers to work. According to the method, kalman filtering processing is performed on sonar data to obtain accurate height data and driver control. According to the system and the method, the autonomous flight capacity of a micro quad-rotor unmanned aerial vehicle and the adaptability to the environment can be effectively enhanced, and the autonomous flight control under indoor environments and outdoor environments can be finished.

Owner:TIANJIN UNIV

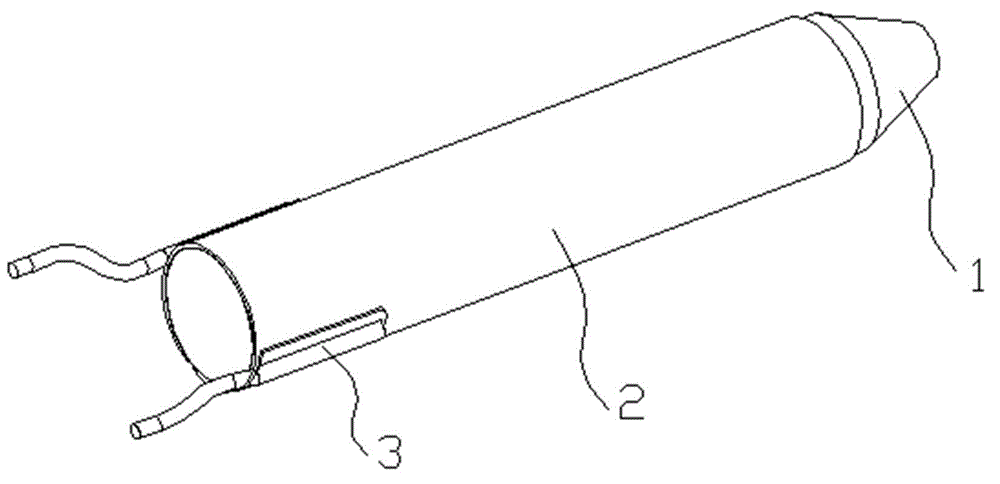

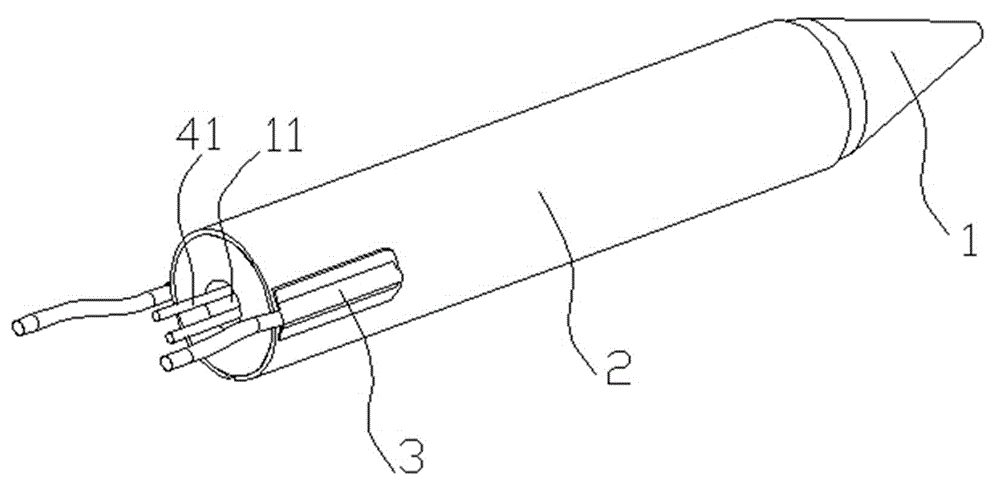

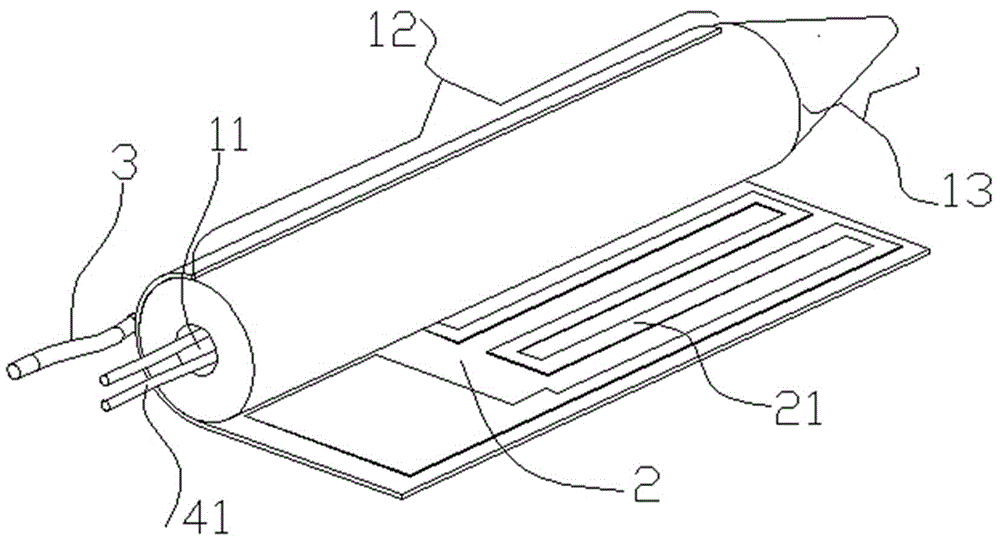

Electronic cigarette smoking set heater with low-temperature heating function

InactiveCN104799438AHigh control precisionRealize closed-loop controlTobacco devicesInsulation layerClosed loop

The invention discloses an electronic cigarette smoking set heater with a low-temperature heating function. The electronic cigarette smoking set heater comprises a core rod (1), an insulation layer (2), anode and cathode pins (3) and a temperature sensor (4), wherein the insulation layer (2) wraps the outer surface of the core rod (1) in a sintering manner; the anode and cathode pins (3) are connected with the insulation layer (2) which wraps the outer surface of the core rod (1); the temperature sensor (4) is embedded in a blind hole (11) which is formed in the tail end of the core rod (1); the rear end of the temperature sensor (4) is connected with pins (41) which extend out of the blind hole (11). The electronic cigarette smoking set heater can be conveniently inserted into core parts of tobacco products for heating; meanwhile, the temperature sensor can be embedded into the core part of the heater for realizing closed-loop control on temperatures; the control precision of an electronic cigarette smoking set heater with a low-temperature heating function on the heating temperature of the tobacco products can be improved.

Owner:云南云智数字科技有限公司

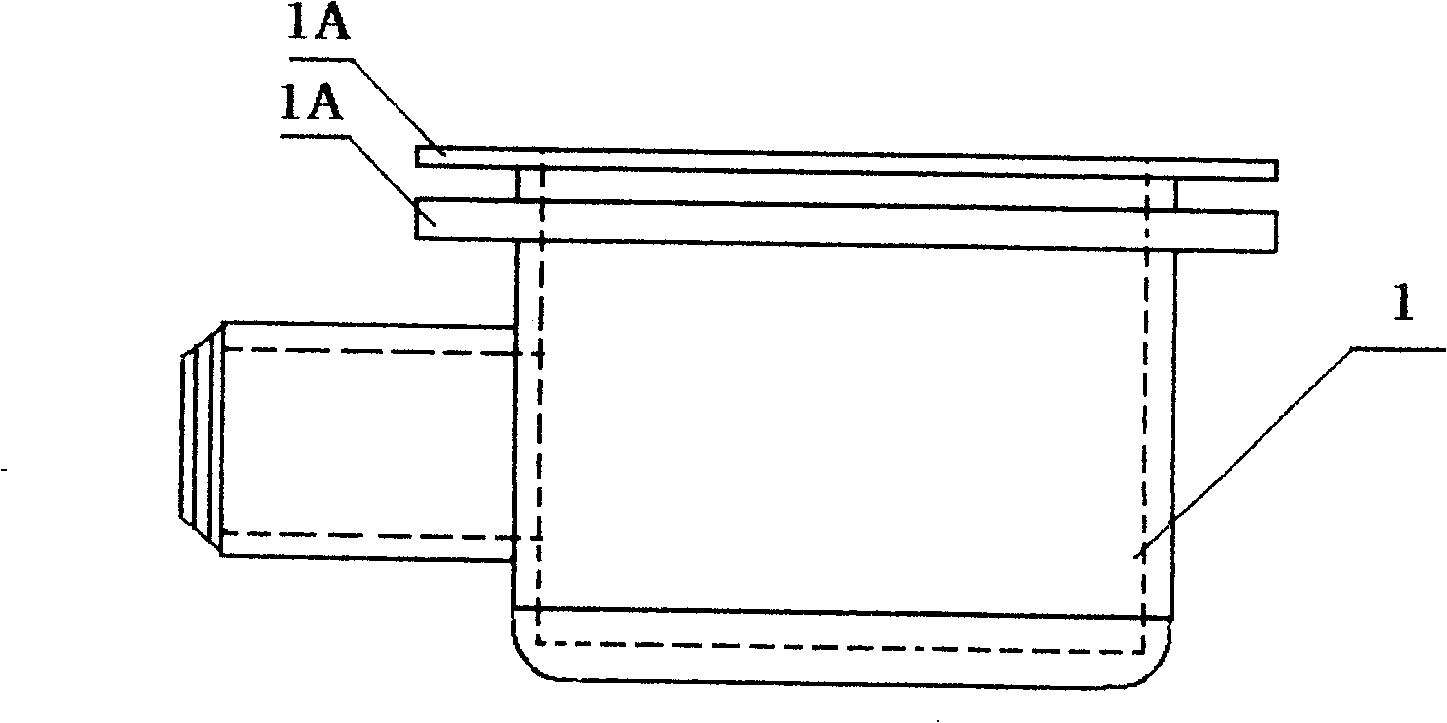

Electric pressure cooker pressure converting device

Owner:FOSHAN FUSHIBAO ELECTRICAL APPLIANCE TECH