Patents

Literature

1011results about How to "Implement extensions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

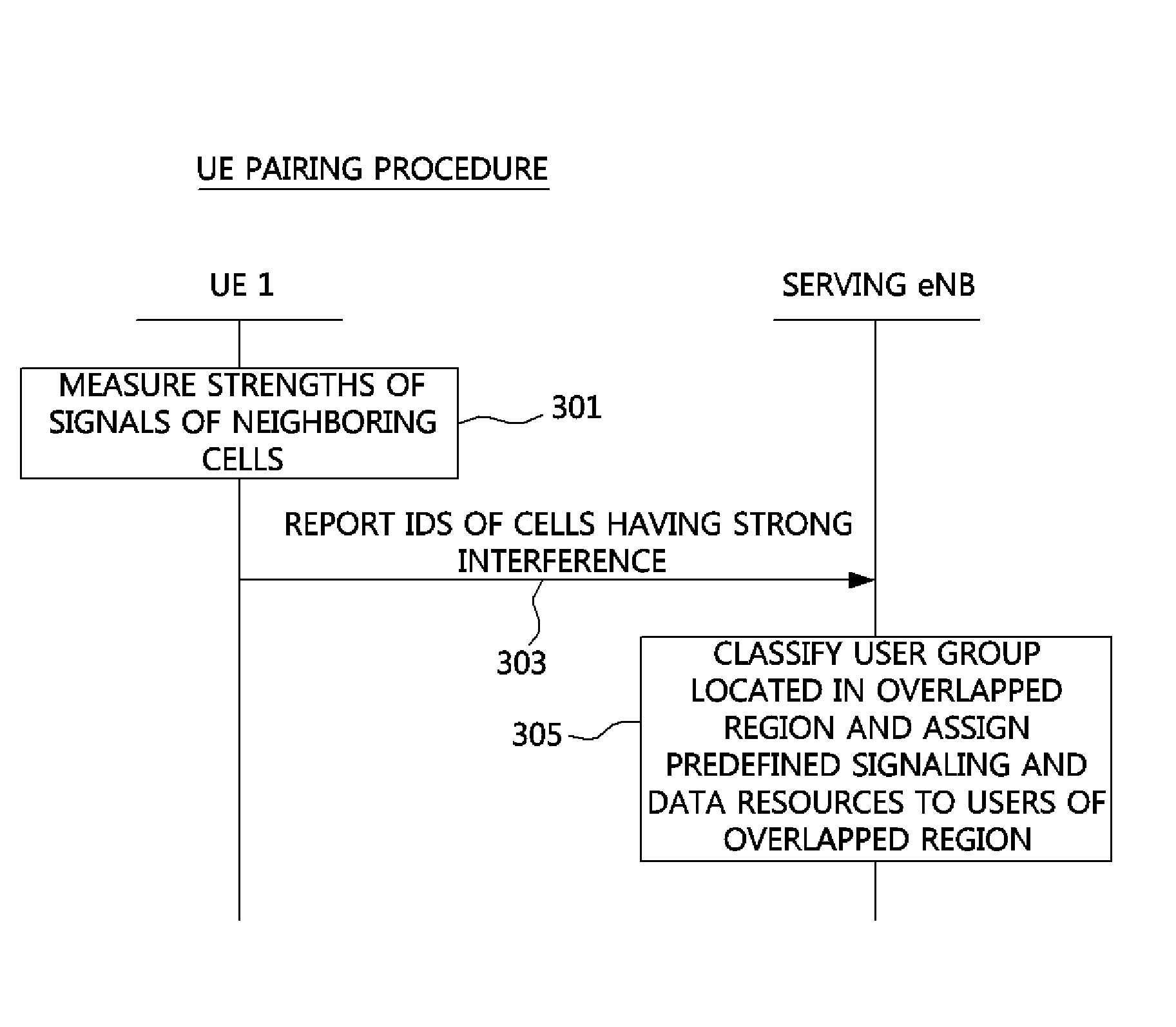

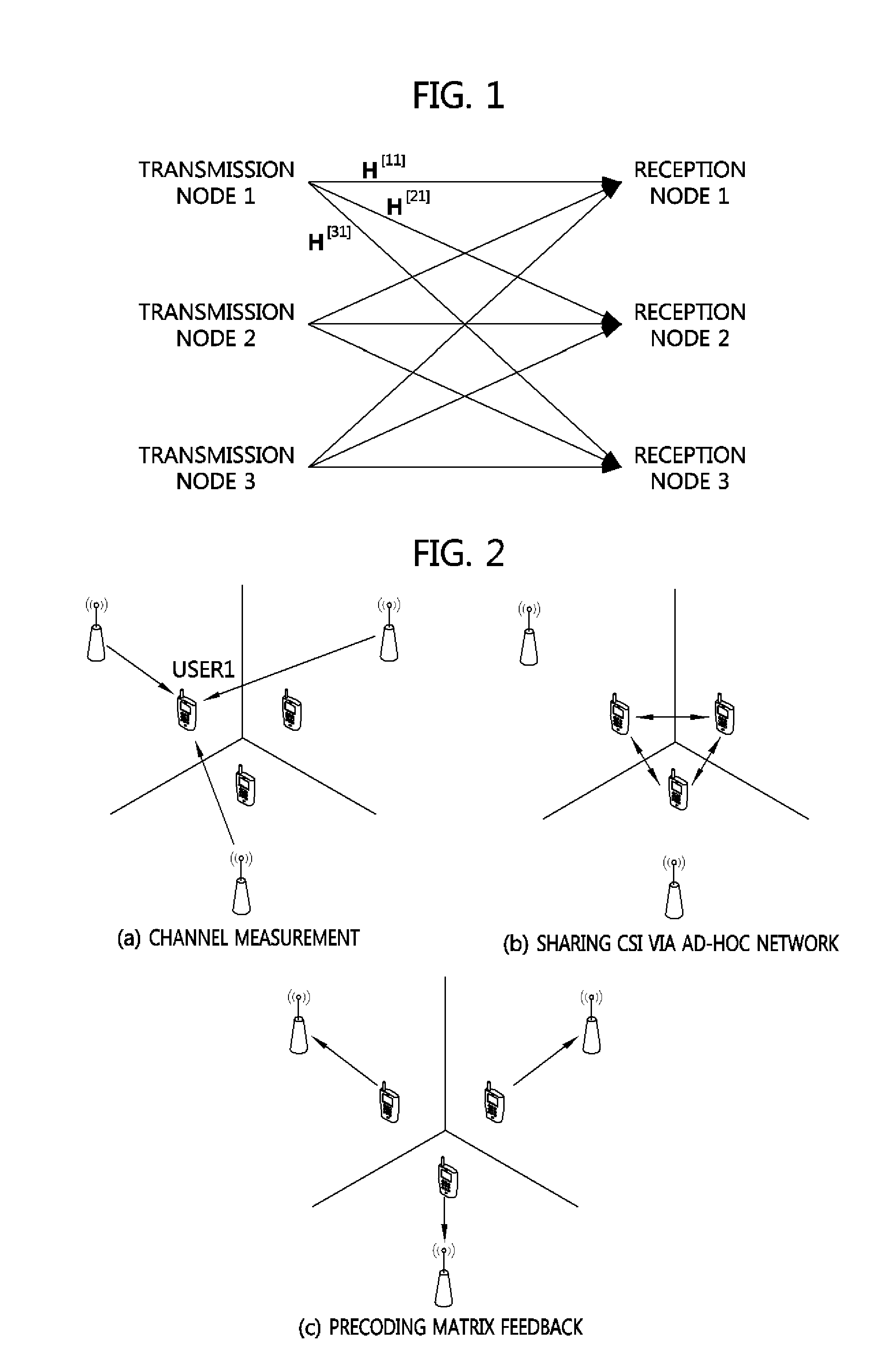

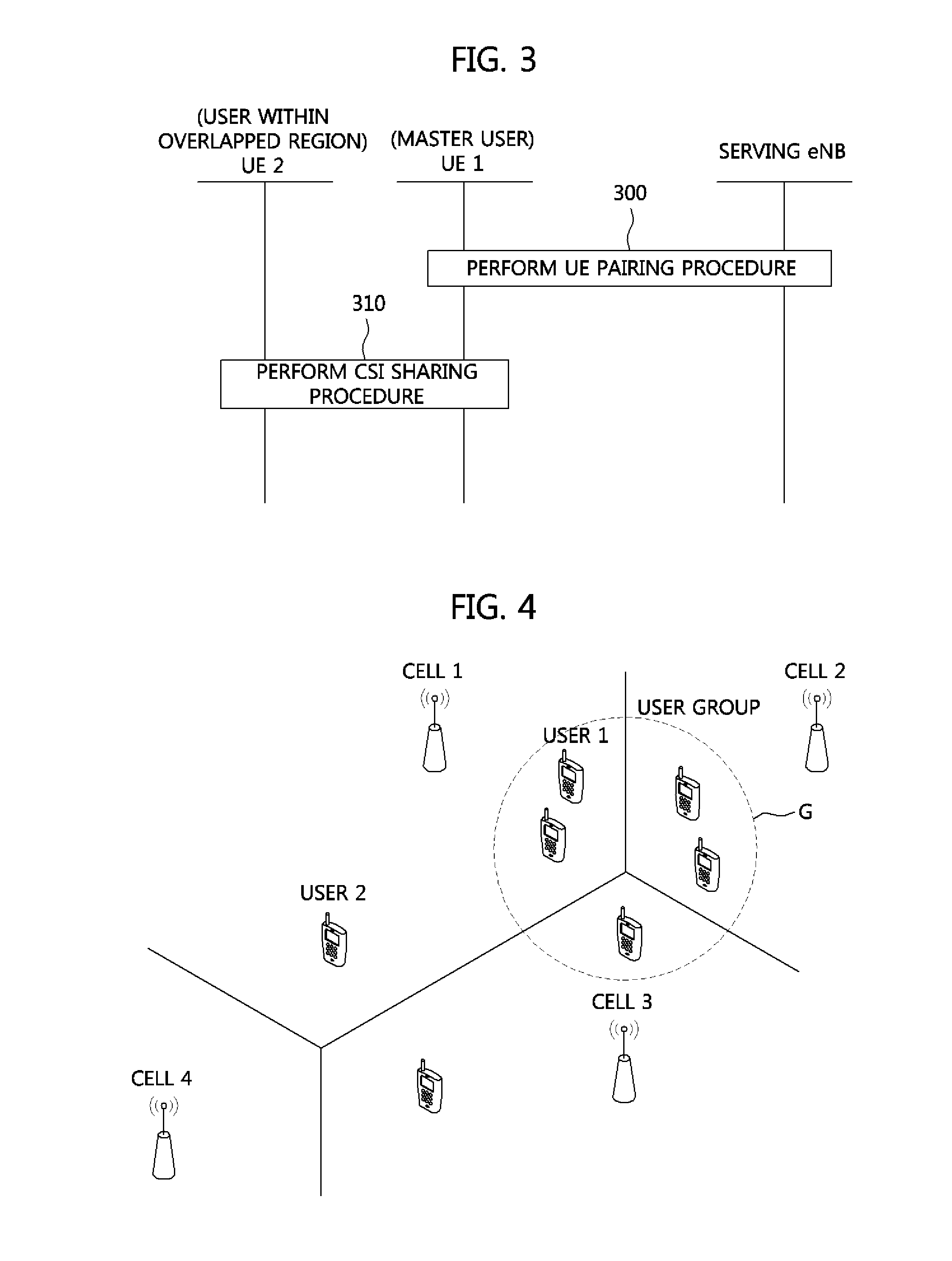

Method and device for managing interference in neighbouring cells having multiple sending and receiving nodes

ActiveUS20130078991A1Improve implementationLimited implementationSite diversityNetwork traffic/resource managementTelecommunicationsWireless systems

Disclosed is method for controlling interference in a wireless system having multiple sending and receiving nodes. In the method for controlling interference in a wireless system having multiple sending and receiving nodes, a plurality of receiving nodes share each other's channel information, each of the receiving nodes uses the shared channel information to calculate a precoding matrix which is fed back to the sending nodes, and each of the sending nodes uses each of the precoding matrices received as feedback to transmit a send signal to the receiving nodes, thereby controlling interference. Complete interference alignment can be achieved even by just sharing channel information between receiving nodes, and the invention can be employed not only for inter-cell interference but also for intra-cell interference environments.

Owner:ELECTRONICS & TELECOMM RES INST

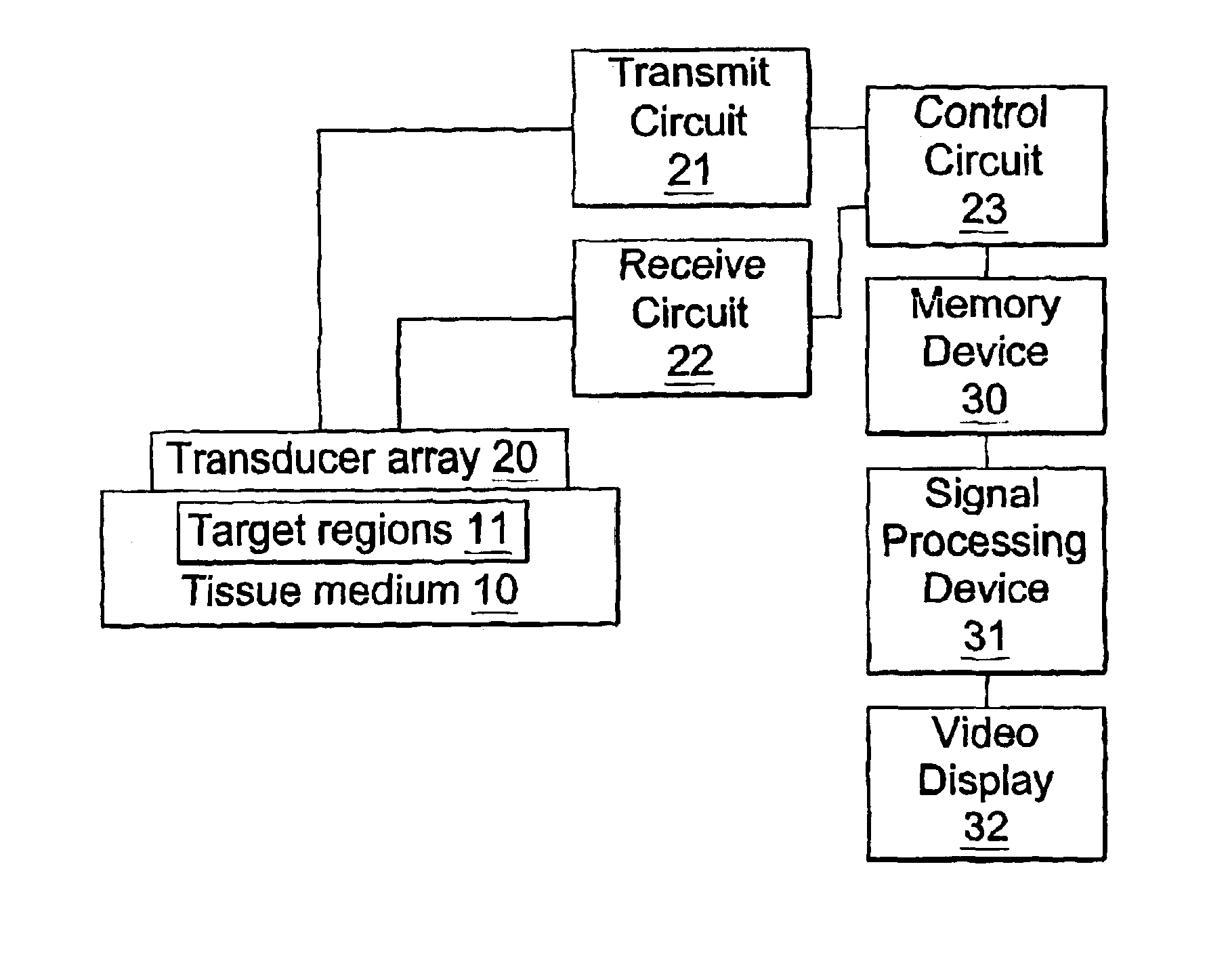

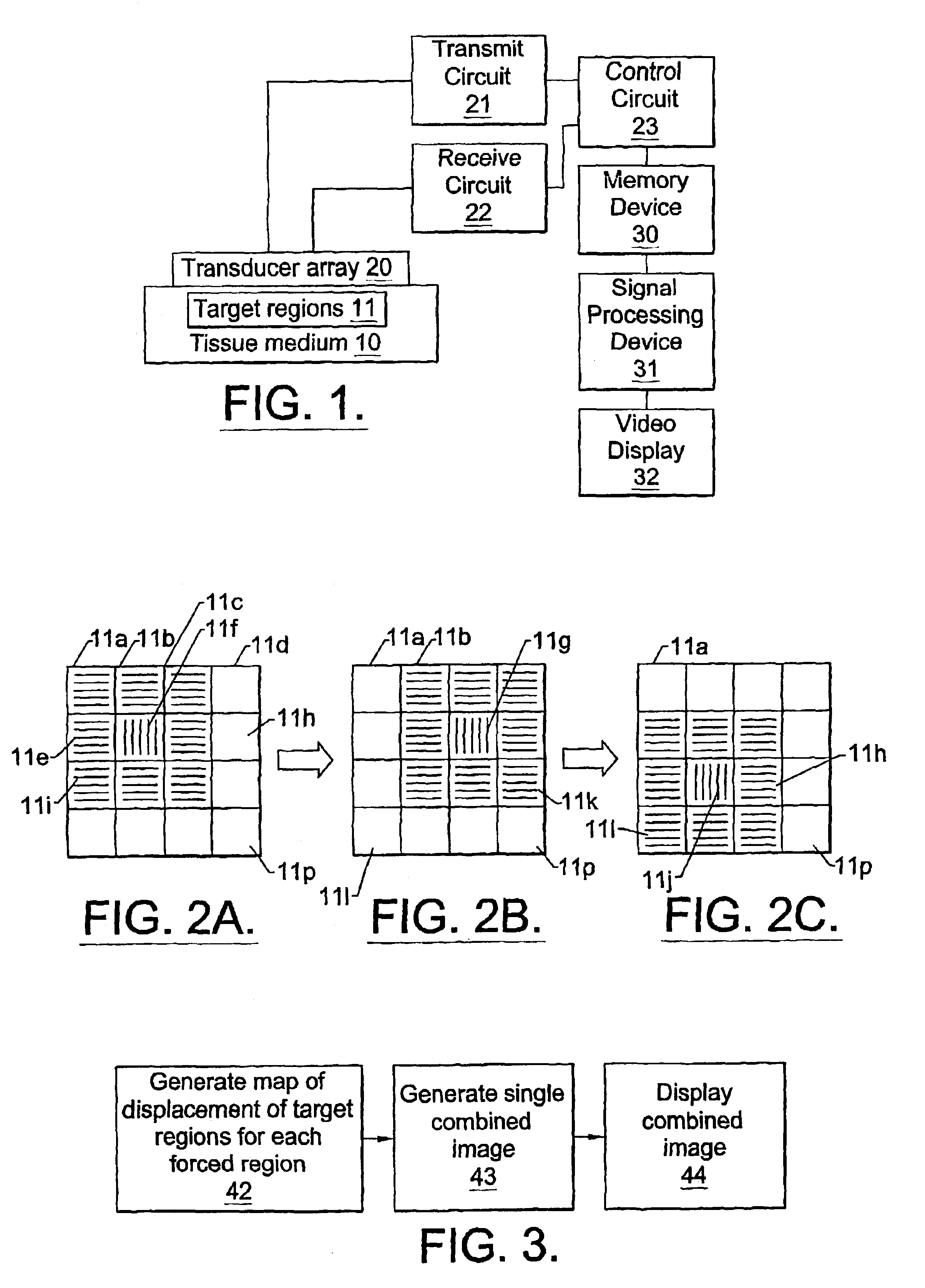

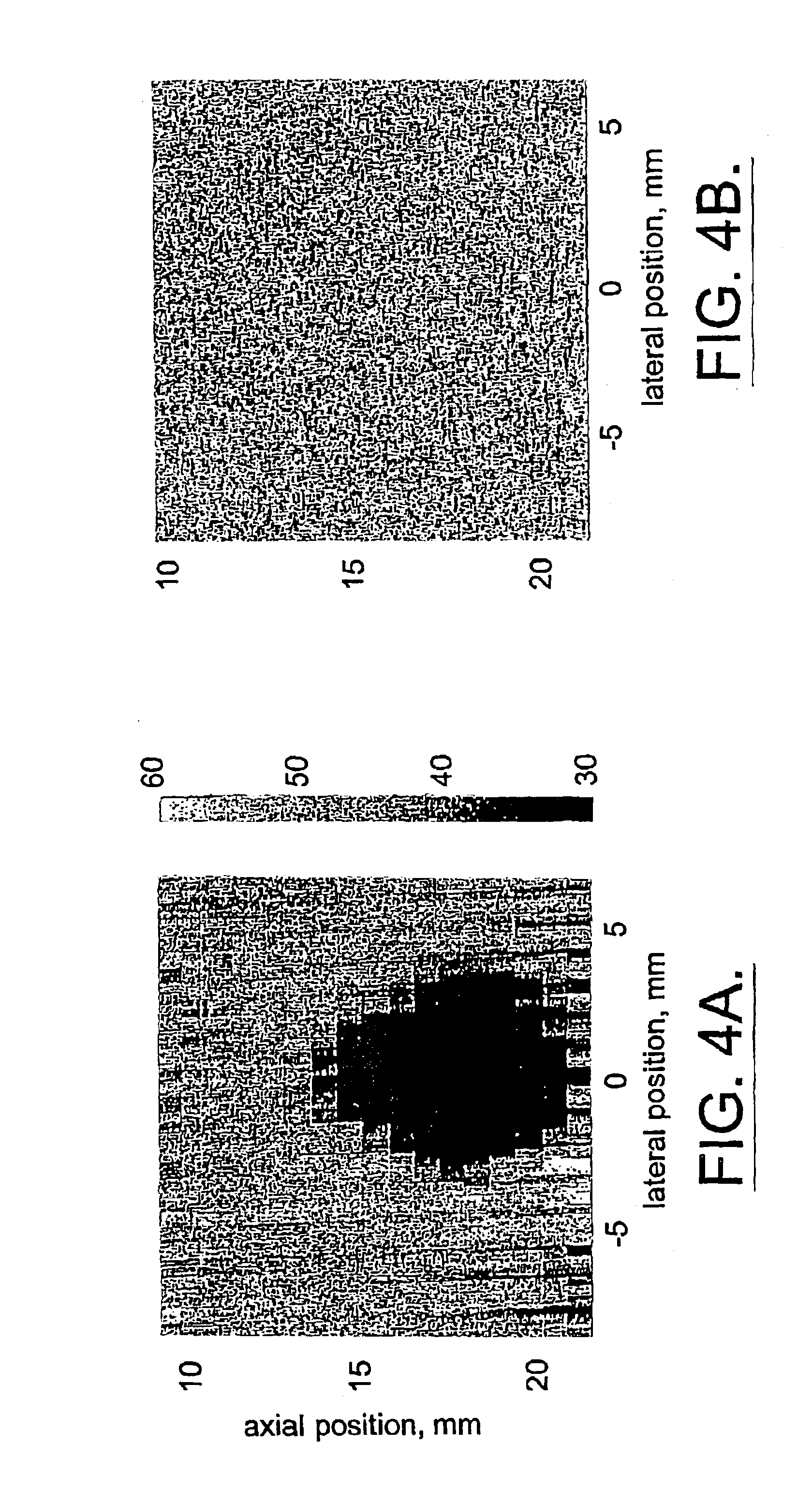

Method and apparatus for the identification and characterization of regions of altered stiffness

InactiveUS6951544B2Facilitate real-timeEasy to implementBlood flow measurement devicesOrgan movement/changes detectionPalpationTarget tissue

A remote palpation technique in breast imaging involves the use of multiple applications of radiation force in rapid succession throughout a two-dimensional plane in the target tissue medium (10), and combination of the small, two-dimensional displacement maps from each force location into a single, larger remote palpation image (block 43). Apparatus for carrying out the foregoing method is also disclosed.

Owner:DUKE UNIV

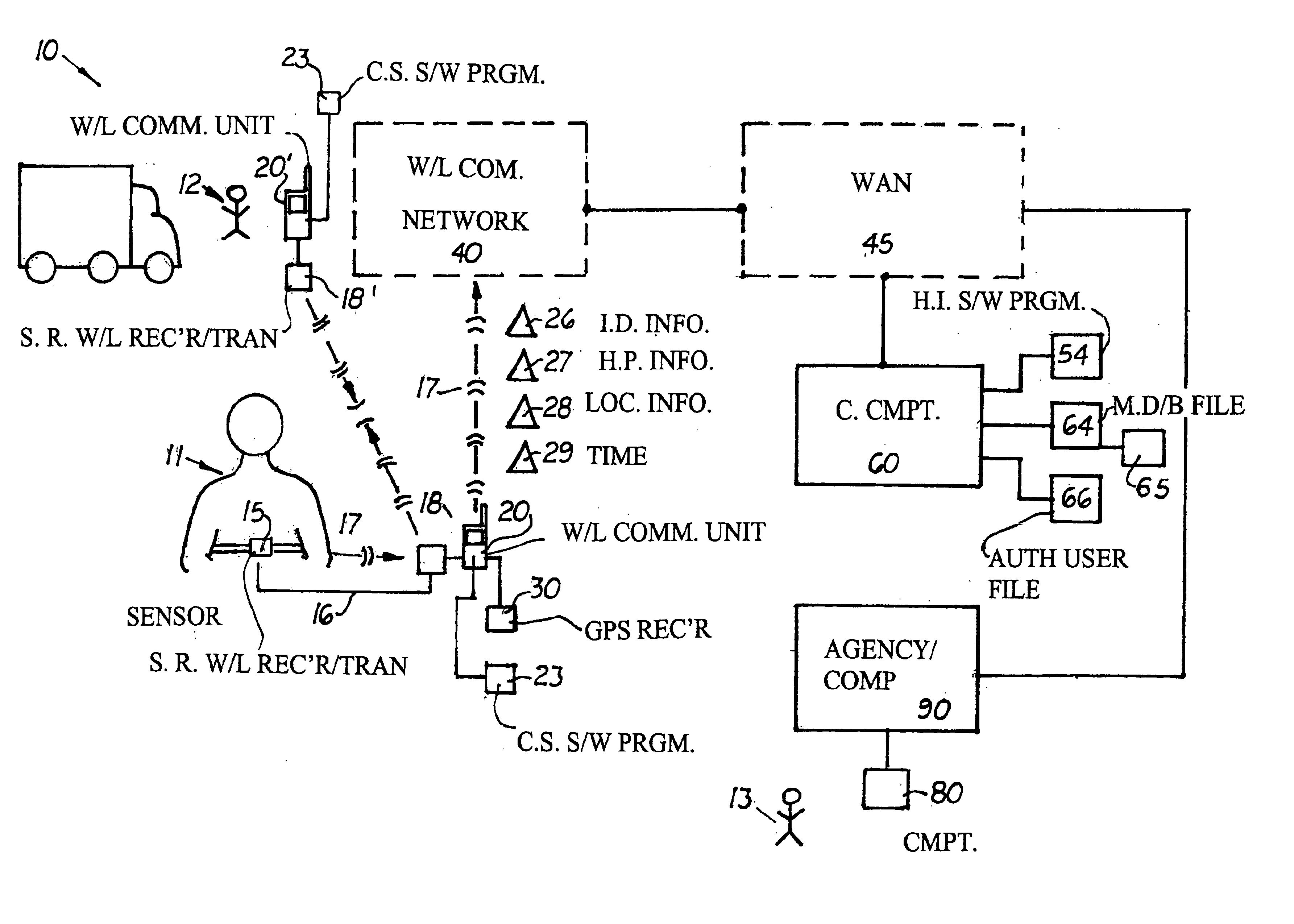

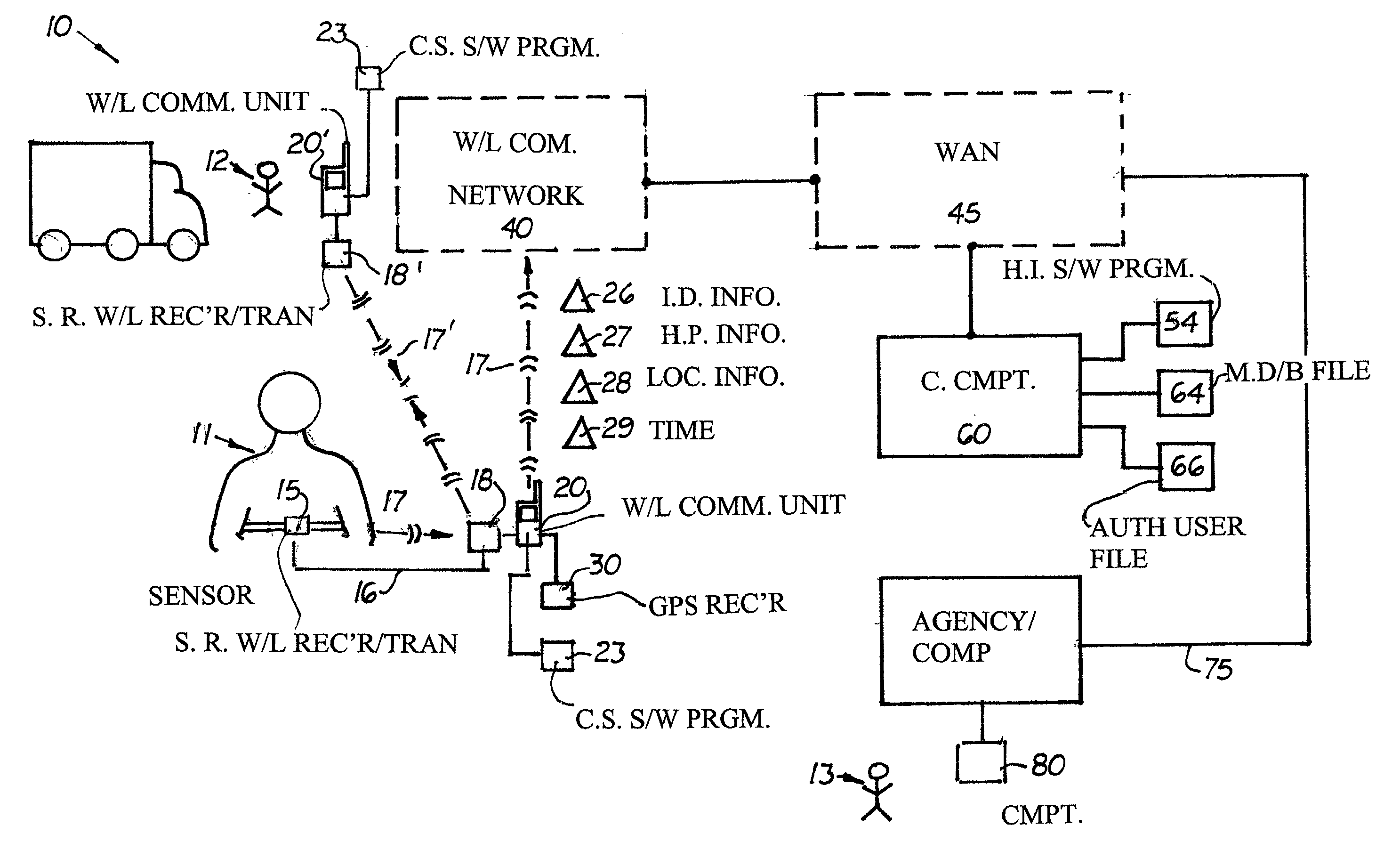

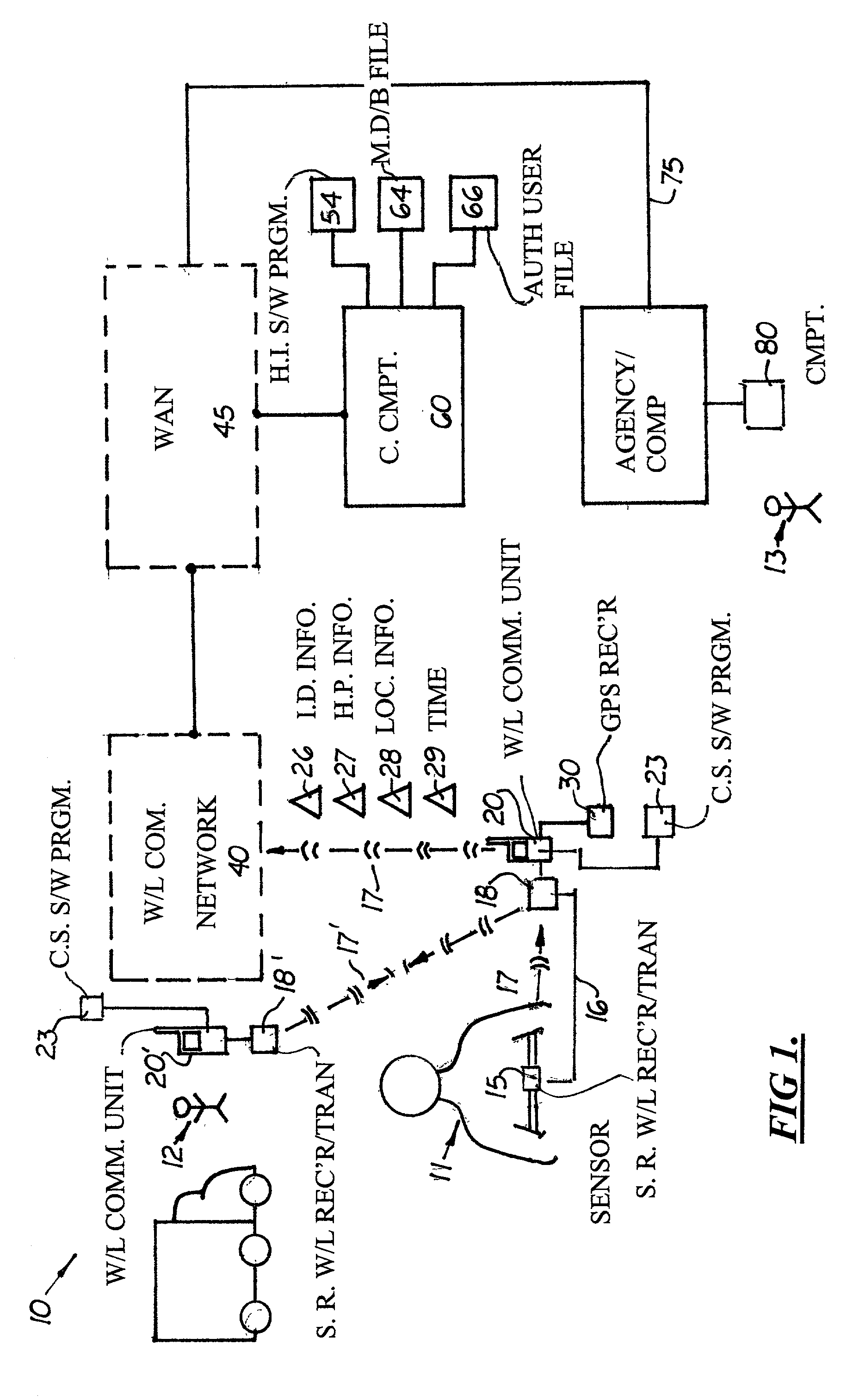

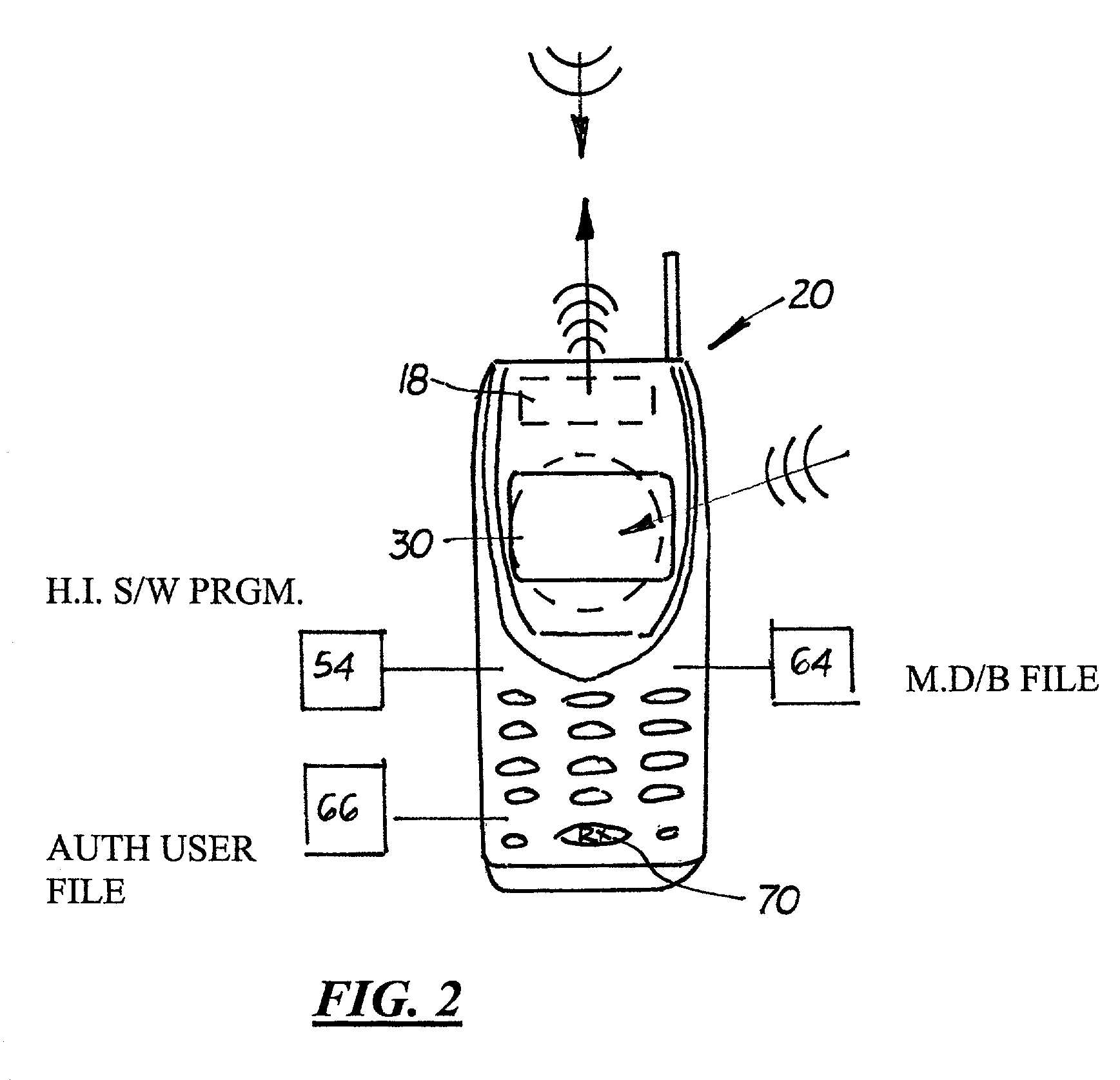

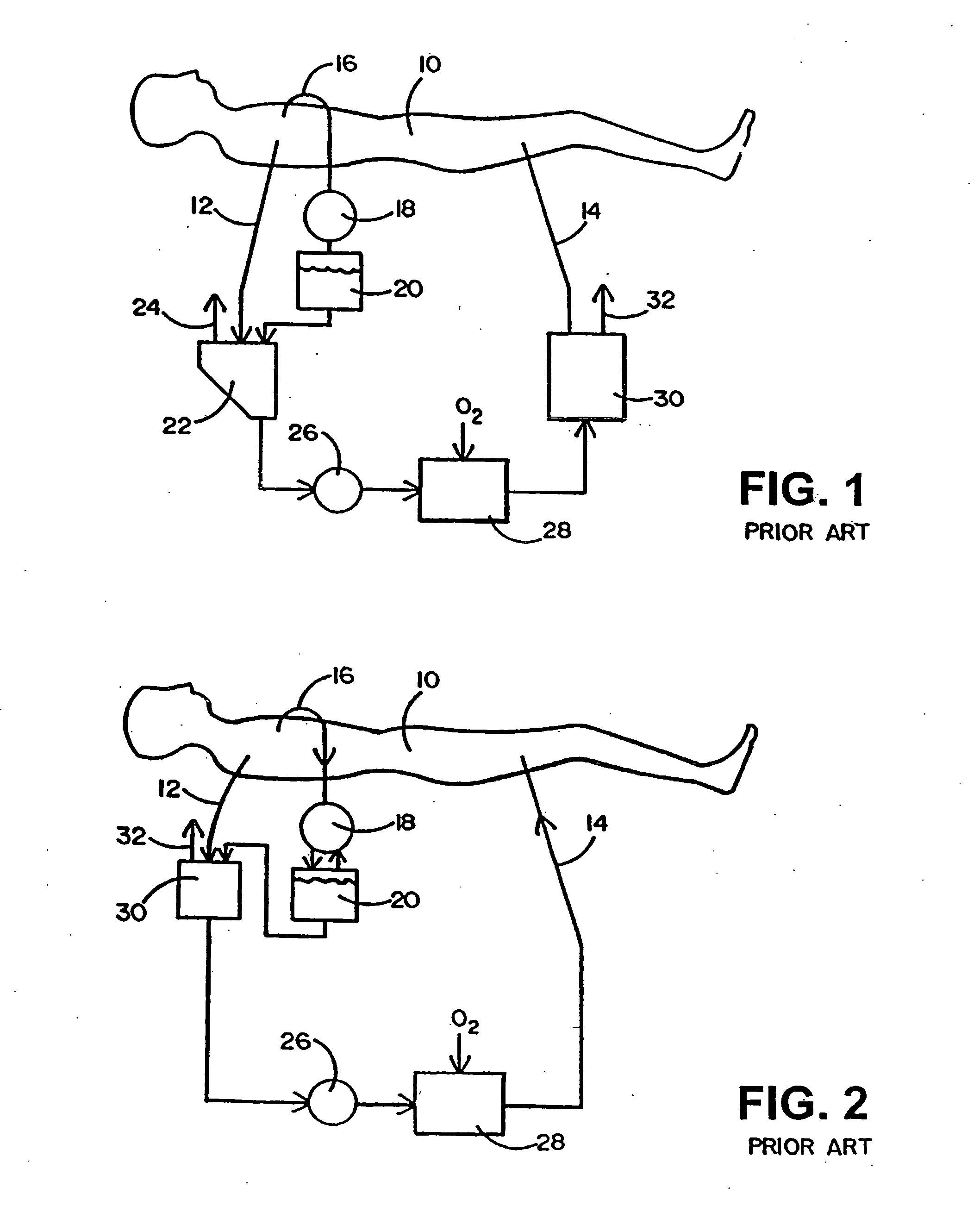

Emergency medical treatment system

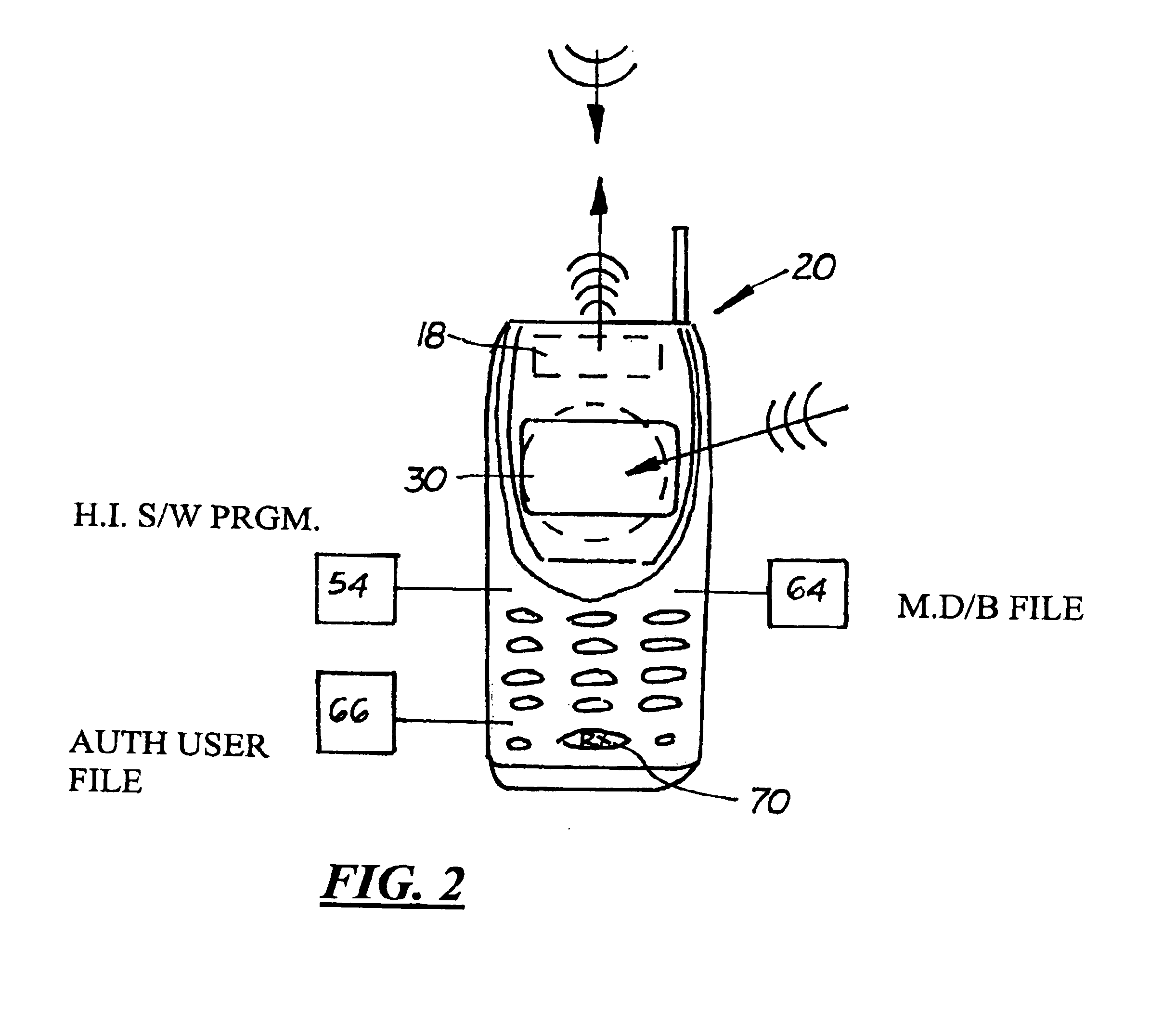

InactiveUS6758812B2Quickly and easily downloadImplement extensionsSurgeryDiagnostic recording/measuringSystems designPhysical health

An emergency medical treatment system that uses medical information recorded in a user file by a central computer connected to a wide area network. The system is designed to be used with a recording and monitoring health and physical fitness system that automatically sends the parameter information from a sensor worn by a subscriber to a central computer. The wireless communication unit is able to connect to a wireless communication network which, in turn, connects to a wide area network. A central computer is connected to a wide area network that is able to continuously download the physiological parameter information from the wireless communication unit via the wireless communication network. The central computer uses a health information recording software program to create a continuously updated subscriber's medical database containing current and historical medical information. The subscriber and authorized medical personnel are able to log onto the central computer to review the medical information on the subscriber's medical database file.

Owner:LANG BROOK W

Universal asynchronous serial extended chip of multi-bus interface

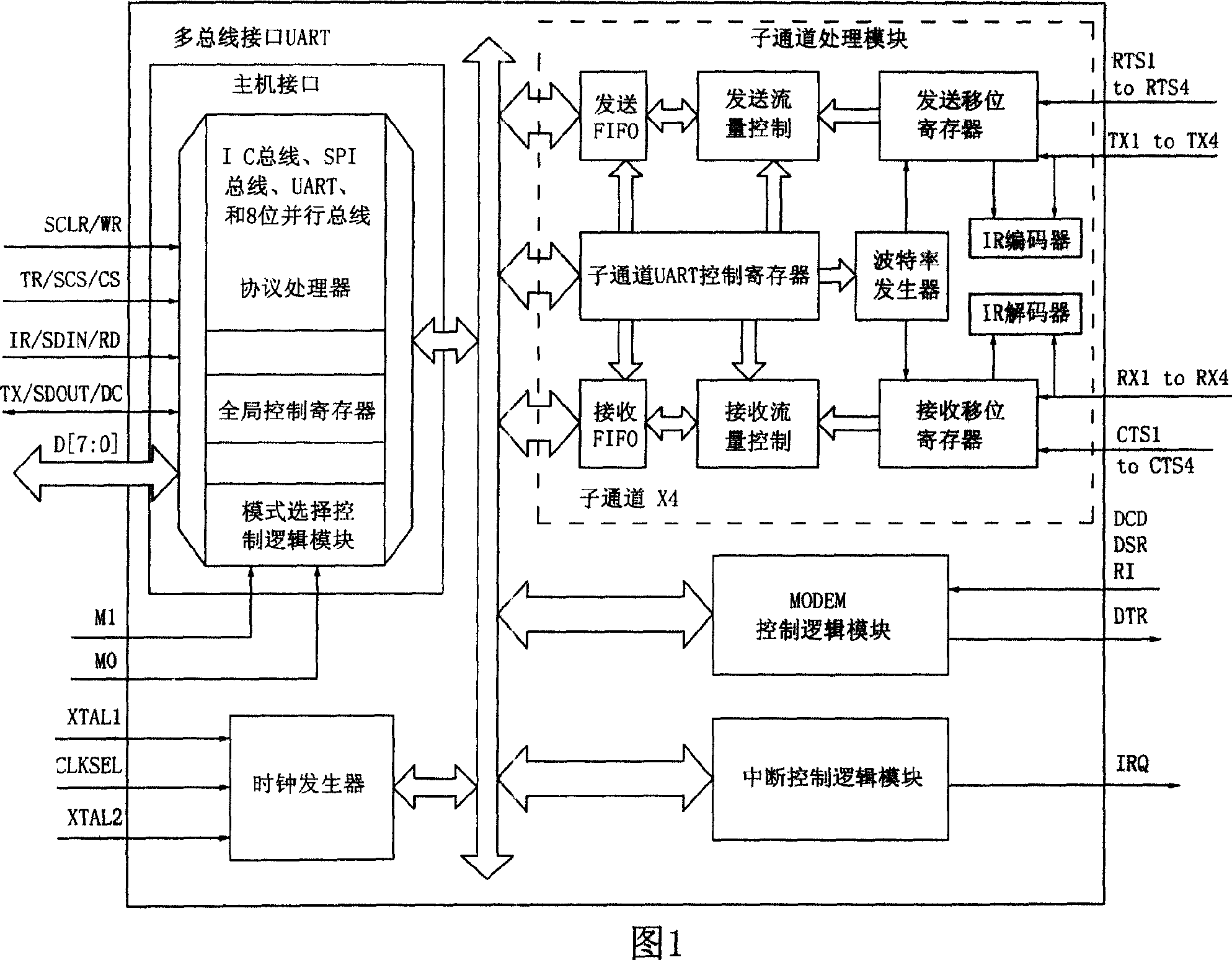

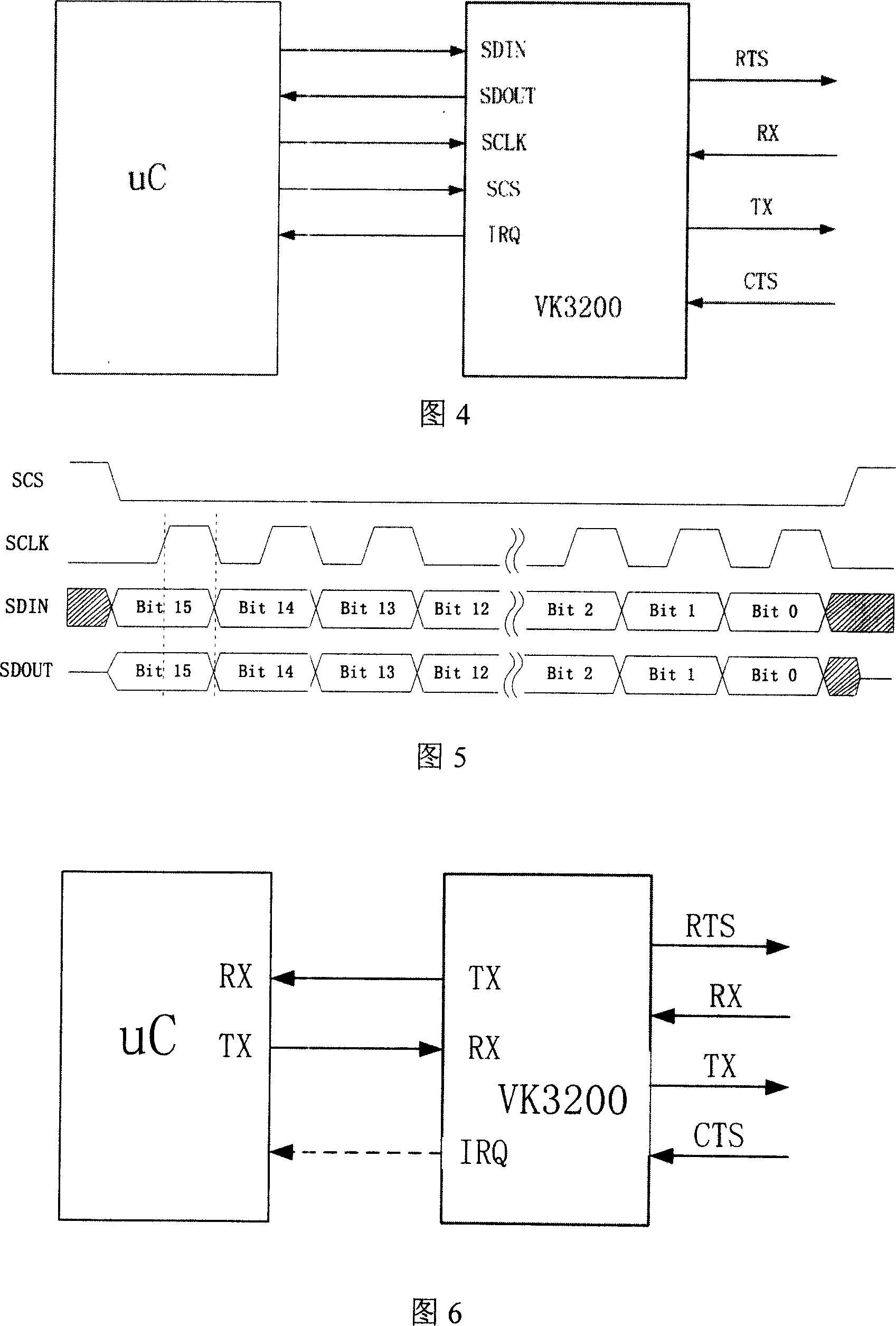

InactiveCN101127023AReduce the burden onImplement extensionsElectric digital data processingIntegrated circuitMode selection

The utility model discloses a multi-bus interface extended chip with general asynchronous serial ports, comprising a host interface, a subchannel processing module, a MODEM control logic module, an interrupt control logic module and a clock generator. The utility model is characterized in that the host interface comprises a 8-bit parallel bus interface, a serial peripheral interface SPI bus interface, a UART bus interface, an internal integrated circuit bus I2C bus interface, a protocol processor, a global register and a mode selection control logic module, wherein the four bus interfaces are all connected with the CPU / DSP host and the bus type corresponding the host is selected through the bus processing logic, in addition, the data and the conversion of data format are processed through the bus processing logic. The working state of the host interface of the chip is setup by the global register and the mode selection, the mode selection control logic module selects the host interface and the signal line through mode. The utility model supports 8-bit parallel bus, SPI bus, I2C, UART and other host bus interfaces, realizes a plurality of extended serial ports for buses, besides, the utility model has compact and perfect configuration register structure and enables multi-working modes set of the sub serial ports independently, and supports high-speed communication, and each channel has independent and controllable data broadcasting and receiving function, and all UARTs support IRDA infrared communication.

Owner:CHENGDU WEIKAI MICROELECTRONICS CO LTD

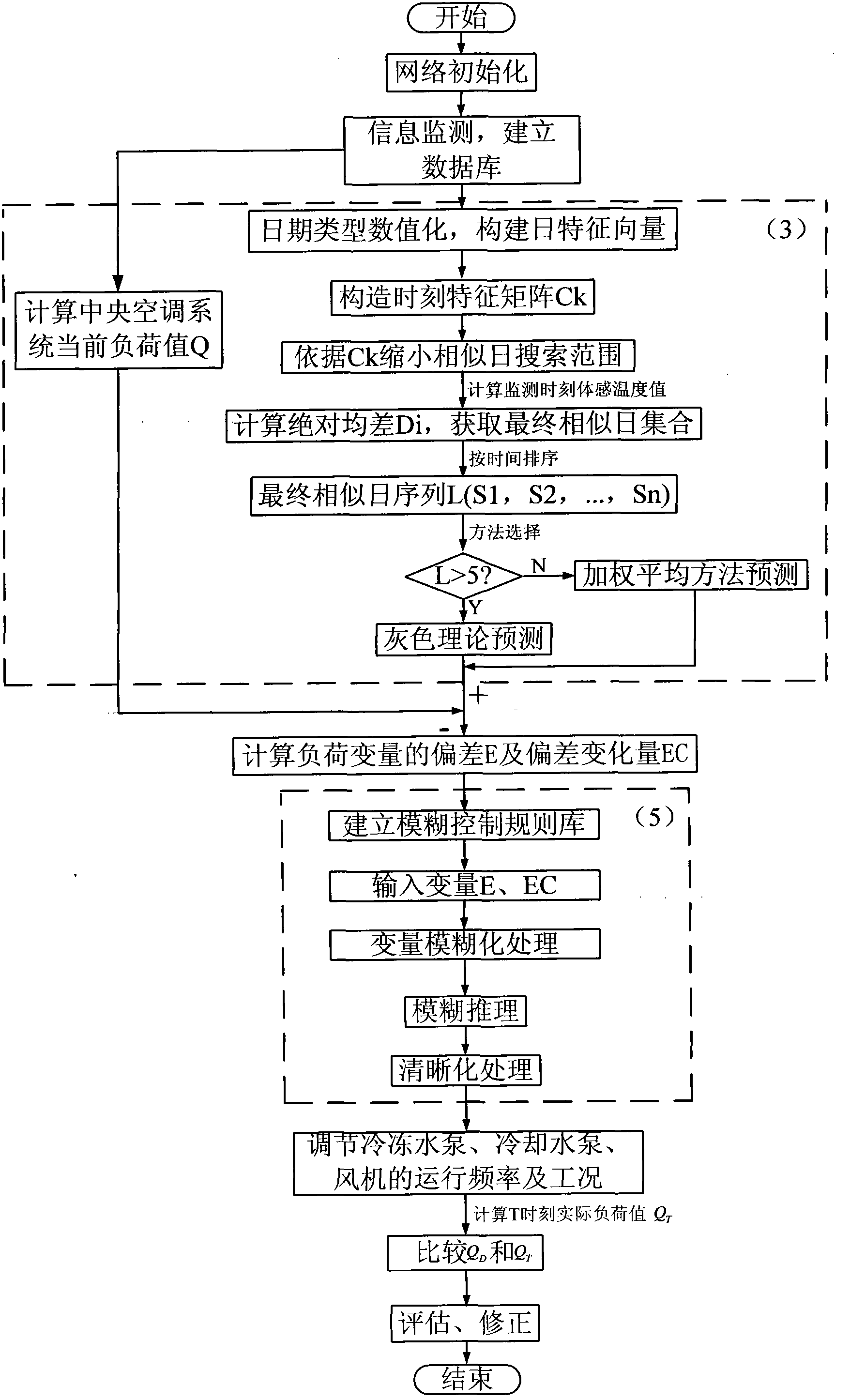

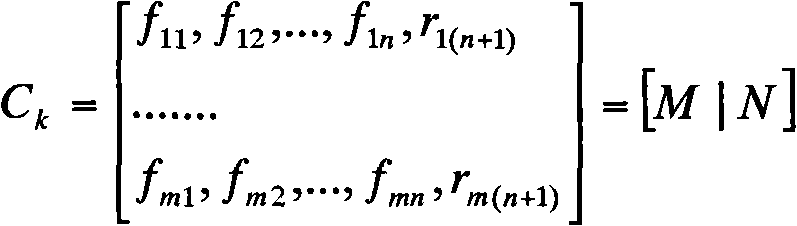

Central air conditioner intelligent control system based on wireless sensor network and method

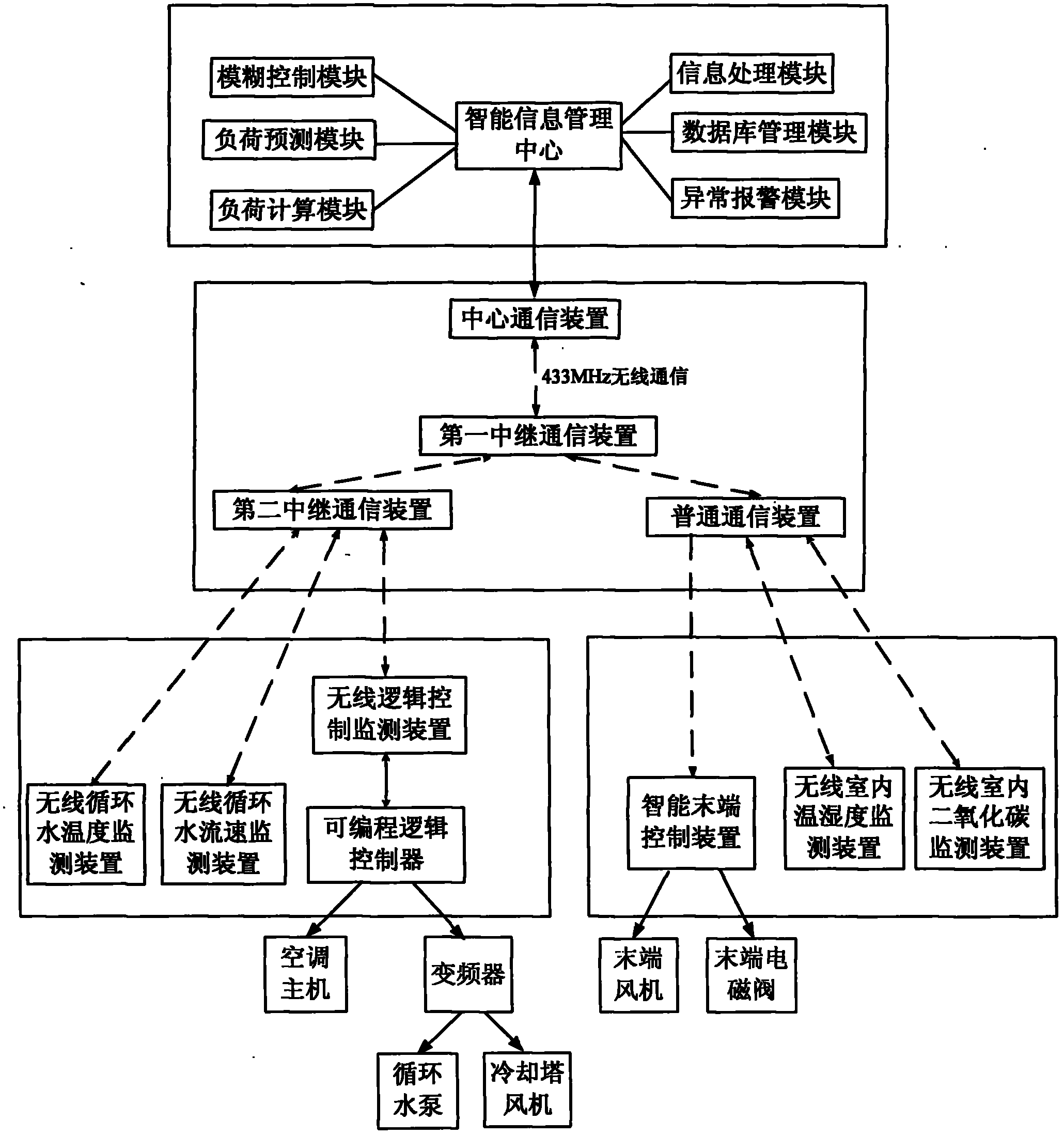

InactiveCN102052739AStrong obstacle avoidance abilityImplement extensionsSpace heating and ventilation safety systemsLighting and heating apparatusShort termsCommunication device

The invention discloses a central air conditioner intelligent control system based on a wireless sensor network and a method, and belongs to the technical field of central air conditioner control. The central air conditioner intelligent control system comprises an intelligent information management center, wireless communication devices, a central air conditioner information monitoring and control module, a room information monitoring and control module and the like. The invention adopts the method that the central air conditioner intelligent control system is used to monitor information, build a data base, calculate current load of the system, and realize advance, accurate and optimized control of a central air conditioner system by combining a short-term loading forecasting method based on similar dates and fuzzy control technology, as well as taking the temperature variation of supply / return chilled / cooling water of a central air conditioner as the manipulated variable. The central air conditioner intelligent control system has the characteristics of great communication capacity, guaranteed communication quality, powerful network functions, wide monitoring range and extensive control quantity of the central air conditioner system, optimized control, high control accuracy, good energy saving effect and the like, and can be widely used in energy-saving optimizing control of various buildings, and is particularly suitable for energy-saving optimizing control of central air conditioners of intelligent buildings.

Owner:CHONGQING UNIV

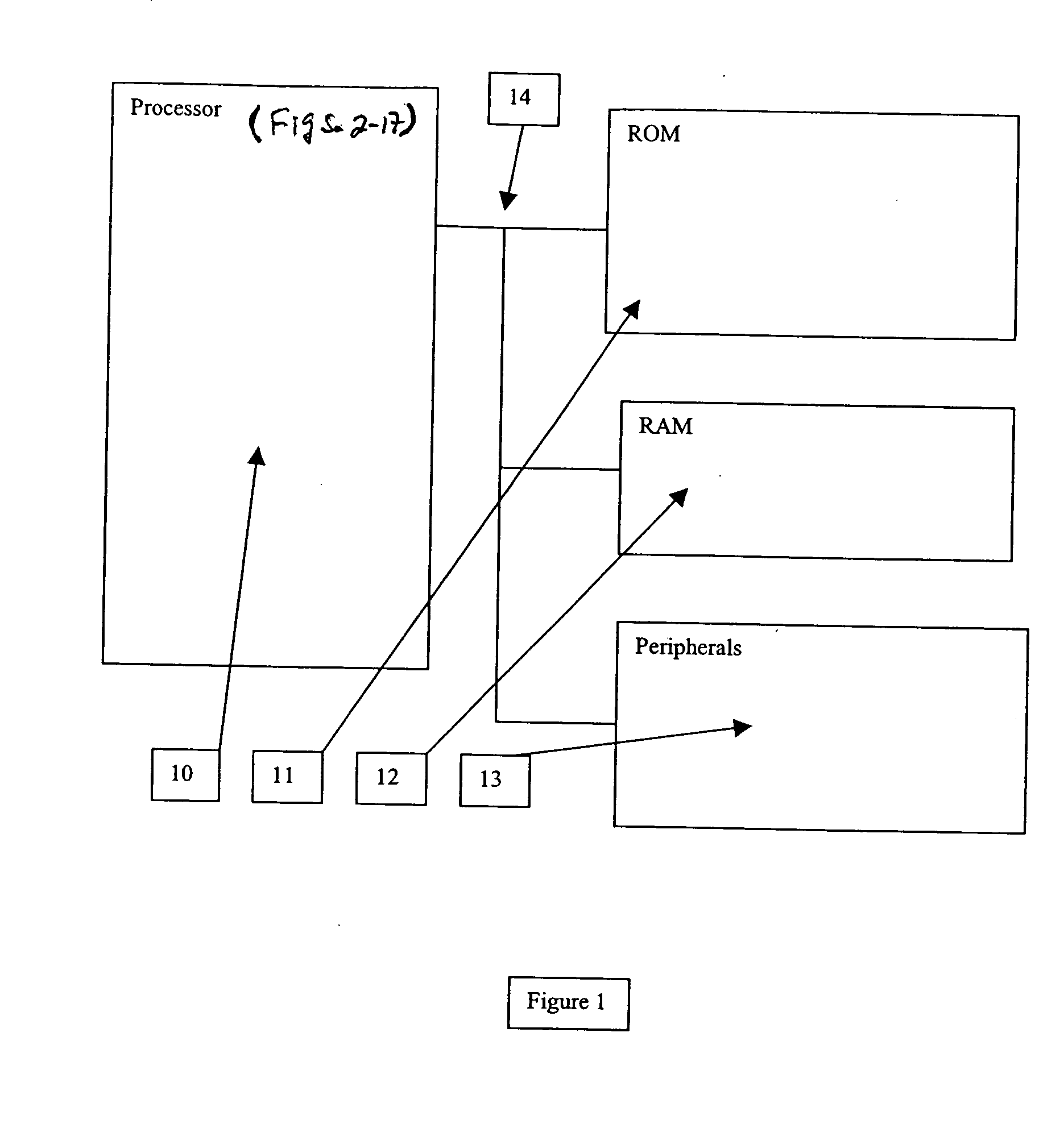

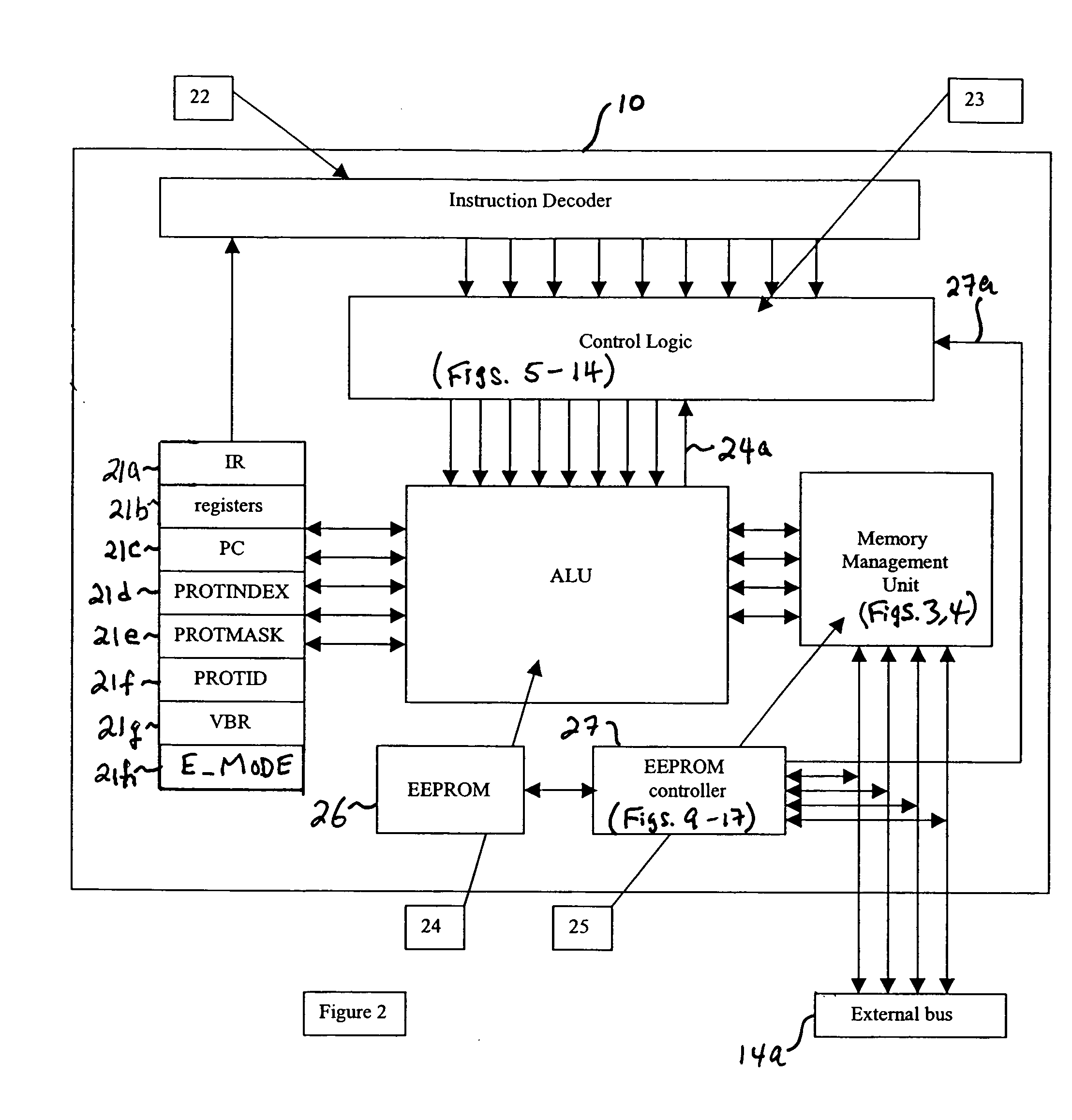

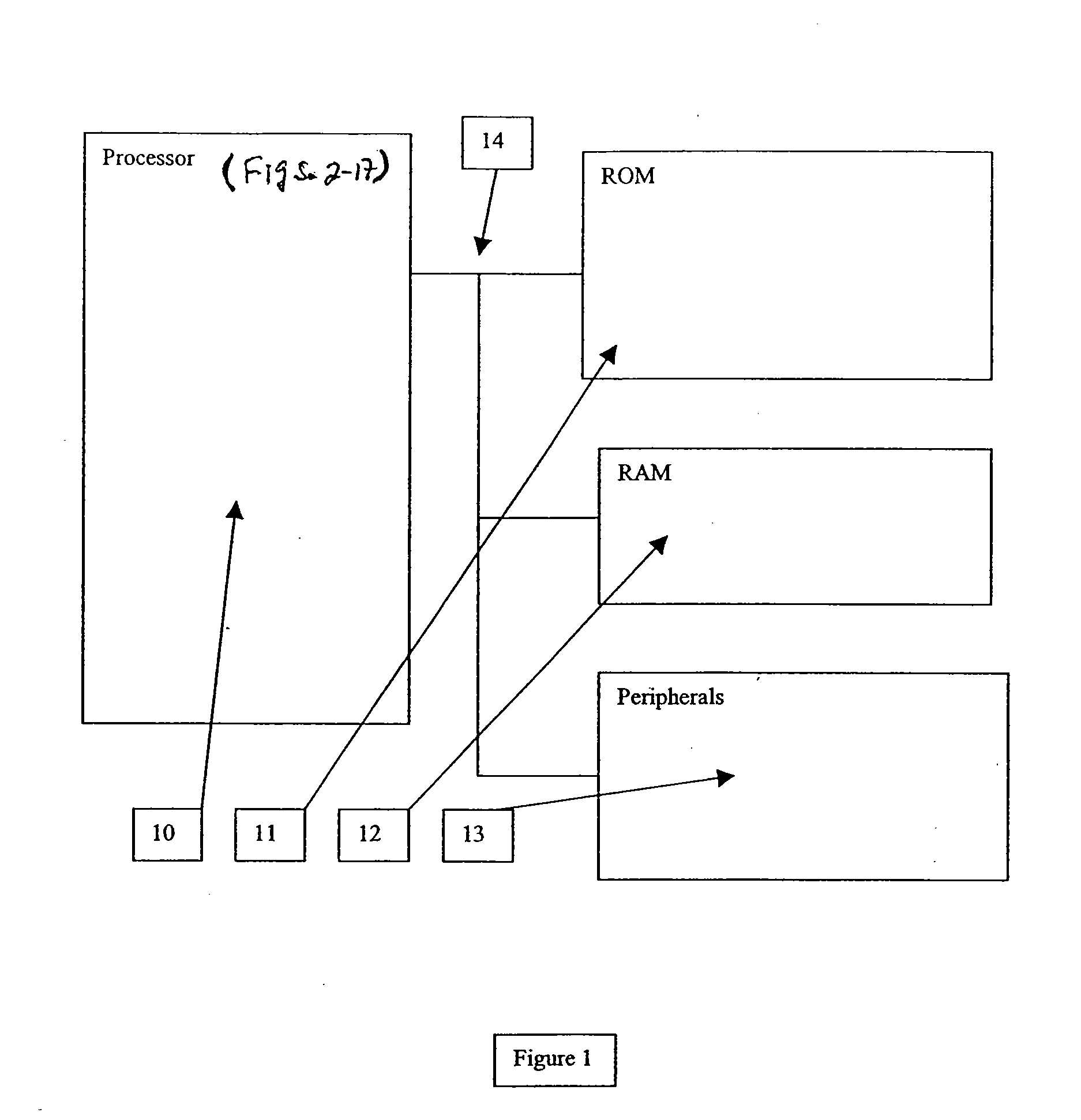

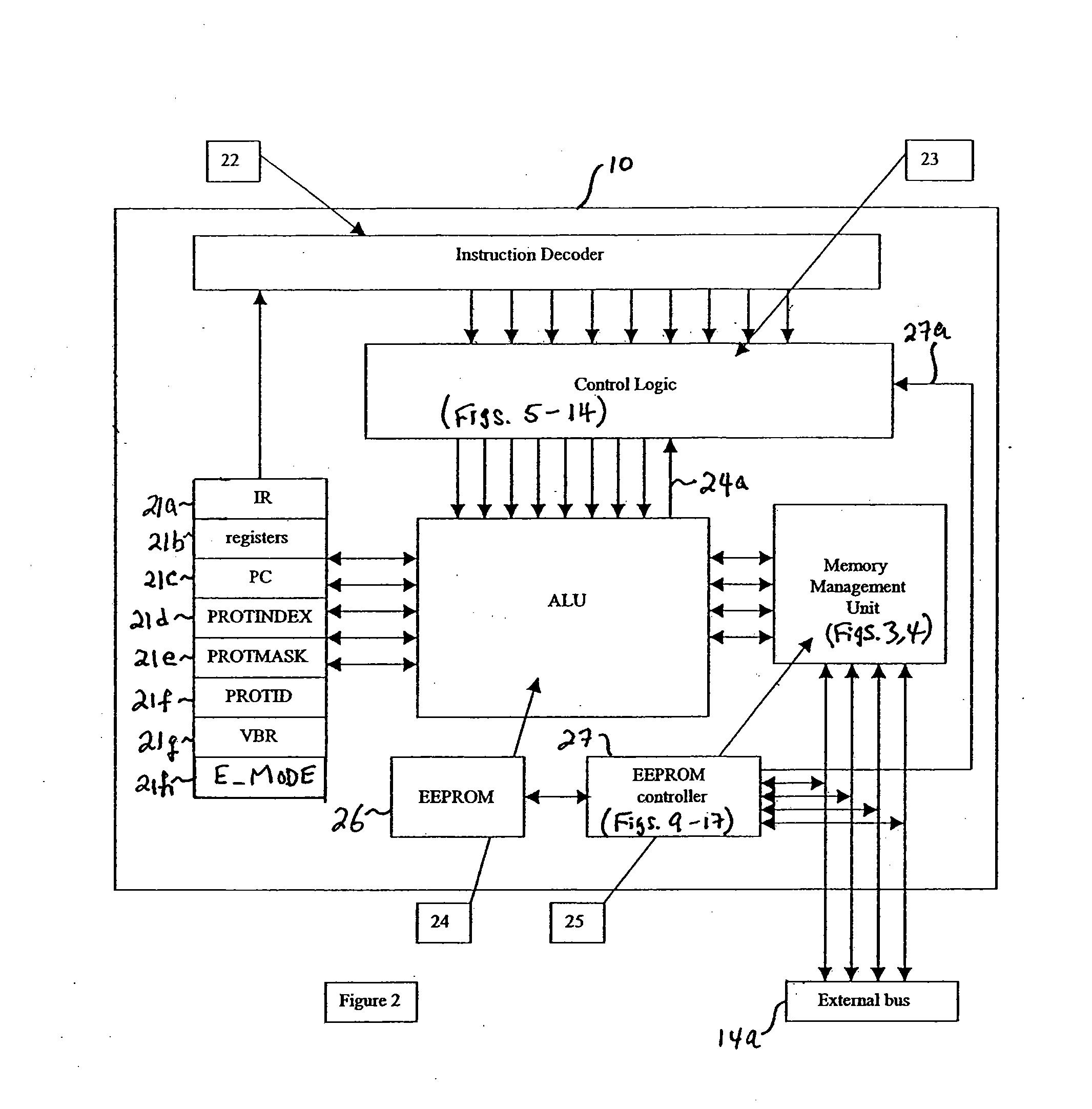

Processor for virtual machines and method therefor

ActiveUS20050091468A1Implement extensionsMemory architecture accessing/allocationMemory adressing/allocation/relocationRandom access memoryTerm memory

Apparatus and method are described for a data processing device. The data processor includes features suitable for executing a software virtual machine. The data processor provides an instruction set that supports object-level memory protection suitable for high speed operation. Memory control logic is provided to accommodate a configuration having relatively less random access memory (RAM) as compared to re-programmable, nonvolatile memory, and to improve access to the re-programmable, nonvolatile memory.

Owner:RENESAS ELECTRONICS AMERICA

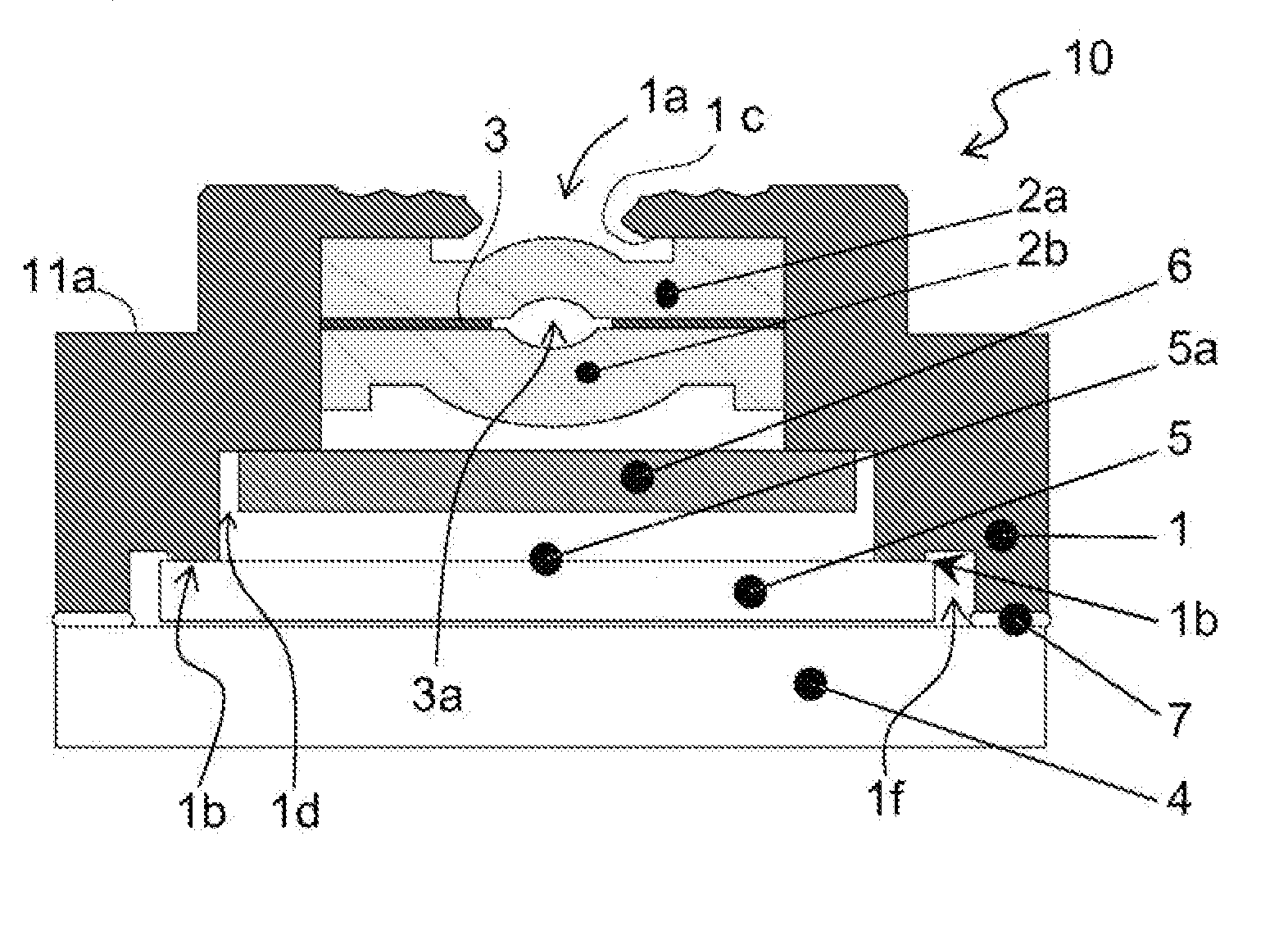

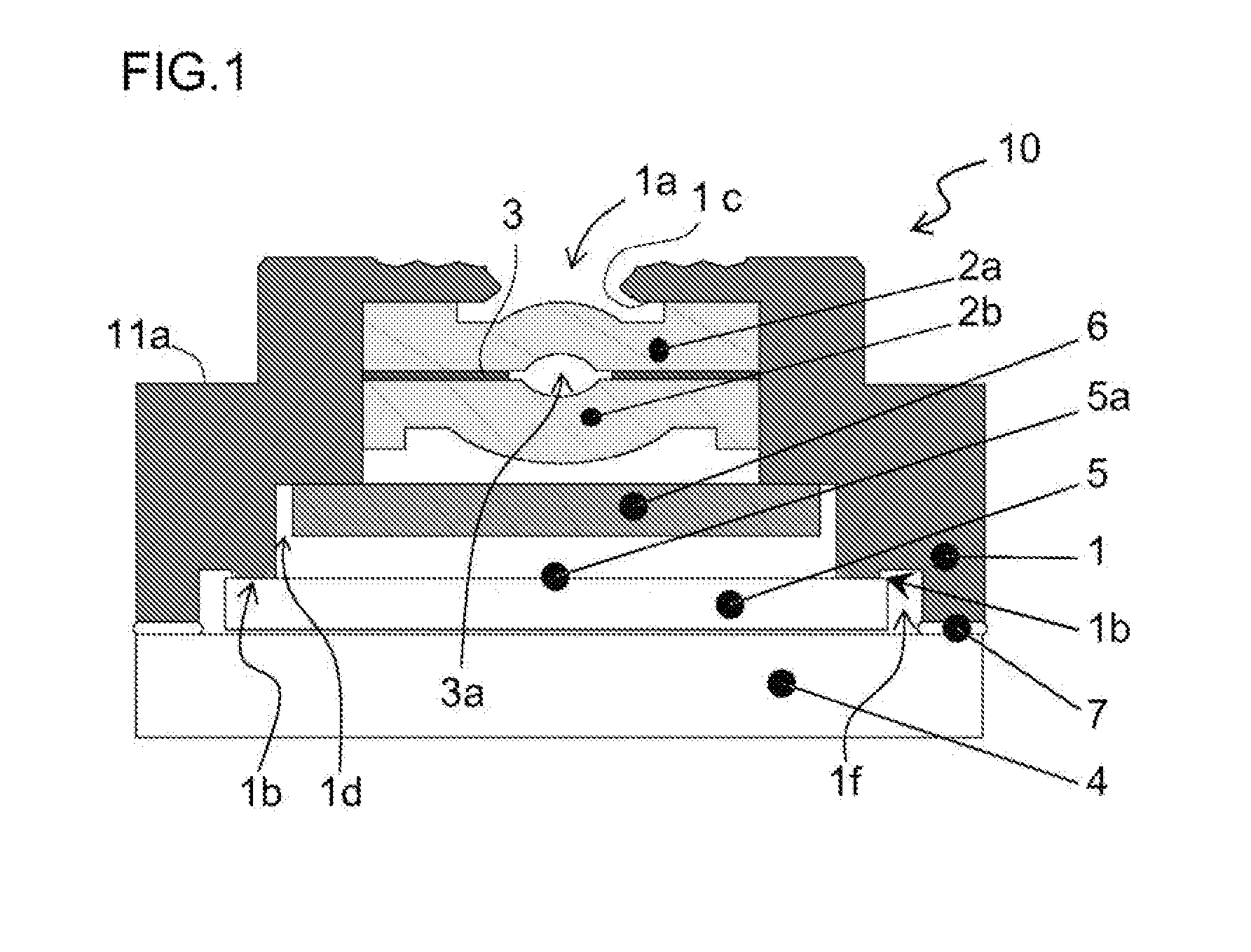

Image capturing module, method for manufacturing the image capturing module, and electronic information device

InactiveUS20090160998A1Improve accuracyFixed and accurateTelevision system detailsLaminationComputer moduleElectronic information

An image capturing module according to the present invention includes a holder member, which accommodates therein a focusing lens for forming an image of a subject light on an image capturing chip attached on a substrate and is attached to the substrate to cover the image capturing chip, where the holder member is directly supported on a surface of the image capturing chip.

Owner:SHARP KK

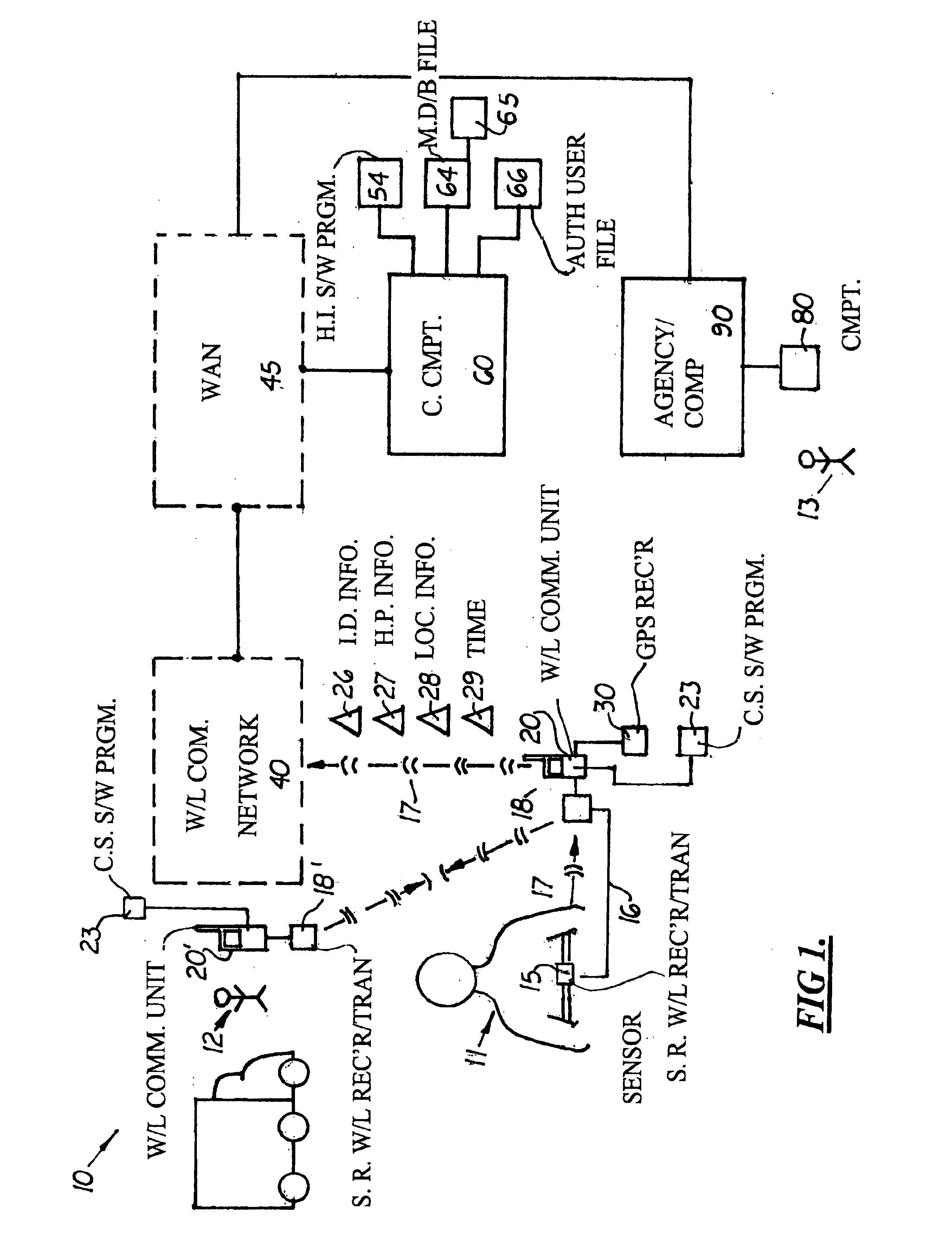

Emergency medical treatment system

InactiveUS20020118112A1Quickly and easily downloadImplement extensionsSurgeryDiagnostic recording/measuringSystems designCommunication unit

An emergency medical treatment system that uses medical information recorded in a user file by a central computer connected to a wide area network. The system is designed to be used with a recording and monitoring health and physical fitness system that automatically sends the parameter information from a sensor worn by a subscriber to a central computer. The wireless communication unit is able to connect to a wireless communication network which, in turn, connects to a wide area network. A central computer is connected to a wide area network that is able to continuously download the physiological parameter information from the wireless communication unit via the wireless communication network. The central computer uses a health information recording software program to create a continuously updated subscriber's medical database containing current and historical medical information. The subscriber and authorized medical personnel are able to log onto the central computer to review the medical information on the subscriber's medical database file.

Owner:LANG BROOK W

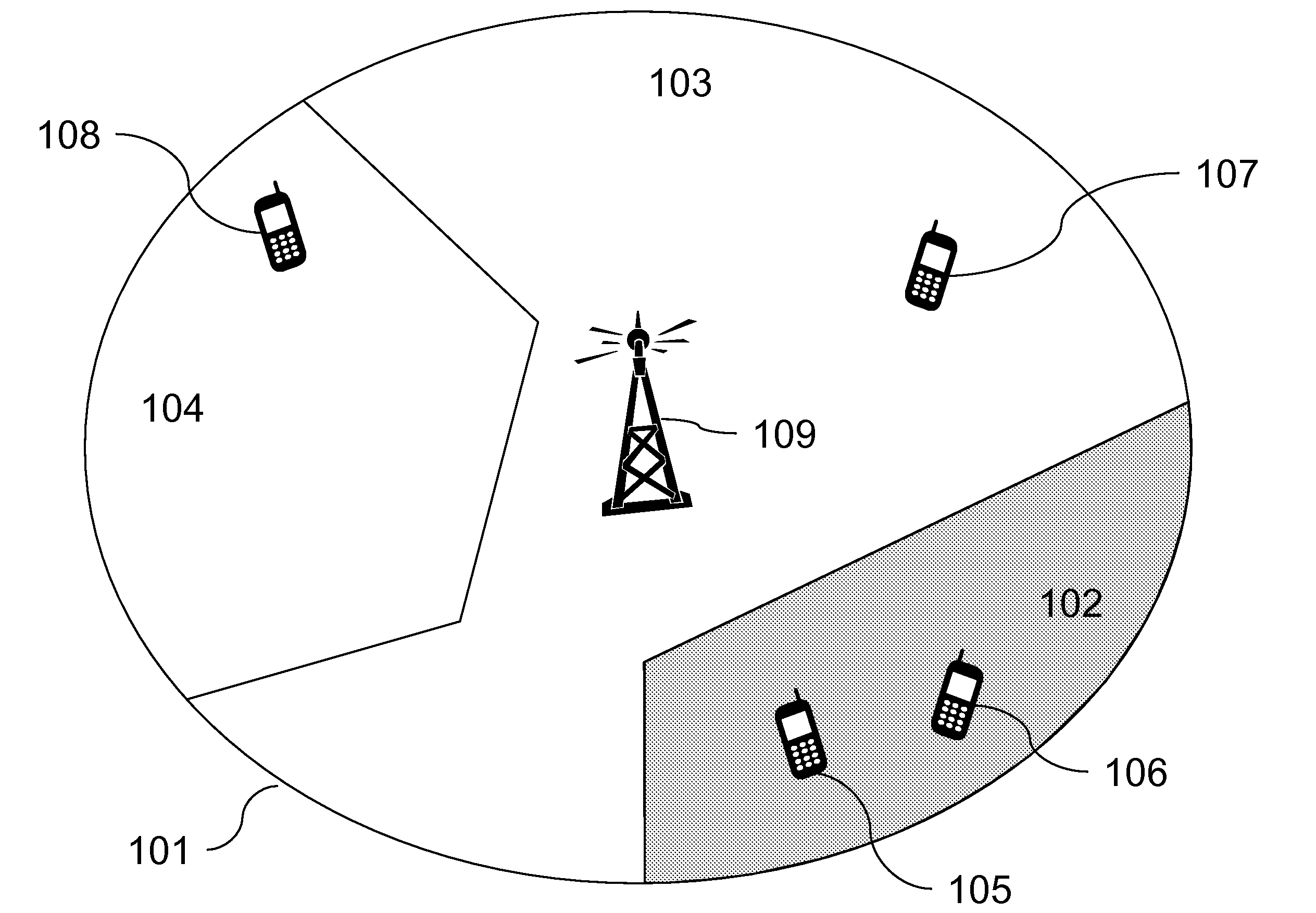

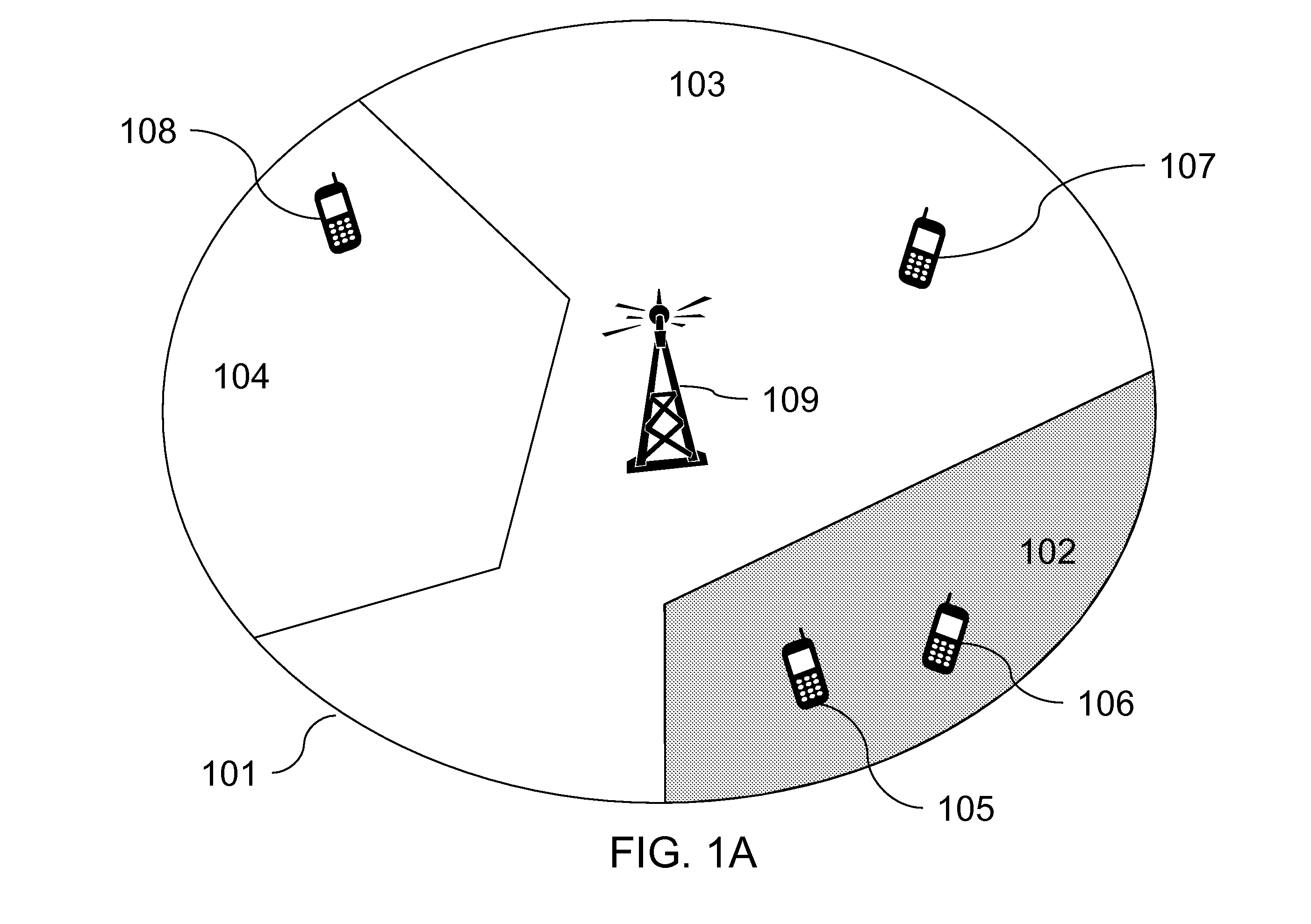

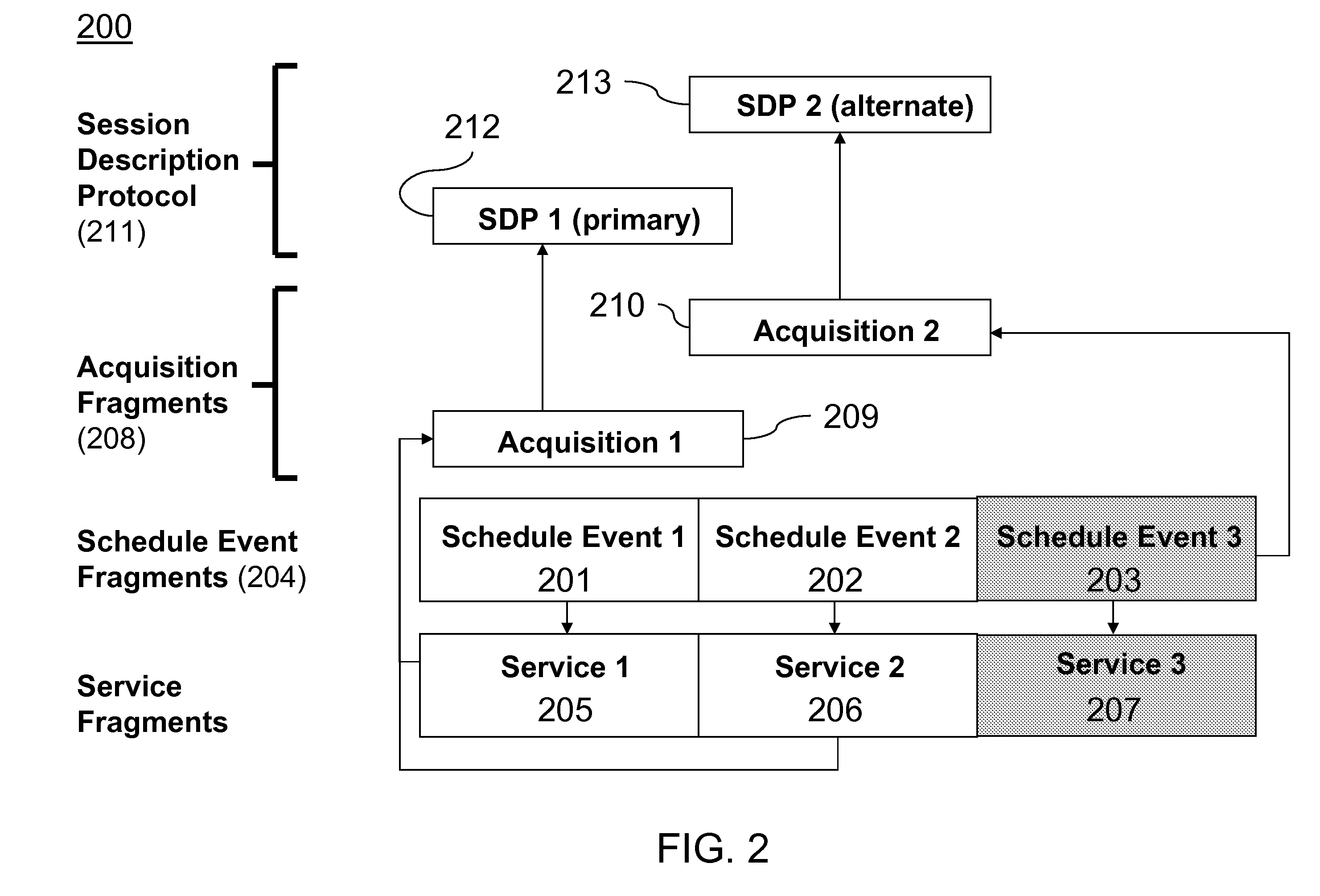

System and Method for Implementing Location-Based Content Restrictions in a Mobile Video Broadcast Environment

InactiveUS20070266396A1Implement extensionsAnalogue secracy/subscription systemsTransmissionMarine navigationAssisted GPS

A system and method for implementing location-based content restrictions in a mobile video broadcast is provided. The invention utilizes DVB-H KSMs to transmit the restrictions and thereby enables the restrictions to be enforced by the mobile terminal receiving a broadcast video signal. This need for enforcement is determined as a function of the received KSMs and the physical location of the receiving terminal (as sensed using one or more accepted navigation technologies (e.g., Global Positioning System (“GPS”) technology, Assisted GPS (“AGPS”) technology, etc.).

Owner:GENERAL INSTR CORP

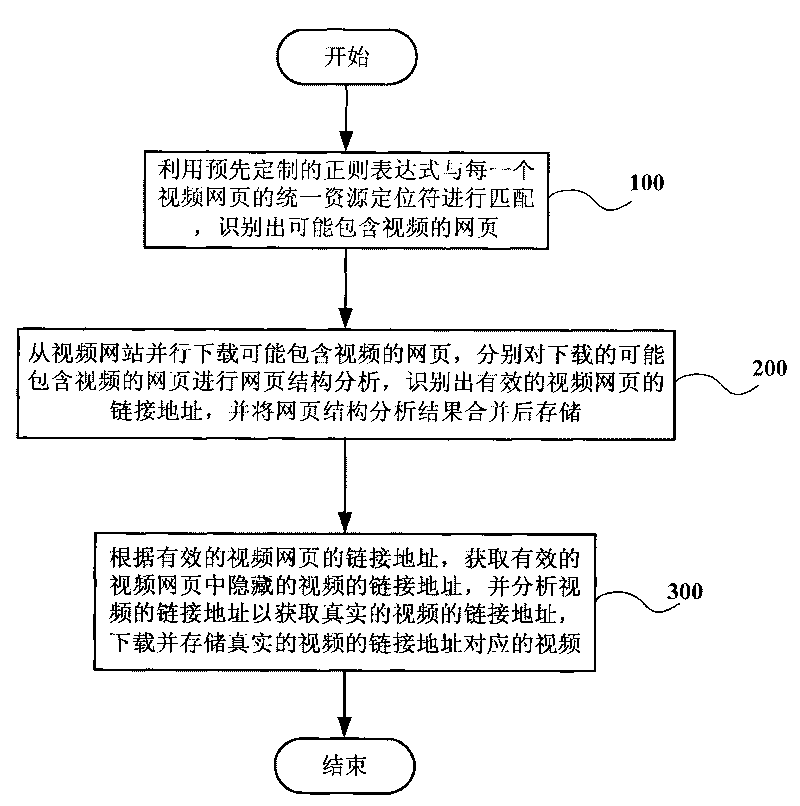

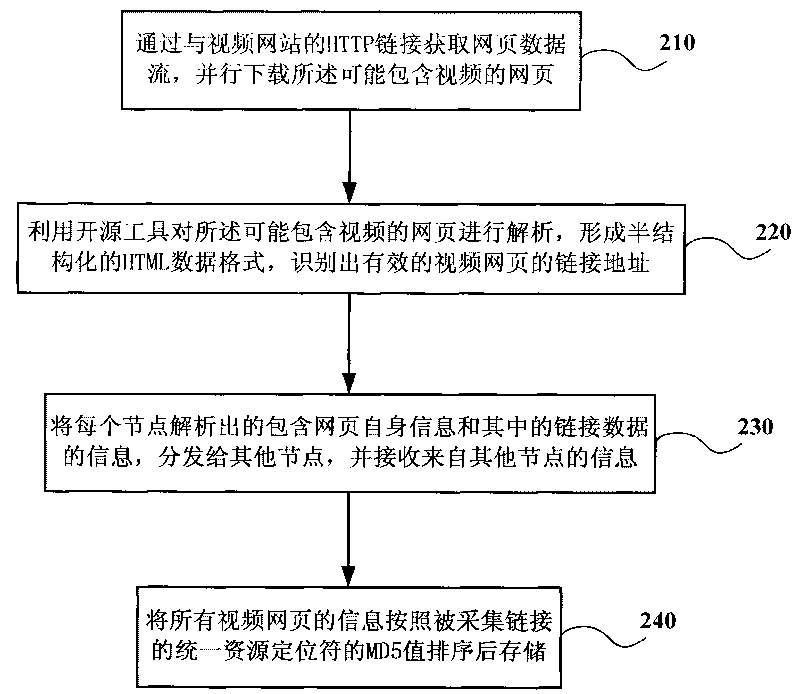

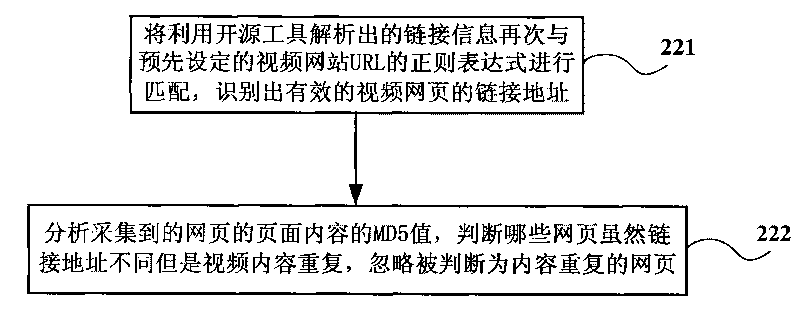

Internet video-oriented distributed acquisition method and system

ActiveCN101715004ARapid deploymentFor quick maintenanceData switching networksSpecial data processing applicationsUniform resource locatorWeb page

The invention discloses Internet video-oriented distributed acquisition method and system. The method comprises the following steps of: utilizing a preliminarily customized regular expression to match the uniform resource locators of each video webpage and identifying a webpage possibly containing video; downloading the webpage possibly containing viedeo in parallel from a video website; respectively analyzing the structure of the downloaded webpage possibly containing the video; identifying the chained address of the effective video webpage; merging and storing the analysis result of the webpage structure; acquiring a video chained address hidden in the effective video webpage according to the chained address of the effective video webpage, analyzing the video chained address to acquire the actual video chained address; and downloading and storing the video corresponding to the actual video chained address.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

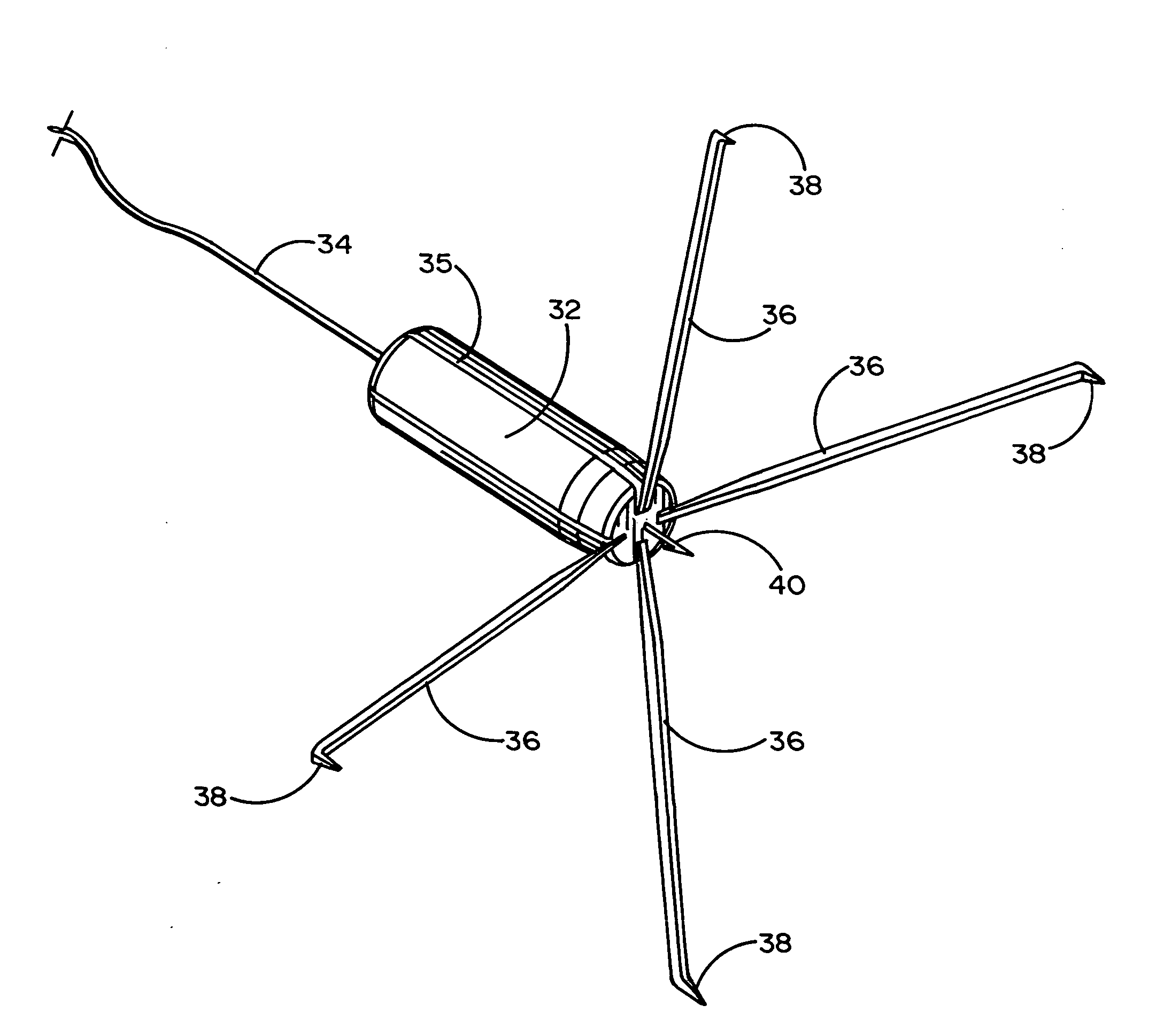

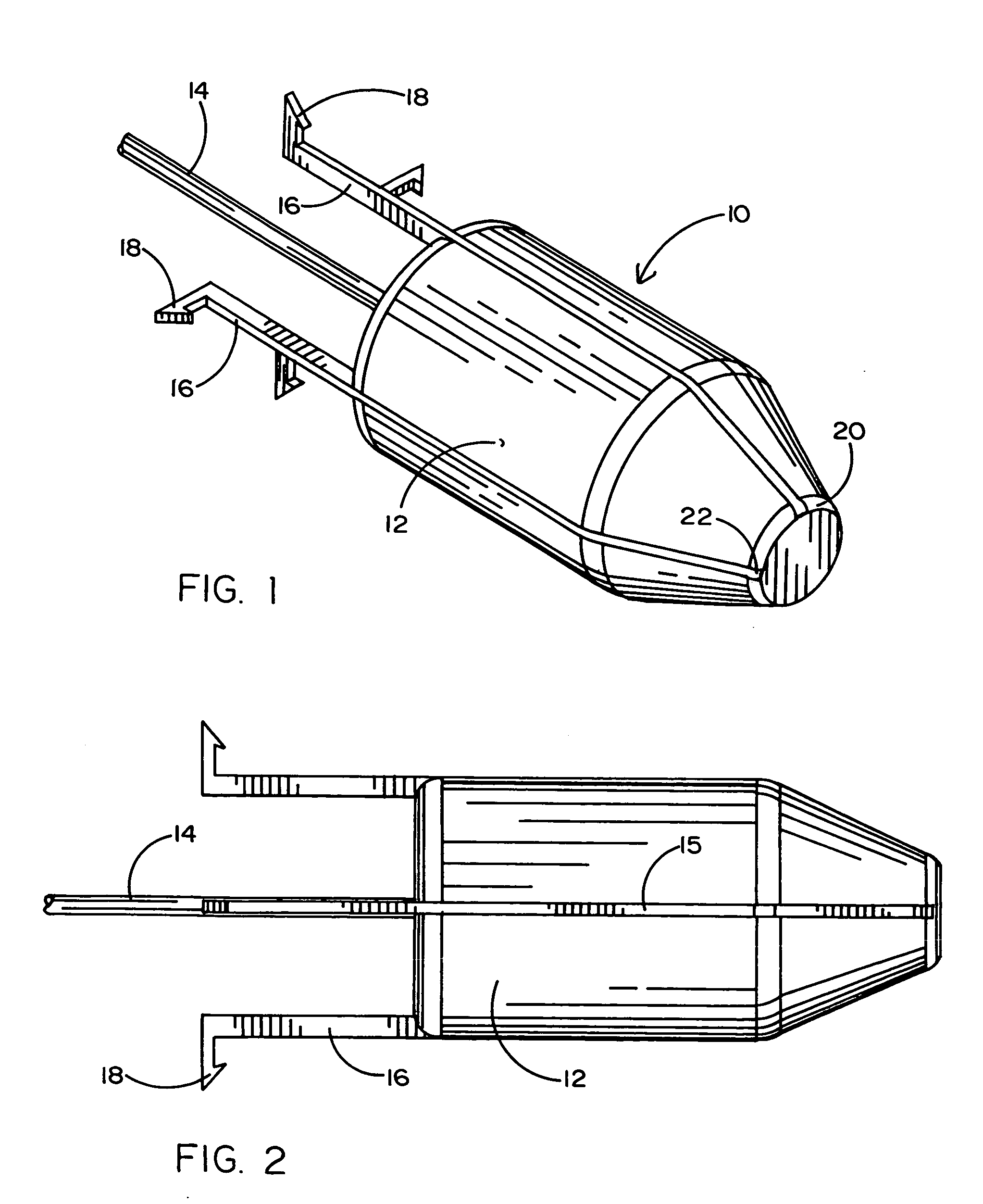

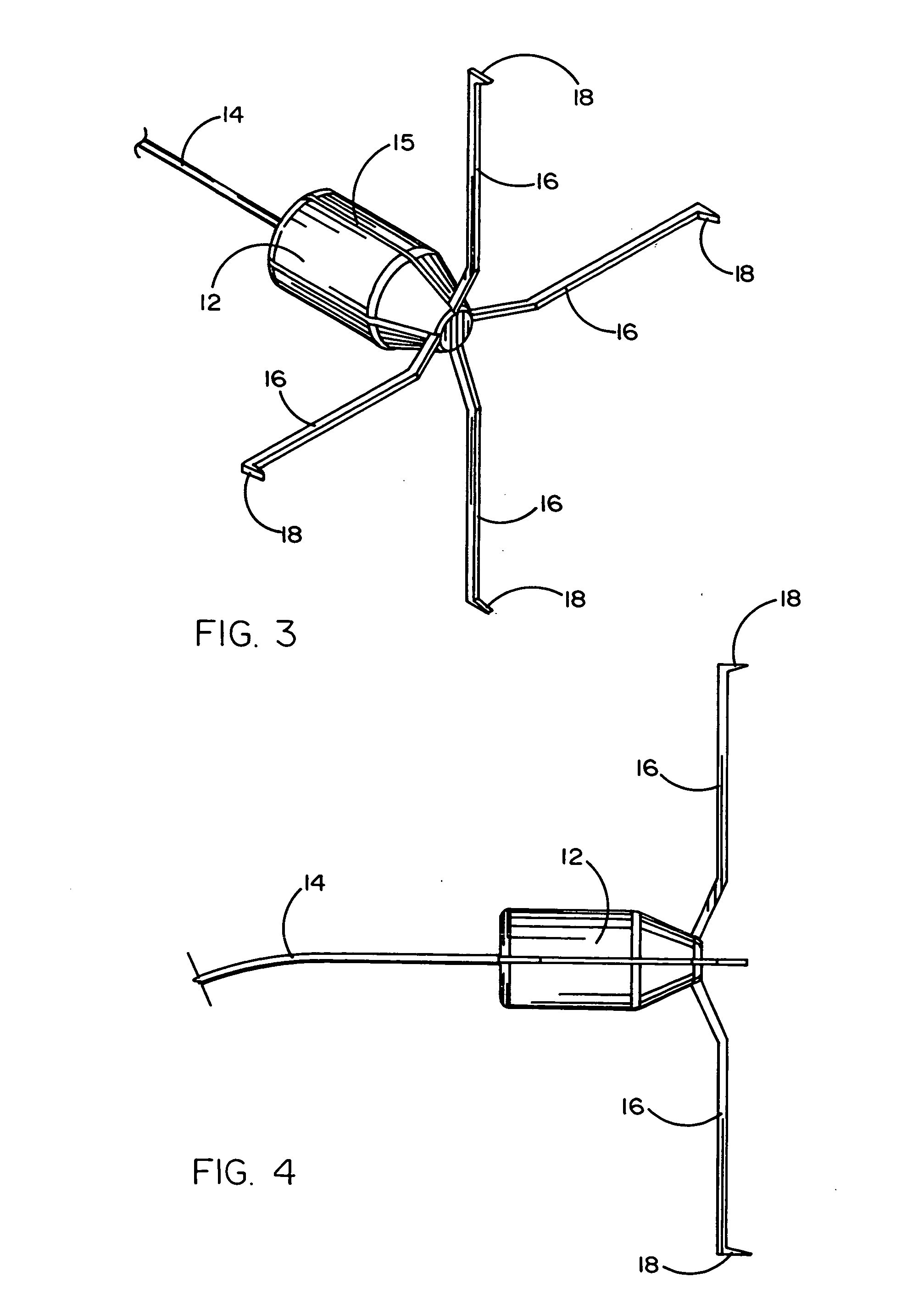

Electrical discharge immobilization weapon projectile having multiple deployed contacts

InactiveUS20060254108A1High effective immobilization currentEasy to deployAmmunition projectilesElectric shock equipmentsElectricityElectrical polarity

A unitary projectile for an immobilization weapon and tethered by two electrical wires, has a plurality of electrical contacts including several contacts dispersed in a spaced pattern around the projectile after target impact. The pattern of several contacts substantially increases the probability that if the projectile hits the target, an immobilization circuit through the target will be completed. The deployment of the second contacts occurs as a result of the sudden deceleration of the projectile when it impacts the target or by the use of an additional spring-biased device. This simplifies the deployment as well as the projectile configuration and likely reduces the risk of misactivation or an ill-timed activation of the second contacts. In a preferred version of the disclosed embodiments, each projectile has its own electrical contact which forms one of the two polarities of the electrical discharge. In addition, there are preferably four second polarity contacts dispersed in a symmetrical arrangement around the projectile.

Owner:PARK YONG S

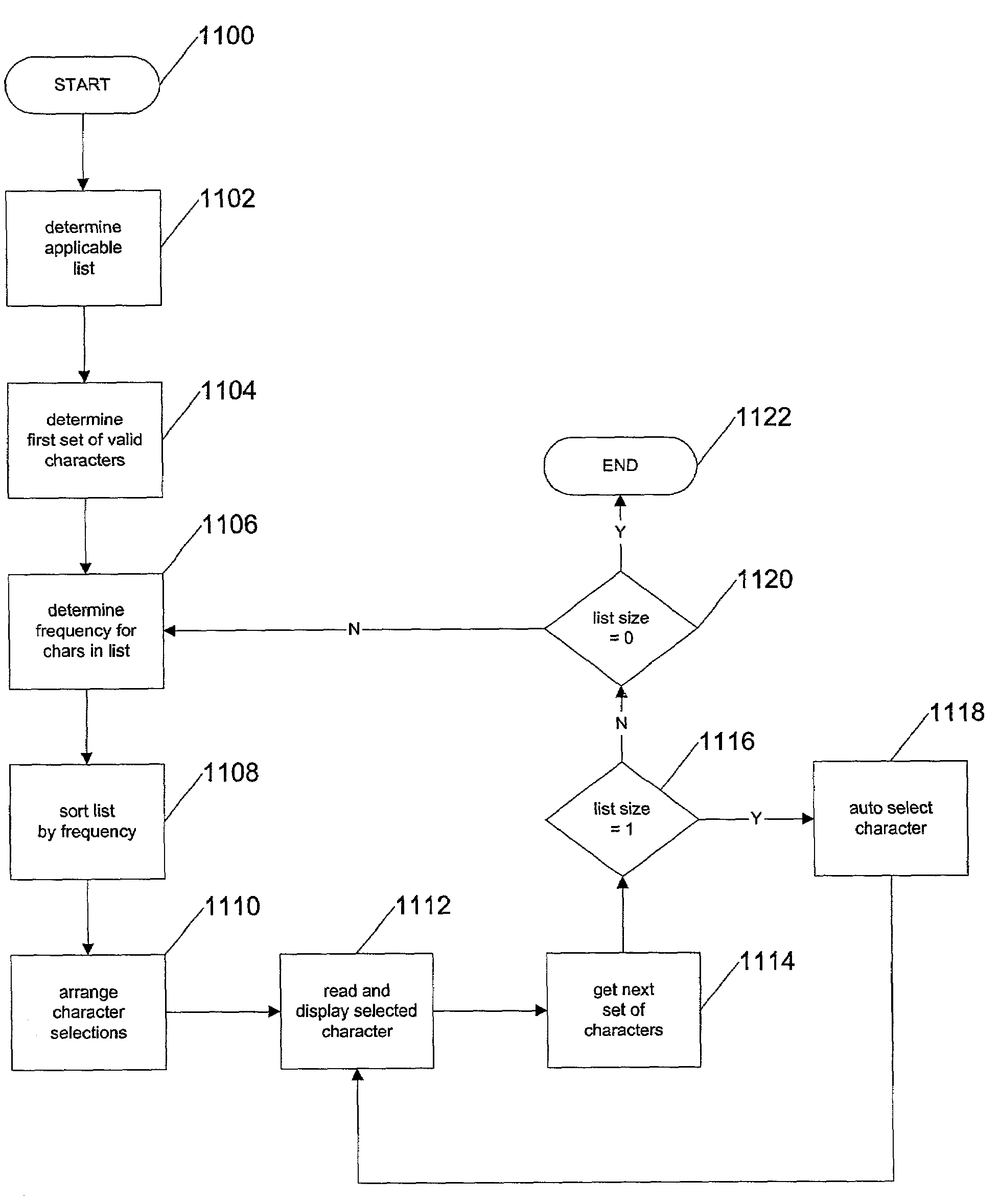

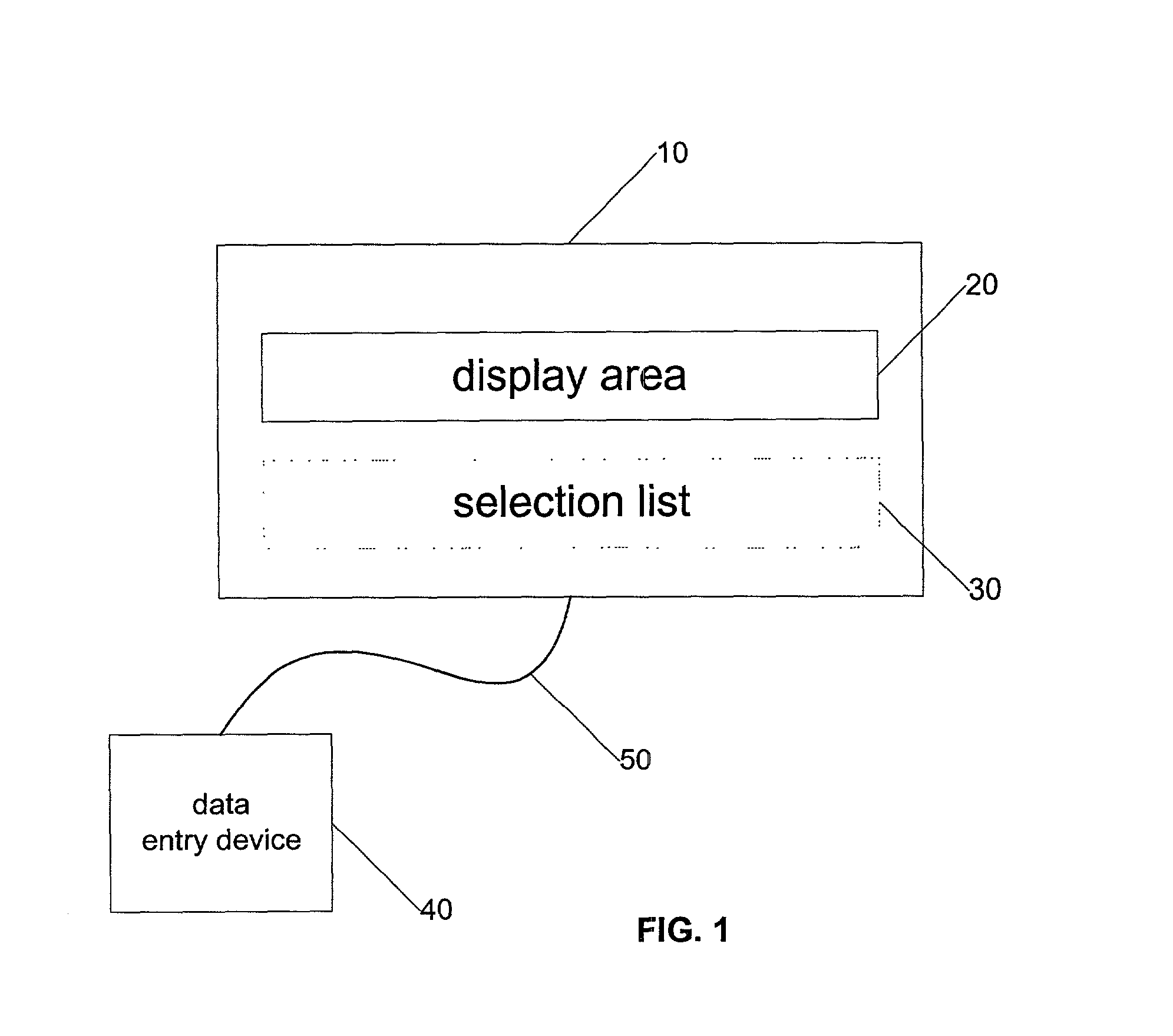

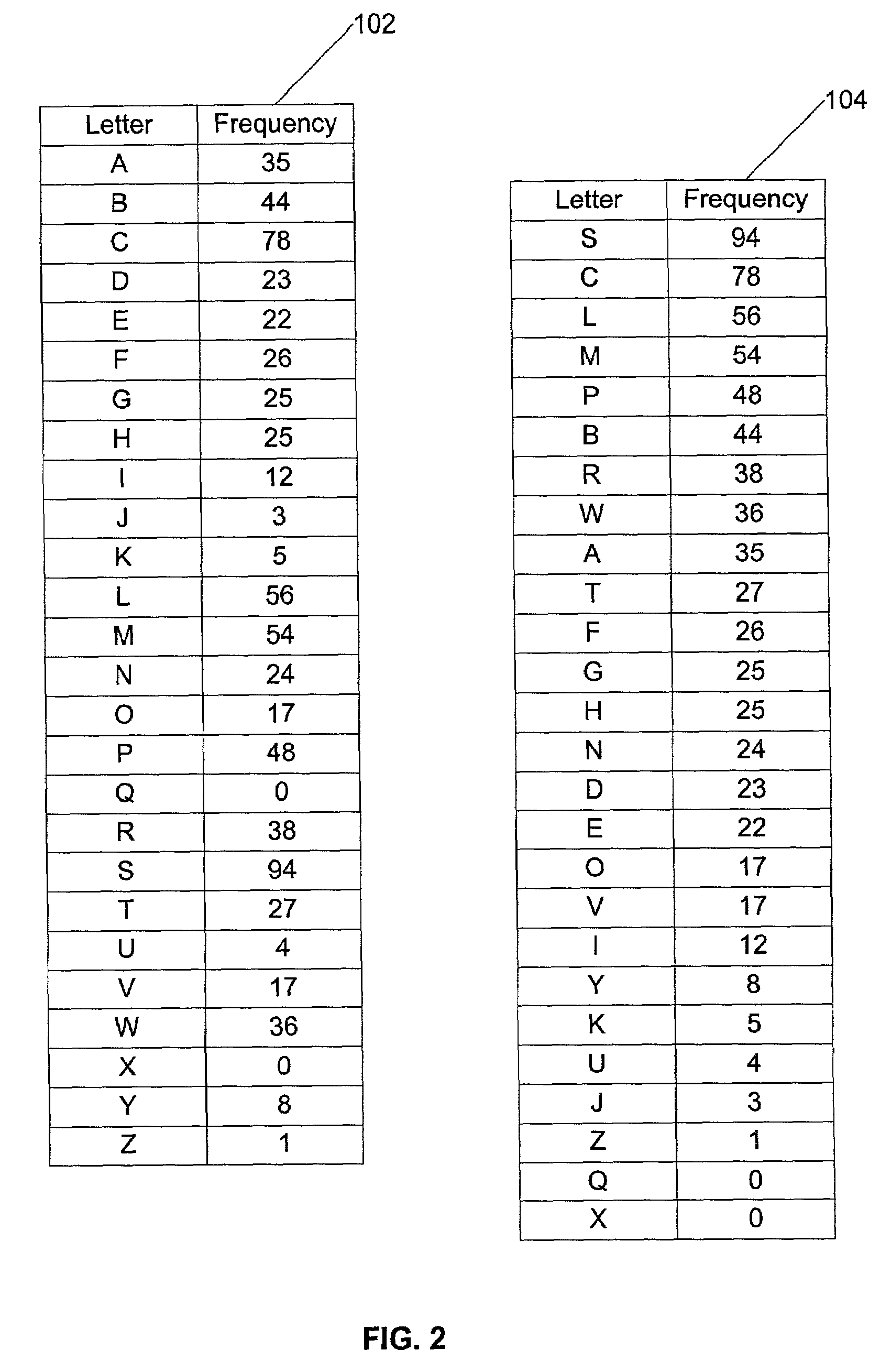

System and method for dynamic key assignment in enhanced user interface

InactiveUS7152213B2Reduce numberMinimize numberInput/output for user-computer interactionVisual data miningData inputHigh frequency

An improved user interface for data input without the use of a standard keyboard is provided. Input is accepted through a data entry means such as a shuttle control system, a standard telephone keypad, or a speech recognition system. The data that is entered is selected from a predefined list that is presented to a user in an arrangement that statistically reduces the number of keystrokes required for data entry. This presentation is the result of determining the relative frequency of each valid selection in the predefined list and presenting those valid selections with the highest frequency items in a position that minimizes the number keystrokes required for data entry. In a speech recognition embodiment, the data entered is selected from an active list containing unique sounding entries. Alternatively, the data entered may be selected by speaking the numbers associated with the keys corresponding to the keystrokes required for data entry.

Owner:INFOGATION CORP

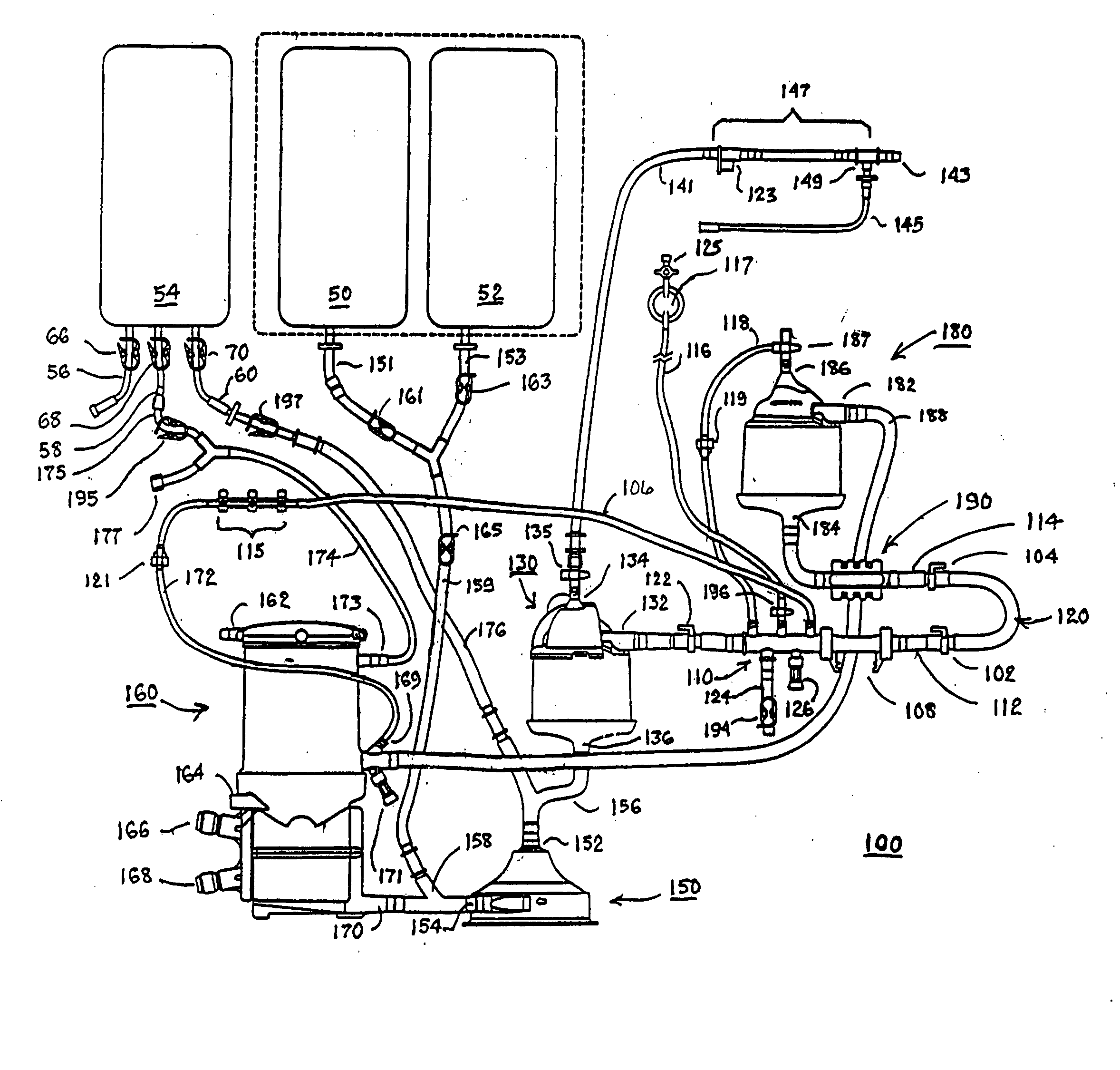

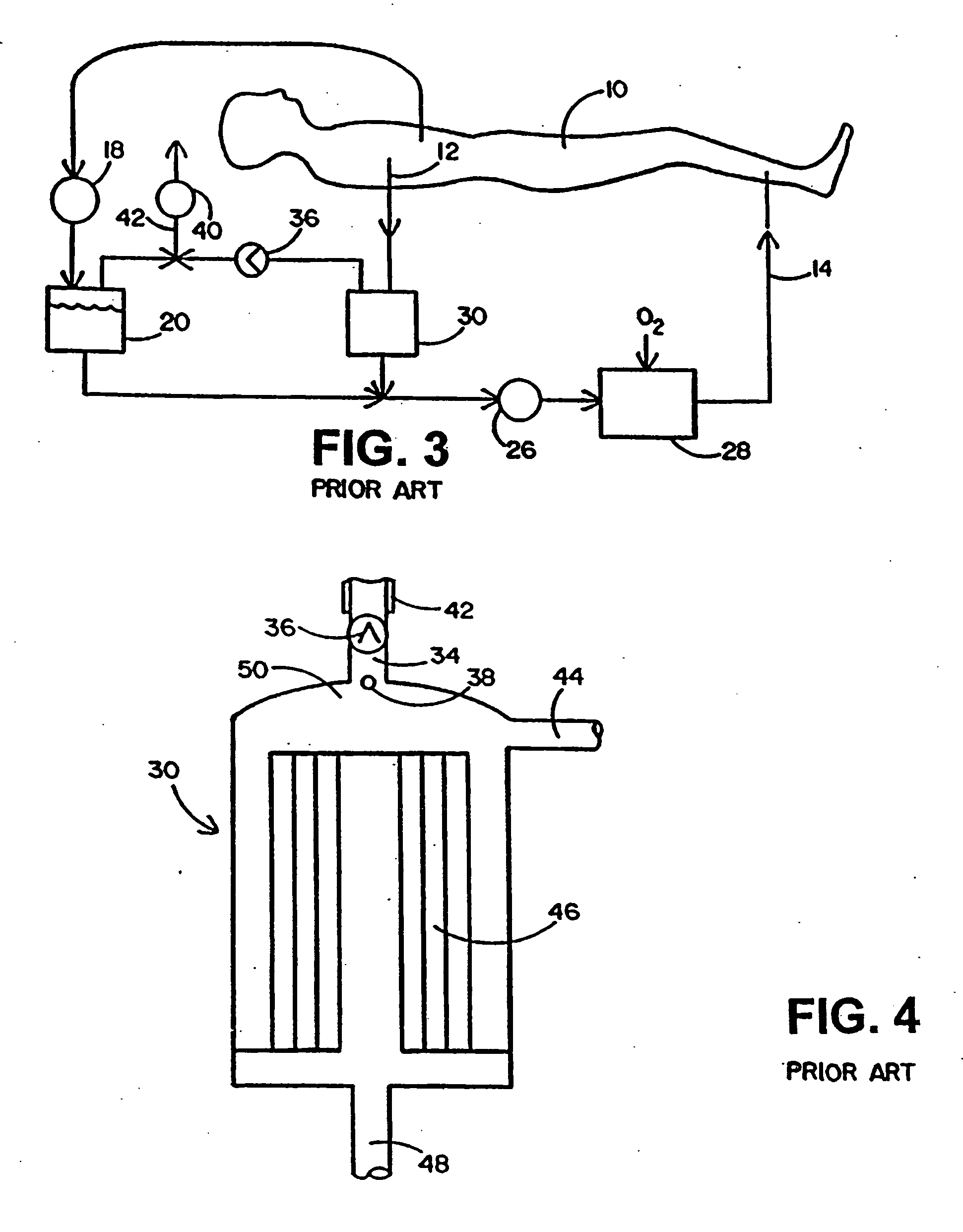

Cardiopulmonary bypass extracorporeal blood circuit apparatus and method

InactiveUS20050118059A1Implement extensionsSignificant improvementOther blood circulation devicesHaemofiltrationBlood levelVein

An extracorporeal blood circuit for use with a venous return line and an arterial line coupled to a patient. The extracorporeal blood circuit can include a venous air removal device coupled to the venous return line. The venous air removal device can perform an active air removal function. The extracorporeal blood circuit can include a sensor that determines a blood level in the venous air removal device, a purge line coupled to the venous air removal device, and a controller connected to the sensor. The controller can cause the venous air removal device to perform the active air removal function through the purge line when the blood level is less than a threshold. The extracorporeal blood circuit can further include a pump coupled to the venous air removal device, an oxygenator coupled to the pump, and a blood filter coupled to the oxygenator and the arterial line.

Owner:MEDTRONIC INC

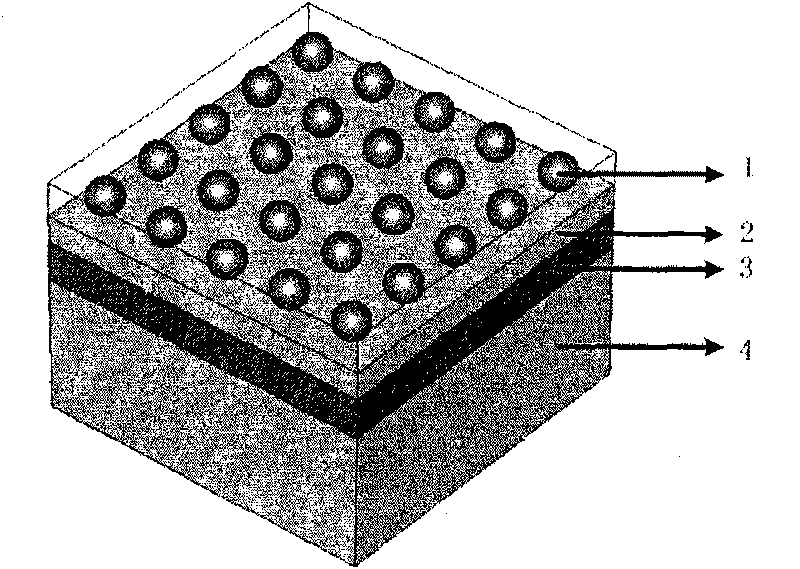

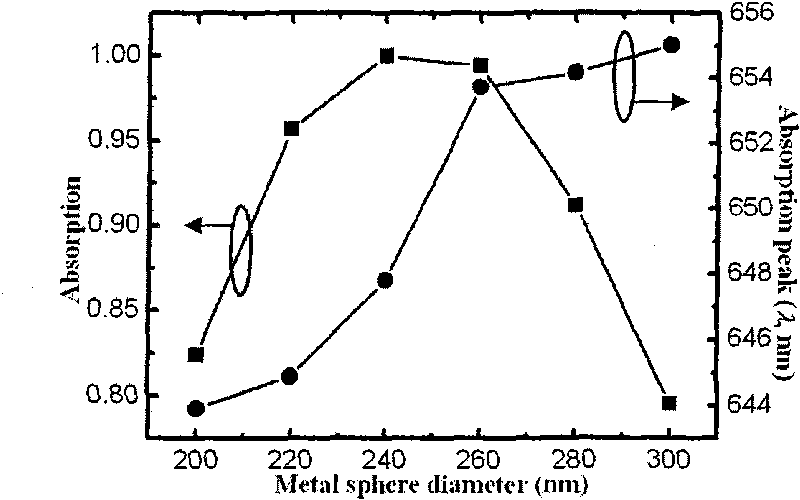

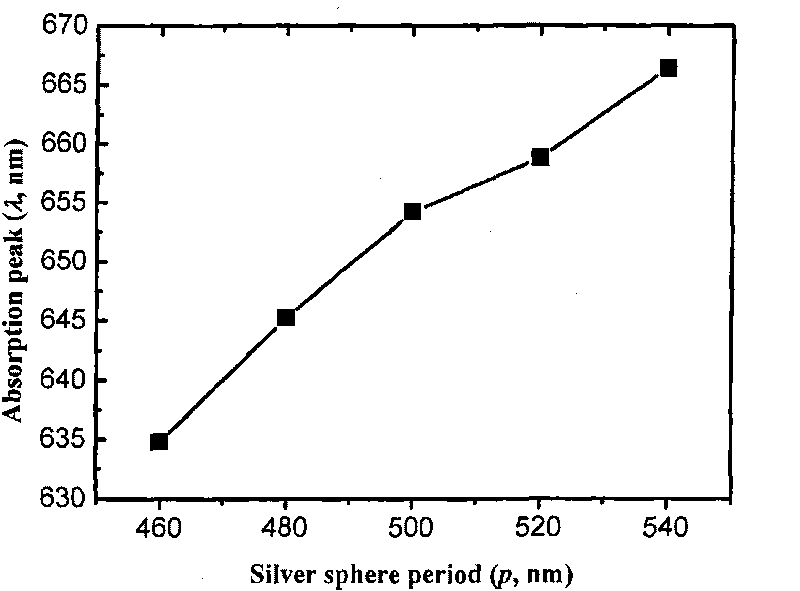

Almost perfect absorbing structure for wide wave band

InactiveCN101740722AEnhance electromagnetic wave absorption efficiencyImplement extensionsFinal product manufactureSolid-state devicesSurface plasmonMetallic materials

The invention relates to an almost perfect absorbing structure for wide wave band, which comprises the following steps: (1) determining absorbing material and metal material according to the incoming wave frequency band; (2) manufacturing structure of apparatus; (3) determining the range of diameter d of metal spherical particles according to the local effect of plasma on the surface of the metalspherical particles; (4) determining the distribution and range of period p according to the electromagnetic resonation effect among metal spherical particles-medium-metal film; and (5) optimizing particle diameter d and distribution period p to realize expansion of the bandwidth of the entire apparatus. The invention realizes almost perfect absorbing function on wide wave band within visible light range.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

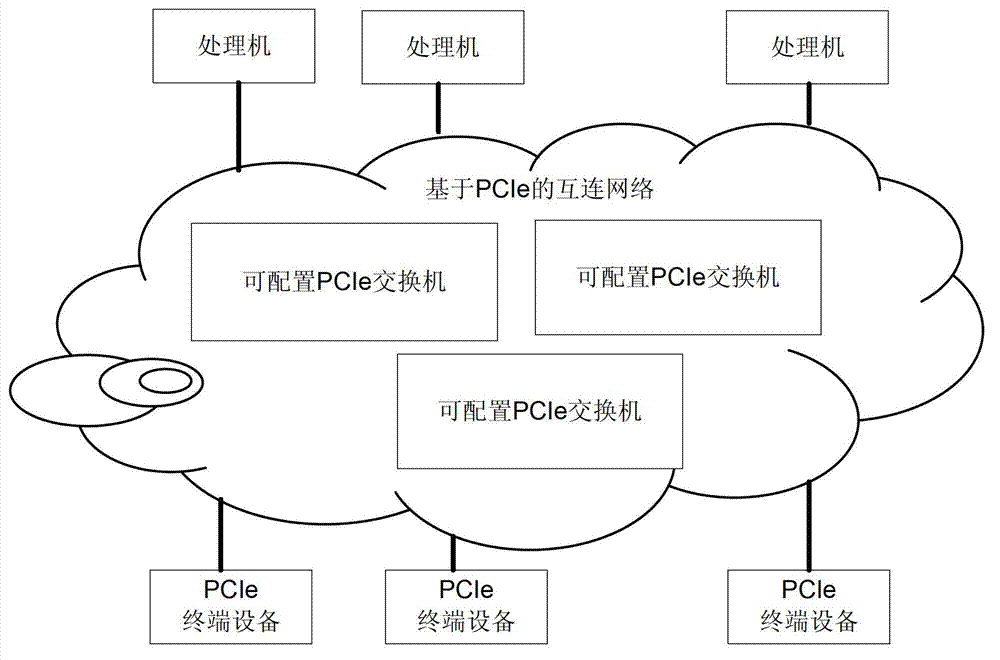

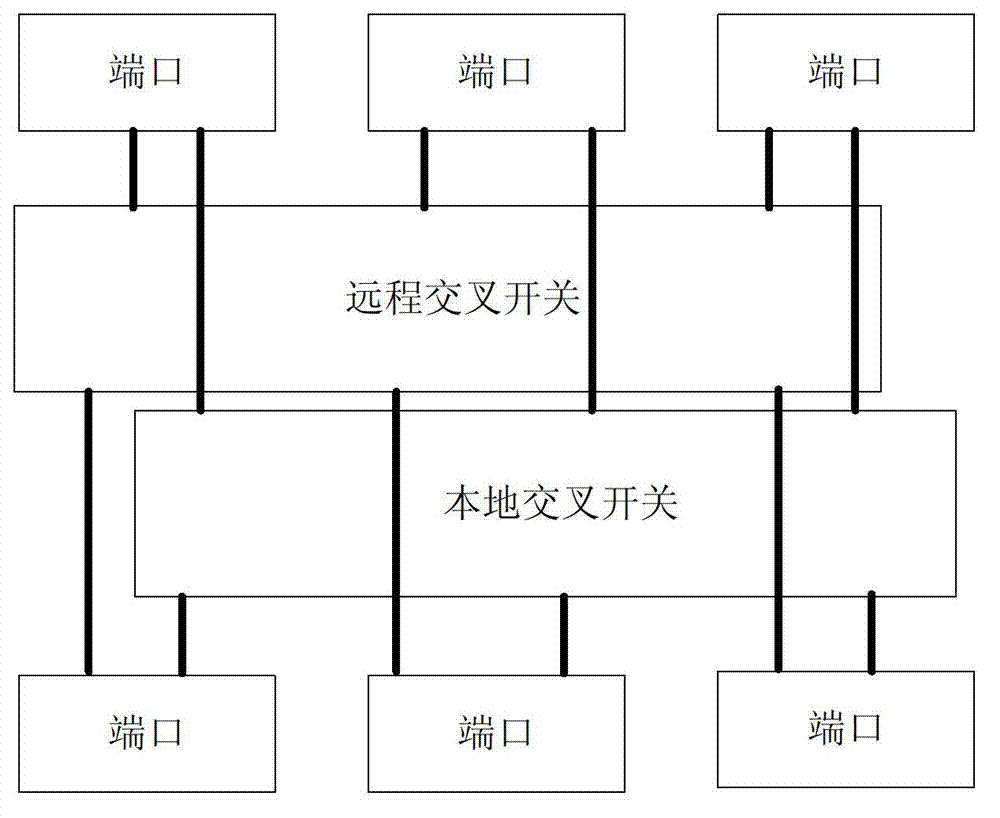

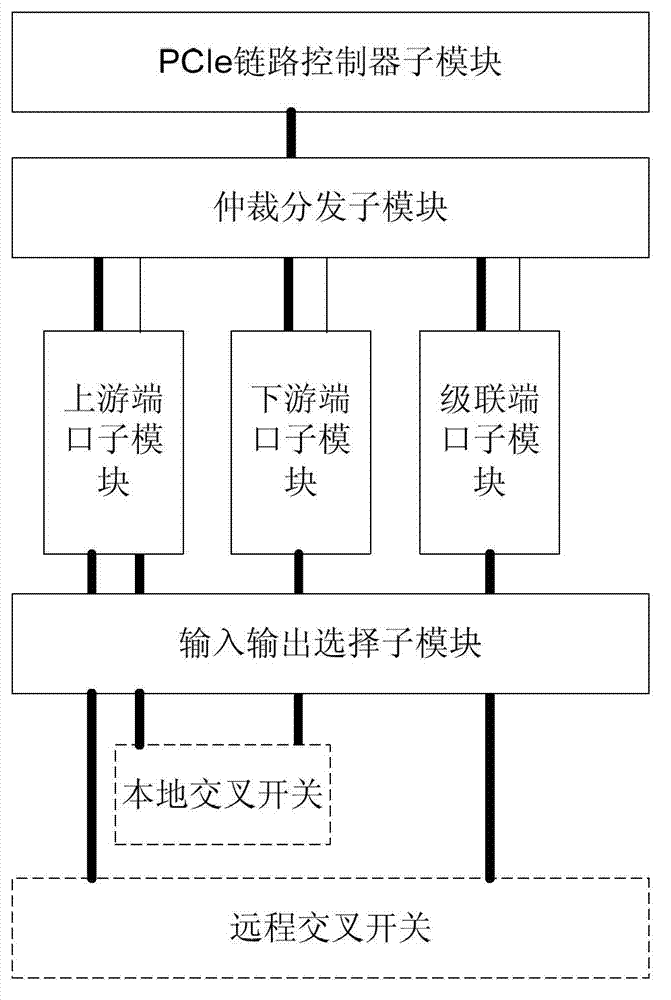

Communication method and system based on PCIe (peripheral component interconnect express) data exchange

ActiveCN103117929AImplement extensionsRealize data communicationData switching networksMulti processorInterconnection

The invention discloses communication method and system based on PCIe (peripheral component interconnect express) data exchange. The method includes the steps of firstly, starting a PCIe switch and subjecting a processor and a PCIe terminal communicated with the PCI3 switch to PCIe equipment search and configuration; secondly, allowing the processor or PCIe terminal to transmit a PCIe read-write request to a port of the PCIe switch according to routing information, allowing the port to structure the PCIe read-write request into a data packet by means of packet format compatible with standard PCIe link layer protocol and extensible routing compatible with standard PCIe routing, and transmitting the data packet to a corresponding port; and thirdly, allowing the corresponding port to restore the data packet into the PCIe read-write request and transmit the request to the processor or PCIe terminal. Multi-processor communication based on PCIe link is achieved by the extended PCIe protocol, and any topological extensible interconnection networks are established.

Owner:SHANGHAI YINGLIAN SOMATOSENSORY INTELLIGENT TECH CO LTD

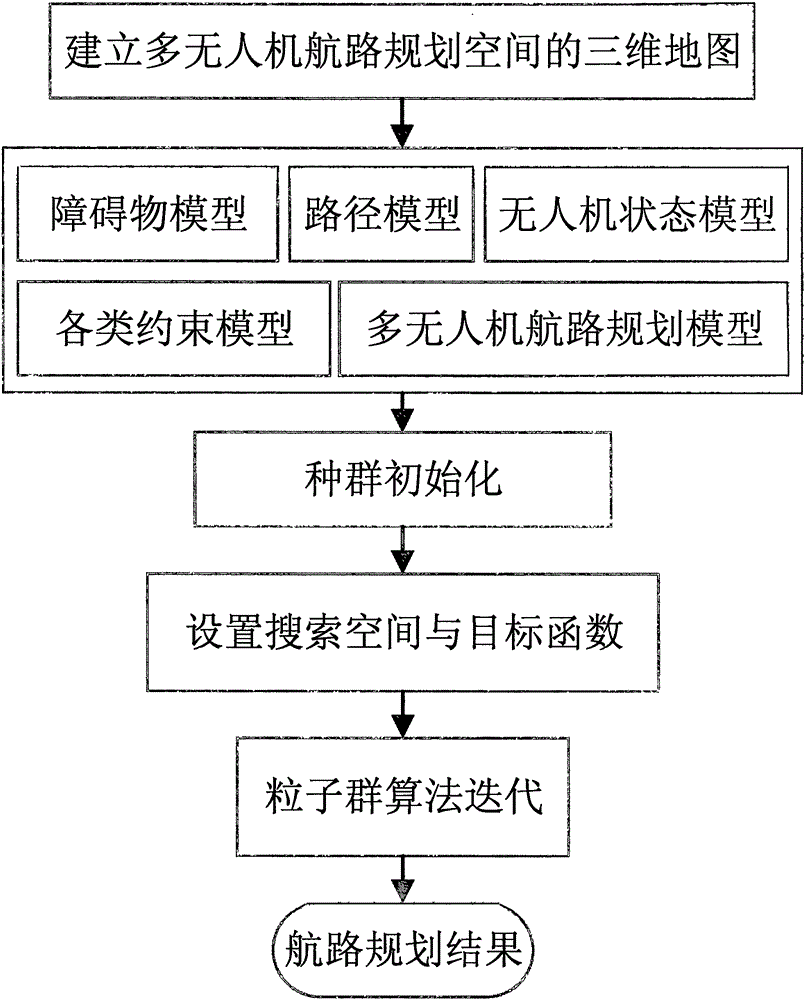

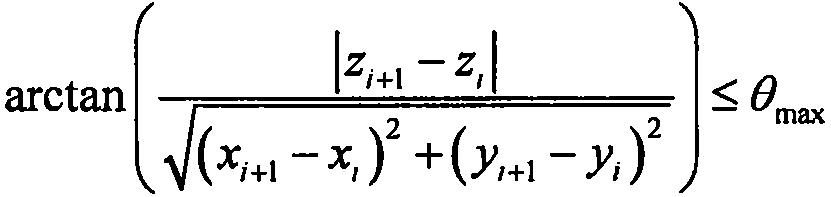

Method for planning routes of multi-unmanned aerial vehicles based on particle swarm optimization algorithm

InactiveCN105841702AImplement extensionsImprove convergence accuracyNavigational calculation instrumentsRouting modelMathematical model

The invention provides a method for planning the routes of multi-unmanned aerial vehicles based on a particle swarm optimization algorithm. The method comprises the following steps: establishing a three-dimensional map for planning space of the routes of the multi-unmanned aerial vehicles at first; then constructing multi-unmanned aerial vehicle route planning models under the three-dimensional map, wherein the models mainly comprise a barrier model, a route model, an unmanned aerial vehicle state model, a constraint model and a multi-unmanned aerial vehicle route planning mathematic model; and solving the problem of multi-unmanned aerial vehicle route planning under the three-dimensional map by using the particle swarm optimization algorithm. The method provided by the invention improves multi-unmanned aerial vehicle route planning capacity in a complex environment and provides technical support for air traffic management platforms for unmanned aerial vehicles, autonomous flight systems for multi-unmanned aerial vehicles, etc.

Owner:SAIDU TECH BEIJING CO LTD

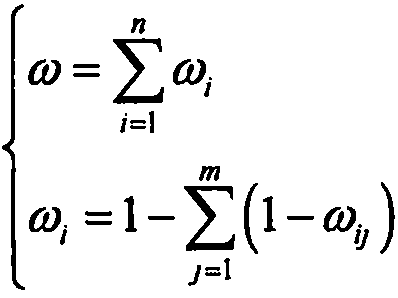

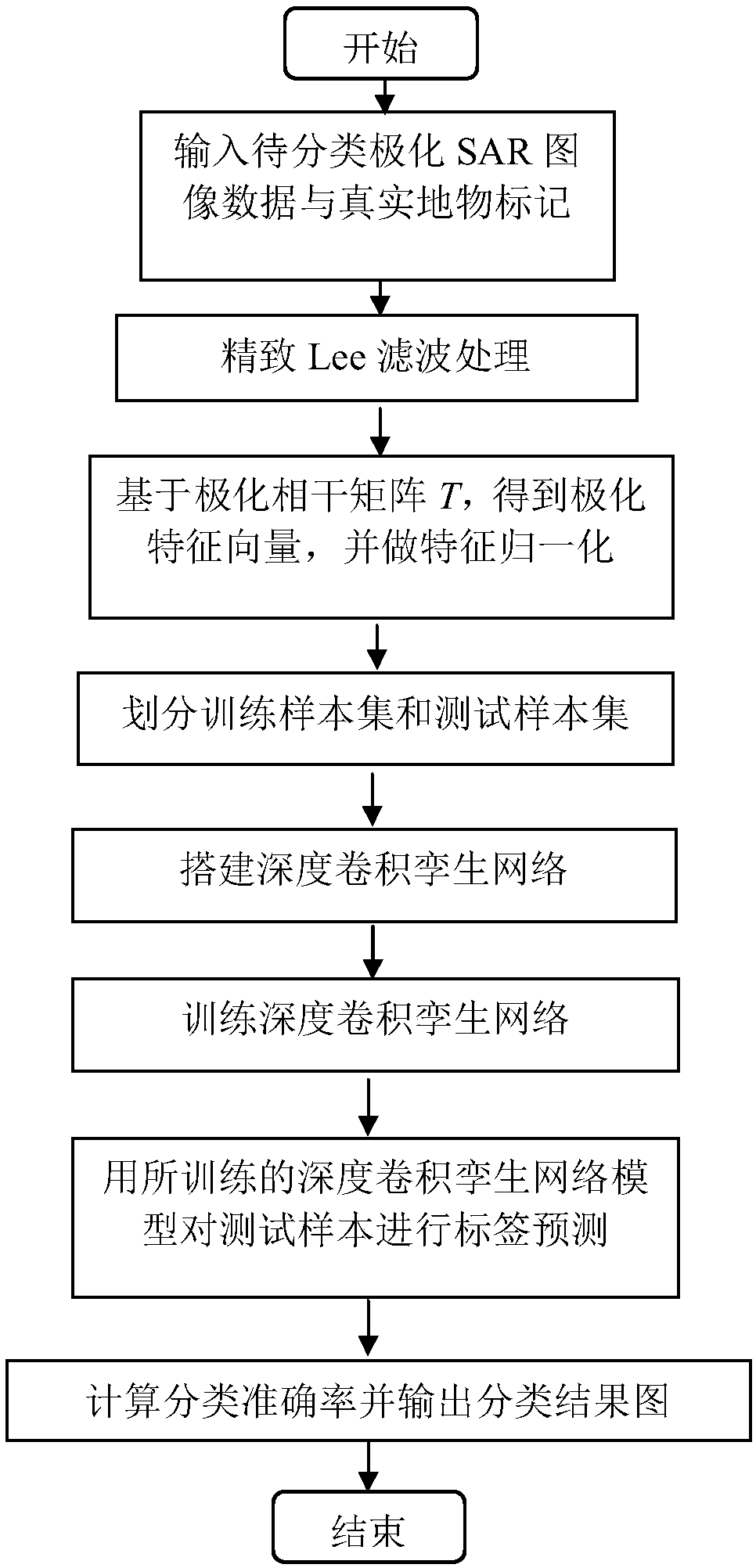

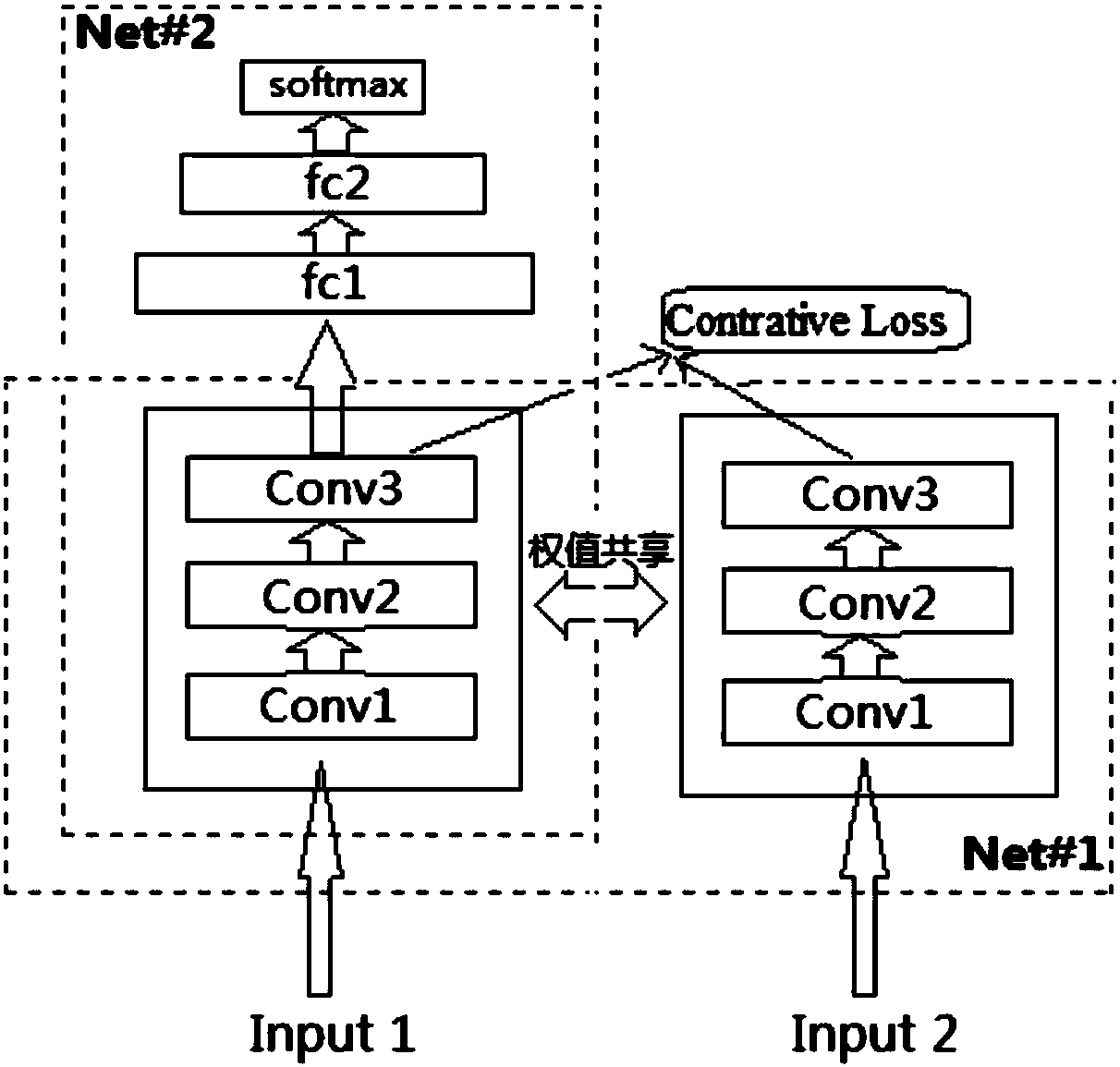

Small-sample polarized SAR ground feature classification method based on deep convolutional twin network

ActiveCN108388927AAchieve trainingImplement classificationImage enhancementImage analysisFeature vectorSmall sample

The invention discloses a small-sample polarized SAR ground feature classification method based on a deep convolutional twin network, and mainly solves a problem that a conventional method is low in classification precision because the number of polarized SAR data mark samples is smaller. The method of the invention comprises the steps: 1), inputting a to-be-classified polarized SAR image and a real ground object mark of the to-be-classified polarized SAR image, and carrying out the Lee filtering; 2), extracting an input feature vector from the filtered to-be-classified polarized SAR data, andcarrying out the dividing of a training sample set and a test sample set; 3), carrying out the combination of each two samples in the training sample set, and obtaining a sample pair training set; 4), building the deep convolutional twin network, and carrying out the training of the deep convolutional twin network through the training sample set and the sample pair training set; 5), carrying outthe classification of the samples in the test set through the trained deep convolutional twin network, and obtaining the classes of ground features. According to the invention, the method expands thetraining set under the twin configuration, achieves the extraction of the difference features, enables the classification precision of a model to be higher, and can be used for the target classification, detection and recognition of a polarized SAR image.

Owner:XIDIAN UNIV

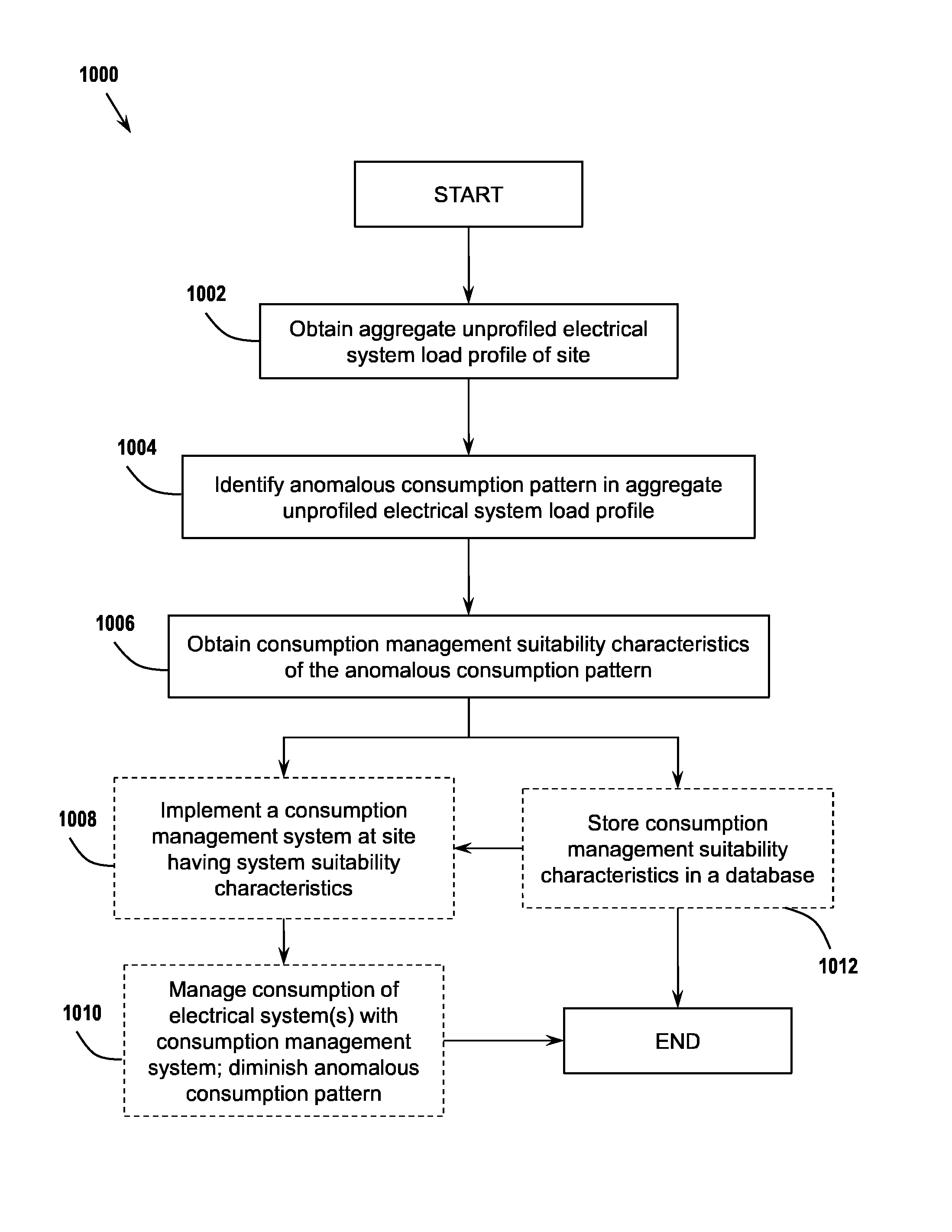

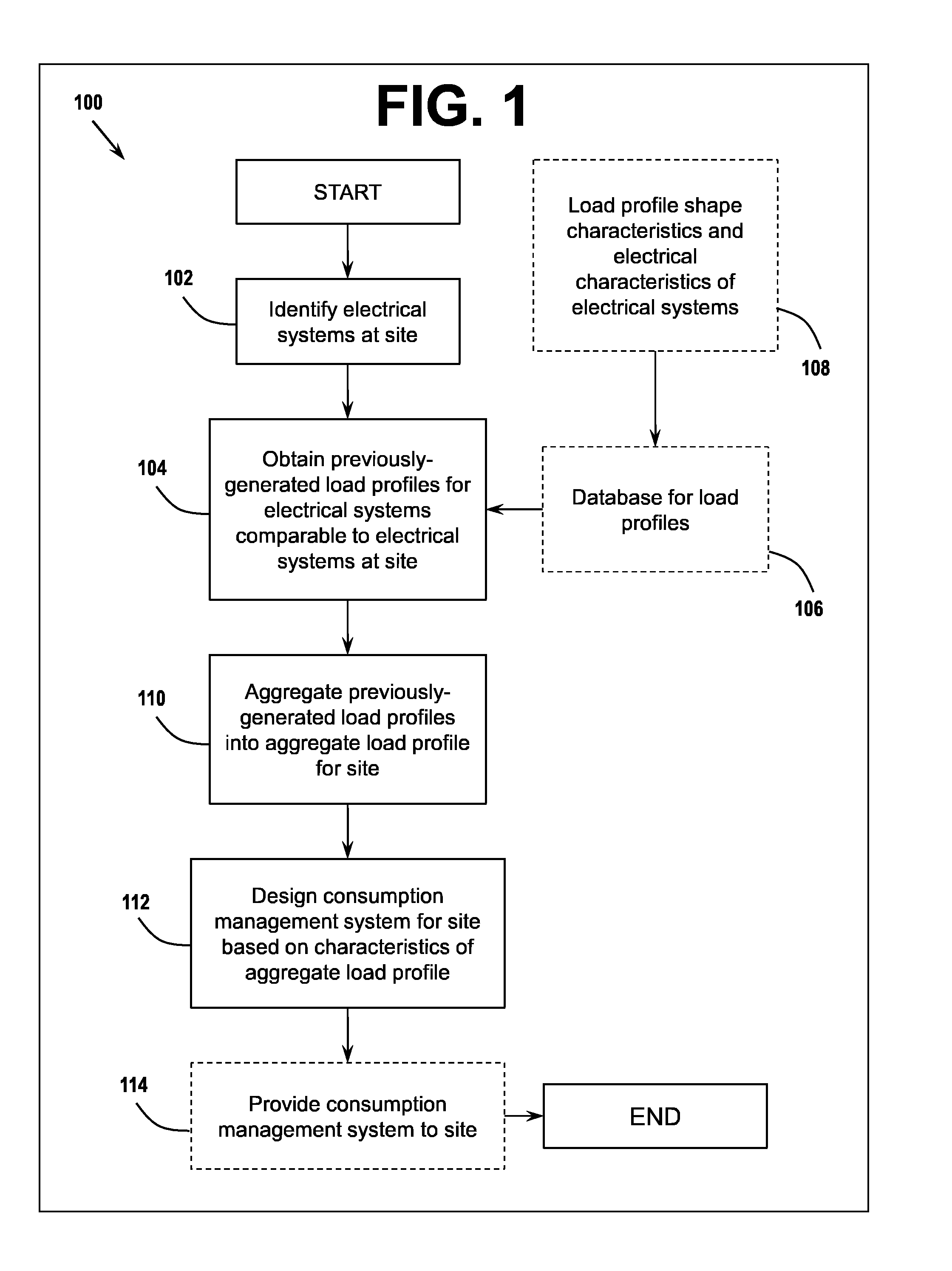

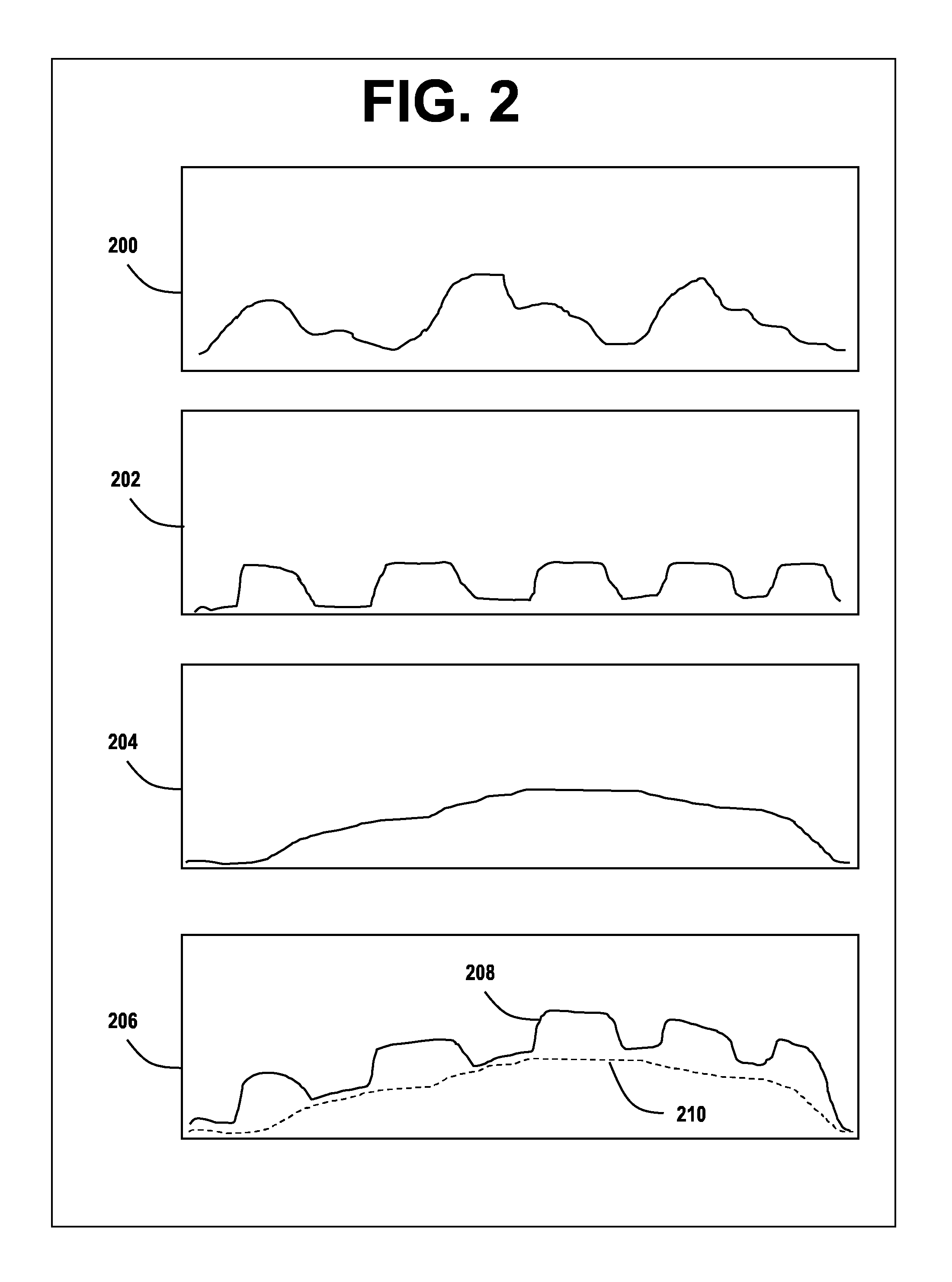

Processing Load Profiles for Consumption Management Systems

ActiveUS20130231790A1Faster and easy energy consumption auditingEffectively manage loadLevel controlVolume/mass flow measurementEngineeringLoad profile

Methods and systems using aggregated electrical system load profiles in determining additional load profiles, and determining consumption management system characteristics, features, and operating requirements at a site are disclosed, along with methods of generating and maintaining databases of load profile information and consumption management system requirements. By using some embodiments of the methods and systems described herein, it is faster and easier to design and implement effective consumption management systems, to determine problematic electrical systems at a site, and to diminish anomalous consumption patterns in an aggregate unprofiled electrical system load profile.

Owner:ENGIE STORAGE SERVICES NA LLC

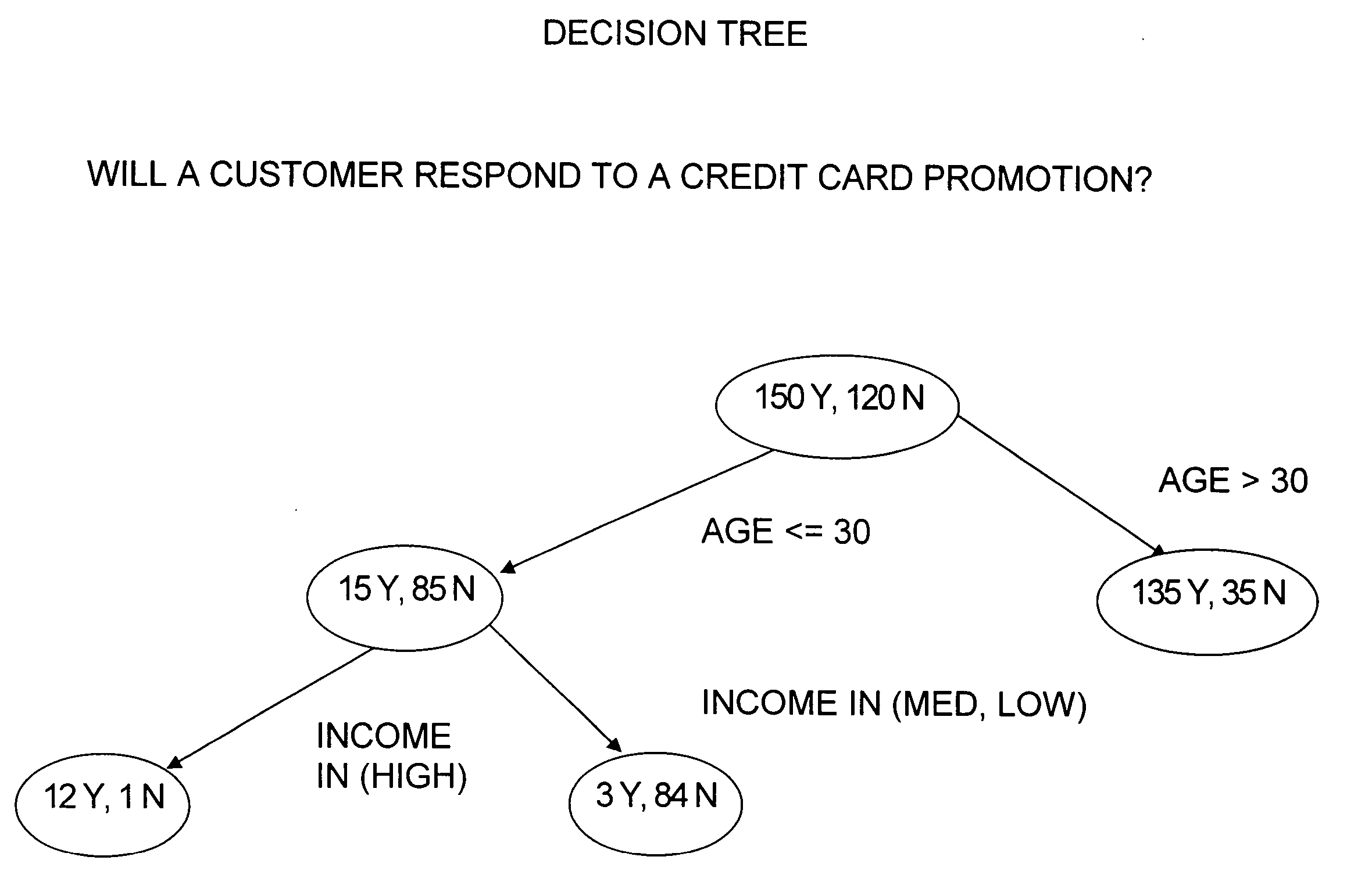

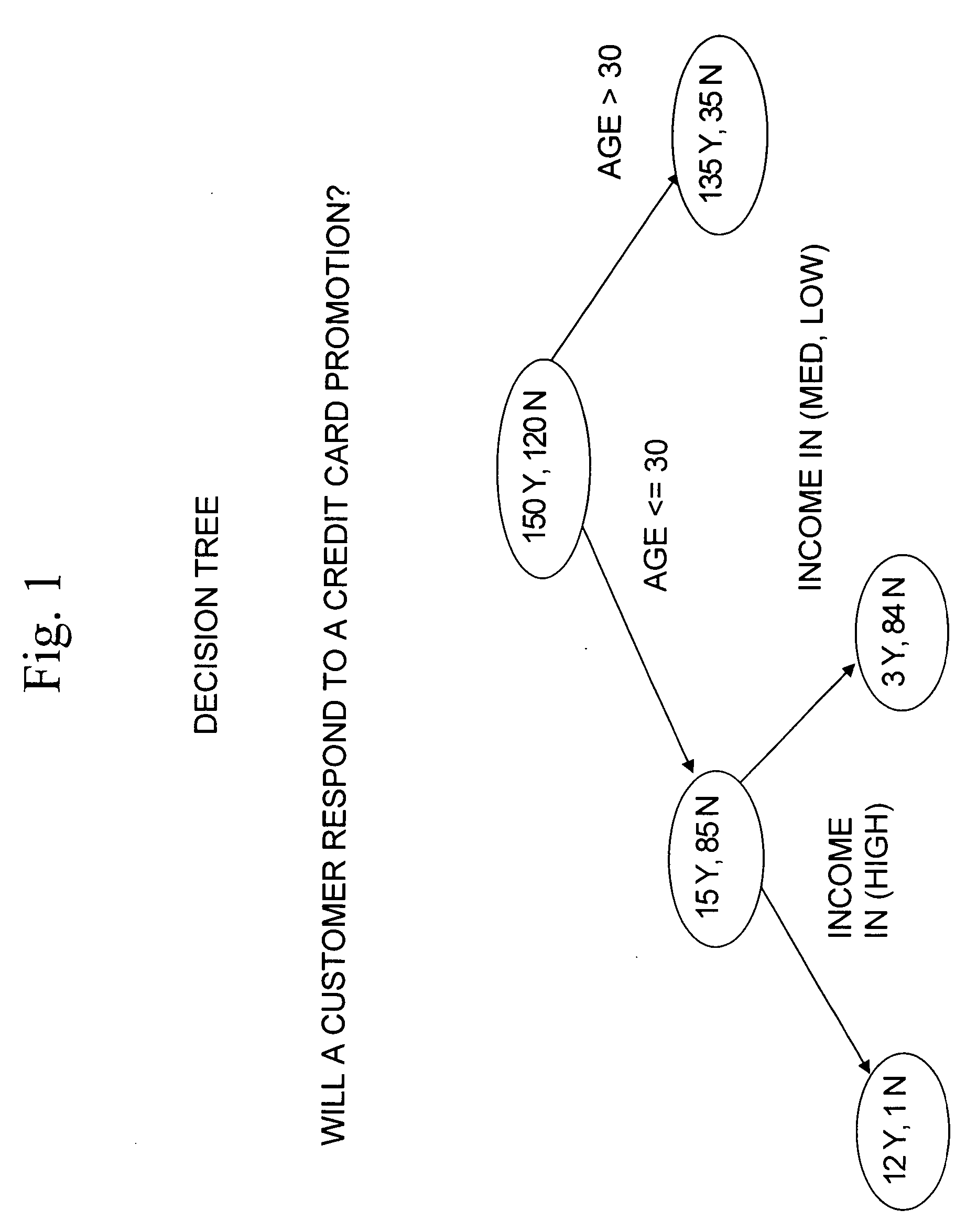

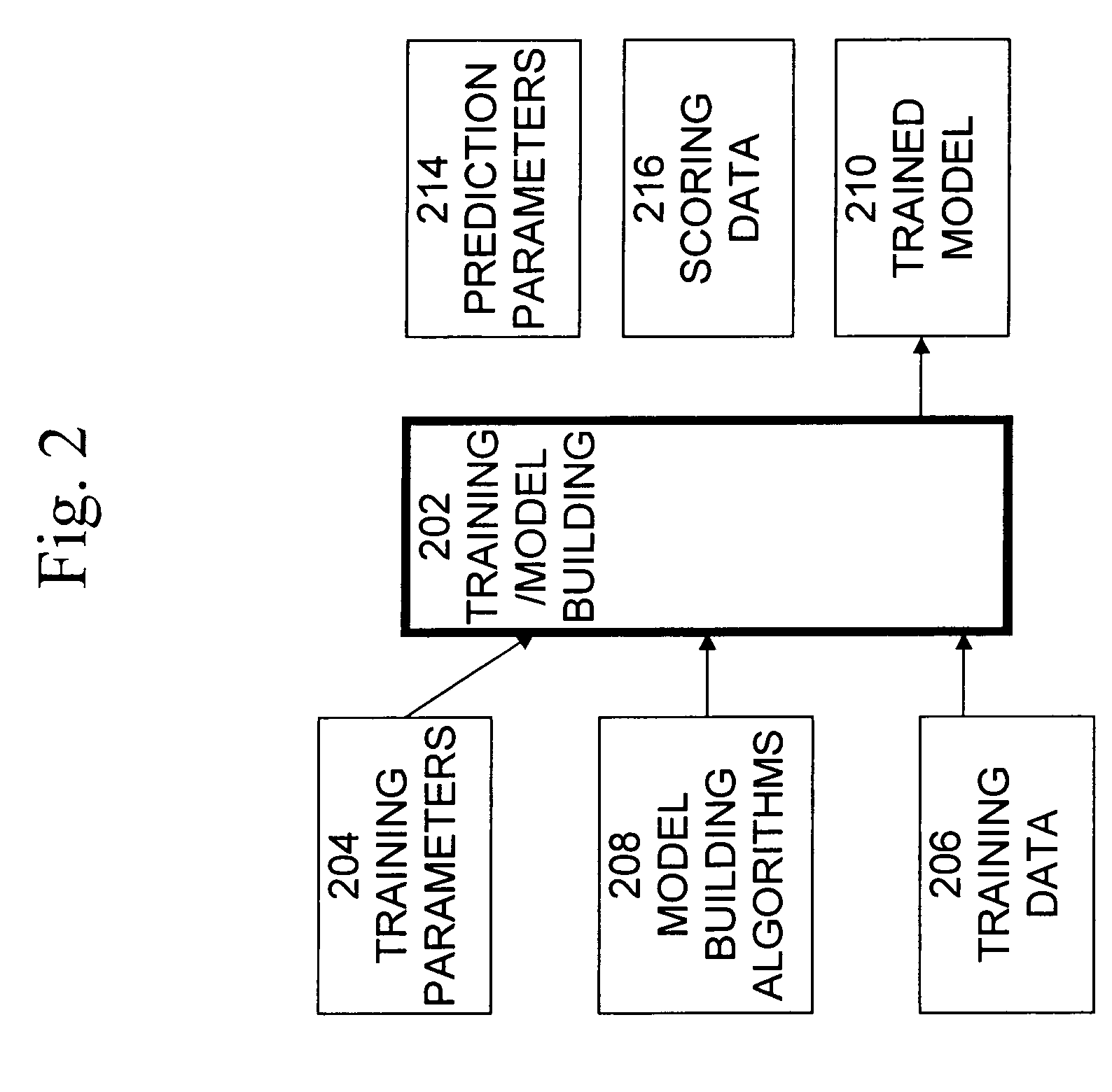

System and method for building decision trees in a database

ActiveUS20070179966A1Improve ease of useImplement extensionsDigital data information retrievalDigital data processing detailsRelational databaseHistogram

Decision trees are efficiently represented in a relational database. A computer-implemented method of representing a decision tree model in relational form comprises providing a directed acyclic graph comprising a plurality of nodes and a plurality of links, each link connecting a plurality of nodes, encoding a tree structure by including in each node a parent-child relationship of the node with other nodes, encoding in each node information relating to a split represented by the node, the split information including a splitting predictor and a split value, and encoding in each node a target histogram.

Owner:ORACLE INT CORP

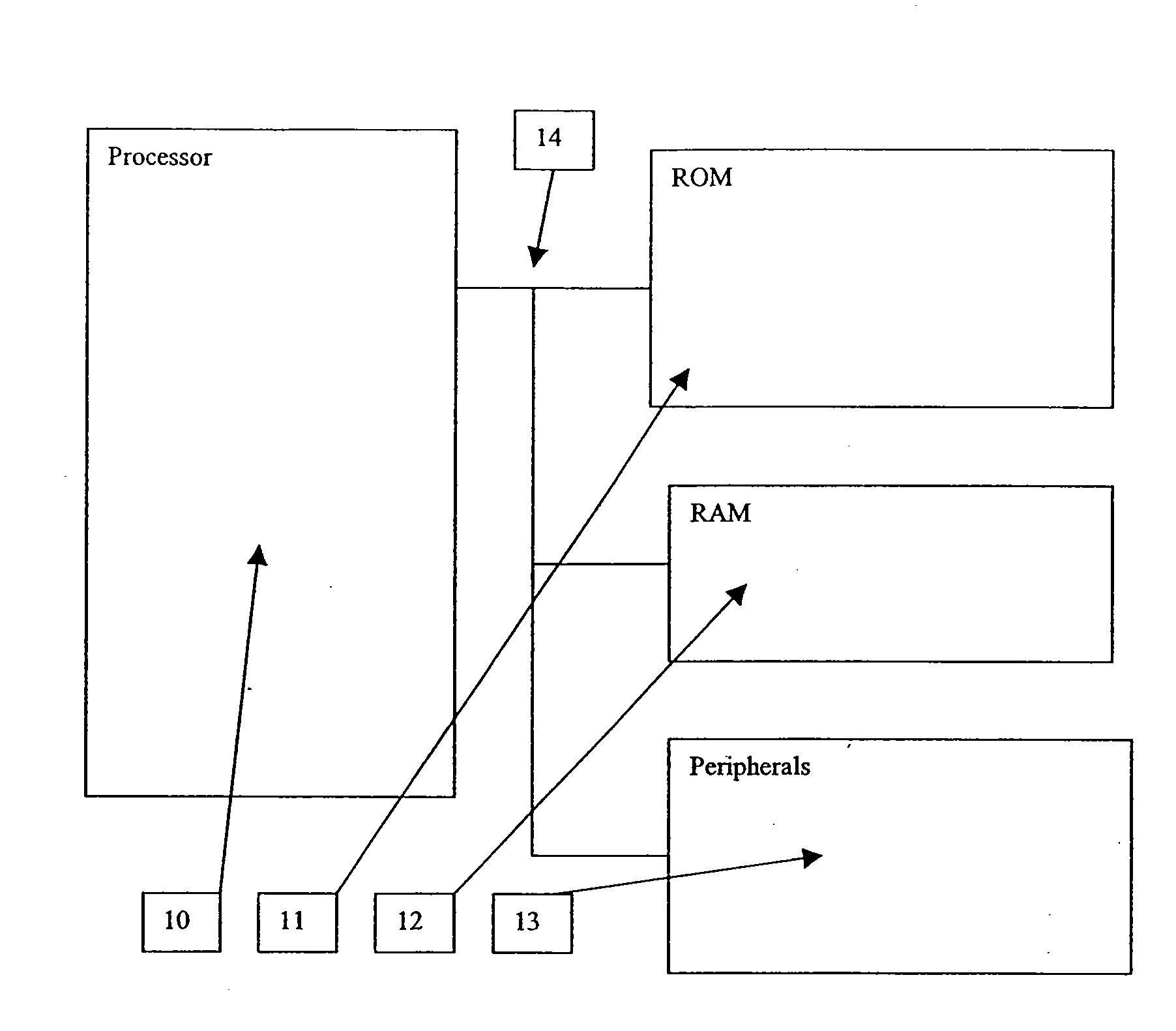

Processor for Virtual Machines and Method Therefor

InactiveUS20080313383A1Implement extensionsMemory architecture accessing/allocationMemory adressing/allocation/relocationRandom access memoryControl logic

Apparatus and method are described for a data processing device. The data processor includes features suitable for executing a software virtual machine. The data processor provides an instruction set that supports object-level memory protection suitable for high speed operation. Memory control logic is provided to accommodate a configuration having relatively less random access memory (RAM) as compared to re-programmable, nonvolatile memory, and to improve access to the re-programmable, nonvolatile memory.

Owner:RENESAS ELECTRONICS AMERICA

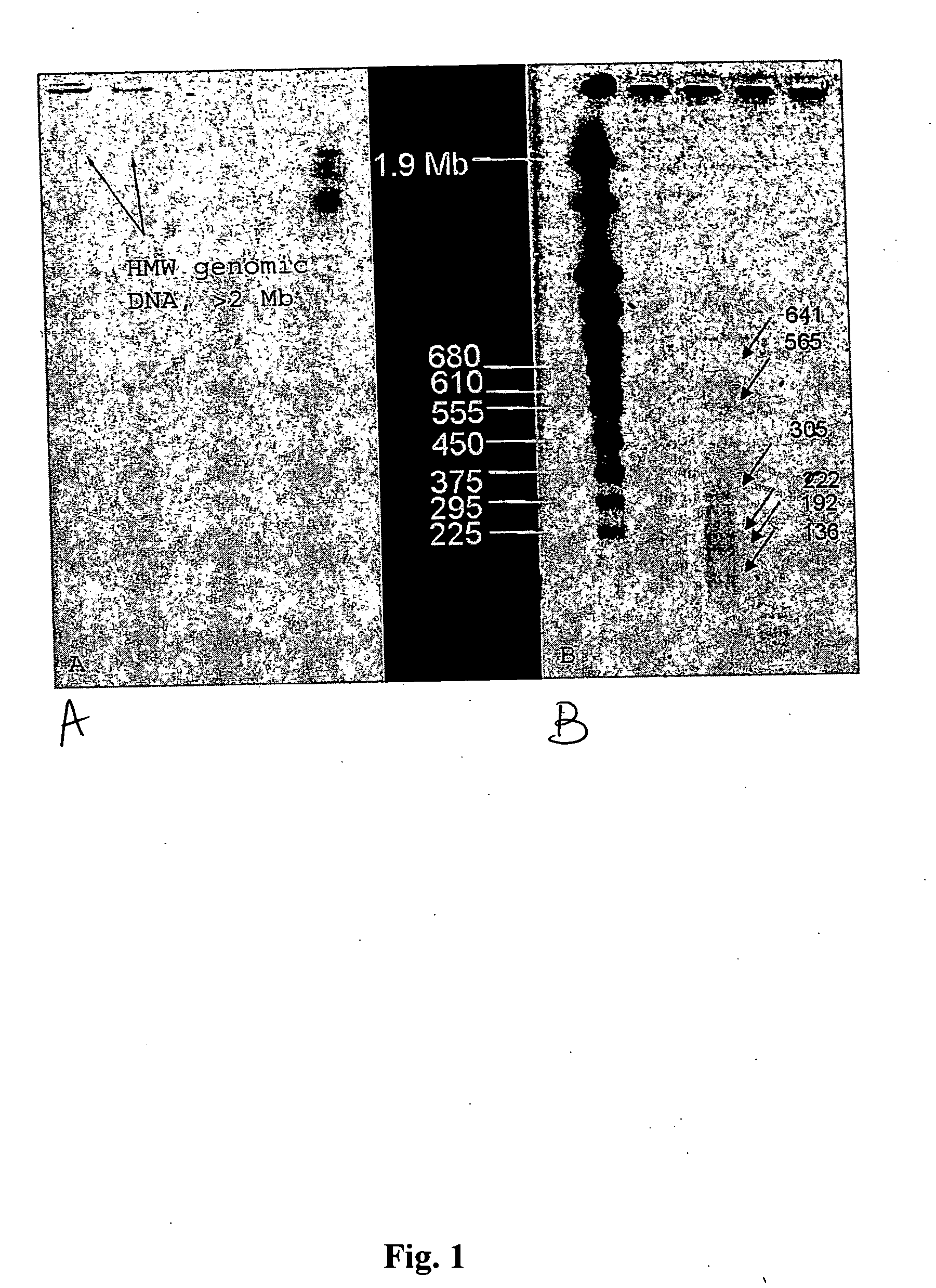

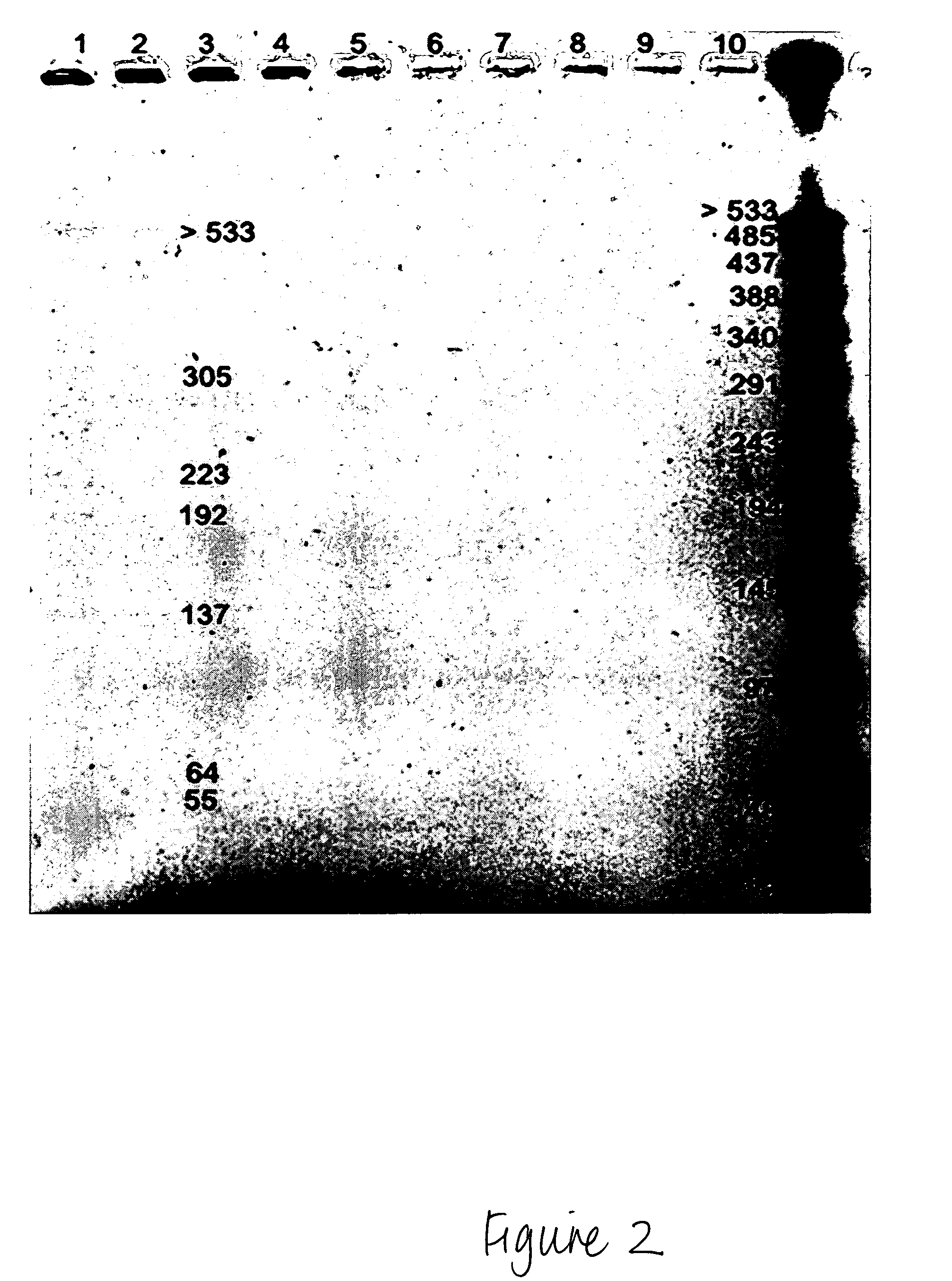

Methods for isolation of nucleic acids from prokaryotic spores

InactiveUS20060204978A1Easy to detectMinimizes potential infectionMicrobiological testing/measurementMicroorganism lysisSporeDNA

The invention provides methods and related products for extracting nucleic acids such as DNA from prokaryotic spores. The invention also encompasses methods for identifying the source of such spores via analysis of the isolated nucleic acids.

Owner:U S GENOMICS INC

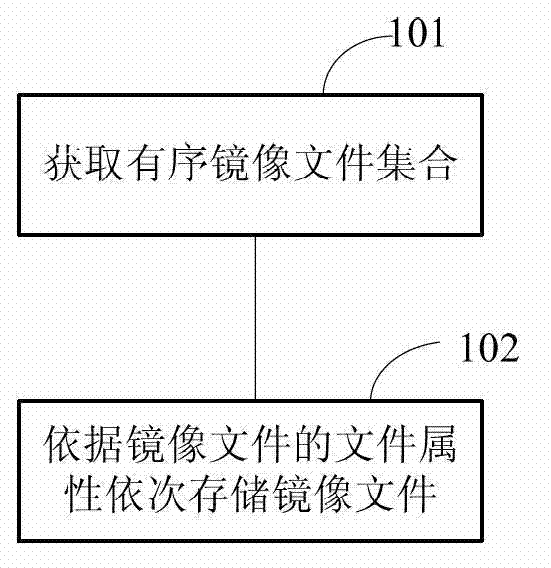

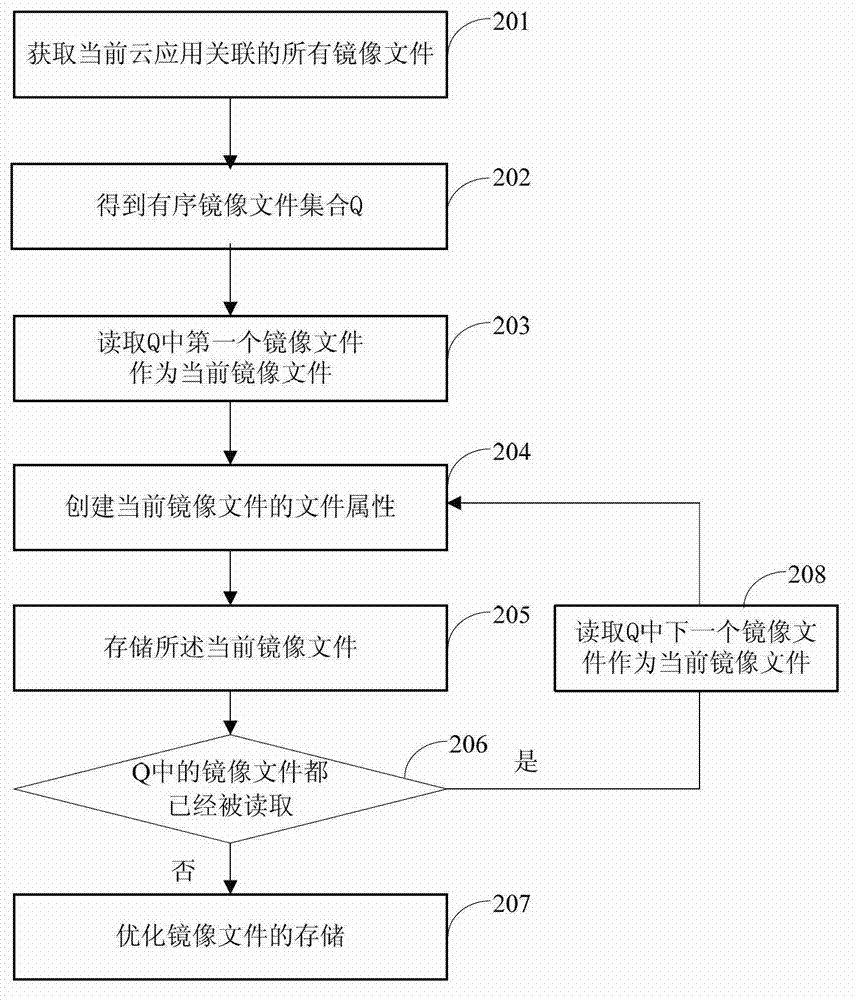

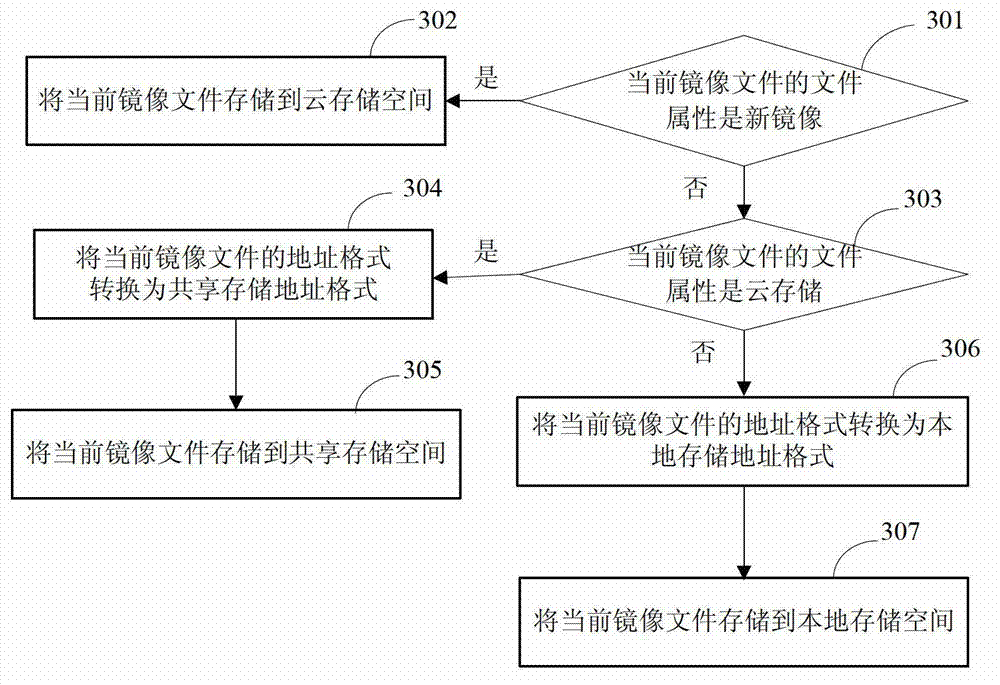

Method and device for storing mirror image document

The invention discloses a method and a device for storing a mirror image document. The method comprises the steps of: acquiring an order mirror image document set corresponding to the current cloud application environment; and storing each mirror image document in a cloud storage space, a sharing storage space or a local storage space in sequence according to the document attribute of each mirror image document in the order mirror image document set. According to the method and the device provided by the invention, the mirror image documents are stored in the cloud storage space, the sharing storage space or the local storage space in sequence according to the document attributes of the related mirror image documents in the current cloud application, the mirror image documents which are stored in the sharing storage space or the local storage space can be run directly and do not need to be copied, so that the starting running speed of the mirror image documents in the cloud application is quickened; and the mirror image documents occupy spare resources in the sharing storage space or the local storage space, so that the storage space utilization is also improved.

Owner:NEUSOFT CORP

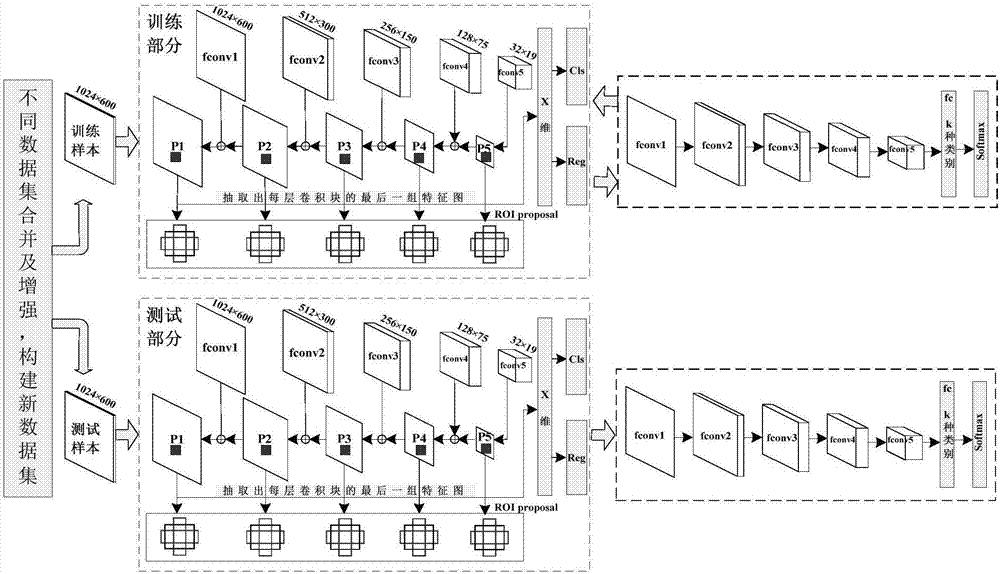

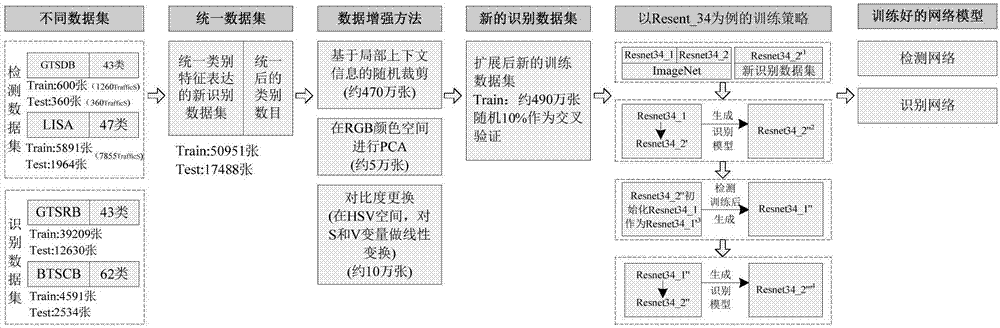

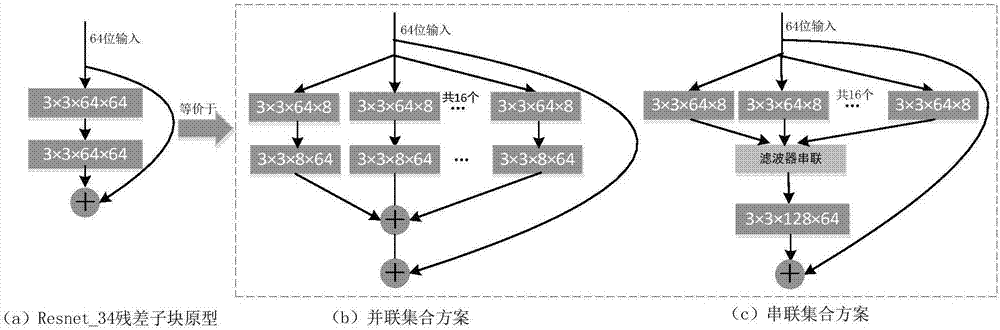

Deep intelligent driving application-oriented traffic sign recognition algorithm

ActiveCN107368787AImprove scalabilityEfficient identificationCharacter and pattern recognitionIdentification rateObject detection

The invention discloses a deep intelligent driving application-oriented traffic sign recognition algorithm, based on consideration of multisource open beta data set translation expansibility and stability by a network, a unified category representation of the multisource open beta data set for traffic signs is built, through a data enhancement strategy randomly clipped based on local context information, expansion of the data set is realized, and a multiscale convolution feature map network and an aggregate network iteration alternate verification training strategy is adopted, a detection network and a recognition network with relatively good performance are obtained, and thus the networks are easy to train and faster in convergence; based on a characteristic of convolution from bottom to top, and through a top-to-down fusion multiscale convolution characteristic network modeling method, the recall ratio of small-sized traffic signs is improved; and design of deeper and more complicated Convnet is not pursued to obtain a higher object recognition rate, but aiming at the characteristics of traffic sign targets, through a contrast experiment, an aggregate network capable of achieving better information flow and better performance is proposed, and efficiency recognition of traffic signs is realized.

Owner:CHANGAN UNIV

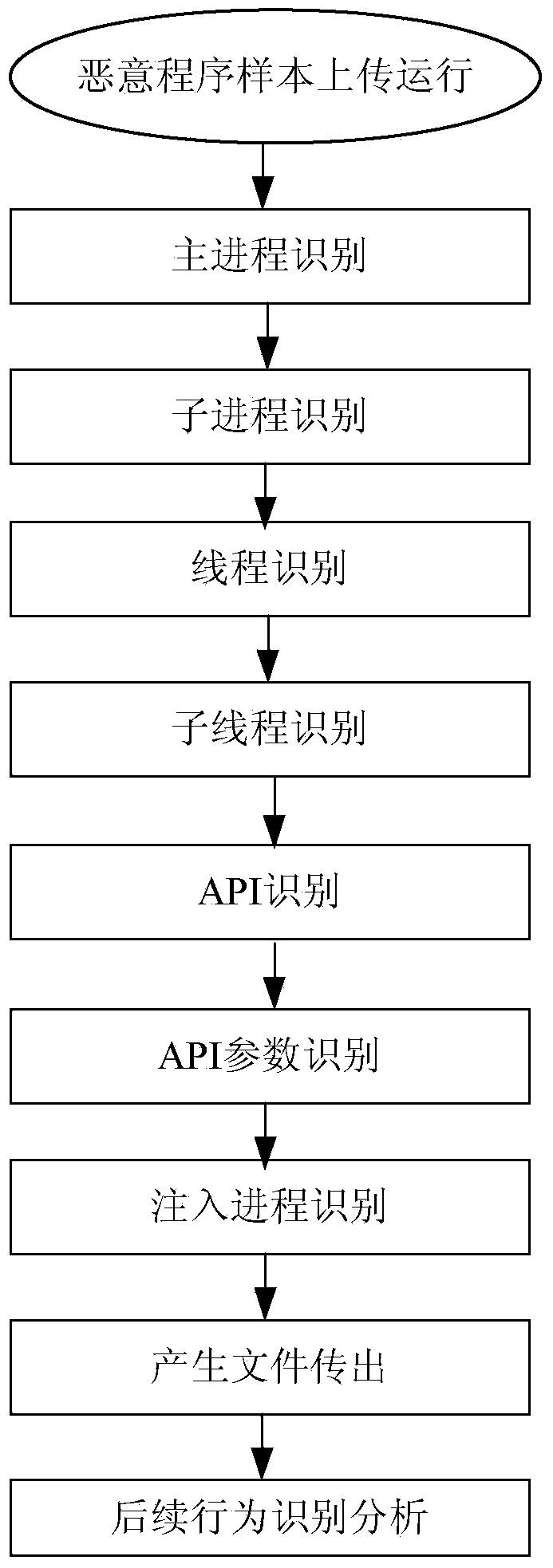

Malicious program behavior capture method based on Qemu

InactiveCN103927484AAchieve captureNo omission semanticsPlatform integrity maintainanceSource codeProgram behavior

The invention relates to a malicious program behavior capture method based on the Qemu. The method is characterized in that a malicious program behavior capture module is directly inserted into a source code of the Qemu, a client operating system is installed on the Qemu, and then behavior capture is carried out on malicious program samples on the client operating system through the malicious program behavior capture module running in the Qemu. The method has the advantages that the malicious program behavior capture module is directly inserted into the source code of the Qemu, completely isolated from the samples running on the client operating system and located on the lower layer of the operating system, and in theory, the malicious program samples can not detect or escape the malicious program behavior capture module easily.

Owner:XIDIAN NINGBO INFORMATION TECH INST

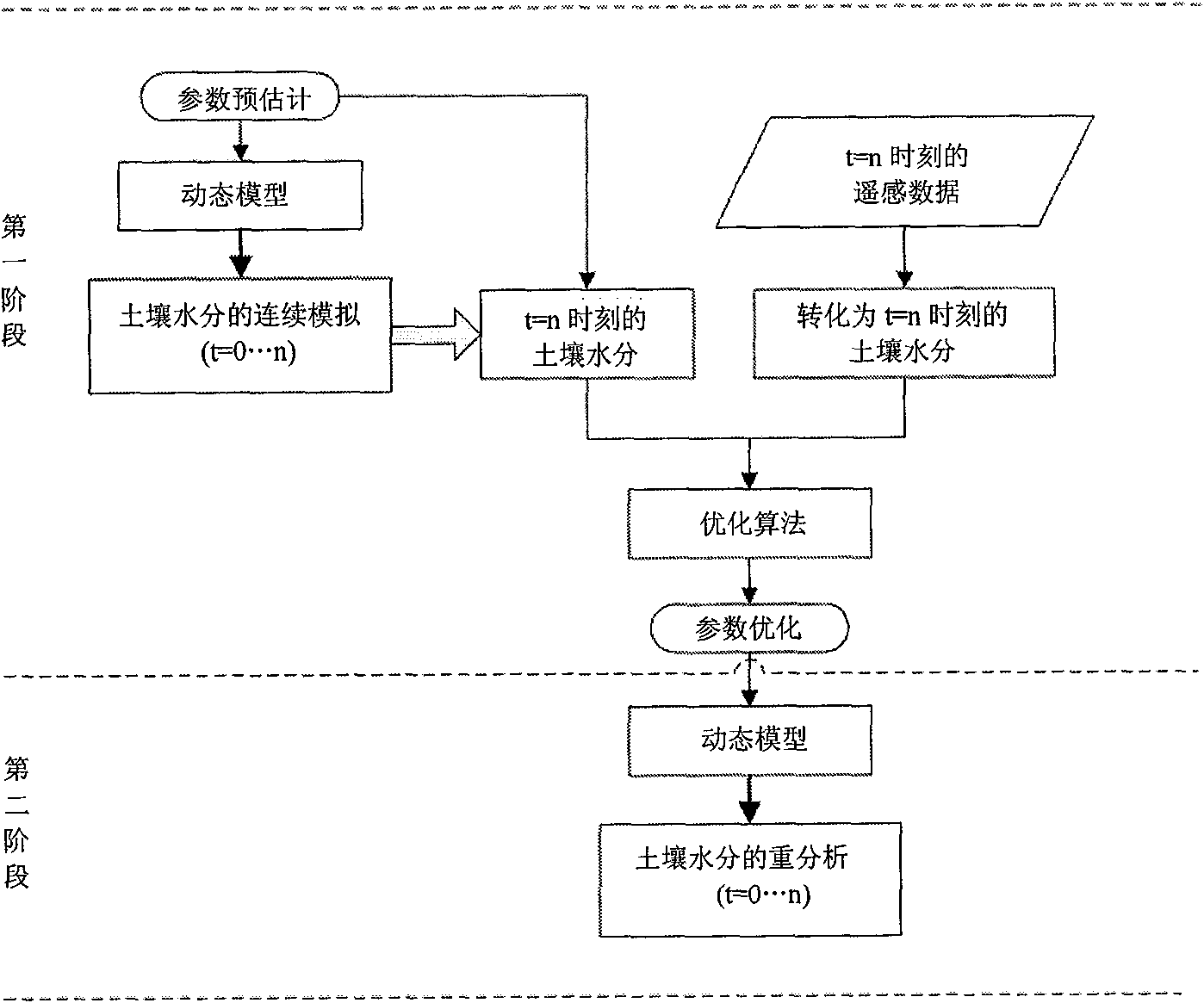

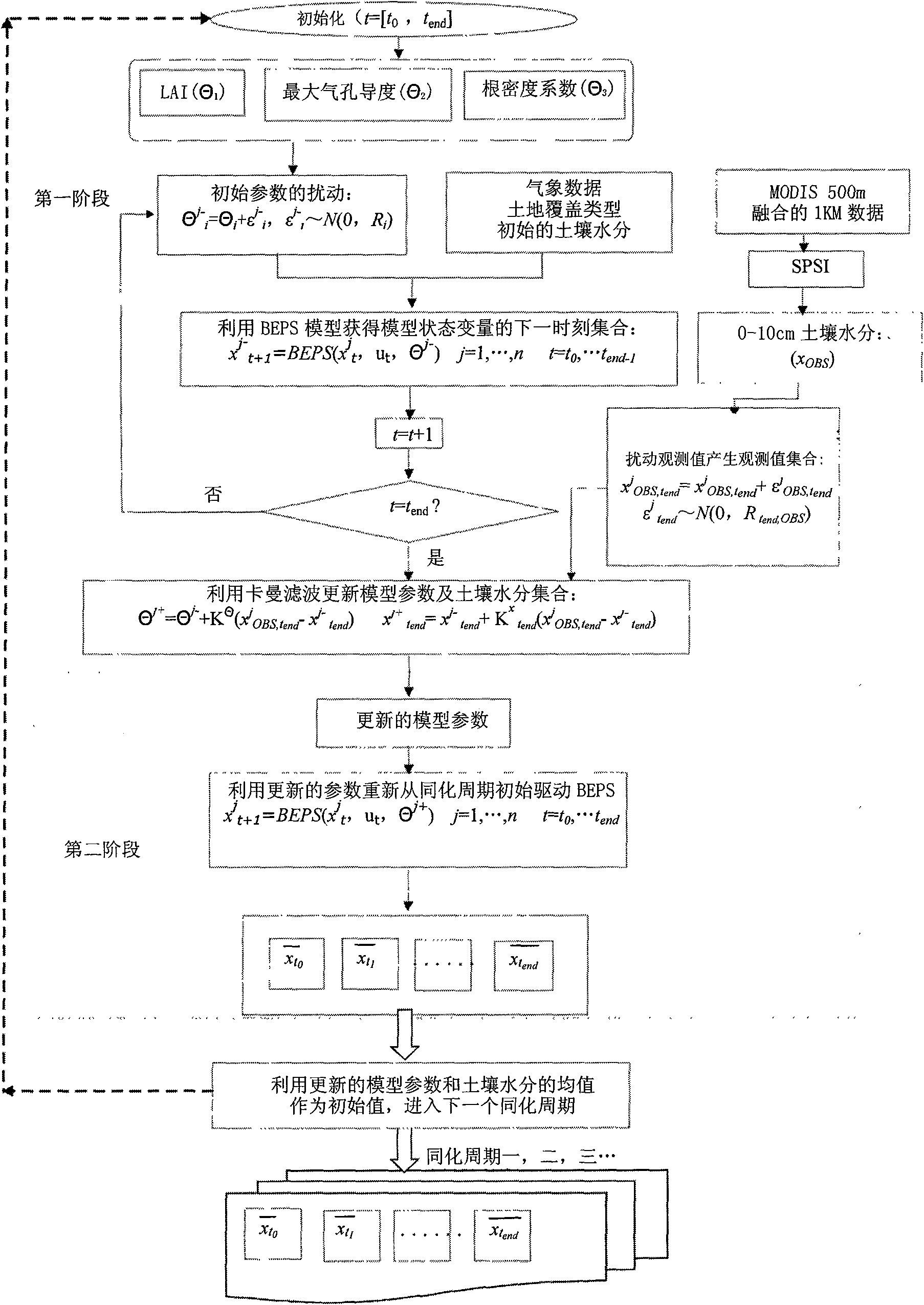

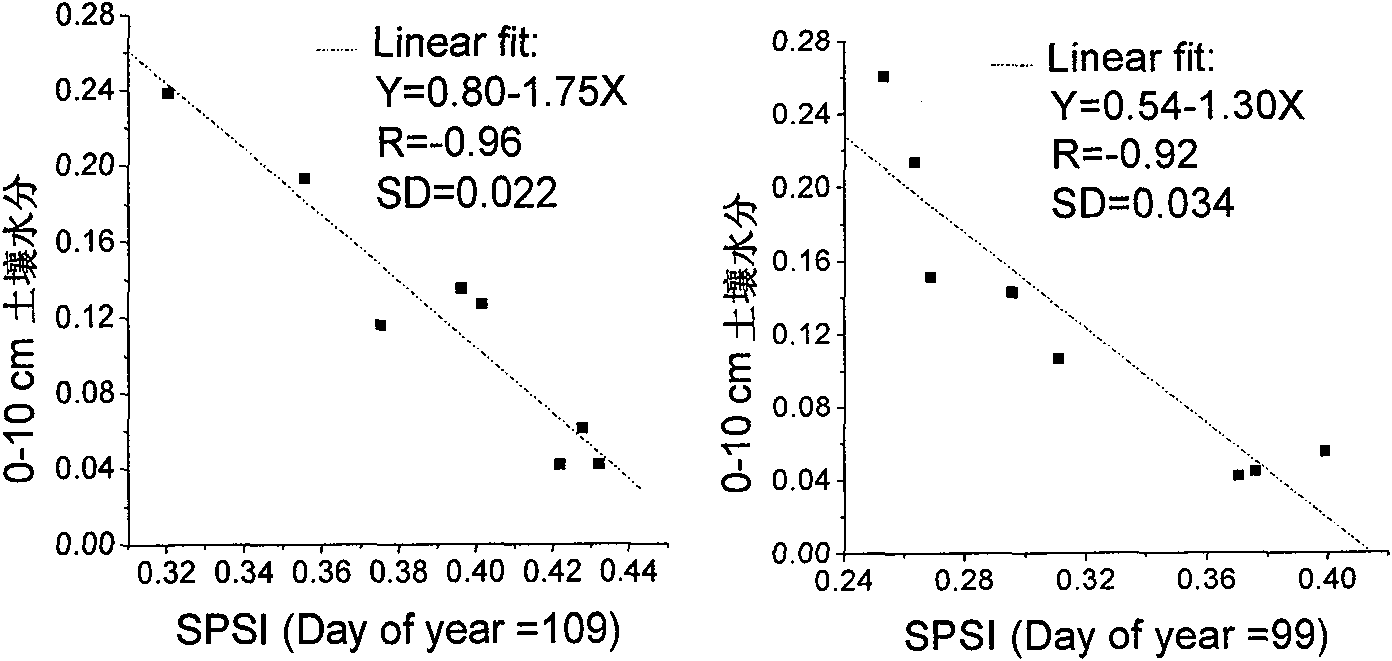

Data assimilation method for monitoring soil moisture

InactiveCN101614651AOptimizing Ecological Process Model ParametersImprove predictive performanceMaterial analysis by optical meansElectromagnetic wave reradiationDynamic modelsModel parameters

The invention discloses a data assimilation method for monitoring soil moisture. The method provided by the invention at least comprises an assimilation cycle, and each assimilation cycle comprises the following steps: (1) an ecological process model serves as a dynamic model to stimulate the space distribution state of soil moisture every day, the initial value in the dynamic model is an initial parameter and an initial soil moisture data, and the dynamic model is operated to output simulative soil moisture data; remotely sensed data on the soil surface is performed with inversion to obtain surface layer soil moisture data; the simulative soil moisture data in the remotely sensed data corresponding date is combined with the surface layer soil moisture data obtained by remotely sensed data inversion for data assimilation so as to obtain an optimized ecological process model parameter; (2) the optimized parameter is substituted into the dynamic model in step (1) to operate the dynamic model so as to obtain simulative soil moisture data every day. The method provided by the invention can connect soil moisture variety with vegetable physiological response mechanism by water deficit and stress, which improves the precision of field soil moisture monitoring and drought evaluation and has important application prospect.

Owner:PEKING UNIV

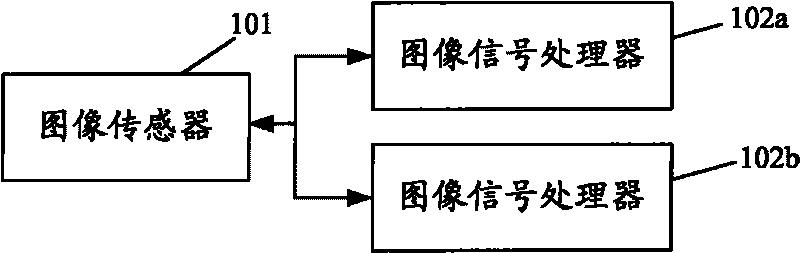

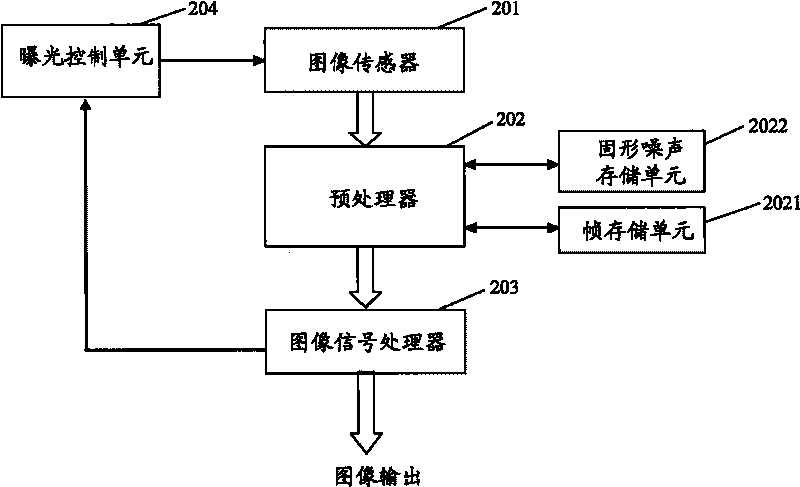

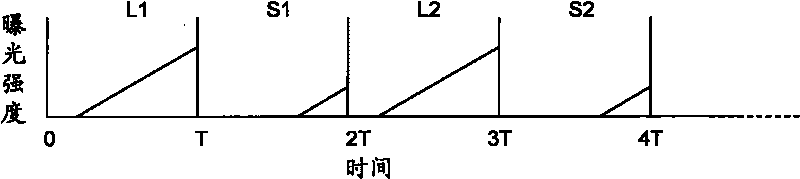

Image pickup system and image processing method

InactiveCN101764959ASimple structureLow costTelevision system detailsColor television detailsImaging processingImage signal

The invention discloses an image pickup system, which includes an image sensor, a preprocessor, and an image signal processor, wherein the image sensor implements alternative exposure according to different exposure time and converts the images into the original image data; the preprocessor implements synthesizing treatment on the original image data according to the length of the exposure time and outputs synthesized image data; the image signal processor implements image recovering treatment on the synthesized image data and outputs an image signal. The invention also discloses a corresponding image processing method. The image pickup system and image processing method realize expansion of dynamic scope under the condition of lower cost.

Owner:BRIGATES MICROELECTRONICS KUNSHAN

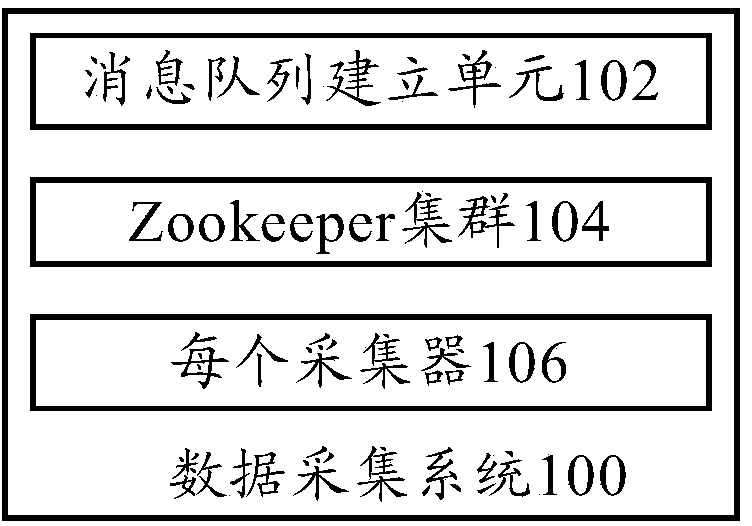

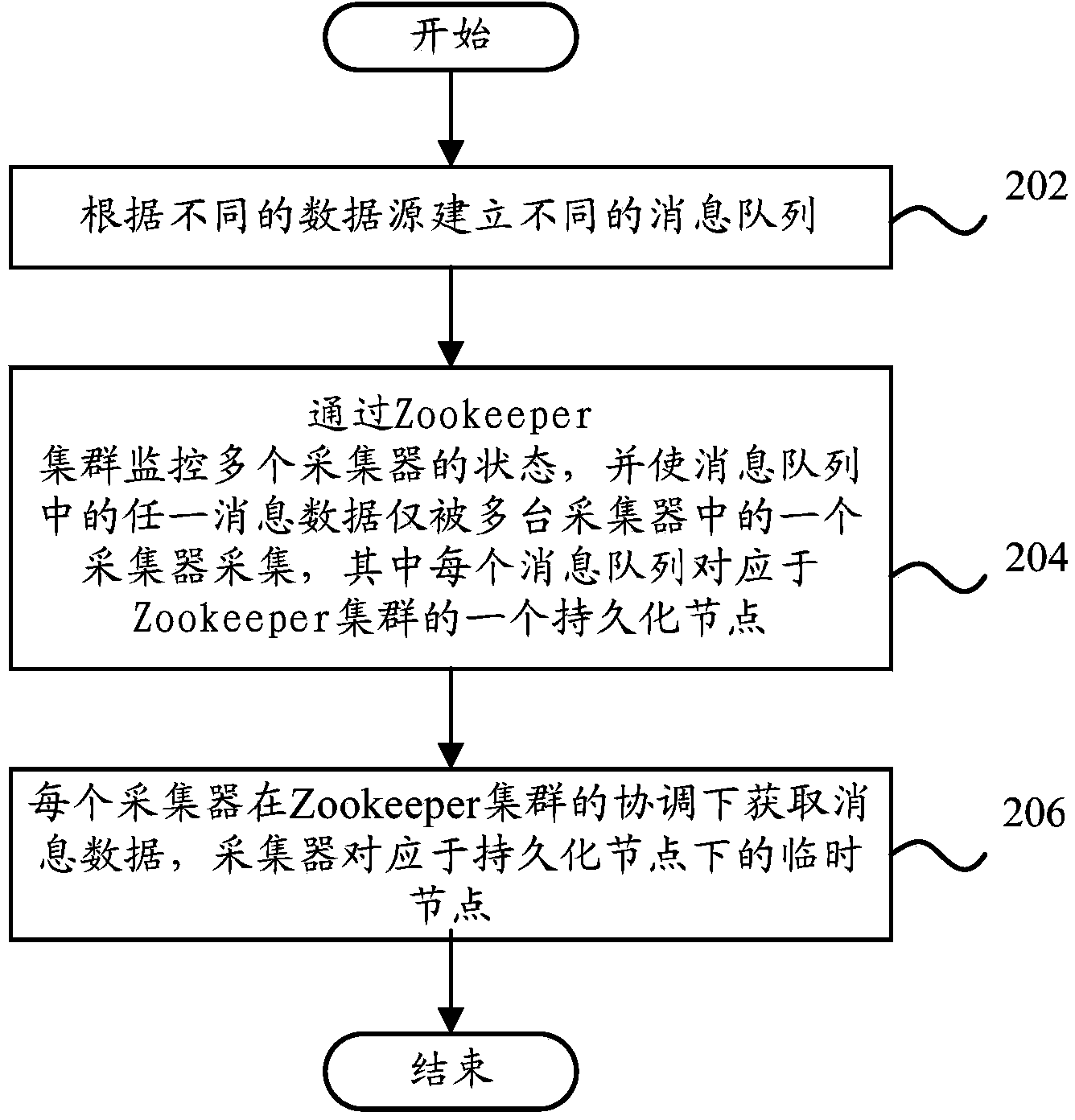

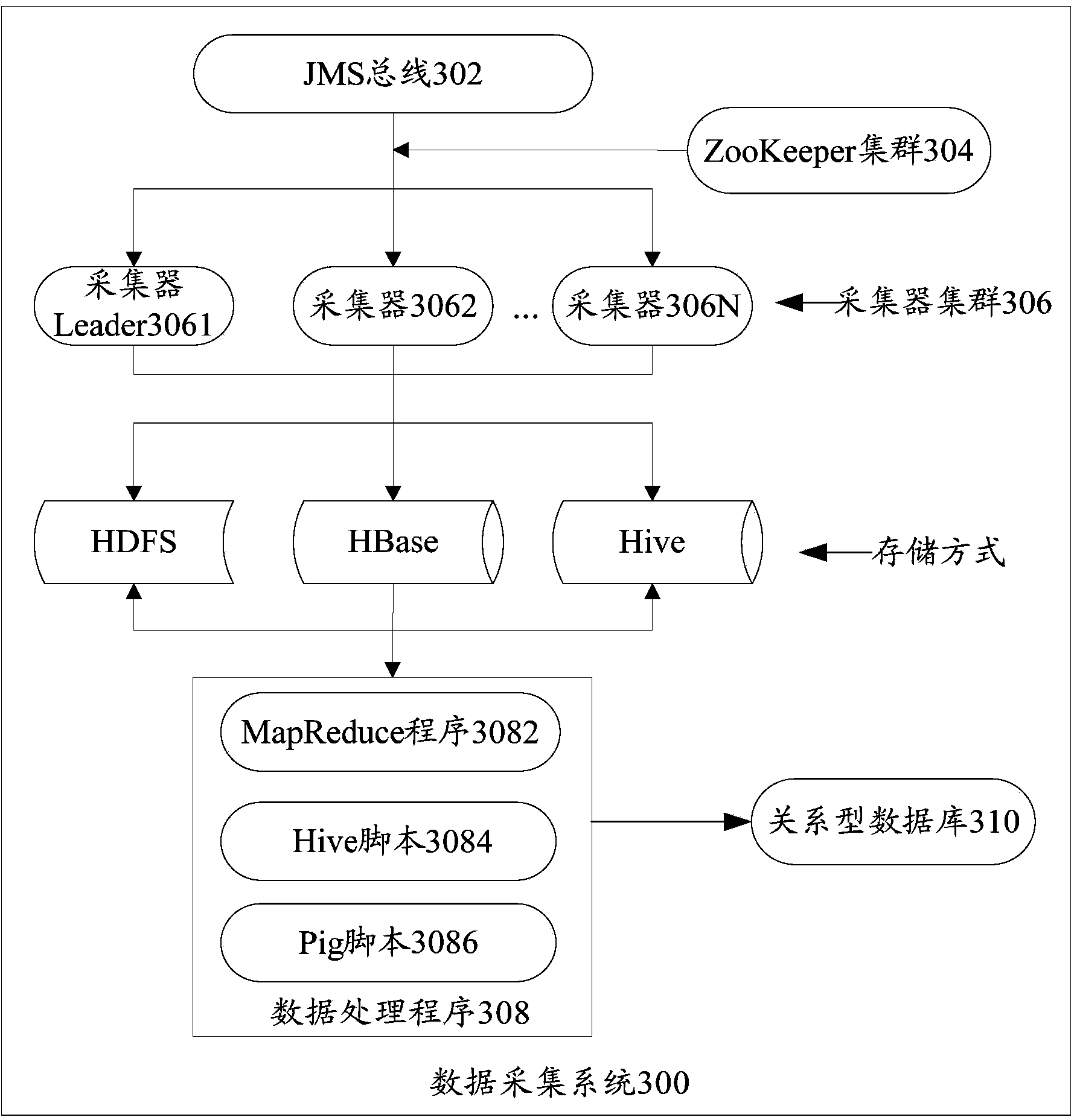

Data collection system and method

ActiveCN104065741AAchieve diversityControl load balancingMultiprogramming arrangementsTransmissionCollections dataMessage queue

The invention provides a data collection system based on a Zookeeper cluster. The system comprises a message queue establishing unit and the Zookeeper cluster. The message queue establishing unit is used for establishing different message queues according to different data sources. The Zookeeper cluster is used for monitoring the states of a plurality of collectors, and enabling any message datum in the message queues to be collected by only one collector, wherein each message queue corresponds to a persistence node of the Zookeeper cluster. Each collector obtains message data under the coordination of the Zookeeper cluster, and corresponds to the temporary node of the persistence node. Correspondingly, the invention further provides a data collection method based on the Zookeeper cluster. According to the technical scheme, different collection modules can be arranged according to different data sources, different storage strategies are set according to different storage requirements, and diversity of data collection and storage is achieved.

Owner:YONYOU NETWORK TECH

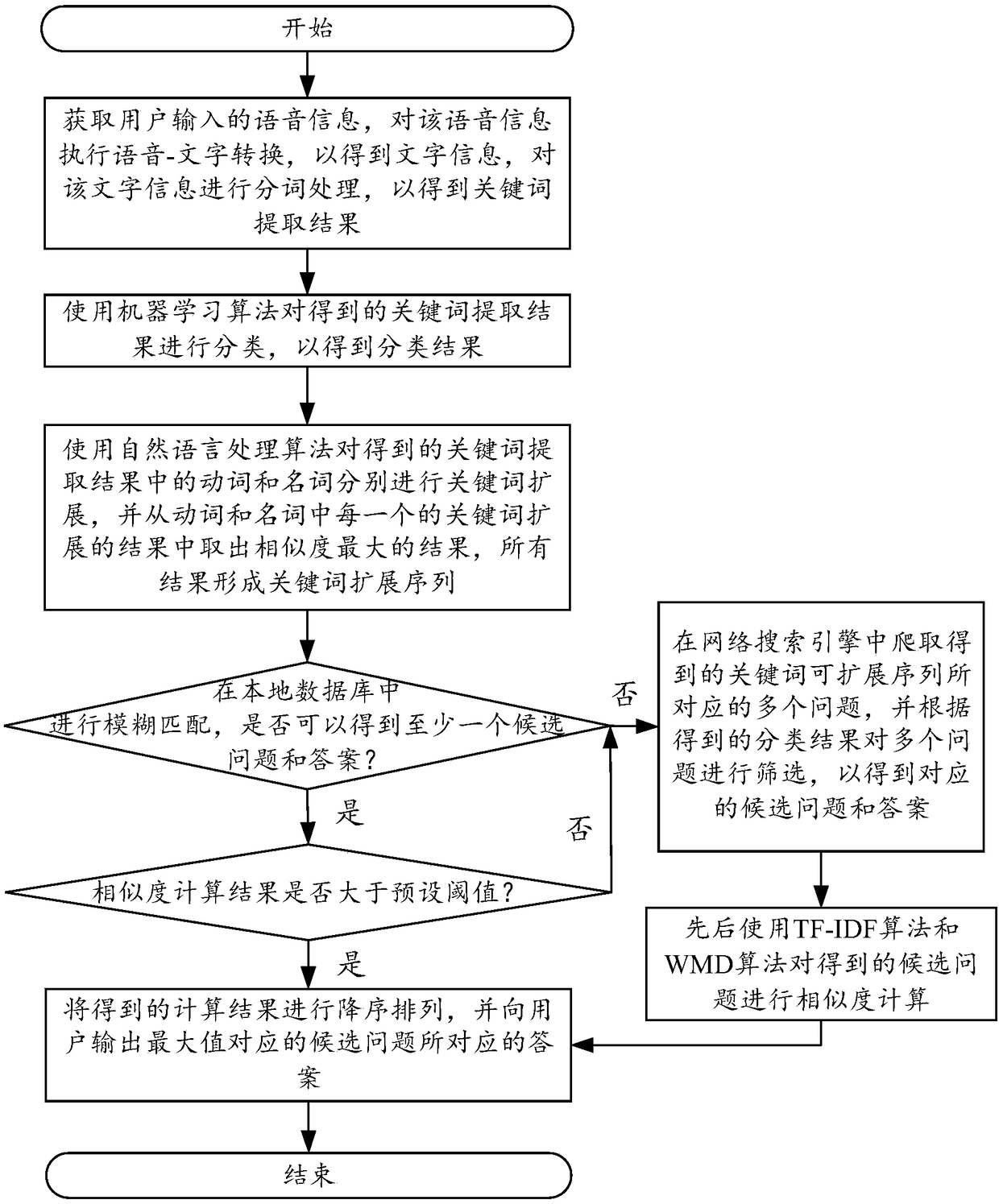

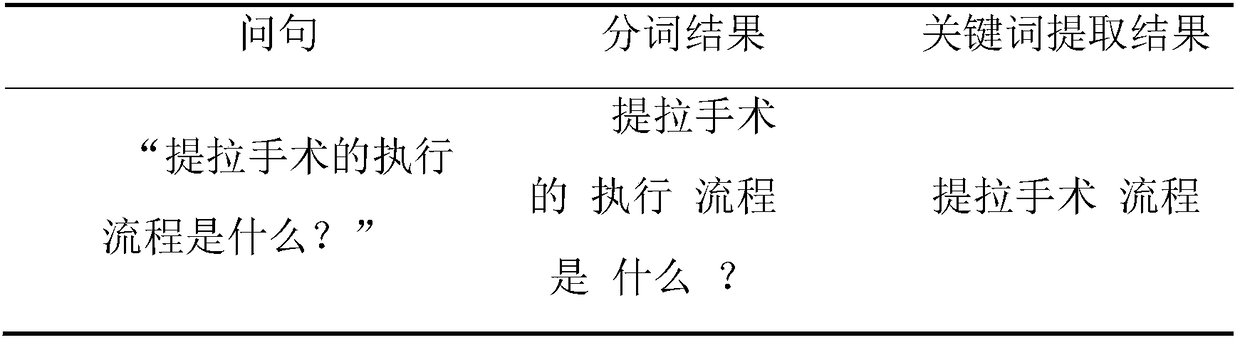

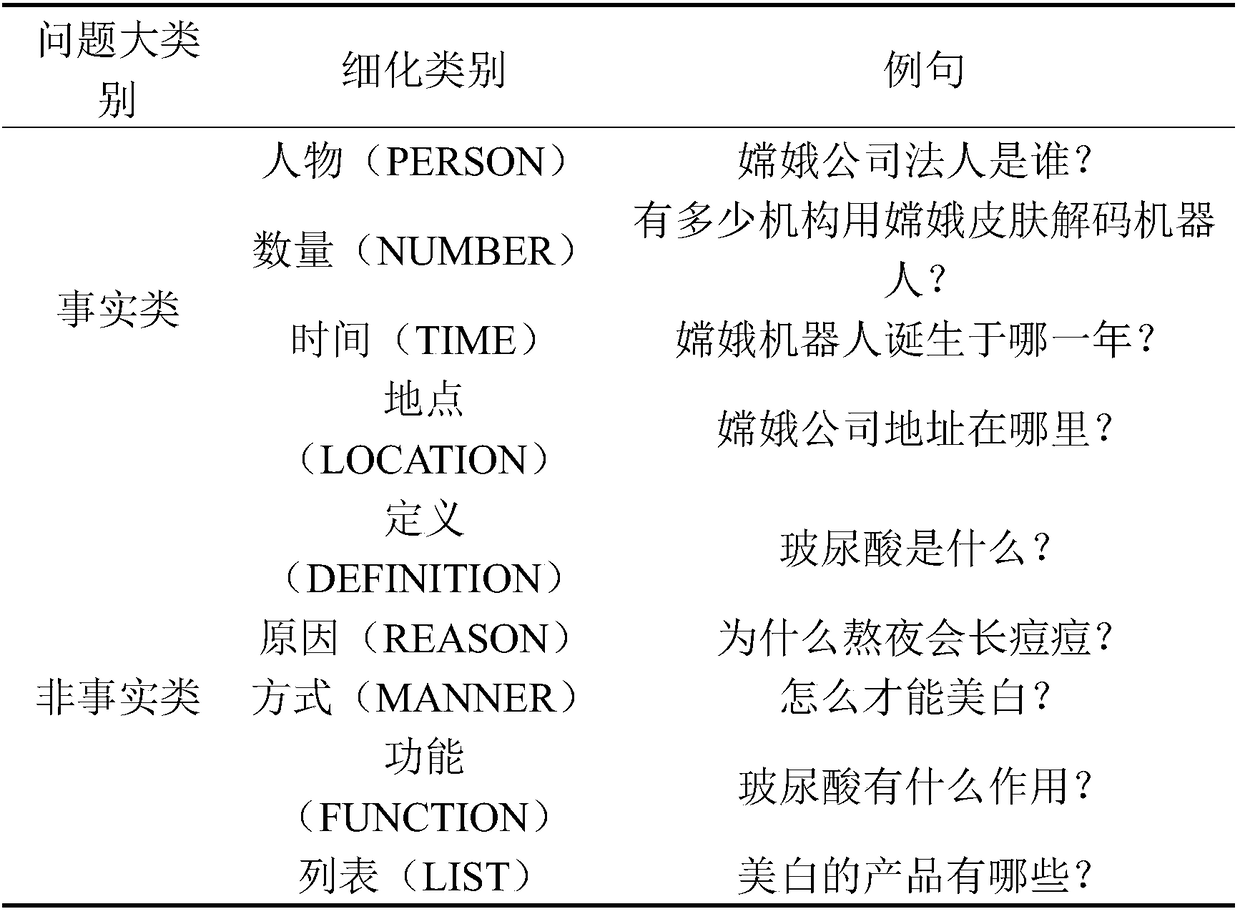

Human-computer interaction intelligent question answering method based on cloud platform

InactiveCN108595696AWord segmentation results are accurateImprove word segmentation accuracyNatural language data processingSpeech recognitionTextual informationKeyword extraction

The invention discloses a human-computer interaction intelligent question answering method based on a cloud platform, which comprises the following steps: acquiring voice information input by a user;performing voice-to-text conversion on the voice information to obtain text information; performing word segmentation processing on the text information to obtain keyword extraction results; using a machine learning algorithm to classify the obtained keyword extraction results so as to obtain classification results; using a natural language processing algorithm to perform keyword expansion on verbs and nouns in the keyword extraction results and taking out a result with the largest similarity from the results of the keyword expansion in each of the verbs and nous, wherein all the results forma keyword expansion sequence; and performing fuzzy matching in a local database according to the classification results and the keyword expandable sequence. The human-computer interaction intelligentquestion answering method based on the cloud platform in the invention can solve the technical problem of low interaction accuracy caused by inaccurate word segmentation, inaccurate keyword expansion,and inaccurate extraction of answers in the existing human-computer interaction question answering system.

Owner:CHANGSHA UNIVERSITY

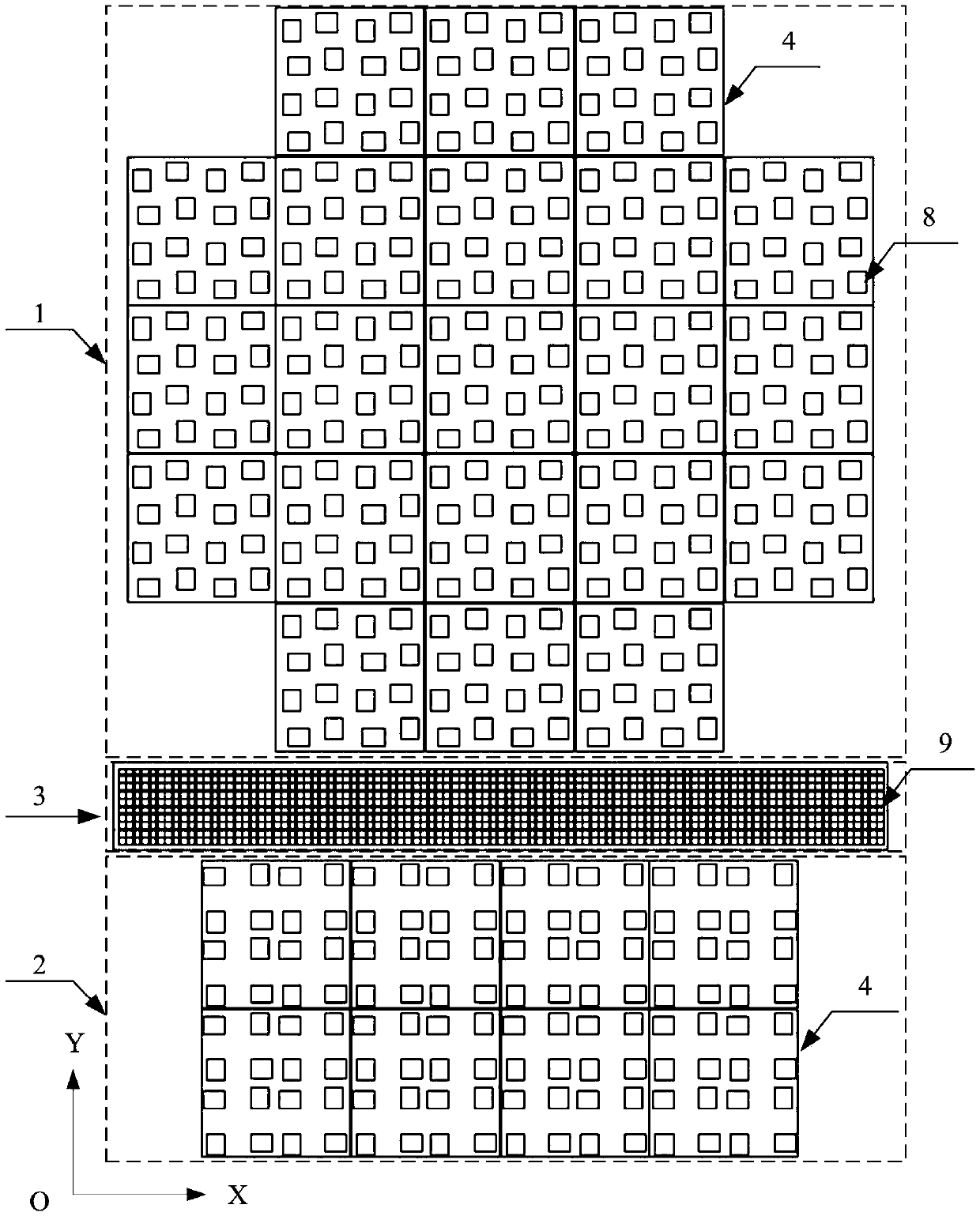

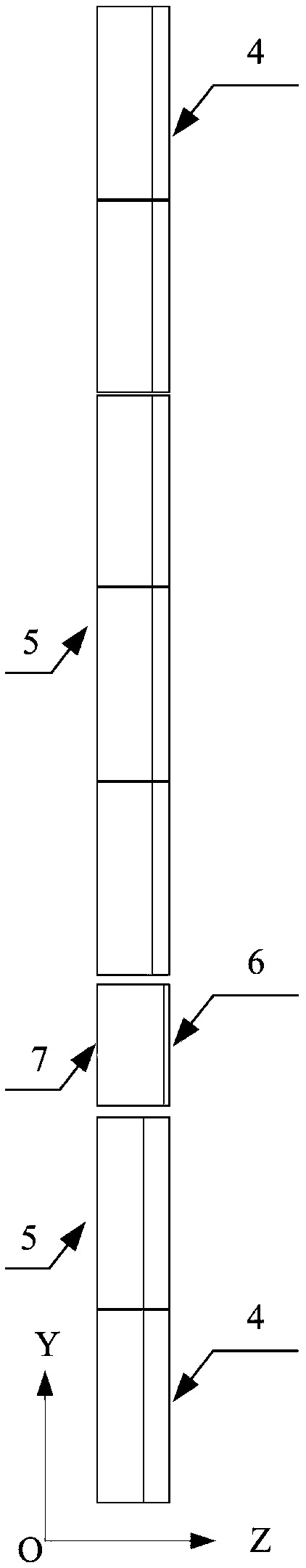

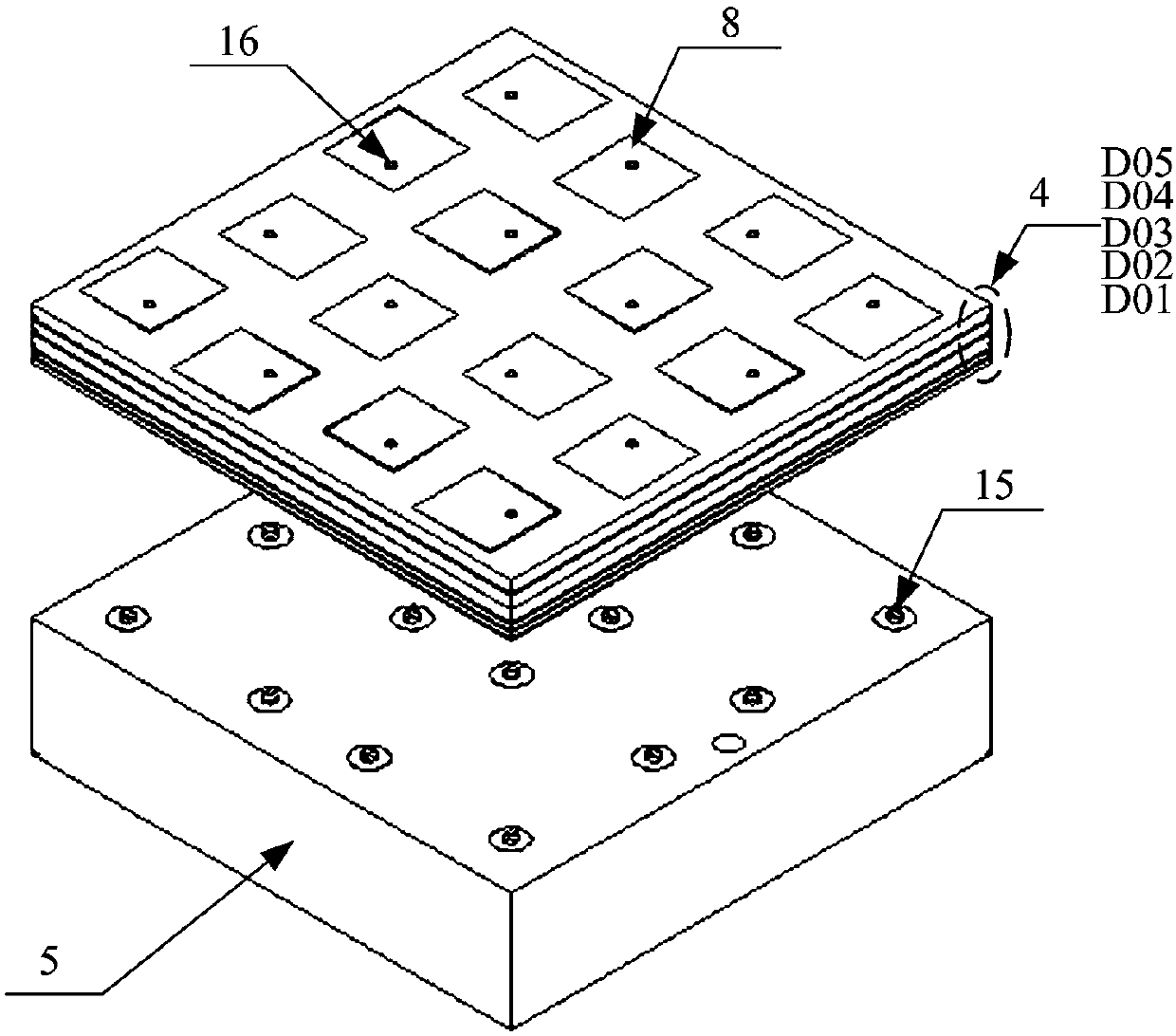

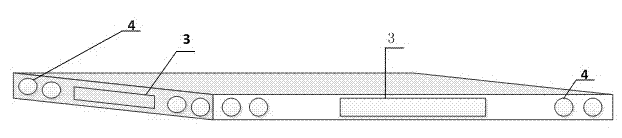

Full-duplex active phased filter antenna array surface

ActiveCN109616759ALow costReduce power consumptionAntenna arraysRadiating elements structural formsRadio frequencyActive phase

The invention discloses a full-duplex active phased filter antenna array surface, and aims at providing an antenna array surface with high-isolation array transmitting and receiving and good filter characteristic. A transmitting antenna array surface of a transmitting array antenna and a receiving antenna array surface of a receiving array antenna consist of a plurality of arrayed radiation units;a multi-layer printed board integrally integrating a radiation circuit, a feed switching circuit and a filter circuit achieves connection between different circuits by vertical interconnection structures of metallized via holes; a metal upper cavity body of a transmitting-receiving component serves as a metal ground; a metal upper cavity body base of a metal floor is consubstantially connected byradio-frequency fuzz button connectors; and then a radiation unit and transmitting-receiving component integrated box-type submatrix module filter antenna unit is formed. With the adoption of the full-duplex active phased filter antenna array surface, high-isolation array transmitting and receiving can be achieved; insertion losses of array transmitting and receiving can be reduced; and high-precision amplitude and phase control can be achieved.

Owner:10TH RES INST OF CETC

Spliced mobile equipment

ActiveCN103209232AHigh resolutionImplement extensionsDigital data processing detailsTelephone set constructionsMulti-core processorImage resolution

The invention relates to the field of mobile equipment, in particular to spliced mobile equipment. The spliced mobile equipment comprises a mobile terminal with an independent application function and a narrow frame, and a plurality of pieces of auxiliary equipment with narrow frames; the mobile terminal and the auxiliary equipment are provided with display screens which have the same resolution ratio and display scale; the sides of the mobile terminal and the auxiliary equipment are provided with signal transmission interfaces; the mobile terminal is provided with a core processor; the auxiliary equipment is provided with auxiliary processors; the mobile terminal and the auxiliary equipment are spliced to form a large screen; during splicing, the signal transmission interfaces of all the splicing sides are butted; the core processor is electrically connected with the adjacent auxiliary processor through the butted signal transmission interface; and the auxiliary processors which are adjacent to each other are electrically connected through the butted signal transmission interfaces. The display screen of the mobile terminal is expanded, and the spliced screen has the high-screen display function and the high-resolution display function, and can bring the high-quality user experience.

Owner:GUANGDONG VTRON TECH CO LTD