Patents

Literature

713results about "Power saving provisions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

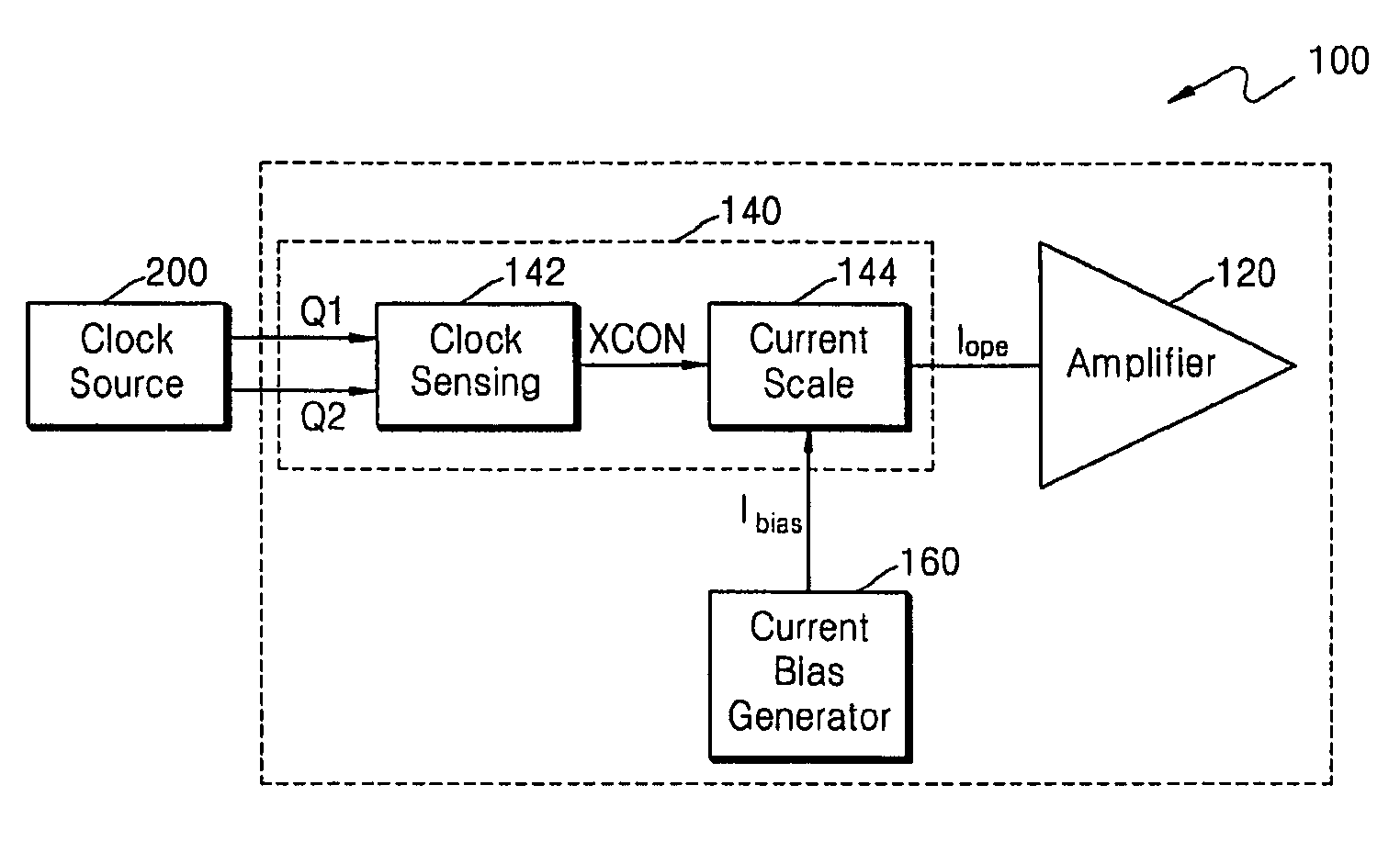

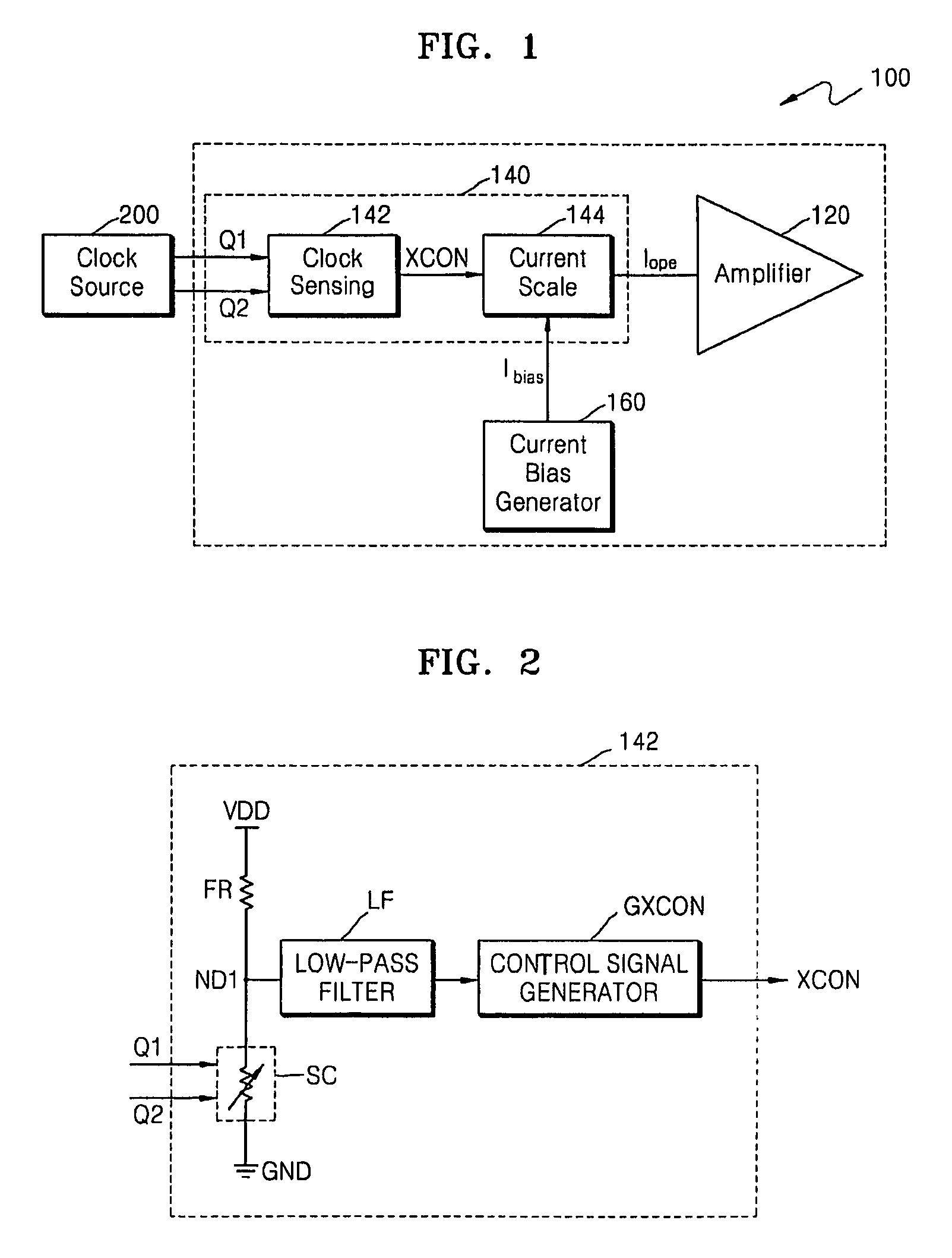

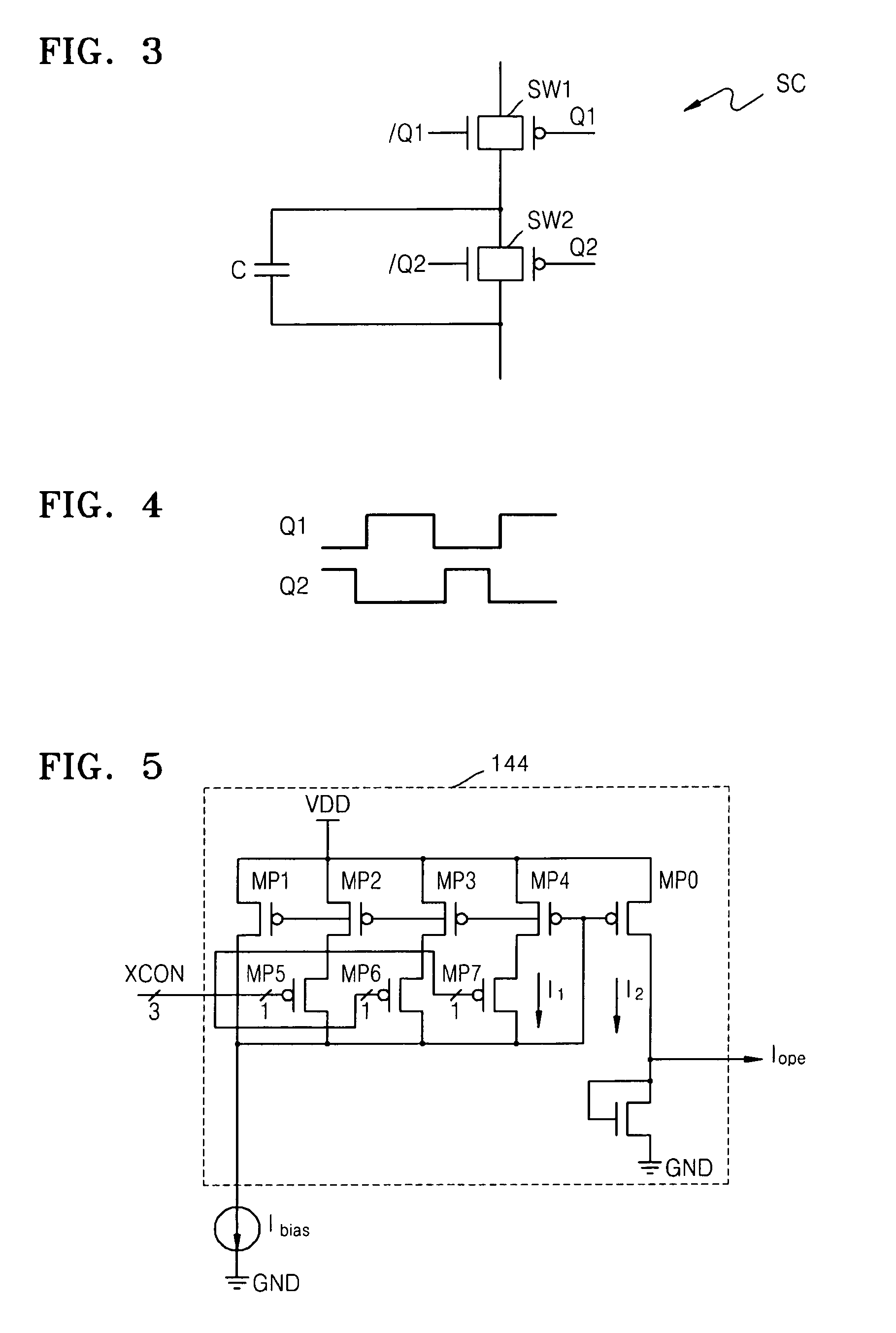

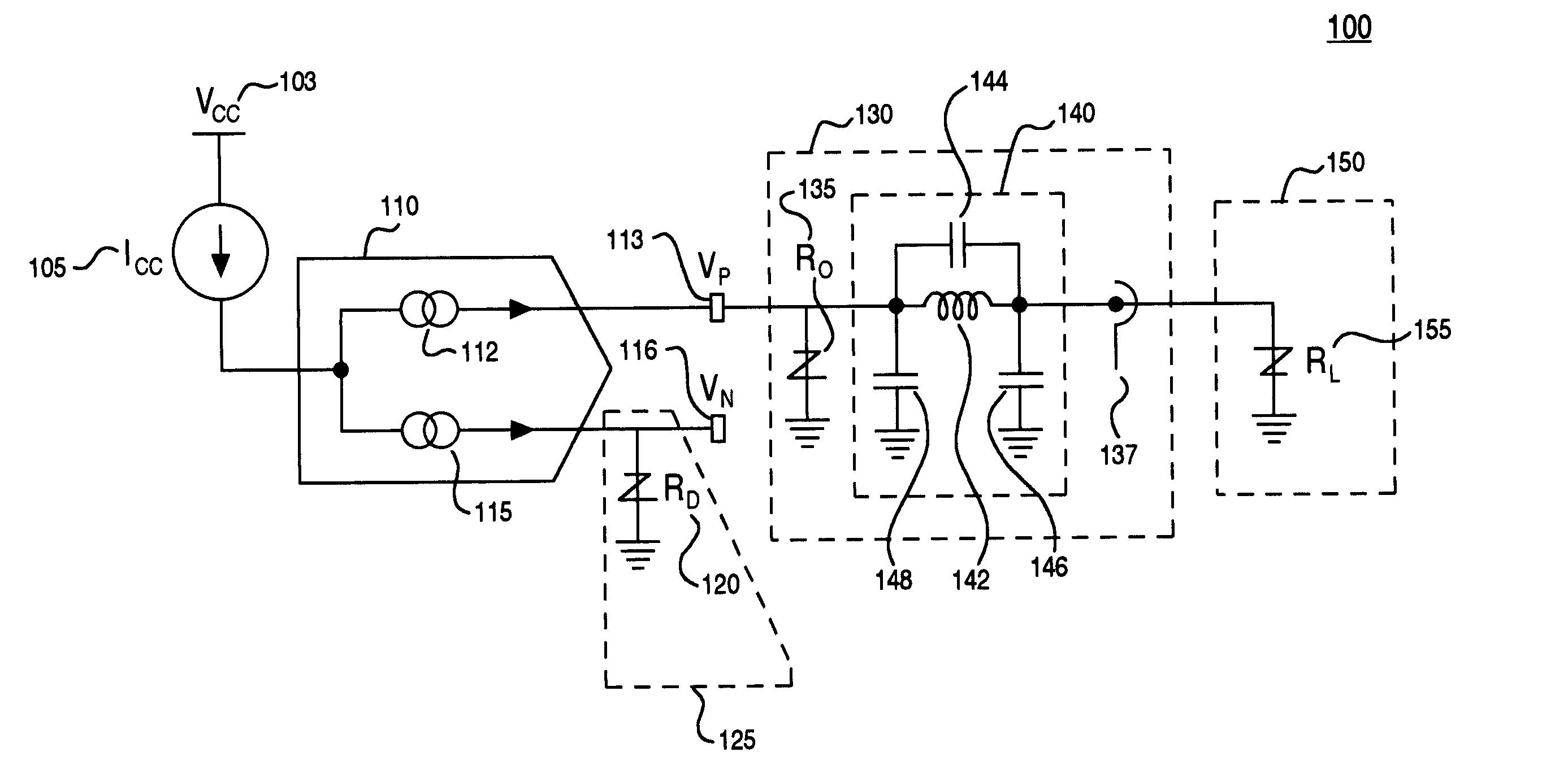

Current control circuit

ActiveUS7808410B2Avoid unnecessary power consumptionPower saving provisionsElectric signal transmission systemsControl signalDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

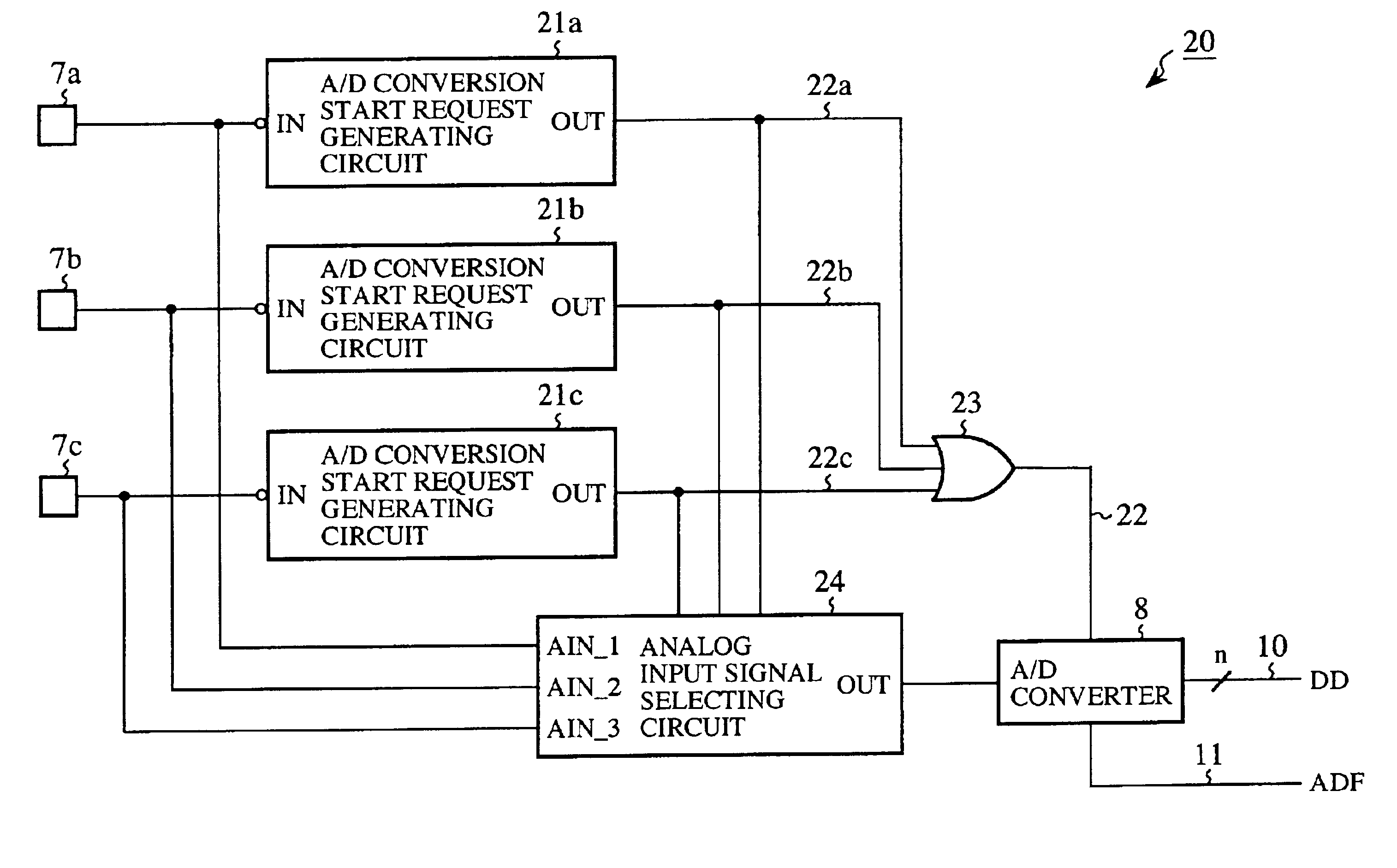

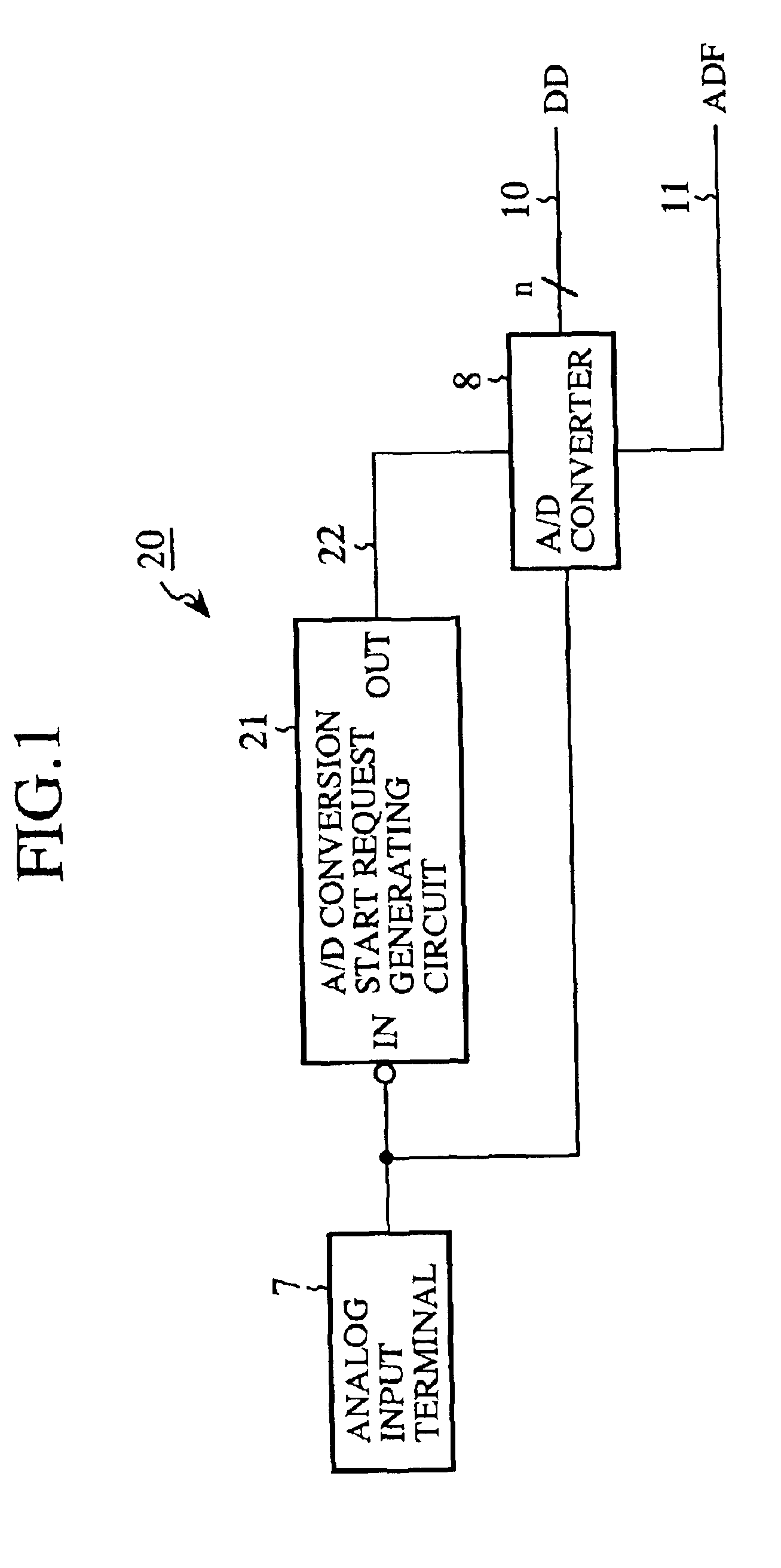

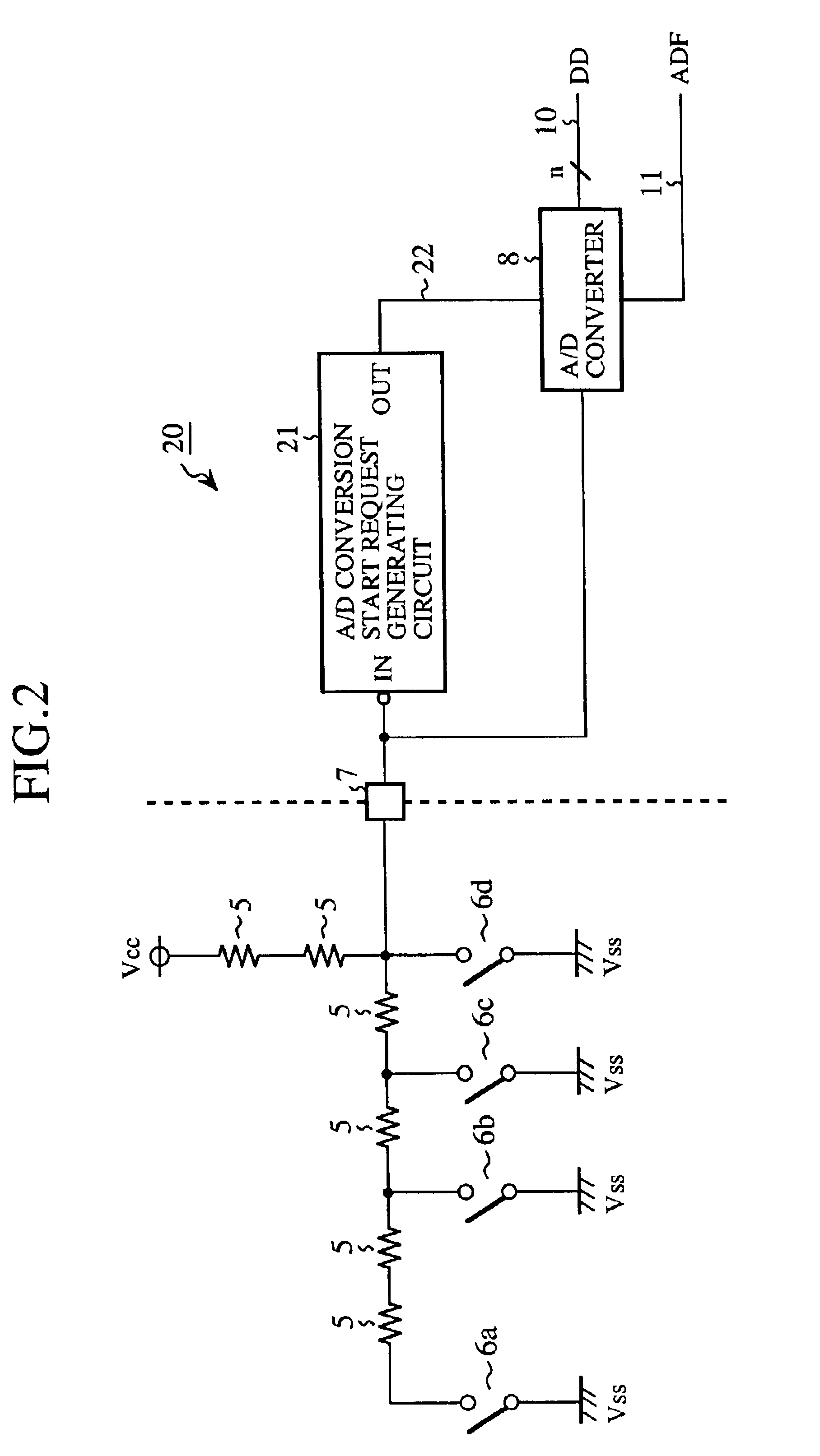

One-chip microcomputer with analog-to-digital converter

InactiveUS6839014B2Reduce electric powerReduce power consumptionPower saving provisionsElectric signal transmission systemsMicrocontrollerDigital data

An input circuit of a one-chip microcomputer is connected to an external switching circuit. When an analog input signal of a significant level generated in the external switching circuit is received at an analog input terminal of the input circuit, an A / D conversion start request signal is generated in an A / D conversion start request generating circuit and is sent to an A / D converter. The operation of the A / D converter is started in response to the A / D conversion start request signal, the analog input signal received at the analog input terminal is converted into digital data, and an A / D conversion finish signal is sent from the A / D converter to a CPU of the one-chip microcomputer. The operation of the CPU is started in response to the A / D conversion finish signal, and the digital data is readout to the CPU. Therefore, the A / D converter, the CPU or a clock is not operated to wait for an analog input signal generated in the external switching circuit, but the A / D converter is operated for the A / D conversion, and the CPU is operated to read out the digital data. Accordingly, an electric power consumed in the A / D converter, the CPU and the clock can be reduced.

Owner:RENESAS ELECTRONICS CORP +1

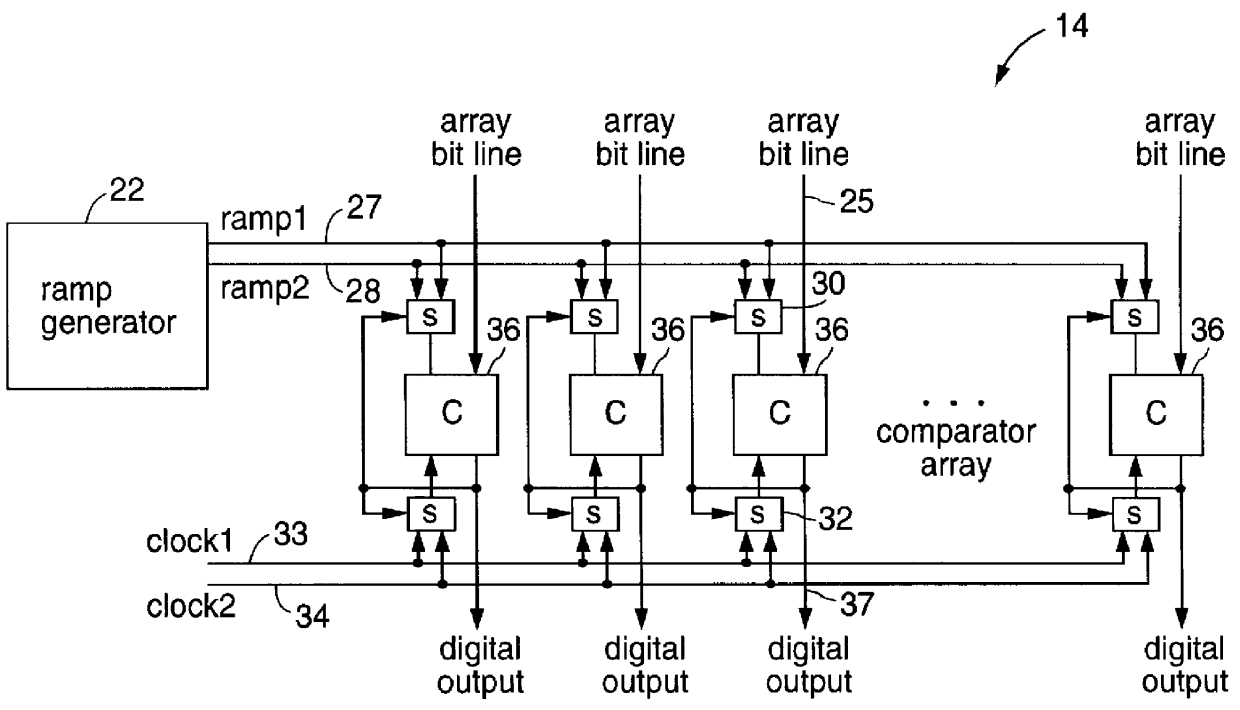

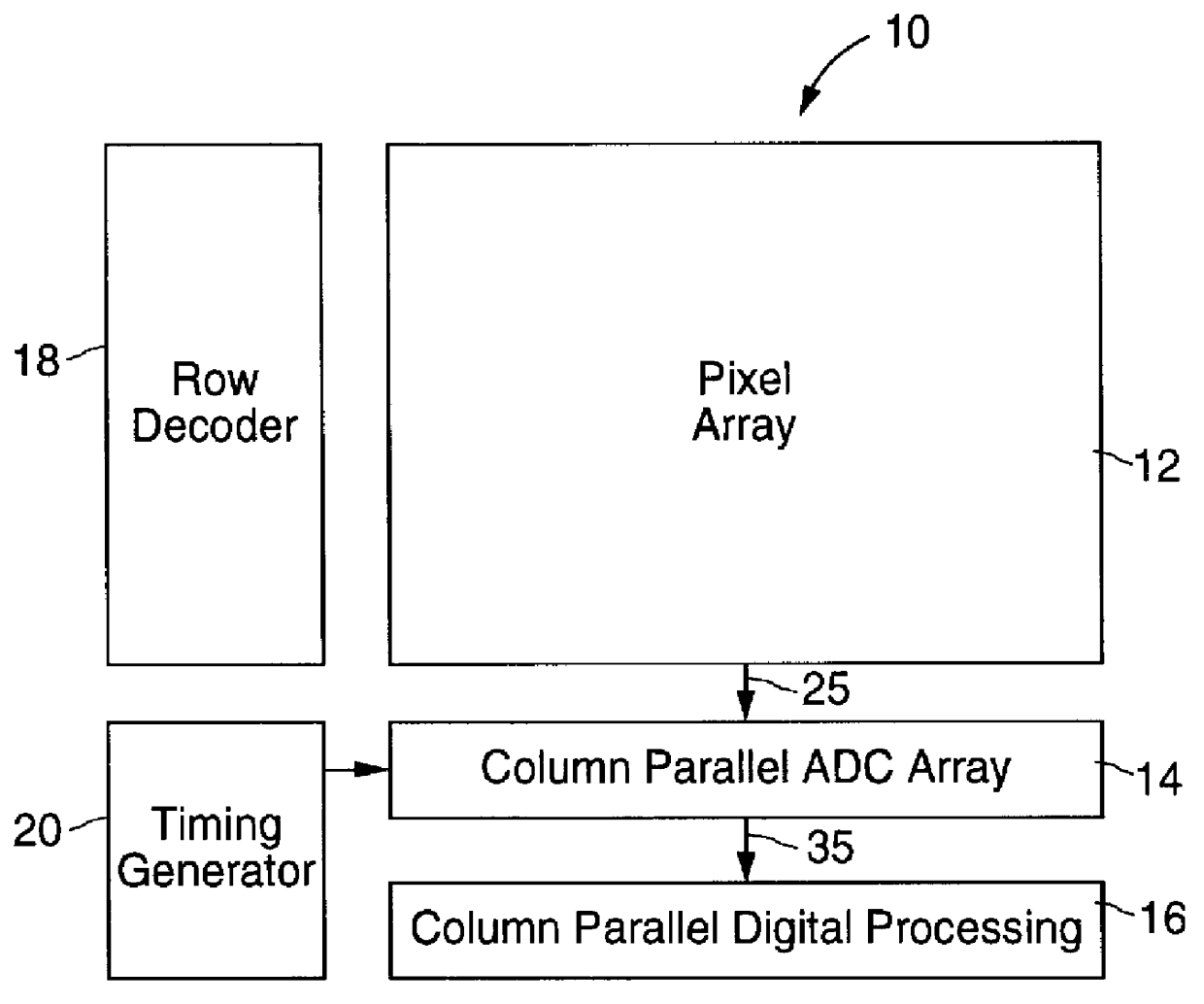

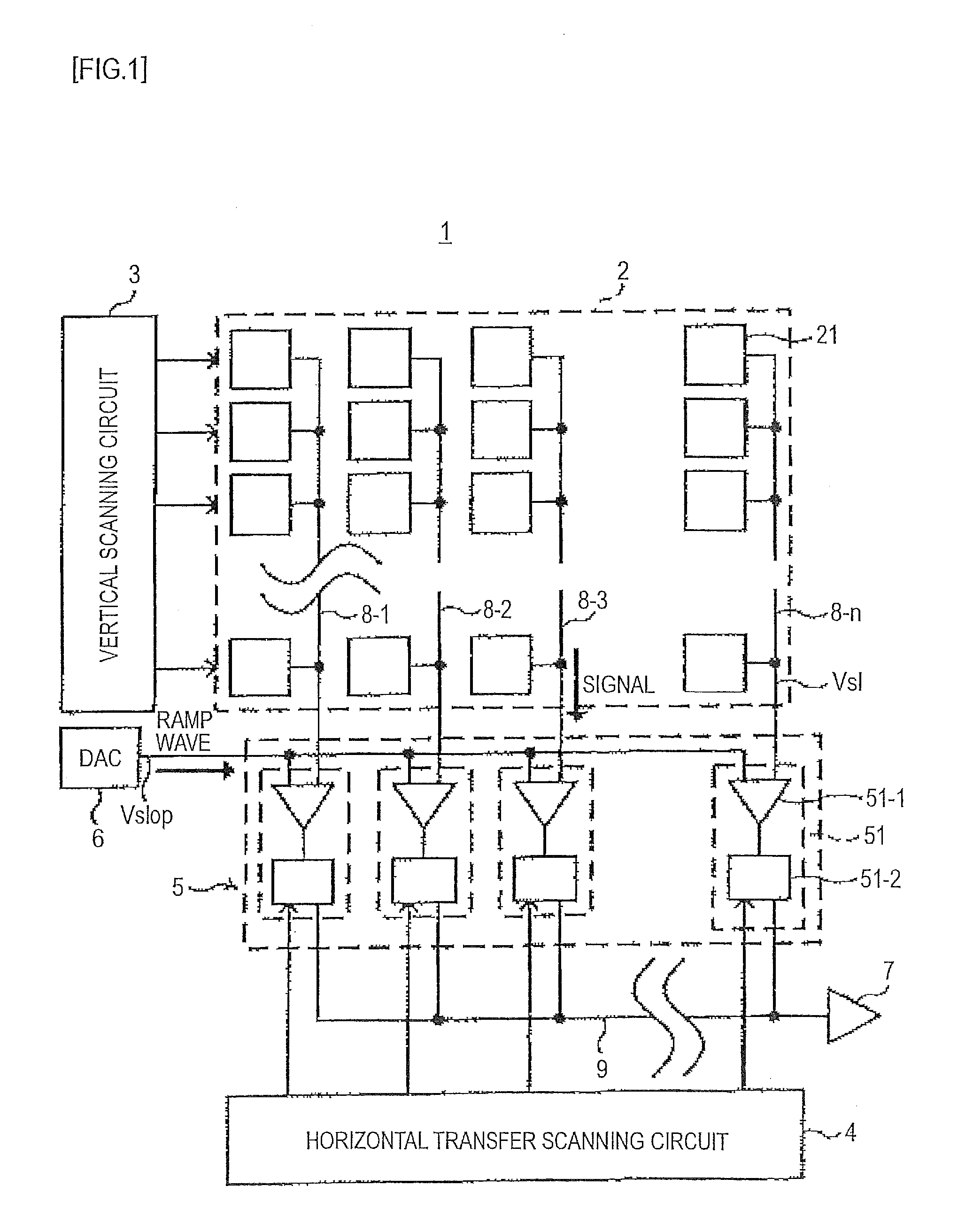

Low-power column parallel ADC in CMOS image sensors

InactiveUS6137432AReduce power consumptionReduce in quantityTelevision system detailsPower saving provisionsCMOSEngineering

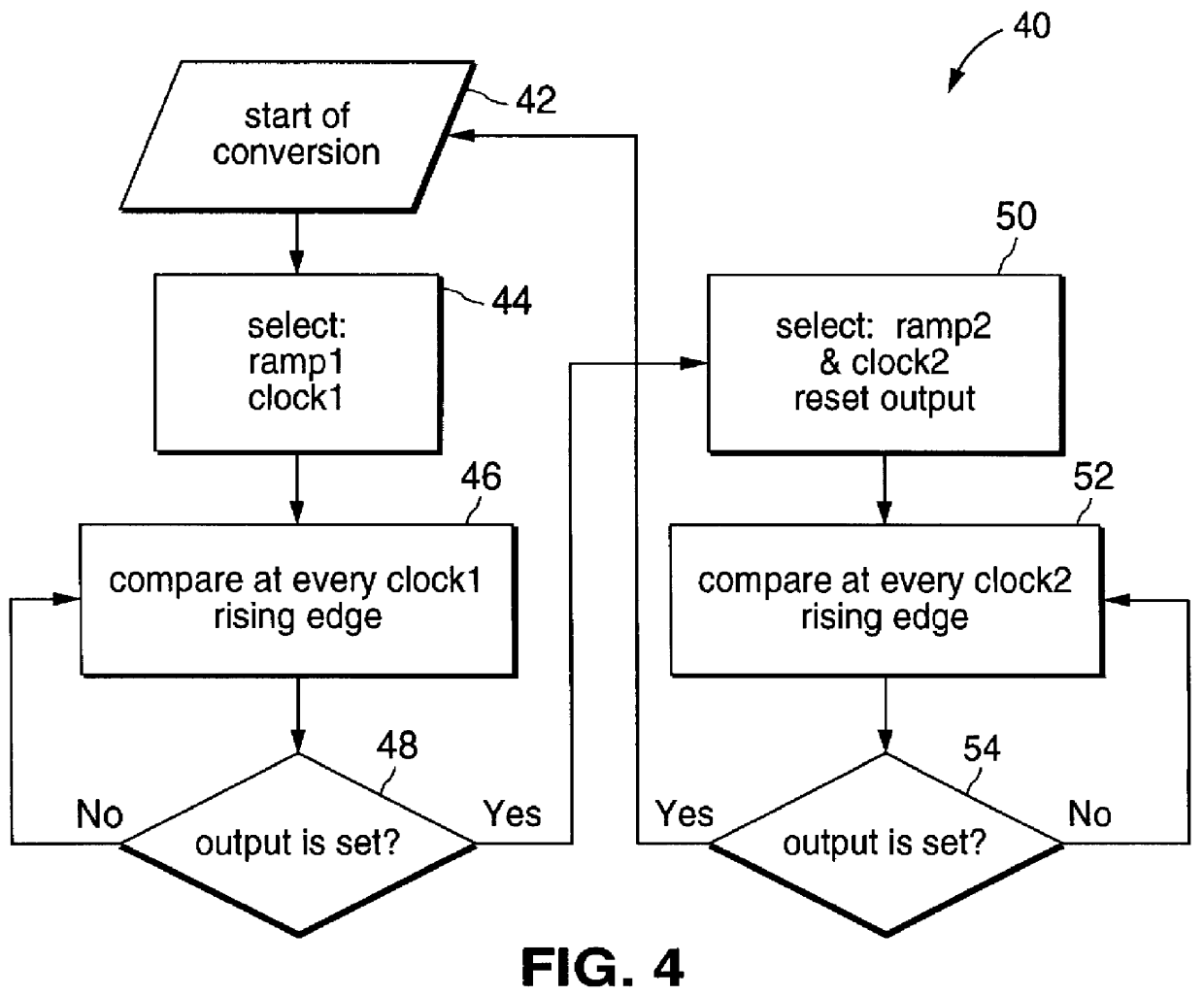

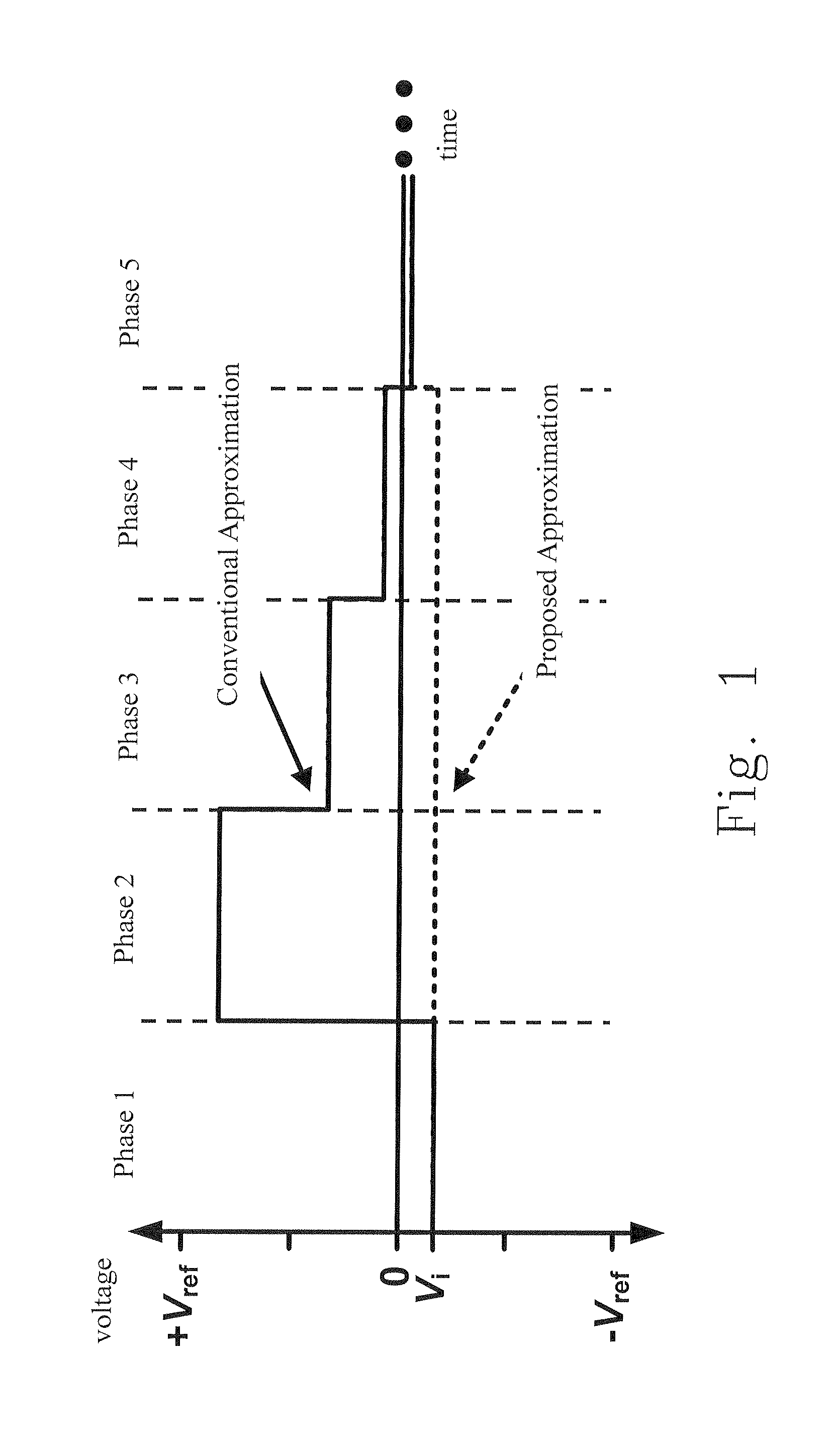

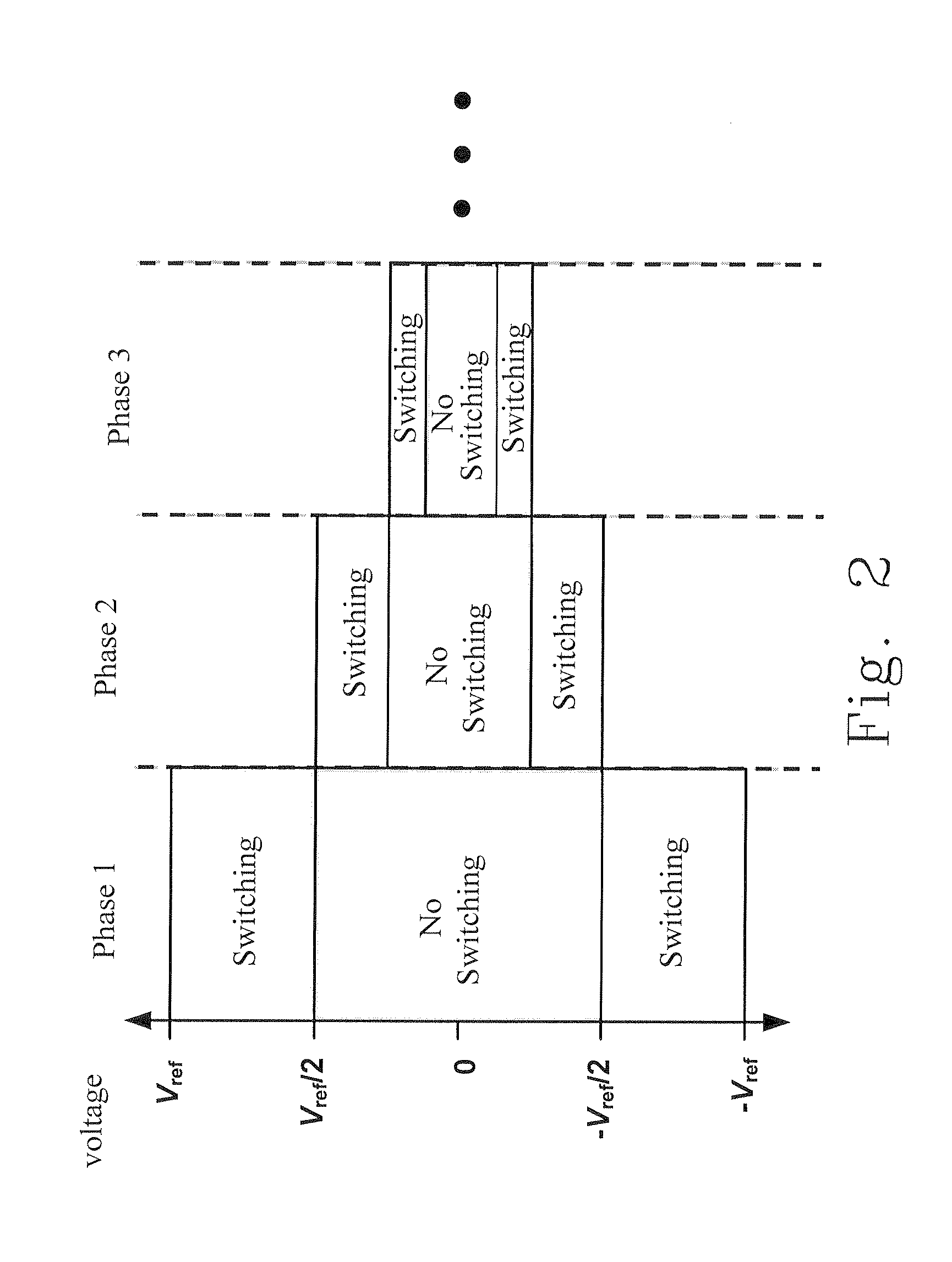

A low-power column parallel ADC architecture for image sensors that reduces the power consumption by reducing the number of switchings of a comparator to digitize a row of pixel data. Two ramp reference signals are provided in accordance with the principles of this invention. A first ramp signal is provided to each comparator that is clocked with an associated first clock signal. In each column comparator, the first ramp signal is compared to the pixel data using clock1, wherein clock1 corresponds to N multiple of a second clock signal (clock2), with N>1. Only when the column comparator detects a first crossover with the first ramp signal, then the comparator switches at every clock cycle of the second clock, clock2, to compare and detect a second crossover point with the second reference signal. This arrangement can greatly reduce the number of switchings required to digitize a row of pixel data, thereby resulting in significant power saving.

Owner:HANGER SOLUTIONS LLC

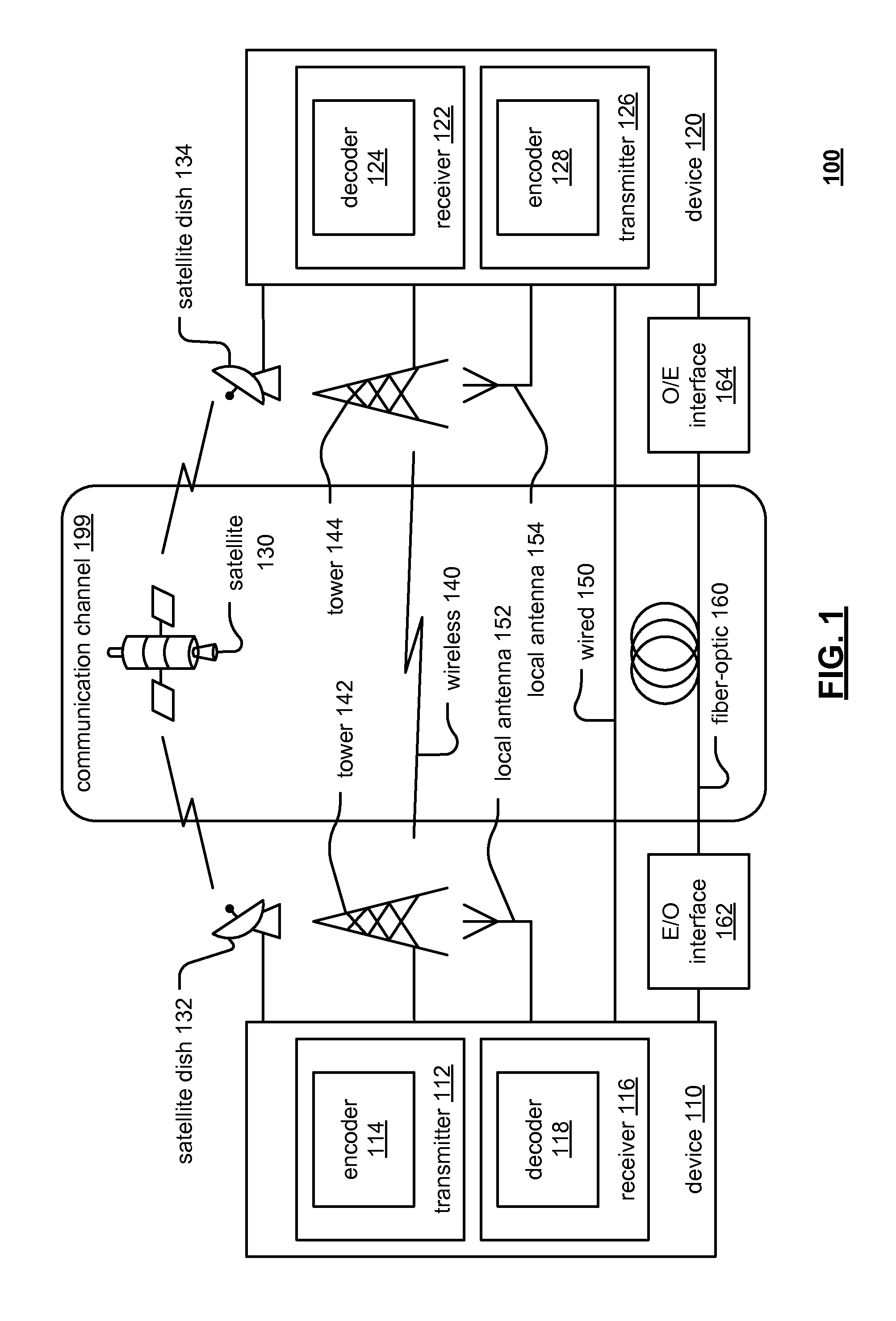

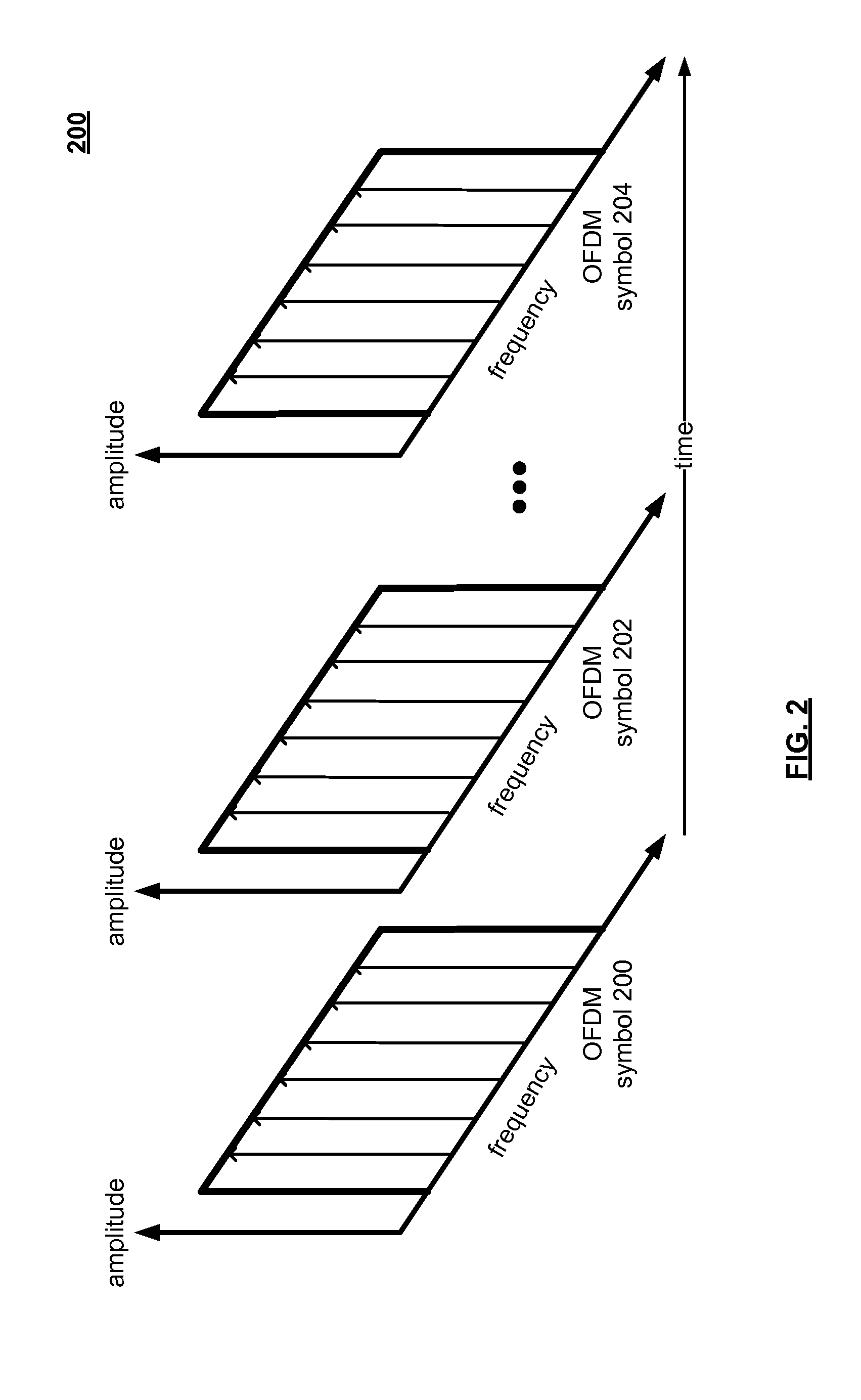

Fractional-N Frequency Synthesizer Incorporating Cyclic Digital-To-Time And Time-To-Digital Circuit Pair

ActiveUS20160056827A1Low spuriousReduce power consumptionPower saving provisionsElectric signal transmission systemsFrequency spectrumFrequency synthesizer

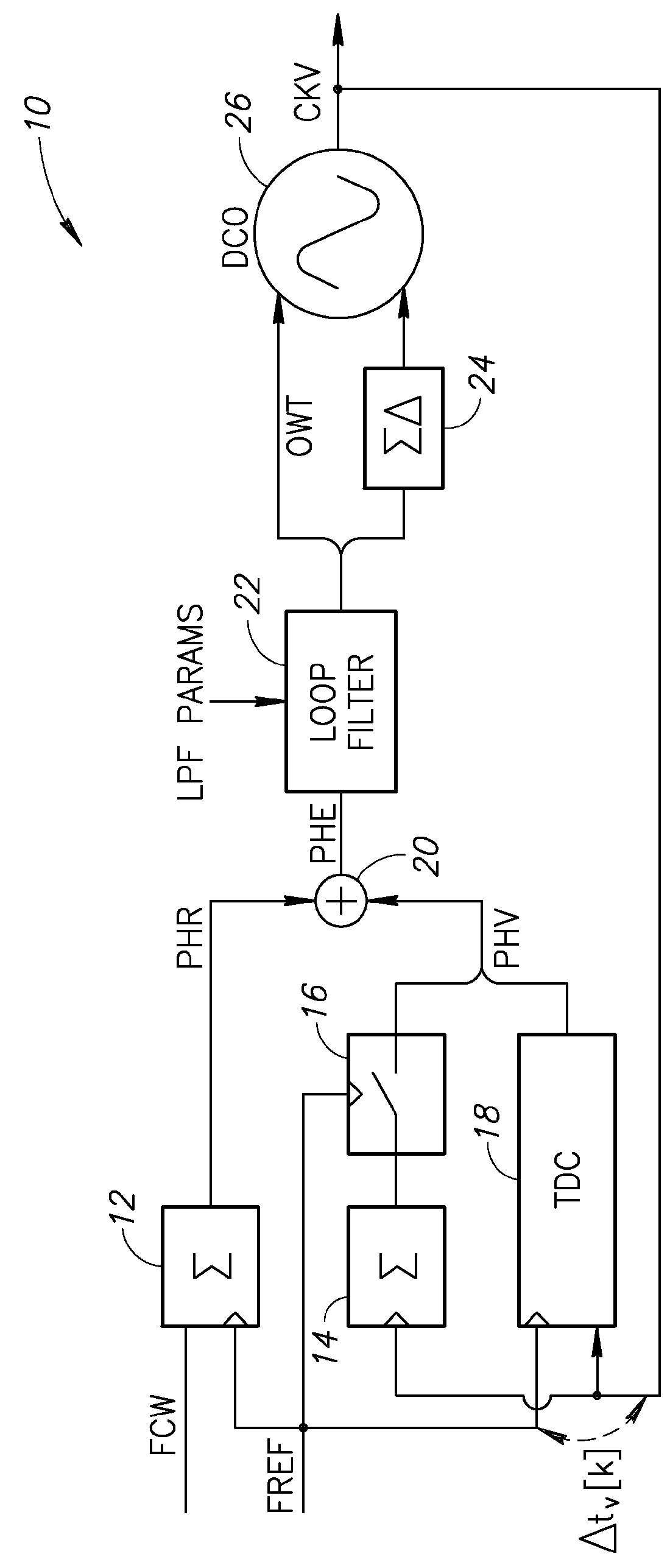

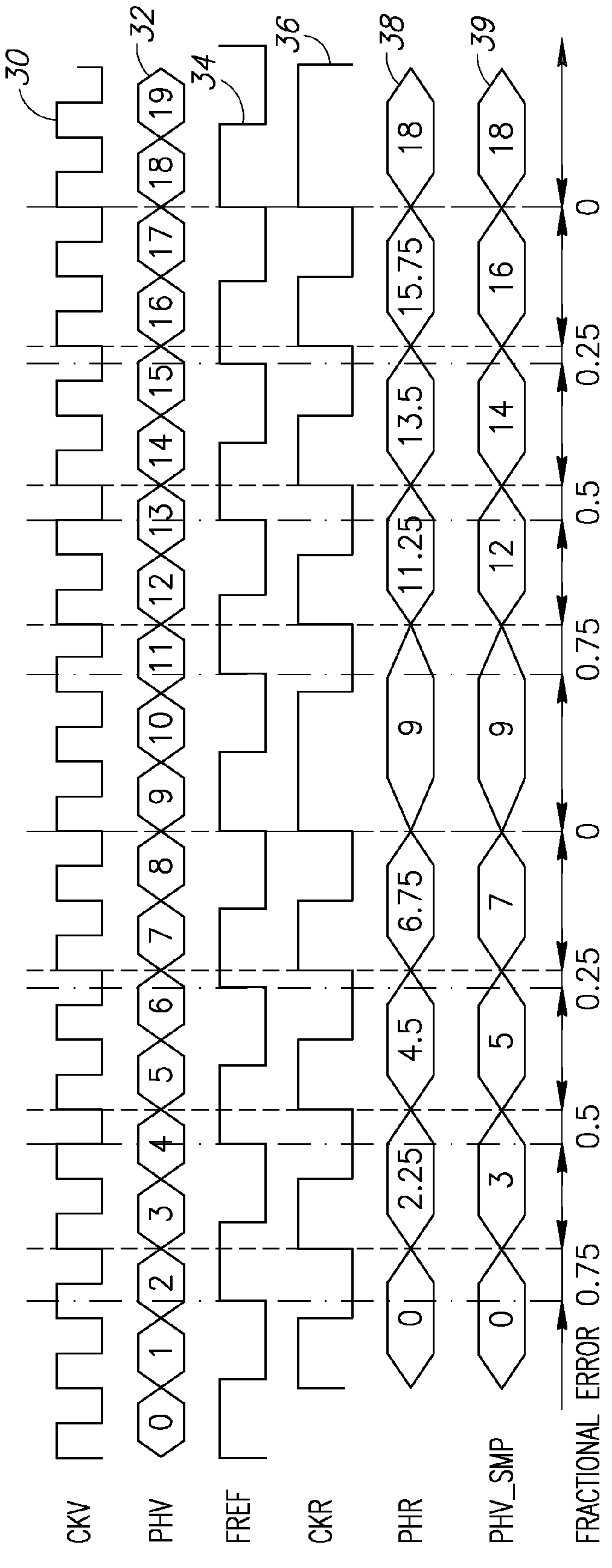

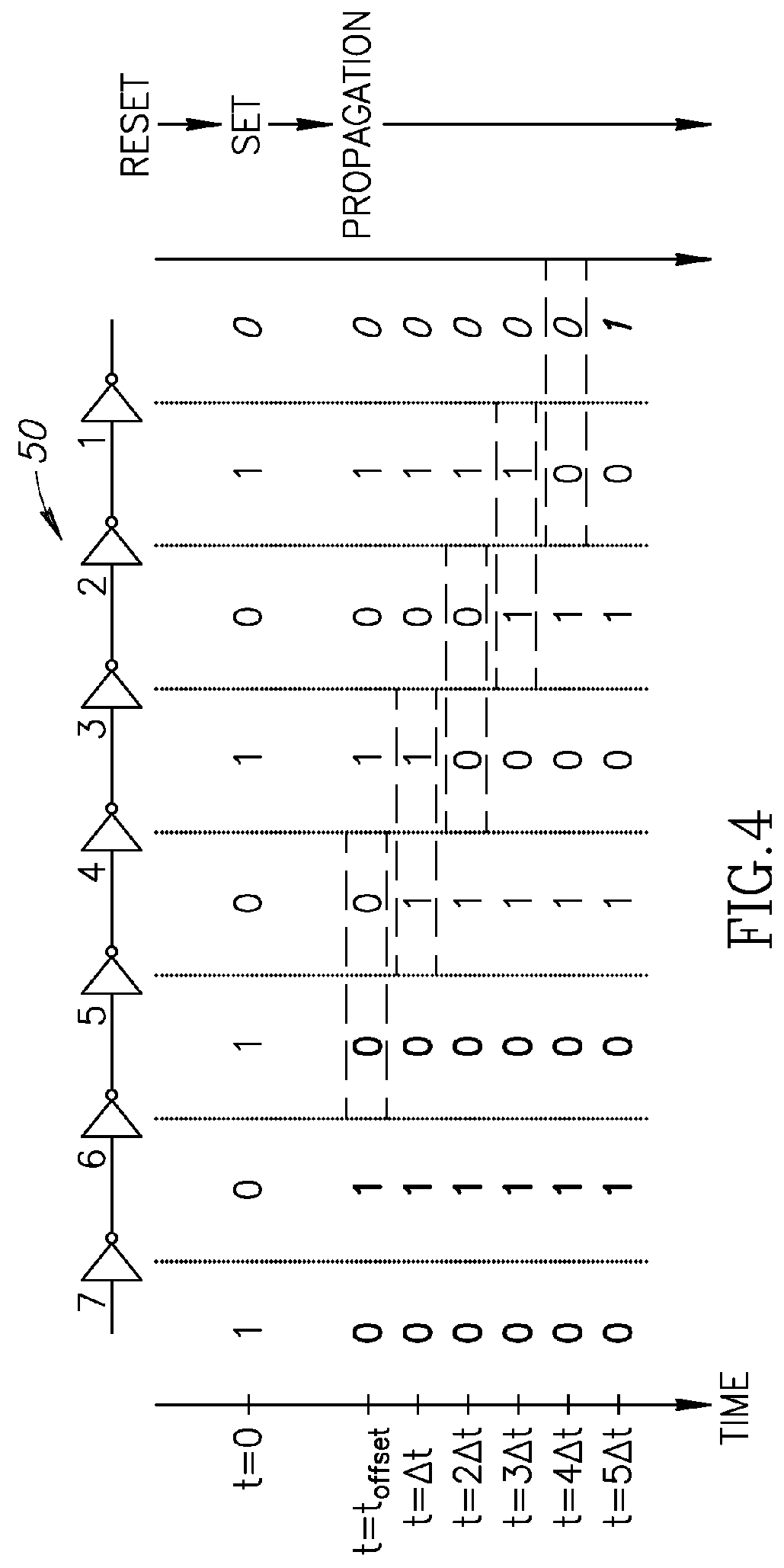

A novel and useful look-ahead time to digital converter (TDC) that is applied to an all digital phase locked loop (ADPLL) as the fractional phase error detector. The deterministic nature of the phase error during frequency / phase lock is exploited to achieve a reduction in power consumption of the TDC. The look-ahead TDC circuit is used to construct a cyclic DTC-TDC pair which functions to reduce fractional spurs of the output spectrum in near-integer channels by randomly rotating the cyclic DTC-TDC structure so that it starts from a different point every reference clock thereby averaging out the mismatch of the elements. Associated rotation and dithering methods are also presented. The ADPLL is achieved using the look-ahead TDC and / or cyclic DTC-TDC pair circuit.

Owner:SHORT CIRCUIT TECH LLC

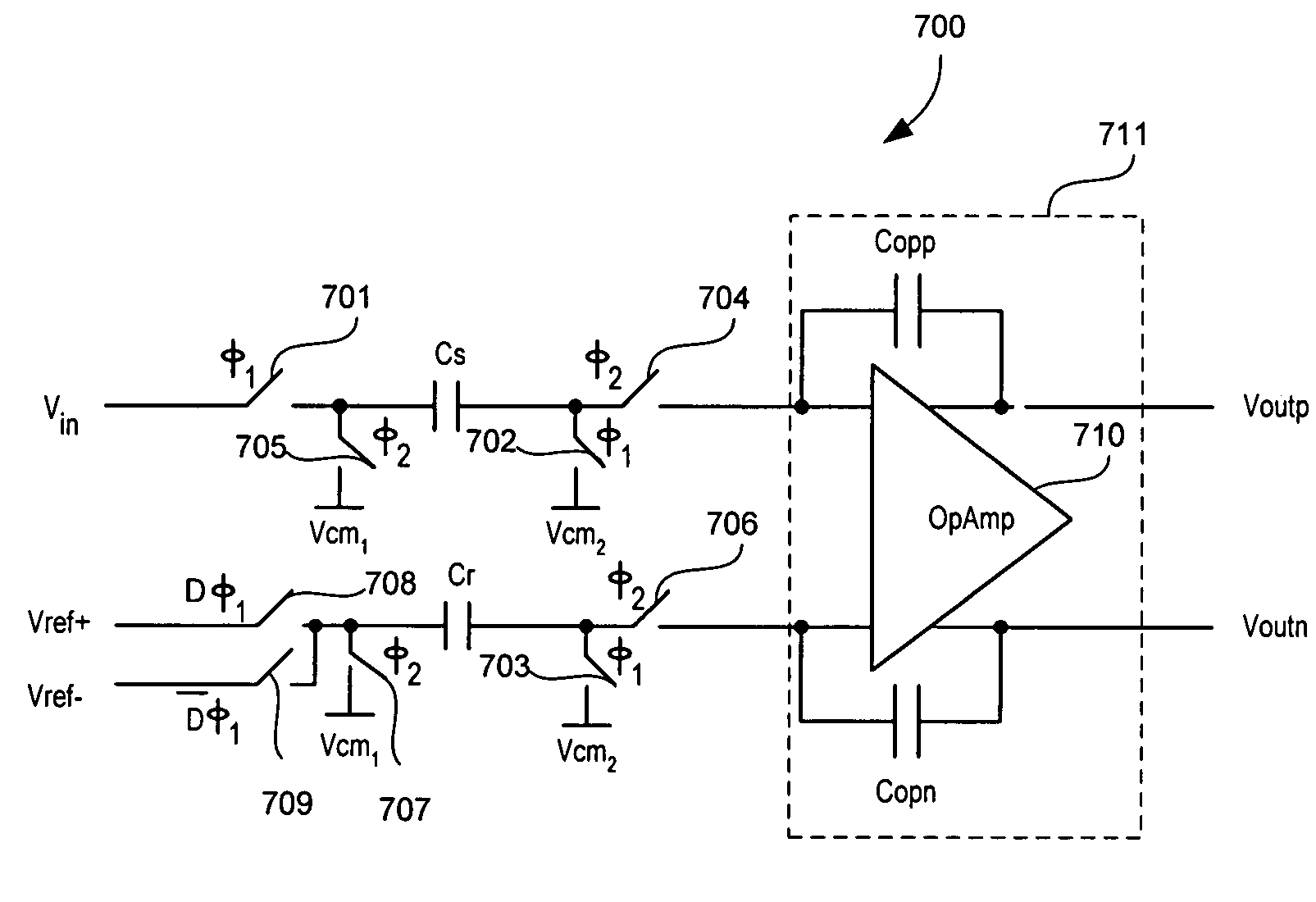

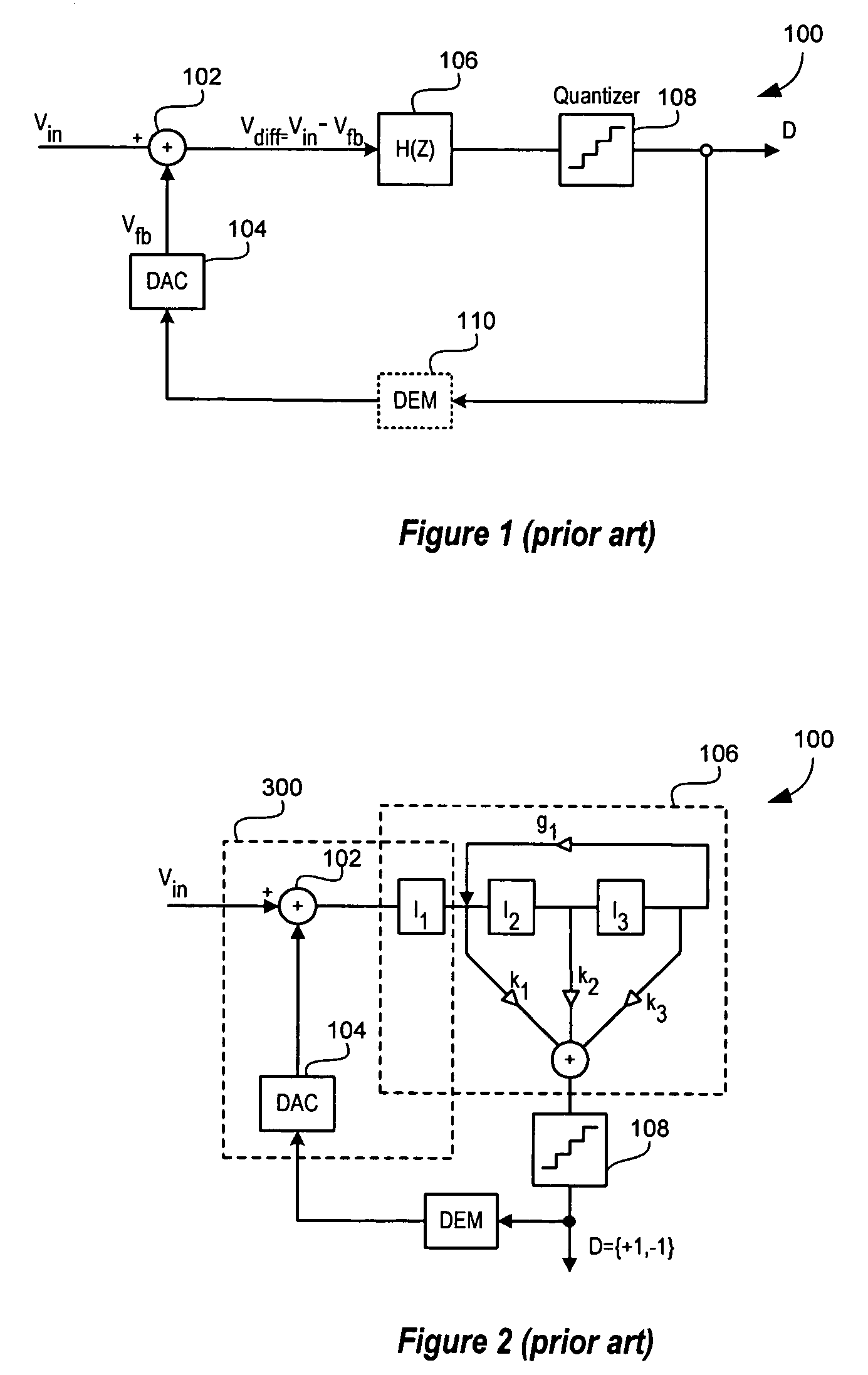

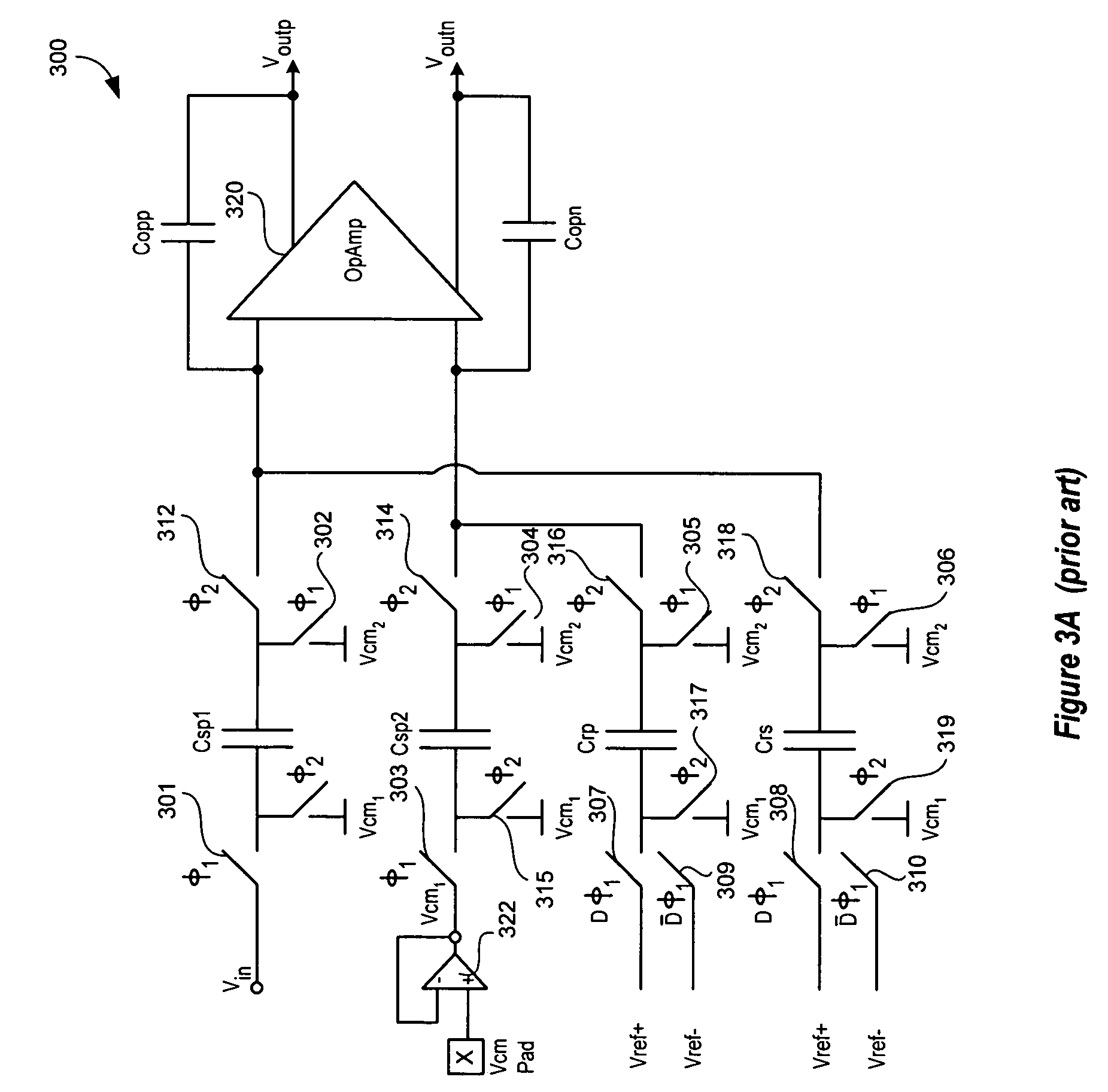

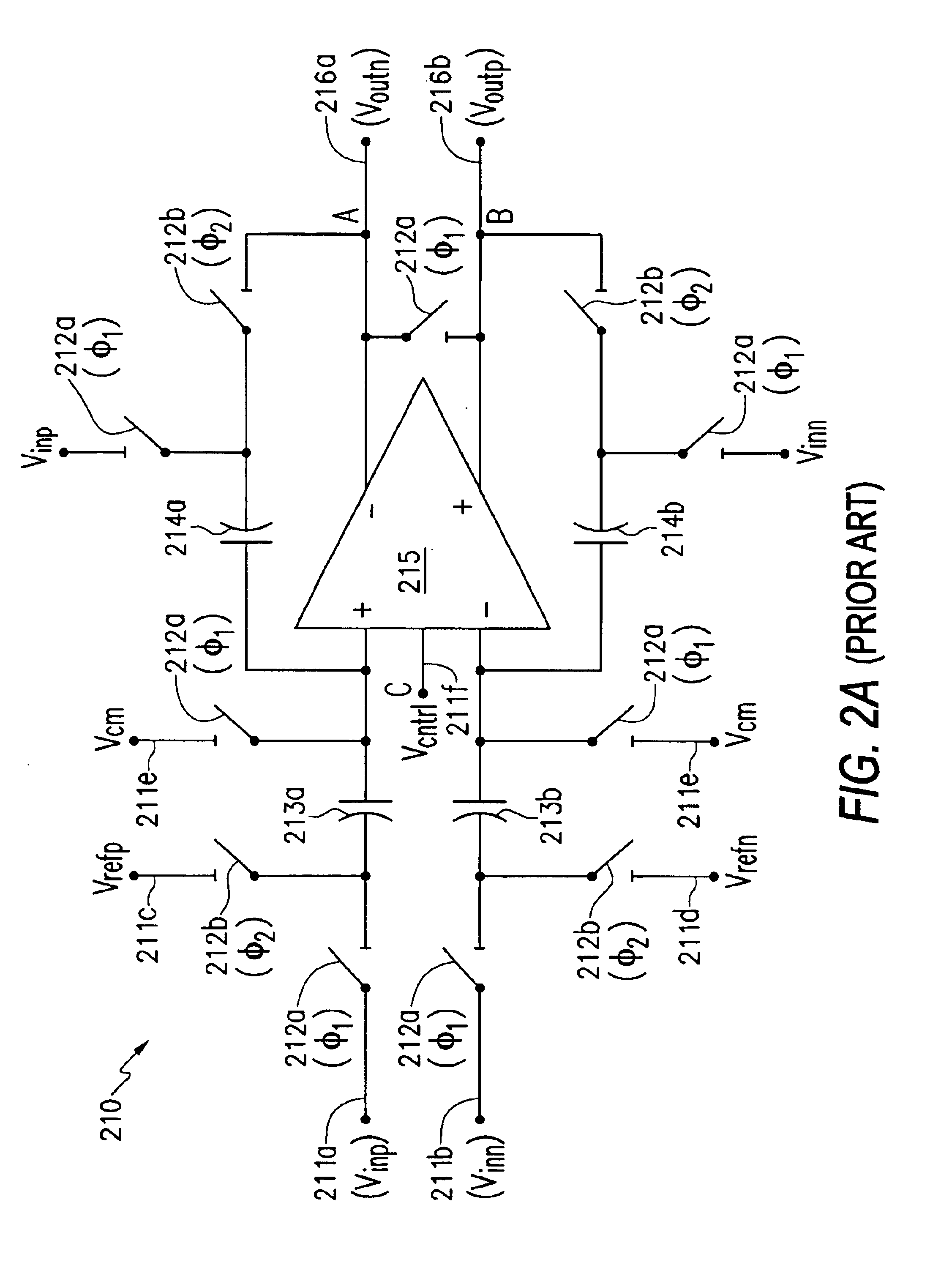

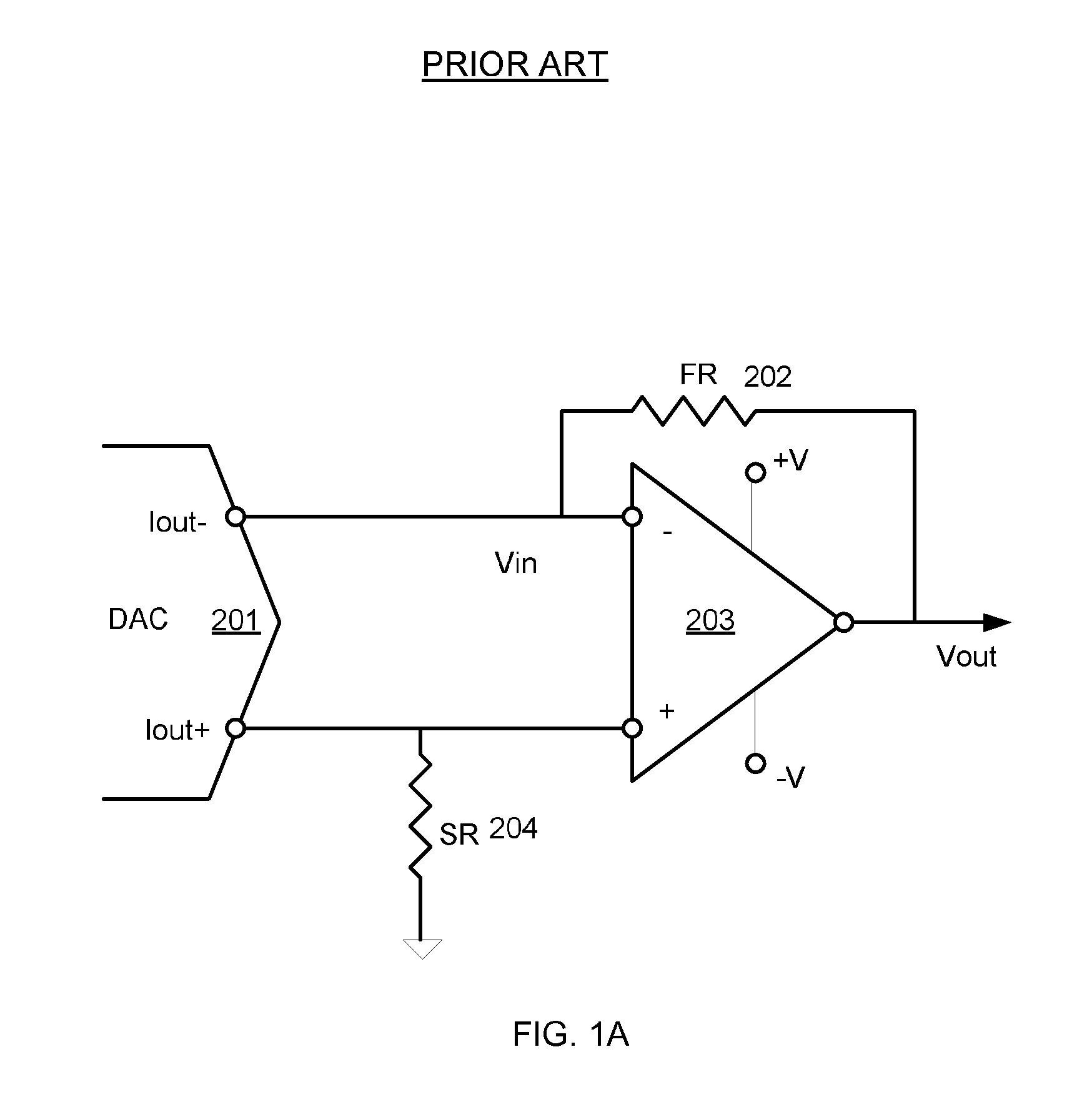

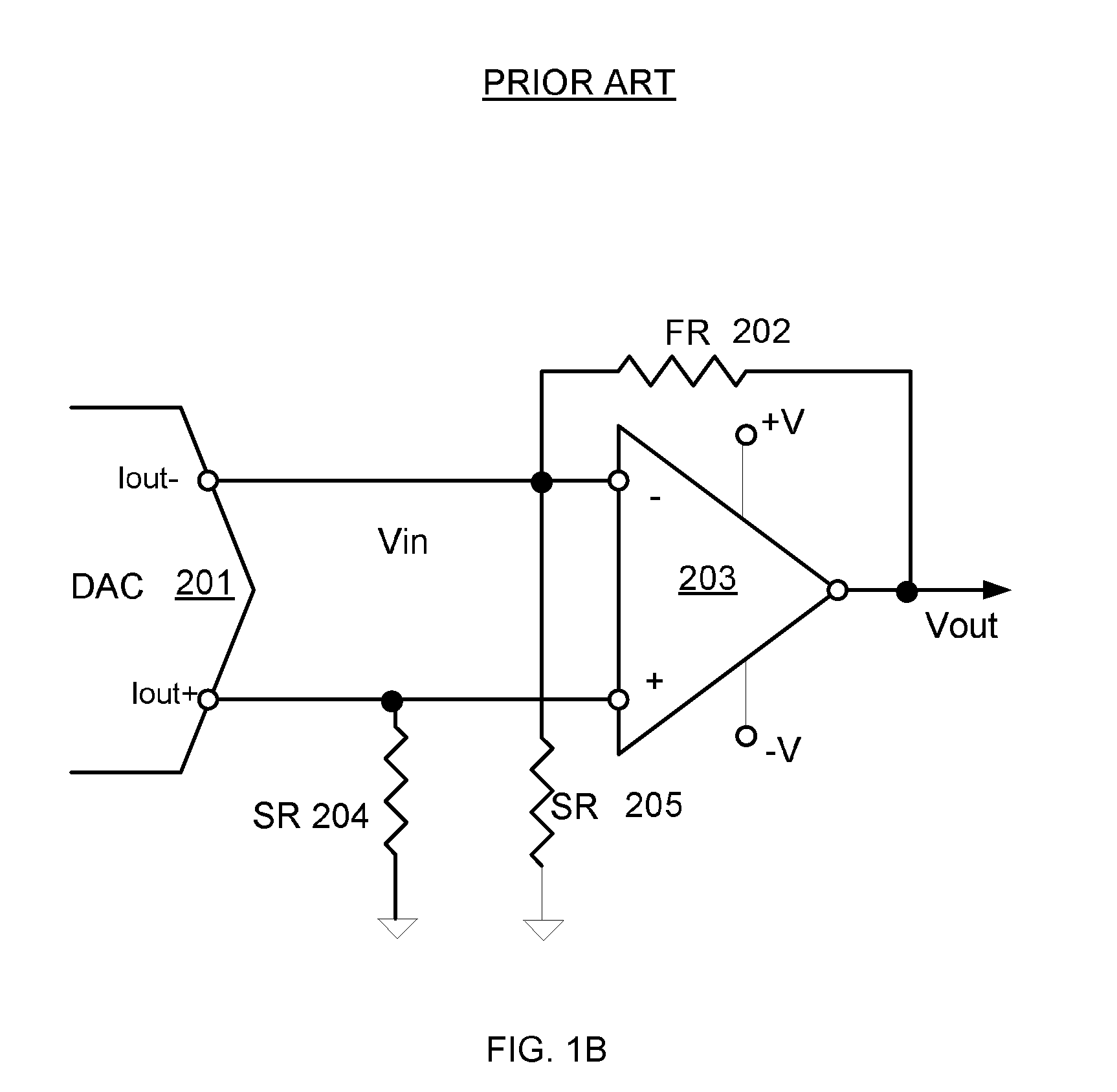

Signal processing system having an ADC delta-sigma modulator with single-ended input and feedback signal inputs

ActiveUS6972705B1Electric signal transmission systemsDifferential modulationAnalog feedbackEngineering

Signal processing systems described herein include an analog-to-digital delta sigma modulator to process a single-ended input signal using a single-ended analog feedback reference signal. The delta sigma modulator includes a switched capacitor circuit that integrates a difference between the single-ended input signal and the single-ended analog feedback signal derived from a quantization output of the delta sigma modulator. Embodiments of the switched capacitor circuit allow the delta sigma modulator to be implemented with fewer switches, less complicated reference signal generators, and smaller capacitors relative to conventional counterparts. Thus, embodiments of the delta sigma modulator described herein can cost less to build and use less power. Embodiments of the signal processing systems can be implemented in single and multi-bit delta sigma modulators and various sampling topologies, including single and double sampling topologies.

Owner:CIRRUS LOGIC INC

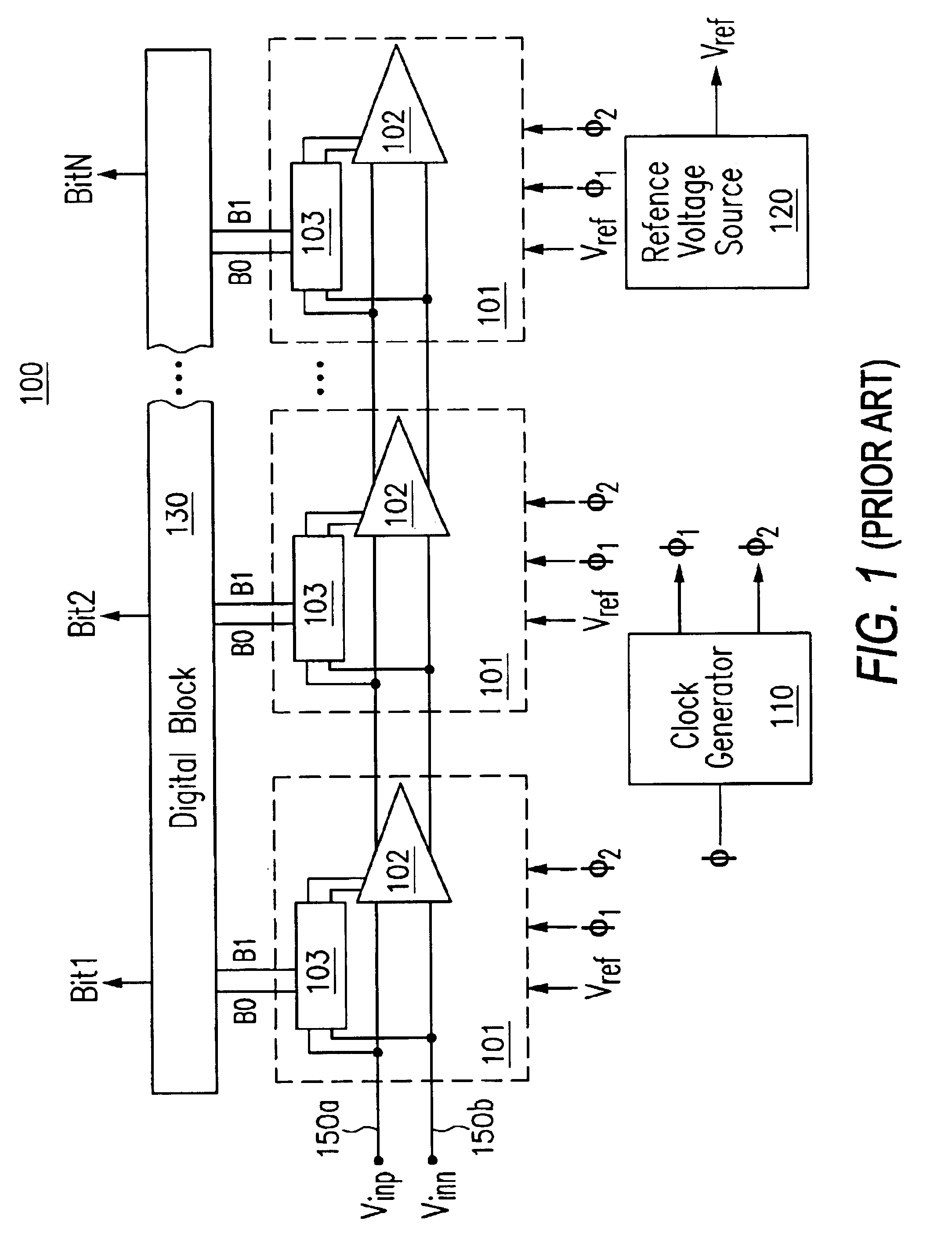

Double throughput analog to digital converter

ActiveUS6870495B1Improve efficiencyImprove throughputPower saving provisionsElectric signal transmission systemsAudio power amplifierEngineering

A pipelined analog-to-digital converter features an amplifier block that includes a switching network to implement a double sampling and double conversion principle of operation. The amplifier block utilizes both phases of a clock for sampling and conversion. Additionally, each stage of the analog-to-digital converter is associated with two independent processing blocks. The analog-to-digital converter can achieve double throughput for approximately the same level of power consumption. Alternatively, throughput may be maintained, but the gain-bandwidth of the amplifier block may be reduced by half, thereby halving the DC bias current consumed by the amplifier. Additionally, the output signal of the amplifier itself is not reset to a common mode voltage.

Owner:MICRON TECH INC

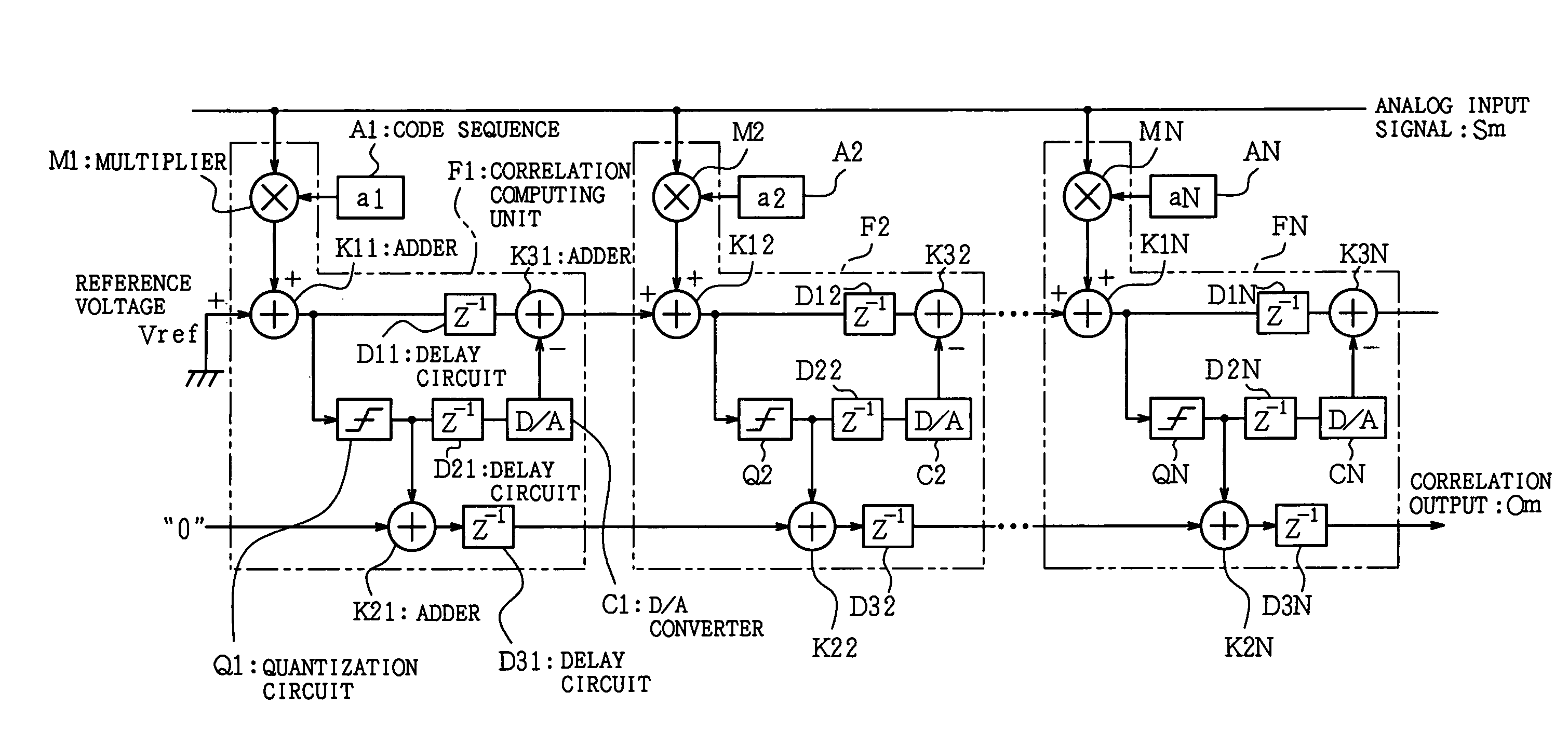

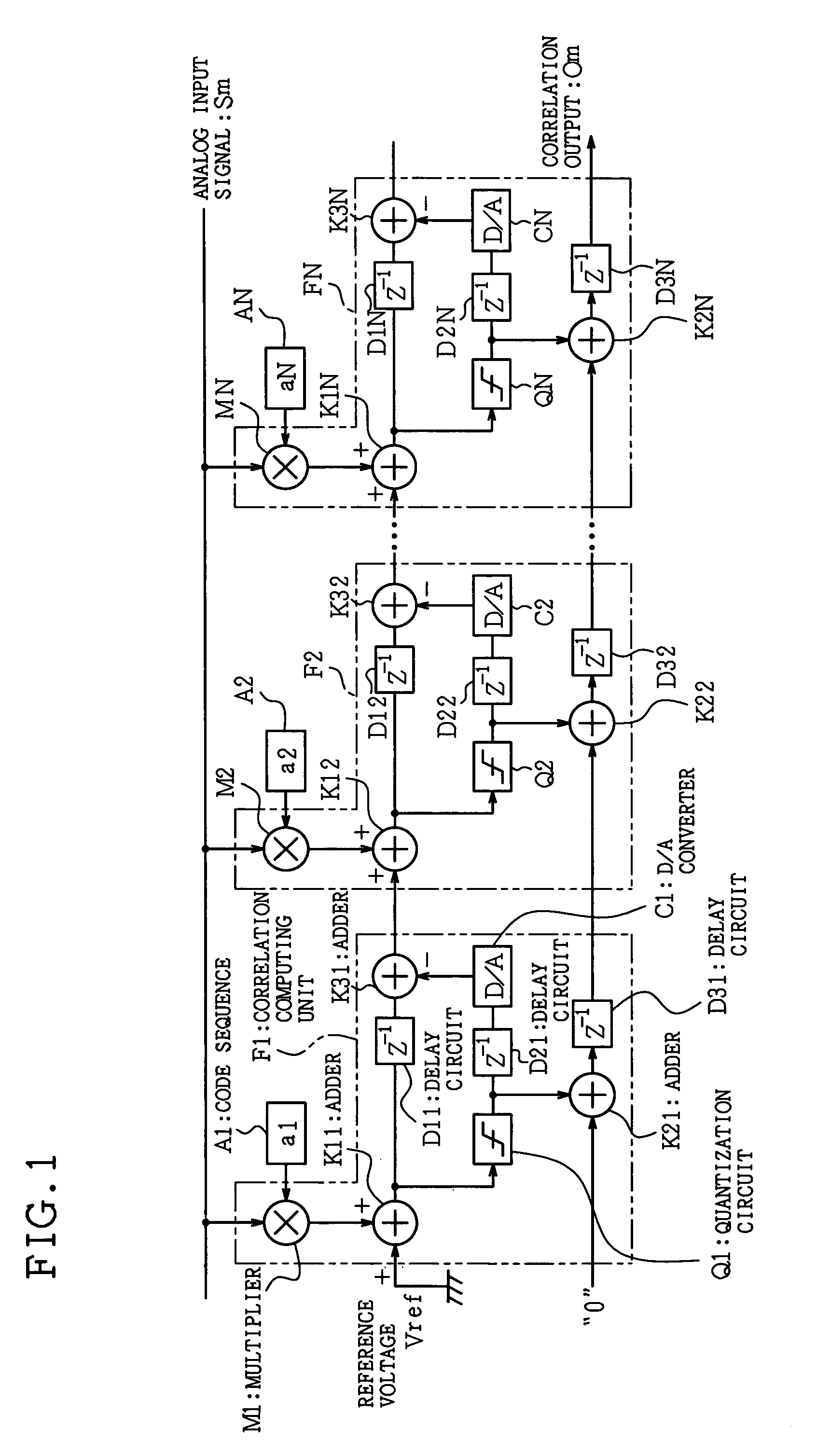

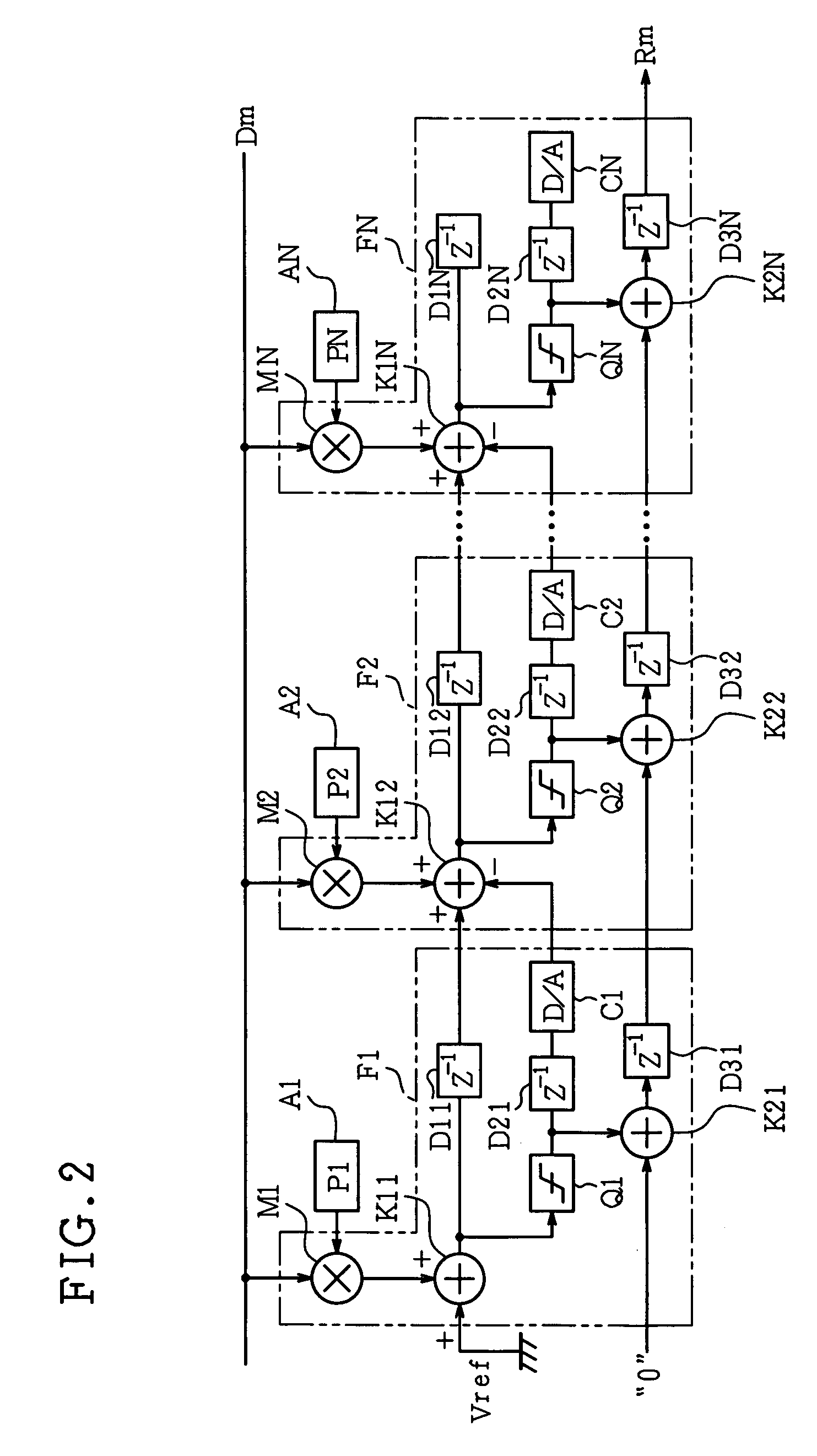

Filter circuit

InactiveUS6983011B1Reduce circuit sizeReduce power consumptionMultiple-port networksPower saving provisionsComputer scienceDynamic range

In a filter circuit of the present invention, a partial quantization value is computed by a quantization circuit according to a spread code and others in a unit at an arbitrary stage, where an integrating value is increased. The partial quantization value is successively added by an adder formed by a counter and is transmitted to a unit of the following stage. In an adder of the following stage, an analog residual is computed by subtracting an analog converted value of the partial quantization value, that is obtained by a D / A converter, from the integrating value so as to suppress an increase in the analog cumulative value. With this arrangement, the cumulative value is increased according to an increase in the number of taps, so that an analog adder can reduce power consumption, which is caused by expansion of a dynamic range at the following stage.

Owner:SHARP KK

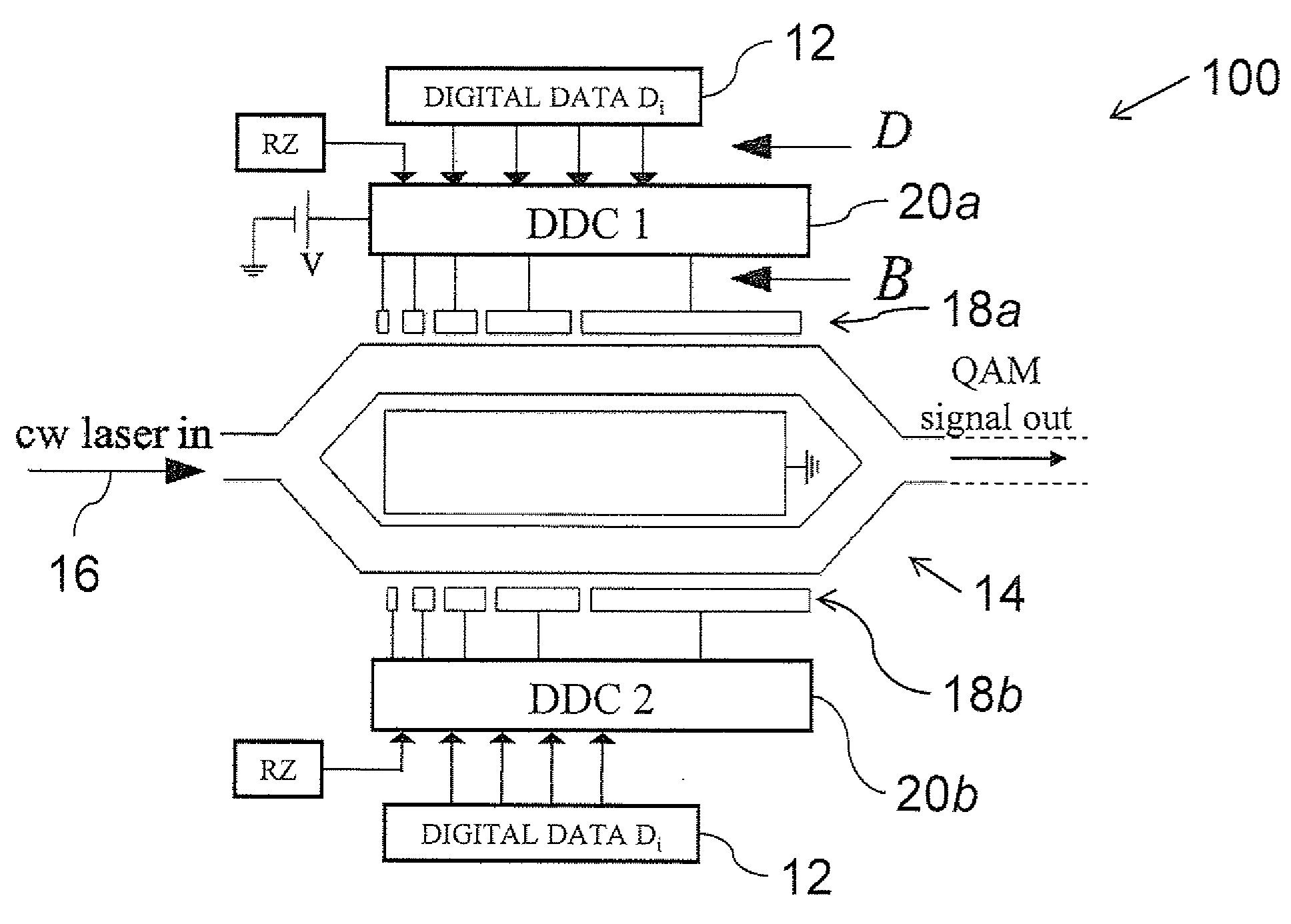

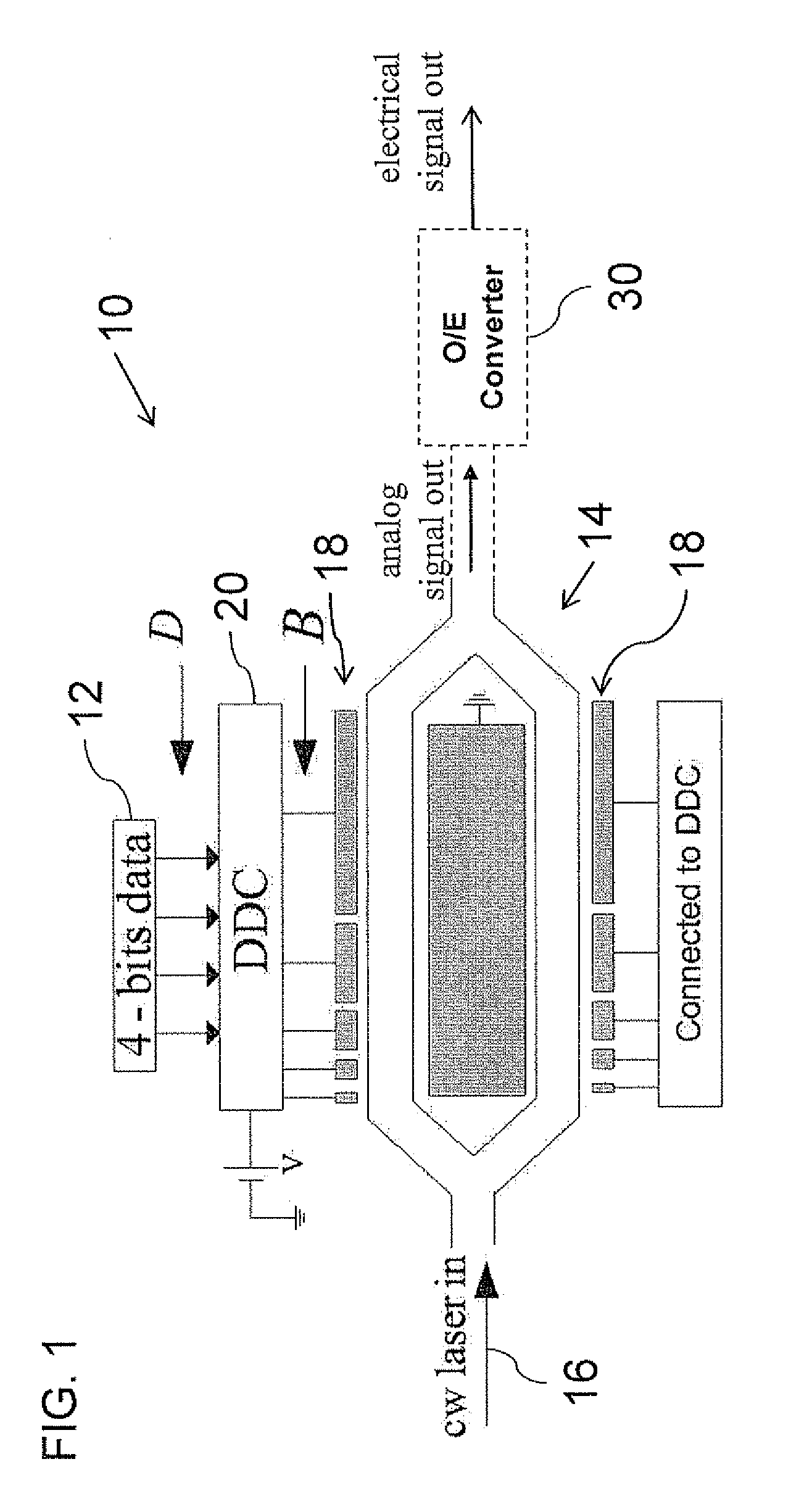

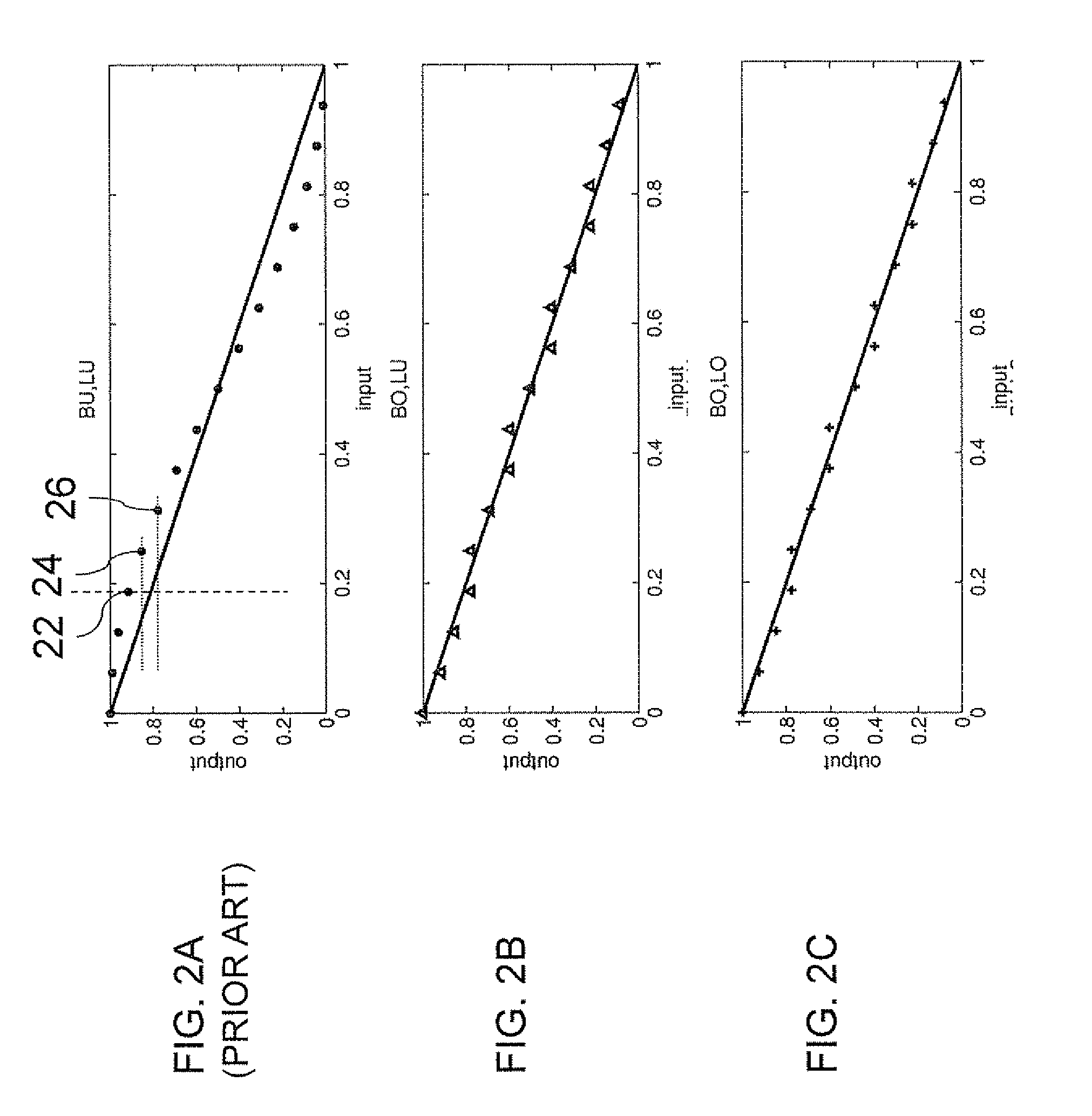

Linearized optical digital-to-analog modulator

ActiveUS20100156679A1Power saving provisionsOptical analogue/digital convertersDigital dataEngineering

A modulator device for converting digital data into modulation of an optical signal includes an electronic input for receiving an input data word of N bits and an electrically controllable modulator for modulating the intensity of an optical signal, the modulator including M actuating electrodes where M≧N. An electrode actuating device, most preferably a digital-to-digital converter, operates actuating electrodes so that at least one electrode is actuated as a function of values of more than one bit of the input data word. According to an alternative, or supplementary, aspect of the invention, the set of electrodes includes at least one electrode having an effective area which is not interrelated to others of the set by factors of two. In one preferred implementation, a Mach-Zehnder modulator also provides phase modulation to give QAM functionality. Another implementation employs a semiconductor laser.

Owner:RAMOT AT TEL AVIV UNIV LTD

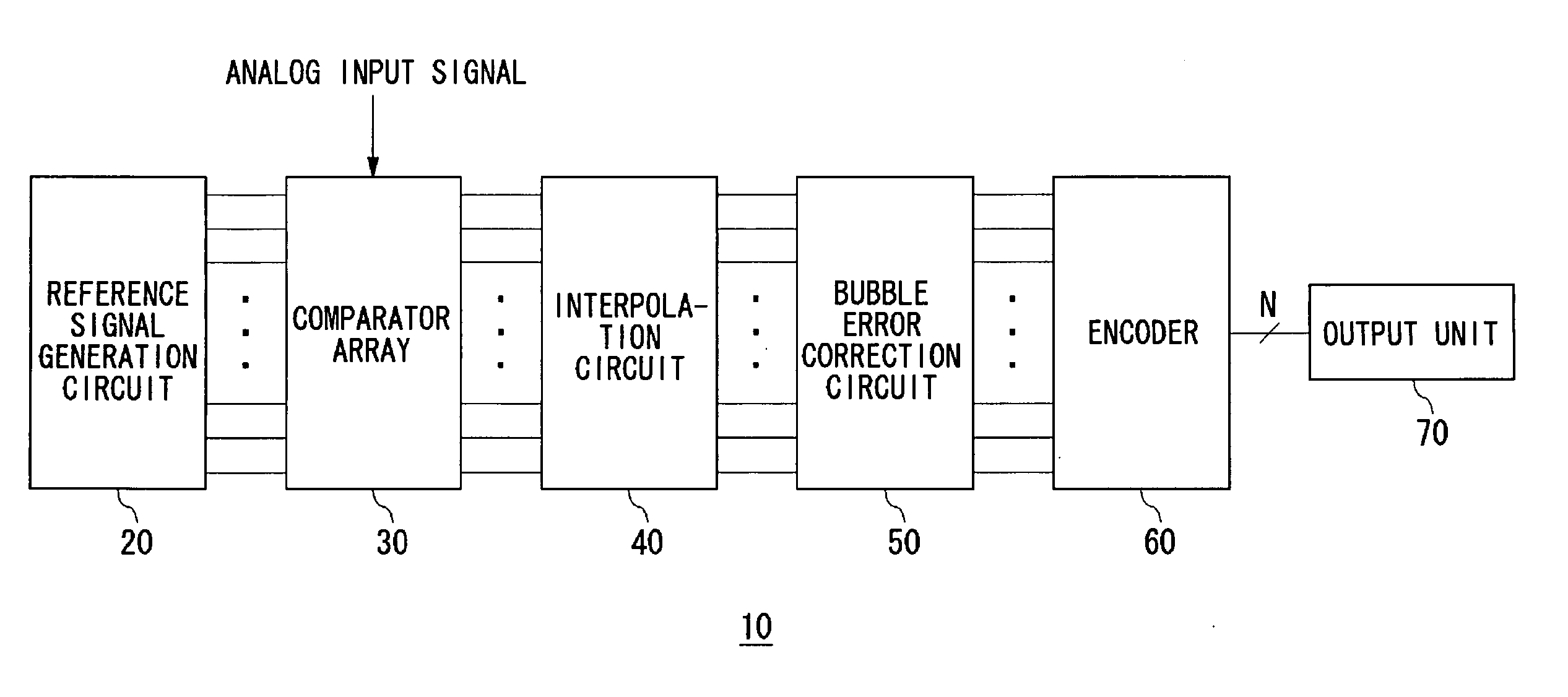

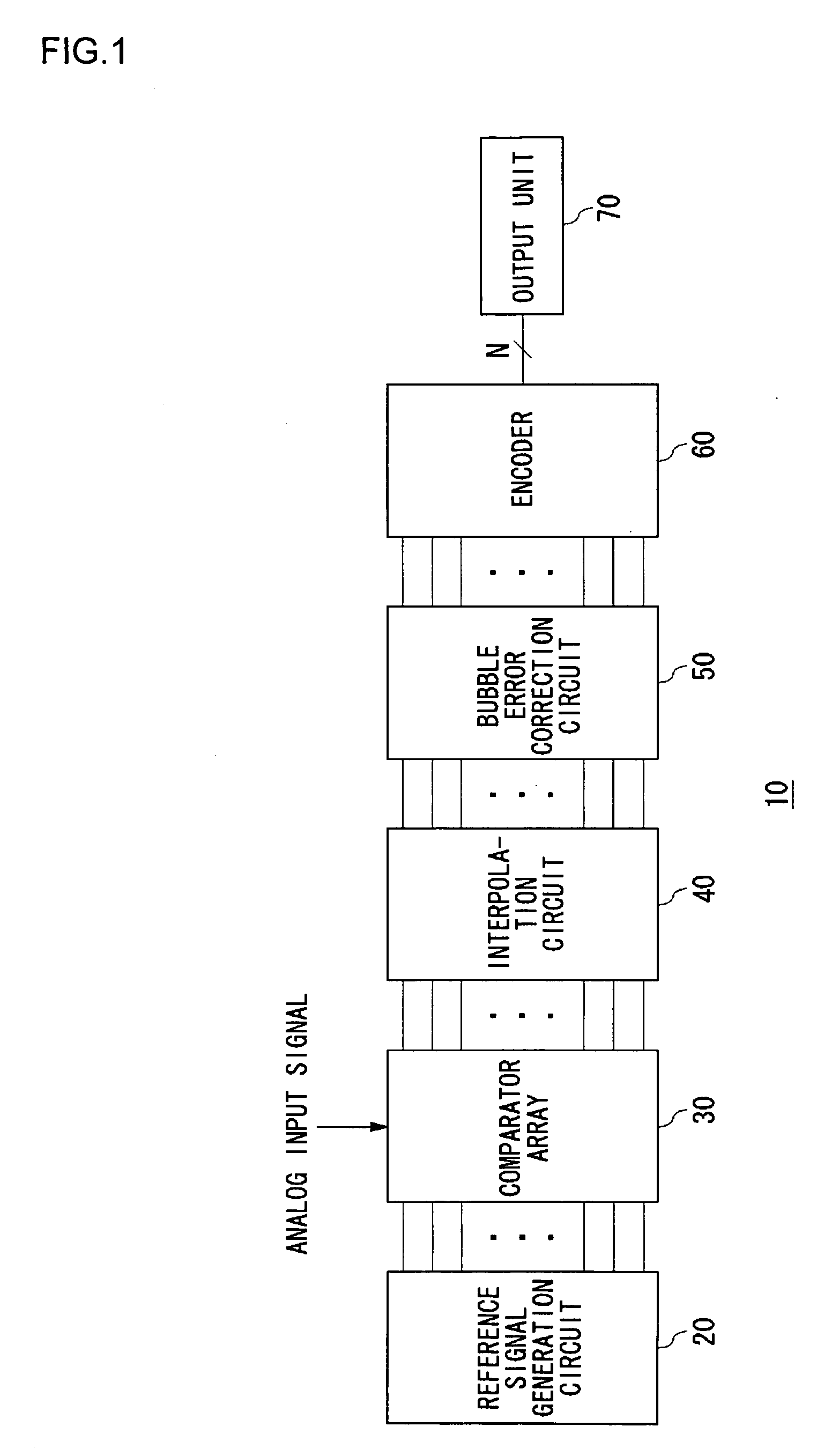

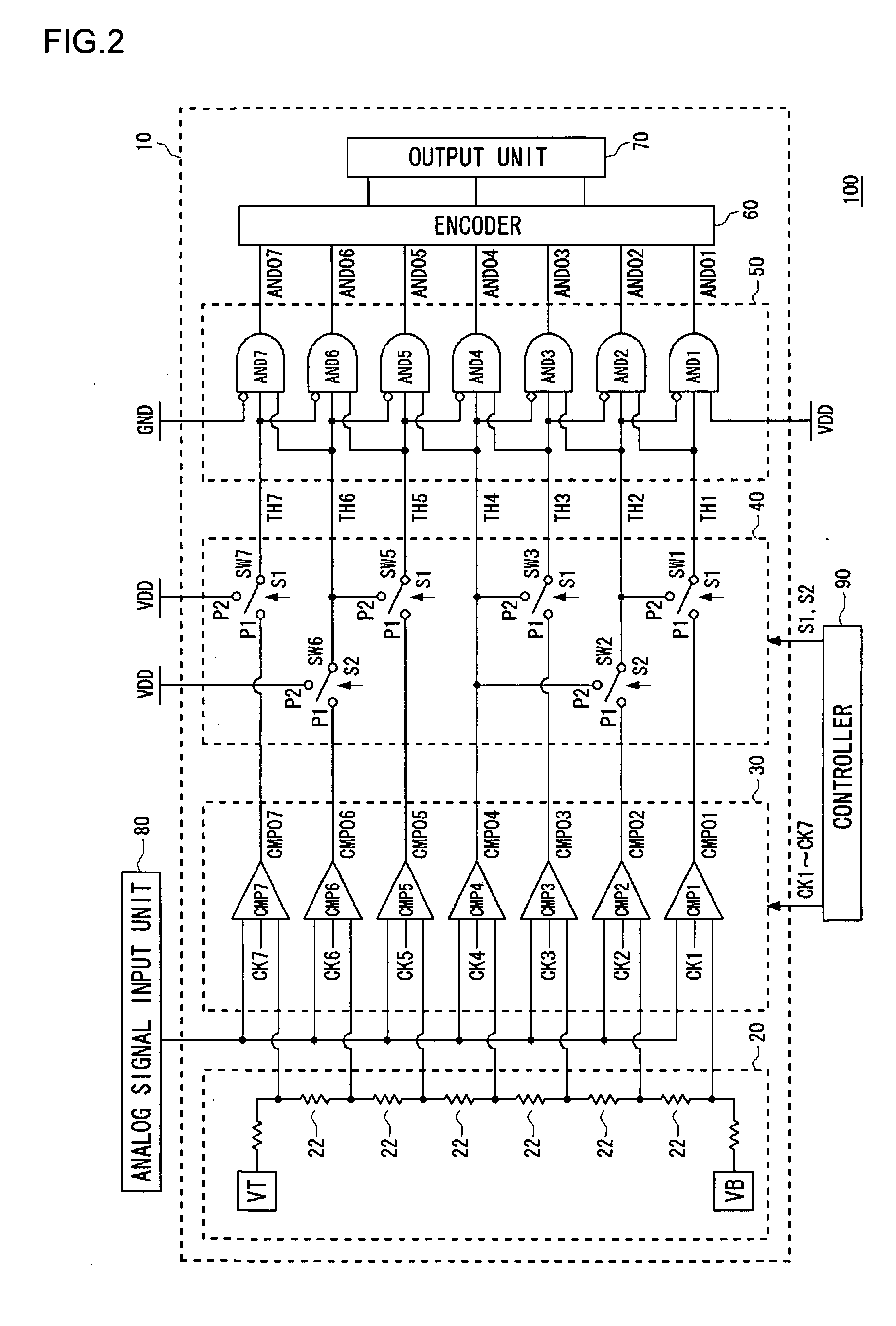

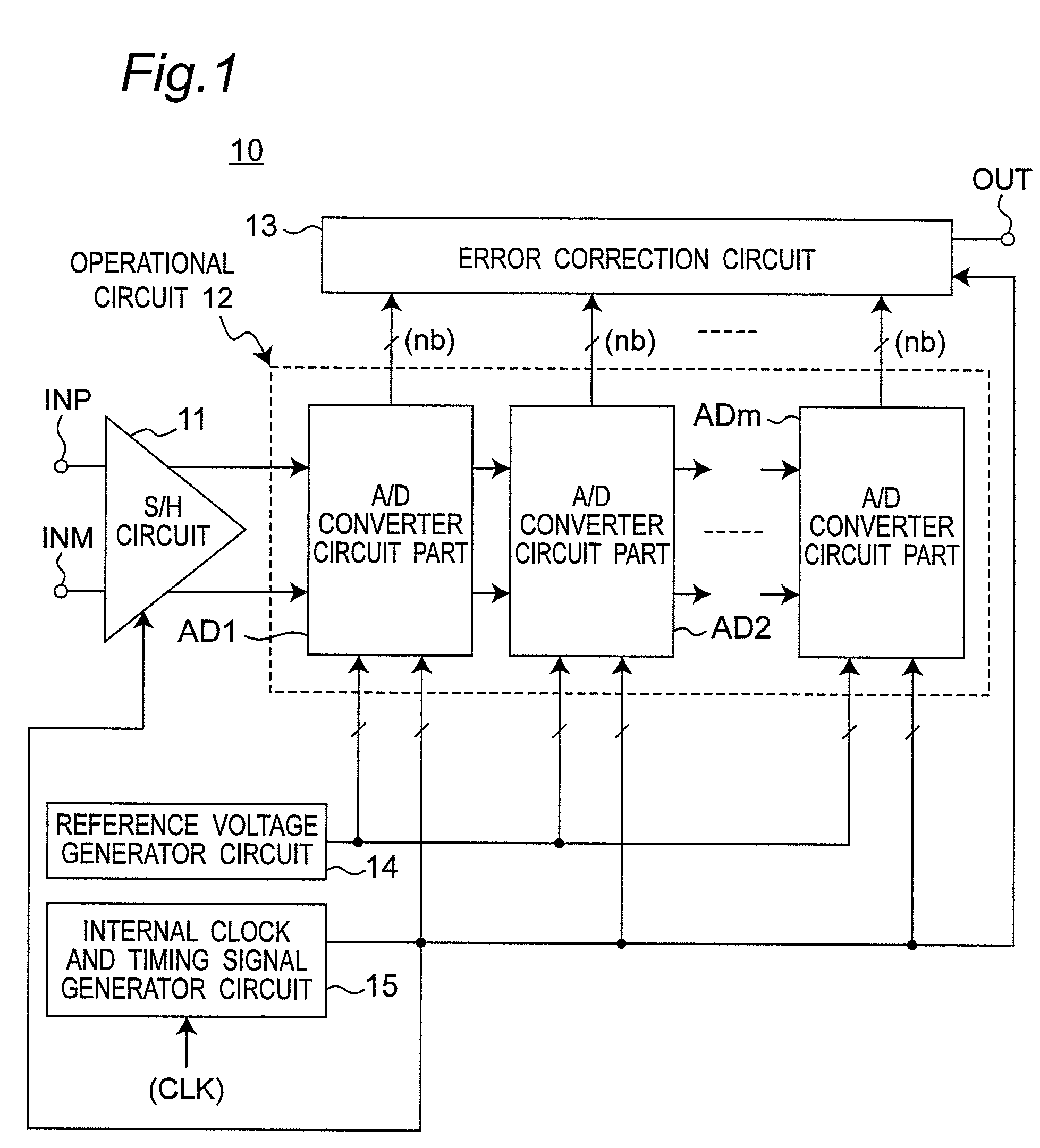

Analog-to digital converter and analog-to digital conversion apparatus

ActiveUS20060187105A1Variable resolutionReduce power consumptionPower saving provisionsElectric signal transmission systemsControl signalImage resolution

An analog-to-digital conversion apparatus which has a variable resolution and allows a reduction in power consumption. This apparatus comprises an analog-to-digital converter (ADC) of parallel type, a controller, and an interpolation circuit. The analog-to-digital converter has a plurality of comparators connected in parallel, each for comparing potentials of an analog input signal and a reference signal. The controller generates a control signal for controlling the resolution of the analog-to-digital converter. Specifically, the controller controls the number of comparators (CMP) to operate by means of the control signal, thereby determining the resolution. The interpolation circuit interpolates the output data of the comparators that are disabled depending on the resolution. The controller avoids simultaneous operation of two adjoining comparators when the analog-to-digital converter is operated at a resolution lower than its maximum resolution.

Owner:SEMICON COMPONENTS IND LLC

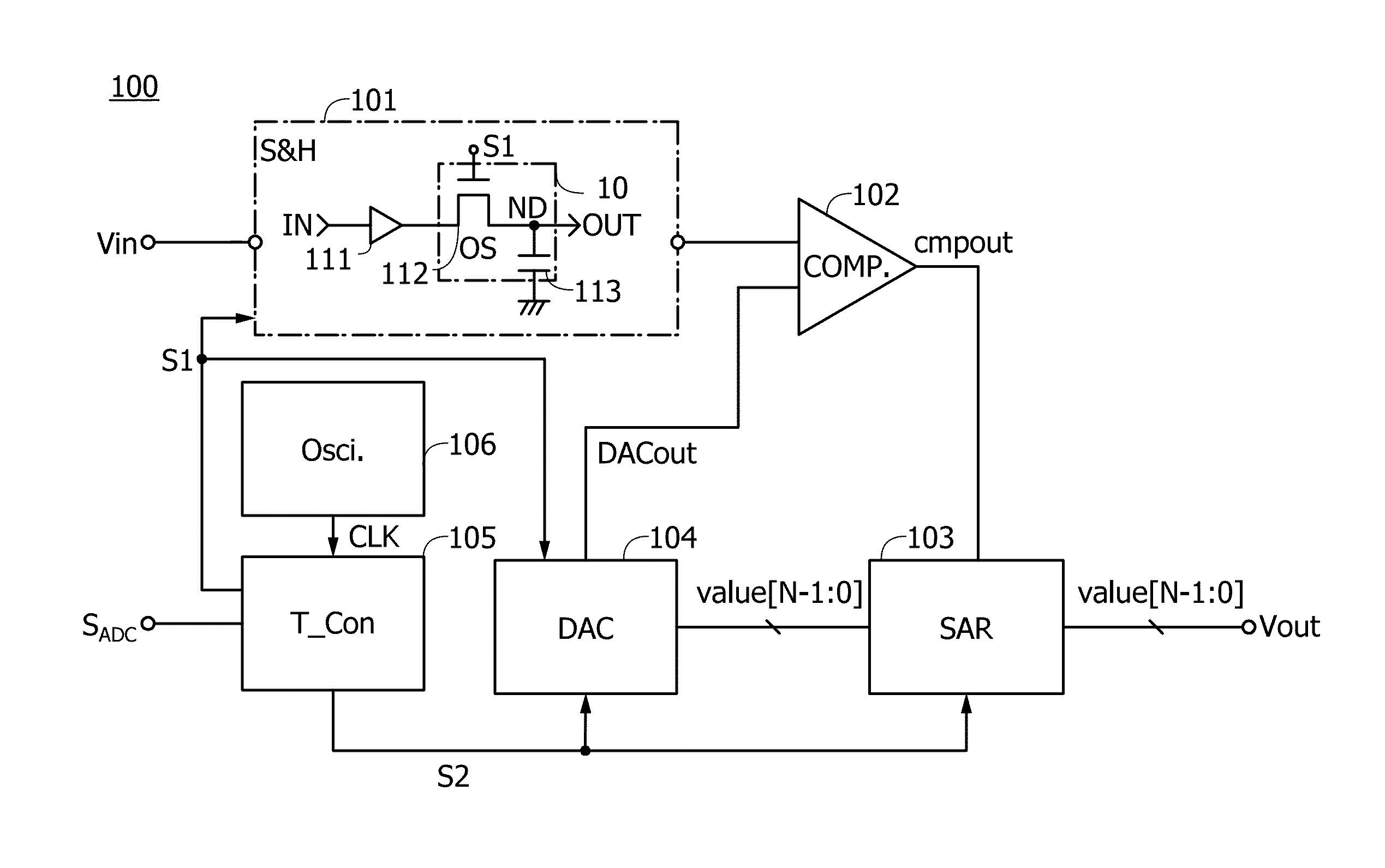

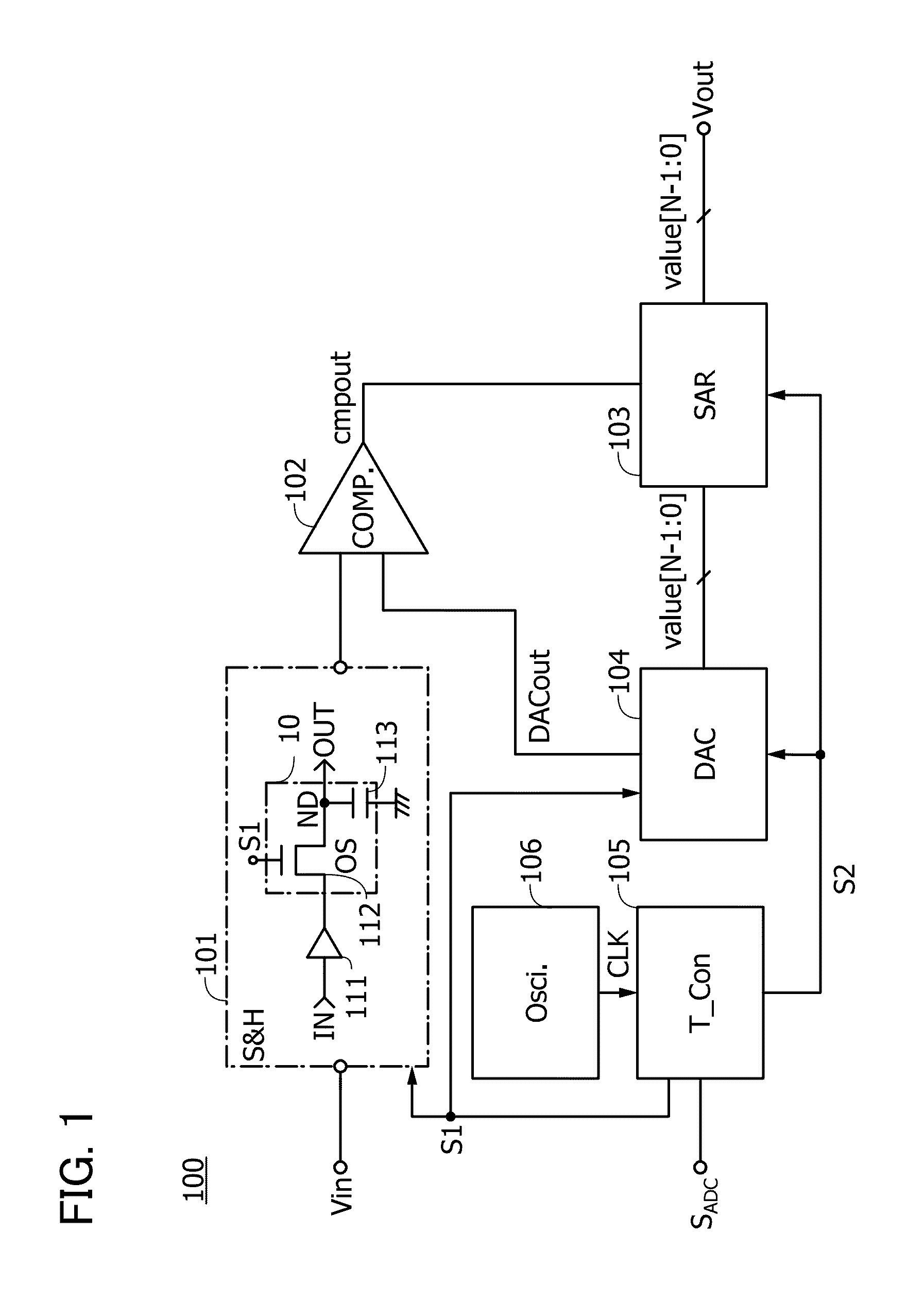

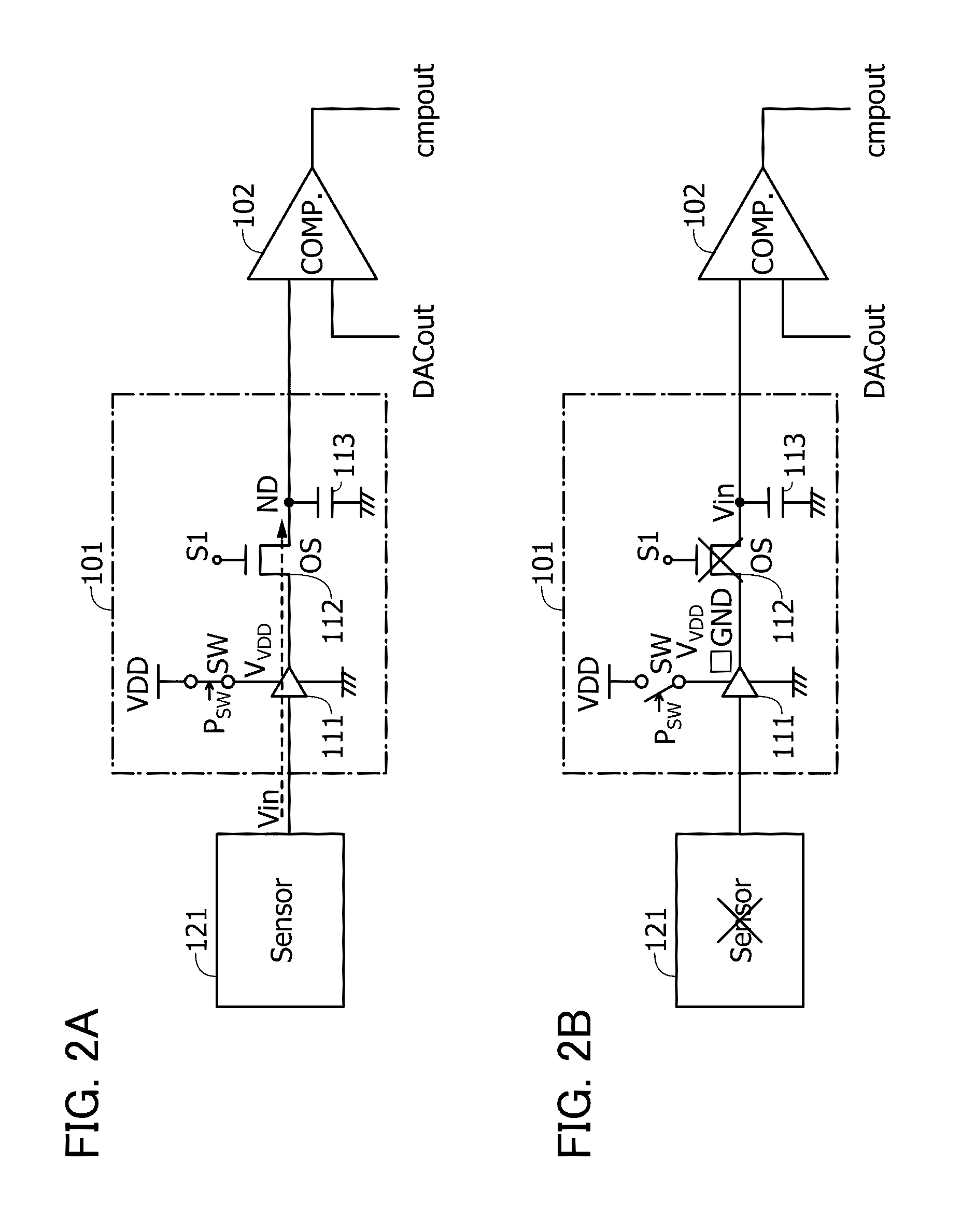

Semiconductor device, wireless sensor, and electronic device

InactiveUS20160094236A1Novel structureImprove ad performancePower saving provisionsElectric signal transmission systemsLine sensorEngineering

An object is to reduce power consumption of an analog-digital converter circuit. An analog potential obtained in a sensor or the like is held in a sample-and-hold circuit including a transistor with an extremely low off-state current. In the sample-and-hold circuit, the analog potential is held in a node which is able to hold a charge by turning off the transistor. Then, power supply to a buffer circuit or the like included in the sample-and-hold circuit is stopped to reduce power consumption. In a structure where a potential is held in each node, power consumption can be further reduced when a transistor with an extremely low off-state current is connected to a node holding a potential of a comparator, a successive approximation register, a digital-analog converter circuit, or the like, and power supply to these circuits is stopped.

Owner:SEMICON ENERGY LAB CO LTD

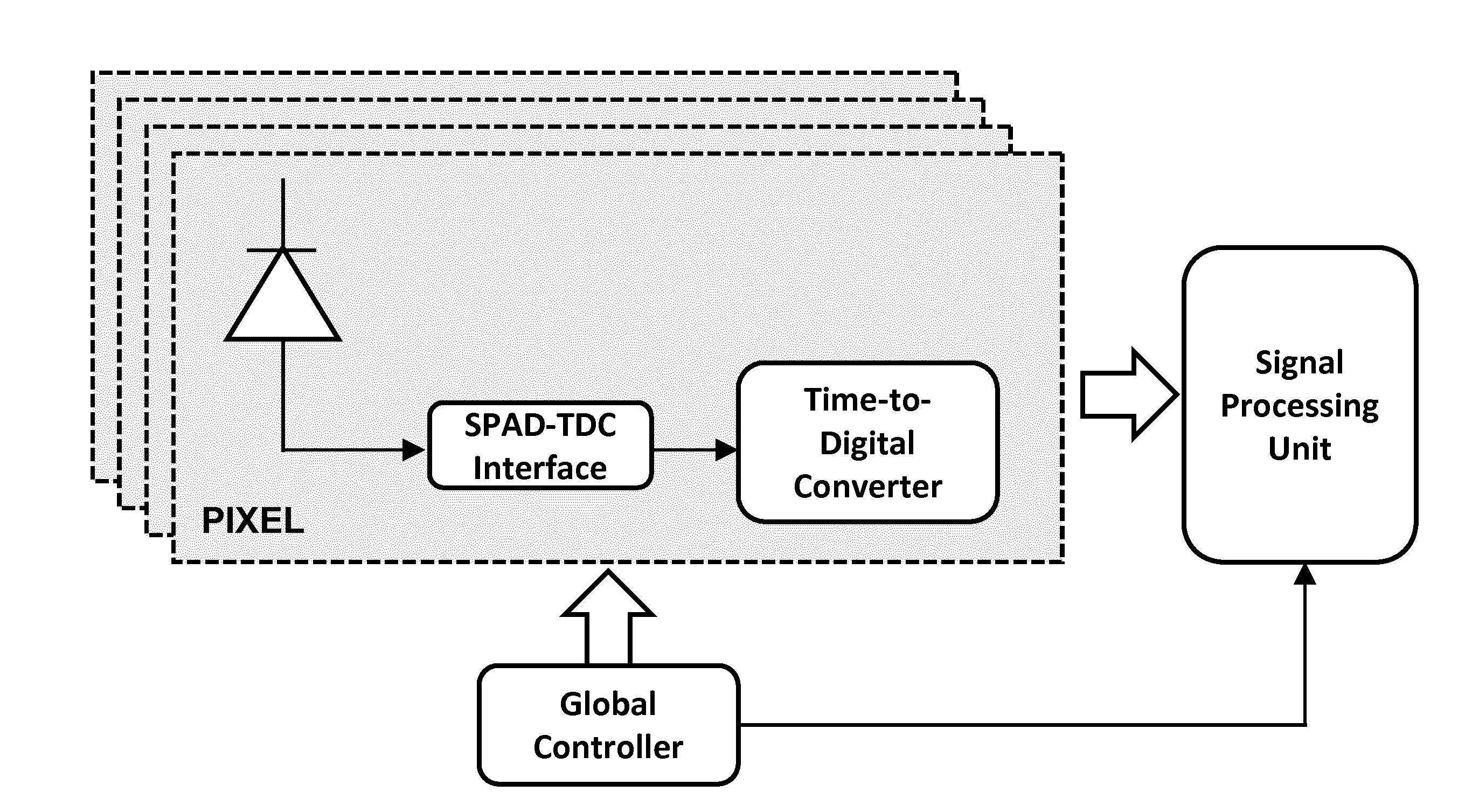

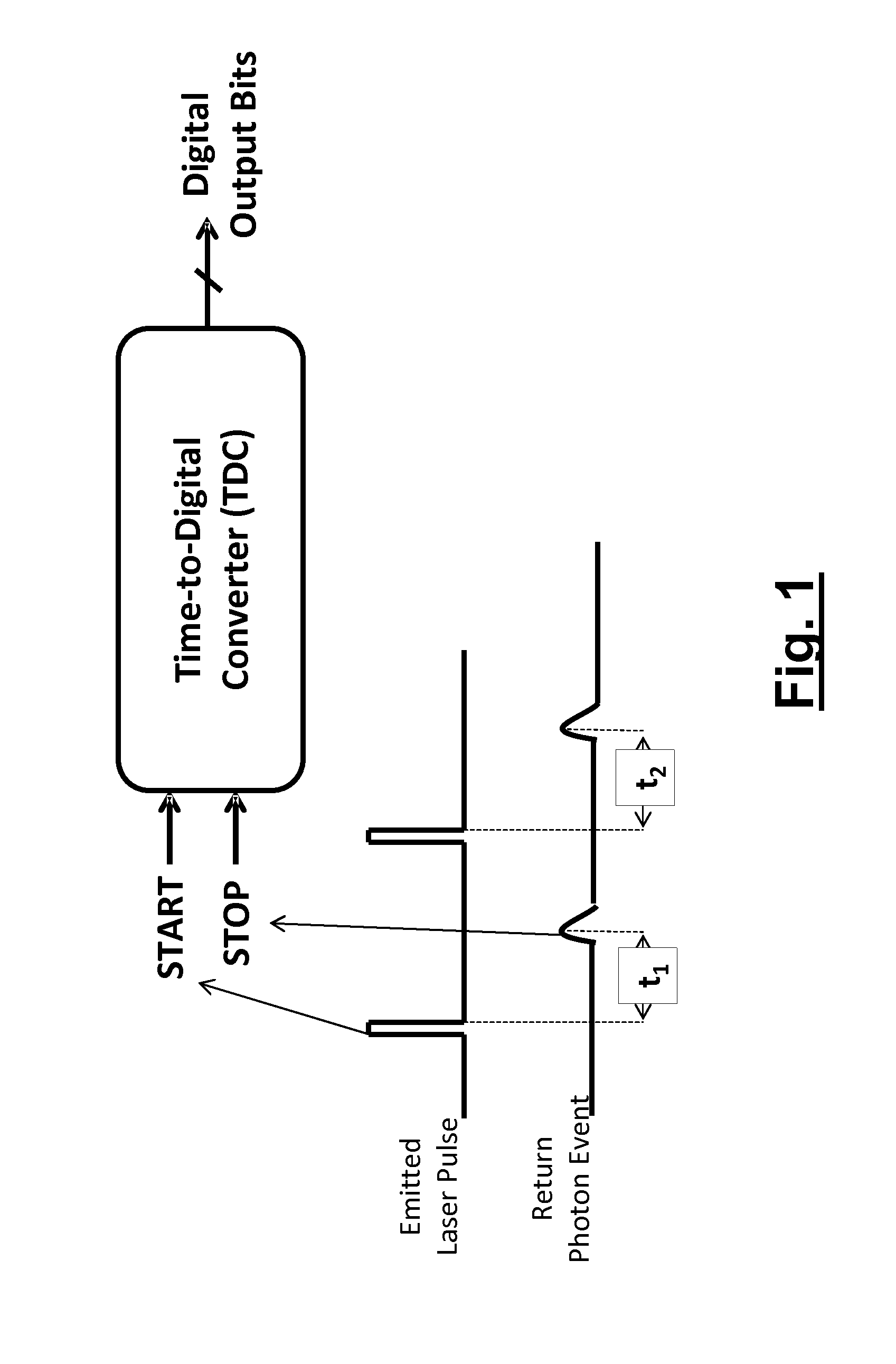

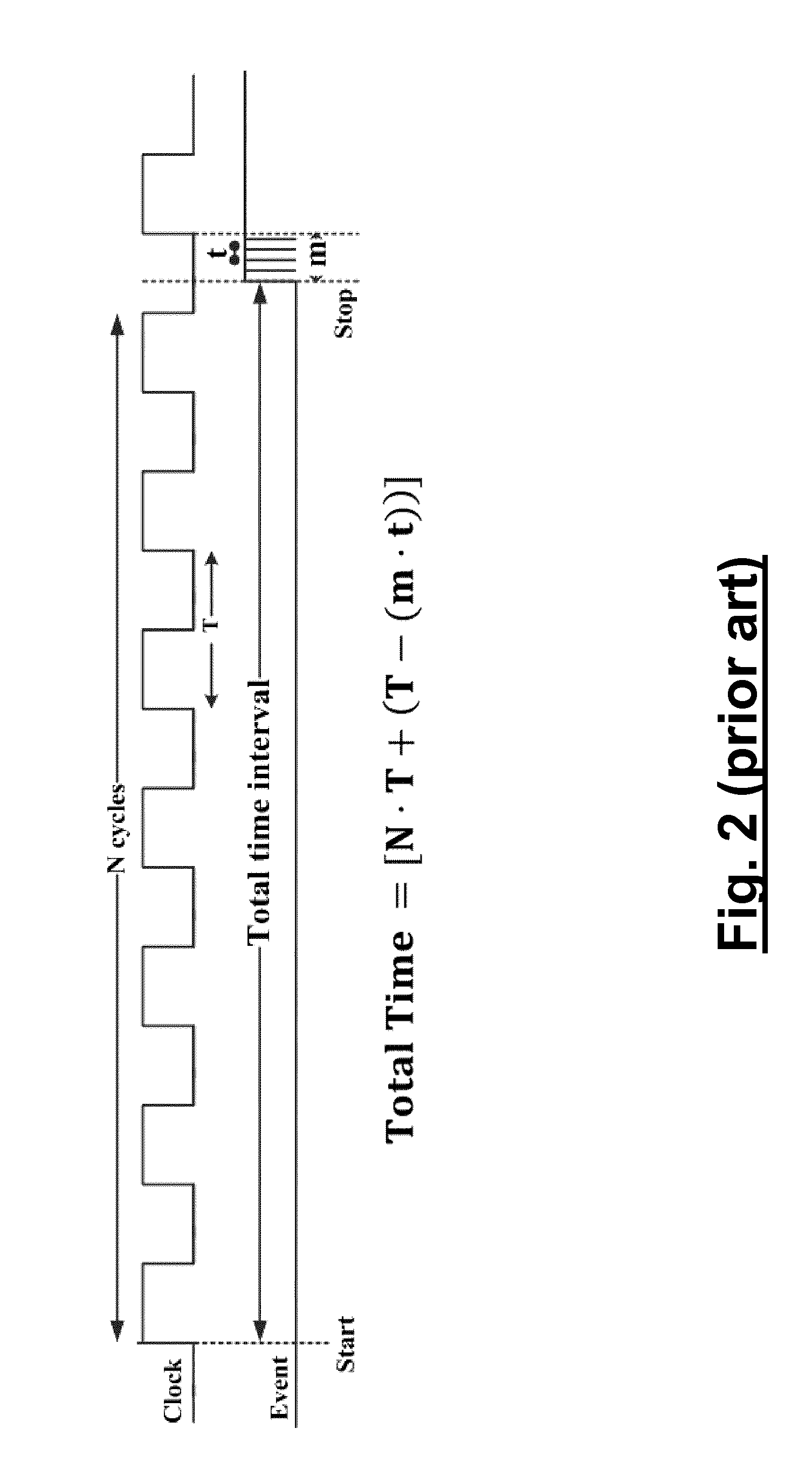

Time-to-digital converter and method therefor

ActiveUS20140232827A1Reduce power consumptionTelevision system detailsPower saving provisionsDigital down converterDigital converter

Time-to-digital converter system including: an event detector configured for detecting an event and generating an event detection signal upon detection of the event; and a time-to-digital converter coupled or connectable to the event detector and including a fine resolution part configured for counting fine time intervals, organized such that the fine resolution part is activated in response to the event detection signal and deactivated in response to a reference clock. 3D imager including an array of pixels, with in each pixel such a time-to-digital converter system, and further including a reference clock generator.

Owner:FASTREE 3D BV

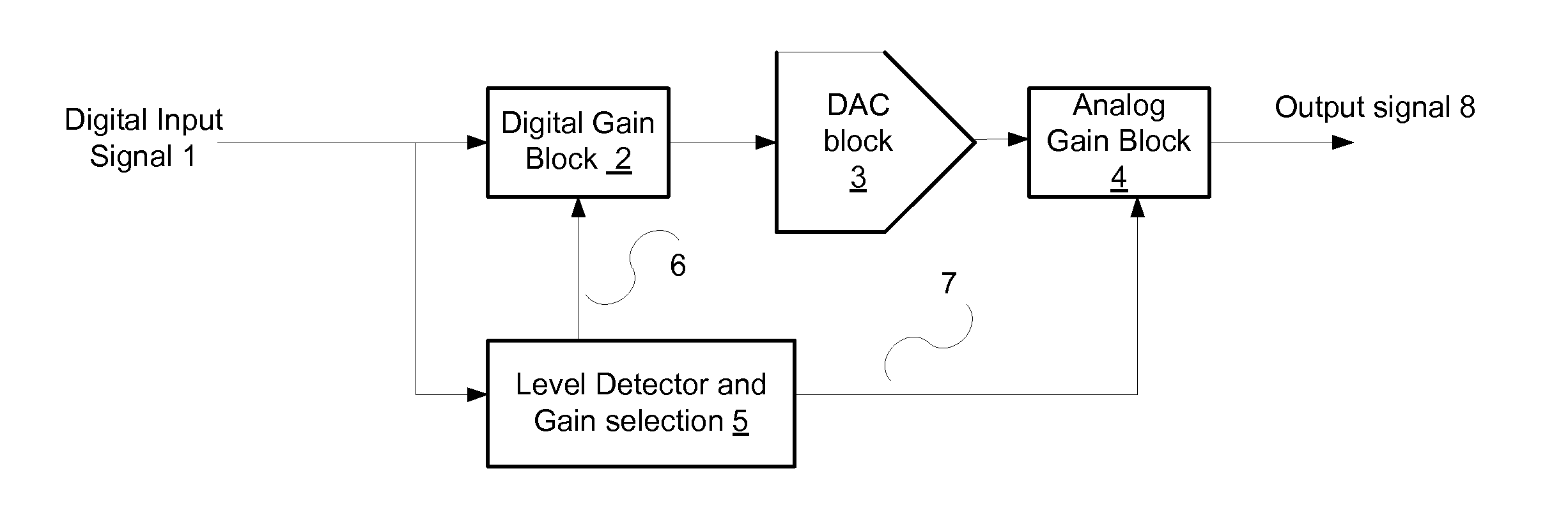

Dynamic gain switching digital to analog converter

ActiveUS20150249466A1Power saving provisionsElectric signal transmission systemsDigital analog converterGain-switching

A digital to analog converter that may include a digital gain block; an analog gain block; a digital to analog conversion (DAC) block and a controller that is configured to: determine a digital gain factor, selected out of multiple digital gain factors, of the digital gain block and an analog gain factor, selected out of multiple analog gain factors of the analog gain block; wherein the DAC block is preceded by the digital gain block and is followed by the analog gain block; wherein the digital gain block is configured to multiply a digital input signal by the digital gain factor to provide an intermediate digital signal; wherein the DAC block is configured to convert the intermediate digital signal to a converted analog signal; and wherein the analog gain block is configured to multiply the converted analog signal by the analog gain factor to provide an output signal; wherein an increment of the analog gain factor results in a decrement of the digital gain factor.

Owner:DSP GROUP

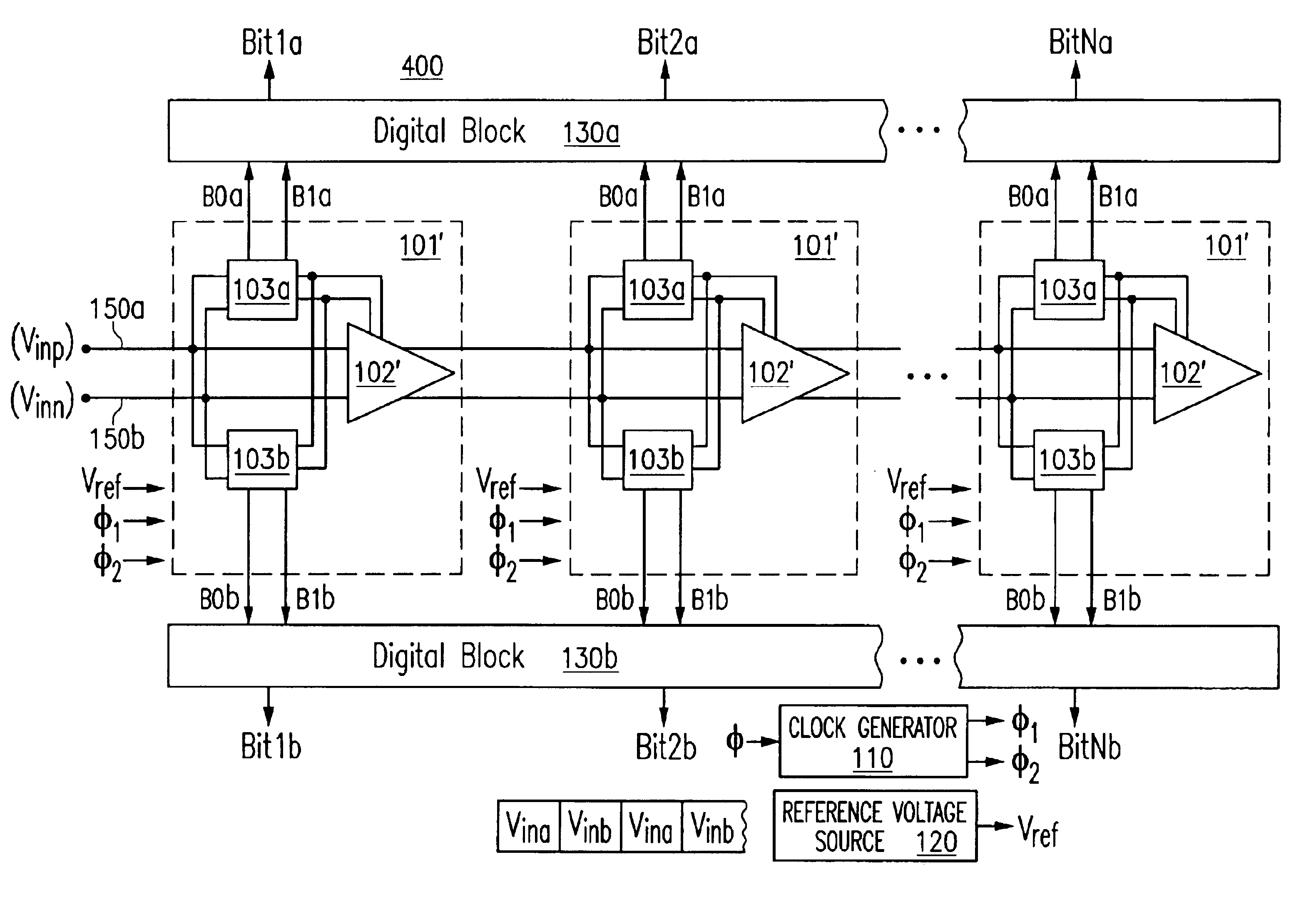

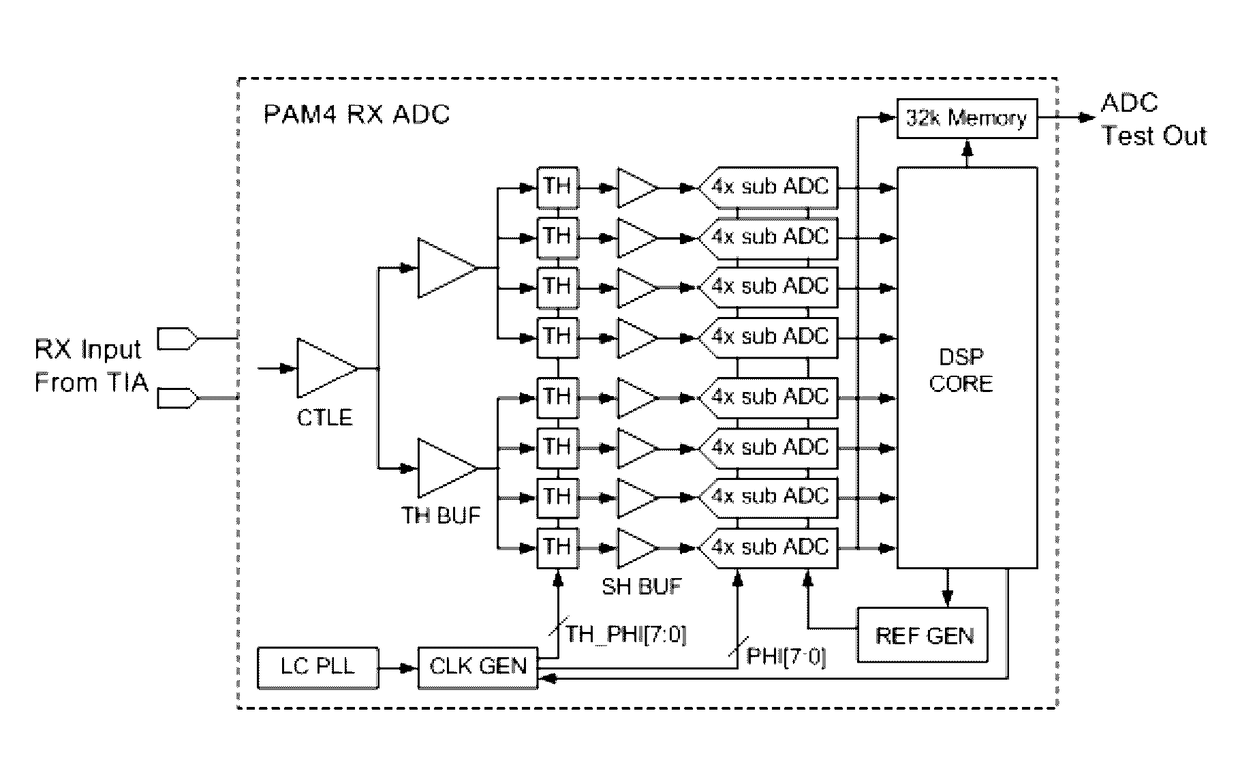

Interleaved successive approximation register analog to digital converter

ActiveUS9602116B1Power saving provisionsElectric signal transmission systemsAudio power amplifierDigital down converter

In an example, the present invention provides an analog to digital converter device for a high speed data transmission from 1 GS-s to 100 GS-s, although there can be other variations. In an example, the device has an input receiver device coupled to a transimpedance amplifier. In an example, the transimpedance amplifier is coupled to an input stream of data at 10 GHz to 100 GHz, or other variations.

Owner:MARVELL ASIA PTE LTD

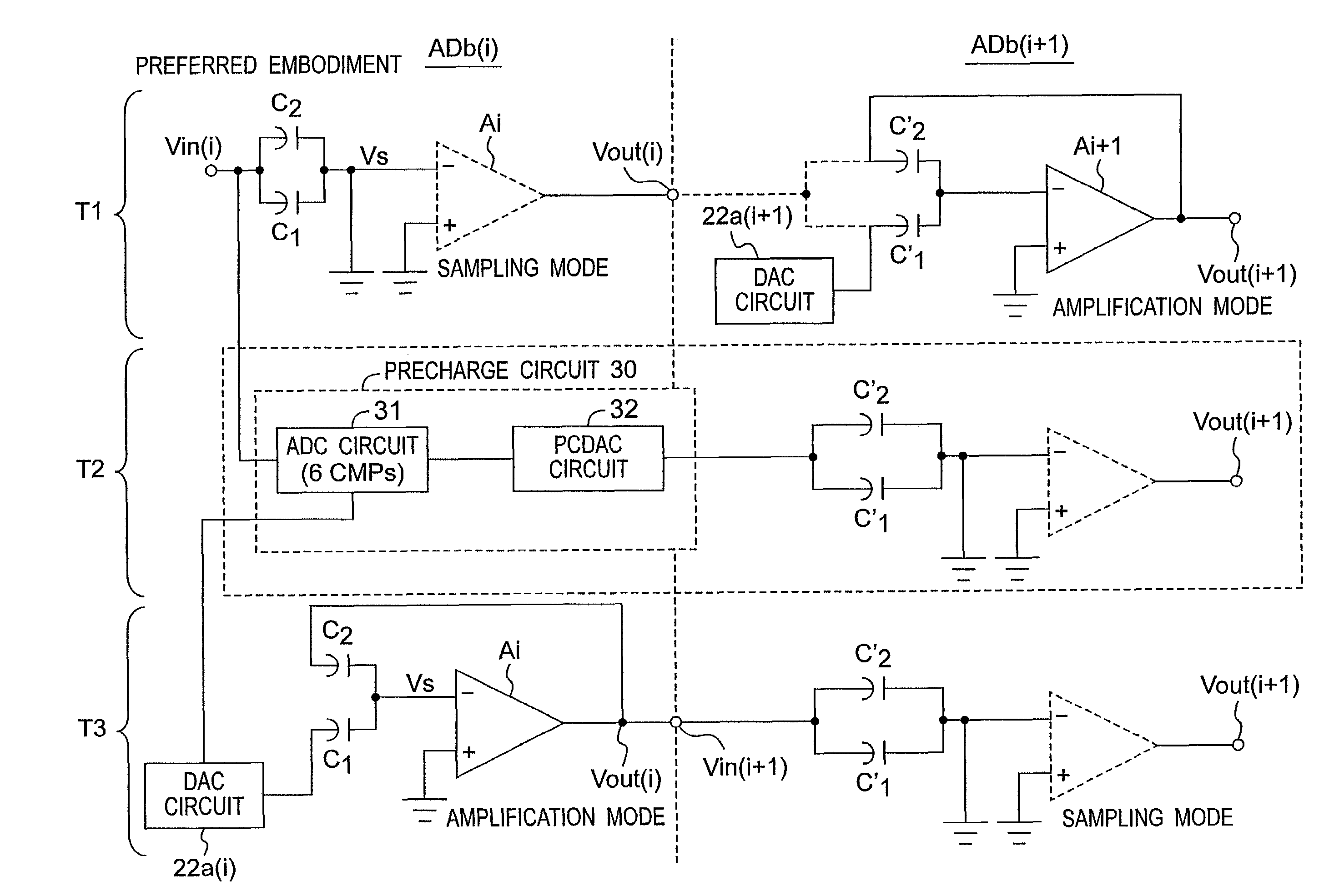

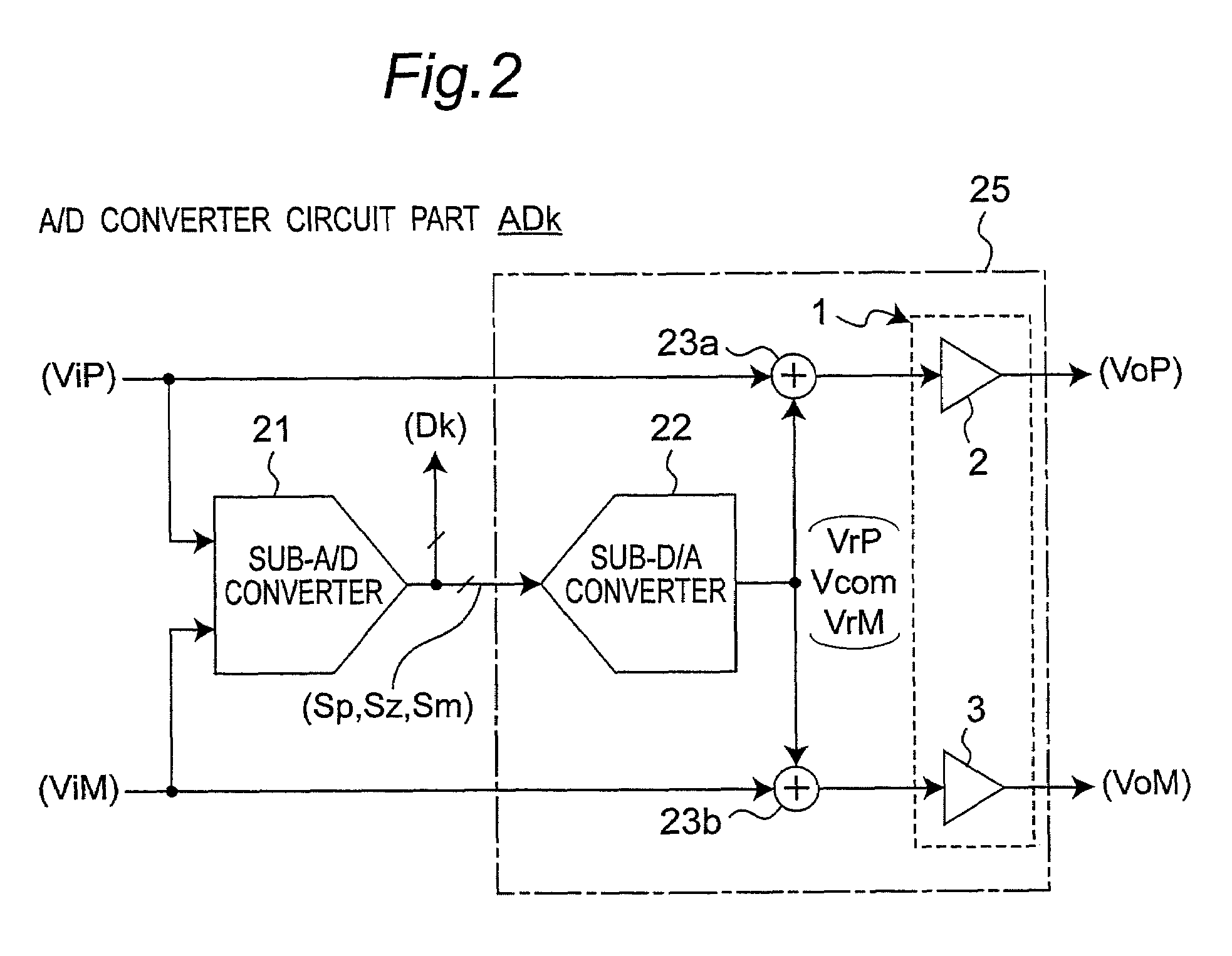

Pipeline type A/D converter apparatus provided with precharge circuit for precharging sampling capacitor

InactiveUS7612700B2Reduce power consumptionHigh speedPower saving provisionsElectric signal transmission systemsCapacitanceEngineering

In a pipeline type A / D converter apparatus including A / D converter circuit parts connected in cascade with each other and A / D converting a sample hold signal in a pipeline form, each A / D converter circuit part includes a pre-A / D converter circuit for A / D converting an input signal into a digital signal, and a multiplying D / A converter circuit for D / A converting the digital signal into an analog control signal, and D / A converting the input signal by sampling, holding and amplifying the input signal using a sampling capacitor based on the analog control signal. A precharge circuit precharges a sampling capacitor before sampling so as to attain a predetermined output value in accordance with a digital input to output characteristic substantially adapted to an input to output characteristic of each A / D converter circuit part that presents an output signal corresponding to the input signal to each A / D converter circuit part.

Owner:SEMICON TECH ACADEMIC RES CENT

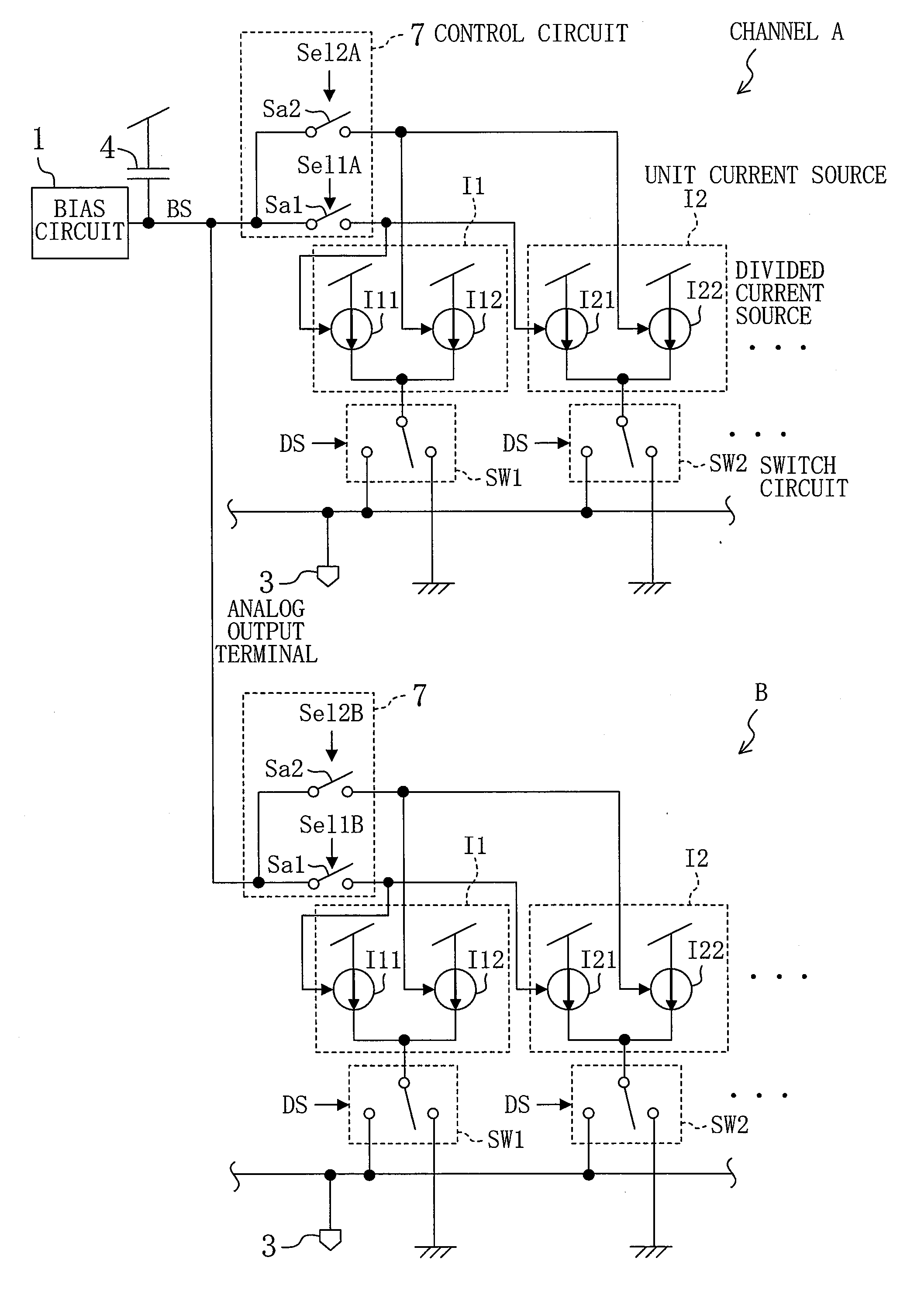

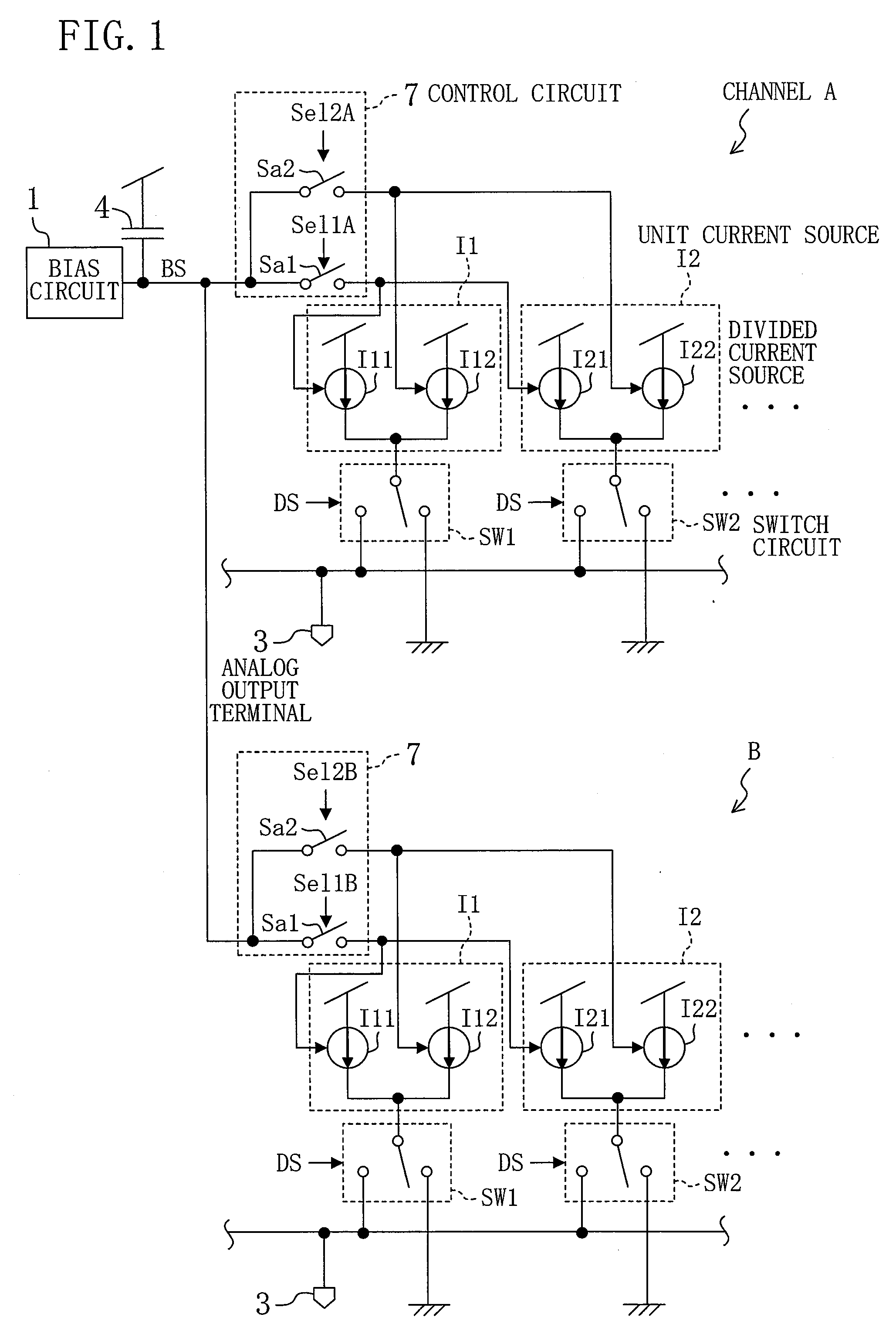

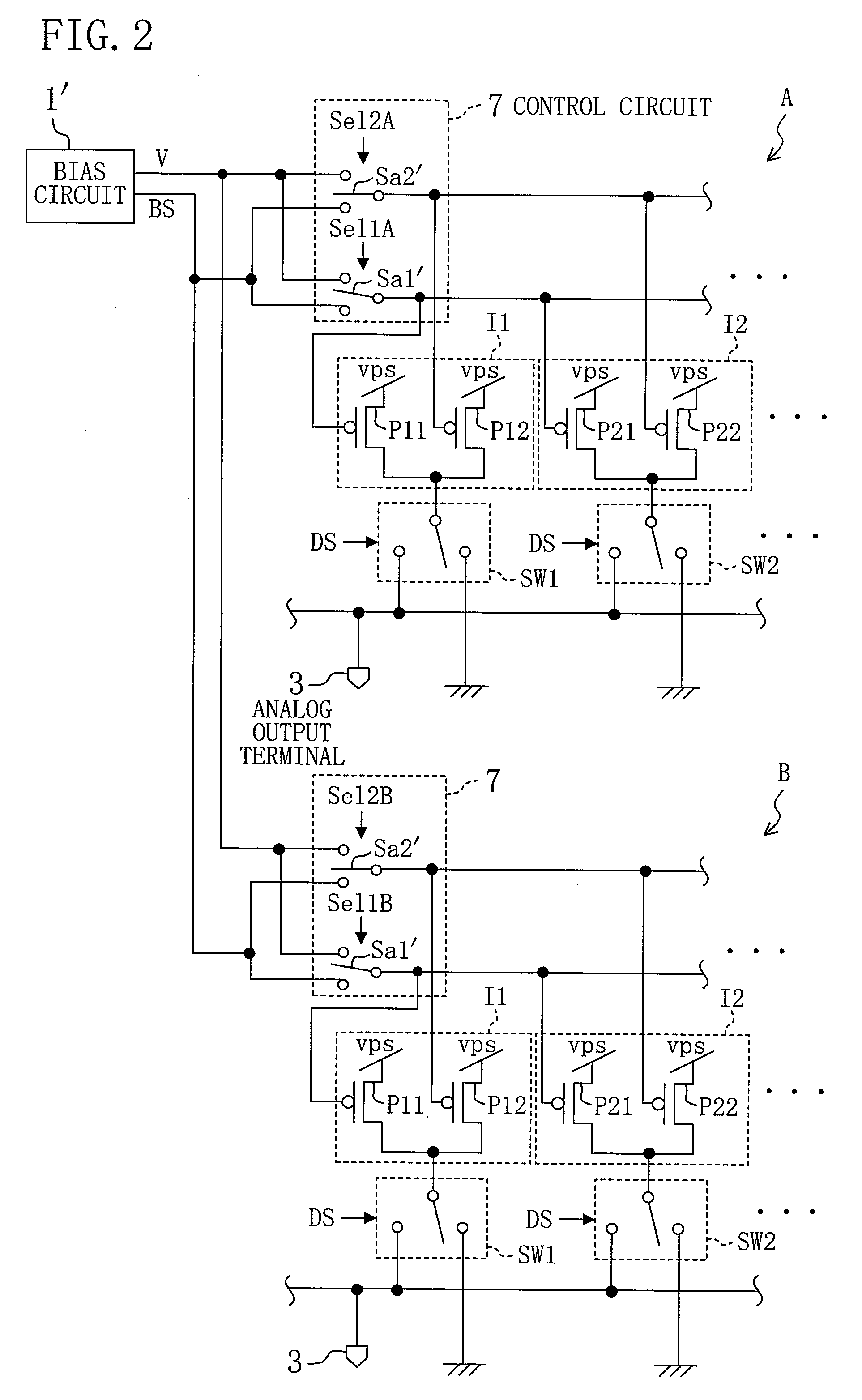

Current steering dac

ActiveUS20090045993A1Without degrading resolutionReduce unnecessary power consumptionPower saving provisionsElectric signal transmission systemsDigital analog converterImage resolution

A multi-channel current steering DAC (Digital-to-Analog Converter), for example, a 2-channel current steering DAC, includes a plurality of current sources I1, I2, . . . corresponding to the number of bits of a digital input signal DS in each of channels A, B. Each of the plurality of current sources I1, I2, . . . is formed by two small-current sources (I11, I12), (I21, I22), . . . . In the case where a full-scale current is limited to a small value in any of the channels, one of the two divided current sources is turned off by switches Sa1, Sa2. Accordingly, a full-scale current of each channel can be adjusted with a common bias circuit without degrading the resolution.

Owner:SOCIONEXT INC

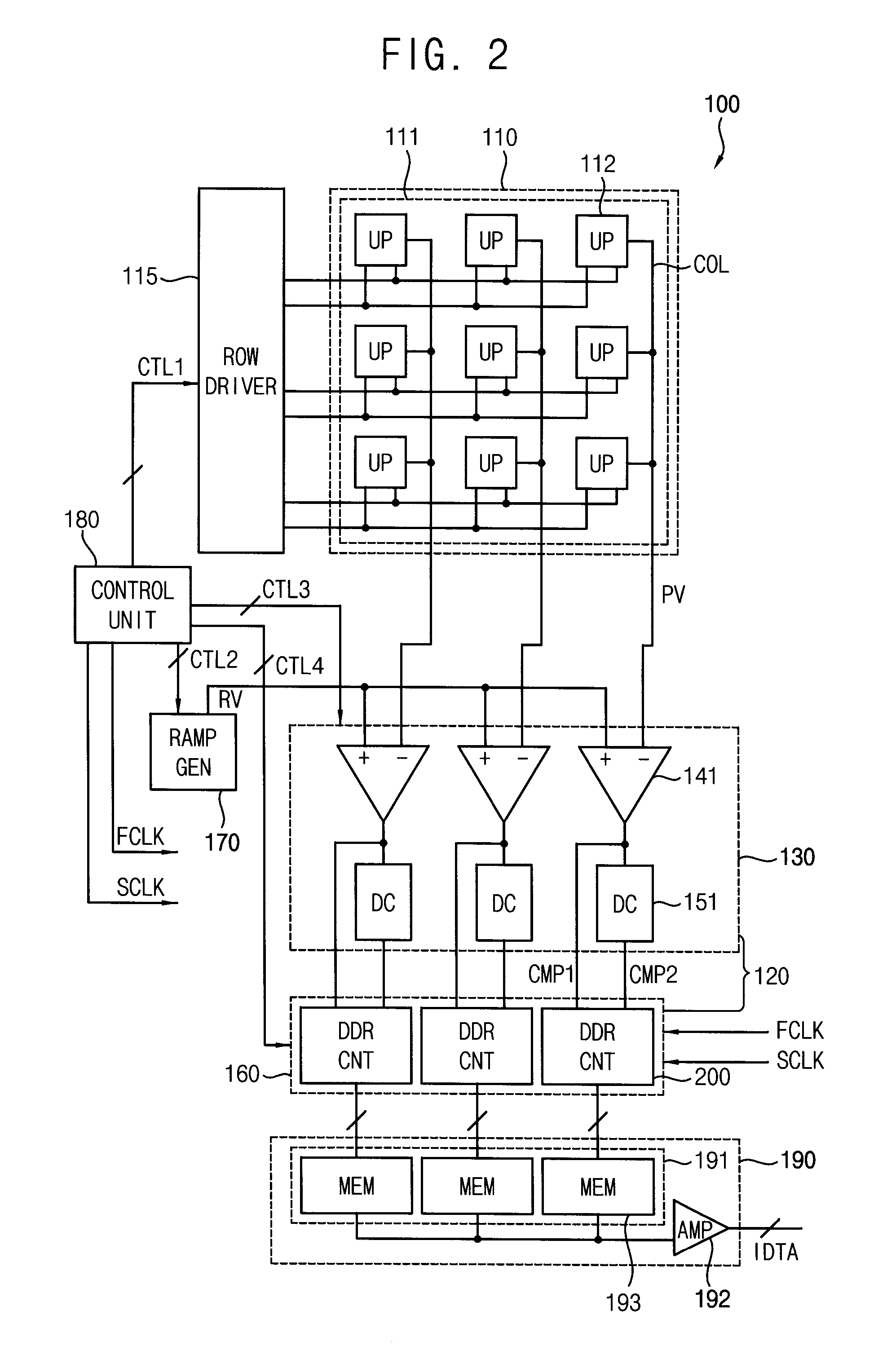

Counter circuit, analog-to-digital converter, and image sensor including the same and method of correlated double sampling

ActiveUS20150028190A1Reduce power consumptionReduce in quantityPower saving provisionsTelevision system detailsAnalog-to-digital converterComputer science

A counter circuit includes a first counter and a second counter. The first counter is configured to count a first counter clock signal which toggles with a first frequency to generate upper (N−M)-bit signals of N-bit counter output signals, in response to a first counting enable signal based on a first comparison signal during a coarse counting interval. N and M are natural numbers, N is greater than M, and M is greater than or equal to 3. The second counter is configured to count a second counter clock signal which toggles with a second frequency which is higher than the first frequency to generate lower M-bit signals of the N-bit counter output signals, in response to a second counting enable signal based on the first comparison signal and a second comparison signal during a fine counting interval which follows the coarse counting interval.

Owner:SAMSUNG ELECTRONICS CO LTD

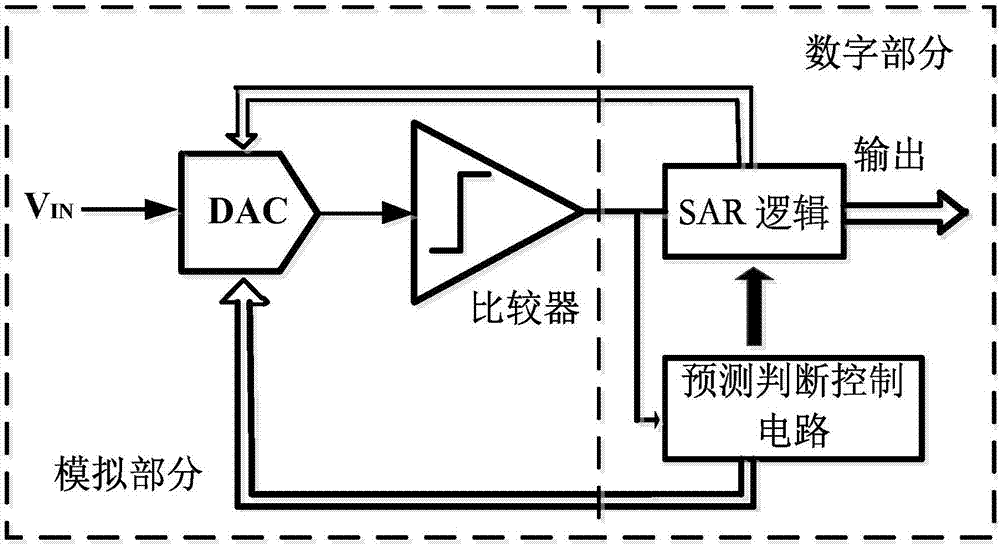

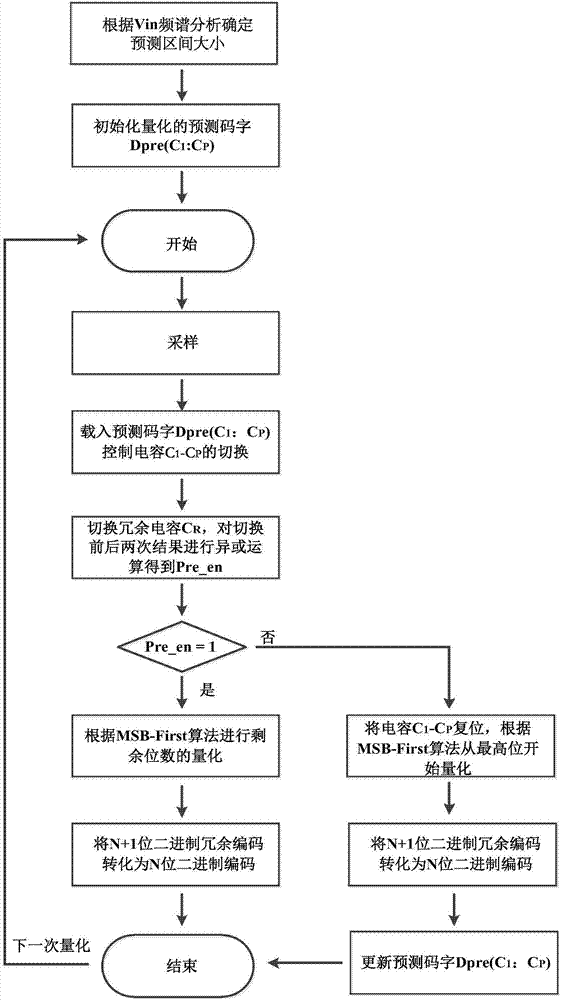

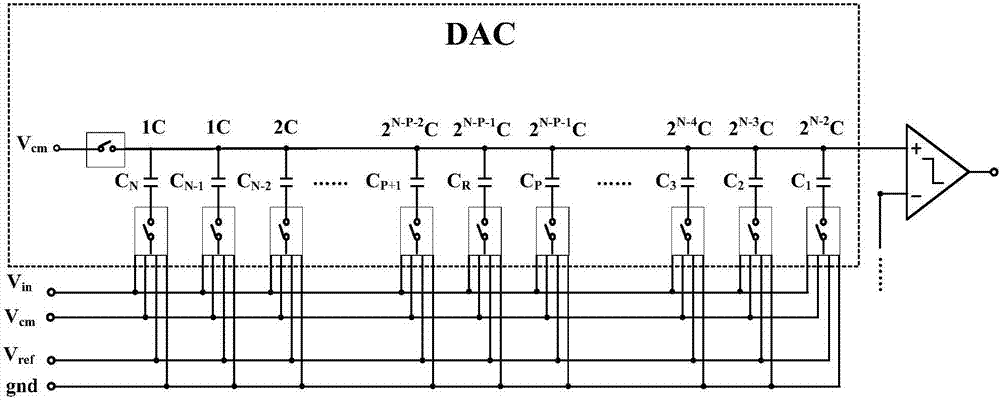

Method for predicting and quantifying binary charge redistribution type successive approximation analog-to-digital converter

InactiveCN106992781AReduced Quantization Power ConsumptionReduce the number of comparisonsPower saving provisionsElectric signal transmission systemsCapacitanceDigital down converter

The invention relates to a method for predicting and quantifying a binary charge redistribution type successive approximation analog-to-digital converter, and belongs to the technical field of analog-to-digital conversion. According to the method provided by the invention, a high P bit code of a previous quantification result is directly loaded in the quantification result of the present high P bit based on a common mode voltage reset structure capacitor array DAC, a prediction result is judged according to twice switching results before and after the switching of a redundant capacitor, the comparison of the residual low bits can be carried out in the case of prediction correctness, the capacitance of a lower polar plate of the high P bit is reset in the case of a prediction error, and the traditional quantification from the most significant bit to the least significant bit (MSB_First) is carried out again. By adoption of the method provided by the invention, the switching frequency of a digital-to-analog converter module and the comparison times of a comparator are maximally reduced, the average quantification power consumption of the low and medium frequency portions of signals are greatly reduced, and a low power consumption design is realized; and the method provided by the invention can be used as a feature parameter extraction means of electrocardiogram (ECG), electroencephalogram (EEG) and other biological medical signals so as to extract extreme values and frequency characteristics of target signals under extremely low power consumption.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

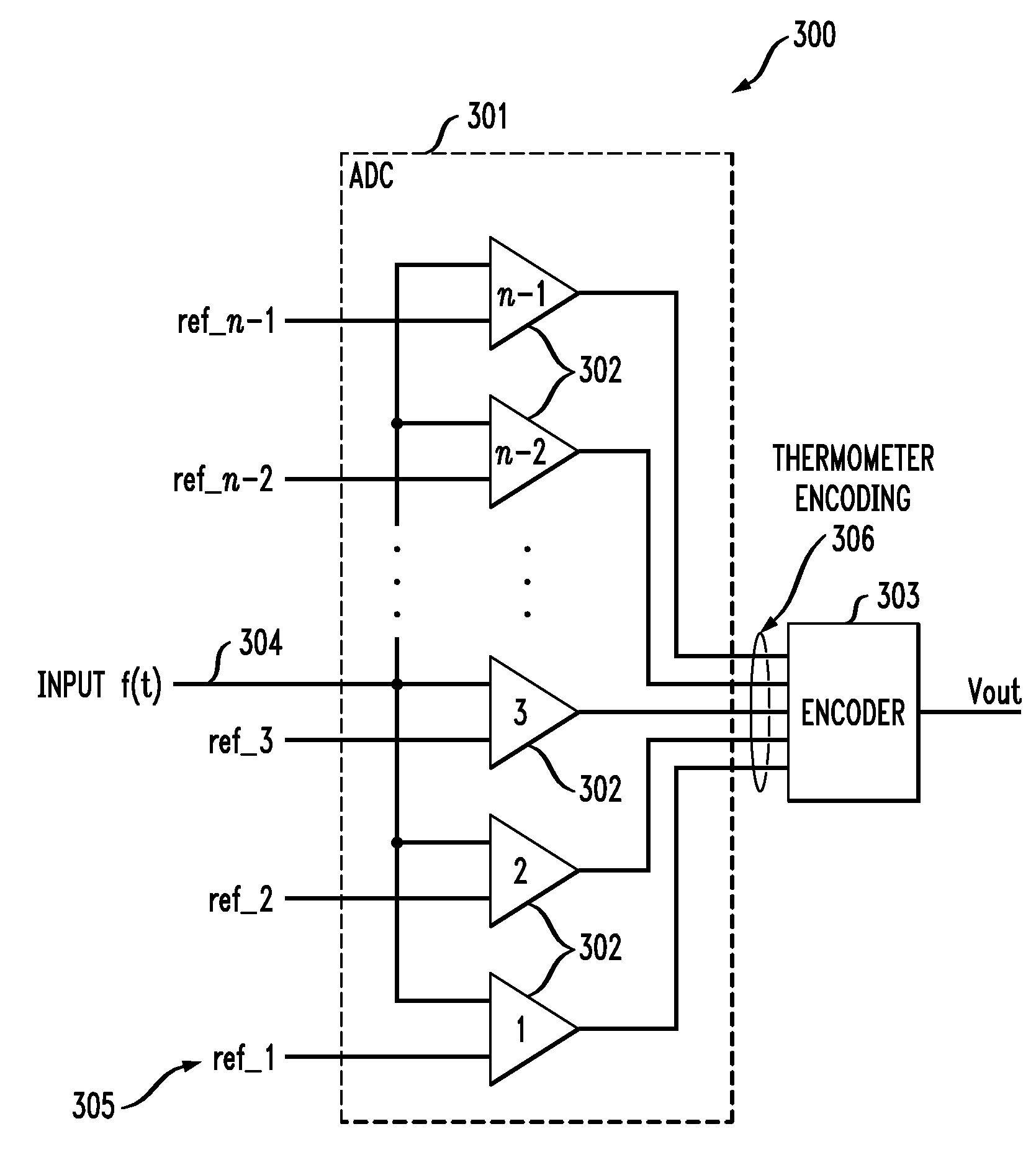

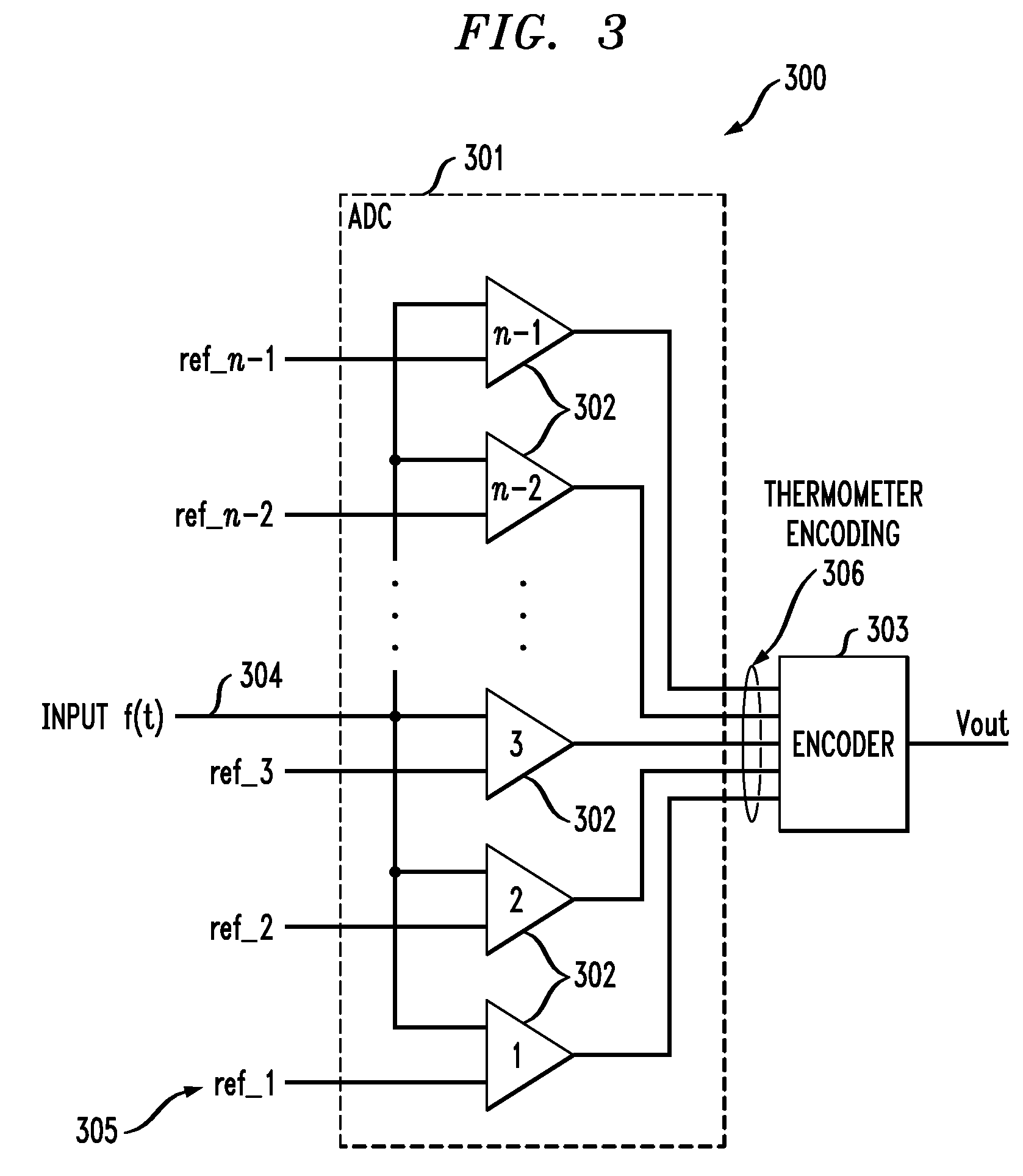

Analog-to-digital converter having reduced number of activated comparators

ActiveUS7696915B2Reduce power consumptionSignificantly degrading performancePower saving provisionsElectric signal transmission systemsControl engineeringA d converter

An ADC circuit includes multiple comparators and a controller coupled to the comparators. Each of the comparators is operative to generate an output indicative of a difference between a first signal representative of an input signal applied to the ADC circuit and a corresponding reference signal. The controller is operative to perform at least one of: (i) activating a subset of the comparators during a given sample period being; and (ii) controlling levels of the corresponding reference signals of the comparators as a function of a level of the input signal. A number of active comparators during the given sample period is no greater than one less than a number of regions into which the input signal is quantized.

Owner:AVAGO TECH INT SALES PTE LTD

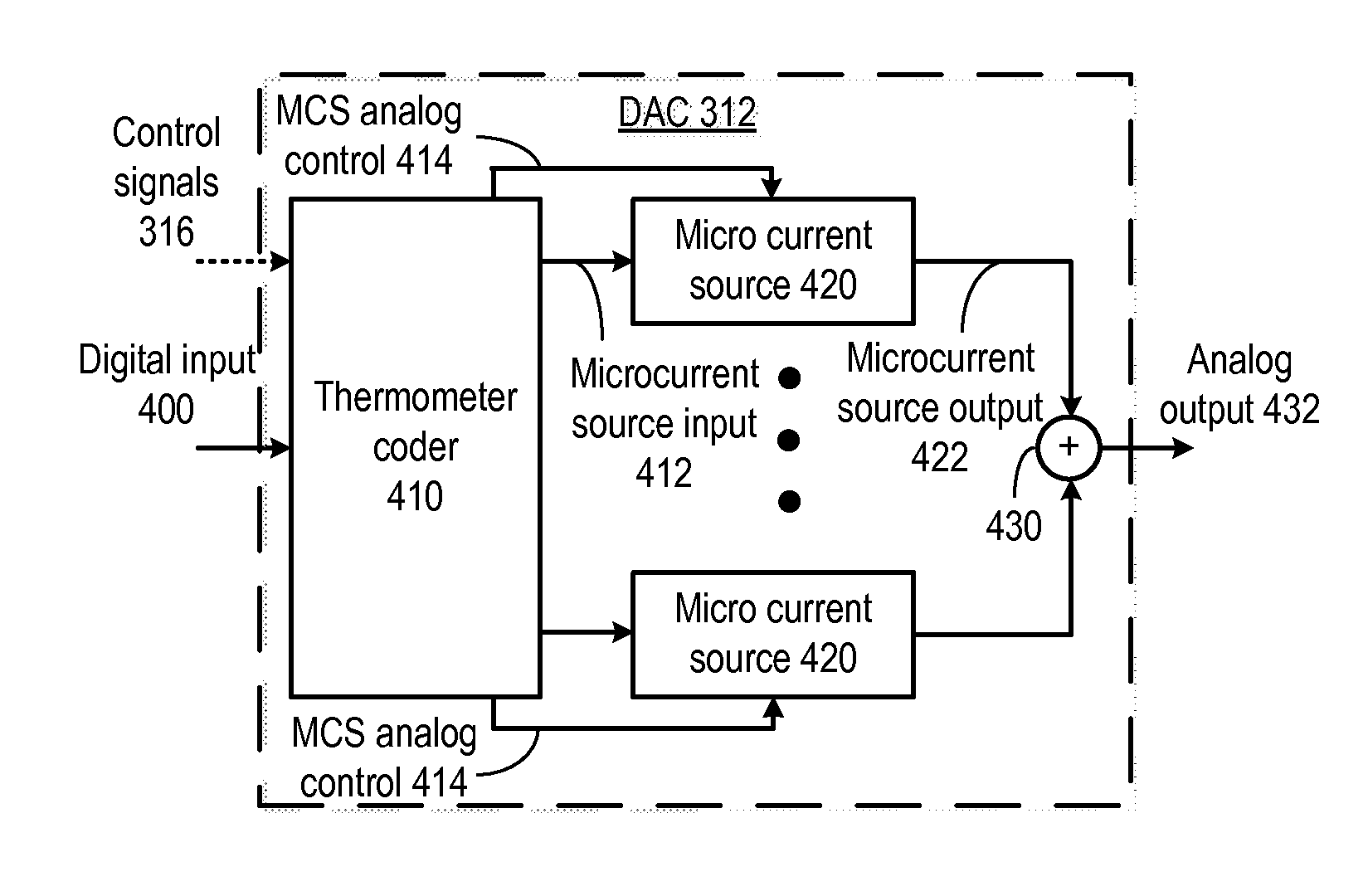

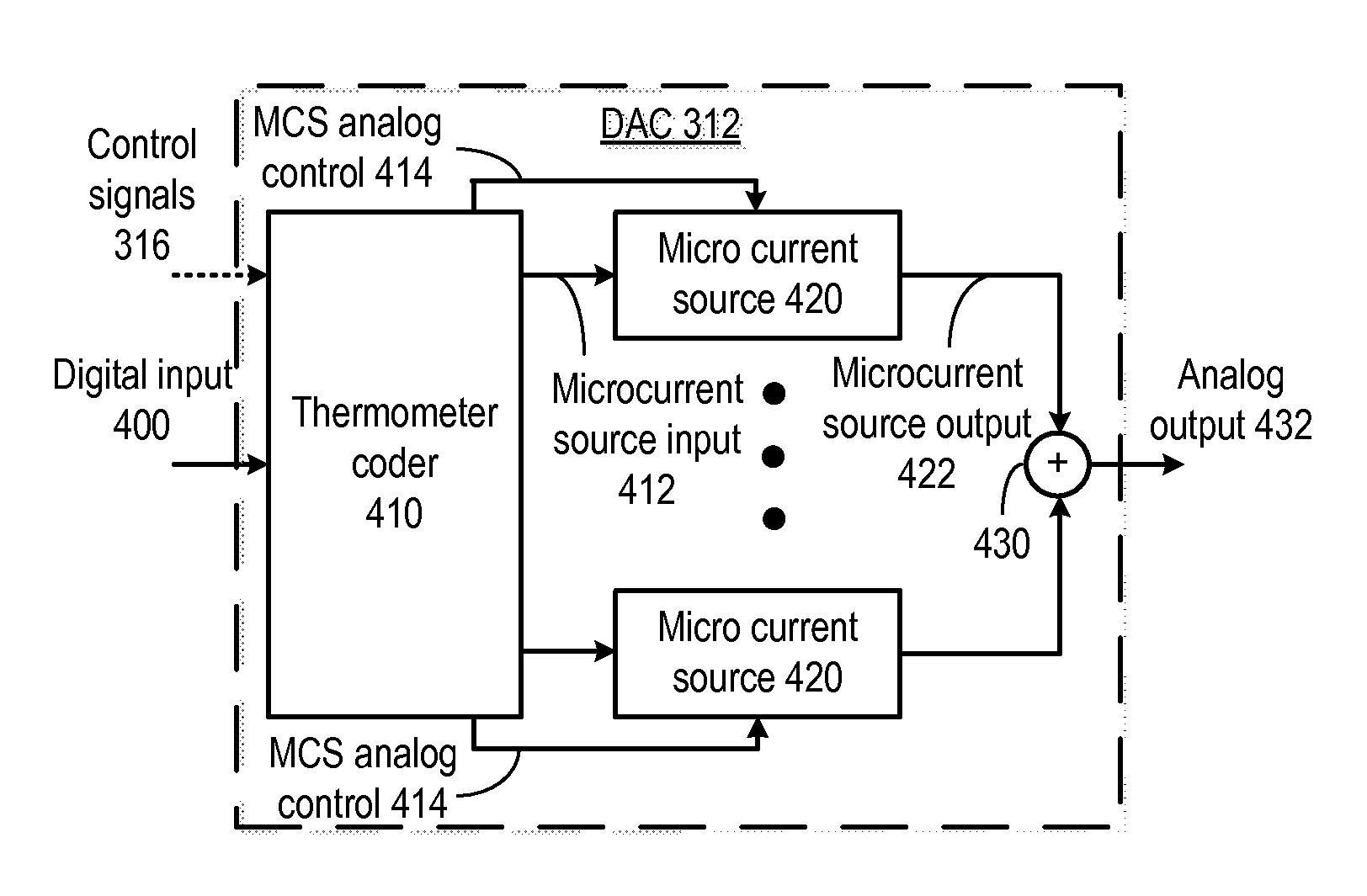

Digital to analog converter with thermometer coding and methods for use therewith

ActiveUS20150214974A1Power saving provisionsElectric signal transmission systemsDigital-to-analog converterThermometer

A digital to analog converter (DAC) includes a thermometer coder that processes a digital input based on a thermometer coding, and generates a plurality of micro-current source inputs and a plurality of micro-current source analog controls. A plurality of micro-current sources generate a corresponding plurality of micro-current source outputs in response to the plurality of micro-current source inputs, wherein first selected ones of the plurality of micro-current sources are powered-off in response to the plurality of micro-current source analog controls. A summing circuit generates an analog output based on a sum of the corresponding plurality of micro-current source outputs.

Owner:AVAGO TECH INT SALES PTE LTD

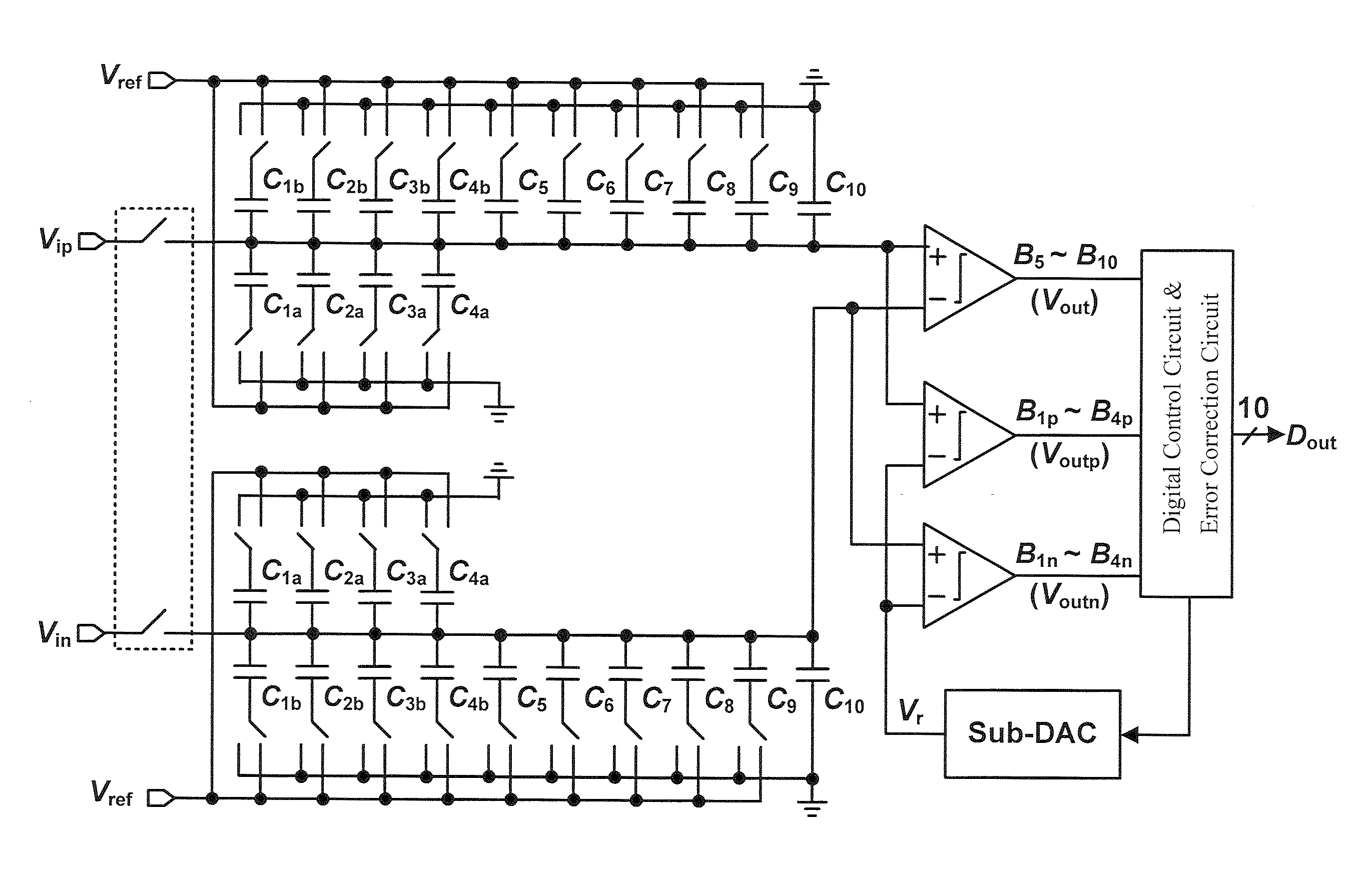

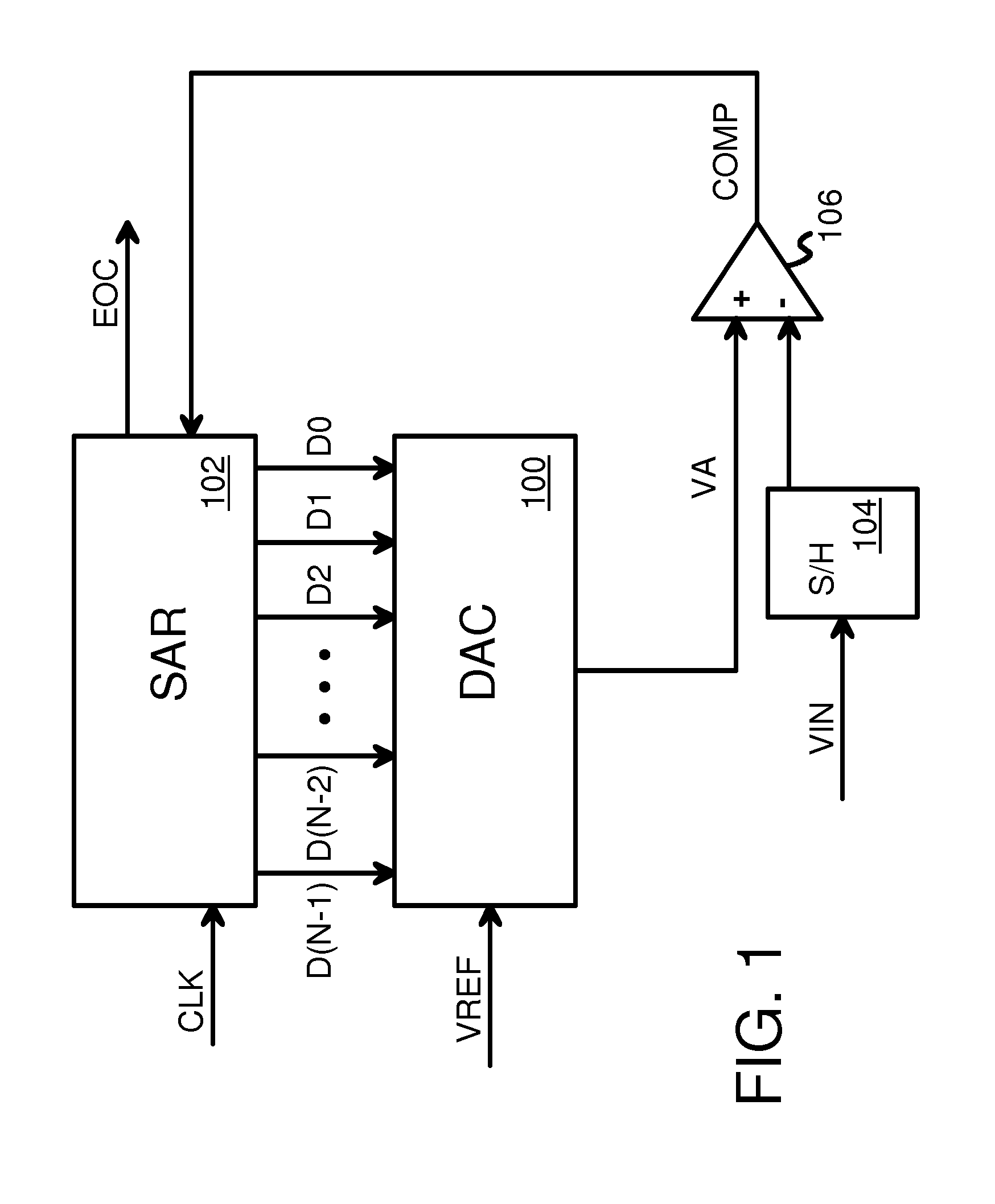

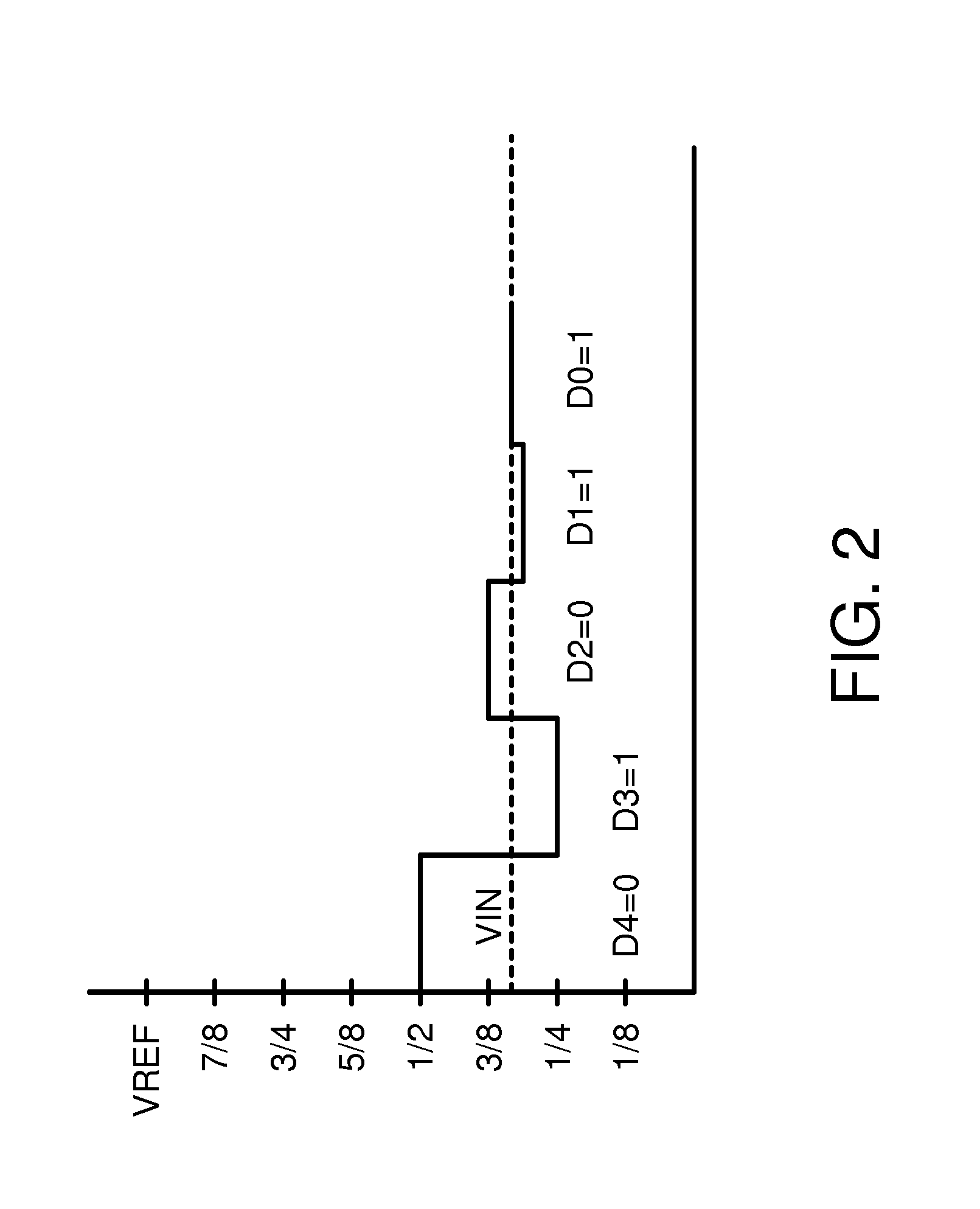

Successive approximation analog-to-digital converter having auxiliary prediction circuit and method thereof

ActiveUS20120154194A1Avoid unnecessary capacitor switchingSave energy consumptionPower saving provisionsElectric signal transmission systemsVoltage referenceEngineering

The configurations and adjusting method of a successive approximation analog-to-digital converter (SAR ADC) are provided. The provided SAR ADC includes at least one capacitor with a first and a second terminals, and a plurality of bits, each of which is connected to the at least one capacitor, wherein the first terminal receives an input signal, and the second terminal selectively receives one of a first and a second reference voltages, and a first comparator receiving an adjustable third reference voltage and a first voltage value generated by the input signal, wherein a connection of the second terminal of each the capacitor of the capacitor array is switched when the first voltage value is larger than the third reference voltage.

Owner:NAT CHENG KUNG UNIV

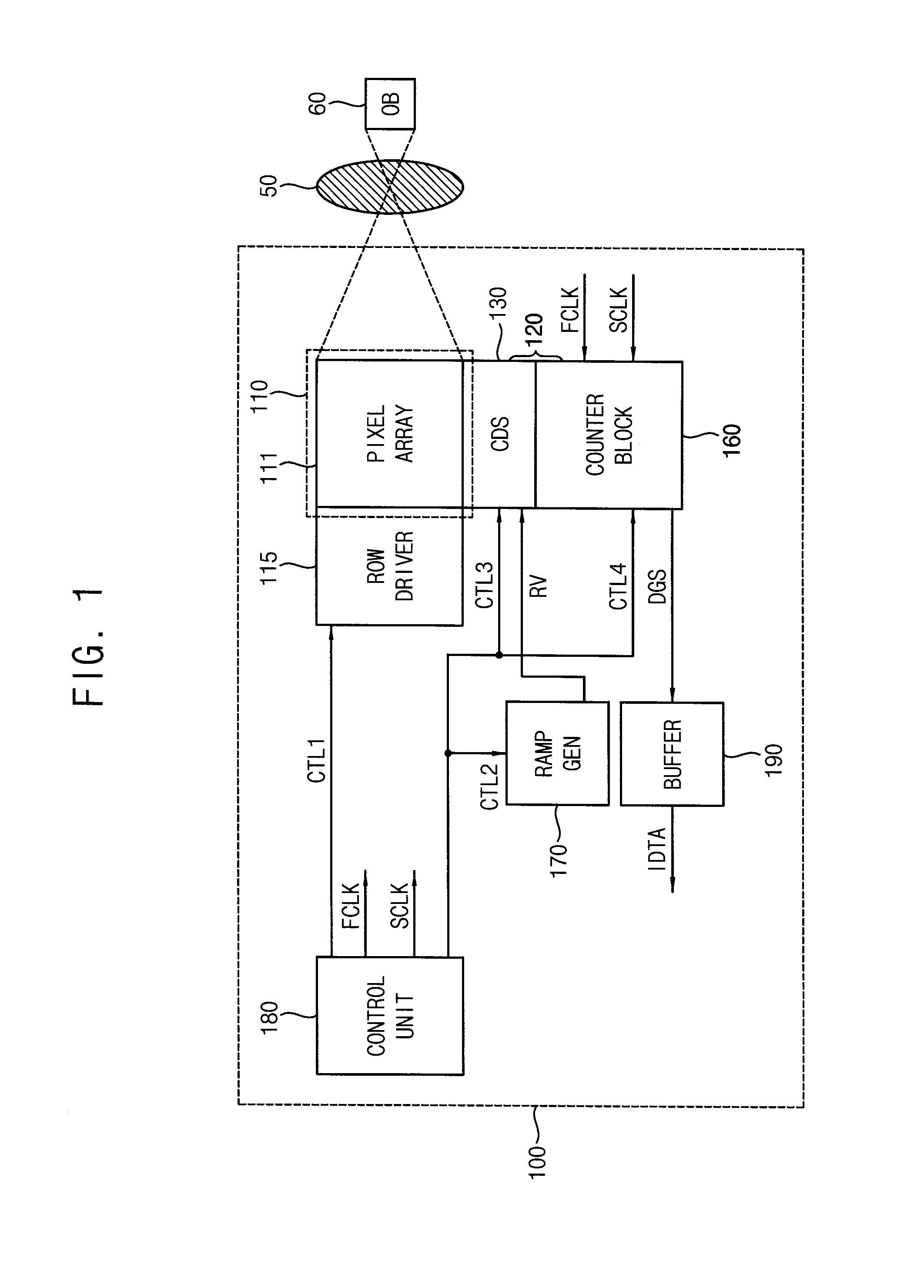

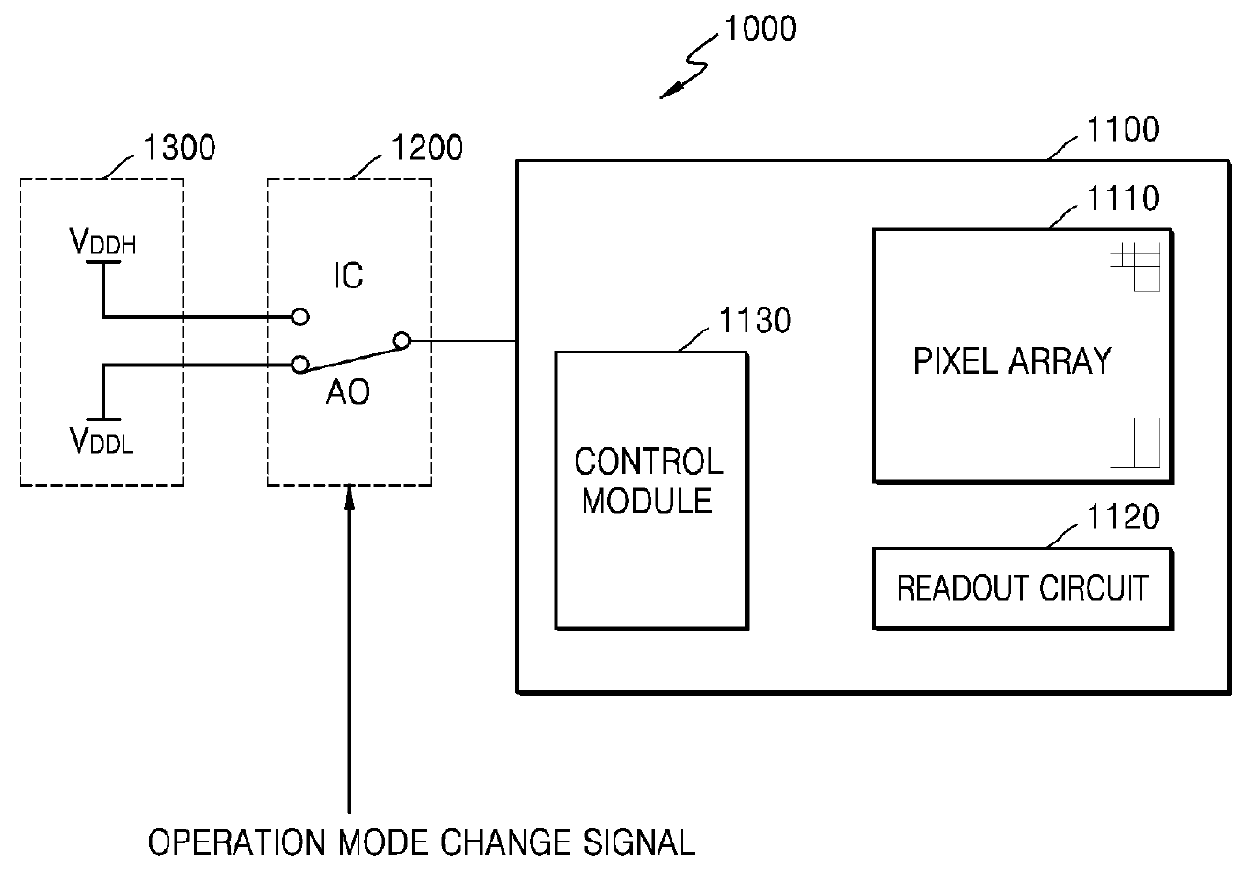

Image sensor and method of driving image sensor, and image capturing apparatus using the same

ActiveUS20160037110A1Minimize power consumptionSize be minimizedPower saving provisionsTelevision system detailsControl signalOperation mode

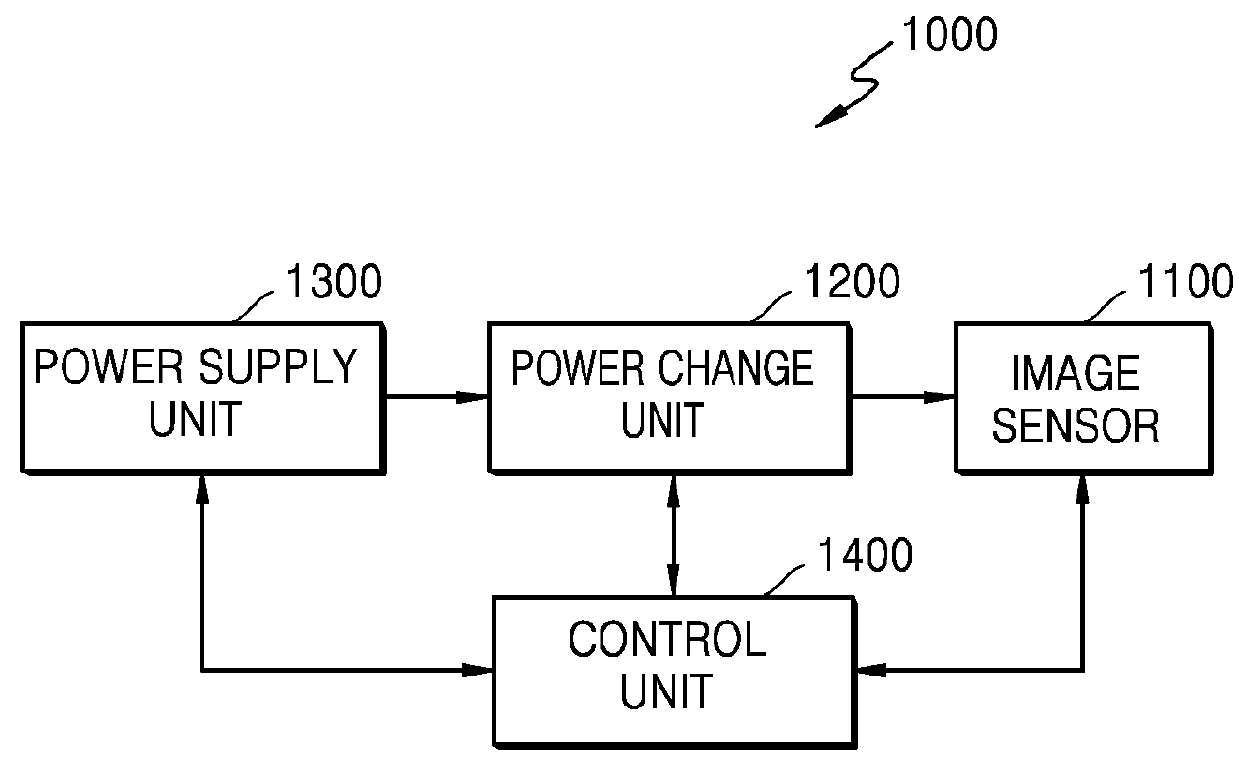

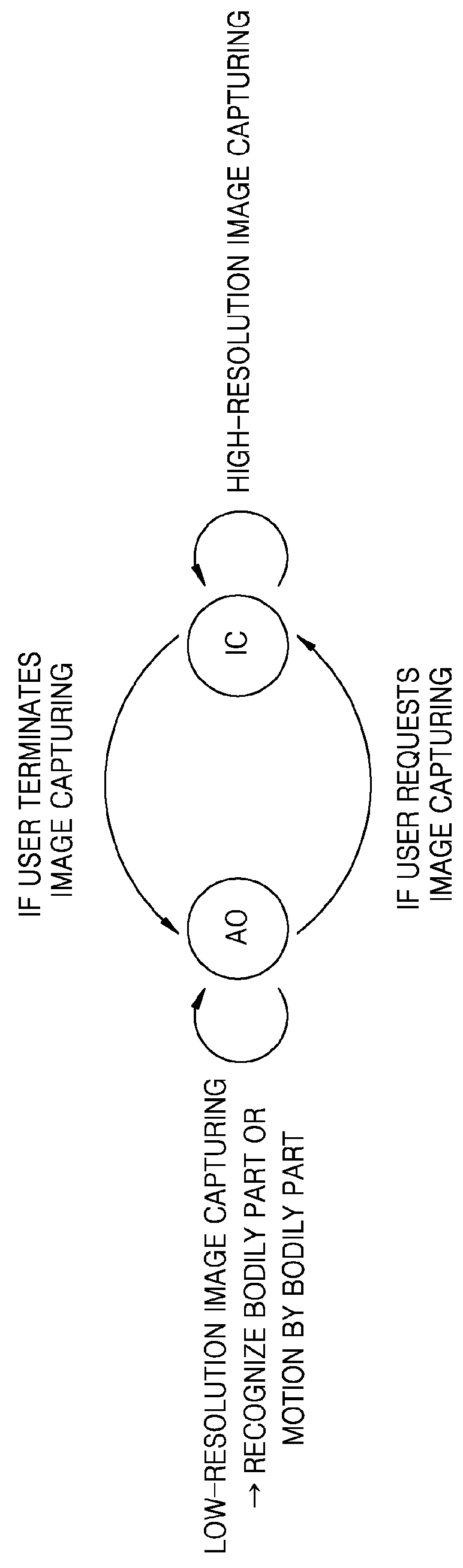

According to one example embodiment, an image sensor is configured to operate in a plurality of operation modes. The image sensor includes a pixel array including unit pixels configured to generate an analog image signal from incident light, a readout circuit configured to generate a digital image signal by converting the analog image signal, and a control module configured to generate control signals for controlling operations of the pixel array and the readout circuit according to an operation mode of the image sensor. A first power voltage for driving the image sensor when the operation mode of the image sensor is an image recognition mode for recognizing a body of a user of the image sensor, is lower than a second power voltage for driving the image sensor when the operation mode of the image sensor is an image capture mode for capturing images by the user.

Owner:SAMSUNG ELECTRONICS CO LTD

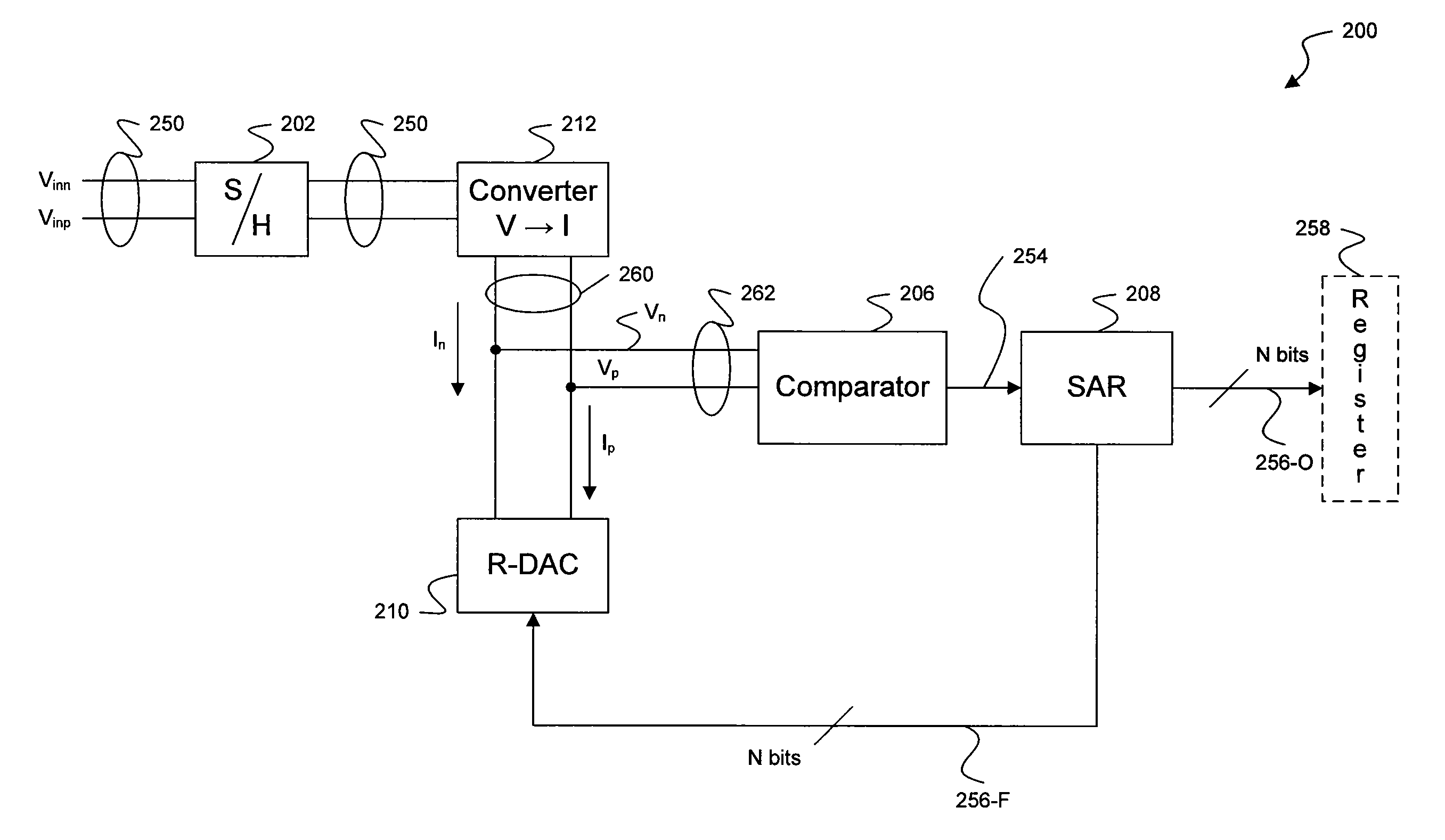

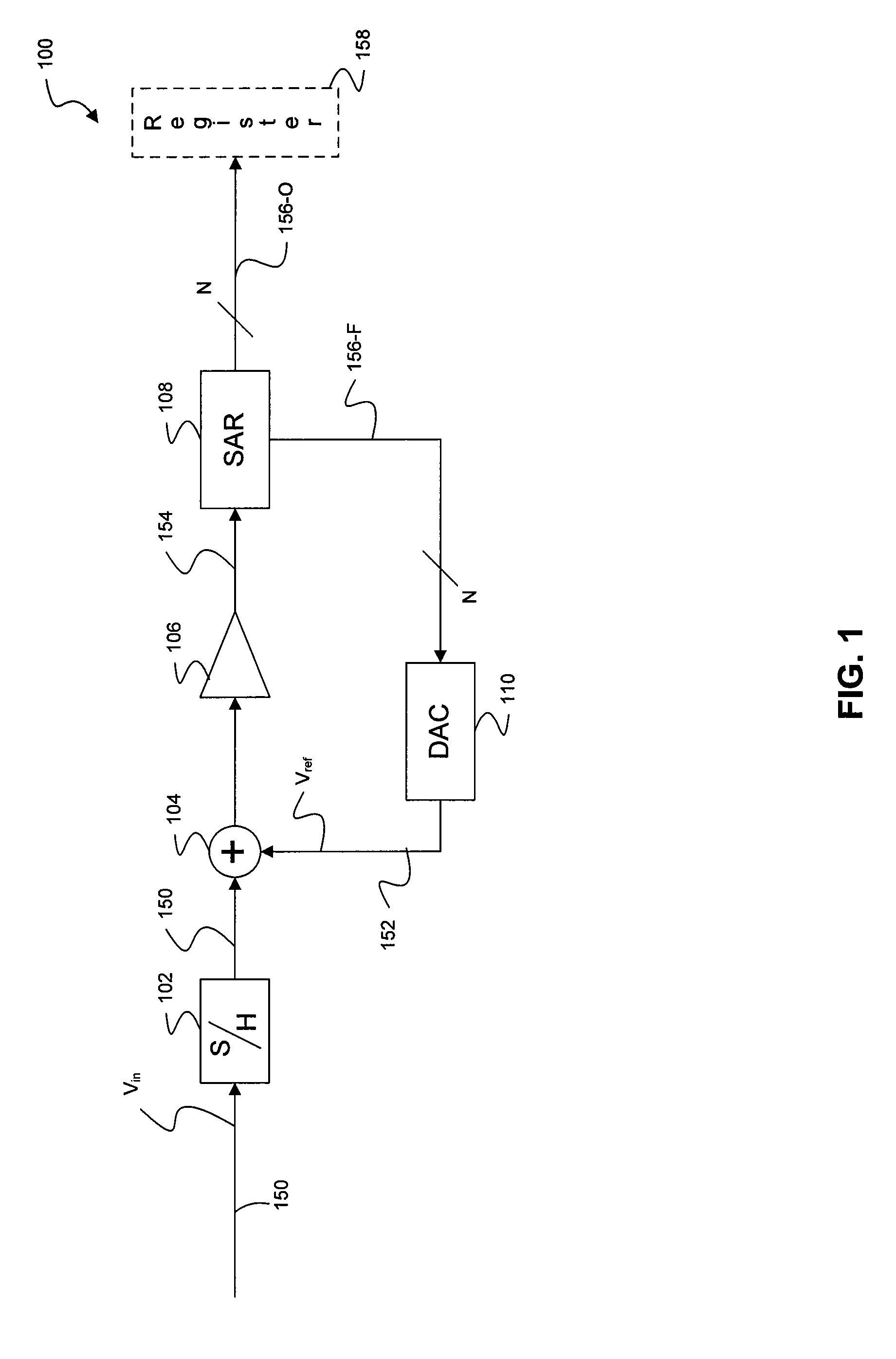

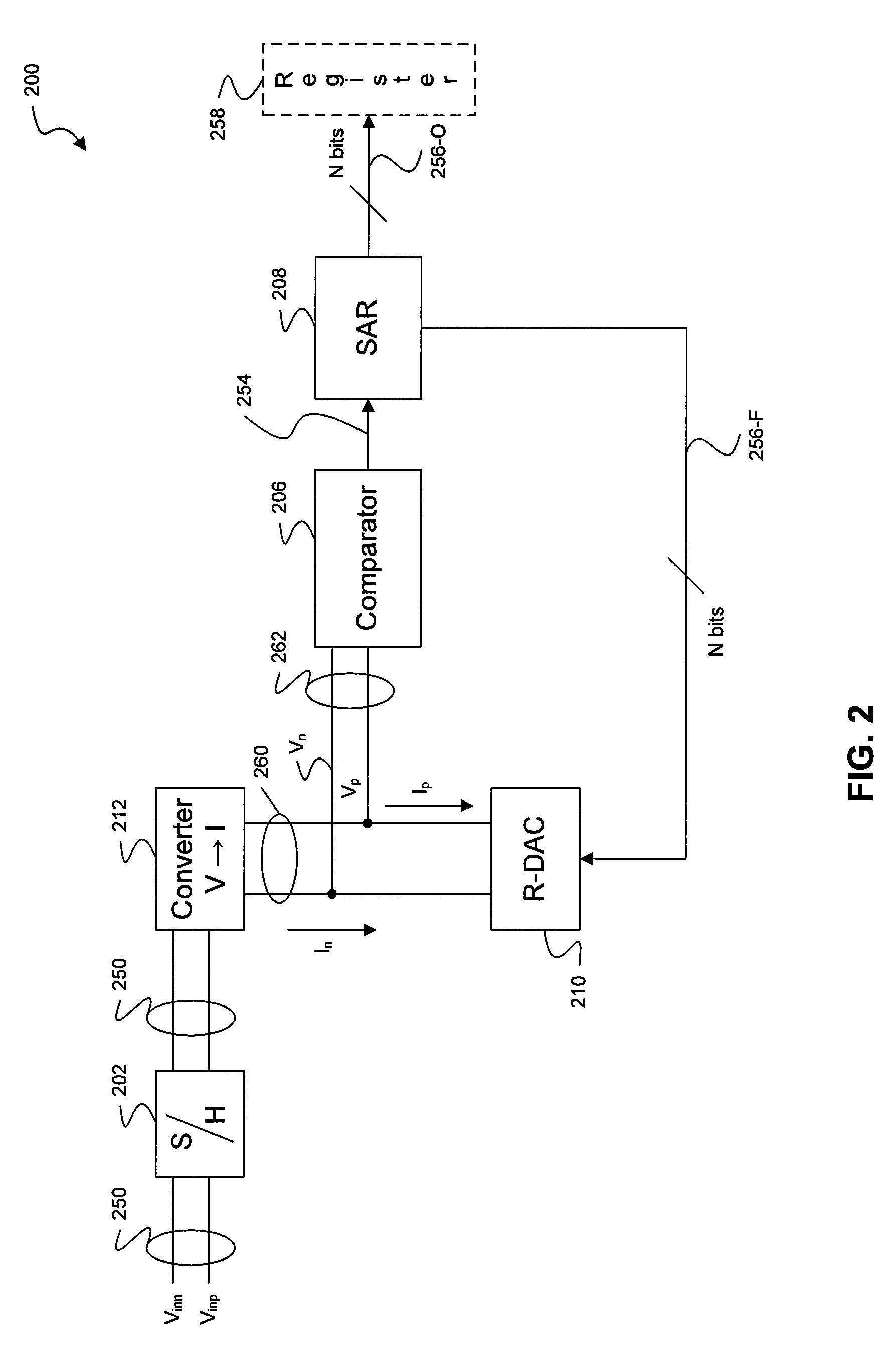

Successive approximation analog to digital converter

ActiveUS7642946B2Power saving provisionsElectric signal transmission systemsElectrical resistance and conductanceA d converter

A system and method are provided allowing for successive approximation analog to digital conversion. A first differential voltage is sampled and held during a first cycle. The first differential voltage is converted to a differential current. A second differential voltage is generated based on the differential current flowing through parallel-coupled respective first and second variable resistances. First and second portions of the second differential voltage are compared to produce a comparison result therefrom. Successive approximation is used to generate a signal based on the comparison result, the signal being an output signal and being used to control resistances of respective ones of the first and second variable resistances during subsequent cycles.

Owner:AVAGO TECH INT SALES PTE LTD

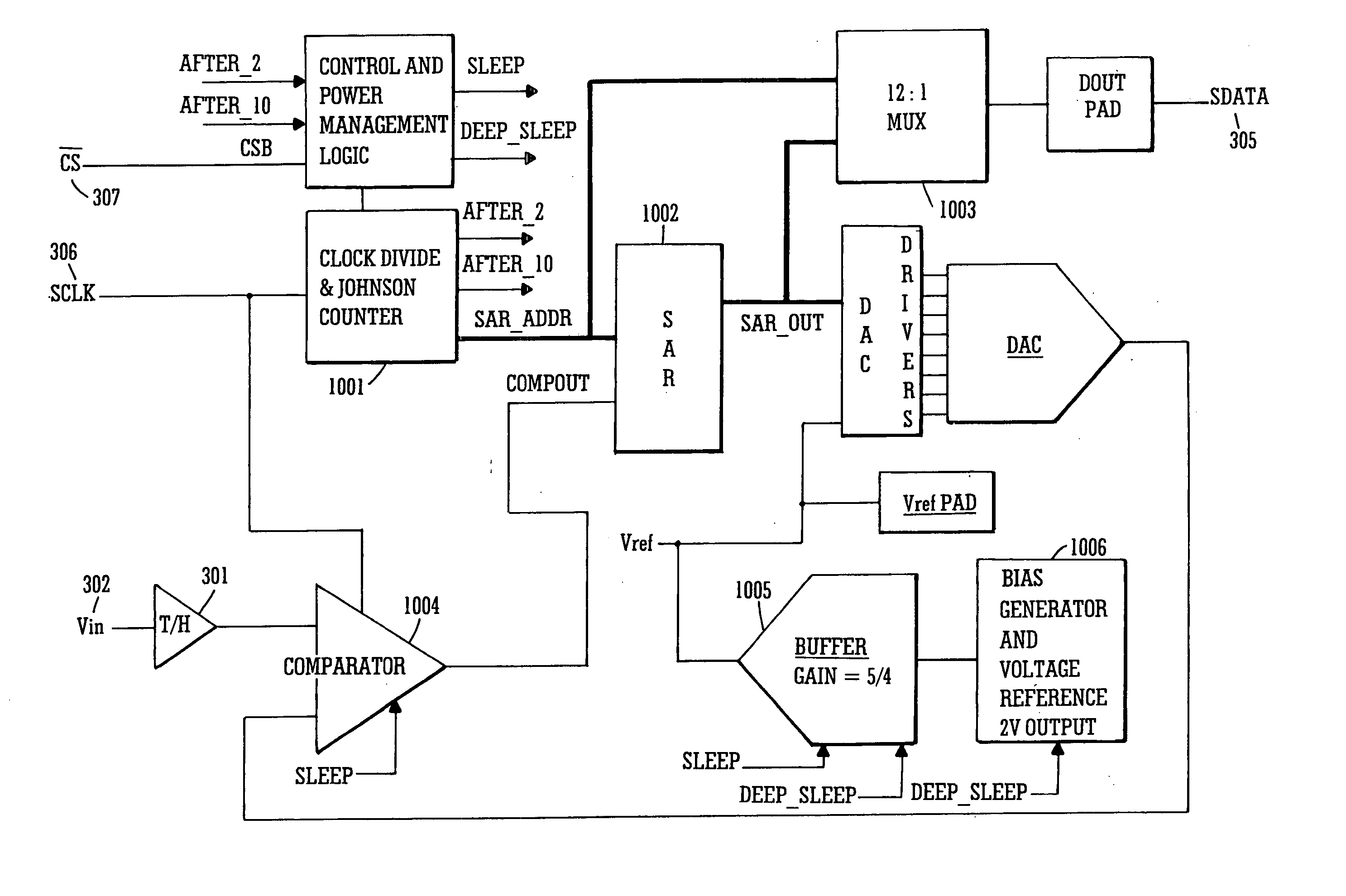

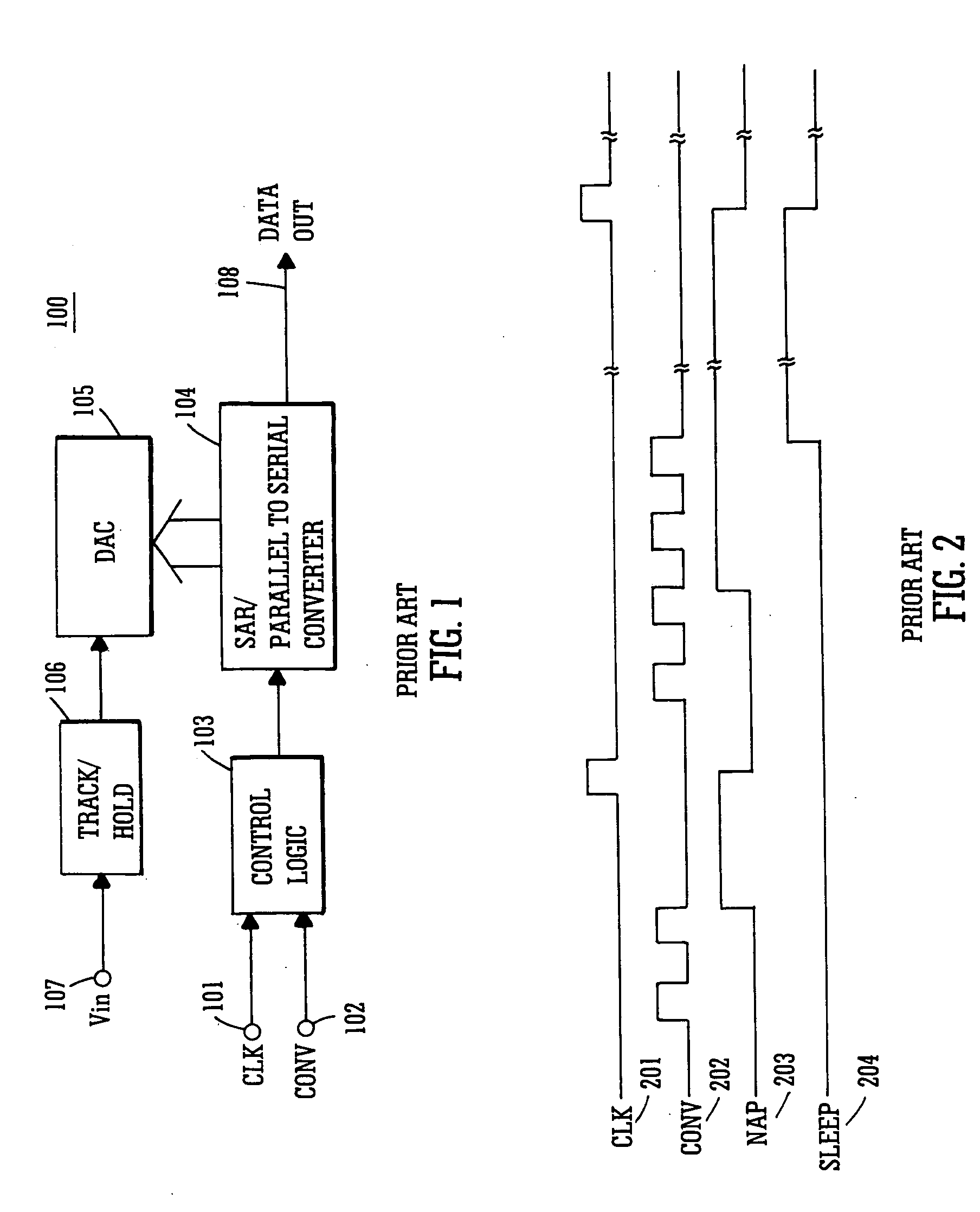

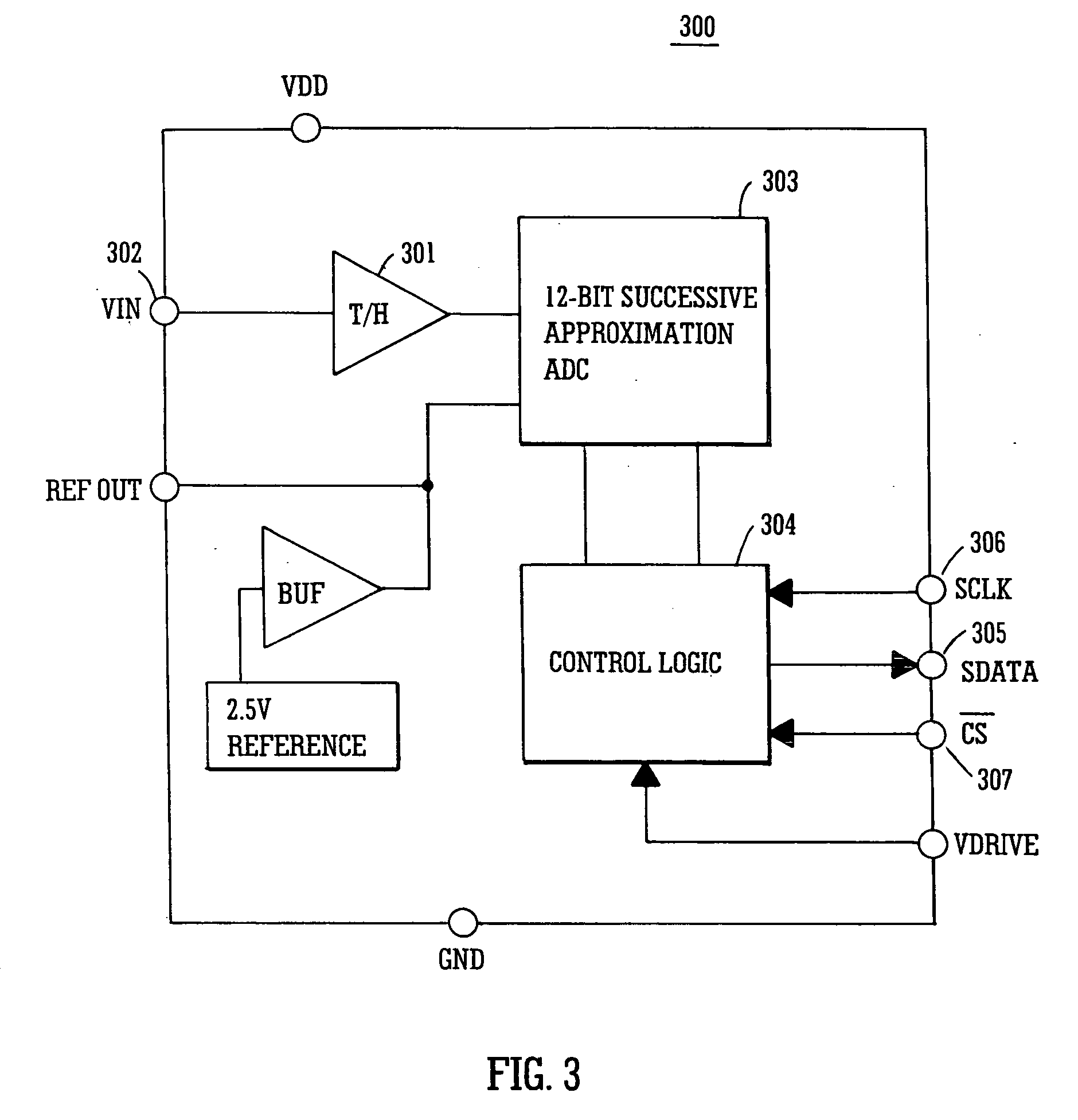

Read-only serial interface with versatile mode programming

InactiveUS20050035895A1Fast device throughputIncreased power consumptionPower managementPower saving provisionsOperation modeLogic state

A method for placing a device in a selected mode of operation. The method comprises the steps of initializing a device select signal into a first logic state, asserting the device select signal in a second logic state, and returning the device select signal to the first logic state within a first user-controlled time window. A device is also described that includes means for detecting logic state transitions at a device select input and a clock input, and means for changing operating mode of the device in response to a predetermined number of logic state transitions at the clock input, occurring between logic state transitions at the device select input. The selected operating mode may be a reduced power consumption mode, for example, or another operating mode of the device, such as a daisy-chain mode of operation, or a mode that accommodates programming of analog input range.

Owner:ANALOG DEVICES INC

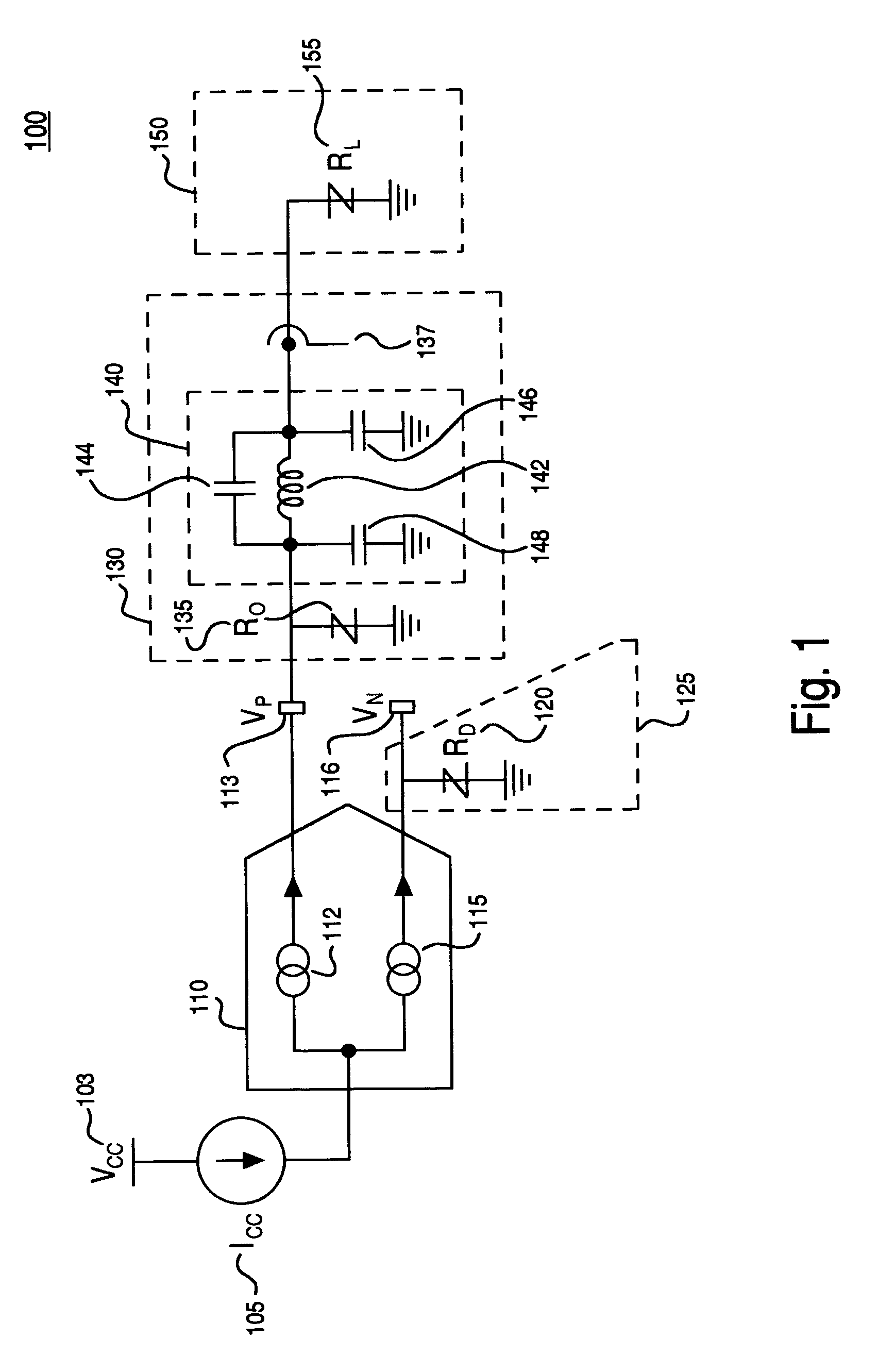

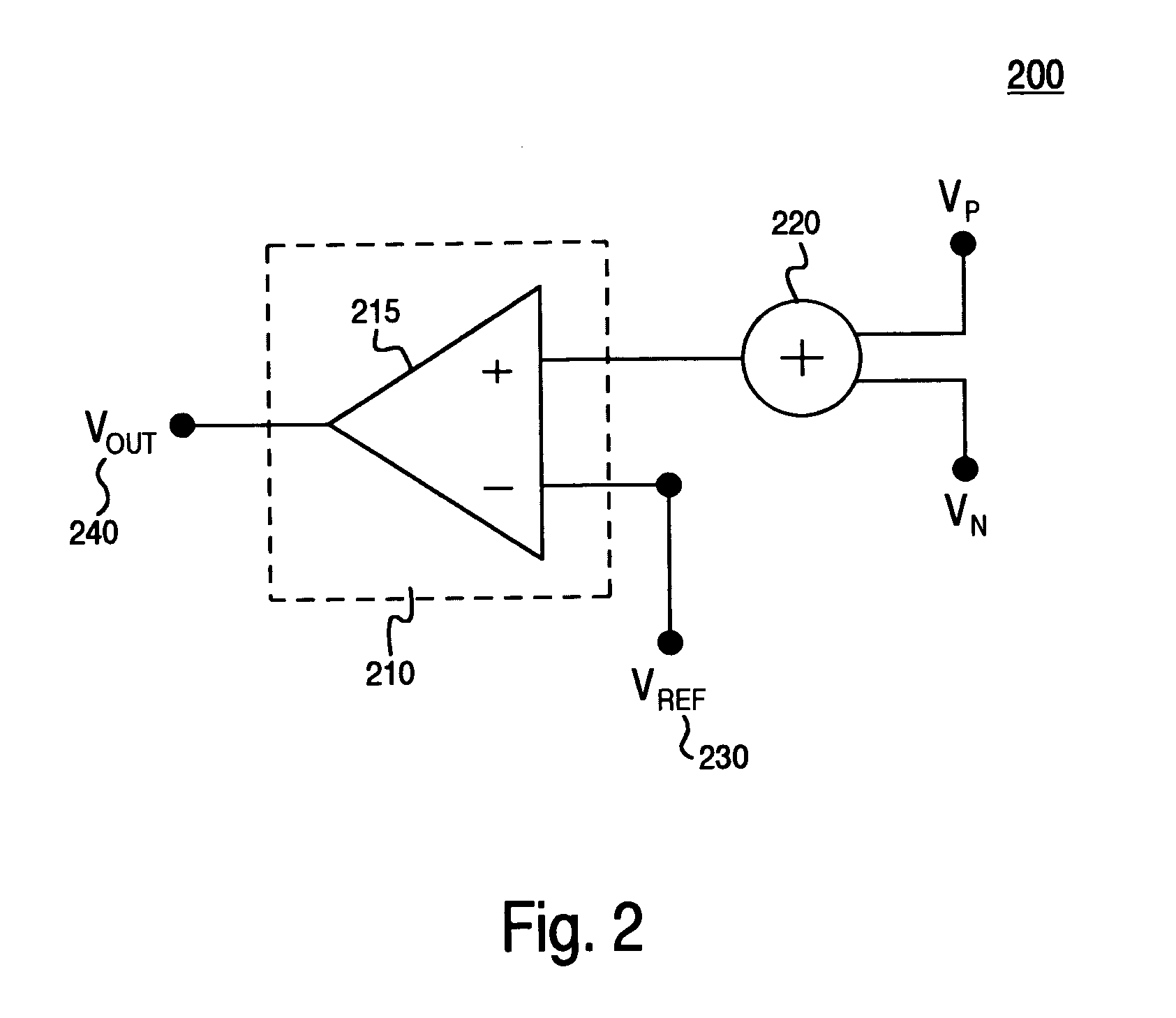

System and method for detecting when an external load is coupled to a video digital-to-analog converter

ActiveUS6940440B1Power saving provisionsElectric signal transmission systemsDigital analog converterDetector circuits

A system and method for determining when an external load is coupled to a digital-to-analog converter (DAC). Specifically, in one embodiment, a load detector circuit comprises a video DAC, an output circuit, a dumping circuit, and a determining circuit. The video DAC comprises a differential architecture including a first output and a second output working in opposite phase. The first DAC output is coupled to the output circuit, which drives the external load. The second DAC output is coupled to a dumping circuit, and is configured such that the dumping circuit is balanced with the output circuit when the external load is present. A determining circuit examines the two outputs of the DAC to determine if the dumping circuit is balanced with the output circuit, and thus if the external load is present.

Owner:NAT SEMICON CORP

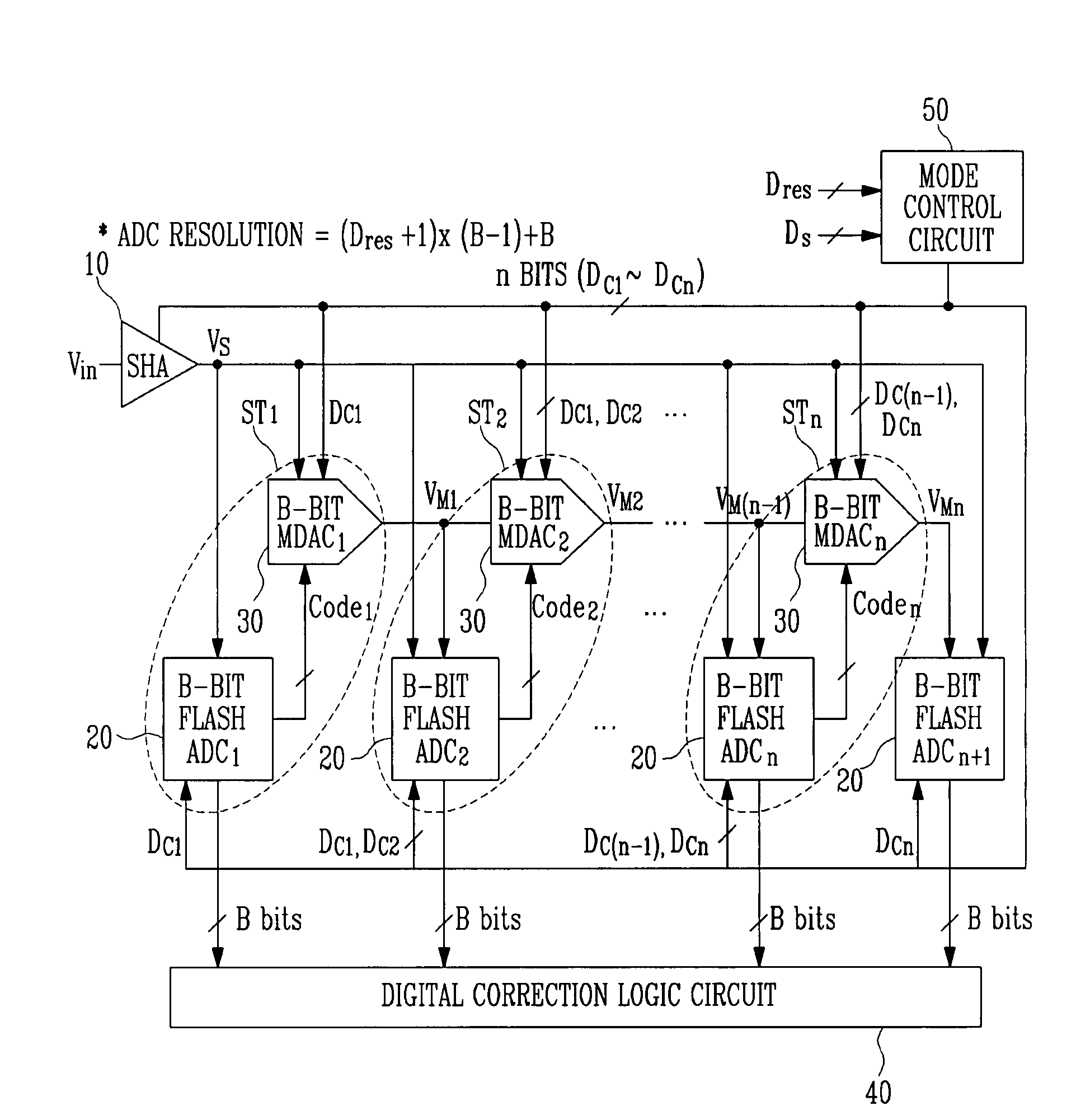

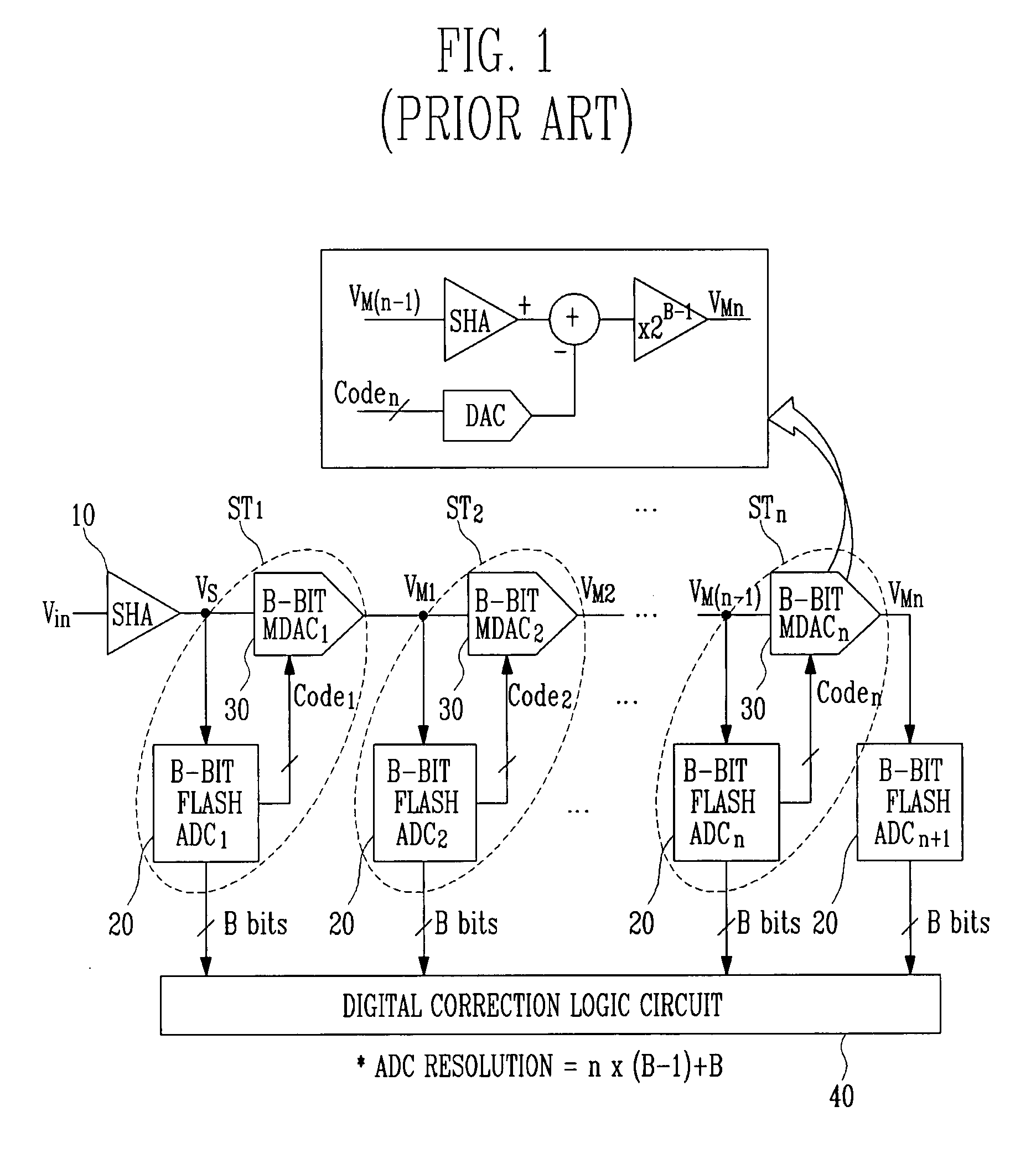

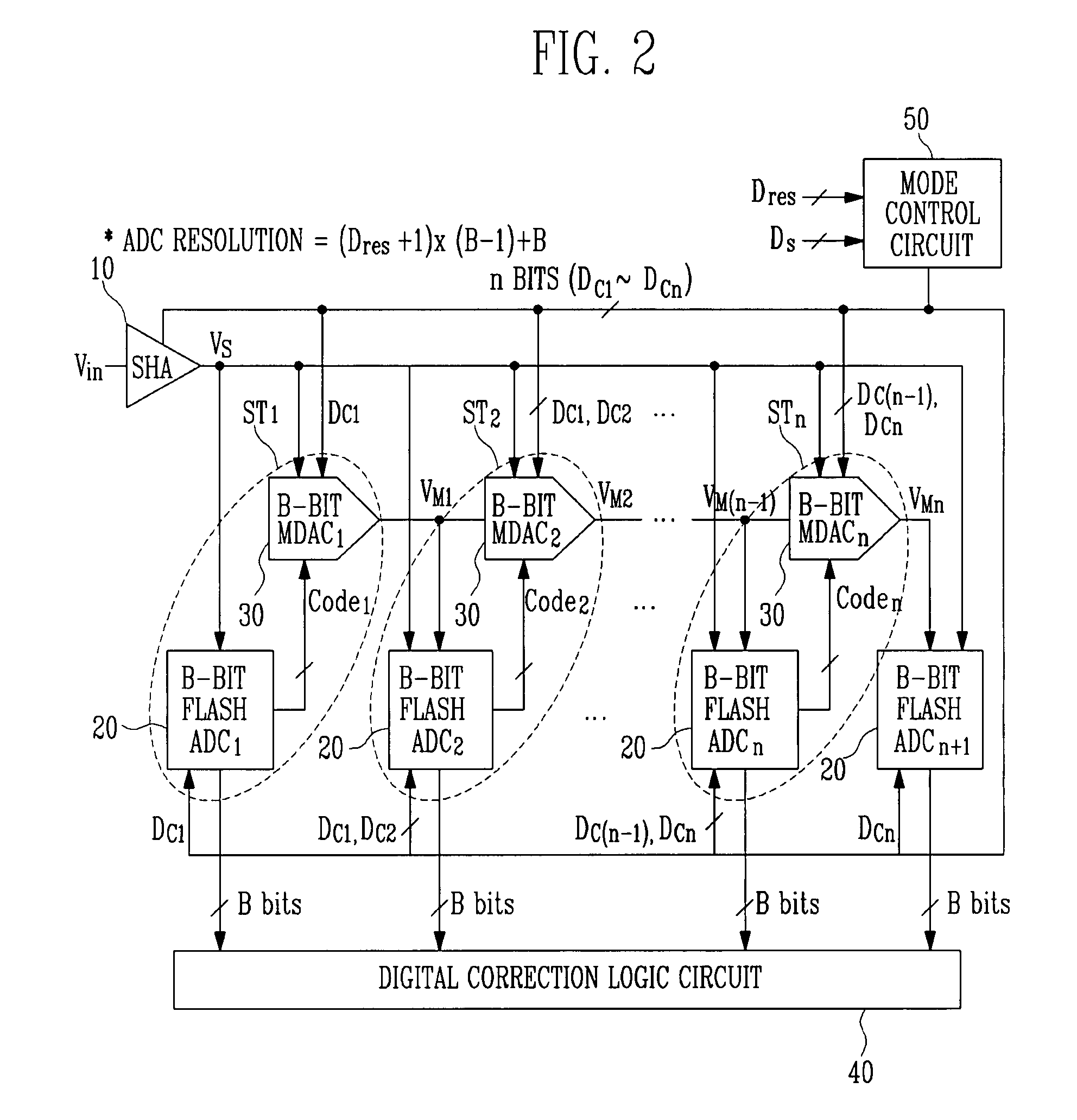

Multi-bit pipeline analog-to-digital converter capable of altering operating mode

InactiveUS20080129567A1Minimize power consumptionPower saving provisionsElectric signal transmission systemsControl signalMode control

Provided is a multi-bit pipeline analog-to-digital converter (ADC) capable of altering an operating mode. The ADC includes: a sample-and-hold amplifier (SHA) for sampling and holding an input analog voltage; an n+1 number of B-bit flash ADCs for receiving an analog signal and converting the analog signal into a digital signal to output the digital signal; an n number of B-bit multiplying digital-to-analog converters (MDACs) for converting a difference between the digital signal output from the B-bit flash ADC and the front-stage output signal into an analog signal to output the analog signal to the next stage; and a mode control circuit for generating n-bit control signals to control the B-bit flash ADC and the B-bit MDAC according to required resolution and operating frequency. In the multi-bit pipeline ADC, an operating mode is altered by controlling the number of stages in a pipeline and a signal path according to required resolution and operating frequency, so that power consumption can be minimized under the corresponding operating condition and signals can be processed in a variety of ways.

Owner:ELECTRONICS & TELECOMM RES INST

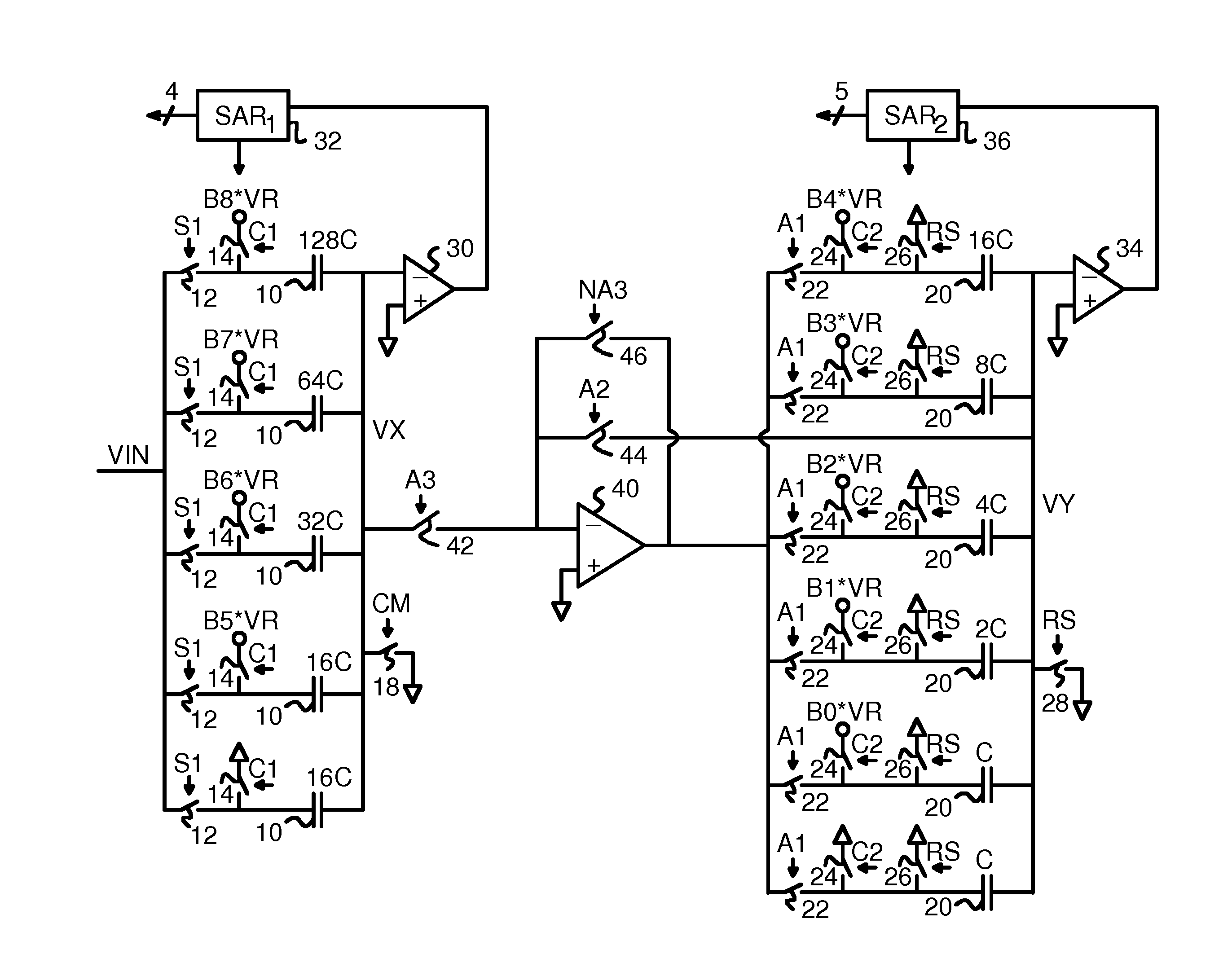

Loading-free multi-stage SAR-assisted pipeline ADC that eliminates amplifier load by re-using second-stage switched capacitors as amplifier feedback capacitor

ActiveUS9219492B1Power saving provisionsElectric signal transmission systemsCapacitanceAudio power amplifier

A multi-stage Successive-Approximation Register (SAR) pipeline Analog-to-Digital Converter (ADC) has an amplifier between two switched capacitor networks, each controlled by a SAR. The load capacitance of the amplifier is magnified due to the amplifier's gain. This magnified load capacitance can disproportionately increase power consumption. The back plates of the second-stage switched capacitors are connected to the amplifier input using a feedback switch during an amplification phase, so that the second-stage switched capacitors are connected between the input and output of the amplifier as a feedback capacitor, rather than a load capacitor. Reset switches are added to drive both plates of the second-stage switched capacitors to ground during a reset phase before the amplification phase. Thus the second-stage switched capacitors function as both the feedback capacitor and as the switched capacitors controlled by the second SAR. Amplifier power is reduced since there is no separate load capacitor during the amplification phase.

Owner:HONG KONG APPLIED SCI & TECH RES INST

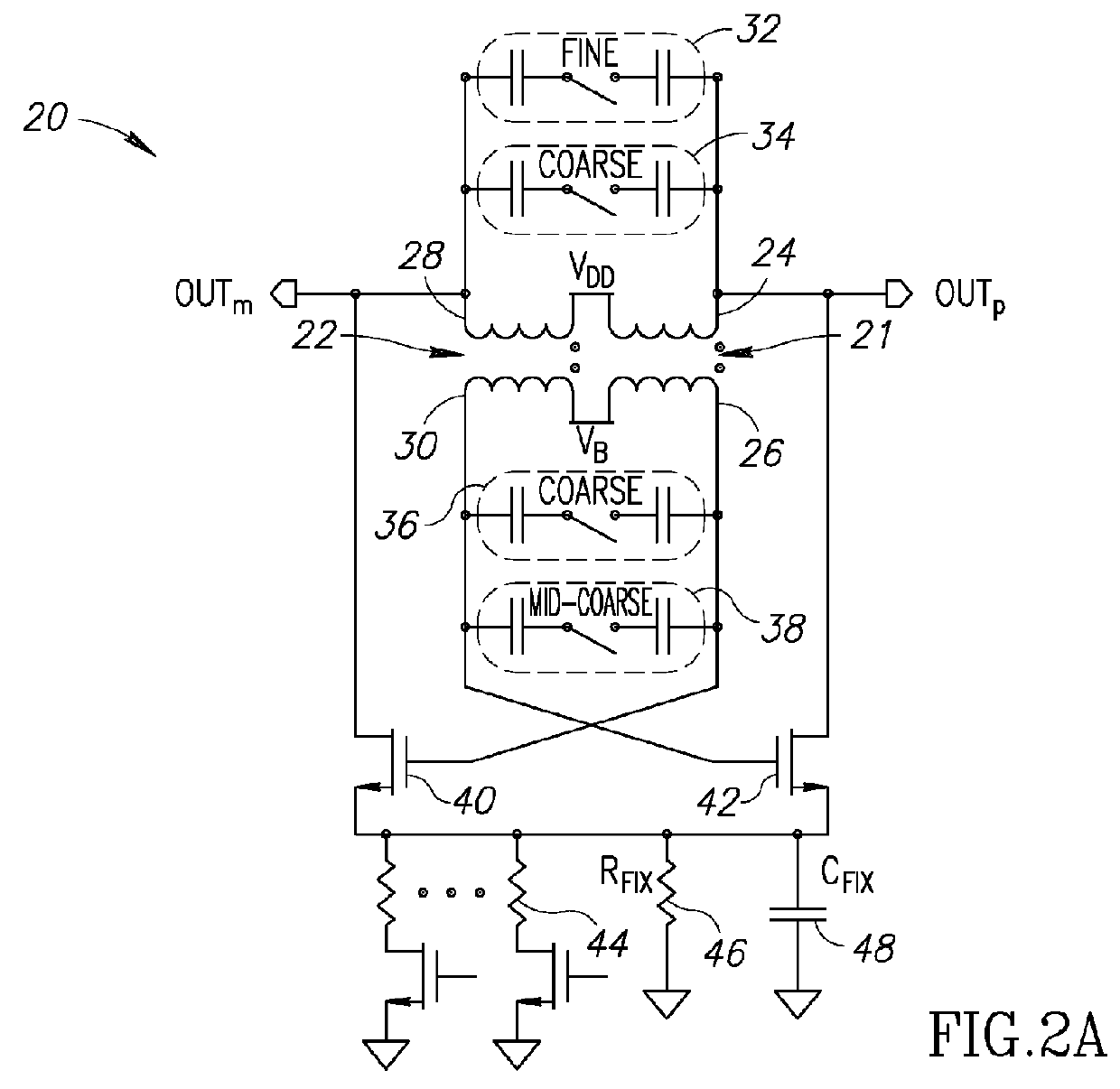

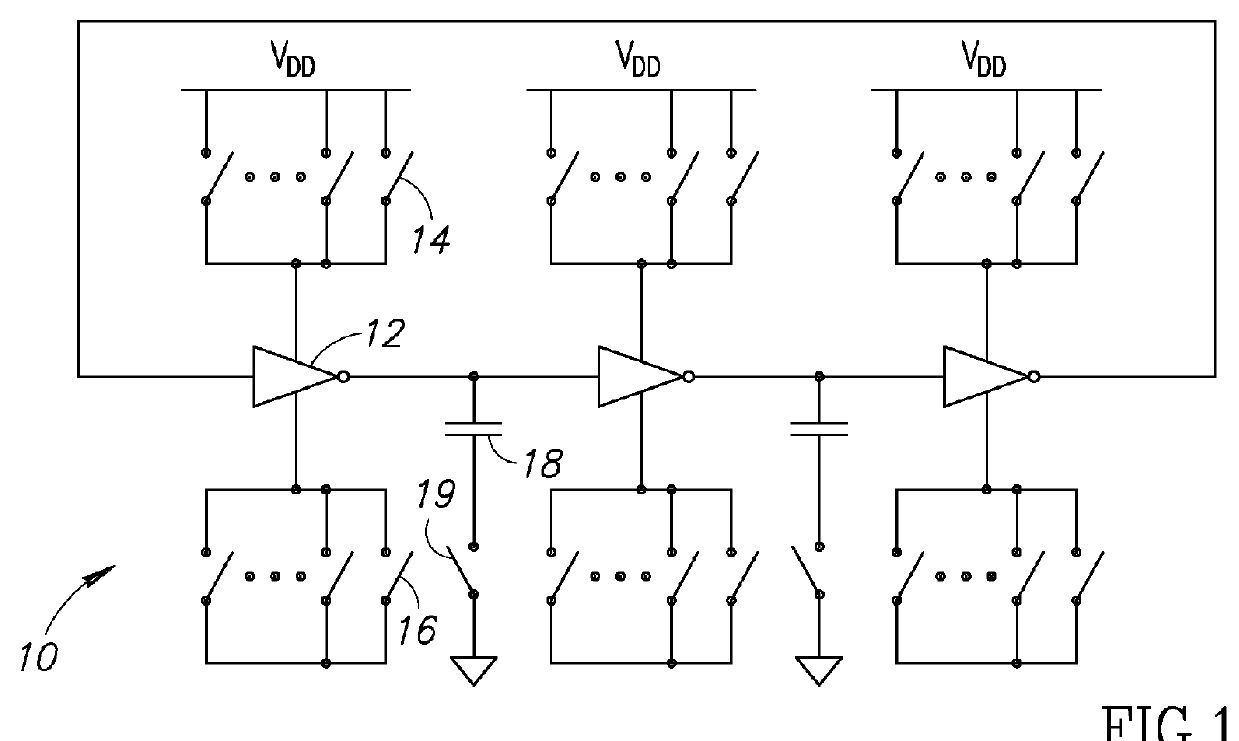

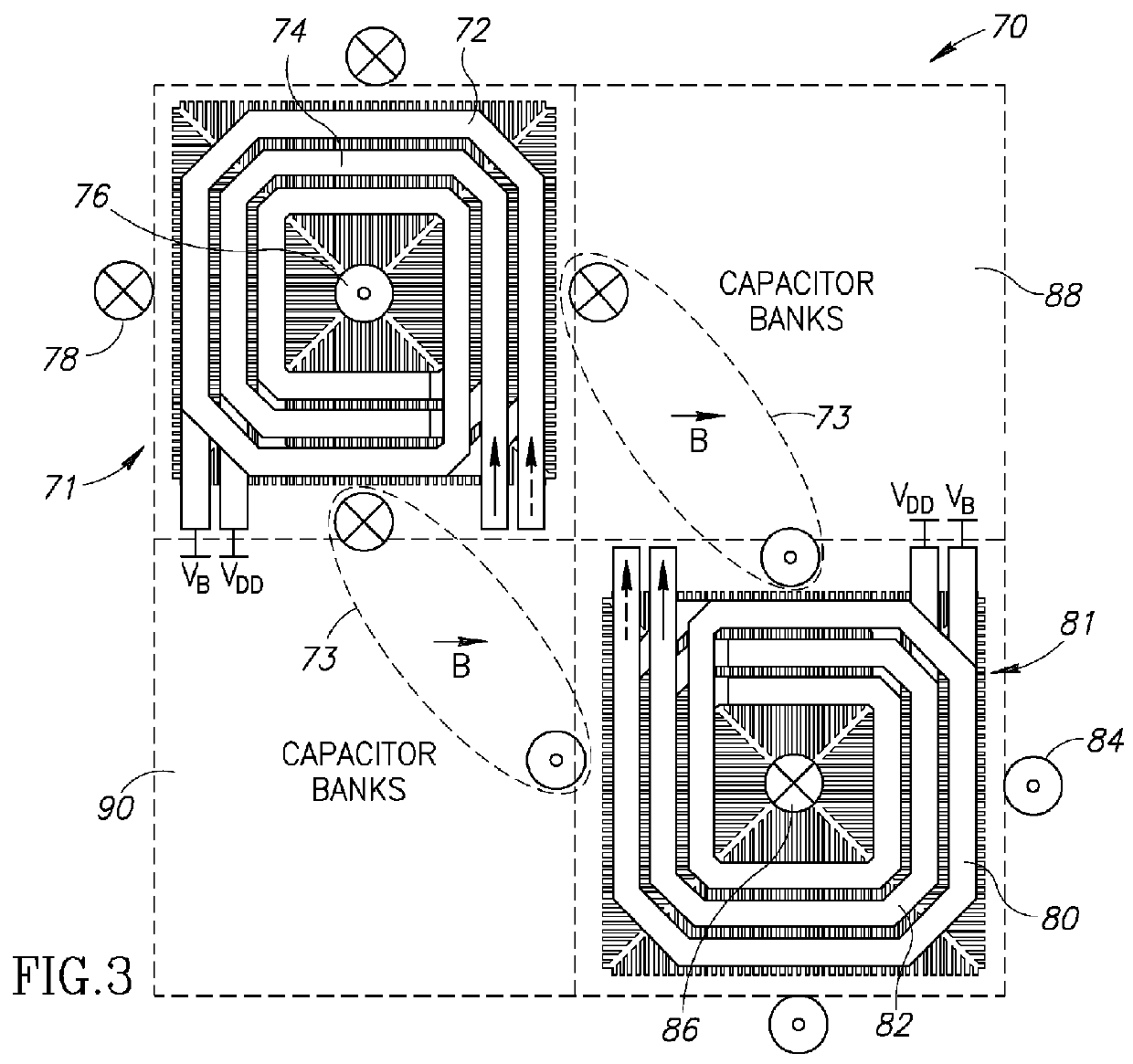

Split Transformer Based LC-Tank Oscillator

A novel and useful LC-tank digitally controlled oscillator (DCO) incorporating a split transformer configuration. The LC-tank oscillator exhibits a significant reduction in area such that it is comparable in size to conventional ring oscillators (ROs) while still retaining its salient features of excellent phase noise and low sensitivity to supply variations. The oscillator incorporates an ultra-compact split transformer topology that is less susceptible to common-mode electromagnetic interference than regular high-Q LC tanks which is highly desirable in SoC environments. The oscillator, together with a novel dc-coupled buffer, can be incorporated within a wide range of circuit applications, including clock generators and an all-digital phase-locked loop (ADPLL) intended for wireline applications.

Owner:SHORT CIRCUIT TECH LLC

Frame adaptive digital to analog converter and methods for use therewith

ActiveUS20150214975A1Power saving provisionsElectric signal transmission systemsDigital-to-analog converterThermometer

A digital to analog converter (DAC) includes a thermometer coder that generates a plurality of micro-current source analog controls on a frame-by-frame or symbol-by-symbol basis and to process digital inputs from symbols or frames of data based on a thermometer coding to generate a plurality of micro-current source inputs. A plurality of micro-current sources generate a corresponding plurality of micro-current source outputs in response to the plurality of micro-current source inputs, wherein first selected ones of the plurality of micro-current sources are powered-off in response to the plurality of micro-current source analog controls for a first symbol or frame of the plurality of symbols or frames of data. A summing circuit generates an analog output based a sum of the corresponding plurality of micro-current source outputs.

Owner:AVAGO TECH INT SALES PTE LTD

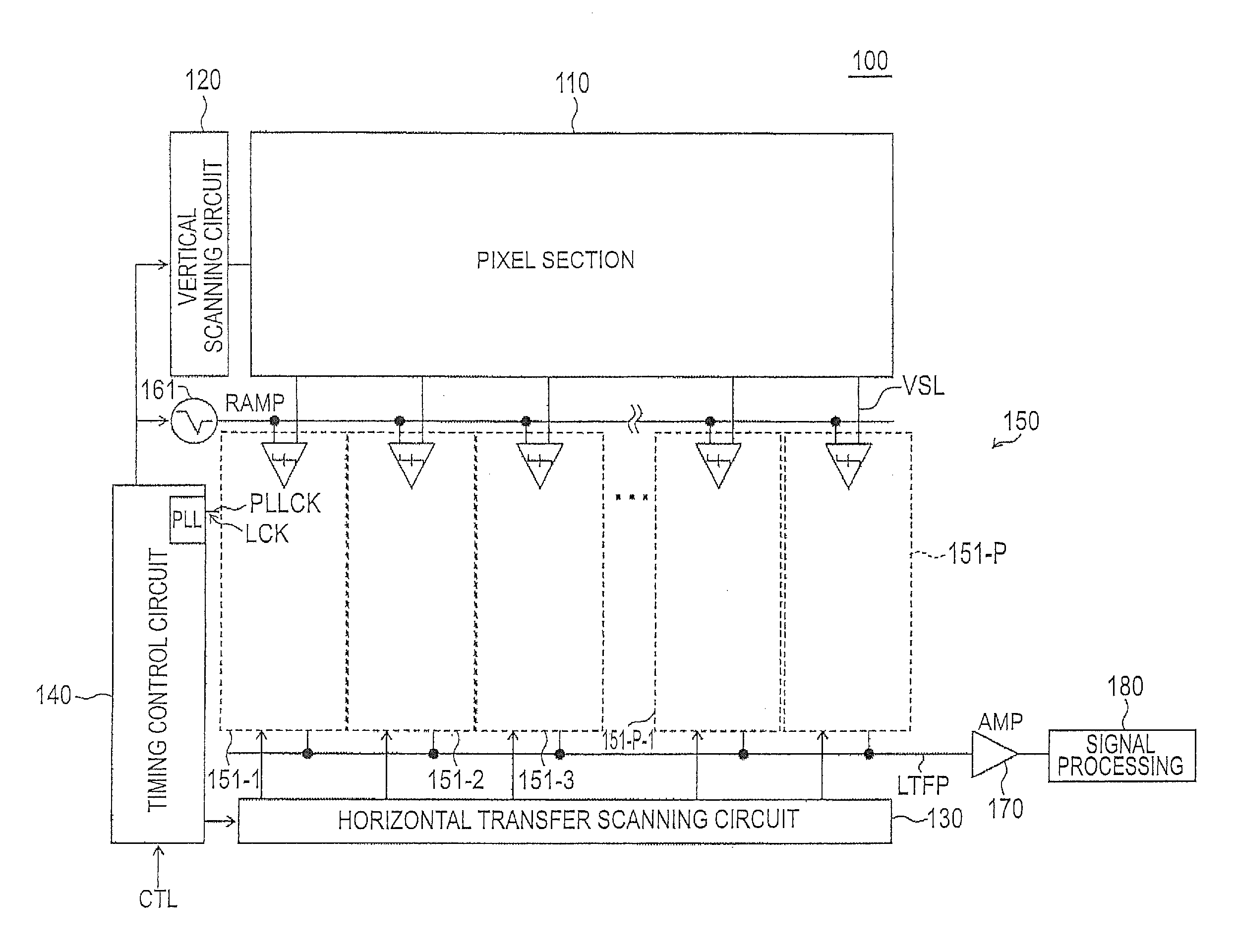

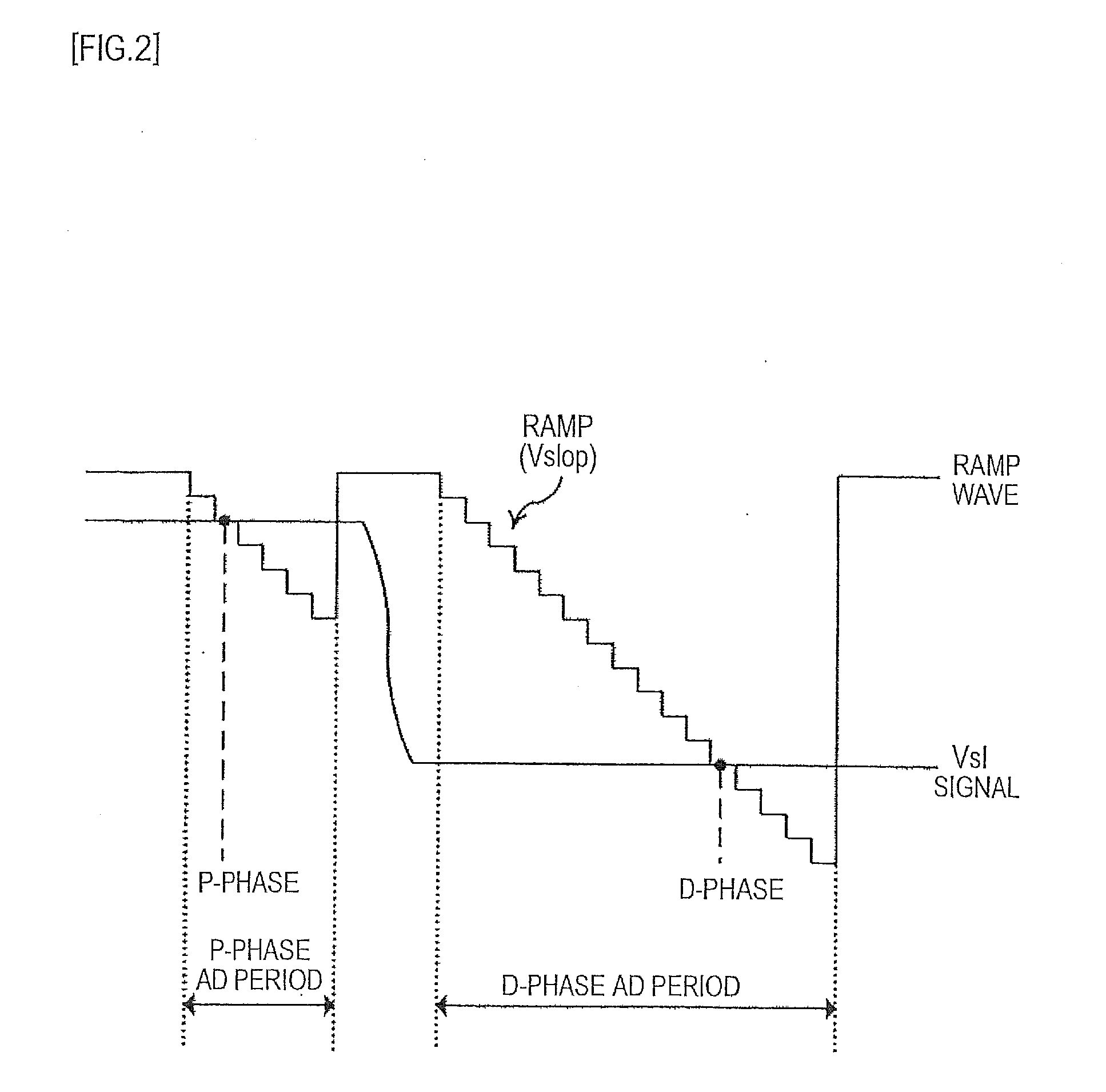

Column a/d converter, column a/d conversion method, solid-state imaging element and camera system

A solid-state imaging device having an analog-digital converter, and an analog-digital conversion method are described herein. An example of a solid-state imaging device includes a column processing section that includes a low-level bit latching section. The low-level bit latching section receives a comparator output from a comparator and a count output from a counter, and the low-level bit latching section latches a count value.

Owner:SONY CORP

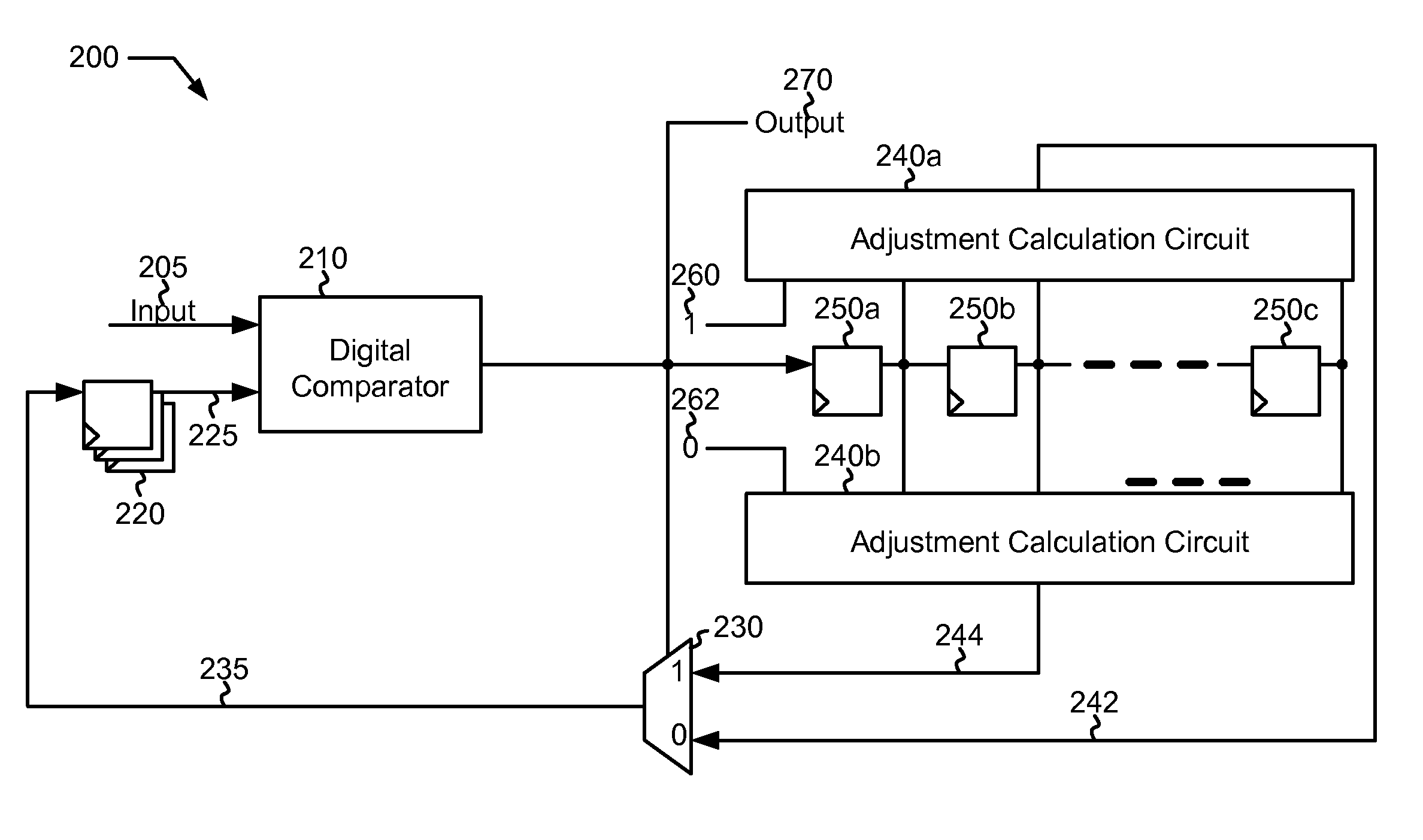

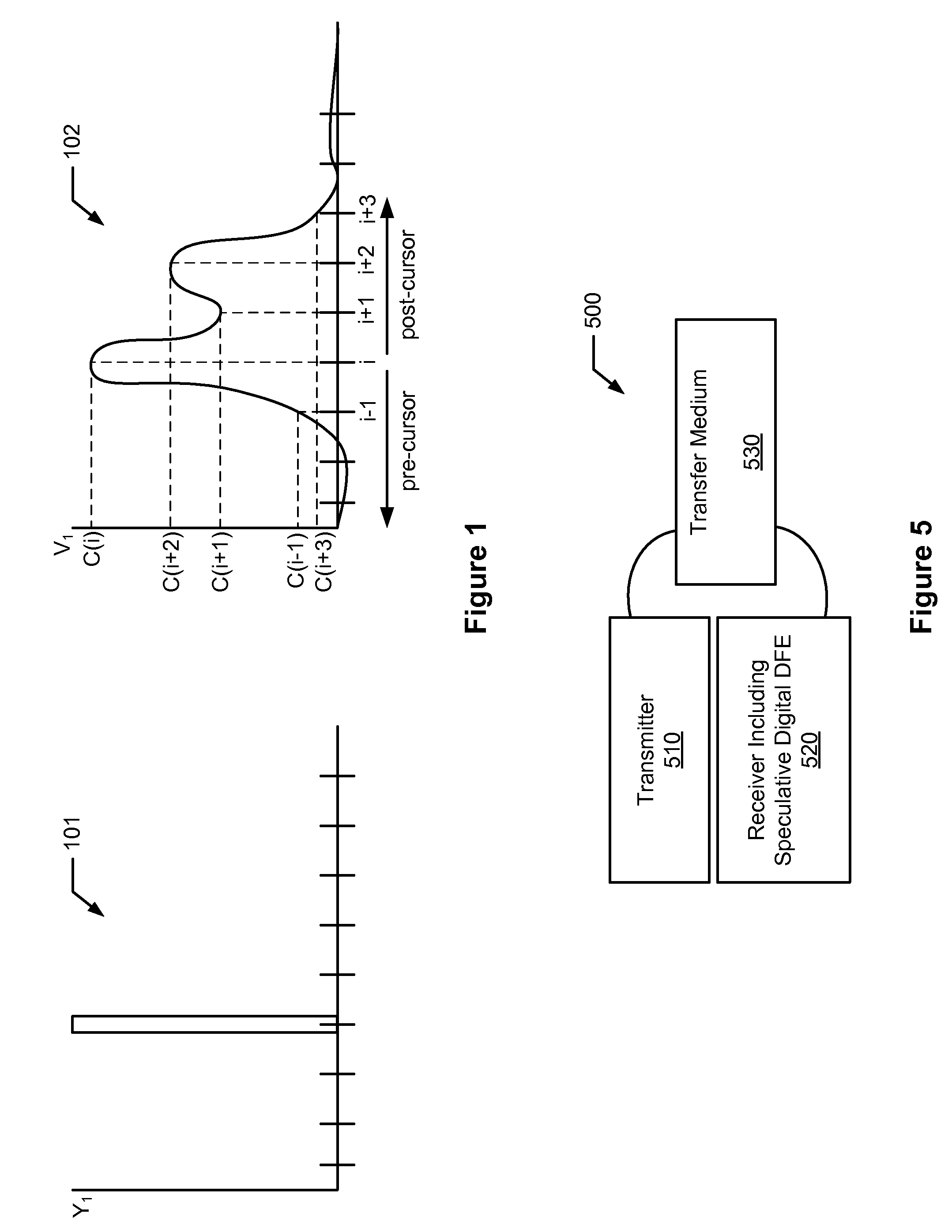

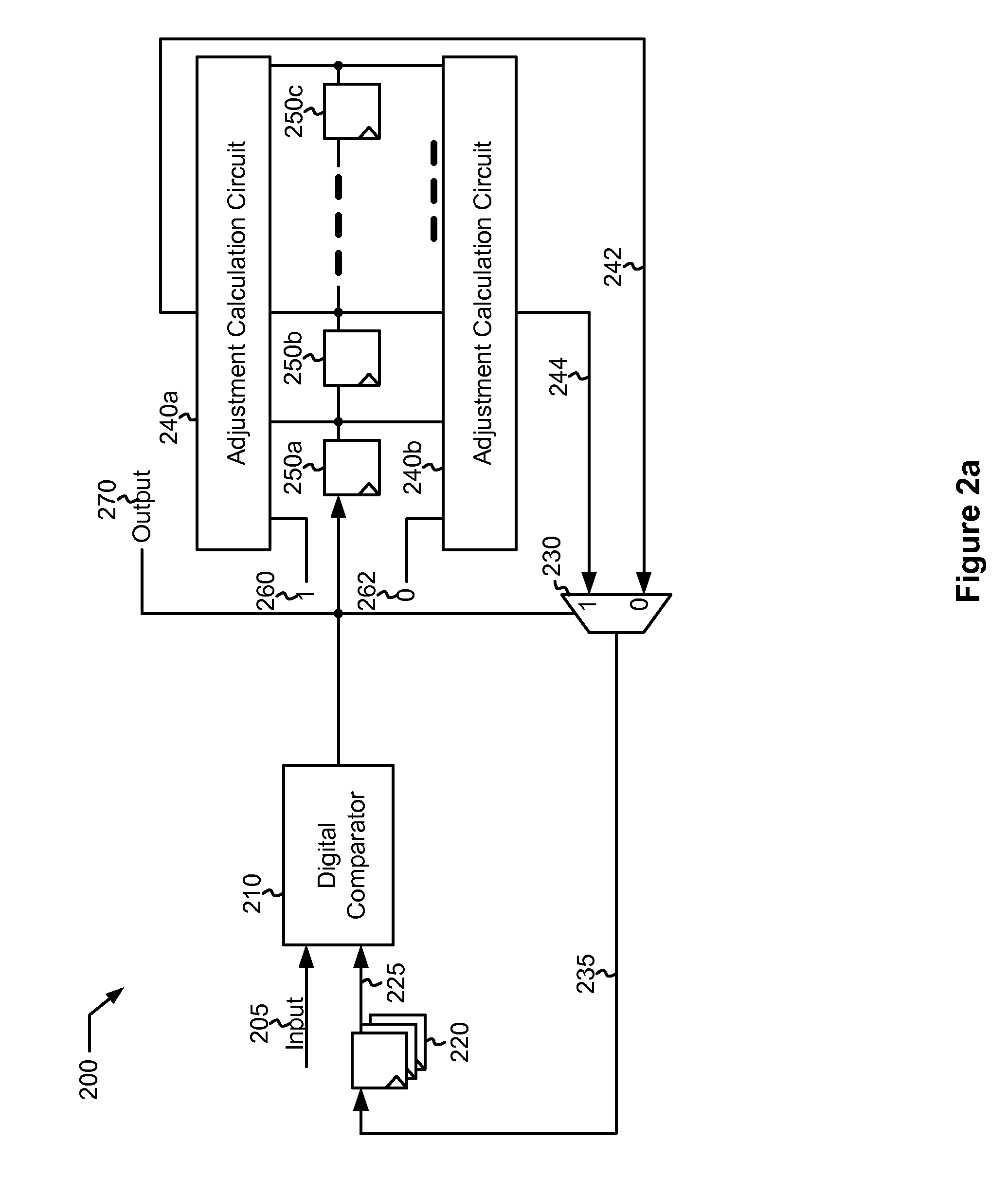

Systems and Methods for Speculative Signal Equalization

Various embodiments of the present invention provide systems and methods for signal equalization, and in some cases analog to digital conversion. For example, an analog to digital converter is disclosed that includes a comparator bank that receives a reference indicator and is operable to provide a decision output based at least in part on a comparison of an analog input with a reference threshold corresponding to the reference indicator. A range selection filter is included that has a first adjustment calculation circuit and a second adjustment calculation circuit. The first adjustment calculation circuit is operable to calculate a first adjustment feedback value based at least in part on a speculation that the decision output is a first logic level, and the second adjustment calculation circuit is operable to calculate a second adjustment feedback value based at least in part on a speculation that the decision output is a second logic level. A selector circuit selects the first adjustment feedback to generate the reference indicator when the decision output is the first logic level, and selects the second adjustment feedback to generate the reference indicator when the decision output is the second logic level.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Popular searches

Reconfigurable analogue/digital converters Pulse automatic control Analogue-digital converters Architecture with single central processing unit Input/output processes for data processing Color television details Electric pulse generator Oscillations generators Time-to-digital converters Physical parameters compensation/prevention