Method for predicting and quantifying binary charge redistribution type successive approximation analog-to-digital converter

A charge redistribution, analog-to-digital converter technology, applied in the direction of analog/digital conversion, energy-saving methods, code conversion, etc., can solve the problems of power consumption increase, speed limit, quantization power consumption, etc., to achieve low power consumption Design, reduce the number of comparisons, and reduce the effect of quantization power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

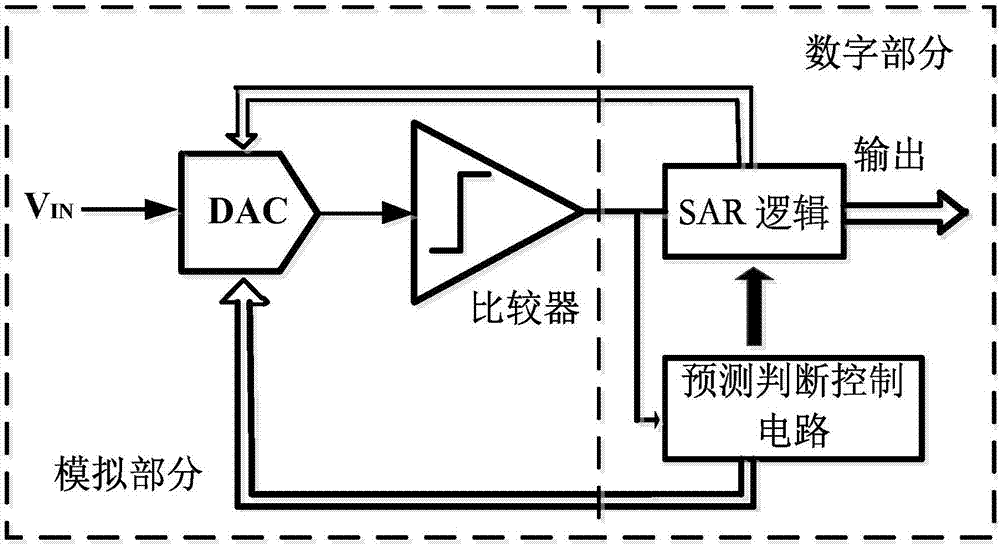

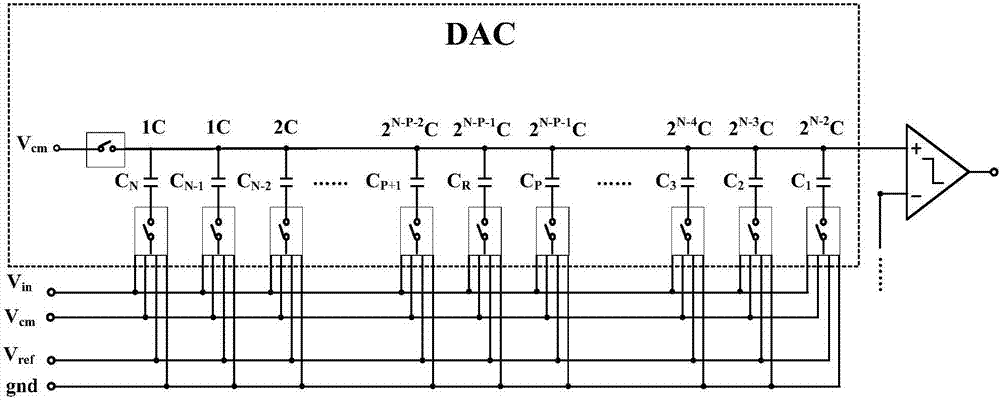

[0042] Such as figure 1 Shown is a system block diagram of a binary charge redistribution type successive approximation analog-to-digital converter applicable to the present invention, including: a digital-to-analog converter module DAC, a comparator module, a SAR logic control circuit module and a predictive judgment control circuit module including a memory, The digital-to-analog converter module DAC consists of at least one set based on the common-mode voltage V cm Composed of reset capacitor arrays, the control terminal of the digital-to-analog converter module DAC is coupled to the output terminals of the SAR logic control circuit module and the prediction and judgment control circuit module; all quantized capacitors in each capacitor array are numbered, denoted as C i , i is any integer from 1 to N-1, C 1 is the highest bit capacitance, where N is the number of digits of the binary charge redistribution successive approximation analog-to-digital converter, and each capa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More