Patents

Literature

271 results about "Right shift" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

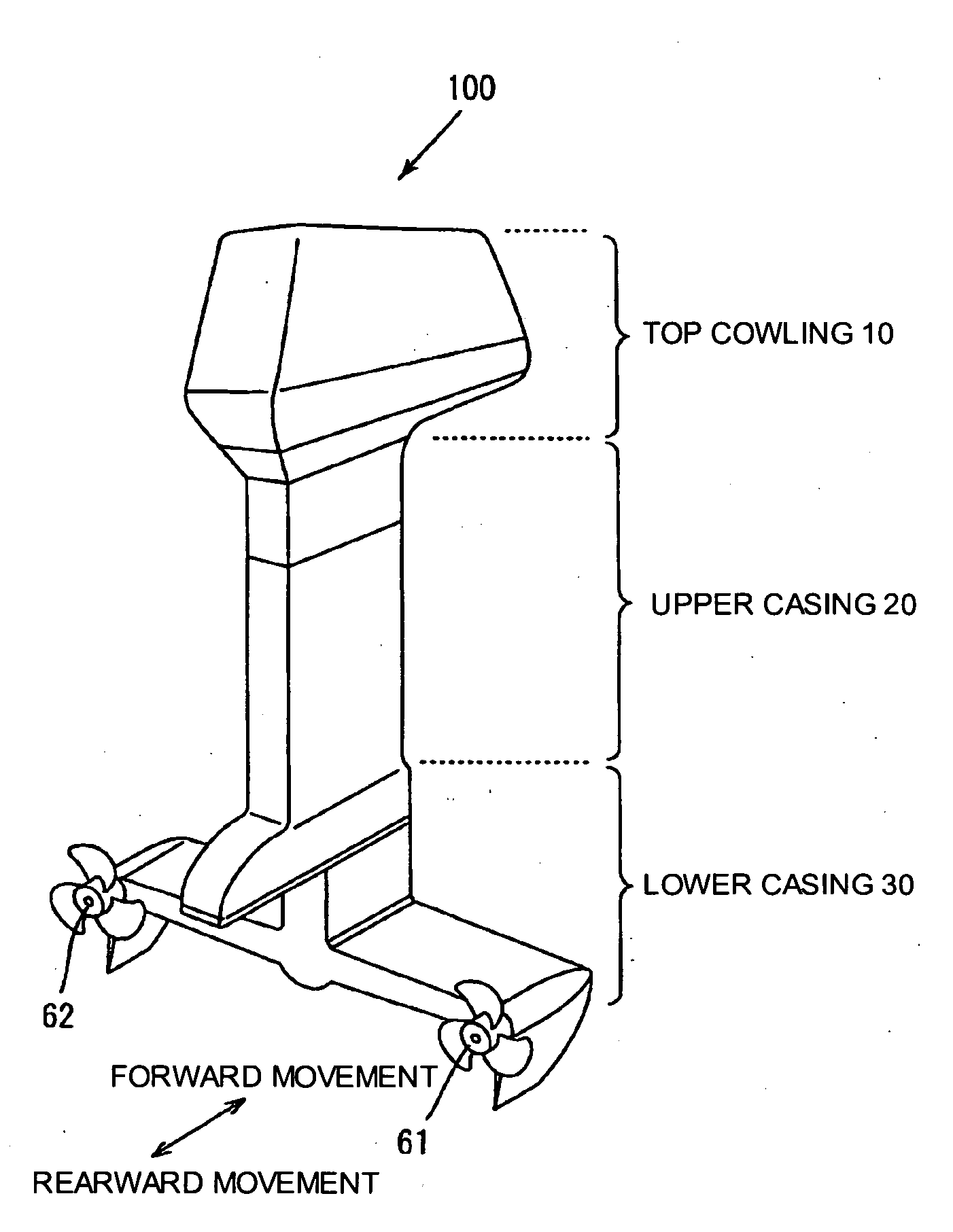

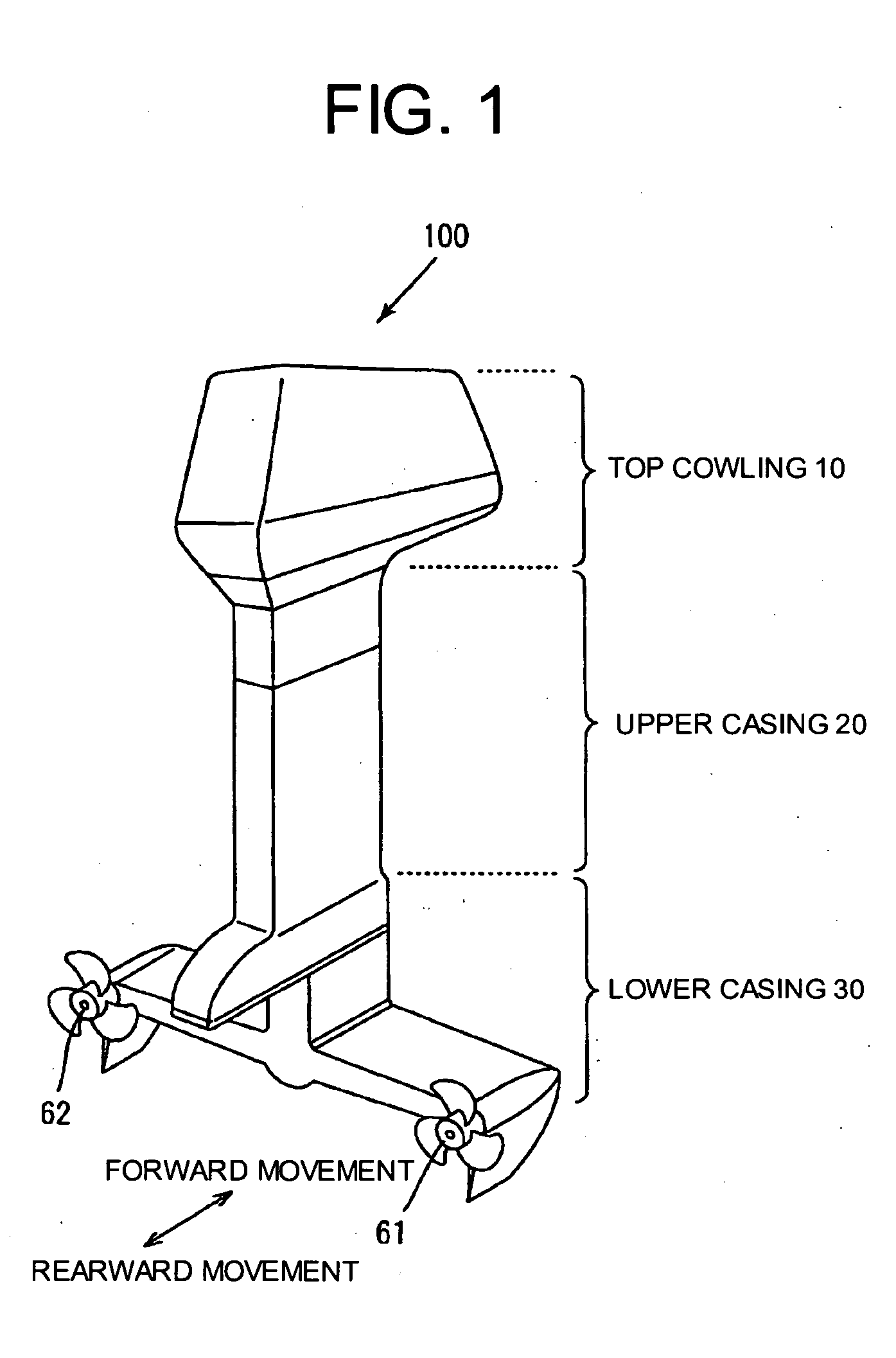

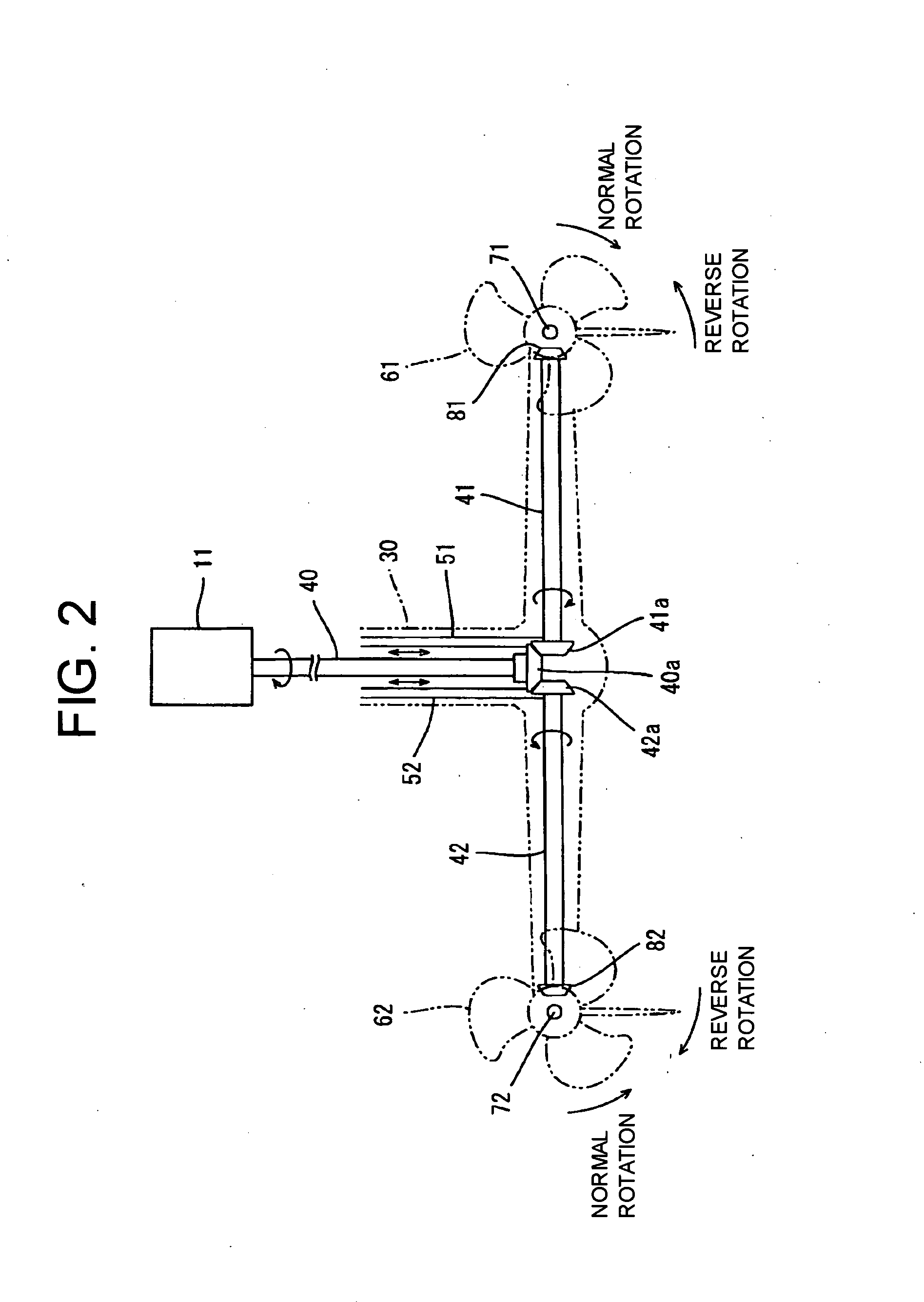

Marine vessel propulsion structure and marine vessel driving apparatus

InactiveUS20060172630A1Improve balanceSimple structurePropulsion power plantsOutboard propulsion unitsDrive shaftRight shift

In an outboard drive or an inboard-outboard drive, power generated by a single engine is transmitted in left and right directions from a main drive shaft, thereby finally causing left and right propellers to be rotated, the left and right propellers being arranged about the main drive shaft so as to be spaced apart from the main drive shaft at approximately equal distances from the main drive shaft and facing a travel direction of a marine vessel, the outboard drive or inboard-outboard drive being provided with left and right shift cam assemblies for causing rotation situations of the propellers to be controlled dependently from each other, the rotation situations including normal rotation, reverse rotation and non-rotation situations of the propellers.

Owner:ARK SYST CORP

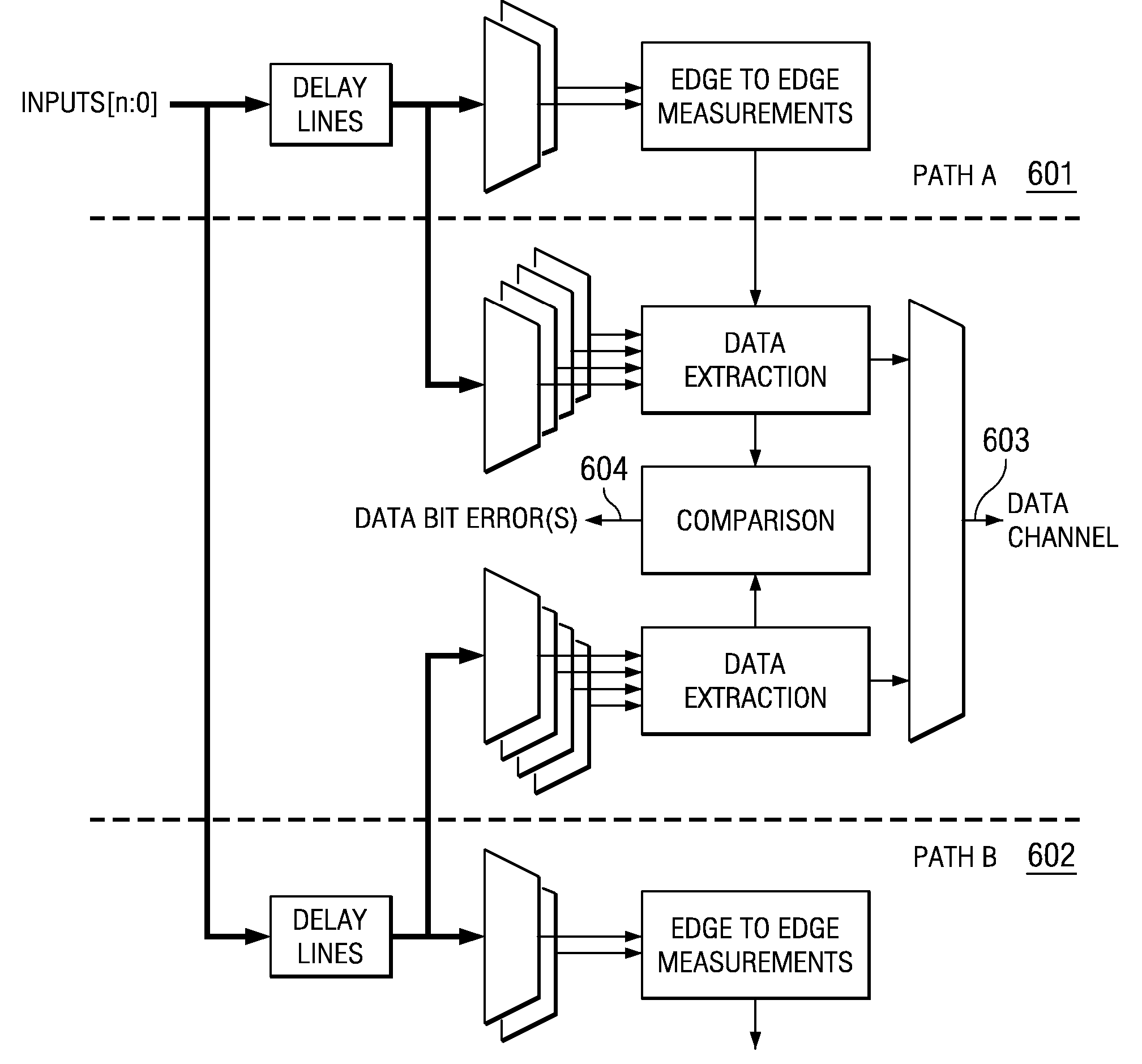

Saving Resources by Deducing the Total Prediction Events

ActiveUS20060267818A1Analogue/digital conversionElectric signal transmission systemsNetwork packetRight shift

While PC trace is o, and the trace is in predication or general event profiling mode, trace hardware captures events in each cycle. Trace hardware inserts this information into data logs, and does a right shift to compact the data. The trace window will eventually close, either because tracing has been turned off, or because a periodic sync point is generated to reset the window. In either of these two cases, the data log may be incomplete, fully packed, or just overflow into the next packet. An index is generated pointing to the last valid location in the data log in order to save transmission bandwidth.

Owner:TEXAS INSTR INC

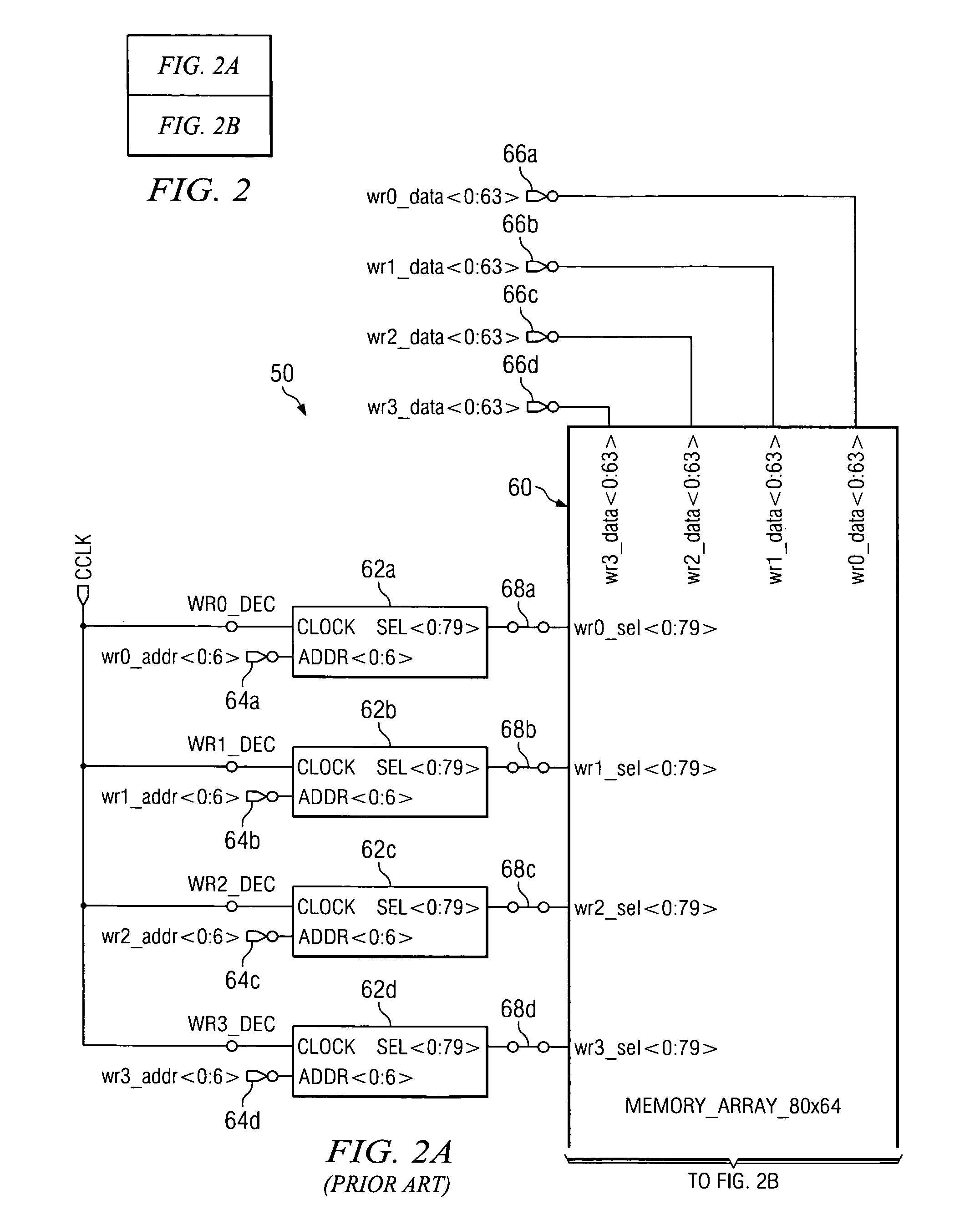

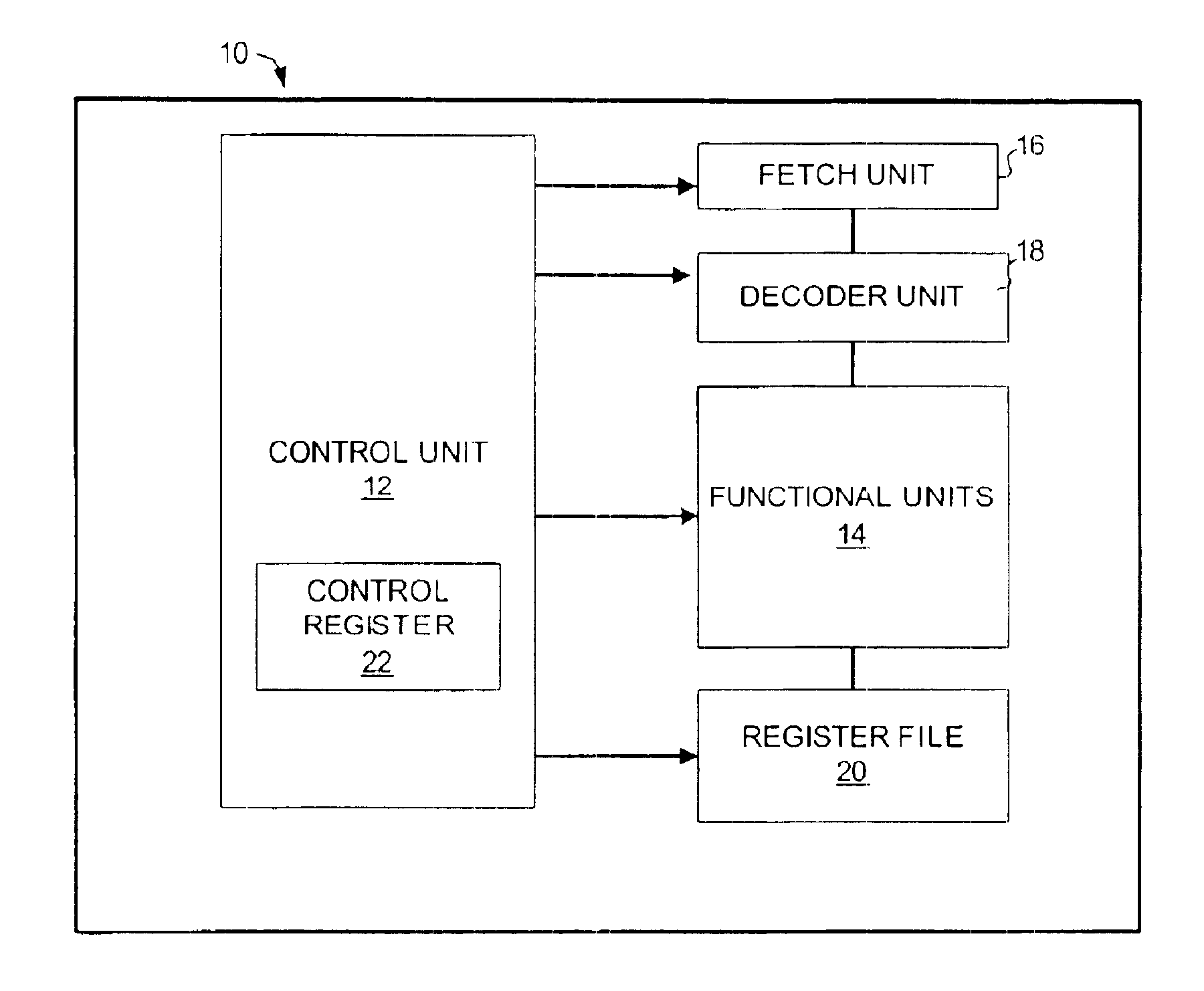

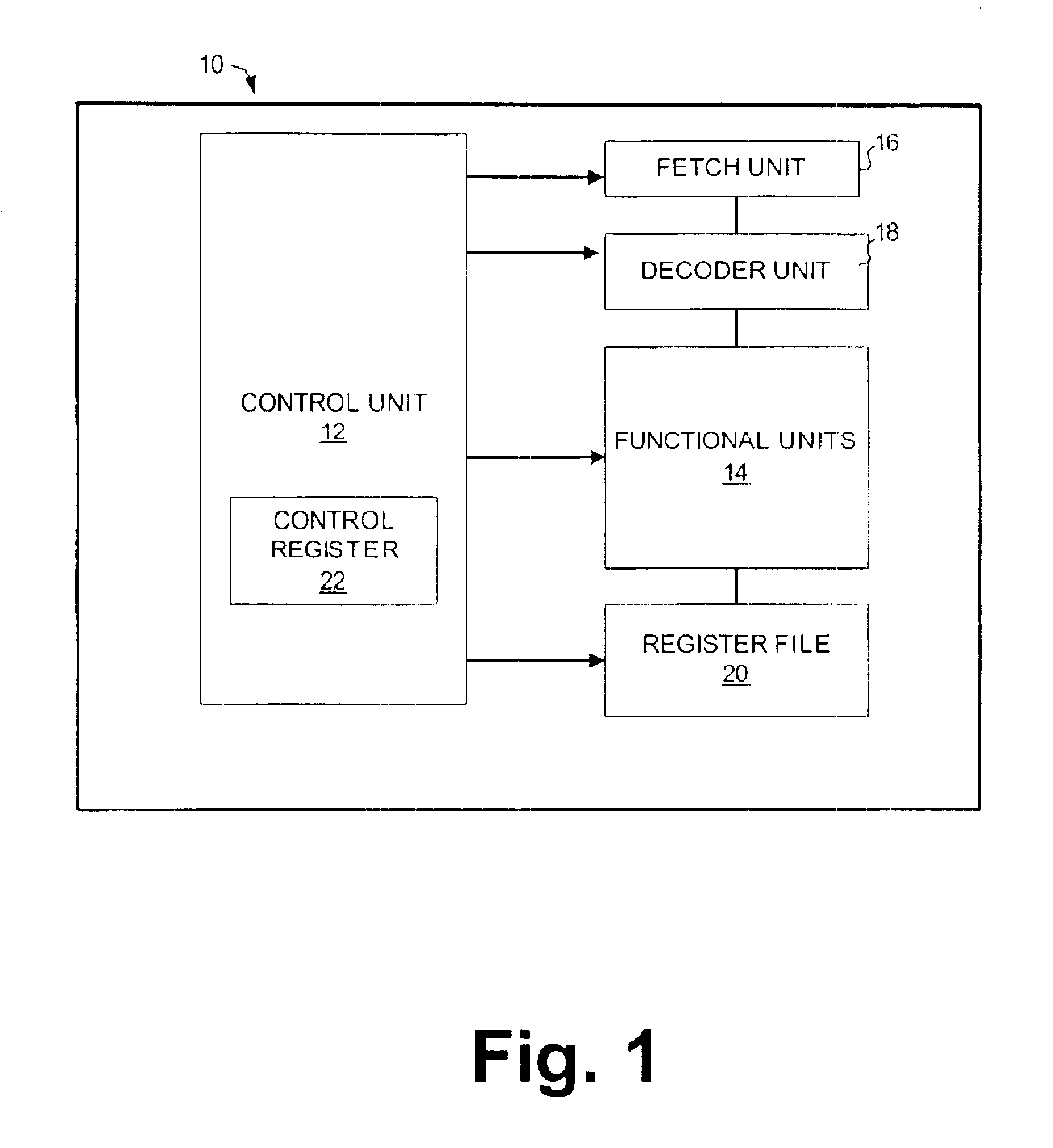

Apparatus and method for dependency tracking and register file bypass controls using a scannable register file

InactiveUS20060168393A1Facilitate inventionSmall and fasterRegister arrangementsUnauthorized memory use protectionRight shiftExecution unit

An apparatus and method for dependency tracking and register file bypass controls using a scannable register file are provided. With the apparatus and method, a scannable register file array is provided and used to track the stage of any instruction in the execution unit. Every entry in the target vector is updated every cycle to stay synchronized with the instructions in the execution unit. To keep the register file array synchronized with the instructions in the execution unit, a right shift of all the data in each entry of the register file array occurs every cycle. The scan port of the register file array cells is used as the shift function.

Owner:IBM CORP

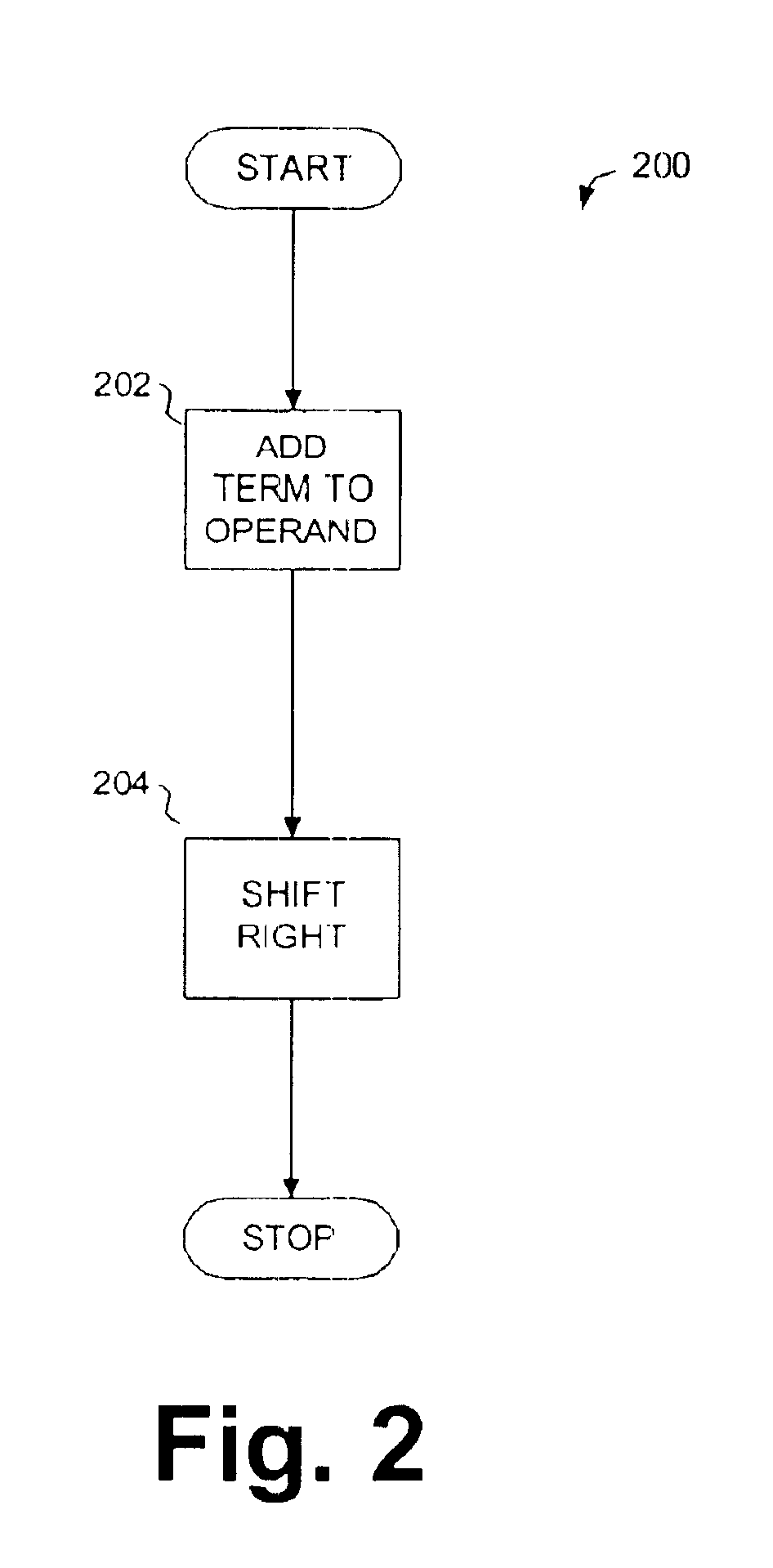

Rounding operations in computer processor

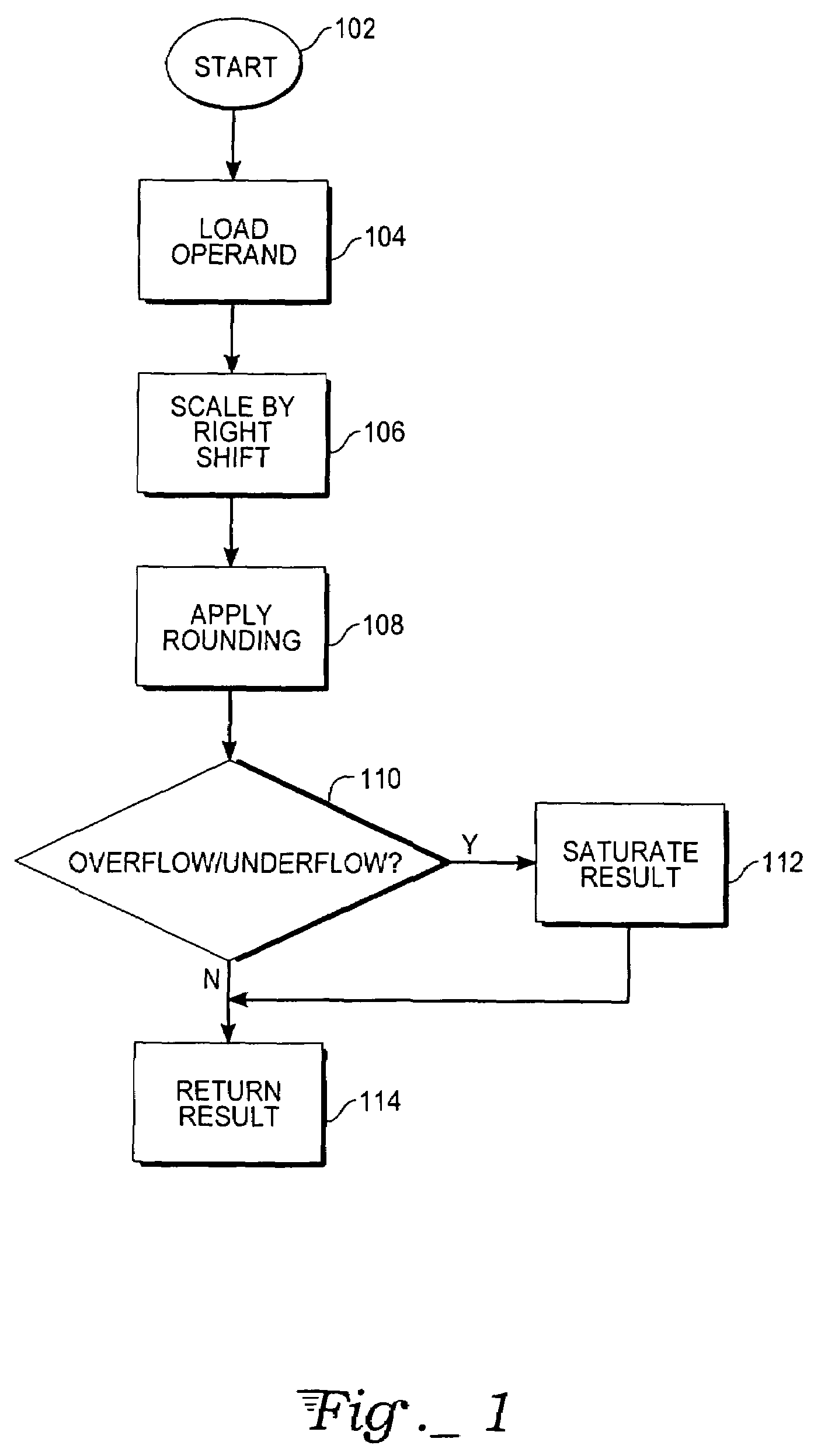

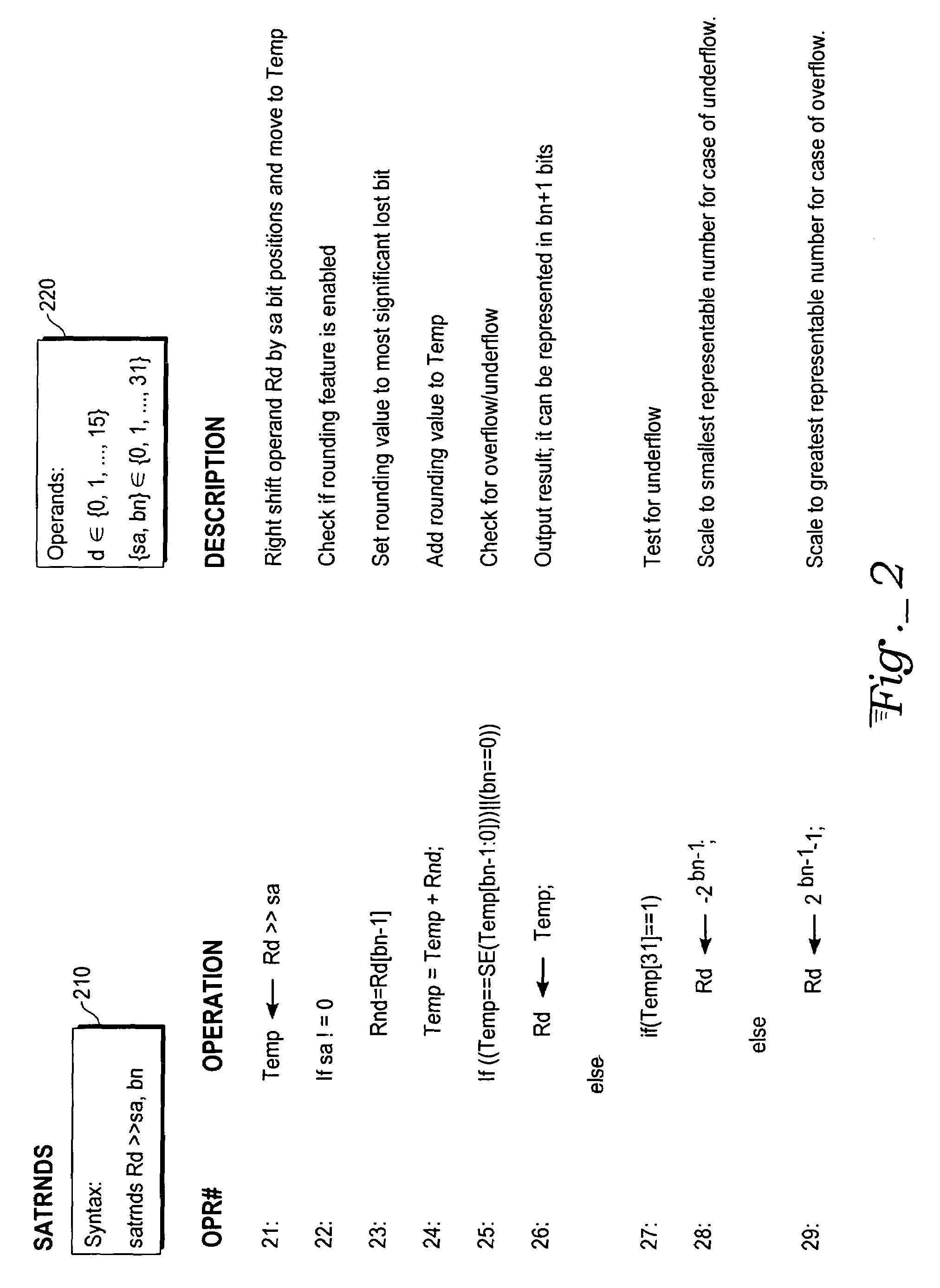

InactiveUS6889242B1Improve execution speedImprove simplicityComputation using denominational number representationRight shiftMachine instruction

Various methods for performing rounding operations in a computer processor are described. A machine instruction sets the rounding mode, which is automatically applied to subsequent machine instructions. Using machine instructions to round results according to the selected rounding mode has several advantages over software-implemented rounding techniques, such as faster execution and concise code. A variety of rounding modes can be specified. Depending in part on the specified rounding mode and on the sign of the value to be rounded, a rounding term is added to the value to be rounded. Adding this rounding term ensures that the desired result is obtained. The value thus obtained is then right-shifted.

Owner:III HLDG 12 LLC

Method and apparatus for formatting numbers in microprocessors

ActiveUS7689640B2Improve execution speedResult is avoidedDigital computer detailsComputation using denominational number representationRight shiftOperand

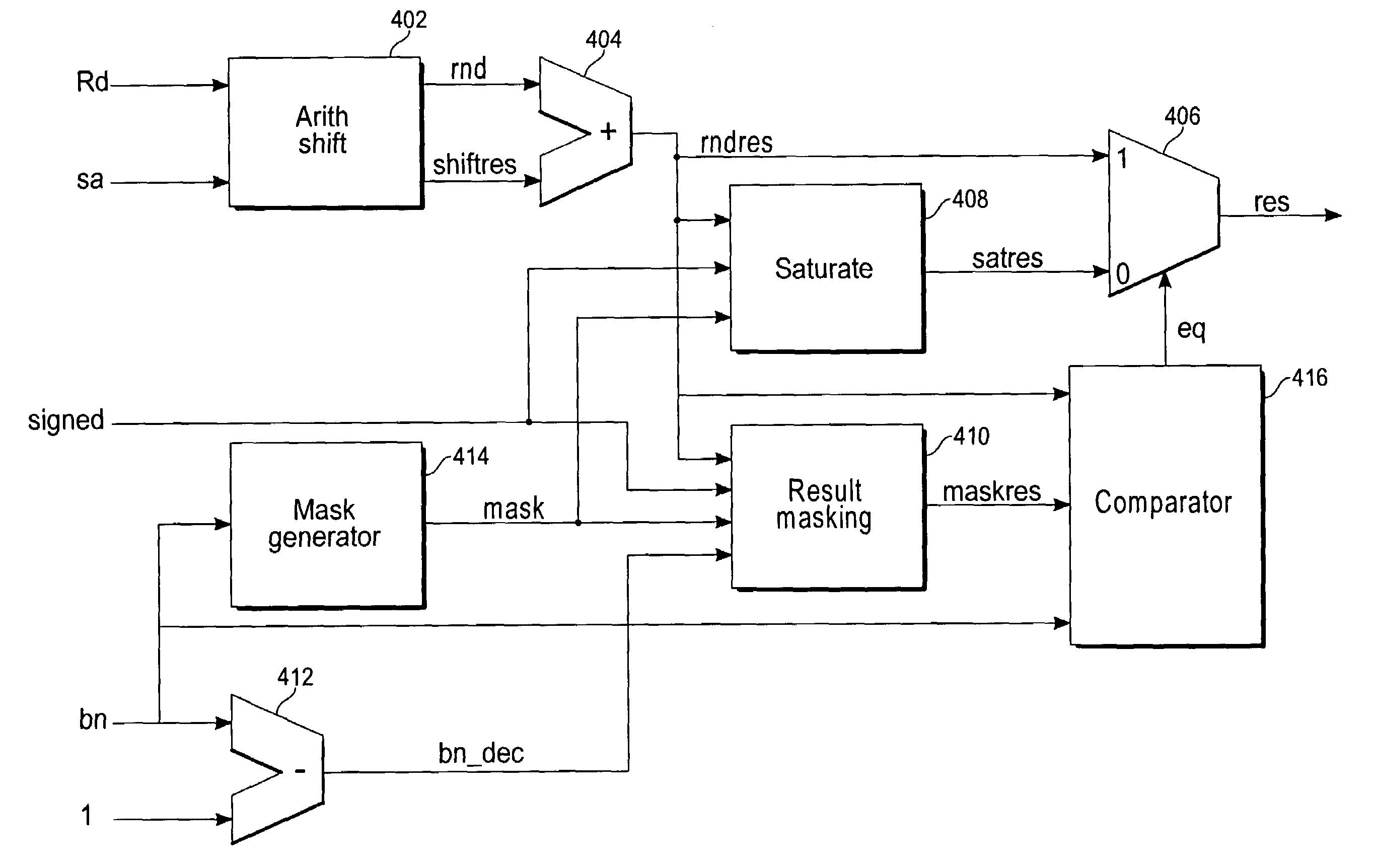

An apparatus for scaling numbers comprises register means for storing an operand to be scaled, bit shifting means for performing a right shift operation on the operand, rounding means, and decision means to test for the existence of at least one of an overflow and an underflow condition.

Owner:ATMEL CORP

Flow electroporation chamber and method

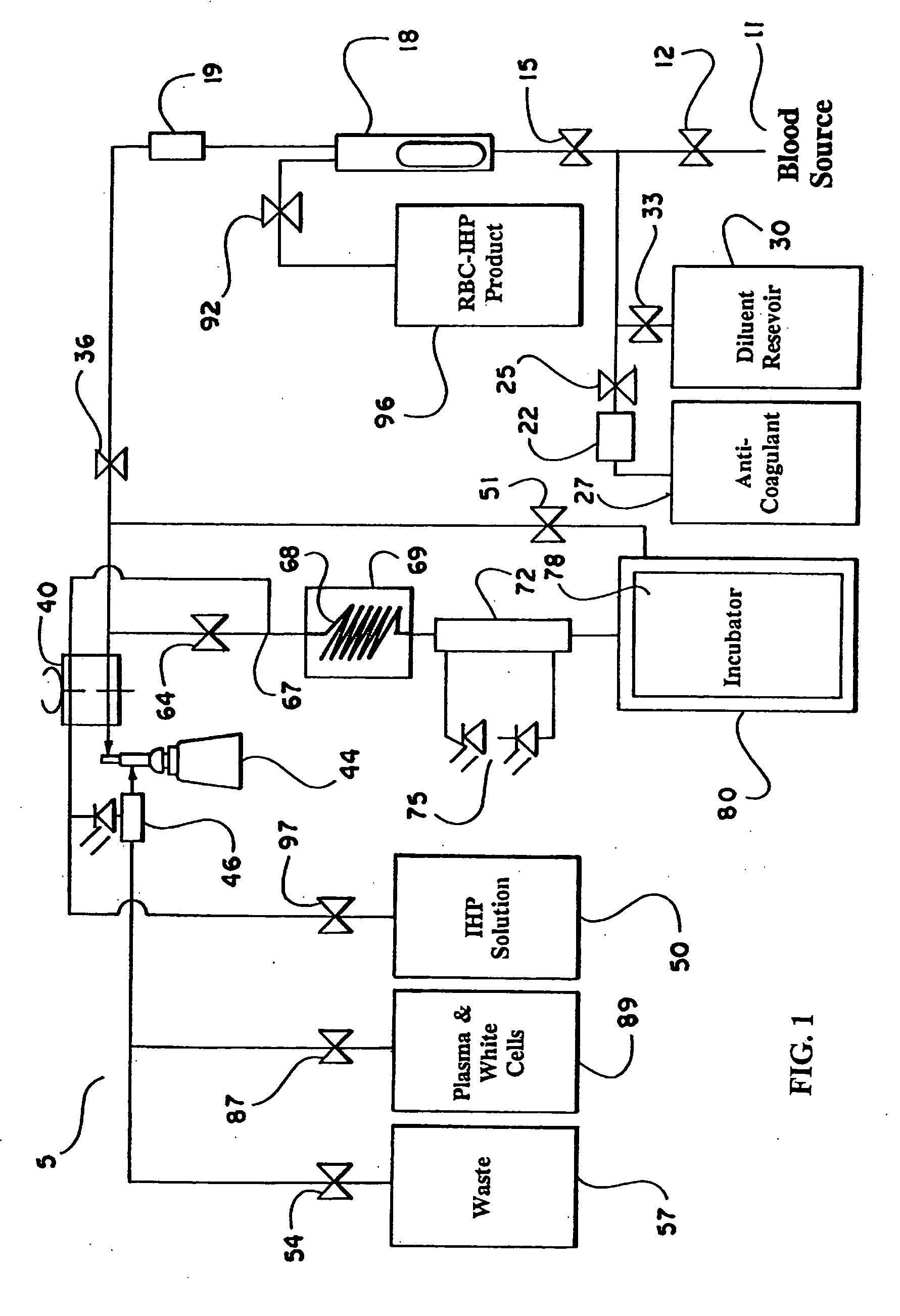

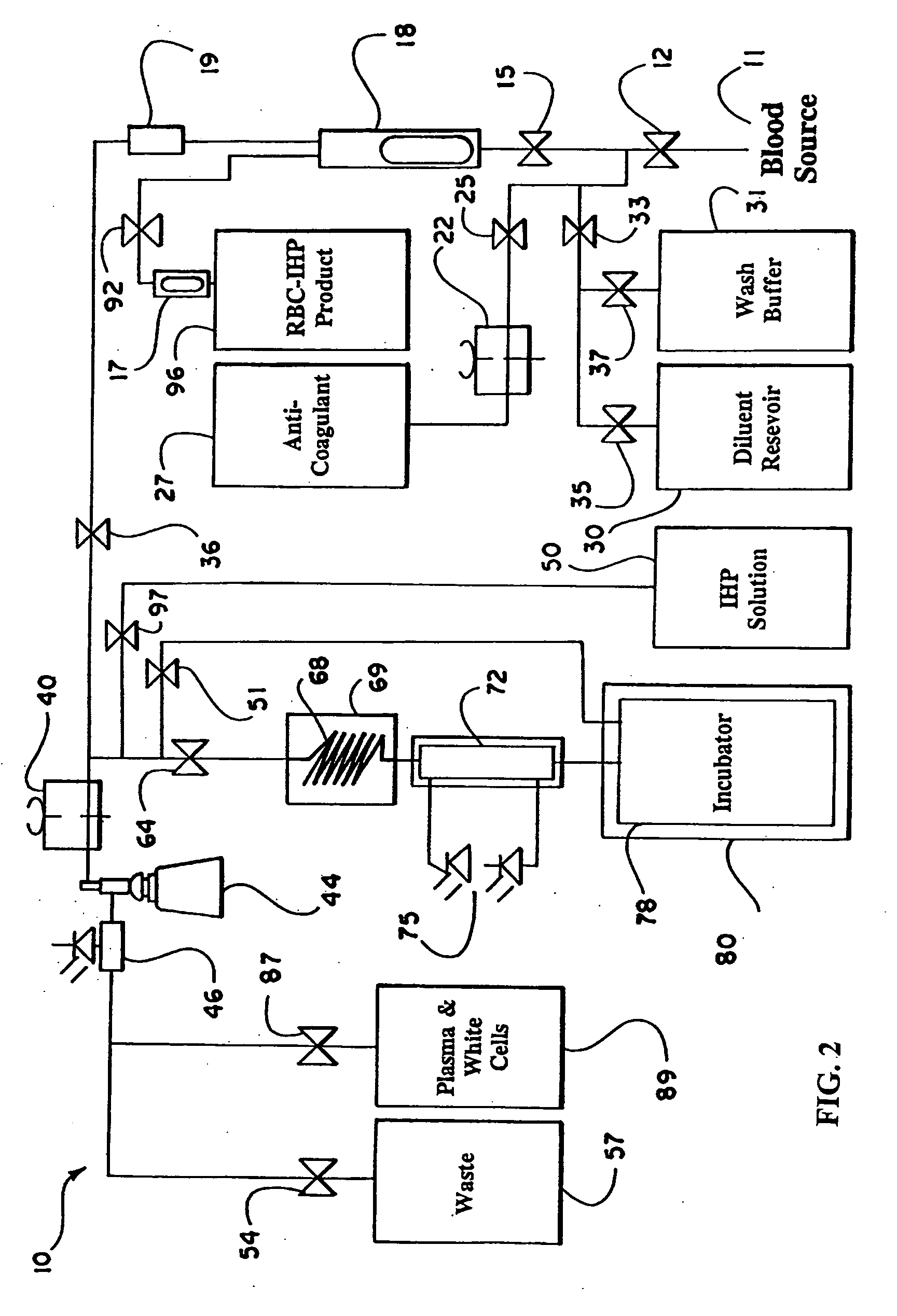

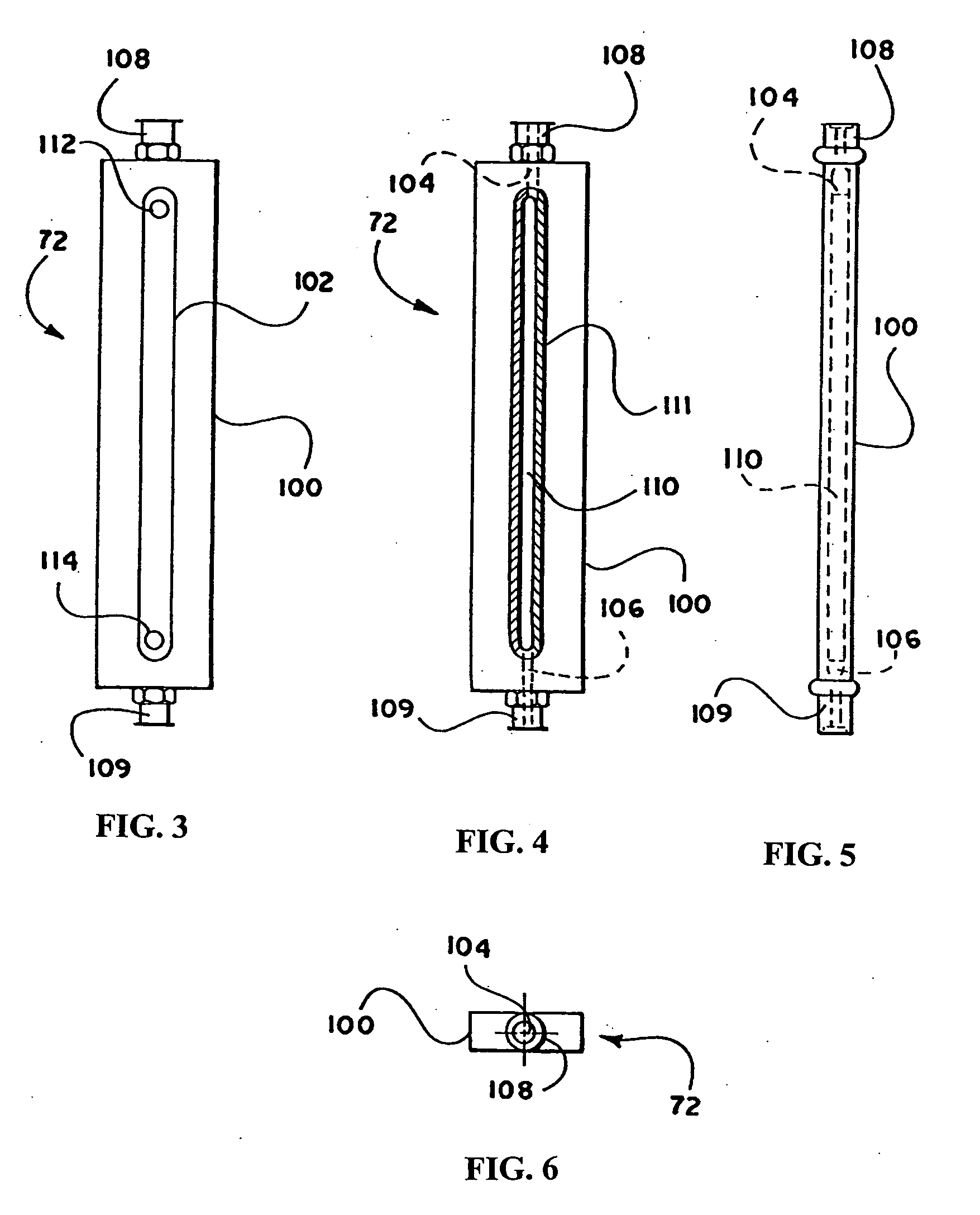

InactiveUS20050019311A1Low affinityIncreased oxygen deliveryBiocideOther blood circulation devicesStreptokinaseMedicine

The present invention relates to a method and apparatus for the encapsulation of substances and drugs into cells and platelets. The present invention is also related to the incorporation of thrombus dissolving drugs, such as tissue plasminogen activator and streptokinase into platelets using the apparatus described herein. The treated platelets can then be used to treat patients suffering from a thrombus blocking a blood vessel. The present invention is also related to a preparation of red blood cells that has a stable right shift of the oxygen dissociation curve.

Owner:HOLADAY JOHN W +4

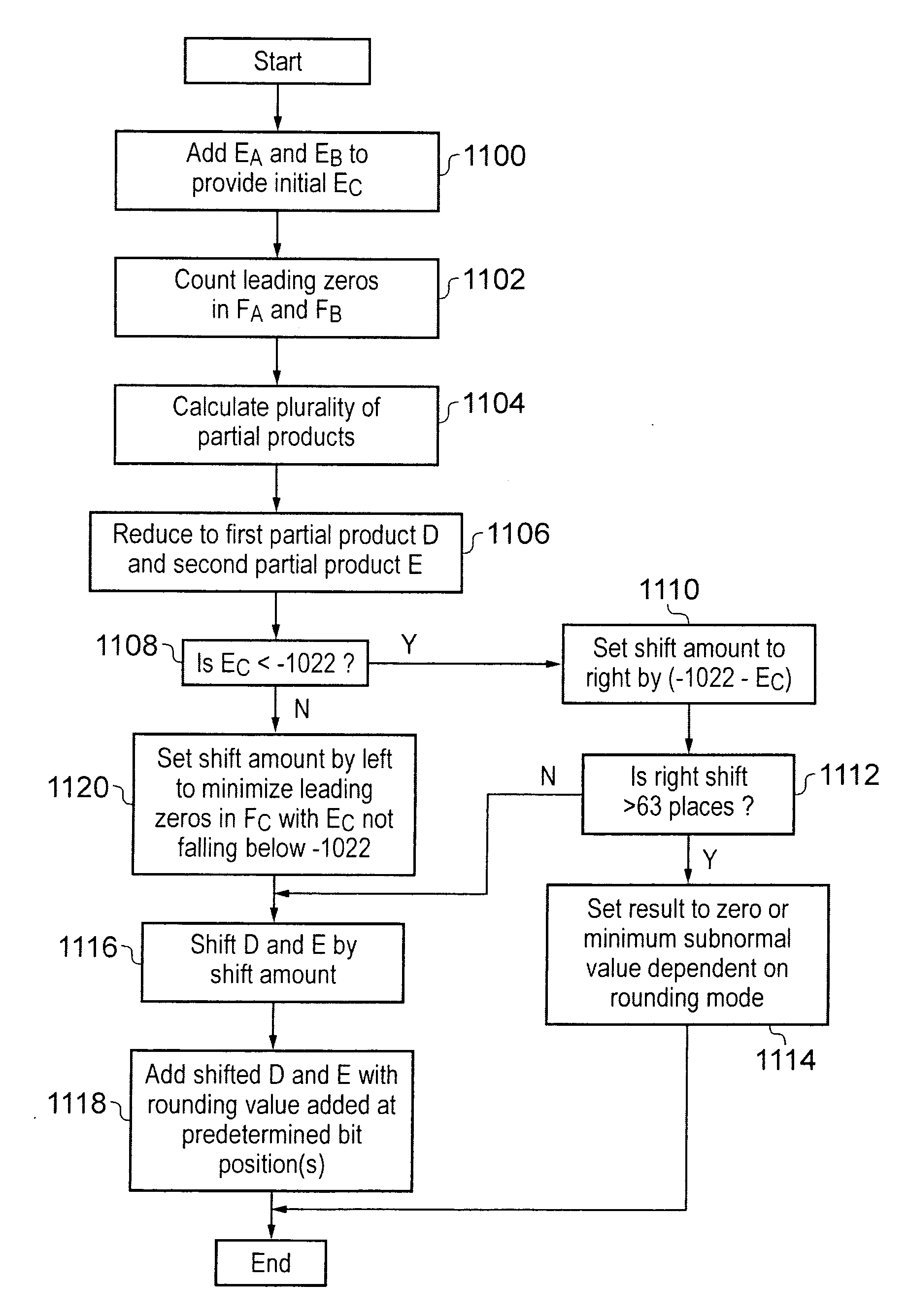

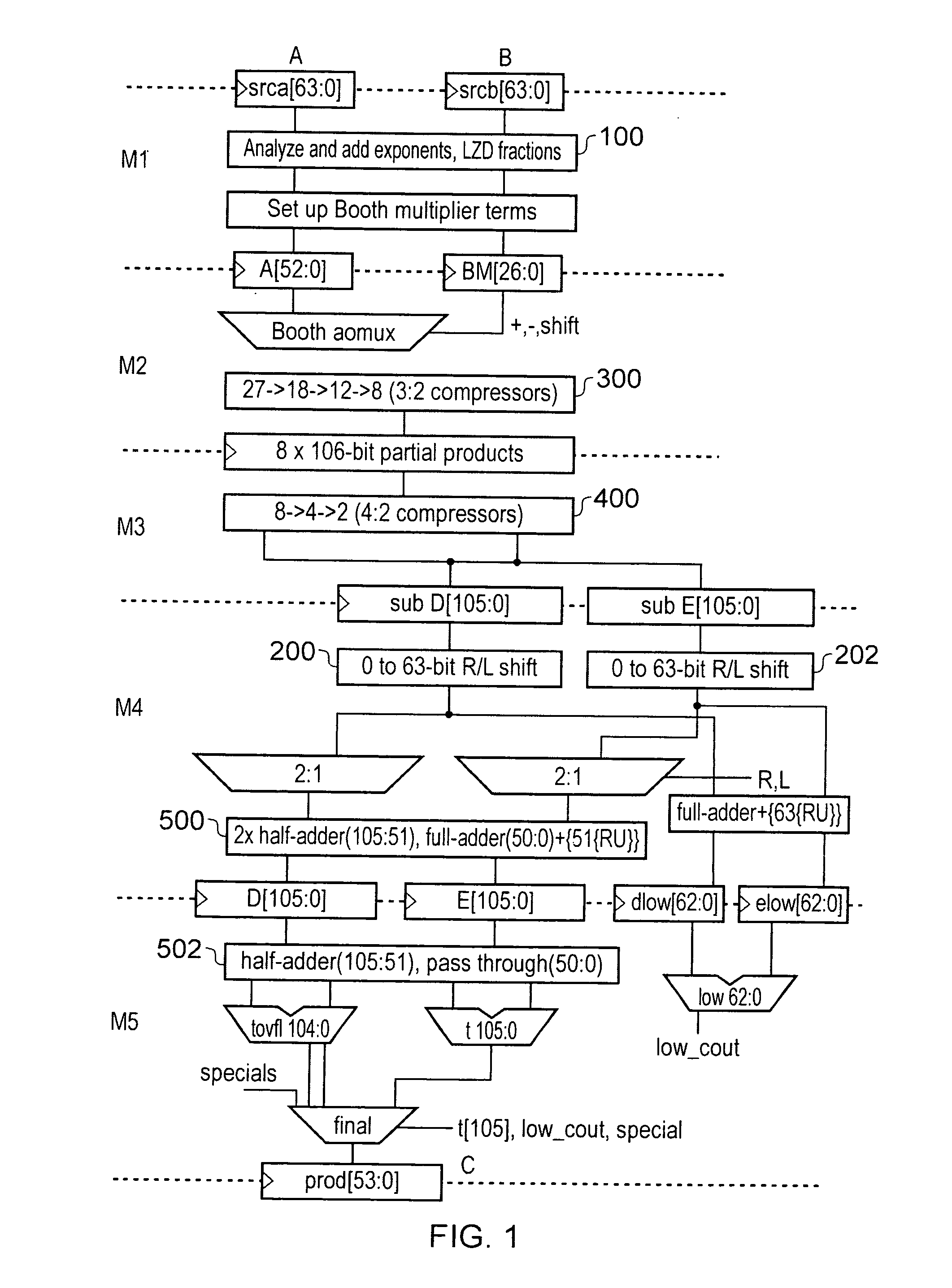

Floating point multiplier with partial product shifting circuitry for result alignment

ActiveUS20110106868A1Minimize the numberReduce delaysDigital computer detailsData conversionRight shiftOperand

A floating point multiplier includes a data path in which a plurality of partial products are calculated and then reduced to a first partial product and a second partial product. Shift amount determining circuitry 100 analyses the exponents of the input operands A and B as well as counting the leading zeros in the fractional portions of these operands to determine an amount of left shift or right shift to be applied by shifting circuitry 200, 202 within the multiplier data path. This shift amount is applied so as to align the partial products so that when they are added they will produce the result C without requiring this to be further shifted. Furthermore, shifting the partial products to the correct alignment in this way in advance of adding these partial products permits injection rounding combined with the adding of the partial products to be employed for cases including subnormal values.

Owner:ARM LTD

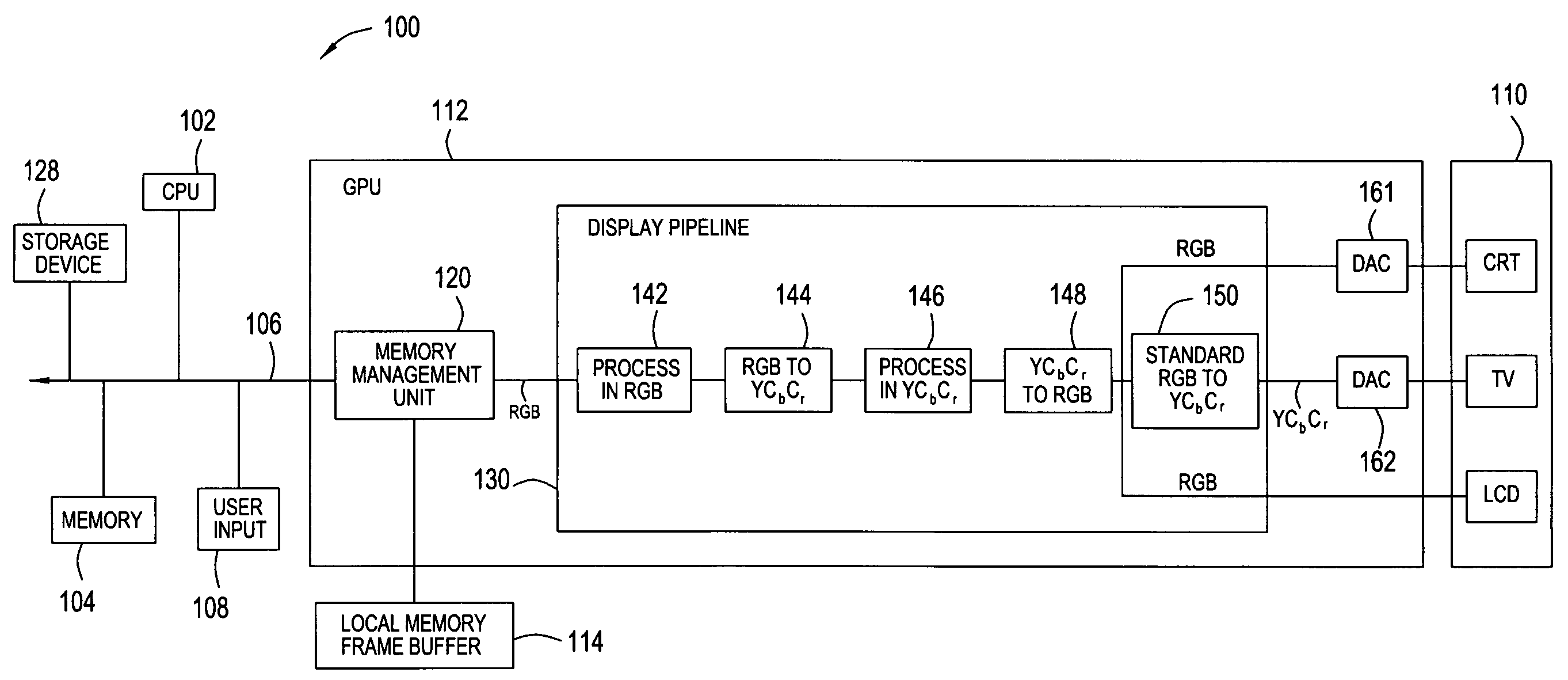

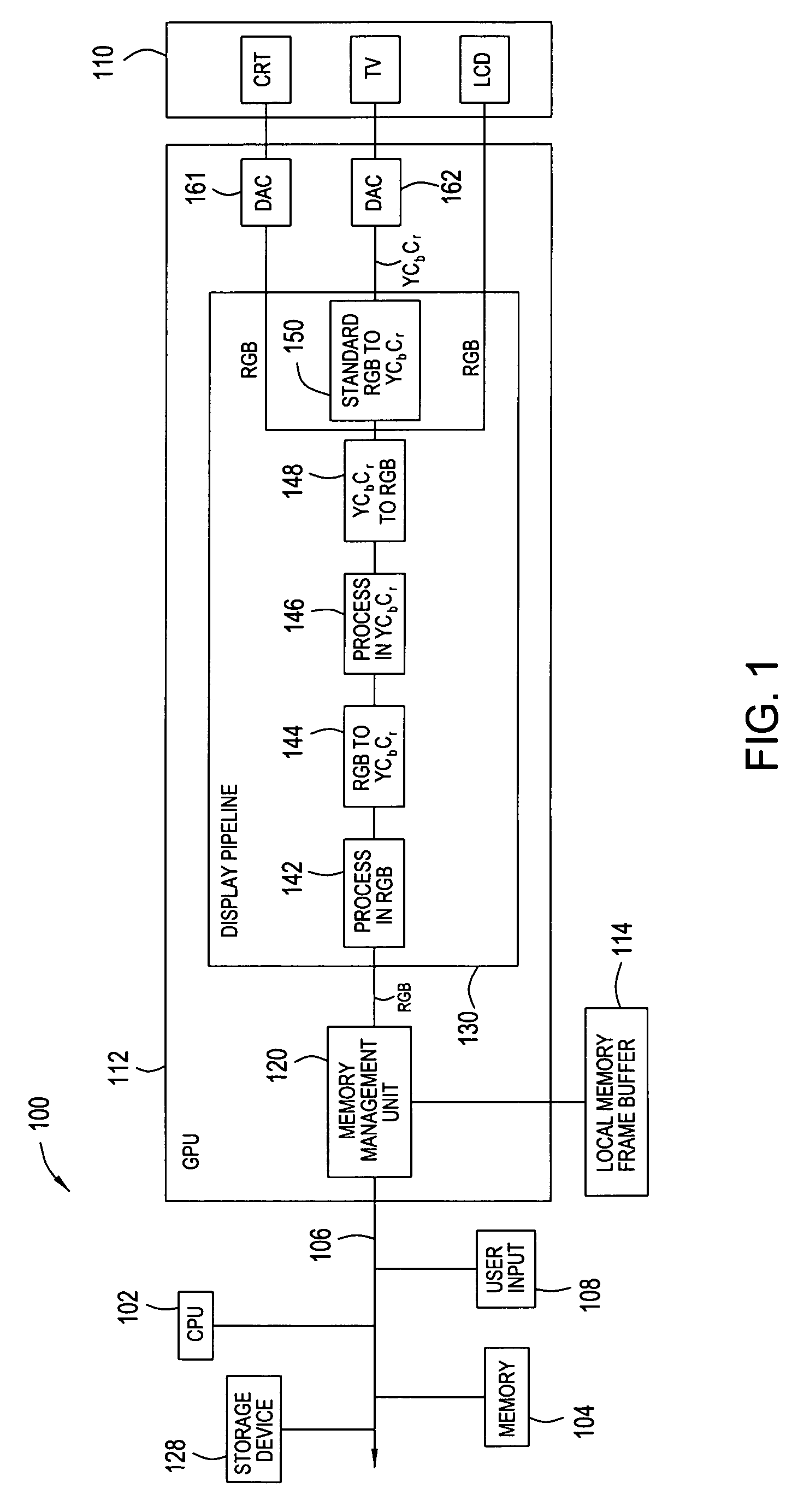

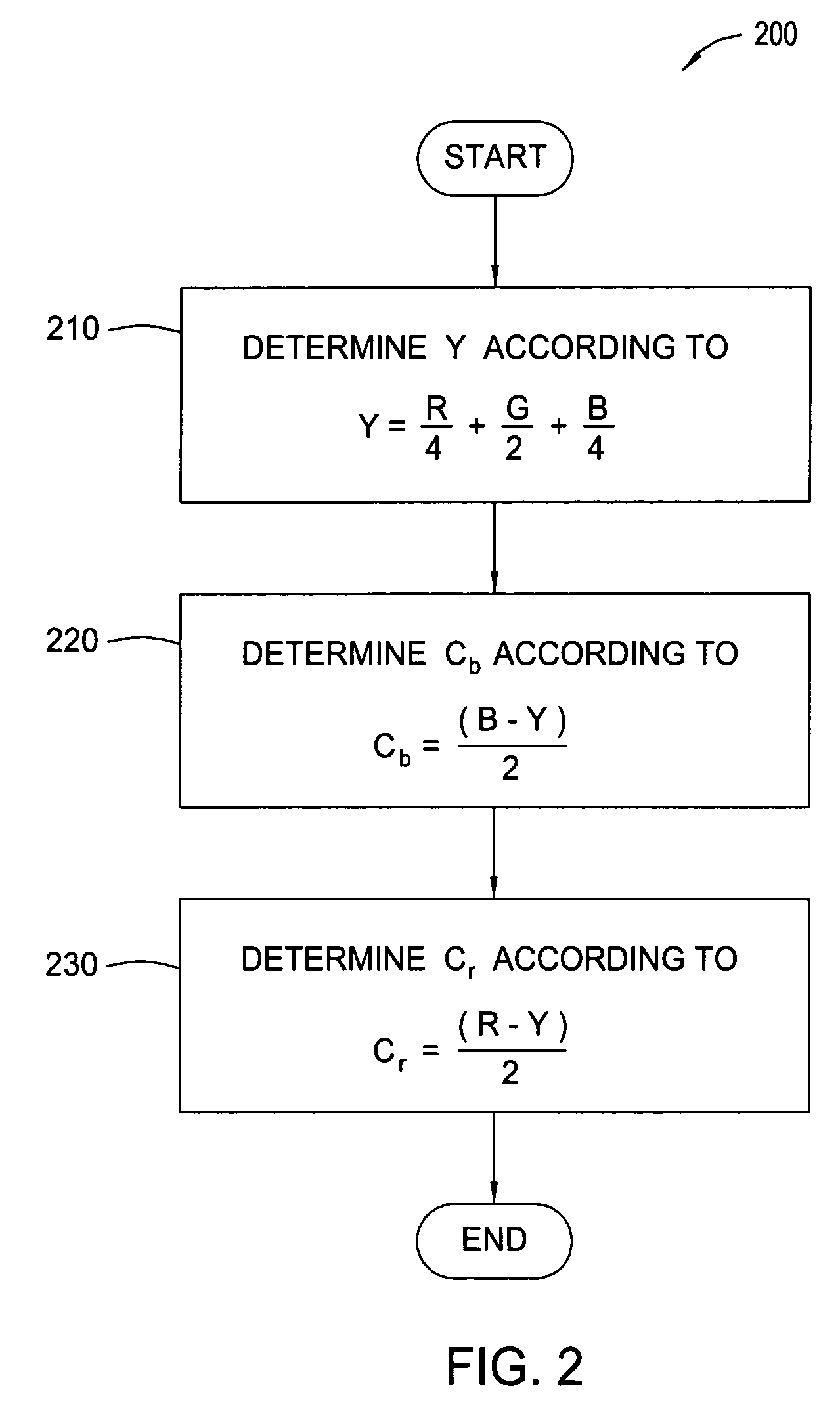

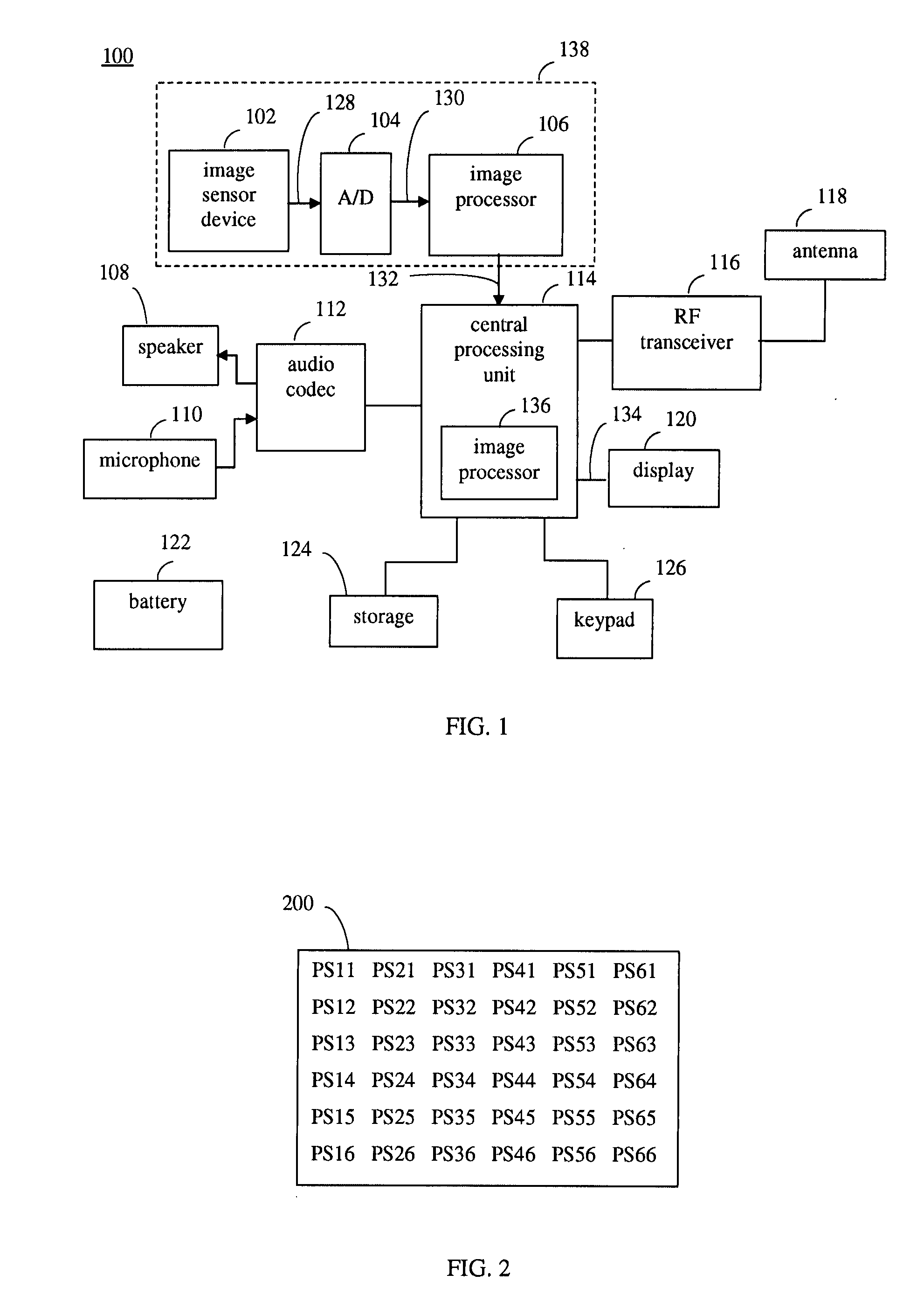

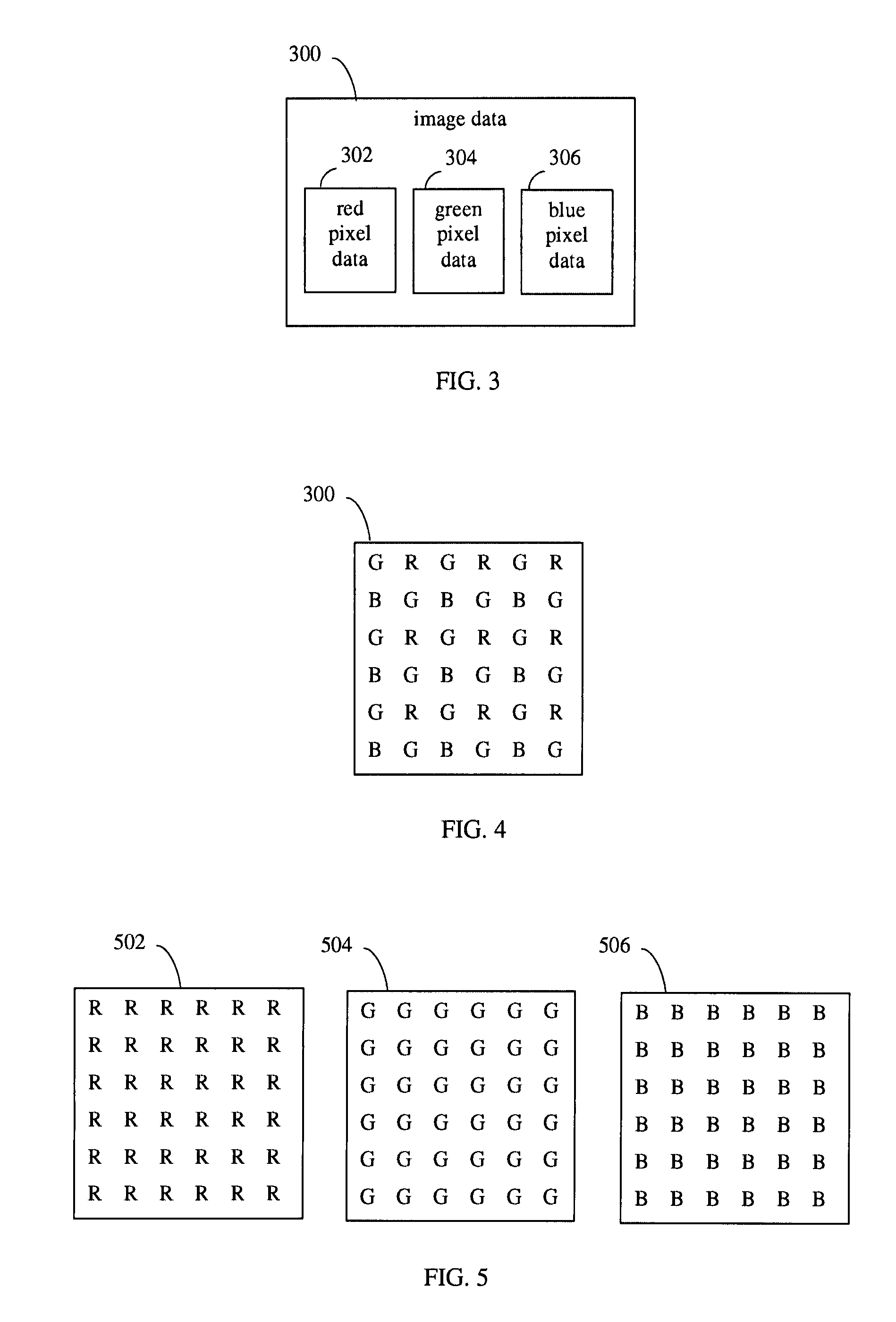

Minimalist color space converters for optimizing image processing operations

ActiveUS7050065B1Low costSimple processCathode-ray tube indicatorsPictoral communicationGraphicsImaging processing

An apparatus for graphics processing unit, which includes a memory for storing pixel data in a red, green and blue (RGB) color space and a display pipeline. The display pipeline includes an RGB color space to a luminance color, blue color difference and red color difference (YCbCr) color space converter module configured to convert the pixel data from the RGB color space to the YCbCr color space. The RGB to YCbCr color space converter module generates a luminance color component (Y) of the pixel data by adding ¼ of a red color (R) component of the pixel data to ½ of a green color (G) component of the pixel data and ¼ of a blue color (B) component of the pixel data. The luminance color component (Y) of the pixel data may be determined by left shifting the green color (G) component of the pixel data by one bit, adding the result to the red color (R) component of the pixel data and the blue color (B) component of the pixel data, and right shifting the sum by two bits.

Owner:NVIDIA CORP

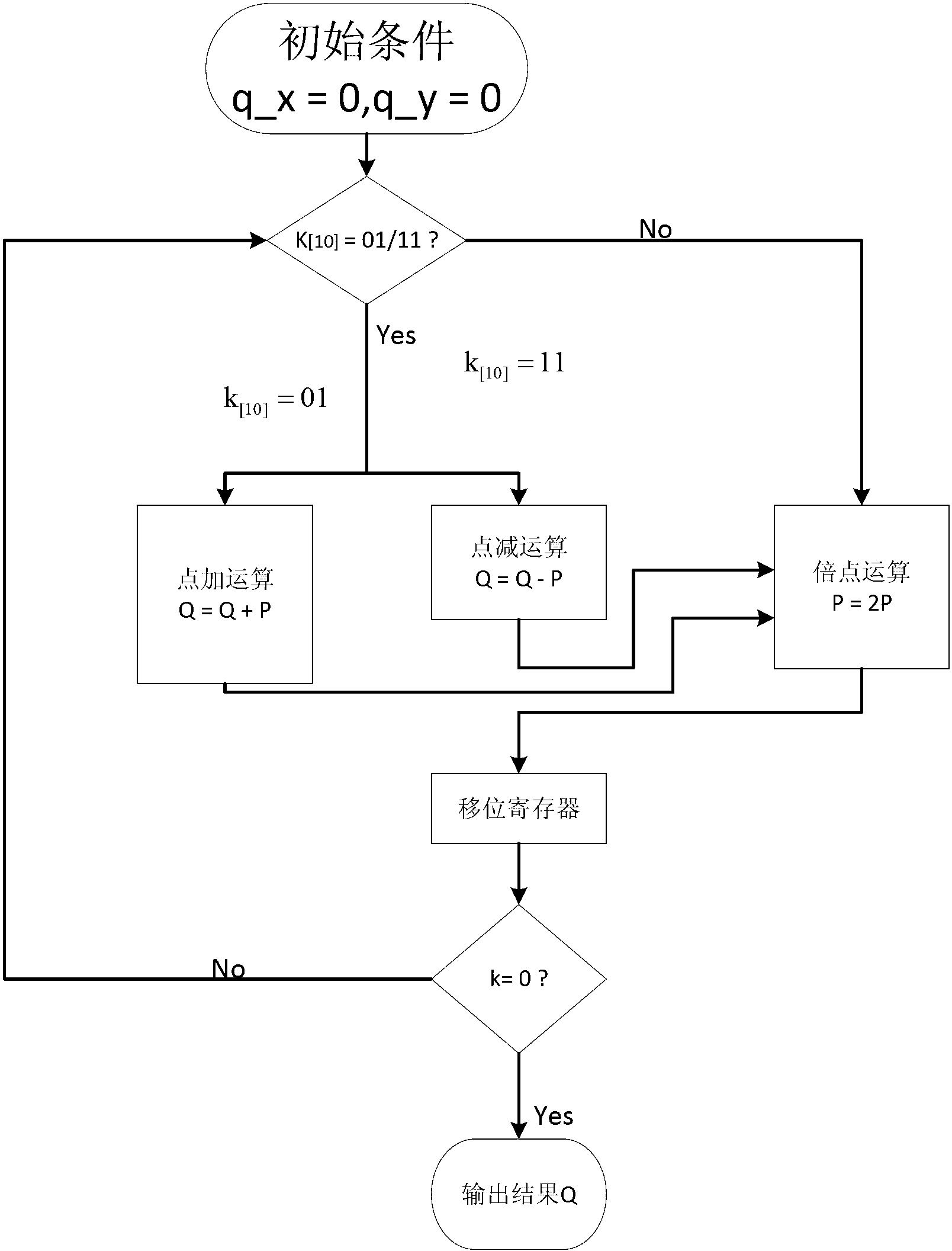

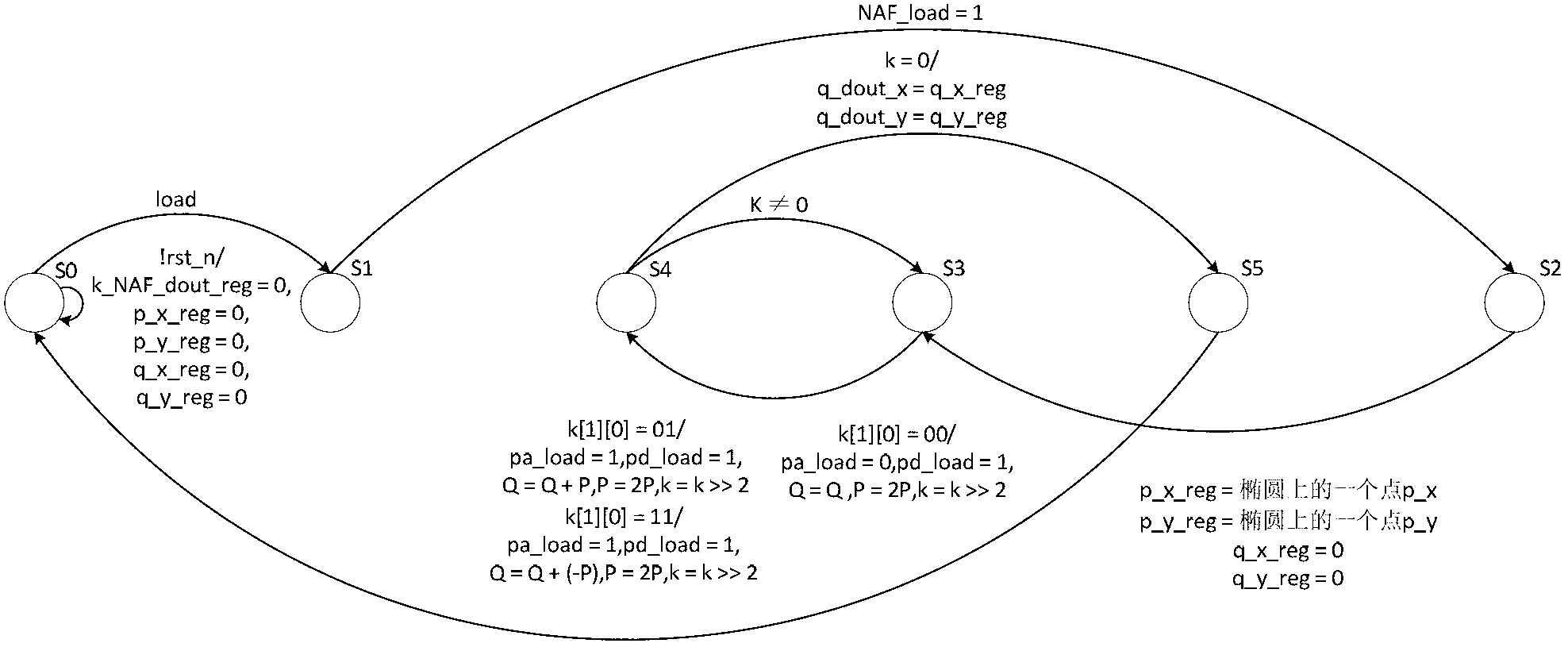

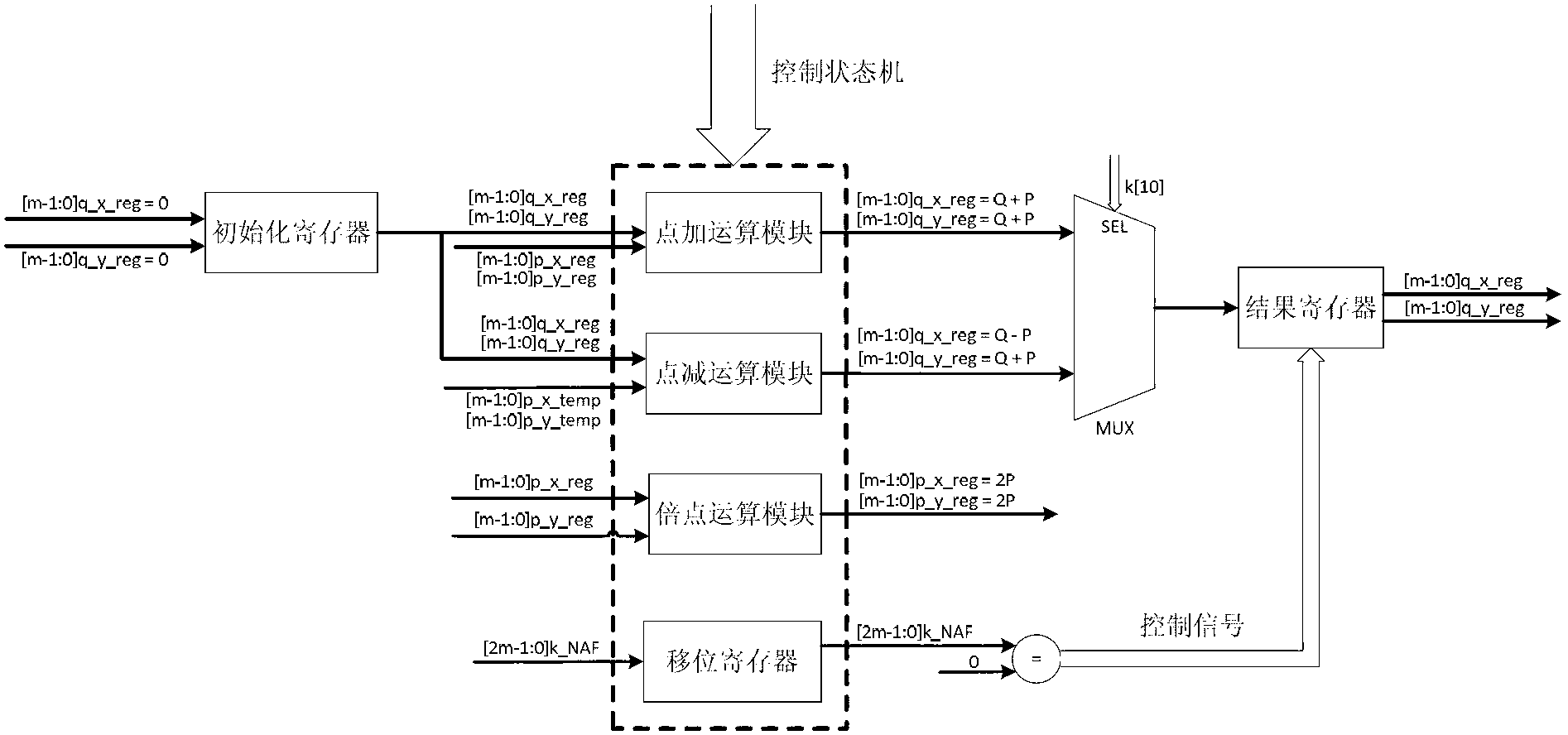

Prime field elliptic curve crypto dot product accelerating circuit

InactiveCN103078732AReduce the numberRun fastEncryption apparatus with shift registers/memoriesShift registerRight shift

The invention relates to a prime field elliptic curve crypto dot product accelerating circuit, which is used for calculating a formula that Q is equal to k*P, wherein the k is times for calculating dot product; the P is a point on an elliptic curve, and the Q is the other point on the elliptic curve. The prime field elliptic curve crypto dot product accelerating circuit comprises an initialization register, a point addition operation module, a point subtraction operation module, a multiple point operation module, a shifting register, a comparator, an alternative selector and a result register, wherein the point addition operation module, the point subtraction operation module, the multiple point operation module and the shifting register are in parallel execution. According to the prime field elliptic curve crypto dot product accelerating circuit, the operation times for point addition and multiple point are controlled through carrying out right shift operation on NAF (k) and judging whether the NAF (k) is '0' or not, wherein the NAF (k) is a non-adjacent expression type numerical value of the k. When a value of the k is '0', the point addition operation can be stopped automatically, so that the operation time is saved. The accelerating circuit is more flexible than regular execution of 2m times of point operation, only a 2m-bit shifter and a corresponding control circuit are needed when an algorithm realizes point multiplication operation of any bit length, the resource demand is less, and the accelerating circuit is suitable to be realized in an FPGA (Field Programmable Gate Array) or an ASIC (Application Specific Integrated Circuit).

Owner:WUHAN UNIV

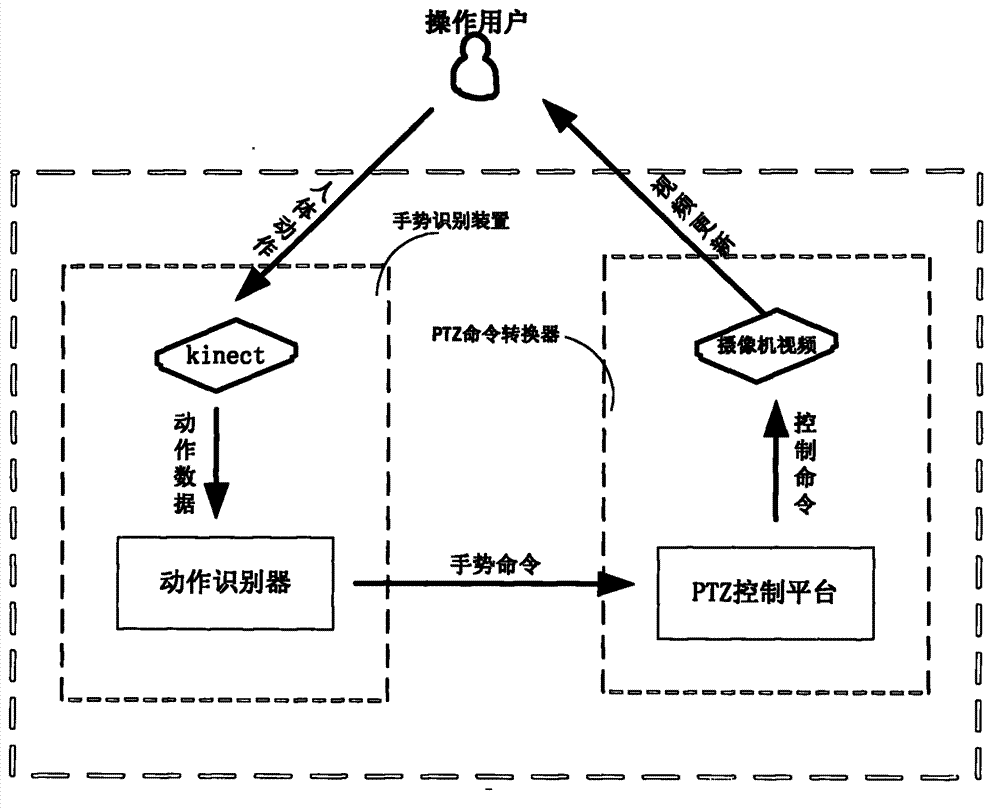

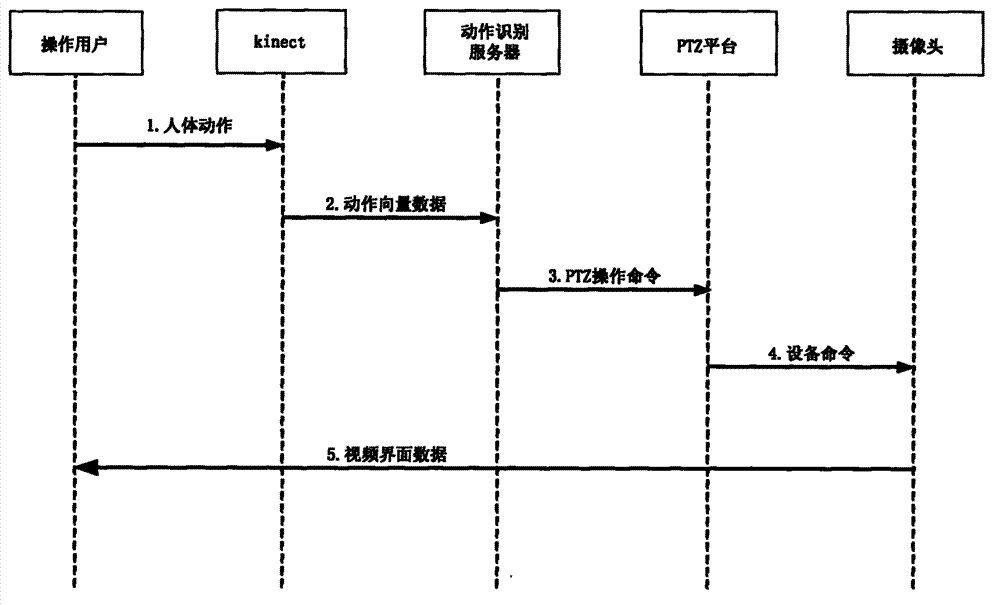

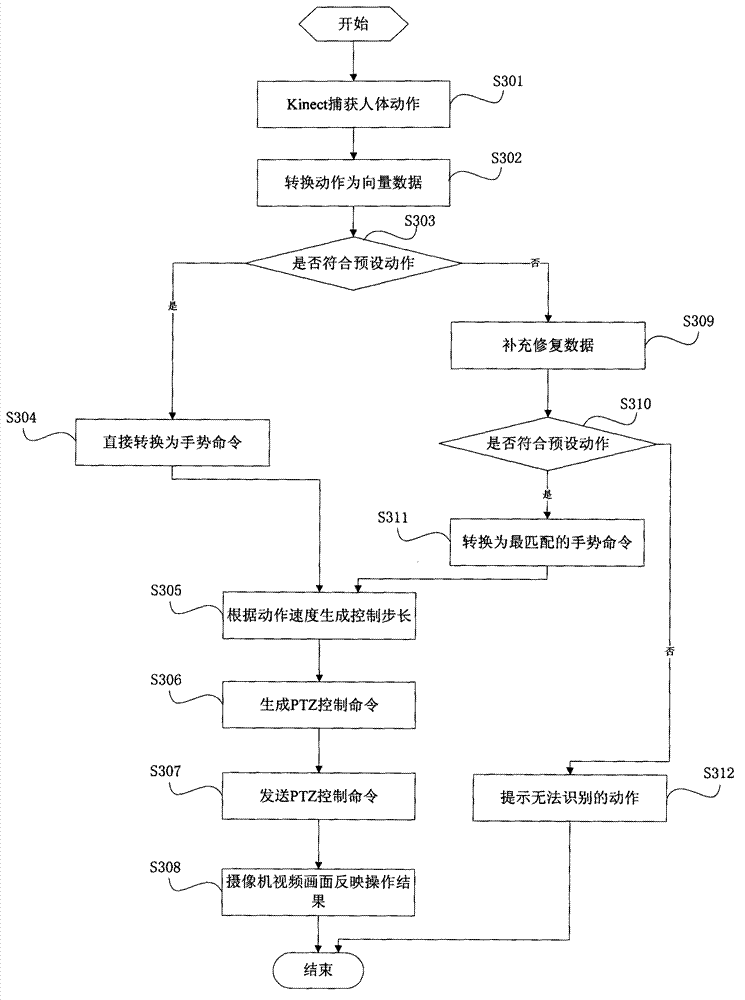

Method, device and system of pan tilt zoom (PTZ) control of video camera based on kinect

InactiveCN103118227AInput/output for user-computer interactionTelevision system detailsVideo monitoringPan tilt zoom

The invention discloses a method, a device and a system of pan tilt zoom (PTZ) control of a video camera based on kinect. PTZ control of the video camera for security and protection monitoring can be achieved through human movements, complex operation interfaces are not required, and PTA control of the video camera is operated simply and conveniently through a video monitoring system. The method, the device and the system comprise that the human movements are caught through the kinect, human movement vector quantity data are input into behavior identification software, after corresponding data optimization, data conversion and behavior judgment, the human movements are converted into PTZ control commands of the monitoring video camera, the PTZ control commands include upward shift, downward shift, left shift, right shift, picture enlargement, picture shrink, preset position switchover, windshield wiper starting and the like, the control commands are sent to the video camera to conduct PTZ control, the video executes corresponding movements, and operation results are displayed in real time through real-time video frames.

Owner:PCI TECH GRP CO LTD

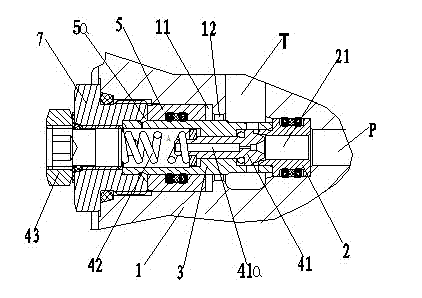

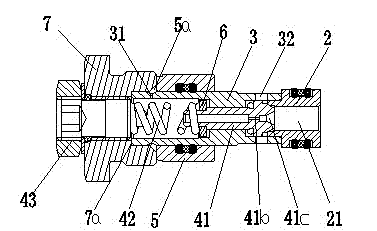

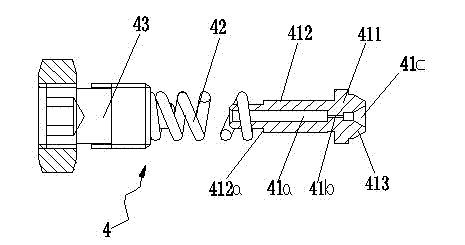

Buffer relief valve for hydraulic motor

The invention discloses a buffer relief valve for a hydraulic motor, which comprises a valve body, a valve seat, a valve sleeve and a screw plug which are matched mutually, wherein the valve sleeve is provided with a valve plug assembly; a buffer piston is sleeved in a sliding cavity position on the valve body on the outer peripheral surface of the valve sleeve in a sliding manner and is provided with a buffer cavity with the screw plug formed at the left end opening of the valve body; the buffer cavity is communicated with an oil inlet of the valve body by a radial damping hole formed by the valve sleeve and an axial hole of the valve plug assembly; and the buffer piston realizes the buffer function of the relief valve by differential pressure delay caused by right shift. The relief valve is compact in a structure and easy to manufacture, and can improve the hydraulic impact of the hydraulic rotation motor during starting and braking and the operability of the hydraulic rotation motor obviously so as to improve prolong the service life of system hydraulic elements.

Owner:SAIKESI HYDRAULIC TECH CO LTD

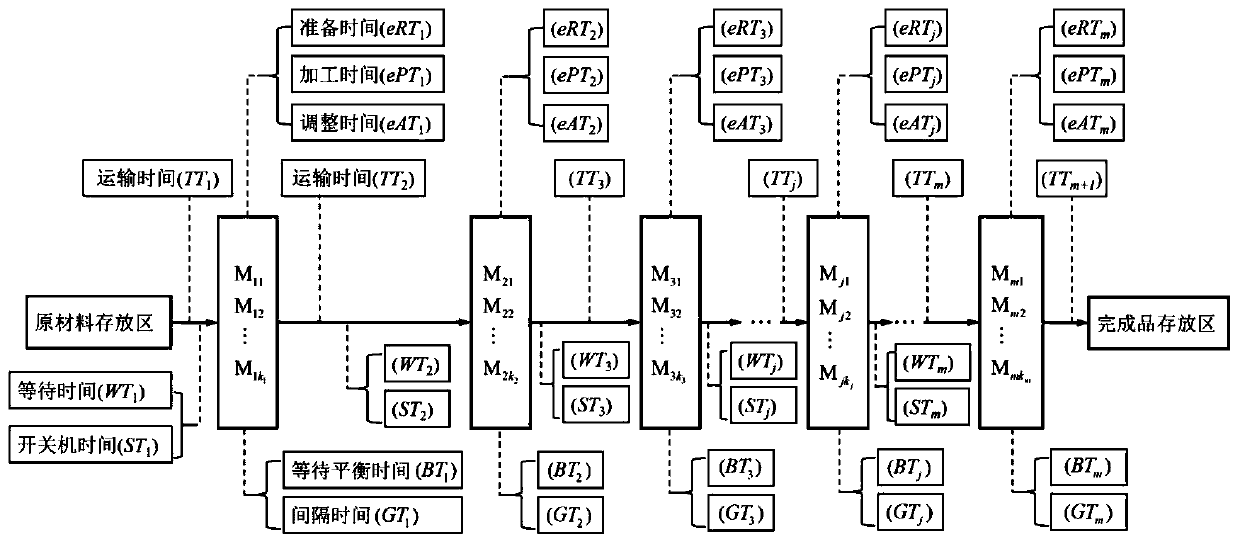

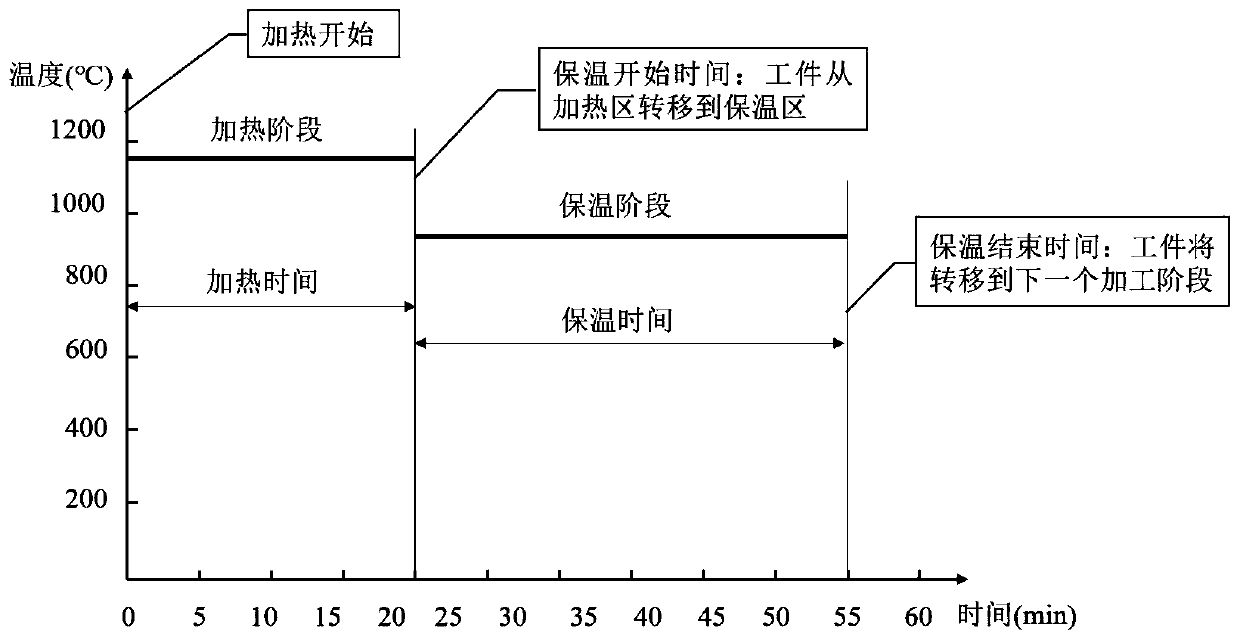

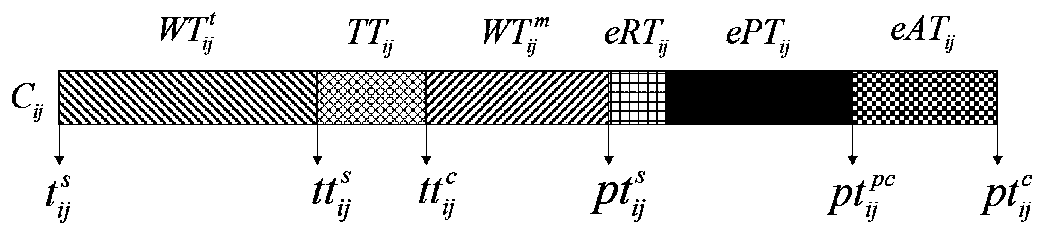

An energy-saving scheduling model of a hybrid assembly line forging workshop under multiple time factors

The invention discloses an energy-saving scheduling model of a hybrid assembly line forging workshop under multiple time factors. The model is established through the following steps that multiple time influence factors of all machining stages of the hybrid assembly line workshop are analyzed, wherein the time influence factors comprise the preparation time, the machining time, the adjustment time, the transportation time, the waiting time and the waiting balance time; Analyzing continuous machining of middle heating furnace equipment and discrete machining processes of other machining equipment in the mixed assembly line forging workshop; Establishing a completion time model by adopting a transportation time right shift sorting rule, and analyzing the relationship of multiple times in workshop scheduling; analyzing the energy consumption scheduling of the mixed flow forging workshop by utilizing a closing / opening scheme, and establishing an energy consumption scheduling model; And establishing a multi-objective function of the mixed flow forging workshop energy-saving scheduling model. According to the invention, a multi-objective model of completion time and energy consumption isestablished for the mixed flow forging workshop, and the model is used for solving the scheduling problem of the mixed flow forging workshop with the continuous machining characteristic of the heating furnace.

Owner:BEIJING UNIV OF TECH

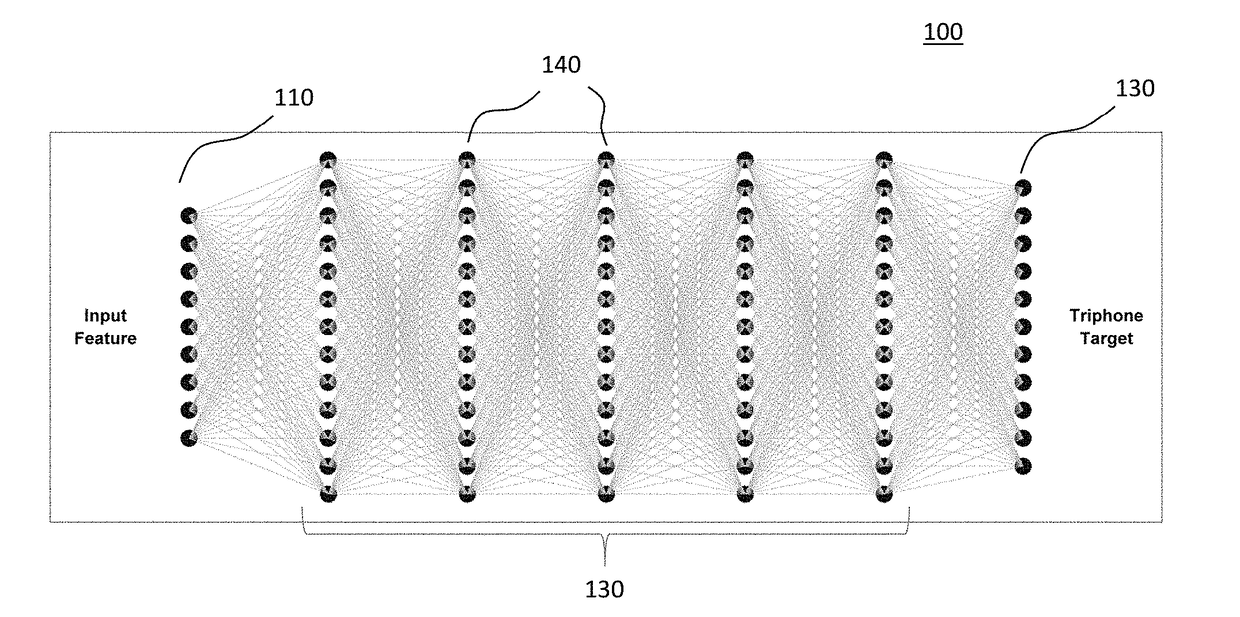

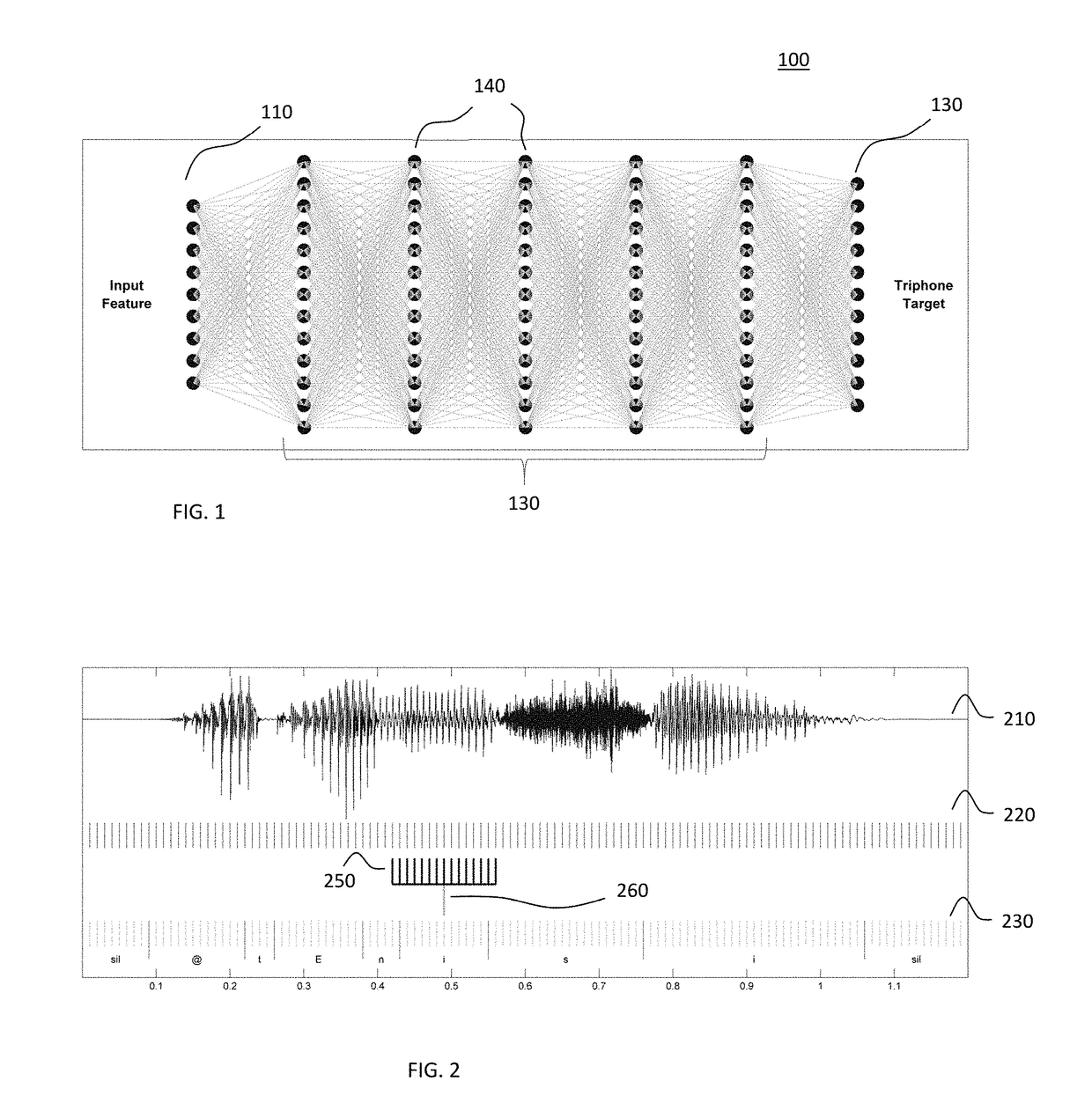

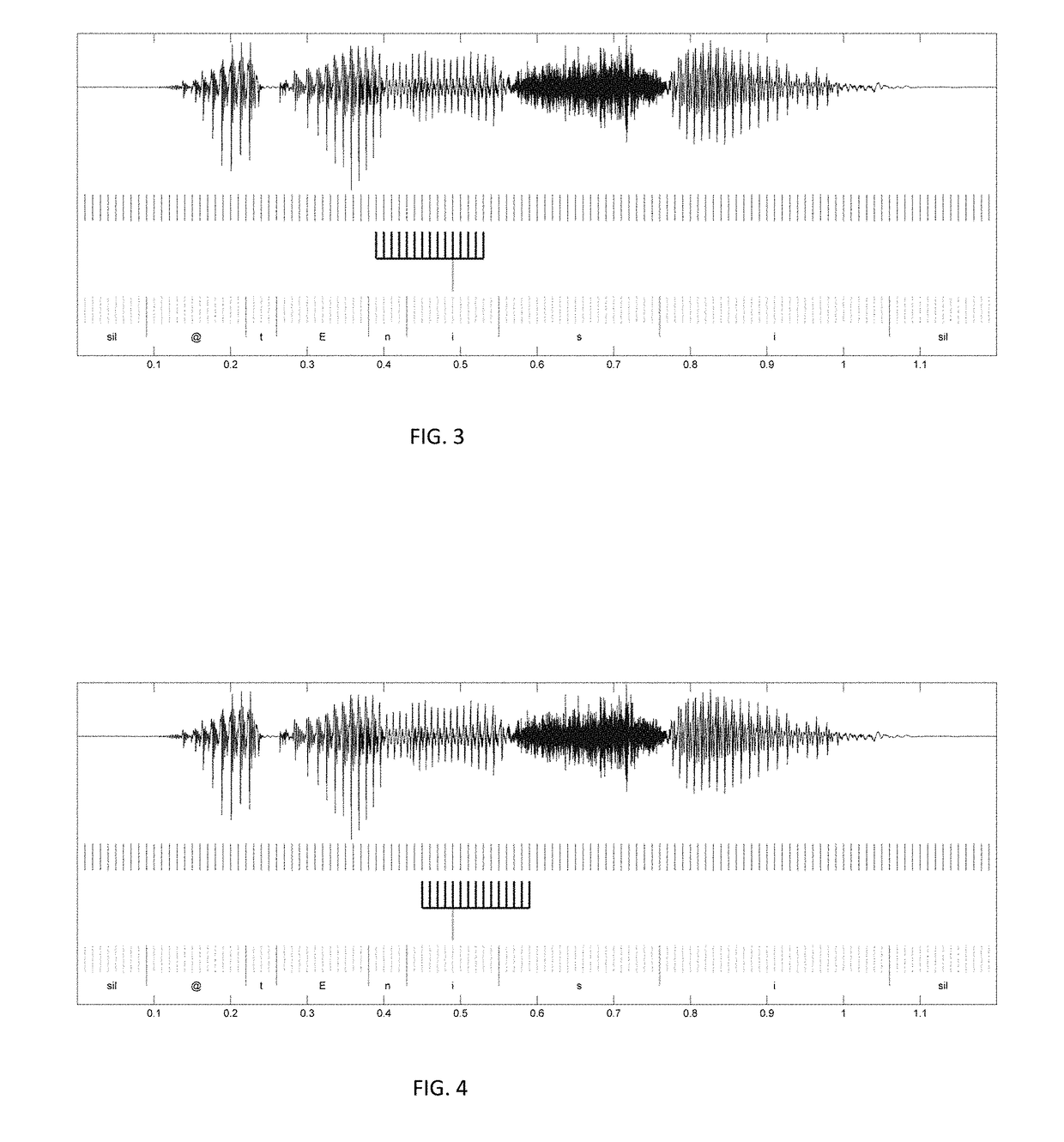

Centered, left- and right-shifted deep neural networks and their combinations

ActiveUS20180082677A1Improve accuracyImprove recognition accuracySpeech recognitionNeural architecturesPattern recognitionHidden layer

Deep Neural Networks (DNN) are time shifted relative to one another and trained. The time-shifted networks may then be combined to improve recognition accuracy. The approach is based on an automatic speech recognition (ASR) system using DNN and using time shifted features. Initially, a regular ASR model is trained to produce a first trained DNN. Then a top layer (e.g., SoftMax layer) and the last hidden layer (e.g., Sigmoid) are fine-tuned with same data set but with a feature window left- and right-shifted to create respective second and third left-shifted and right-shifted DNNs. From these three DNN networks, four combination networks may be generated: left- and right-shifted, left-shifted and centered, centered and right-shifted, and left-shifted, centered, and right-shifted. The centered networks are used to perform the initial (first-pass) ASR. Then the other six networks are used to perform rescoring. The resulting are combined using ROVER (recognizer output voting error reduction) or another technique to improve recognition performance as compared to the centered DNN by itself

Owner:APPTEK INC

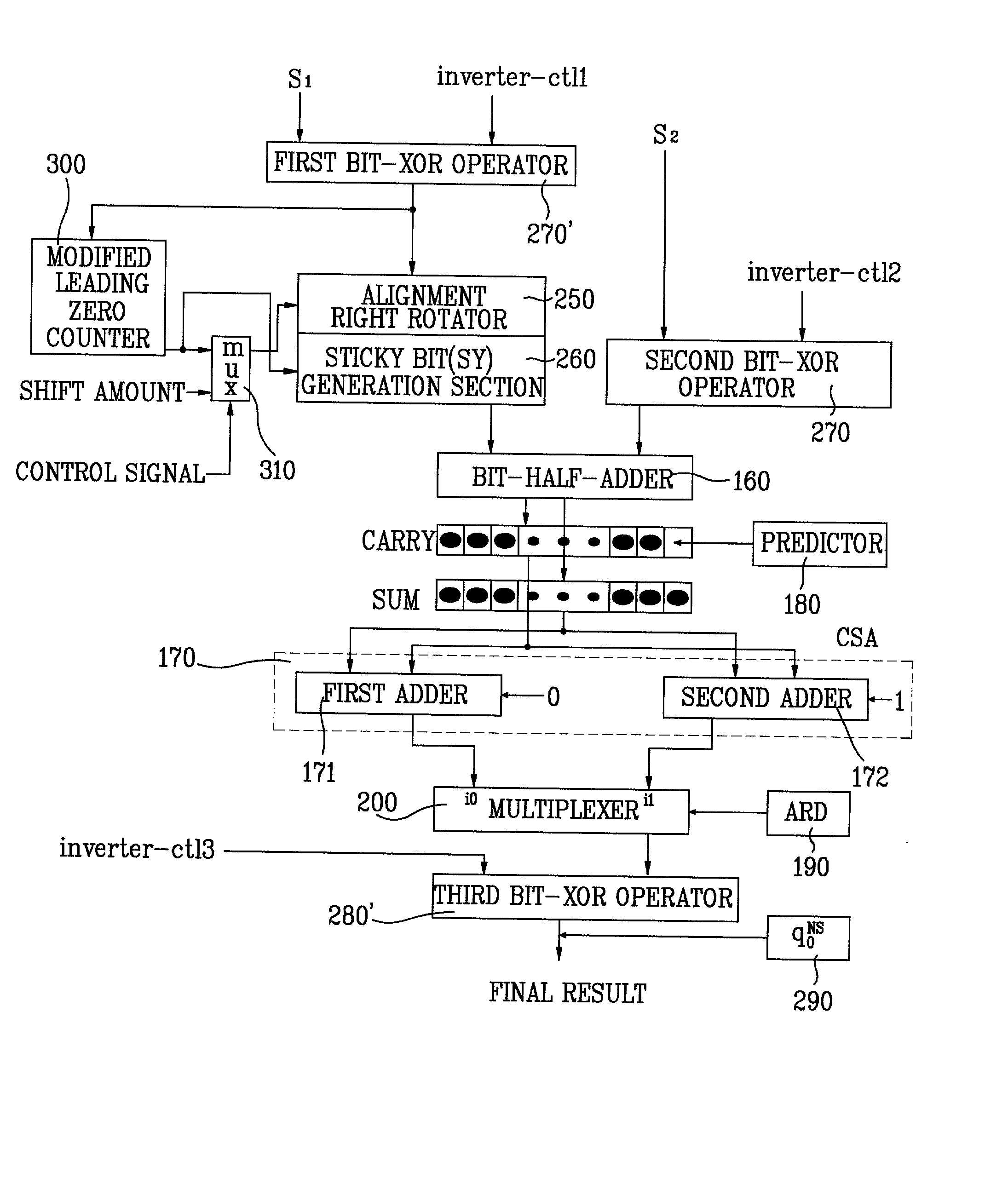

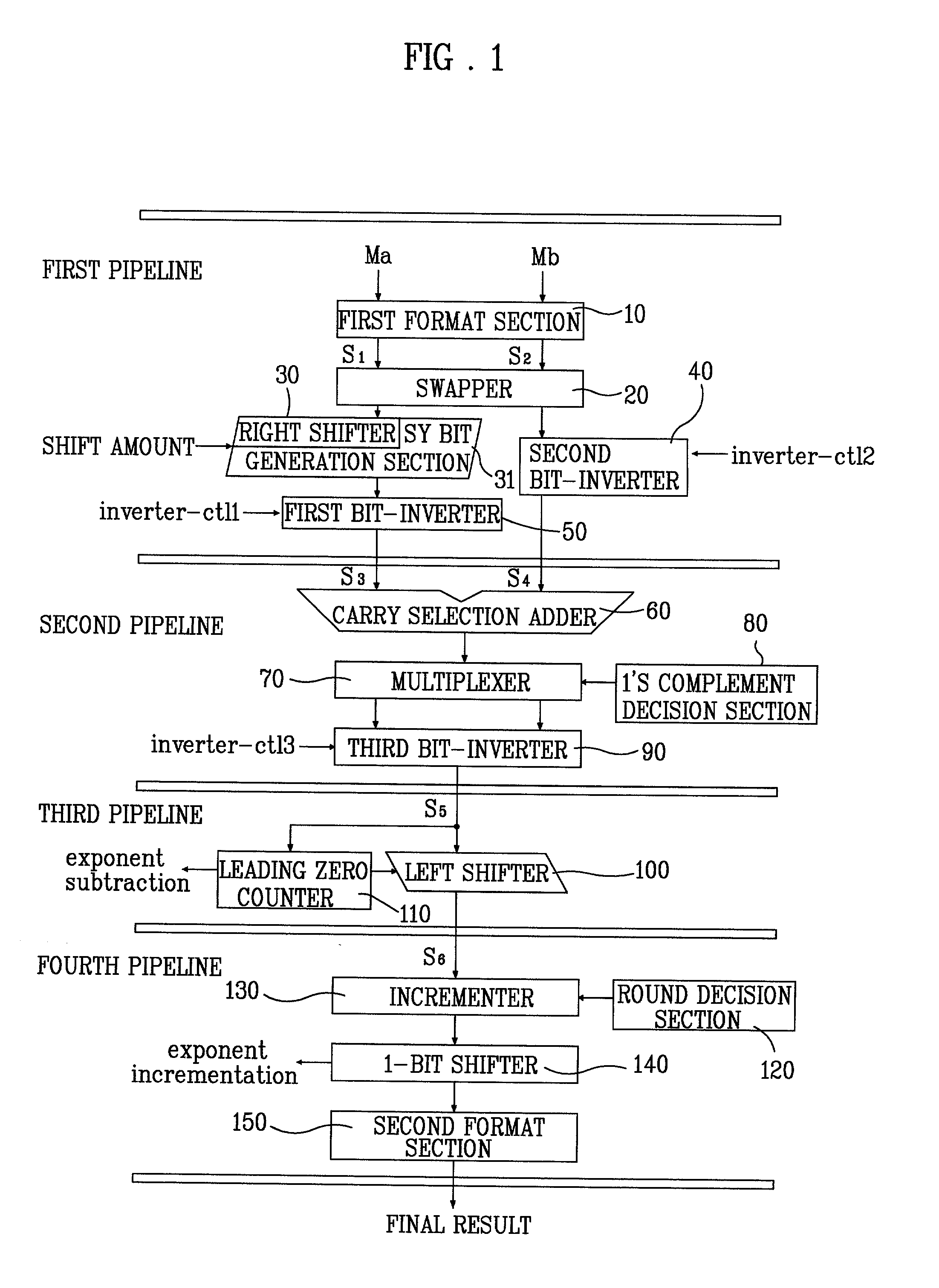

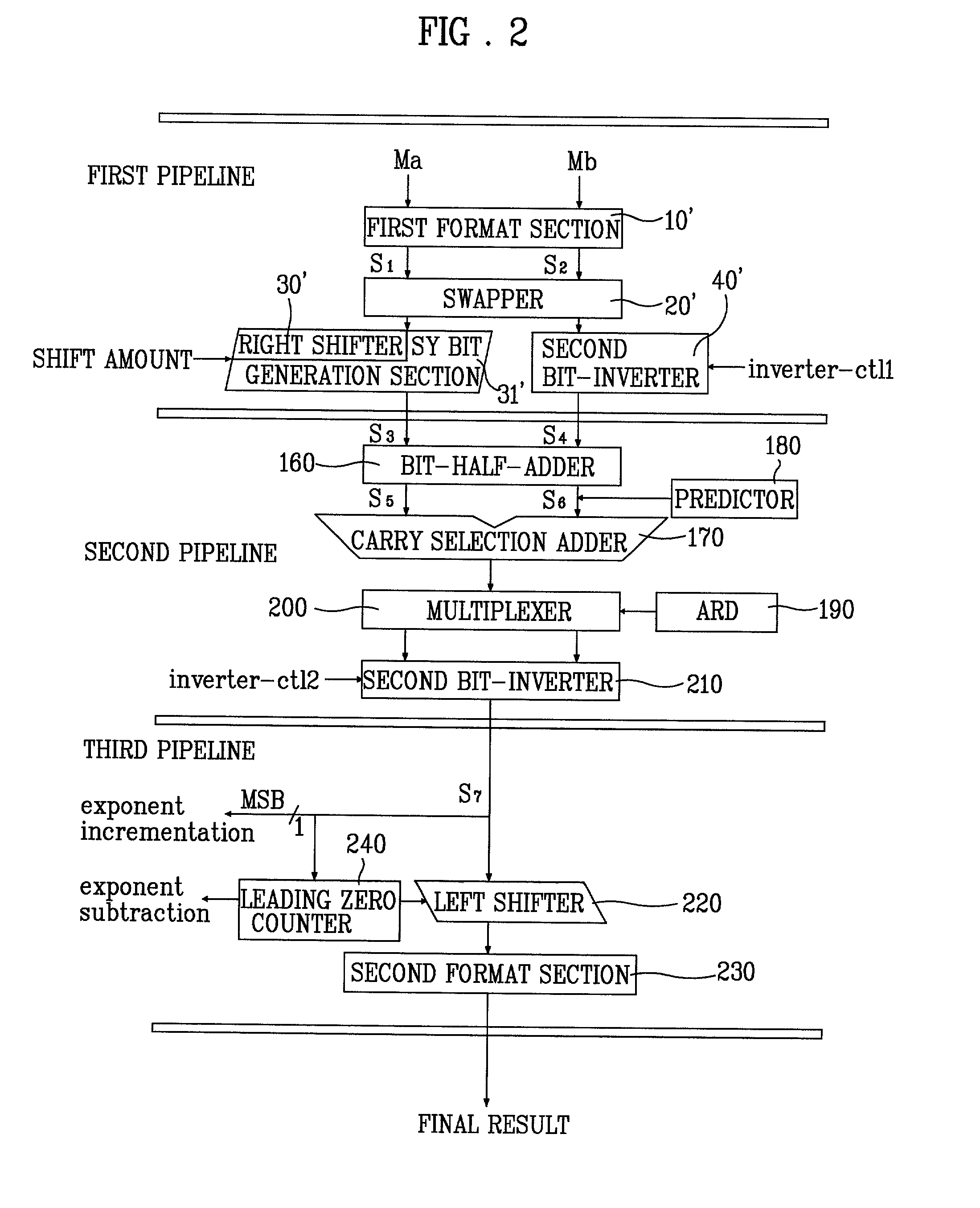

Apparatus and method of performing addition and rounding operation in parallel for floating-point arithmetic logical unit

InactiveUS20020129075A1Computations using contact-making devicesComputation using non-contact making devicesArithmetic logic unitRight shift

A floating-point ALU that performs an IEEE rounding and an addition in parallel in a simultaneous rounding method (SRM) type floating-point adder. The floating-point ALU includes an alignment / normalization section for bypassing or inverting a first fraction part and a second fraction part, performing an alignment by performing a right shift as much as a value obtained from an exponent part or performing a normalization through a left shift by calculating a leading zero with respect to the first fraction part, and obtaining a guard bit (G), round bit (R), and sticky bit (Sy); and an addition and rounding operation section for performing a addition and rounding with respect to the first fraction part and second fraction part outputted through the alignment / normalization section. According to the floating-point ALU, the processing time and the hardware size can be reduced, and the hardware of the SRM can be used as it is.

Owner:YONSEI UNIVERSITY

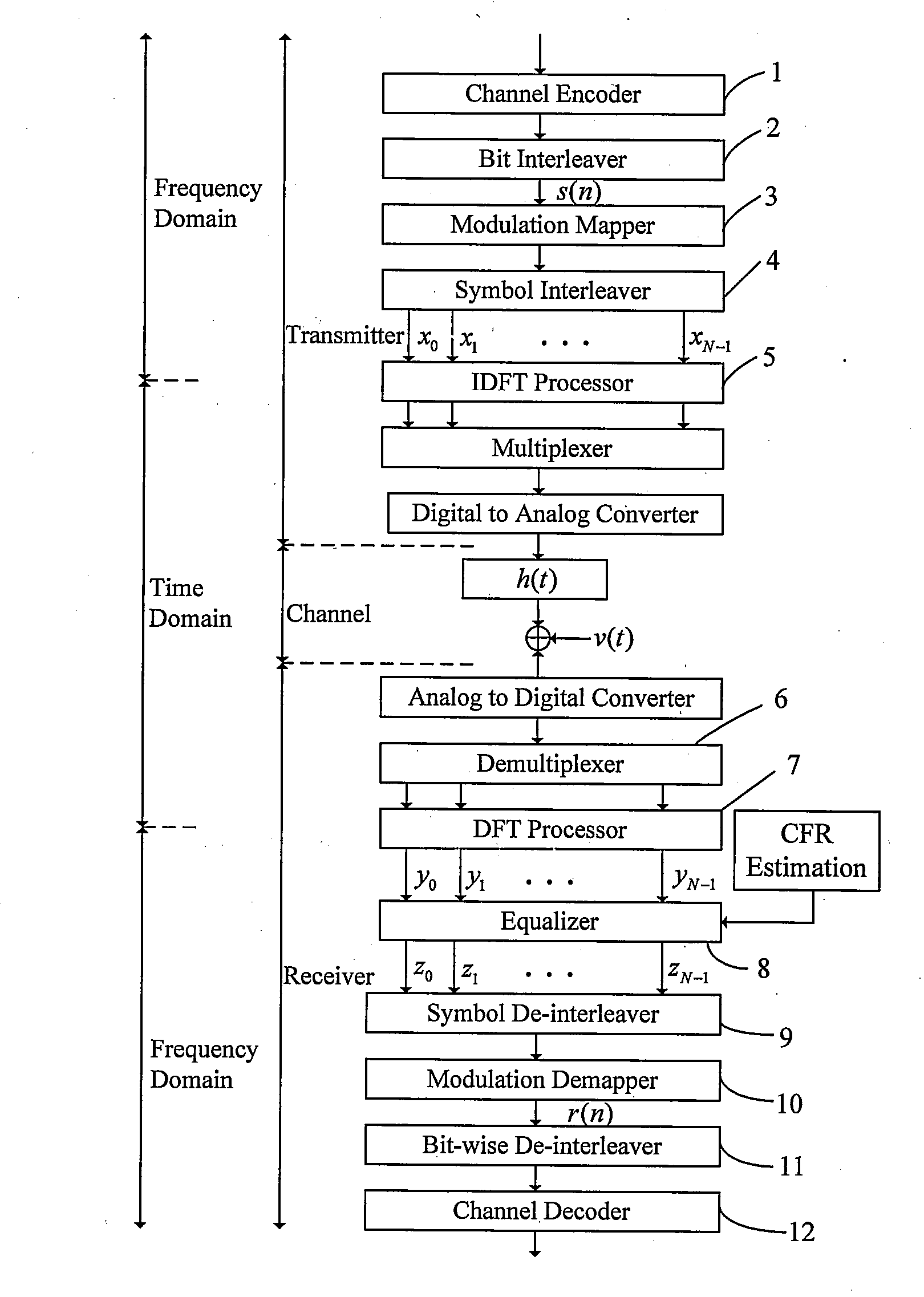

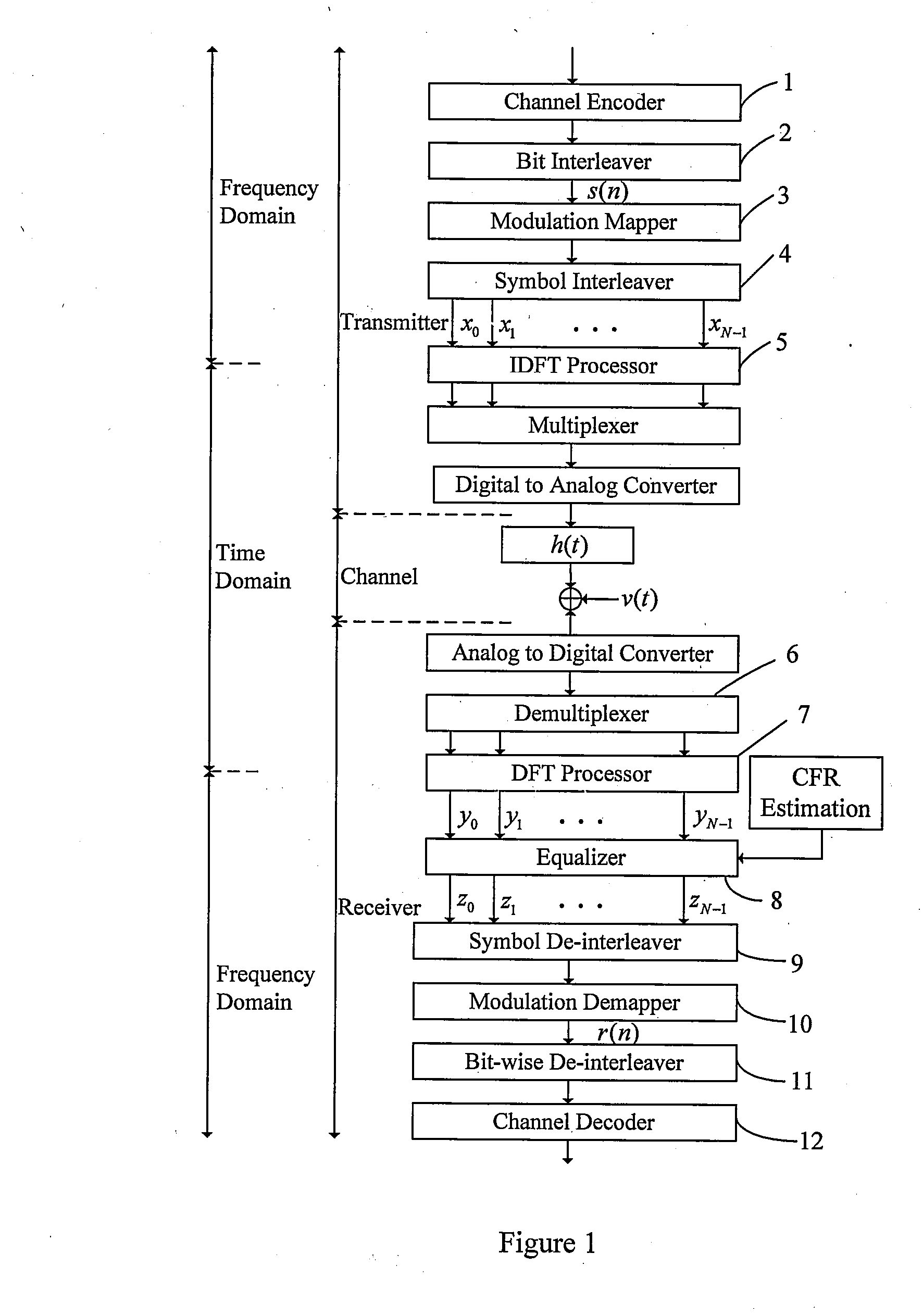

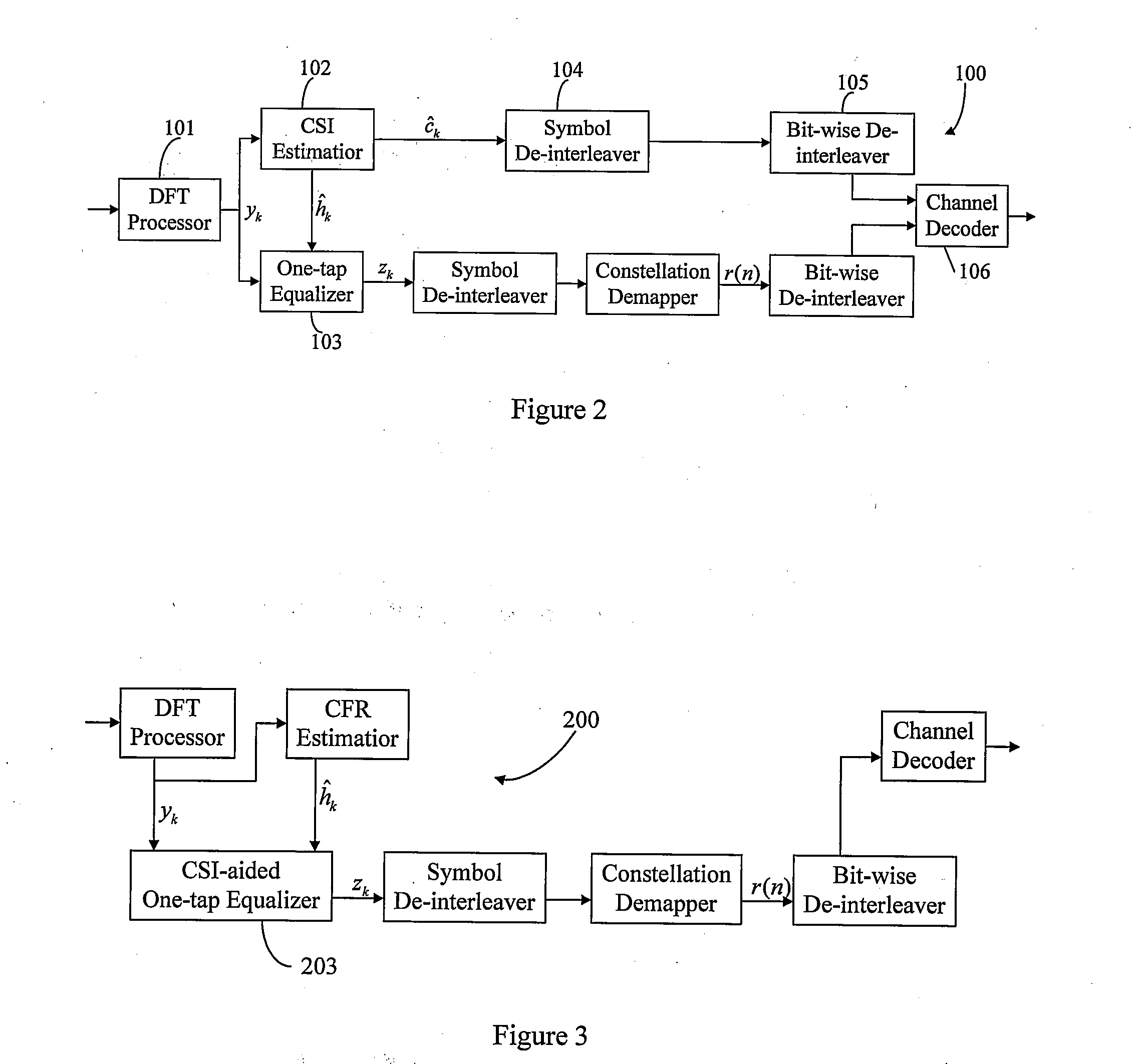

Method and apparatus for receiving coded signals with the aid of channel state information

ActiveUS20090074050A1Easy to keepMultiple-port networksError preventionChannel state informationDecision boundary

Method and apparatus for receiving coded signals with the aid of CSI are provided. The method comprises: performing channel estimation to obtain a CFR estimation vector; computing a squared magnitude of the CFR estimation vector, and obtaining a normalization factor α by averaging the squared magnitudes of CFR estimations on all N subcarriers; finding a norm-shift operand m satisfying the condition that α0=2m is a power of 2 number closest to the normalization factor α; performing a CSI-aided one-tap channel equalization on an output signal vector from a DFT processor by using the norm-shift operand m; performing constellation demapping; and performing channel decoding. The method further comprises obtaining a weighting factor vector by right shifting m bits of the squared magnitude of the CFR estimation vector so that the constellation demapping can use the weighted decision boundary values in case that its input signal is sensitive to both amplitude and phase.

Owner:WIPRO LTD

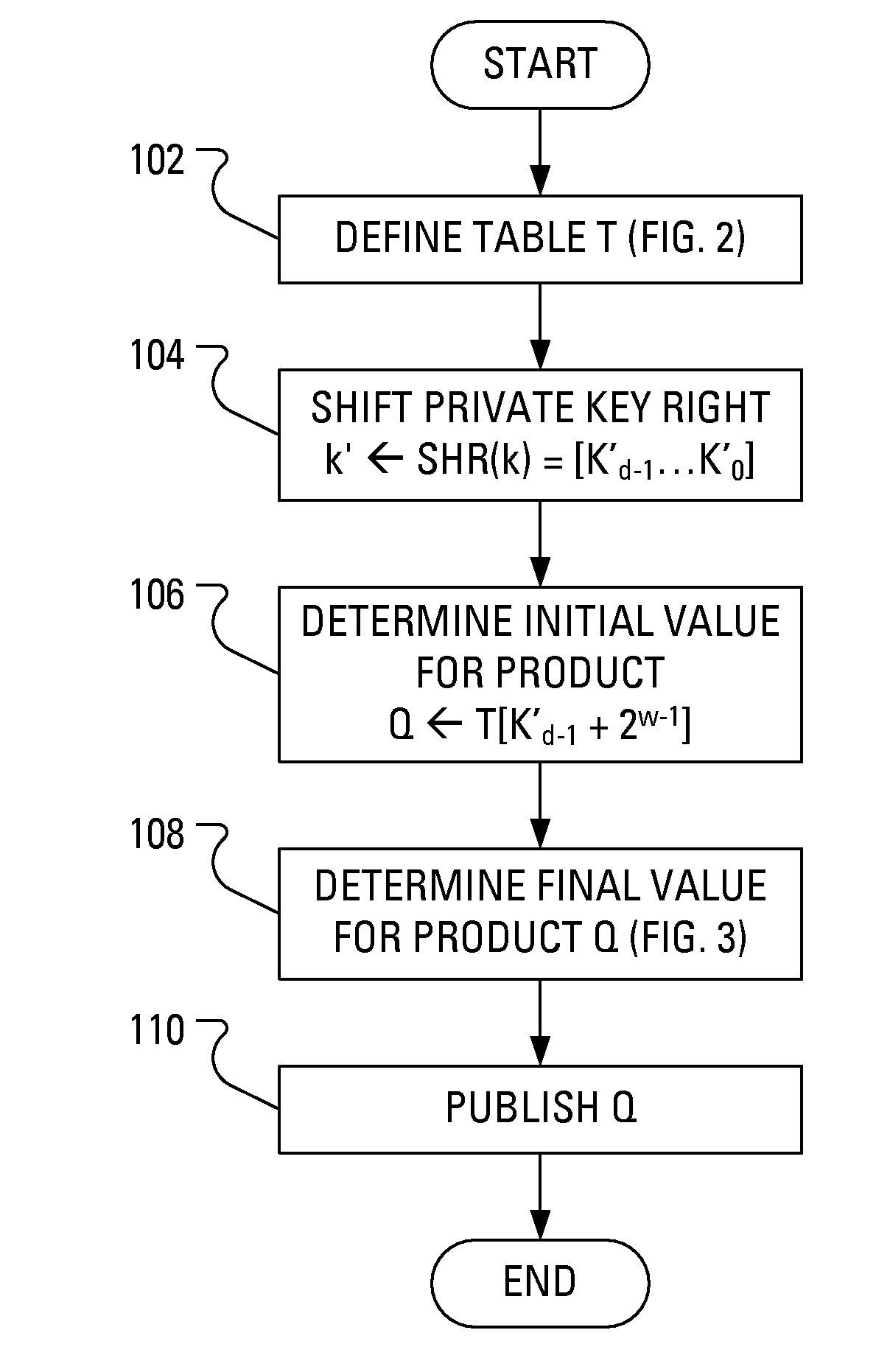

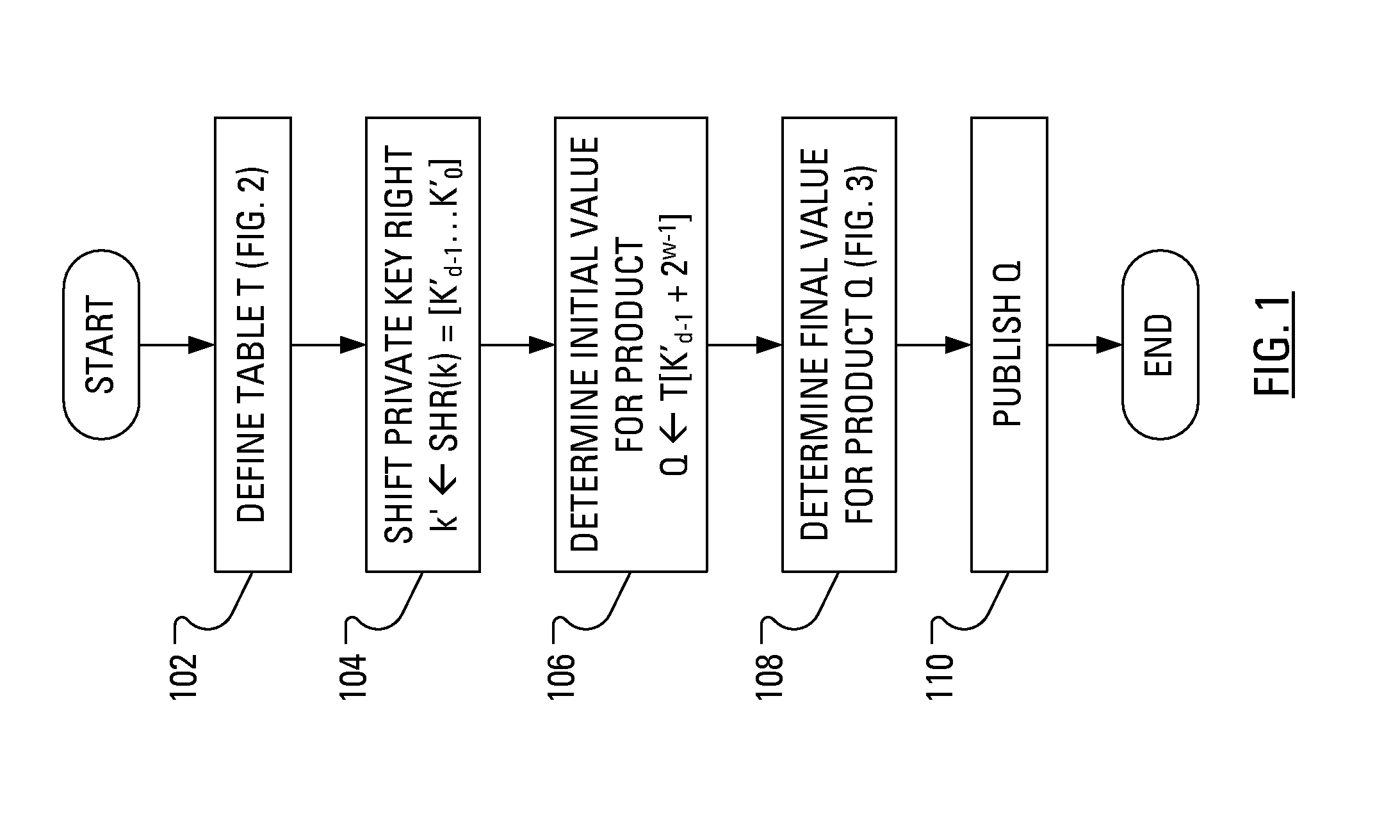

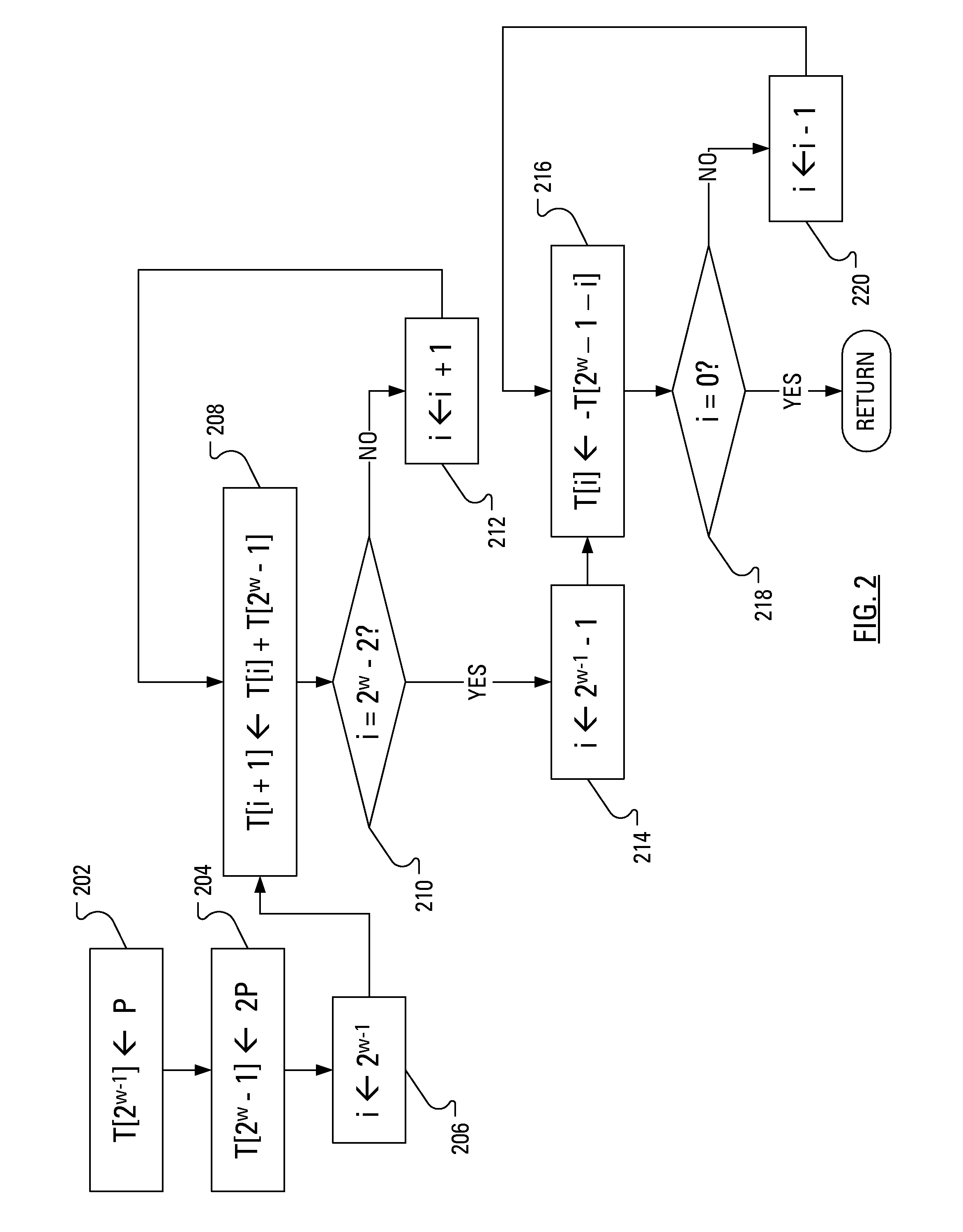

Method and Apparatus for Generating a Public Key in a Manner That Counters Power Analysis Attacks

ActiveUS20080219438A1Key distribution for secure communicationPublic key for secure communicationPower analysisCountermeasure

A public key for an Elliptic Curve Cryptosystem is generated in a manner that acts as a countermeasure to power analysis attacks. In particular, a known scalar multiplication method is enhanced by, in one aspect, performing a right shift on the private key. The fixed-sequence window method includes creation and handling of a translated private key. Conveniently, as a result of the right shift, the handling of the translated private key is made easier and more efficient.

Owner:MALIKIE INNOVATIONS LTD

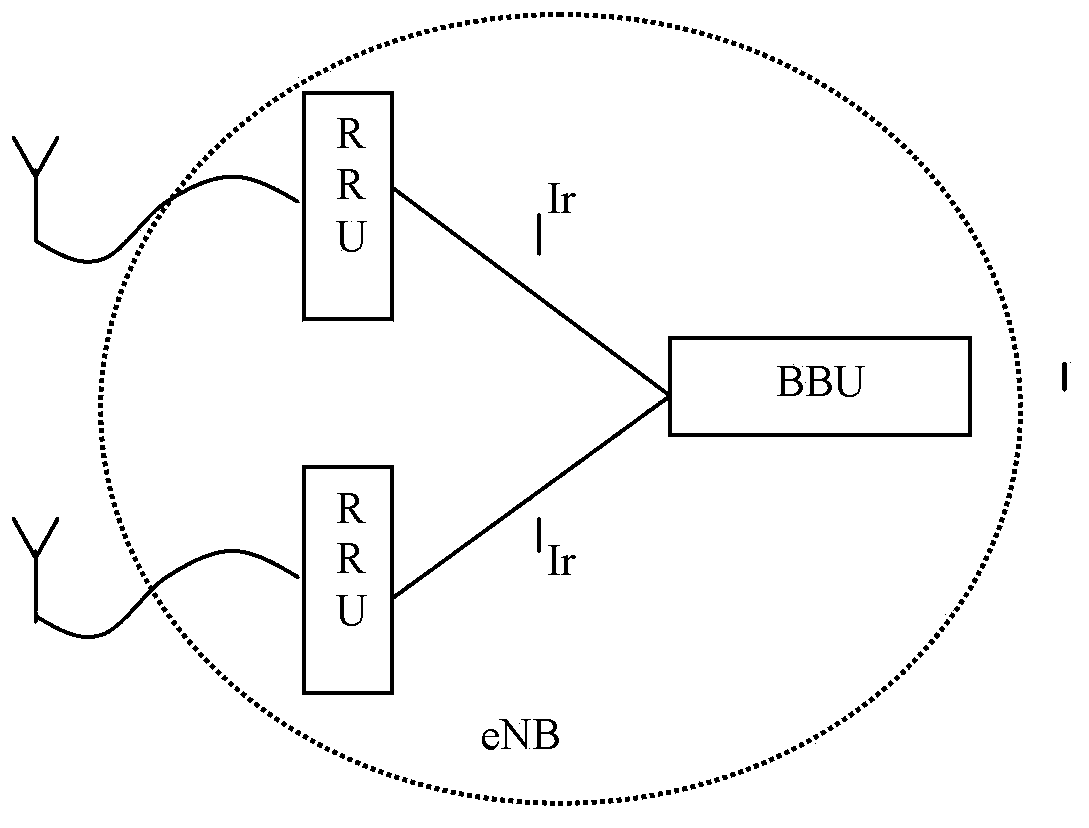

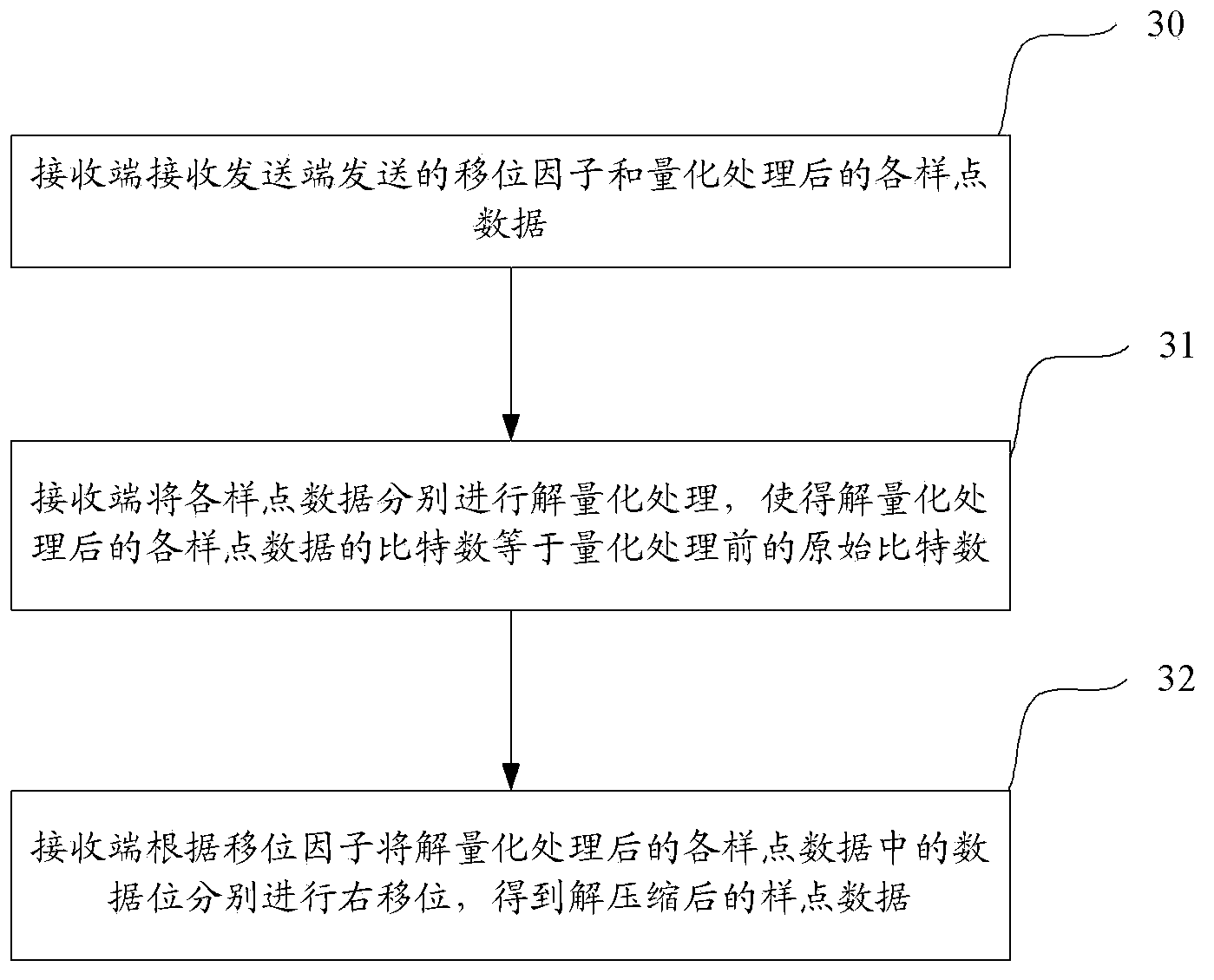

Data compression transmitting and decompression method and apparatus

InactiveCN103634273AEasy to compressModulated-carrier systemsPolarisation/directional diversityData compressionRight shift

An embodiment of the invention discloses a data compression transmitting and decompression method and an apparatus, relates to the field of wireless communication, and is used for optimizing a data compression scheme. In the method, a transmitting terminal divides data to be transmitted into packets, and as for each packet: a shift factor is determined according to a highest order bit of sampling point data of the largest value after a sign bit is removed in the packet, and left shift is conducted respectively for data bits of the sampling point data in the packet according to the shift factor; quantization processing is carried out respectively for the sampling point data after the left shift, so that the number of bits of the sampling point data after the quantization processing is equal to the target number of bits of compression; and the shift factor and the sampling point data after the quantization processing are transmitted to the receiving terminal, the receiving terminal carries out de-quantization processing respectively for the sampling point data, right shift is conducted respectively for the data in the sampling point data after the de-quantization processing according to the shift factor, and decompressed sampling point data are obtained. According to the invention, the performance of the data compression is optimized.

Owner:CHINA ACAD OF TELECOMM TECH

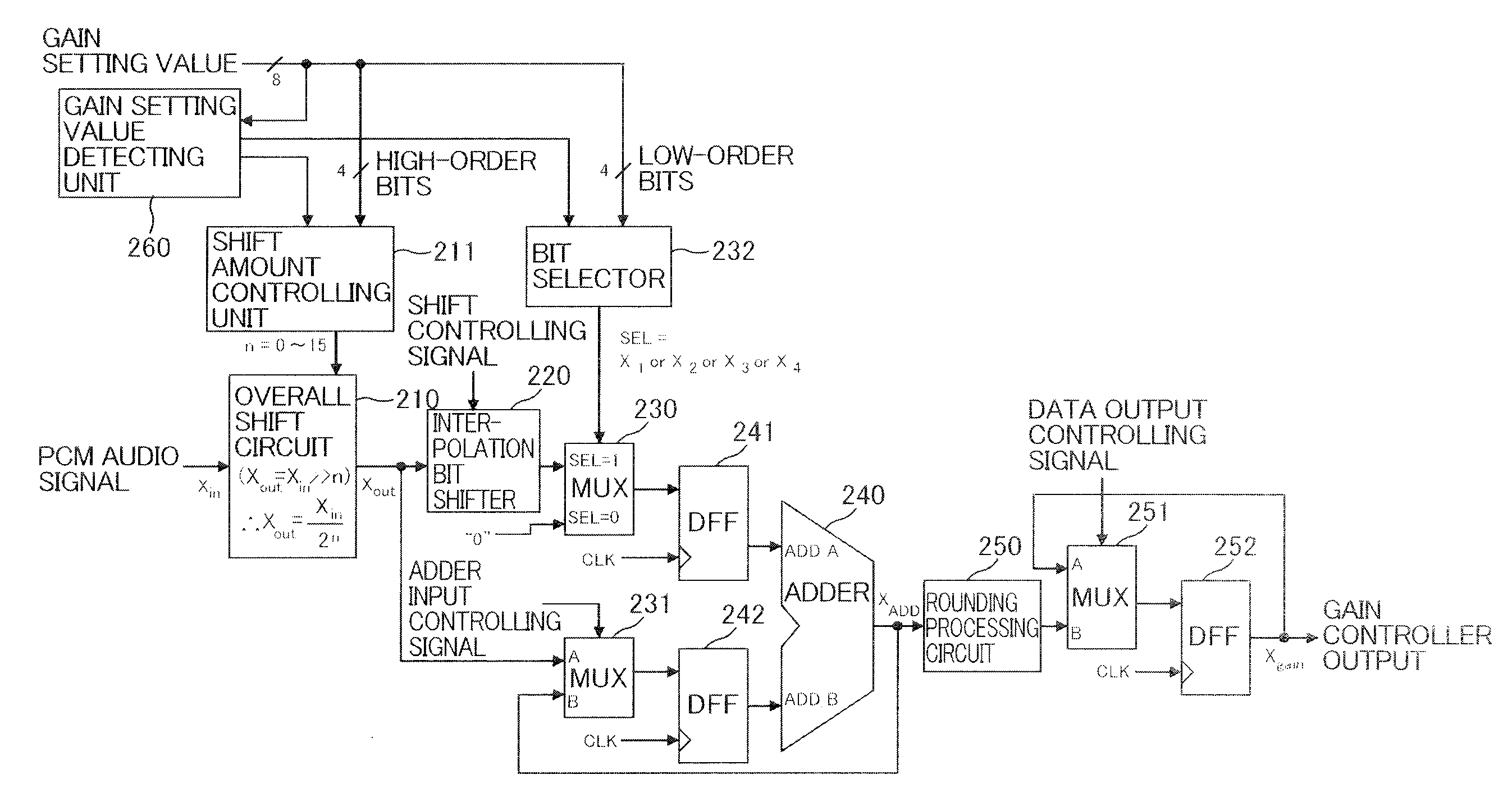

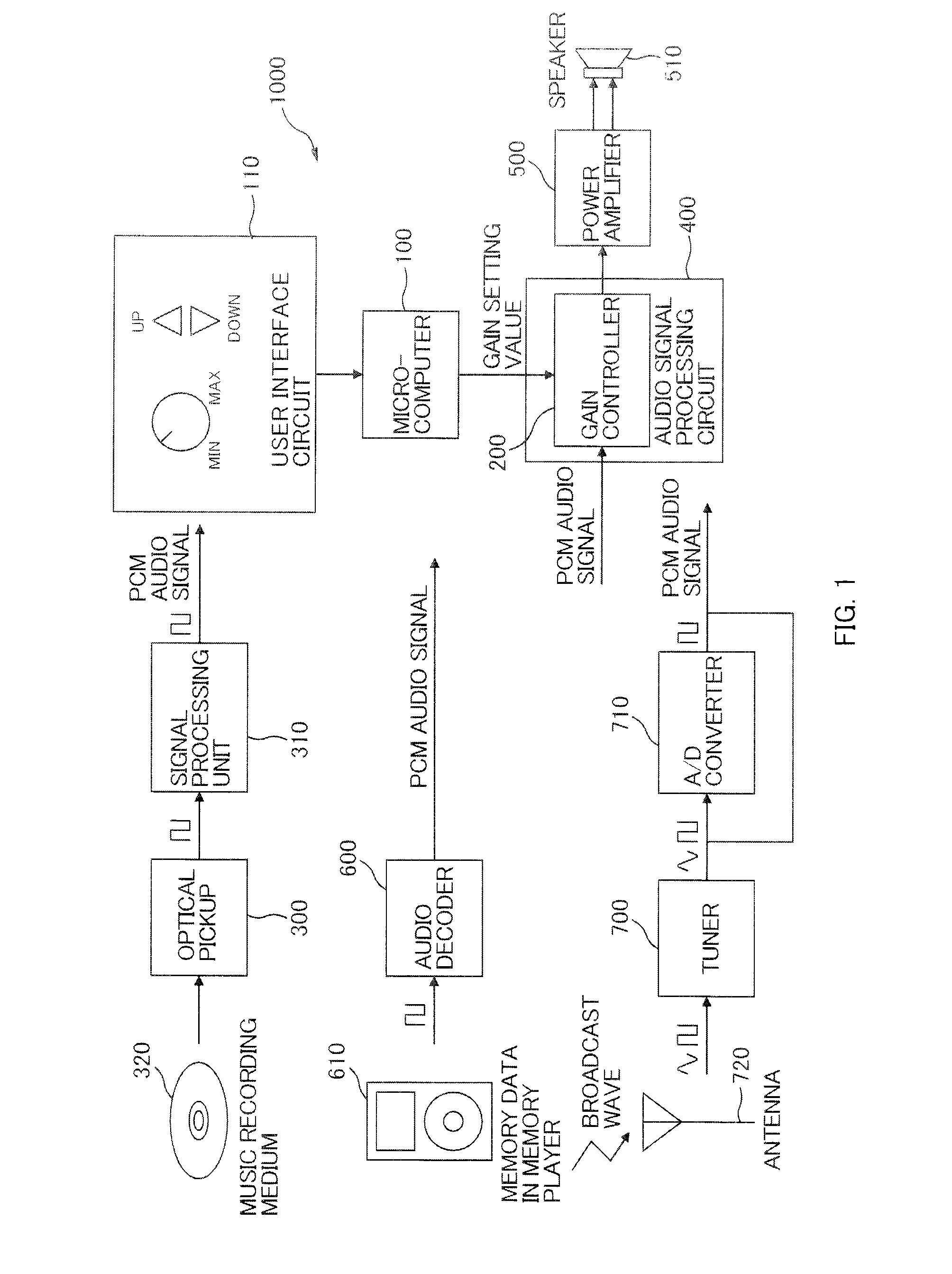

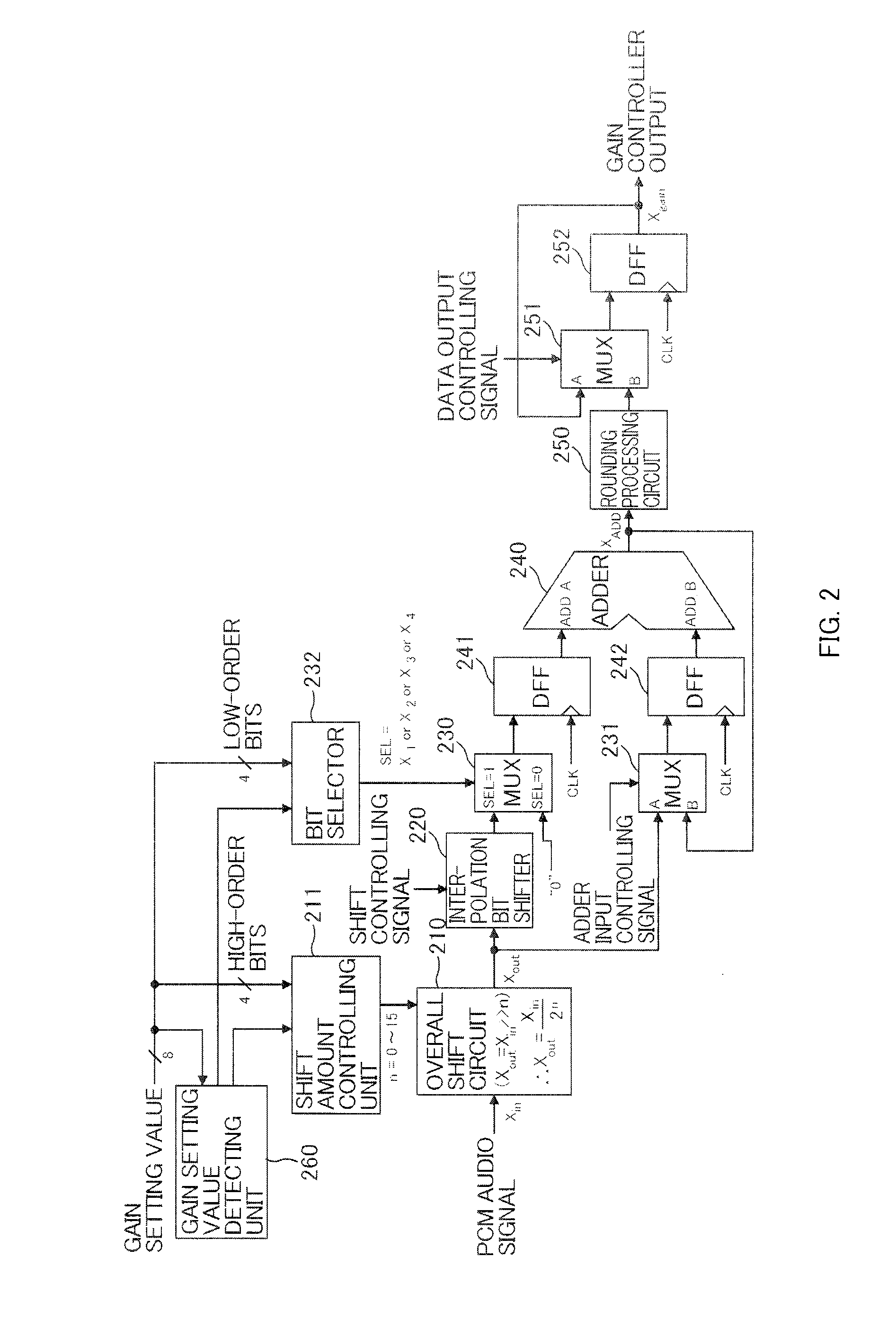

Sound Volume Converting Apparatus

InactiveUS20070244587A1Digital/coded signal controlAnalog signal digital controlRight shiftAudio frequency

A sound volume converting apparatus comprises a data shift unit configured to shift digital audio data by a predetermined number of bits to the right based on first sound volume adjustment data; a correction value calculating unit configured to calculate a correction value based on the right-shifted digital audio data and second sound volume adjustment data; and an adding unit configured to add the correction value to the right-shifted digital audio data to be output.

Owner:SANYO ELECTRIC CO LTD

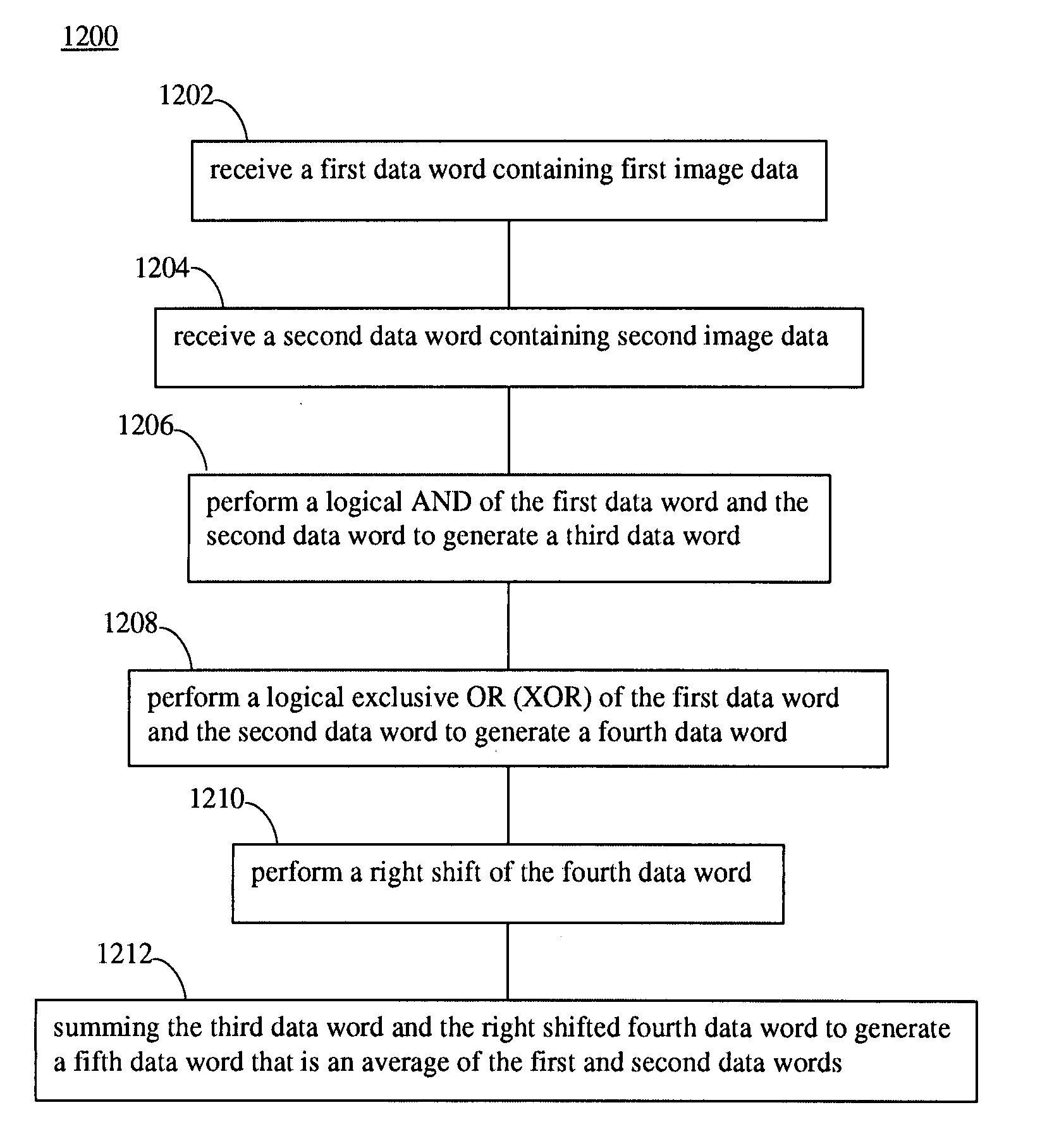

In-place averaging of packed pixel data

Methods, systems, and apparatuses for averaging data in packed format are provided. The data may be image data, such as data words containing color-specific data portions representative of pixels of a captured image. A first data word containing first image data is received. A second data word containing second image data is received. A logical AND of the first data word and the second data word is performed to generate a third data word. A logical exclusive OR (XOR) of the first data word and the second data word is performed to generate a fourth data word. A right shift of the fourth data word is performed. The third data word and the right shifted fourth data word are summed to generate a fifth data word that is an average of the first and second data words.

Owner:AVAGO TECH INT SALES PTE LTD

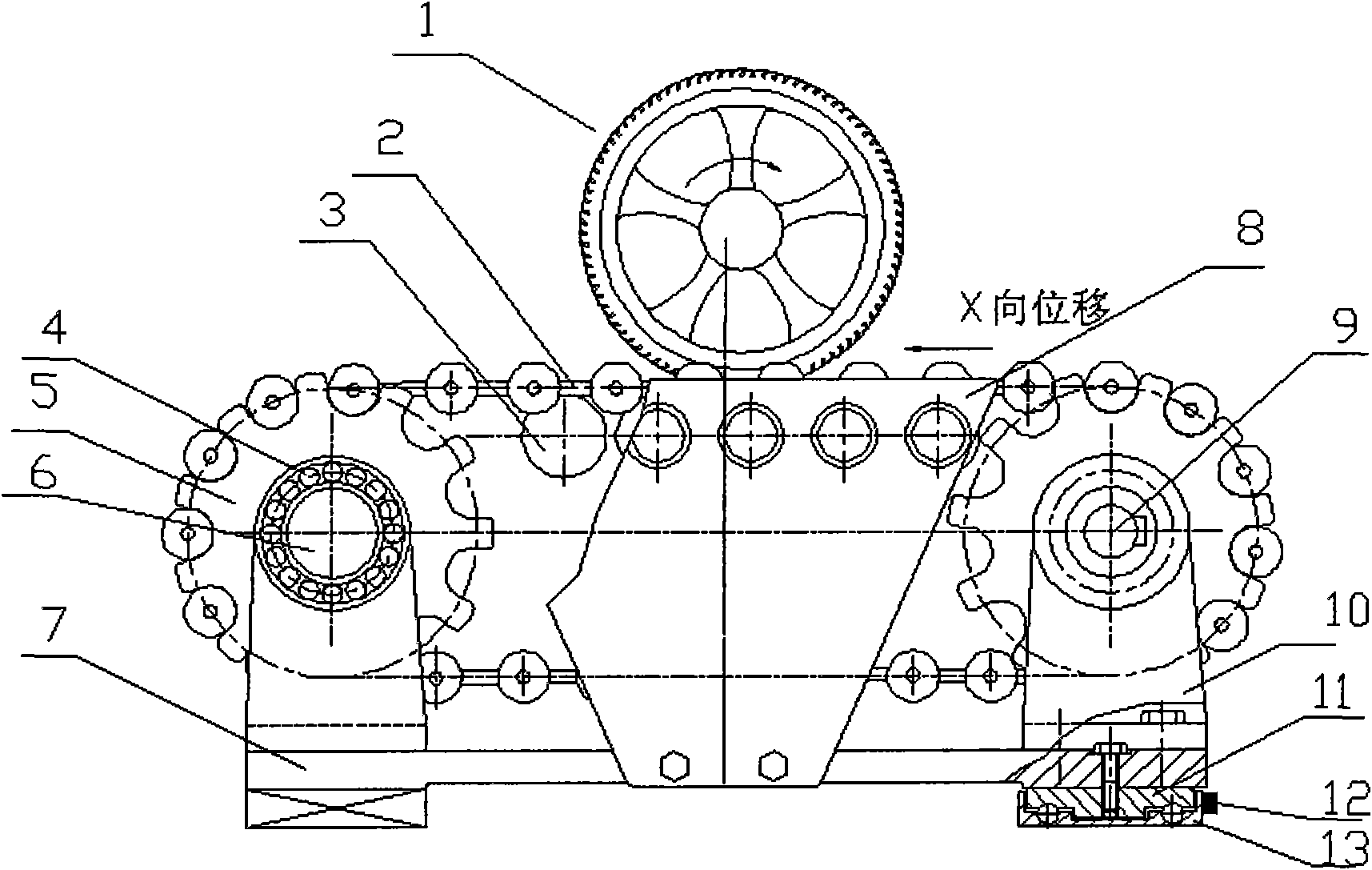

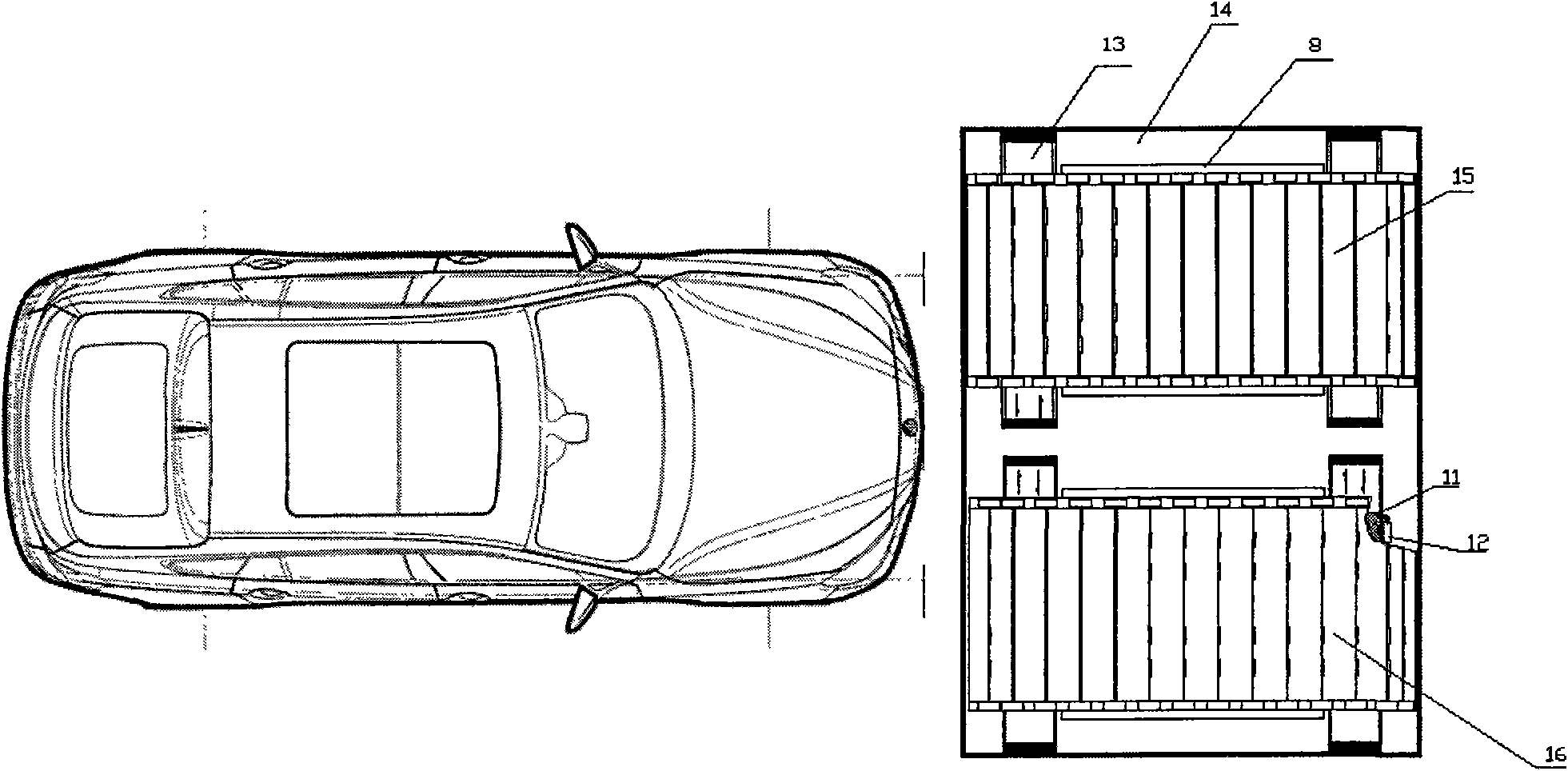

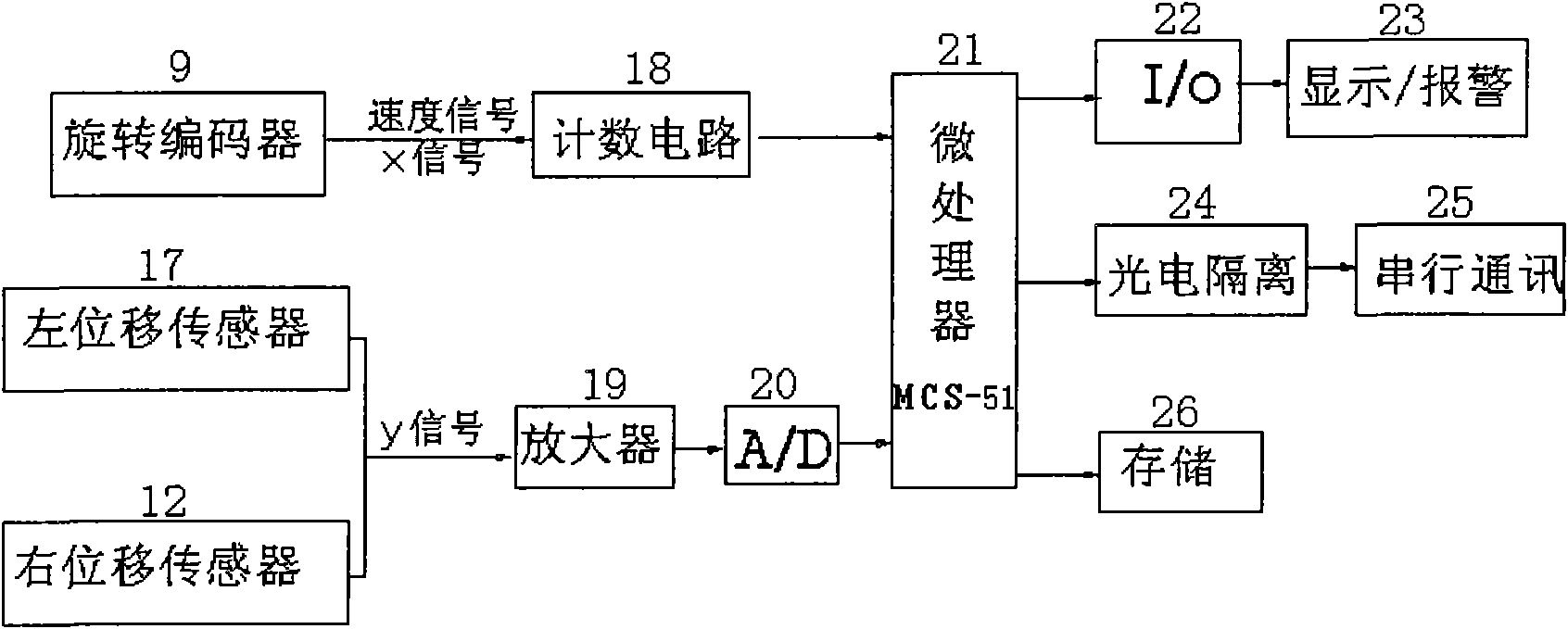

Automobile sideslip detector and method for detecting sideslip

InactiveCN101592557AThe test result is reasonableIn line with actual operating conditionsUsing electrical meansVehicle wheel testingBall bearingAudio power amplifier

The invention discloses an automobile sideslip detector and a method for detecting sideslip. The automobile sideslip detector consists of a mechanical part and an electric part, wherein chain wheels of the mechanical part are fixed on a chain wheel shaft, and a plane link plate and two chain wheels form chain drive connection; a base plate is arranged on a sliding plate, the sliding plate is connected with a plate type linear guide rail through a ball bearing, and the sliding plate can reciprocate on the plate type guide rail transversely; a left-shift sensor and a right-shift sensor of the electric part are connected with an amplifier respectively, and the amplifier is connected with a microprocessor through an A / D converter; a rotary encoder is connected with the microprocessor through a counting circuit; and a rotating shaft of the rotary encoder and the chain wheel shaft are arranged coaxially, and the fixed parts of the left-shift sensor and the right-shift sensor are arranged on the plate type linear guide rail. The sideslip detector amplifies the detection running distance X of a detected automobile so that the detection is more accurate, and can measure sideslip values at different speeds and different loads for accurately matching suspension fork positional parameters of a front steering wheel.

Owner:SOUTH CHINA UNIV OF TECH

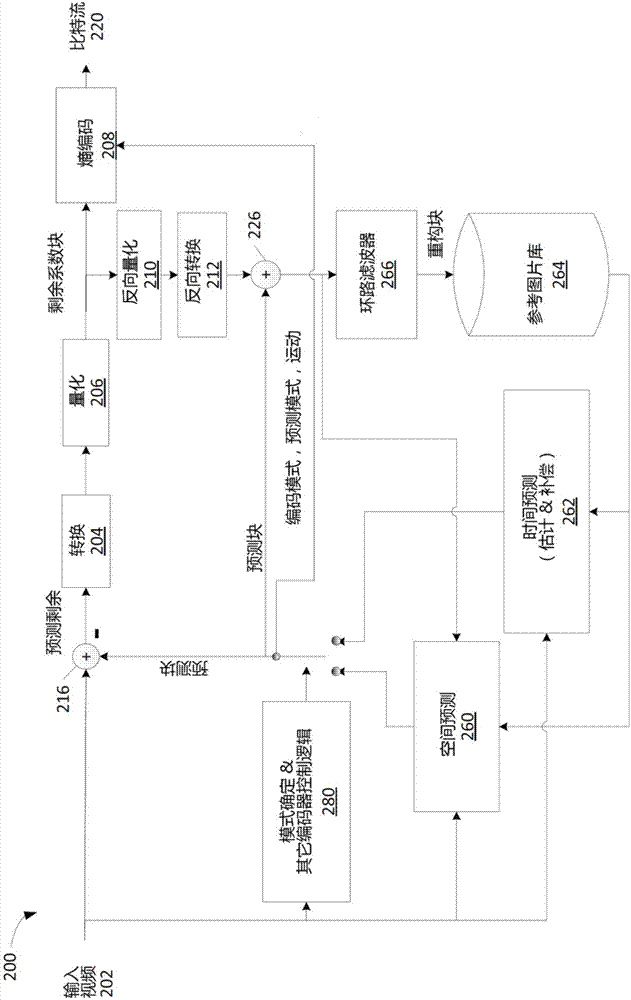

Escape color coding for palette coding mode

Systems, methods, and instrumentalities are disclosed for escape color coding for palette coding mode. A video bitstream may be received. The video bitstream may comprise a quantization parameter (QP) and / or a quantized escape color value that corresponds to an escape color pixel. A scaled escape color value may be generated by scaling the quantized escape color value by a scaling factor. A left- shift parameter may be determined based on the QP. A left-shifted escape color value may be generated by left-shifting the scaled escape color value based on the left-shift parameter. A right-shifted escape color value may be generated by right-shifting the left-shifted escape color value based on a constant parameter. A reconstructed escape color value may be determined based on the right-shifted escape color value. The device may decode the video bitstream based on the reconstructed escape color value.

Owner:VID SCALE INC

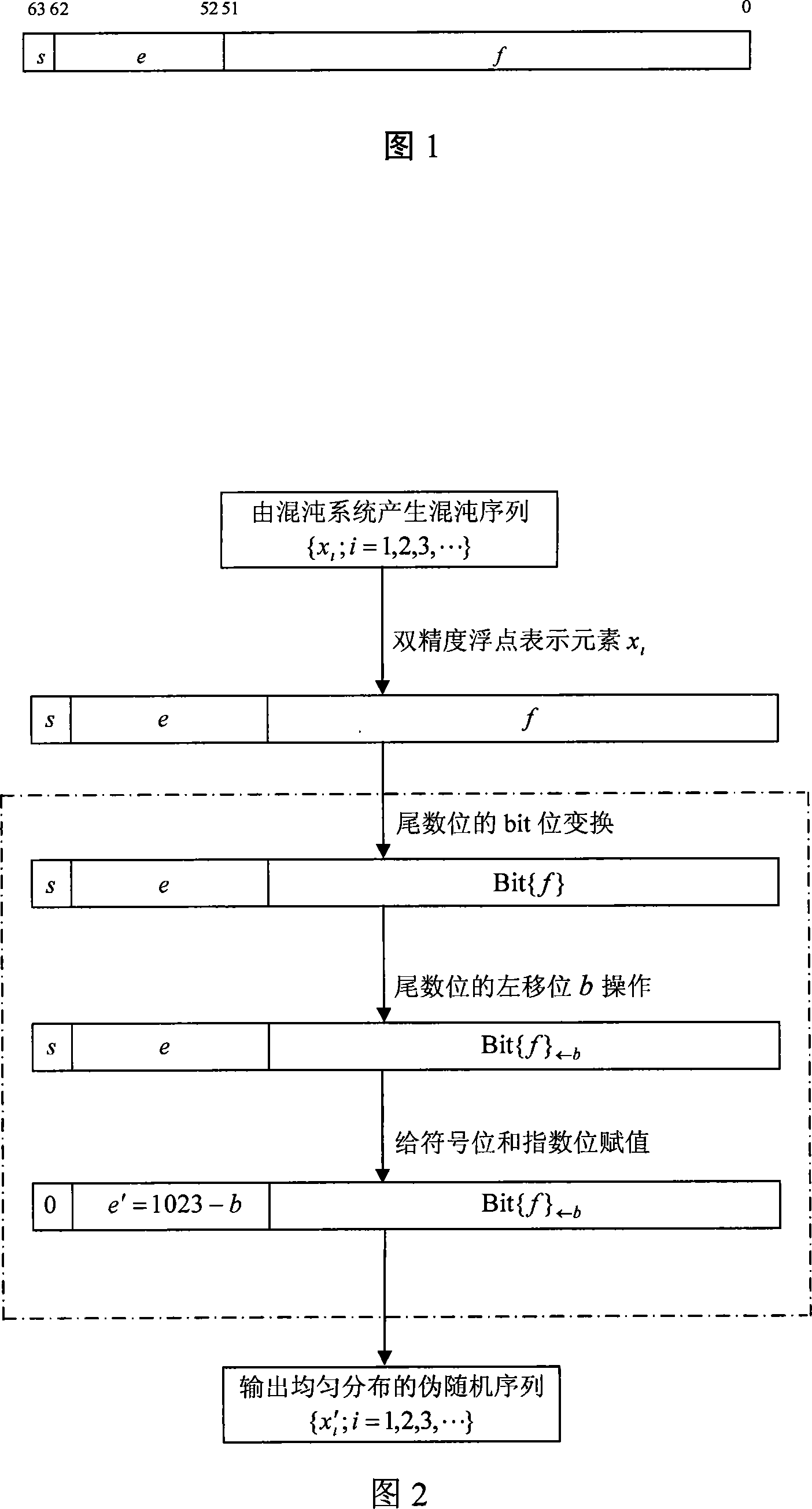

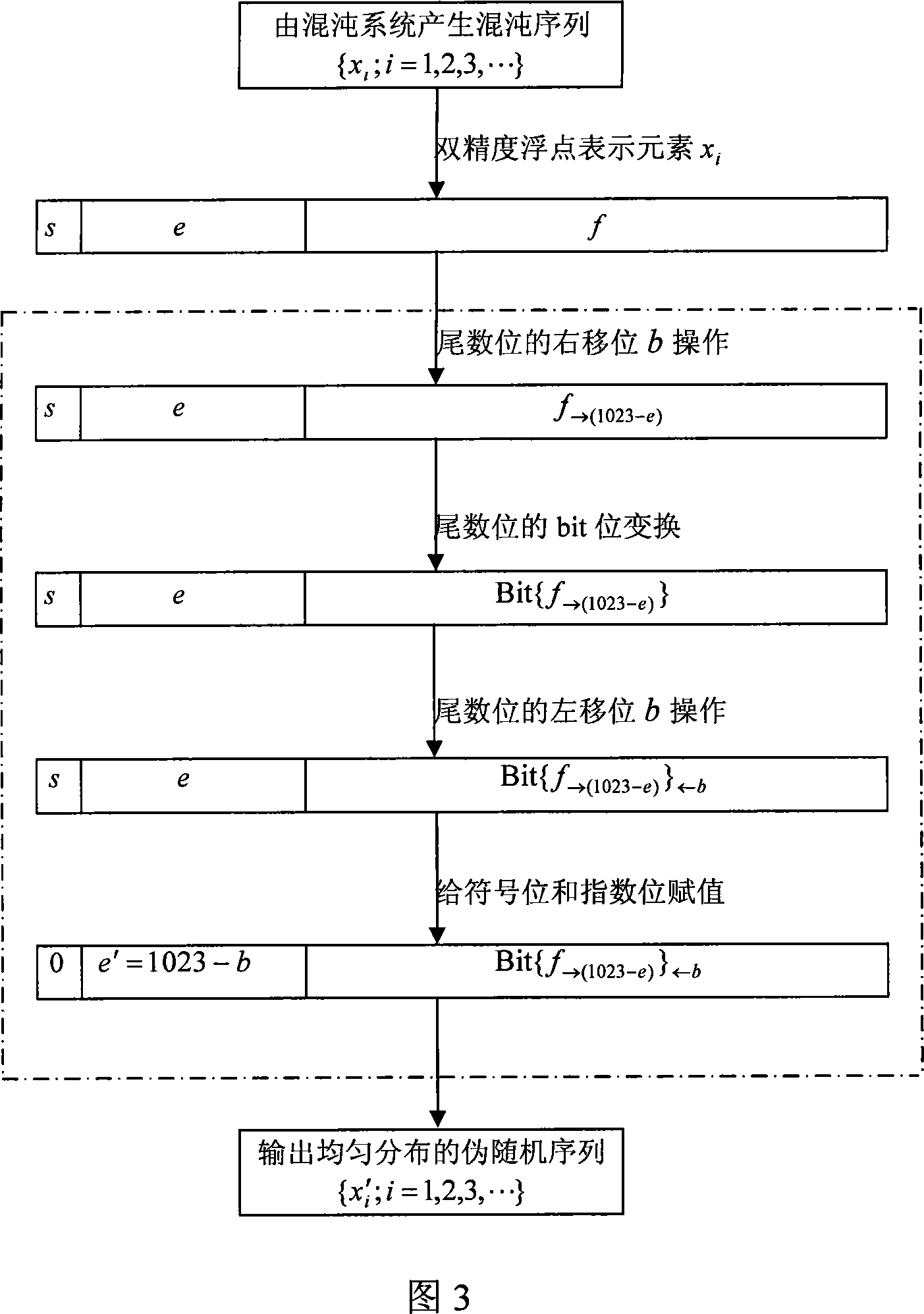

A method to obtain uniform distributed pseudo random sequence in random chaos system

InactiveCN101217360AEvenly distributedEasy to implementSecret communicationSecuring communicationRight shiftSign bit

The invention discloses a pseudo-random sequence even obtaining method from an arbitrary chaotic system. The invention comprises the following steps: for an arbitrary solid pattern chaotic sequence from a chaotic map system or a chaotic differential dynamic system, if the field of definitions of the chaotic sequence is (-1, 1), a real number converter carries on right shift b operations successively to the mantissas of each element in the arbitrary solid pattern chaotic sequence, switches the bit position of mantissa and carries on left shift b operations to the mantissas; the sign bit is endowed with a value '0' and an asynchronous exponential bit is endowed with a value '1023-b' to obtain an even-distributed pseudo-random sequence; or the real number converter switches the position of bit successively of the mantissas of each element in the arbitrary solid pattern chaotic sequence, carries on left shift b operations to the mantissas; the sign bit is endowed with a value '0' and an asynchronous exponential bit is endowed with a value '1023-b' to obtain the even-distributed pseudo-random sequence. The invention can obtain good-homogeneity pseudorandom number from an arbitrary chaotic system, in particular to be convenient for the realization of digital system.

Owner:CENT SOUTH UNIV

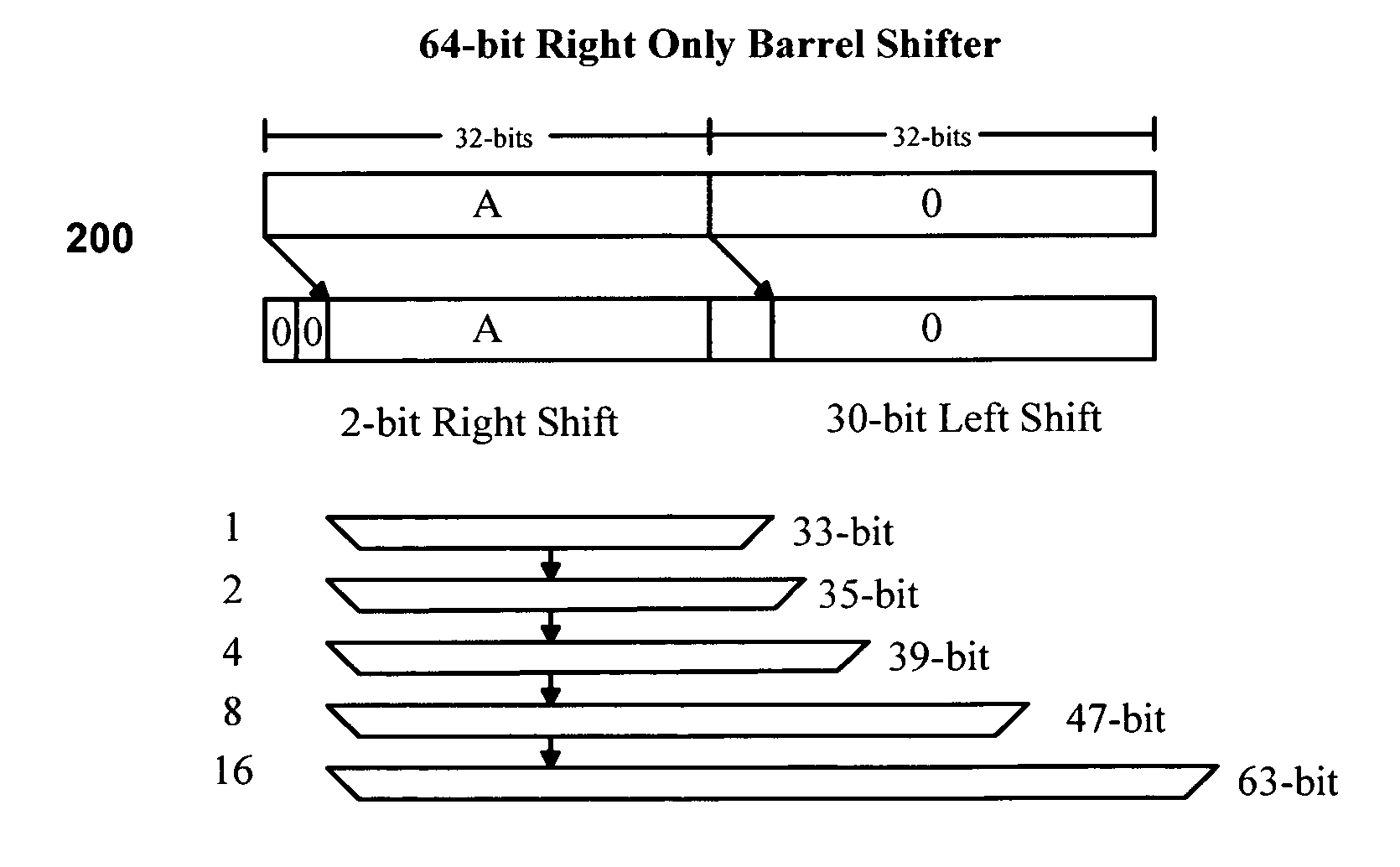

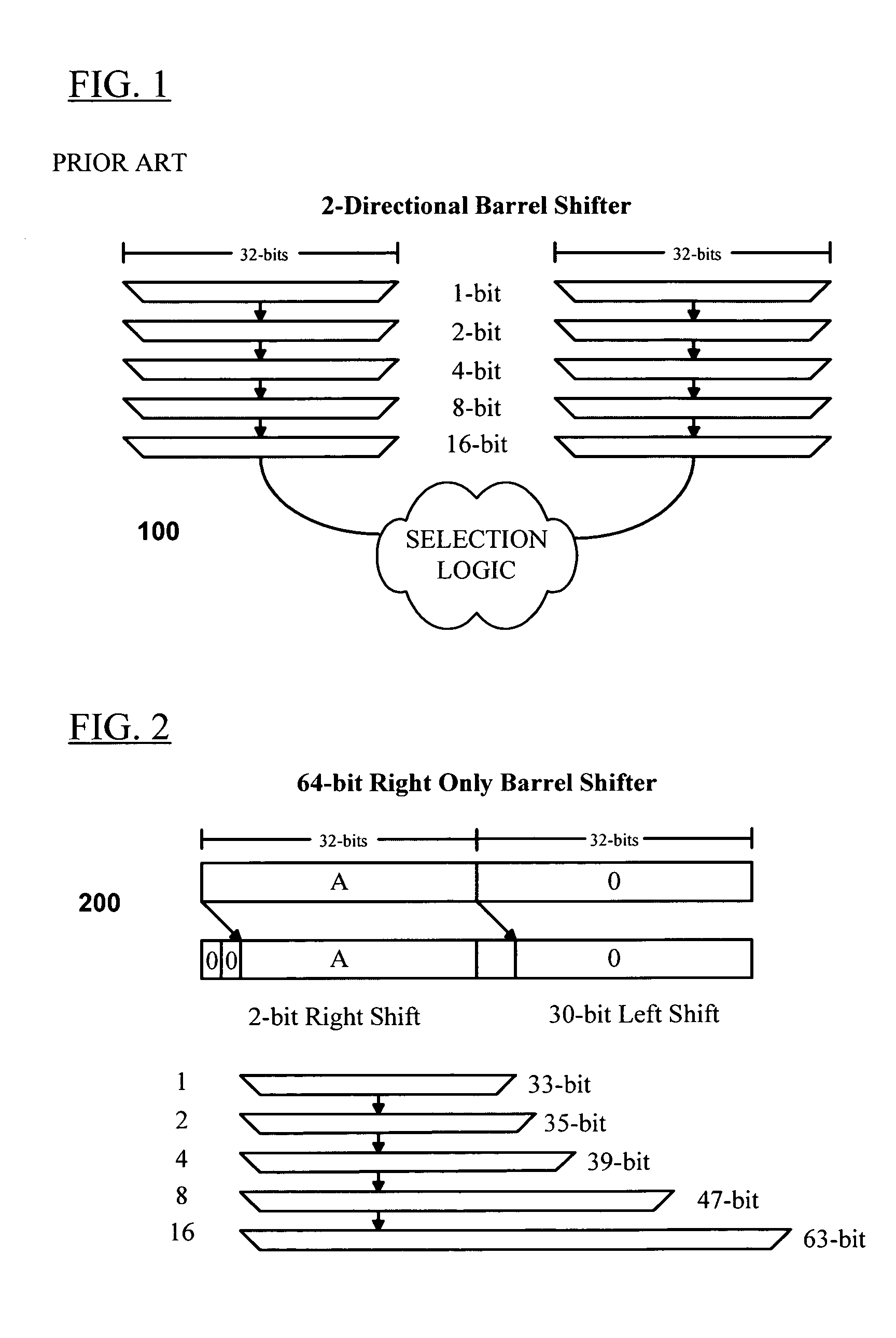

Barrel shifter for a microprocessor

InactiveUS20050289323A1Reduce power consumptionImprove performanceEnergy efficient ICTError detection/correctionRight shiftMultiplexer

A 2N bit right only barrel shifter for a microprocessor comprising upper and lower N bit shifter portions. A N bit input is put in the upper portion. An X bit right shift of the N bit number yields the results in the N bit upper portion and the result of an N-X bit left shift in the lower portion. The N bit shifter is comprised of a Log2N stage multiplexer where in each successive stage of the multiplexer adds 2x additional bits where x increments from 0 to (Log2N-1).

Owner:ARC INT LTD

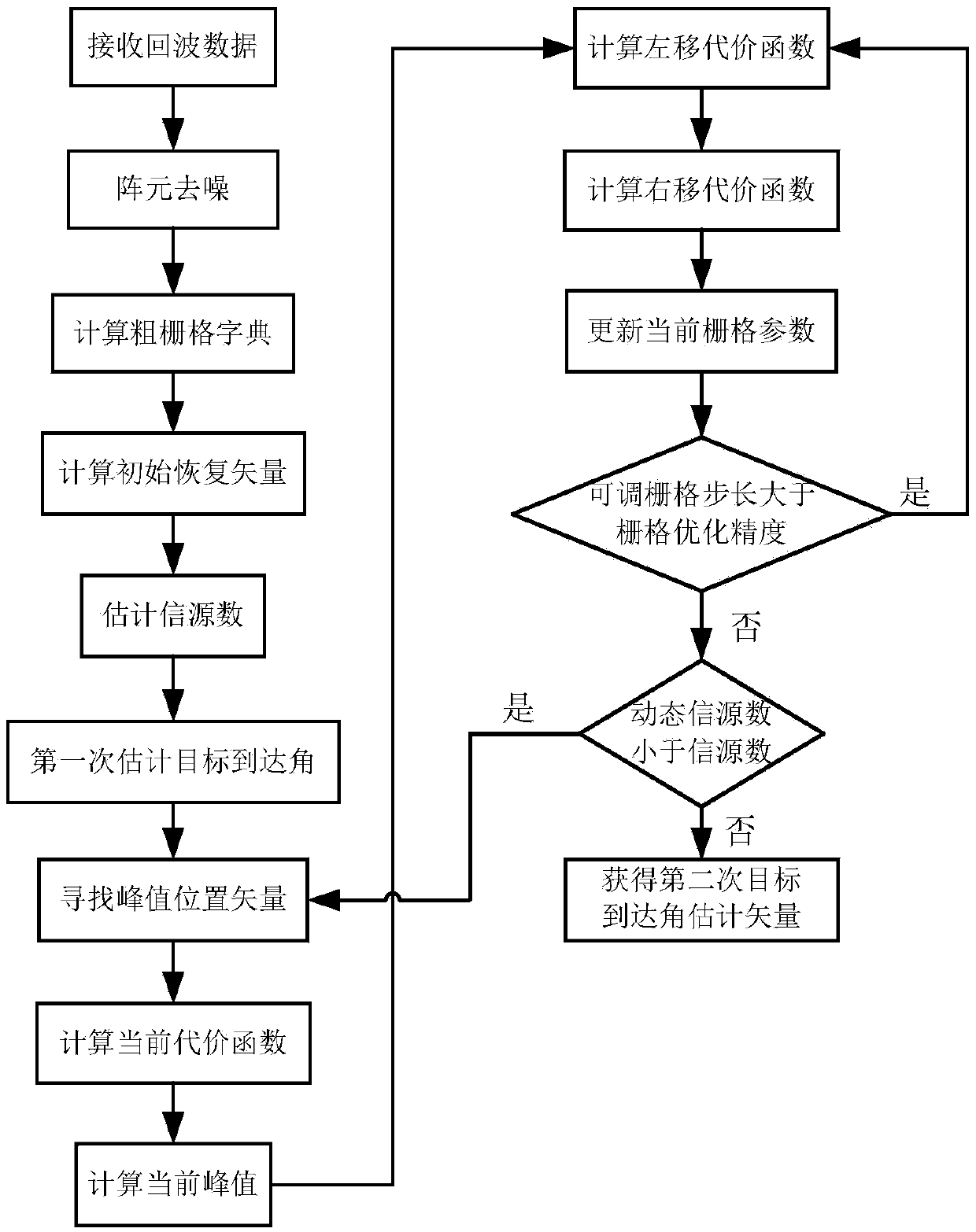

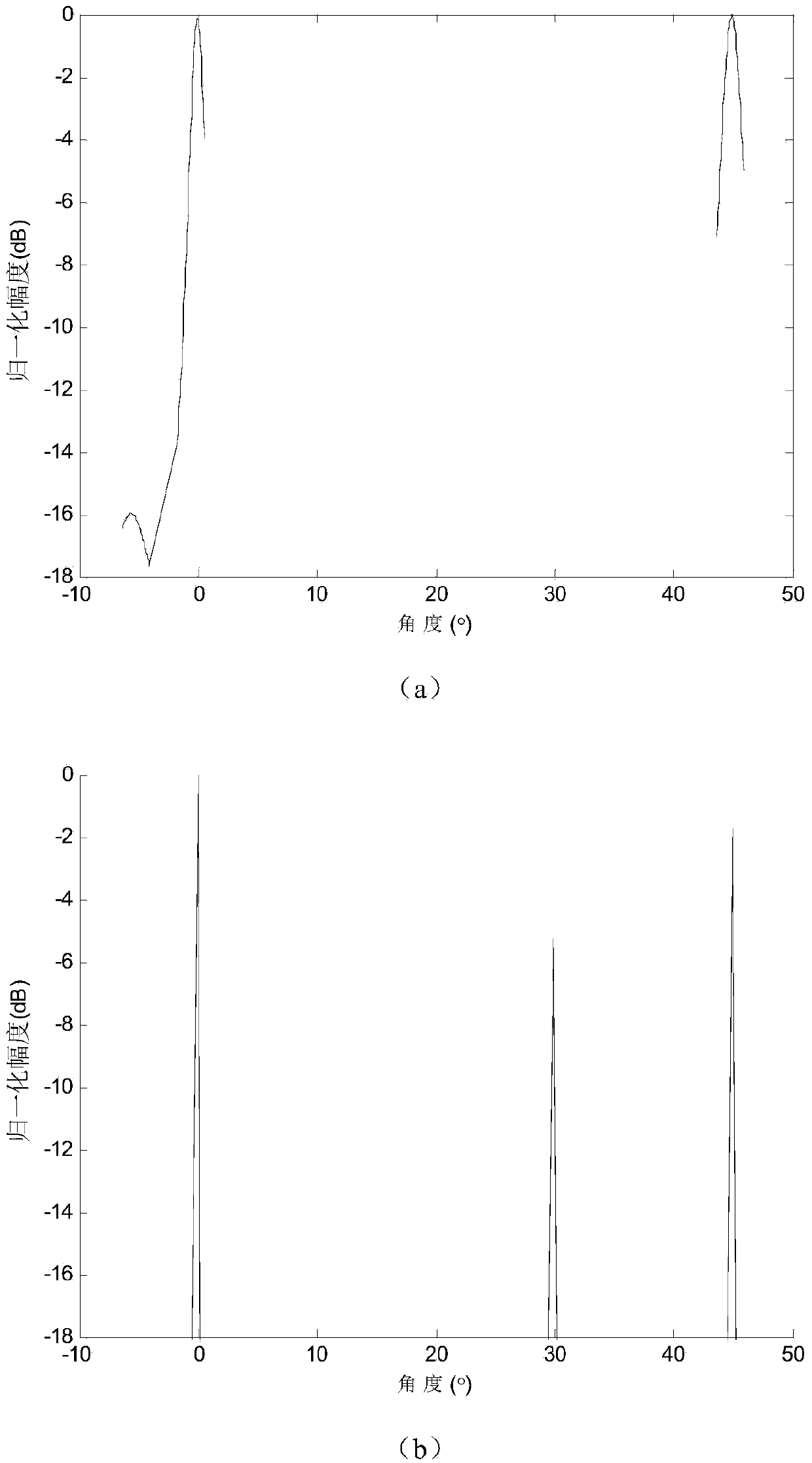

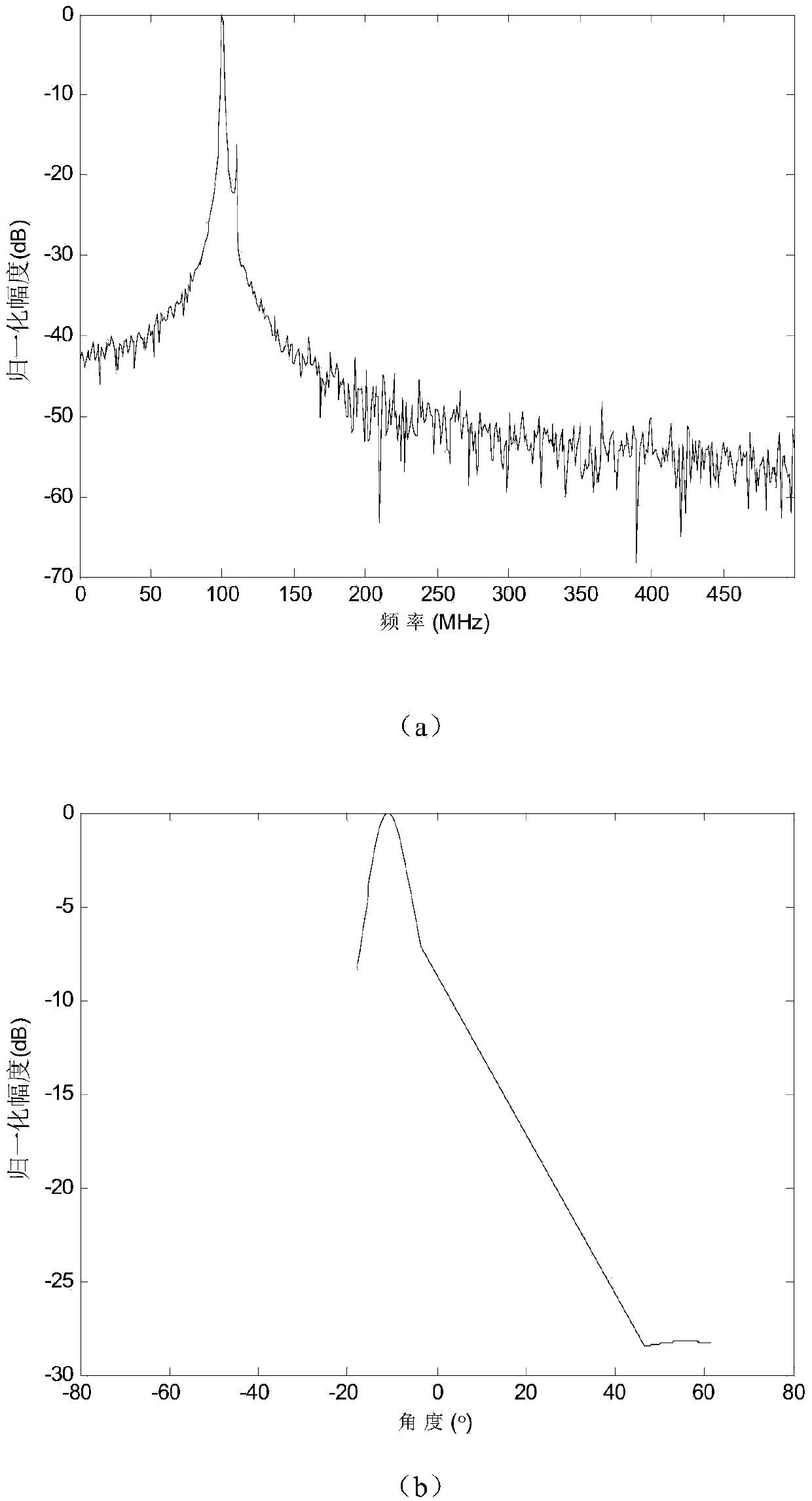

Grid offset optimization object DOA (Direction of Arrival) estimation method based on source number estimation

ActiveCN105334488AOvercome the problem of estimated performance degradation or even failureOvercome the rank deficit problemRadio wave direction/deviation determination systemsEstimation methodsRight shift

The invention discloses a grid offset optimization object DOA (Direction of Arrival) estimation method based on source number estimation. The grid offset optimization object DOA estimation method based on source number estimation mainly solves the problem that the prior art is low the DOA estimation performance when the source number is unknown and the sample is small and under the coherent source situation. The implementation process of the method comprises: utilizing array element denoising to perform denoising processing for the received data so as to acquire a data observation vector; solving the peak value for the recovery vector acquired through calculation so as to estimate the source number and the primary target DOA; calculating the current peak value and the current cost function; calculating and comparing the left shift cost function value and the right shift cost function value to update the current grid parameter; and not stopping the angle estimation until the adjustable grid step length satisfies the grid precision and the dynamic source number is greater than the estimated source number, and obtaining the secondary DOA estimation vector. The grid offset optimization object DOA estimation method based on source number estimation realizes high-precision DOA estimation for sparse multi targets when the source number is unknown and the sample is small and under the coherent source situation.

Owner:XIDIAN UNIV

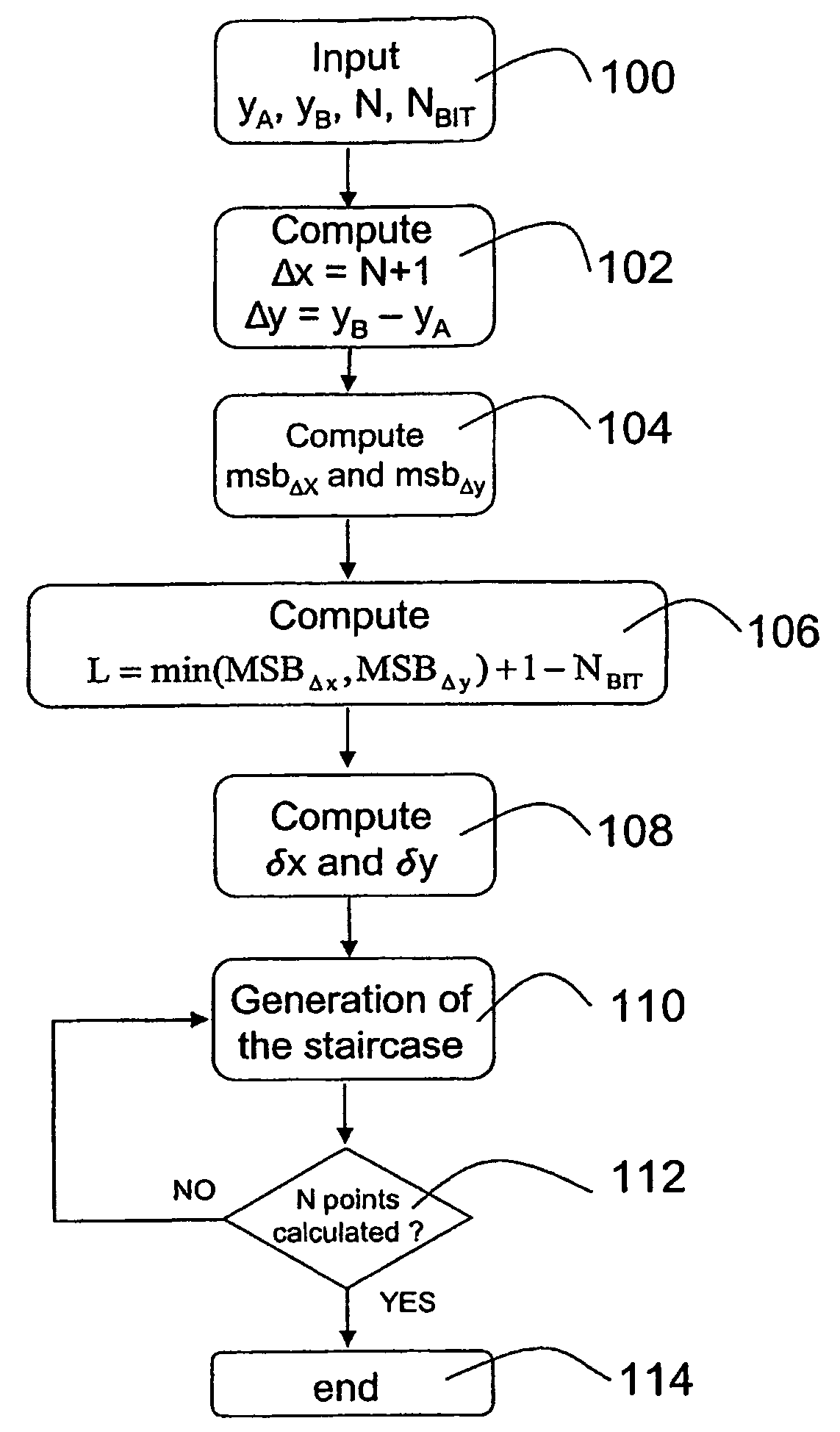

Interpolation Method and a Related Device for Channel Estimation in Communication Systems

InactiveUS20090067518A1Flexible processCost-effectiveBaseband system detailsSecret communicationCommunications systemRight shift

A method for interpolating between a first and a second point includes the steps of calculating a first distance between a first and a second independent value and a second distance between a first and a second dependent value, right shifting the first and the second distances by a predetermined number of bits for obtaining respectively a hold step and a variations step and generating a number of interpolated points, having independent values between the first and the second independent values and corresponding dependent values obtained by alternating hold and variations phases, wherein the hold phase consists of generating a number of points corresponding to the hold step having the same dependent value, and wherein the variations phase consists of varying the dependent value by the variations step until the number of interpolated points has been calculated. The method is particularly suitable for channel estimation in communication systems.

Owner:TELECOM ITALIA SPA

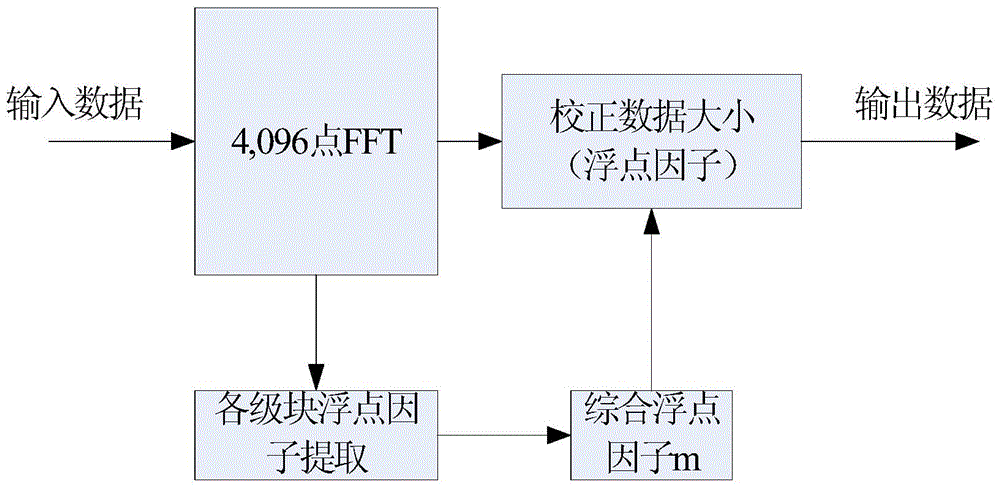

Floating point calculation method based on FPGA

ActiveCN104679719ASolve conflictsImprove the efficiency of floating-point operationsComplex mathematical operationsRight shiftParallel computing

The invention provides a floating point calculation method based on a FPGA. The method comprises the steps of processing a group of data which is identical in index and different in mantissa and used as a data block, expressing the data in calculation by adopting a fixed point format, adjusting the data precision by virtue of left shifting, right shifting the data to avoid the overflow error in the fixed point calculation, and dividing result data by a preset gain to obtain correct data after the calculation is ended. By adopting the floating point calculation method, the contradiction between a fixed point algorithm and a floating point algorithm is solved, the floating point calculation efficiency is improved, and the cost is reduced.

Owner:南京晶达微电子科技有限公司

High rate, long block length, low density parity check encoder

InactiveUS8020063B2Error detection/correctionError correction/detection using multiple parity bitsHigh rateRight shift

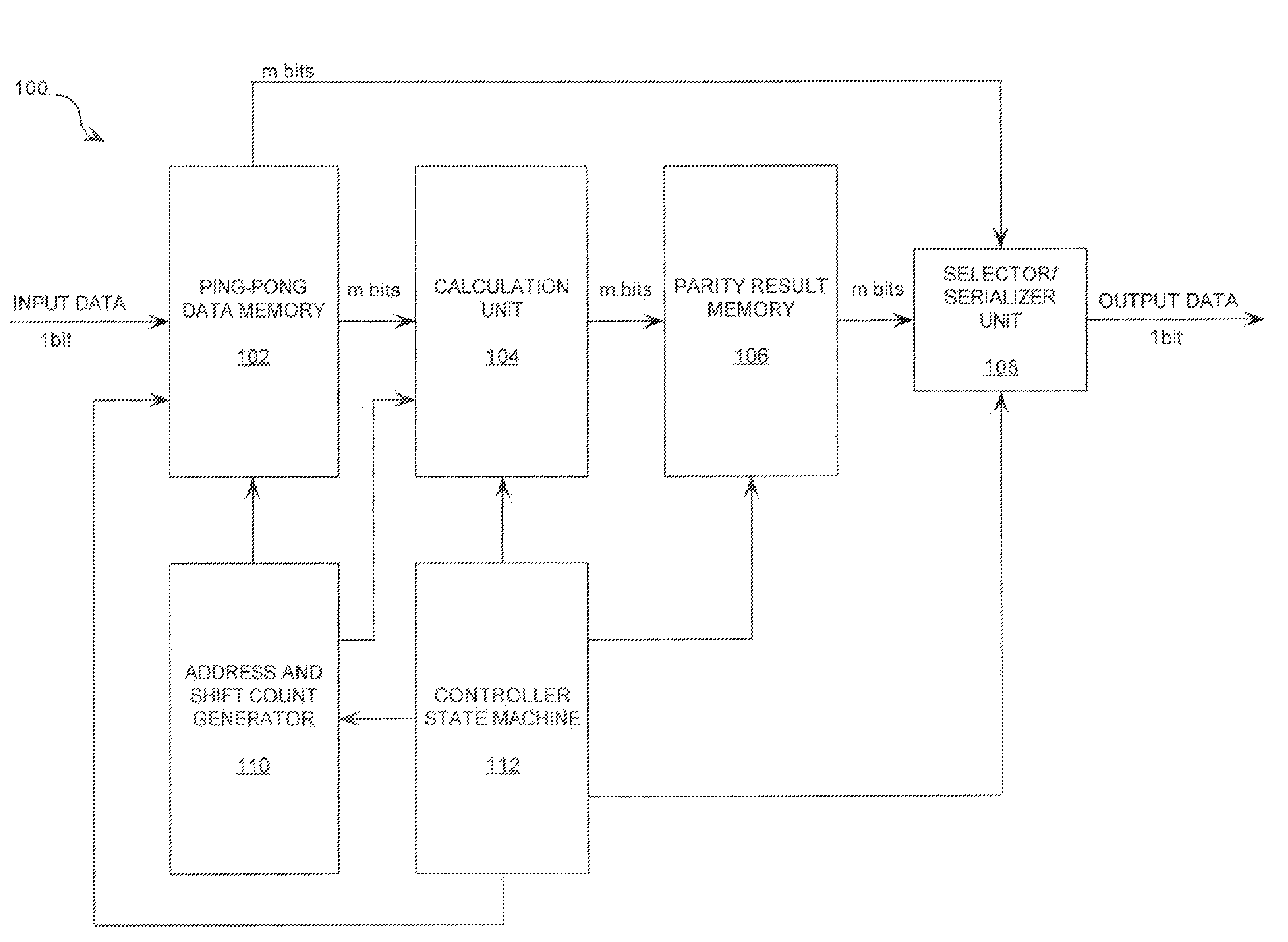

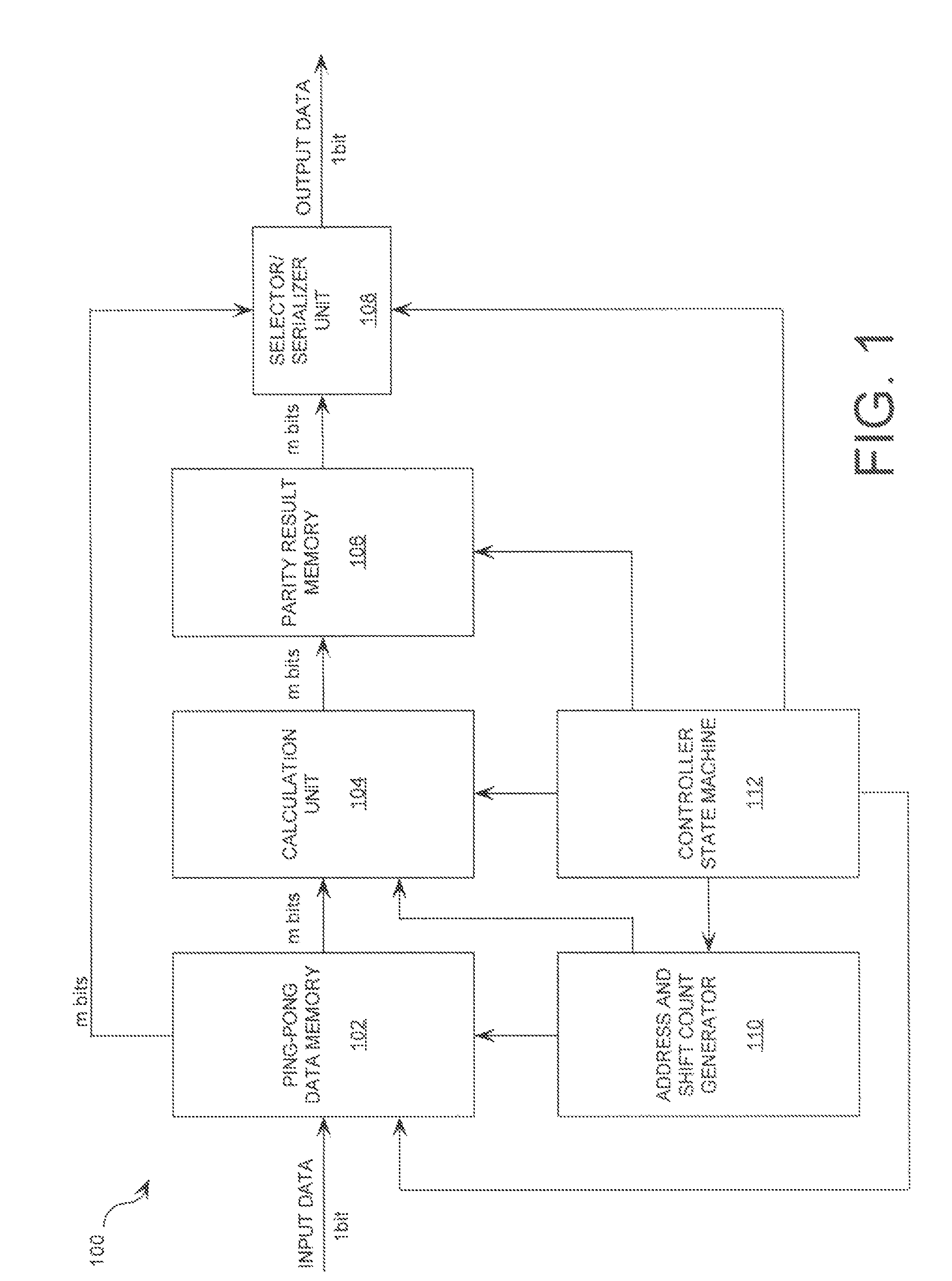

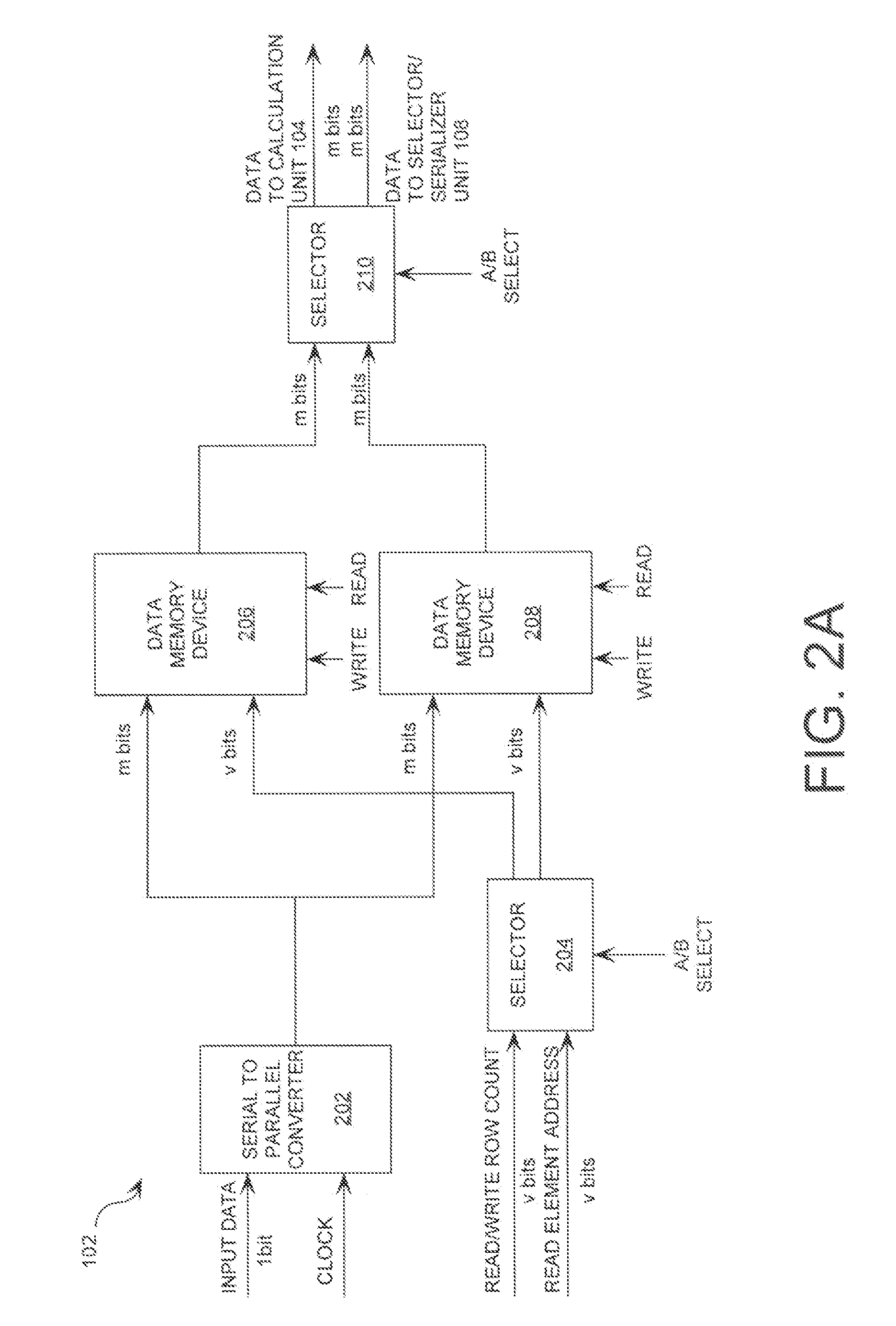

There is provided a parity check encoder (100) comprising a data memory (PPDM) configured for storing input data, a calculation / parity result data store (CPRDS), and a selector / serializer (SS). The CPRDS (104,106) is coupled to the PPDM (102) and is configured to calculate parity bits in parallel using input data and information contained in a parity check matrix H. The SS (108) is coupled to the PPDM and CPRDS. The SS is configured to generate an encoded output sequence using the input data and parity bits. The matrix H is formed of a plurality of sub-matrices. Each sub-matrix of the sub-matrices is an all zero (0) matrix, an identity matrix, or a circular right shifted version of the identity matrix. A portion B of the matrix H includes a plurality of rows having two (2) ones (1), except for a first row which includes a single one (1).

Owner:HARRIS CORP

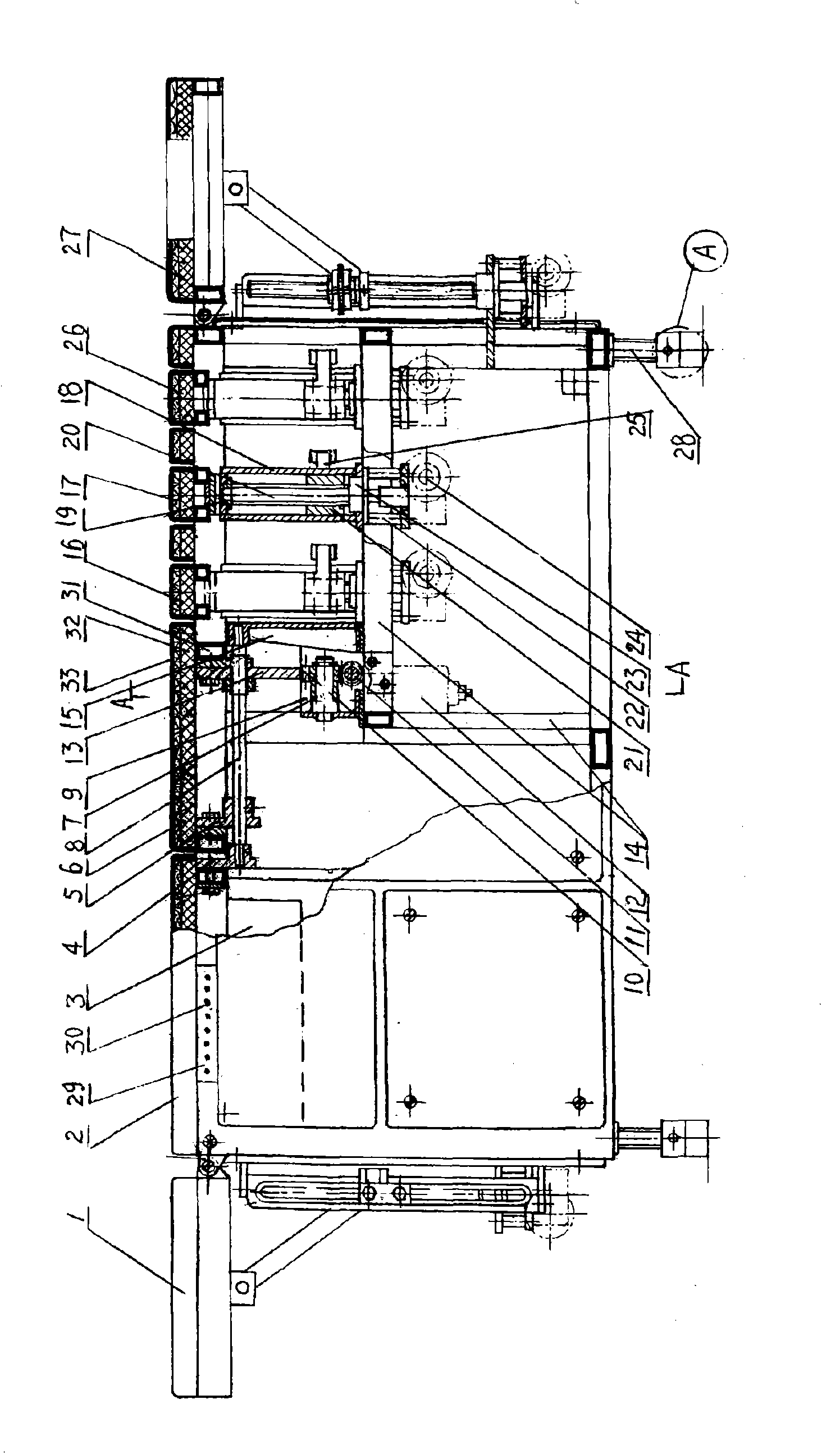

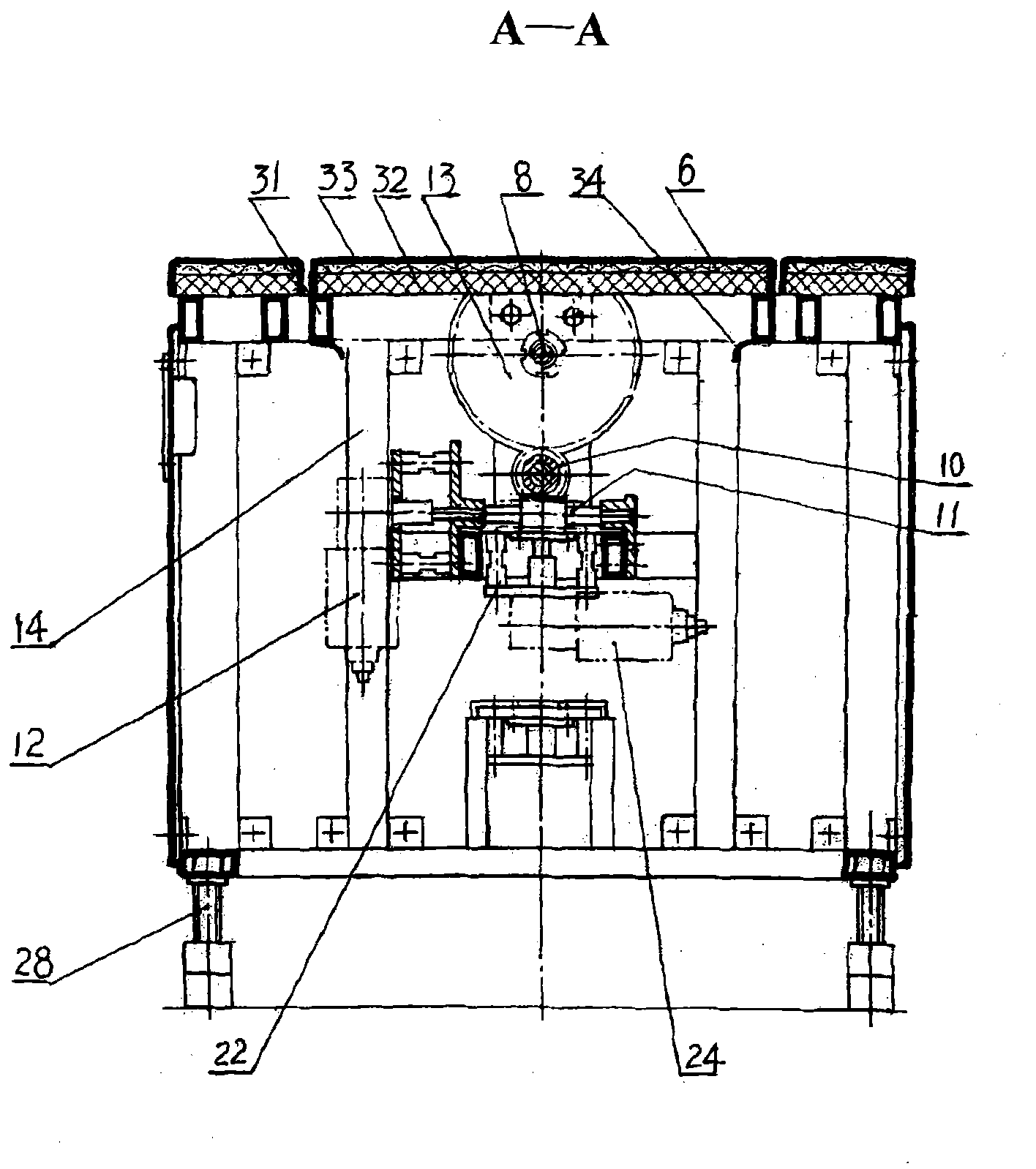

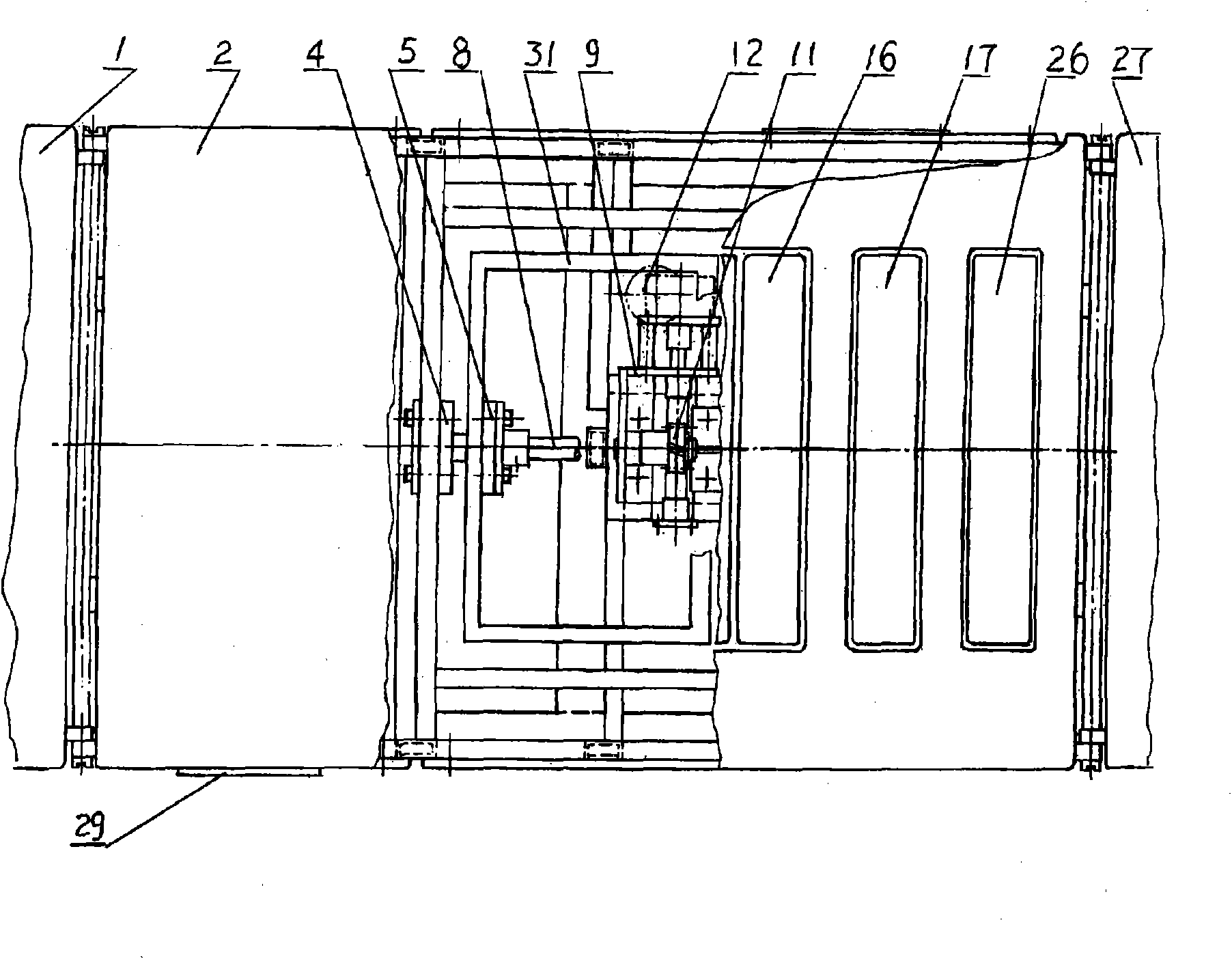

Pelvis-rotating electric spinal column massage correcting bed

InactiveCN101849867AReduce physical laborEffective corrective treatmentChiropractic devicesNon-surgical orthopedic devicesSpinal columnGear wheel

The invention relates to a pelvis-rotating electric spinal column massage correcting bed which is characterized in that after a middle-section bed body is provided with electric lifting mechanisms of a shoulders correcting plate, a back correcting plate and a waist correcting plate, an electric pelvis correcting plate left and right rotating mechanism comprising a motor base, a first direct-current gear motor, a worm, a support, a pinion, a pinion shaft, a gear wheel shaft, a gear wheel, a first shaft seat, a coupling band, a stroke limiting stopper and a stroke catch is additionally arranged; the worm, the pinion and the gear wheel are driven by the first direct-current gear motor to make left and right shift to drive a pelvis correcting plate to make left and right rotation, and thereby, the left and right correction of the pelvis is realized. The bed not only has reasonable design and compact structure, but also is simple and practical, uses safe voltages, not only can carry out massage correcting treatment on bent and deformed thoracic vertebras and lumbar vertebras, but also can carry out correcting treatment on rotating distorted pelvises and has the advantages of good massage correcting effect, low price, attractive appearance, very convenient use and the like and still can carry out treatment when powered off, and moreover, the manual labor is replaced with electric operation.

Owner:BEIJING ZHANG DEHONG SPINE BENDING DISEASE INST

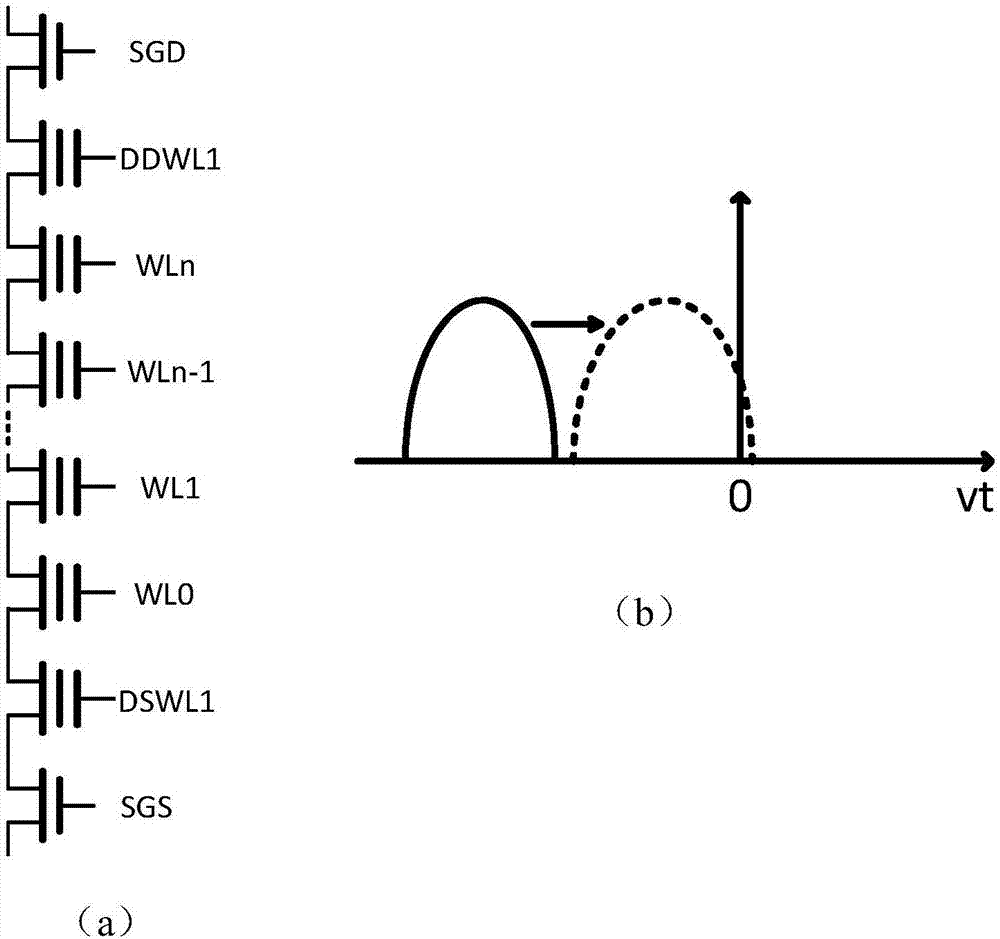

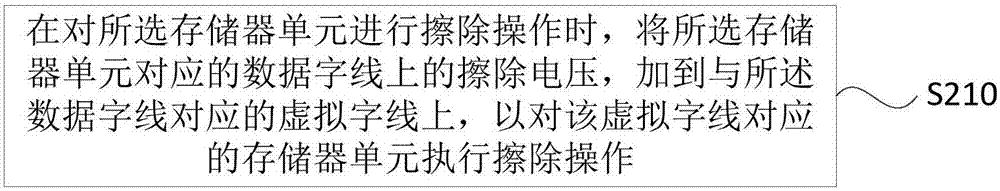

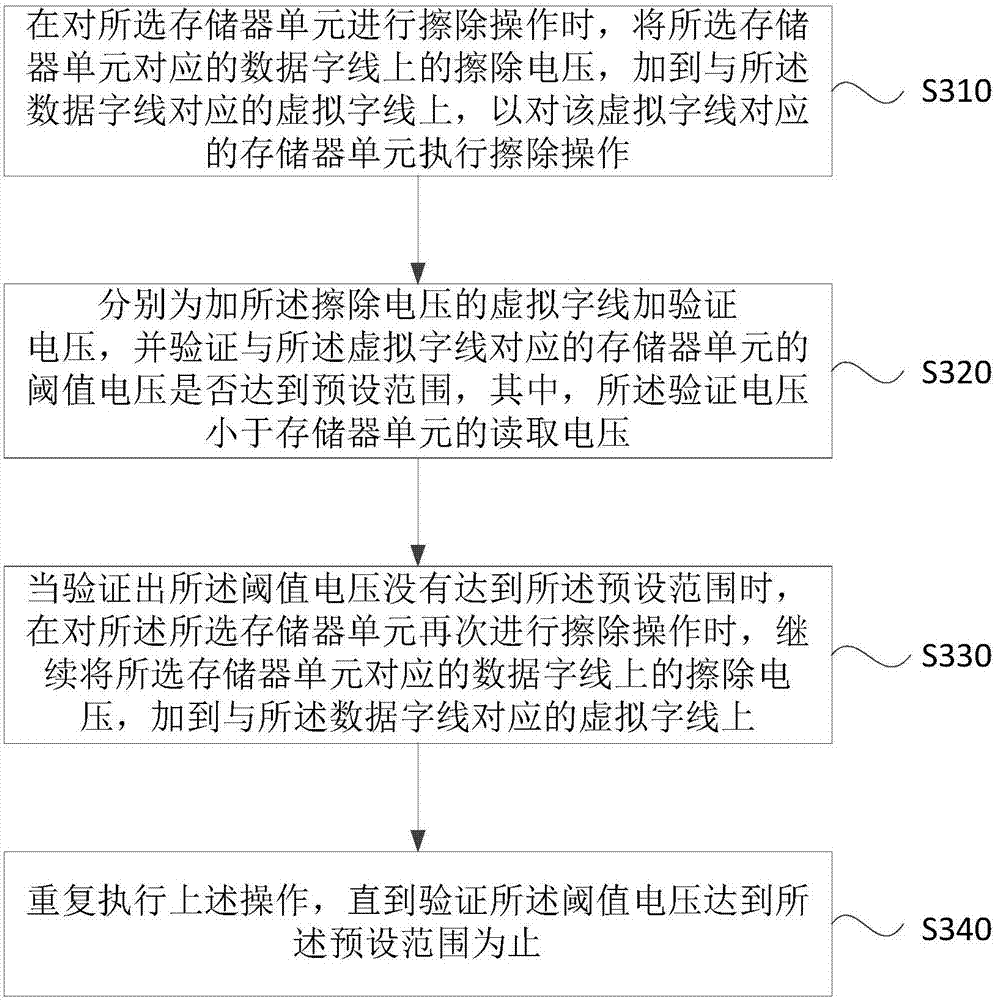

NAND flash-based threshold voltage check method and apparatus, and NAND storage device

InactiveCN106971760APrevent the impact of data read and write accuracyRead-only memoriesDigital storageRight shiftComputer science

Embodiments of the invention disclose an NAND flash-based threshold voltage check method and apparatus, and an NAND storage device. The method is applied to the NAND storage device. The storage device comprises a plurality of word lines and a plurality of NAND memory units; each word line is connected with the corresponding memory unit; the word lines include virtual word lines and data word lines; and each group of the data word lines corresponds to each group of the virtual word lines. The method comprises the steps of loading an erasure voltage on the data word line, corresponding to the selected memory unit, to the virtual word line corresponding to the data word line when the selected storage unit is subjected to erasure operation, thereby executing the erasure operation on the memory unit corresponding to the virtual word line. According to the method and the apparatus, the influence on data reading / writing accuracy of the memory unit corresponding to the data word line due to right shift of a threshold voltage of the memory unit corresponding to the virtual word line can be prevented; and the threshold voltage of the memory unit corresponding to the virtual word line is adjusted to be in a normal range.

Owner:GIGADEVICE SEMICON (BEIJING) INC

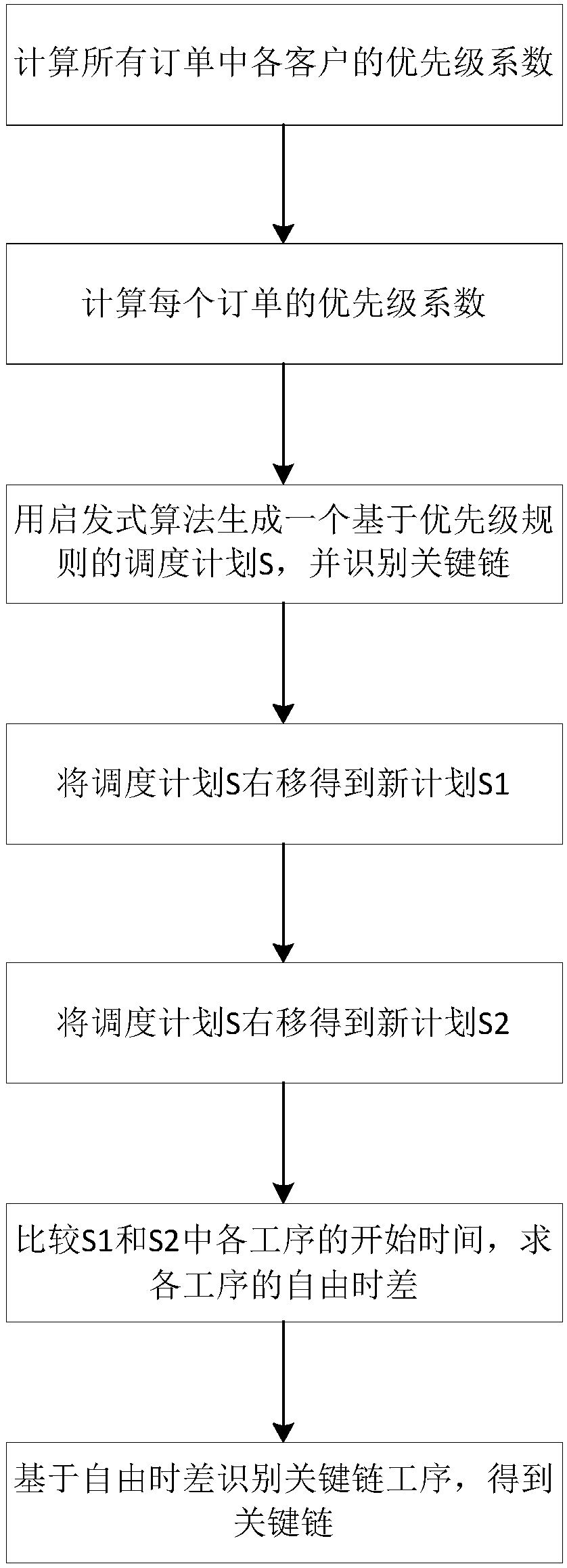

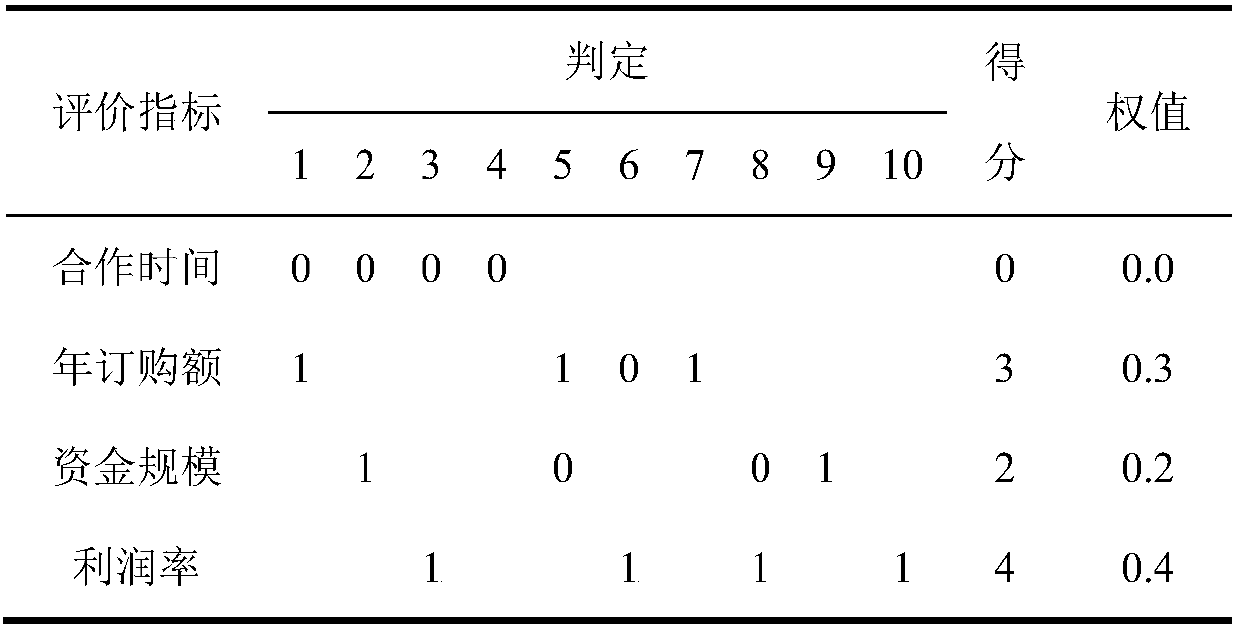

Critical chain buffer area arrangement method based on production uncertainty

ActiveCN107944695AImprove accuracyIn line with the actual production situationResourcesManufacturing computing systemsStart timeRight shift

The invention discloses a critical chain buffer area arrangement method based on production uncertainty. Firstly the priority coefficient of the customer and the priority coefficient of the order areacquired, then a dispatching plan based on the priority rules is generated by using a heuristic algorithm, then left and right shift operation is performed on the obtained dispatching plan to obtain two new dispatching plans, the start time of all the processes is compared and the free time difference of each process is acquired, the process of which the free time difference is zero is the critical chain process and the critical chain is obtained, and then the input, the items and the buffer area size of the resource buffer area are set based on the free time difference and the improved root square difference method. The root square difference method is improved through combination of the resource utilization degree and the variability measurement, and the calculation result of the root square difference method is corrected through accurate measurement of the processing time variability of the process by aiming at the influence problem of a lot of uncertain factors on buffer area calculation under the complex production environment so that the accuracy of buffer area calculation can be effectively enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA