Patents

Literature

133 results about "Leading zero" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A leading zero is any 0 digit that comes before the first nonzero digit in a number string in positional notation. For example, James Bond's famous identifier, 007, has two leading zeros. When leading zeros occupy the most significant digits of an integer, they could be left blank or omitted for the same numeric value. Therefore, the usual decimal notation of integers does not use leading zeros except for the zero itself, which would be denoted as an empty string otherwise. However, in decimal fractions strictly between −1 and 1, the leading zeros digits between the decimal point and the first nonzero digit are necessary for conveying the magnitude of a number and cannot be omitted, while trailing zeros – zeros occurring after the decimal point and after the last nonzero digit – can be omitted without changing the meaning.

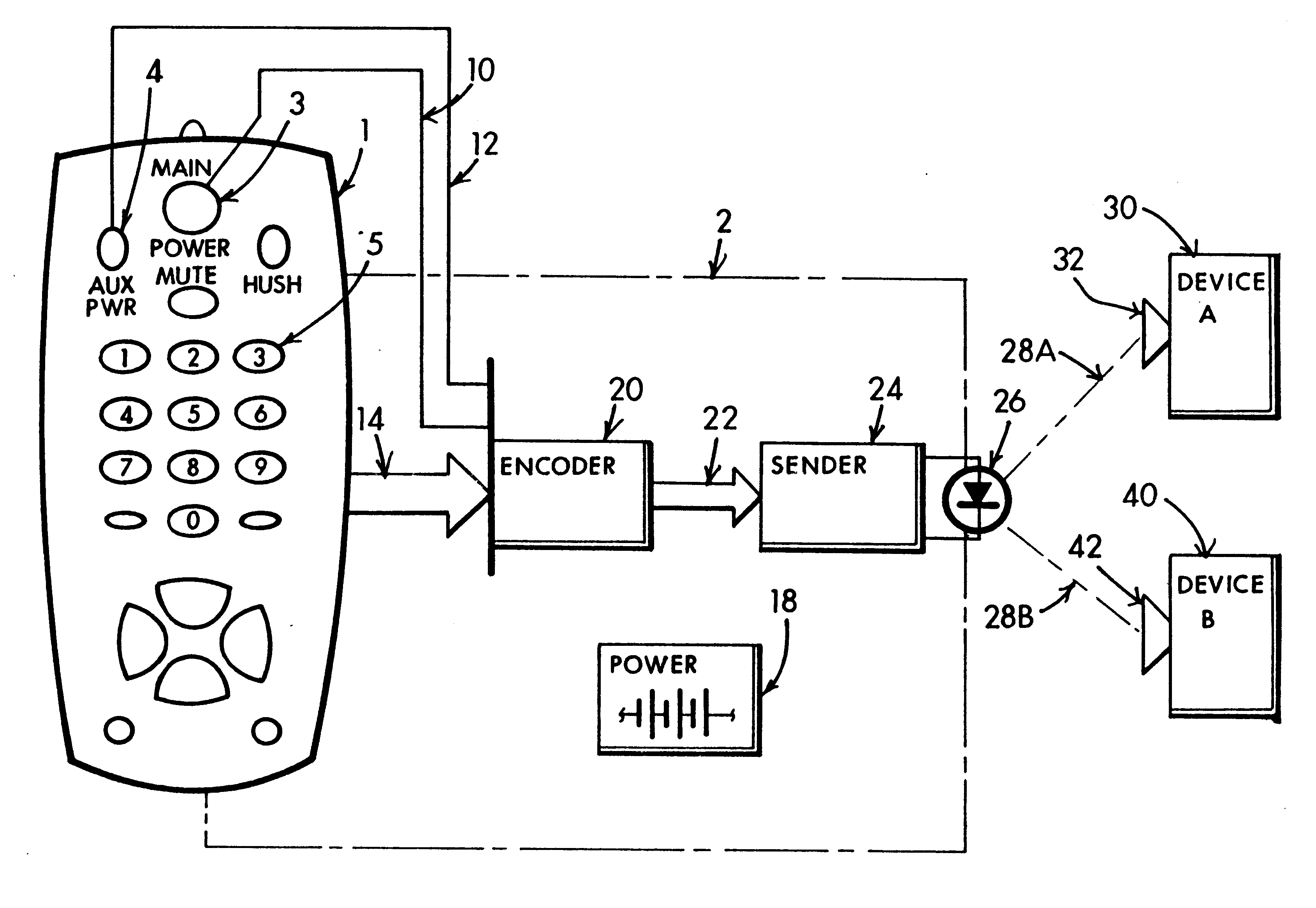

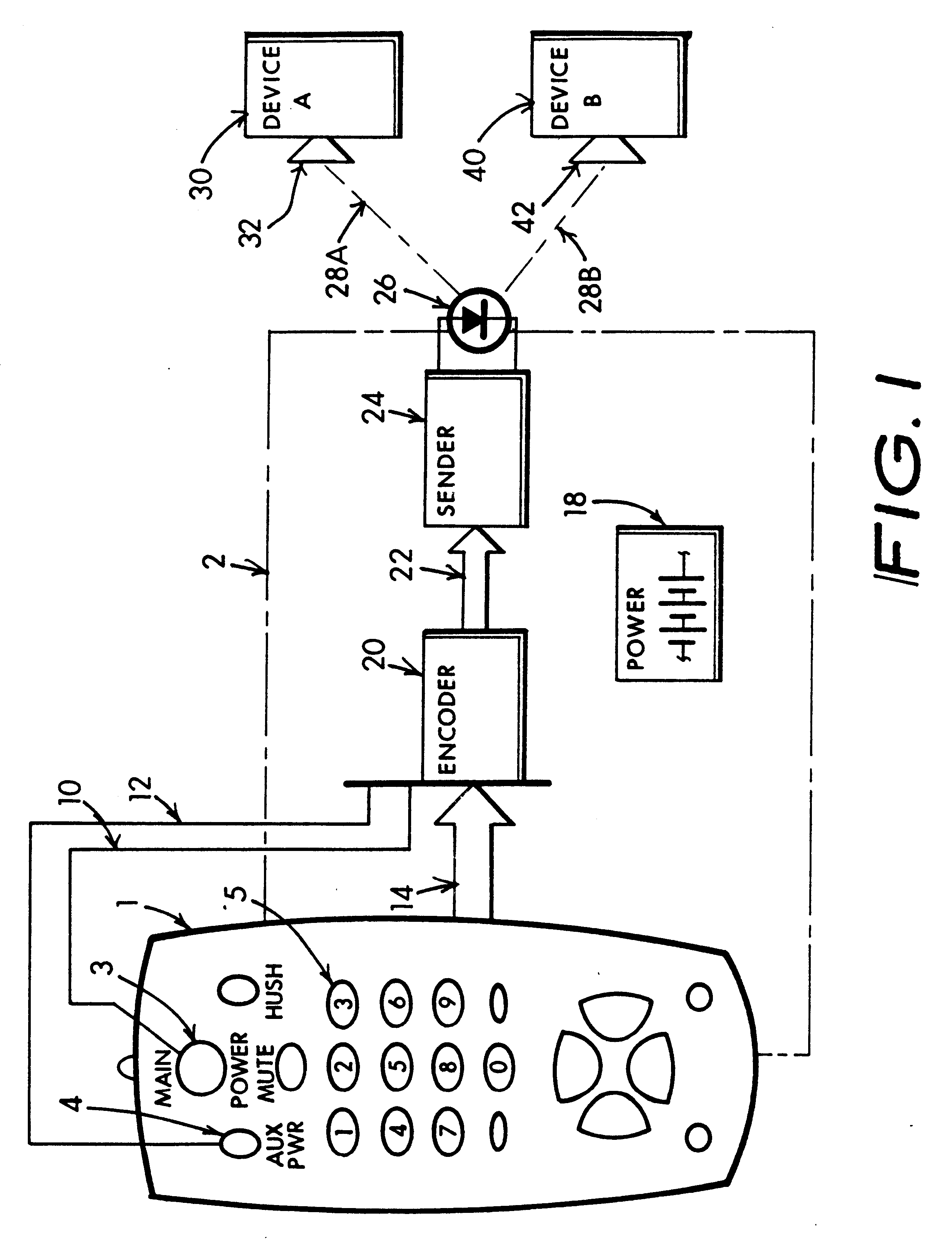

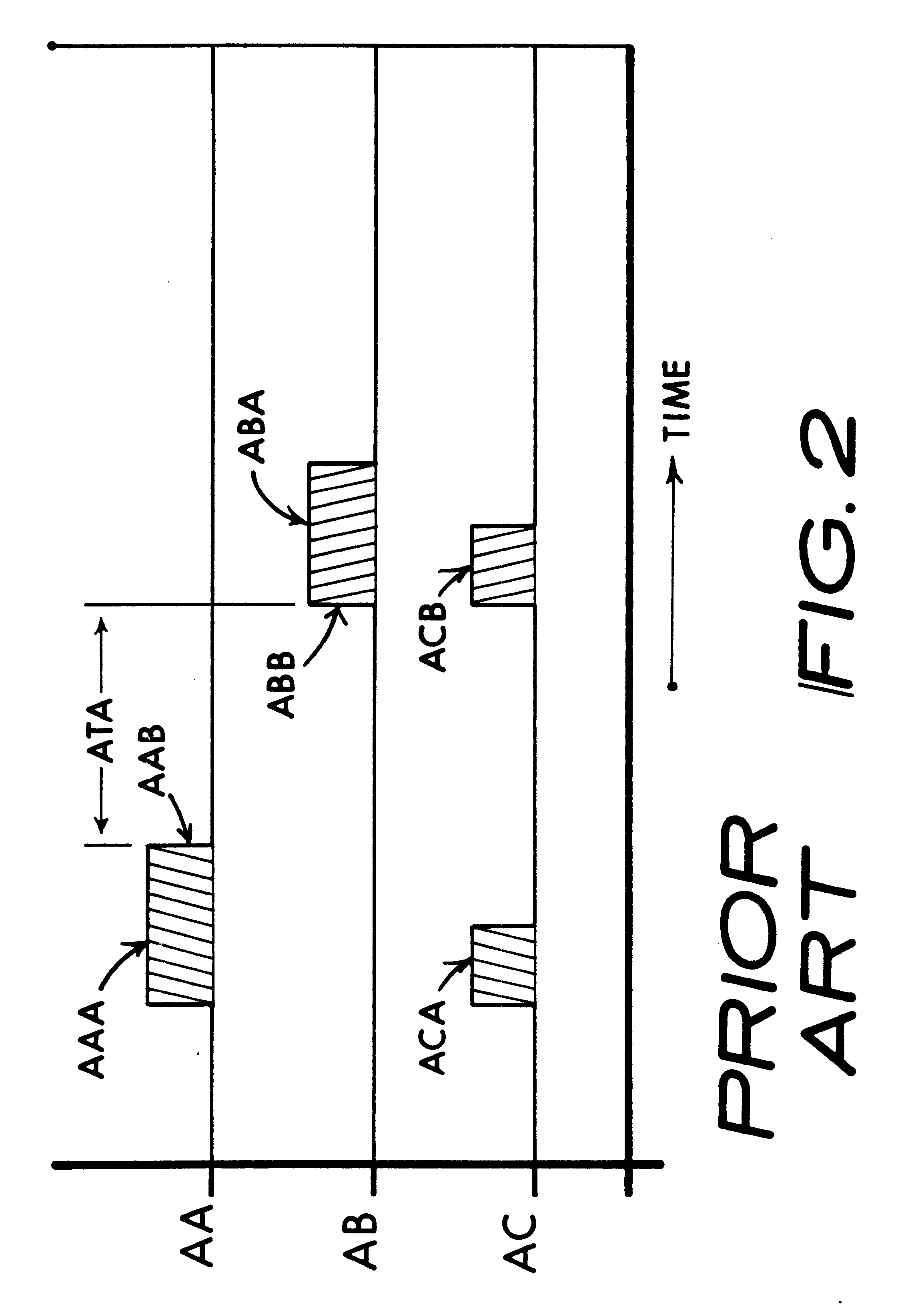

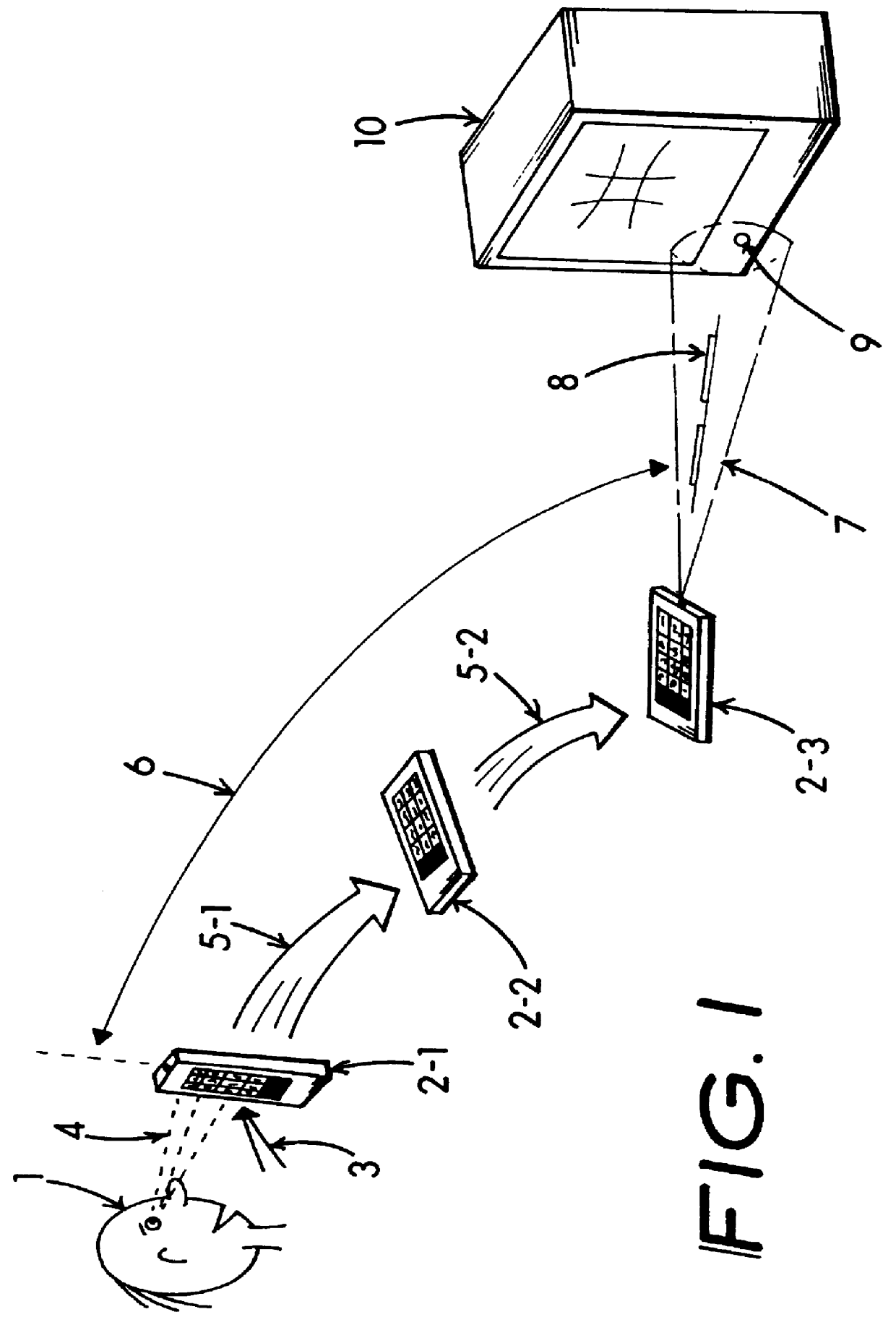

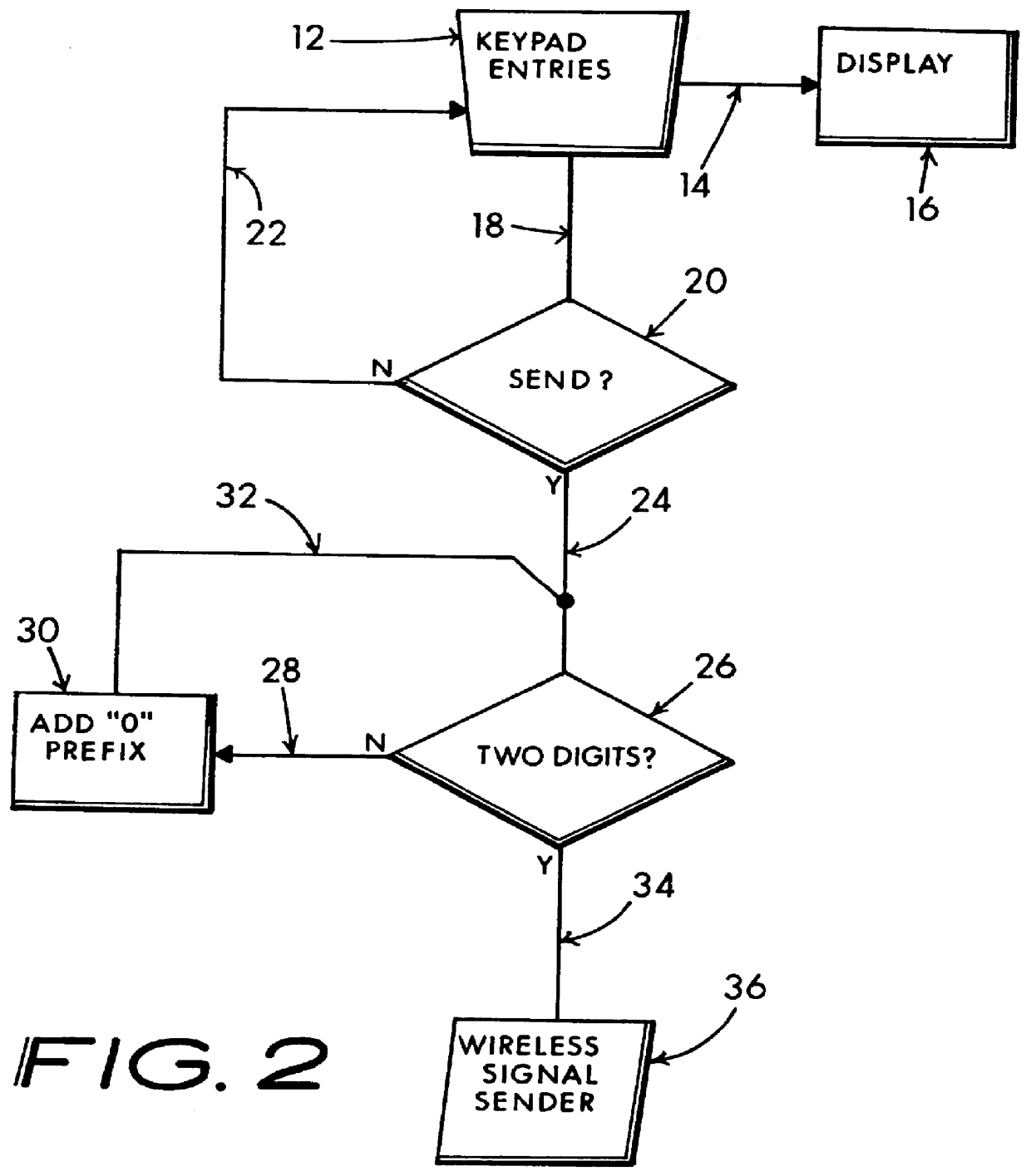

Remote controller for a multi-device television receiving system providing channel number auto-completion, presettable audio hush level and base channel auto-reaffirm

InactiveUS6396549B1Quiet noiseLower requirementTelevision system detailsElectric signal transmission systemsLeading zeroCable television

A handheld remote controller for a televisor that automatically prefixes a single-digit program channel selection, typically between 2 and 9, with a leading zero in response to a prolonged single digit keybutton actuation exceeding about 3 seconds or by an intended ersatz key entry, such as a star "*" key, either preceding or following the channel digit key entry. A HUSH control provides audio volume reduction intermediate between mute and normal volume levels, obtainable by pressing a HUSH keybutton, or automatically hushed concurrent with a program channel change. Maintaining a televisor's necessitous channel 3 or 4 selection when used in conjunction with a cable box, VCR or other intermediate device is assured by concurrently sending a reiterative channel 3 (or channel 4) tuning command to the televisor whenever a program channel change command or other function signal is dispatched to the cable box, VCR or other television signal tuning apparatus.

Owner:HANGER SOLUTIONS LLC

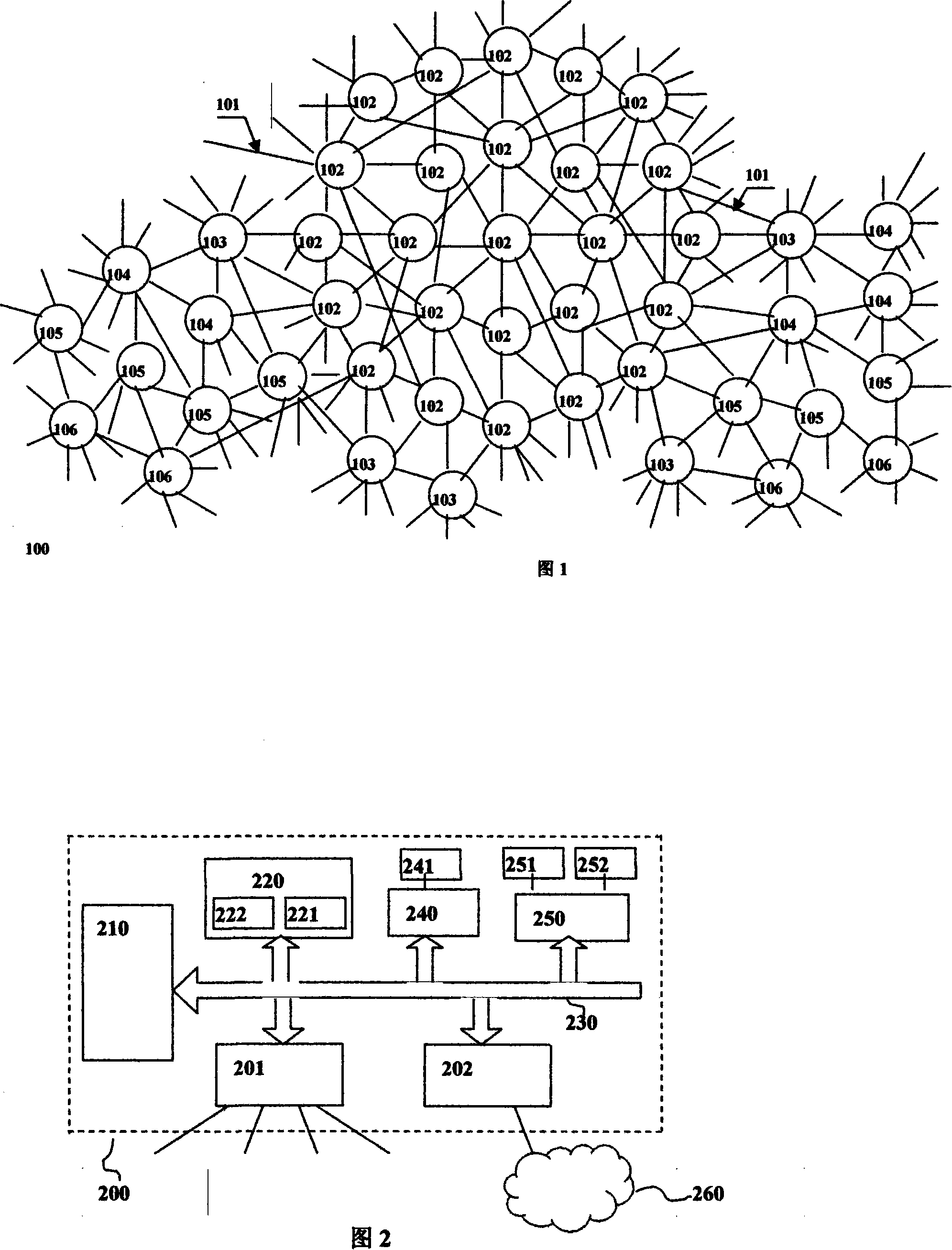

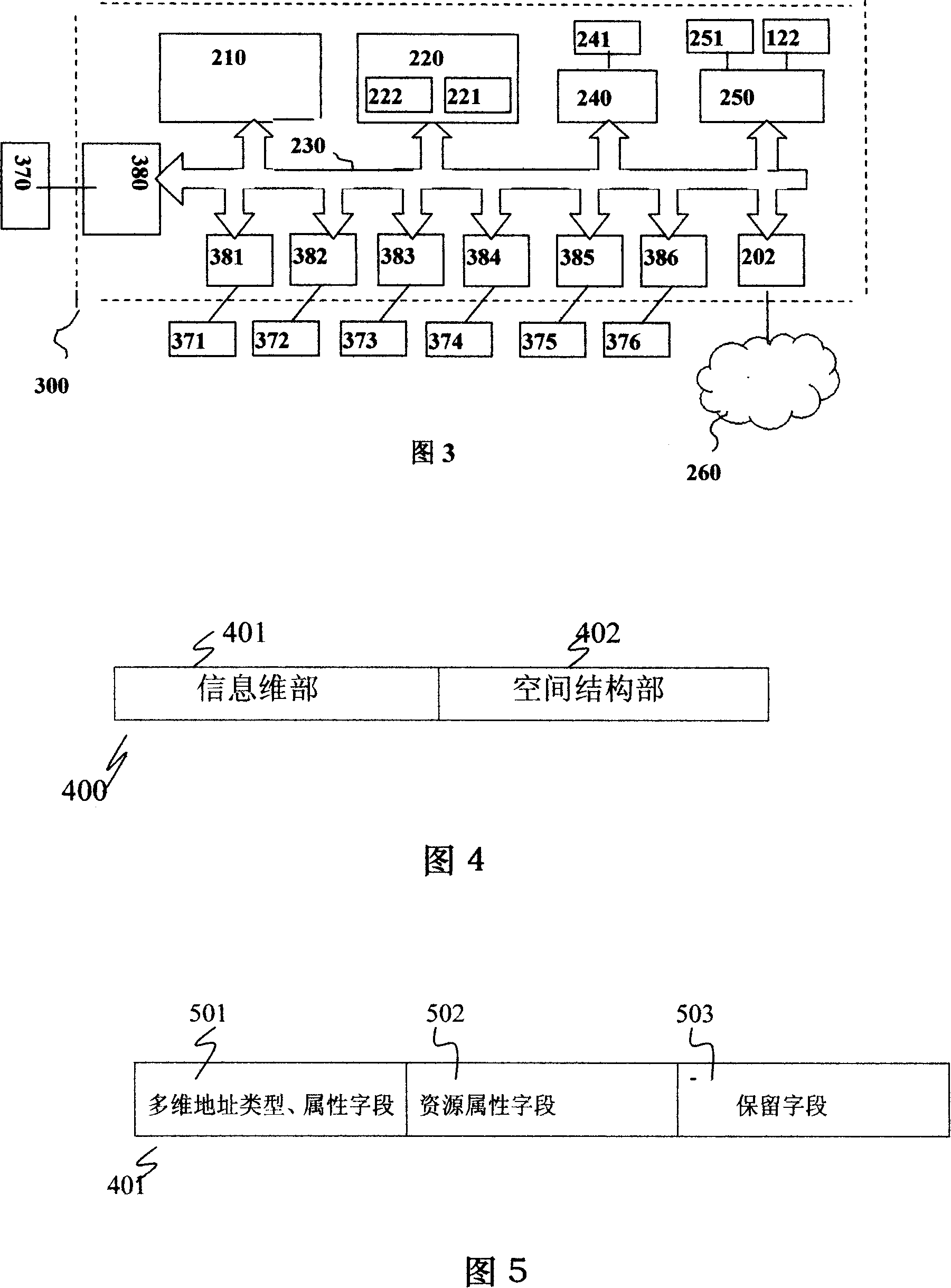

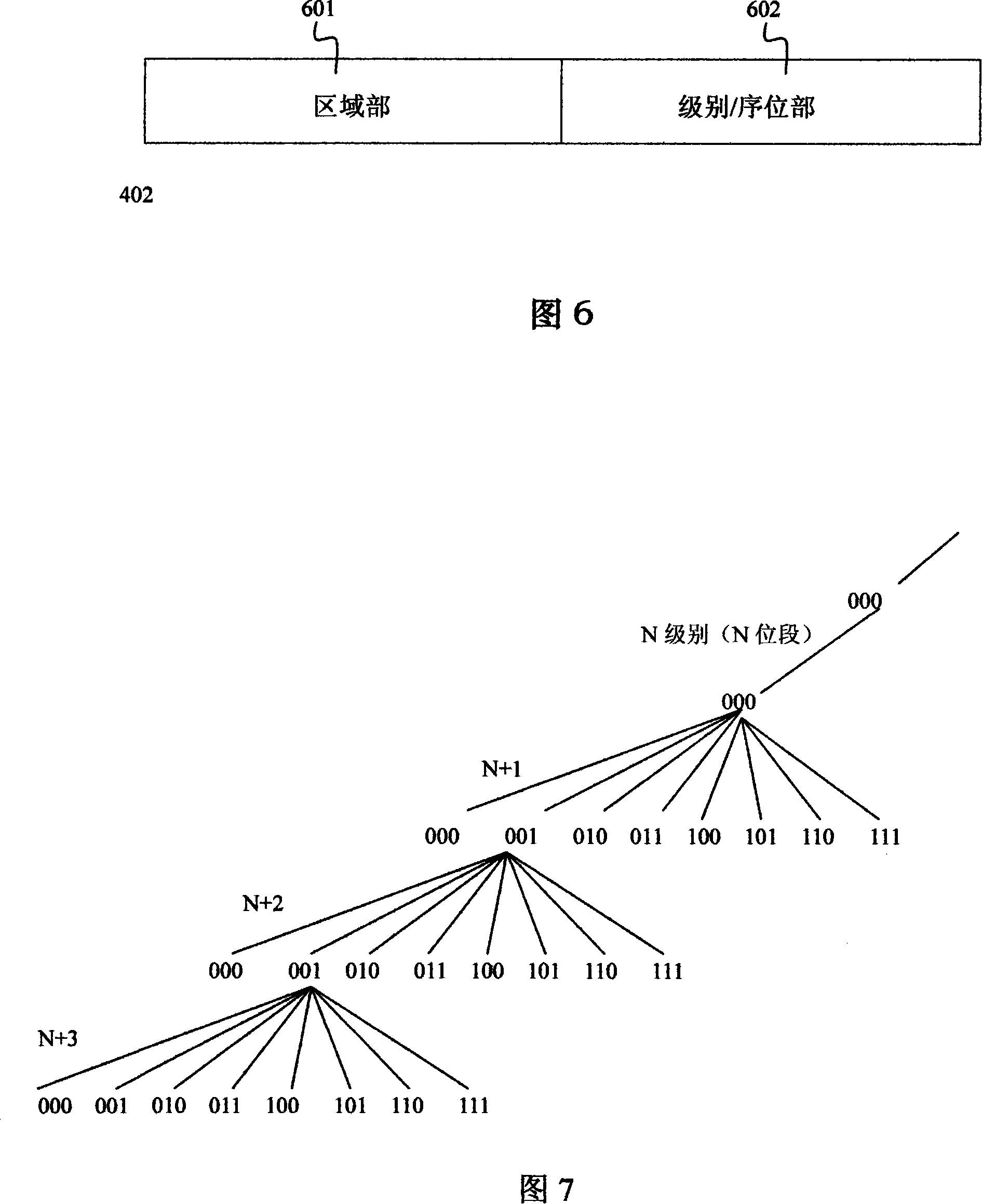

A coding method and device and system for multi-dimension address

ActiveCN101123613AReduce transfer volumeFunction increaseTransmissionSpecial data processing applicationsBit fieldSpatial structure

The invention discloses a method, a device and a system for addressing a multi-dimensional address. The invention comprises that through establishing a standard of format, grammar and type of the multi-dimensional address data, an effective multi-dimensional address format, which is generated by a first resource, can be output, input, processed and stored by the first and the second resources. The invention also comprises that the multi-dimensional address is defined by a binary digit series identifier, and the length of the binary digit series identifier is an arbitrary digit number from 1 bit to 1536 bit. An information dimension part is included in the multi-dimensional address through the bit segment division; the invention comprises that the object and attribute data is constructed through the bit, the bit segment and the data in the information dimension part; a virtual space structural part is also included in the multi-dimensional address; the invention comprises that the space structure and relation data of the object and attribute data is constructed through the bit, and the bit segment and the data in the virtual space structural part. The invention also comprises that each bit segment is seperated by a symbol; each bit segment carries out an automatic conversion of carry counting system; a leading zero of each bit segment is compressed; and the zero of an all -zerocontinuous bit segment in the multi-dimensional address carries out zero compression.

Owner:张建中

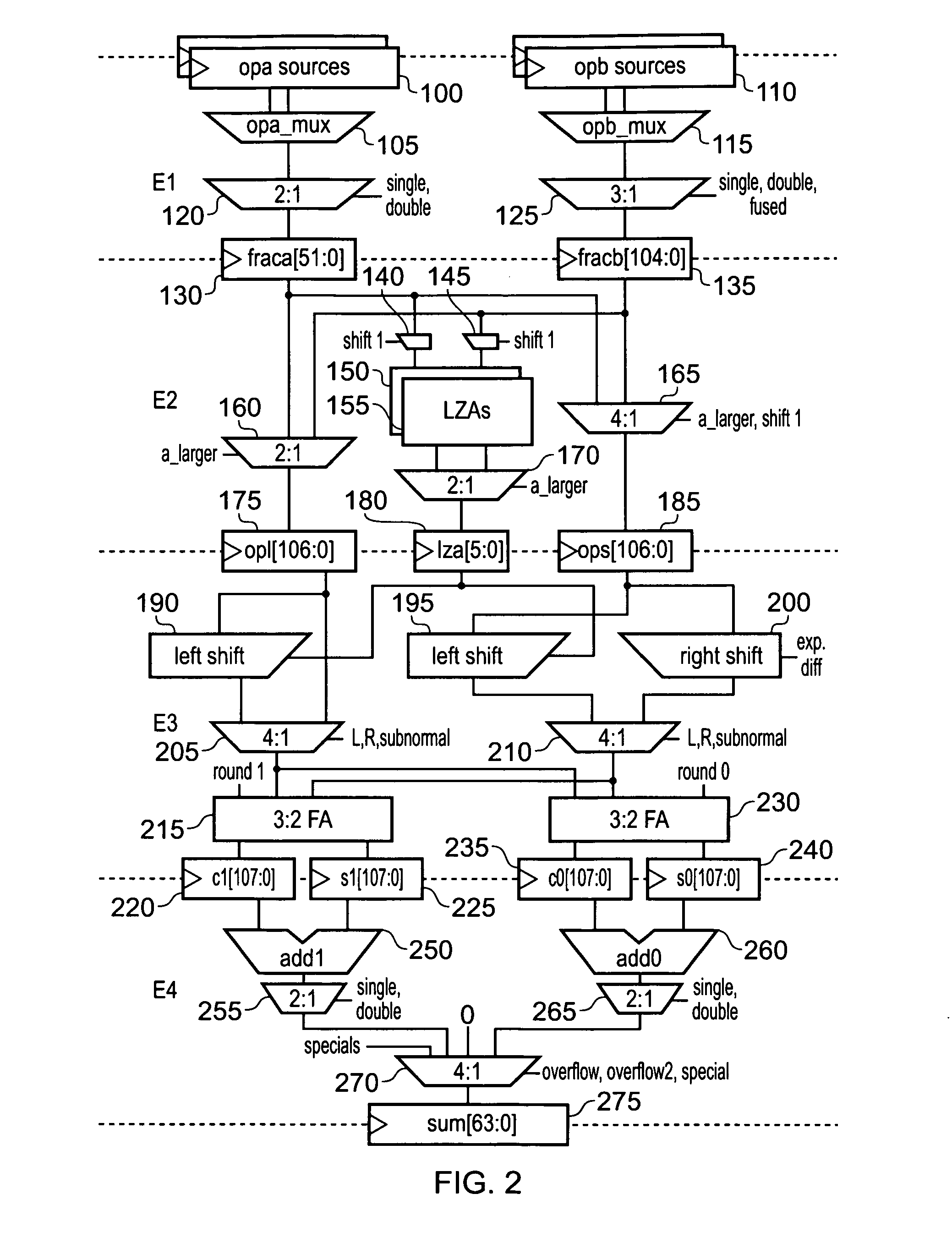

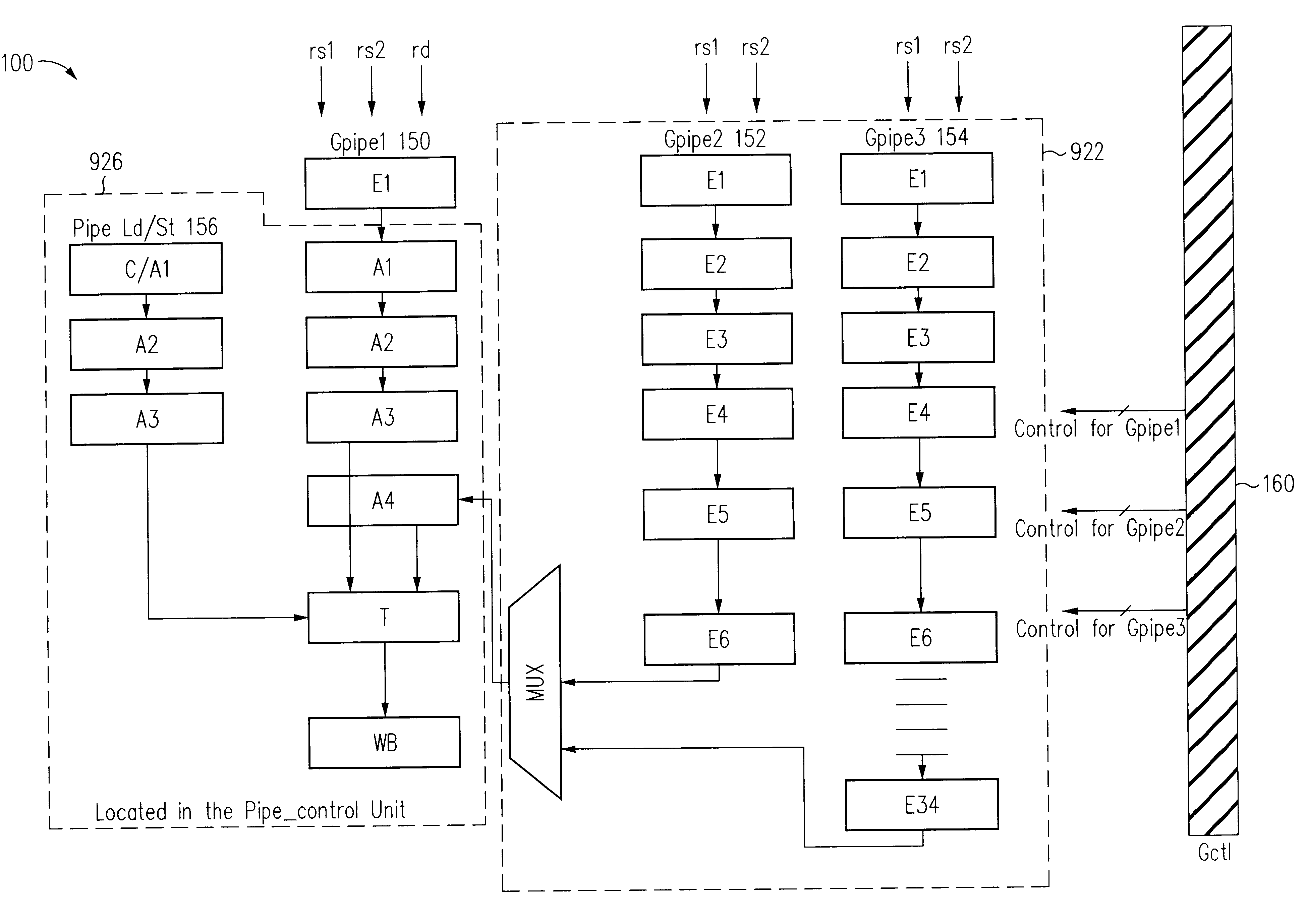

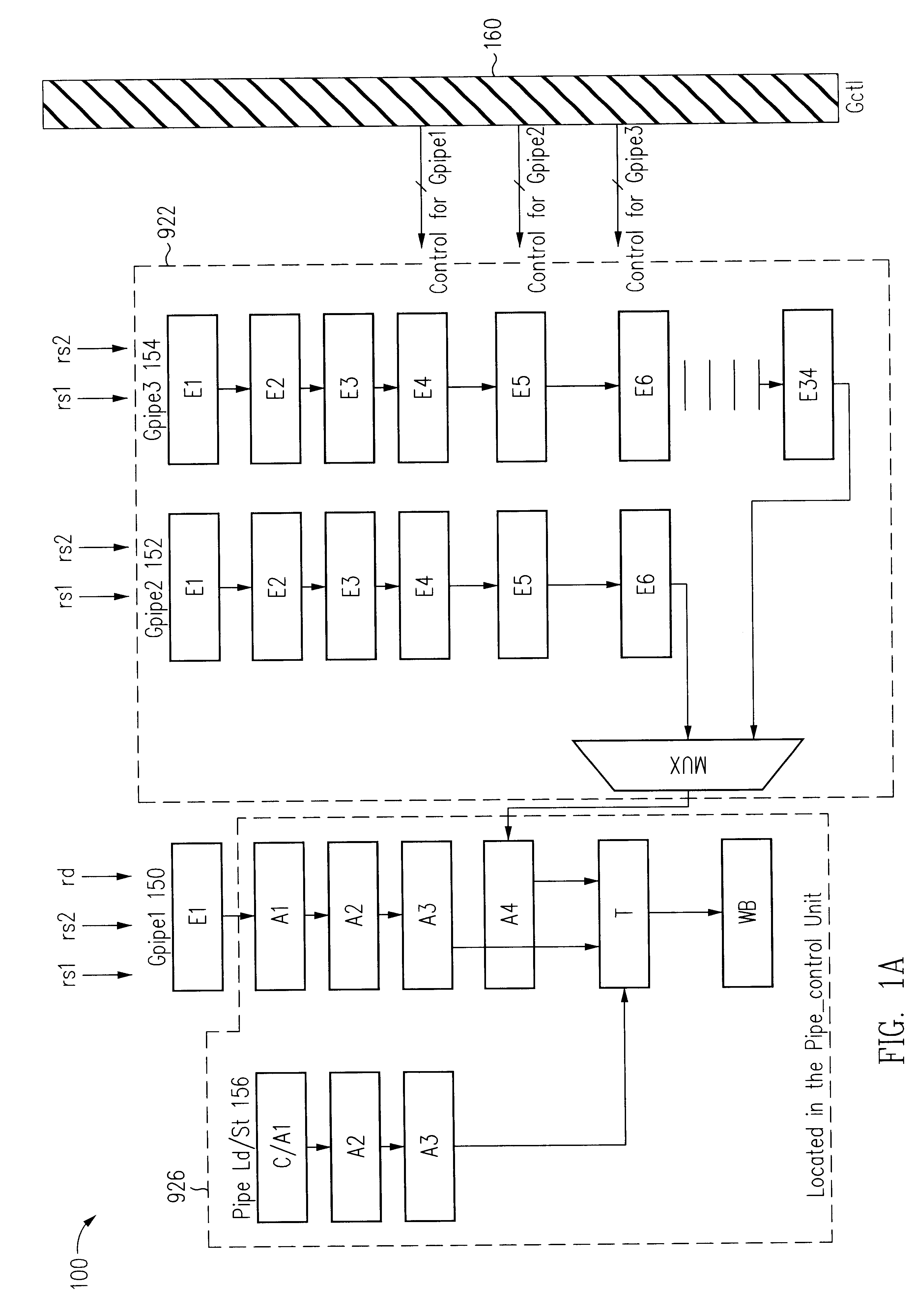

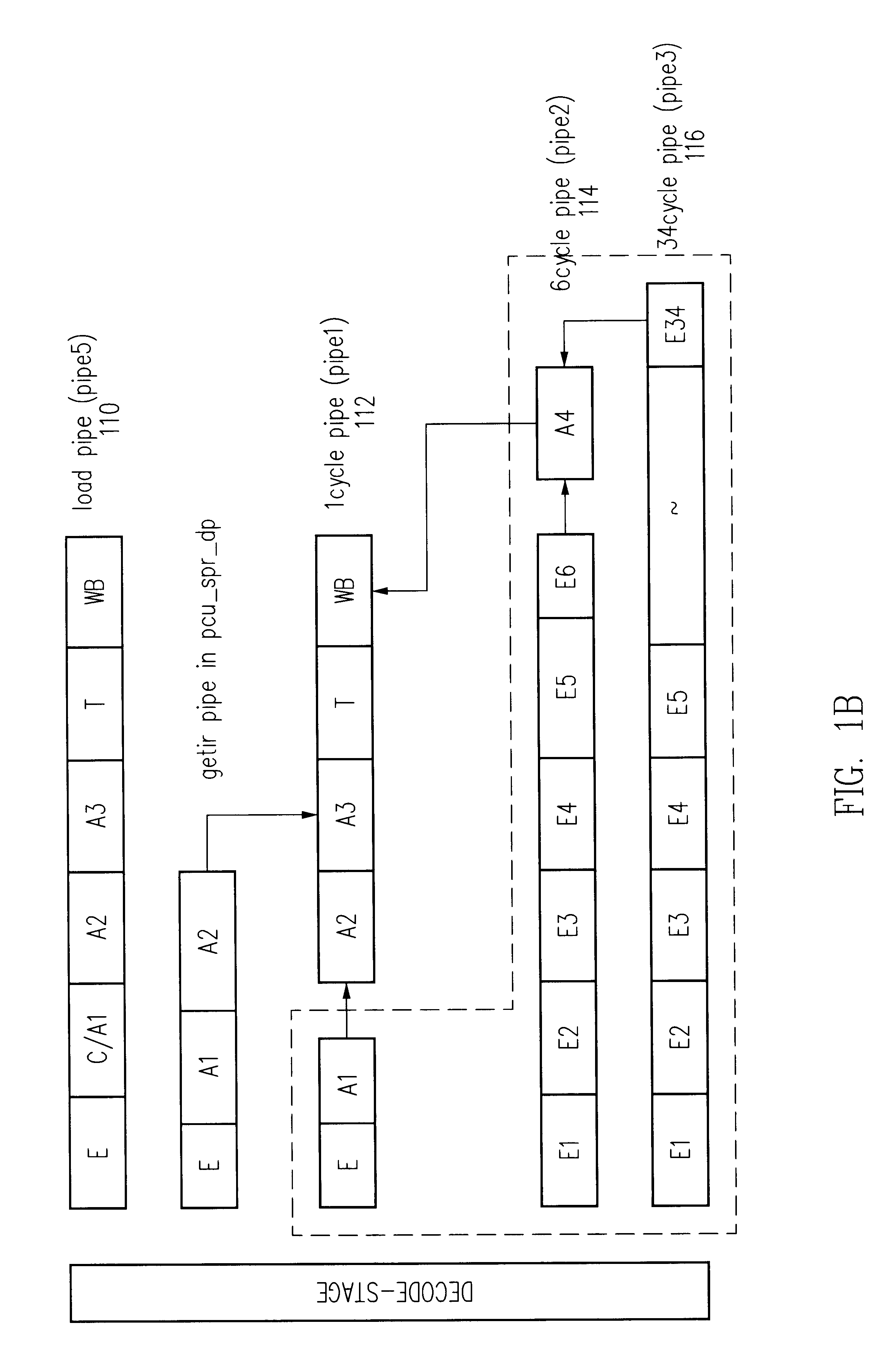

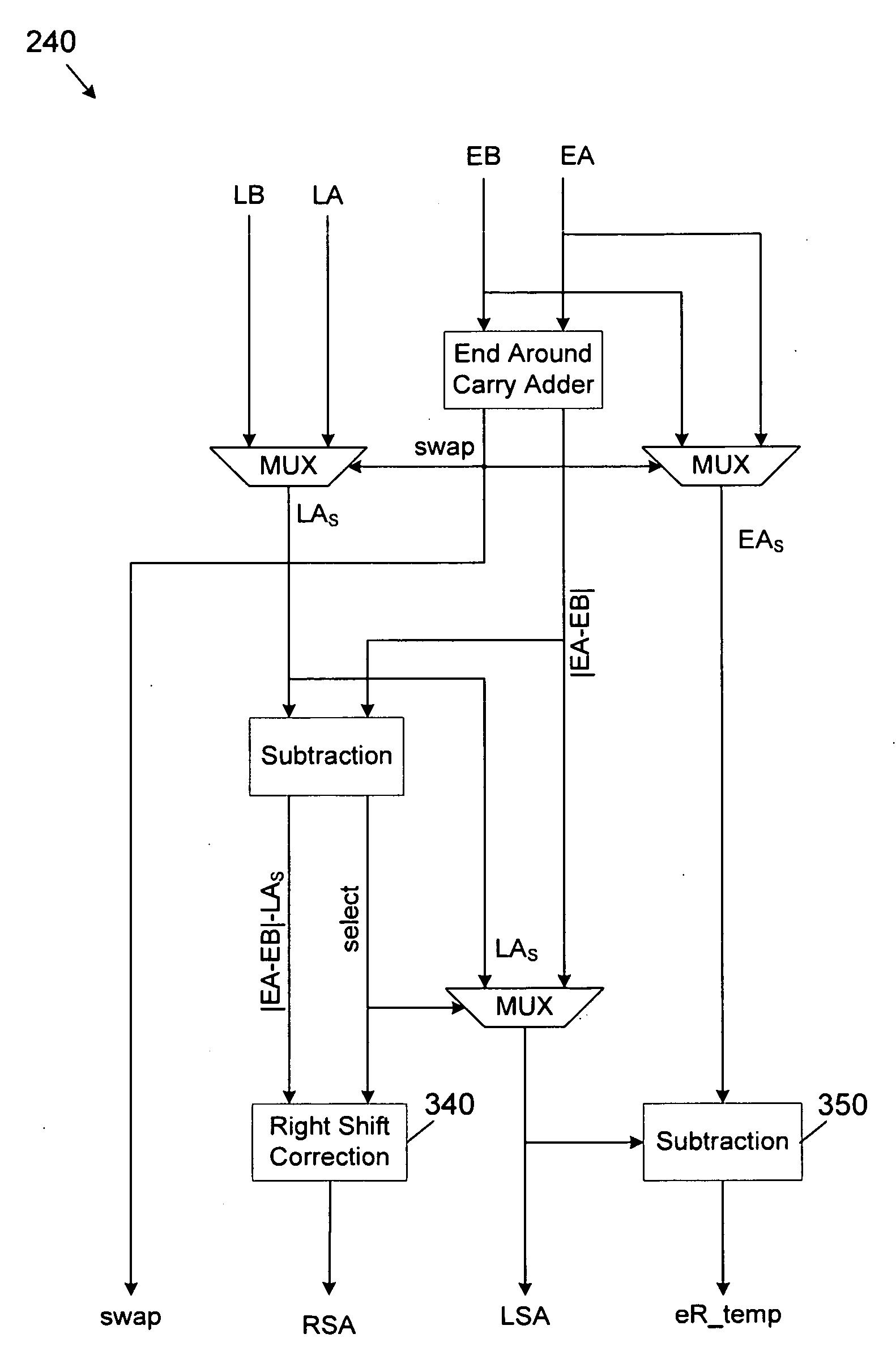

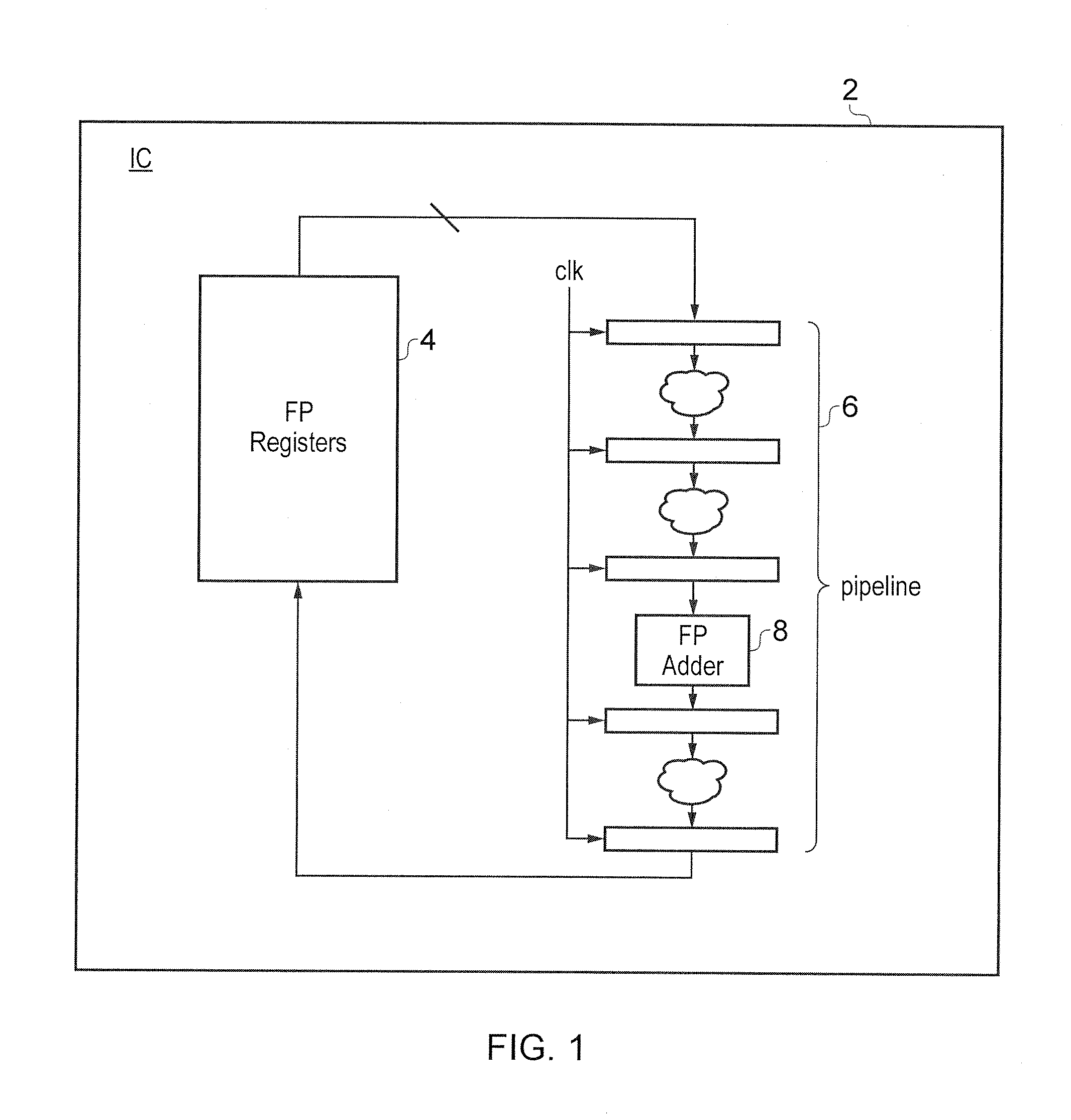

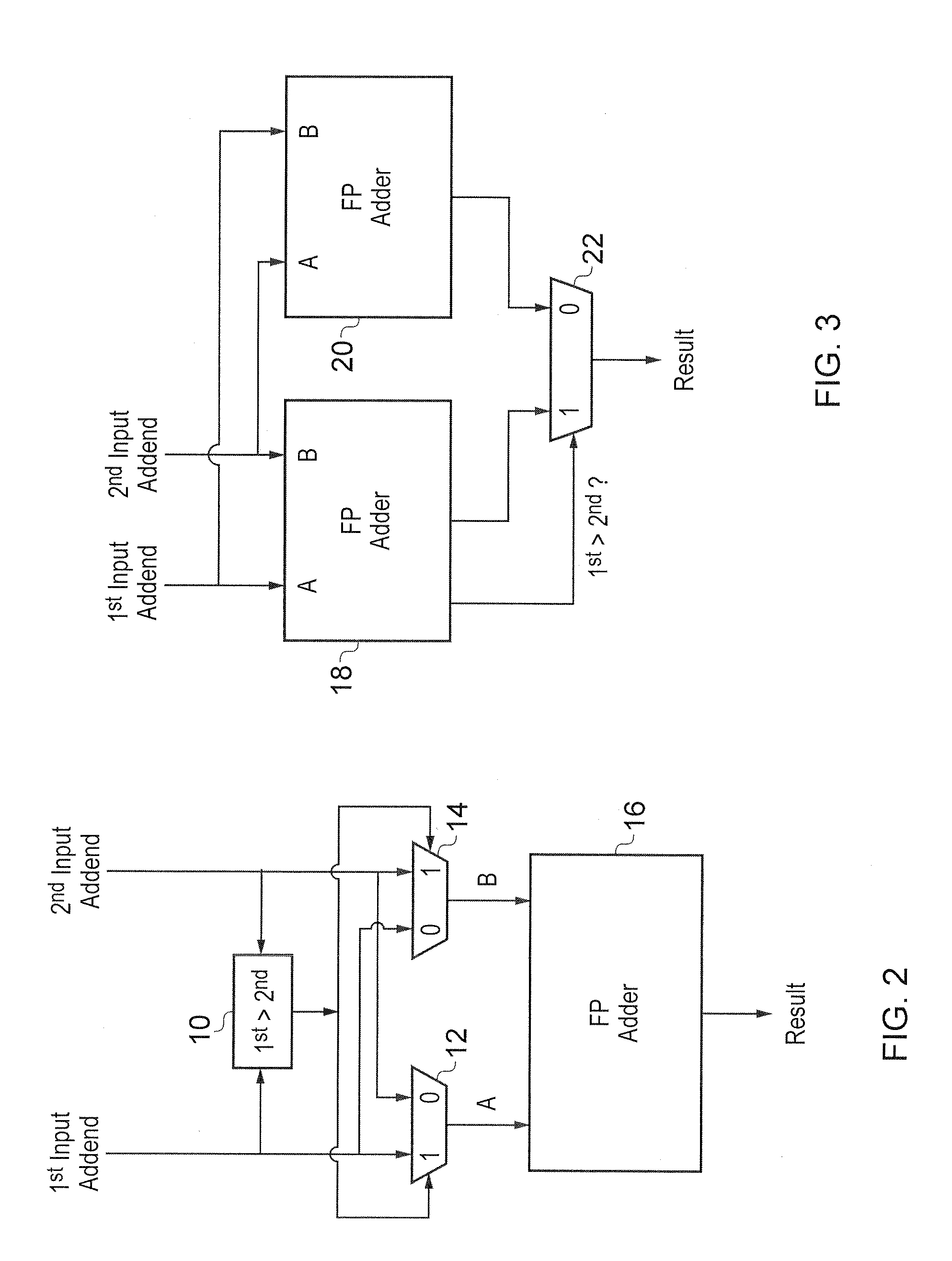

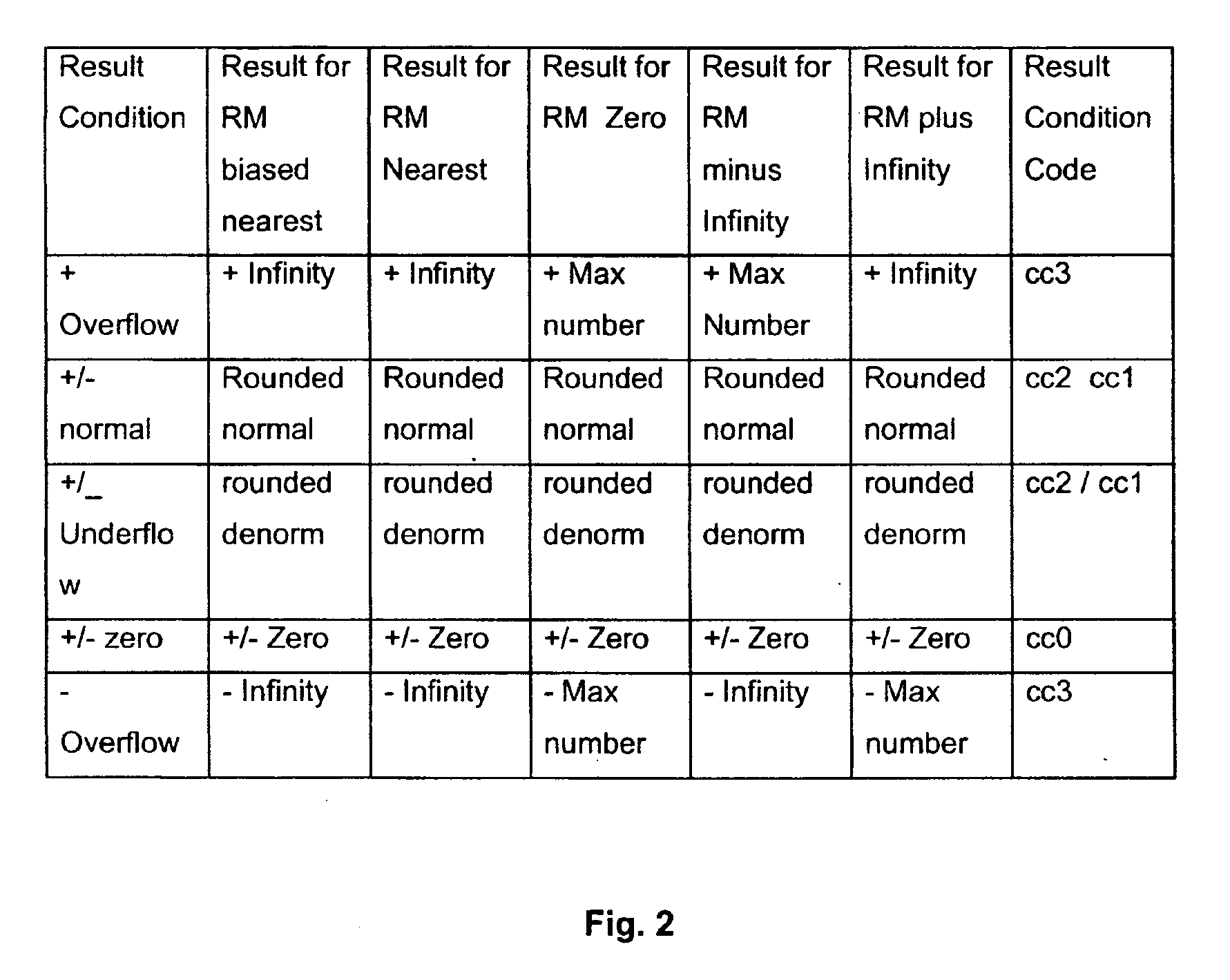

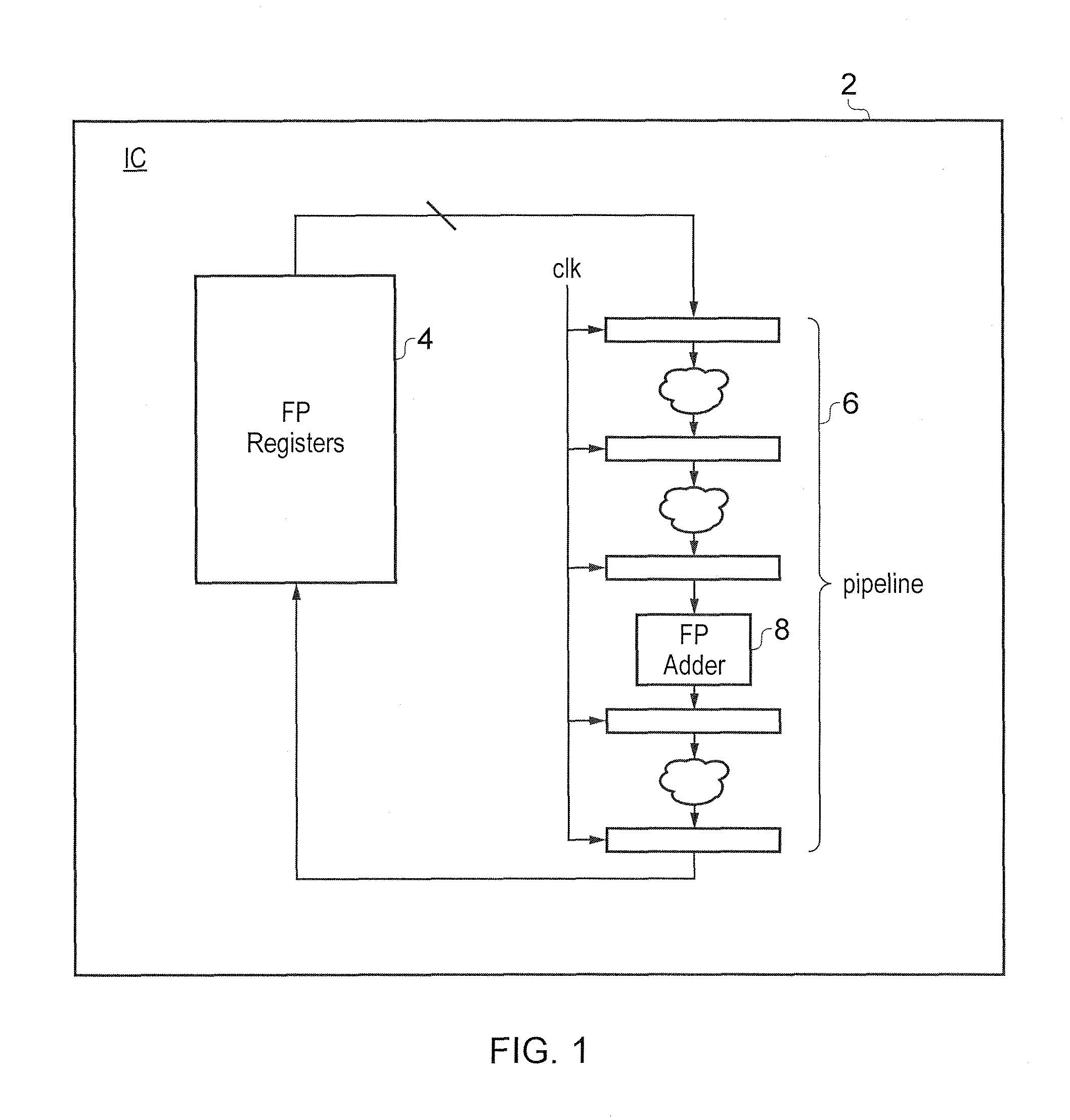

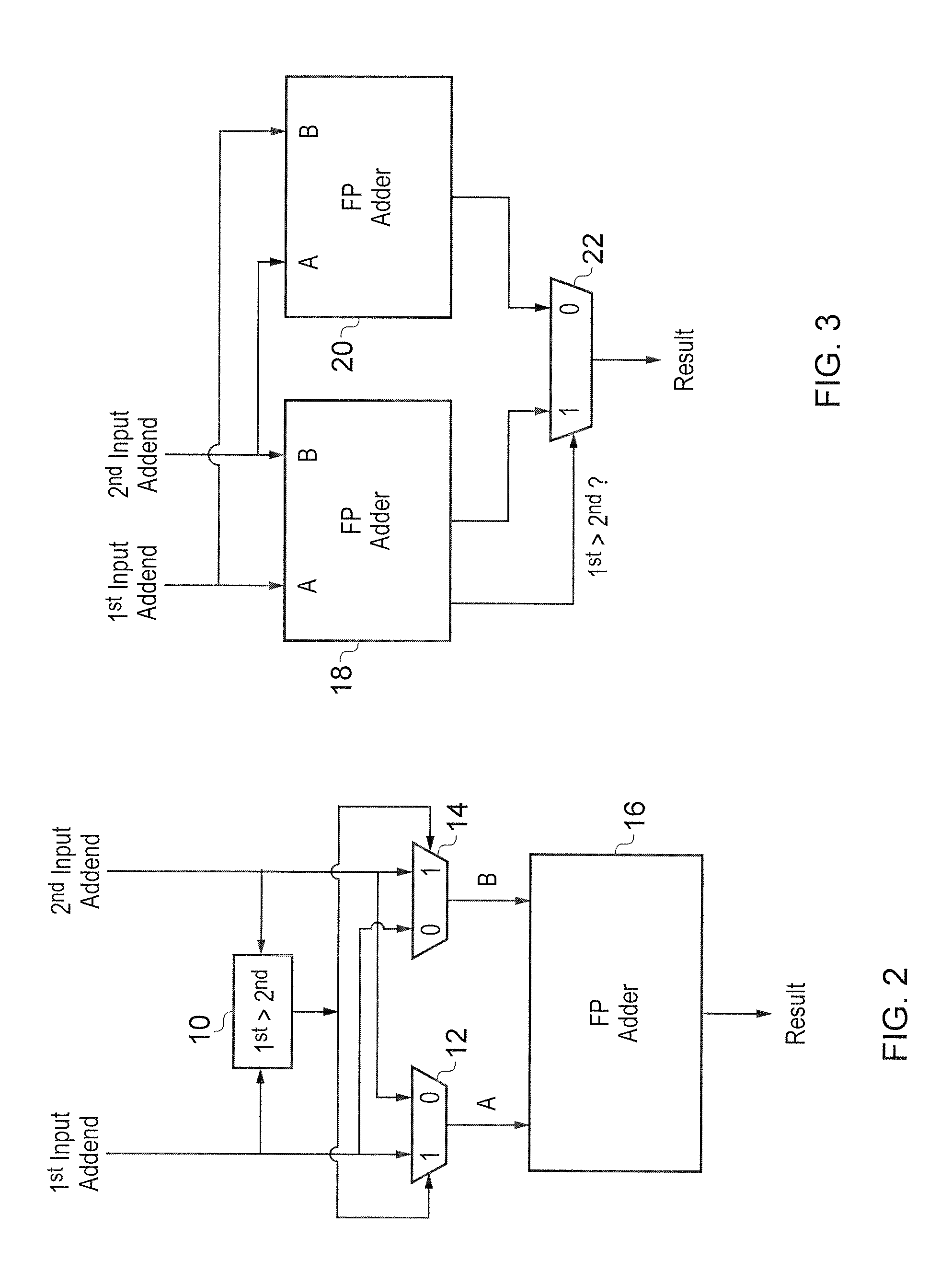

Apparatus and method for performing floating point addition

ActiveUS20120215823A1Small and simpleSignificant comprehensive benefitsComputations using contact-making devicesDigital computer detailsOperandLeading zero

An apparatus and method are provided for performing an addition operation on operands A and B in order to produce a result R, the operands A and B and the result R being floating point values each having a significand and an exponent. The apparatus comprises prediction circuitry for generating a shift indication based on a prediction of the number of leading zeros that would be present in an output produced by subjecting the operands A and B to an unlike signed addition. Further, result pre-normalization circuitry performs a shift operation on the significands of both operand A and operand B prior to addition of the significands, this serving to discard a number of most significant bits of the significands of both operands as determined by the shift indication in order to produce modified significands for operands A and B. Operand analysis circuitry detects, with reference to the exponents of operands A and B, the presence of a leading bit cancellation condition, and addition circuitry is configured, in the presence of the leading bit cancellation condition, to perform an addition of the modified significands for operands A and B, in order to produce the significand of the result R. Such an approach provides a particularly simple and efficient apparatus for performing addition operations.

Owner:ARM LTD

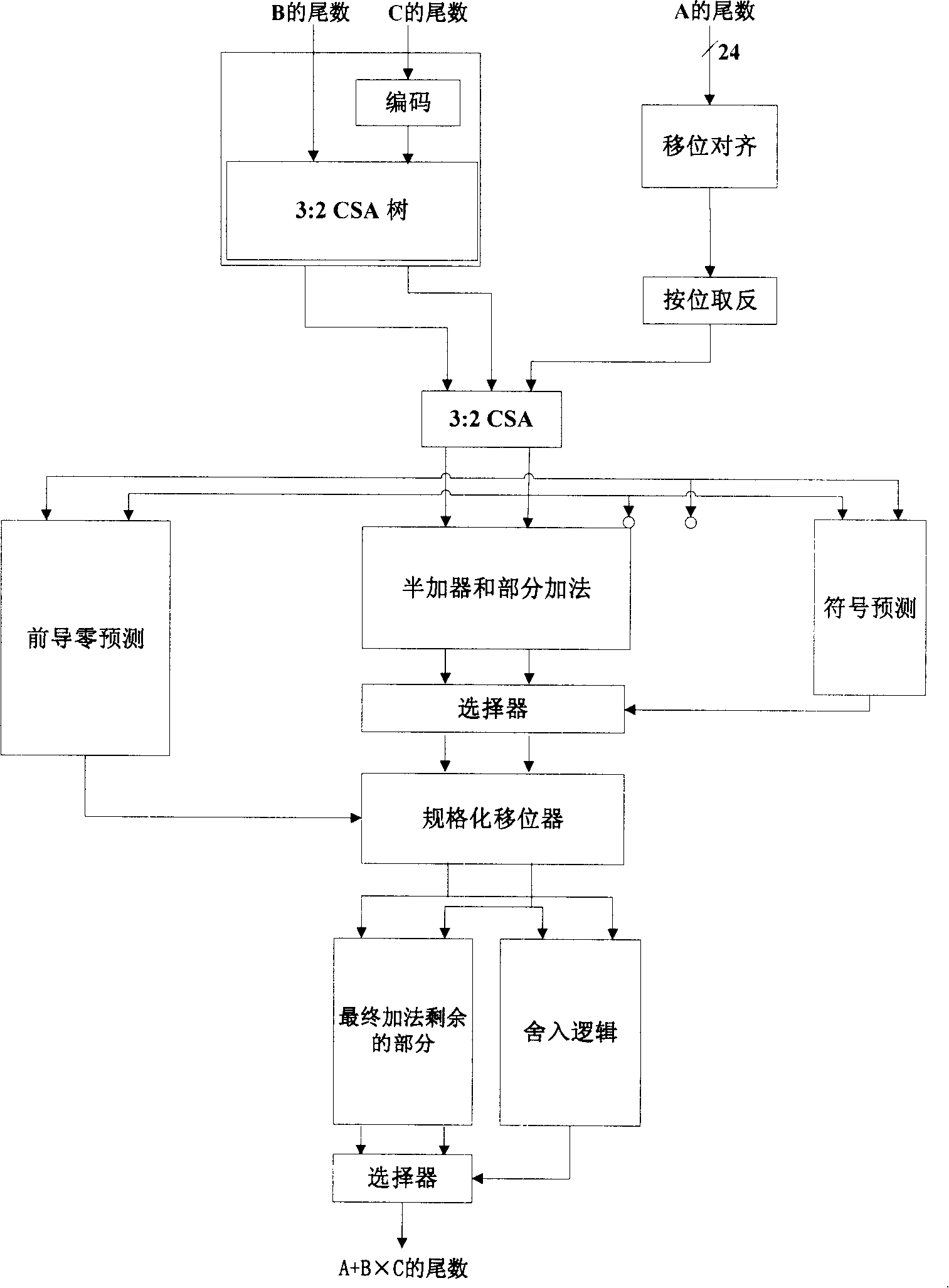

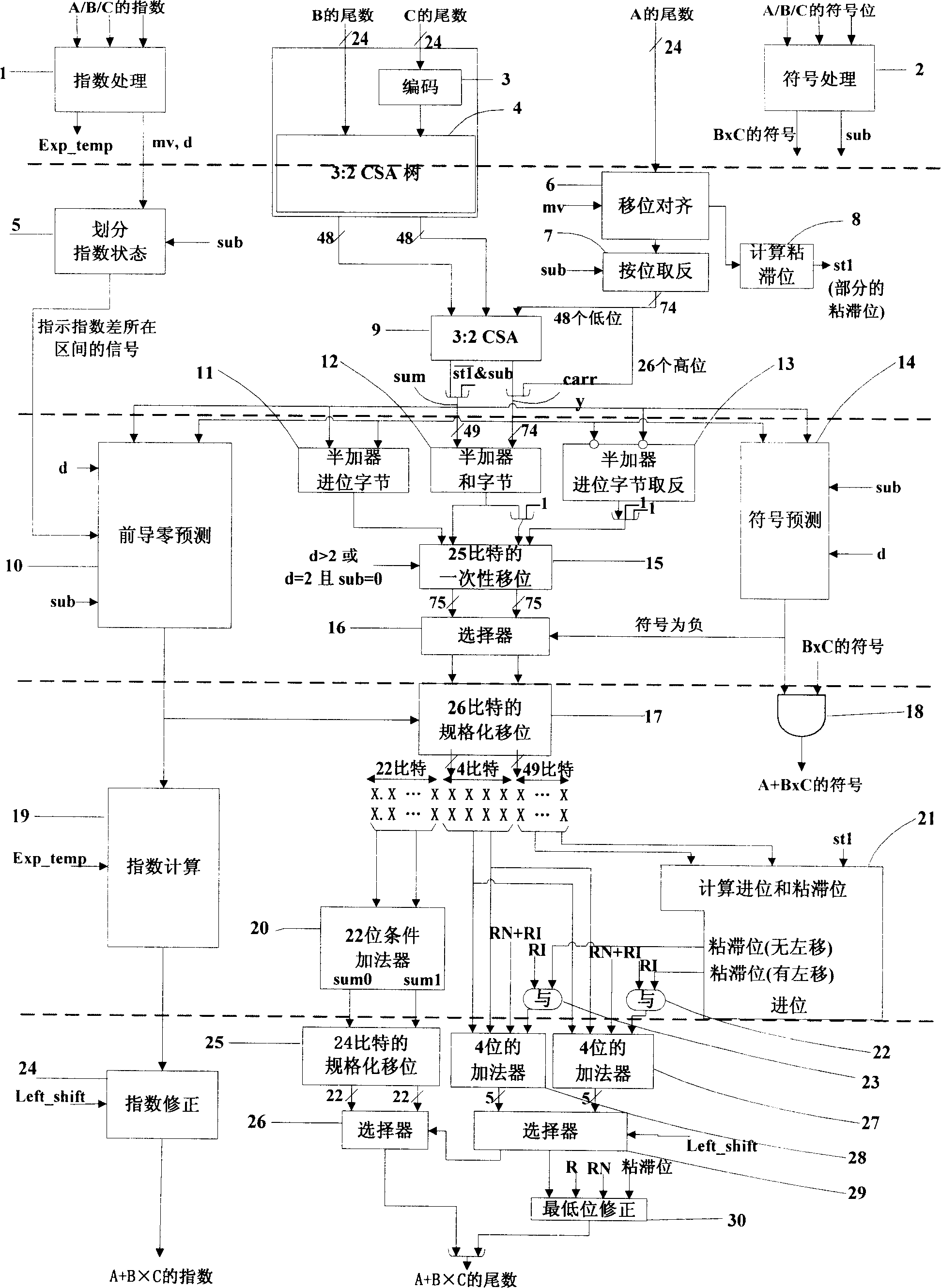

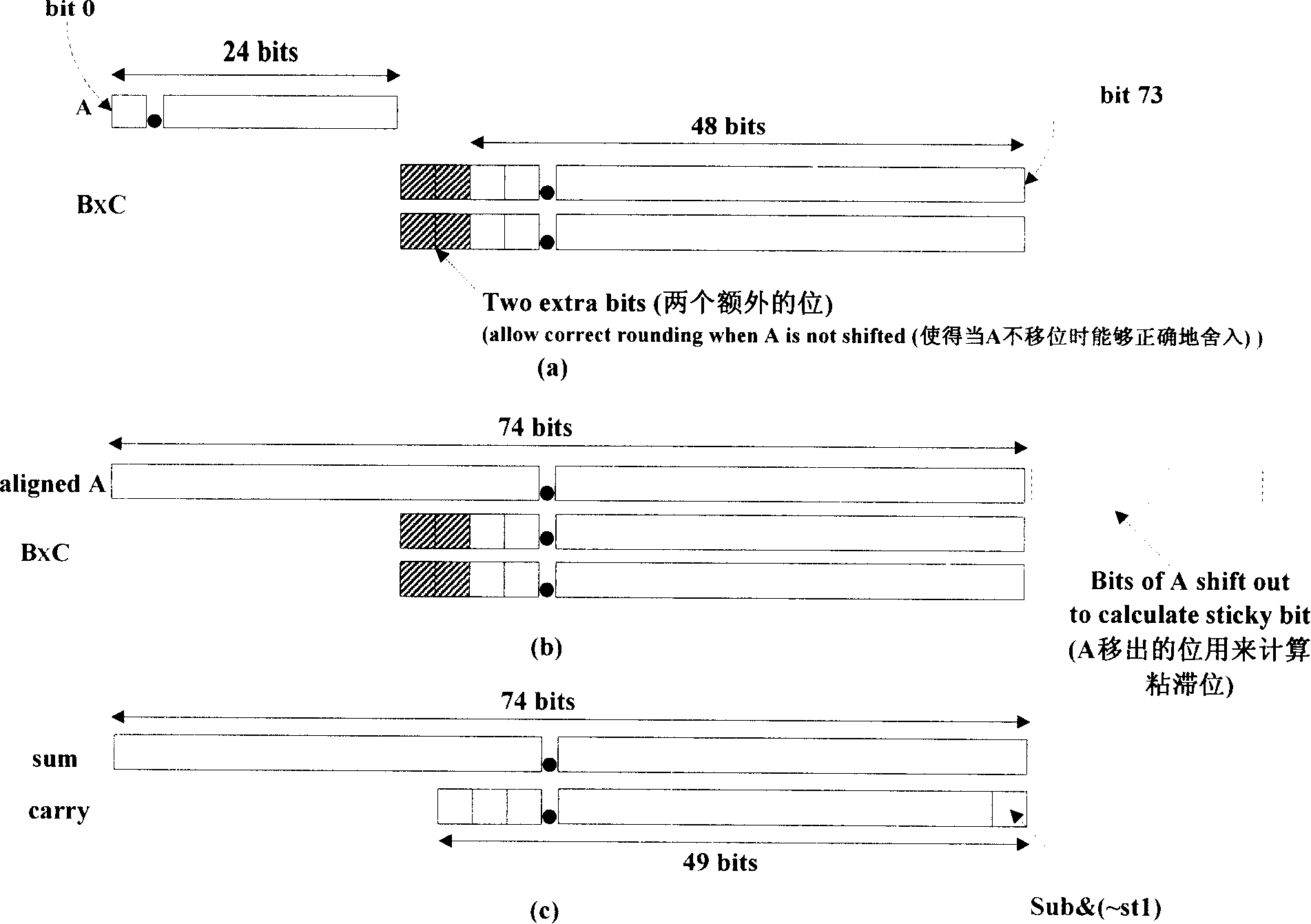

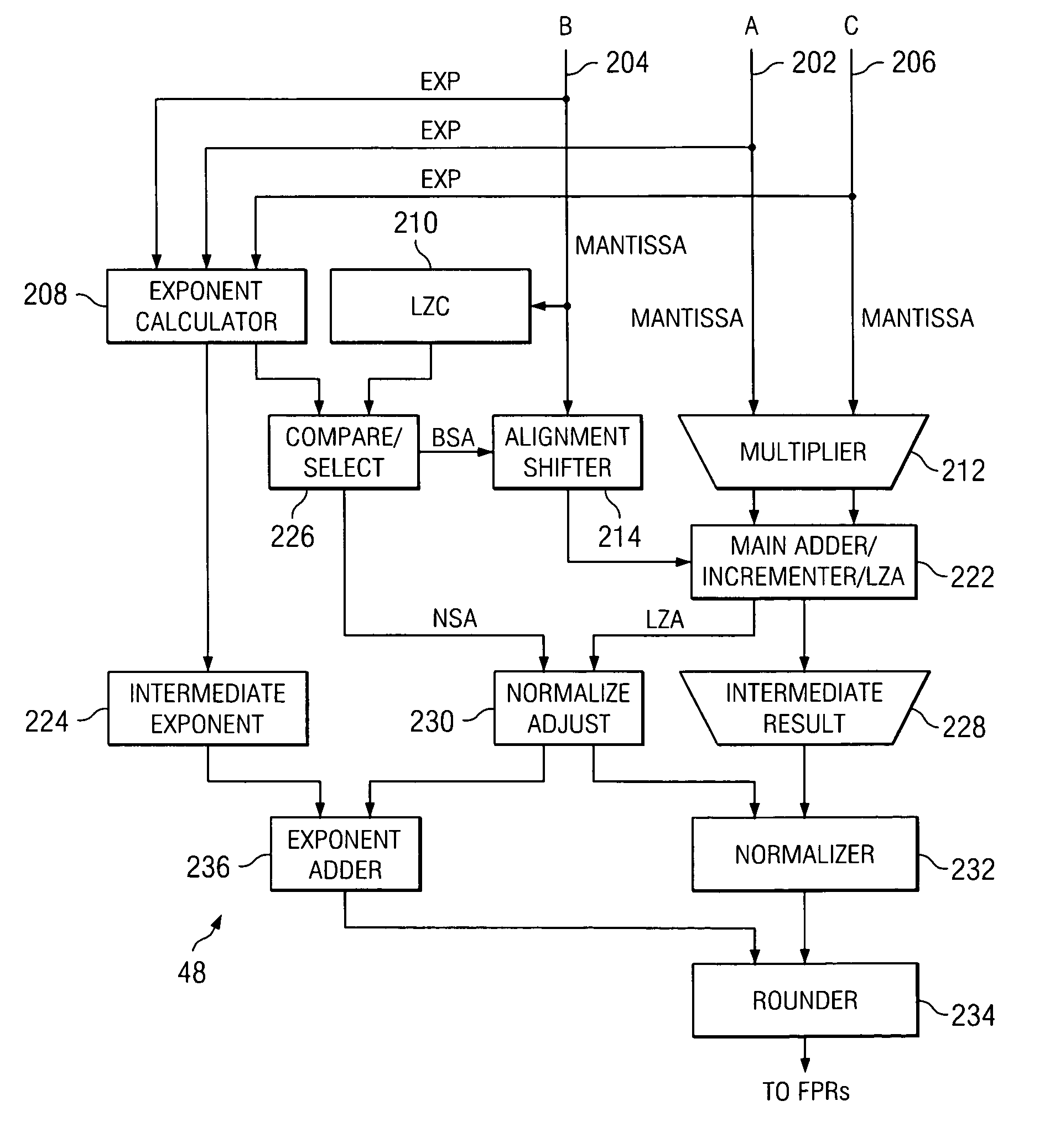

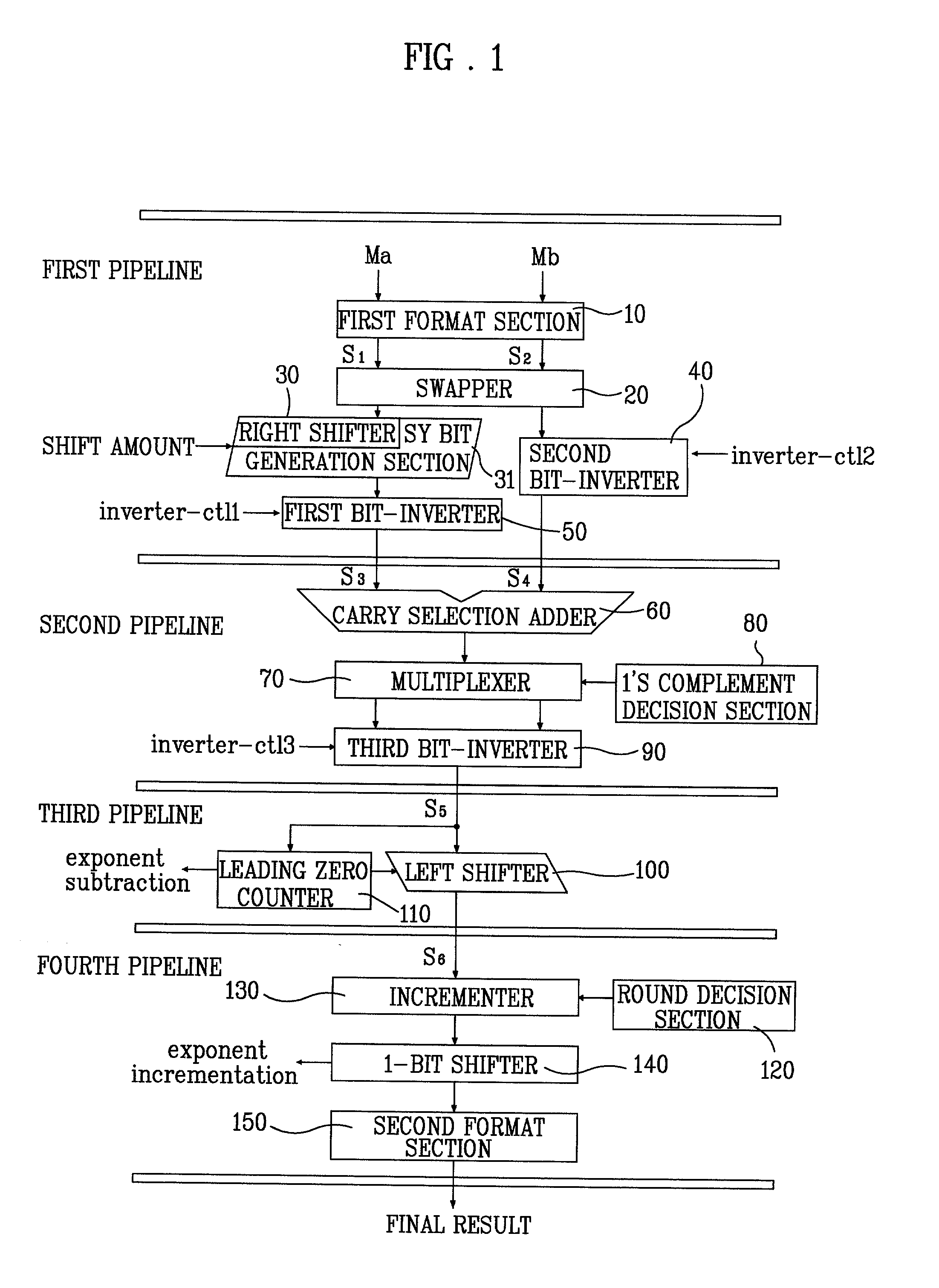

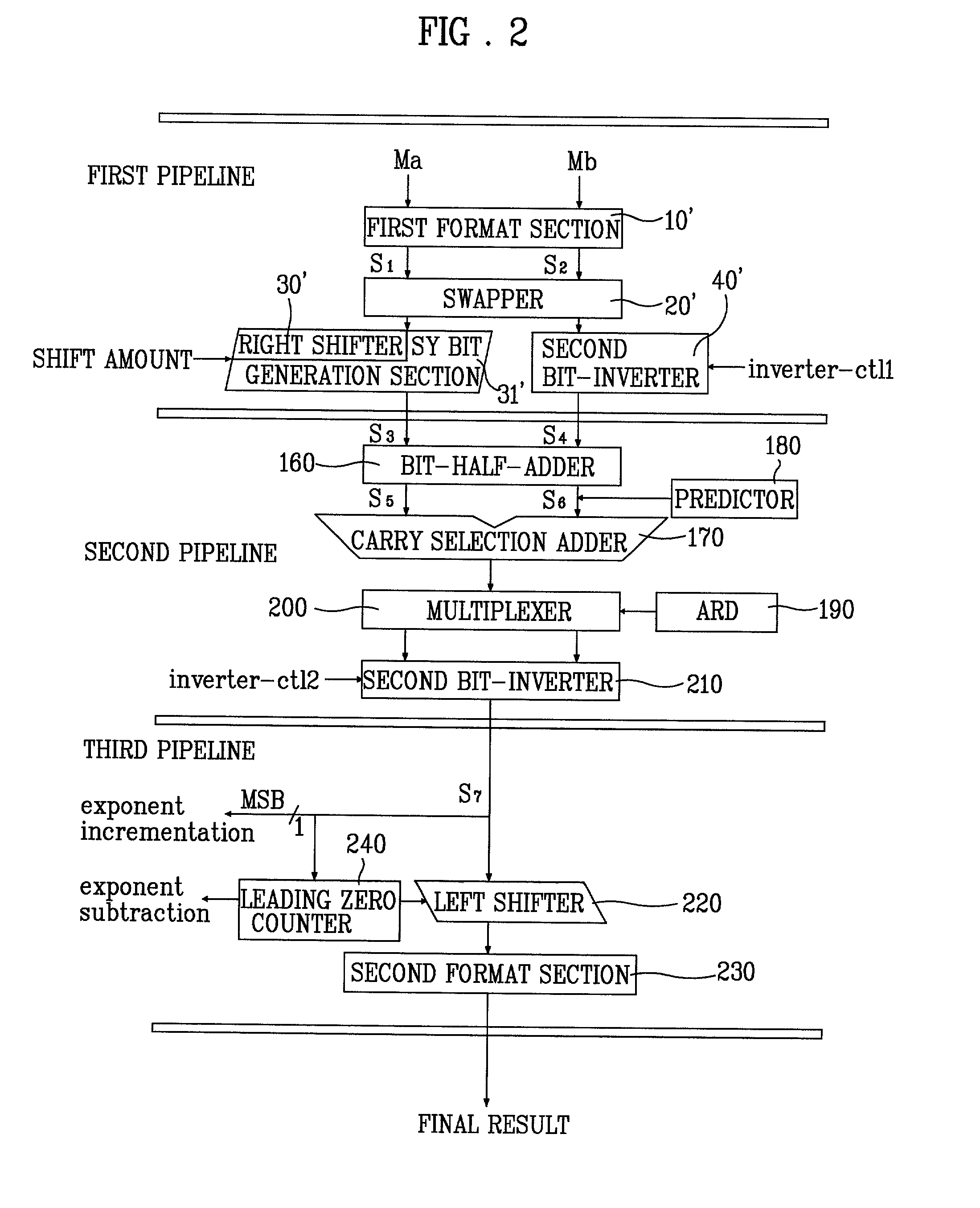

5-grade stream line structure of floating point multiplier adder integrated unit

ActiveCN101174200AHigh precisionDigital data processing detailsSymbol of a differential operatorLeading zero

The invention discloses a design of a full pipeline of a single precision floating point multiplication-add fused unit, which realizes multiplication-add operation in the form of A+B x C. the multiplication-add operation is realized in the following five pipelines: in the first stage pipeline, exponential difference is calculated and a part of the multiplication is completed; in the second stage pipeline, A and B x C are aligned according to the exponential difference, effective subtraction and complement are performed, the rest multiplication is completed, simultaneously, the exponent is divided into six states, and the calculation method of normalized shift amount in different states are different; in the third stage pipeline, the number of leading zero is pre-estimated, simultaneously the sign of the final result is synchronously pre-estimated, and finally first stage normalized shift is performed; in the fourth stage pipeline, second normalized shift is performed first, and then addition and a part of half adjust are performed; in the last stage pipeline, addition and half adjust are completed, exponential terms are amended, and third stage normalized shift is completed in the spacing of the half adjust. The invention has the advantages that high performance and high precision are realized in the condition of low hardware cost.

Owner:TSINGHUA UNIV

Methods, apparatus, instructions, and logic to provide permute controls with leading zero count functionality

Instructions and logic provide SIMD permute controls with leading zero count functionality. Some embodiments include processors with a register with a plurality of data fields, each of the data fields to store a second plurality of bits. A destination register has corresponding data fields, each of these data fields to store a count of the number of most significant contiguous bits set to zero for corresponding data fields. Responsive to decoding a vector leading zero count instruction, execution units count the number of most significant contiguous bits set to zero for each of data fields in the register, and store the counts in corresponding data fields of the first destination register. Vector leading zero count instructions can be used to generate permute controls and completion masks to be used along with the set of permute controls, to resolve dependencies in gather-modify-scatter SIMD operations.

Owner:INTEL CORP

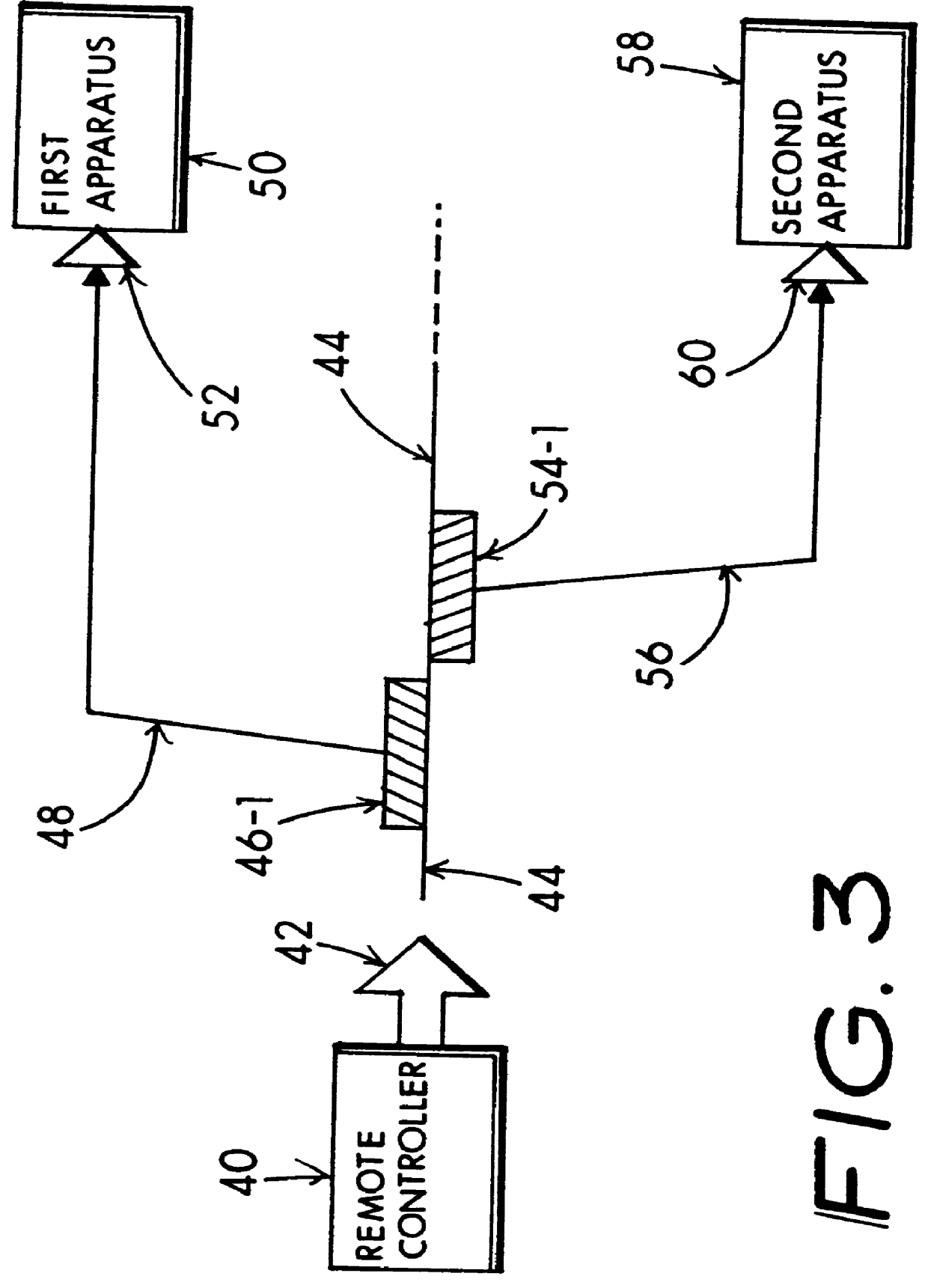

Remote control for a television enabling a user to enter and review a channel selection choice immediately prior to sending an encoded channel selection command to the television

InactiveUS6094239AEasy entryPreventing irritating switchingTelevision system detailsResonant circuit detailsNetwork packetRemote control

A handheld remote controller device that may be manually programmed while the keypad is conveniently supported in an easy to actuate and readily viewable position in front of a user. Individual keybutton entries are temporarily stored until the entry sequence is complete. Each keybutton entry may be visually displayed for review by the user. When the entry sequence is completed the remote controller device is then aimed at a remotely controlled television set, video tape or video disk player, cable or satellite signal converter. The user initiates a SEND command and the stored entries are retrieved and transmitted from the remote controller device to the receptor of the remotely controlled device as a packet of data which acts to change channel selection or accomplish other tasks in the remotely controlled device. A keybutton entry filter reduces a likelihood for accidental multiple entries which may be caused by tremors and other physical or mental maladies. In this way, physically challenged persons, or elderly persons in particular, may be enabled to utilize a remote control function with less chance for error. When only a single number channel, such as channel 5 is selected, a necessitous leading zero is automatically added to the SEND dispatched command.

Owner:HANGER SOLUTIONS LLC +1

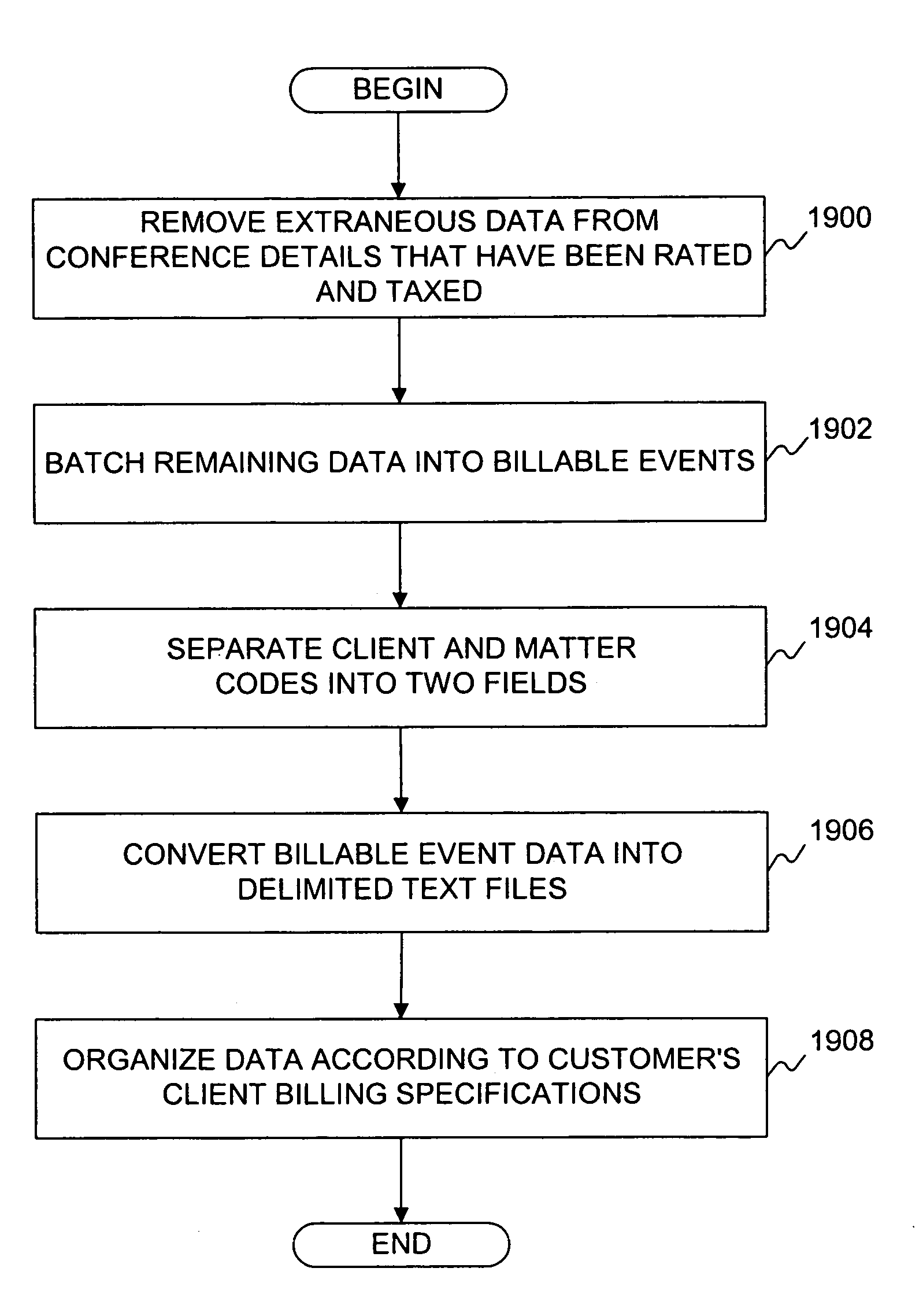

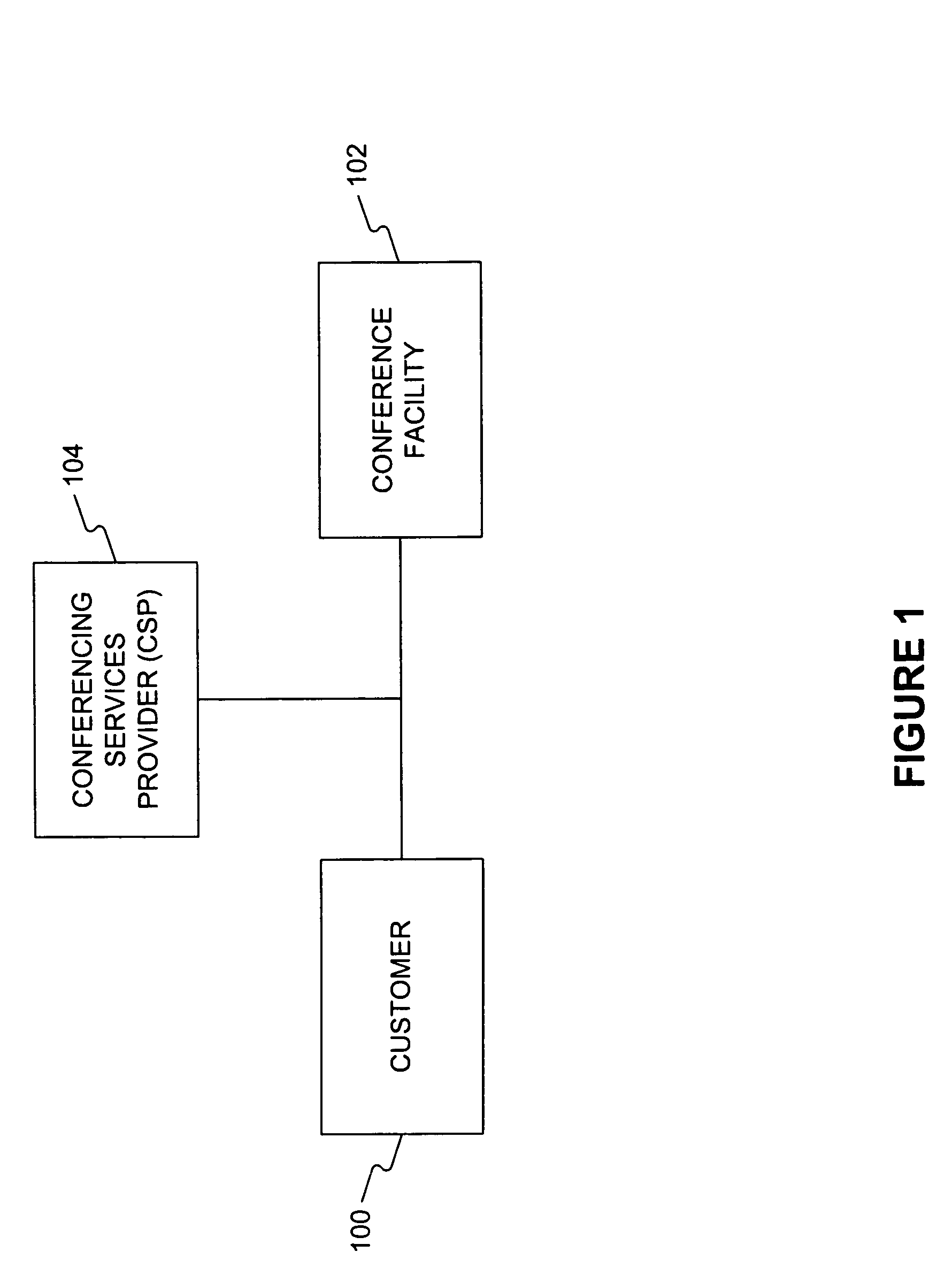

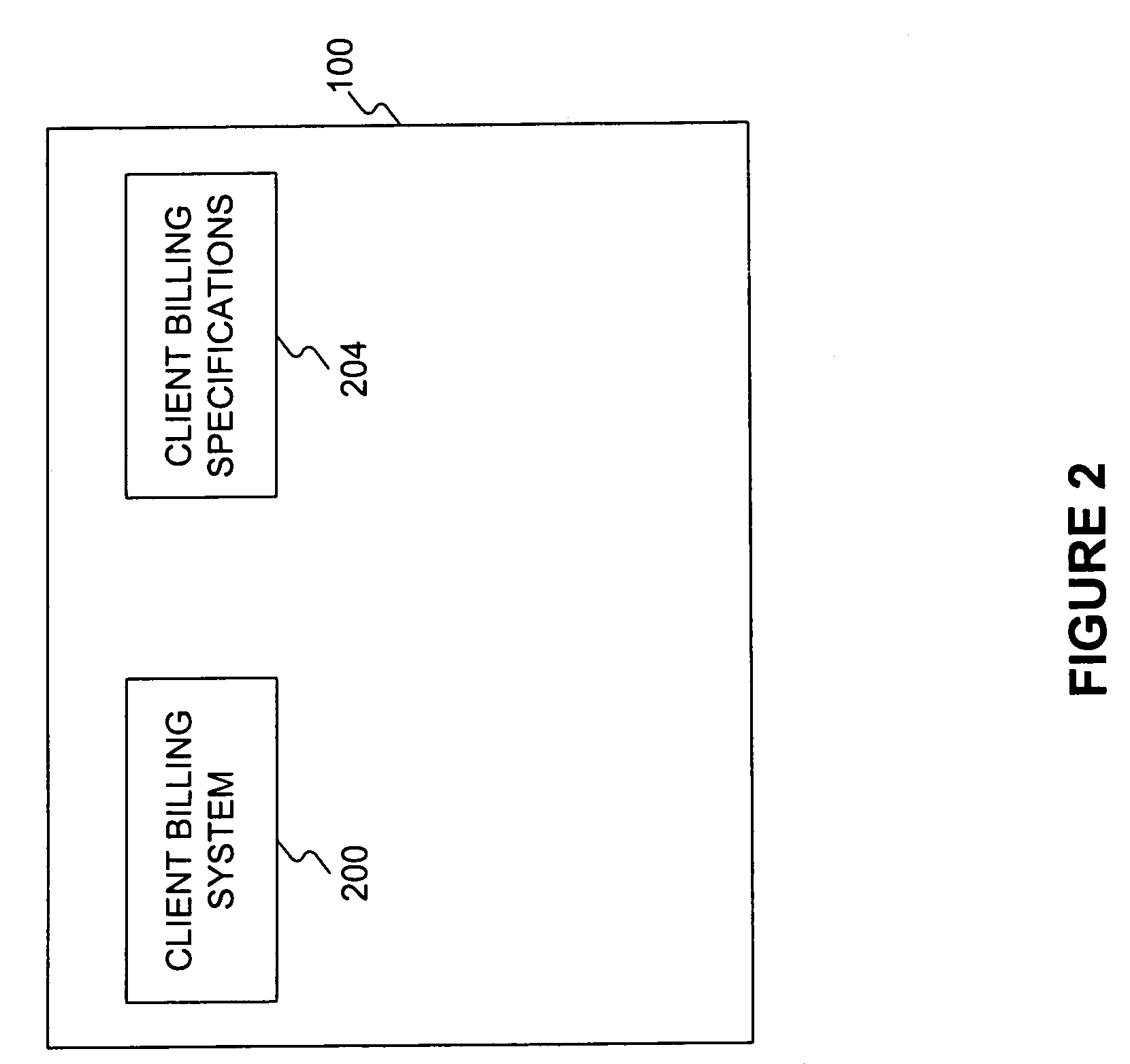

Billing data interface for conferencing customers

ActiveUS20060233334A1Meet data requirementsSpecial service for subscribersBilling/invoicingData fileData treatment

A billing data interface provides billing data to customers in an accurate and efficient manner. Billing data is processed to preserve client billing information and to meet a customer's individual data requirements. The billing data may be presented in such a way that the customer may input the billing data directly into its client billing system. The billing data may be processed according to client billing specifications corresponding to a client billing system used by the customer. The processed data may preserve leading zeros, separate client code and matter code into two fields, etc. The resulting data file may be delivered to the customer for entry into the customer's client billing system.

Owner:AMERICAN TELECONFERENCING SERVICES

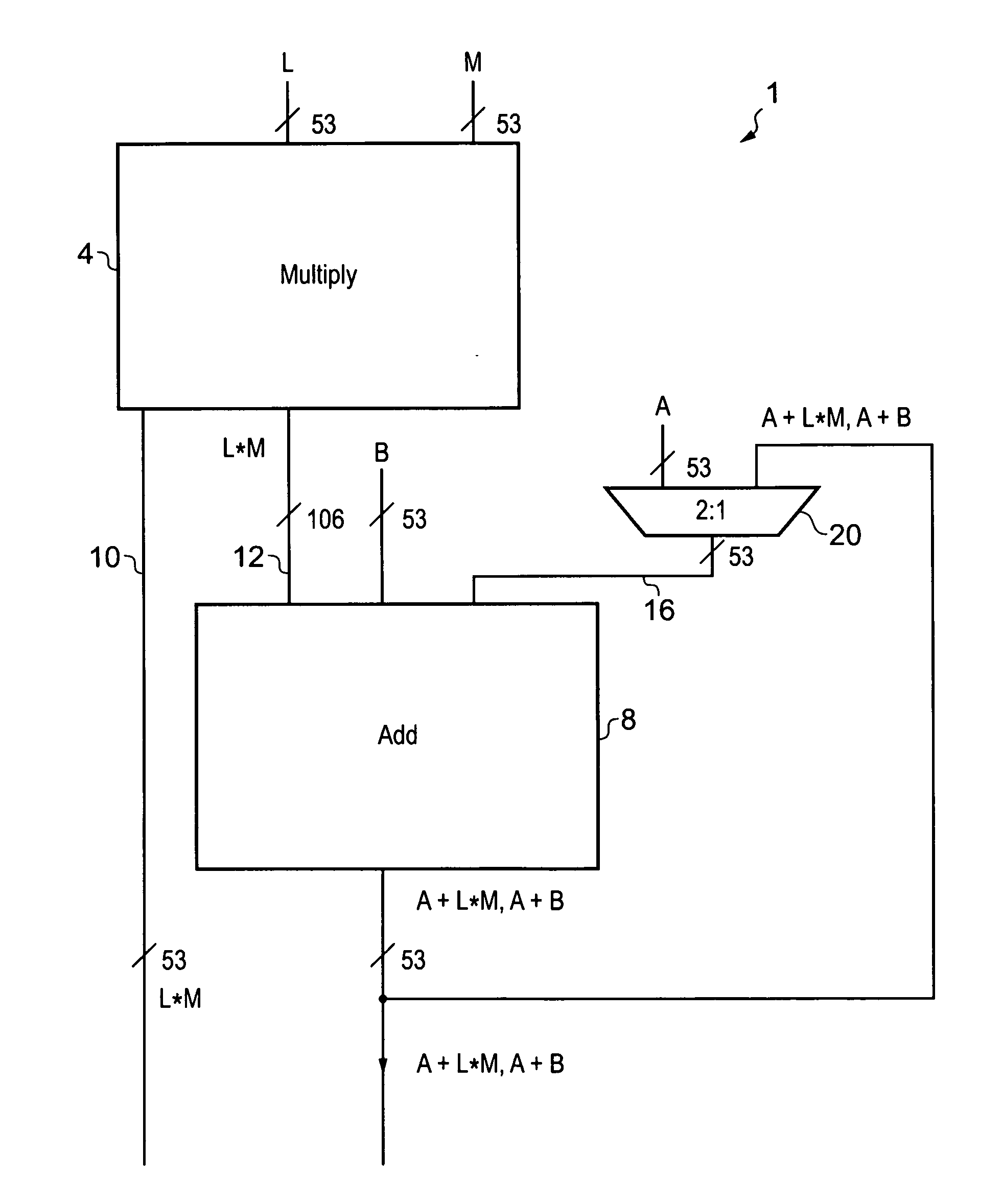

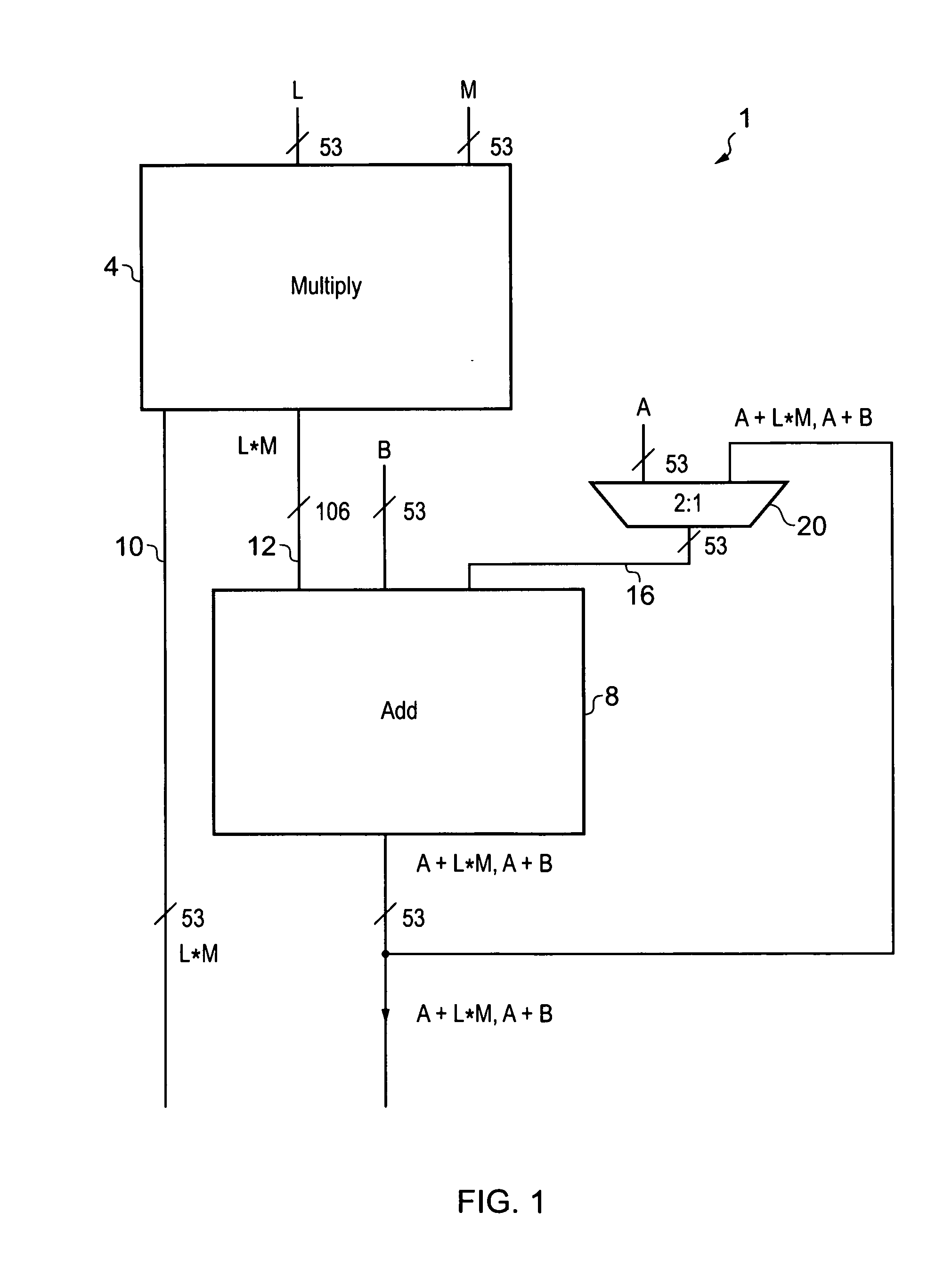

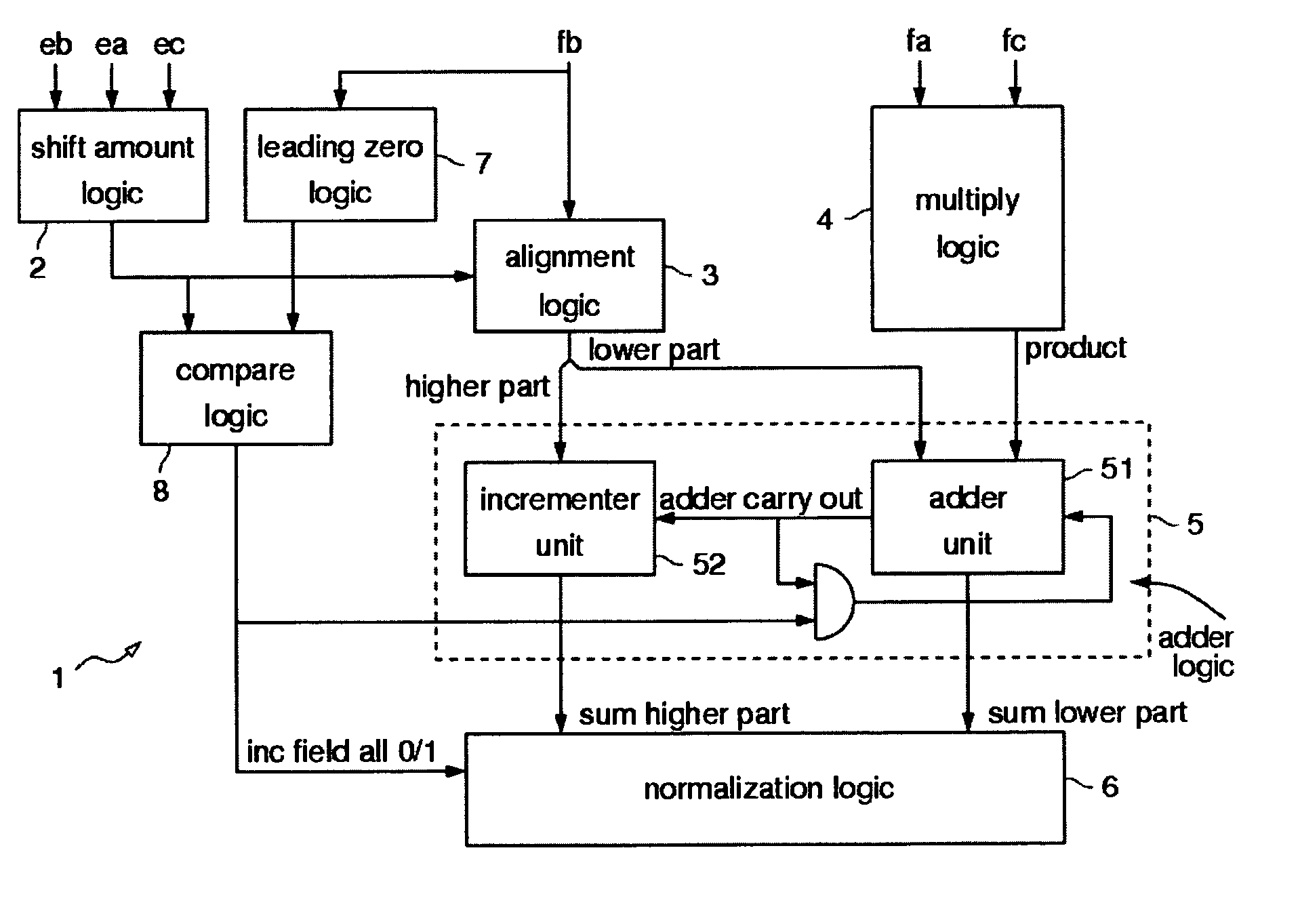

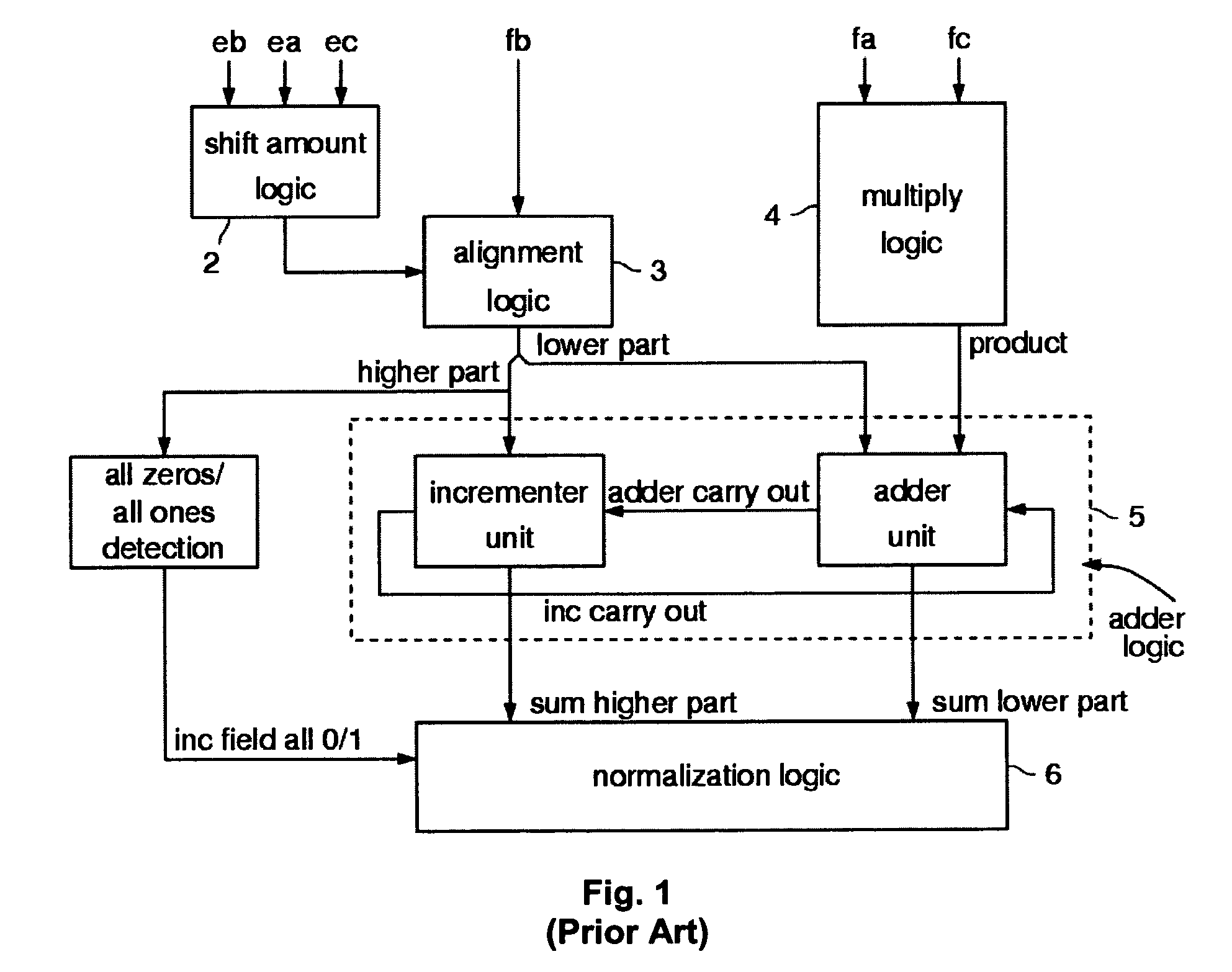

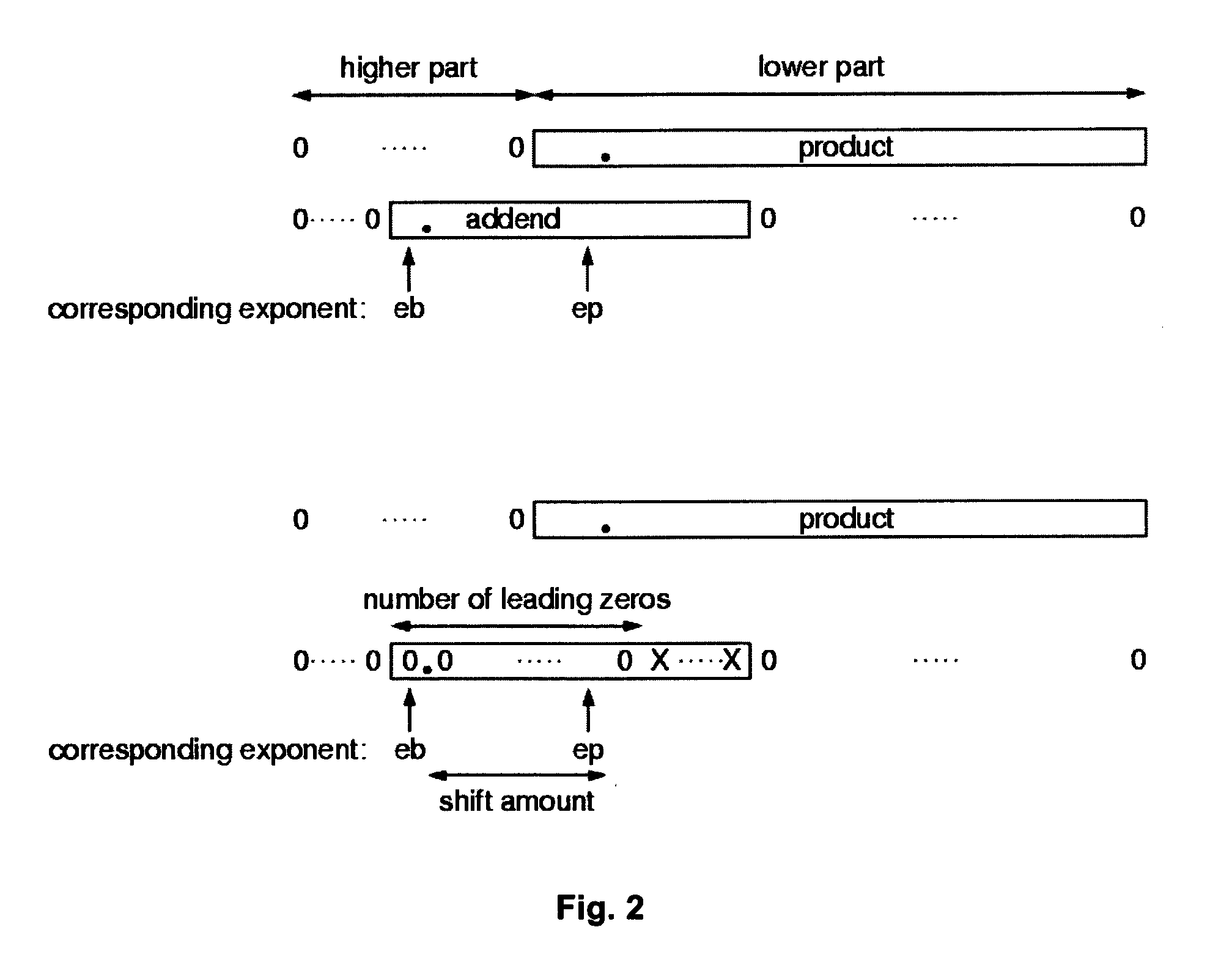

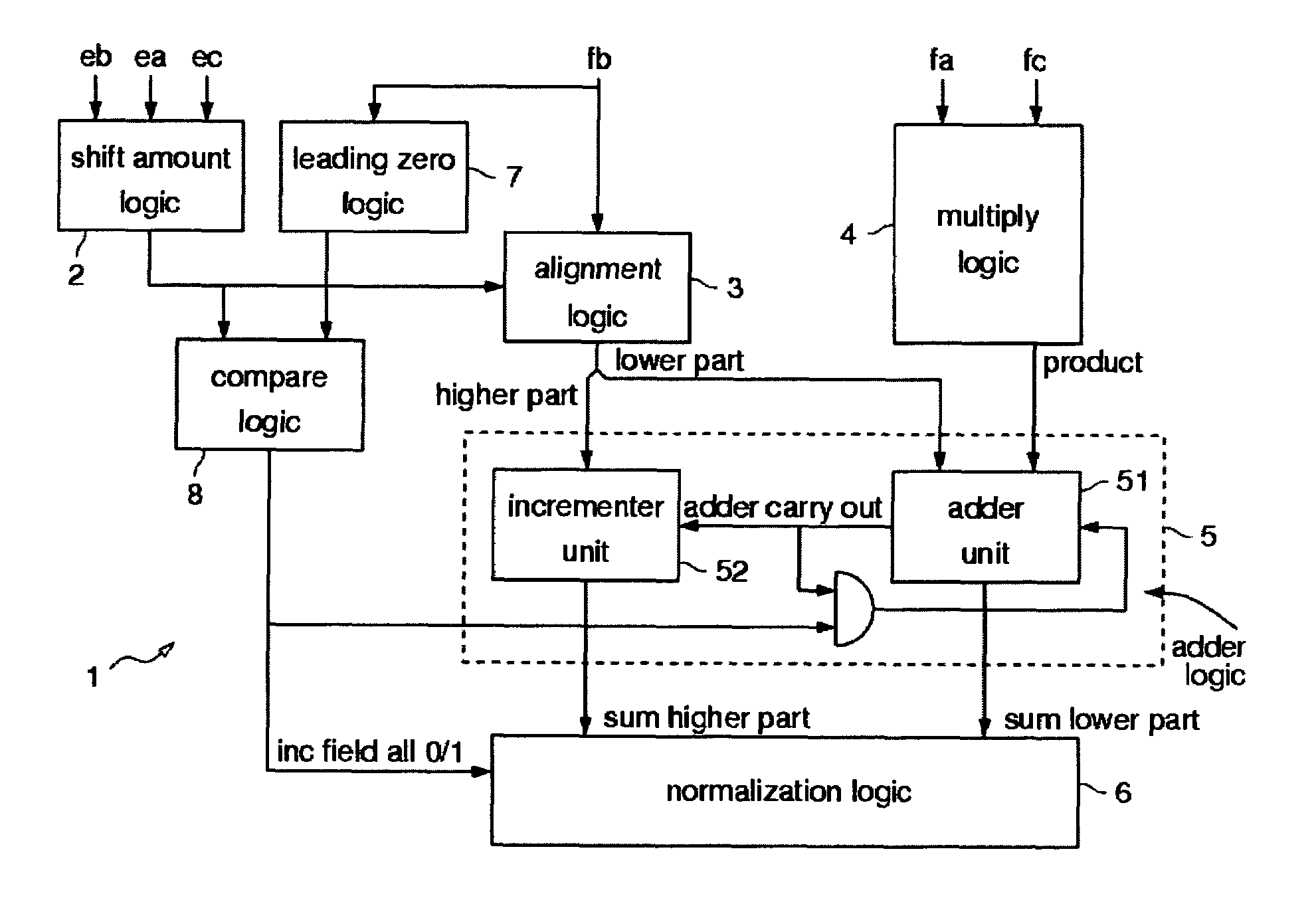

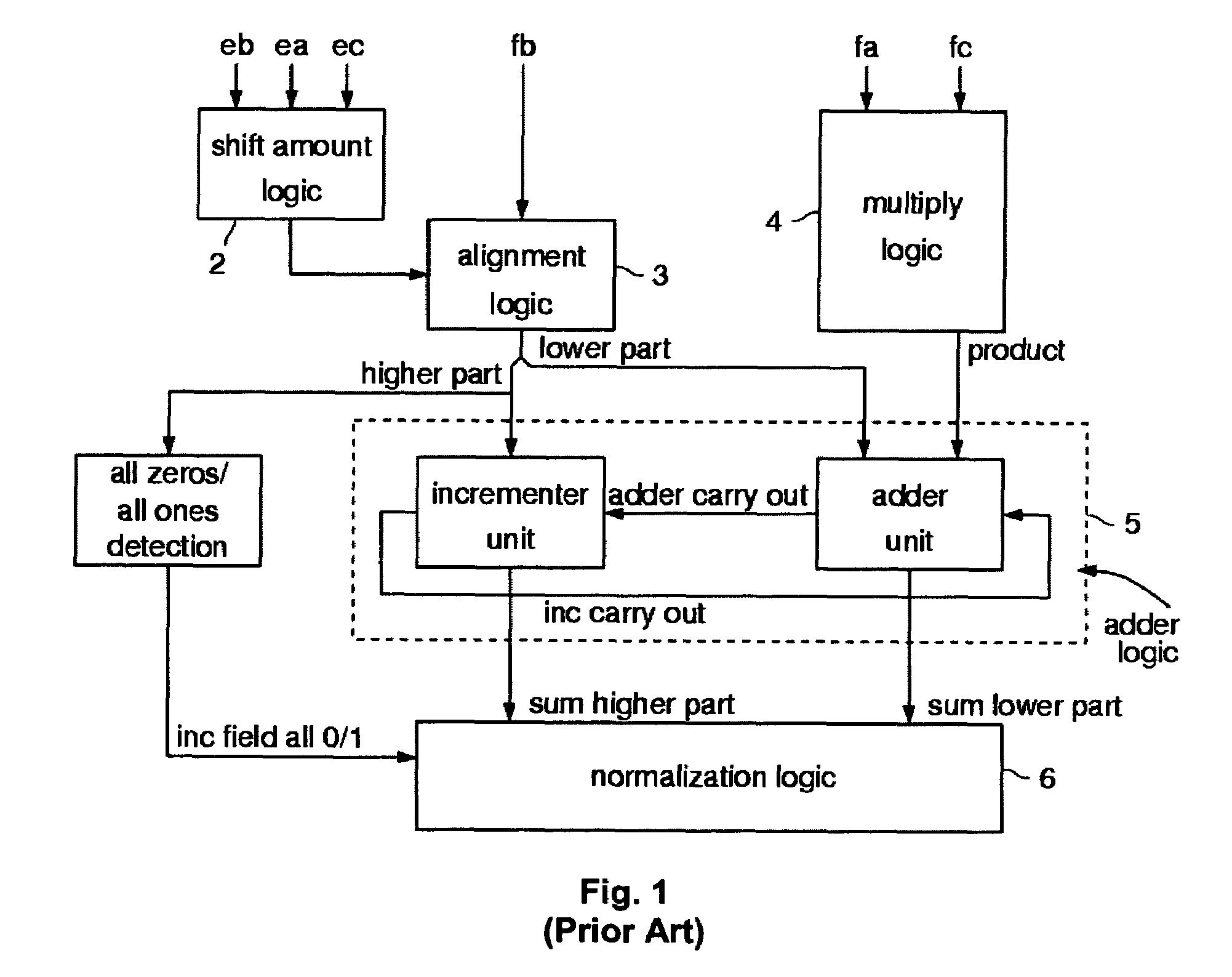

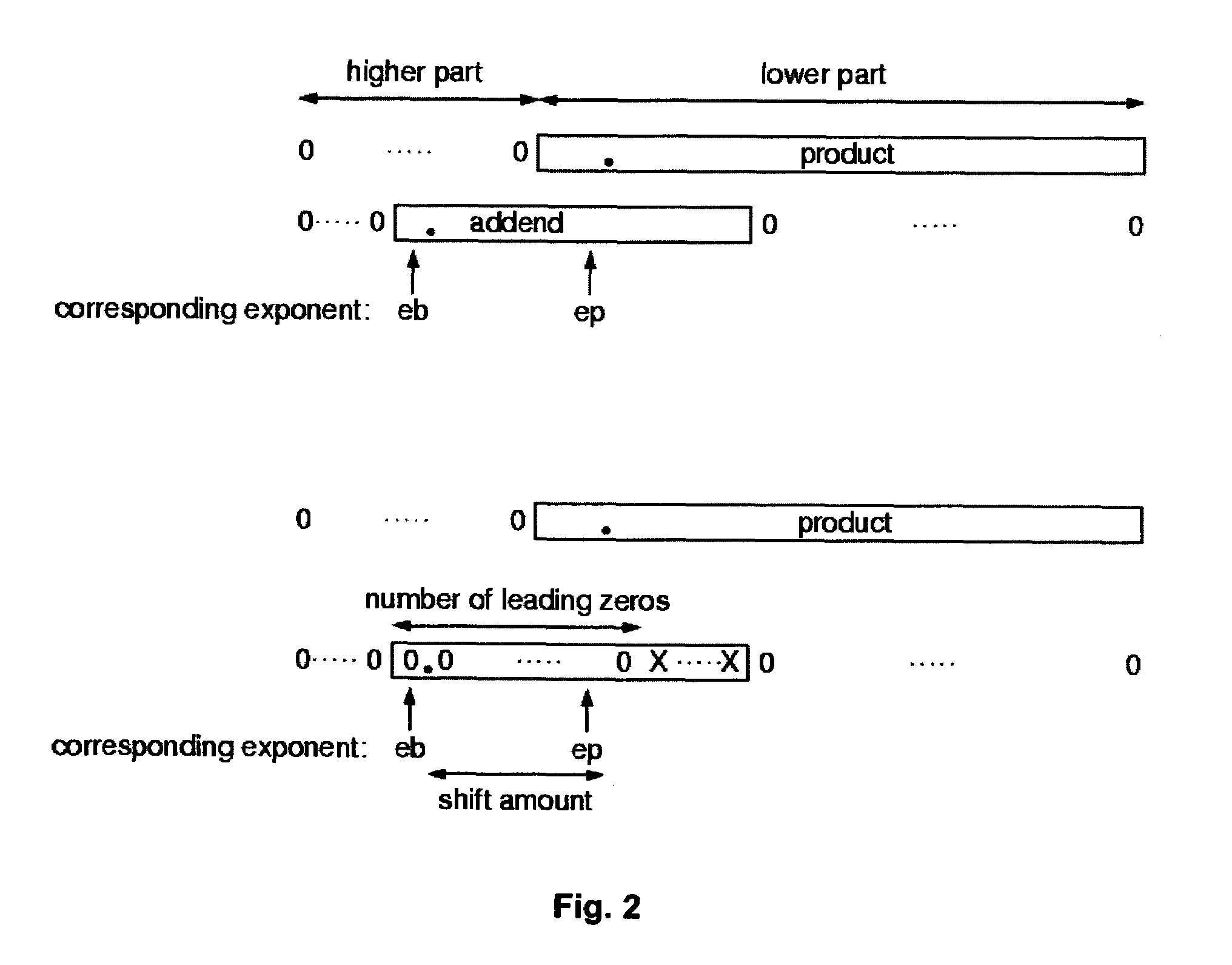

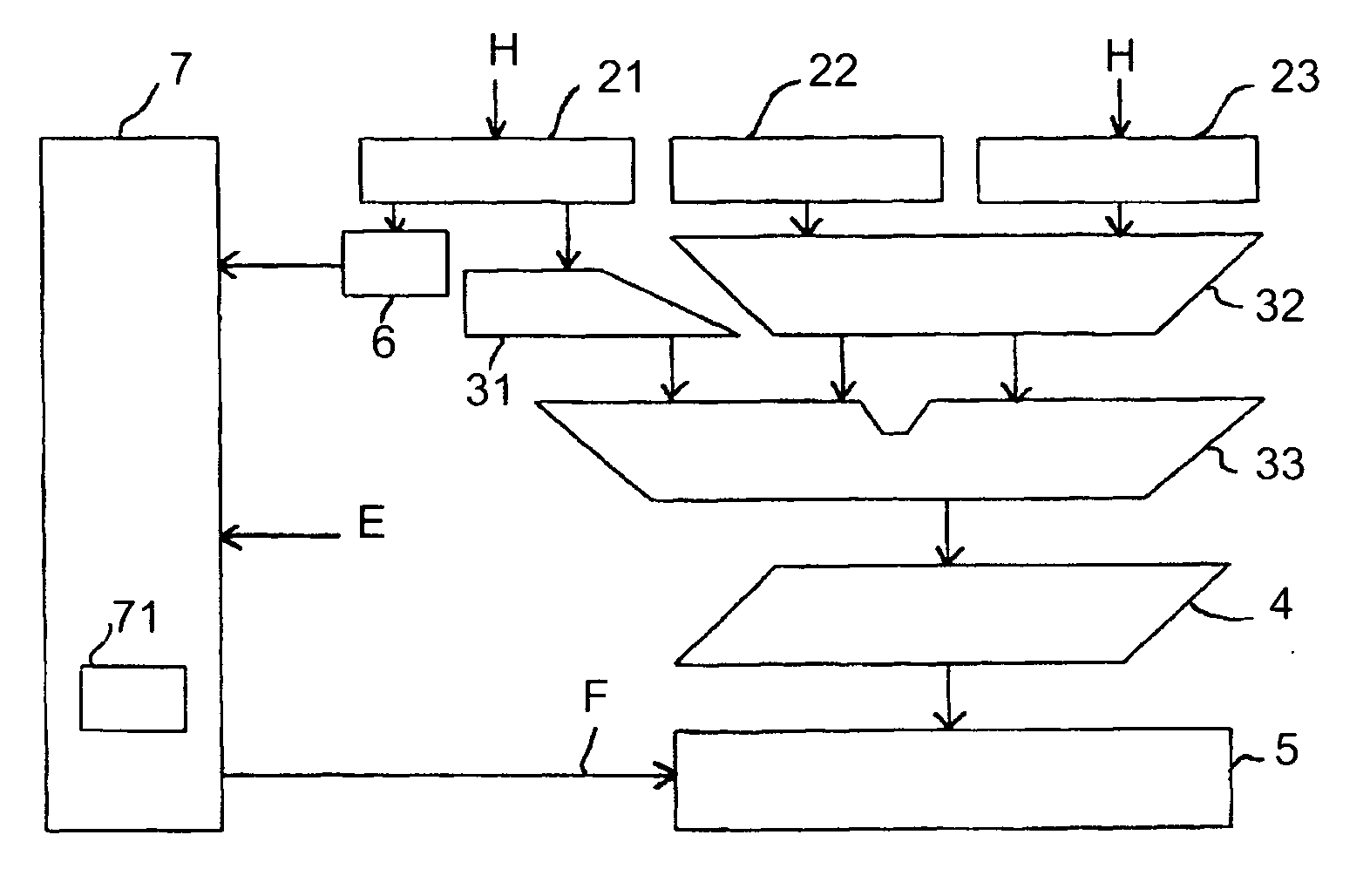

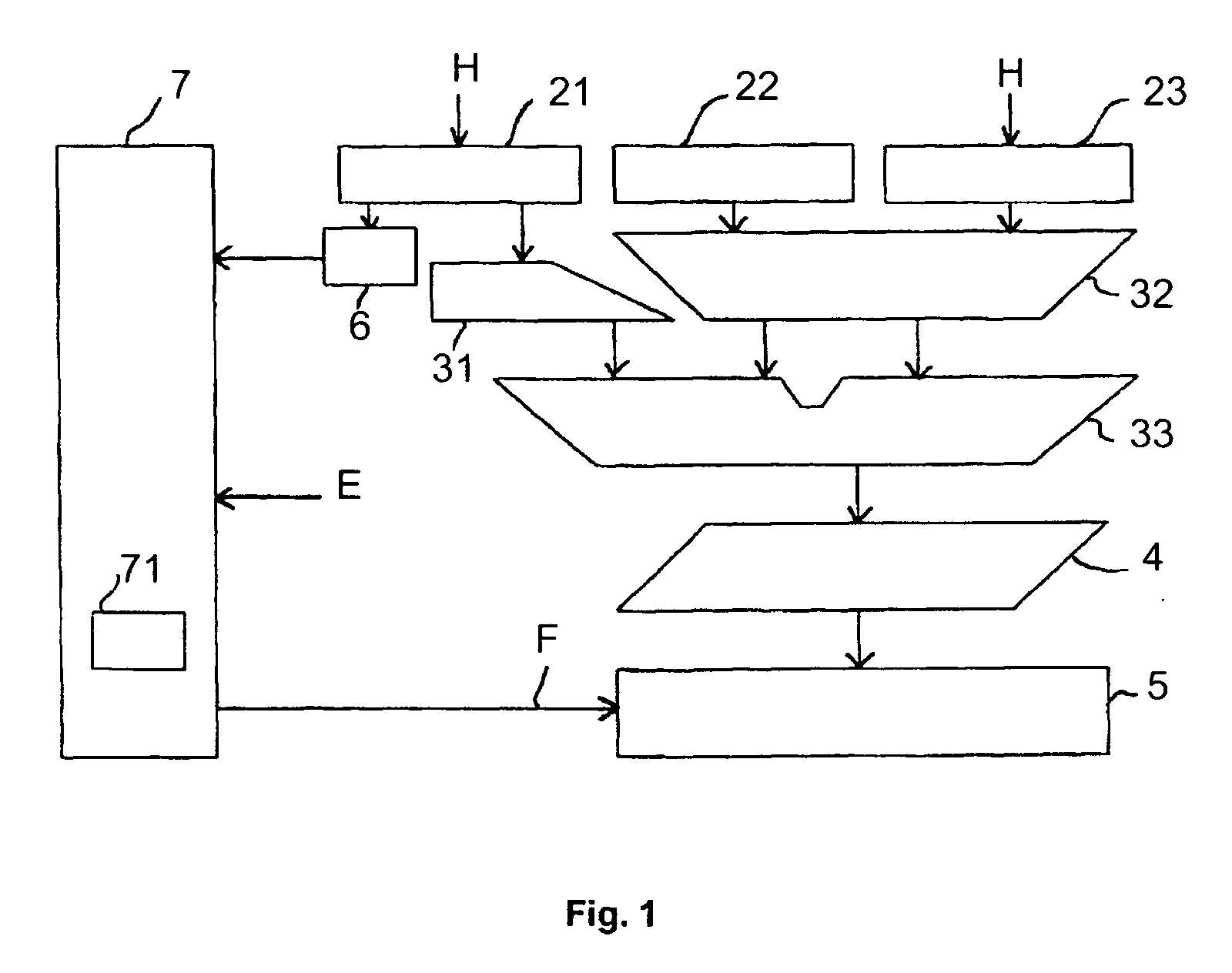

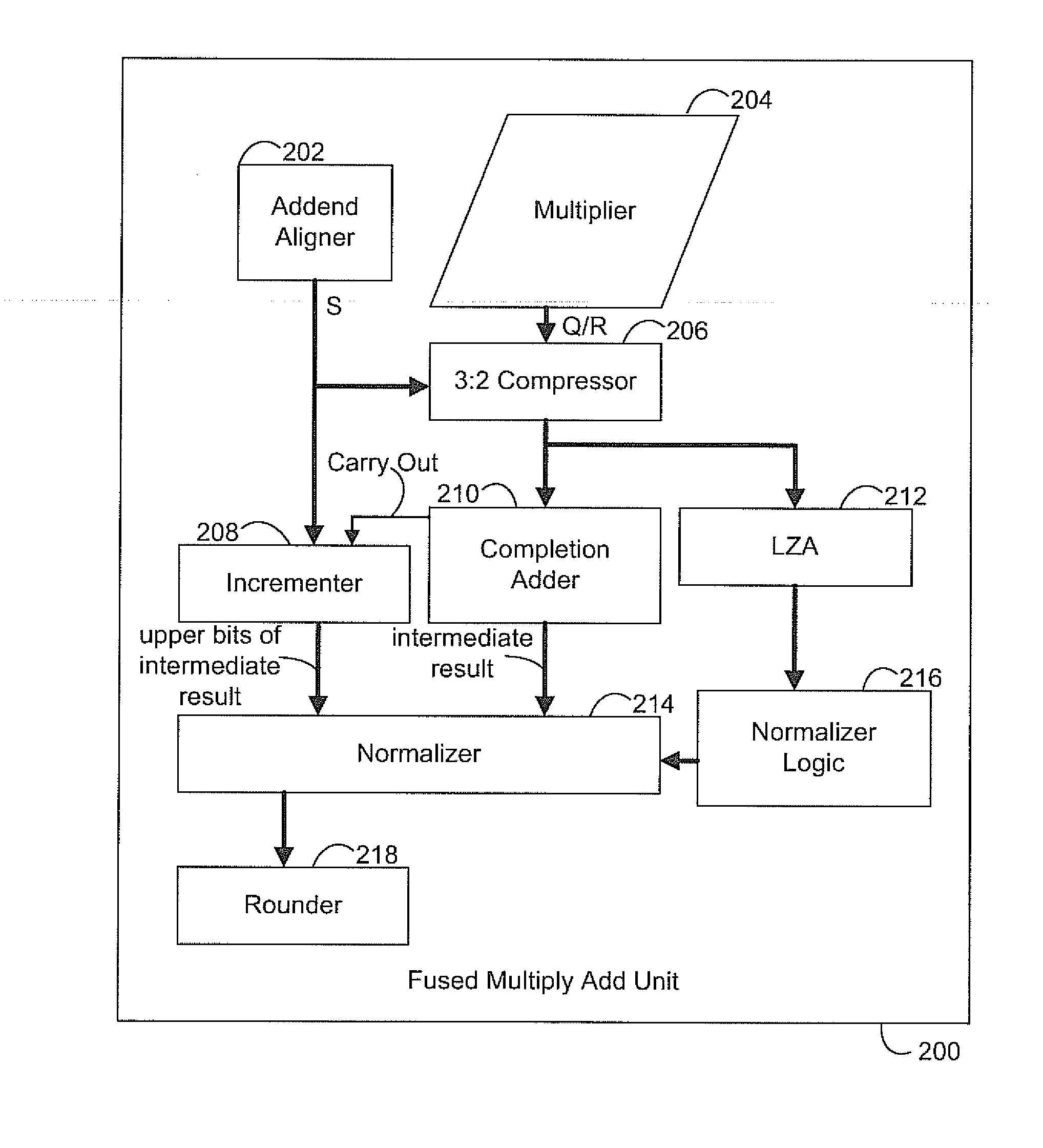

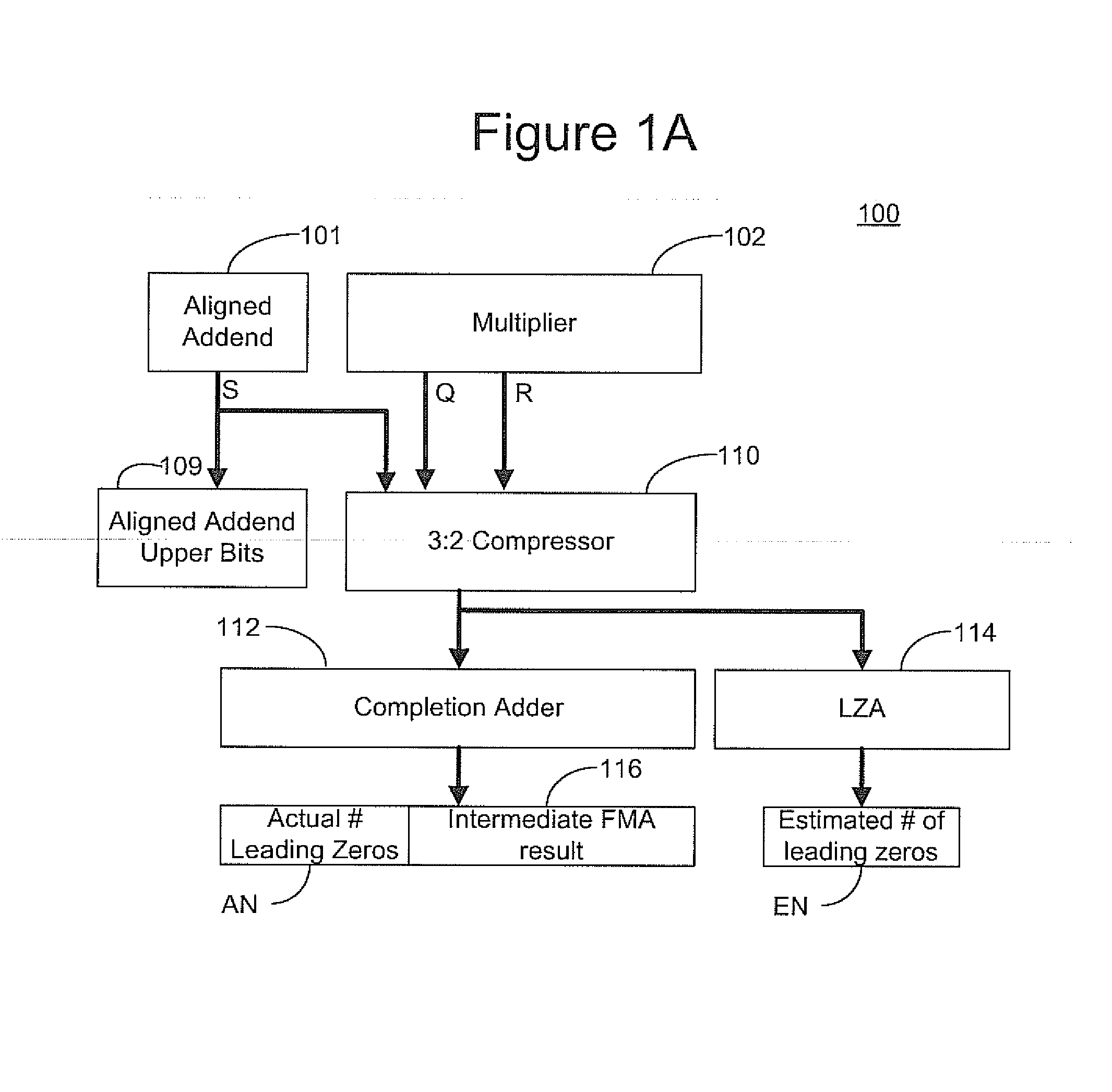

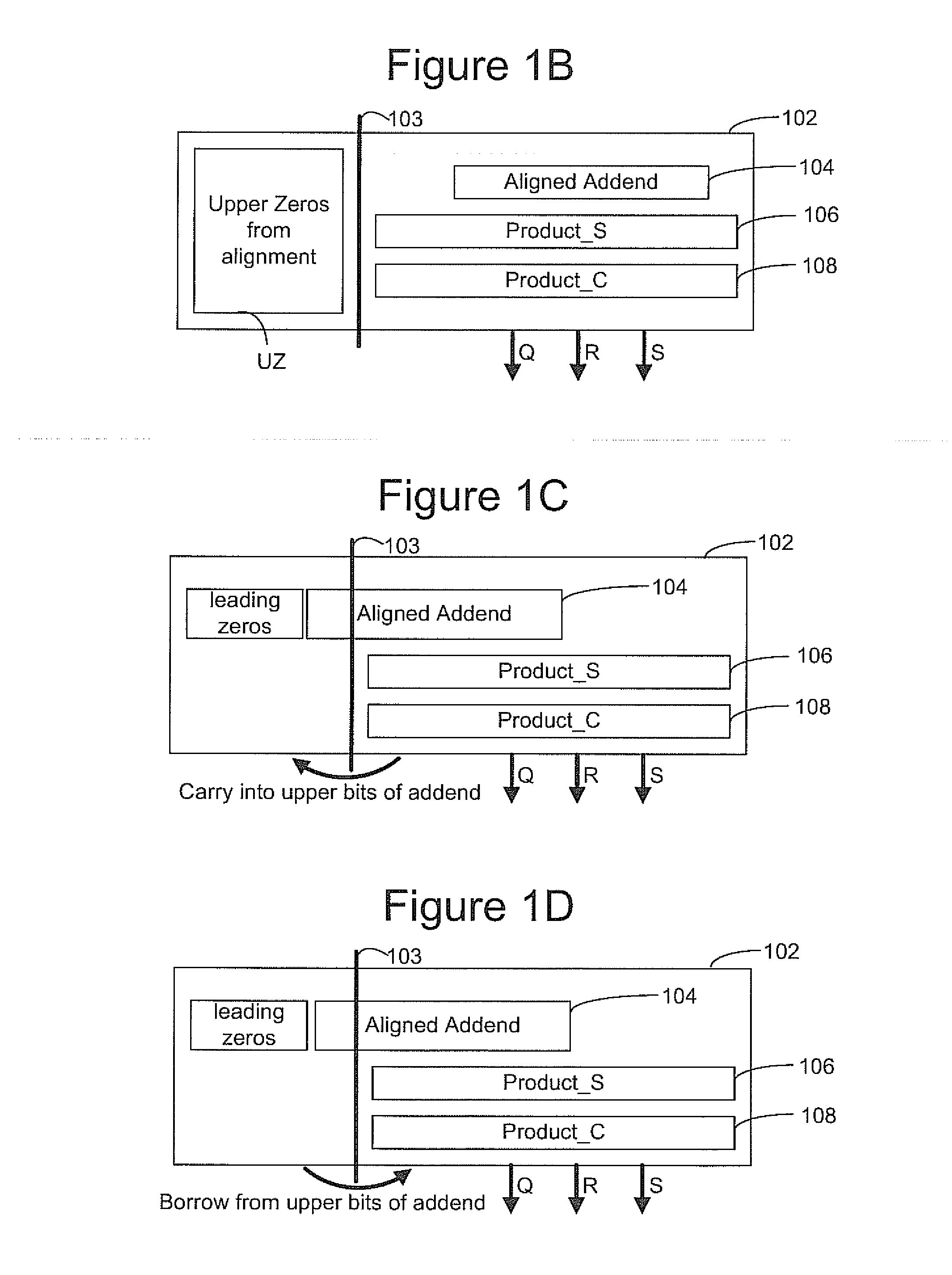

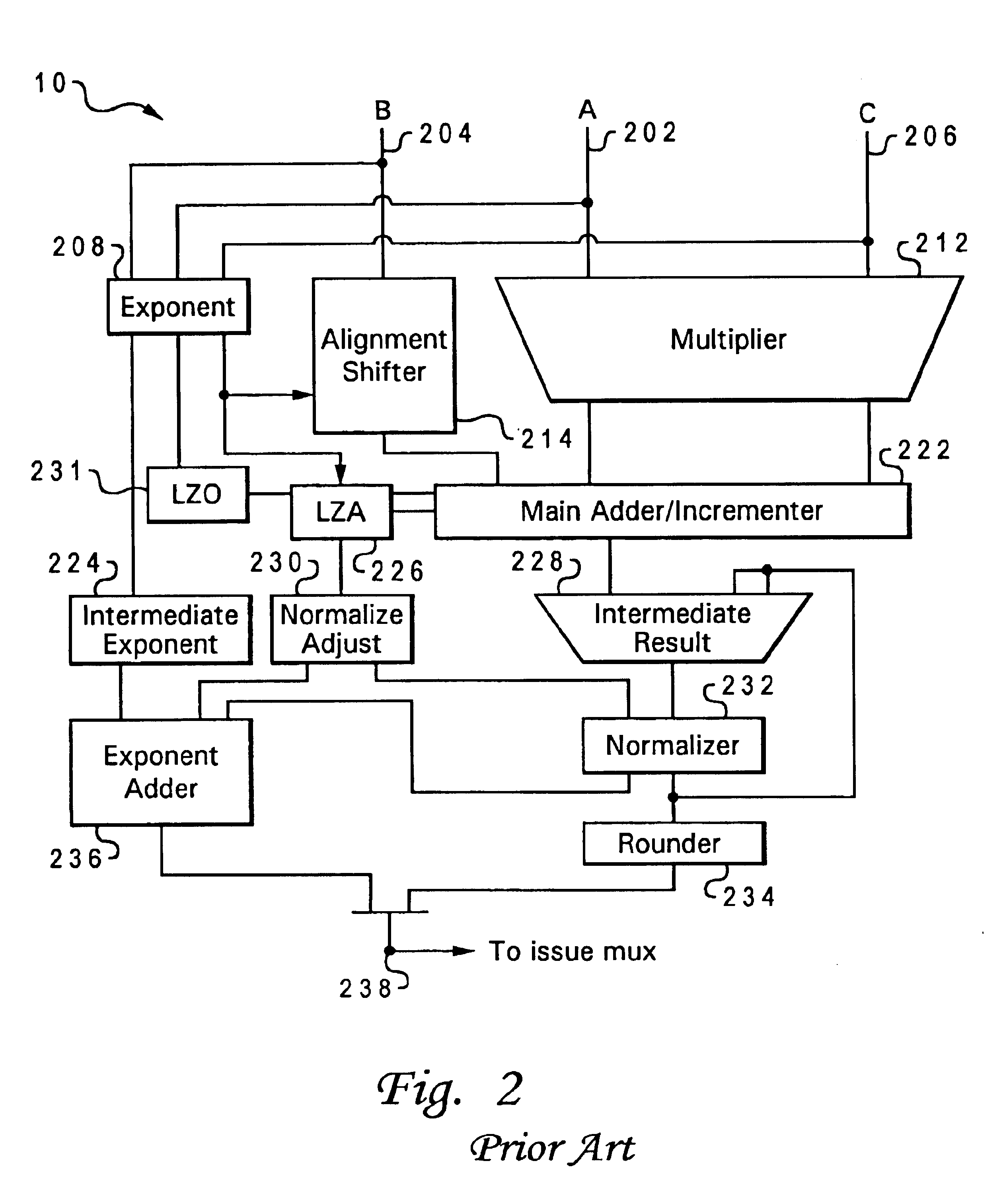

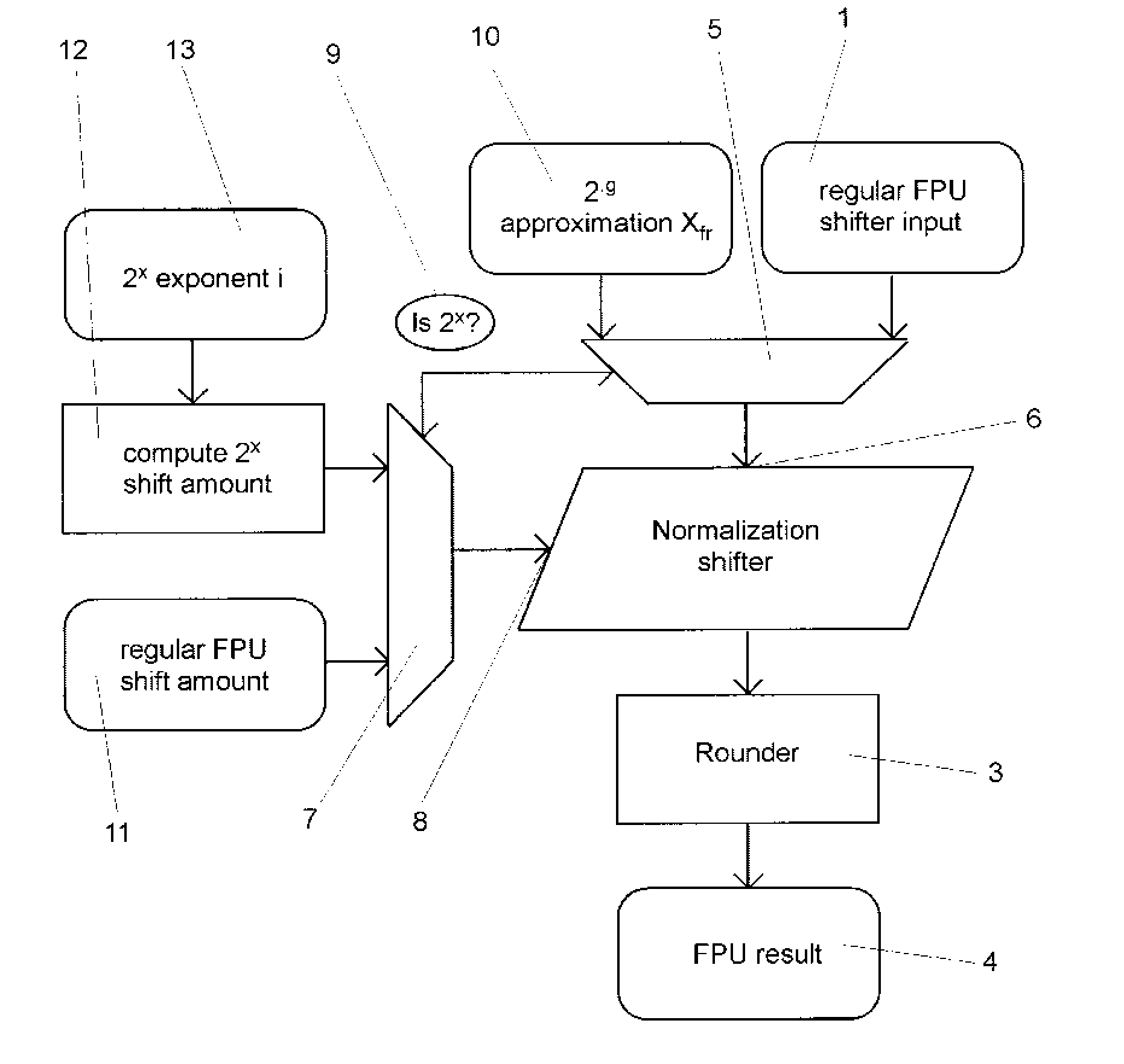

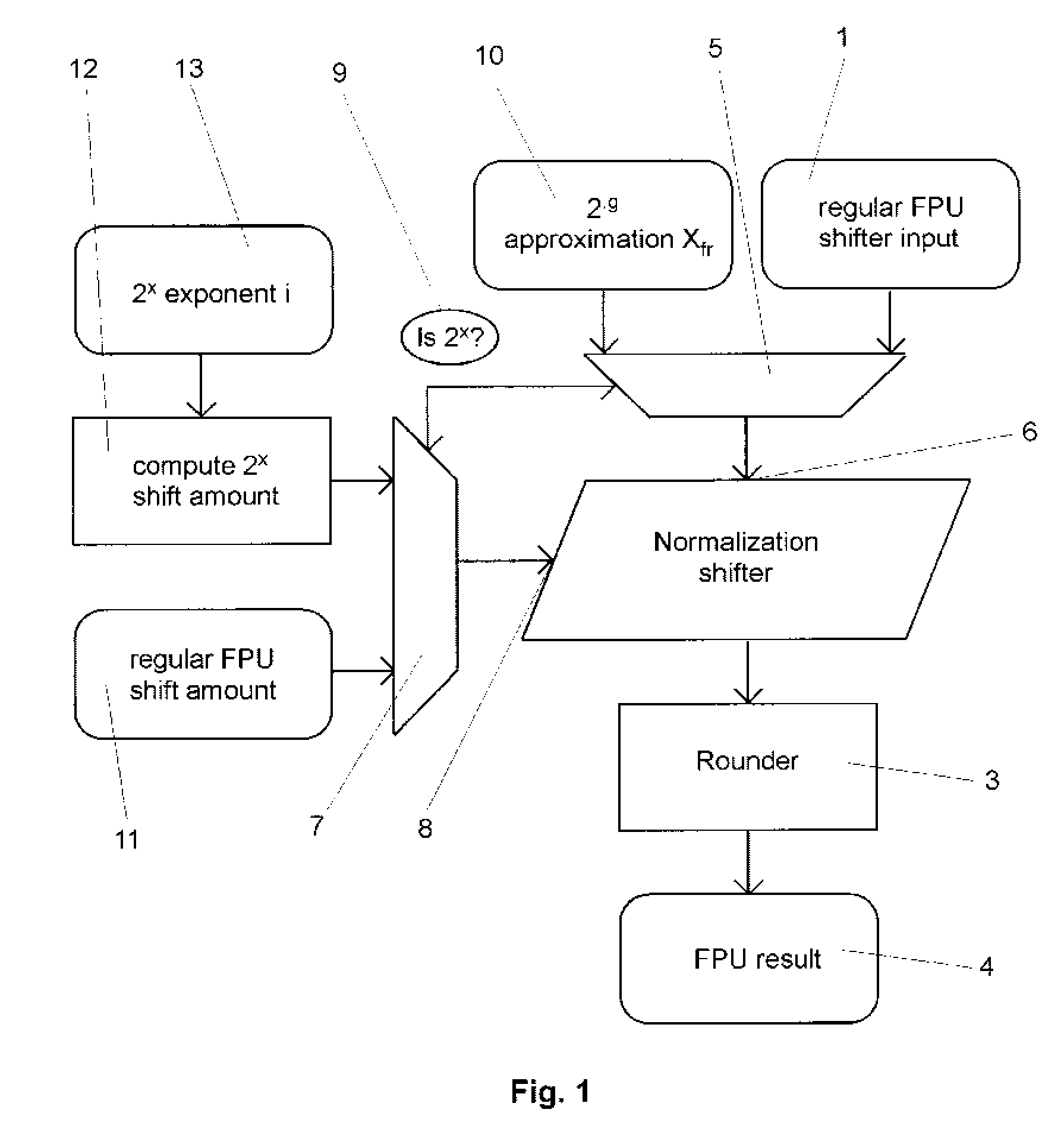

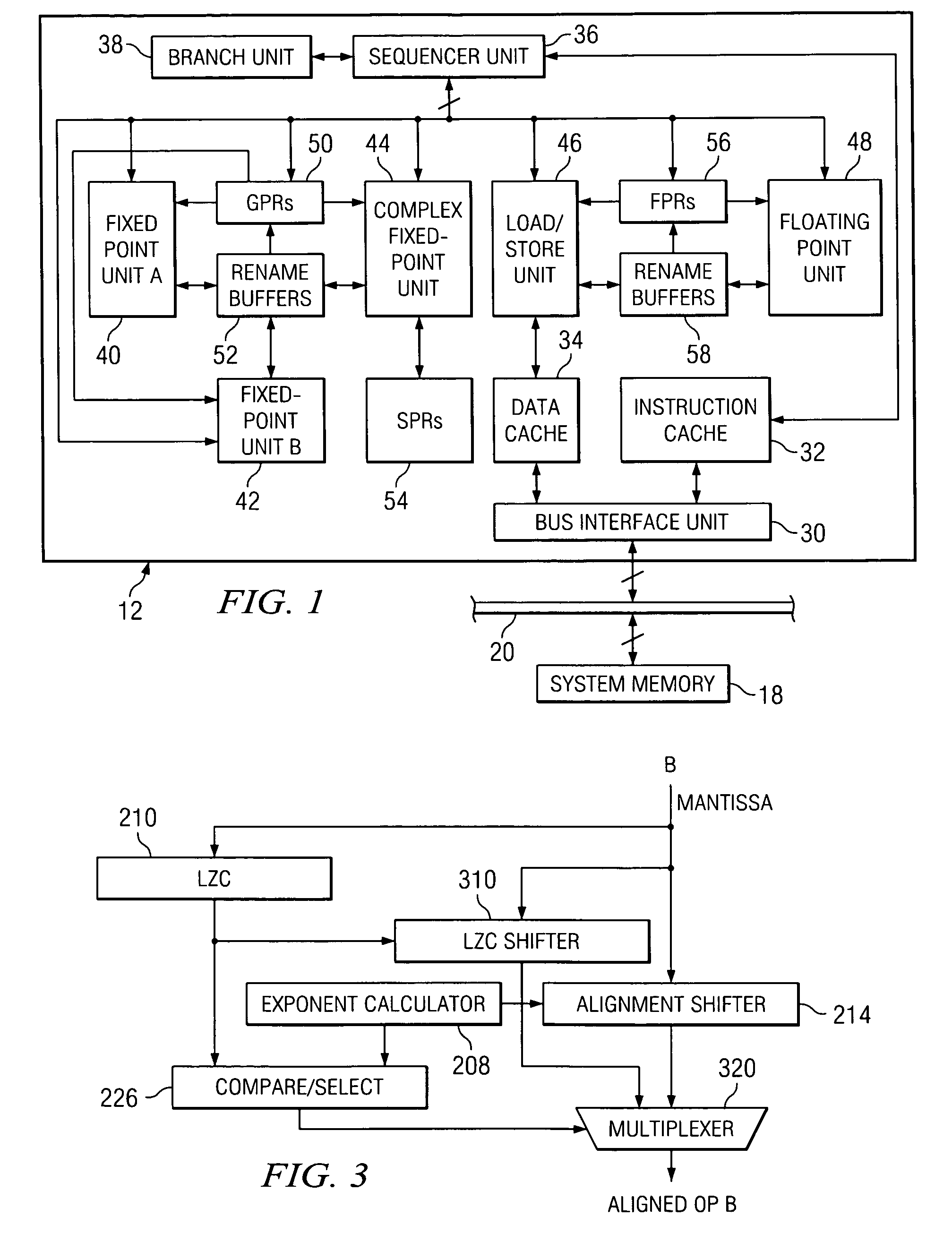

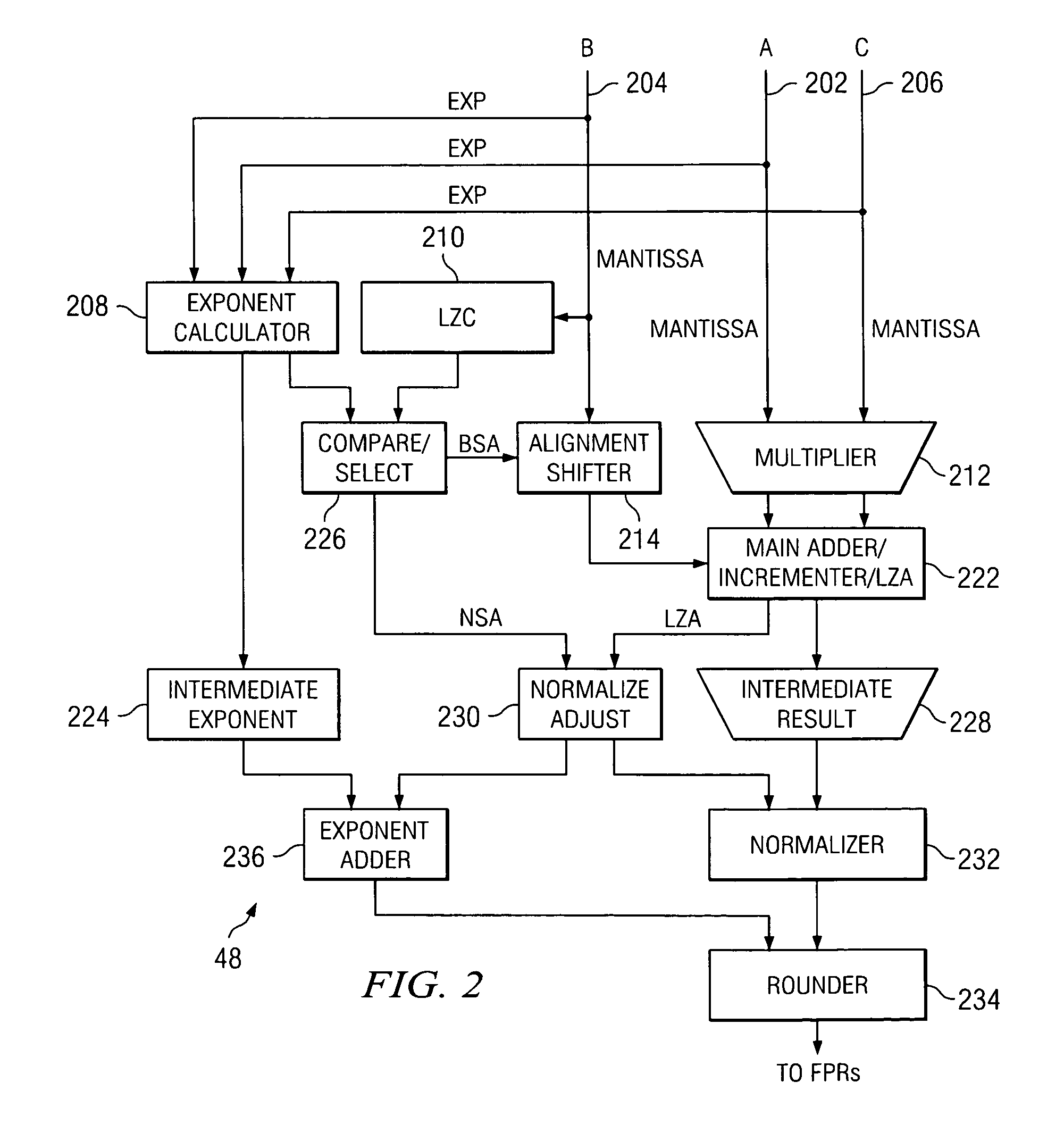

Floating point unit with fused multiply add and method for calculating a result with a floating point unit

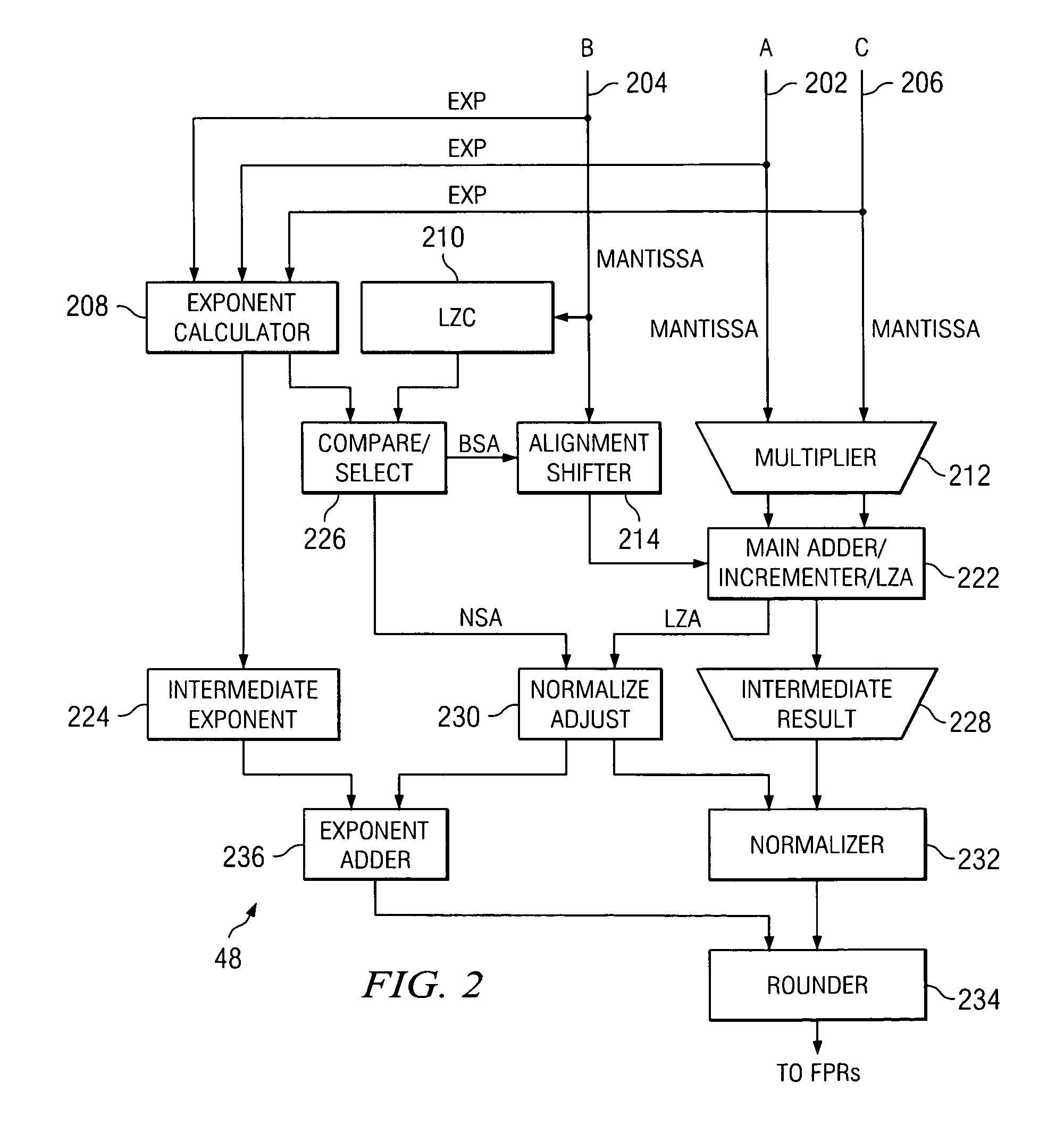

InactiveUS20060184601A1Reduce delaysSimplify carry logicComputation using denominational number representationFloating-point unitOperand

The invention proposes a Floating Point Unit (1) with fused multiply add, with one addend operand (eb, fb) and two multiplicand operands (ea, fa; ec, fc), with a shift amount logic (2) which based on the exponents of the operands (ea, eb and ec) computes an alignment shift amount, with an alignment logic (3) which uses the alignment shift amount to align the fraction (fb) of the addend operand, with a multiply logic (4) which multiplies the fractions of the multiplicand operands (fa, fc), with a adder logic (5) which adds the outputs of the alignment logic (3) and the multiply logic (4), with a normalization logic (6) which normalizes the output of the adder logic (5), which is characterized in that a leading zero logic (7) is provided which computes the number of leading zeros of the fraction of the addend operand (fb), and that a compare logic (8) is provided which based on the number of leading zeros and the alignment shift amount computes select signals that indicate whether the most significant bits of the alignment logic (3) output have all the same value in order to: a) control the carry logic of the adder logic (5) and / or b) control a stage of the normalization logic (6).

Owner:IBM CORP

Parallel fixed point square root and reciprocal square root computation unit in a processor

InactiveUS6341300B1Register arrangementsComputation using non-contact making devicesParallel computingLeading zero

A parallel fixed-point square root and reciprocal square root computation uses the same coefficient tables as the floating point square root and reciprocal square root computation by converting the fixed-point numbers into a floating-point structure with a leading implicit 1. The value of a number X is stored as two fixed-point numbers. In one embodiment, the fixed-point numbers are converted to the special floating-point structure using a leading zero detector and a shifter. Following the square root computation or the reciprocal square root computation, the floating point result is shifted back into the two-entry fixed-point format. The shift count is determined by the number of leaded zeros detected during the conversion from fixed-point to floating-point format.

Owner:ORACLE INT CORP

Decimal Floating-Point Adder with Leading Zero Anticipation

ActiveUS20100312812A1Computations using contact-making devicesDigital computer detailsOperandLeading zero

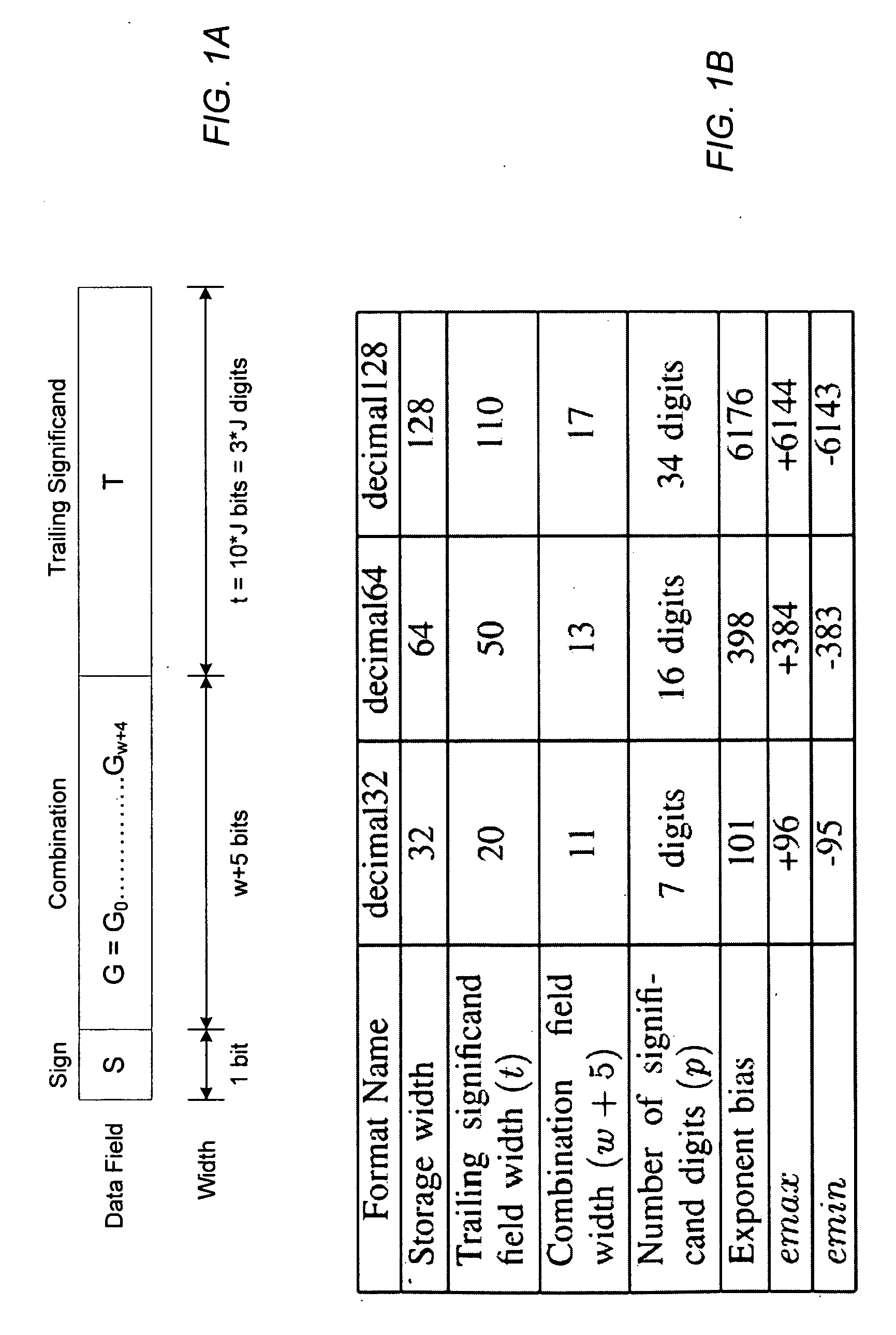

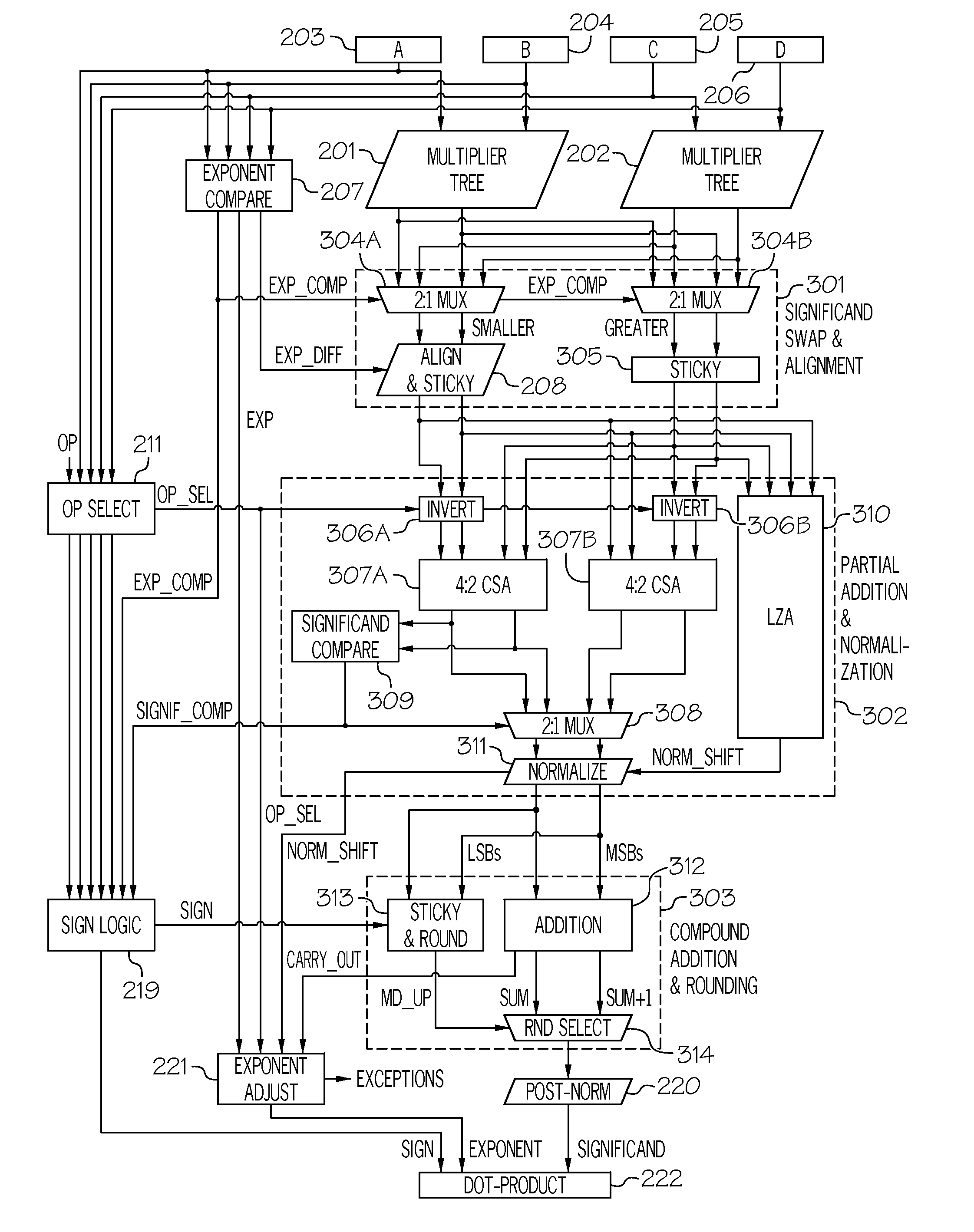

A decimal floating-point (DFP) adder includes a decimal leading-zero anticipator (LZA). The DFP adder receives DFP operands. Each operand includes a significand, an exponent, a sign bit and a leading zero count for the significand. The DFP adder adds or subtracts the DFP operands to obtain a DFP result. The LZA determines the leading zero count associated with the significand of the DFP result. The LZA operates at least partially in parallel with circuitry (in the DFP adder) that computes the DFP result. The LZA does not wait for that circuitry to finish computation of the DFP result. Instead it “anticipates” the number of leading zeros that the result's significand will contain.

Owner:ADVANCED MICRO DEVICES INC

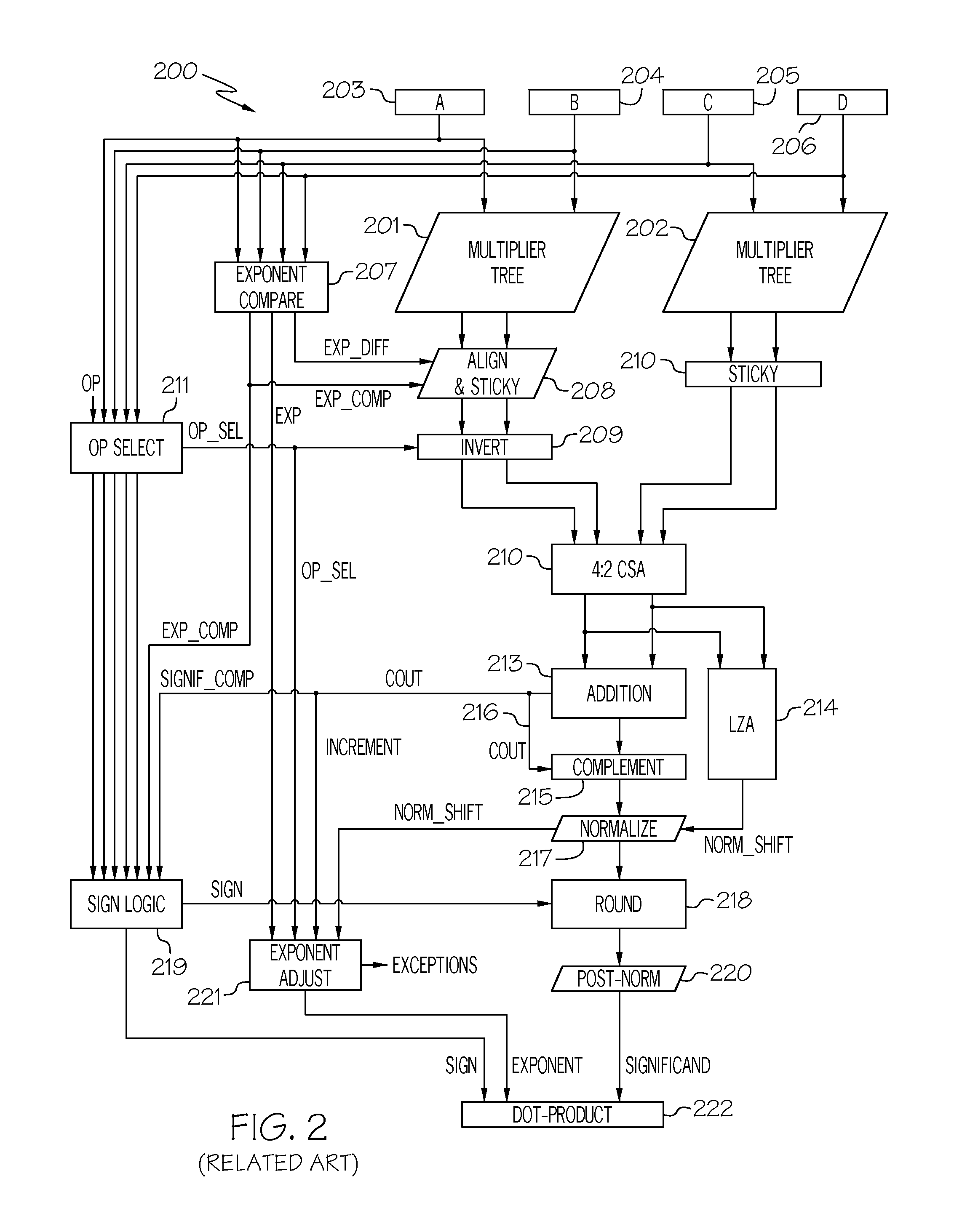

Dual-path fused floating-point two-term dot product unit

InactiveUS8626813B1Shorten the lengthComputation using denominational number representationLeading zeroComputer science

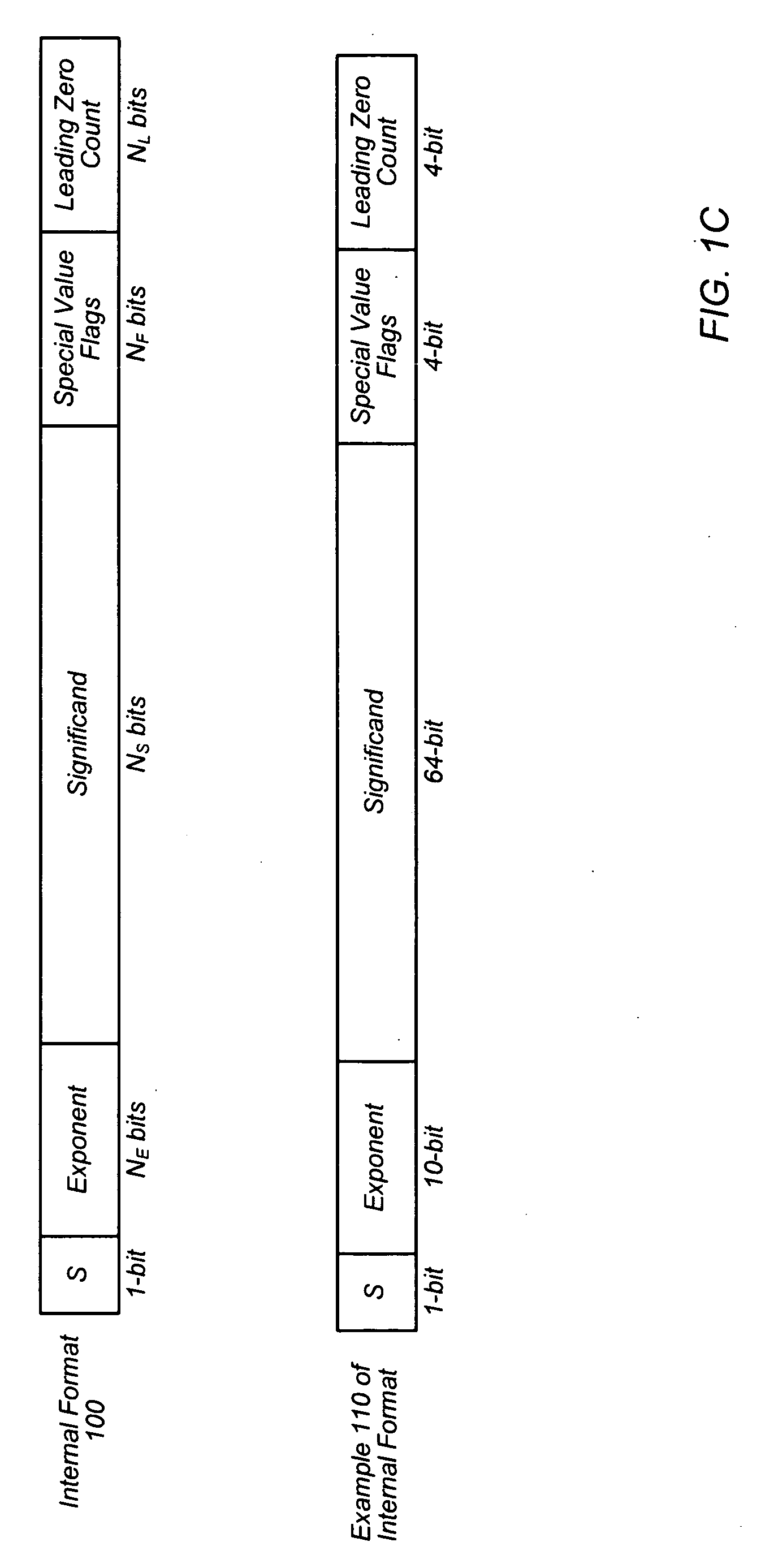

A fused floating-point dot product unit. The fused dot product unit includes an improved alignment scheme that generates smaller significand pairs compared to the traditional alignment due to the reduced shift amount and sticky logic. Furthermore, the fused dot product unit implements early normalization and a fast rounding scheme. By normalizing the significands prior to the significand addition, the length of the adder can be reduced and the round logic can be performed in parallel. Additionally, the fused dot product unit implements a four-input leading zero anticipation unit thereby reducing the overhead of the reduction tree by encoding the four inputs at once. The fused floating-point dot product unit may also employ a dual-path (a far path and a close path) algorithm to improve performance. Pipelining may also be applied to the dual-path fused dot product unit to increase the throughput.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Floating point unit with fused multiply add and method for calculating a result with a floating point unit

InactiveUS7461117B2Simplify carry logicReduce delaysComputation using denominational number representationFloating-point unitOperand

The invention proposes a Floating Point Unit (1) with fused multiply add, with one addend operand (eb, fb) and two multiplicand operands (ea, fa; ec, fc), with a shift amount logic (2) which based on the exponents of the operands (ea, eb and ec) computes an alignment shift amount, with an alignment logic (3) which uses the alignment shift amount to align the fraction (fb) of the addend operand, with a multiply logic (4) which multiplies the fractions of the multiplicand operands (fa, fc), with a adder logic (5) which adds the outputs of the alignment logic (3) and the multiply logic (4), with a normalization logic (6) which normalizes the output of the adder logic (5), which is characterized in that a leading zero logic (7) is provided which computes the number of leading zeros of the fraction of the addend operand (fb), and that a compare logic (8) is provided which based on the number of leading zeros and the alignment shift amount computes select signals that indicate whether the most significant bits of the alignment logic (3) output have all the same value in order to: a) control the carry logic of the adder logic (5) and / or b) control a stage of the normalization logic (6).

Owner:INT BUSINESS MASCH CORP

Floating point multiplier with partial product shifting circuitry for result alignment

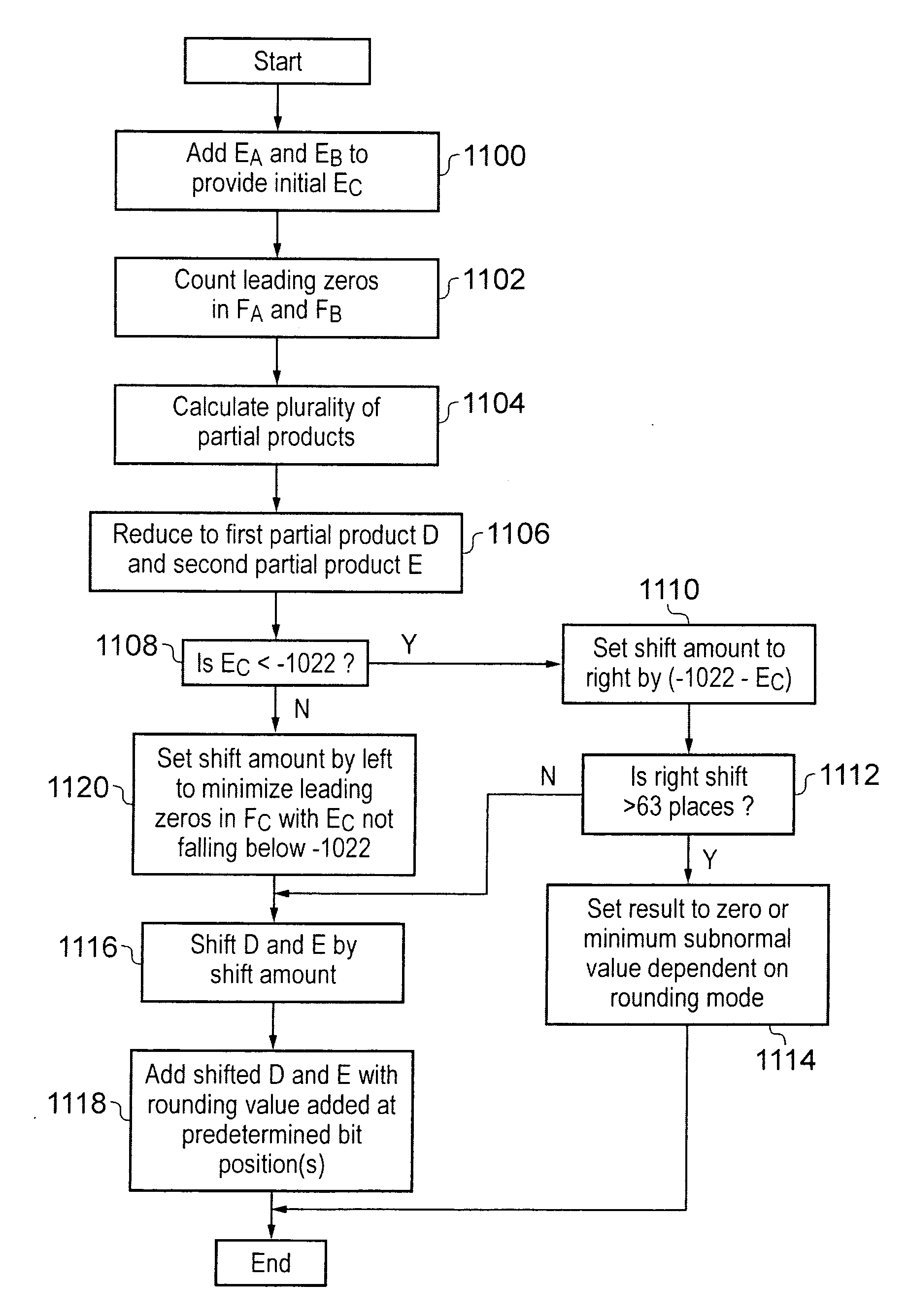

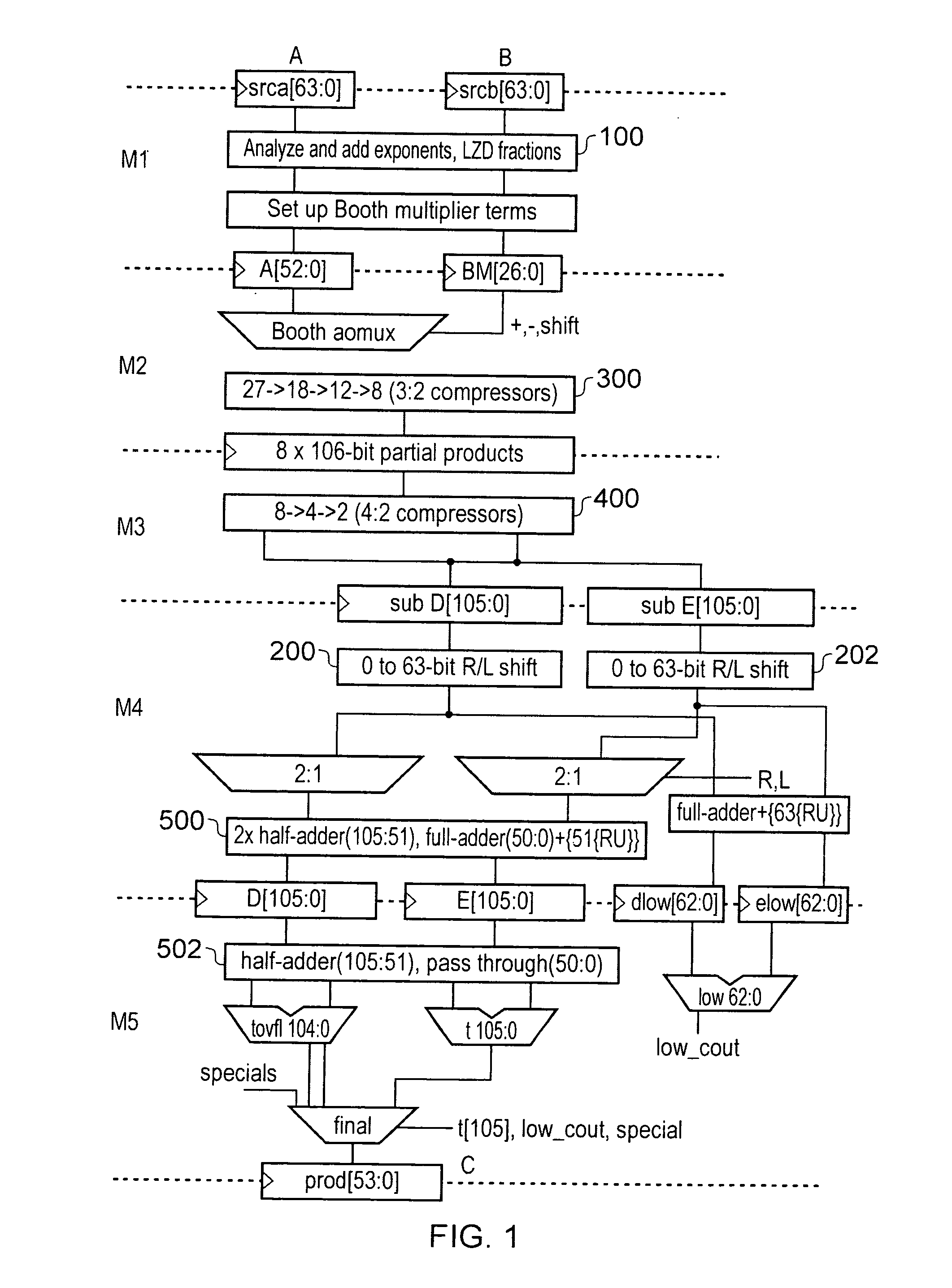

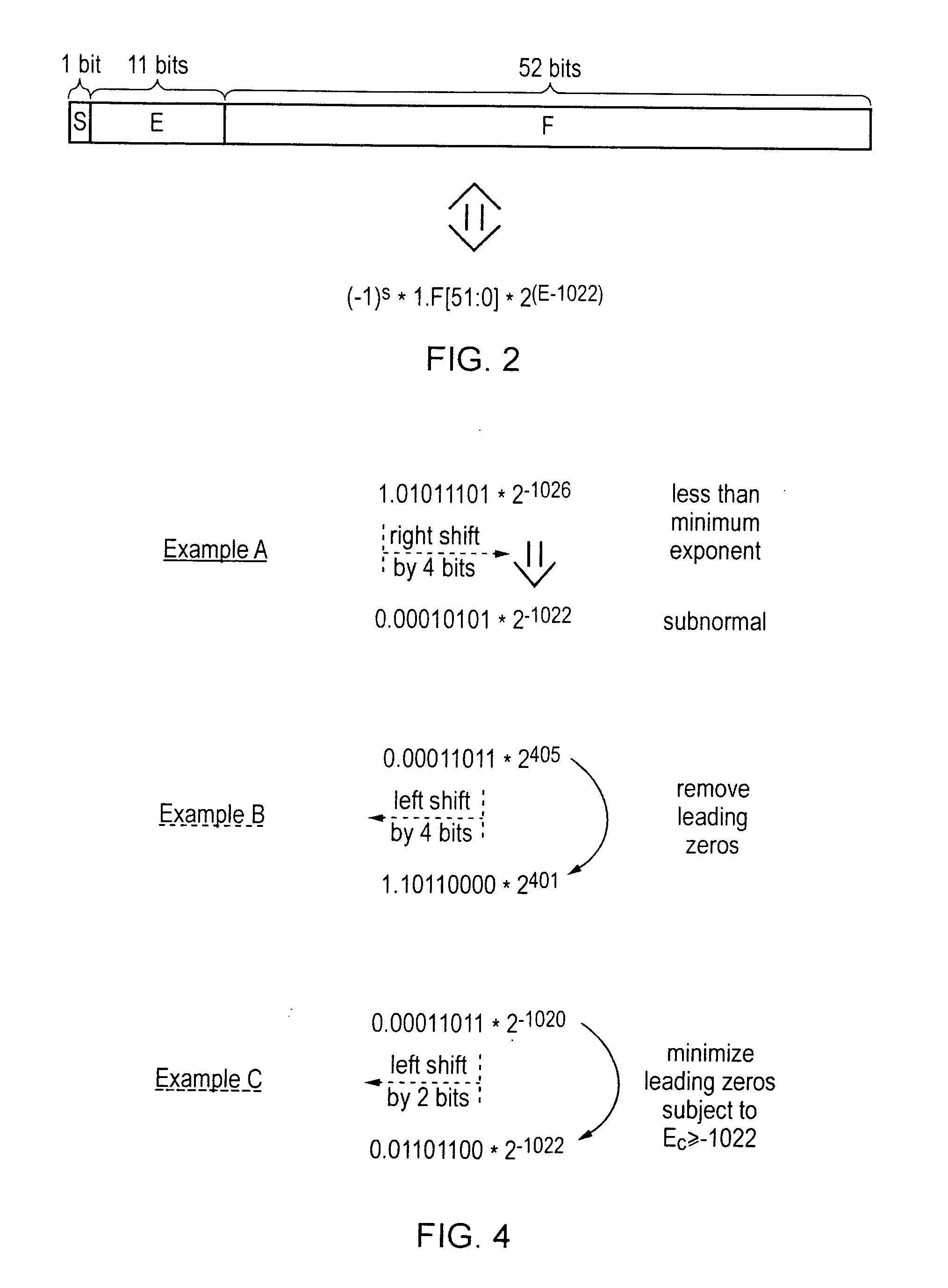

ActiveUS20110106868A1Minimize the numberReduce delaysDigital computer detailsData conversionRight shiftOperand

A floating point multiplier includes a data path in which a plurality of partial products are calculated and then reduced to a first partial product and a second partial product. Shift amount determining circuitry 100 analyses the exponents of the input operands A and B as well as counting the leading zeros in the fractional portions of these operands to determine an amount of left shift or right shift to be applied by shifting circuitry 200, 202 within the multiplier data path. This shift amount is applied so as to align the partial products so that when they are added they will produce the result C without requiring this to be further shifted. Furthermore, shifting the partial products to the correct alignment in this way in advance of adding these partial products permits injection rounding combined with the adding of the partial products to be employed for cases including subnormal values.

Owner:ARM LTD

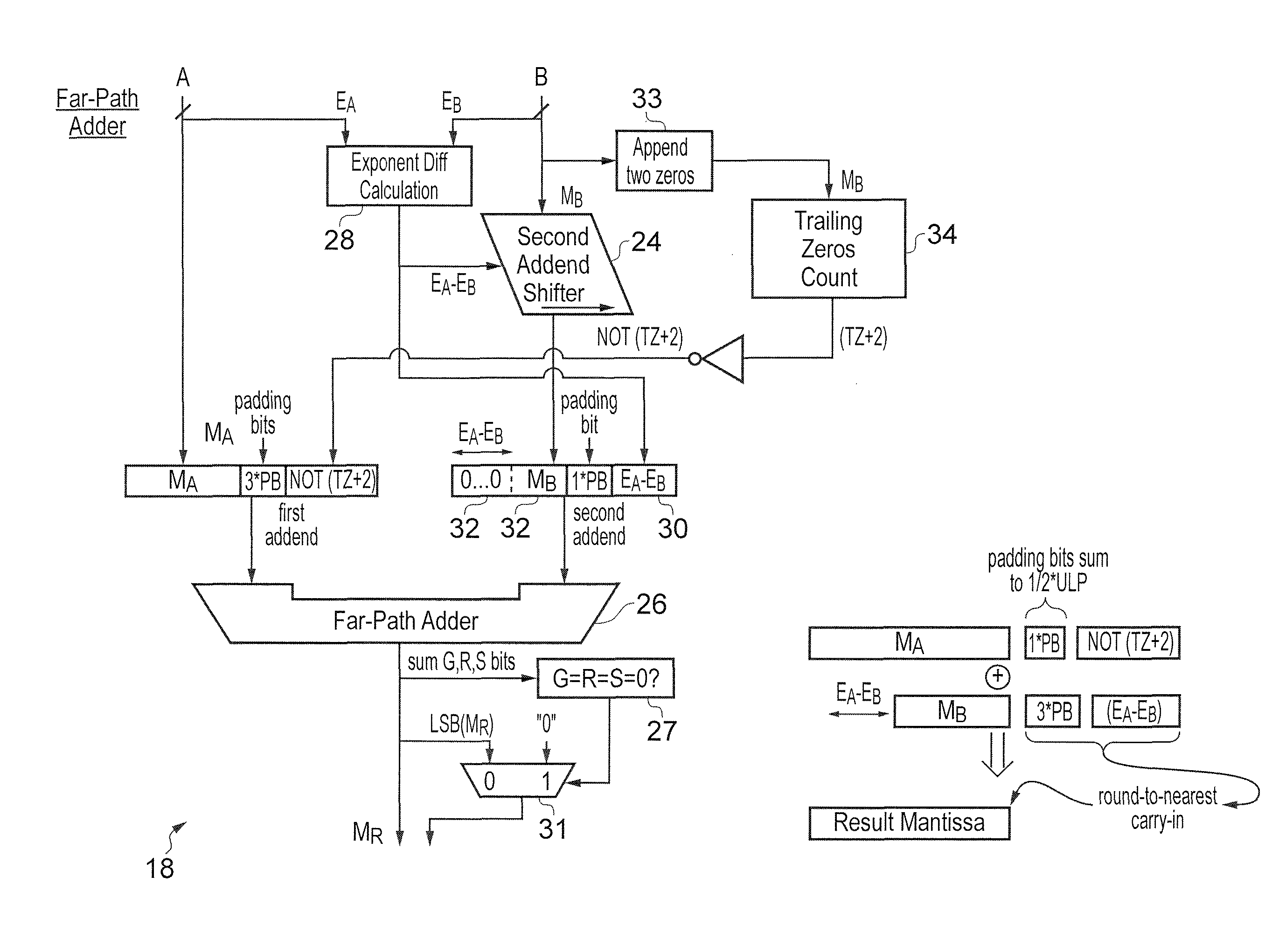

Floating-point adder

ActiveUS20130007084A1Lower latencyMaintain balanceComputations using contact-making devicesComputer architectureOperand

Floating point adder circuitry 16, 18, 20 is provided with far-path circuitry 18 and near-path circuitry 20. The far-path circuitry utilises a count of trailing zeros TZ and a difference in the input operand exponents to form respective suffix values which are concatenated with the mantissas of the input addends and serve when summed to generate a carry out taking the place of a conventionally calculated sticky bit. Within the near-path, minimum value circuitry 46 is used to calculate the lower of a leading zeros count of the intermediate mantissa produced in a subtraction and the larger of the input operand exponent values such that a left shift applied to the intermediate mantissa value is not able to produce a invalid floating point result due to applying a left shift to remove leading zeros that is too larger and accordingly corresponds to an exponent which cannot be validly represented.

Owner:ARM LTD

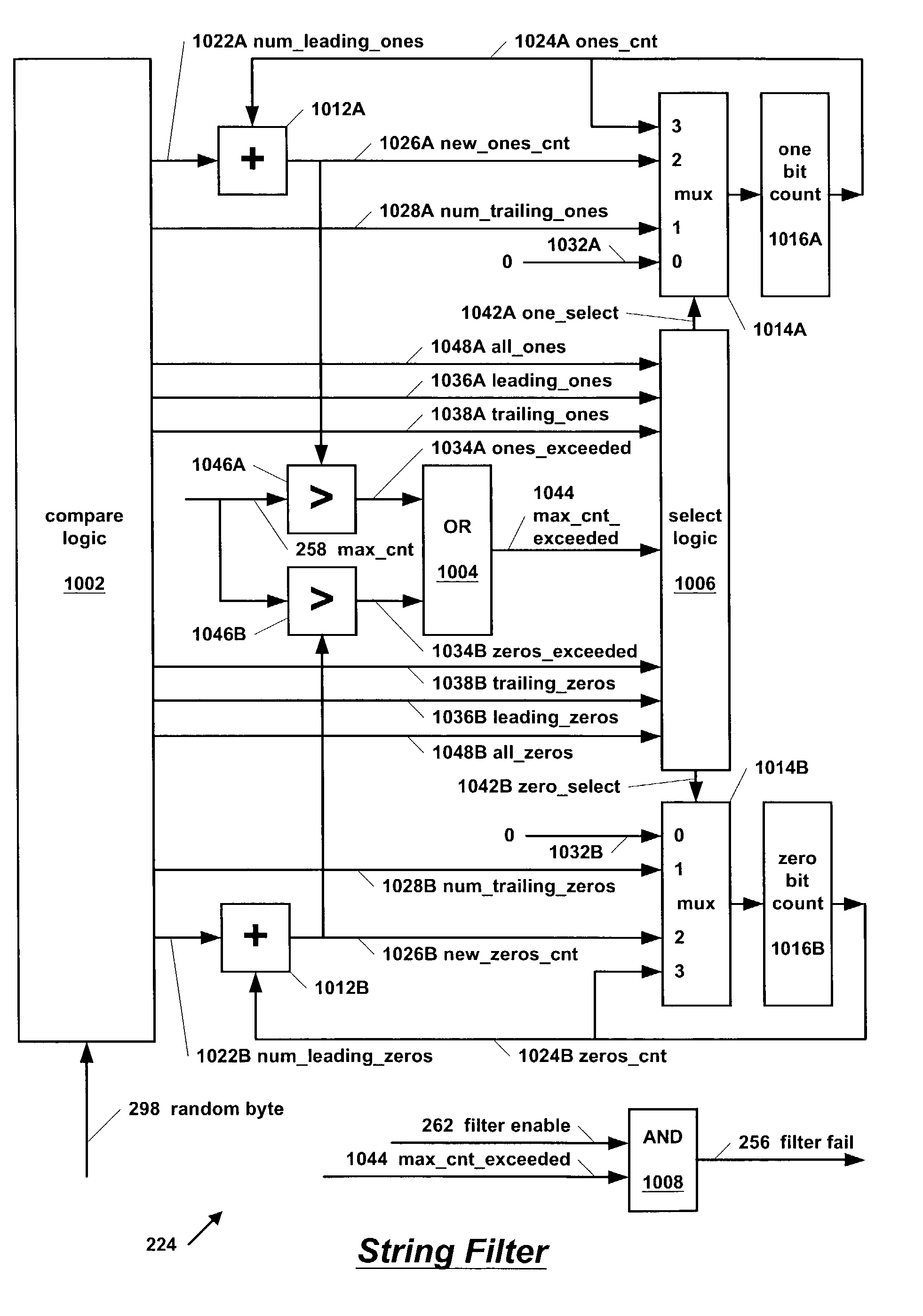

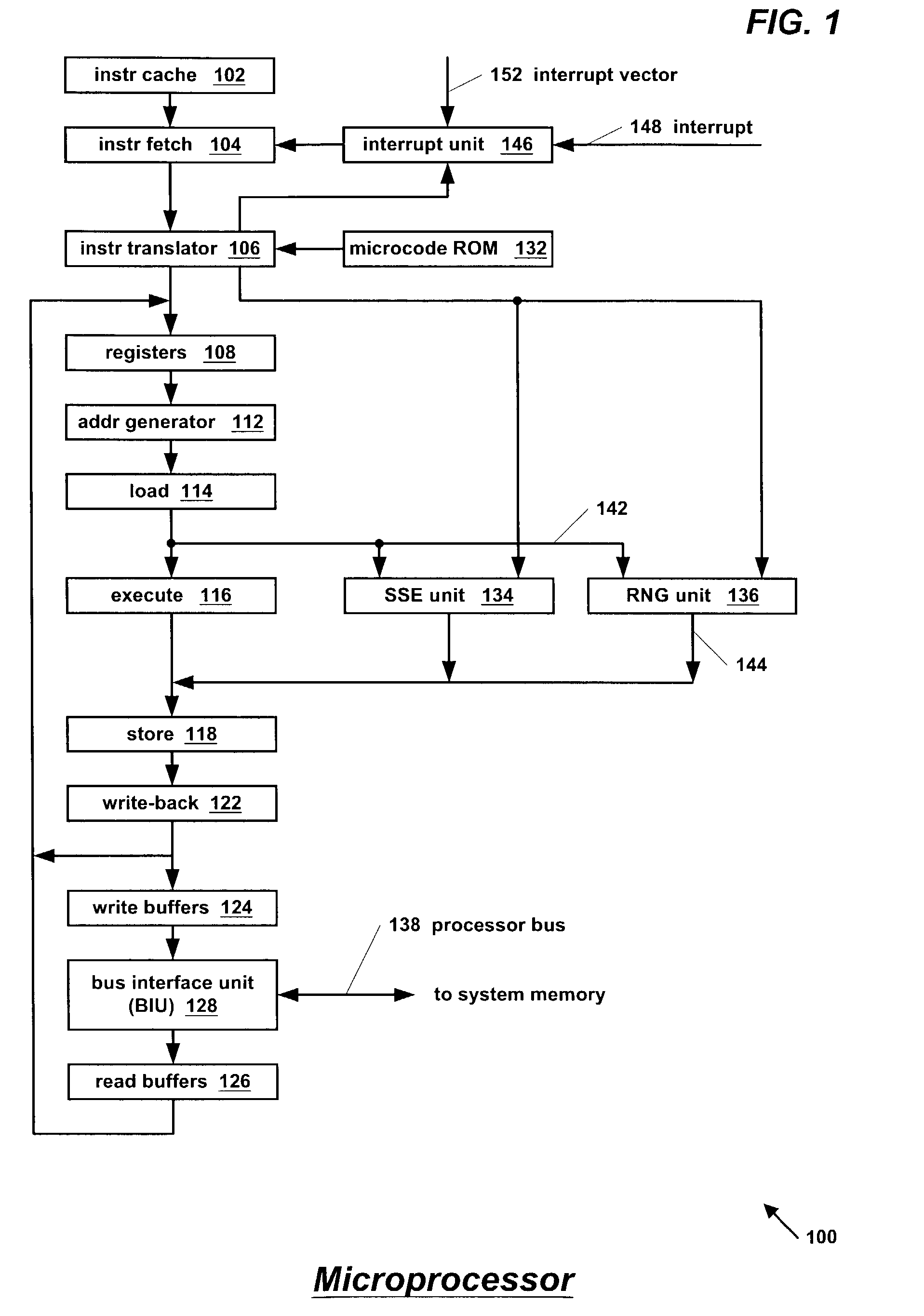

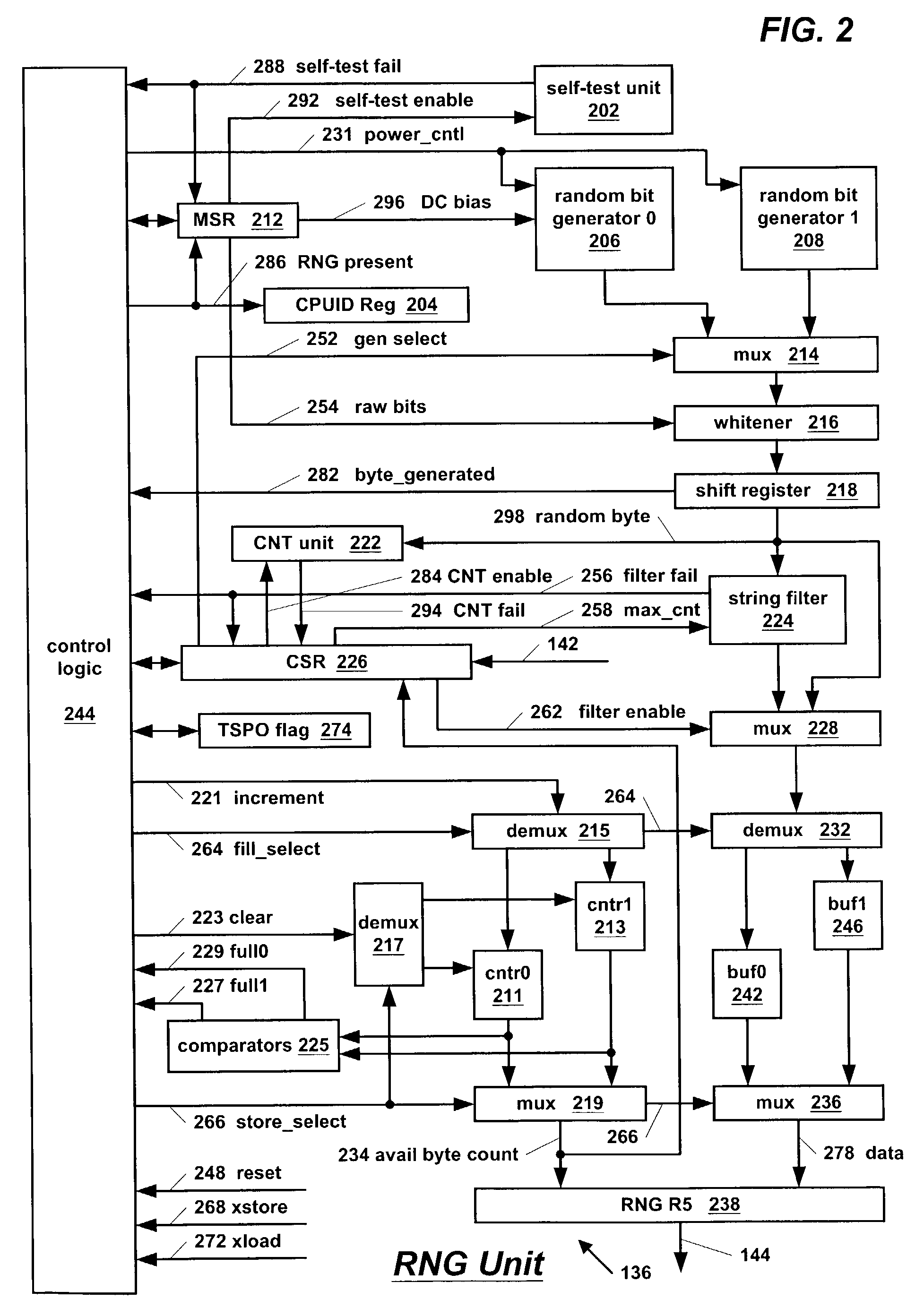

Random number generator bit string filter

ActiveUS7149764B2Faster rateRandom number generatorsDigital function generatorsLeading zeroNumber generator

A filtering apparatus in a hardware random number generator that prevents the random number generator (RNG) from outputting a contiguous string of zeros or ones longer than a specified length. The maximum length is programmable in the apparatus. The apparatus includes a counter that keeps a current count of contiguous zero bits in a series of bytes generated by the RNG. An adder generates a sum of the current zero bit count and the number of leading zeros in the next byte generated. If the sum exceeds the maximum length, then the filter throws out the byte rather than accumulating it. Otherwise, if the byte contains all zeros, the counter is updated with the sum; or if the byte contains trailing zeros, the counter is updated with the number of trailing zeros; otherwise the counter is cleared. The apparatus does the same for contiguous one bits.

Owner:IP FIRST

Method and floating point unit to convert a hexadecimal floating point number to a binary floating point number

InactiveUS20070022152A1Improve performanceComputation using non-contact making devicesDigital computer detailsComputational scienceFloating-point unit

Method to convert a hexadecimal floating point number (H) into a binary floating point number by using a Floating Point Unit (FPU) with fused multiply add with an A-register a B-register for two multiplicand operands and a C-register for an addend operand, wherein a leading zero counting unit (LZC) is associated to the addend C-register, wherein the difference of the leading zero result provided by the LZC and the input exponent (E) is calculated by a control unit and determines based on the Raw-Result-Exponent a force signal (F) with special conditions like ‘Exponent Overflow’, ‘Exponent Underflow’, and ‘Zero Result’.

Owner:IBM CORP

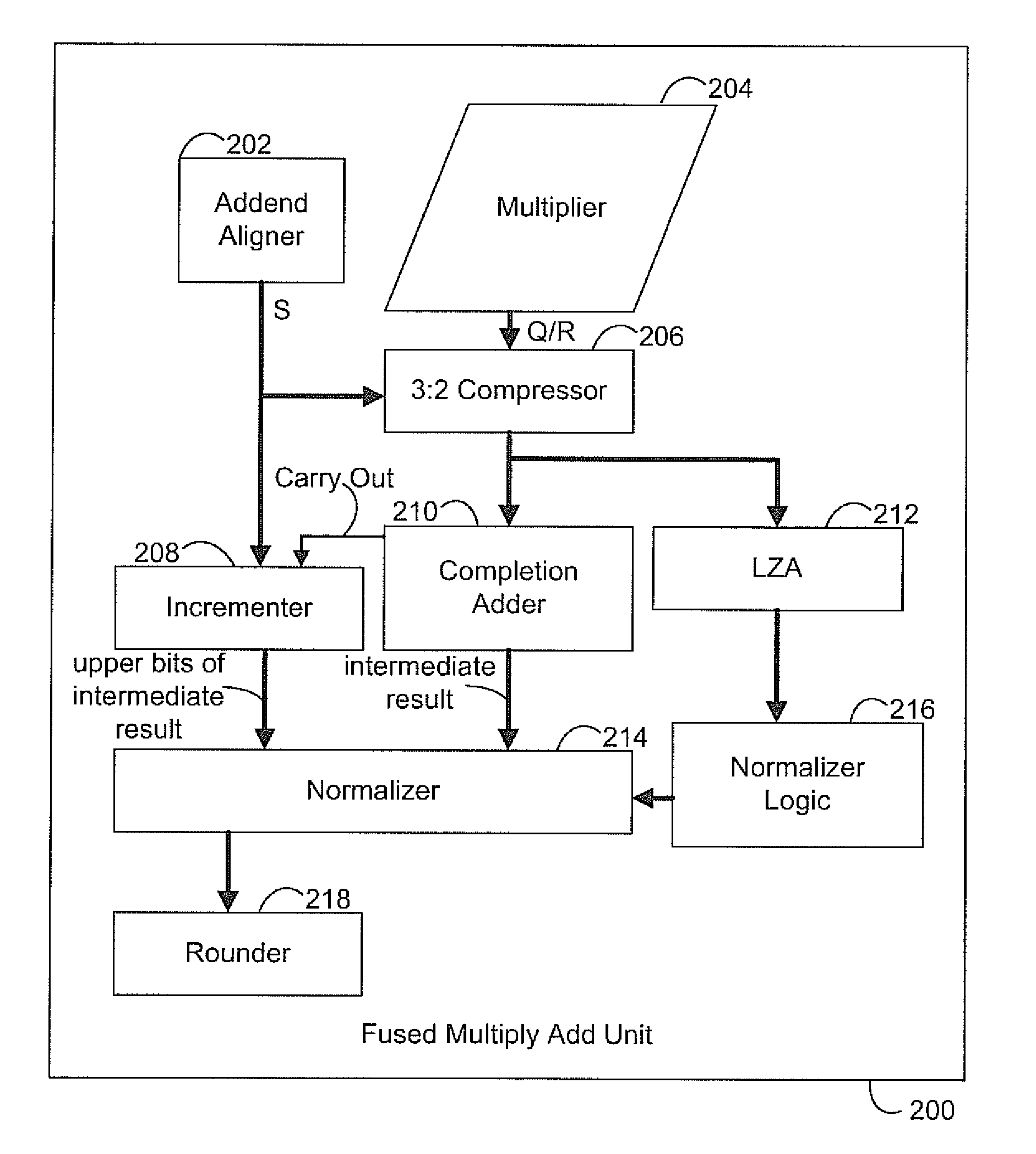

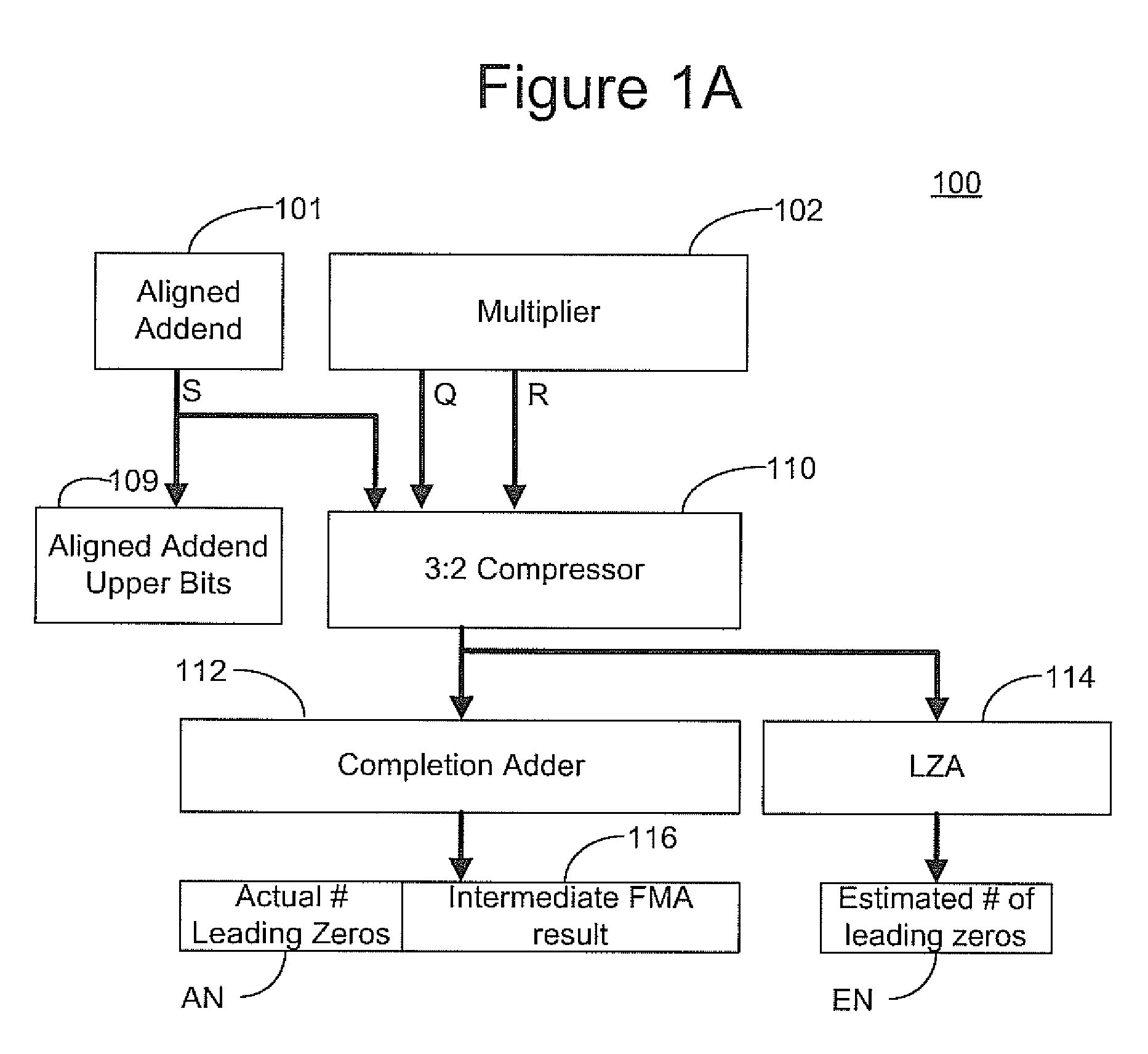

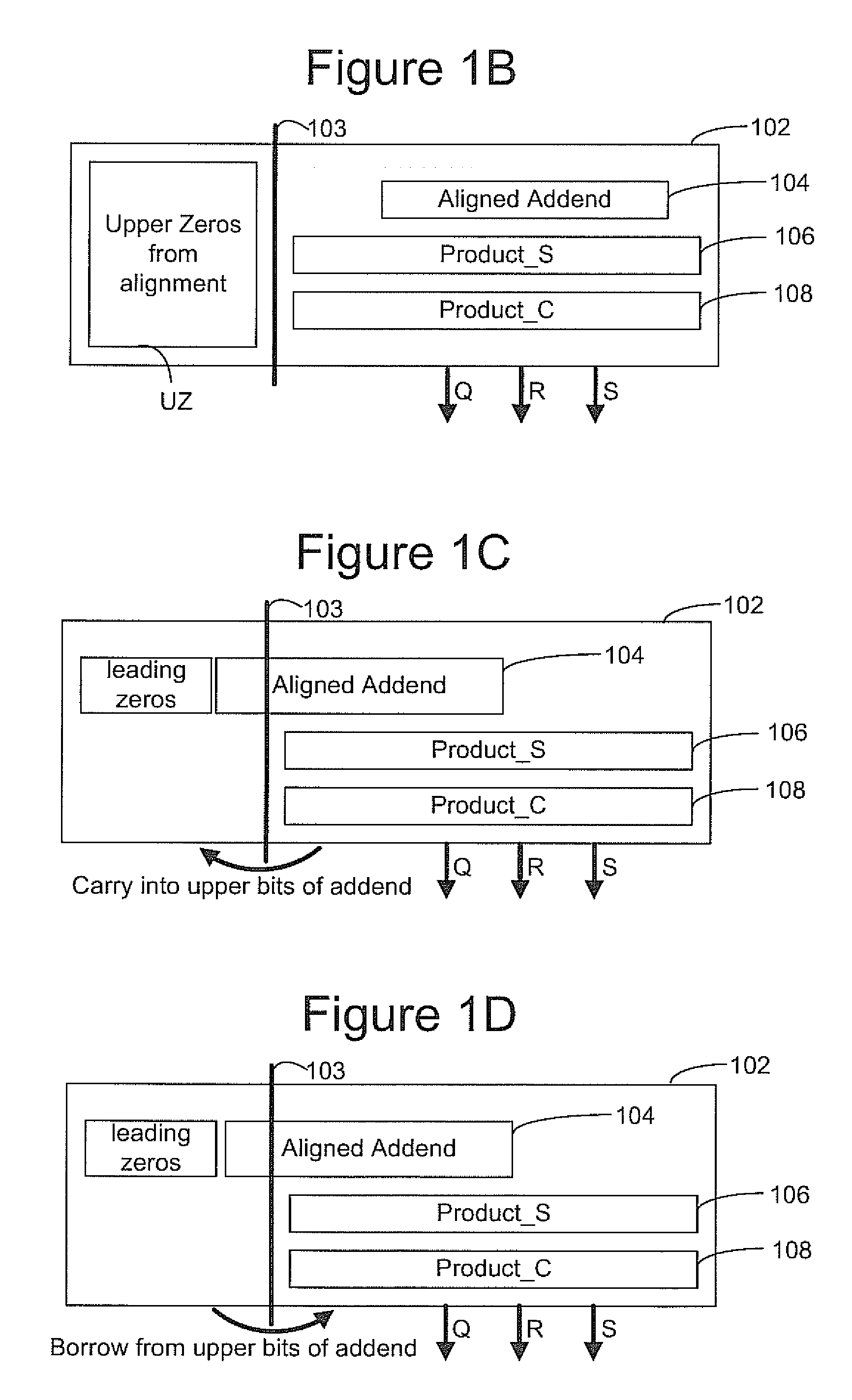

Efficient correction of normalizer shift amount errors in fused multiply add operations

ActiveUS20140188963A1Improve normalizationLess logicDigital data processing detailsDigital computer detailsFloating pointErrors and residuals

Owner:NVIDIA CORP

Billing data interface for conferencing customers

ActiveUS7151824B1Meet data requirementsSpecial service for subscribersBilling/invoicingData fileClient-side

A billing data interface provides billing data to customers in an accurate and efficient manner. Billing data is processed to preserve client billing information and to meet a customer's individual data requirements. The billing data may be presented in such a way that the customer may input the billing data directly into its client billing system. The billing data may be processed according to client billing specifications corresponding to a client billing system used by the customer. The processed data may preserve leading zeros, separate client code and matter code into two fields, etc. The resulting data file may be delivered to the customer for entry into the customer's client billing system.

Owner:AMERICAN TELECONFERENCING SERVICES

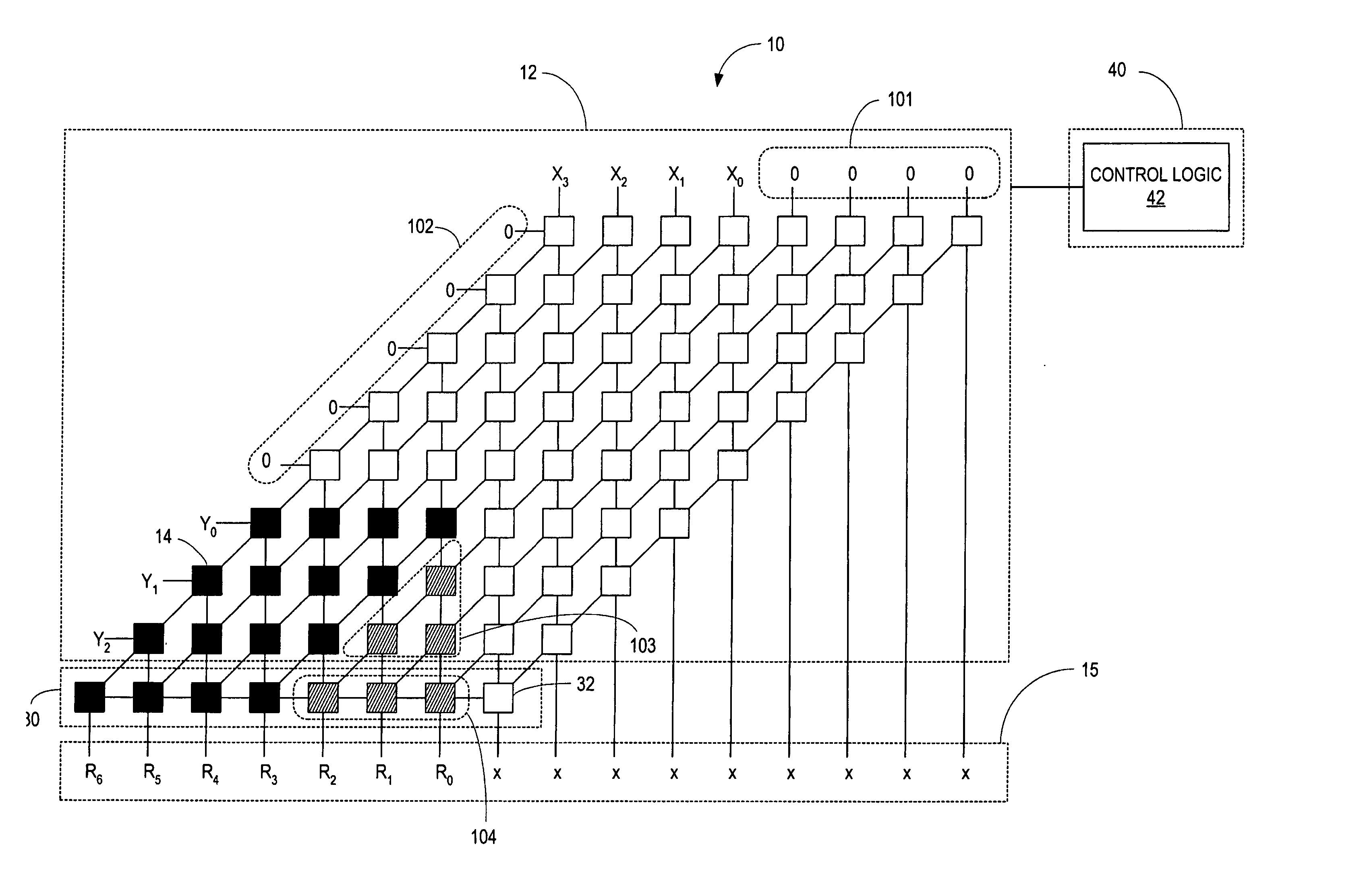

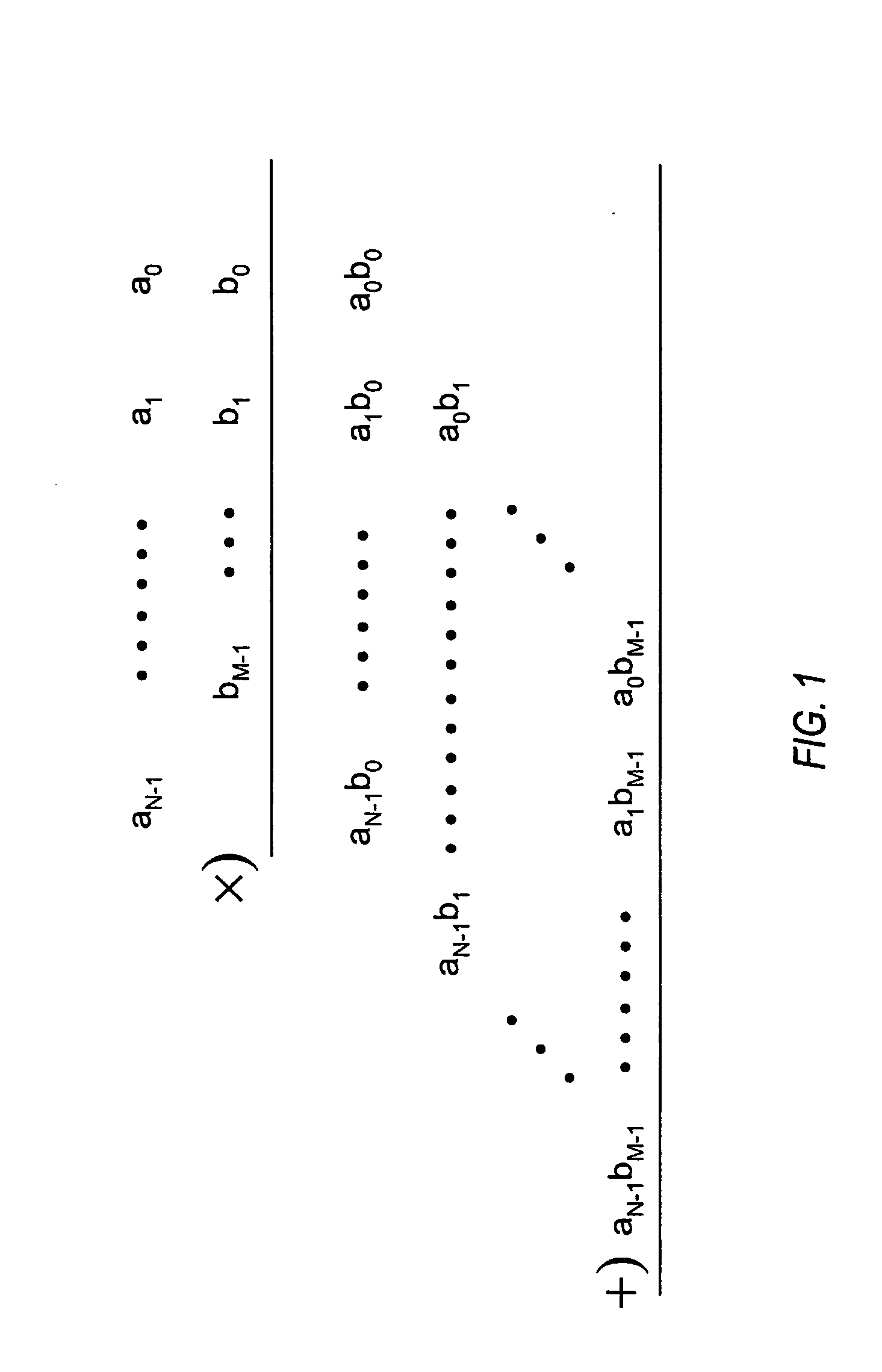

Low Power array multiplier

InactiveUS20060212505A1Lower latencyReduce power consumptionComputation using non-contact making devicesEngineeringOperand

An array multiplier comprises a partial product array including a plurality of array elements and a final carry propagate adder. Operands smaller than a corresponding dimension of the partial product array are shifted toward the most significant row or column of the array to reduce the number of array elements used to compute the product of the operands. Switching activity in the unused array elements may be reduced by turning off power to the array elements or by padding the shifted operands with leading zeros. Additional power saving may be achieved by having bypass lines in the partial product array that bypasses non-essential array elements and by feeding partial sum and carry directly to the final carry propagate adder. Elements of the carry propagate adder may also be bypassed to achieve further power reduction.

Owner:QUALCOMM INC

Method and apparatus for binary leading zero counting with constant-biased result

InactiveUS6779008B1Computation using non-contact making devicesDigital computer detailsFloating pointLeading zero

Owner:IBM CORP

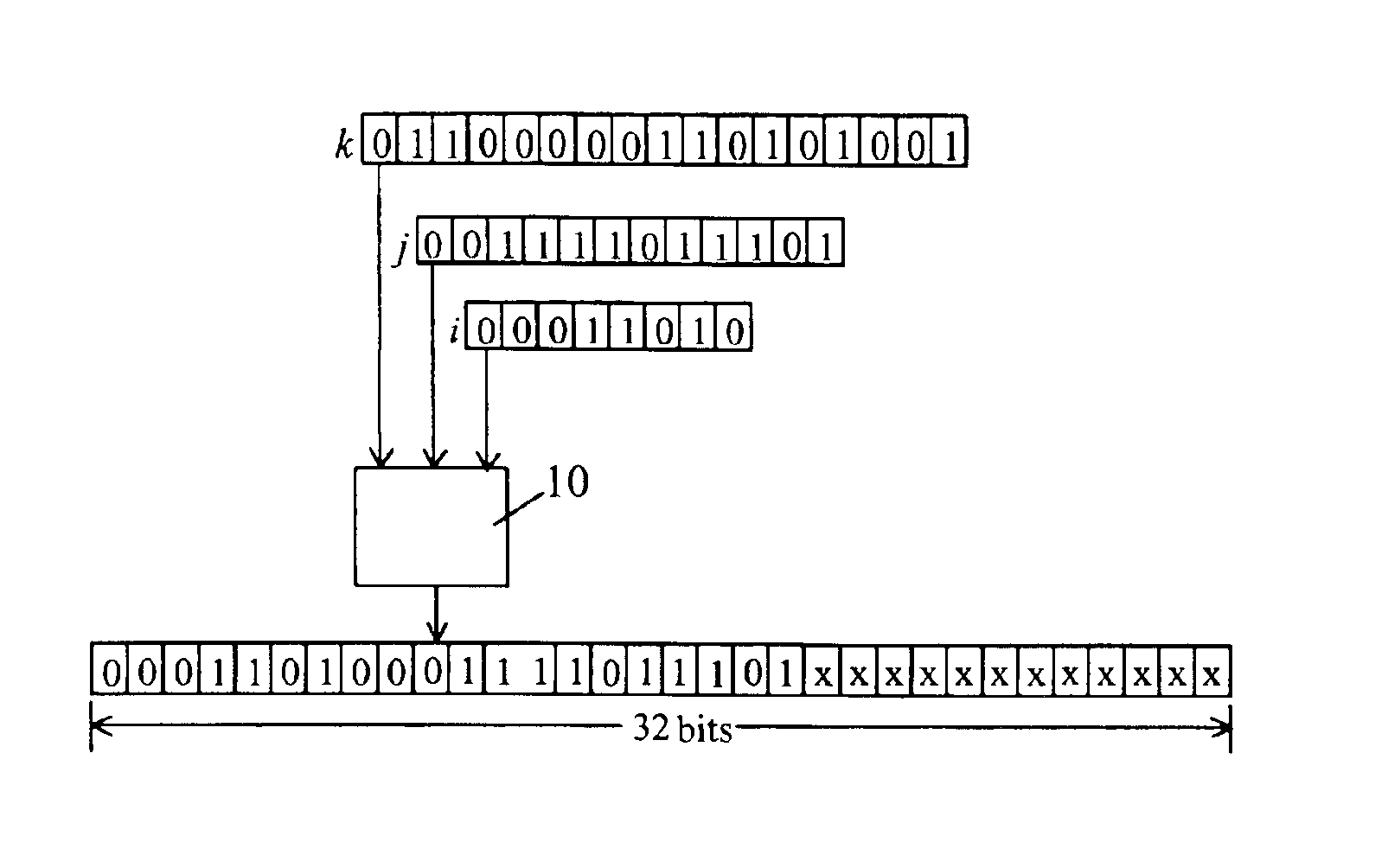

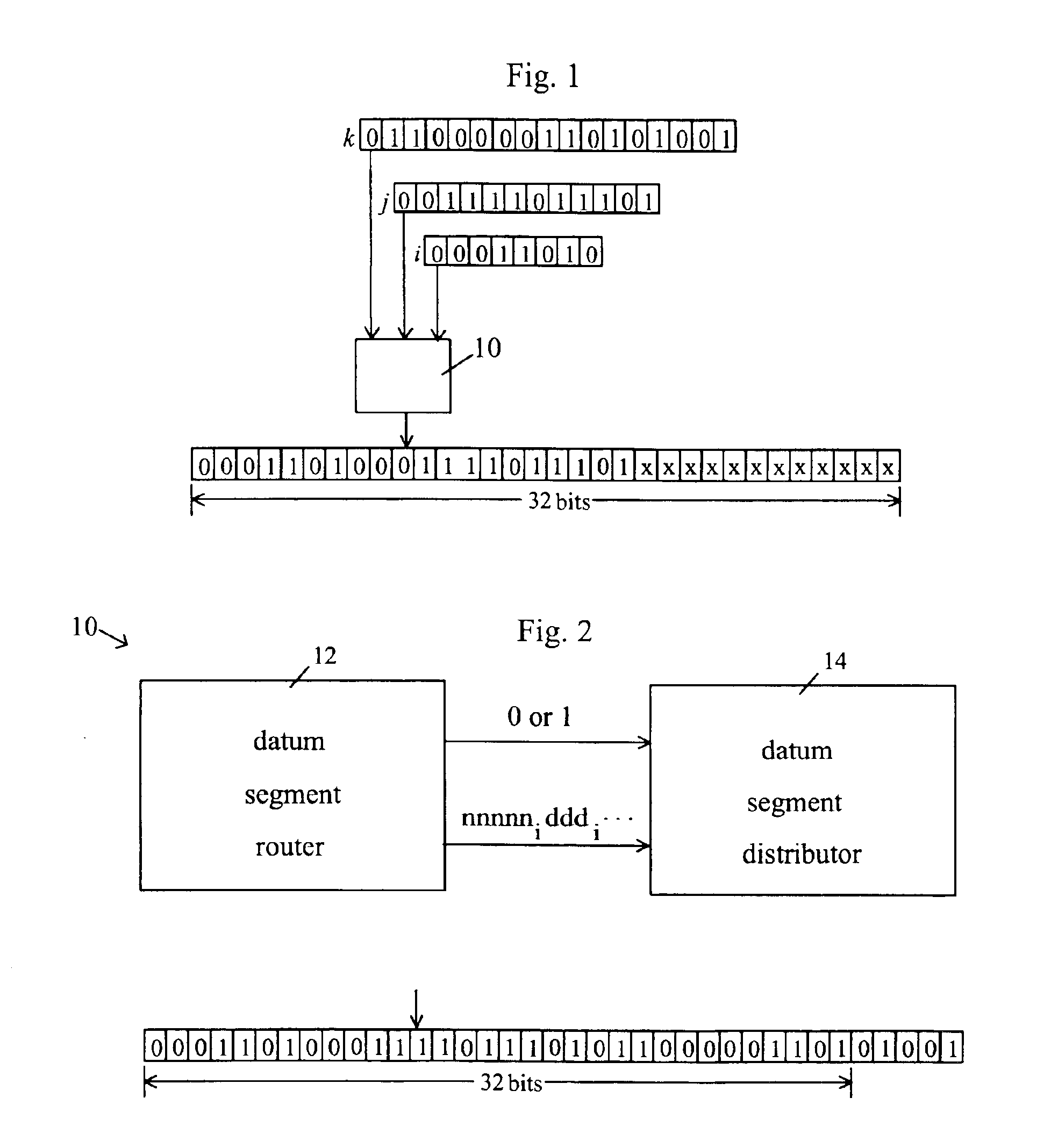

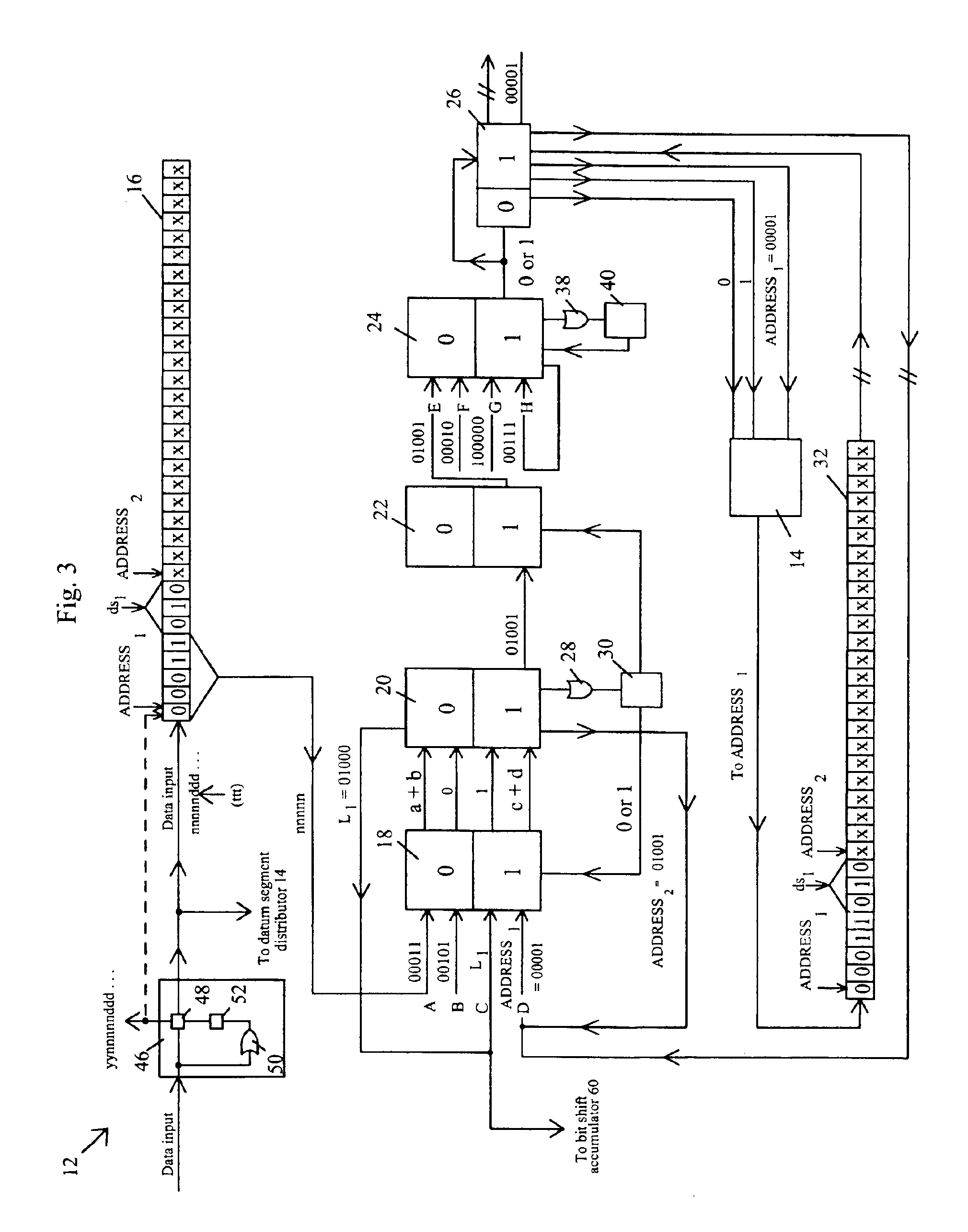

Asynchronous, data-activated concatenator for variable length datum segments

InactiveUS6900746B1Improve transmission efficiencyImprove efficiencyParallel/series conversionDigital dataData segment

An apparatus accepts randomly arriving blacks of parallel digital data of varying bit lengths termed datum segments that may have been generated by stripping leading zeros from bytes of a fixed size, each having associated therewith a bit count code that expresses the bit length of each datum segment in the form nnnnndddd . . . , the “n” being the bits of the bit count code in such number as to encompass the memory capacity of a receiving device to which the datum segments are to be sent, and the “d” representing the actual datum segment bits. The apparatus concatenates the nnnnndddd . . . expressions to form a continuous bit sequence that is saved so that each nnnnndddd . . . expression is accessible thereafter through the computer address therefor, such use preferably being by a circuit of matching bit length, the format, however, allowing the original form of the data to be recovered if desired.

Owner:WEND

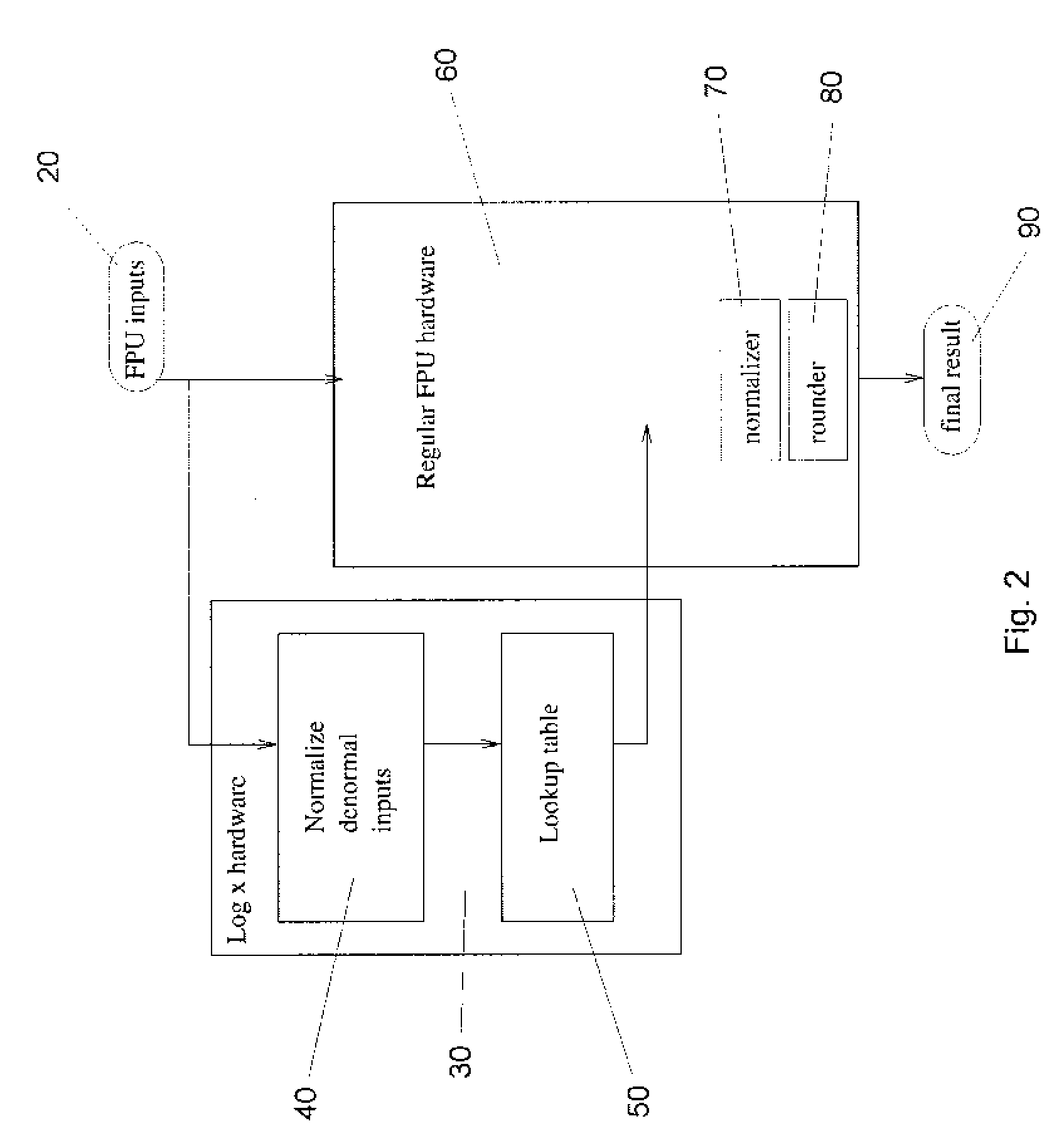

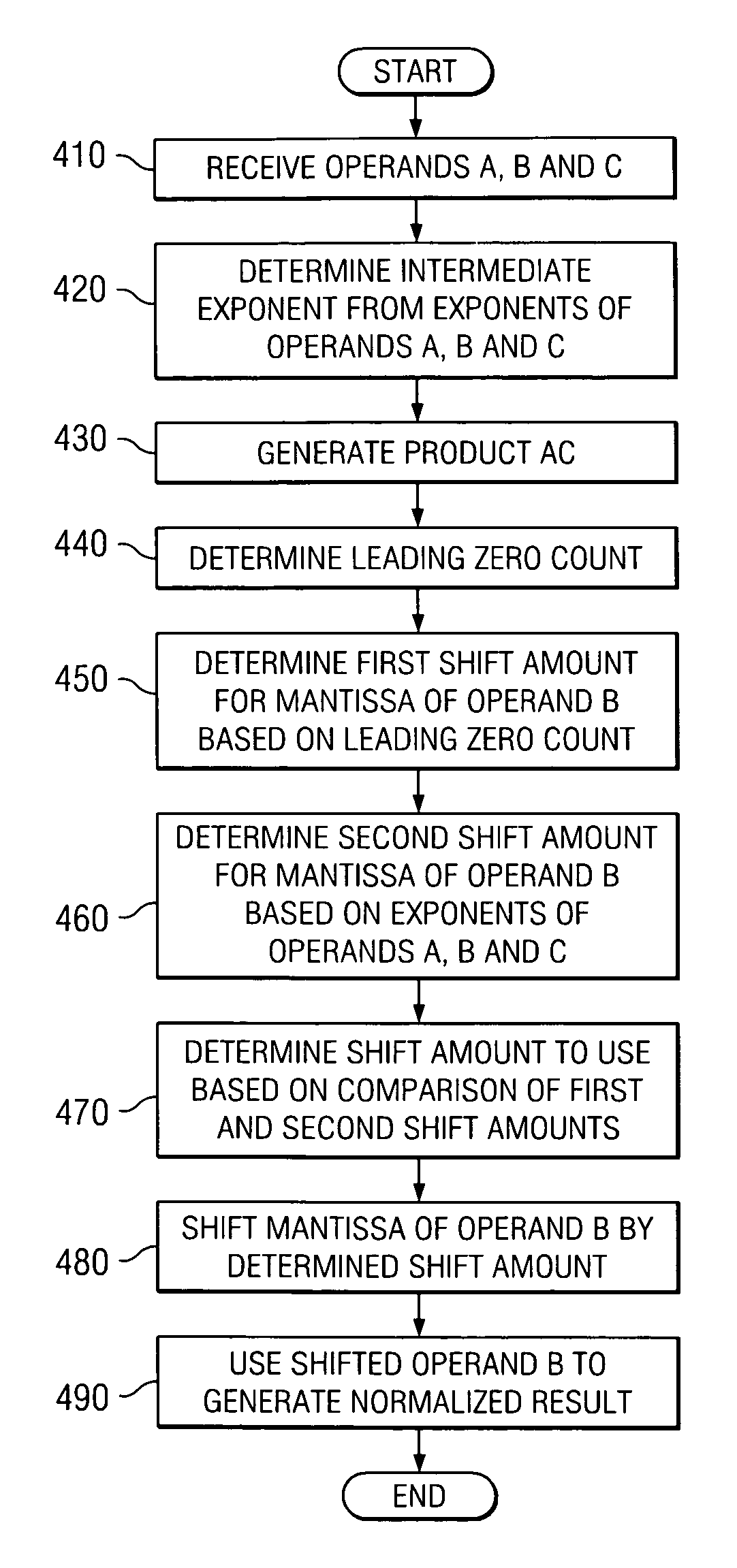

System and method for handling denormal floating point operands when result must be normalized

InactiveUS20060179093A1Eliminate needMinimize powerDigital computer detailsComputation using denominational number representationEngineeringFloating point

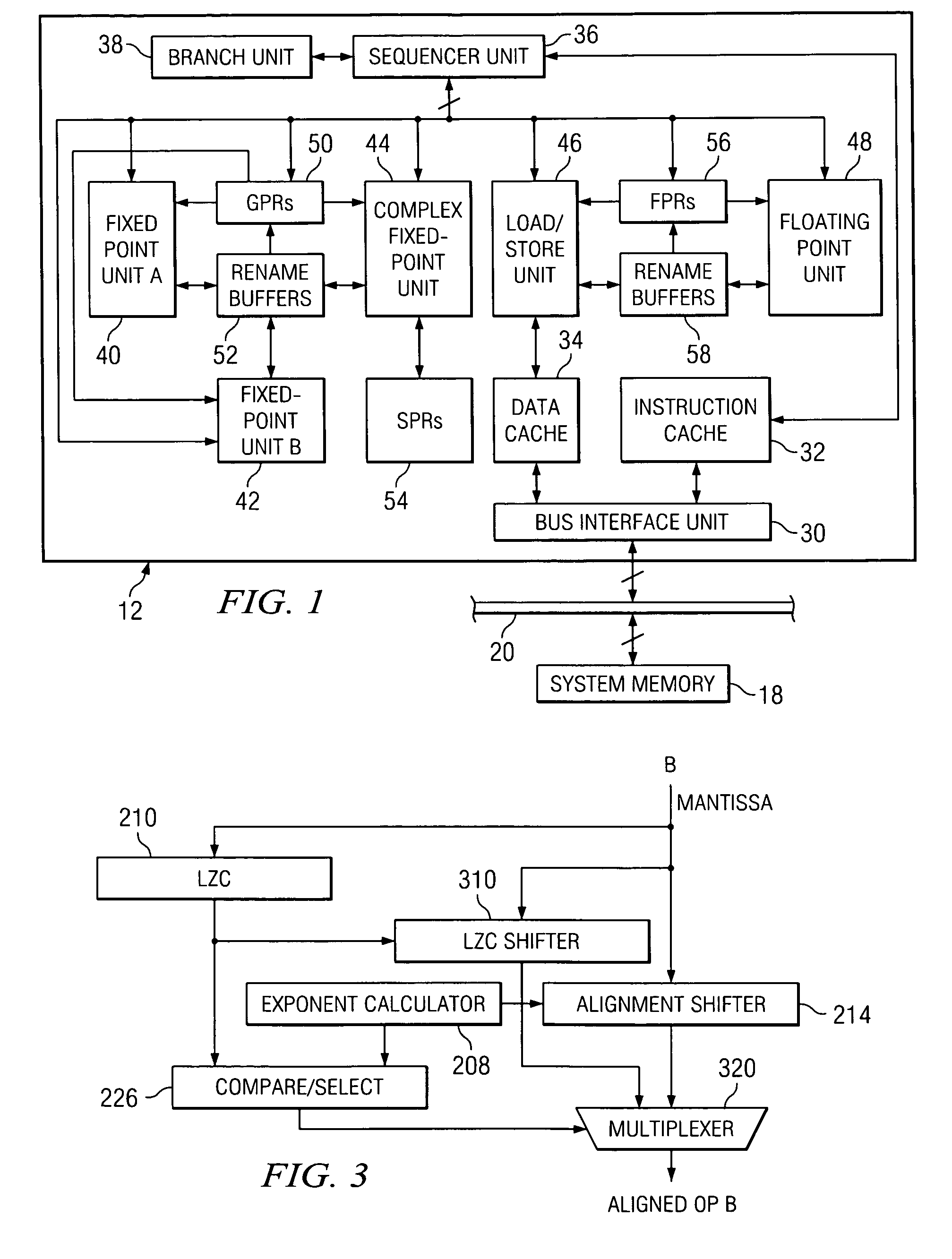

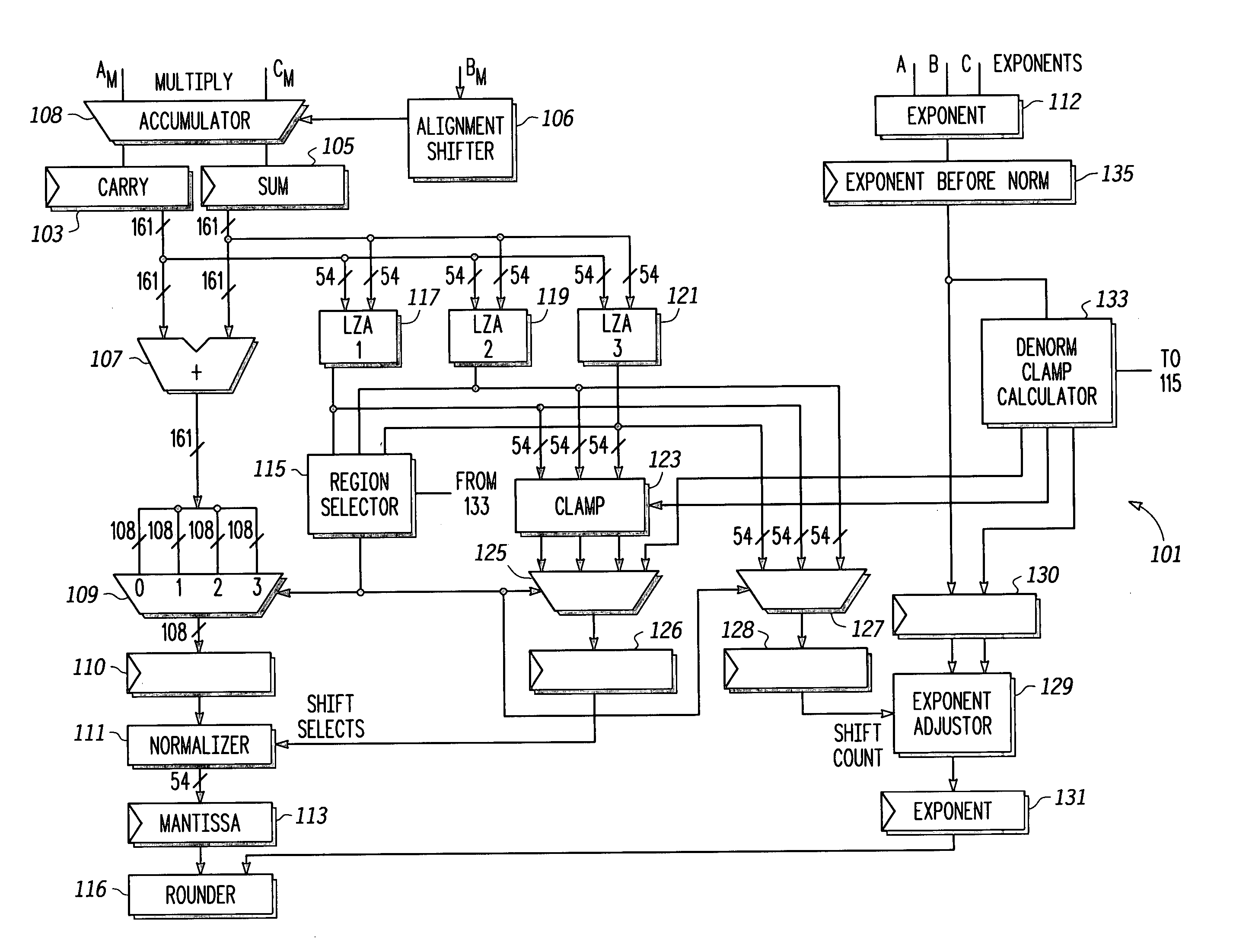

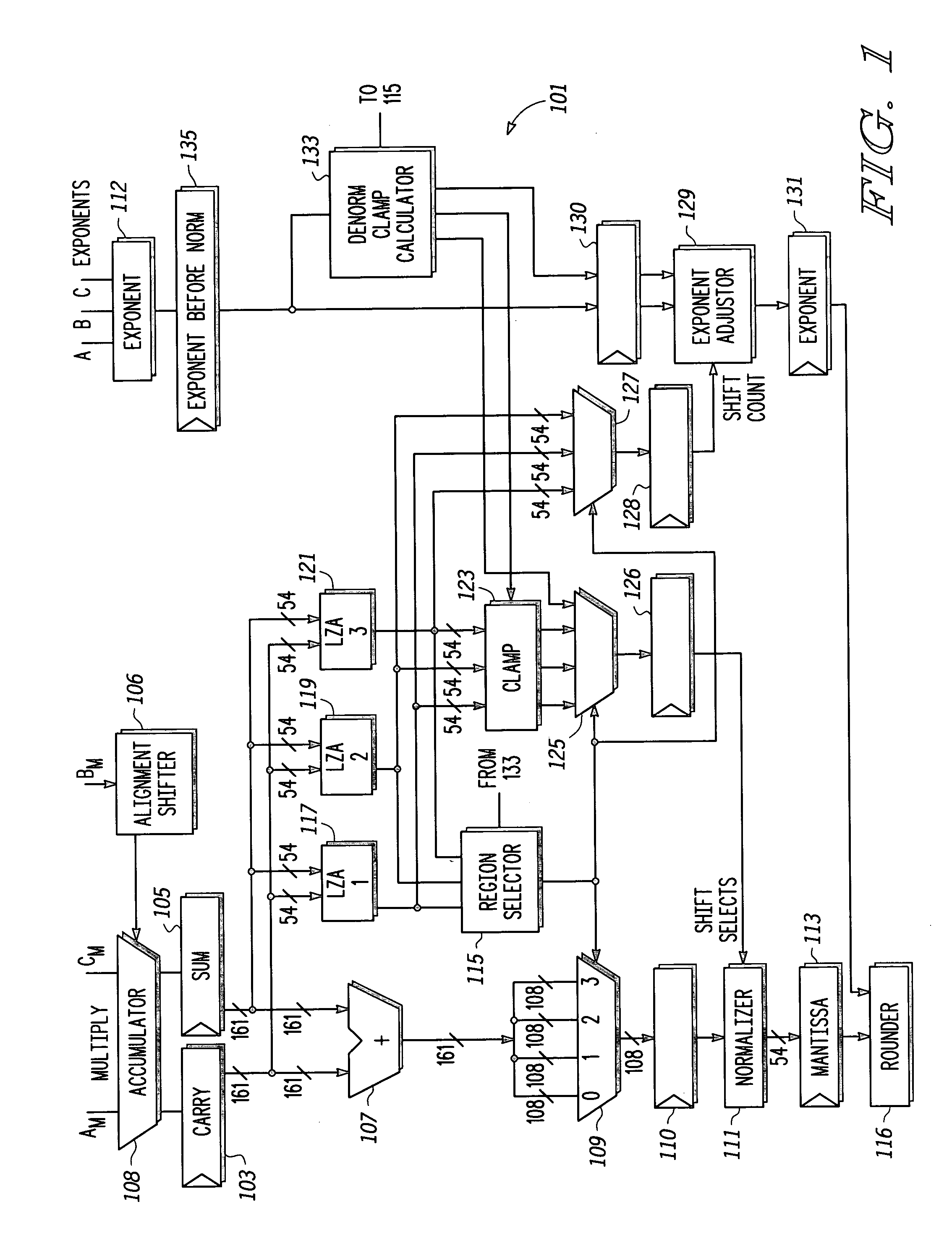

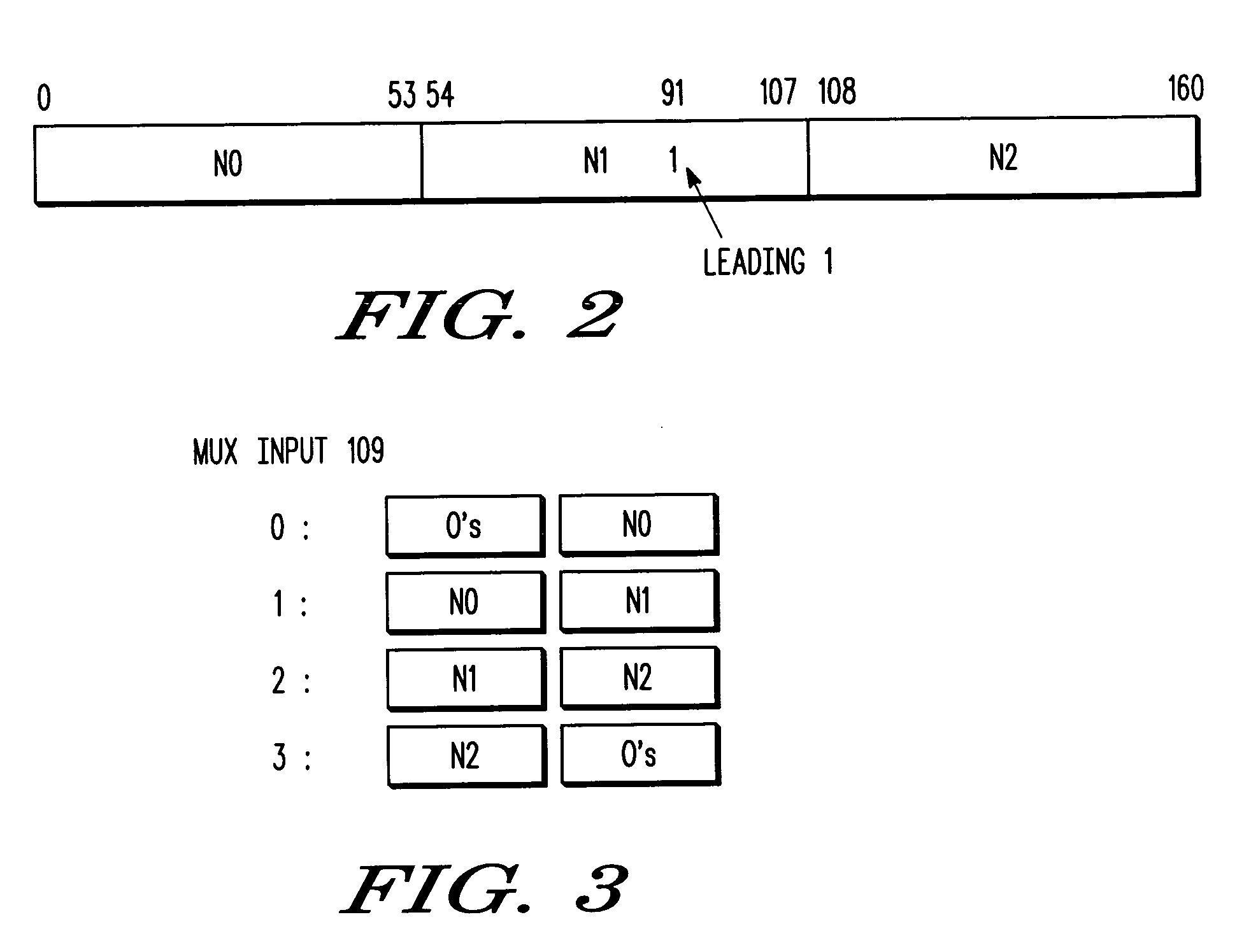

A system and method for handling denormal floating point operands when the result must be normalized. A leading zero counter (lzc) on the operand B (opB) is used to limit alignment shifts when opB is denormal but is much greater than the product of operands A and C, i.e. AC. By limiting the additional shift of B during normalization, by the number of leading zeros in opB, no increase is needed in the output bus of the alignment shifter. Furthermore, the additional shift may be done either in the alignment shifter, or postponed to a later stage in the pipeline, where the result is normalized.

Owner:IBM CORP

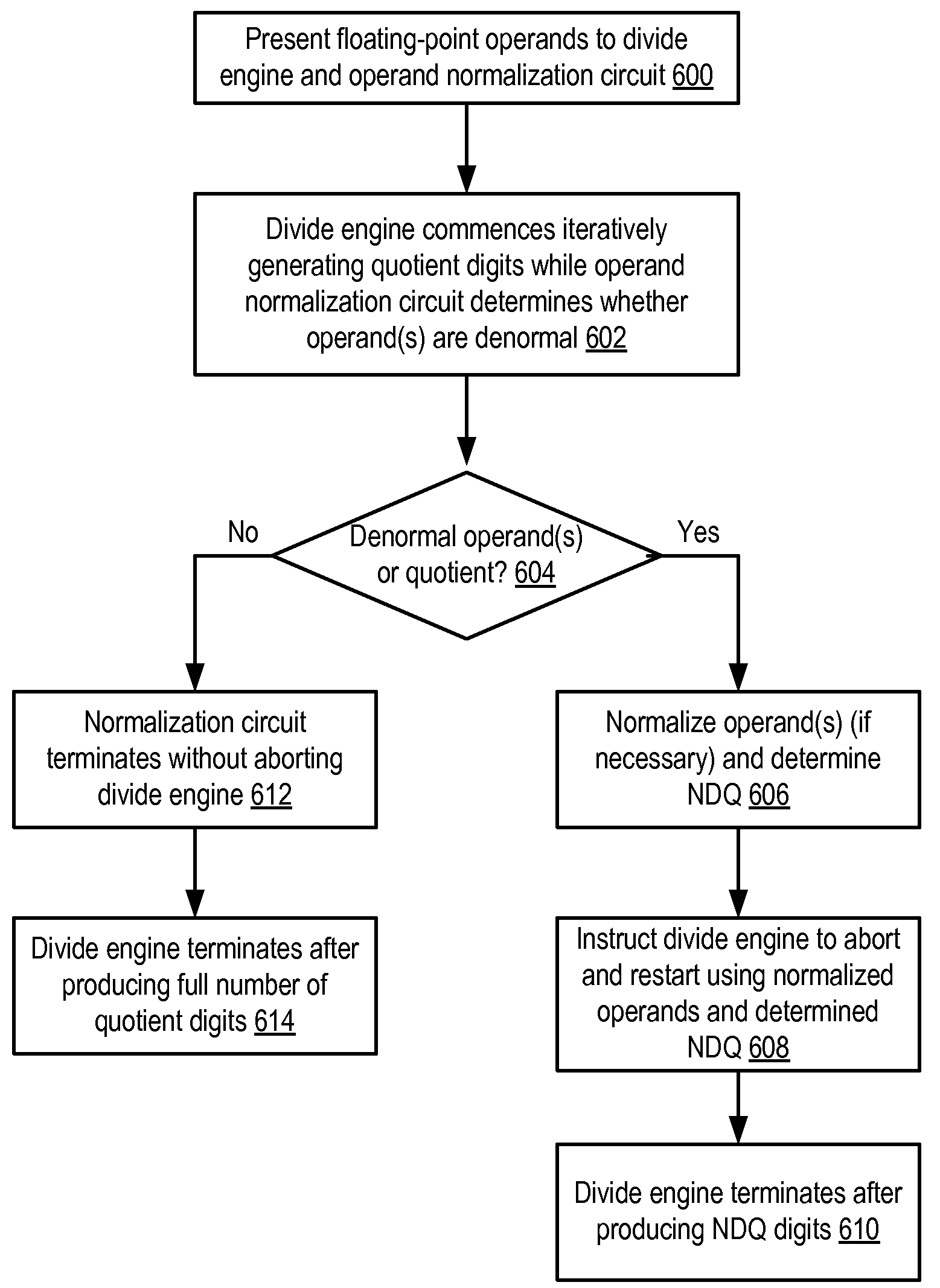

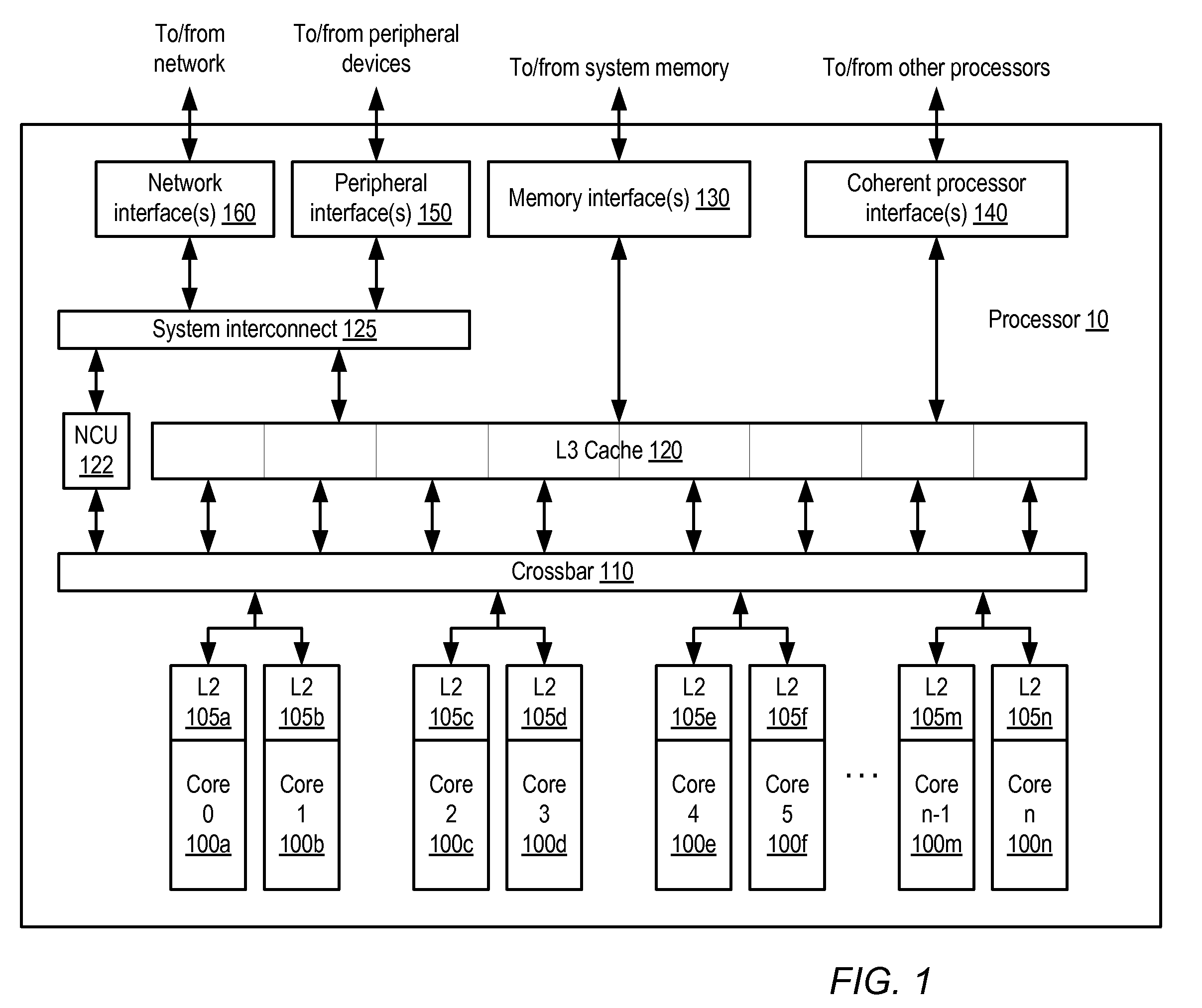

Apparatus and method for implementing hardware support for denormalized operands for floating-point divide operations

ActiveUS20100250639A1Computations using contact-making devicesComputation using non-contact making devicesFloating pointOperand

A floating-point circuit may include a floating-point operand normalization circuit configured to receive input floating-point operands of a given floating-point divide operation, the operands comprising a dividend and a divisor, as well as a divide engine coupled to the normalization circuit. In response to determining that one or more of the input floating-point operands is a denormal number, the operand normalization circuit may be further configured to normalize the one or more of the input floating-point operands and output a normalized dividend and normalized divisor to the divide engine, and dependent upon respective numbers of leading zeros of the dividend and divisor prior to normalization, generate a value indicative of a maximum possible number of digits of a quotient (NDQ). The divide engine may be configured to iteratively generate NDQ digits of a floating-point quotient from the normalized dividend and the normalized divisor provided by the floating-point operand normalization circuit.

Owner:ORACLE INT CORP

Floating point normalization and denormalization

ActiveUS20070061391A1Digital computer detailsComputation using denominational number representationBit fieldFloating point

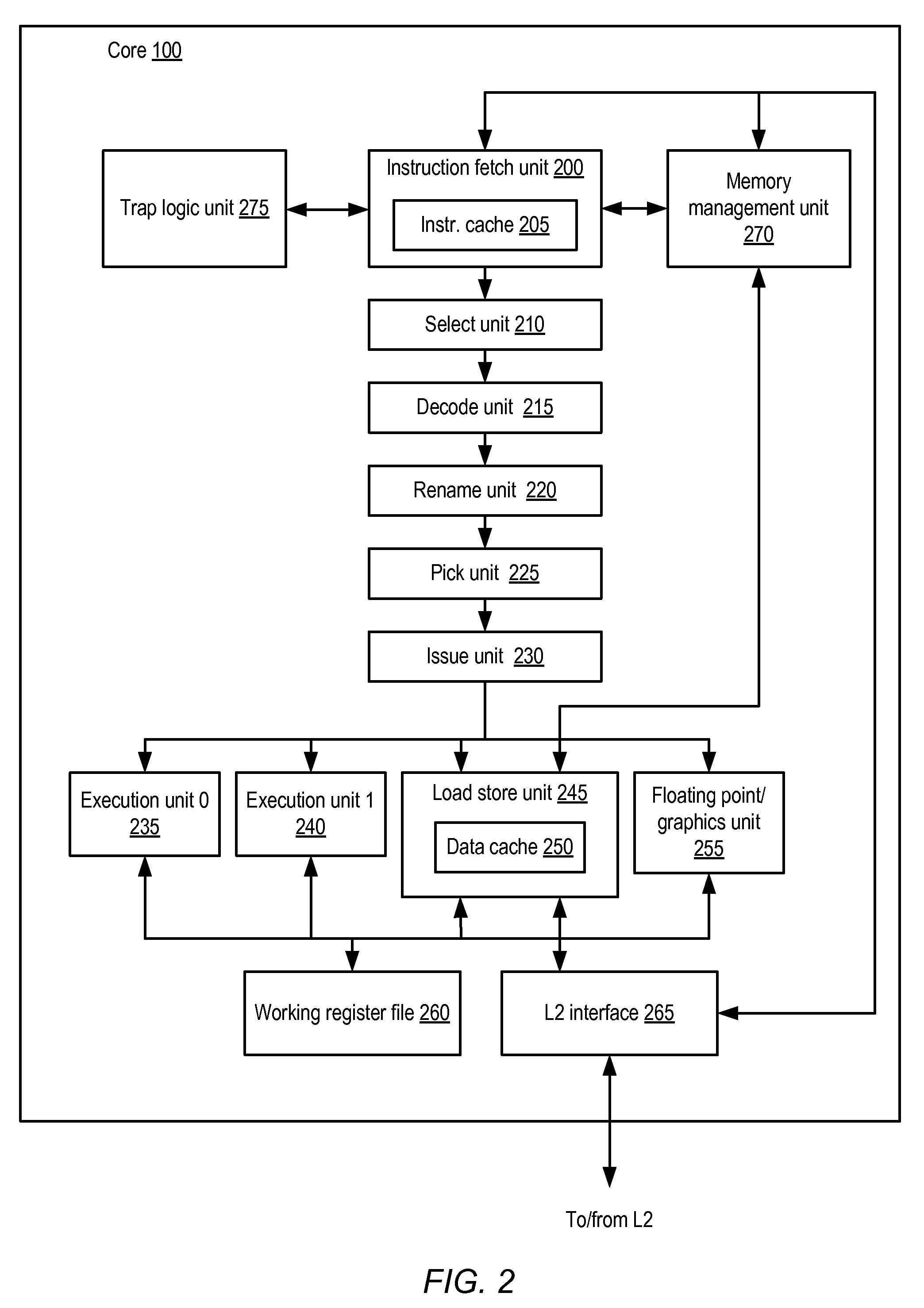

A data processor includes a first bit field of a first plurality of bits representing a mantissa of a floating point number and a second bit field of a second plurality of bits representing an exponent of the floating point number. The first plurality of bits is partitioned into a plurality of regions, each of the plurality of regions comprises more than one bit of the first plurality of bits. A leading zero anticipator or other type of leading bit indication circuit is coupled to each region and determines a position of a leading bit of the first plurality of bits. A normalizer is coupled to receive a region of the plurality of regions that contains the leading bit, the normalizer may normalize or denormalize the region to produce a normalized or denormalized floating point number.

Owner:NXP USA INC

Efficient correction of normalizer shift amount errors in fused multiply add operations

ActiveUS9317251B2Improved latency and power and areaImprove normalizationDigital data processing detailsFloating pointLeading zero

Owner:NVIDIA CORP

Method and Processor for Performing a Floating-Point Instruction Within a Processor

InactiveUS20070038693A1Computation using denominational number representationData processing systemParallel computing

The invention relates to a method for performing floating-point instructions within a processor of a data processing system is described, wherein an input of said floating-point instruction comprises a normal or a denormal floating-point number. Said method comprises the steps of storing said floating-point number, normalization of said floating-point number by counting the leading zeros of the mantissa, shifting the fraction part to the left by the number of leading zeros and simultaneously decrementing the exponent by one for every position that the fraction part is shifted to the left, wherein it the input is a normal floating point number the normalization is done after counting no leading zero of the mantissa, execution of a floating point instruction, wherein said normalized floating-point number is utilized as input for the floating point instruction, and storing of a floating-point result. Furthermore a processor to be used to perform said method is described.

Owner:IBM CORP

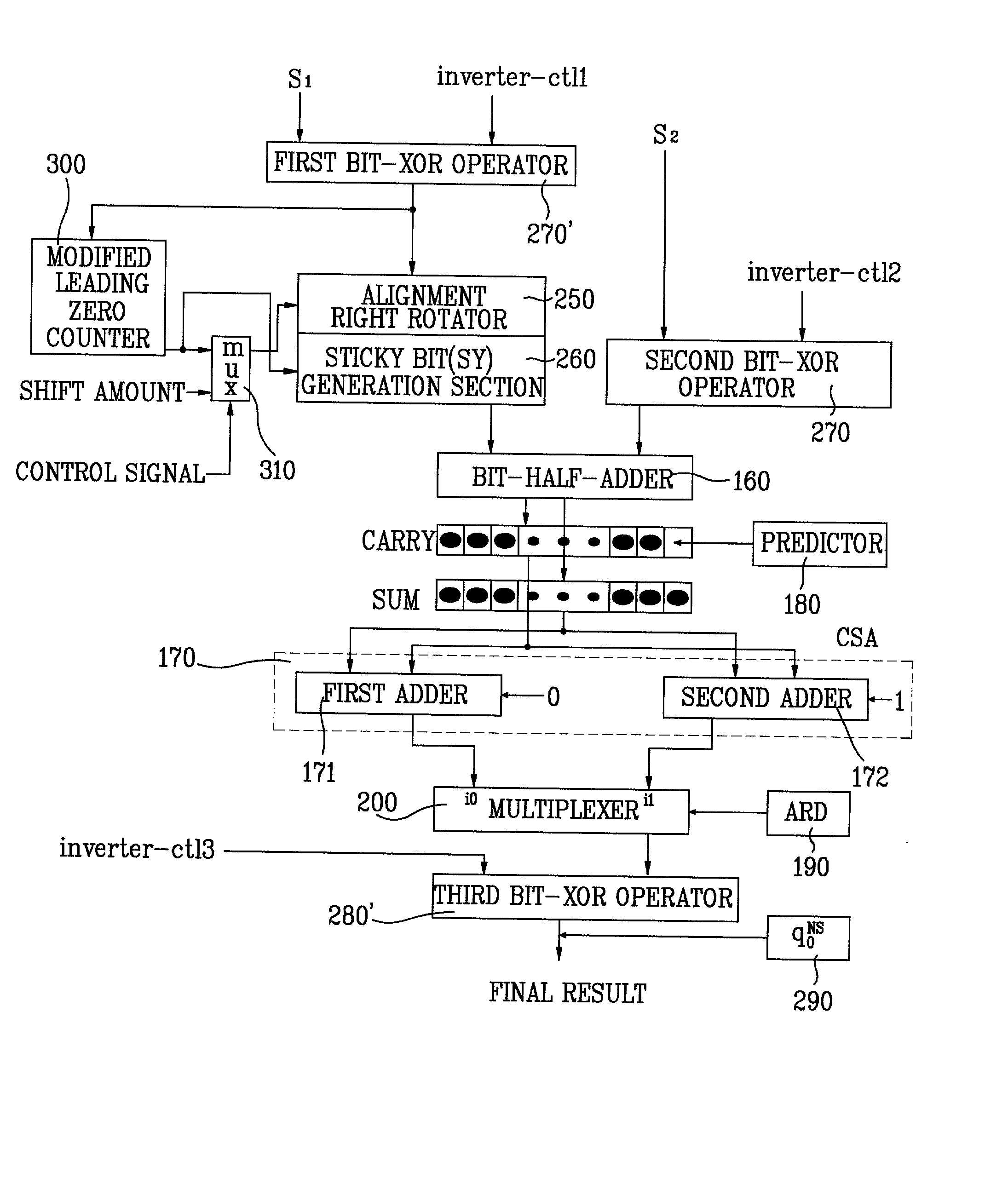

Apparatus and method of performing addition and rounding operation in parallel for floating-point arithmetic logical unit

InactiveUS20020129075A1Computations using contact-making devicesComputation using non-contact making devicesArithmetic logic unitRight shift

A floating-point ALU that performs an IEEE rounding and an addition in parallel in a simultaneous rounding method (SRM) type floating-point adder. The floating-point ALU includes an alignment / normalization section for bypassing or inverting a first fraction part and a second fraction part, performing an alignment by performing a right shift as much as a value obtained from an exponent part or performing a normalization through a left shift by calculating a leading zero with respect to the first fraction part, and obtaining a guard bit (G), round bit (R), and sticky bit (Sy); and an addition and rounding operation section for performing a addition and rounding with respect to the first fraction part and second fraction part outputted through the alignment / normalization section. According to the floating-point ALU, the processing time and the hardware size can be reduced, and the hardware of the SRM can be used as it is.

Owner:YONSEI UNIVERSITY

Handling denormal floating point operands when result must be normalized

InactiveUS7451172B2Digital computer detailsComputation using denominational number representationFloating pointEngineering

Owner:INT BUSINESS MASCH CORP

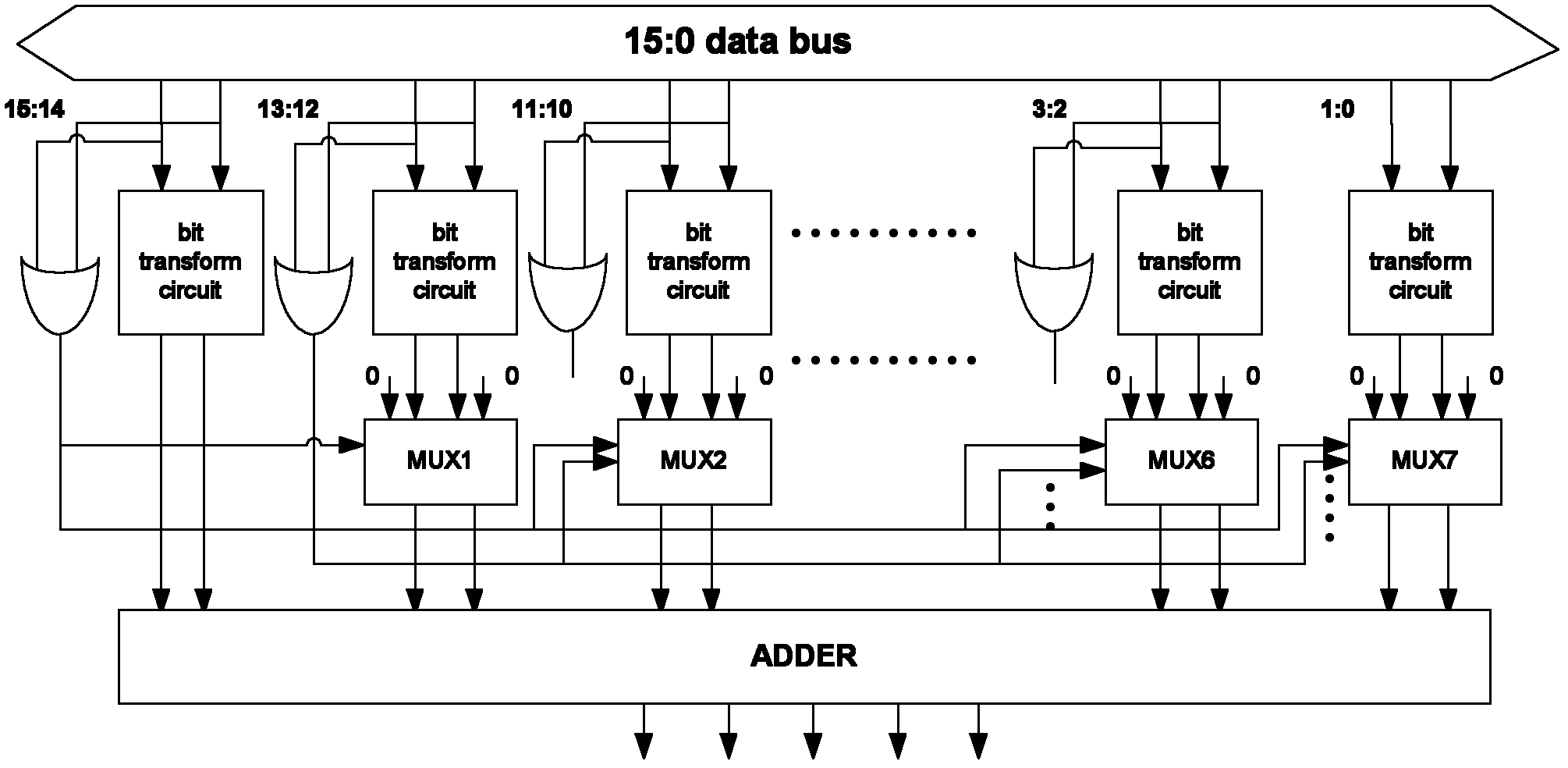

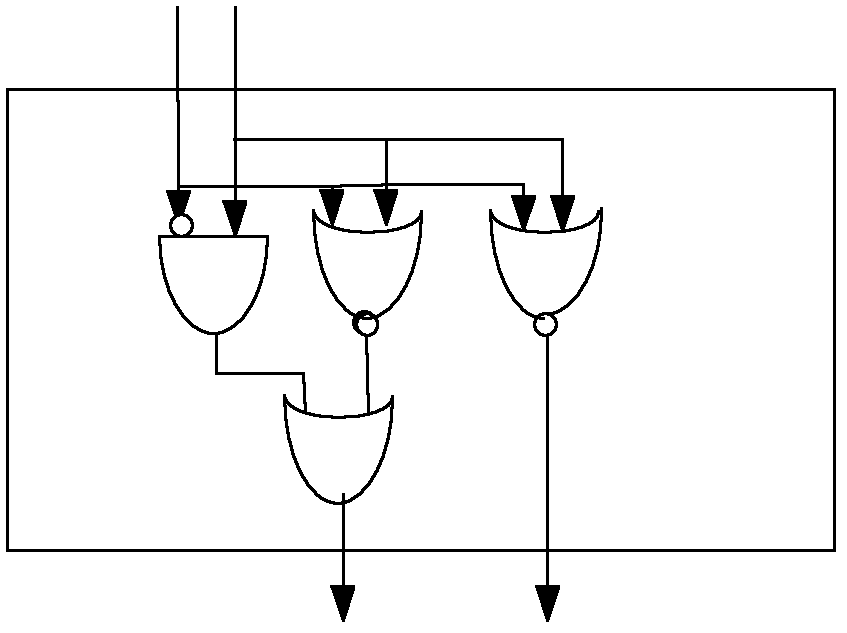

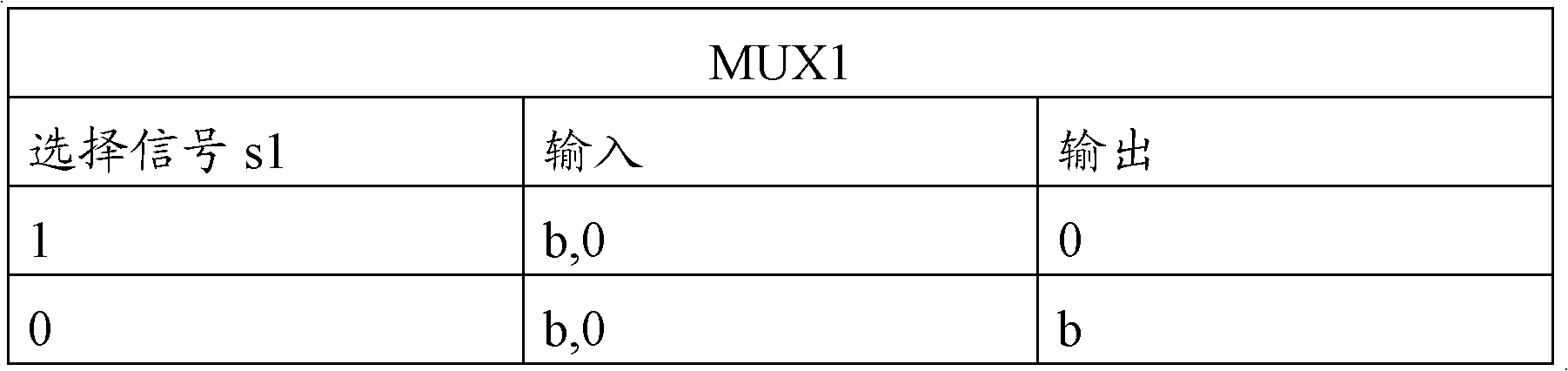

Method and device for confirming leading zero number of binary data

ActiveCN102664637AImprove performanceAvoid problems with indeterminate processing cyclesDynamic codingHierarchical designLeading zero

The invention discloses a method for confirming leading zero number of binary data. The method comprises the following steps: converting the leading zero number in the binary data into a corresponding number of 1; converting all the data behind the first 1 on the highest order side in the binary data into zero; and then calculating the leading zero number in the binary data by addition. The method adopts a completely different design idea; and the input and output data in each part structure is identical in length, so that the problem that the processing period is uncertain along with the different data length caused by hierarchical design is avoided, and the delay is fixed. The method can be applied in a processor to improve the performance of the processor.

Owner:北京中科晶上科技股份有限公司

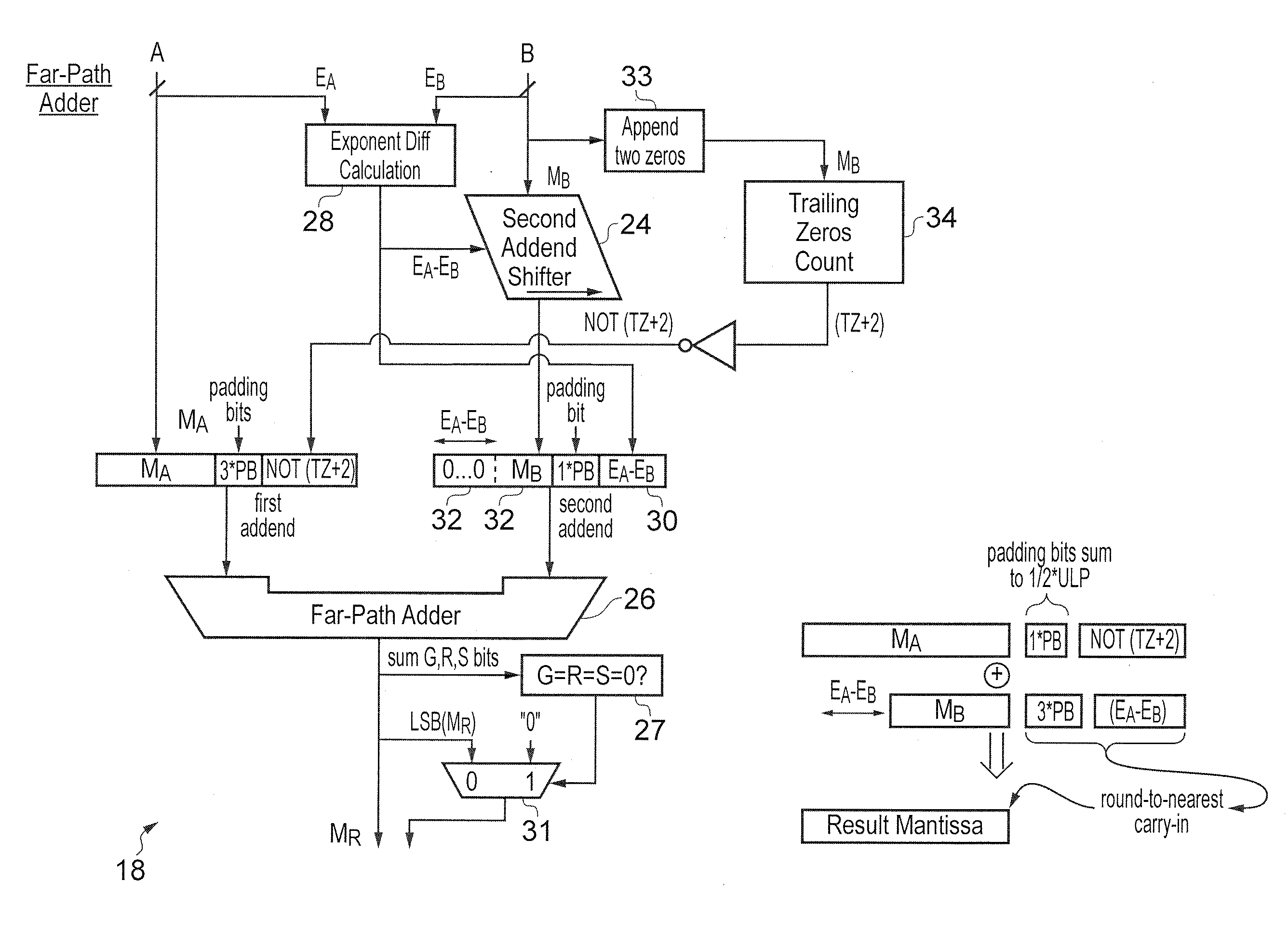

Floating-point adder

ActiveUS9009208B2Lower latencyLittle countComputations using contact-making devicesComputer architectureOperand

Floating point adder circuitry 16, 18, 20 is provided with far-path circuitry 18 and near-path circuitry 20. The far-path circuitry utilises a count of trailing zeros TZ and a difference in the input operand exponents to form respective suffix values which are concatenated with the mantissas of the input addends and serve when summed to generate a carry out taking the place of a conventionally calculated sticky bit. Within the near-path, minimum value circuitry 46 is used to calculate the lower of a leading zeros count of the intermediate mantissa produced in a subtraction and the larger of the input operand exponent values such that a left shift applied to the intermediate mantissa value is not able to produce a invalid floating point result due to applying a left shift to remove leading zeros that is too larger and accordingly corresponds to an exponent which cannot be validly represented.

Owner:ARM LTD