5-grade stream line structure of floating point multiplier adder integrated unit

A pipeline and floating-point multiplication technology, applied in the direction of instruments, electrical digital data processing, digital data processing components, etc., can solve problems such as increased delay, unprocessed leading zero prediction logic processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

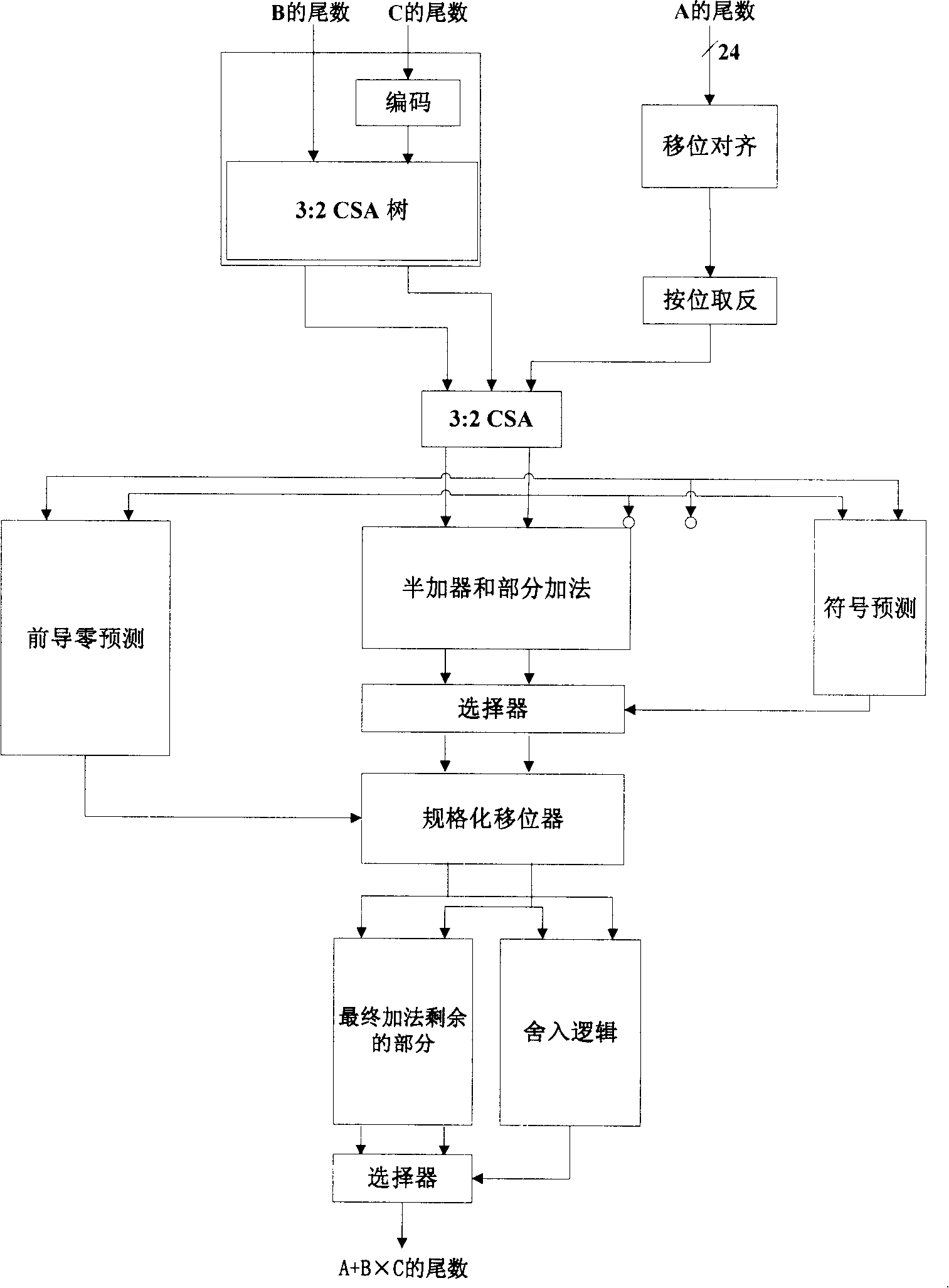

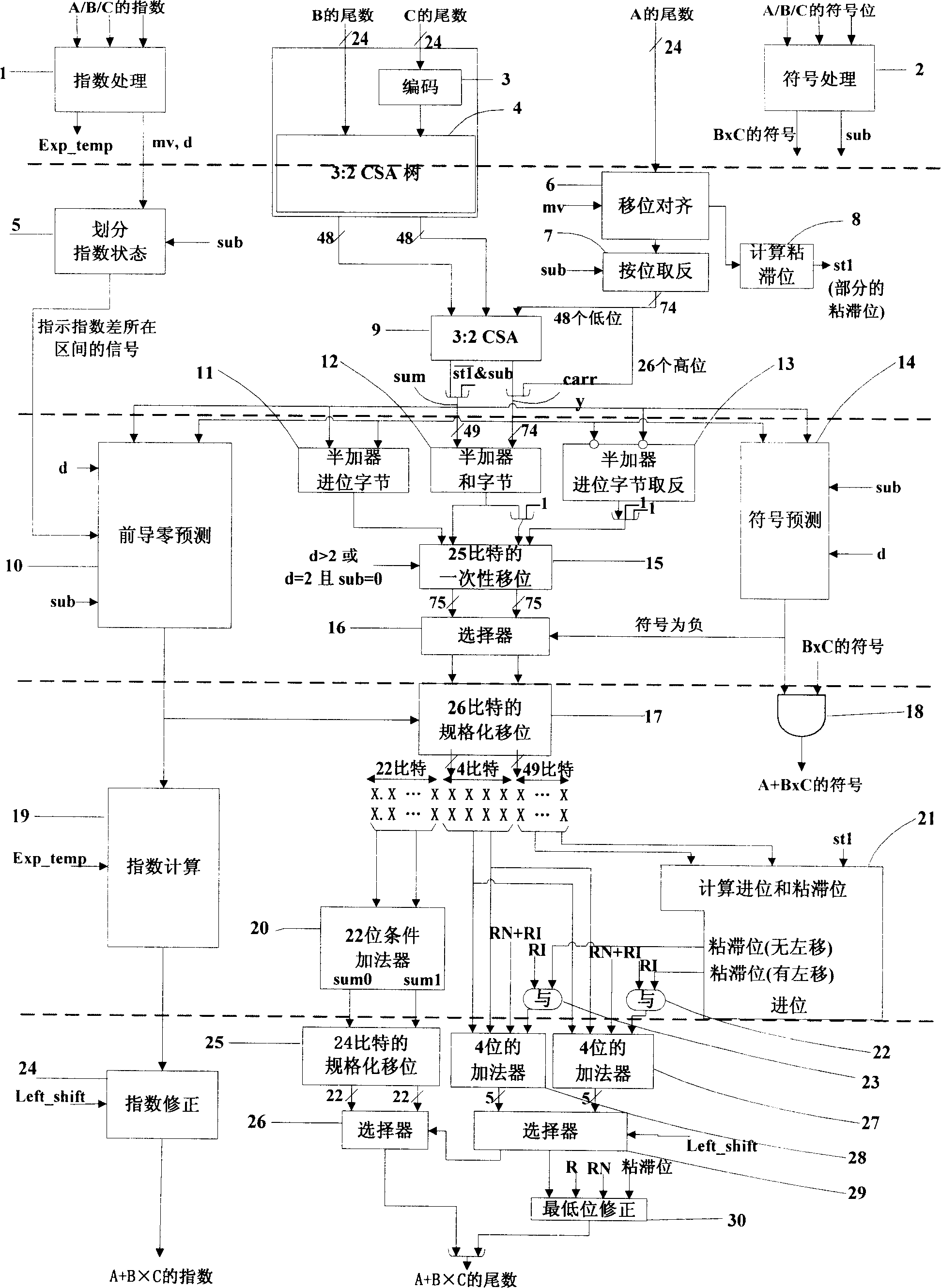

[0117] Concrete function realization process of the present invention is as follows:

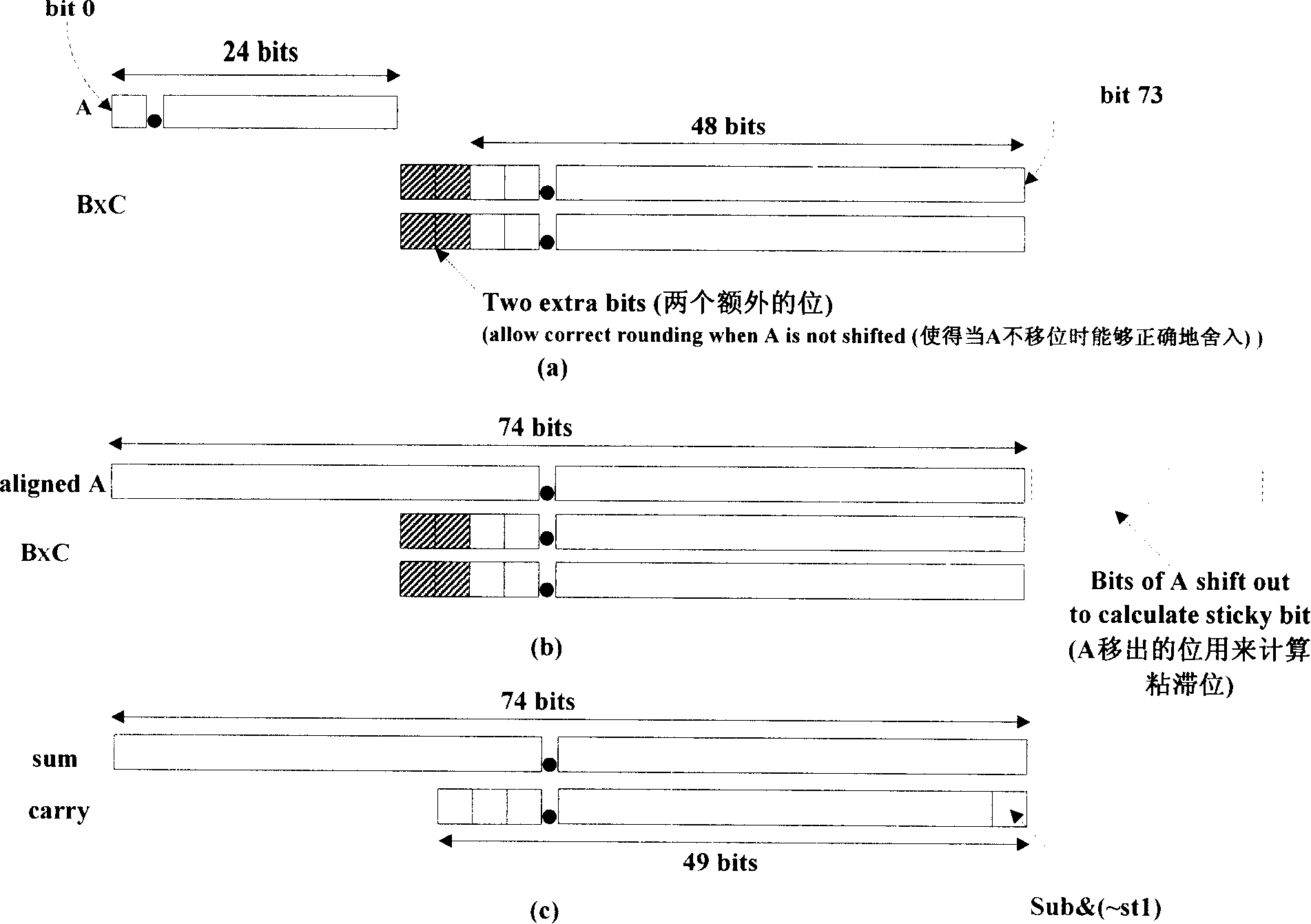

[0118] The shift alignment and inversion of A are performed in parallel with the Persian encoding and partial product compression of B×C. The addition of 1 required for complementation is accomplished using the vacant bit in the lowest bit of the 3:2 CSA carry byte. then A inv The partial product after compression with B*C is input into the 3:2CSA. A inv Indicates the output of bit-aligning the mantissa of A and inverting (if the sign bit of A is the same as the sign bit of B×C, no inversion is required). Since the partial product of B×C is only 48 bits, only A inv The lower 48 bits of the input 3: 2 CSA, the upper 55 bits are connected with the sum byte output by the CSA to obtain a 74-bit sum byte. While performing multiplication and alignment, it is judged whether the sign of A is the same as that of B×C, and the exponent difference d is calculated.

[0119] The next step is to dete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More