Patents

Literature

1542results about How to "Less power" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

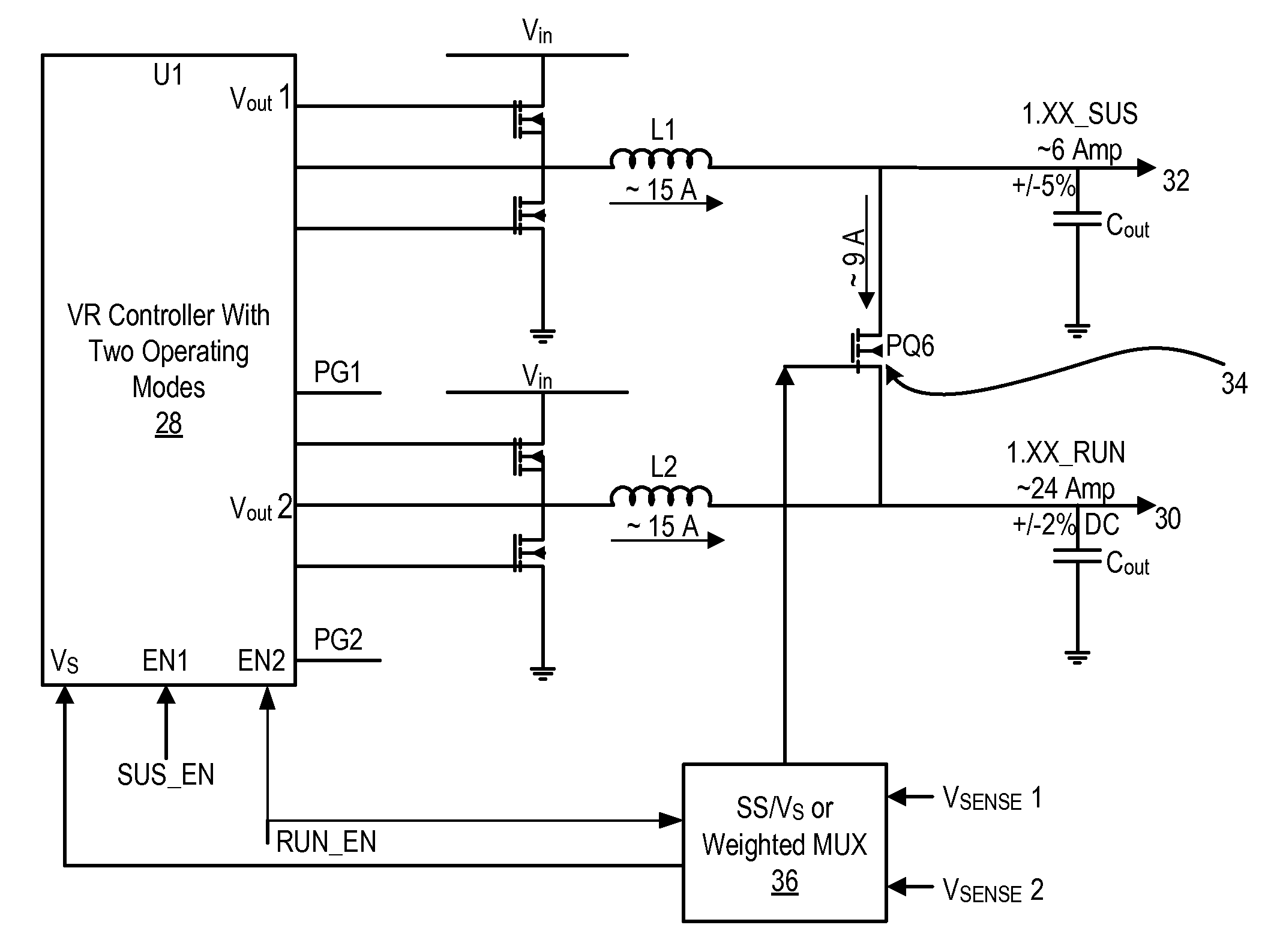

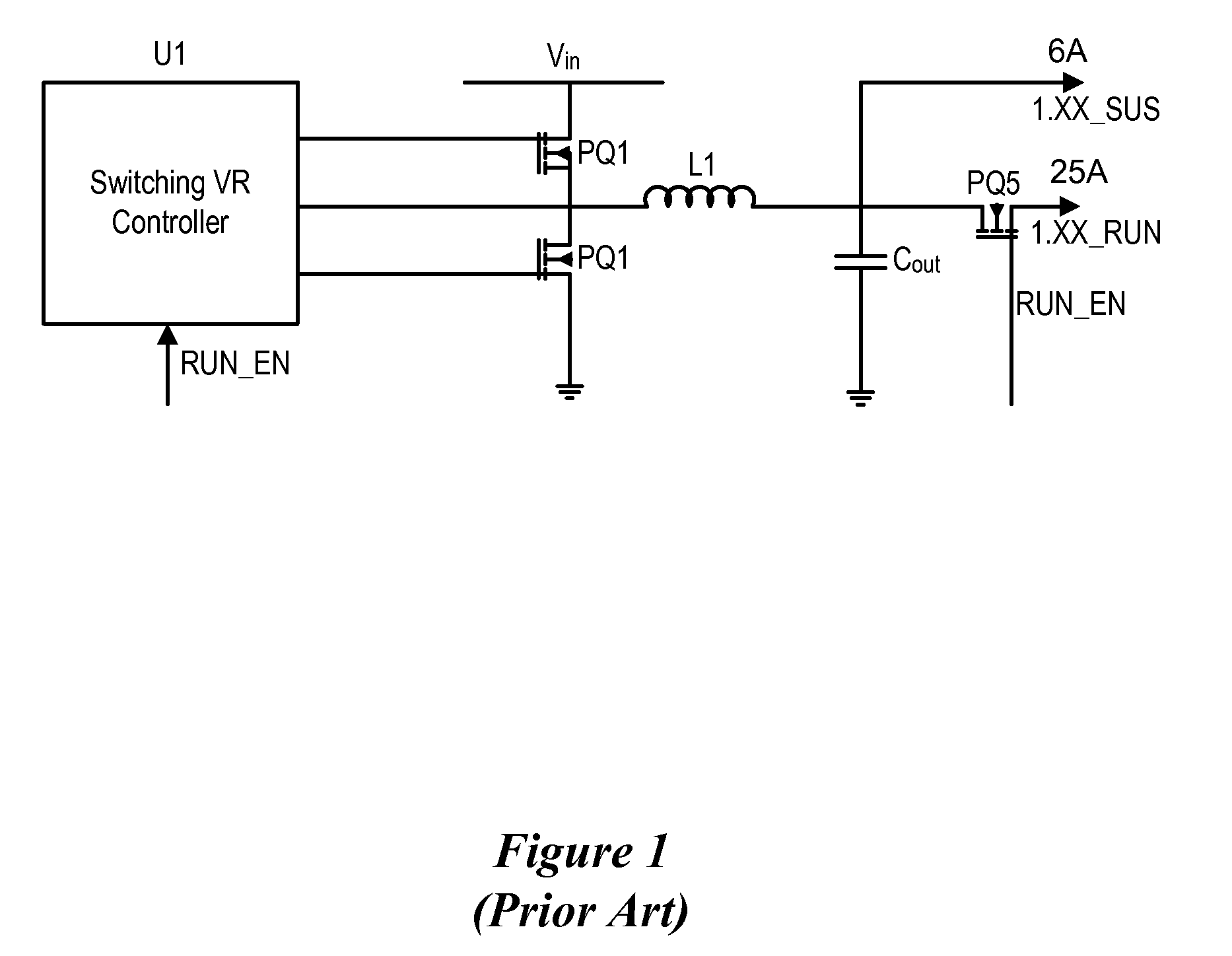

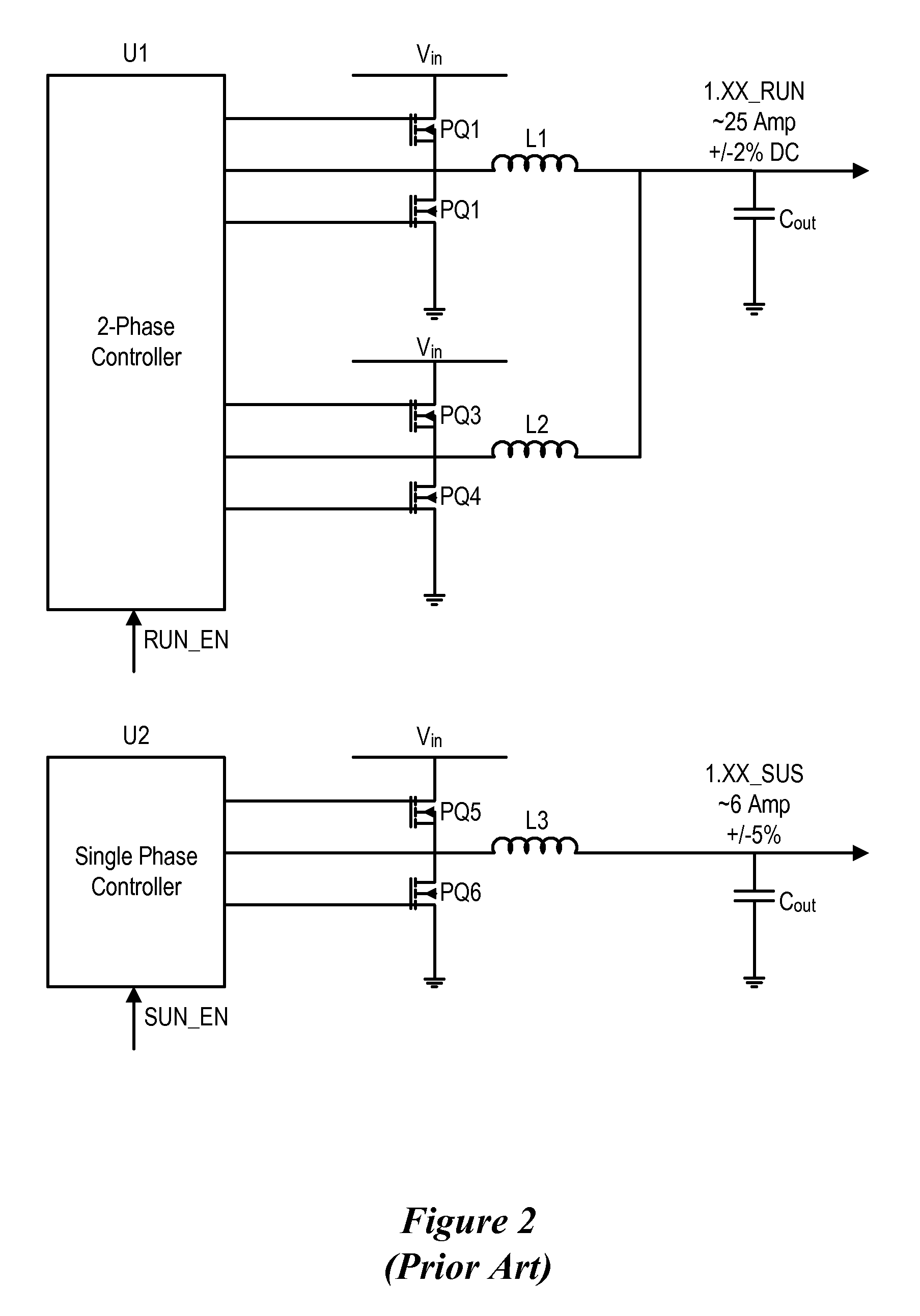

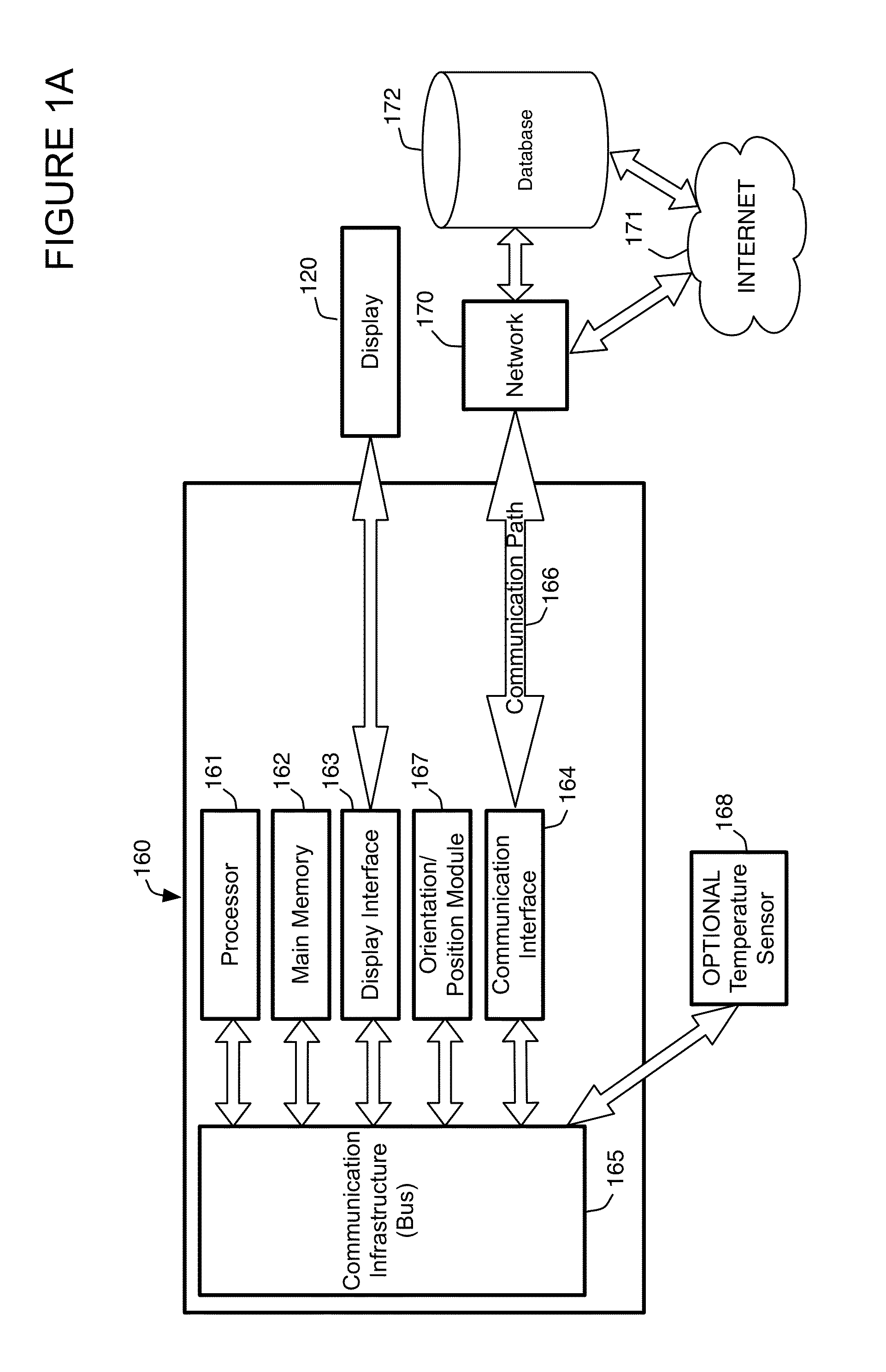

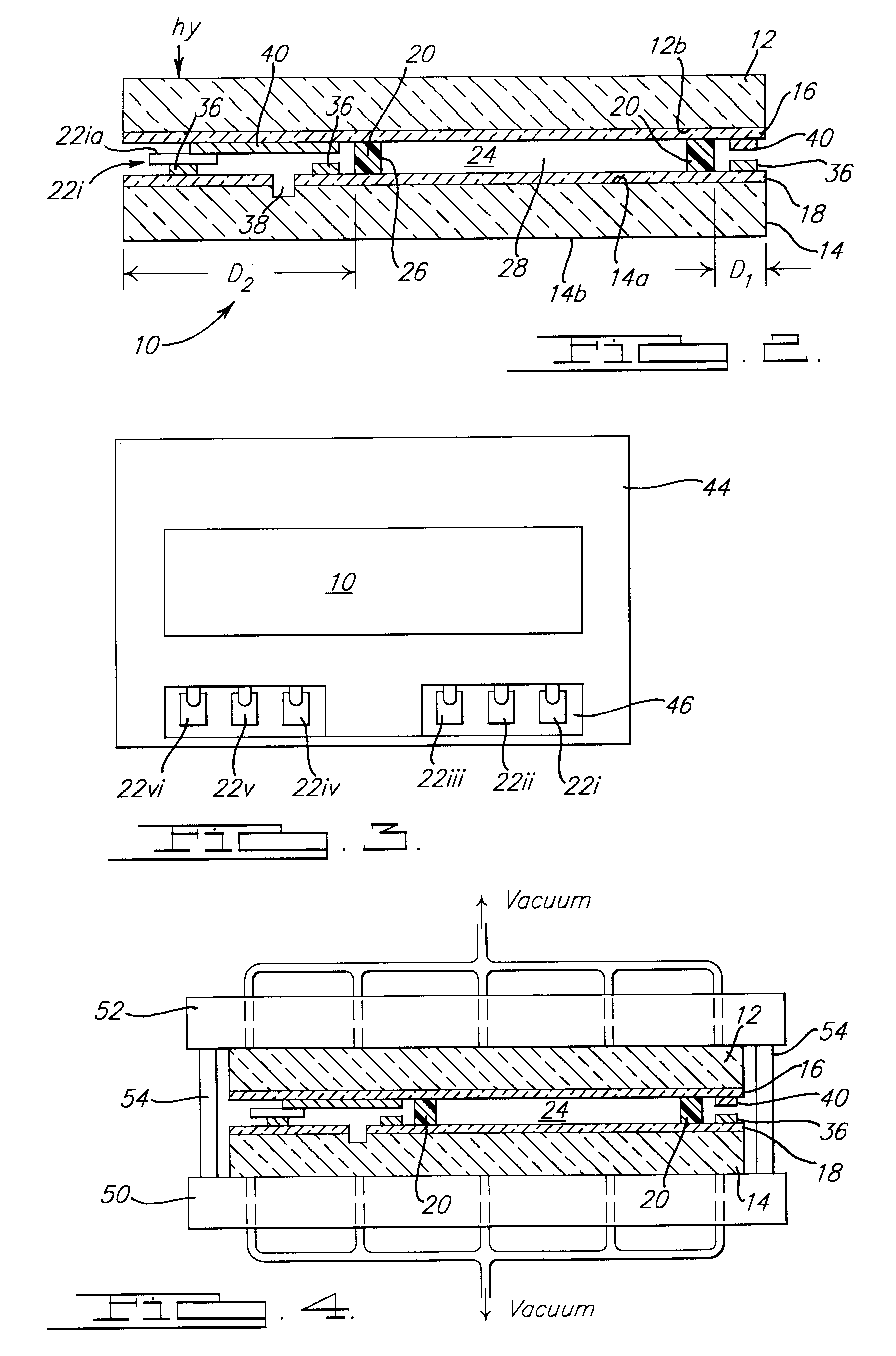

System and method for powering an information handling system in multiple power states

ActiveUS8063619B2Reduce disadvantagesReduce problemsElectric signal transmission systemsDc network circuit arrangementsMOSFETVoltage regulation

Power is supplied to an information handling system chipset with a single voltage regulator having dual phases. A first phase of the voltage regulator provides power to a low power state power rail in an independent mode to support a low power state, such as a suspend or hibernate state. A second phase of the voltage regulator provides power to a run power state power rail in combination with the first phase by activation of a switch, such as a MOSFET load switch, that connects the low power state power rail and the run power state power rail. Voltage sensed from both power rails is applied to control voltage output so that the run power state power rail is maintained within more precise constraints than the low power state power rail.

Owner:DELL PROD LP

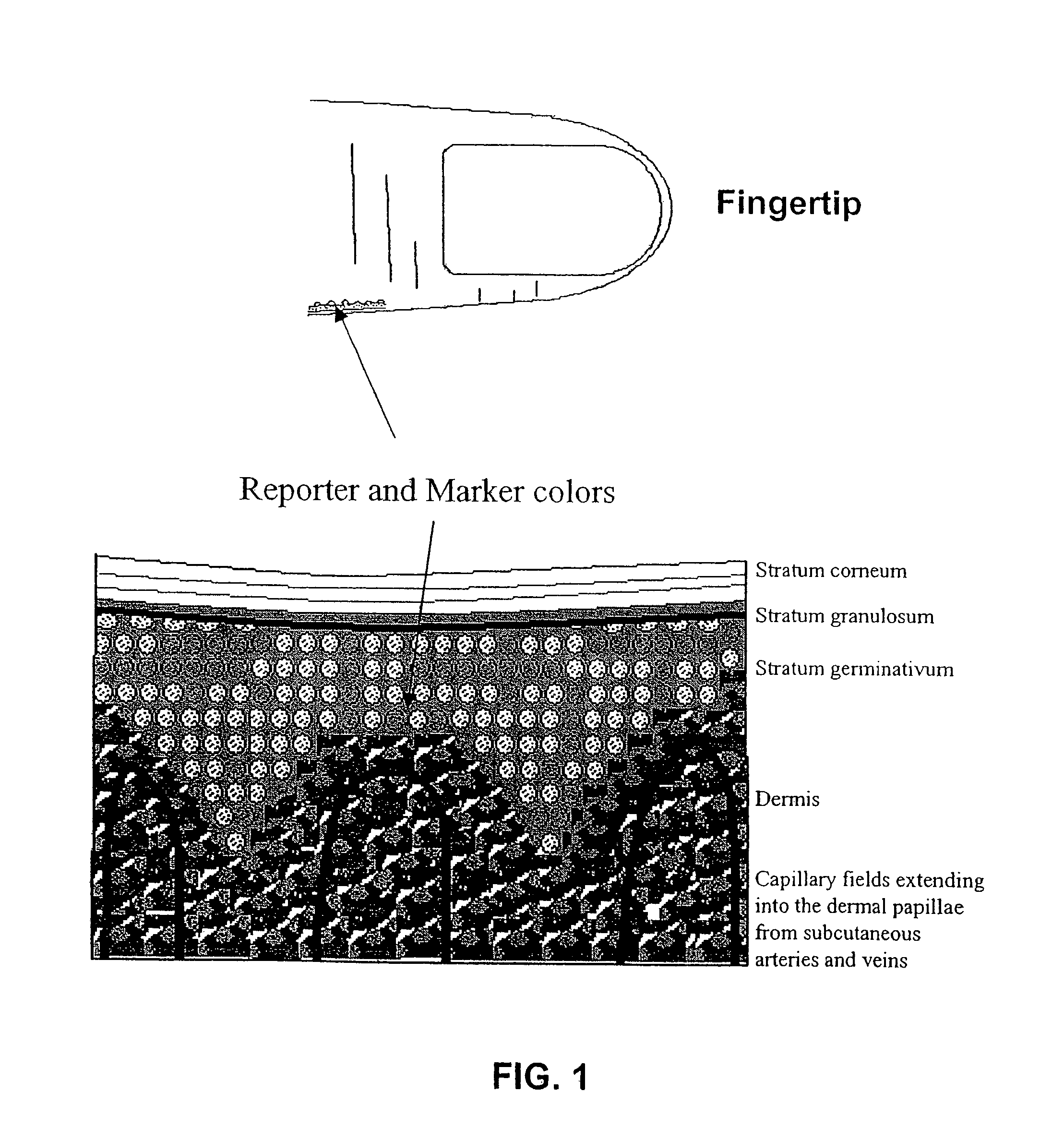

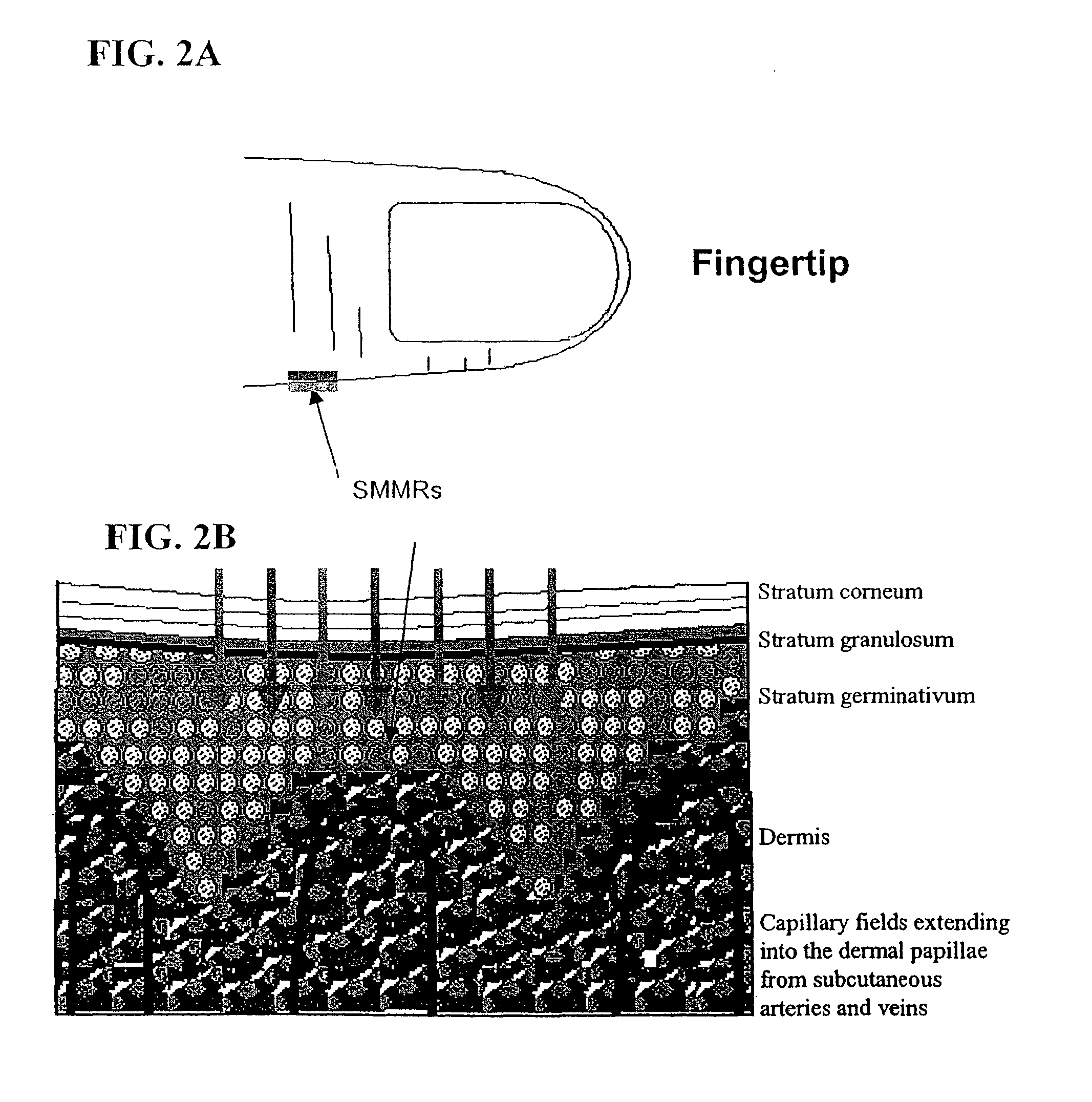

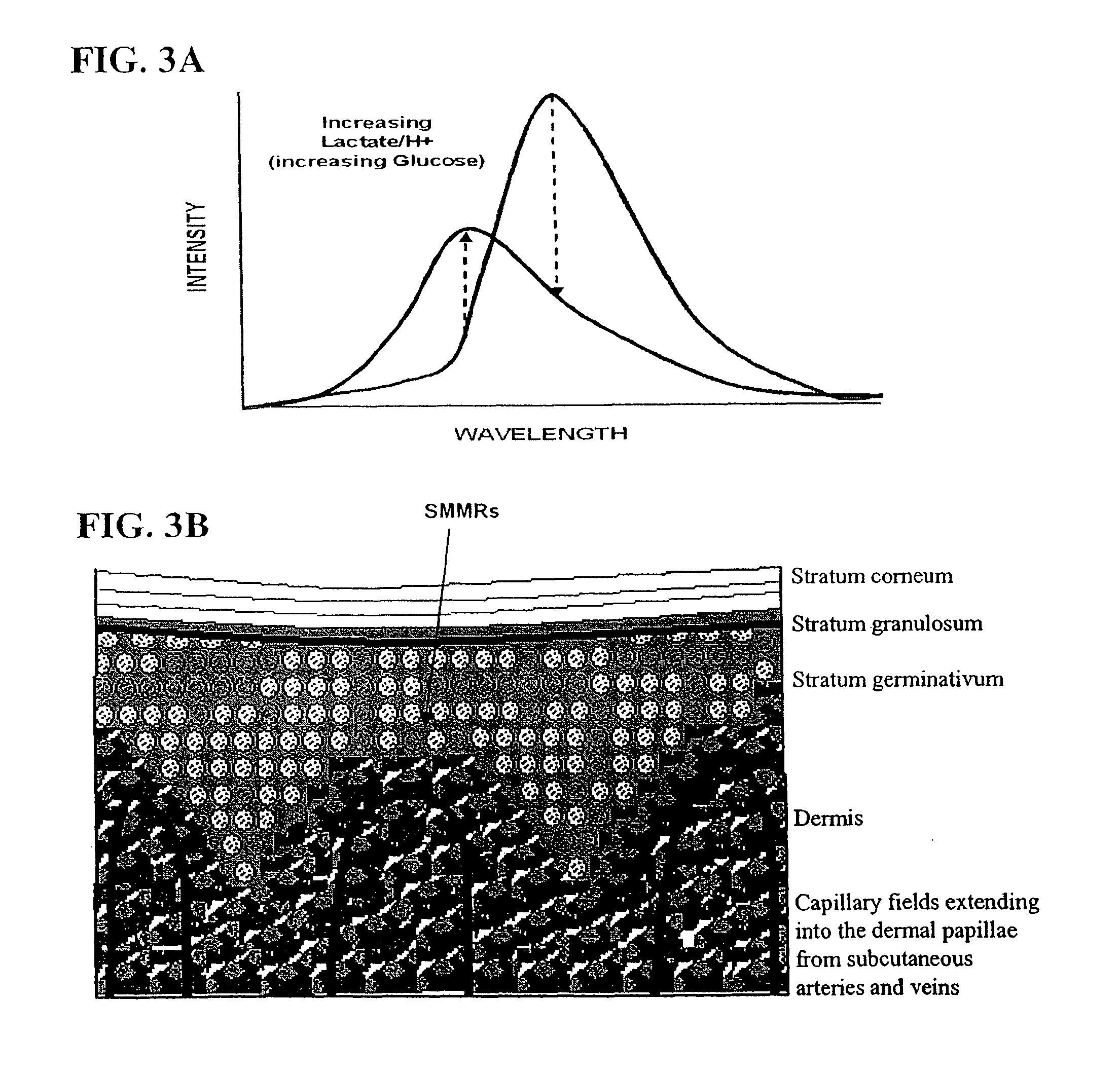

Non-invasive measurement of analytes

ActiveUS8509867B2Great simplicityHigh sensitivityMicrobiological testing/measurementChemiluminescene/bioluminescenceBiological bodyMetabolite

Owner:CERCACOR LAB INC

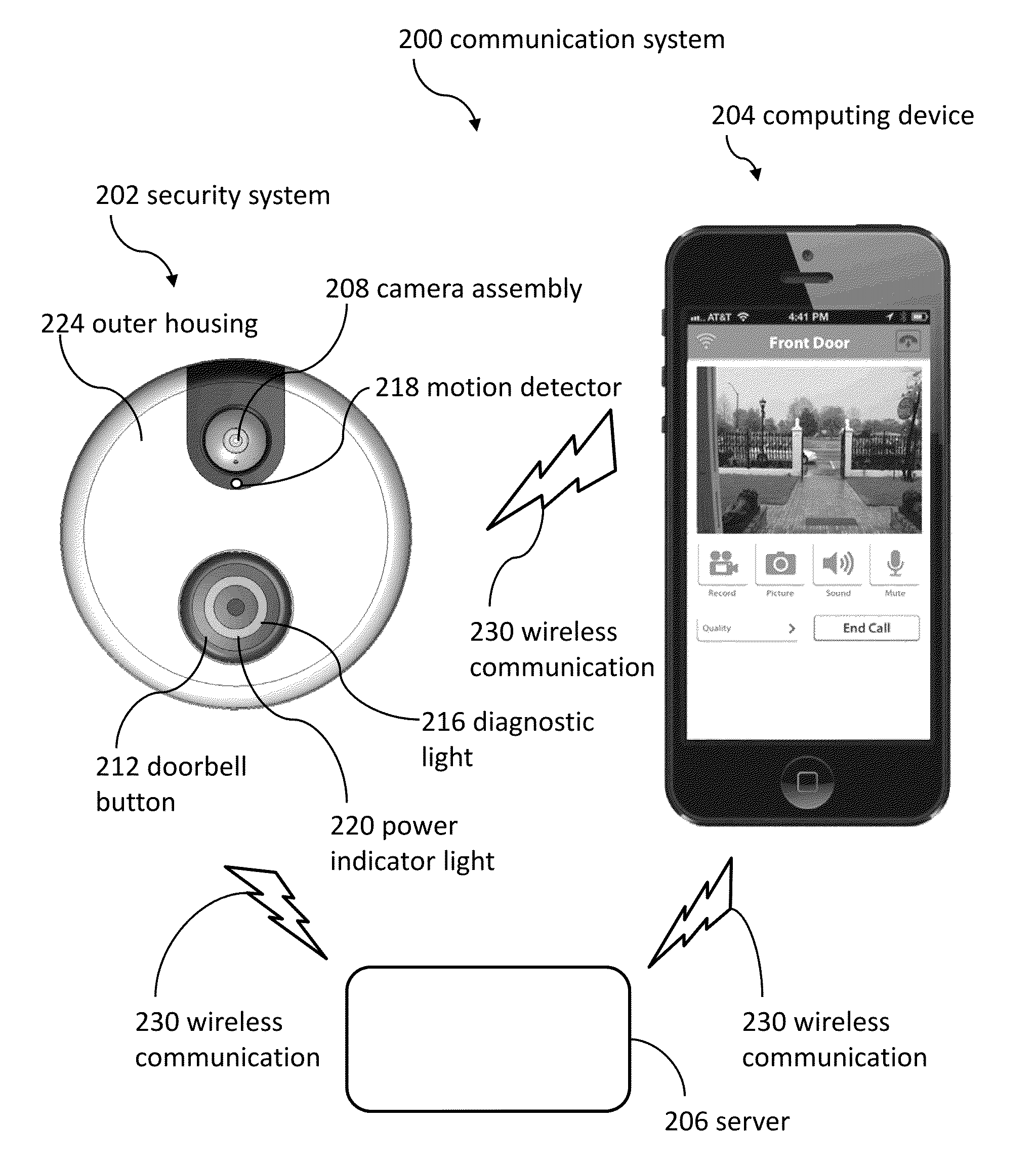

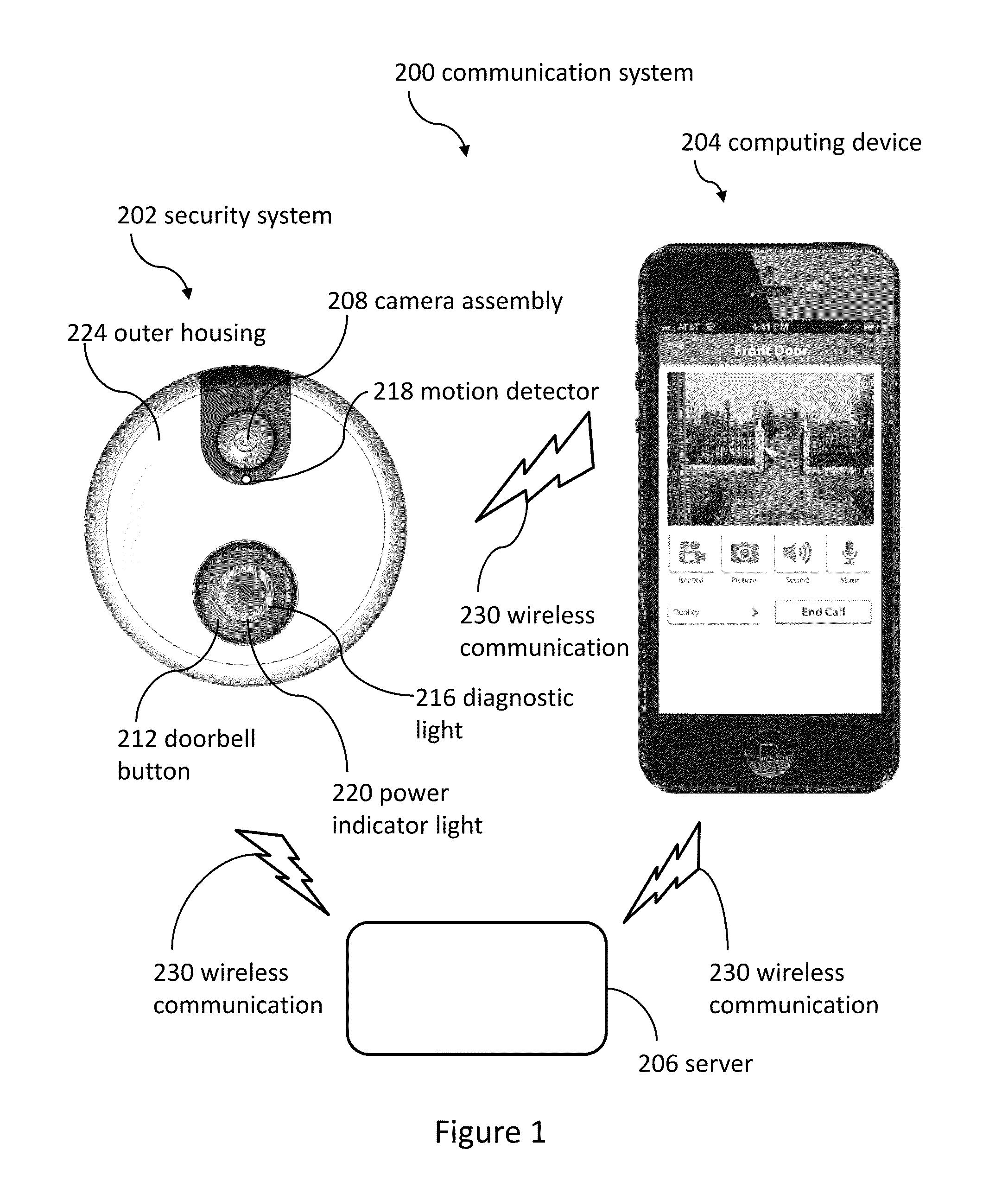

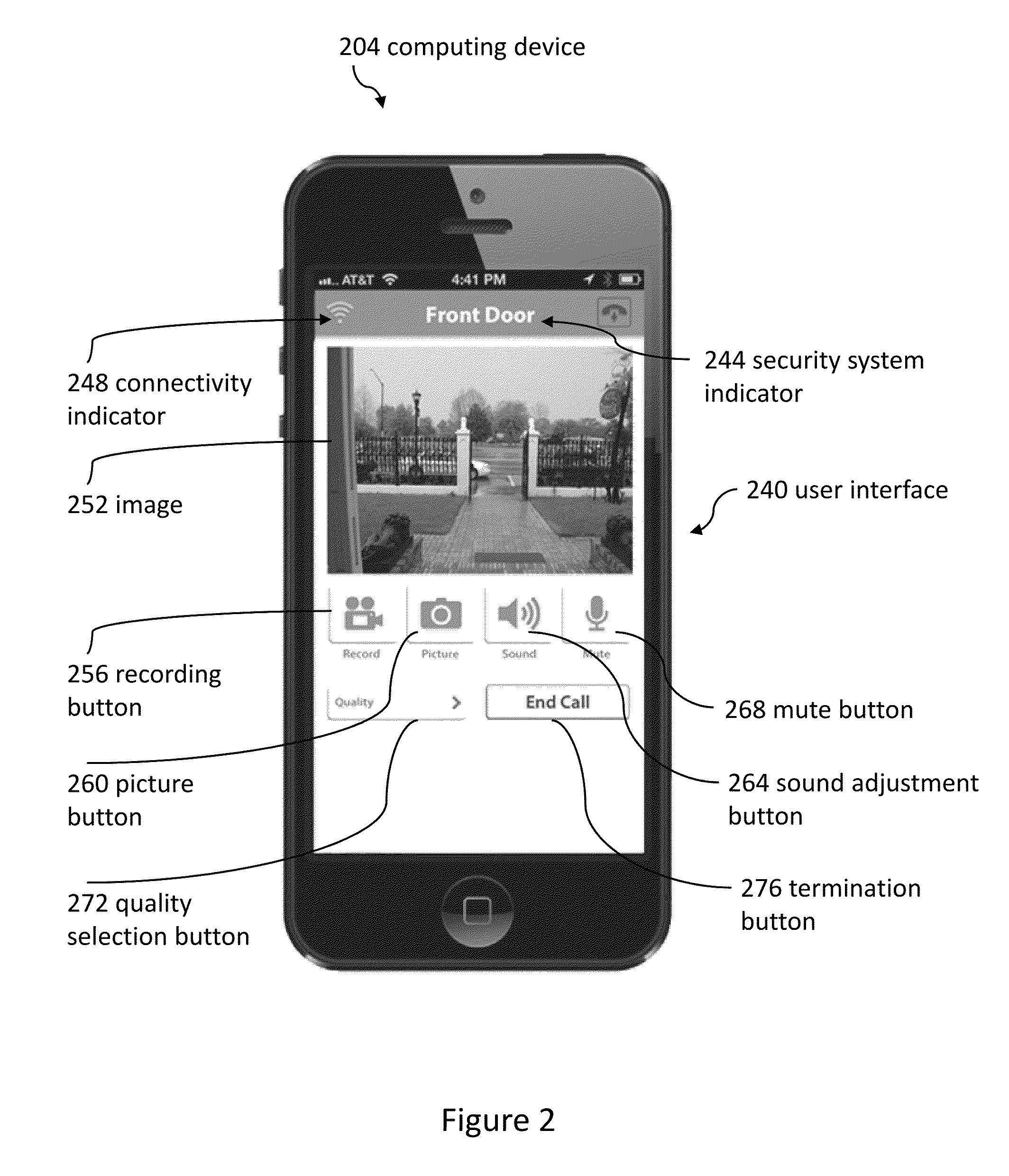

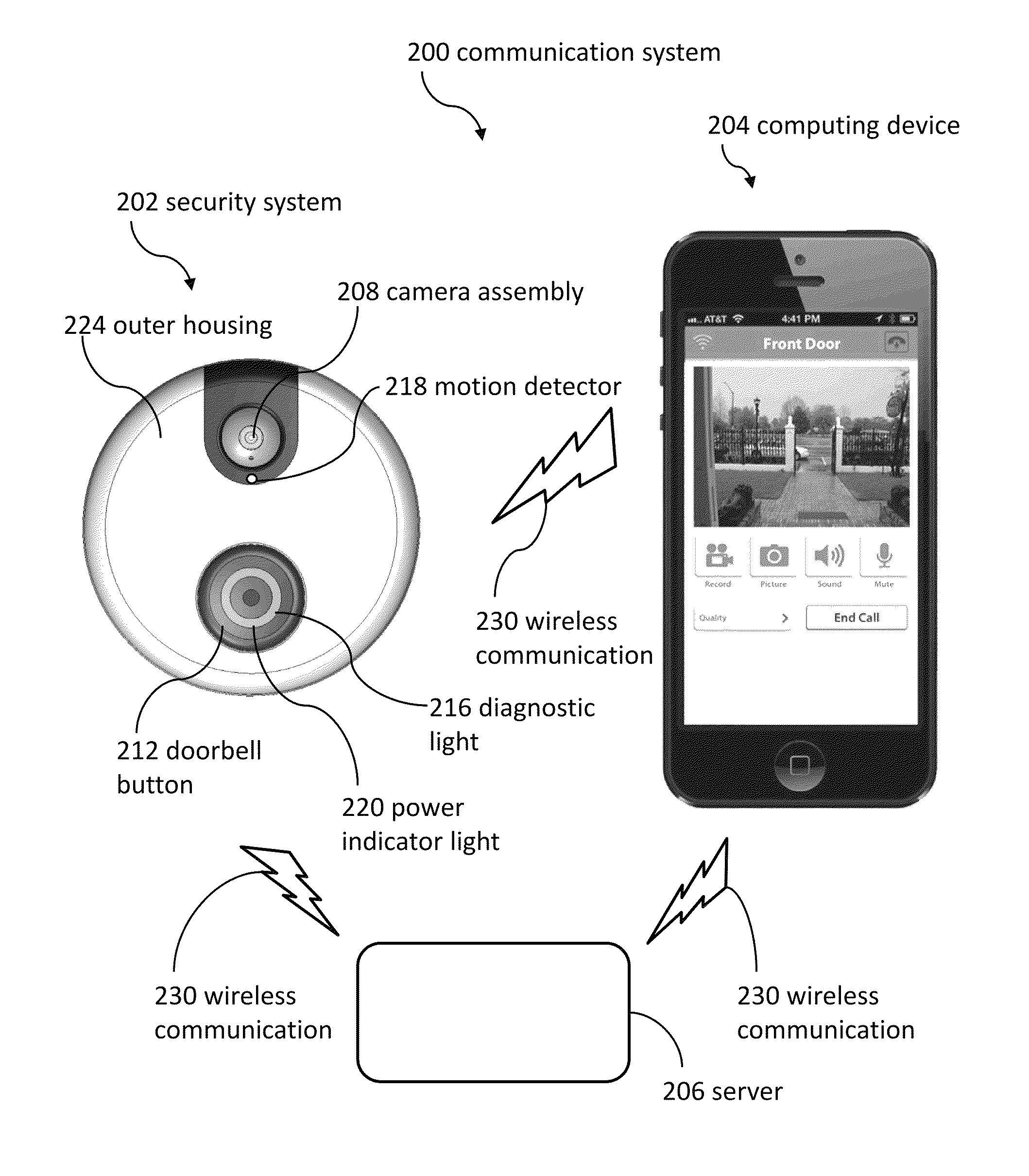

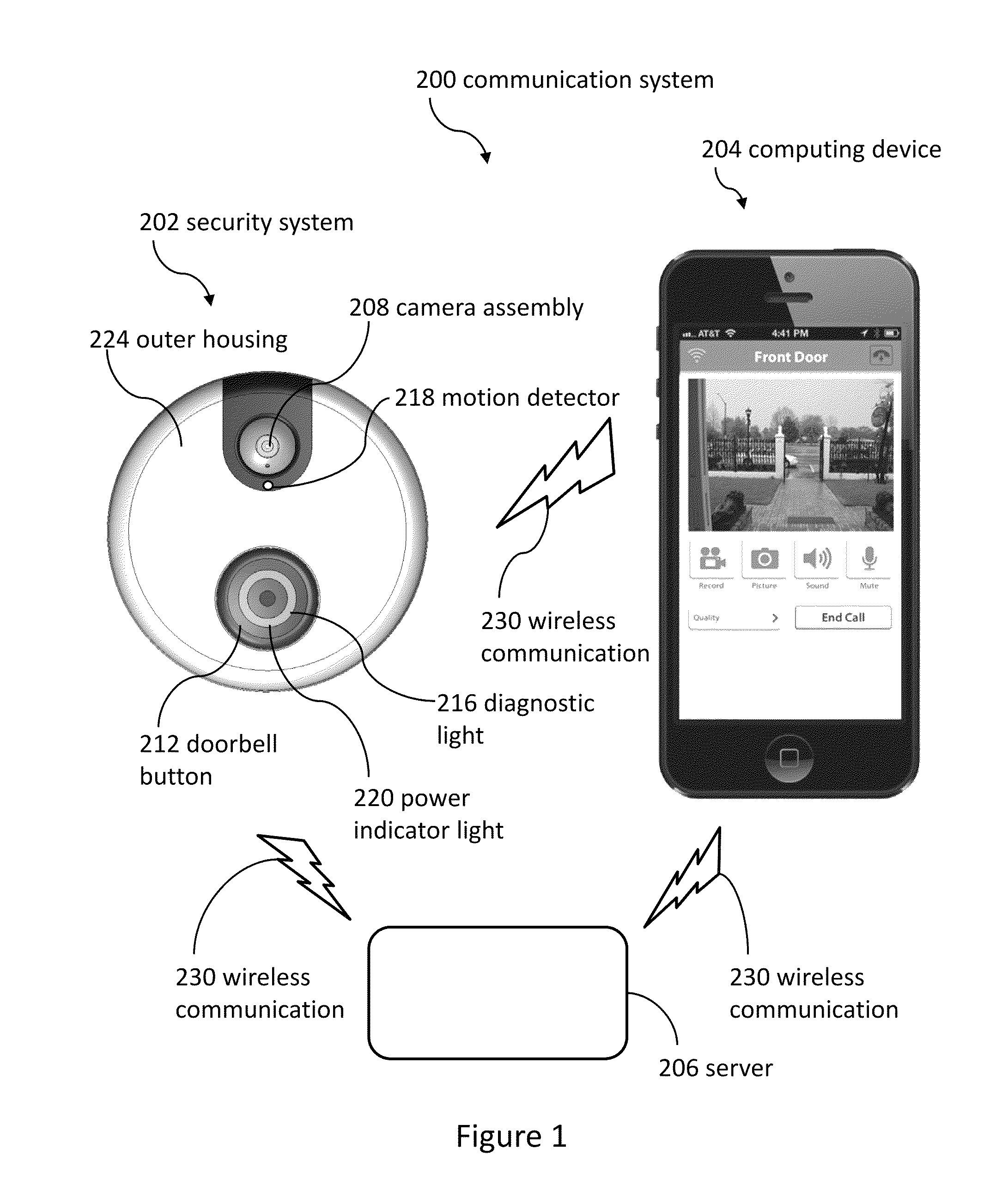

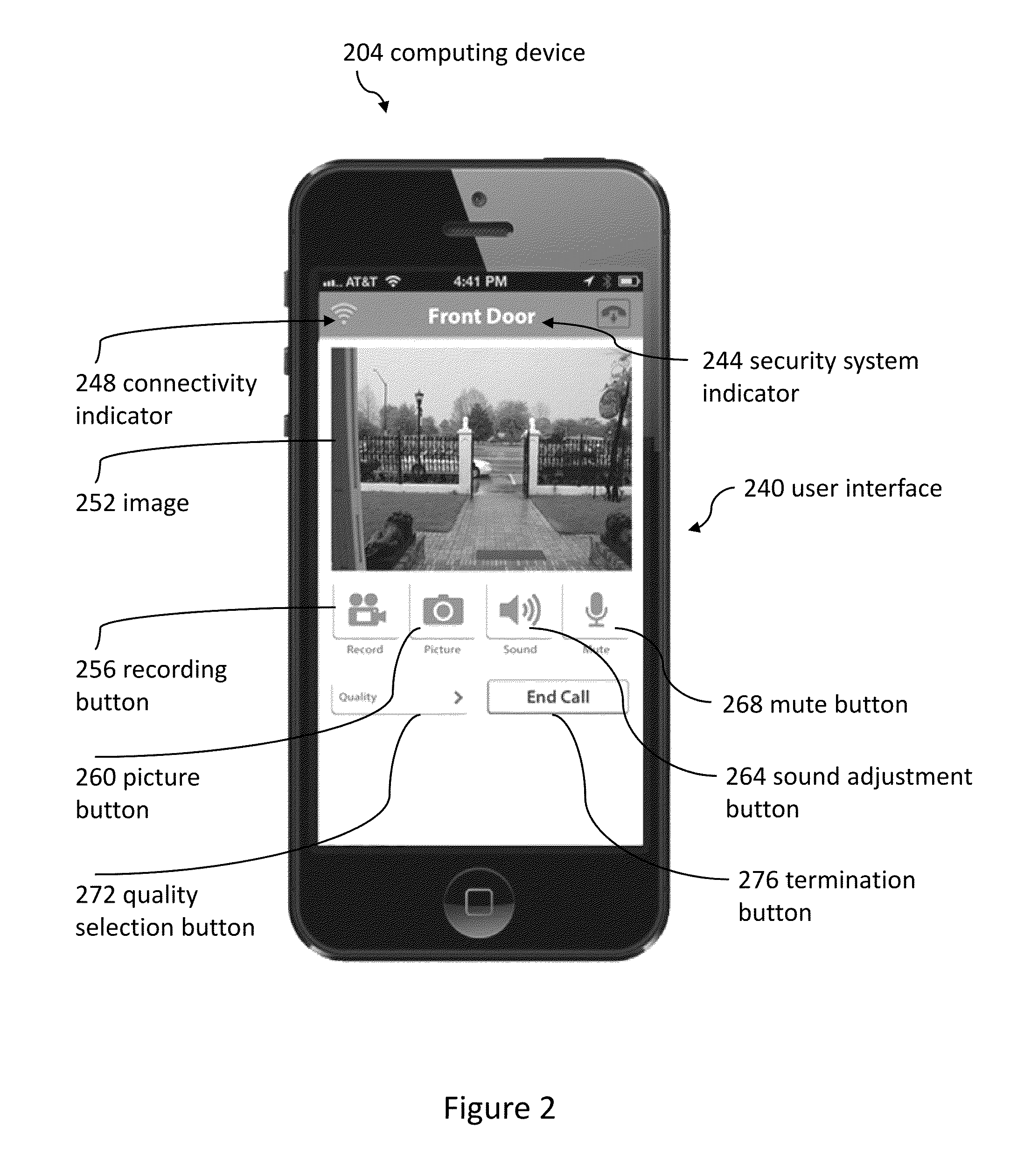

Doorbell communication systems and methods

ActiveUS8780201B1Reduce generationHigh activityColor television detailsClosed circuit television systemsDoorbellElectricity

Methods for using a doorbell that is configurable to wirelessly communicate with a remotely located computing device can include obtaining the doorbell that comprises a speaker, a microphone, and a camera. Methods can include entering a sleep mode in which the doorbell's wireless communication, the camera, and the microphone are disabled. Methods can include exiting the sleep mode and entering a standby mode in response to the doorbell detecting a first indication of a visitor. The standby mode can increase electrical activities of the doorbell's camera and microphone relative to the sleep mode. Methods can include entering an alert mode in response to detecting a second indication of the visitor. The doorbell can record an image using the camera during the alert mode. Wireless communication can be enabled during the alert mode to send an alert to the remotely located computing device.

Owner:SKYBELL TECH IP LLC

Energy harvesting computer device in association with a communication device configured with apparatus for boosting signal reception

ActiveUS20130157729A1Improve consumer electronics hybrid consumer electronics performanceLow densityMaterial nanotechnologyEnergy efficient ICTCellular telephoneCommunication device

Disclosed embodiments comprise an energy harvesting computer device in association with a communication device comprising interactive user interface operatively configured with CMOS multiple antennas on chip for boosting signal receptions and for providing faster data transmission speed. Disclosed embodiment encompasses three modes of communications—the Cell phone, wireless Internet applications, and Global communication and media information. Embodiments provide communication apparatus operable to enhance mobile communication efficiency with touch sensitive display comprising energy harvesting platform in communication with a charging circuit board configured with memories, processors, sensors, and modules. Embodiments further provide a gaming device, a wireless media device configured with touch pads comprising sensors being embedded in silicon substrate and fused in nano-fiber / microfiber material having excellent electrical characteristics. Certain embodiments provide communication apparatus configured for voice enabled applications comprising human voice auditory operable to convert text into voice auditory and / or voice auditory into text applications.

Owner:TABE JOSEPH AKWO

Doorbell communication systems and methods

ActiveUS8823795B1High activityLess powerColor television detailsClosed circuit television systemsDoorbellEntryway

Communication systems configured to monitor an entryway to a building can include a security system configured to wirelessly communicate with a remote computing device. The security system can include a doorbell that comprises a camera, a speaker, and a microphone.

Owner:SKYBELL TECH IP LLC

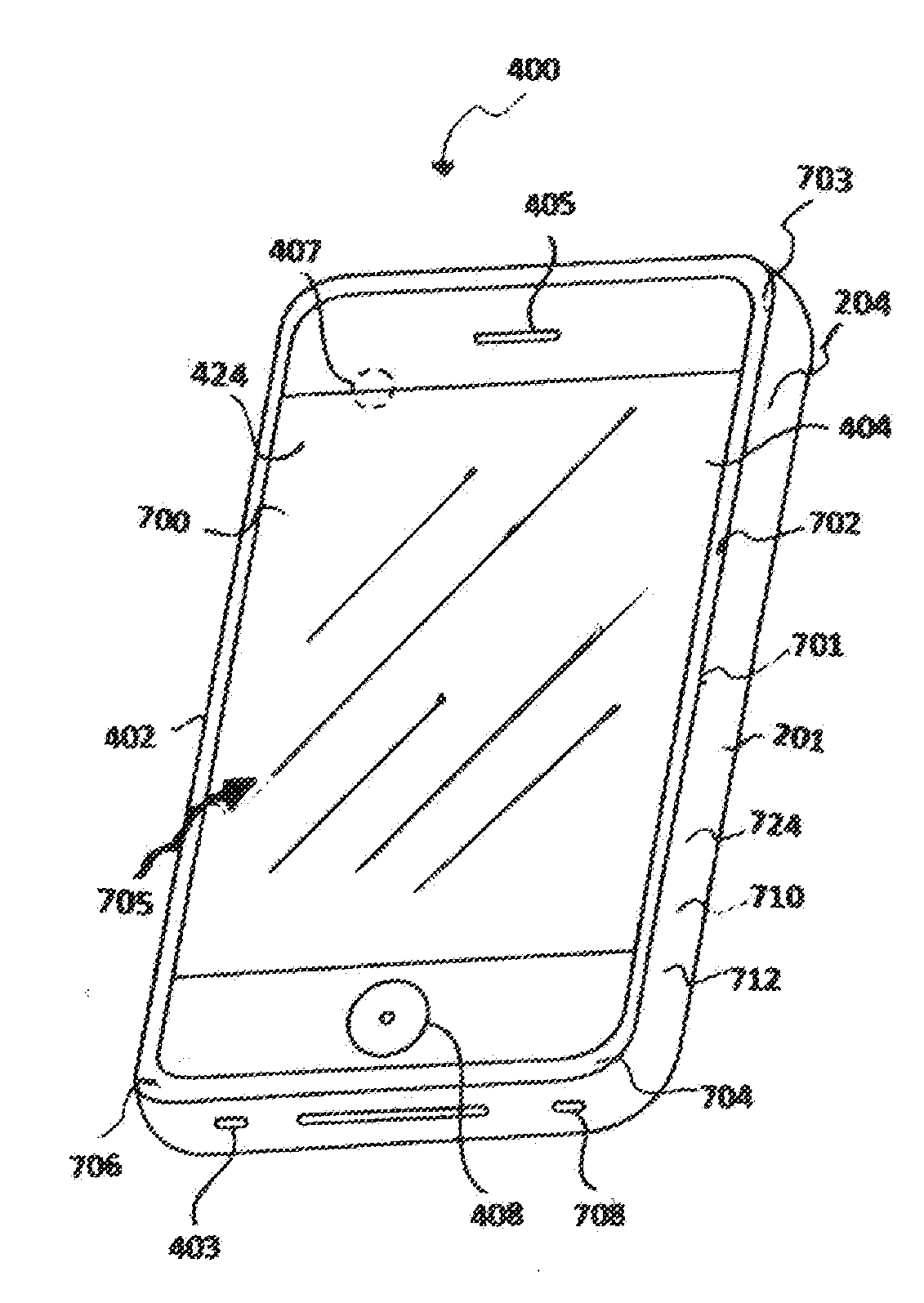

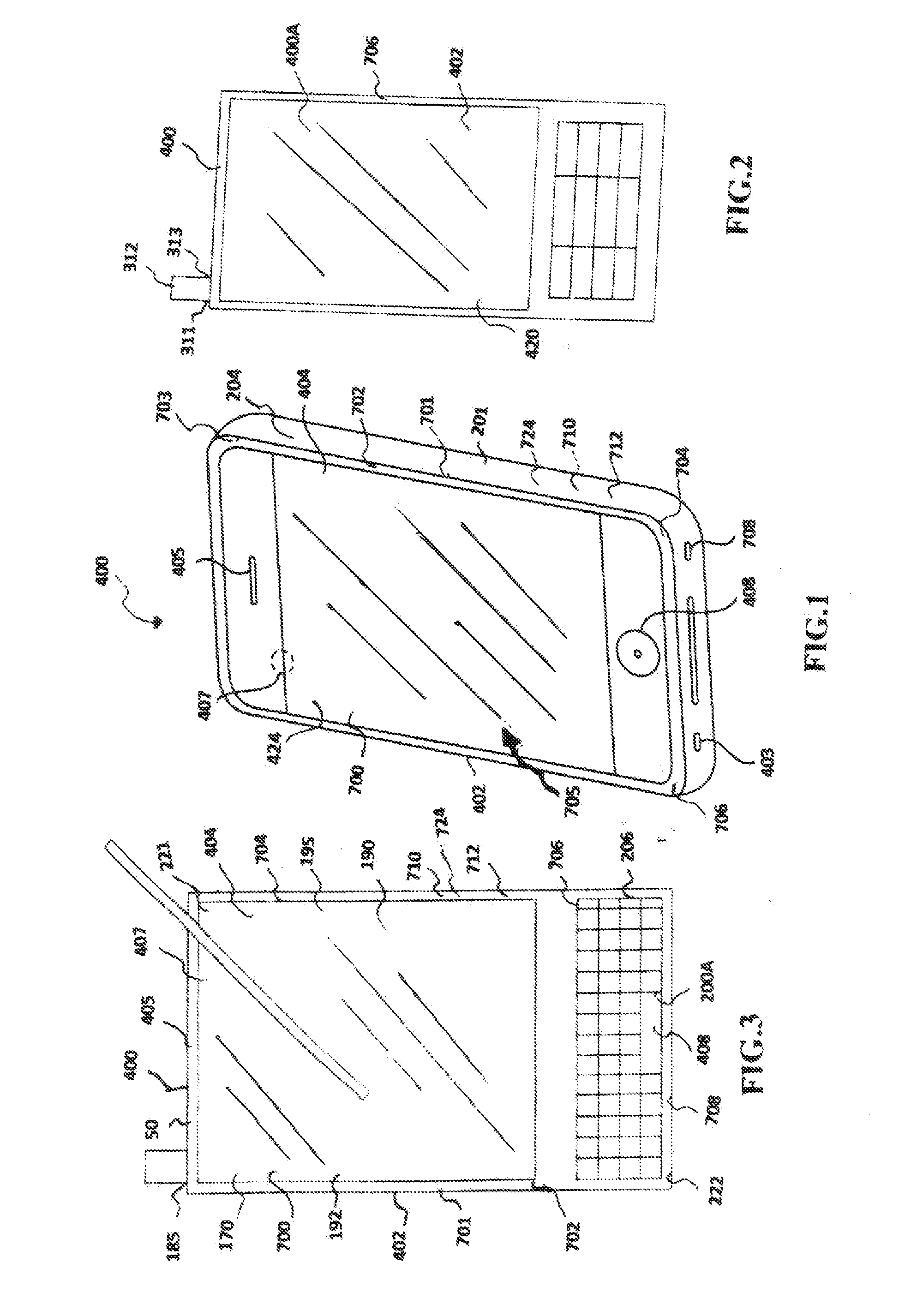

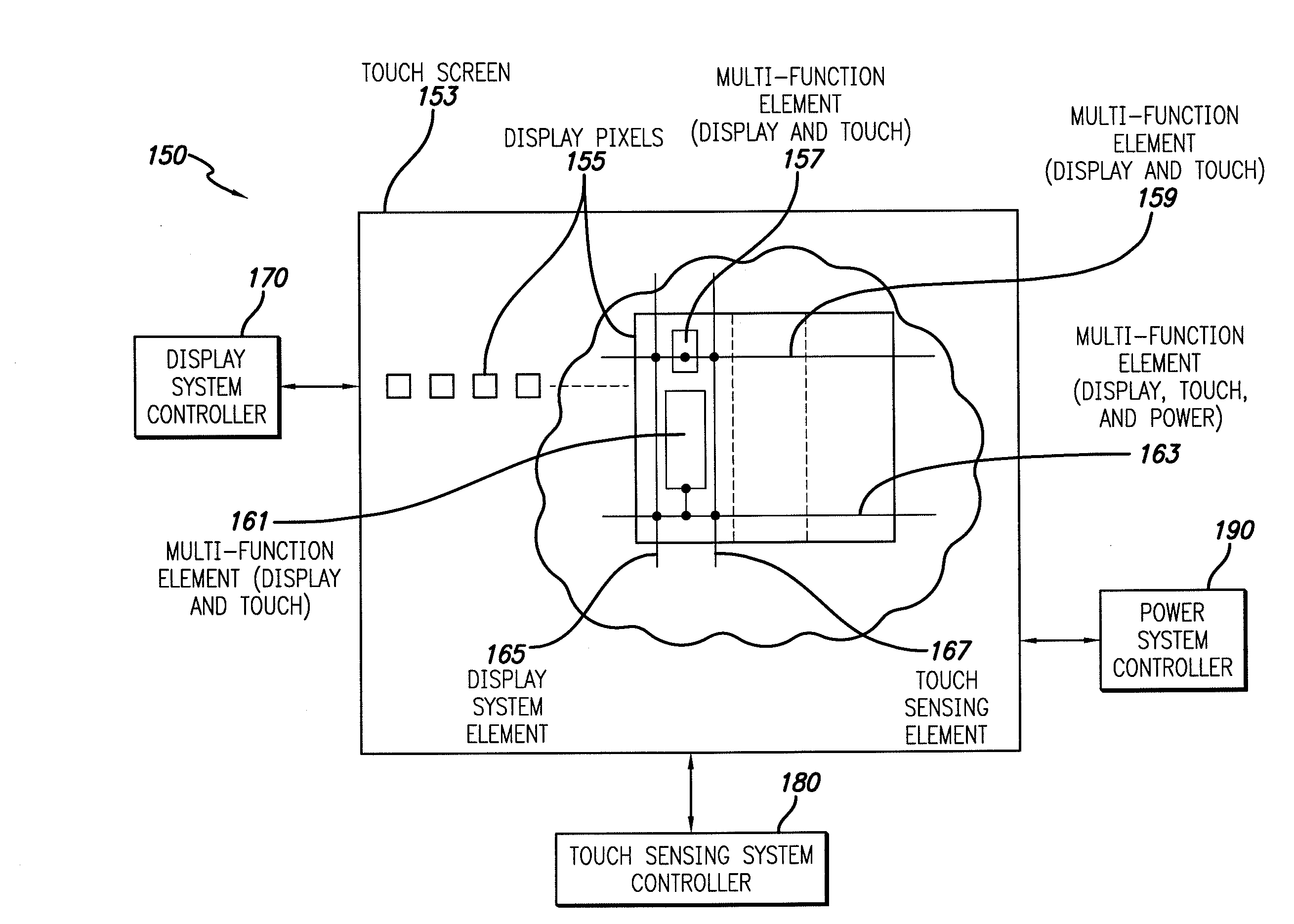

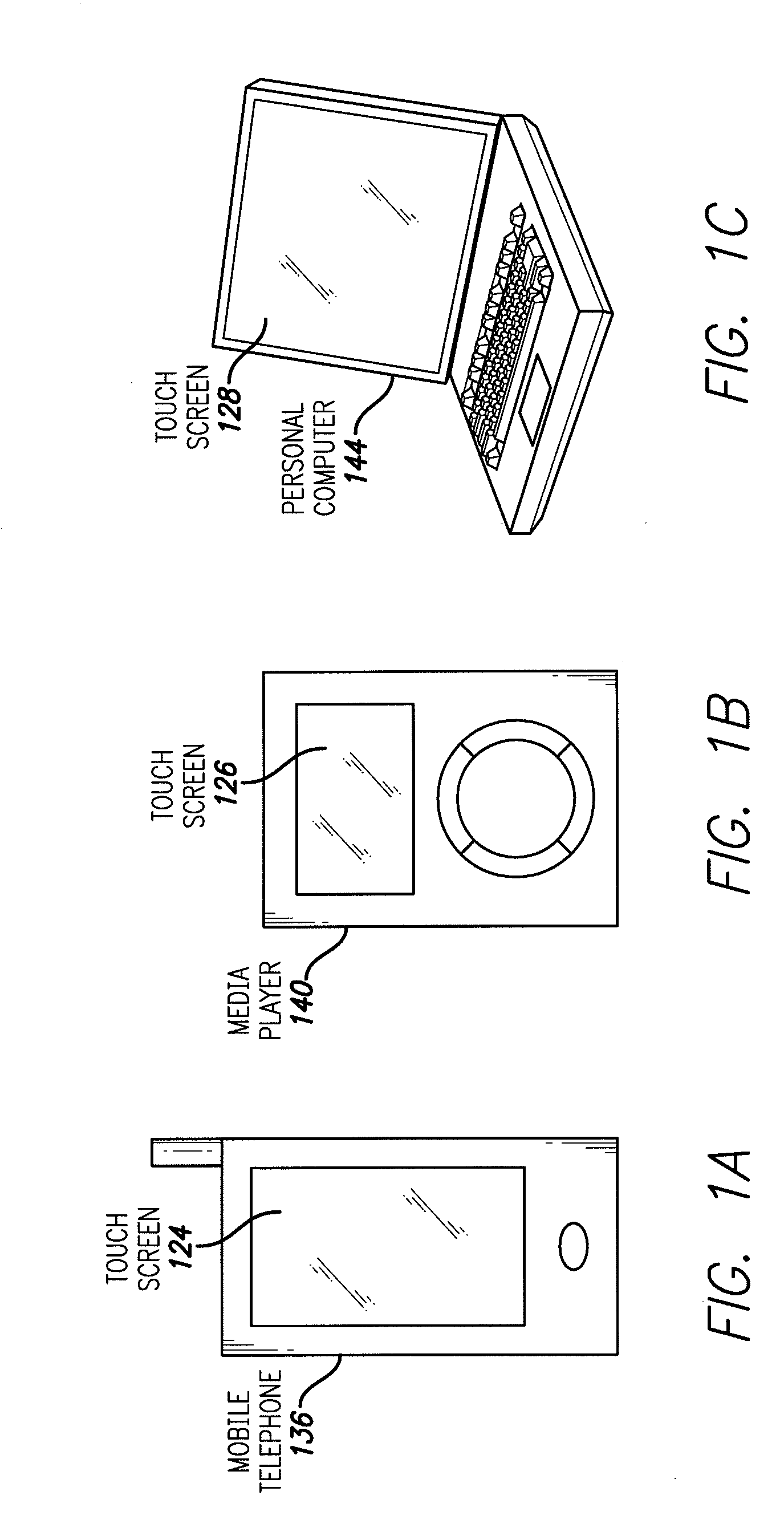

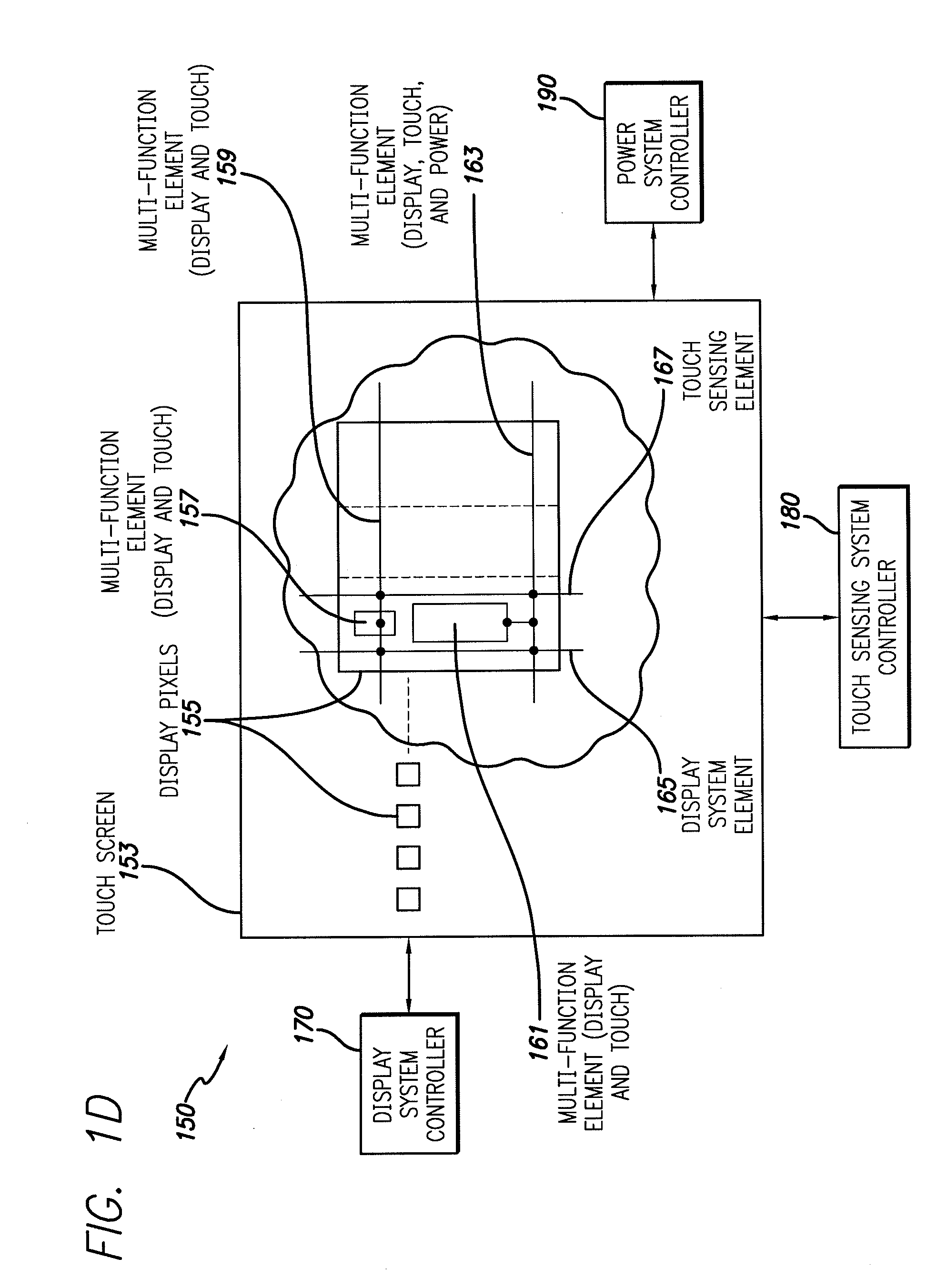

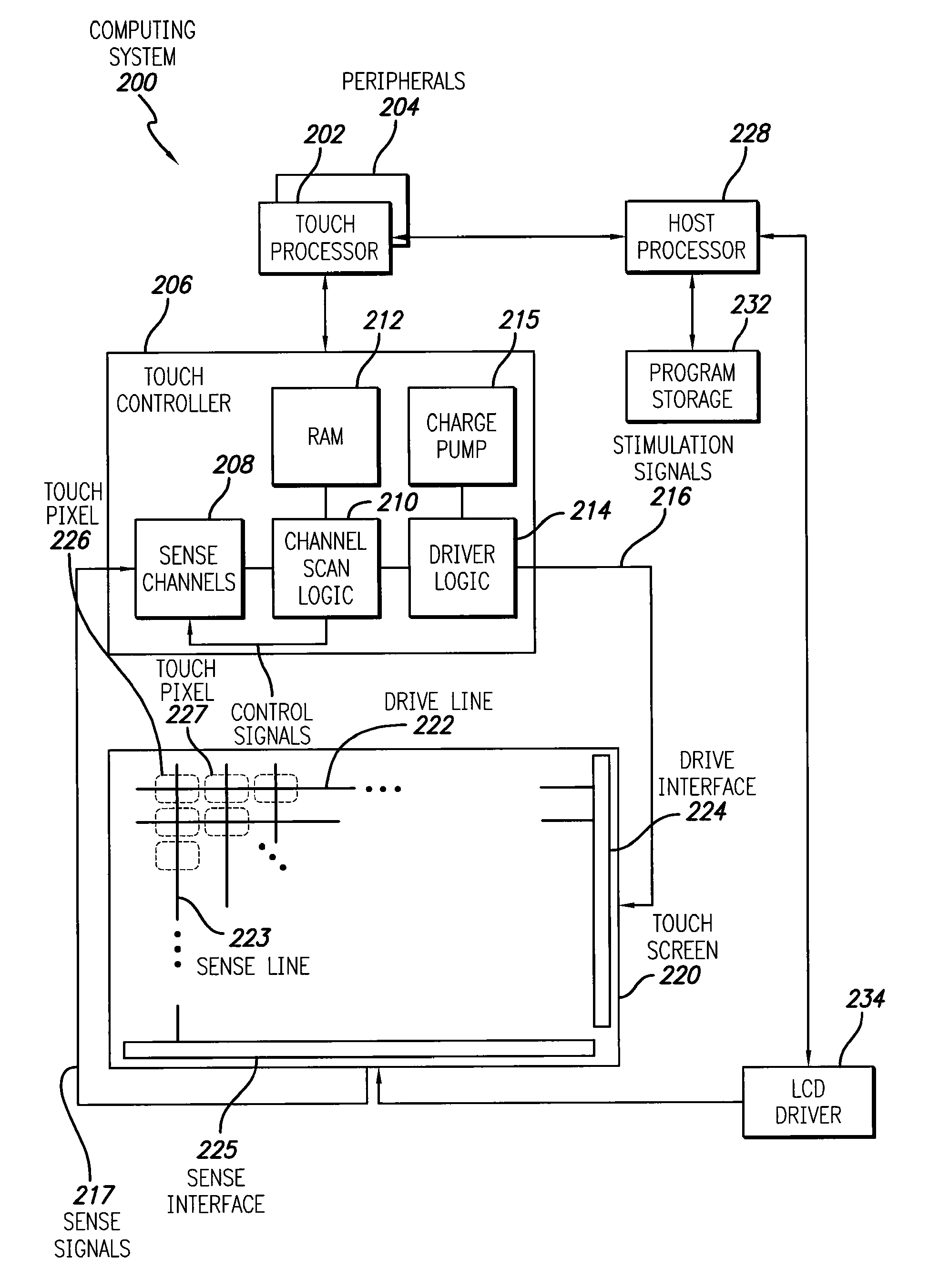

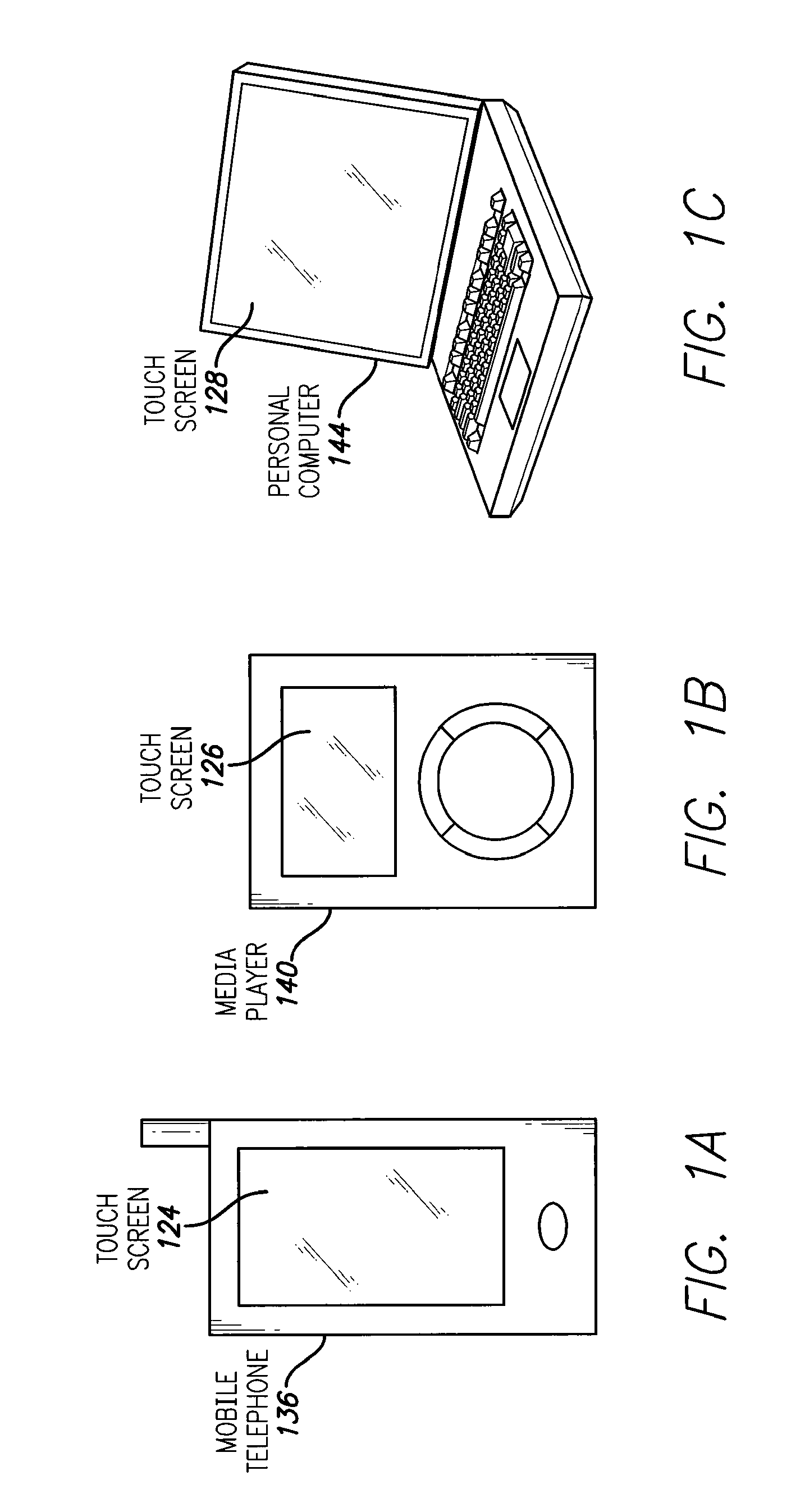

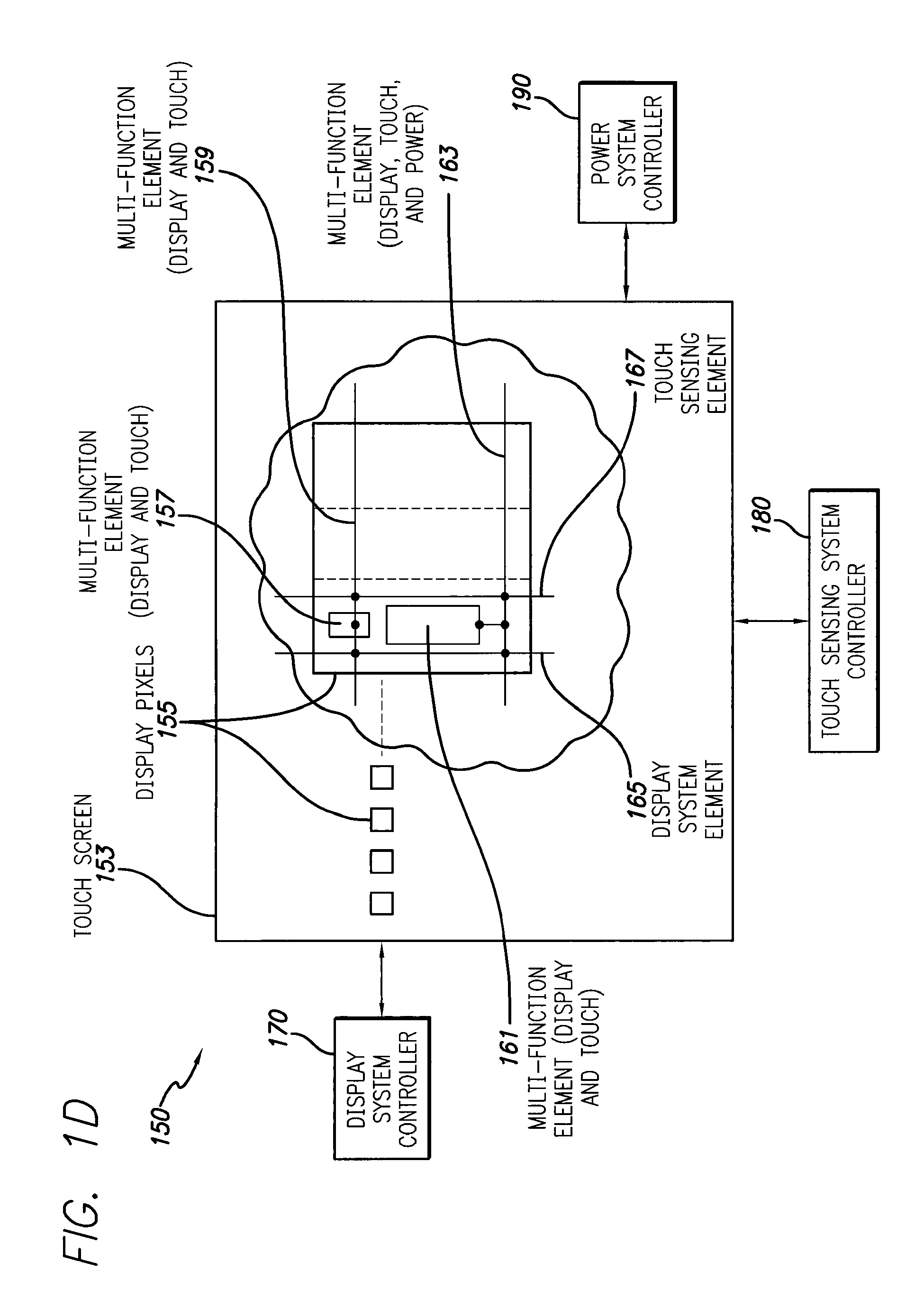

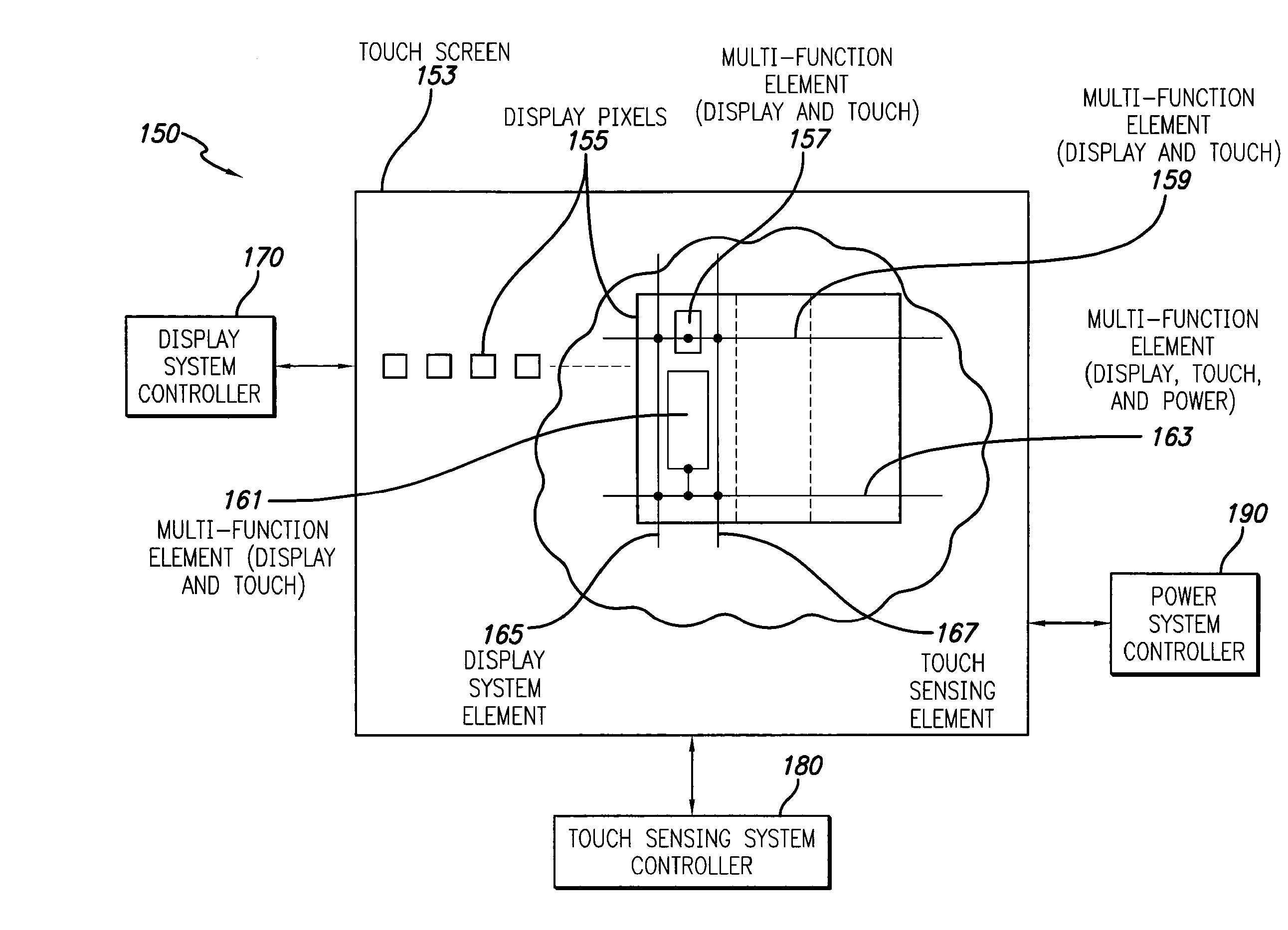

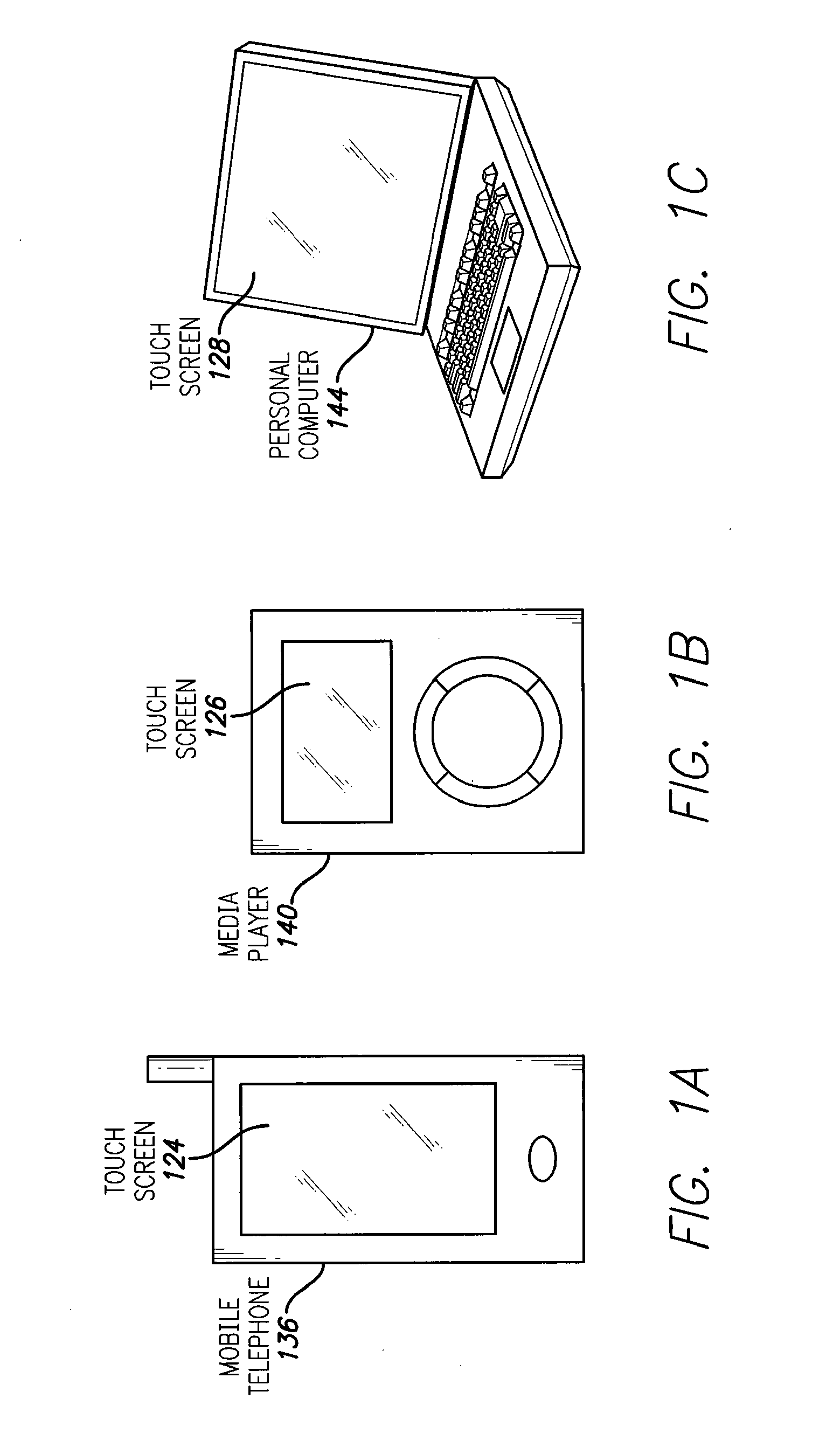

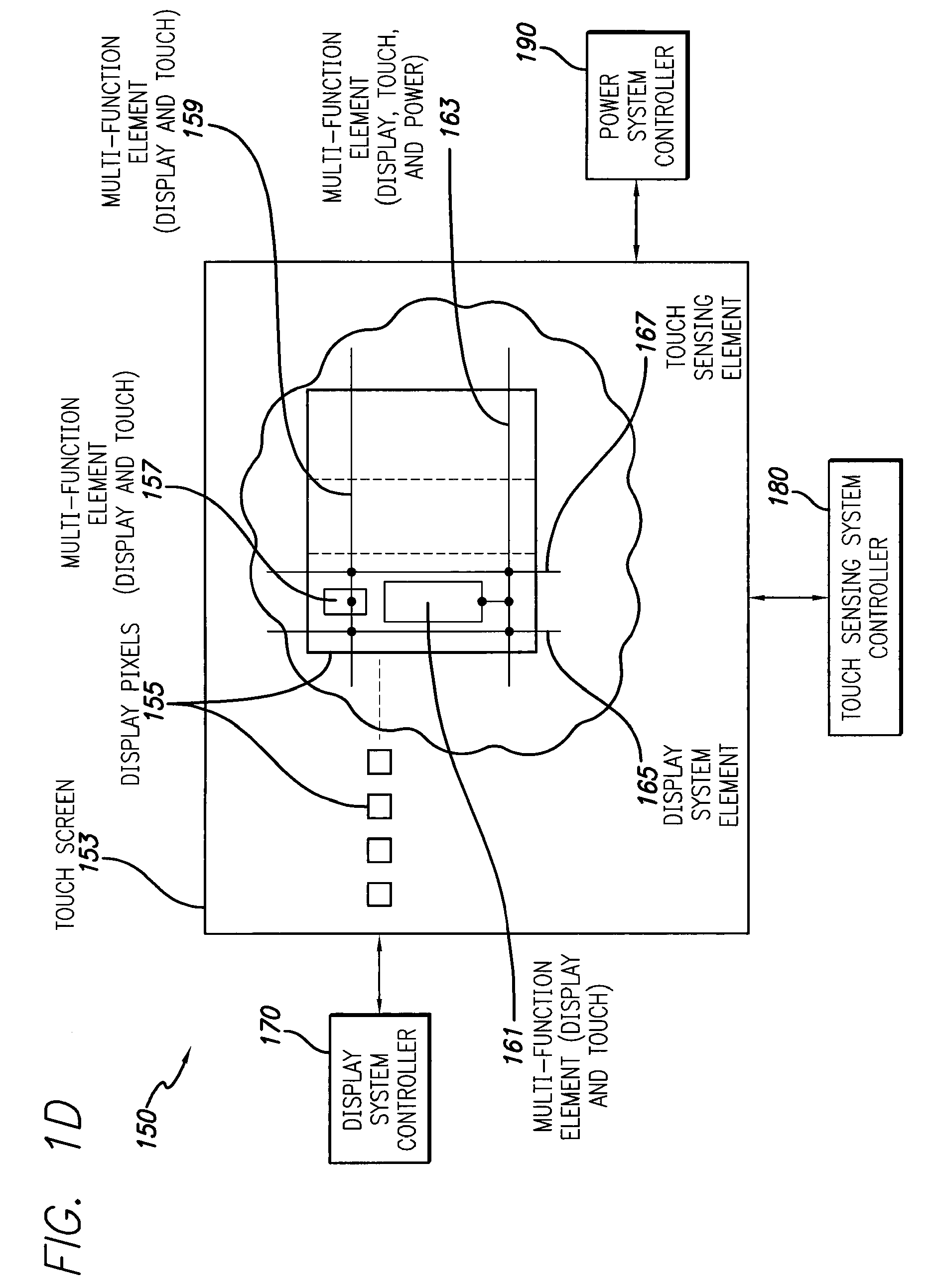

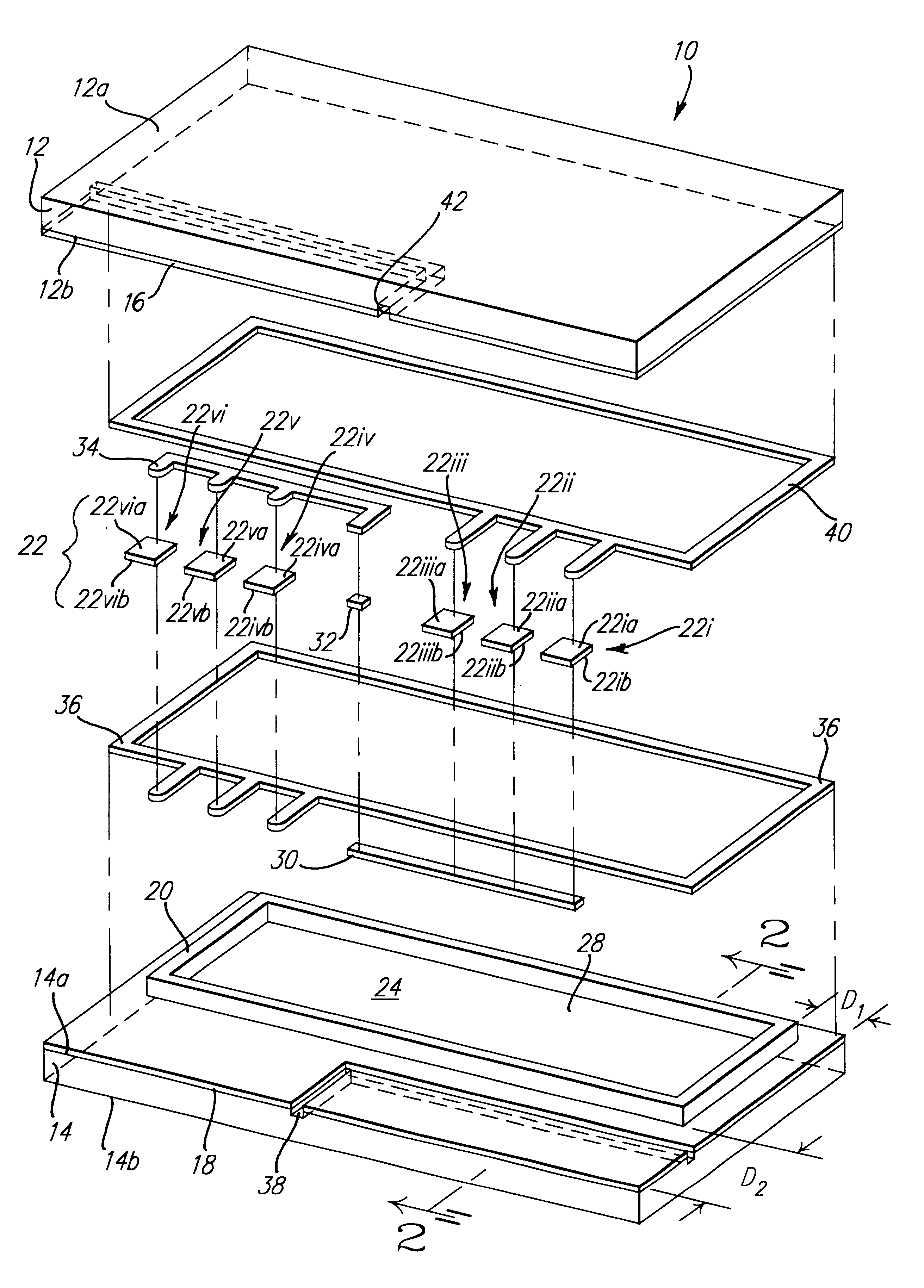

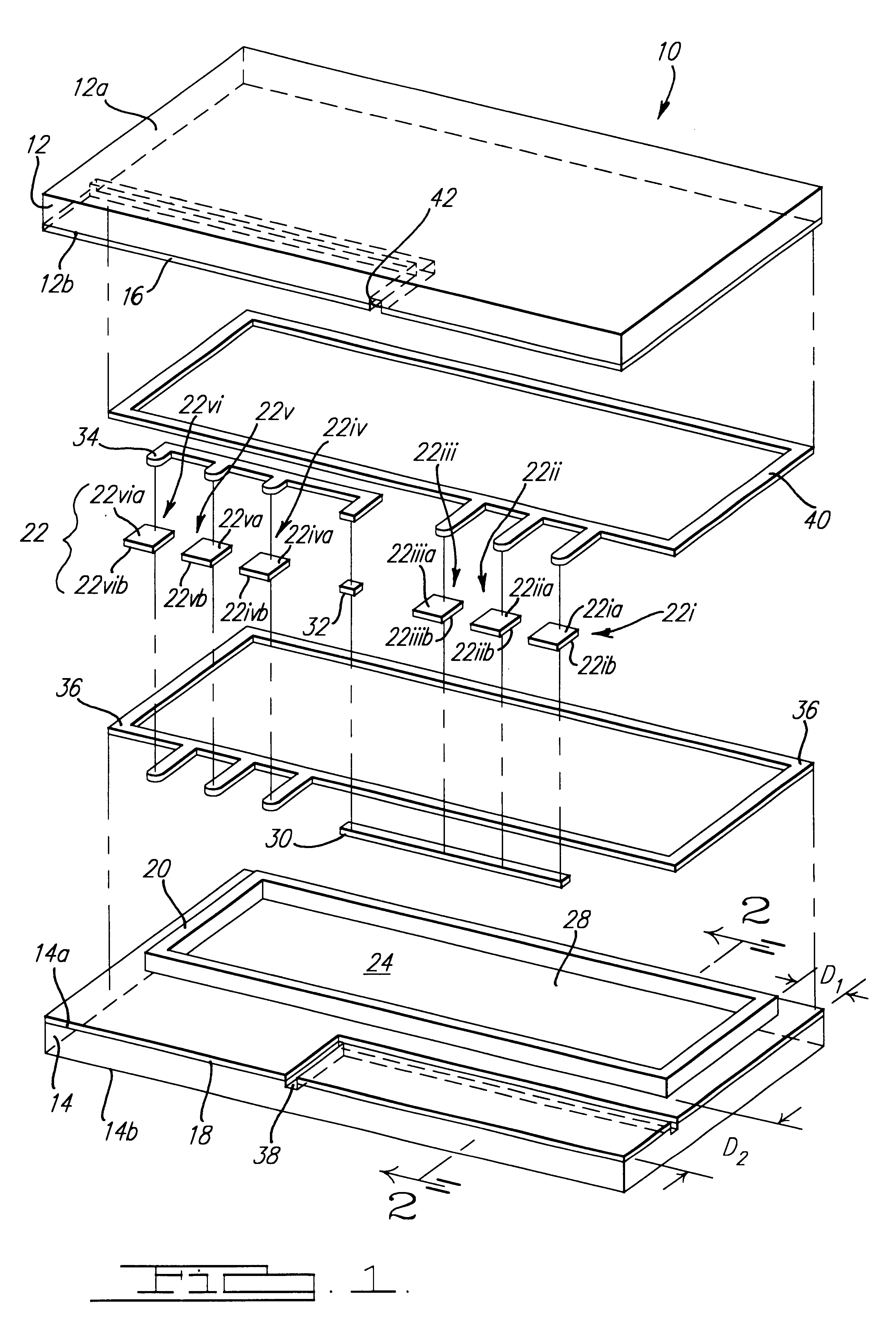

Integrated Touch Screen

ActiveUS20100194697A1Less powerFew partsStatic indicating devicesVessels or leading-in conductors manufactureTouch SensesDisplay device

Displays with touch sensing circuitry integrated into the display pixel stackup are provided. Circuit elements, such as touch signal lines, such as drive lines and sense lines, grounding regions, in the display pixel stackups can be grouped together to form touch sensing circuitry that senses a touch on or near the display. An integrated touch screen can include multi-function circuit elements that can operate as circuitry of the display system to generate an image on the display, and can also form part of a touch sensing system that senses one or more touches on or near the display. The multi-function circuit elements can be, for example, capacitors in display pixels that can be configured to operate as storage capacitors / electrodes, common electrodes, conductive wires / pathways, etc., of the display circuitry in the display system, and that may also be configured to operate as circuit elements of the touch sensing circuitry.

Owner:APPLE INC

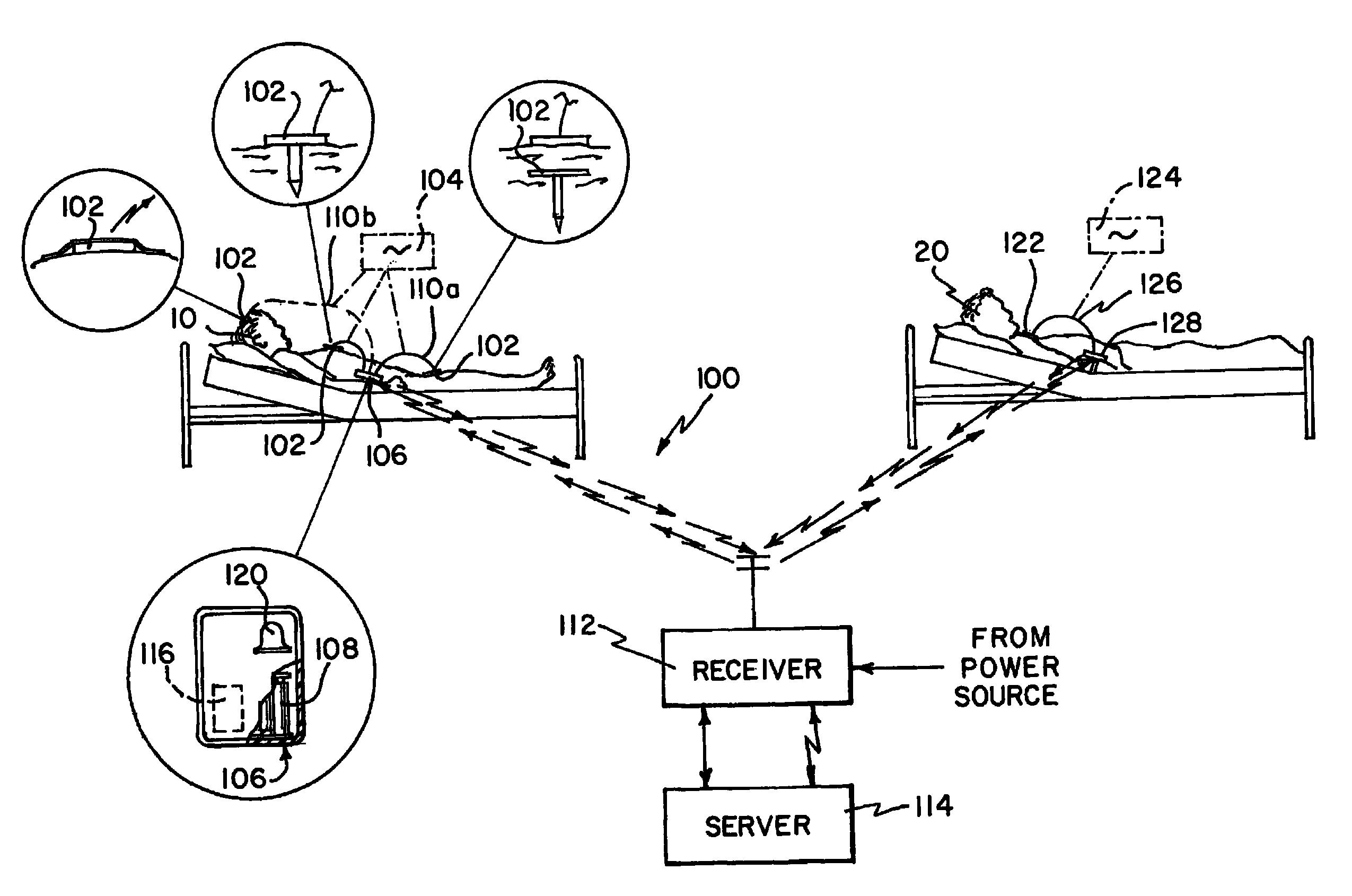

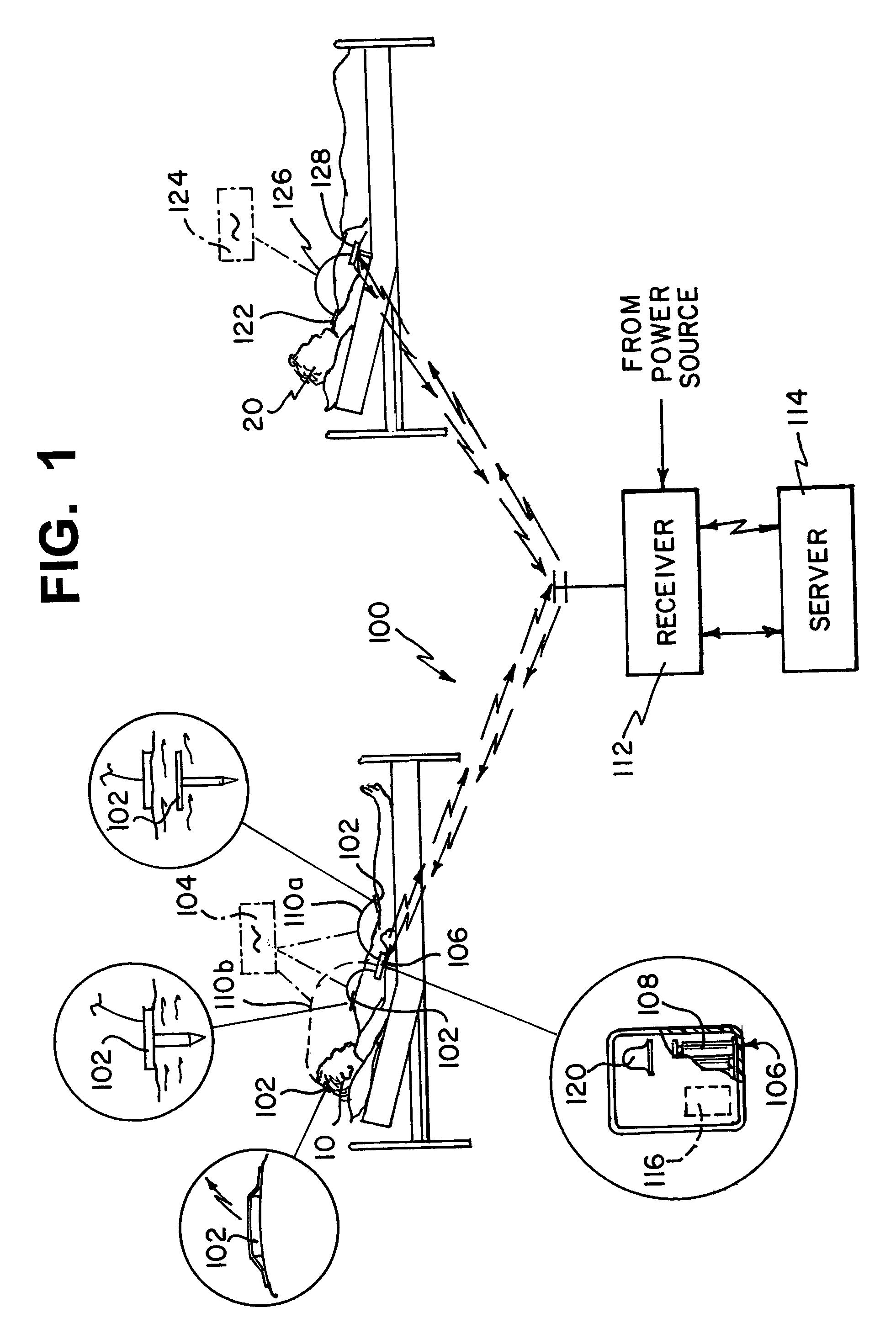

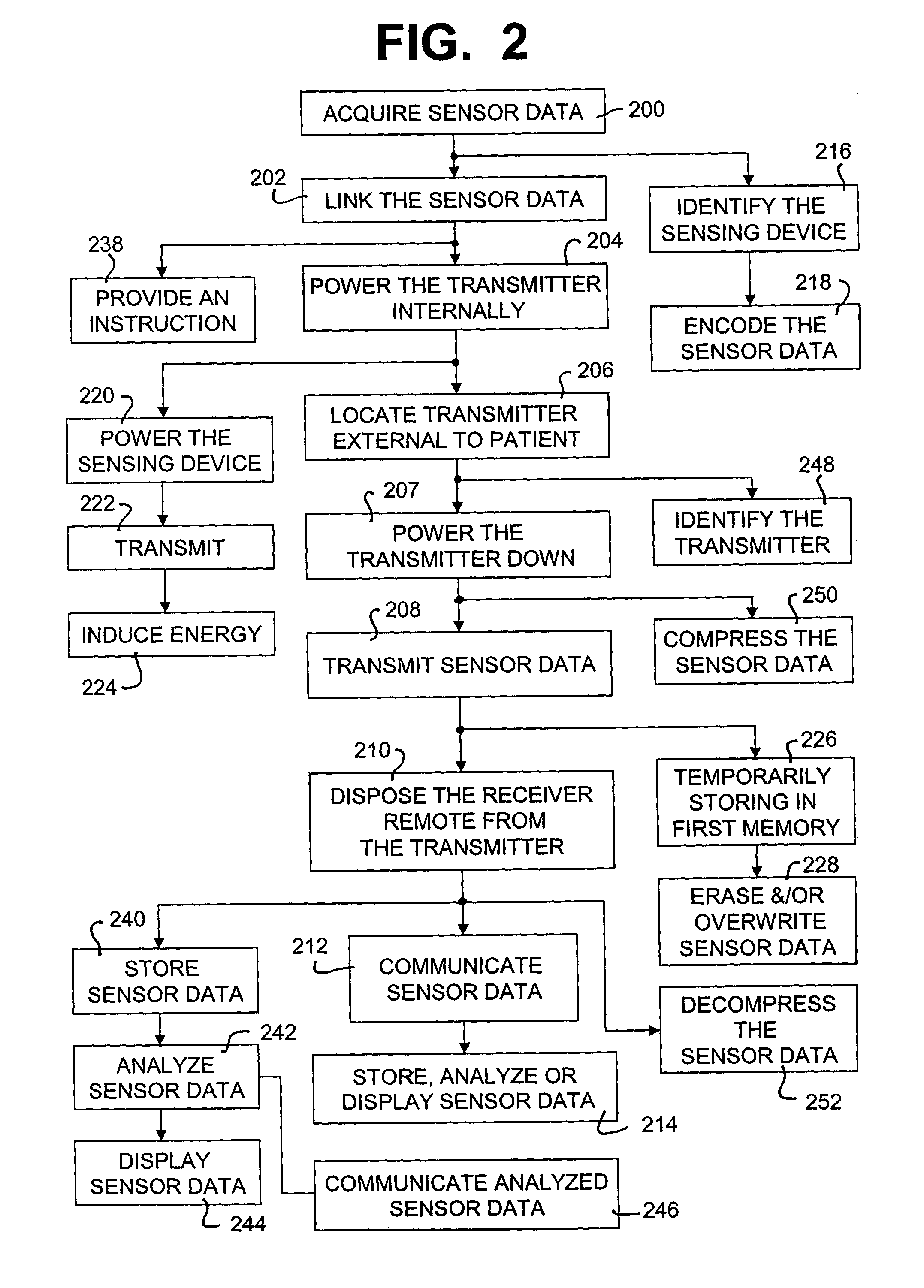

Wireless patient monitoring system

A device and method for monitoring a patient having a sensing device taking sensor data continuously and a transmitter located on the patient and internally powered. The transmitter is normally in a power-down state and powered-up for transmitting the sensor data. A receiver is located remote from the patient and receives the sensor data transmitted wirelessly from the transmitter. The transmission is typically a burst and can also be initiated on a command. For the burst, the sensor data is accumulated over a first period. The transmitter can transmit the sensor data over a second period of time. The second period of time is shorter than the first period of time. Once the transmission is complete, transmitter can be powered down. A further step displays the sensor data at the receiver in pseudo real-time. The display is shifted by a sum of the first and the second period of time.

Owner:INTEGRA LIFESCI

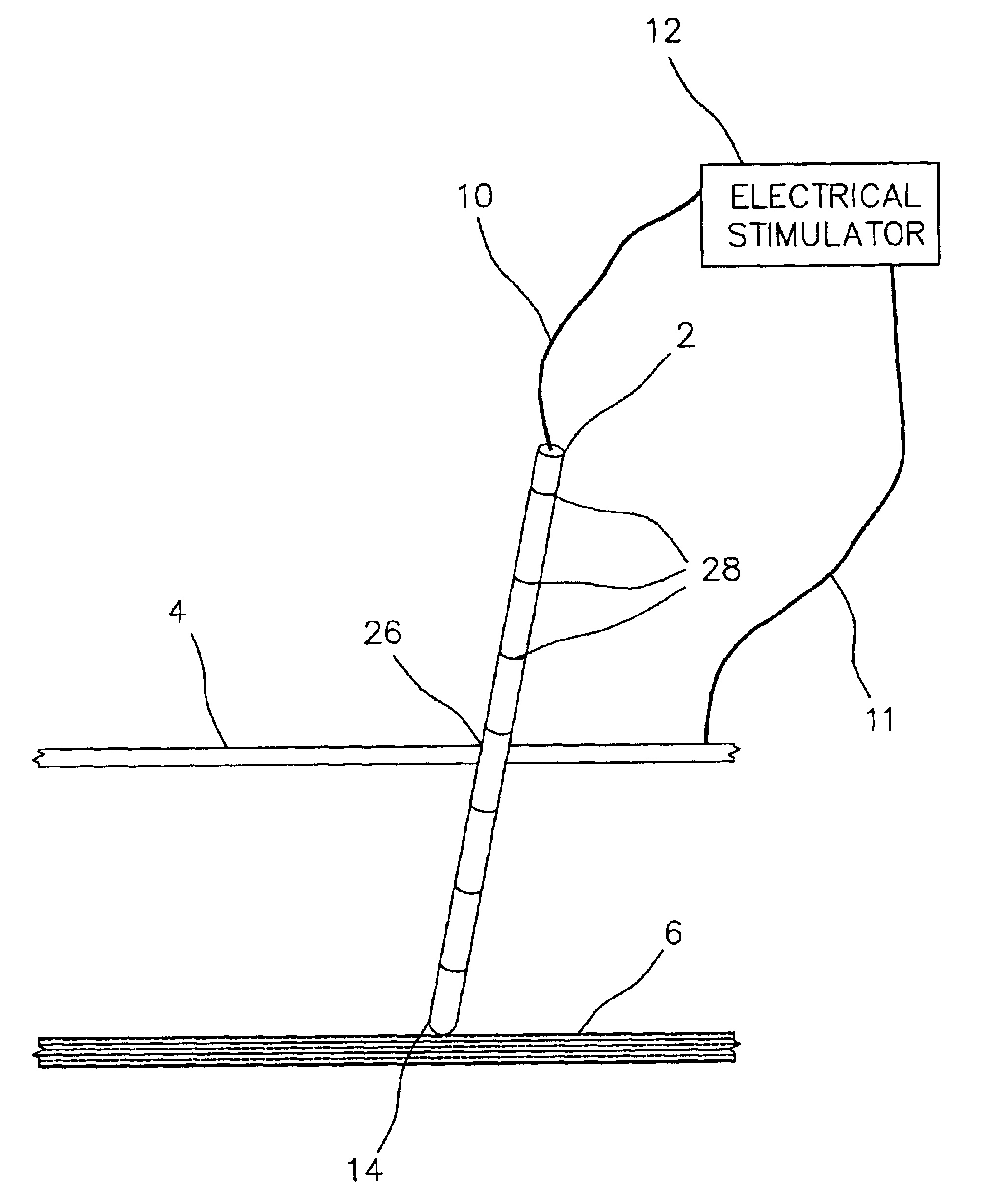

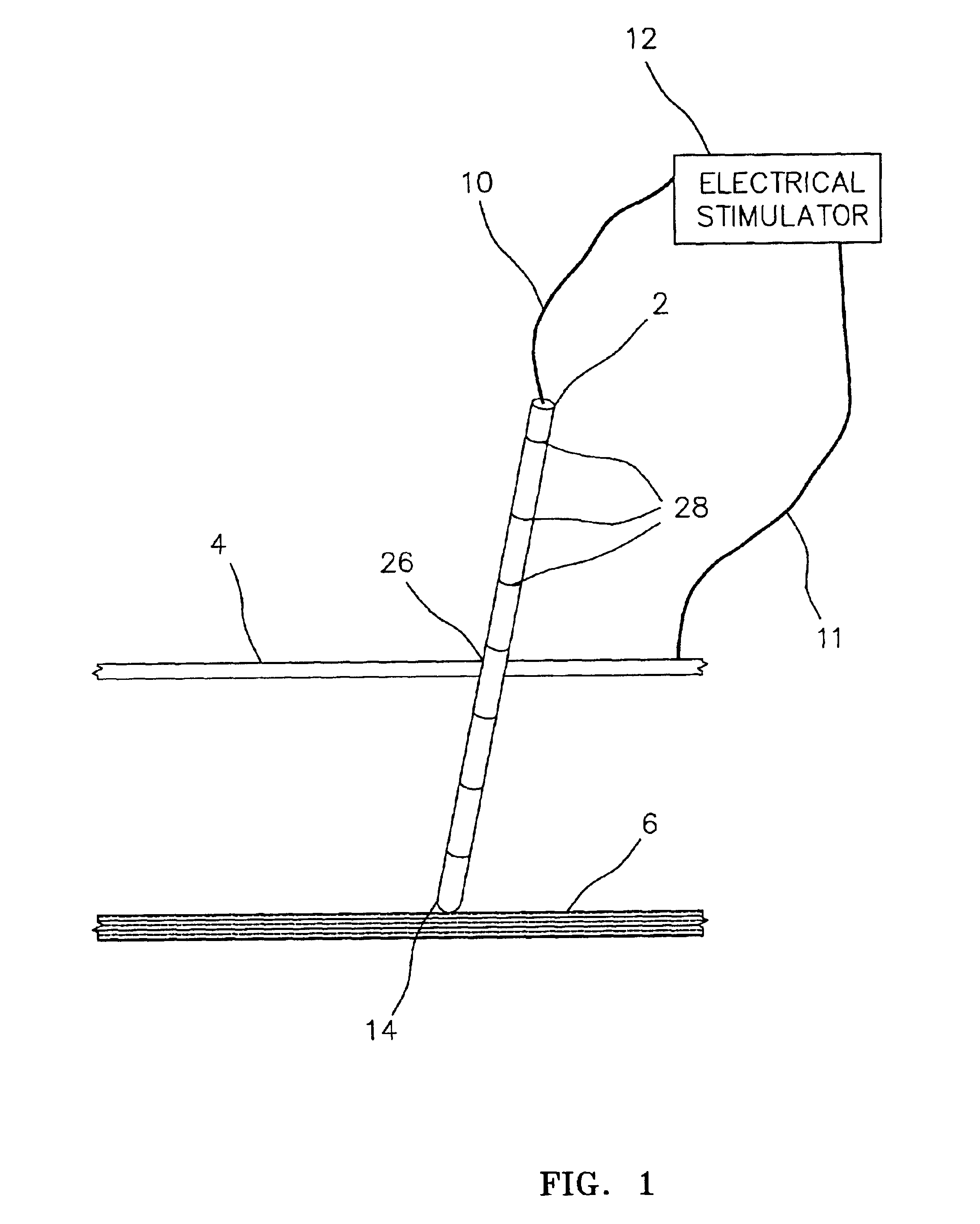

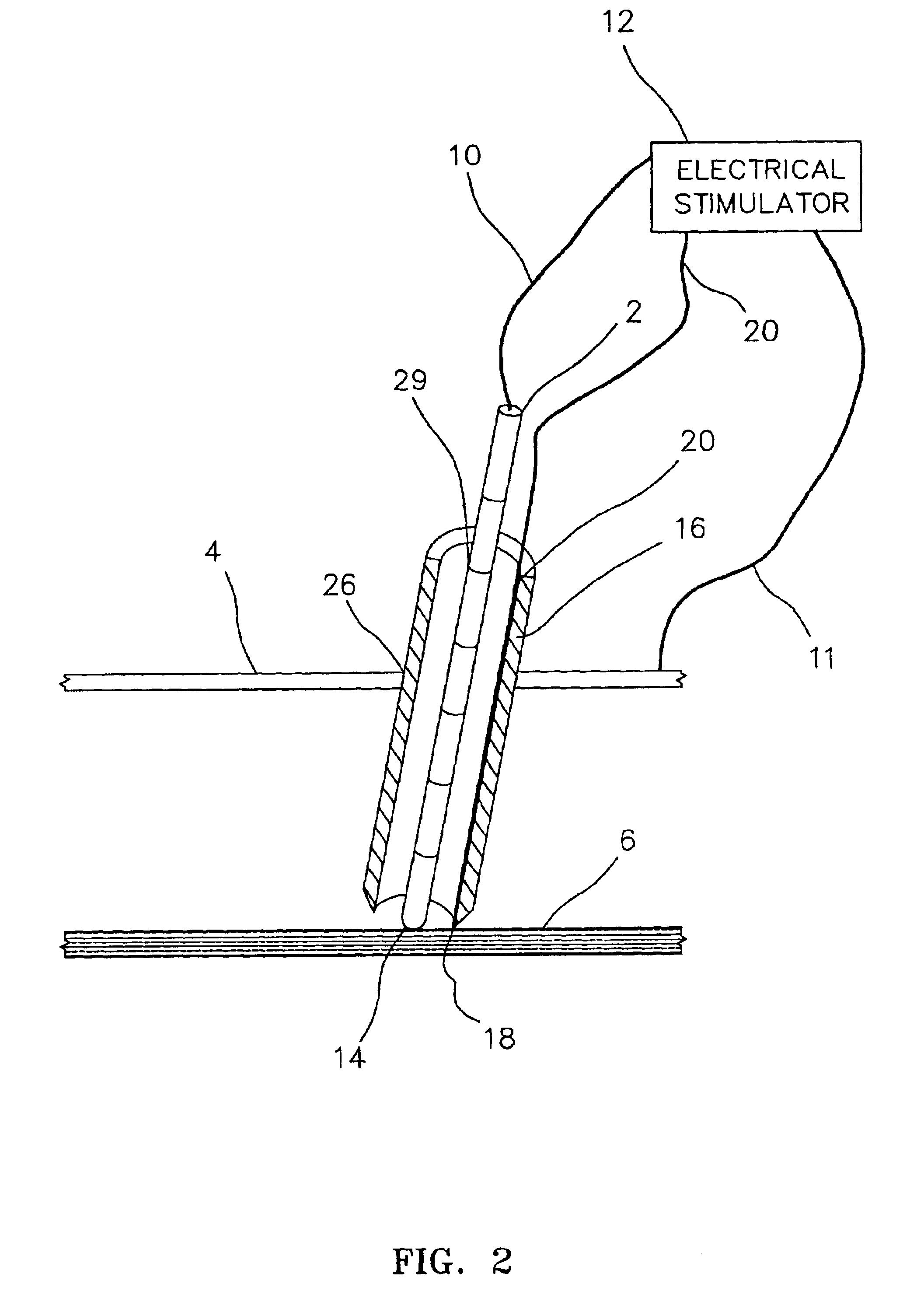

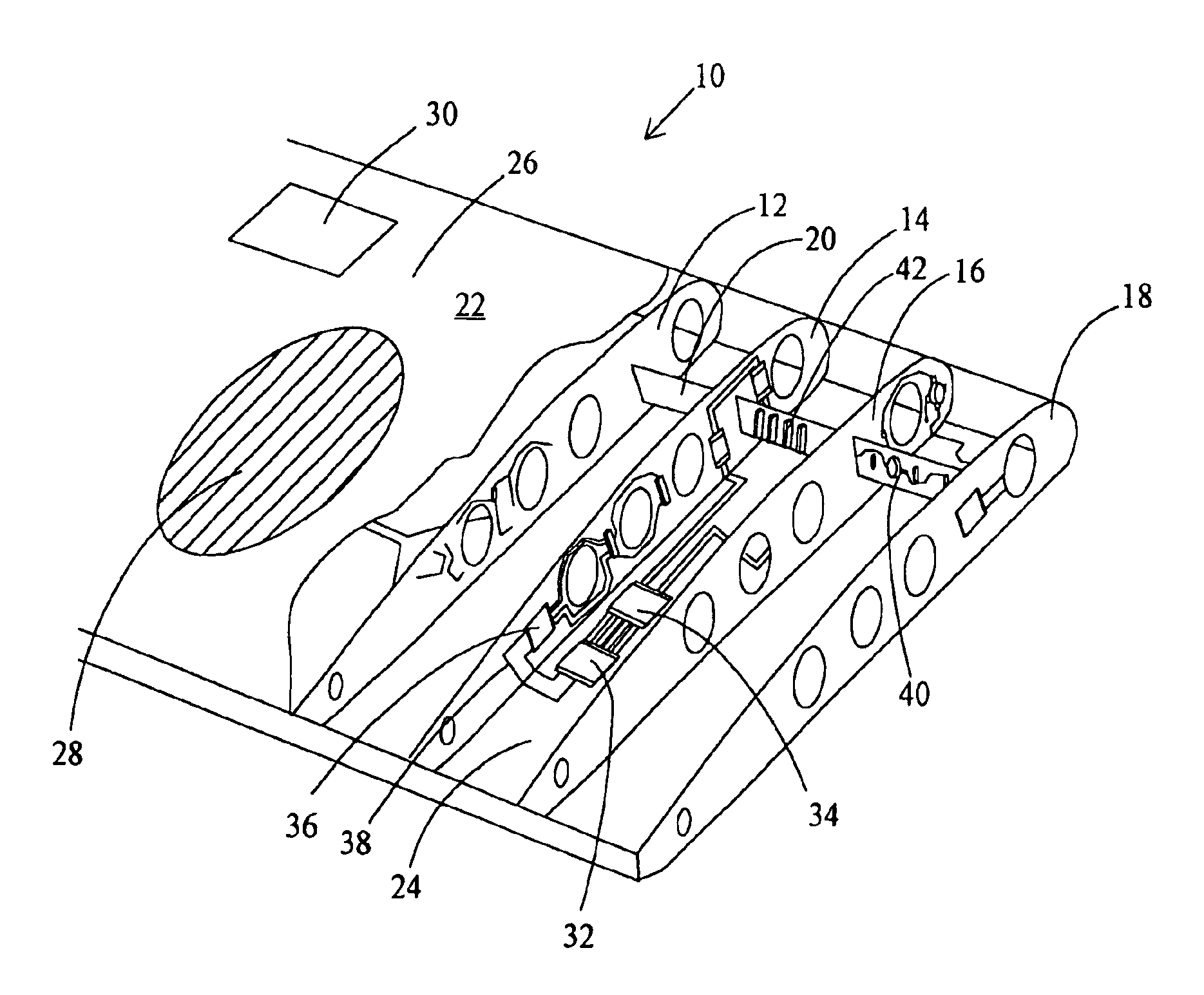

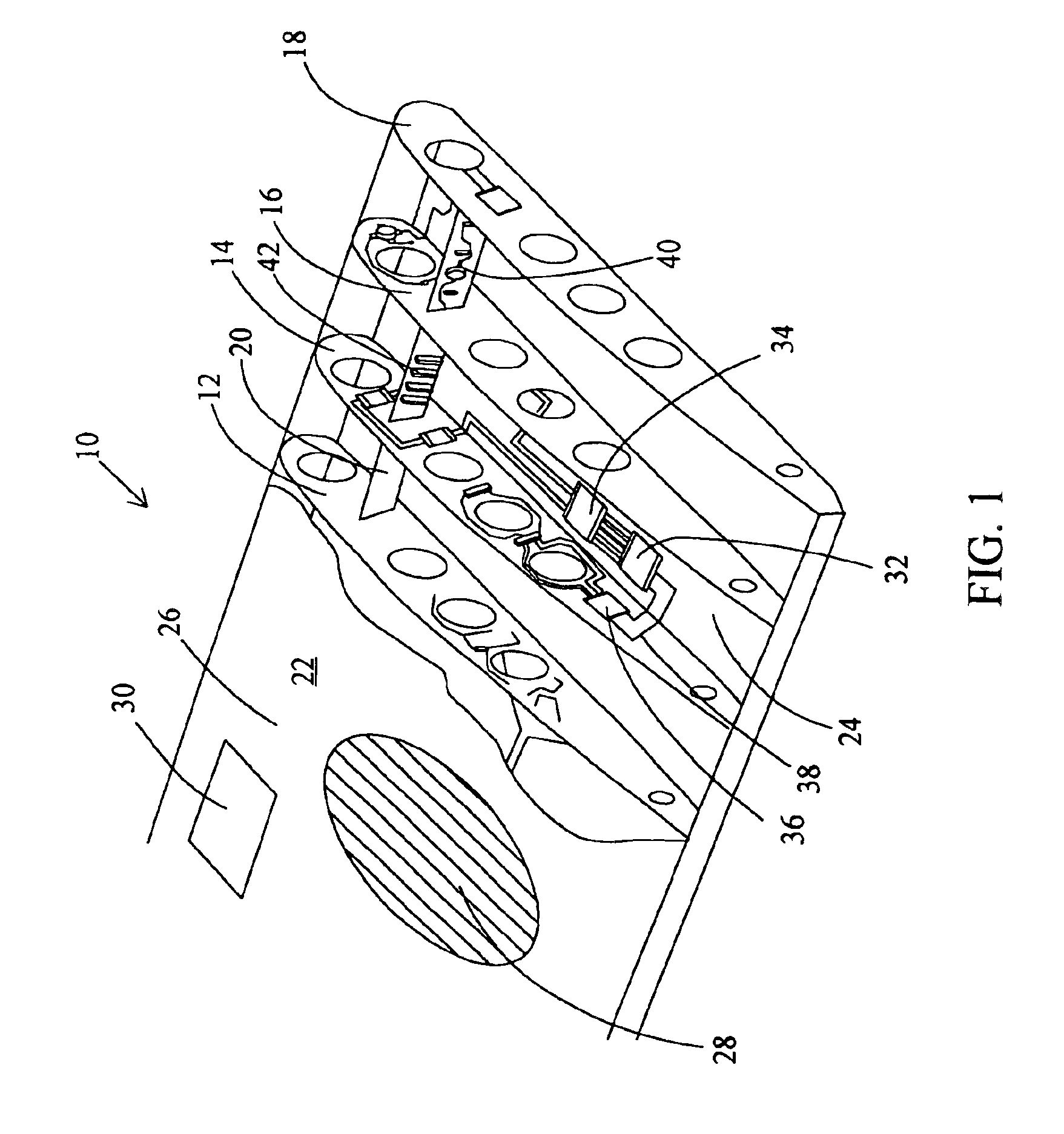

Electrically sensing and stimulating system for placement of a nerve stimulator or sensor

InactiveUS6829508B2Easy to installLongerSpinal electrodesSurgical needlesSurgical departmentSurgical procedures

An electrically sensing and stimulating outer sheath for ensuring accurate surgical placement of a microsensor or a microstimulator near a nerve in living tissue is disclosed. The electrically sensing outer sheath may also be used to verify the function of the microstimulator or microsensor during surgical placement but before the outer sheath is removed. In the event that the microstimulator is not optimally placed near the nerve, or if the microstimulator is malfunctioning, this can be determined prior to removal of the outer sheath, thus reducing the possibility of nerve or tissue damage that might be incurred during a separate operation to remove the microstimulator.

Owner:ALFRED E MANN FOUND FOR SCI RES

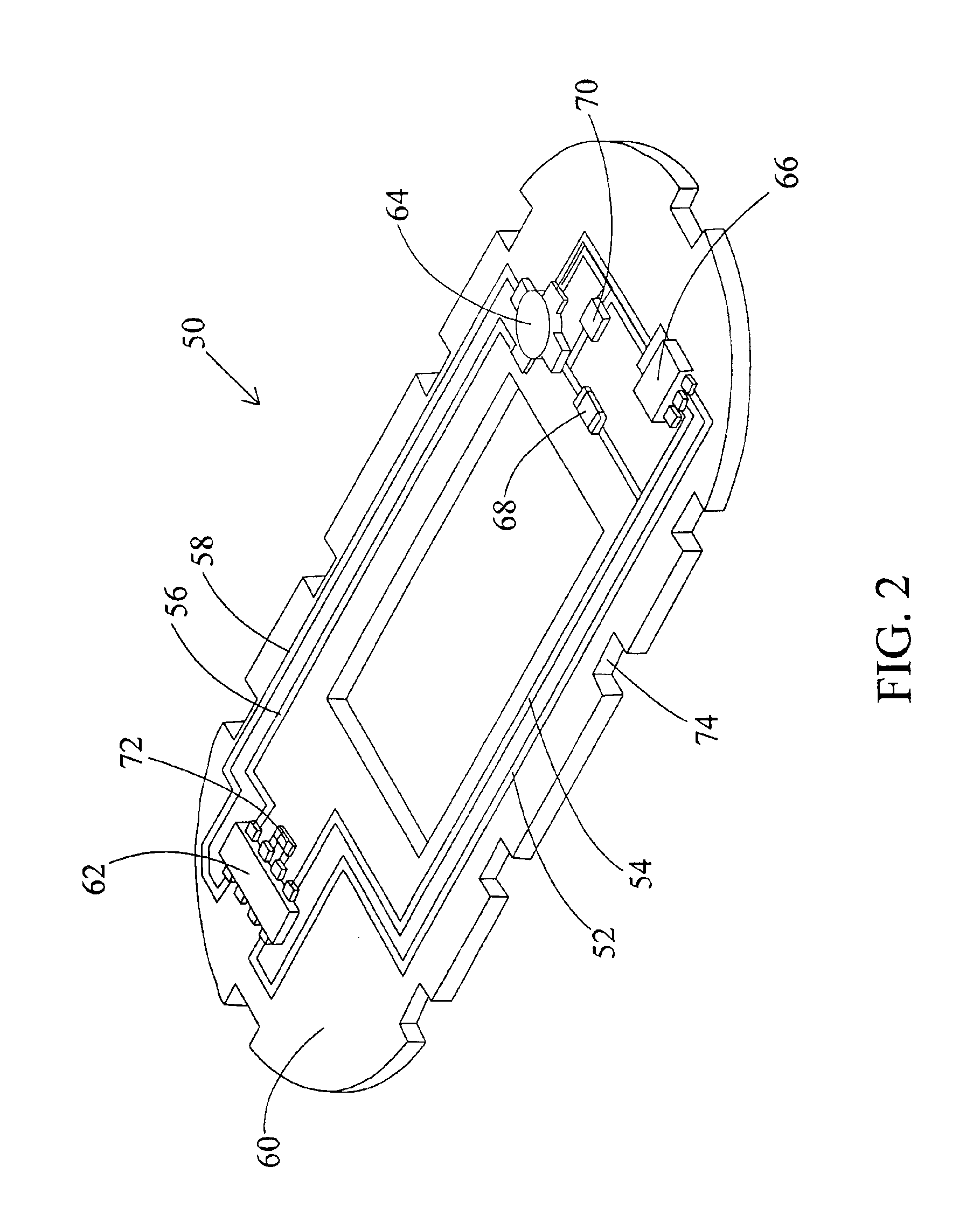

Unmanned aerial vehicle apparatus, system and method for retrieving data

InactiveUS6868314B1Unacceptable costHigh maintenance costFuselage framesDigital data processing detailsTerrainWireless transceiver

The present invention relates to a system for retrieving data from remote difficult to reach terrain, such as wilderness areas, etc. and in particular to a system comprised of one or more surface based data collectors in communication with one or more wireless transceivers adapted to transmit the collected data to an unmanned aerial vehicle adapted to fly within a predetermined distance from the data collector and receive data collected therefrom. The present invention further relates to an unmanned aerial vehicle adapted to fly a flight pattern relative to a moveable surface object or for controlling the position of a moveable surface object relative to the flight path of the unmanned aerial vehicle. Finally, the present invention relates to an improved unmanned aerial vehicle having airframe structural elements with electrical circuits adhered to the surfaces of the structural elements.

Owner:FRINK BENTLEY D

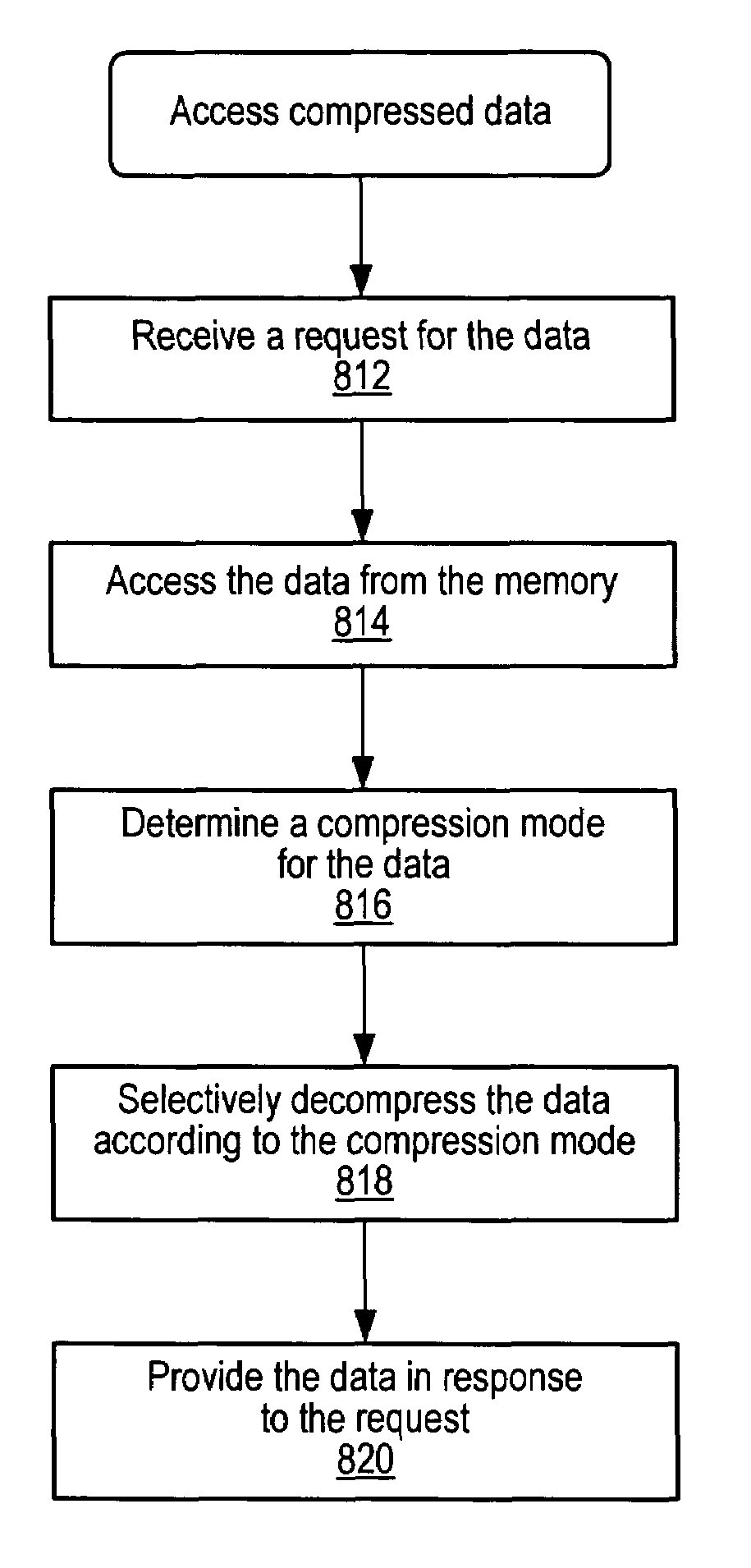

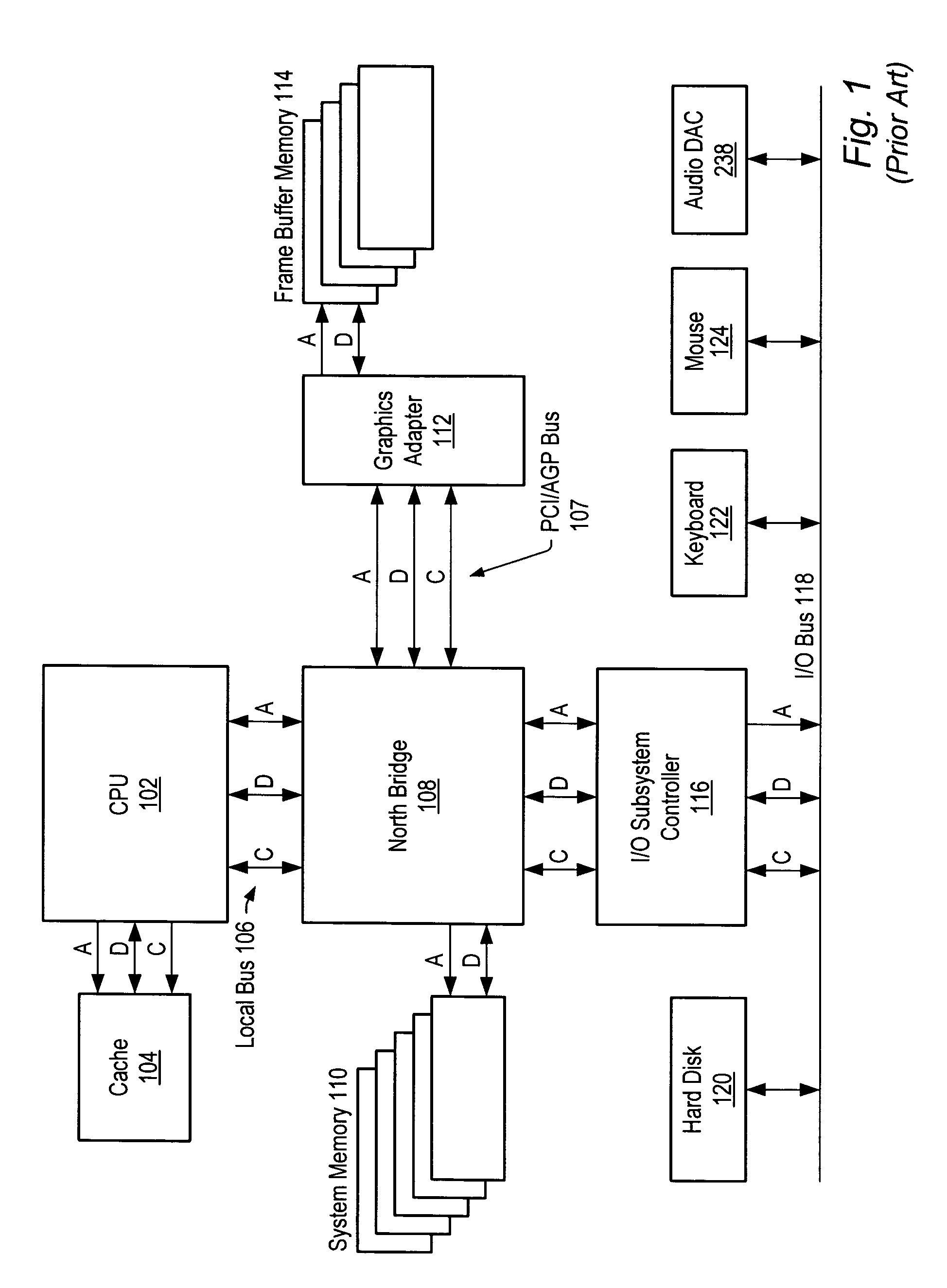

Selective lossless, lossy, or no compression of data based on address range, data type, and/or requesting agent

InactiveUS7190284B1Increase performanceIncrease system bandwidthMemory architecture accessing/allocationEnergy efficient ICTMemory controllerData transmission

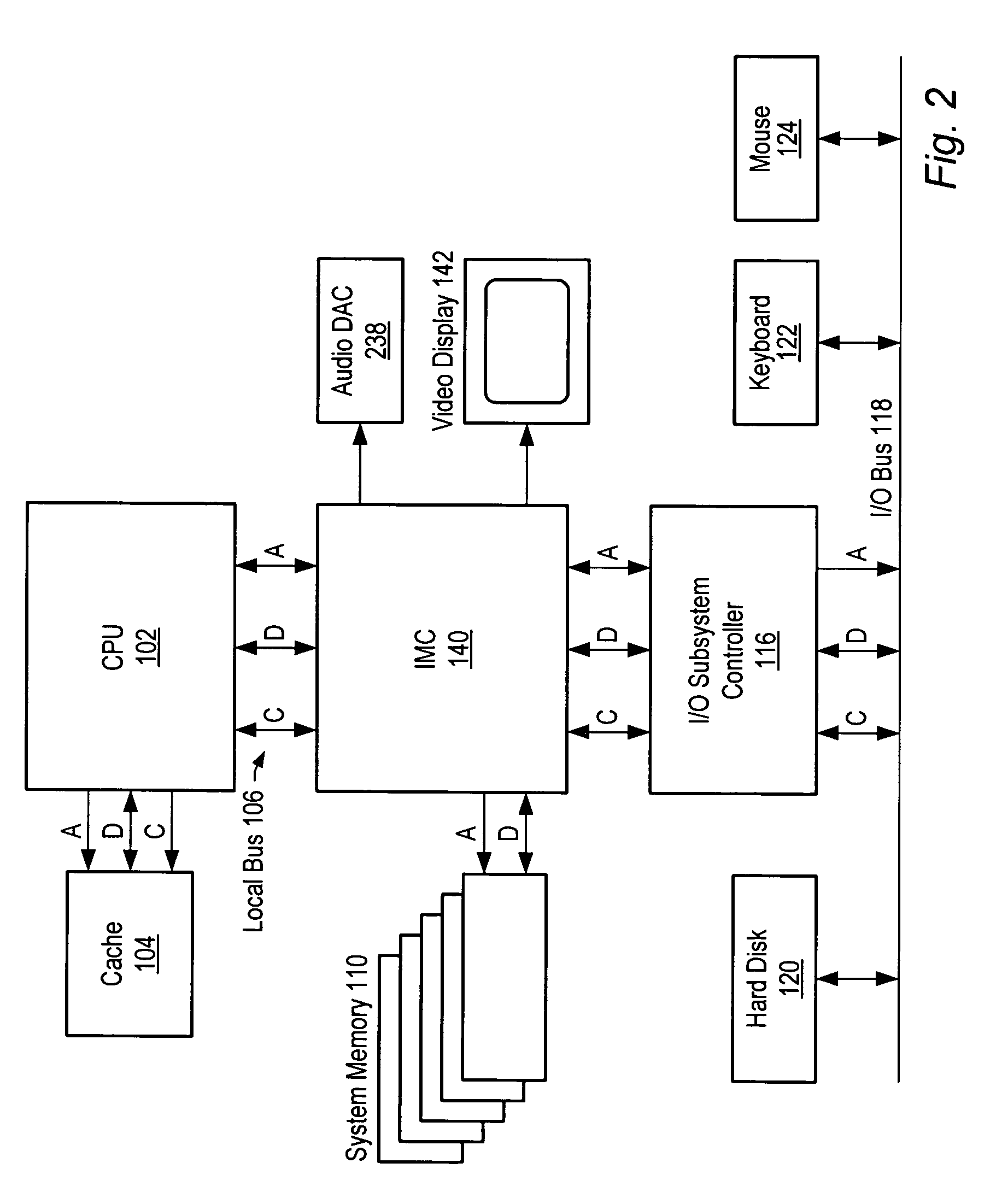

An integrated memory controller (IMC) including MemoryF / X Technology which includes data compression and decompression engines for improved performance. The memory controller (IMC) of the present invention preferably selectively uses a combination of lossless, lossy, and no compression modes. Data transfers to and from the integrated memory controller of the present invention can thus be in a plurality of formats, these being compressed or normal (non-compressed), compressed lossy or lossless, or compressed with a combination of lossy and lossless. The invention also indicates preferred methods for specific compression and decompression of particular data formats such as digital video, 3D textures and image data using a combination of novel lossy and lossless compression algorithms in block or span addressable formats. To improve latency and reduce performance degradations normally associated with compression and decompression techniques, the MemoryF / X Technology encompasses multiple novel techniques such as: 1) parallel lossless compression / decompression; 2) selectable compression modes such as lossless, lossy or no compression; 3) priority compression mode; 4) data cache techniques; 5) variable compression block sizes; 6) compression reordering; and 7) unique address translation, attribute, and address caches. The parallel compression and decompression algorithm allows high-speed parallel compression and high speed parallel decompression operation. The IMC also preferably uses a special memory allocation and directory technique for reduction of table size and low latency operation. The integrated data compression and decompression capabilities of the IMC remove system bottle-necks and increase performance. This allows lower cost systems due to smaller data storage, reduced bandwidth requirements, reduced power and noise.

Owner:INTELLECTUAL VENTURES I LLC

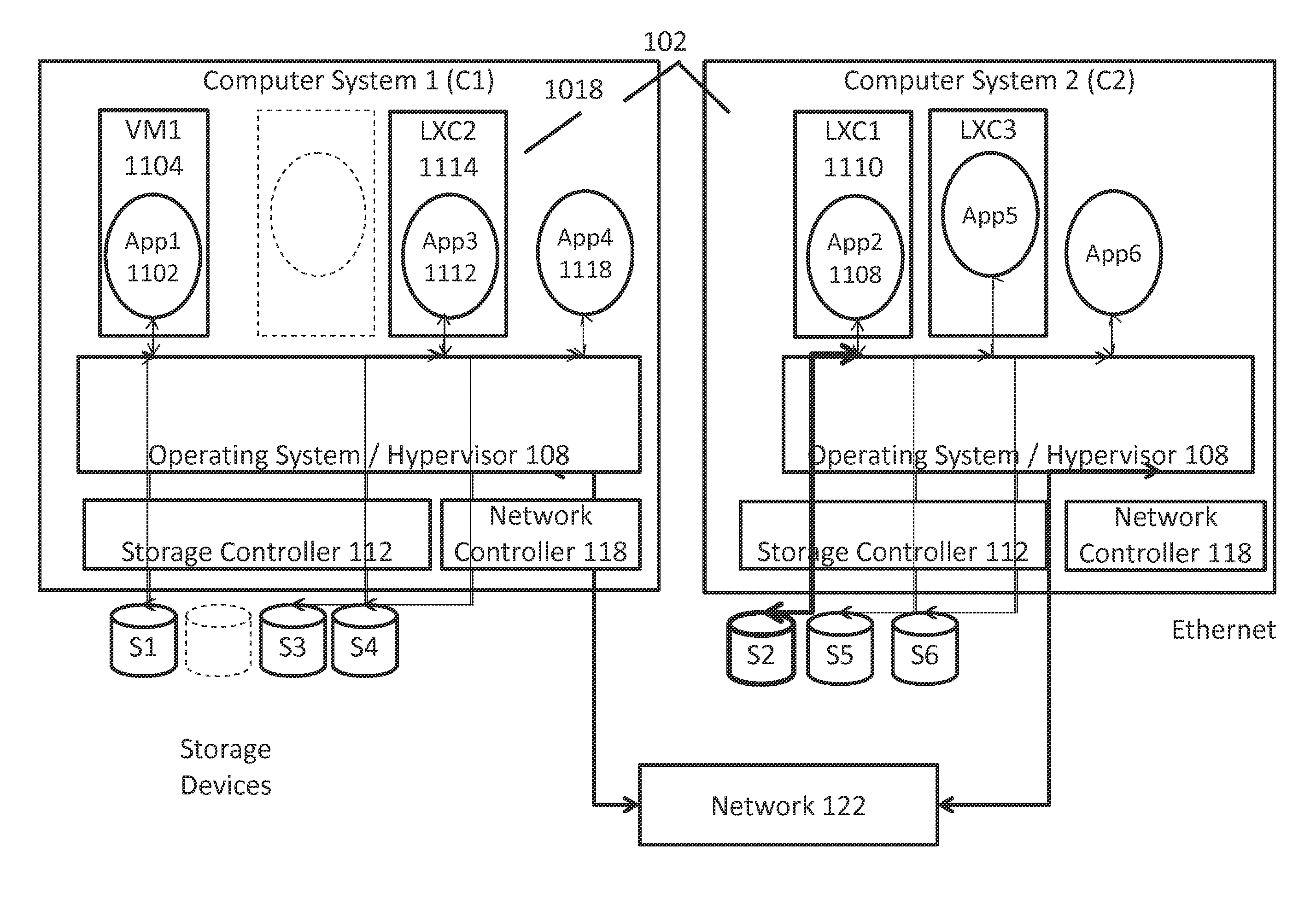

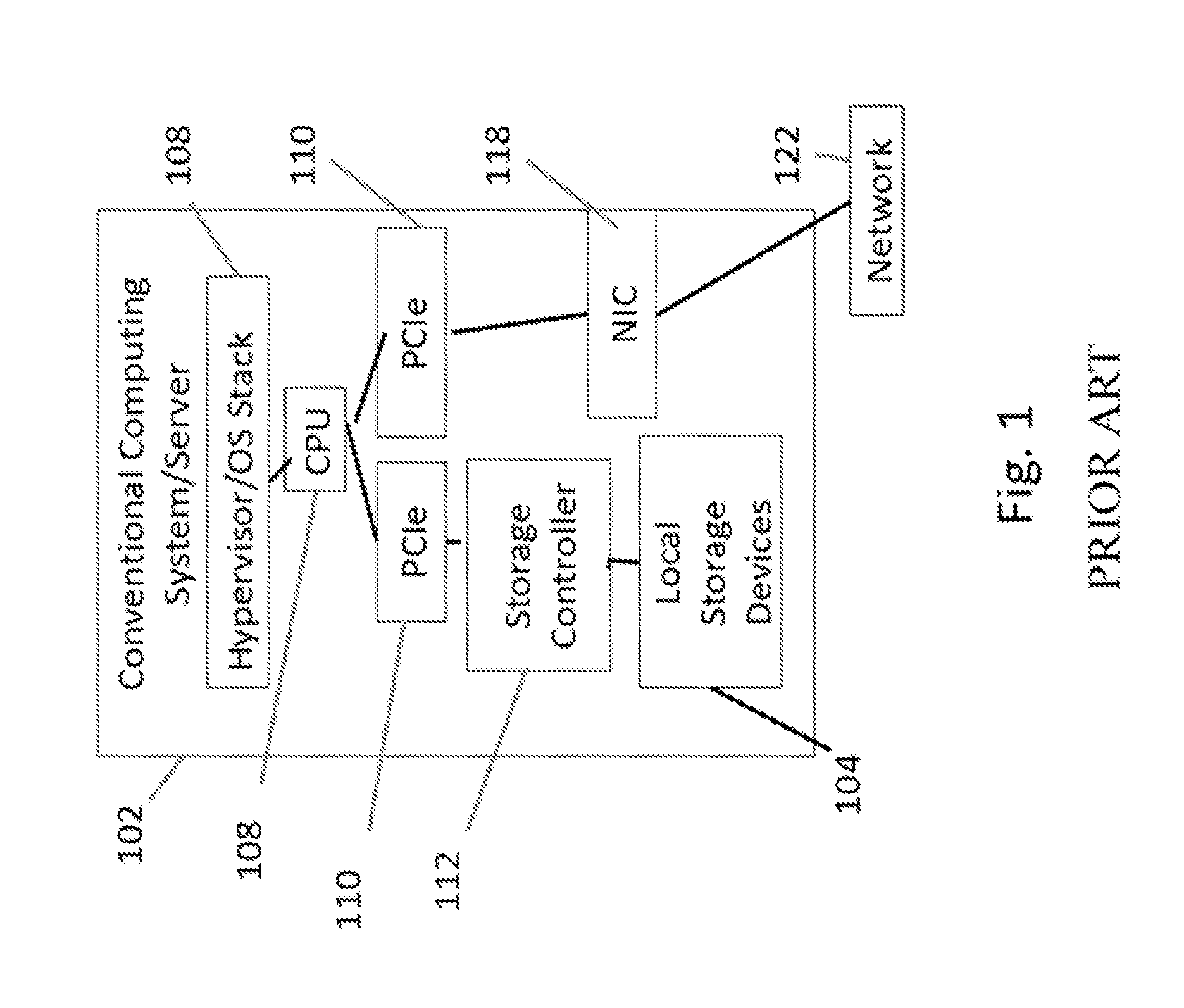

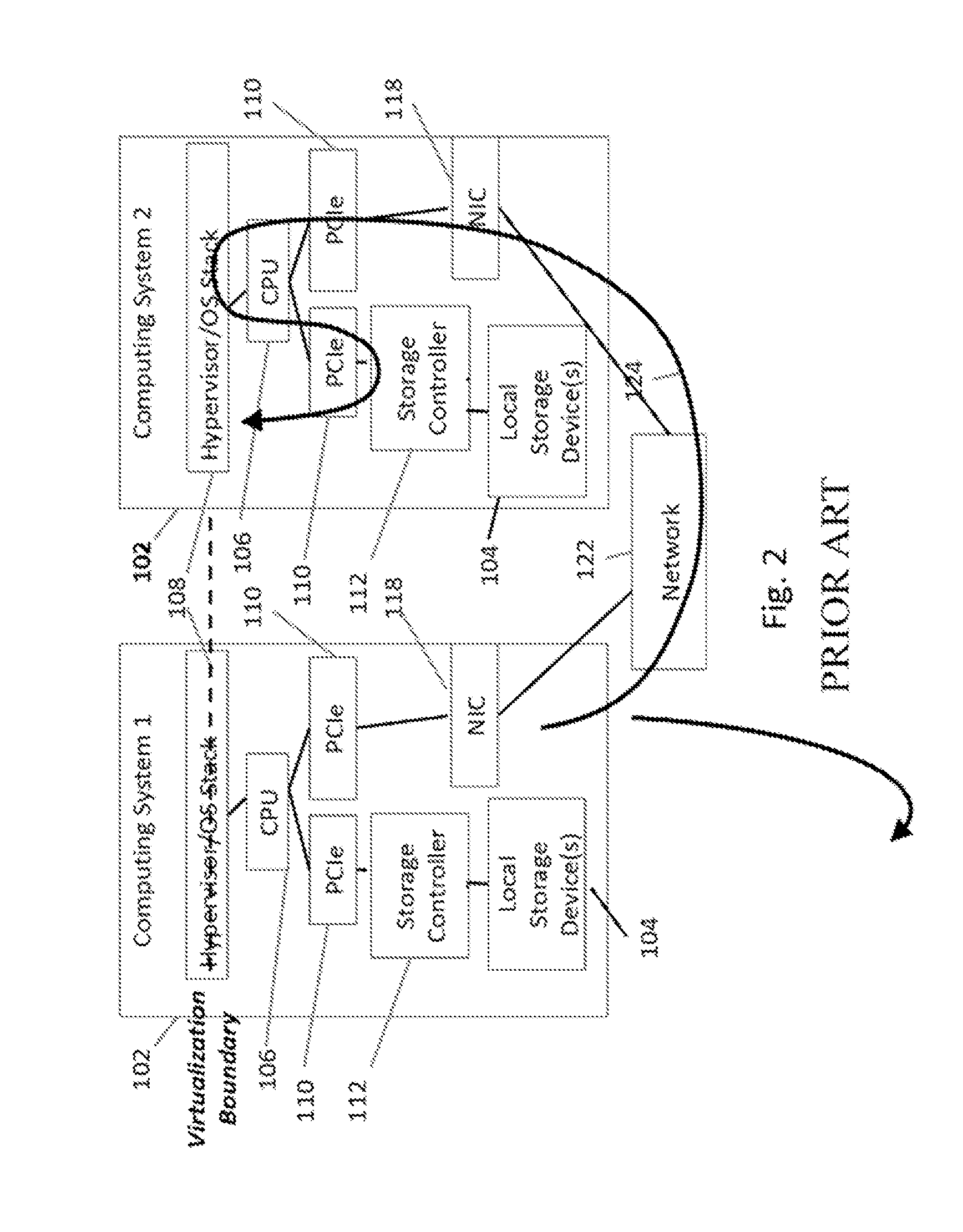

Methods and systems for converged networking and storage

InactiveUS20150254088A1Easy programmingImprove performanceResource allocationDigital computer detailsTraffic capacityNetwork interface controller

A device includes a converged input / output controller that includes a physical target storage media controller, a physical network interface controller and a gateway between the storage media controller and the network interface controller, wherein gateway provides a direct connection for storage traffic and network traffic between the storage media controller and the network interface controller.

Owner:DIAMANTI INC

Integrated touch screen

ActiveUS7859521B2Less powerFew partsTransmission systemsCathode-ray tube indicatorsTouch SensesDisplay device

Owner:APPLE INC

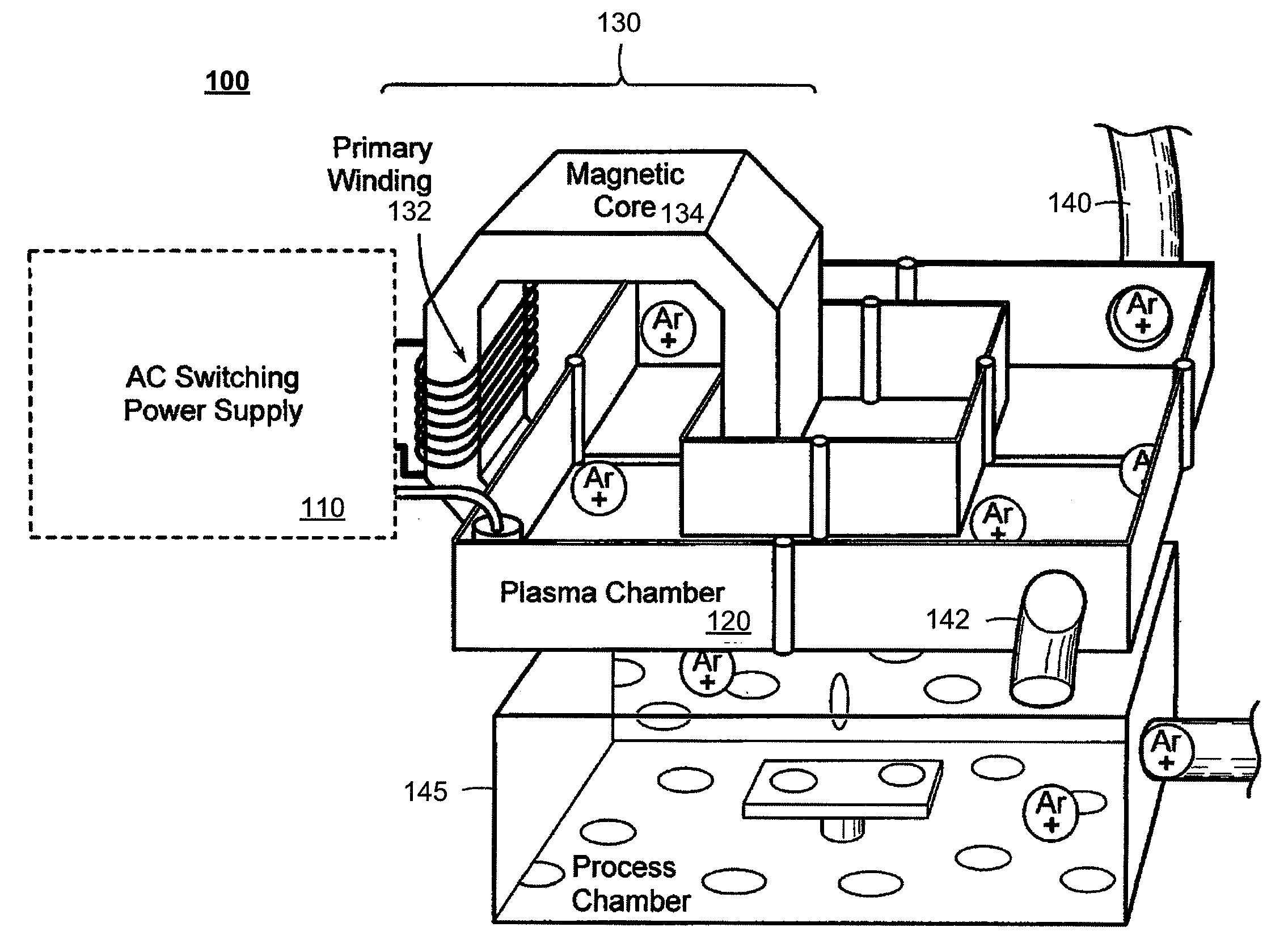

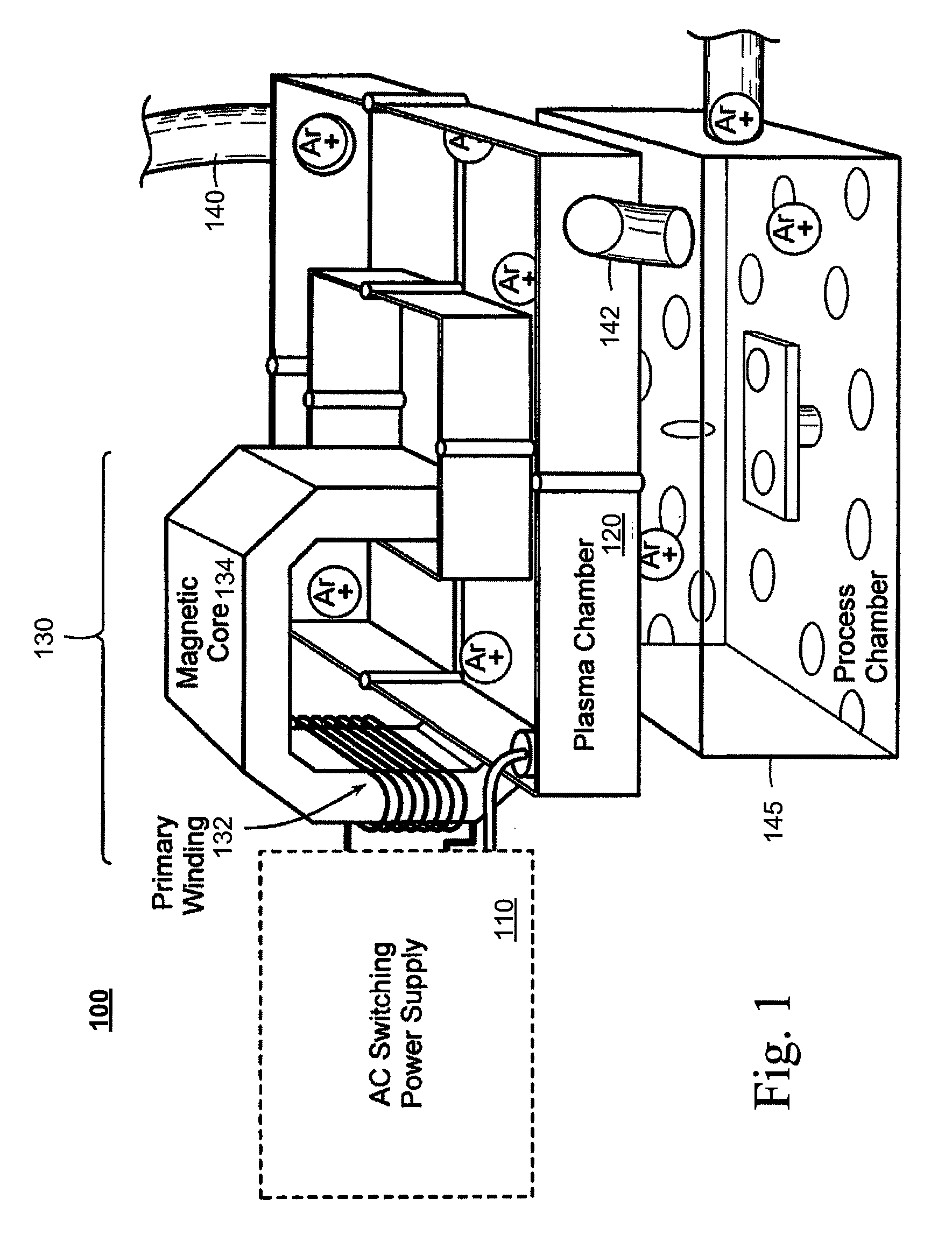

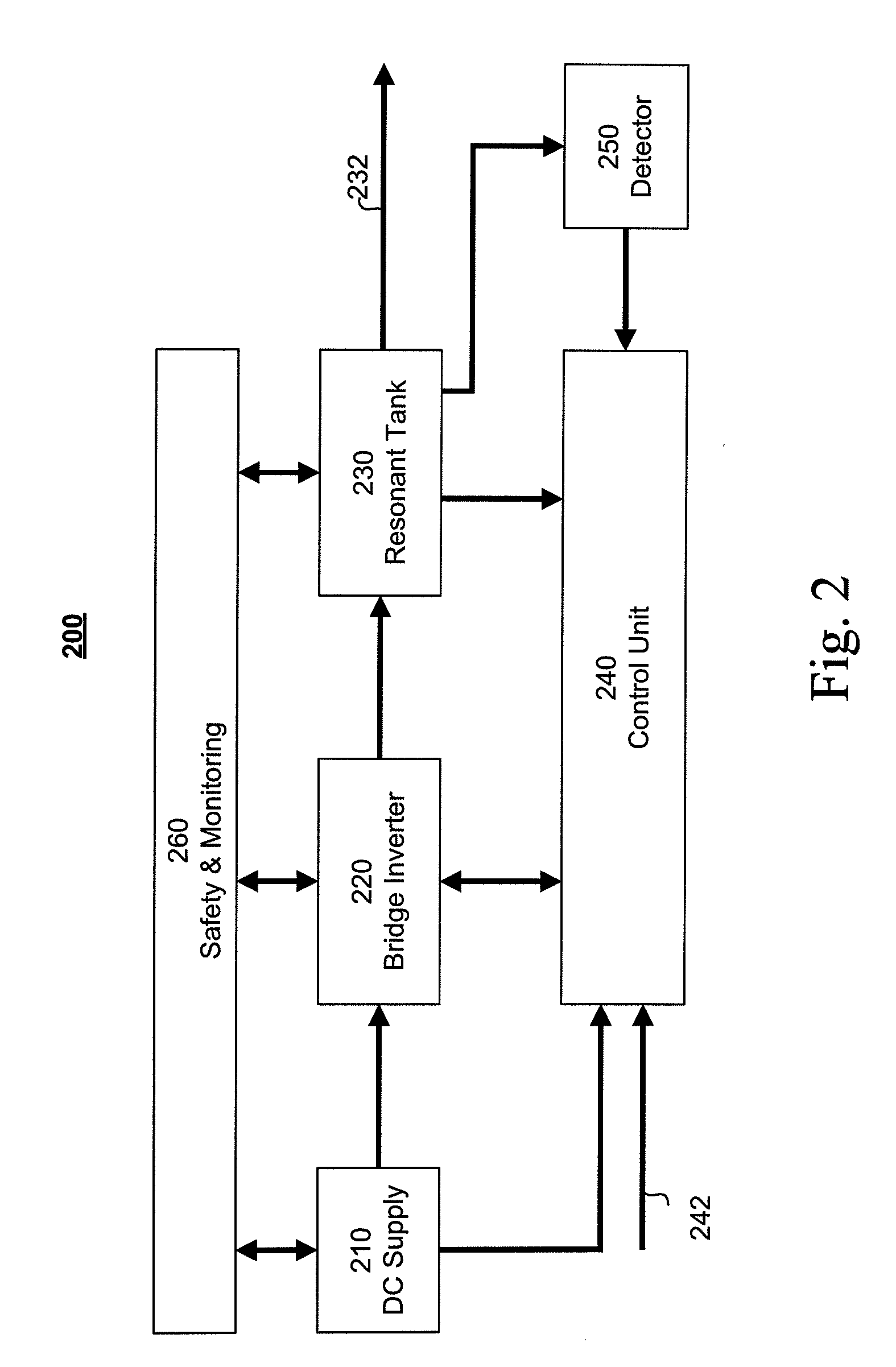

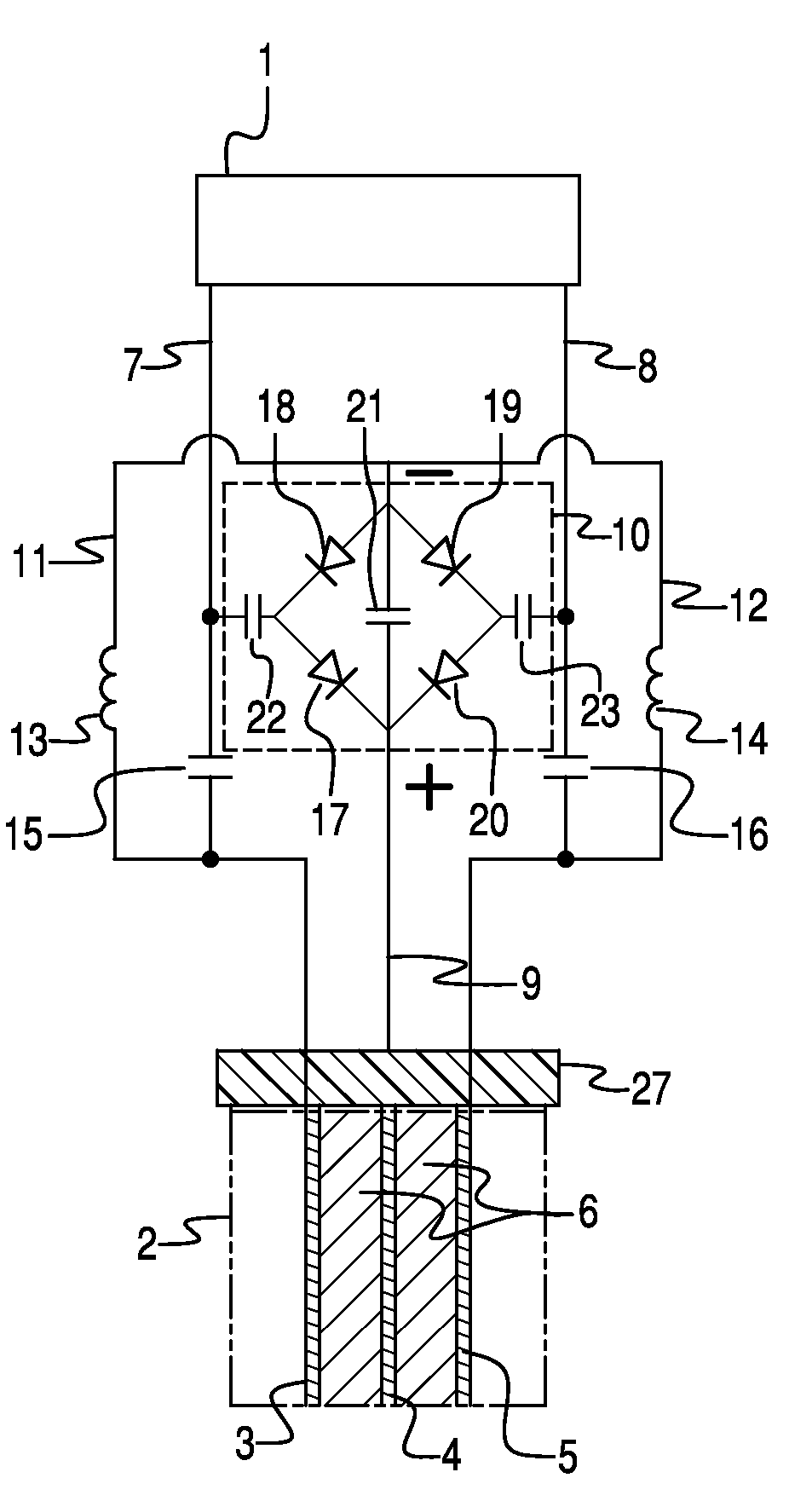

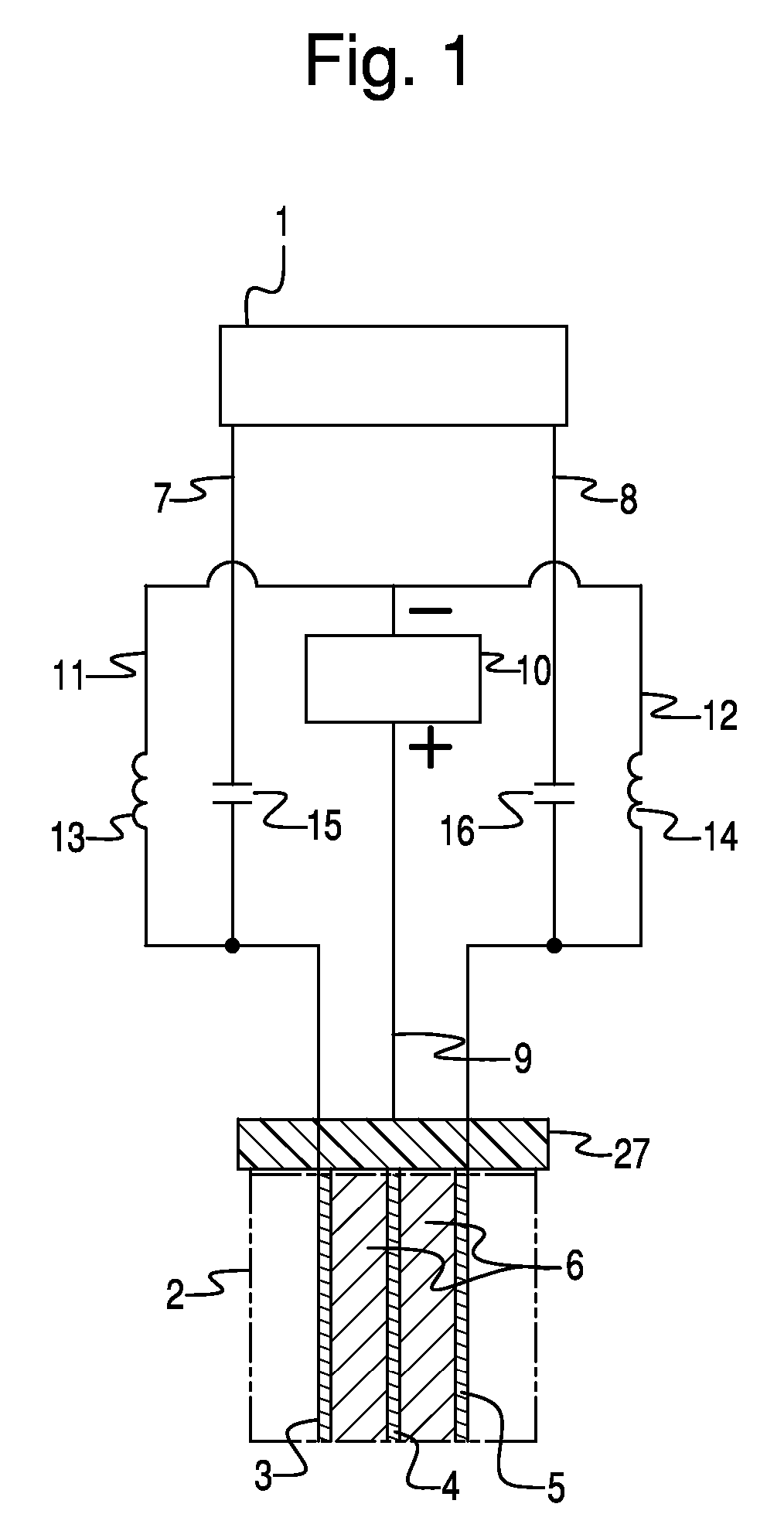

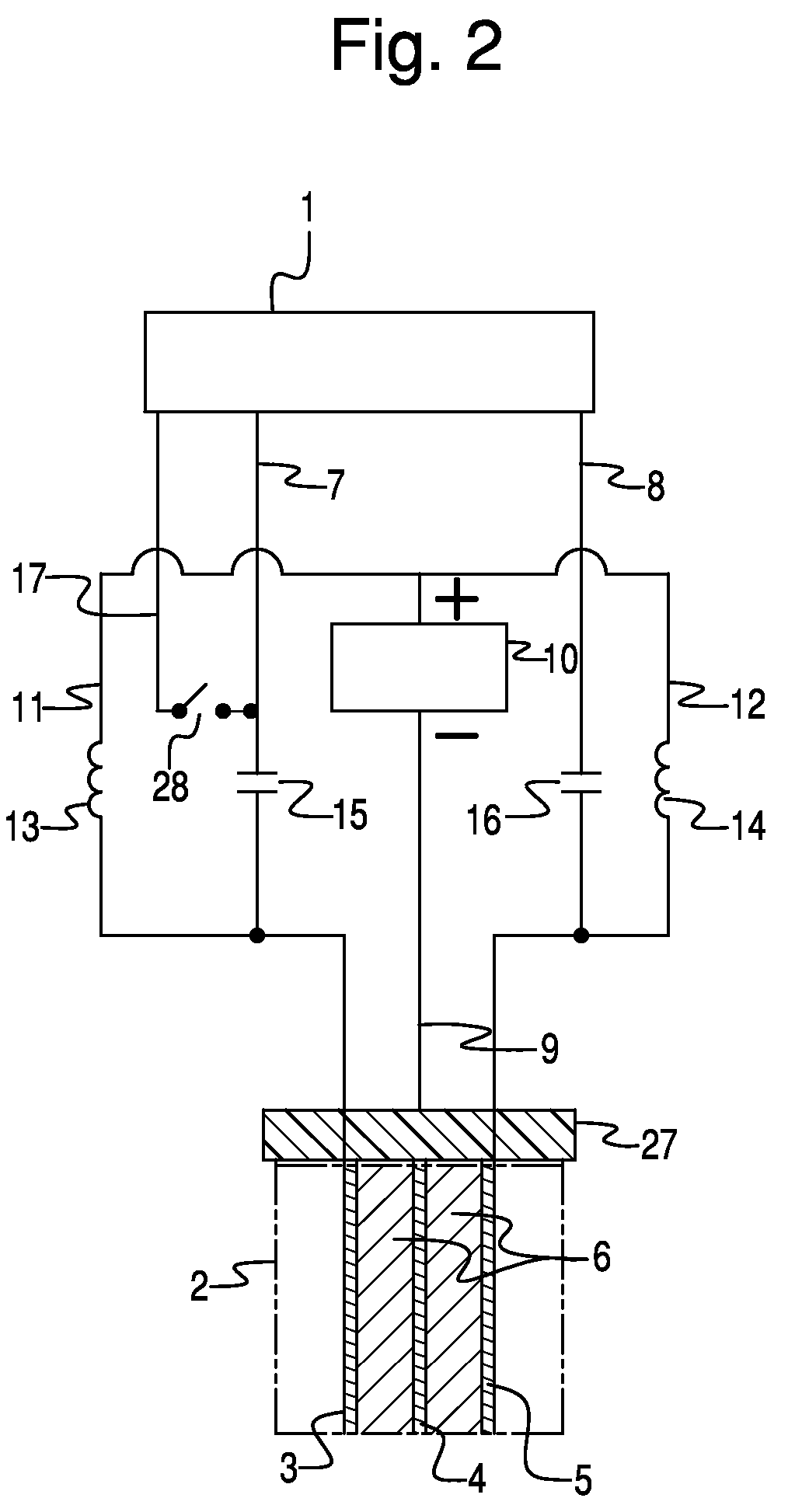

Method and Apparatus of Providing Power to Ignite and Sustain a Plasma in a Reactive Gas Generator

ActiveUS20100219757A1Eliminating and minimizing riskBig spaceElectric discharge tubesElectric arc lampsReactive gasPlasma ignition

Described are methods and apparatuses, including computer program products, for igniting and / or sustaining a plasma in a reactive gas generator. Power is provided from an ignition power supply to a plasma ignition circuit. A pre-ignition signal of the plasma ignition circuit is measured. The power provided to the plasma ignition circuit is adjusted based on the measured pre-ignition signal and an adjustable pre-ignition control signal. The adjustable pre-ignition control signal is adjusted after a period of time has elapsed.

Owner:MKS INSTR INC

Battery powered electrosurgical system

ActiveUS7896875B2Avoid excessive accumulationMinimize durationSurgical instruments for heatingCoatingsInsulation layerElectrical conductor

An battery-powered electrosurgical instrument includes a blade having a conductor edge portion and insulation layer with geometric shapes and composition that concentrate electrosurgical energy and reduce or eliminate the production of smoke and eschar and reduce tissue damage, thereby providing more efficient application of electrosurgical energy. The more efficient use of electrosurgical energy permits configuring the system to be battery-powered. The system may be portable or configured as a battery-backup powered system.

Owner:SURGINETICS

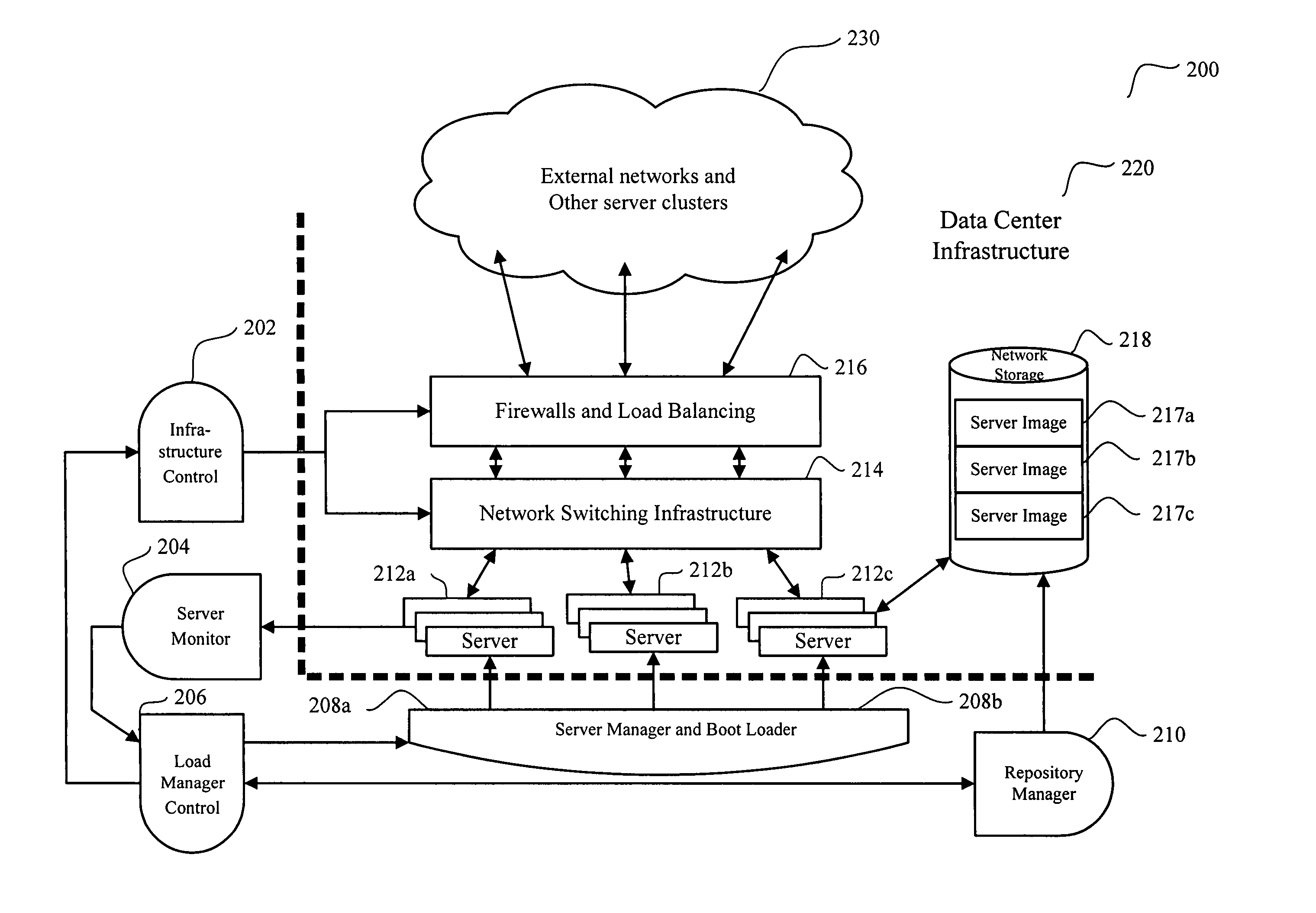

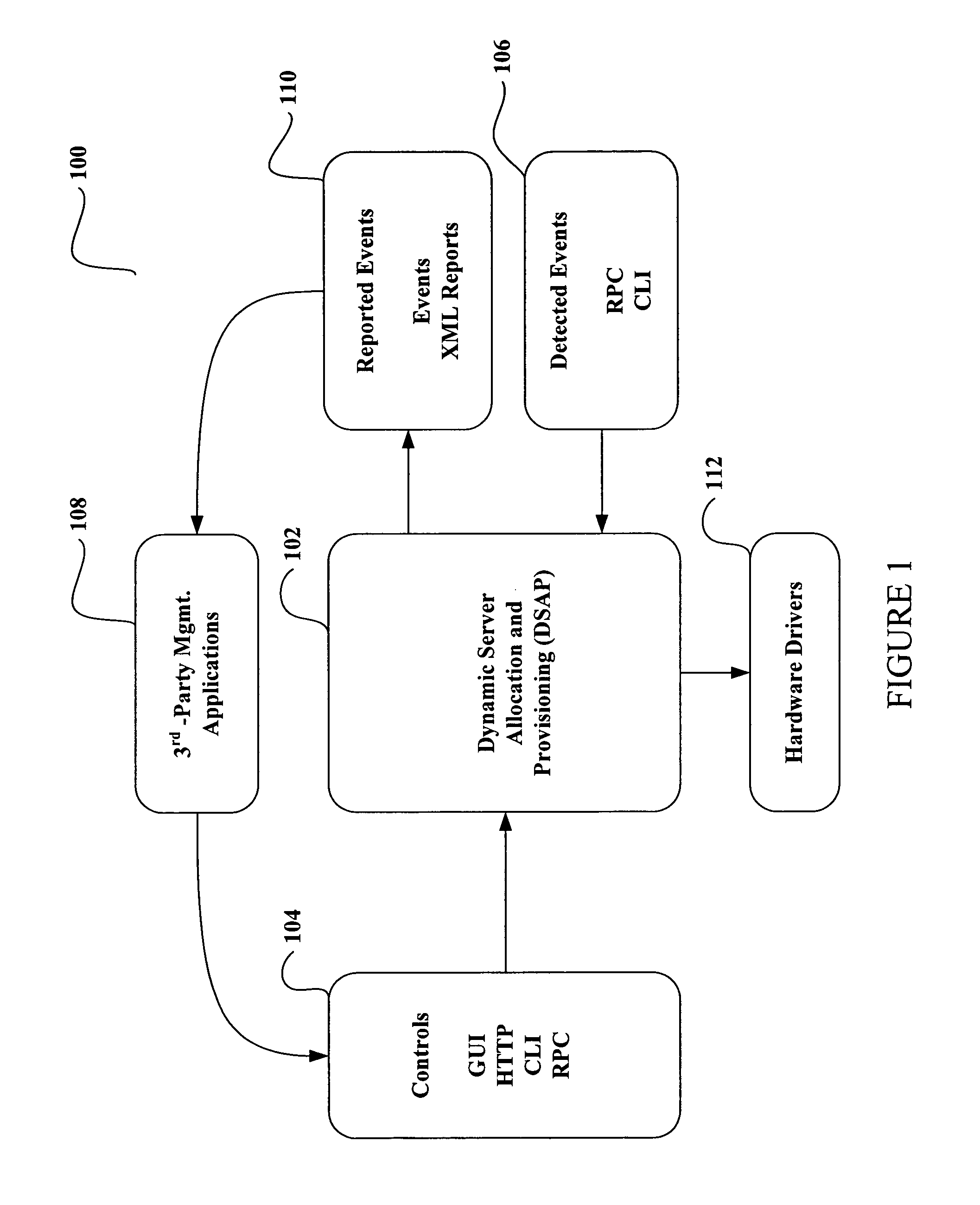

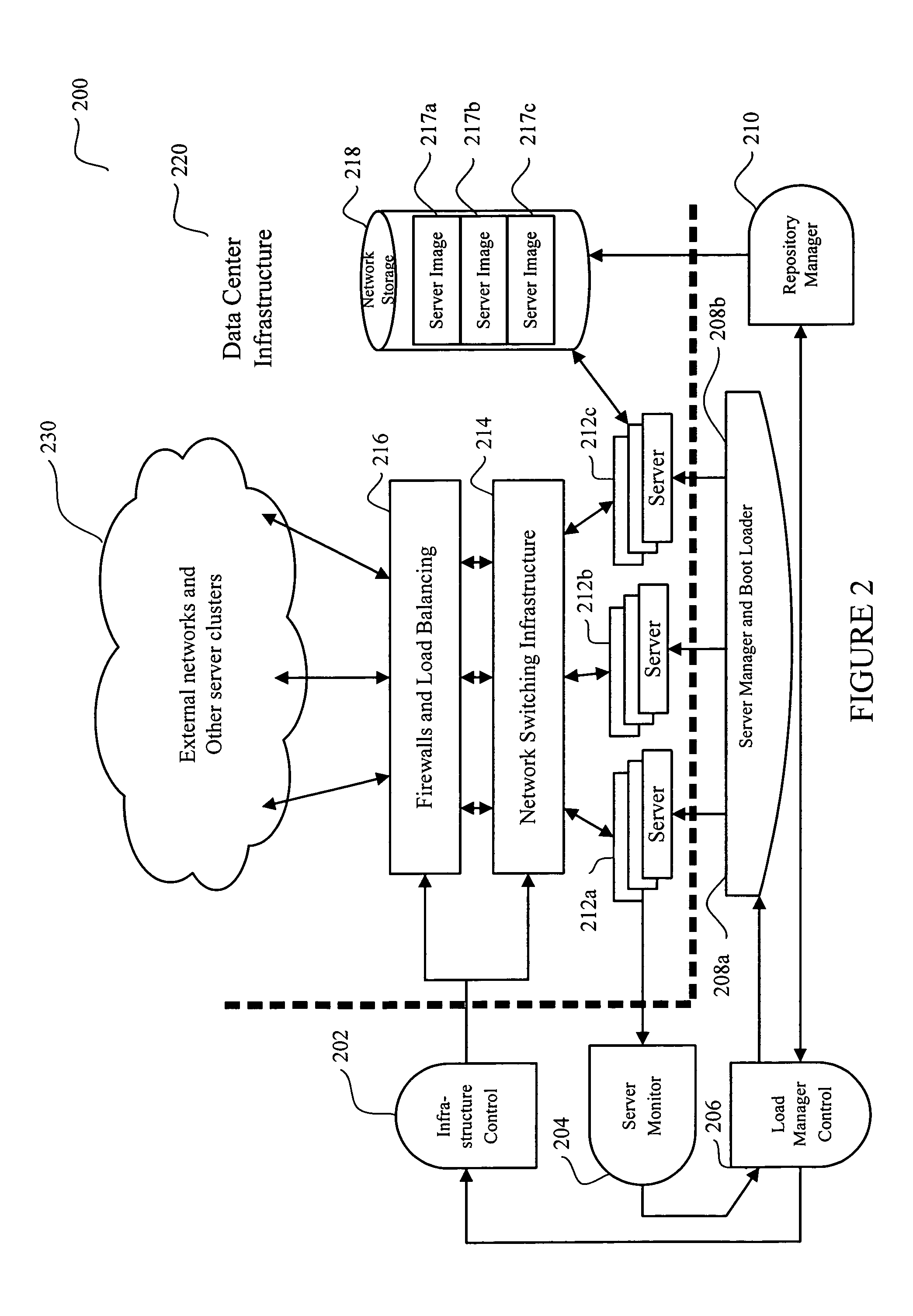

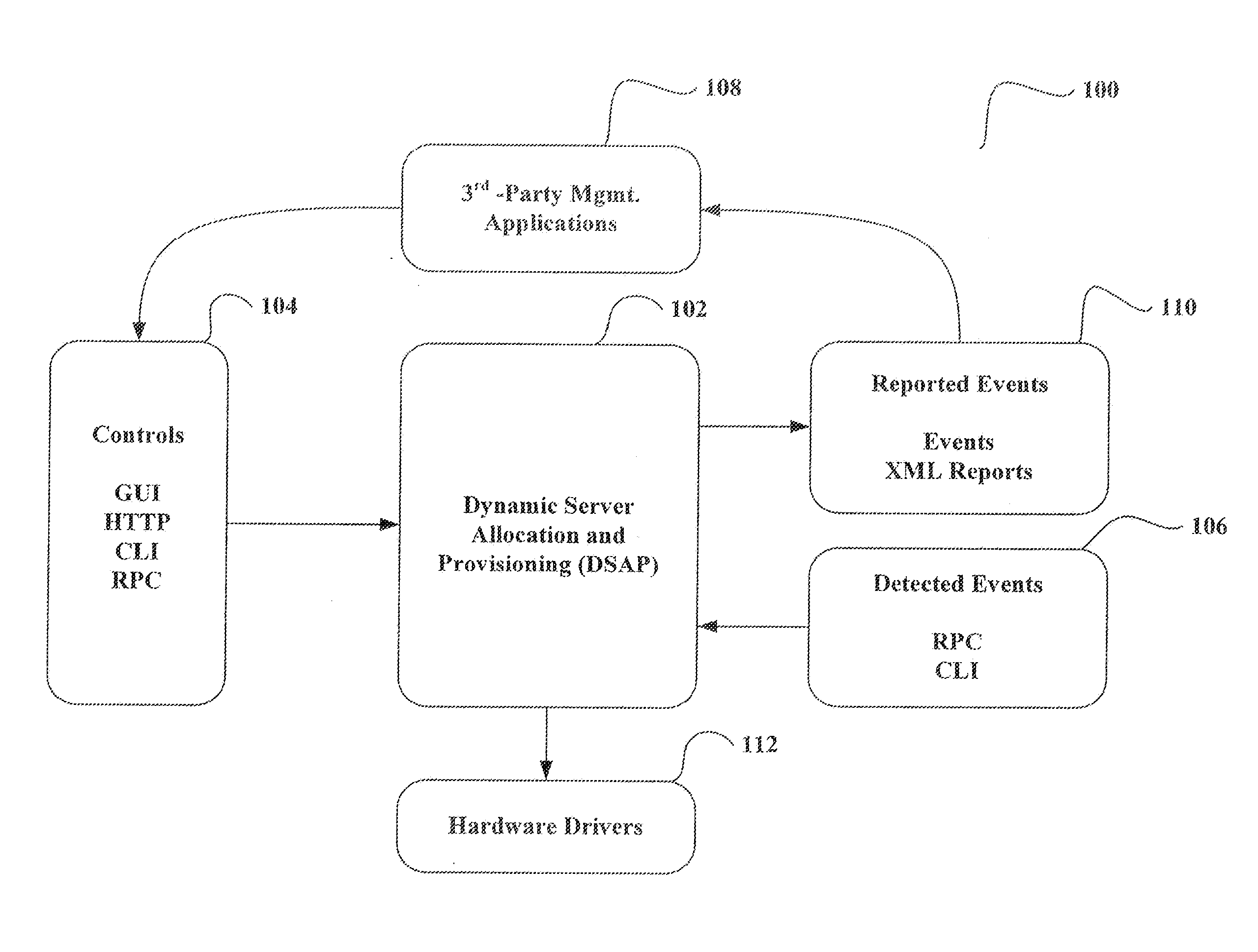

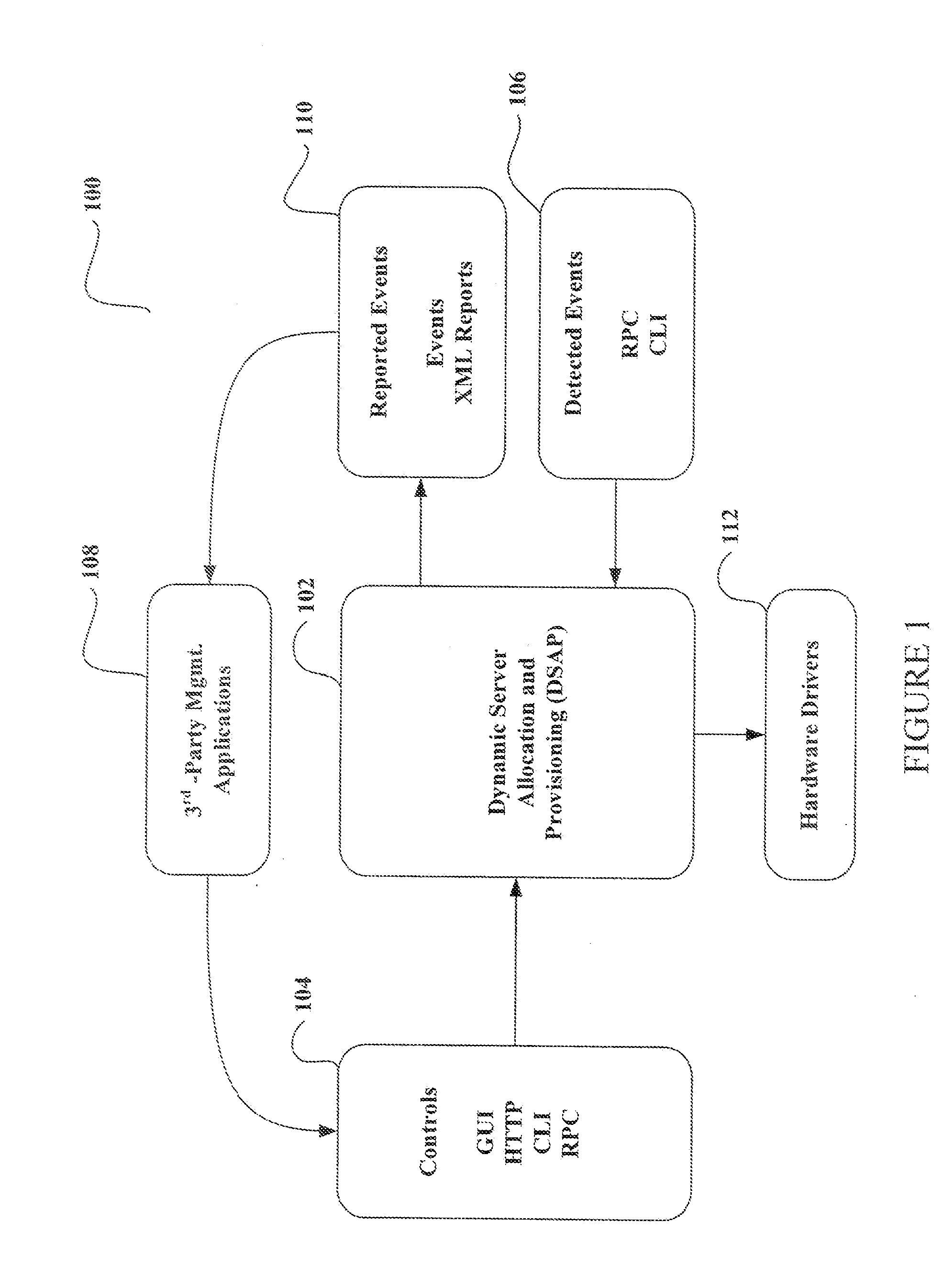

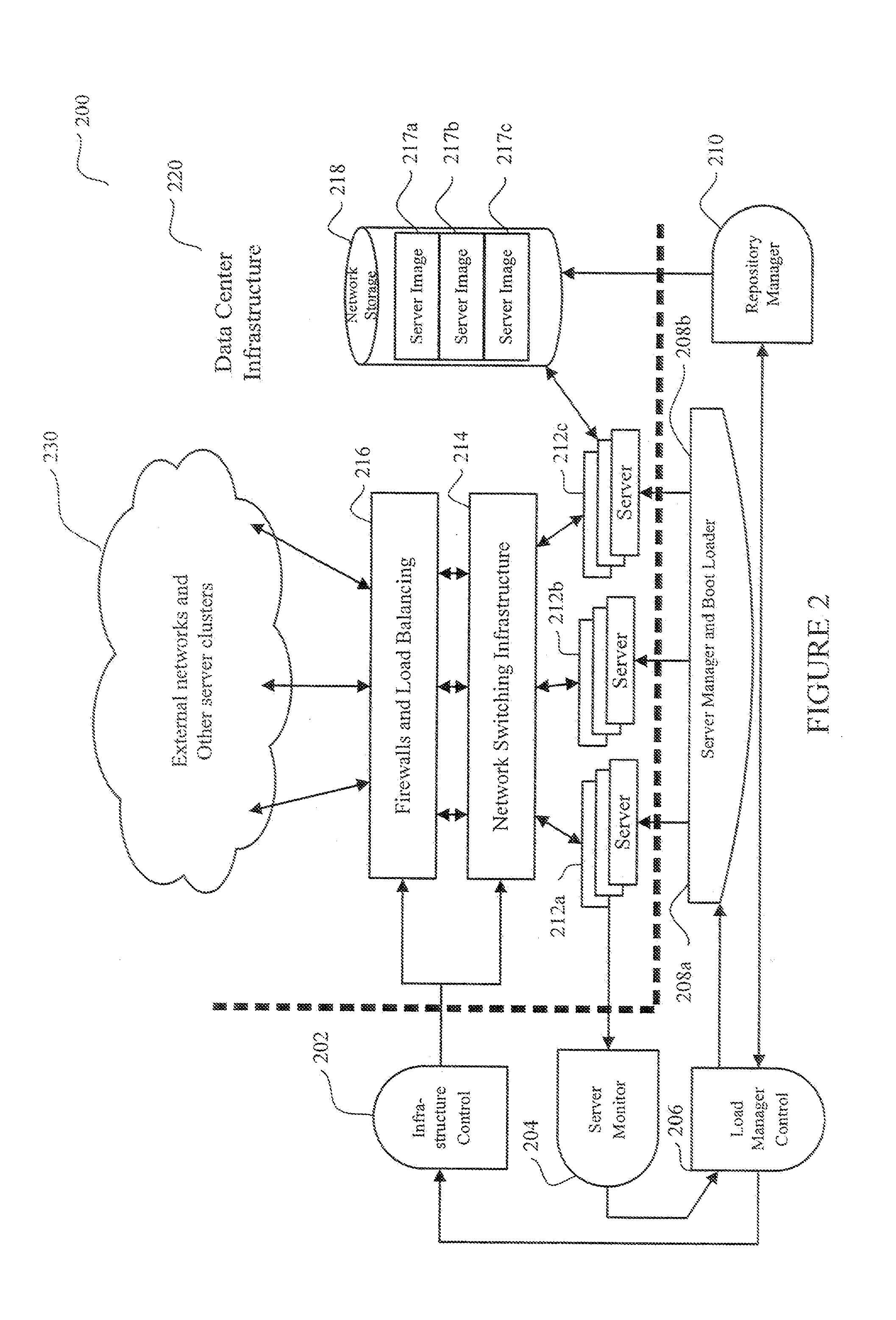

System and method for dynamic server allocation and provisioning

ActiveUS7213065B2Lower cost of capitalQuality improvementResource allocationDigital computer detailsManagement toolVirtual LAN

A management tool that streamlines the server allocation and provisioning processes within a data center is provided. The system, method, and computer program product divide the server provisioning and allocation into two separate tasks. Provisioning a server is accomplished by generating a fully configured, bootable system image, complete with network address assignments, virtual LAN (VLAN) configuration, load balancing configuration, and the like. System images are stored in a storage repository and are accessible to more than one server. Allocation is accomplished using a switching mechanism which matches each server with an appropriate system image based upon current configuration or requirements of the data center. Thus, real-time provisioning and allocation of servers in the form of automated responses to changing conditions within the data center is possible. The ability to instantly re-provision servers, safely and securely switch under-utilized server capacity to more productive tasks, and improve server utilization is also provided.

Owner:RACEMI

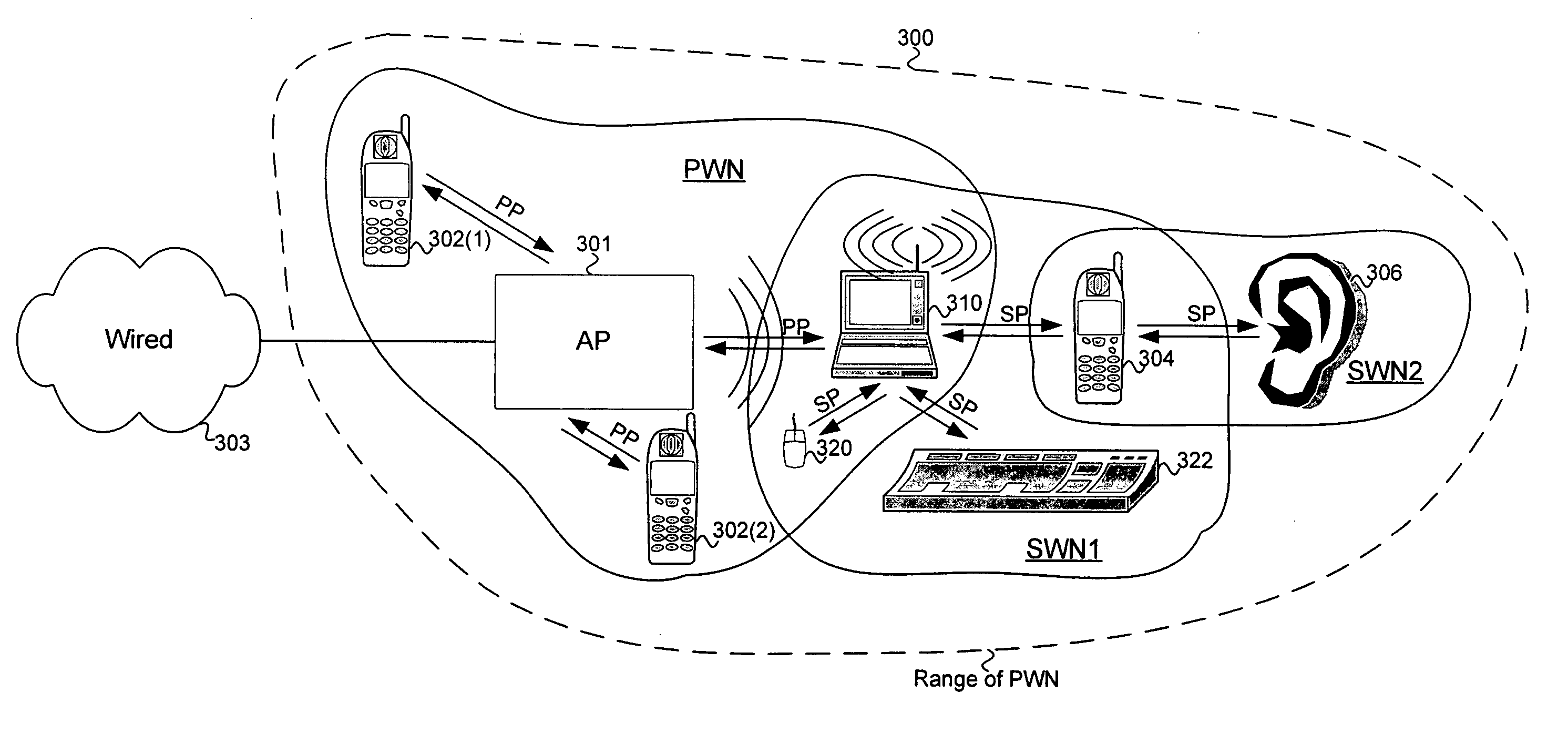

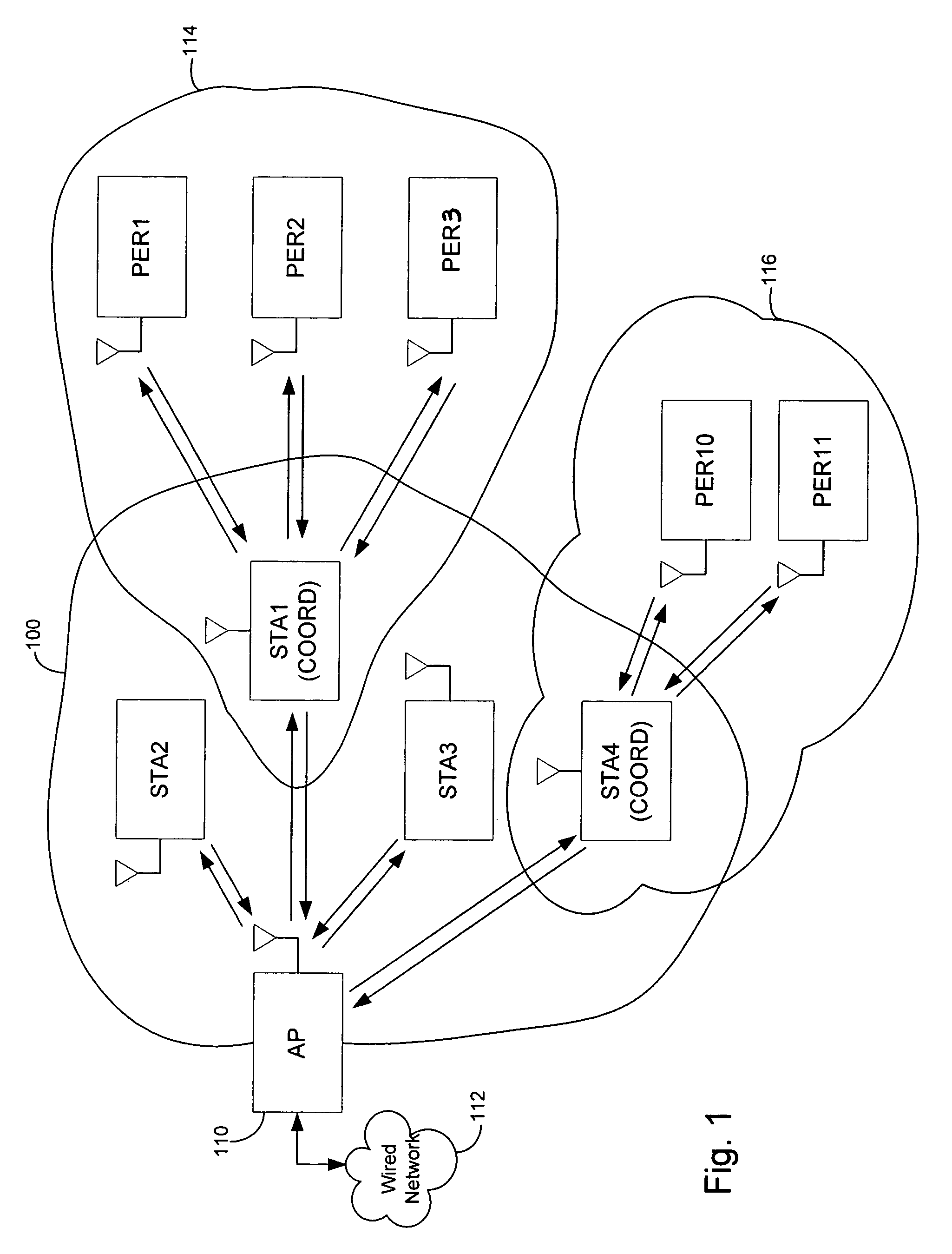

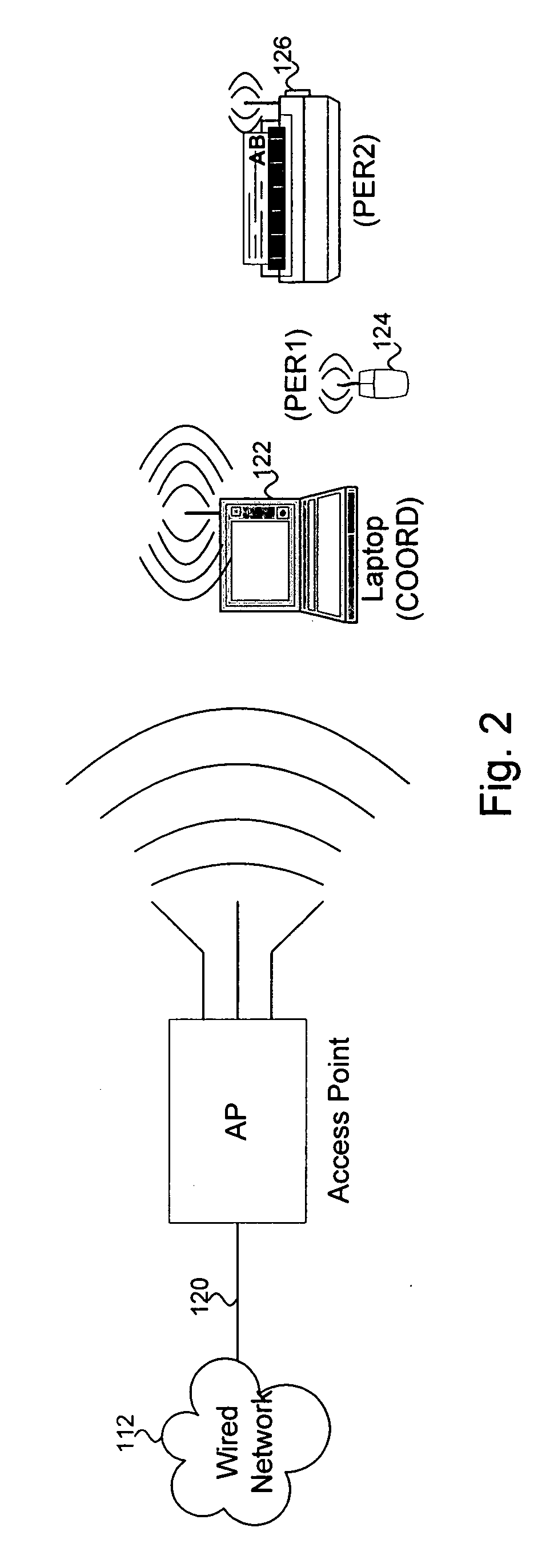

Method and apparatus for coordinating a wireless PAN network and a wireless LAN network

InactiveUS20060215601A1Less powerPower managementEnergy efficient ICTWireless lanPersonal area network

Devices of a personal area network (PAN) use a wireless medium that is shared with a wireless local area network (WLAN). WLAN devices communicate using protocols of the WLAN and PAN devices communicate using PAN protocols allowing for lower power transmissions over the wireless medium relative to transmissions over the WLAN. A PAN coordinator device obtains access to the wireless medium for the PAN devices by signalling a reservation of the medium by the PAN coordinator device, such that the other devices defer use of the wireless medium, including at least one WLAN device, for a reservation period. During the reservation period, the communication is done using the PAN protocol. The signalling can be implicit in that the PAN coordinator device transmits one or more frame using the PAN protocol but that is at least partially understandable by WLAN devices such that they defer upon receipt of one or more of the PAN protocol frames, which may be a standard or modified HCCA-CF poll frame, a CTS frame with an increased duration field, or other variation. A PAN coordinator might also signal an access point to set up a DLS link between the PAN coordinator and itself and use the DLS period for PAN traffic.

Owner:ATMEL WI FI SOLUTIONS

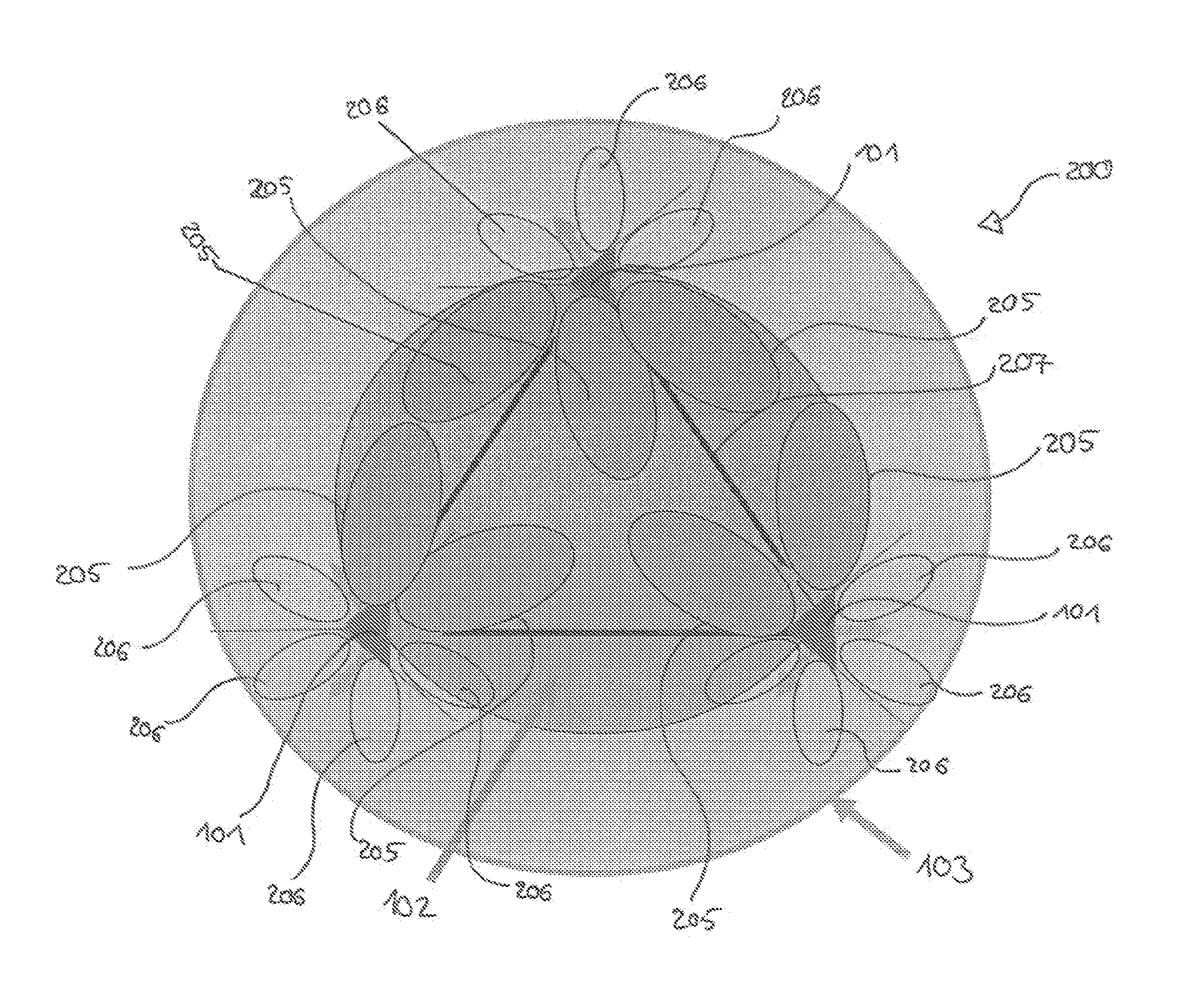

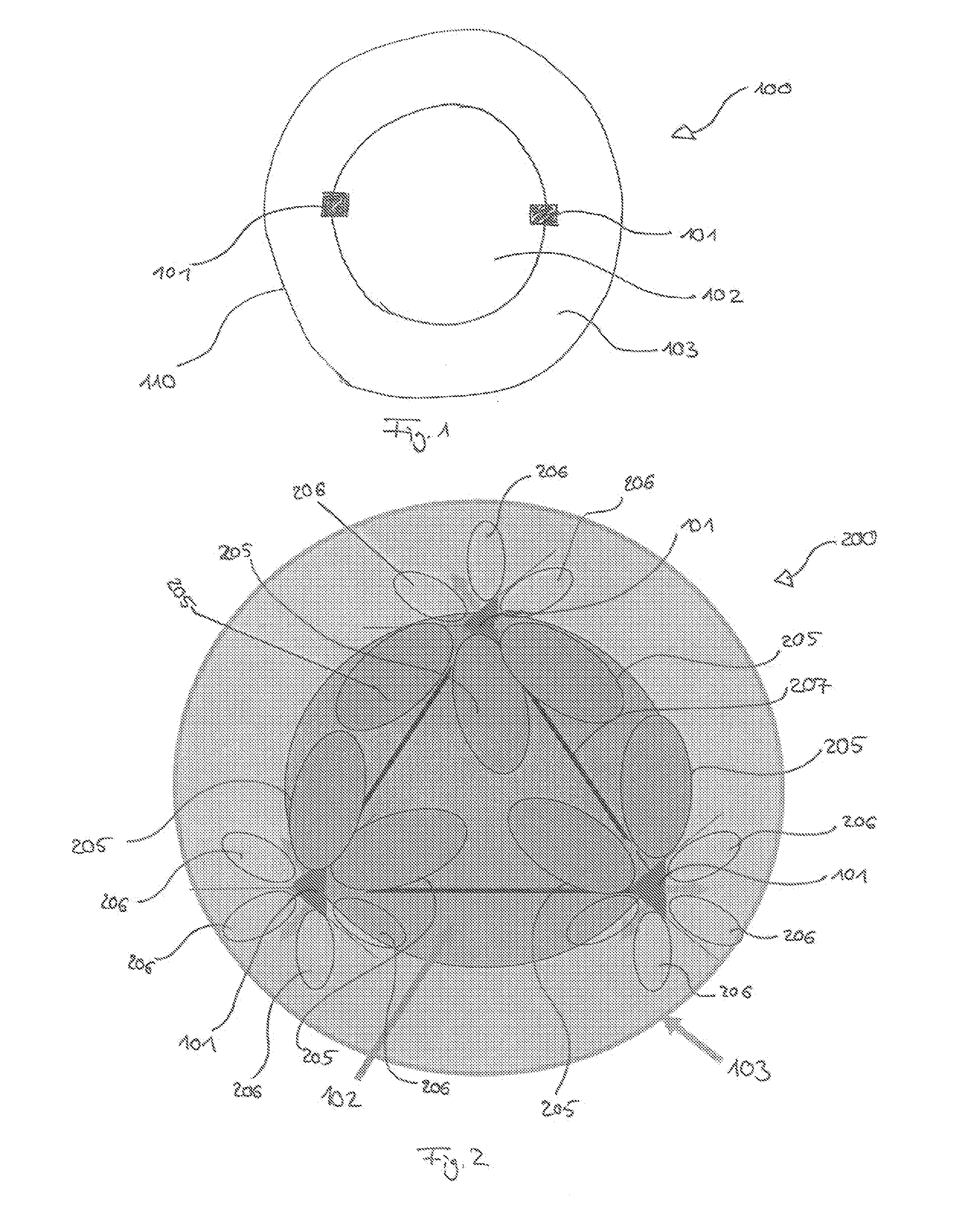

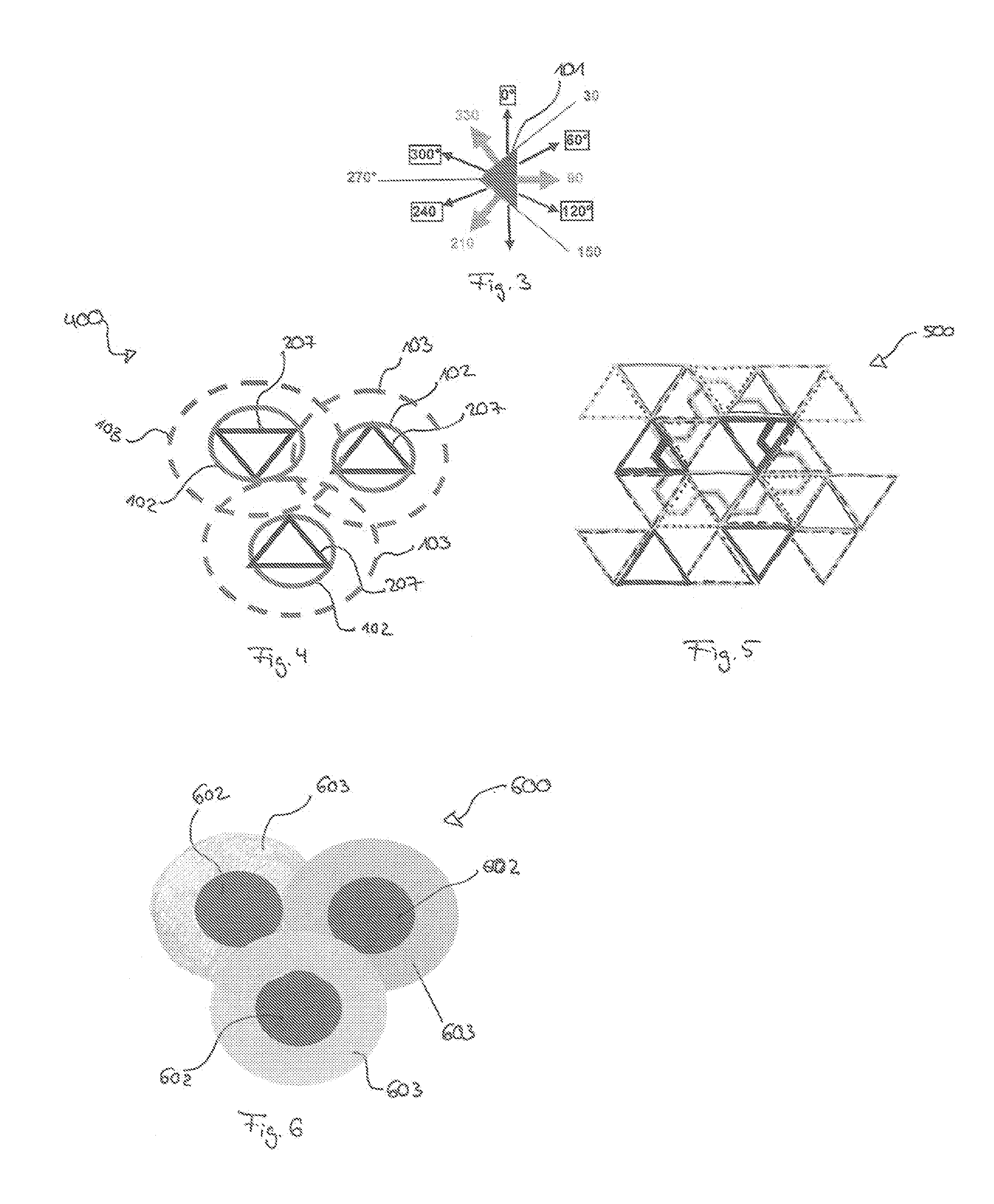

Configuring Power Distribution Within Cooperation Areas of Cellular Communication Networks

ActiveUS20140057618A1Reduce distractionsMore powerPower managementSite diversityTransmitted powerEngineering

There is provided a method for configuring a power distribution within a cellular network system. The cellular network system includes at least one cooperation area. The at least one cooperation area is defined by at least two base stations, each including at least one antenna, wherein each base station has at least one beam. The method includes configuring the base stations to transmit at a first transmit power level for providing a first receiving power level for a user equipment at a center region of the cooperation area, and configuring the base stations to transmit at a second transmit power level for providing a second receiving power level at a border region of the cooperation area, wherein the second receiving power level is lower than the first receiving power level.

Owner:NOKIA SOLUTIONS & NETWORKS OY

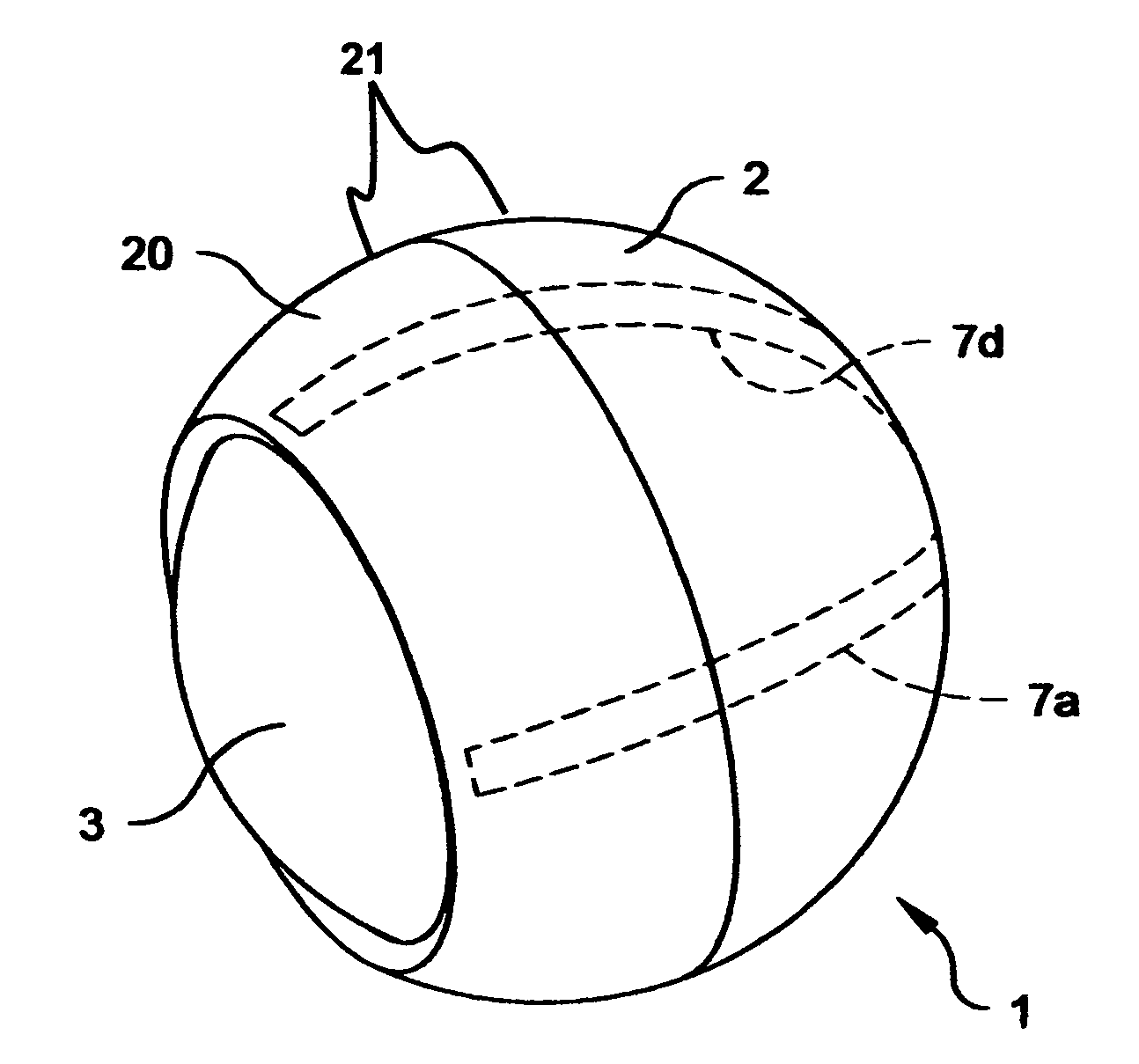

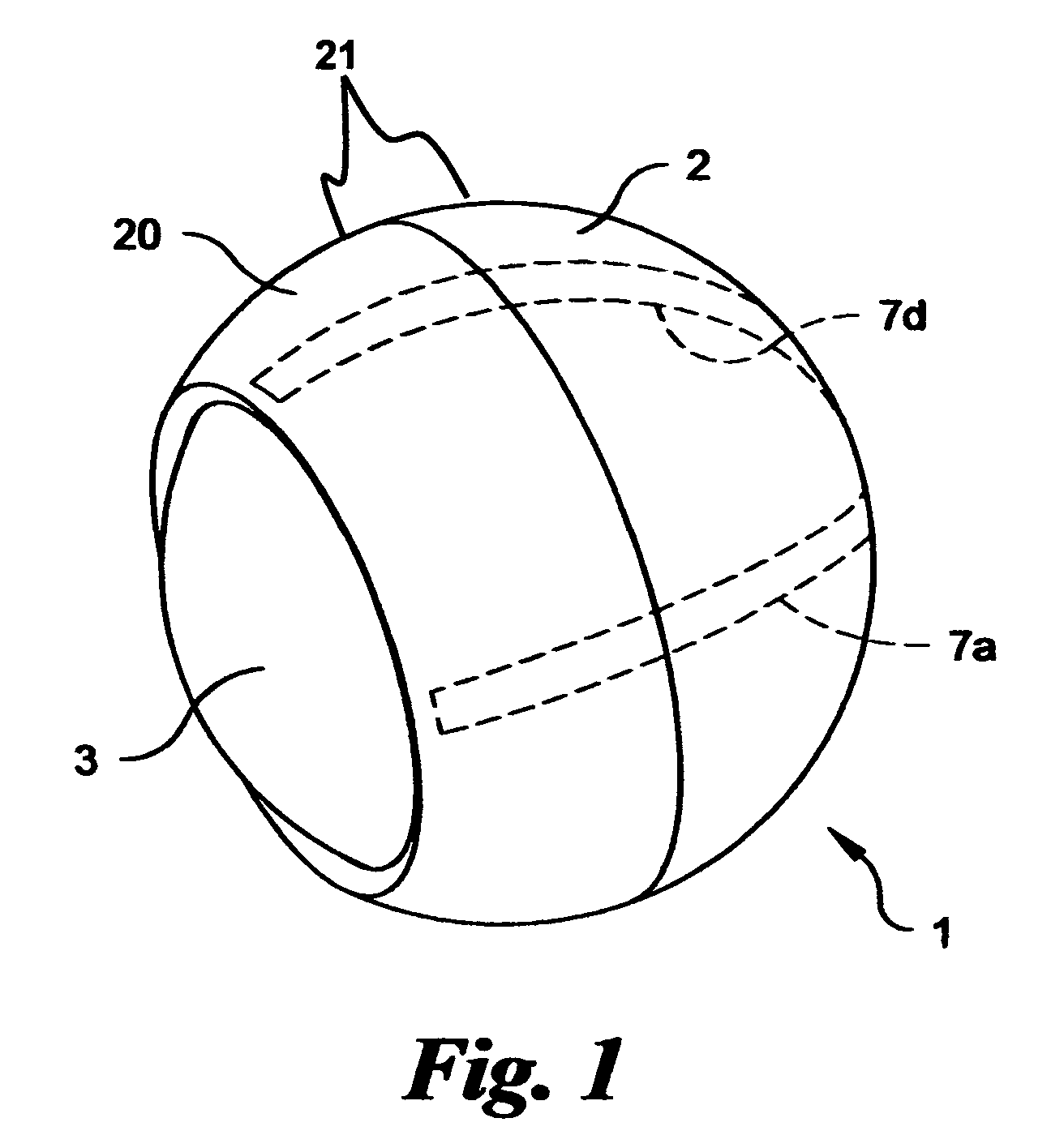

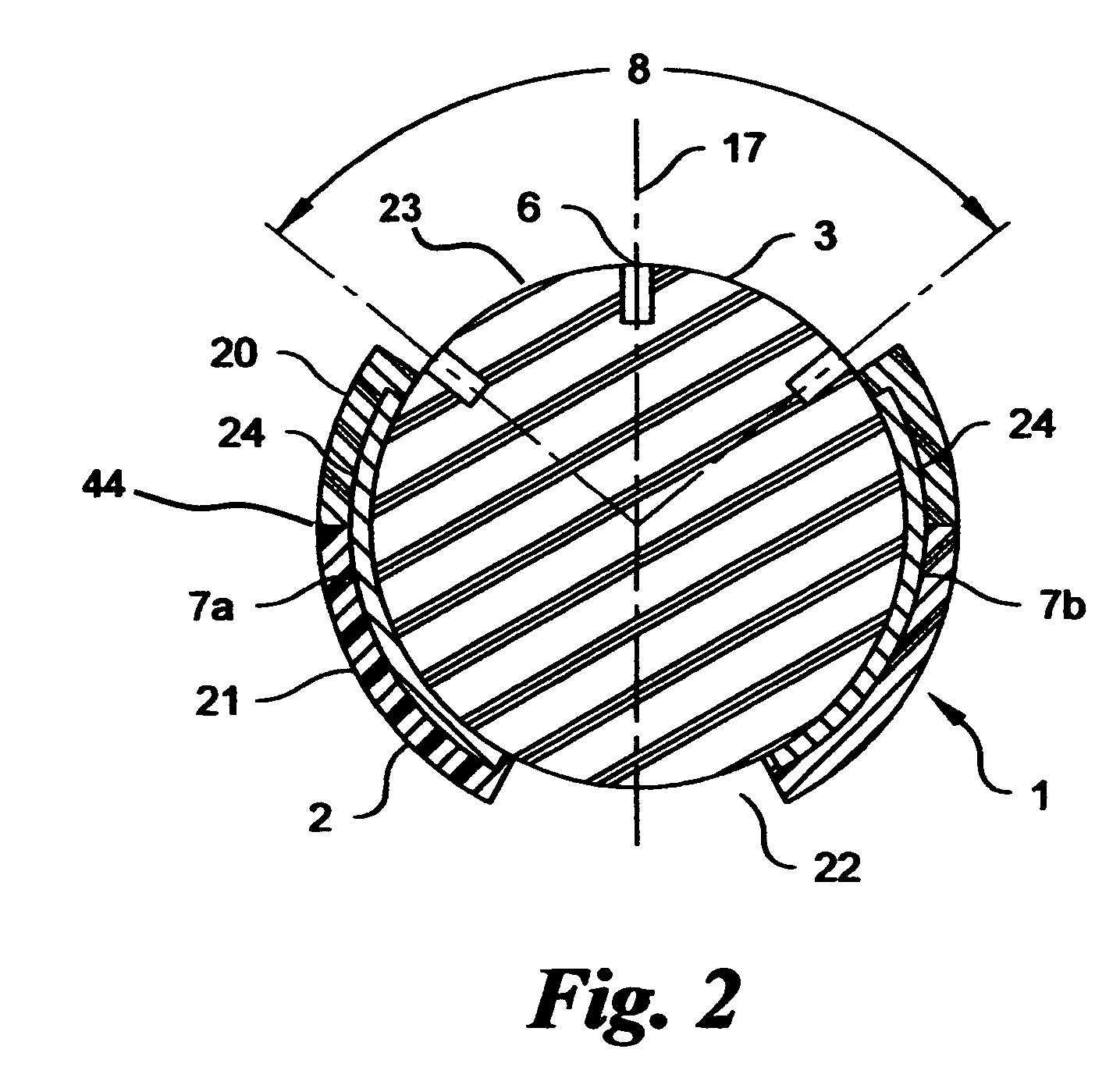

Solid state gimbal system

InactiveUS7459834B2Less powerHigh operating requirementsAdditive manufacturing apparatusPiezoelectric/electrostriction/magnetostriction machinesGuidance systemCommunications system

A non-mechanical gimbal system is presented. The gimbal system includes a gimbal housing, including hemispherical and annular caps, rotatable sphere, and at least two curvilinear actuators. The hemispherical cap is attached to the annular cap in a removable fashion so as to surround the rotatable sphere. The curvilinear actuators are disposed between the rotatable sphere and gimbal housing. Curvilinear actuators rotate the rotatable sphere, via shear induced motion, with respect to the interior surface of the gimbal housing. The present invention has immediate applicability within security devices, games, toys, weapons (including guidance systems and aiming), and communication systems.

Owner:QORTEK

Integrated Touch Screen

ActiveUS20100194707A1Less powerFew partsStatic indicating devicesNon-linear opticsTouch SensesDisplay device

Displays with touch sensing circuitry integrated into the display pixel stackup are provided. Circuit elements, such as touch signal lines, such as drive lines and sense lines, grounding regions, in the display pixel stackups can be grouped together to form touch sensing circuitry that senses a touch on or near the display. An integrated touch screen can include multi-function circuit elements that can operate as circuitry of the display system to generate an image on the display, and can also form part of a touch sensing system that senses one or more touches on or near the display. The multi-function circuit elements can be, for example, capacitors in display pixels that can be configured to operate as storage capacitors / electrodes, common electrodes, conductive wires / pathways, etc., of the display circuitry in the display system, and that may also be configured to operate as circuit elements of the touch sensing circuitry.

Owner:APPLE INC

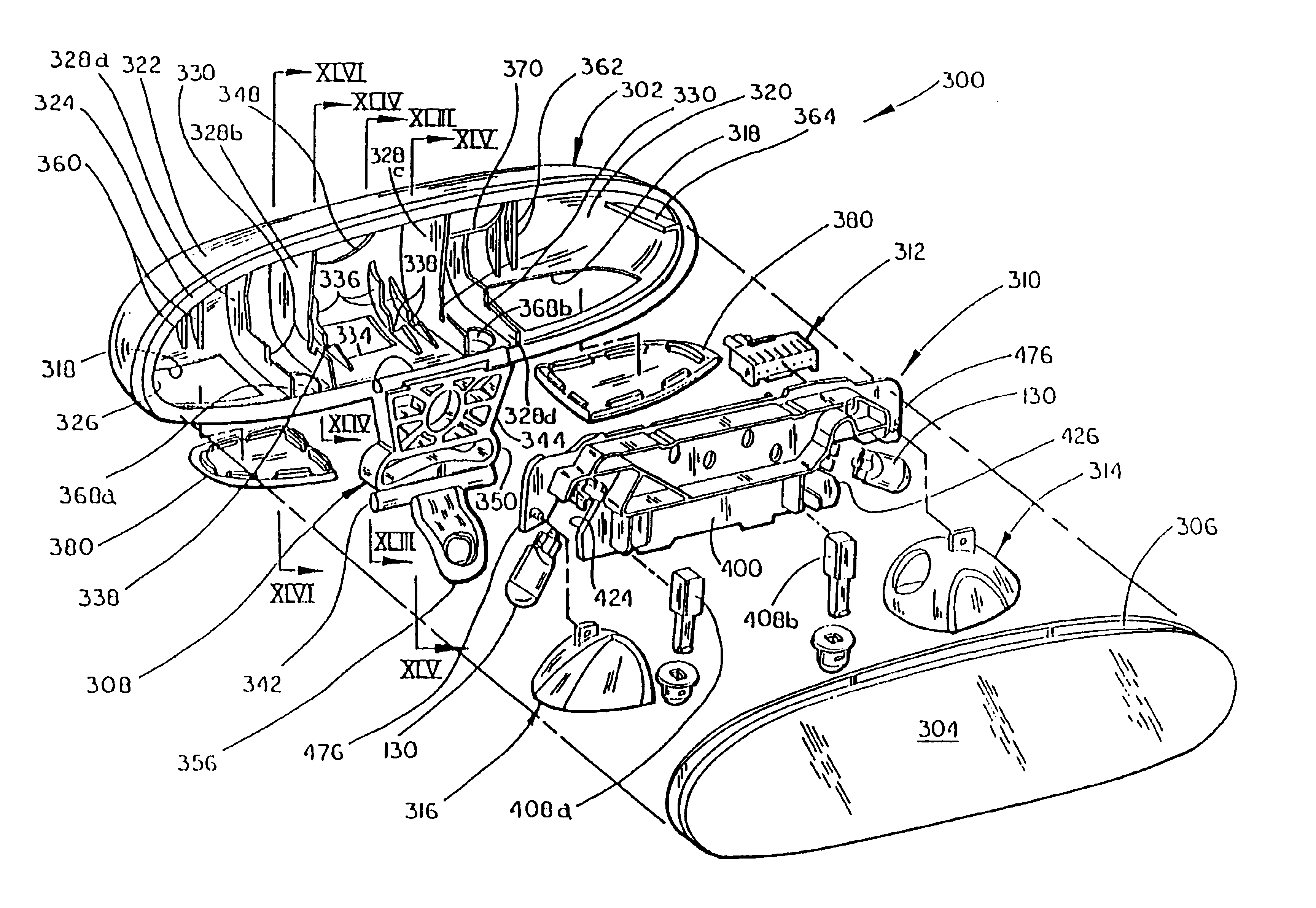

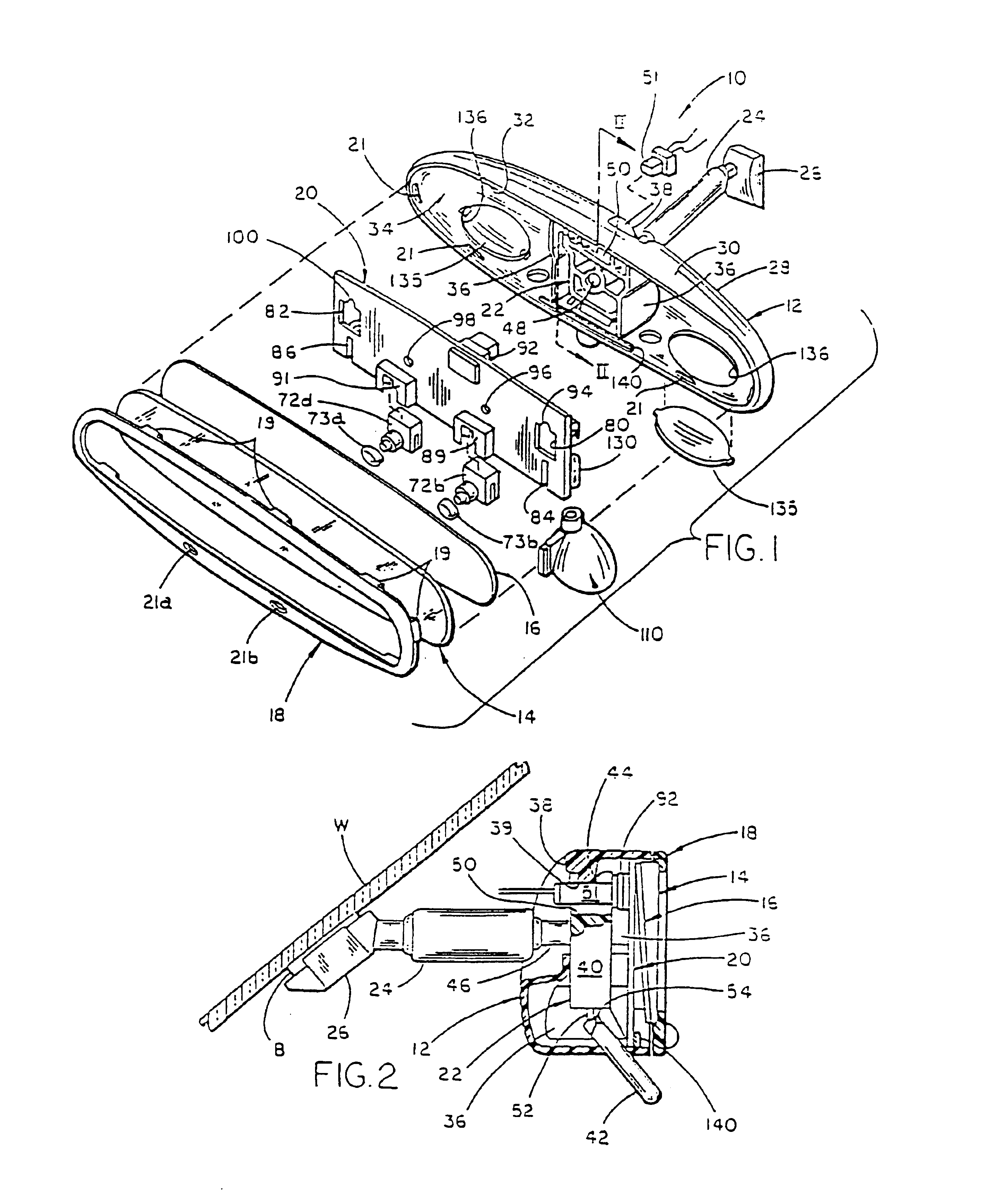

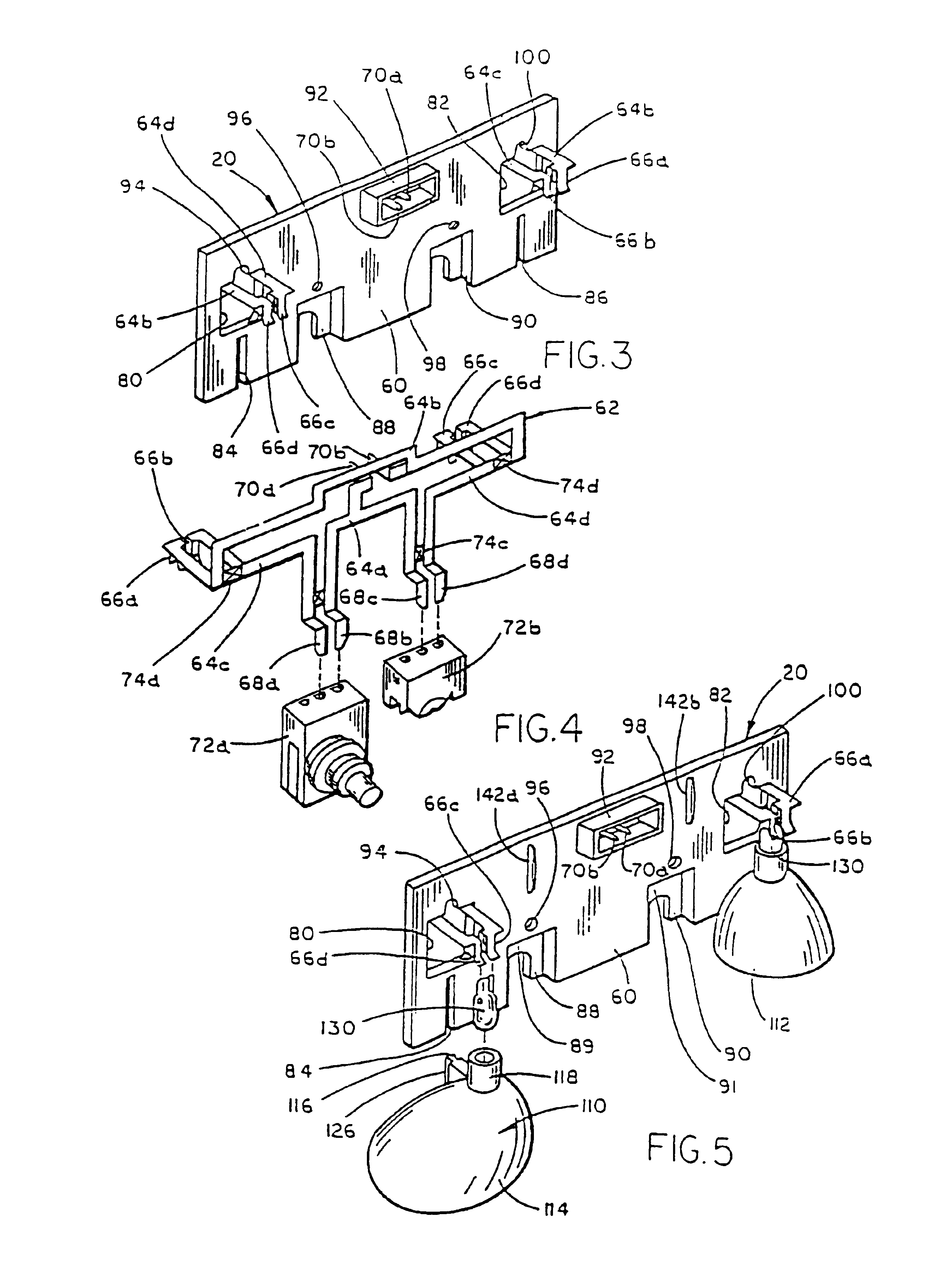

Modular rearview mirror assembly

InactiveUS6877888B2Increased durabilityImprove reliabilityLighting elementsClosed circuit television systemsPolymer resinElectrical devices

An interior rearview mirror assembly for vehicles incorporates a reflective mirror element for viewing by a user of the mirror assembly, a lip formed from moldable polymeric resin selected to expand sufficiently when heated to allow snap in insertion of the reflective mirror element while the lip is warm and flexable, a carrier located to the rear of the reflective element such that the carrier is closer to a windshield of the vehicle than the mirror element when the mirror element is mounted in the vehicle, at least one electrical accessory, and an electrical connector adapted to receive a connector from the vehicle electrical system with the electrical accessory connected to the electrical connector. Preferably, the electrical accessory is supported by the carrier and is selected from a variety of electrical devices, lamps, lights, sensors and the like.

Owner:DONNELLY CORP

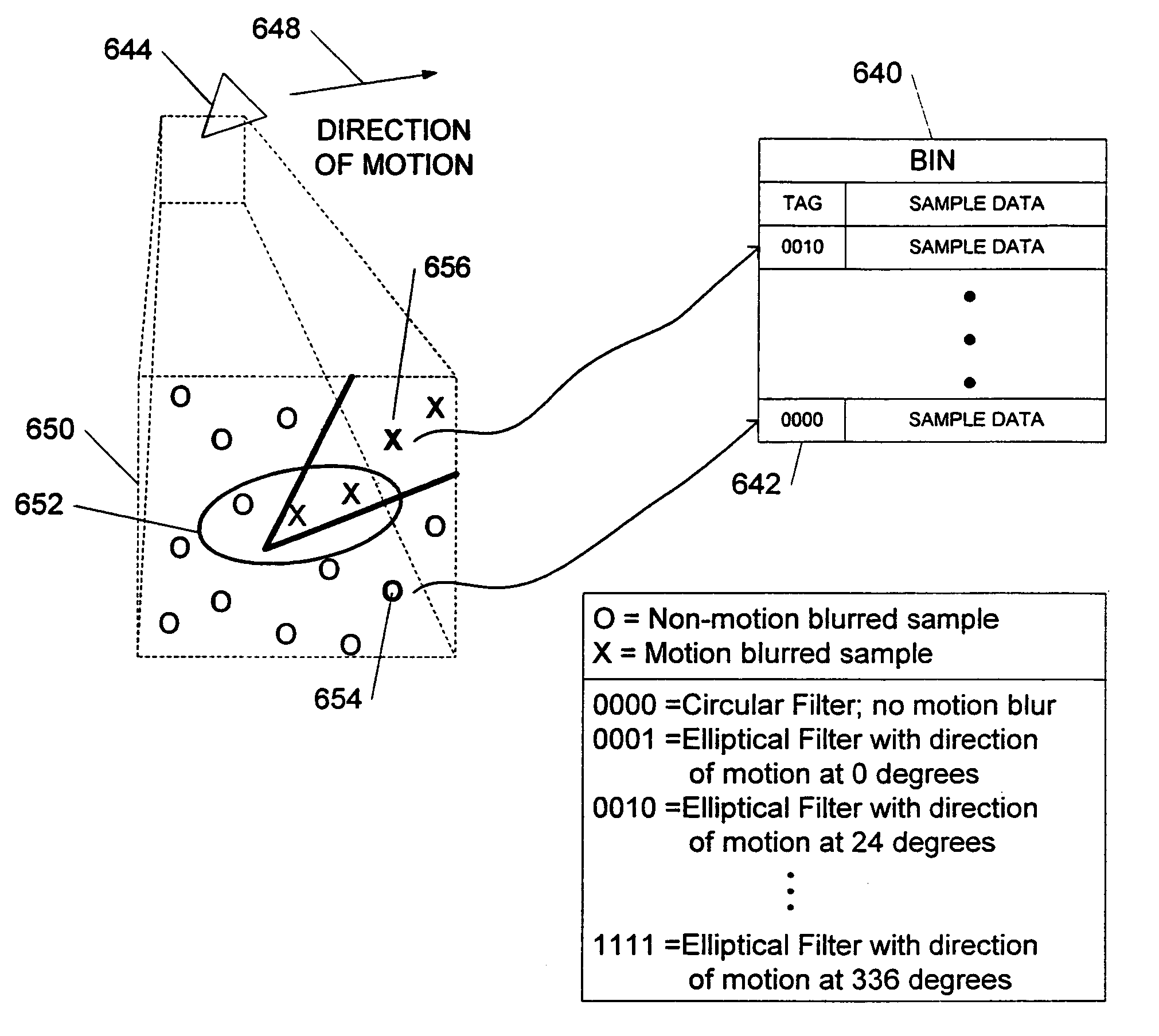

Graphics system using sample masks for motion blur, depth of field, and transparency

InactiveUS6956576B1Quality improvementHigh quality imagingCathode-ray tube indicatorsAnimationScreen-door effectGeometric primitive

A method and apparatus for creating motion blur, depth of field, and screen door effects when rendering three-dimensional graphics data are disclosed. A graphics system configured with a graphics processor, a super-sampled sample buffer, and a sample-to-pixel calculation unit is disclosed. The graphics processor may be configured to use a sample mask to select different subsets of sample coordinates to be rendered for a particular frame. Each subset may be rendered applying a different set of attributes, and the resulting samples may then be stored together in the sample buffer. The sample-to-pixel calculation unit may be configured to filter the samples into output pixels that are provided to a display device. The attributes that may be changed from subset to subset include the viewpoint, the time at which objects in the data are rendered, which objects or geometric primitives in the data are rendered, the position of objects in the data, the color of objects in the data, the transparency of objects in the data, and the shape of objects in the data.

Owner:ORACLE INT CORP

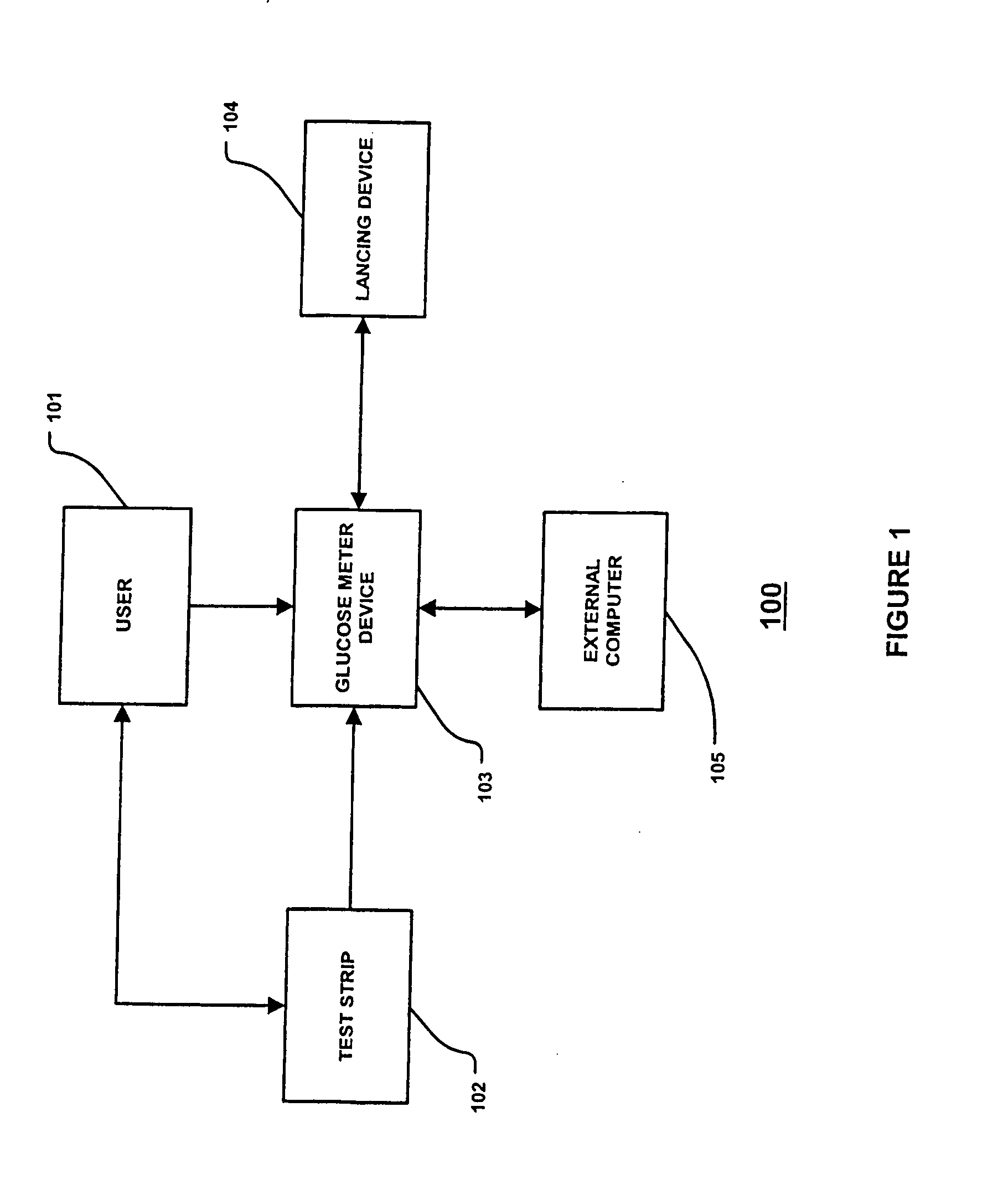

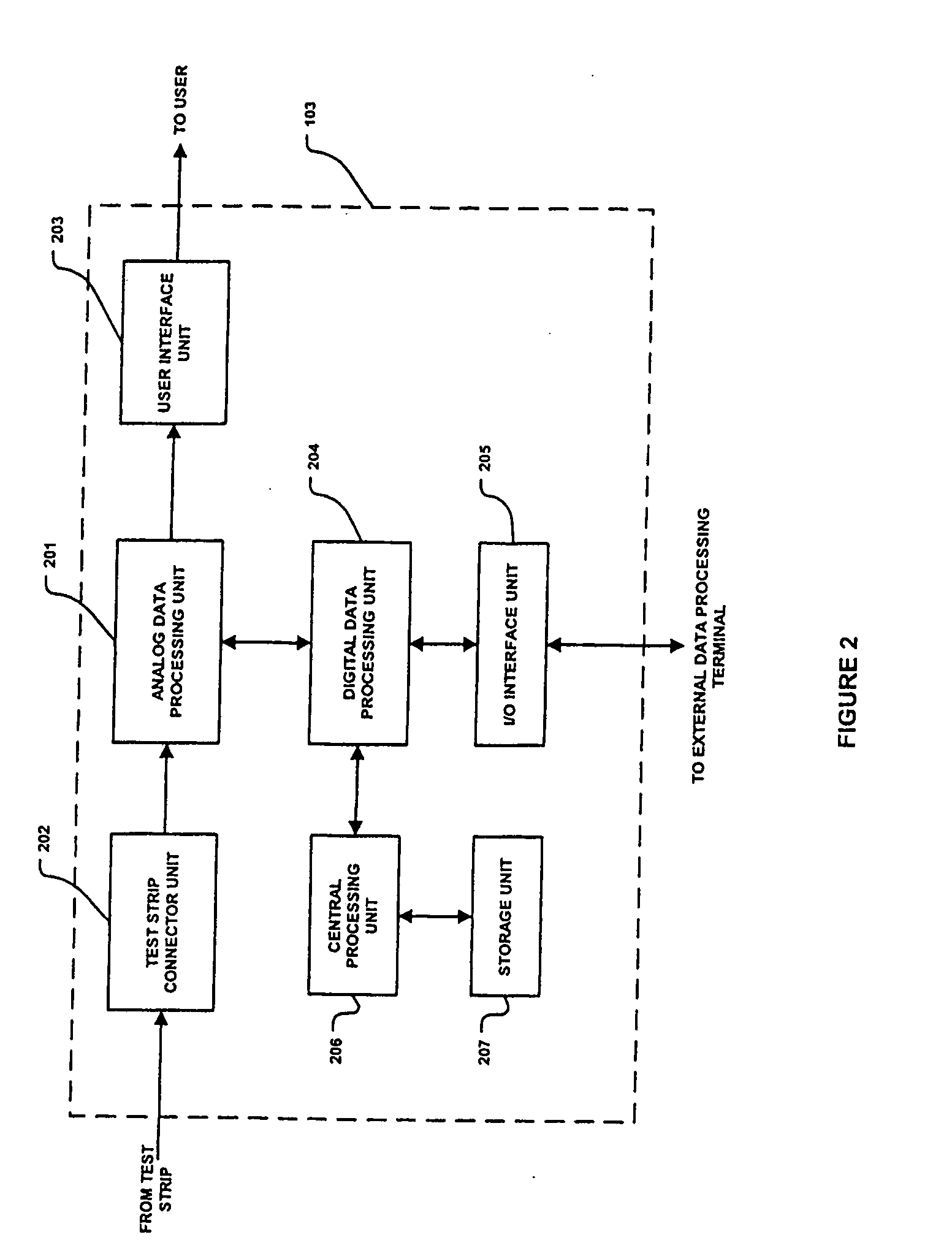

Method and apparatus for providing power management in data communication systems

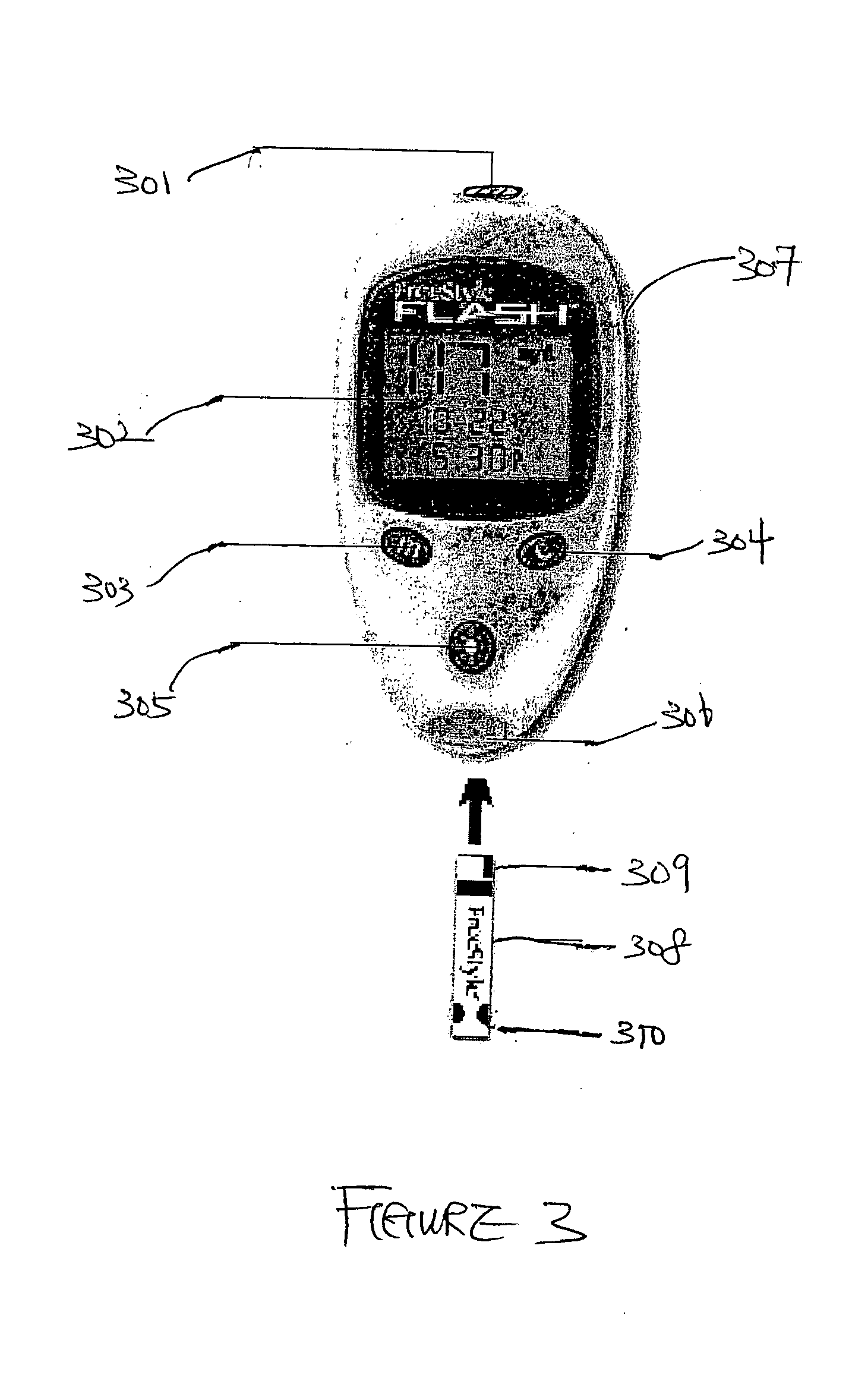

ActiveUS20050009126A1Good for healthEarly detectionBioreactor/fermenter combinationsBiological substance pretreatmentsCommunications systemBlood glucose meters

A blood glucose meter having a compact housing, a display unit disposed on the housing, the display unit including a display light source to illuminate the display unit,an input unit disposed on the housing, the input unit configured to provide input functions for the blood glucose meter, and a power source provided within the housing for providing power to the blood glucose meter, where the housing includes a port integrated on said housing configured to receive a blood glucose test strip, and corresponding methods of measuring blood glucose meter is provided.

Owner:ABBOTT DIABETES CARE INC

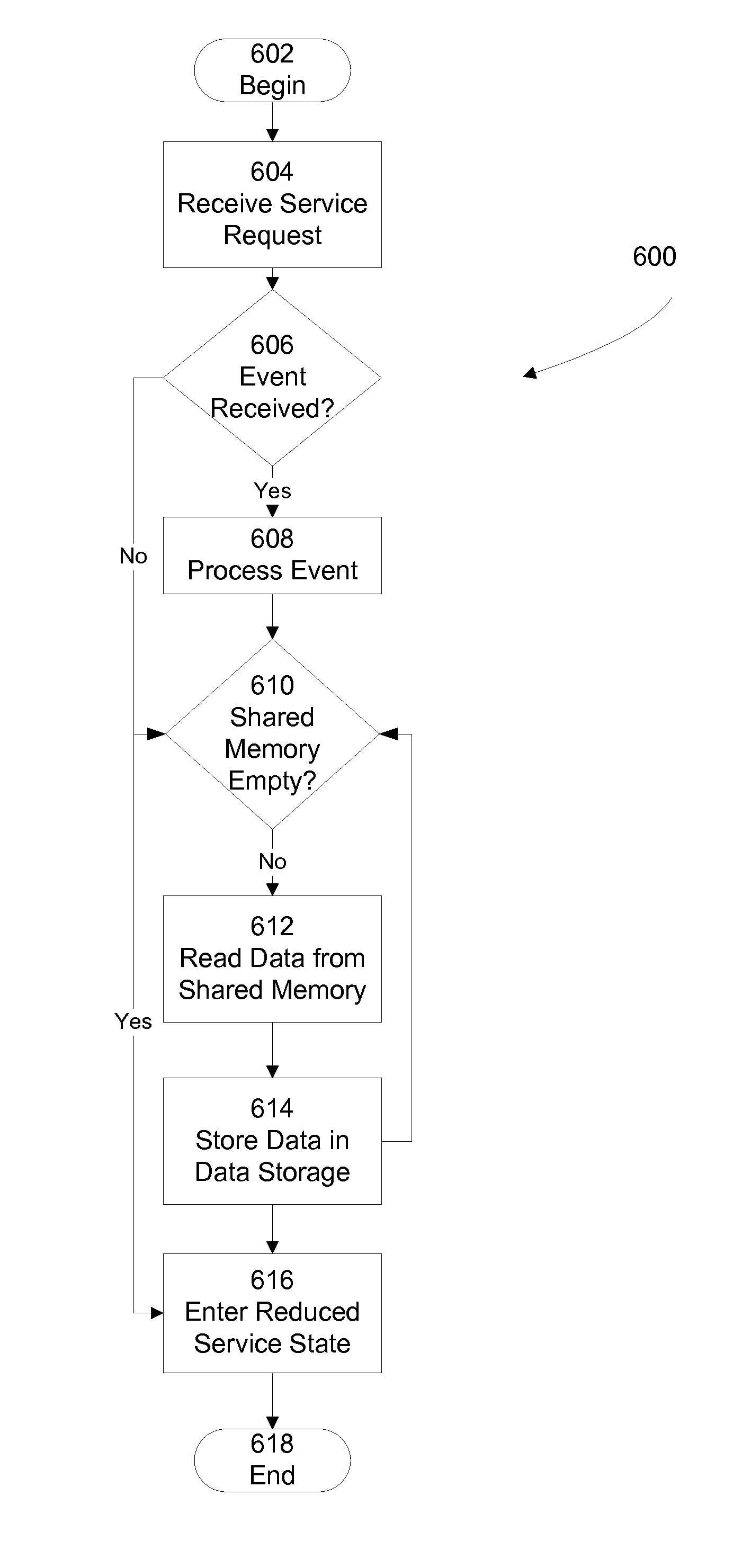

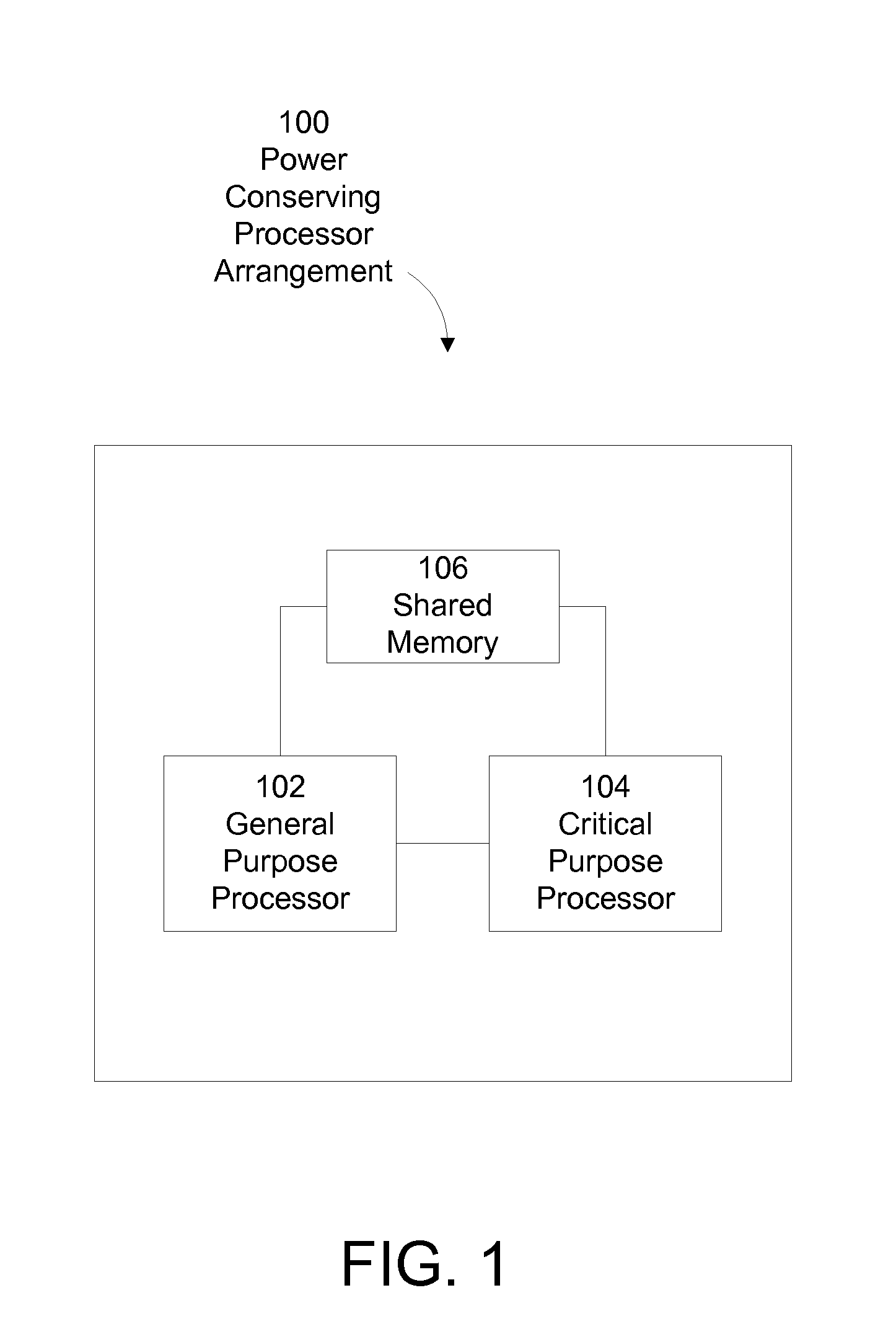

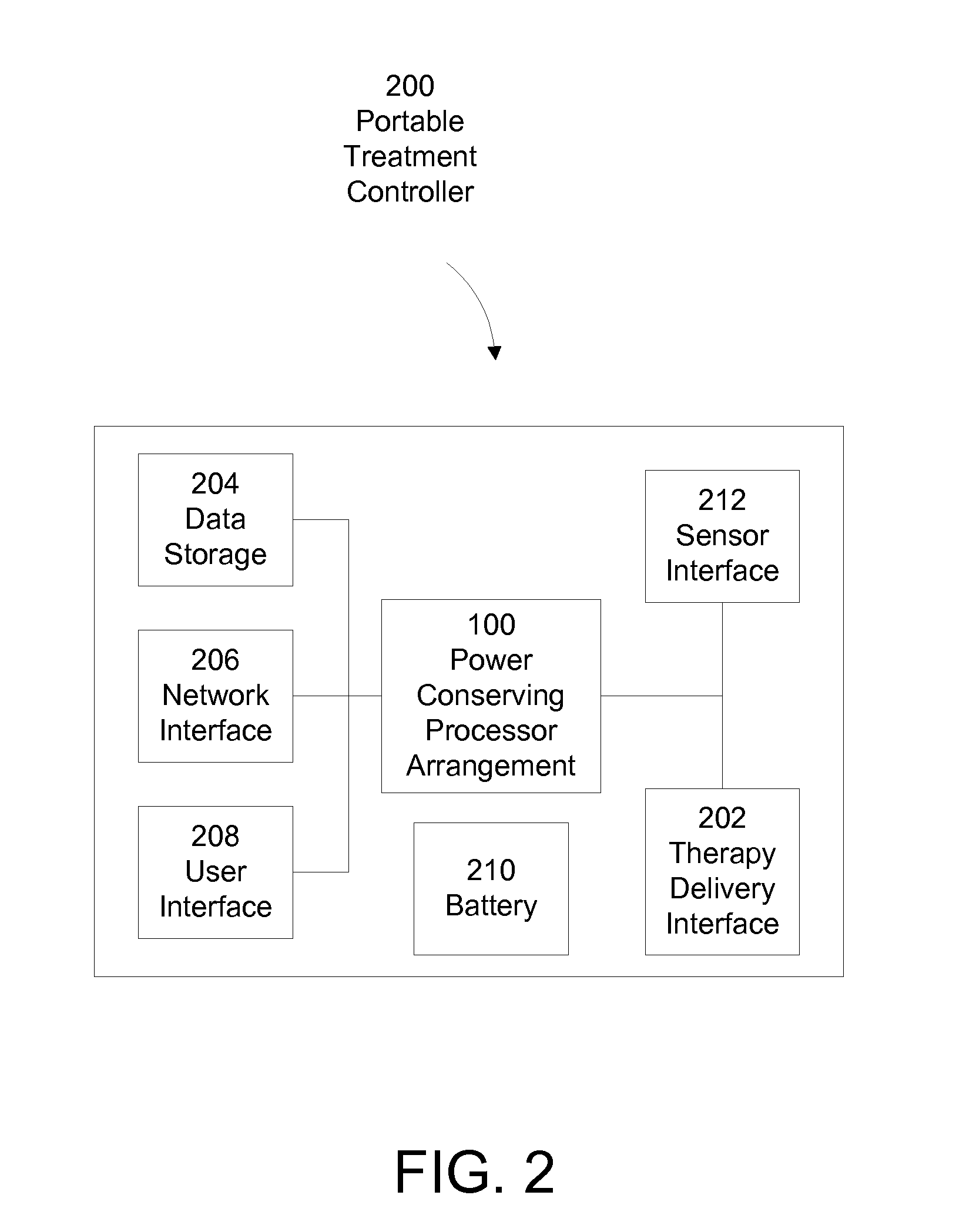

System and method for conserving power in a medical device

ActiveUS20120011382A1Useful lifespan of batteryEfficient treatment methodEnergy efficient ICTElectrotherapyCritical functionMedical device

A system and method for conservation of battery power in a portable medical device is provided. In one example, a processor arrangement that includes a plurality of processors is implemented. At least one of these processors is configured to execute the critical functions of the medical device, while one or more other processors assume a reduced service level, thereby drawing significantly less power. According to this arrangement, the medical device conserves energy by drawing the additional electrical power needed to activate the additional processing power only when needed.

Owner:ZOLL MEDICAL CORPORATION

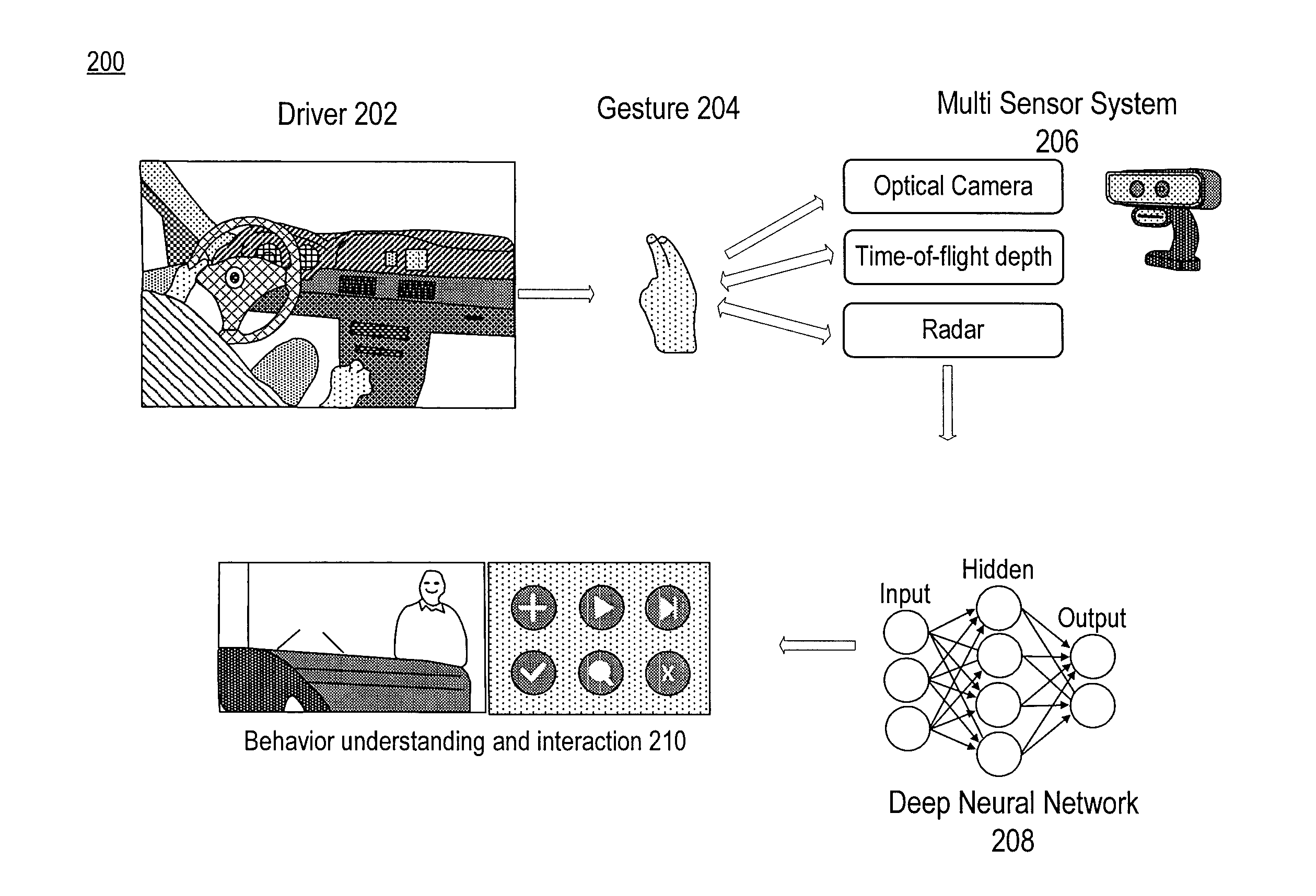

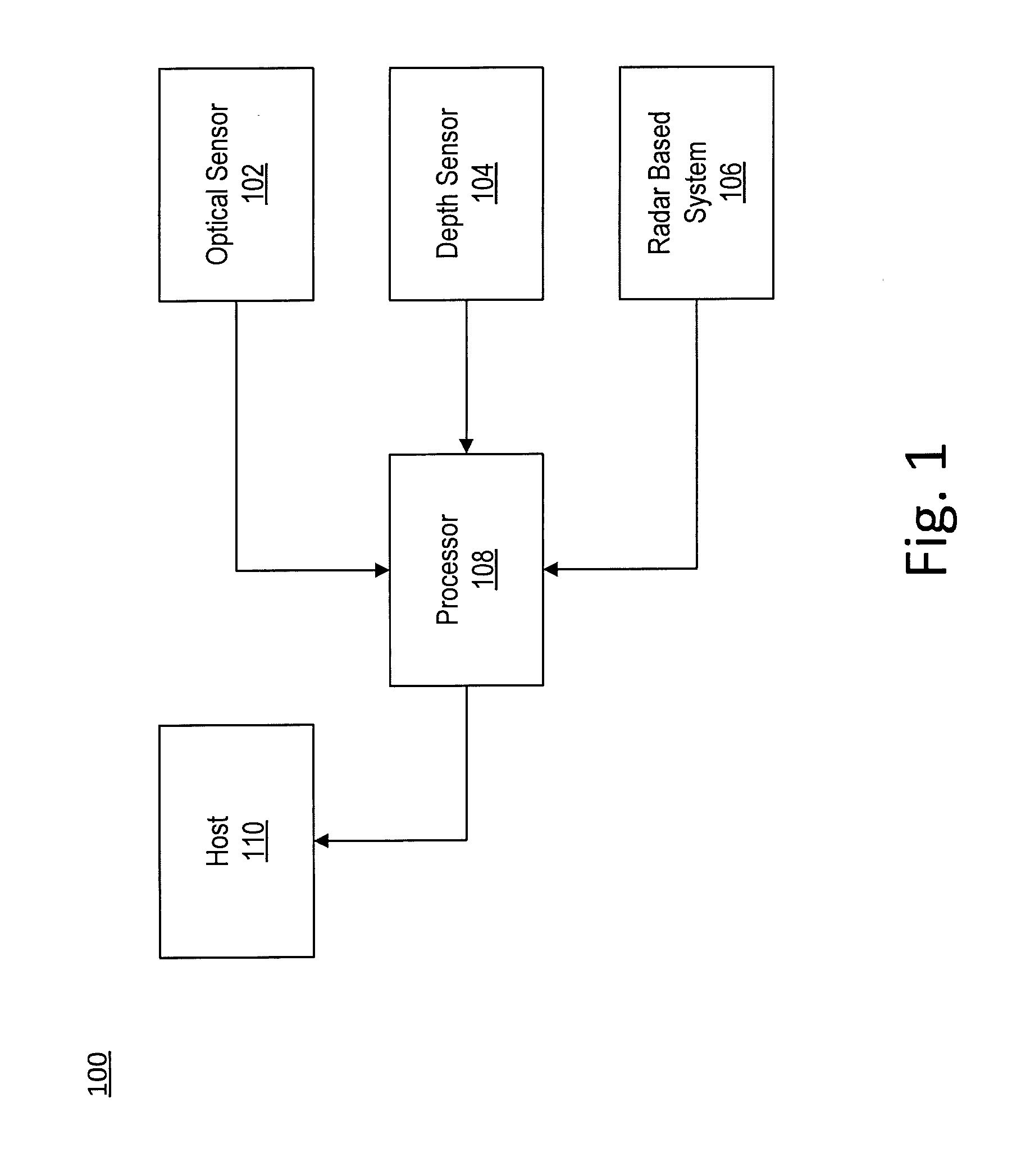

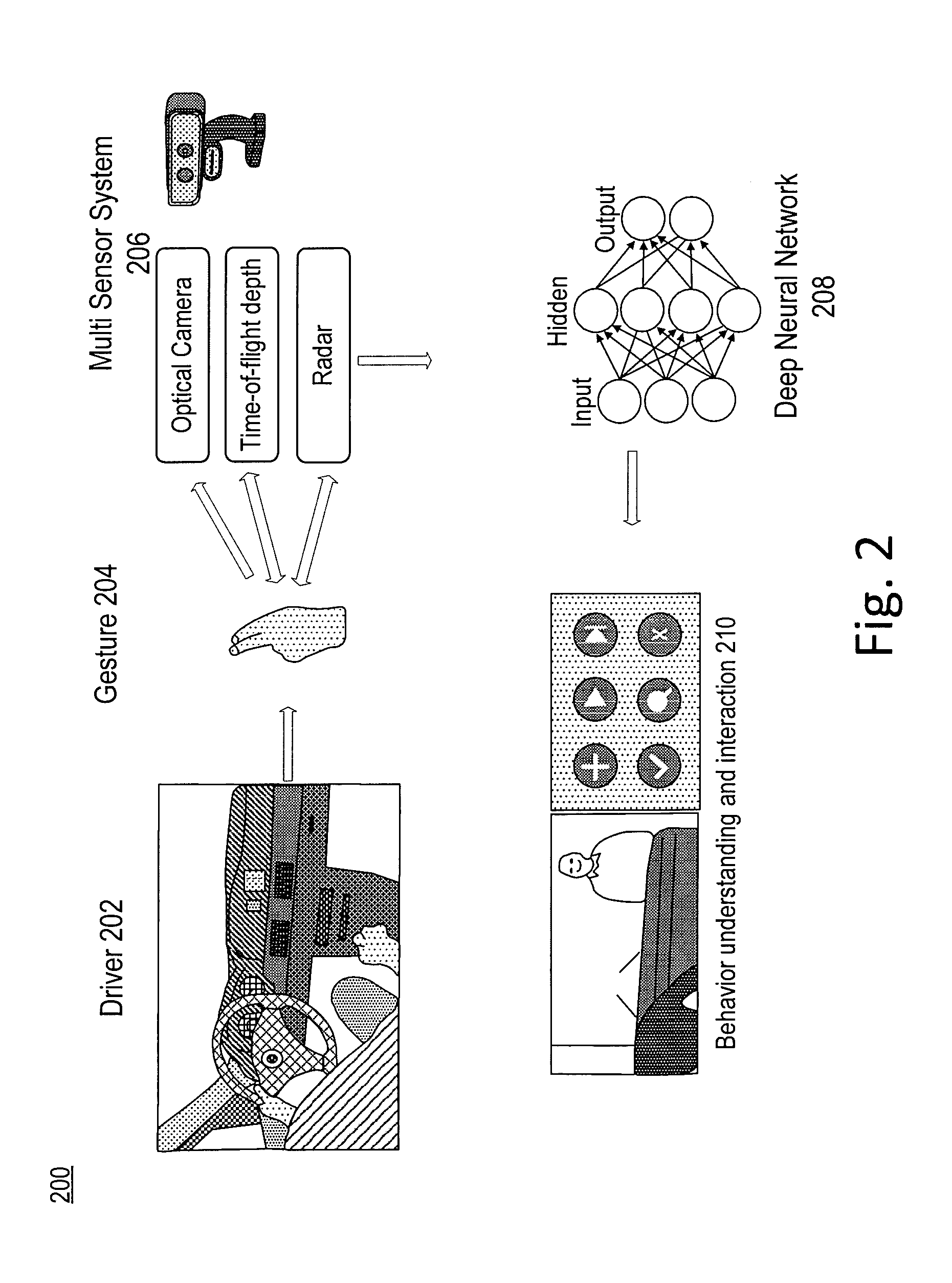

Multi-sensor based user interface

ActiveUS20170060254A1Minimize distractionReduce distractionsInput/output for user-computer interactionCharacter and pattern recognitionRadarProcessing element

An apparatus and method for gesture detection and recognition. The apparatus includes a processing element, a radar sensor, a depth sensor, and an optical sensor. The radar sensor, the depth sensor, and the optical sensor are coupled to the processing element, and the radar sensor, the depth sensor, and the optical sensor are configured for short range gesture detection and recognition. The processing element is further configured to detect and recognize a hand gesture based on data acquired with the radar sensor, the depth sensor, and the optical sensor.

Owner:NVIDIA CORP

System and method for dynamic server allocation and provisioning

InactiveUS20070250608A1Lower cost of capitalQuality improvementResource allocationDigital computer detailsLoad SheddingManagement tool

A management tool that streamlines the server allocation and provisioning processes within a data center is provided. The system, method, and computer program product divide the server provisioning and allocation into two separate tasks. Provisioning a server is accomplished by generating a fully configured, bootable system image, complete with network address assignments, virtual LAN (VLAN) configuration, load balancing configuration, and the like. System images are stored in a storage repository and are accessible to more than one server. Allocation is accomplished using a switching mechanism which matches each server with an appropriate system image based upon current configuration or requirements of the data center. Thus, real-time provisioning and allocation of servers in the form of automated responses to changing conditions within the data center is possible. The ability to instantly re-provision servers, safely and securely switch under-utilized server capacity to more productive tasks, and improve server utilization is also provided.

Owner:RACEMI

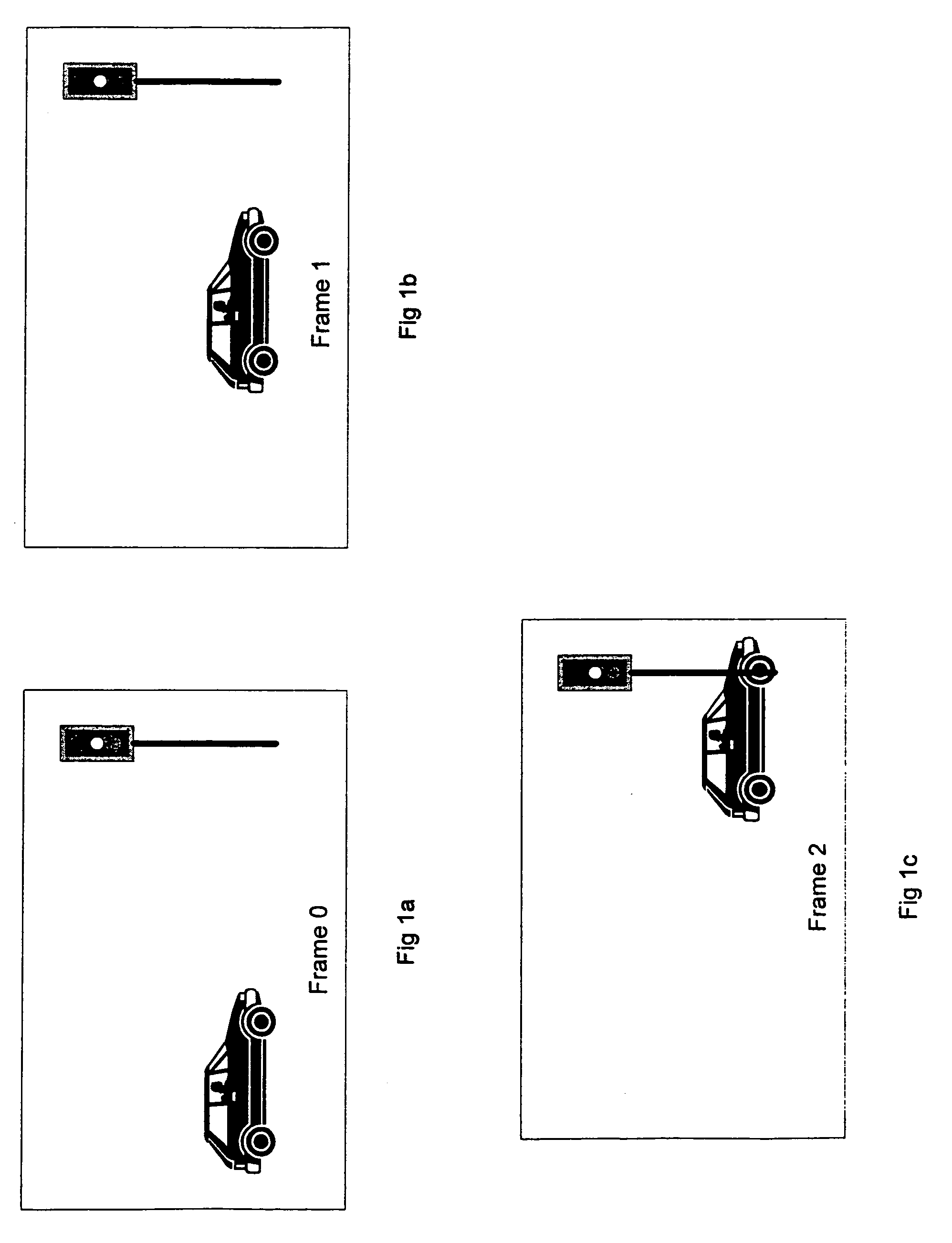

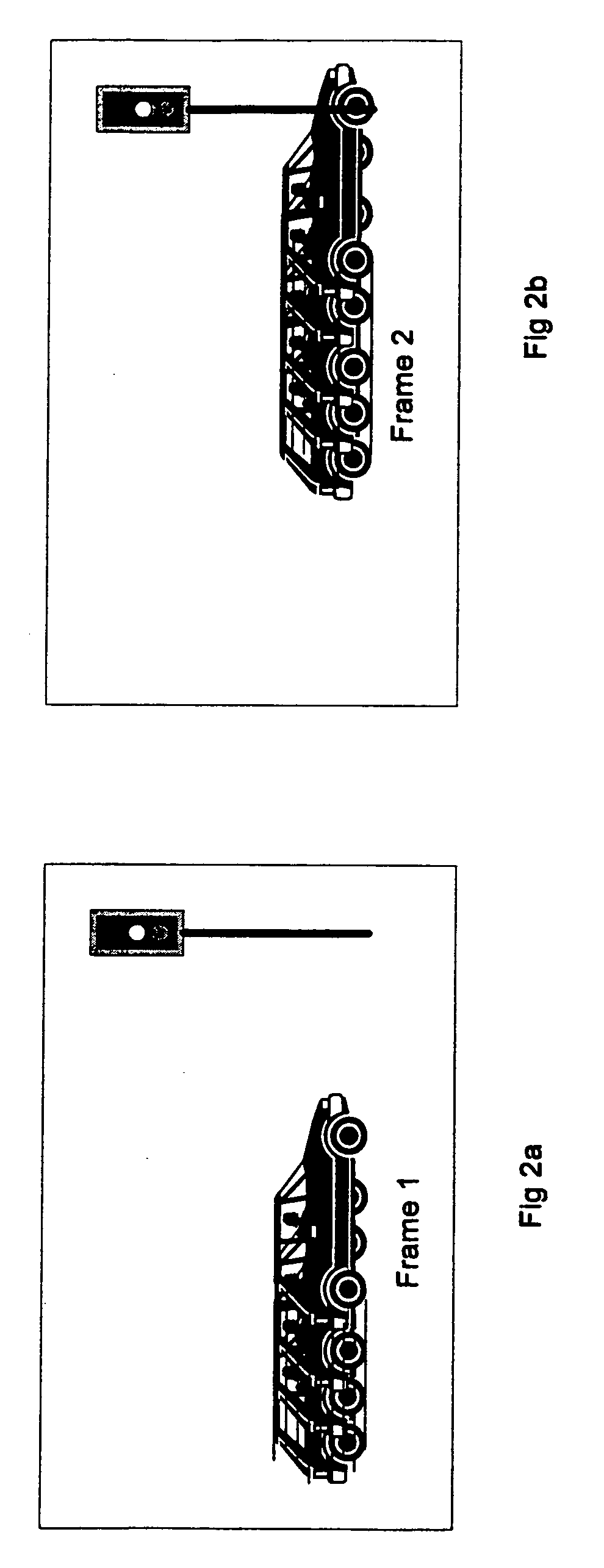

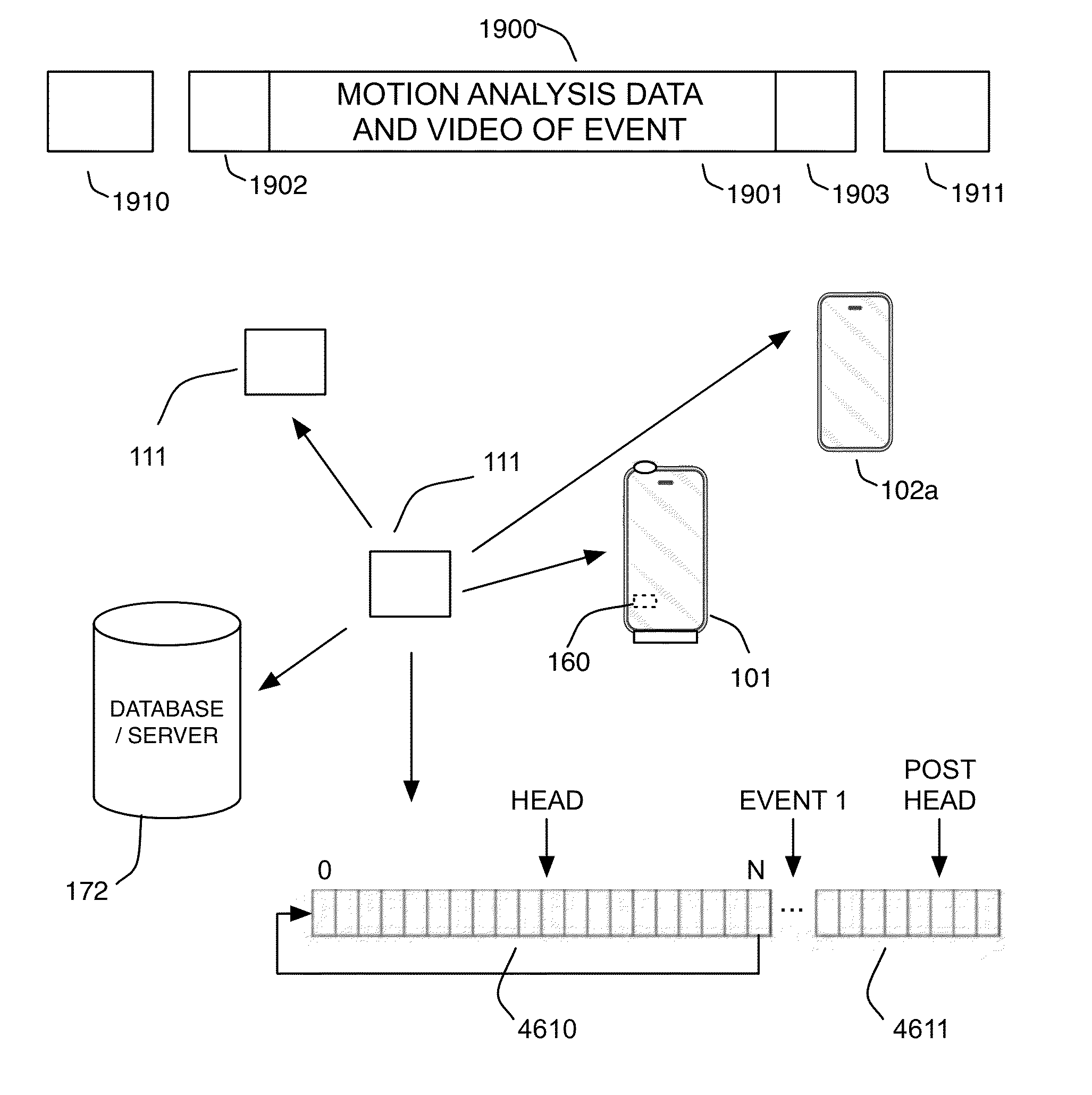

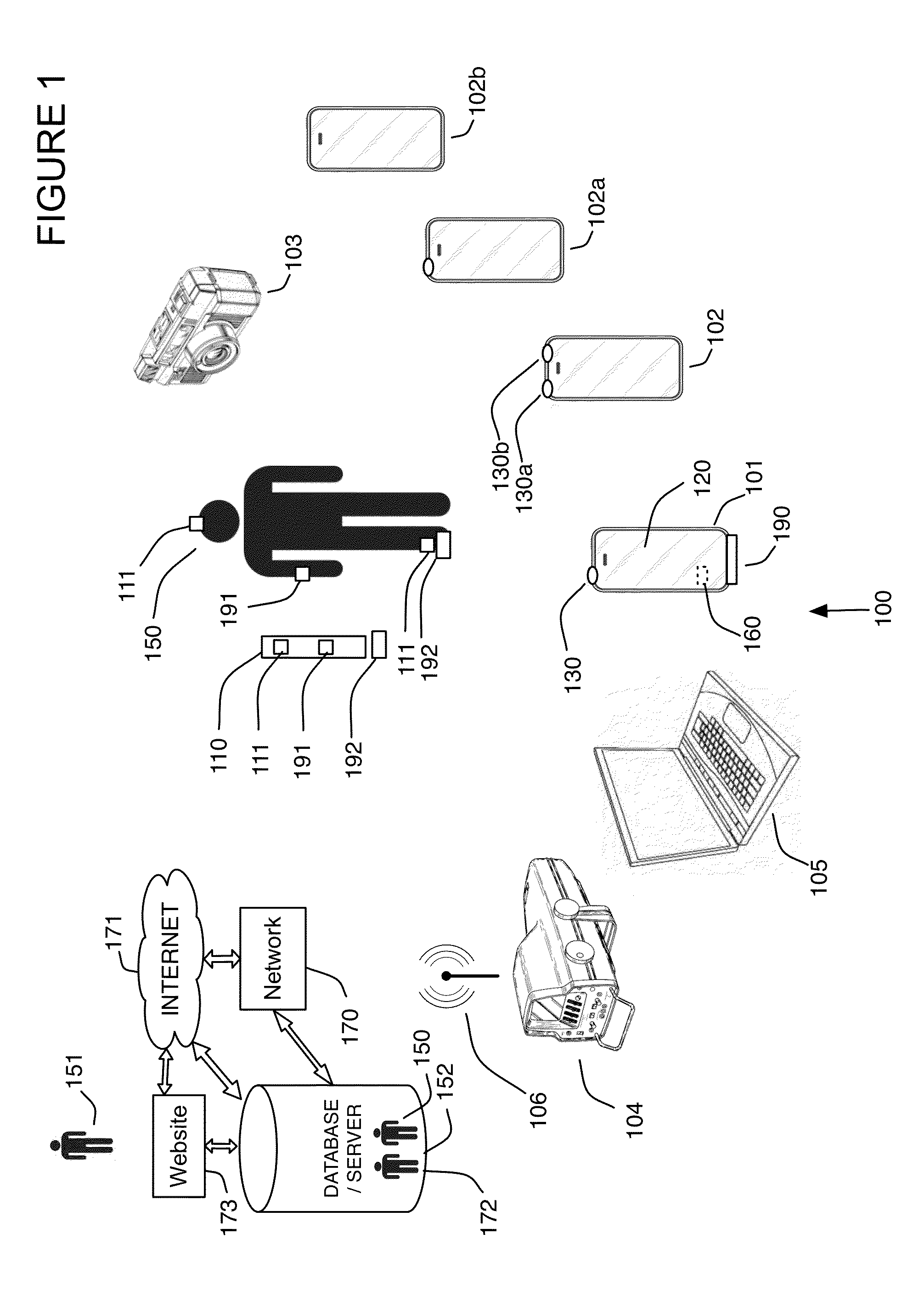

Motion event recognition and video synchronization system and method

ActiveUS20140376876A1Improve accuracy of synchronizationImprove dataImage enhancementTelevision system detailsUser groupReal-time computing

Enables recognition of events within motion data obtained from portable wireless motion capture elements and video synchronization of the events with video as the events occur or at a later time, based on location and / or time of the event or both. May use integrated camera or external cameras with respect to mobile device to automatically generate generally smaller event videos of the event on the mobile device or server. Also enables analysis or comparison of movement associated with the same user, other user, historical user or group of users. Provides low memory and power utilization and greatly reduces storage for video data that corresponds to events such as a shot, move or swing of a player, a concussion of a player, or other medical related events or events, such as the first steps of a child, or falling events.

Owner:NEWLIGHT CAPITAL LLC

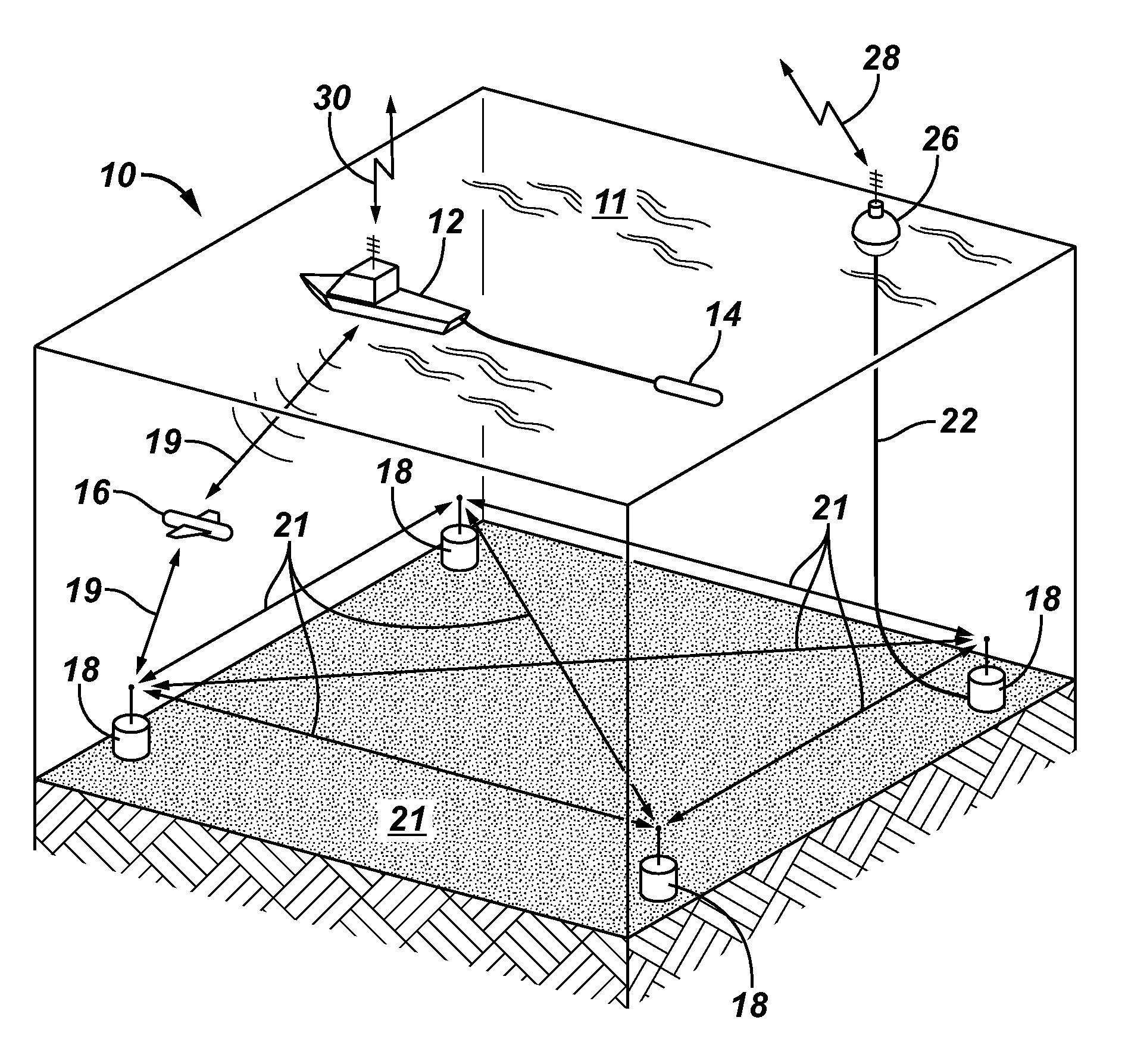

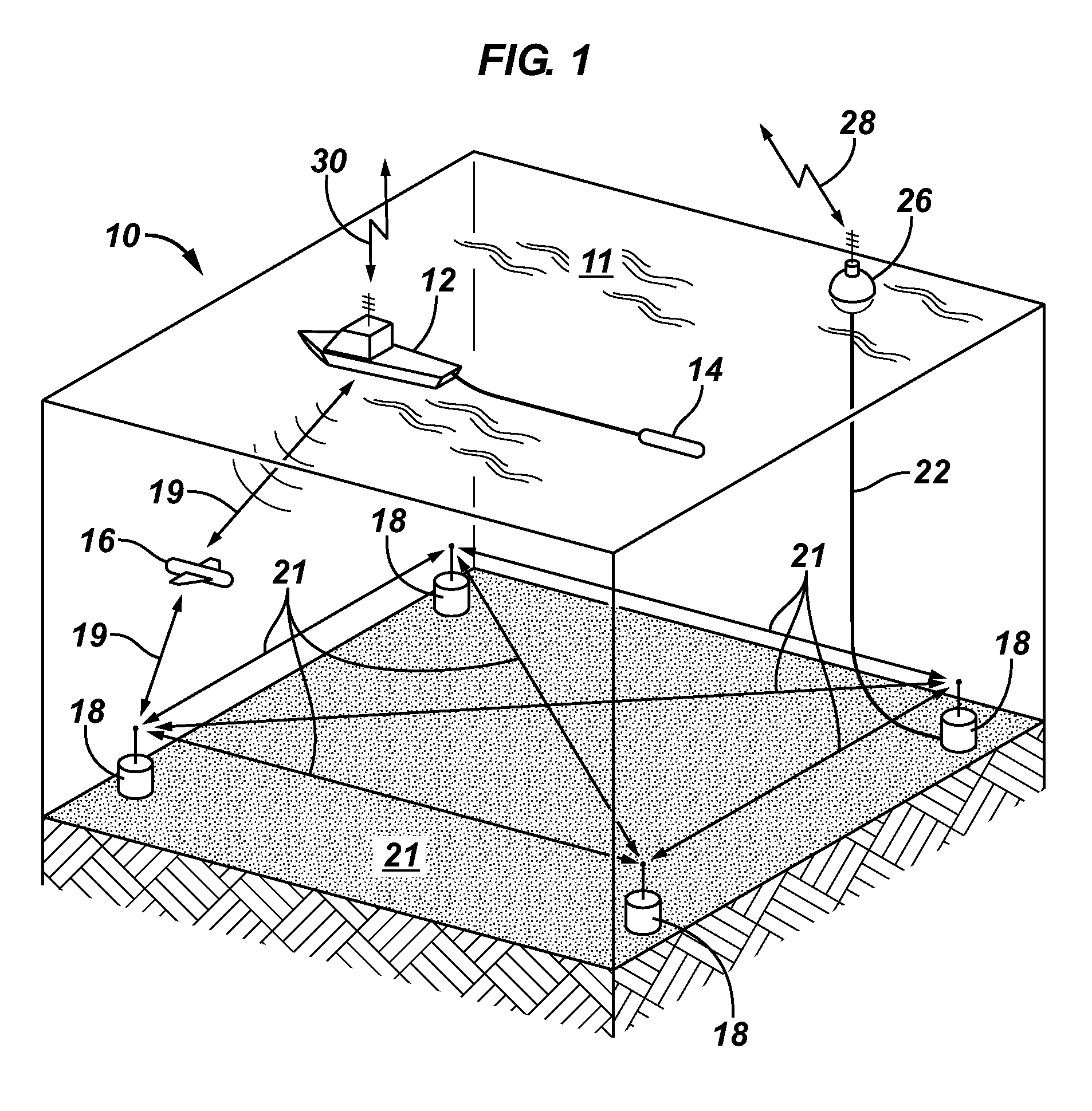

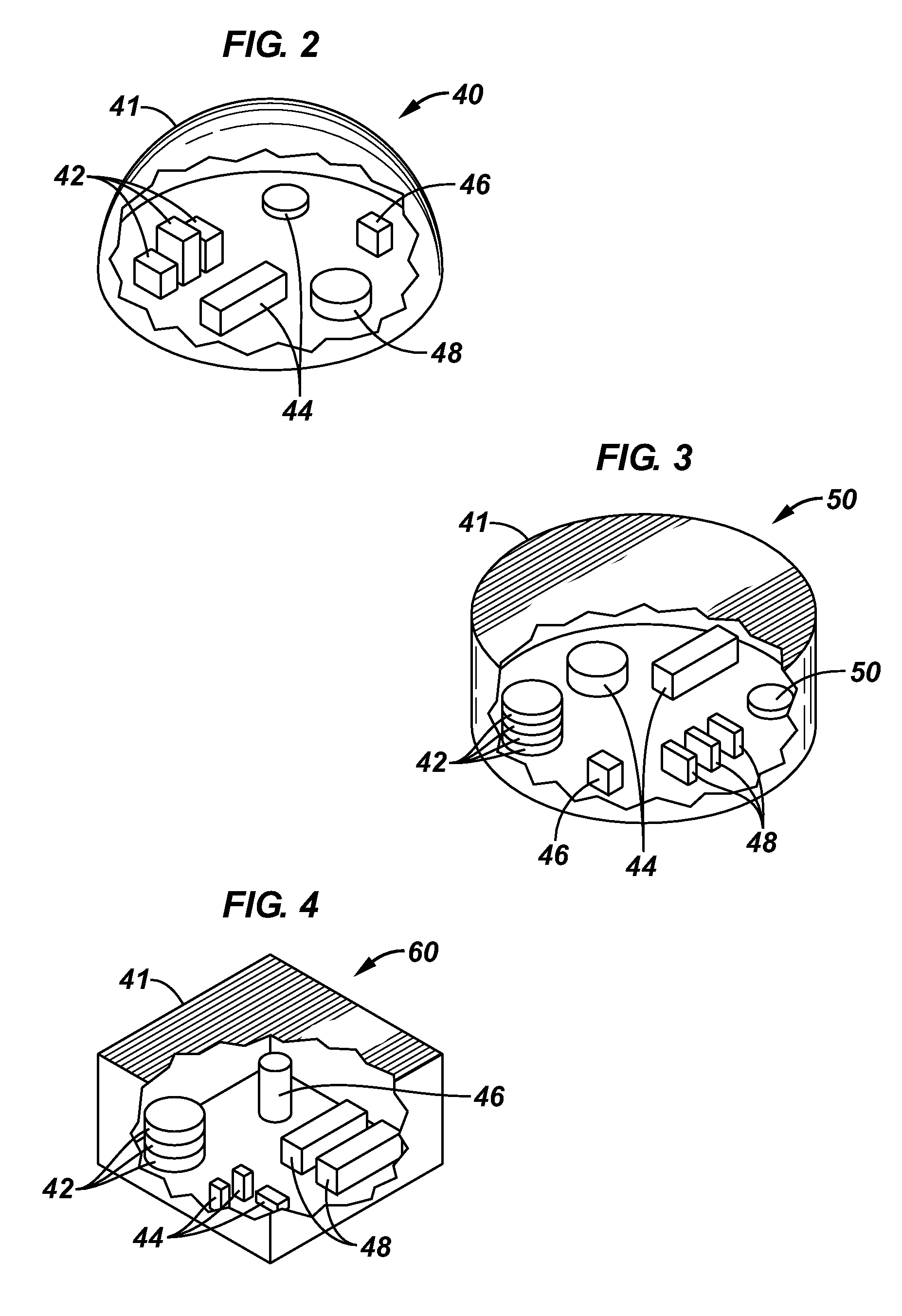

Apparatus, systems and methods for seabed data acquisition

ActiveUS20080144442A1Reduce errorsThe effect is accurateSonic/ultrasonic/infrasonic transmissionSeismic signal transmissionOcean bottomData acquisition

Seabed sensor units, systems including same, and methods for acquiring seabed data are described, one seabed sensor unit comprising a base, the base containing at least one sensor able to detect a seismic signal, electronics comprising a clock and one or more electronic components enabling the sensor to communicate seismic data to one or more memory modules, and a local autonomous power source. This abstract is provided to comply with the rules requiring an abstract, which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims. 37 CFR 1.72(b).

Owner:WESTERNGECO LLC

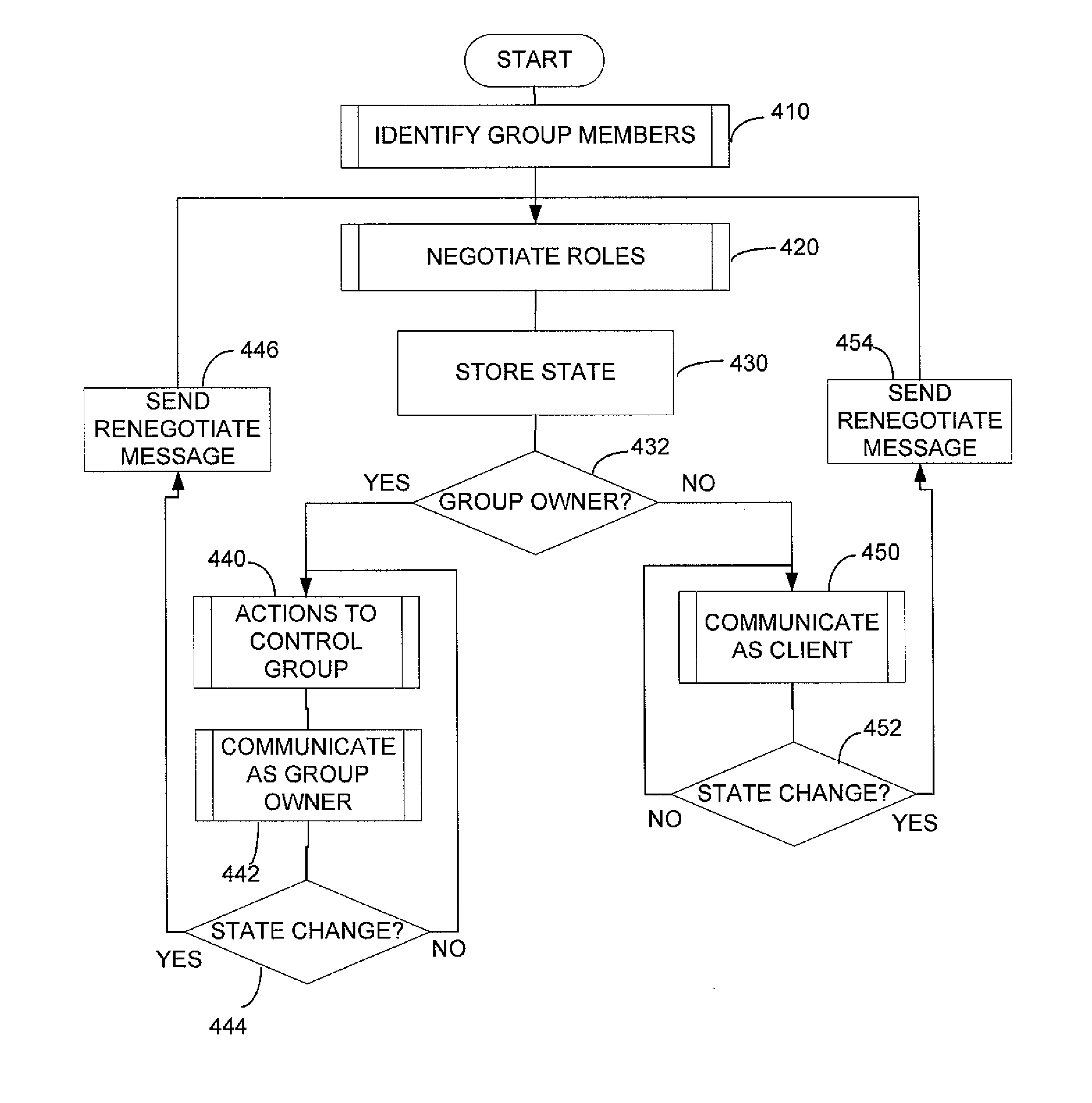

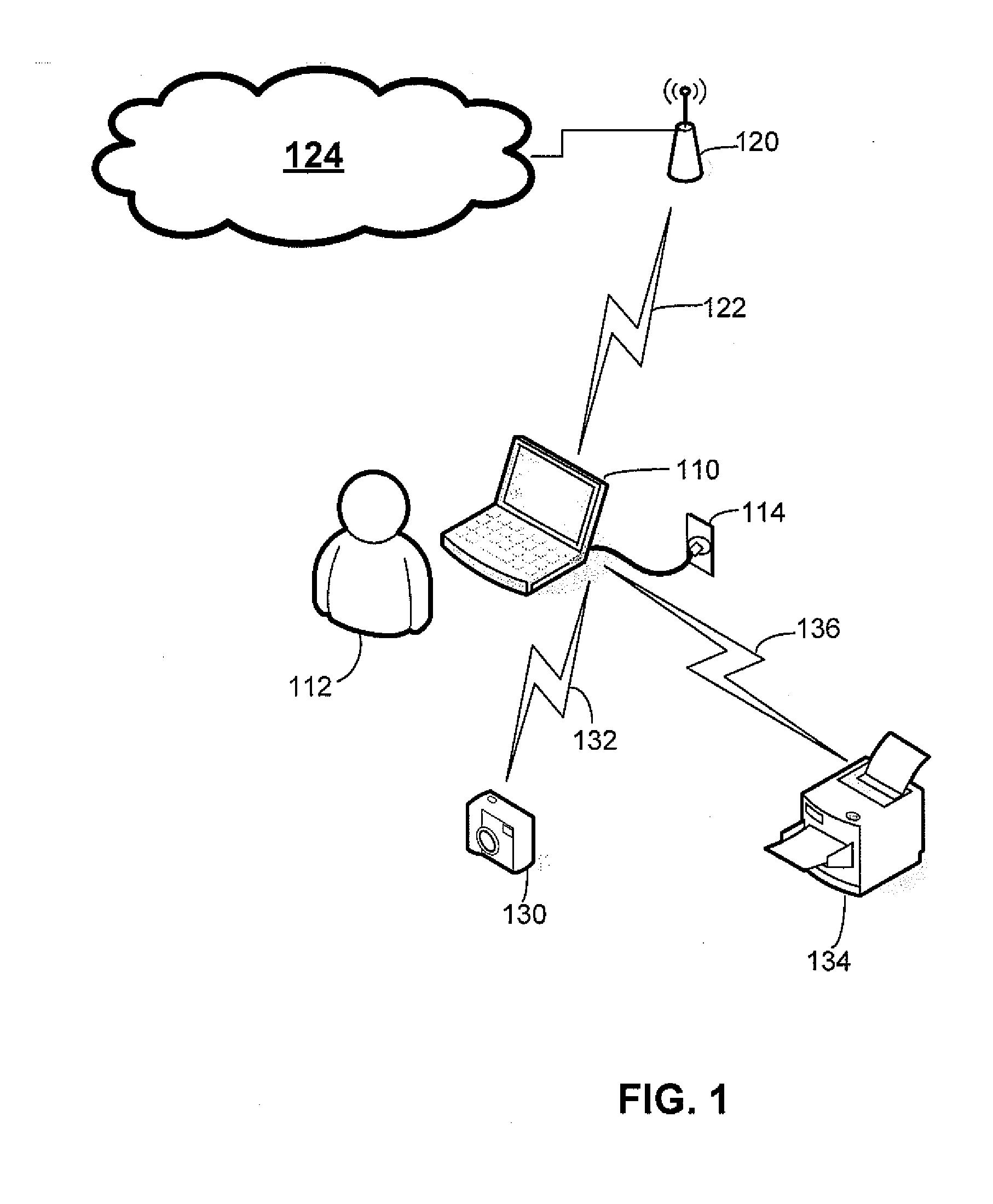

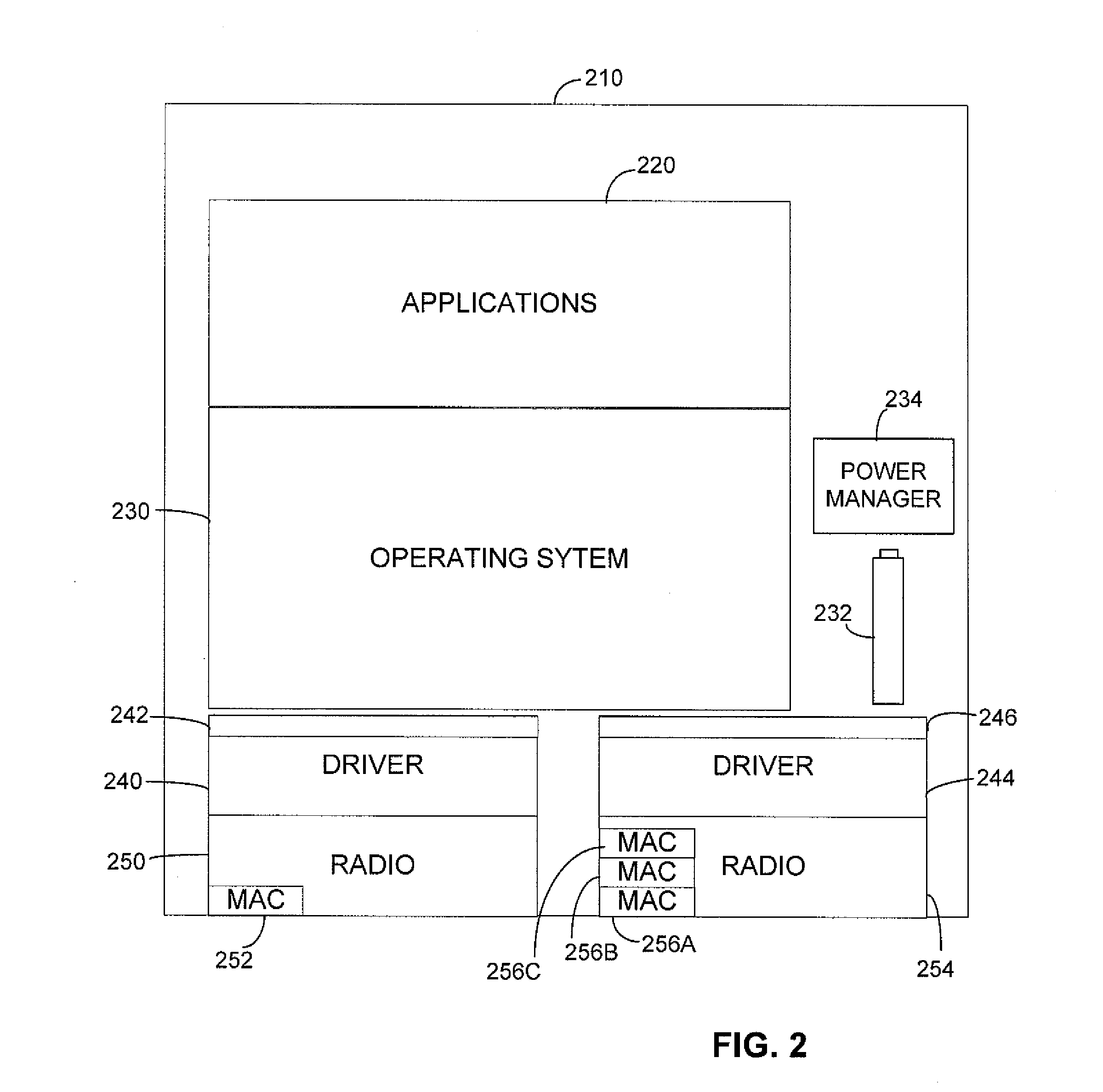

Peer-to-peer group with renegotiation of group owner

InactiveUS20120233266A1Power consumptionLess powerPower managementNetwork topologiesClient-sideControl equipment

A computing device that selectively renegotiates roles of devices in an existing peer-to-peer group. As the group is formed, the device may negotiate with other devices to select a device to control the group. During operation of the group, a device in the group may initiate a renegotiation that may lead to the selection of an alternative device to control the group. Renegotiation may be triggered by a message containing an information element signifying a request for renegotiation. Such a message may be sent either by the controlling device or other device in the group, and may be sent based on a state of the device. The state may relate to a source of power to the device such that a client that is connected to a source of power or a controlling device that is running low on battery power may request a renegotiation.

Owner:MICROSOFT TECH LICENSING LLC

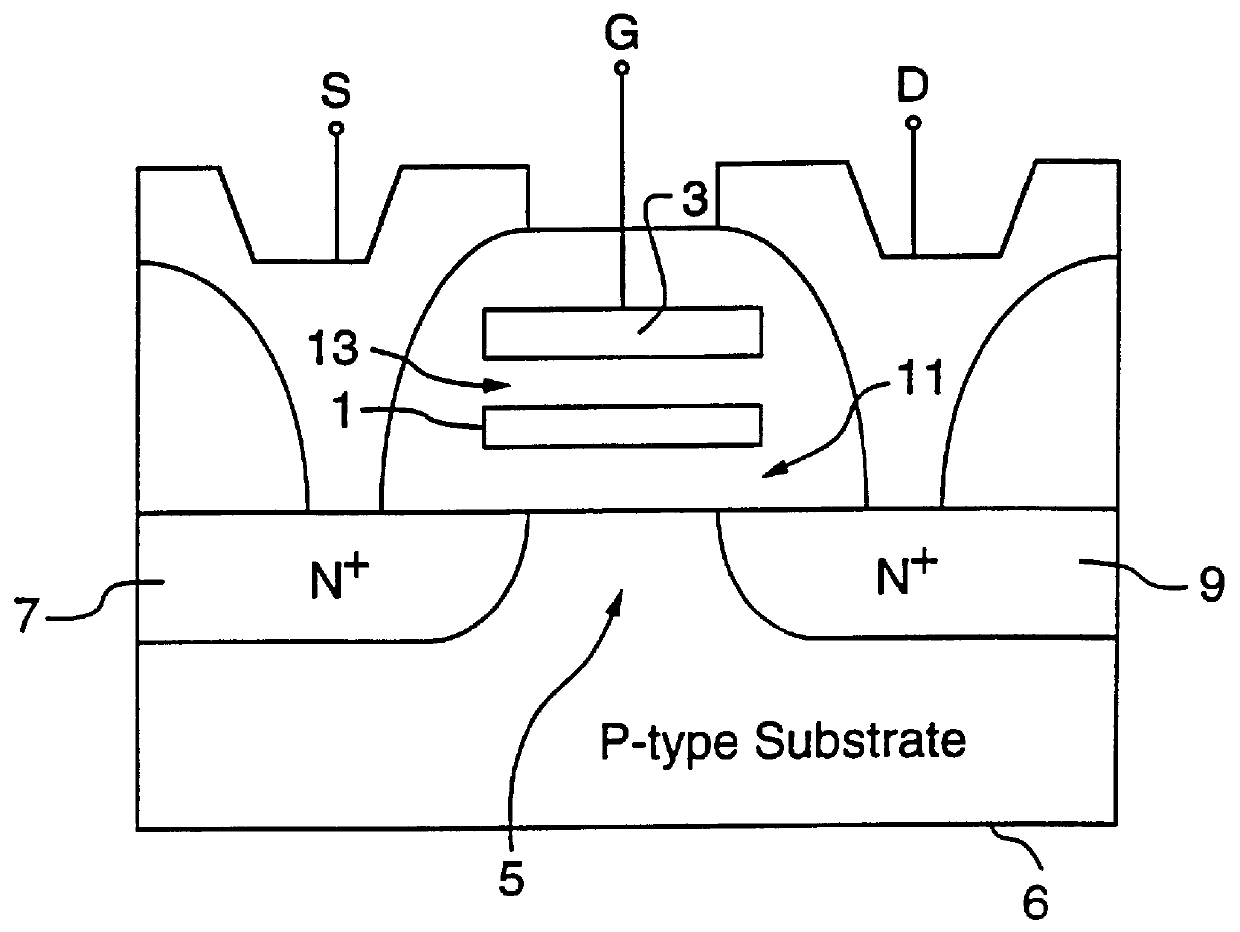

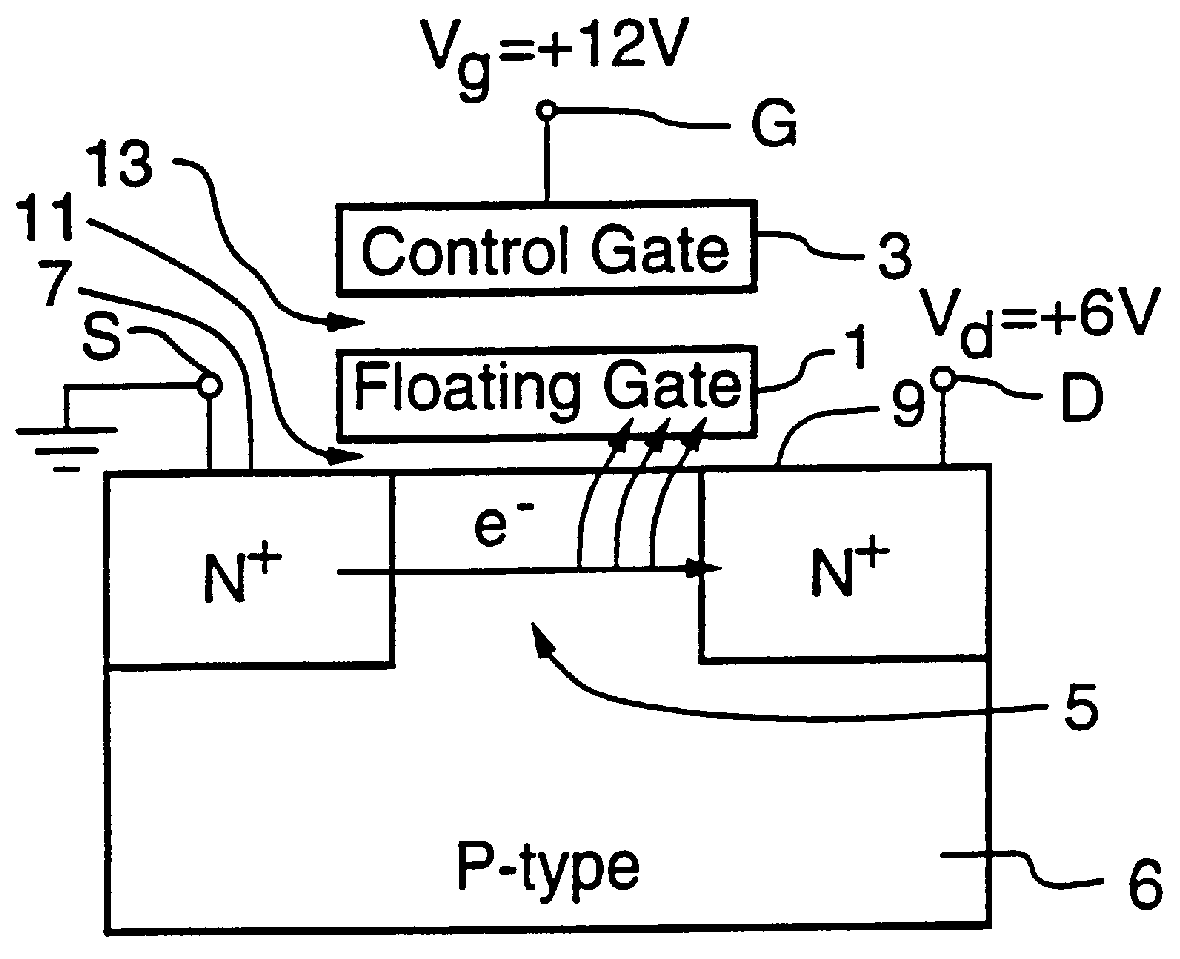

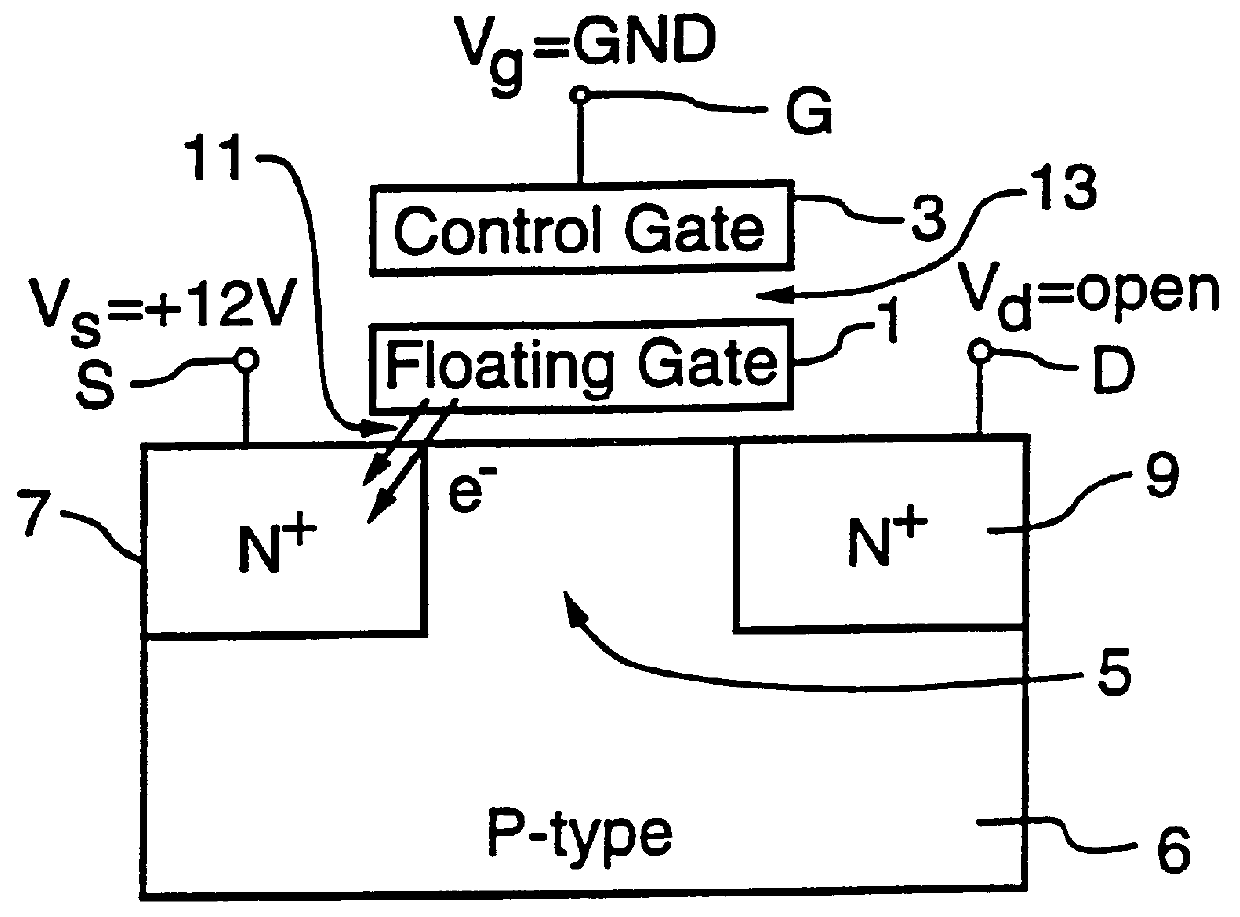

Method of fabricating a fast programmable flash E2PROM cell

InactiveUS6034896ALarge capacitySuitable for battery operated portable equipmentTransistorRead-only memoriesElectric fieldHot electron

PCT No. PCT / CA96 / 00446 Sec. 371 Date Jun. 24, 1998 Sec. 102(e) Date Jun. 24, 1998 PCT Filed Jul. 3, 1996 PCT Pub. No. WO97 / 02605 PCT Pub. Date Jan. 23, 1997A flash E2PROM cell having source and drain regions disposed in a substrate, a channel region intermediate to the source and drain regions, a tunnel dielectric layer overlying the channel region, a floating gate overlying the tunnel dielectric layer, an inter-poly dielectric layer overlying the floating gate, and a control gate overlying the inter-poly dielectric layer. The flash E2PROM cell further having a highly doped p+ pocket implant covering a portion of the cell width and adjacent to at least one of the drain and source regions. The flash E2PROM cell is comprised of two sections butted together. The portion (width-wise) that is covered by the highly doped p+ pocket implant is referred to as a program section. The remaining portion (width-wise) not covered by the highly doped p+ pocket implant resembles a conventional flash E2PROM cell and is referred to as a sense section. The highly doped p+ pocket implant and the n+ drain and / or source regions create a junction having narrow depletion width so that when the junction is reversed biased, an electric field is created for generating hot electrons for storage on the floating gate, thereby programming the flash E2PROM cell when a high positive potential is applied to the control gate.

Owner:UNIV OF TORONTO INNOVATIONS FOUND THE

Electro-optic device incorporating a discrete photovoltaic device and method and apparatus for making same

InactiveUS6433913B1Less powerStatic indicating devicesLaminationElectrical resistance and conductanceDisplay device

Improved electro-optic devices are provided which may be in the configuration of variable transmittance windows, variable transmittance eyeglasses, variable transmittance light filters and displays and other devices wherein the transmittance of light therethrough automatically varies as a function of light impinging thereon. The electro-optic devices include a self-erasing electro-optic medium, and the transmittance of light through such medium varies as a function of electrical signals applied thereto through the agency of at least one photovoltaic cell, enclosed within the electro-optic device, and obviating the necessity of providing external drive voltage or external bleeder resistors or external wiring. In addition, a method and apparatus are provided for making such electro-optic devices.

Owner:GENTEX CORP