Vector floating point unit

a floating point unit and vector technology, applied in the field of vector floating point units, can solve the problems of conventional vector processor conventional vector processors that cannot meet the processing speed requirements of high-performance digital signal processing systems, and the pipeline latency of conventional vector processors cannot be reduced below a certain point, so as to achieve the effect of fine-tuning the performance to a particular application, rapid configuration of vfpu, and reducing pipeline la

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021]The invention is particularly applicable to a vector FPU for vector floating point operatons, and it is in this context that the invention will be described. It will be appreciated, however, that the VFPU in accordance with the invention has greater utility, such as to other types of floating point or non-floating point calculations. To understand the VFPU in accordance with the invention, the basic structure of the VFPU and its operations will be described.

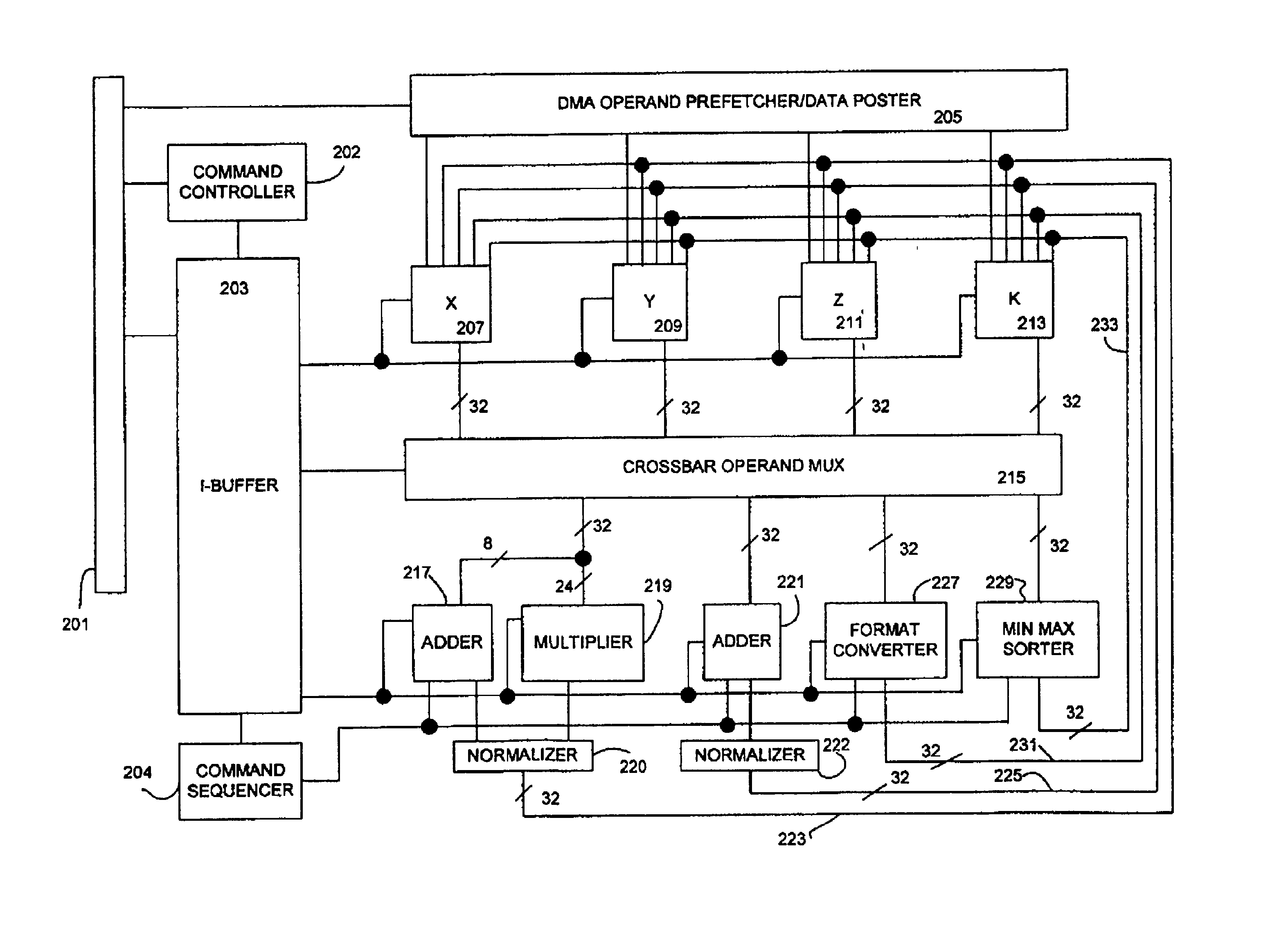

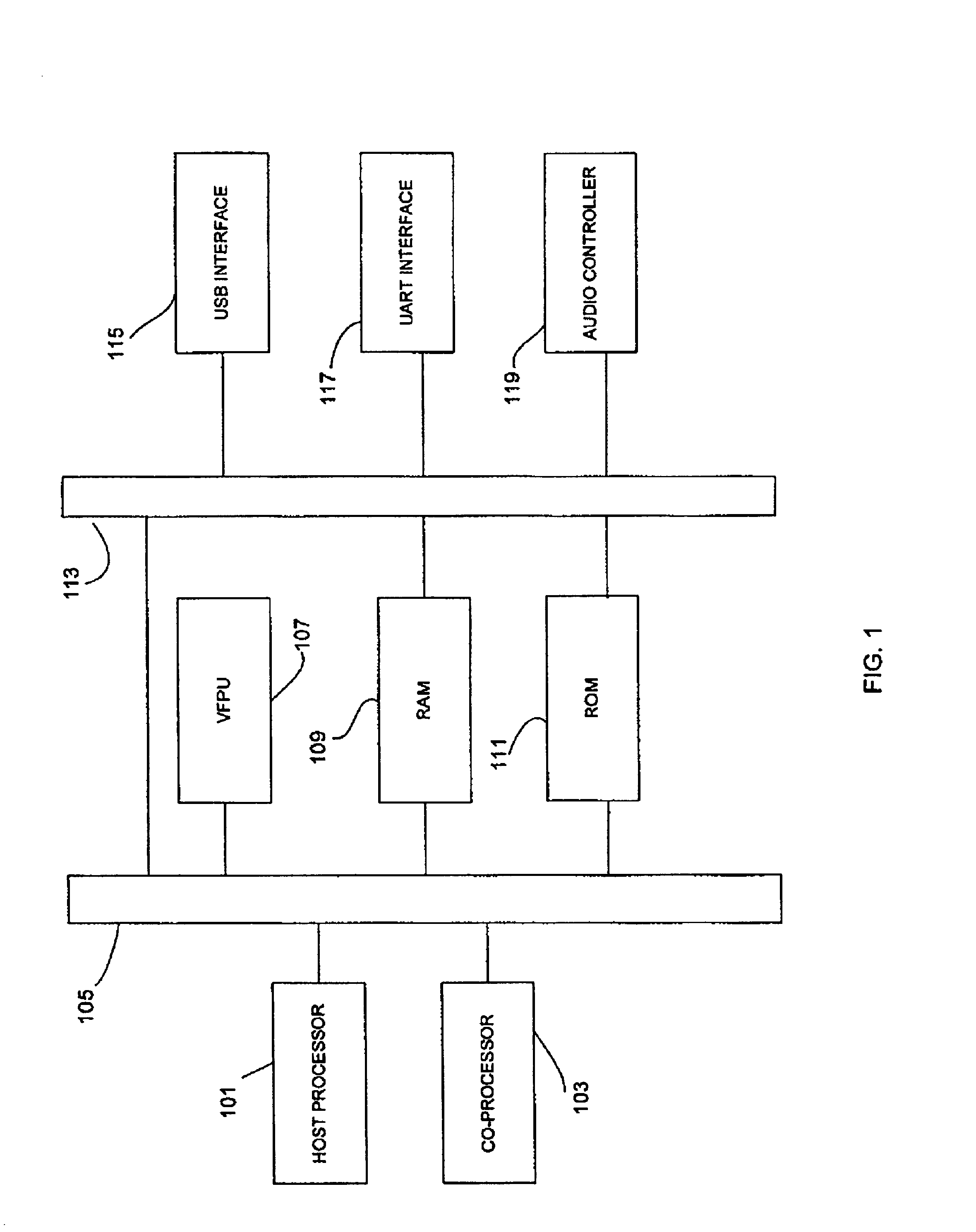

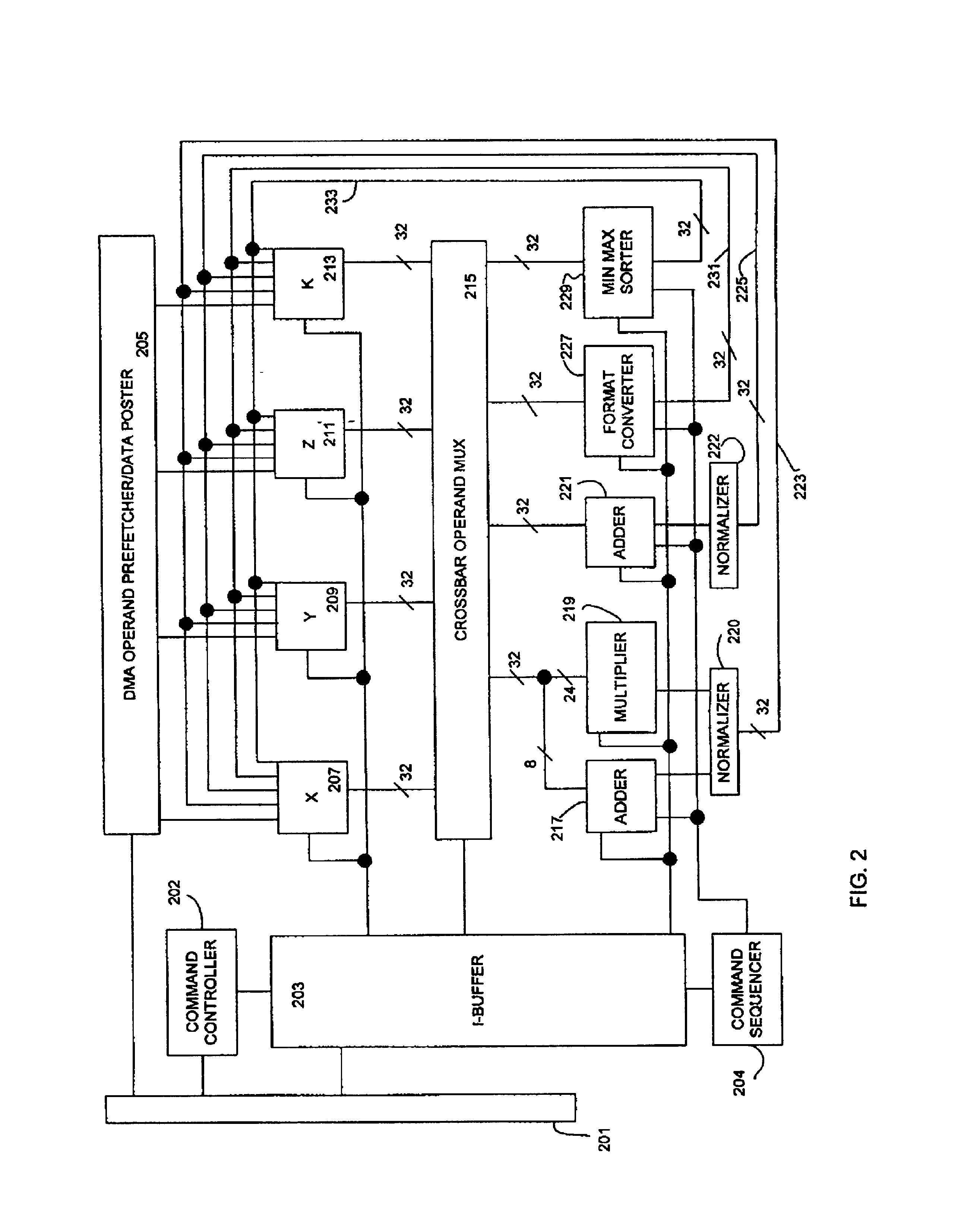

[0022]Overview—Vector FPU

[0023]FIG. 1. Illustrates a system diagram where a vector floating point unit (VFPU) 107 of the invention is provided to perform floating point calculations. As shown in FIG. 1, a VFPU is typically used in conjunction with one or more general microprocessor(s). In FIG. 1, a host processor 101 and a co-processor 103 are coupled to a VFPU 107 via a bus 105. A RAM (random access memory) 109 and a ROM (read only memory) 111 are also coupled to the bus 105. In addition, USB (universal serial bus) interfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More