Patents

Literature

89 results about "Product term" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

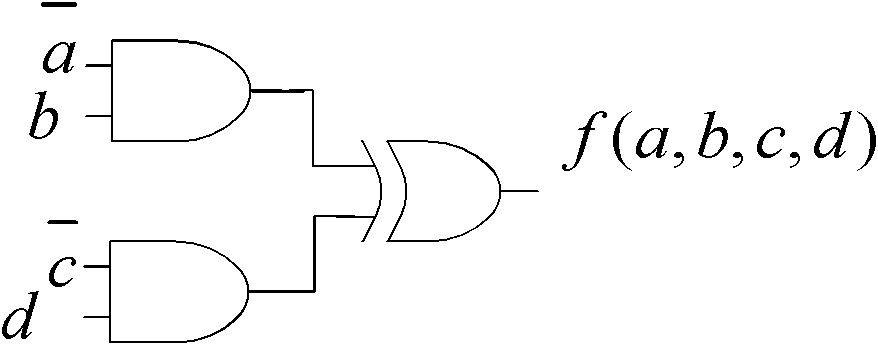

In Boolean logic, a product term is a conjunction of literals, where each literal is either a variable or its negation.

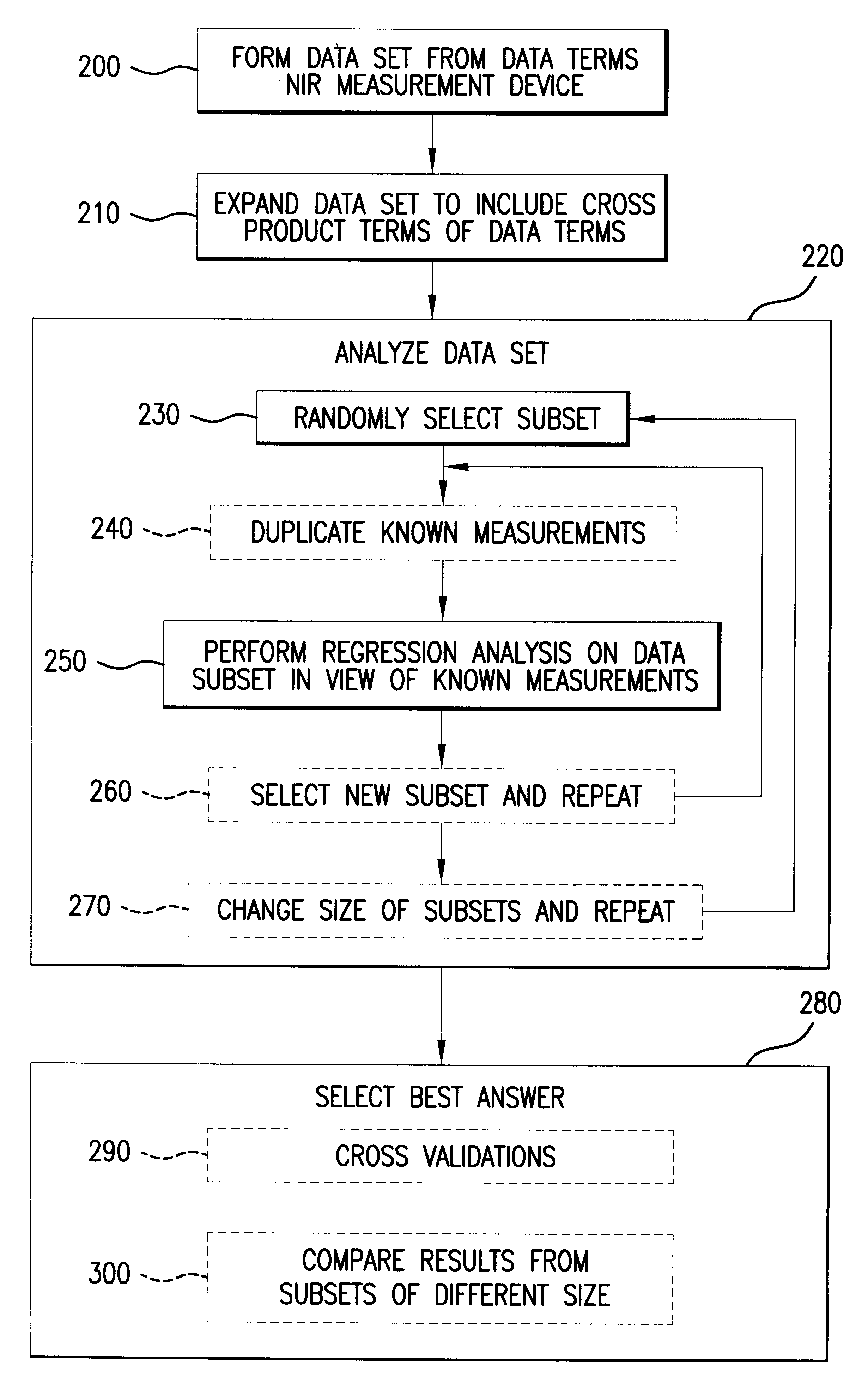

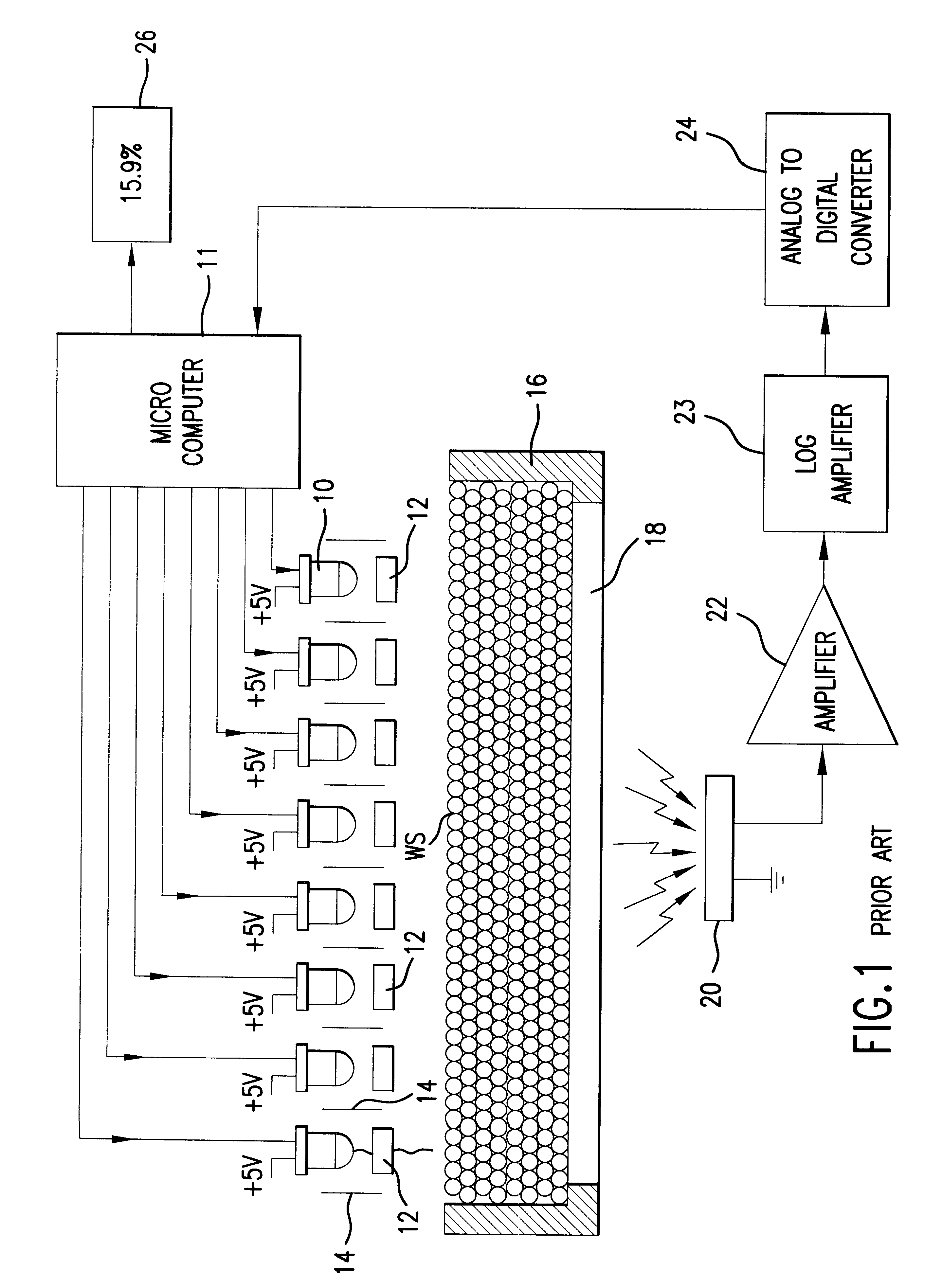

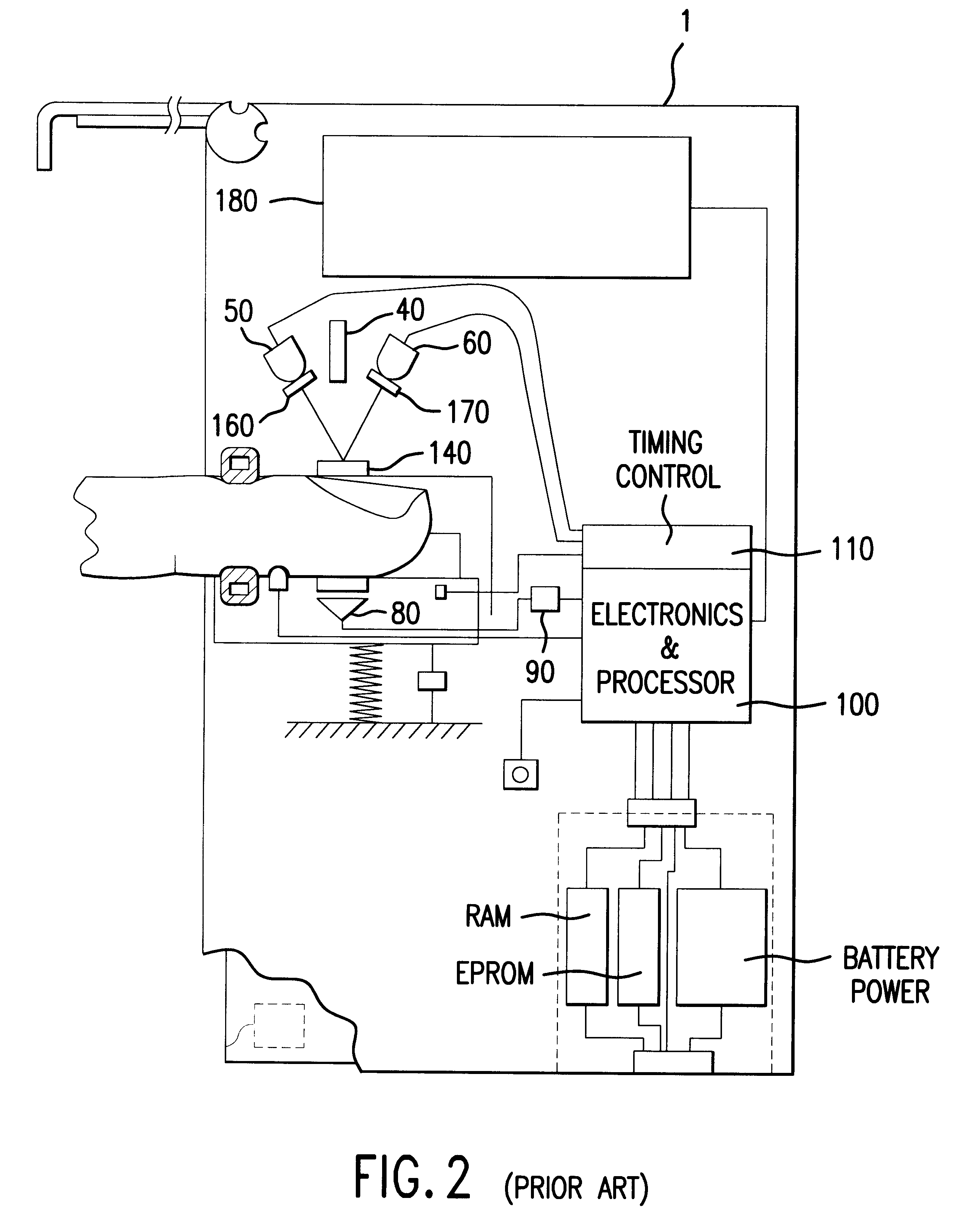

Calibration of near infrared quantitative measurement device using optical measurement cross-products

In a method to improve the calibration of a non-invasive, near infrared (NIR) measurement device, a plurality of data terms is formed for the NIR measurement device. Then the codependence of the data terms is evaluated by forming cross-products terms using the data terms. Next, sets of prespecified sizes are randomly formed from the data terms and the cross-product terms. Each of these sets of terms is evaluated by testing the ability of the set to predict a set of accurate measurements using regression analysis. The method then selects one of the sets based on preselected criteria and uses the selected set to calibrate the NIR measurement device.

Owner:FUTREX

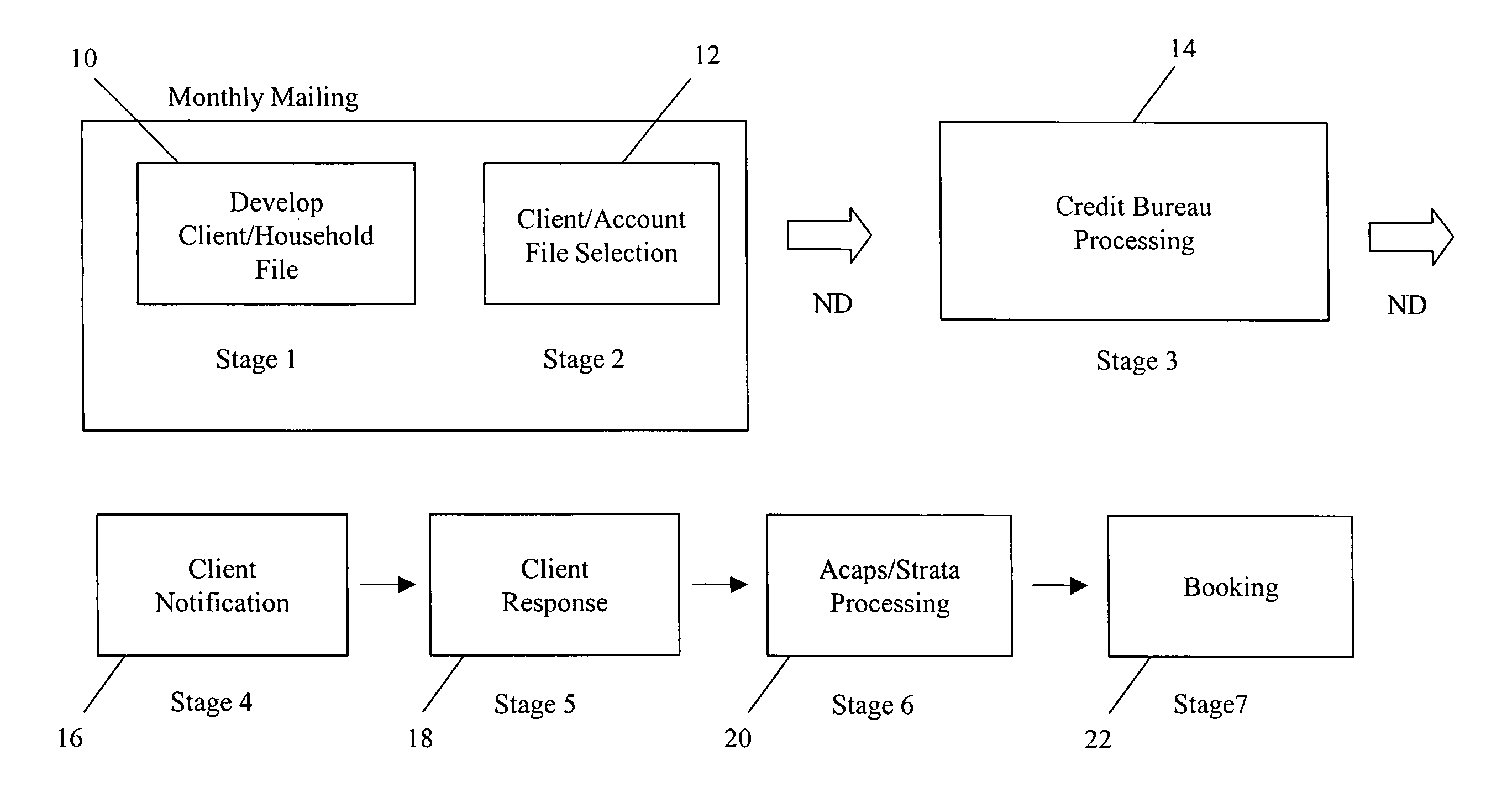

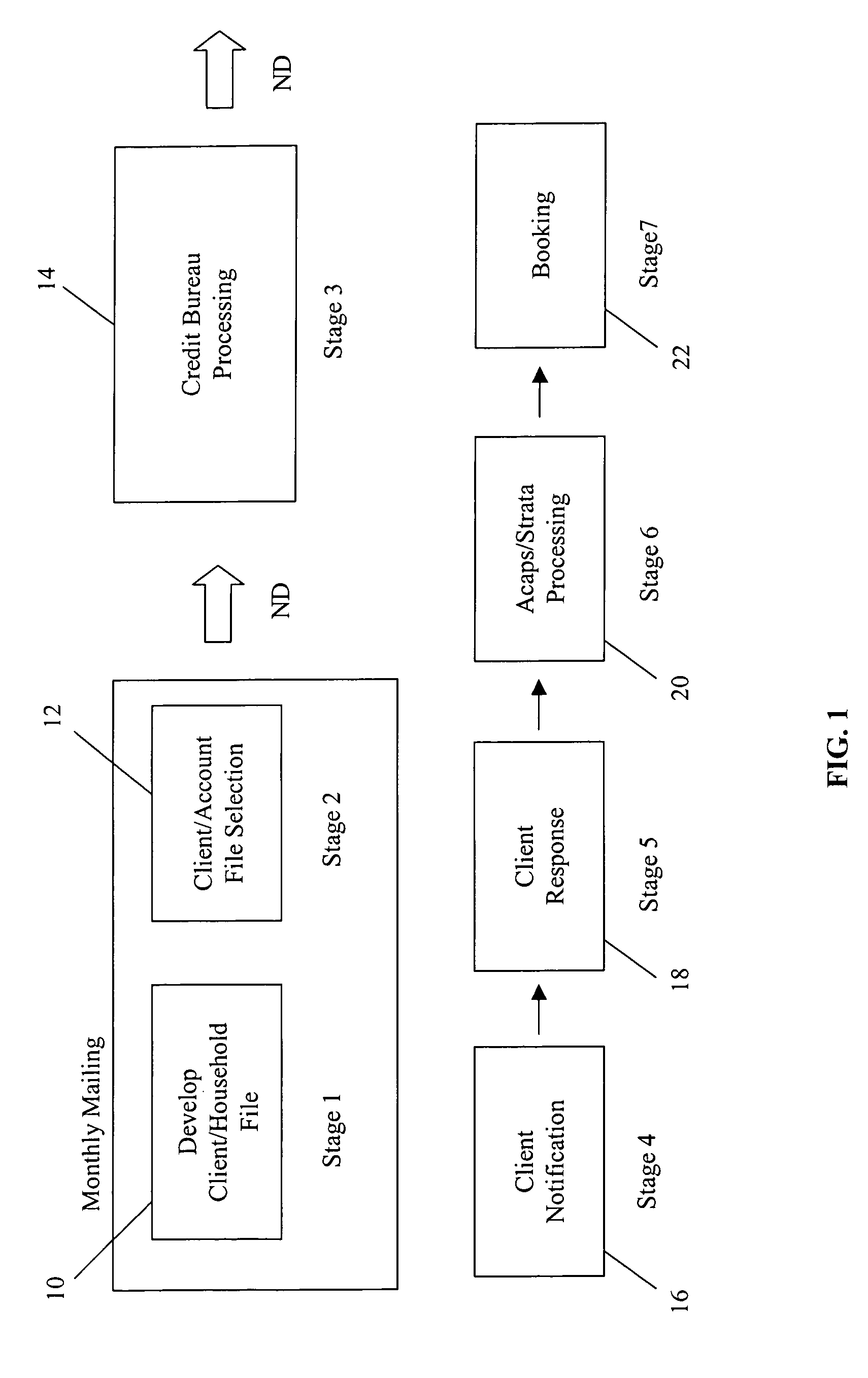

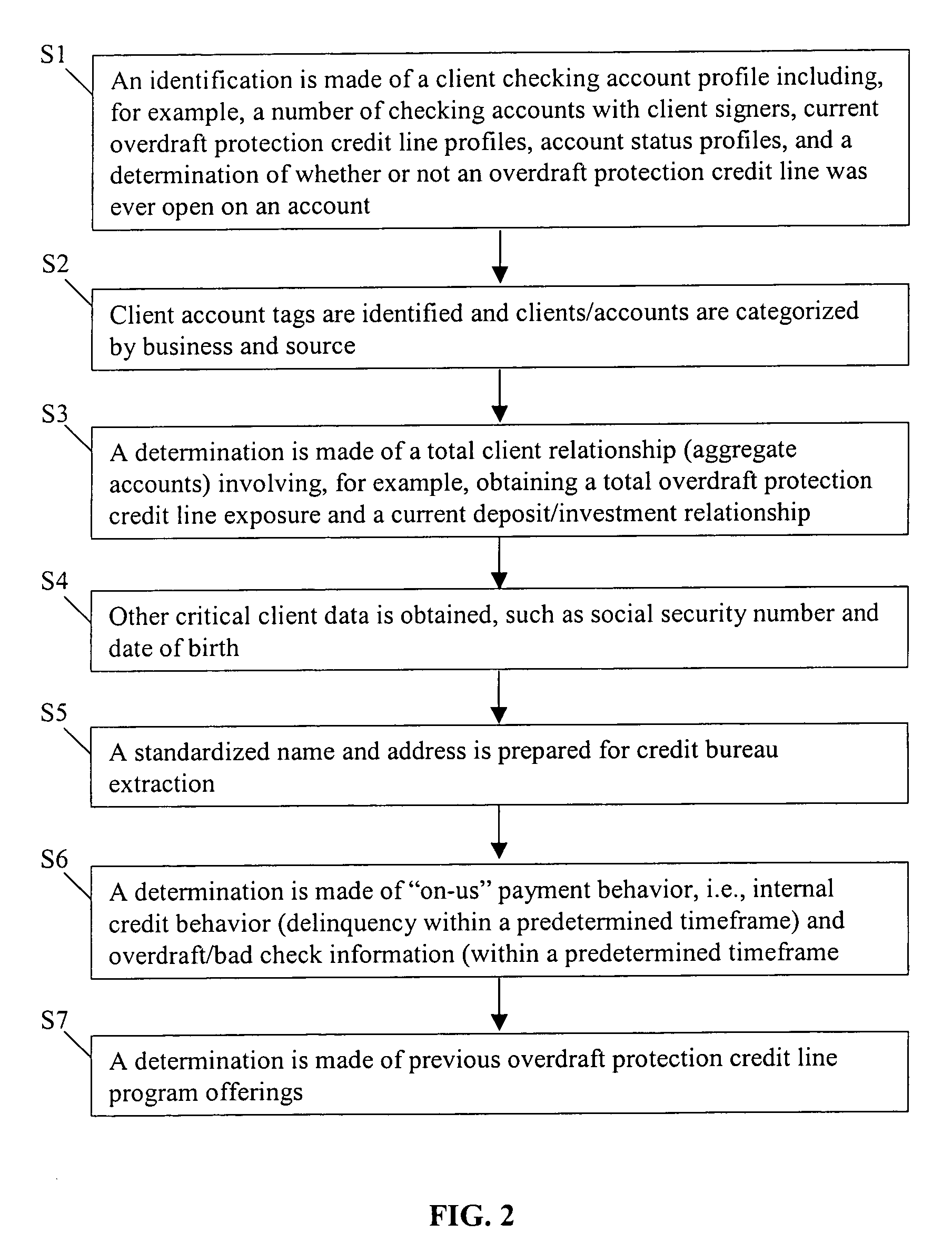

Systems and methods for offering credit line products

InactiveUS20060080251A1Improve experienceGenerate additional revenueFinancePayment architectureCredit limitDatabase

Computer implemented methods and systems for offering a credit line product to customers of a financial institution in which client household level files are created for financial institution customers, particular ones of which are then selected for a credit-line product offering based on client level and account level selection parameters, and the selected files are transferred electronically to a credit bureau. Thereafter, credit-screened account files corresponding to each of the selected client household level files with an appended credit score and credit line product terms are received from the credit bureau electronically by the financial institution for customer solicitations as determined by the credit bureau, and the customer solicitations are sent out by the financial institution.

Owner:CITIBANK

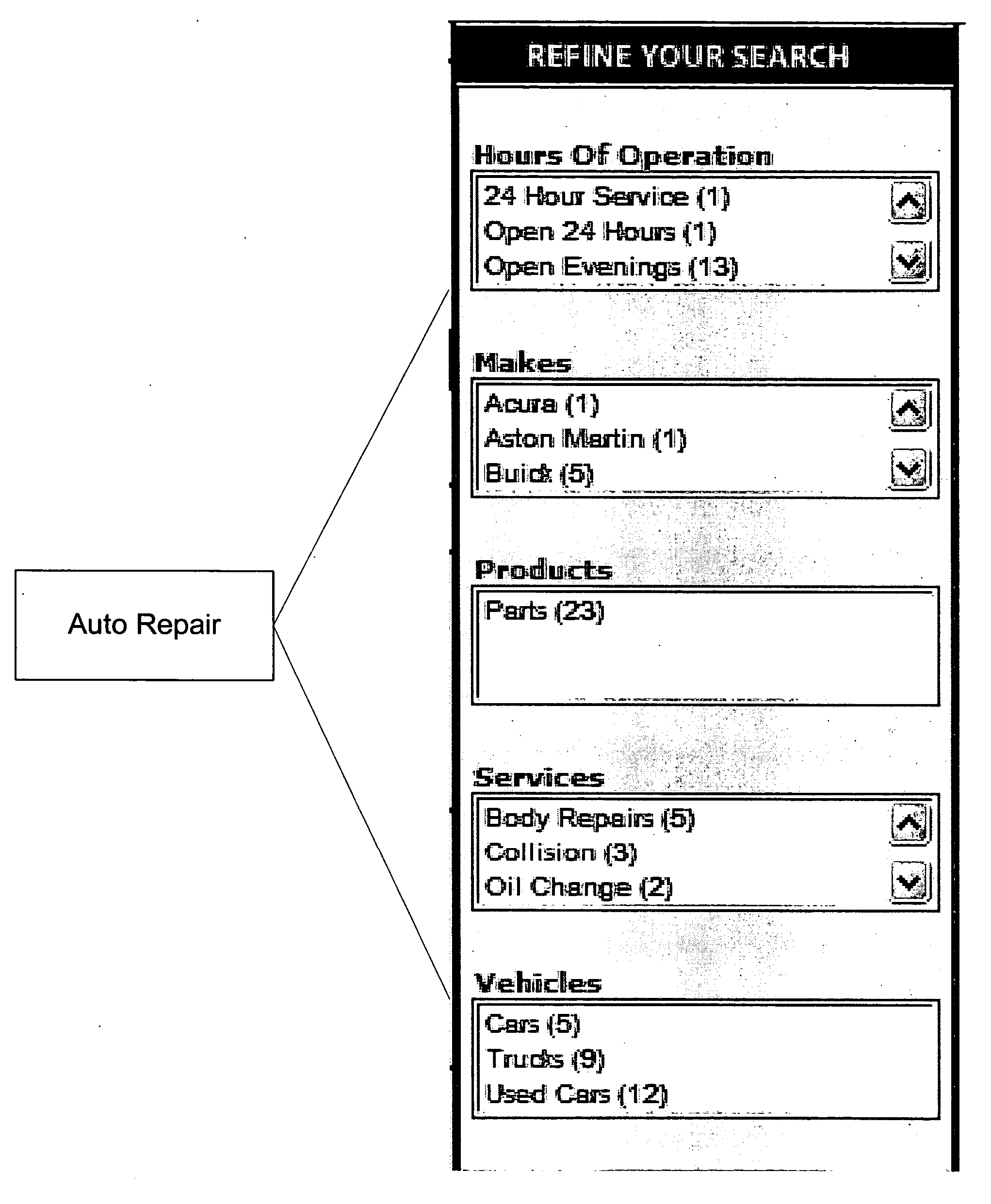

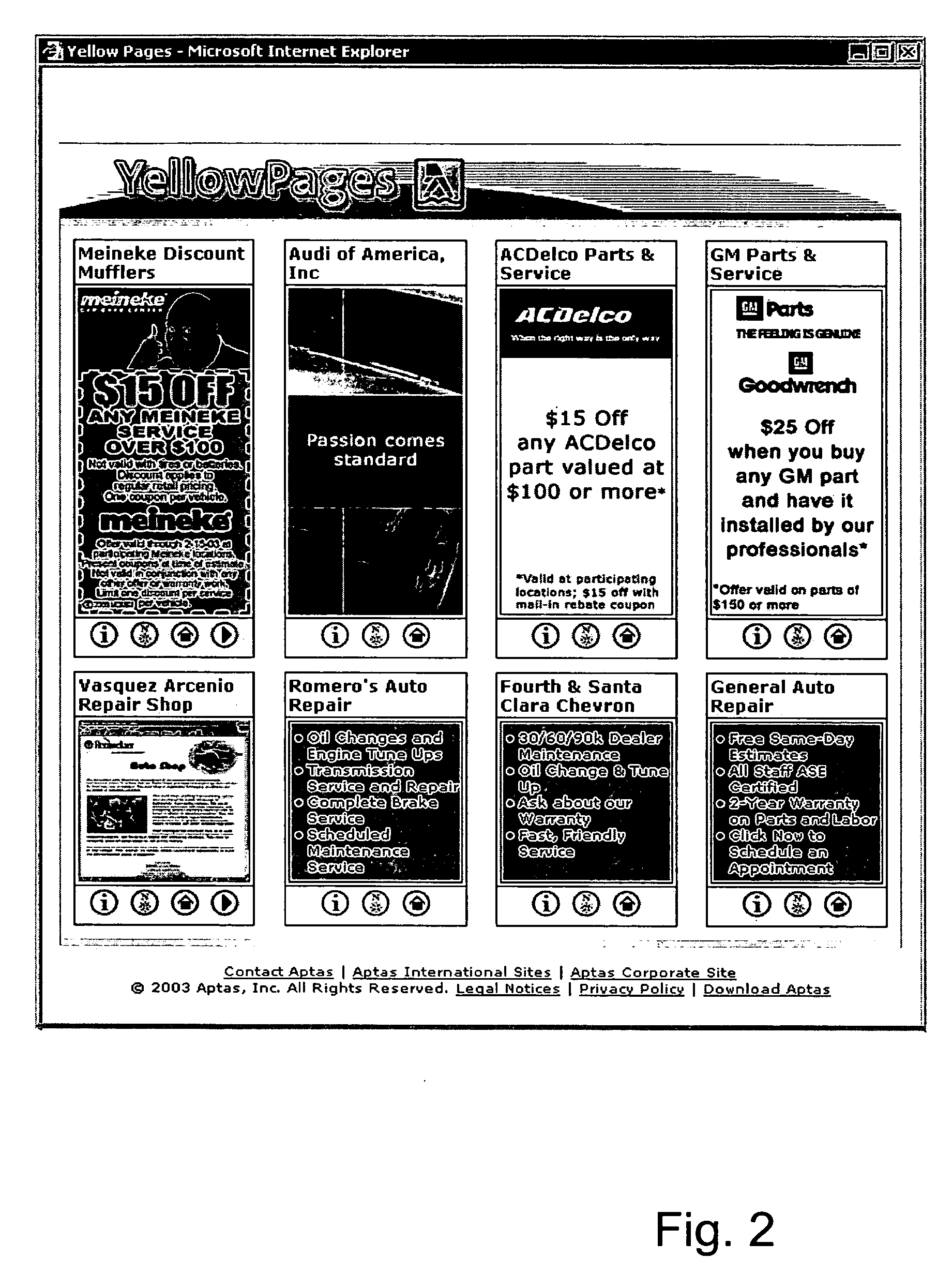

System and method for mining and searching localized business-marketing and informational data

InactiveUS20050278309A1Digital data information retrievalDigital data processing detailsData miningMarine navigation

A system and method for searching records. One embodiment includes a method for searching comprising: receiving a search a term comprising a product term and a geography limitation; identifying a normalized term corresponding to the product term; identify a first set of records corresponding to the normalized term; sorting the first set of records according to the geography limitation; returning at least some of the first set of records according to the sort; identifying navigation links corresponding to the normalized term; identifying a second set of records corresponding to at least one of the navigation links; and returning at least some of the second set of records.

Owner:APTAS INC

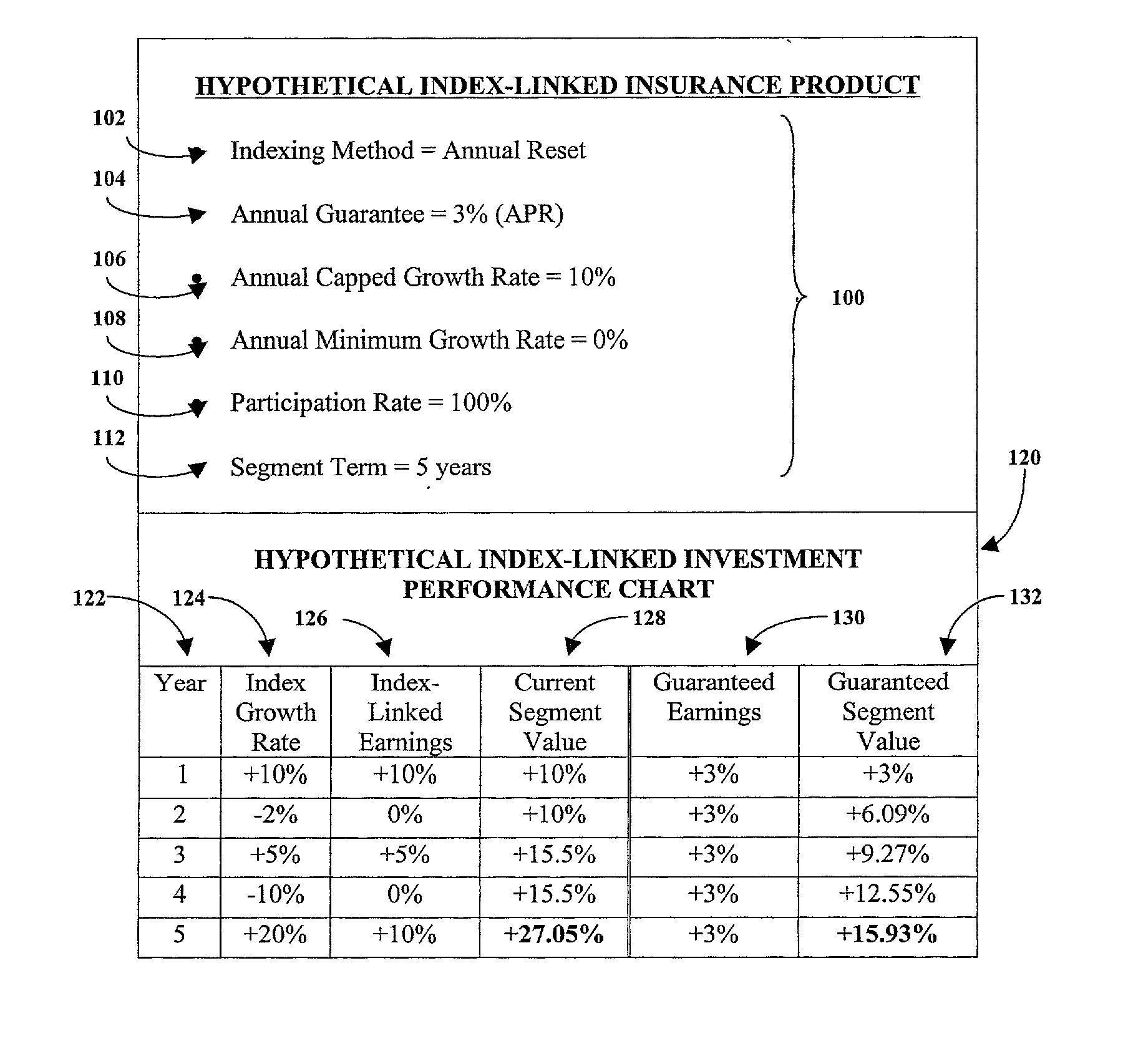

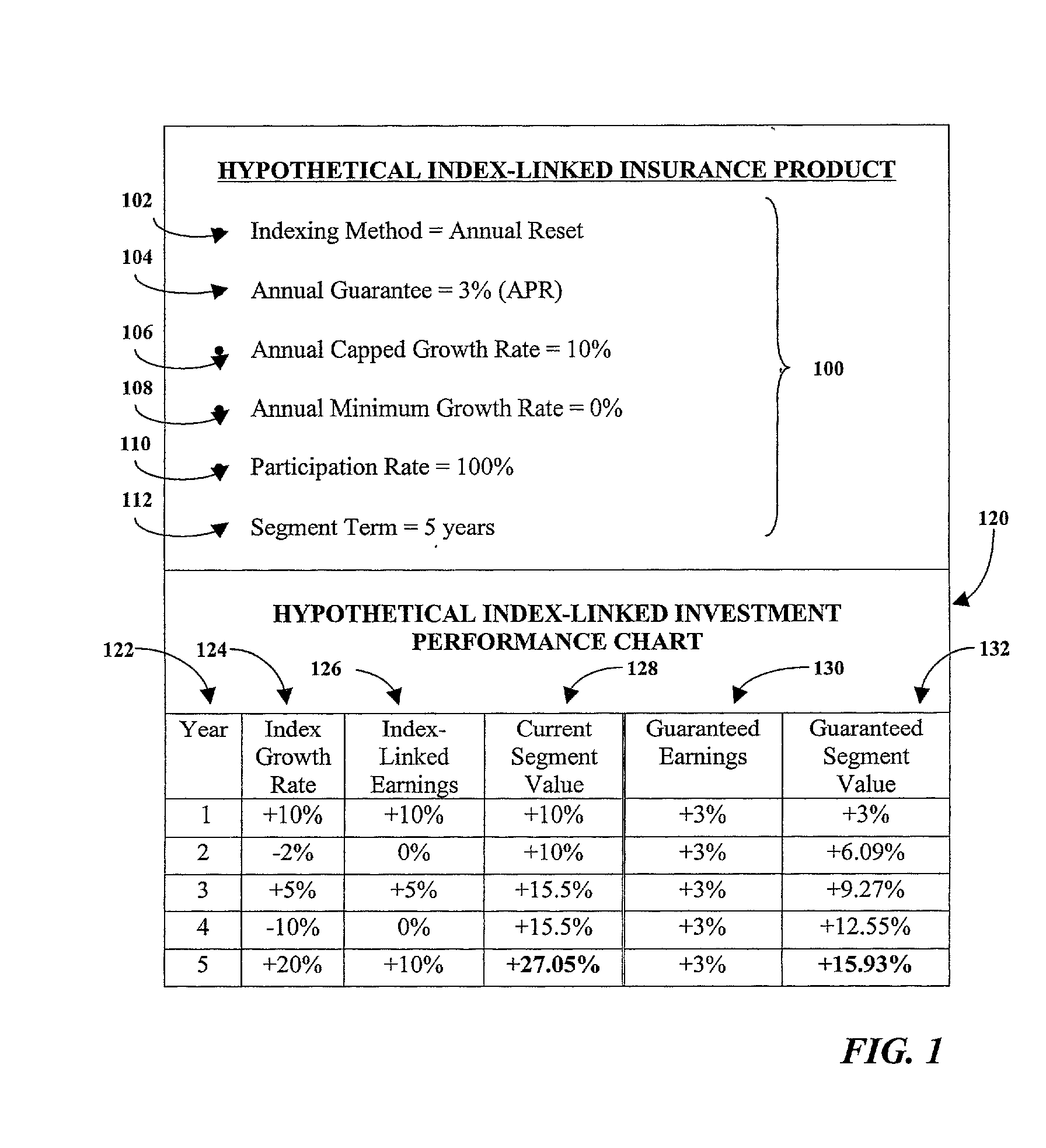

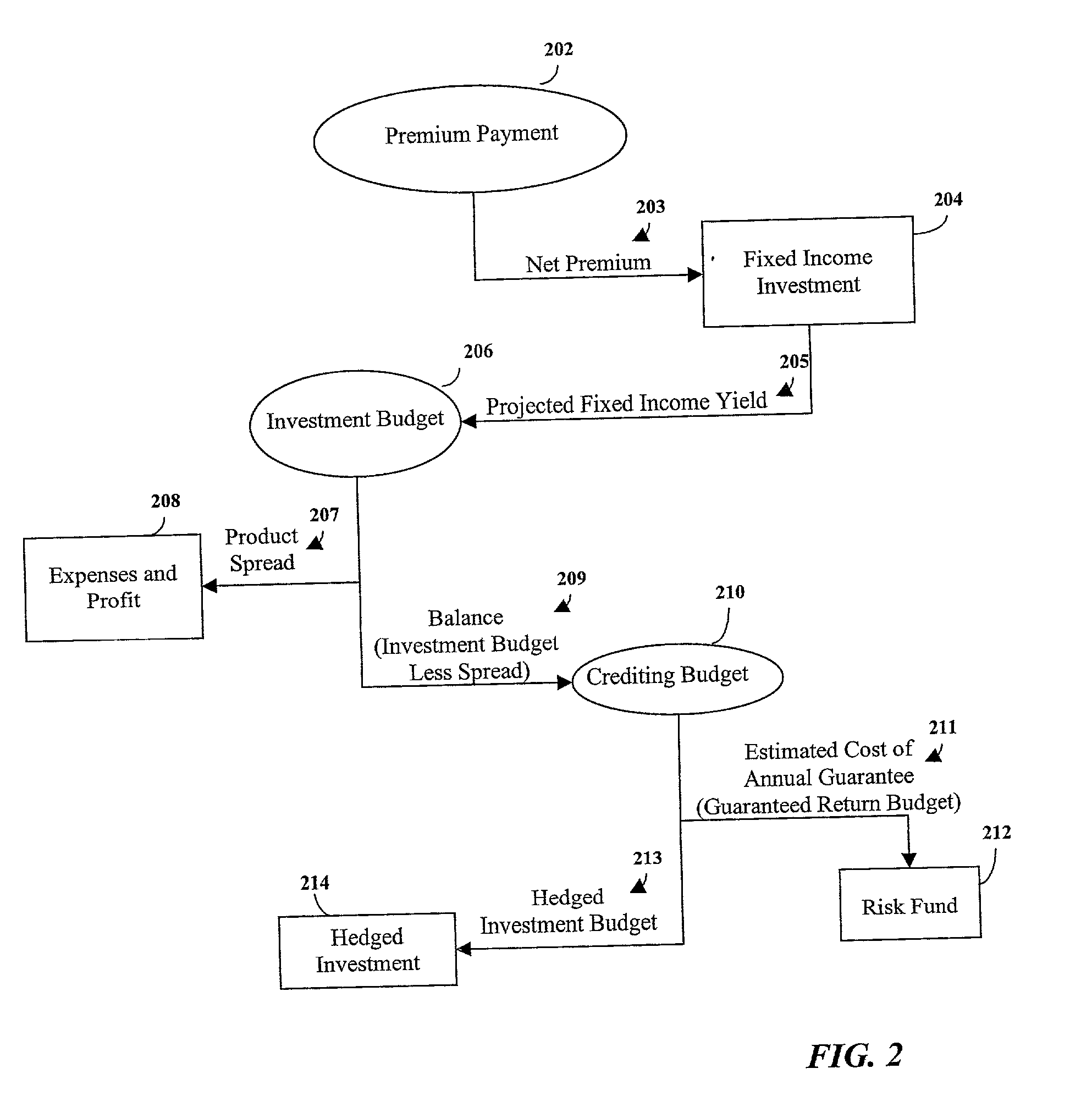

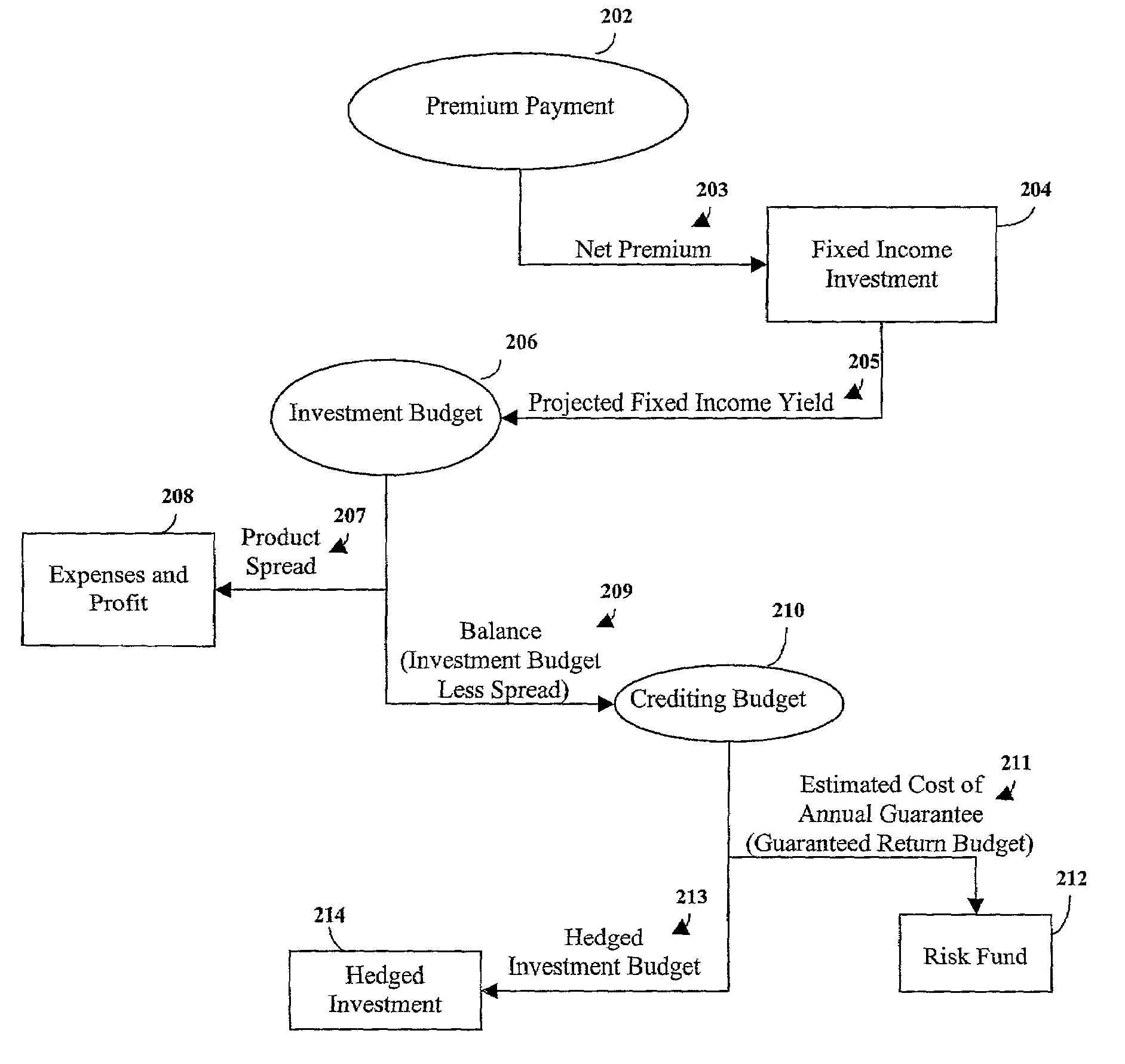

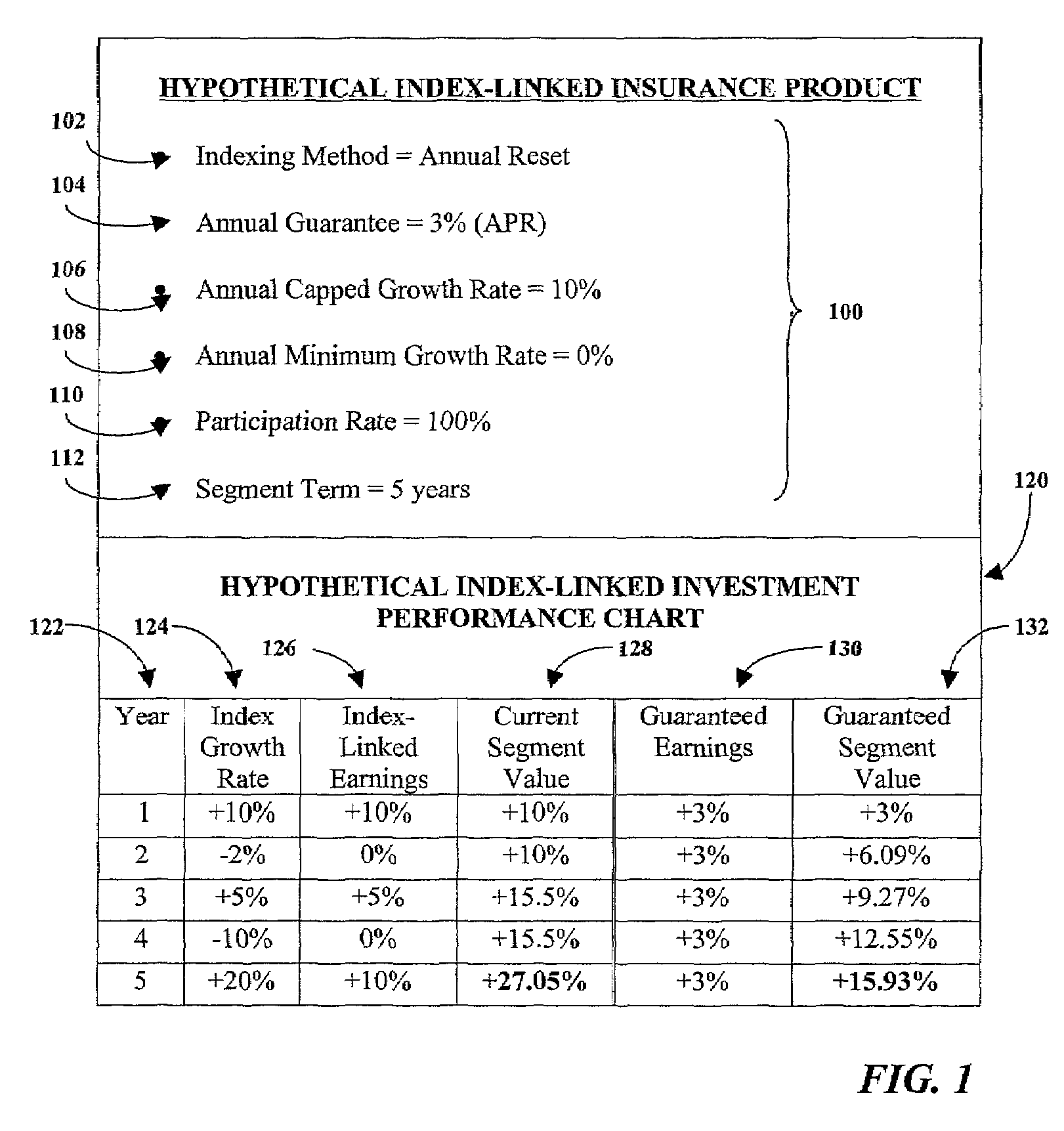

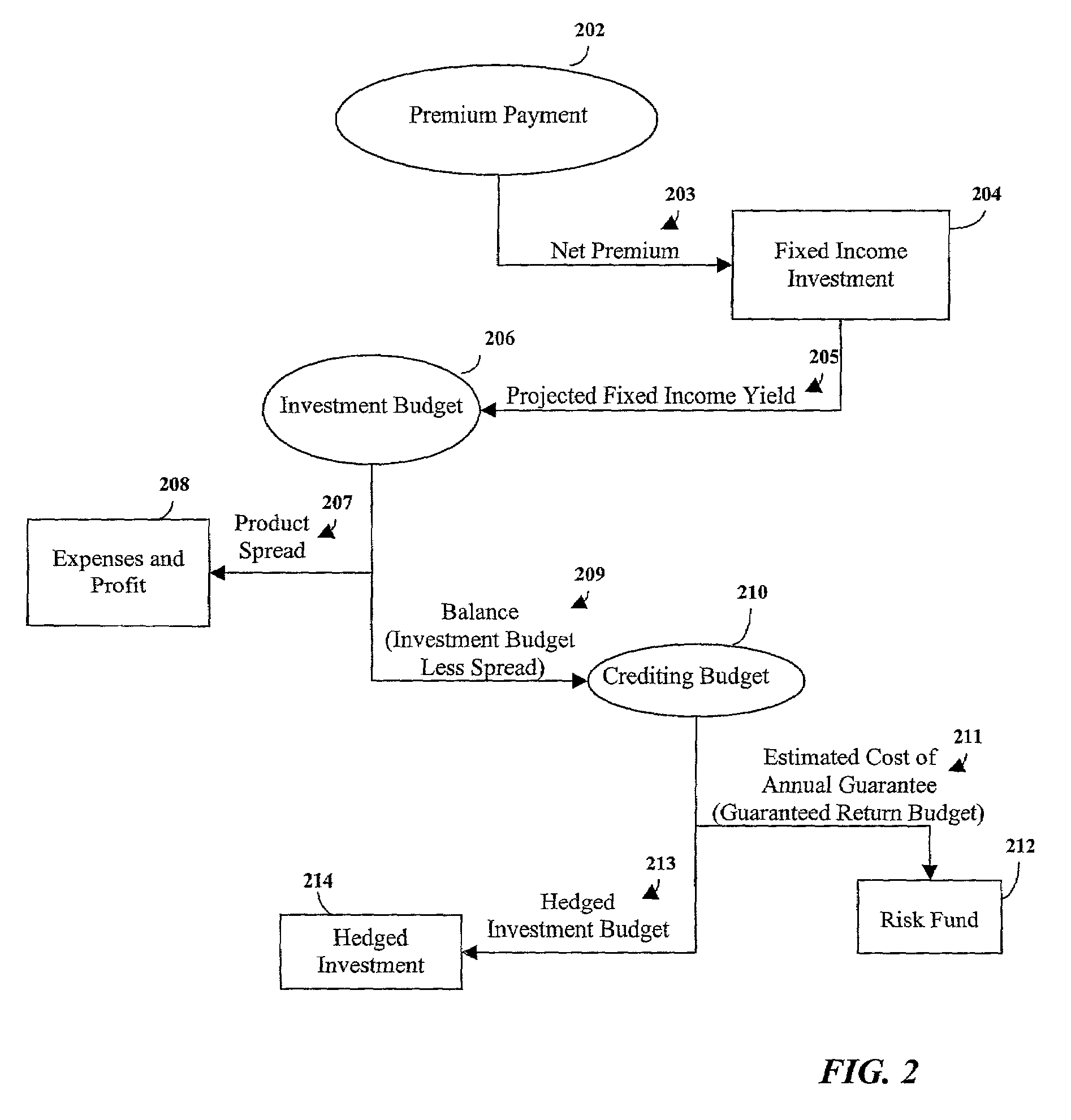

Maximization of a hedged investment budget for an index-linked insurance product

An index-linked insurance product having an annual guarantee is implemented having a maximized hedged investment budget. A net premium payment is allocated to a fixed income investment and an annual fixed income yield is projected. The maximized hedged investment budget is determined by deducting from the projected annual fixed income a product spread and an estimated cost of the annual guarantee. The deducted estimated cost of the annual guarantee is allocated to a risk fund. The maximized hedged investment budget is allocated to a hedged investment designed to generate proceeds for supporting index-linked earnings credited to the index-linked insurance product. Upon expiration of the product term, if the amount credited based on the index-linked earnings does not equal to at least the compounded annual guarantee, the amount credited is increased to be equal to the compounded annual guarantee. The increased credit may be supported using funds from the risk fund and other reserves if necessary.

Owner:ACCORDIA LIFE & ANNUITY

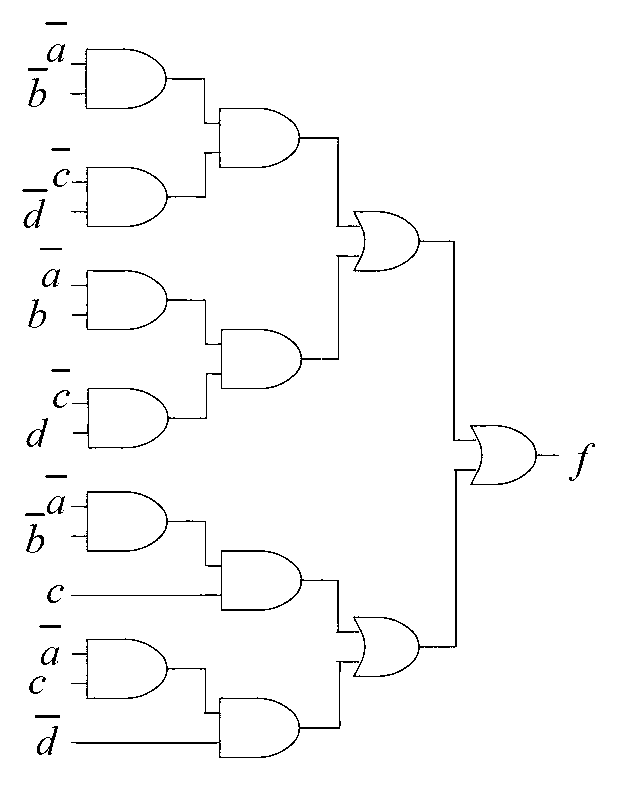

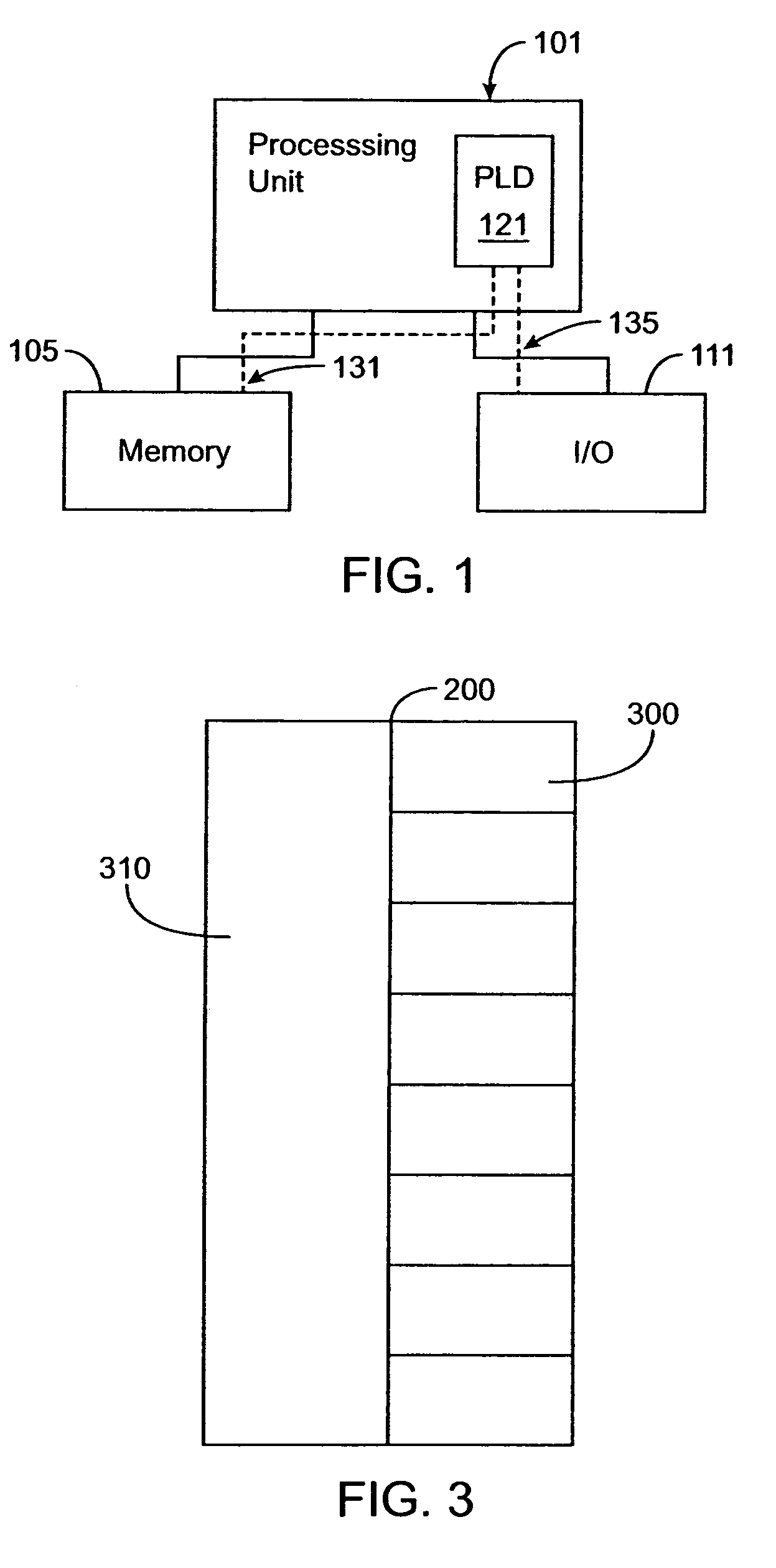

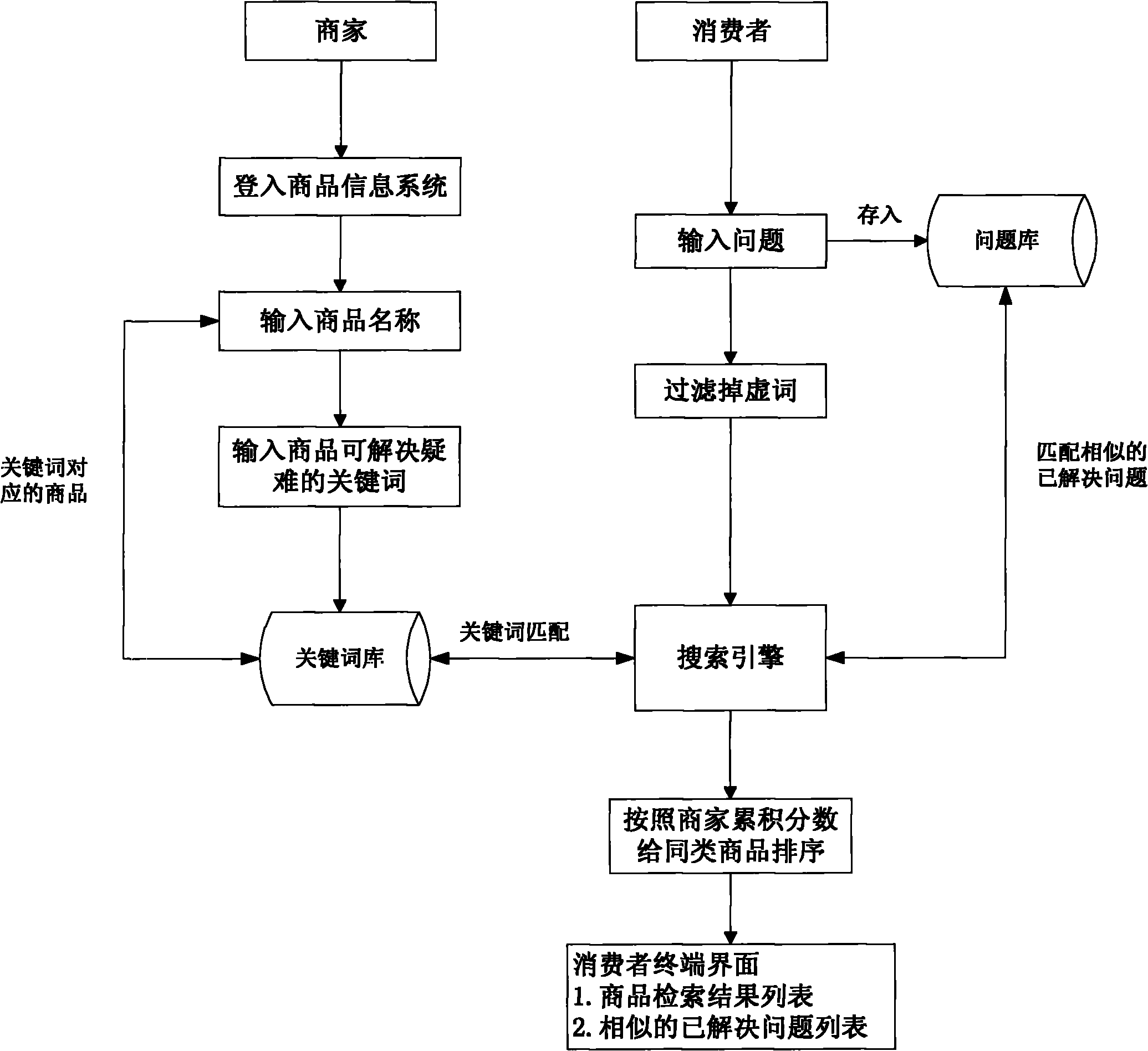

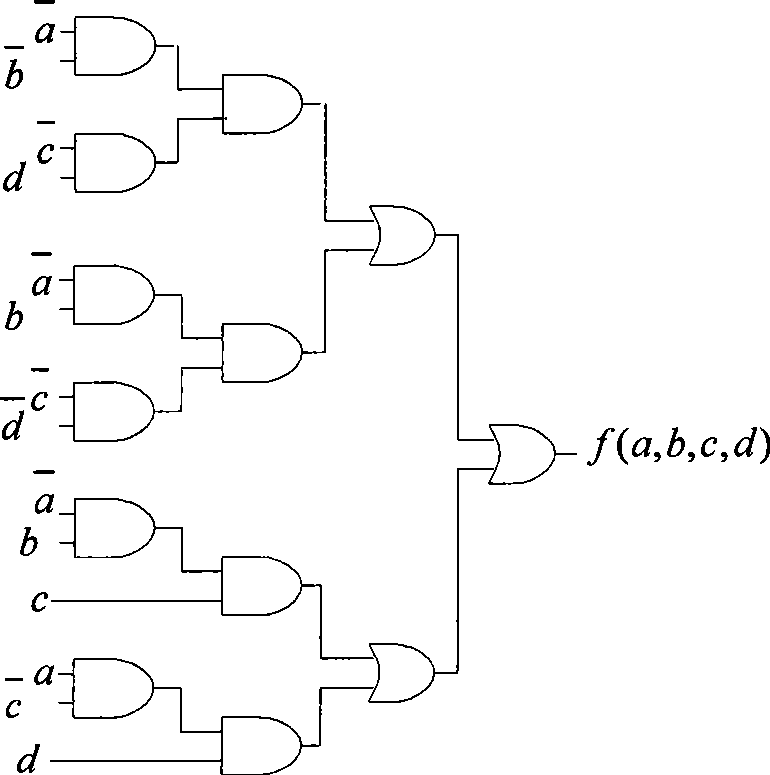

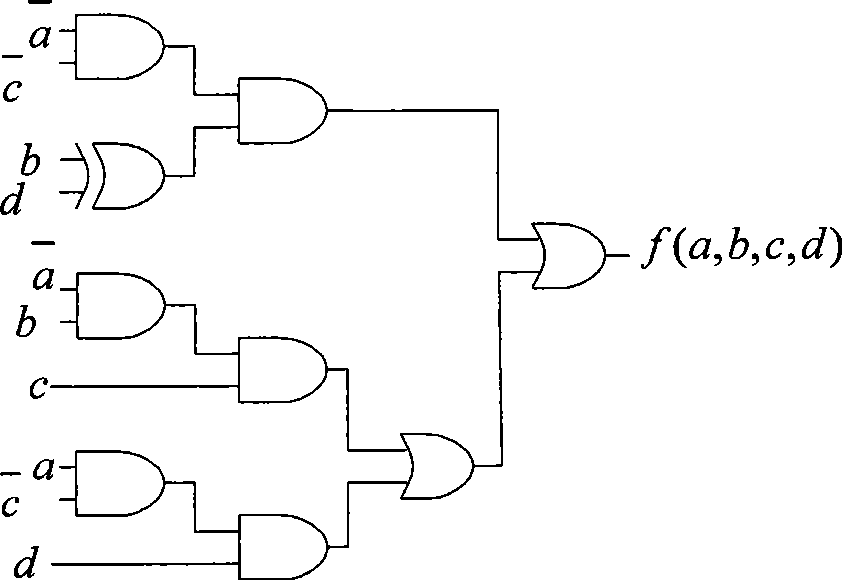

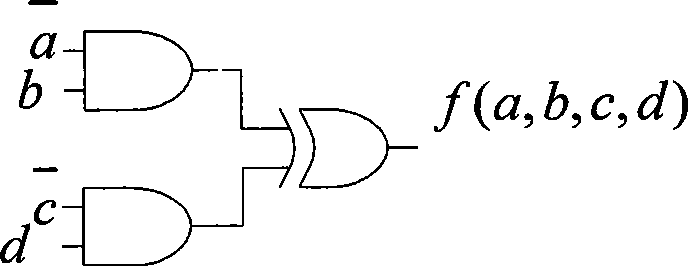

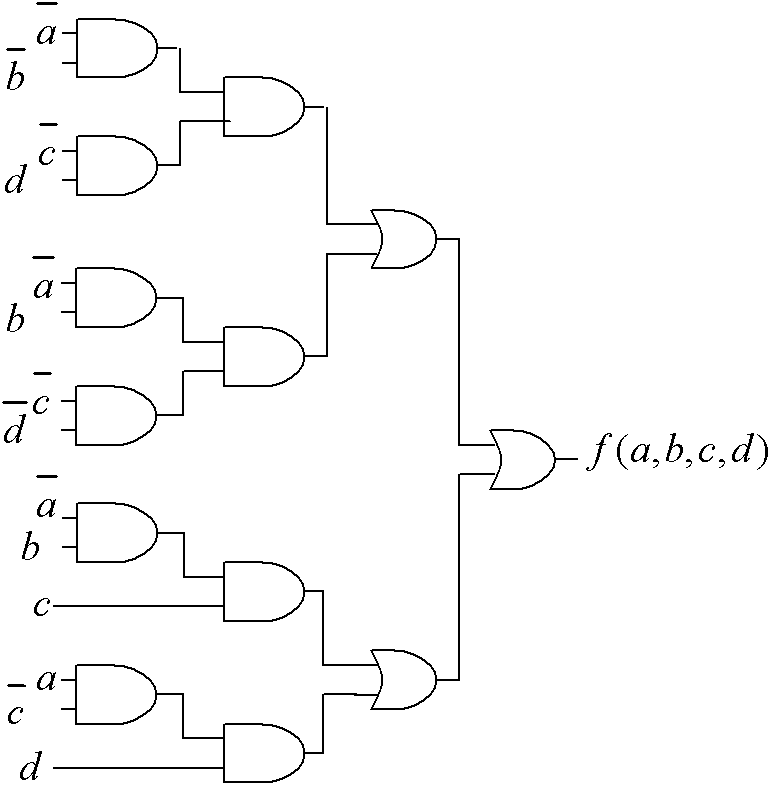

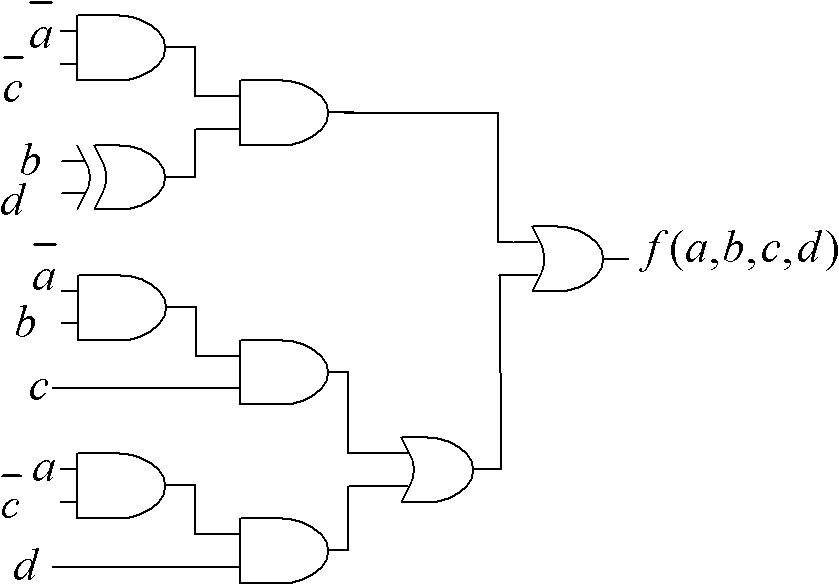

Method and VLSI circuits allowing to change dynamically the logical behavior

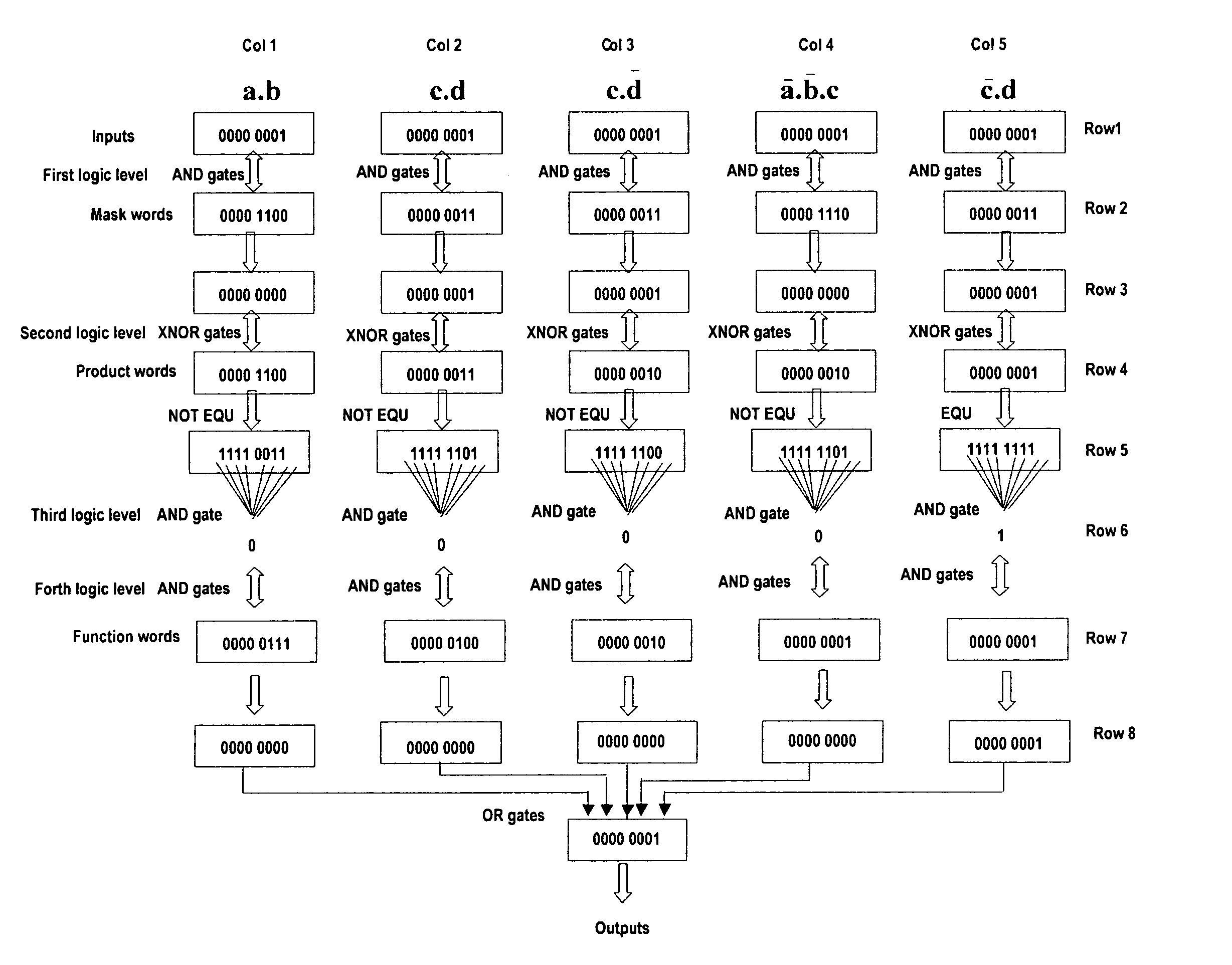

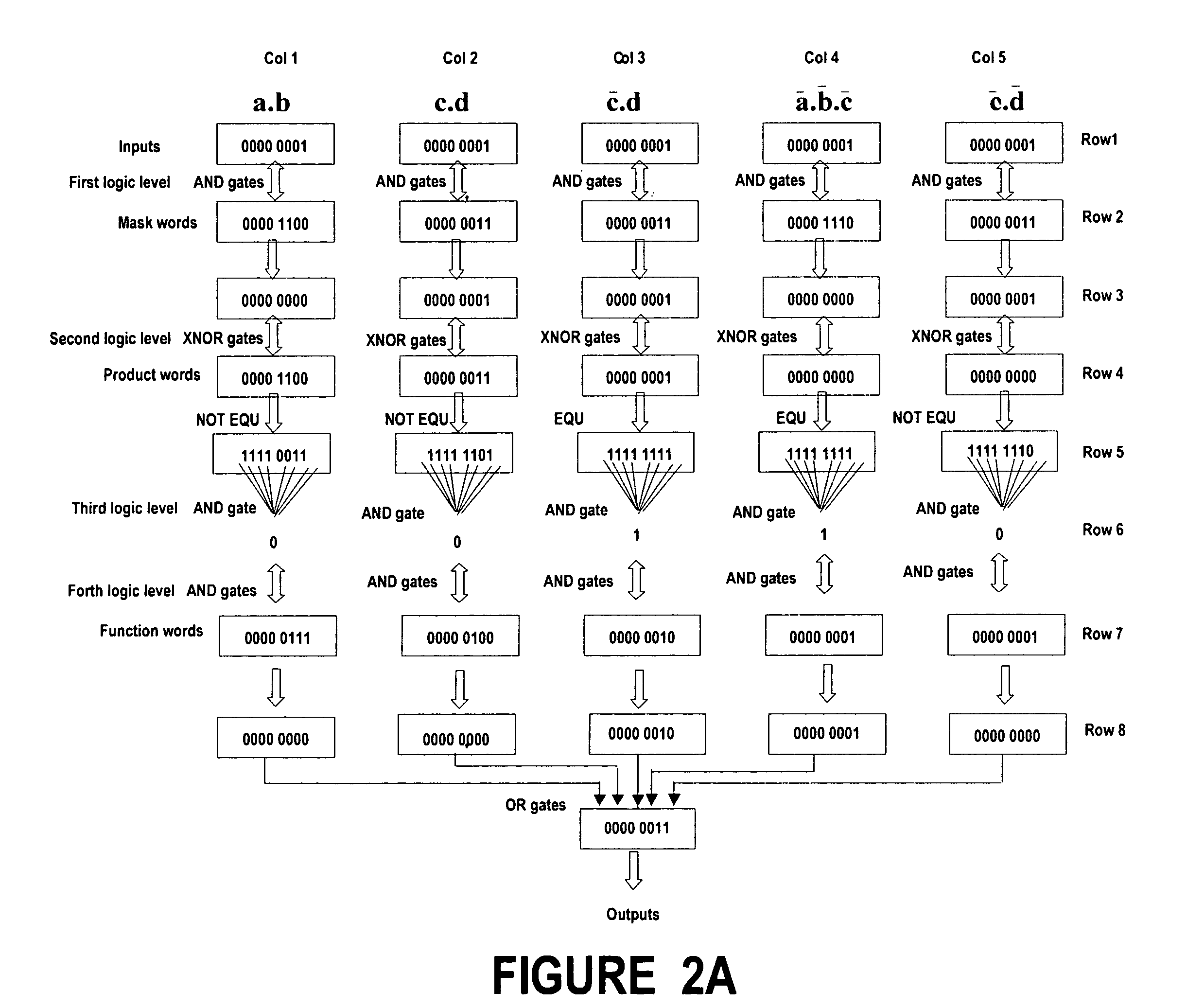

InactiveUS7047166B2Improve accuracyReduce manufacturing costSolid-state devicesAnalogue computers for electric apparatusFunction wordHardware structure

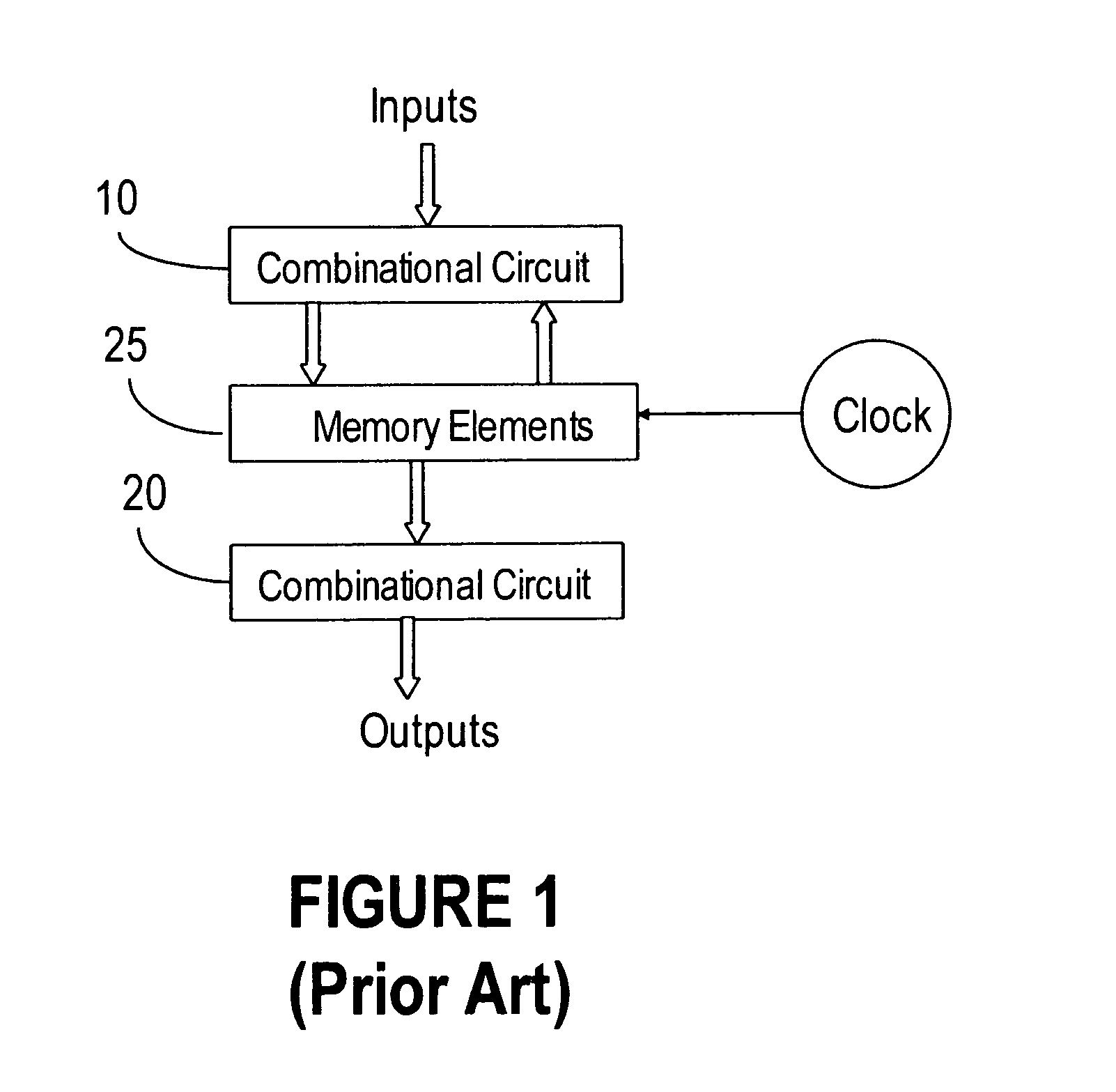

A method, named the product terms method that allows to implement and / or to change dynamically the logical behavior of any combinational or synchronous sequential circuits has been presented. The method uses for every product term of logical equations, expressed as a sum-of-product, three memory words: mask word, product word and function word. The words of all product terms are ranged in a table, which characterize the logical behavior of the circuit.The invention provides the hardware structure of several new types of VSLI circuits, having re-configurable logic behaviors. A first embodiment implements any type of multiple output combinational circuit, a second embodiment implements any synchronous sequential circuit with only clock input and, a third embodiment implements any synchronous sequential circuit s with data inputs and clock input.An expert system capable to generate the tables used for the product terms method by interpreting and analysing the logical equations either supplied by the user or found in a database is also provided.

Owner:IOAN DANCEA

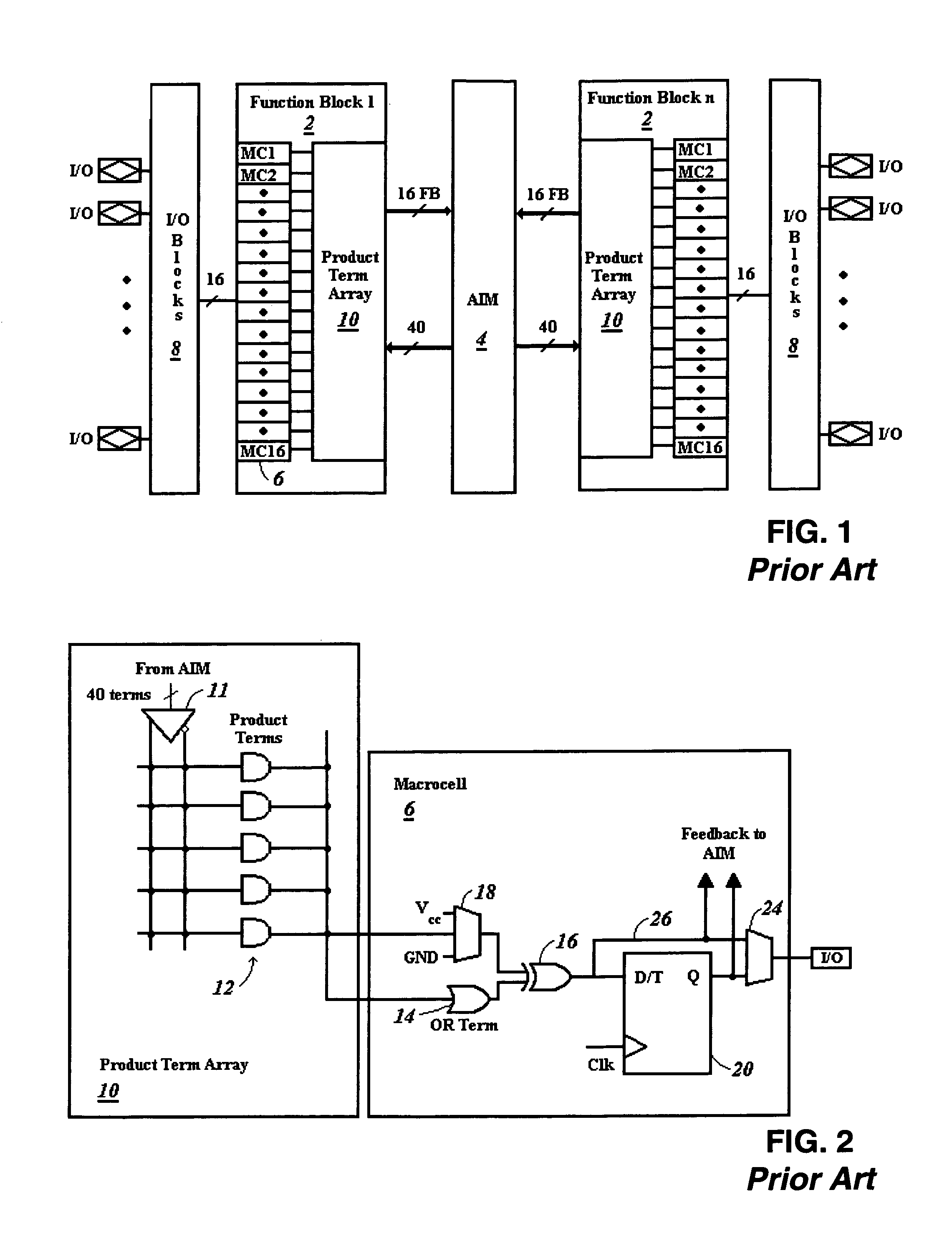

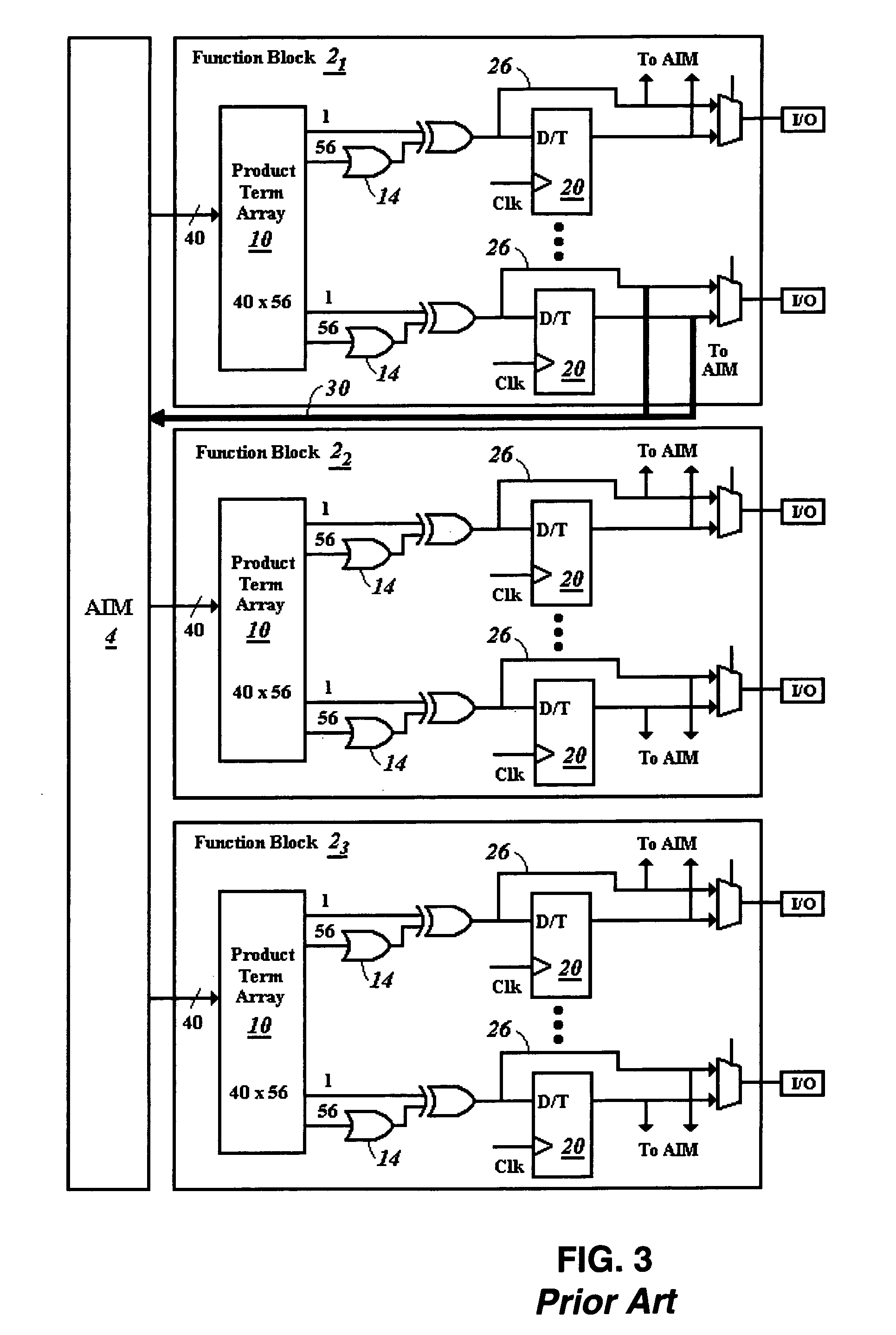

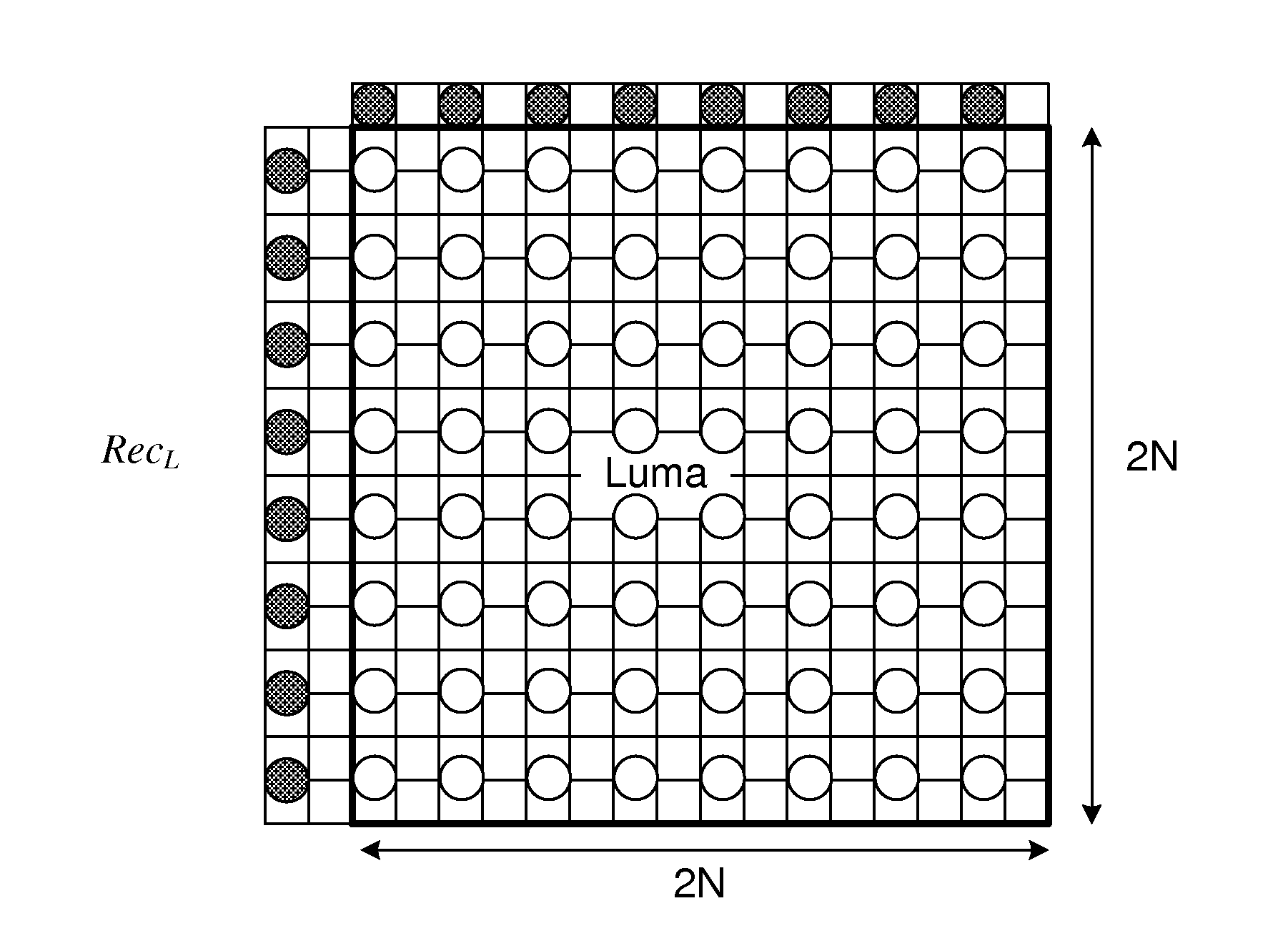

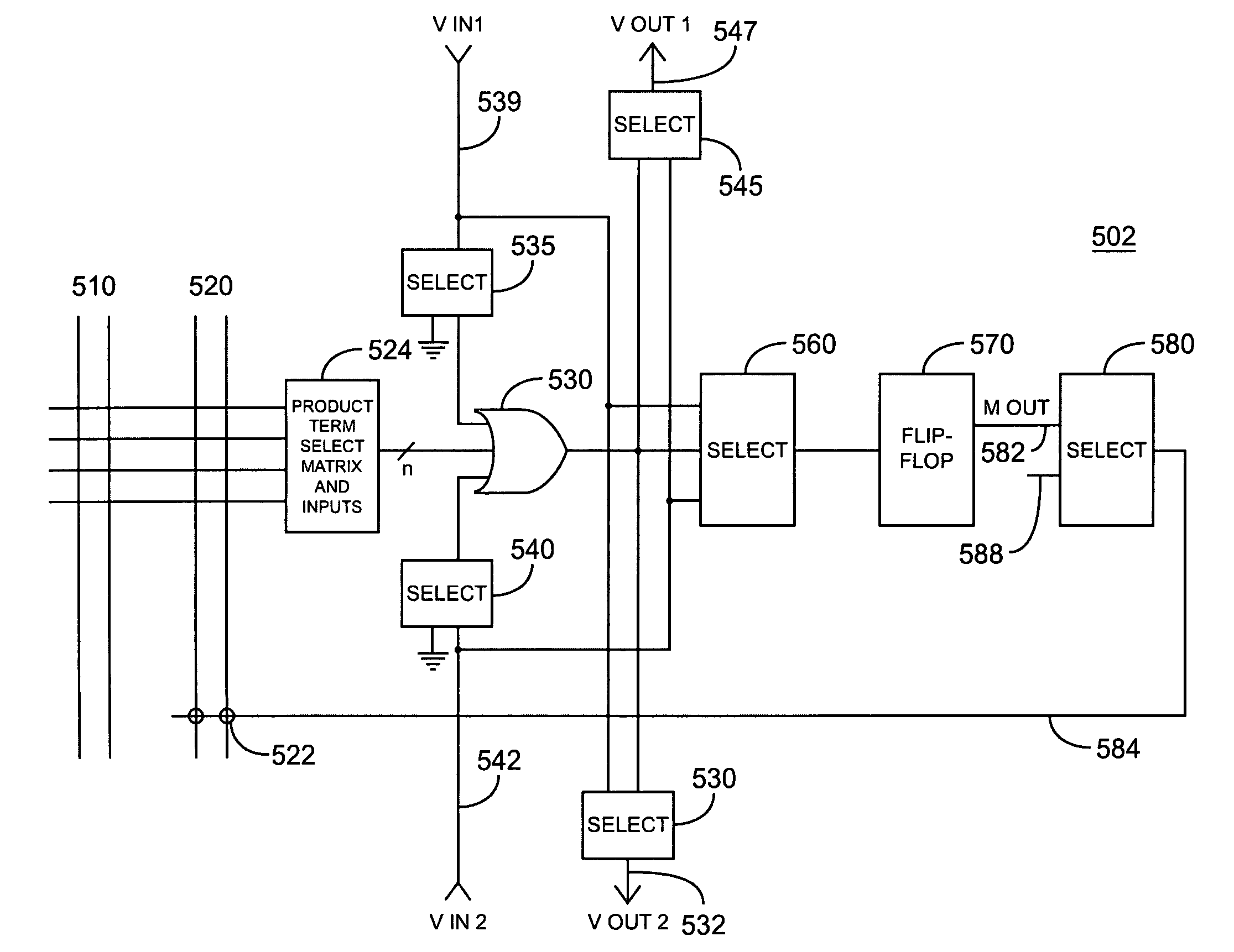

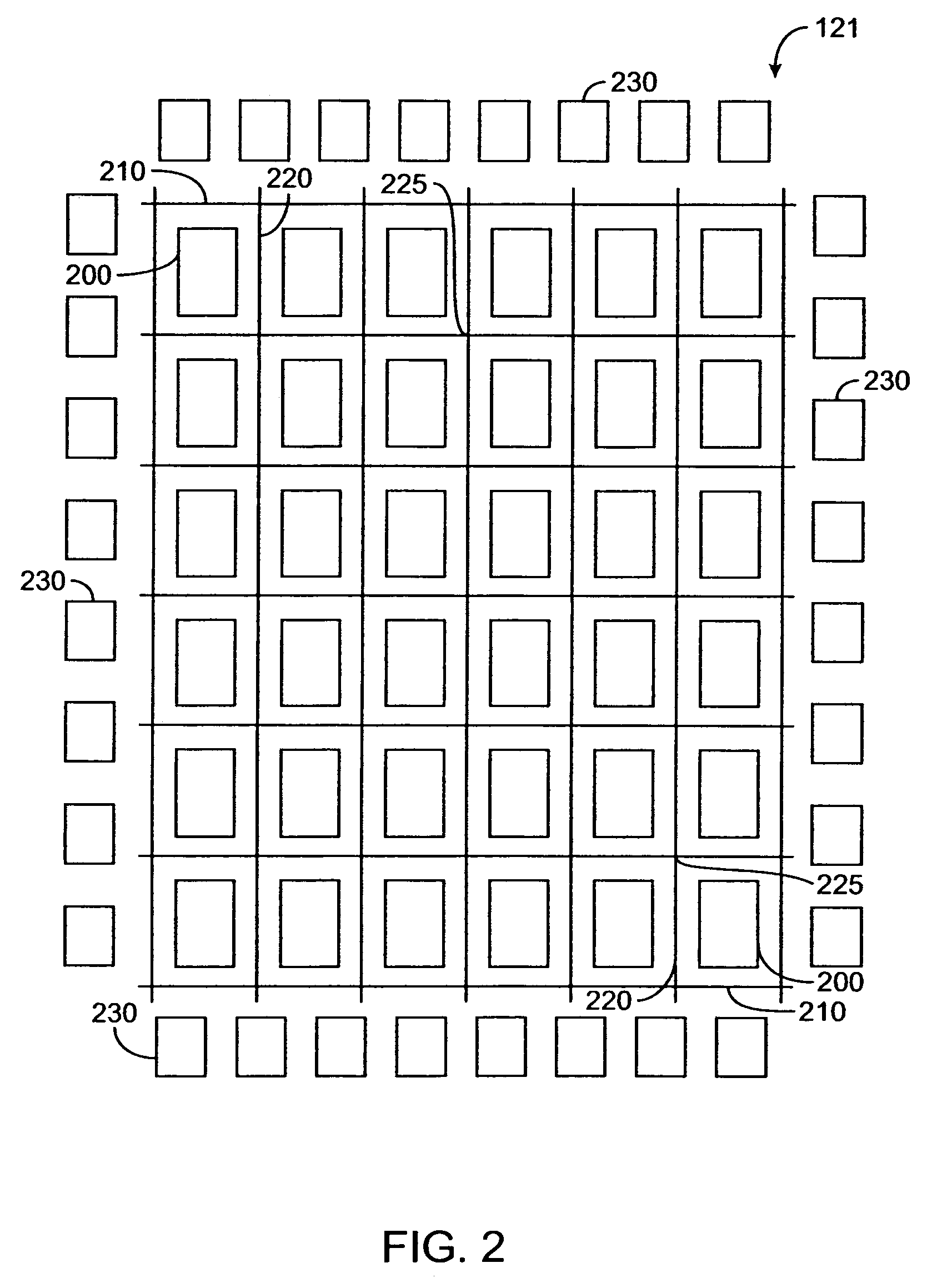

CPLD with fast logic sharing between function blocks

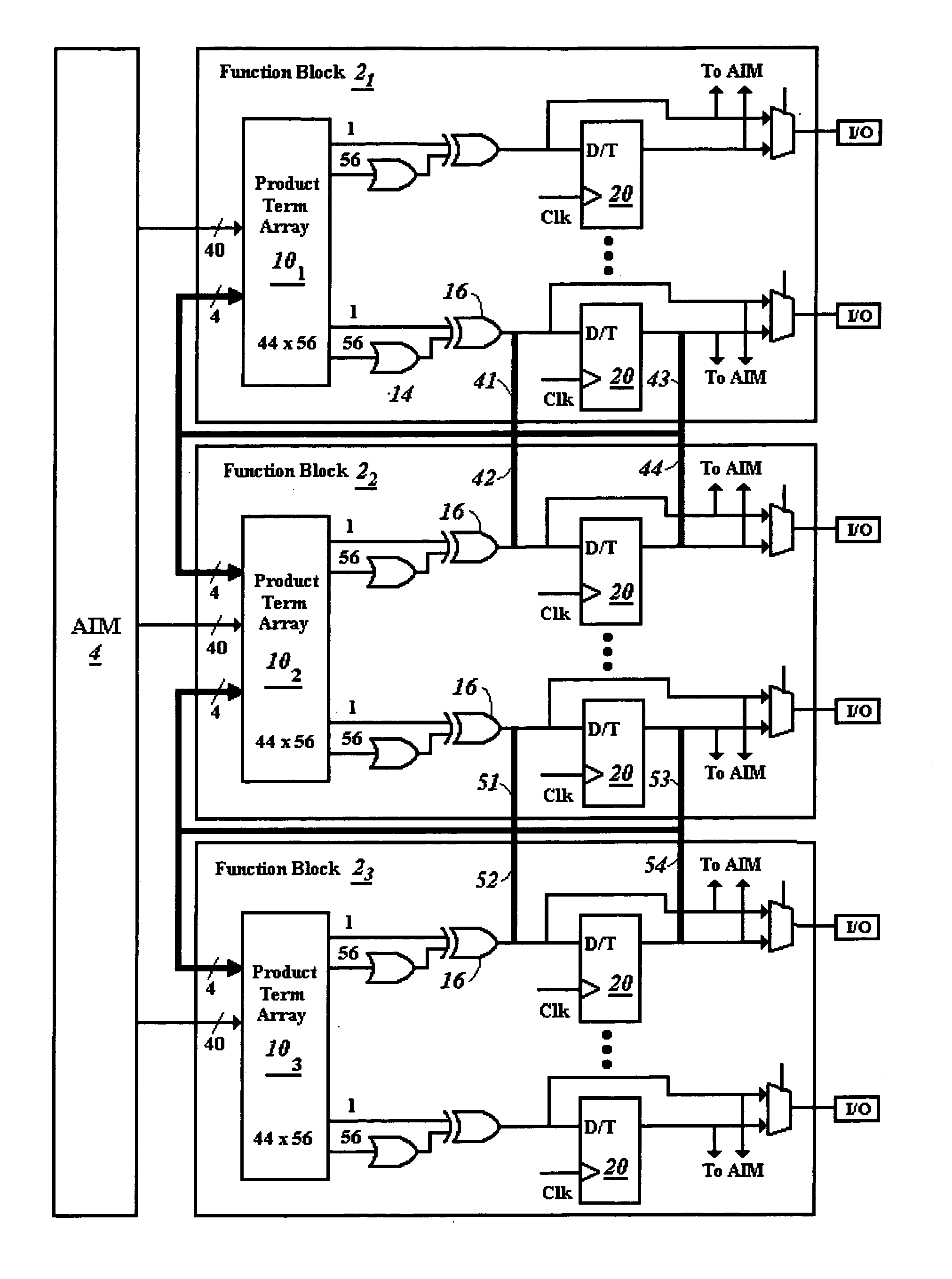

InactiveUS7129747B1OptimizationOperational shortcomings of conventional CPLDsSolid-state devicesSpecial data processing applicationsComputer architectureProcessor register

Fast logic sharing is created using a feedback path from the output logic macrocell of one functional block to the product term inputs of another function block without going through an advanced interconnect matrix (AIM). The fast feedback path may be provided from the macrocell after the product terms XOR gate without registering, and / or after the register in the macrocell. The fast logic sharing avoids the slow AIM for feedback logic, and allows additional resources to be borrowed from other function blocks with a limited delay penalty. In particular, delay penalties resulting from dividing wide operations requiring multiple product terms between the product terms of multiple functional blocks are significantly reduced.

Owner:XILINX INC

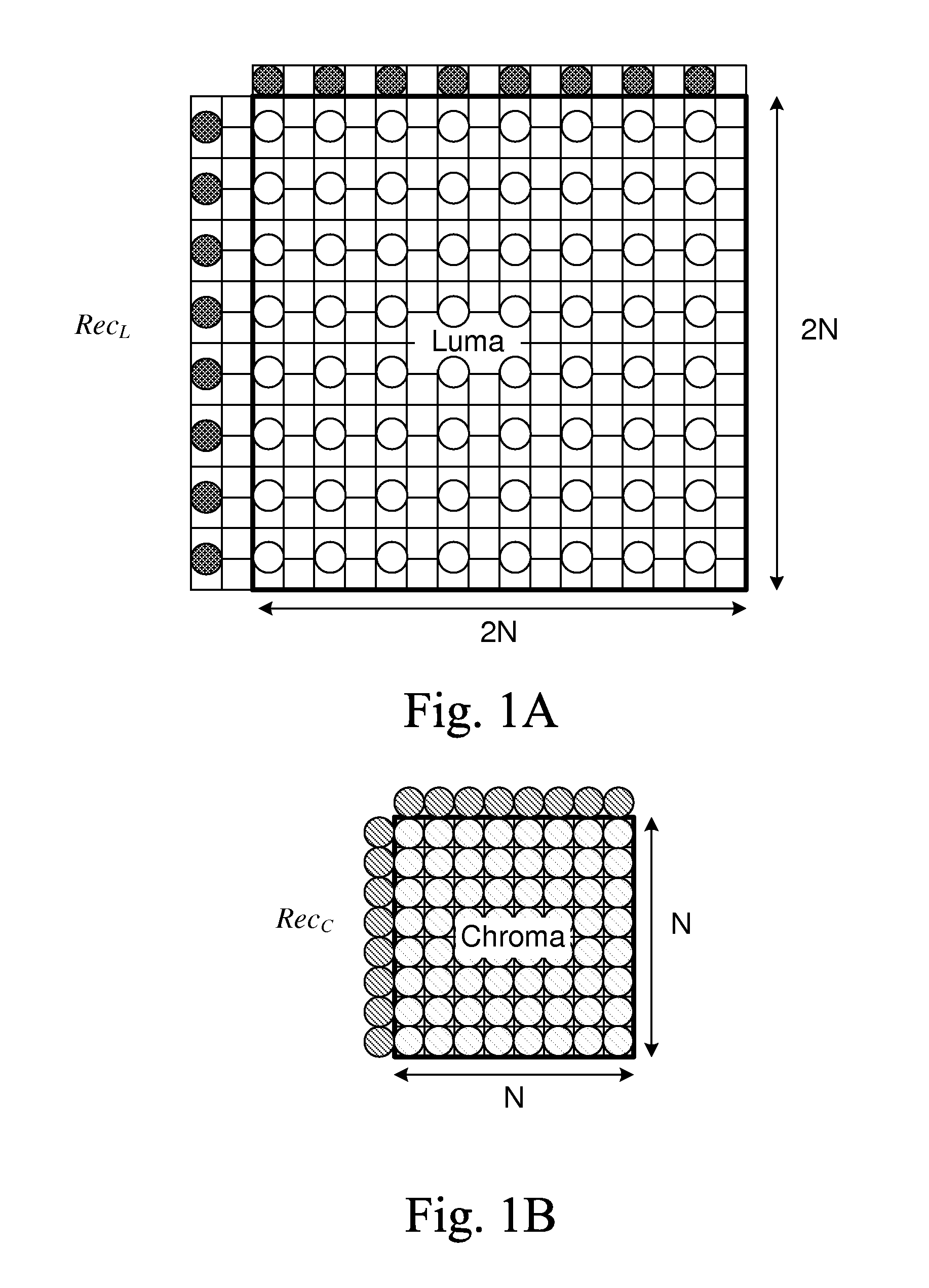

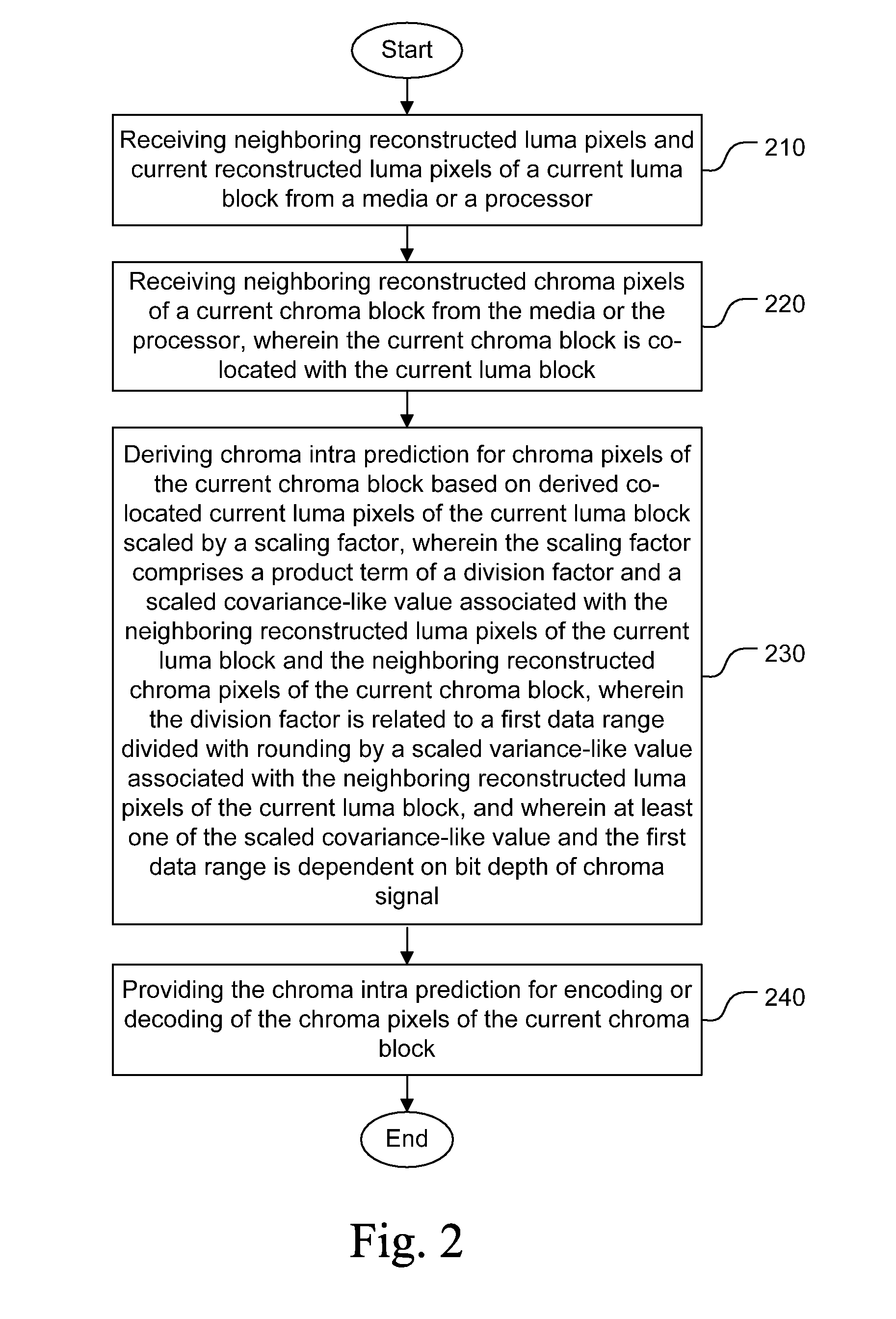

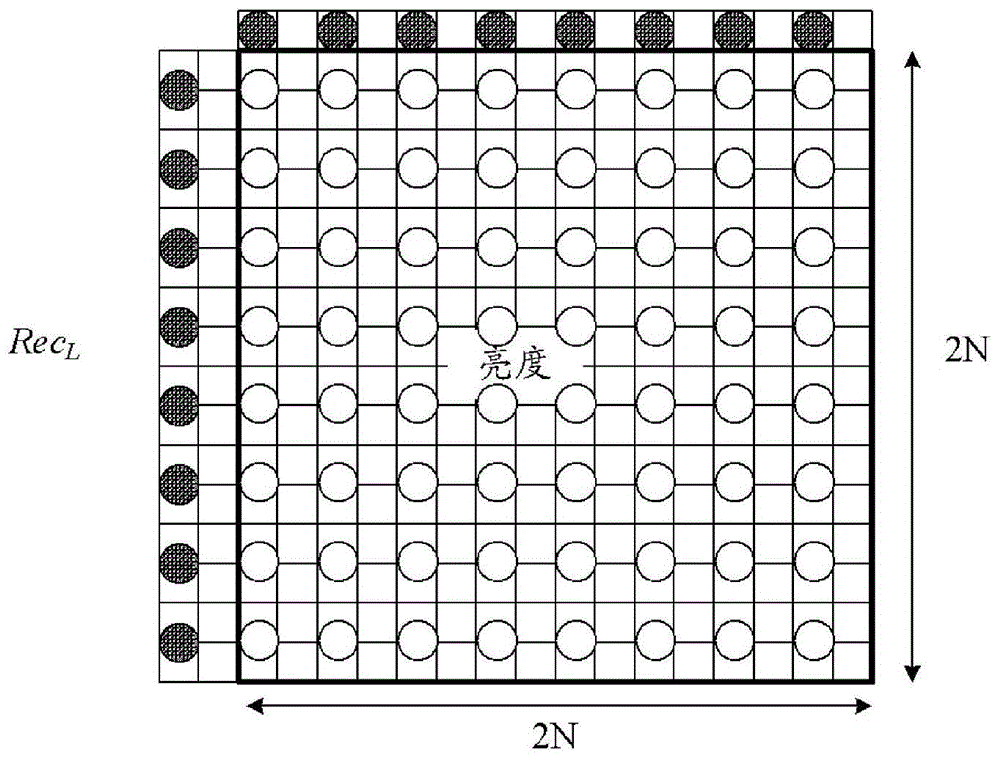

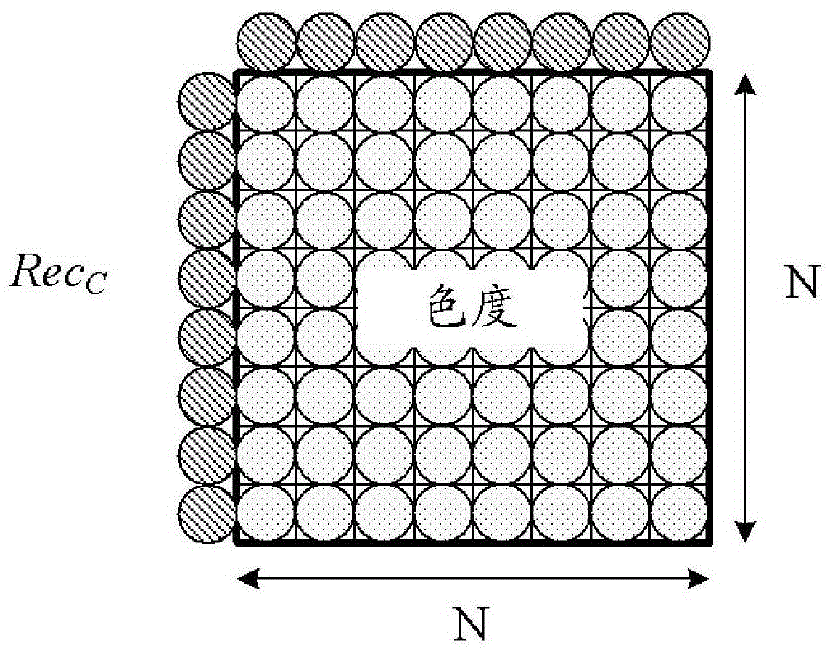

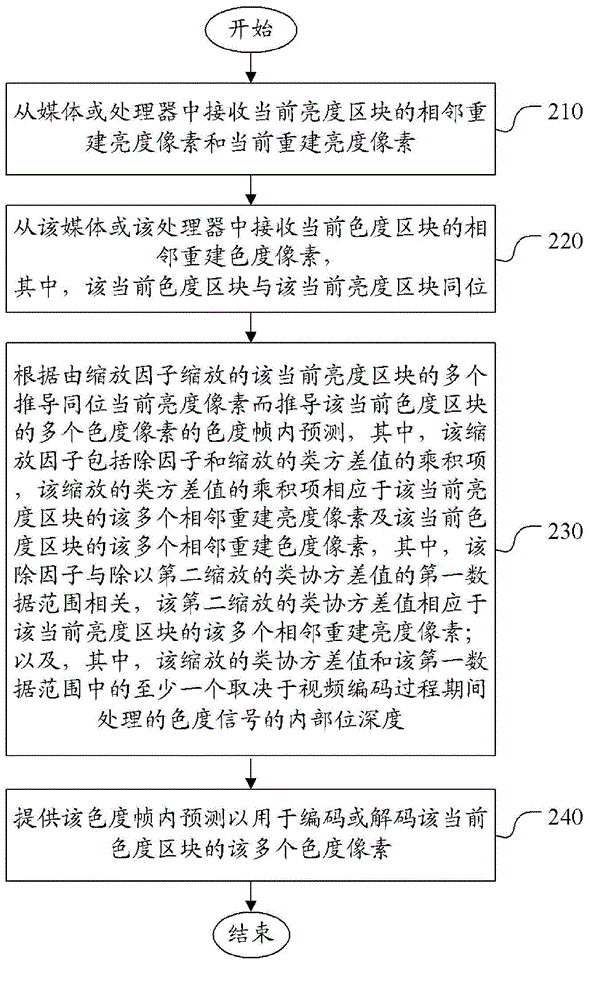

Method and apparatus of simplified luma-based chroma intra prediction

ActiveUS20150036745A1Color television with pulse code modulationColor television with bandwidth reductionCovarianceLinear model

A method and apparatus for chroma intra prediction based on reconstructed luma pixels and chroma pixels are disclosed. The chroma intra prediction is based on a linear model of derived co-located current luma pixels of the current luma block scaled by a scaling factor. The scaling factor comprises a product term of a division factor and a scaled covariance-like value associated with neighboring reconstructed luma and chroma pixels of a current block. The division factor is related to a first data range divided with rounding by a scaled variance-like value associated with the neighboring reconstructed luma pixels of the current block. The scaled covariance-like value, the first data range, or both of the scaled covariance-like value and the first data range are dependent on the internal bit depth, with which the chroma signal is processed during video coding process, according to an embodiment of the present invention.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

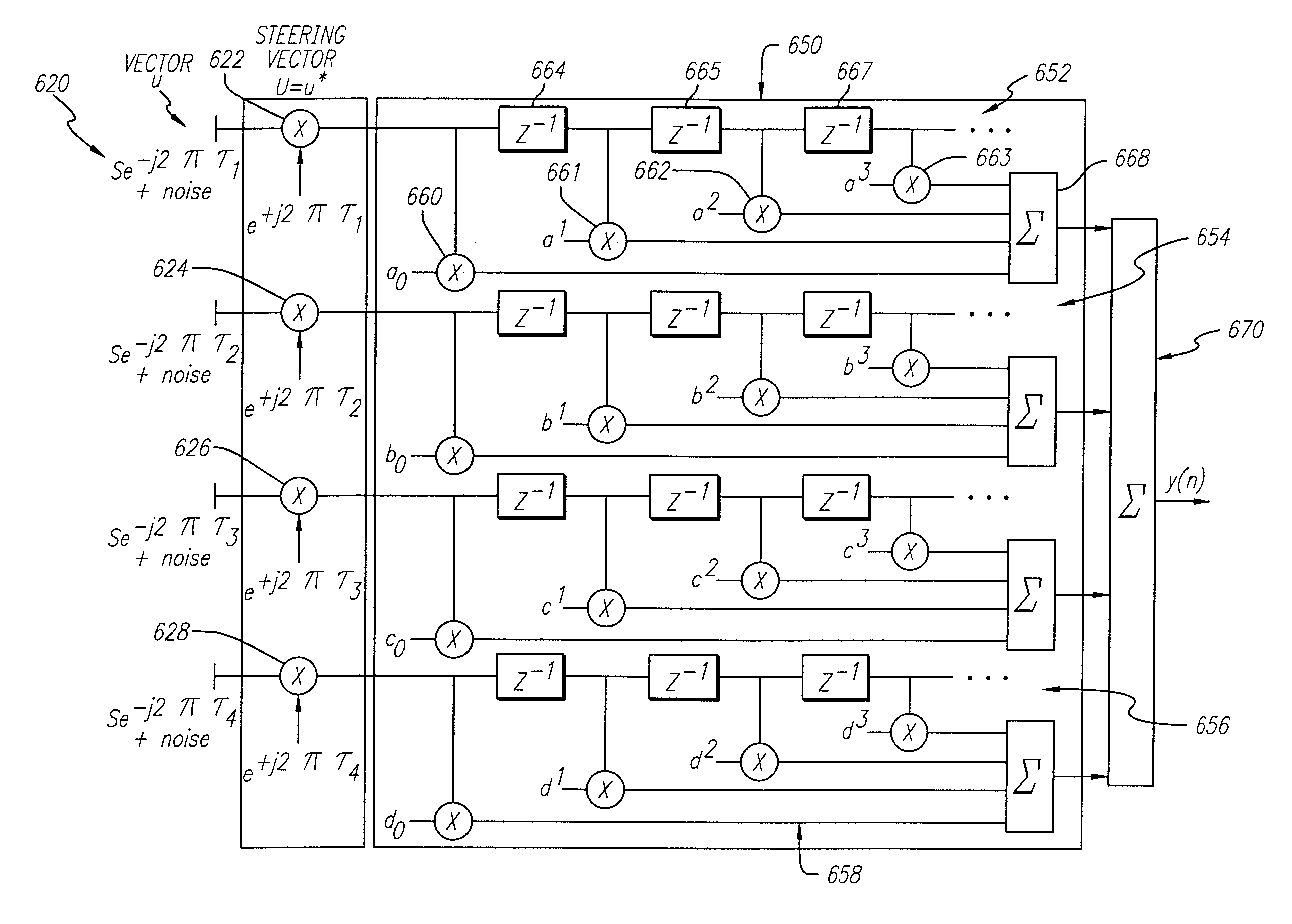

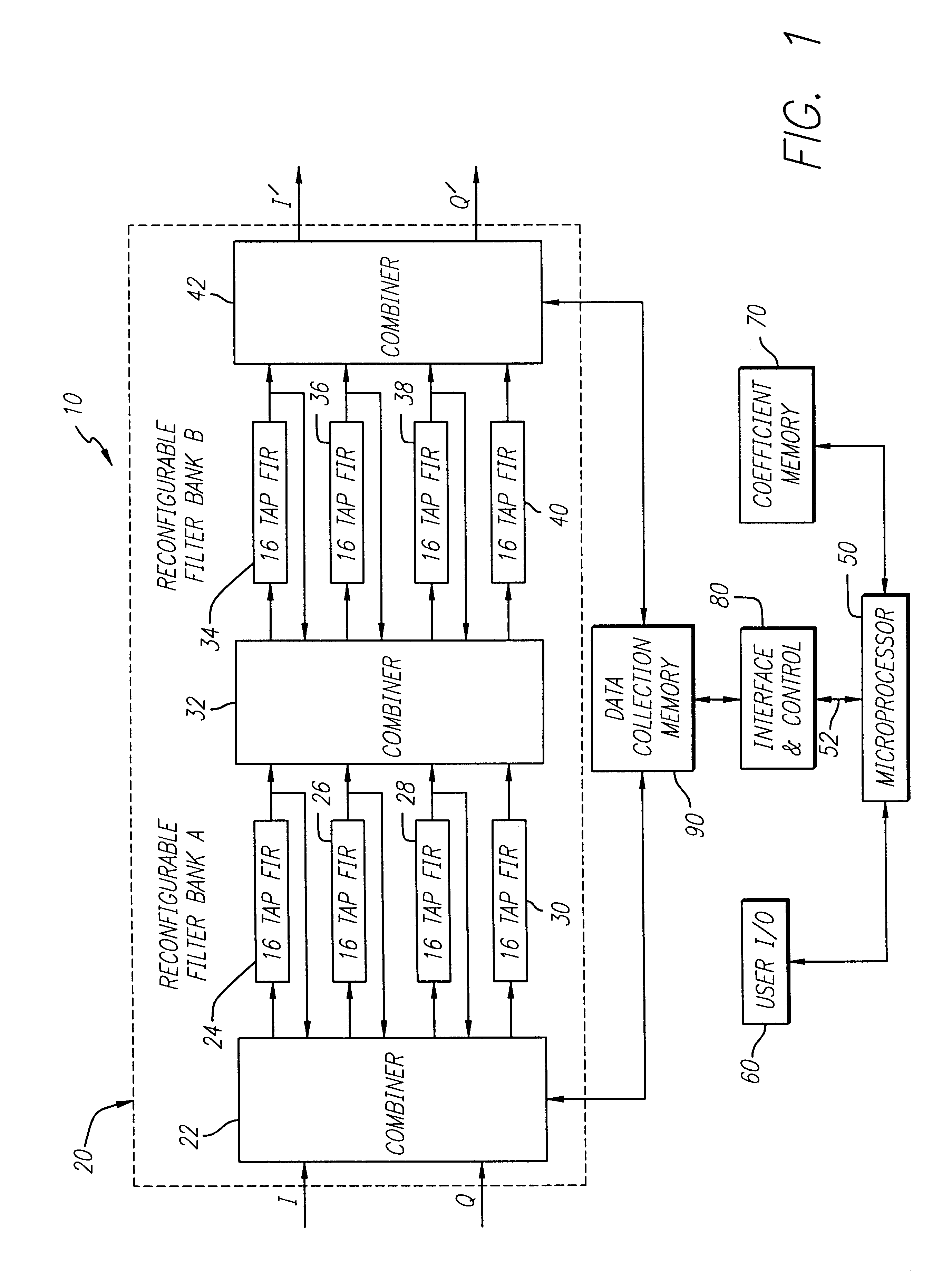

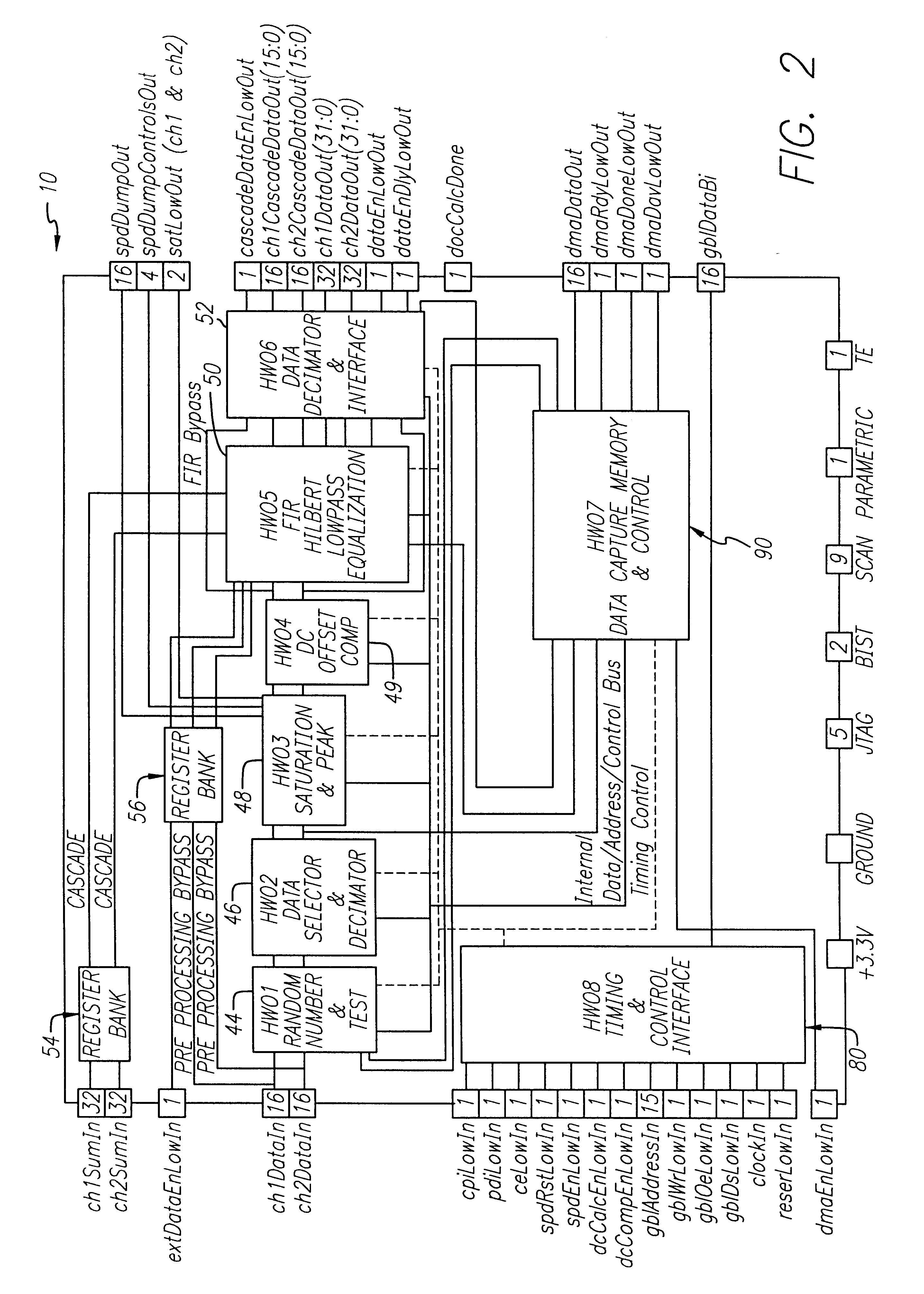

Beamforming and interference cancellation system using general purpose filter architecture

InactiveUS6317467B1Multiple-port networksSpatial transmit diversityGeneral purposeInterference cancelation

A beamforming system including a multiplier stage for providing a plurality of steered signal terms, each term being a product of an input signal term and a steering signal term. A filter multiplies the steered signal terms by a plurality of respective filter weights to provide a plurality of weighted products. The weighted products are summed to provide an output beam directionally responsive to the steering signal. A microprocessor provides the steering signal terms and the filter weights in response to the input signal and / or user input. In the preferred embodiment, the filter is a reconfigurable, general purpose matched filter configured to multiply a plurality of delayed representations of a respective one of the steered signal terms by a plurality of the weights to provide a plurality of intermediate weighted product terms. The filter further includes a summing circuit for accumulating the intermediate weighted product terms to provide a respective one of the plurality of weighted products. The inventive beamforming system cancels unwanted interference, while forming a beam to allow a desired signal to be received with a maximum signal-to-interference-plus-noise ratio (SINR). Through a data-capture RAM, the system allows interference samples to be collected and passed to a microprocessor to calculate the optimum filter weights. The received beam may be steered to any desired direction to form an optimal space-time adaptive matched filter.

Owner:RAYTHEON CO

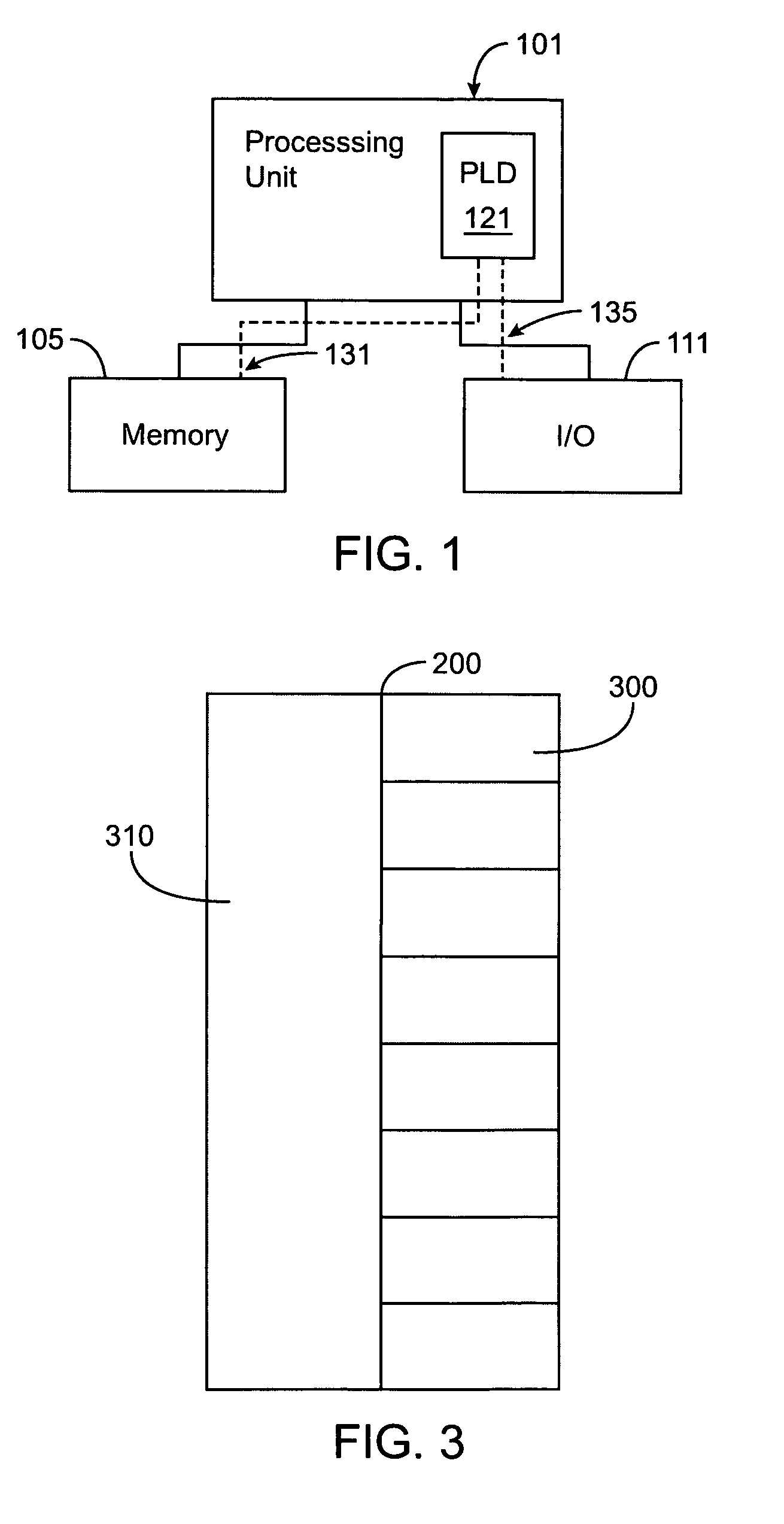

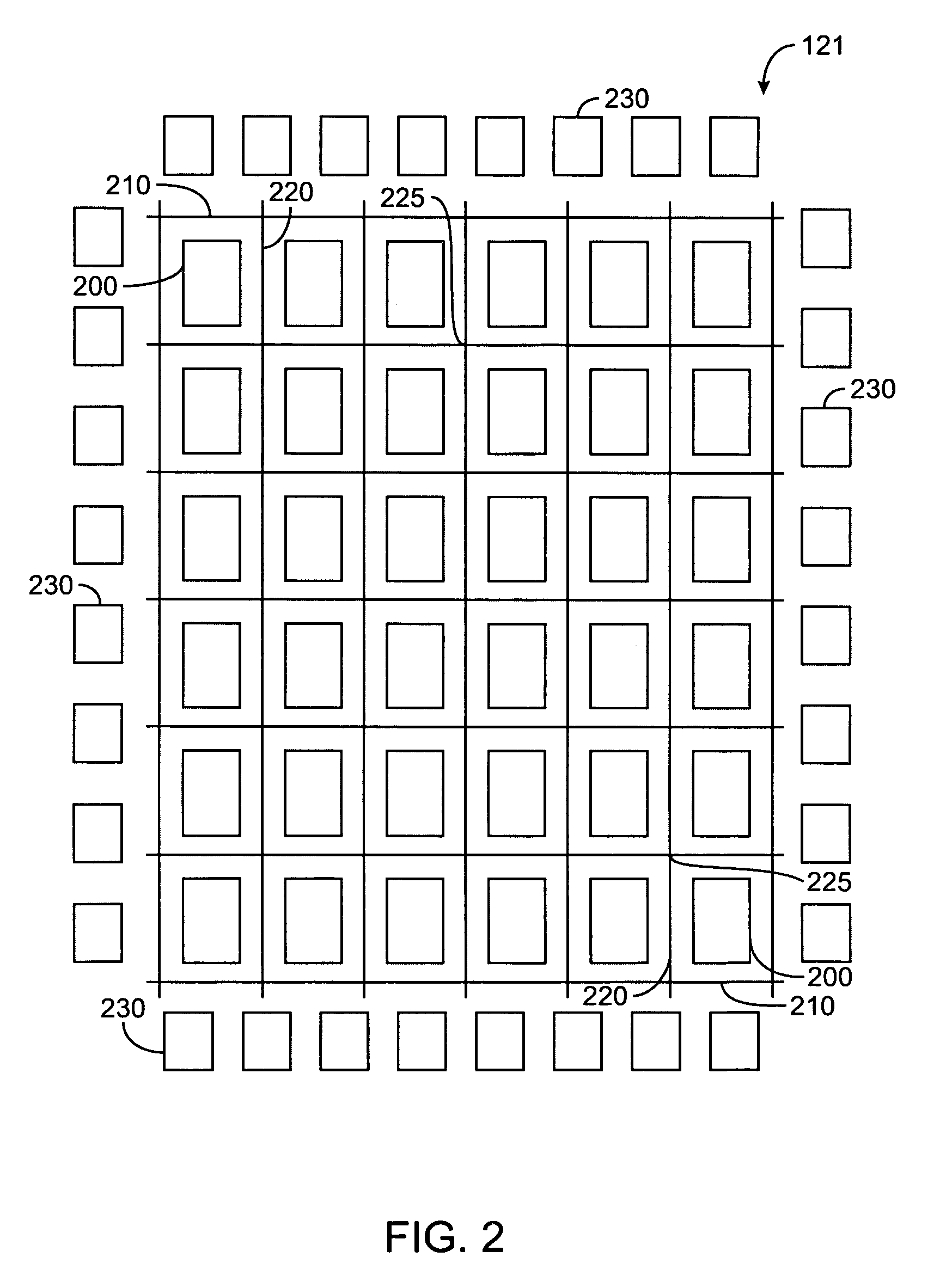

Flexible macrocell interconnect

InactiveUS6927601B1Improve fitGood flexibilitySolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceEngineering

Methods and apparatus for novel routing structures and methods that improve fitting of user-defined functions onto programmable logic devices. In particular, second time fitting is improved. Exemplary structures and methods include allowing product terms to be expanded using inputs from more than one neighboring macrocell by providing multiple expansion and bypassing paths. Also, product term OR shifting prevents macrocell output stages from being buried and made inaccessible, and macrocell outputs are provided on expander word lines, increasing efficiency of those lines, as well as conserving routing resources. Expansion, bypassing, OR shifting, and expander word lines may terminate at logic array block boundaries or may continue beyond these boundaries to other logic array blocks.

Owner:ALTERA CORP

Maximization of a hedged investment budget for an index-linked insurance product

An index-linked insurance product having an annual guarantee is implemented having a maximized hedged investment budget. A net premium payment is allocated to a fixed income investment and an annual fixed income yield is projected. The maximized hedged investment budget is determined by deducting from the projected annual fixed income a product spread and an estimated cost of the annual guarantee. The deducted estimated cost of the annual guarantee is allocated to a risk fund. The maximized hedged investment budget is allocated to a hedged investment designed to generate proceeds for supporting index-linked earnings credited to the index-linked insurance product. Upon expiration of the product term, if the amount credited based on the index-linked earnings does not equal to at least the compounded annual guarantee, the amount credited is increased to be equal to the compounded annual guarantee. The increased credit may be supported using funds from the risk fund and other reserves if necessary.

Owner:ACCORDIA LIFE & ANNUITY

Method and apparatus of simplified luma-based chroma intra prediction

A method and apparatus for chroma intra prediction based on reconstructed luma pixels and chroma pixels are disclosed. The chroma intra prediction is based on a linear model of derived co-located current luma pixels of the current luma block scaled by a scaling factor. The scaling factor comprises a product term of a division factor and a scaled covariance-like value associated with neighboring reconstructed luma and chroma pixels of a current block. The division factor is related to a first data range divided with rounding by a scaled variance-like value associated with the neighboring reconstructed luma pixels of the current block. The scaled covariance-like value, the first data range, or both of the scaled covariance-like value and the first data range are dependent on the internal bit depth, with which the chroma signal is processed during video coding process, according to an embodiment of the present invention.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

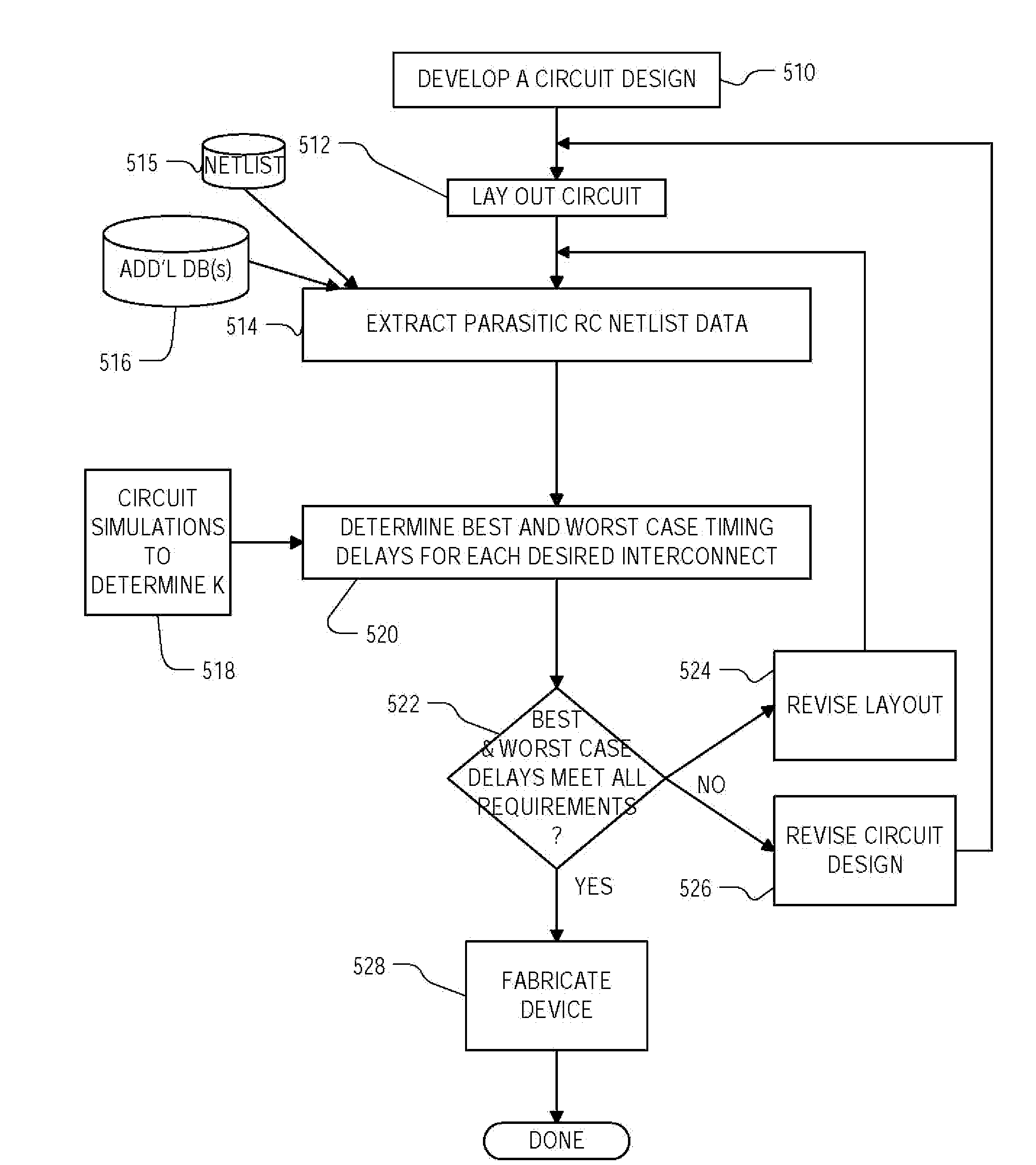

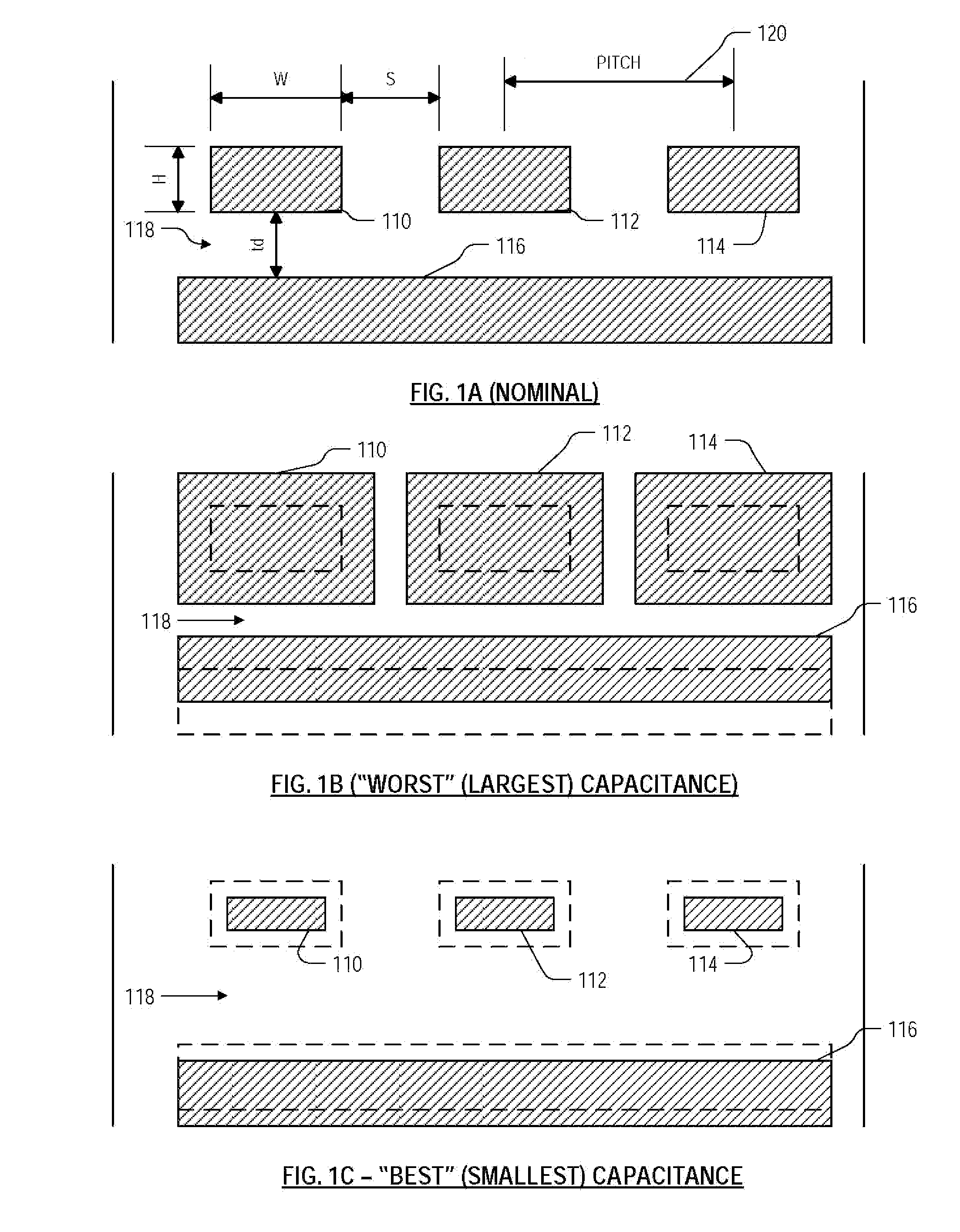

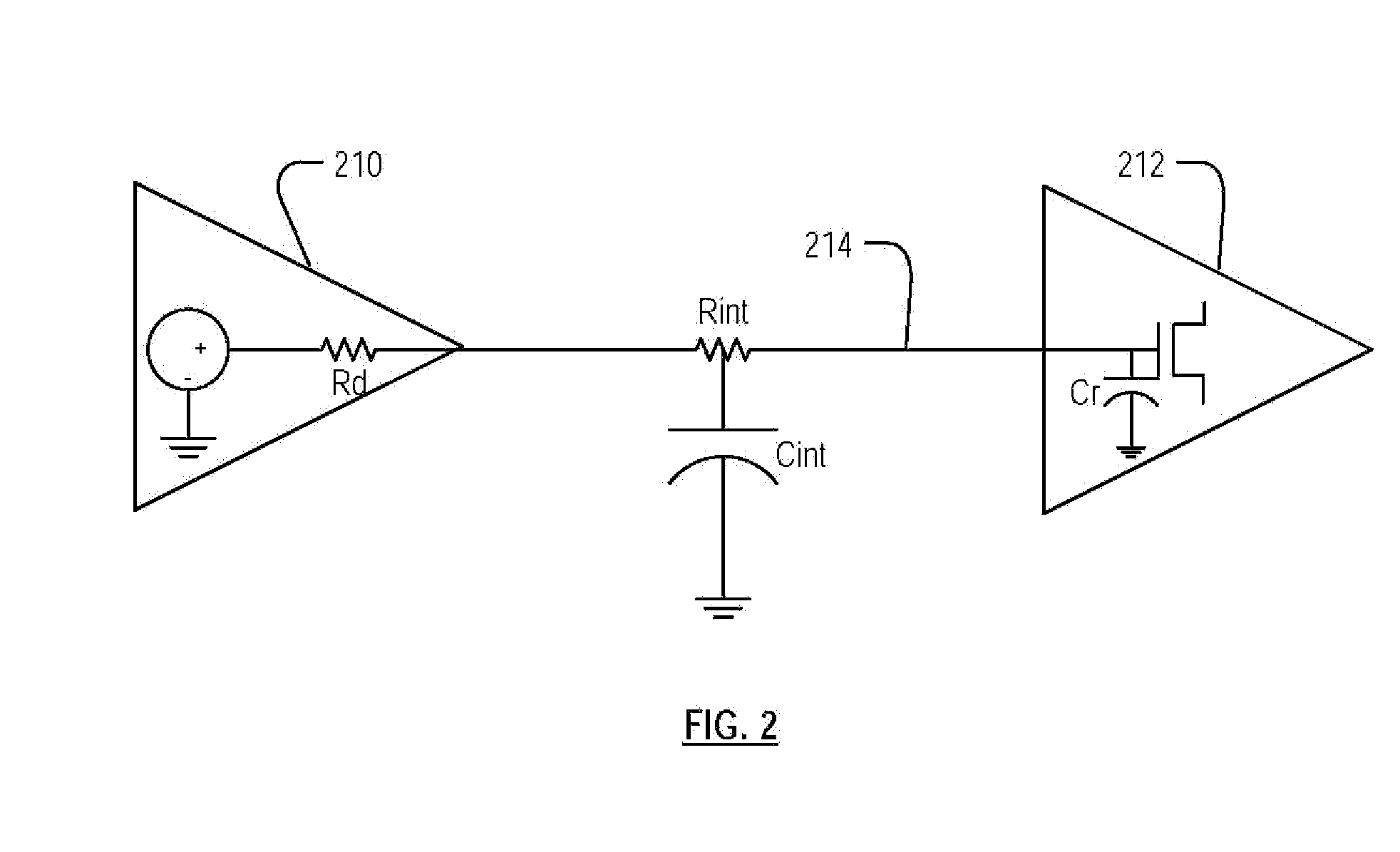

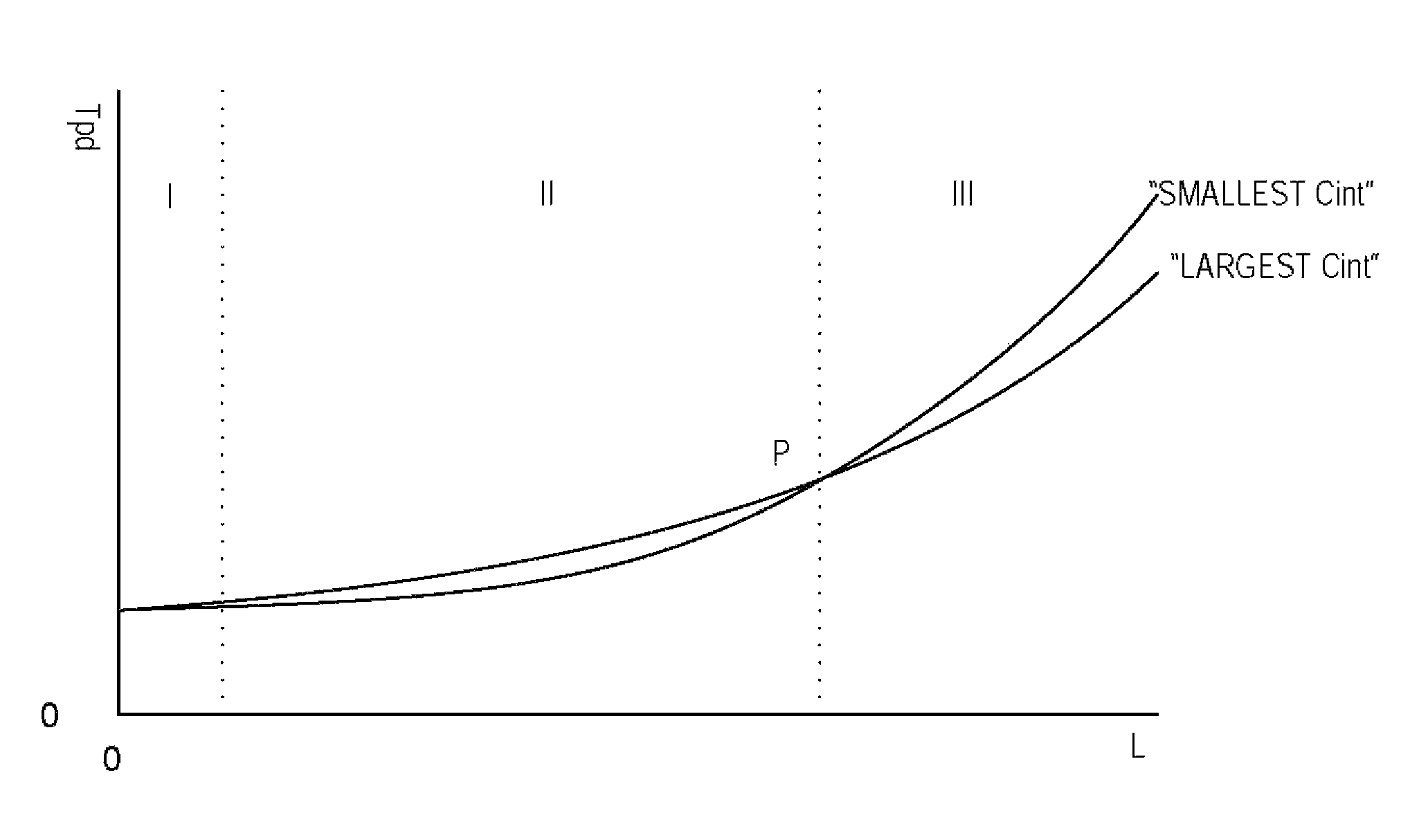

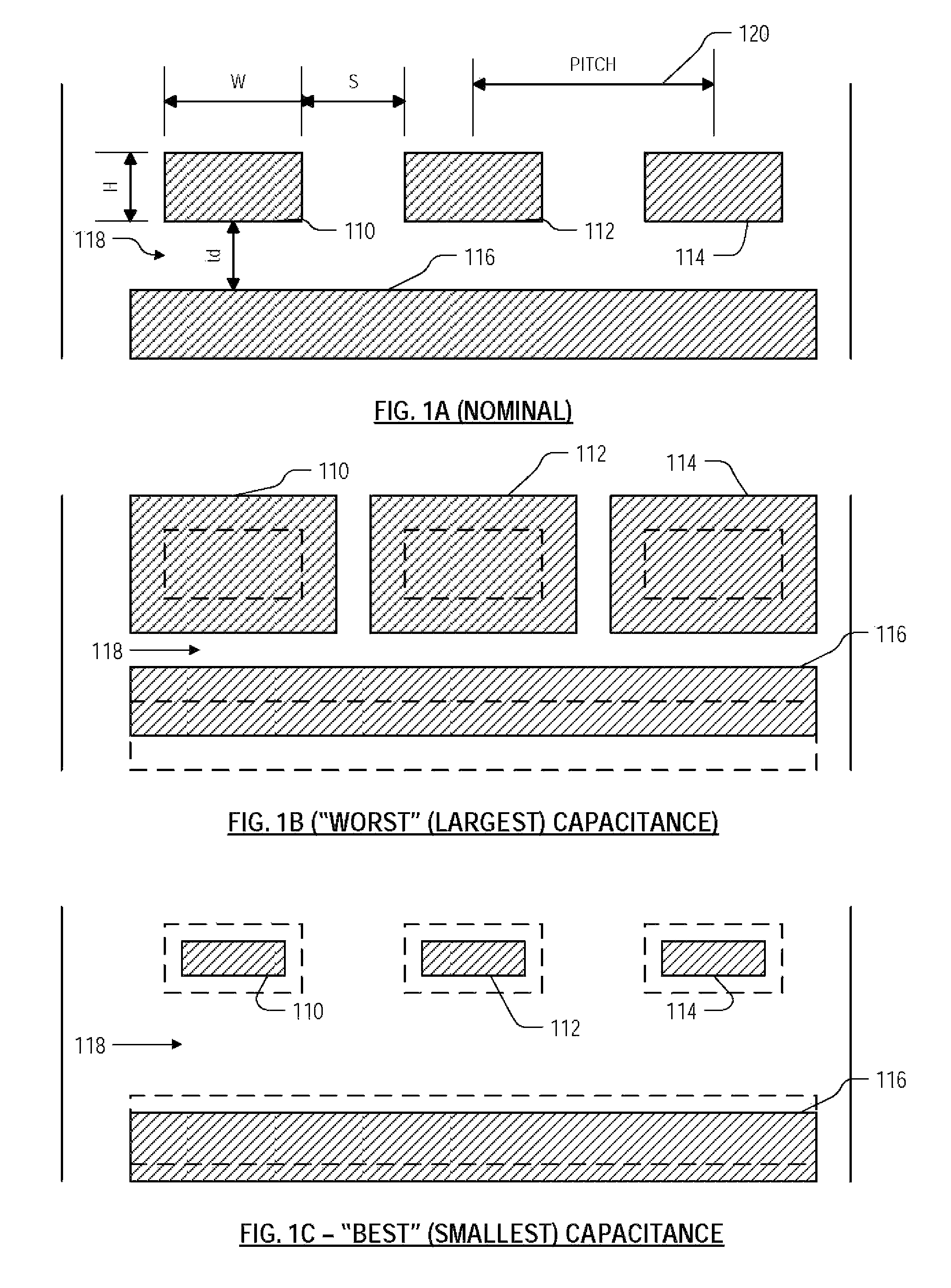

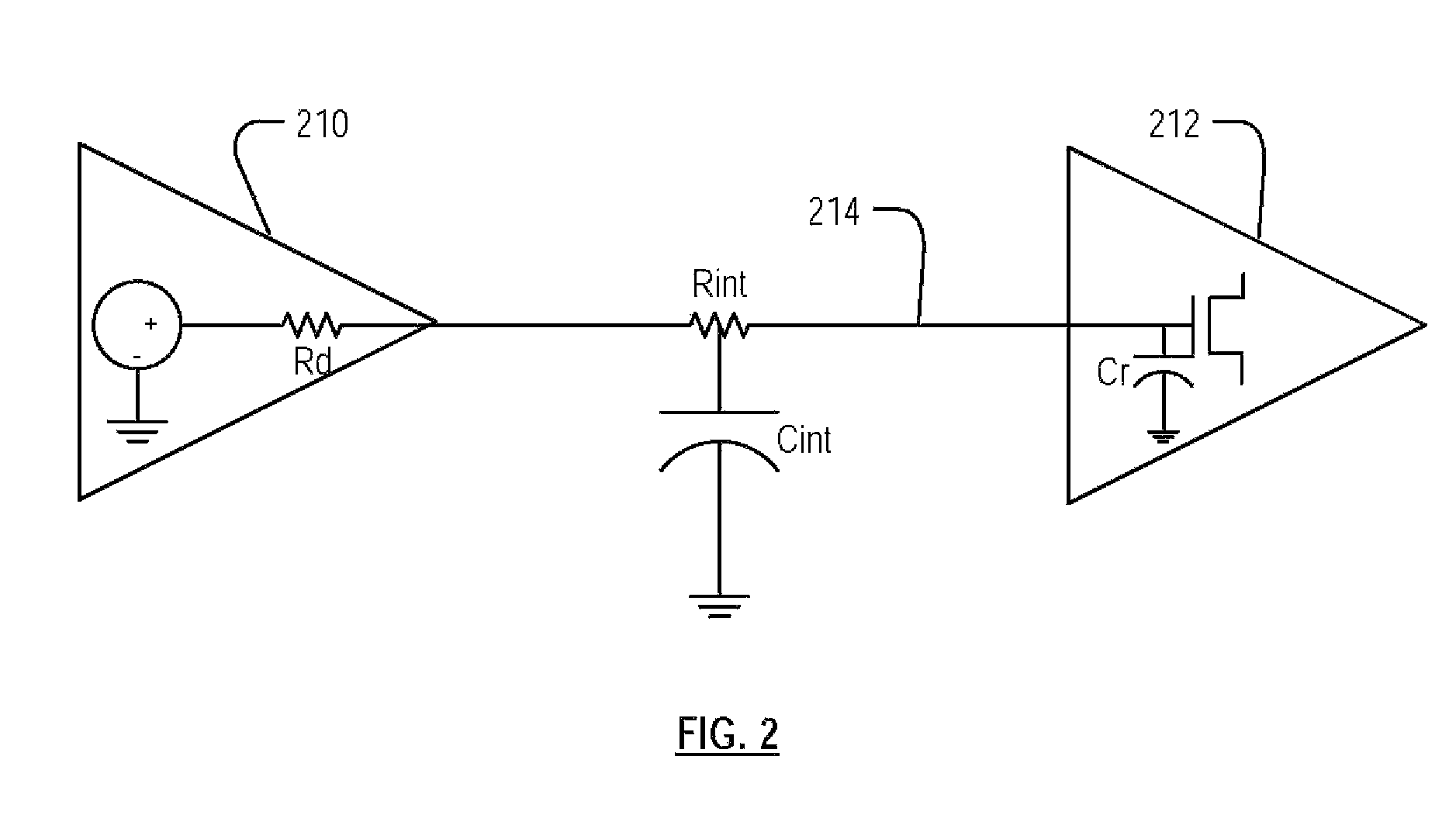

Method for determining best and worst cases for interconnects in timing analysis

ActiveUS20080228460A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingPropagation delayCapacitance

Roughly described, signal propagation delay values are estimated for a plurality of interconnects in a circuit design. For each interconnect, the propagation delay value(s) are estimated in dependence upon a preliminary approximate determination of whether the signal propagation delay is dominated more by an interconnect capacitance term or by an interconnect capacitance and resistance product term. If it is dominated more by the interconnect capacitance term, then the parameter values used for a minimum propagation delay calculation are obtained assuming a smallest capacitance process variation case and the parameter values used for a maximum propagation delay calculation are obtained assuming a largest capacitance process variation case. If the signal propagation delay is dominated more by the interconnect capacitance and resistance product term, then the opposite assumptions are made. Preferably the approximate determination is made by comparing Rint to k*Rd.

Owner:SYNOPSYS INC

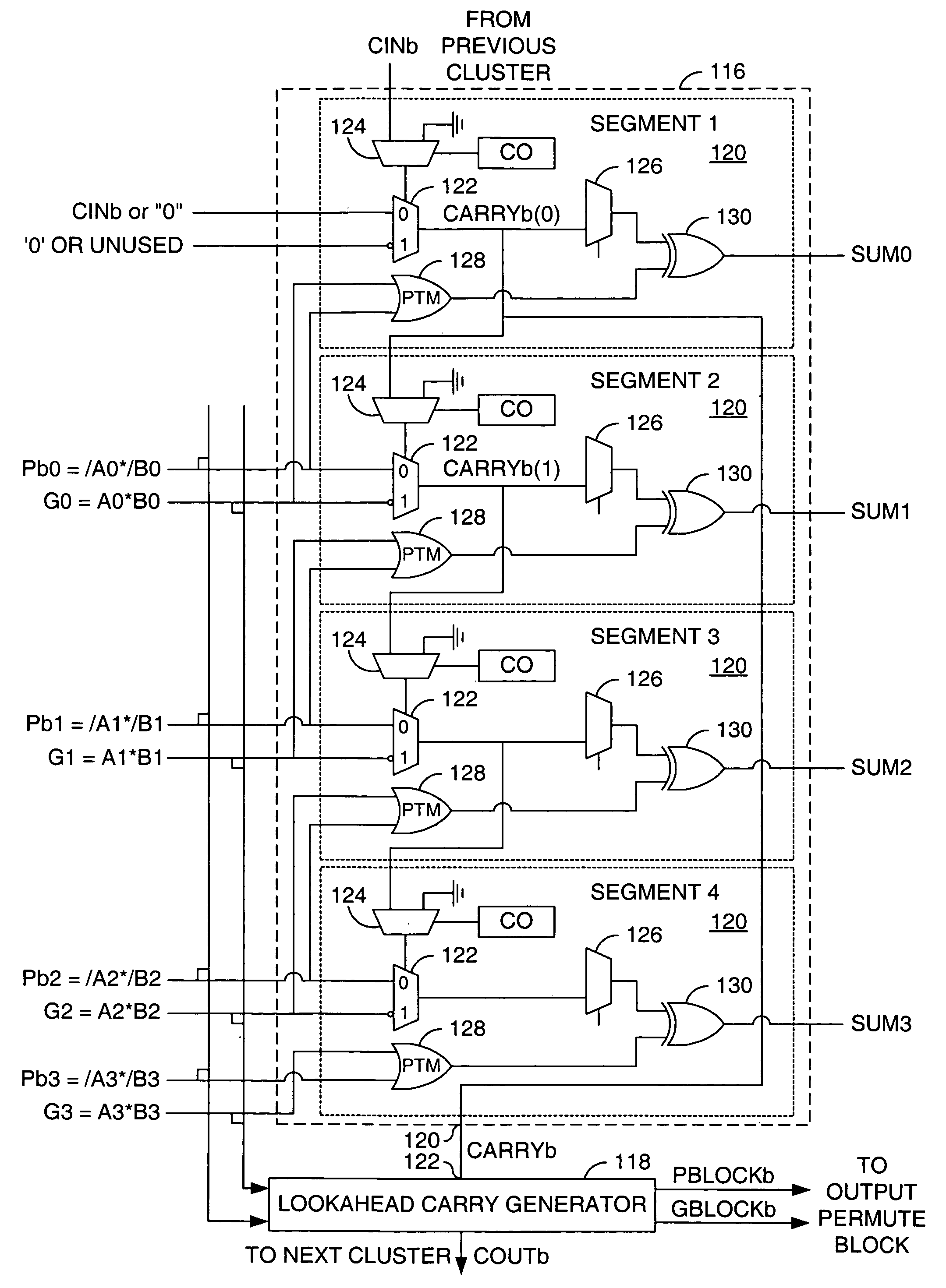

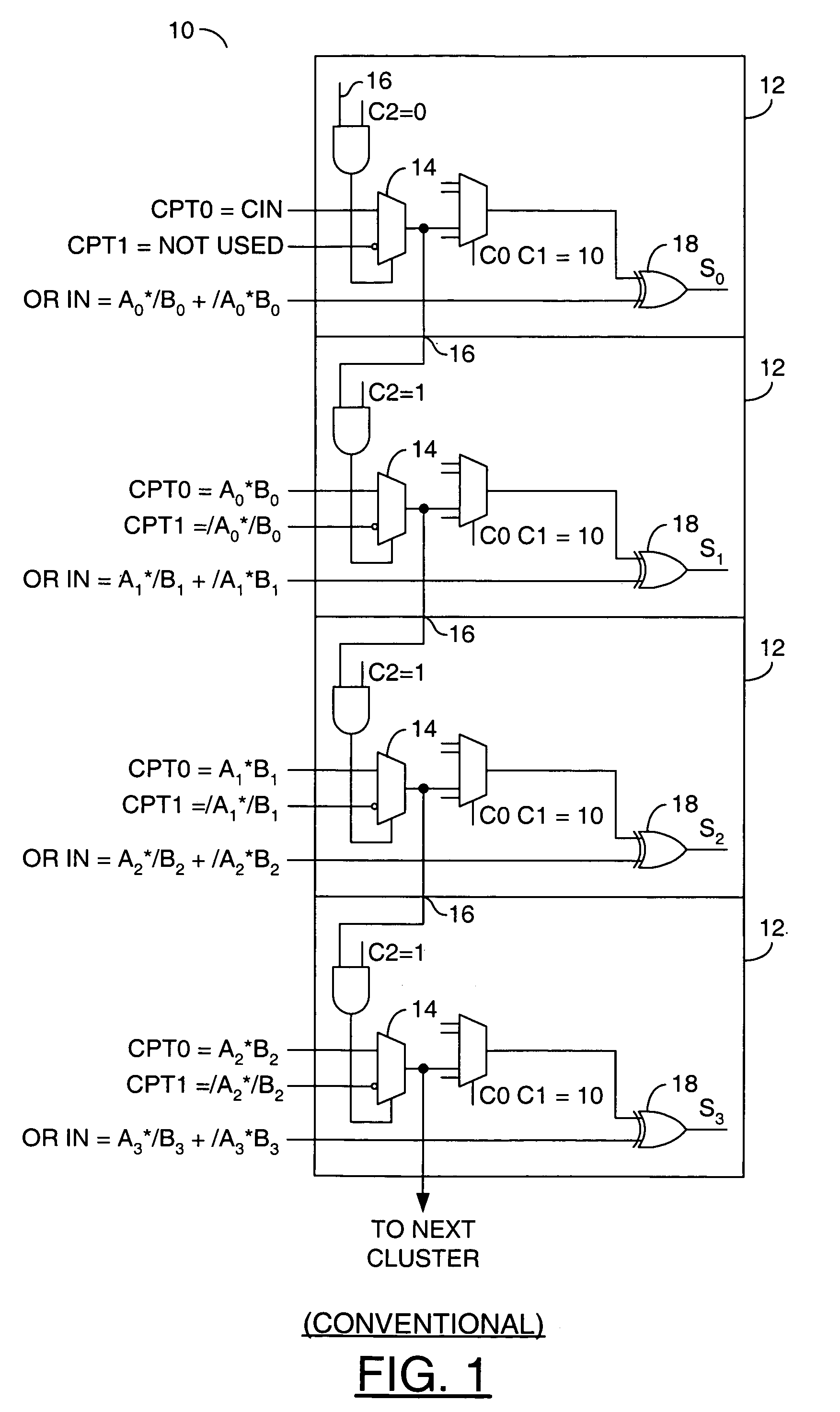

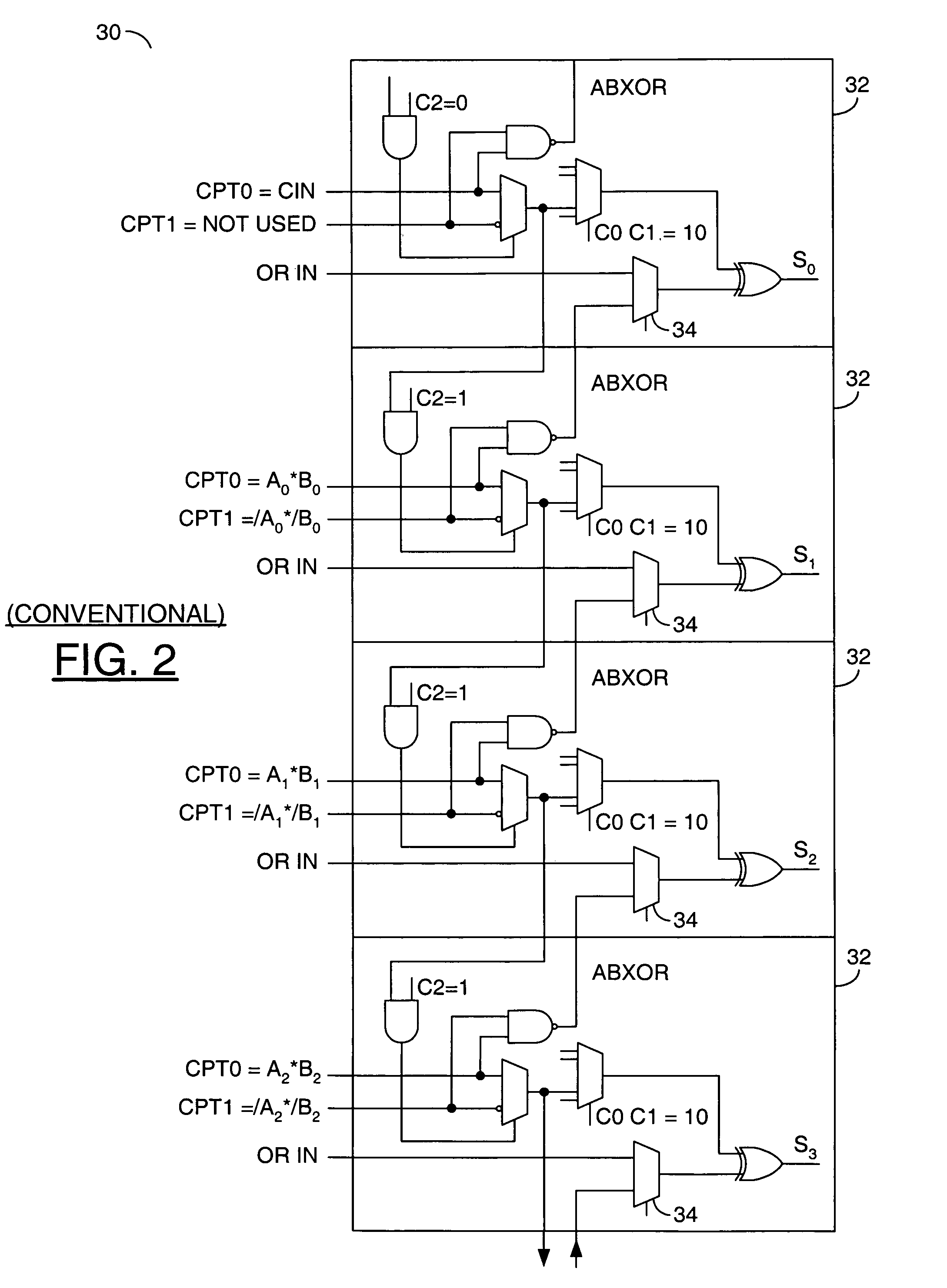

High performance carry chain with reduced macrocell logic and fast carry lookahead

InactiveUS6990508B1Improve performanceReduced macrocell logicComputation using non-contact making devicesProgrammable logic deviceComputer science

A programmable logic block in an integrated circuit comprising a plurality of macrocells, an AND-array, an OR-array, and a logic circuit. The plurality of macrocells may comprise logic that may be configured to (i) generate and propagate an inverted carry-input signal and (ii) generate a sum bit. The AND-array may comprise at least two product terms per macrocell. The OR-array may be configured to generate a sum-of-products term for each macrocell in response to the two product terms. The logic circuit may be configured to (a) receive (i) the product terms and (ii) the carry-input signal generated by a first macrocell of the plurality of macrocells and (b) generate (i) a block carry-propagate signal, (ii) a block carry-generate signal, and (iii) a block carry-output signal.

Owner:MONTEREY RES LLC

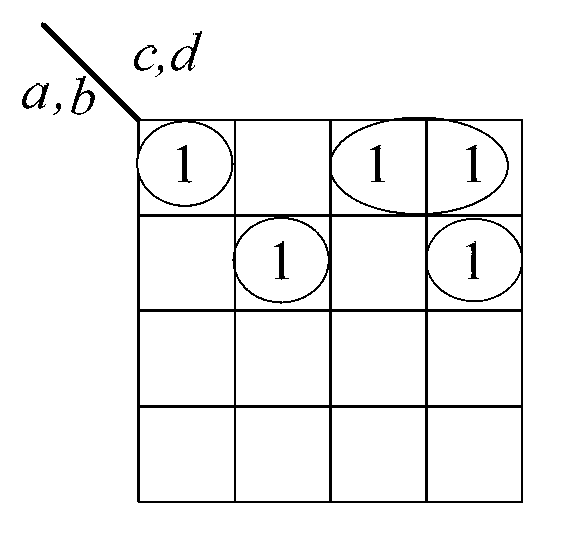

Sub-circuit extracting method of digital logic circuit

ActiveCN103236837AImprove general performanceRelaxed constraintsLogic circuits characterised by logic functionCircuit extractionComputer science

The invention discloses a sub-circuit extracting method of a digital logic circuit. By the aid of disjoint sharp-operations between logic function product terms, the product term set belonging to the logic functions corresponding to the sub circuits is eliminated from the product term set of the logic functions corresponding to original circuits, so that sub-circuit extraction from the original circuits is realized. A novel circuit construction method with sub circuits is further provided to be equivalent to logic functions of the original circuits.

Owner:NINGBO UNIV

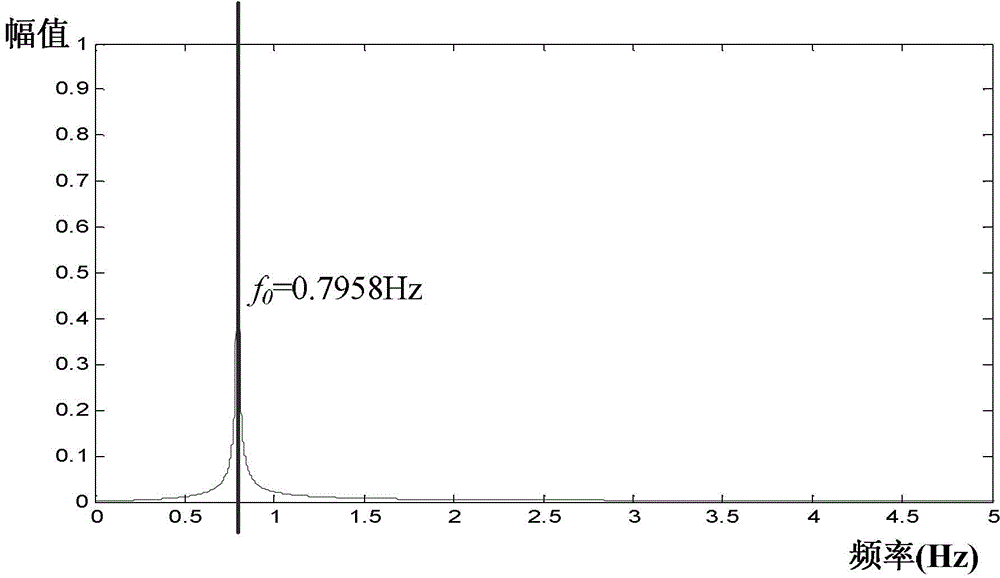

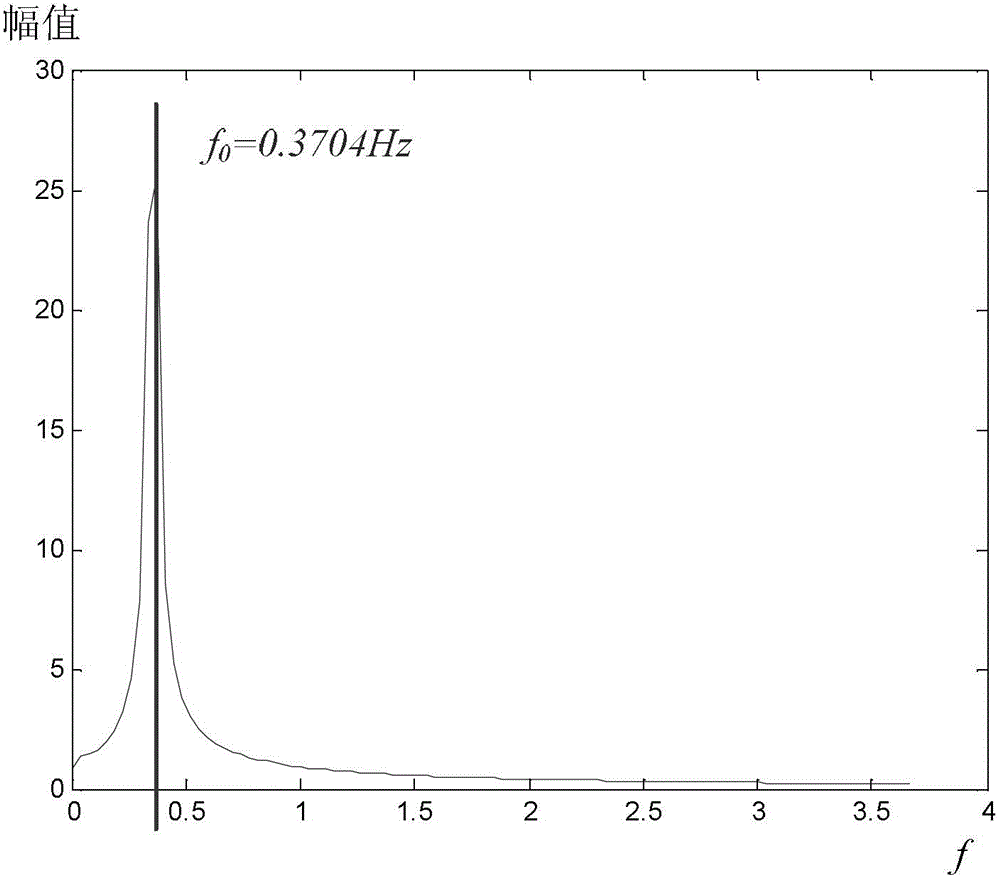

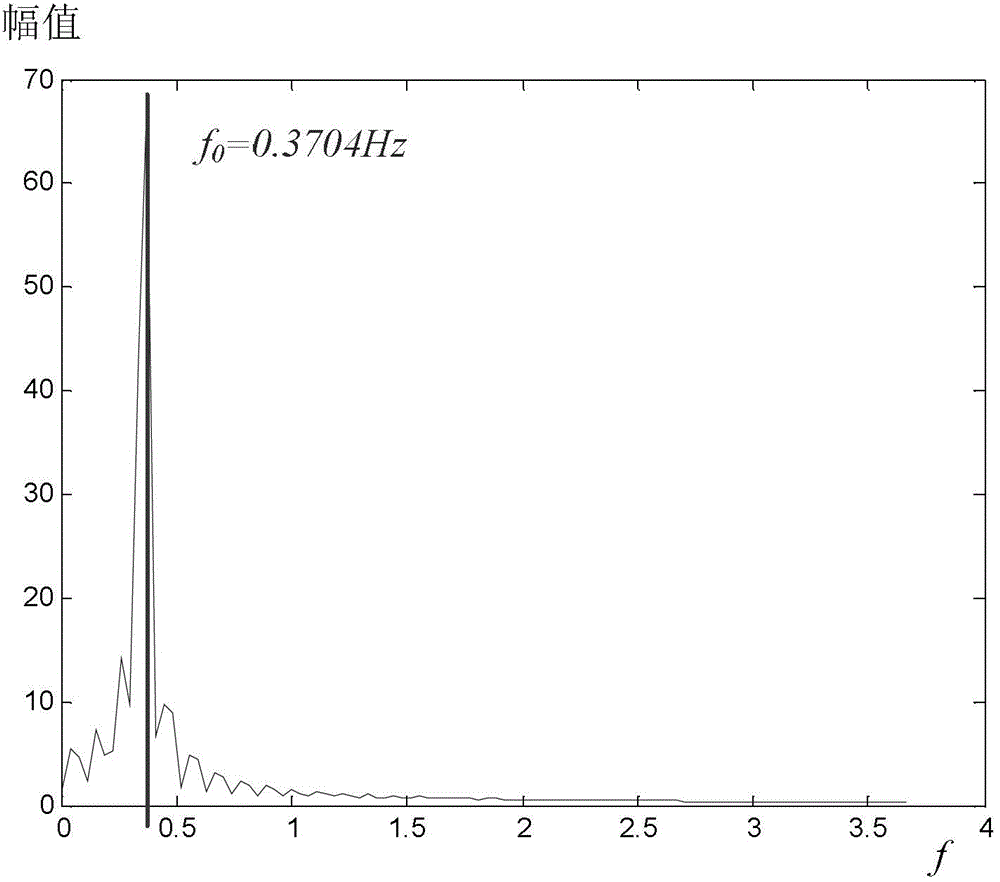

Rotational inertia frequency domain detection method based on floating torsion pendulum table

ActiveCN104155054AEasy to determineSmooth spectrum distribution curveStatic/dynamic balance measurementLaws of thermodynamicsDamping ratio

The invention provides a rotational inertia frequency domain detection method based on a floating torsion pendulum table, belonging to the technical field of rotational inertia detection. According to the method, a problem that an existing time domain measurement method of torsion method rotational inertia is influenced by a cycle measurement precision and finally the measurement precision of the rotational inertia is influenced is solved. The technical points of the method are that in the condition of a damping linear model, a pendulum motion differential equation can be written according to the law of rotation, the equation is solved to obtain the function of pendulum motion angle about time, an expression is subjected to approximate processing, a product term is subjected to power series expansion and a higher-order term is neglected, then the expression is subjected to continuous Fourier transform to obtain an analysis formula, finally the magnitude of the undamped natural vibration frequency of a detected product can be calculated according to the peak frequency and damping ratio, and the magnitude of the product rotational inertia is obtained. The method is mainly applied to the rotational inertia measurement of an air vehicle such as a missile, an interceptor and an unmanned aerial vehicle and can be applied to the rotational inertia measurement of other large equipment.

Owner:严格集团股份有限公司

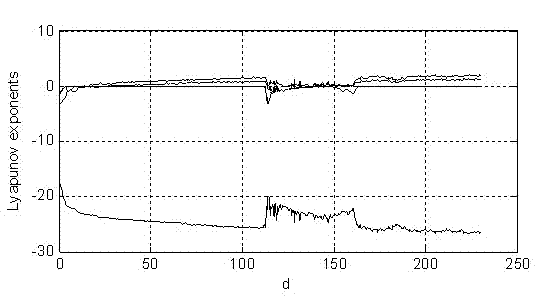

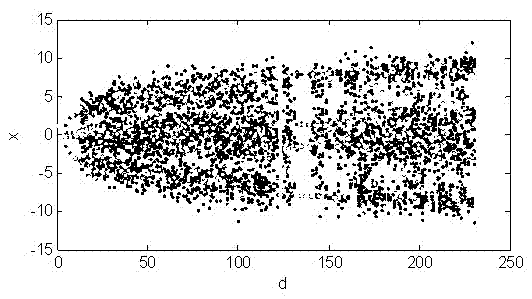

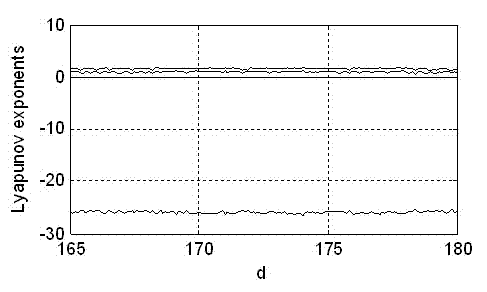

Dual-parameter constant-Lyapunov-exponent four-dimensional autonomous super-chaos system

InactiveCN103248473AEasy to implementRich Dynamic BehaviorSecuring communicationCapacitanceElectrical resistance and conductance

The invention discloses a dual-parameter constant-Lyapunov-exponent four-dimensional autonomous super-chaos system. The dual-parameter constant-Lyapunov-exponent four-dimensional autonomous super-chaos system comprises a math model and a realization circuit, and is characterized in that the realization circuit comprises a first channel circuit, a second channel circuit, a third channel circuit and a fourth channel circuit; the first channel circuit, the second channel circuit, the third channel circuit and the fourth channel circuit comprise three operational amplifiers, and auxiliary resistance and capacitor components that can realize four functions of the math model, respectively; and the realization circuit also comprises four analog multipliers used for realizing two quadratic product terms and a cubic product term of the math model. The realization circuit of the invention is simple in structure and convenient for integration, and can greatly promote the development of the chaos system in the technical fields of electronic measuring, weak signal detection, image encryption and privacy communication.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

Flexible macrocell interconnect

InactiveUS7161384B1Improve fitGood flexibilitySolid-state devicesLogic circuits using elementary logic circuit componentsProgrammable logic deviceEngineering

Methods and apparatus for novel routing structures and methods that improve fitting of user-defined functions onto programmable logic devices. In particular, second time fitting is improved. Exemplary structures and methods include allowing product terms to be expanded using inputs from more than one neighboring macrocell by providing multiple expansion and bypassing paths. Also, product term OR shifting prevents macrocell output stages from being buried and made inaccessible, and macrocell outputs are provided on expander word lines, increasing efficiency of those lines, as well as conserving routing resources. Expansion, bypassing, OR shifting, and expander word lines may terminate at logic array block boundaries or may continue beyond these boundaries to other logic array blocks.

Owner:ALTERA CORP

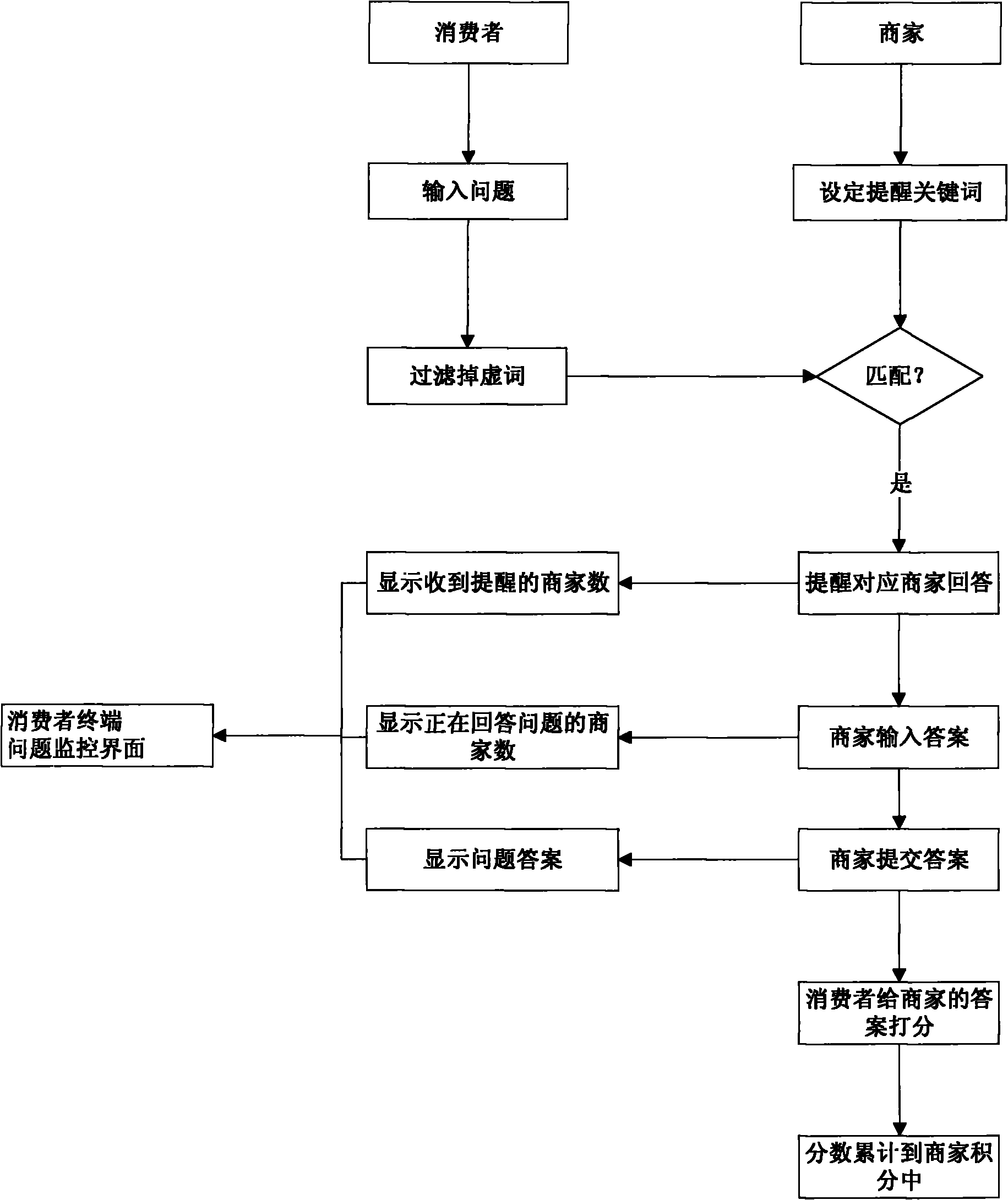

Problem-posing commodity information consultation method based on search engine technique

InactiveCN101882291AAccurate marketingCommerceSpecial data processing applicationsThe InternetSales promotion

The invention discloses a problem-posing commodity information consultation method based on a search engine technique, which relates to the technique of the computer Internet. The method comprises the following steps that a merchant stores commodities and the resoluble consumer's problem information of the commodities to a data base; a consumer inputs knotty problems in life, and then a computer searches in the data base to find out the commodity capable of solving the problems of the consumer, and the problems of the consumer are immediately transmitted to the merchant in front of the computer to remind the merchant of carrying out online solution; the consumer can grade answers provided by the merchant; the mark can be accumulated to the account number of the merchant and is used for deciding the rank of the commodity of the merchant in a search results. By adopting the method, as long as the problems that the consumer meet in lift are input, the consumer can find products and service for solving the problems without mastering any product term; similarly, the merchant can accurately carry out sales promotion on target users without carrying out large-scale propaganda.

Owner:万昌洵 +1

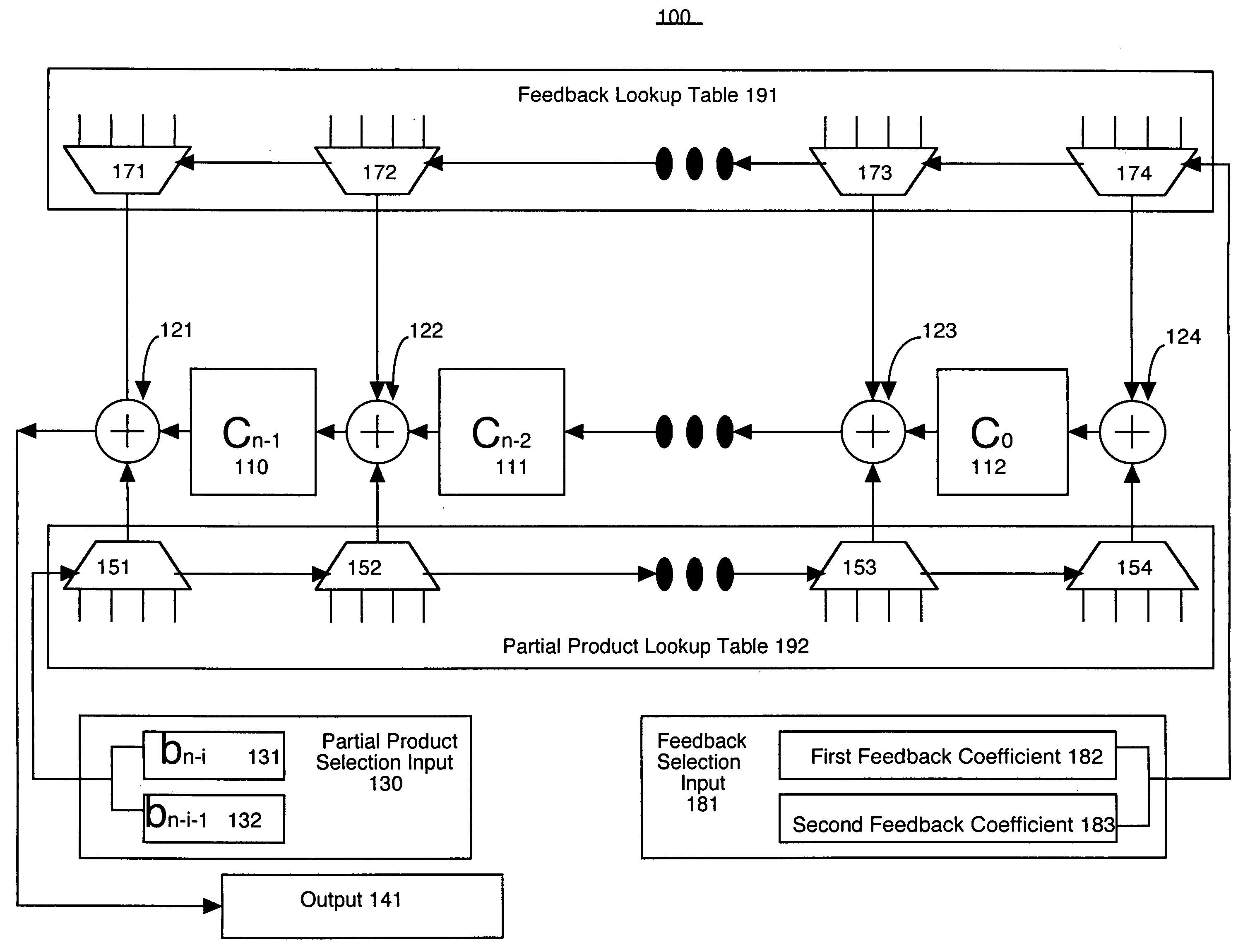

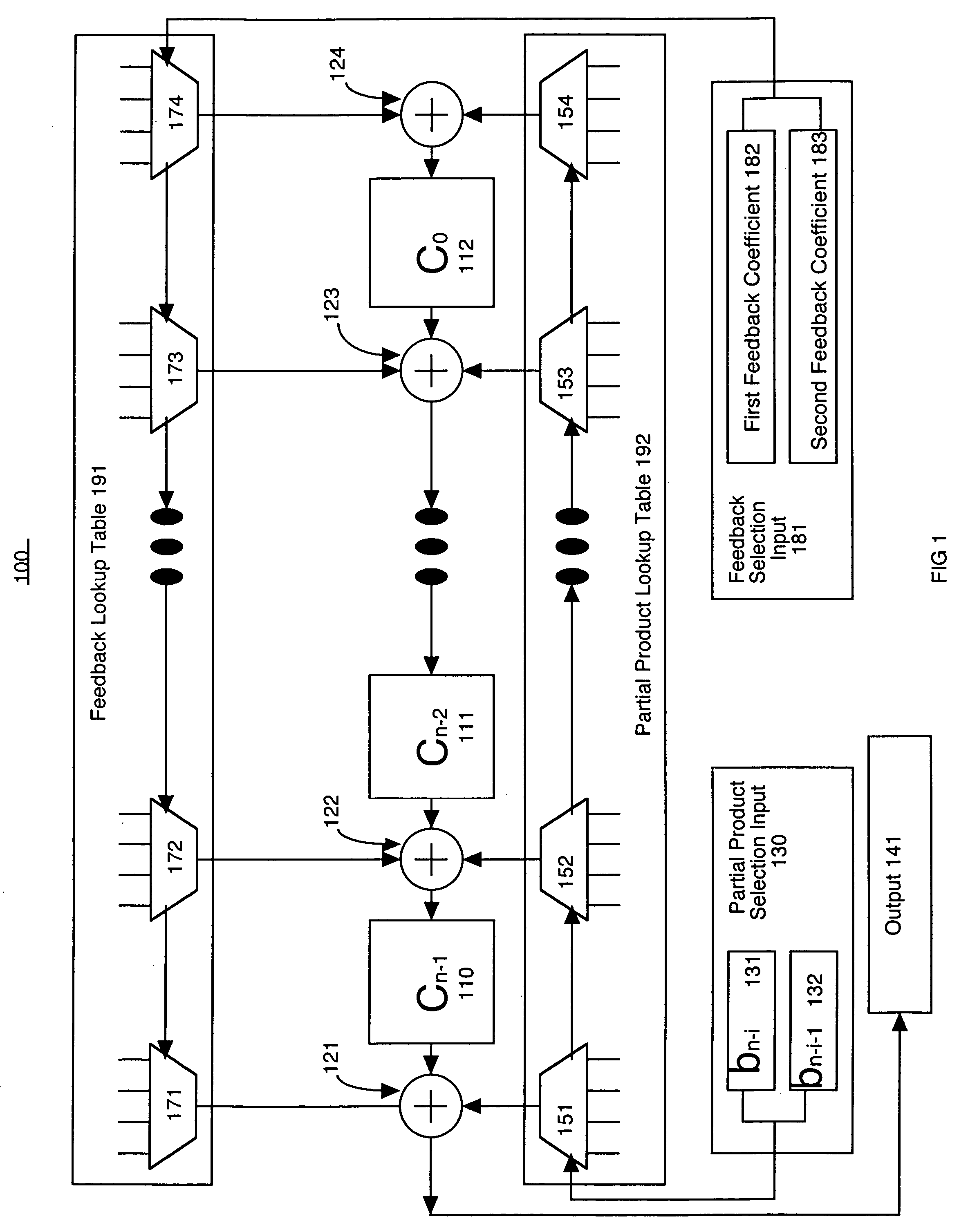

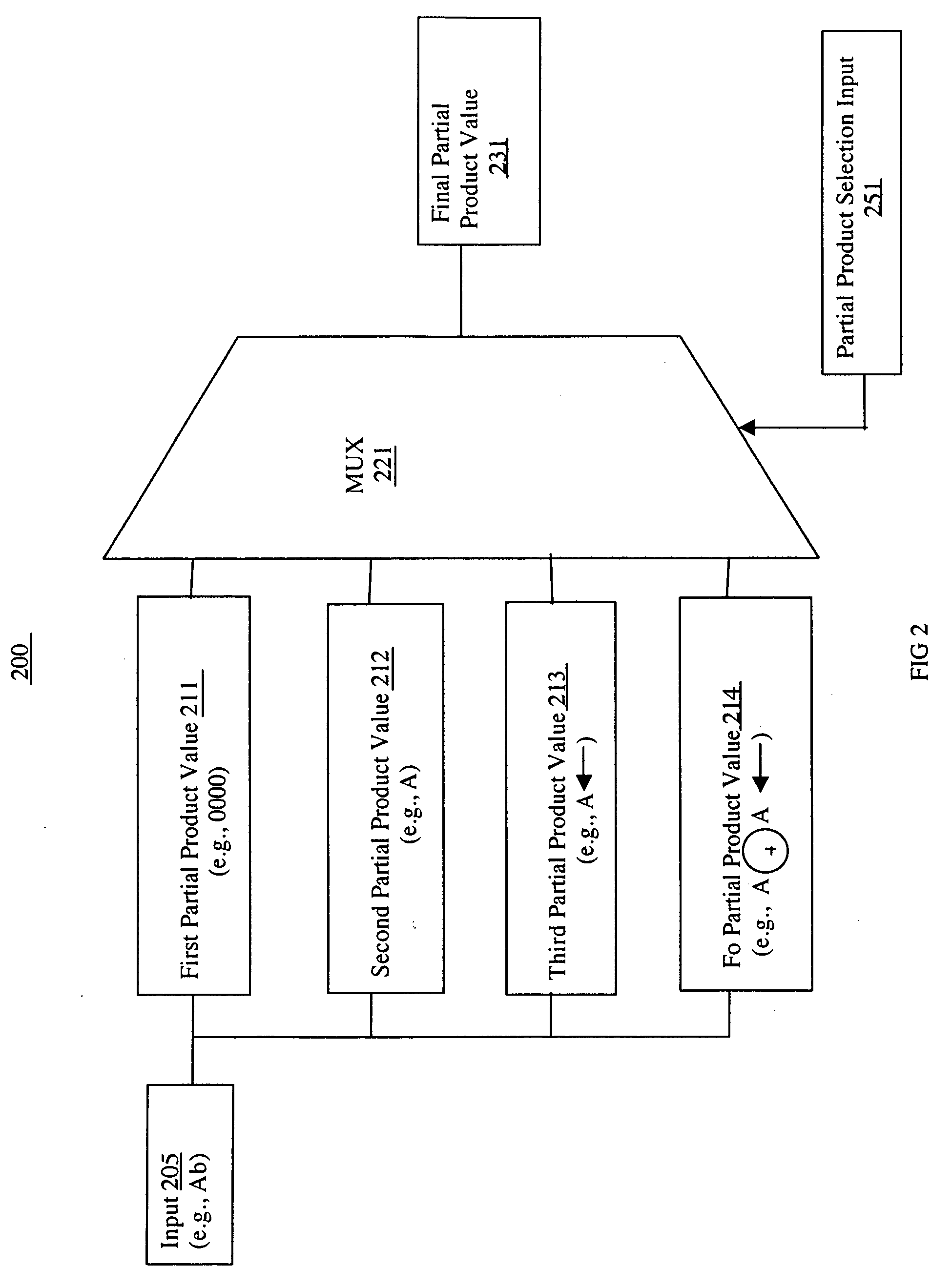

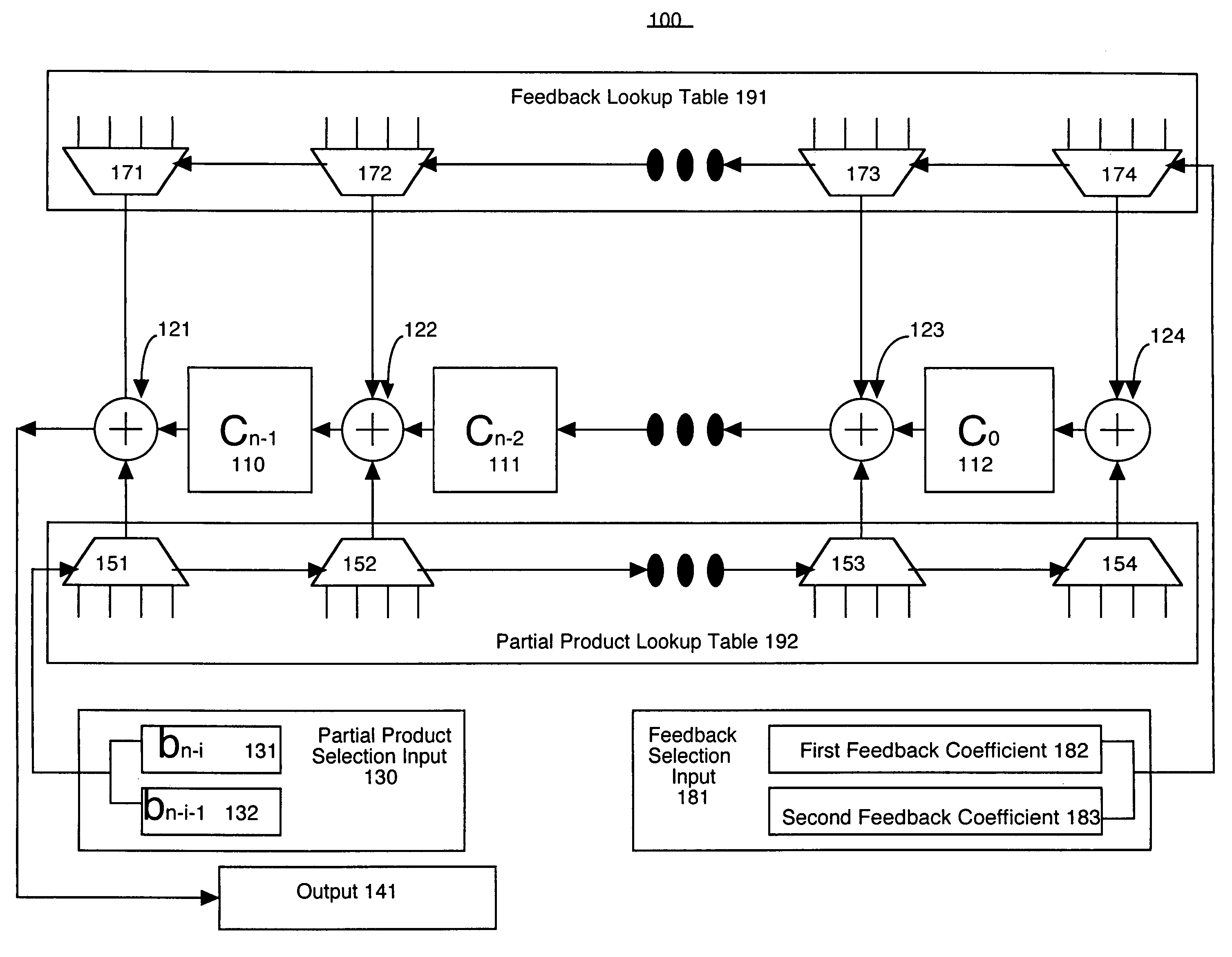

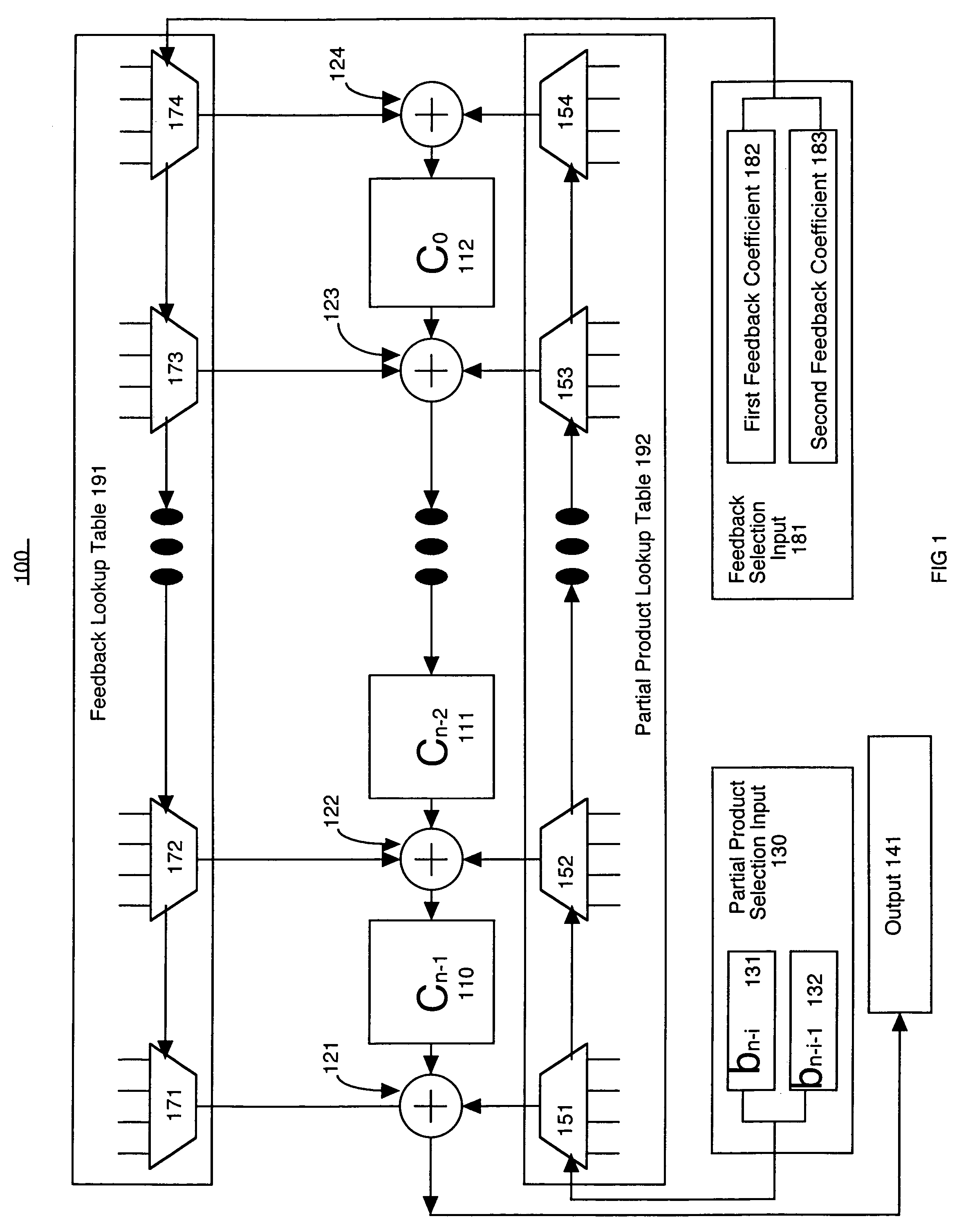

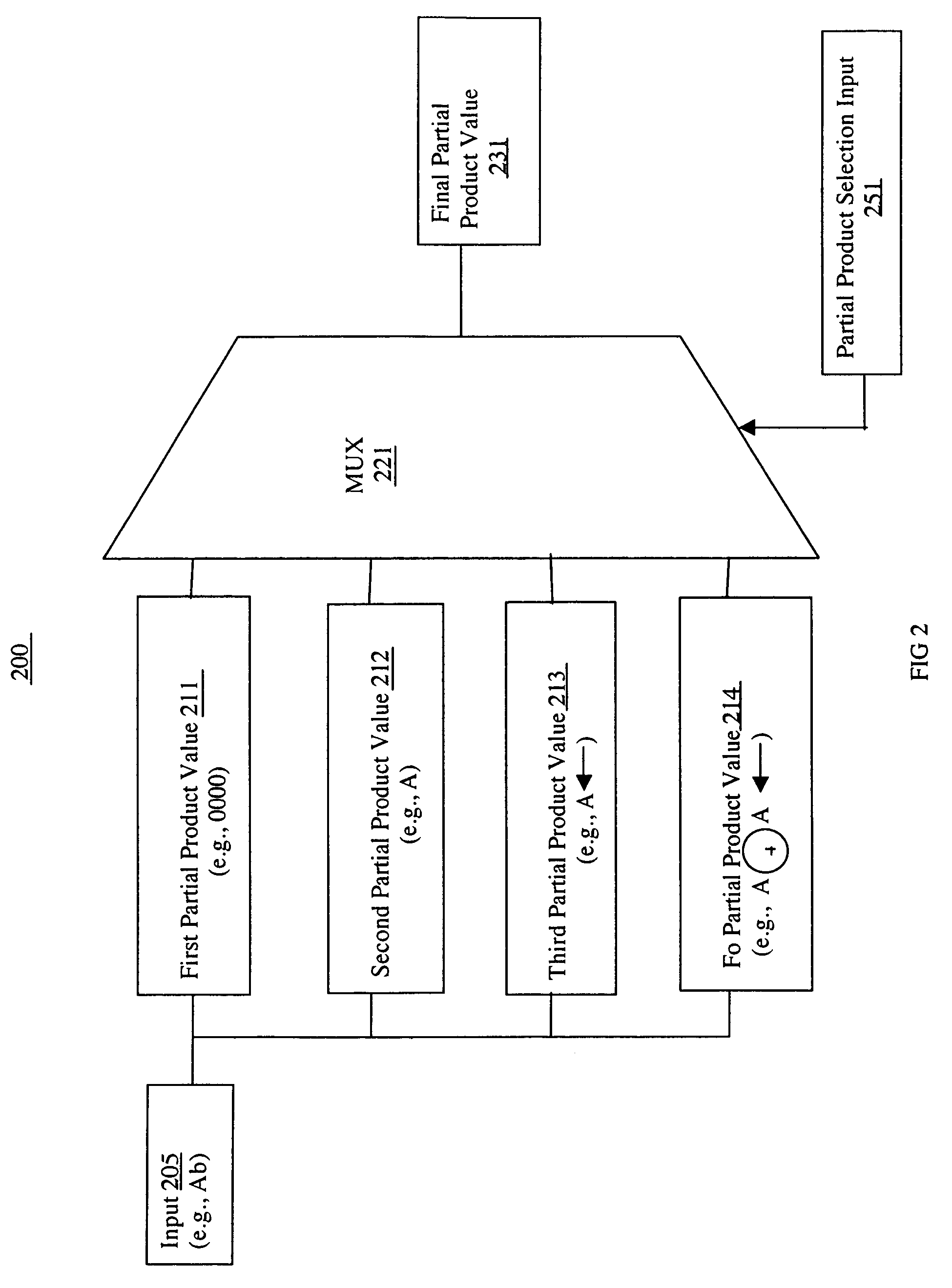

Galois field multiplication system and method

InactiveUS20060080376A1Digital data processing detailsDigital computer detailsShift registerExclusive or

A present invention Galois field multiplier system and method utilize lookup tables to generate one partial product term and one feedback term in one clock cycle. In one embodiment, a Galois field multiplier system includes a plurality of shift registers, a plurality of exclusive OR components, a partial product lookup table, and a feedback table lookup table. The plurality of shift registers perform shift multiplication operation and are coupled to the plurality of shift registers that perform addition operations. The partial product lookup table and feedback lookup tables are selectively coupled to the exclusive OR components and values from the partial product lookup table and feedback lookup tables are fed into the selectively coupled exclusive OR components. Coefficients of the partial product term and feedback term are utilized as indexes to the partial product lookup table and feedback lookup table respectively.

Owner:CISCO TECH INC

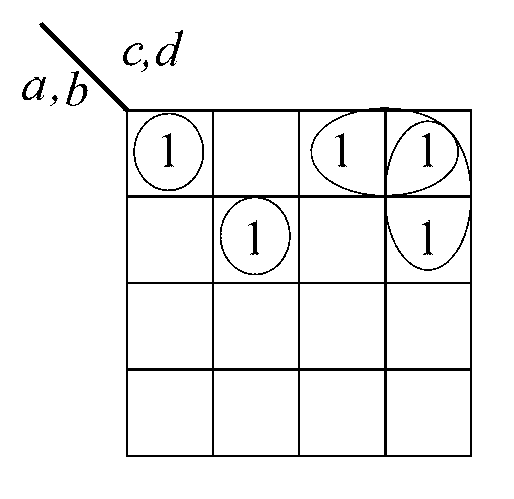

Method for reducing area of digital logic circuit

InactiveCN101488745AReduce areaLogic circuits using elementary logic circuit componentsLogic optimizationTheoretical computer science

The invention discloses a method for reducing the area of a digital logical circuit; a specific product term is generated and added in an optimized function by using characteristics of exclusive OR operation 1 OR 1=0; as the new product term is added, original logically nonadjacent product terms become logically adjacent due to the inserting of added items so as to realize logic optimization; the advantages are as follows: two product terms do not constitute an OR expression right now but an added item p is firstly generated after the two product terms are judged to have a broad hamming distance of 2, and then whether the added item p is fit for simplification of function is judged by a corresponding evaluation method. As the complexity of the logic function is closely related with the complexity of the corresponding digital circuit, simple logic function always corresponds to smaller circuit area, thereby achieving the purpose of reducing the area of digital logic circuit by a method for simplifying the logic function.

Owner:NINGBO UNIV

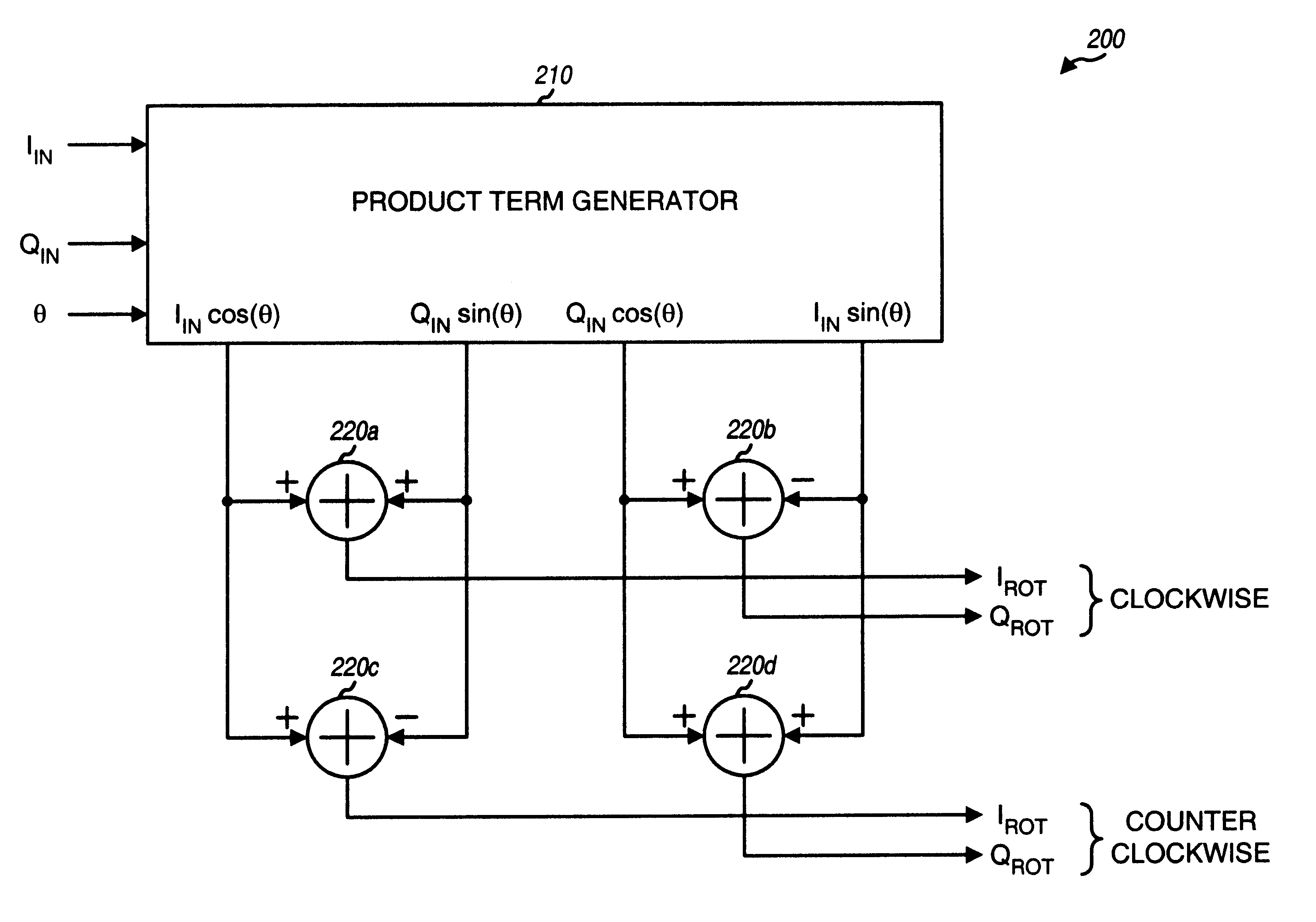

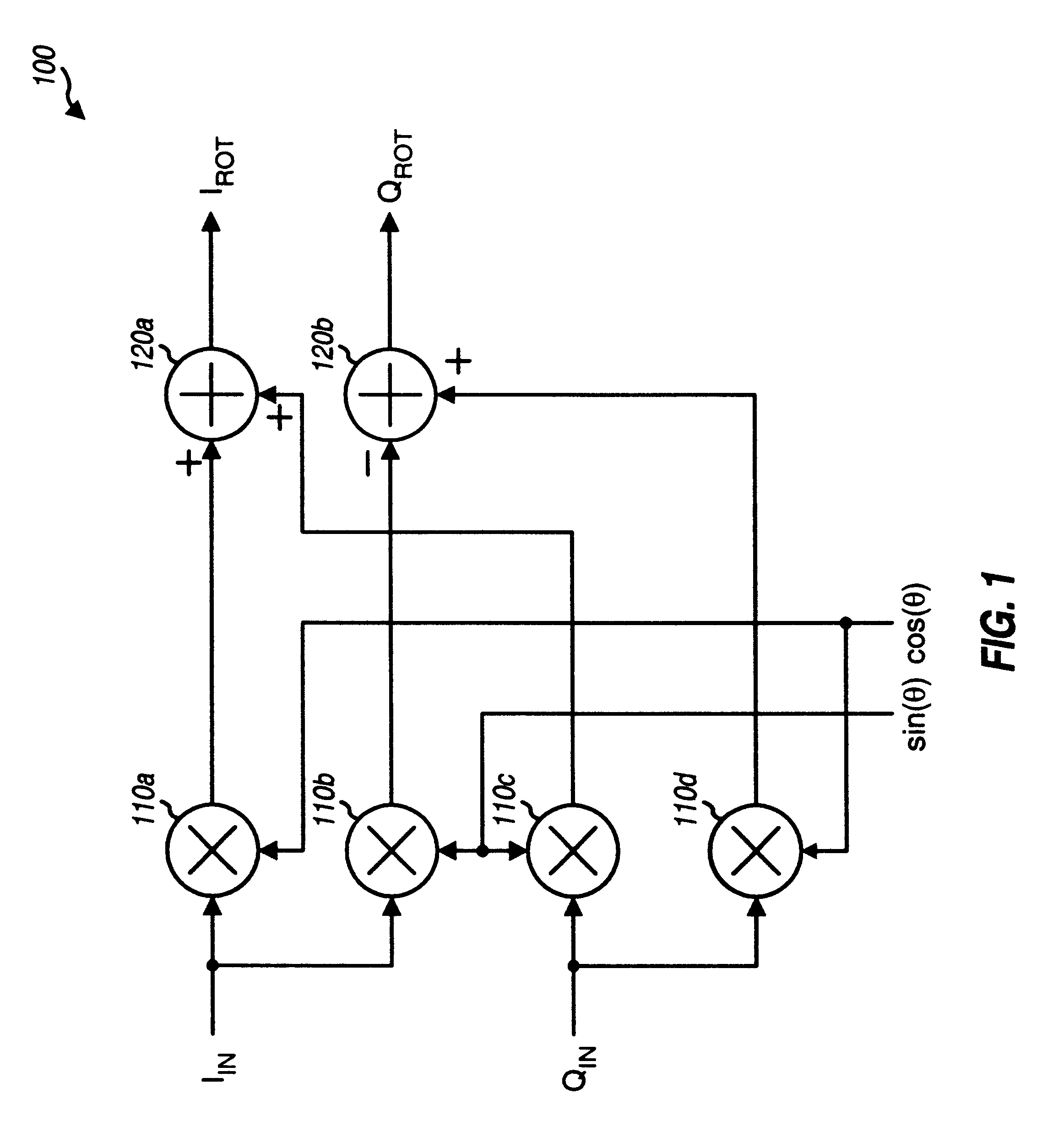

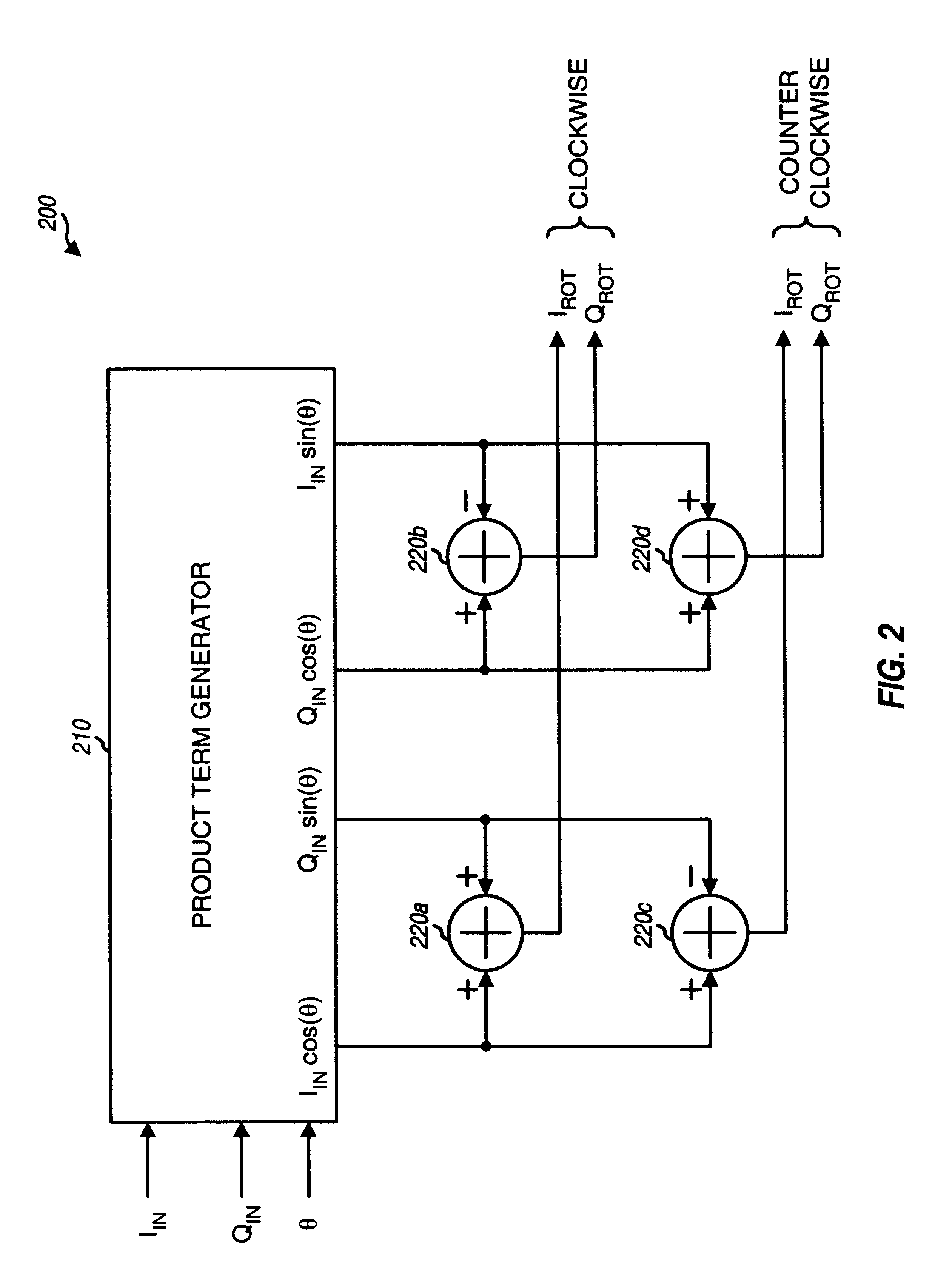

Bi-directional vector rotator

InactiveUS6661851B1Carrier regulationFrequency/rate-modulated pulse demodulationInput selectionCarrier signal

A bi-directional vector rotator that can be used to provide outputs having phases that are rotated in clockwise and counter clockwise directions relative to that of the input signal. The bi-directional vector rotator includes a product term generator that receives a complex input and a complex carrier signal and generates product terms. Combiners then selectively combine the product terms to generate the outputs. By sharing the same product term generator for both clockwise and counter clockwise phase rotations, the bi-directional vector rotator can be implemented using less circuitry than that for a conventional design employing two uni-directional vector rotators. Moreover, only one complex carrier signal is needed by the bi-directional vector rotator instead of two for the conventional design. Further simplification in the design of the bi-directional vector rotator can be achieved by selecting the proper sampling rate for the complex input. The bi-directional vector rotator can be advantageously used in a receiver device, and is especially efficient in demodulating a multi-carrier signal having multiple (e.g., three) modulated signals.

Owner:QUALCOMM INC

Method for reducing area of digital logic circuit

InactiveCN102185606AReduce areaLogic circuits using elementary logic circuit componentsLogic optimizationTheoretical computer science

The invention discloses a method for reducing area of a digital logic circuit. By utilizing the characteristic of xor operation, a specified product term is generated and added into the optimized function; owning to the adding of the new product term, the original product term with nonadjacent logics becomes logically adjacent owning to the interposing of the product term, thus realizing logic optimization; the method has the advantages that after the existence of two product terms with the generalized hamming distance of 2 is judged, the two product terms do not form an xor expression immediately; a corresponding addition term is generated; and subsequently whether the addition term is suitable for function simplification is judged by a corresponding evaluation method. As the complexity of the logic function is related to the complexity of the corresponding digital circuit, the simple logic function always corresponds to a smaller circuit area; and the aim of reducing the area of digital logic circuit can be achieved by the method of simplifying logic function.

Owner:NINGBO UNIV

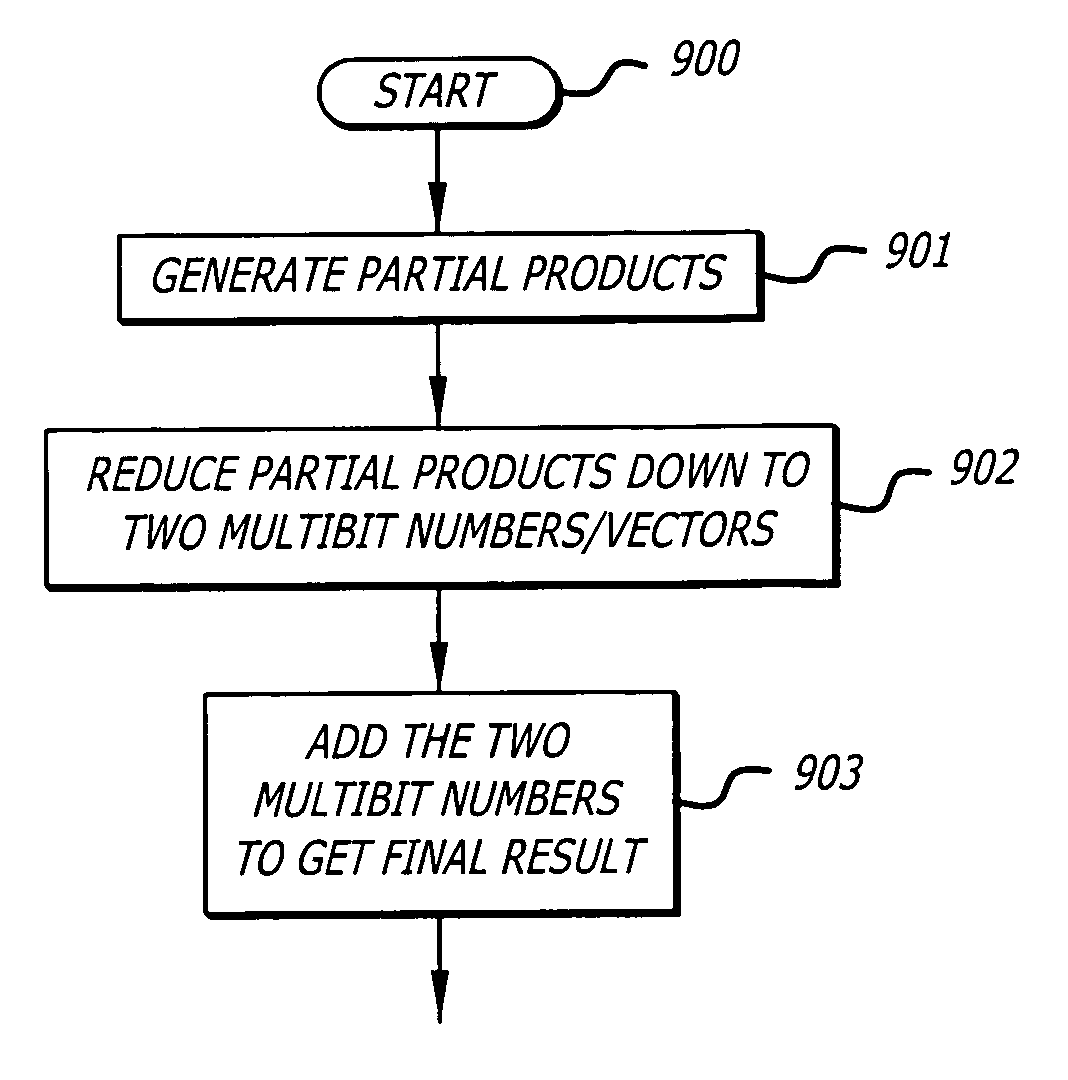

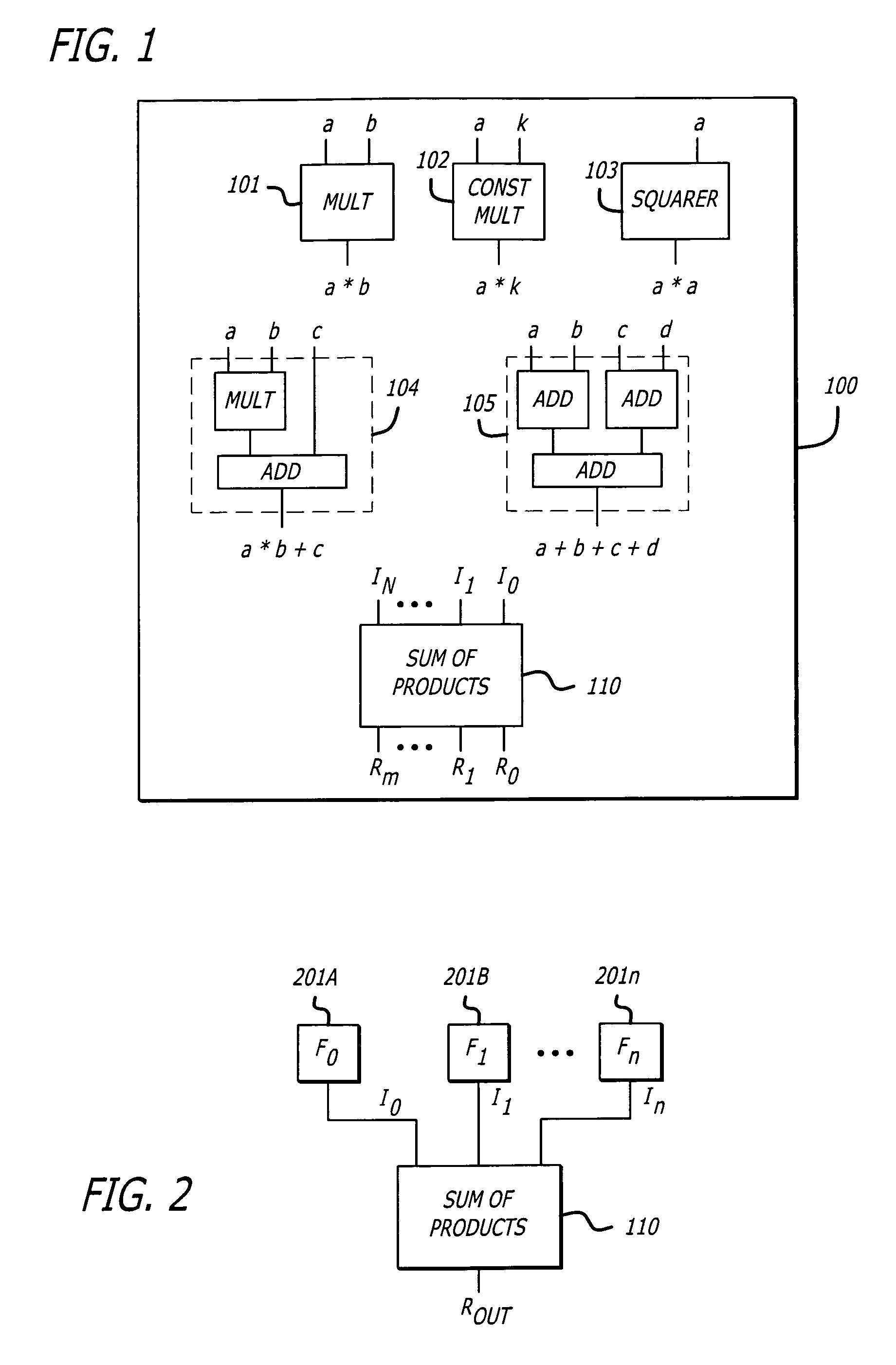

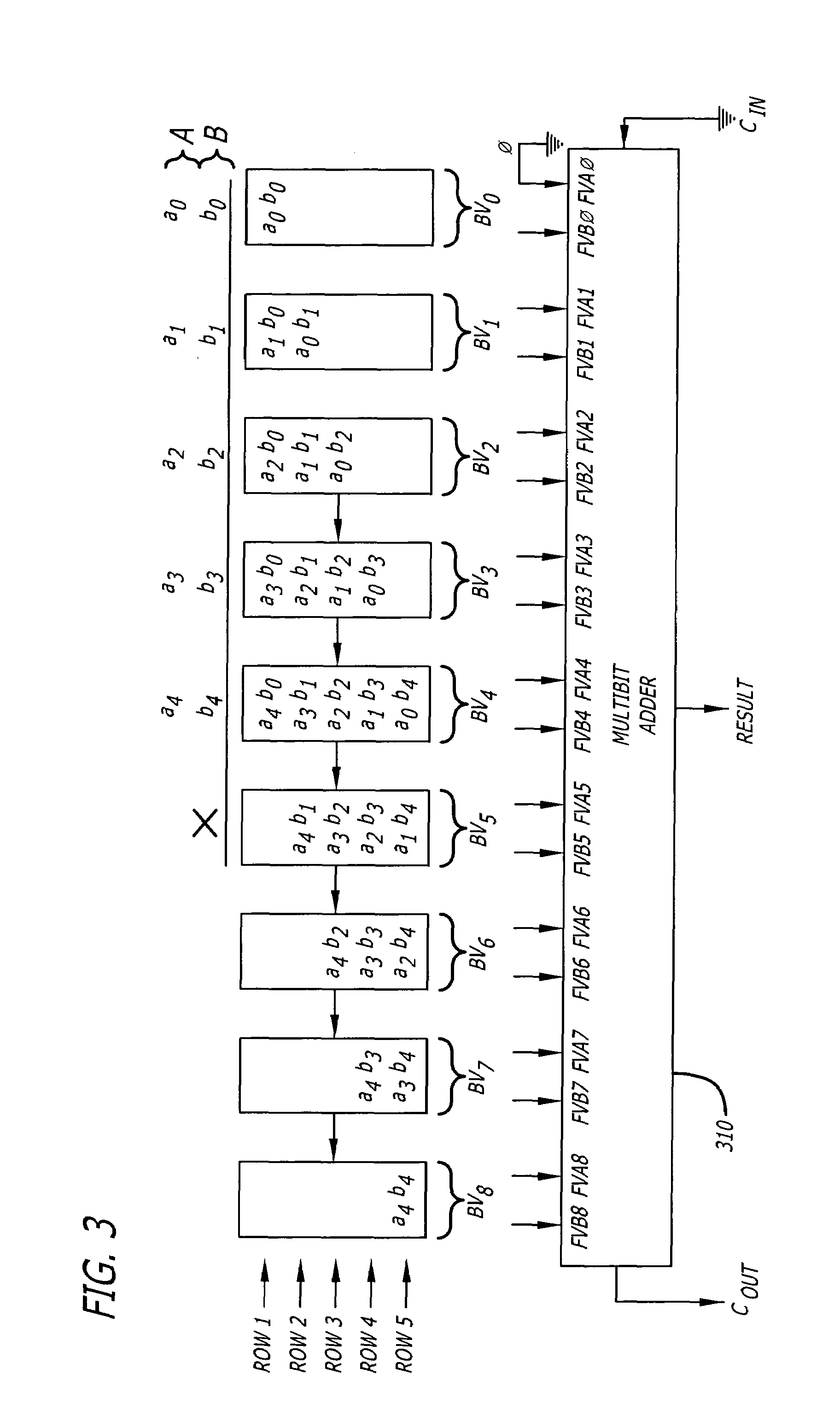

Timing driven synthesis of sum-of-product functional blocks

ActiveUS7739324B1Digital data processing detailsDigital computer detailsPartial product reductionProcessor register

In one embodiment of the invention, an integrated circuit (IC) design tool is provided that has a sum-of-products (SOP) synthesizer. The SOP synthesizer receives expected arrival times of signals including partial product terms of each bit-vector of a SOP functional block, a comparison gate delay, and a register-transfer-level (RTL) netlist in order to synthesize a gate-level netlist of the SOP functional block. The SOP synthesizer includes software modules to synthesize a partial products generator, a partial product reduction tree, and an adder. The synthesis of the partial product reduction tree is responsive to a comparison gate delay and the expected arrival times of the partial product terms in each bit vector.

Owner:CADENCE DESIGN SYST INC

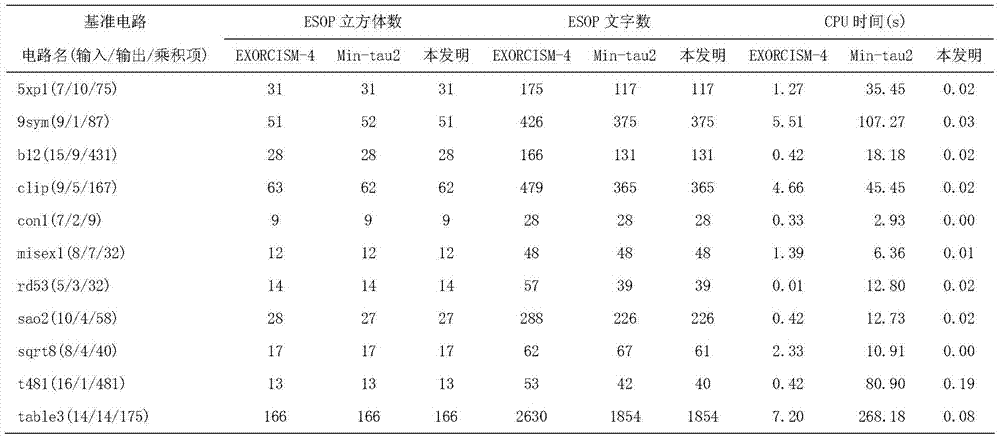

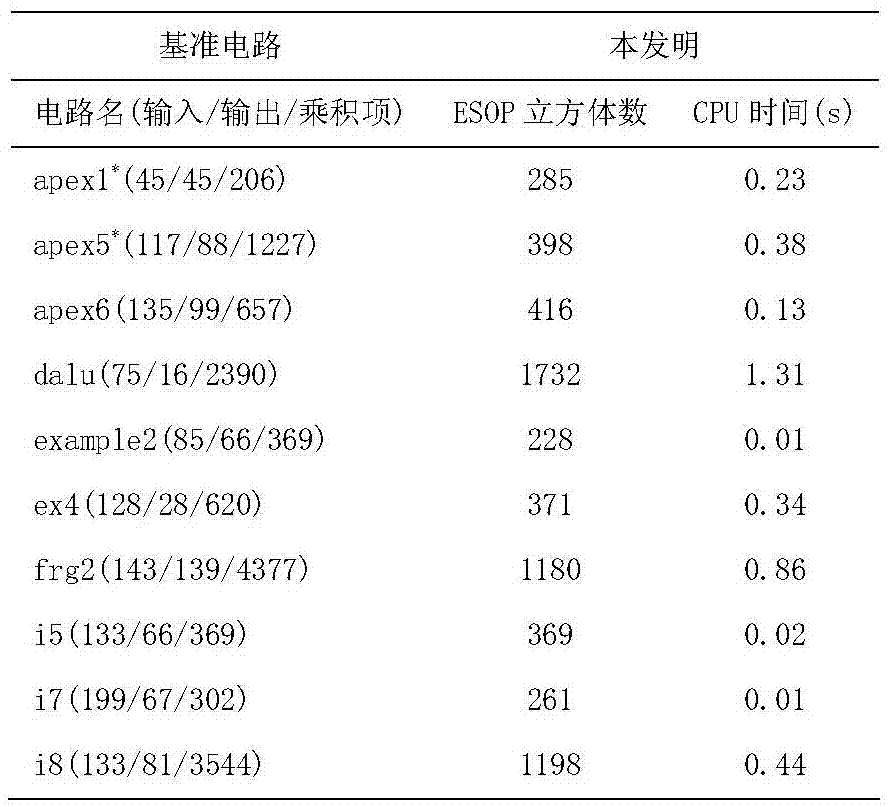

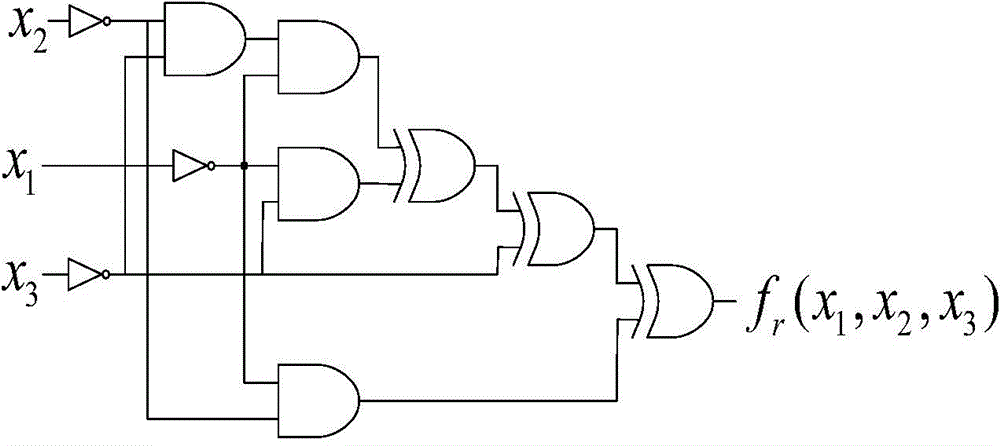

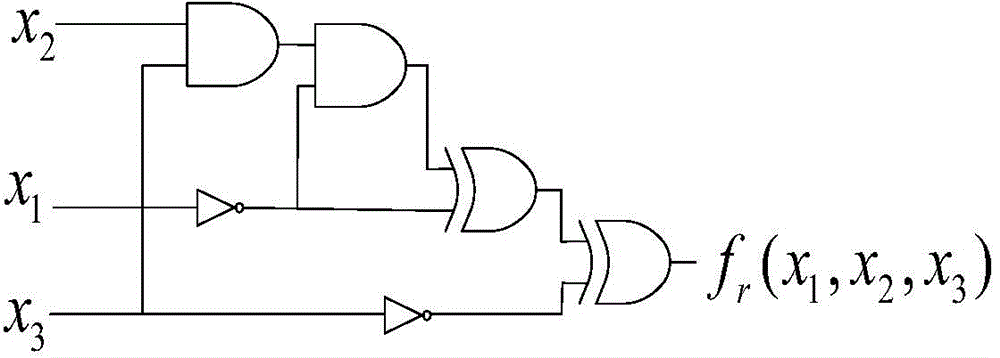

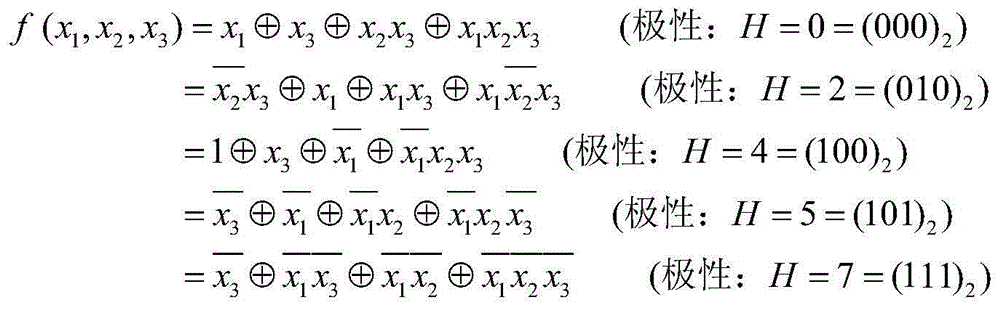

ESOP minimization method for logic function

InactiveCN105447241AMinimizeGet rid of constraintsComputer aided designSpecial data processing applicationsSearch problemRound complexity

The present invention discloses an ESOP minimization method for a logic function. By converting the optimal coverage searching problem of a 3n global space in the ESOP minimization process of an n variable logic function into the simplest connection problem in a plurality of cube blocks, a search space is reduced, thereby breaking away from a constraint of a variable scale; moreover, a cube set is directly operated without being converted into a minterm set, so that limitation to a product term number is avoided; and in order to achieve accurate minimization of rapid ESOP, a minimized conversion algorithm of a cube EXOR conversion diagram is adopted to improve operation efficiency so as to effectively reduce calculation complexity and a memory occupied quantity, and the characteristics that calculation time is insensitive to the number of input variables and is only related to the number of product terms included by the logic function and intersection can effectively achieve an effect that random n variables totally regulate the ESOP minimization of the logic function. The ESOP minimization method has the advantages of no limitation to the number of the product items and the number of the variables in the logic function and capacity of carrying out minimization processing on an ESOP of a random logic function.

Owner:ZHEJIANG WANLI UNIV

Polarity fast conversion method for Reed-Muller logic circuit

ActiveCN104539298AScale upAvoid searchingError correction/detection using linear codesElectrical polarityRepeatability

The invention discloses a polarity fast conversion method for a Reed-Muller logic circuit. Fixed polarity conversion of the RM logic is achieved through the method for deleting common parts in the logic coverage corresponding to different product terms, the steps such as product term expanding, searching and deleting in a previous RM logic polarity conversion process are omitted, multiple times of expanding, repeated product term searching and deleting operation do not need to be conducted on the product terms in the whole searching process, only one time of product term expanding needs to be conducted in the whole process, repeated examination does not need to be conducted, and therefore the conversion speed is higher in the RM logic polarity conversion process through the method, the scale of circuits which can be processed is larger, and the method has higher efficiency in the aspect of polarity searching.

Owner:NINGBO UNIV

Method for determining best and worst cases for interconnects in timing analysis

ActiveUS7739095B2Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingPropagation delayCapacitance

Roughly described, signal propagation delay values are estimated for a plurality of interconnects in a circuit design. For each interconnect, the propagation delay value(s) are estimated in dependence upon a preliminary approximate determination of whether the signal propagation delay is dominated more by an interconnect capacitance term or by an interconnect capacitance and resistance product term. If it is dominated more by the interconnect capacitance term, then the parameter values used for a minimum propagation delay calculation are obtained assuming a smallest capacitance process variation case and the parameter values used for a maximum propagation delay calculation are obtained assuming a largest capacitance process variation case. If the signal propagation delay is dominated more by the interconnect capacitance and resistance product term, then the opposite assumptions are made. Preferably the approximate determination is made by comparing Rint to k*Rd.

Owner:SYNOPSYS INC

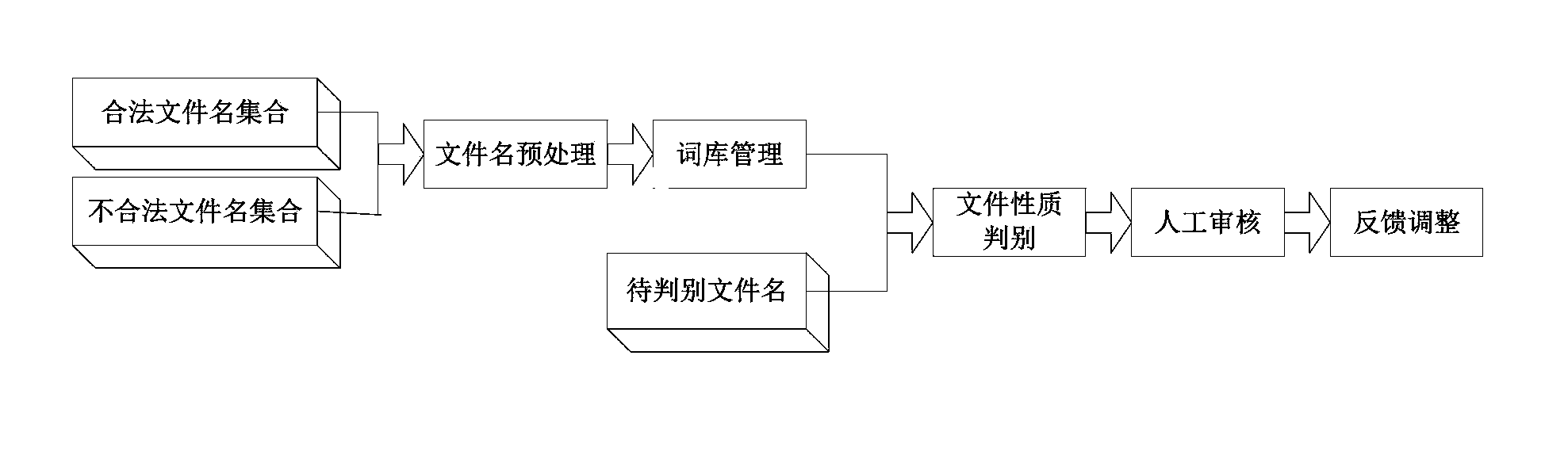

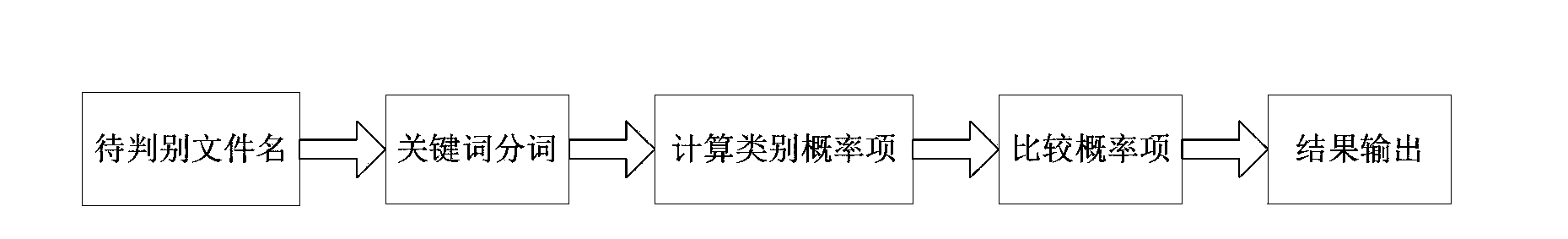

Neural-network-based self-learning semantic detection method and system

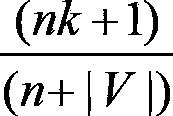

InactiveCN103853701ATimely Correct Semantic DiscriminationSolve the problem of not detecting semantics correctlySpecial data processing applicationsSemanticsData mining

The invention discloses a neural-network-based self-learning semantic detection method and system. The method includes the steps: 101, a dictionary base is imported to segment filenames to be recognized so as to obtain keywords in the filenames, and a probability item of each keyword is calculated on the basis of a Bayesian algorithm; the probability items are analyzed and acquired on the basis of judgment results of good or bad filenames; 102, a product of multiplying a product of probabilities of all keywords occurring in good semantic string names and prior probabilities of the good semantic string names is obtained; a product of multiplying a product of probabilities of all keywords occurring in bad semantic string names and prior probabilities of bad semantic string names is obtained; 103, the two products are compared; if the product item of the good semantic string is larger than that of the bad semantic strings, the strings are determined as to have good semantics; if not, the strings are determined to have bad semantics; judgment results are stored in a storage medium.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI +1

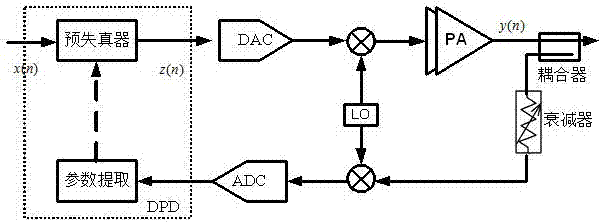

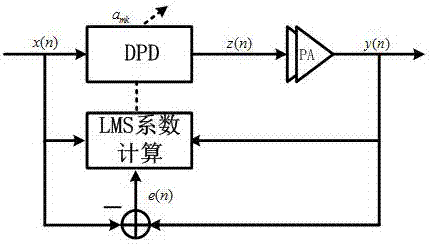

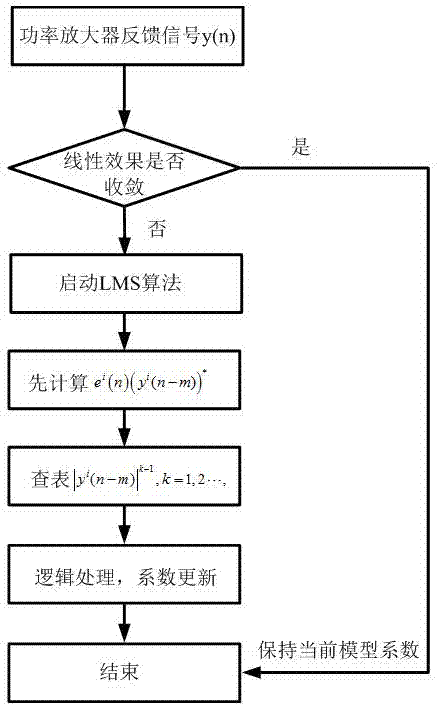

Digital pre-distortion adaptive processing method

InactiveCN108011598ASave resourcesAvoid errorsAmplifier modifications to reduce non-linear distortionCommunications systemBinary multiplier

The invention discloses a digital pre-distortion adaptive processing method, and relates to the technical field of wireless communication system signal processing. According to the method, in an LMS coefficient updating algorithm, magnitude high order terms are mapped into a lookup table, errors caused by the quantification bit width and the bit cut effect during FPGA fixed-point operation are reduced, then same product terms of factors are calculated step by step, multiplier resources consumed by the coefficient updating algorithm are reduced, and then the power consumption of an FPGA is reduced.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

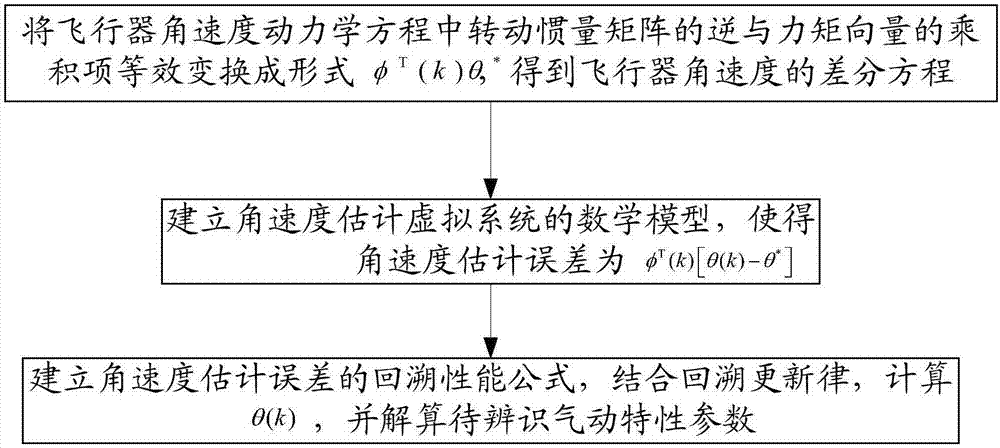

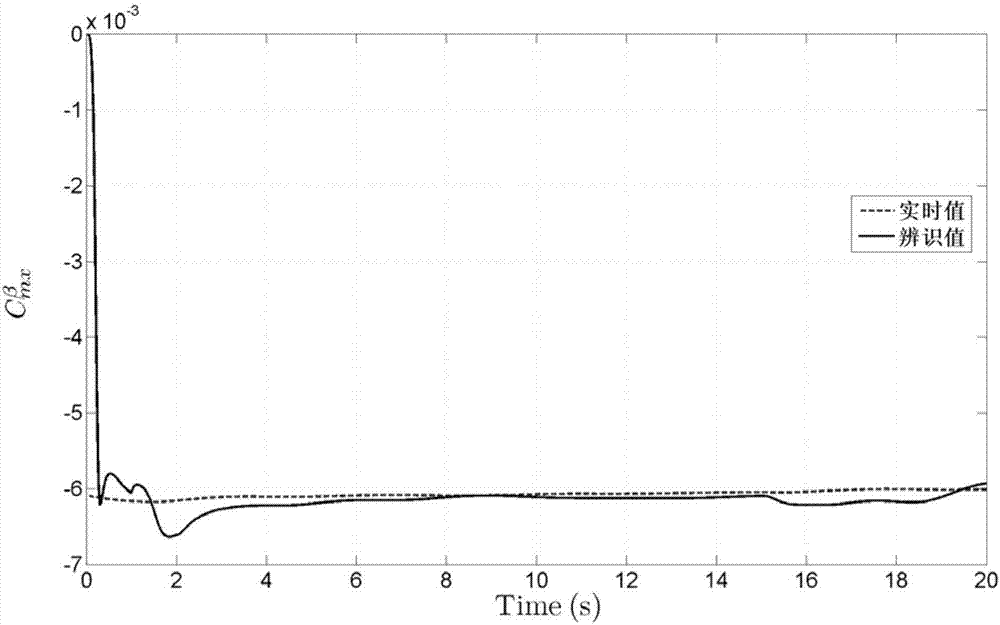

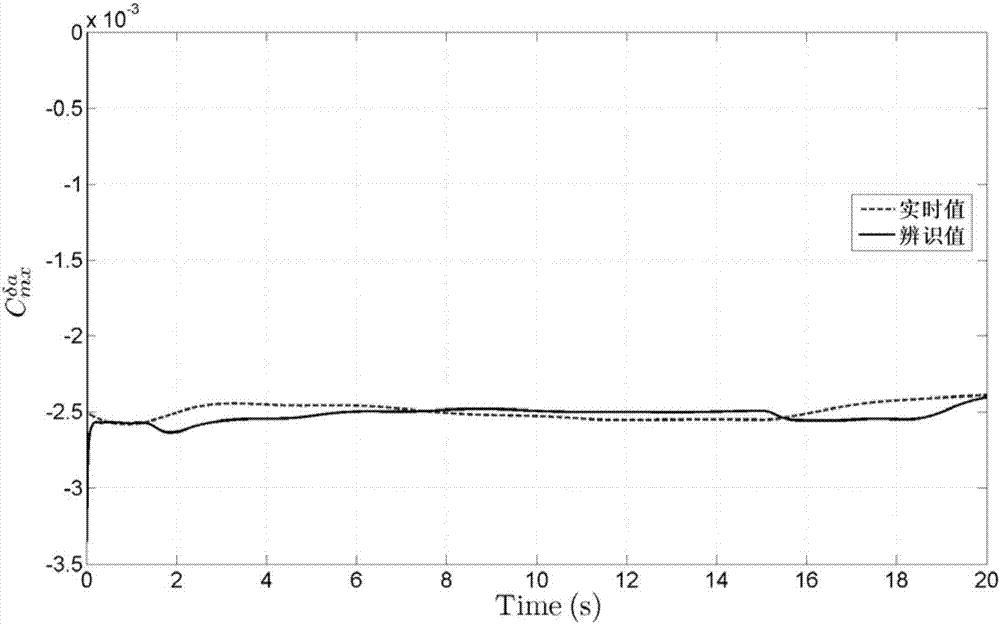

Aircraft aerodynamic characteristic on-line identification method based on backtracking self-adaptive algorithm

ActiveCN107976296ALower requirementSimplify the design processAerodynamic testingAircraft components testingLow demandAngular velocity

The invention provides an aircraft aerodynamic characteristic on-line identification method based on a backtracking self-adaptive algorithm. The aircraft aerodynamic characteristic on-line identification method comprises steps: (1) equivalently transforming the product term of the inverse of a rotational inertia matrix and a moment vector in an aircraft angular velocity kinetic equation into a Phi<T>(k)Theta* form, carrying out discretization processing on the transformed product term, and obtaining an aircraft angular velocity difference equation; wherein Phi<T>(k) represents a signal vector,Theta* represents a parameter truth vector, and the parameter truth vector is a column vector including an aerodynamic characteristic parameter to be identified; (2) establishing a mathematical modelof an angular velocity estimation virtual system, and making an angular velocity estimation error and a parameter estimation error be Phi<T>(k)[Theta(k)-Theta*], wherein Theta(k) represents an estimated value of the parameter truth vector; (3) establishing a backtracking performance formula of the angular velocity estimation error, combining a backtracking updating rule to obtain Phi (k) in realtime, resolving the Theta(k) by means of the backtracking self-adaptive algorithm, making the angular velocity estimation error omega-wave(k) approach zero, and resolving the aerodynamic characteristic parameter to be identified according to the value of the Theta(k). The aircraft aerodynamic characteristic on-line identification method has a lower calculated amount and a lower demand on the computer, and has operability.

Owner:BEIJING LINJIN SPACE AIRCRAFT SYST ENG INST +1

Galois field multiplication system and method

InactiveUS7526518B2Digital data processing detailsDigital computer detailsShift registerExclusive or

A present invention Galois field multiplier system and method utilize lookup tables to generate one partial product term and one feedback term in one clock cycle. In one embodiment, a Galois field multiplier system includes a plurality of shift registers, a plurality of exclusive OR components, a partial product lookup table, and a feedback table lookup table. The plurality of shift registers perform shift multiplication operation and are coupled to the plurality of shift registers that perform addition operations. The partial product lookup table and feedback lookup tables are selectively coupled to the exclusive OR components and values from the partial product lookup table and feedback lookup tables are fed into the selectively coupled exclusive OR components. Coefficients of the partial product term and feedback term are utilized as indexes to the partial product lookup table and feedback lookup table respectively.

Owner:CISCO TECH INC