ESOP minimization method for logic function

A logic function and minimization technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as reduced efficiency of simplification, difficulty in solving ESOP minimization, and inability to ensure ESOP.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

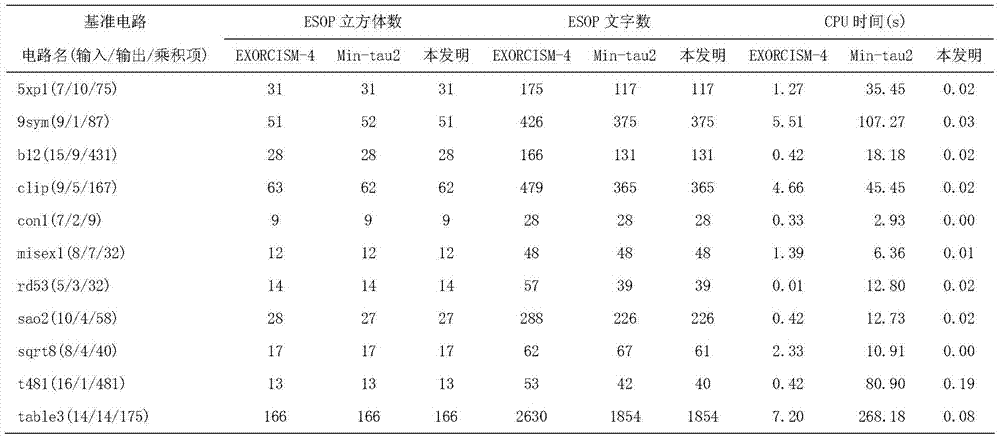

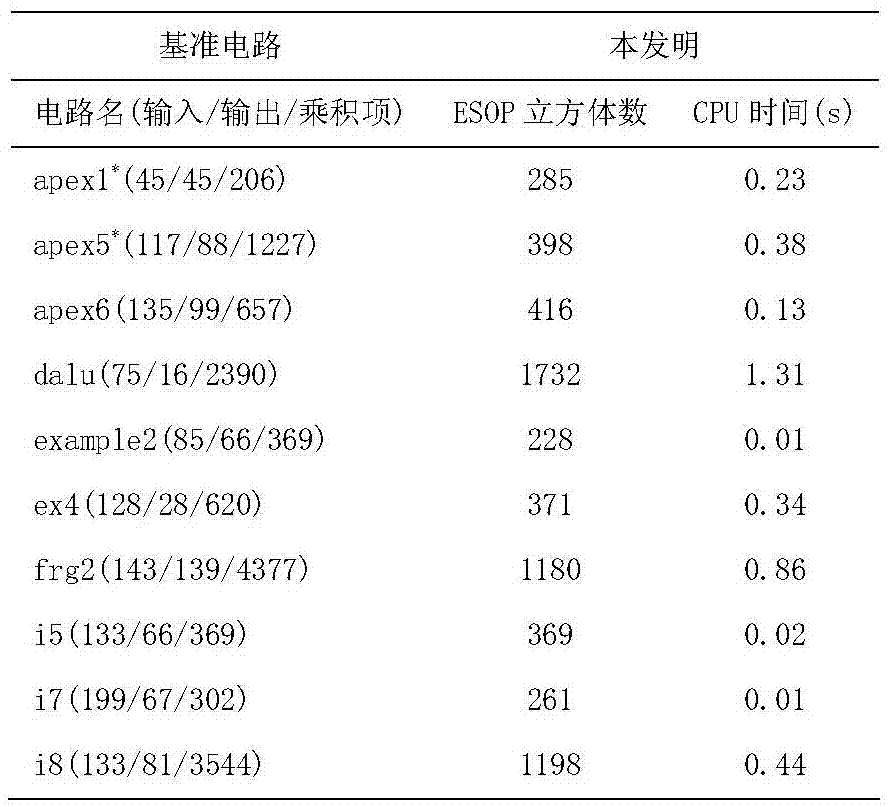

Examples

Embodiment

[0038] Embodiment: a kind of ESOP minimization method of logistic function, comprises the following steps:

[0039] ① Read in the ESOP formula of the logic function n is the number of variables of the logic function f and n>3, k is an integer and 1≤k≤n, (x n ,x n-1 ,...,x k ,...,x 1 ) are n input variables of ESOP formula f, i is an integer and 0≤i≤3 n -1; π i is the ith cube of ESOP formula f, π i Expressed as a sequence of input variables as in Indicates the kth input variable x k in cube π i The appearance form in will be are called variable literals, or literals for short, when When , the kth input variable x k in cube π i The original variable x k appear when When , the kth input variable x k in cube π i China-Israel contravariant appear when When , the kth input variable x k in cube π i does not appear in; b i is the cube π i Coefficient of b i is a constant and b i ∈{0,1}, when b i =0, the cube π i does not exist in ESOP formula f, whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More