Patents

Literature

435 results about "Digital logic circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Storage elements using nanotube switching elements

Owner:NANTERO

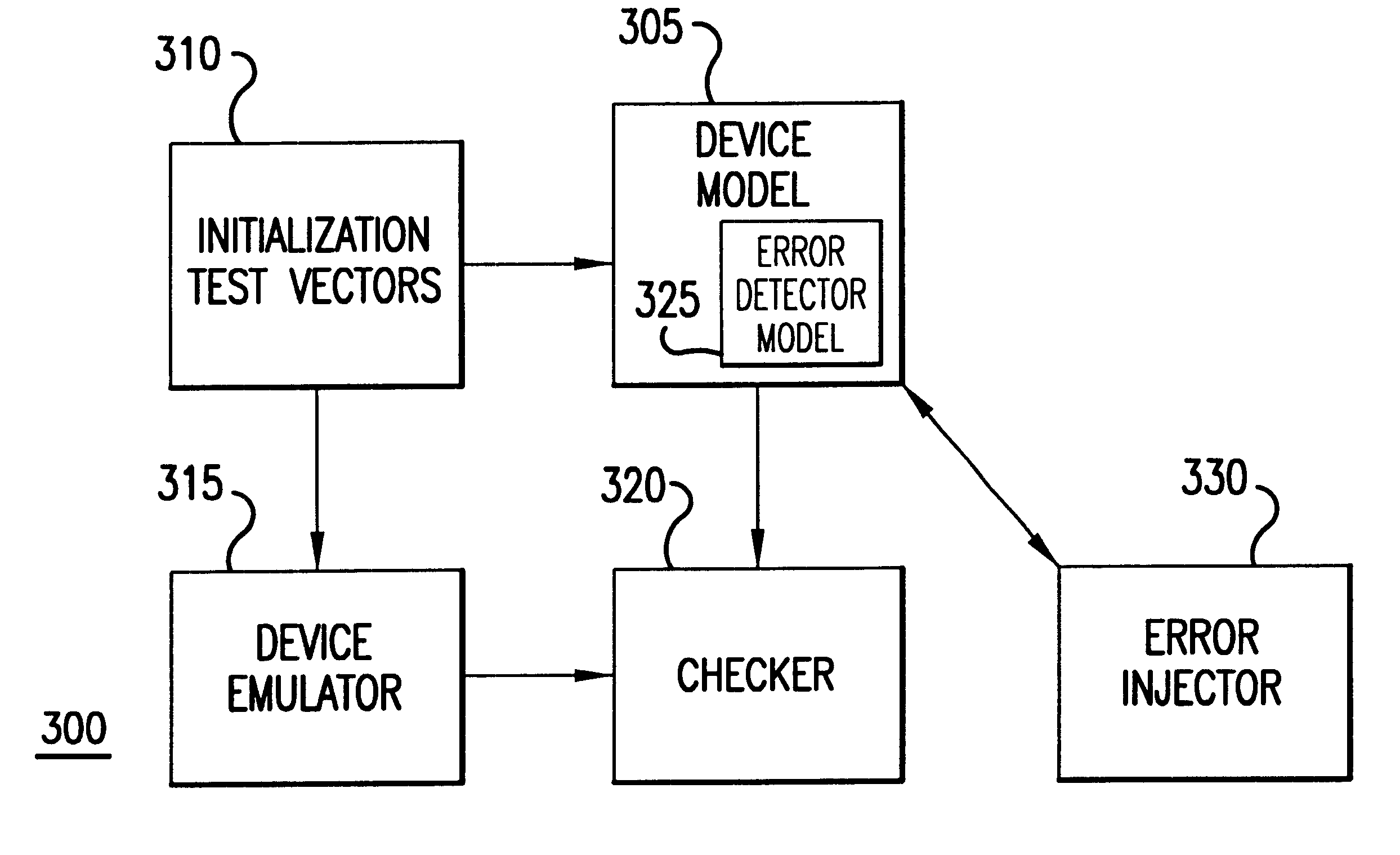

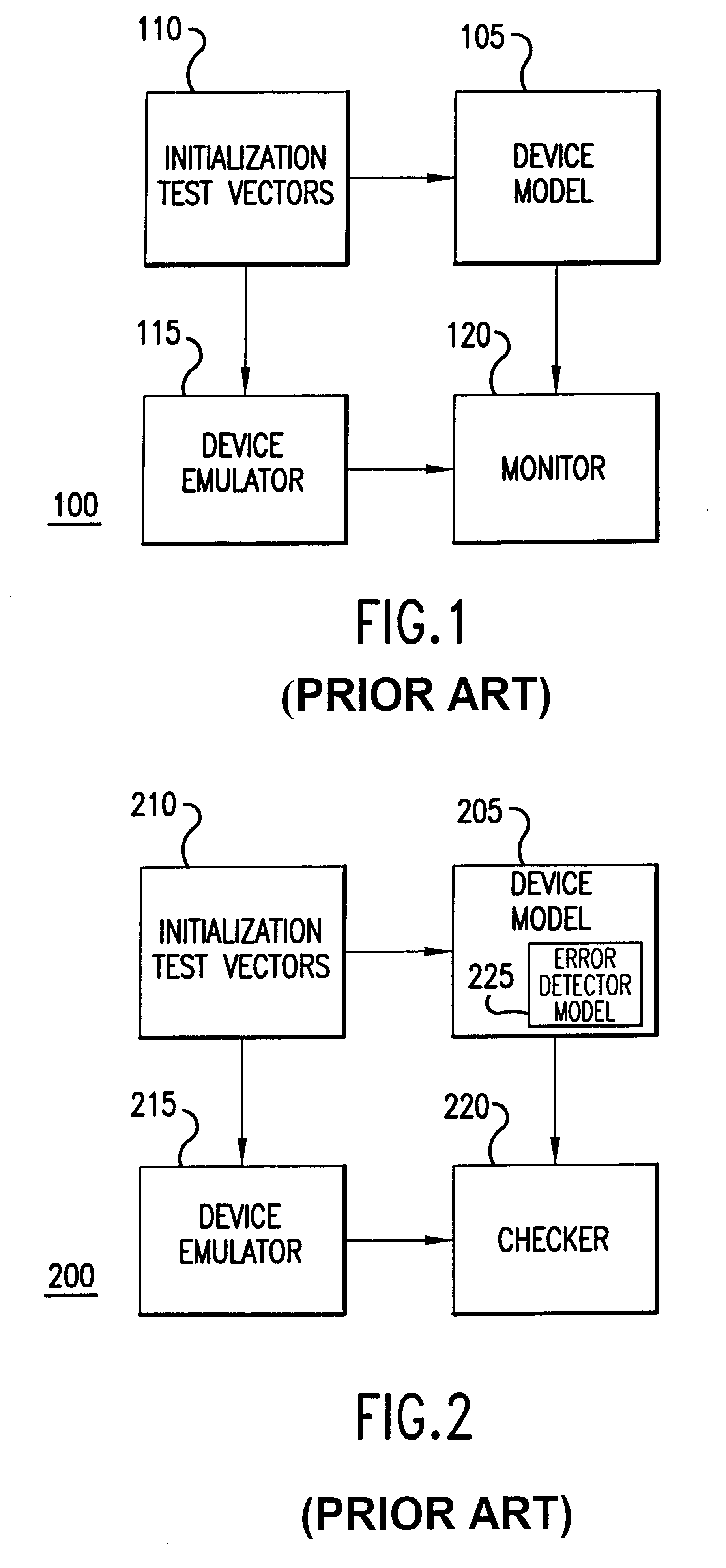

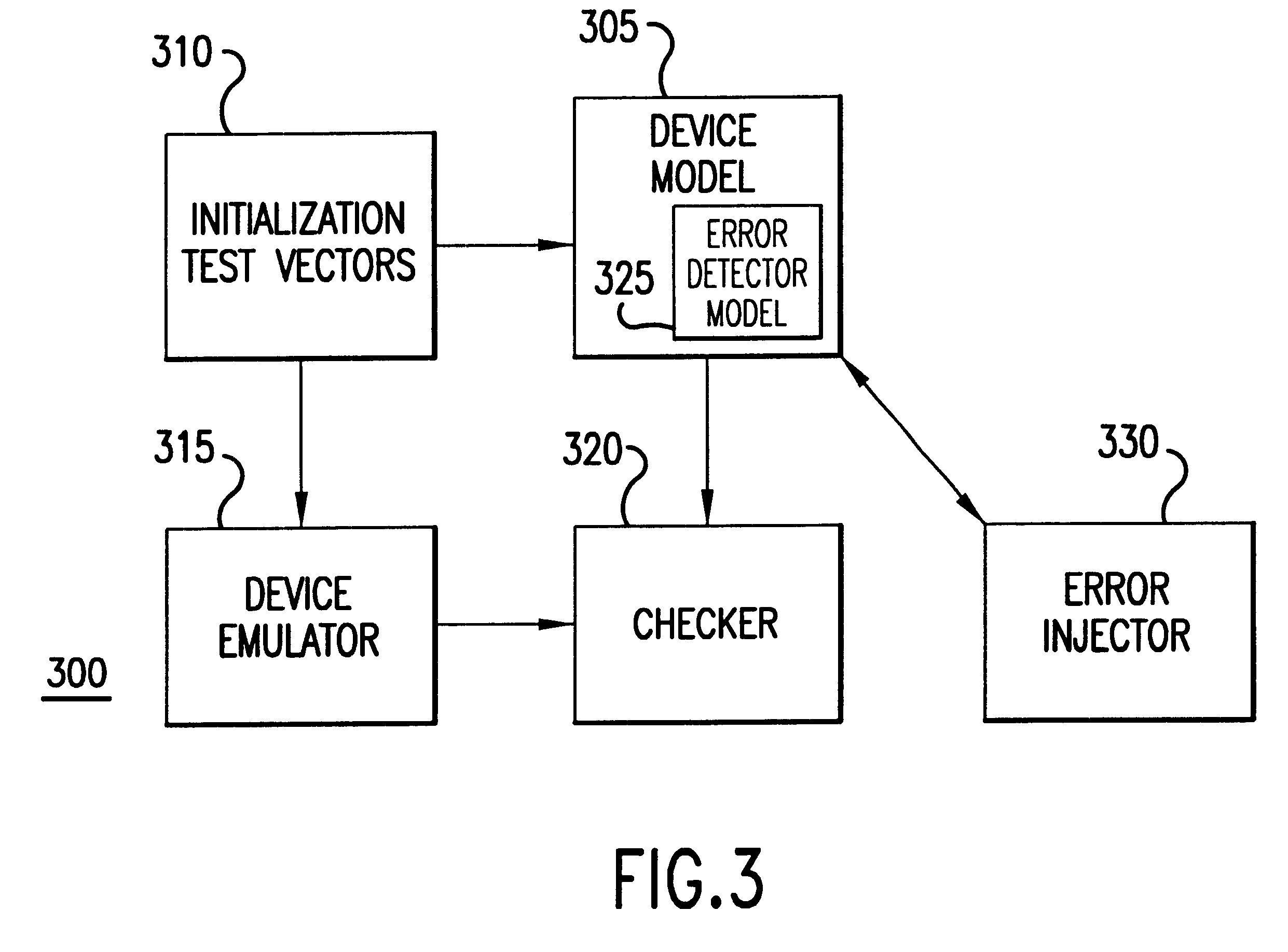

Method and apparatus for testing error detection

InactiveUS6539503B1Easy to testFocusElectronic circuit testingError detection/correctionComputer softwareProcessor design

Disclosed is a device and method for testing of a program or a design of an electronic device comprising digital logic circuitry. The method comprises testing the design of software or an electronic device and injecting, after initiation of the testing step, a predetermined error pattern into a value operated upon by the design of the digital logic circuitry. In a preferred embodiment, the software is a simulation of the design of a processor having a cache with error detection and / or correction circuitry. A triggering condition is preferably a cache hit, in response to which a detectable error is injected into the cache. The simulated operations of the model are observed to determine whether the injected error is detected, as should happen if the processor's error detection circuitry has been designed properly. In another respect, the invention is an apparatus, or computer software embedded on a computer readable medium, for testing a program comprising an error detector. The apparatus or software comprises the program, an error injector module connected to the program; and a checker module connected to the program. The checker module is capable of determining whether the program responds appropriately to an error dynamically produced by the error injector module during execution of the program. By injecting errors dynamically the invention easily facilitates precisely focused testing at any time during simulated operation regardless of initialization conditions.

Owner:SAMSUNG ELECTRONICS CO LTD

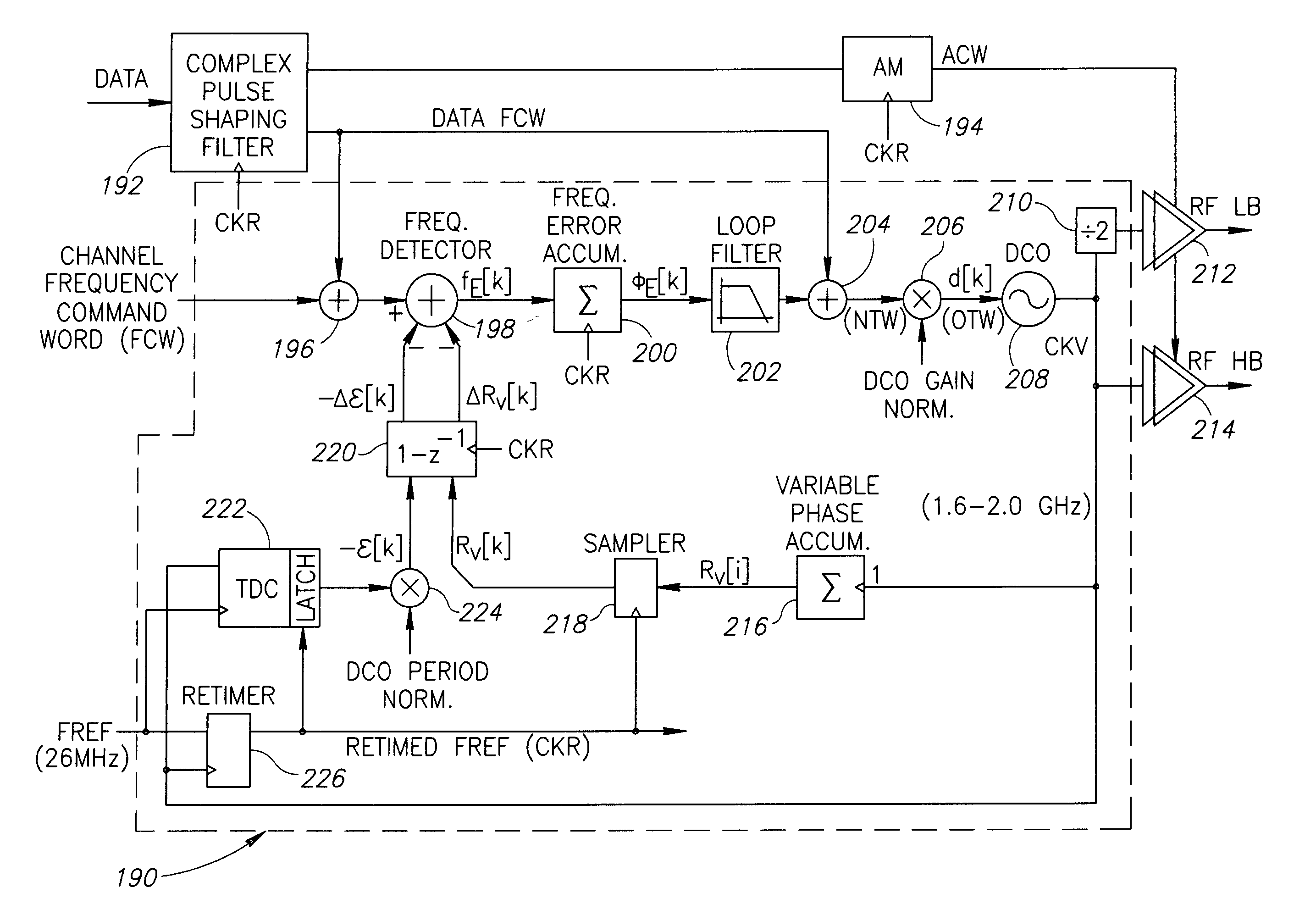

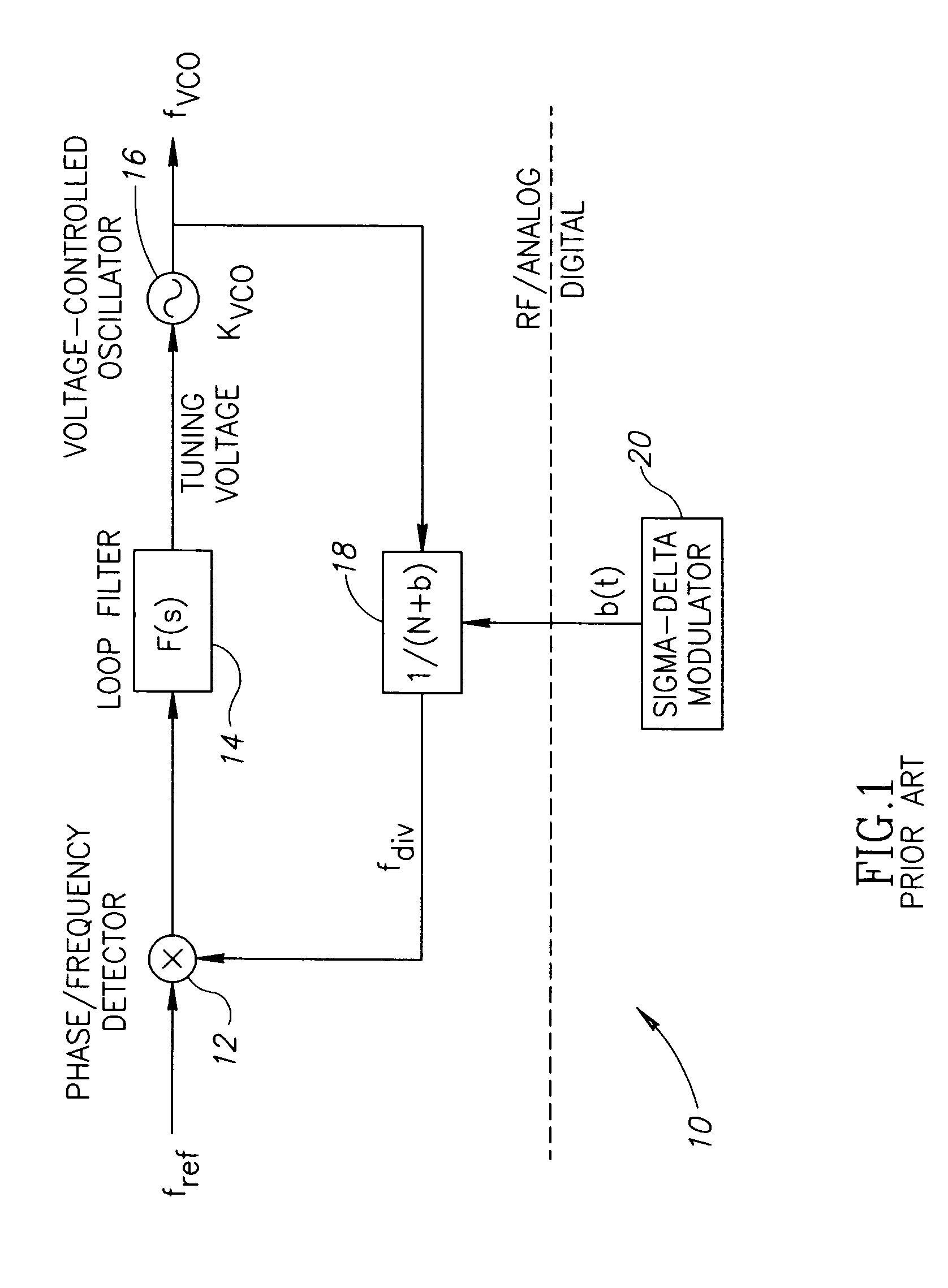

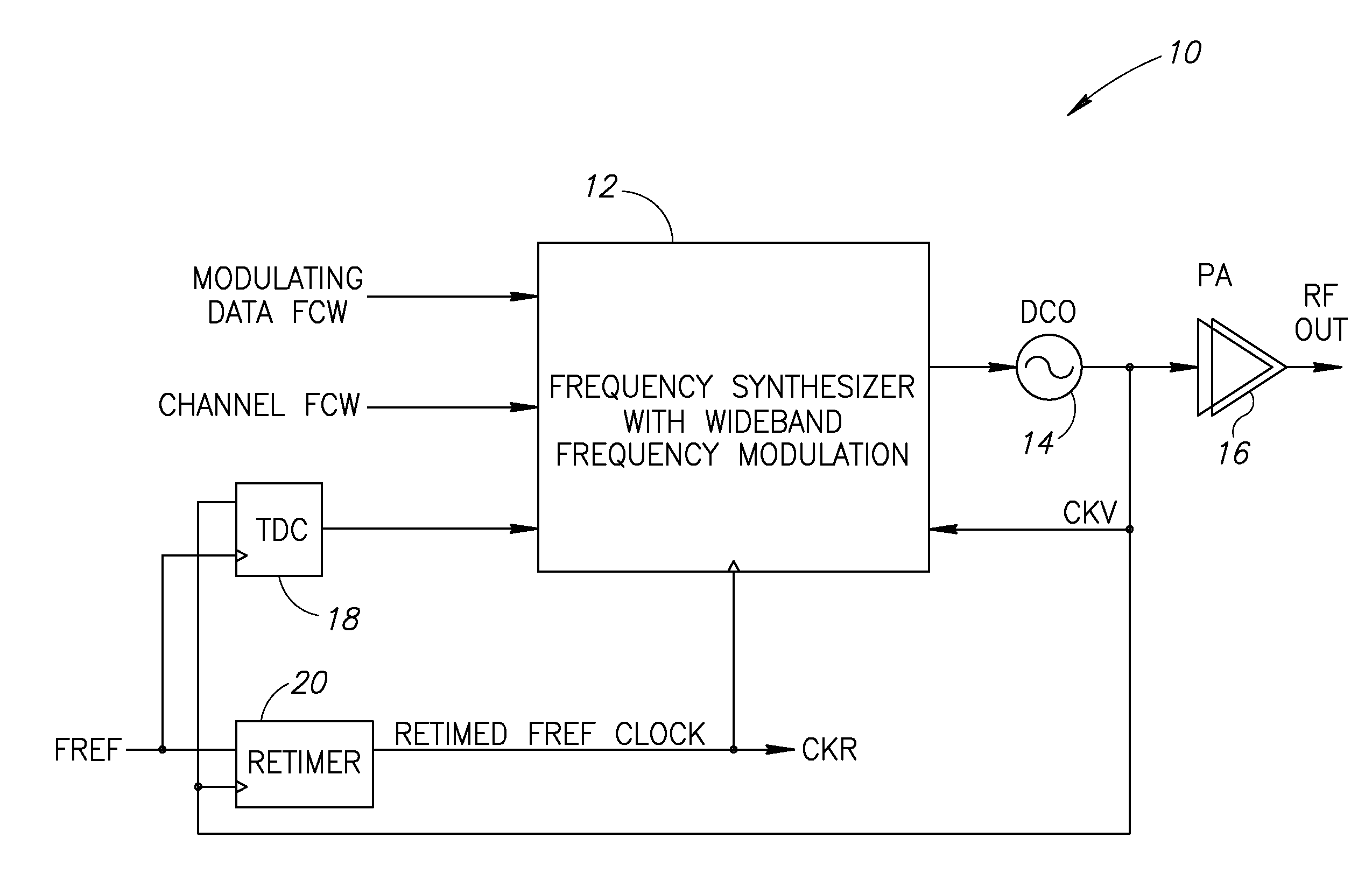

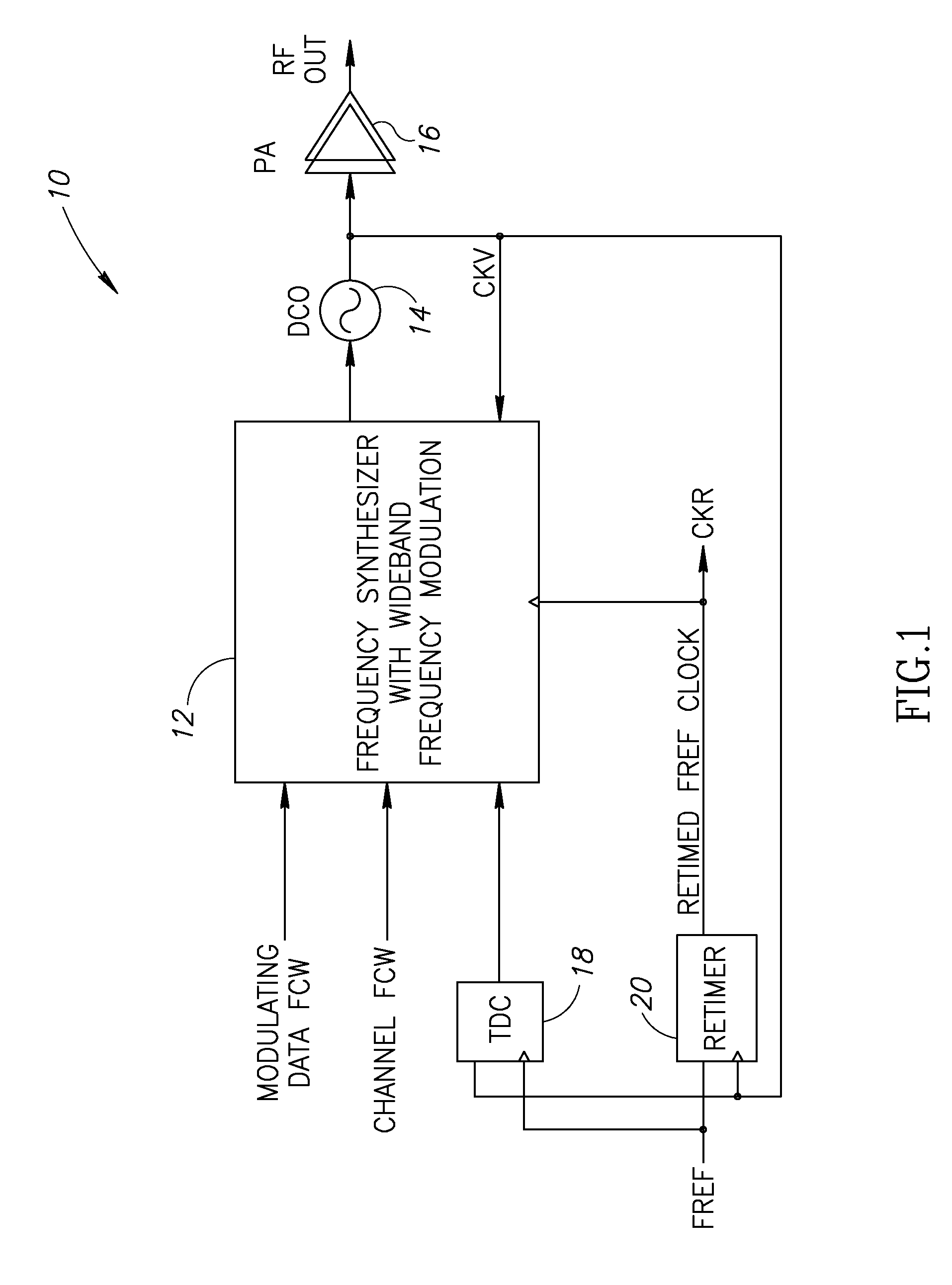

Apparatus for and method of noise suppression and dithering to improve resolution quality in a digital RF processor

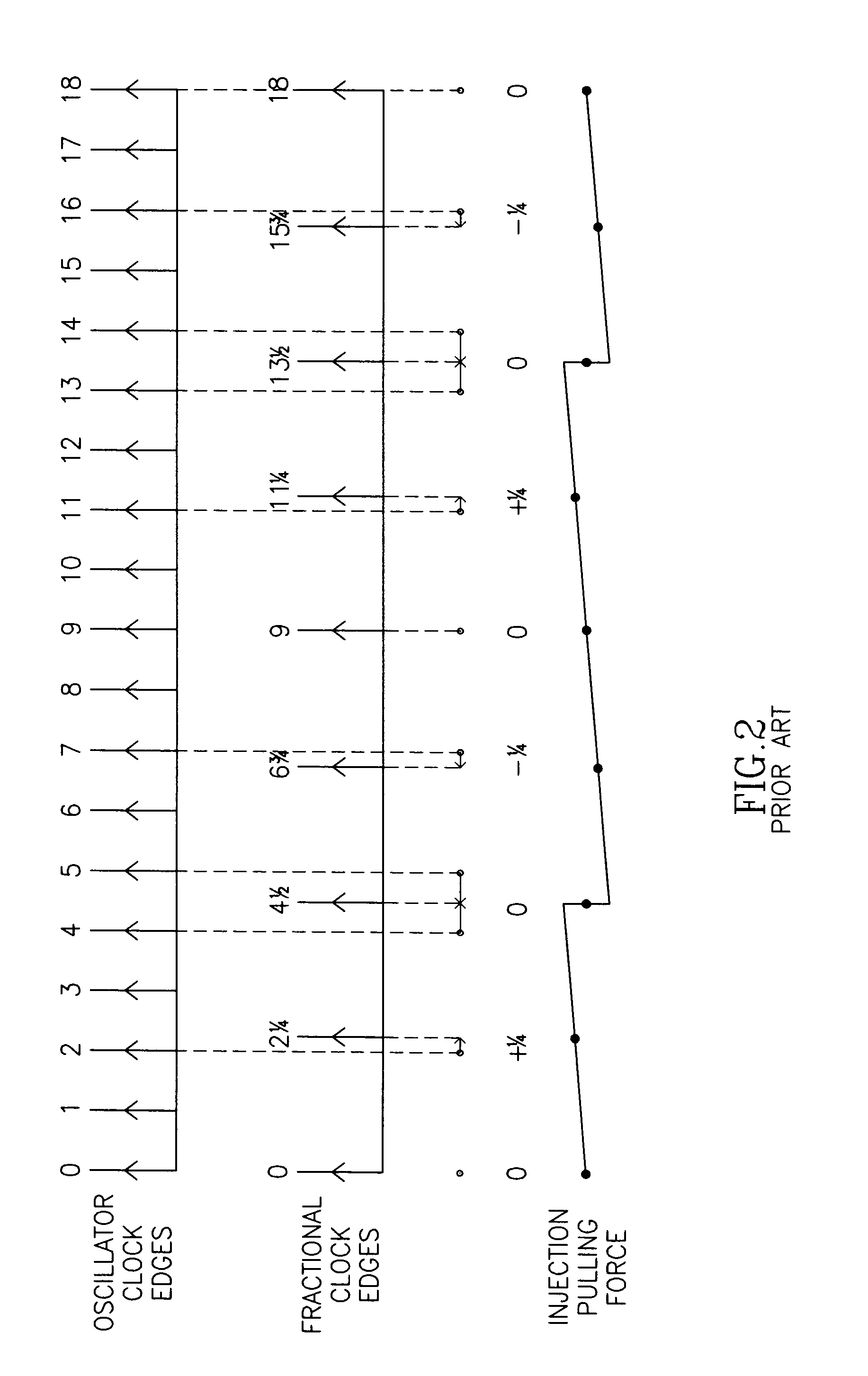

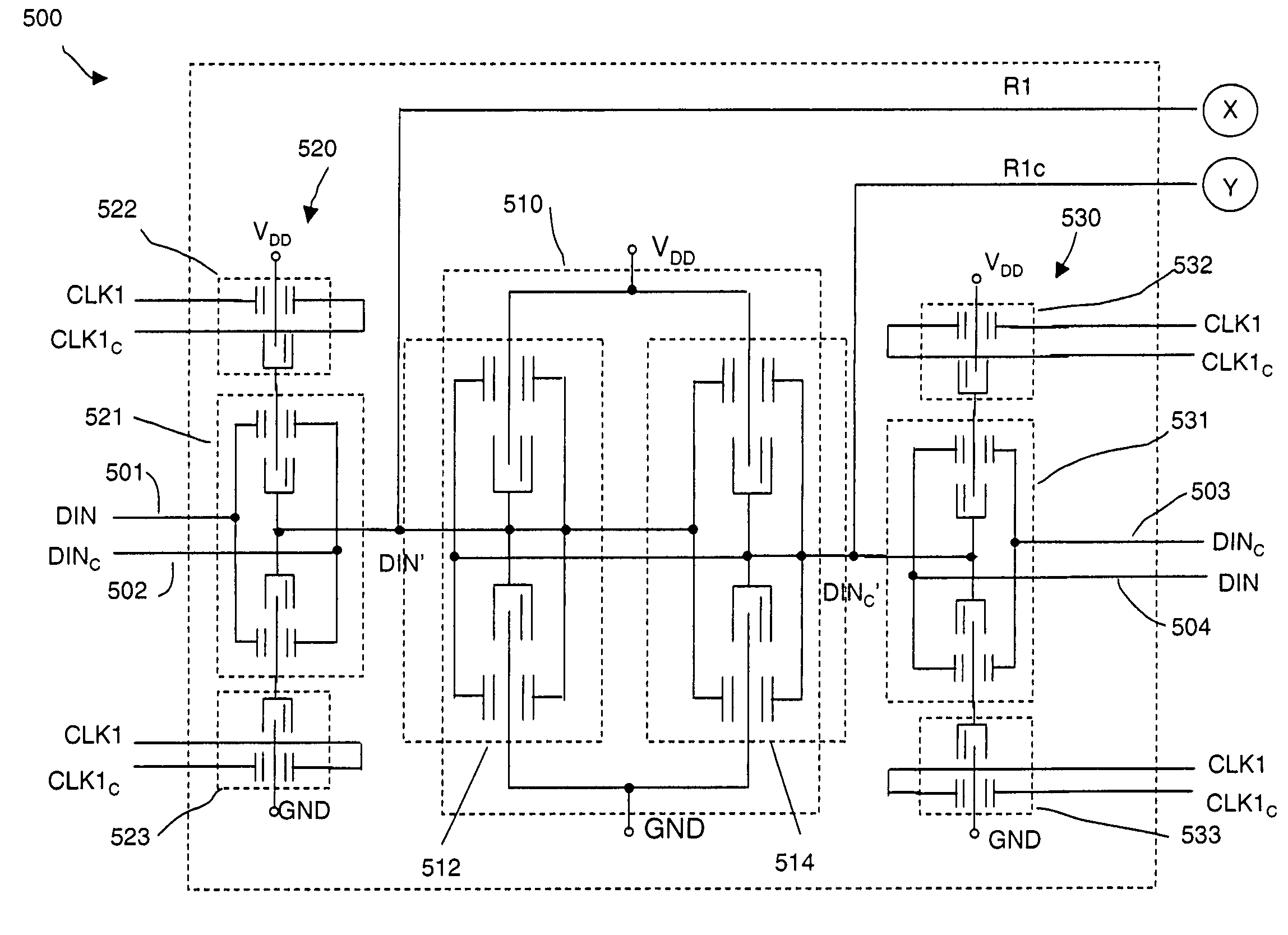

InactiveUS20050186920A1Cancel noiseAvoid it happening againPulse automatic controlAngle modulationImage resolutionEngineering

A novel apparatus for and a method of noise and spurious tones suppression in a digital RF processor (DRP). The invention is well suited for use in highly integrated system on a chip (SoC) radio solutions that incorporate a very large amount of digital logic circuitry. The noise suppression scheme eliminates the noise caused by various on chip interference sources transmitted through electromagnetic, power, ground and substrate paths. The noise suppression scheme permits an all digital PLL (ADPLL) to operate in such a way to avoid generating the spurs that would normally be generated from the injection pulling effect of interfering sources on the chip. The frequency reference clock is retimed to be synchronous to the RF oscillator clock and used to drive the entire digital logic circuitry of the DRP. This ensures that the different clock edges throughout the system will not exhibit mutual drift. A method of improving the resolution quality of a time to digital converter within the ADPLL is also taught. The method dithers the reference clock by passing it through a delay circuit that is controlled by a sigma-delta modulator. The dithered reference clock reduces the affect on the phase noise at the output of the ADPLL due to ill-behaved quantization of the TDC timing estimation.

Owner:TEXAS INSTR INC

Storage elements using nanotube switching elements

Data storage circuits and components of such circuits constructed using nanotube switching elements. The storage circuits may be stand-alone devices or cells incorporated into other devices or circuits. The data storage circuits include or can be used in latches, master-slave flip-flops, digital logic circuits, memory devices and other circuits. In one aspect of the invention, a master-slave flip-flop is constructed using one or more nanotube switching element-based storage devices. The master storage element or the slave storage element or both may be constructed using nanotube switching elements, for example, using two nanotube switching element-based inverters. The storage elements may be volatile or non-volatile. An equilibration device is provided for protecting the stored data from fluctuations on the inputs. Input buffers and output buffers for data storage circuits of the invention may also be constructed using nanotube switching elements.

Owner:NANTERO

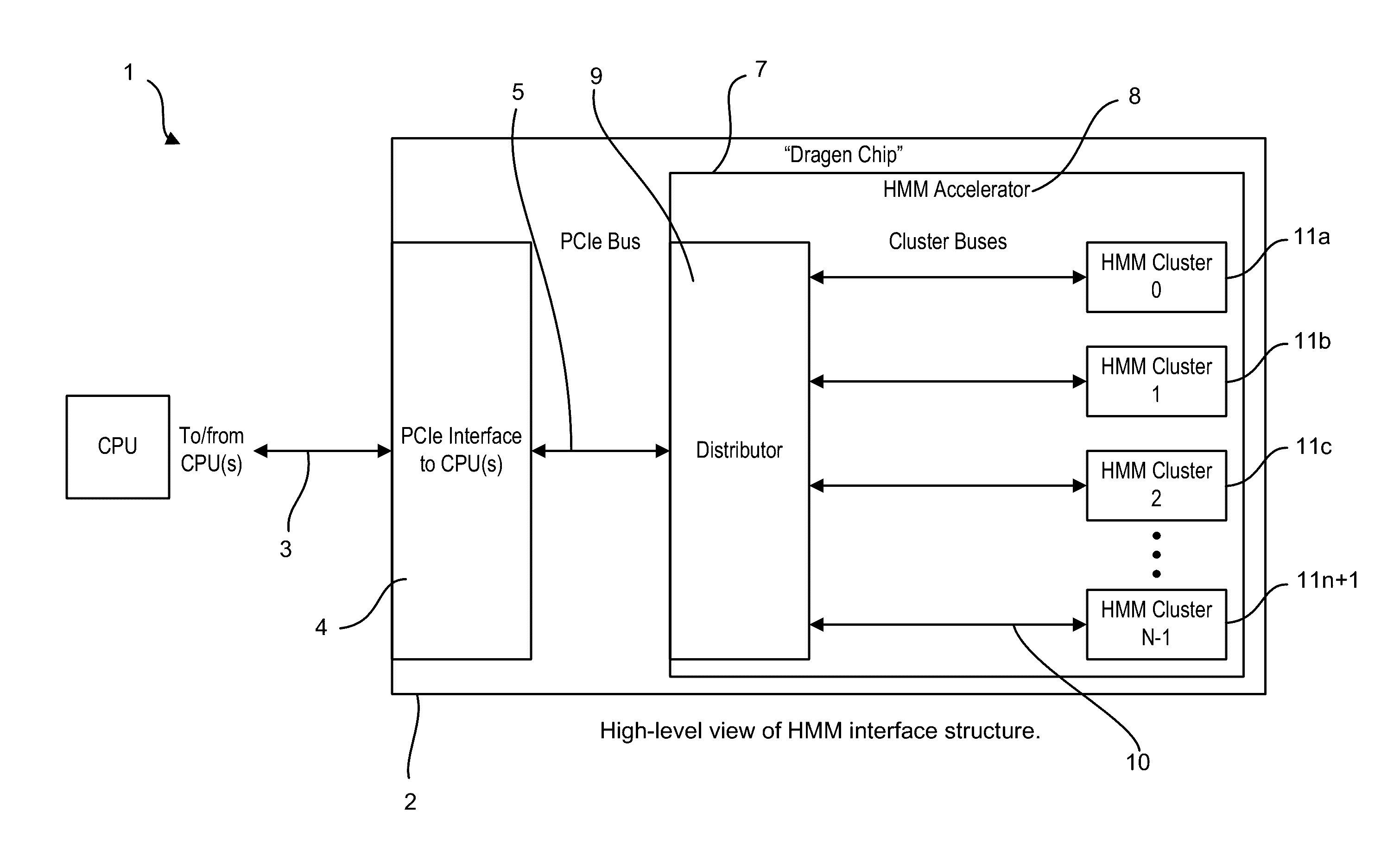

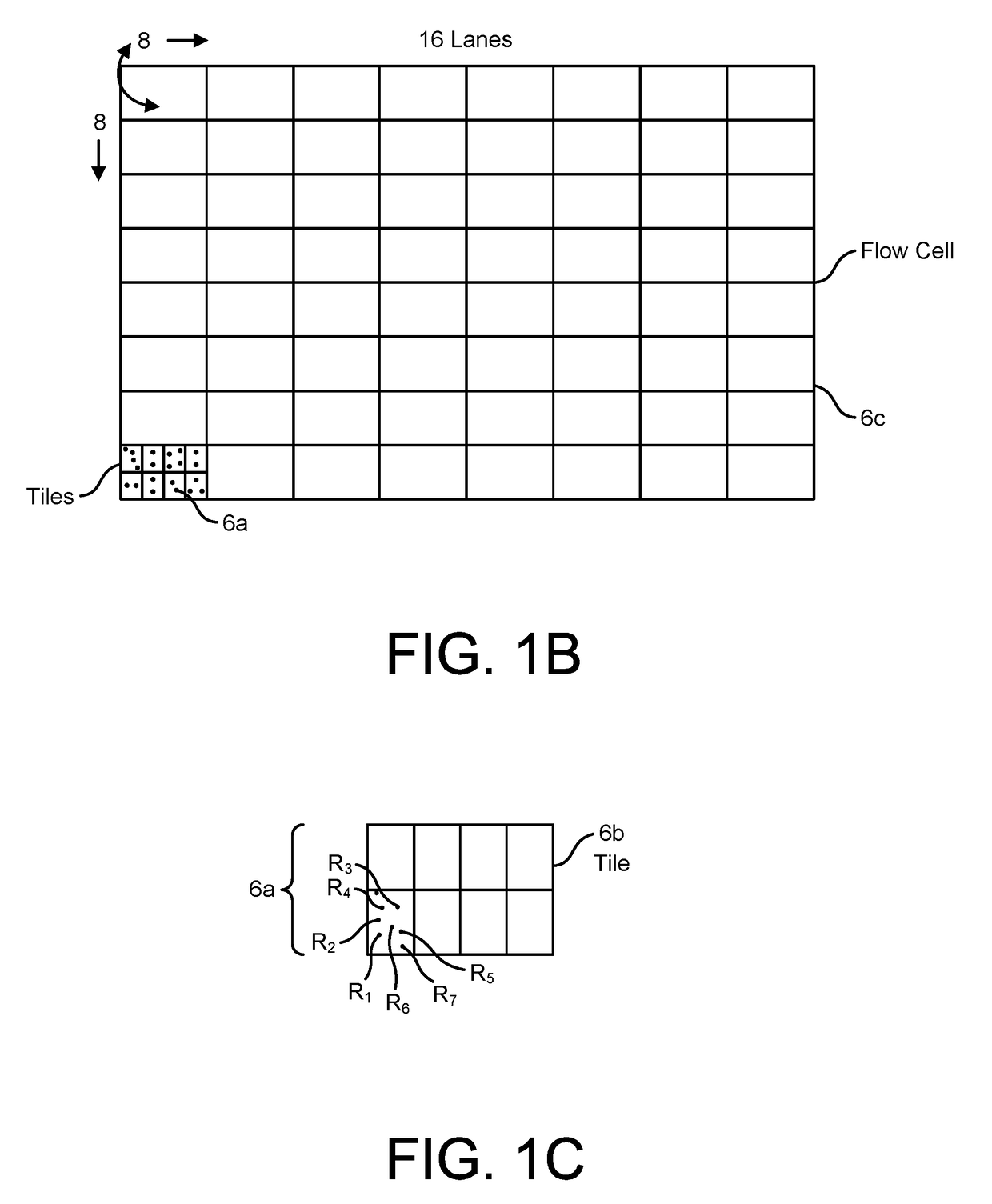

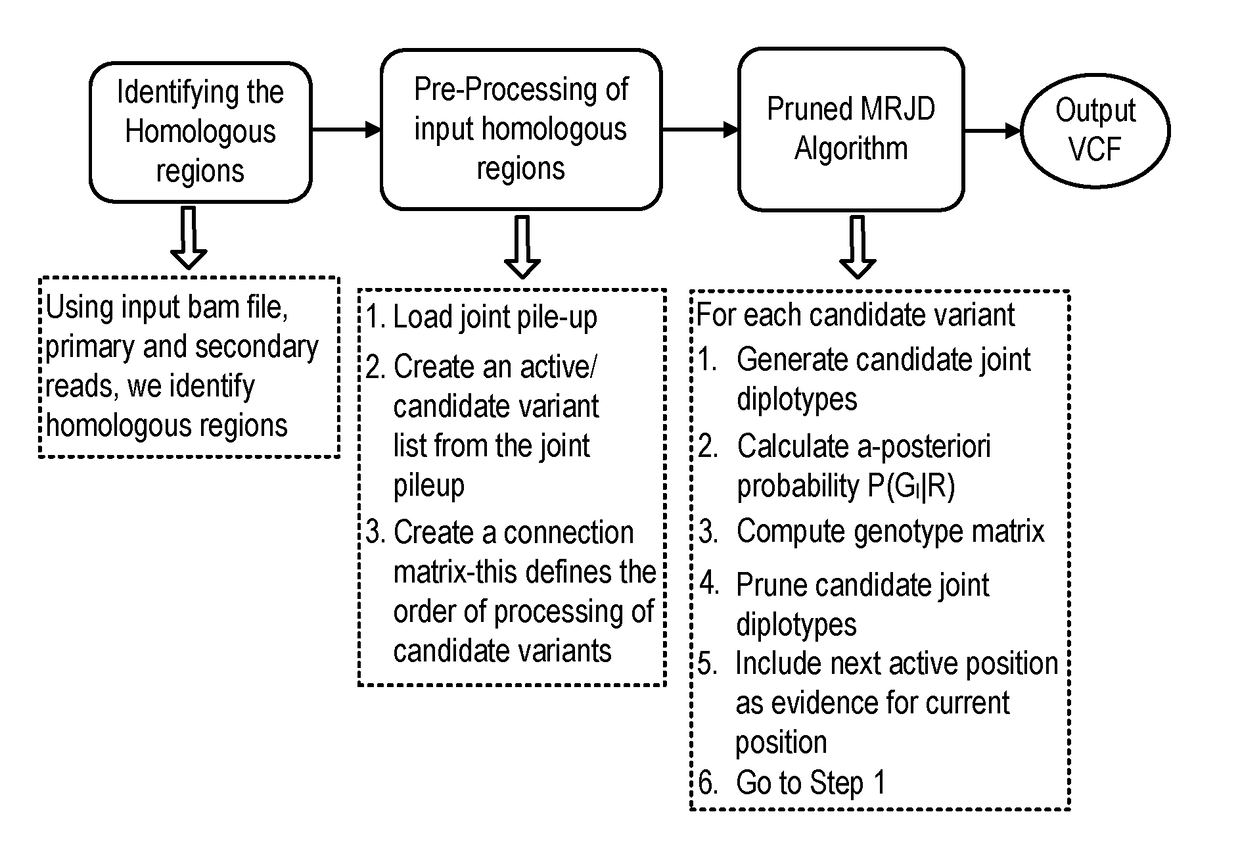

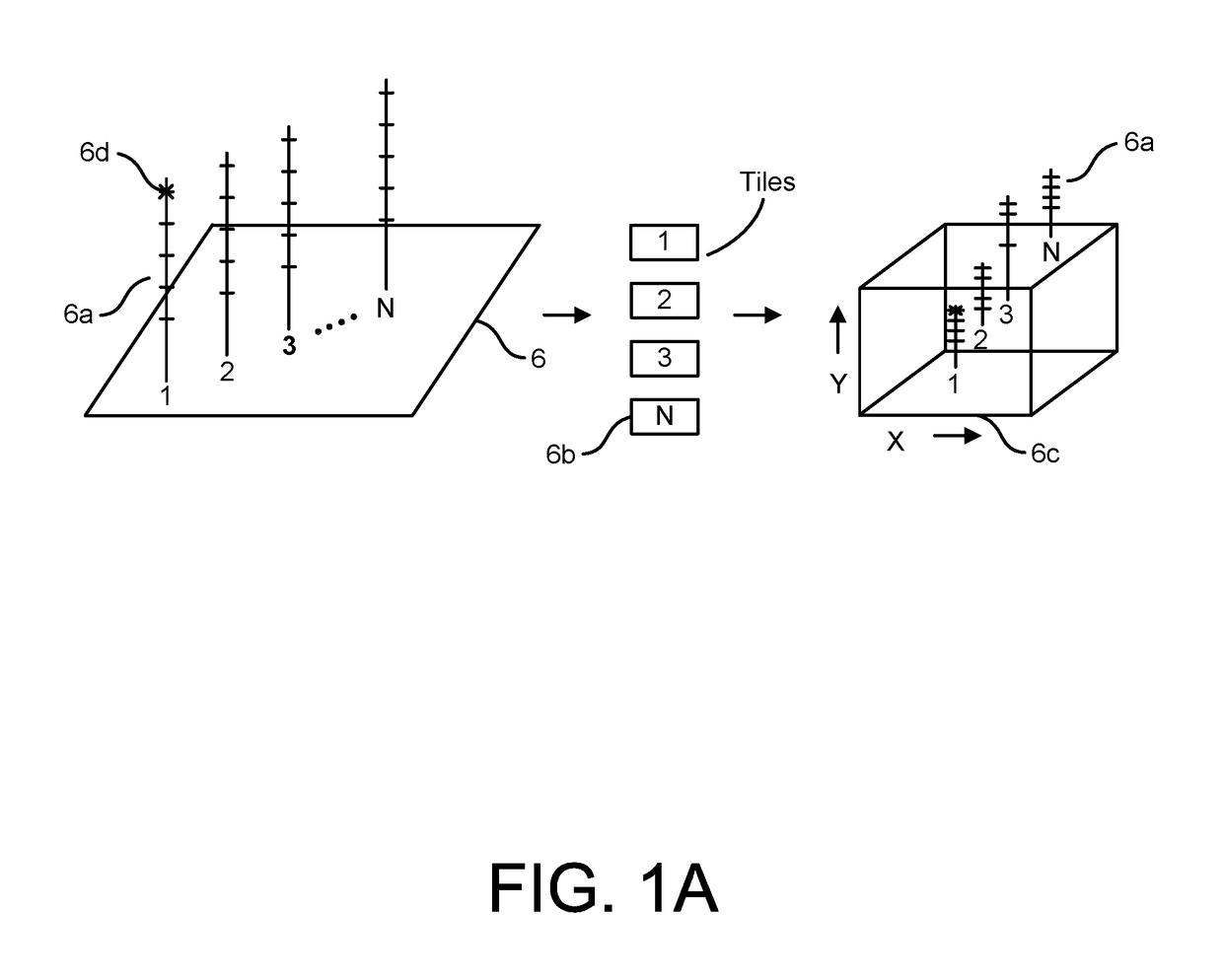

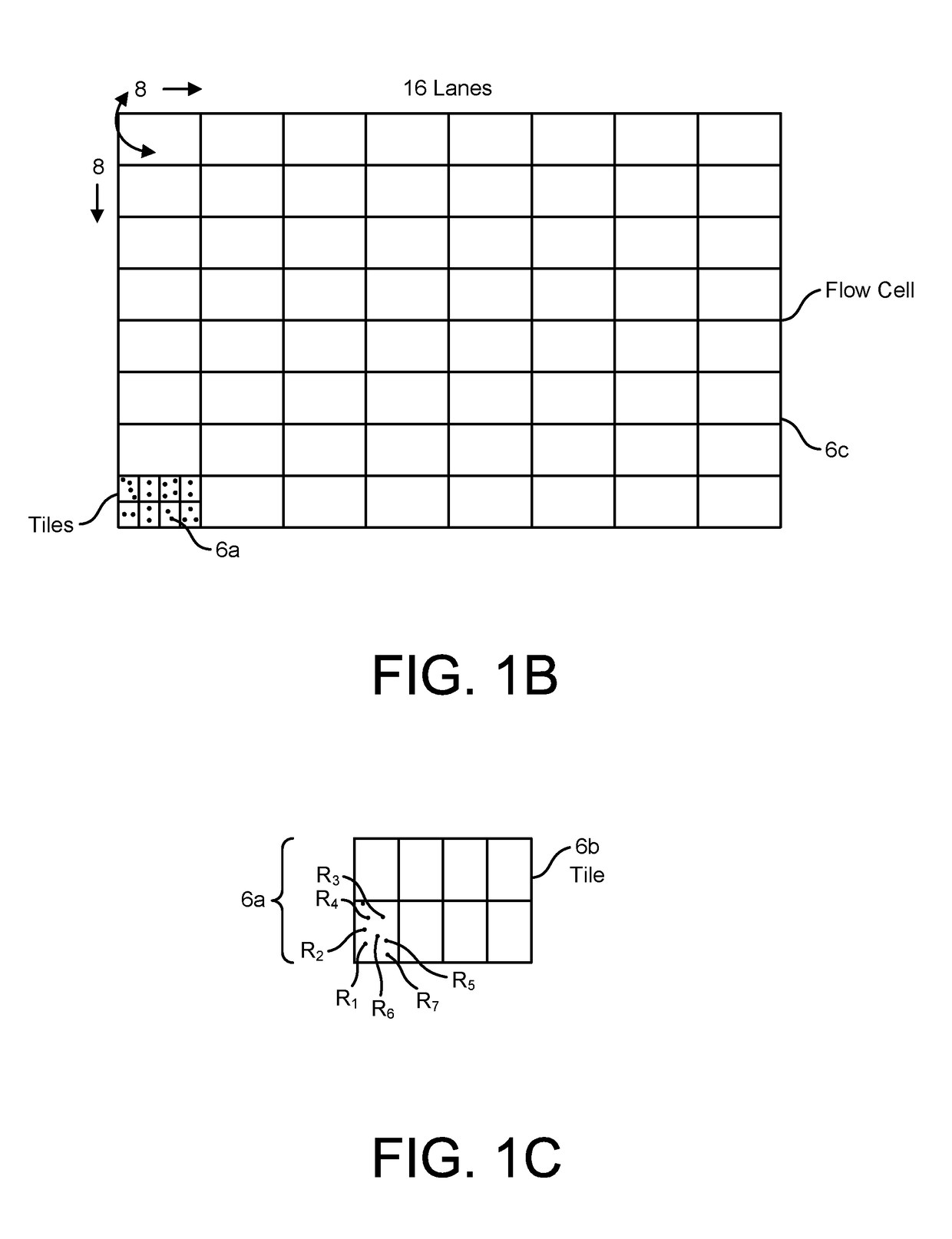

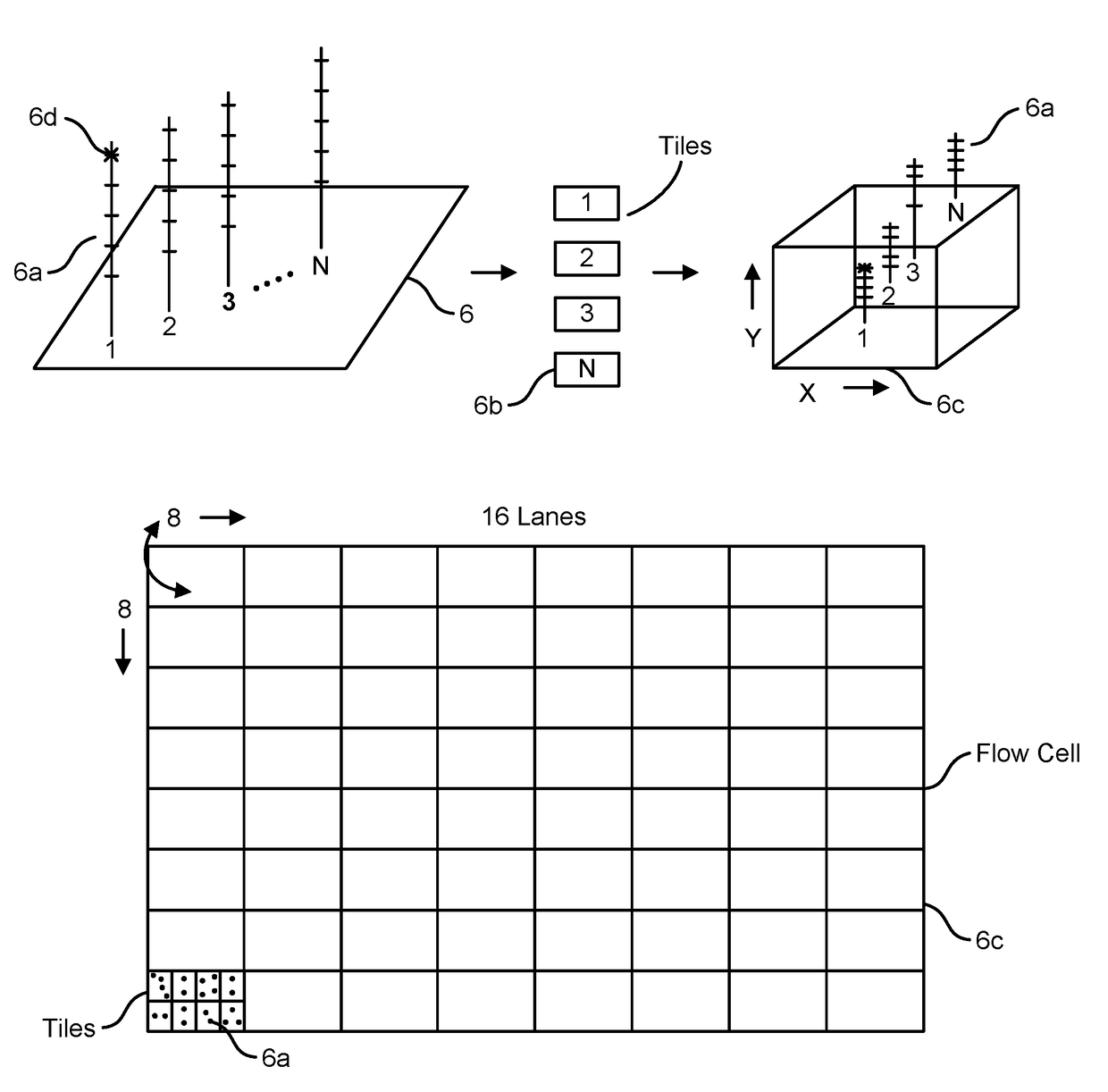

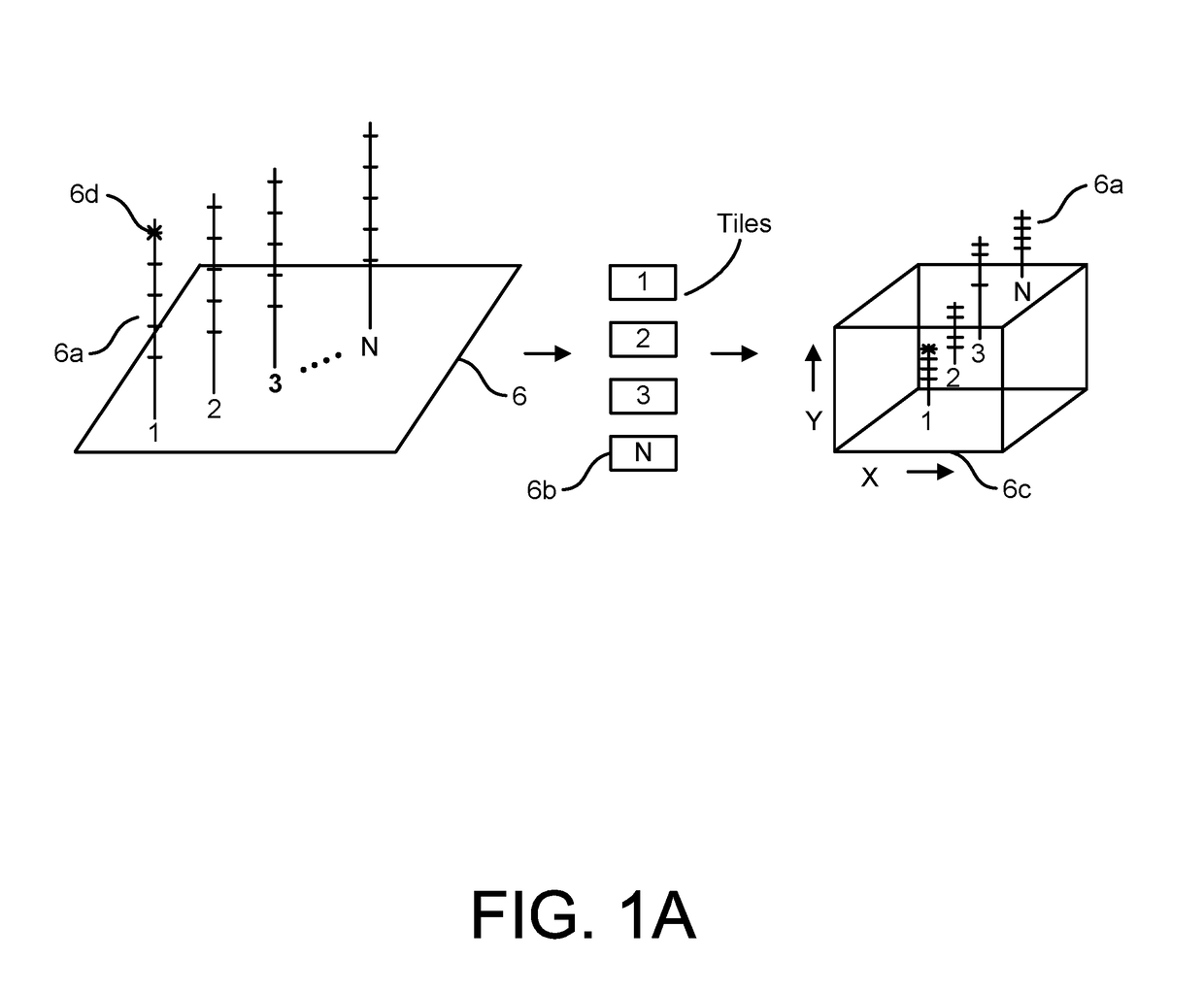

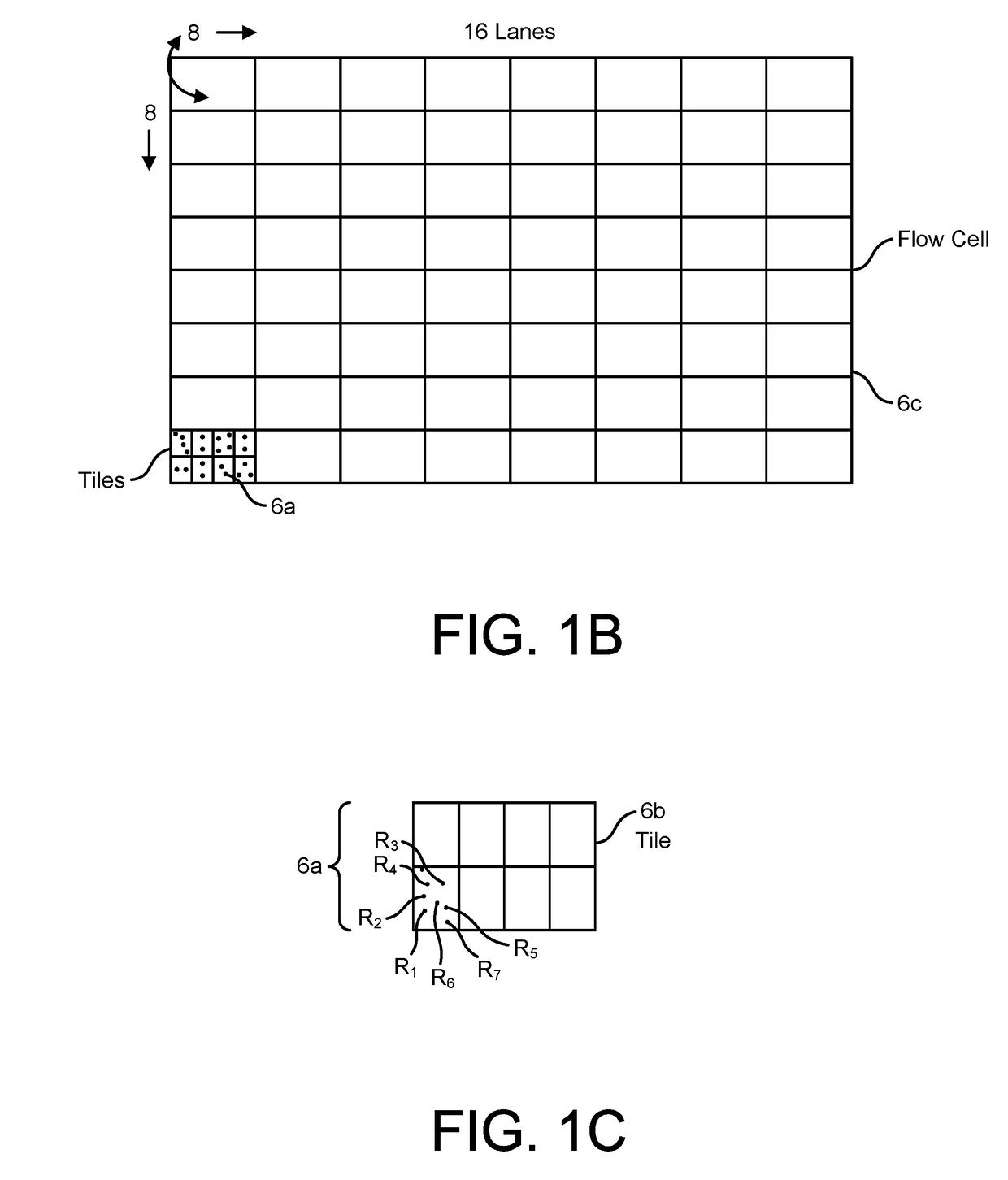

Bioinformatics systems, apparatuses, and methods executed on an integrated circuit processing platform

ActiveUS20160306922A1High sensitivityImprove accuracyHealth-index calculationTelemedicineElectricityData source

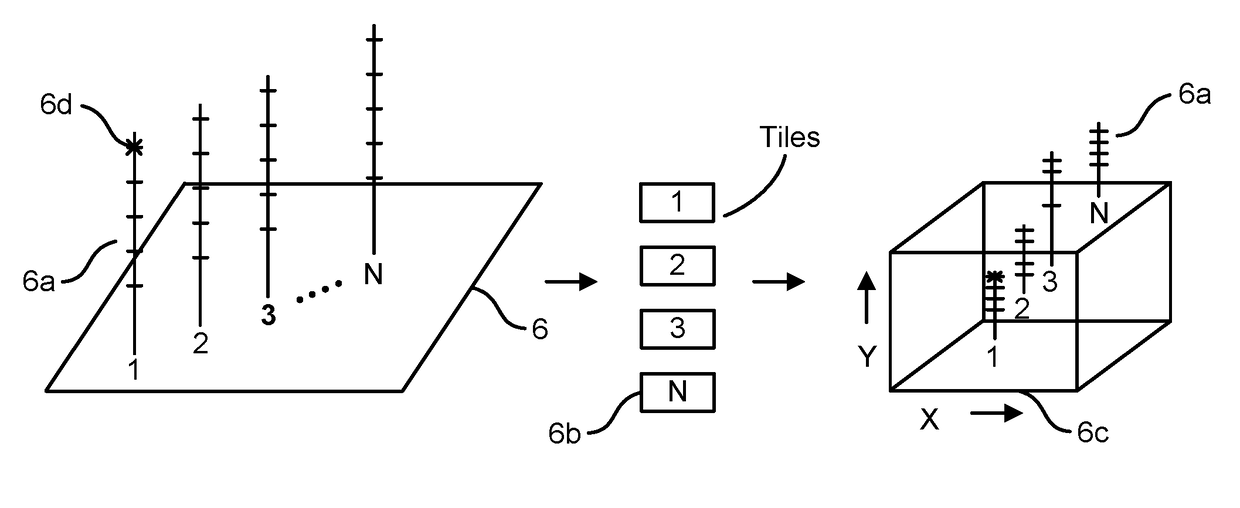

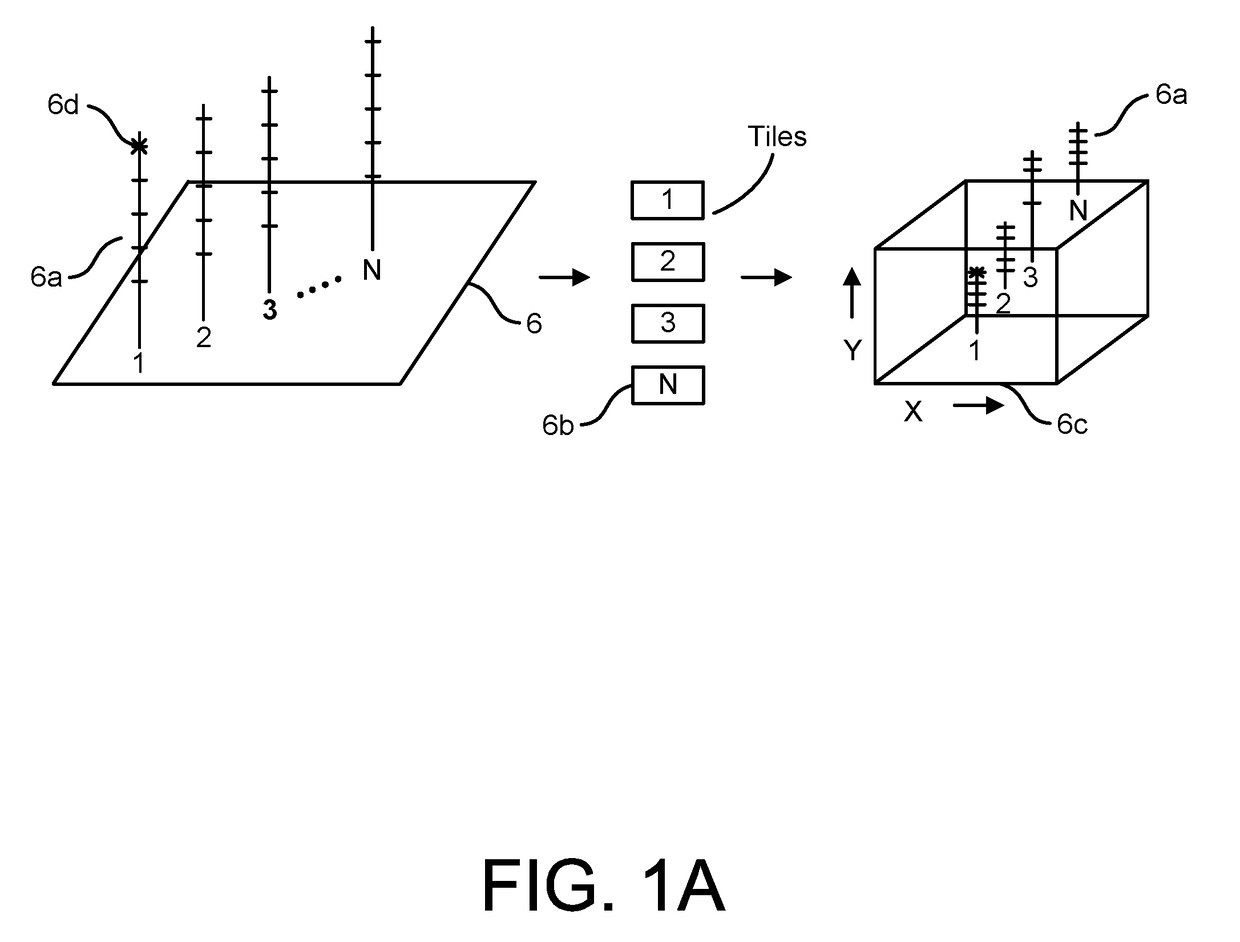

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data includes an integrated circuit formed of a set of hardwired digital logic circuits that are interconnected by physical electrical interconnects. One of the physical electrical interconnects forms an input to the integrated circuit that may be connected with an electronic data source for receiving reads of genomic data. The hardwired digital logic circuits may be arranged as a set of processing engines, each processing engine being formed of a subset of the hardwired digital logic circuits to perform one or more steps in the bioinformatics analysis on the reads of genomic data. Each subset of the hardwired digital logic circuits may be formed in a wired configuration to perform the one or more steps in the bioinformatics analysis.

Owner:EDICO GENOME

Bioinformatics systems, apparatuses, and methods executed on an integrated circuit processing platform

ActiveUS20160306923A1Processing speedProcessed result accuracyMemory architecture accessing/allocationMathematical modelsData sourceGenomic data

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data includes an integrated circuit formed of a set of hardwired digital logic circuits that are interconnected by physical electrical interconnects. One of the physical electrical interconnects forms an input to the integrated circuit that may be connected with an electronic data source for receiving reads of genomic data. The hardwired digital logic circuits may be arranged as a set of processing engines, each processing engine being formed of a subset of the hardwired digital logic circuits to perform one or more steps in the bioinformatics analysis on the reads of genomic data. Each subset of the hardwired digital logic circuits may be formed in a wired configuration to perform the one or more steps in the bioinformatics analysis.

Owner:EDICO GENOME

Bioinformatics systems, apparatuses, and methods for performing secondary and/or tertiary processing

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data is provided. Particularly, a genomics analysis platform for executing a sequence analysis pipeline is provided. The genomics analysis platform includes one or more of a first integrated circuit, where each first integrated circuit forms a central processing unit (CPU) that is responsive to one or more software algorithms that are configured to instruct the CPU to perform a first set of genomic processing steps of the sequence analysis pipeline. Additionally, a second integrated circuit is also provided, where each second integrated circuit forming a field programmable gate array (FPGA), the FPGA being configured by firmware to arrange a set of hardwired digital logic circuits that are interconnected by a plurality of physical interconnects to perform a second set of genomic processing steps of the sequence analysis pipeline, the set of hardwired digital logic circuits of each FPGA being arranged as a set of processing engines to perform the second set of genomic processing steps. A shared memory is also provided.

Owner:EDICO GENOME

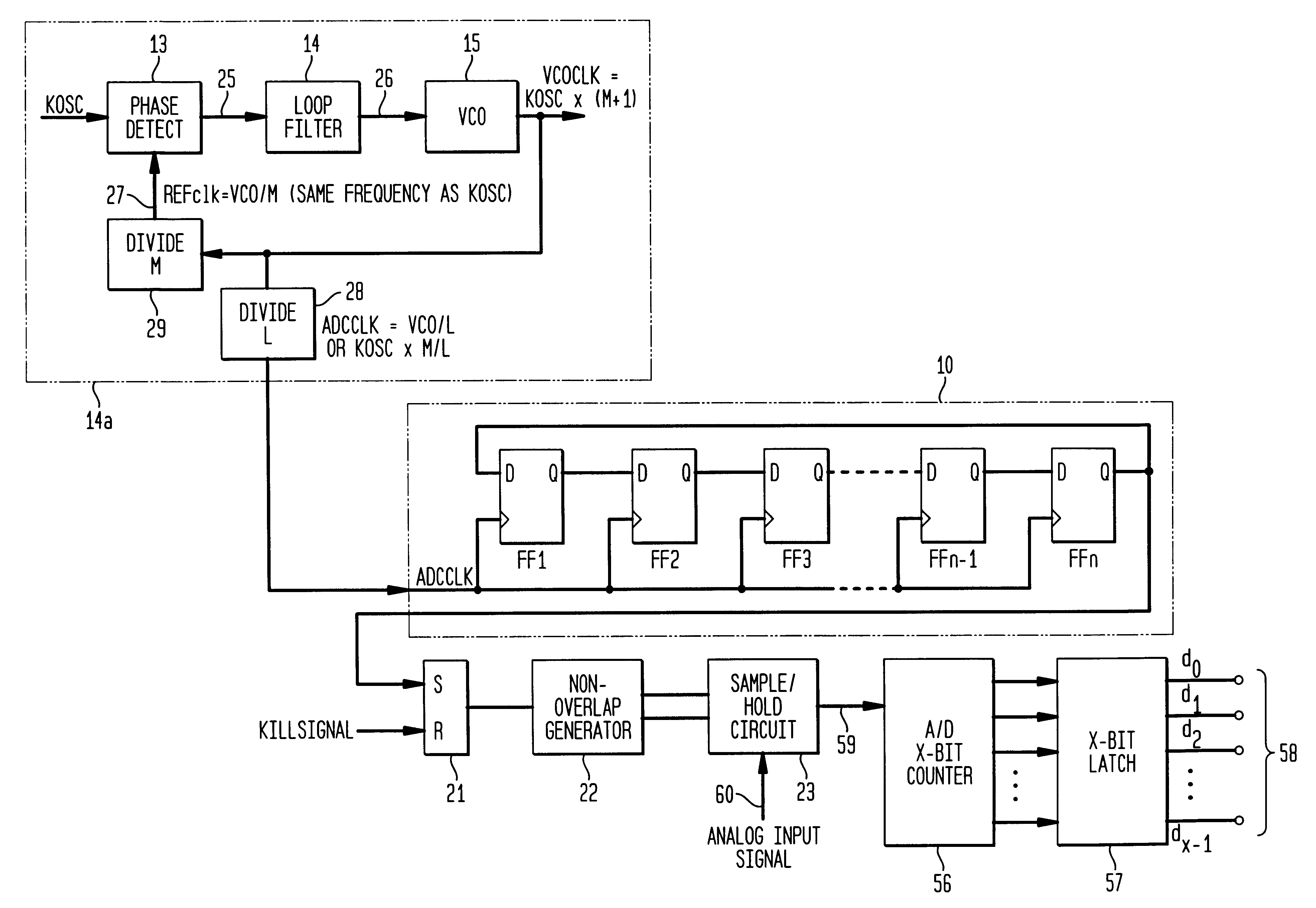

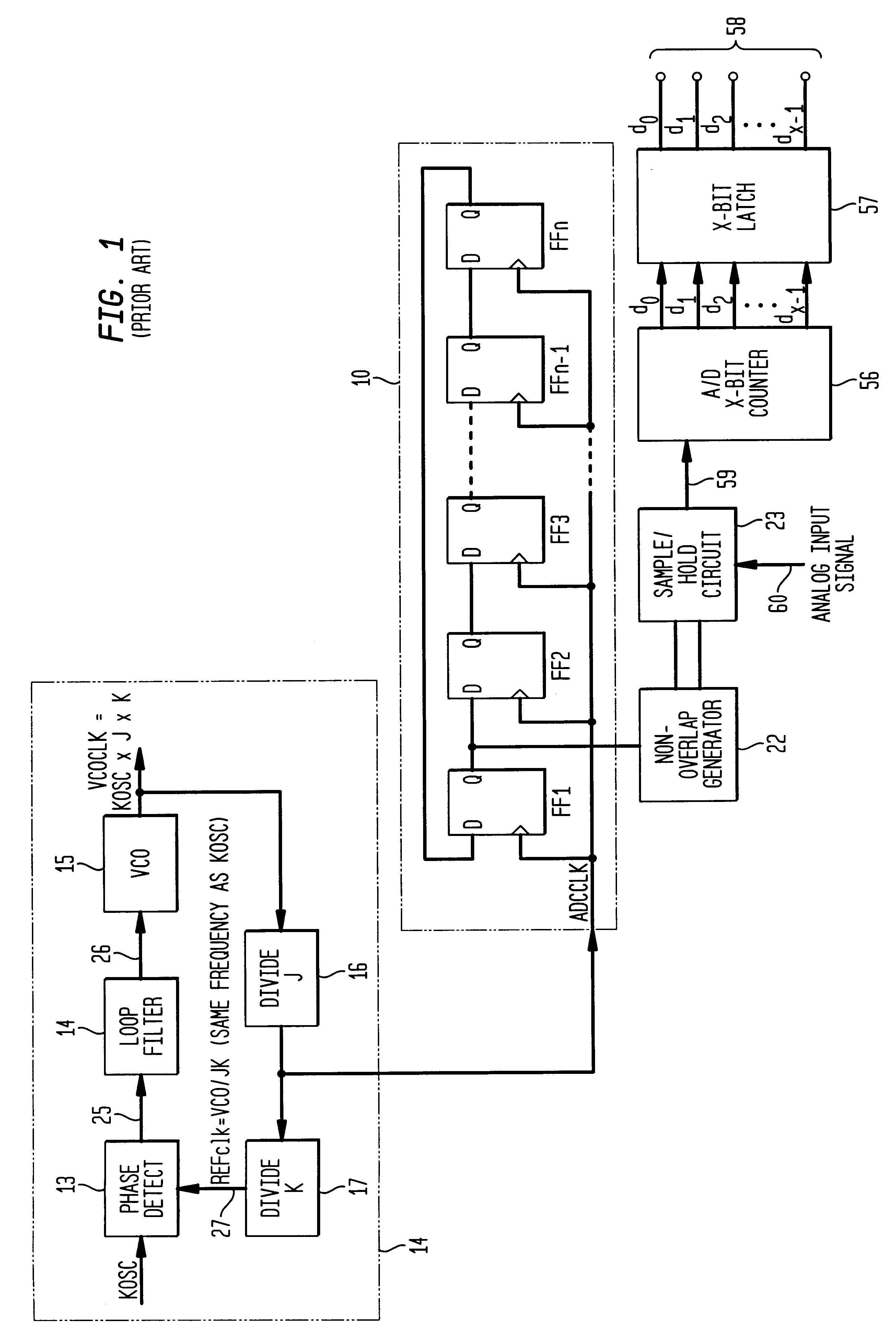

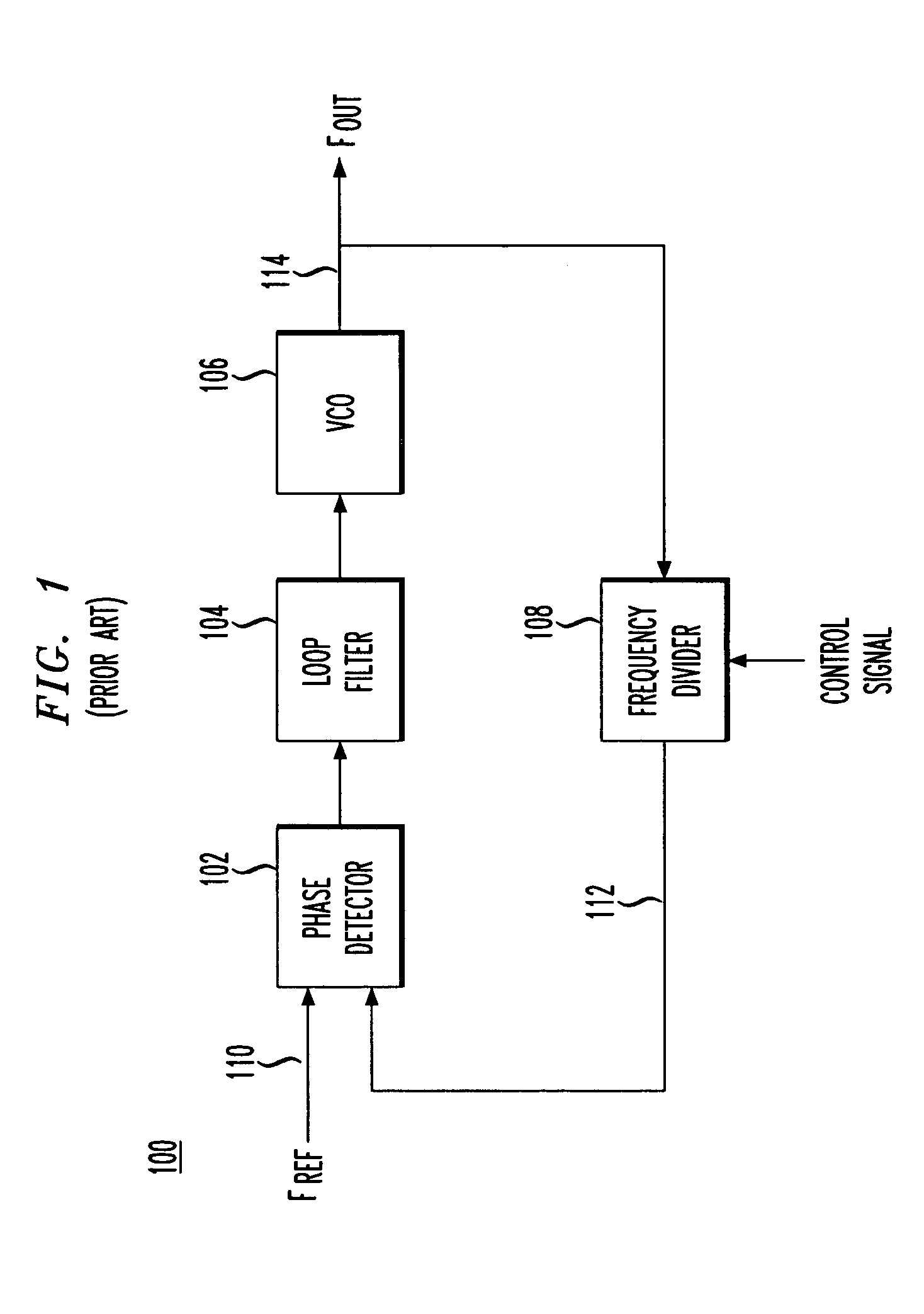

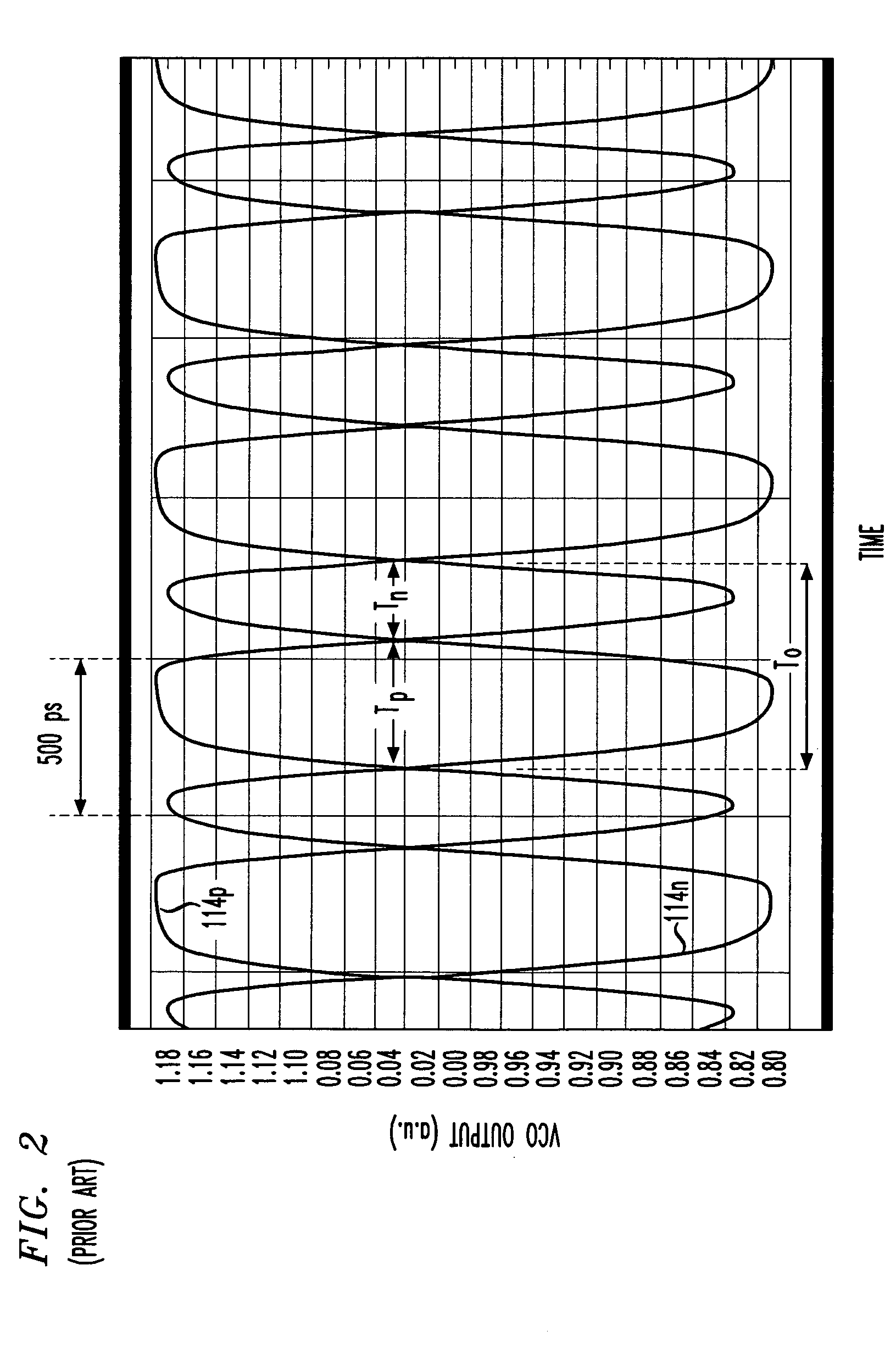

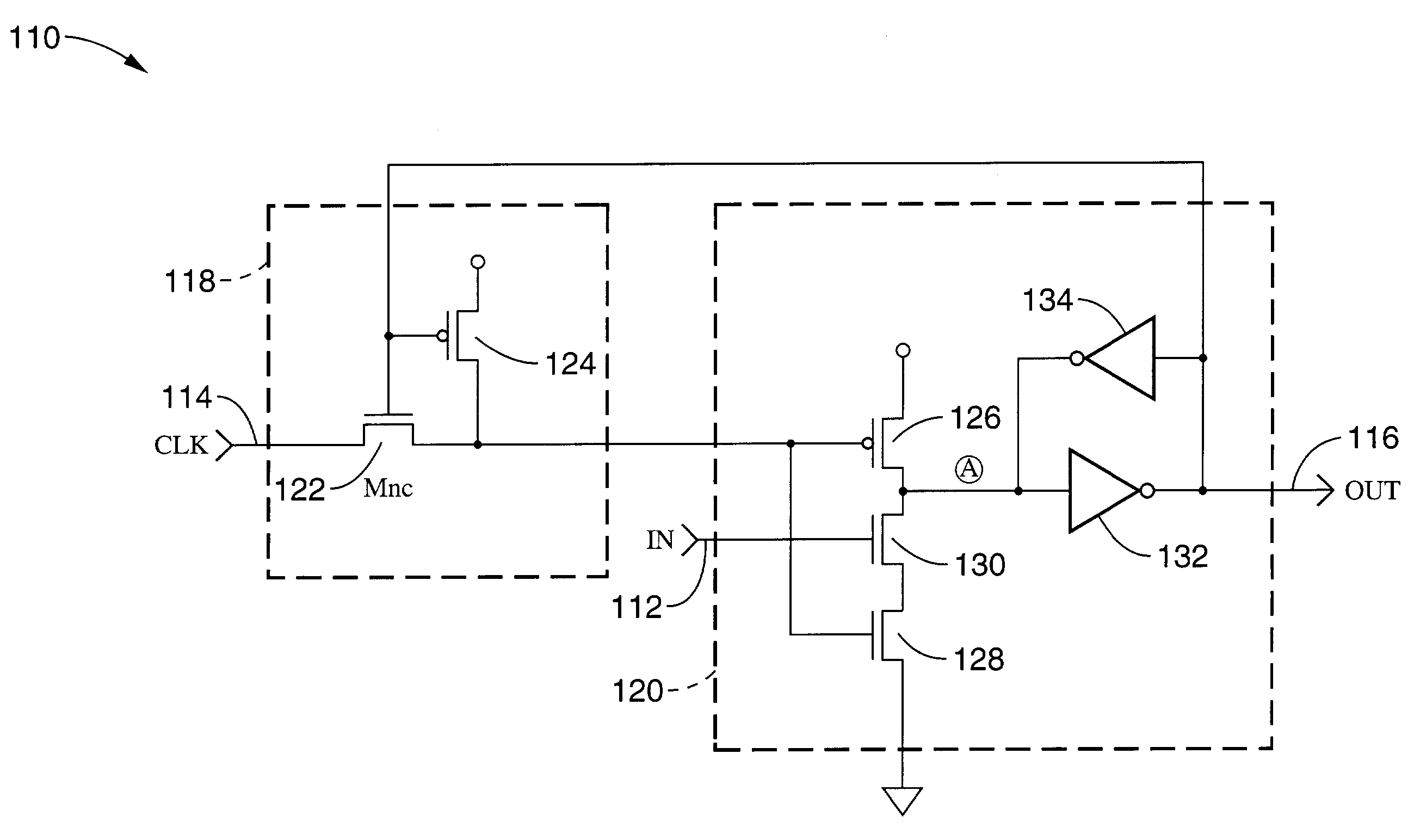

Clocking technique for reducing sampling noise in an analog-to-digital converter

InactiveUS6232905B1Low costHigh resolutionElectric signal transmission systemsAnalogue-digital convertersLeading edgeDigital down converter

A method and apparatus are disclosed for improving the operation of an analog-to-digital converter ("ADC"). A separate "clean" oscillator clock is to be used in combination with a "noisy" ADC clock being regulated by a phase-locked-loop (PLL) circuit. The "noisy" ADC clock drives the digital control logic and also turns on the sample signal for the purpose of sampling. The second clock, which has a substantially fixed (i.e., "clean") frequency is used to generate a short pulse, the leading edge of which turns off the sample signal, thereby providing an improved sampling process with greater resolution. The interaction of the two clocks is controlled with digital logic circuitry.

Owner:LUCENT TECH INC

Bioinformatics systems, apparatuses, and methods for performing secondary and/or tertiary processing

InactiveUS20180121601A1Improve processing speedImprove accuracyInternal/peripheral component protectionProteomicsSequence analysisGenomics

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data is provided. Particularly, a genomics analysis platform for executing a sequence analysis pipeline is provided. The genomics analysis platform includes one or more of a first integrated circuit, where each first integrated circuit forms a central processing unit (CPU) that is responsive to one or more software algorithms that are configured to instruct the CPU to perform a first set of genomic processing steps of the sequence analysis pipeline. Additionally, a second integrated circuit is also provided, where each second integrated circuit forming a field programmable gate array (FPGA), the FPGA being configured by firmware to arrange a set of hardwired digital logic circuits that are interconnected by a plurality of physical interconnects to perform a second set of genomic processing steps of the sequence analysis pipeline, the set of hardwired digital logic circuits of each FPGA being arranged as a set of processing engines to perform the second set of genomic processing steps. A shared memory is also provided.

Owner:EDICO GENOME

Power consumption stabilization system & method

InactiveUS20050078016A1Reduce maximum power consumptionLimiting designReliability increasing modificationsCode conversionNumber generatorComputer science

A source signal is provided. The source signal is XORed with a scrambling random signal to generate a scrambled signal. The scrambled signal is transmitted through the digital logic circuit. The scrambled signal is XORed with the descrambling random signal logically identical to the scrambling random signal to produce a descrambled signal identical to the source signal. In one embodiment, the scrambling random signal is transmitted through the digital logic circuit and used as the descrambling random signal. In another embodiment, the scrambling random signal and descrambling random signal are generated independently using pseudo-random number generators. In yet another embodiment, the scrambling random signal is self-synchronizing and is contained within the pattern of the scrambled signal.

Owner:AGILENT TECH INC

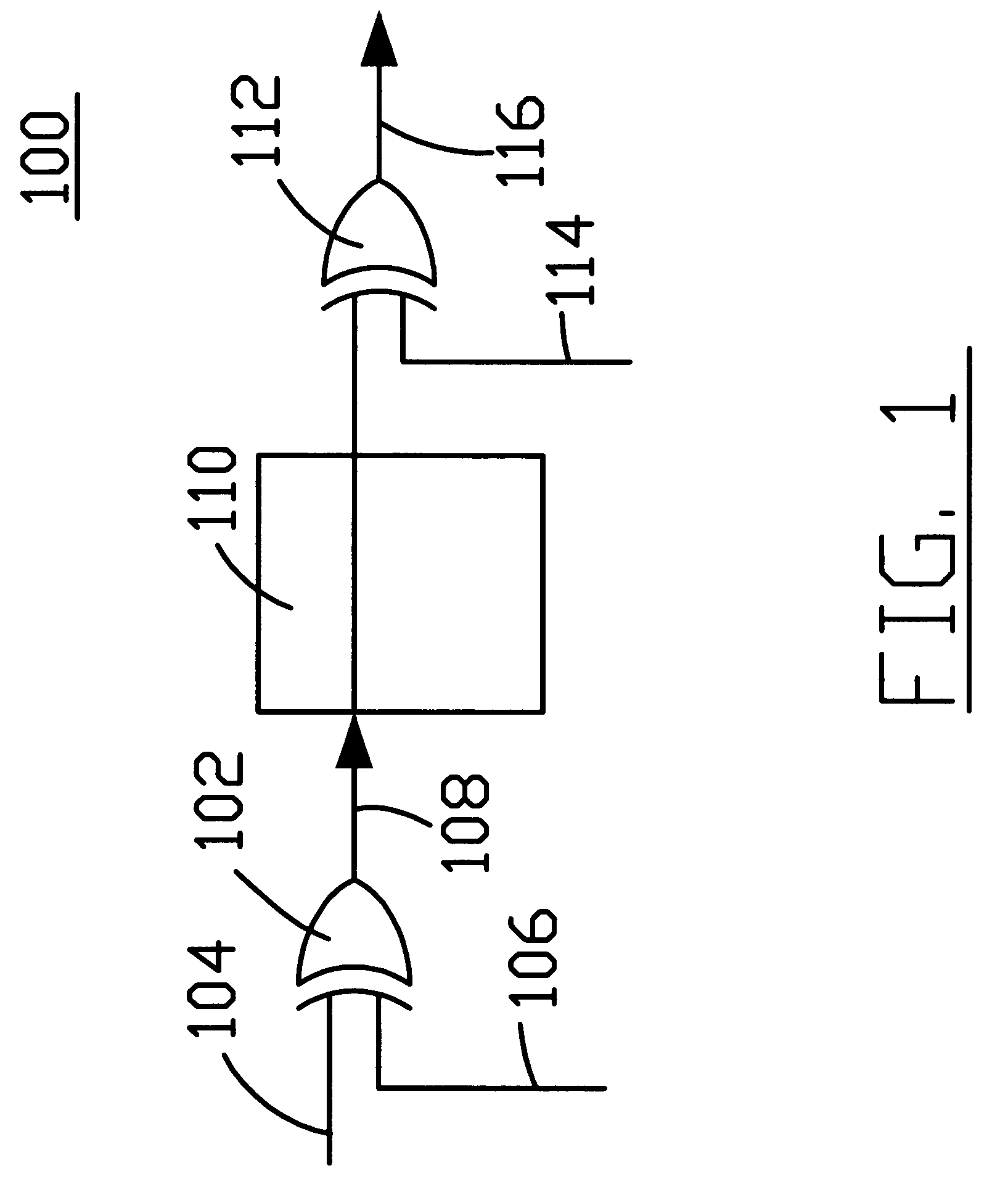

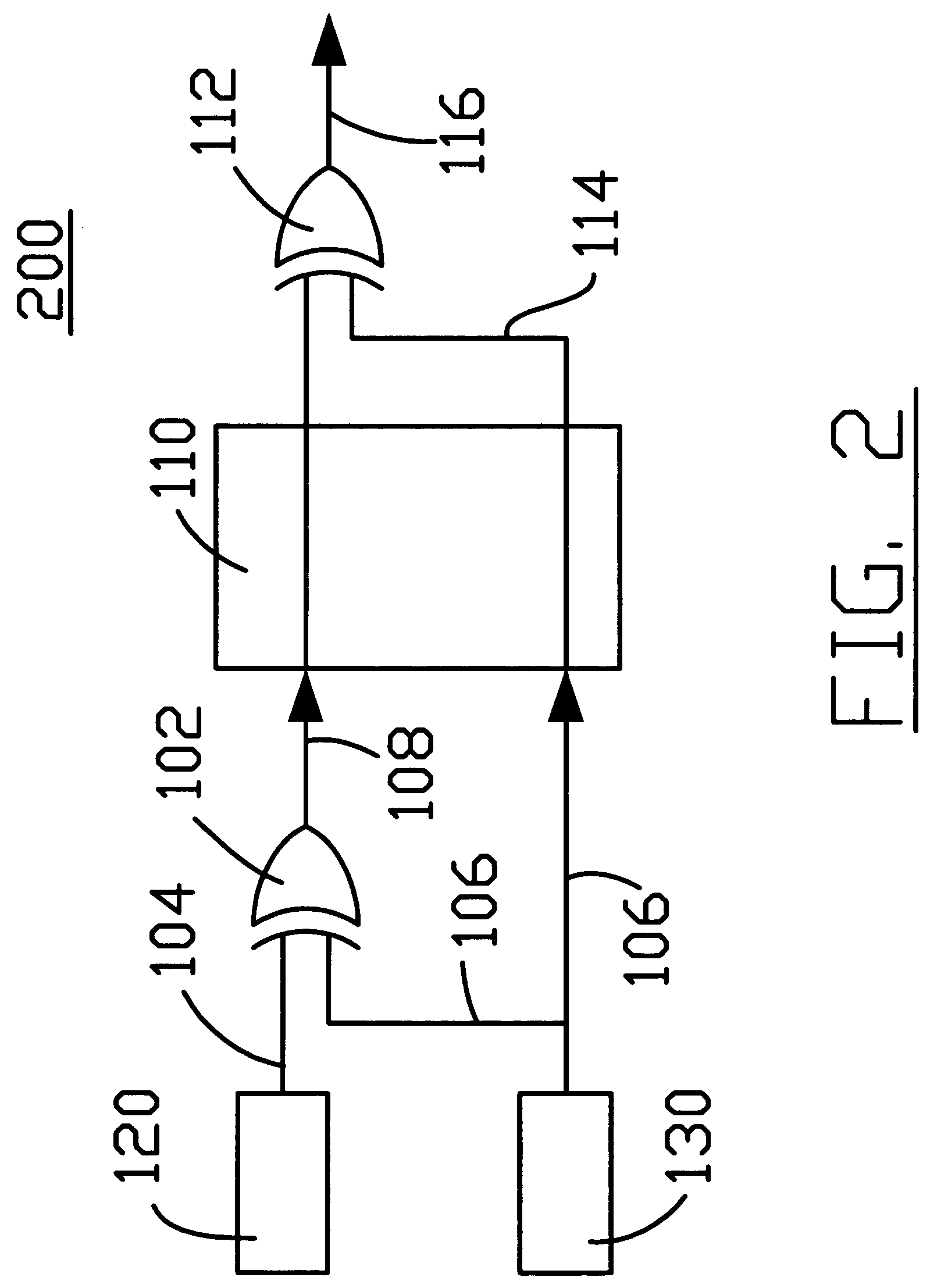

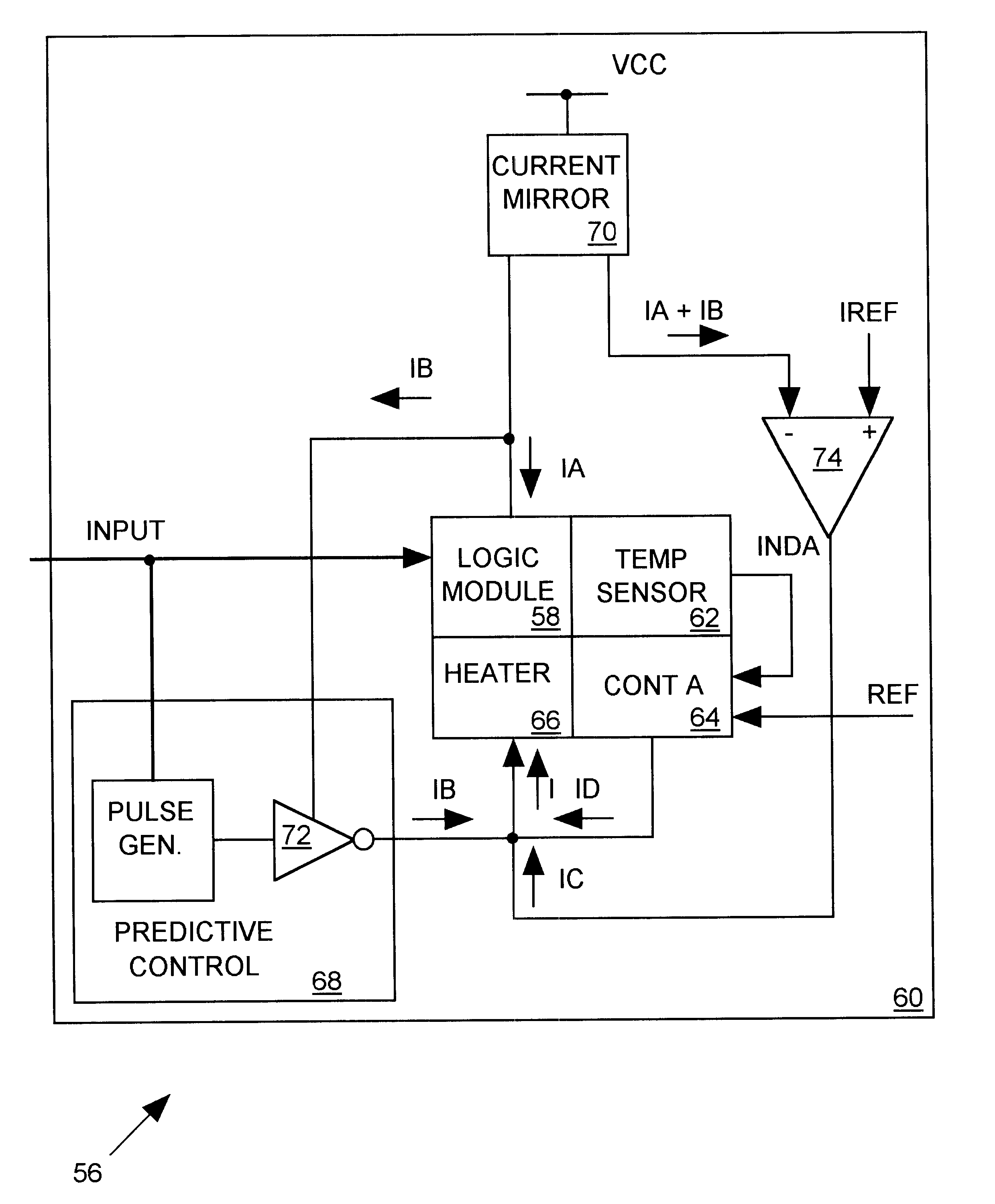

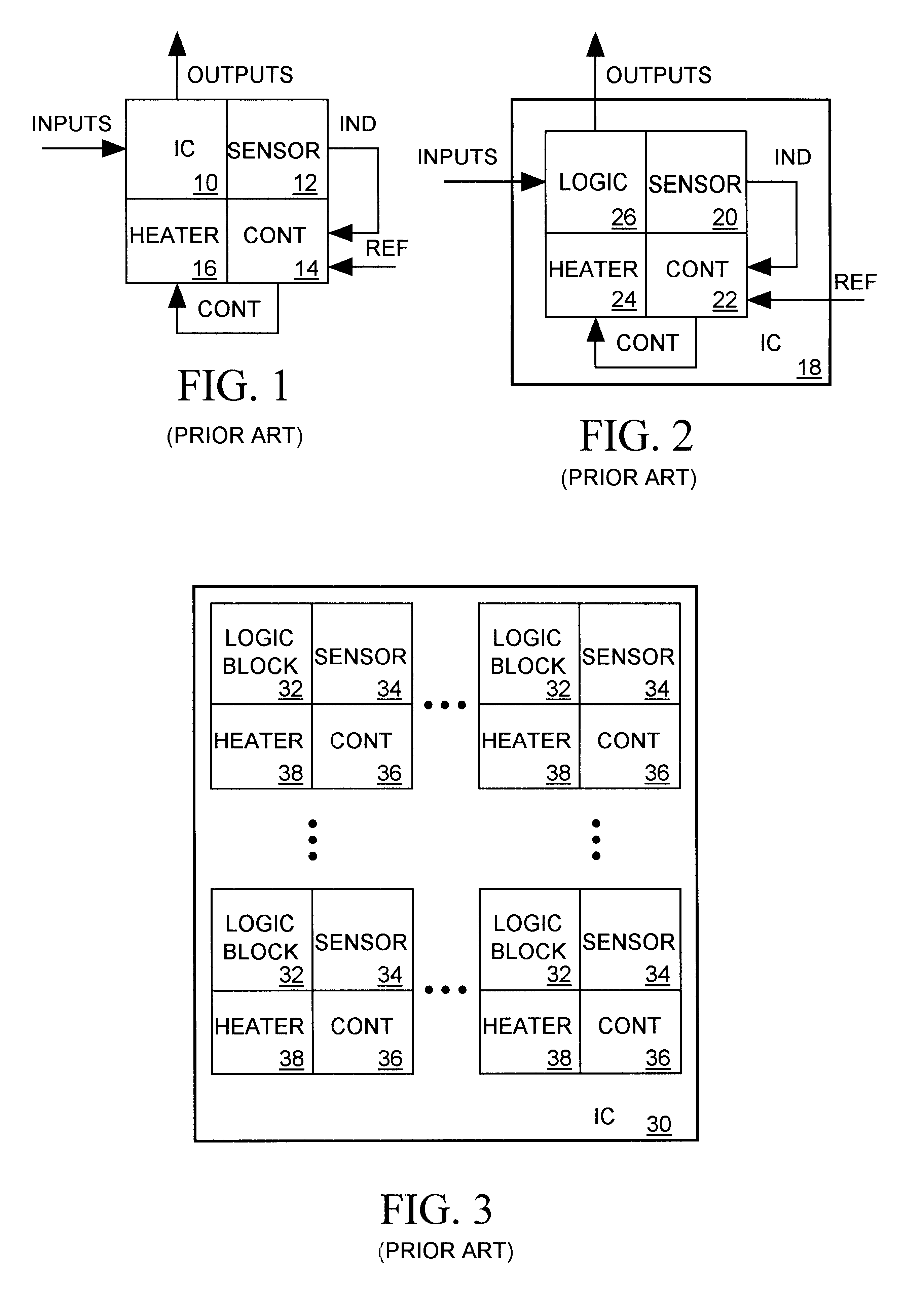

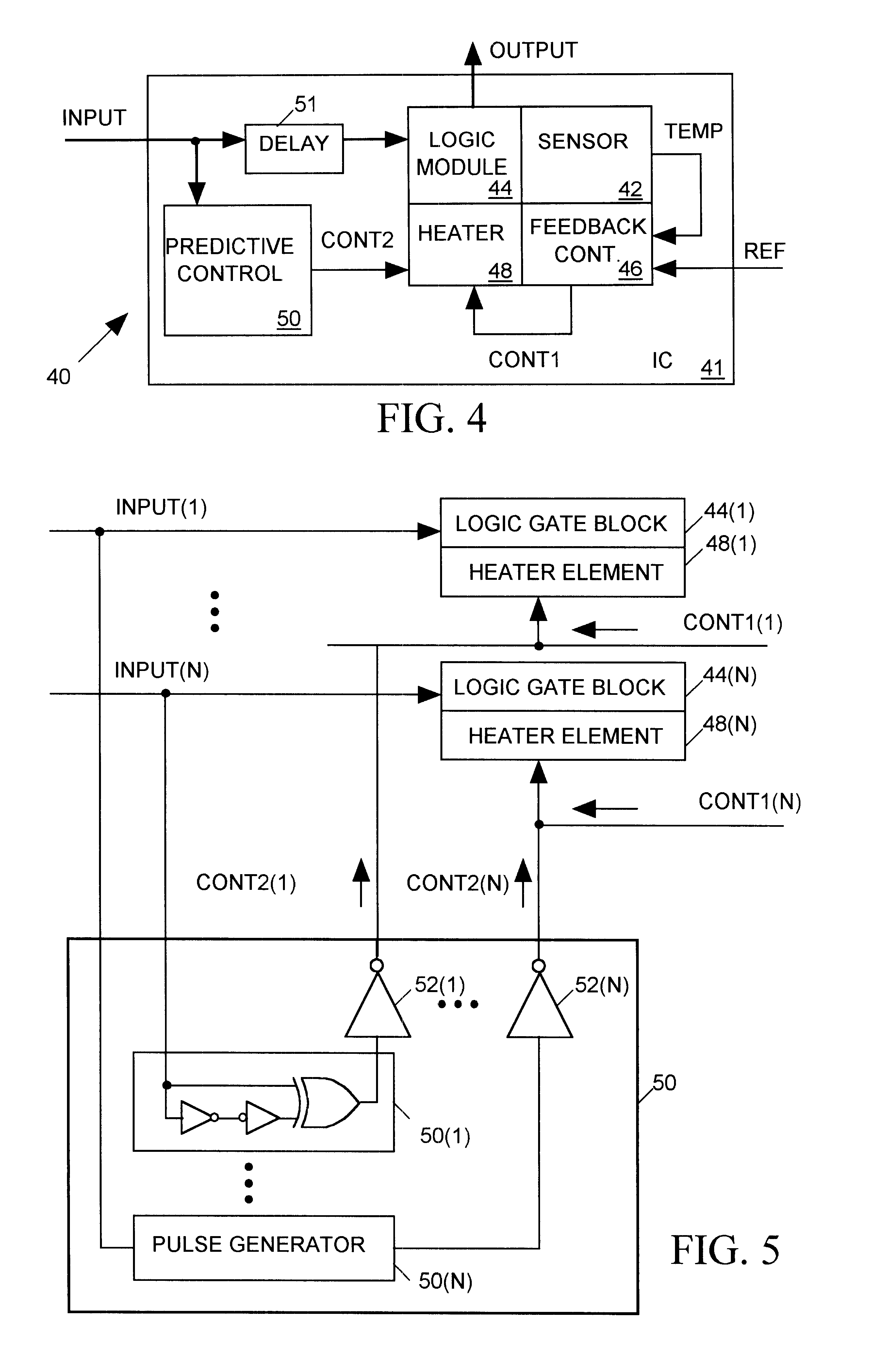

Predictive temperature control system for an integrated circuit

InactiveUS6484117B1Thermometer detailsThermometers using electric/magnetic elementsTemperature controlControl system

Variation in temperature of a digital logic circuit that temporarily increases its heat production after a digital input signal changes state is limited using a heater that applies heat to the digital logic circuit at a variable rate. A control circuit monitors all of the circuit's digital input signals and temporarily decreases the rate at which the heater applies heat to the digital logic circuit after each state change in a digital input signal. The amount of temporary reduction in heater output is sized to substantially match the amount of temporary increase in logic circuit heat production so that the temperature of the logic circuit remains largely unaffected. A feedback circuit is also provided to monitor the temperature of the digital logic circuit and to further adjust the heater output so as to help maintain the logic circuit at a desired temperature.

Owner:CREDENCE SYSTEMS

Bioinformatics systems, apparatuses, and methods for performing secondary and/or tertiary processing

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data is provided. Particularly, a genomics analysis platform for executing a sequence analysis pipeline is provided. The genomics analysis platform includes one or more of a first integrated circuit, where each first integrated circuit forms a central processing unit (CPU) that is responsive to one or more software algorithms that are configured to instruct the CPU to perform a first set of genomic processing steps of the sequence analysis pipeline. Additionally, a second integrated circuit is also provided, where each second integrated circuit forming a field programmable gate array (FPGA), the FPGA being configured by firmware to arrange a set of hardwired digital logic circuits that are interconnected by a plurality of physical interconnects to perform a second set of genomic processing steps of the sequence analysis pipeline, the set of hardwired digital logic circuits of each FPGA being arranged as a set of processing engines to perform the second set of genomic processing steps. A shared memory is also provided.

Owner:EDICO GENOME

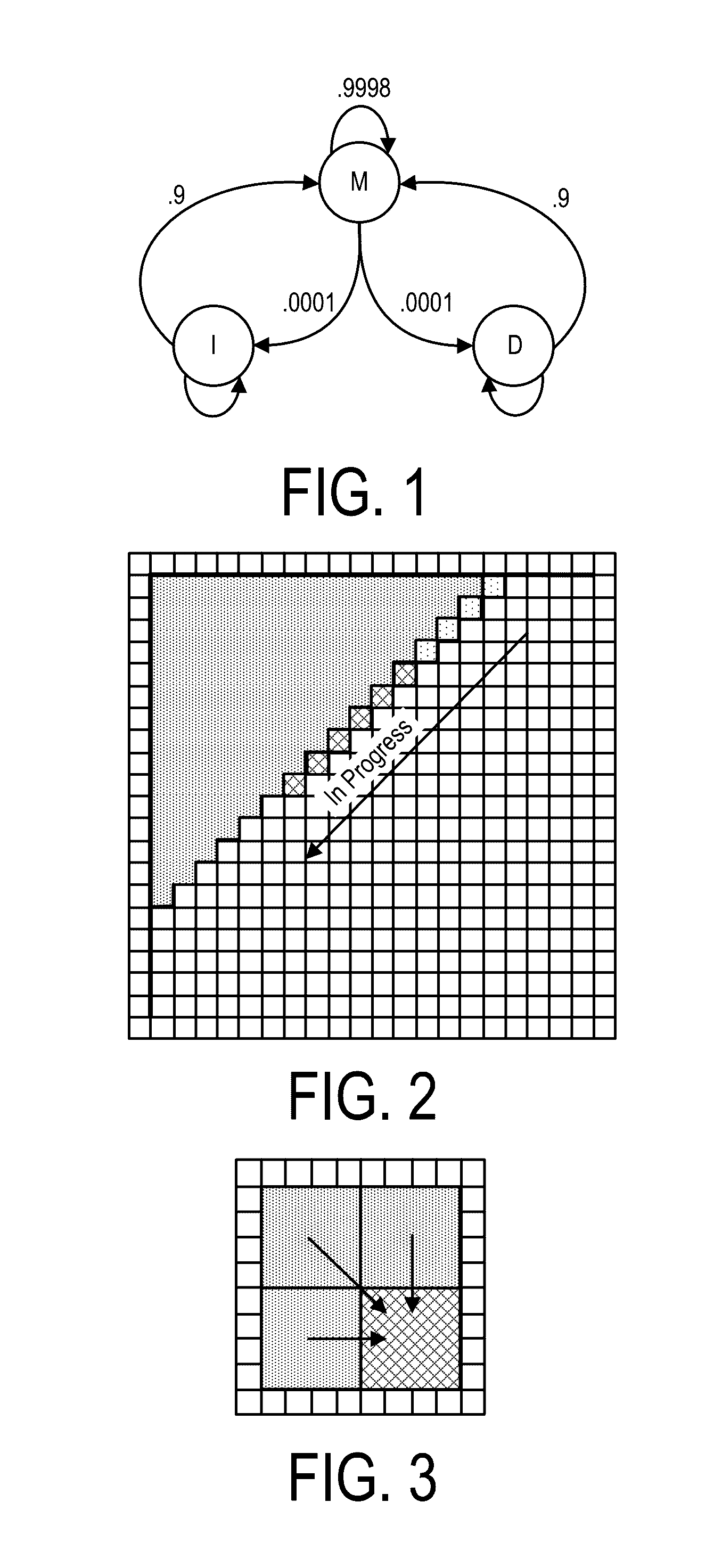

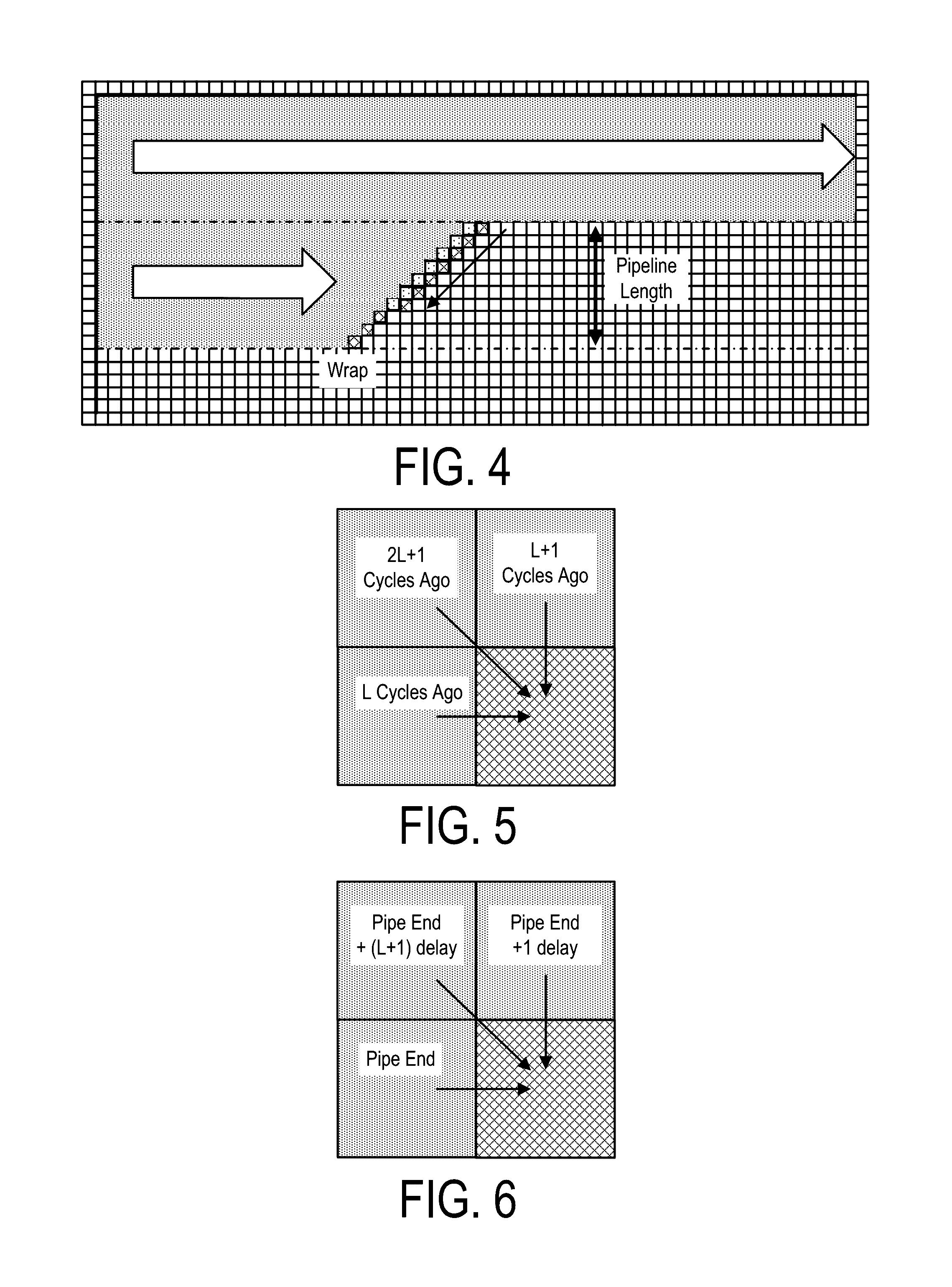

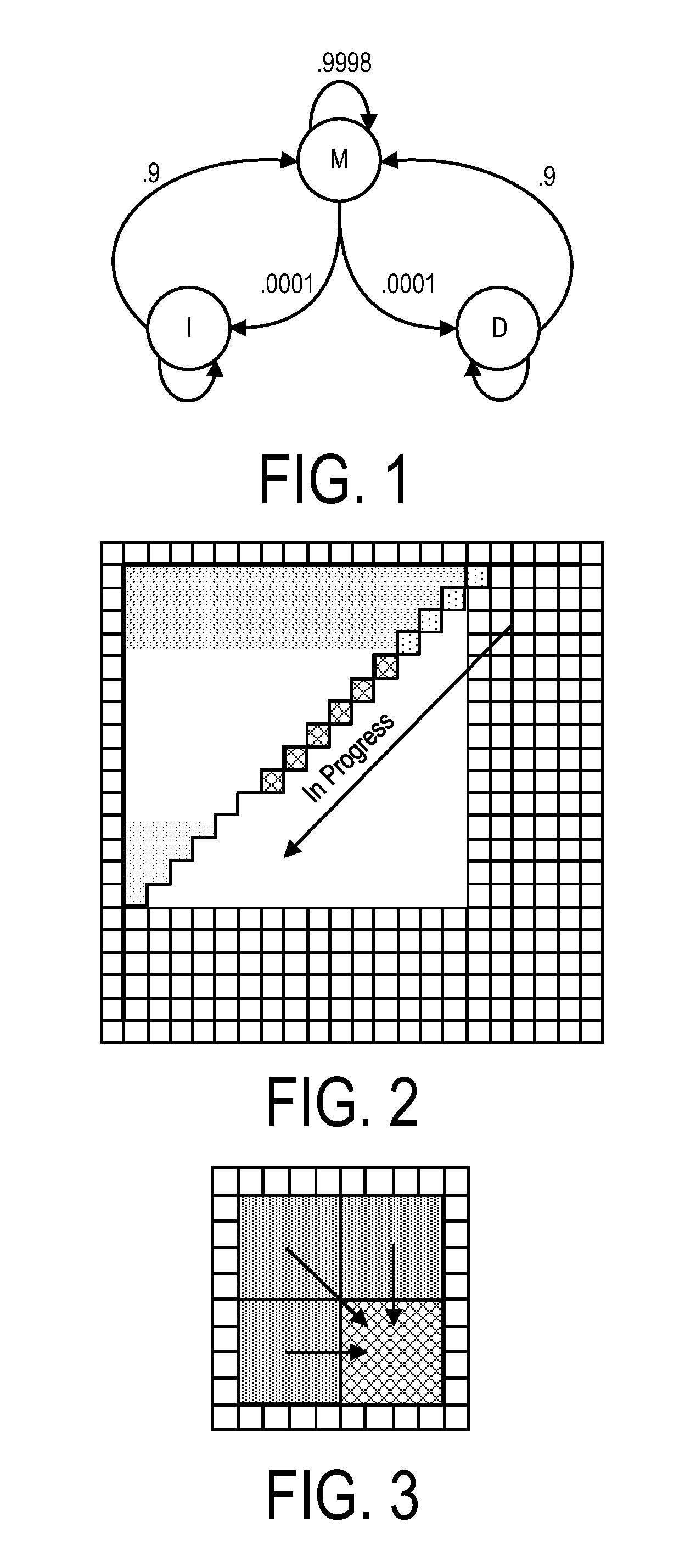

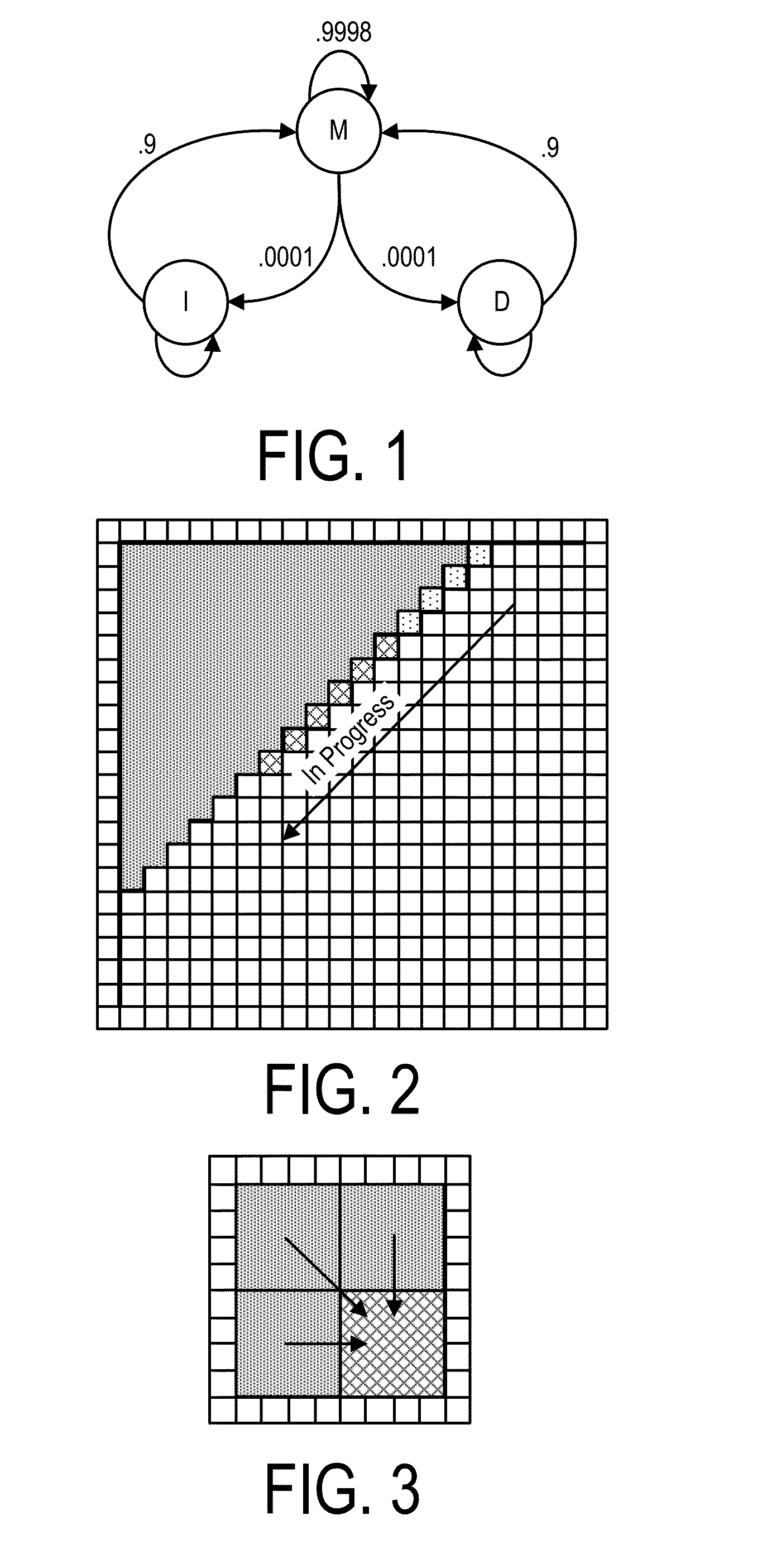

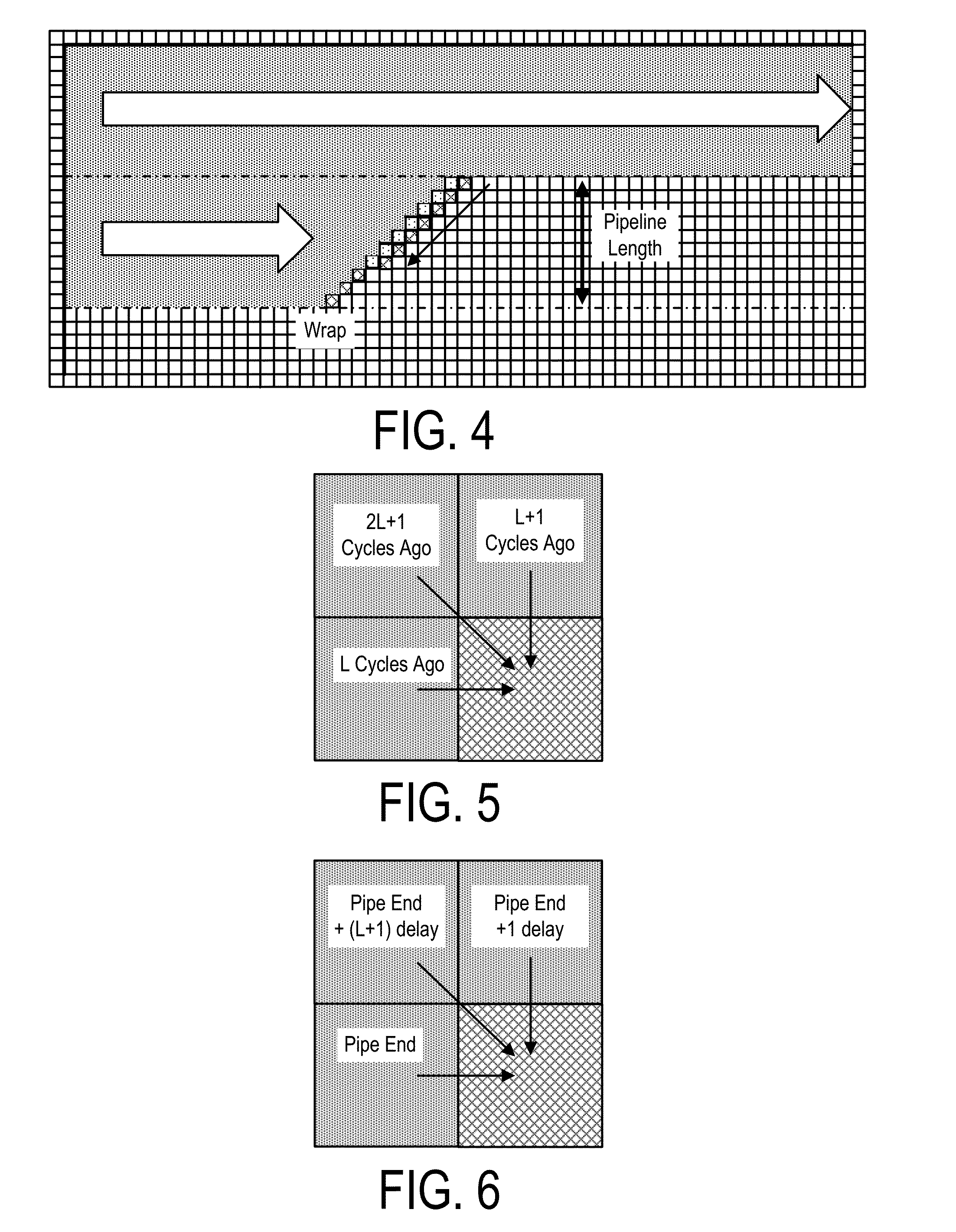

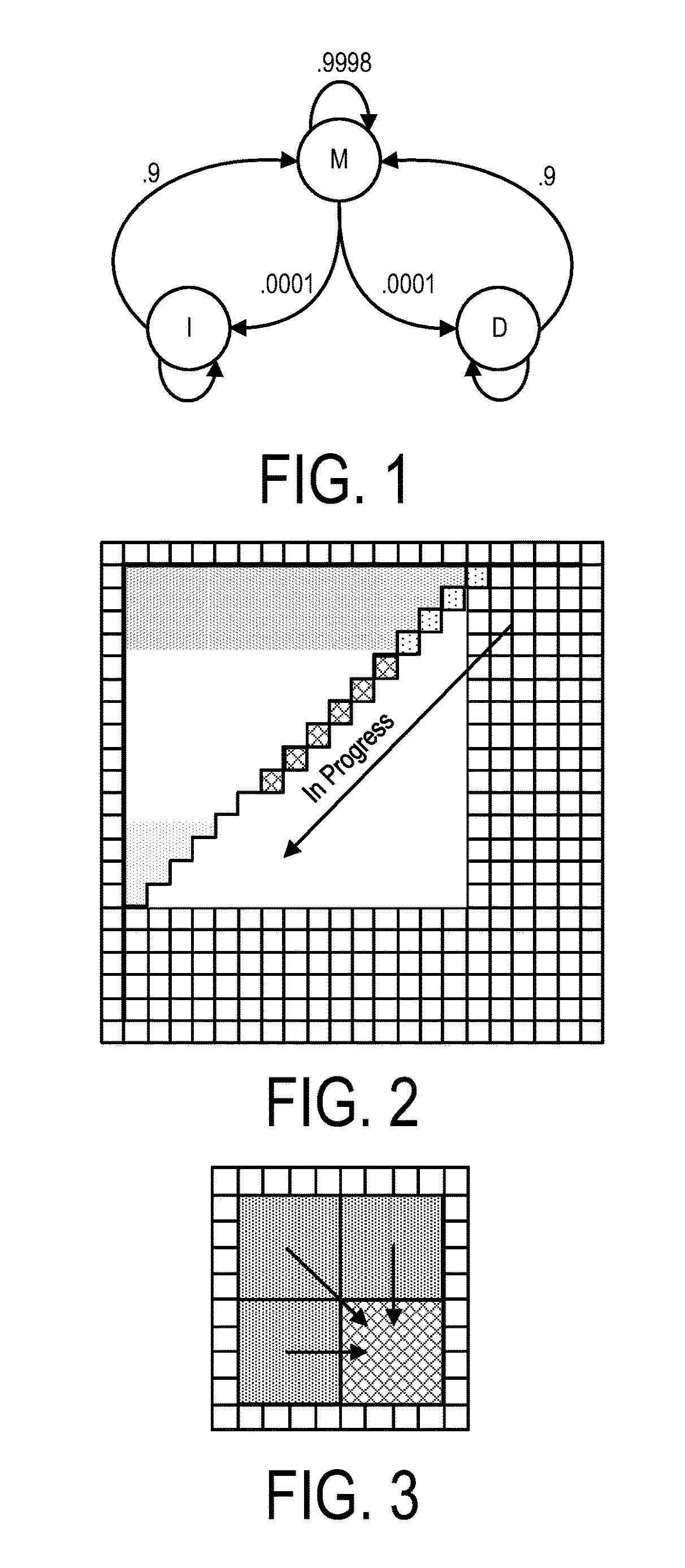

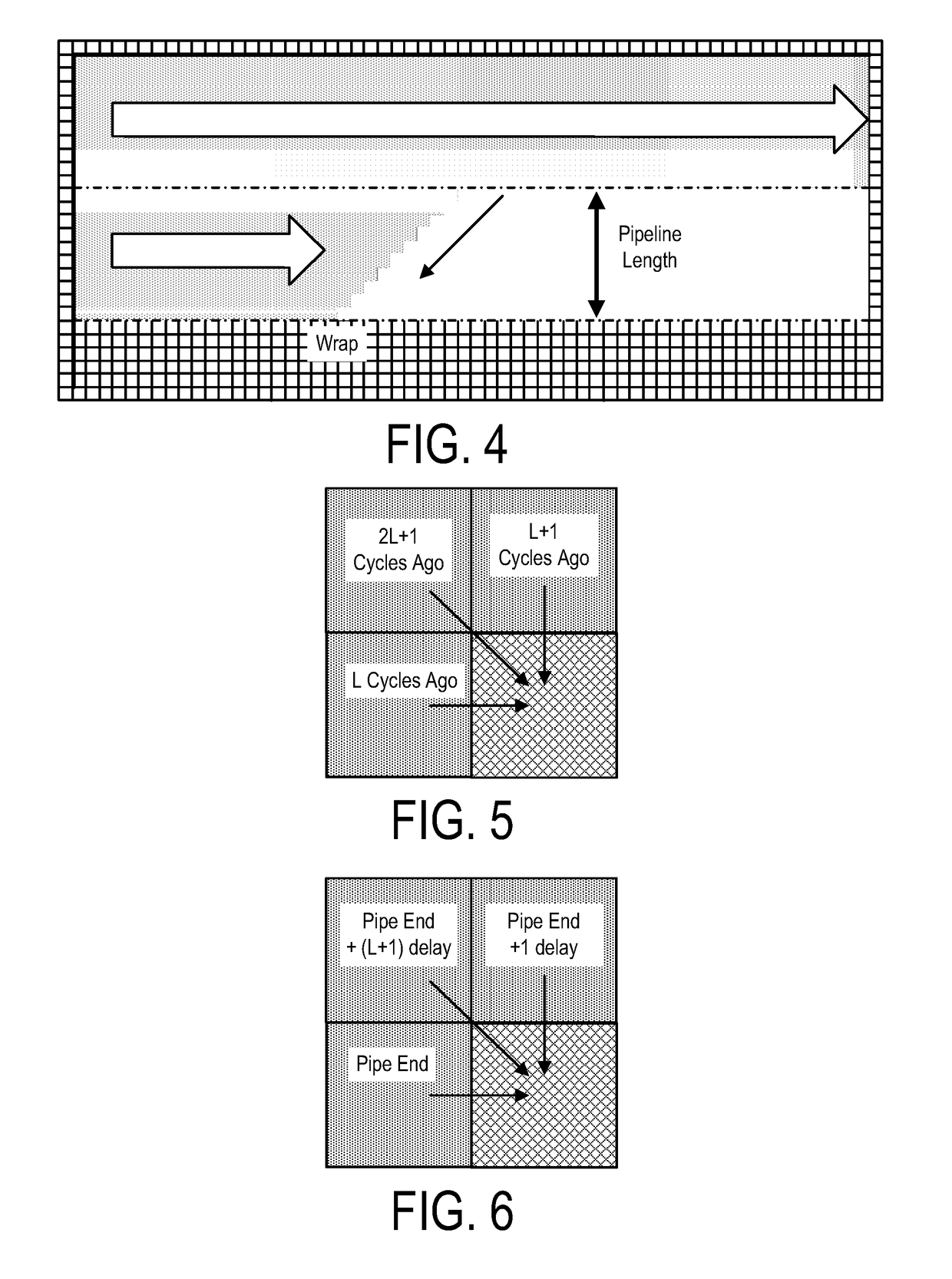

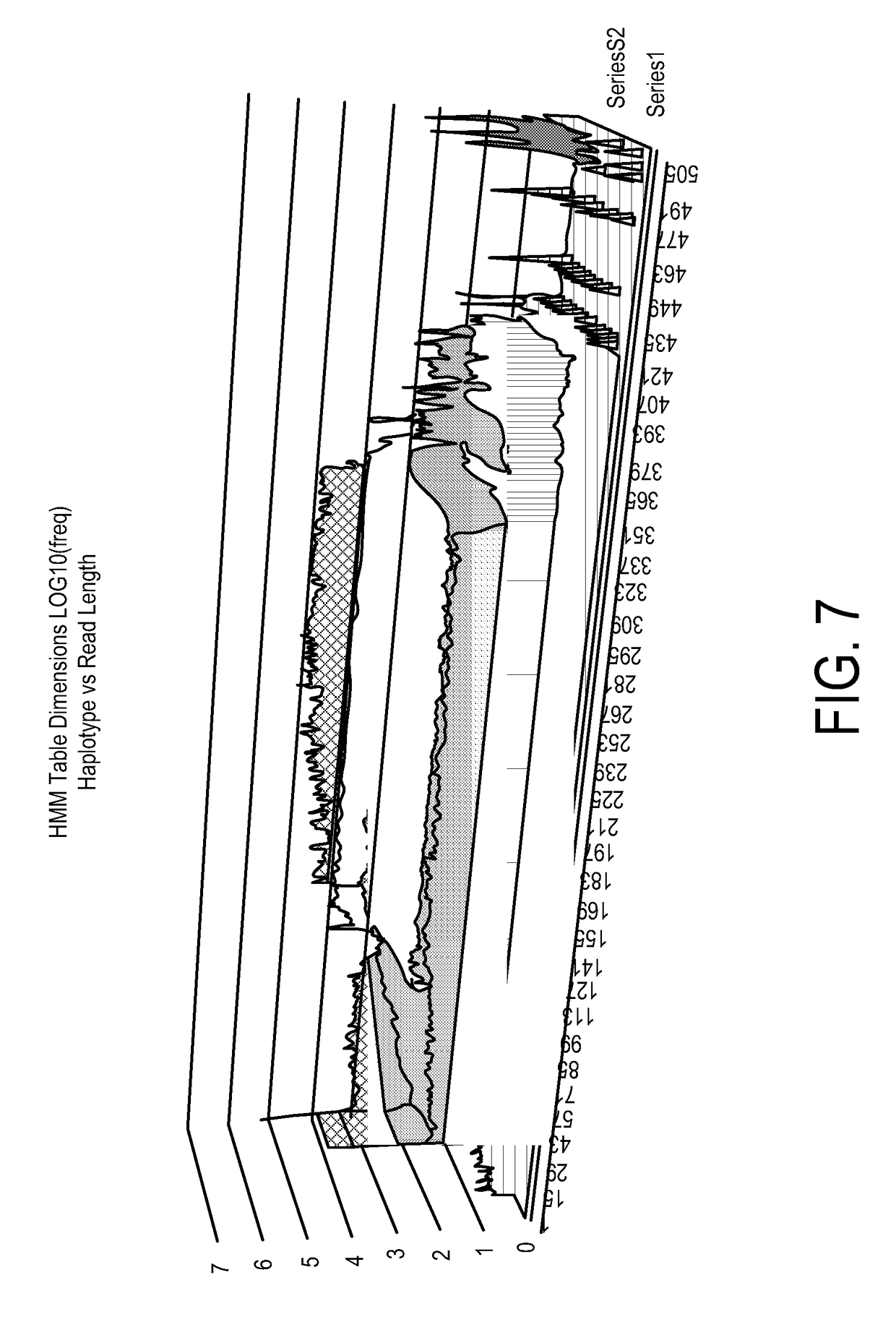

Bioinformatics Systems, Apparatuses, And Methods Executed On An Integrated Circuit Processing Platform

PendingUS20160171153A1Processing speedProcessed result accuracyBiostatisticsBiological testingData sourceGenomic data

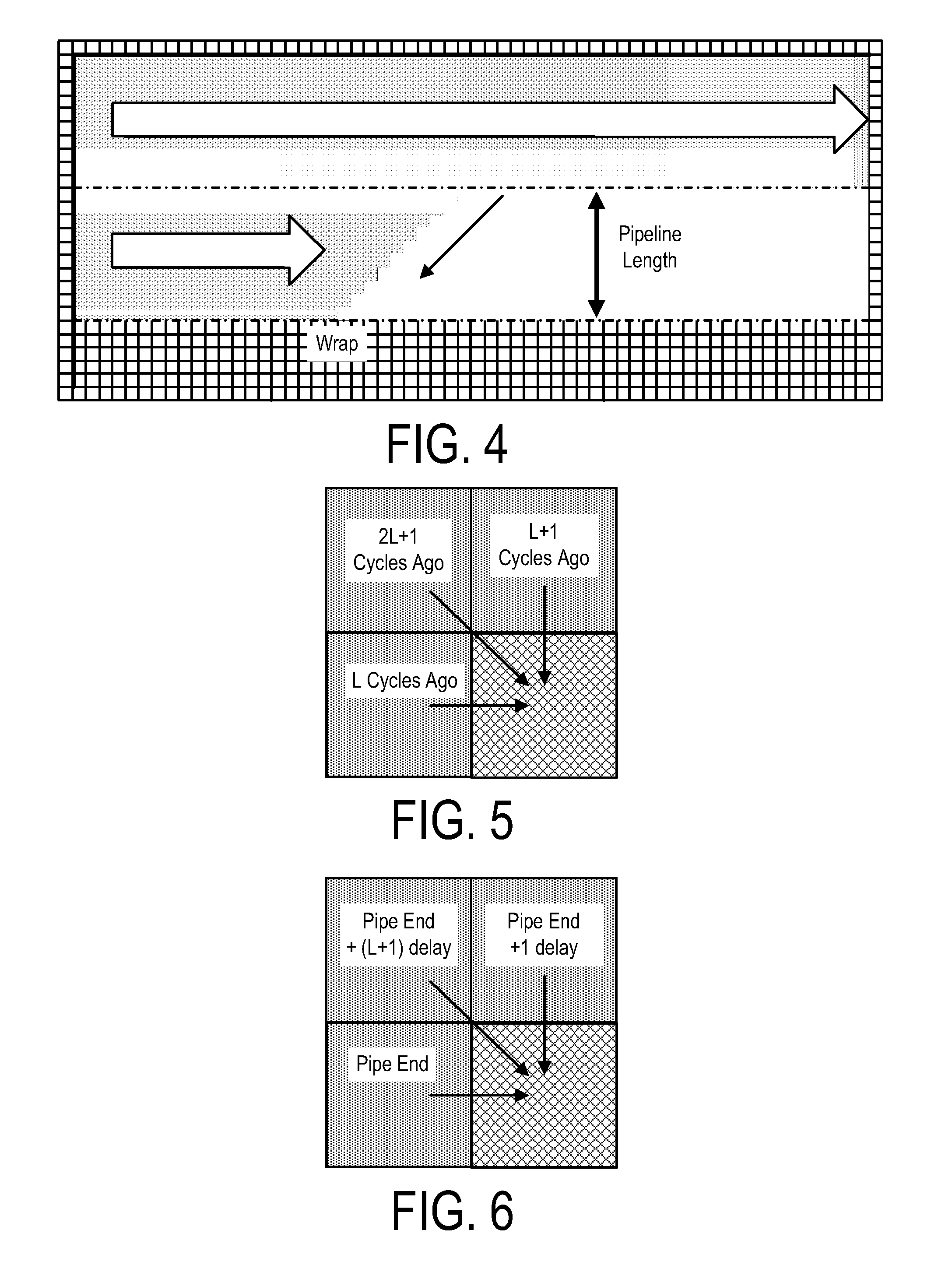

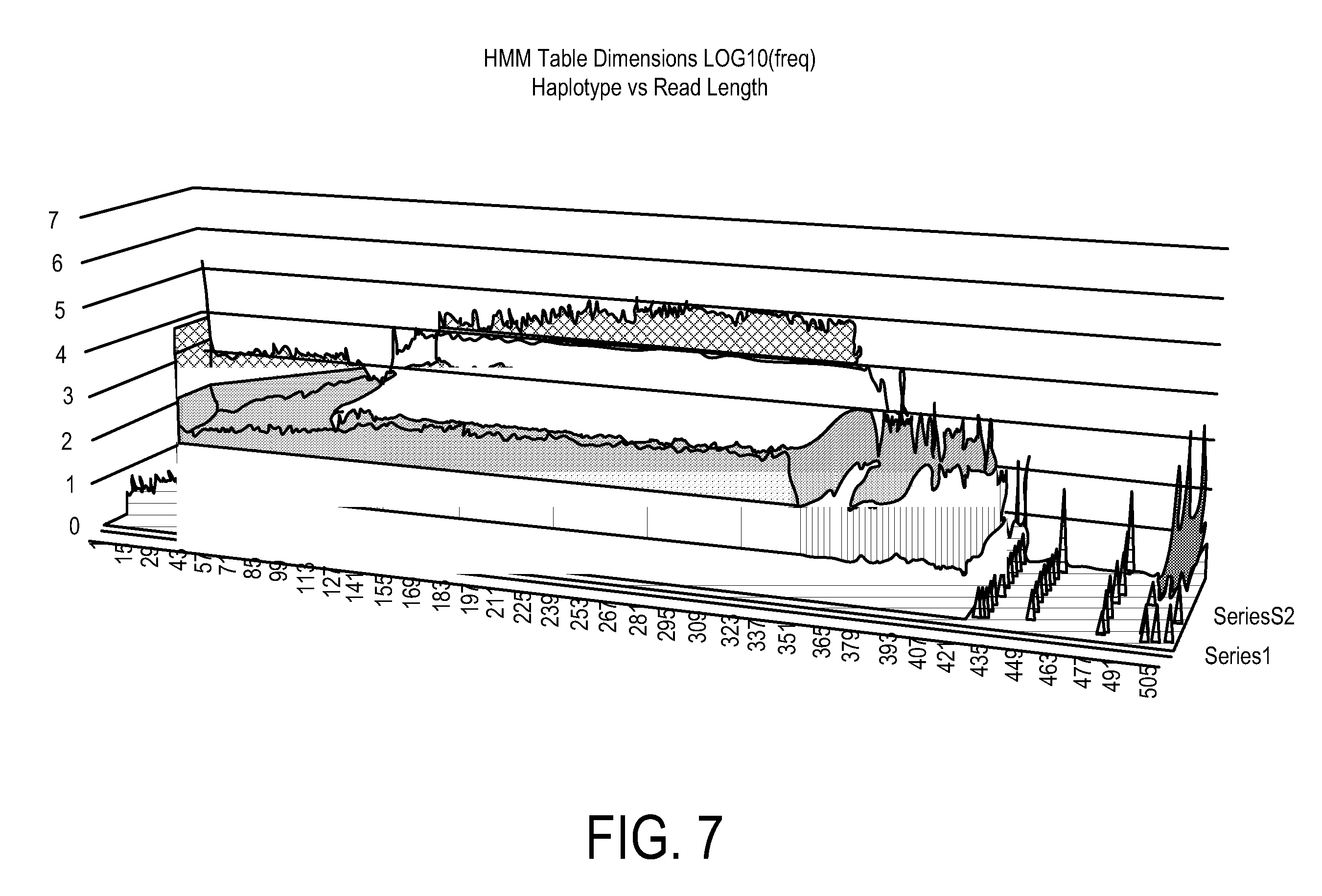

A system, method and apparatus for executing an HMM analysis on genetic sequence data includes an integrated circuit formed of a set of hardwired digital logic circuits that are interconnected by physical electrical interconnects. One of the physical electrical interconnects forms an input to the integrated circuit that may be connected with an electronic data source for receiving reads of genomic data. The hardwired digital logic circuits may be arranged as a set of processing engines, each processing engine being formed of a subset of the hardwired digital logic circuits to perform one or more steps in the HMM analysis on the reads of genomic data. Each subset of the hardwired digital logic circuits may be formed in a wired configuration to perform the one or more steps in the HMM analysis.

Owner:EDICO GENOME

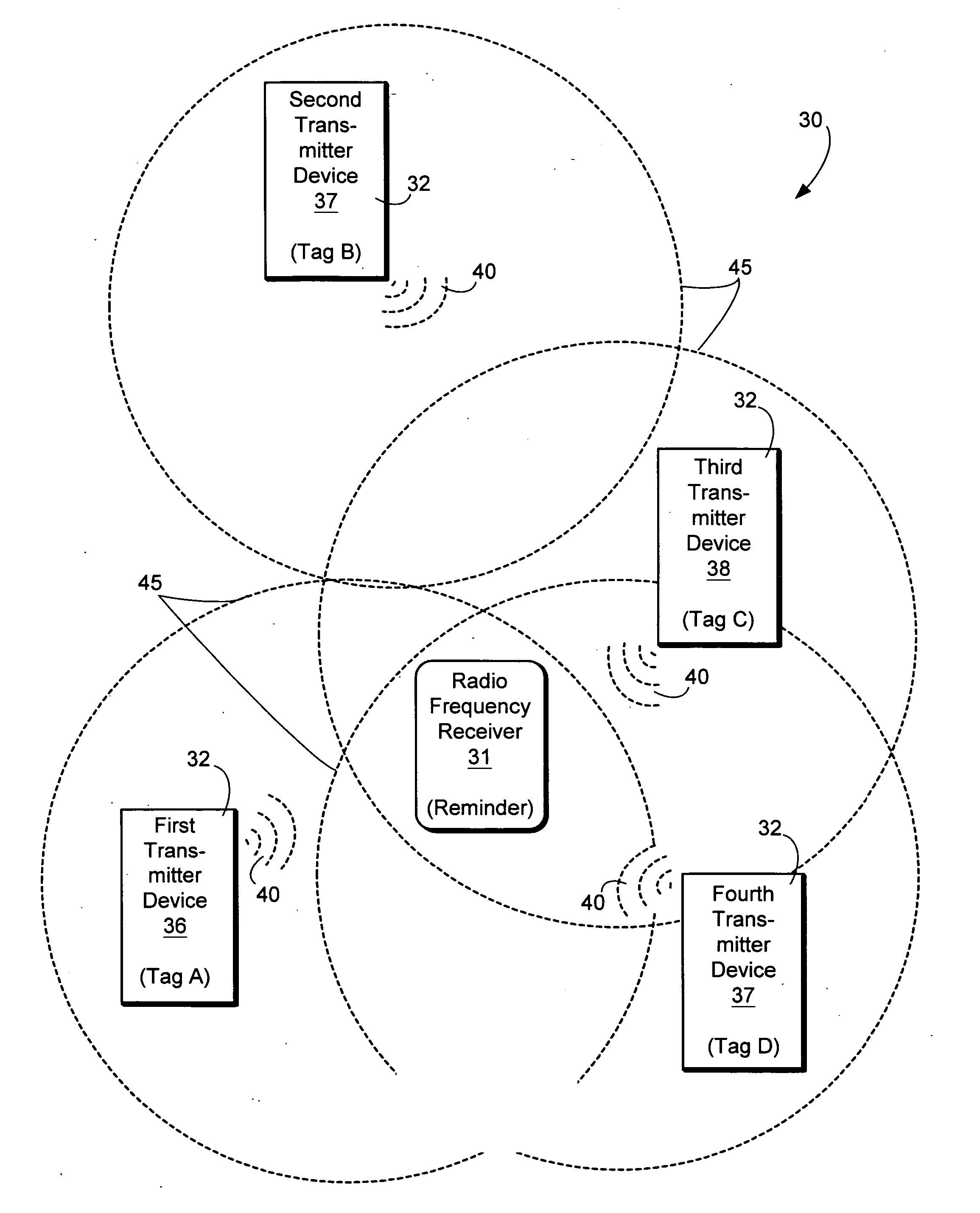

Wireless tracking system for personal items

InactiveUS20060135178A1Radio/inductive link selection arrangementsSubstation equipmentEngineeringCompanion animal

A radio frequency transmission device including electronic circuitry. A digital logic circuit is alternate-able from a sleep mode to an active mode after a pre-determined time period, and back to the sleep mode immediately after transmission of a digital signal. The digital signal includes a unique and pre-determined sequence of fixed length pulses routed to a transmission circuit to transmit a radio signal in a specific frequency range. An output display signal from the output circuitry is displayed with an LED. An input circuitry is manually activated. A radio frequency signal is received with a receiver circuitry, sensed to determine if the received signal has a compatible characteristic of an expected signal. The radio frequency signal is converted into a digital form and sent to the microprocessor. Every associated transmitter device is tracked with a counter maintained by a microprocessor. Personnel, belongings and pets can be tracked with this device.

Owner:J3KEEPER L L C

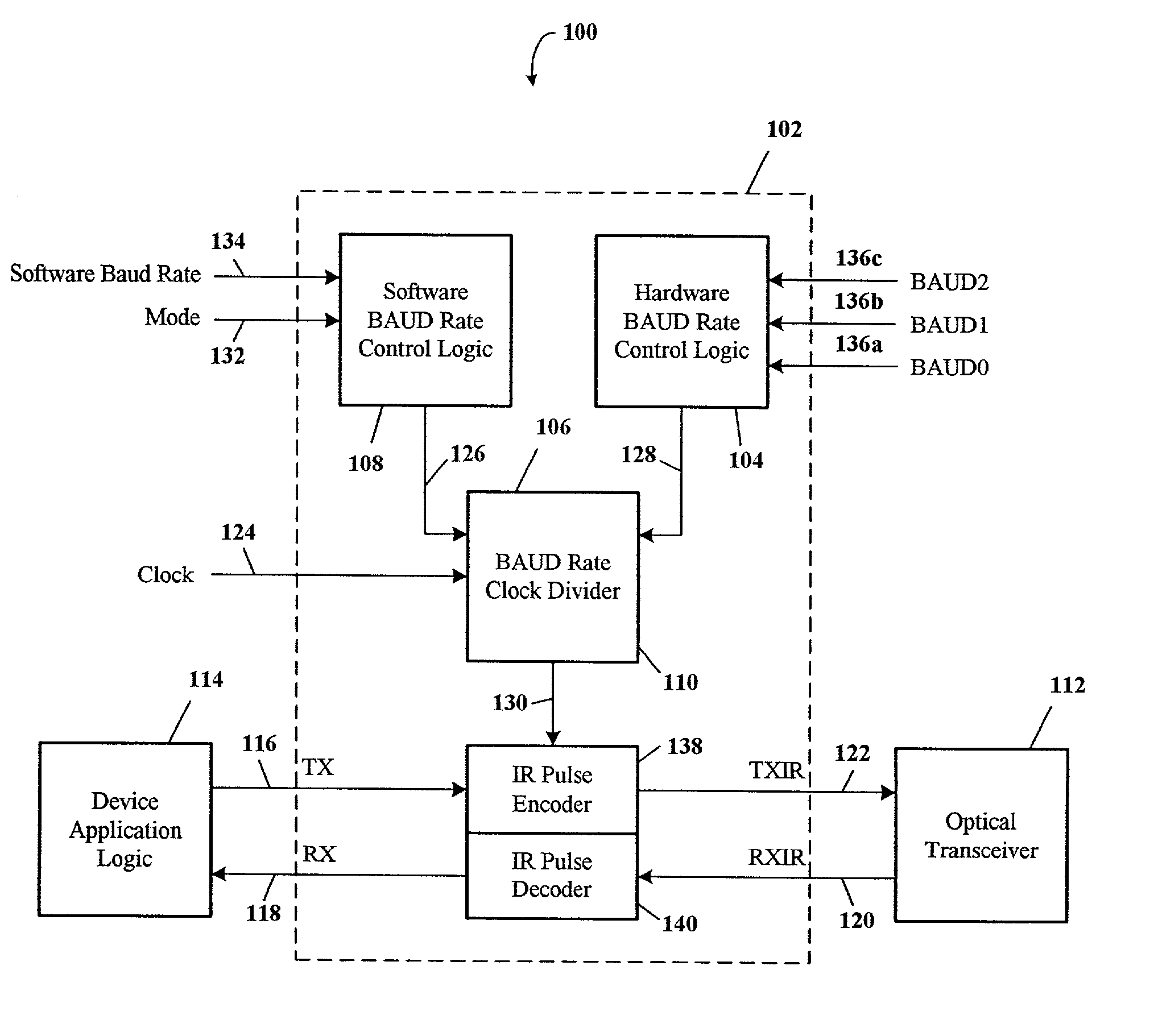

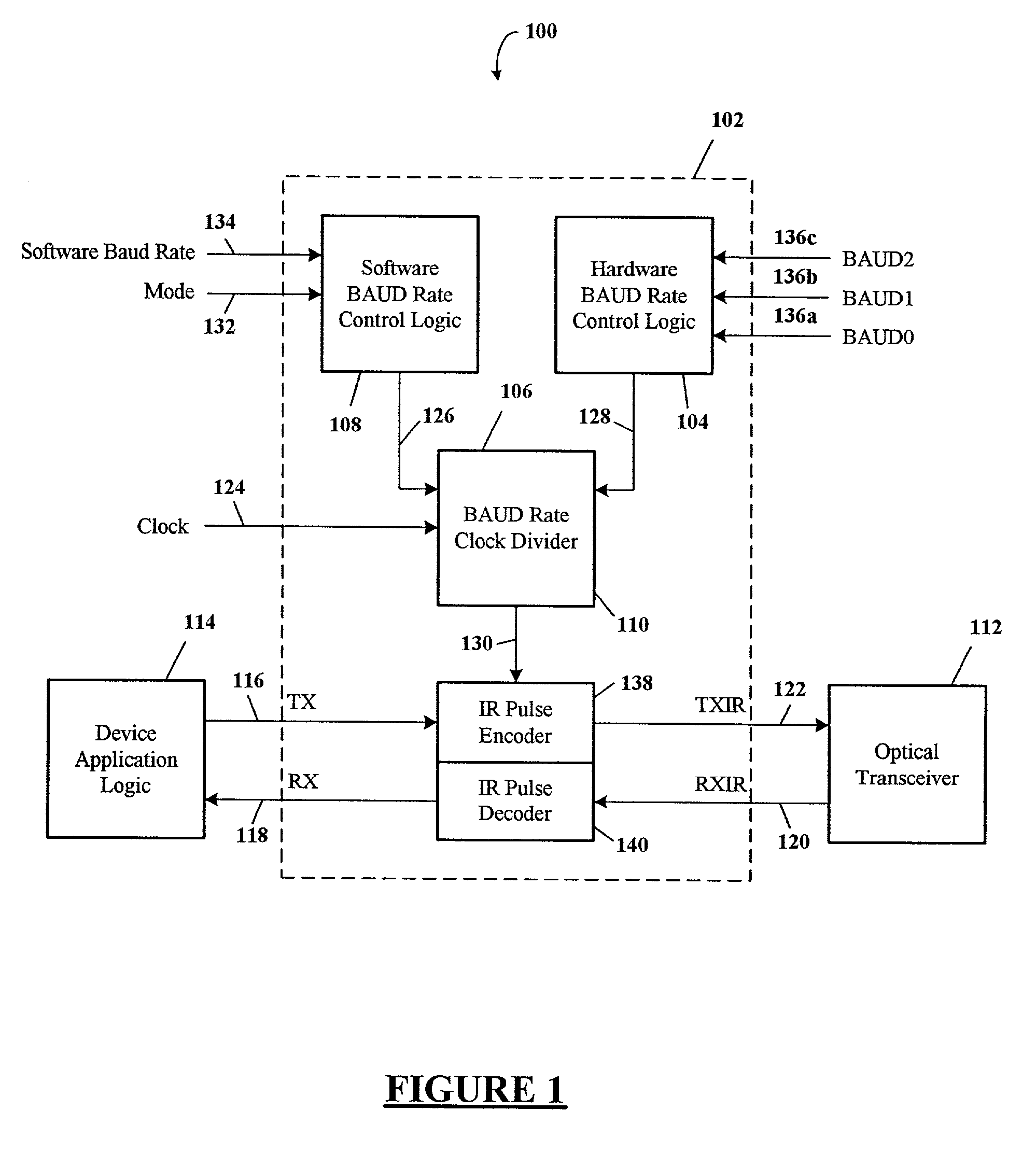

Infrared encoder/decoder having hardware and software data rate selection

InactiveUS20020176138A1Reduce system resourceClose-range type systemsElectromagnetic transmittersInfraredSerial transfer

An infrared encoder / decoder selects the data rate of a serial transmission of data by changing an input clock speed, setting the operating characteristics of a clock divider circuit by hardware inputs or selecting a clock speed by software commands that program the operating characteristics of a clock divider circuit. Having three alternate ways, two hardware and one software, of selecting the data rate of the serial transmission allows greater flexibility in the application and interfacing of a single integrated circuit package infrared encoder / decoder with all types of digital logic circuits and systems. An encoder / decoder having standard pulse width output and input compatibility with infrared industry standards, e.g., IrDA, and infrared transceivers is achieved in a flexible and cost effective low power integrated circuit package.

Owner:MICROCHIP TECH INC

Method of defining semiconductor fabrication process utilizing transistor inverter delay period

ActiveUS20070110194A1Improve performanceError preventionPulse automatic controlManufacturing technologyTime delays

A novel method and apparatus for defining process variation in a digital RF processor (DRP). The invention is well suited for use in highly integrated system on a chip (SoC) radio solutions that incorporate a very large amount of digital logic circuitry. The method and apparatus provide direct measurement of fabrication process variation in circuits without requiring any additional test equipment by utilizing a time to digital converter (TDC) circuit already present in the chip. The TDC circuit relies on the time delay in an inverter chain to sample a high speed CKV clock using a slow FREF clock. Calculation of inverse time provides a direct correlation for fabrication process variation in each die.

Owner:DE OBALDIA ELIDA ISABEL +3

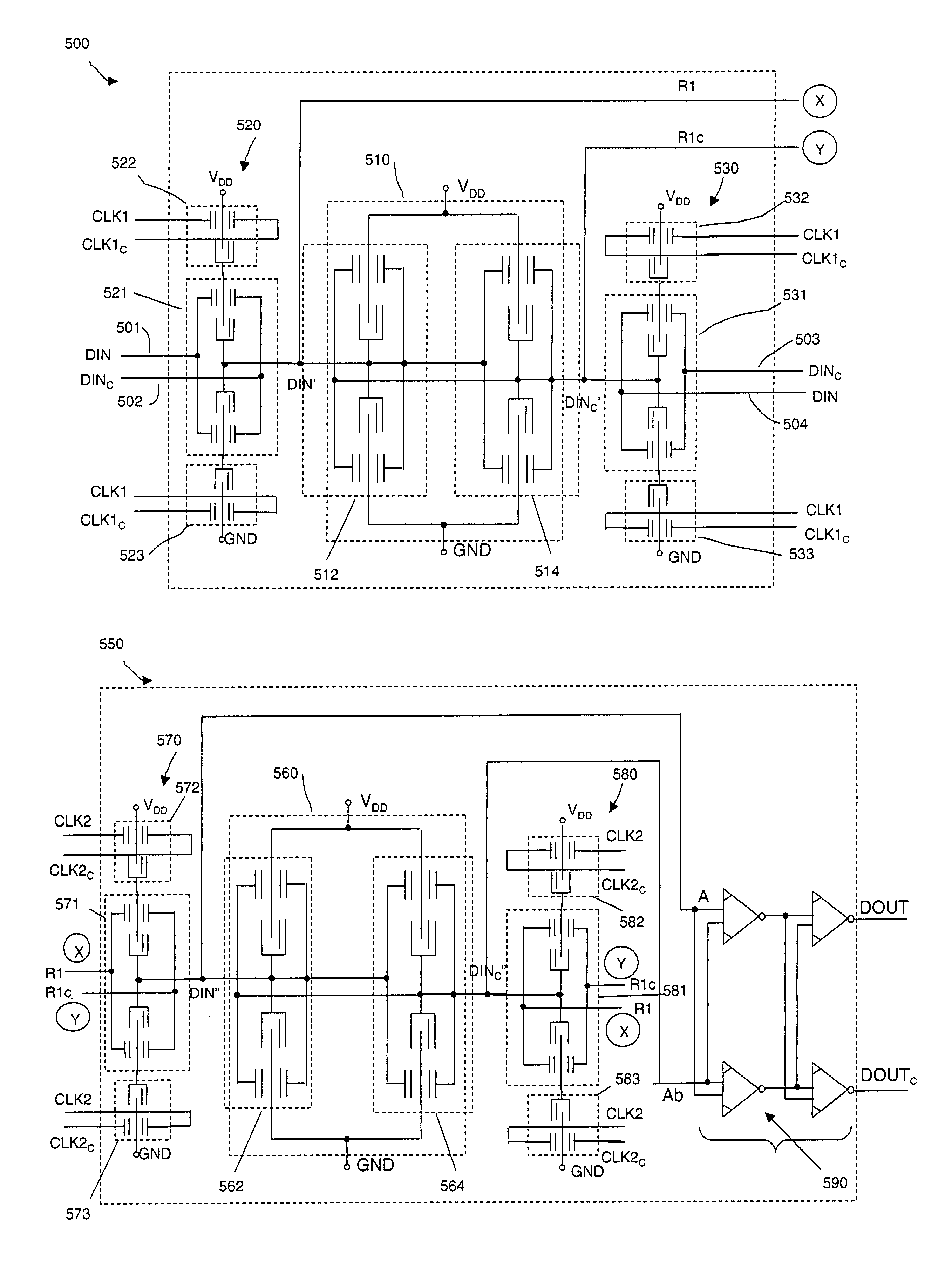

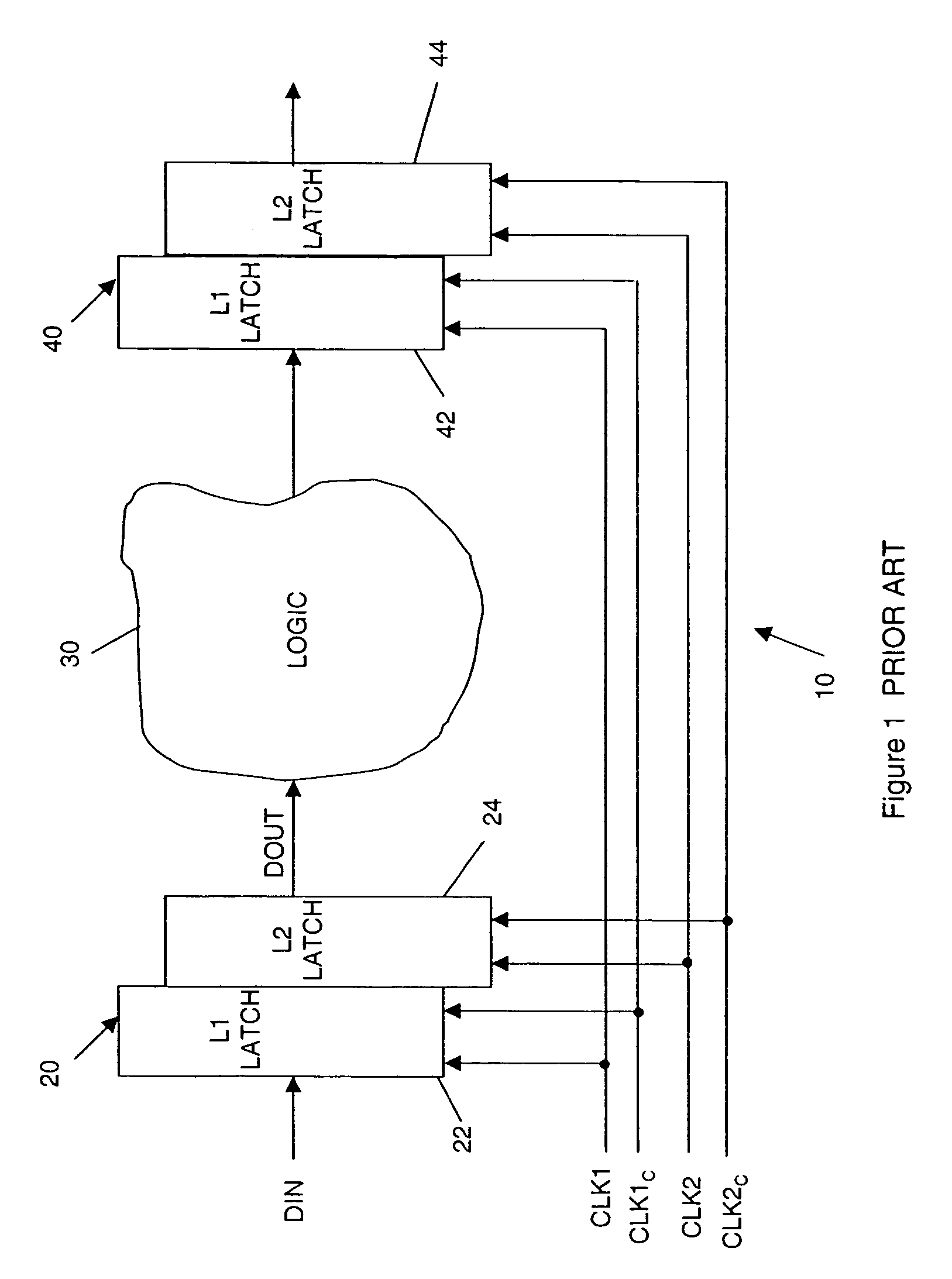

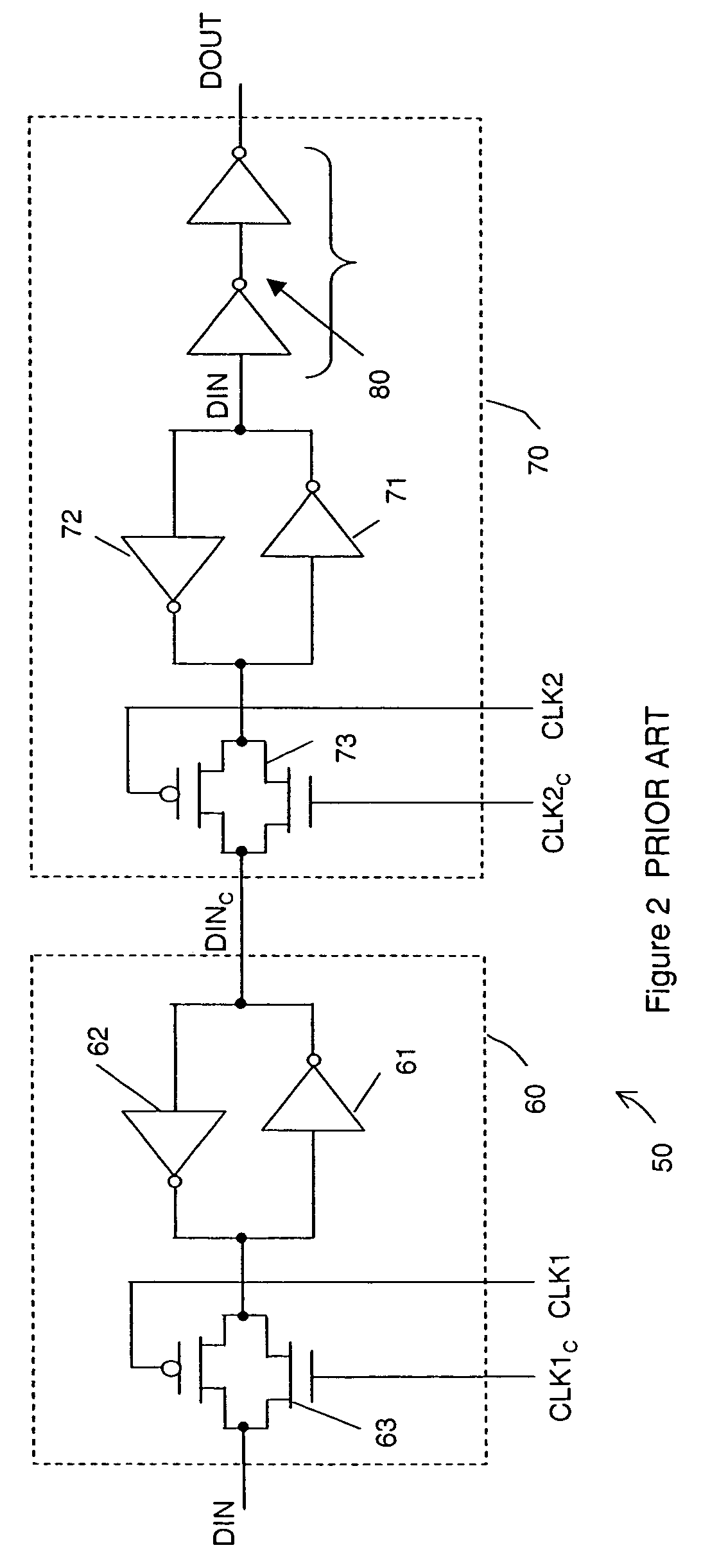

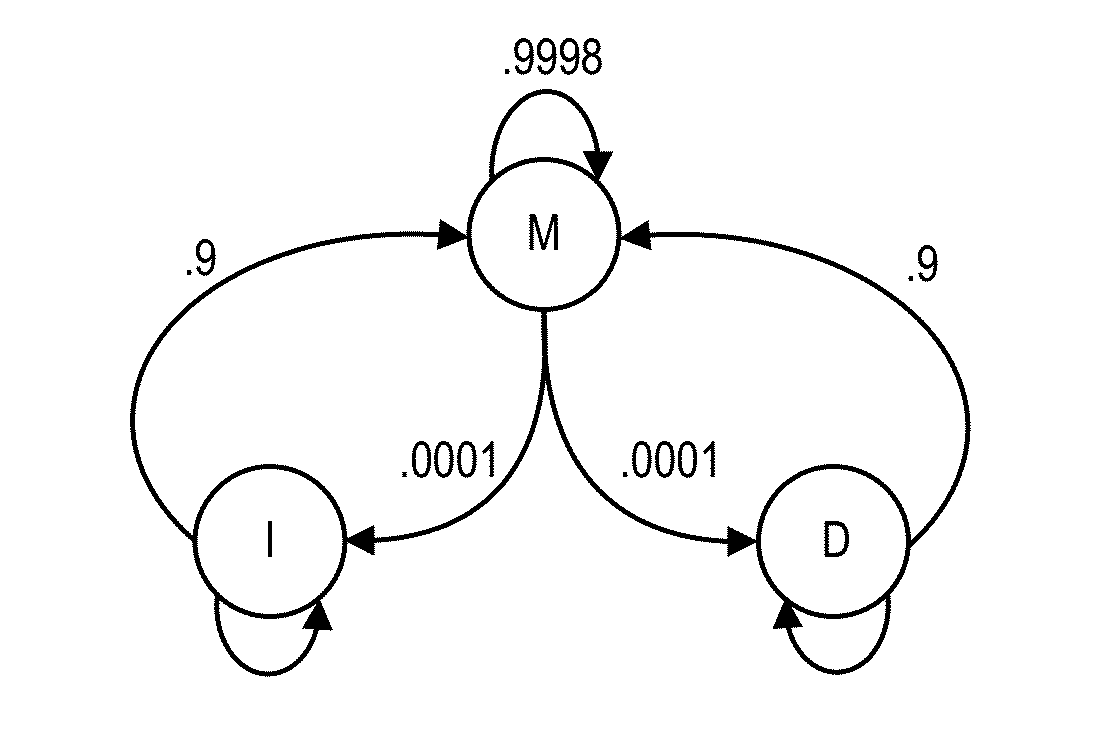

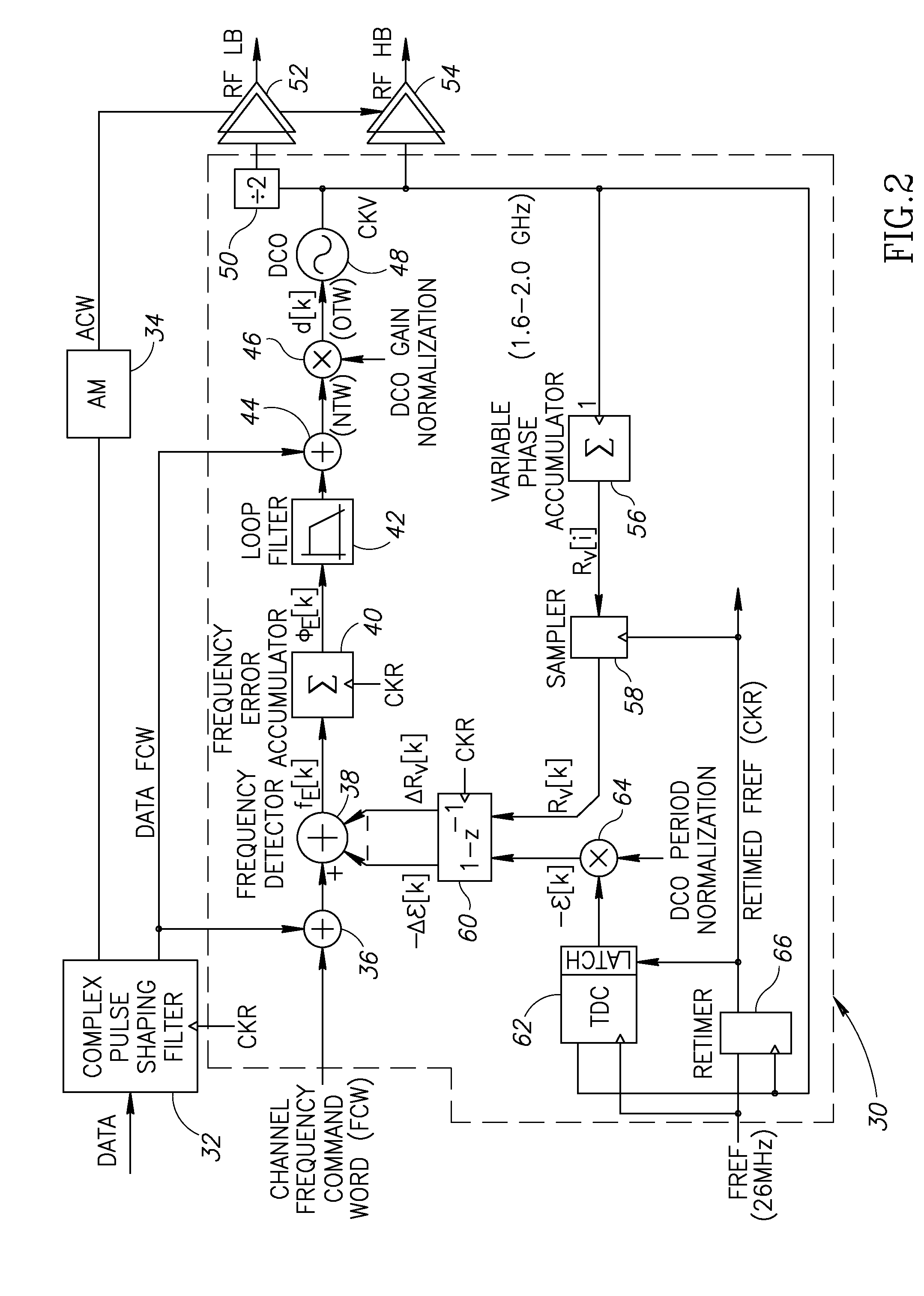

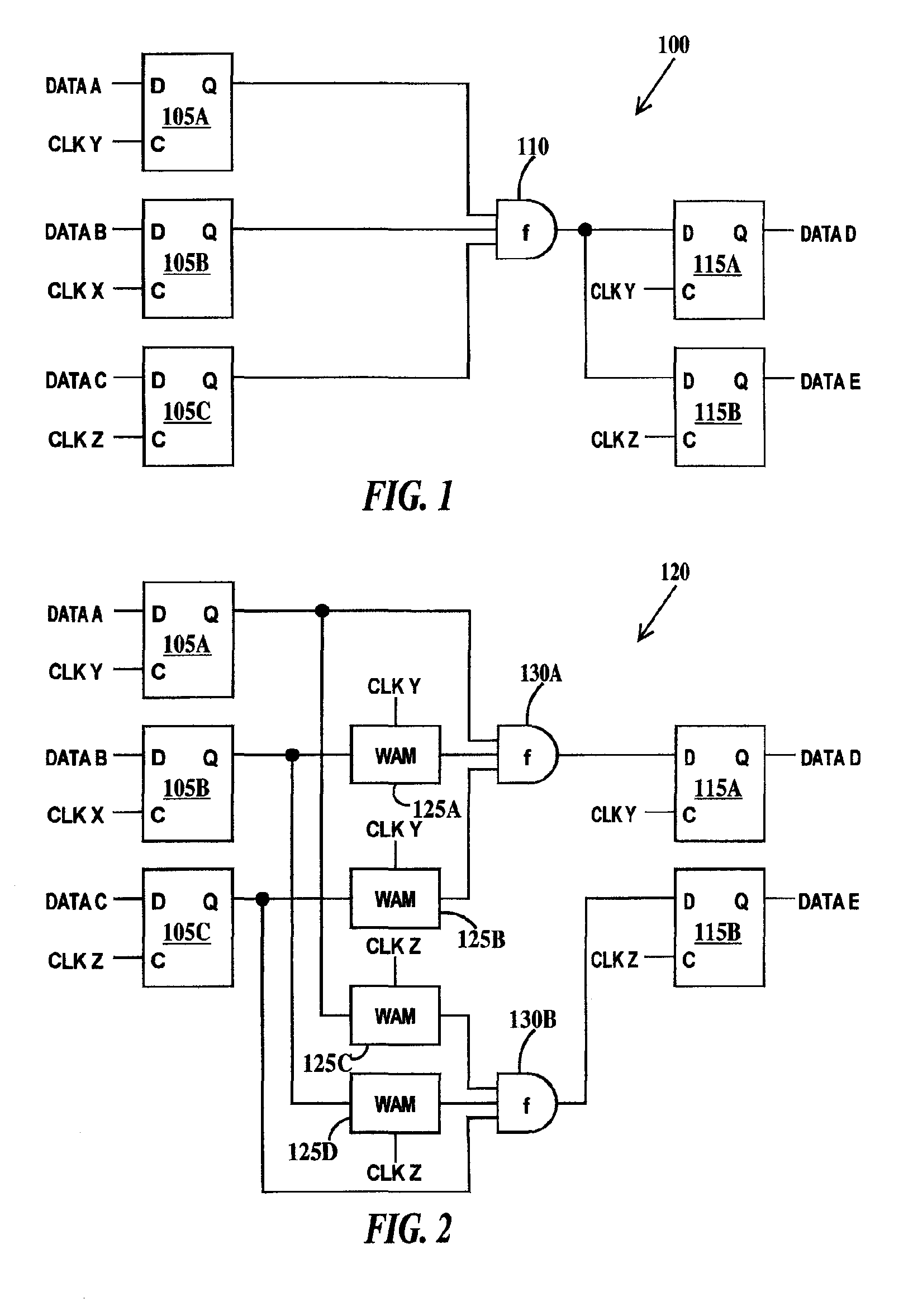

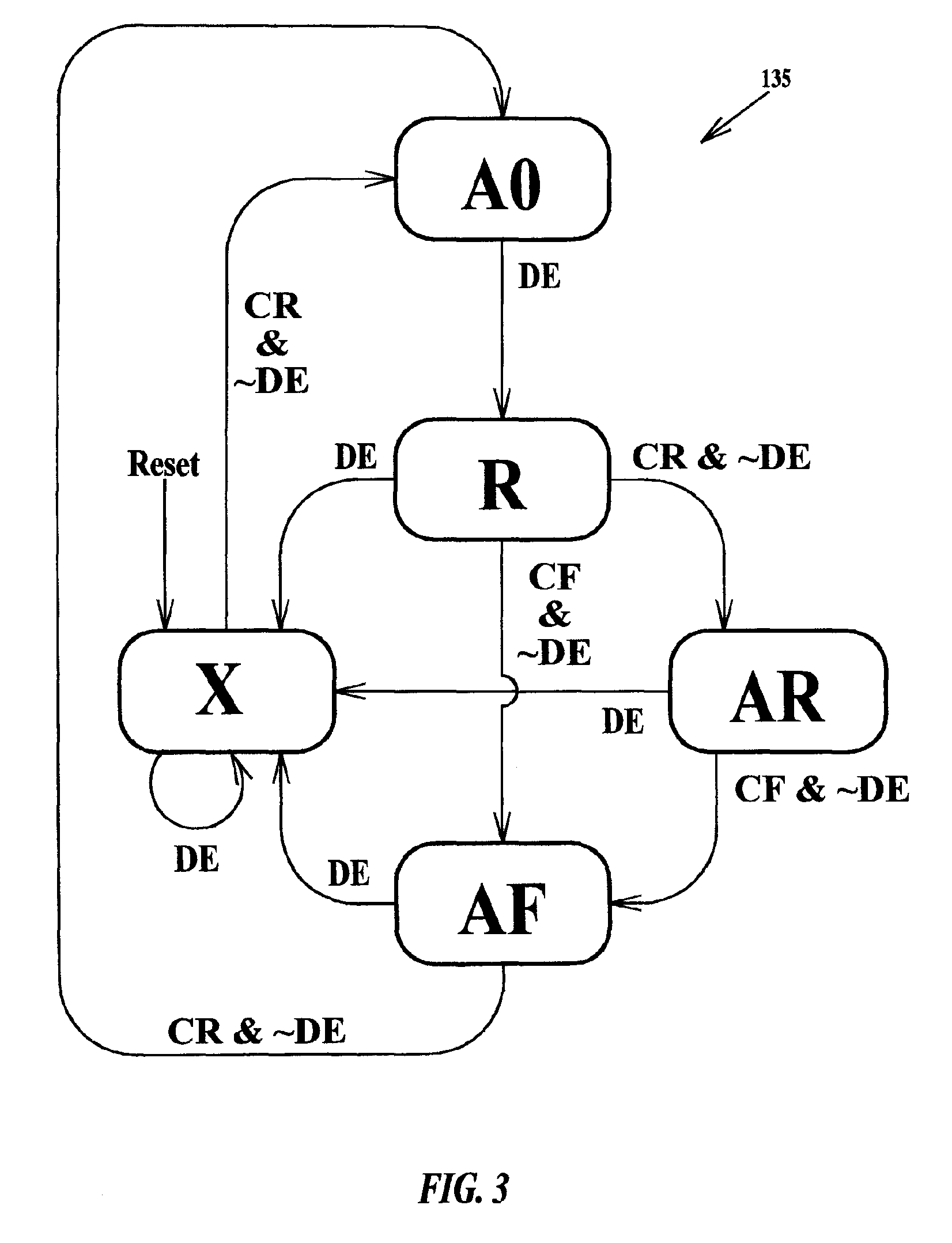

Simulation testing of digital logic circuit designs

InactiveUS7251794B2Computer aided designSoftware simulation/interpretation/emulationComputer architectureSimulation testing

Owner:GLOBALFOUNDRIES INC

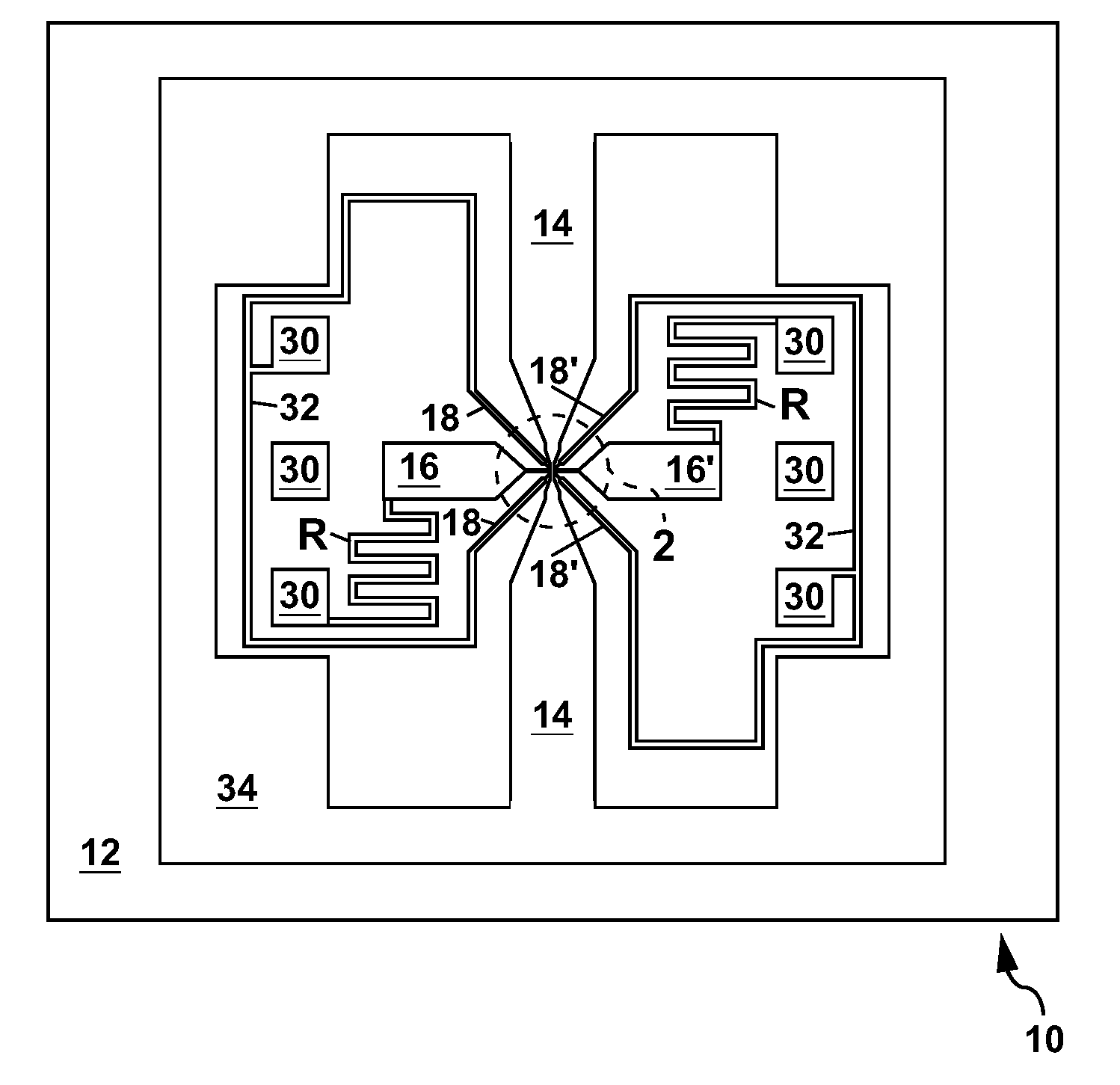

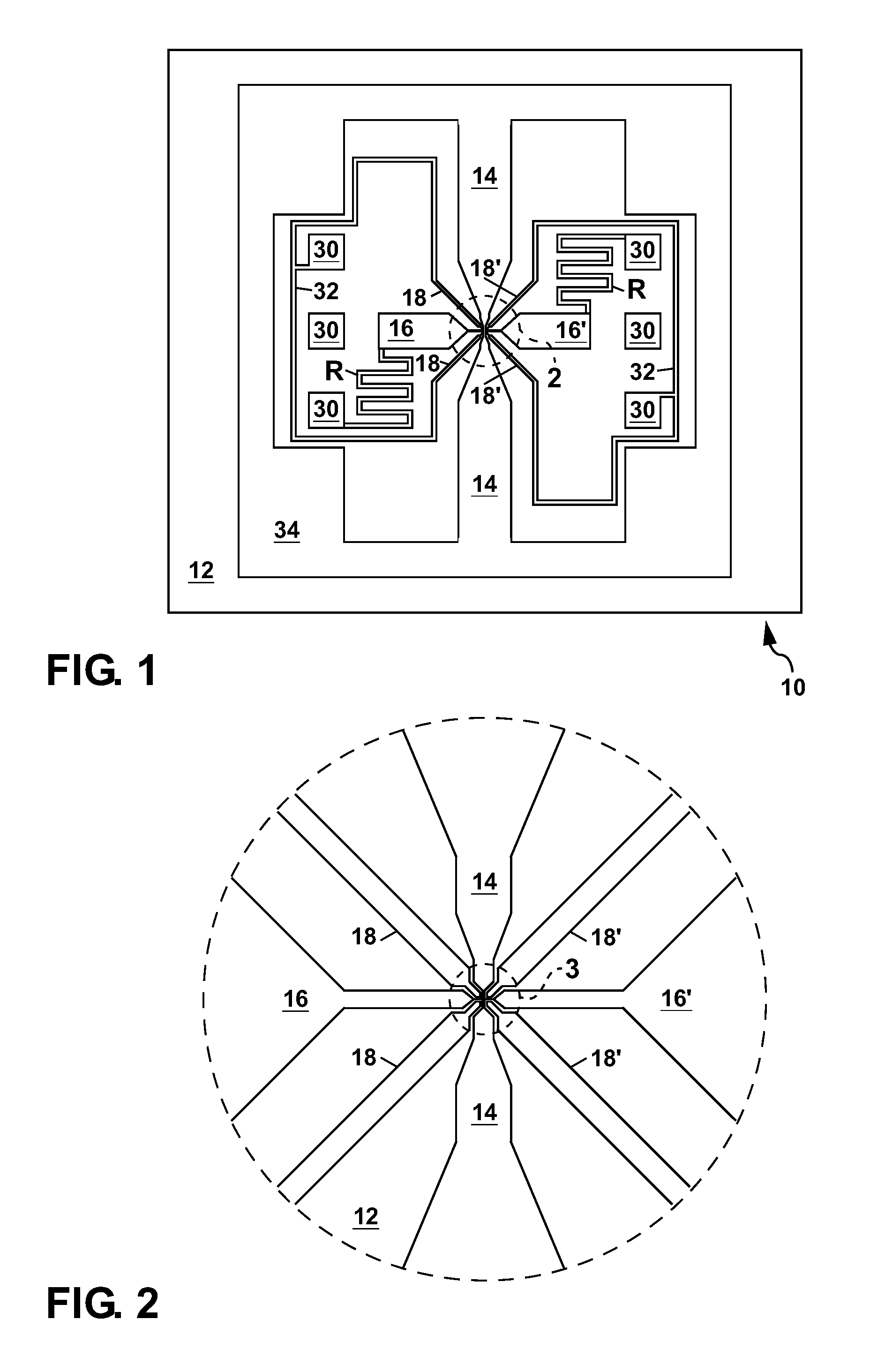

Nanoeletromechanical switch and logic circuits formed therefrom

A nanoelectromechanical (NEM) switch is formed on a substrate with a source electrode containing a suspended electrically-conductive beam which is anchored to the substrate at each end. This beam, which can be formed of ruthenium, bows laterally in response to a voltage applied between a pair of gate electrodes and the source electrode to form an electrical connection between the source electrode and a drain electrode located near a midpoint of the beam. Another pair of gate electrodes and another drain electrode can be located on an opposite side of the beam to allow for switching in an opposite direction. The NEM switch can be used to form digital logic circuits including NAND gates, NOR gates, programmable logic gates, and SRAM and DRAM memory cells which can be used in place of conventional CMOS circuits, or in combination therewith.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

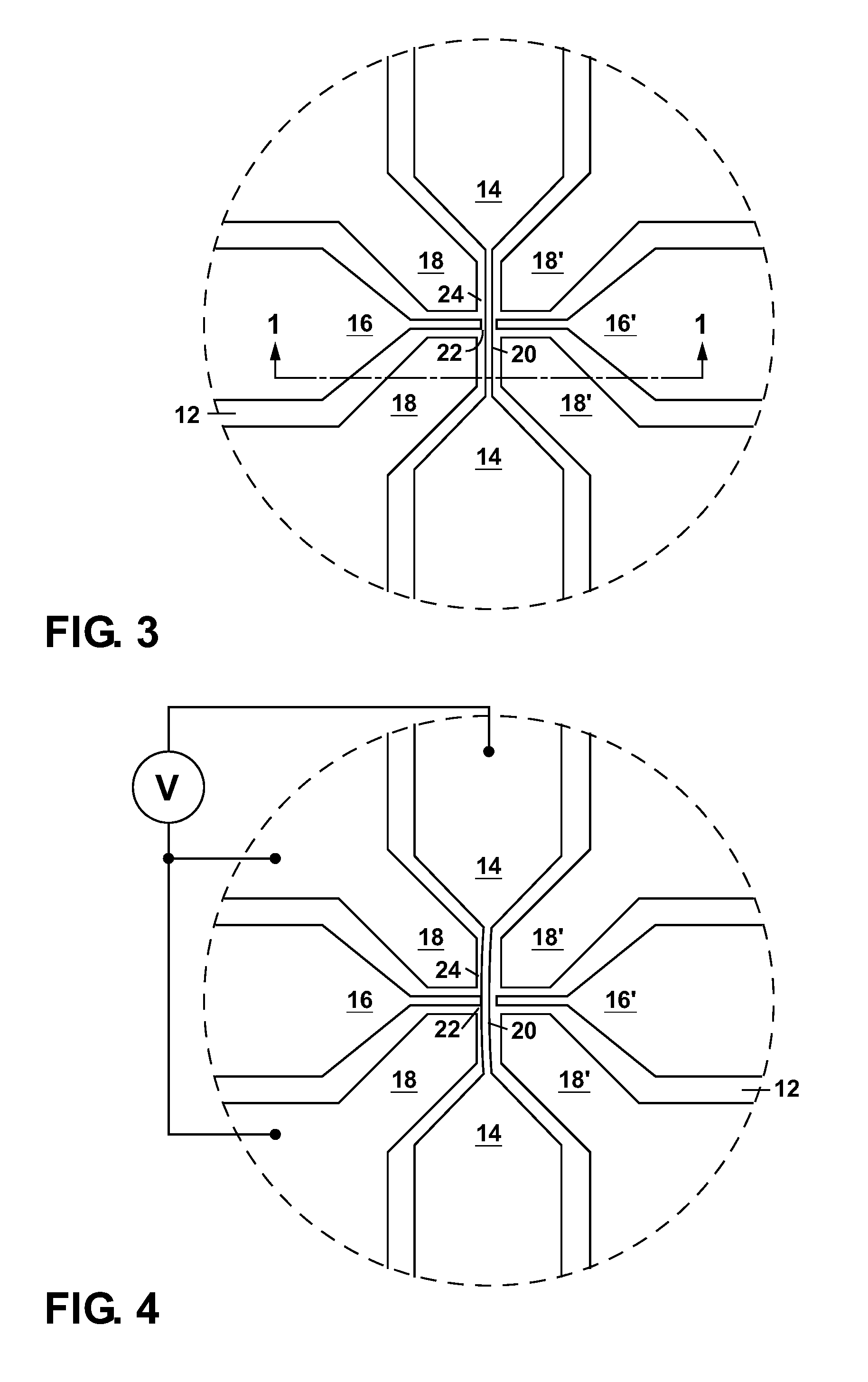

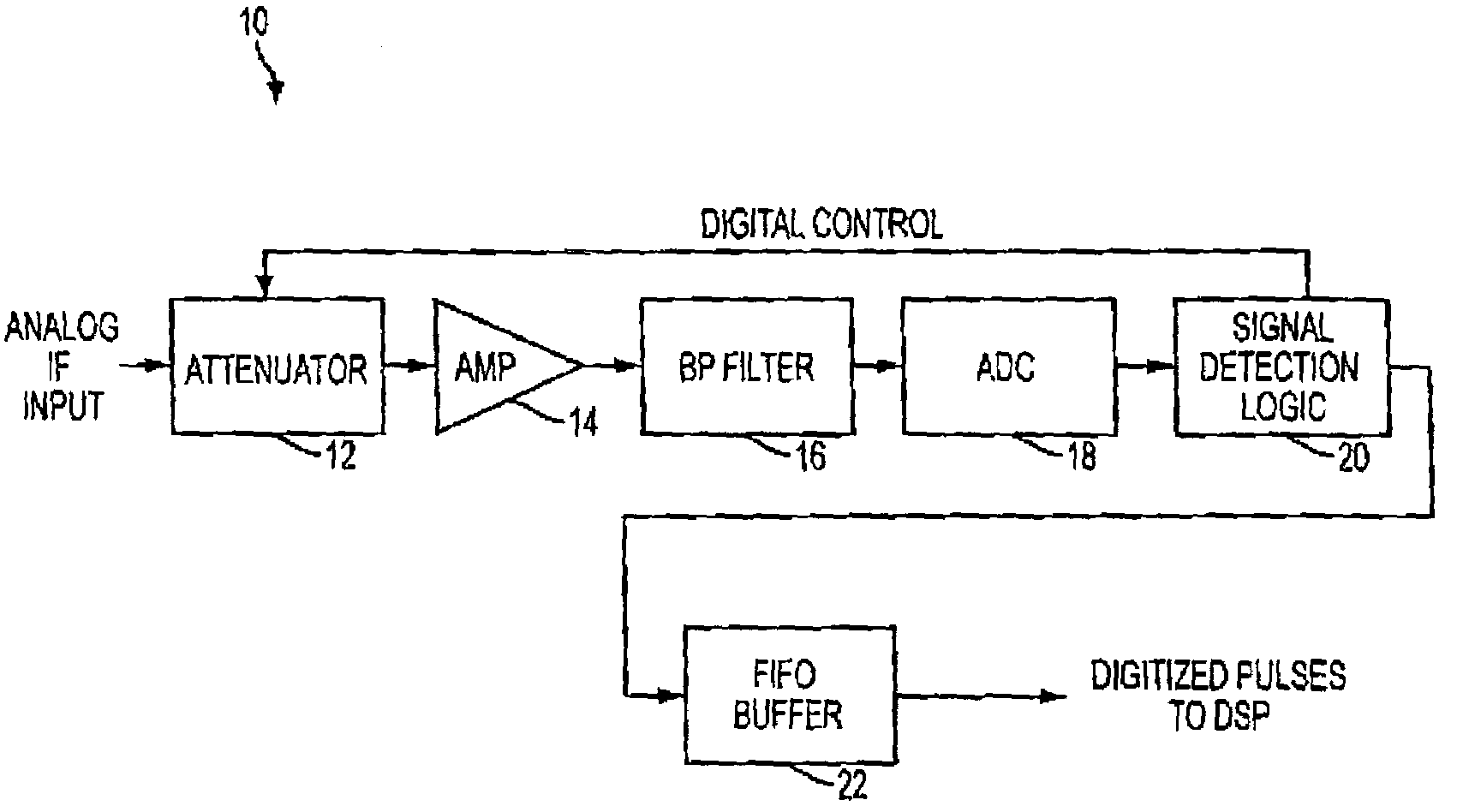

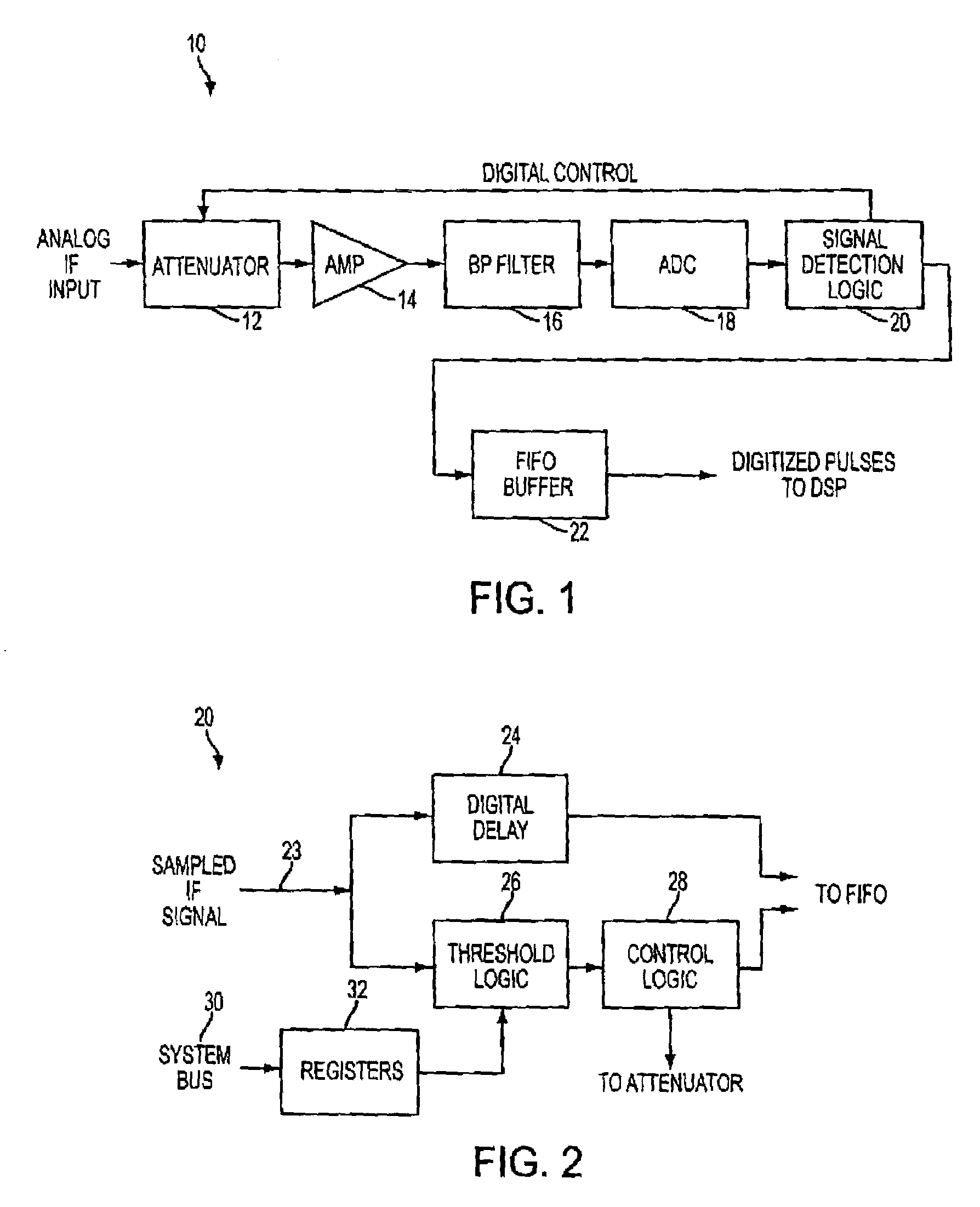

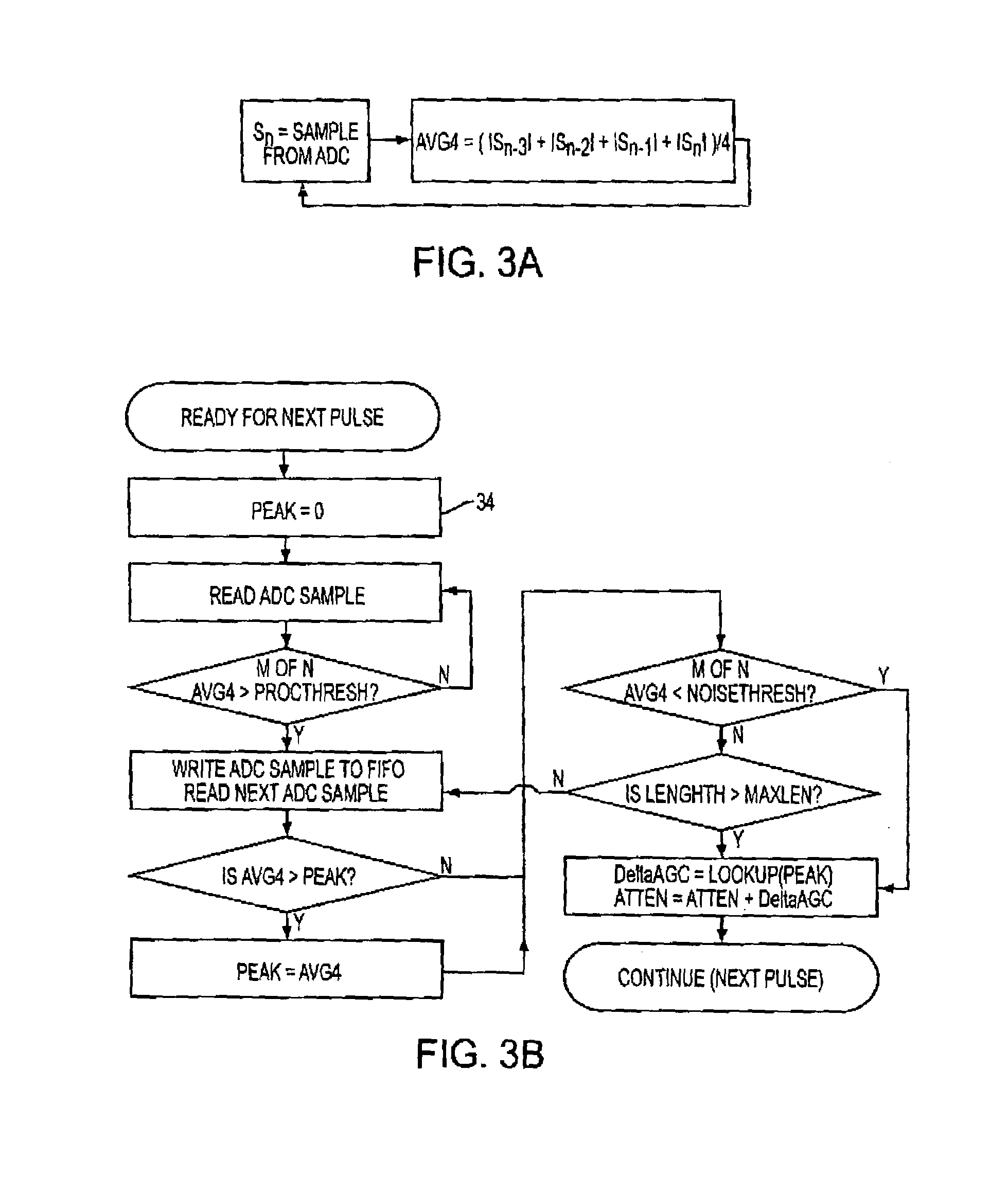

Automatic gain control for digitized RF signal processing

ActiveUS7088794B2Lower performance requirementsFunction increaseAnalogue/digital conversionElectric signal transmission systemsBandpass filteringMoving average

An automatic gain control RF signal processor for receiver systems, such as radar intercept receivers, includes an attenuator having an input for receiving an analog RF input signal, an amplifier coupled to the attenuator, a bandpass filter coupled to the amplifier output, a single ADC coupled to the bandpass filter, a digital logic circuit, and a FIFO buffer. The digital logic circuit has an input for receiving the ADC output signal, a first output coupled to a variable gain control input of the attenuator, and a second output. The logic circuit includes signal detection logic for detecting the presence of a pulse within the ADC signal, determining a peak amplitude value of the pulse, and based on the peak amplitude value generating an attenuation value at the first output that is applied to the variable gain control input of the attenuator. The sampling logic averages a number of ADC data samples to determine a moving average pulse amplitude, and compares this moving average pulse amplitude to a processing threshold value to determine a delta value with which to adjust an attenuation value for the attenuator, and to determine when to terminate a pulse and reset the attenuation value to zero. The averaging is carried out to determine whether an assigned number m of n samples is above the processing threshold value or whether the pulse should be terminated.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Duty-cycle correction circuit

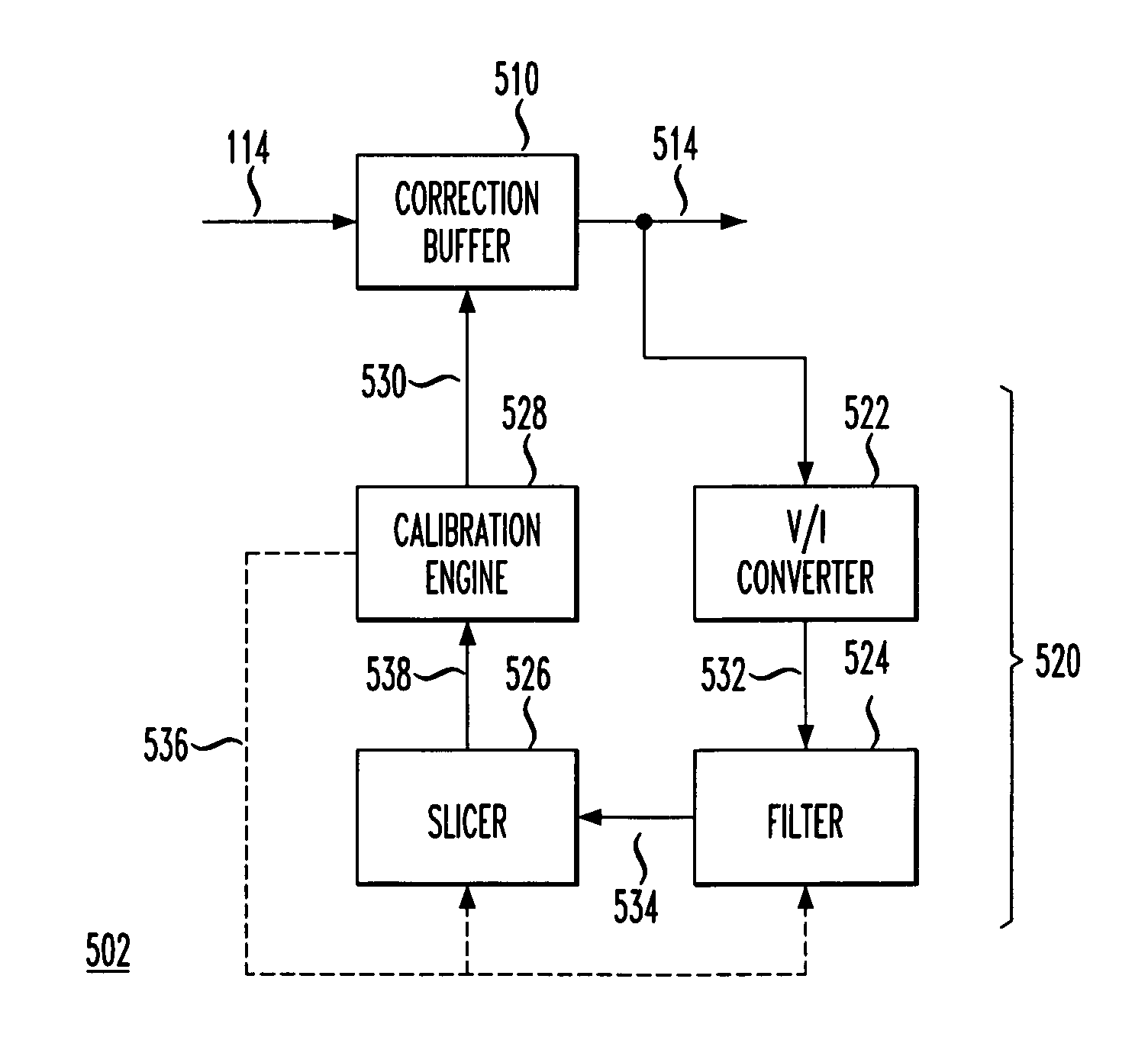

InactiveUS7202722B2Continuous to patterned pulse manipulationElectric pulse generatorEngineeringData buffer

A duty-cycle correction (DCC) circuit adapted to adjust the duty cycle of a differential clock signal to conform it to the requirements of a half-rate clocking system. In a representative embodiment, the DCC circuit has a buffer circuit adapted to generate a differential output clock signal by adding offset voltage to a differential input clock signal. A feedback loop coupled to the buffer circuit processes the output clock signal to evaluate deviation of its duty-cycle value from 50% and, based on the evaluation, configures the buffer circuit to adjust the offset voltage such that the duty-cycle deviation is reduced. The feedback loop and the buffer circuit are controlled by a duty-cycle calibration engine, e.g., a digital logic circuit adapted to determine an appropriate value for the offset voltage, which causes the duty-cycle value in the output clock signal to be substantially 50% regardless of the duty-cycle value in the input clock signal. As a result, technological limitations in the circuit-fabrication process do not significantly reduce the yield of chips for half-rate clocking systems.

Owner:CADENCE DESIGN SYST INC +2

Event driven dynamic logic for reducing power consumption

InactiveUS6977528B2Reduce power consumptionReduce capacitive loadReliability increasing modificationsPower reduction by control/clock signalCapacitanceState variation

Methods and circuits are described for reducing power consumption within digital logic circuits by blocking the passage of clock signal transitions to the logic circuits when the clock signal would not produce a desired change of state within the logic circuit, such as at inputs, intermediary nodes, outputs, or combinations. By way of example, the incoming clock is blocked if a given set of logic inputs will not result in an output change of state if a clock signal transition were to be received. By way of further example, the incoming clock is blocked in a data flip-flop if the input signal matches the output signal, such that receipt of a clock transition would not produce a desired change of state in the latched output. The invention may be utilized for creating lower power combinatorial and / or sequential logic circuit stages subject to less unproductive charging and discharging of gate capacitances.

Owner:RGT UNIV OF CALIFORNIA

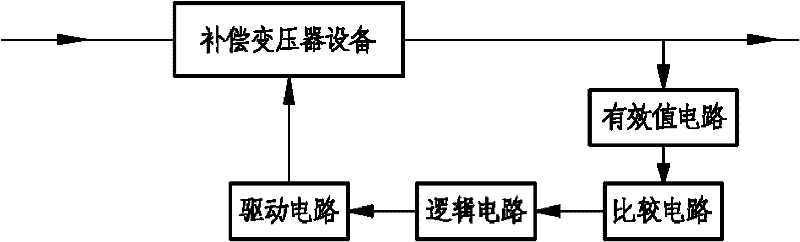

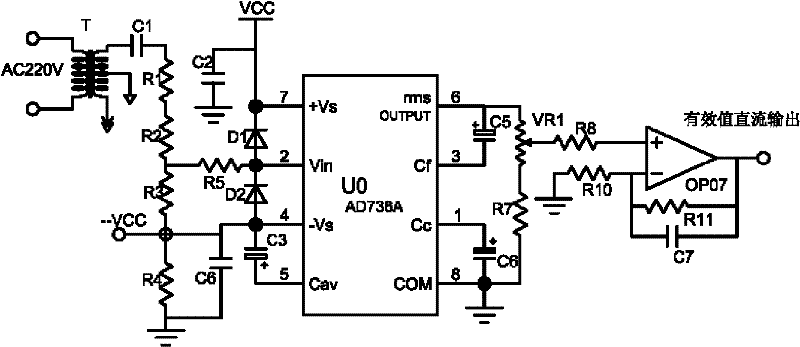

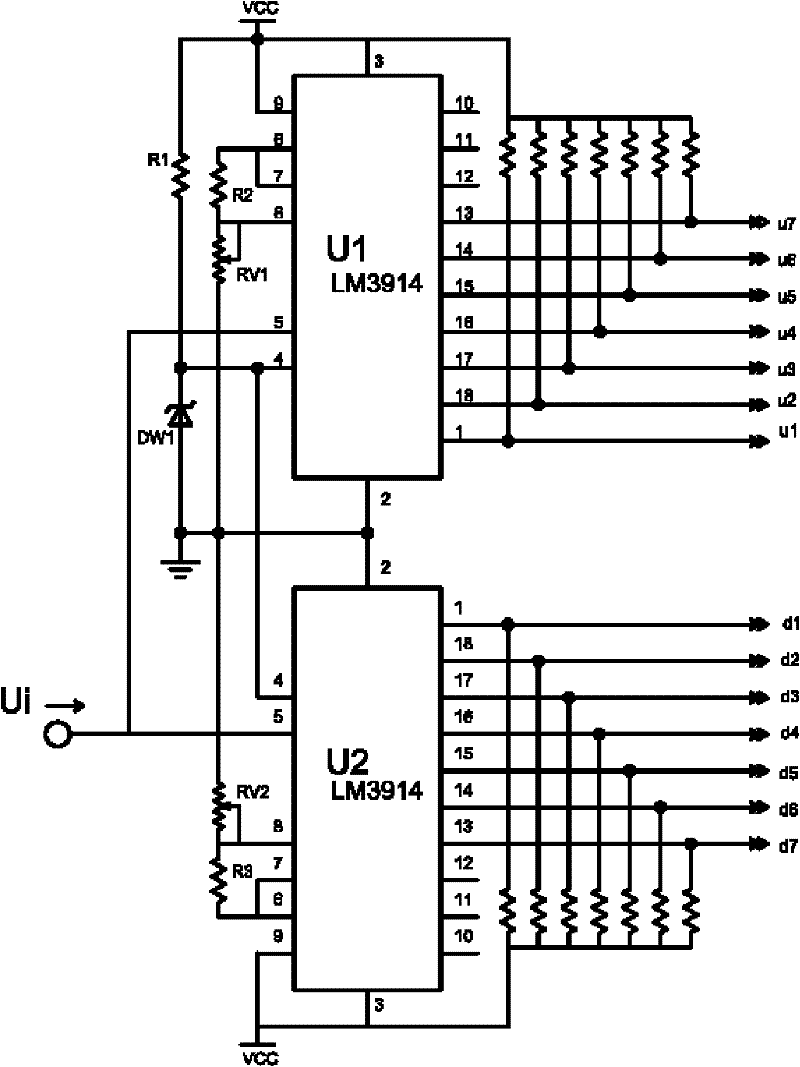

Digital stabilized power supply control circuit based on SPLD (simple programmable logic device)

InactiveCN102163930ASmall scaleEliminate competitionAc-dc conversion without reversalLoop controlTransformer

The invention provides a digital stabilized power supply control circuit based on an SPLD (simple programmable logic device). The alternating power frequency power supply of the control circuit is input from a main circuit, and output by a compensation equipment transformer; an effective value circuit samples the output voltage to obtain a direct current signal, and a digital signal of the output voltage through a comparing circuit; and the digital signal is processed by a programmable digital logic circuit to drive a switch circuit to control a compensation transformer for stabilizing compensation so as to form a typical constant voltage closed loop control system. The digital stabilized power supply control circuit has the following advantages that: a control signal in the digital stabilized power supply control circuit is based on a power frequency alternating current effective value signal, and the problem sensitive to the waveform is not existed in alternating current synchronous collection. The SPLD uses the programmable devices to realize combination logic, so that the control method is optimized, the stabilizing responding speed is fast, the system instantaneity is strong, and the work is reliable. By the application of the SPLD chip, the scale of the stabilized control circuit is small; the production and manufacturing techniques are simplified; and the efficiency is improved; furthermore, the fault of the circuit board is conveniently debugged and maintained.

Owner:CHUANTIE ELECTRIC TIANJIN GRP

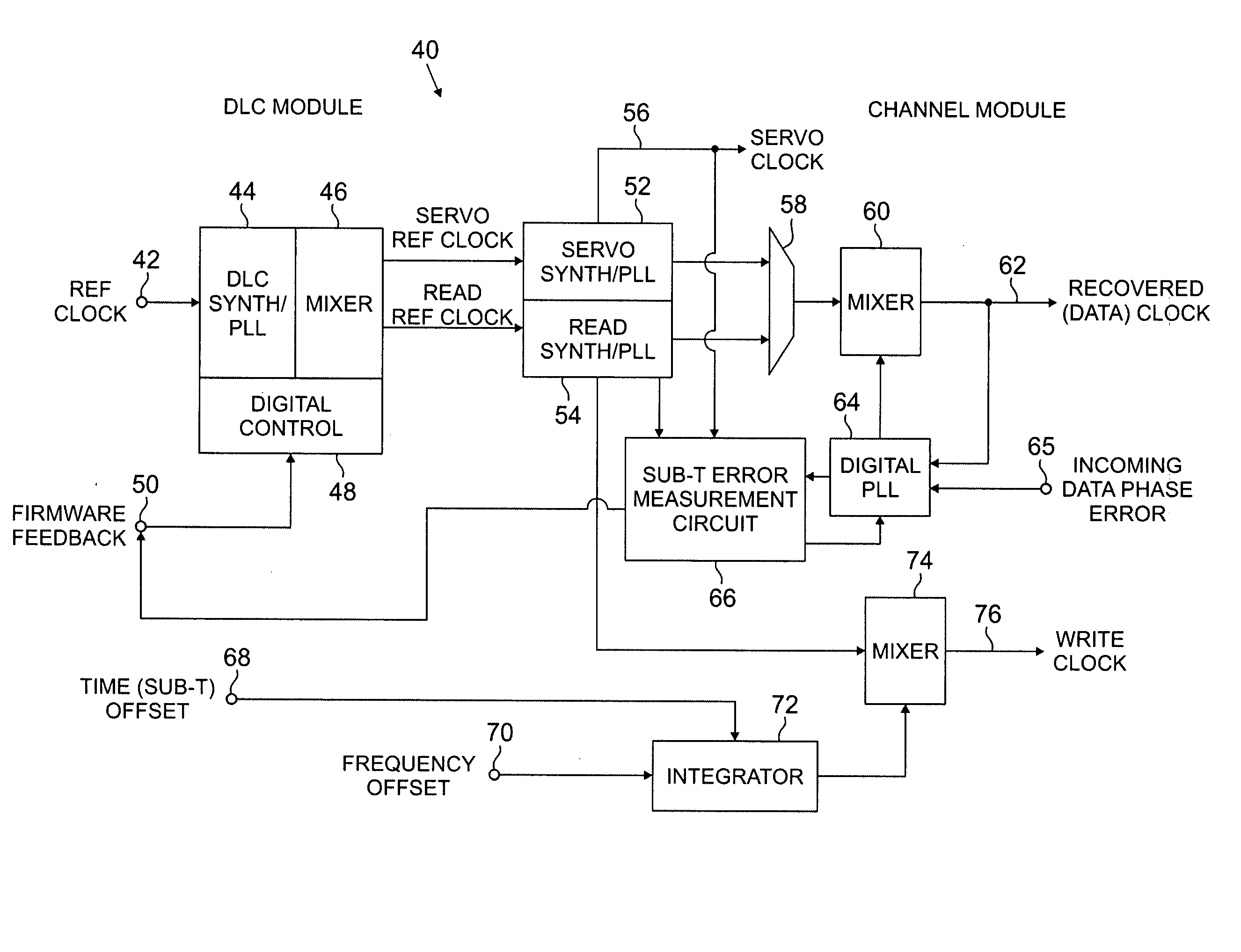

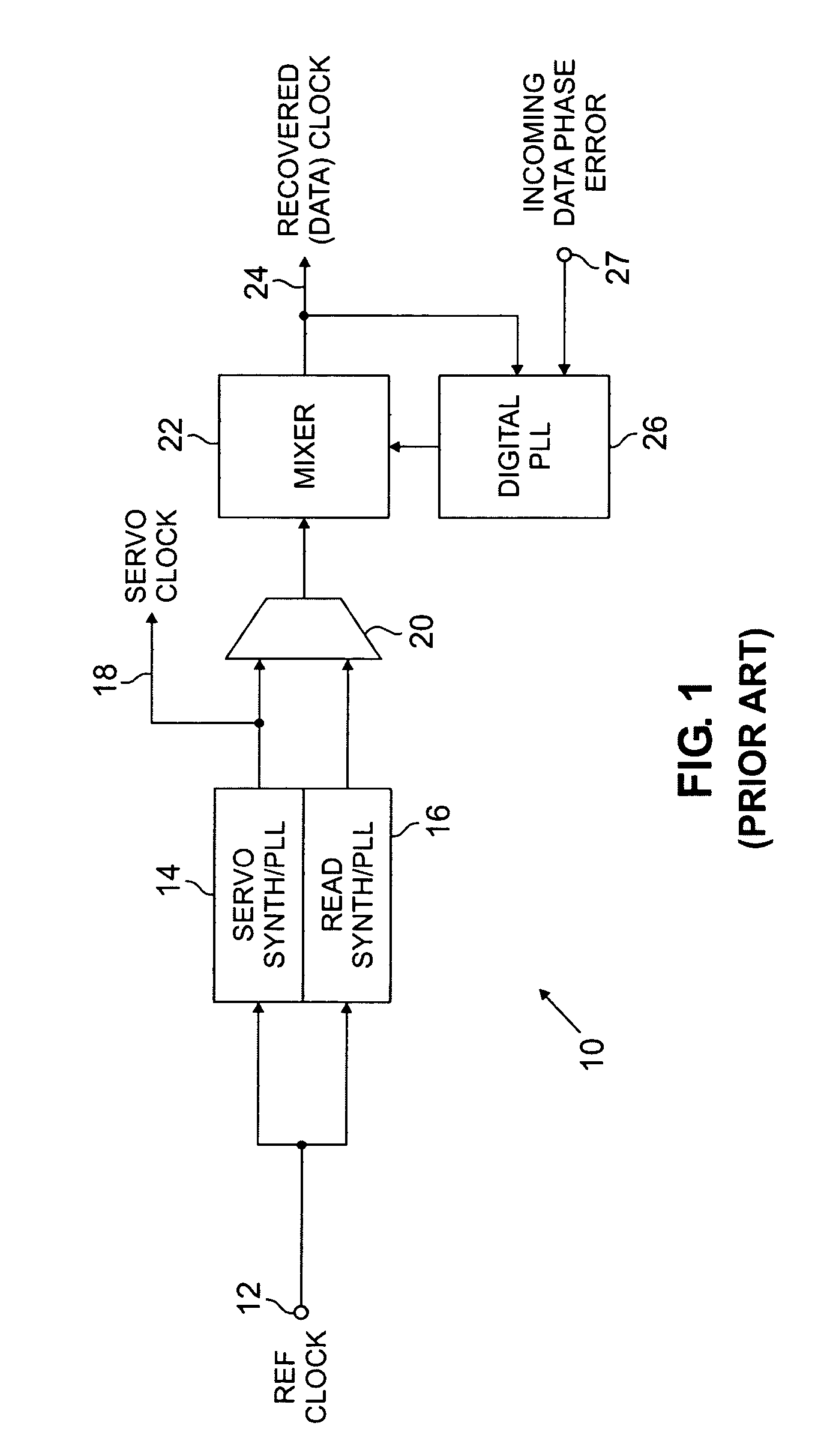

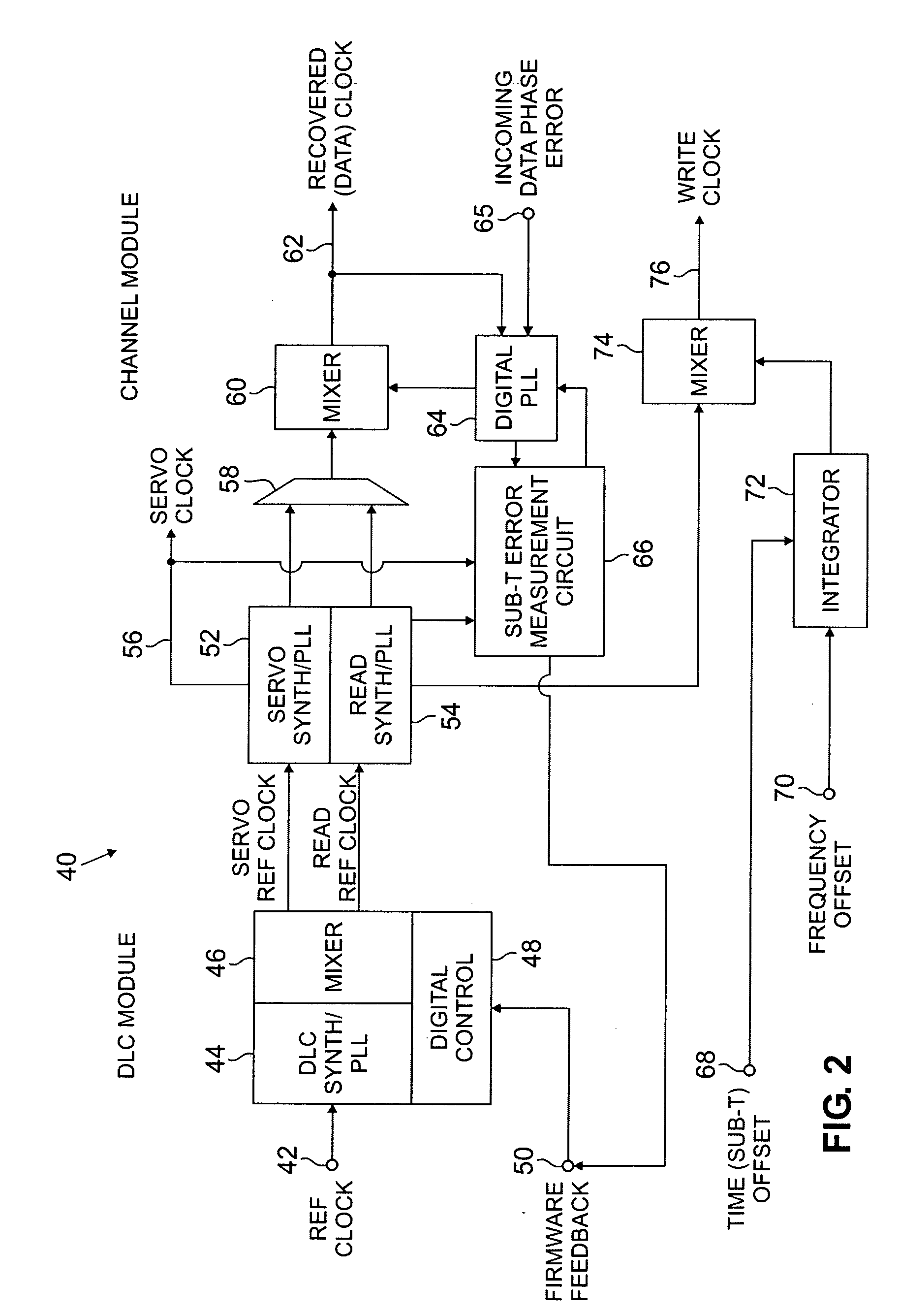

System for locking a clock onto the frequency of data recorded on a storage medium

InactiveUS20060023602A1Television system detailsPulse automatic controlDigital controlErrors measurement

A circuit locks onto a frequency of data encoded on a medium, taking frequency variations in the physical travel of the medium into account. The circuit includes a disk locked clock (DLC) circuit having a synthesizer operating under digital control based on a feedback signal to produce a servo reference clock and a read reference clock that track frequency variations in the physical travel of the medium. A recovered clock signal is produced based on the servo reference clock and the read reference clock. A digital phase locked loop maintains a frequency lock of the recovered clock signal. An error measurement circuit is connected to the digital phase locked loop. The error measurement circuit produces the feedback signal for digitally controlling the digital logic circuit synthesizer to produce the servo reference clock and the read reference clock that track frequency variations in the physical travel of the medium.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Apparatus and method for a programmable security processor

InactiveUS20060206727A1Unauthorized memory use protectionHardware monitoringProgrammable logic deviceOperational safety

A digital logic circuit comprises a programmable logic device and a programmable security circuit. The programmable security circuit stores a set of authorized configuration security keys. The programmable security circuit compares the authorized configuration security keys with an incoming configuration request, and selectively enables a new configuration for the programmable logic device in response to the configuration request. In another exemplary embodiment, a programmable security circuit also stores a set of authorized operation security keys. The programmable security circuit compares the authorized operation security keys with an incoming operation request from the programmable logic device, and selectively enables an operation within the programmable logic device in response to the operation request.

Owner:INTEL MOBILE COMM GMBH

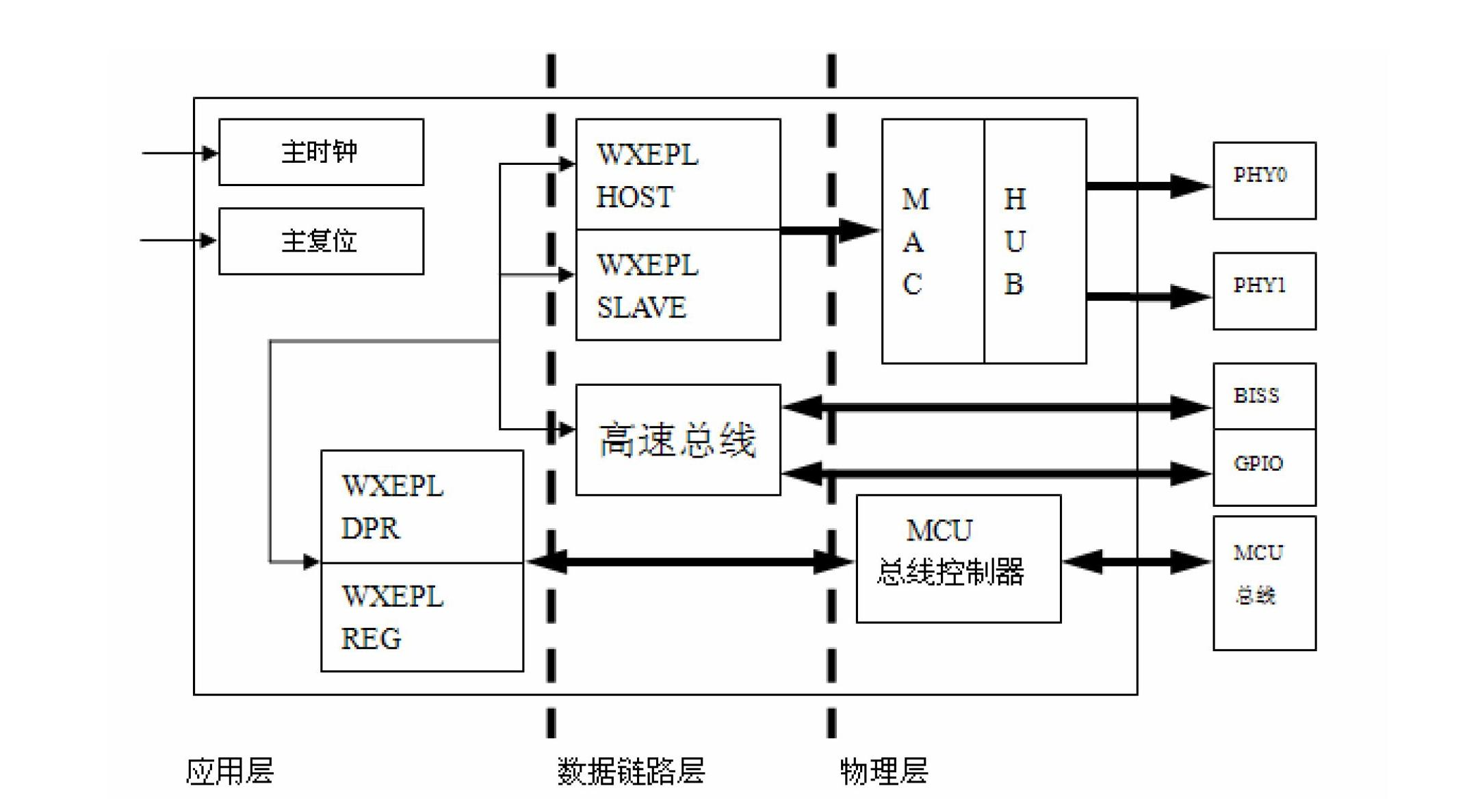

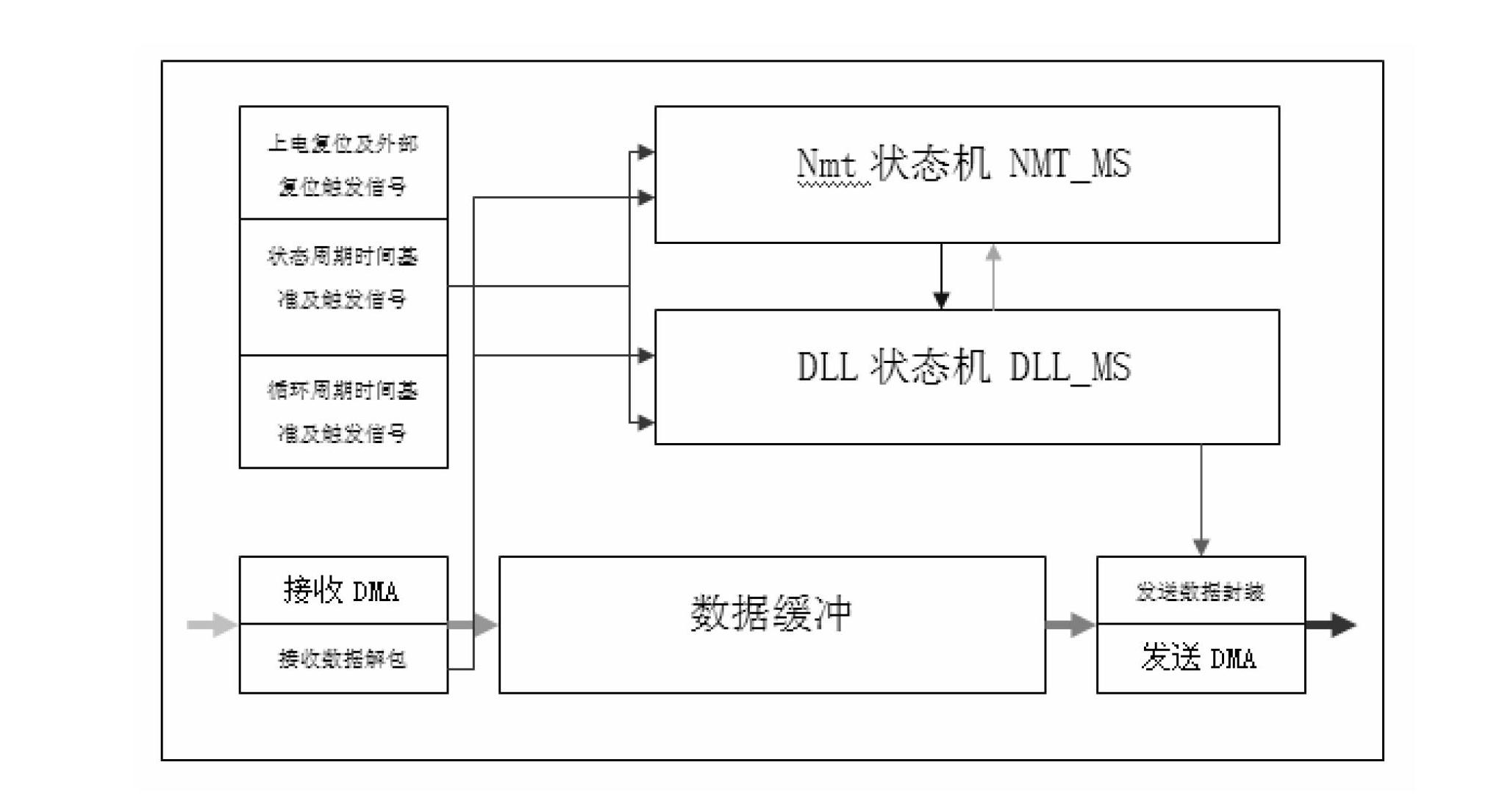

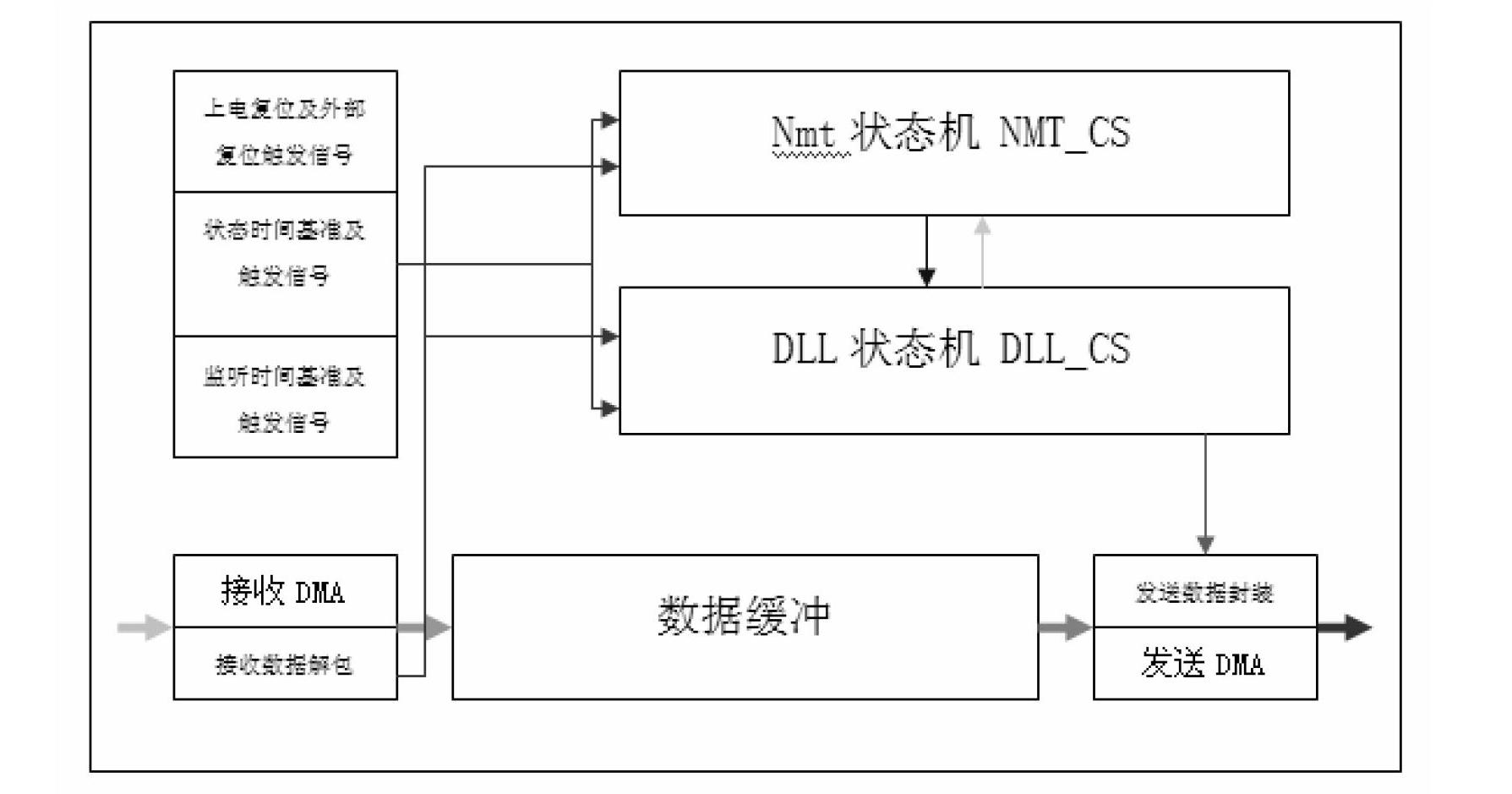

Hardware implementing method for kernels of POWERLINK communication protocol master and slave stations

ActiveCN102664902AQuick responseReduce the burden onTransmissionReal-time dataProgrammable logic device

The invention discloses a hardware implementing method for kernels of POWERLINK communication protocol master and slave stations. A data link layer, an application layer and a synchronous bus of the POWERLINK communication protocol master and slave stations are implemented on the basis of a programmable logic device and a customization / semi-customization hardware chip, wherein the data link layer comprises a master station and slave station data link layer controller, and the application layer comprises an application layer dial pulse receiver (DPR) and an application layer register (REG); each sub-module of the data link layer and the application layers DPR and REG are mounted on the synchronous bus; and the modules are integrated by integrated software, bit stream files are generated from codes by using implementing software, and the bit stream files are downloaded to target hardware to realize the kernels of the master and slave stations. Through the method, the kernels of the master and slave stations of a POWERLINK protocol are implemented in a complete hardware mode, the response speed of the kernels is improved from millisecond level of a central processing unit (CPU) to microsecond level of a digital logic circuit, and the real-time data processing burden of the master CPU is greatly lightened.

Owner:NANJING WASHING CNC TECH

Bioinformatics systems, apparatuses, and methods executed on an integrated circuit processing platform

ActiveUS9792405B2High sensitivityImprove accuracyMemory architecture accessing/allocationMathematical modelsElectricityData source

A system, method and apparatus for executing a bioinformatics analysis on genetic sequence data includes an integrated circuit formed of a set of hardwired digital logic circuits that are interconnected by physical electrical interconnects. One of the physical electrical interconnects forms an input to the integrated circuit that may be connected with an electronic data source for receiving reads of genomic data. The hardwired digital logic circuits may be arranged as a set of processing engines, each processing engine being formed of a subset of the hardwired digital logic circuits to perform one or more steps in the bioinformatics analysis on the reads of genomic data. Each subset of the hardwired digital logic circuits may be formed in a wired configuration to perform the one or more steps in the bioinformatics analysis.

Owner:EDICO GENOME

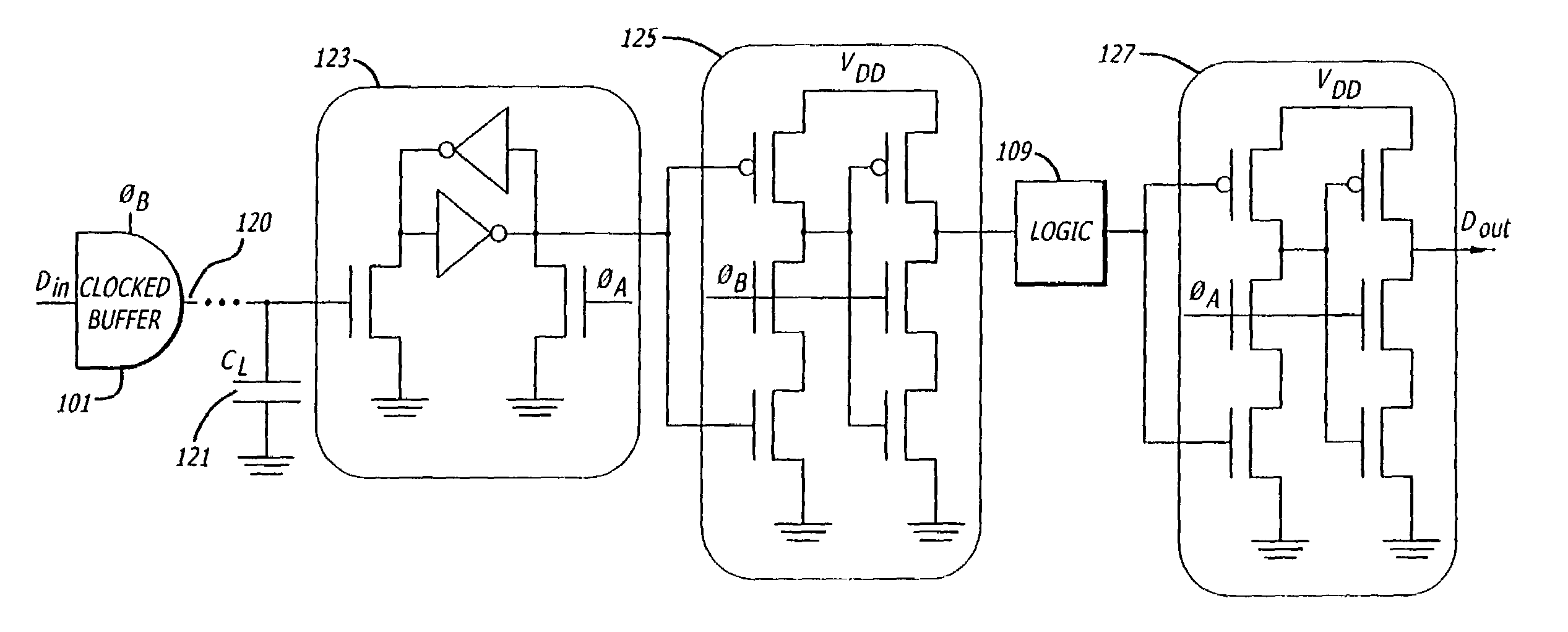

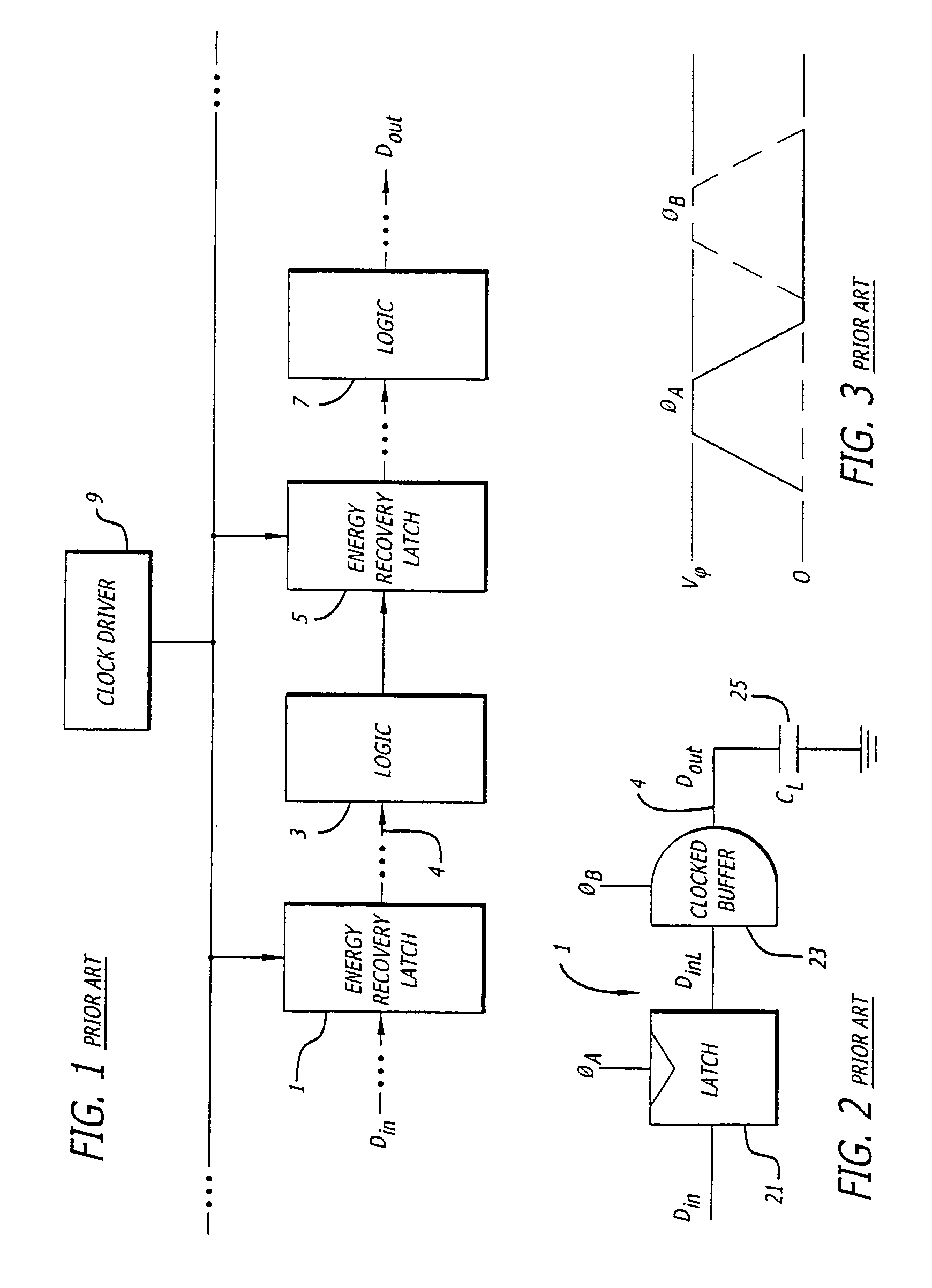

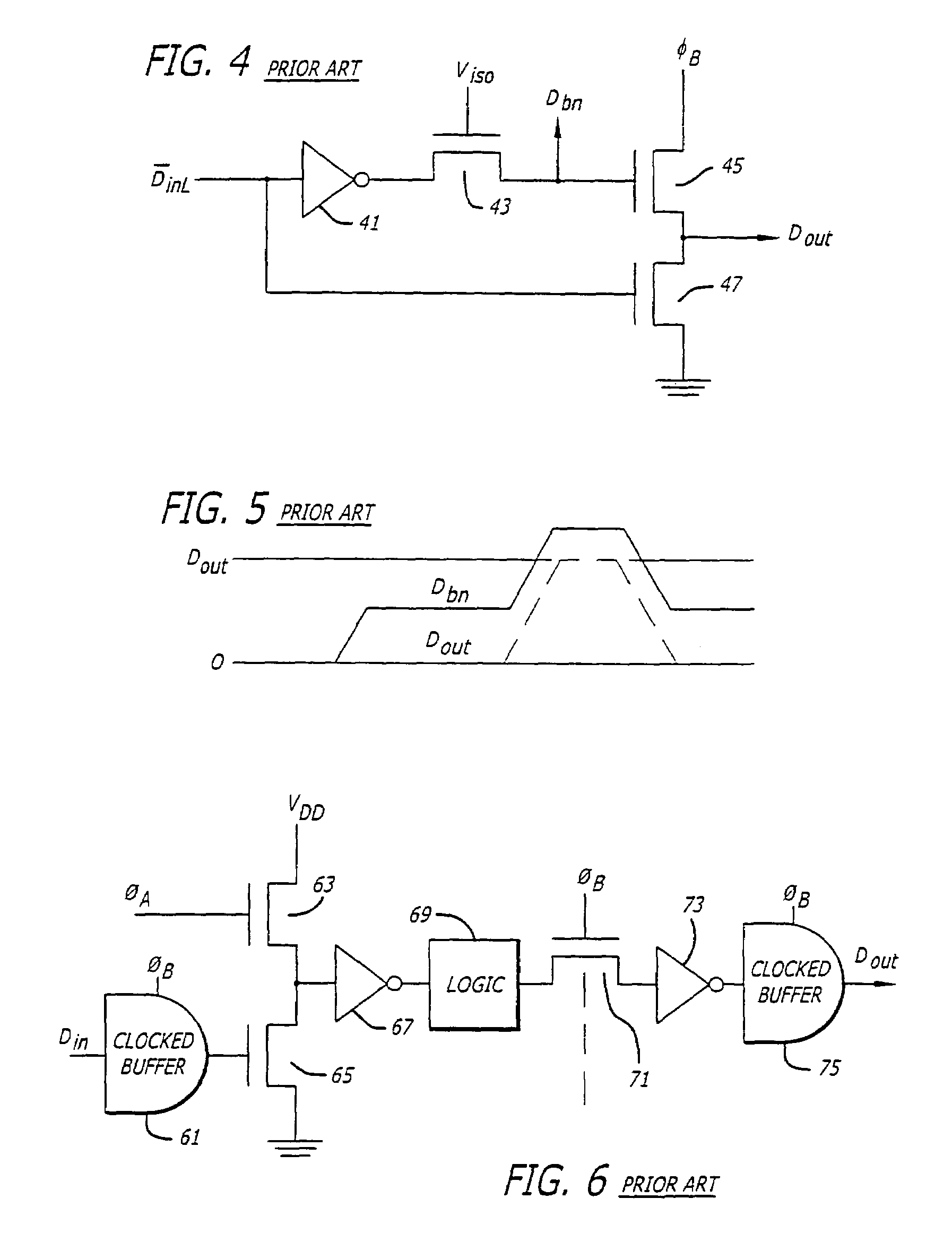

High-performance clock-powered logic

InactiveUS7005893B1Reduce energy consumptionIncrease speedReliability increasing modificationsPower reduction by energy recoveryEngineeringLogic circuitry

High performance clock-powered logic runs at below supply levels and reduces the need for faster digital logic circuitry. In a preferred embodiment, a clocked buffer (101) is used to drive the signal line. The receiving end of the line is connected to a jam latch (123), preferably followed by an n-latch (125), followed by the digital logic (109), and followed by a second n-latch (127). The first n-latch is eliminated in an alternative embodiment, preferably one that uses complementary data signals.

Owner:UNIV OF SOUTHERN CALIFORNIA

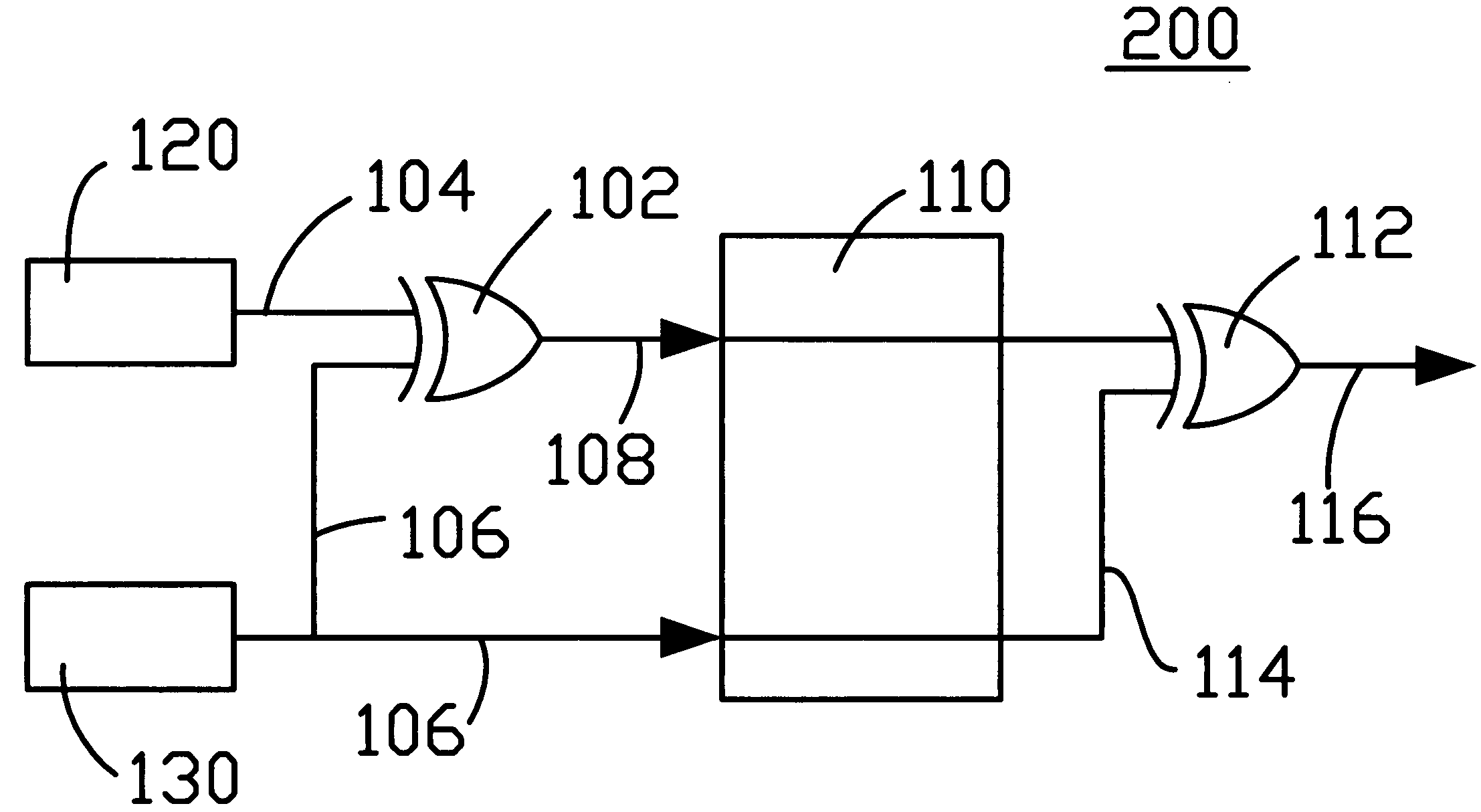

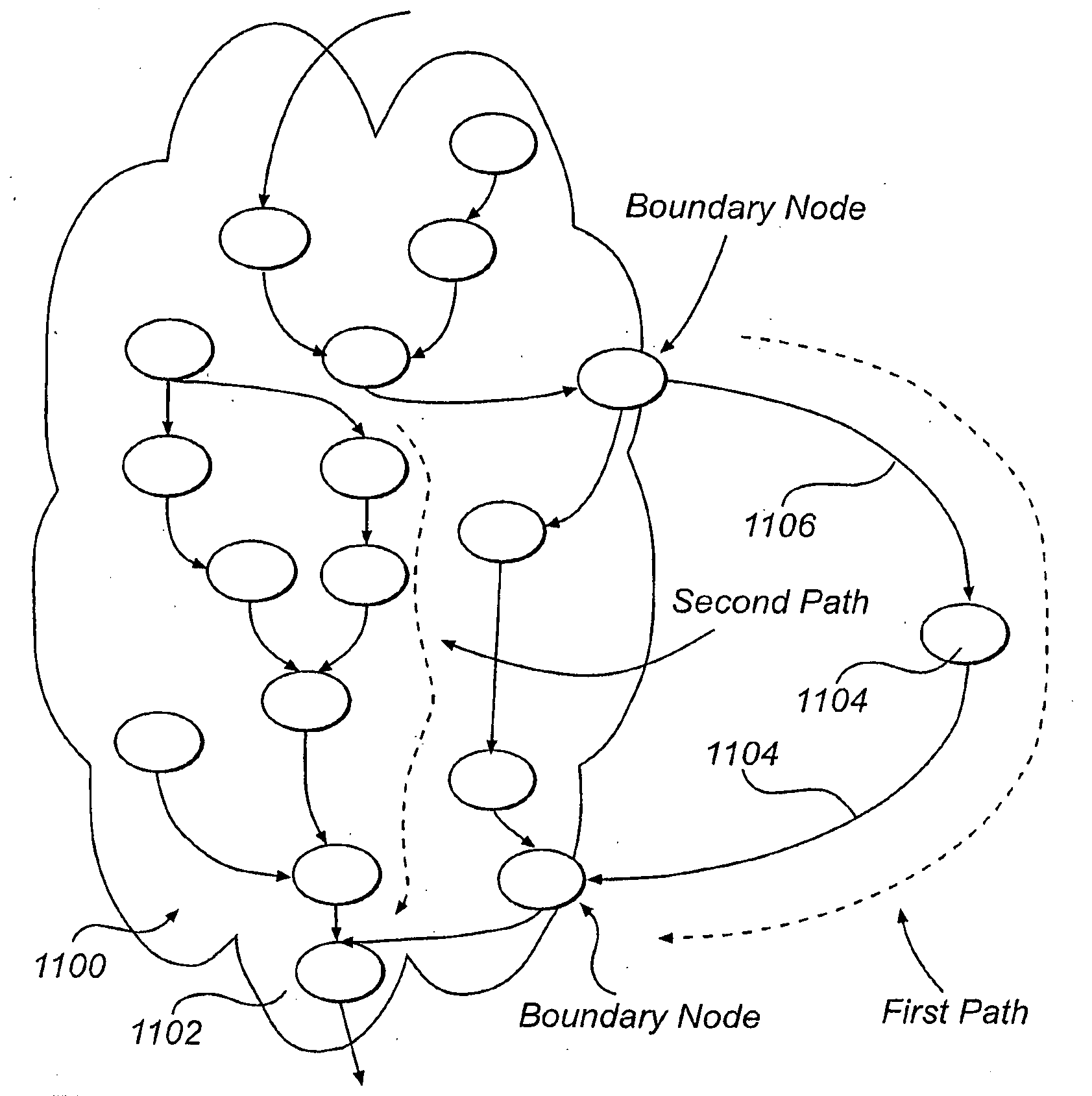

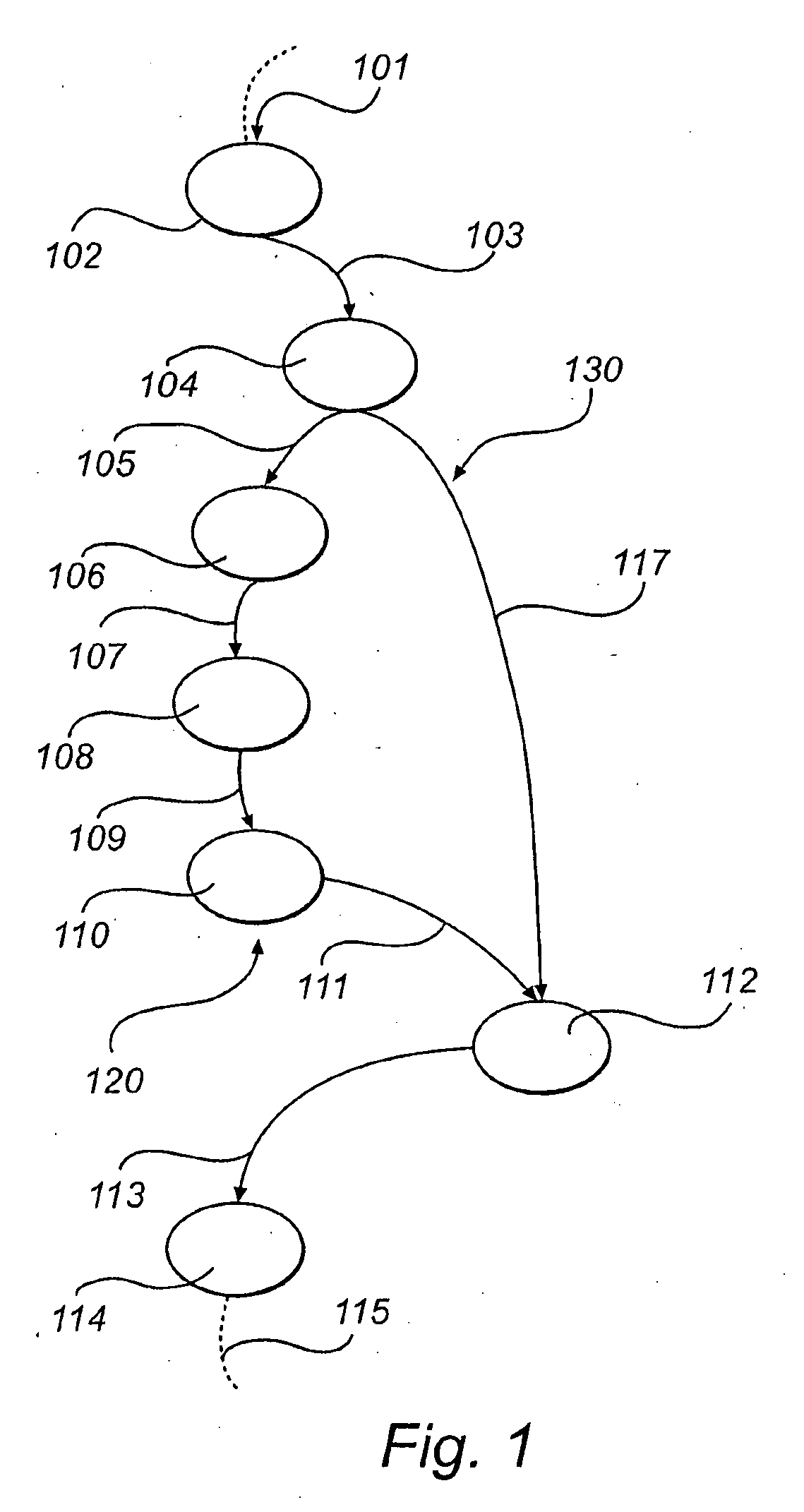

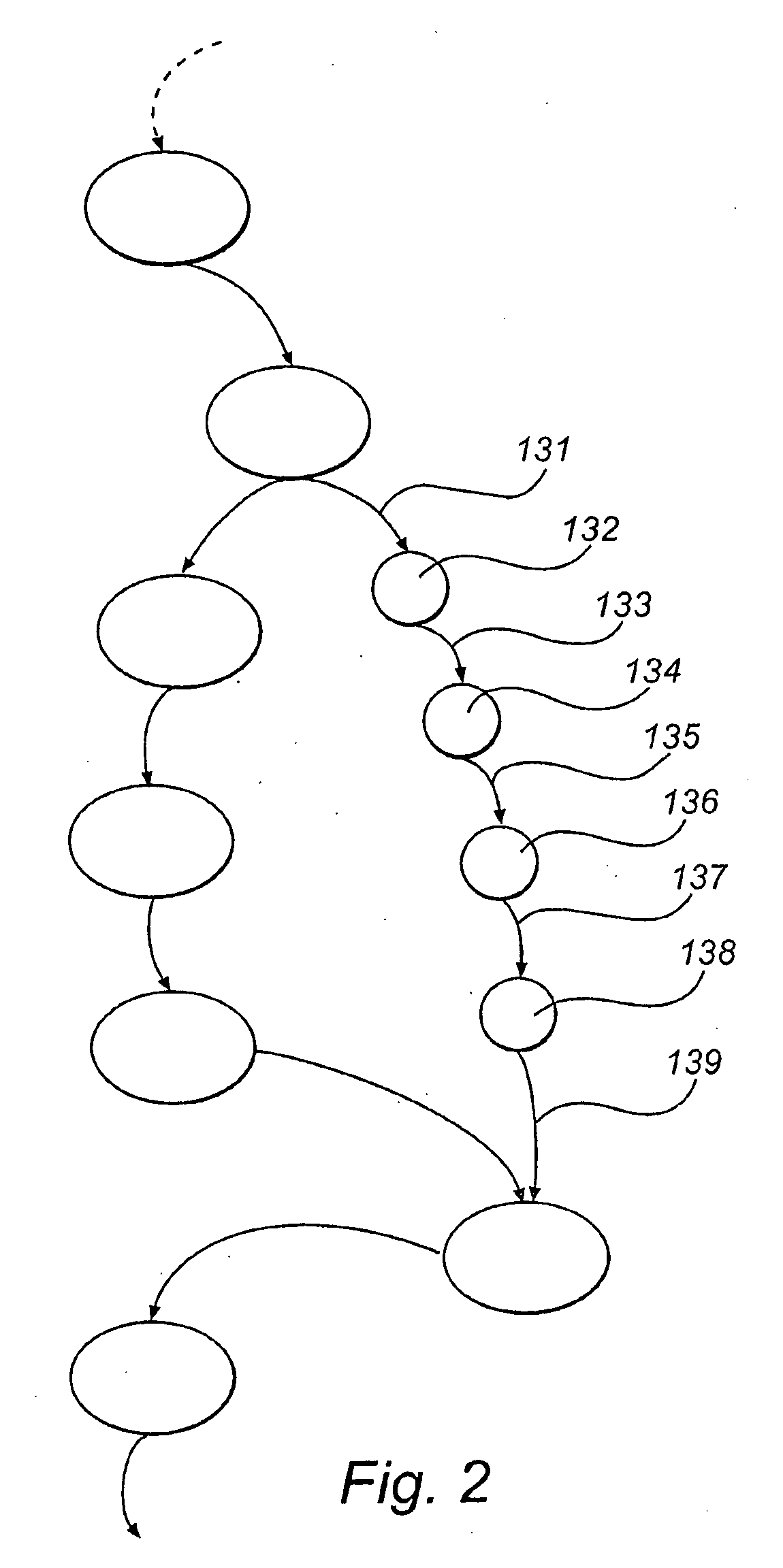

Method and Apparatus for Implementing Digital Logic Circuitry

InactiveUS20090119484A1Fast programmingImprove practicalityProgram control using stored programsDigital computer detailsData streamInterconnection

A method of generating digital control parameters for implementing digital logic circuitry comprising functional nodes with at least one input or at least one output and connections indicating interconnections between said functional nodes, wherein said digital logic circuitry comprises a first path streamed by successive tokens, and a second path streamed by said tokens is disclosed. The method comprises determining a necessary relative throughput for data flow to said paths; assigning buffers to one of said paths to balance throughput of said paths; removing assigned buffers until said necessary relative throughput is obtained with minimized number of buffers; and generating digital control parameters for implementing said digital logic circuitry comprising said minimized number of buffers. An apparatus, a computer implemented digital logic circuitry, a Data Flow Machine, methods and computer program products are also disclosed.

Owner:ZIQTAG SASAN FALLAHI

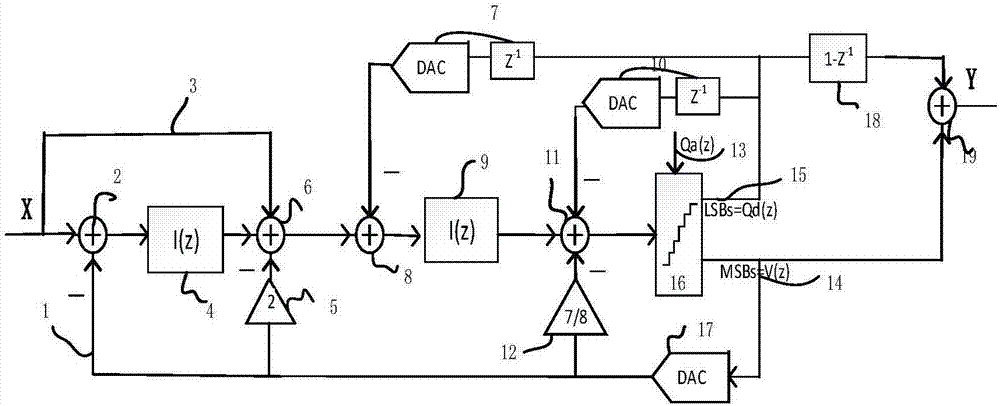

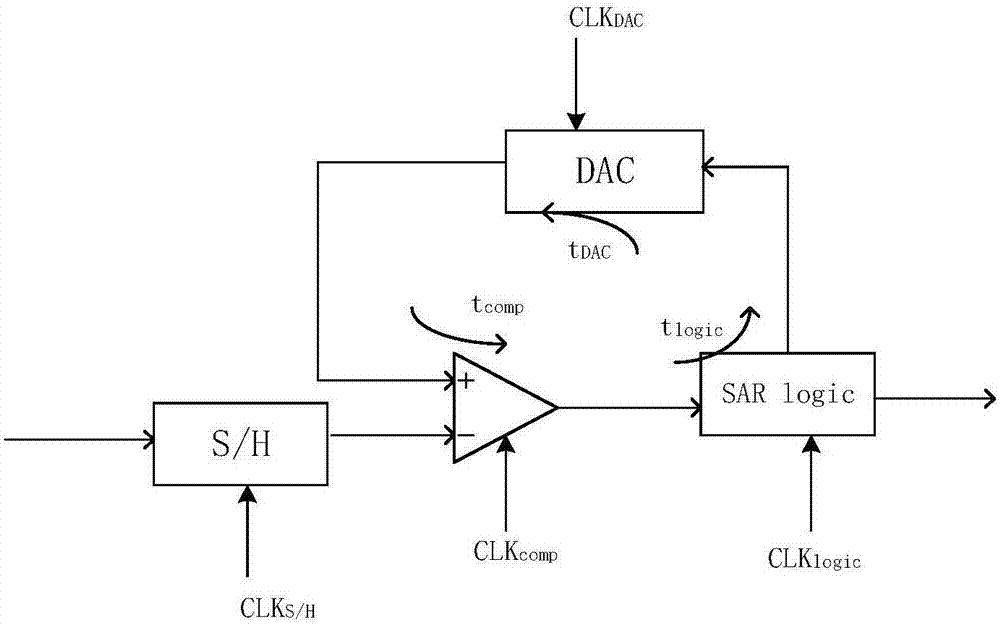

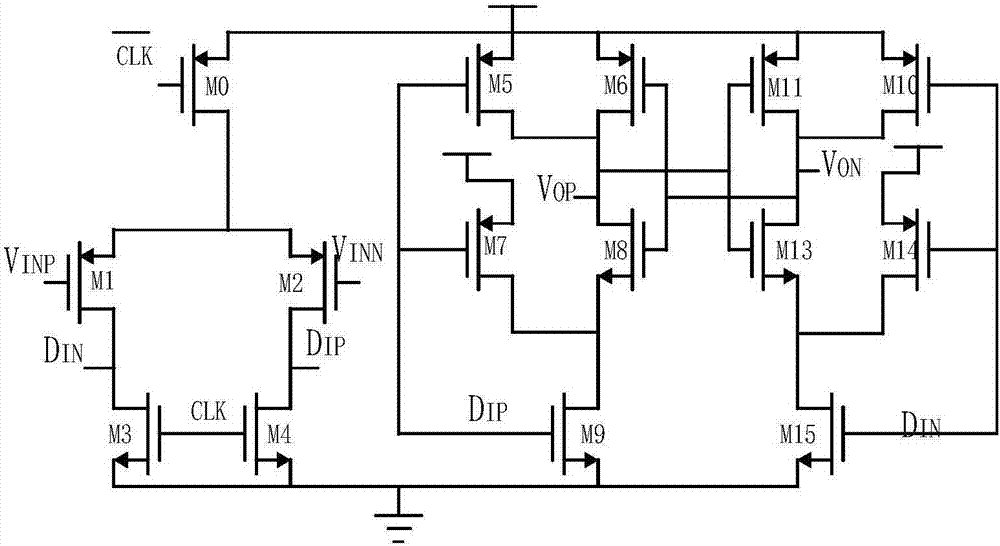

Successive-approximation type digital-analog converter with feedback advanced setting, and corresponding Delta-Sigma ADC configuration

ActiveCN107395206AReduce power consumptionReduce the difficulty of buildingPower saving provisionsElectric signal transmission systemsCapacitanceIntegrator

The invention discloses a successive-approximation type digital-analog converter with feedback advanced setting in a Delta-Sigma ADC configuration. The digital-analog converter is characterized in that the digital-analog converter is used for feeding back an output signal of a quantizer to an output node of a second-stage integrator, thereby completing the non-zero loop delay compensation and noise coupling; the digital-analog converter comprises two DAC capacitor arrays in the same structure; each DAC capacitor array comprises a plurality of capacitors in parallel connection; one end of each capacitor of each DAC capacitor array is connected with a VDD or VSS through an independent switch; the other end of each capacitor in one DAC capacitor array is connected to a link of an input Vinp and the positive input end Vp of a dynamic comparator, and the other end of each capacitor in the other DAC capacitor array is connected to a link of an input Vinn and the negative input end Vn of the dynamic comparator; the dynamic comparator, a digital logic circuit and a decoder are connected sequentially; the output end of the decoder is connected with the capacitor switches in the two DAC capacitor arrays. The DAC can reduce the building difficulty and power consumption of the Delta-Sigma ADC configuration.

Owner:UNIV OF SCI & TECH OF CHINA

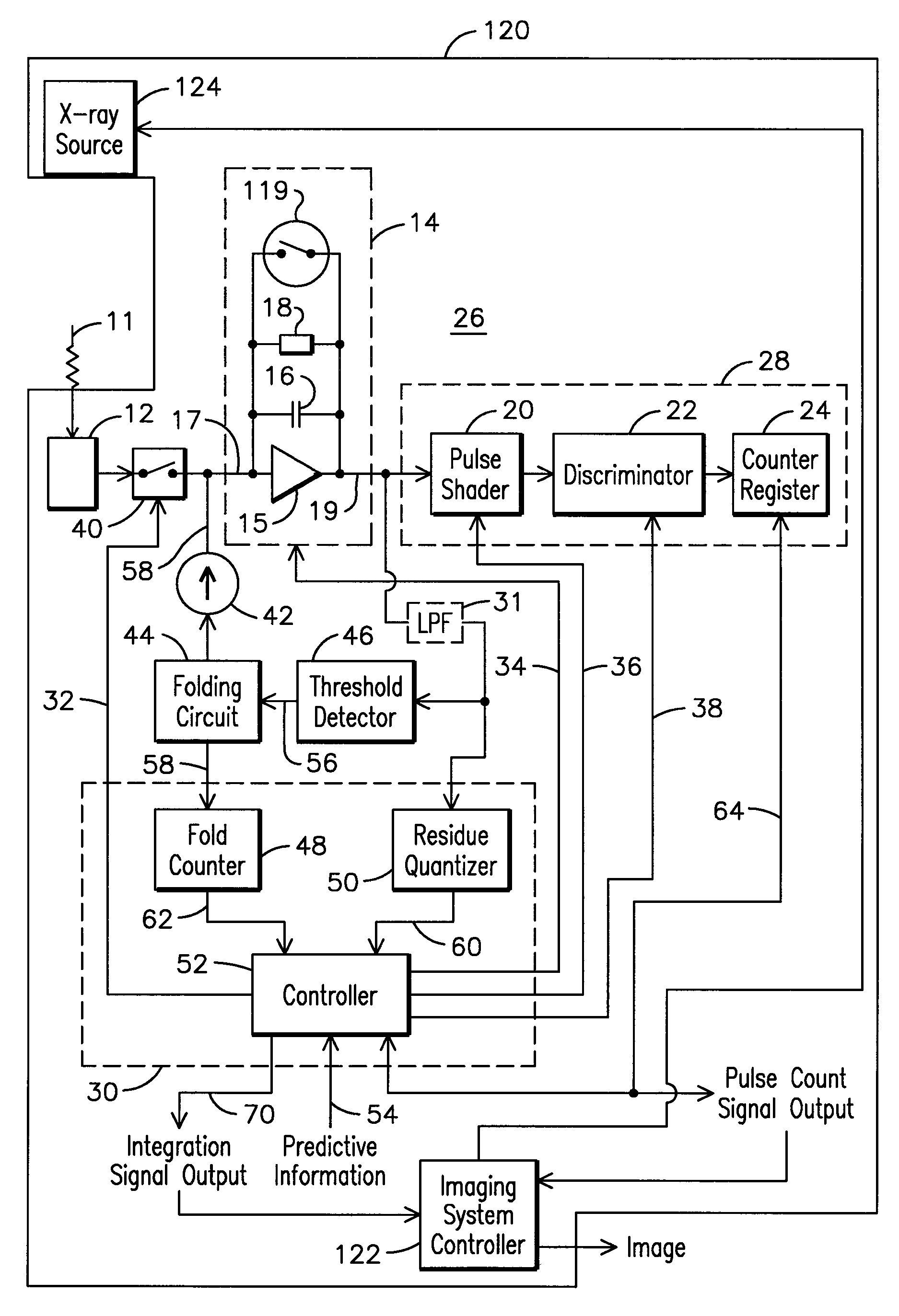

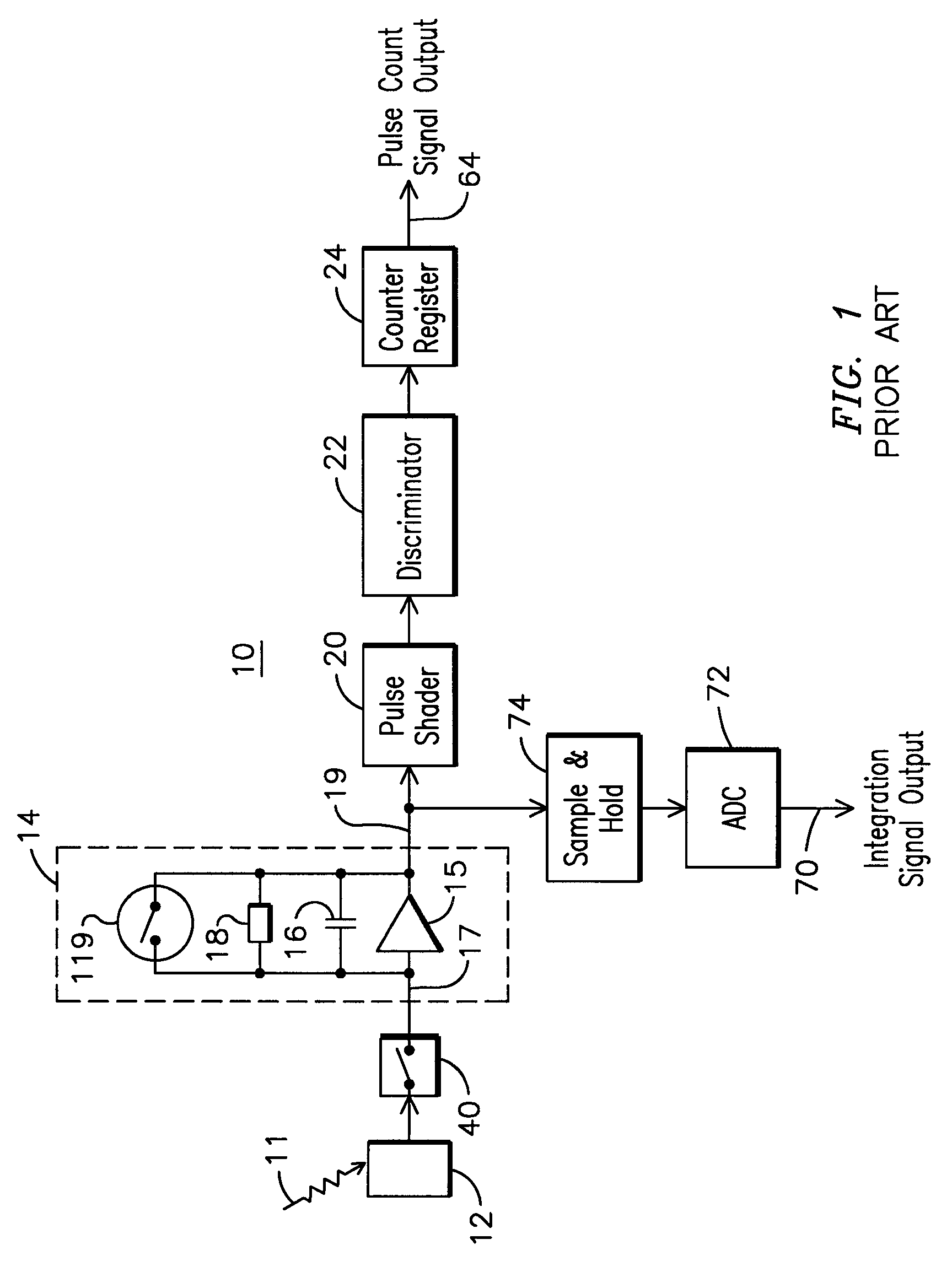

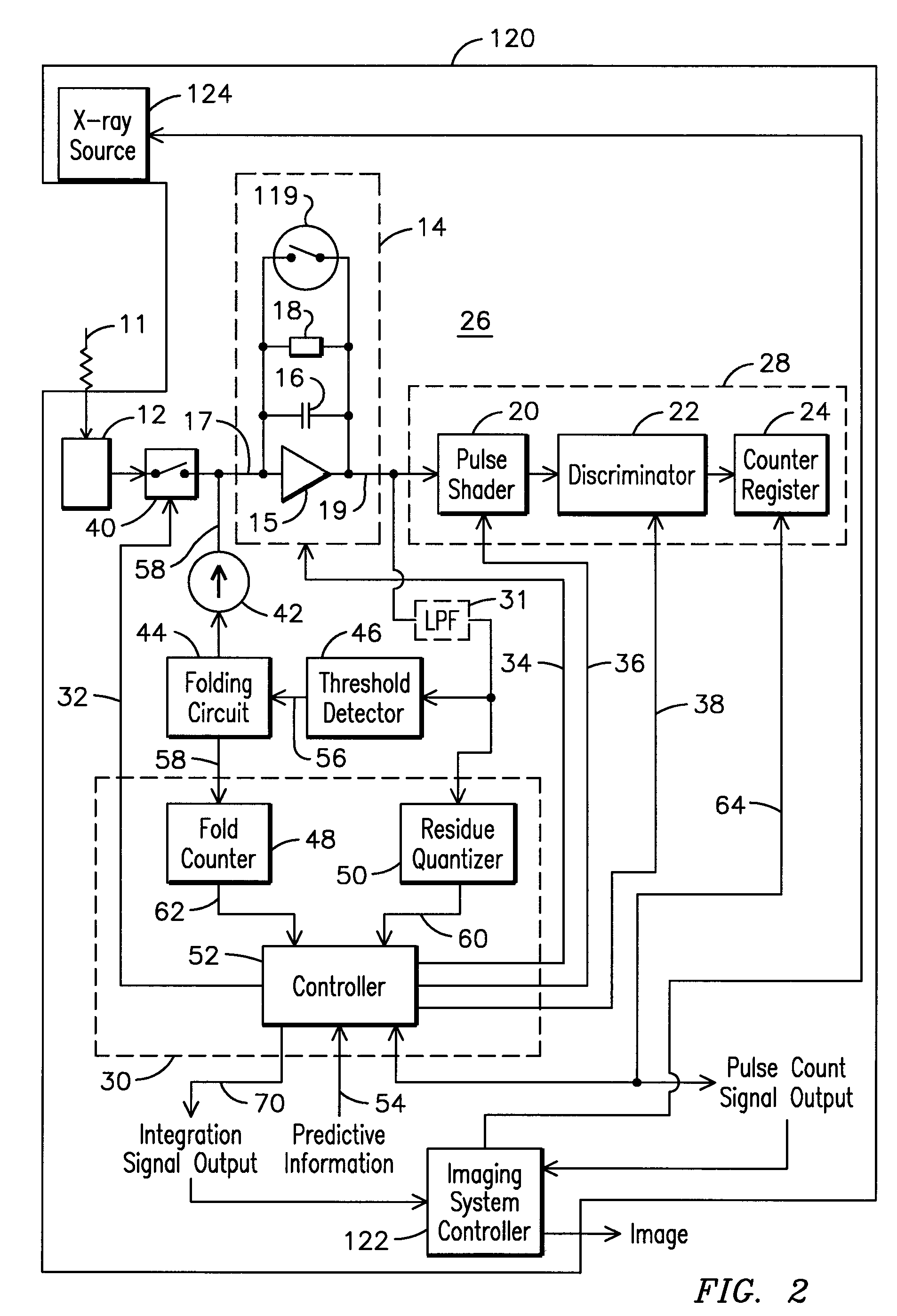

Adaptive data acquisition for an imaging system

ActiveUS20080018505A1Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierControl signal

An adaptive data acquisition circuit (26) includes an amplifier (14) for amplifying electrical pulses generated by a detector (12) responsive to energy incident at the detector. The adaptive data acquisition circuit also includes a counting circuit (28) for counting amplified electrical pulses generated by the amplifier. In addition, the adaptive data acquisition circuit includes a digital logic circuit (30) for determining a pulse parameter indicative of a pulse rate and an amount of energy present in the amplified electrical pulses and for generating a control signal (34) responsive to the pulse parameter for controlling an operating parameter of the data acquisition circuit.

Owner:GENERAL ELECTRIC CO