Patents

Literature

103results about How to "Reduce capacitive load" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

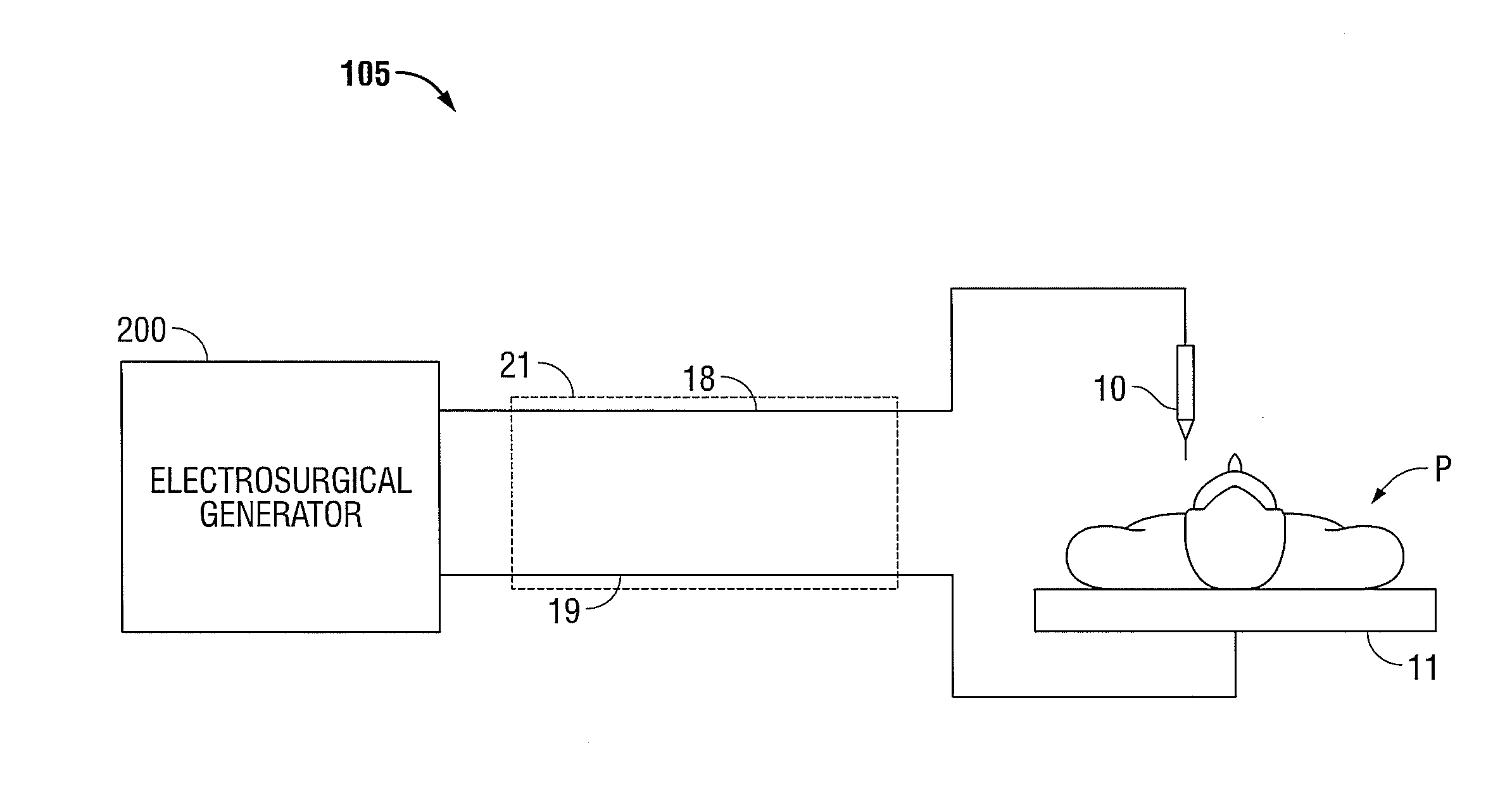

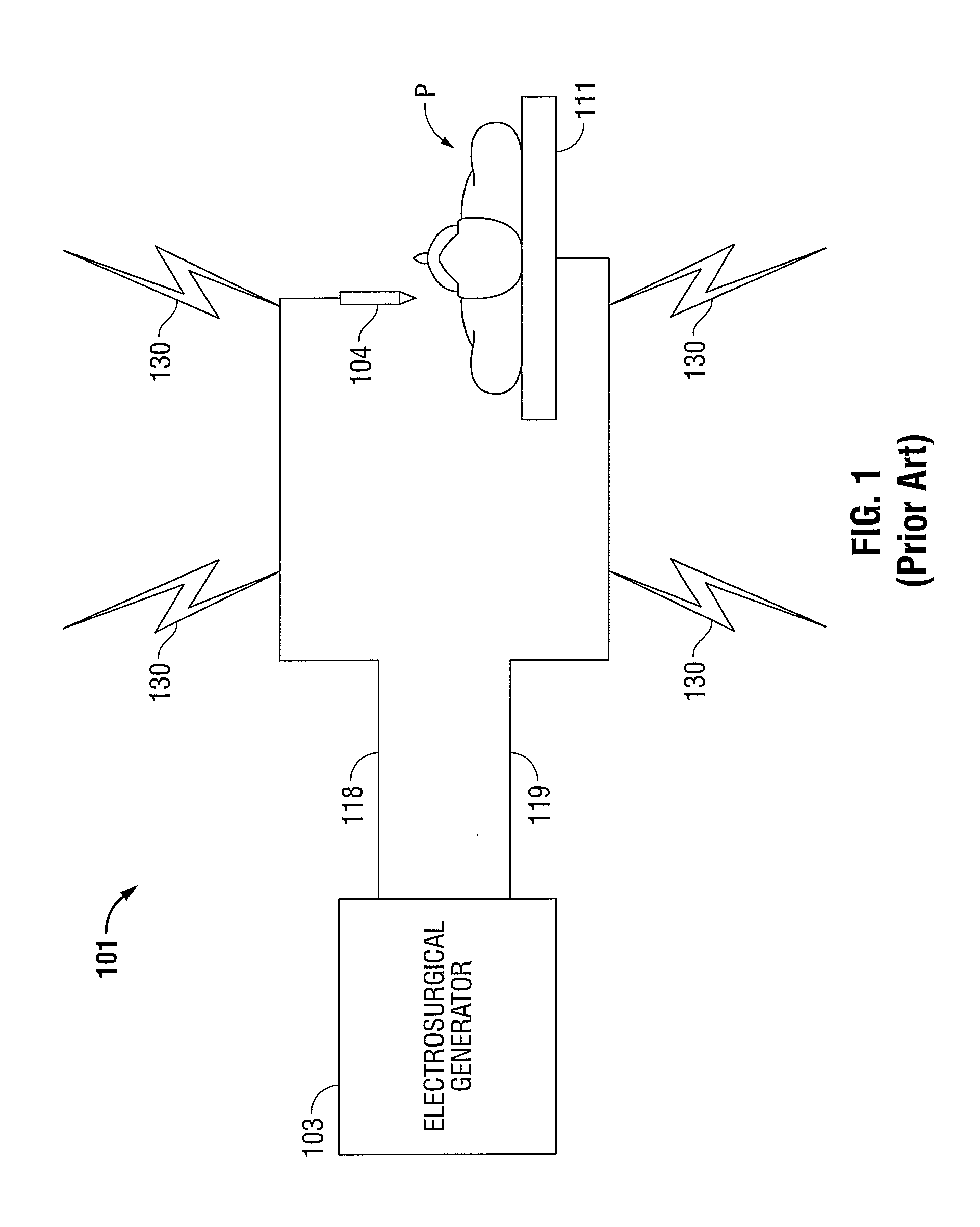

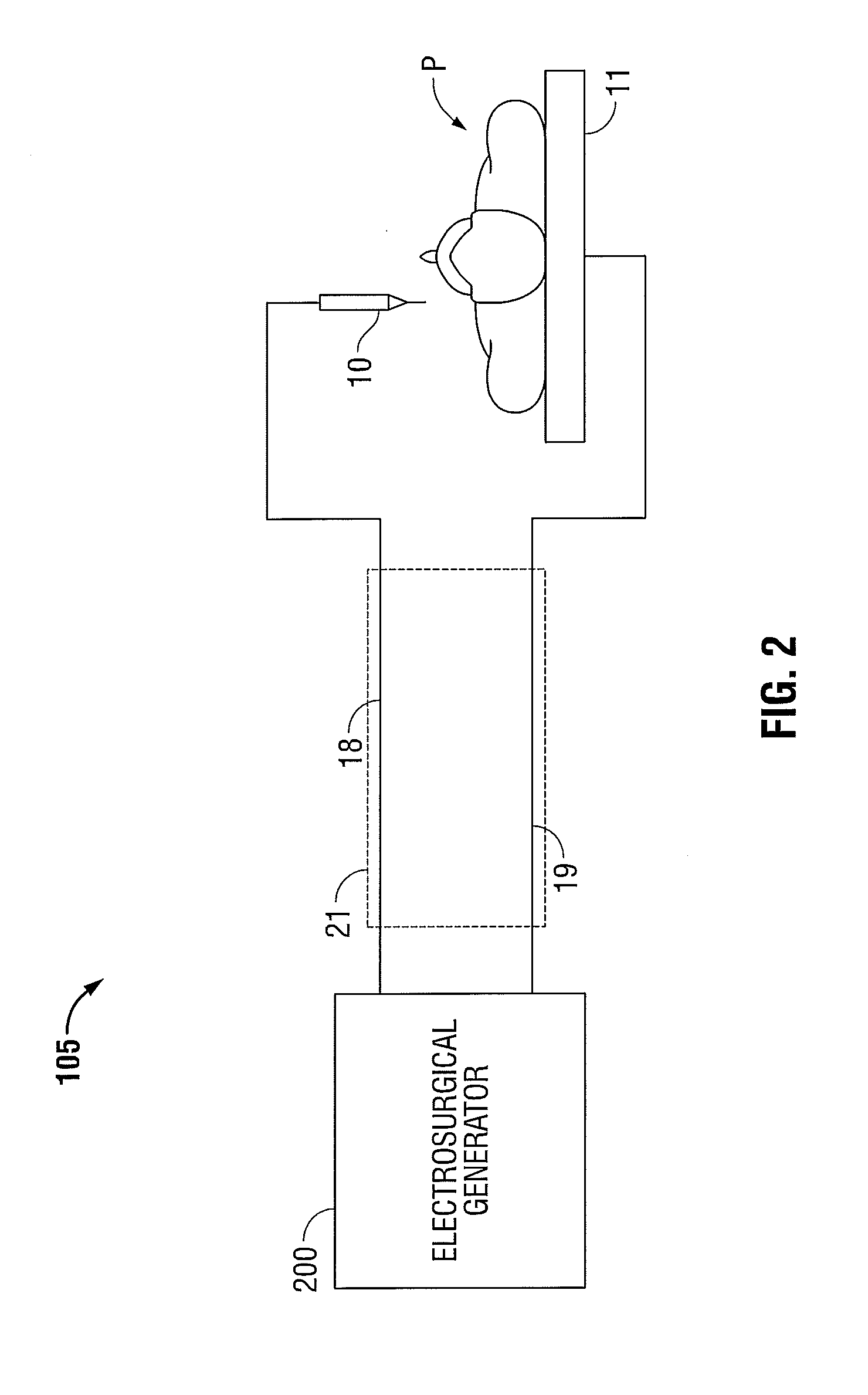

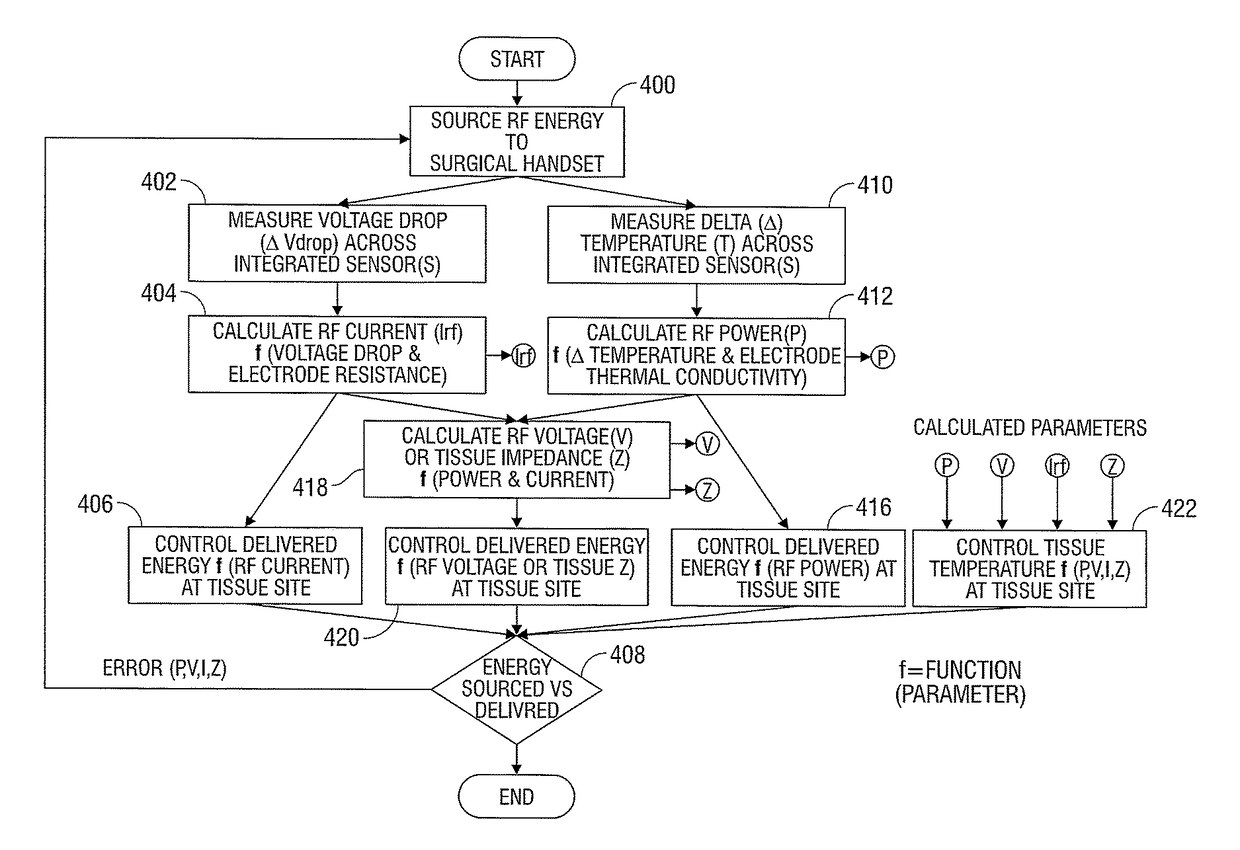

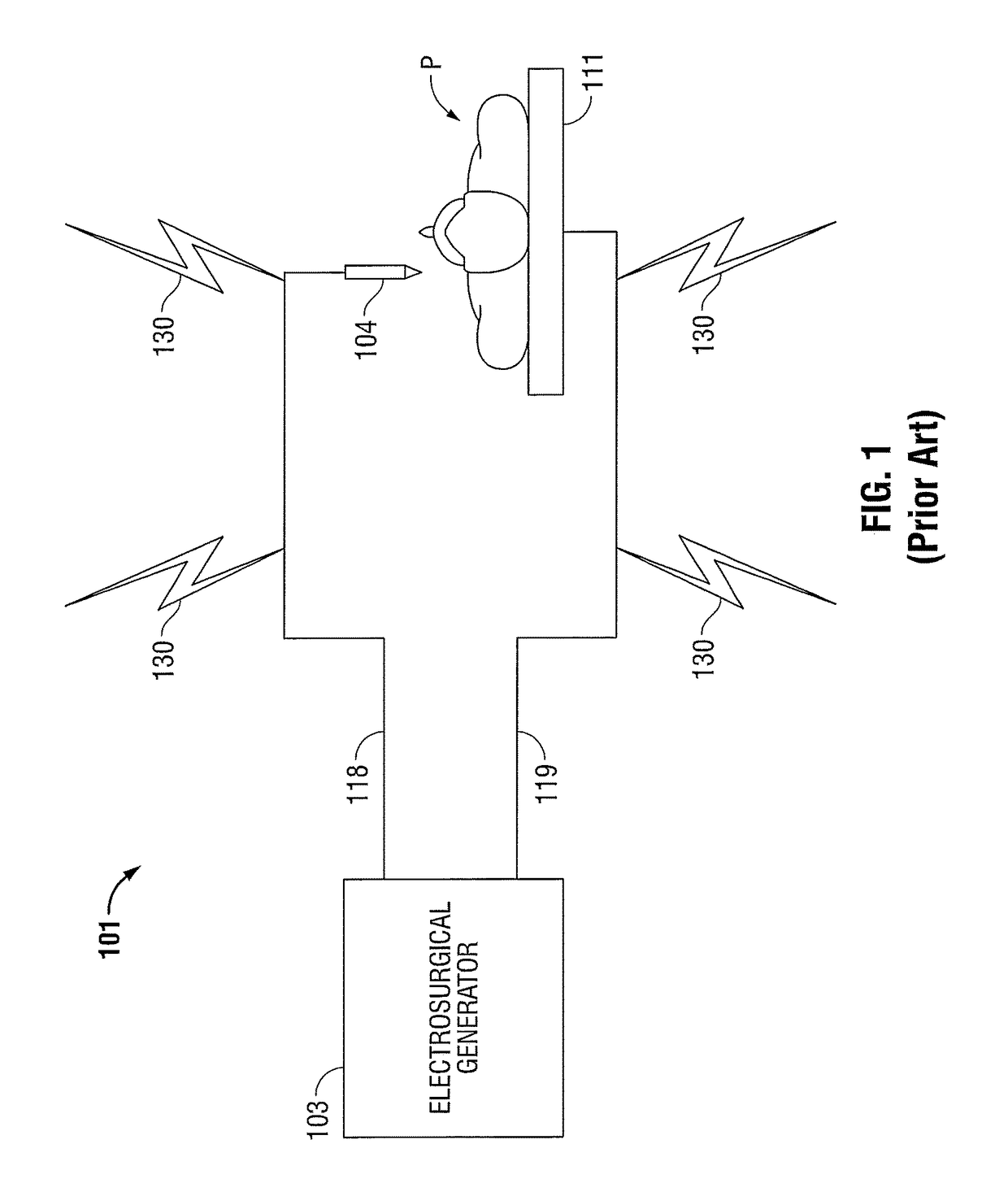

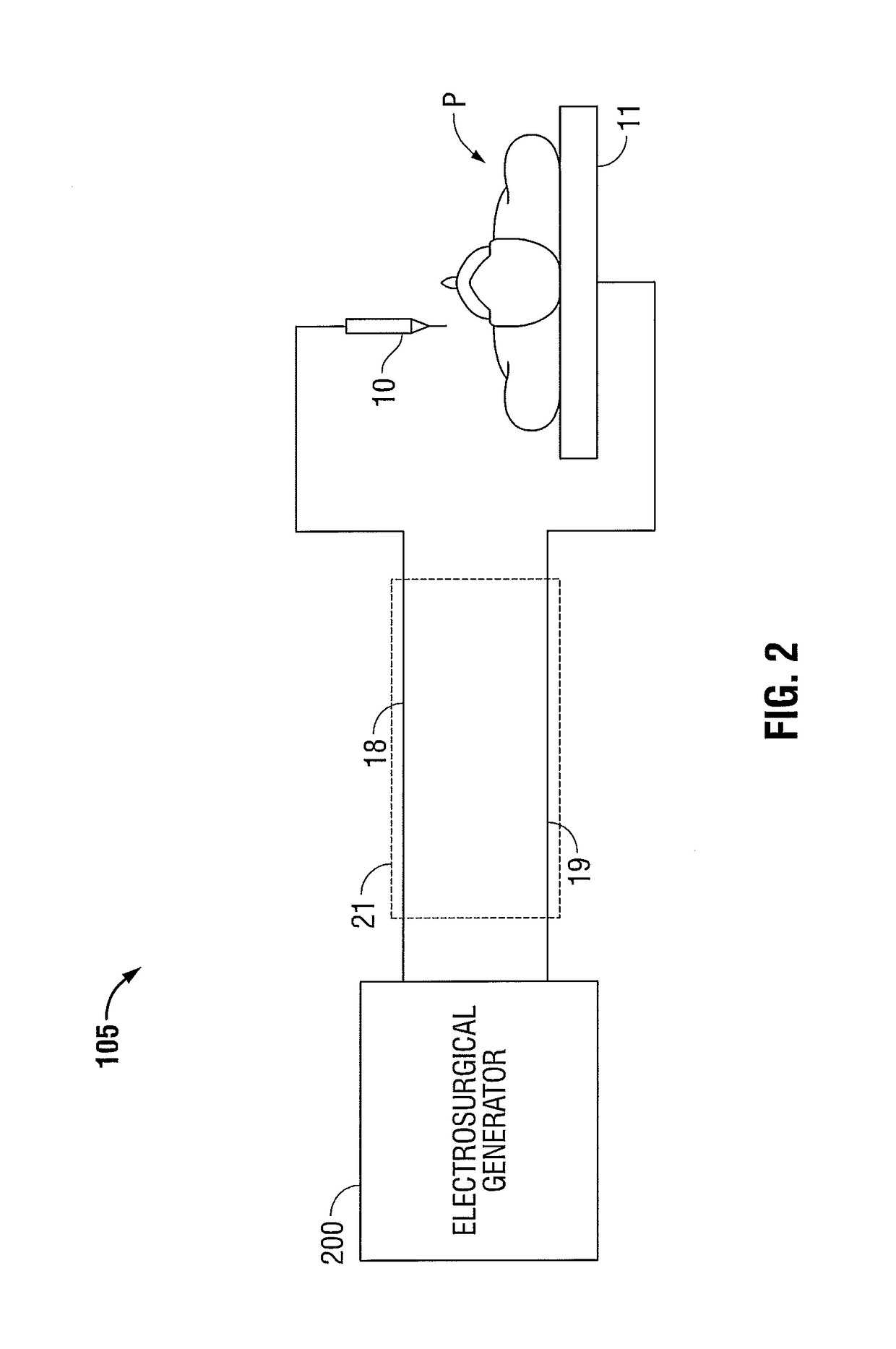

Electrosurgical Apparatus with Integrated Energy Sensing at Tissue Site

ActiveUS20130197503A1Increase safetyReduce coupleSurgical instruments for heatingSurgical forcepsRadio frequencyThermal conductivity

An electrosurgical system is disclosed. The system includes an electrosurgical instrument having at least one electrode configured as a first sensor for measuring a voltage drop therethrough and a temperature sensor for a thermal sensor configured to measure a temperature difference across the at least one electrode; and a generator including an output stage coupled to the at least one electrode, the output stage configured to generate radio frequency energy; and a controller configured to determine actual radio frequency current based on the voltage drop and electrical resistivity of the at least one electrode and radio frequency power based on the measured temperature difference and the thermal conductivity of the at least one electrode.

Owner:TYCO HEALTHCARE GRP LP

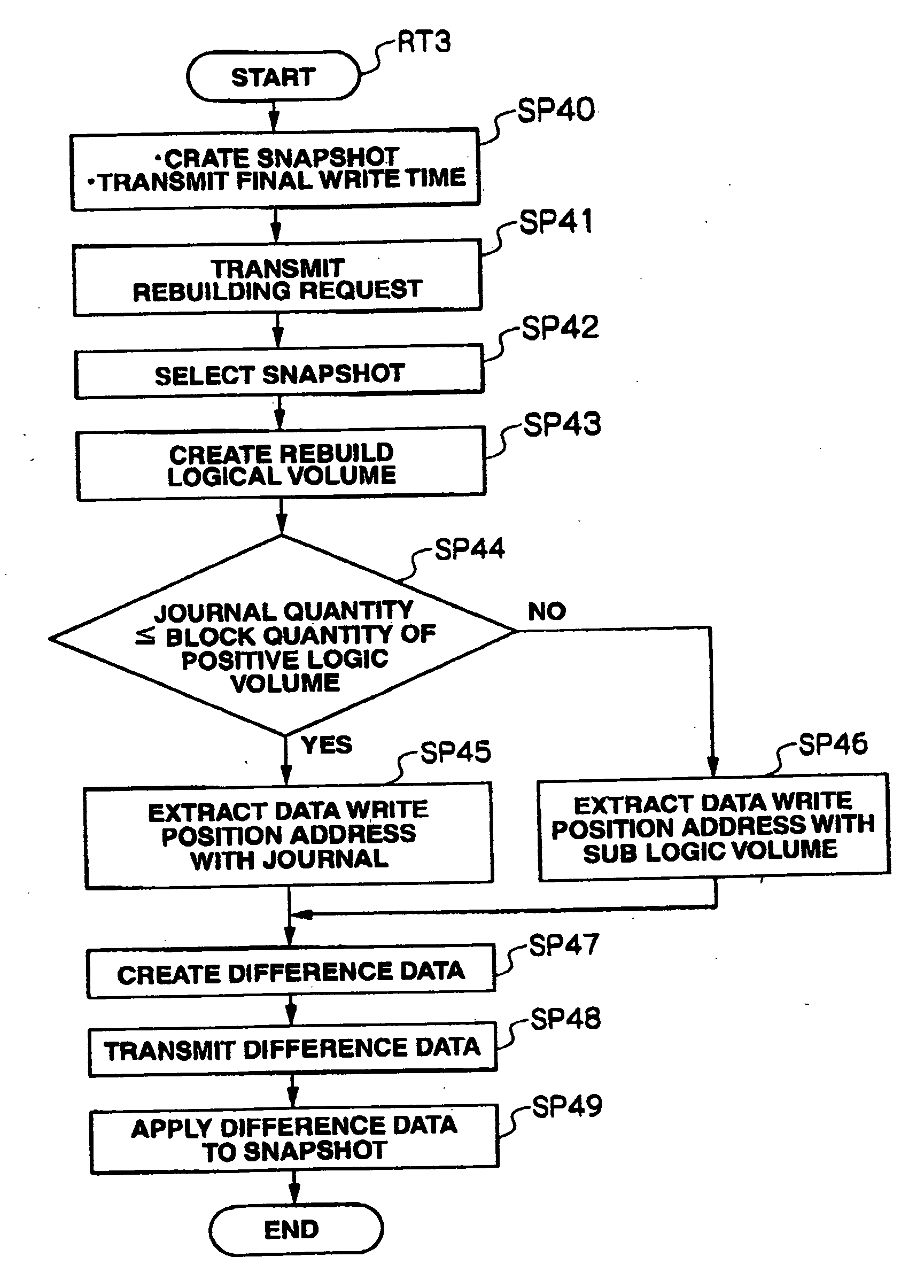

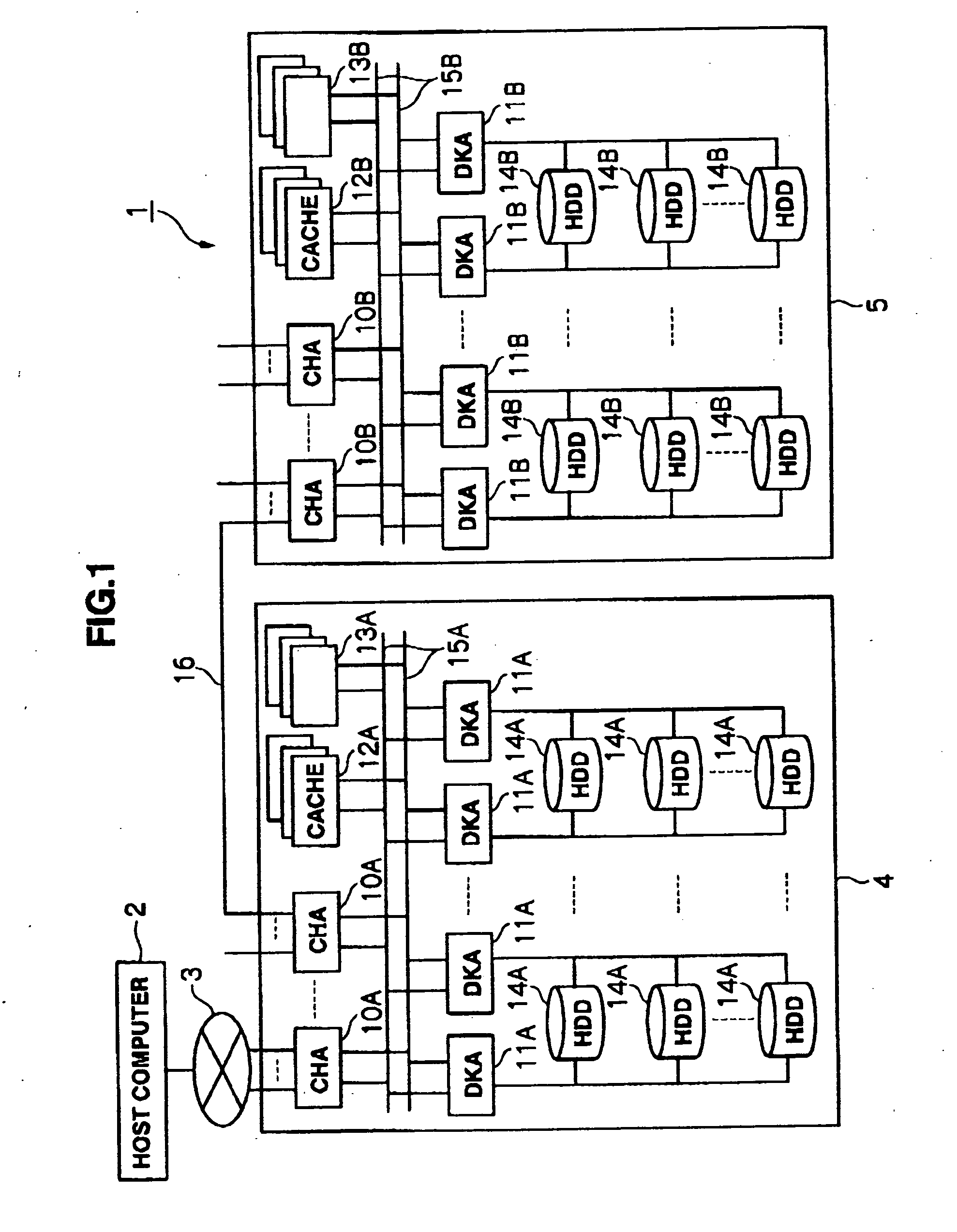

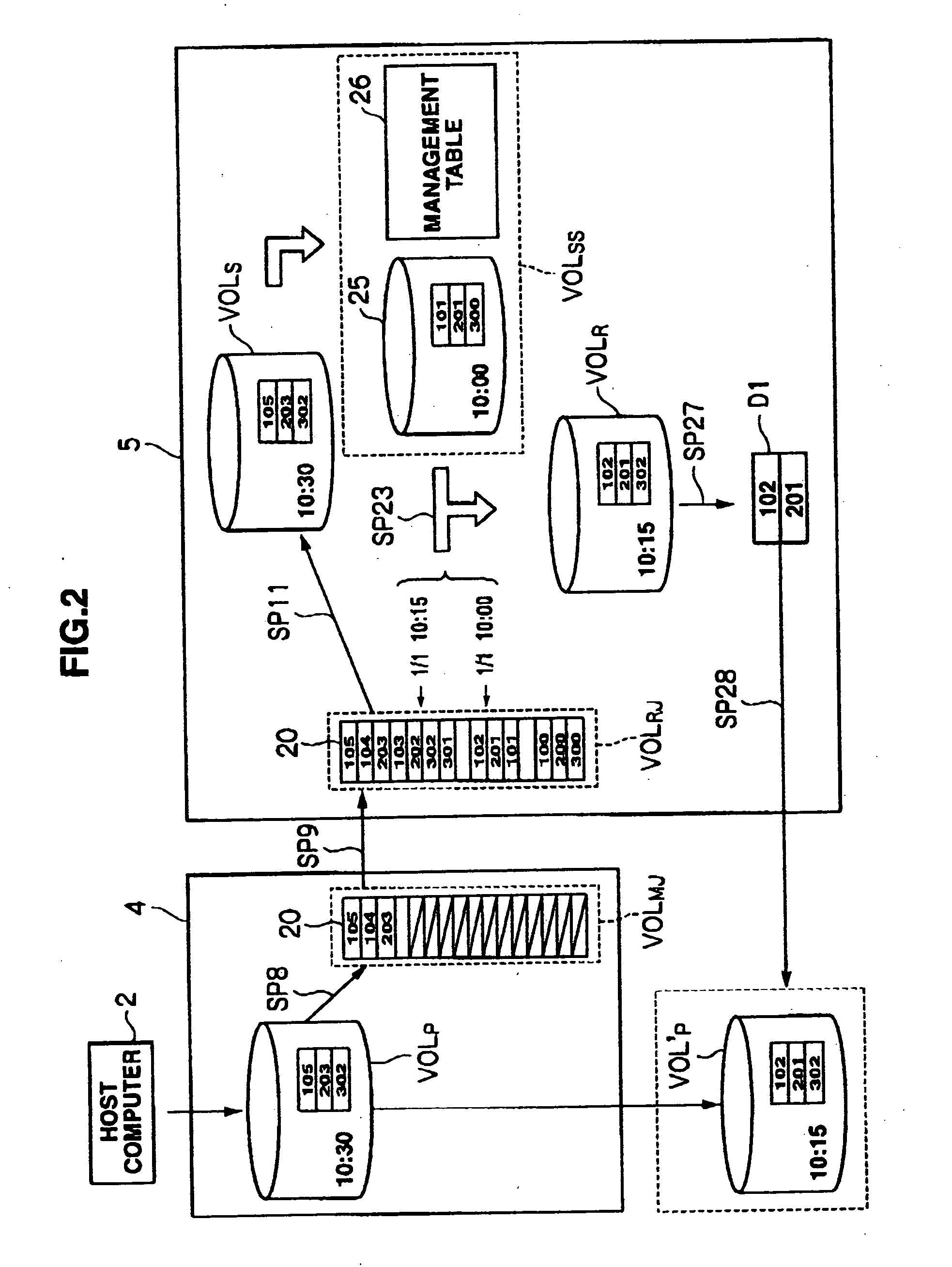

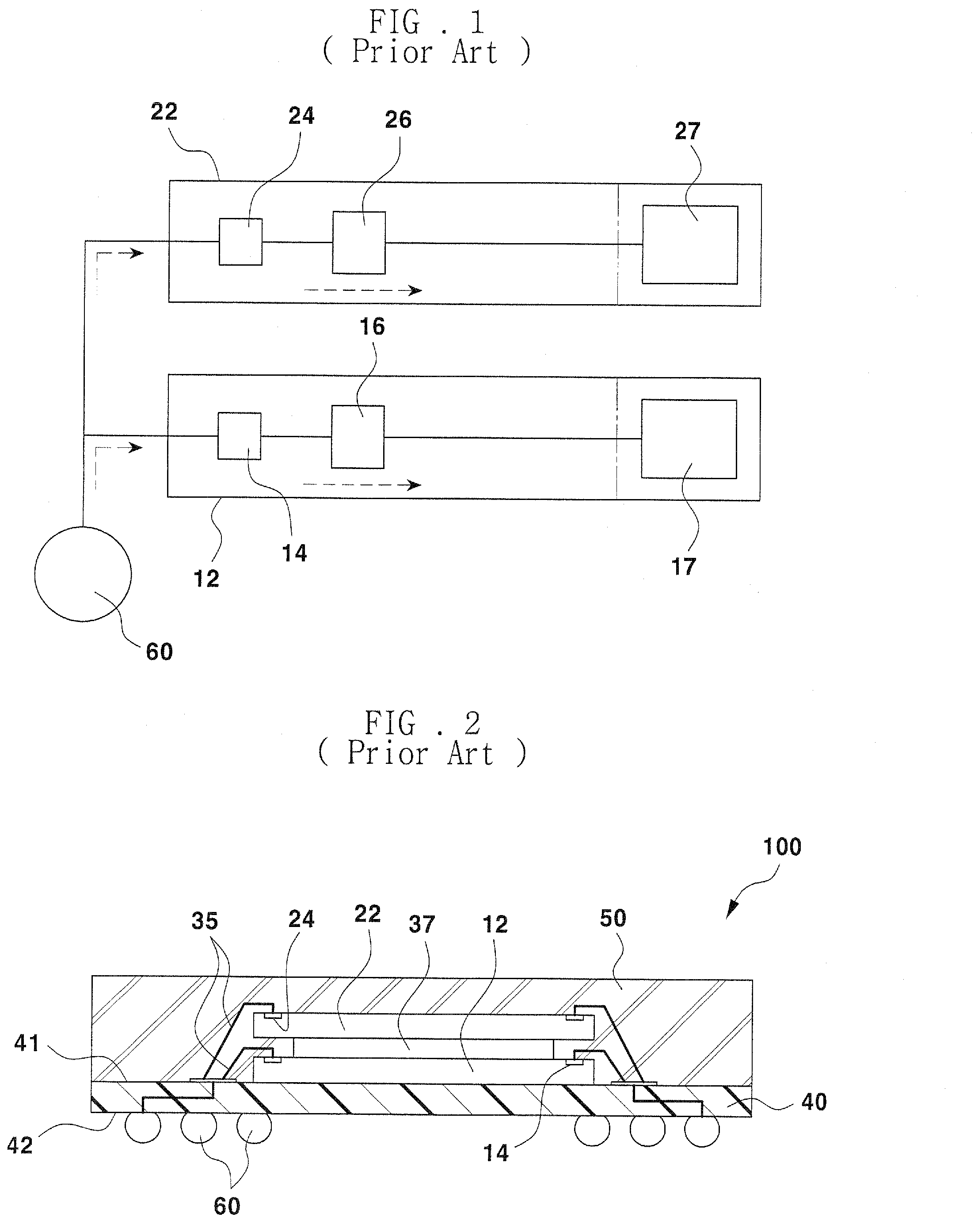

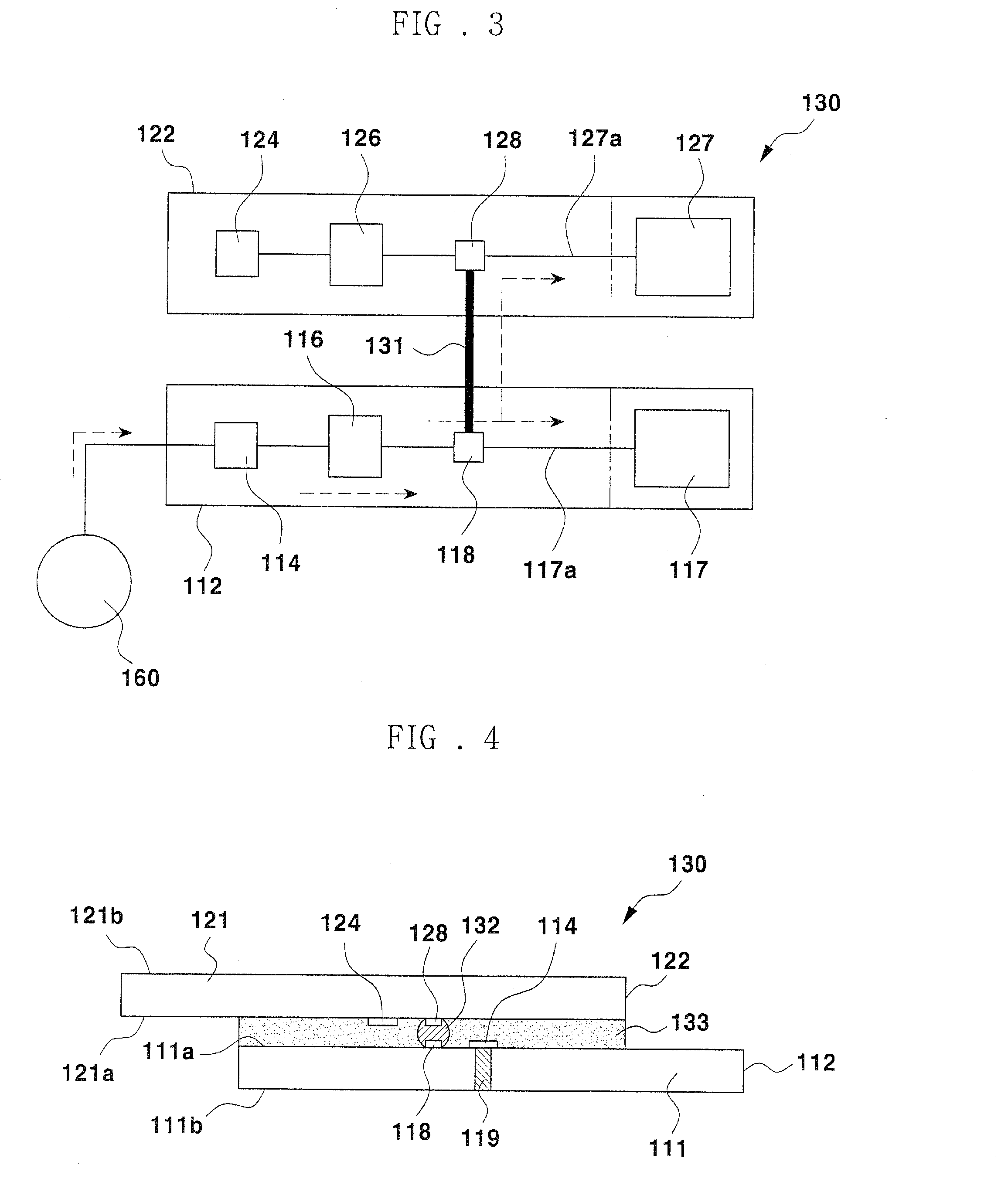

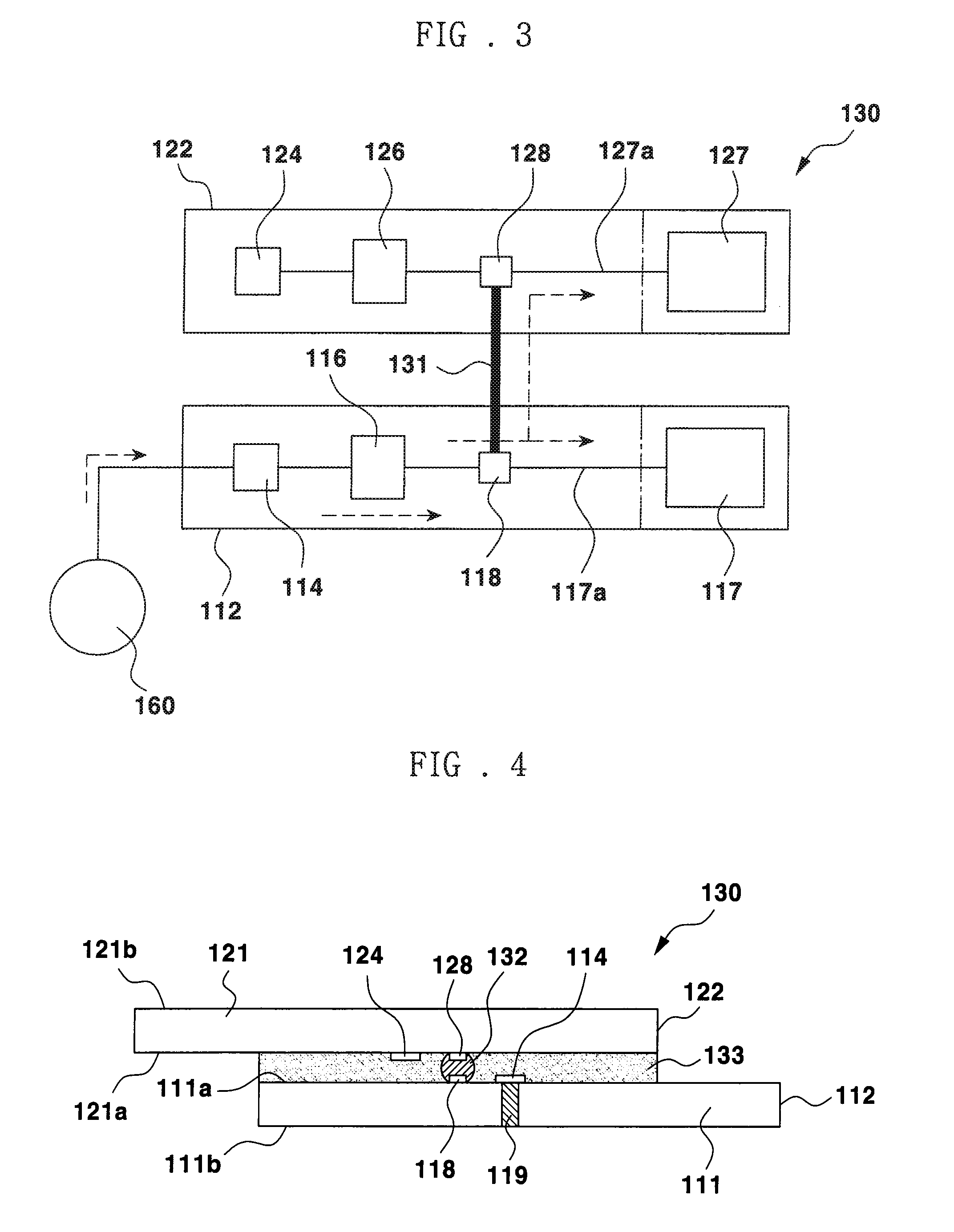

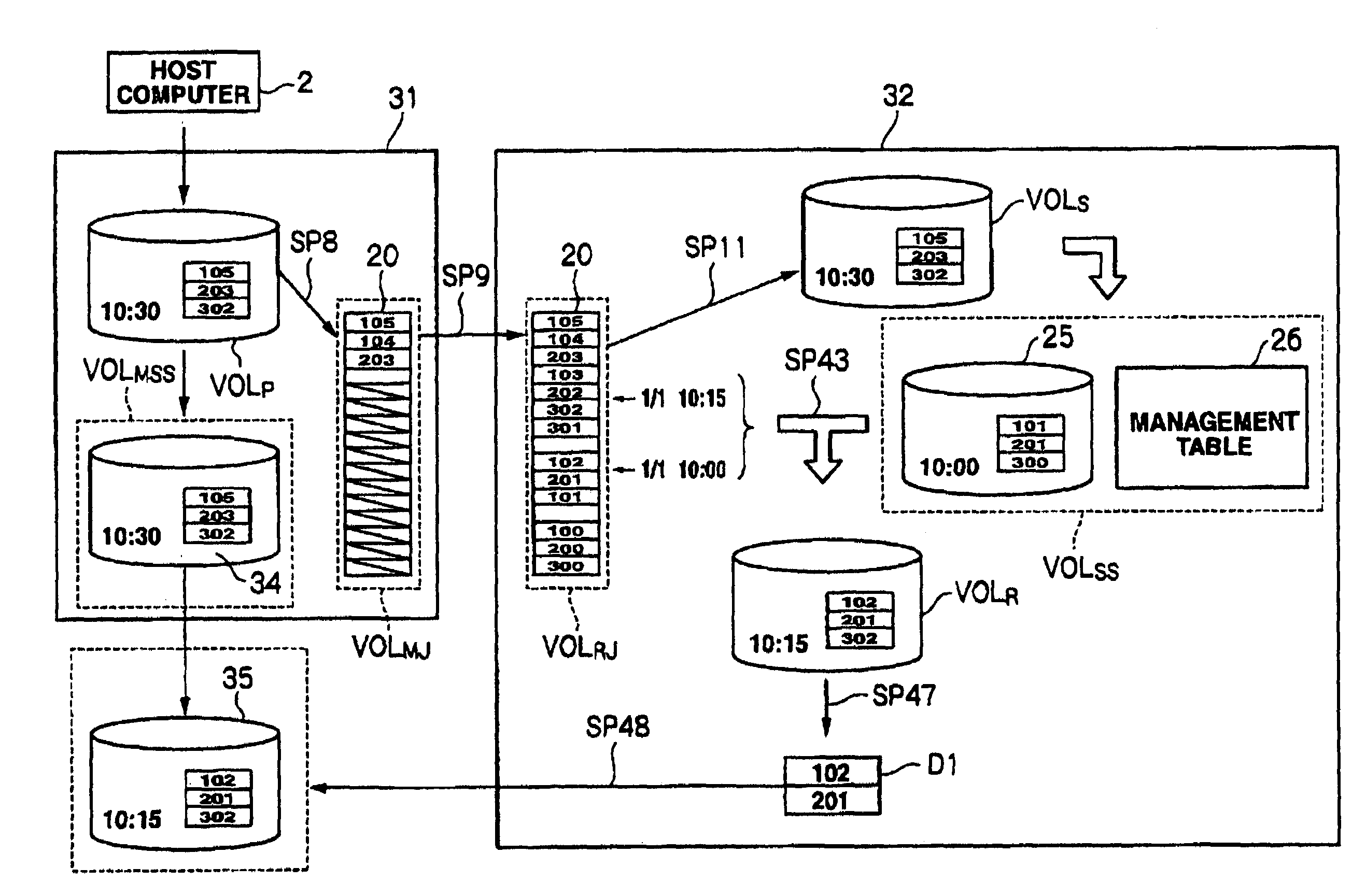

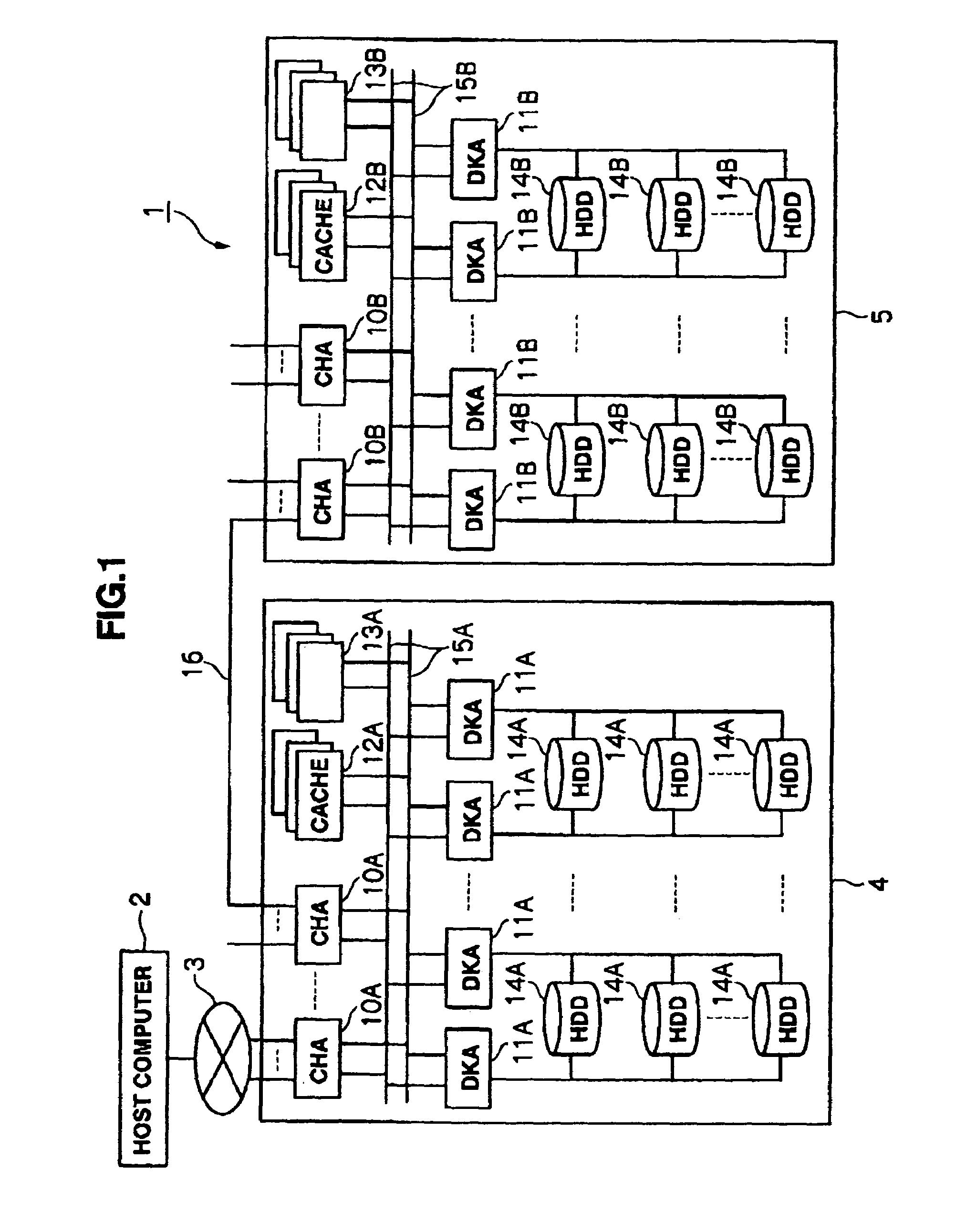

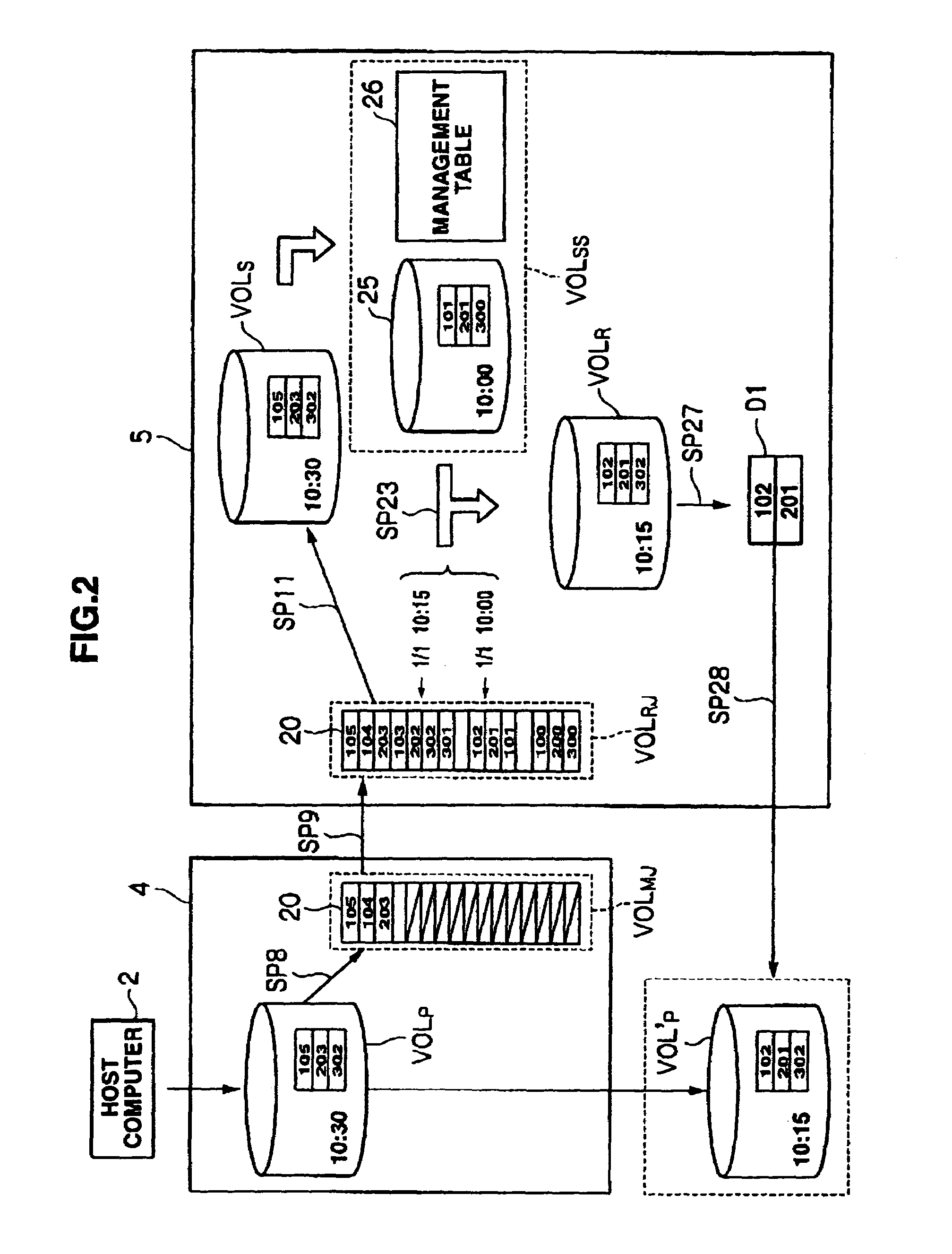

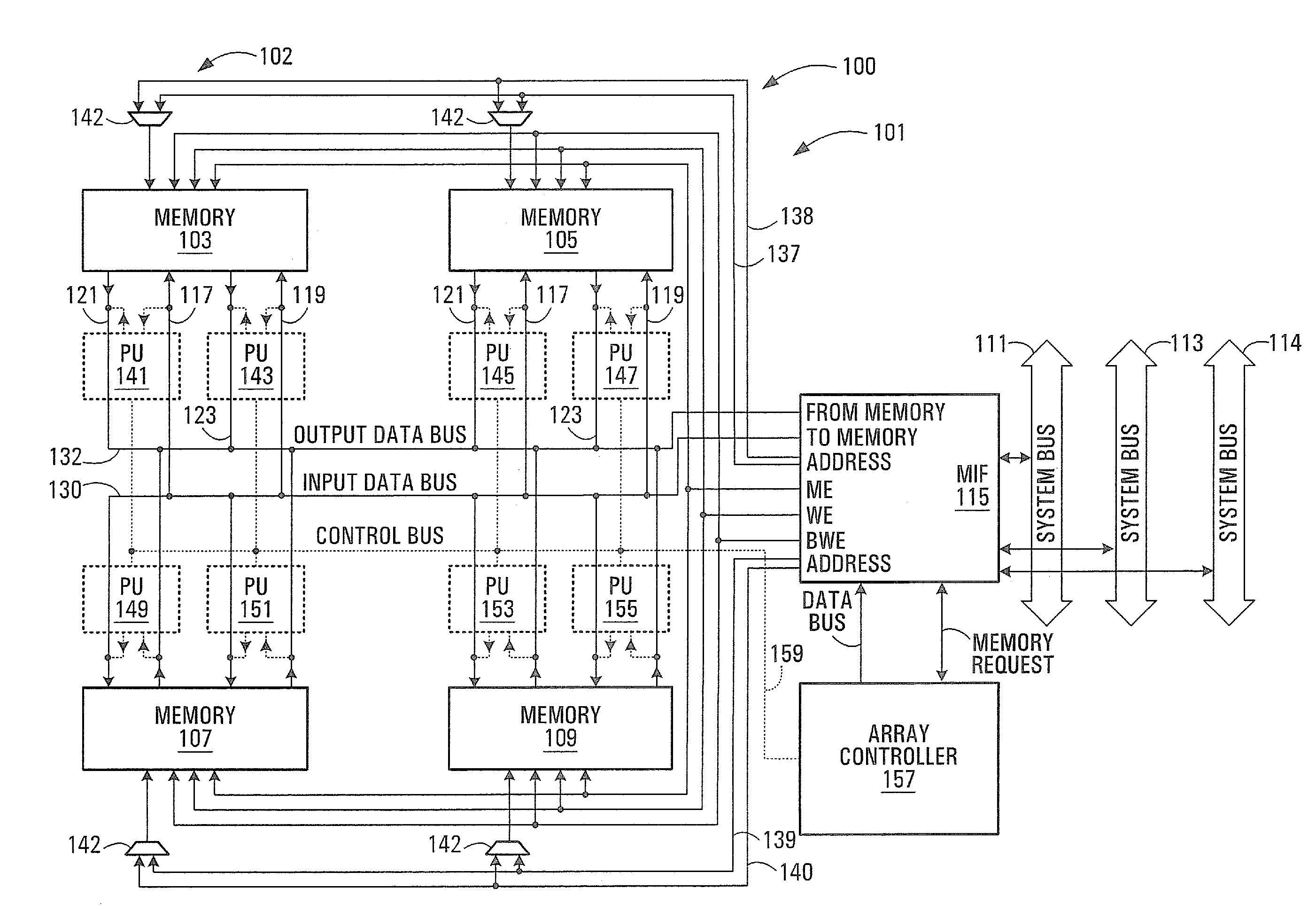

Storage system and data management method

InactiveUS20060242371A1Prevent overload of memory capacityImposing burdenData processing applicationsMemory loss protectionData managementData reconstruction

On the first storage device side, when data is written in a first volume, a journal of such data is transmitted to a second storage device; on the second storage device side, a snapshot of a second volume and the respective journals are stored; on the second storage device side, the first volume is rebuilt at a rebuilding time according to a rebuilding order; on the second storage device side, data of an address rewritten from the rebuilding time onward is transmitted as difference data to the first storage device; and on the first storage device side, the first volume is rebuilt at the rebuilding time based on the difference data.

Owner:HITACHI LTD

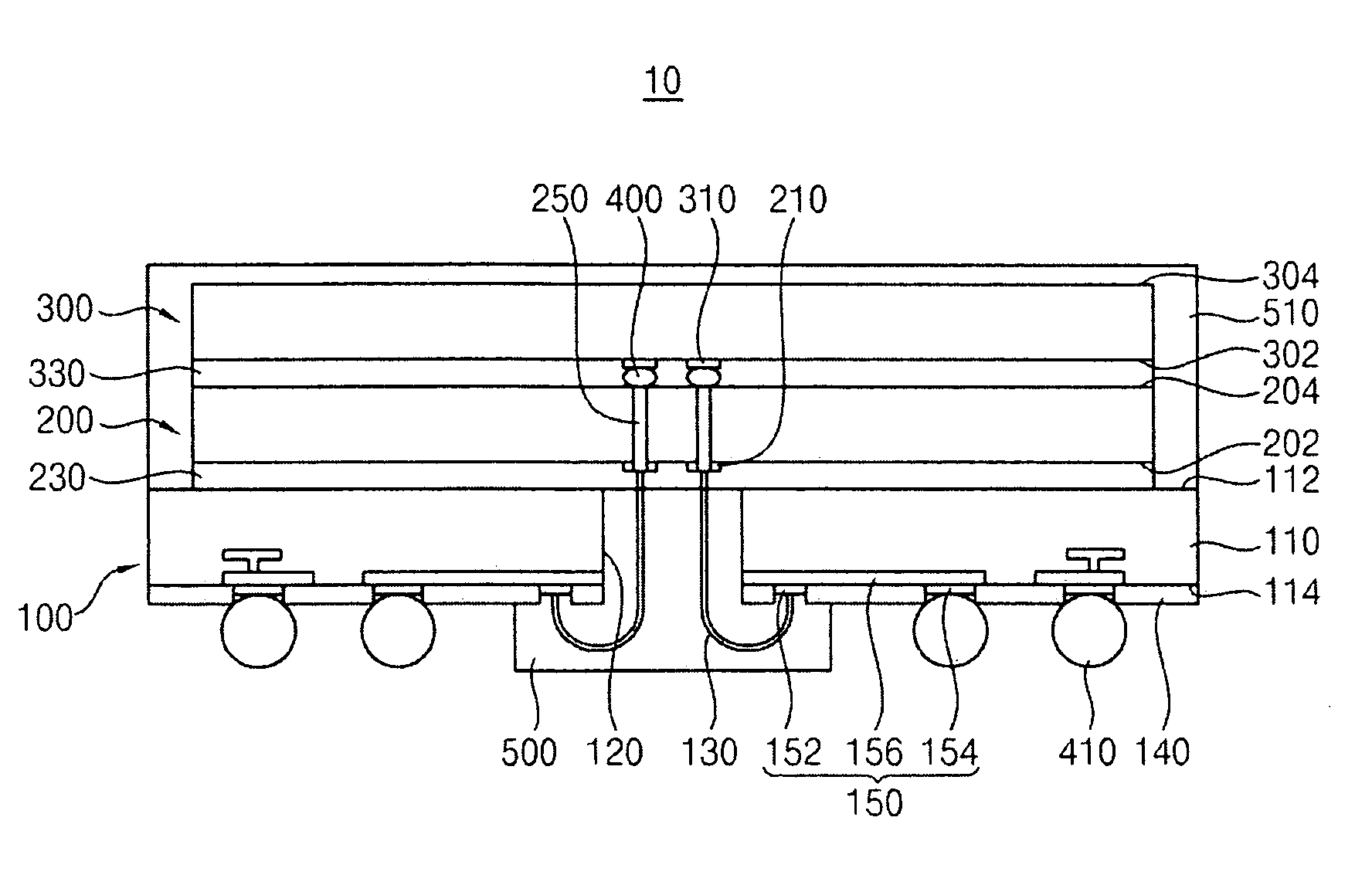

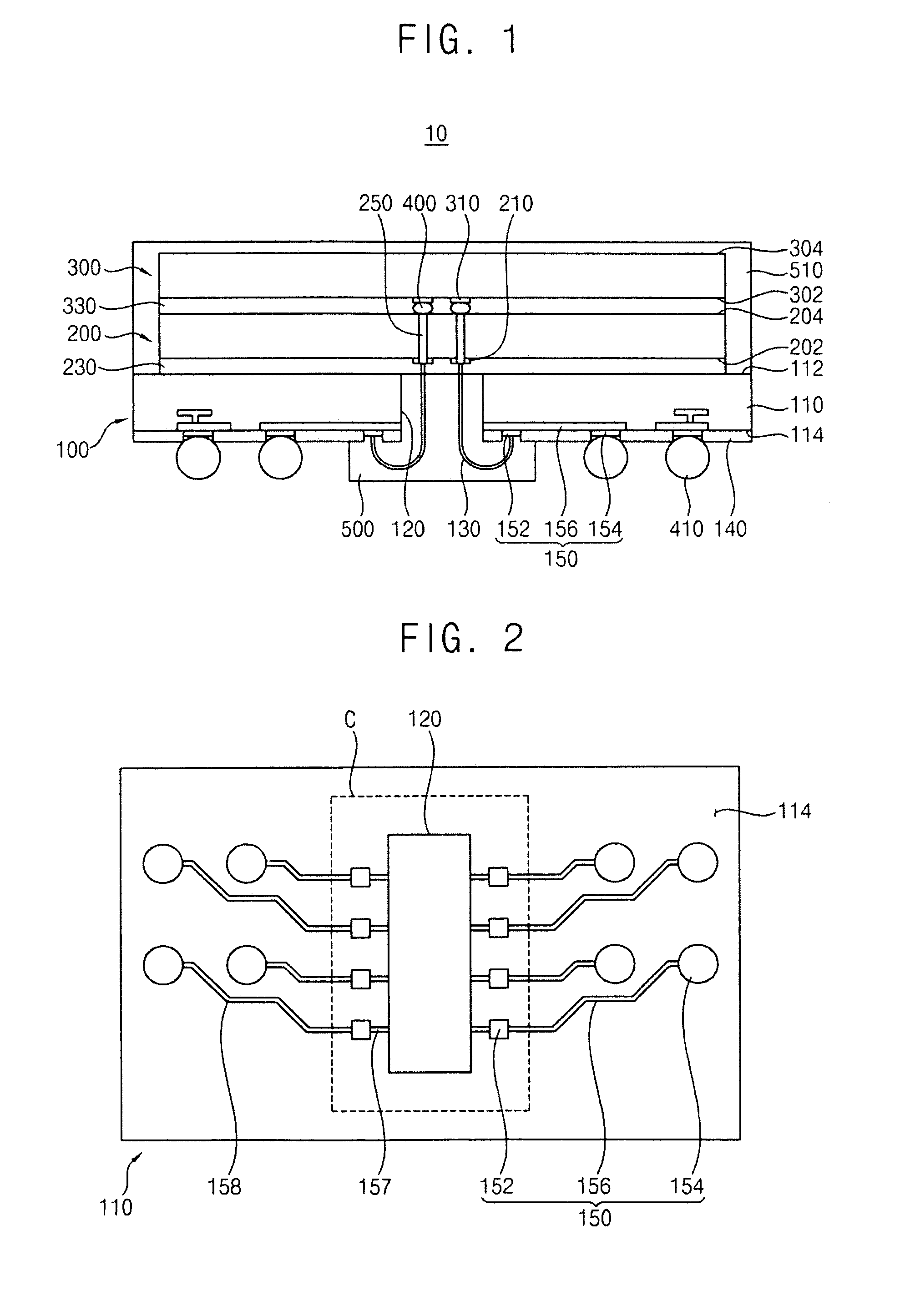

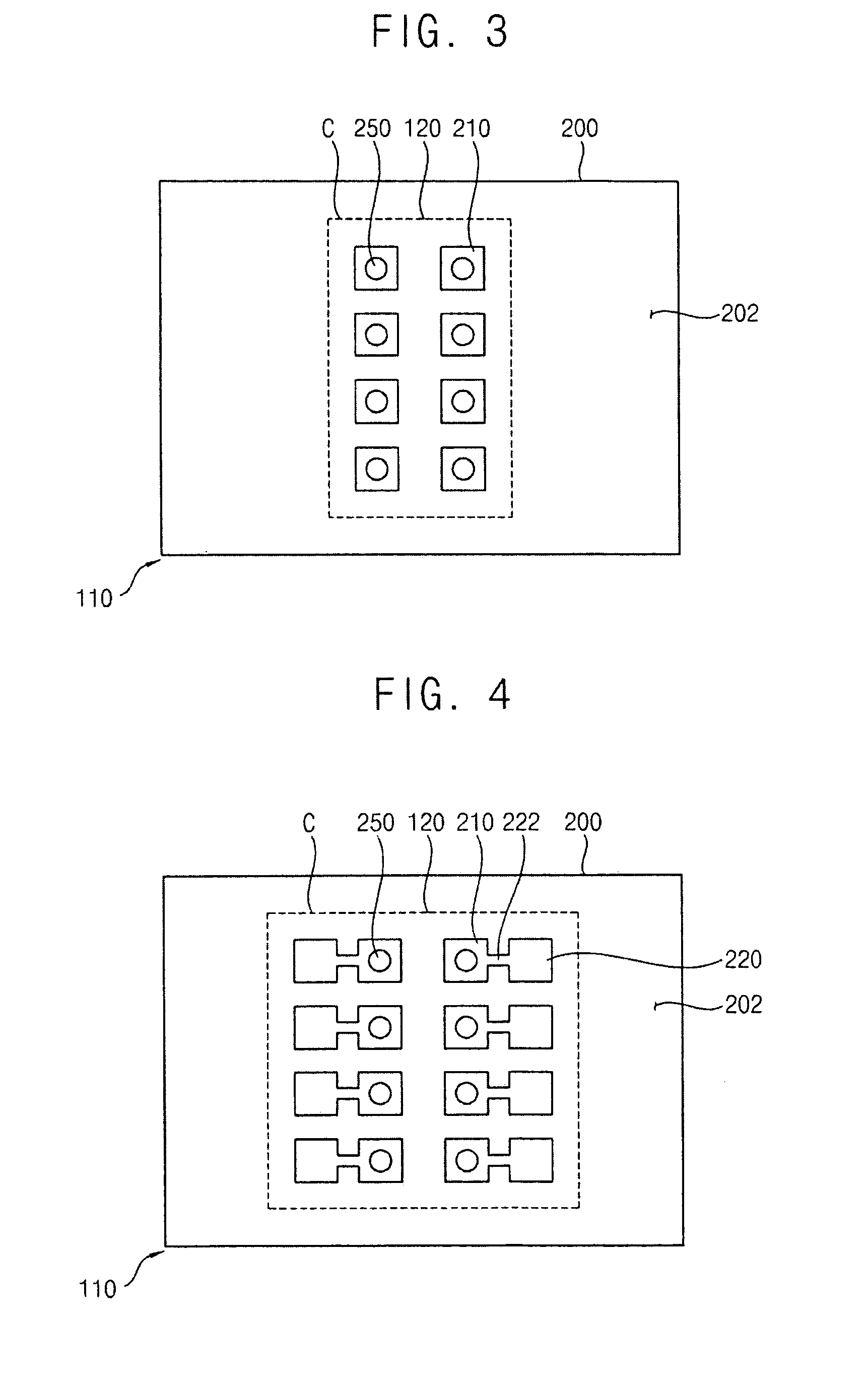

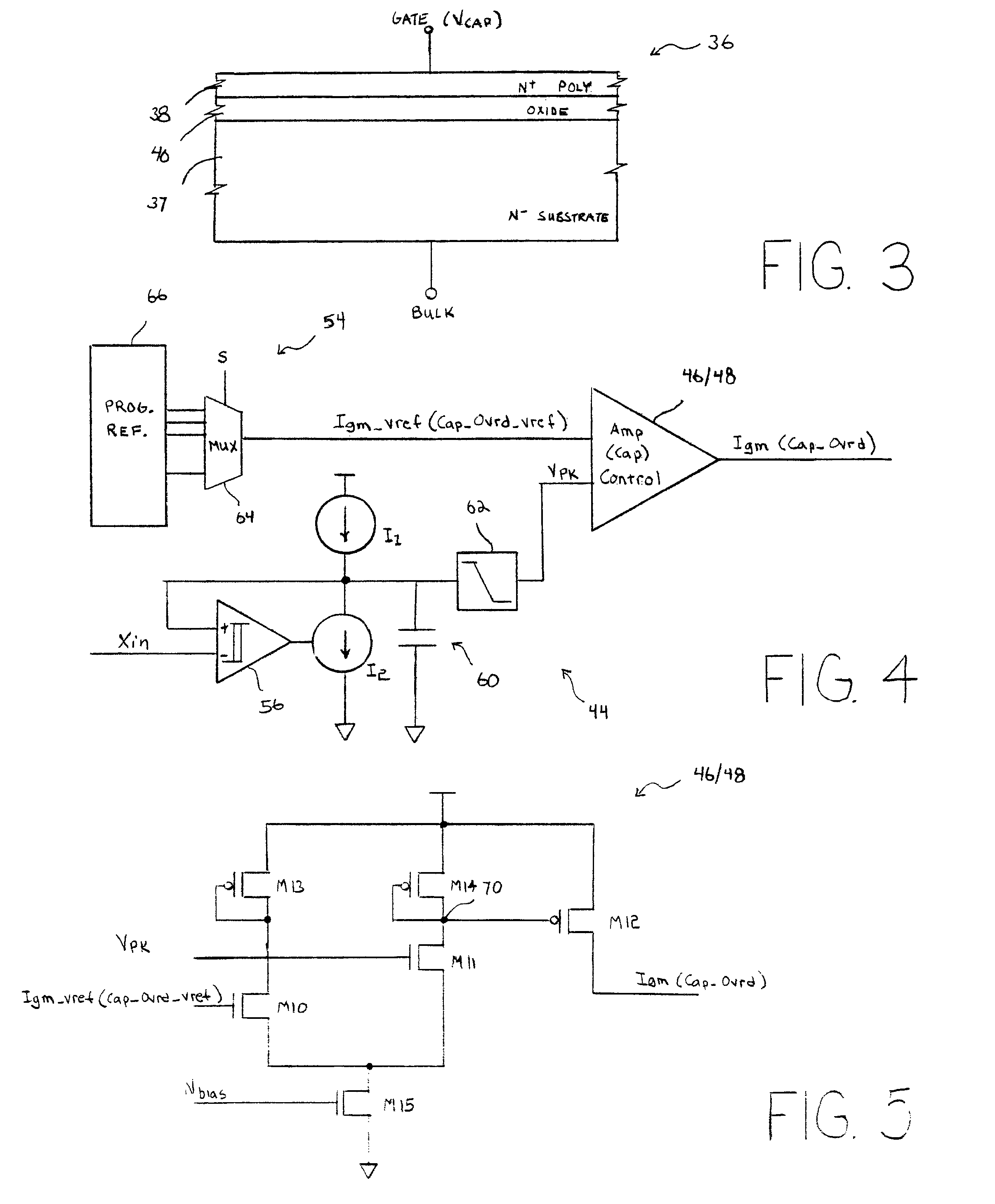

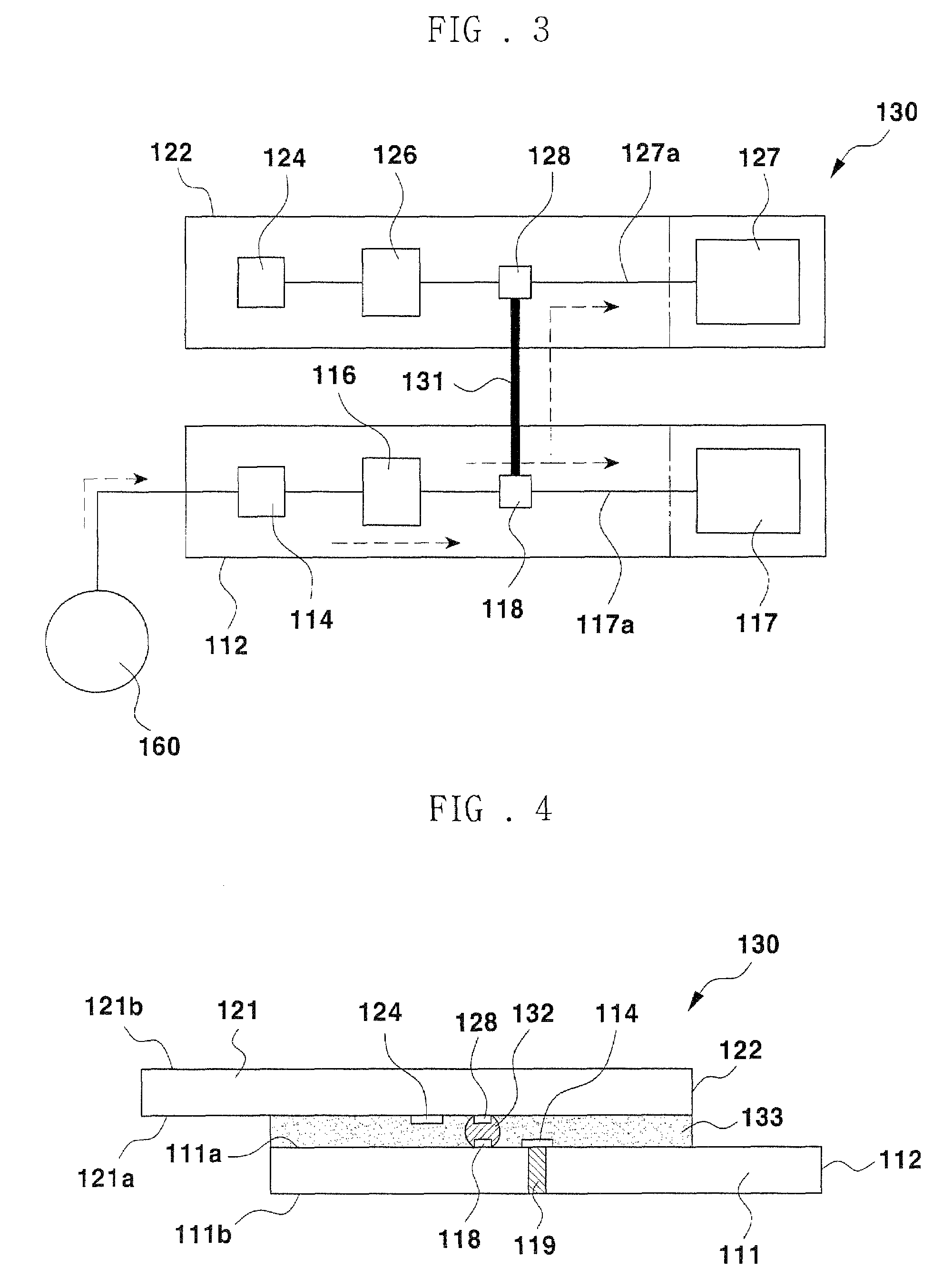

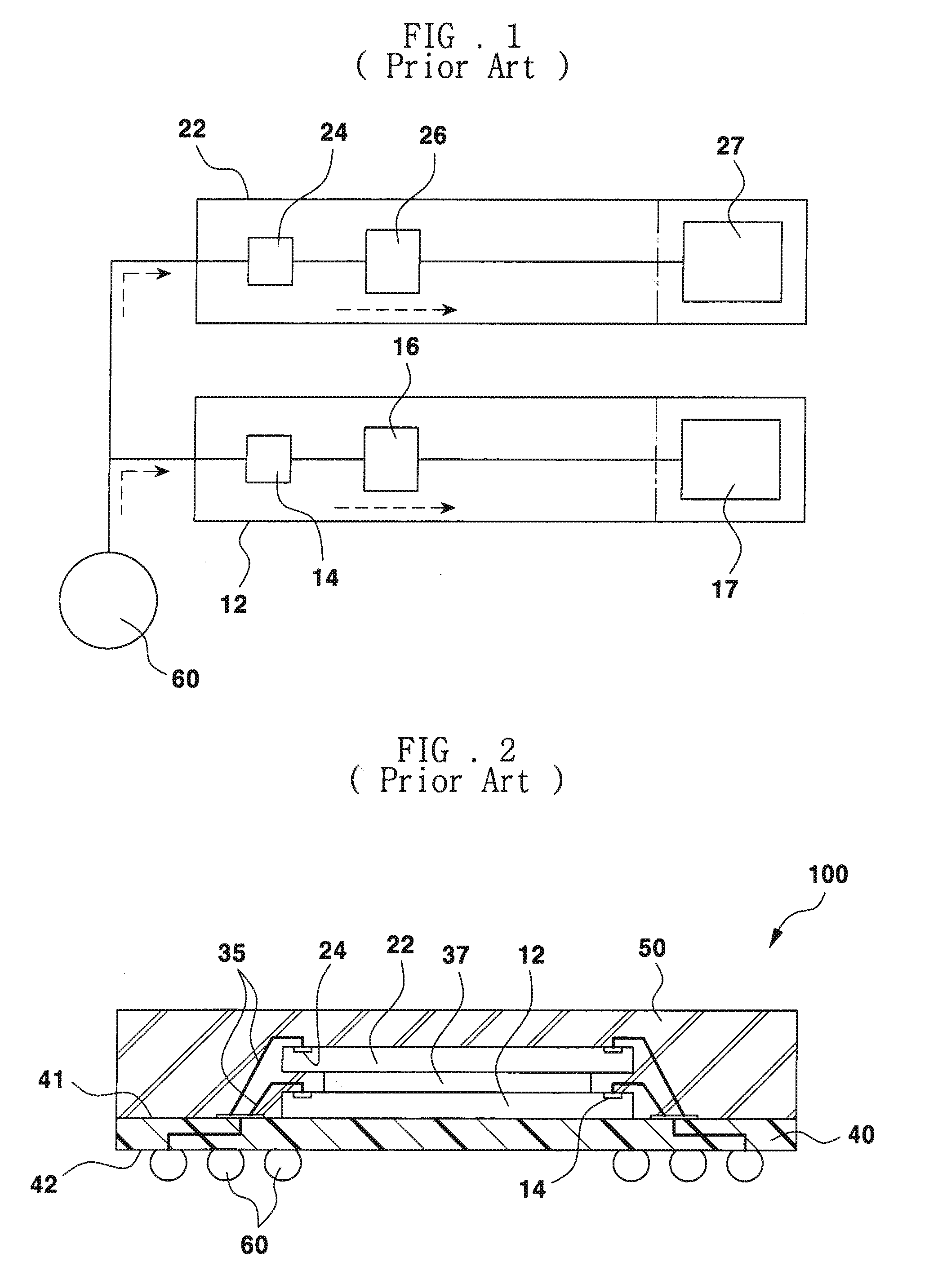

Stack package

ActiveUS20100090326A1Increase computing speedSmall overall lengthSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A stack package may include a substrate having first and second faces opposite each other and an opening formed therein. The first semiconductor chip may be mounted on the first face of the substrate and include a through electrode in the middle region of the first semiconductor chip that is exposed through the opening. The second semiconductor chip may be stacked on the first semiconductor chip and electrically connected to the first semiconductor chip by the through electrode of the first semiconductor chip. The circuit pattern may be formed on the second face of the substrate and include a bonding pad arranged adjacent to the opening and electrically connected to the through electrode of the first semiconductor chip through the opening, an outer connection pad spaced apart from the bonding pad and a connection wiring extending from the opening to the outer connection pad via the bonding pad.

Owner:SAMSUNG ELECTRONICS CO LTD

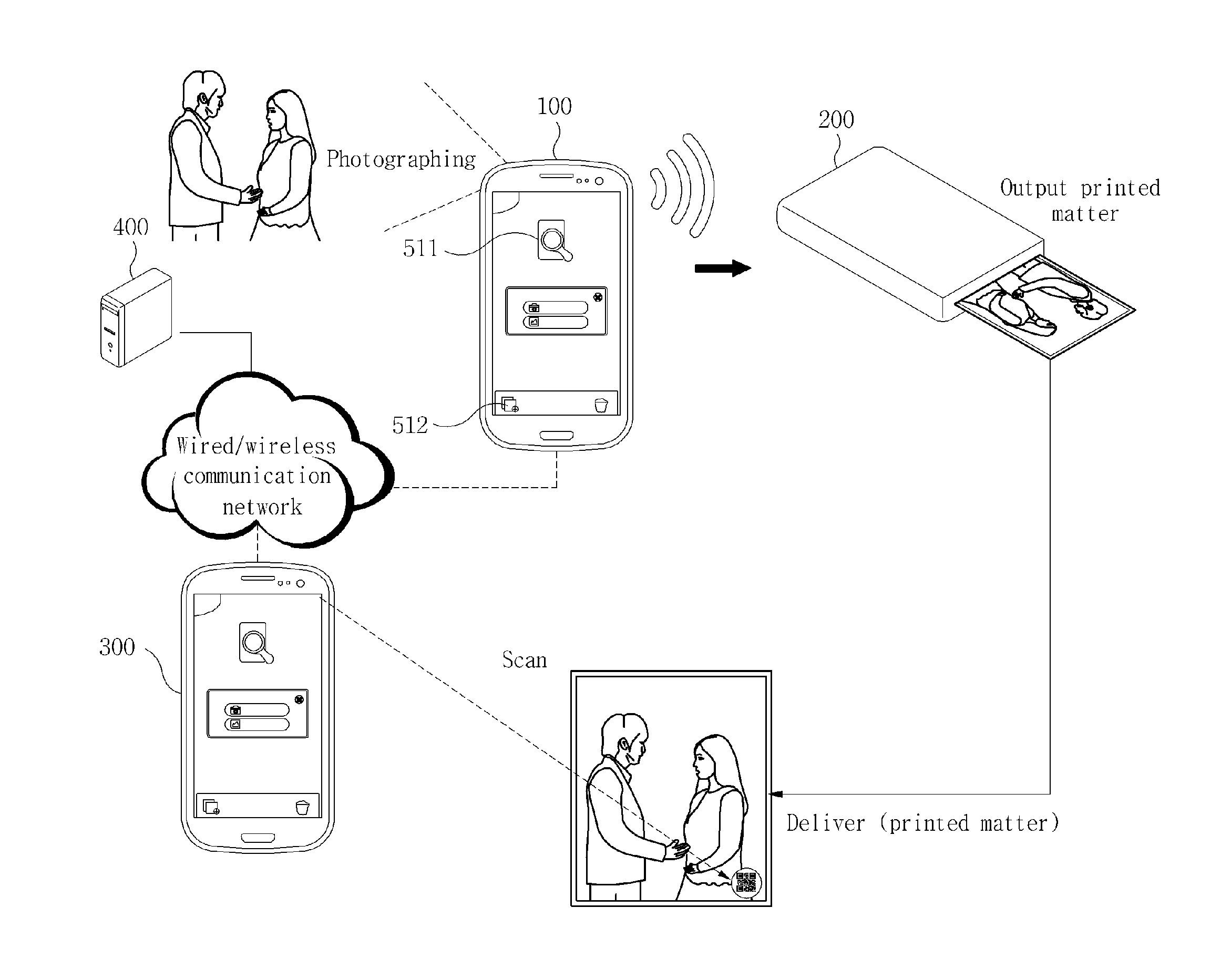

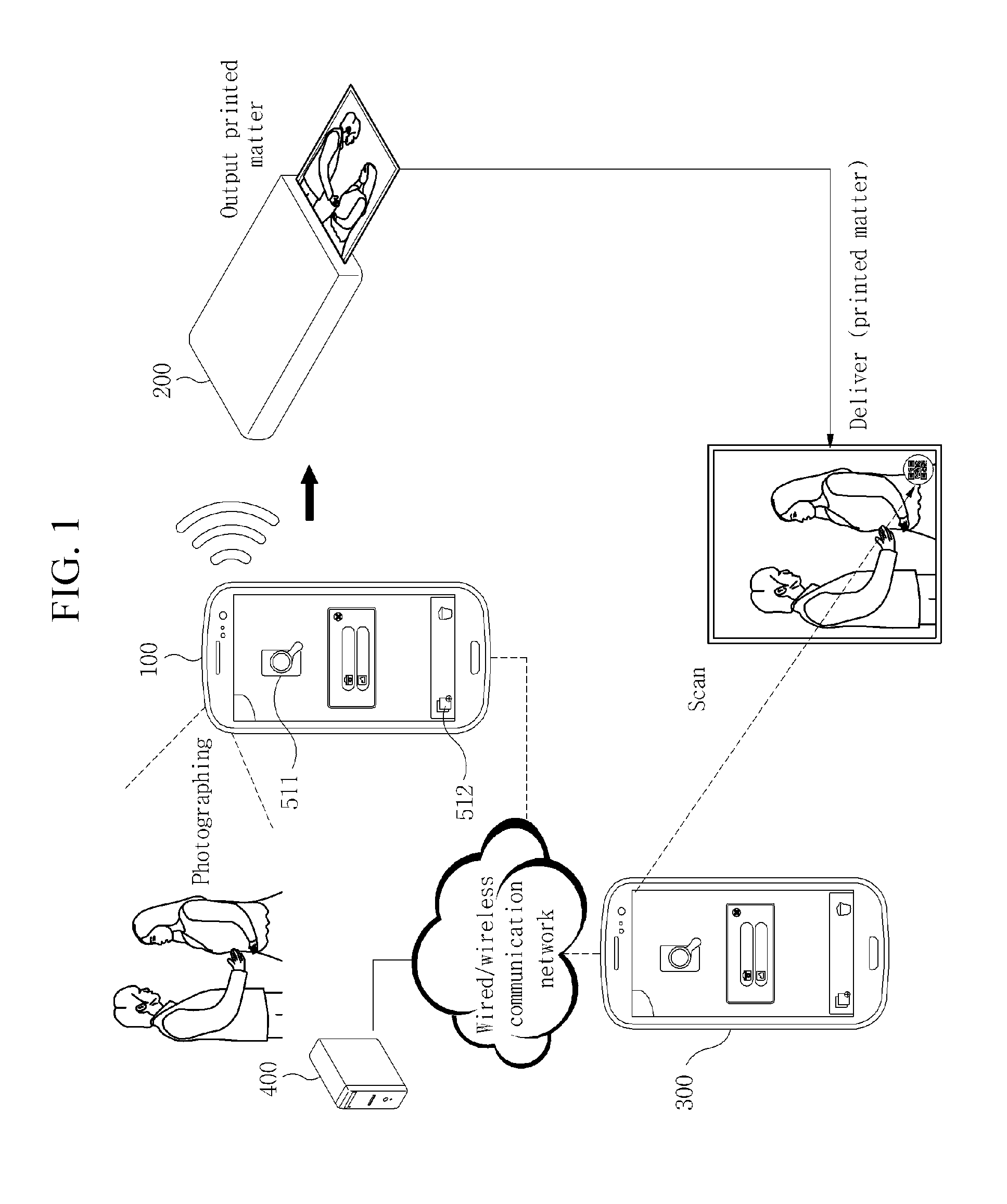

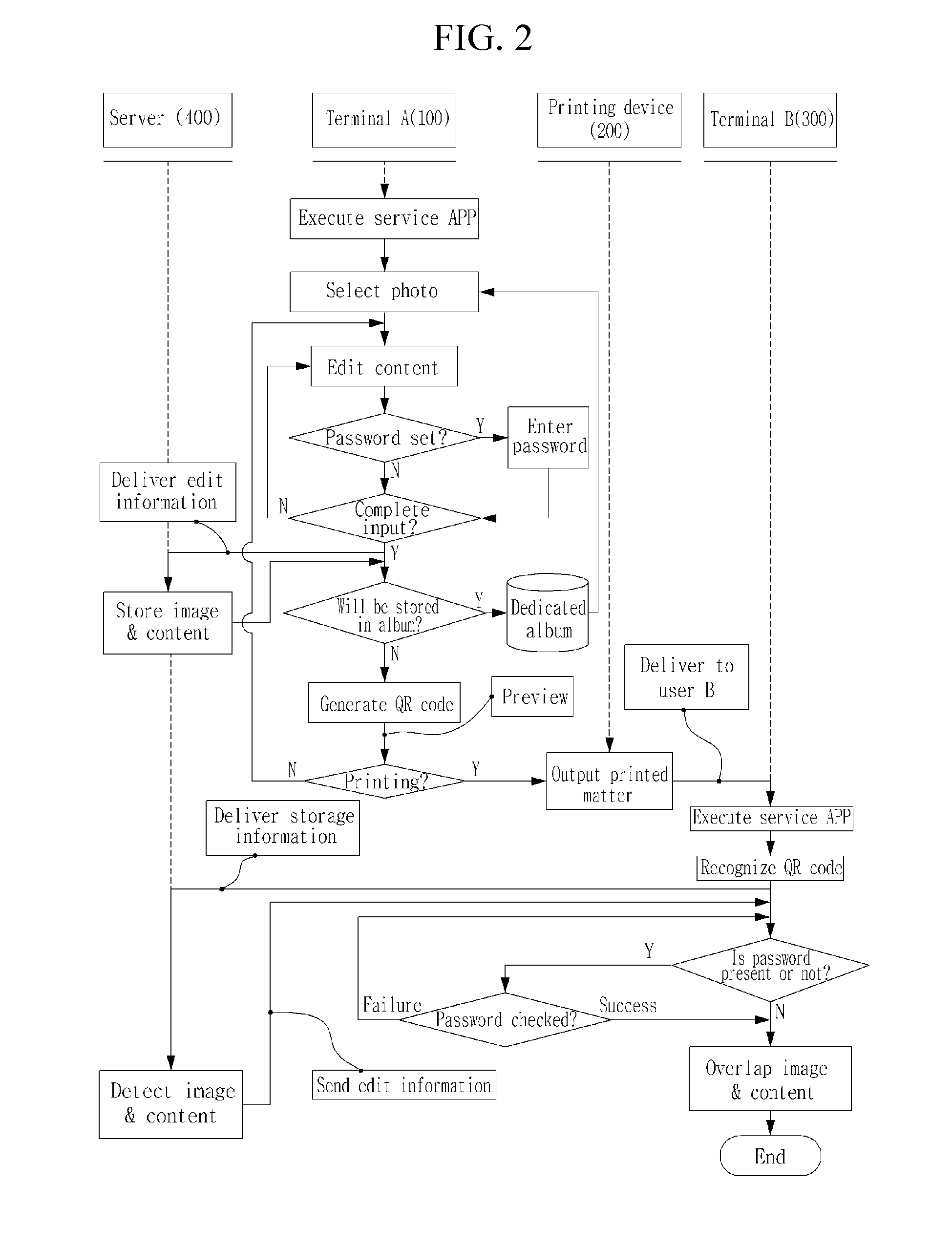

Method of providing content transmission service by using printed matter

ActiveUS20160171357A1Reduce capacitive loadingReduce capacitive loadData processing applicationsCharacter and pattern recognitionContent deliveryWorld Wide Web

Provided is a content delivery service method using printed matter. The content delivery service method using printed matter may include executing, by a first terminal, a service app and selecting an image, editing content on the selected image in an app screen, sending, by the first terminal, the image and information about the edited content to a server, storing, by the server, the image and the information about the edited content and sending information about the storage to the first terminal, generating, by the first terminal, specific recognition code in which the storage information has been recorded and inserting the specific recognition code into the image, and sending, by the first terminal, the image into which the recognition code has been inserted to a printing device so that the image is printed by the printing device.

Owner:DS GLOBAL

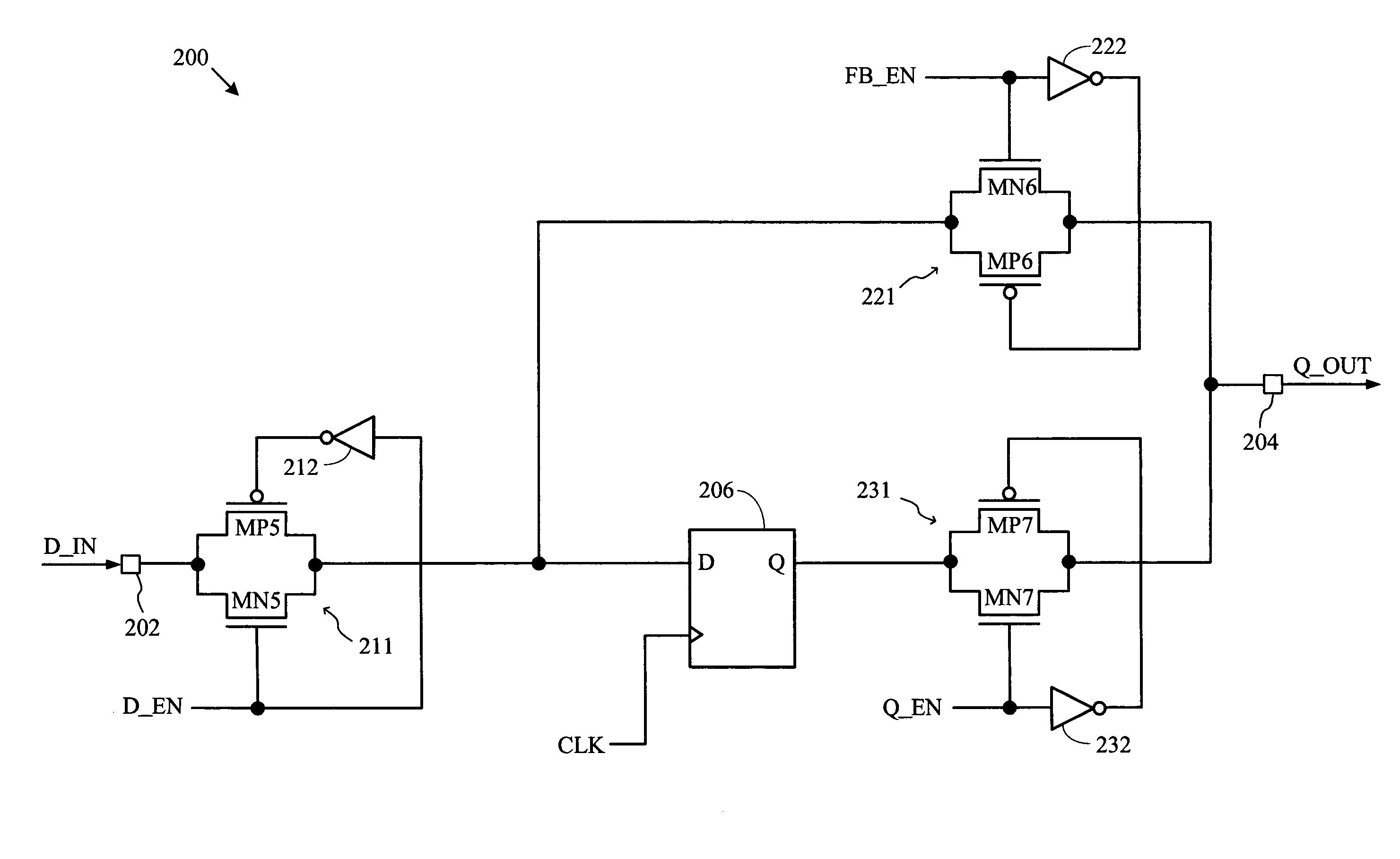

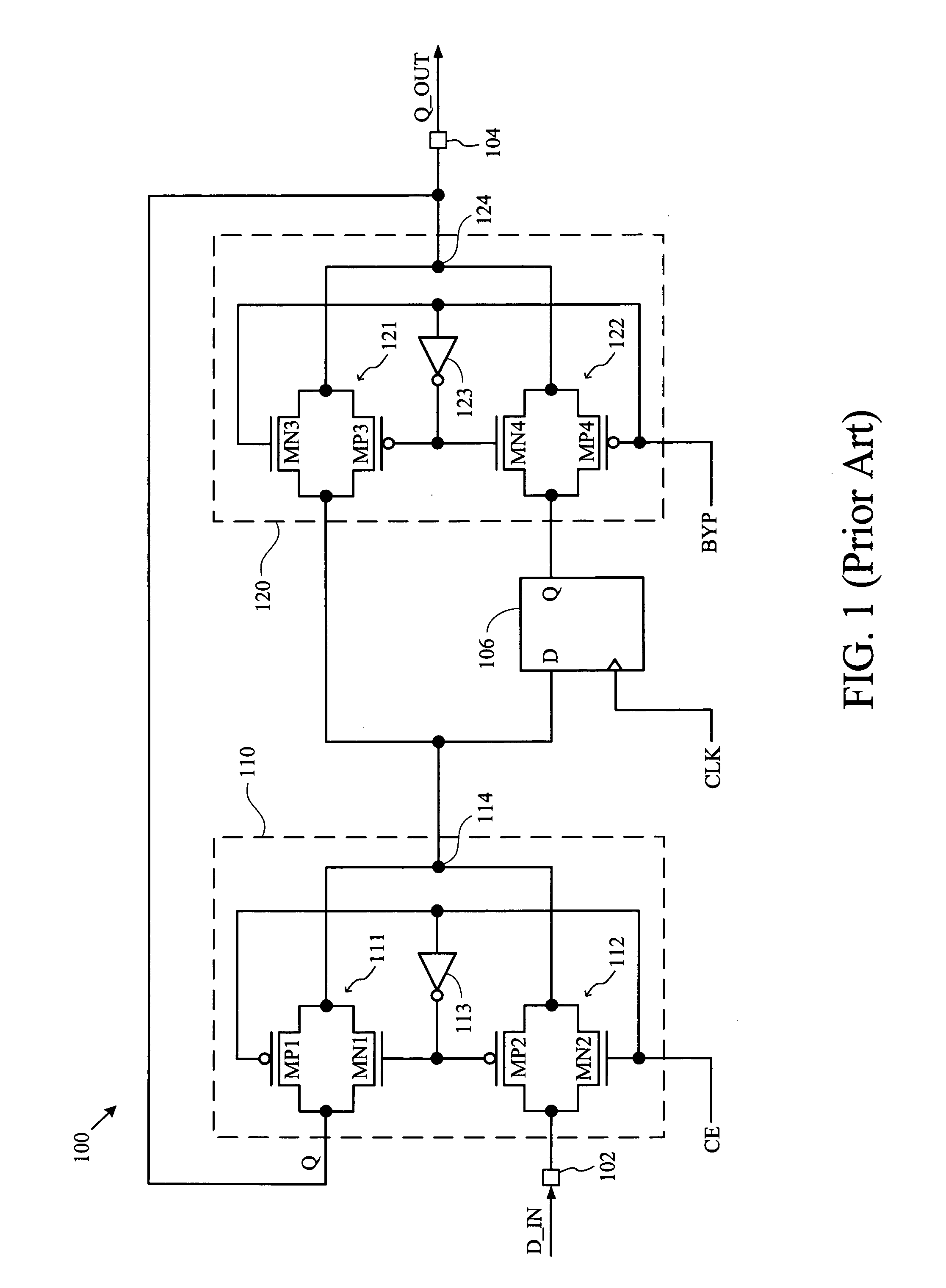

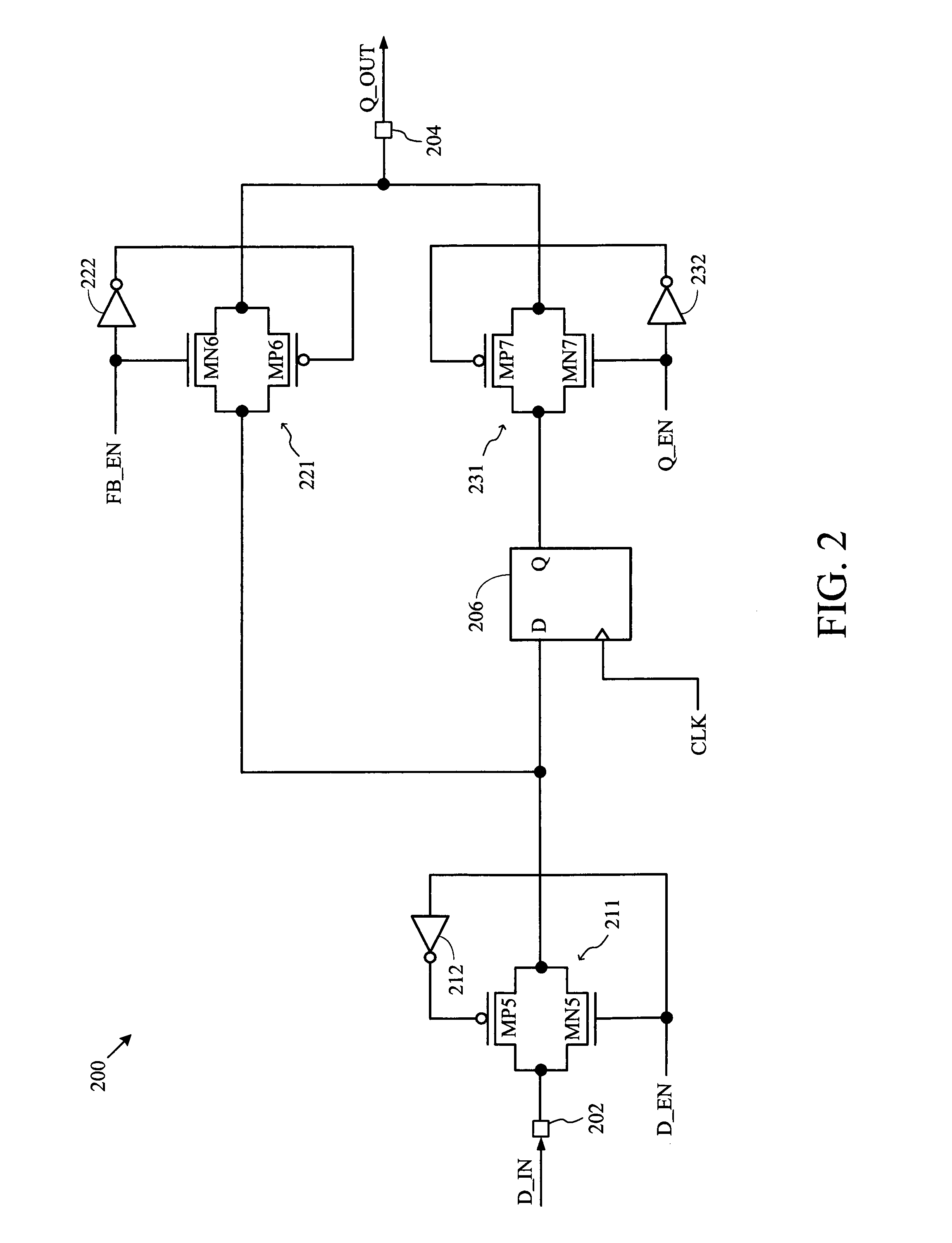

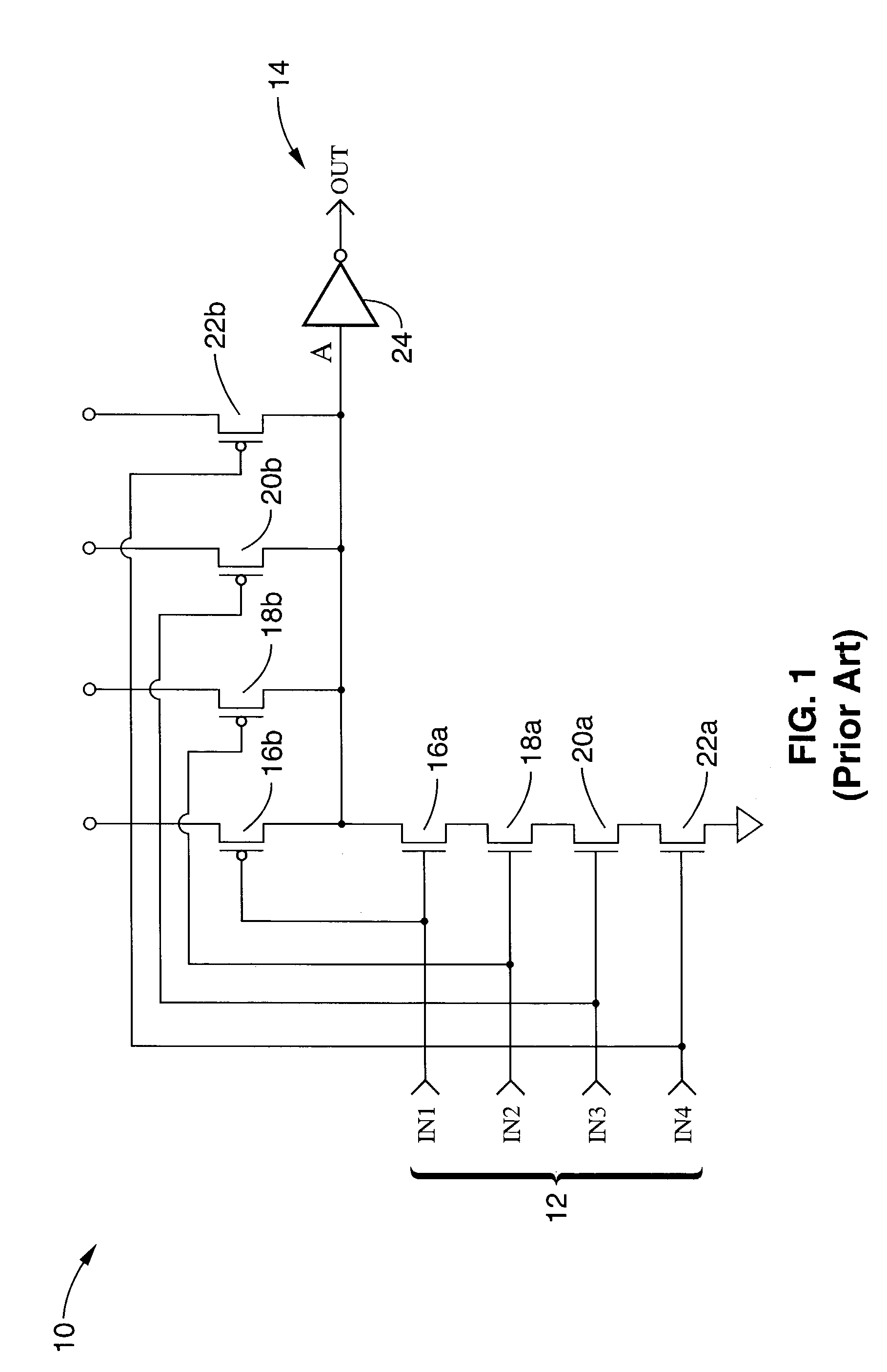

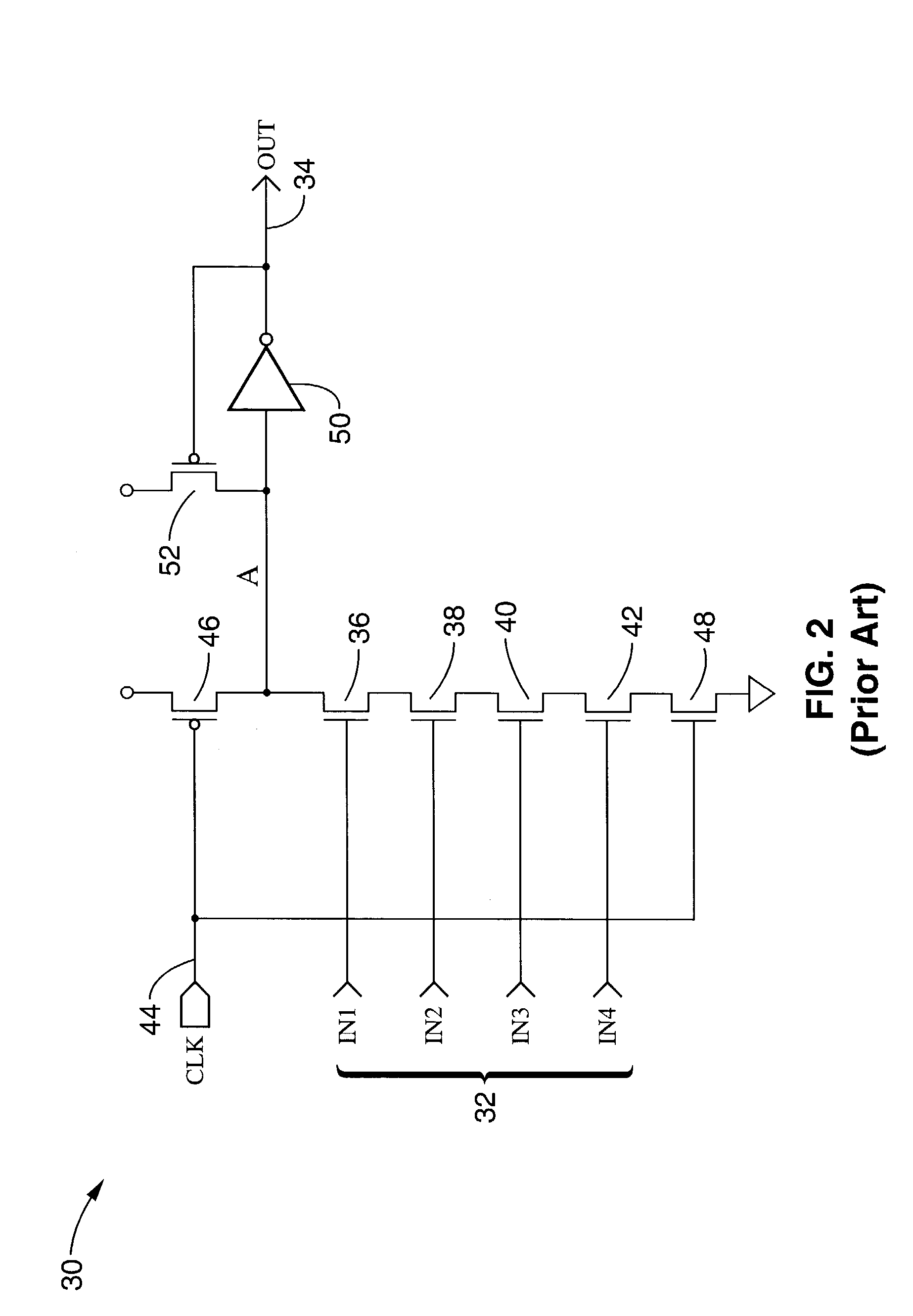

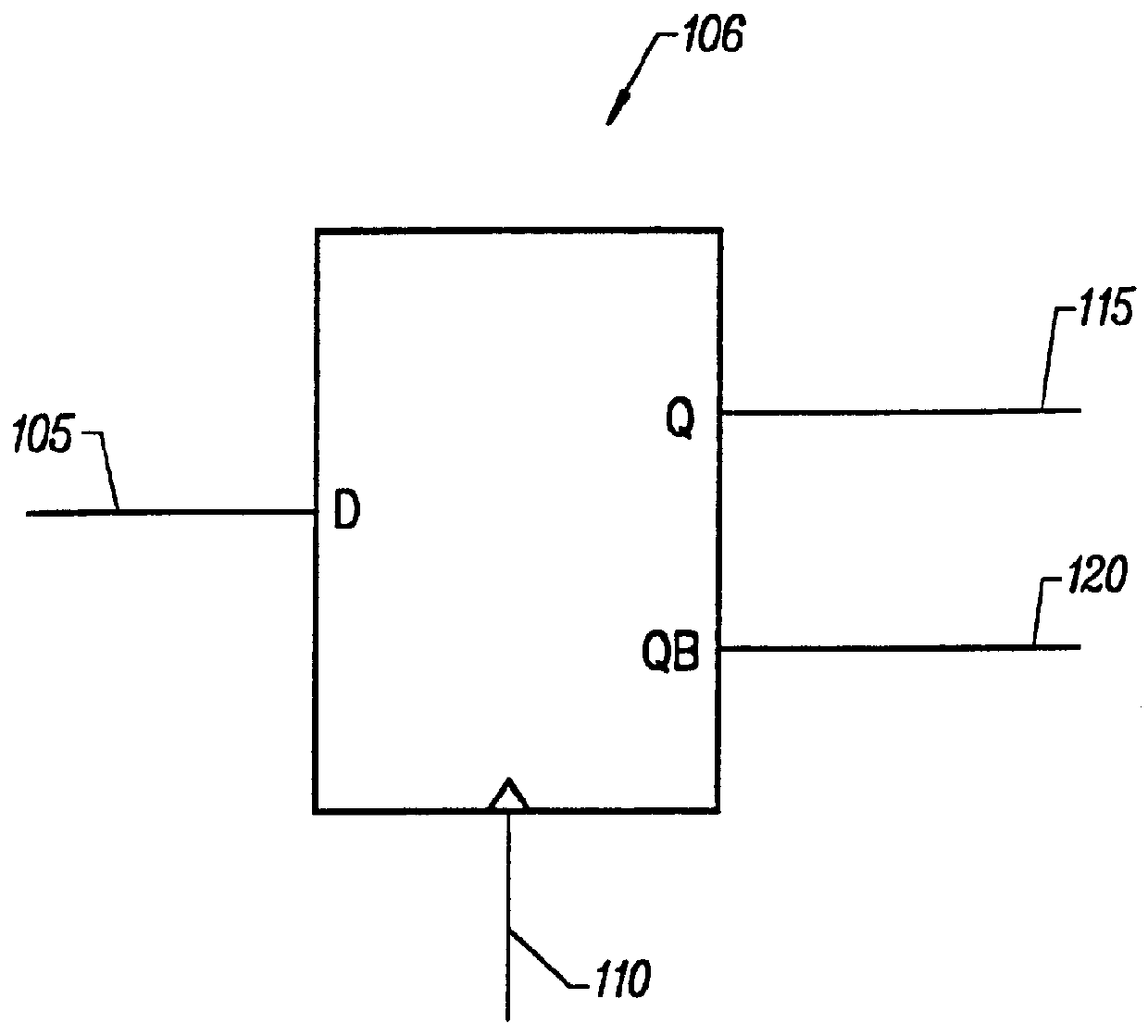

Efficient implementation of a bypassable flip-flop with a clock enable

ActiveUS7129762B1Area minimizationReduce degradationElectric pulse generatorControl signalLogical combination

A flip-flop circuit includes a flip-flop, a first pass gate, a second pass gate, and a third pass gate. The first pass gate has an input to receive an input signal, an output coupled to the flip-flop's data input, and a control terminal to receive a first control signal. The second pass gate has an input coupled to the flip-flop's data input, an output coupled to the circuit's output, and a control terminal to receive a second control signal. The third pass gate has an input coupled to the flip-flop's data output, an output coupled to the circuit's output, and a control terminal to receive a third control signal. The first, second, and third control signals may be generated in response to various logical combinations of a bypass signal and a clock enable signal.

Owner:XILINX INC

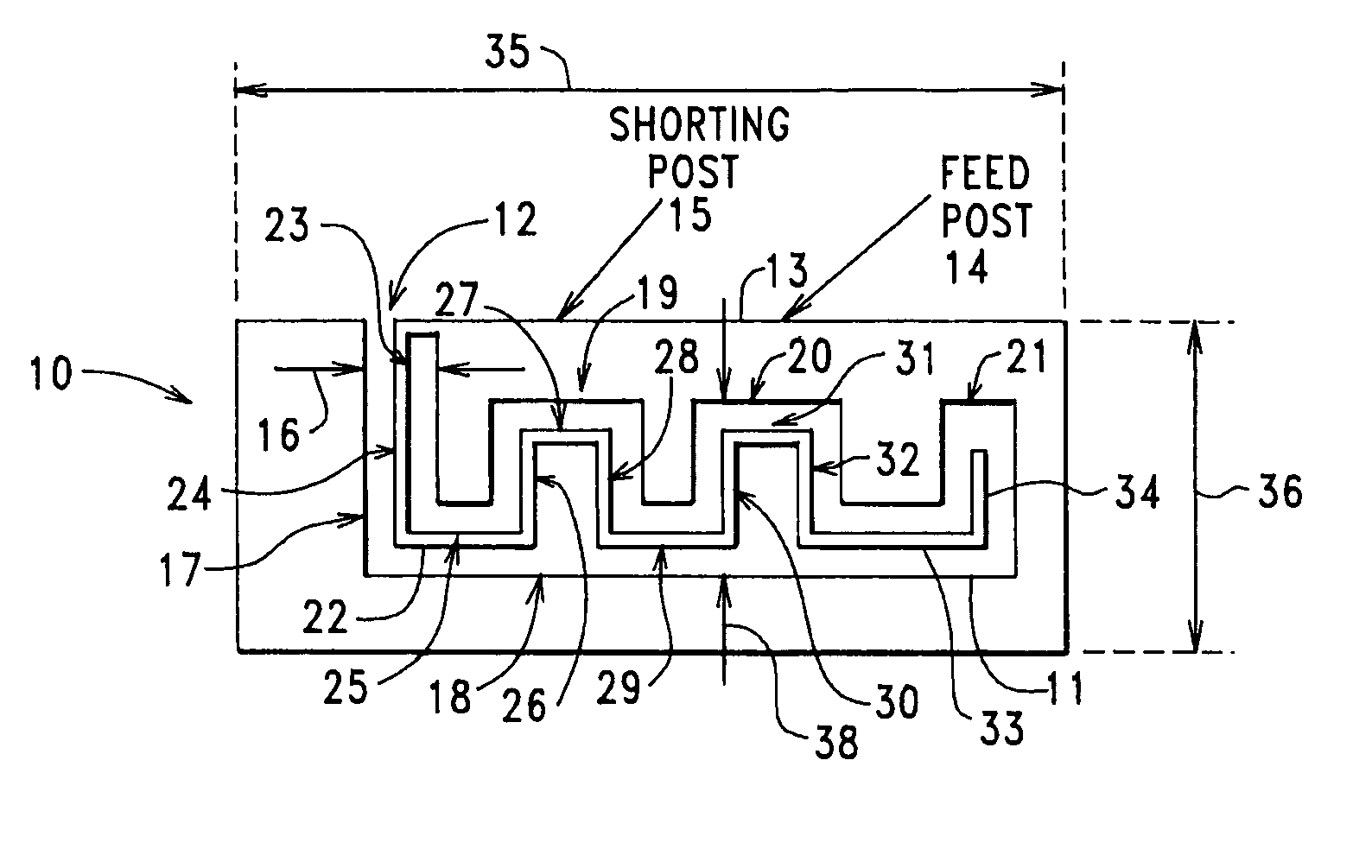

Optimum Utilization of slot gap in PIFA design

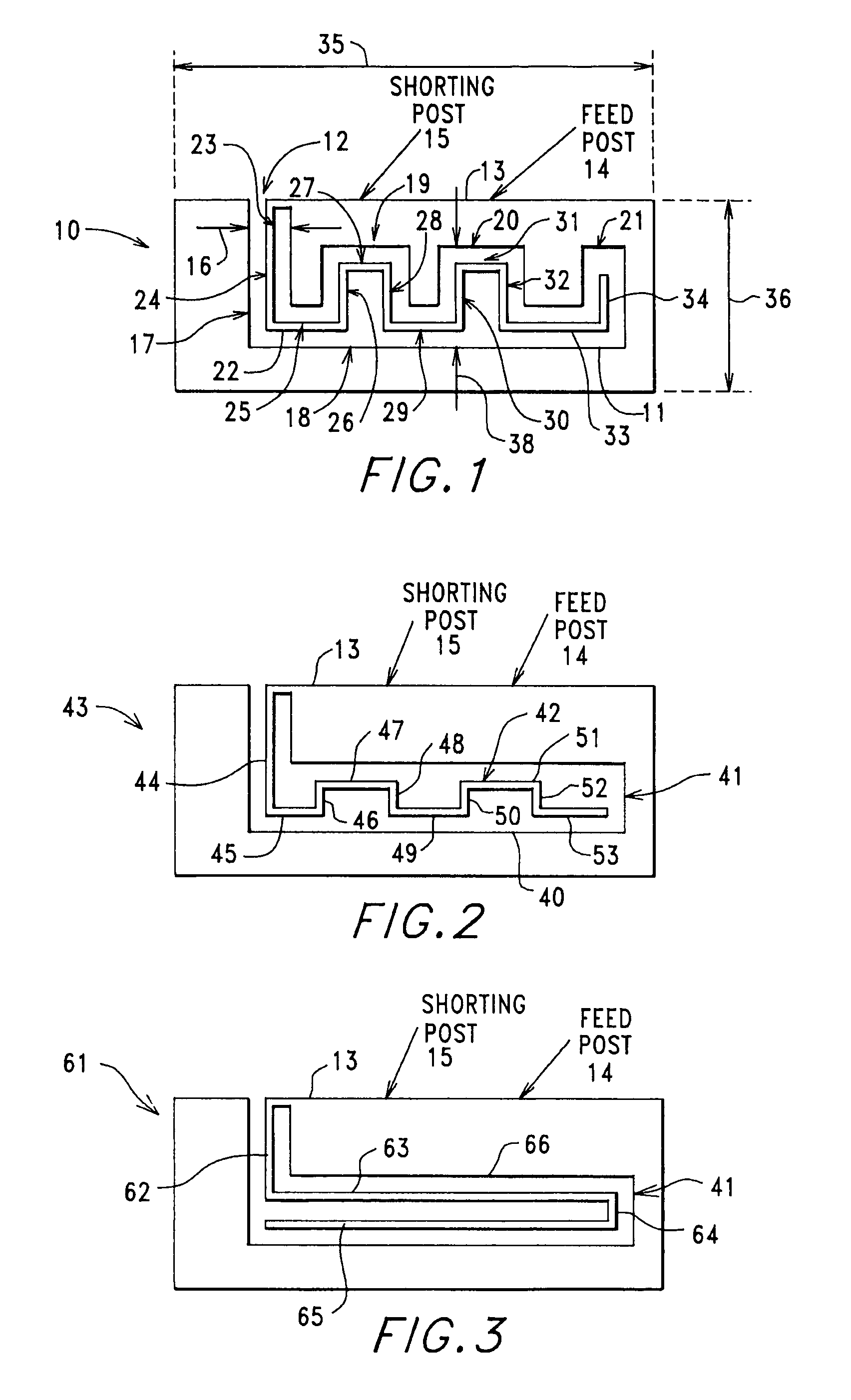

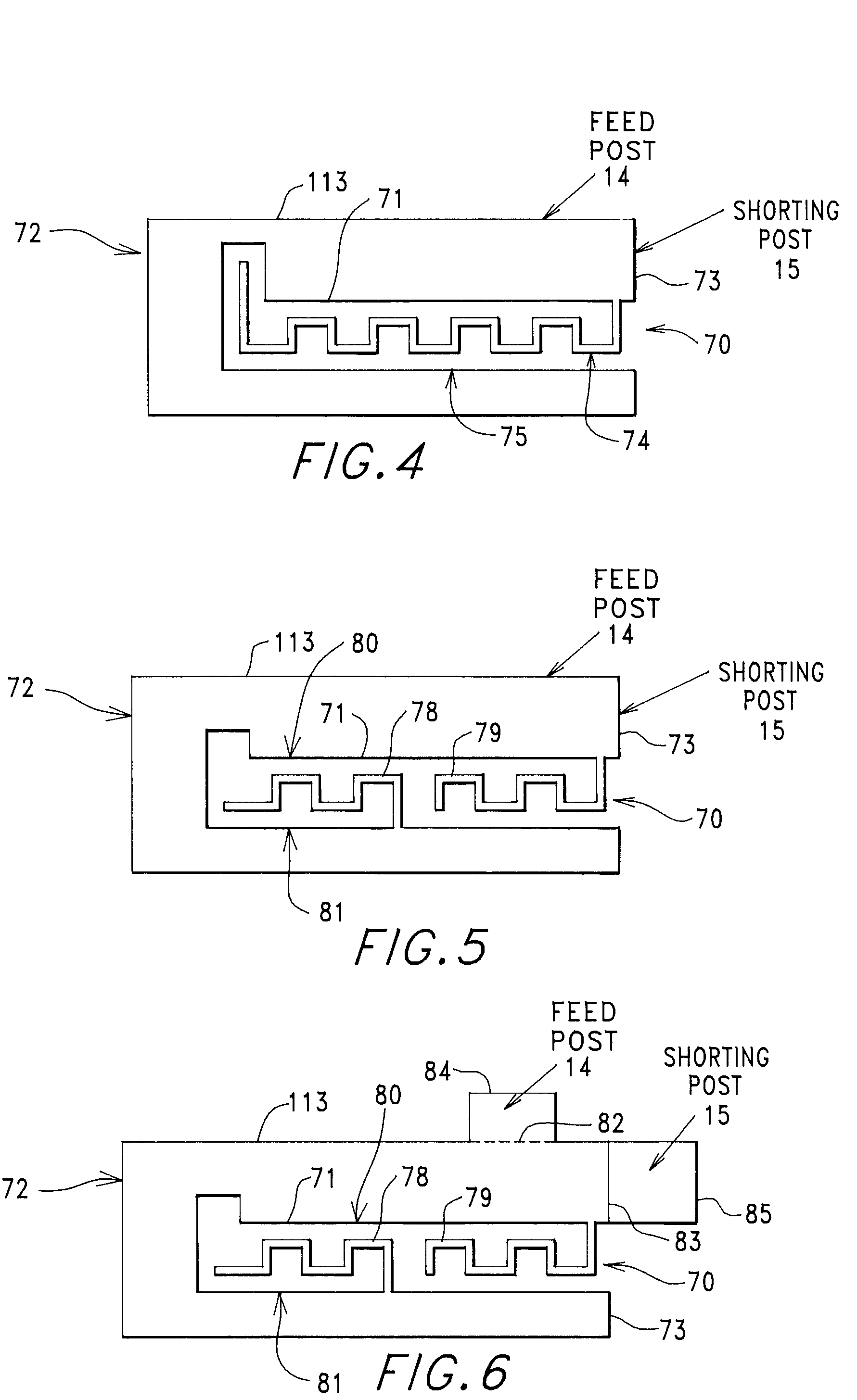

InactiveUS7183982B2Easy to manufactureIncreasing effective and virtual physical dimensionSimultaneous aerial operationsAntenna supports/mountingsEngineeringGround plane

Operating parameters of a planar antenna are controlled by providing a planar metal radiating element having an edge, by providing a slot within the radiating element, the slot having side walls, an open slot-end that lies on the edge of the radiating element, and a closed slot-end the lies within the radiating element, and by providing a thin, line-like, and metal segment, at least a portion of which is coplanar with the radiating element and that extends from the open slot-end to the closed slot-end without physically engaging the slot's side walls. The metal segment can be connected to the antenna's ground plane to thereby form a parasitic element, or the metal segment can be connected to the radiating element to thereby form an extension of the radiating element.

Owner:CENTURION WIRELESS TECH INC

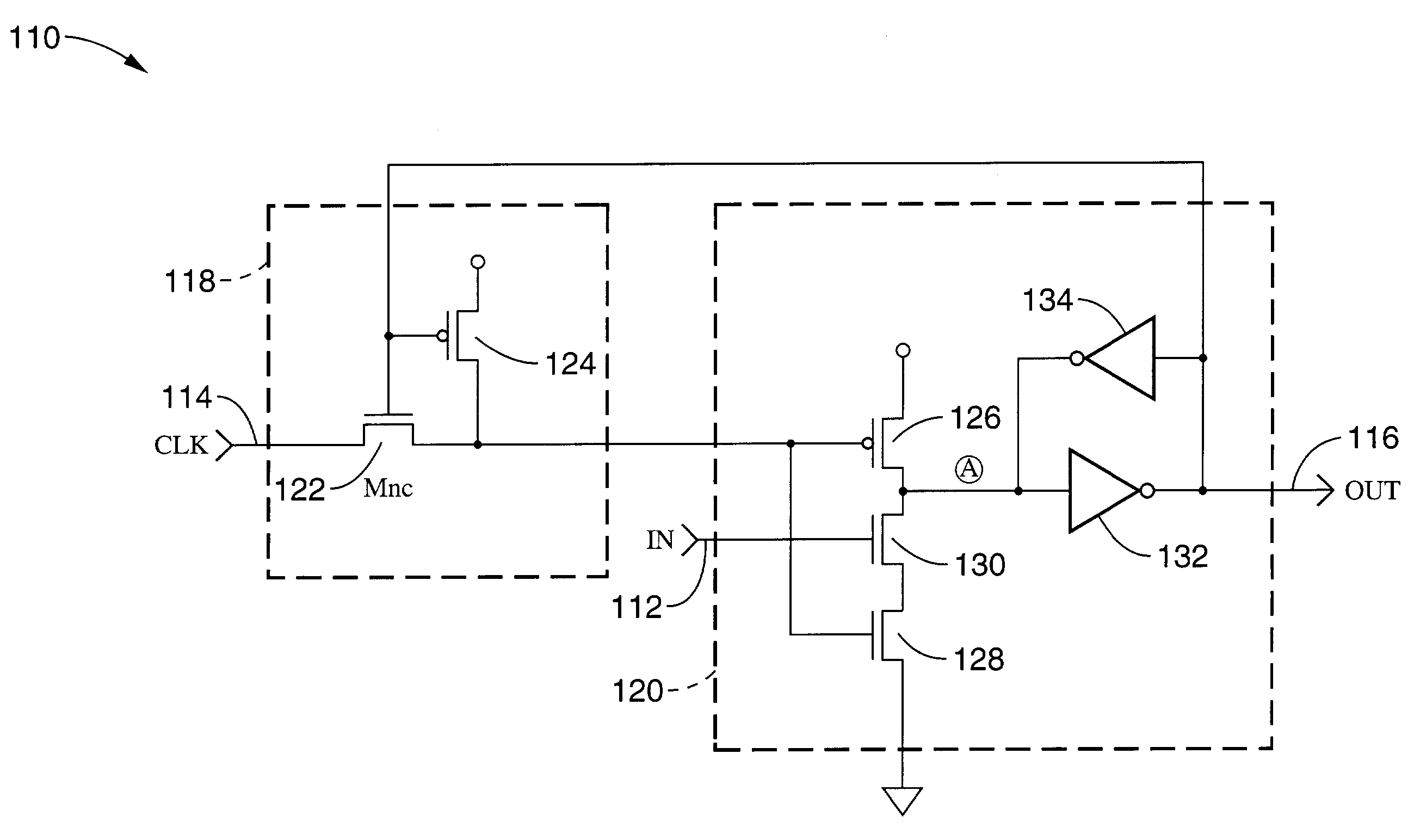

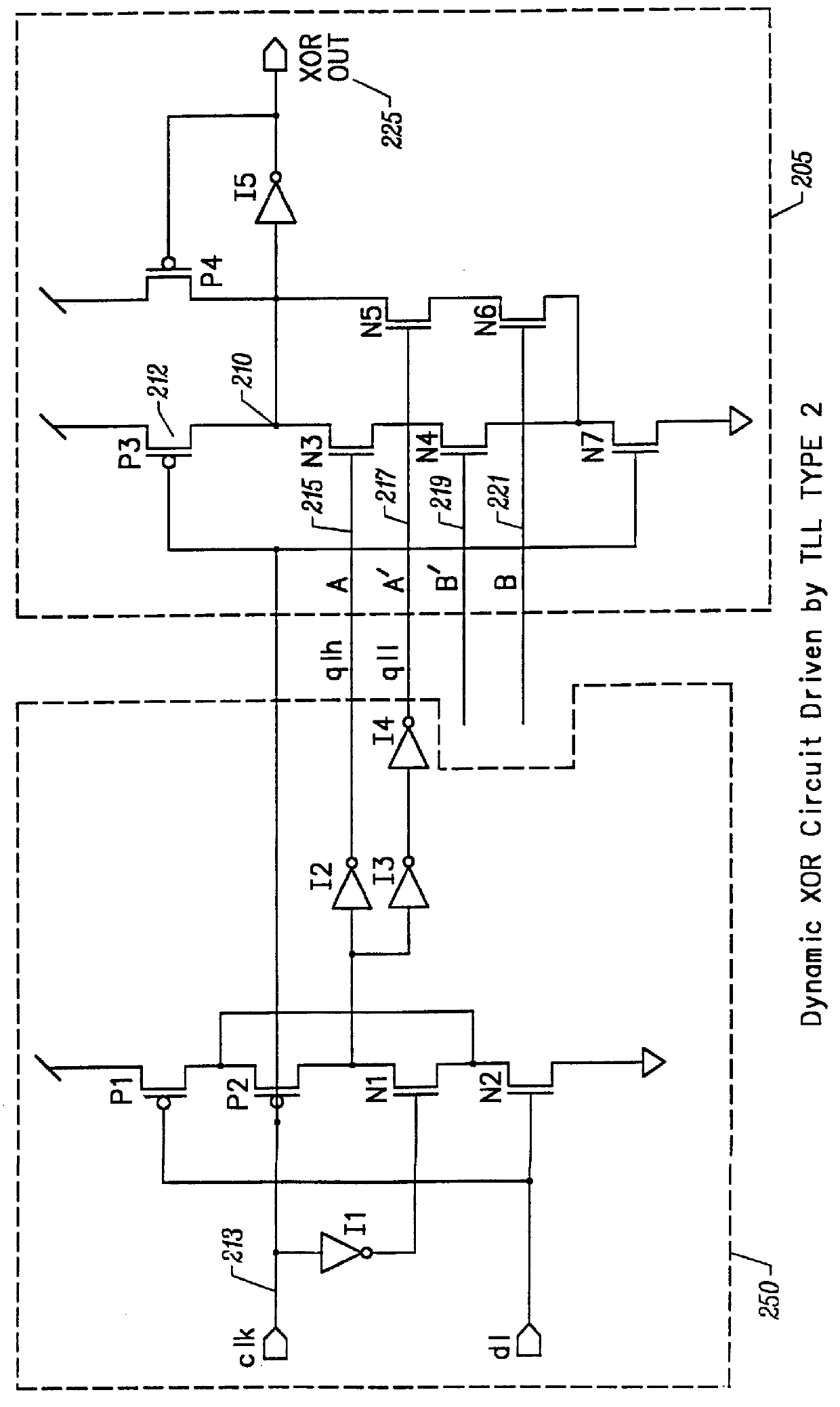

Event driven dynamic logic for reducing power consumption

InactiveUS6977528B2Reduce power consumptionReduce capacitive loadReliability increasing modificationsPower reduction by control/clock signalCapacitanceState variation

Methods and circuits are described for reducing power consumption within digital logic circuits by blocking the passage of clock signal transitions to the logic circuits when the clock signal would not produce a desired change of state within the logic circuit, such as at inputs, intermediary nodes, outputs, or combinations. By way of example, the incoming clock is blocked if a given set of logic inputs will not result in an output change of state if a clock signal transition were to be received. By way of further example, the incoming clock is blocked in a data flip-flop if the input signal matches the output signal, such that receipt of a clock transition would not produce a desired change of state in the latched output. The invention may be utilized for creating lower power combinatorial and / or sequential logic circuit stages subject to less unproductive charging and discharging of gate capacitances.

Owner:RGT UNIV OF CALIFORNIA

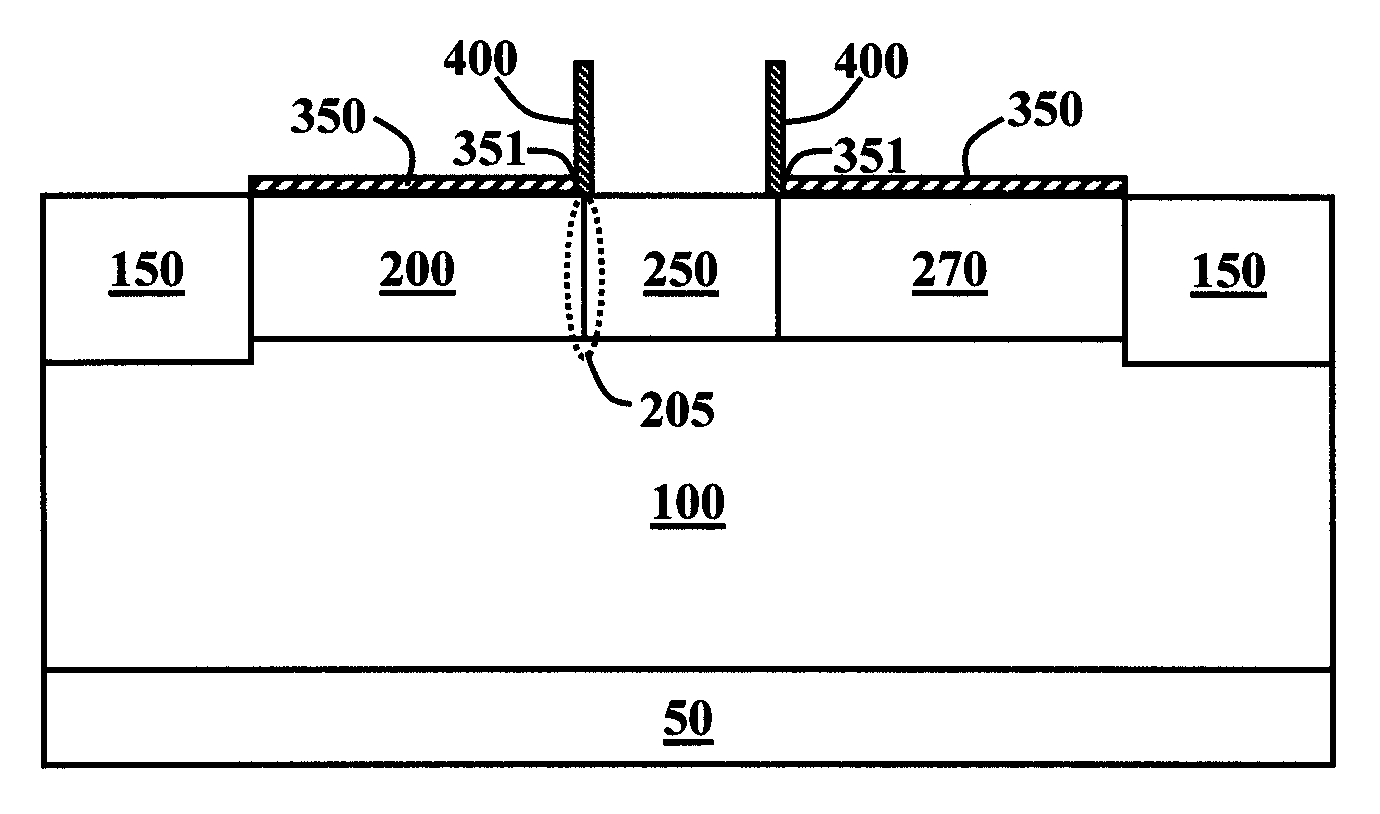

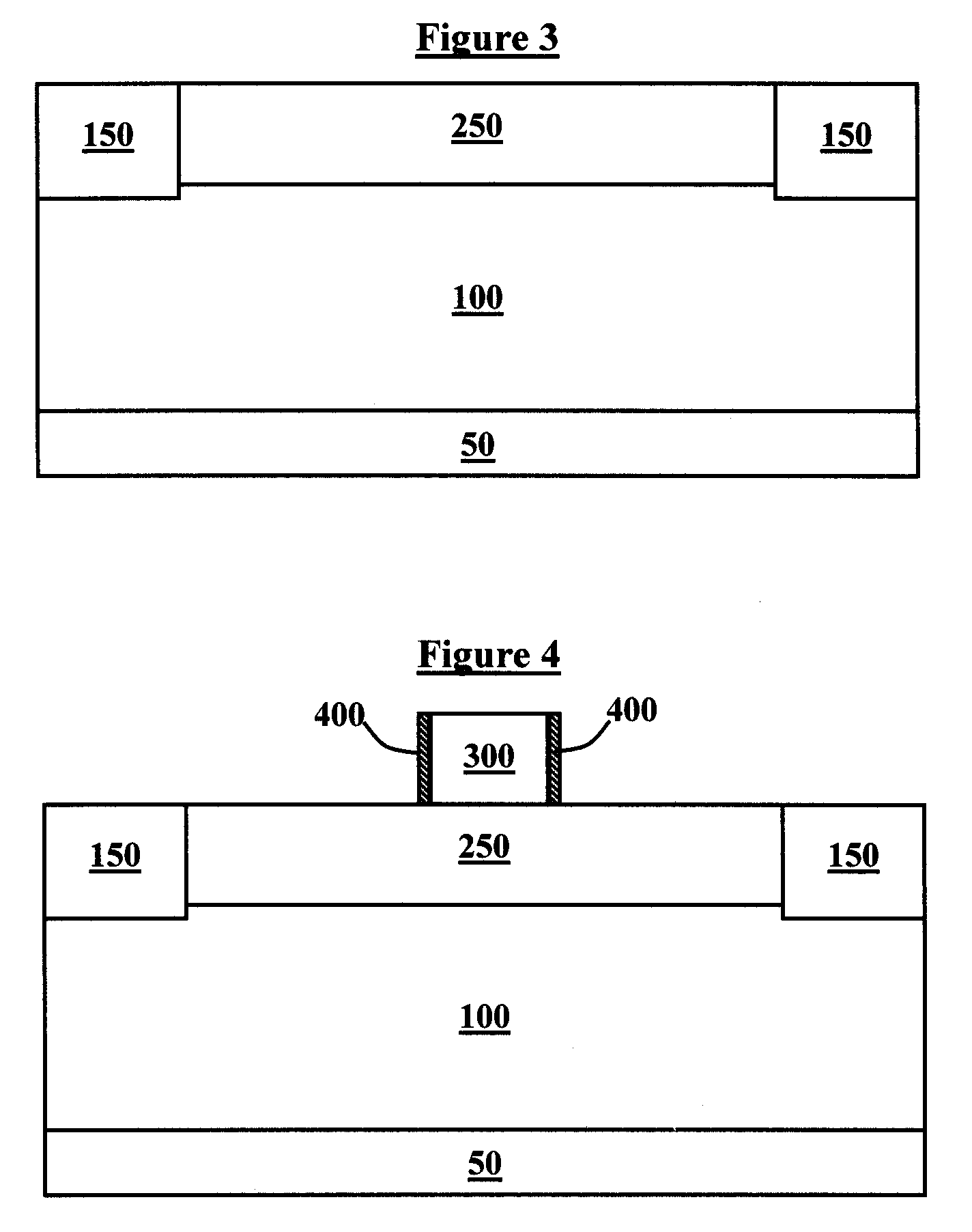

Electrostatic Discharge (ESD) Silicon Controlled Rectifier (SCR) with Lateral Gated Section

ActiveUS20160056146A1Rapid responseReduce capacitive loadTransistorThyristorSilicon-controlled rectifierEngineering

In an embodiment, an ESD protection circuit may include an STI-bound SCR and a gated SCR that may be electrically in parallel with the STI-bound SCR. The gated SCR may be perpendicular to the STI-bound SCR in a plane of the semiconductor substrate. In an embodiment, the gated SCR may trigger more quickly and turn on more quickly than the STI-bound SCR. The STI-bound SCR may form the main current path for an ESD event. A low capacitive load with rapid response to ESD events may thus be formed. In an embodiment, the anode of the two SCRs may be shared.

Owner:APPLE INC

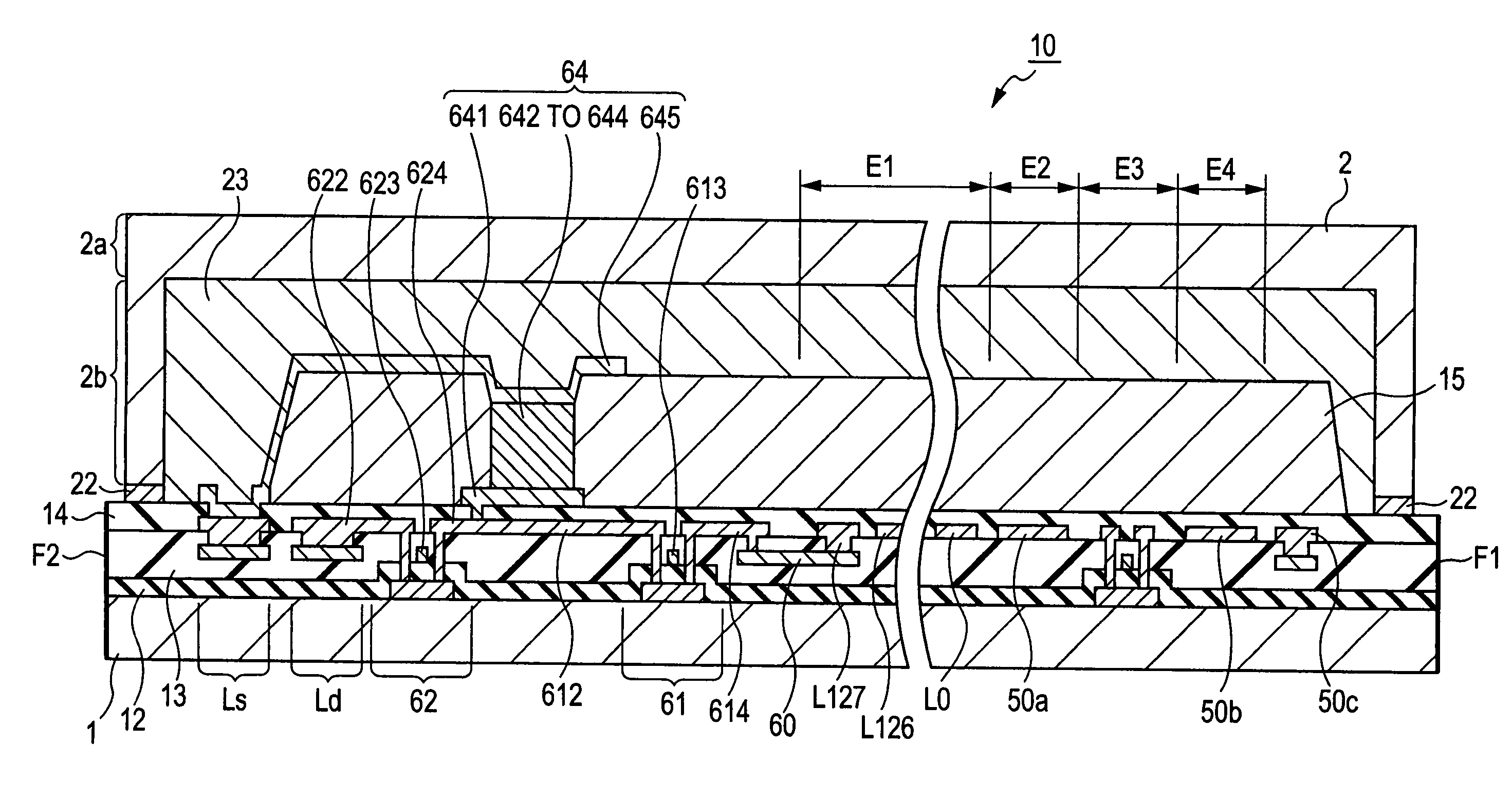

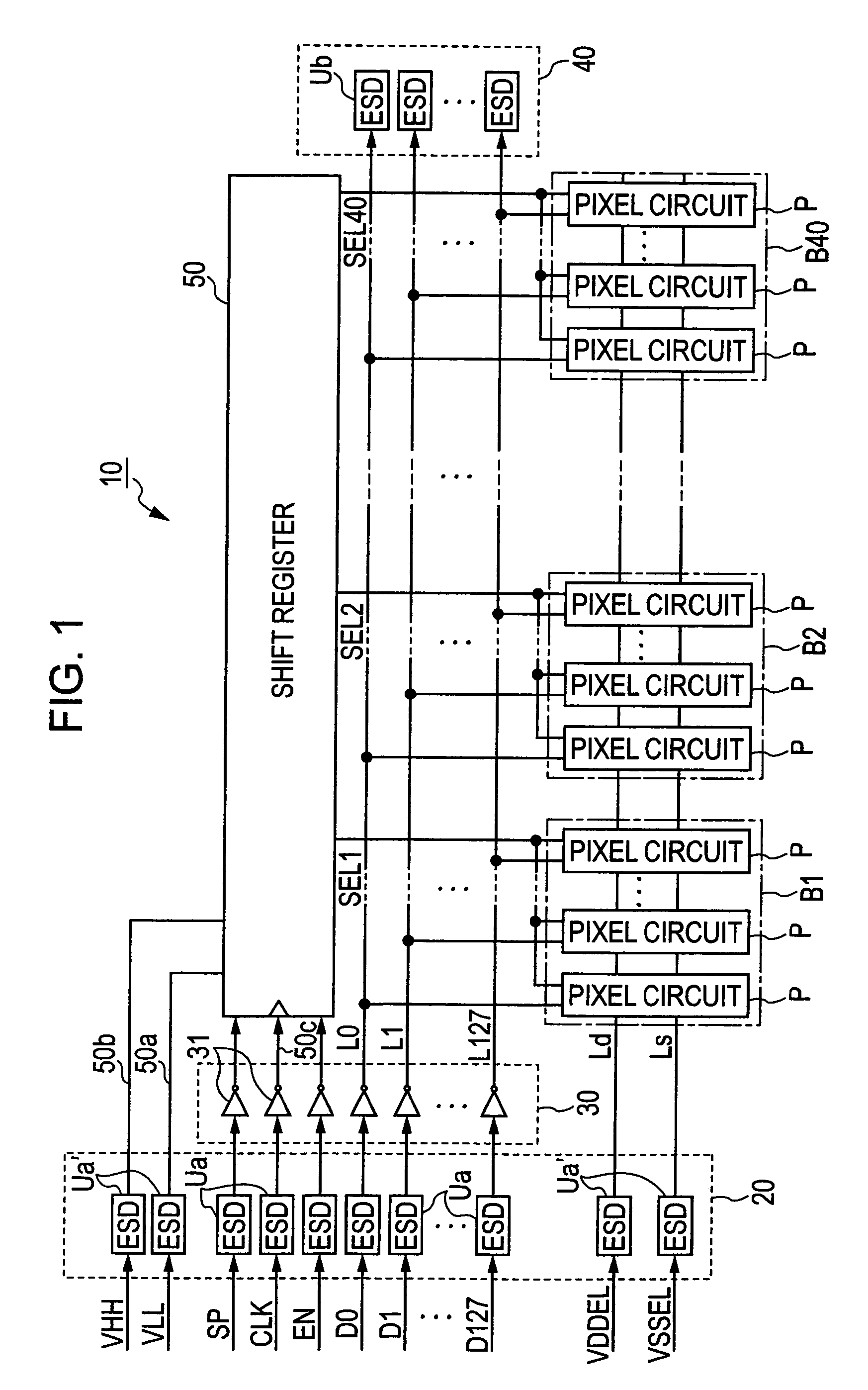

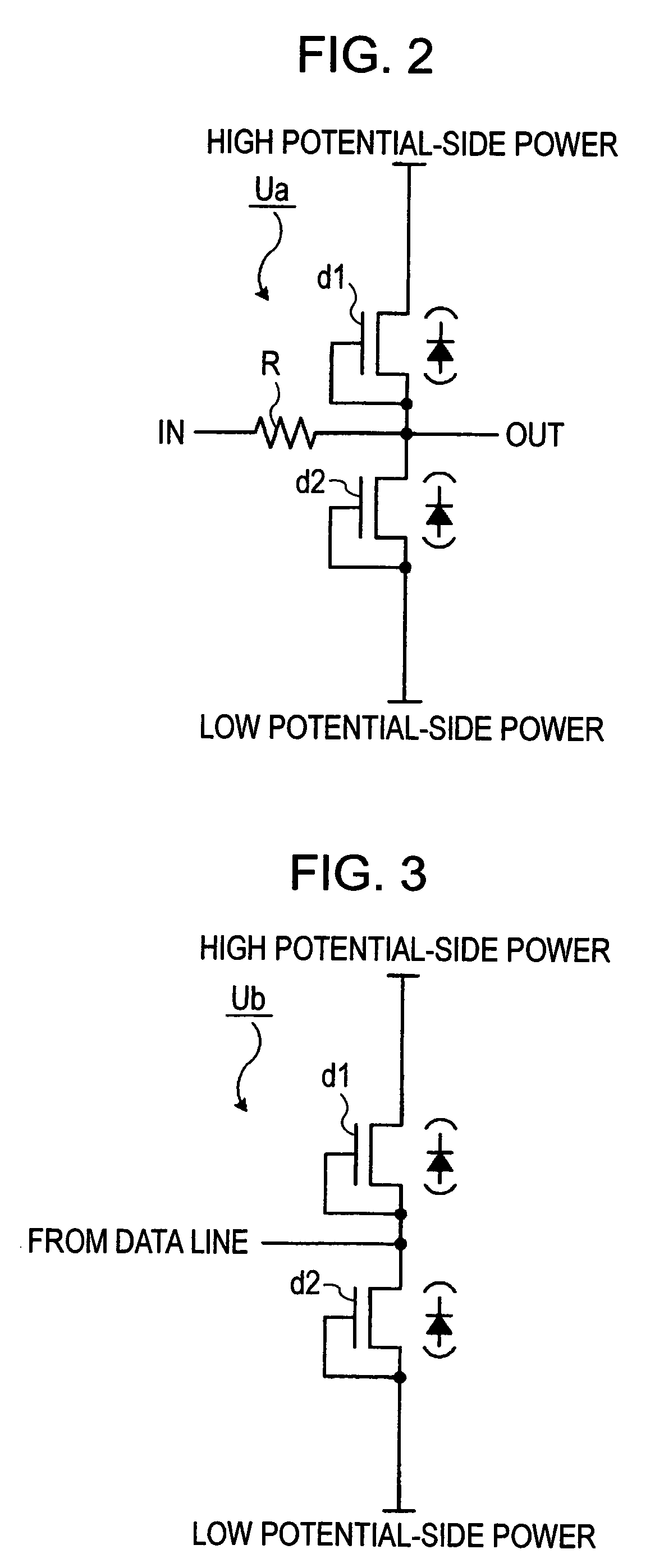

Light-emitting device, image forming apparatus, and display apparatus

ActiveUS7126268B2Suppress brightnessReduce power consumptionDischarge tube luminescnet screensStatic indicating devicesDriving currentLight emitting device

Owner:LUMITEK DISPLAY TECH LTD

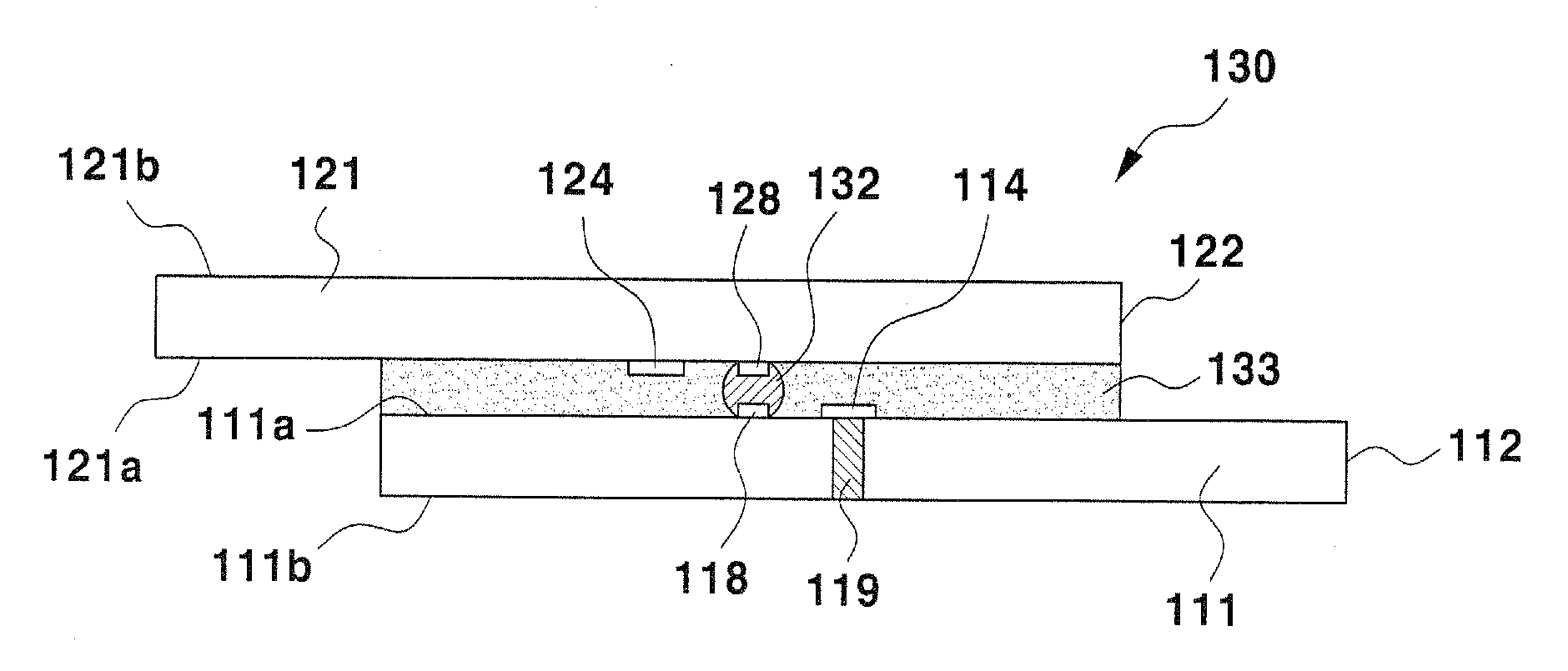

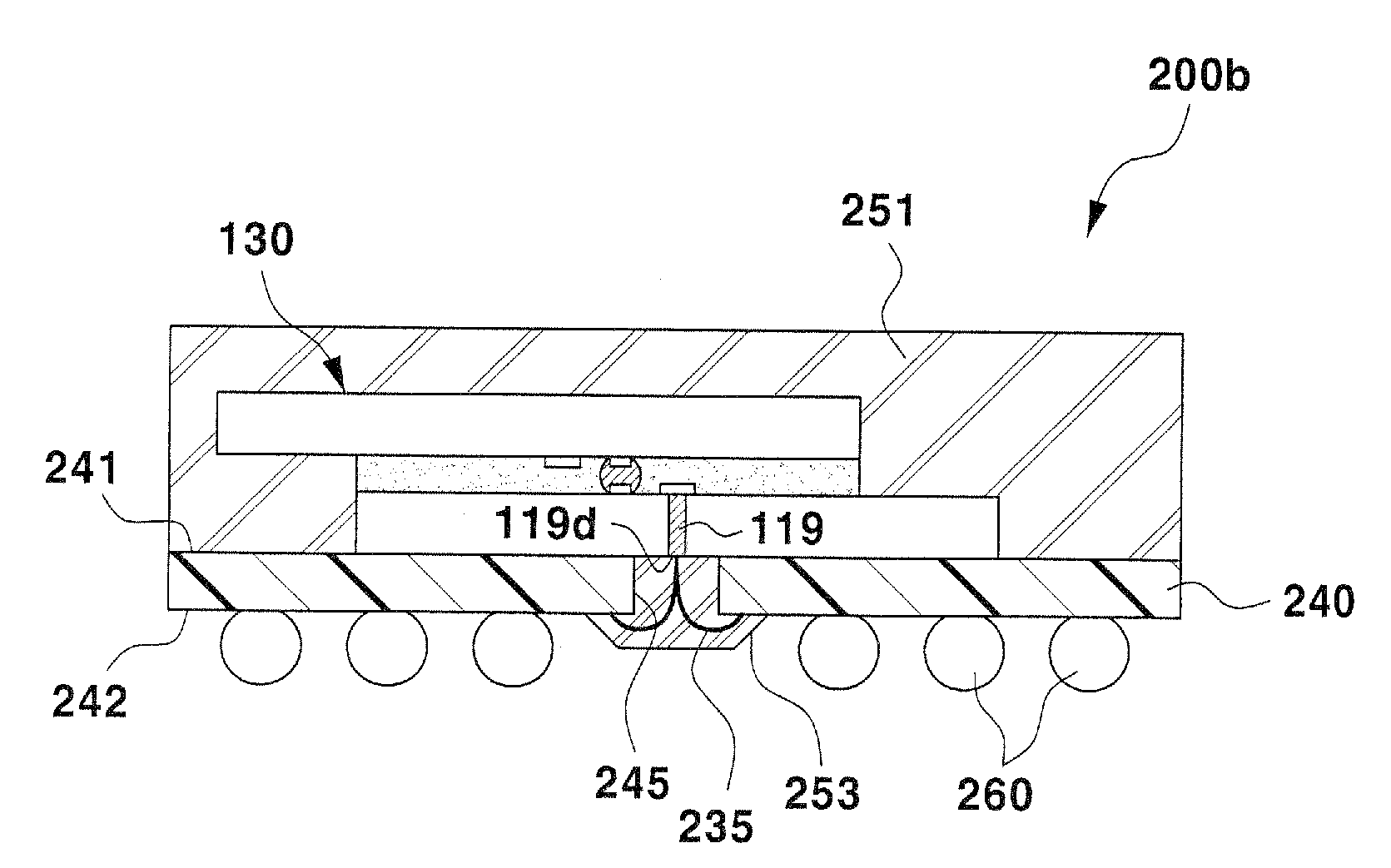

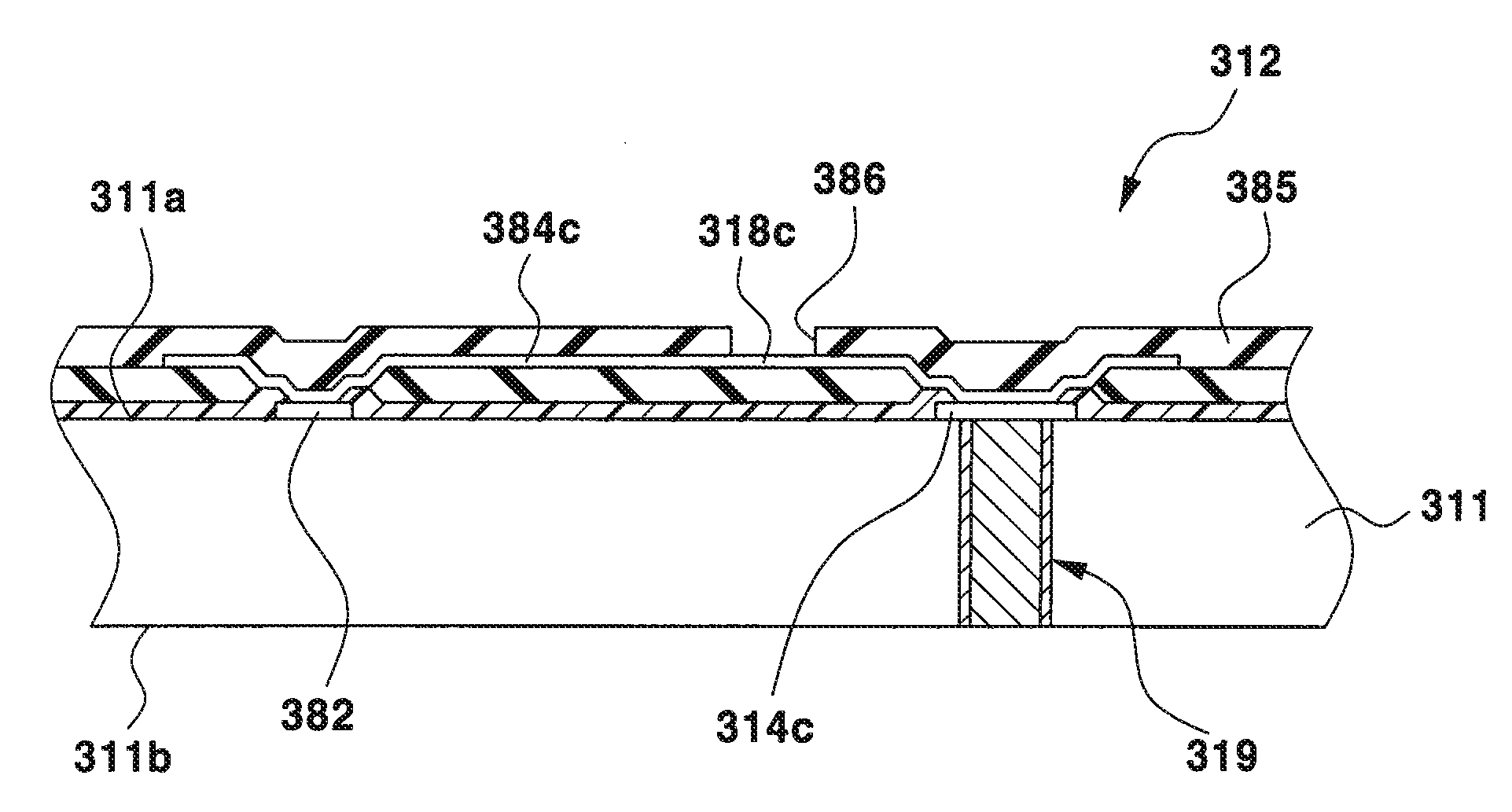

Stack chip and stack chip package having the same

ActiveUS20070170575A1Reduce capacitive loadIncrease speedLighting circuitsSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

Provided are a stack chip and a stack chip package having the stack chip. Internal circuits of two semiconductor chips are electrically connected to each other through an input / output buffer connected to an external connection terminal. The semiconductor chip has chip pads, input / output buffers and internal circuits connected through circuit wirings. The semiconductor chip also has connection pads connected to the circuit wirings connecting the input / output buffers to the internal circuits. The semiconductor chips include a first chip and a second chip. The connection pads of the first chip are electrically connected to the connection pads of the second chip through electrical connection means. Input signals input through the external connection terminals are input to the internal circuits of the first chip or the second chip via the chip pads and the input / output buffers of the first chip, and the connection pads of the first chip and the second chip.

Owner:SAMSUNG ELECTRONICS CO LTD

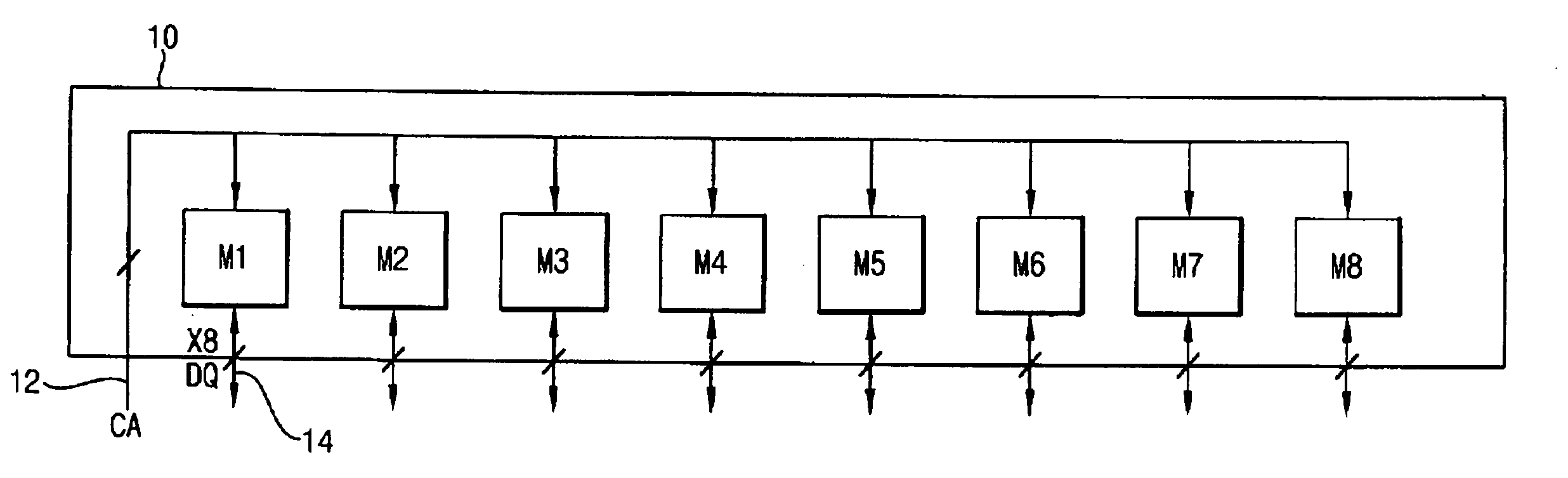

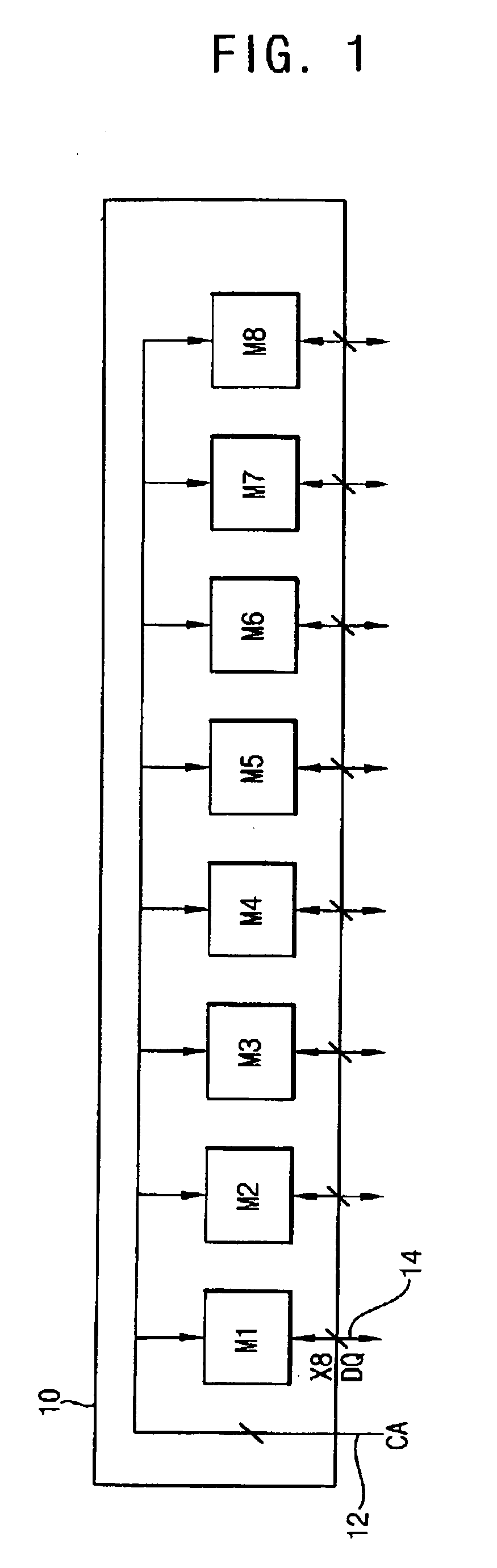

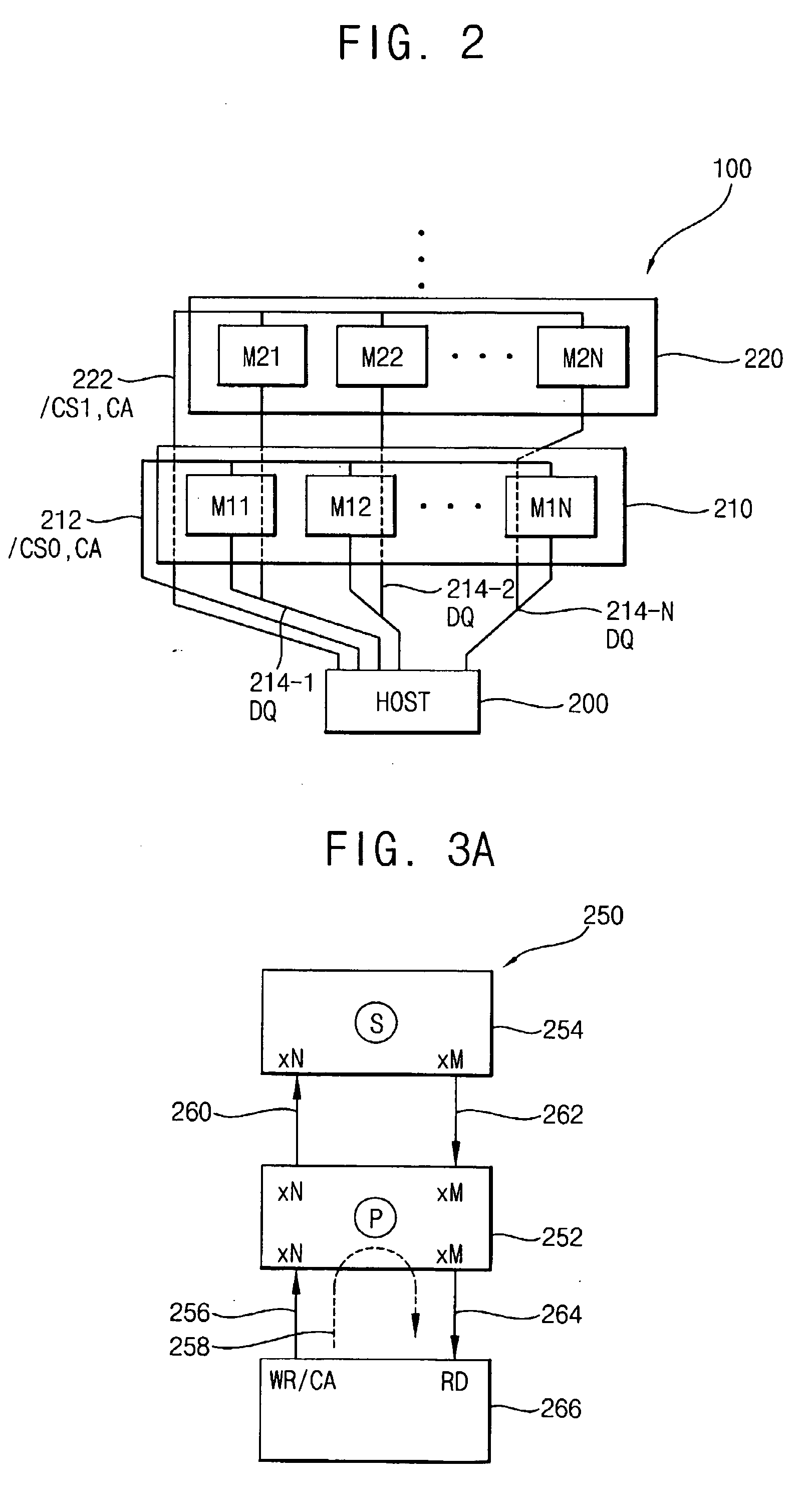

Memory system and method having point-to-point link

ActiveUS20070061614A1Minimize difficultyReduce package sizeError detection/correctionMemory adressing/allocation/relocationOn boardControl signal

A memory system includes a controller for generating a control signal and a primary memory for receiving the control signal from the controller. A secondary memory is coupled to the primary memory, the secondary memory being adapted to receive the control signal from the primary memory. The control signal defines a background operation to be performed by one of the primary and secondary memories and a foreground operation to be performed by the other of the primary and secondary memories. The primary memory and the secondary memory are connected by a point-to-point link. At least one of the links between the primary and secondary memories can be an at least partially serialized link. At least one of the primary and secondary memories can include an on-board internal cache memory.

Owner:SAMSUNG ELECTRONICS CO LTD

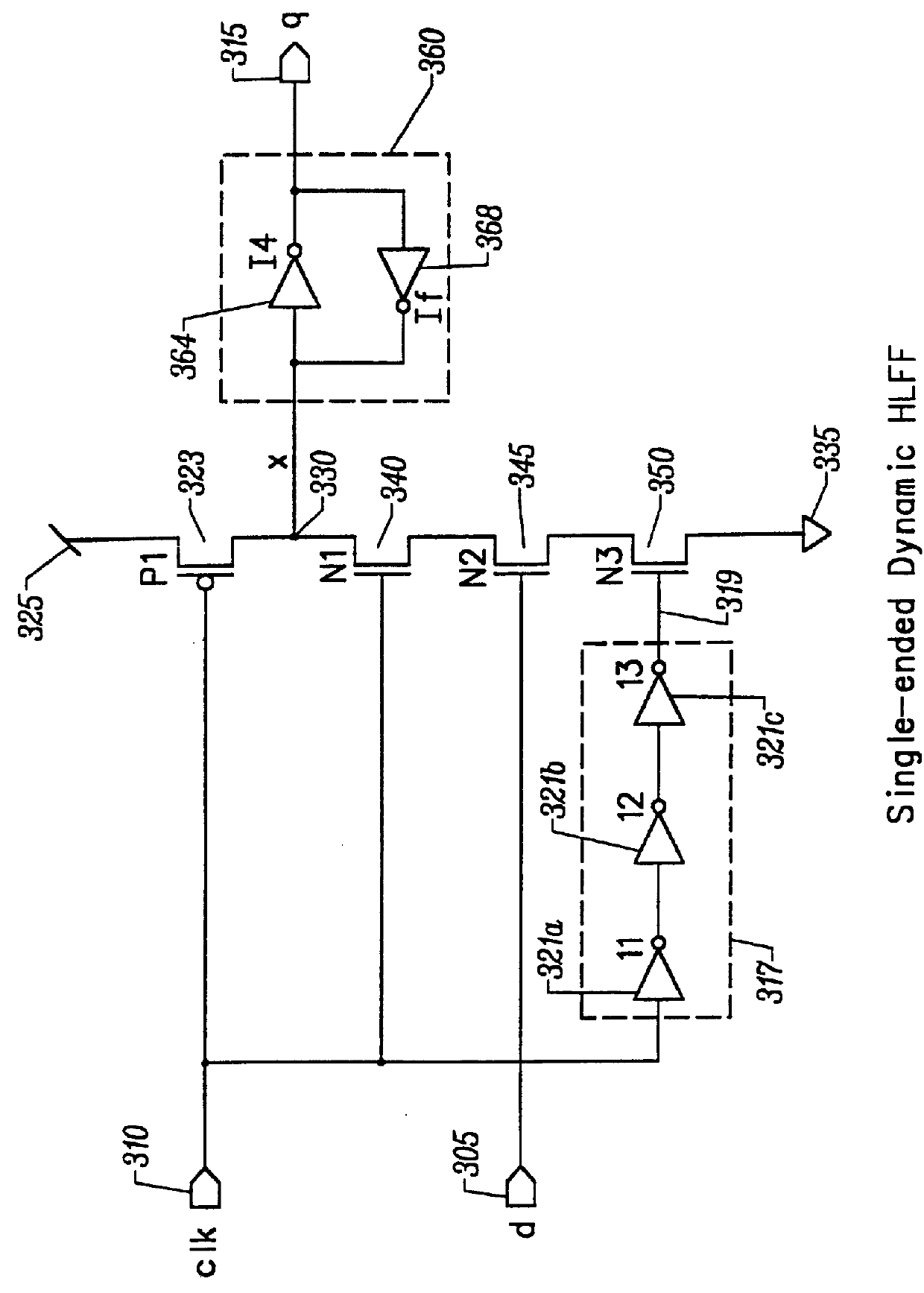

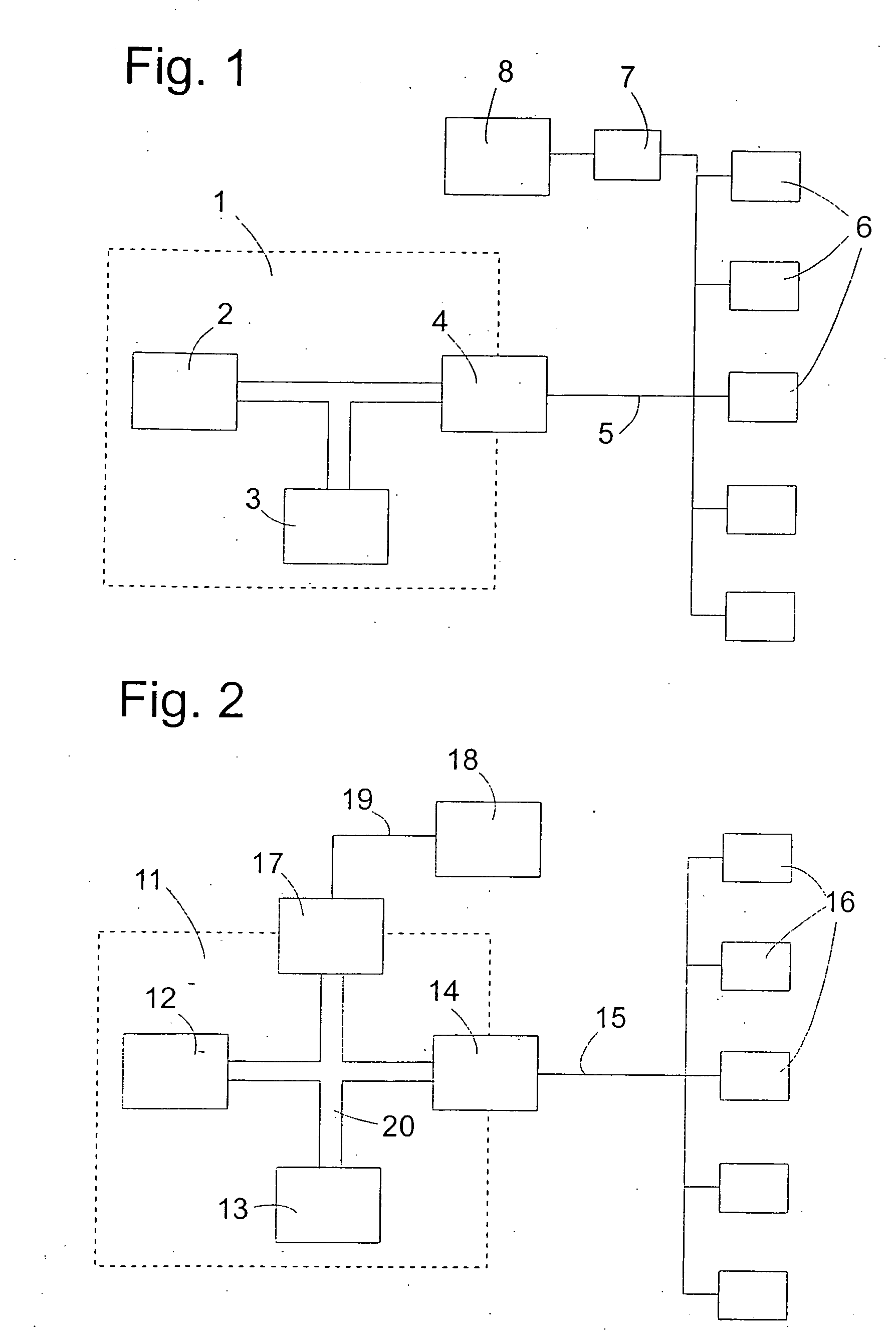

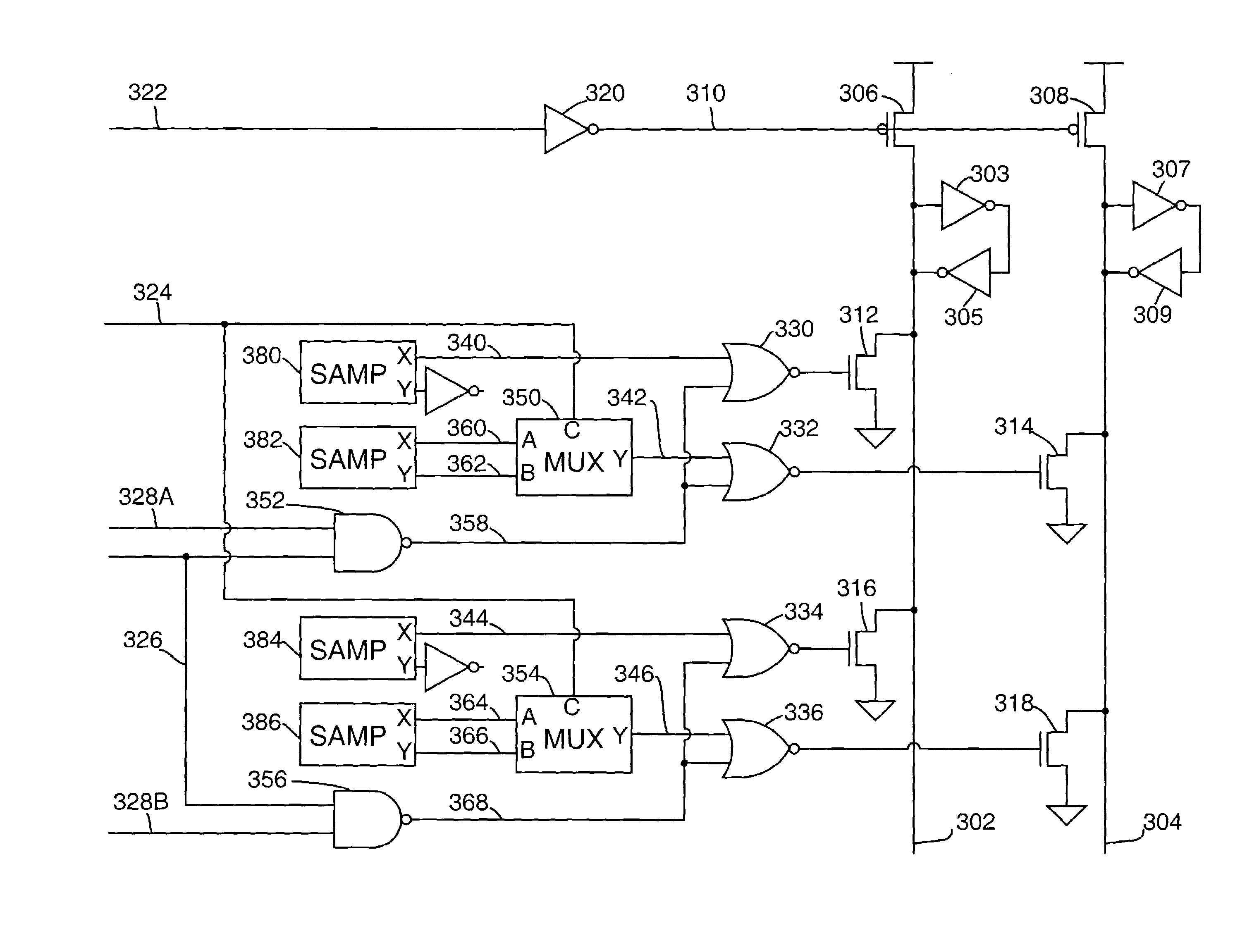

Dynamic latch circuitry

InactiveUS6087872AImprove efficiencyImprove operating characteristicsElectric pulse generator circuitsLogic circuitsDelayed periodsOne shot

A high-performance dynamic flip-flop circuit implementation. The dynamic flip-flop circuit comprises an "implicit" one-shot to generate a delayed clock output (319). The flip-flop comprises a delay block (317) coupled to a clock input (305). The flip-flop may be a D-type flip-flop. In a positive-edge-triggered embodiment of the flip-flop, a falling edge (440) of the delayed clock output (319) follows a rising edge (444) of a clock signal after a delay period (448). The flip-flop clocks in new data at a data input (305) in response to the clock input (310) during this delay period (448). Data is held in a storage block (360). The flip-flop has extremely good transient characteristics, especially set-up and clock-to-output times. The flip-flop consumes no static power.

Owner:GLOBALFOUNDRIES INC

Electrosurgical apparatus with integrated energy sensing at tissue site

ActiveUS9693816B2Maximize applicationReduce lossSurgical instruments for heatingSurgical forcepsRadio frequency energyVoltage drop

An electrosurgical system is disclosed. The system includes an electrosurgical instrument having at least one electrode configured as a first sensor for measuring a voltage drop therethrough and a temperature sensor for a thermal sensor configured to measure a temperature difference across the at least one electrode; and a generator including an output stage coupled to the at least one electrode, the output stage configured to generate radio frequency energy; and a controller configured to determine actual radio frequency current based on the voltage drop and electrical resistivity of the at least one electrode and radio frequency power based on the measured temperature difference and the thermal conductivity of the at least one electrode.

Owner:COVIDIEN LP

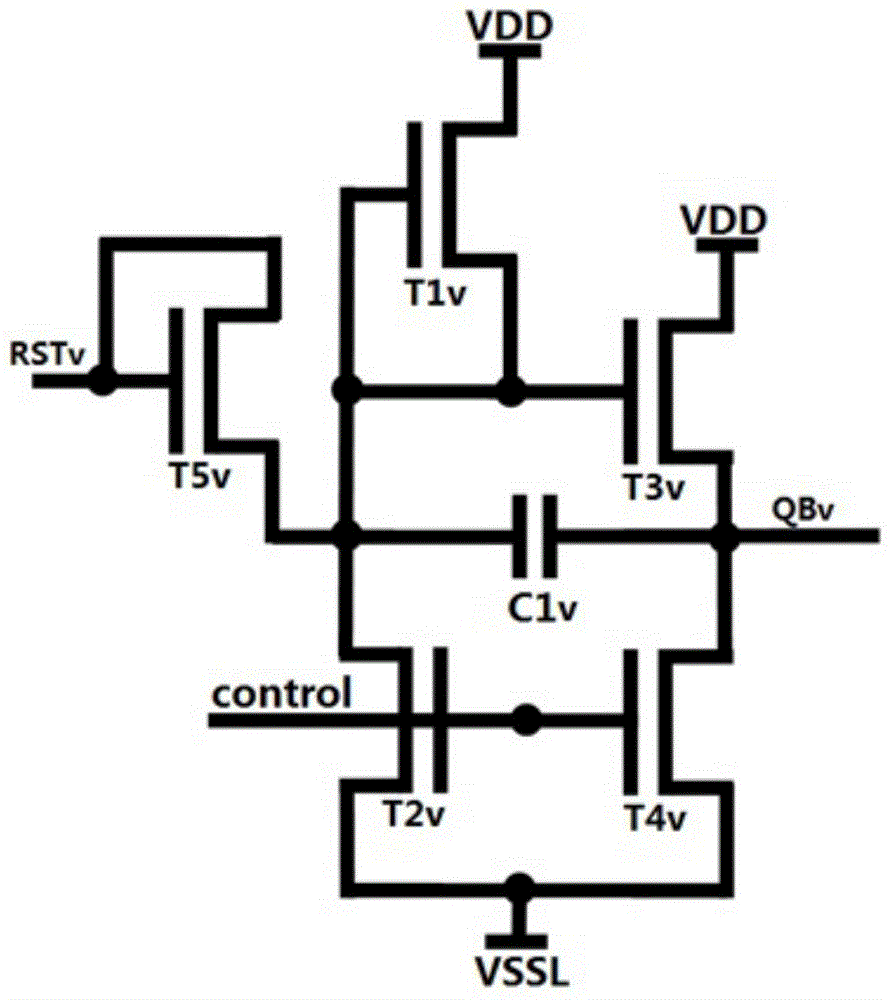

Inverter of grid integrated driving circuit, grid integrated driver and driving method

ActiveCN104599620AReduce power consumptionQuick switchStatic indicating devicesCapacitanceAnti jamming

The invention discloses an inverter of a grid integrated driving circuit. The inverter comprises transistors T1v-T5v and a coupling capacitor C1v, a second electrode of the T1v and a second electrode of the T3v are connected with positive level VDD, a grid and a first electrode of the T1v are connected with a second electrode of the T2v, a grid of the T3v, a first electrode of the T5v and one end of the C1v, a grid of the T2v and a grid of the T4v are connected with a control signal, the grid and a second electrode of the T5v are connected with a feedback signal RSTv, a first electrode of the T2v and a first electrode of the T4v are connected with first negative level, a second electrode of the T3v and a second electrode of the T4v are connected with the other end of the C1v, and an output node QBv of the inverter is formed. The invention further discloses the grid integrated driving circuit with the inverter and a driving method of the grid integrated driving circuit. The inverter is low in power consumption and noise and excellent in anti-jamming capability, and the output pull-up transistors and the inverter are rapid in action and can work under high frequency.

Owner:王磊 +1

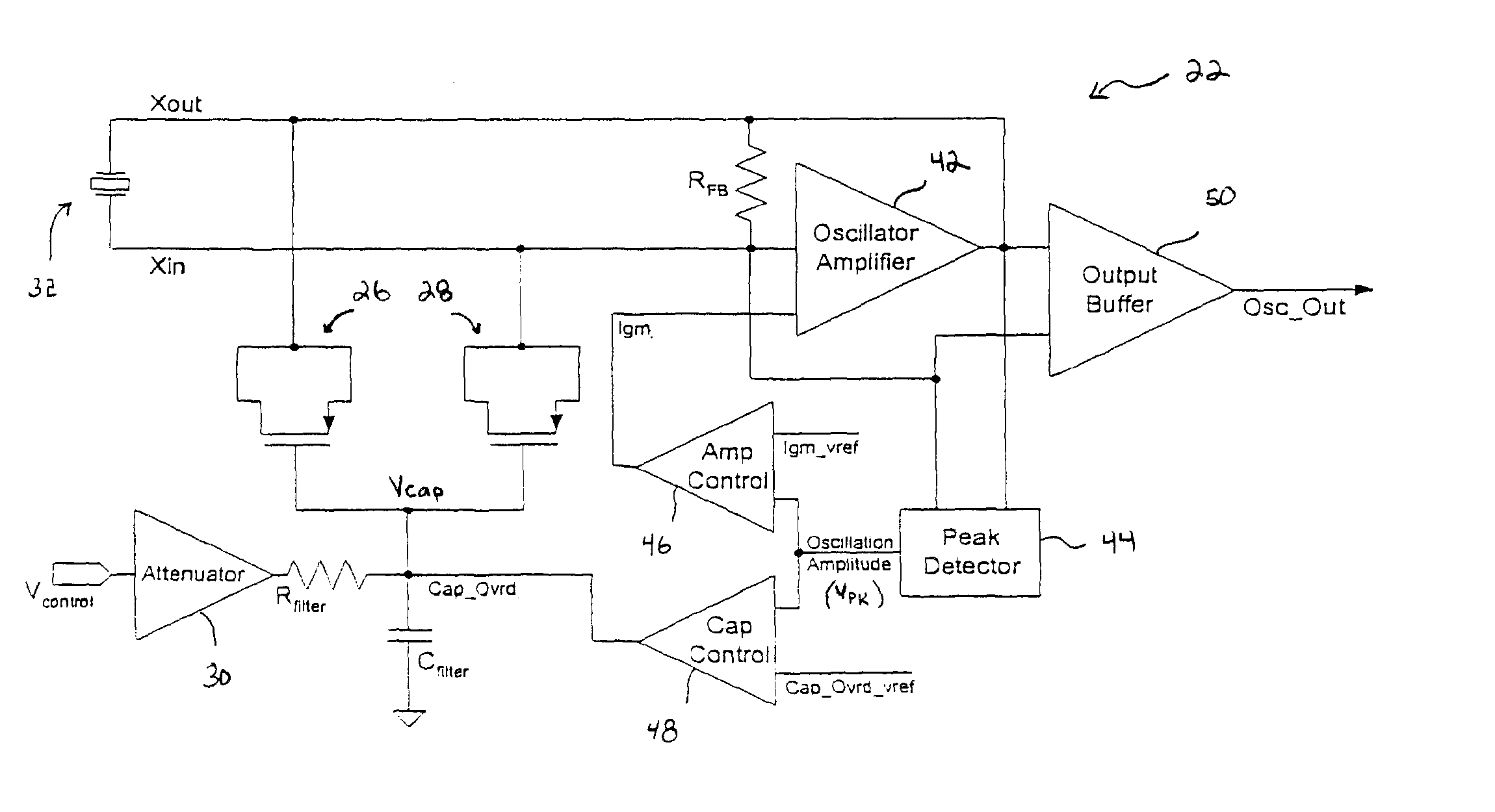

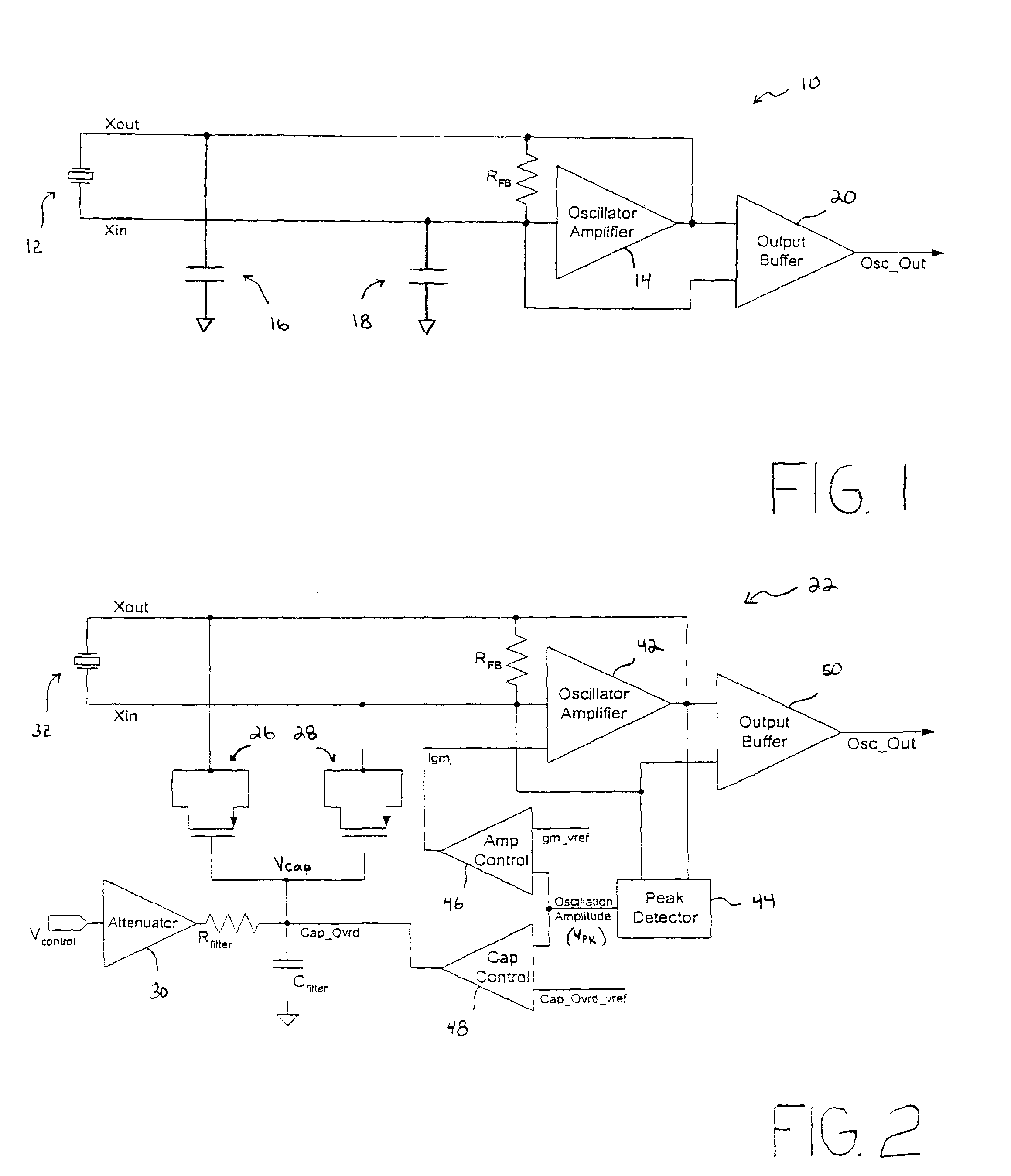

Regulated capacitive loading and gain control of a crystal oscillator during startup and steady state operation

InactiveUS7859355B2Start fastHigh resistanceAngle modulation by variable impedencePulse automatic controlVariable-gain amplifierAudio power amplifier

An oscillator circuit and system are provided having a peak detector that can determine a peak voltage value from the oscillator. The peak voltage value can then be compared against a predetermined voltage value by a controller coupled to the peak detector. The comparison value is then used to change a bias signal if the peak voltage value is dissimilar from the predetermined voltage value. A variable capacitor or varactor can be formed from a transistor and is coupled to the oscillator for receiving the bias signal upon a varactor bias node. The bias signal is used to regulate the capacitance within the varactor as applied to the oscillator nodes. Another controller can also be coupled to the peak detector to produce a second bias signal if the peak voltage is dissimilar from a second predetermined voltage value. The second bias signal can then be forwarded into an amplifier having a variable gain to regulate the gain applied to the oscillator. The combination of a varactor and variable gain amplifier regulate the negative resistance applied to the resonating circuit during startup and steady state operations to ensure a relatively fast startup, and to maintain optimal loading and accurate steady state amplitude after startup has completed.

Owner:MONTEREY RES LLC

Stack chip and stack chip package having the same

ActiveUS7462930B2Reduce capacitive loadIncrease speedLighting circuitsSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

Owner:SAMSUNG ELECTRONICS CO LTD

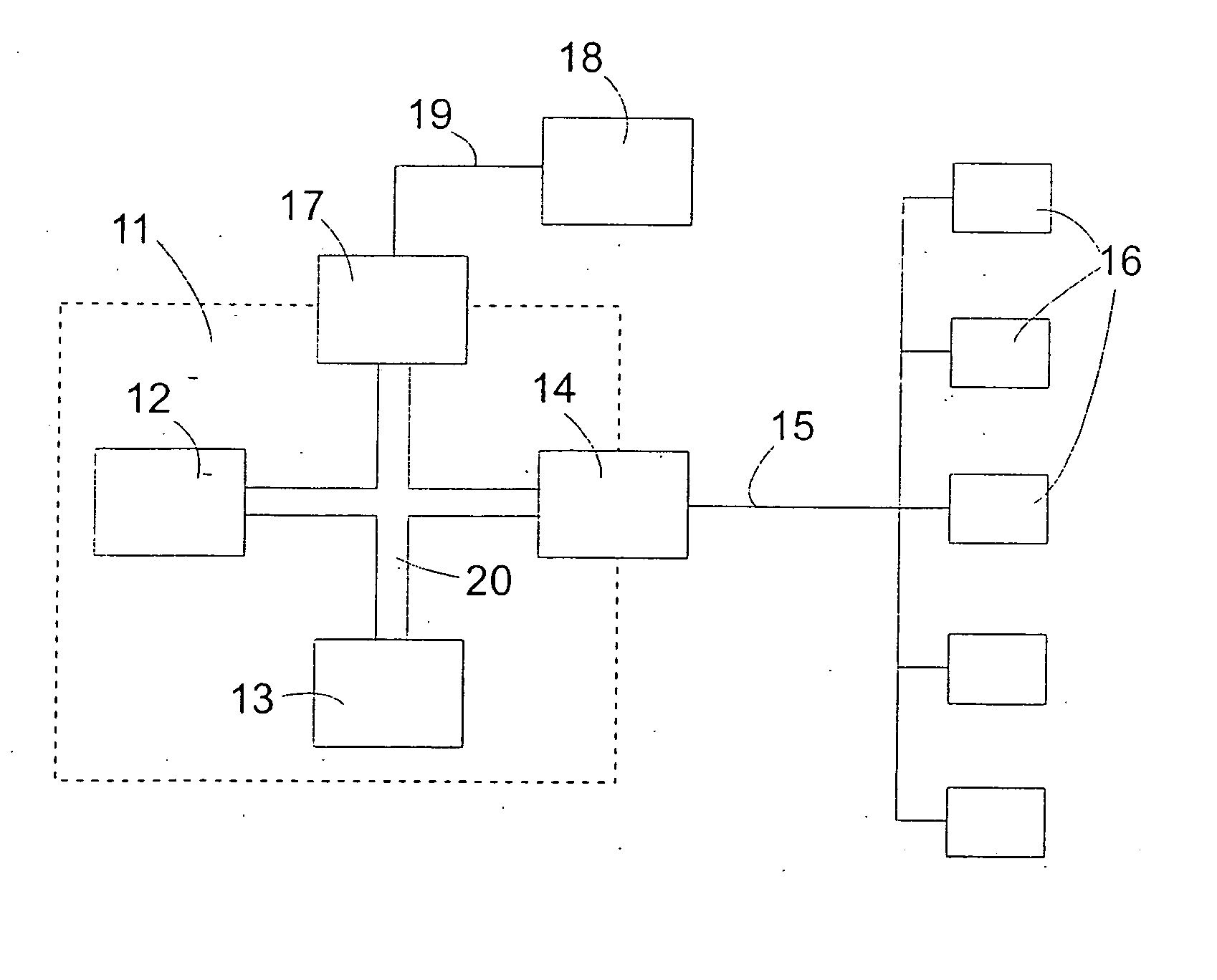

Control device for a motor vehicle and communication method therefor

InactiveUS20060178804A1Simple and cost-effectiveSimple possibilityAnalogue computers for vehiclesElectrical controlEngine control unitMotorized vehicle

A motor vehicle control unit, in particular an engine control unit, includes a processor, a first interface for the communication with functional units of the motor vehicle and at least one second interface, which is combined with the processor in a sub-assembly.

Owner:ROBERT BOSCH GMBH

Stack chip and stack chip package having the same

ActiveUS20090065950A1Reduce capacitive loadIncrease speedLighting circuitsSemiconductor/solid-state device detailsElectrical connectionSemiconductor chip

Provided are a stack chip and a stack chip package having the stack chip. Internal circuits of two semiconductor chips are electrically connected to each other through an input / output buffer connected to an external connection terminal. The semiconductor chip has chip pads, input / output buffers and internal circuits connected through circuit wirings. The semiconductor chip also has connection pads connected to the circuit wirings connecting the input / output buffers to the internal circuits. The semiconductor chips include a first chip and a second chip. The connection pads of the first chip are electrically connected to the connection pads of the second chip through electrical connection means. Input signals input through the external connection terminals are input to the internal circuits of the first chip or the second chip via the chip pads and the input / output buffers of the first chip, and the connection pads of the first chip and the second chip.

Owner:SAMSUNG ELECTRONICS CO LTD

Storage system and data management method

InactiveUS7360046B2Reducing processing load and capacity loadPrevent overload of memory capacityData processing applicationsMemory systemsData management

Owner:HITACHI LTD

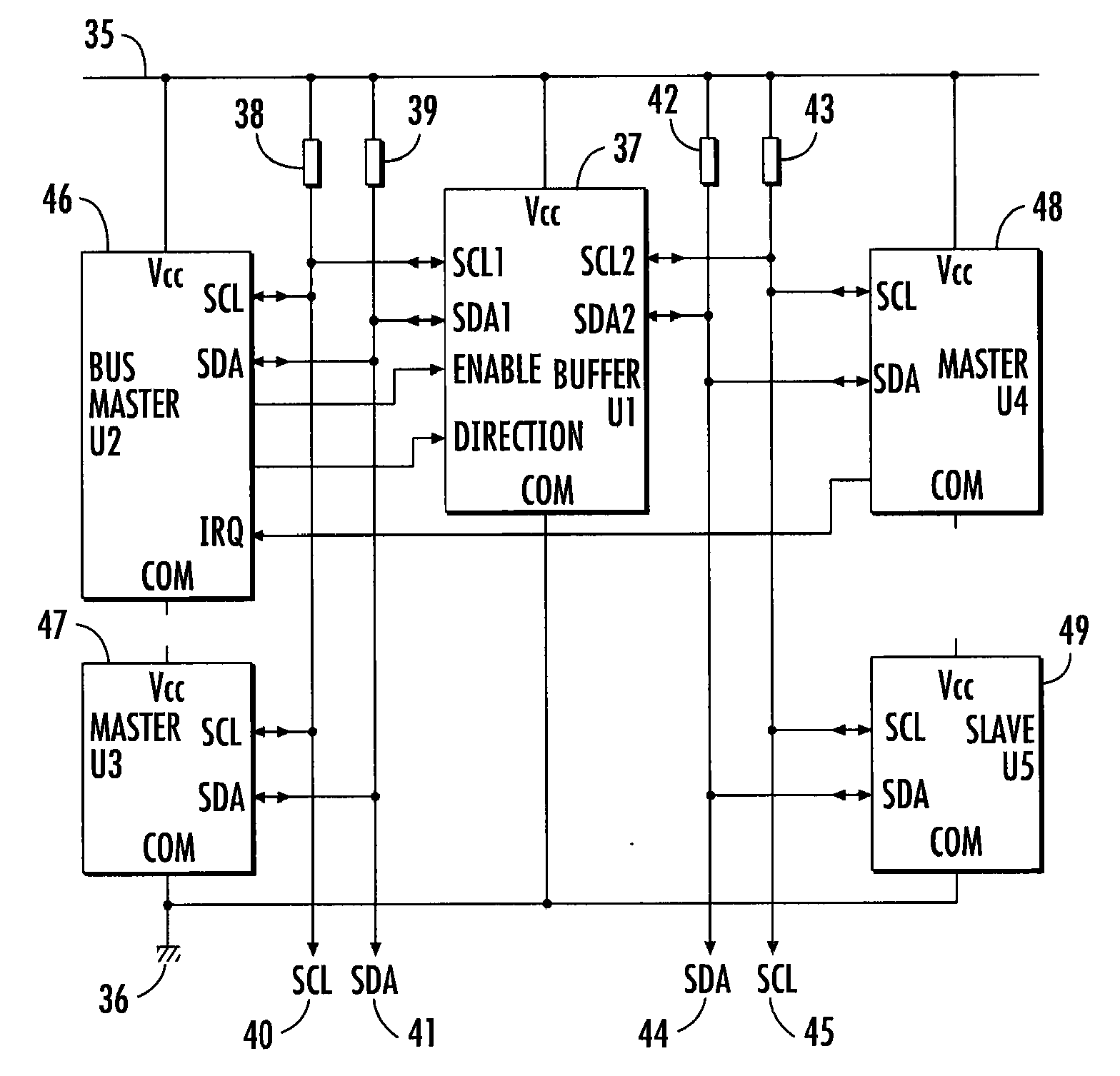

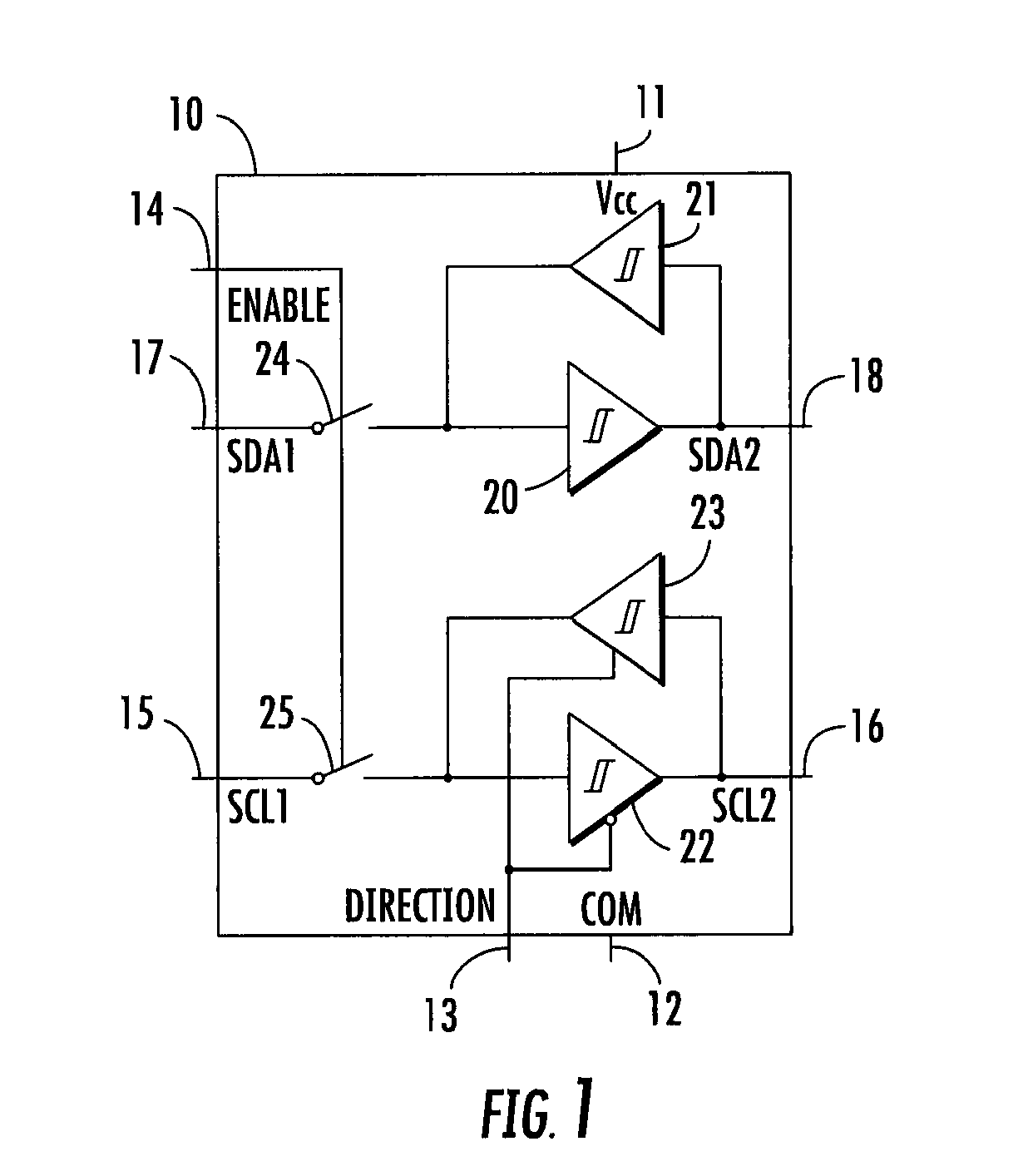

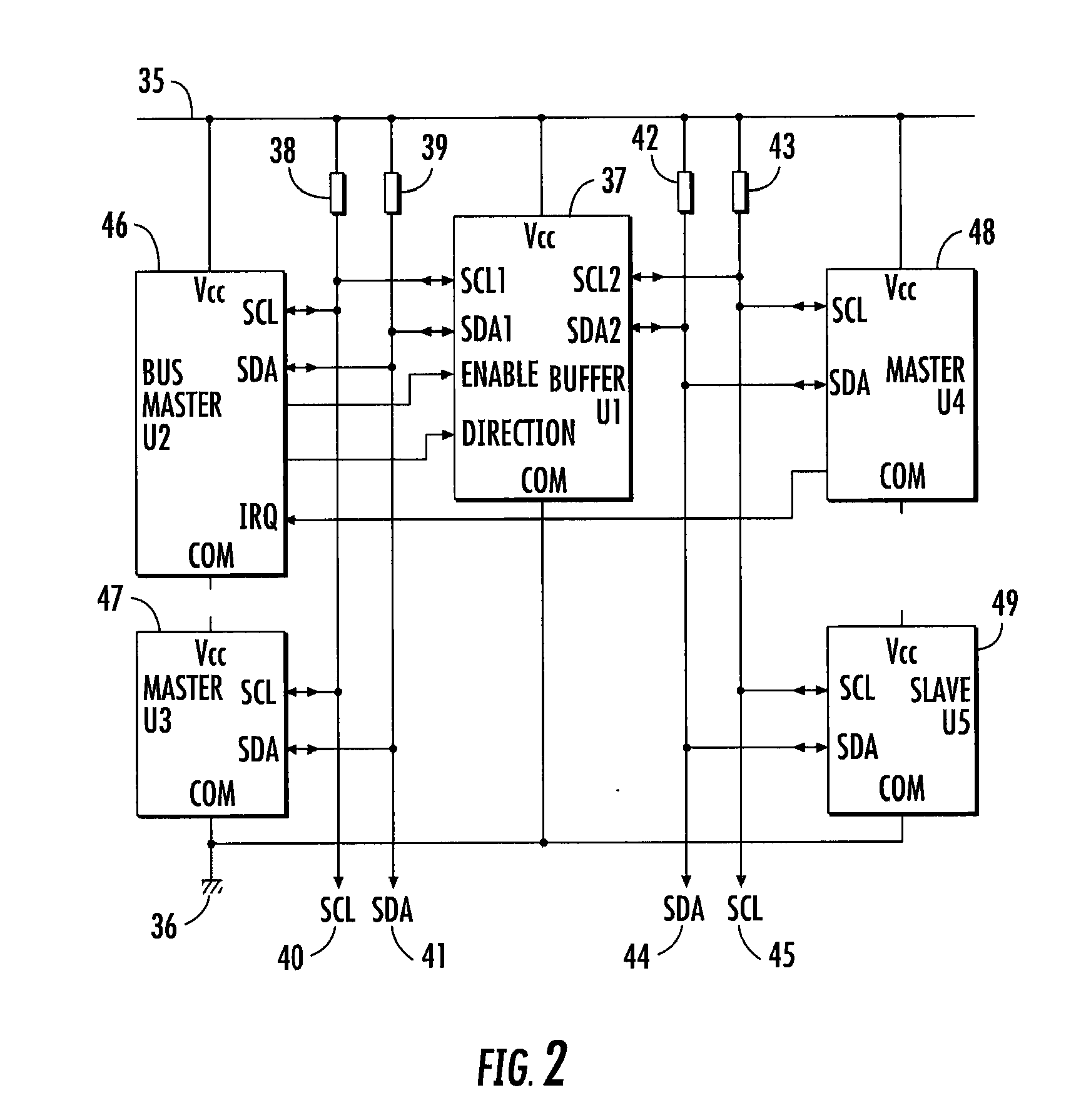

Simple Bus Buffer

ActiveUS20080183919A1Free designAvoid constraintsLogic circuit coupling/interface arrangementsInput/output processes for data processingData bufferVoltage

A bus buffer can include a data buffer and a clock signal buffer. The data buffer for can include two symmetrical buffer circuits with an output signal that can follow the input voltage to provide bi-directional buffer action for a data path of the bus buffer. The clock buffer can operate in a forward or reverse direction, where the signal direction for the clock signal path in the bus buffer can be controlled with a direction input. The bus buffer can also include an enable circuit for enabling the data path and the clock signal path.

Owner:HENDON SEMICON

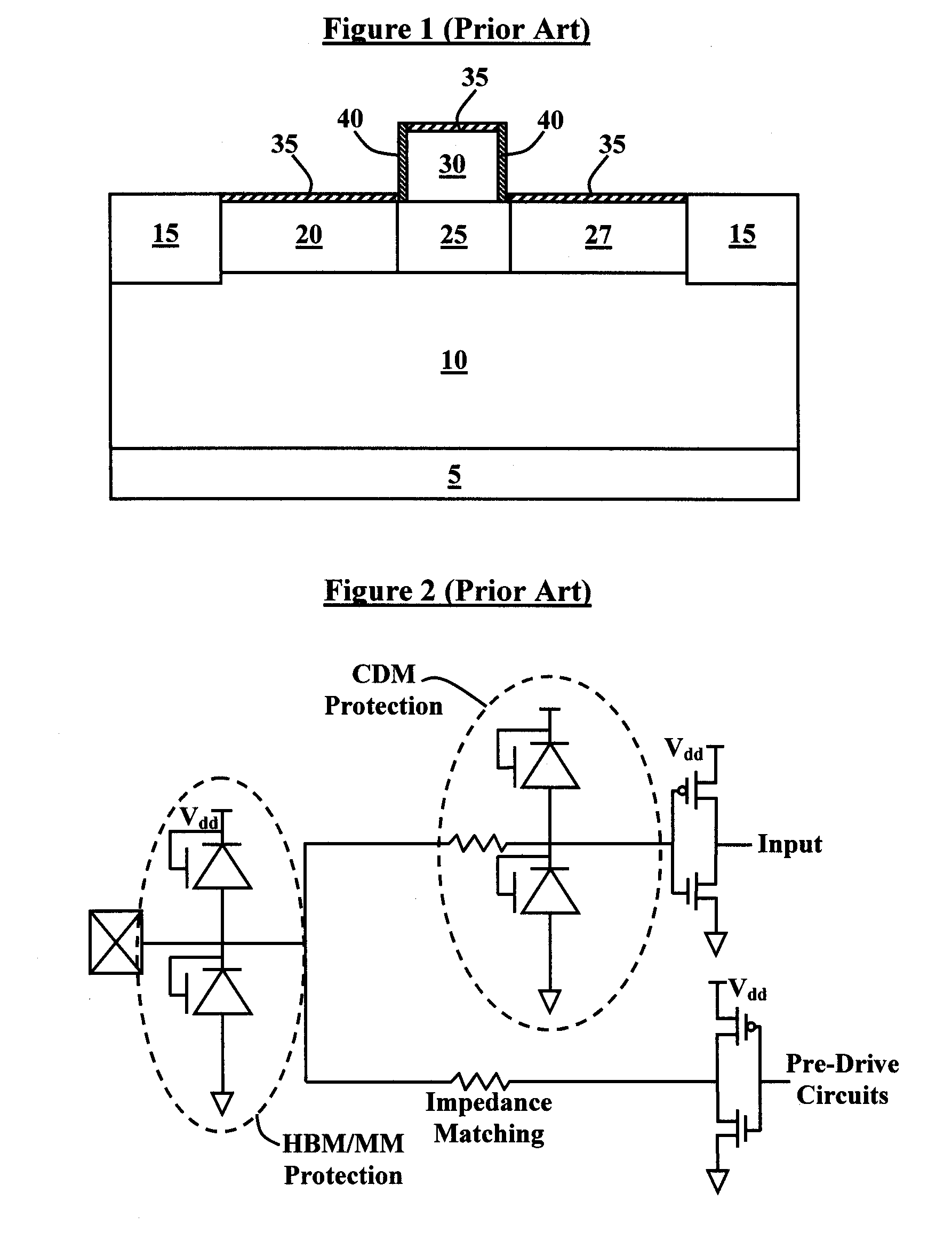

Method for creating a self-aligned SOI diode by removing a polysilicon gate during processing

InactiveUS7138313B2Reduce capacitive loadEliminate requirementsSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringPolysilicon gate

Owner:INT BUSINESS MASCH CORP

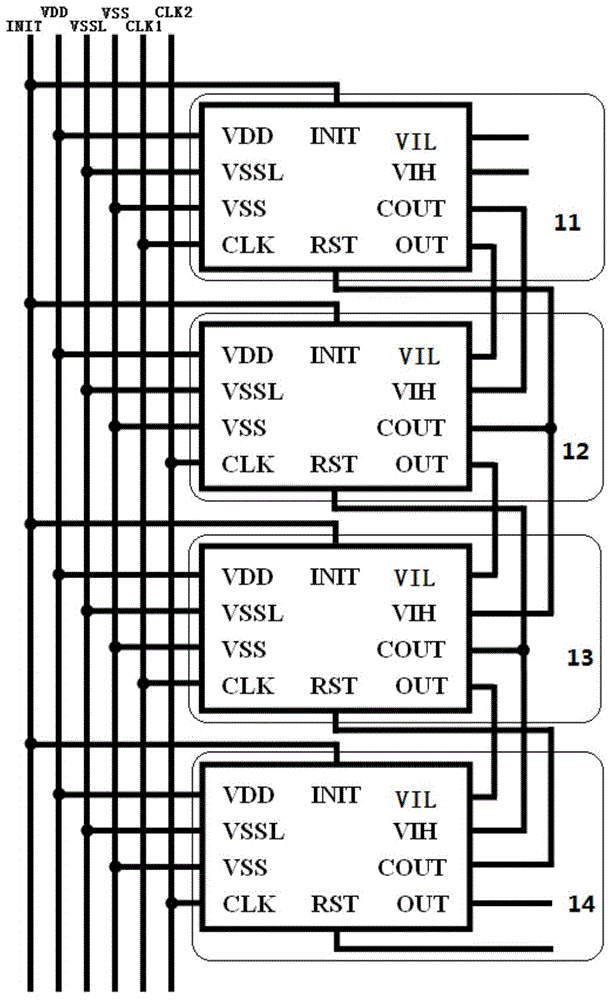

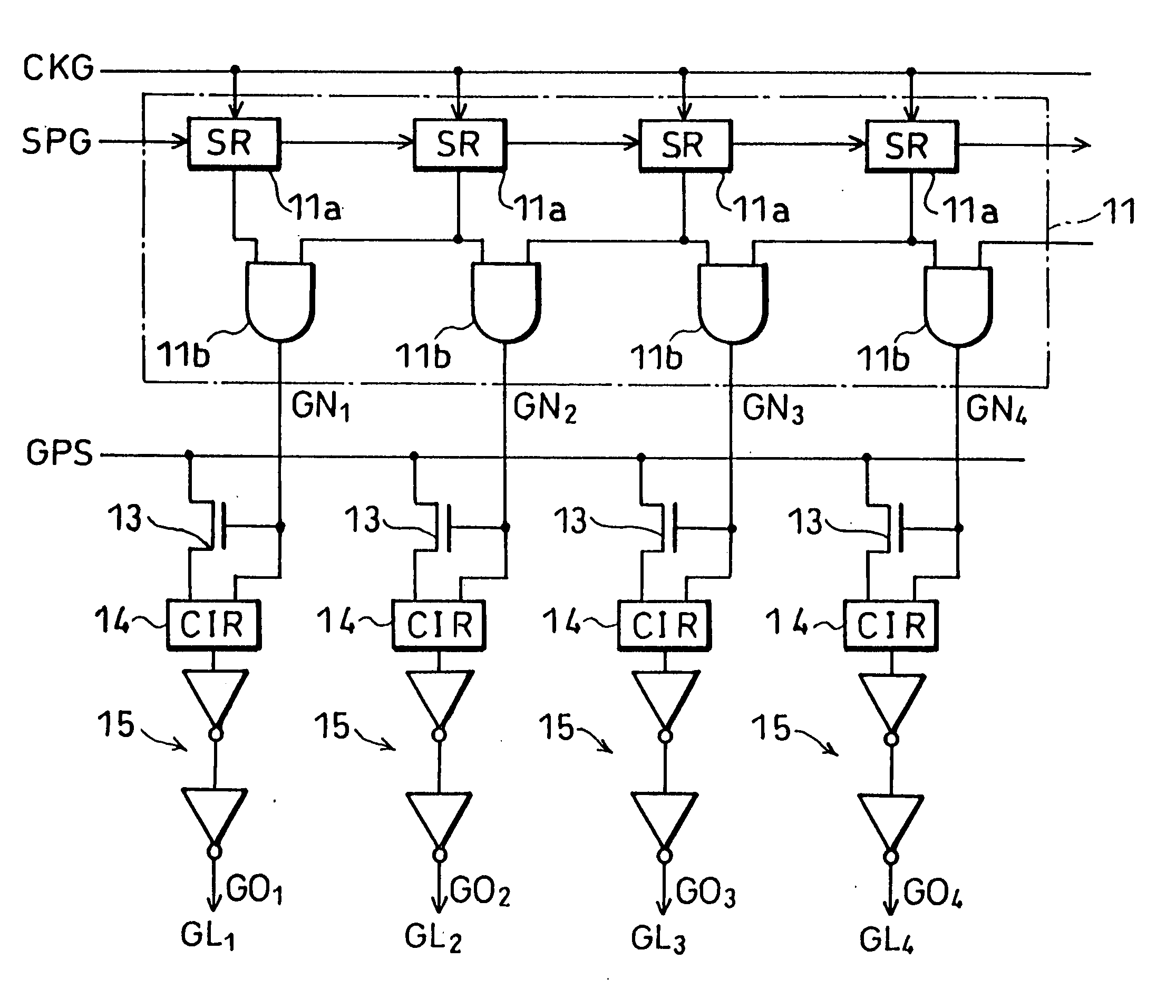

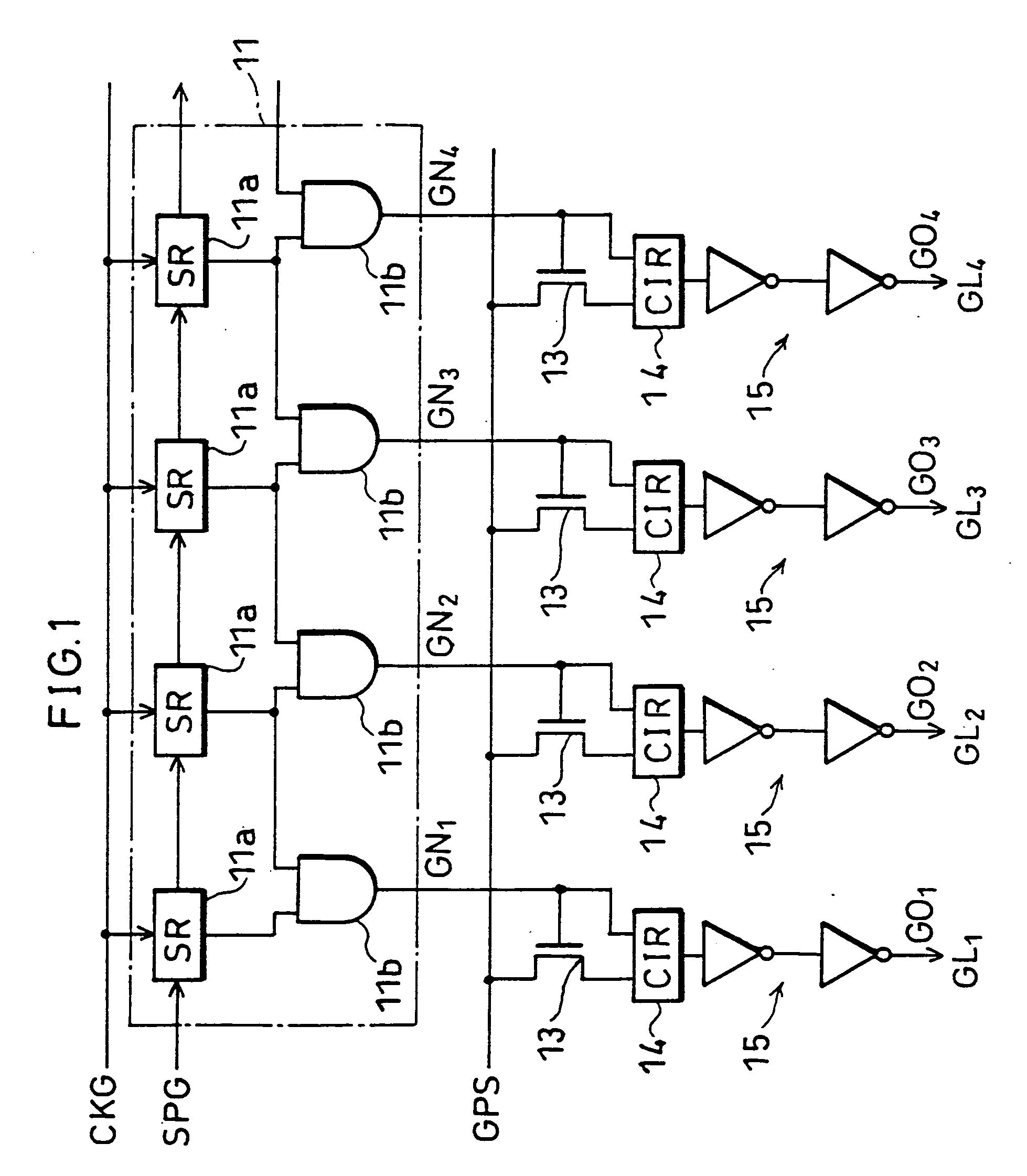

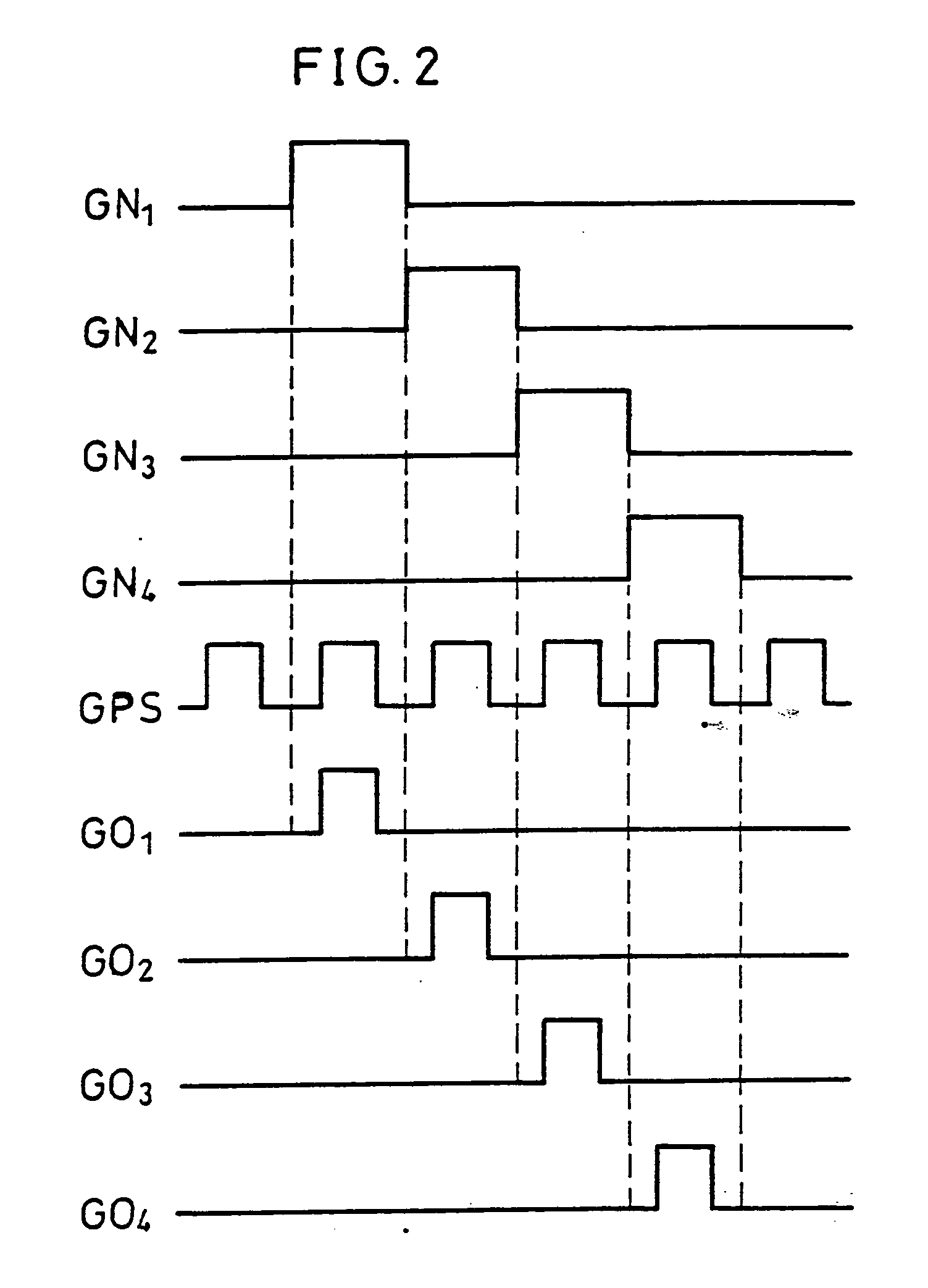

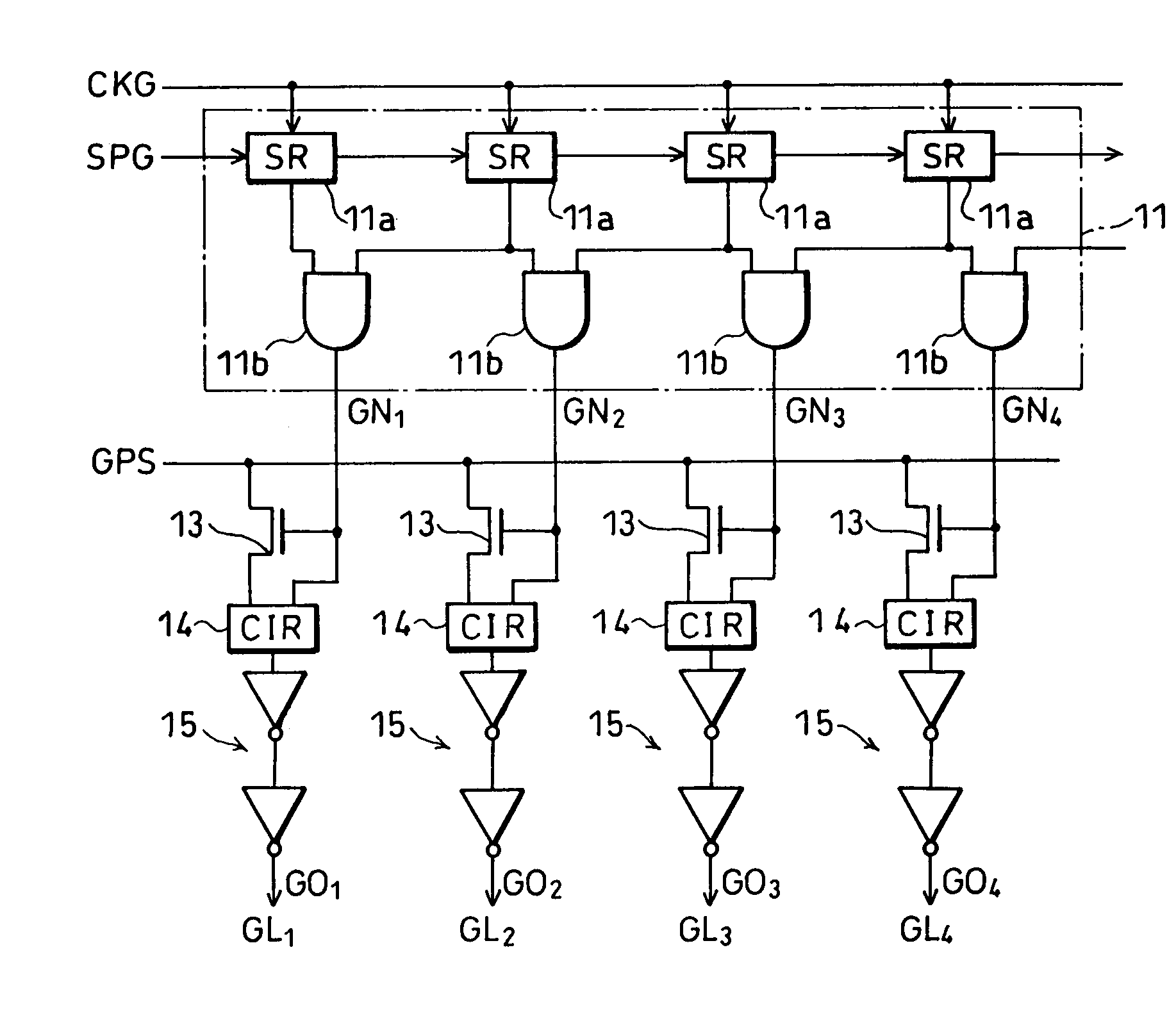

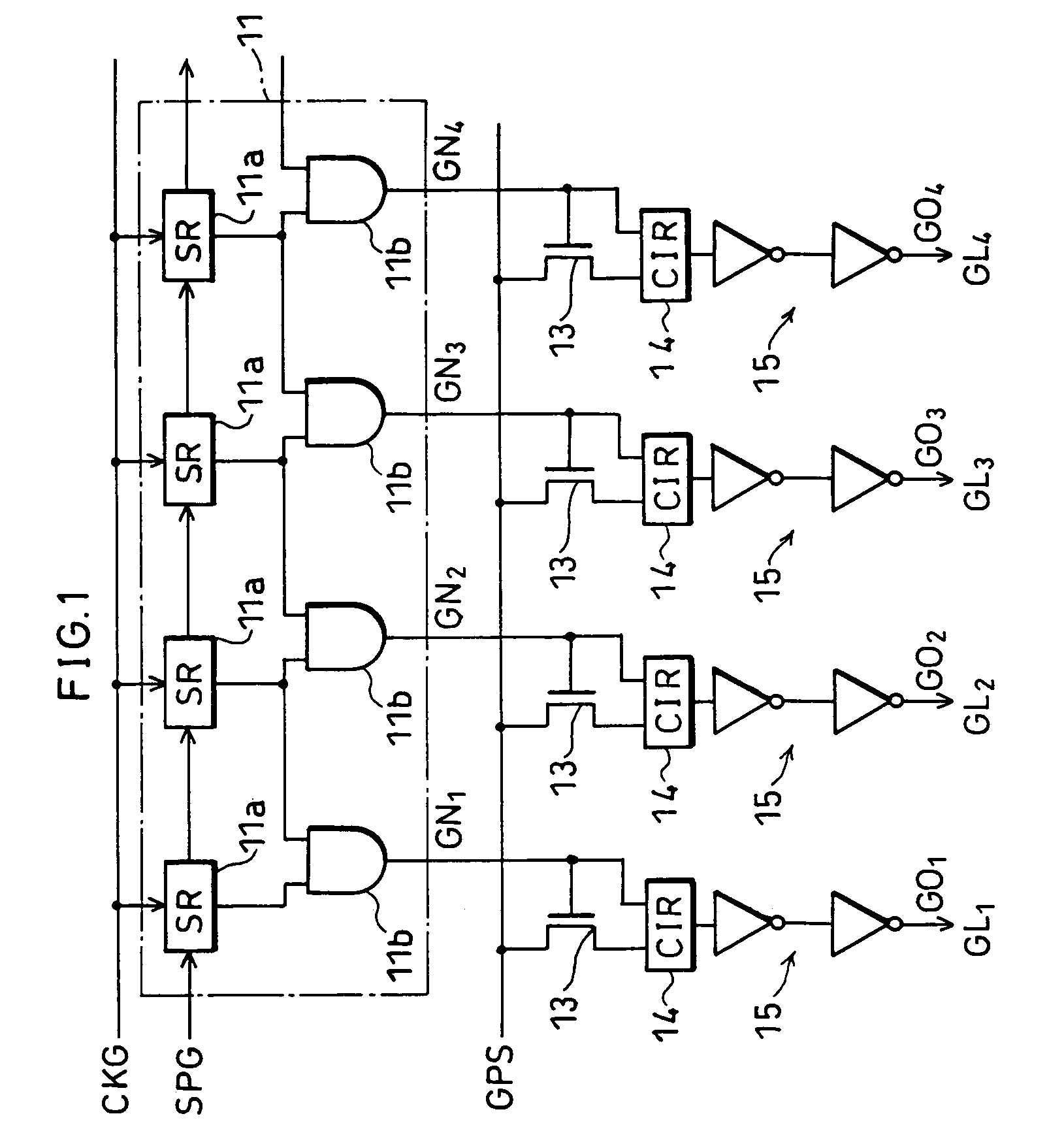

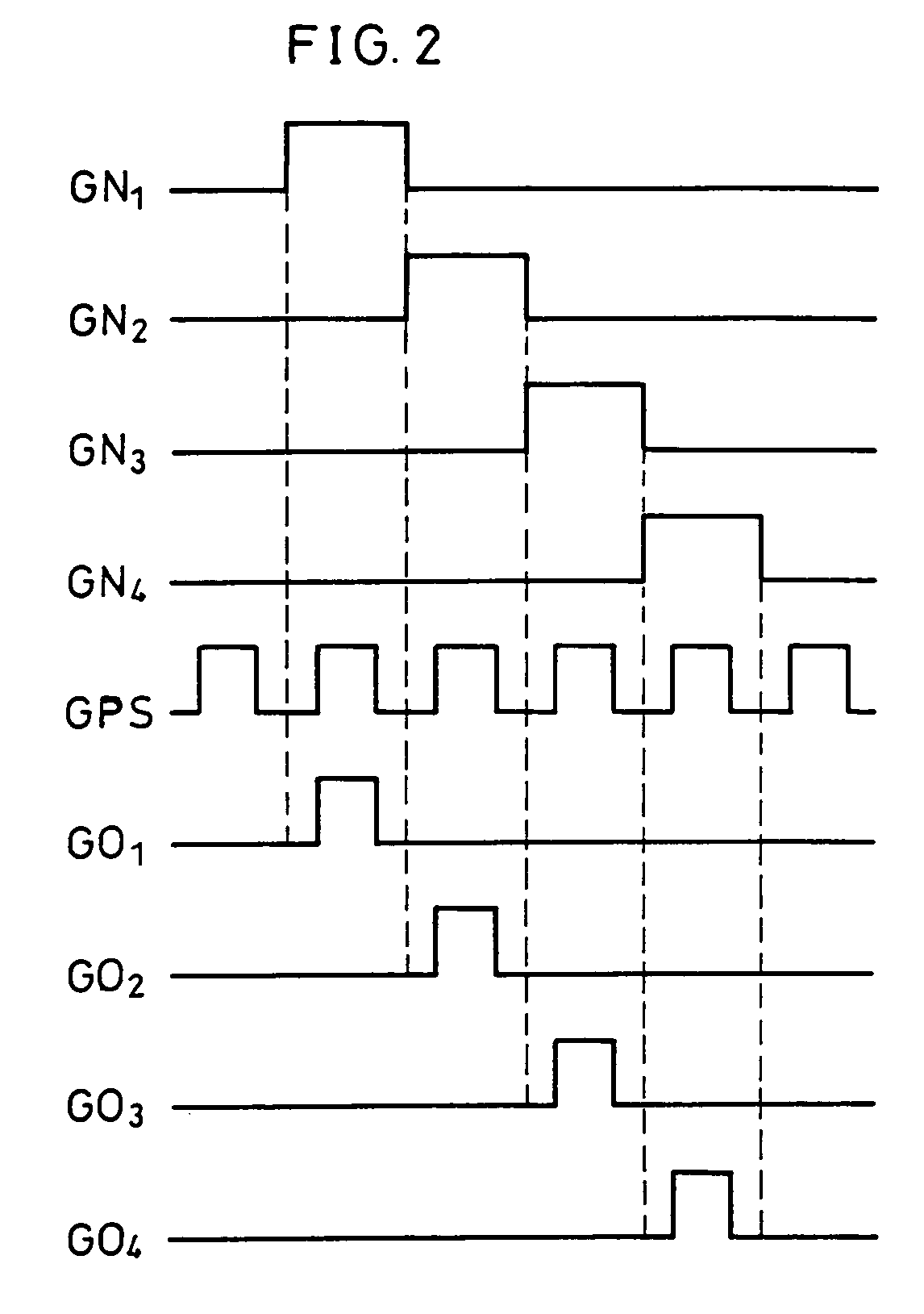

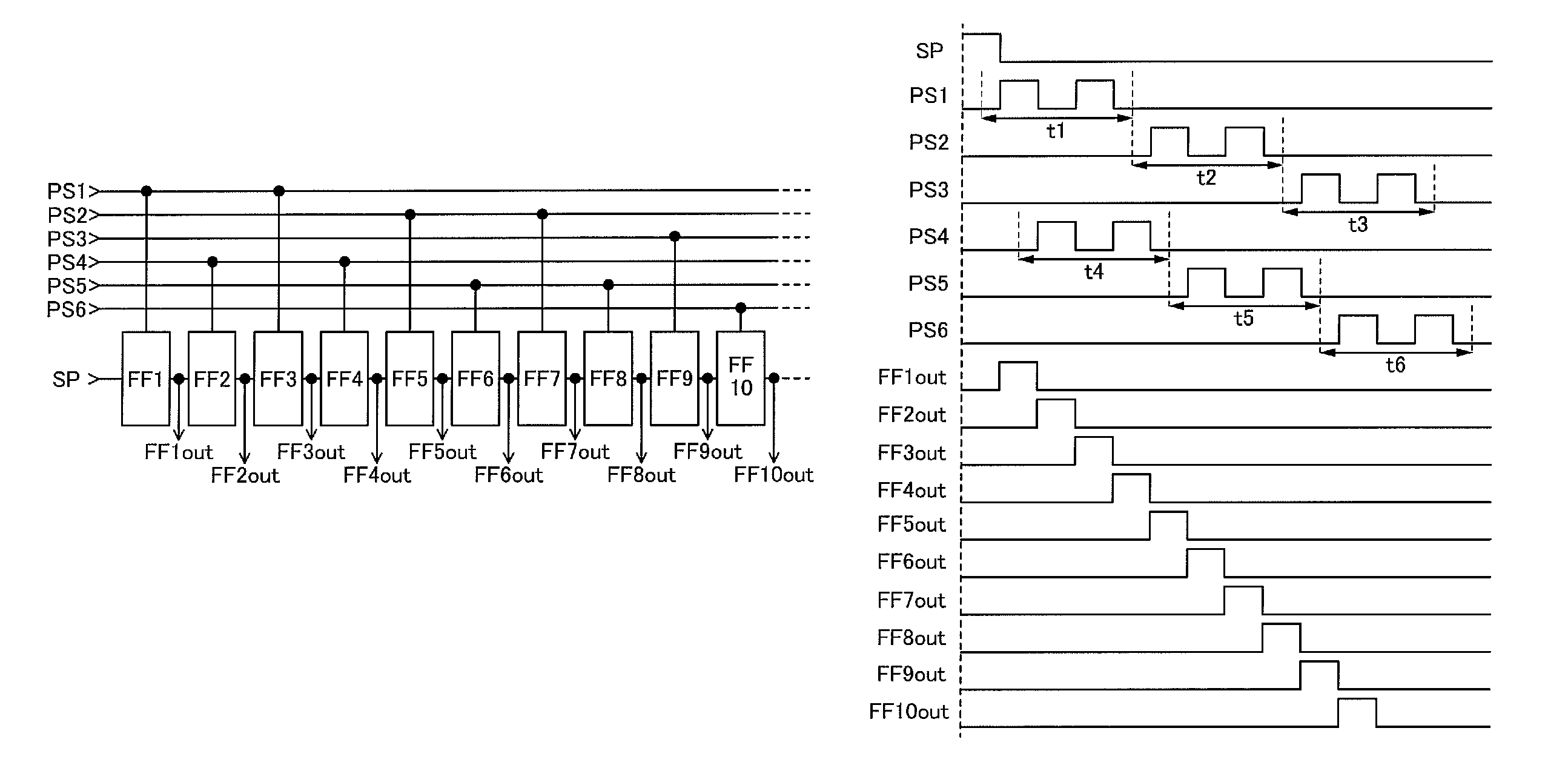

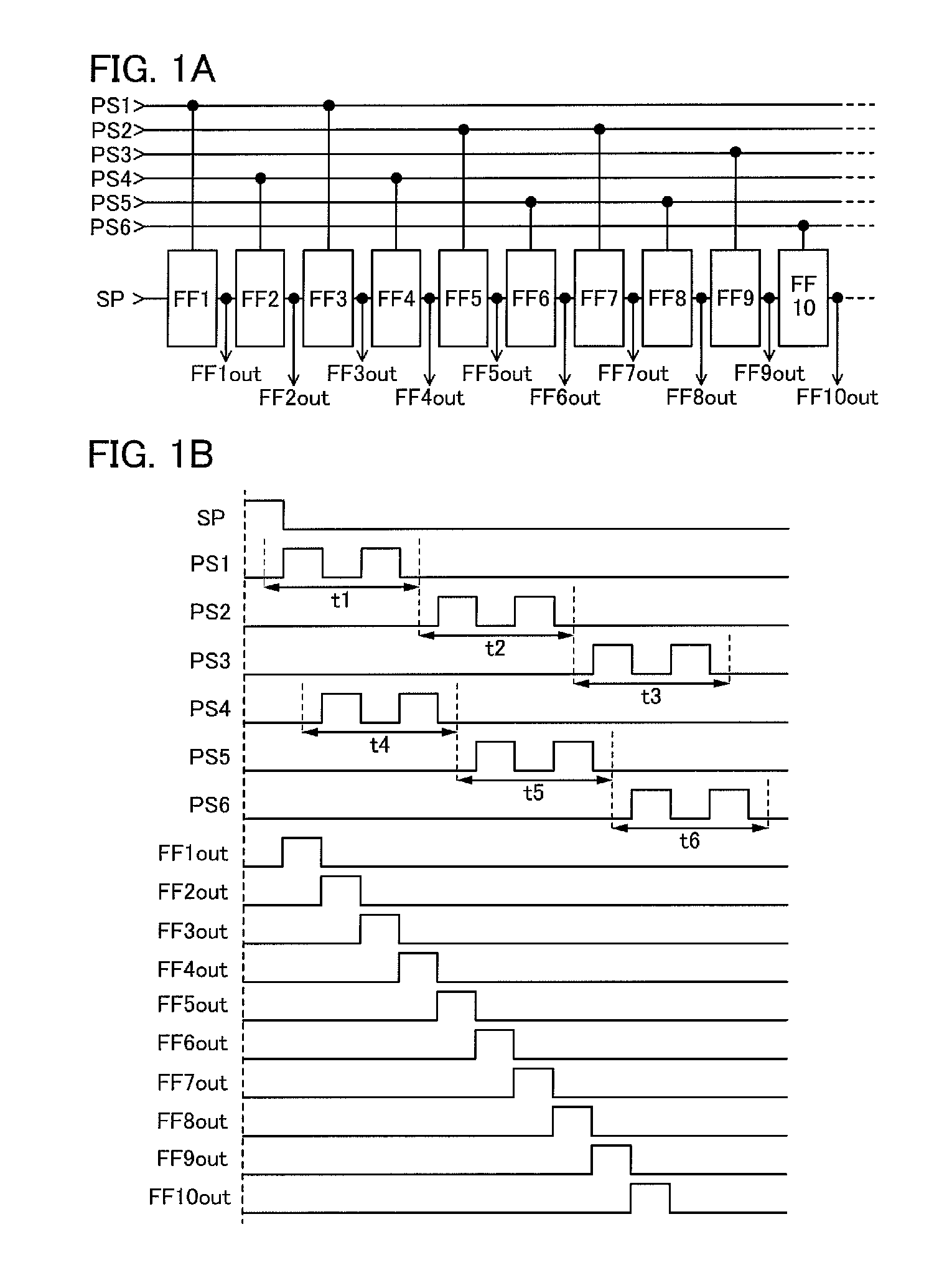

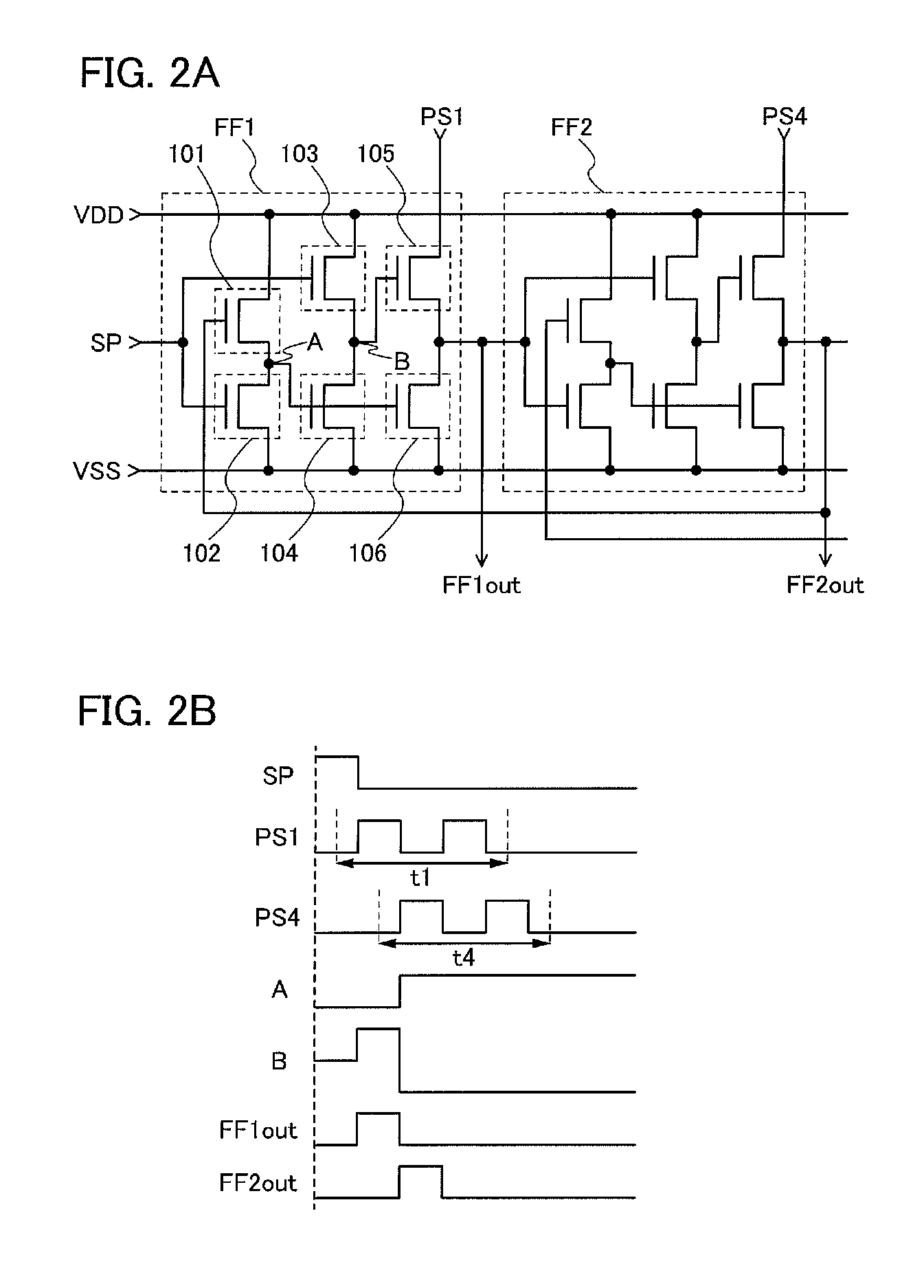

Signal line driving circuit and image display device

InactiveUS20060181502A1Reduce capacitanceReduce the numberTelevision system detailsStatic indicating devicesCapacitanceShift register

A signal line driving circuit includes a shift register having a plurality of shift circuits, each of which shifts a start pulse successively to the next stage, synchronizing with the timing of a clock signal. In this signal line driving circuit, shift pulses are outputted from an AND gate based on output pulses of two adjacent shift circuits. Meanwhile, a width specifying pulse for specifying a pulse width of the shift pulse is inputted via a transistor whose ON / OFF operation is controlled by the shift pulse. A logical operation circuit operates an AND of the shift pulse and the width specifying pulse and outputs the result of operation to a signal line. When the shift pulse is non-active, the transistor becomes OFF, which causes the signal line transmitting the width specifying pulse to be disconnected from the signal line driving circuit, thereby reducing a capacitive load of wiring. As a result, reduction of a parasitic capacitance of the wiring, reduction in the number of elements, reduction in the size of an amplitude of an input signal, etc. in the signal line driving circuit are attained.

Owner:SHARP KK

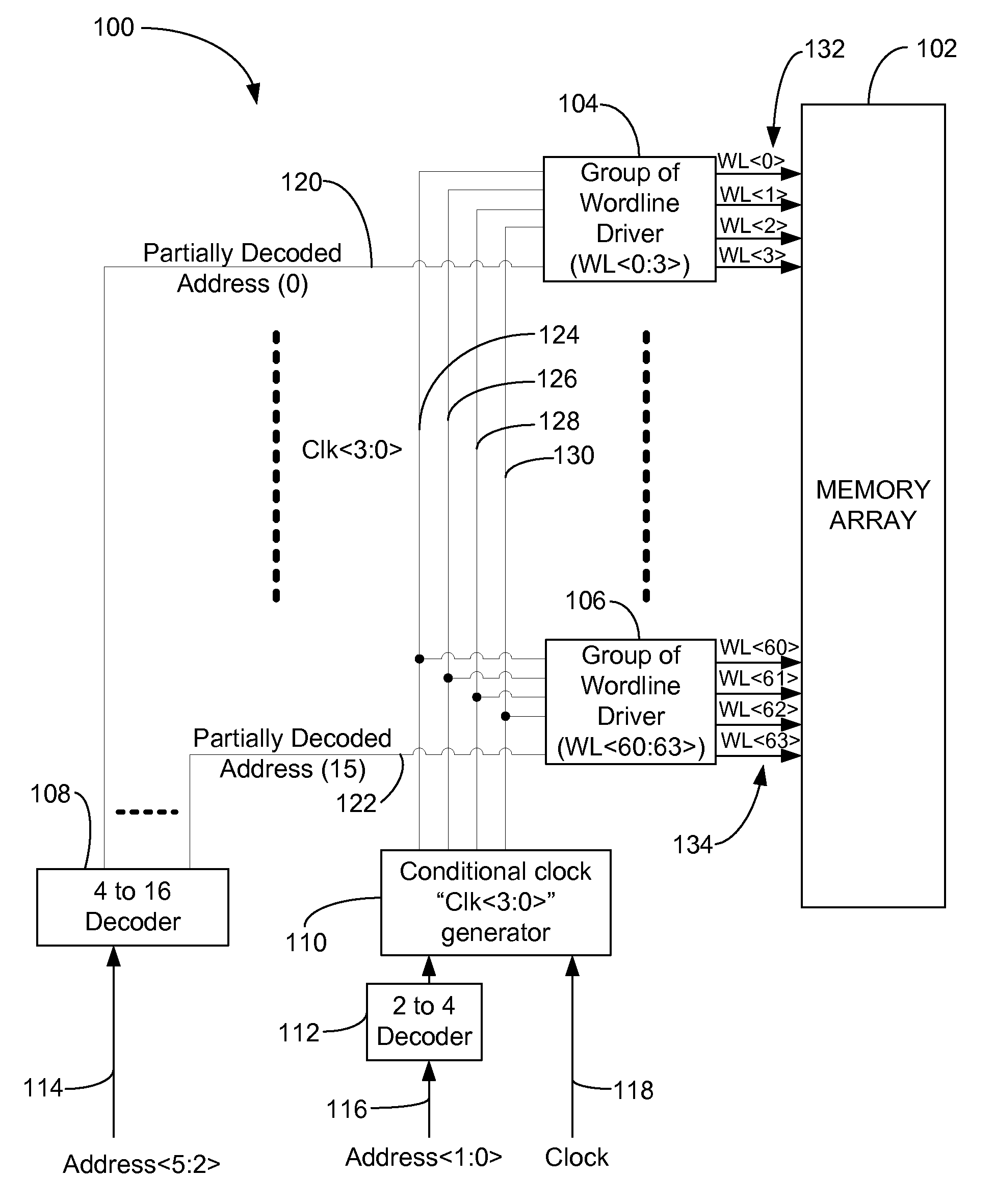

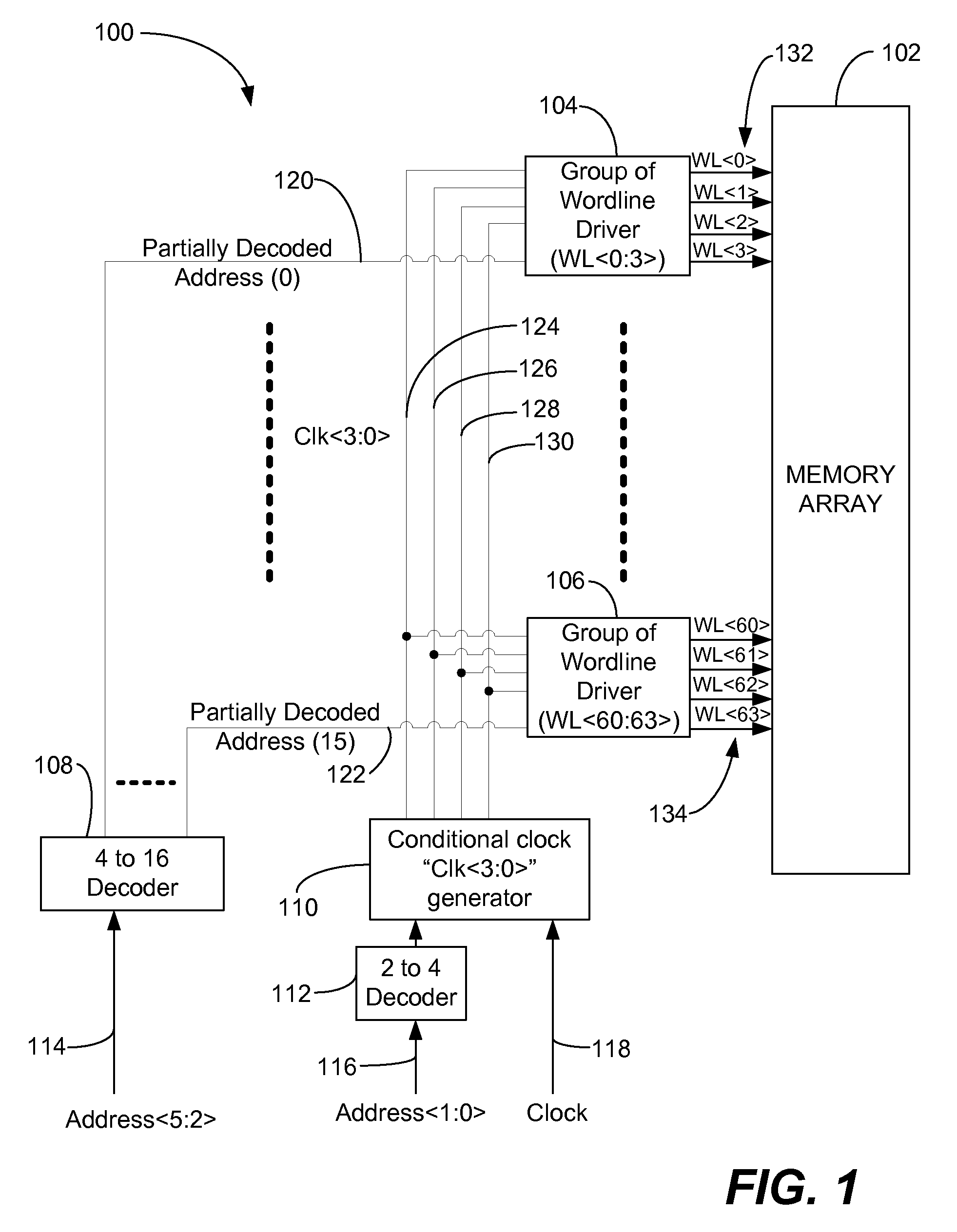

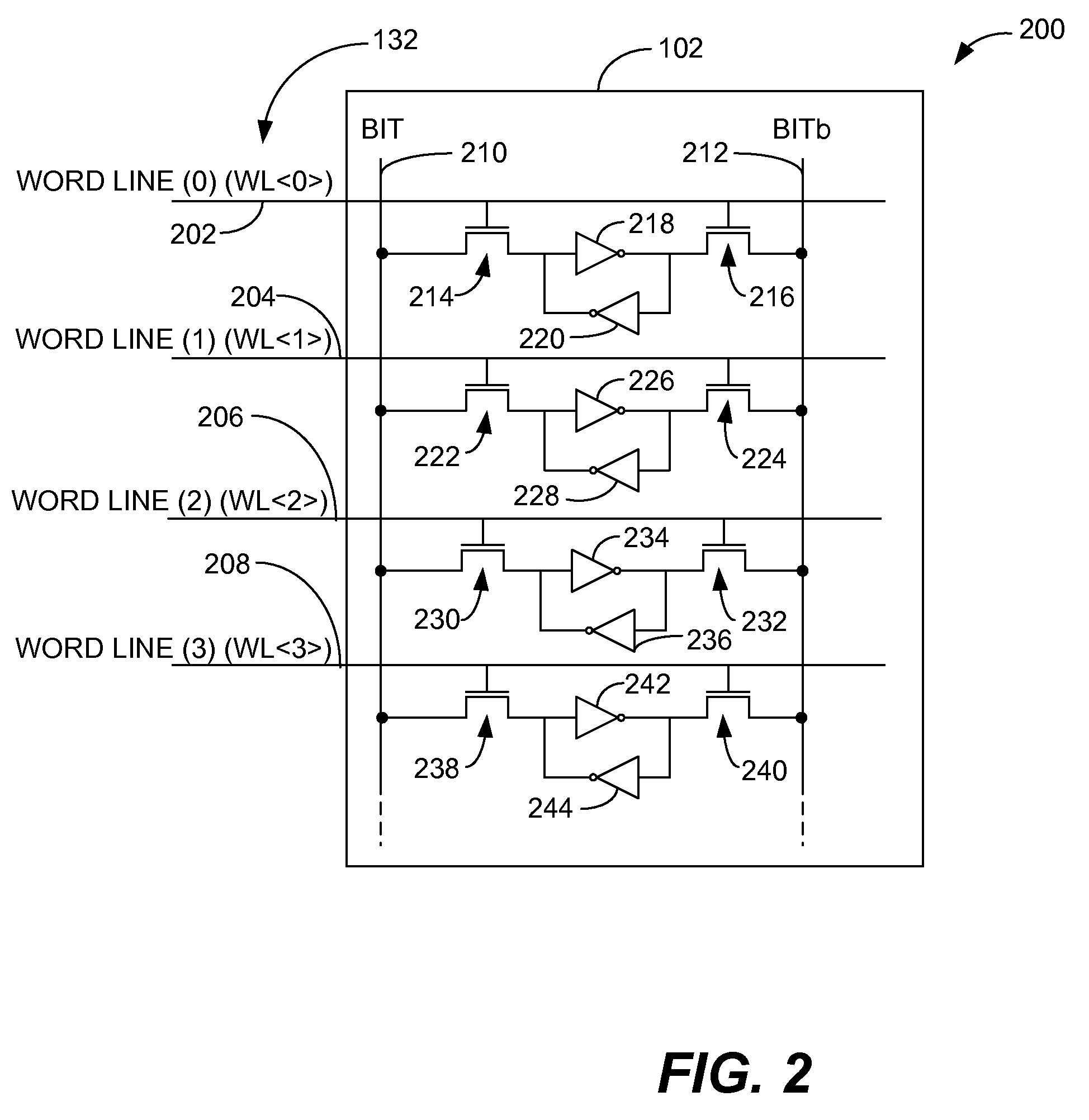

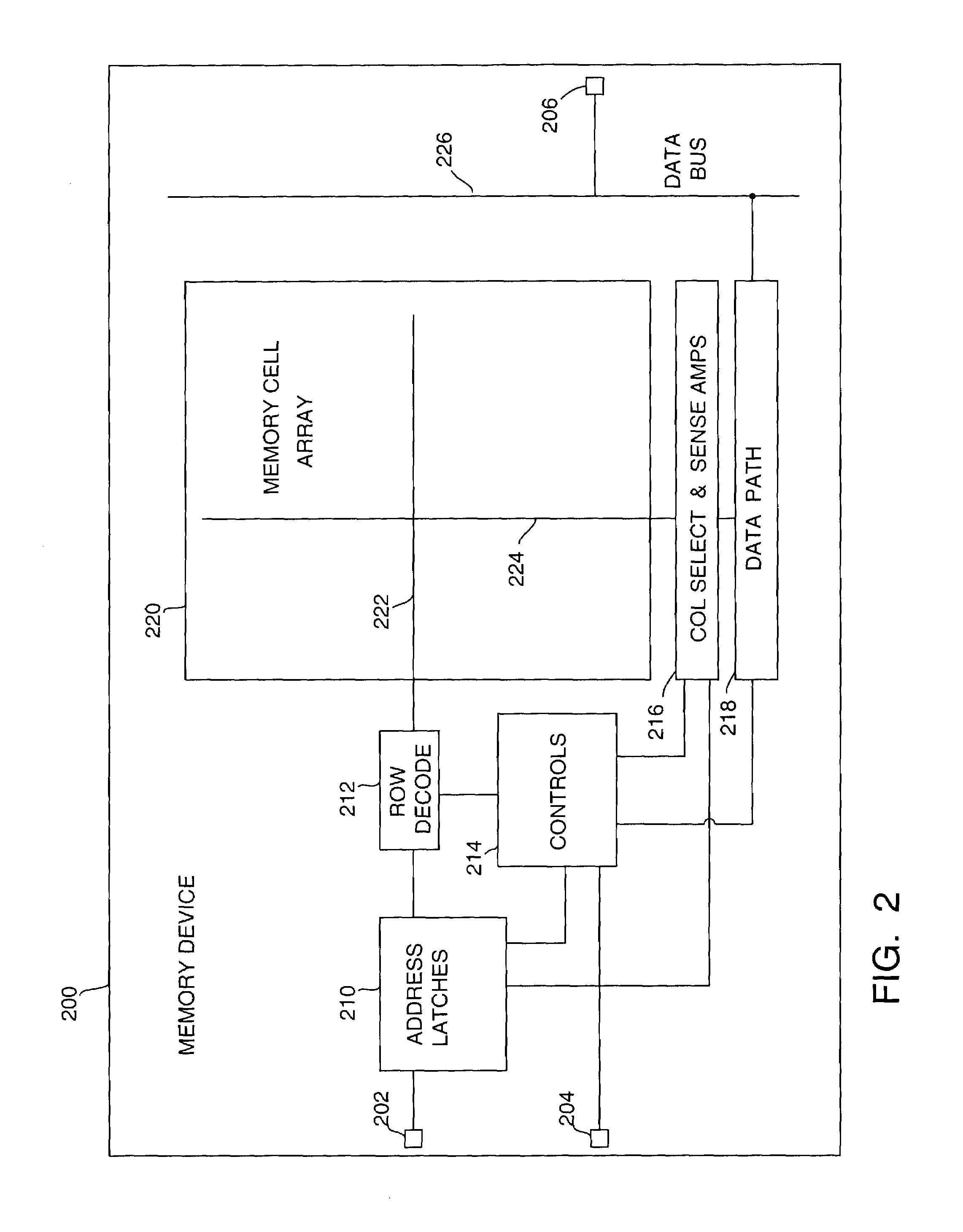

Dynamic word line drivers and decoders for memory arrays

In a particular illustrative embodiment, a circuit device that includes first logic and second logic is disclosed. The first logic receives a clock signal and a first portion of a memory address of a memory array, decodes the first portion of the memory address, and selectively applies the clock signal to a selected group of wordline drivers associated with the memory array. The second logic decodes a second portion of the memory address and selectively activates a particular wordline driver of the selected group of wordline drivers according to the second portion of the memory address.

Owner:QUALCOMM INC

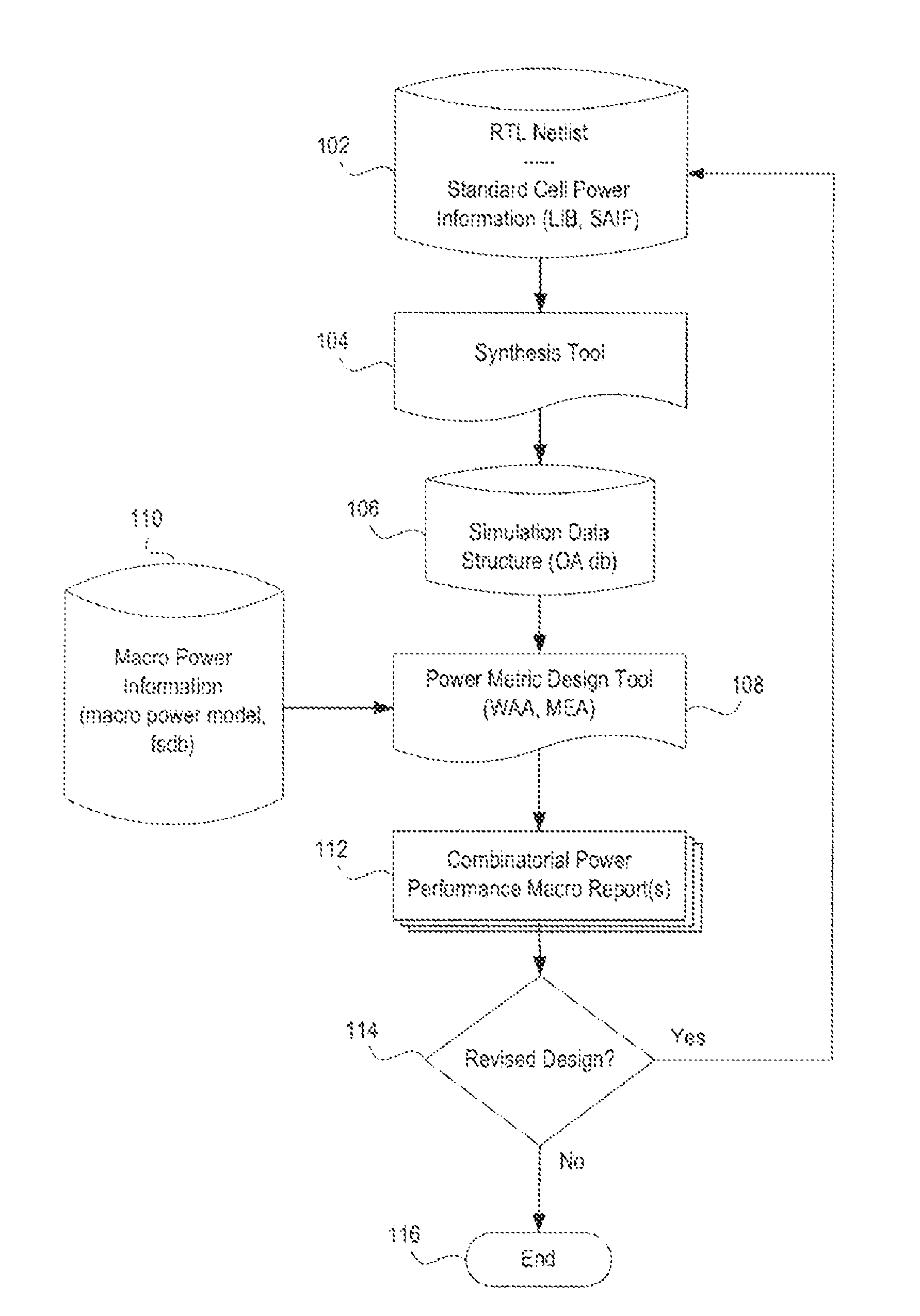

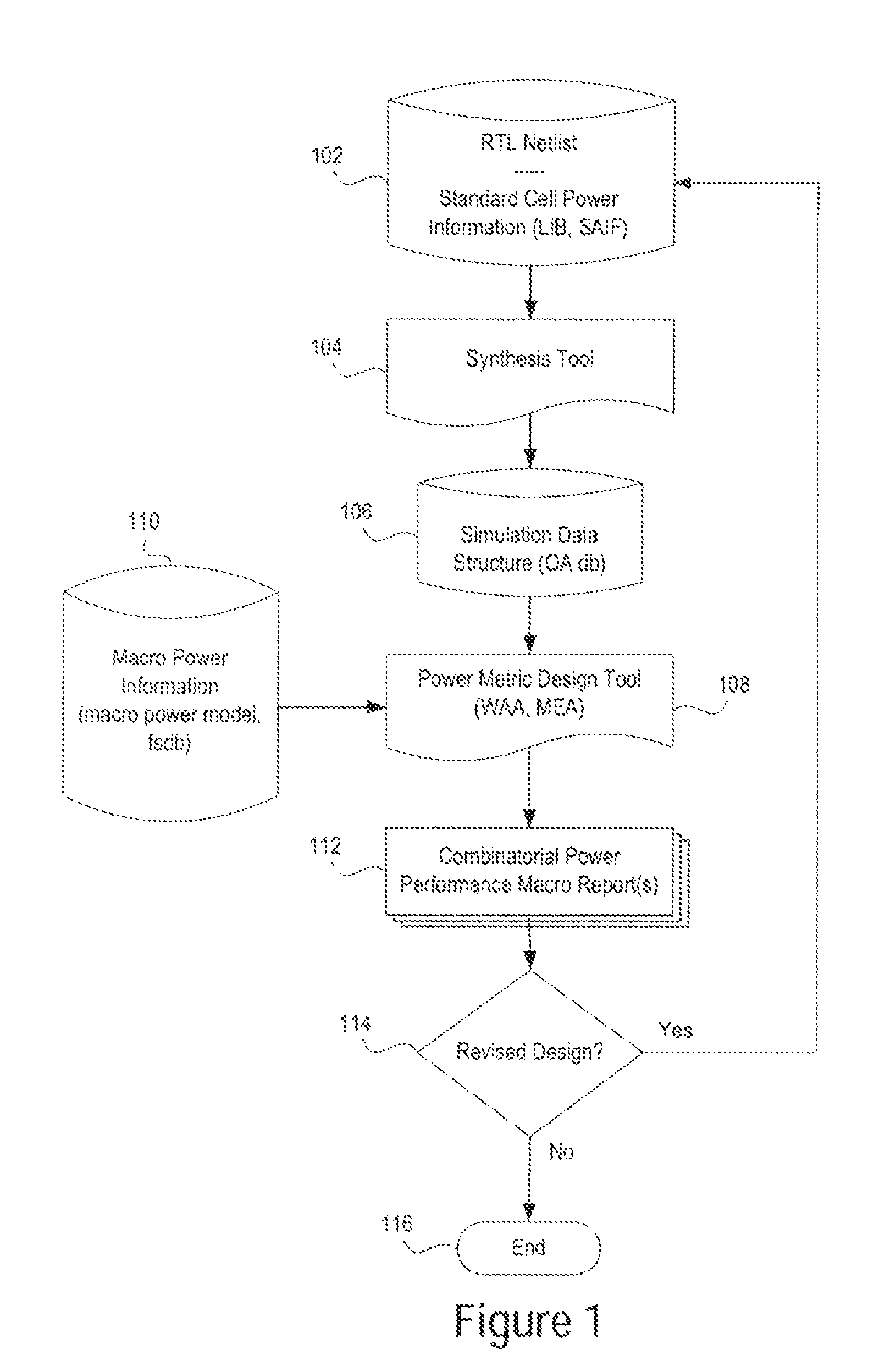

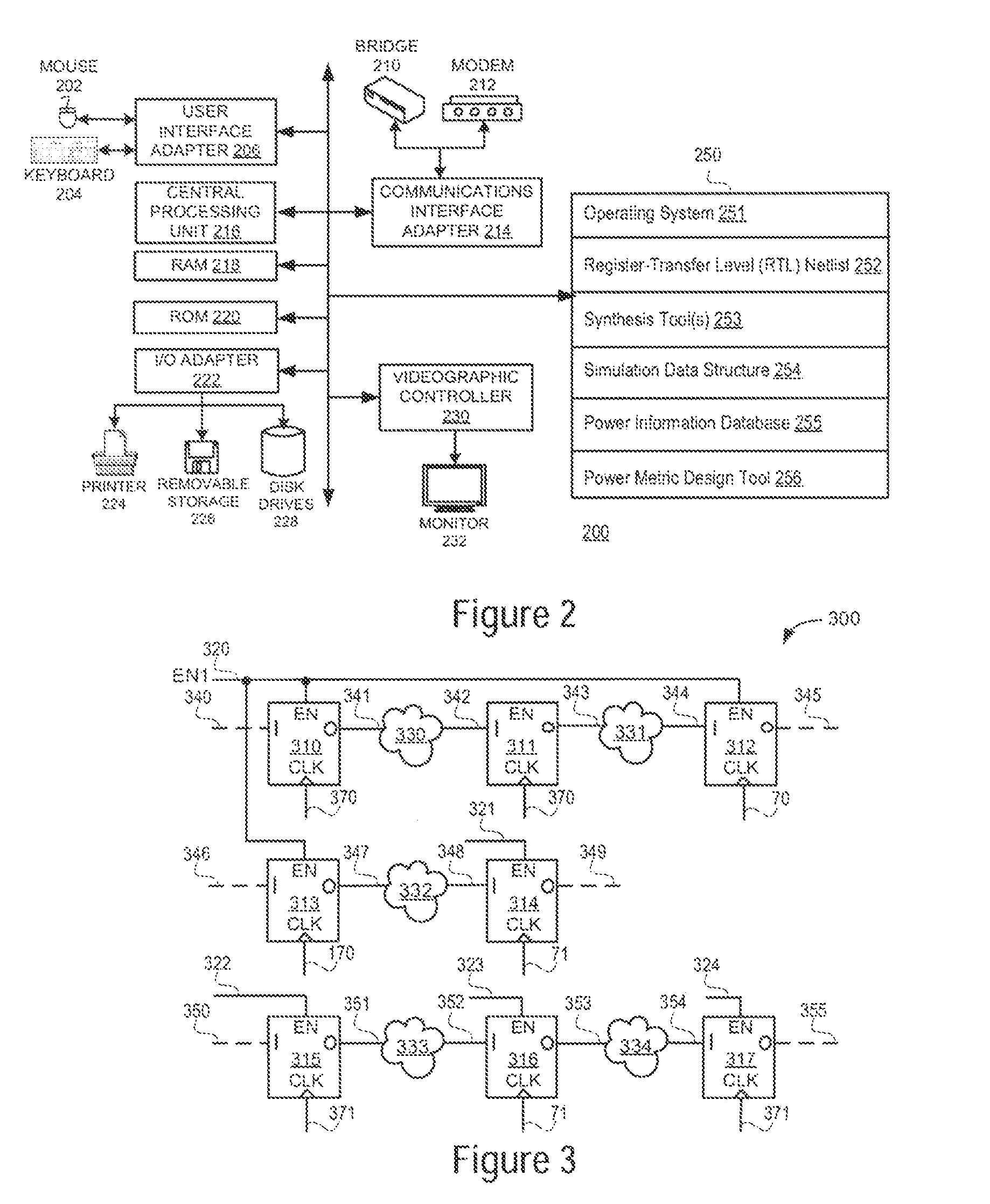

Identification of critical enables using MEA and WAA metrics

InactiveUS8266569B2Improve power performanceReduce power consumptionComputation using non-denominational number representationComputer aided designCapacitancePower performance

A plurality of sequential nodes in a design file for an electronic device are identified and one or more combinatorial power metric values are computed for the plurality of sequential nodes based upon an effective switching capacitance, a switching activity measure, and a power effort measure for at least a first device downstream from the each sequential node at a specified depth. The combinatorial power metric values for the plurality of sequential node are stored and compared to a target power metric value to determine if power consumption at the electronic device meets a predetermined power performance goal.

Owner:ADVANCED MICRO DEVICES INC

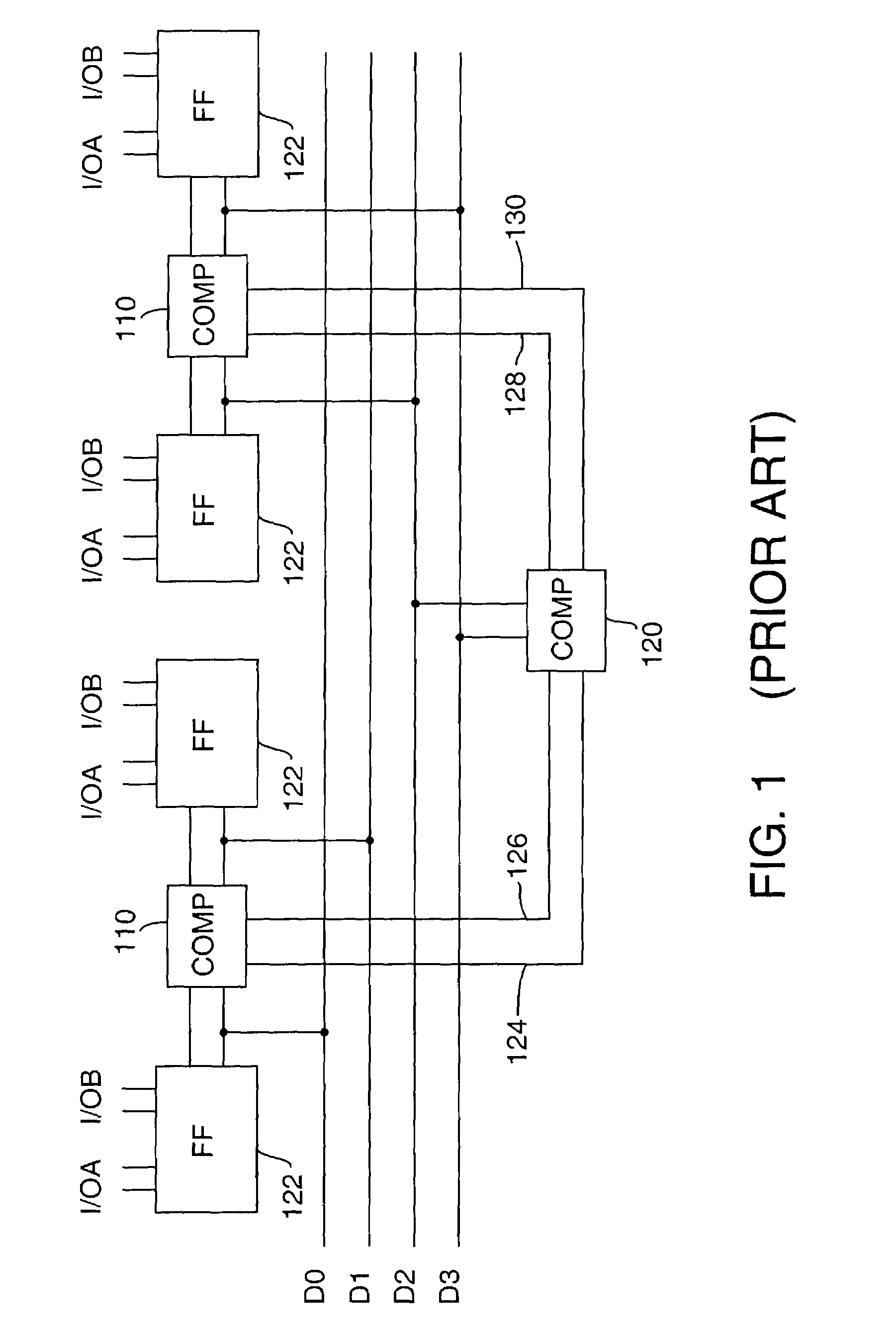

Memory data path circuit

InactiveUS7032143B1Improve scalabilityIncrease the compression ratioDigital storageDatapath circuitsNOR logic

A memory device with a data path circuit having support in the sense-amp region for compression testing of the device. The data path circuit uses NOR logic compression to provide a scalable design which may be extended to large circuits.

Owner:WALLER WILLIAM KENNETH

Signal line driving circuit and image display device

InactiveUS7042433B1Reduce the numberReduce parasitic capacitanceTelevision system detailsElectronic switchingShift registerDisplay device

A signal line driving circuit includes a shift register having a plurality of shift circuits, each of which shifts a start pulse successively to the next stage, synchronizing with the timing of a clock signal. In this signal line driving circuit, shift pulses are outputted from an AND gate based on output pulses of two adjacent shift circuits. Meanwhile, a width specifying pulse for specifying a pulse width of the shift pulse is inputted via a transistor whose ON / OFF operation is controlled by the shift pulse. A logical operation circuit operates an AND of the shift pulse and the width specifying pulse and outputs the result of operation to a signal line. When the shift pulse is non-active, the transistor becomes OFF, which causes the signal line transmitting the width specifying pulse to be disconnected from the signal line driving circuit, thereby reducing a capacitive load of wiring. As a result, reduction of a parasitic capacitance of the wiring, reduction in the number of elements, reduction in the size of an amplitude of an input signal, etc. in the signal line driving circuit are attained.

Owner:SHARP KK

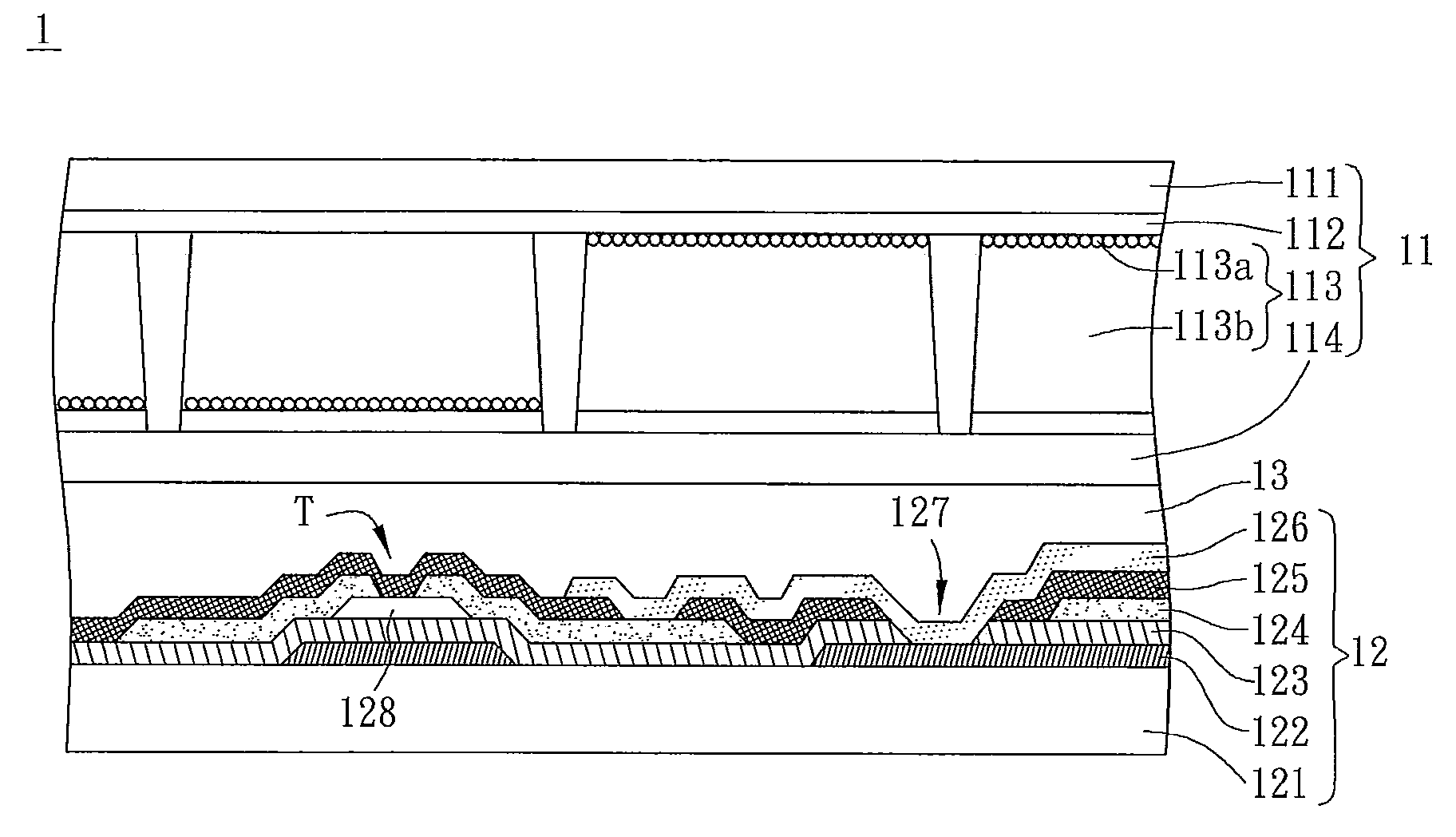

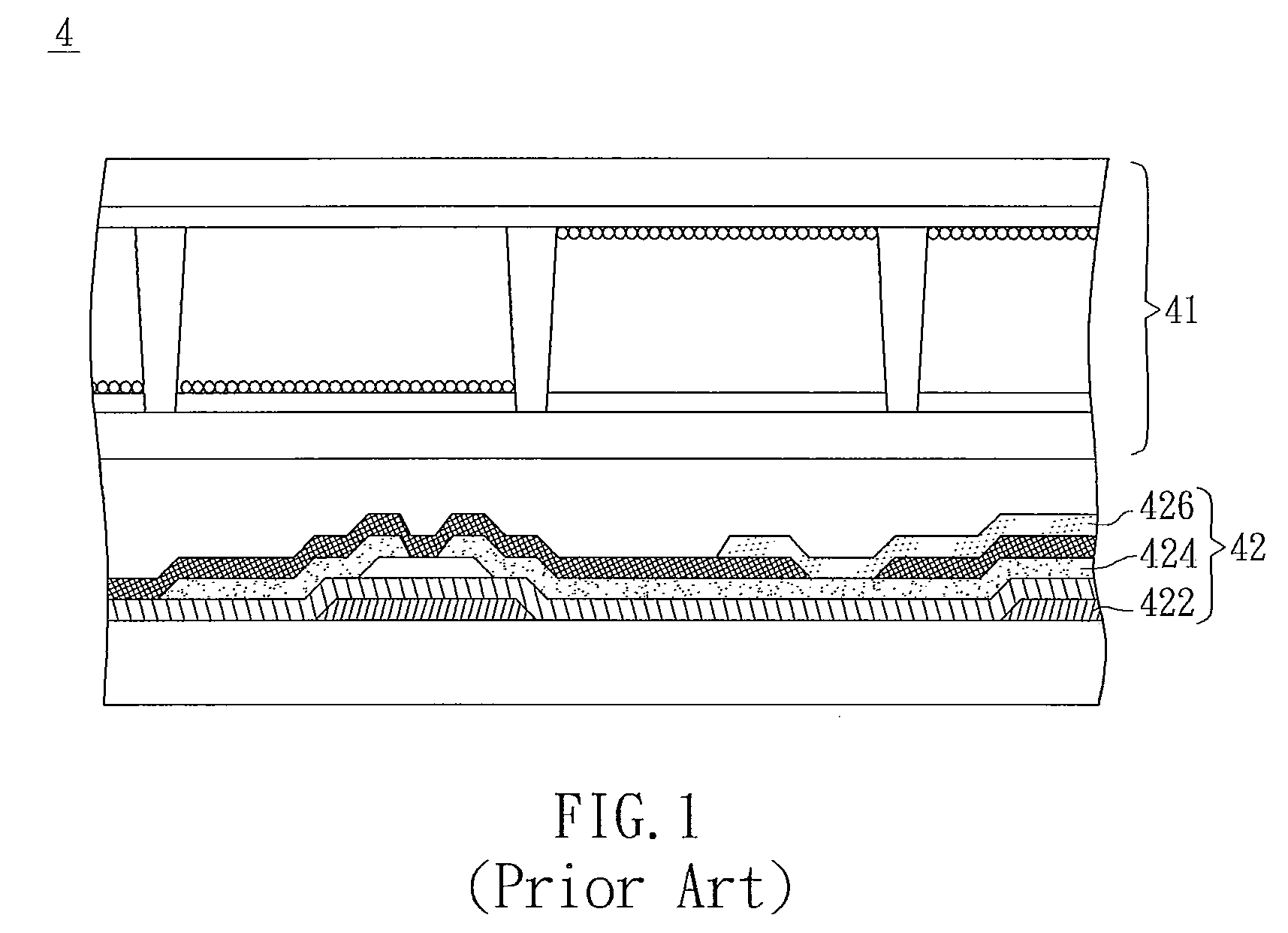

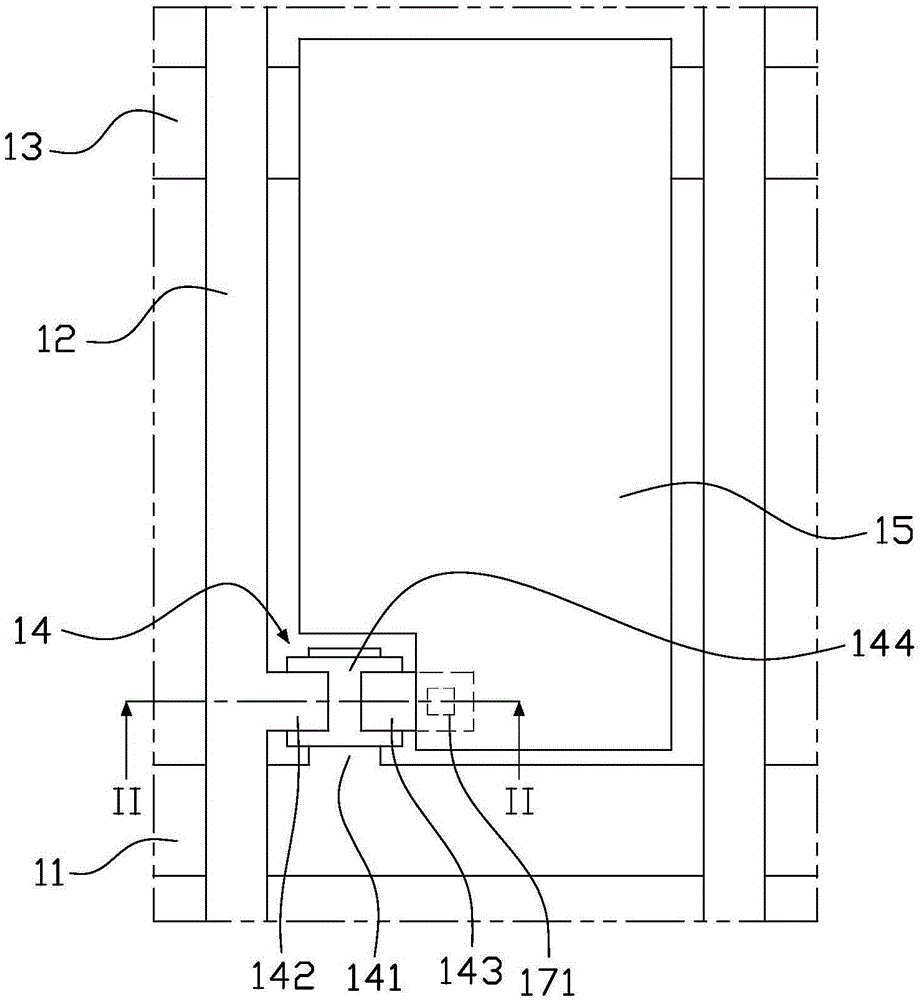

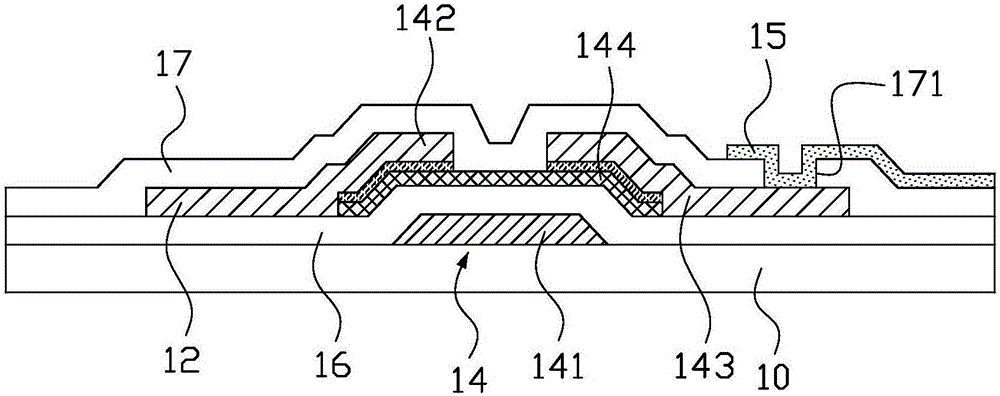

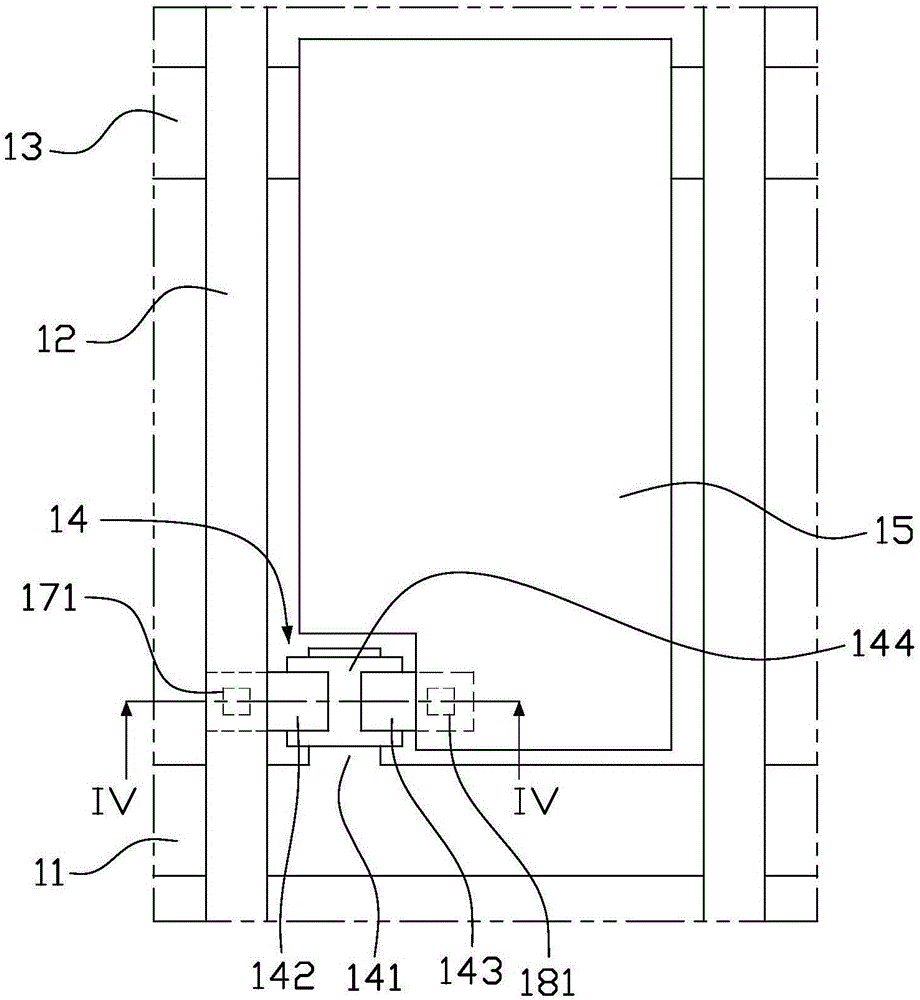

E-paper apparatus and driving substrate thereof

InactiveUS20090244689A1Reduce power consumptionReduce data loadStatic indicating devicesPrinted electric component incorporationScan lineCommon line

A driving substrate of an e-paper apparatus includes a first metal layer, a second metal layer and a pixel electrode. The first metal layer has a scan line and a first storage electrode. The second metal layer has a data line and a common line. The scan line and the data line are disposed crossingly. The common line is disposed parallel to the data line substantially. The common line and the scan line are disposed crossingly. The pixel electrode is disposed over the common line and is electrically connected to the first storage electrode through a via.

Owner:AUSK OPTOELECTRONICS

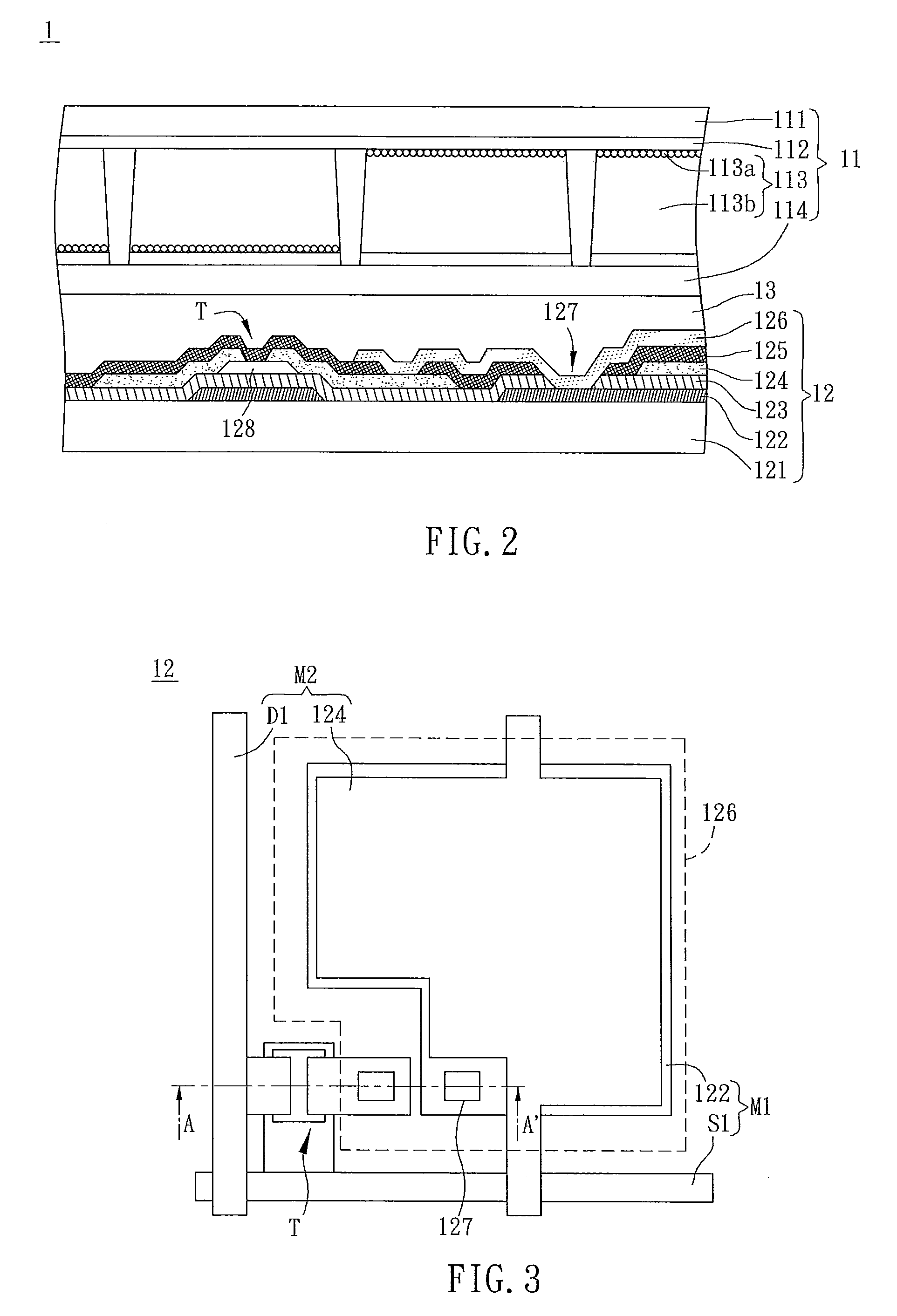

Thin film transistor array substrate, manufacturing method and liquid crystal display panel

ActiveCN106483726AIncreasing the thicknessImprove alignment accuracySolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayInsulation layer

Provided are a thin film transistor array substrate, a manufacturing method and a liquid crystal display panel. The thin film transistor array substrate comprises a substrate, a first metal layer, a first insulation layer, an active layer, a second metal layer, a second insulation layer, a third metal layer, a third insulation layer and a pixel electrode. The first metal layer is formed on the substrate and comprises a scanning line and a grid. The first metal layer is covered with the first insulation layer, and the active layer is formed on the first insulation layer. The second metal layer is formed on the first insulation layer and comprises a source electrode and a drain electrode. The second metal layer is covered with the second insulation layer, and a first contact hole and a second contact hole are formed in the second insulation layer. The third metal layer is formed on the second insulation layer and comprises a data line and a conductive block, the data line is connected with the source electrode through the first contact hole, and the conductive block is connected with the drain electrode through the second contact hole. The third metal layer is covered with the third insulation layer, and a third contact hole is formed in the third insulation layer. The pixel electrode is formed on the third insulation layer, and the pixel electrode is connected with the conductive block through the third contact hole.

Owner:KUSN INFOVISION OPTOELECTRONICS

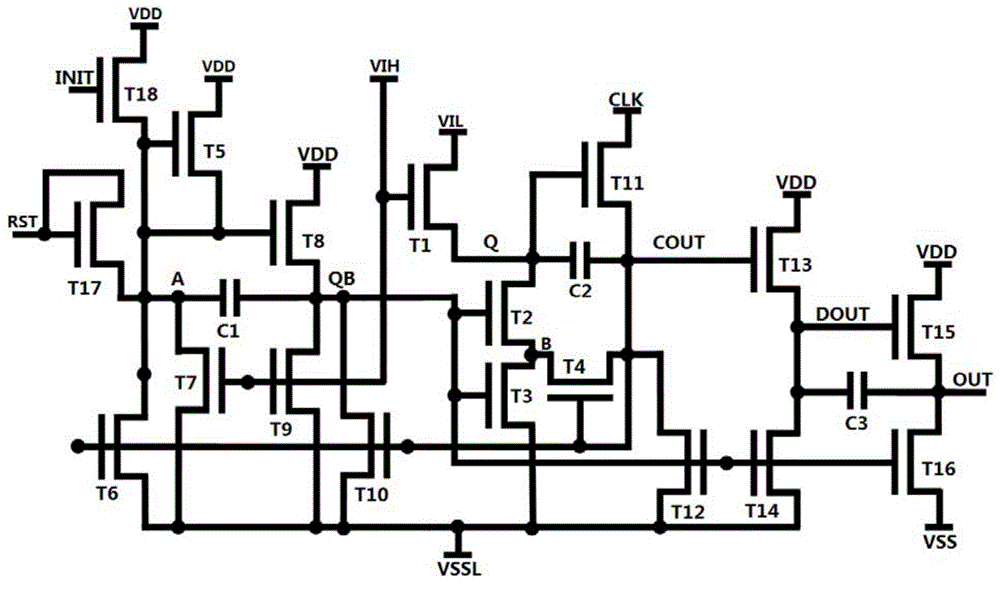

Shift register and display device and driving method thereof

ActiveUS8526567B2Reduce power consumptionReduce capacitive loadStatic indicating devicesSolid-state devicesShift registerDisplay device

The power consumption of a shift register or a display device including the shift register is reduced. A clock signal is supplied to a shift register by a plurality of wirings, not by one wiring. Any one of the plurality of wirings supplies a clock signal in only part of the operation period of the shift register, not during the whole operation period of the shift register. Therefore, the capacity load caused with the supply of clock signals can be reduced, leading to reduction in power consumption of the shift register.

Owner:SEMICON ENERGY LAB CO LTD

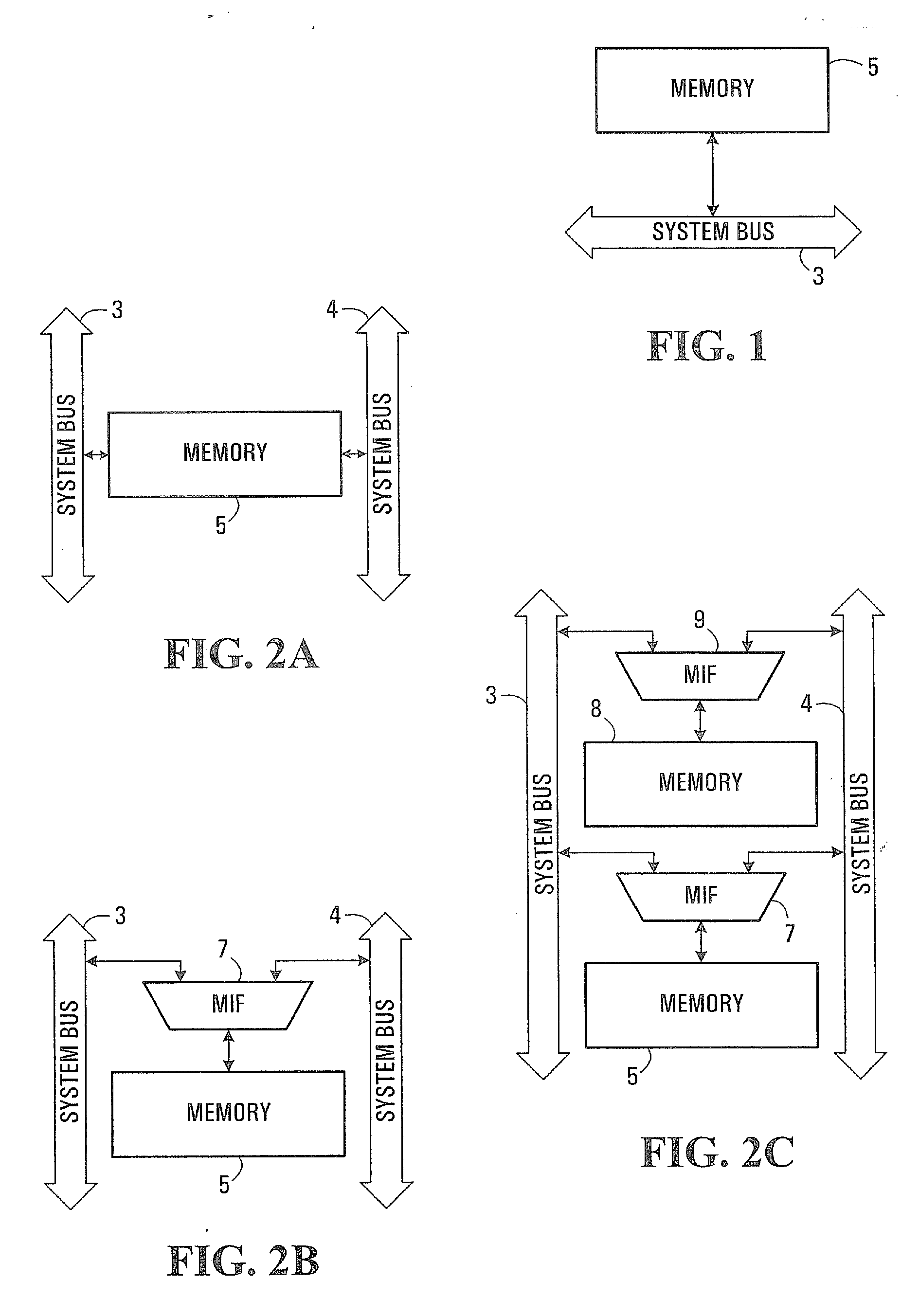

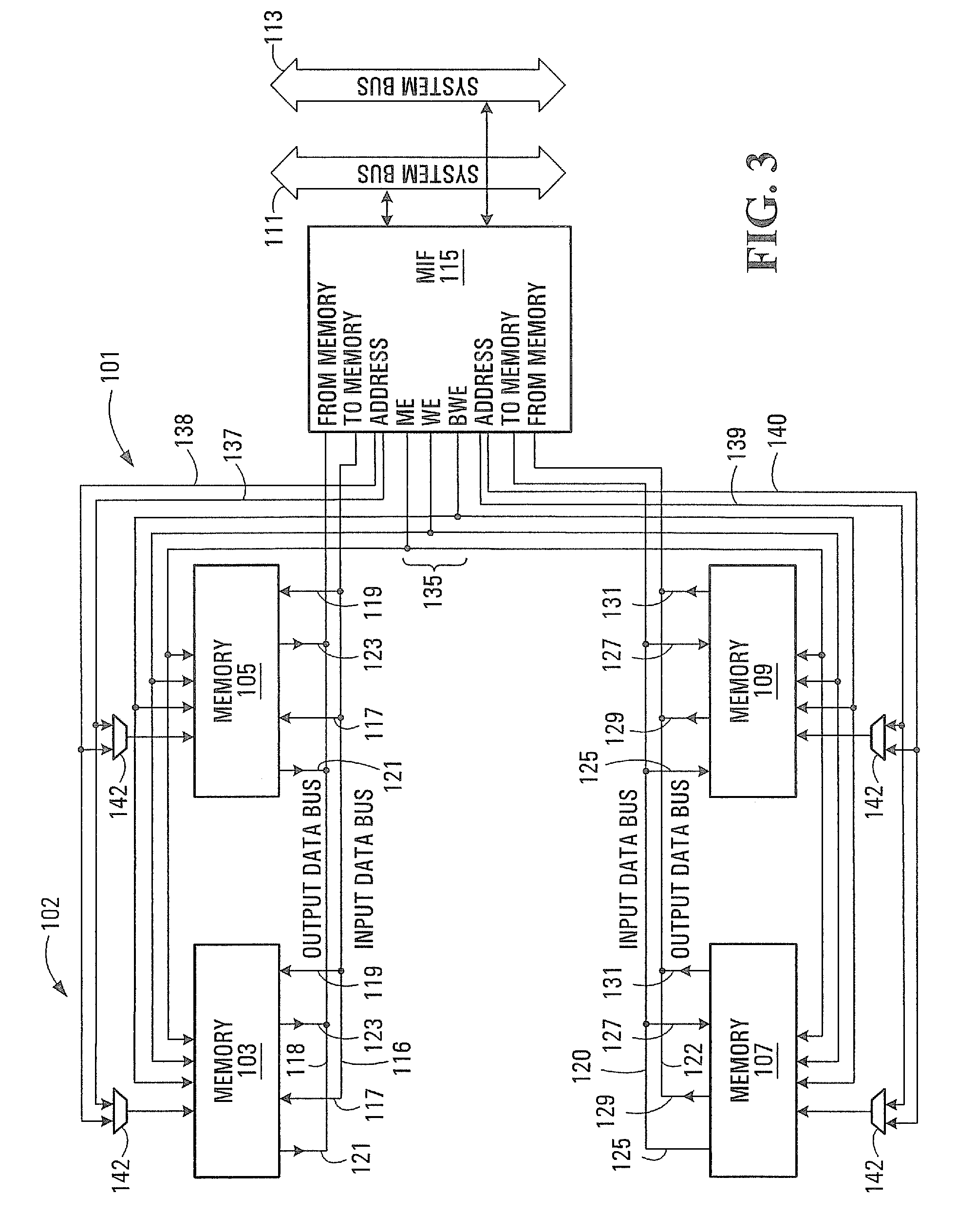

Apparatus and method for controlling access to a memory

InactiveUS20060248247A1Reduce capacitive loadIncrease speedElectric digital data processingEmbedded systemControl memory

An apparatus and method are provided for producing an assembly comprising a memory, a plurality of data buses and an interface for controlling access to the memory by each data bus. The interface is arranged to control memory access so that the plurality of devices can access different parts of the memory substantially simultaneously. A single interface is used to control memory accesses to different parts or elements of a memory substantially simultaneously so that a plurality of, or multiple memory accesses can be performed at the same time.

Owner:MTEKVISION CO LTD