Patents

Literature

69 results about "NOR logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A NOR gate is a logic gate which gives a positive output only when both inputs are negative. Like NAND gates, NOR gates are so-called "universal gates" that can be combined to form any other kind of logic gate. For example, the first embedded system, the Apollo Guidance Computer, was built exclusively from NOR gates, about 5,600 in total for the later versions. Today, integrated circuits are not constructed exclusively from a single type of gate. Instead, EDA tools are used to convert the description of a logical circuit to a netlist of complex gates (standard cells) or transistors (full custom approach).

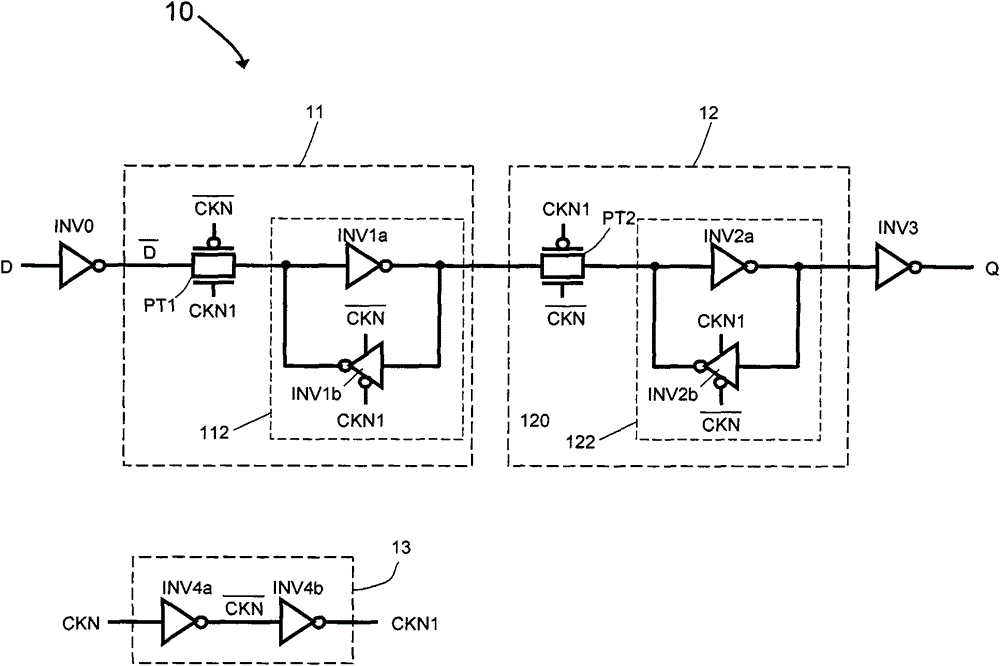

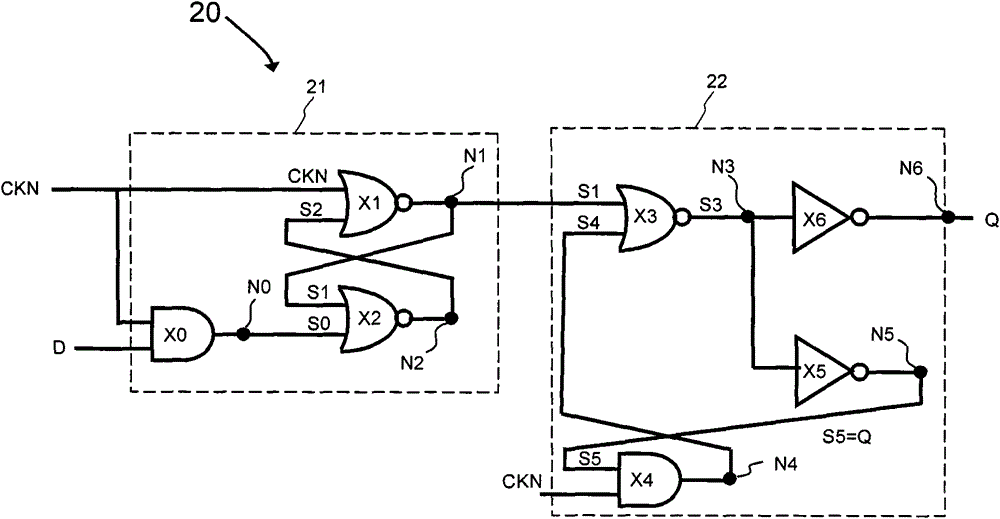

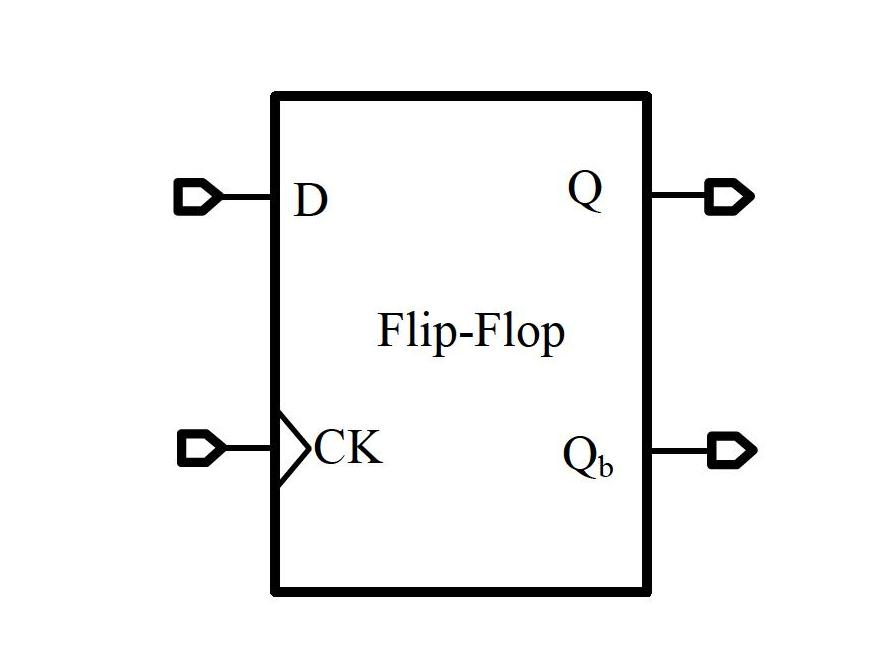

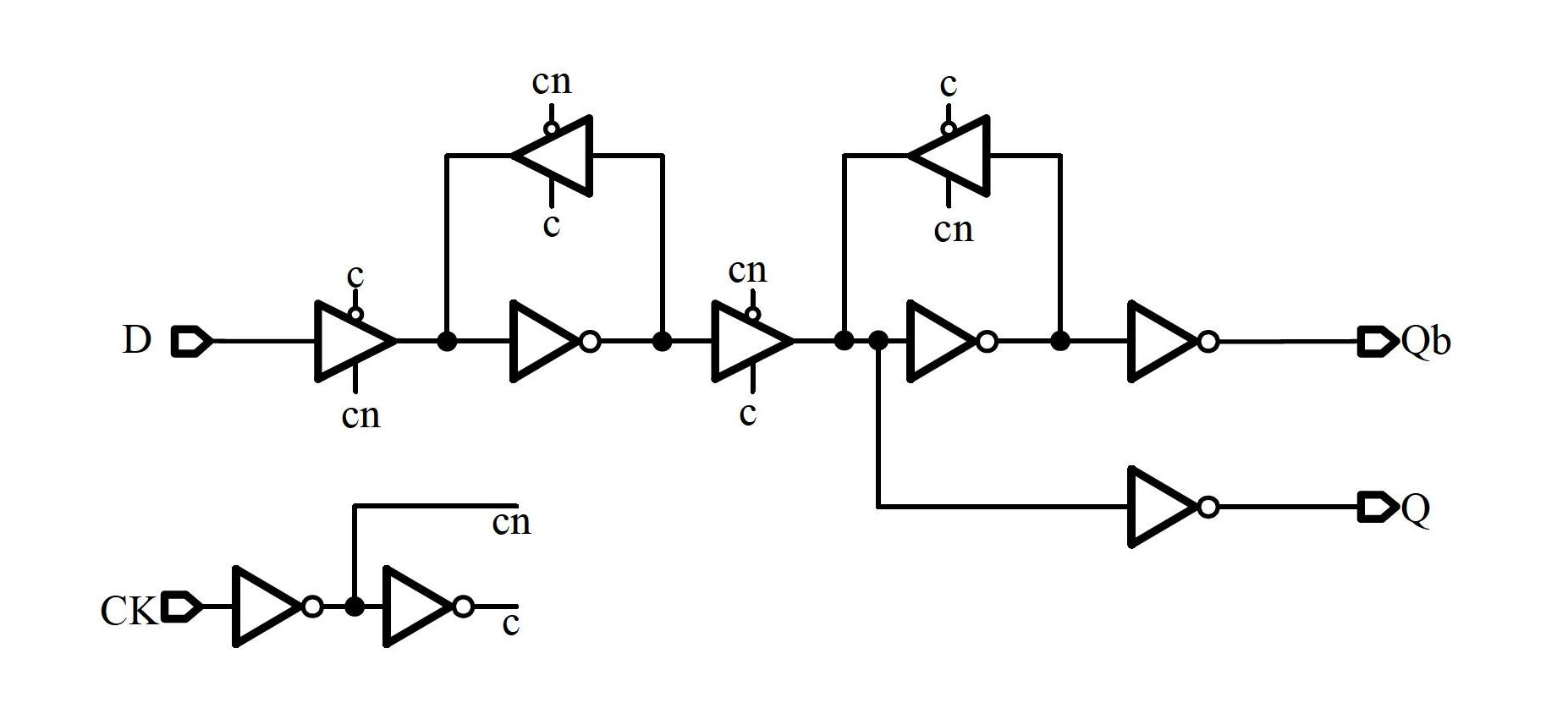

Flip-flop circuit

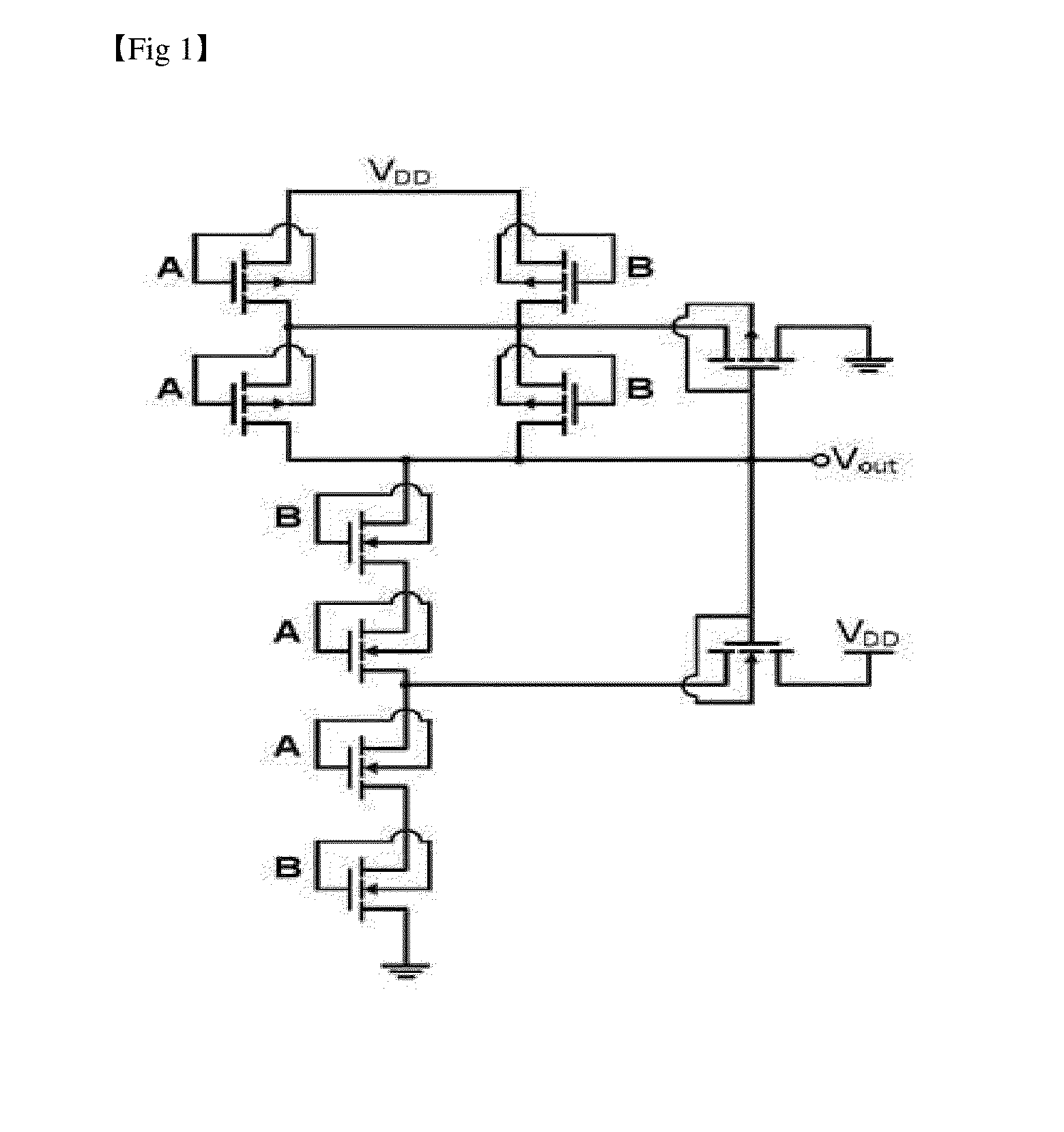

ActiveCN104796132ASimple structureReduce dynamic power consumptionLogic circuitsNOR logicData signal

The invention provides a flip-flop circuit, and belongs to the technical field of semiconductor integrated circuits. The flip-flop circuit comprises a master latch and a secondary latch driven by clocking signals with same phases; the master latch comprises a first logic module for selectively and at least performing AND logic processing on an input data signal and the clock signal, a second logic module for at least performing NOR logic processing on the clock signal and an output signal of a third logic module, and the third logic module for selectively and at least performing the NOR logic processing on the output signal of the first logic module and the output signal of the second logic module so as to output a result to the second logic module; the secondary latch comprises a fourth logic module for at least performing the NOR logic processing on the output signal of the second logic module and the output signal of a fifth logic module, and the fifth logic module for at least performing the AND logic processing on the clock signal and an inversion signal of the output signal of the fourth logic module. The flip-flop circuit is low in dynamic power consumption.

Owner:陈祺琦

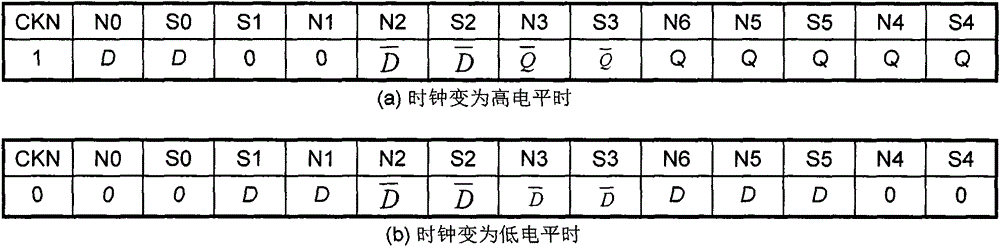

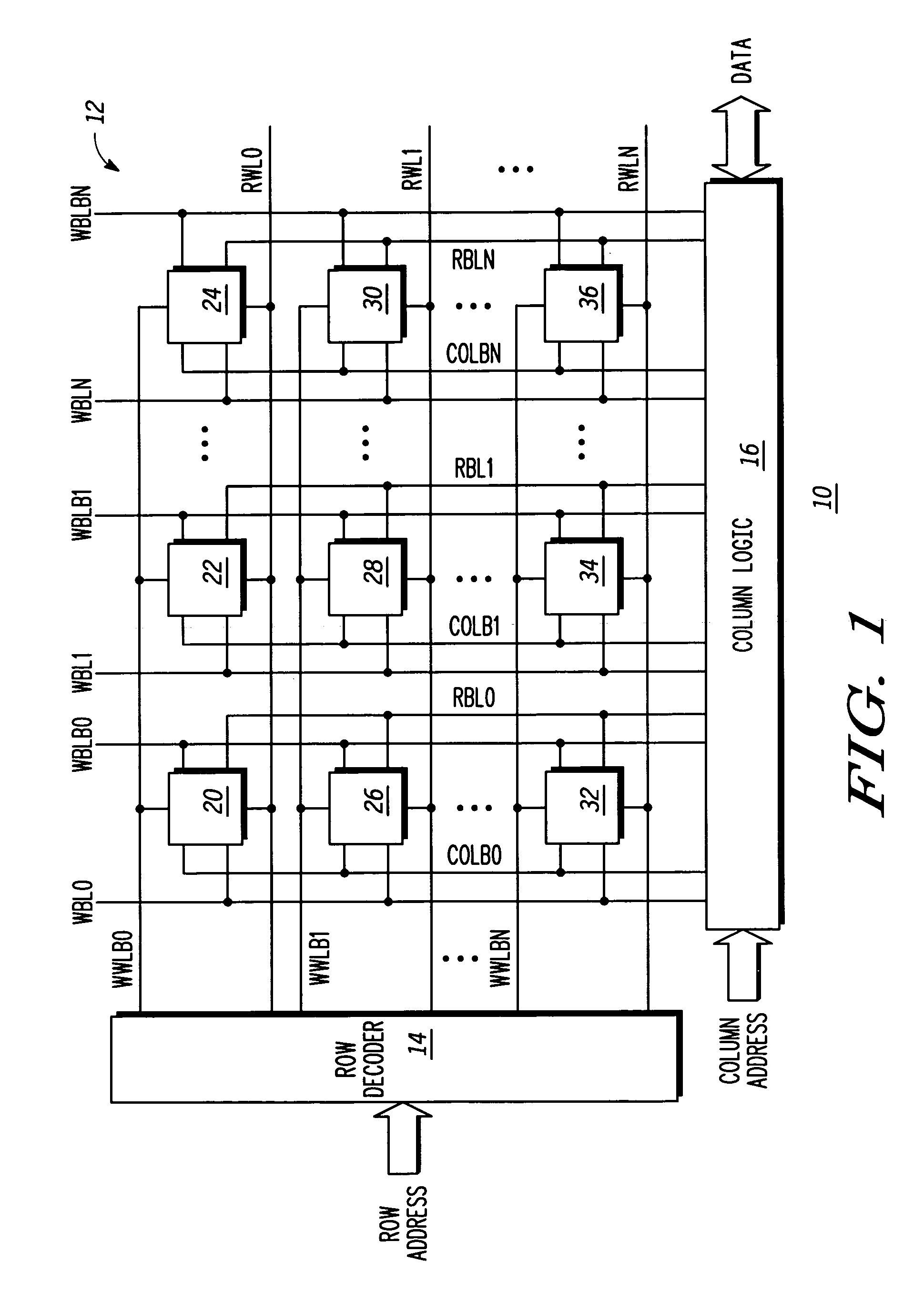

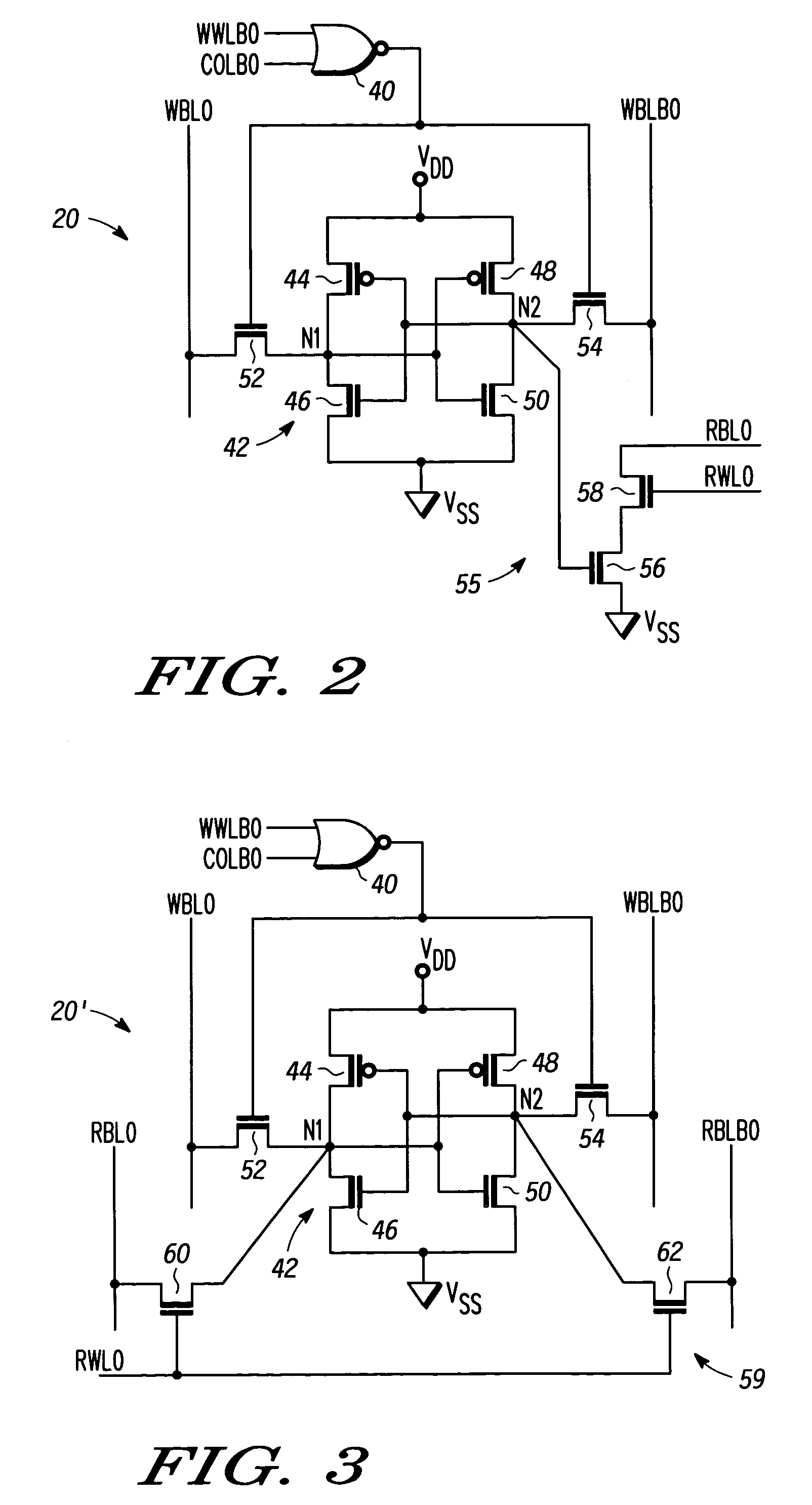

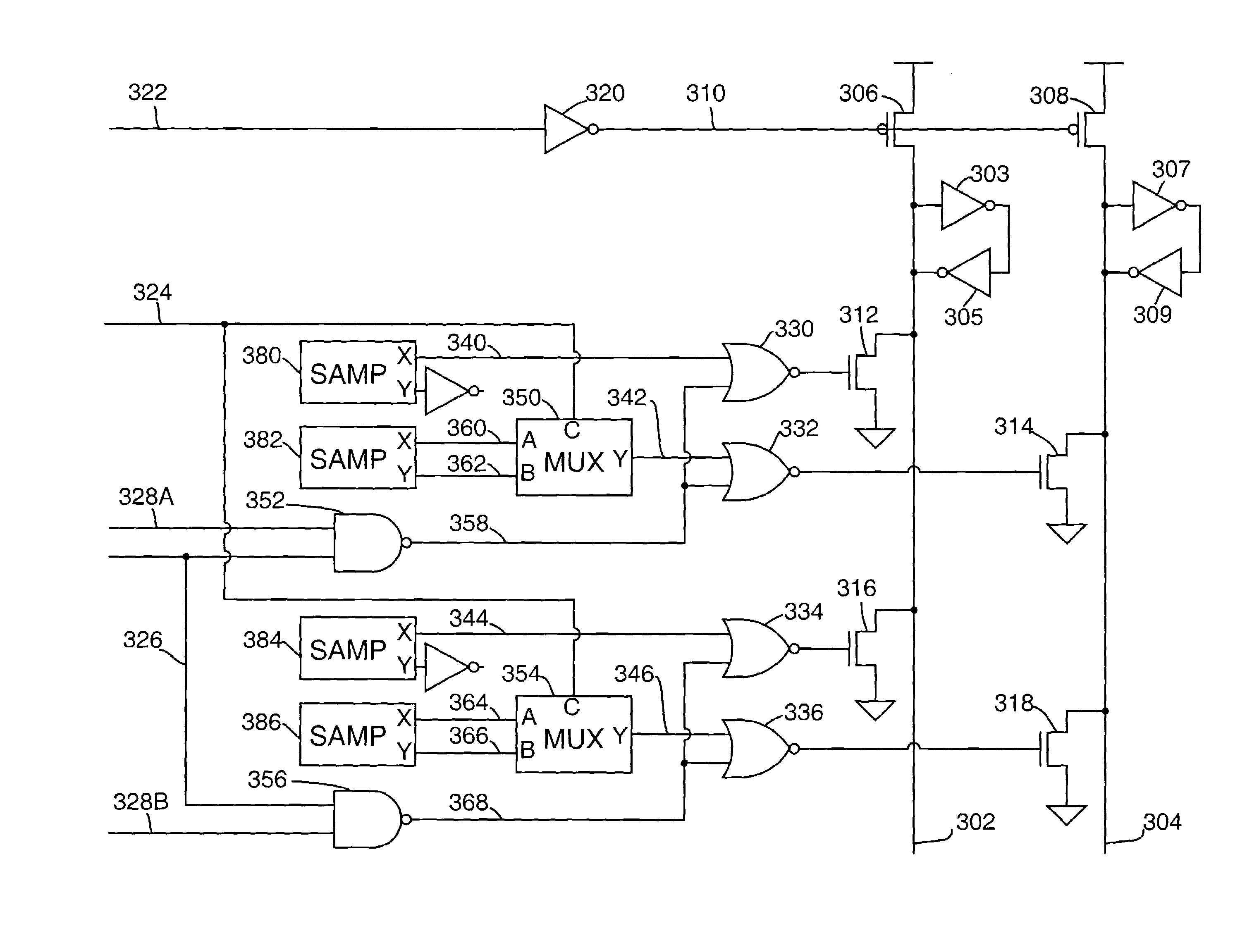

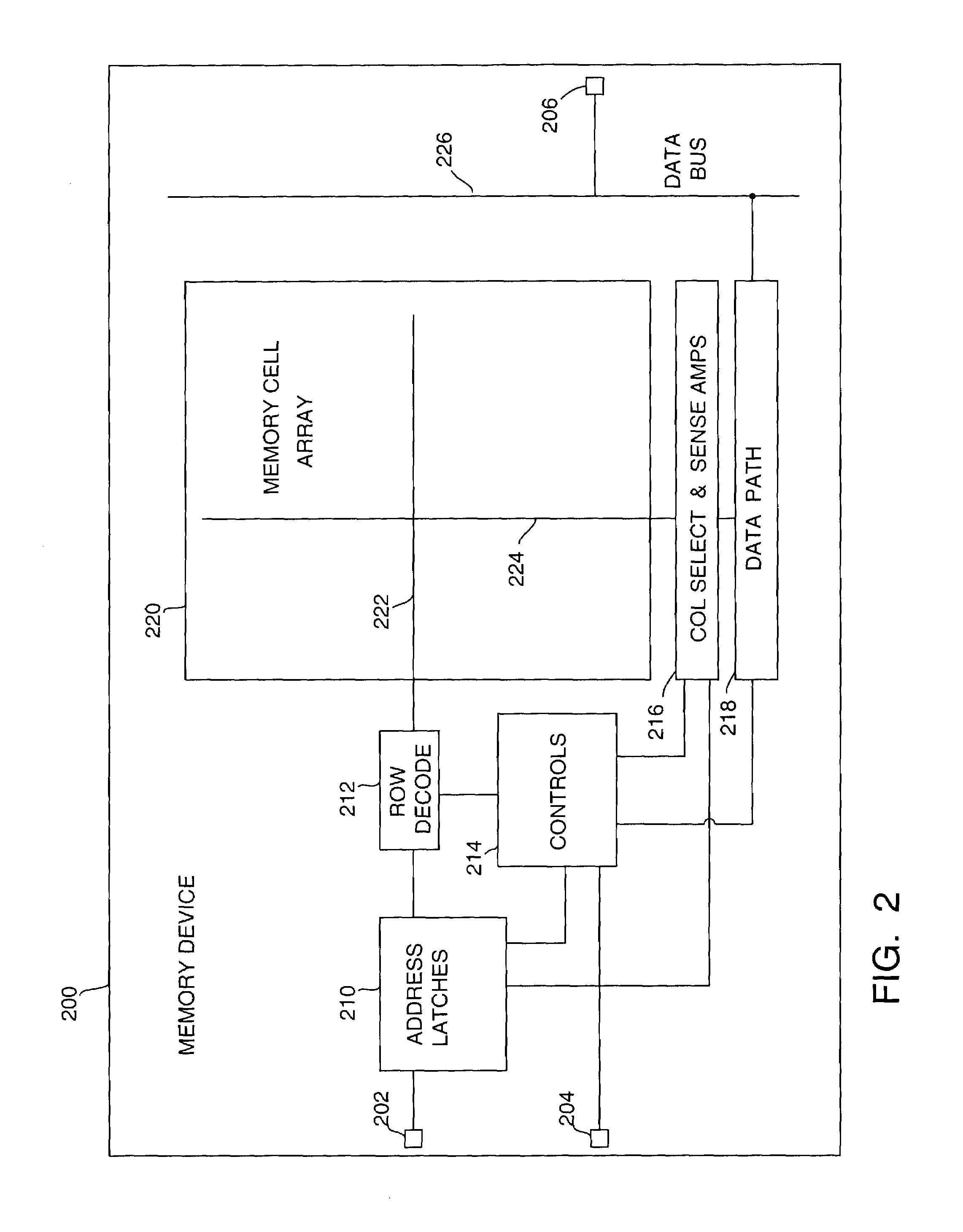

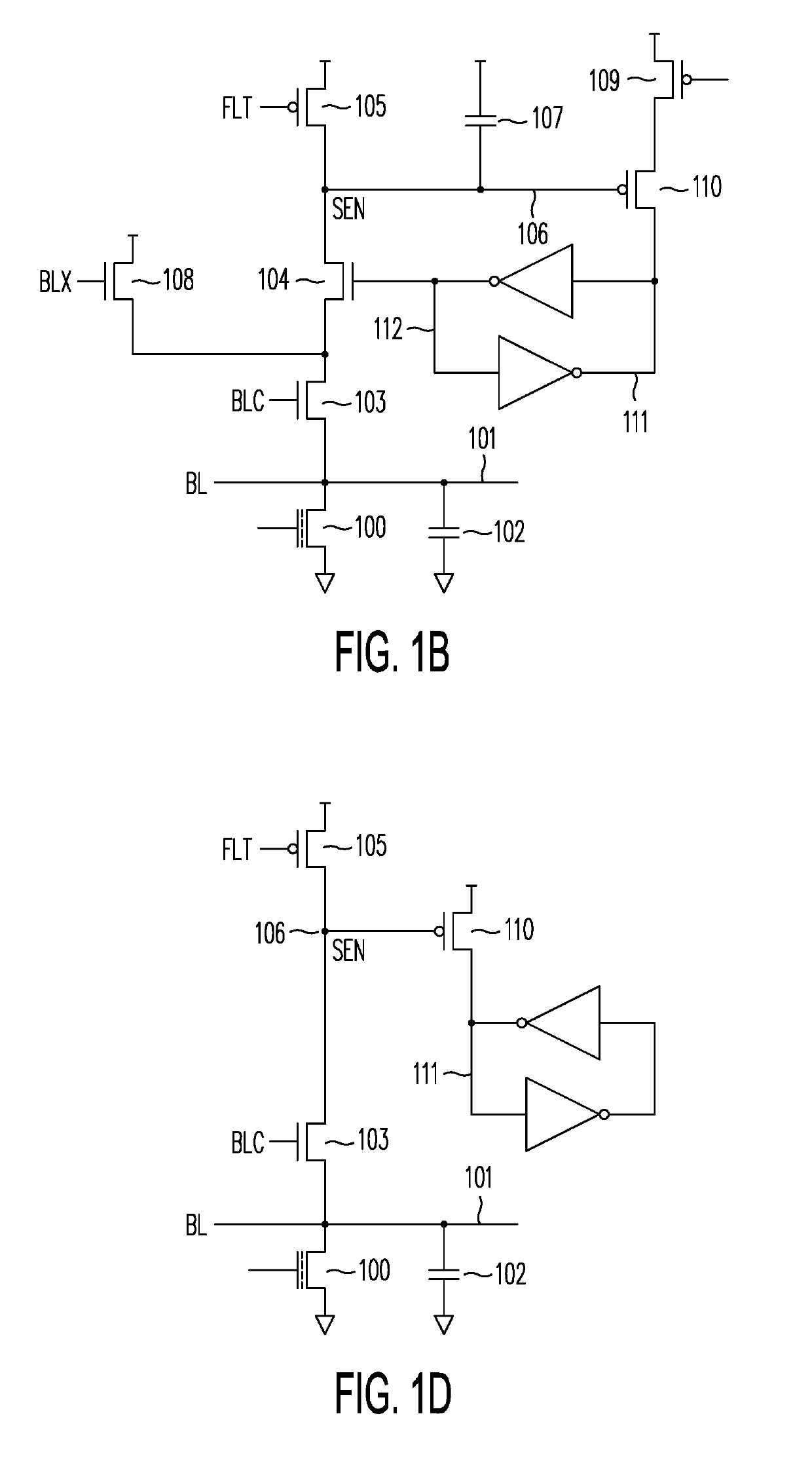

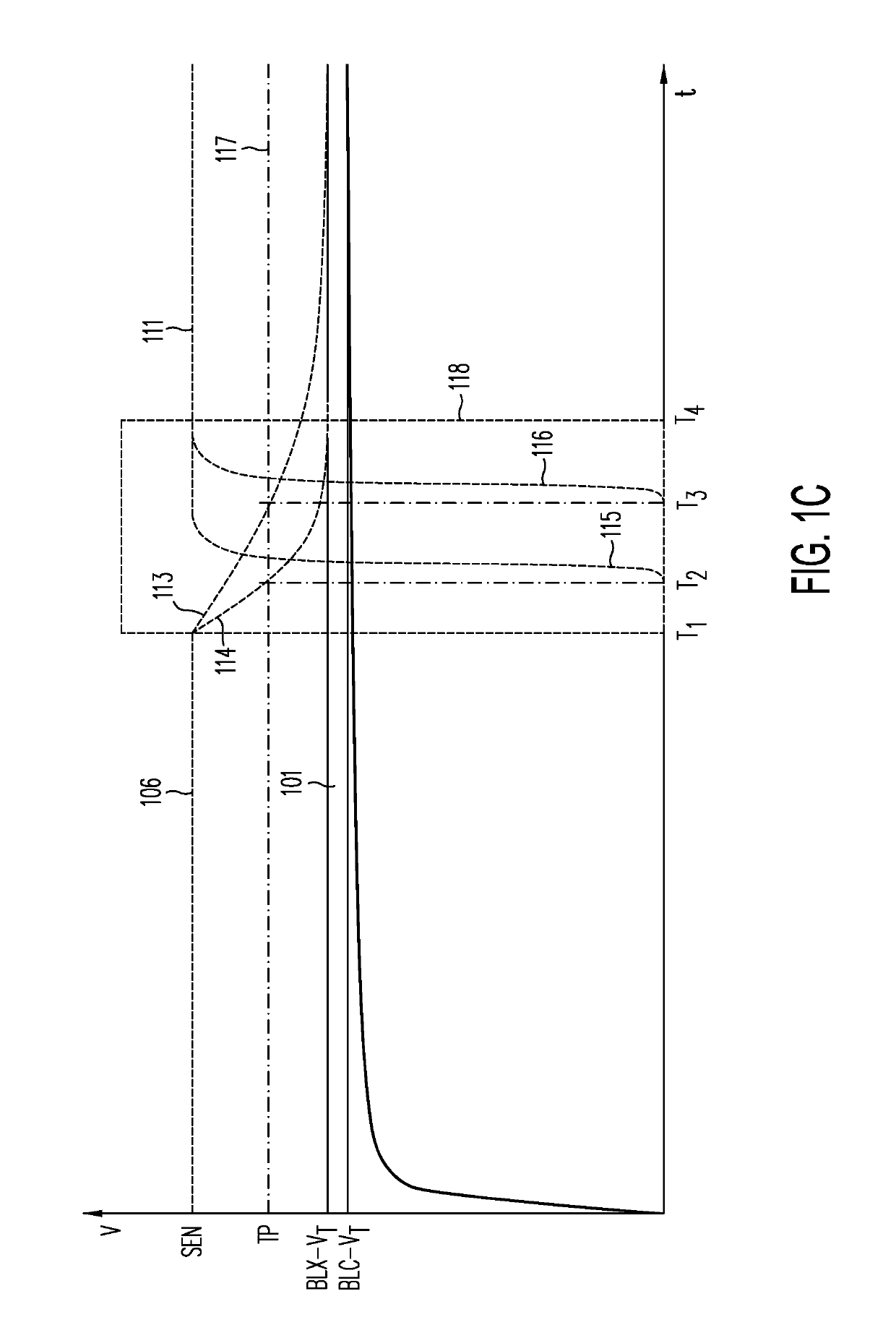

Dual-port static random access memory having improved cell stability and write margin

A dual-port memory includes a plurality of memory cells coupled to a row decoder and column logic. Each memory cell includes two storage nodes, where each storage node is coupled to a bit line via an access transistor. Each memory cell also includes a logic gate for logically combining a word line signal with a column address signal and providing the resulting output signal to the gates of the access transistors. In one embodiment, the logic gate is a NOR logic gate and in another embodiment, the logic gate is a transmission gate. This prevents a potential read disturb problem with unselected memory cells of a row. This also reduces power consumption in the memory.

Owner:NORTH STAR INNOVATIONS

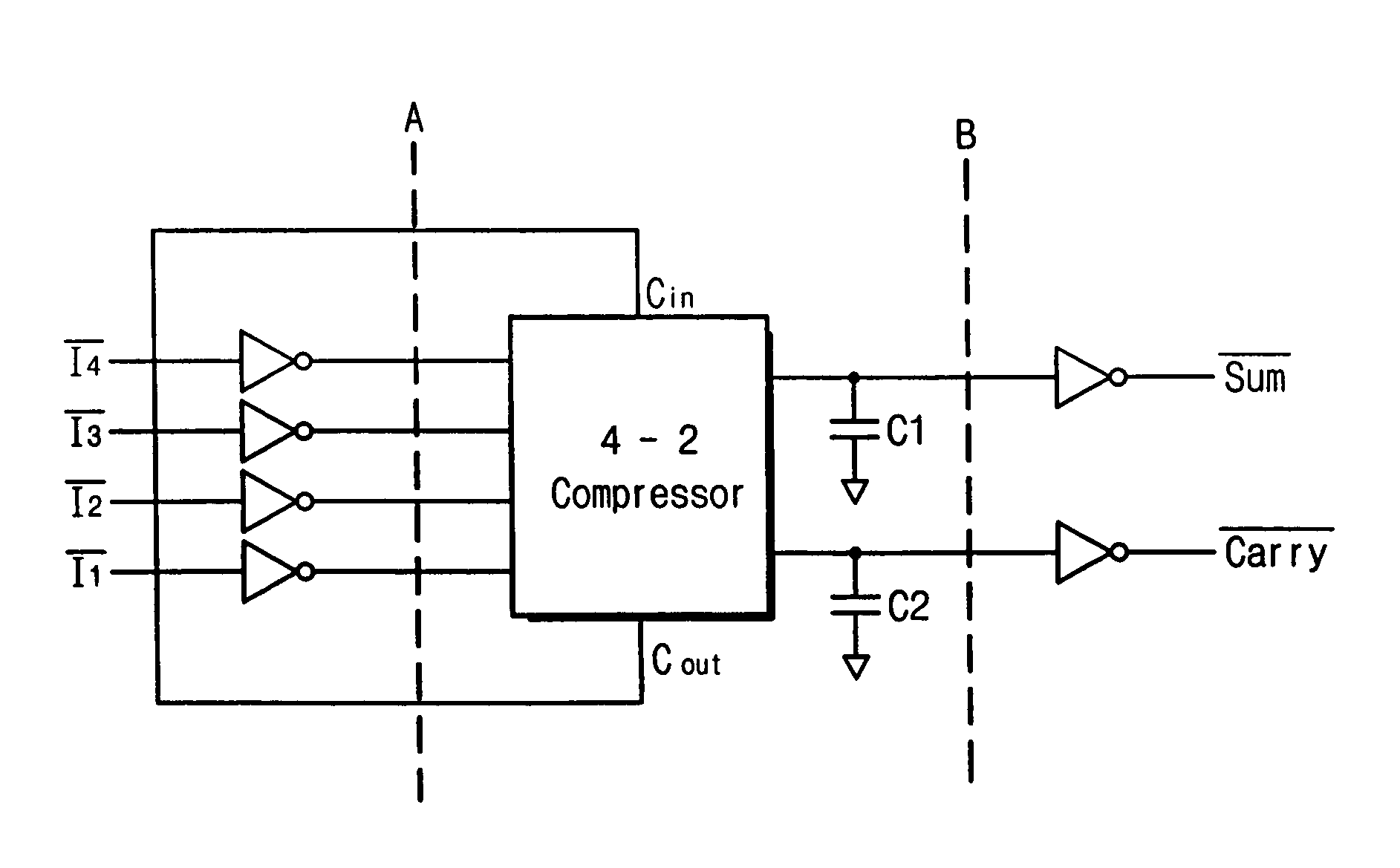

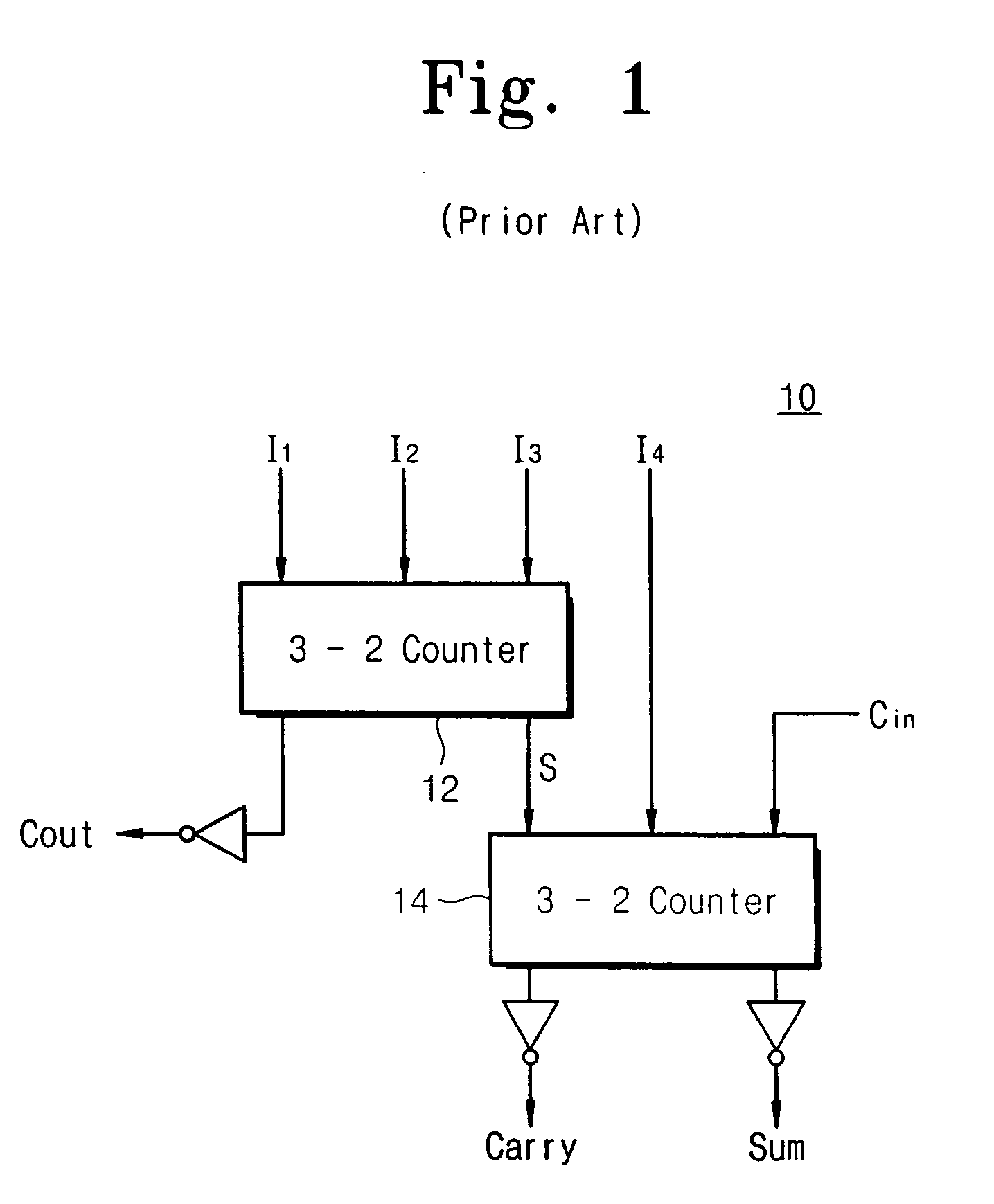

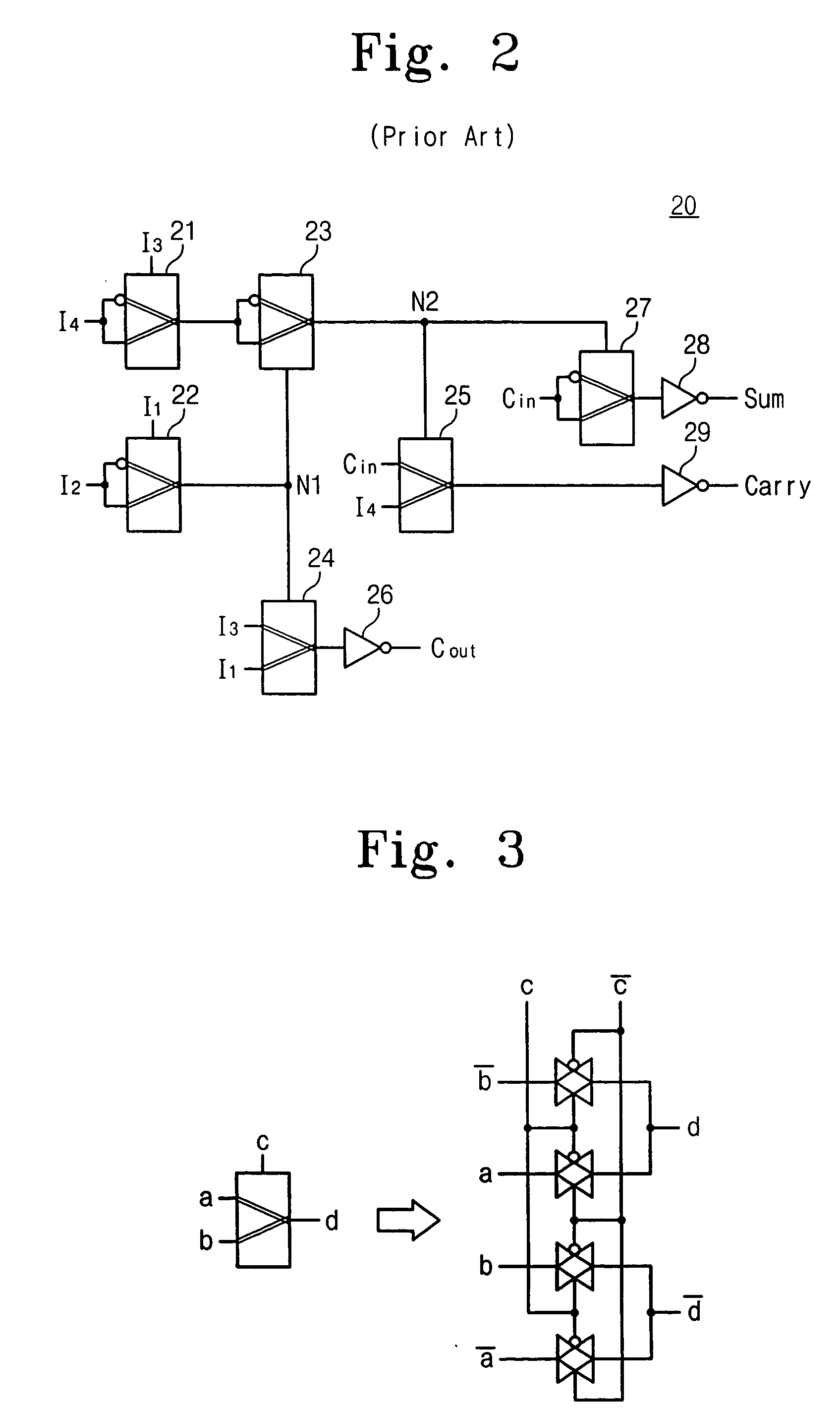

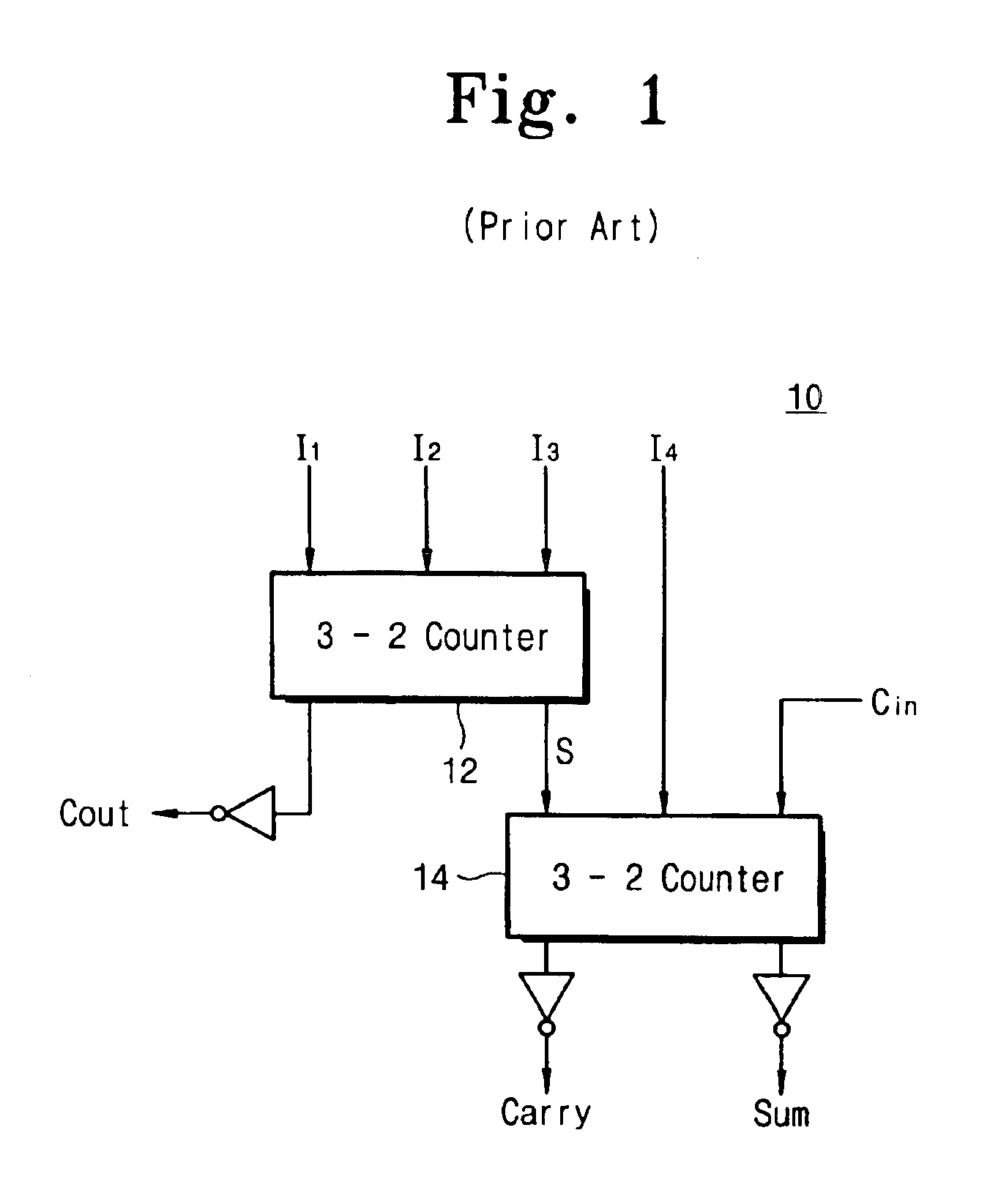

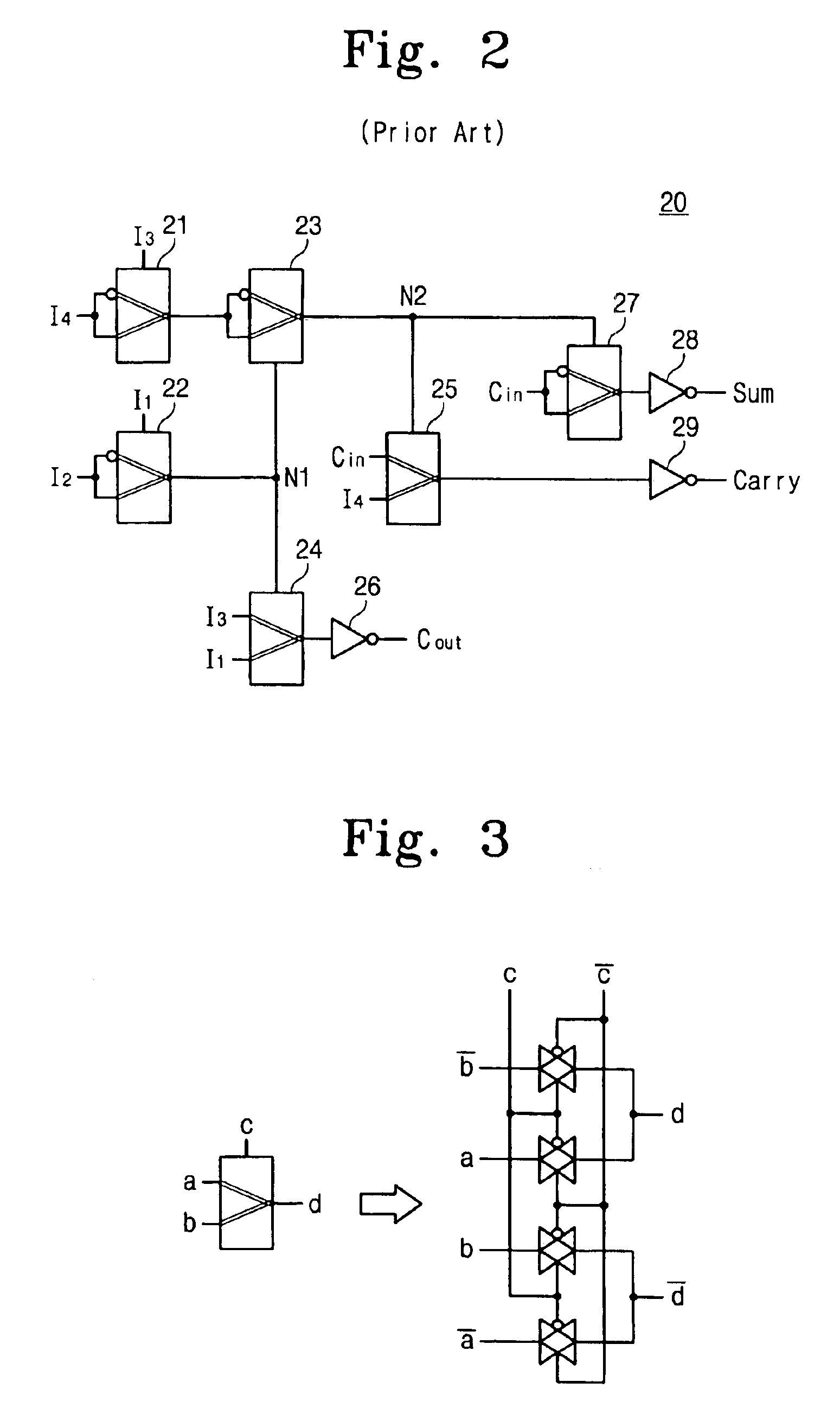

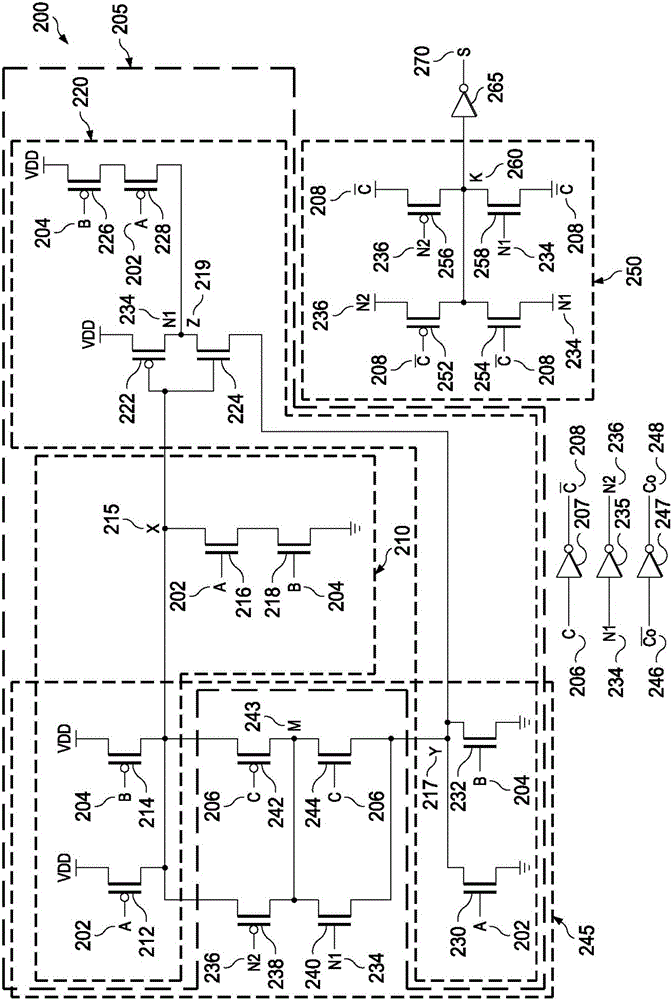

High speed low power 4-2 compressor

InactiveUS20050027777A1Raise the voltage levelReduce the voltage levelComputation using non-contact making devicesNumber-of-one countersCapacitanceMultiplexer

A high speed low powered 4-2 compressor according to the present invention performs an XOR / XNOR operation of input data by using a single input type NAND / NOR logic circuit and a dual input type NAND / NOR logic circuit. Thus, delays to generate complementary signals are avoided. In addition, the 4-2 compressor uses a single railed multiplexer instead of a dual railed multiplexer, so that gate drive nodes and internal load capacitance are reduced. As a result, circuit area and power consumption of the 4-2 compressor are reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

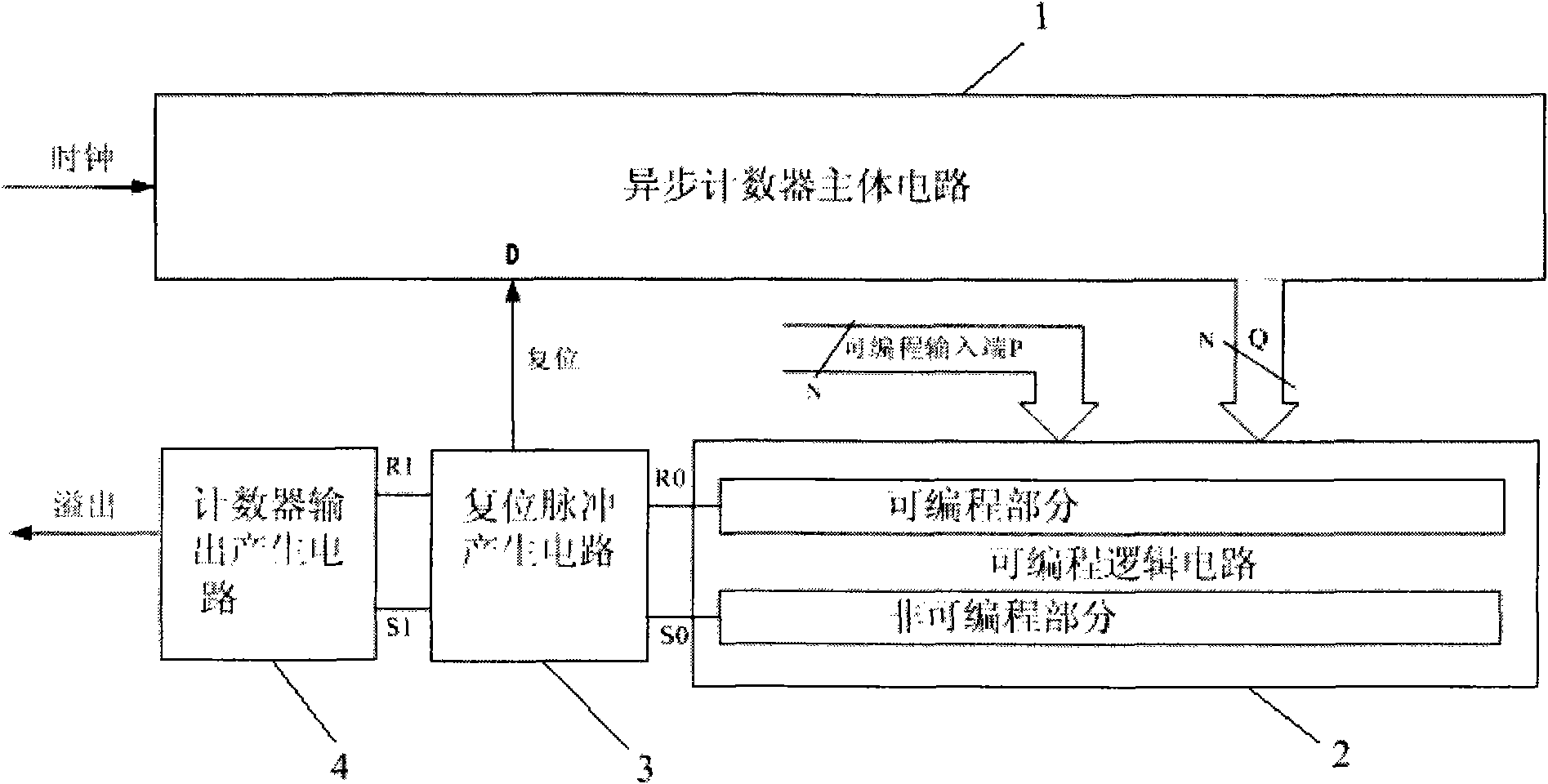

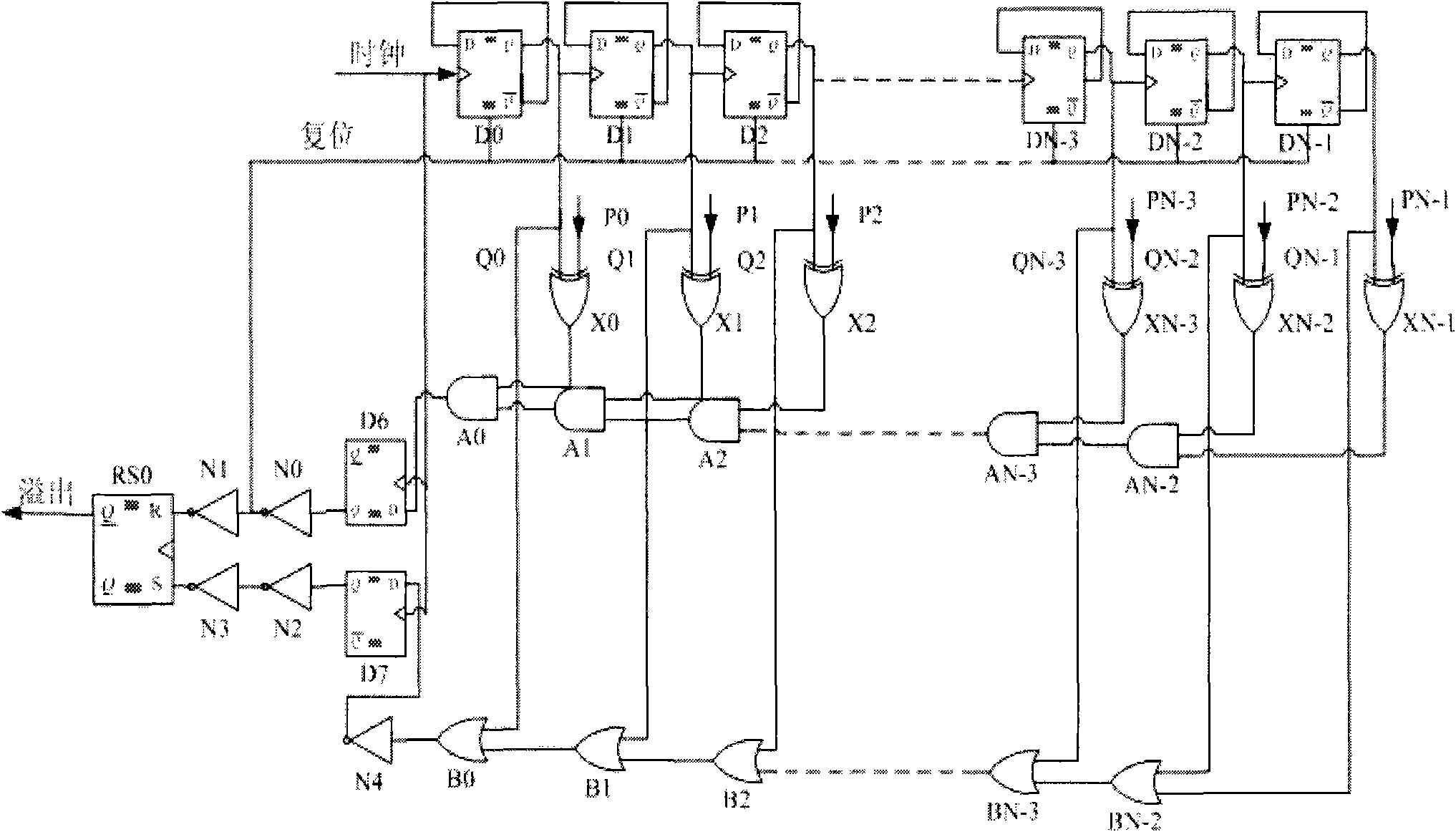

Glitch-eliminating programmable counter

InactiveCN101944907ANovel structureStrong elimination abilityCounting chain asynchronous pulse countersNAND logicNOR logic

The invention discloses a glitch-eliminating programmable counter, which comprises an asynchronous counter main body circuit, a programmable logic circuit, an reset pulse generation circuit and a counter output generation circuit, wherein the asynchronous counter main body circuit is provided with N-bit frequency division output end (Q0...QN-1), a programmable input end P and a trigger D; the programmable logic circuit is divided into a programmable part and a non-programmable part, the programmable part adopts a NAND logic, while the non-programmable part adopts a NOR logic; the reset pulse generation circuit is provided with two input ends R0 and S0 and three output ends; and the counter output generation circuit is provided with two input ends R1 and S1 and one outlet end. The glitch-eliminating programmable counter has the characteristics of simple design, novel circuit structure, high glitch-eliminating capability, easy realization and the like.

Owner:SOUTHEAST UNIV

Memory data path circuit

InactiveUS7032143B1Improve scalabilityIncrease the compression ratioDigital storageDatapath circuitsNOR logic

A memory device with a data path circuit having support in the sense-amp region for compression testing of the device. The data path circuit uses NOR logic compression to provide a scalable design which may be extended to large circuits.

Owner:WALLER WILLIAM KENNETH

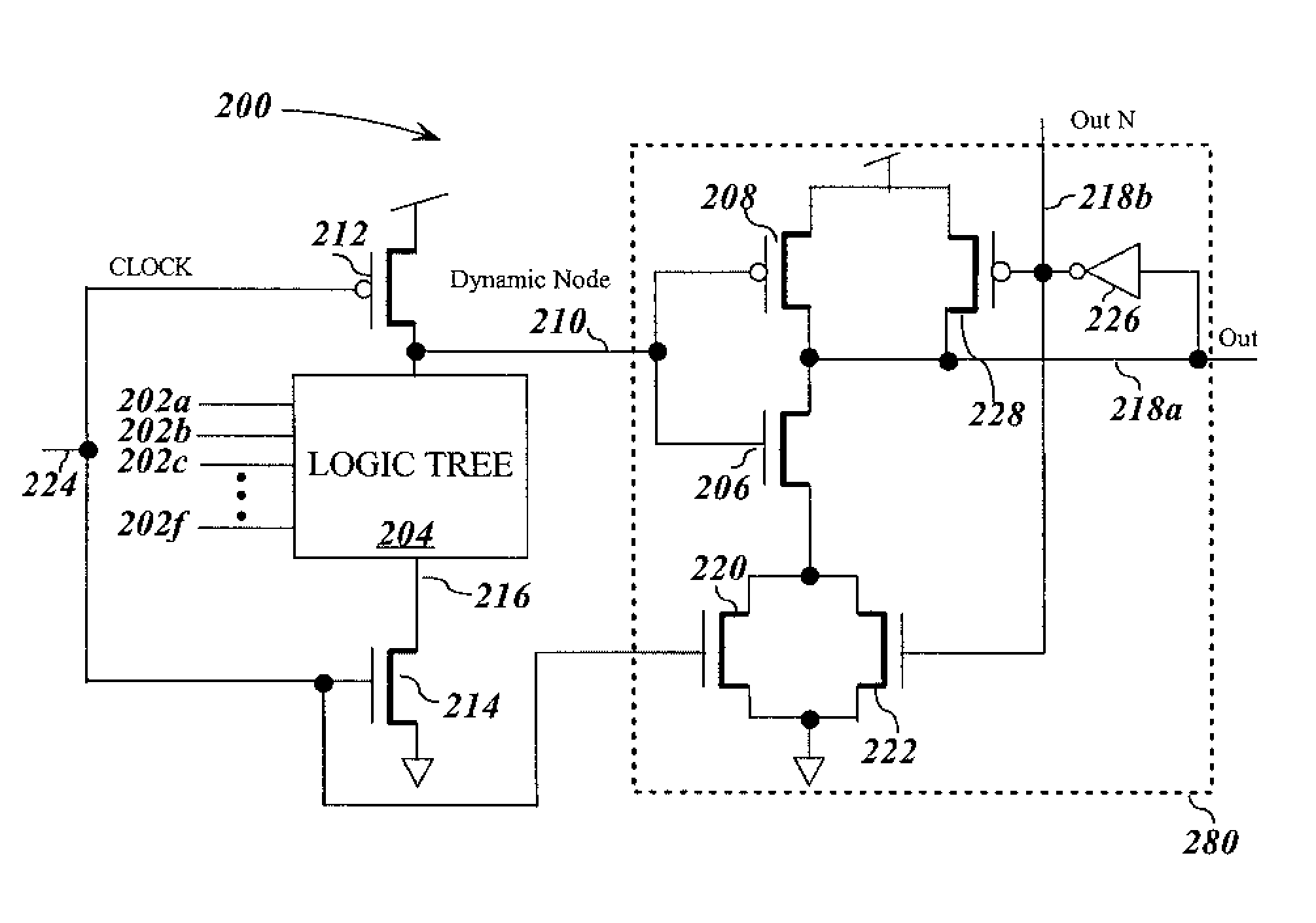

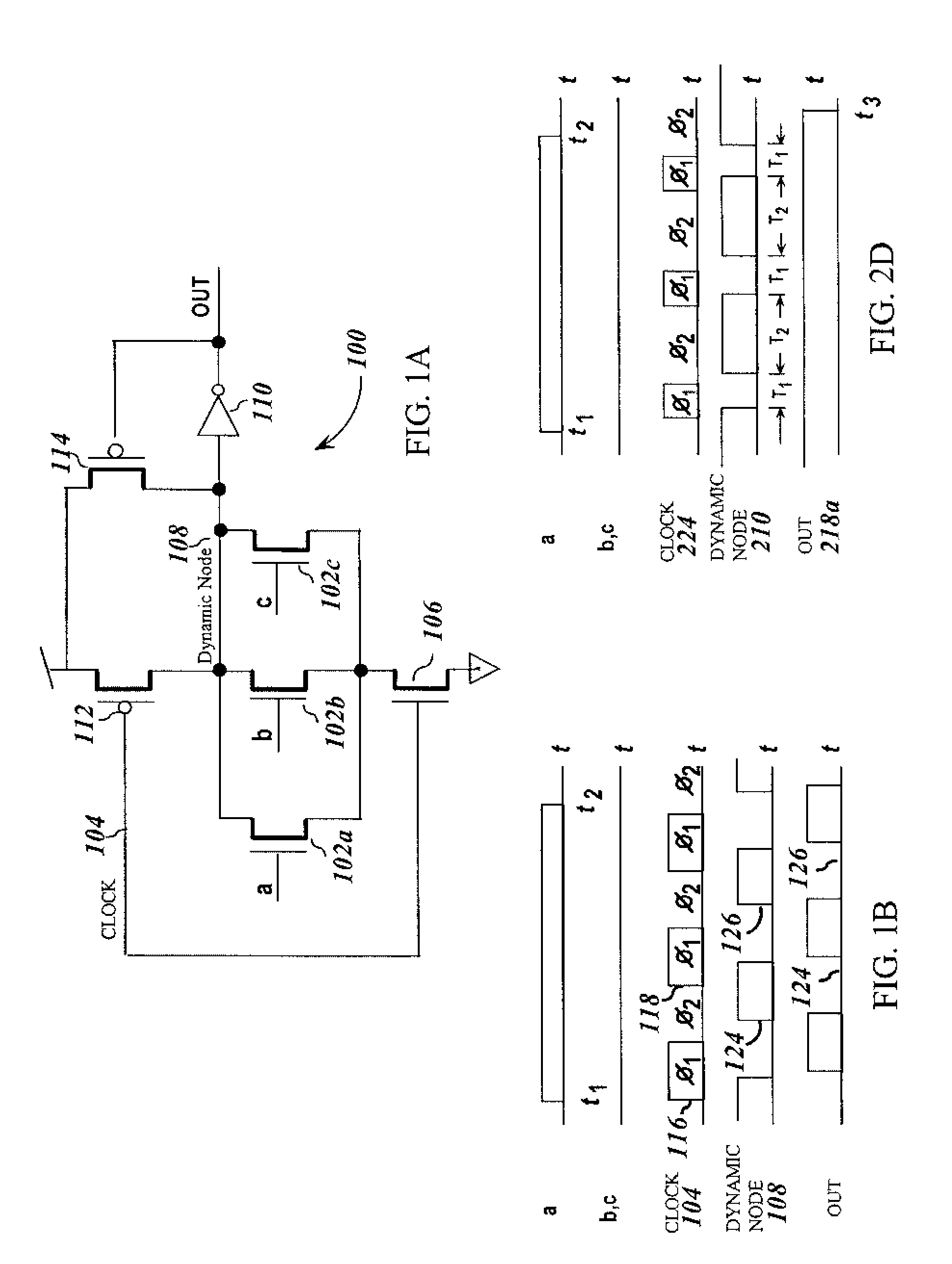

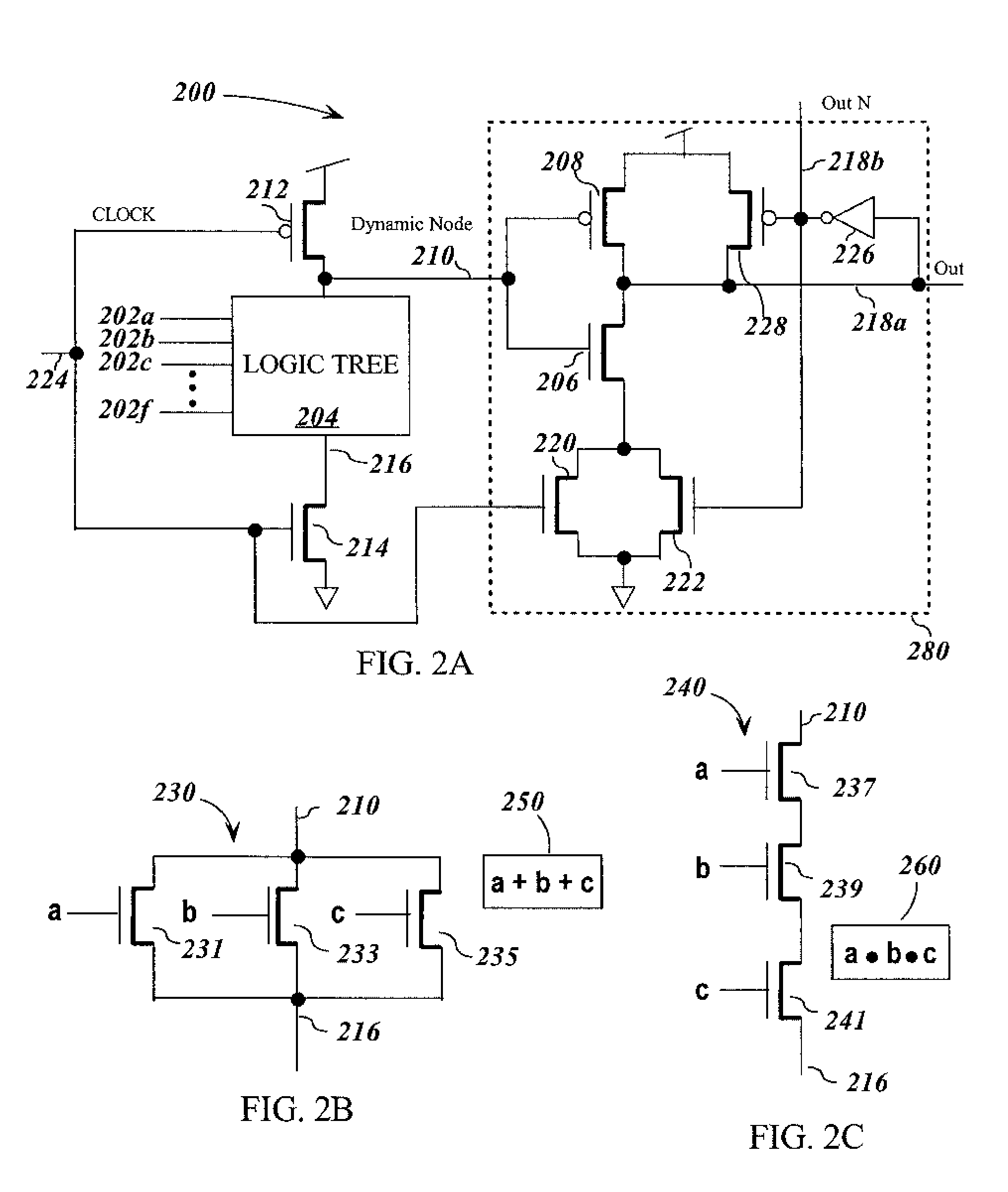

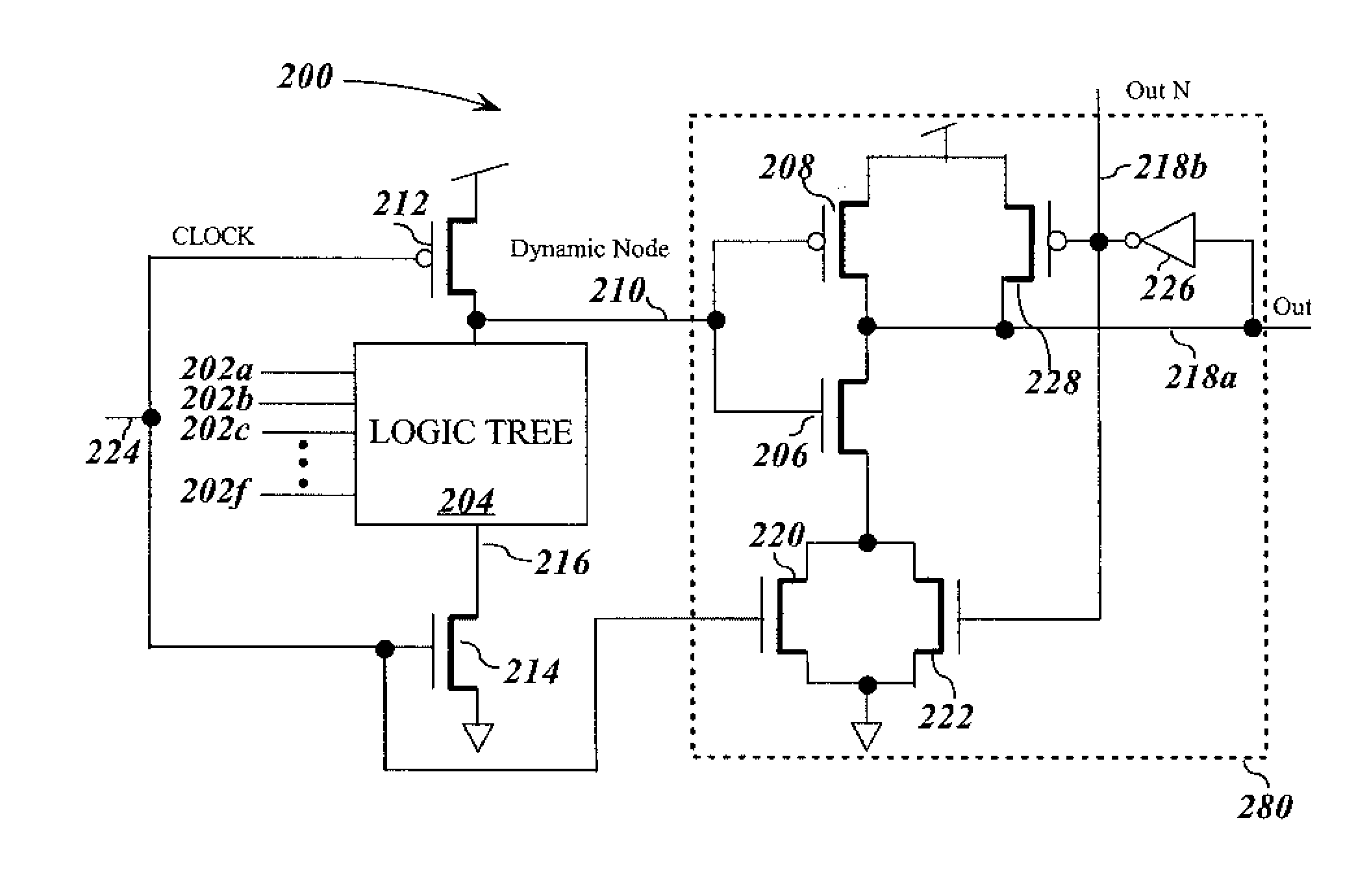

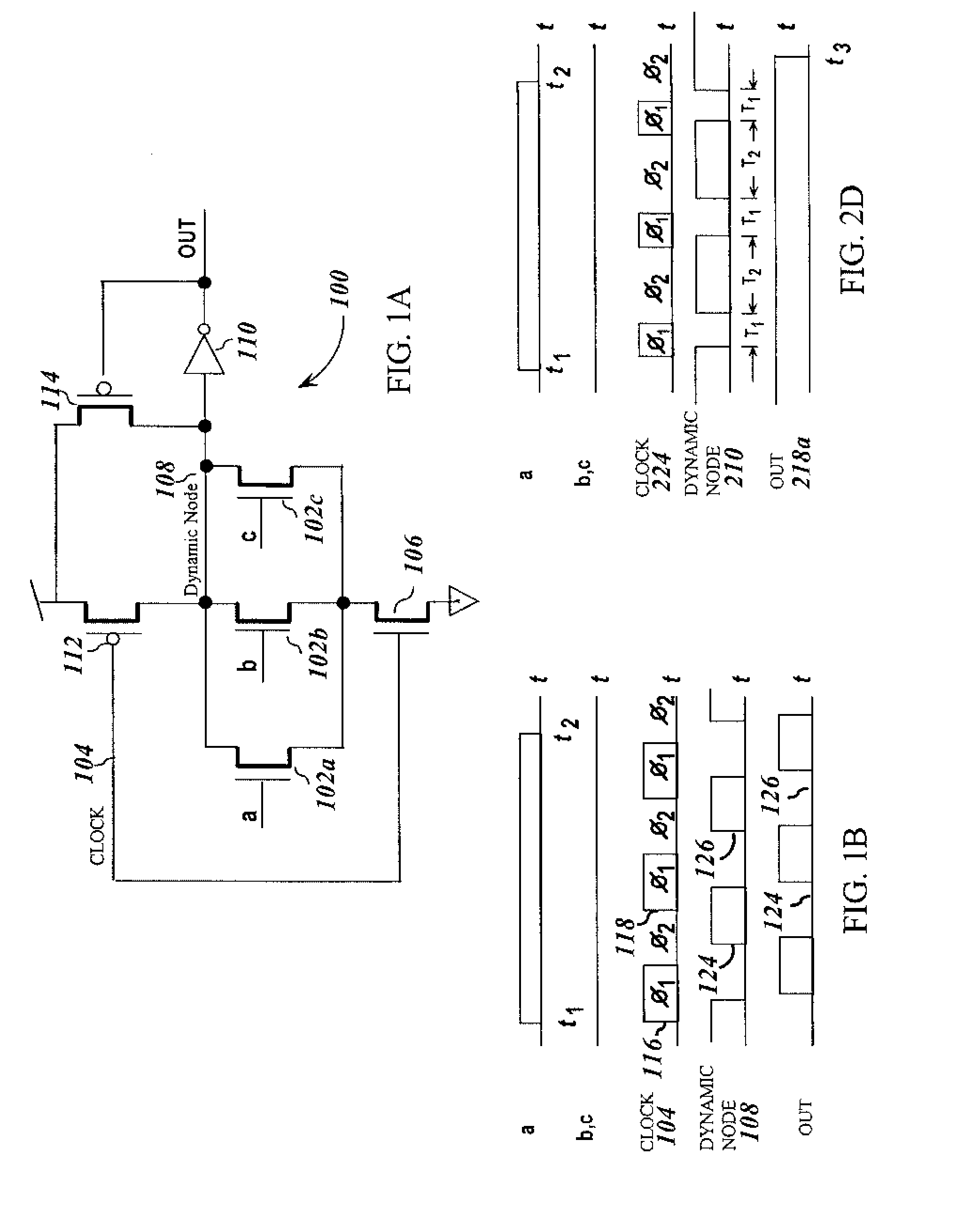

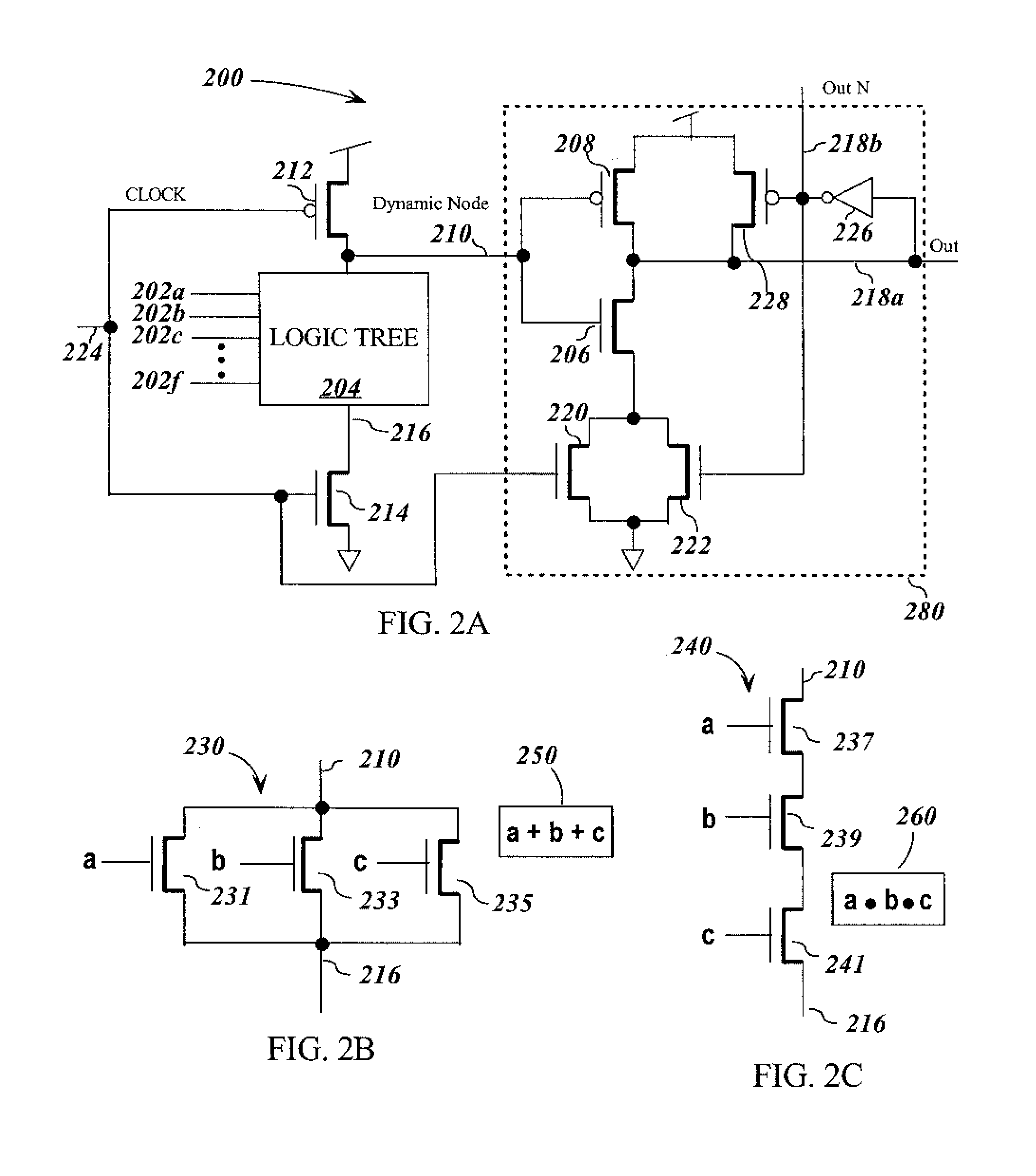

Ultra high-speed Nor-type LSDL/Domino combined address decoder

An ultra high speed address decoder uses a combination of Domino logic circuits and LSDL logic circuits. N address bits are converted into N logic true address bits and N complementary address bits. A partial address decoder generates two bit groups using selected of the N logic true address bits and N complementary address bits in NOR logic structures such only two cascaded NFETS are used in a logic tree. The bit groups are partitioned to optimize the layout of the parallel bit lines in the address decoder.

Owner:GOOGLE LLC

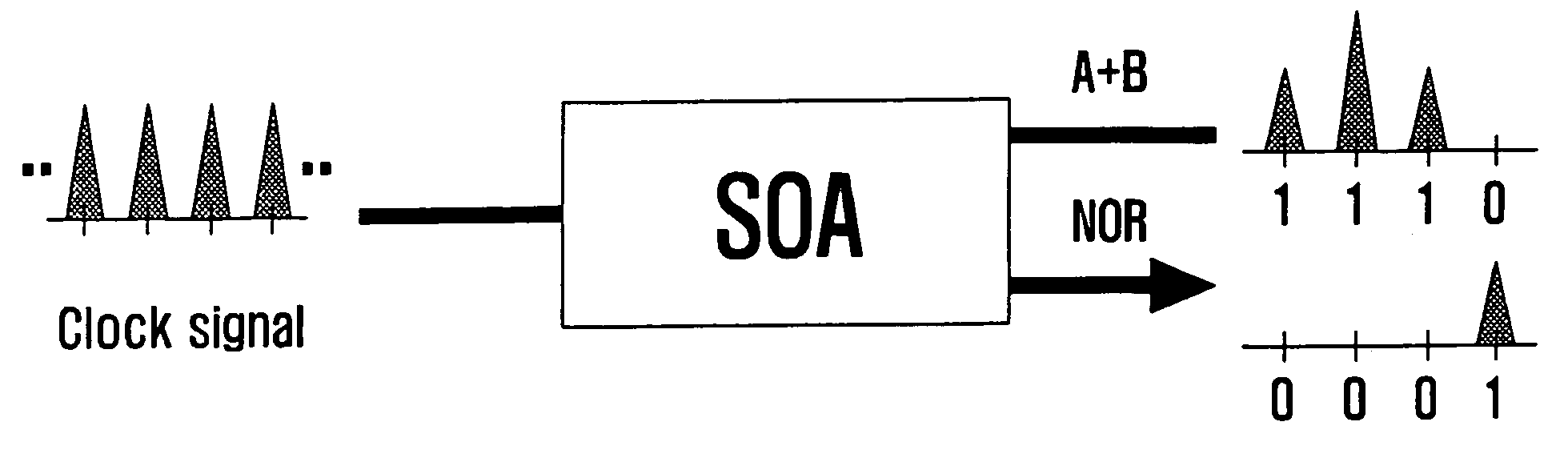

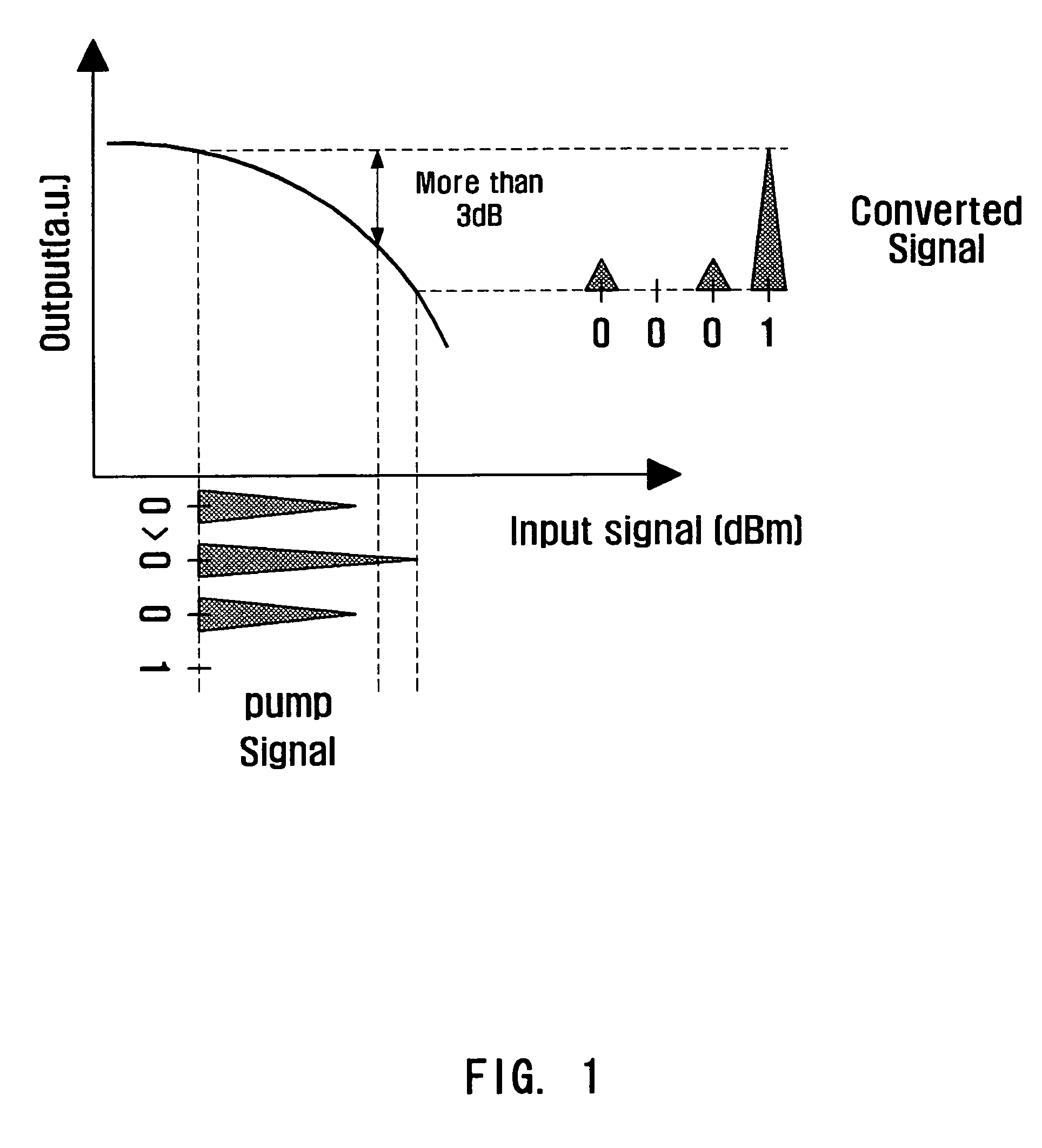

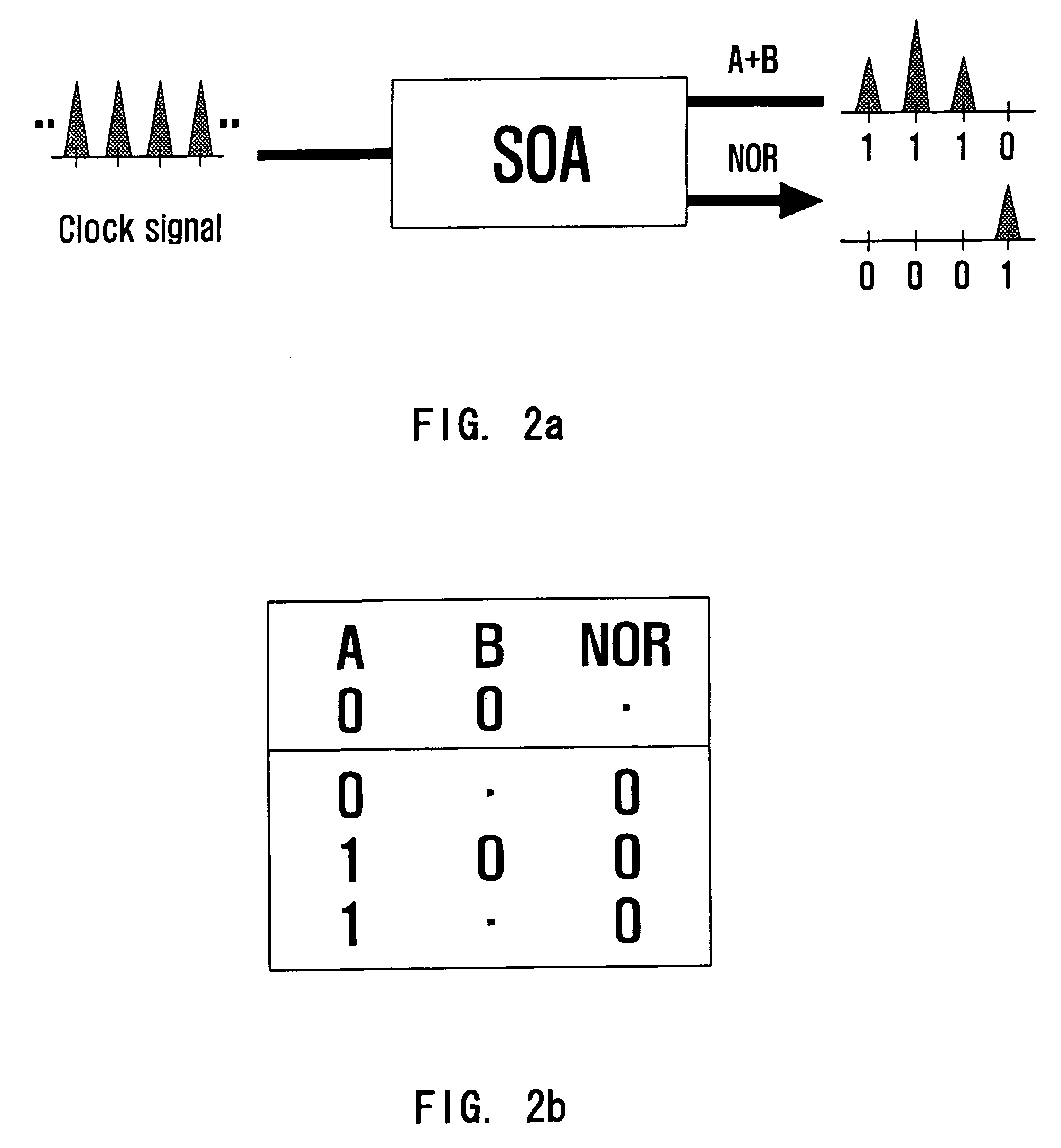

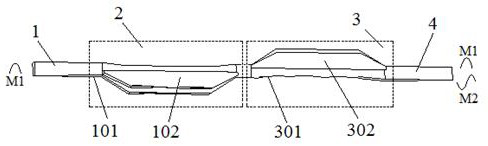

Apparatus and method for realizing all-optical NOR logic device using gain saturation characteristics of a semiconductor optical amplifier

InactiveUS7123407B2Laser detailsLogic circuits using opto-electronic devicesCross gain modulationNOR logic

The present invention relates to an apparatus and a method for realizing all-optical NOR logic device using the gain saturation characteristics of a semiconductor optical amplifier(SOA). More particularly, the invention relates to a 10 Gbit / s all-optical NOR logic device among all-optical logic devices, in which a signal transmitted from a given point of an optical circuit such as an optical computing circuit is used as a pump signal and a probe signal.The method for realizing an all-optical NOR logic device using the gain saturation characteristics of the SOA according to the present invention comprises the steps of: utilizing A+B signal which couples together an input signal pattern A (1100) and an input signal pattern B (0110) as a pump signal (1110); utilizing a probe signal (1111) by generating a clock signal out of said input signal pattern A (1100); and obtaining a Boolean equation {overscore (A+B)} by making said probe signal and said pump signal incident upon the SOA simultaneously from the opposite direction.The all-optical logic device according to the present invention has a simple construction since it is realized through the XGM (Cross Gain Modulation) method which utilizes the gain saturation characteristics. Also, it is expected that the method employed in the present invention could be used for realizing other all-optical logic circuits and devices.

Owner:KOREA INST OF SCI & TECH

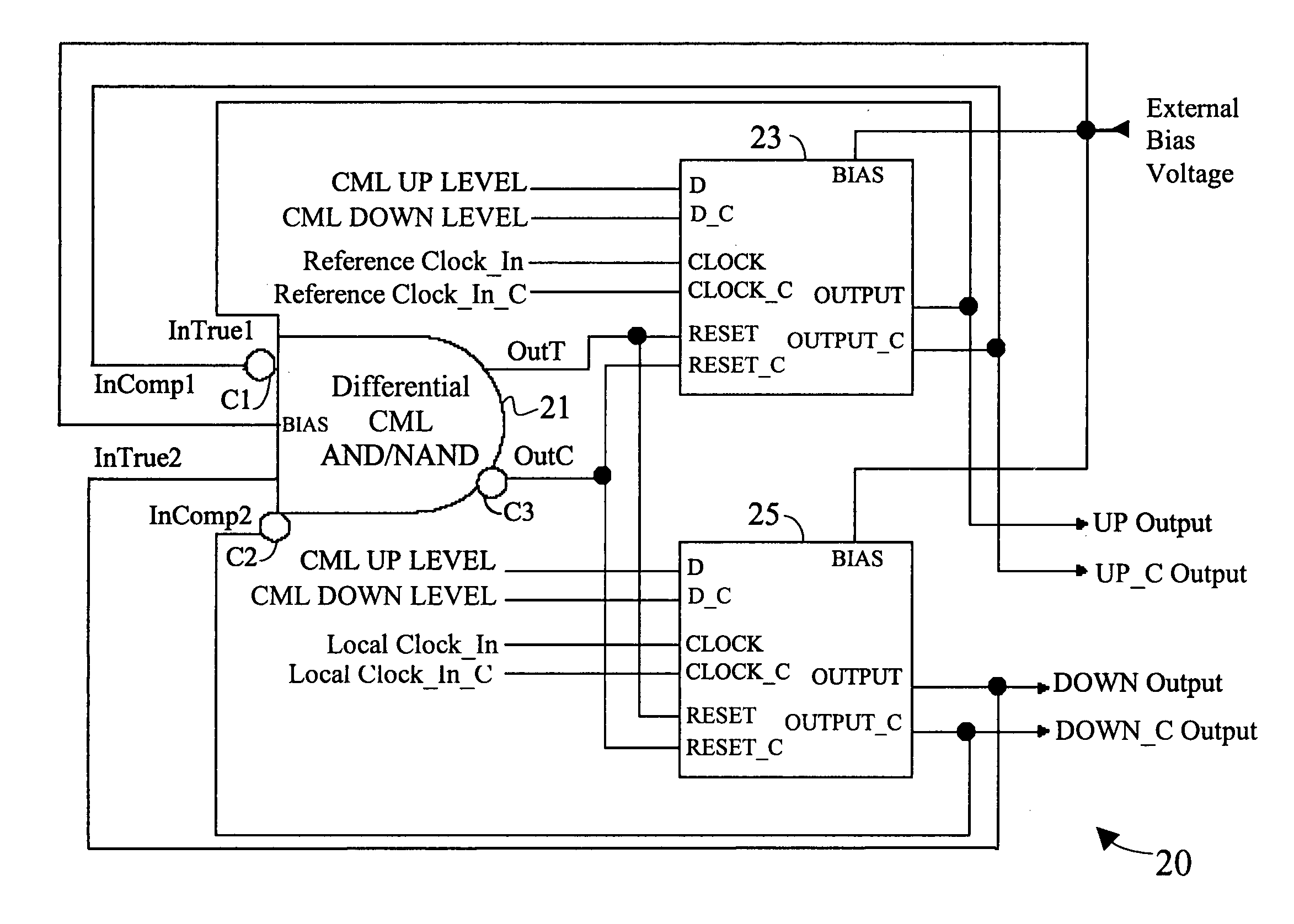

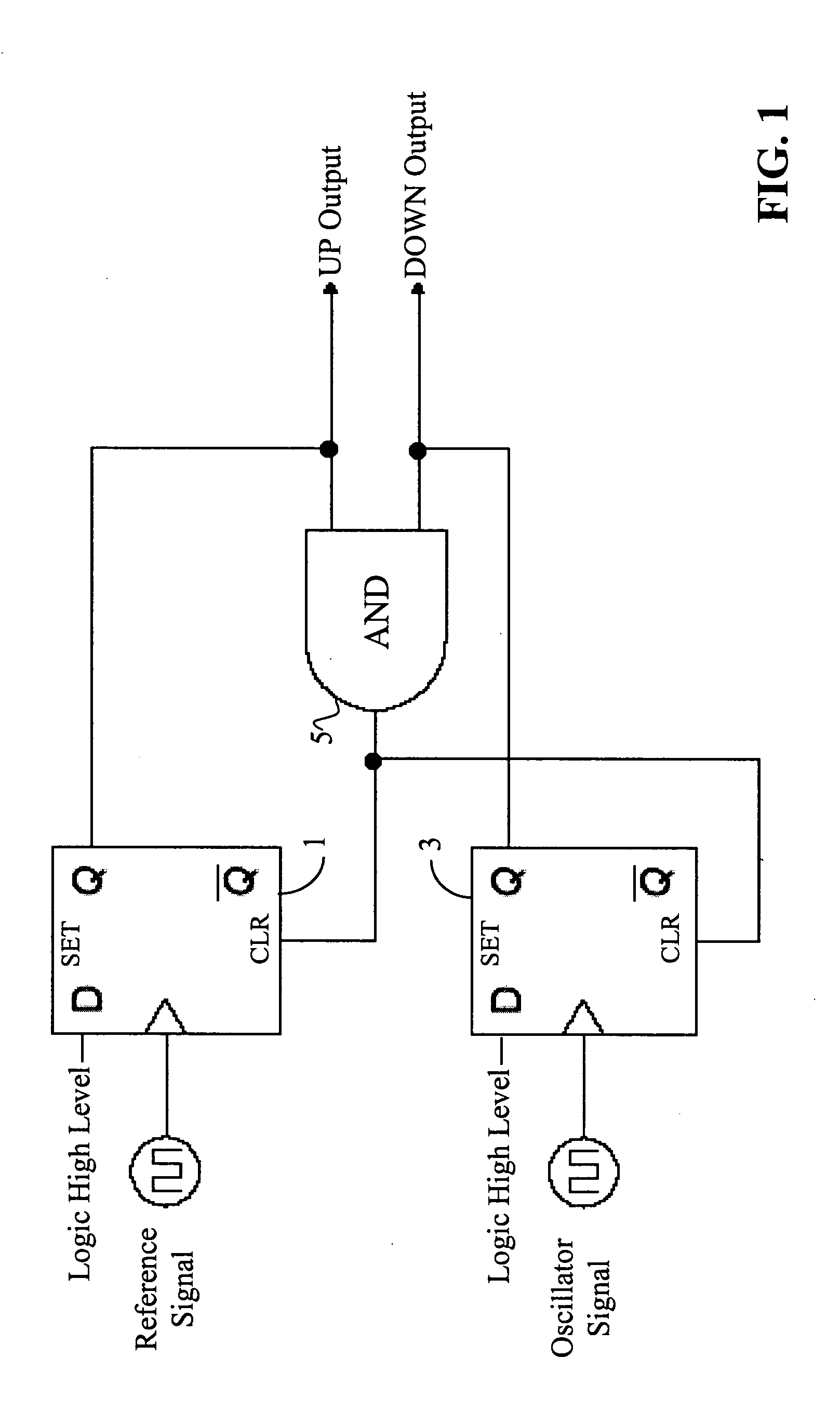

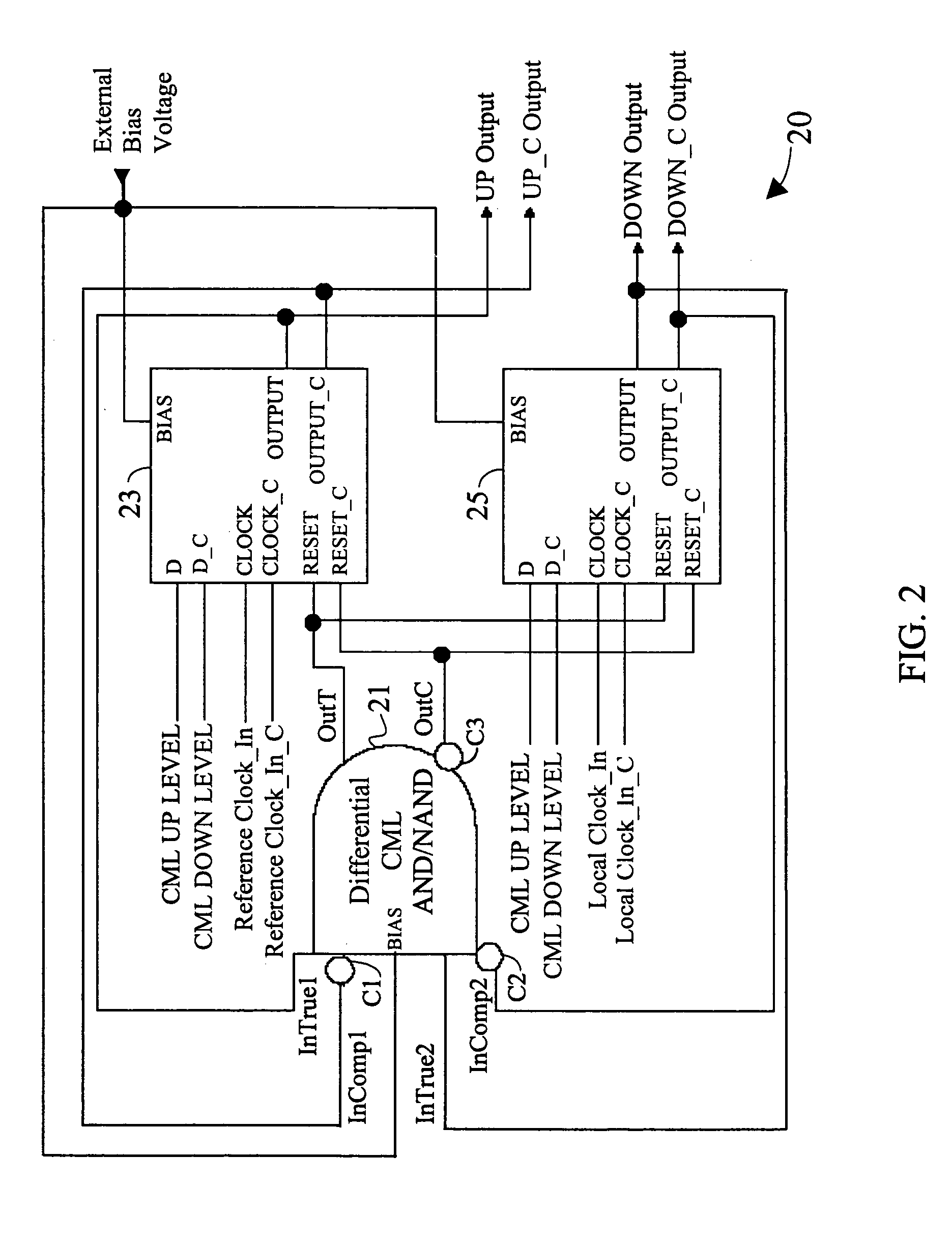

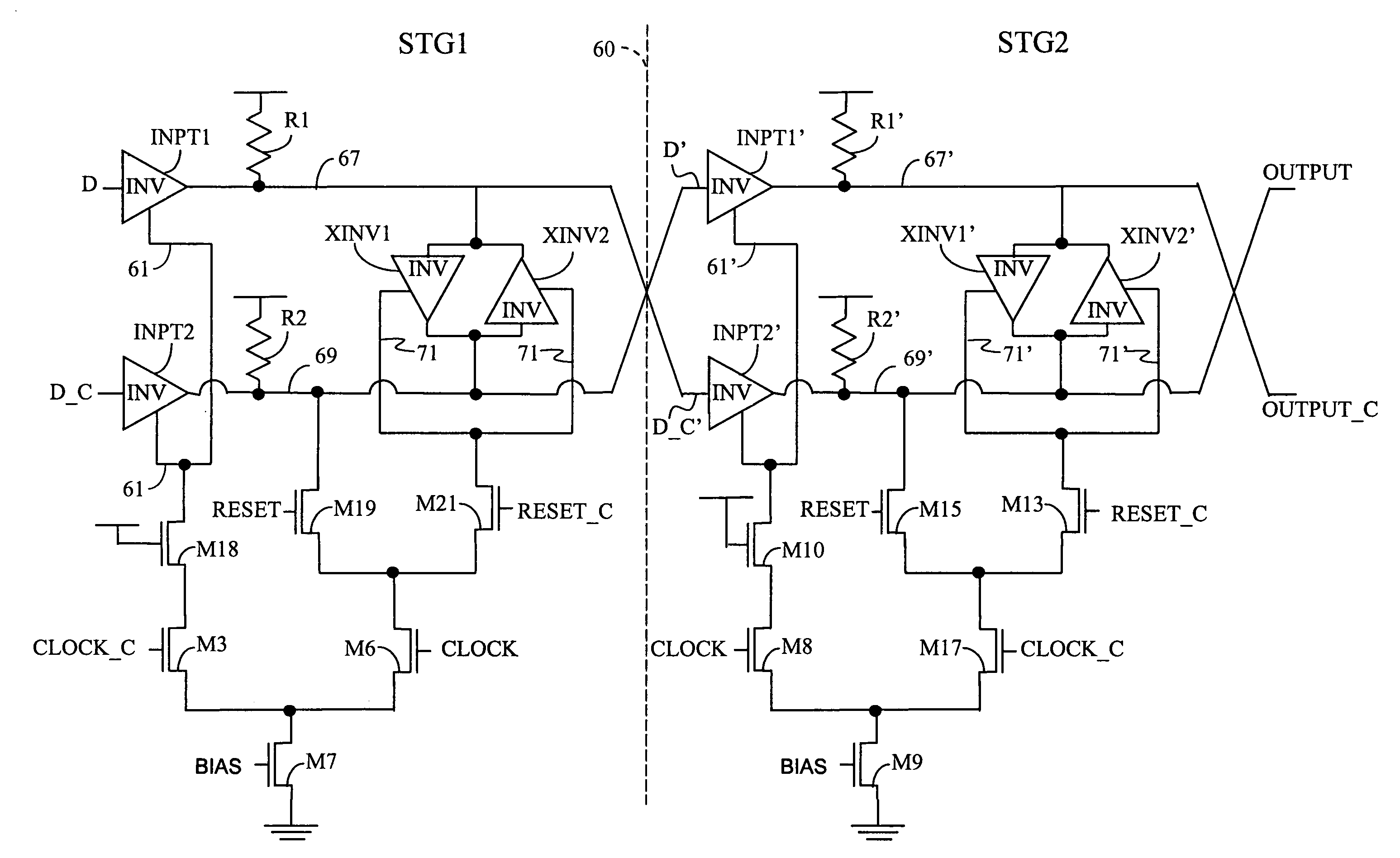

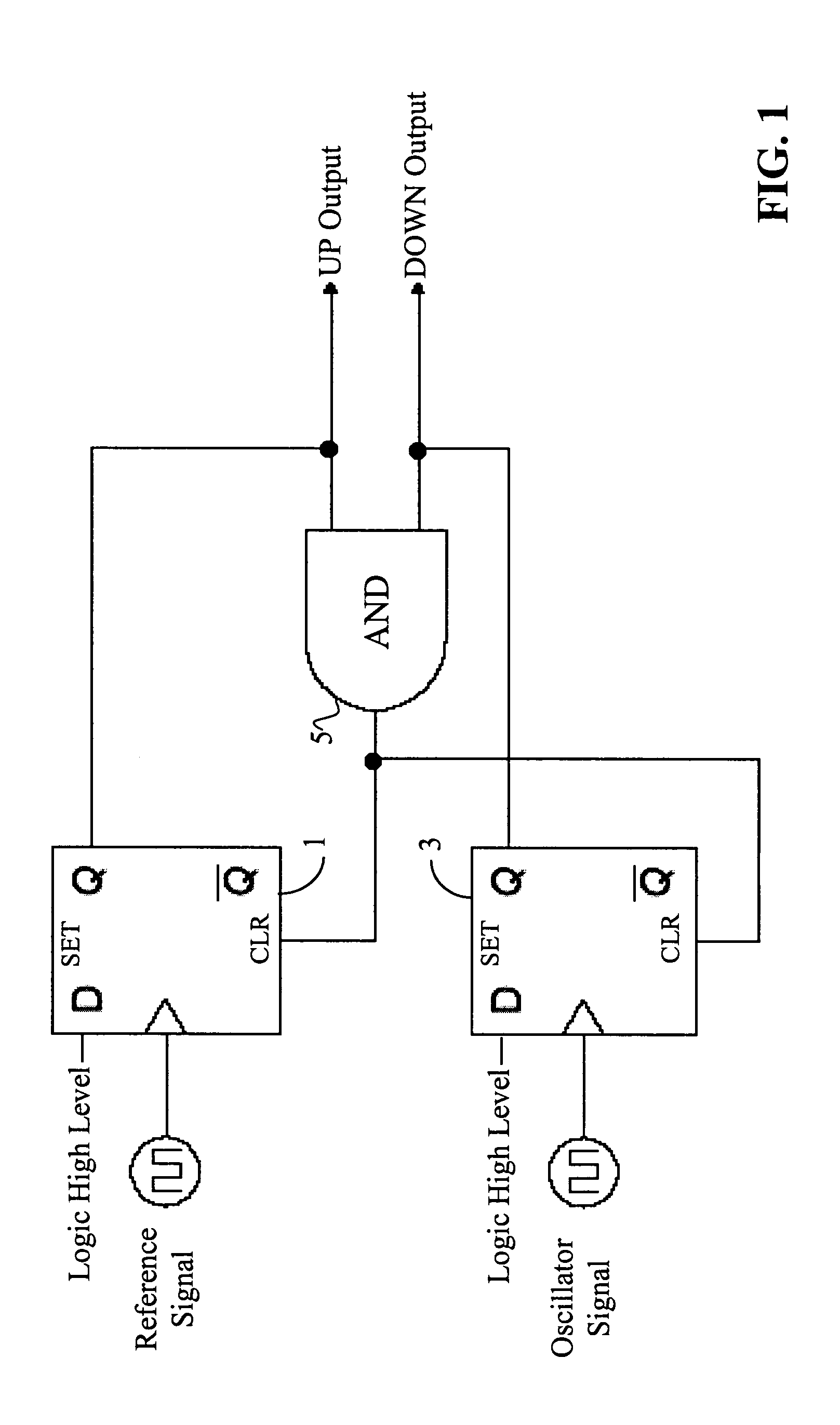

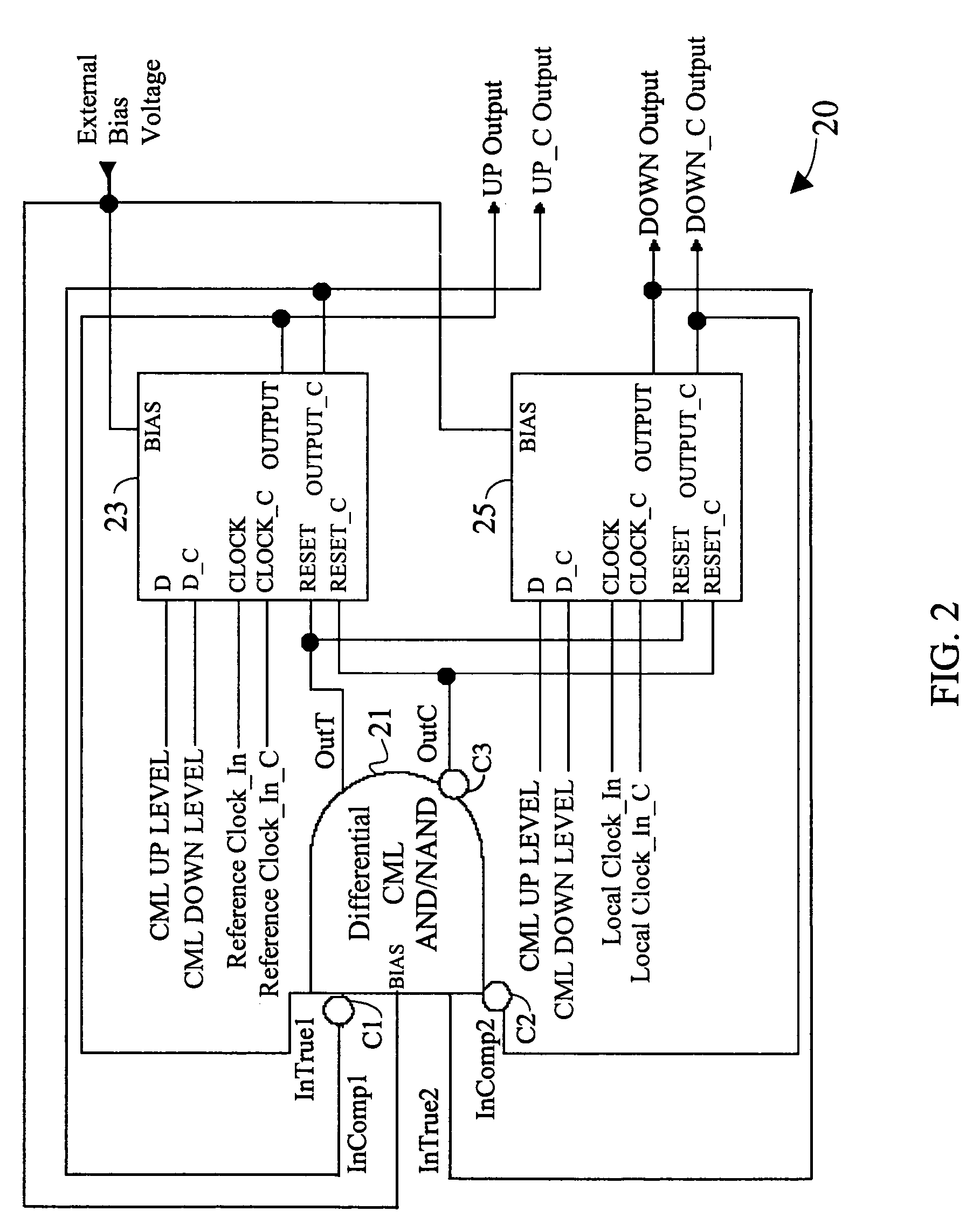

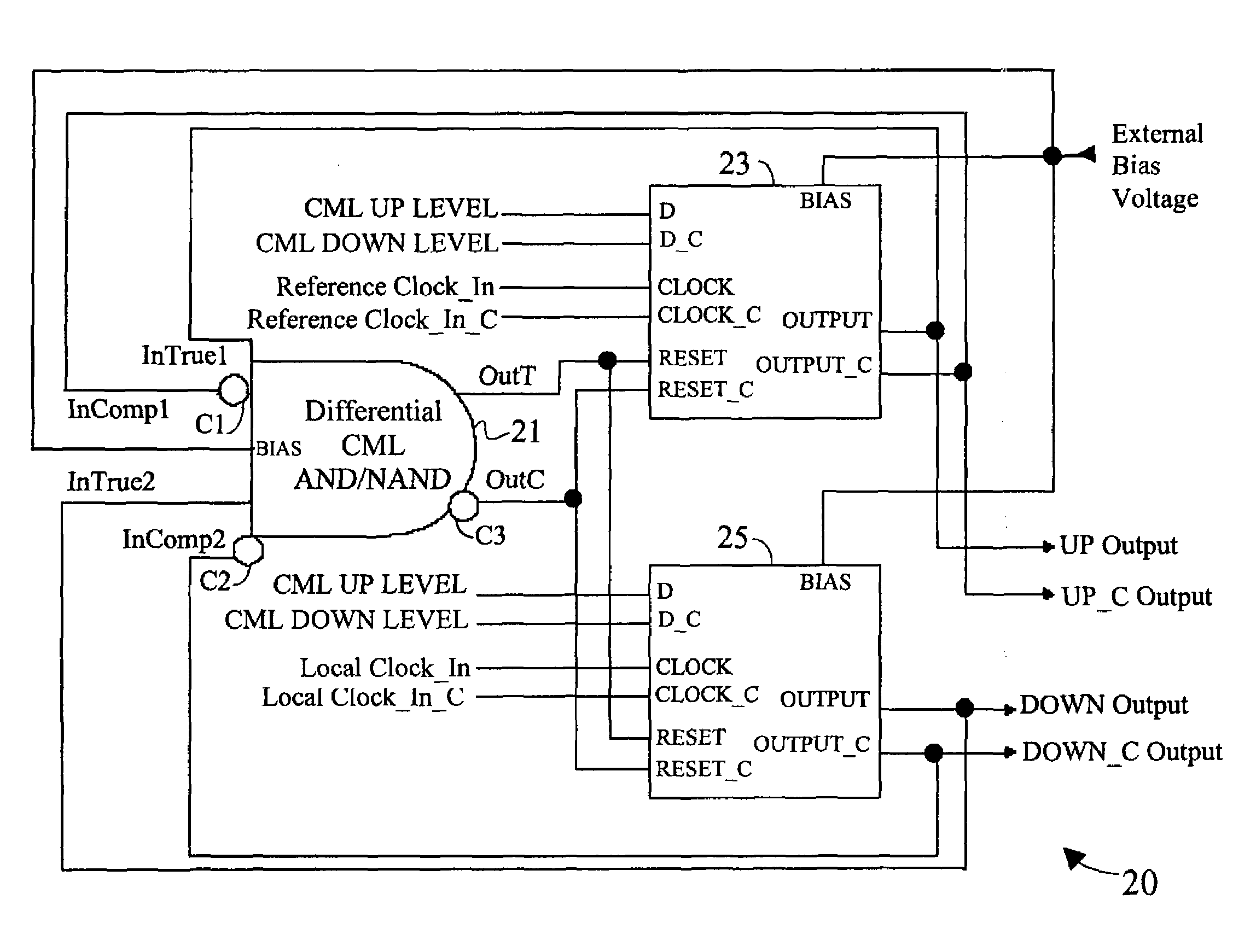

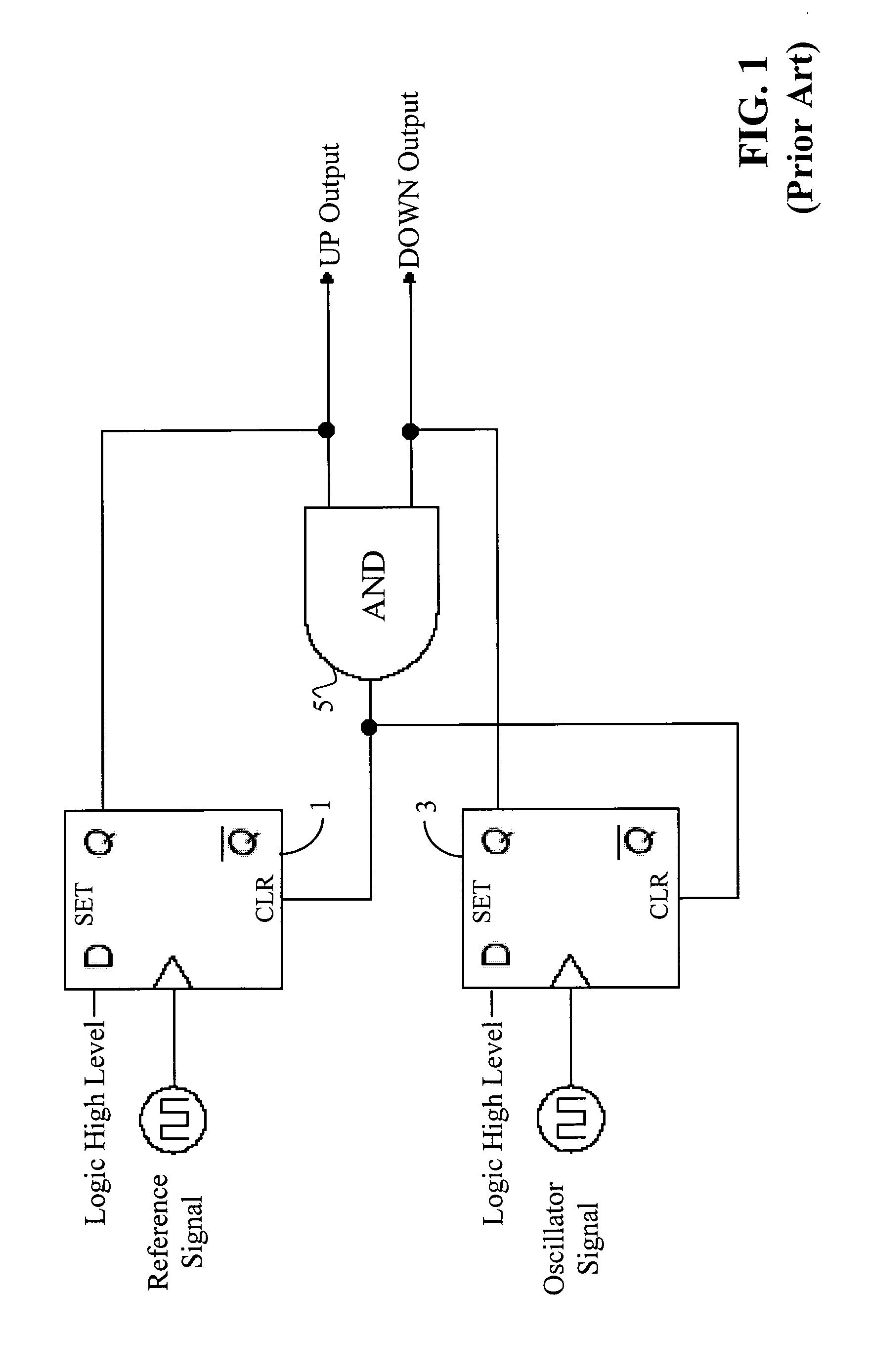

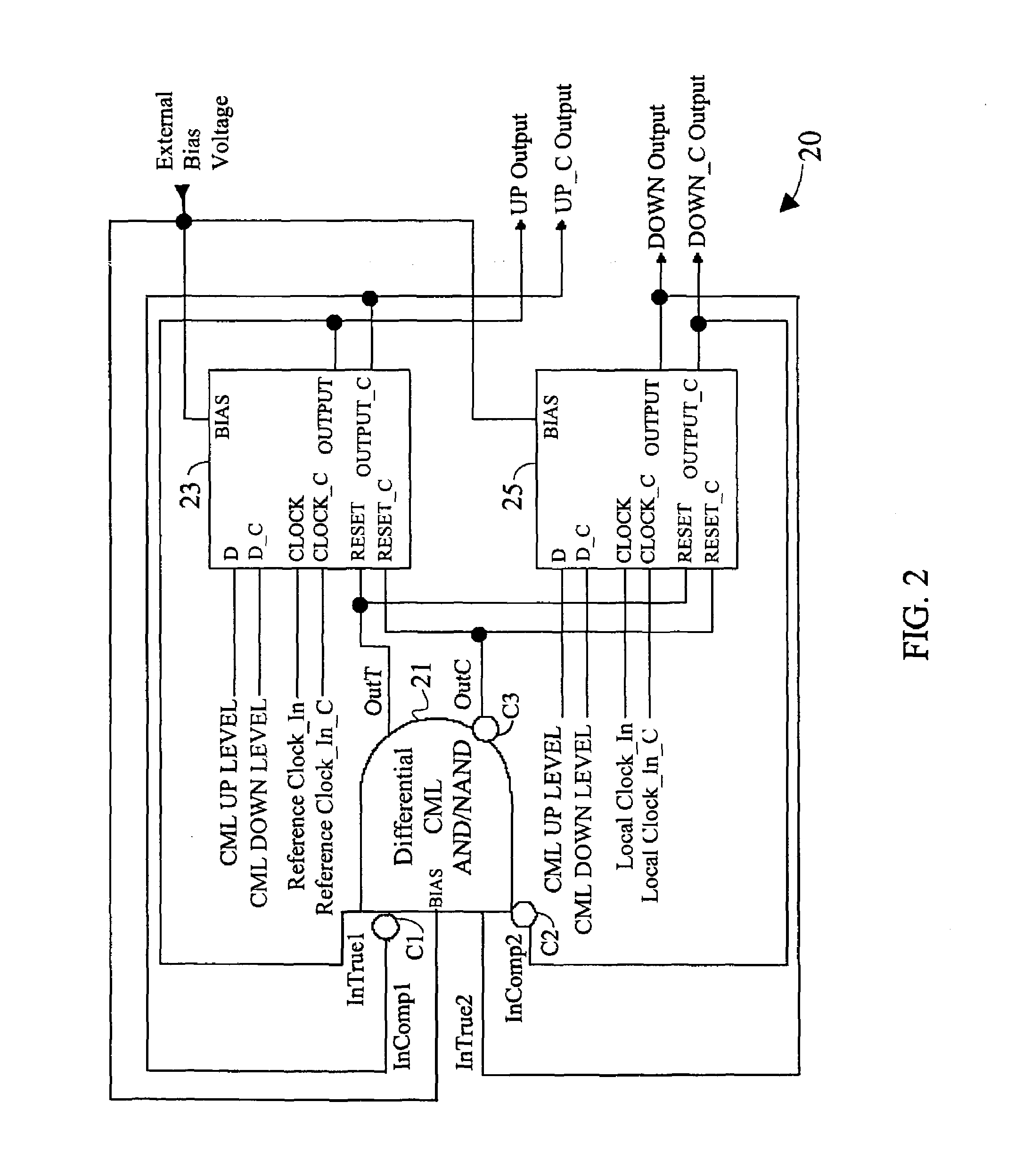

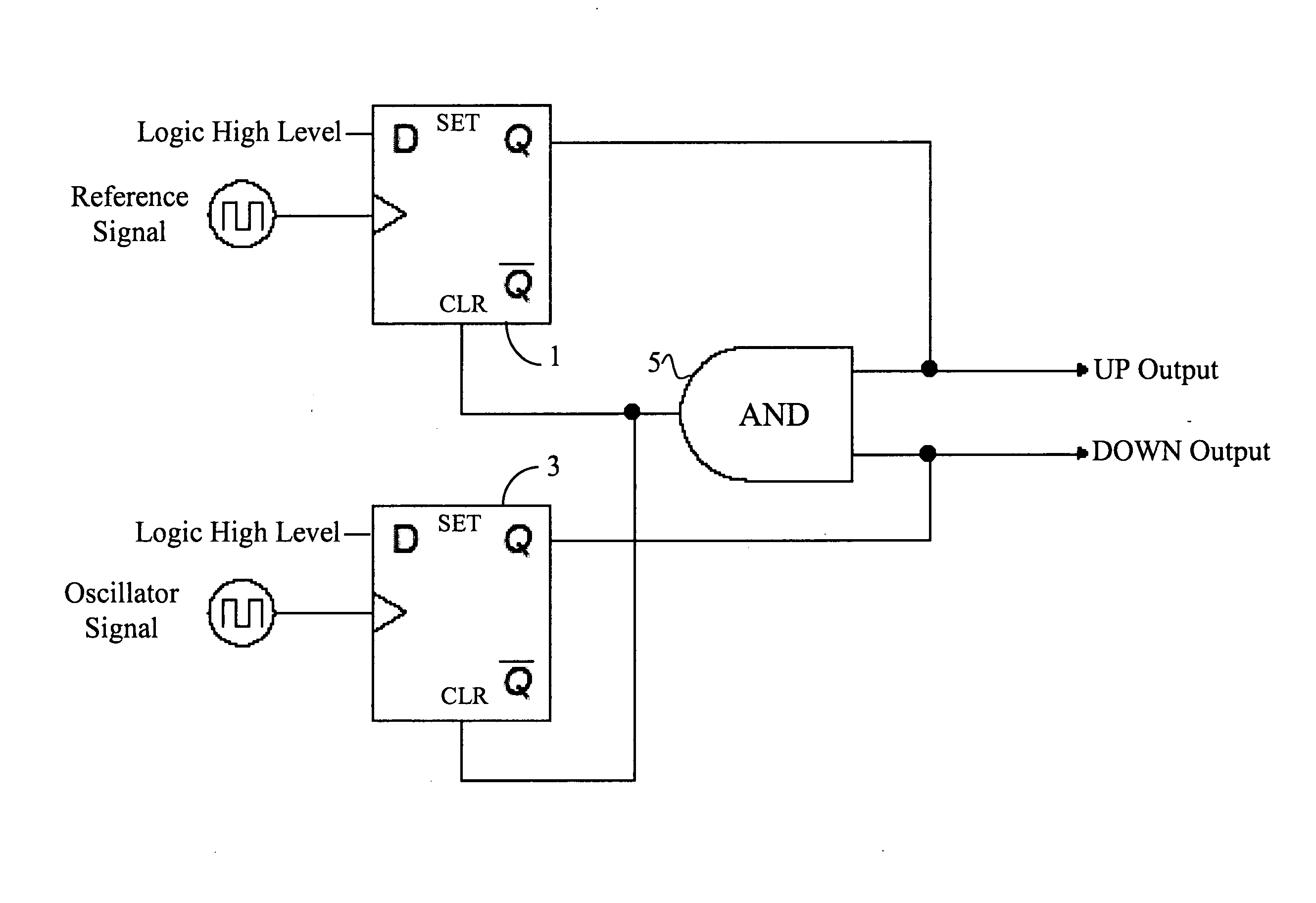

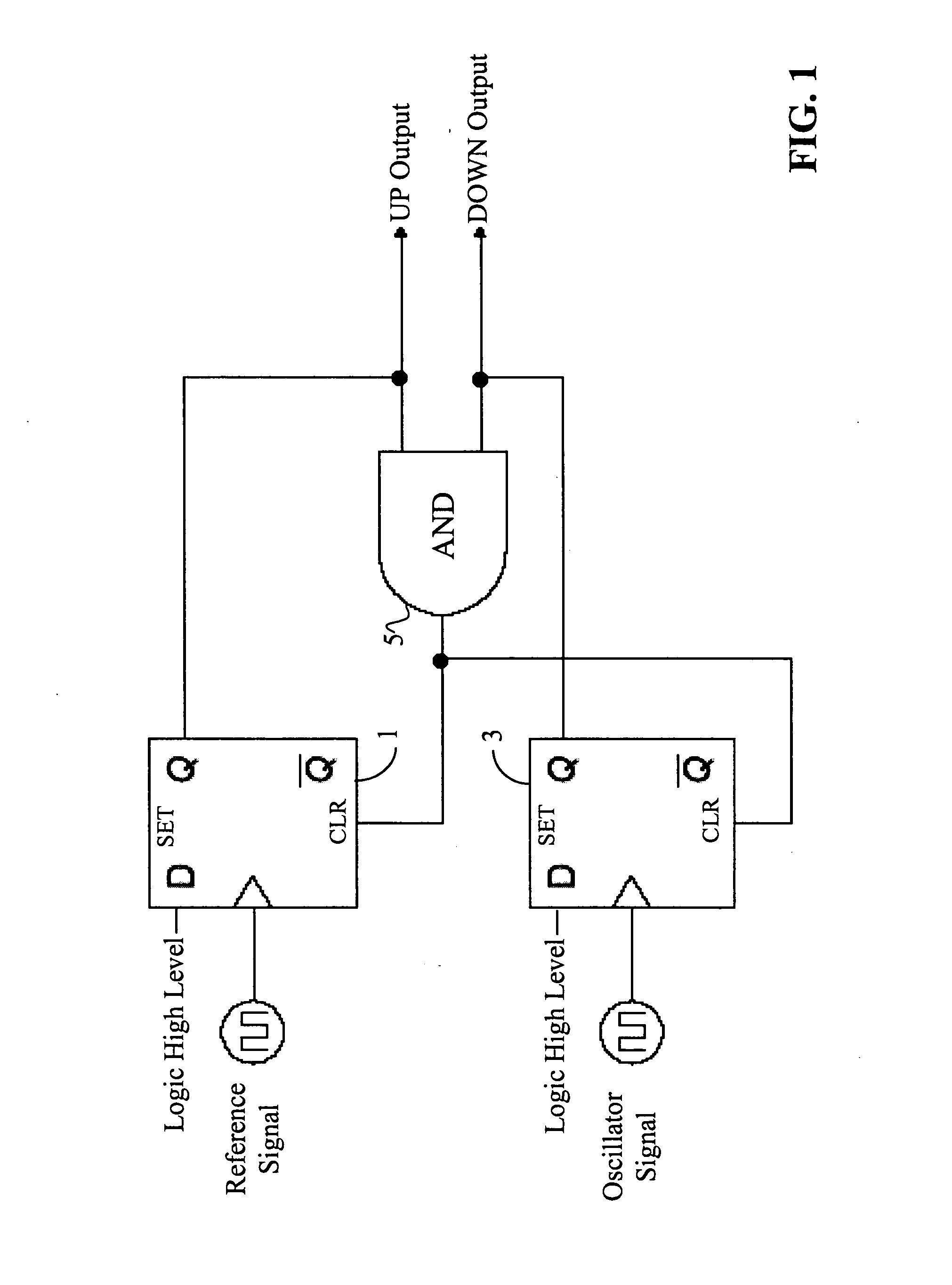

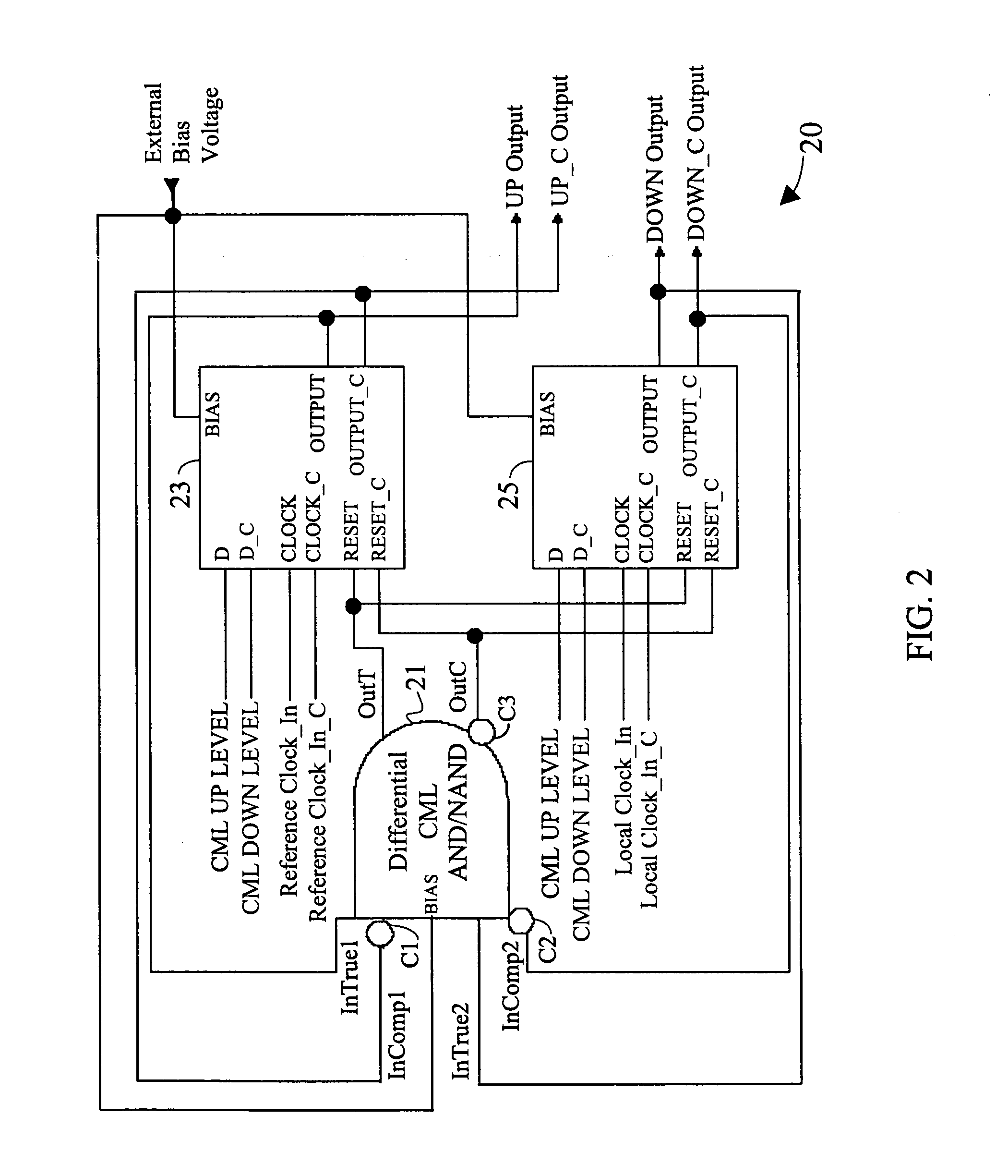

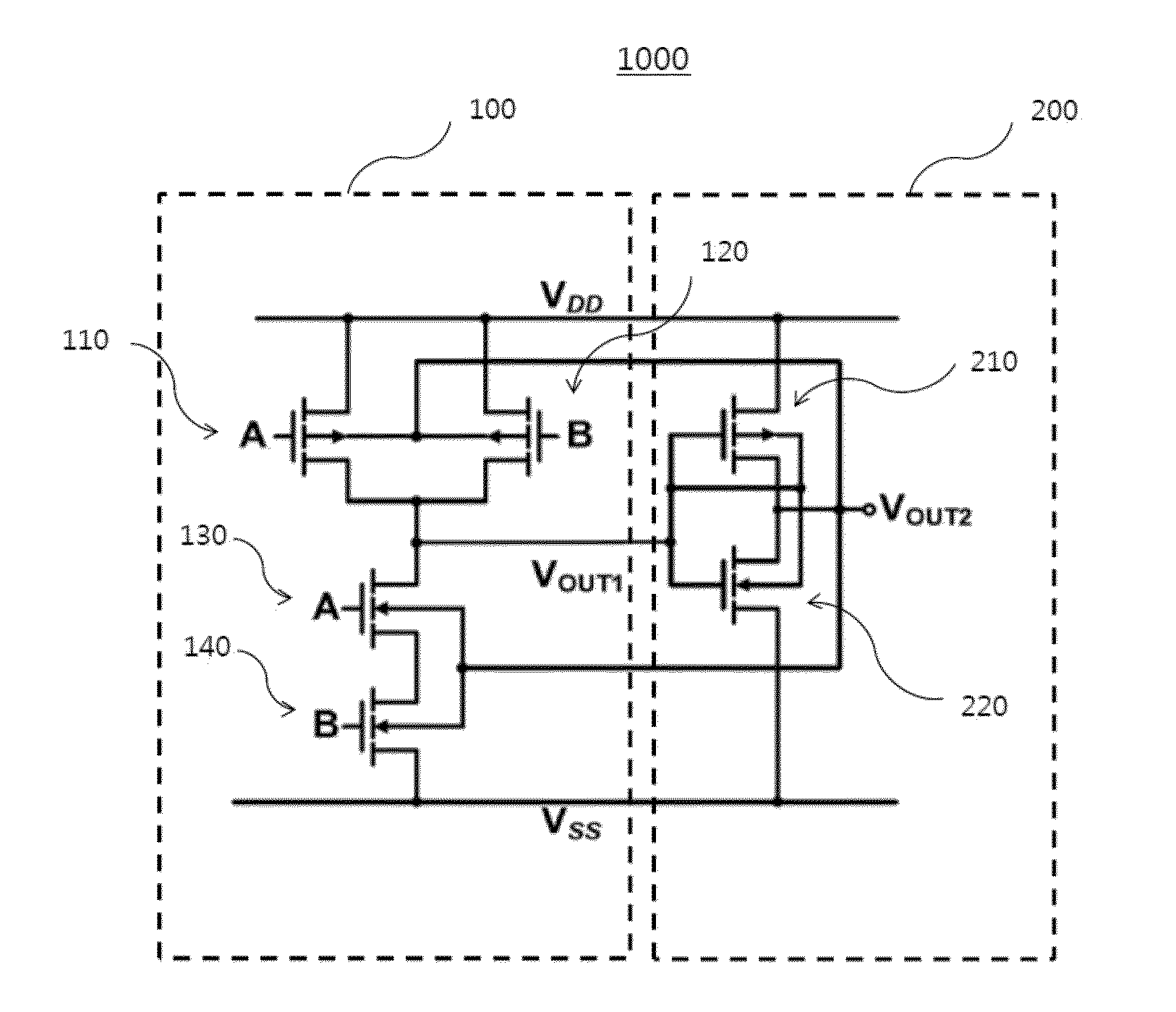

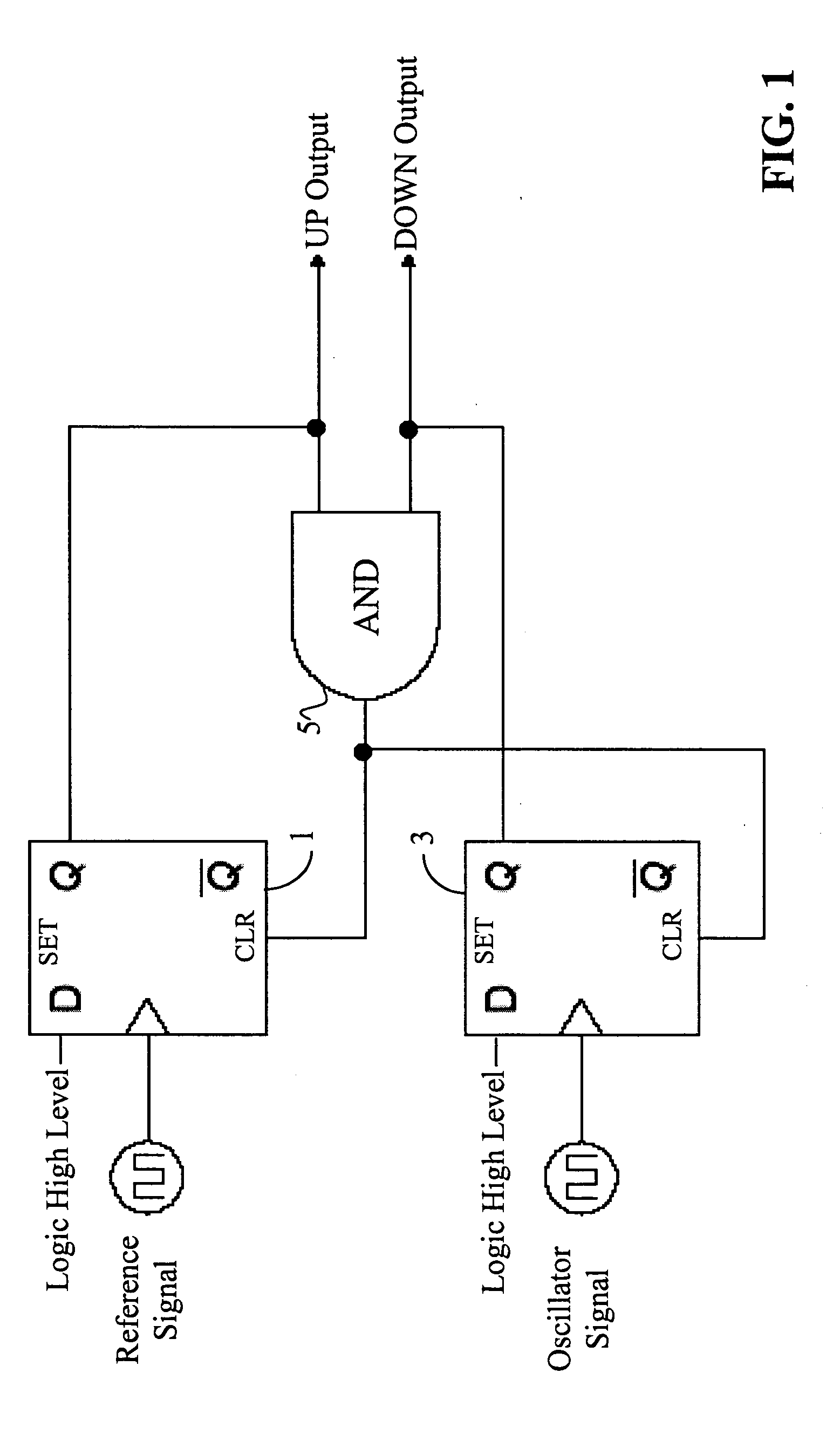

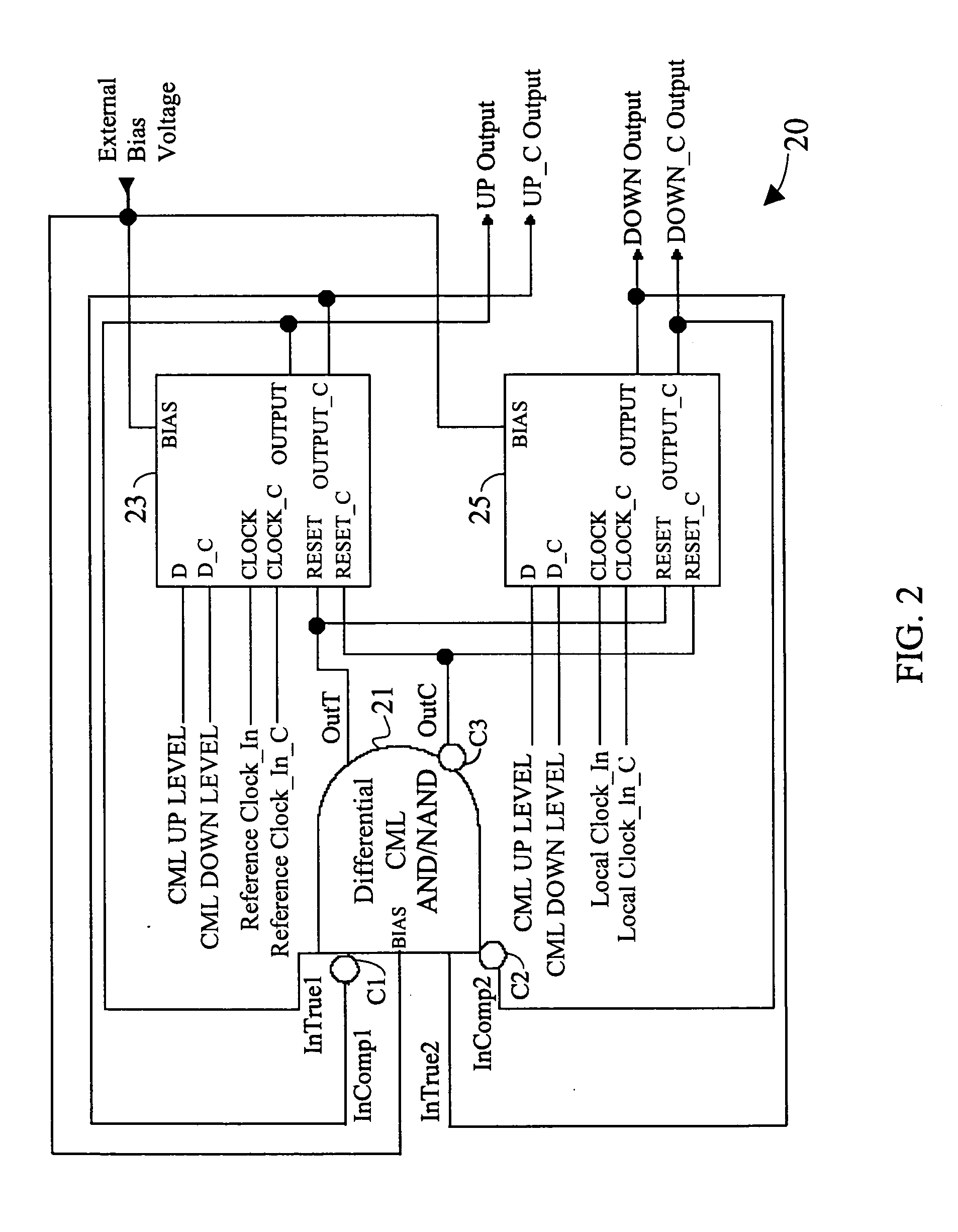

Differential master/slave CML latch

InactiveUS20050242859A1High frequencyReduce noiseReliability increasing modificationsMultiple input and output pulse circuitsDifferential phaseNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

Differential master/slave CML latch

InactiveUS7034594B2High frequencyReduce noiseReliability increasing modificationsMultiple input and output pulse circuitsDifferential phaseNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

Differential current mode phase/frequency detector circuit

InactiveUS7038497B2High frequencyReduce noiseMultiple input and output pulse circuitsPulse automatic controlNAND logicDetector circuits

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

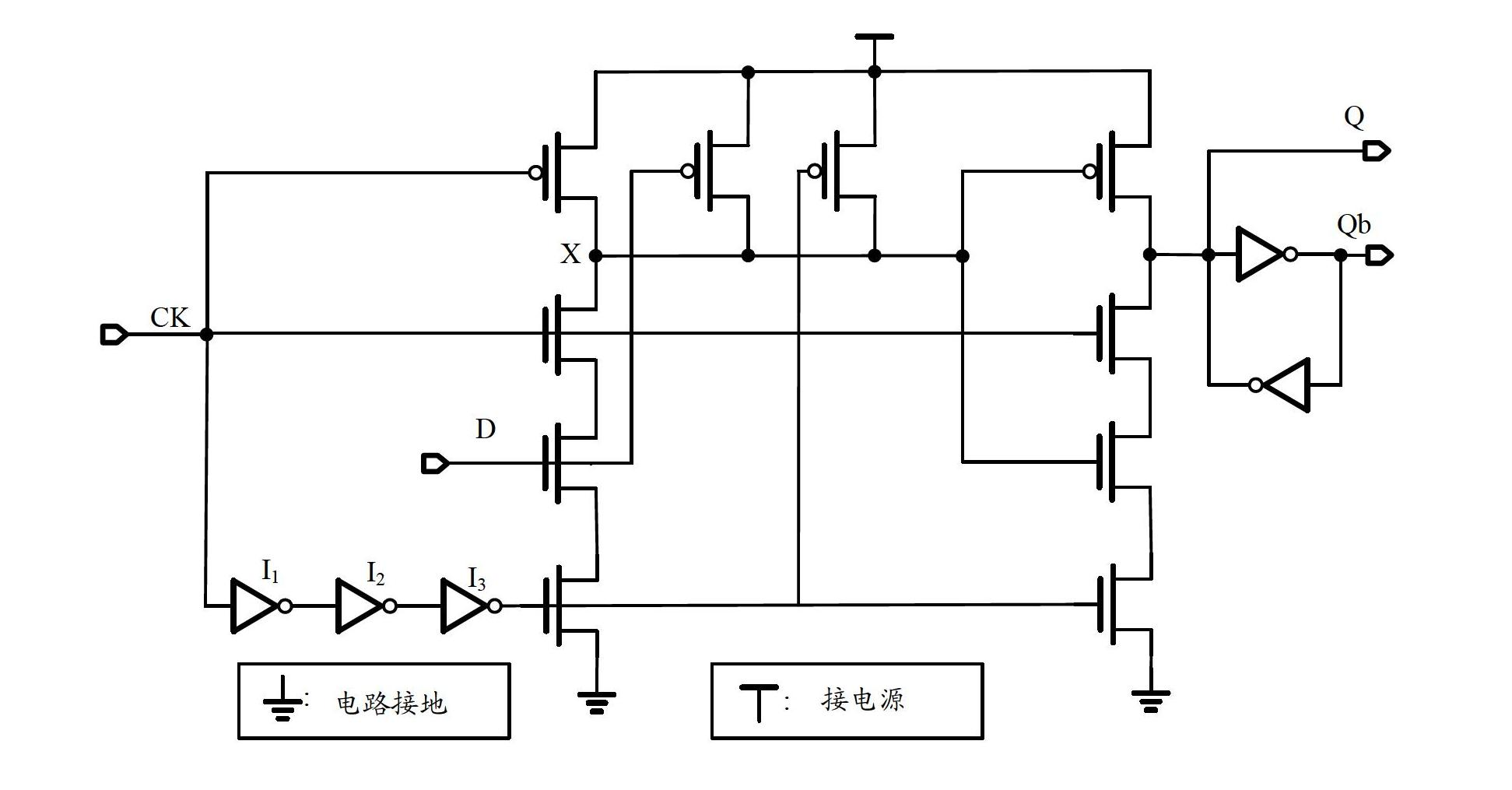

Sampling pulse type trigger

ActiveCN102684647AHigh speedReduce power consumptionElectric pulse generator circuitsElectricityData signal

The invention provides a sampling pulse type trigger comprising a first data signal input unit and a second data signal input unit, a clock signal input unit, a first signal output unit and a second signal output unit, a first NOR logic unit, a second NOR logic unit, a first charging / discharging unit, a second charging / discharging unit and a maintaining unit, wherein the first NOR logic unit is used for outputting a delay clock signal of a first gating under the control of a clock signal, a first signal and a second signal; the second NOR logic unit is used for outputting a delaying clock signal of a second gating under the control of the clock signal, the first signal and the second signal; the first charging / discharging unit is used for carrying out condition sampling on a first data signal when the clock signal and the clock signal of the first gating are high electrical levels; the second charging / discharging unit is used for carrying out the condition sampling on a second data signal when the clock signal and the clock signal of the second gating are the high electrical levels; and the maintaining unit is used for switching off an upper maintaining access or a lower maintaining access of the first signal. The trigger not only has a flexible edge property, but also reduces the power consumption.

Owner:TSINGHUA UNIV

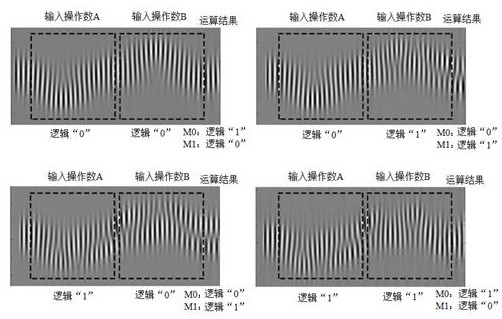

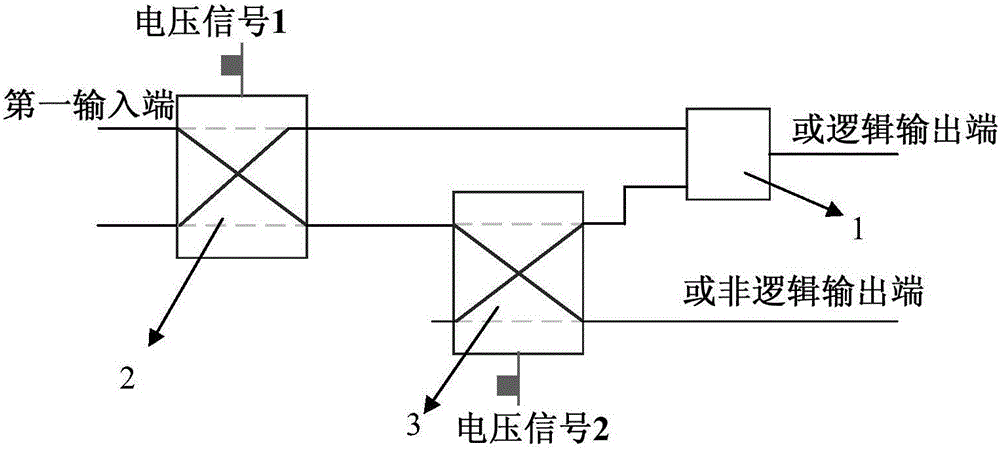

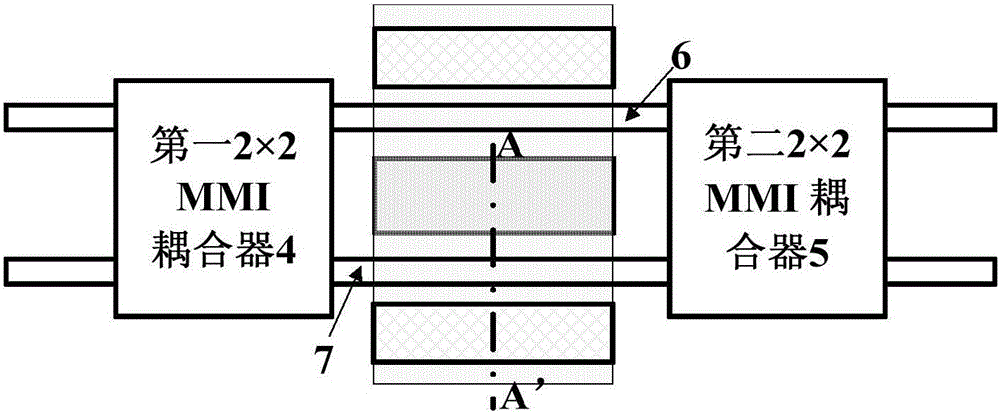

Exclusive OR and exclusive NOR logic operation unit based on optical mode

ActiveCN112180653ALow wavelength requirementLow costDigital dataLogic circuits using opto-electronic devicesNOR logicSoftware engineering

The invention discloses an exclusive OR and exclusive NOR logic operation unit based on an optical mode. The exclusive OR and exclusive NOR logic operation unit comprises a set of input waveguide andoutput waveguide which support multi-mode transmission and two sets of dynamic mode conversion devices which are controlled by operand signals. A single-mode input light source serves as a carrier andsequentially passes through the two sets of mode conversion devices, whether the mode conversion devices convert an input mode into another mode or not is controlled through each operand, and the component of each mode is detected at the output waveguide, and exclusive OR and exclusive NOR logic operation results can be obtained at the same time through one-time light propagation and collection.The logic operation unit can use different waveguide modes to calculate within the same wavelength, so that the cost of the whole optical logic loop is reduced; and meanwhile, the method is insensitive to input wavelength and ambient temperature change. The unit can be realized by adopting various material platforms, and parallel logic operation of electro-optic and all-optical exclusive OR and exclusive NOR can be realized according to different modulation modes.

Owner:LANZHOU UNIVERSITY

High speed low power 4-2 compressor

InactiveUS6904447B2Reduce load capacitanceReduce areaComputation using non-contact making devicesNumber-of-one countersCapacitanceNOR logic

A high speed low powered 4-2 compressor according to the present invention performs an XOR / XNOR operation of input data by using a single input type NAND / NOR logic circuit and a dual input type NAND / NOR logic circuit. Thus, delays to generate complementary signals are avoided. In addition, the 4-2 compressor uses a single railed multiplexer instead of a dual railed multiplexer, so that gate drive nodes and internal load capacitance are reduced. As a result, circuit area and power consumption of the 4-2 compressor are reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

Differential current mode phase/frequency detector circuit

InactiveUS20050242843A1Reduce noiseHigh frequencyReliability increasing modificationsMultiple input and output pulse circuitsDetector circuitsNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

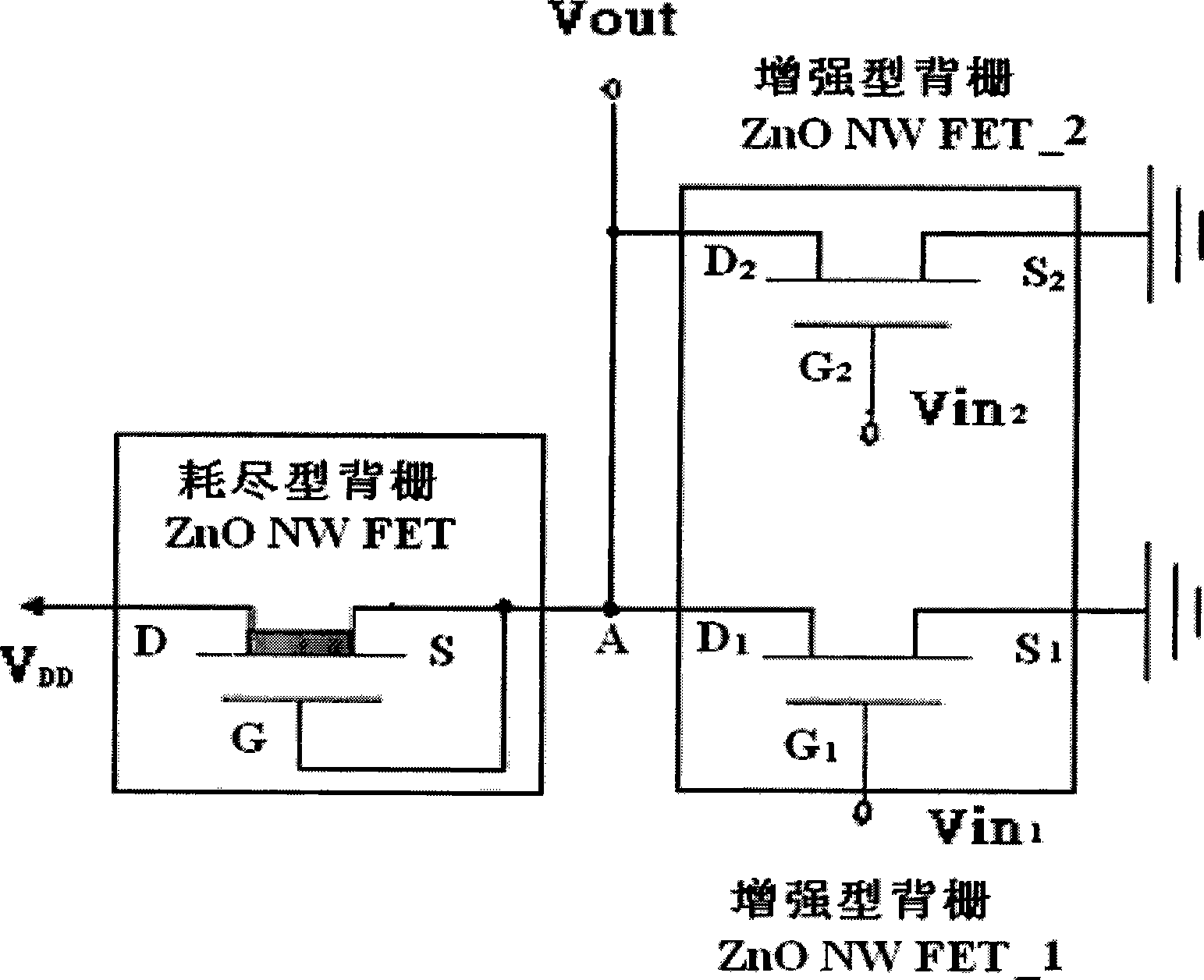

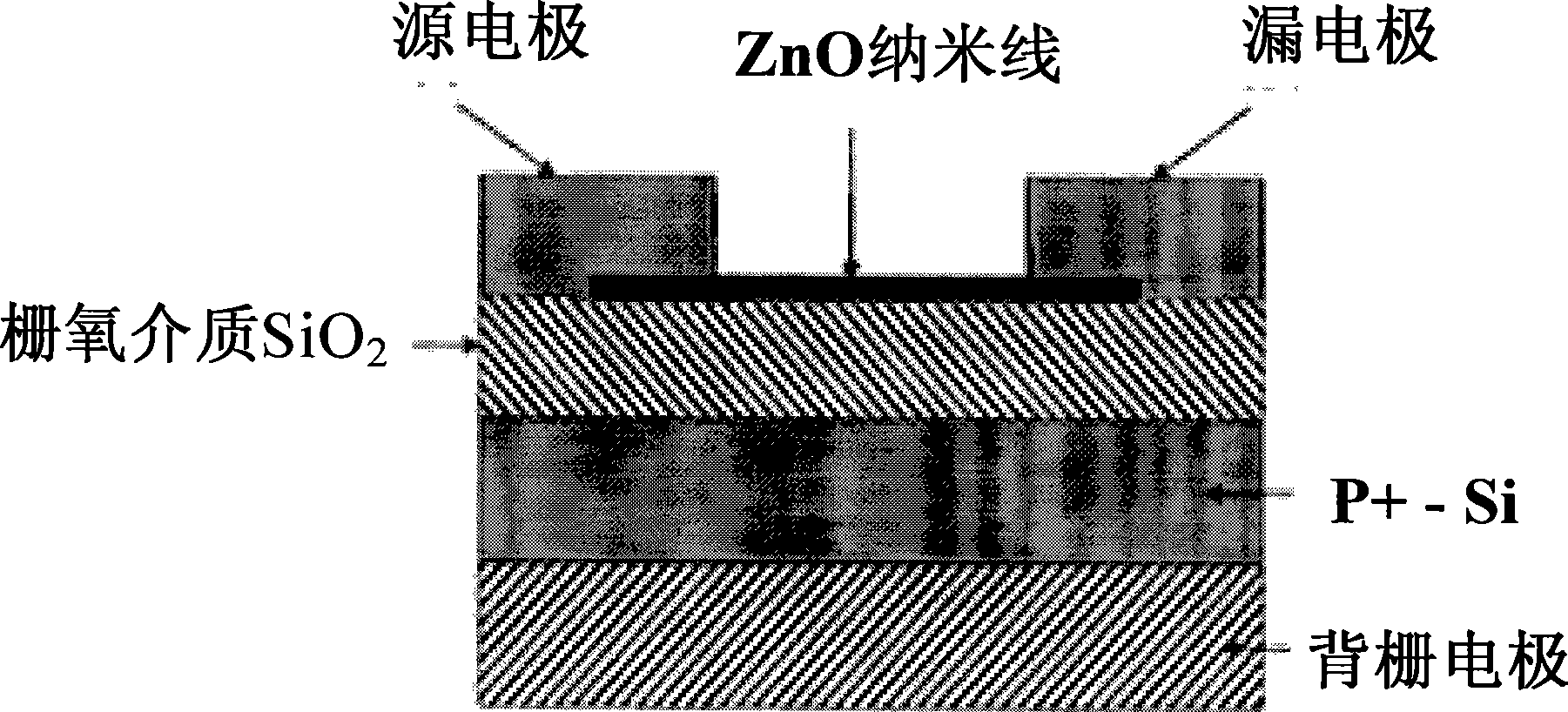

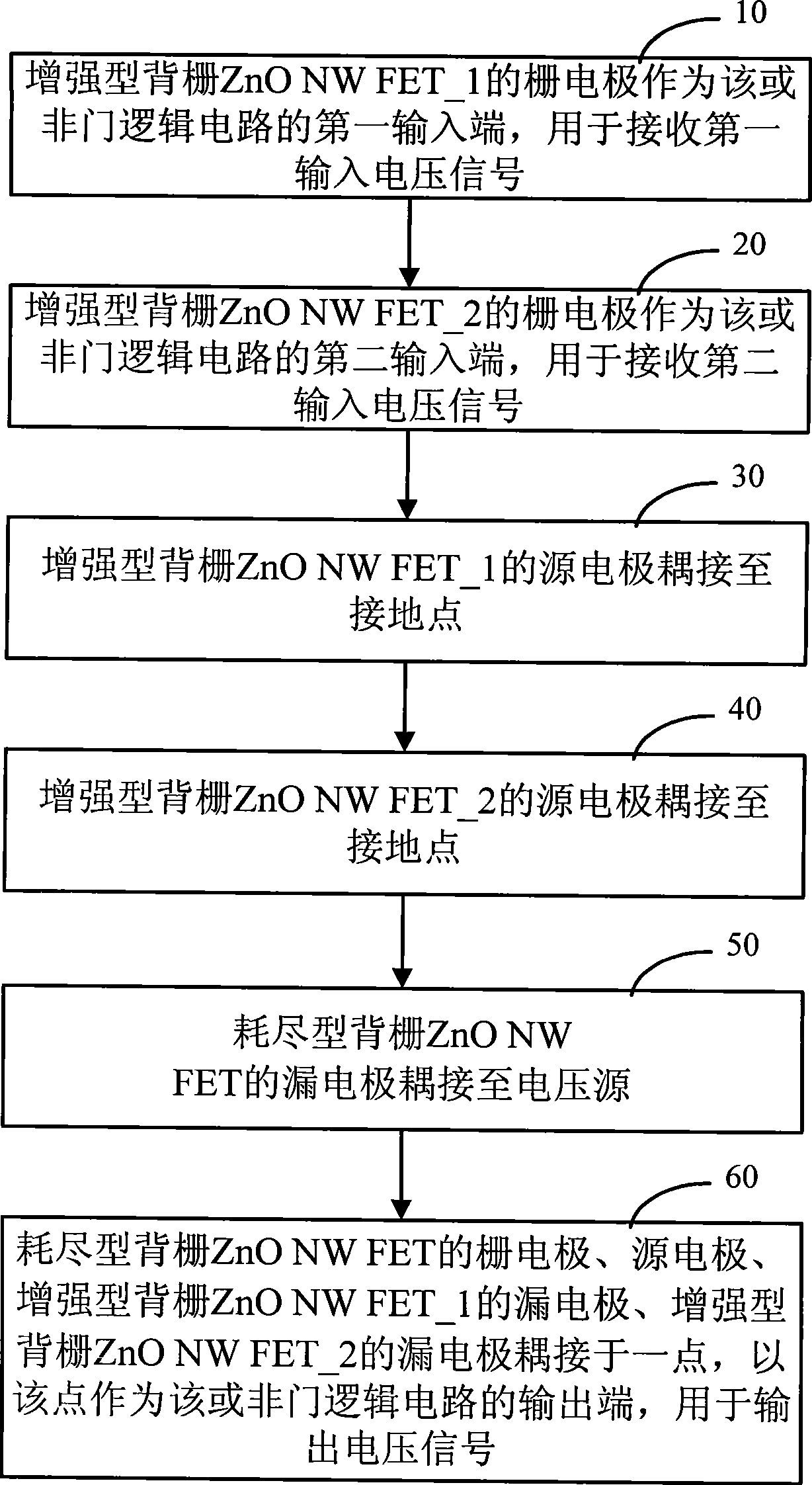

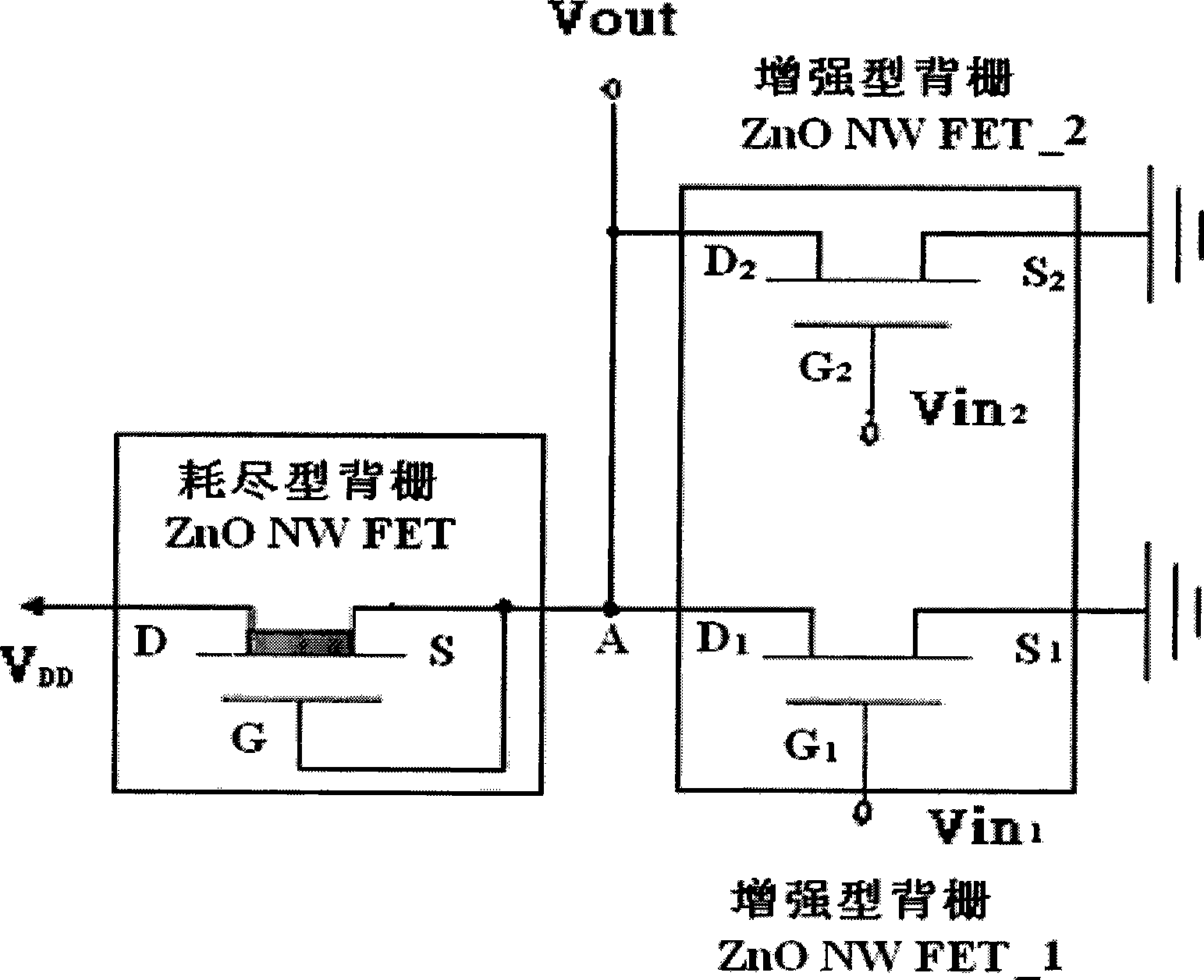

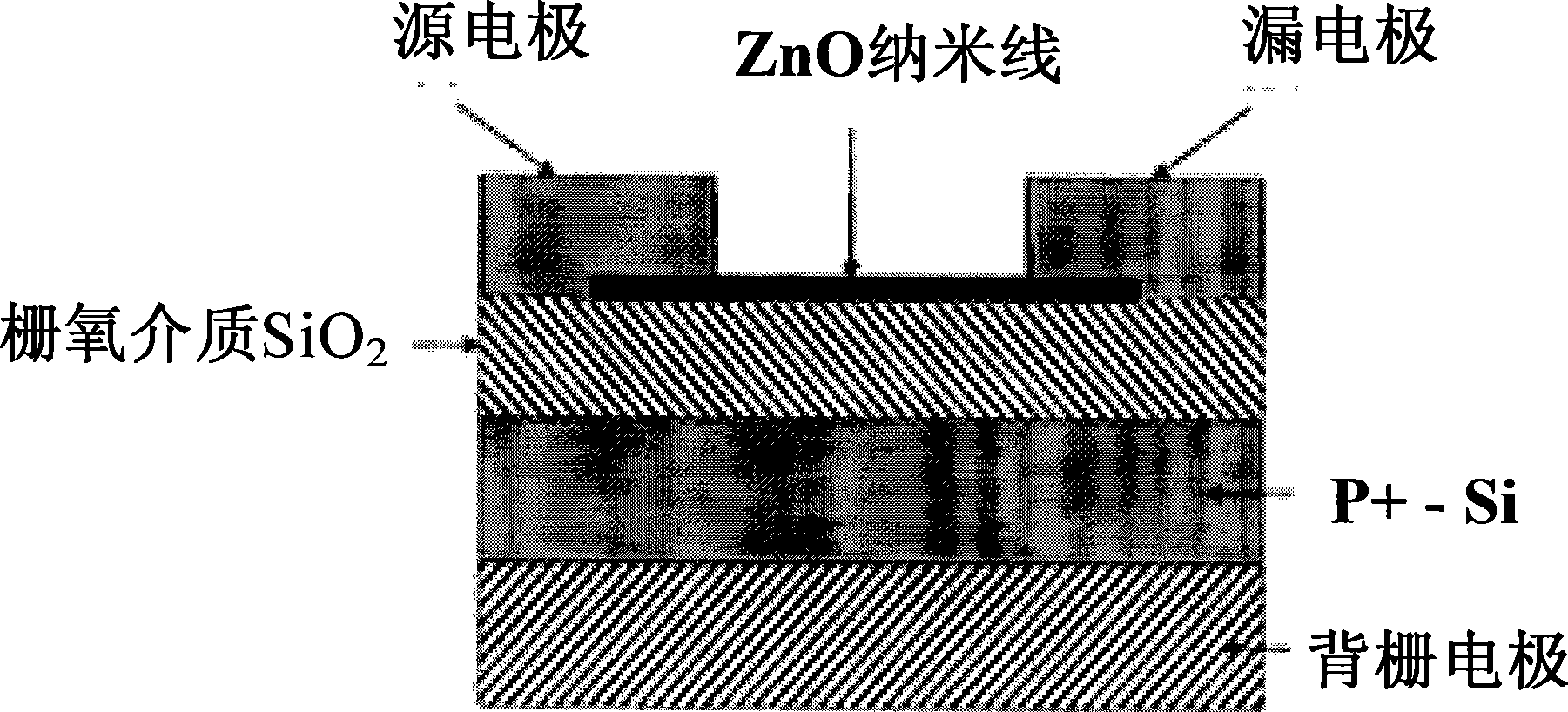

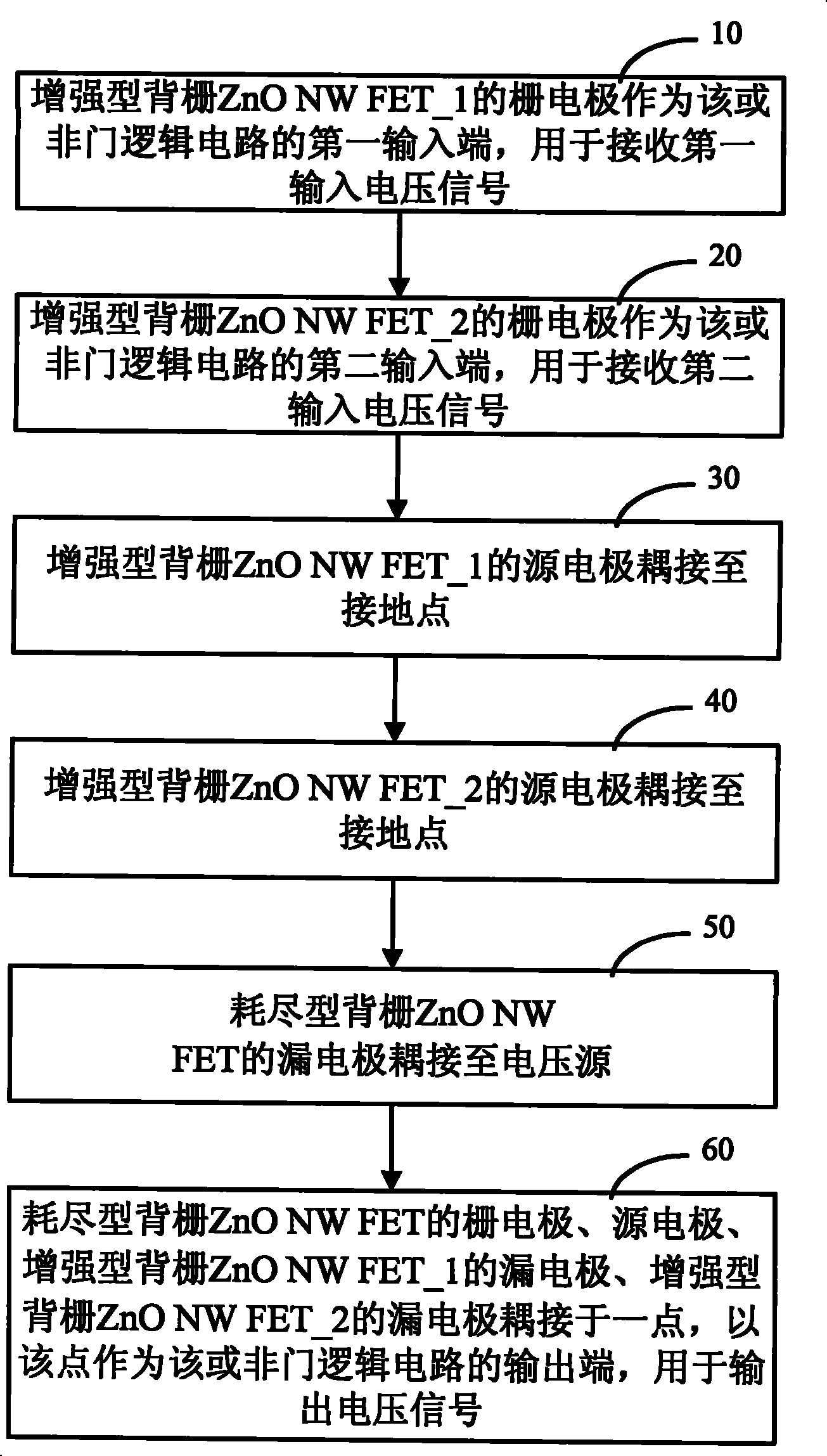

NOR gate logic circuit and its forming method

ActiveCN101431330AOvercome limitationsActive connectionTransistorLogic circuits characterised by logic functionManufacturing technologyNOR gate

The invention relates to a NOR logic circuit and a fabricating method thereof. The NOR logic circuit comprises two input terminals, two enhancement type back-gate ZnO nanowire field effect transistors, and a depletion mode back-gate ZnO nanowire field effect transistor. The input terminals are respectively used for receiving input voltage signals; the gate electrodes of the two enhancement type back-gate ZnO nanowire field effect transistors are coupled to the two input terminals respectively, and the source electrodes thereof are coupled to an earth point respectively; the drain electrode of the depletion mode back-gate ZnO nanowire field effect transistor is coupled to a voltage source, and the gate electrode and the source electrode of the depletion mode back-gate ZnO nanowire field effect transistor, and the drain electrodes of the two enhancement type back-gate ZnO nanowire field effect transistors are coupled at a point; and the point serves as an output terminal used for outputting the voltage signals. The invention utilizes the manufacturing technology and the interconnection technology of ZnO nanowire materials and ZnO nanowire field effect transistors, and fabricates the NOR logic circuit based on the direct coupling field effect of the ZnO nanowire field effect transistor.

Owner:SOI MICRO CO LTD

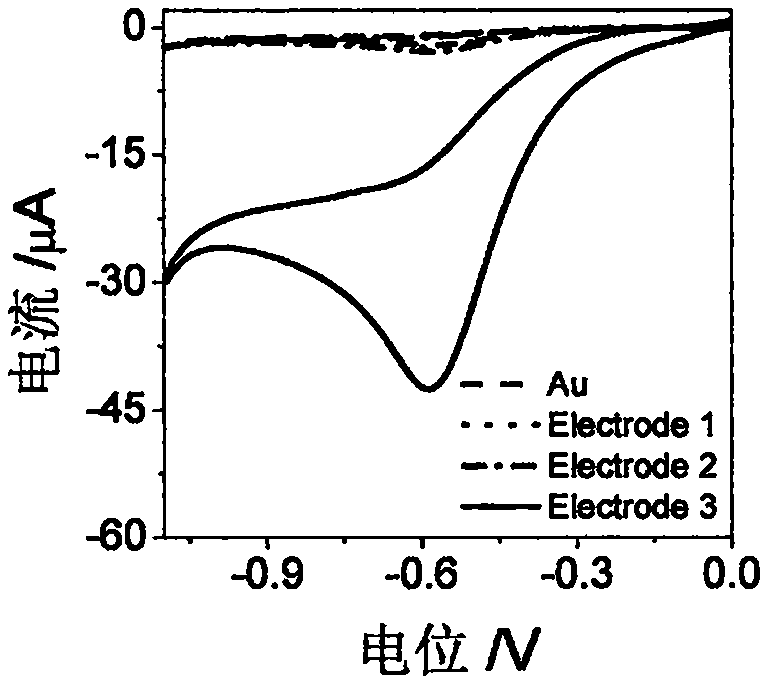

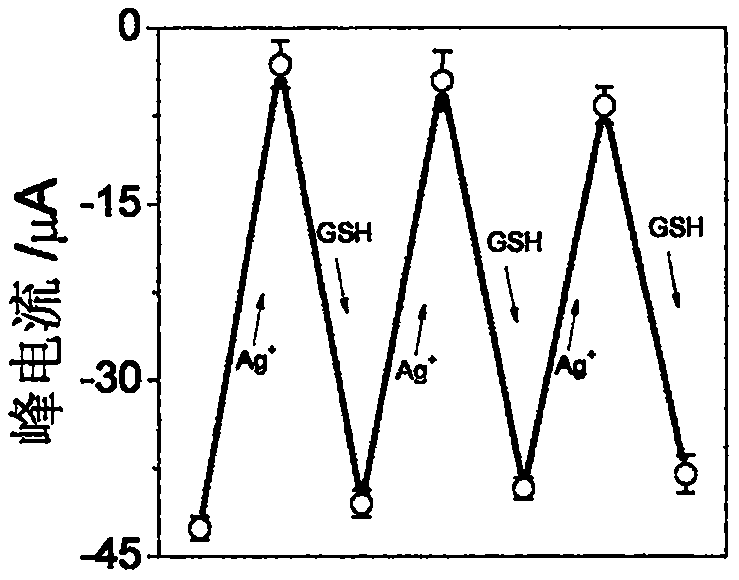

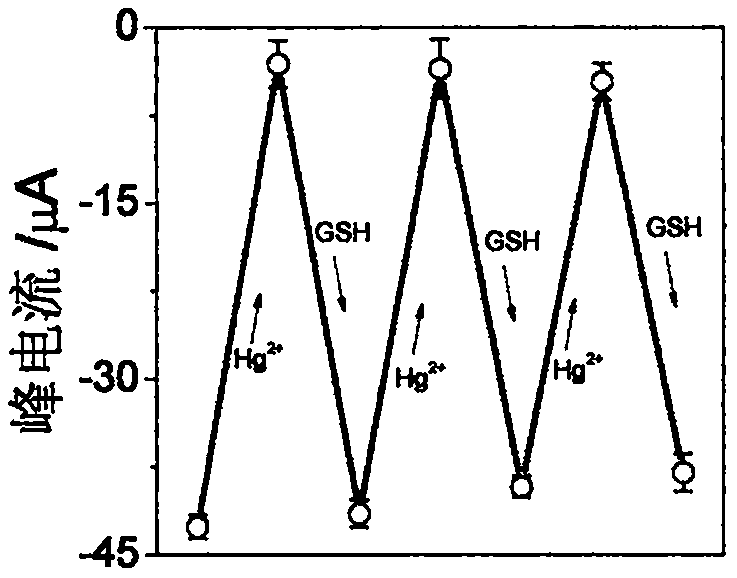

Electrochemical logic operation method based on DNA template-free amplification and metal ion-glutathione switch

ActiveCN110895259AIncrease flexibilityThe result is accurateMaterial electrochemical variablesIceboxNOR logic

The invention discloses a series of electrochemical logic operation methods constructed on the basis of DNA template-free amplification and a metal ion-glutathione switch, and the method comprises thefollowing specific steps: pretreating a gold electrode (Au), dropwise coating a DNA solution on the surface of the Au, incubating in a refrigerator at 4 DEG C overnight, and treating with mercaptohexanol (MCH); uniformly mixing distilled water, a TdT buffer solution, dNTP (dTTP+dGTP) and TdT, and dripping the mixture on the surface of the electrode; after the polymerization reaction, adding a buffer solution (Tris-HCl, KCl, pH 7.4), and incubating at room temperature; dropwise adding hemin to the electrode, and incubating at room temperature; after the electrode is prepared in each step, slowly washing the electrode with distilled water to remove impurities. Two NOT logic gates, two IMPLY logic gates and one NOR logic gate are constructed. The method has the advantages of simple preparation, high detection speed, accurate and reliable result and low cost.

Owner:NINGBO UNIV

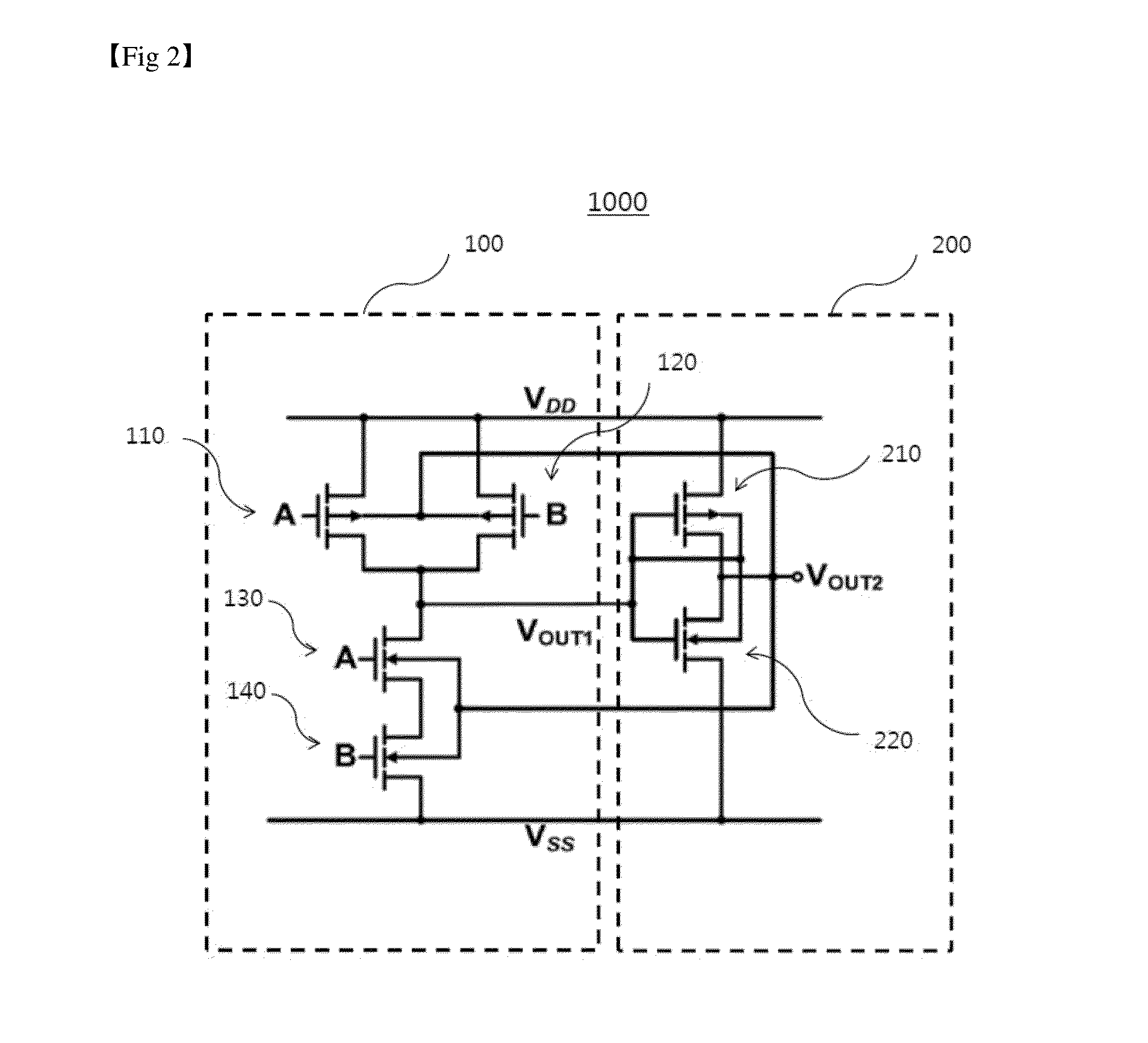

Logic gate using schmitt trigger circuit

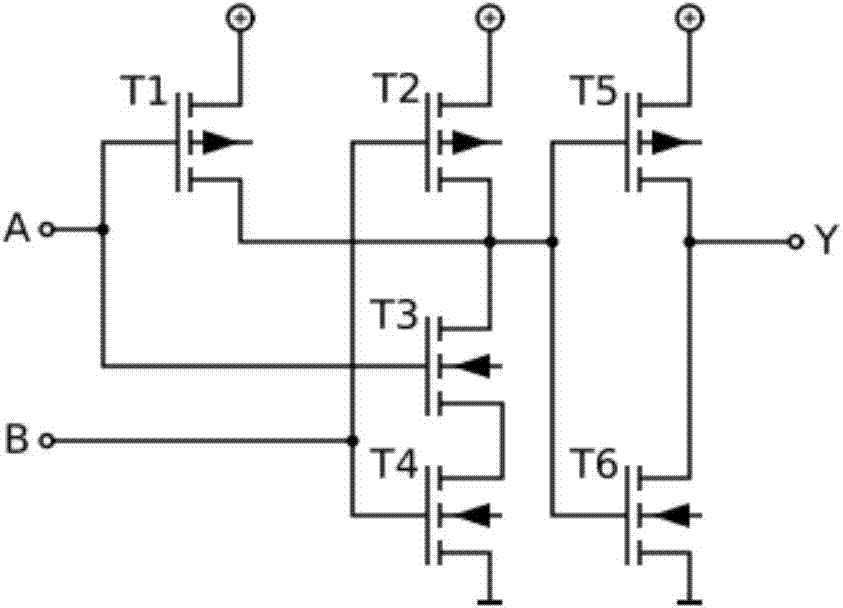

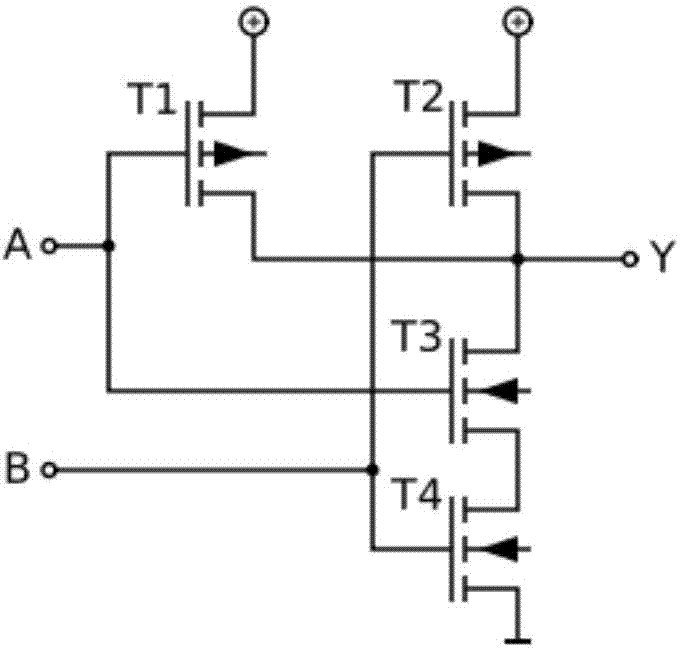

ActiveUS20150303918A1Low noise immunityReduce power consumptionPower reduction by control/clock signalLogic circuits characterised by logic functionSchmitt triggerNAND logic

Logic gates using Schmitt trigger circuits are provided. An AND gate using the Schmitt trigger circuit includes: a NAND gate configured to receive two input signals, perform a NAND logic operation, and output a first output signal; and a DTMOS inverter configured to invert the first output signal, and output the inverted first output signal as a second output signal, and a threshold voltage of the NAND gate is controlled using the second output signal. A OR gate using the Schmitt trigger circuit includes: a NOR gate configured to receive two input signals, perform a NOR logic operation, and output a first output signal; and a DTMOS inverter configured to invert the first output signal, and output the inverted first output signal as a second output signal, and a threshold voltage of the NOR gate is controlled using the second output signal.

Owner:RES & BUSINESS FOUND SUNGKYUNKWAN UNIV

Ultra high-speed nor-type lsdl/domino combined address decoder

An ultra high speed address decoder uses a combination of Domino logic circuits and LSDL logic circuits. N address hits are converted into N logic true address bits and N complementary address bits. A partial address decoder generates two bit groups using selected of the N logic true address bits and N complementary address bits in NOR logic structures such only two cascaded NFETS are used in a logic tree. The bit groups are partitioned to optimize the layout of the parallel bit lines in the address decoder.

Owner:GOOGLE LLC

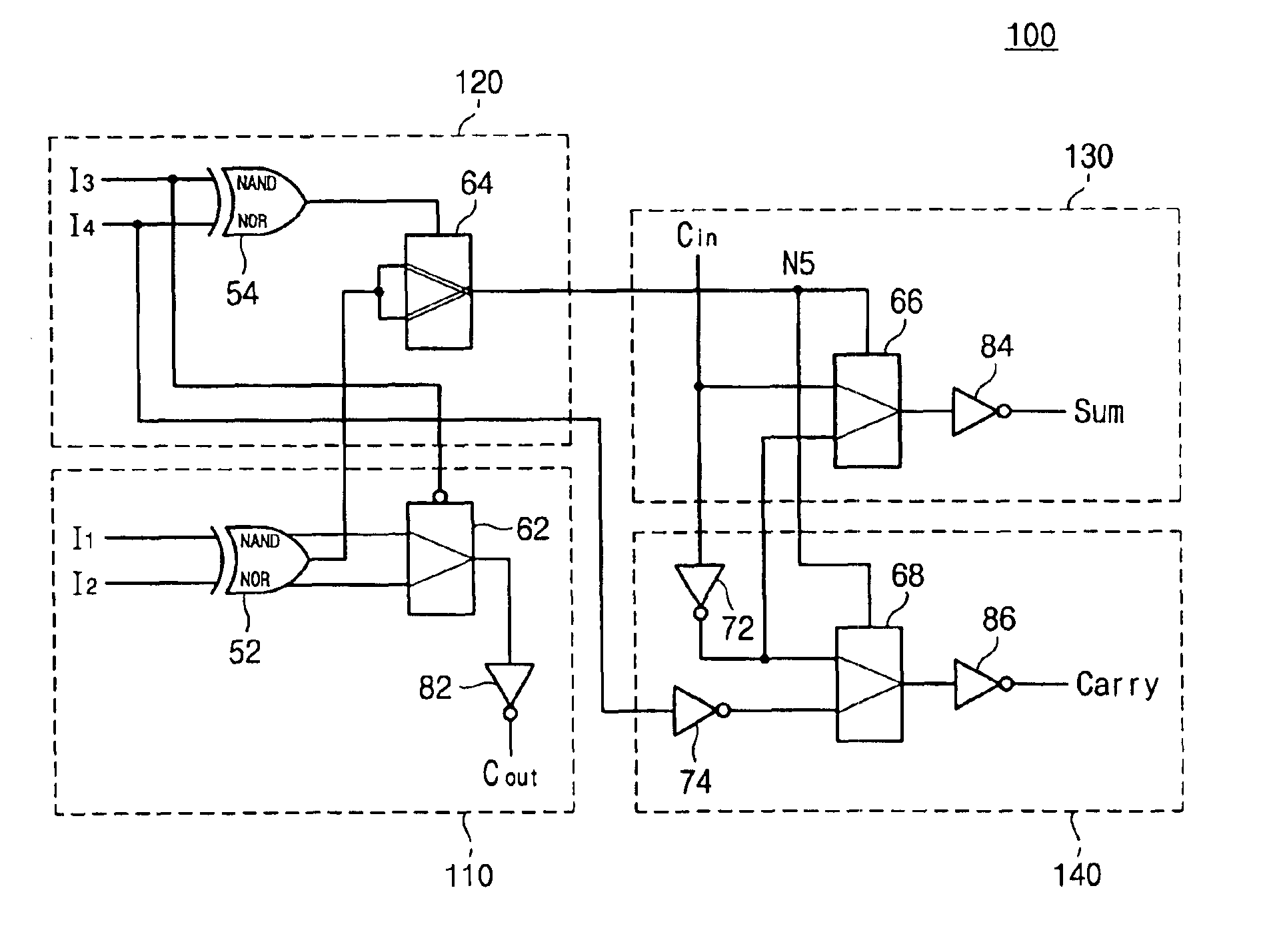

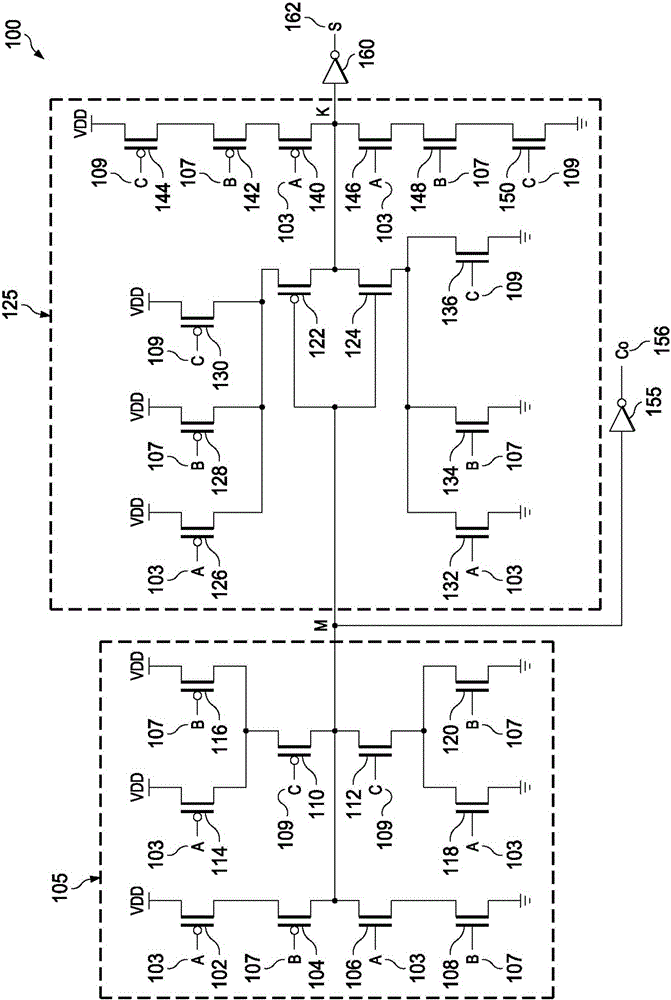

Low area full adder with shared transistors

ActiveCN105471424APower reduction in field effect transistorsLogic circuits characterised by logic functionNOR logicExclusive or

The invention relates to a low area full adder with shared transistors. A full adder (200) is disclosed that utilizes low area. The full adder (200) includes an exclusive NOR logic circuit (205). The exclusive NOR logic circuit (205) receives a first input (202) and a second input (204). A first inverter (235) receives an output (234) of the exclusive NOR logic circuit (205) and generates an exclusive OR output (236). A carry generation circuit (245) receives the output (234) of the exclusive NOR logic circuit (205), the exclusive OR output (236) and a third input (206). The carry generation circuit (245) generates an inverted carry (246). A second inverter (247) is coupled to the carry generation circuit (245) and generates a carry (248) on receiving the inverted carry (246). A sum generation circuit (250) receives the output (234) of the exclusive NOR logic circuit (205), the exclusive OR output (236) and the third input (206). The sum generation circuit (250) generates an inverted sum. A third inverter (265) is coupled to the sum generation circuit (250) and generates a sum (270) on receiving the inverted sum.

Owner:TEXAS INSTR INC

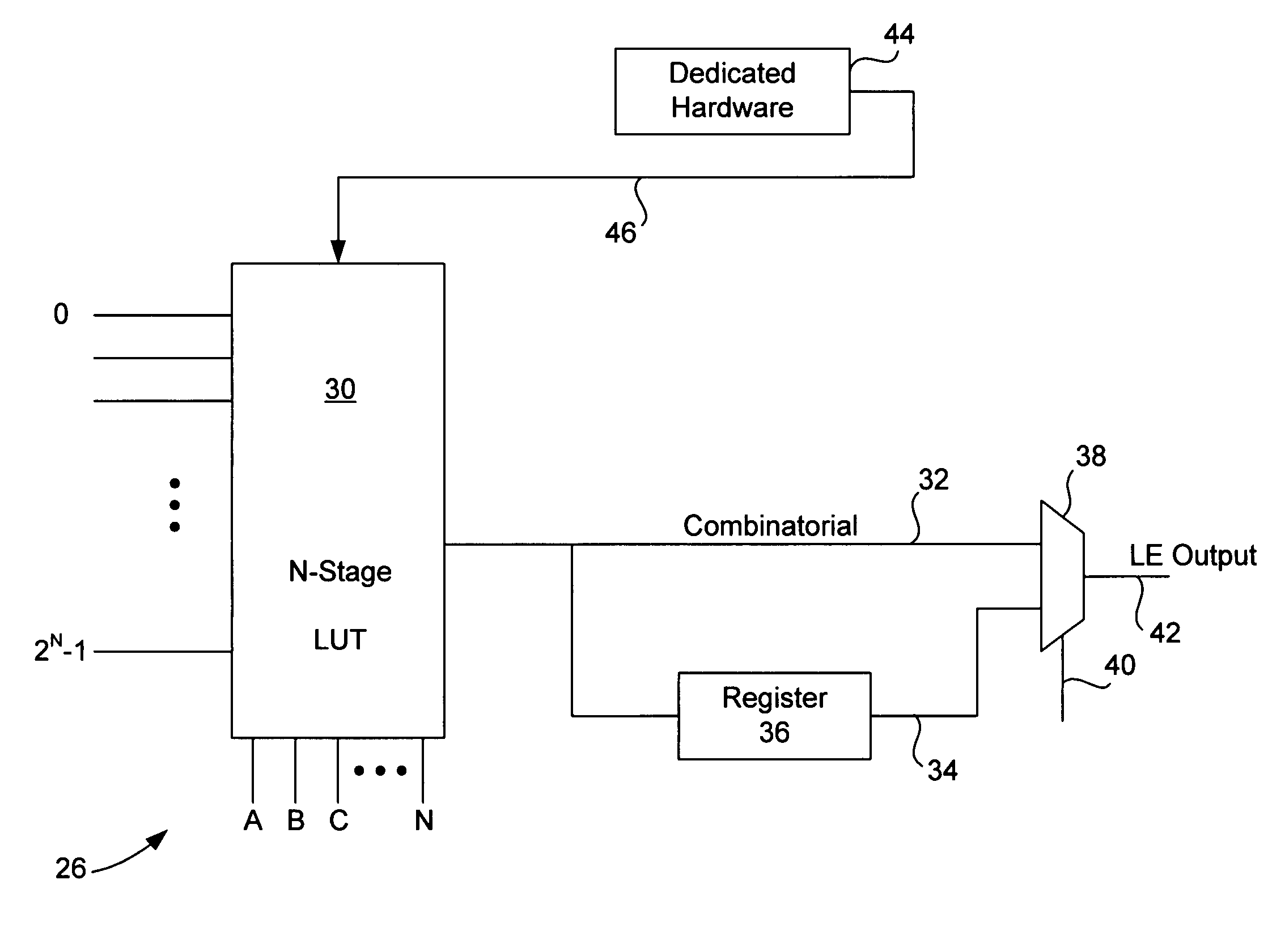

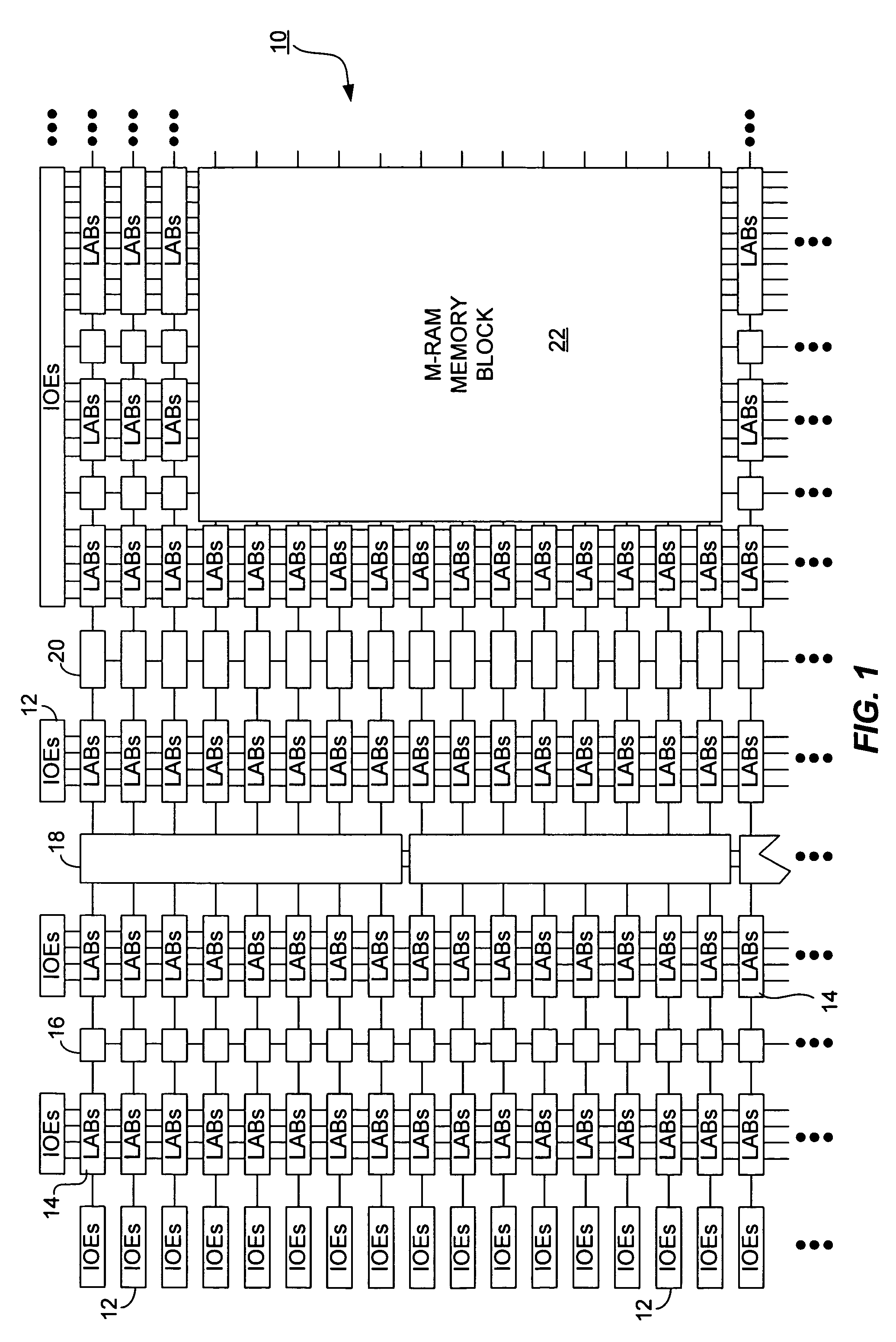

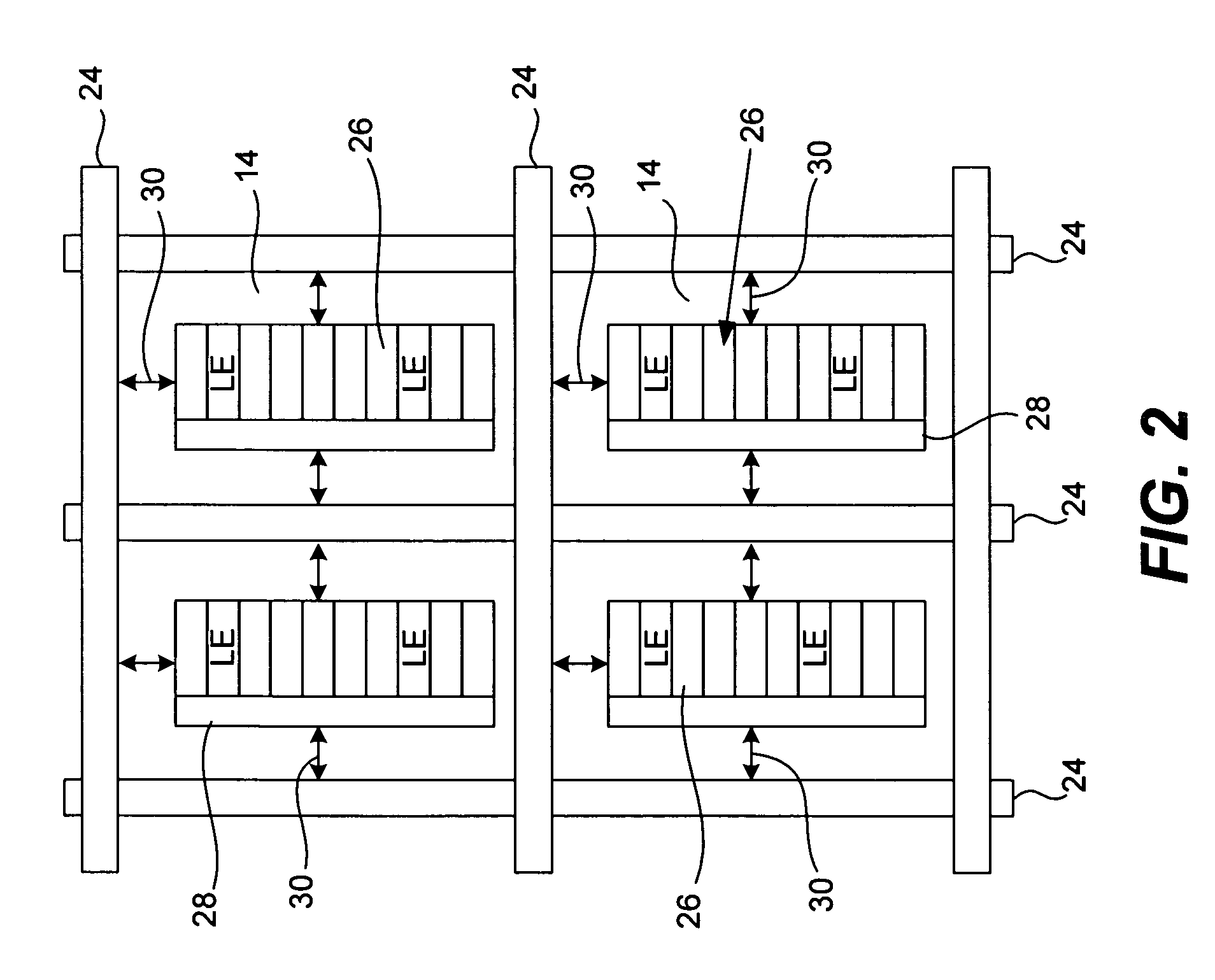

Apparatus and method for the arithmetic over-ride of look up table outputs in a programmable logic device

ActiveUS7812633B1Solid-state devicesLogic circuits using elementary logic circuit componentsMultiplexingDigital signal processing

A programmable logic device having a Logic Element with an N-stage Look Up Table (LUT), dedicated hardware for performing a non-LUT logic function, and an over-ride element configured to selectively force a muxing stage within the N-stage LUT to select either one or more LUT configuration bit inputs or the output of the non-LUT logic function as the output of the LUT. In various embodiments, the non-LUT functions can include addition, subtraction, multiplication, division, digital signal processing, memory storage, etc.

Owner:ALTERA CORP

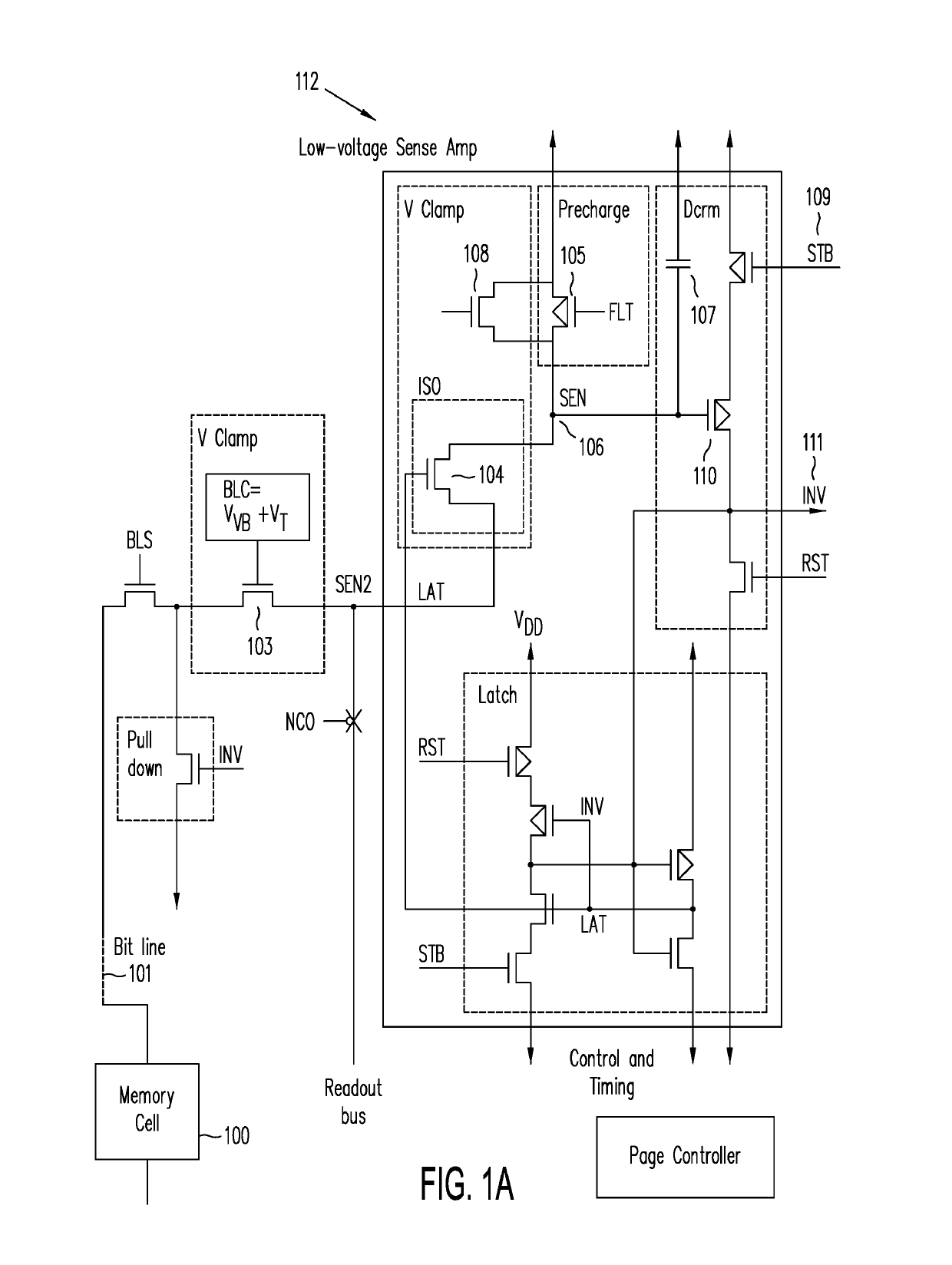

Sensing in floating source string nor architecture

Algorithms for fast data retrieval, low power consumption in a 3D or planar non-volatile array of memory cells, connected between an accessible drain string and a floating, not directly accessible, source string, in a NOR-logic type of architecture, are presented.

Owner:SUNRISE MEMORY CORP

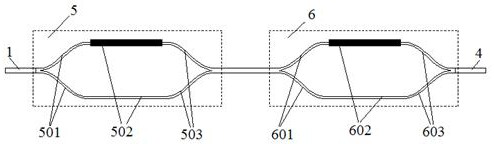

Silicon-based electro-optic logic OR/NOR gate

ActiveCN105759533AHigh extinction ratioHigh bandwidthLogic circuits using opto-electronic devicesInstrumentsNOR gateNOR logic

The invention discloses a silicon-based electro-optic logic OR / NOR gate. The silicon-based electro-optic logic OR / NOR gate comprises two 2*2MZI type electro-optic switches and a 2*1MMI coupler. Each 2*2MZI type electro-optic switch comprises a first input end, a second input end, a first output end and a second output end, the 2*1MMI coupler comprises a first input end, a second input and an output end, and the two 2*2MZI type electro-optic switches include a first 2*2MZI type electro-optic switch and a second 2*2MZI type electro-optic switch. The first output end of the first 2*2MZI type electro-optic switch is connected with the first input end of the 2*1MMI coupler, and the second output end of the first 2*2MZI type electro-optic switch is connected with the first input end of the second 2*2MZI type electro-optic switch. The first output end of the second 2*2MZI type electro-optic switch is connected with the second input end of the 2*1MMI coupler, the output end of the 2*1MMI coupler is an OR logic output end, and the second output end of the second 2*2MZI type electro-optic switch is a NOR logic output end. The silicon-based electro-optic logic OR / NOR gate has the advantages of high extinction ratio, high speed, large broadband and large fabrication tolerance.

Owner:NINGBO UNIV

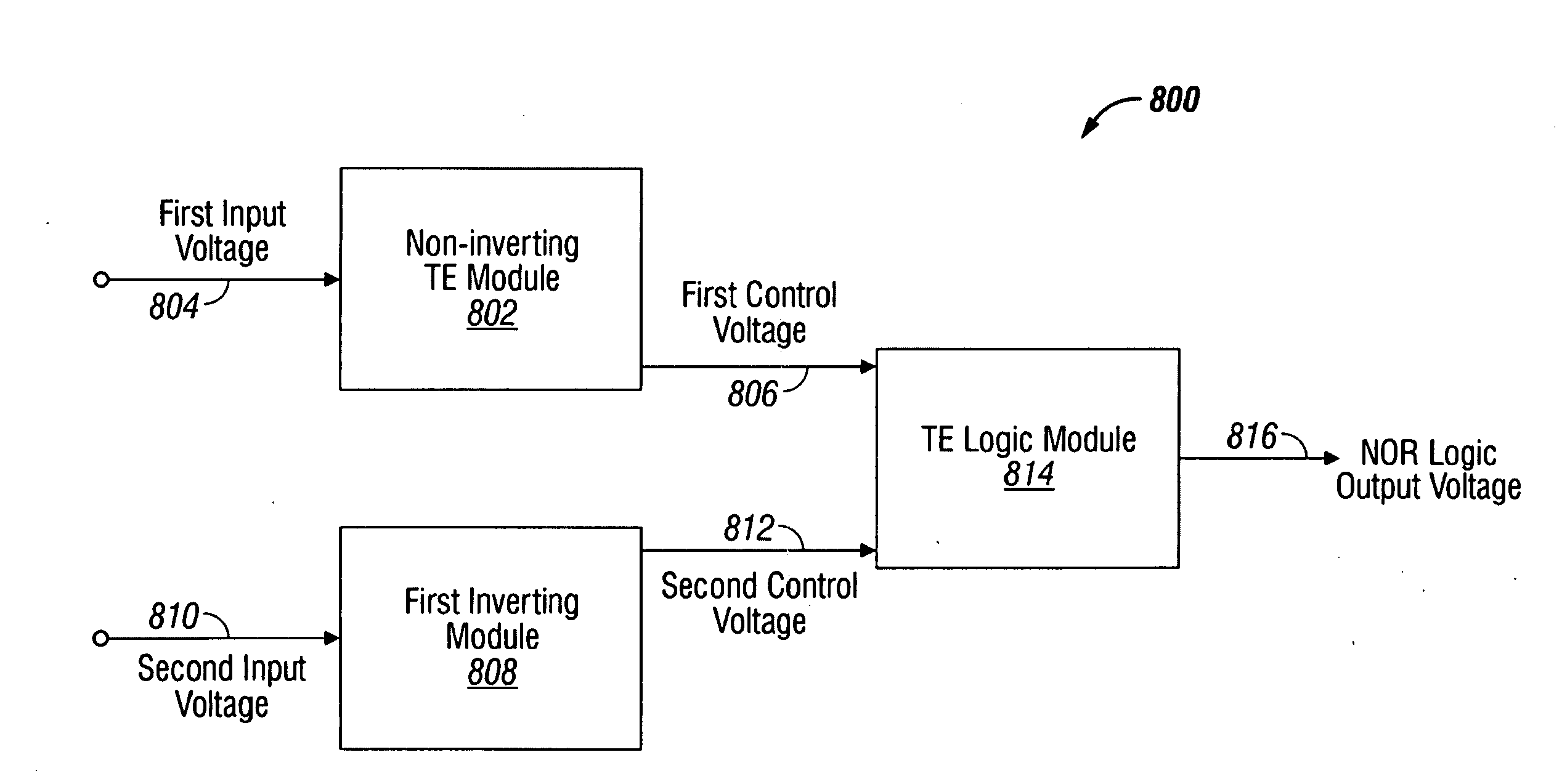

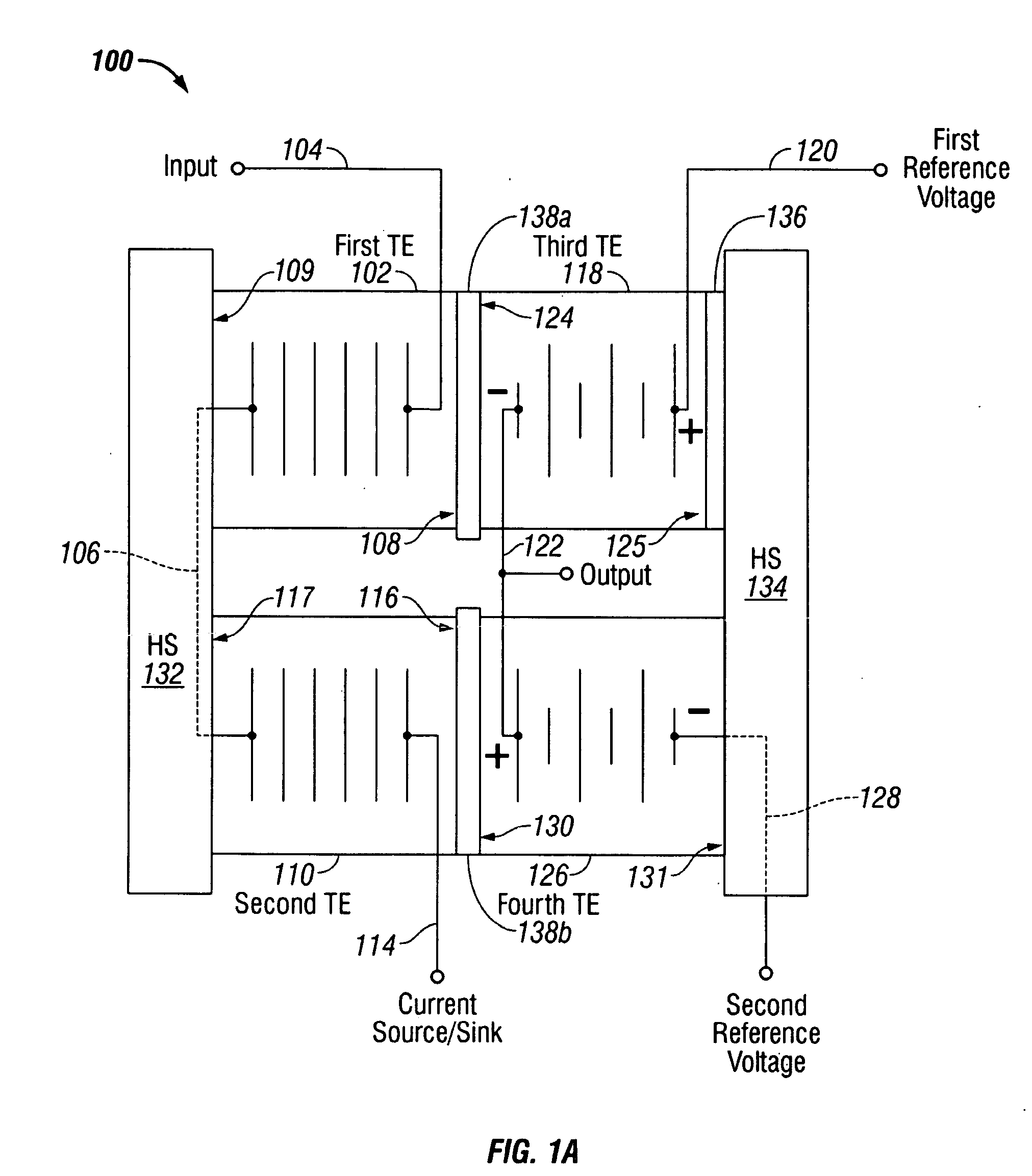

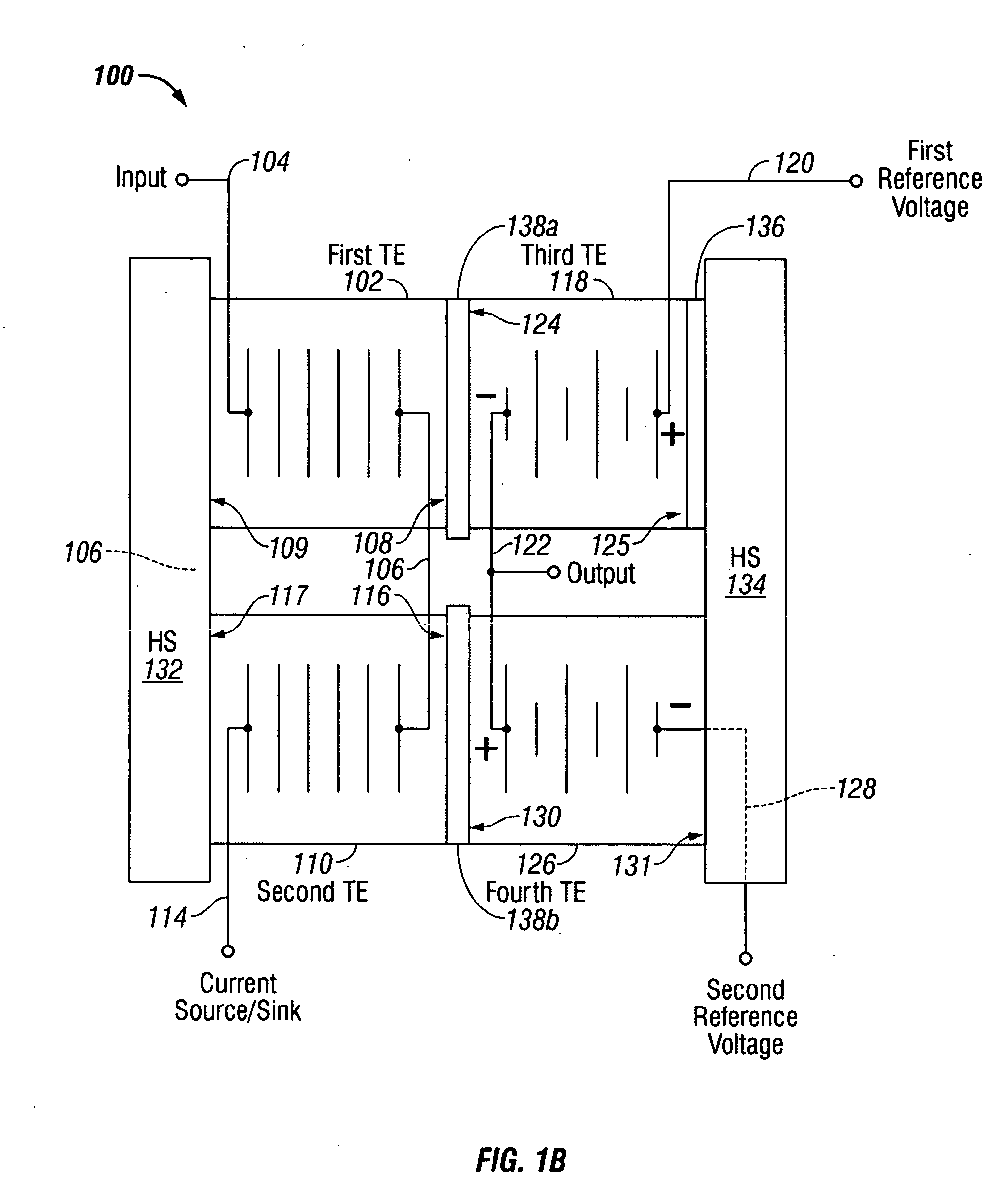

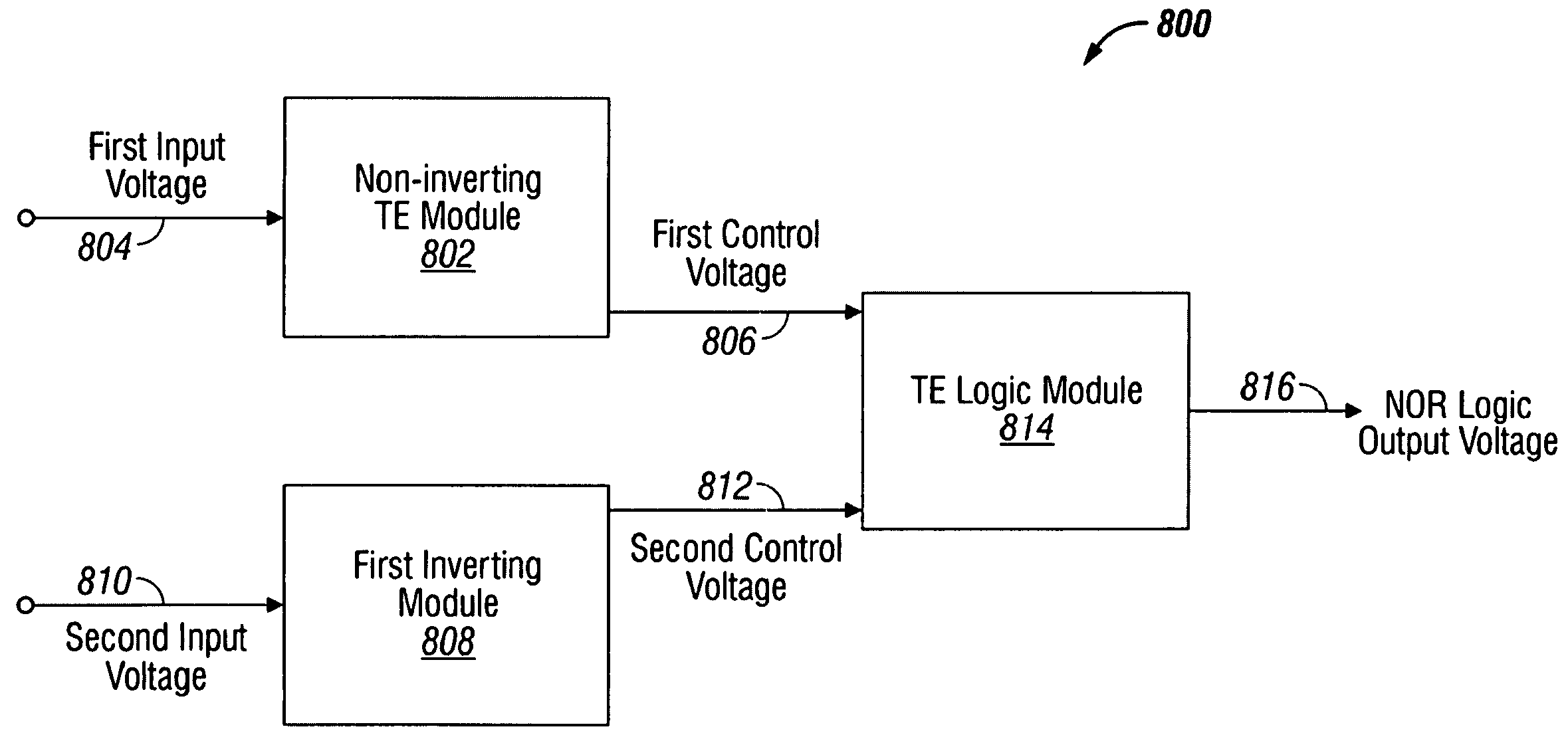

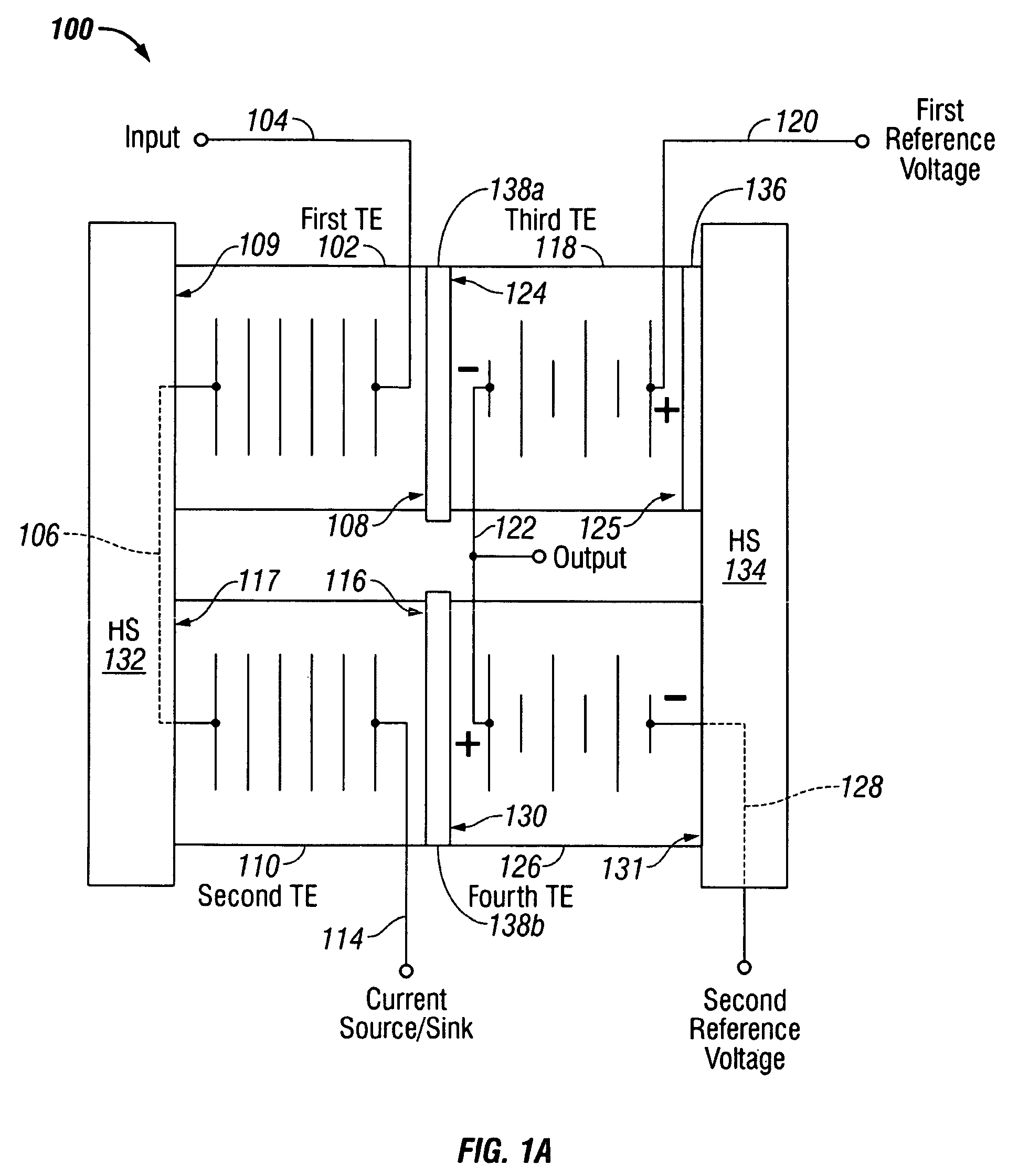

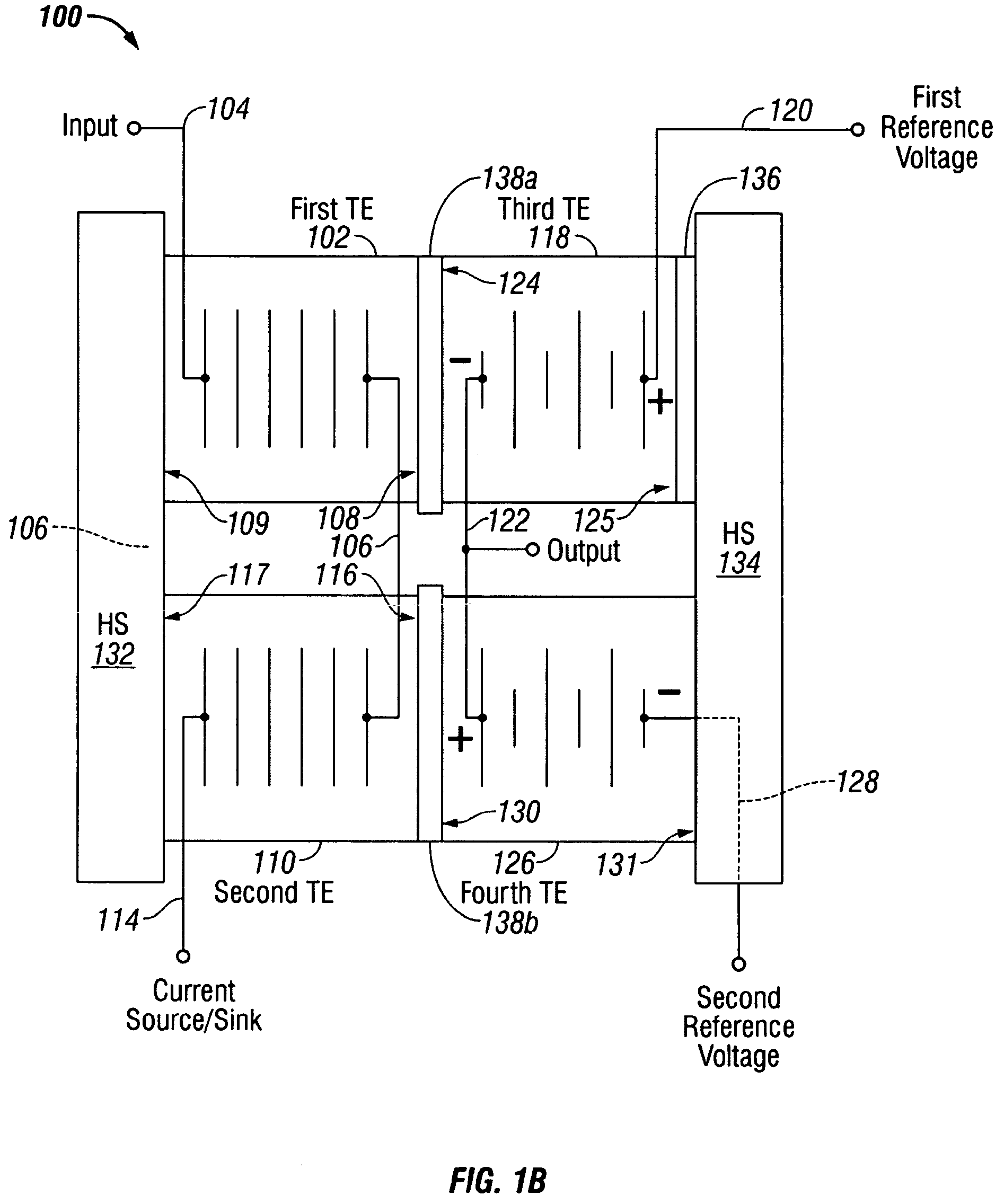

Thermal Electric NOR Gate

ActiveUS20090206882A1Less overall consumptionHigh densityLogic circuits characterised by logic functionLogic circuits using superconductive devicesNOR logicNOR gate

A thermal electric (TE) binary NOR gate logic circuit is provided with a method for NOR logic gating. The method accepts a first input voltage representing an input binary logic state and generates a first thermal electric (TE) temperature in response to the first input voltage. A second input voltage is accepted representing an input binary logic state, and a second TE temperature is generated in response to the second input voltage. In response to the first and second TE temperatures, a NOR logic state output voltage is generated. More explicitly, a first control voltage is generated in response to the first TE temperature, and a second control voltage is generated in response to the second TE temperature. Then, a third TE temperature is generated in response to the first and second control voltages, which in turn generates the output voltage.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

Thermal electric NOR gate

ActiveUS7659750B2Low volumeLess overall consumptionLogic circuits characterised by logic functionLogic circuits using superconductive devicesNOR logicNOR gate

A thermal electric (TE) binary NOR gate logic circuit is provided with a method for NOR logic gating. The method accepts a first input voltage representing an input binary logic state and generates a first thermal electric (TE) temperature in response to the first input voltage. A second input voltage is accepted representing an input binary logic state, and a second TE temperature is generated in response to the second input voltage. In response to the first and second TE temperatures, a NOR logic state output voltage is generated. More explicitly, a first control voltage is generated in response to the first TE temperature, and a second control voltage is generated in response to the second TE temperature. Then, a third TE temperature is generated in response to the first and second control voltages, which in turn generates the output voltage.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

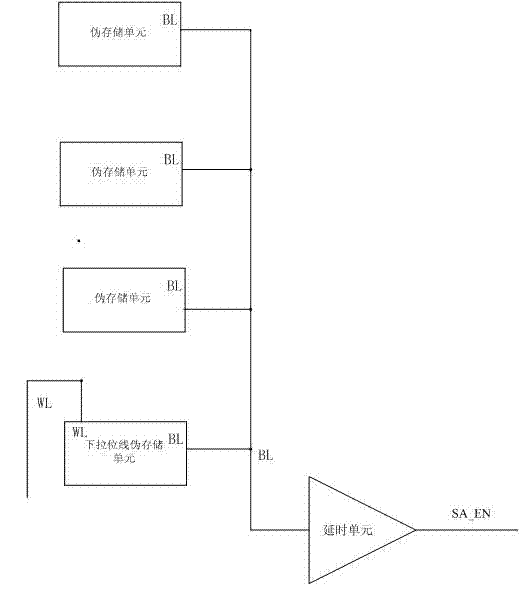

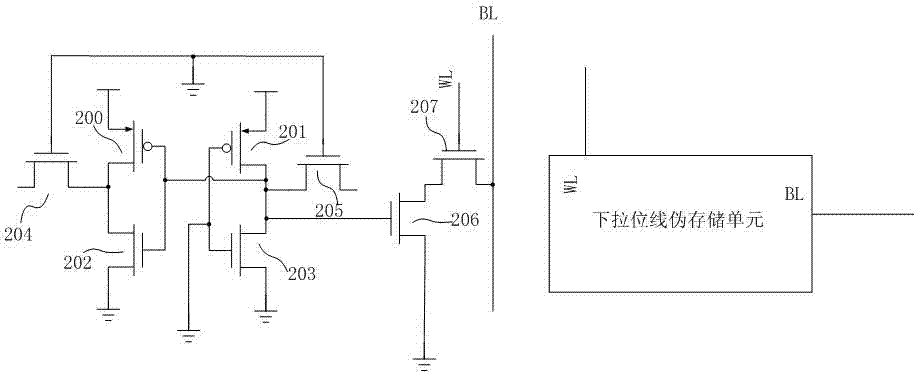

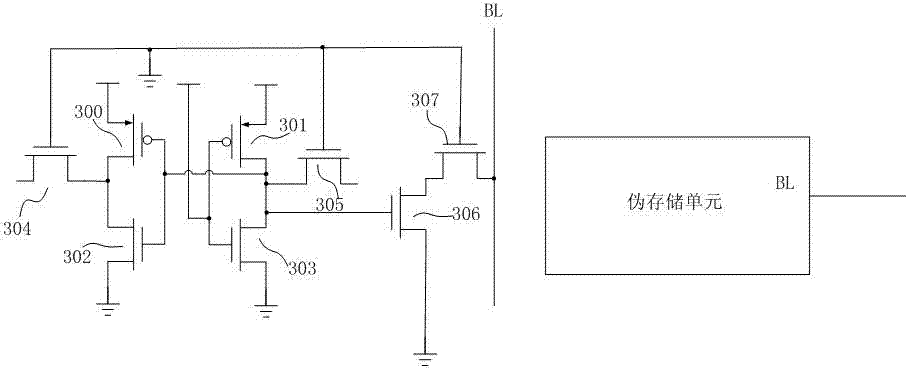

Sensitivity amplifying sequential control signal generating circuit based on self-timing

The invention, belonging to the technical field of integrated circuit memory cell, particularly relates to a sensitivity amplifying sequential control signal generating circuit based on self-timing. The circuit comprises two configurable memory cell pseudo arrays, and a double-input NOR-logic and a delay unit, wherein the bit lines of the pseudo memory array is pre-charged to a high level, while working, when word line signals (WL signals) of the pseudo array are changed from low level to high level, the bit lines (BL) of the two configurable memory cell pseudo arrays start to discharge, the bit line voltage is reduced so that the NOR gate is overturned to complete the sequential control function. According to the invention, the function failure problem of the memory caused by process variation in the manufacturing process can be effectively reduced, the yield of the memory is raised, and the reading speed of the memory is raised.

Owner:FUDAN UNIV

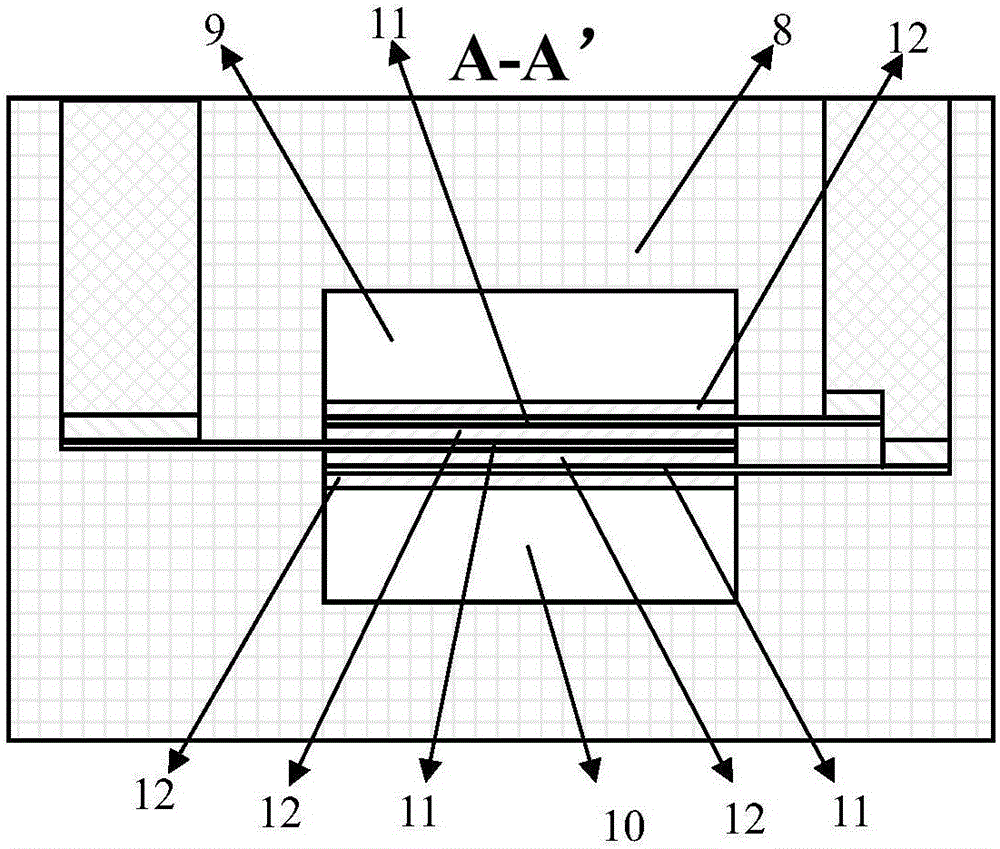

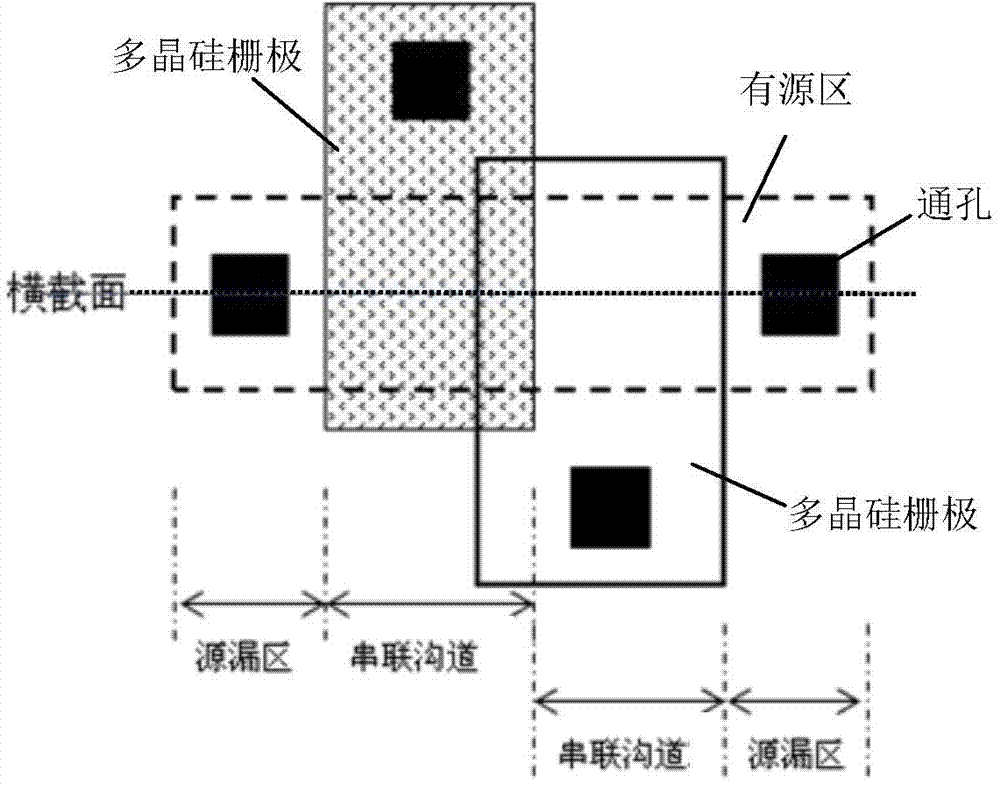

Structure of AND and NOR-logic devices and making method

InactiveCN104752430ASimple structureReduce areaSolid-state devicesSemiconductor/solid-state device manufacturingNOR logicConducting channel

The invention discloses a structure of AND and NOR-logic devices. The AND-logic device is made on a P-trap or P-type substrate, the P-trap or P-type substrate is connected to the ground, the upper face is provided with two neighboring control gates, for respectively controlling two neighboring n-type conducting channels which are connected in series; two ends of each control gate are provided with a highly doped n-type source region and a drain region, used as the leading-out ends of two n-type conducting channels; a polycrystalline silicon grid electrode is located above each control gate, and two polycrystalline silicon grid electrodes are mutually electrically separated and leaded out independently. The structure of the NOR-logic device is similar to the structure of the AND-logic device, the difference is to be made in a n-trap or n-type substrate, and the source and drain regions are the highly doped p-type. The invention further discloses a making method for the structure of AND and NOR-logic devices. The structure of the AND and NOR-logic devices is capable of, through designing the novel AND and NOR-logic device structure, simplifying the device and circuit structure, reducing the circuit area and making cost, and simplifying the sequential control of the circuit.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

NOR gate logic circuit and its forming method

ActiveCN101431330BOvercome limitationsActive connectionTransistorLogic circuits characterised by logic functionManufacturing technologyNOR logic

The invention relates to a NOR logic circuit and a fabricating method thereof. The NOR logic circuit comprises two input terminals, two enhancement type back-gate ZnO nanowire field effect transistors, and a depletion mode back-gate ZnO nanowire field effect transistor. The input terminals are respectively used for receiving input voltage signals; the gate electrodes of the two enhancement type back-gate ZnO nanowire field effect transistors are coupled to the two input terminals respectively, and the source electrodes thereof are coupled to an earth point respectively; the drain electrode ofthe depletion mode back-gate ZnO nanowire field effect transistor is coupled to a voltage source, and the gate electrode and the source electrode of the depletion mode back-gate ZnO nanowire field effect transistor, and the drain electrodes of the two enhancement type back-gate ZnO nanowire field effect transistors are coupled at a point; and the point serves as an output terminal used for outputting the voltage signals. The invention utilizes the manufacturing technology and the interconnection technology of ZnO nanowire materials and ZnO nanowire field effect transistors, and fabricates theNOR logic circuit based on the direct coupling field effect of the ZnO nanowire field effect transistor.

Owner:SOI MICRO CO LTD

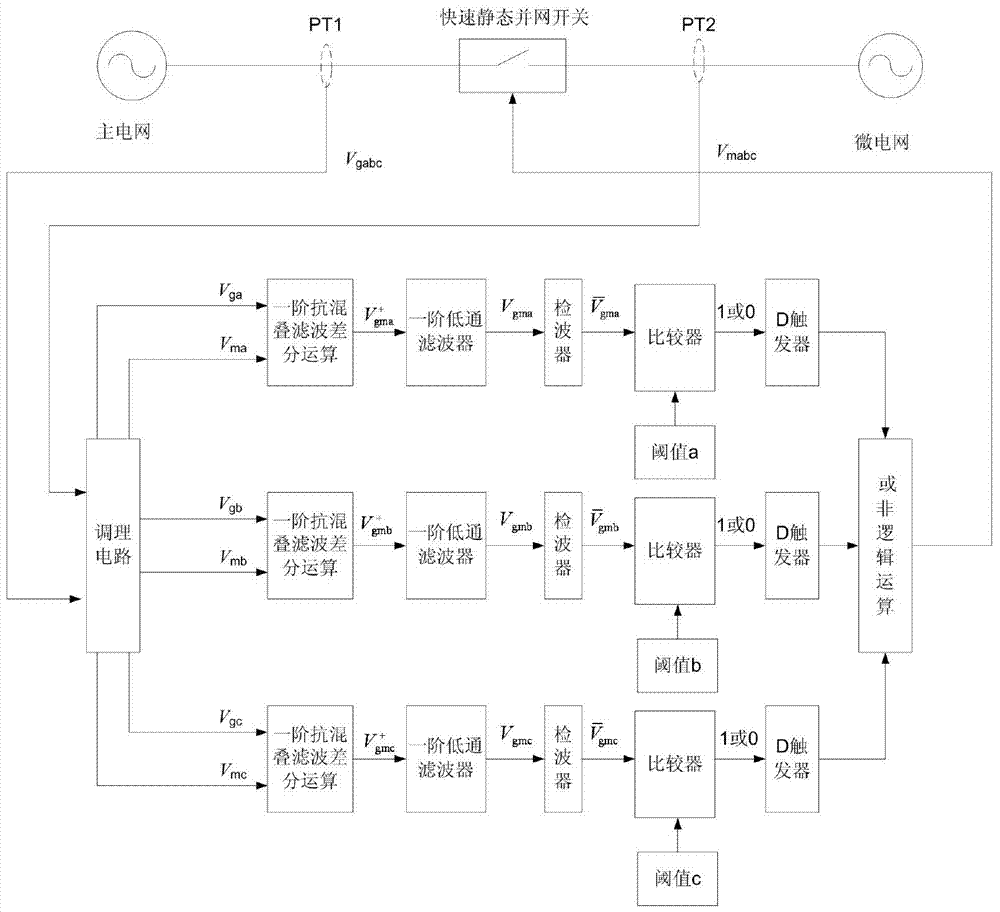

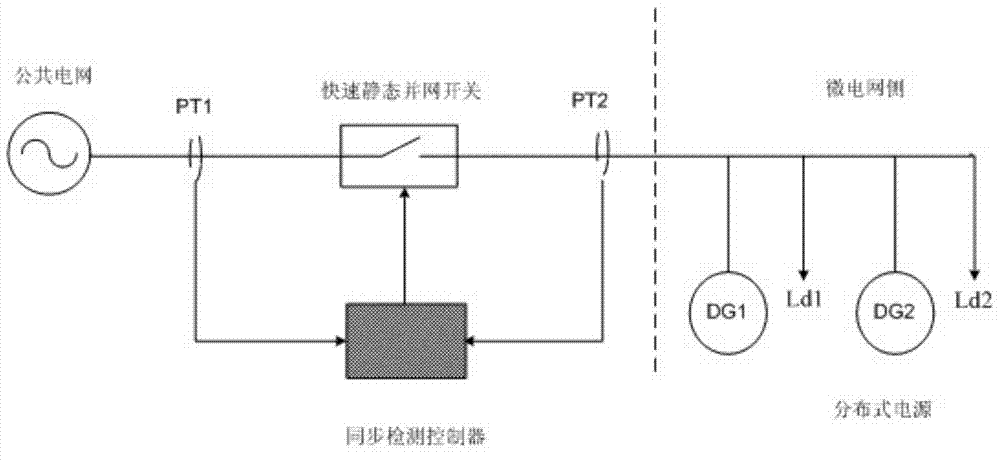

Synchronous detection controller and control method for grid connection of micro-grid

InactiveCN103501019AImprove securityImprove stabilityClimate change adaptationSingle network parallel feeding arrangementsPower qualityAnti-aliasing

The invention discloses a synchronous detection controller and control method for grid connection of a micro-grid. Each phase of a three-phase circuit comprises a conditioning circuit module, a first-order anti-aliasing filter difference operation module, a first-order low-pass filter, a detector, a comparator and a D trigger. The synchronous detection controller further comprises a NOR-logic operation module; the synchronous detection controller is applied to the grid connection control of the micro-grid and a public electric network and can effectively ensure the synchronous grid connection, out-of-sync rate is limited within the acceptable range, a large transient state of the micro-grid is avoided, misoperation of a relaying protection system is avoided, safety and stability of operation of the micro-grid are enhanced, and quality of electric energy of the micro-grid is improved. Meanwhile, detection precision is high, wiring is easy, size is small, weight is light, energy consumption and cost are low, high flexibility is achieved, and the synchronous detection controller and control method for the grid connection of the micro-grid are applicable to the grid connection control of the micro-grid.

Owner:NORTH CHINA UNIV OF WATER RESOURCES & ELECTRIC POWER

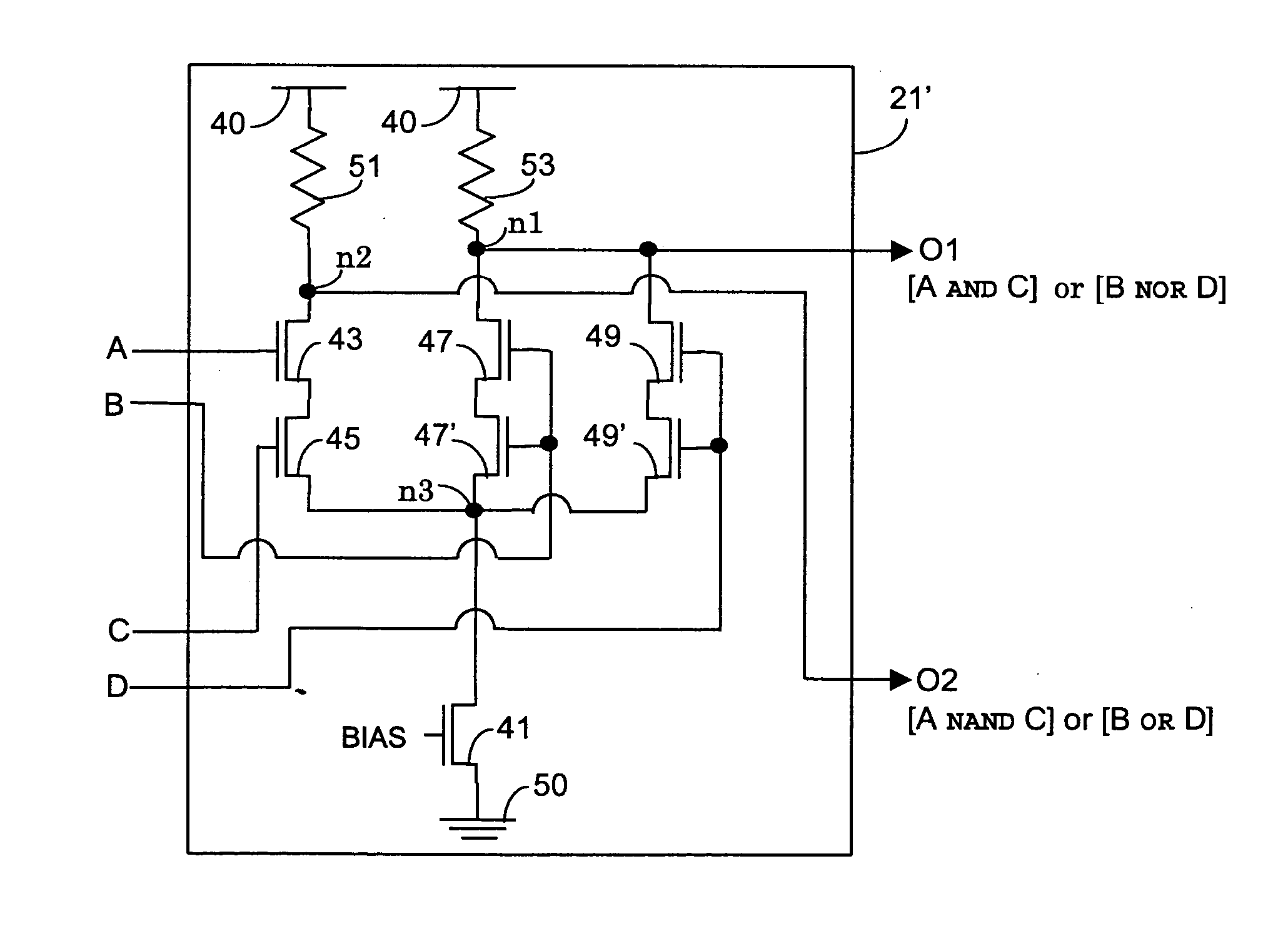

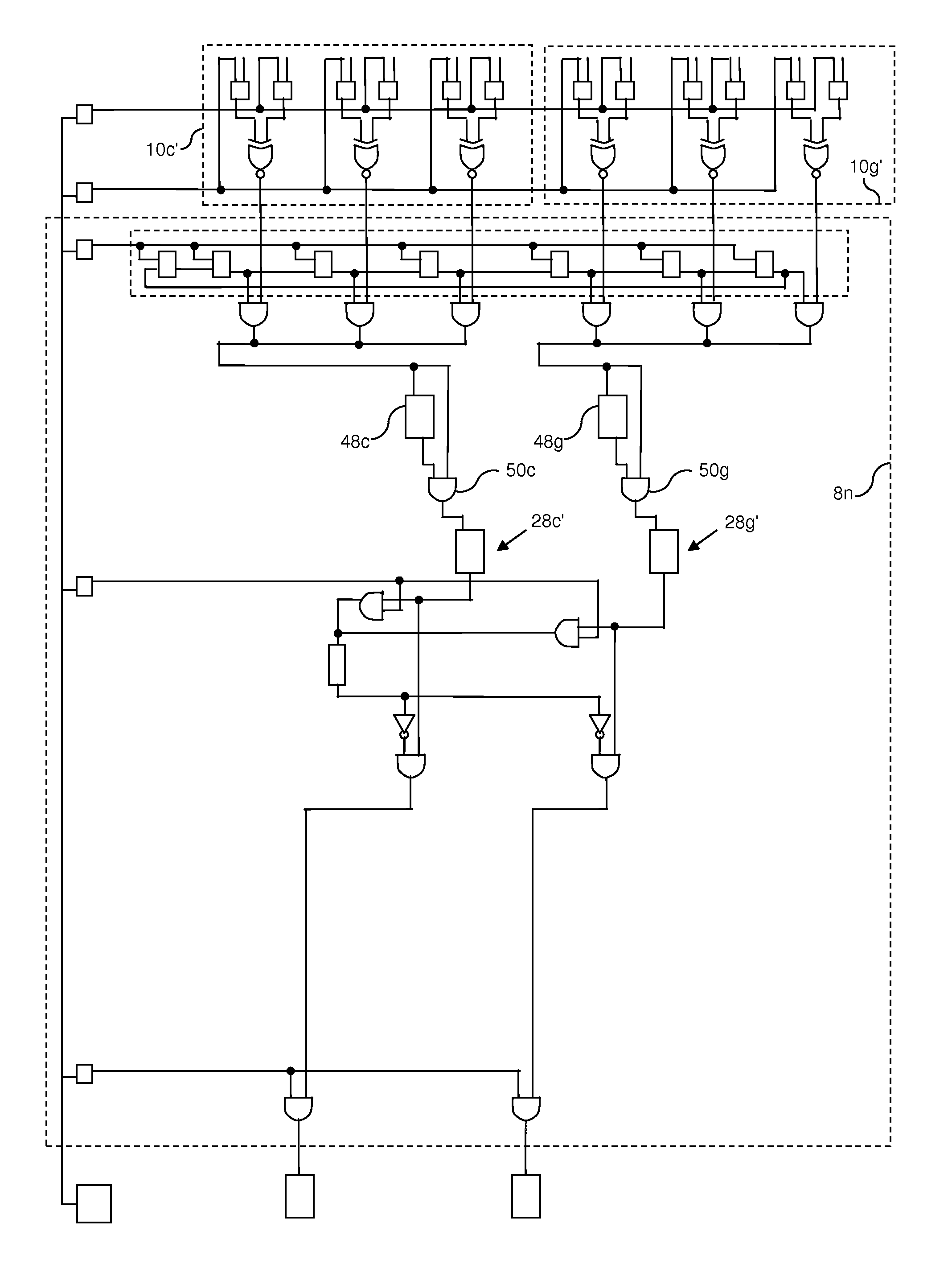

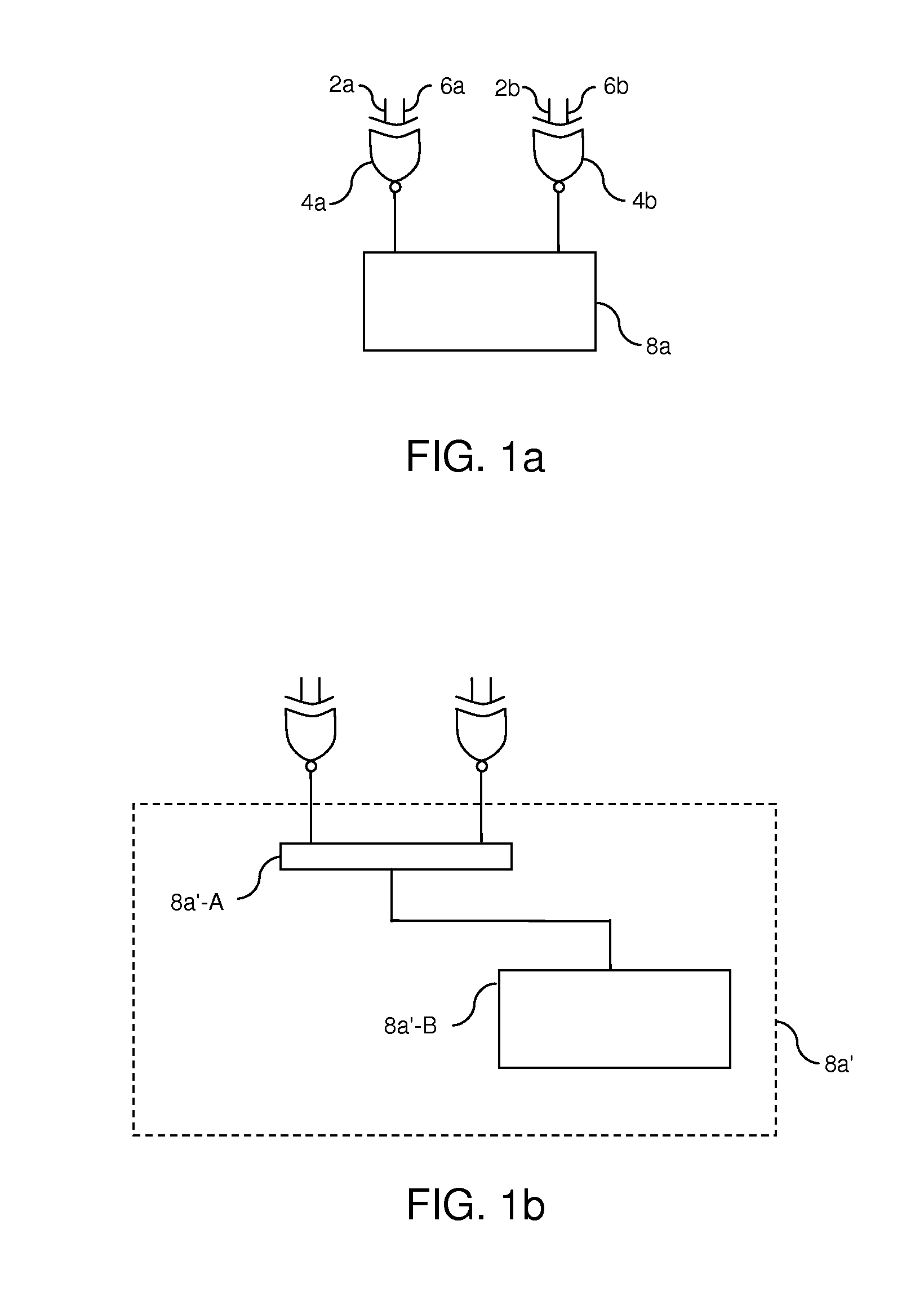

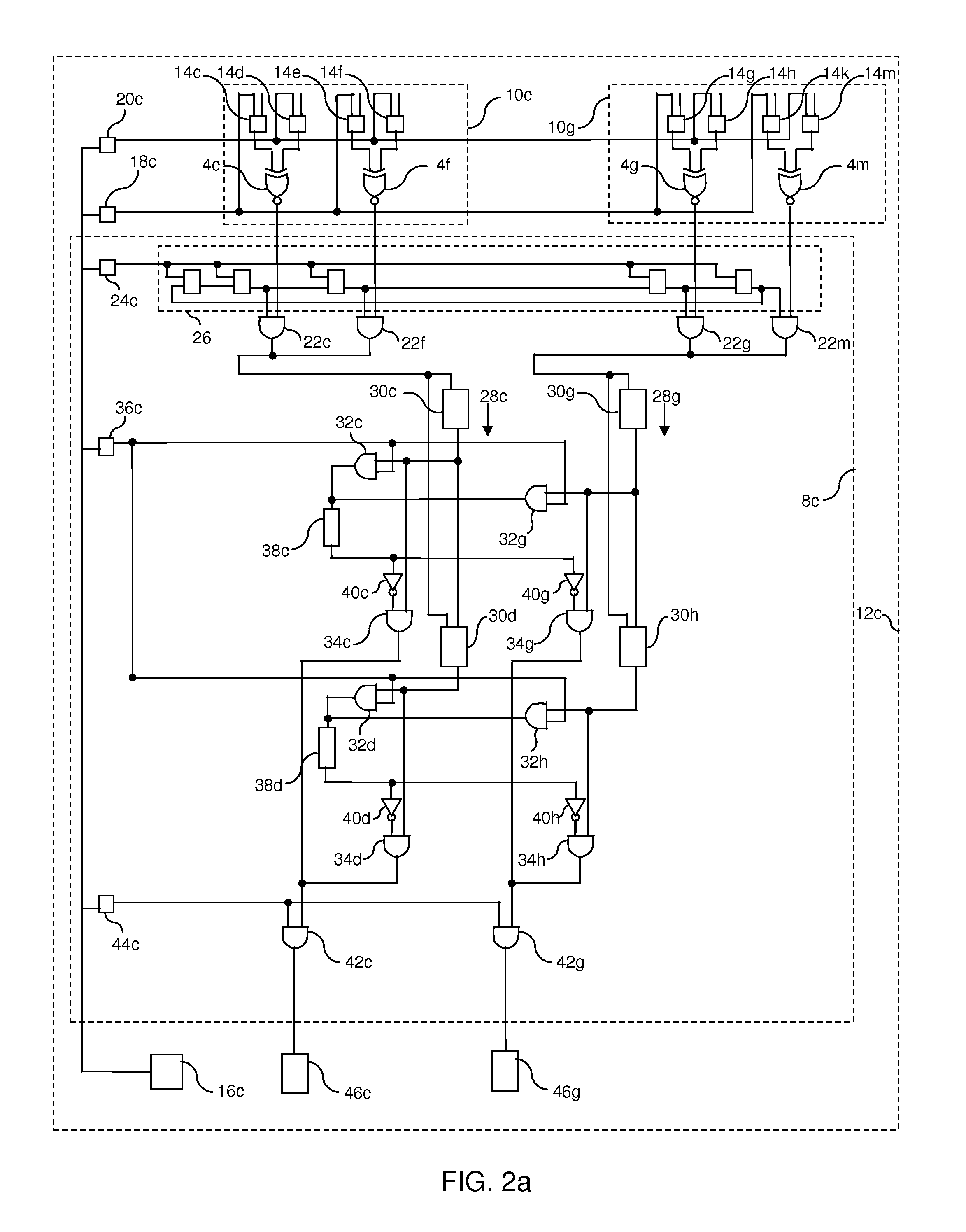

Multi-function differential logic gate

InactiveUS20050242842A1Control inputLogic circuits characterised by logic functionPulse automatic controlDifferential phaseNAND logic

A fully differential phase and frequency detector utilizes a multi-function differential logic gate to implement a differential AND gate operation and provides a fully differential D-flip-flop. The multi-function differential logic gate has four inputs, which can be grouped into two pairs of true and complement signals. By selectively re-assigning the inputs to different signal pairs, the differential logic gate can be made to provide one of either simultaneous AND / NAND logic operations or simultaneous OR / NOR logic operations. The differential D-flip-flop is implemented following a master / slave configuration and is response to the true and complement forms of an input clock signal, an input reset input, and input data signal, and also provides true and complement forms of an output signal. All components within the phase and frequency detector are exemplified in CML circuit configuration.

Owner:SEIKO EPSON CORP

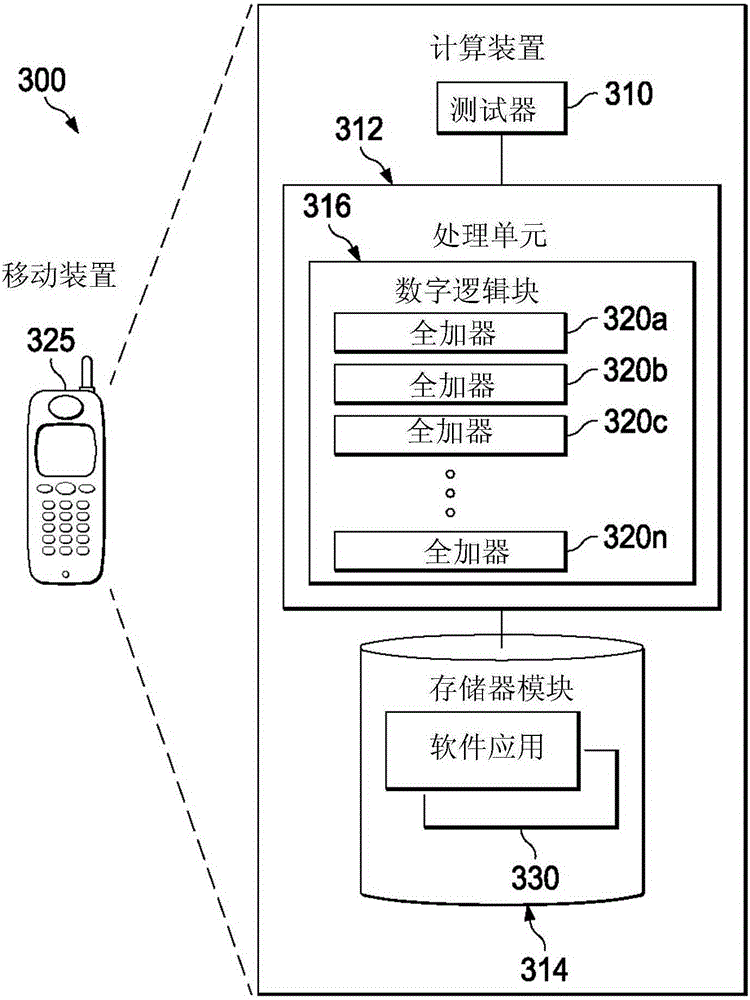

Method of Pattern Recognition for Artificial Intelligence

ActiveUS20130054504A1Character and pattern recognitionNumber-of-one countersPattern recognitionNOR logic

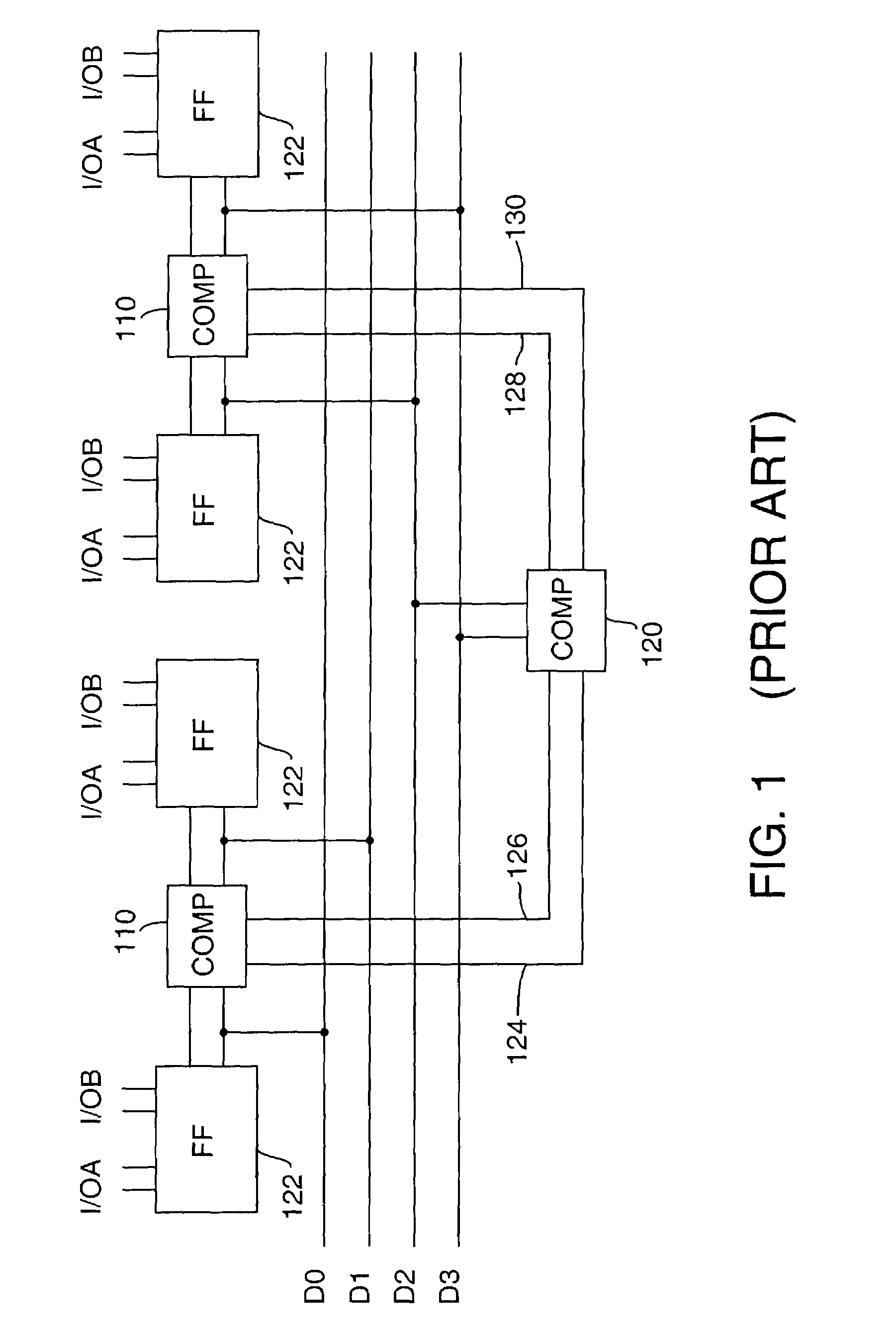

Invention for pattern recognition and artificial intelligence comprising:1) storing data in parallel by applying a logic level (1) input or a logic level (0) input to one input of each of at least two exclusive-nor logic gates;2) comparing data in parallel by applying a logic level (1) input or a logic level (0) input to the other input of each of the exclusive-nor gates, wherein each exclusive-nor gate produces a logic level (1) output when both inputs have the same datum input, and each exclusive-nor gate produces a logic level (0) output when both inputs have different datum input; and3) measuring the outputs of the exclusive-nor logic circuits collectively with a measuring apparatus, wherein the percentage of the pattern input for comparison which matches the pattern of data stored in the exclusive-nor gates is directly proportional to the magnitude of the collective output of the exclusive-nor gates.

Owner:SNYDER STEVEN HOWARD