Sensitivity amplifying sequential control signal generating circuit based on self-timing

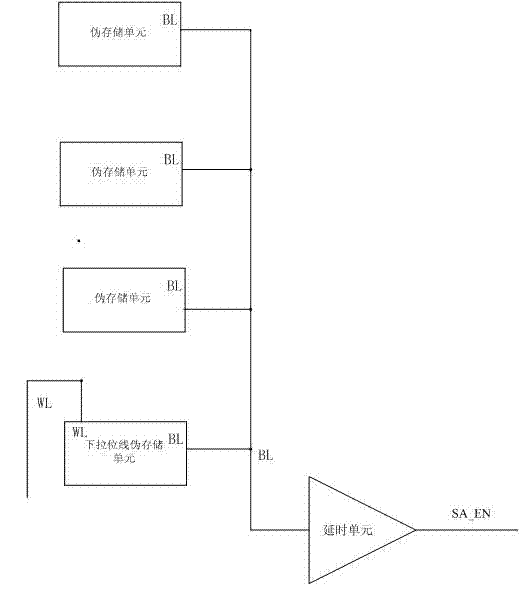

A signal generation circuit and sensitive amplification technology, which is applied in the field of sensitive amplification timing control signal generation circuit, can solve the problems of different discharge speed and discharge time, inoperable memory, poor time followability of pseudo-array memory cells, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The invention describes a high-reliability, high-speed sensitive amplification timing control signal generation circuit based on a self-timing structure. Various relevant examples and design ideas therein are described below.

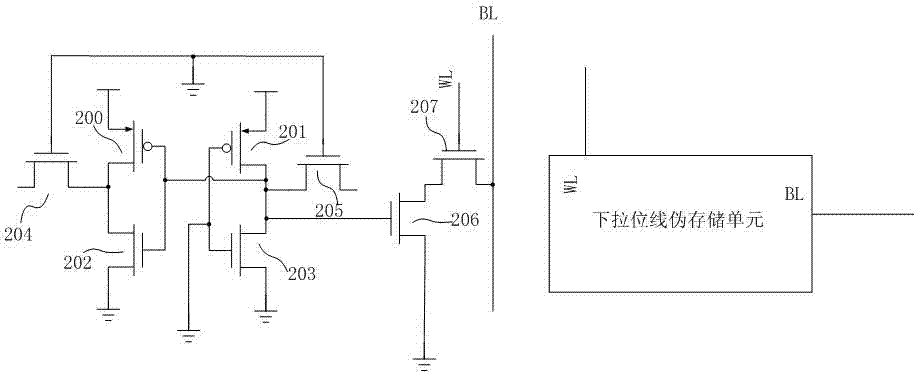

[0020] figure 2 It exemplarily shows the pull-down bit line dummy memory cell. Among them, 200 and 201 are pull-up PMOS transistors, their source terminals are connected to the power supply voltage, 202 and 203 are pull-down NMOS transistors, and their source terminals are grounded to the ground voltage. 204 and 205 are NMOS tubes, and in this structure, the gate terminal is grounded, which has no practical effect. 201, 203 constitute a first inverter, and 200, 202 constitute a second inverter. The first inverter and the second inverter constitute the core part of the pull-down bit line dummy memory cell. Since the input terminal of the first inverter is fixed at the ground voltage, the output voltage of the inverter is the power supply volt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More