Patents

Literature

71results about How to "Reduce load capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

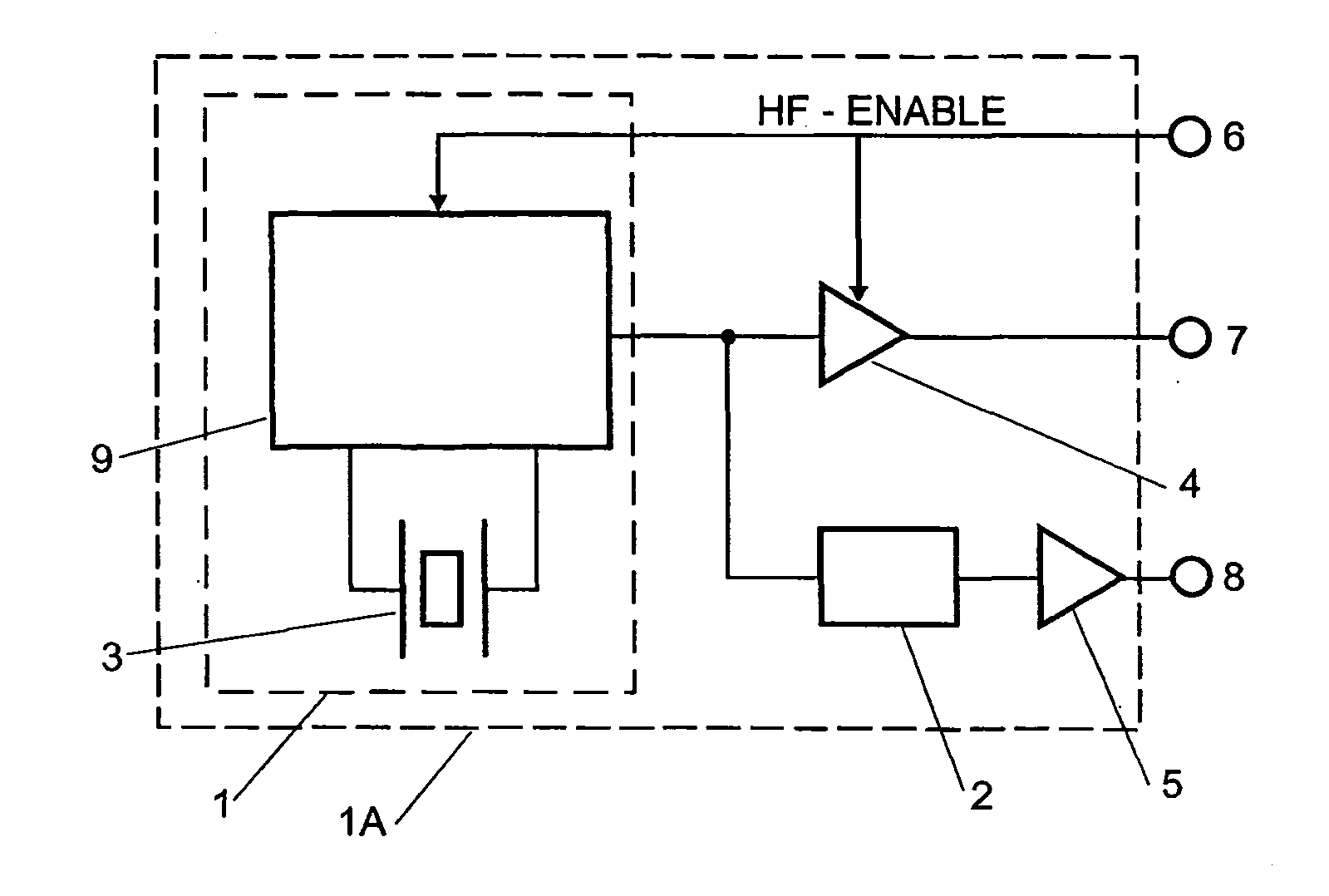

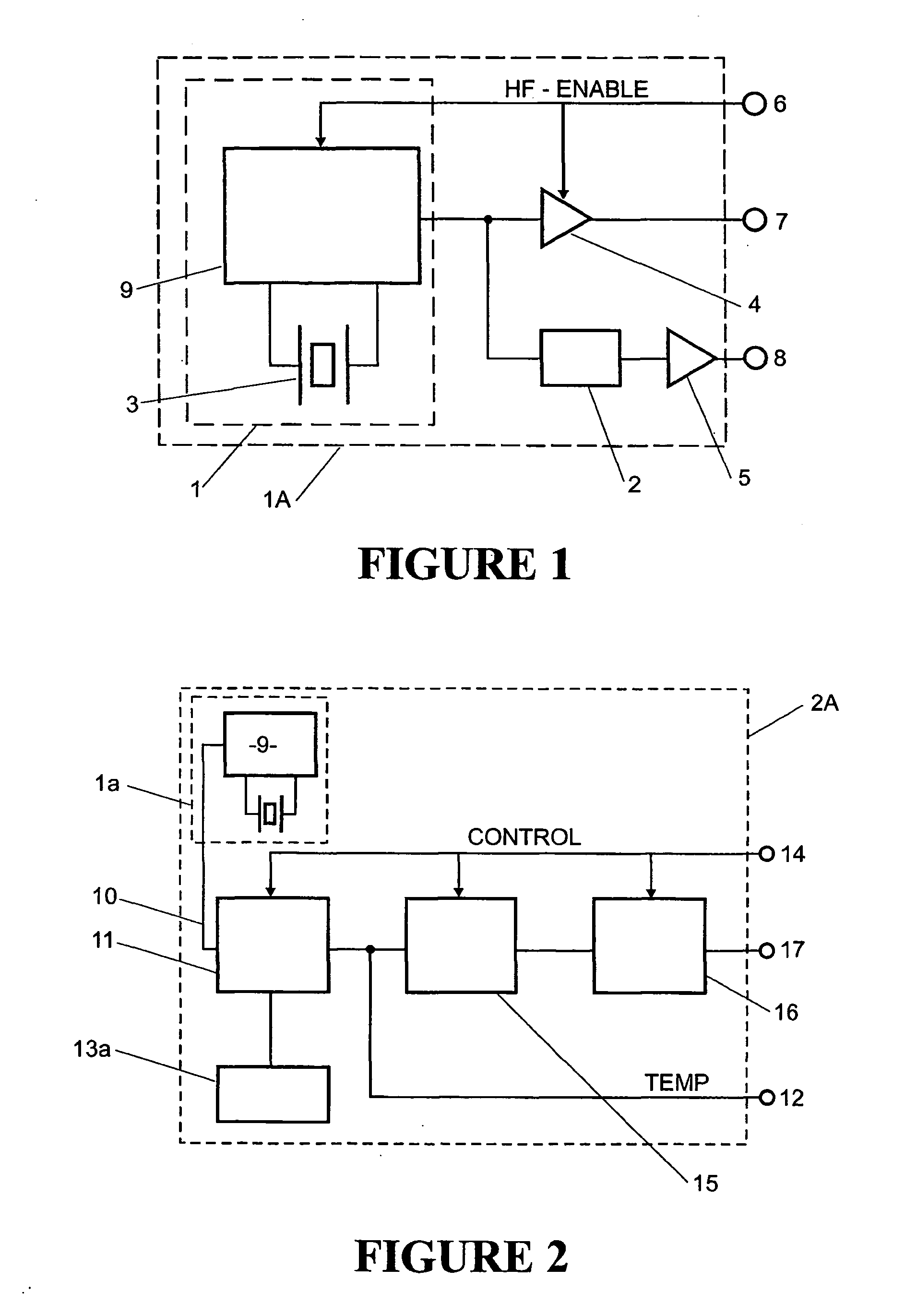

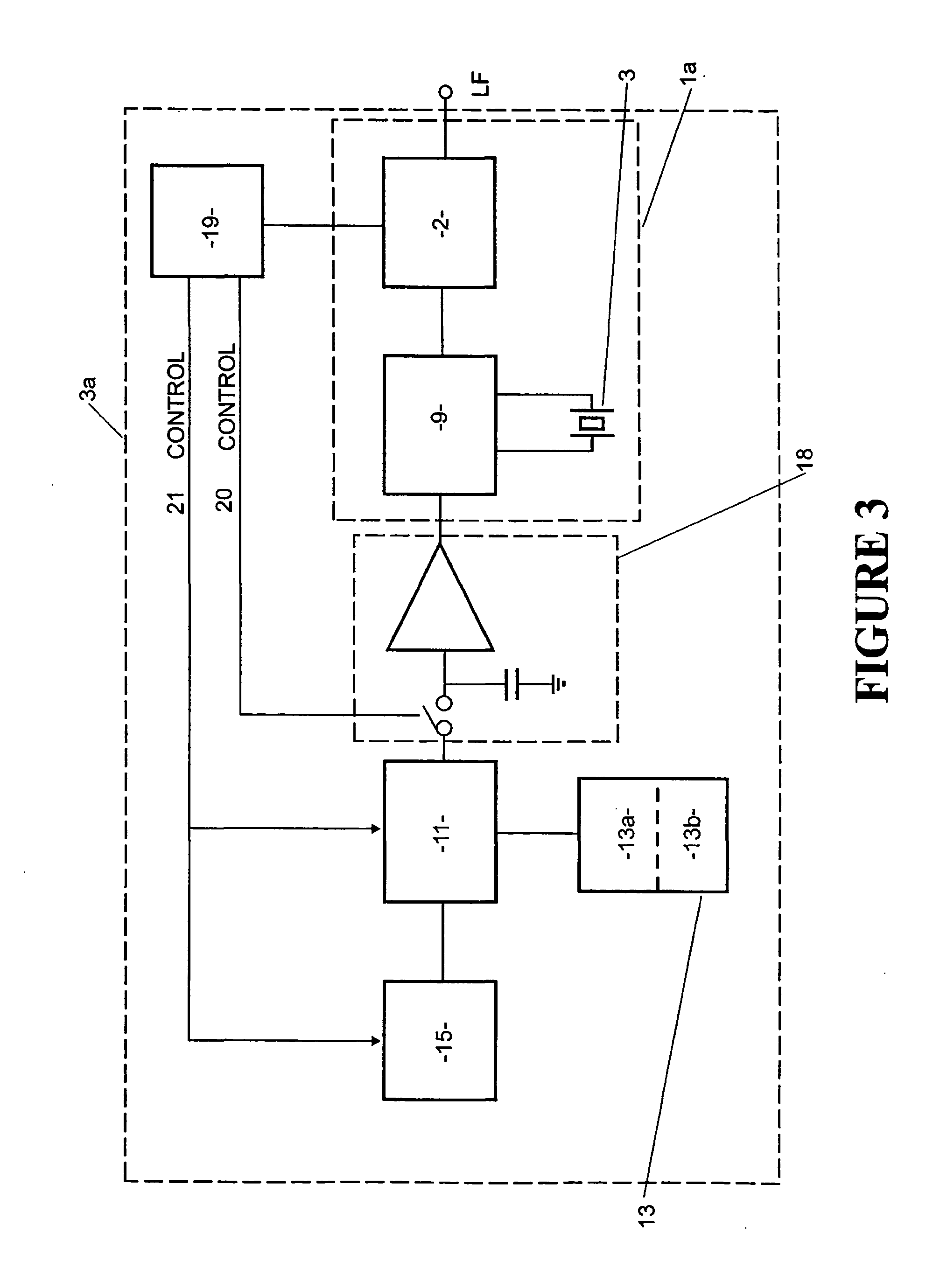

Low power crystal oscillator

InactiveUS20050007205A1Reduce frequencyReduce bias currentGenerator stabilizationOscillations generatorsPhase noiseEngineering

The present invention relates to a timing system including an integrated circuit having an oscillator that provides both high and low frequency clock signals from a single high frequency crystal without the necessity of a tuning fork crystal. The low frequency signal is available for time-keeping applications, with low power consumption during “idle” periods. The high performance high frequency signal is available on demand for clock and frequency reference use. The oscillator of the present invention provides improved time-keeping accuracy, whilst size, cost and component count is reduced. Furthermore, phase noise and other critical parameters of the high frequency oscillator are not compromised. Shock vulnerability, a known problem for tuning fork crystals, is reduced.

Owner:RAKON

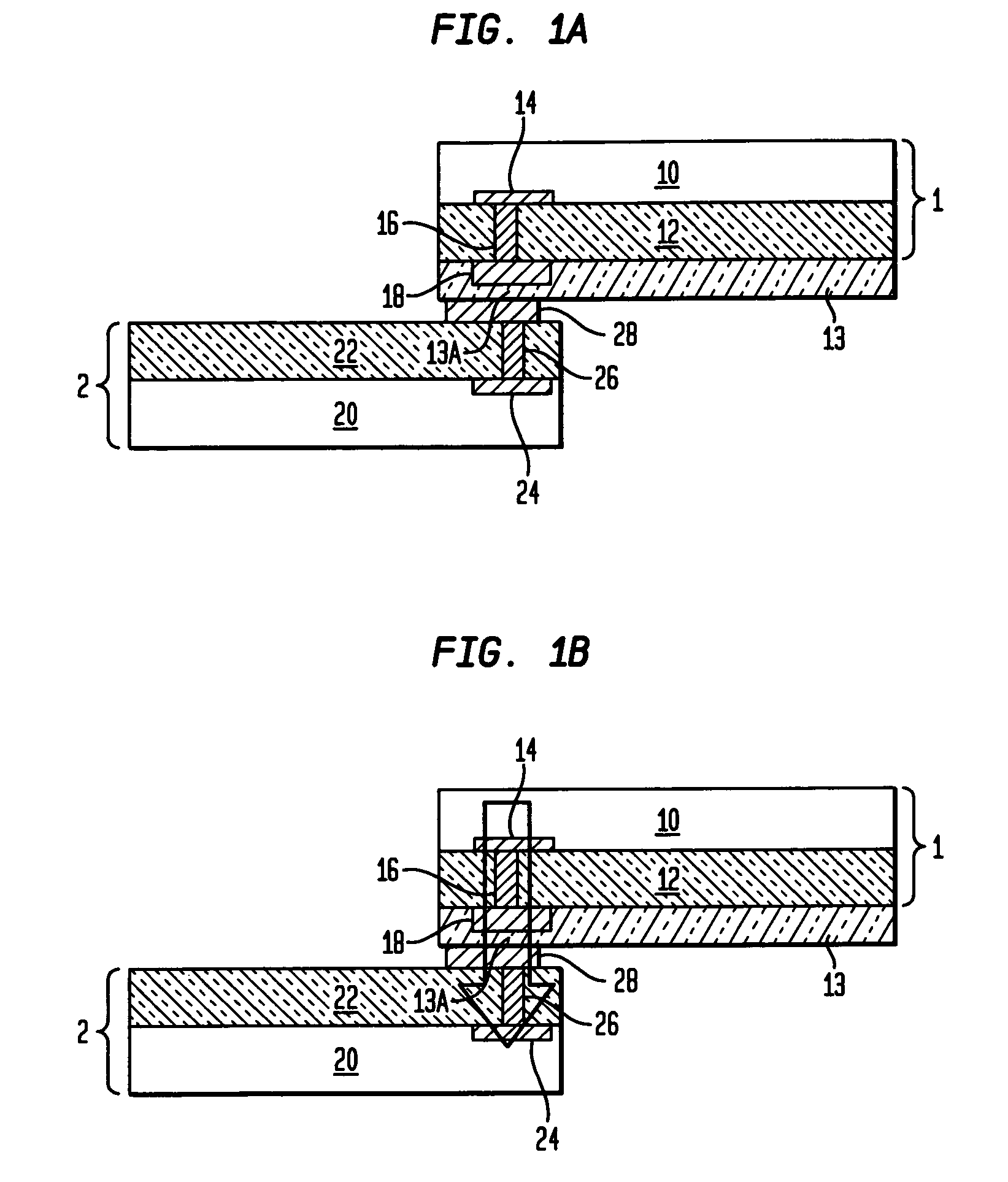

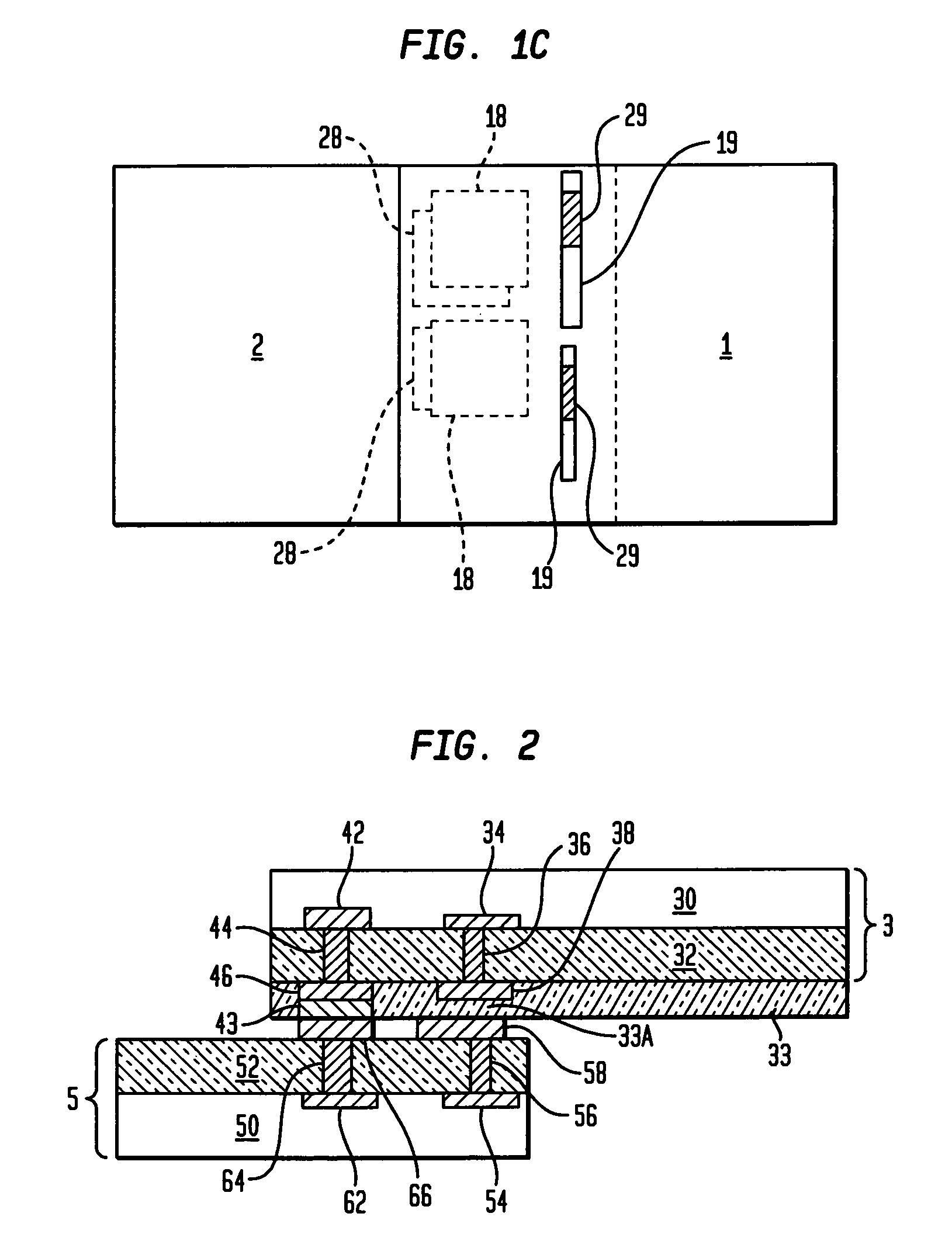

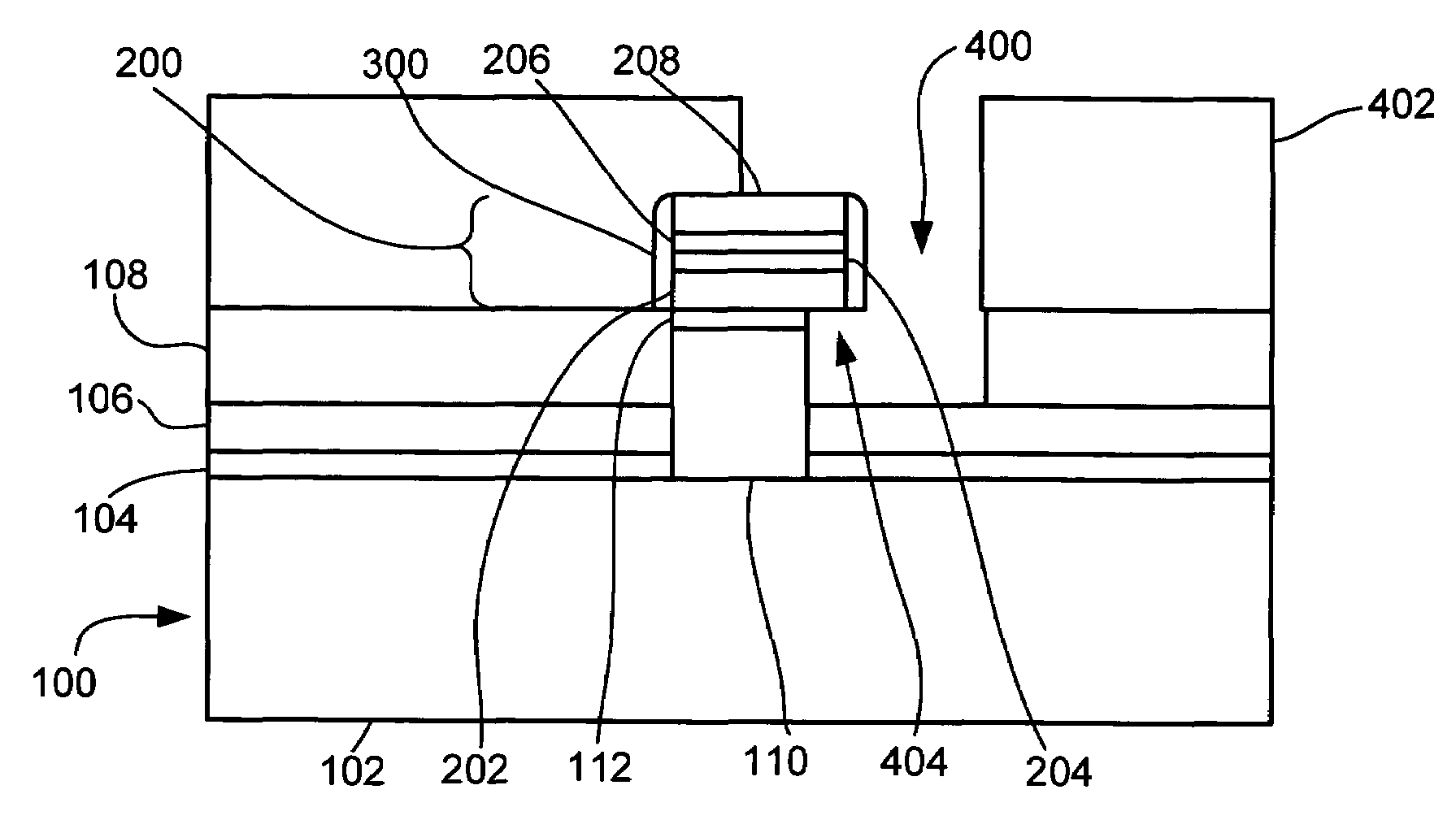

Inter-chip ESD protection structure for high speed and high frequency devices

ActiveUS7535105B2Reduce electrical impedanceReduce load capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringHigh velocity

Owner:GLOBALFOUNDRIES U S INC

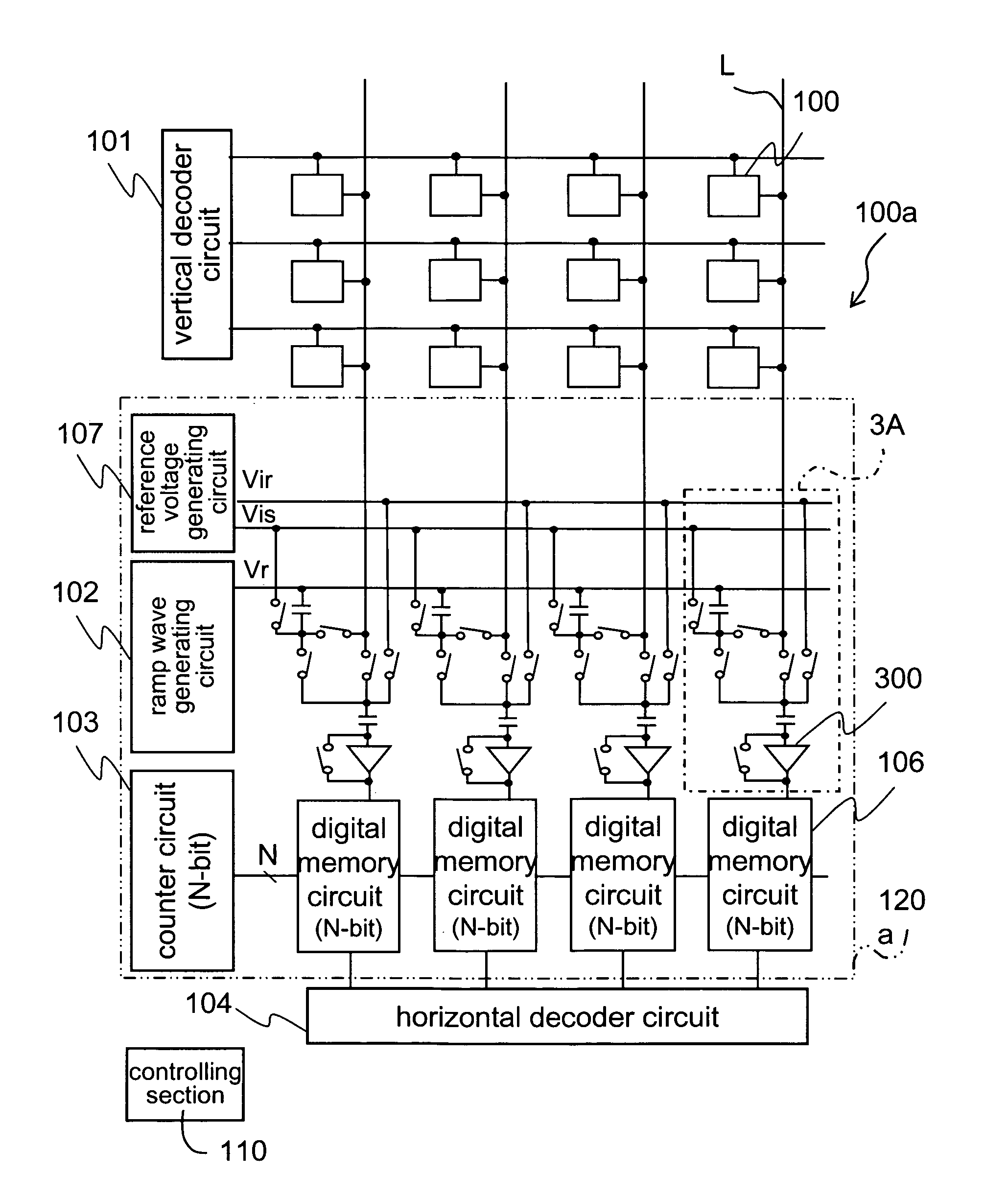

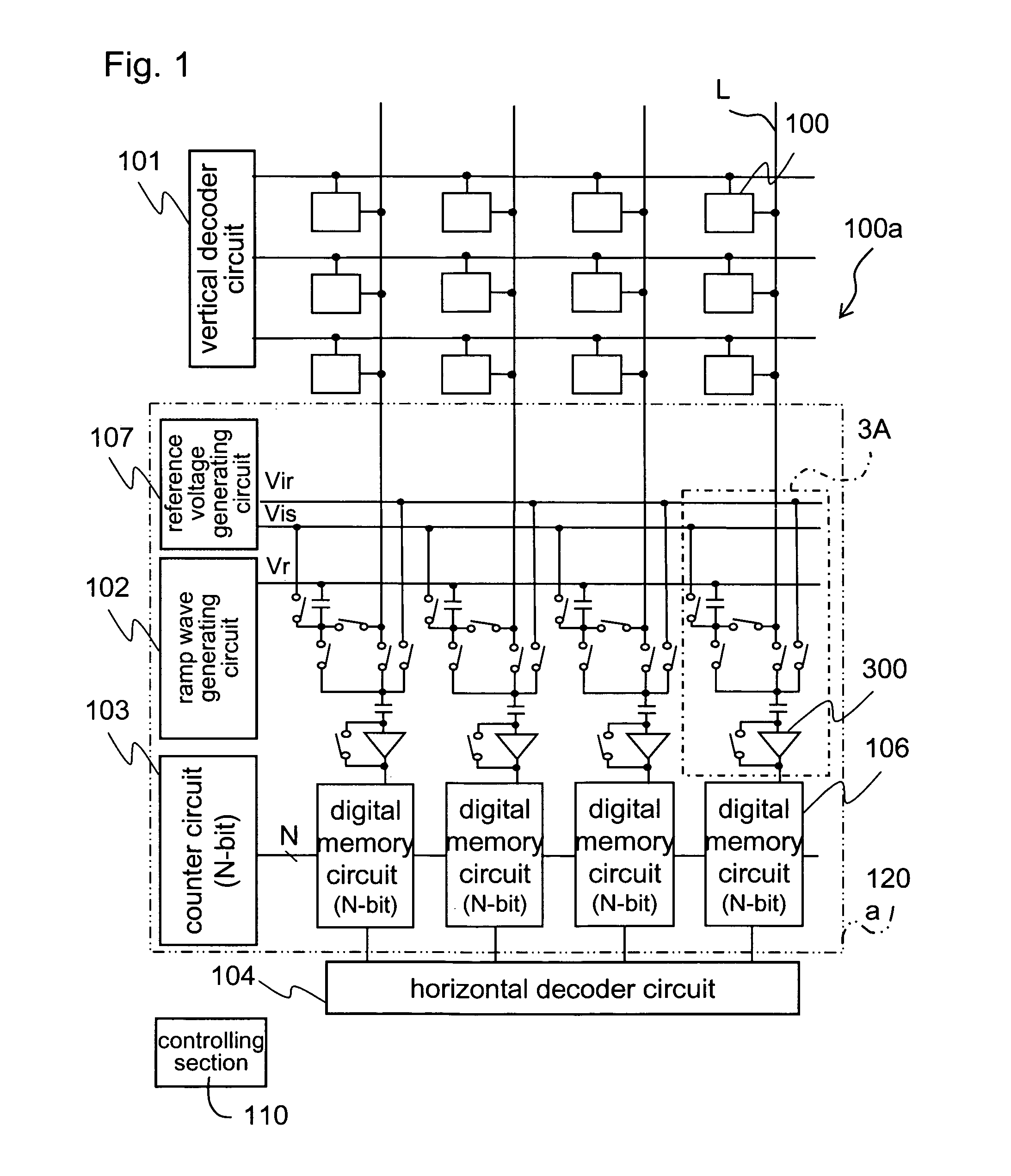

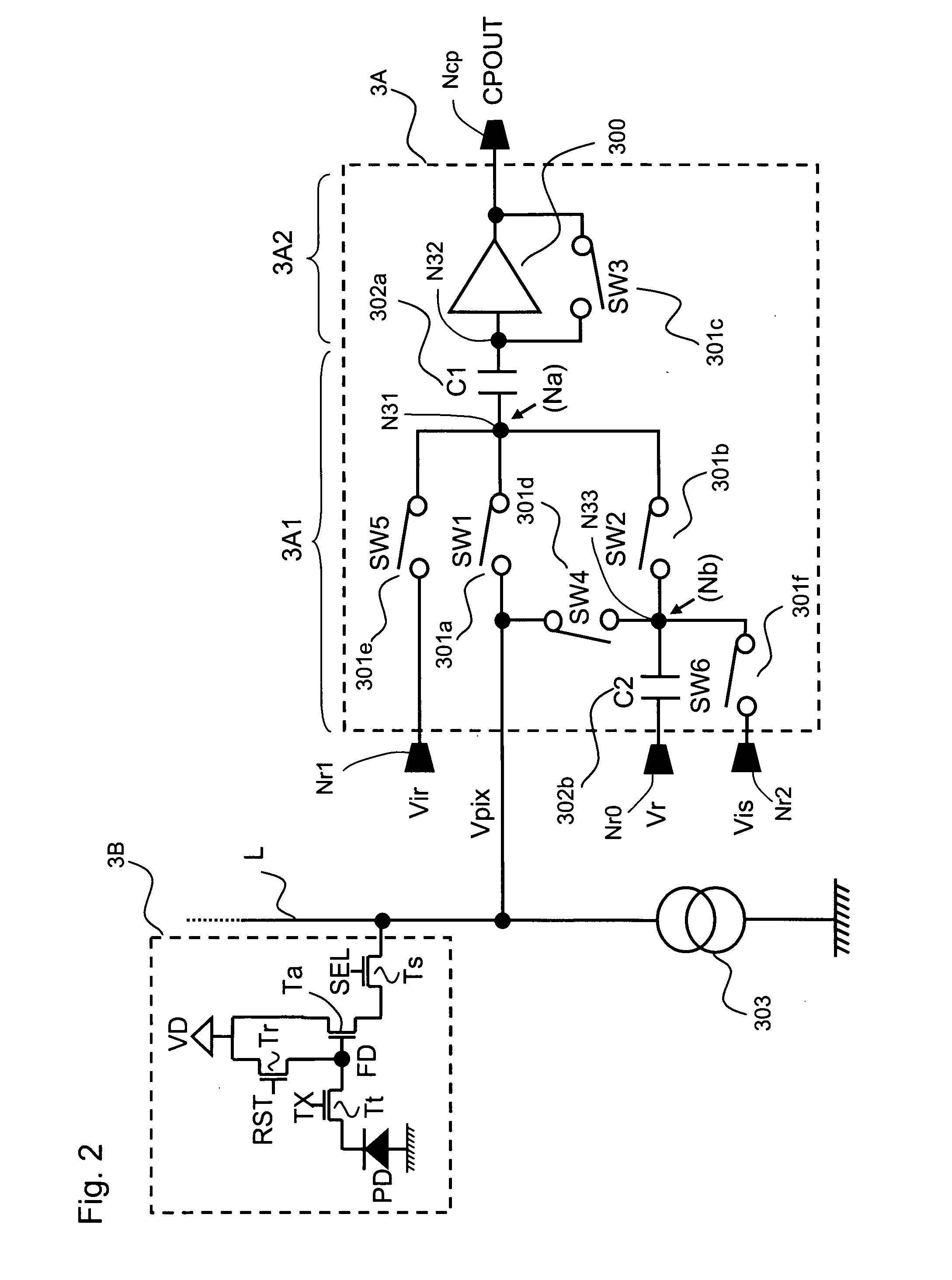

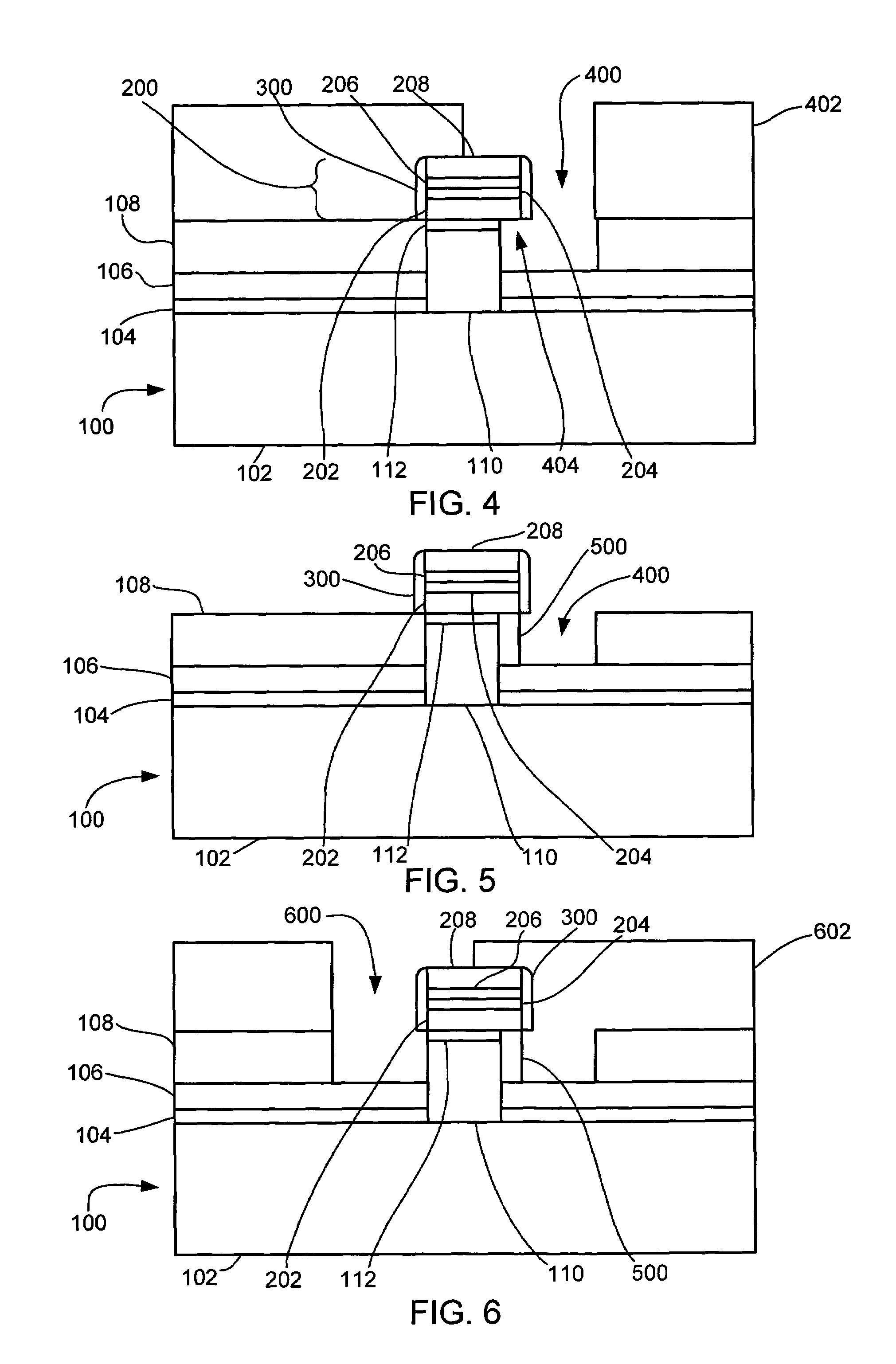

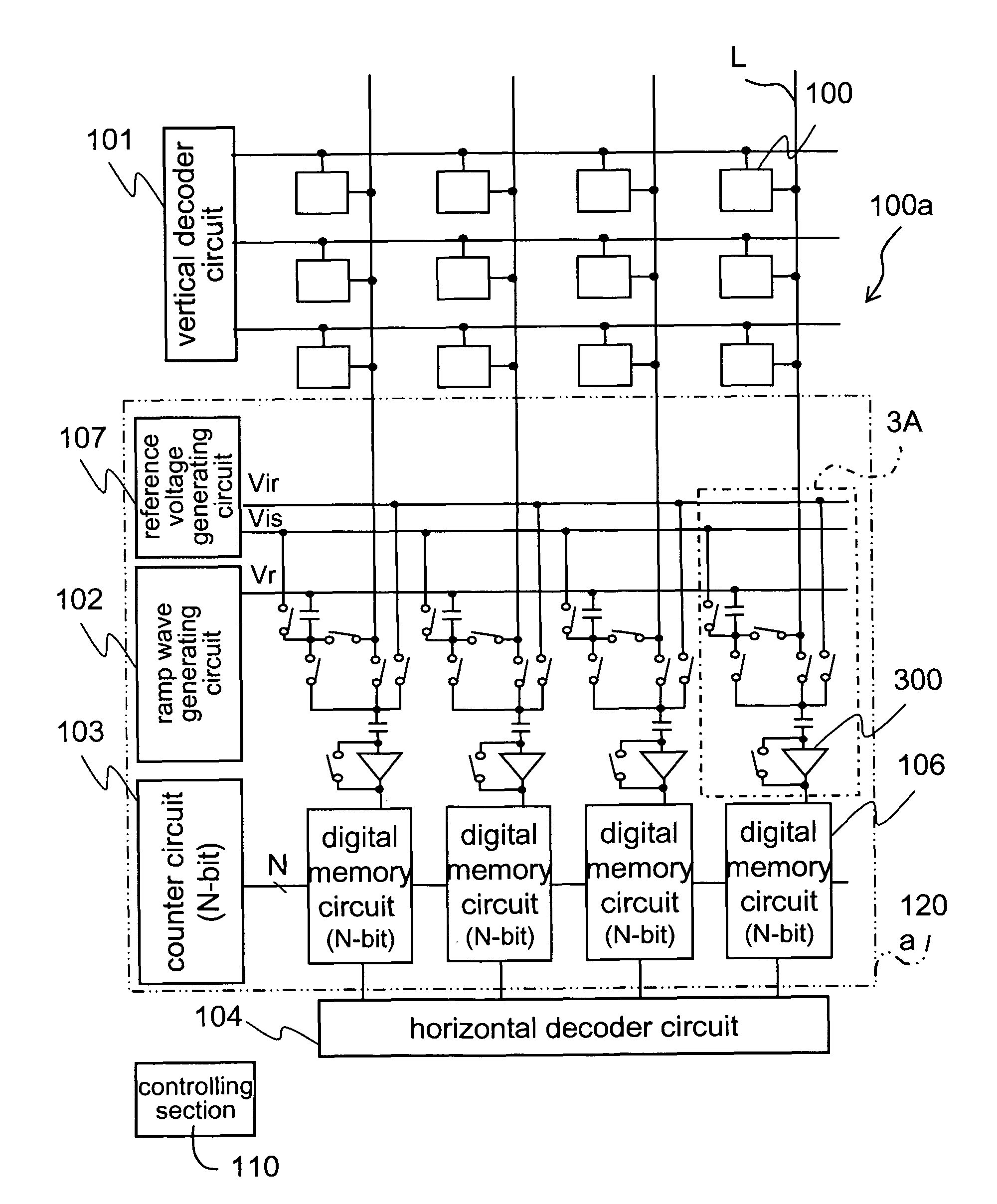

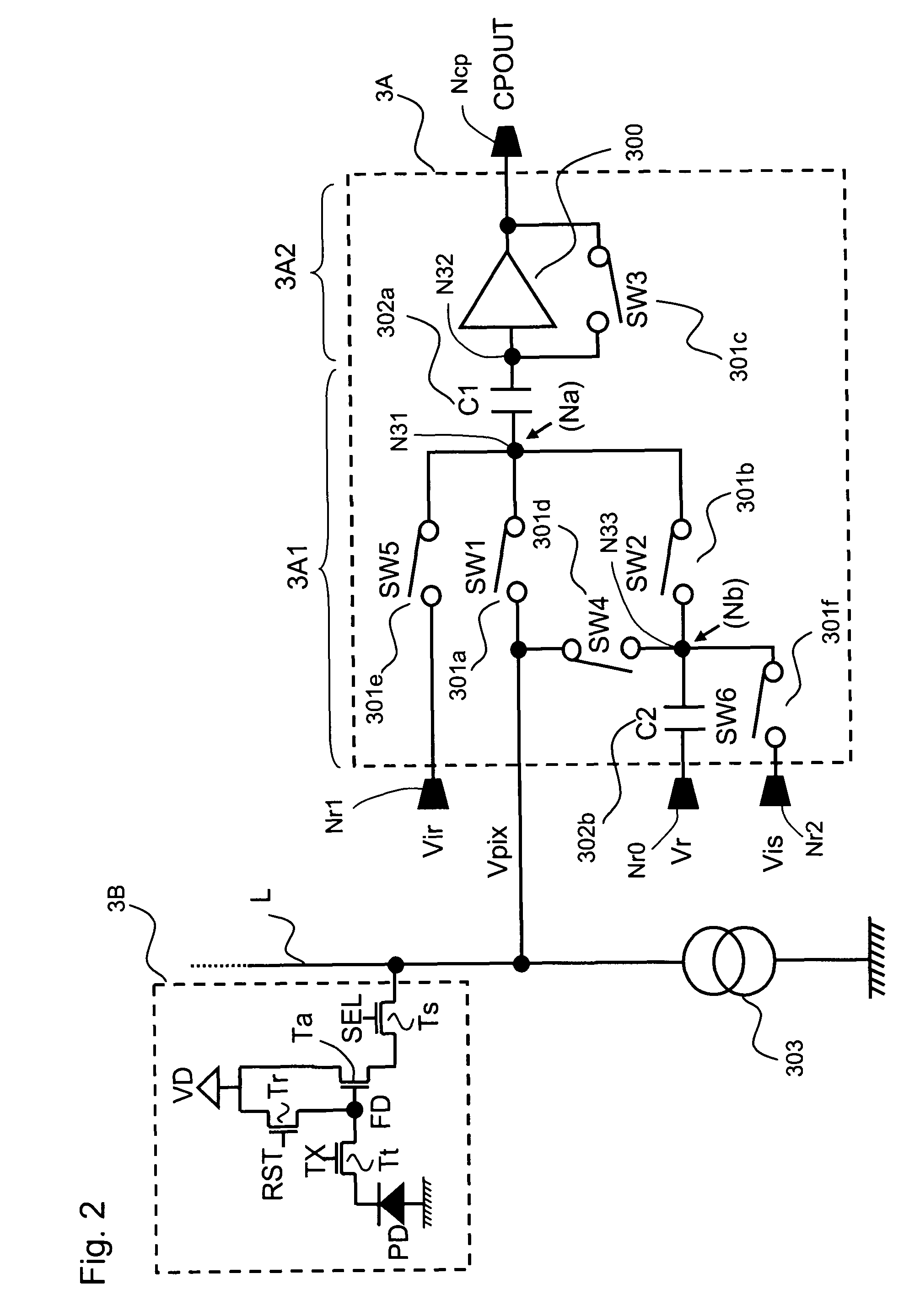

A/D converter, solid-state image capturing apparatus and electronic information device

ActiveUS20100315540A1Faster rateAccurate samplingTelevision system detailsElectric signal transmission systemsCapacitanceCMOS

The CMOS image sensor according to the present invention includes a sample hold section 3A1 for retaining an analog input signal voltage and a ramp wave signal voltage; and a comparing section 3A2 for taking an output from the sample hold section 3A1 as an input to compare it with a reverse level of itself, in which the sample hold section 3A1 applies a stabilization promoting voltage to a terminal of the sampling capacitance element so that an electric potential level of the terminal of the sampling capacitance element is promoted to become stabilized at a predetermined voltage, when the analog input signal is applied to the terminal of the sampling capacitance element.

Owner:SHARP KK

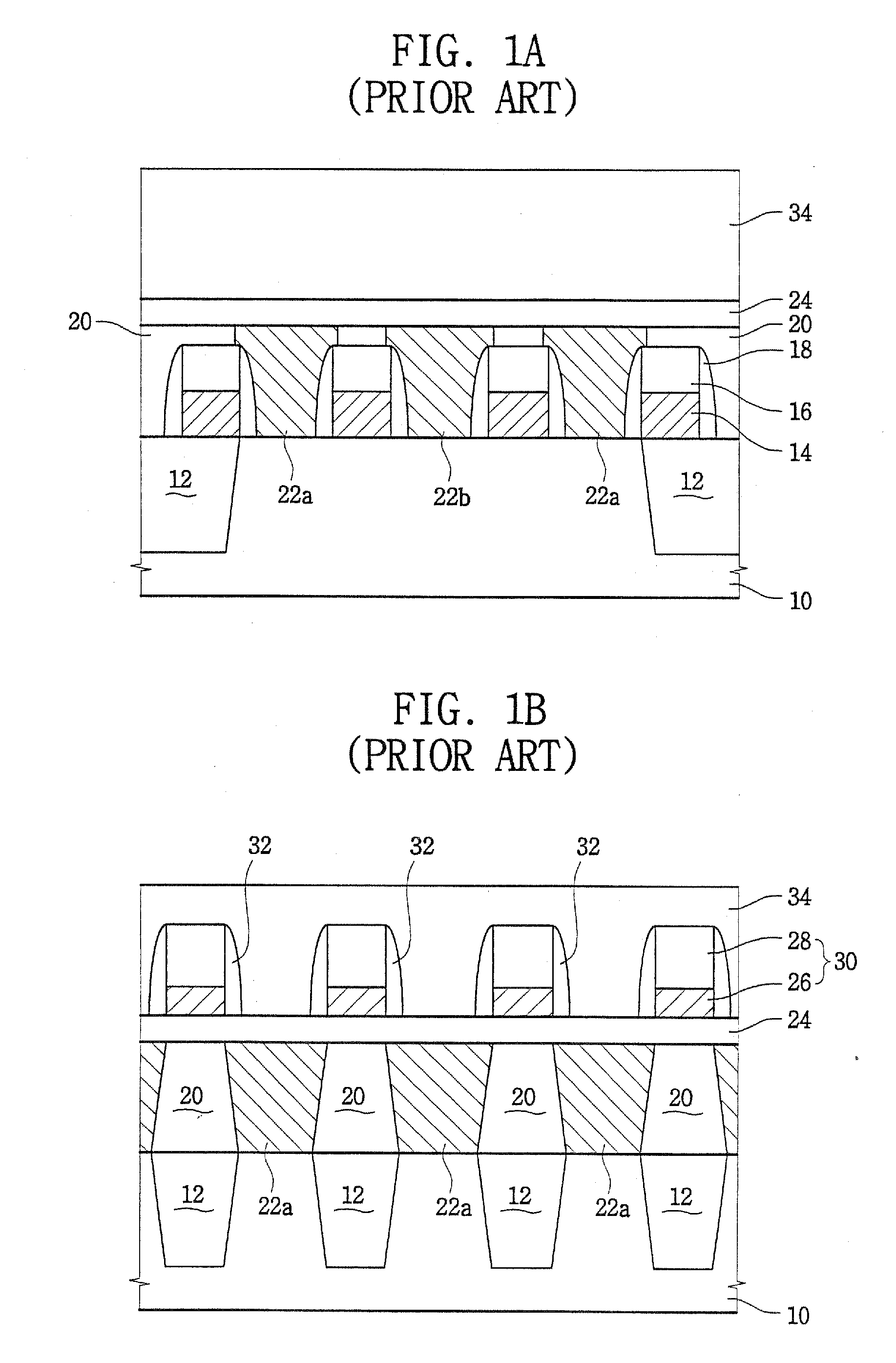

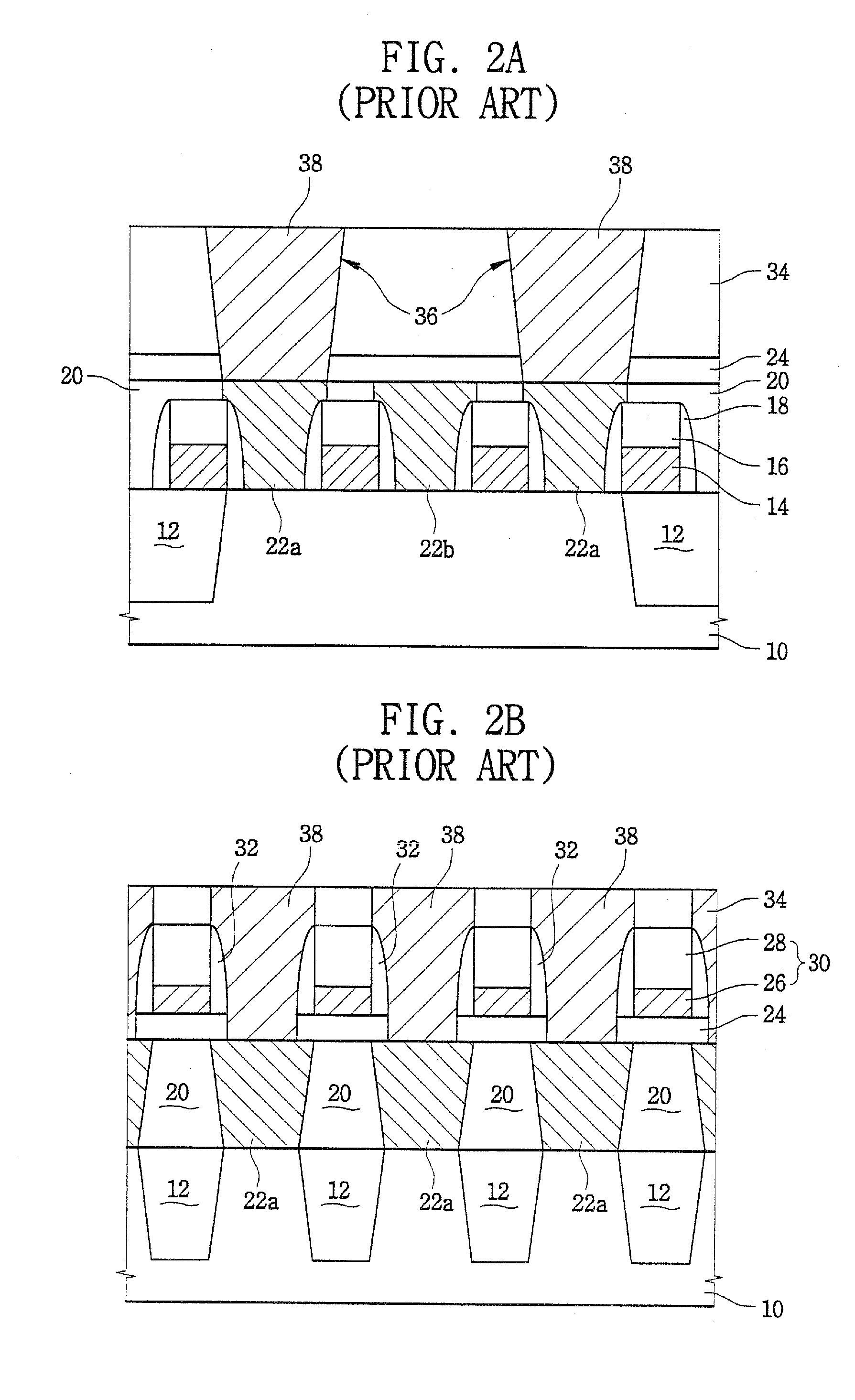

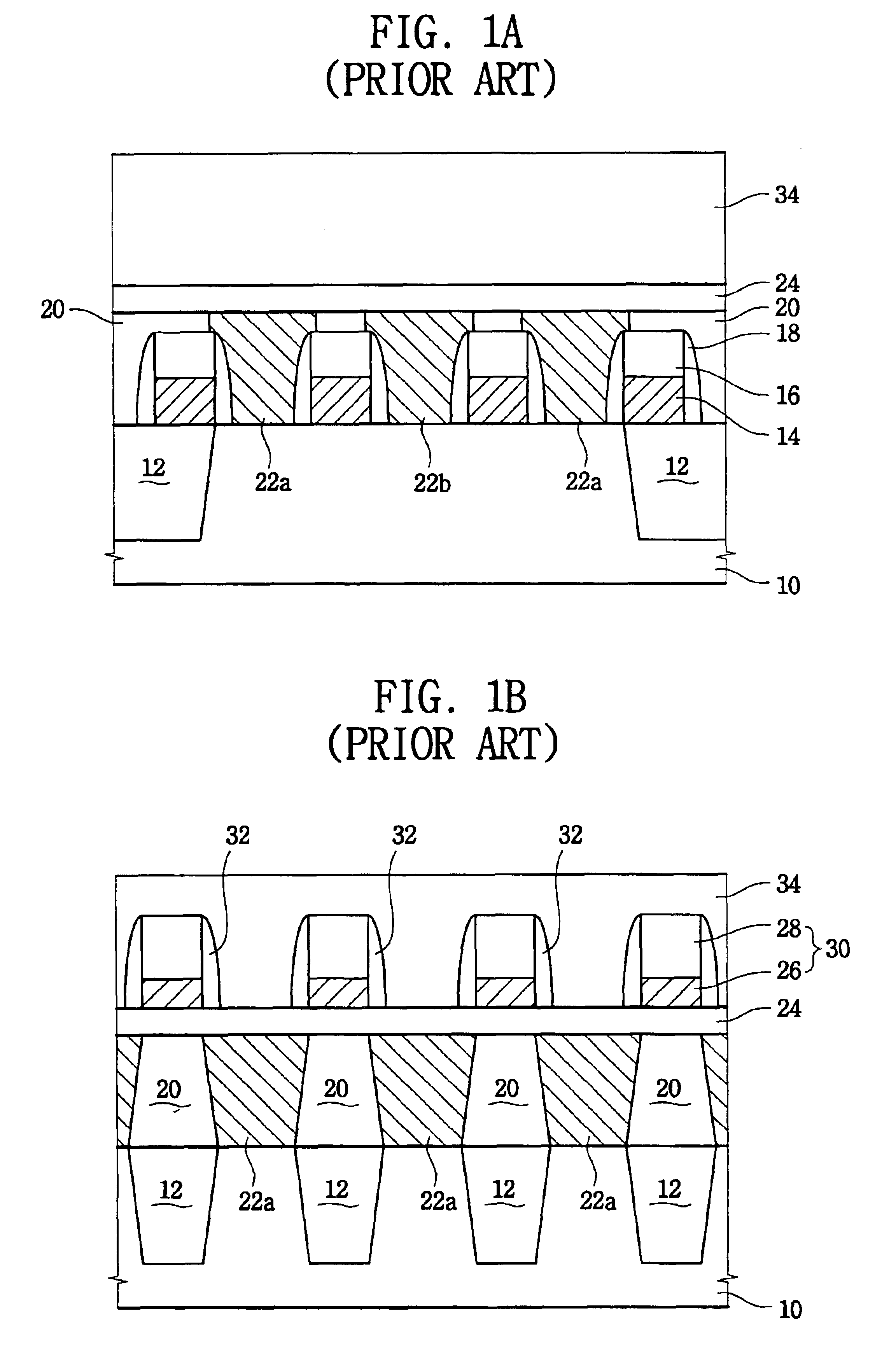

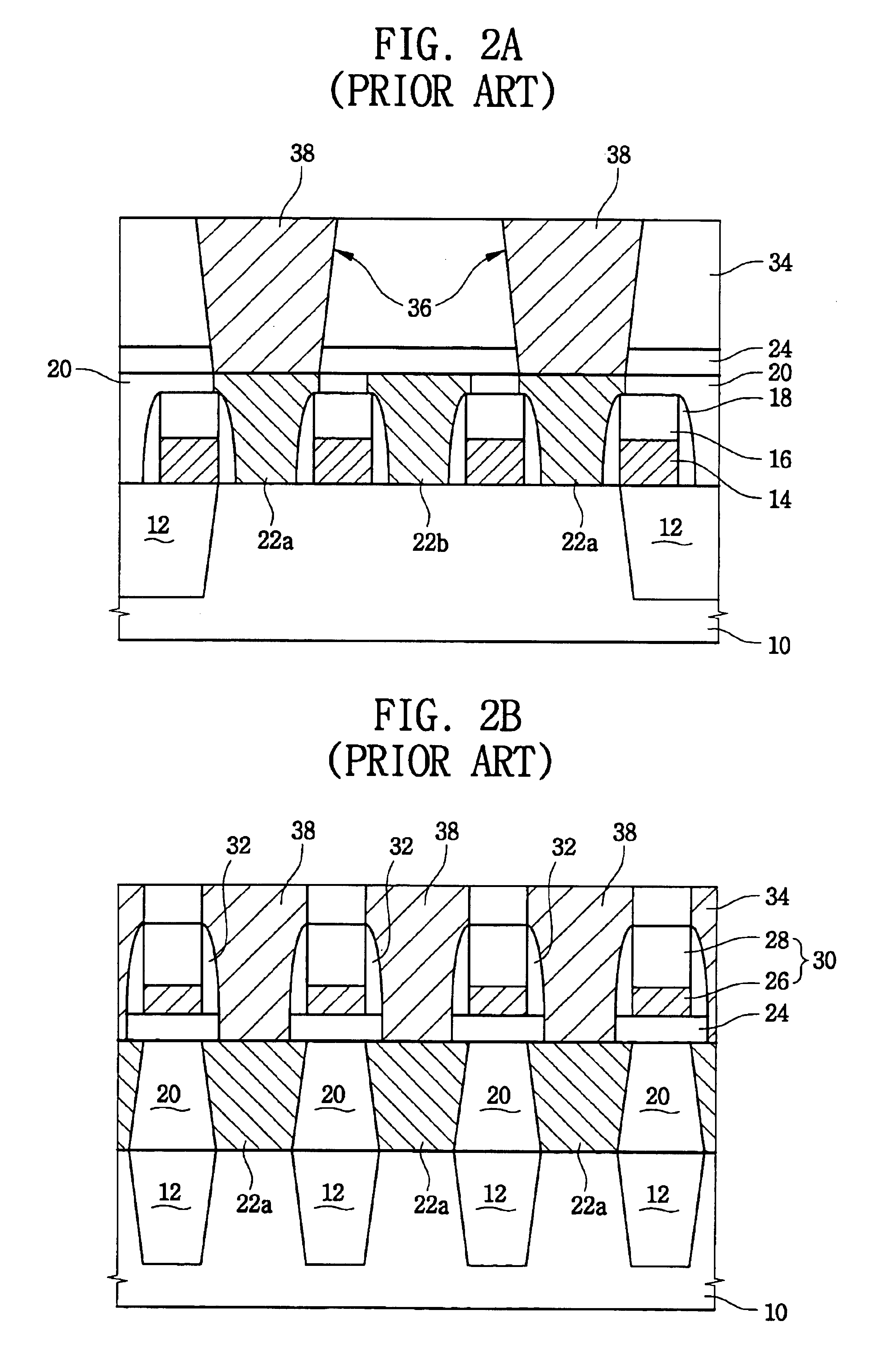

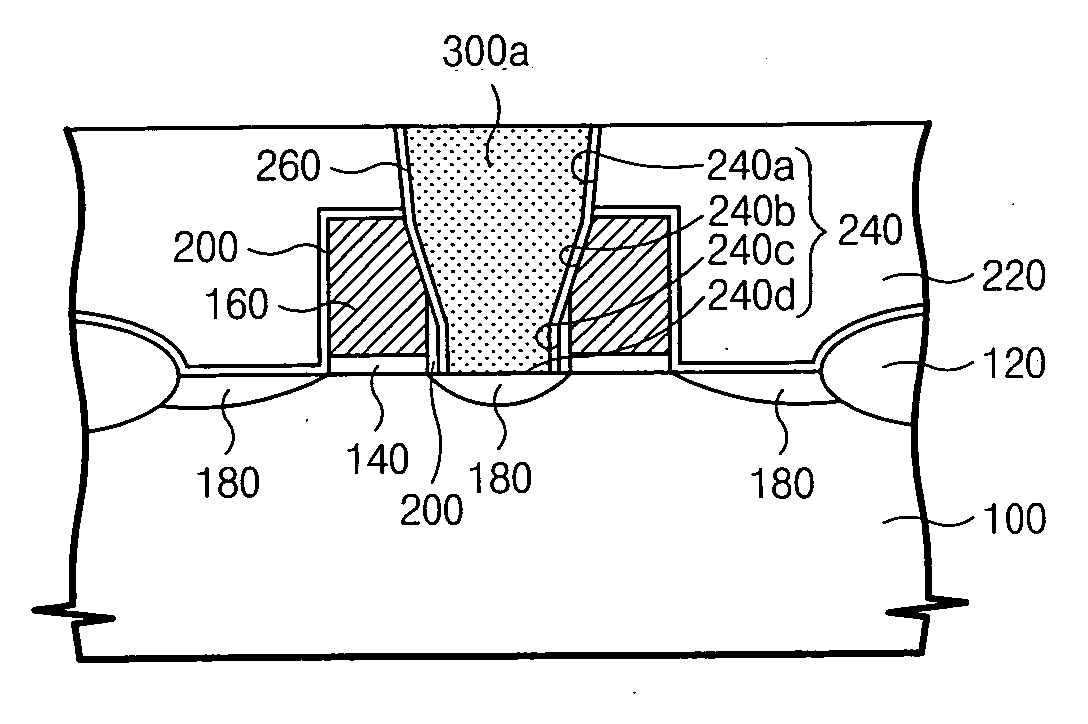

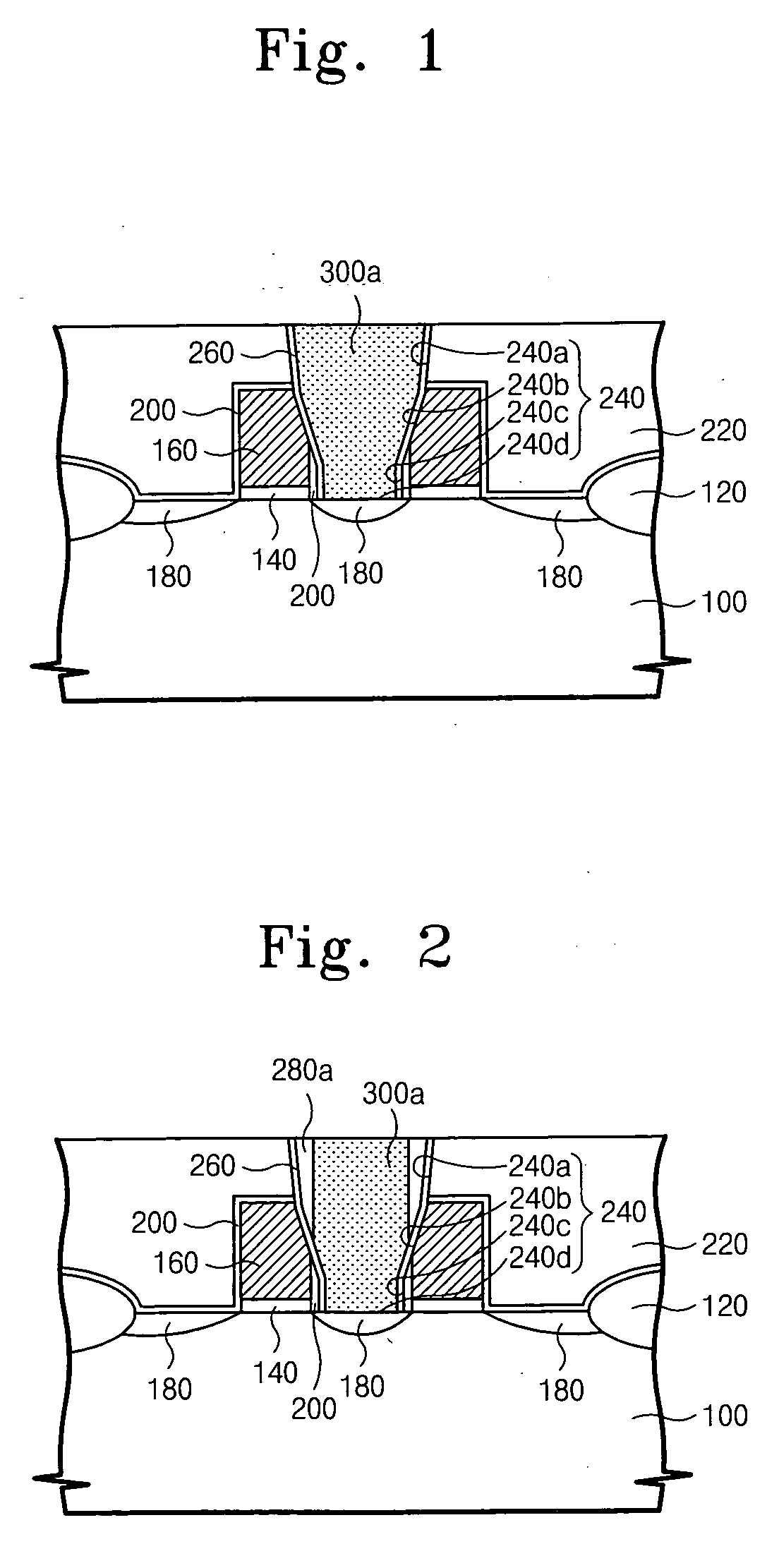

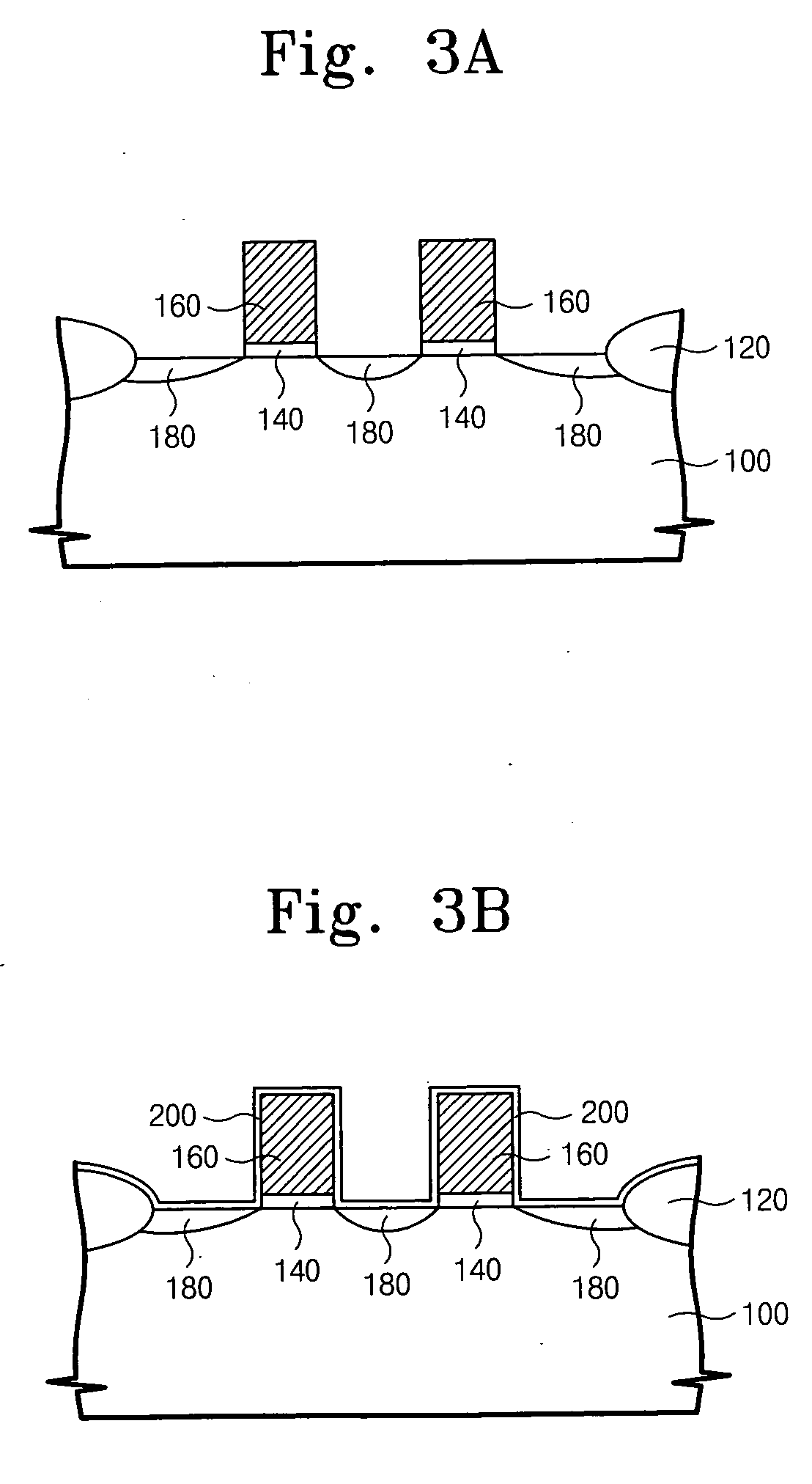

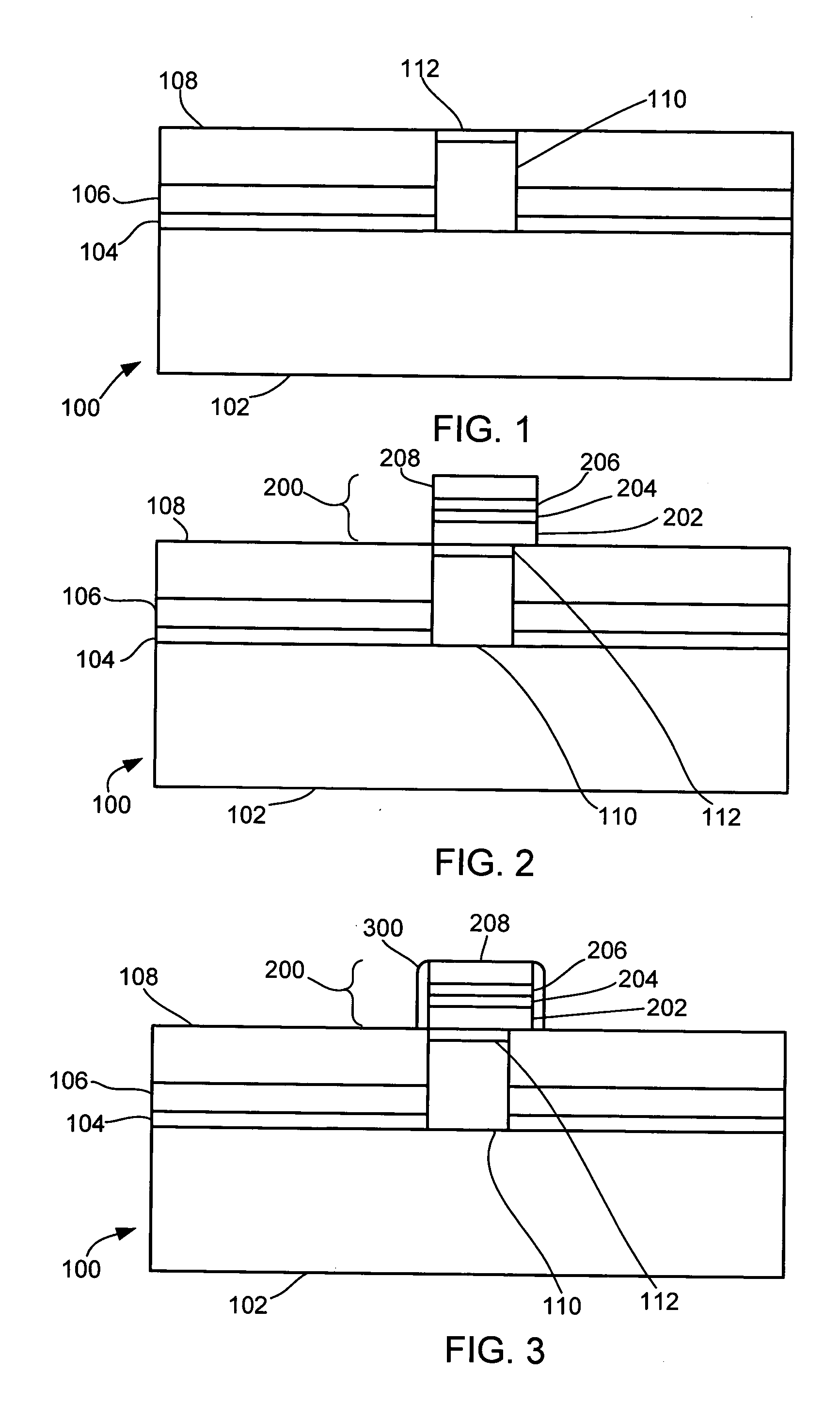

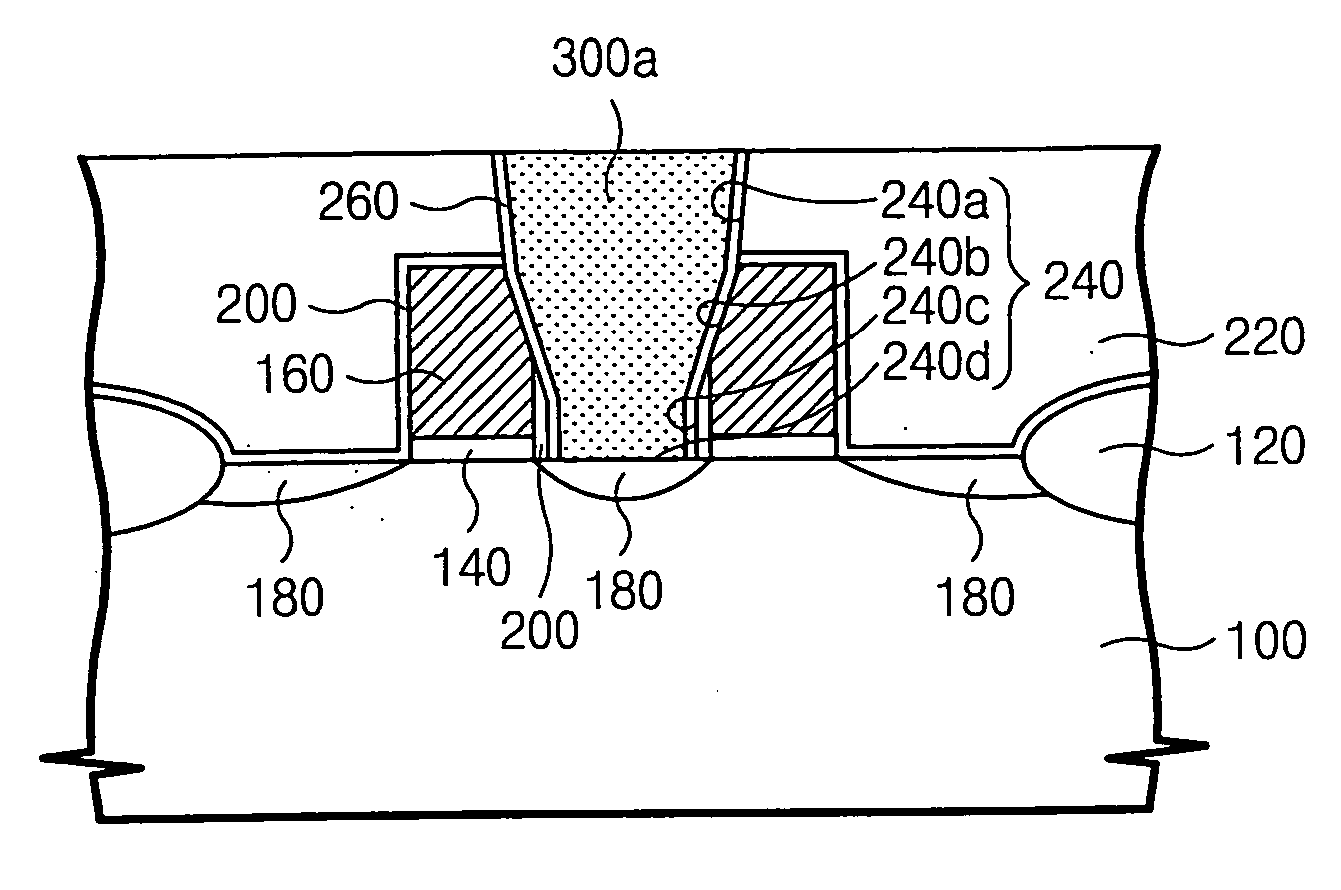

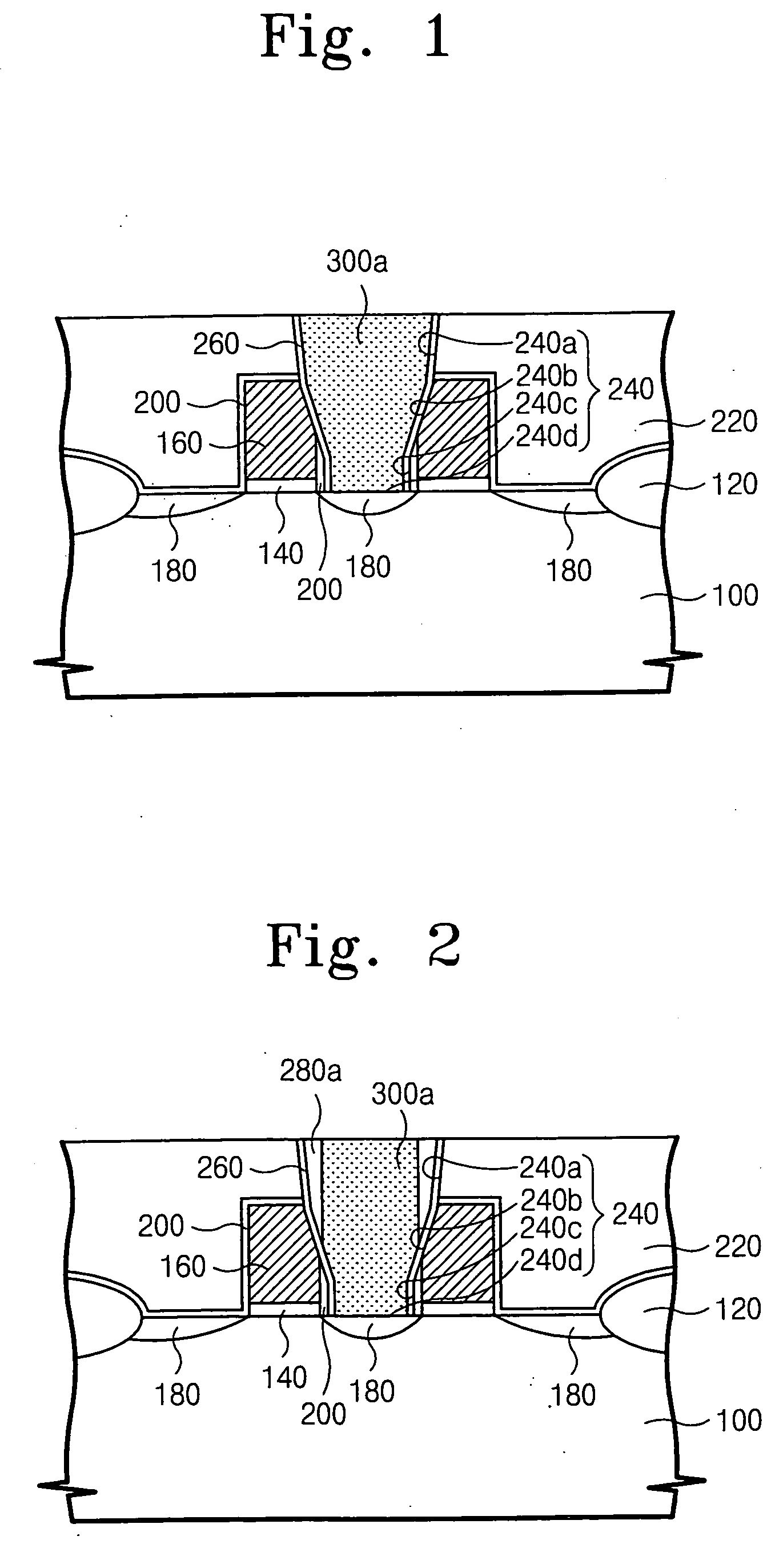

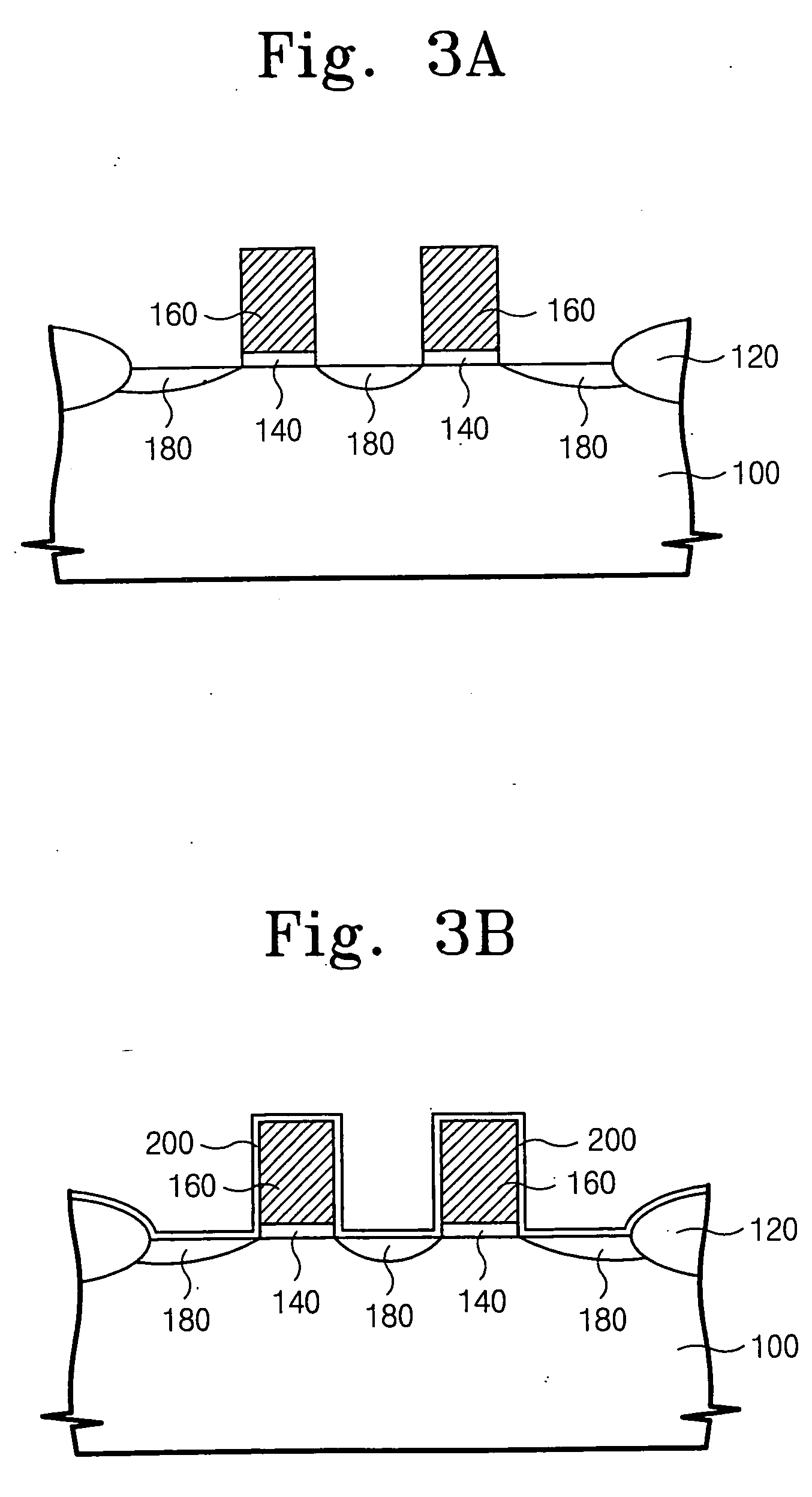

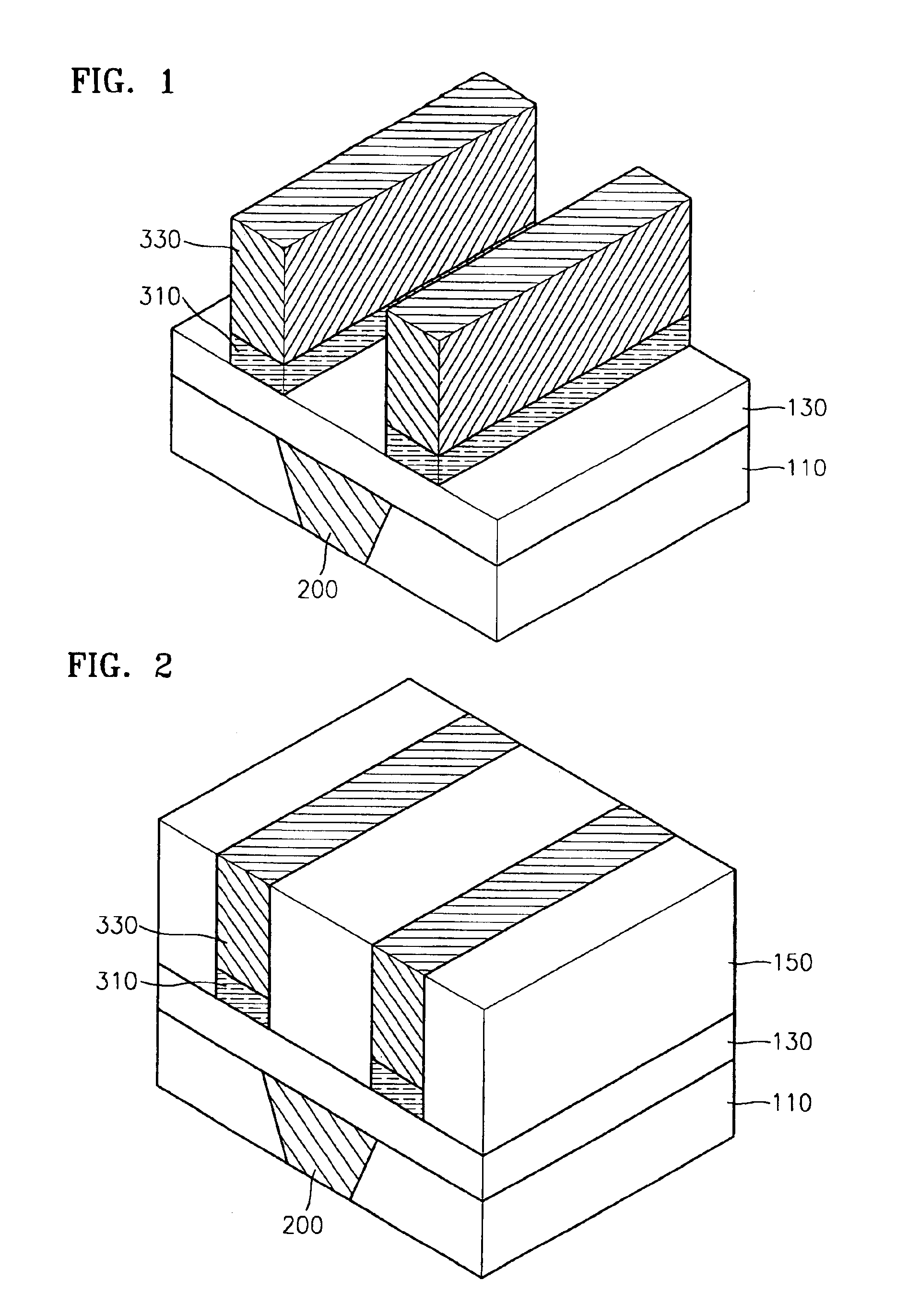

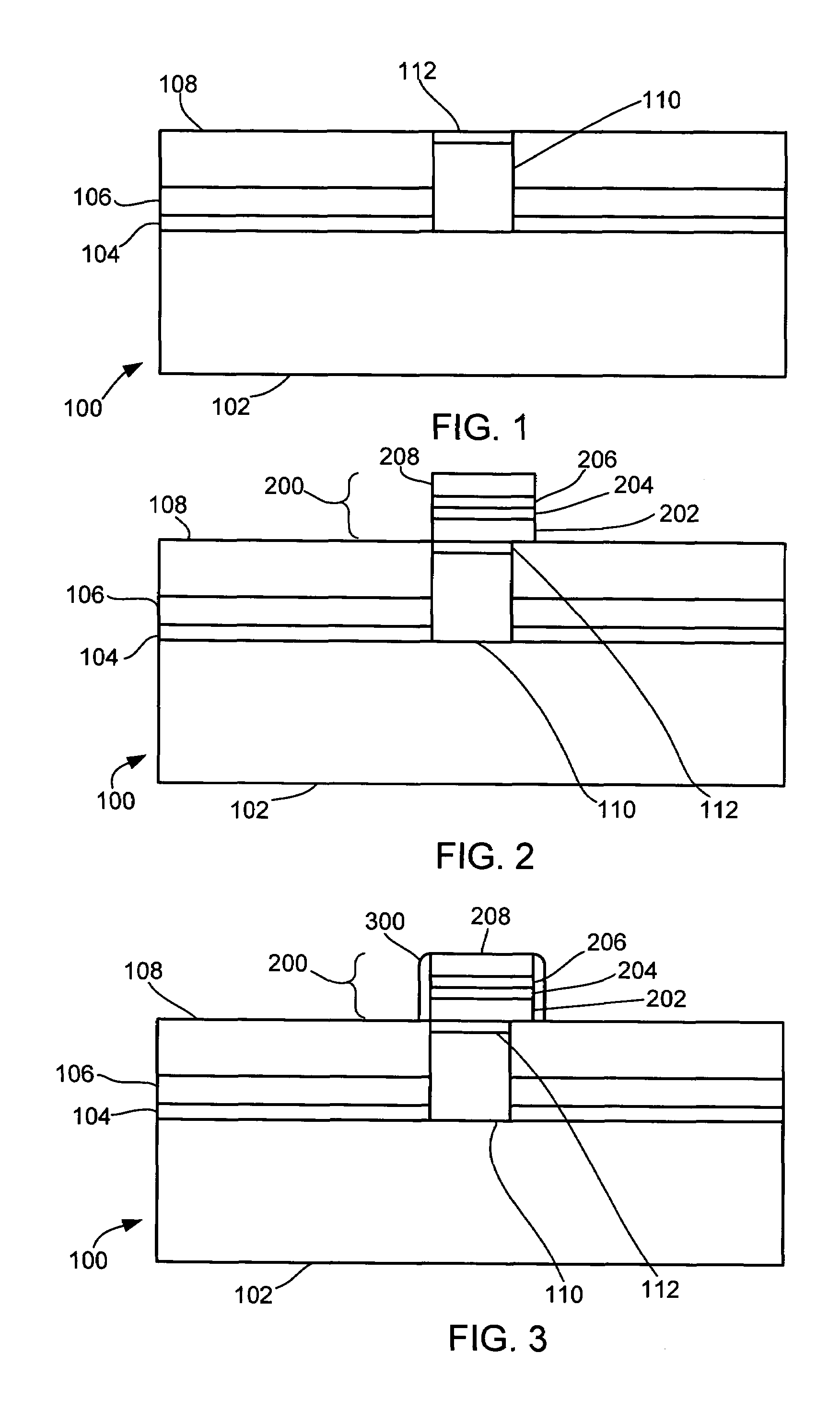

Self-aligned semiconductor contact structures and methods for fabricating the same

InactiveUS7071517B2Easily exposedWell formedTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

Owner:SAMSUNG ELECTRONICS CO LTD

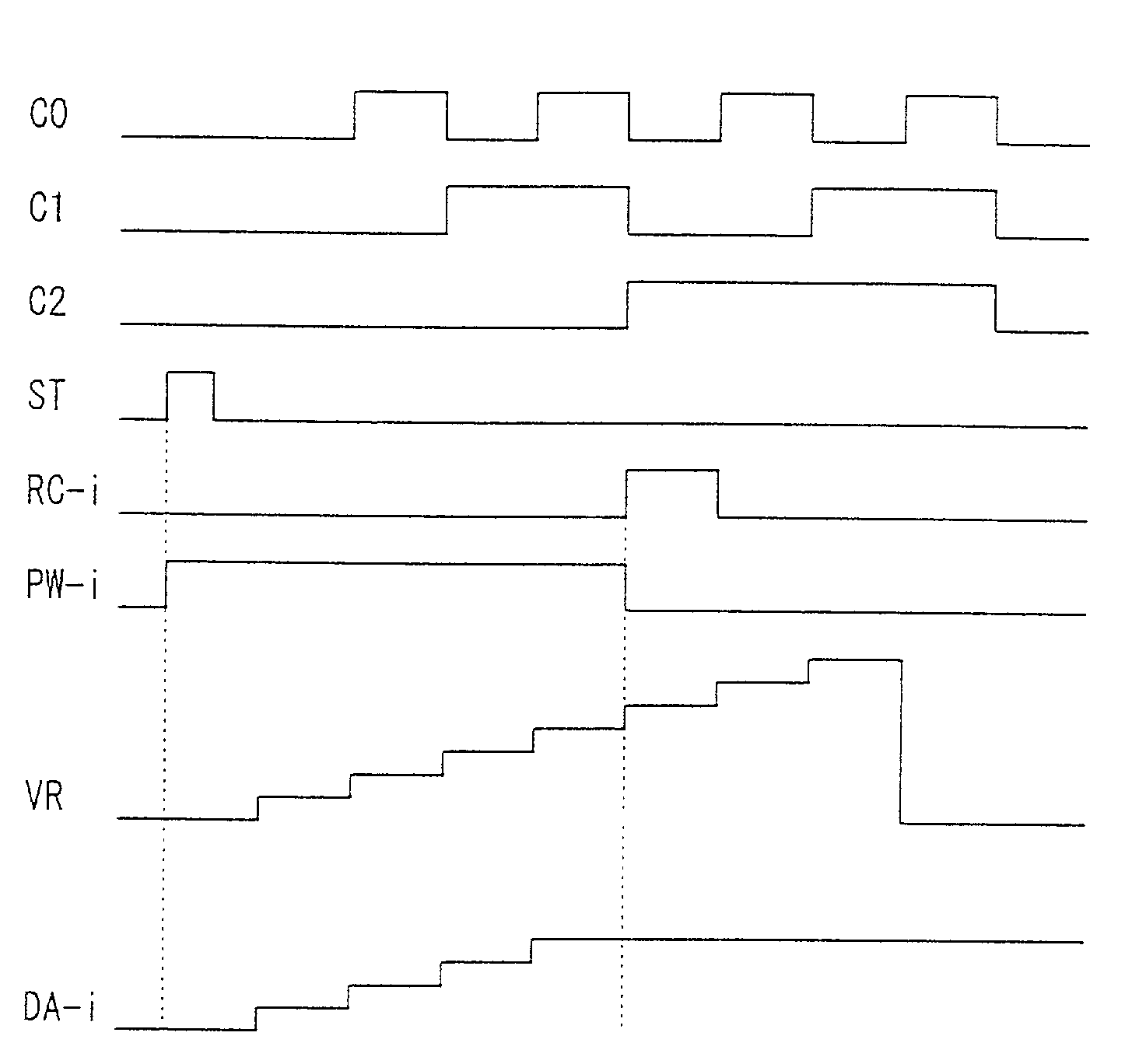

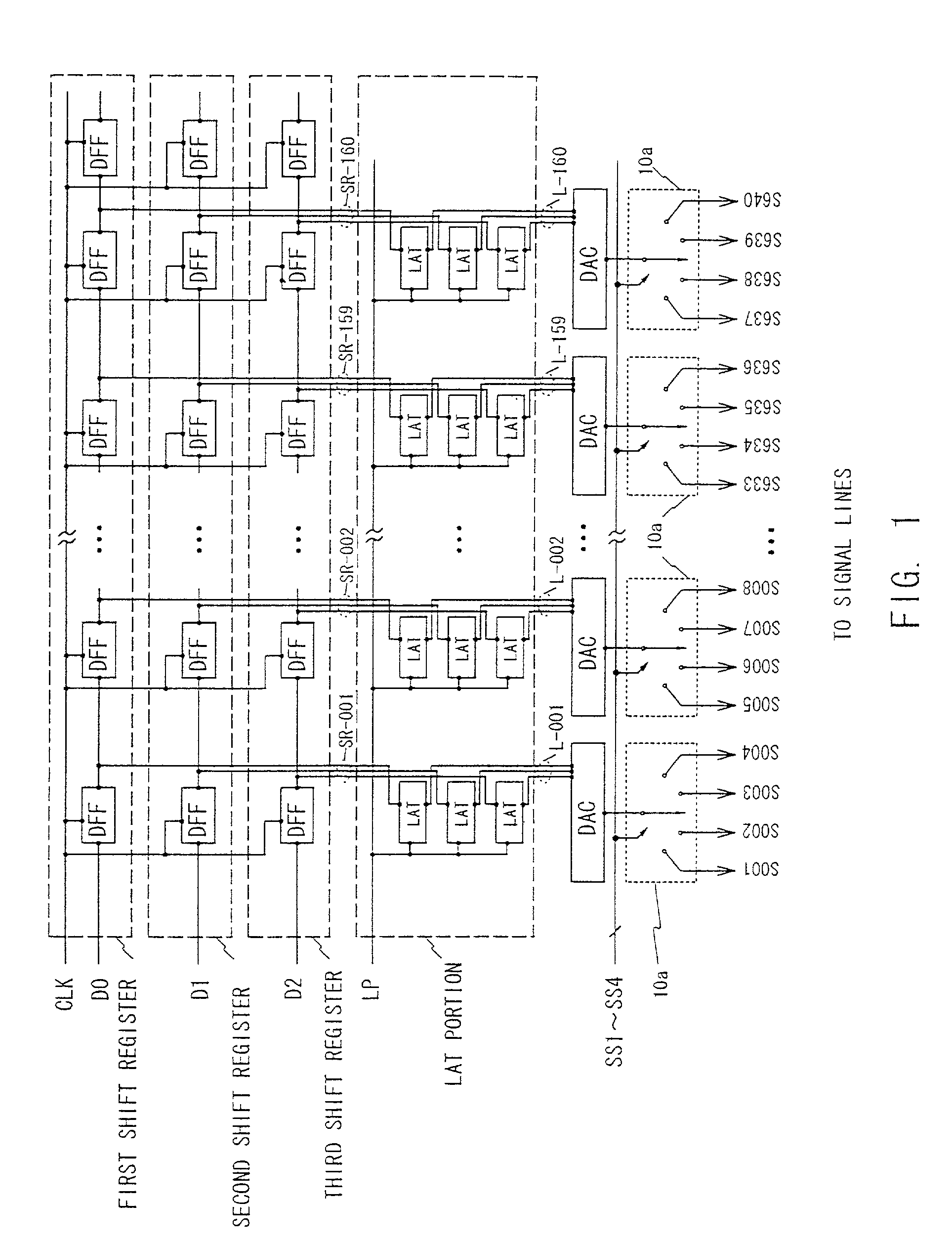

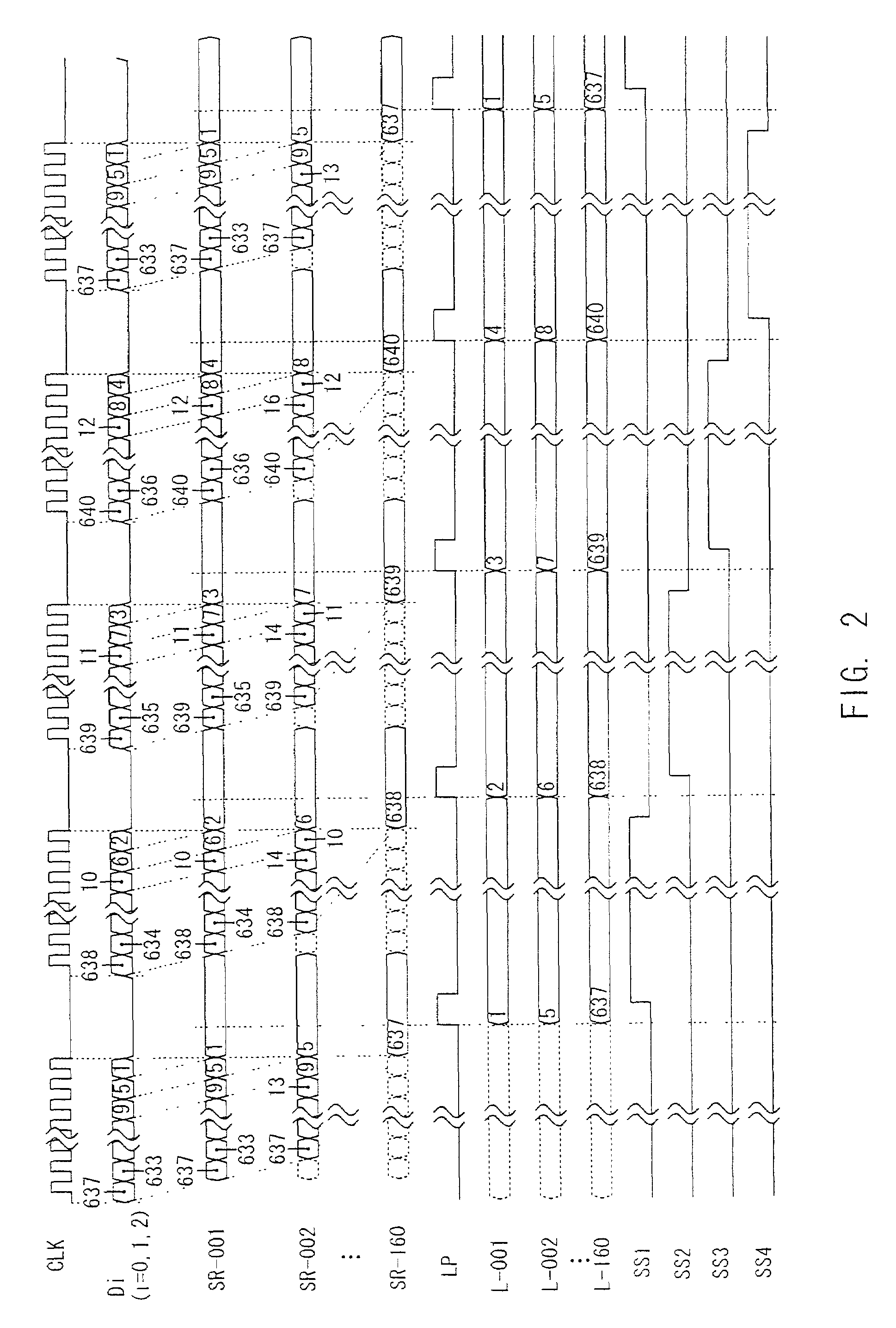

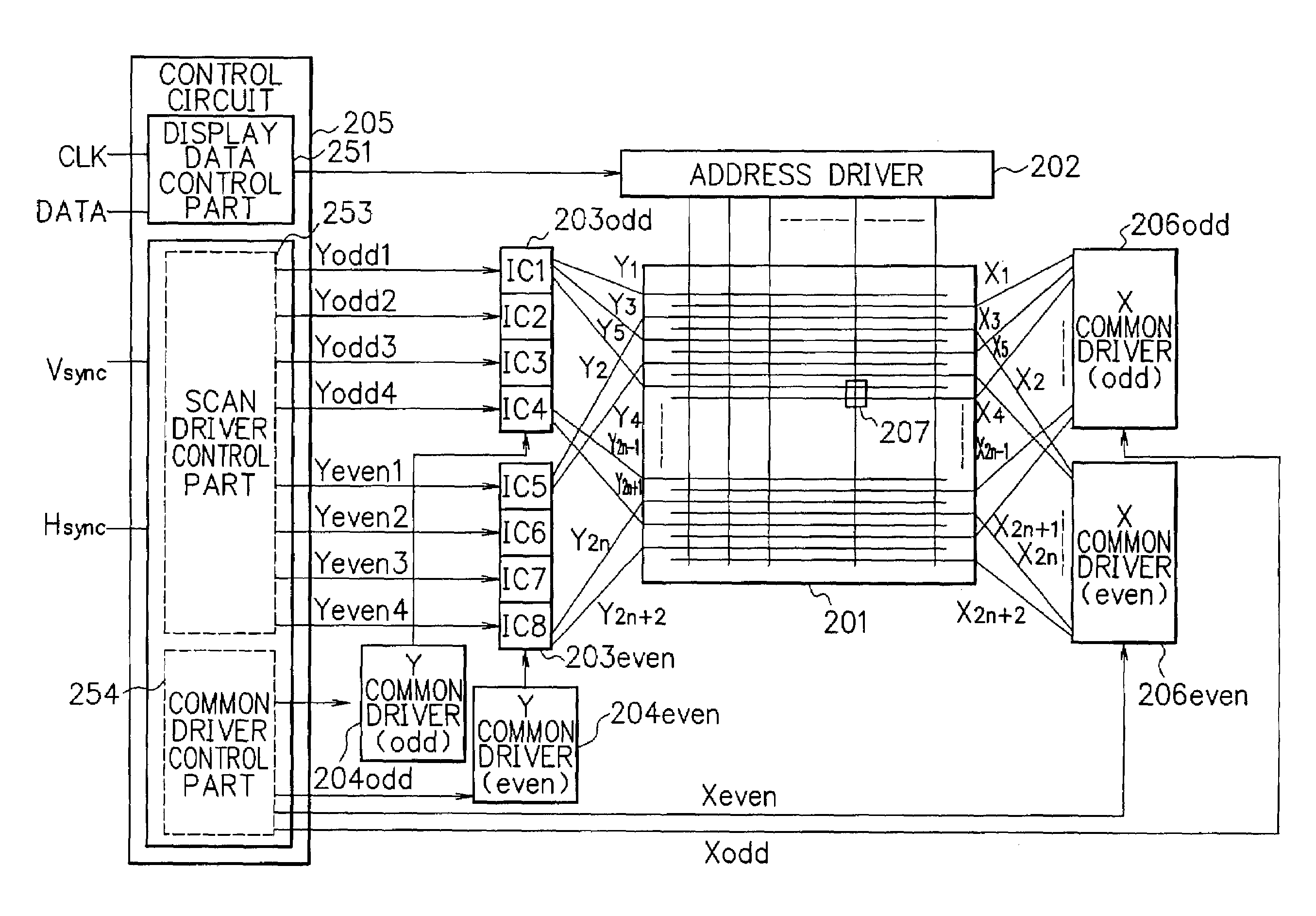

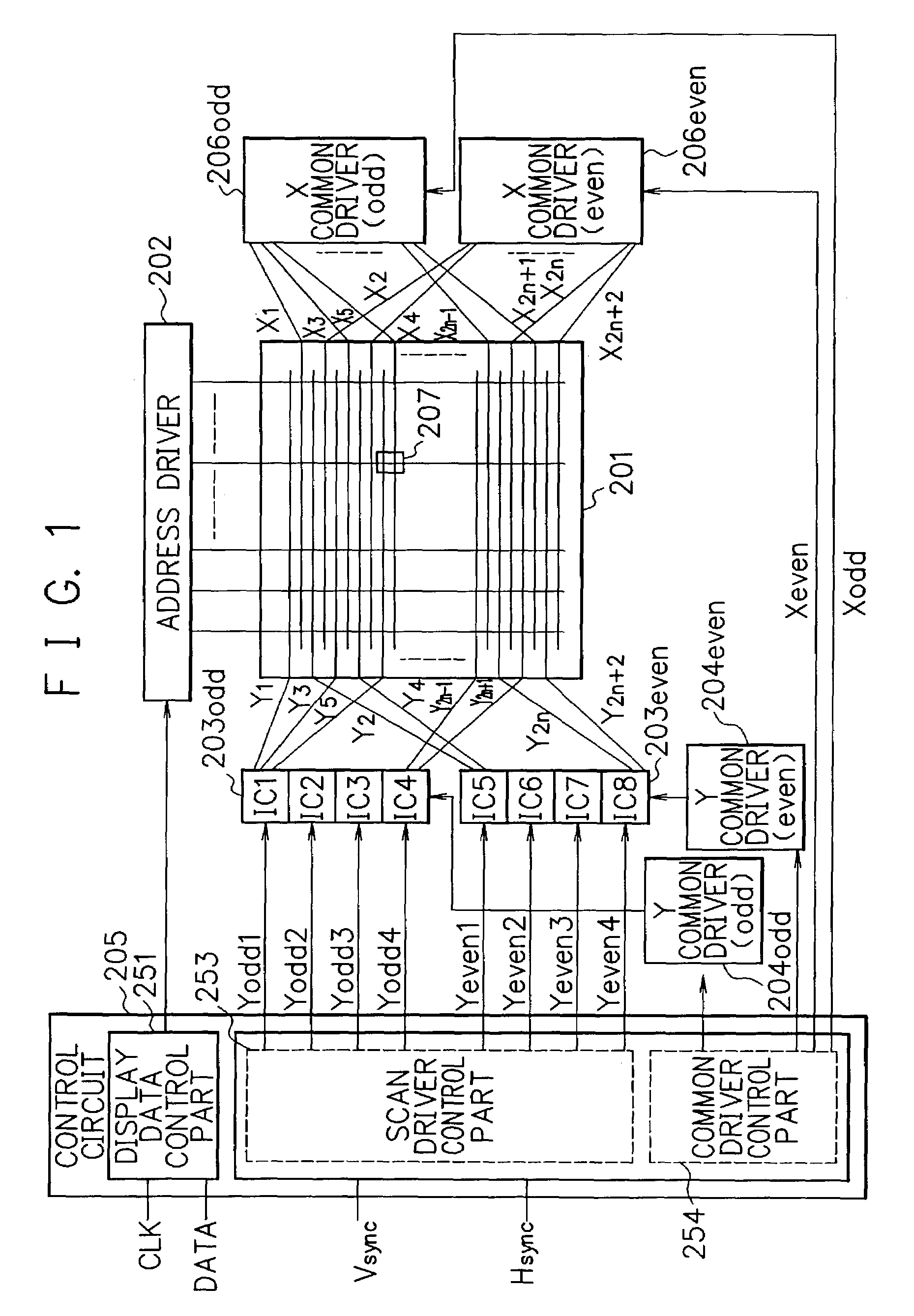

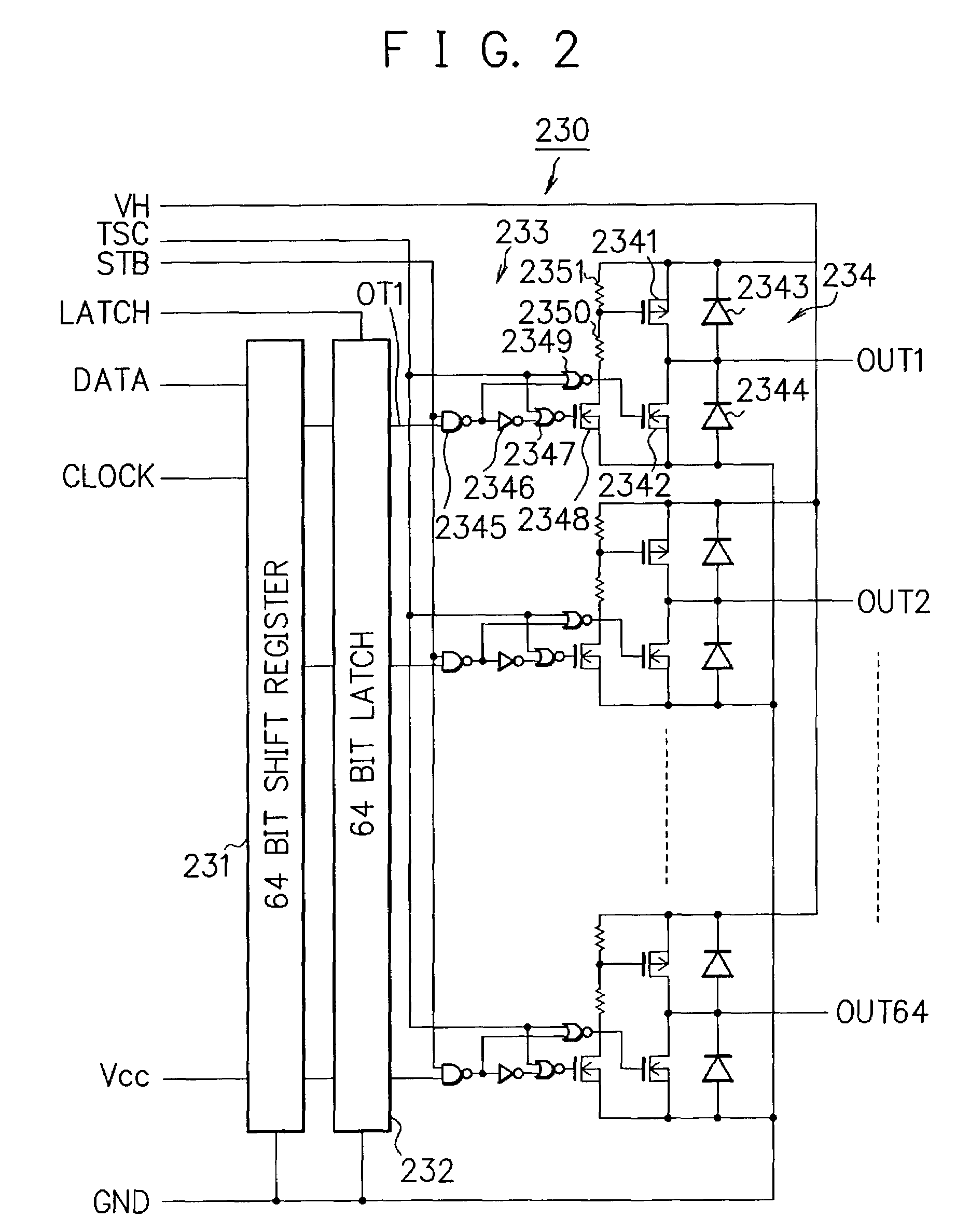

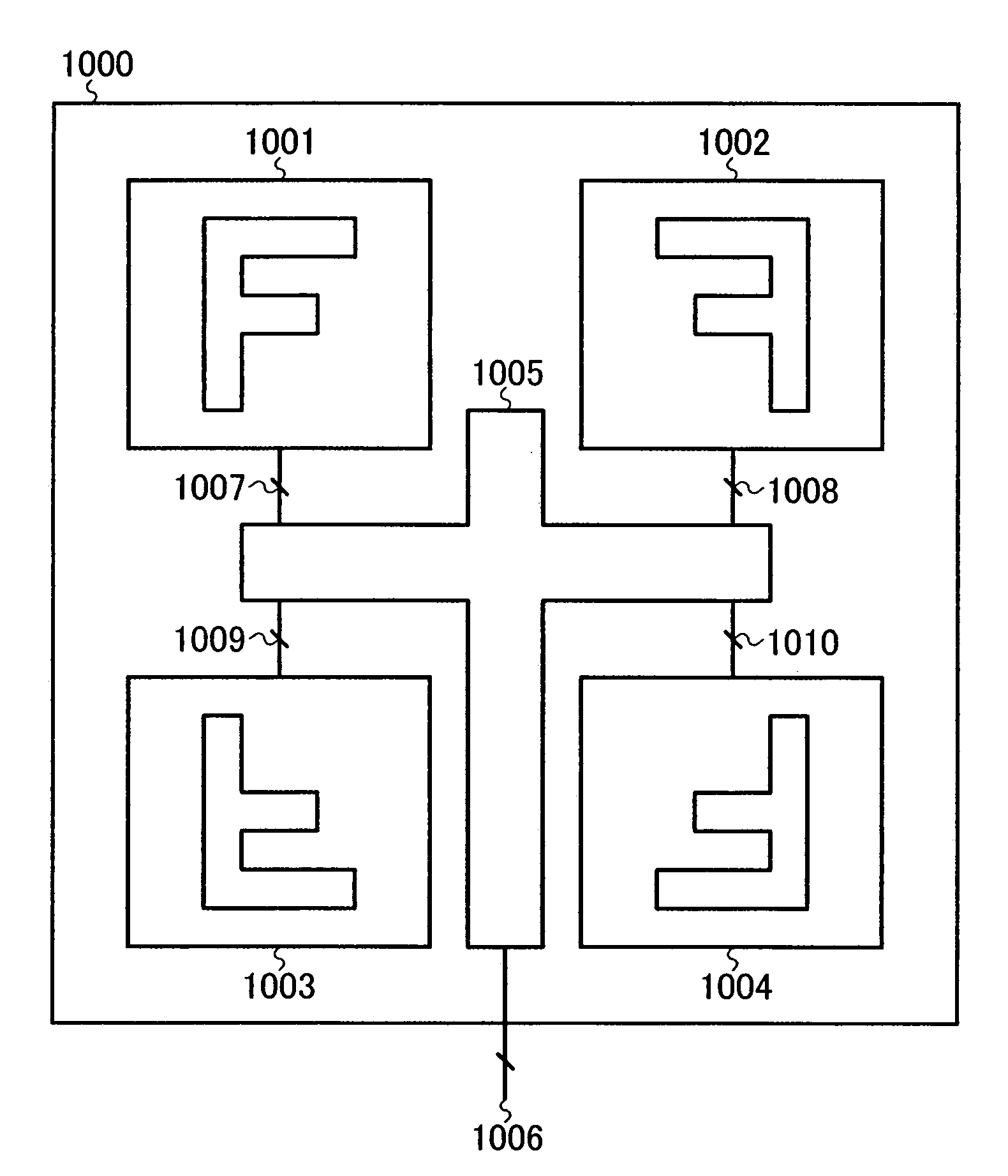

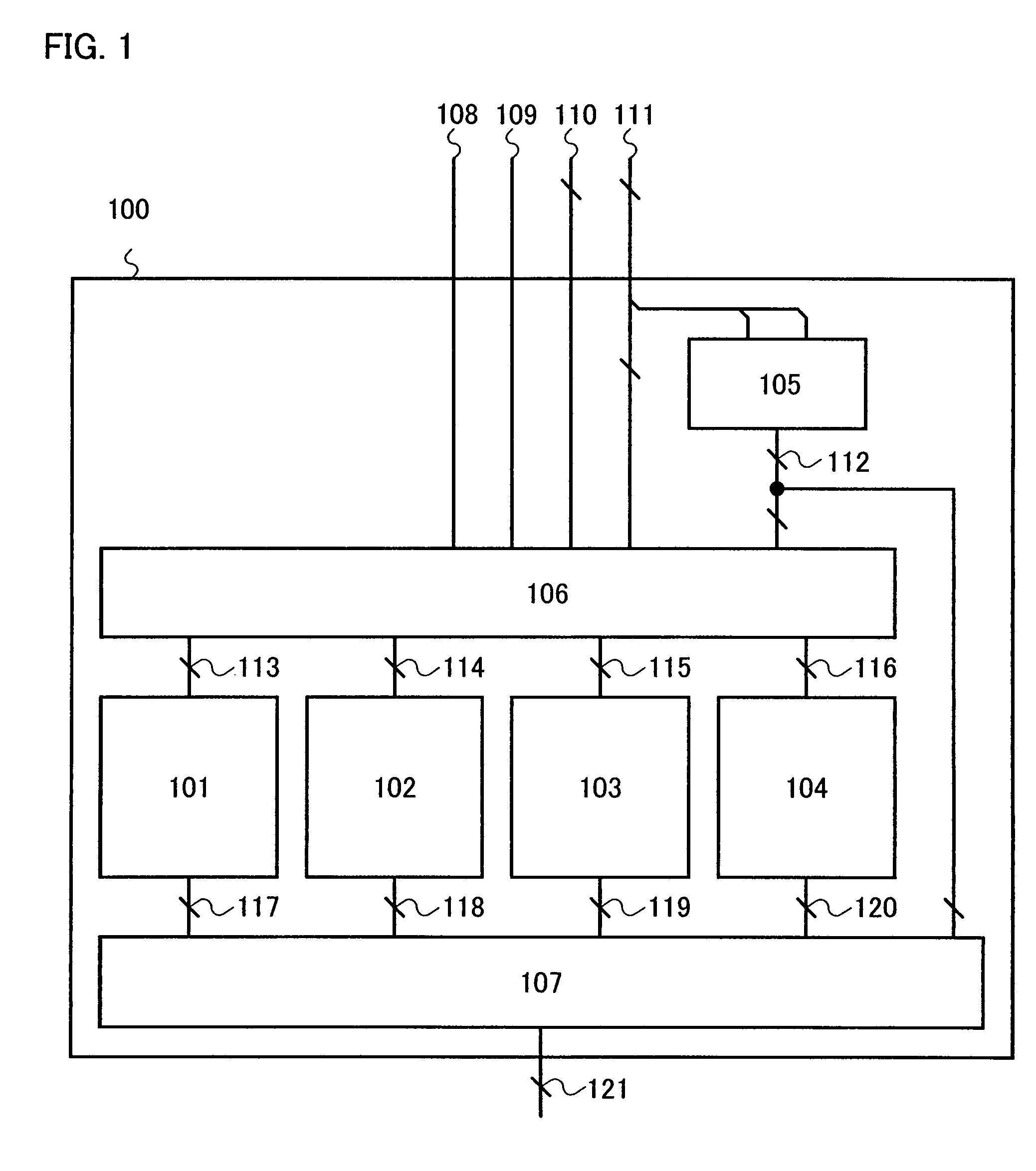

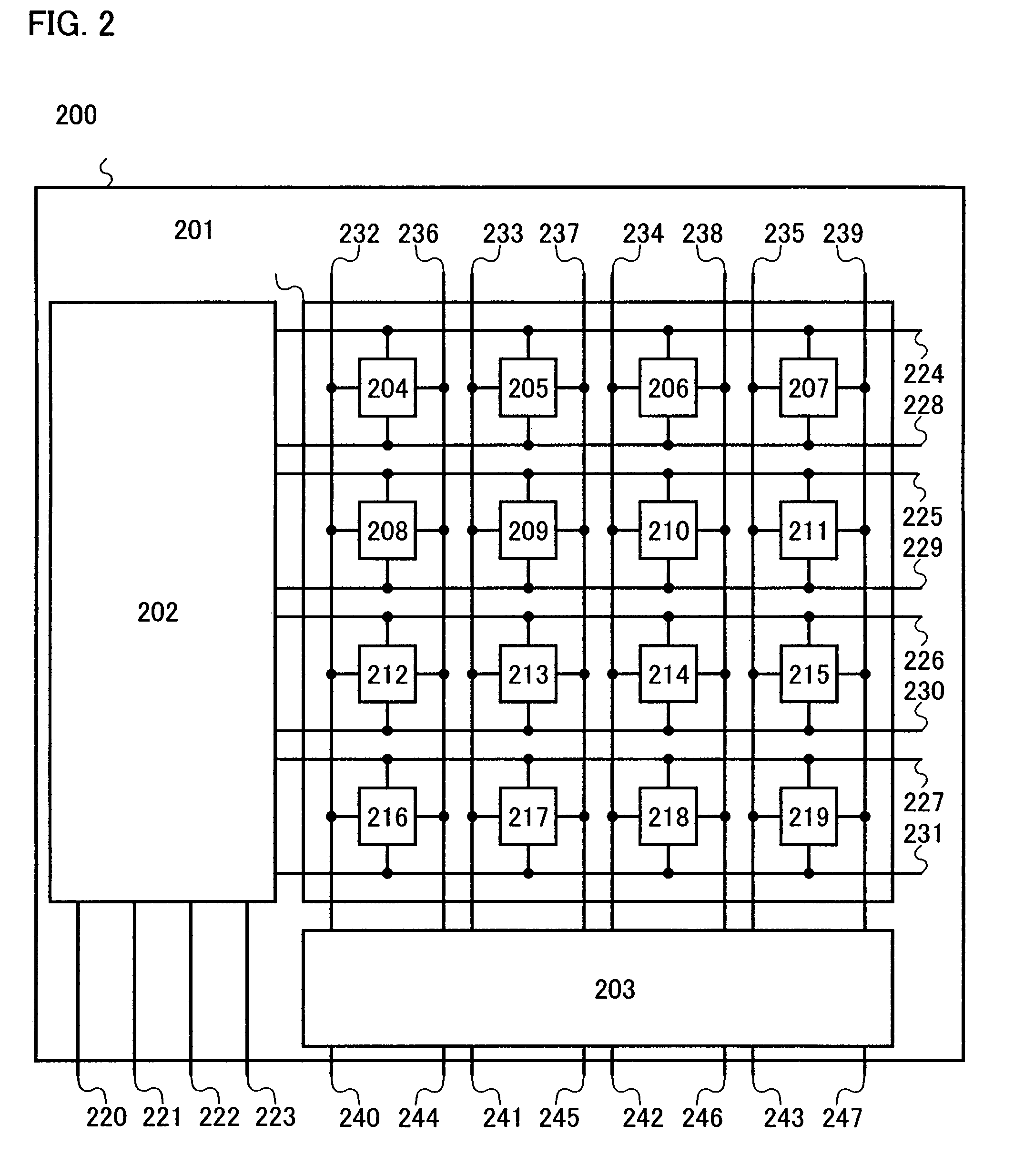

Image display device and driver circuit therefor

InactiveUS7301520B2Reduce degradationReduce signal distortionStatic indicating devicesShift registerElectrical resistance and conductance

There is provided an image display device operating in response to the input of digital picture signals, in which the occupied area of a signal line driver circuit thereof is reduced, and the parasitic capacitance and resistance of input transmission lines of the digital picture signals are reduced. The device includes both a unit for directly inputting the digital picture signals to shift registers and for performing series parallel conversion, and a unit for causing n (n is a natural number not less than 2) signal lines to jointly own storage circuits and D / A converter circuits in the signal line driver circuit. One horizontal scan period is divided into n periods, and the storage circuits and the D / A converter circuits perform a processing to signal lines different in each of the divided periods.

Owner:SEMICON ENERGY LAB CO LTD

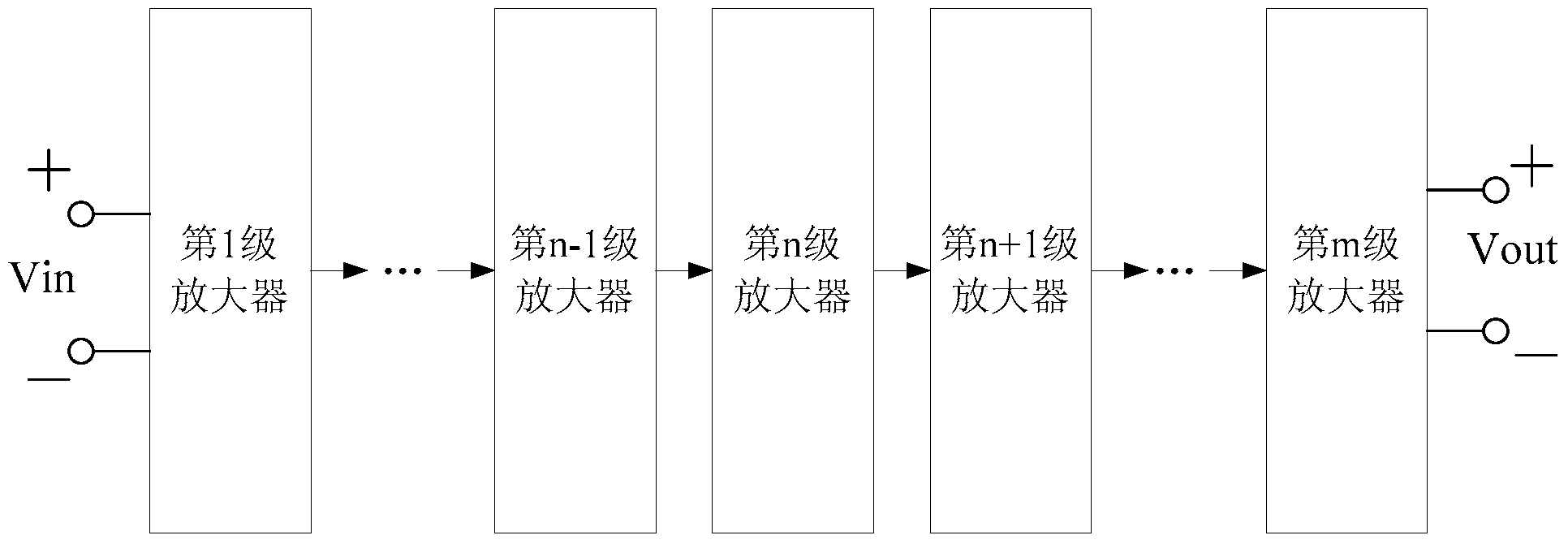

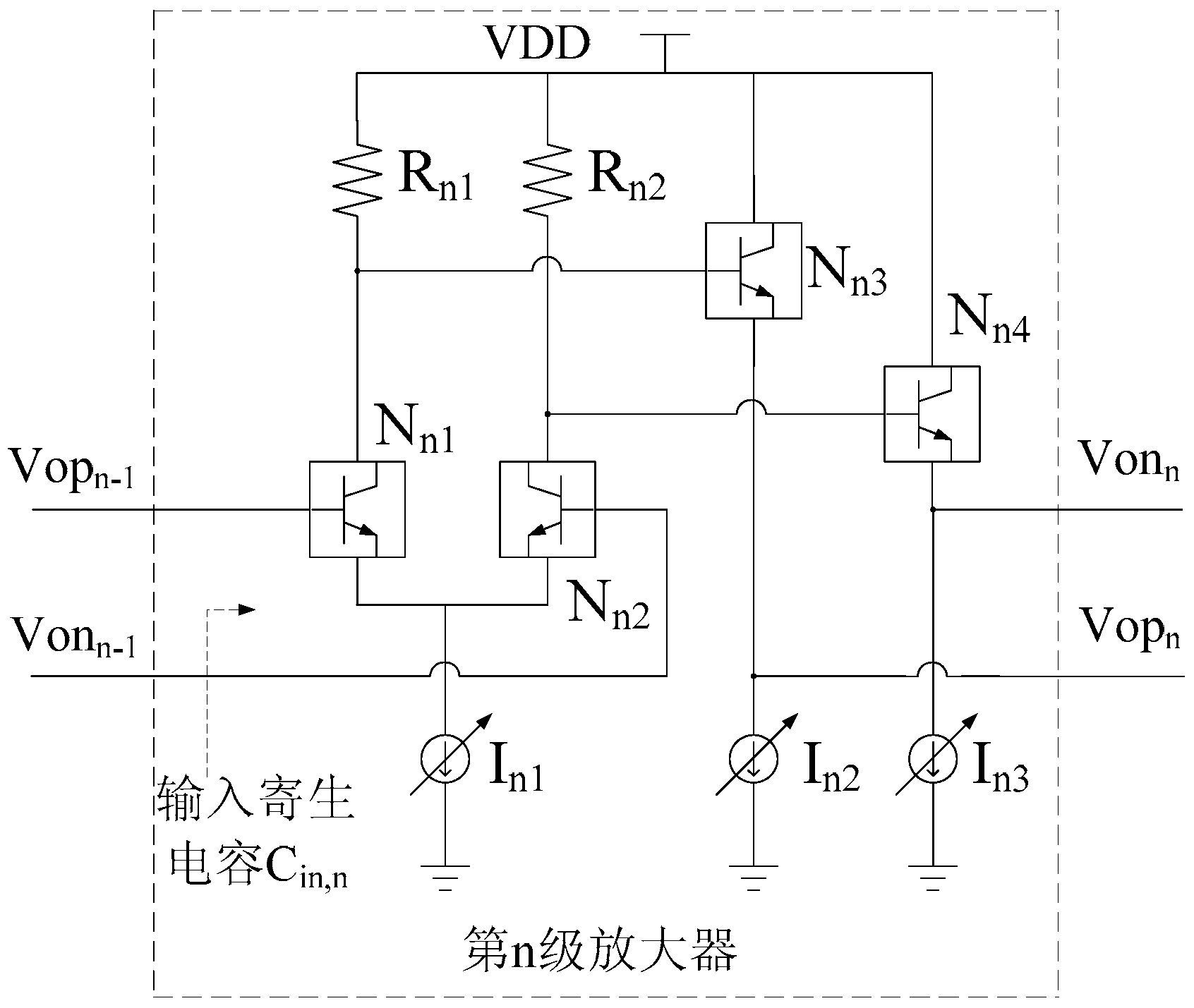

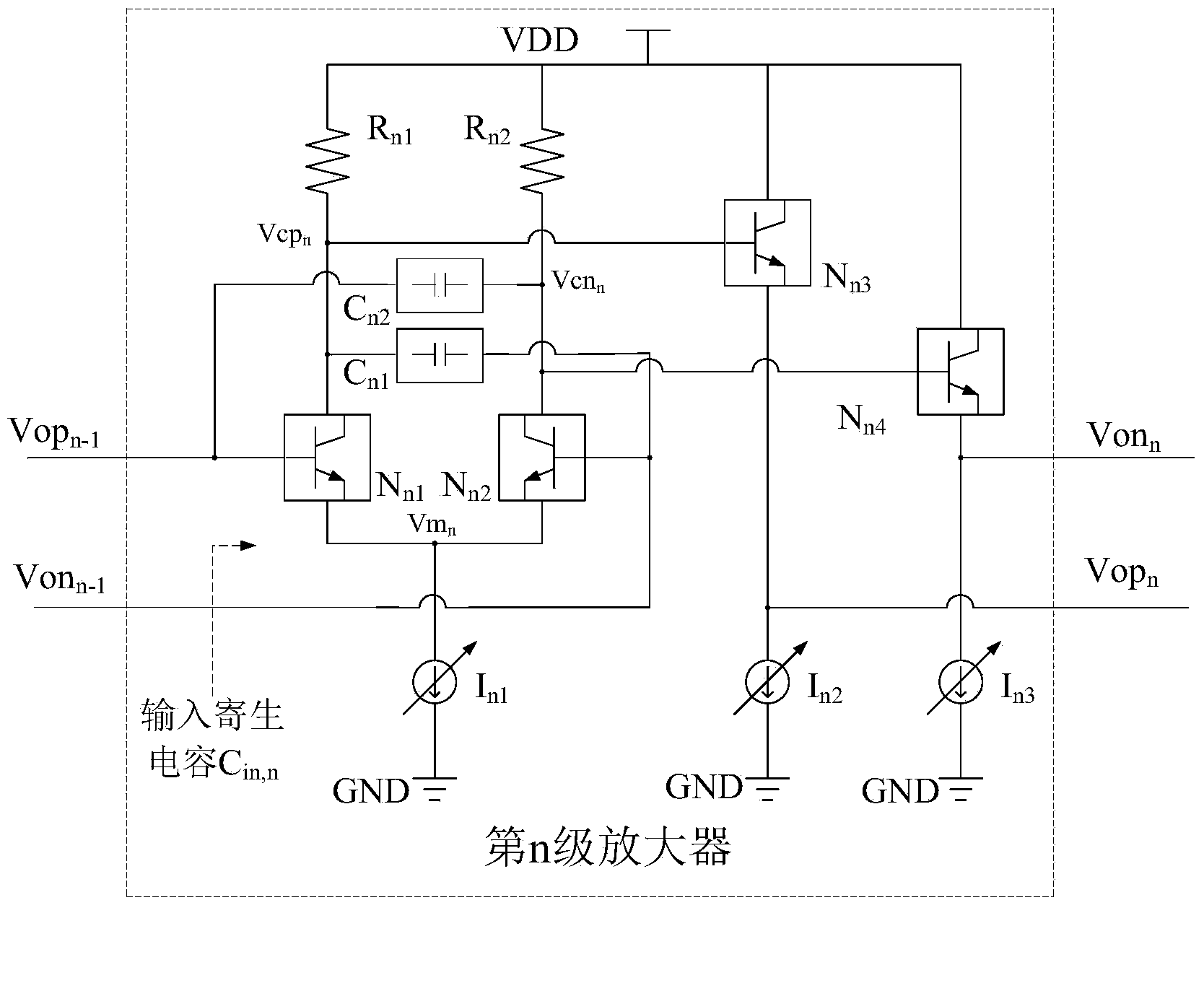

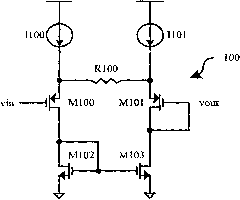

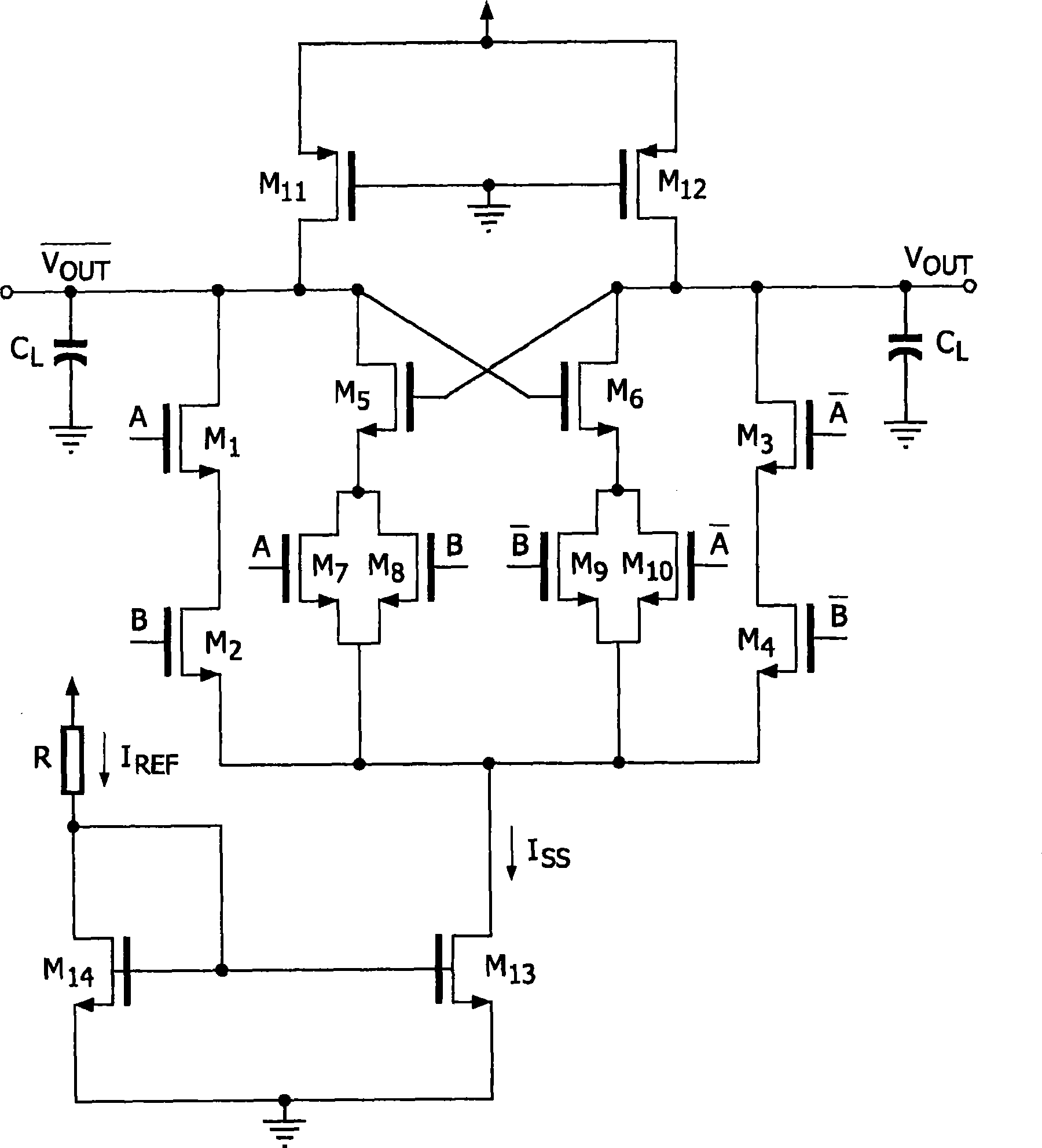

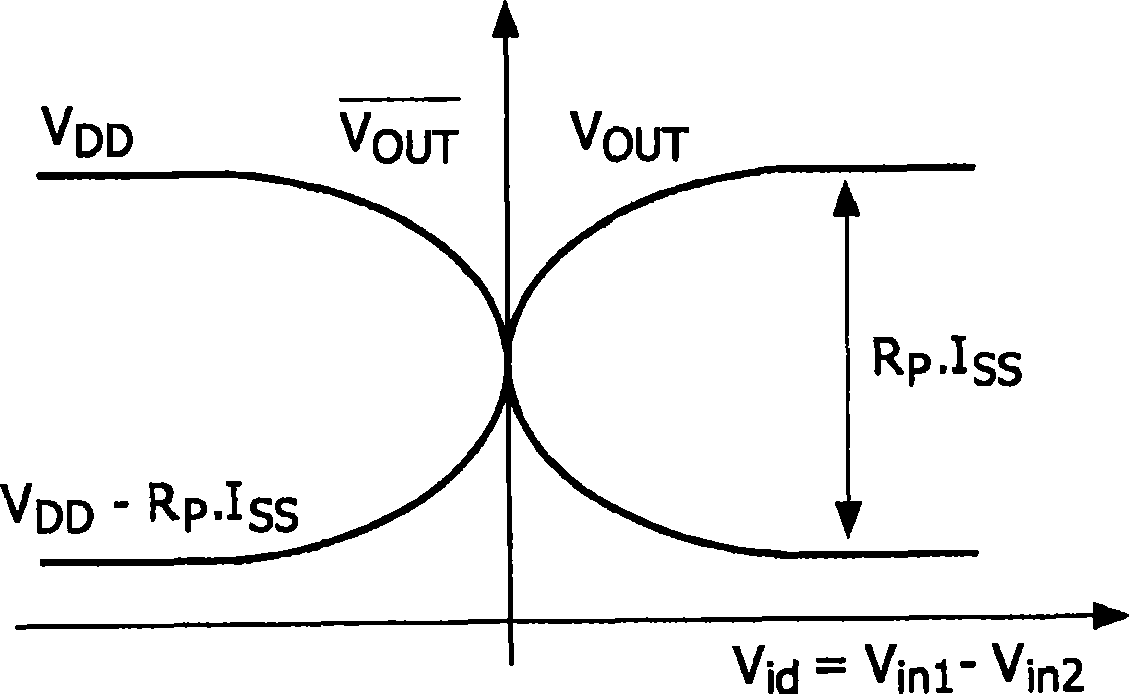

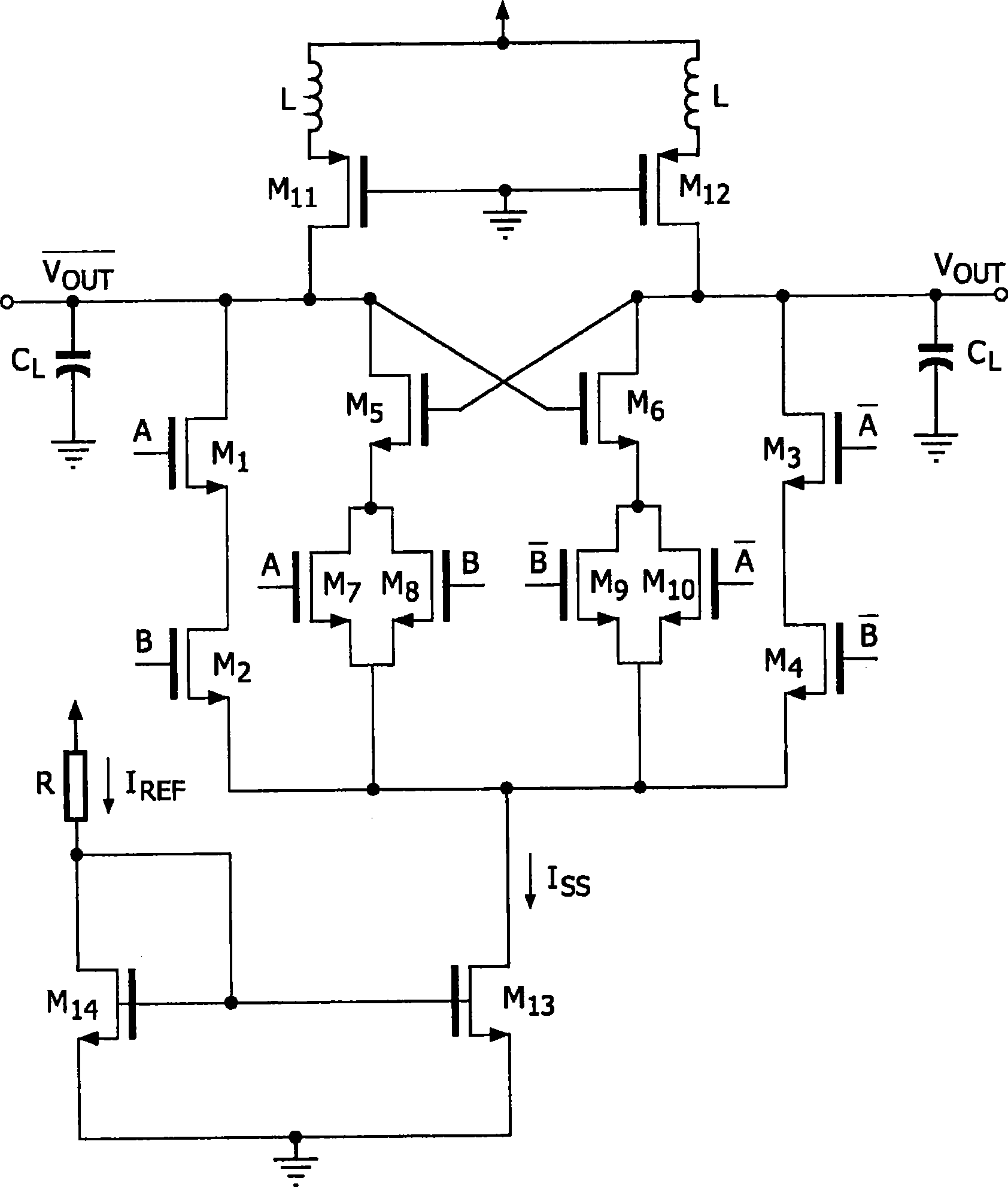

High-speed laser diode driver integrated circuit adopting negative capacitance neutralizing technology

ActiveCN103928842AImprove output performanceIncreased Voltage Gain BandwidthLaser detailsSemiconductor lasersCapacitanceEngineering

The invention relates to a high-speed laser diode driver integrated circuit adopting a negative capacitance neutralizing technology, and belongs to the field of integrated circuits. The high-speed laser diode driver integrated circuit adopting the negative capacitance neutralizing technology aims to enlarge voltage gain -3dB bandwidths of a driver, enhance high-frequency modulation current output capability and improve eye pattern characteristics of output high-frequency current signals under the premise that the power consumption of the driver is not increased. The high-speed laser diode driver integrated circuit adopting the negative capacitance neutralizing technology is formed by m levels of amplifiers in a cascading connection mode, and the m is a natural number larger than or equal to 1. The nth-level amplifier in the m levels of the amplifiers is a controllable gain amplifier adopting the negative capacitance neutralizing technology, the n is smaller than or equal to the m, and the nth-level amplifier comprises a differential amplifier and a source electrode follower. The differential amplifier comprises a controllable current source In1, an NMOS transistor Nn1, an NMOS transistor Nn2, a load resistor Rn1, a load resistor Rn2, a capacitor Cn1 and a capacitor Cn2. The source electrode follower comprises a controllable current source In2, a controllable current source In3, an NMOS transistor Nn3 and an NMOS transistor Nn4.

Owner:QIANDU TONGCHIP XIAMEN MICROELECTRONICS TECH CO LTD

Semiconductor device

InactiveUS20070218682A1Reduce load capacitanceEfficient fillingTransistorSolid-state devicesCapacitanceBit line

Bit lines having first conductive patterns and bit line mask patterns are formed on a first insulating layer between capacitor contact regions of a substrate. An oxide second insulating layer is formed on the bit lines and contact patterns are formed to open storage node contact hole regions corresponding to portions of the second insulating layer. First spacers are formed on sidewalls of the etched portions. The second and first insulating layers are etched to form storage node contact holes exposing the capacitor contact regions. Simultaneously, second spacers of the second insulating layer are formed beneath the first spacers. A second conductive layer fills the storage node contact holes to form storage node contact pads. A loss of the bit line mask pattern decreases due to the reduced thickness of the bit line mask pattern and a bit line loading capacitance decreases due to the second spacers.

Owner:SAMSUNG ELECTRONICS CO LTD

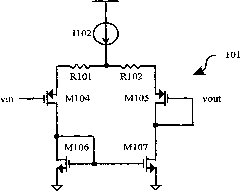

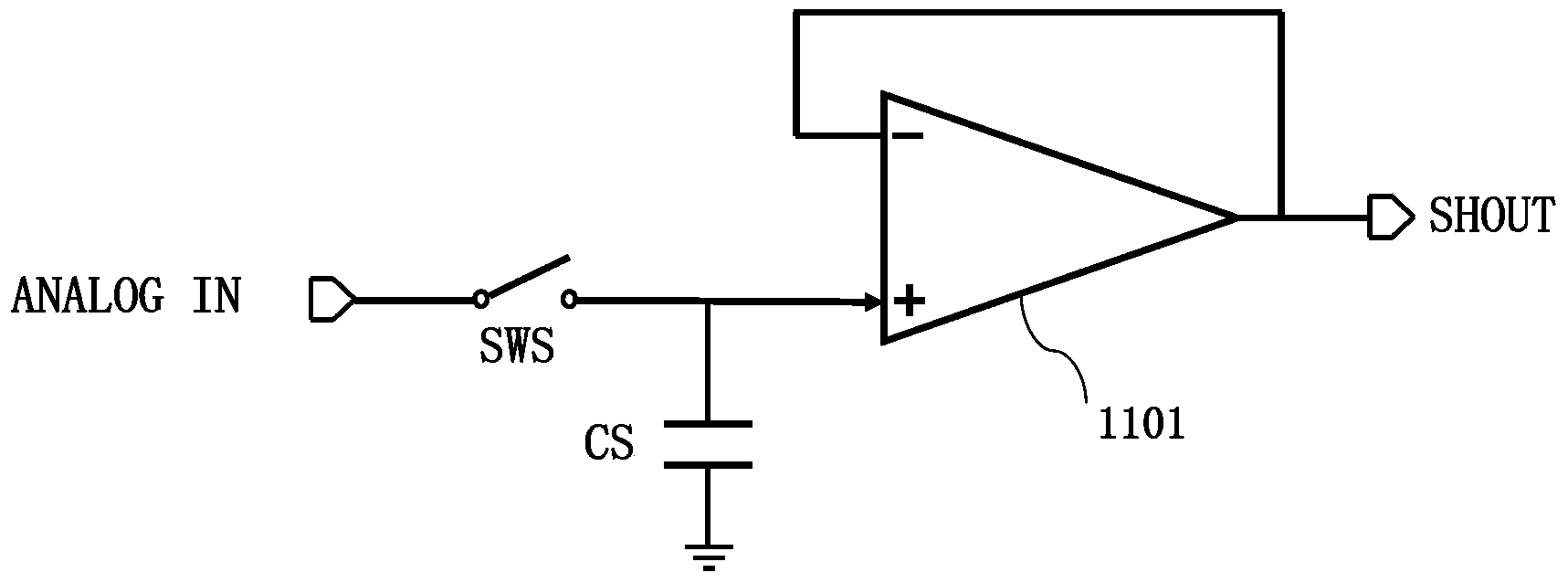

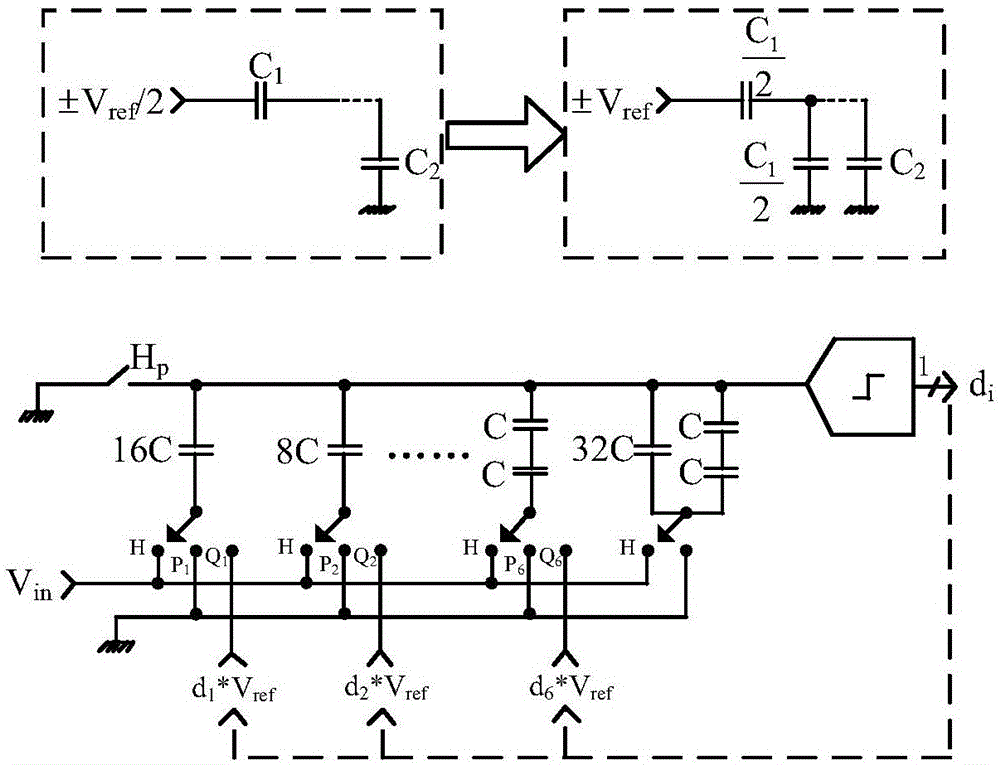

Input buffer circuit for high-speed pipeline analog-to-digital converter

InactiveCN101800550AMeet the input requirementsReduce load capacitanceAnalogue-digital convertersCapacitanceNegative feedback

The invention provides a input buffer circuit for high-speed pipeline analog-to-digital converter (ADC). The input buffer circuit comprises an input pair transistor, a current mirror load, a gain-boosted amplifier and a compensation capacitor, wherein the input pair transistor consists of a first MOS (metal oxide semi-conductor) transistor and a second MOS transistor of a source negative-feedback resistor; the current mirror load consists of a third MOS transistor and a fourth transistor which are connected to each other by a gate; the positive input terminal of the gain-boosted amplifier is connected with the drain of the first MOS transistor, the negative input terminal thereof is connected with the drain of the second MOS transistor, and the output terminal thereof is connected with the gate of the third MOS resistor; and one terminal of the compensation capacitor is connected with the gate of the third MOS transistor, and the other terminal thereof is connected with the drain of the third MOS transistor. The input buffer circuit of the invention is capable of meeting the requirements for the input of high-speed signals, effectively reducing the inputted load capacitance and increasing the outputted impedance.

Owner:ZHEJIANG UNIV

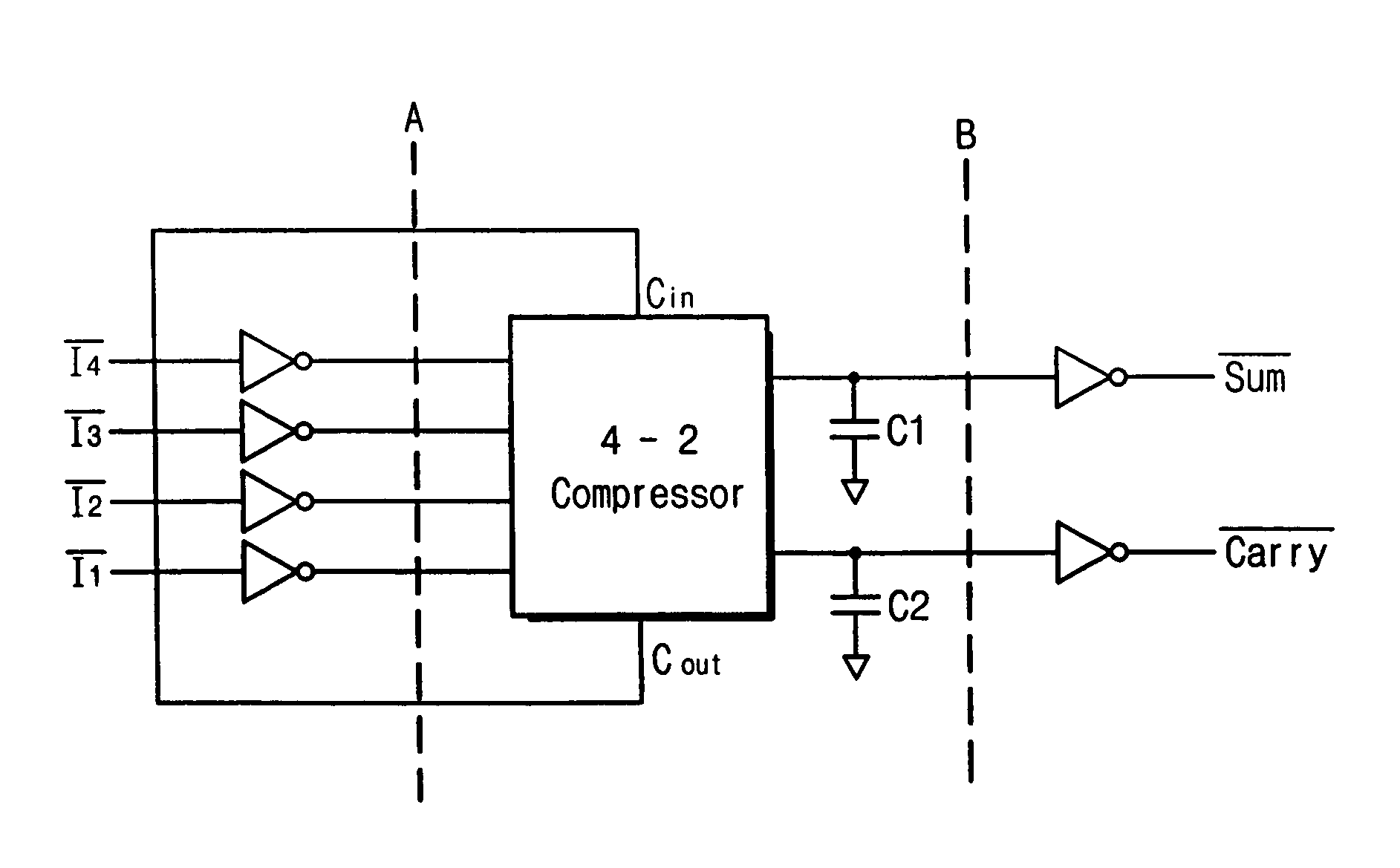

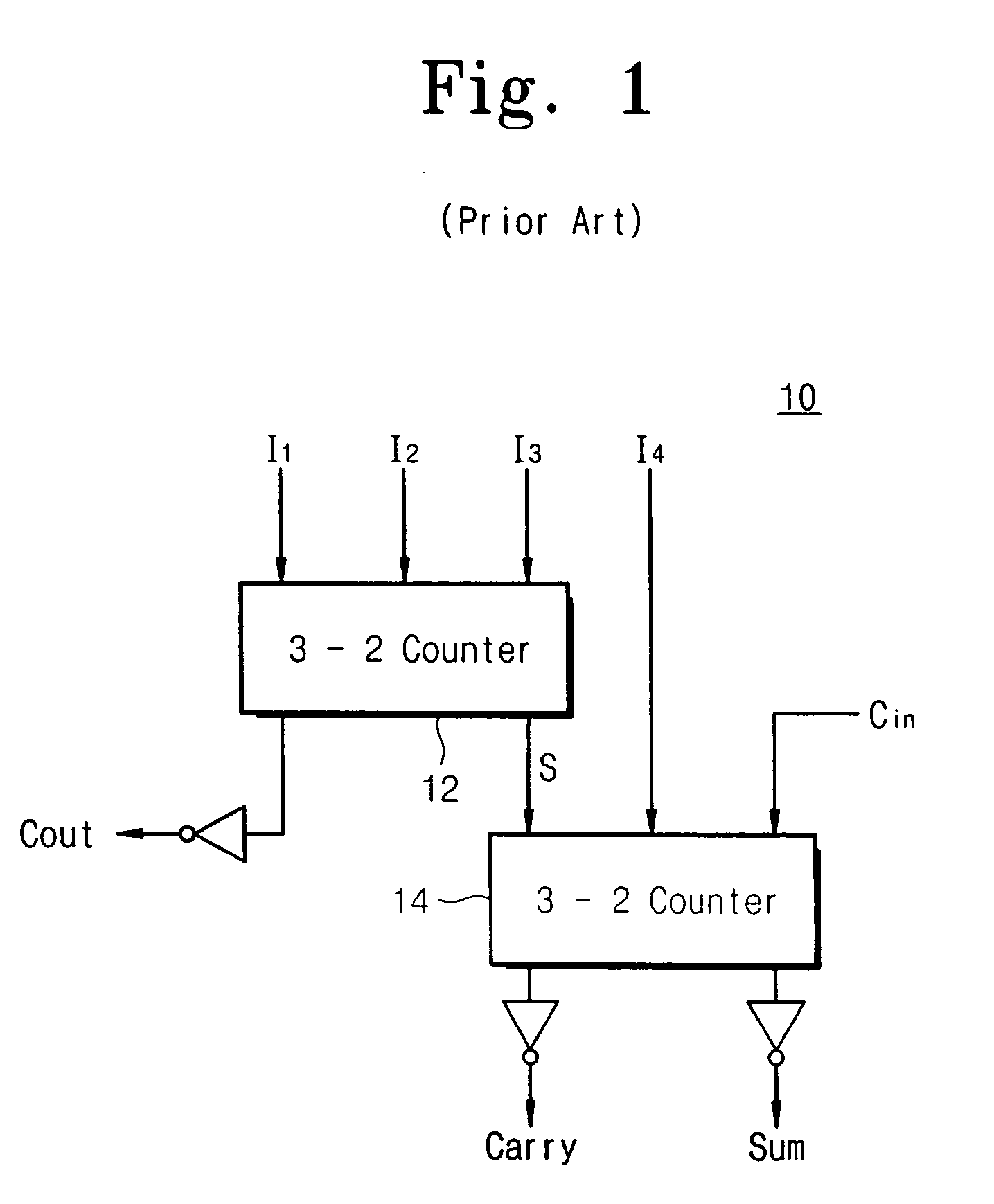

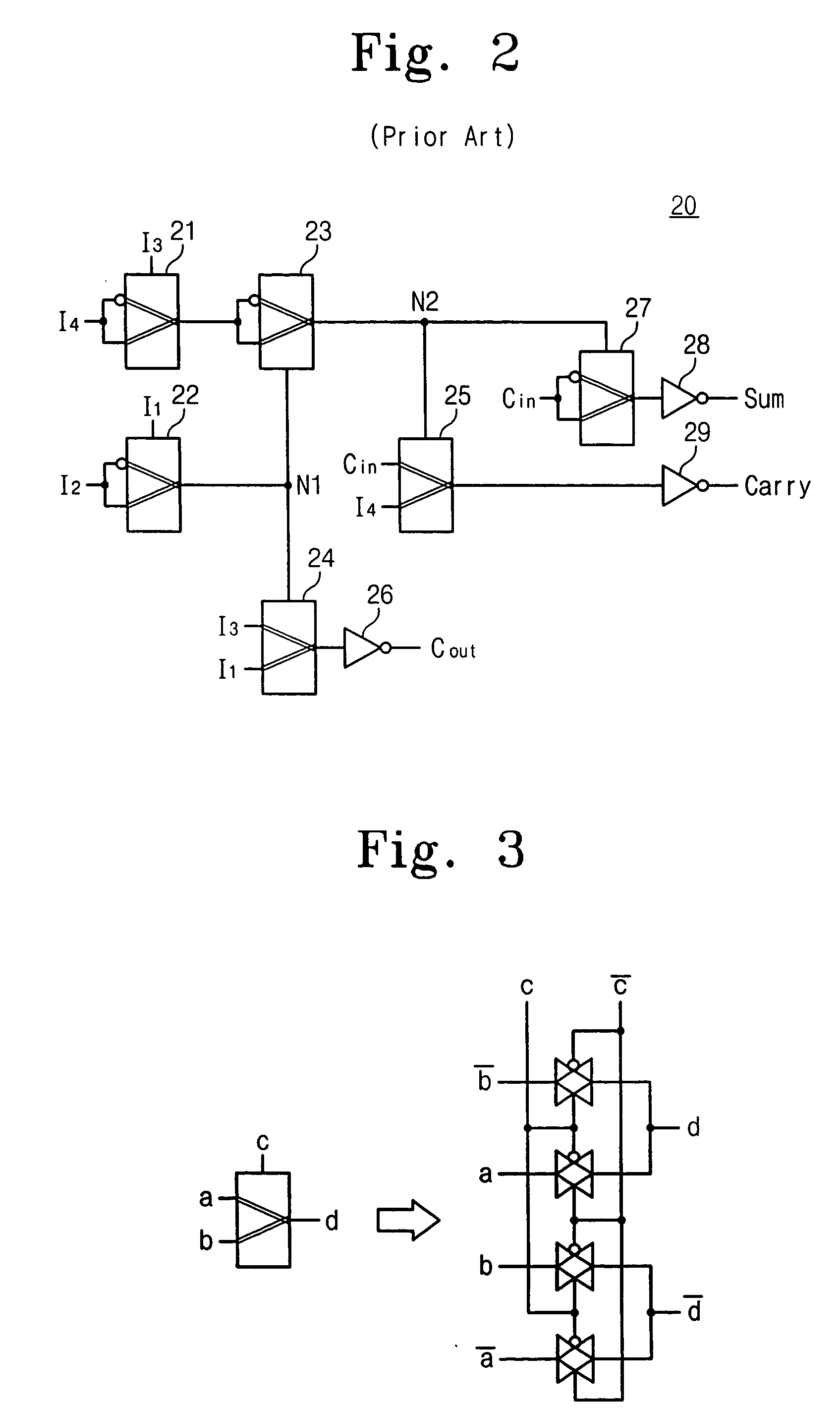

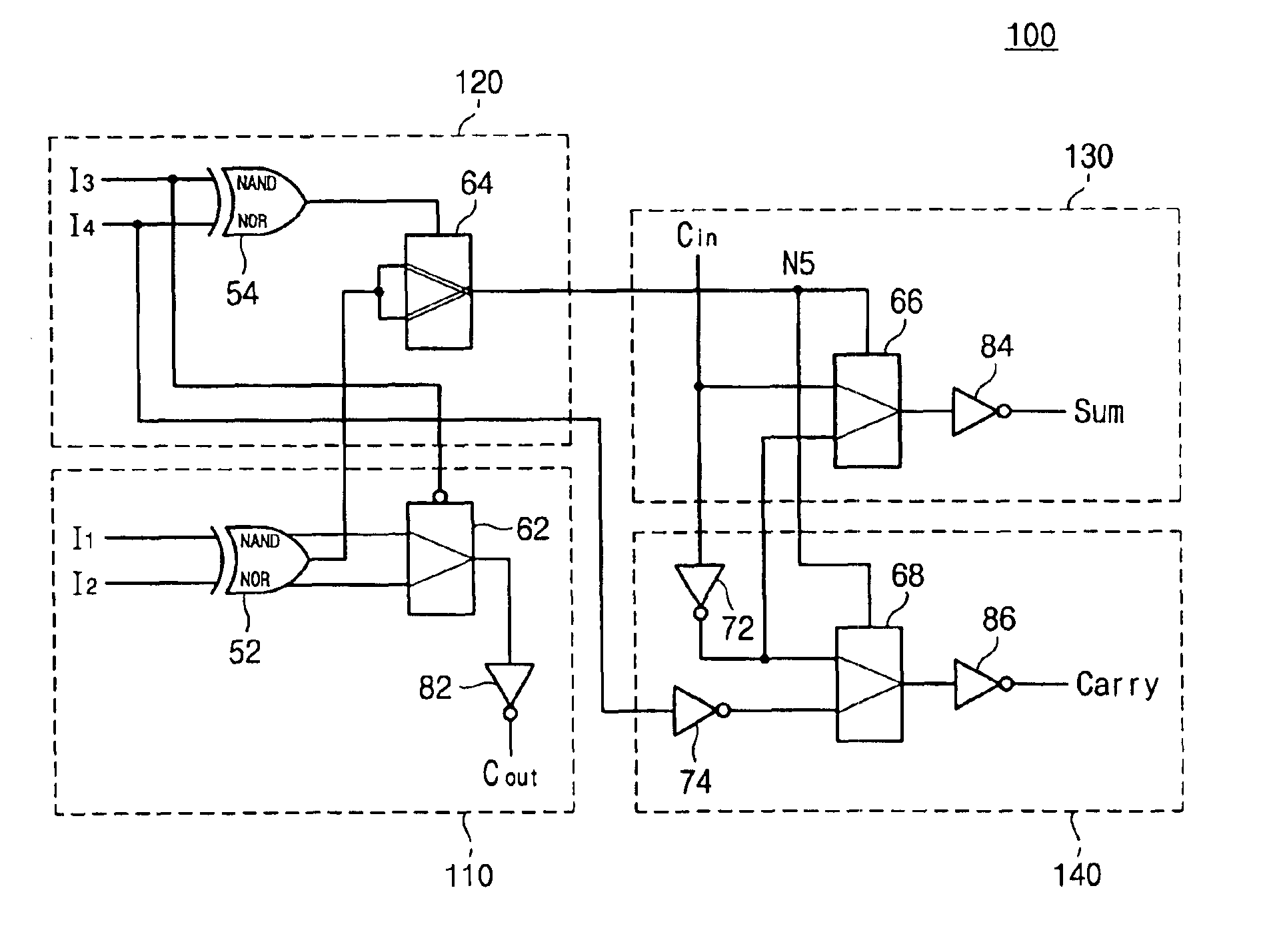

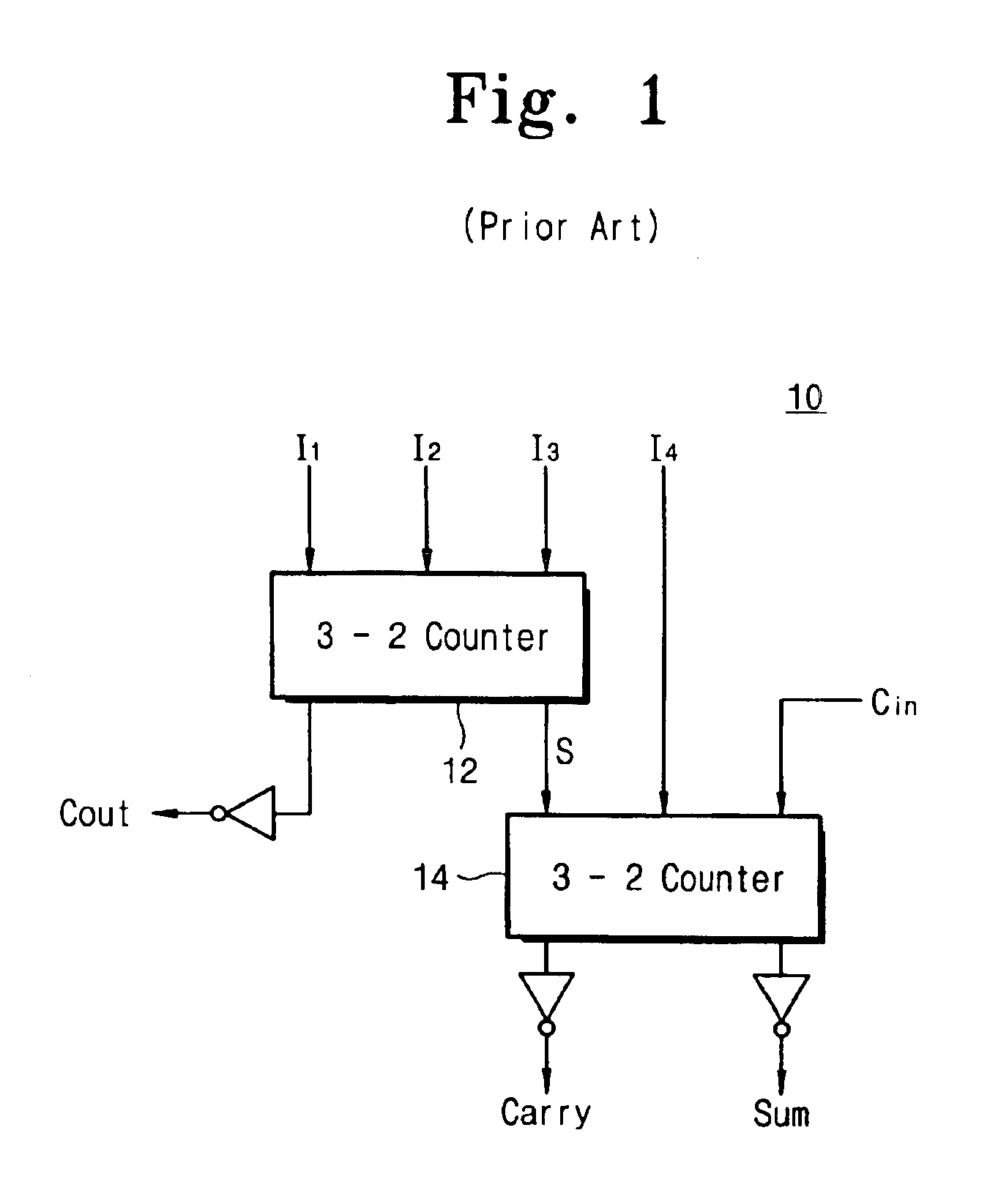

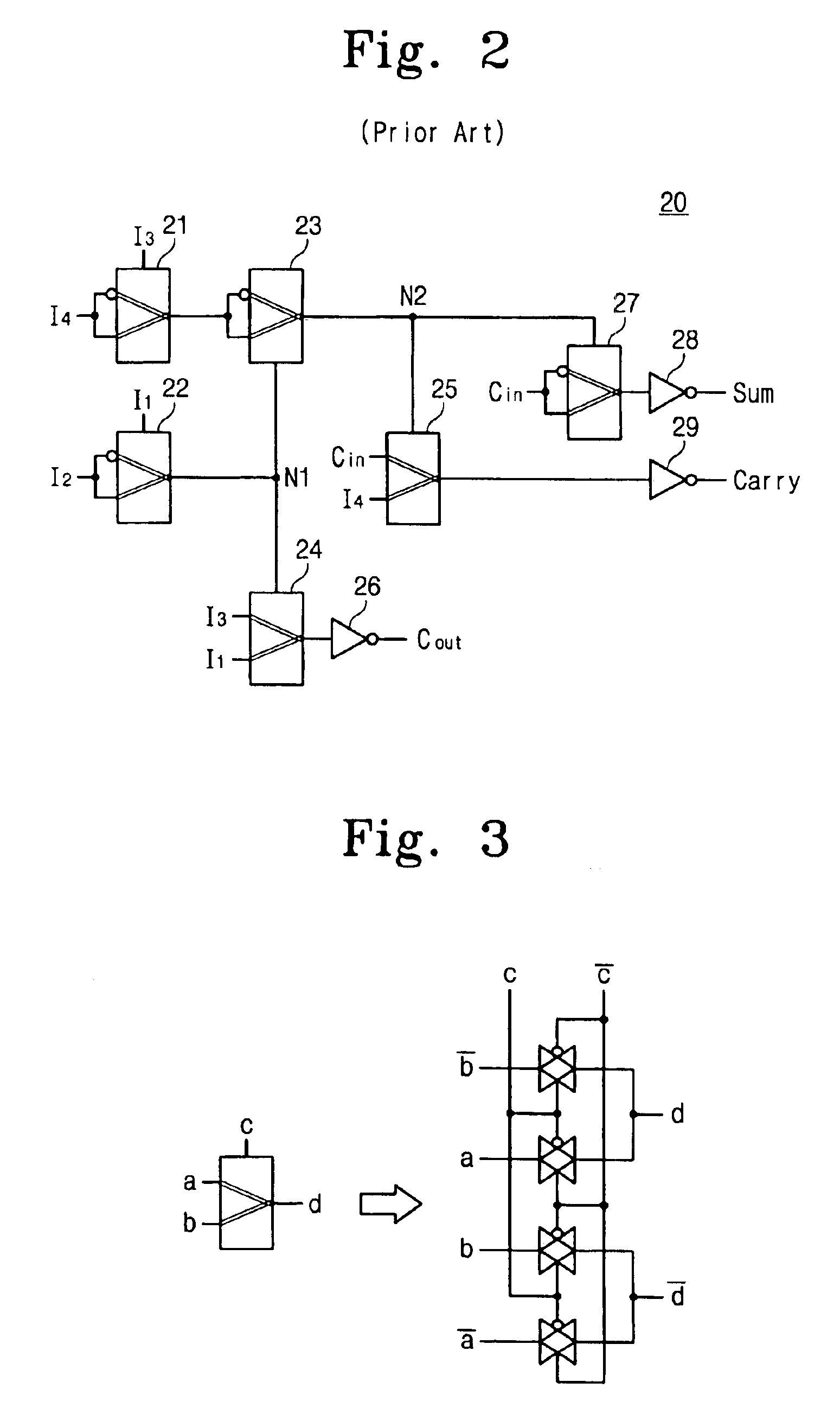

High speed low power 4-2 compressor

InactiveUS20050027777A1Raise the voltage levelReduce the voltage levelComputation using non-contact making devicesNumber-of-one countersCapacitanceMultiplexer

A high speed low powered 4-2 compressor according to the present invention performs an XOR / XNOR operation of input data by using a single input type NAND / NOR logic circuit and a dual input type NAND / NOR logic circuit. Thus, delays to generate complementary signals are avoided. In addition, the 4-2 compressor uses a single railed multiplexer instead of a dual railed multiplexer, so that gate drive nodes and internal load capacitance are reduced. As a result, circuit area and power consumption of the 4-2 compressor are reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

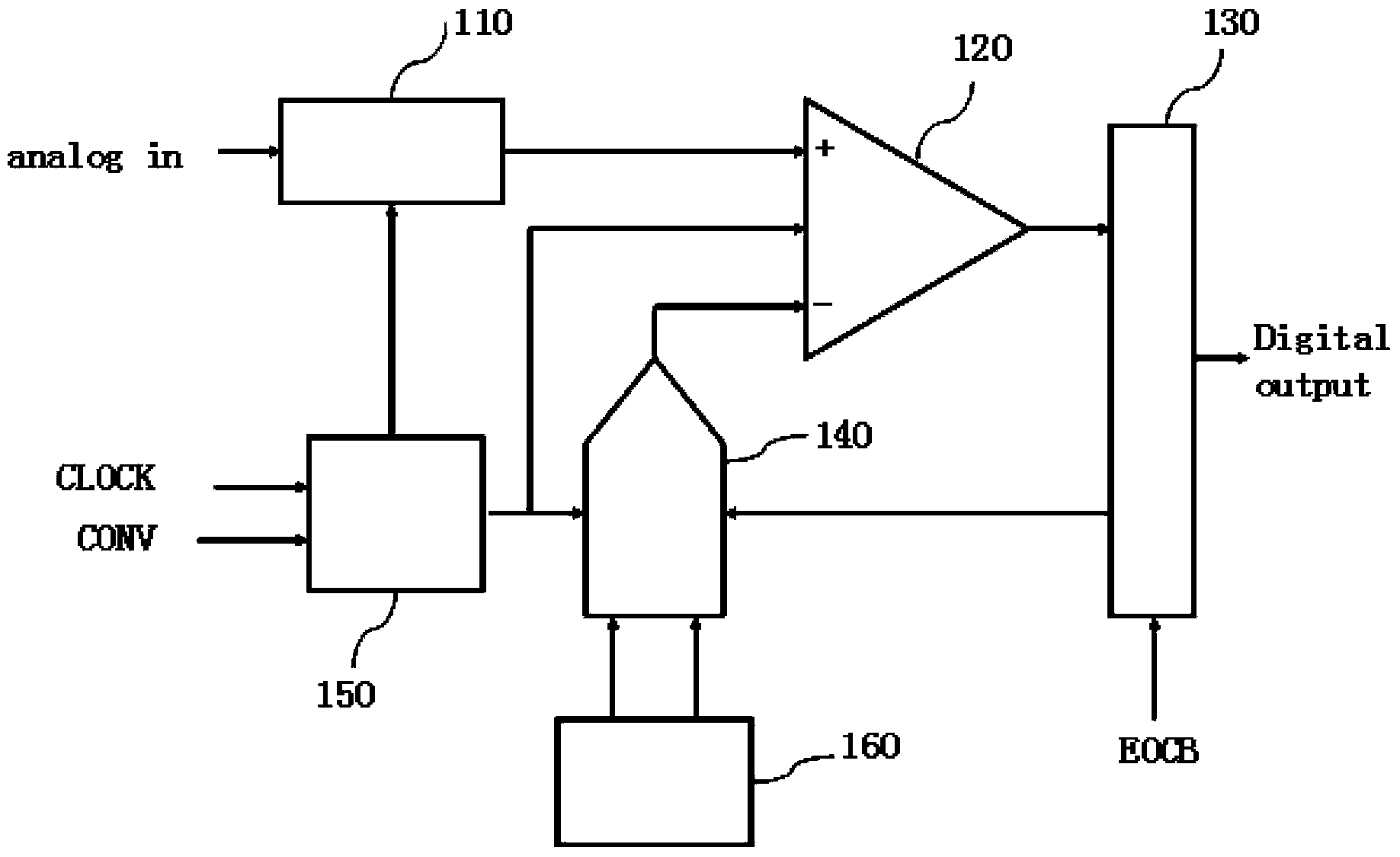

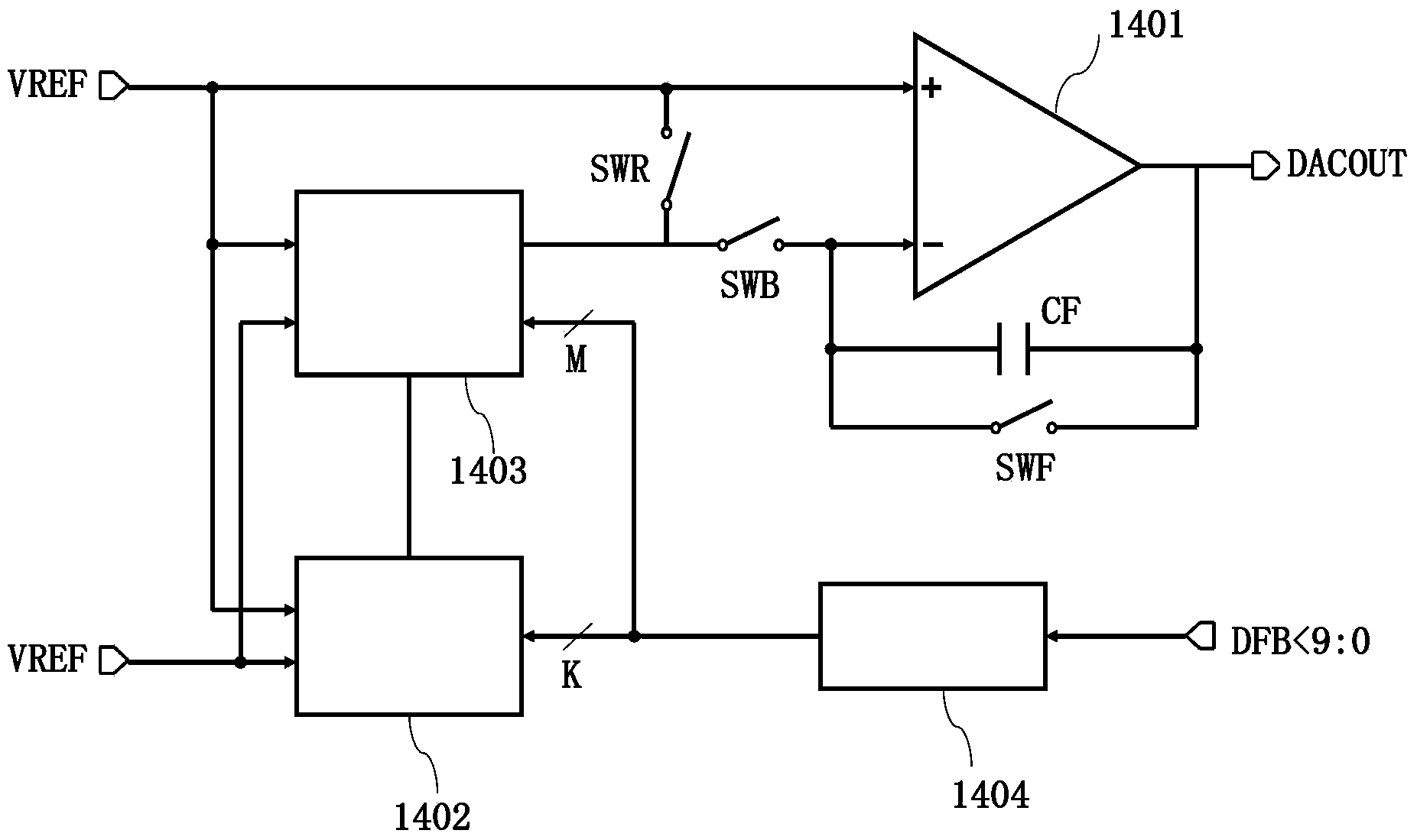

Successive approximation type analog-to-digital conversion device

InactiveCN104283562AReduce load capacitanceSmall working currentAnalogue/digital conversionElectric signal transmission systemsShift registerCapacitance

The invention discloses a successive approximation type analog-to-digital conversion device. The successive approximation type analog-to-digital conversion device comprises a sample-and-hold circuit, a comparator, a shift register, a digital-to-analog converter, a clock generation circuit and a reference voltage generation circuit. The minimum sampling error can be obtained by adopting the independent sample-and-hold circuit, and a most significant bit charge scaling digital-to-analog converter body, a least significant bit voltage scaling digital-to-analog converter body, an amplifier and the like of the digital-to-analog converter form a closed-loop switched capacitor amplifier. Due to the structure, the influence of charge injection and clock feed-through can be eliminated, the load capacitance of the amplifier can be reduced, and accordingly the power consumption can be reduced. In addition, a gapping switch is additionally arranged between the charge scaling digital-to-analog converter body and the amplifier for isolation, and therefore additional charging current caused by charge averaging can be eliminated.

Owner:上海明波通信技术股份有限公司

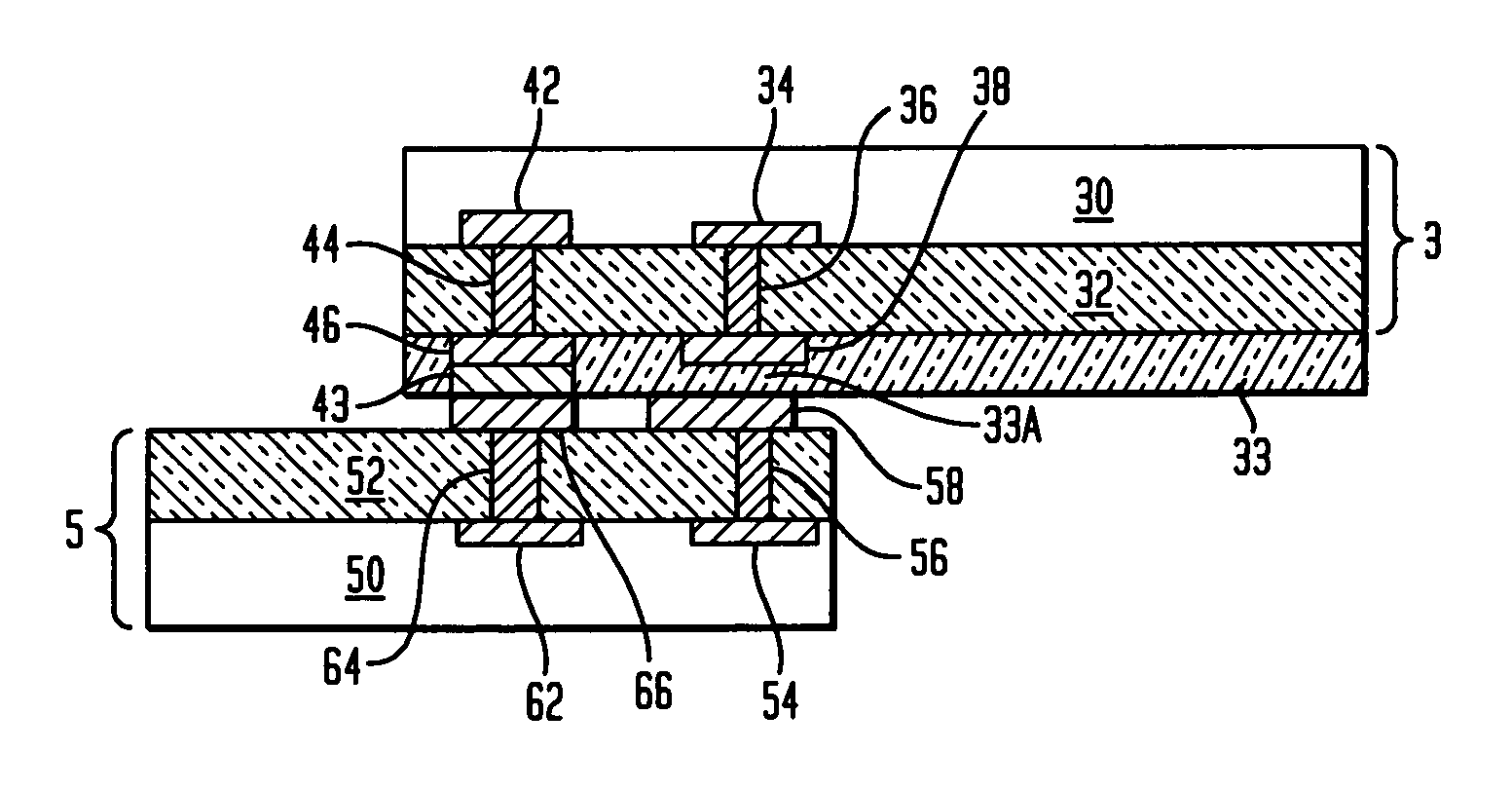

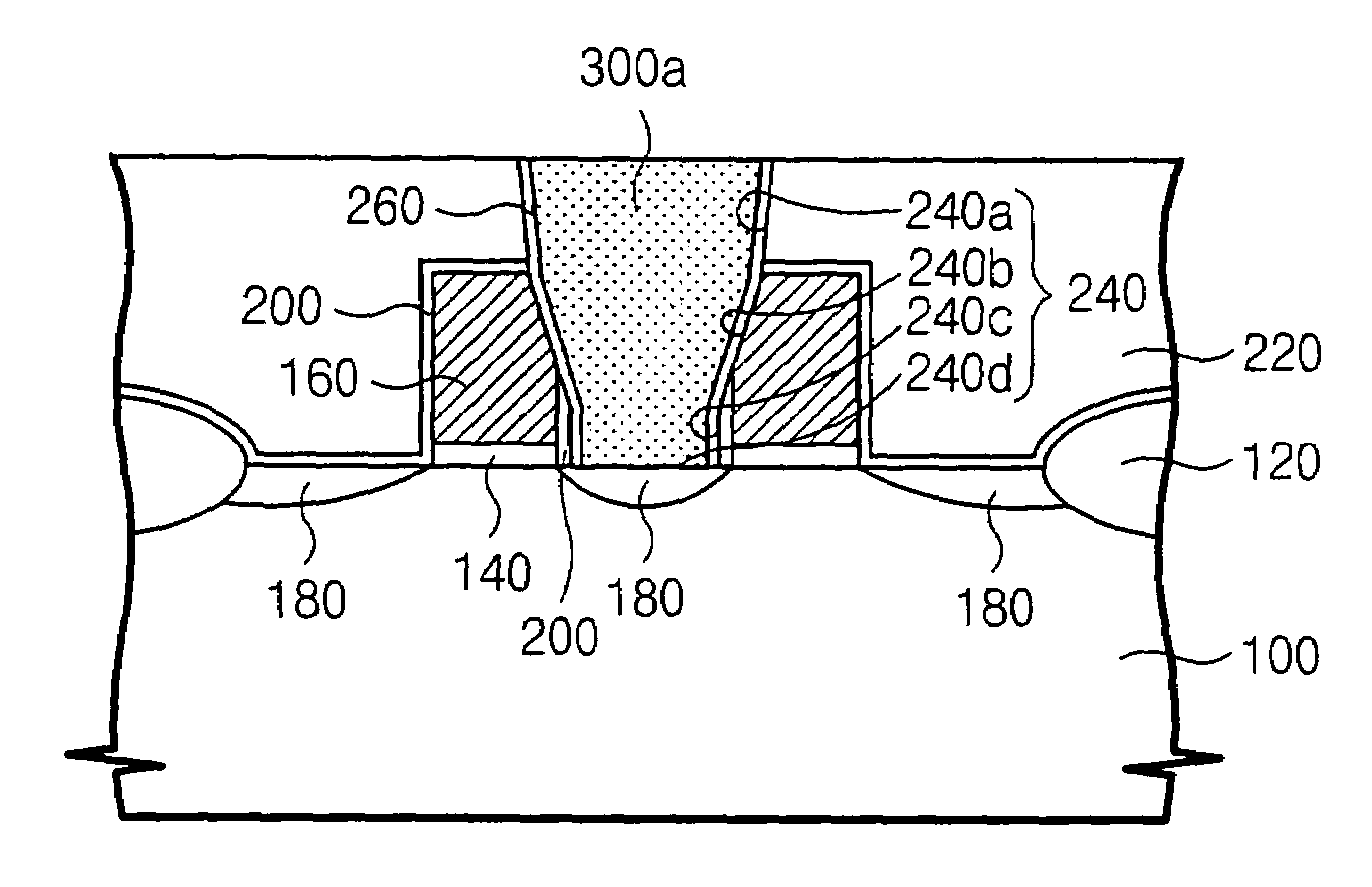

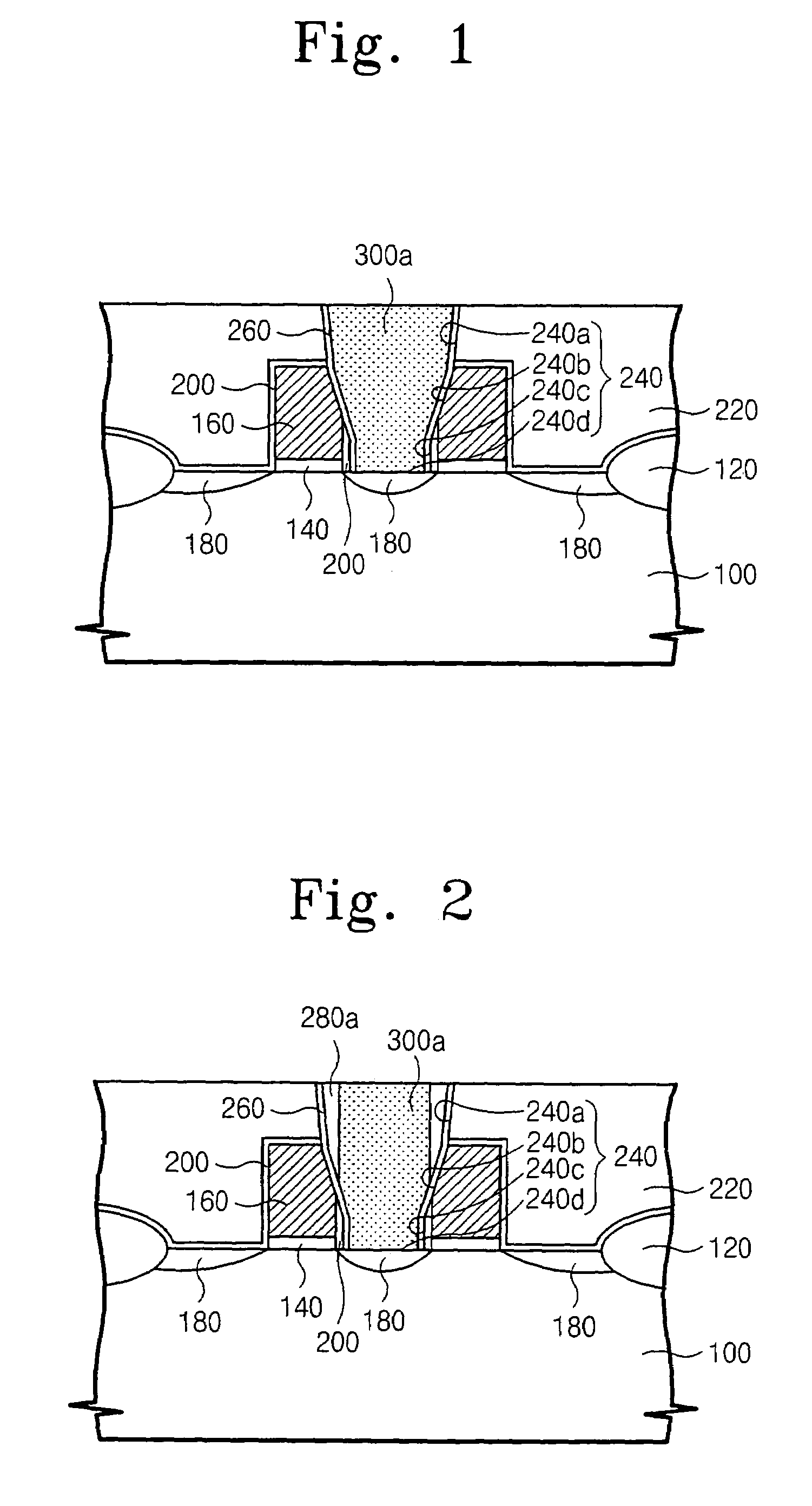

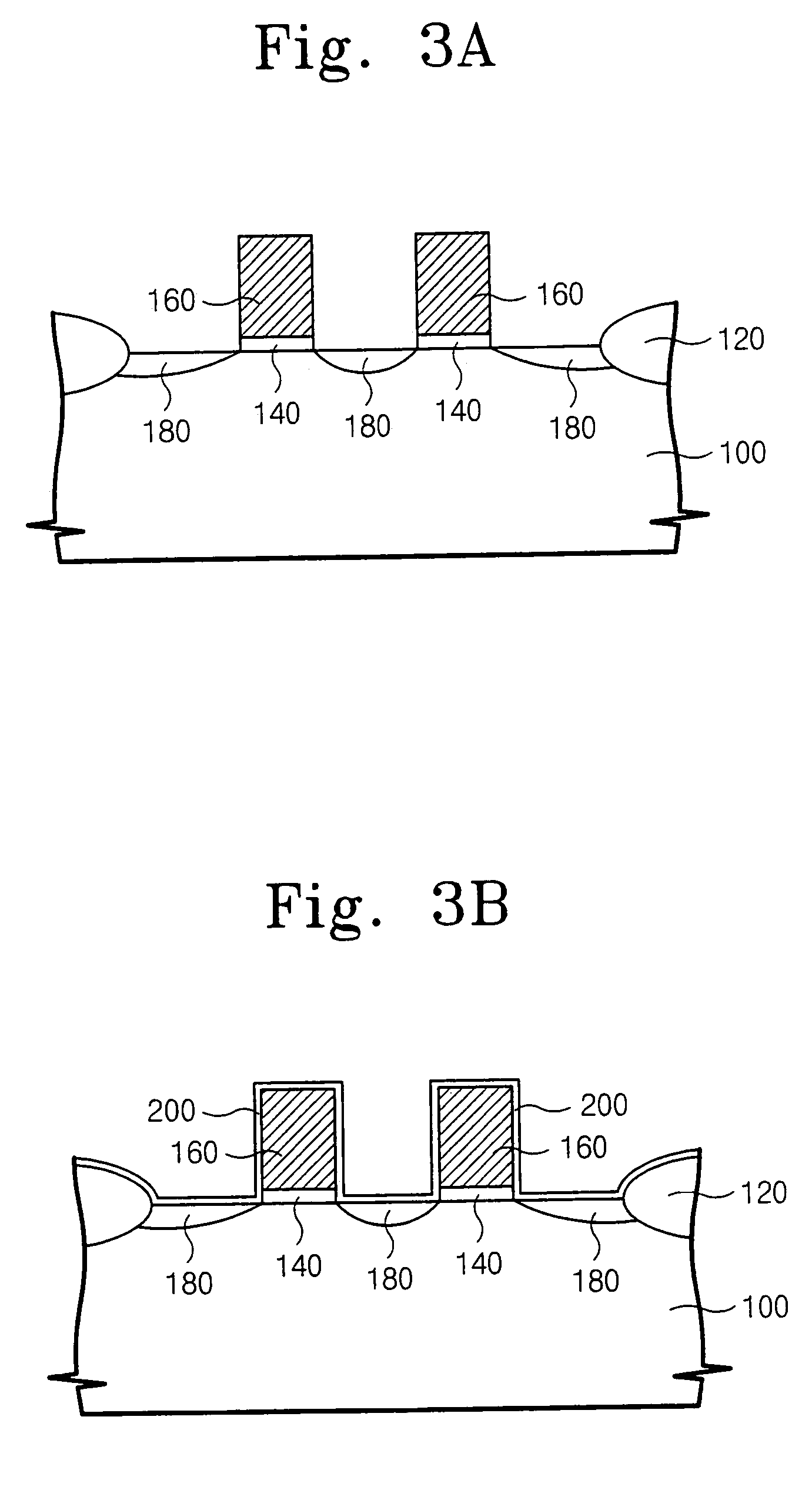

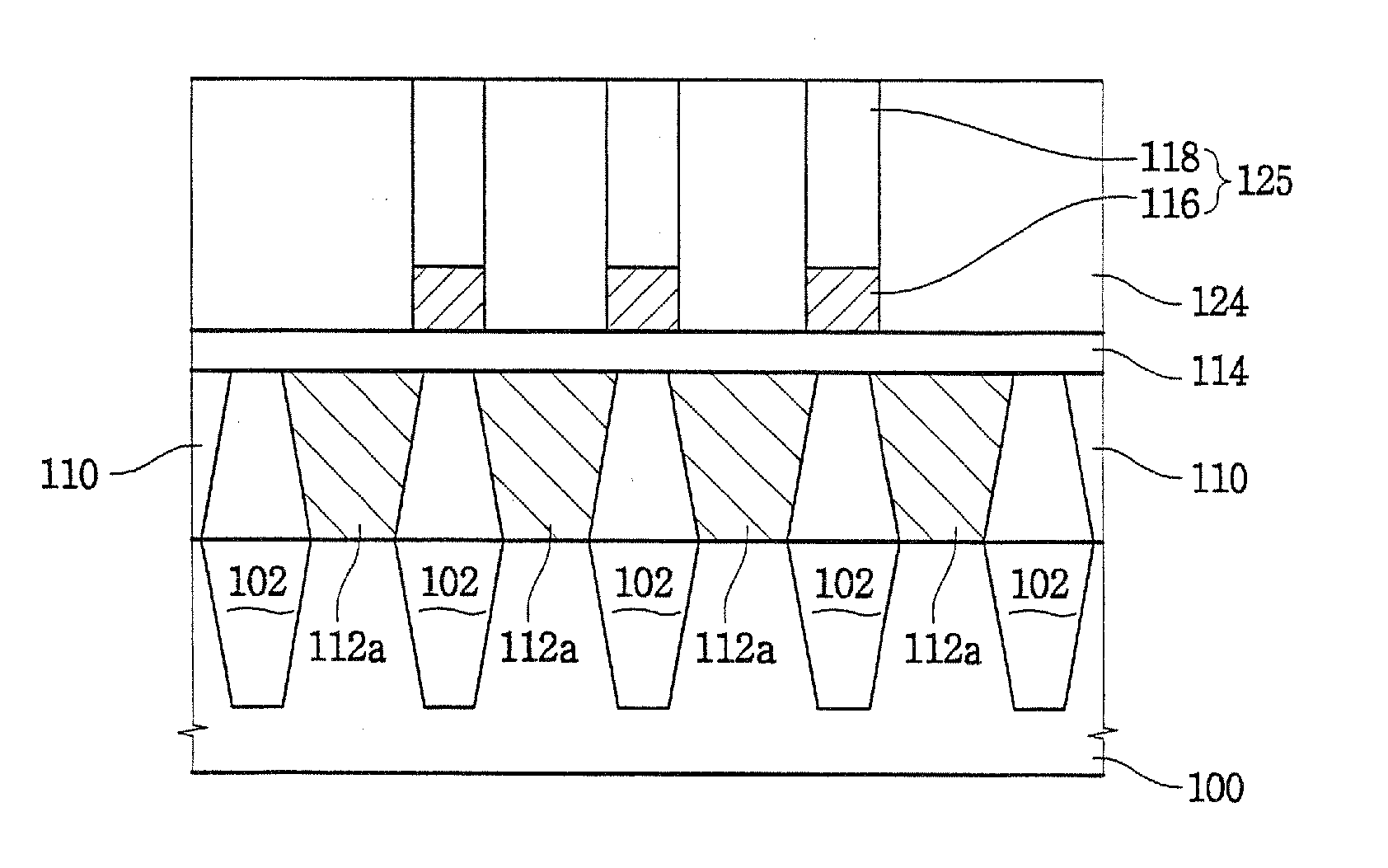

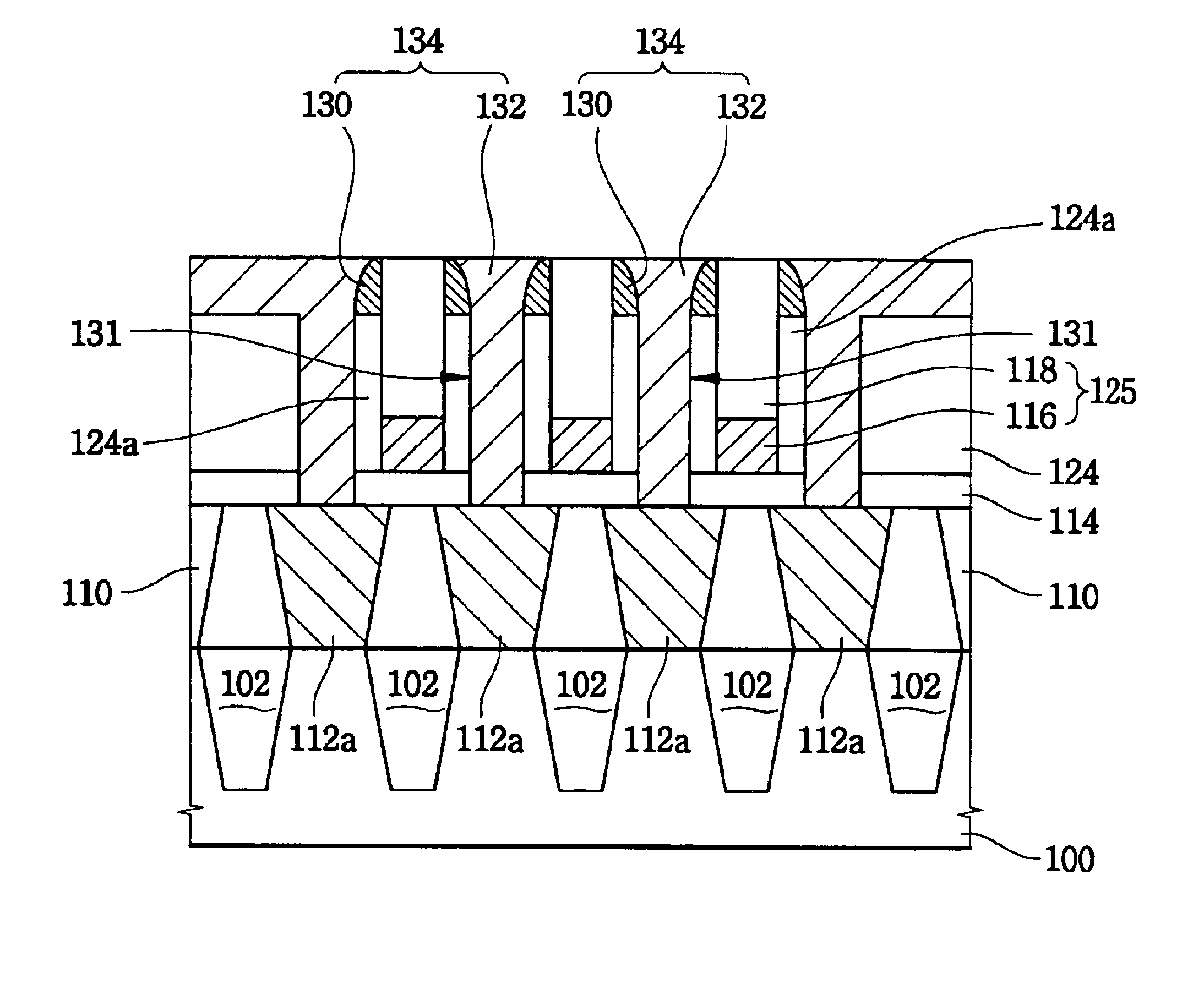

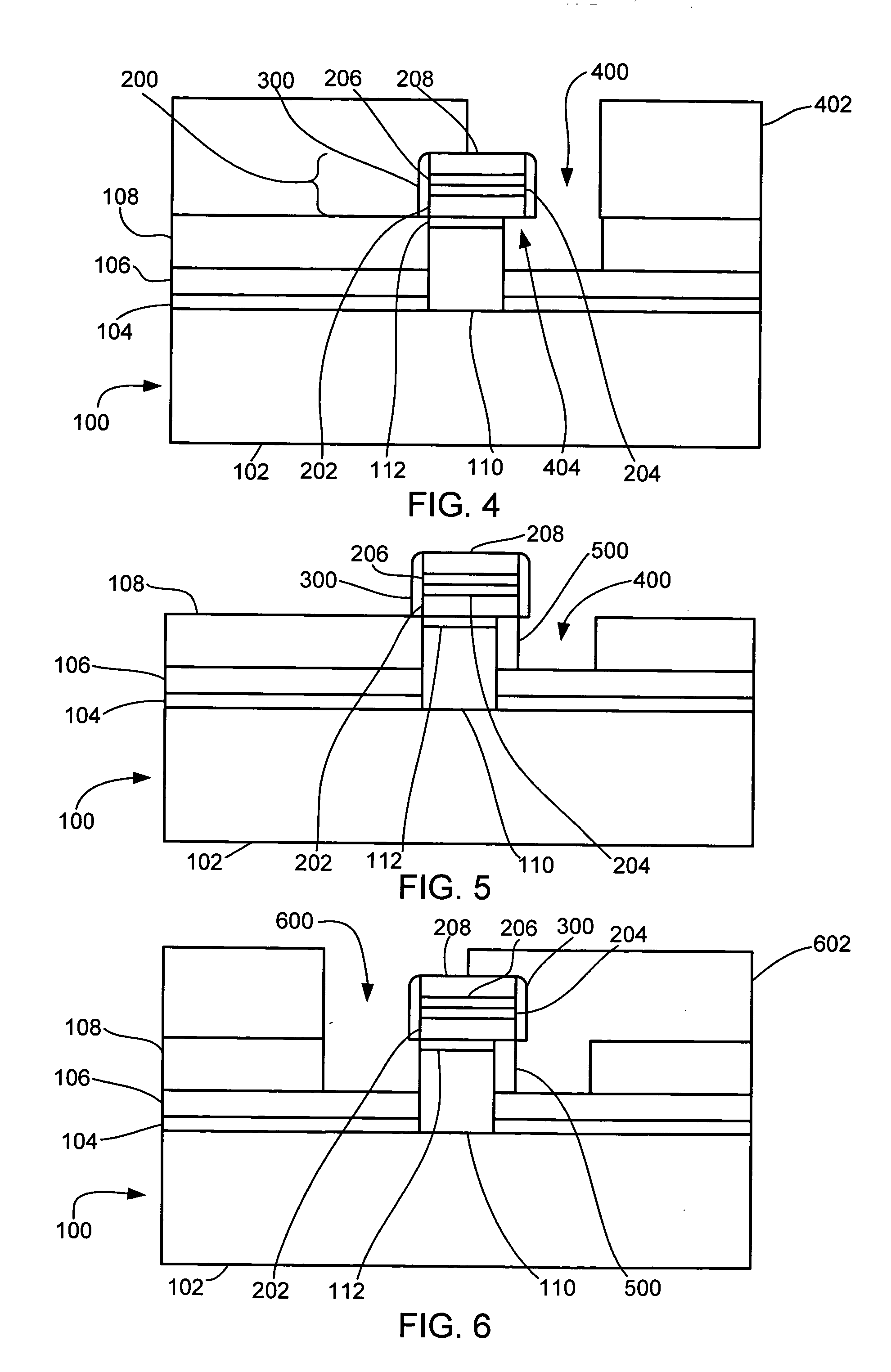

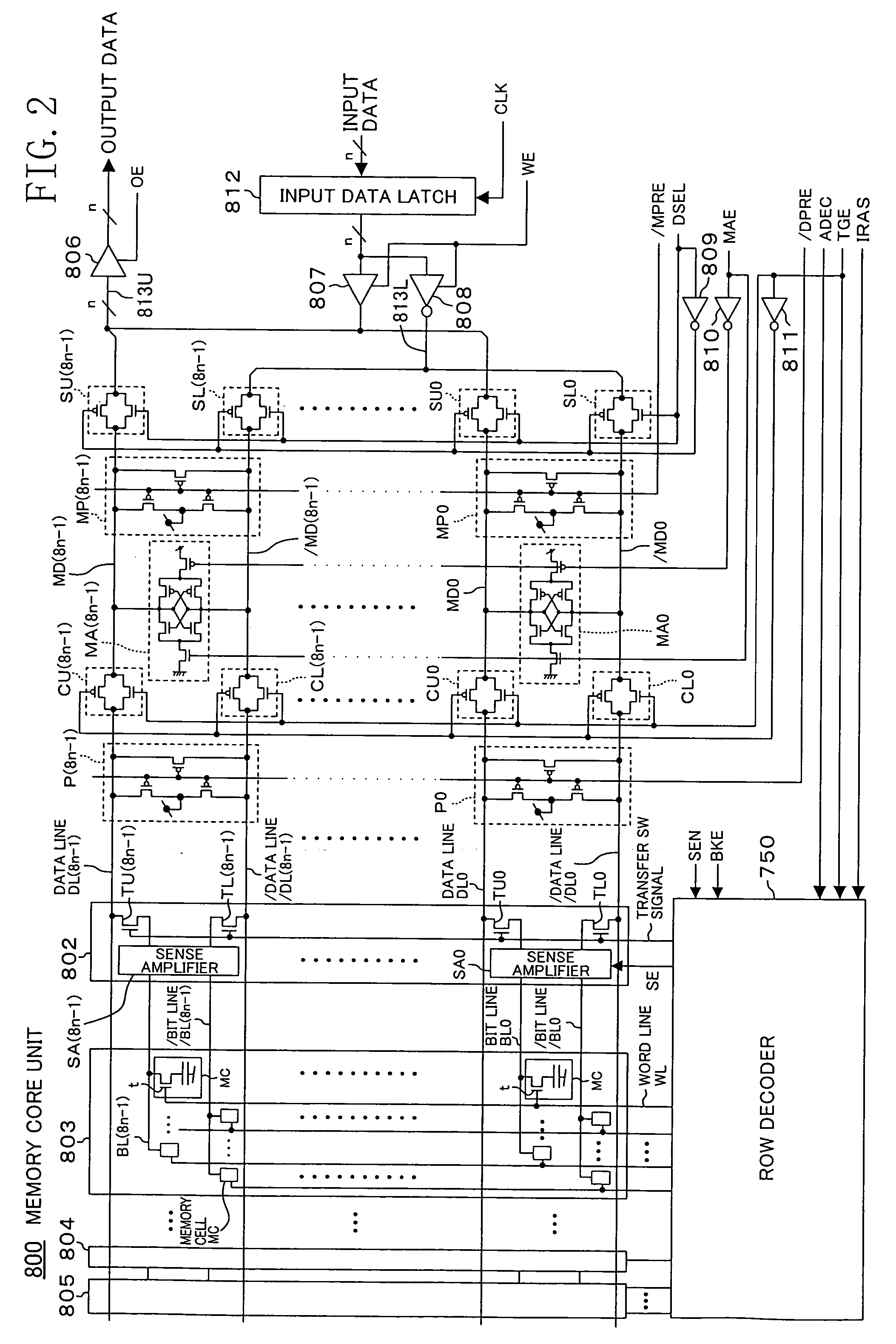

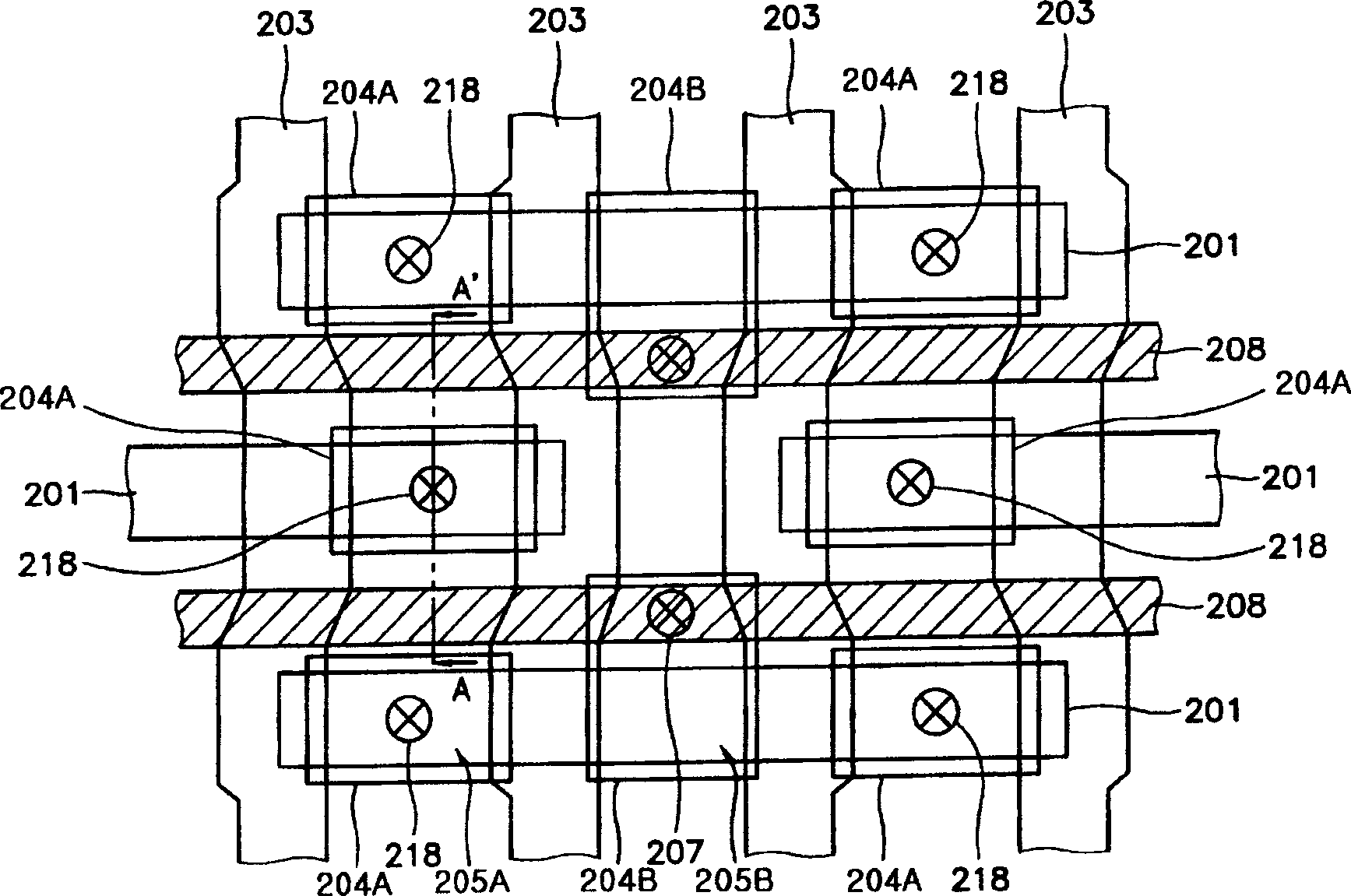

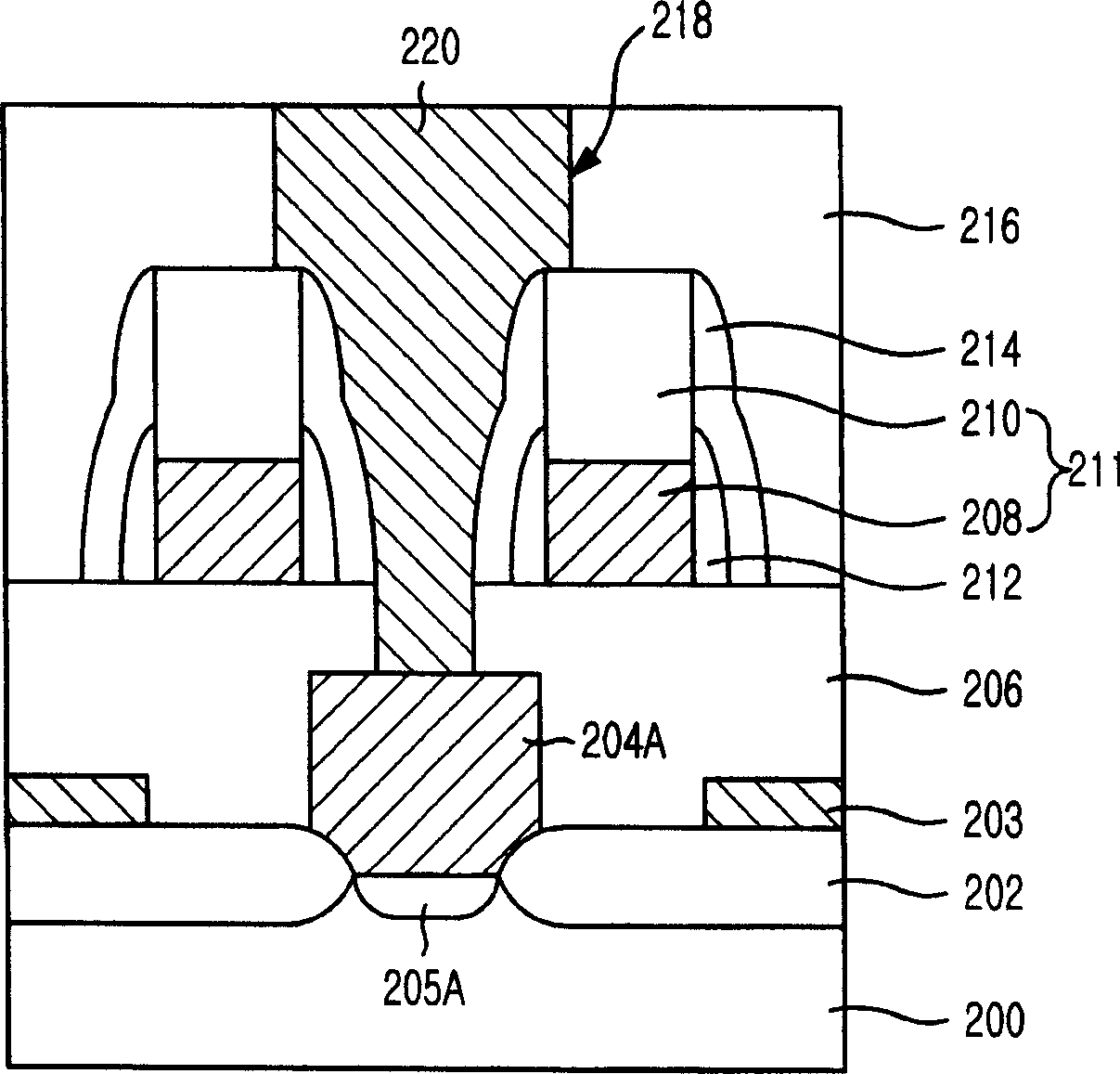

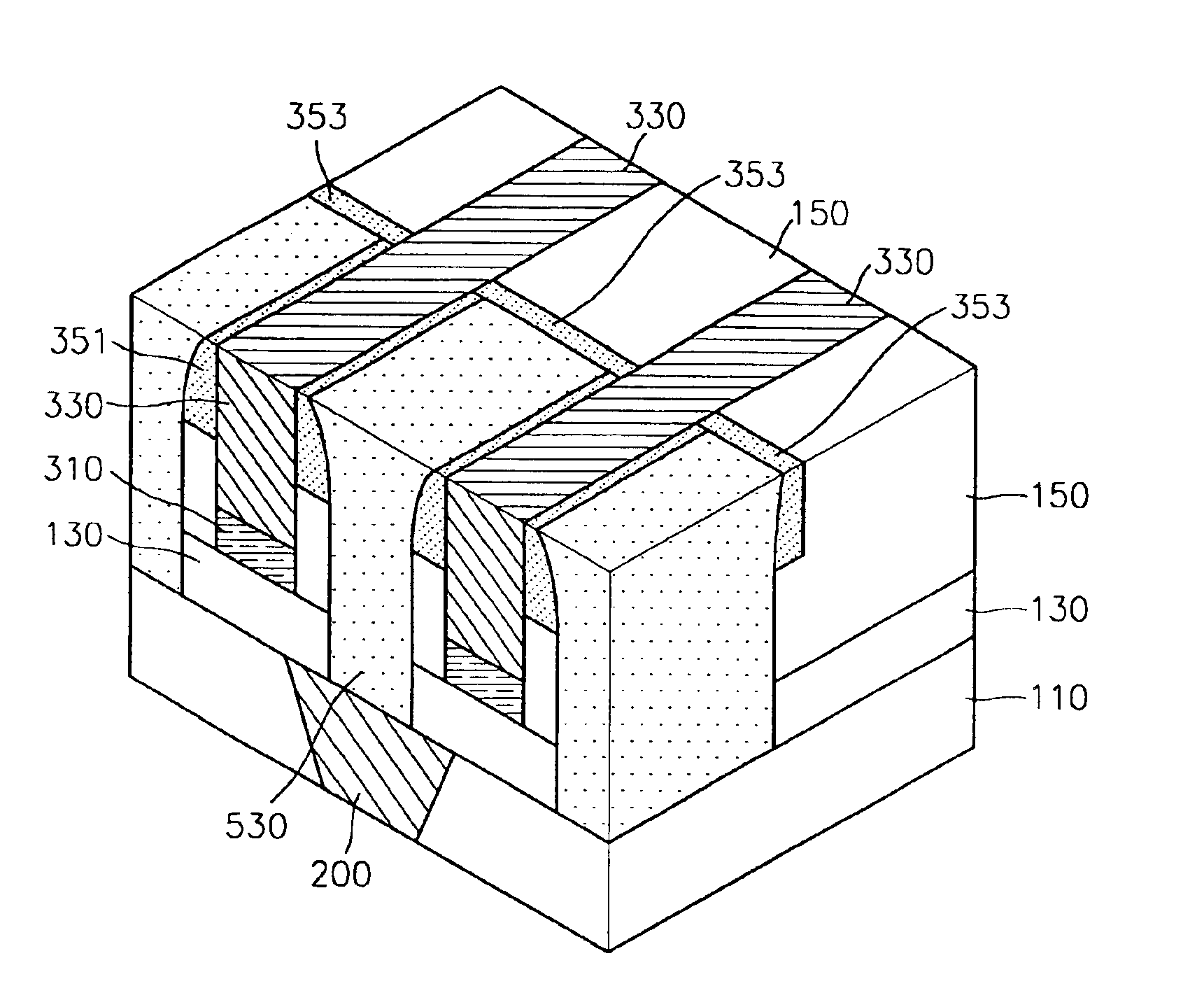

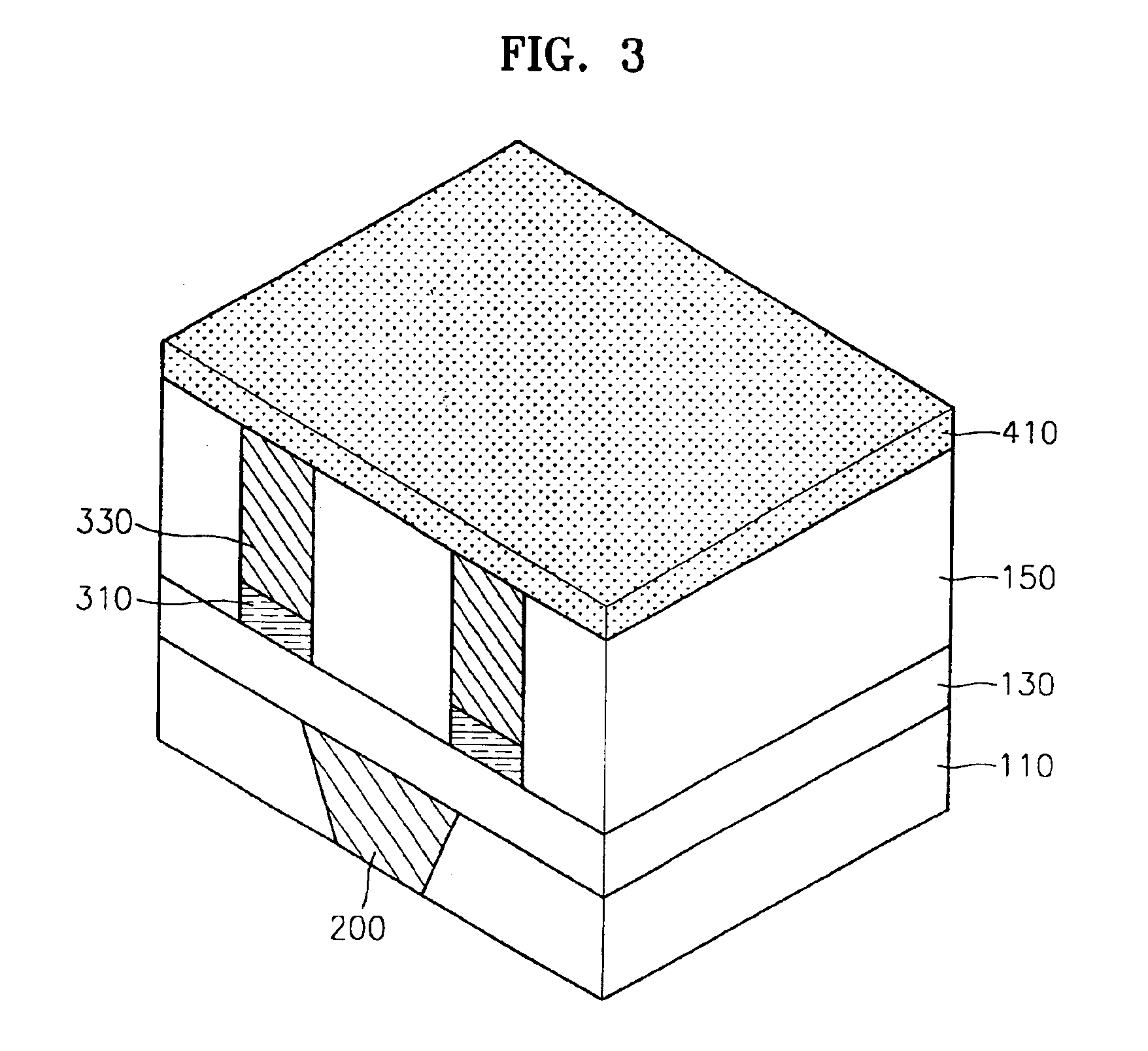

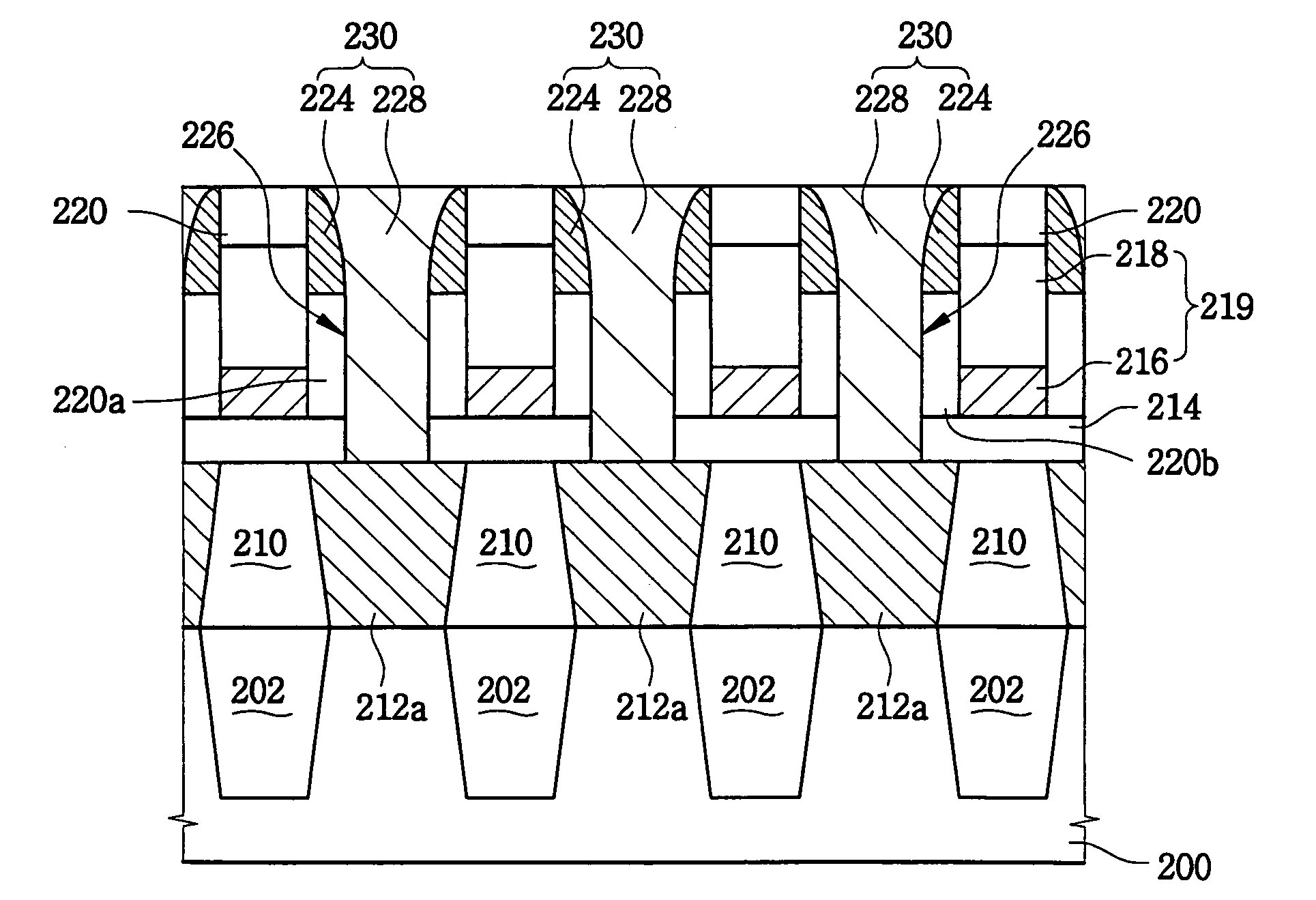

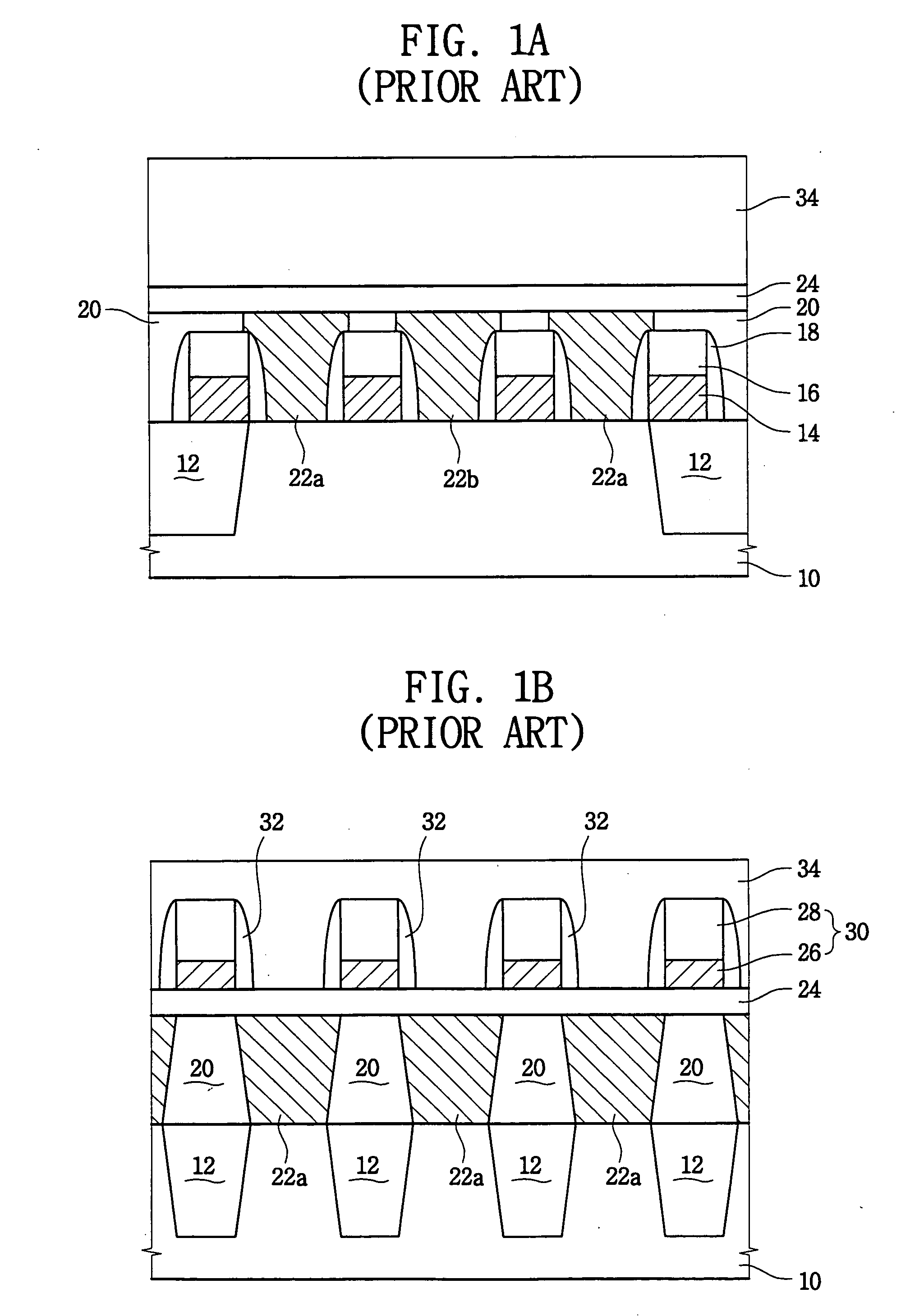

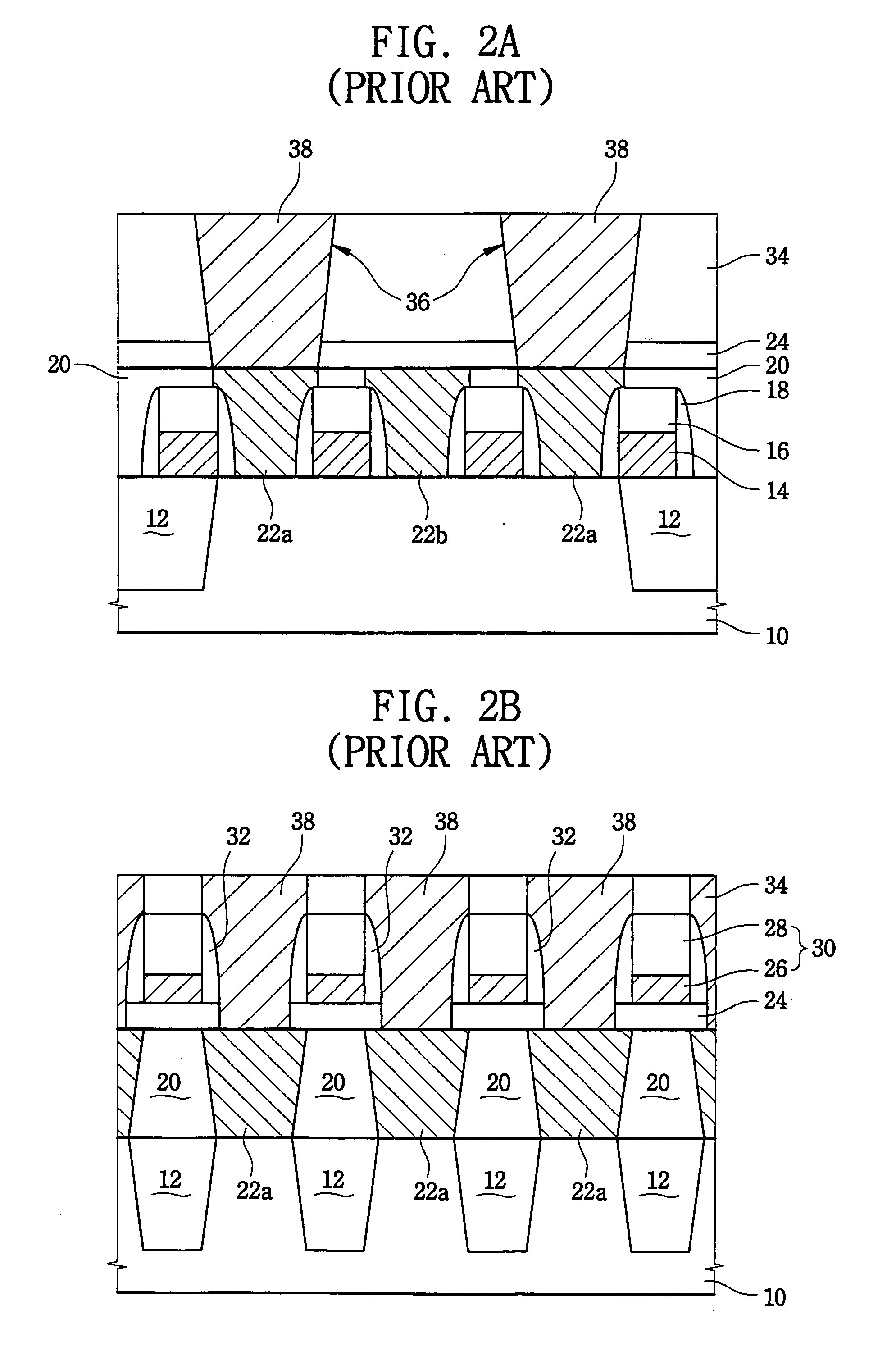

Semiconductor device and method of manufacturing the same

ActiveUS6916738B2Reduce load capacitanceEfficient fillingTransistorSolid-state devicesCapacitanceBit line

Bit lines having first conductive patterns and bit line mask patterns are formed on a first insulating layer between capacitor contact regions of a substrate. An oxide second insulating layer is formed on the bit lines and contact patterns are formed to open storage node contact hole regions corresponding to portions of the second insulating layer. First spacers are formed on sidewalls of the etched portions. The second and first insulating layers are etched to form storage node contact holes exposing the capacitor contact regions. Simultaneously, second spacers of the second insulating layer are formed beneath the first spacers. A second conductive layer fills the storage node contact holes to form storage node contact pads. A loss of the bit line mask pattern decreases due to the reduced thickness of the bit line mask pattern and a bit line loading capacitance decreases due to the second spacers.

Owner:SAMSUNG ELECTRONICS CO LTD

Muller-c element

InactiveCN101479942ASmall dampingEnlarged size to avoidSwitching accelaration modificationsLogic circuits characterised by logic functionDamping factorCapacitance

The invention relates to an electronic device that includes an MCML Muller-c element. The MCML Muller-c element has a first differential stage for operating in a trans- conductance state converting the differential input to a differential output current implementing the logical behavior of the MCML Muller-c element and a second stage operating as a trans-impedance stage being coupled to the first stage. Further, the MCML Muller-c element has peaking circuitry being coupled to the first stage, such that the peaking circuitry and the first stage provide a negative capacitance to the MCML Muller-c element for reducing the damping factor of the MCML Muller-c element.

Owner:NXP BV

Self-aligned semiconductor contact structures and methods for fabricating the same

InactiveUS20060170062A1Reduce aspect ratioReduce contact resistanceTransistorSolid-state devicesEngineeringSemiconductor

Owner:KIM SEONG HO +5

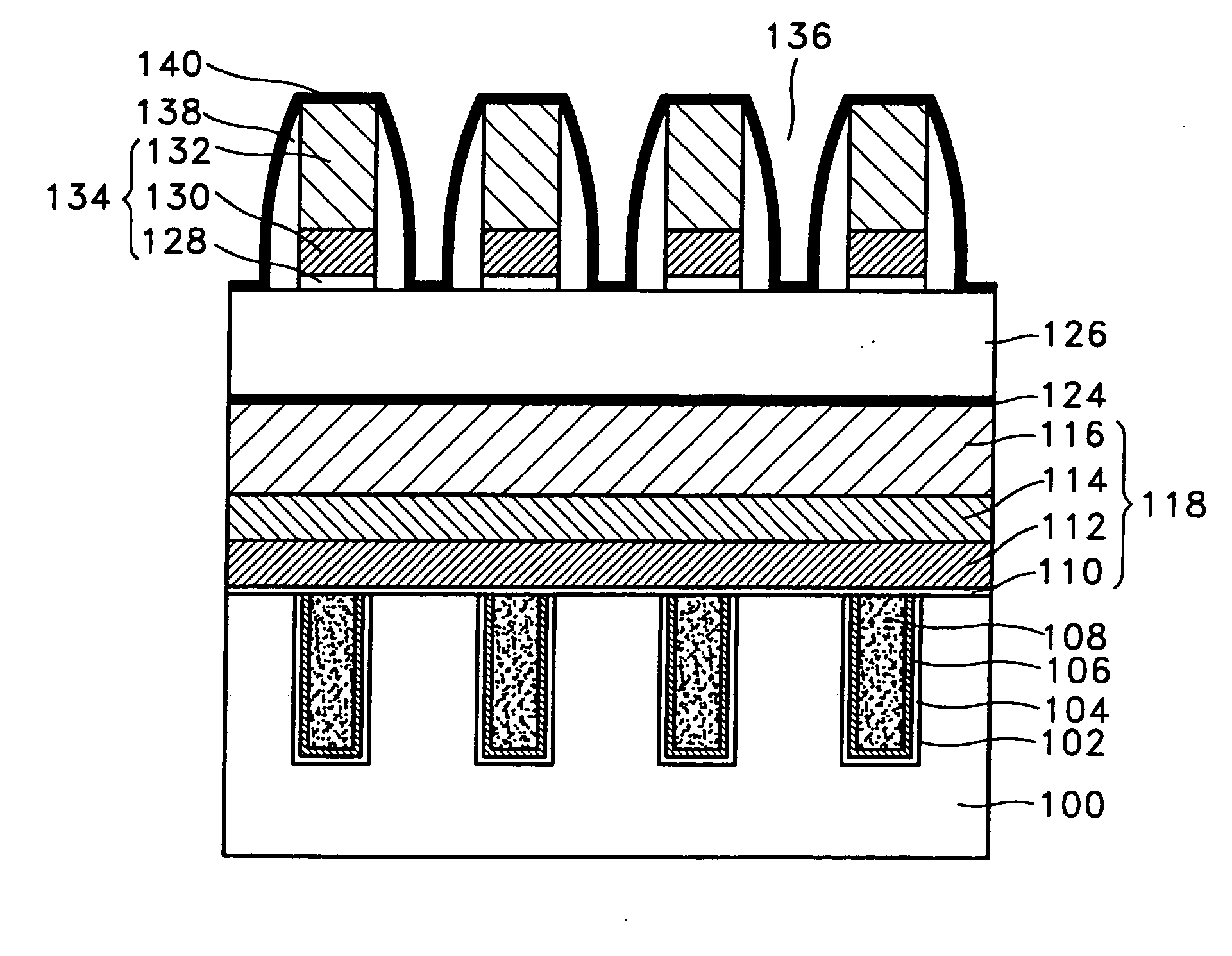

Lateral heterojunction bipolar transistor and method of manufacture using selective epitaxial growth

ActiveUS20050116254A1Reduce load capacitanceReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

A method for manufacturing a heterojunction bipolar transistor is provided. An intrinsic collector structure is formed on a substrate. An extrinsic base structure partially overlaps the intrinsic collector structure. An intrinsic base structure is formed adjacent the intrinsic collector structure and under the extrinsic base structure. An emitter structure is formed adjacent the intrinsic base structure. An extrinsic collector structure is formed adjacent the intrinsic collector structure. A plurality of contacts is formed through an interlevel dielectric layer to the extrinsic collector structure, the extrinsic base structure, and the emitter structure.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Semiconductor device having thin film formed by atomic layer deposition and method for fabricating the same

InactiveUS20050087828A1Low thermal budgetLow budgetSolid-state devicesSemiconductor/solid-state device manufacturingBit lineDevice material

A semiconductor device having a thin film formed by atomic layer deposition and a method for fabricating the same, wherein the semiconductor device includes a liner layer formed on an internal wall and bottom of a trench, gate spacers formed on the sidewalls of gate stack patterns functioning as a gate line, a first bubble prevention layer formed on the gate spacers and the gate stack patterns, bit line spacers formed on the sidewalls of bit line stack patterns functioning as a bit line, and a second bubble prevention layer formed on the bit line spacers and the gate stack patterns and at least one of the above is formed of a multi-layer of a silicon nitride layer and a silicon oxide layer, or a multi-layer of a silicon oxide layer and a silicon nitride layer, thereby filling the trench, gate stack patterns, or bit line stack patterns without a void.

Owner:SAMSUNG ELECTRONICS CO LTD

Display panel drive circuit and plasma display

InactiveUS7075528B2Reduce power consumptionImprovement in power recovery efficiencyCathode-ray tube indicatorsInput/output processes for data processingEngineeringOutput impedance

A display panel drive circuit having a plurality of first and second electrodes for connecting to a display panel, a first drive circuit for driving the first electrodes, and a second drive circuit for driving the second electrodes. The second drive circuit is connected to drive all or a part of a plurality of the second electrodes, or interrupted to increase output impedance.

Owner:HITACHI LTD

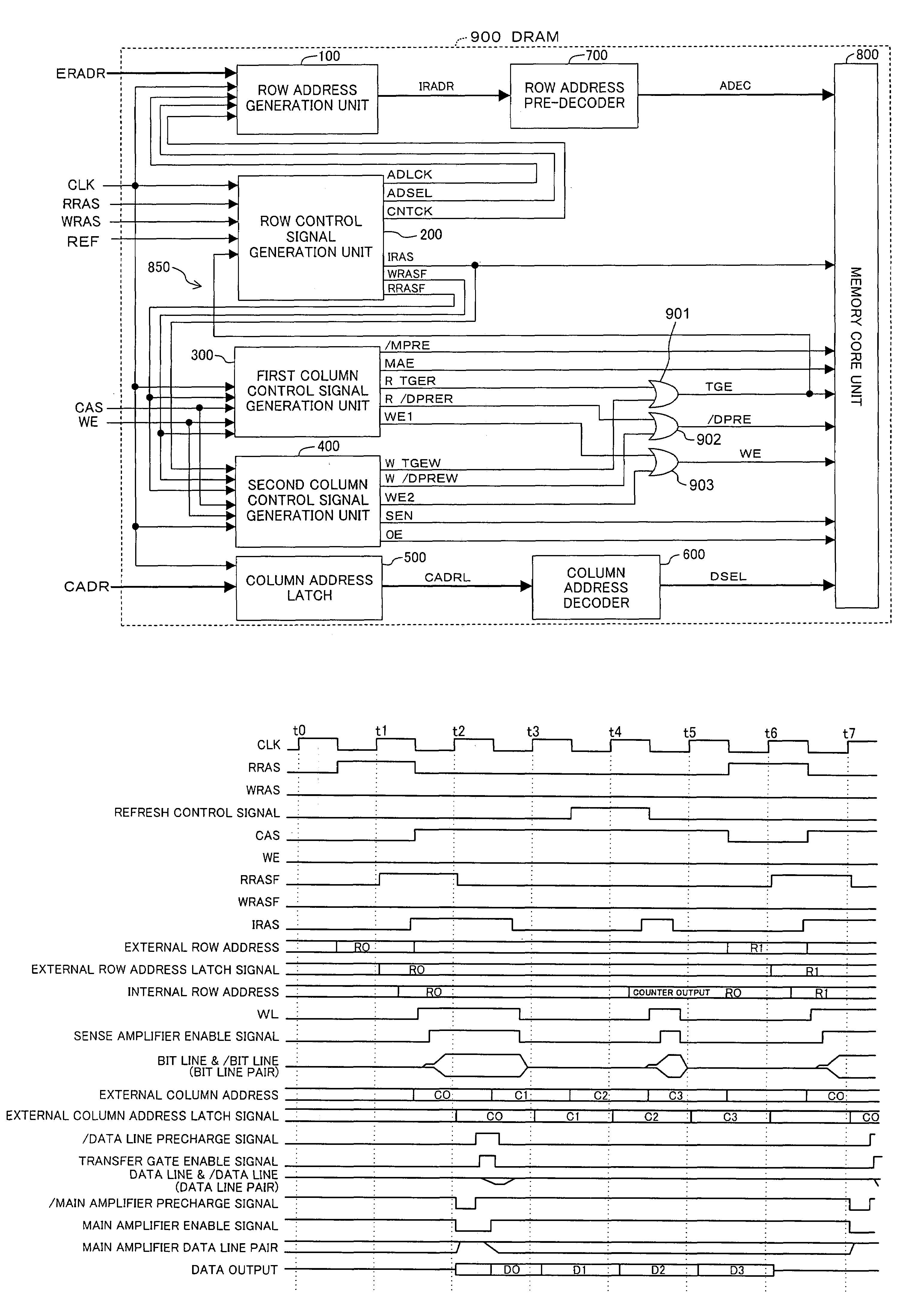

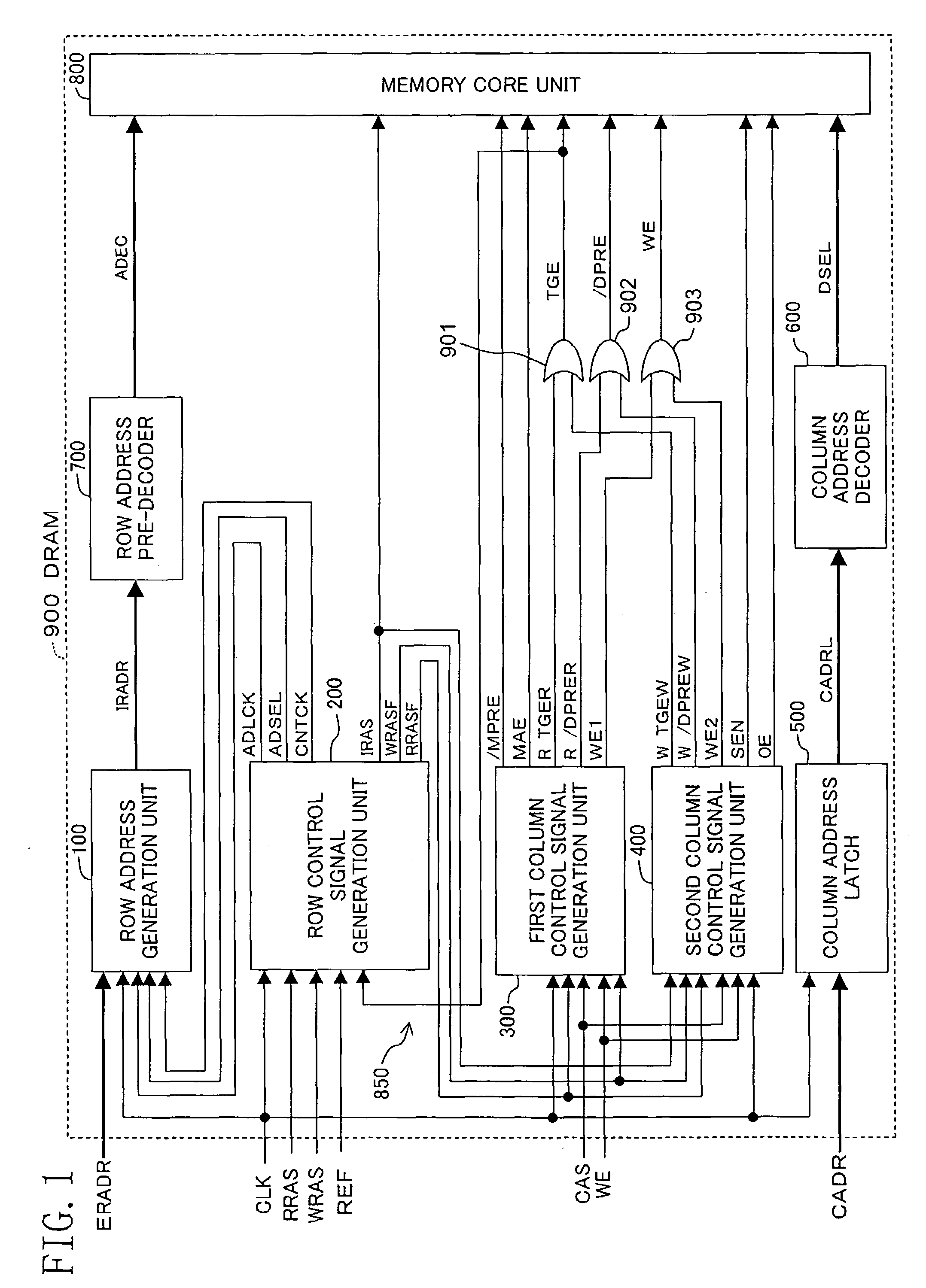

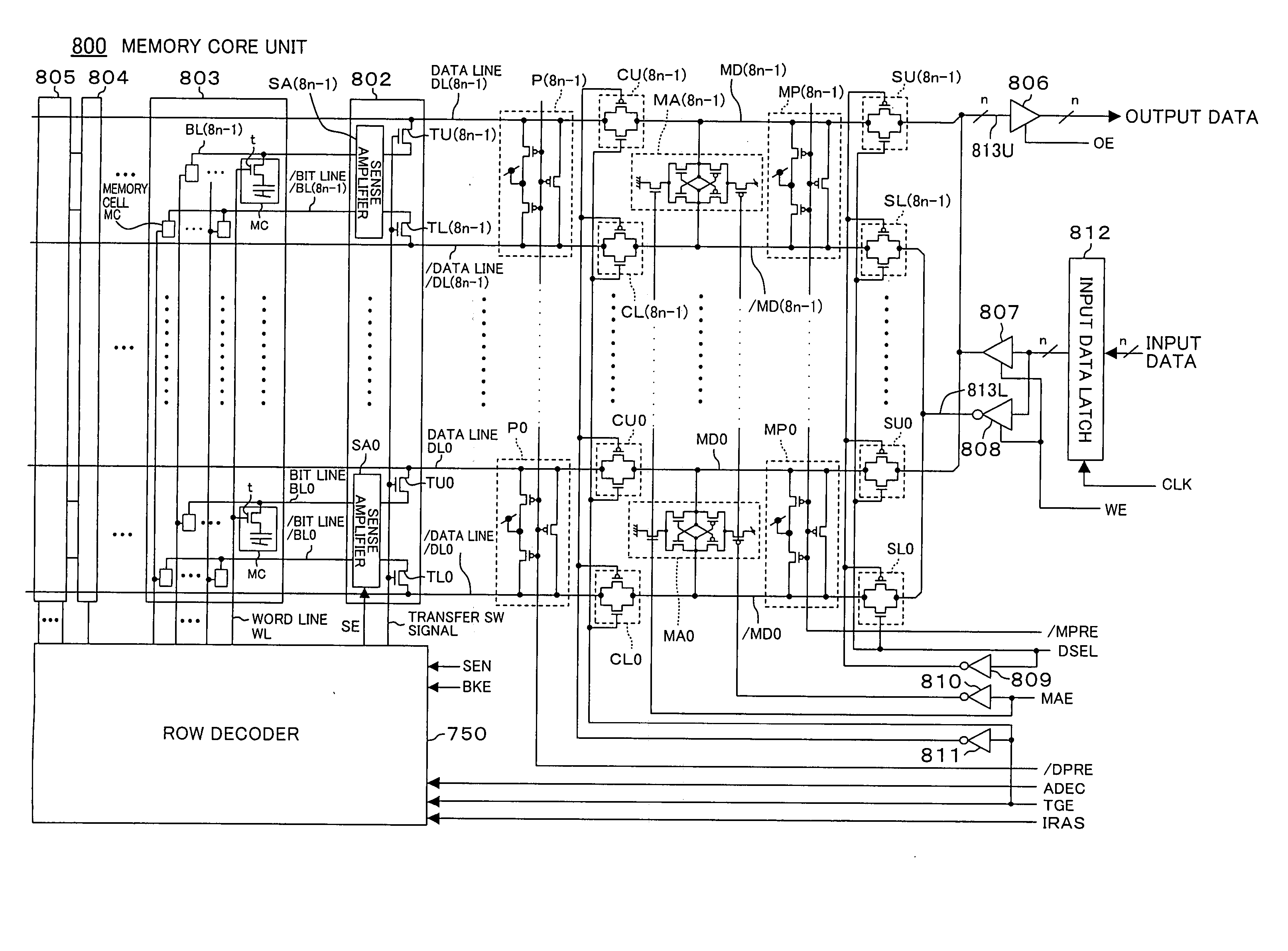

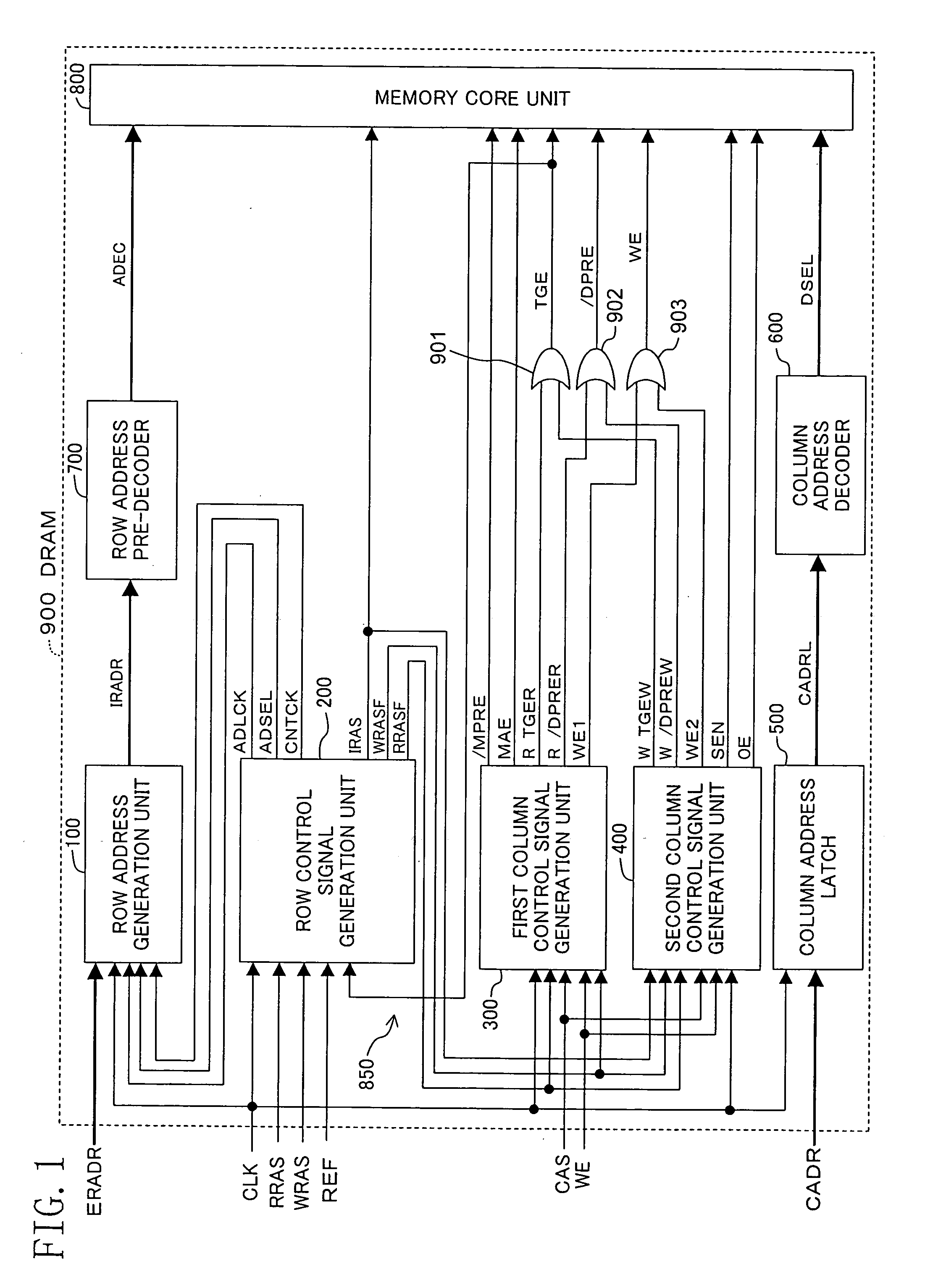

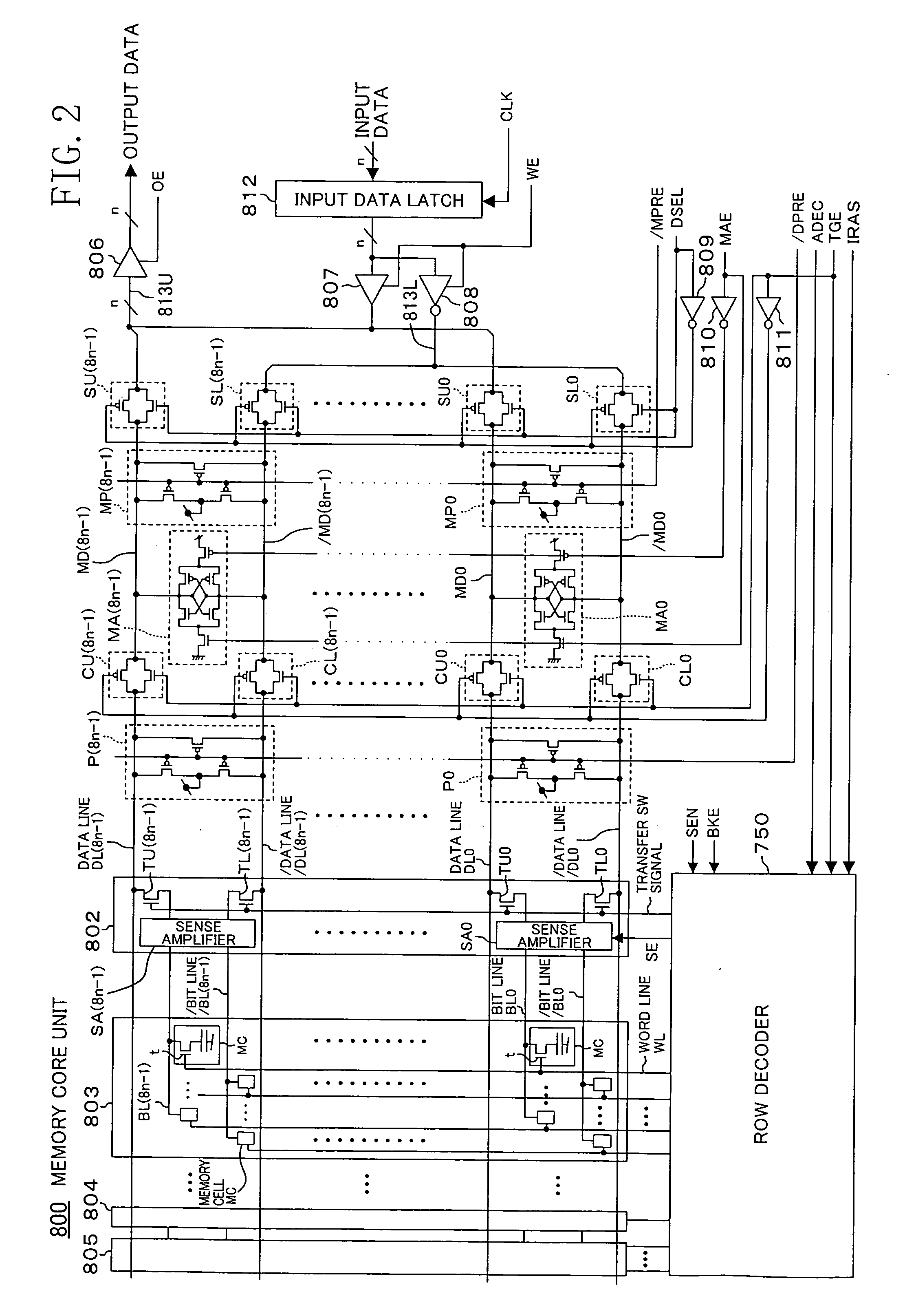

Semiconductor device having read and write operations corresponding to read and write row control signals

In a semiconductor device that needs a refresh operation for storing data, data of memory cells selected in response to a row address is read to main amplifiers through bit line pairs, sense amplifiers and data line pairs in a page-mode read operation. Thereafter, while outputting the data held in the main amplifiers to the outside, connecting transistors are turned off so as to disconnect the main amplifiers from the memory cells, and thus, the memory cells can be precharged. Also, in a page-mode write operation, while writing externally supplied input data in the main amplifiers, the memory cells can be precharged.

Owner:CETUS TECH INC

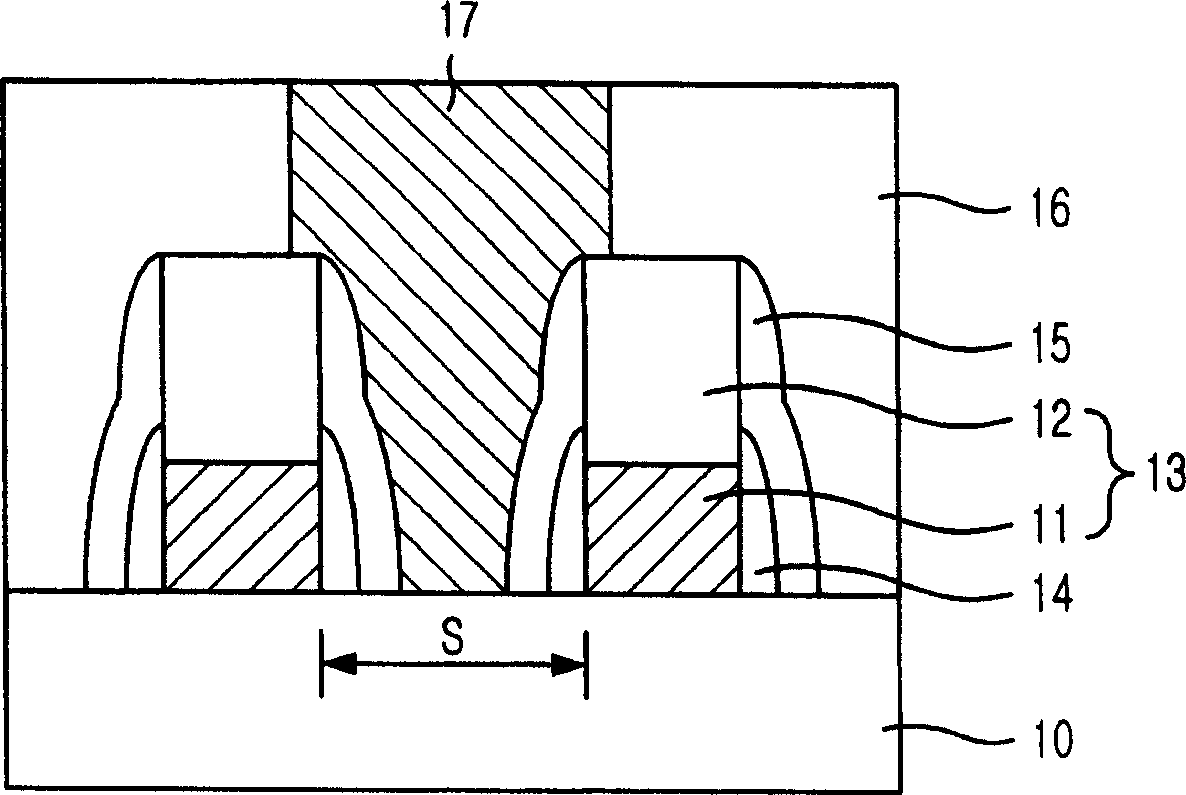

Method for producing semi-conductor

InactiveCN1469428AAvoid lostReduce load capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideSilicon dioxide

The present invention provides a method for producing semi-conductor. The inventive method includes the steps of: forming a plurality of patterns on a substrate, wherein the patterns are formed by stacking and patterning a first conductive layer, a silicon nitride mask layer and a metal mask layer on the substrate; depositing a first silicon oxide layer along the profile containing the patterns; etching the first silicon oxide layer for forming a silicon oxide spacer with a height lower than a top part of the silicon nitride mask layer so as to partially expose a top part of lateral sides of patterns and simultaneously etching the metal mask layer to expose the silicon nitride mask layer, wherein the metal mask layer prevents losses of the silicon nitride mask layer; forming a silicon nitride spacer on a surface of the silicon oxide spacer and the lateral sides of the patterns; forming a second silicon oxide layer on an entire structure in which the silicon nitride spacer is formed; etching selectively the second silicon oxide layer to expose silicon nitride layer spacer and forming a self-align contact hole that is partially expanded to the top portion of the patterns; and forming a self-align contact structure by filling the self-align contact hole with a second conductive layer.

Owner:SK HYNIX INC

Semiconductor device

According to the invention, in a semiconductor device that needs a refresh operation for storing data, data of memory cells selected in response to a row address is read to main amplifiers through bit line pairs, sense amplifiers and data line pairs in a page-mode read operation. Thereafter, while outputting the data held in the main amplifiers to the outside, connecting transistors are turned off so as to disconnect the main amplifiers from the memory cells, and thus, the memory cells can be precharged. Also, in a page-mode write operation, while writing externally supplied input data in the main amplifiers, the memory cells can be precharged.

Owner:CETUS TECH INC

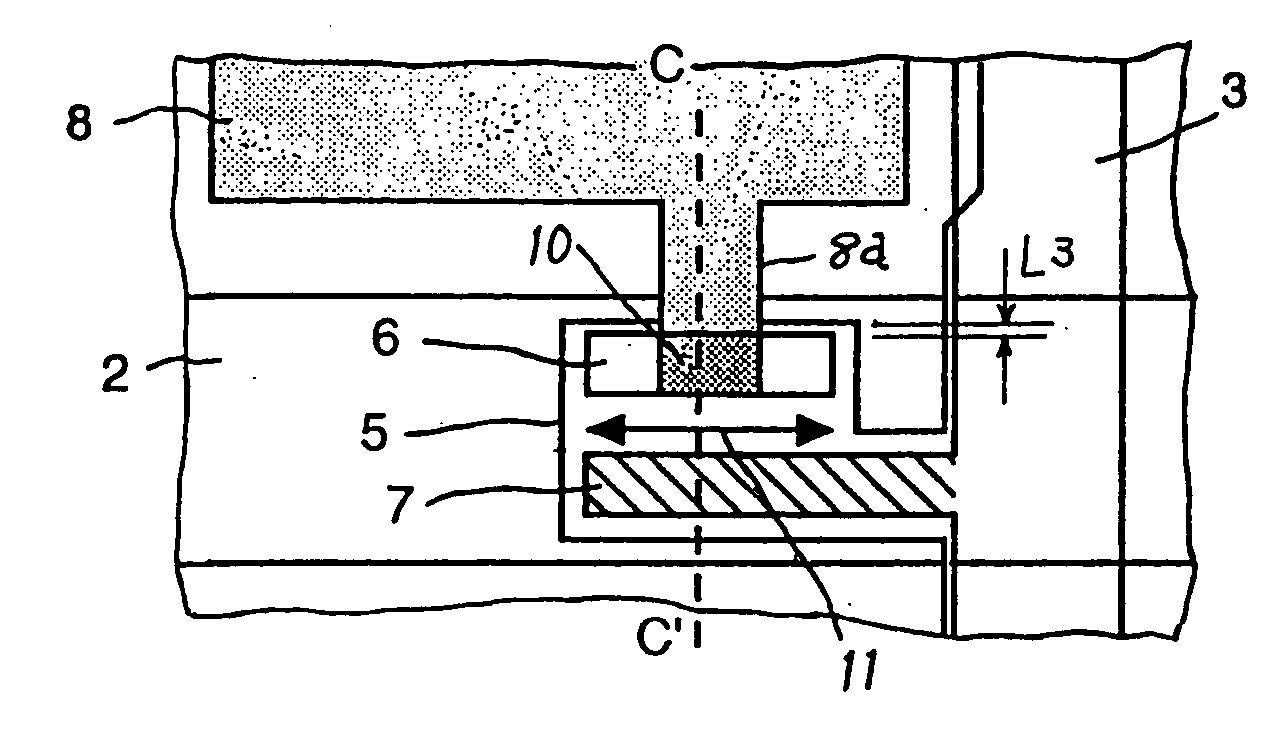

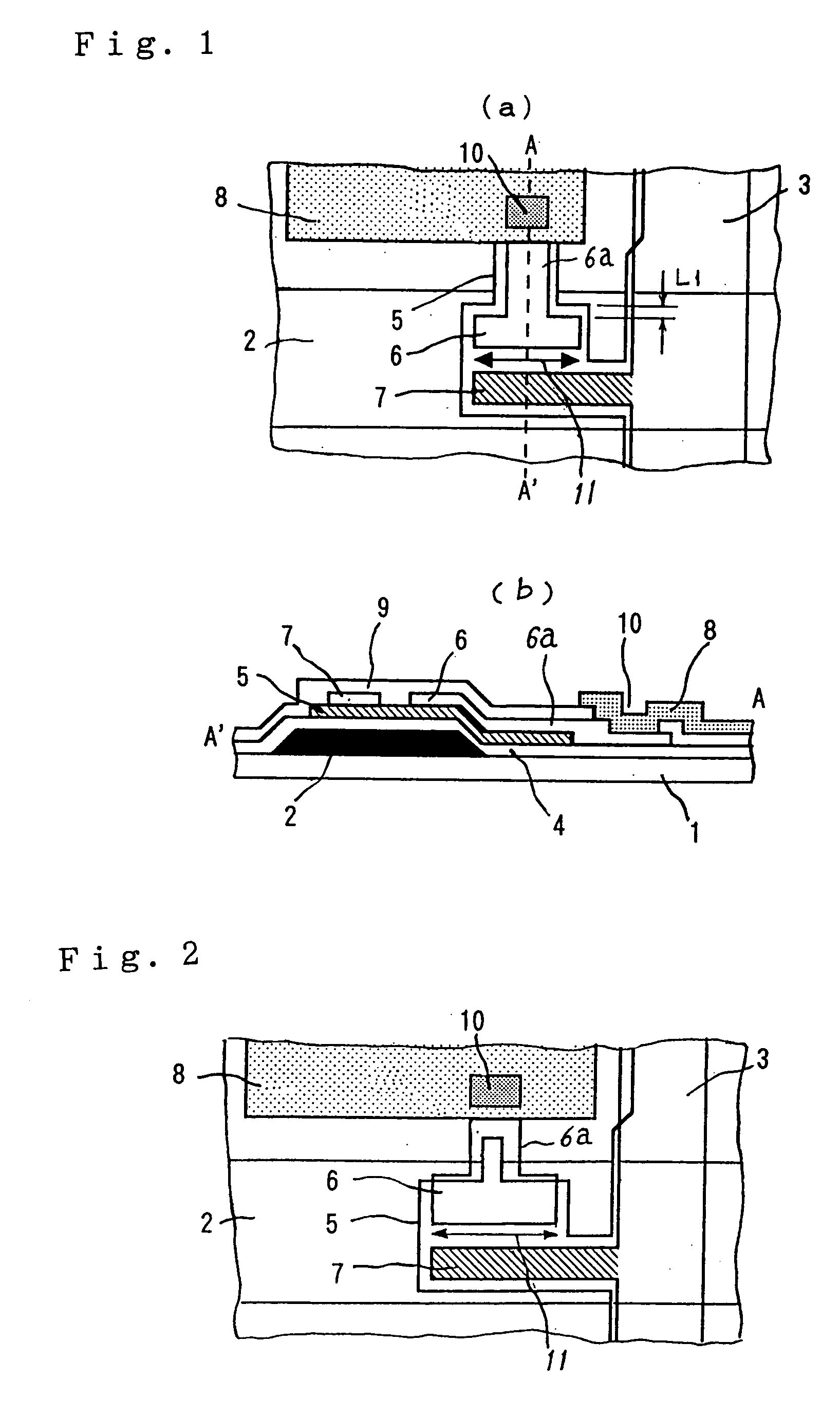

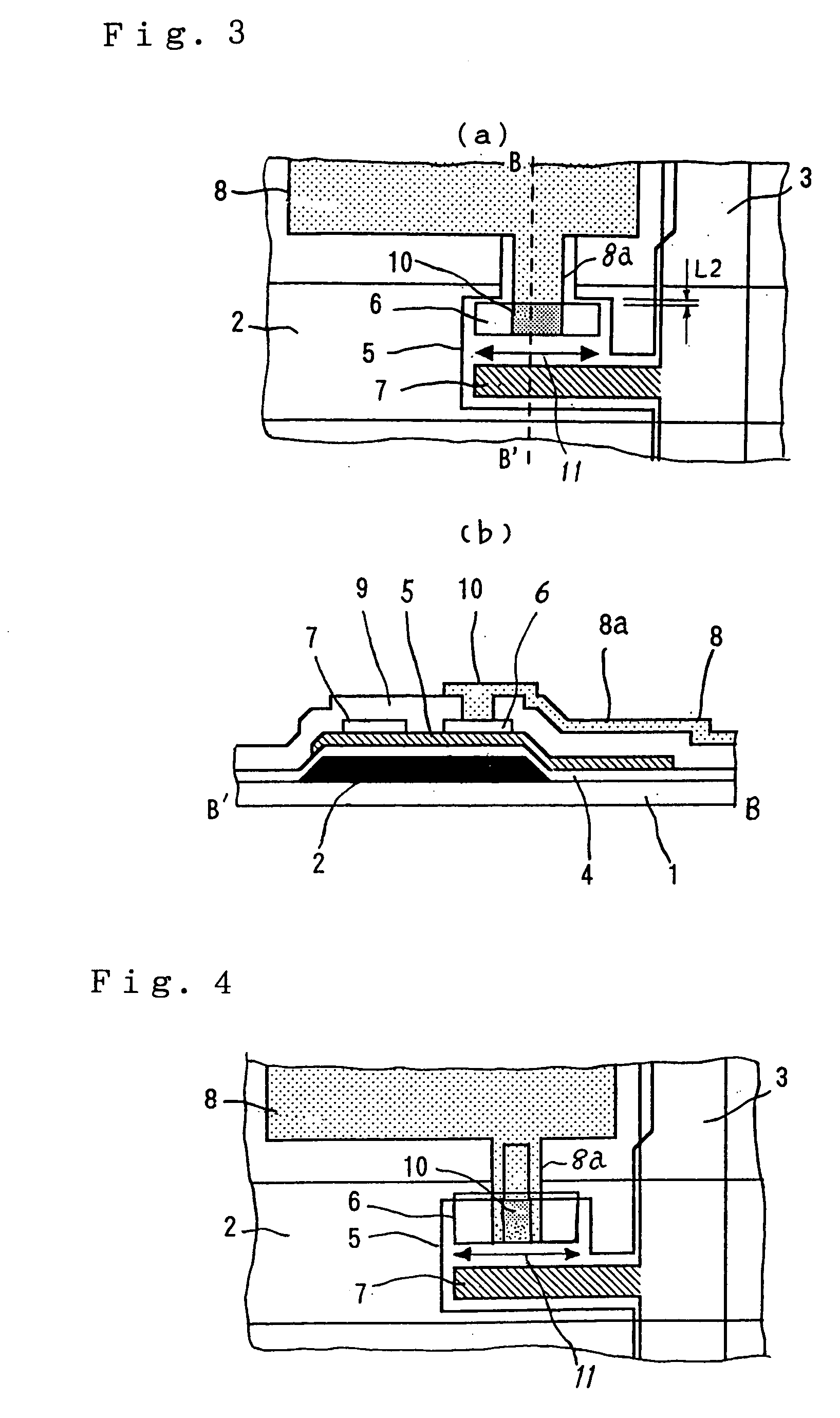

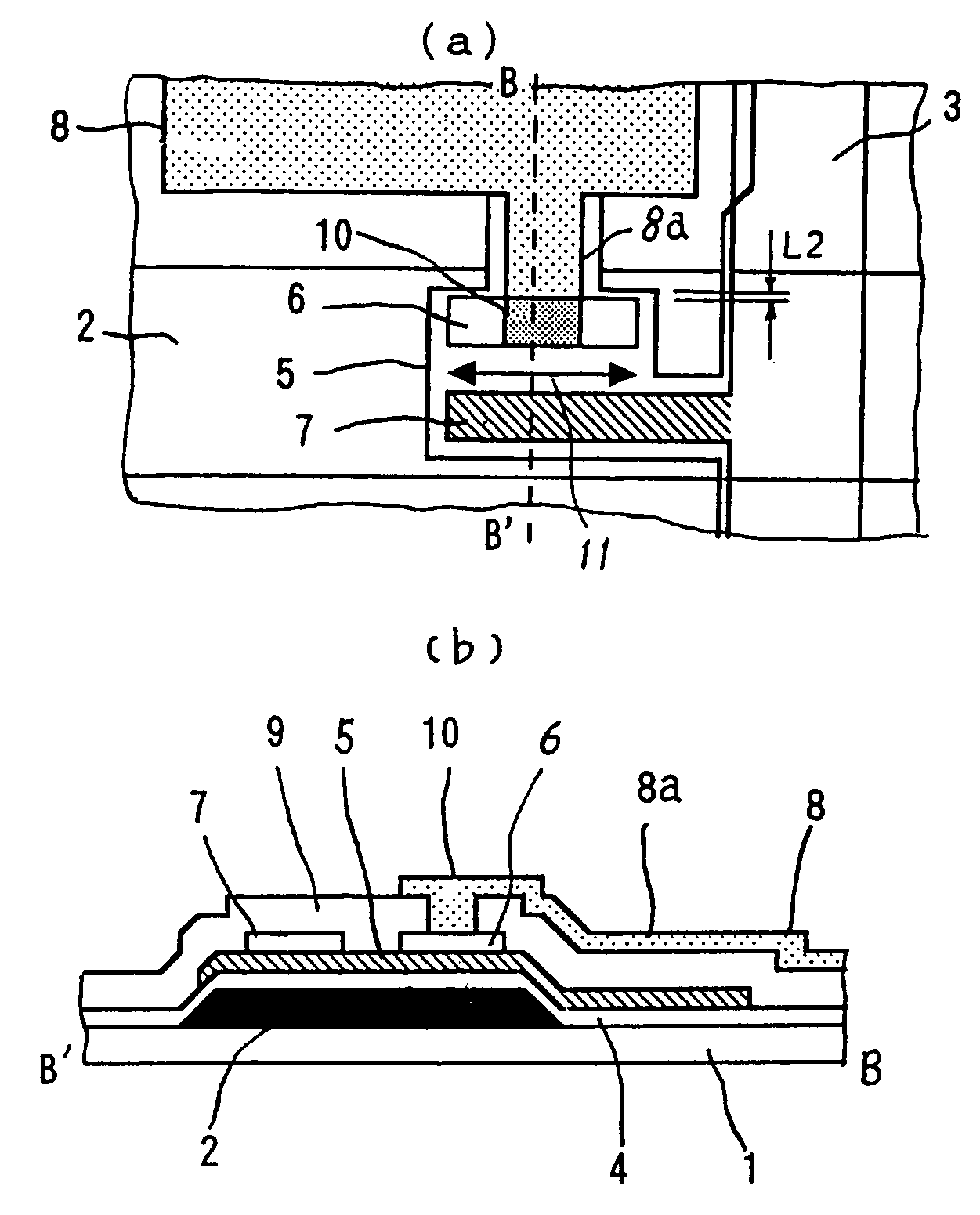

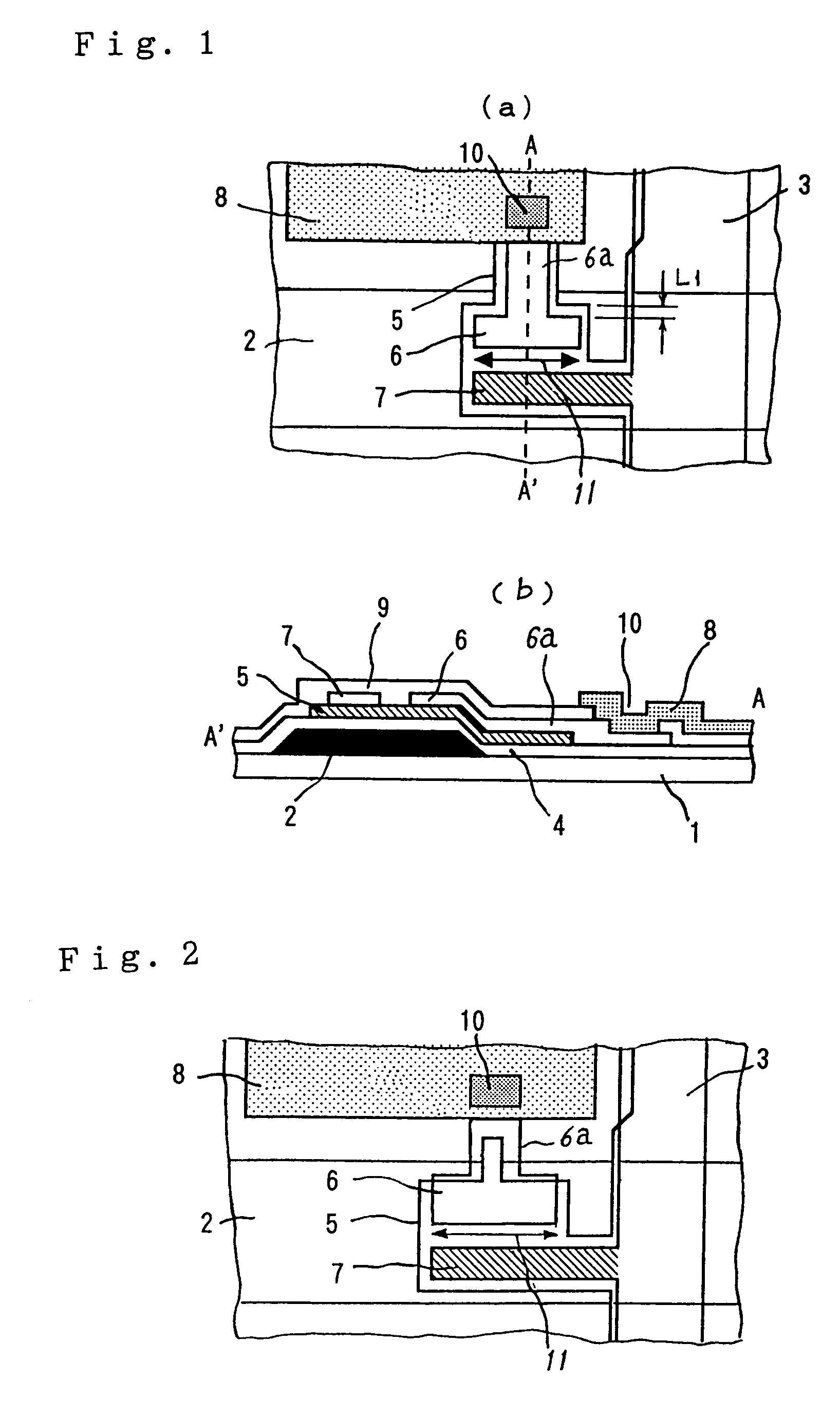

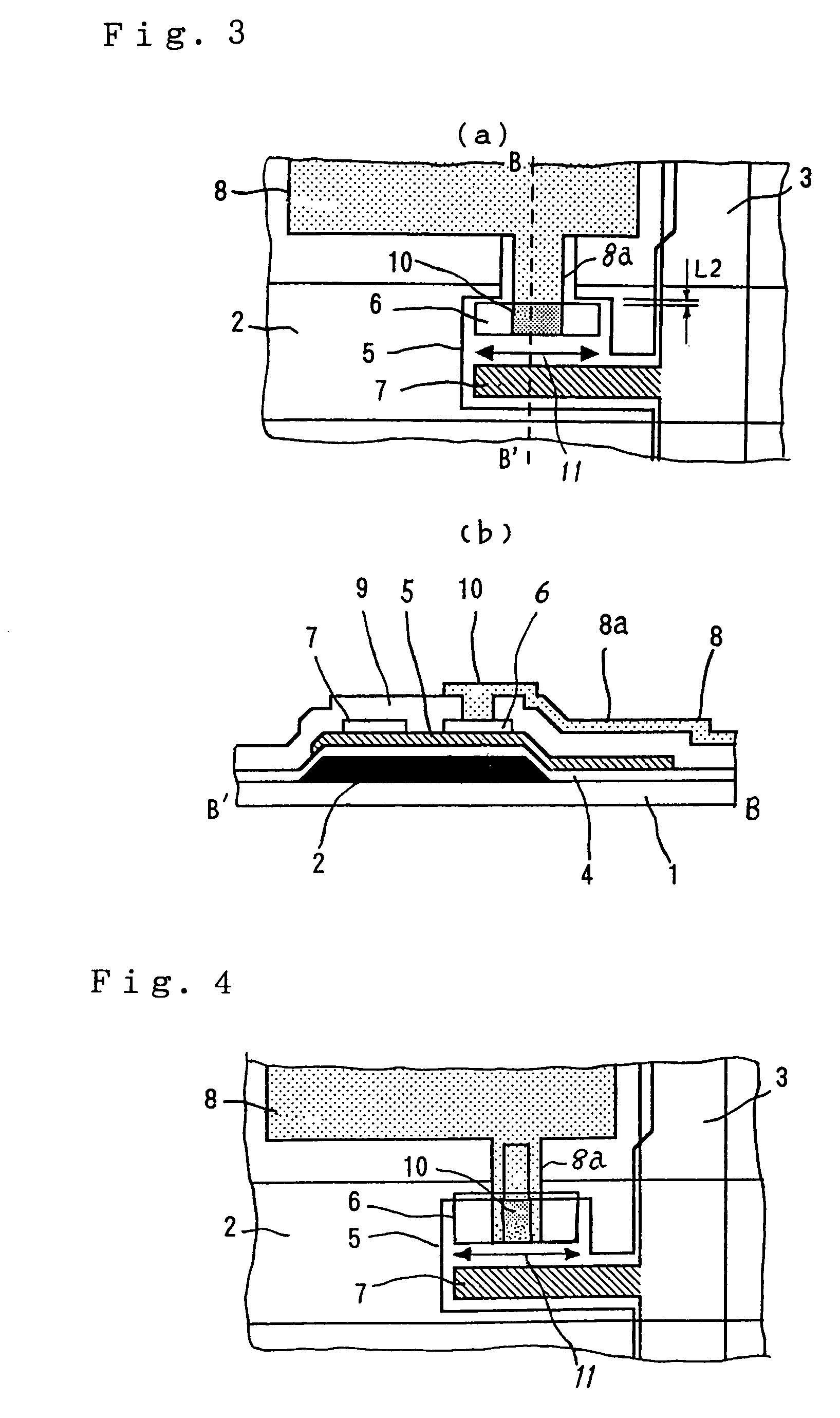

TFT array substrate and liquid crystal display device using it

InactiveUS20050088599A1Small differenceReduce variationTransistorSolid-state devicesLiquid-crystal displayEngineering

The widths of those portions of a semiconductor layer 5 and a drain line 6a overlapping with it which cross an edge line of a gate electrode 2 are made smaller than the channel width of a thin-film transistor. With this measure, the overlap area of the gate electrode 2 and a drain electrode 6 is reduced. As a result, a variation of the above overlap area due to alignment errors in a photolithography apparatus used in patterning the gate lines 2, the drain electrodes 6, and source electrodes 7 can be reduced and the frequency of occurrence of display defects can be decreased.

Owner:TRIVALE TECH

Self-aligned semiconductor contact structures and methods for fabricating the same

InactiveUS20060192255A1Reduce aspect ratioReduce contact resistanceTransistorSolid-state devicesEngineeringSemiconductor

Owner:SAMSUNG ELECTRONICS CO LTD

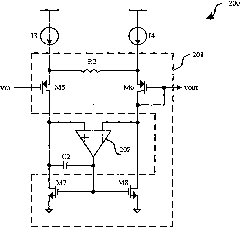

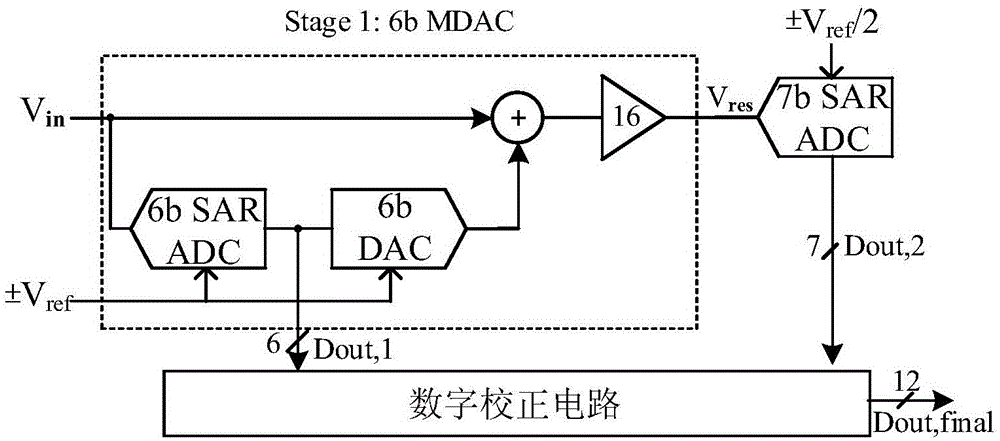

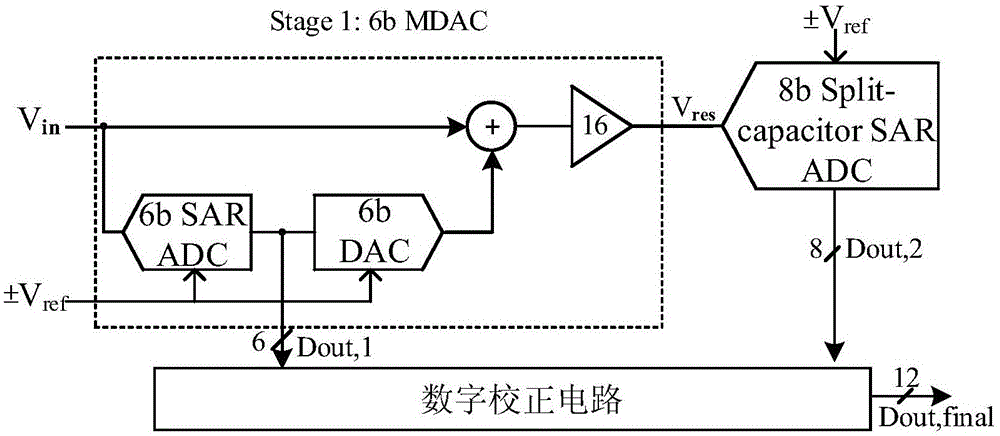

Pipeline successive-approximation analog-to-digital converter

InactiveCN105119603AReduce load capacitanceSampling Capacitance ReductionAnalogue/digital conversionElectric signal transmission systemsCapacitanceVoltage reference

The invention discloses a pipeline successive-approximation analog-to-digital converter used for solving the technical problem that the existing pipeline successive-approximation analog-to-digital converter is high in power consumption. The technical scheme is as follows: a first stage circuit adopts a 6-bit half-gain MDAC (Multiplying Digital To Analog Converter) circuit, and a second stage circuit adopts an 8-bit full-reference voltage multiple-segment capacitor SAR ADC (successive-approximation analog-to-digital converter). The whole capacitor network of the 8-bit full-reference voltage multiple-segment capacitor SAR ADC is divided into a high 4-bit binary weighted capacitor network and a low 4-bit binary weighted capacitor network. Since a sampling capacitance of the 8-bit full-reference voltage multiple-segment capacitor SAR ADC is significantly reduced, thus a load capacitance of a residue amplifier in the 6-bit half-gain MDAC circuit is significantly reduced. For the same error requirement, current consumed by the residue amplifier in the 6-bit half-gain MDAC circuit can be reduced, so that the power consumption of the pipeline successive-approximation analog-to-digital converter can be reduced.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

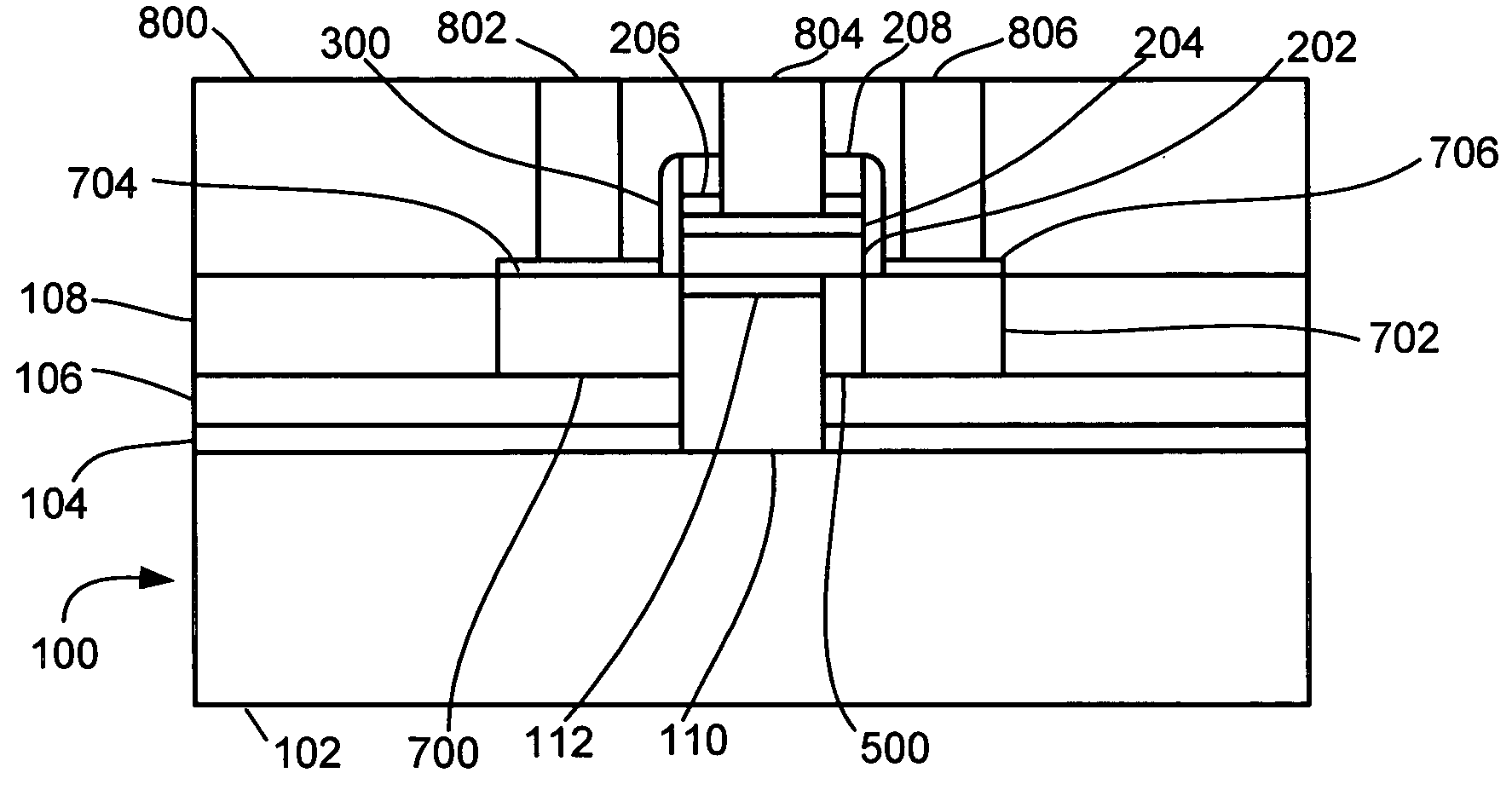

Method of manufacturing semiconductor device with interconnections and interconnection contacts and a device formed thereby

ActiveUS6927126B2Load capacitanceReduce load capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingBit lineDevice material

A second insulating layer is formed on a first insulating layer. A plurality of stacks each including a bit line and a bit line mask are formed on the second insulating layer. A third insulating layer is formed overlying the second insulating layer to fill gaps between the plurality of stacks. A hard mask layer is formed on the third insulating layer. A photoresist pattern is formed on the hard mask layer. The photoresist pattern has an opening region that intersects the plurality of stacks. The hard mask layer and the third insulating layer are sequentially etched, using the photoresist pattern as an etching mask, thereby forming a hard mask pattern and forming a recess in the third insulating layer. The recess exposes a portion of upper sidewalls of the bit line mask. Spacers are formed on the exposed upper sidewalls of the bit line mask.

Owner:SAMSUNG ELECTRONICS CO LTD

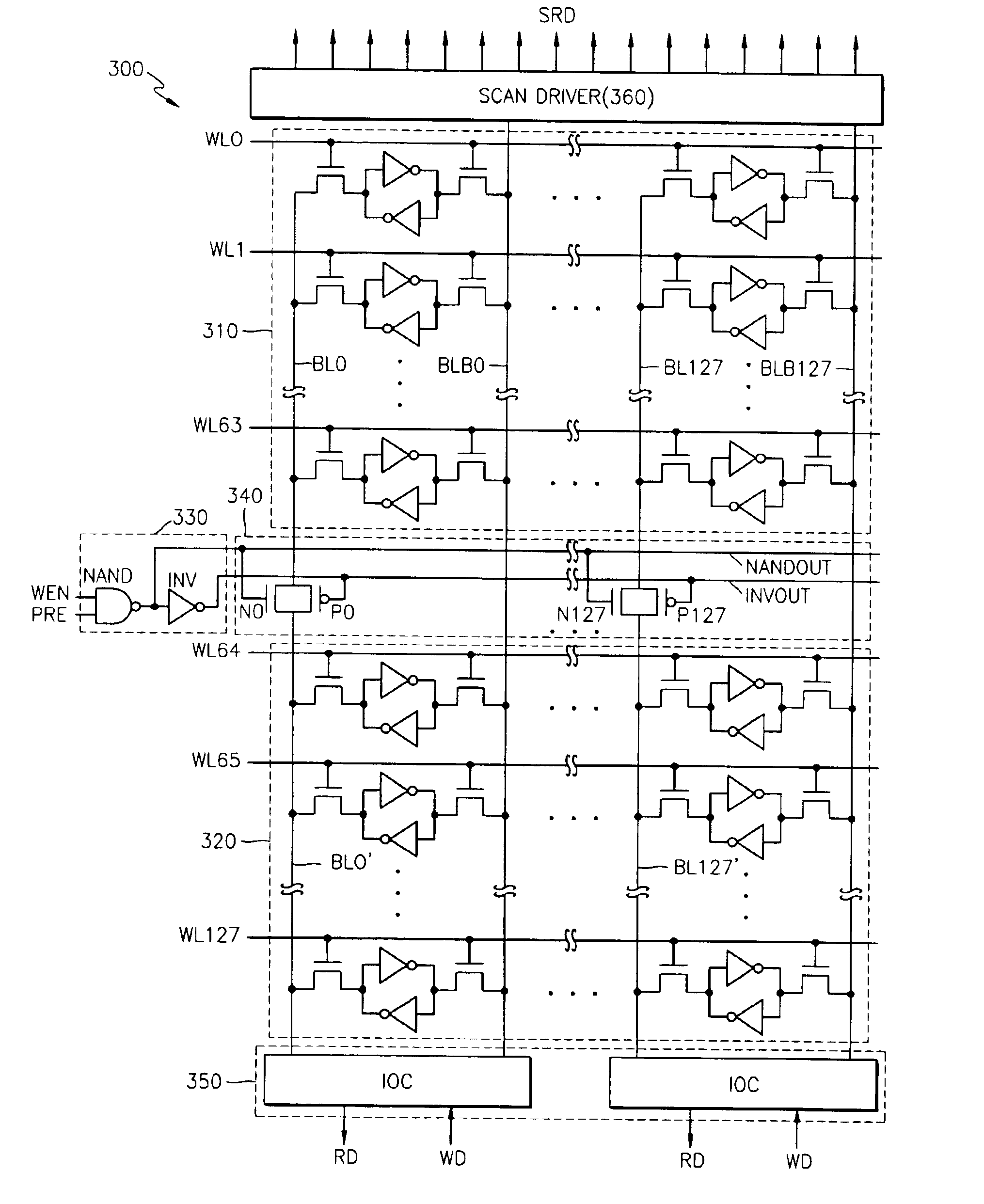

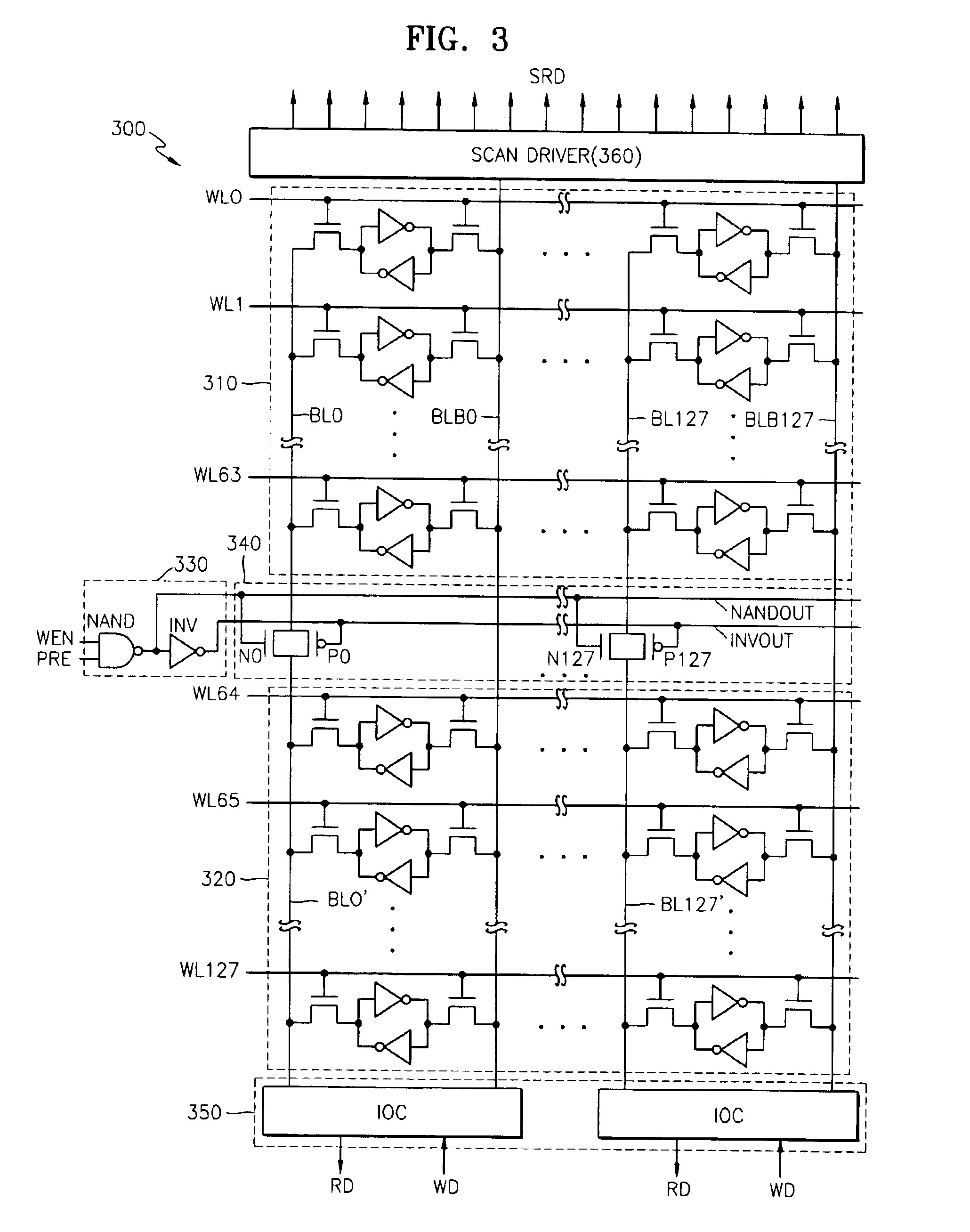

Semiconductor memory device with selectively connectable segmented bit line member and method of driving the same

A semiconductor memory device, that reduces load capacitance of write-only bit lines, may include: a first bit cell array block, in which bit cells thereof are defined by intersections of first bit lines and first word lines, the first bit lines being arranged as pairs of first signal lines and second signal lines, respectively; a second bit cell array block, in which bit cells thereof are defined by intersections of second bit lines and second word lines, the second bit lines being arranged as pairs of third signal lines and the second signal lines; respectively; a block division circuit operable to generate and output block division control signals; and a write bit line divider circuit operable to either open-circuit or connect together the first signal lines and the third signal lines, respectively, according to the block division control signals.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS20050218439A1Reduce load capacitanceEfficient fillingTransistorSolid-state devicesCapacitanceBit line

Bit lines having first conductive patterns and bit line mask patterns are formed on a first insulating layer between capacitor contact regions of a substrate. An oxide second insulating layer is formed on the bit lines and contact patterns are formed to open storage node contact hole regions corresponding to portions of the second insulating layer. First spacers are formed on sidewalls of the etched portions. The second and first insulating layers are etched to form storage node contact holes exposing the capacitor contact regions. Simultaneously, second spacers of the second insulating layer are formed beneath the first spacers. A second conductive layer fills the storage node contact holes to form storage node contact pads. A loss of the bit line mask pattern decreases due to the reduced thickness of the bit line mask pattern and a bit line loading capacitance decreases due to the second spacers.

Owner:SAMSUNG ELECTRONICS CO LTD

Lateral heterojunction bipolar transistor and method of manufacture using selective epitaxial growth

ActiveUS6972237B2Reduce parasitic capacitanceReduce capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

A method for manufacturing a heterojunction bipolar transistor is provided. An intrinsic collector structure is formed on a substrate. An extrinsic base structure partially overlaps the intrinsic collector structure. An intrinsic base structure is formed adjacent the intrinsic collector structure and under the extrinsic base structure. An emitter structure is formed adjacent the intrinsic base structure. An extrinsic collector structure is formed adjacent the intrinsic collector structure. A plurality of contacts is formed through an interlevel dielectric layer to the extrinsic collector structure, the extrinsic base structure, and the emitter structure.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

A/D converter, solid-state image capturing apparatus and electronic information device

ActiveUS8130125B2Reduce load capacitanceReduce capacitanceTelevision system detailsElectric signal transmission systemsCapacitanceCMOS

The CMOS image sensor according to the present invention includes a sample hold section 3A1 for retaining an analog input signal voltage and a ramp wave signal voltage; and a comparing section 3A2 for taking an output from the sample hold section 3A1 as an input to compare it with a reverse level of itself, in which the sample hold section 3A1 applies a stabilization promoting voltage to a terminal of the sampling capacitance element so that an electric potential level of the terminal of the sampling capacitance element is promoted to become stabilized at a predetermined voltage, when the analog input signal is applied to the terminal of the sampling capacitance element.

Owner:SHARP KK

High speed low power 4-2 compressor

InactiveUS6904447B2Reduce load capacitanceReduce areaComputation using non-contact making devicesNumber-of-one countersCapacitanceNOR logic

A high speed low powered 4-2 compressor according to the present invention performs an XOR / XNOR operation of input data by using a single input type NAND / NOR logic circuit and a dual input type NAND / NOR logic circuit. Thus, delays to generate complementary signals are avoided. In addition, the 4-2 compressor uses a single railed multiplexer instead of a dual railed multiplexer, so that gate drive nodes and internal load capacitance are reduced. As a result, circuit area and power consumption of the 4-2 compressor are reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

TFT array substrate and liquid crystal display device using it

InactiveUS7098969B2Big ratioReduce load capacitanceTransistorSolid-state devicesLiquid-crystal displayFrequency of occurrence

The widths of those portions of a semiconductor layer 5 and a drain line 6a overlapping with it which cross an edge line of a gate electrode 2 are made smaller than the channel width of a thin-film transistor. With this measure, the overlap area of the gate electrode 2 and a drain electrode 6 is reduced. As a result, a variation of the above overlap area due to alignment errors in a photolithography apparatus used in patterning the gate lines 2, the drain electrodes 6, and source electrodes 7 can be reduced and the frequency of occurrence of display defects can be decreased.

Owner:TRIVALE TECH

Semiconductor device

InactiveUS7675808B2Reduce power consumptionIncrease power consumptionTransistorSolid-state devicesCapacitanceBit line

An object is to realize high-capacity of a memory while reducing power consumption and making the power consumption even throughout the memory. A memory includes a plurality of memory block arranged to be symmetrically to each other. Also, a specific combination of signals among address signals supplied to the memory, a memory block including a memory cell to be read from or written to is specified. Further, signals supplied to other memory blocks than the above memory block is maintained at a constant value. Consequently, a wiring length of a bit line in a memory array can be shortened, and current consumption can be made to be even among data reading or writing from / to memory cells of a variety of addresses within the memory, at the same time as reducing load capacitance.

Owner:SEMICON ENERGY LAB CO LTD