Pipeline successive-approximation analog-to-digital converter

An analog-to-digital converter and successive approximation technology, applied in analog/digital conversion, code conversion, instruments, etc., can solve the problems of high power consumption and achieve the effects of reducing power consumption, reducing sampling capacitance, and reducing current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

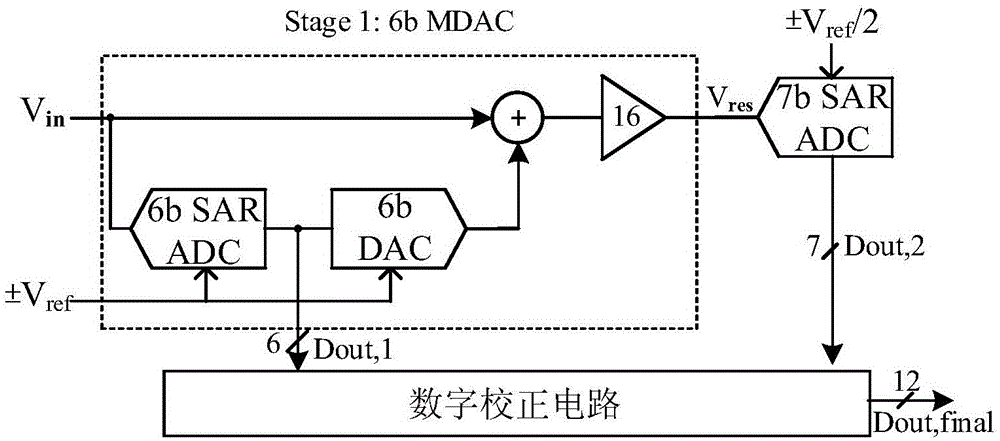

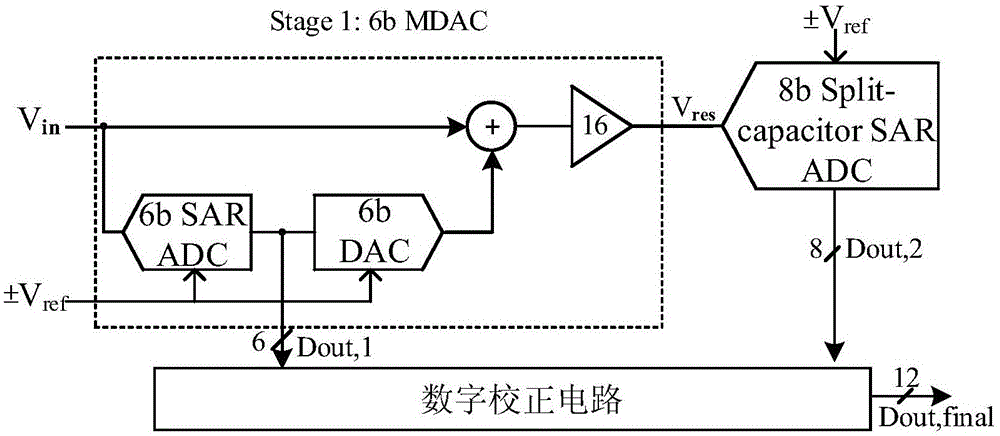

[0020] refer to Figure 3-5 . The pipeline successive approximation analog-to-digital converter of the present invention adopts a two-stage pipeline structure circuit, the first-stage circuit adopts a 6-bit half-gain MDAC circuit, and the second-stage circuit adopts an 8-bit full reference voltage segment capacitor SARADC instead of the background technology 7-bit "half reference voltage" binary capacitor SARADC. The 14-bit digital output code output by the two-stage pipeline circuit is superimposed and added by two bits, and the digital offset code 10000000 is subtracted to obtain the final 12-bitADC digital code.

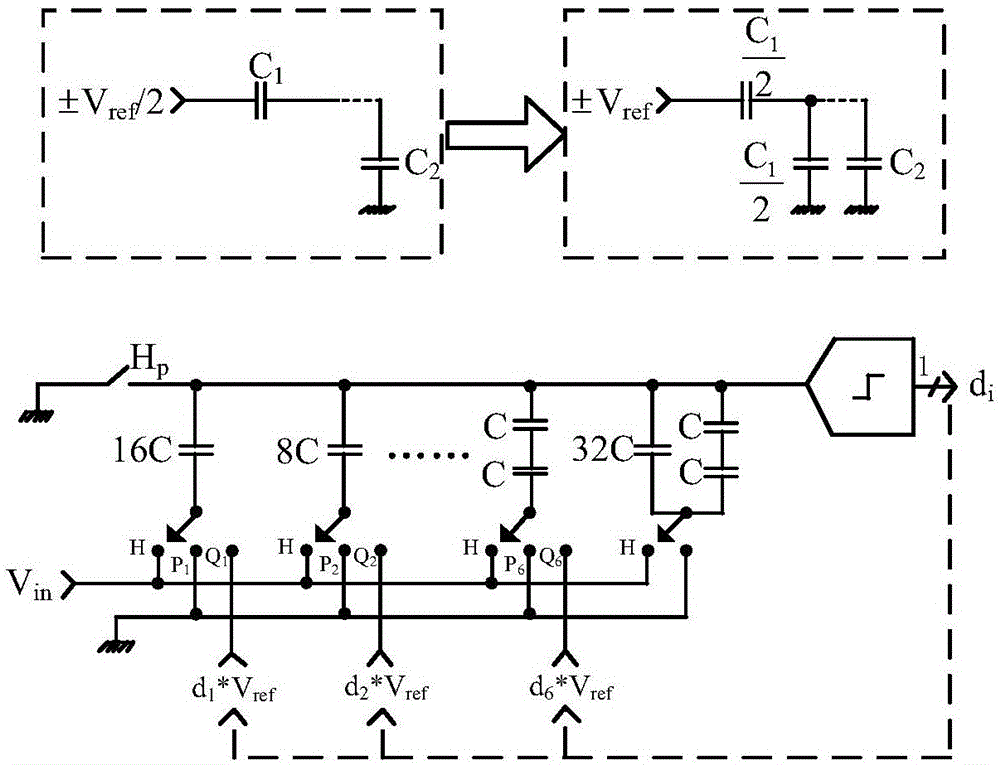

[0021] The entire capacitor network of the 8-bit segmented capacitor SARADC is divided into two parts: the high 4-bit binary weighted capacitor network and the low 4-bit binary weighted capacitor network. Its working process is divided into two stages: sampling stage and conversion stage. During the sampling phase, switch S, switch S 1e and switch S 1f closur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More