Method for producing semi-conductor

A semiconductor and device technology, applied in the field of manufacturing semiconductor devices, can solve problems such as mask layer damage, infeasibility, and difficulty in conducting patterns

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] Other objects and aspects of the present invention will become apparent through the following description of the preferred embodiments together with the related drawings, which are related as follows.

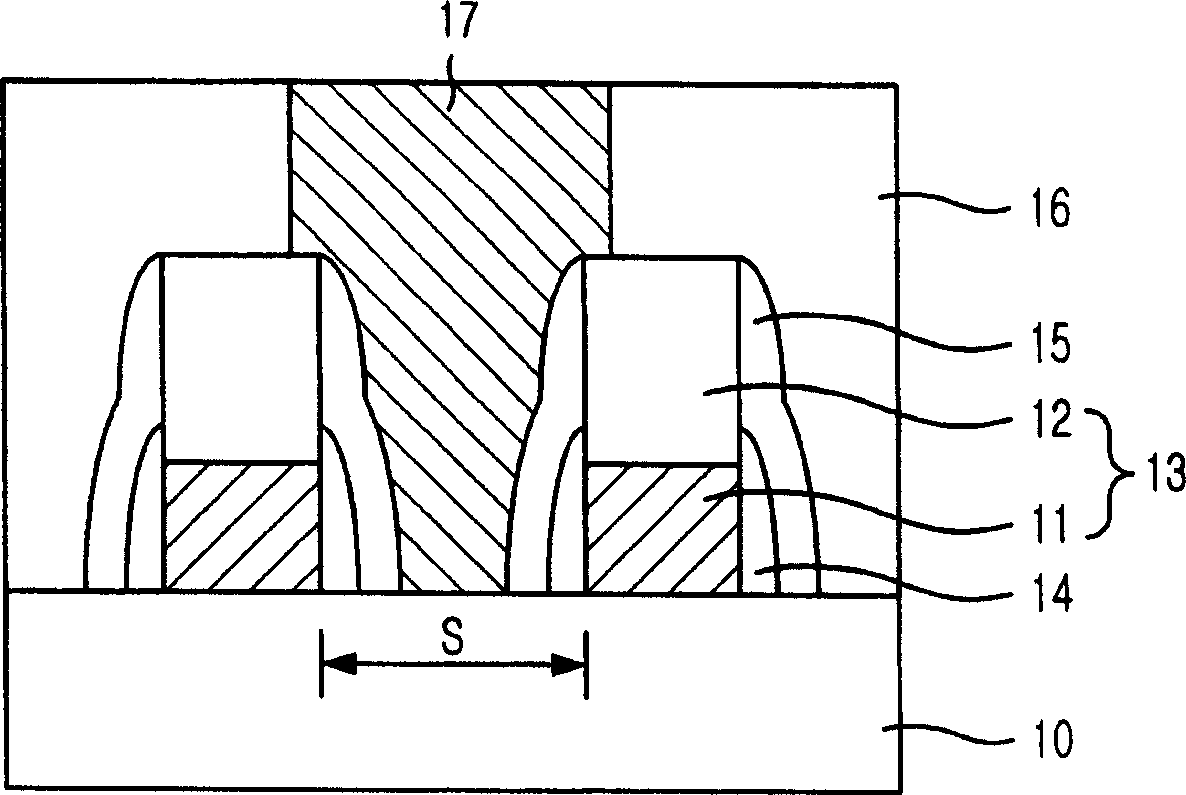

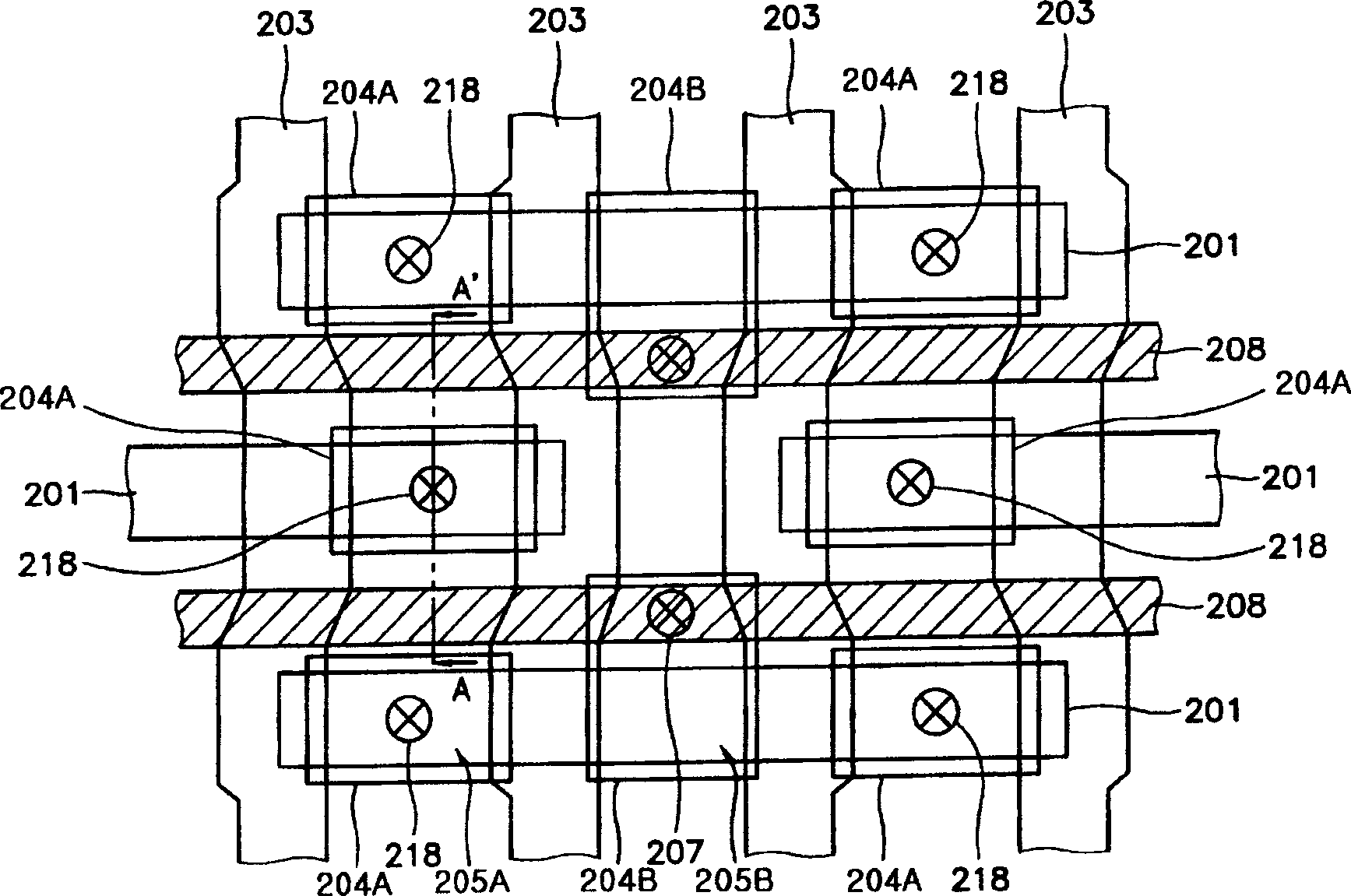

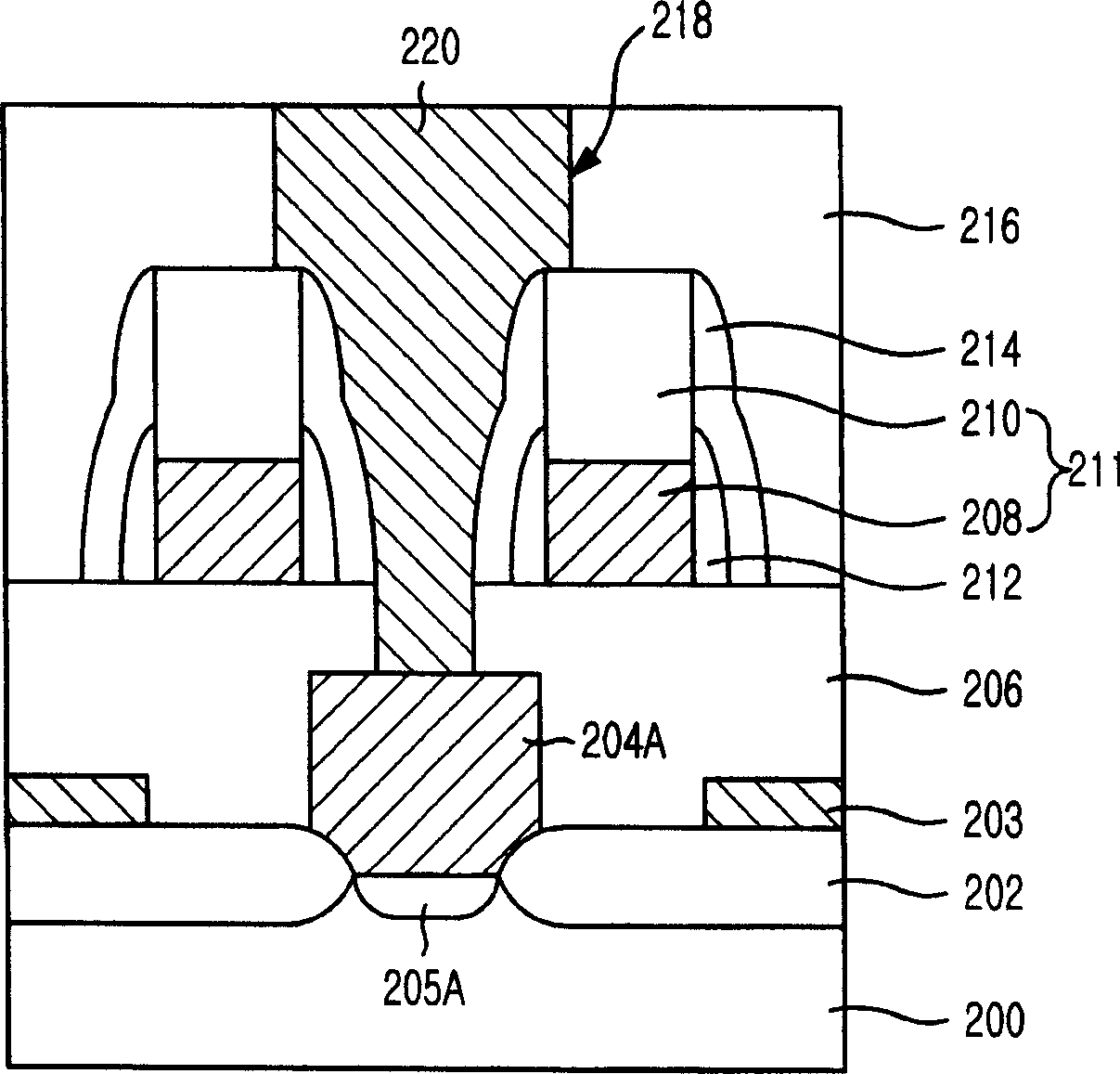

[0054] figure 2 A cross-sectional view of a semiconductor device applied according to a preferred embodiment of the present invention, in particular, a memory cell region is shown in figure 2 middle. image 3 for figure 2 A cross-sectional view along the direction A-A' in FIG. 1 illustrates a semiconductor device with a self-aligned contact (SAC) structure according to a preferred embodiment of the present invention.

[0055] refer to figure 2 and image 3 , a transistor comprising a gate 203 provided to a word line, a capacitive contact region such as a source region 205A and a bit line contact region such as a drain region 205B is formed on a semiconducting substrate 200 . Here, the semiconductor substrate 200 is divided into an active region 201 and a device...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More