Patents

Literature

60results about How to "Reduce bias current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

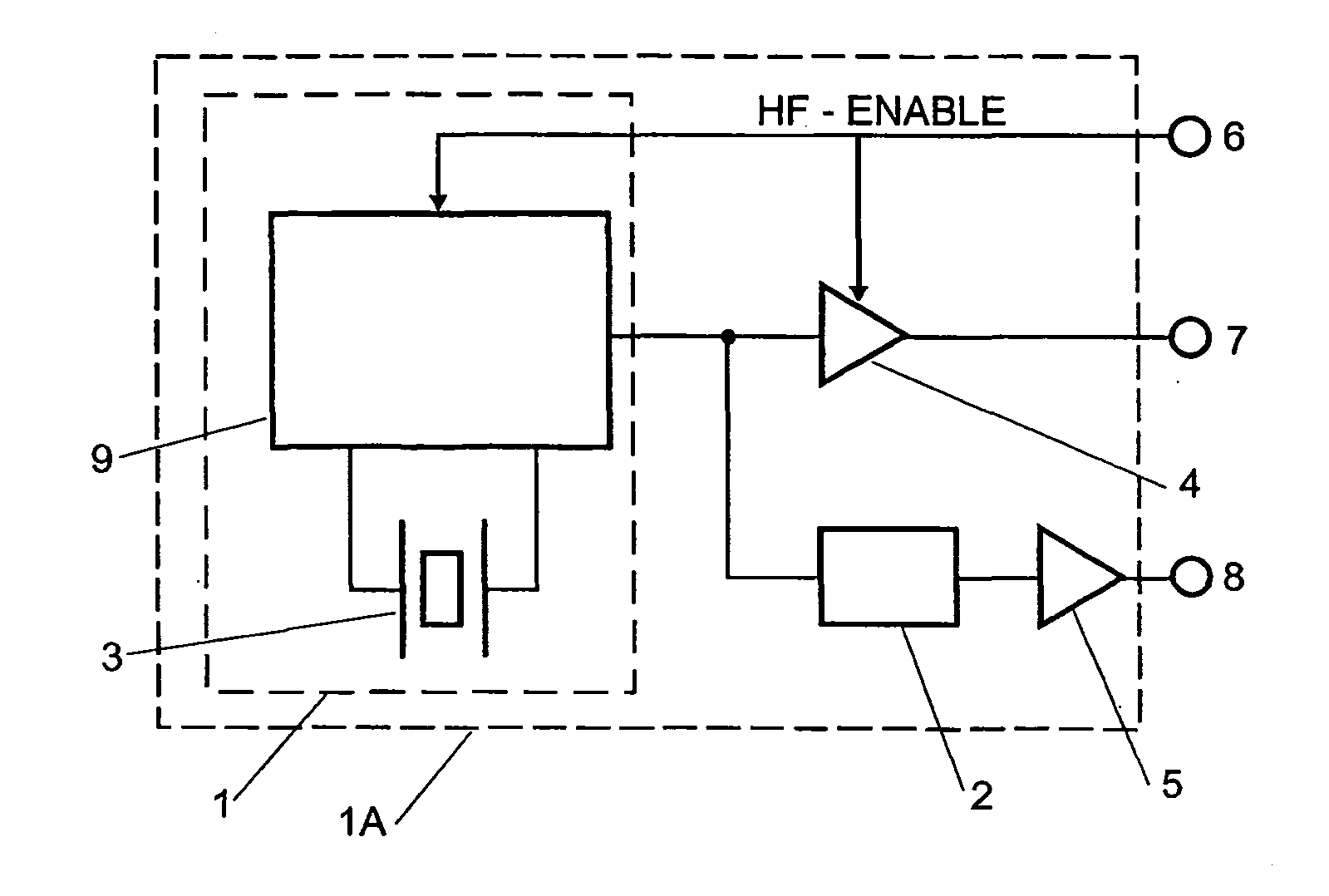

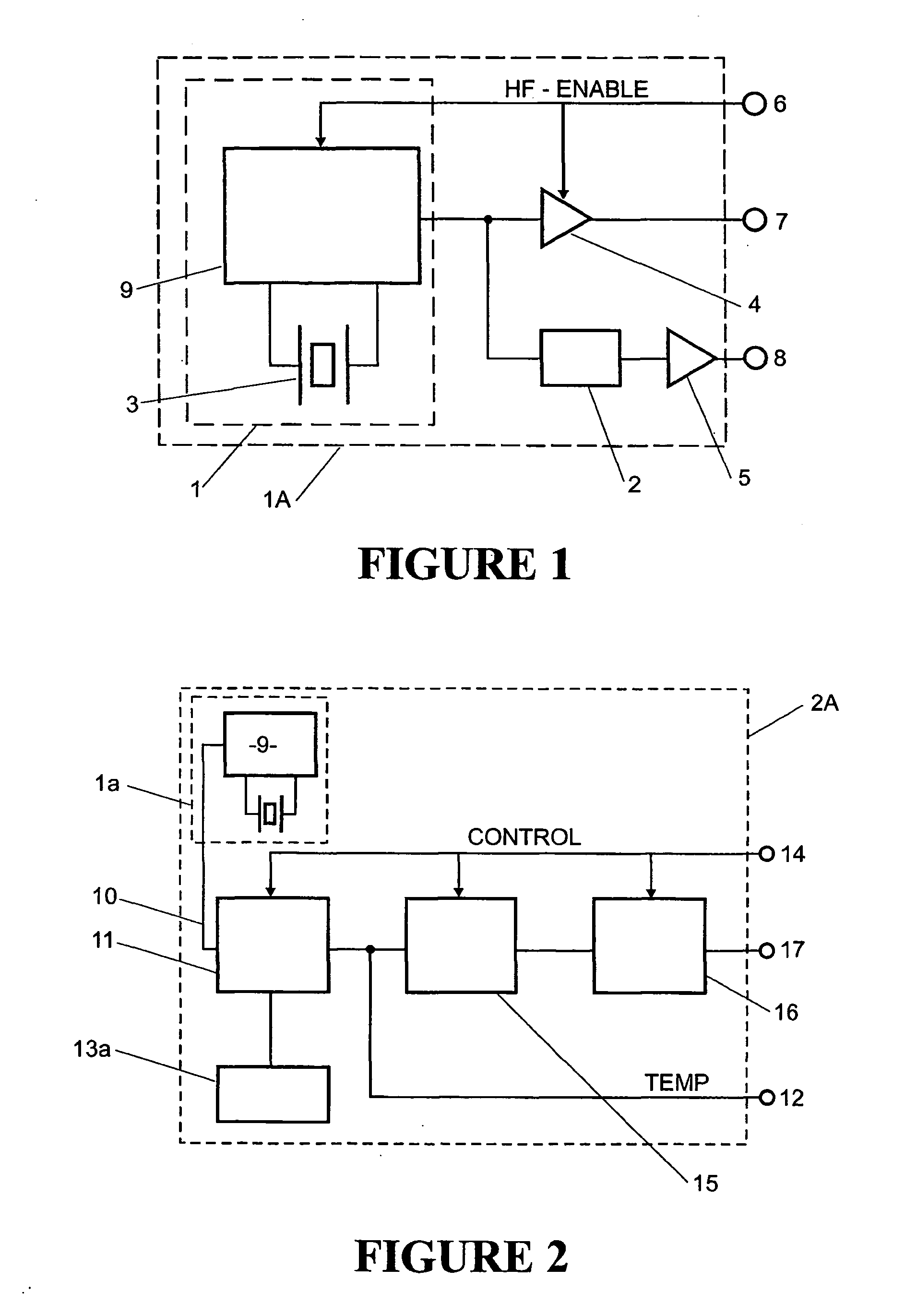

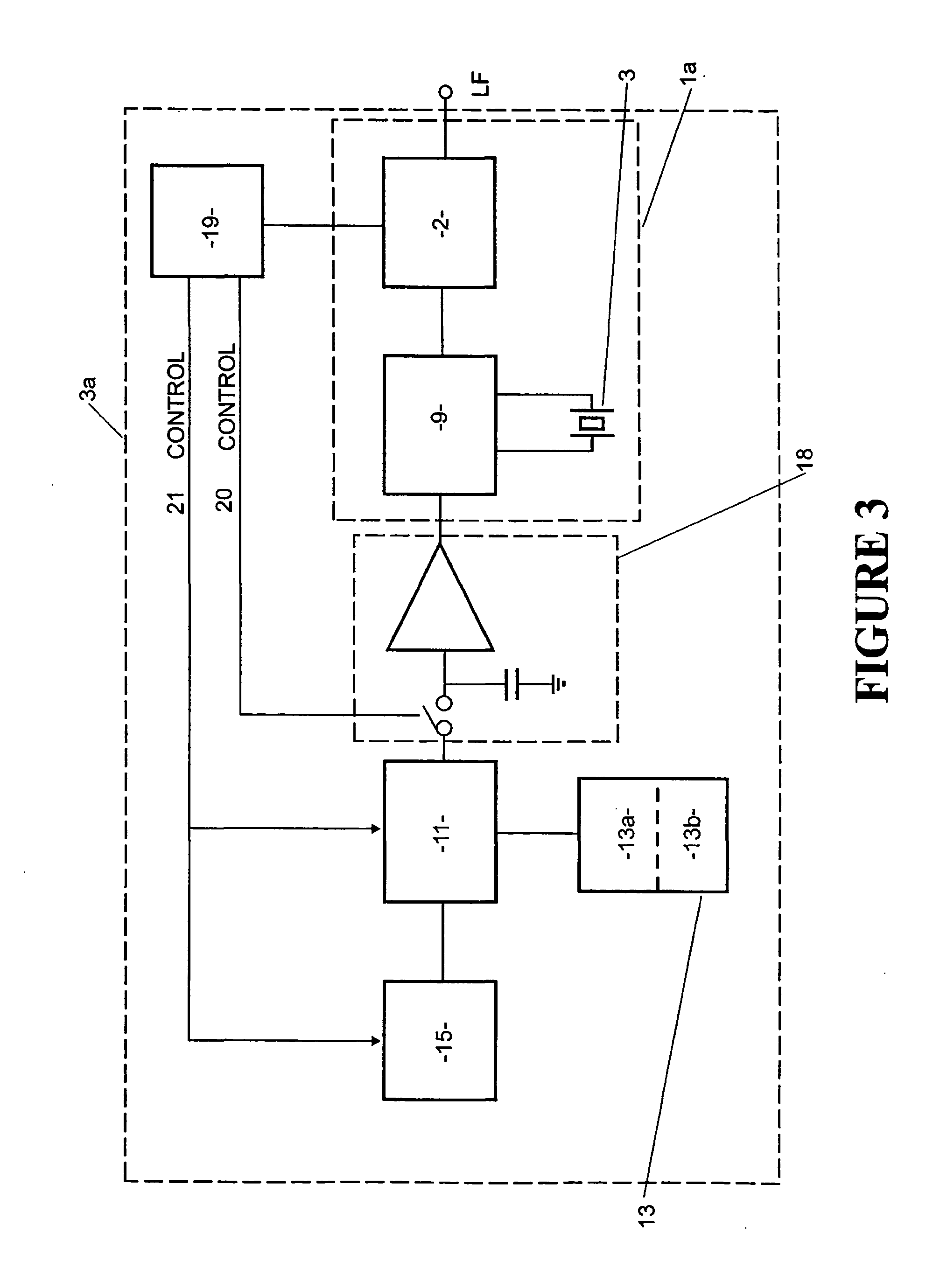

Low power crystal oscillator

InactiveUS20050007205A1Reduce frequencyReduce bias currentGenerator stabilizationOscillations generatorsPhase noiseEngineering

The present invention relates to a timing system including an integrated circuit having an oscillator that provides both high and low frequency clock signals from a single high frequency crystal without the necessity of a tuning fork crystal. The low frequency signal is available for time-keeping applications, with low power consumption during “idle” periods. The high performance high frequency signal is available on demand for clock and frequency reference use. The oscillator of the present invention provides improved time-keeping accuracy, whilst size, cost and component count is reduced. Furthermore, phase noise and other critical parameters of the high frequency oscillator are not compromised. Shock vulnerability, a known problem for tuning fork crystals, is reduced.

Owner:RAKON

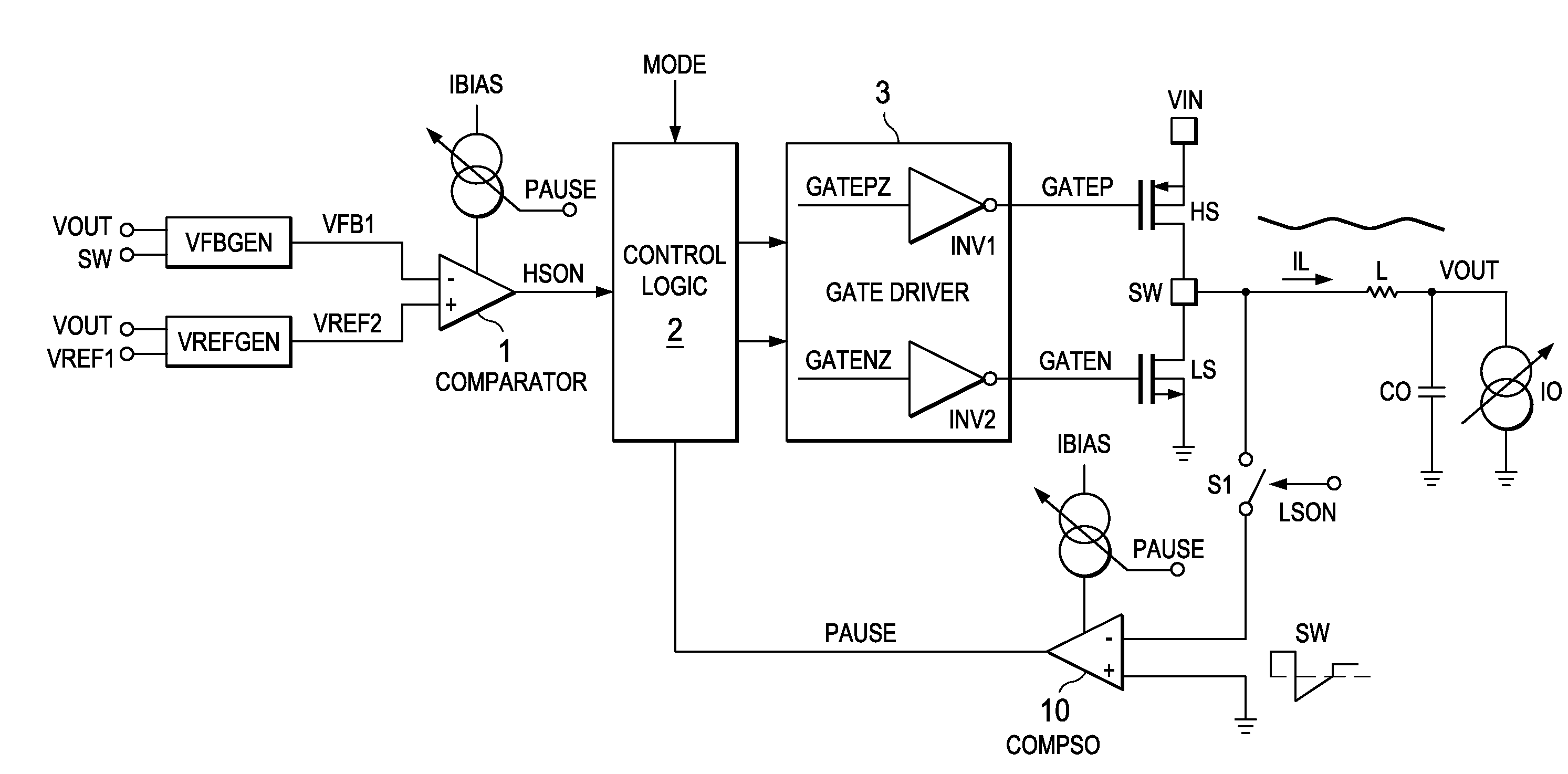

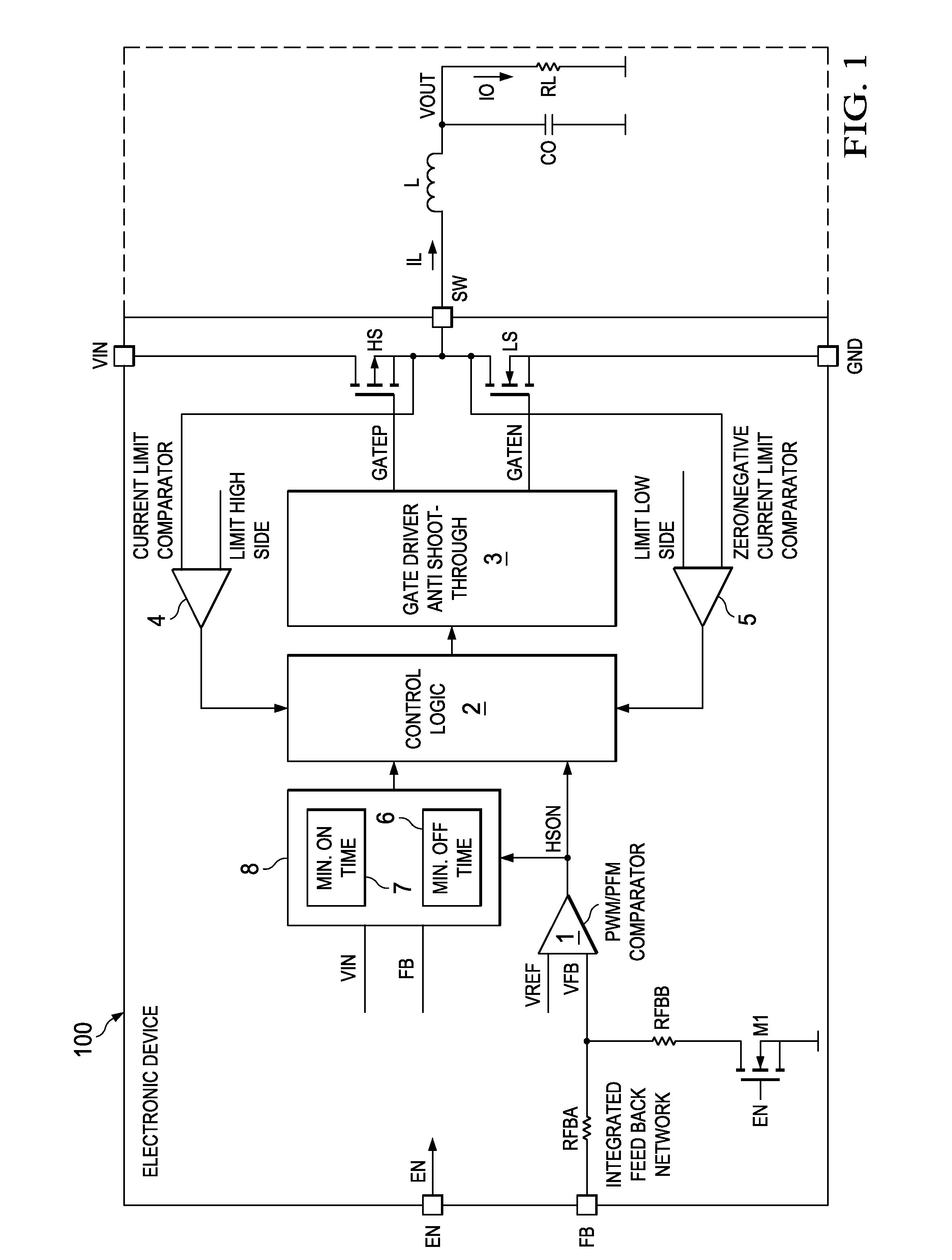

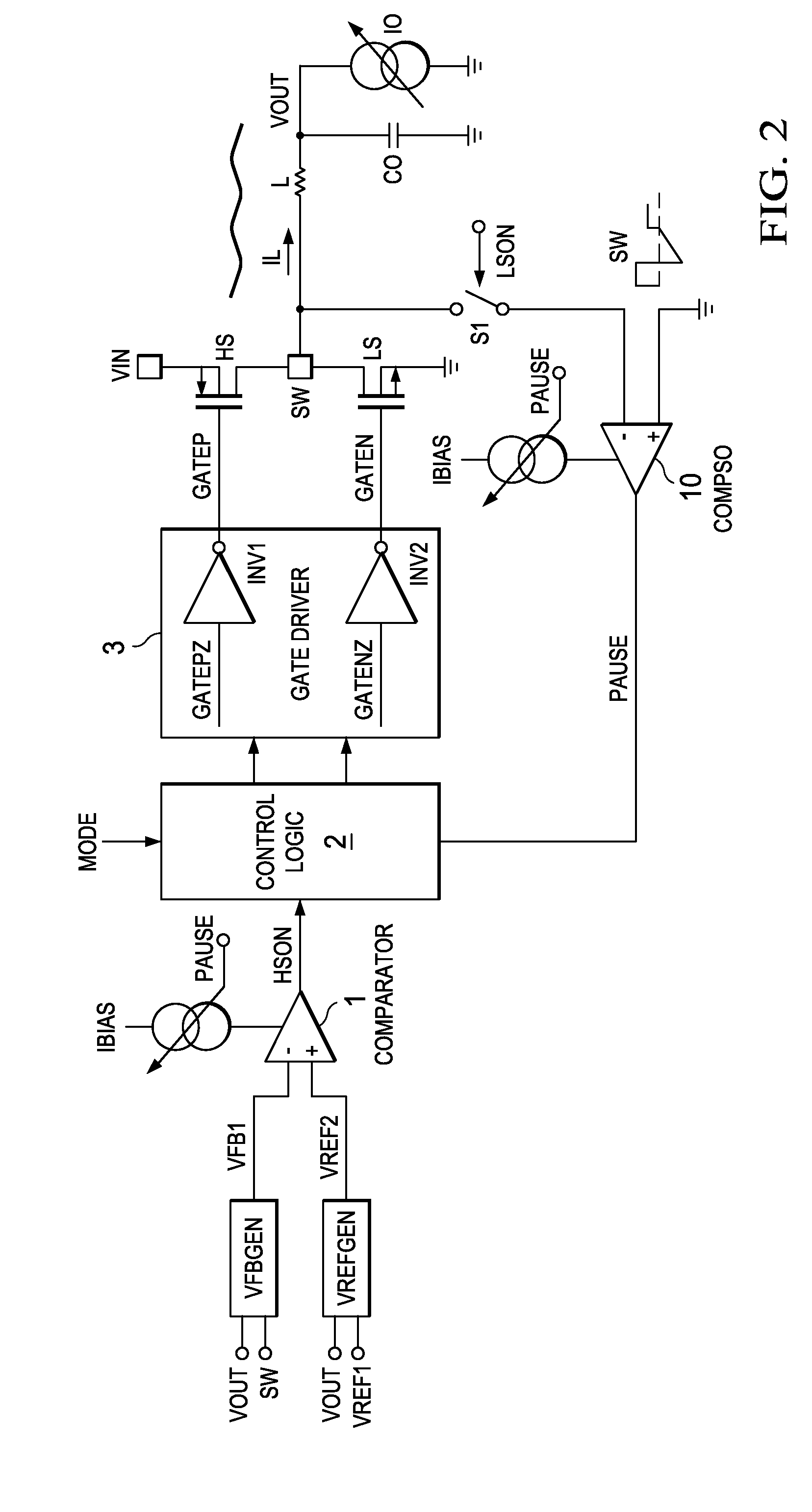

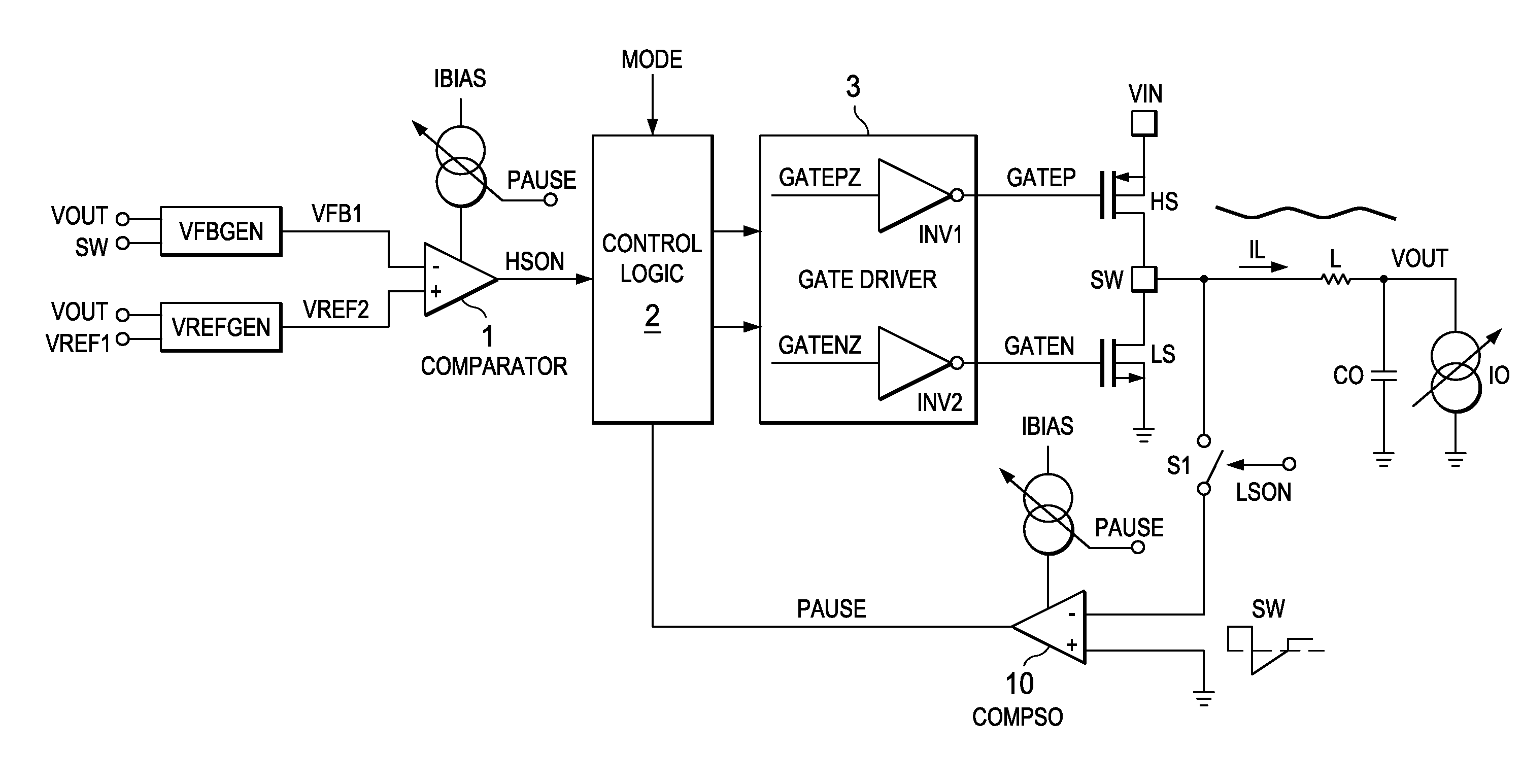

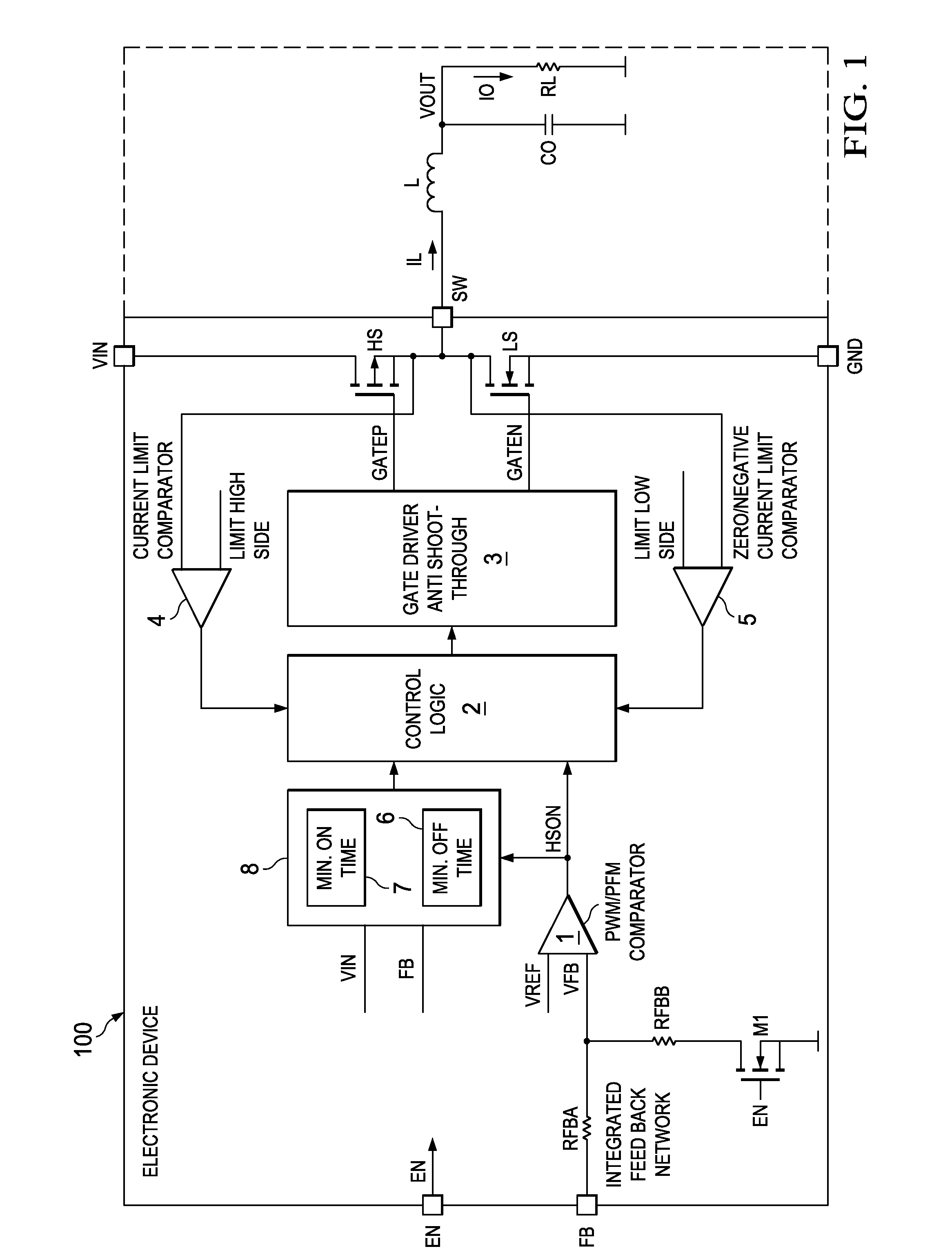

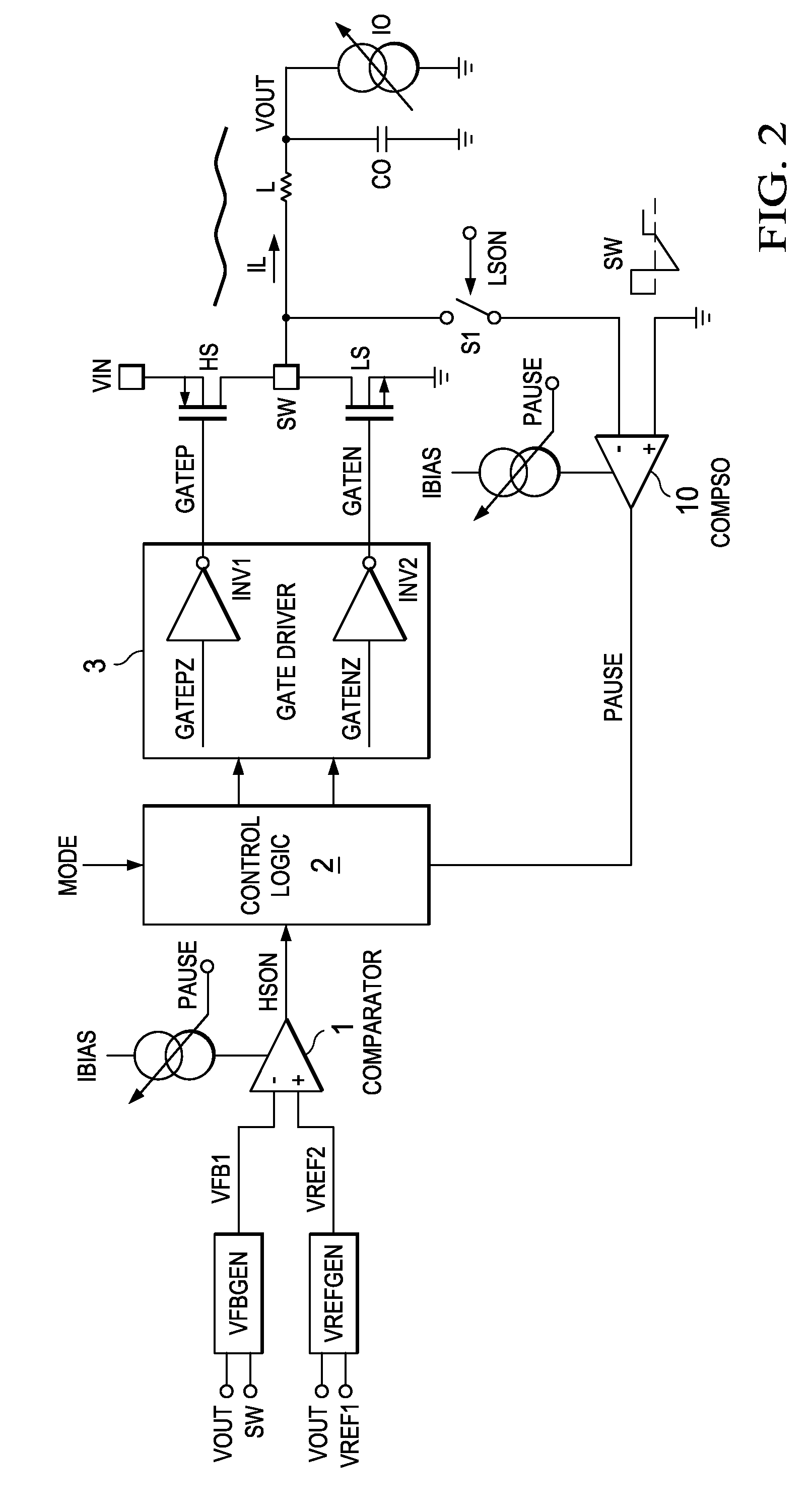

Electronic device and method for dc-dc conversion with variable bias current

ActiveUS20100308784A1Reduce sensitivityReduce bias currentEfficient power electronics conversionDc-dc conversionDc dc converterComparator

The invention relates to an electronic device and a method for DC-DC conversion using a comparator for generating an output signal for driving a power switch of a switch mode DC-DC converter. The electronic device is configured to reduce a bias current of the comparator with a first slope in response to a decreasing load and to increase the bias current of the comparator with a second slope in response to an increasing load, wherein the second slope is steeper than the first slope.

Owner:TEXAS INSTR INC

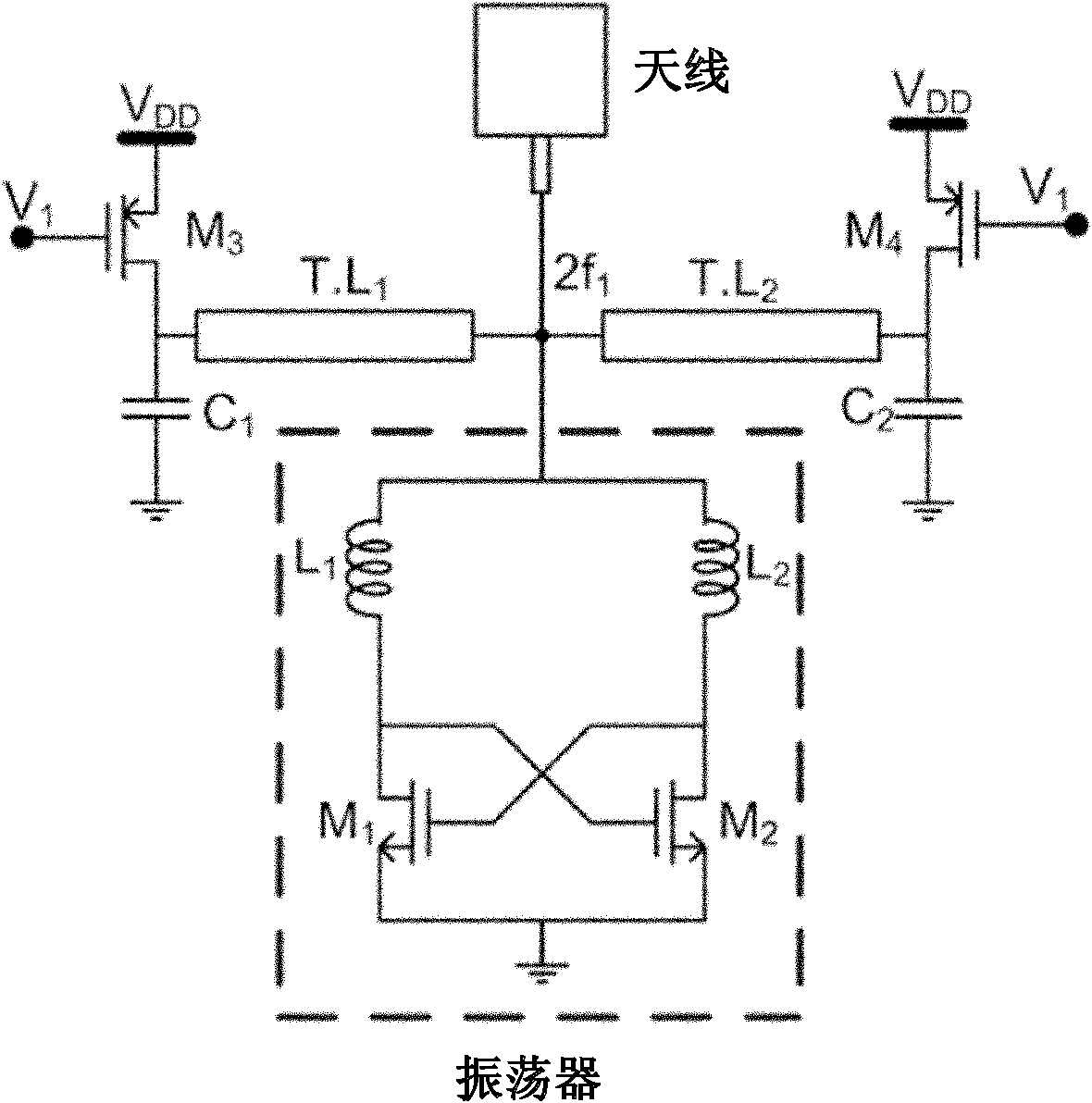

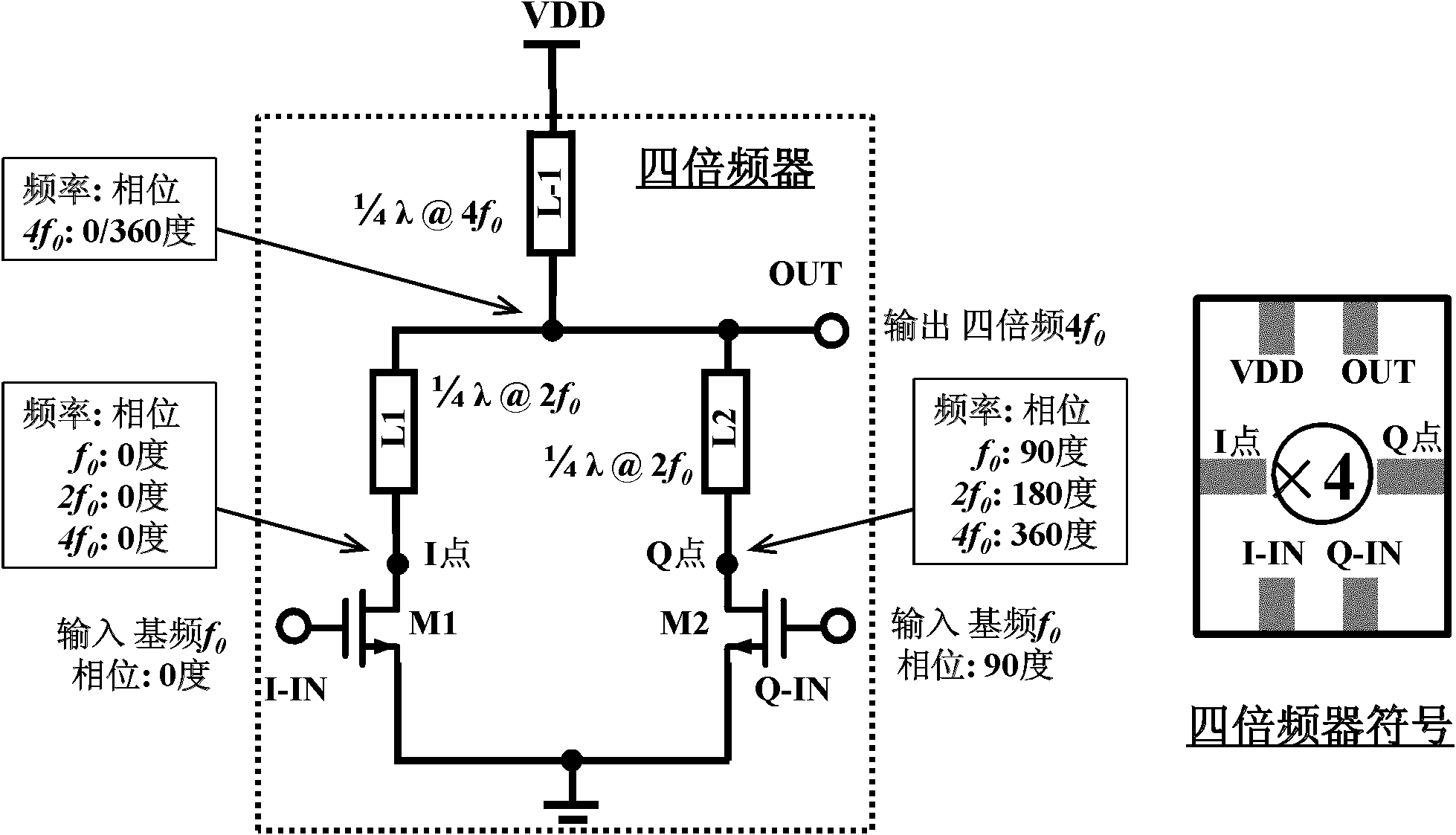

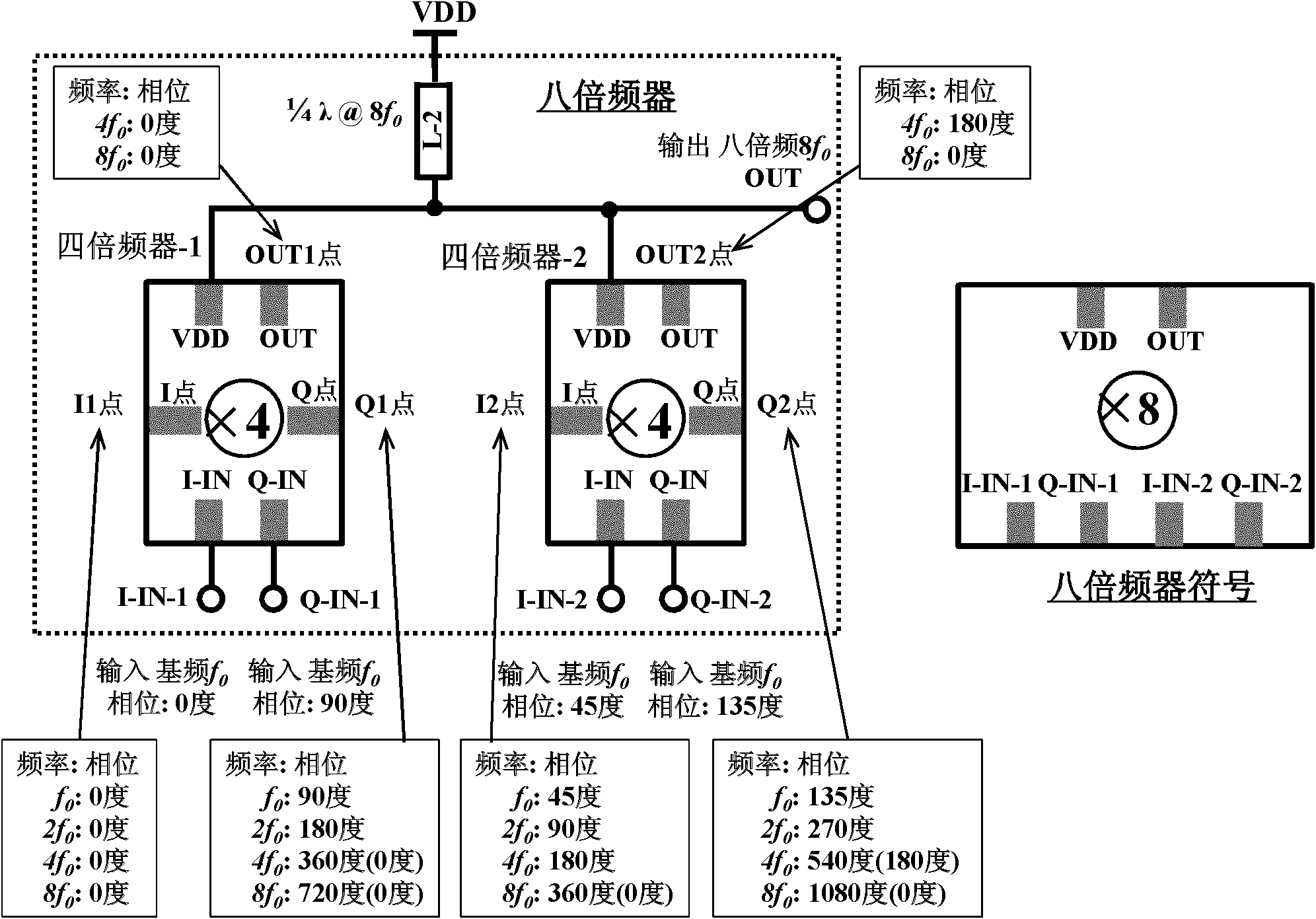

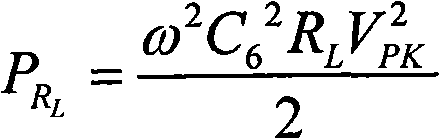

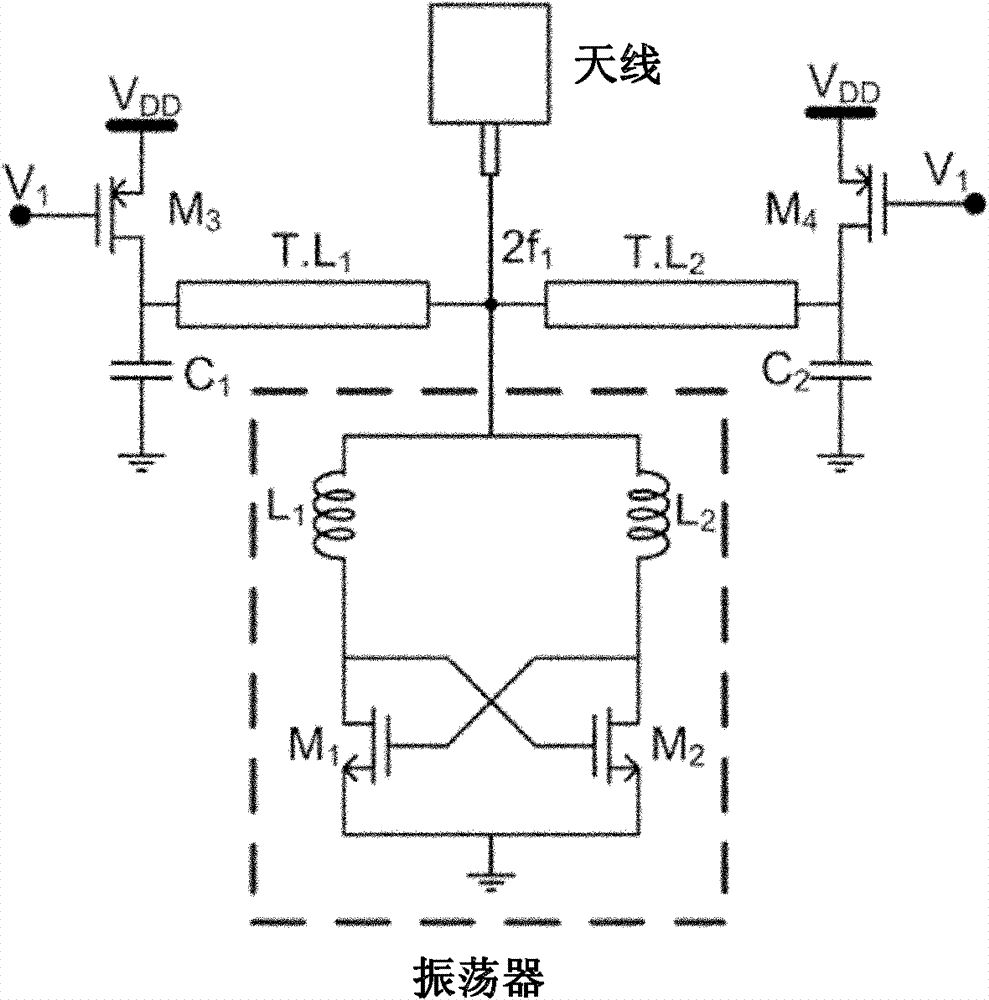

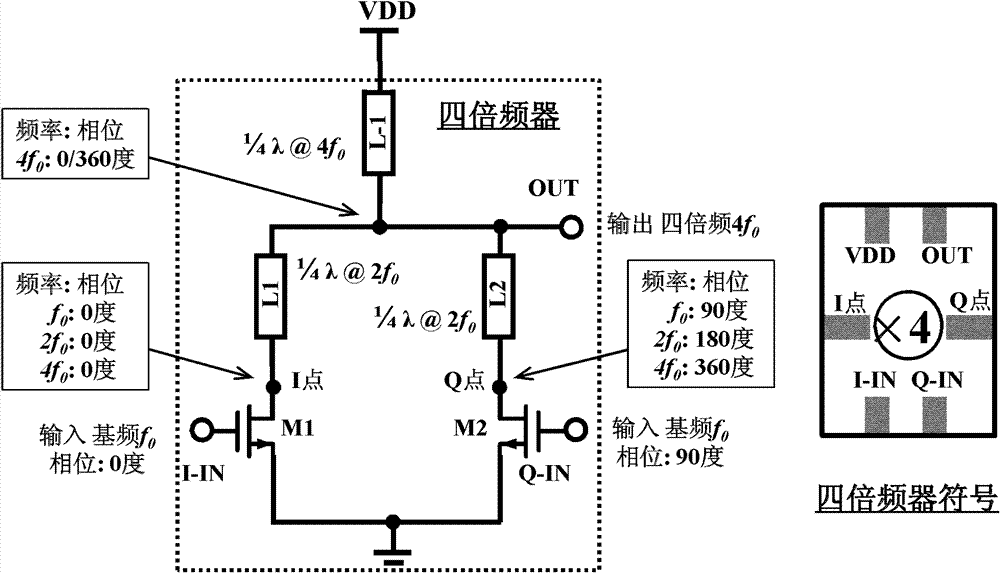

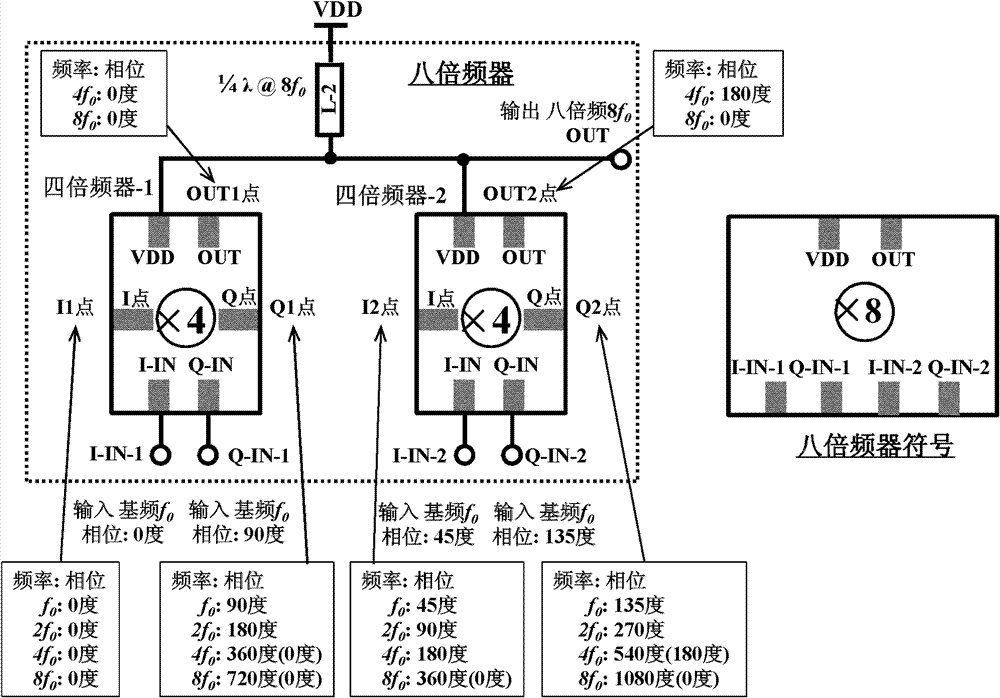

Tera-hertz silica-based quadrupler and frequency multiplier

InactiveCN102104363AIncrease the output frequencyHigh multiplierOscillations generatorsFrequency spectrumRFIC

The invention discloses a tera-hertz silica-based quadrupler and a frequency multiplier, belonging to the field of RFIC (Radio Frequency Integrated Circuit). The quadrupler comprises transistors (M1 and M2) and transmission lines (L1, L2 and L-1), wherein the drain ends of the transistors (M1 and M2) are respectively connected to an output port through the transmission lines (L1 and L2), source ends are connected with a ground line, grid ends are respectively connected with the signal input ends of an path (I) and the path (Q) of a baseband signal (f0); the transmission line (L-1) is connected between the output port and a power supply; and the length of the transmission lines (L1 and L2) are 1 / 4 of that of the corresponding wavelength of a signal (2f0), the length of the transmission line (L-1) is 1 / 4 of that of the corresponding wavelength of a signal (4f0). The multi-frequency multiplier comprises a 2n frequency multiplier (1), a 2n frequency multiplier (2) and a transmission line (L), wherein the output ports of the 2n frequency multiplier (1) and the 2n frequency multiplier (2) are connected to be used as the output port of a 2n+1 frequency multiplier, the transmission line (L) is connected between the output port of the 2n+1 frequency multiplier and the power supply, and the length of the transmission line (L) is 1 / 4 of that of the corresponding wavelength of a signal (2n+1f0). The tera-hertz silica-based quadrupler and the multi-frequency multiplier, provided by invention, have the advantages of high output frequency, pure frequency spectrum, low power consumption and easiness for integration.

Owner:PEKING UNIV

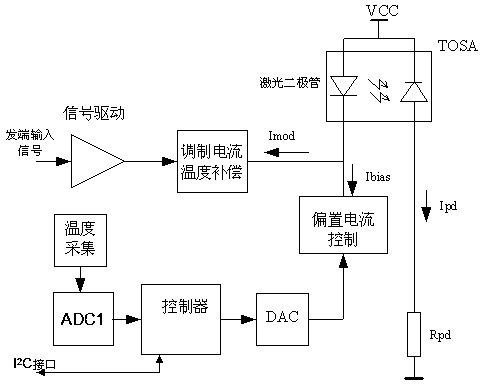

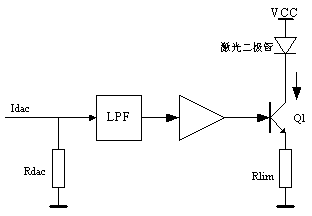

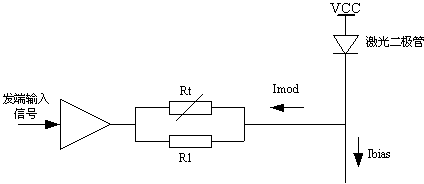

Digital open loop temperature compensation system of optical module laser device

ActiveCN104078841AReduce power consumptionAvoid performance degradationLaser detailsElectromagnetic transmittersOptical ModuleHemt circuits

The invention relates to the field of optical communication, in particular to the laser temperature compensation technology, and discloses a digital open loop temperature compensation system of an optical module laser device. Temperature compensation is carried out on the laser device in an optical module through a digital open loop circuit to guarantee the stable output light power and the stable extinction ratio. Meanwhile, the operating temperature, the bias currents, the backlight currents, the operating voltage and the light collection power value of the digital open loop temperature compensation system are effectively monitored in real time, the power consumption of the optical module is greatly lowered, the risk of performance deterioration and failures of the optical module at high temperature for a long time is avoided, and stable operation of the system is guaranteed. Meanwhile, hardware of the scheme is simple, the cost is lower compared with an integrated dedicated chip scheme, and production is simple and practicable.

Owner:成都新易盛通信技术股份有限公司

Current type terahertz pyroelectricity detector reading circuit

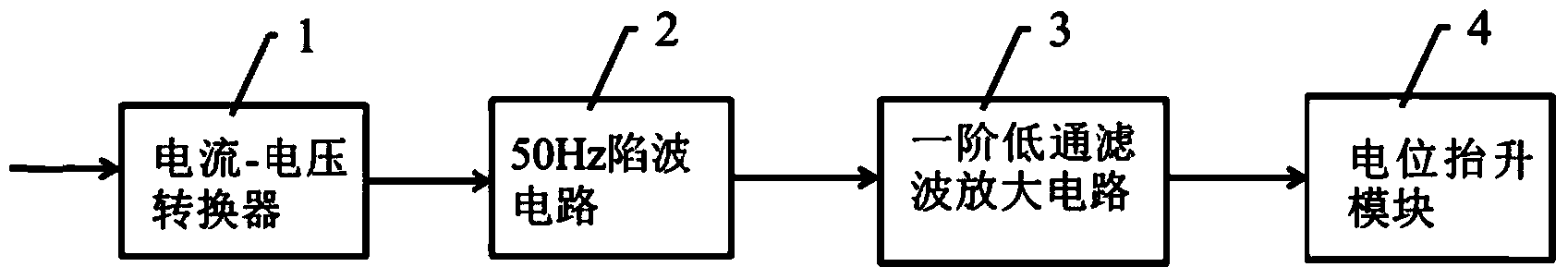

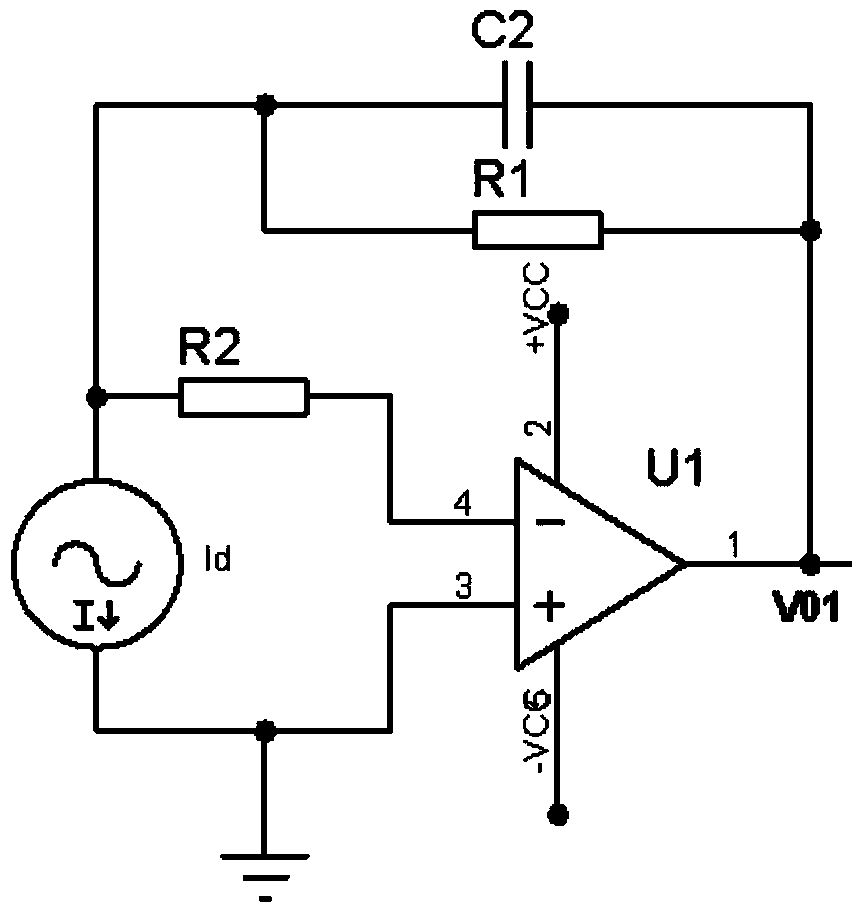

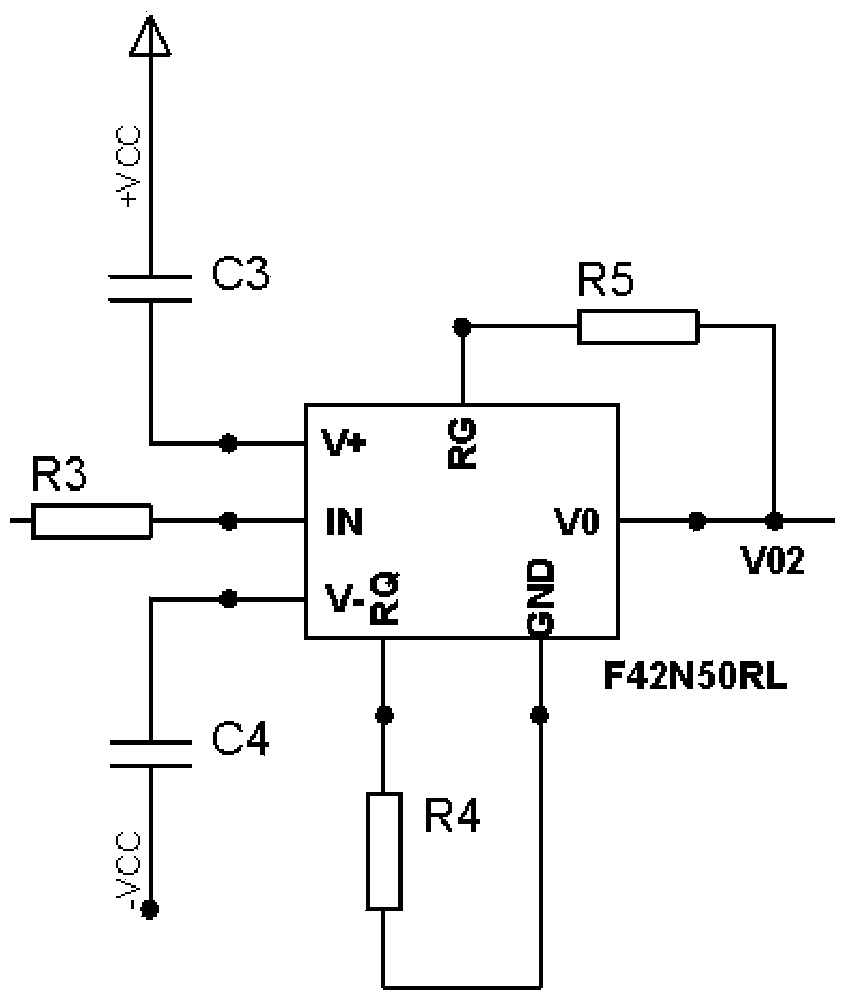

InactiveCN103913240AEliminate power frequency interferenceFilter out the signalRadiation pyrometryVoltage converterComputer module

The invention discloses a current type terahertz pyroelectricity detector reading circuit, and belongs to the field of terahertz detecting and imaging. The reading circuit comprises a current-voltage converter, a 50Hz trap circuit, a first-order lowpass filtering amplifying circuit and an electric potential raising module. Signals output by the terahertz pyroelectricity detector are input into the current-voltage converter so that the current signals can be converted into voltage signals; the signals output by the current-voltage converter are input into the 50Hz trap circuit so that power frequency interference can be eliminated; the signals output by the 50Hz trap circuit are input into the first-order lowpass filtering amplifying circuit so that the signals can be further amplified; the signals output by the first-order lowpass filtering amplifying circuit are input into the electric potential raising module so that a voltage can be raised and the voltage signals output by the circuit can be matched with a voltage required by a rear digital collecting circuit. The voltage signals output by the circuit are pure, and the circuit is suitable for collecting and outputting a weak current of the terahertz pyroelectricity detector.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

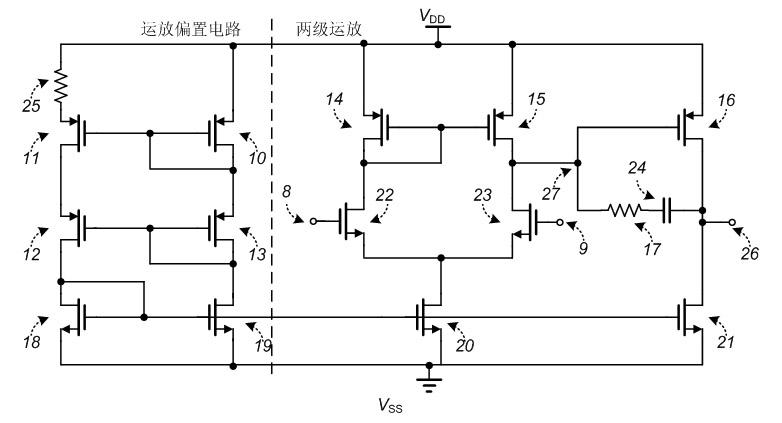

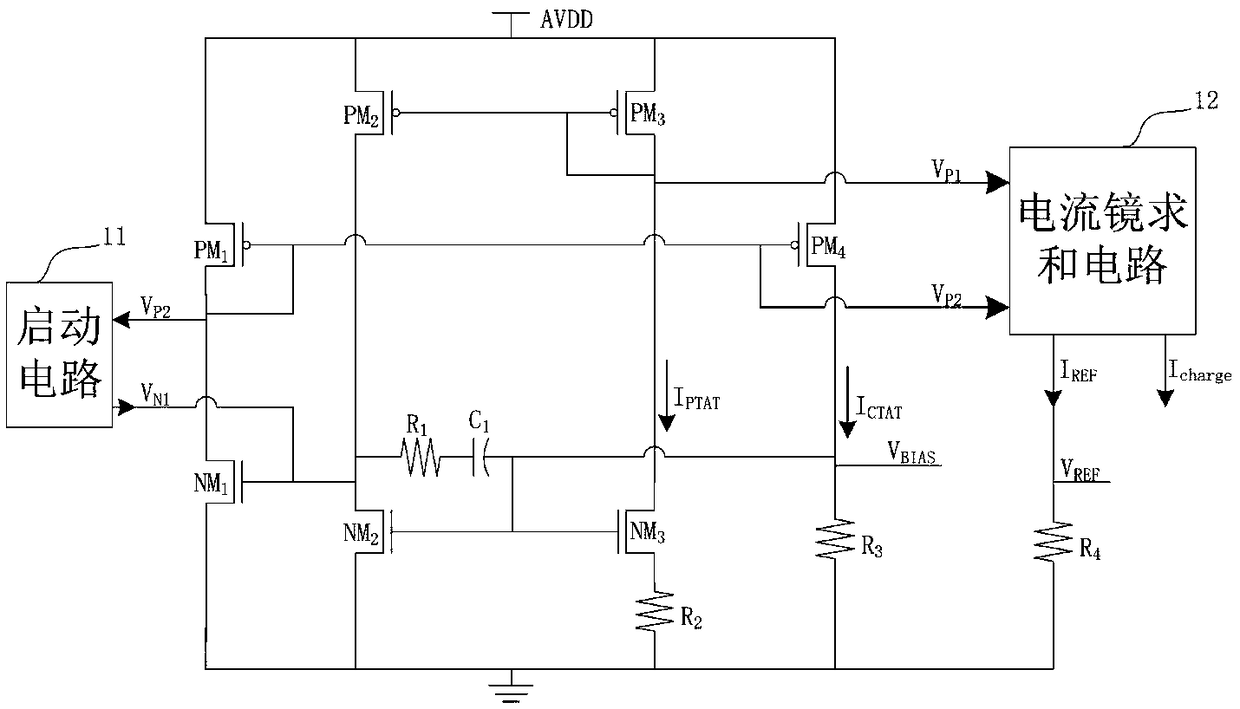

Temperature compensation current source having wide temperature scope and being compatible with CMOS (complementary metal-oxide-semiconductor transistor) technique

InactiveCN102122189AReduce power consumptionReduce bias currentElectric variable regulationP channelIntegrated circuit

The invention belongs to the technical field of integrated circuit and particularly relates to a temperature compensation current source having wide temperature scope and being compatible with CMOS (complementary metal-oxide-semiconductor transistor) technique, which comprises four NMOS (n-channel metal oxide semiconductor)tubes, three PMOS (p-channel metal oxide semiconductor) tubes, a compensation resistor and an operational amplifier, wherein the operational amplifier is a traditional two-stage miller compensation operational amplifier and has a biasing circuit; the high-gain operational amplifier can be used for ensuring that the voltages at difference input ends are the same; a main circuit of the temperature compensation current source is formed by the four NMOS tubes, three PMOS tubes and the compensation resistor; and by utilizing the resistance, the mobility of MOS tubes and different temperature coefficients of threshold voltages, the novel temperature compensation current source which is low in temperature coefficient, has small area, is fit for wide range of temperature change and is compatible with the standard CMOS technique, is realized.

Owner:FUDAN UNIV

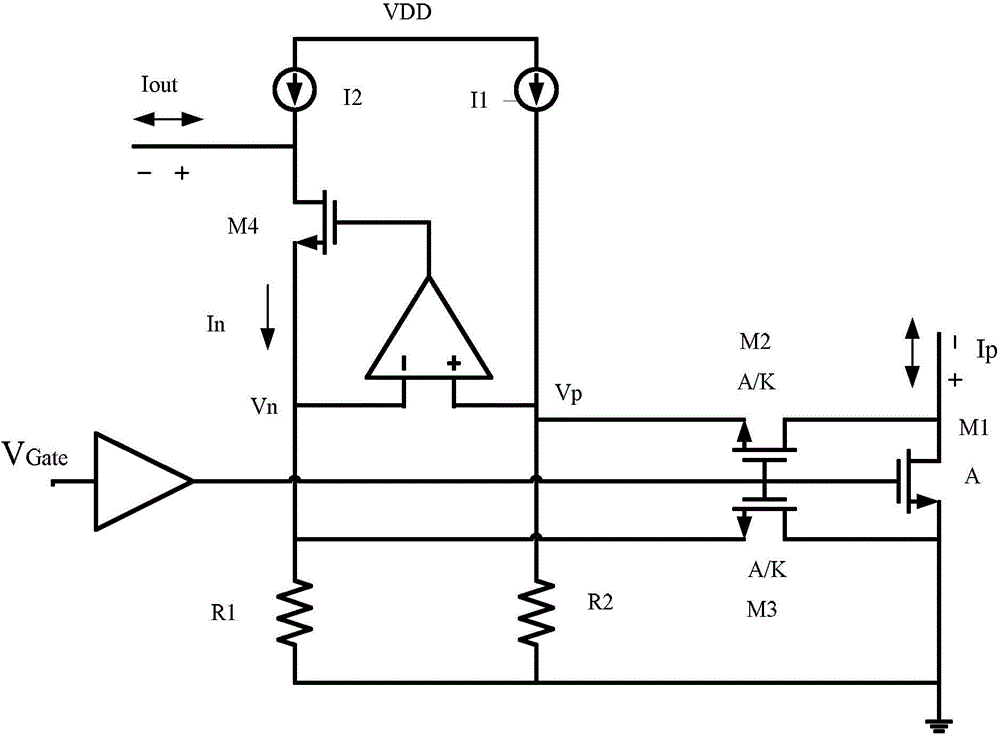

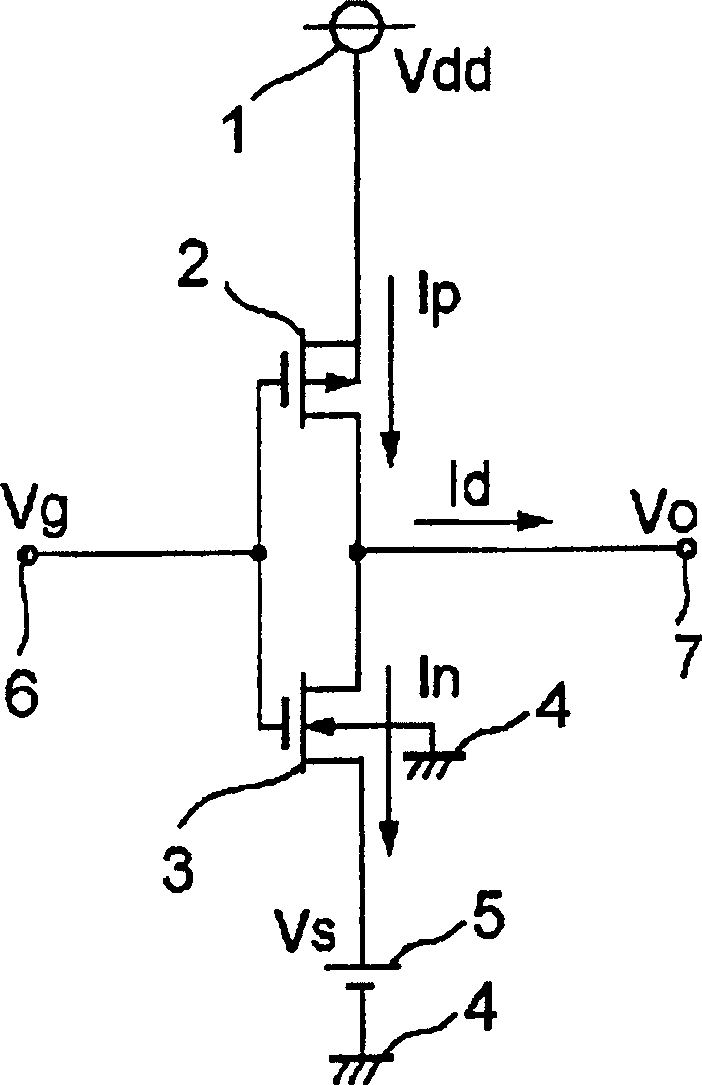

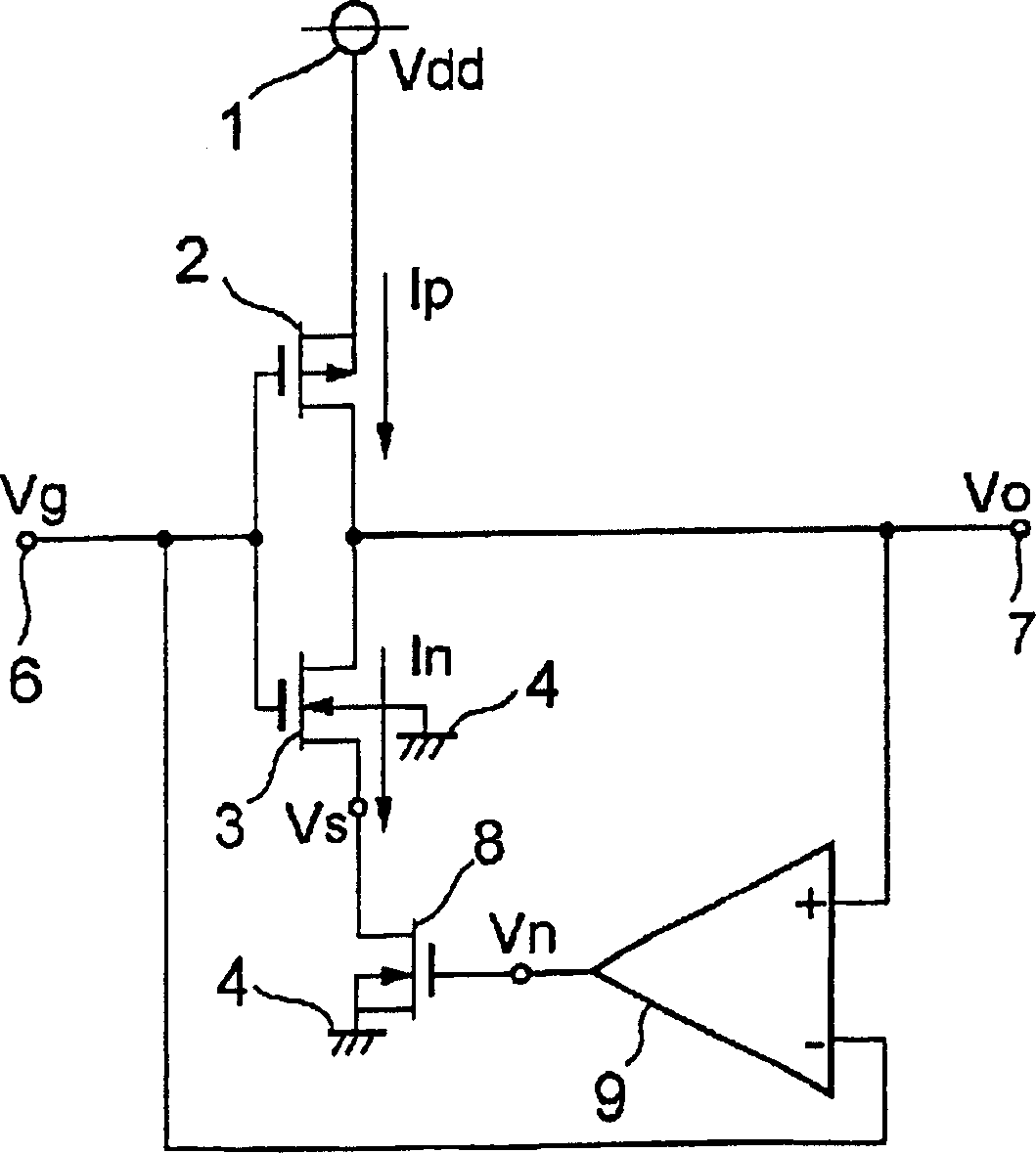

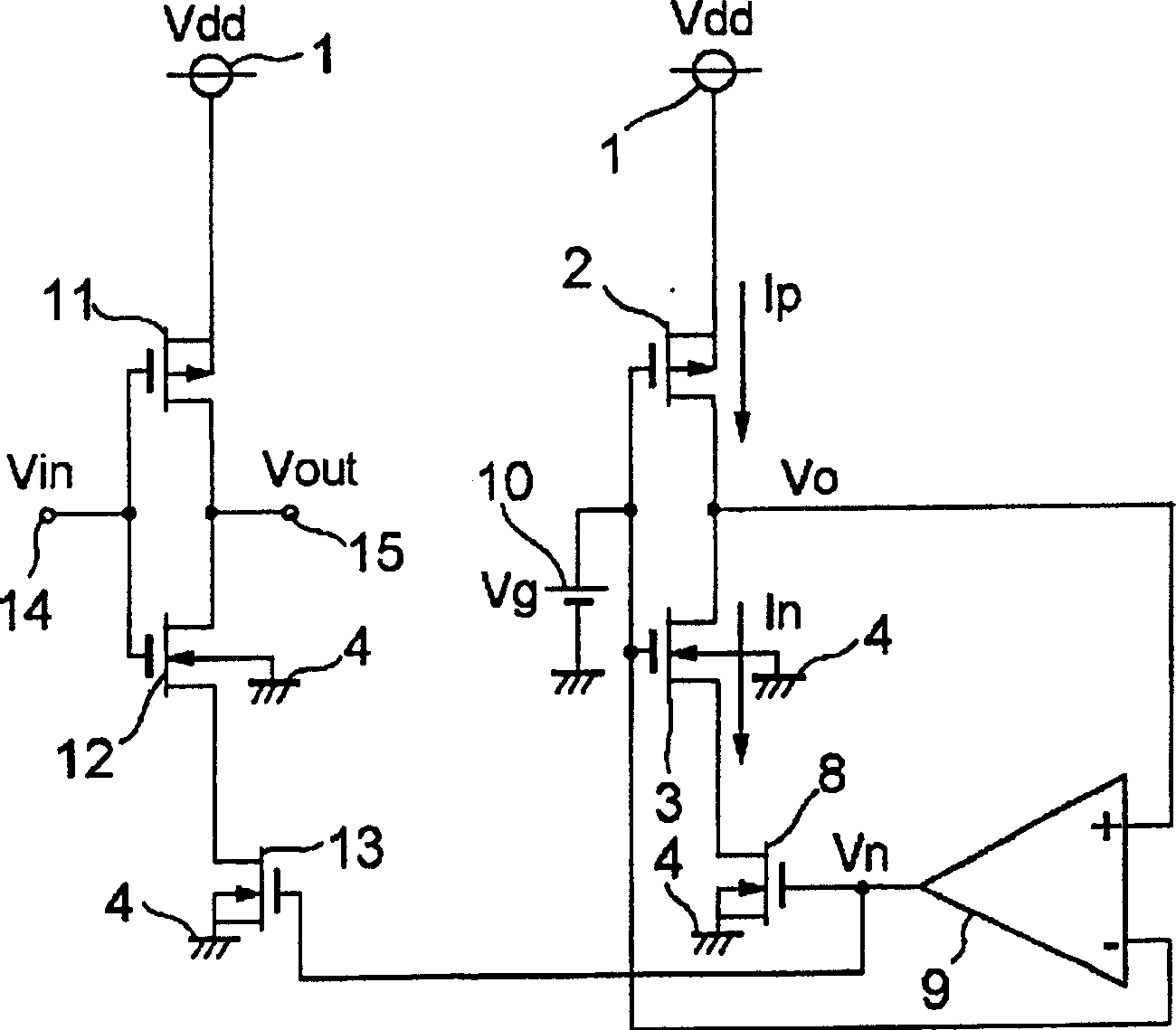

Electronic device and method for DC-DC conversion with variable bias current

ActiveUS8970199B2Reduce sensitivityReduce bias currentEfficient power electronics conversionDc-dc conversionDc dc converterComparator

The invention relates to an electronic device and a method for DC-DC conversion using a comparator for generating an output signal for driving a power switch of a switch mode DC-DC converter. The electronic device is configured to reduce a bias current of the comparator with a first slope in response to a decreasing load and to increase the bias current of the comparator with a second slope in response to an increasing load, wherein the second slope is steeper than the first slope.

Owner:TEXAS INSTR INC

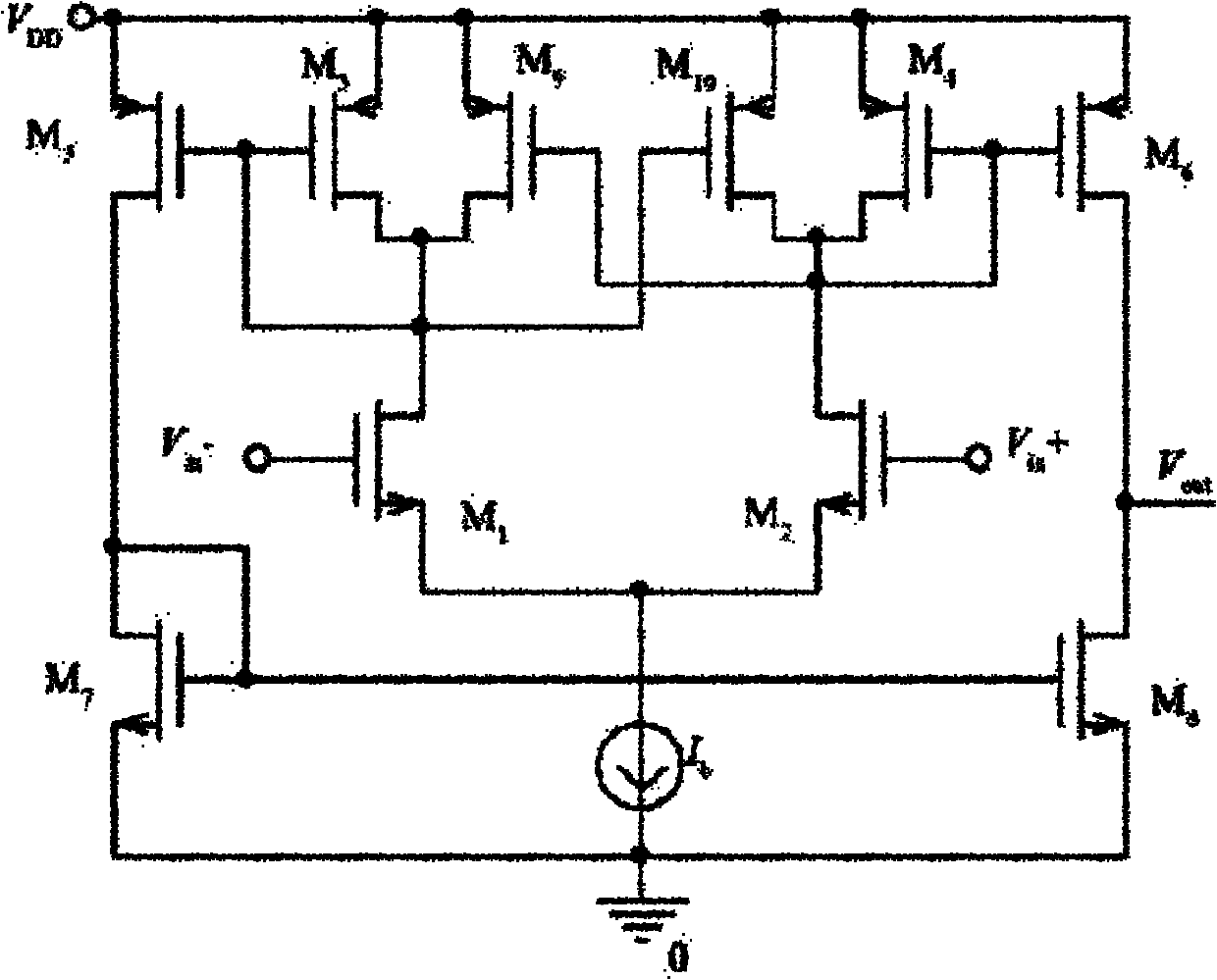

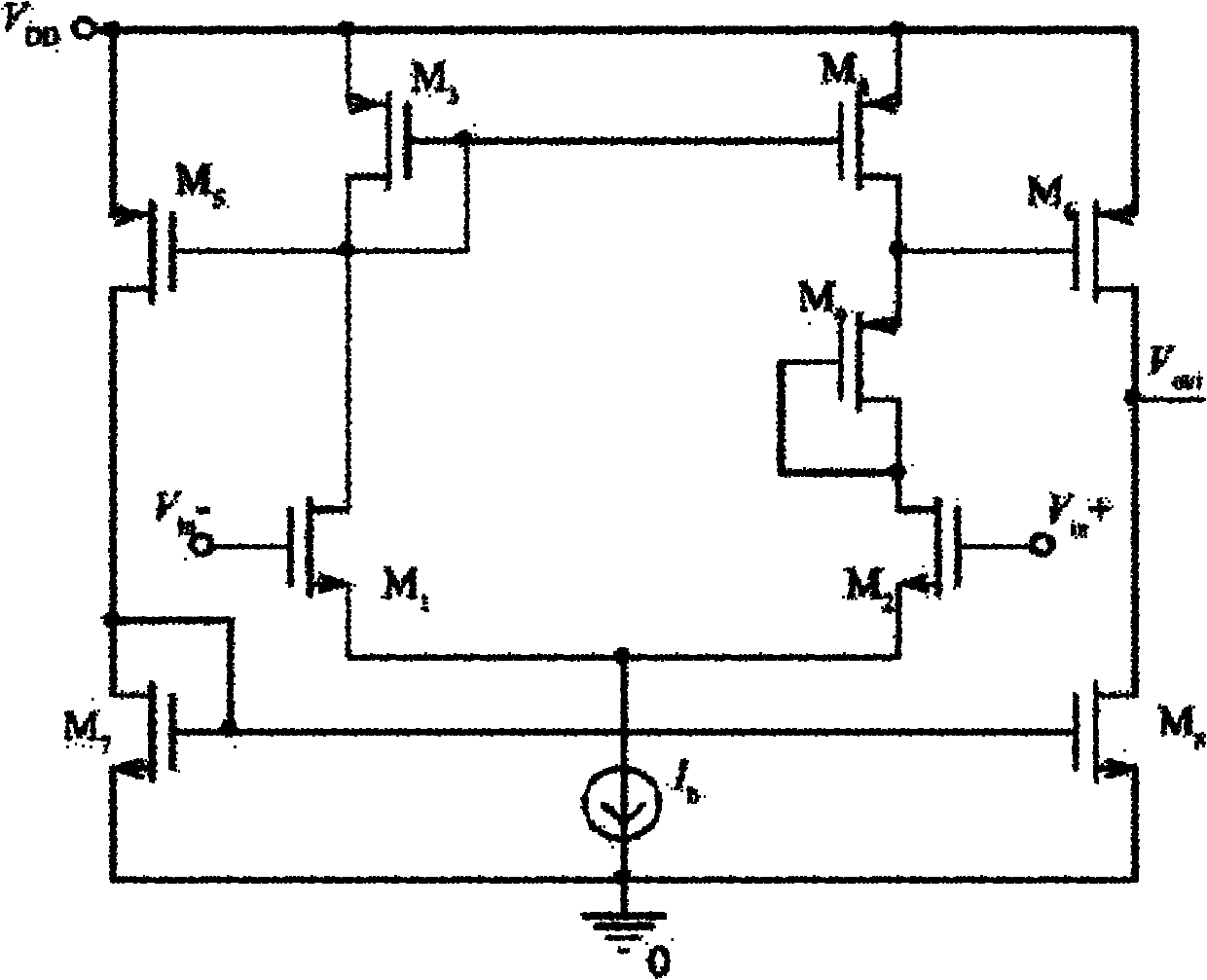

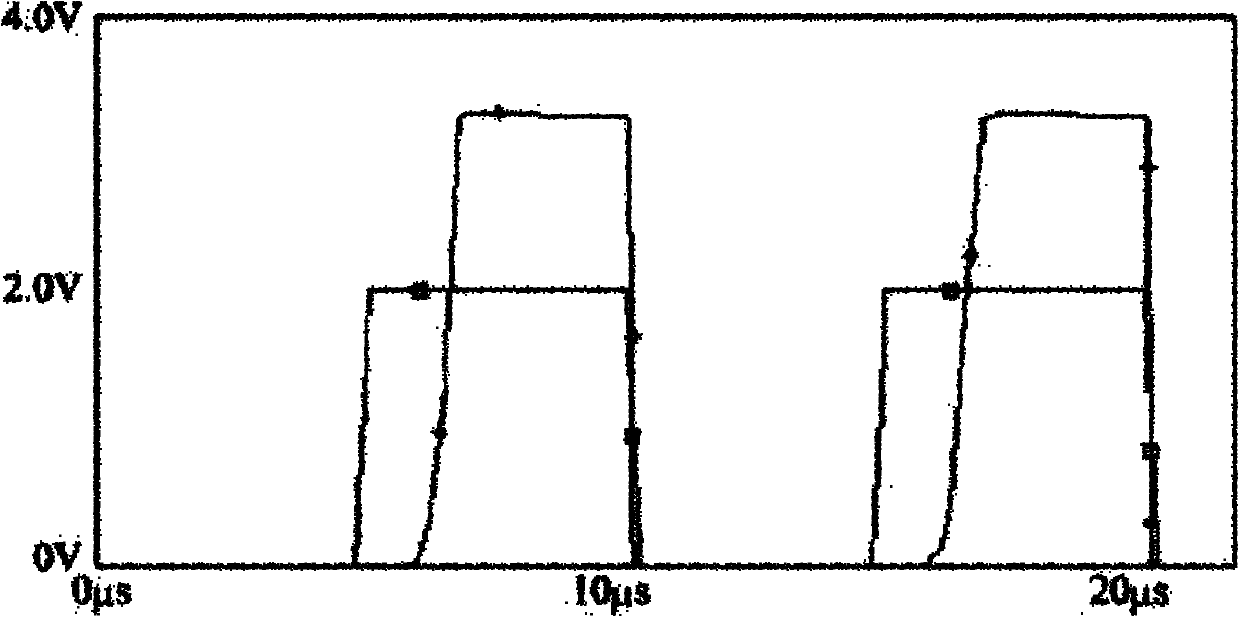

Voltage comparator

InactiveCN102571044AReduce bias currentLower latencyMultiple input and output pulse circuitsElectric variable regulationSub thresholdComputer module

The invention provides a voltage comparator, which comprises a current source, a differential gain module and a conversion module, wherein the current magnitude of the current source is of nanoampere level; the differential gain module comprises a first transistor, a second transistor, a third transistor and a fourth transistor; the first transistor and the second transistor are connected with the current source respectively; the third transistor and the fourth transistor form a current mirror structure; the third transistor is connected with the first transistor; and the fourth transistor is connected with the second transistor through a ninth transistor for forming asymmetric differential gain. According to the voltage comparator provided by the invention, since the transistor which works in a sub-threshold region has higher transconductance-to-current ratio Gm / Ib than the transistor which works in a saturation region, the power consumption is lower; and in order to reduce the power consumption, the bias current in the voltage comparator provided by the embodiment is low, and the time delay of the voltage comparator is also low.

Owner:CSMC TECH FAB1 +1

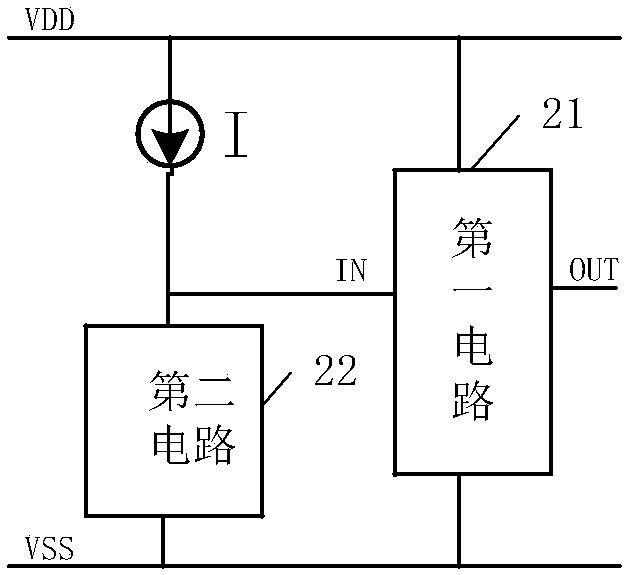

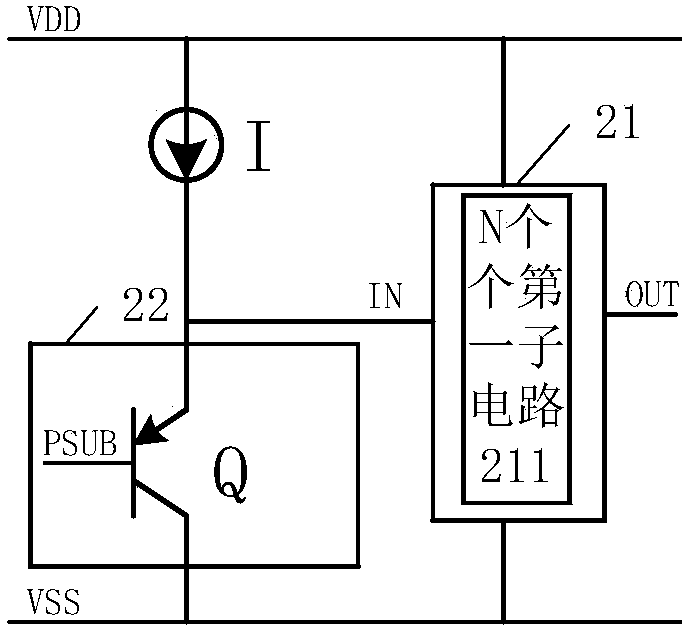

Band-gap reference voltage generation method and circuit

InactiveCN105955391AReduce power consumptionReduce bias currentElectric variable regulationElectronic communicationTransistor

The invention relates to the technical field of electronic communications, and discloses a voltage generation circuit and a voltage generation method which are used for generating band-gap reference voltage. The voltage generation circuit comprises a first circuit used for generating first voltage which is in direct proportion to temperature and a second circuit used for generating second voltage which is in inverse proportion to the temperature, wherein the first circuit and the second circuit are connected to enable the first voltage and the second voltage to be superposed, and therefore the band-gap reference voltage is provided; the first circuit is obtained by means of transistors. By means of the band-gap reference voltage generation method and circuit, the band-gap reference voltage is generated, the circuit power consumption can be reduced, and the chip area can be decreased.

Owner:TELINK SEMICON SHANGHAI

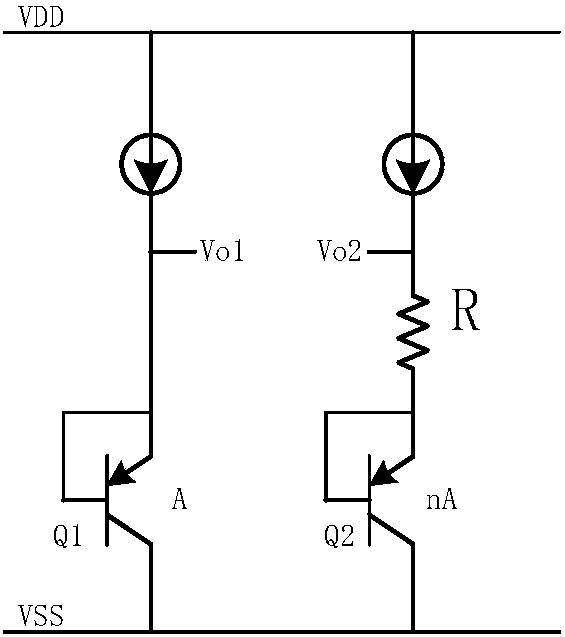

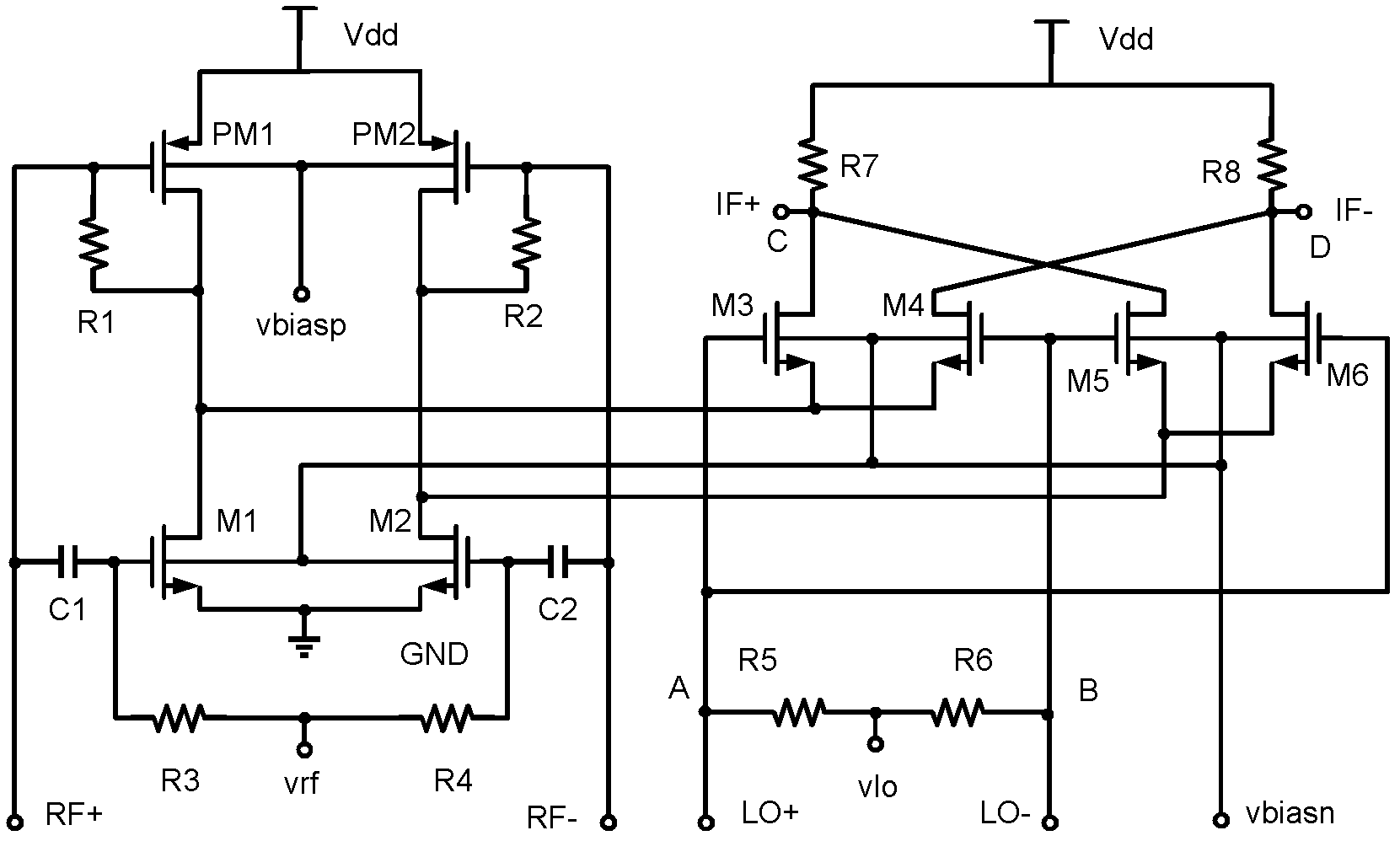

Ultralow consumption current multiplexing mixer based on substrate bias

ActiveCN102611392AReduce bias currentHigh currentModulation transference by semiconductor devices with minimum 2 electrodesLinearityP channel

The invention discloses an ultralow consumption current multiplexing mixer based on substrate bias. The mixer comprises the following parts: a transconductance grade consisting of a pair of NMOS (N-channel Metal Oxide Semiconductor) pipes and a pair of PMOS (P-channel Metal Oxide Semiconductor) pipes, a switch grade consisting of two pairs of NMOS pipes, and a load grade consisting of resistors. The transconductance grade of the mixer utilizes a self-bias complementary transconductance structure and forms a folding structure with the switch grade to greatly reduce voltage of a power supply; substrates of all the MOS pipes in a circuit are additionally provided with fixed bias voltage to reduce threshold voltage of the MOS pipe and realize the design of ultralow voltage ultralow power consumption; and through a current multiplexing technique, the noise performance of the circuit is modified, and the conversion gain and the linearity are improved. The ultralow consumption current multiplexing mixer based on the substrate bias, disclosed by the invention, can be applied to deep submicron radio frequency CMOS (Complementary Metal Oxide Semiconductor) integrated circuits and can be widely applied to electronic systems in the aerospace field.

Owner:BEIHANG UNIV

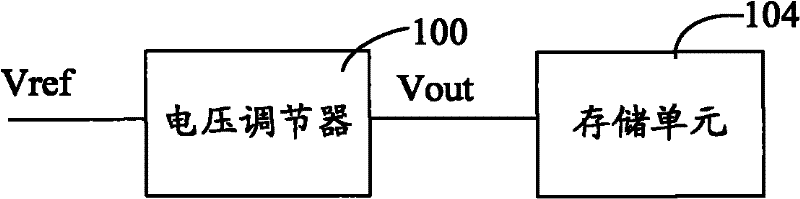

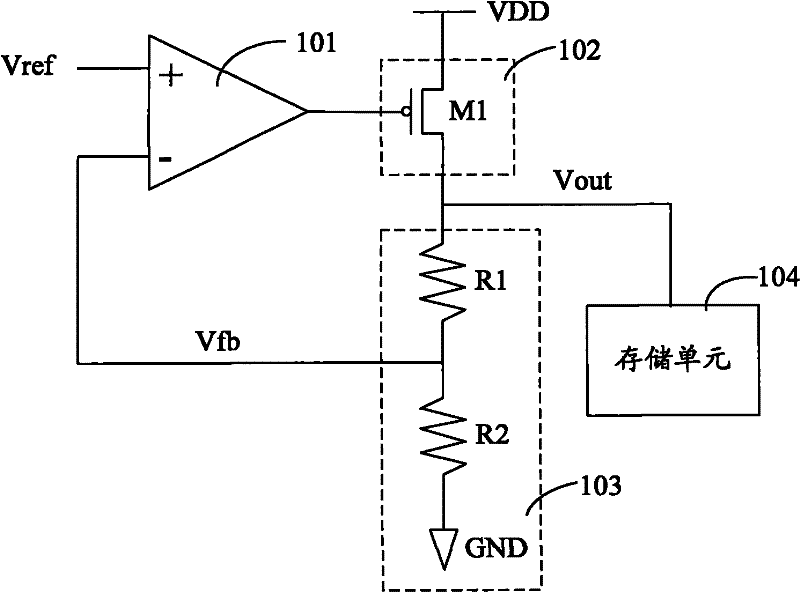

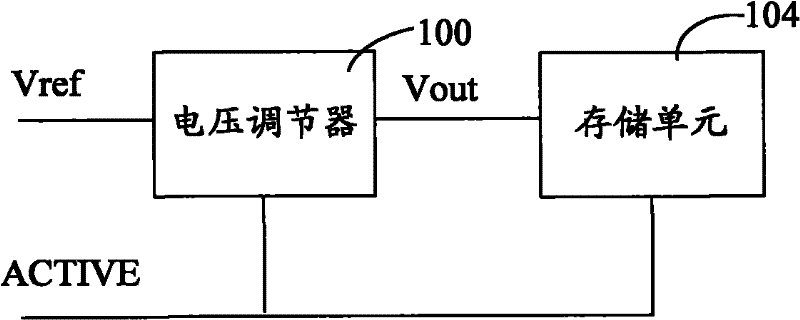

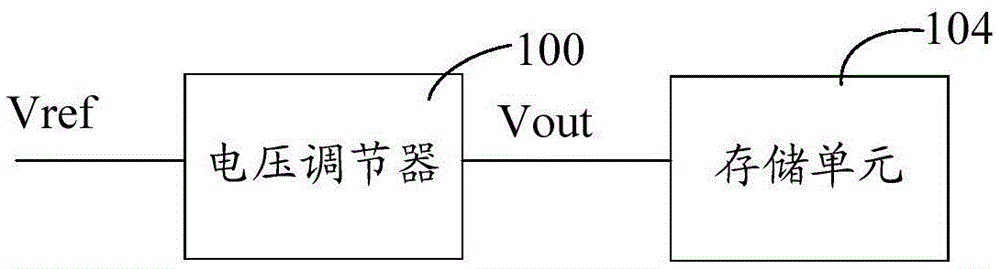

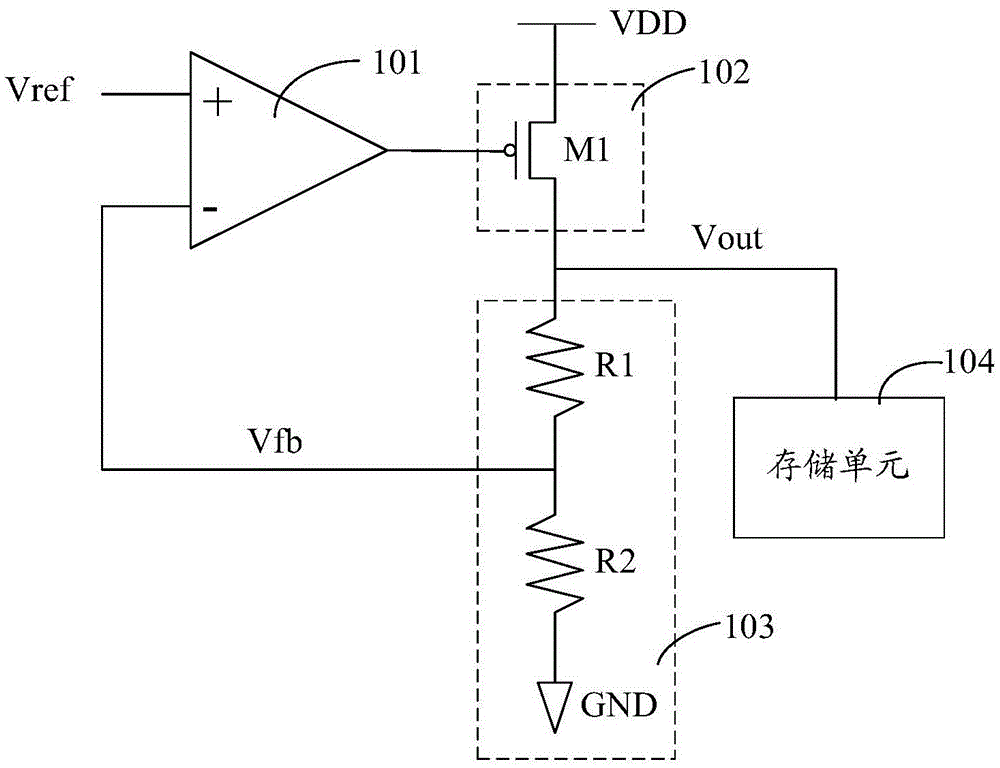

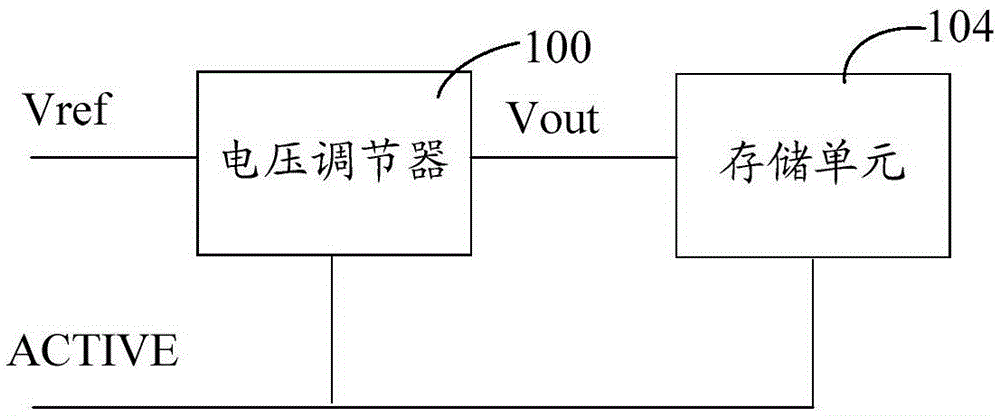

Voltage supply circuit

ActiveCN102237138AQuick responseReduce power consumptionRead-only memoriesElectric variable regulationStopped workVoltage regulation

The invention provides a voltage supply circuit used for supplying voltage to a memory unit. The memory unit comprises a voltage input end. The voltage supply circuit comprises a first voltage regulator, a second voltage regulator and a control unit, wherein the first voltage regulator is used for regulating reference voltage to generate working voltage when the memory unit works and stops working when the memory unit does not work; the second voltage regulator is used for regulating the reference voltage to generate standby voltage; and the control unit is used for controlling the voltage input end to receive the working voltage after the memory unit works for a preset time, or receiving the standby voltage. The voltage supply circuit has the following advantage: the problem of slow response of the memory unit caused by delay of the voltage regulators is avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

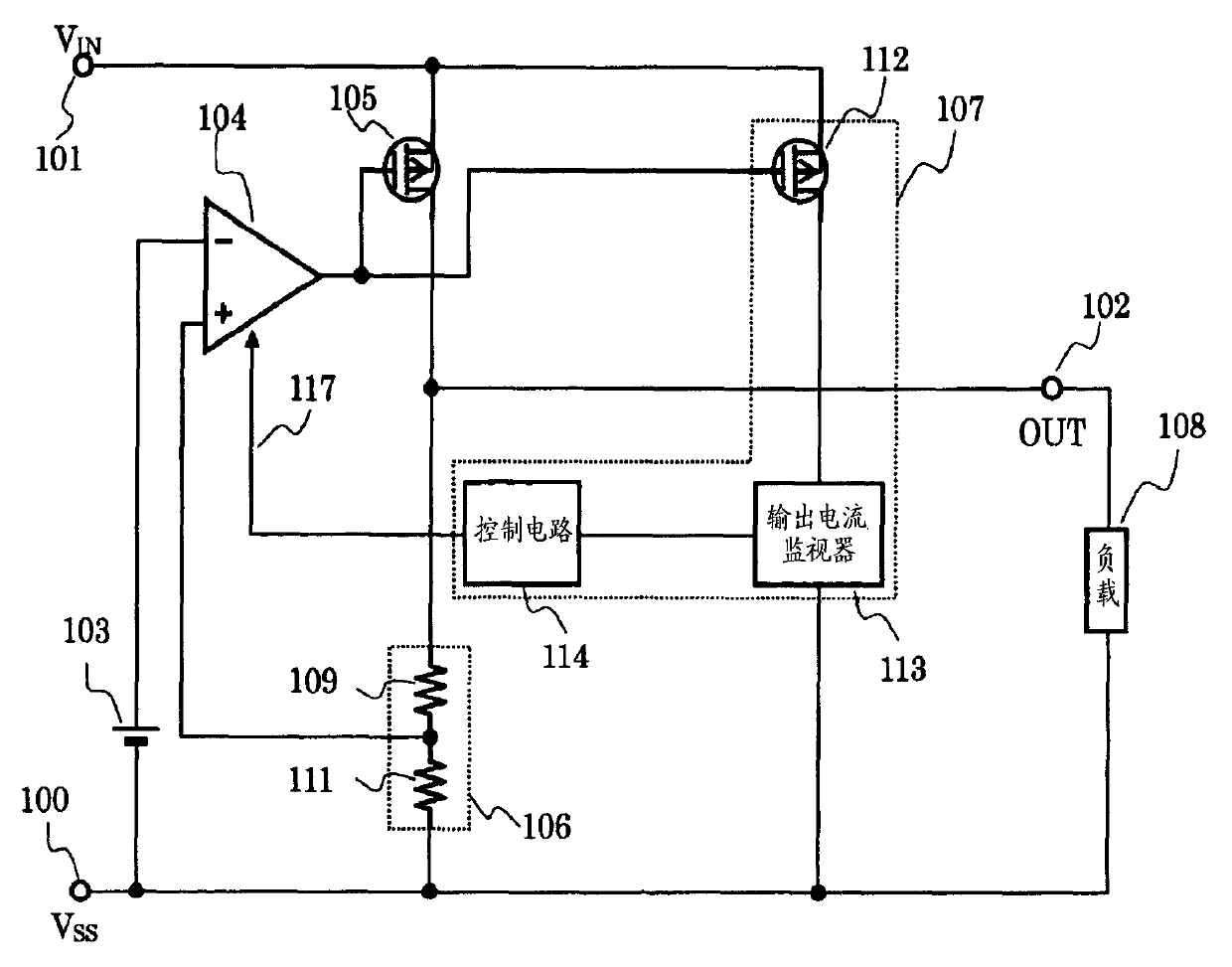

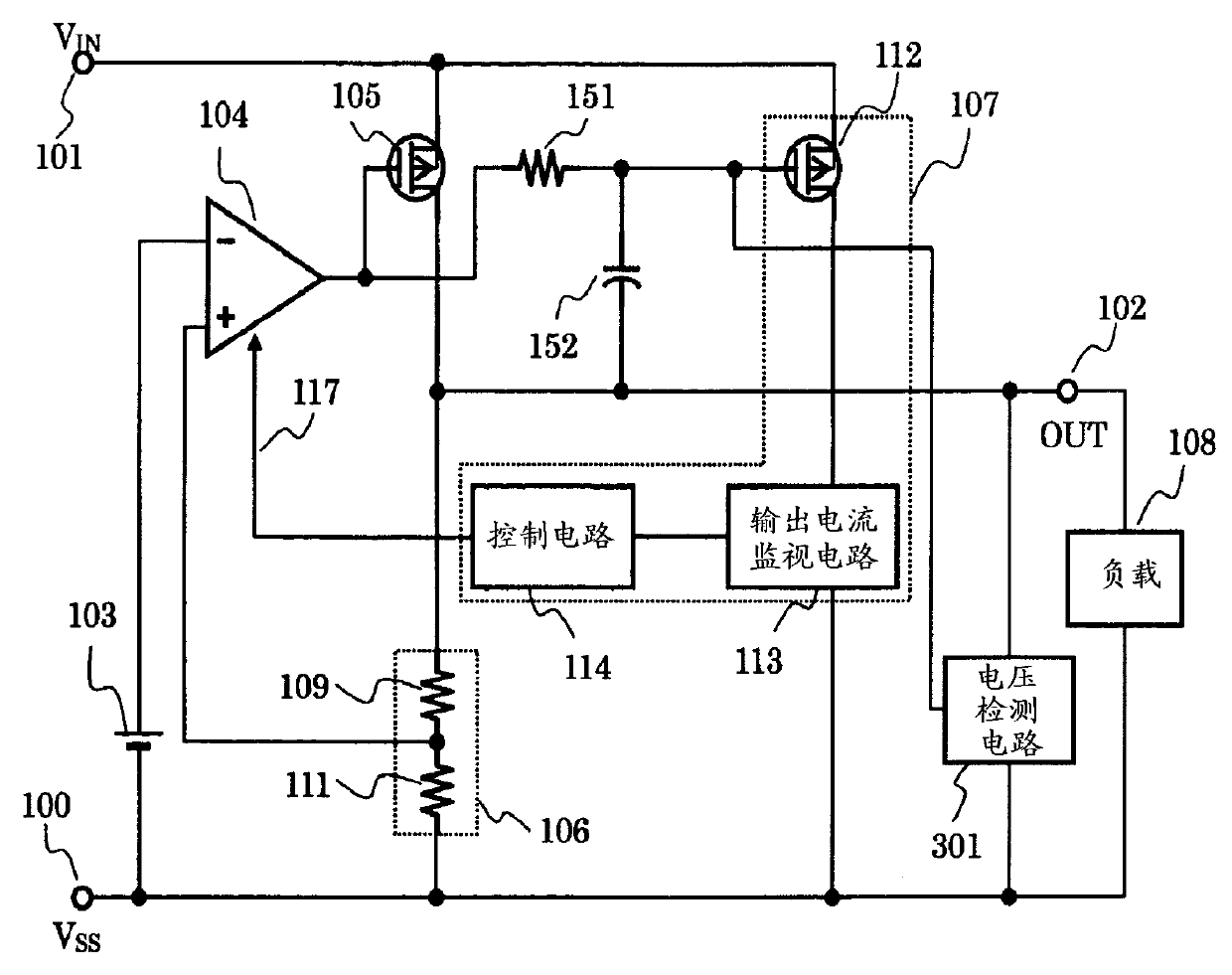

Voltage regulator

InactiveCN103309387AReduce bias currentReduced output voltage dropElectric variable regulationCapacitanceElectrical resistance and conductance

Provided is a voltage regulator having improved transient response characteristics even when a load current is switched from a light load to a heavy load. The voltage regulator includes, to a gate of a detection transistor constituting an output current detection circuit: a resistive element for interrupting the gate of the detection transistor from an output terminal of a differential amplifier circuit in an AC manner; and a capacitive element connected to an output terminal of the voltage regulator in an AC manner.

Owner:SII SEMICONDUCTOR CORP

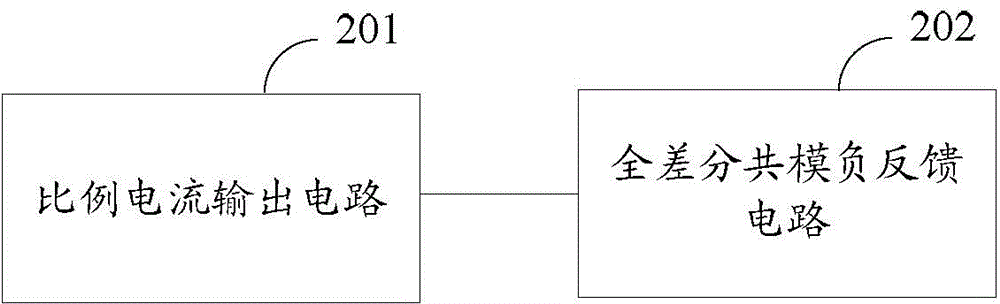

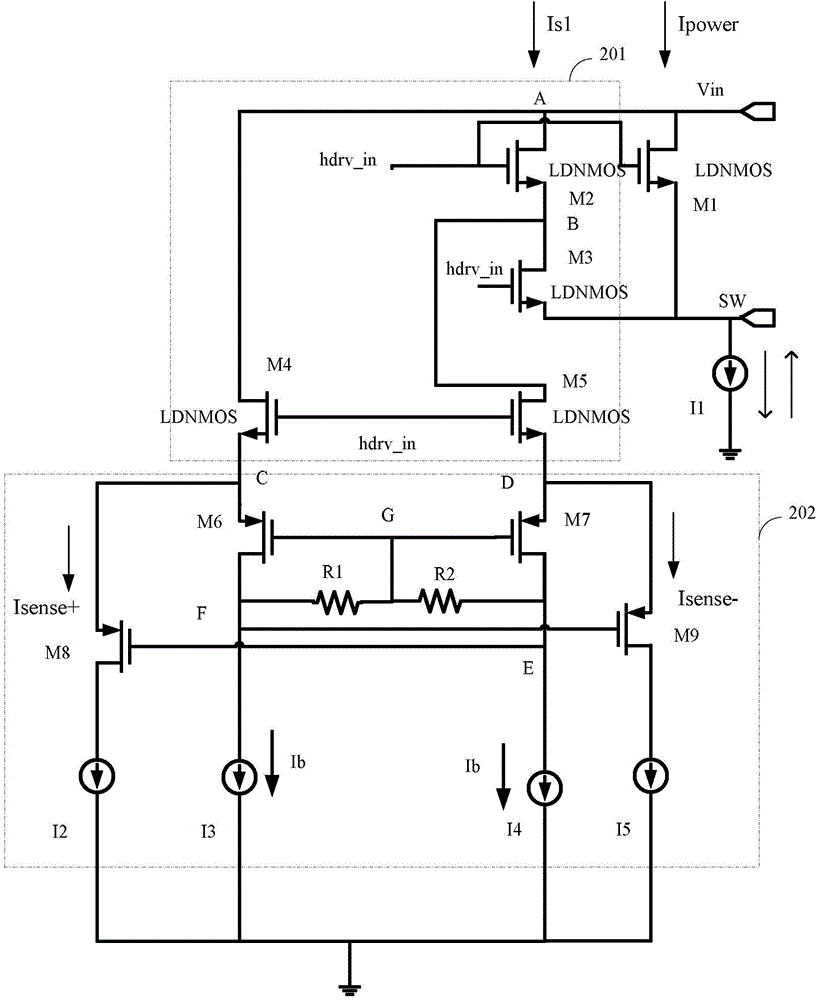

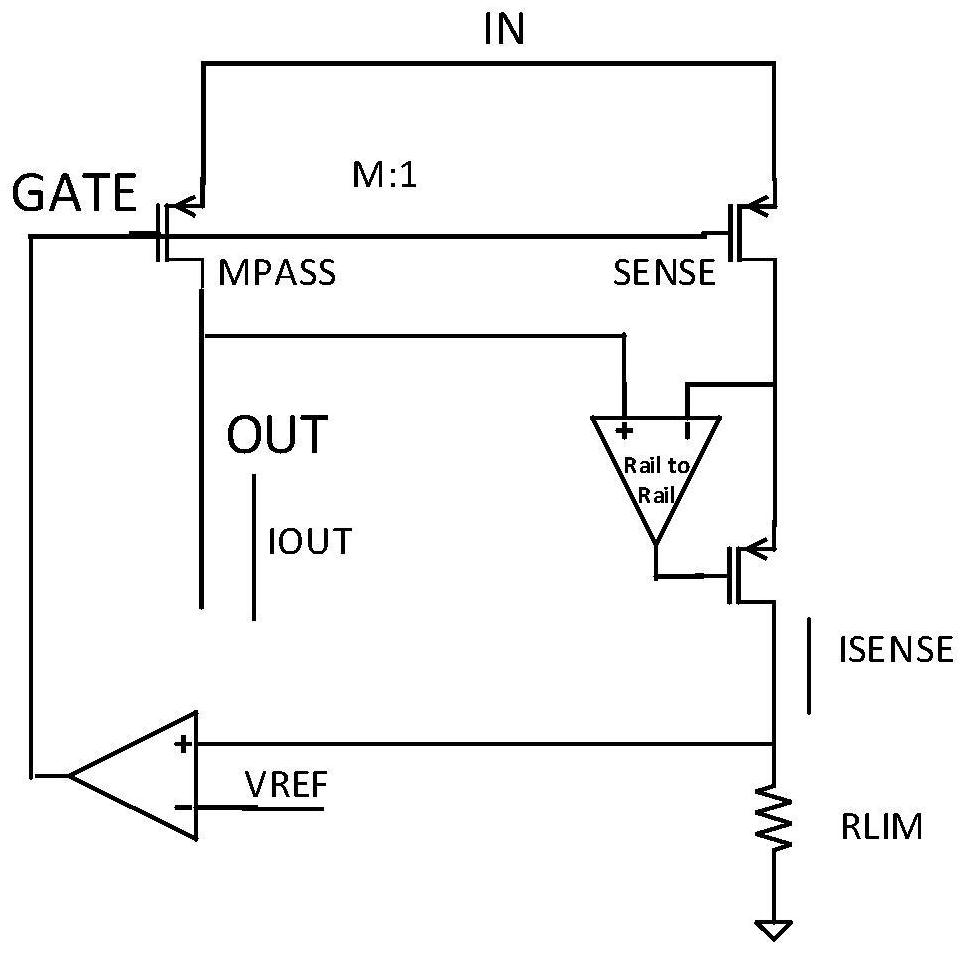

Current sampling circuit and method

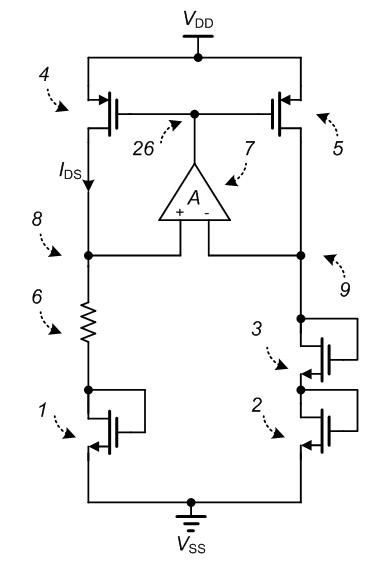

ActiveCN104977450ASimple structureGuaranteed growthElectronic switchingCurrent measurements onlyNegative feedbackEngineering

A current sampling circuit and method, the current sampling circuit comprising a proportional current outputting circuit (201) and a fully differential common-mode negative feedback circuit (202); the proportional current output circuit (201) is used to calculate the current outputted by a power device based on a preset proportion, and obtain the first proportional current and the second proportional current for output to the fully differential common-mode negative feedback circuit (202); the fully differential common-mode negative feedback circuit (202)is used to shunt the first proportional current and the second proportional current by using a fully differential common-mode negative feedback network and the bias current of the microampere level, and obtain a first sampling current and a second sampling current for constant output.

Owner:SANECHIPS TECH CO LTD

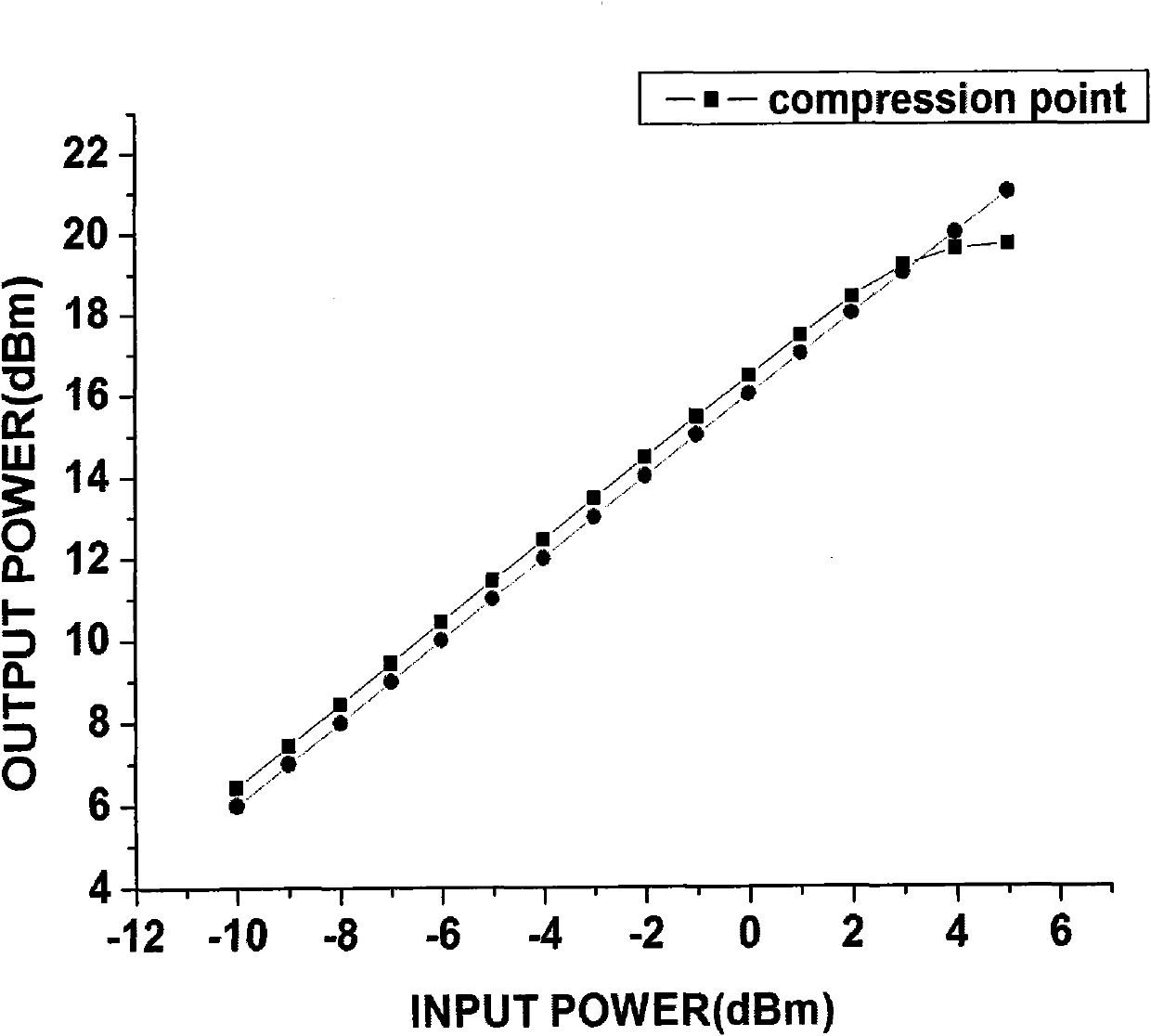

Silicon germanide bipolar-complementary metal oxide semiconductor AB power amplifier

InactiveCN101951226AImprove linearityReduce power consumptionPower amplifiersAmplifier modifications to raise efficiencyAudio power amplifierNegative temperature

The invention discloses a silicon germanide bipolar-complementary metal oxide semiconductor AB power amplifier. The circuit structure of the amplifier is divided into a first pre-amplification stage and a second power amplification stage, wherein the amplifying tube of the first stage is a standard silicon germanide bipolar transistor, and the amplifying tube of the second stage is a high-voltage silicon germanide bipolar transistor so as to obtain high power output; and bias current is provided in a form of current mirror, and the temperature stability of a bias circuit is improved by using negative temperature feedback. The amplifier has high linearity, low power consumption and good temperature stability. When P1dB is output, the compression point is about 18.5dBm. After 5.5GHz, the simulation S11 is less than -15dB, the S22 is less than -6.6dB, and the S21 is more than 16dB.

Owner:EAST CHINA NORMAL UNIV

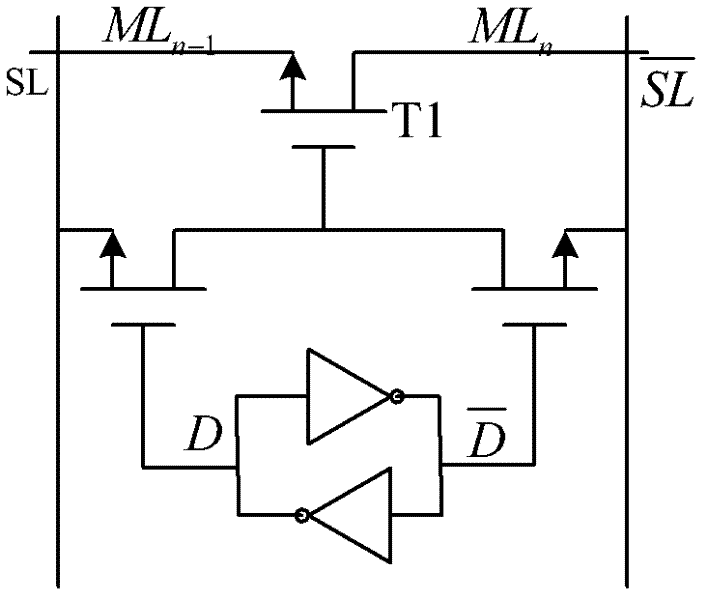

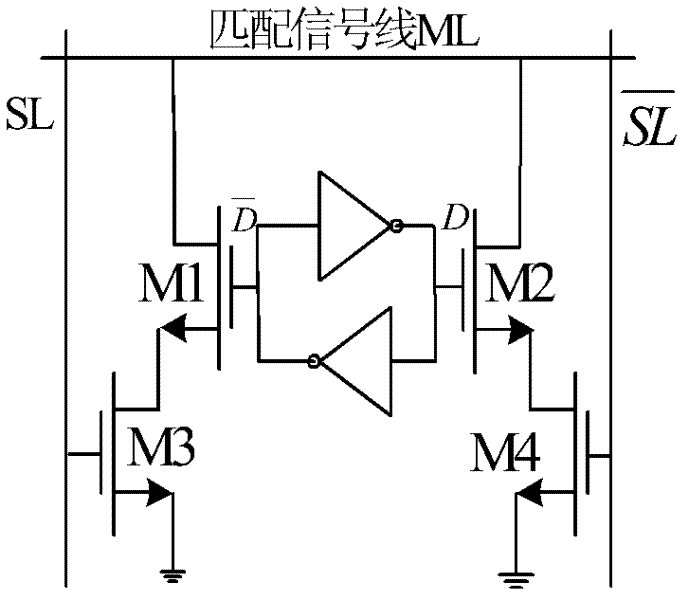

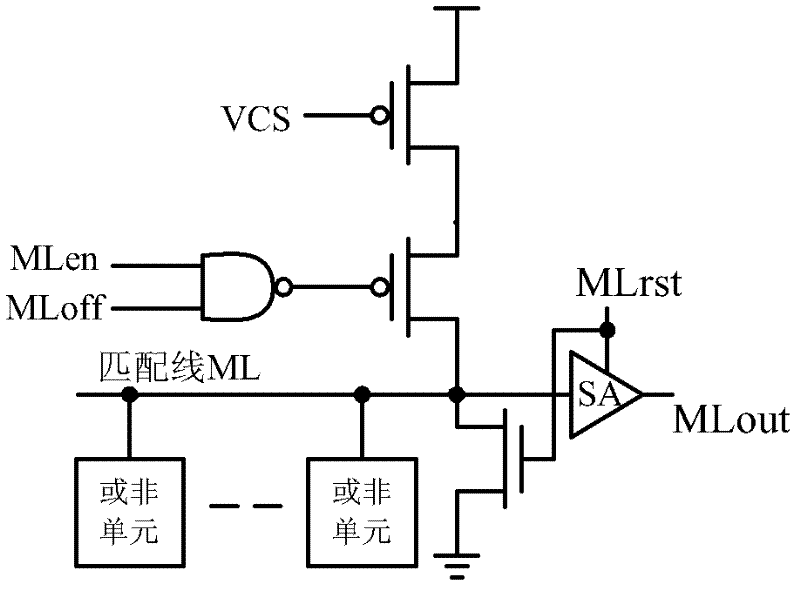

Matching detection method and circuit of content addressable memory cell

InactiveCN102403018AReduce consumptionReduce bias voltageDigital storageCharge controlFeedback control

The invention relates to a matching detection method and circuit of a content addressable memory cell. The matching detection method comprises the steps of: carrying out charging or charging control on a charge circuit of a first matching signal wire and a feedback control circuit of a second matching signal wire; when contents of an NOR memory cell are matched and a voltage difference exists between the matching signal wires, outputting a matching signal; and when the contents of the NOR memory cell are mismatched and no voltage difference exists between the matching signal wires, not outputting the matching signal. The matching detection method is simple and reliable, and has the advantages of reduction in additional offset voltage and offset current and further reduction in power consumption in comparison with the traditional matching detection method of the memory cell.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

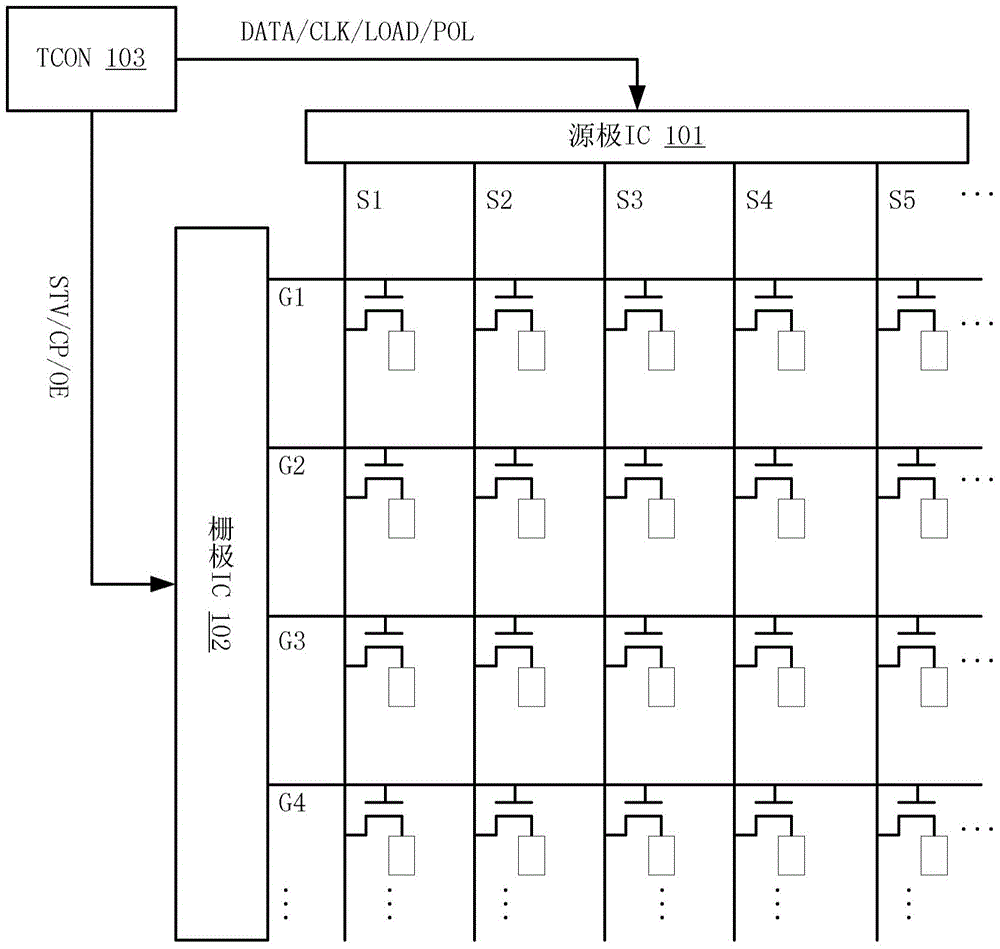

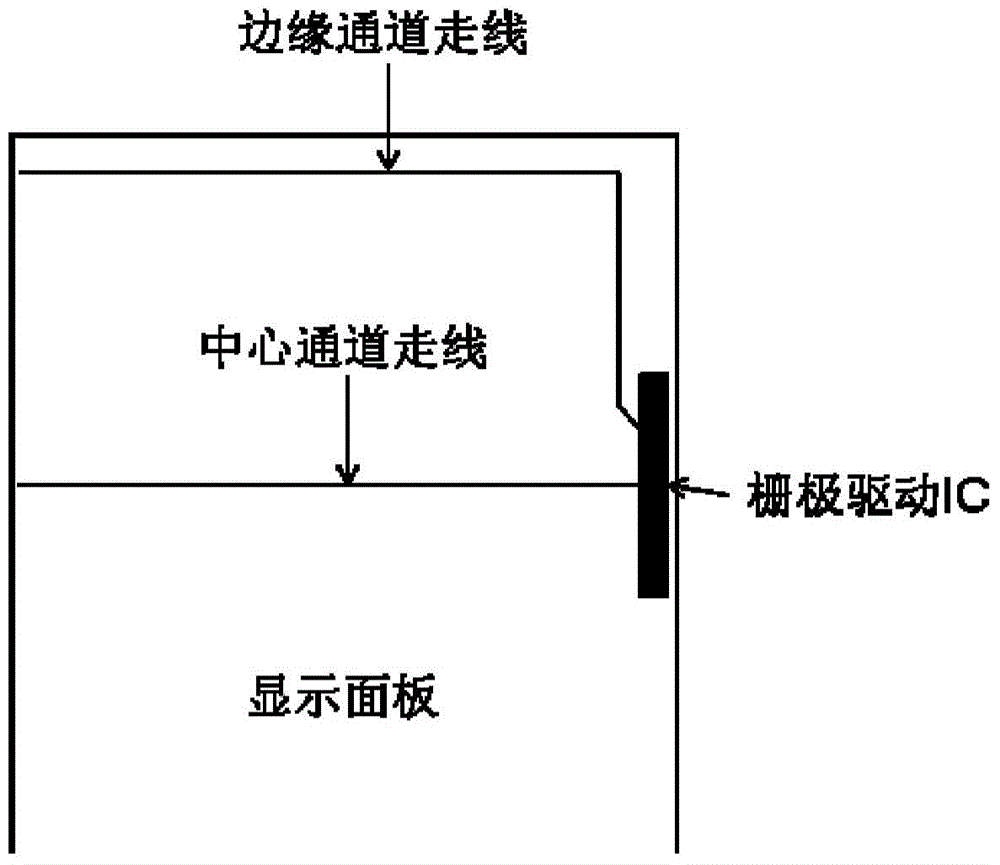

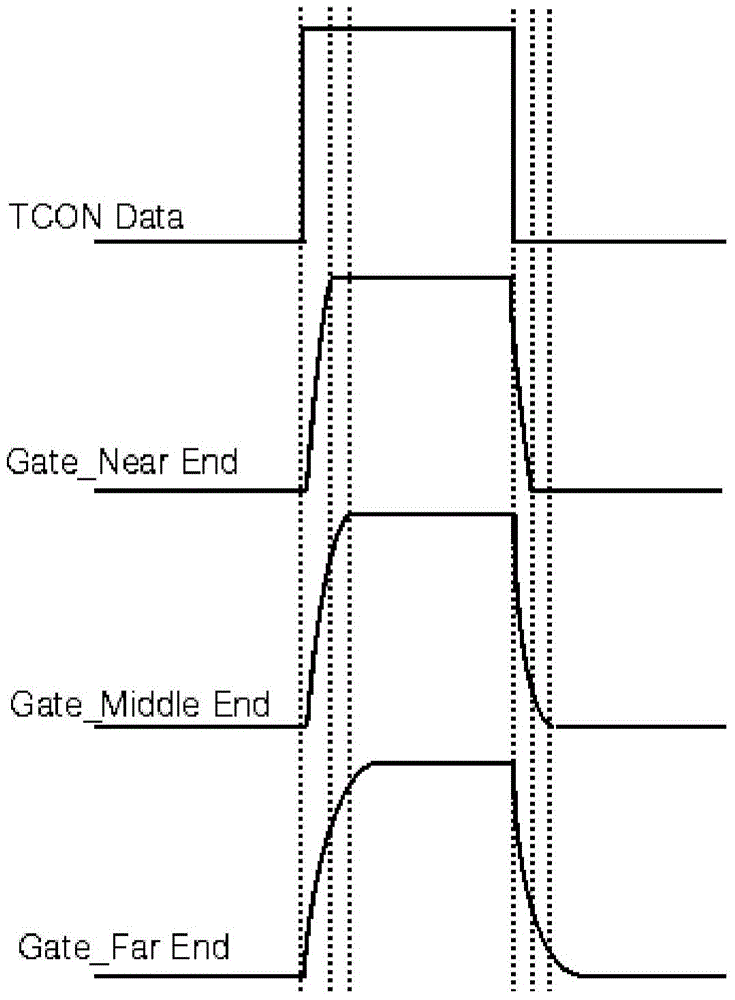

Gate driving method and structure

InactiveCN105118452AReduce power consumptionReduce bias currentStatic indicating devicesLiquid-crystal displayAudio power amplifier

The invention provides a gate driving method and a gate driving device, so as to drive a gate of a liquid crystal display. The driving method comprises the steps that according to parts, which are away from the center of a panel, of the gate driving device, the gate driving device of a liquid crystal display panel is classified into a panel edge gate driving device, a panel middle driving device and a panel center gate driving device; and from the panel edge gate driving device to the panel center gate driving device, the bias current of an output operational amplifier of a gate drive IC gradually decreases. According to the invention, a gate drive IC output resistor and the gate drive IC output operational amplifier are designed; under the condition of normal panel drive display, the power consumption of the gate drive IC is minimized; and the power consumption of the liquid crystal panel is further reduced.

Owner:BOE TECH GRP CO LTD +1

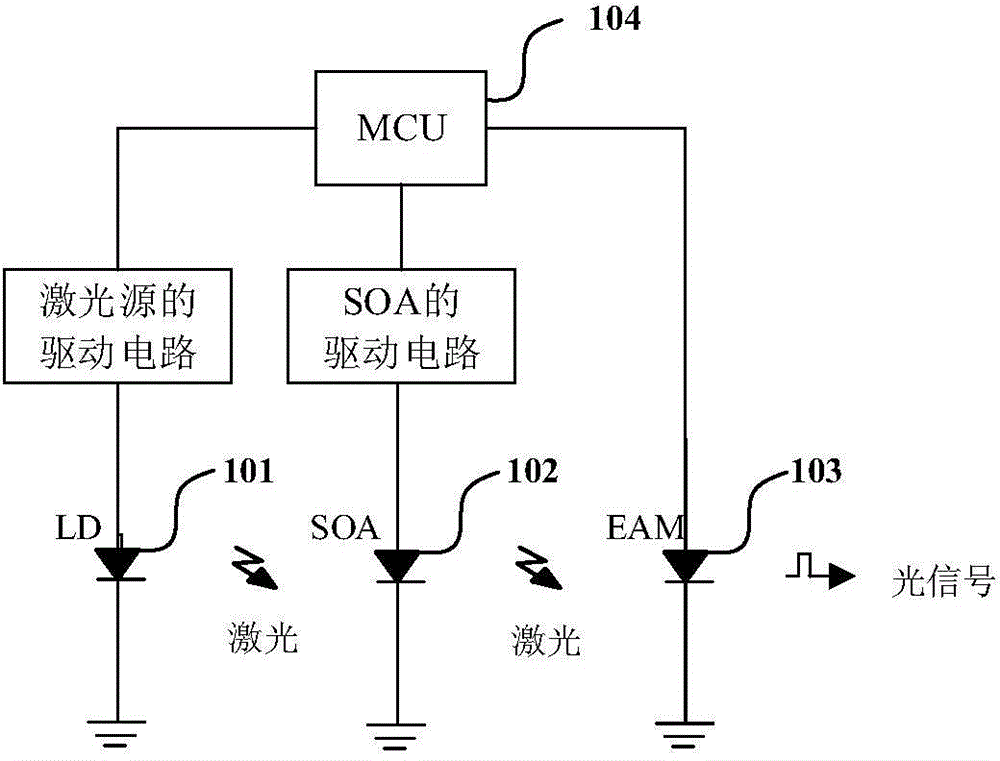

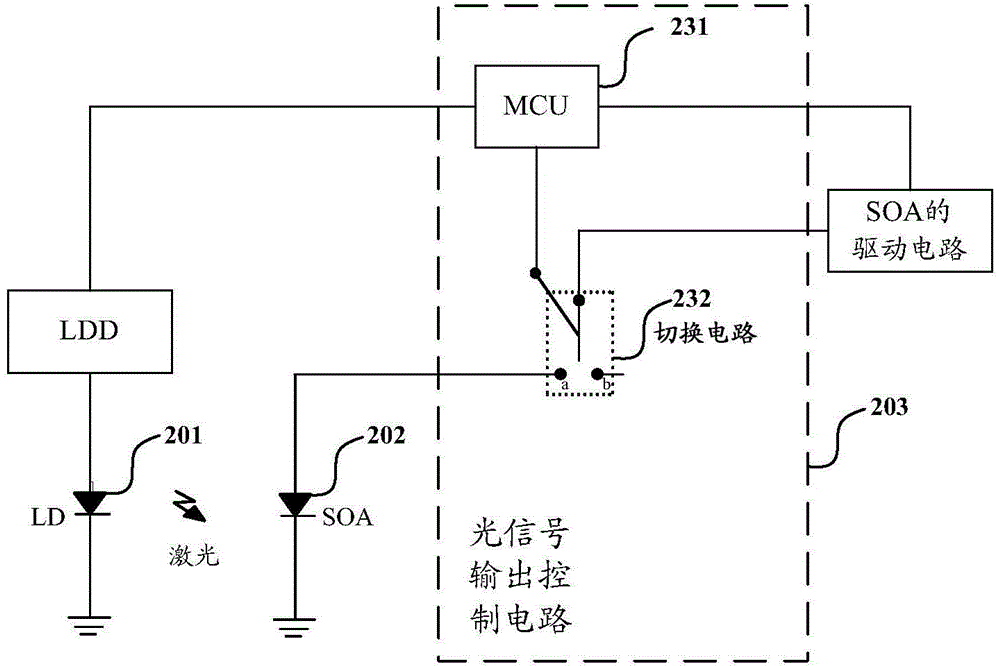

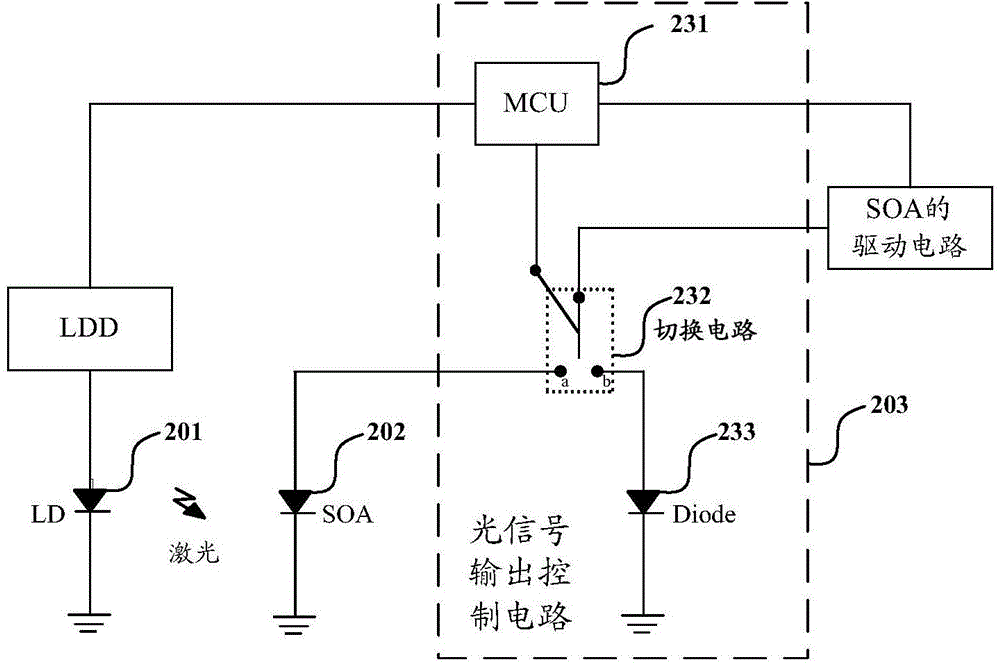

Optical module and optical signal output control method

ActiveCN106253989AReduce turn-on timeShorten off timeDistortion/dispersion eliminationElectromagnetic repeatersOptical ModuleSemiconductor laser amplifier

Embodiments of the invention provide an optical module and an optical signal output control method. The optical module comprises a laser source, a semiconductor laser amplifier, and a drive circuit of the semiconductor laser amplifier. The optical module further comprises a switching circuit of which one end is connected with the bias current output end of the drive circuit of the semiconductor laser amplifier, and a controller which is used for making the switching circuit connect the bias current output end of the drive circuit to the semiconductor laser amplifier after receiving an optical signal transmission instruction, and making the switching circuit disconnect the bias current output end of the drive circuit from the semiconductor laser amplifier after receiving an optical signal stop instruction. According to the technical scheme of the invention, the on time and off time of optical signal output of the optical module can be shortened greatly, and quick start and cutoff of optical signal output of the optical module is realized.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

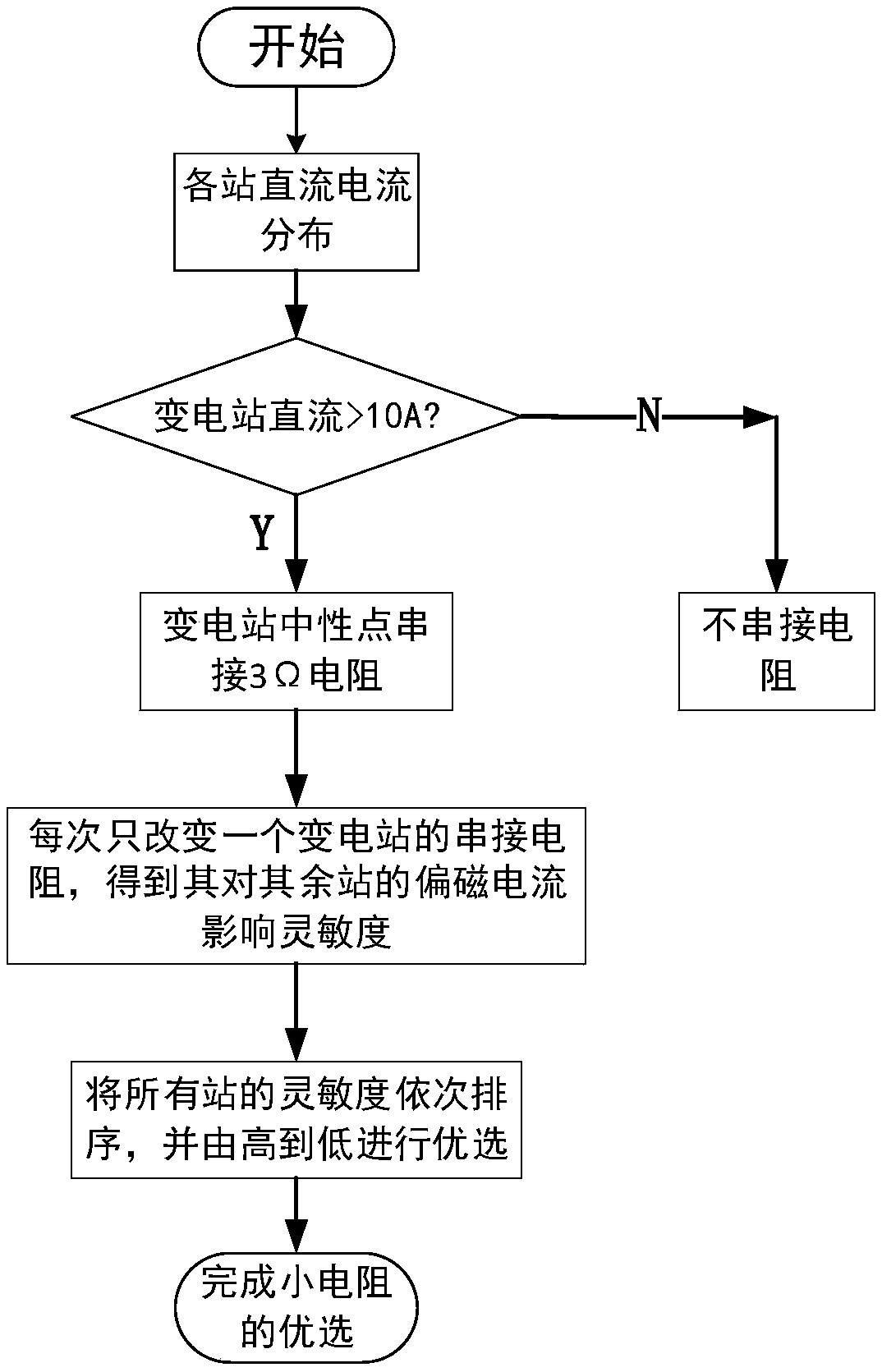

A method for optimally selecting a resistor for suppressing a DC bias current

ActiveCN109149542AReduce mutual interferenceGuaranteed immutabilityEmergency protective arrangements for limiting excess voltage/currentElectrical resistance and conductanceDc current

The invention relates to a resistance optimization selection method for restraining DC bias current. The method comprises the following steps: building a simulation model, modeling a calculation gridframe, and calculating the distribution of the DC current in each substation; Select the substation whose DC current is more than 10A to carry out DC bias treatment; the selected substation neural point is serially connected with the 3 omega small resistor, According to the principle of single variable, the resistance of one substation is changed to 3.5 omega at a time, and the sensitivity to thebias current of other substations is obtained. The sensitivity of each substation is sorted in turn, and the series resistance of substation is selected in the order of sensitivity from high to low, and the small resistance of neutral point series connection of each substation is finally determined. The invention can reduce the mutual interference of the series connection resistors of the neutralpoints of each substation, and reduce the total bias current flowing into the AC power network.

Owner:STATE GRID CORP OF CHINA +2

Tera-hertz silica-based quadrupler and frequency multiplier

InactiveCN102104363BIncrease the output frequencyHigh multiplierOscillations generatorsFrequency spectrumFrequency multiplier

The invention discloses a tera-hertz silica-based quadrupler and a frequency multiplier, belonging to the field of RFIC (Radio Frequency Integrated Circuit). The quadrupler comprises transistors (M1 and M2) and transmission lines (L1, L2 and L-1), wherein the drain ends of the transistors (M1 and M2) are respectively connected to an output port through the transmission lines (L1 and L2), source ends are connected with a ground line, grid ends are respectively connected with the signal input ends of an path (I) and the path (Q) of a baseband signal (f0); the transmission line (L-1) is connected between the output port and a power supply; and the length of the transmission lines (L1 and L2) are 1 / 4 of that of the corresponding wavelength of a signal (2f0), the length of the transmission line (L-1) is 1 / 4 of that of the corresponding wavelength of a signal (4f0). The multi-frequency multiplier comprises a 2n frequency multiplier (1), a 2n frequency multiplier (2) and a transmission line (L), wherein the output ports of the 2n frequency multiplier (1) and the 2n frequency multiplier (2) are connected to be used as the output port of a 2n+1 frequency multiplier, the transmission line (L) is connected between the output port of the 2n+1 frequency multiplier and the power supply, and the length of the transmission line (L) is 1 / 4 of that of the corresponding wavelength of a signal (2n+1f0). The tera-hertz silica-based quadrupler and the multi-frequency multiplier, provided by invention, have the advantages of high output frequency, pure frequency spectrum, low power consumption and easiness for integration.

Owner:PEKING UNIV

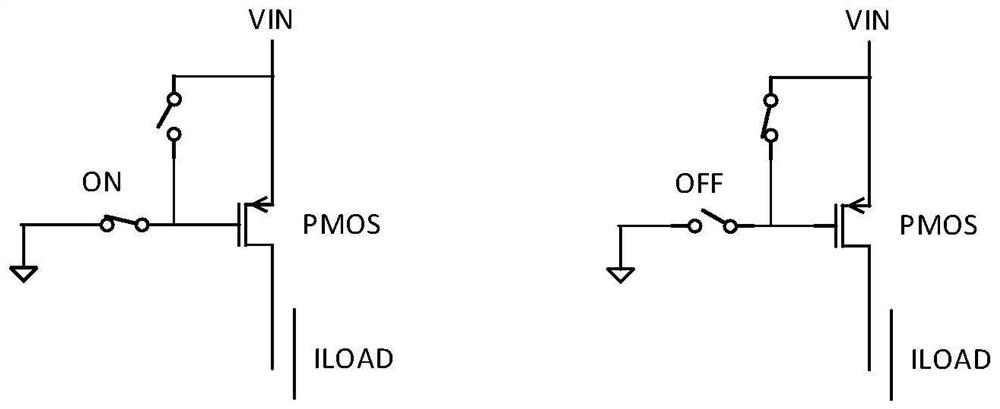

Protection circuit of power tube, power supply protection chip and equipment

PendingCN114337226AProtection securityReduce bias currentEmergency protective circuit arrangementsPower conversion systemsCurrent limitingHemt circuits

The invention provides a protection circuit of a power tube, the circuit comprises a bias branch connected to a grid electrode of the power tube and a clamping branch connected between a source electrode and a drain electrode of the power tube, the source electrode of the power tube is connected with an input end, the drain electrode of the power tube is connected with an output end, the bias branch is used for providing bias current, and the clamping branch is used for clamping the bias current. The output current of the power tube is limited by the bias current, and the clamping branch is used for reducing the bias current when the source-drain voltage of the power tube is greater than a source-drain clamping voltage threshold, so that the output current of the power tube is reduced, and the power tube enters a current-limiting protection mode to control the power. Thus, current limiting and clamping can be combined, the power of the power tube is limited, and the safety of the power tube is protected fundamentally.

Owner:SHANGHAI AWINIC MICROELECTRONIC TECH CO LTD

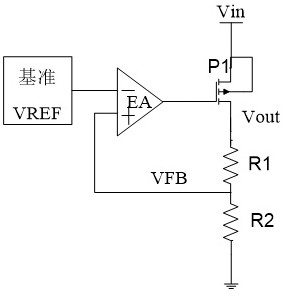

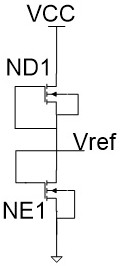

Linear voltage regulator integrating reference and operational amplifier

ActiveCN114115425AImprove static power consumptionAchieve performanceElectric variable regulationPower applicationControl engineering

According to the reference and operational amplifier integrated linear voltage regulator, a depletion tube is introduced, and the depletion tube reference is used as the reference and the first stage of the operational amplifier, so that the operational amplifier and the reference are integrated, a starting circuit is not needed, the circuit is very simple, and the circuit performance is greatly improved on the basis of realizing the circuit performance of the linear voltage regulator. The depletion reference is used as a reference and a first stage of the operational amplifier, so that the static power consumption of low-power application can be obviously improved, and the optimal combination of performance and cost is realized.

Owner:江苏长晶科技股份有限公司

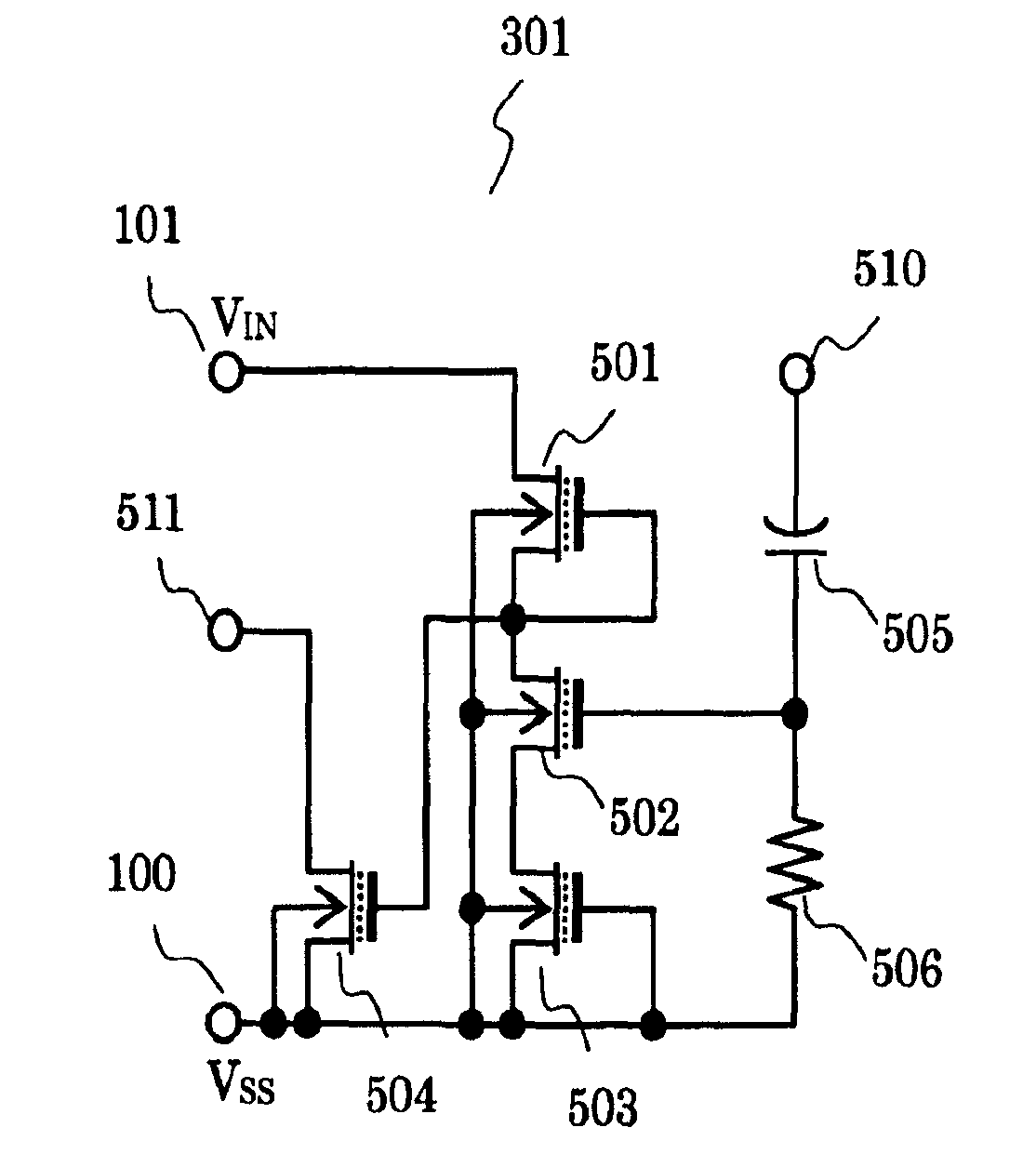

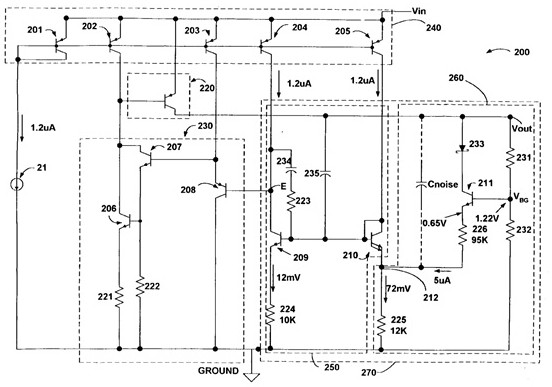

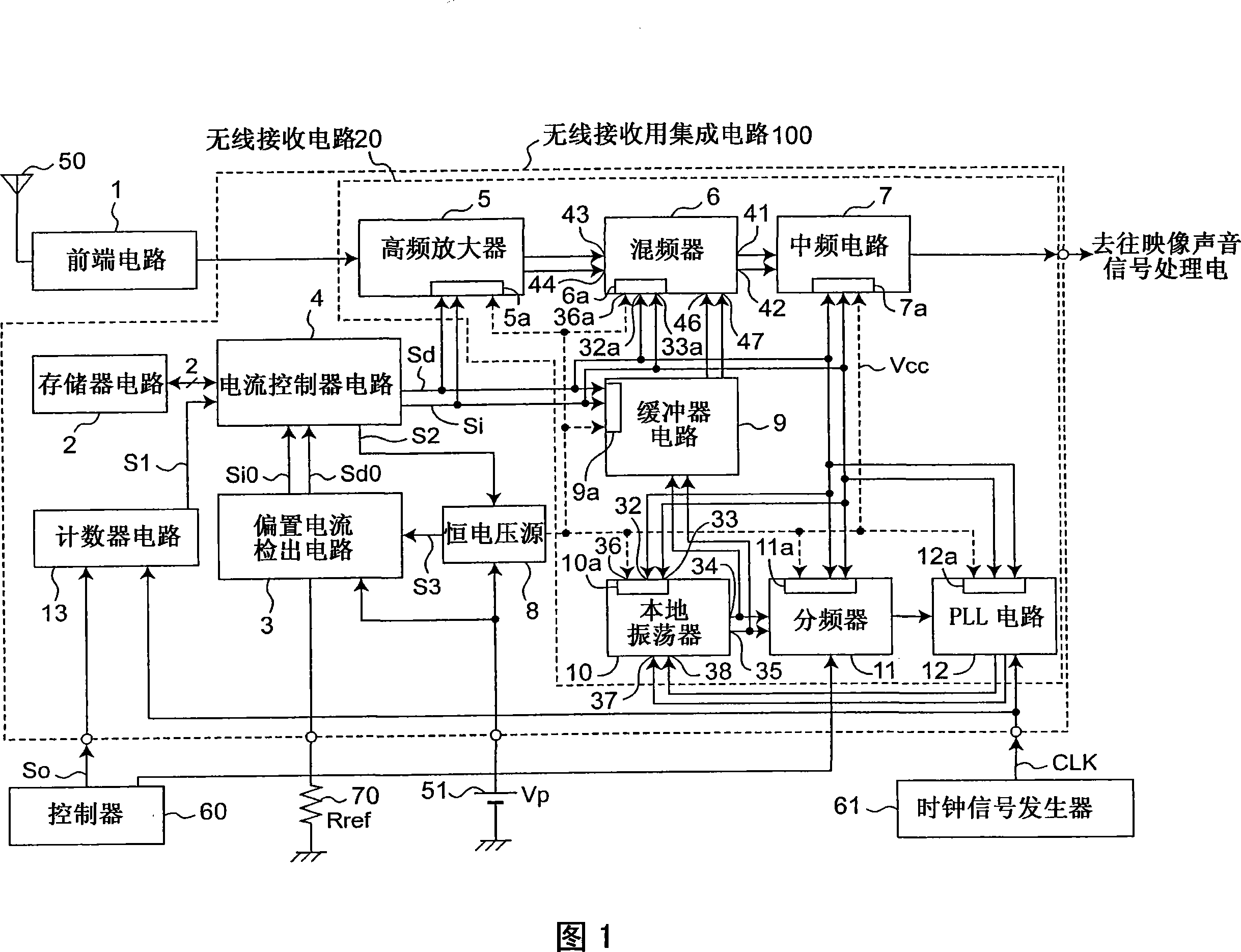

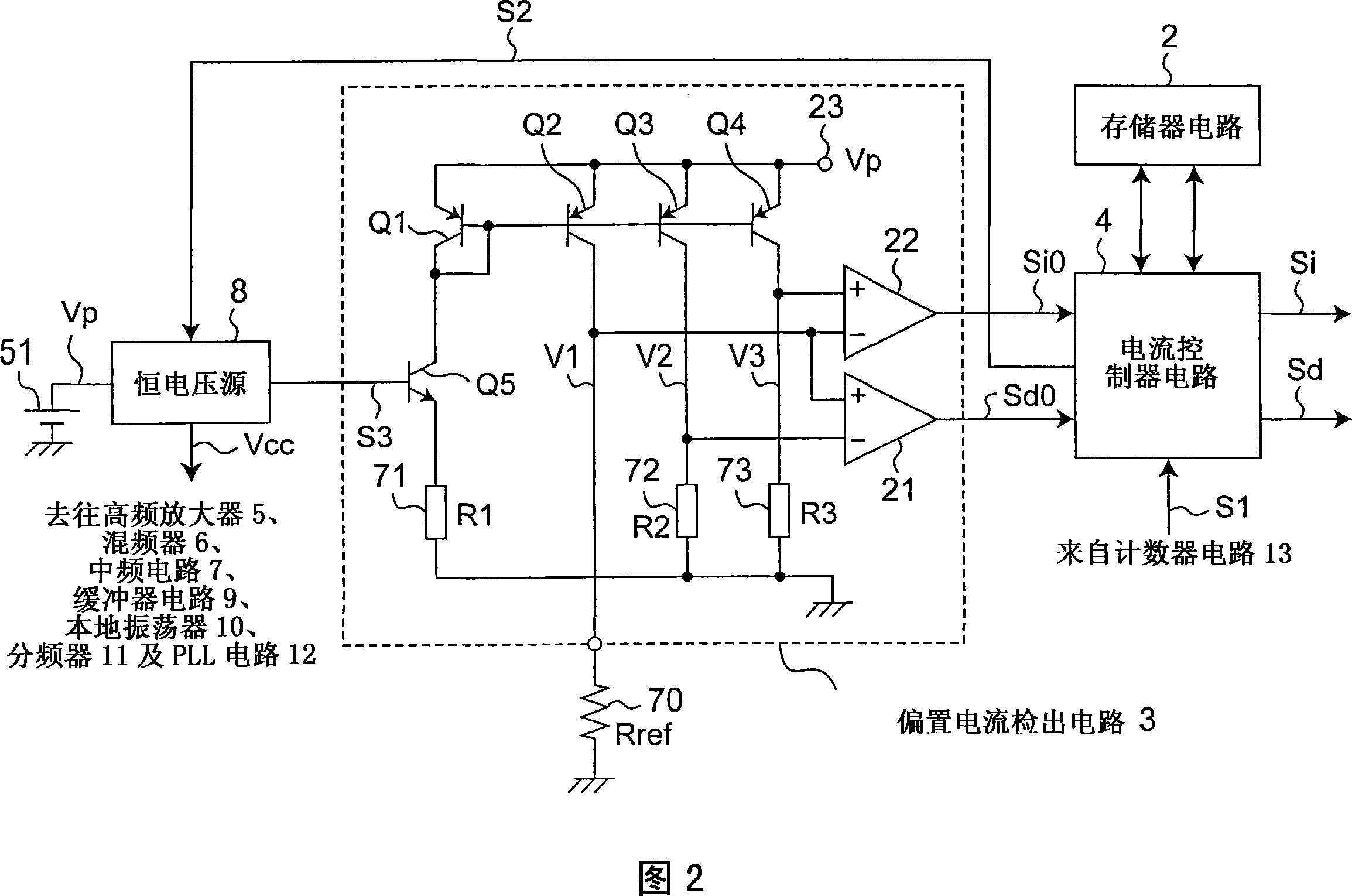

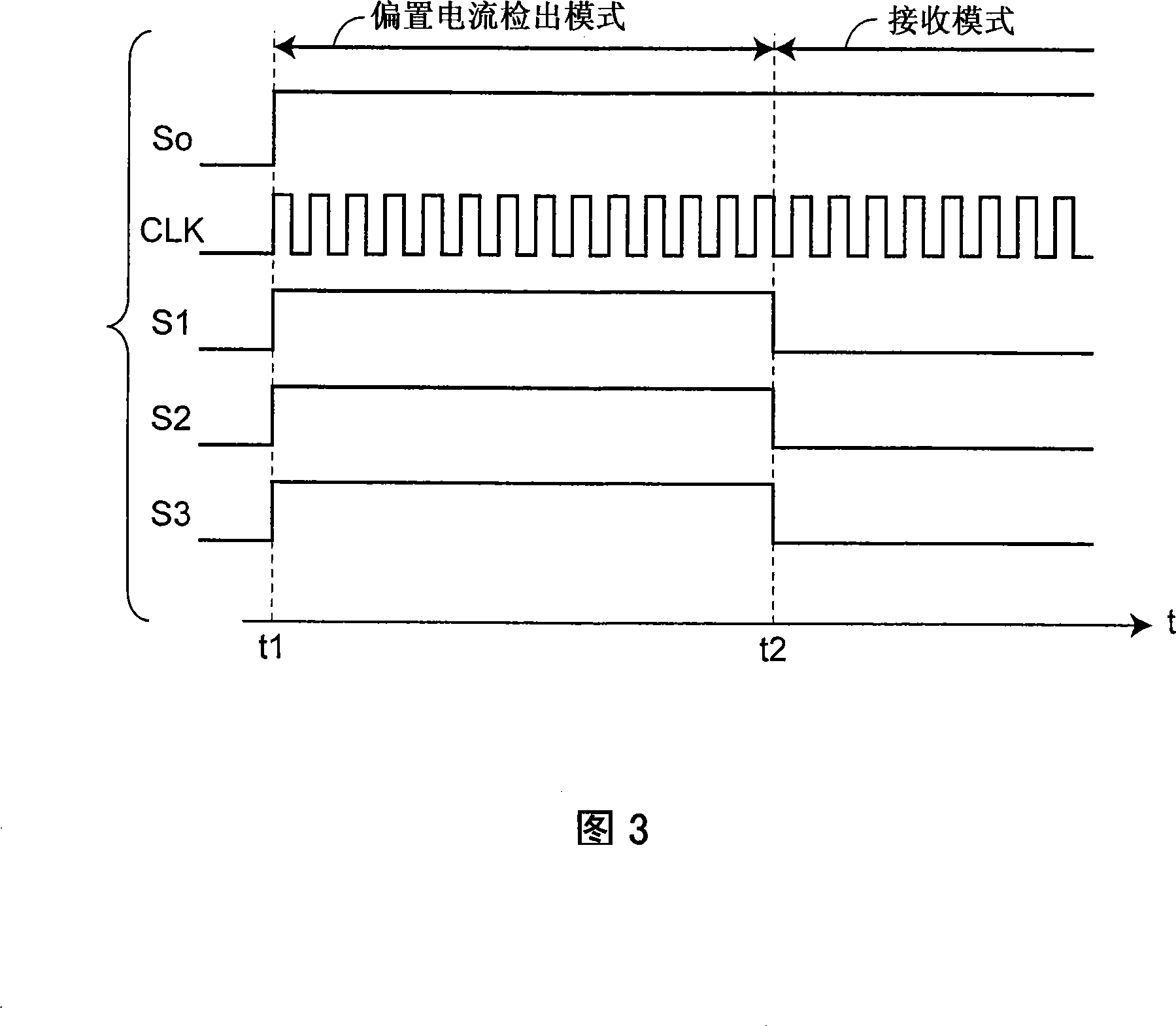

Semiconductor circuit for wireless receiving provided with controller circuit for controlling bias current

InactiveCN101197583AReduce bias currentReduce current consumptionGain controlTransmissionDetector circuitsSignal processing circuits

The invention relates to a wireless receiving semiconductor circuit and a wireless receiving device having the semiconductor circuit, wherein, the wireless receiving circuit (20) outputs the medium-frequency signal to a rear image and sound signal processing circuit after converting a wireless receiving signal received by an antenna (50) into the medium-frequency signal. A constant voltage source (8) supplies a bias current to the wireless receiver circuit (20). A bias current detector circuit detects the bias current, and outputs a detection result to a current controller circuit (4). The current controller circuit (4) outputs the detection result of the bias current to a memory circuit (2). The current controller circuit (4) controls the bias current detector circuit (3) to stop operating thereof, and then controls the bias current to decrease when the detected bias current is larger than a predetermined first threshold value and controls the bias current to increase when the detected bias current is smaller than a second threshold value smaller than the first threshold value, based on the detection result stored in the memory circuit (2).

Owner:PANASONIC CORP

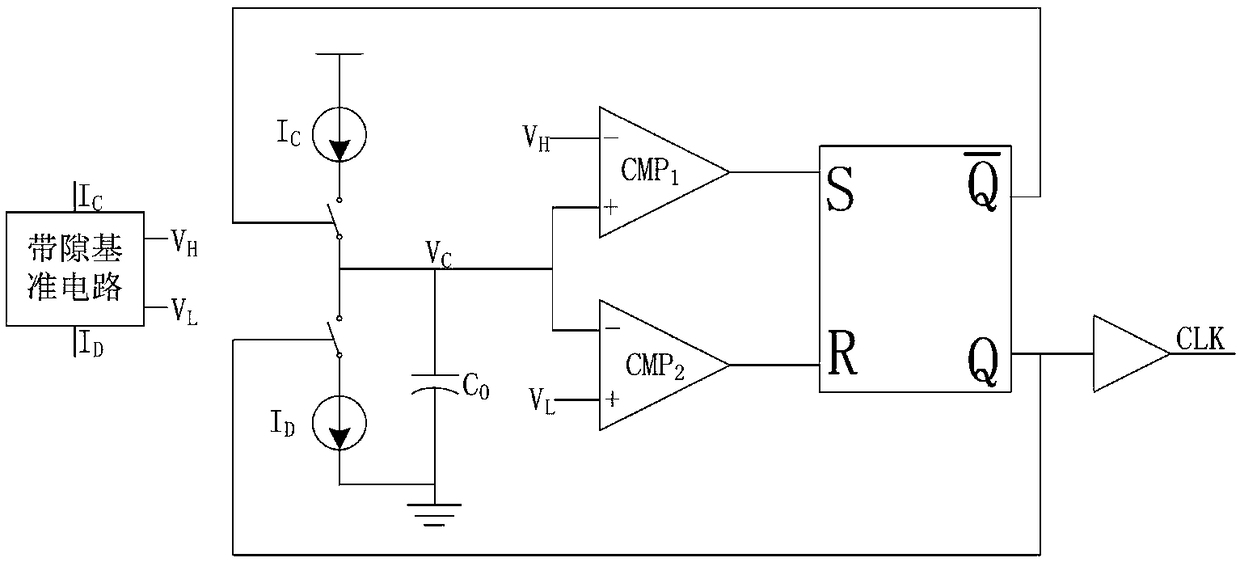

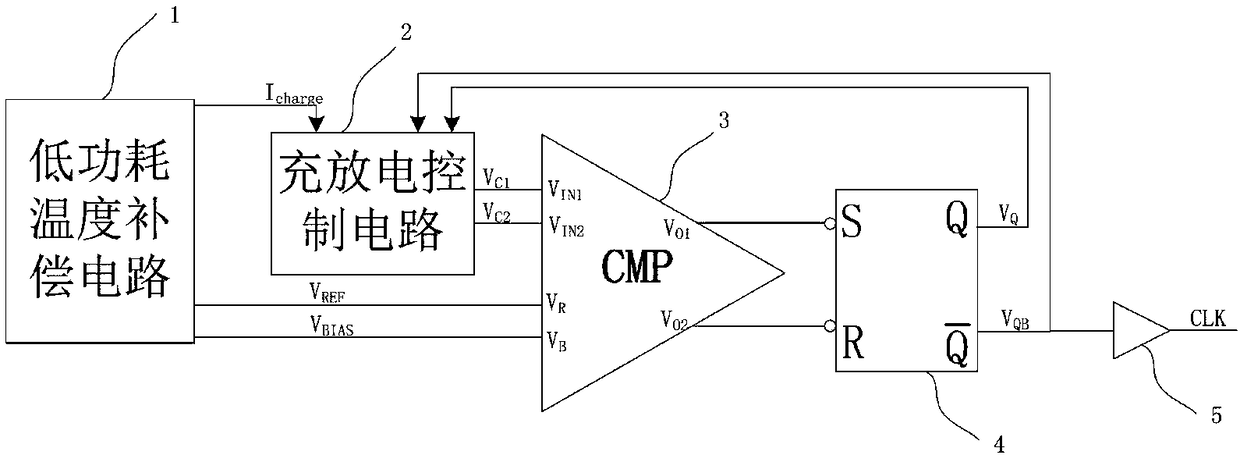

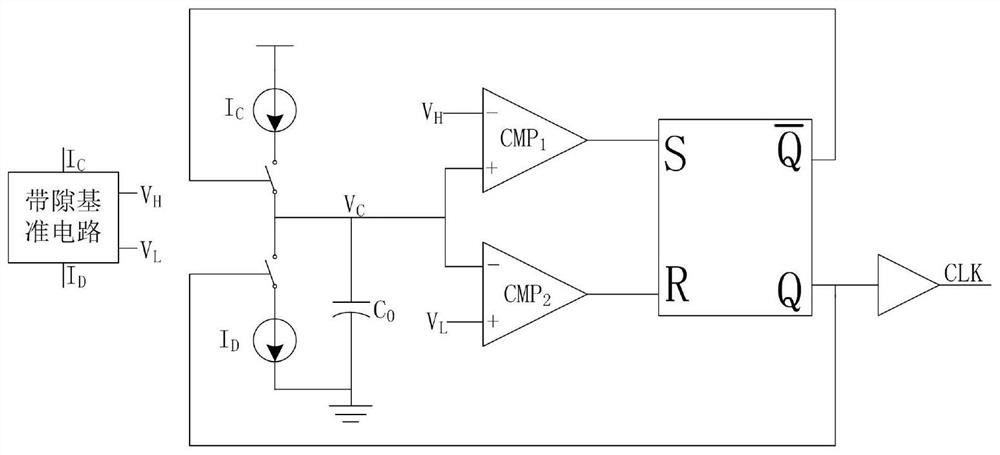

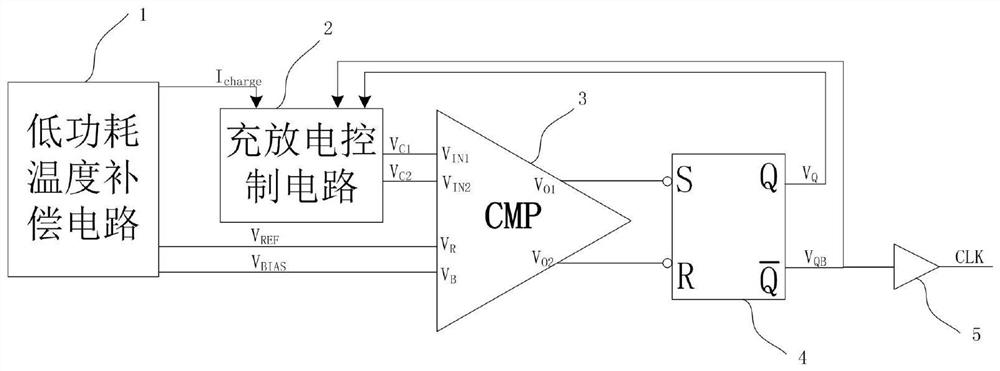

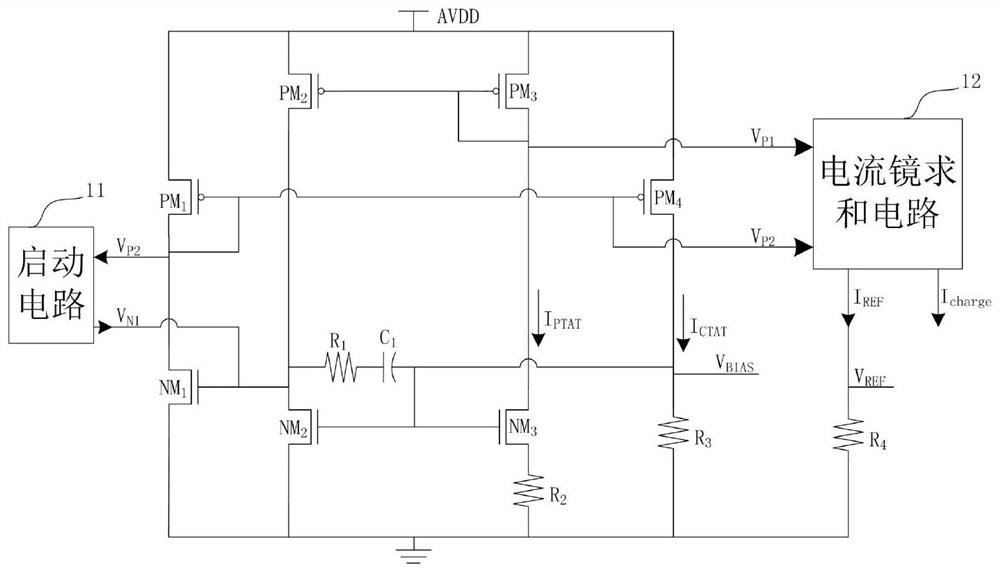

On-chip RC oscillator circuit

ActiveCN109245723AReduce power consumptionSimple structureOscillations generatorsCapacitanceEngineering

The invention discloses an on-chip RC oscillator circuit, and belongs to the technical field of integrated circuits. The on-chip RC oscillator circuit includes a low-power-consumption temperature compensation circuit, a charge and discharge control circuit, a comparator circuit, an RS flip flop, and a buffer. A first NMOS transistor, a first PMOS transistor, a fourth PMOS transistor, a third resistor and a second NMOS transistor in the low-power-consumption temperature compensation circuit form a loop for generating a bias current with a negative temperature coefficient. A second NMOS transistor, a second PMOS tube, a third PMOS transistor, a third NMOS transistor and a second resistor form a loop that generates a positive temperature coefficient current. The two loops implement a negativefeedback connection through the second NMOS transistor, and the first capacitor and the first resistor perform the miller compensation for a negative feedback loop to improve stability. The oscillator circuit only needs four current branches, and the positive and negative temperature coefficient current structure required for temperature compensation is very simple, and the power consumption is low. The first NMOS transistor, the second NMOS transistor and the third NMOS transistor operate at a sub-threshold section, achieving a smaller bias current and consuming less power.

Owner:CHINA KEY SYST & INTEGRATED CIRCUIT

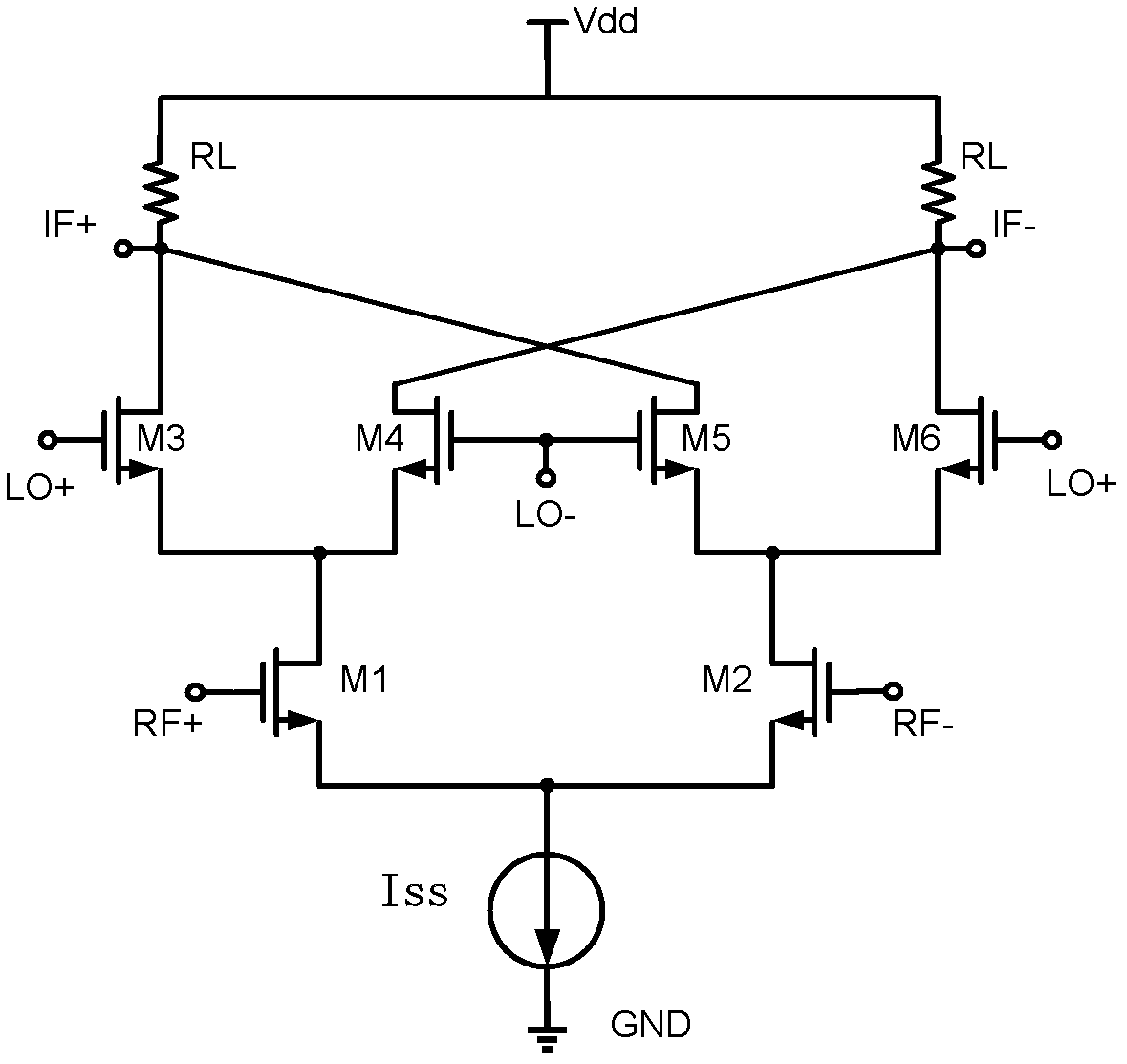

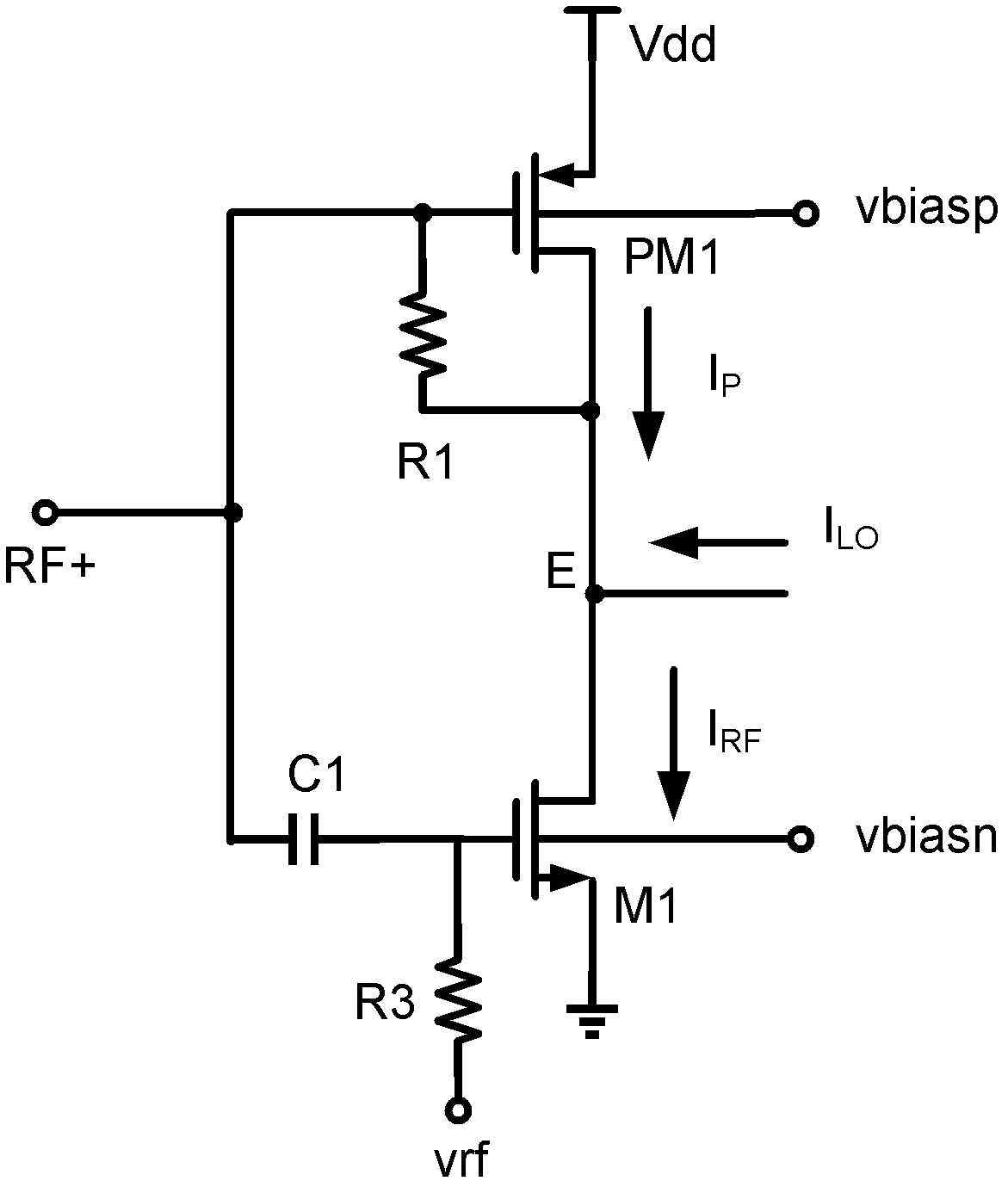

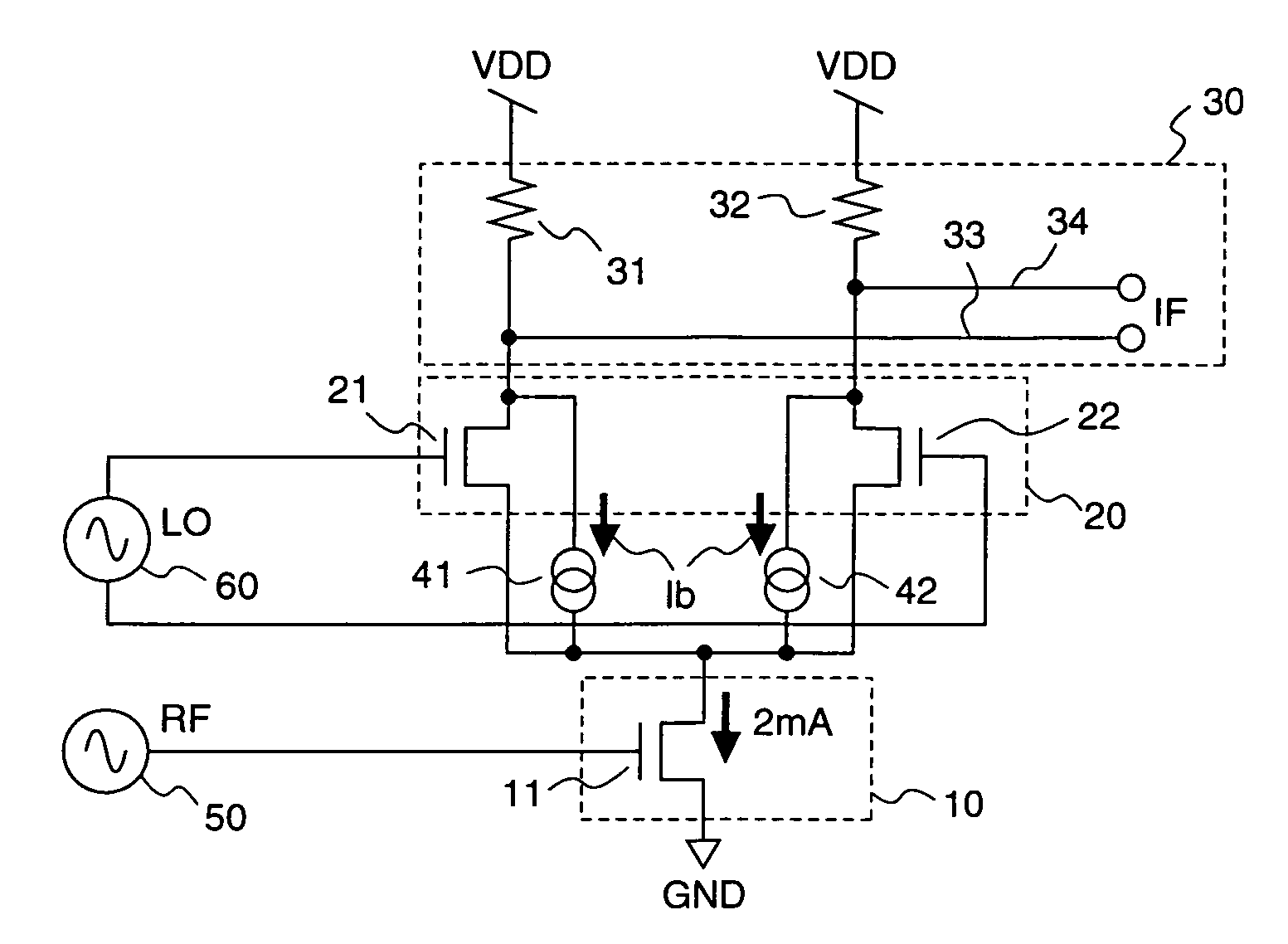

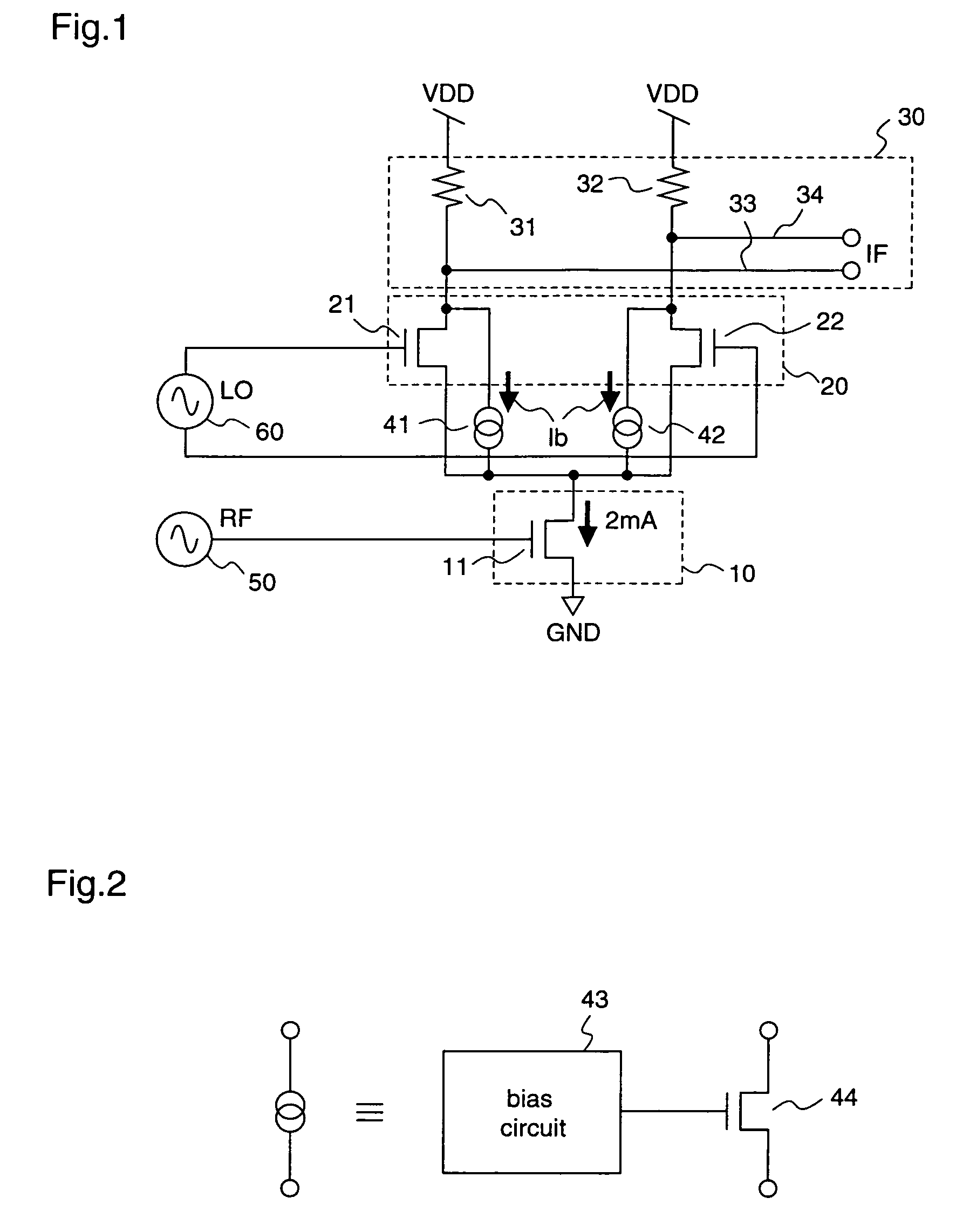

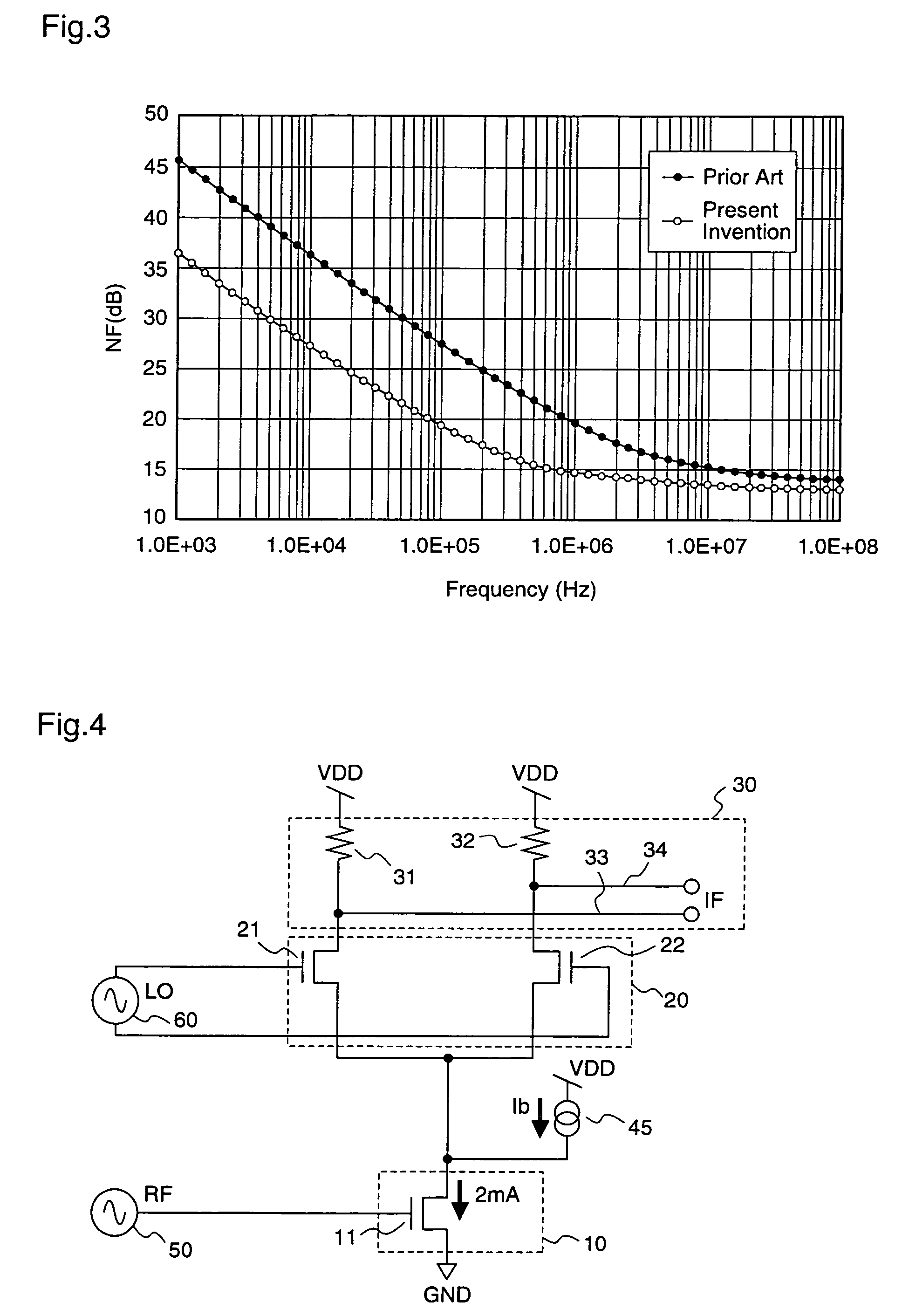

Mixer circuit

ActiveUS7613440B2Reduce flicker noiseImprove noise characteristicsModulation transference balanced arrangementsTransmissionLow noiseEngineering

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

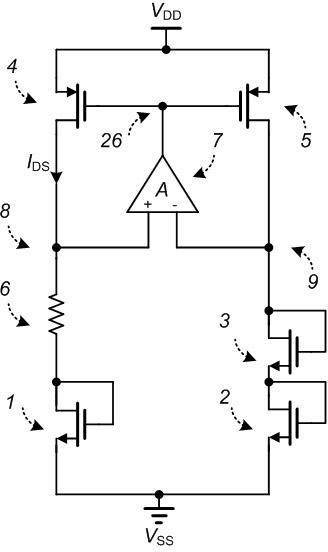

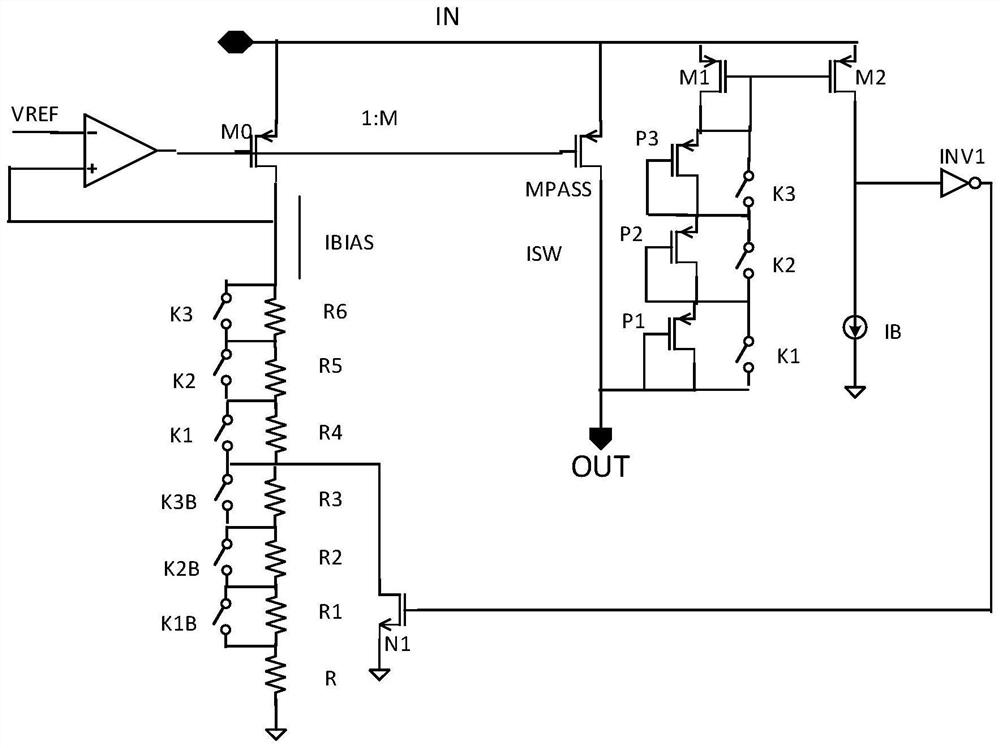

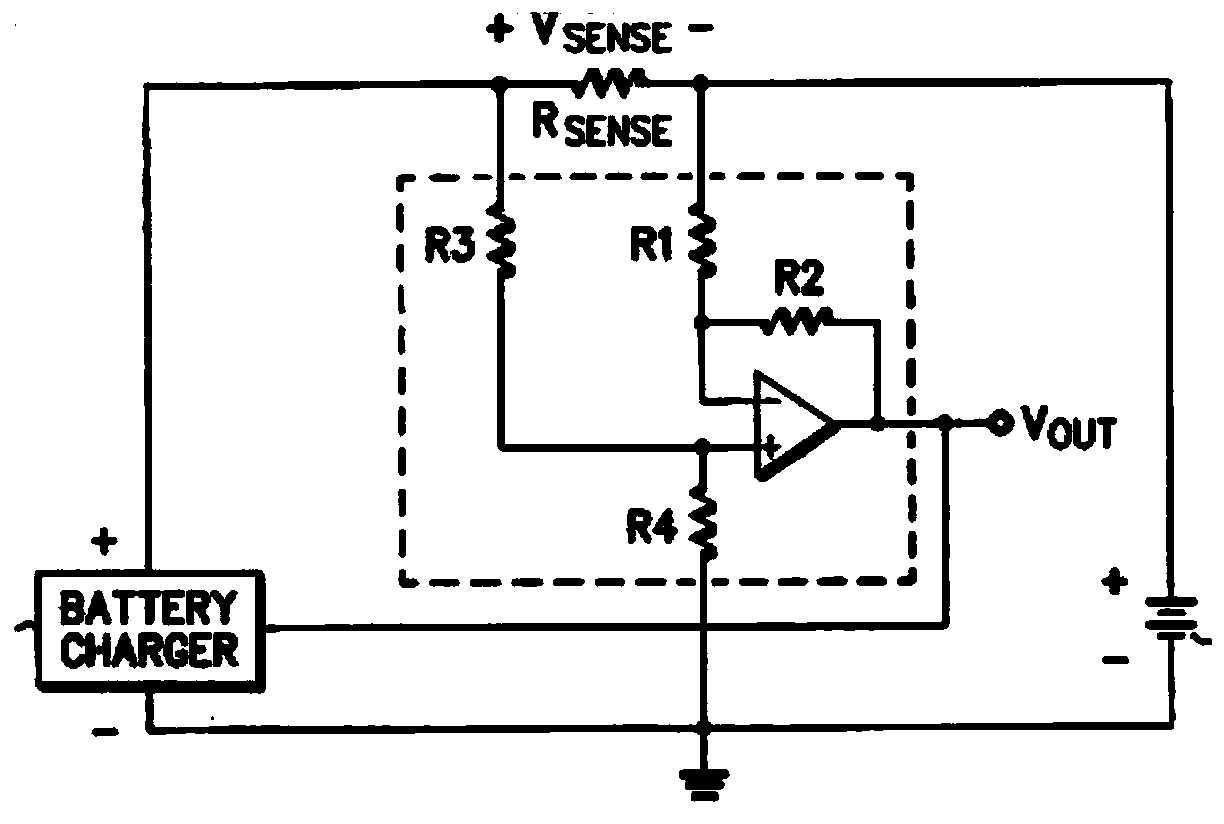

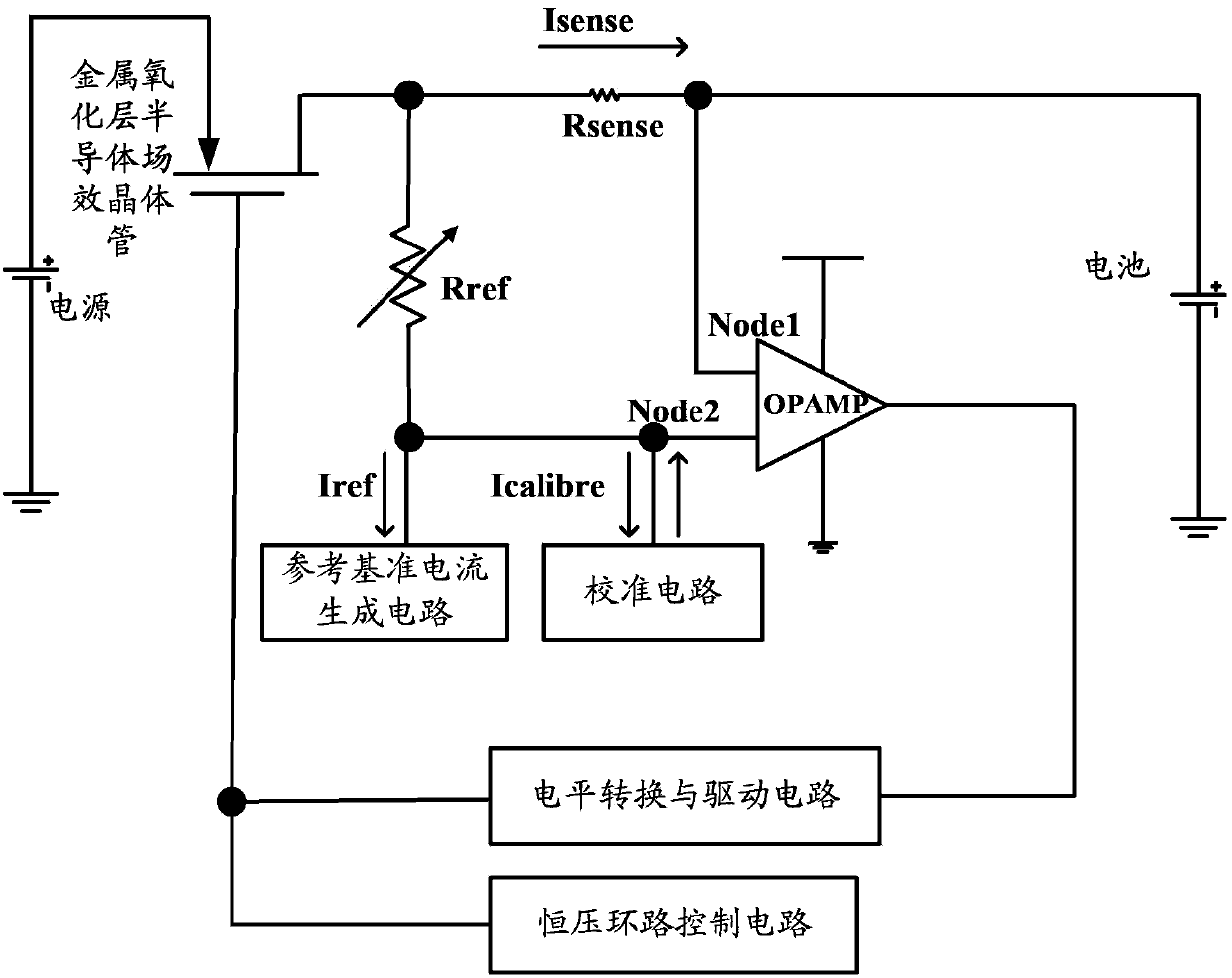

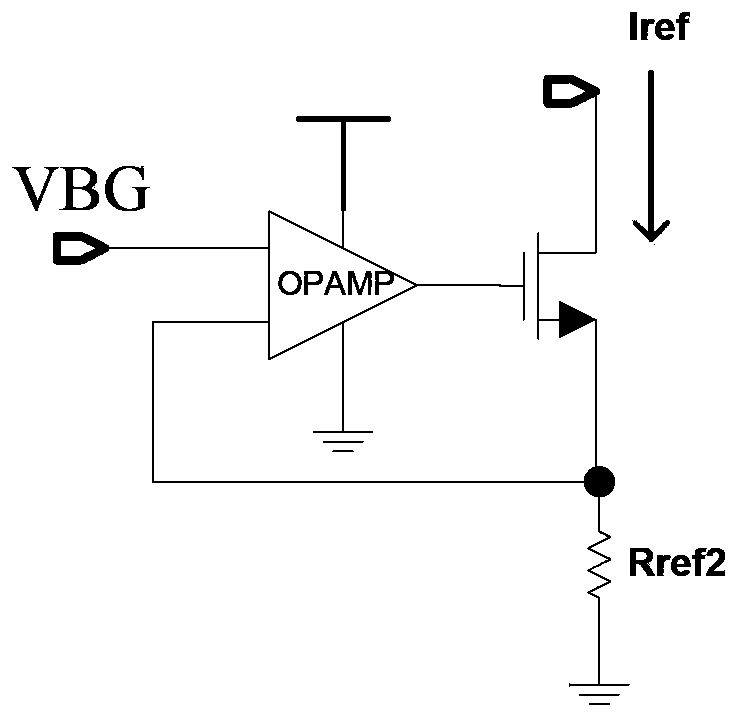

Constant current loop

ActiveCN103970170ALower Offset VoltageReduce bias currentElectric variable regulationField-effect transistorControl theory

The invention discloses a constant current loop, which comprises an EA (error amplifier) and a power supply, wherein one end of the EA is connected with one end of a current detection element, and the other end of the EA is connected with the other end of the current detection element through a reference generation element; one end of the power supply is grounded, and the other end of the power supply is connected with the source or drain of a metal oxide layer semiconductor field effect transistor; the drain or source of the metal oxide layer semiconductor field effect transistor is connected with the other end of the current detection element. According to the constant current loop, the EA is directly used for forming a negative feedback closed loop, and the whole loop has only one EA gain stage; the offset voltage and bias current of the whole loop are reduced, so that constant current is higher in accuracy; in addition, the structure of the loop is simplified, and the implementation cost is lowered.

Owner:SANECHIPS TECH CO LTD

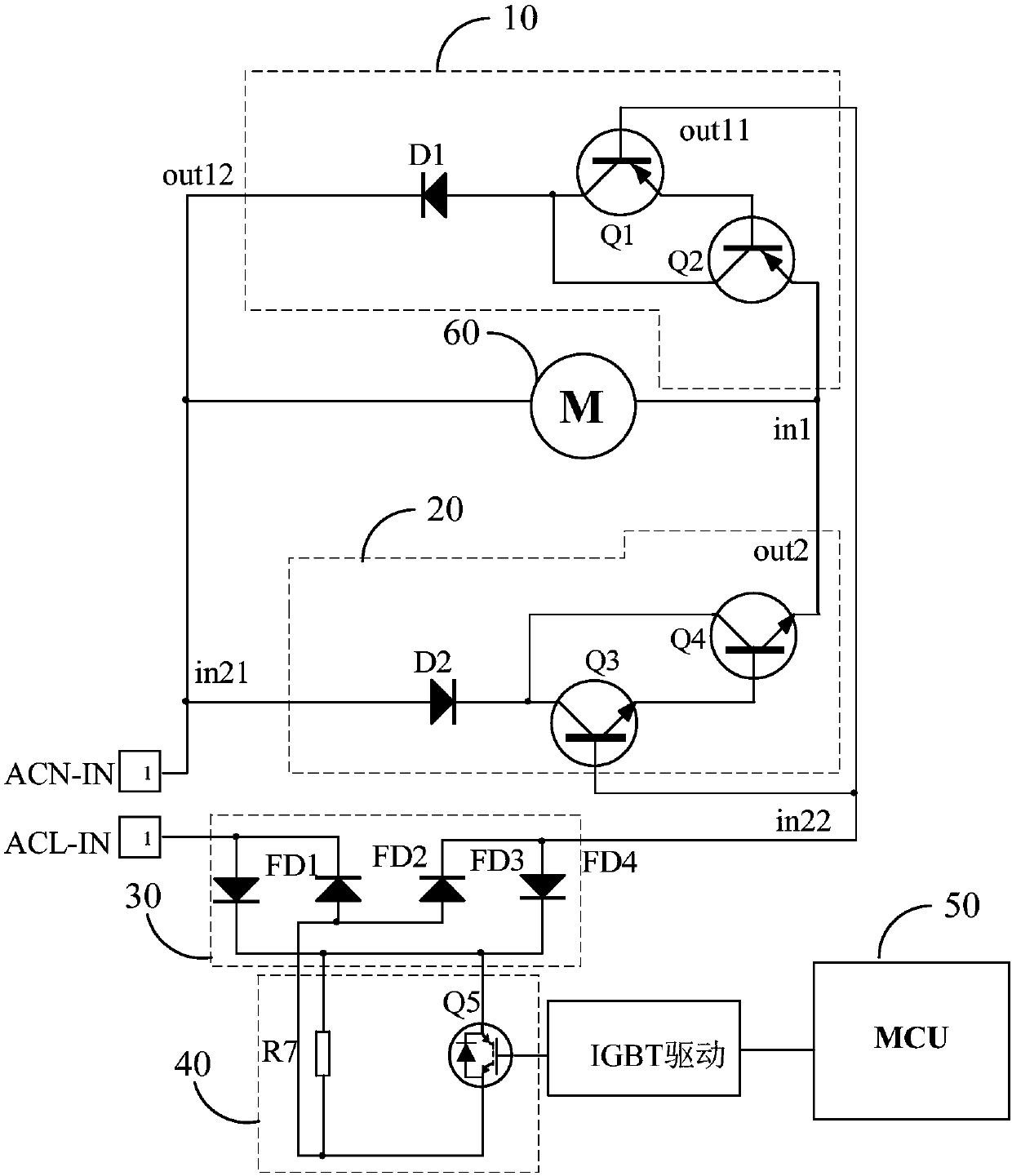

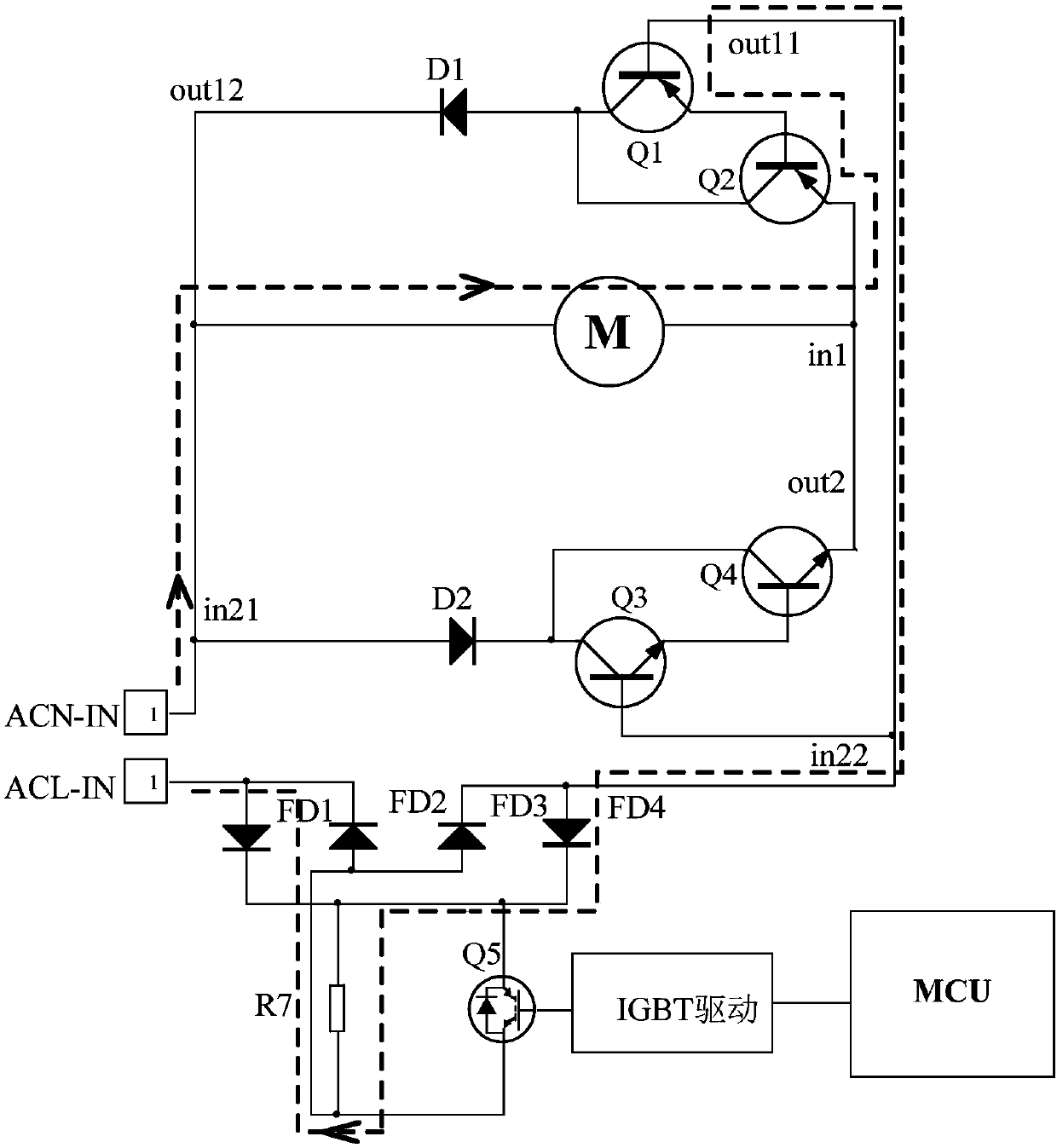

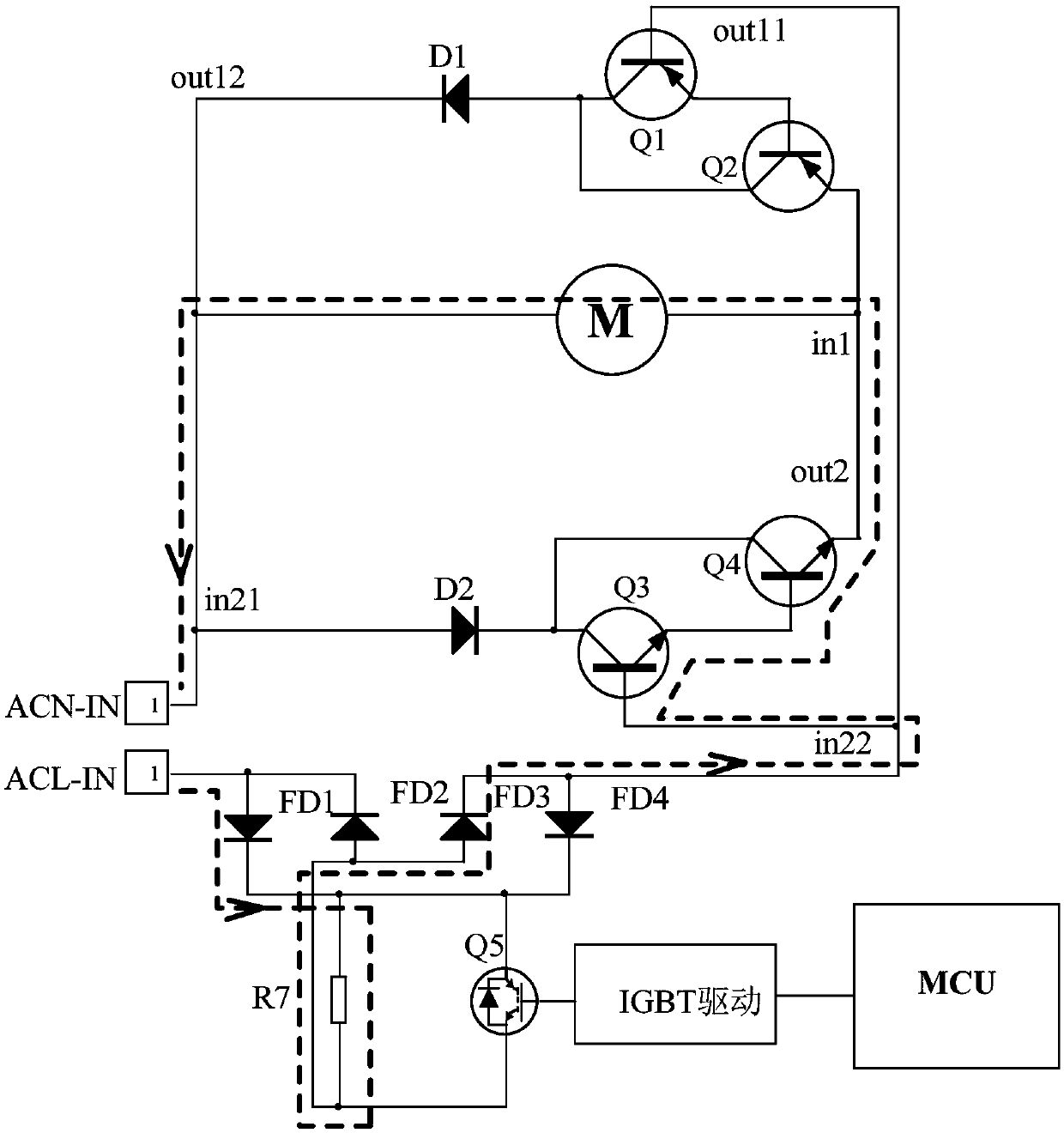

Alternating-current motor speed regulation circuit

The invention provides an alternating-current motor speed regulation circuit. A first freewheel module or a second freewheel module, a rectifier module and a switch module form a motor power supply circuit to supply power to an alternating-current motor, an alternating-current power supply supplies power to the first freewheel module or the second freewheel module through the switch module, and the induced electromotive force generated on a main winding of the alternating-current motor is discharged through the first freewheel module or the second freewheel module, so that normal operation ofthe alternating-current motor is guaranteed. Moreover, each of the first freewheel module and the second freewheel module has a composite tube structure composed of two triodes. When the switch moduleis turned off, the induced electromotive force generated on the alternating-current motor is subjected to current discharge. Due to the triode composite structure, the bias current provided by the switch module for maintaining the conduction of the freewheel module is very small, so that the consumption of the bias power provided by the switch module can be greatly reduced, the size of the circuit is reduced, and the heating loss is reduced.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

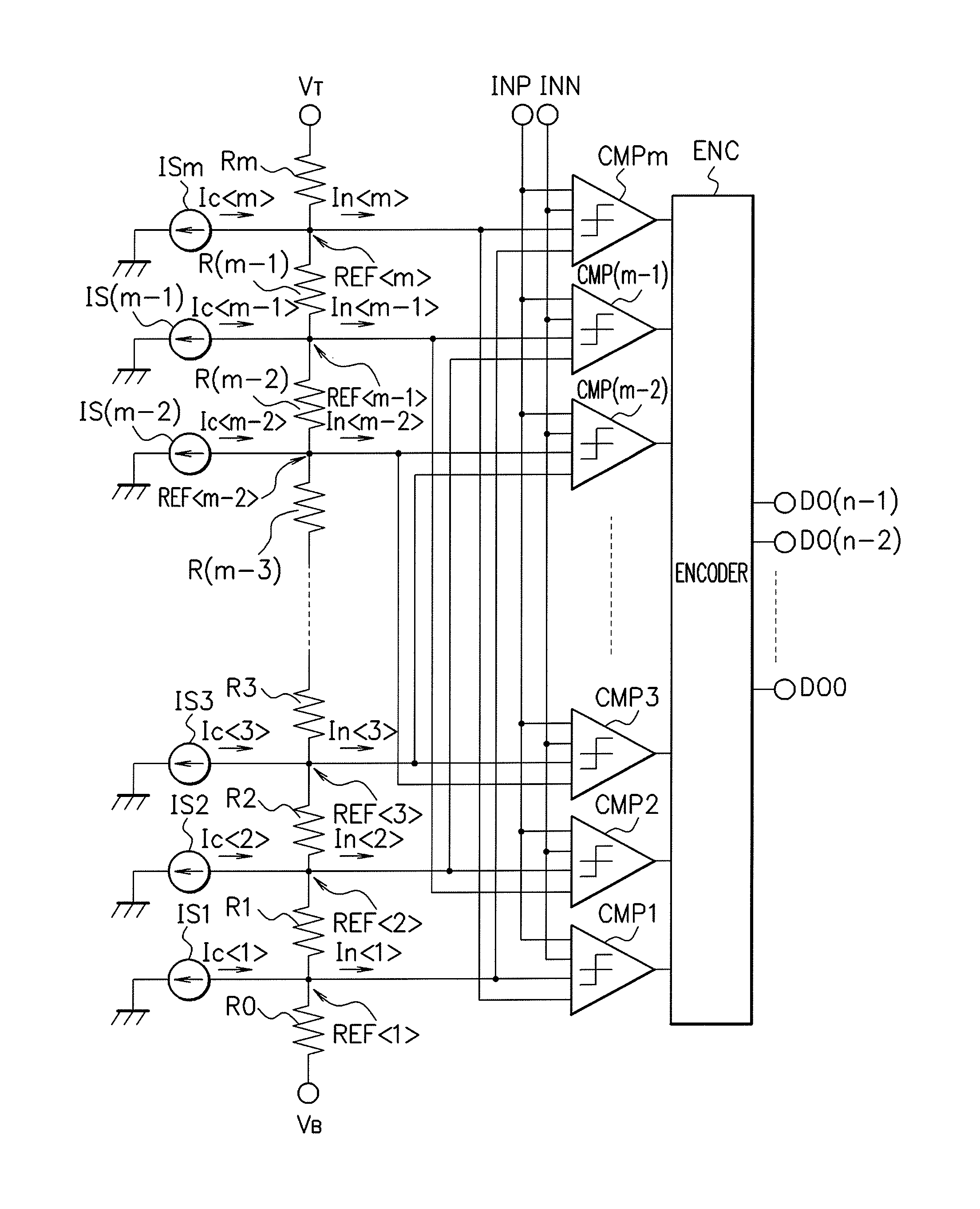

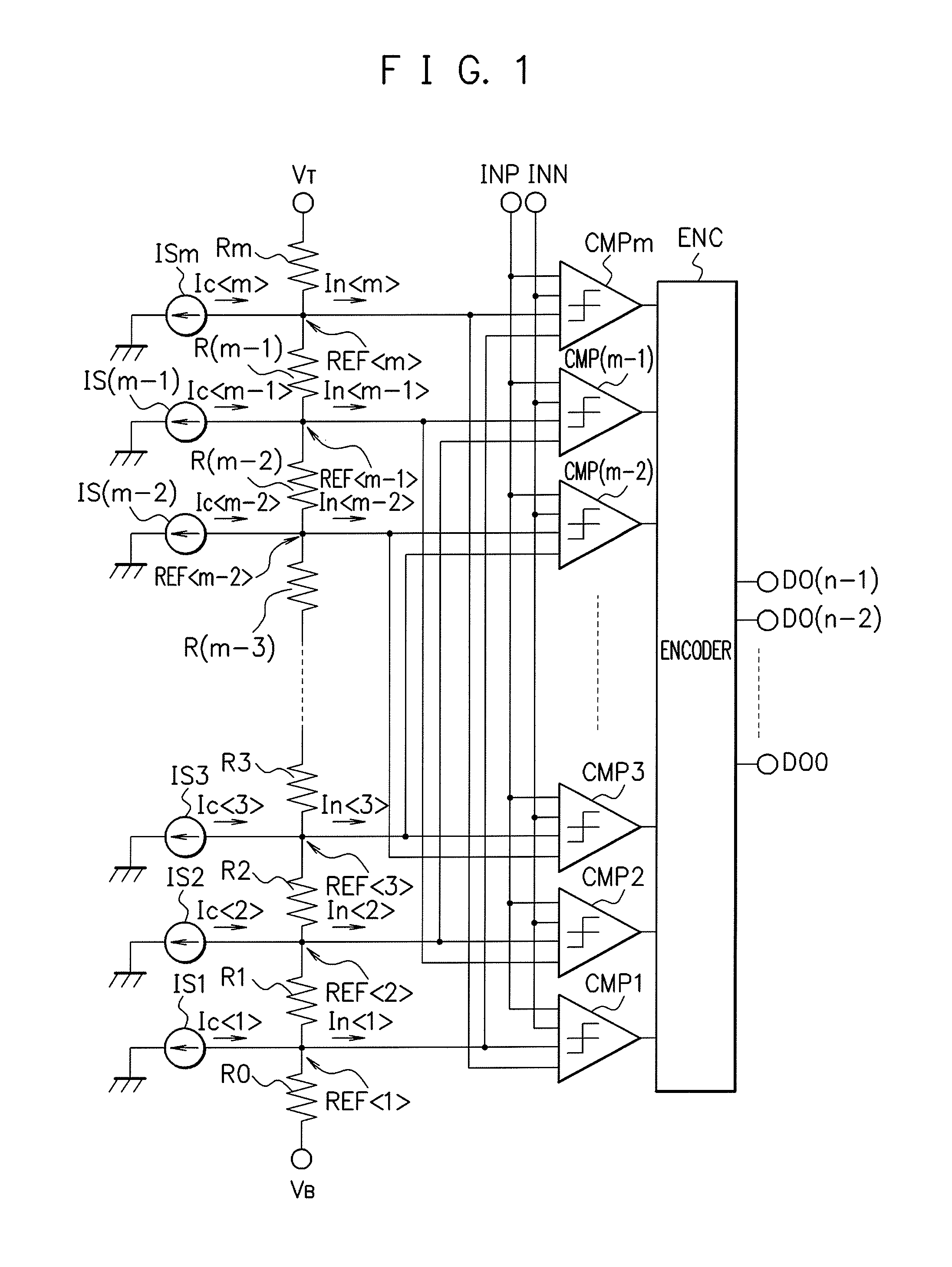

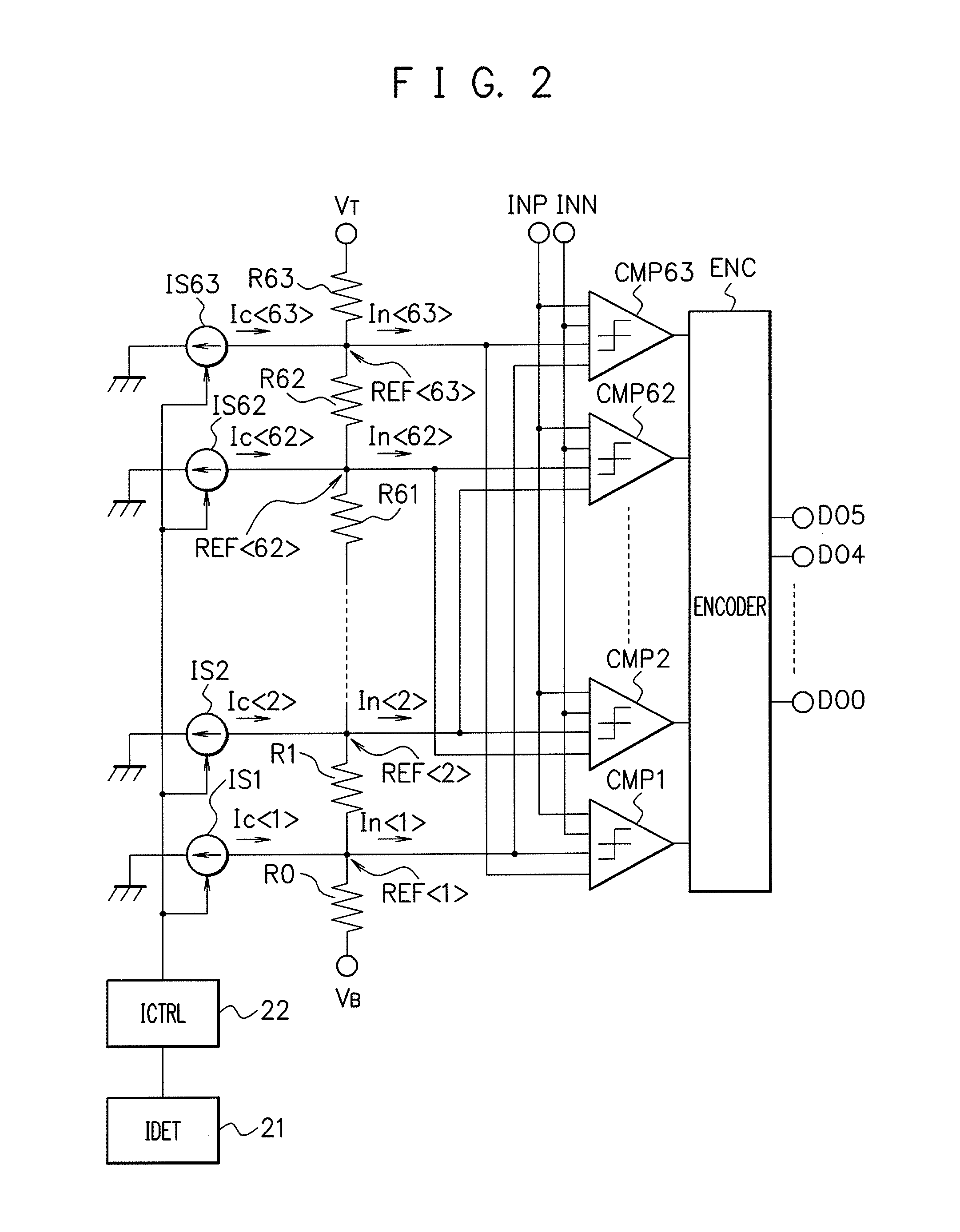

Analog-digital converter

InactiveUS20150180494A1Reduce bias currentImprove accuracyPower saving provisionsElectric signal transmission systemsElectrical resistance and conductanceDigital down converter

A parallel-type AD converter includes: a plurality of comparators that receive comparison reference potentials different from one another and compare the comparison reference potentials and received analog input signals; an encoder that encodes outputs of the plurality of comparators to output digital signals; and a resistor ladder circuit that resistance-divides a reference voltage to generate the comparison reference potentials and supplies the comparison reference potentials to the comparators through output nodes each positioned between resistors, and is designed to supply a correction current corresponding to noise currents that the comparators generate to the output nodes of the comparison reference potentials in the resistor ladder circuit, and thereby the noise currents that the comparators generate are offset by the correction current, a bias current in the resistor ladder circuit can be decreased, and accuracy deterioration in AD conversion can be suppressed.

Owner:KAGOSHIMA UNIV

Amplification circuit

InactiveCN1568573ASmall scaleSmall sizeAmplifier modifications to reduce temperature/voltage variationLogic circuitsCMOSEngineering

An amplifier circuit including a CMOS inverter circuit that eliminates a DC offset caused by variations in characteristics of elements in each manufacturing process and is thus applicable to analog signal processing. The CMOS inverter circuit including a PMOS transistor (11), an NMOS transistor (12), and the like is provided with an NMOS transistor (13) connected to the NMOS transistor (12) to increase a source voltage of the NMOS transistor (12) and DC offset detecting means for detecting a DC offset and applying a voltage adjusted so as to reduce the DC offset to a gate of the NMOS transistor (13).

Owner:SONY CORP

voltage supply circuit

ActiveCN102237138BQuick responseReduce power consumptionRead-only memoriesElectric variable regulationStopped workVoltage regulator module

The invention provides a voltage supply circuit used for supplying voltage to a memory unit. The memory unit comprises a voltage input end. The voltage supply circuit comprises a first voltage regulator, a second voltage regulator and a control unit, wherein the first voltage regulator is used for regulating reference voltage to generate working voltage when the memory unit works and stops working when the memory unit does not work; the second voltage regulator is used for regulating the reference voltage to generate standby voltage; and the control unit is used for controlling the voltage input end to receive the working voltage after the memory unit works for a preset time, or receiving the standby voltage. The voltage supply circuit has the following advantage: the problem of slow response of the memory unit caused by delay of the voltage regulators is avoided.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

An on-chip rc oscillator circuit

ActiveCN109245723BReduce power consumptionSimple structureOscillations generatorsCapacitanceHemt circuits

The invention discloses an on-chip RC oscillator circuit, which belongs to the technical field of integrated circuits. The on-chip RC oscillator circuit includes a low power consumption temperature compensation circuit, a charge and discharge control circuit, a comparator circuit, an RS flip-flop and a buffer. In the low power consumption stable compensation circuit, the first NMOS transistor, the first PMOS transistor, the fourth PMOS transistor, the third resistor and the second NMOS transistor constitute a circuit that generates a bias current with a negative temperature coefficient; the second NMOS transistor, the second PMOS transistor The tube, the third PMOS tube, the third NMOS tube, and the second resistor form a loop that generates a positive temperature coefficient current; the two loops are connected through the second NMOS tube to achieve negative feedback, and the first capacitor and the first resistor are connected to the negative feedback loop. Le compensation improves stability, only four current branches are required to realize the positive and negative temperature coefficient current structure required for temperature compensation, and the power consumption is reduced; the first NMOS tube, the second NMOS tube, and the third NMOS tube work at sub-threshold The region realizes smaller bias current and lower power consumption.

Owner:CHINA KEY SYST & INTEGRATED CIRCUIT