Patents

Literature

97results about How to "Low budget" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

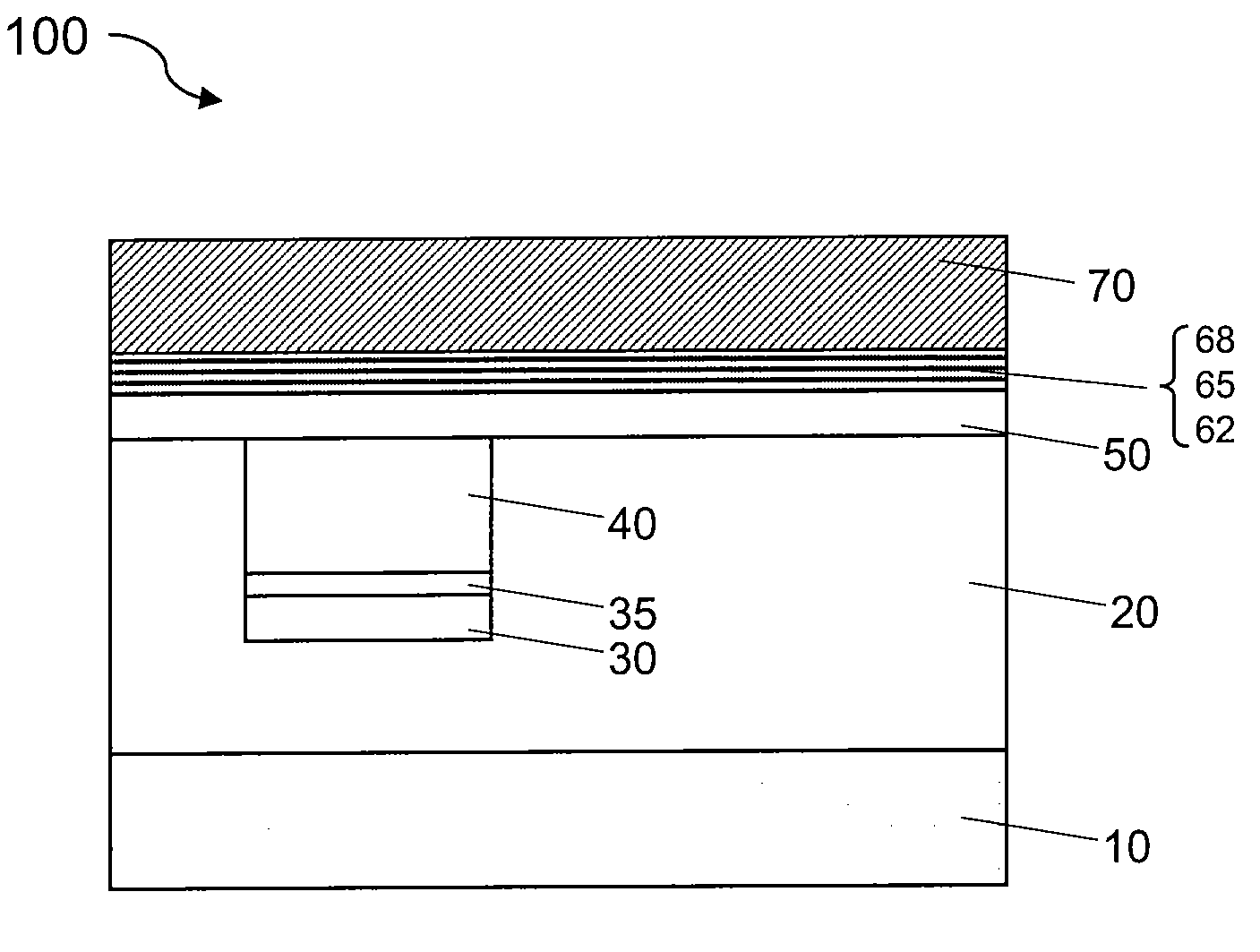

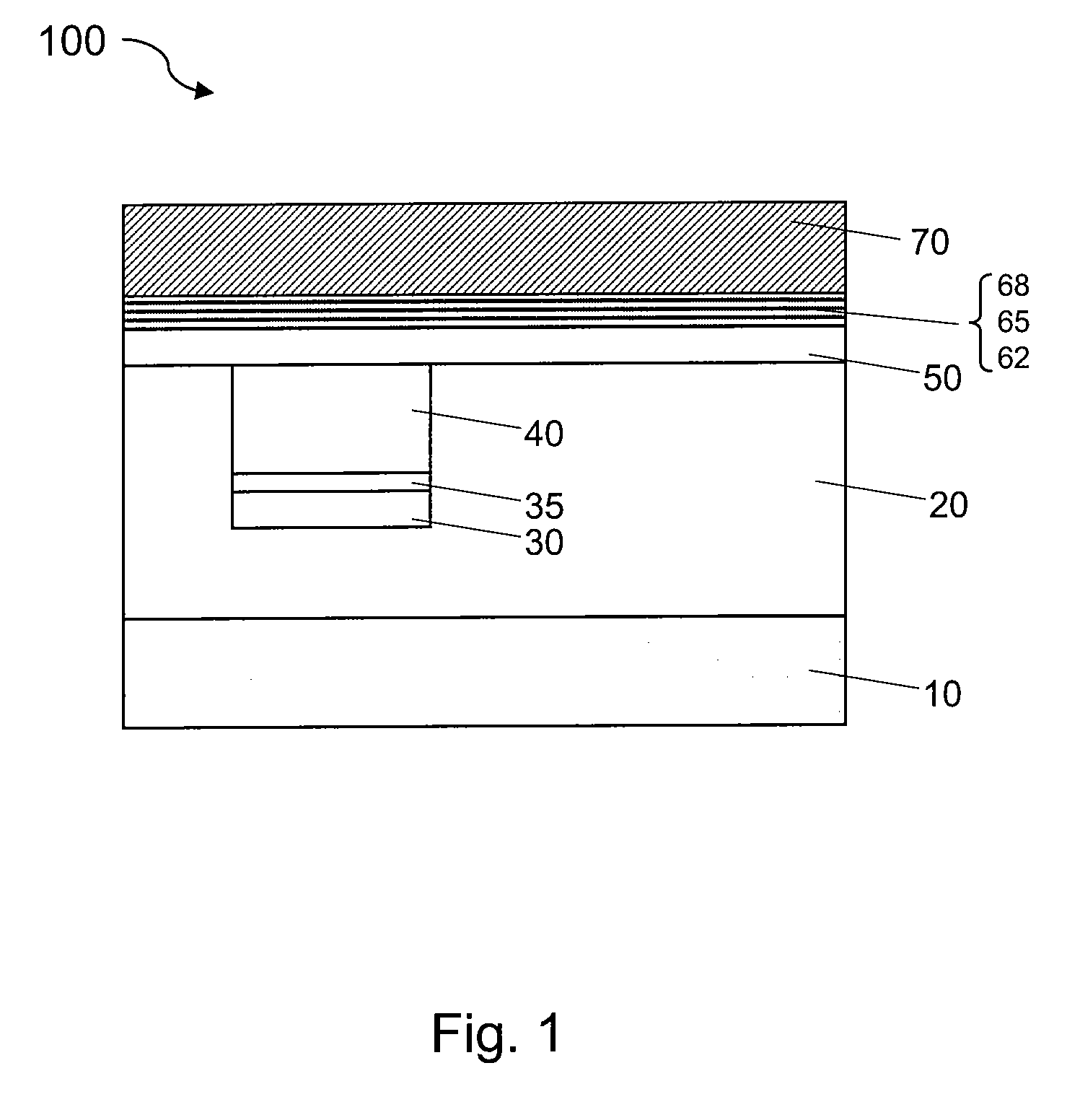

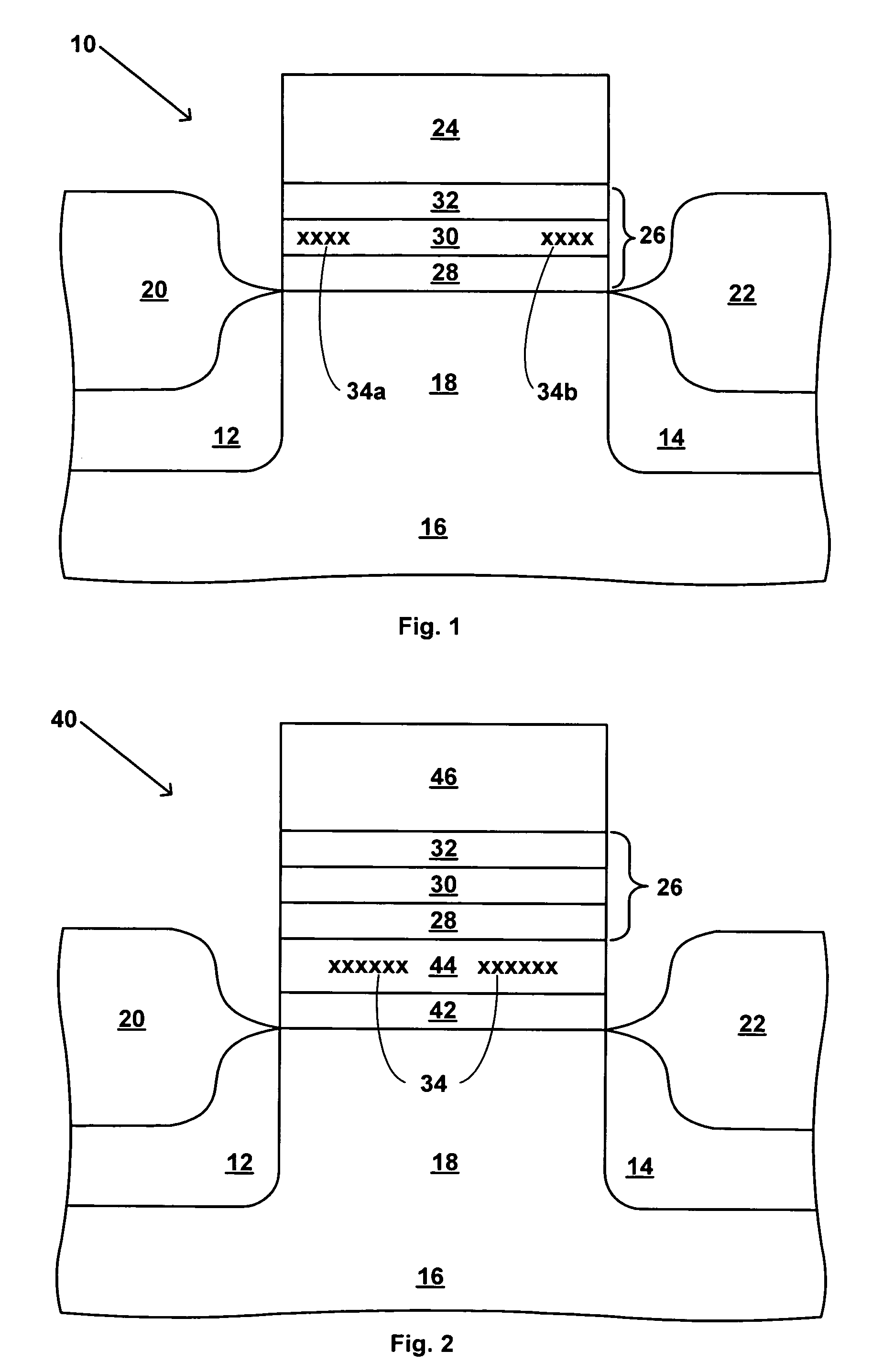

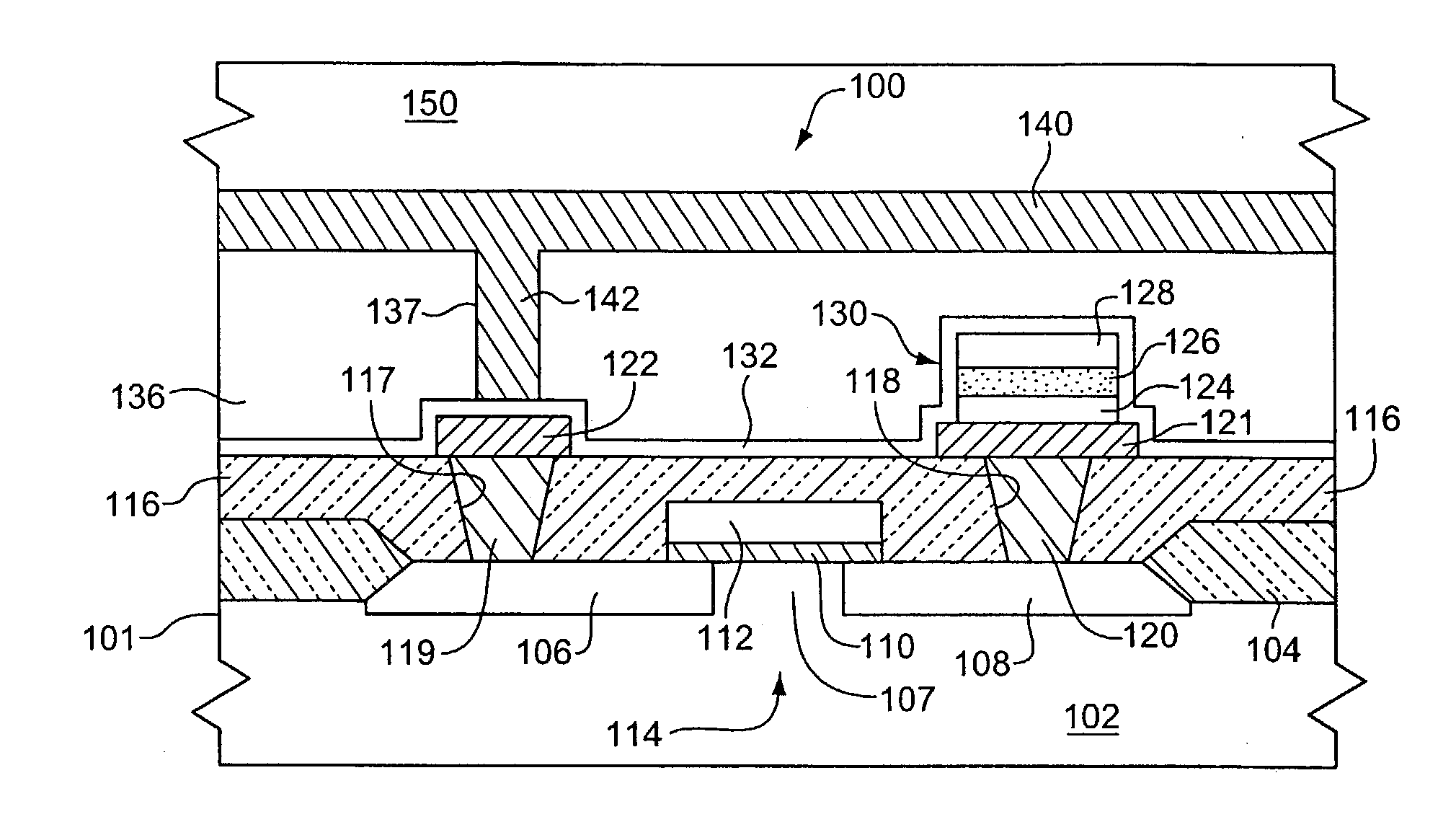

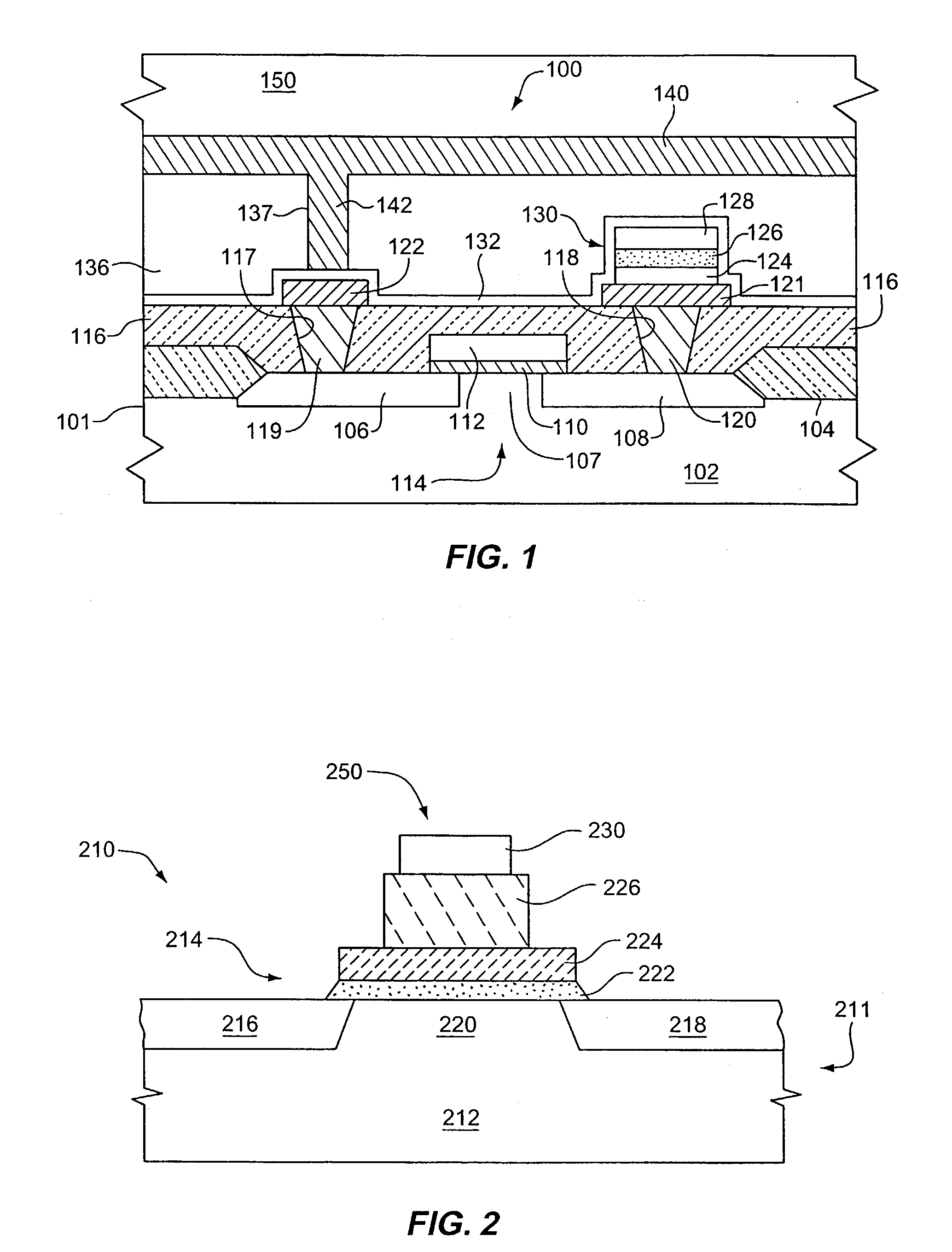

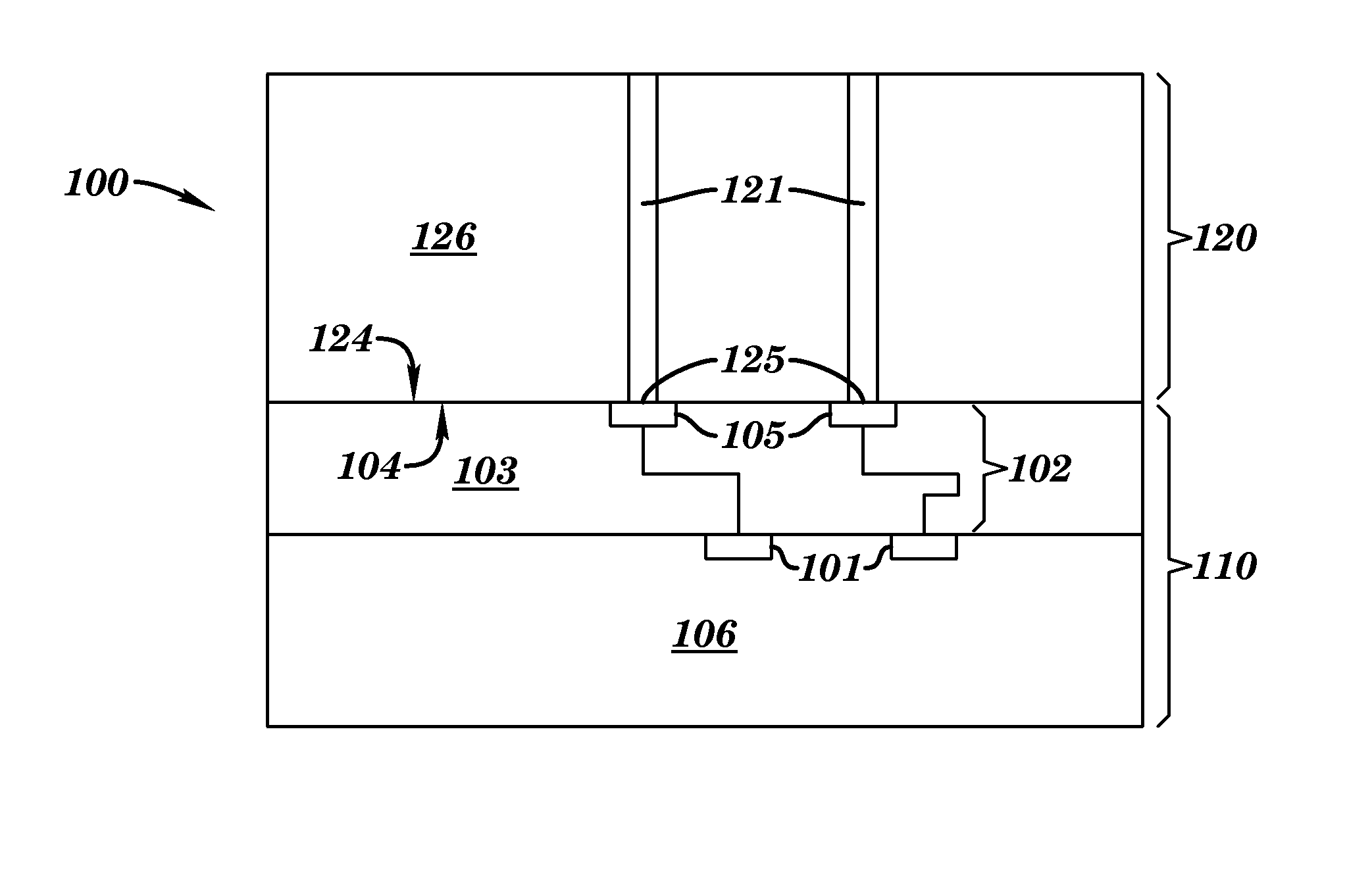

TFT floating gate memory cell structures

ActiveUS20100001282A1Improve reliabilitySmall geometric cell sizeTransistorSemiconductor/solid-state device manufacturingDiffusion barrierDielectric layer

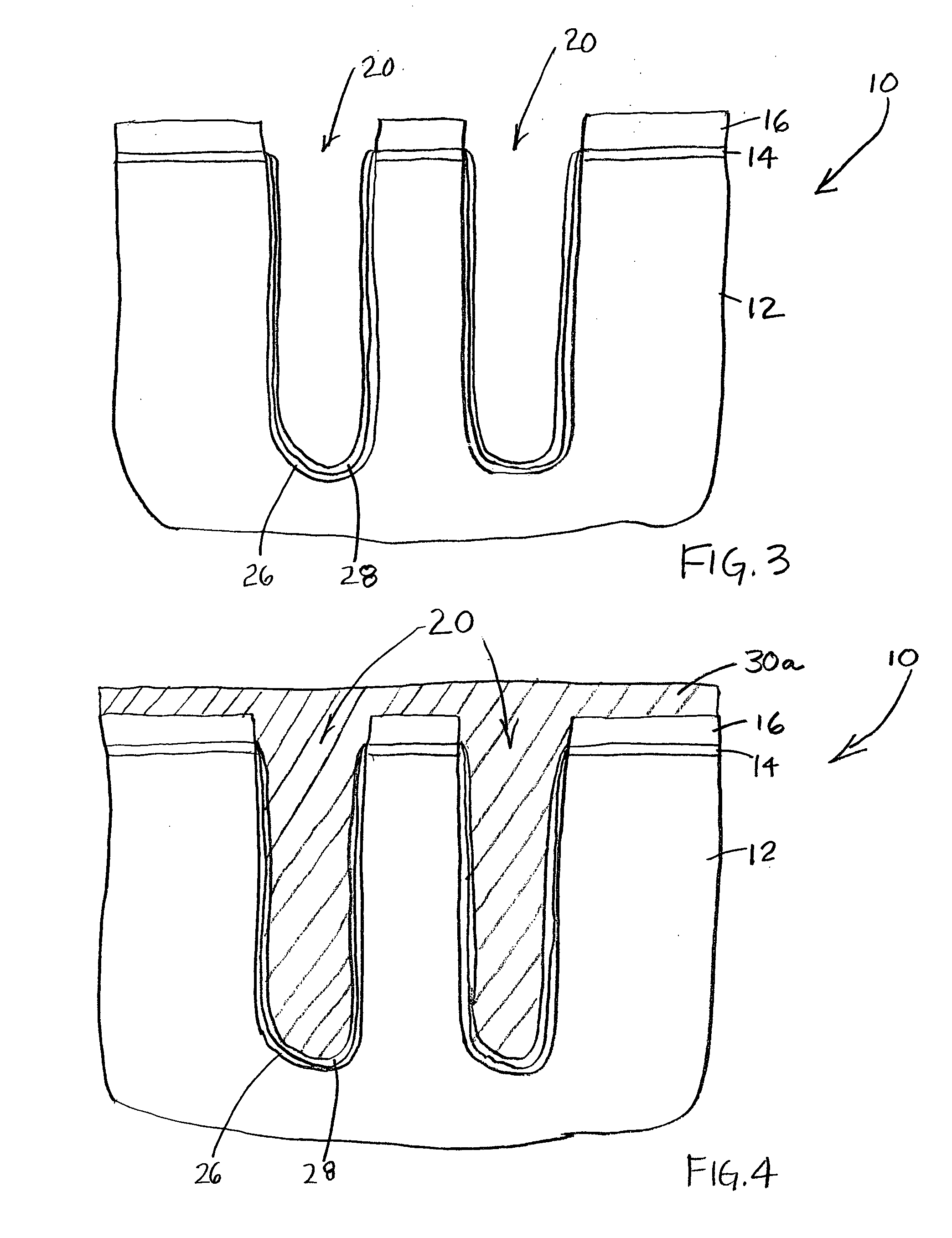

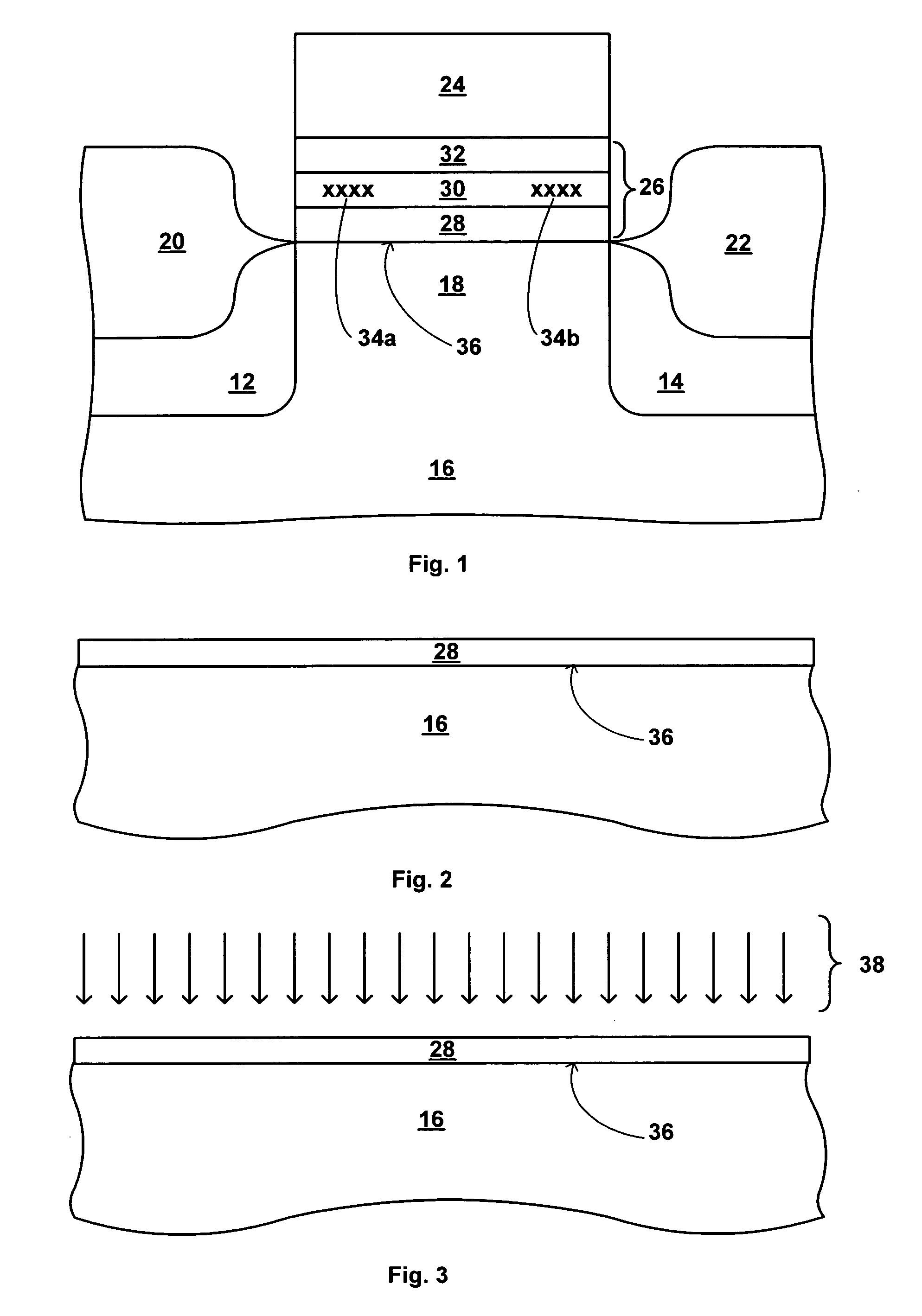

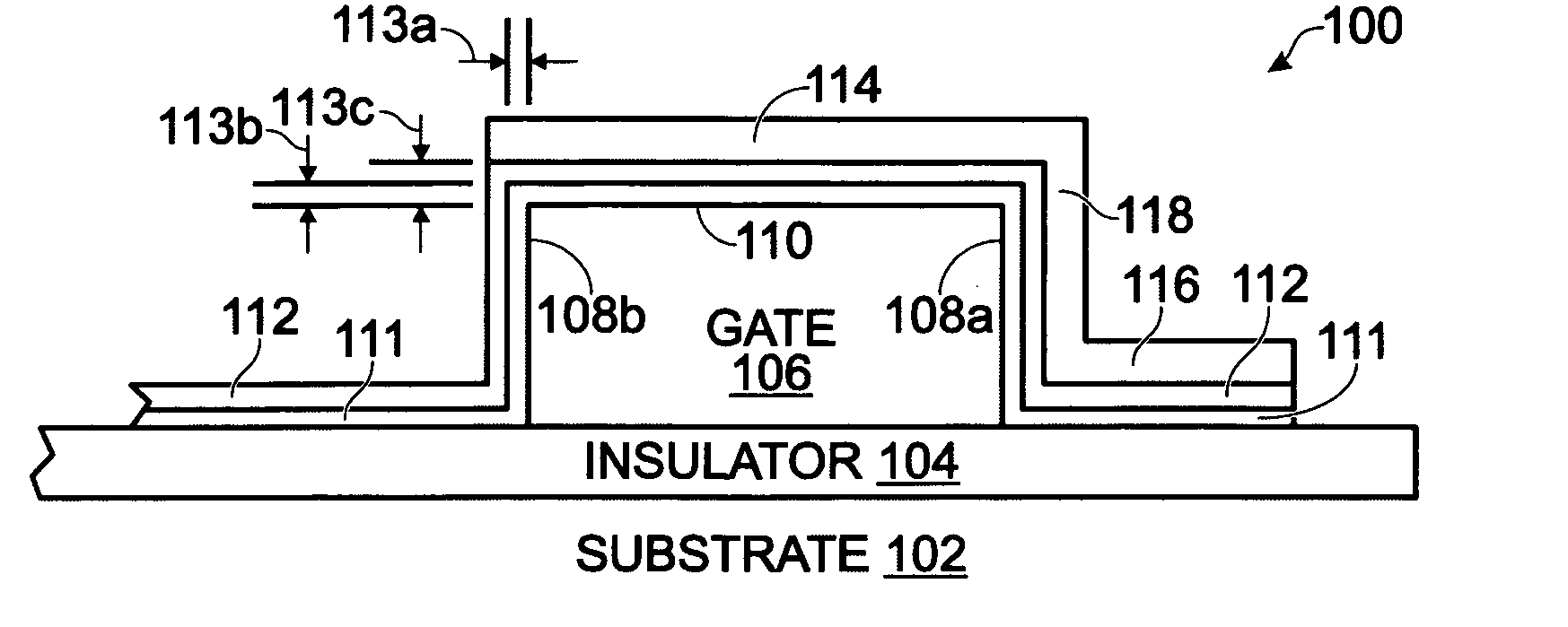

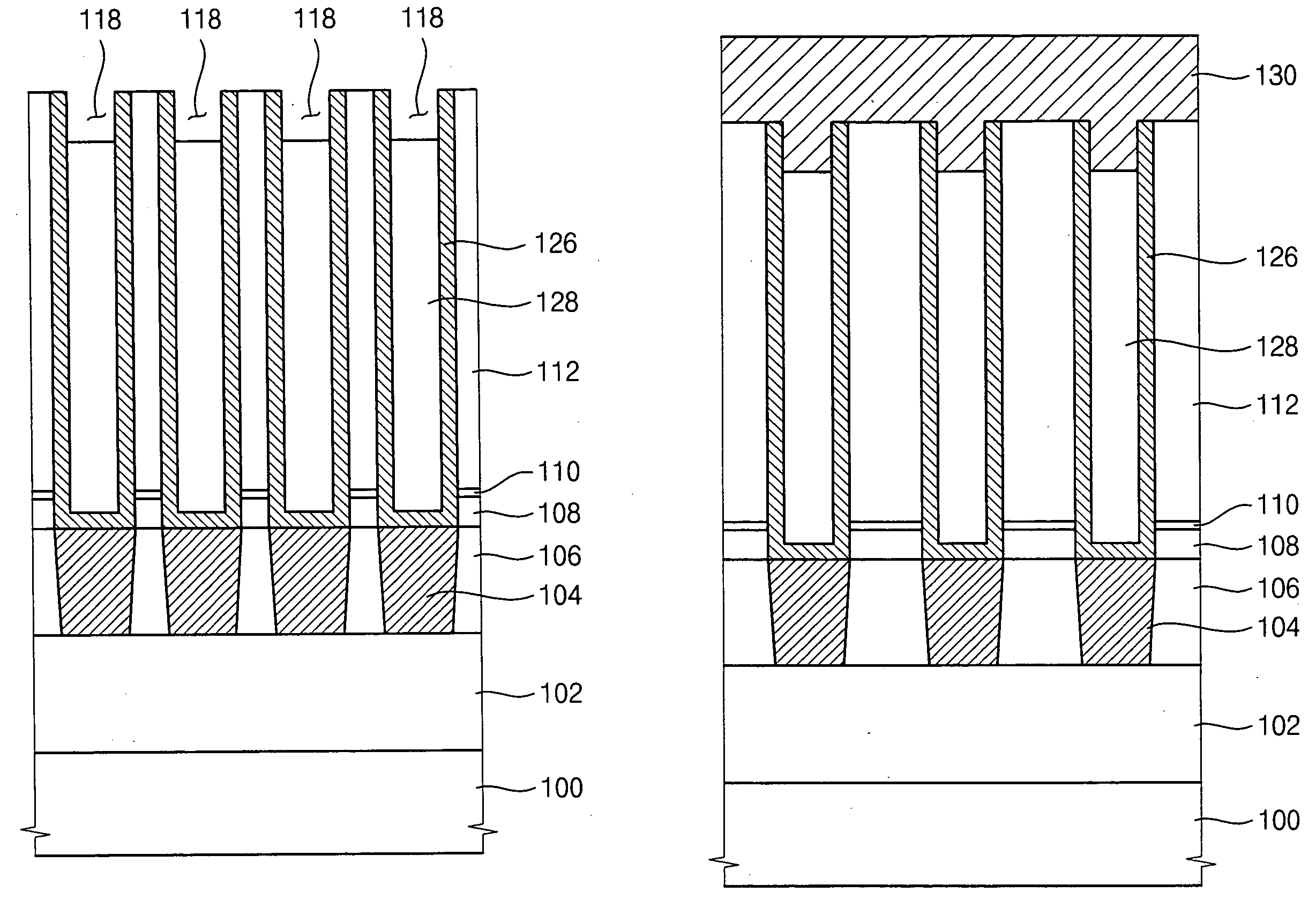

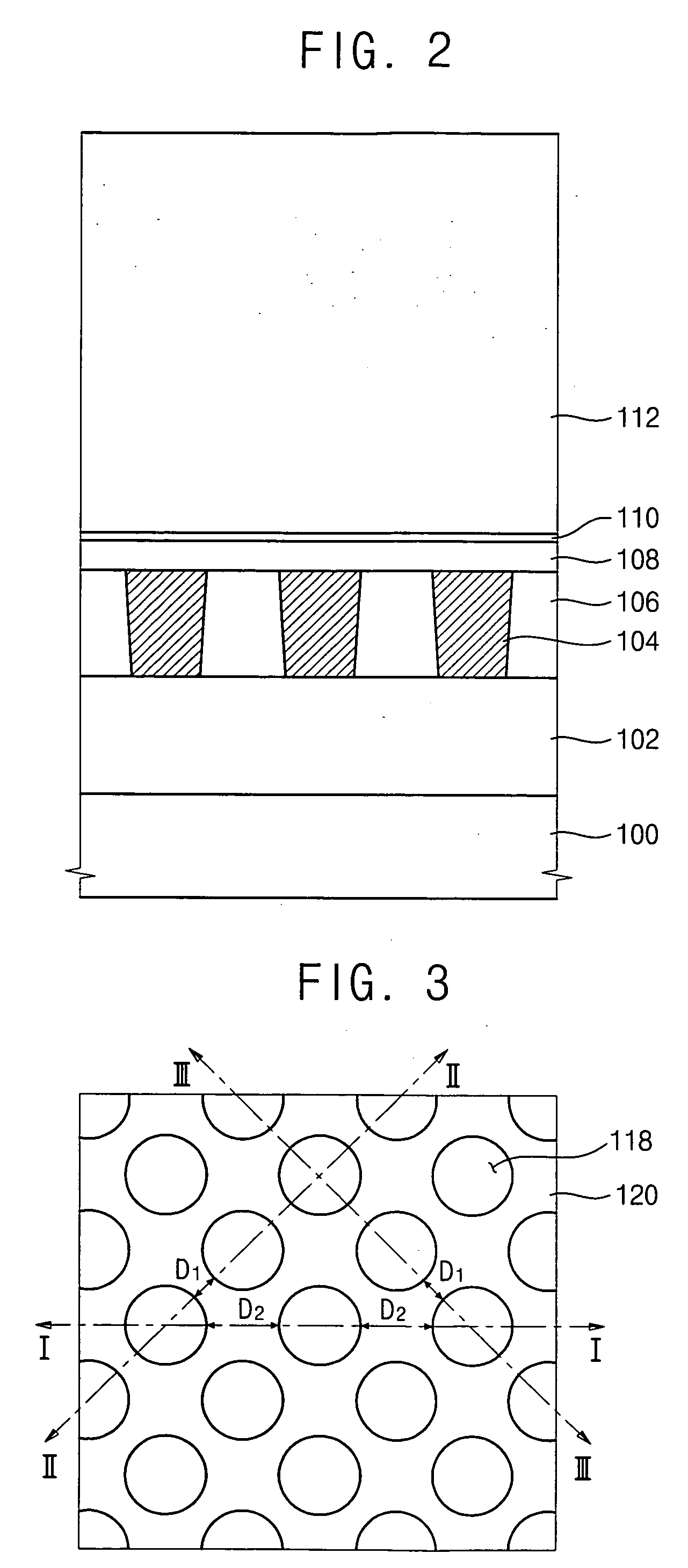

A device having thin-film transistor (TFT) floating gate memory cell structures is provided. The device includes a substrate, a dielectric layer on the substrate, and one or more source or drain regions being embedded in the dielectric layer. the dielectric layer being associated with a first surface. Each of the one or more source or drain regions includes an N+ polysilicon layer on a diffusion barrier layer which is on a first conductive layer. The N+ polysilicon layer has a second surface substantially co-planar with the first surface. Additionally, the device includes a P− polysilicon layer overlying the co-planar surface and a floating gate on the P− polysilicon layer. The floating gate is a low-pressure CVD-deposited silicon layer sandwiched by a bottom oxide tunnel layer and an upper oxide block layer. Moreover, the device includes at least one control gate made of a P+ polysilicon layer overlying the upper oxide block layer. A method of making the same memory cell structure is provided and can be repeated to integrate the structure three-dimensionally.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

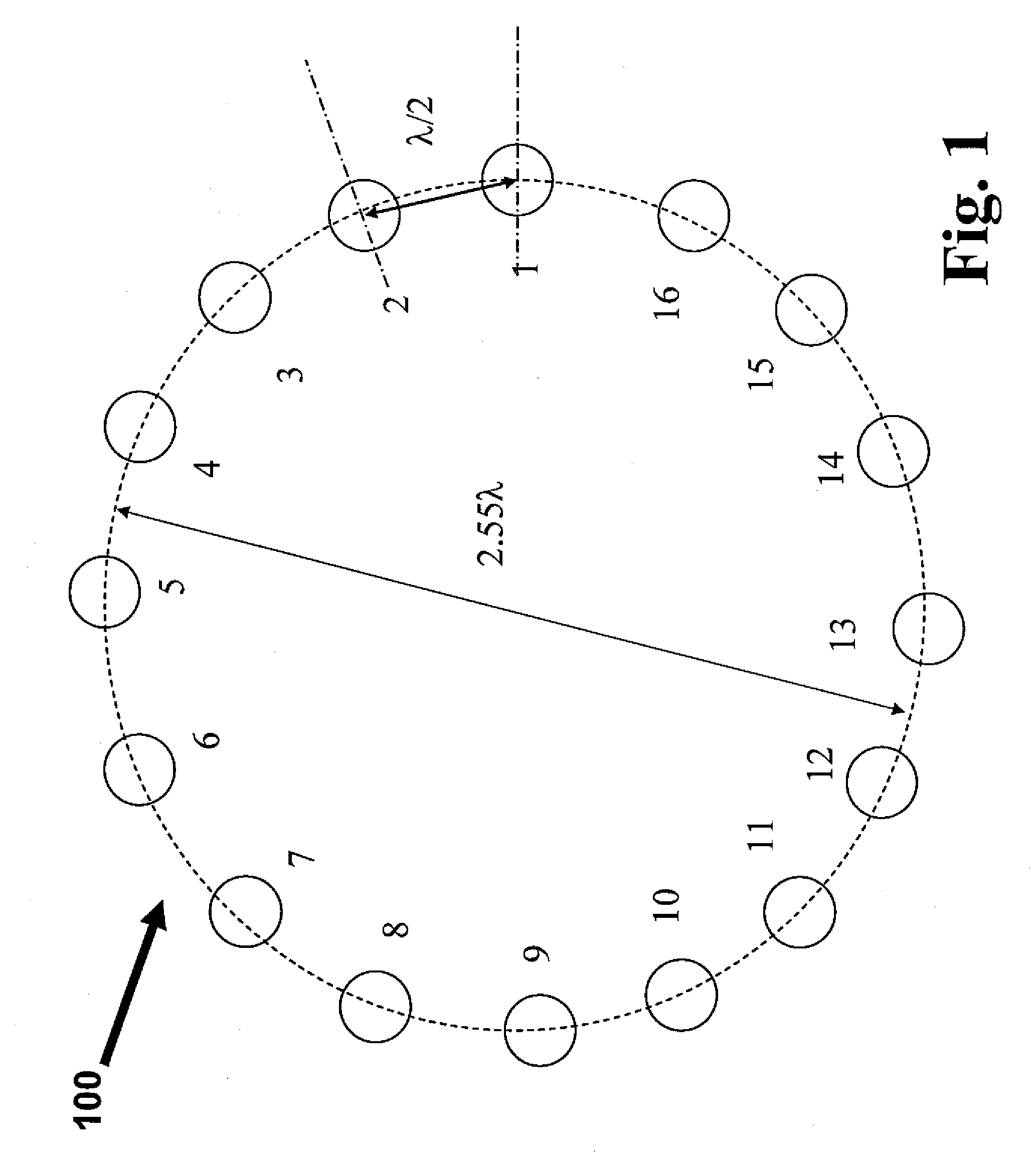

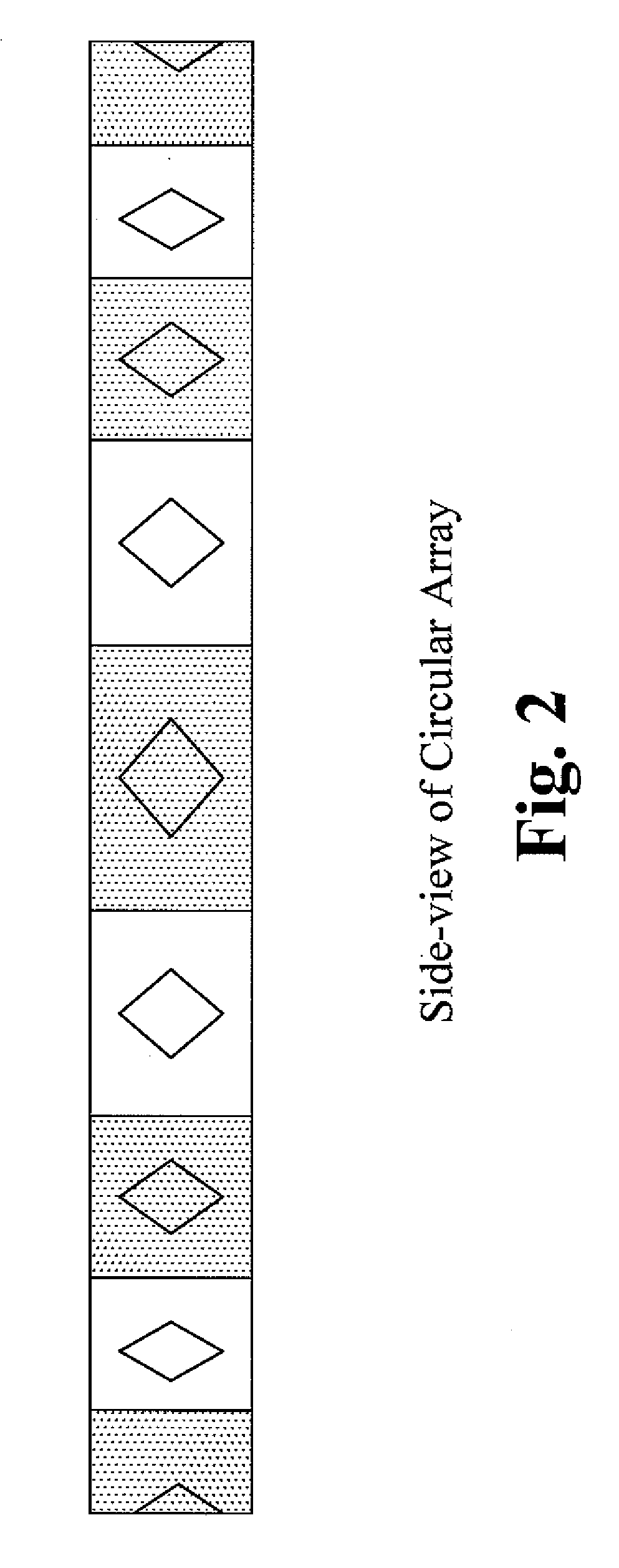

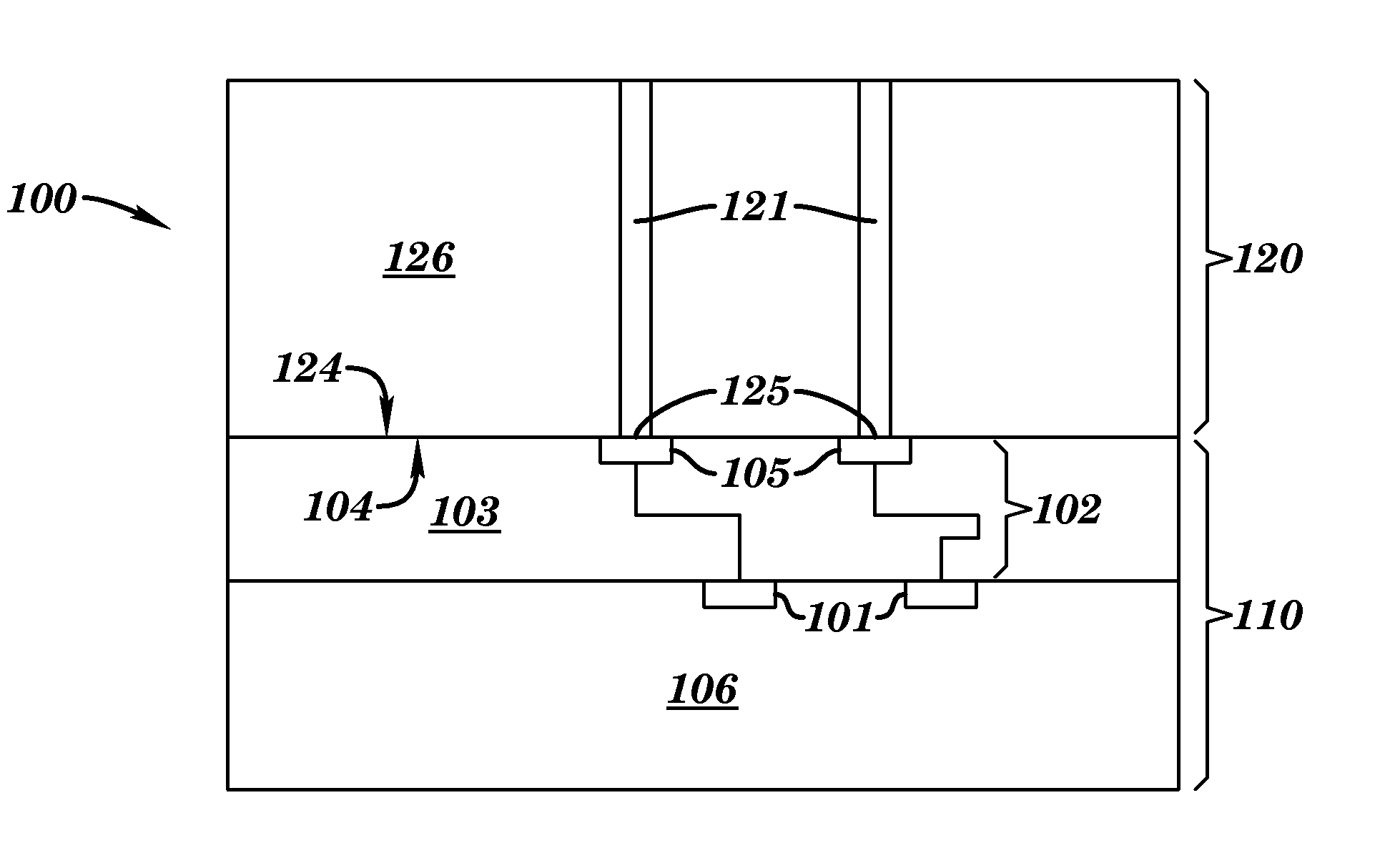

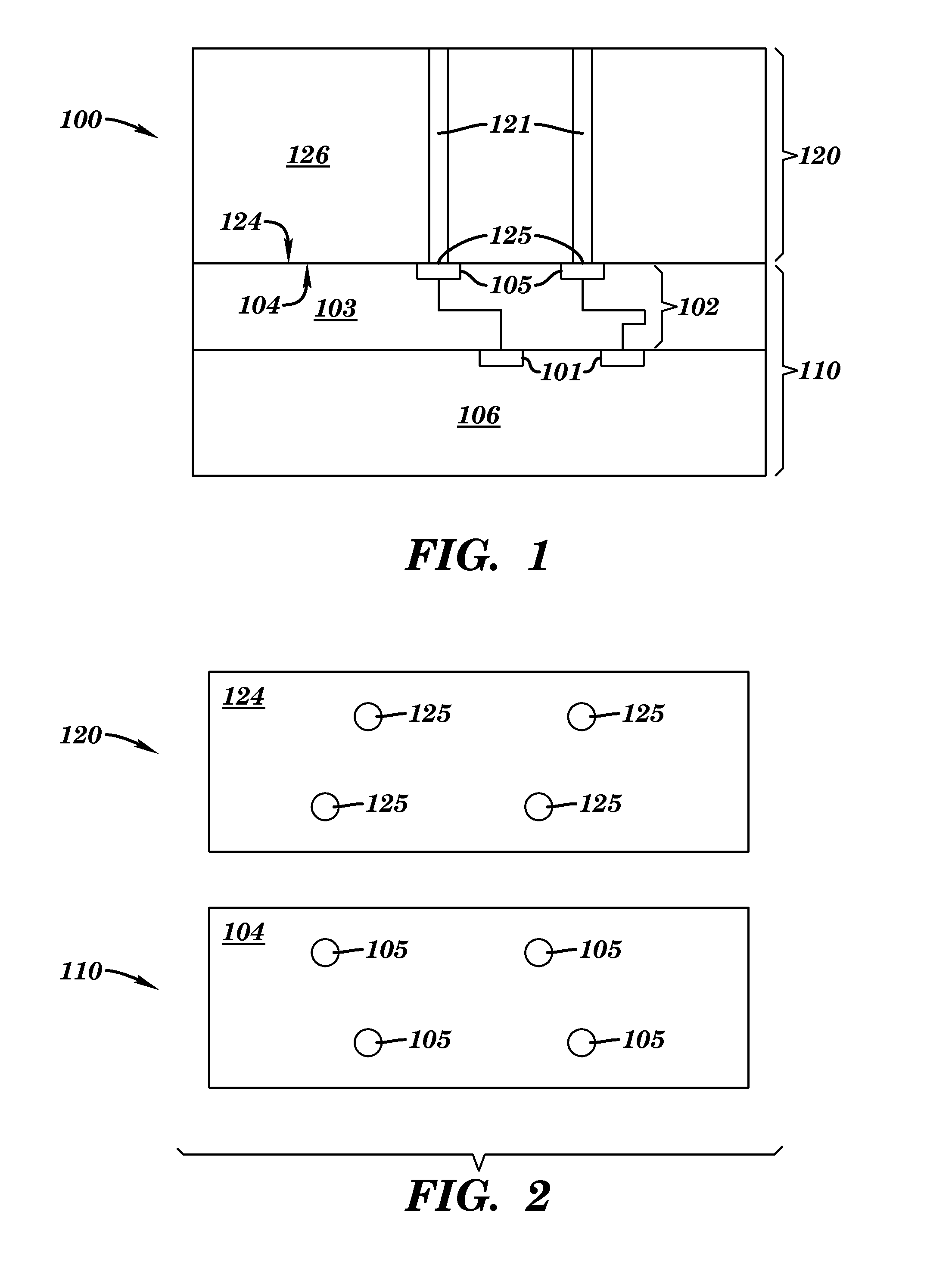

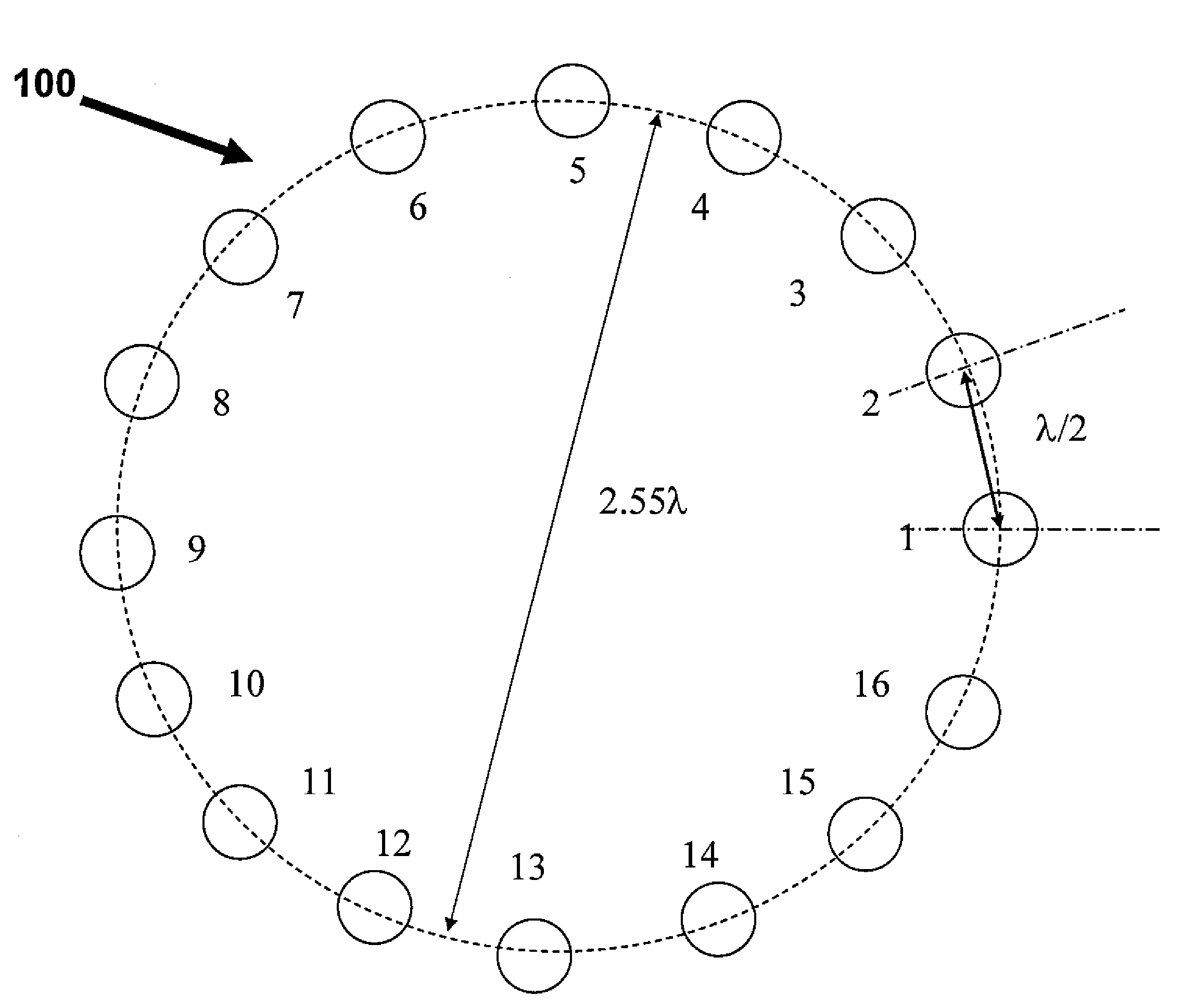

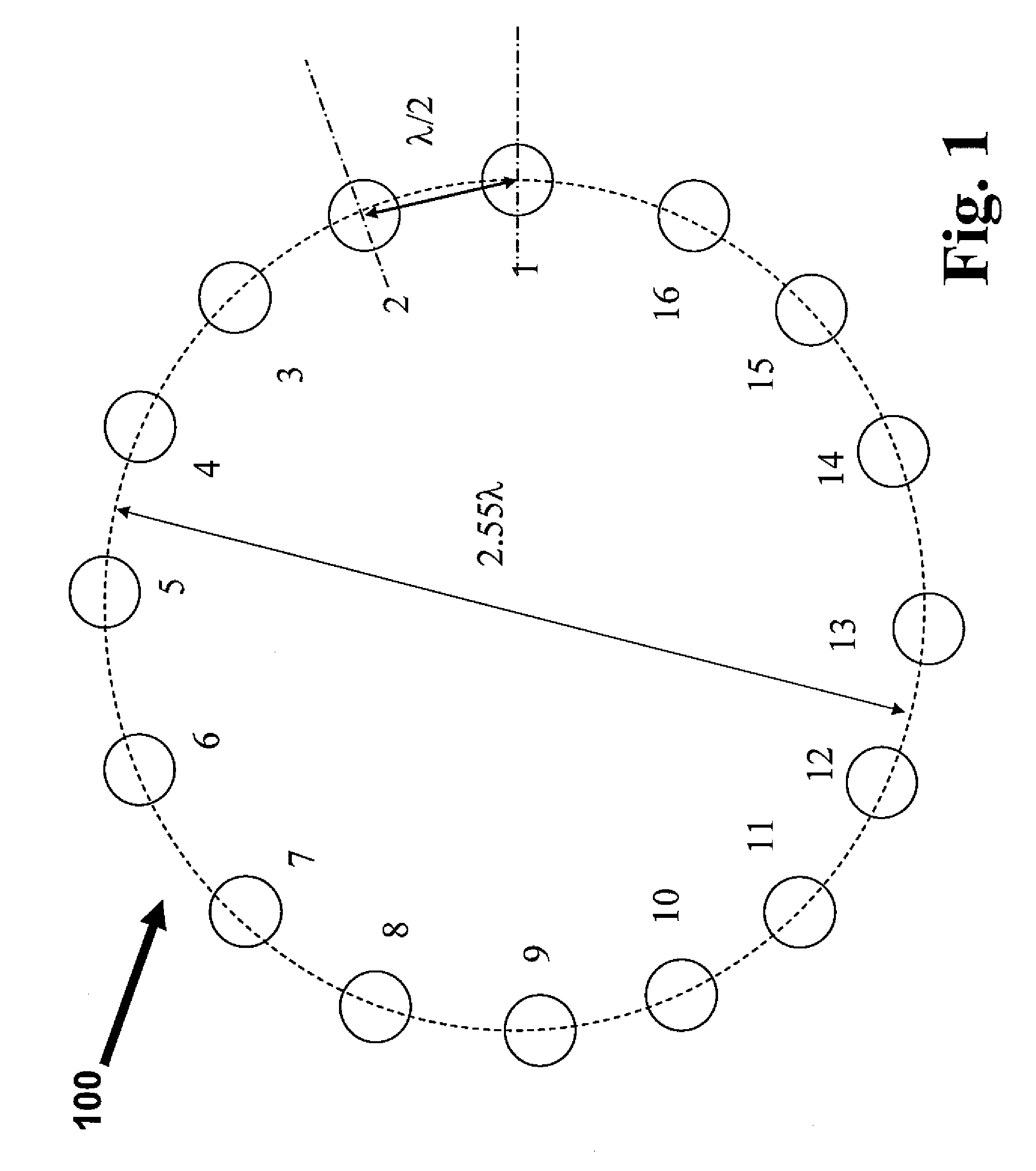

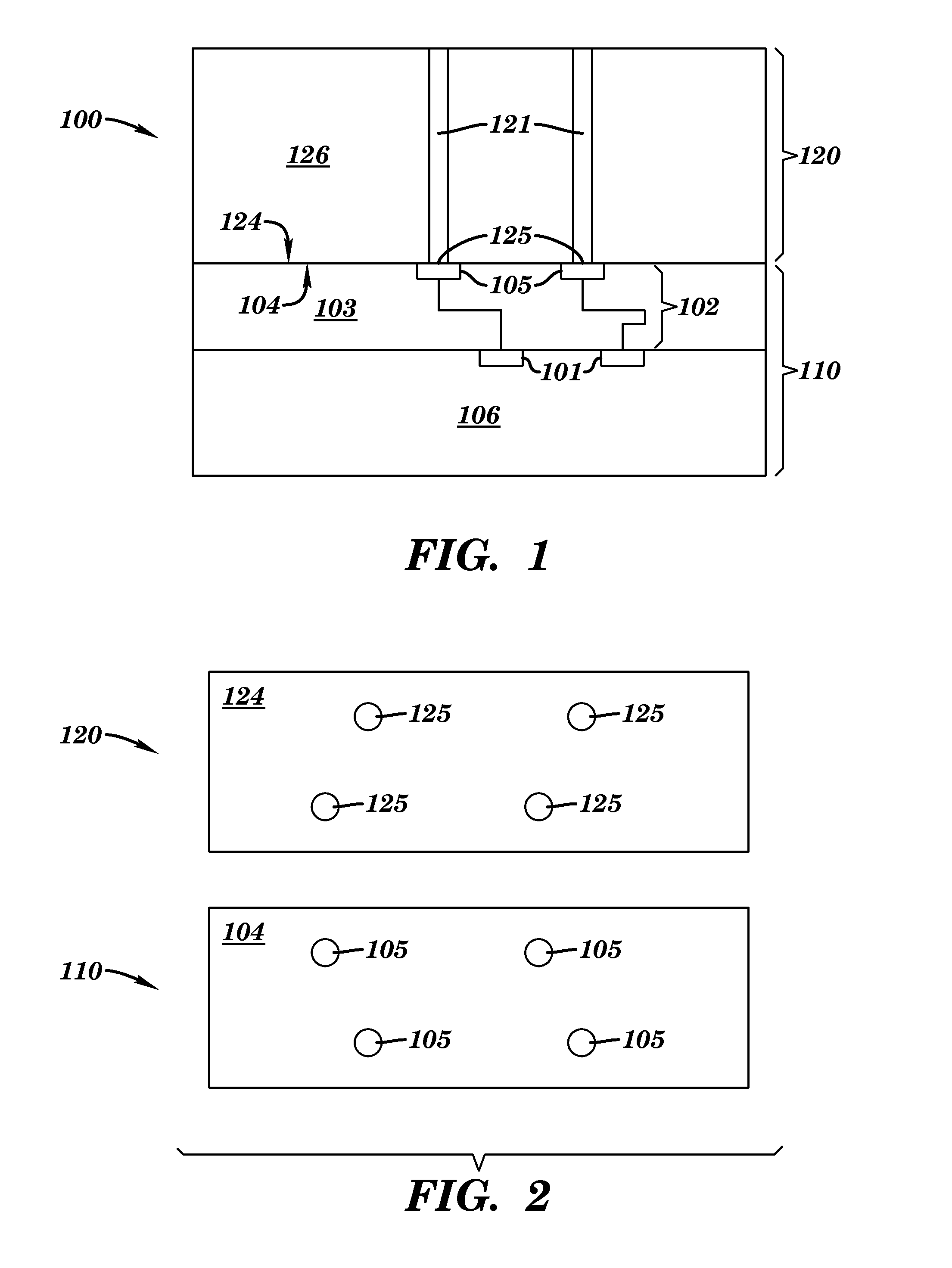

Array structure for the application to wireless switch of WLAN and wman

InactiveUS20070257858A1Improve efficiencyLow budgetIndoor communication adaptationIndividually energised antenna arraysArea networkArray data structure

The present invention provides an antenna array structure which includes multiple array elements, and the antenna array structure is using for the application of the WLAN (wireless local area network) or WMAN (wireless metro area network.) Furthermore, the array elements of the present invention are phased arrays or attenuated arrays, and when configuration with different type of the array element is used, the corresponding BFN (beam forming network) can also be implemented in various possibilities. With all the configuration of the present invention, the manufacturers can have a stable array structure for their applications.

Owner:ACCTON TECHNOLOGY CORPORATION

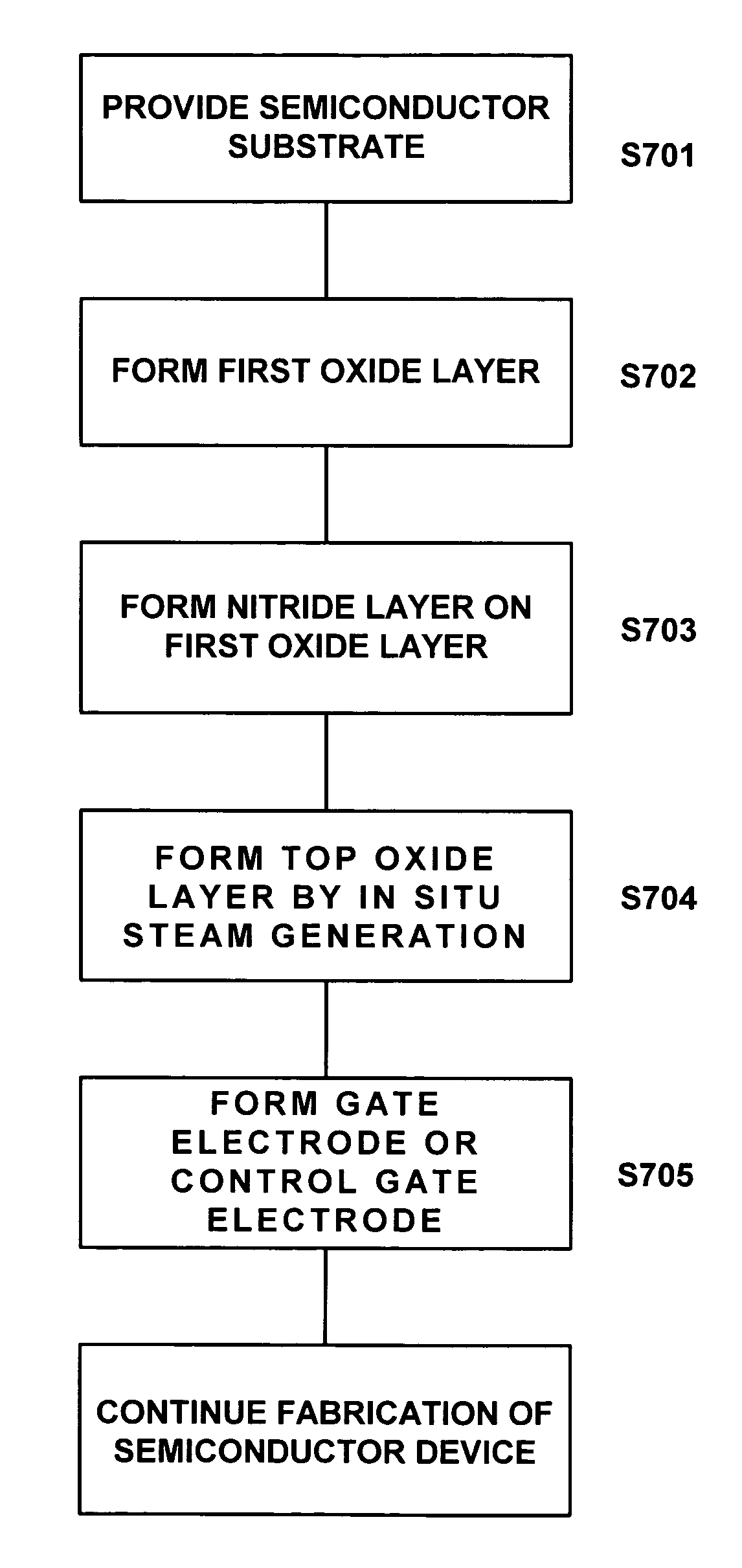

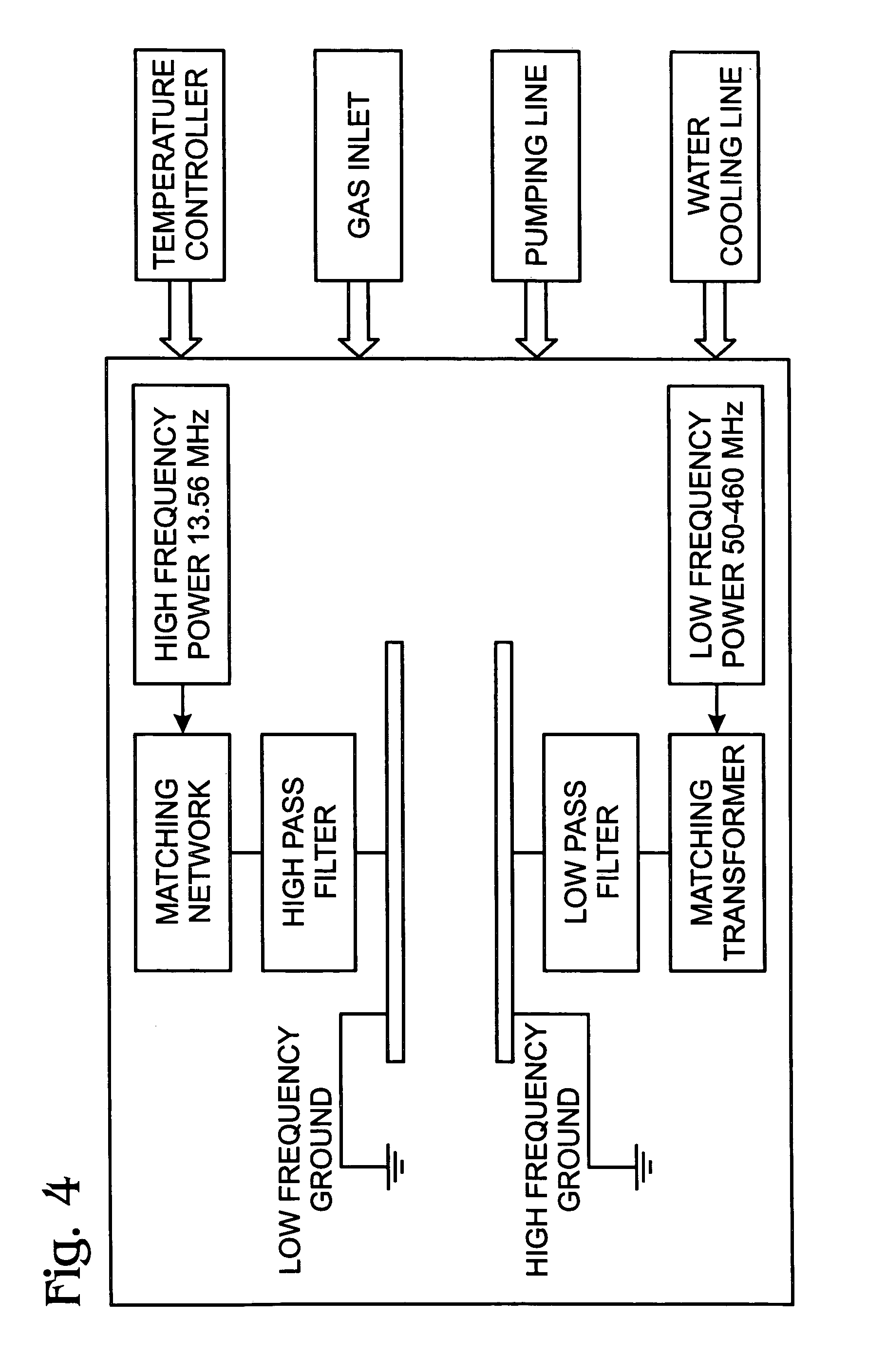

Integrated ONO processing for semiconductor devices using in-situ steam generation (ISSG) process

InactiveUS7115469B1Less carbonThermal budgetSemiconductor/solid-state device manufacturingSemiconductor devicesSteam generationSemiconductor

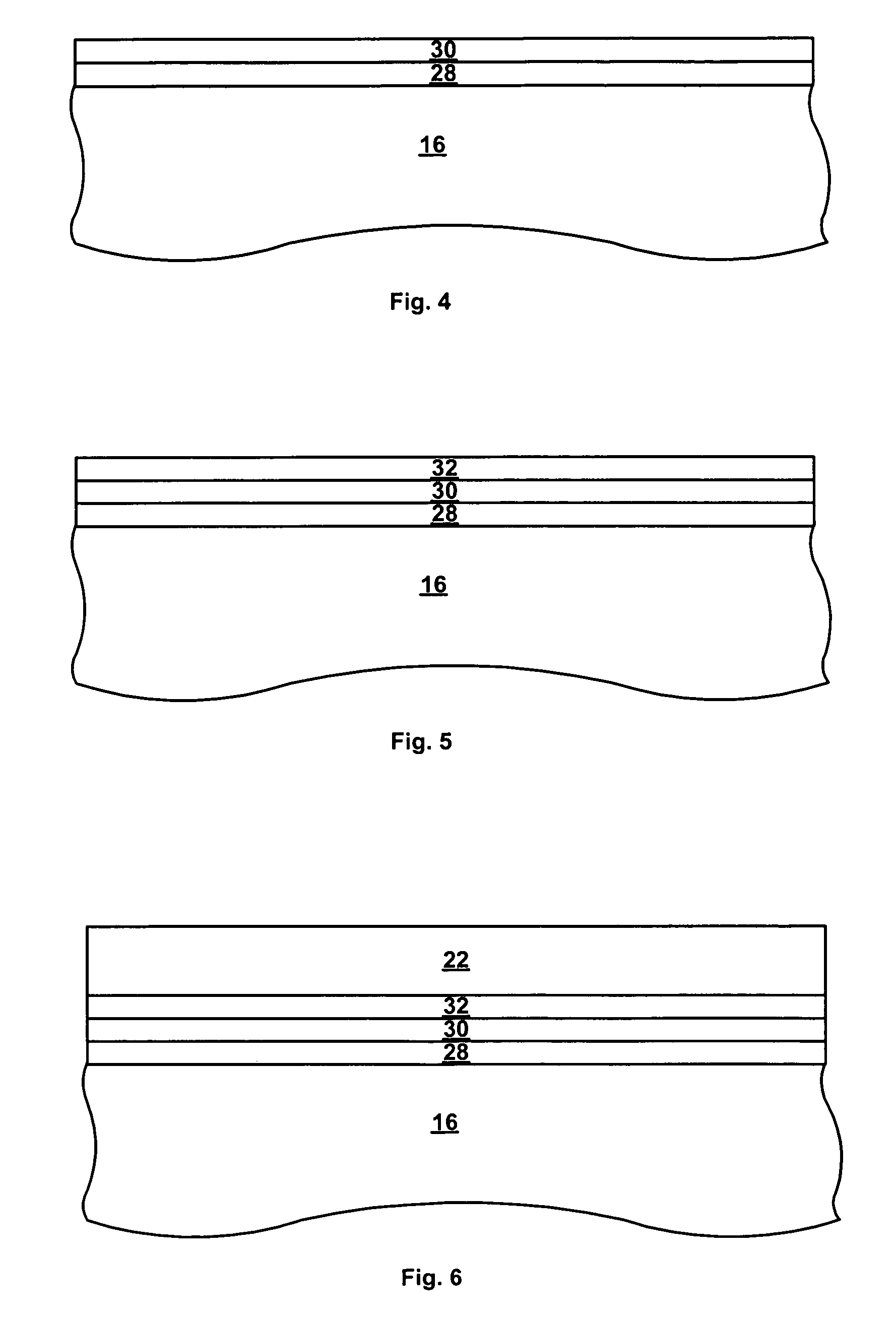

A process for fabrication of a semiconductor device including an ONO structure as a component of a flash memory device, comprising forming the ONO structure by providing a semiconductor substrate having a silicon surface; forming a first oxide layer on the silicon surface; depositing a silicon nitride layer on the first oxide layer; and forming a top oxide layer on the silicon nitride layer, wherein the top oxide layer is formed by an in-situ steam generation oxidation of a surface of the silicon nitride layer. The semiconductor device may be, e.g., a SONOS two-bit EEPROM device or a floating gate FLASH memory device including an ONO structure.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

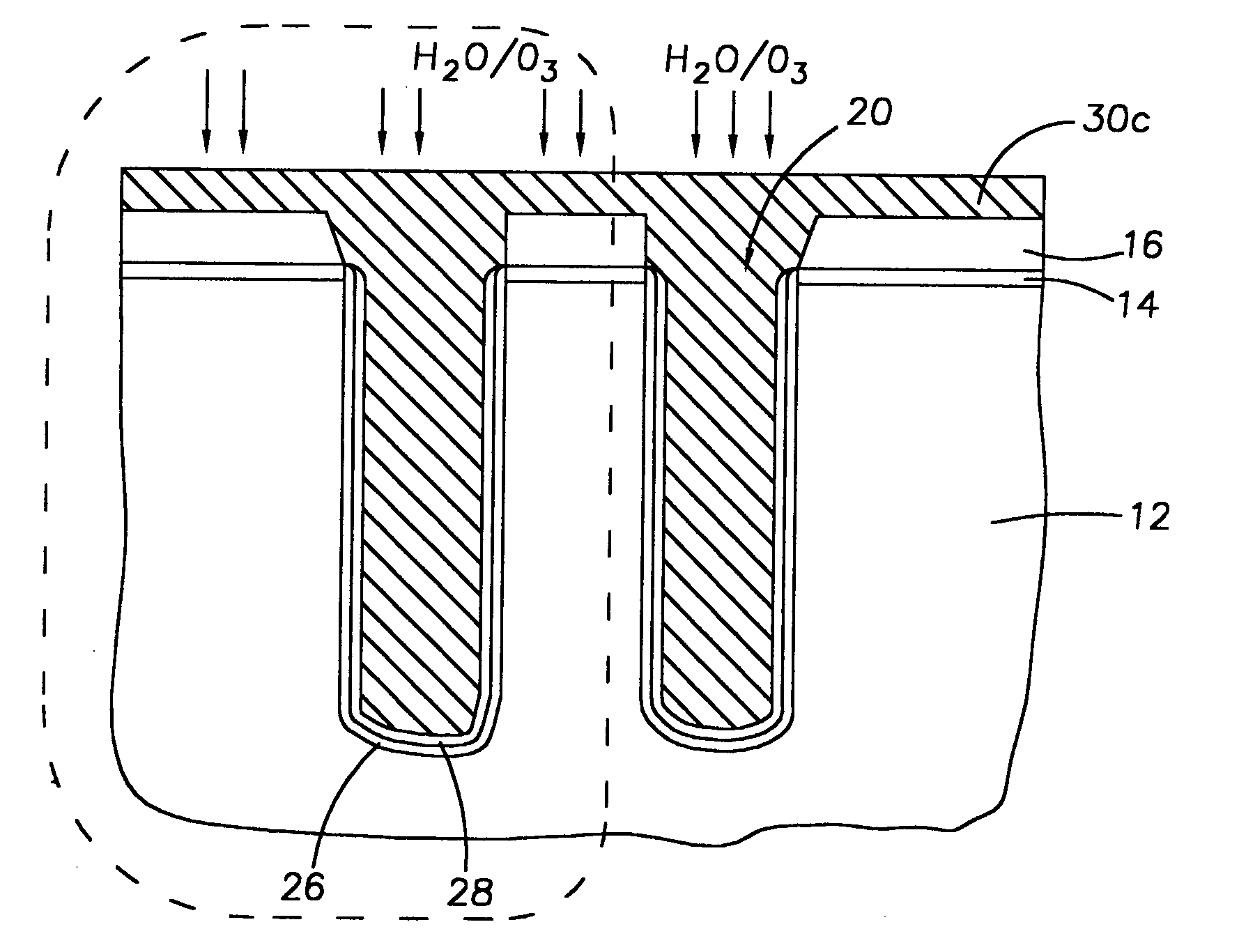

Low temperature process for polysilazane oxidation/densification

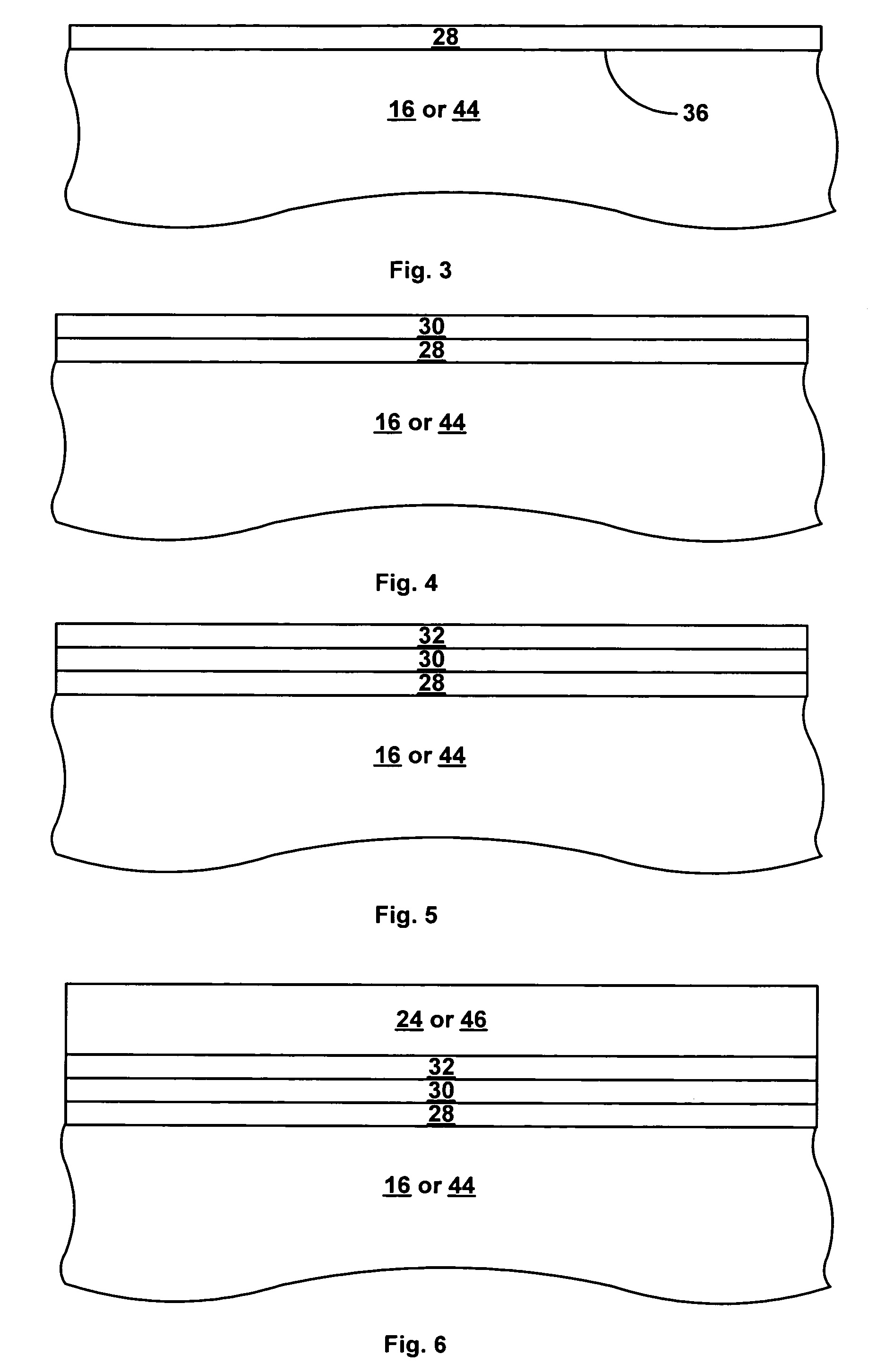

ActiveUS20060003596A1Easy to processHigh oxygen contentPretreated surfacesSemiconductor/solid-state device manufacturingPolysilazaneSilicon oxide

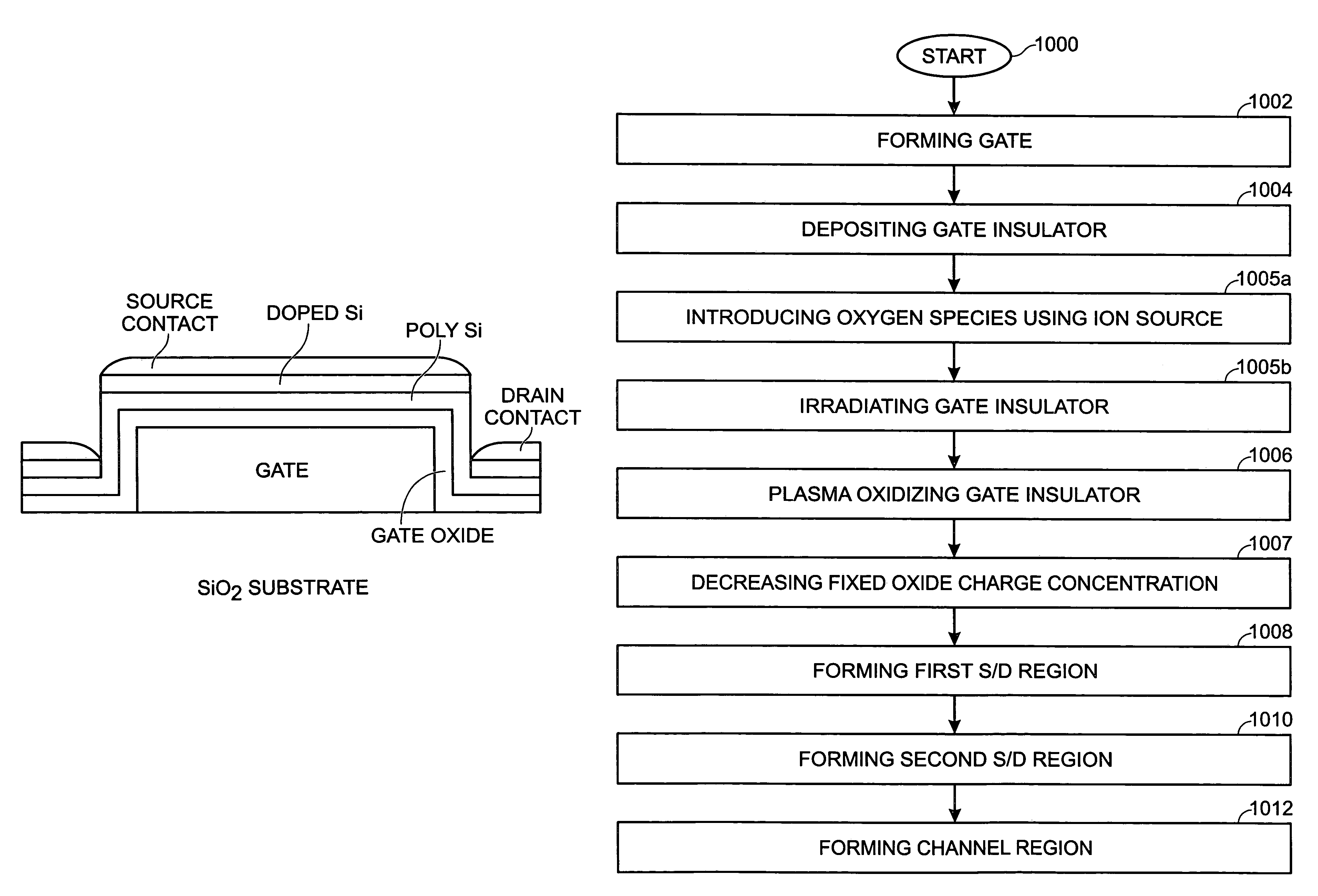

Semiconductor devices, structures and systems that utilize a polysilazane-based silicon oxide layer or fill, and methods of making the oxide layer are disclosed. In one embodiment, a polysilazane solution is deposited on a substrate and processed with ozone in a wet oxidation at low temperature to chemically modify the polysilazane material to a silicon oxide layer.

Owner:MICRON TECH INC

Low temperature process for polysilazane oxidation/densification

InactiveUS20060102977A1Easy to processIncrease contentSemiconductor/solid-state device manufacturingSemiconductor devicesPolysilazaneSilicon oxide

Semiconductor devices, structures and systems that utilize a polysilazane-based silicon oxide layer or fill, and methods of making the oxide layer are disclosed. In one embodiment, a polysilazane solution is deposited on a substrate and processed with ozone in a wet oxidation at low temperature to chemically modify the polysilazane material to a silicon oxide layer.

Owner:MICRON TECH INC

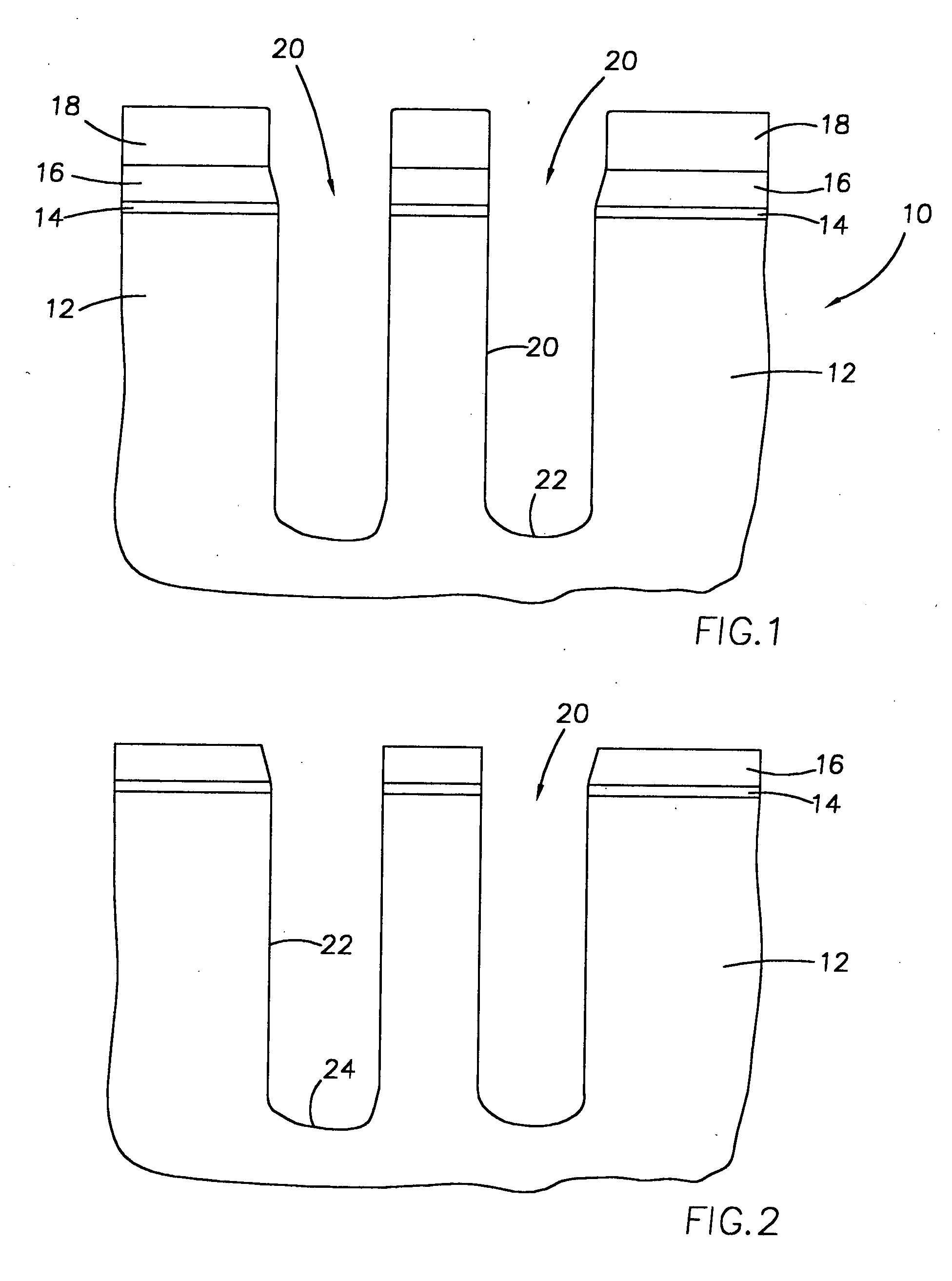

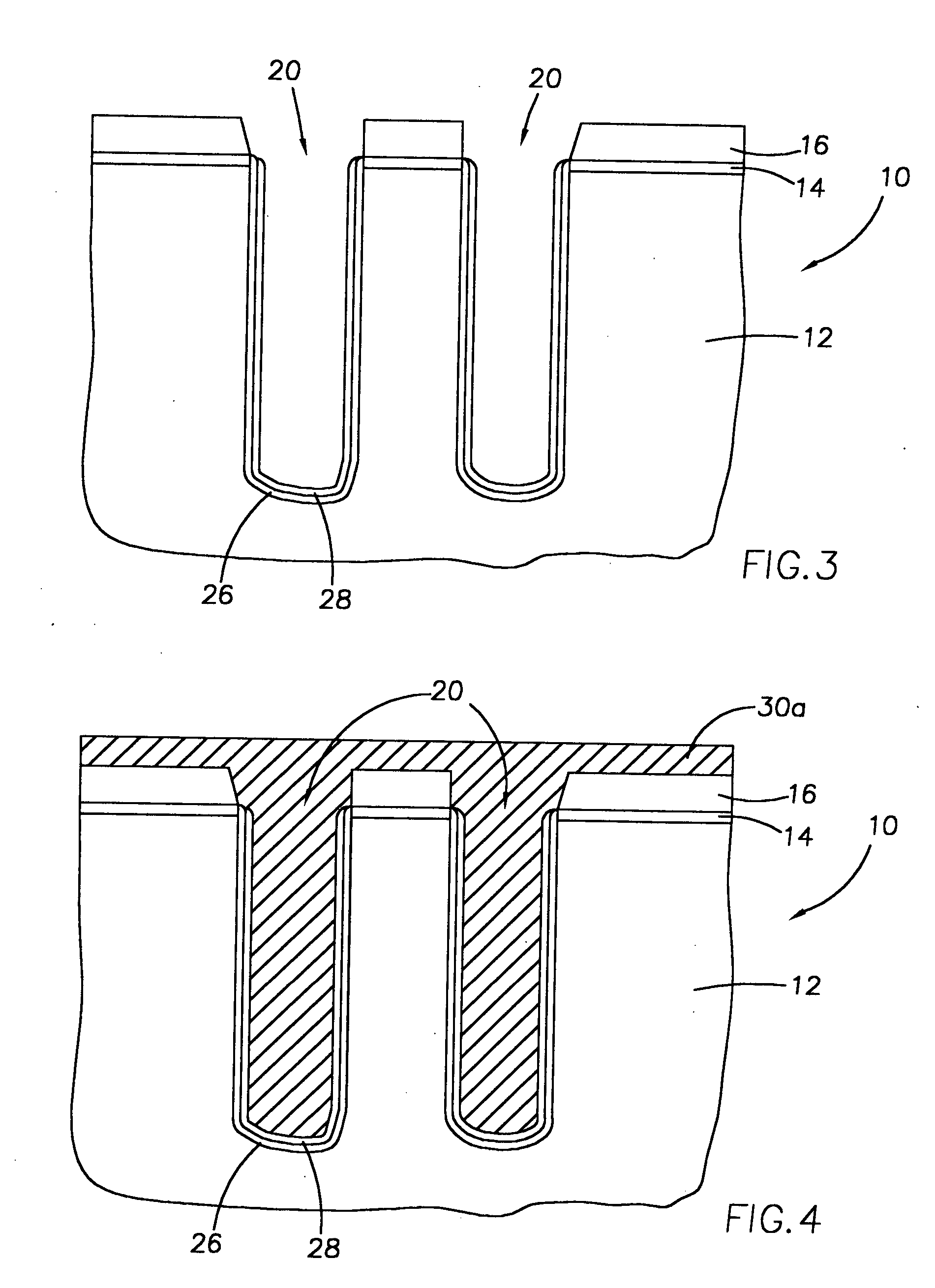

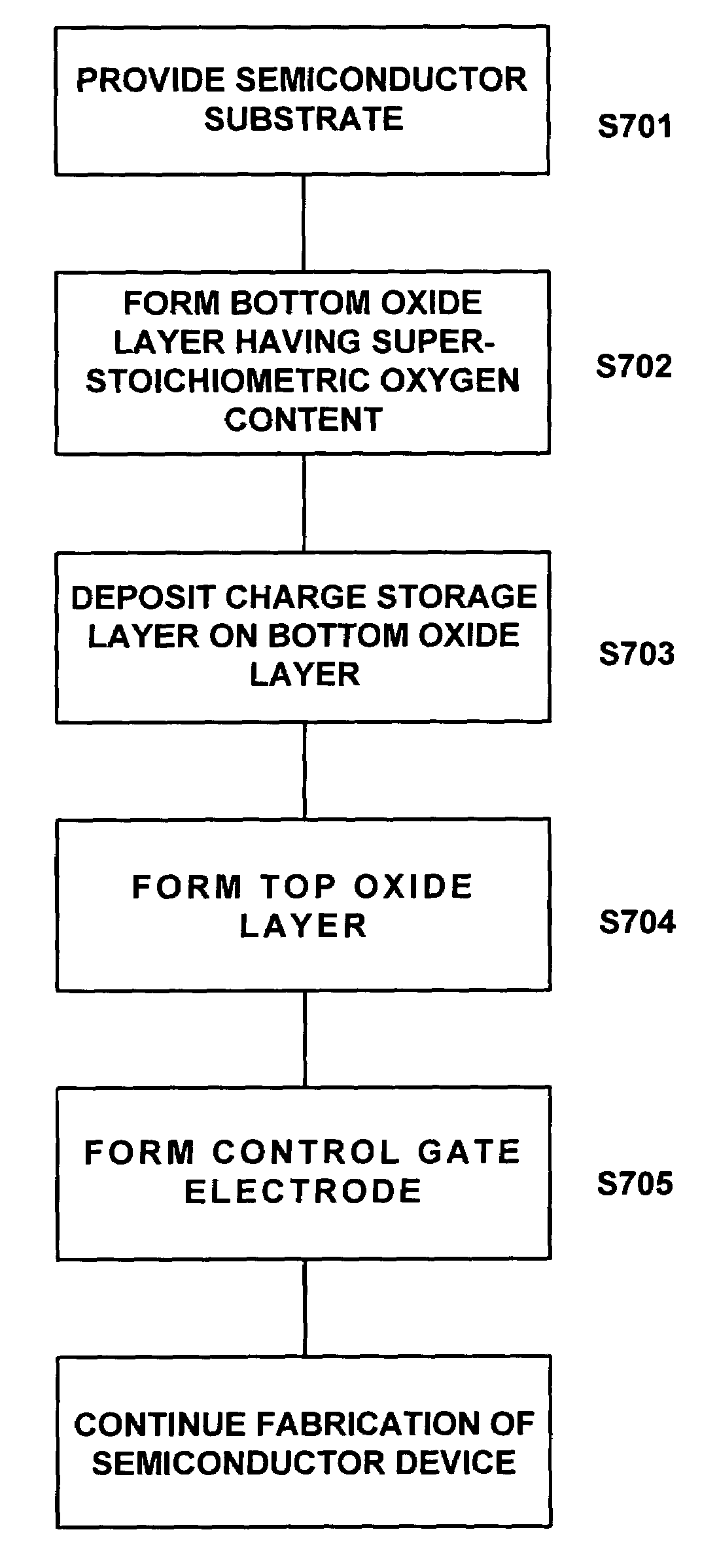

ONO fabrication process for increasing oxygen content at bottom oxide-substrate interface in flash memory devices

InactiveUS7033957B1Increase oxygen contentThermal budgetSemiconductor/solid-state device manufacturingSemiconductor devicesOxygen contentNitride

Process for reducing charge leakage in a SONOS flash memory device, including in one embodiment, forming a bottom oxide layer of an ONO structure on the semiconductor substrate to form an oxide / silicon interface having a first oxygen content adjacent the oxide / silicon interface; treating the bottom oxide layer to increase the first oxygen content to a second oxygen content adjacent the oxide / silicon interface; and depositing a nitride charge-storage layer on the bottom oxide layer. In another embodiment, process for reducing charge leakage in a SONOS flash memory device, including forming a bottom oxide layer of an ONO structure on a surface of the semiconductor substrate having an oxide / silicon interface with a super-stoichiometric oxygen content adjacent the oxide / silicon interface; and depositing a nitride charge-storage layer on the bottom oxide layer.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

High-density plasma oxidation for enhanced gate oxide performance

InactiveUS7381595B2Improve bulk and interfacial qualityPromote efficient oxidationTransistorSolid-state devicesLow temperature depositionHigh density

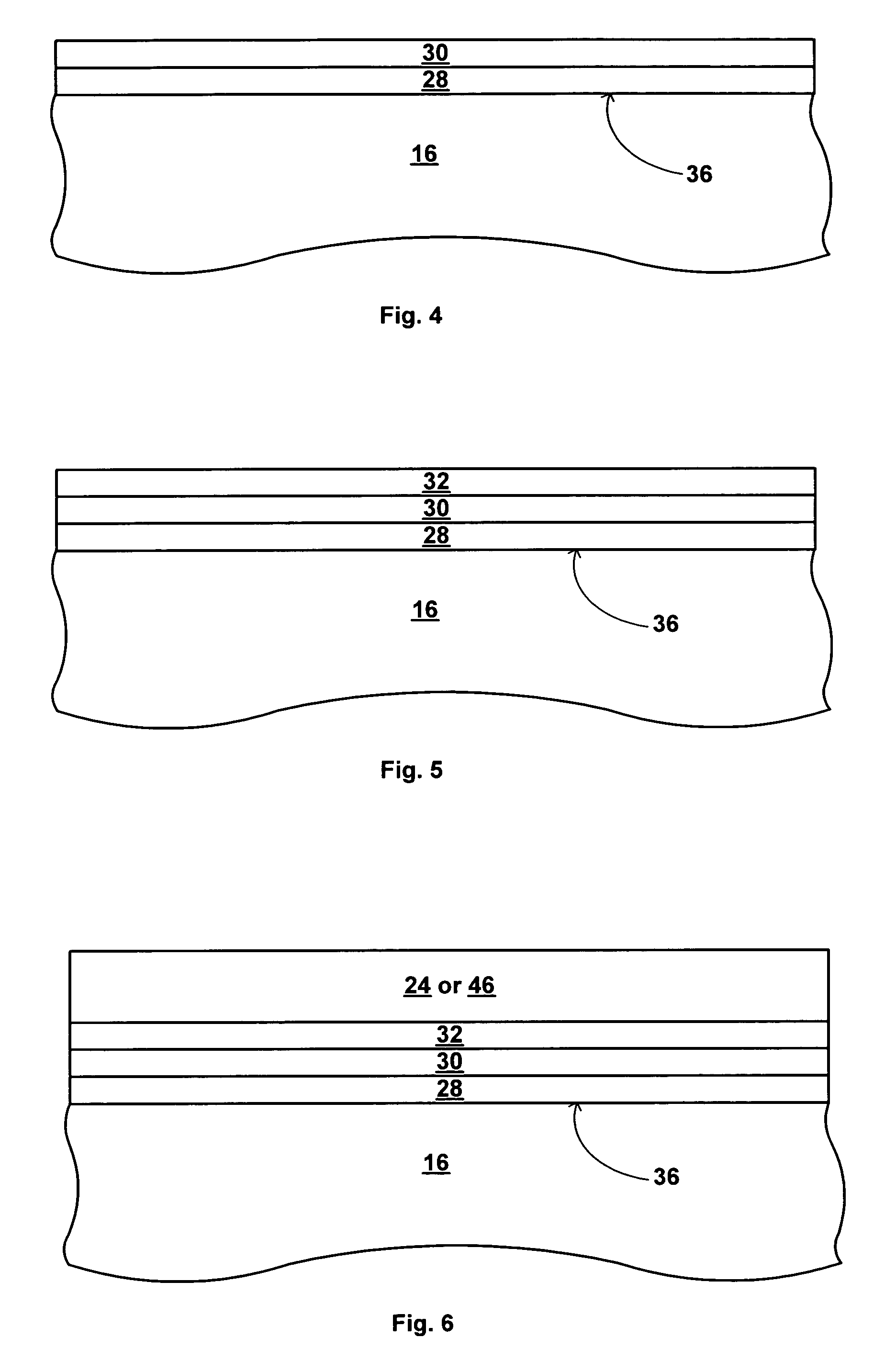

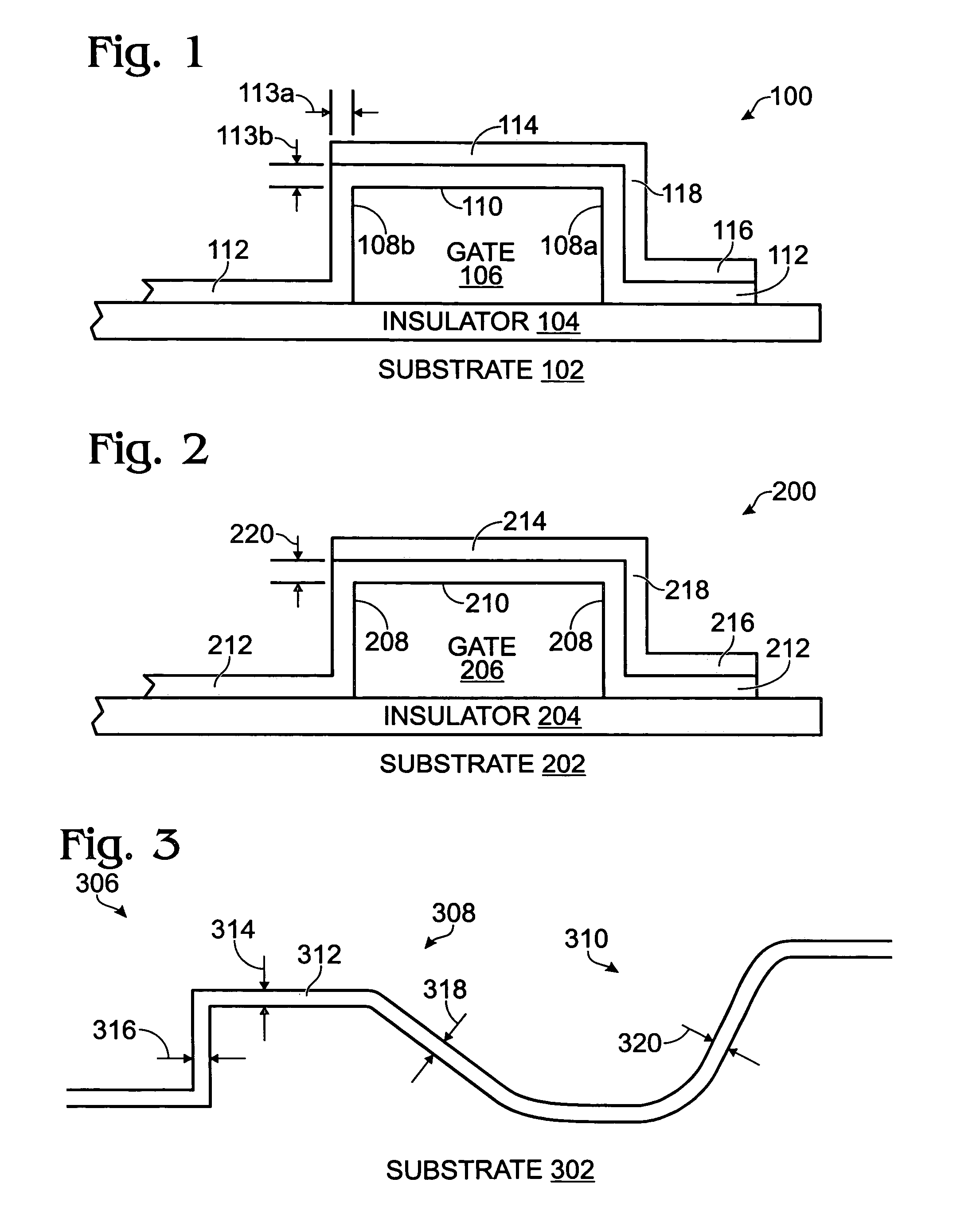

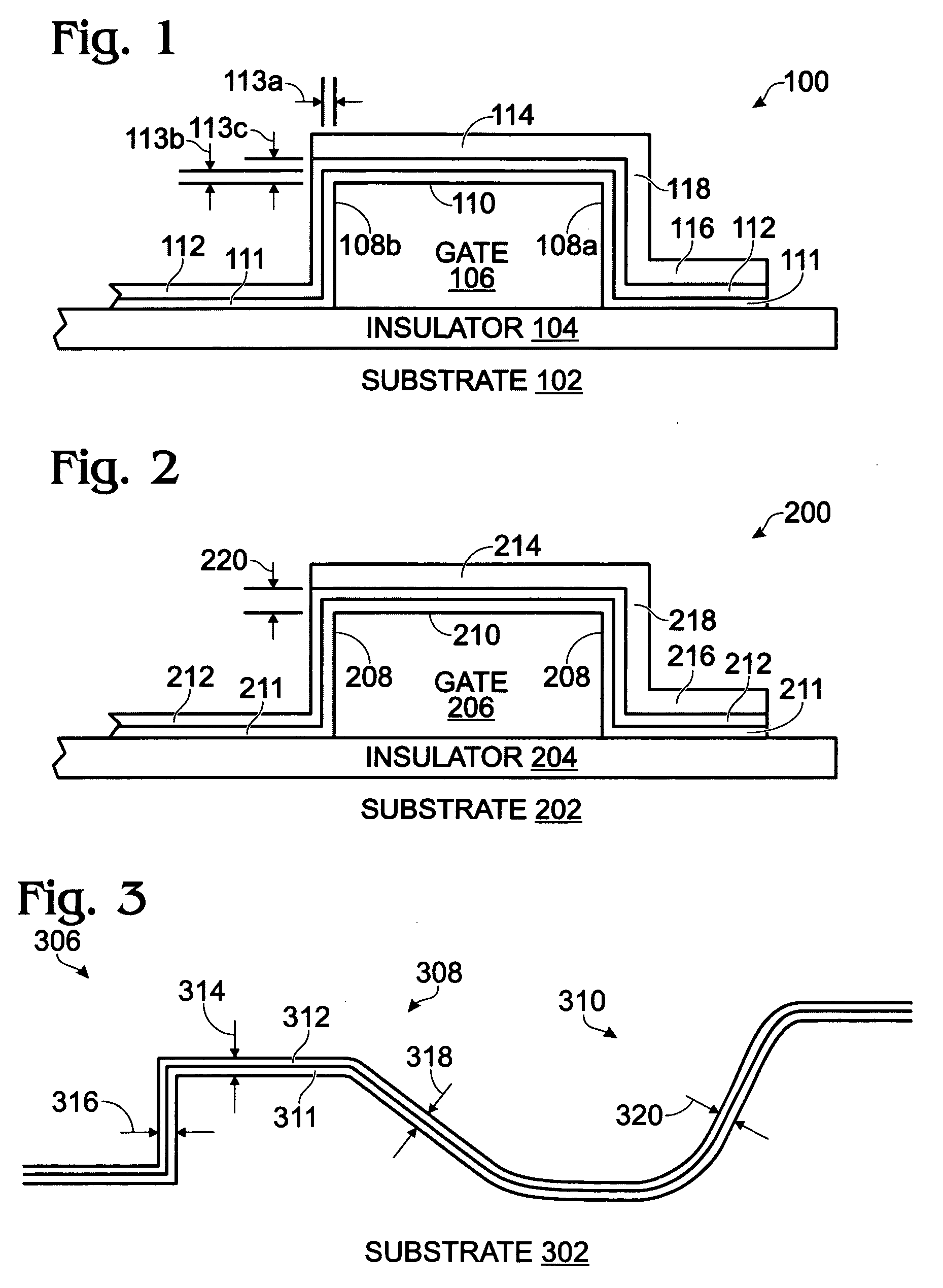

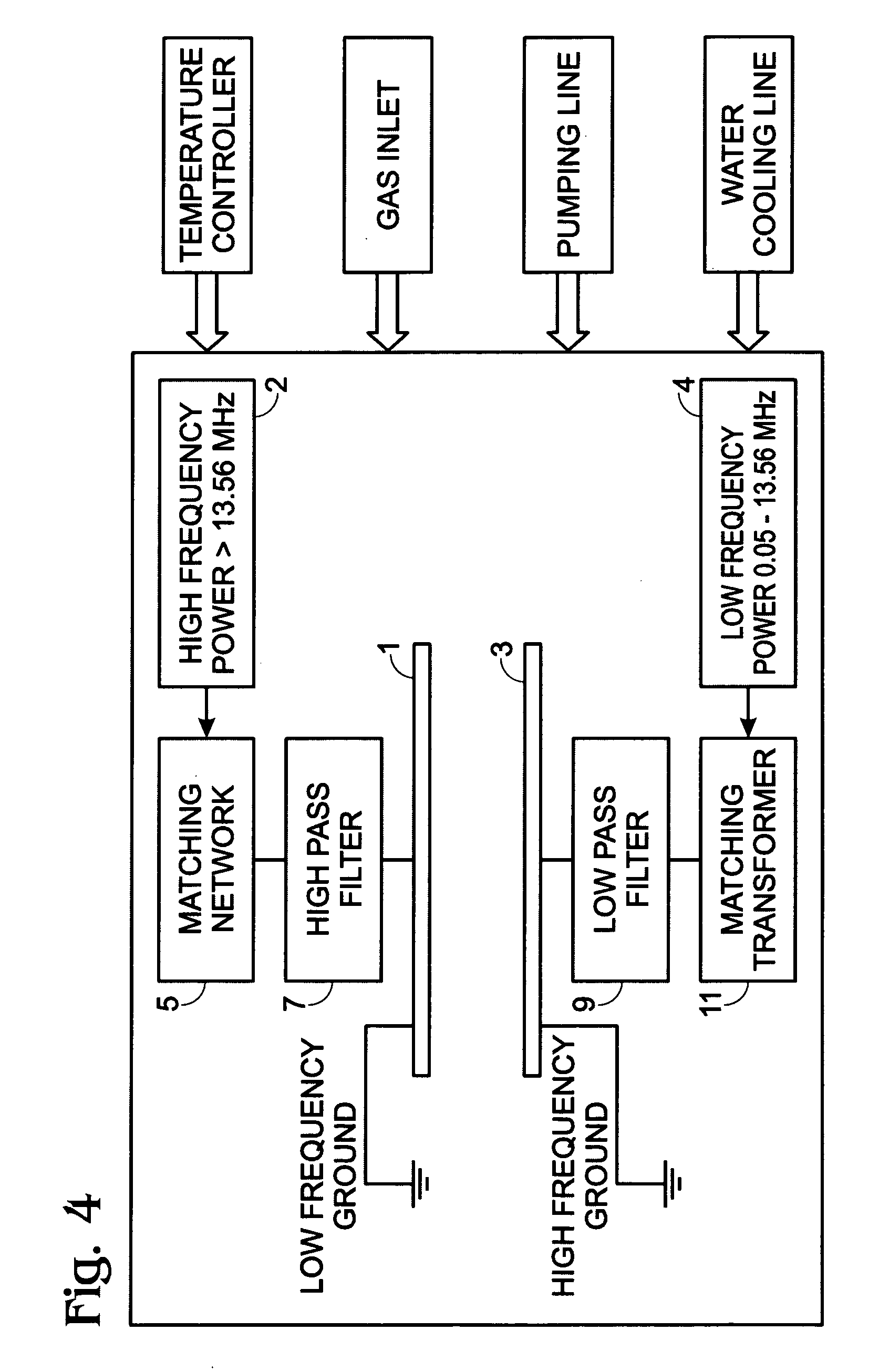

A method is provided for forming a low-temperature vertical gate insulator in a vertical thin-film transistor (V-TFT) fabrication process. The method comprises: forming a gate, having vertical sidewalls and a top surface, overlying a substrate insulation layer; depositing a silicon oxide thin-film gate insulator overlying the gate; plasma oxidizing the gate insulator at a temperature of less than 400° C., using a high-density plasma source; forming a first source / drain region overlying the gate top surface; forming a second source / drain region overlying the substrate insulation layer, adjacent a first gate sidewall; and, forming a channel region overlying the first gate sidewall, in the gate insulator interposed between the first and second source / drain regions. When the silicon oxide thin-film gate insulator is deposited overlying the gate a Si oxide layer, a low temperature deposition process can be used, so that a step-coverage of greater than 65% can be obtained.

Owner:SHARP KK

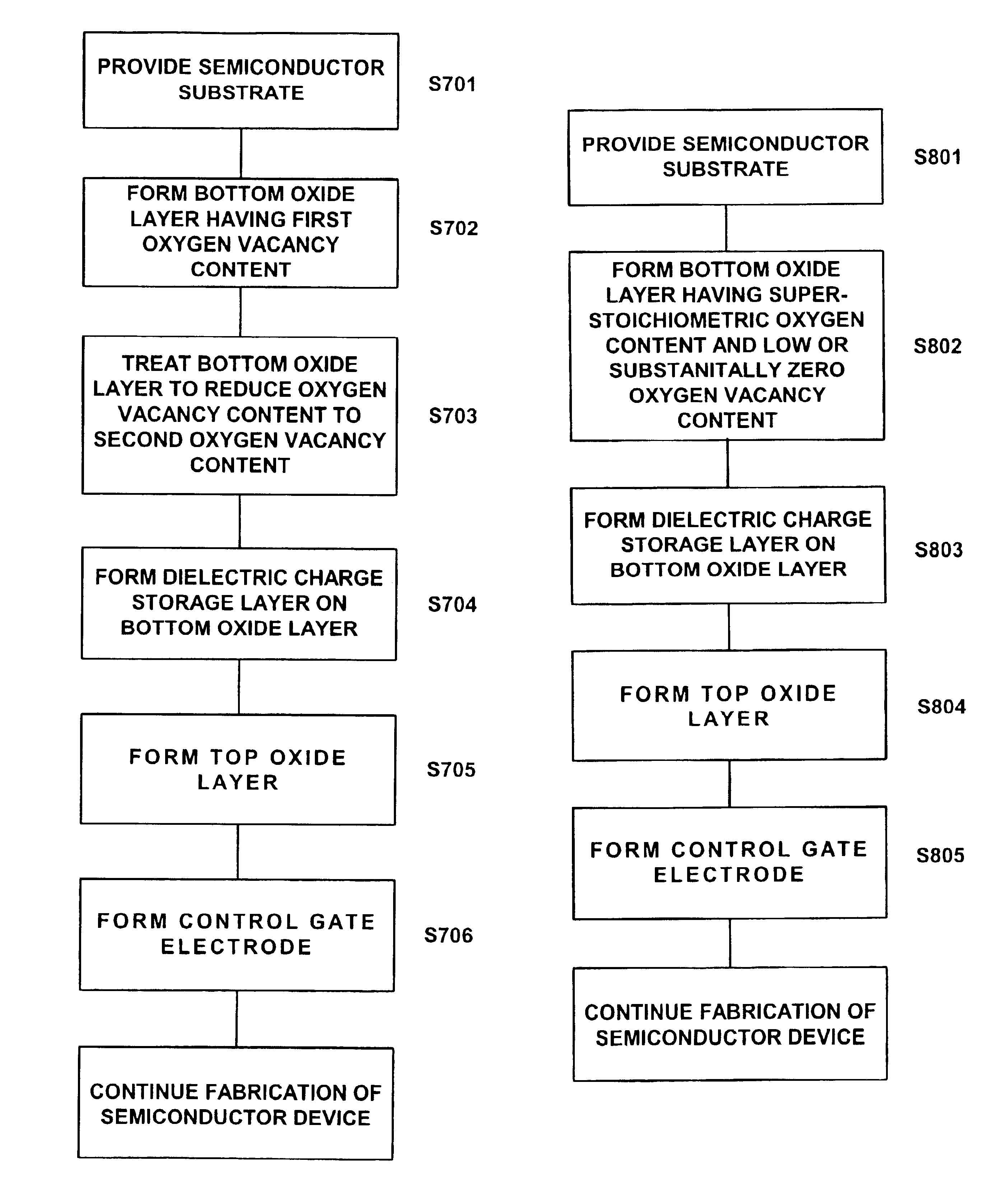

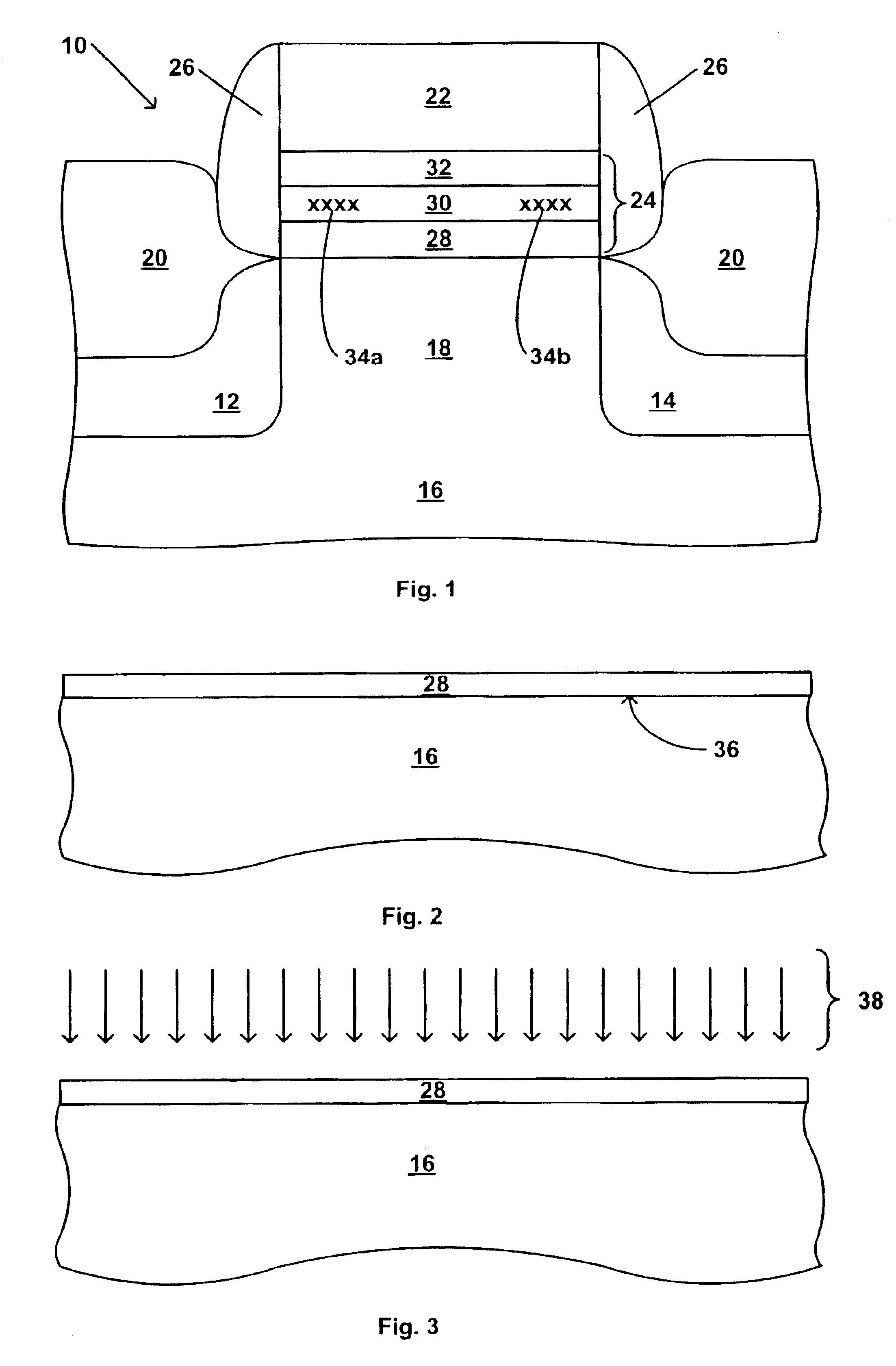

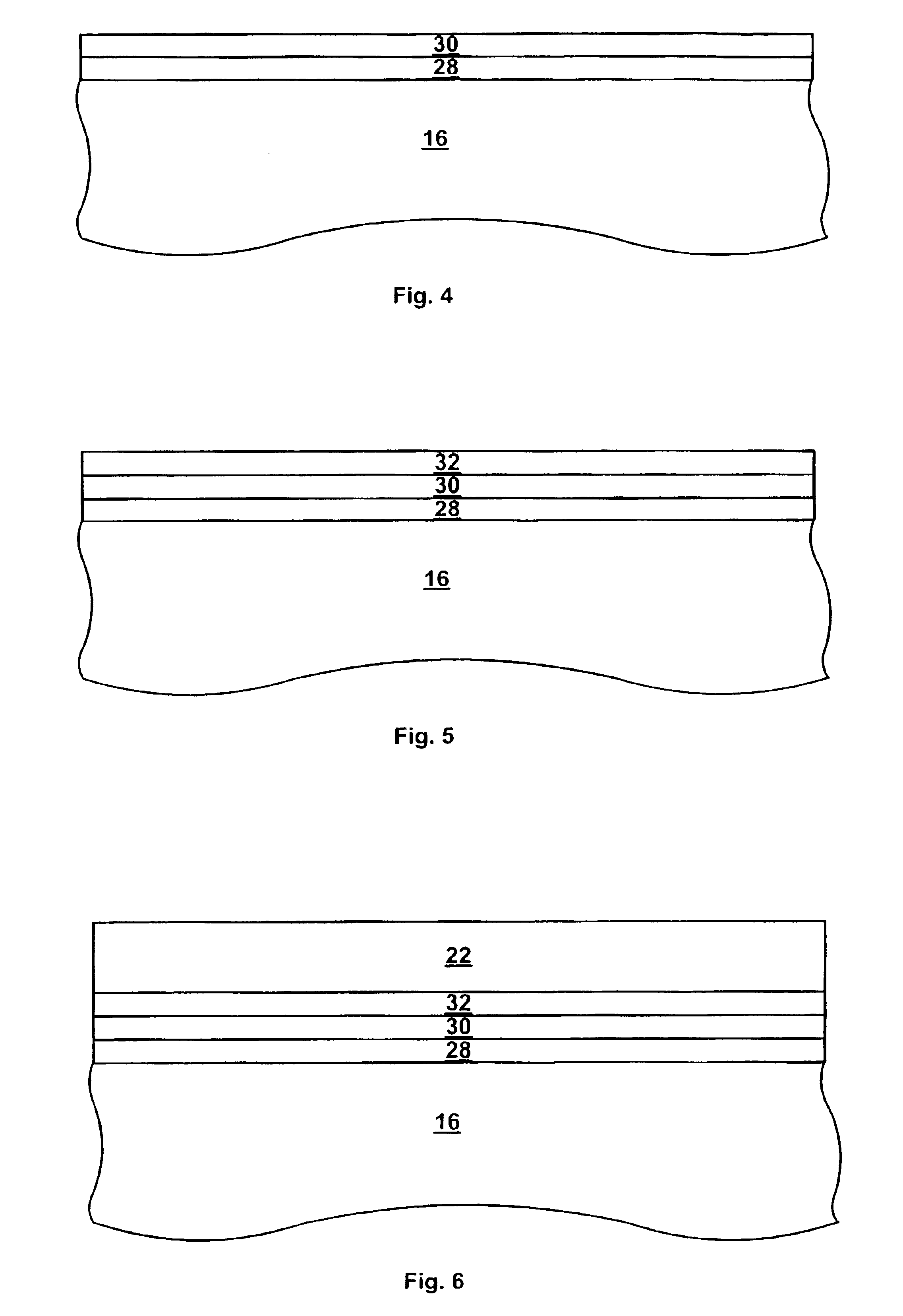

ONO fabrication process for reducing oxygen vacancy content in bottom oxide layer in flash memory devices

InactiveUS6803275B1High oxygen contentReduce contentSemiconductor/solid-state device manufacturingSemiconductor devicesOxygen vacancyOxygen content

Process for fabricating a SONOS flash memory device, including in one embodiment, forming a bottom oxide layer of an ONO structure on a semiconductor substrate, wherein the bottom oxide layer has a first oxygen vacancy content; treating the bottom oxide layer to decrease the first oxygen vacancy content to a second oxygen vacancy content; and depositing a dielectric charge-storage layer on the bottom oxide layer. In another embodiment, a process for fabricating a SONOS flash memory device includes forming a bottom oxide layer of an ONO structure on the semiconductor substrate under strongly oxidizing conditions, wherein the bottom oxide layer has a super-stoichiometric oxygen content and an oxygen vacancy content reduced relative to a bottom oxide layer formed by a conventional process; and depositing a dielectric charge-storage layer on the bottom oxide layer.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

Metal to metal bonding for stacked (3D) integrated circuits

ActiveUS8916448B2Reduce the temperatureShorten the timeSemiconductor/solid-state device detailsSolid-state devicesMetal microstructureIntegrated circuit

The present invention provides a stabilized fine textured metal microstructure that constitutes a durable activated surface usable for bonding a 3D stacked chip. A fine-grain layer that resists self anneal enables metal to metal bonding at moderate time and temperature and wider process flexibility.

Owner:INT BUSINESS MASCH CORP

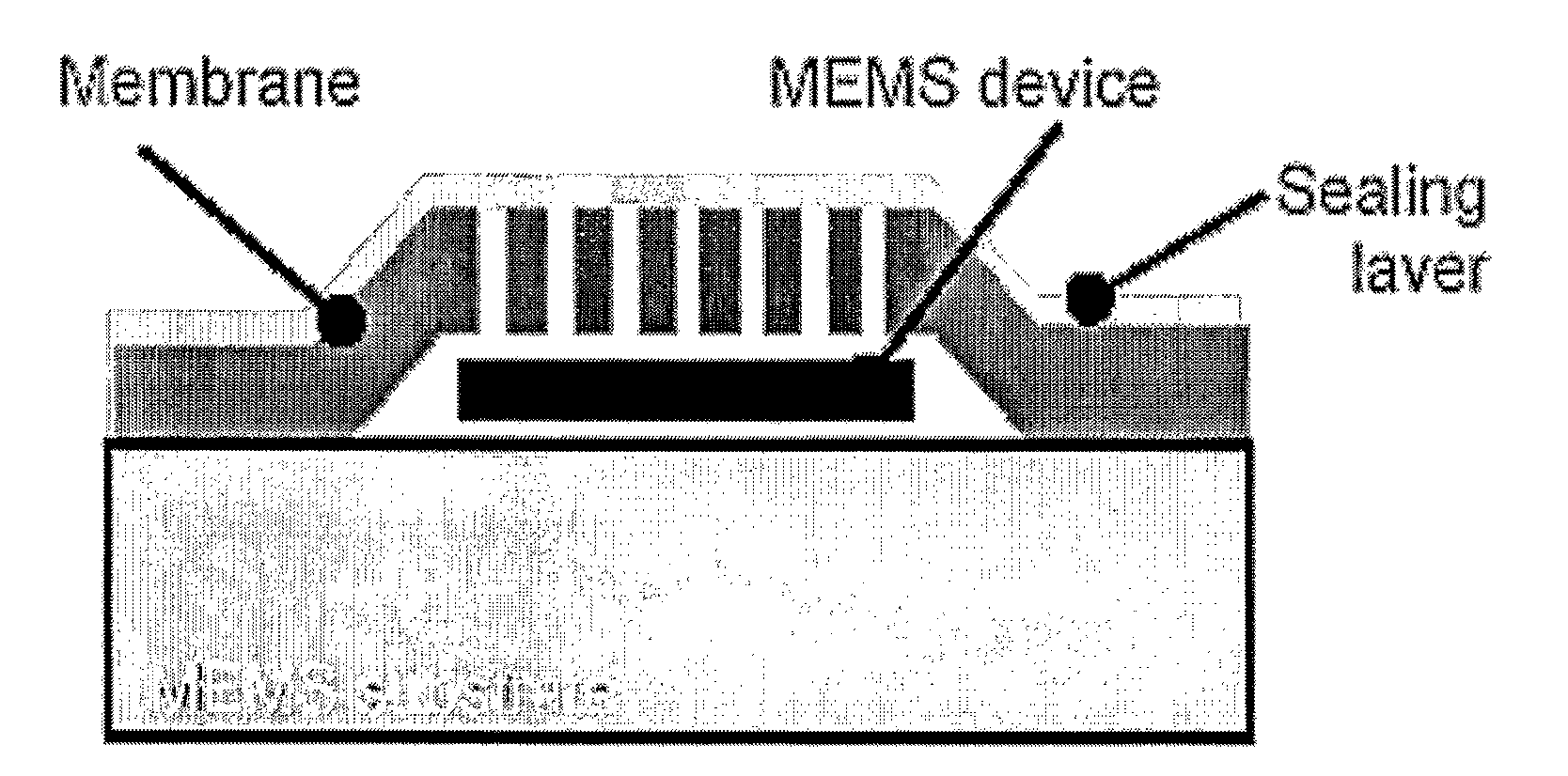

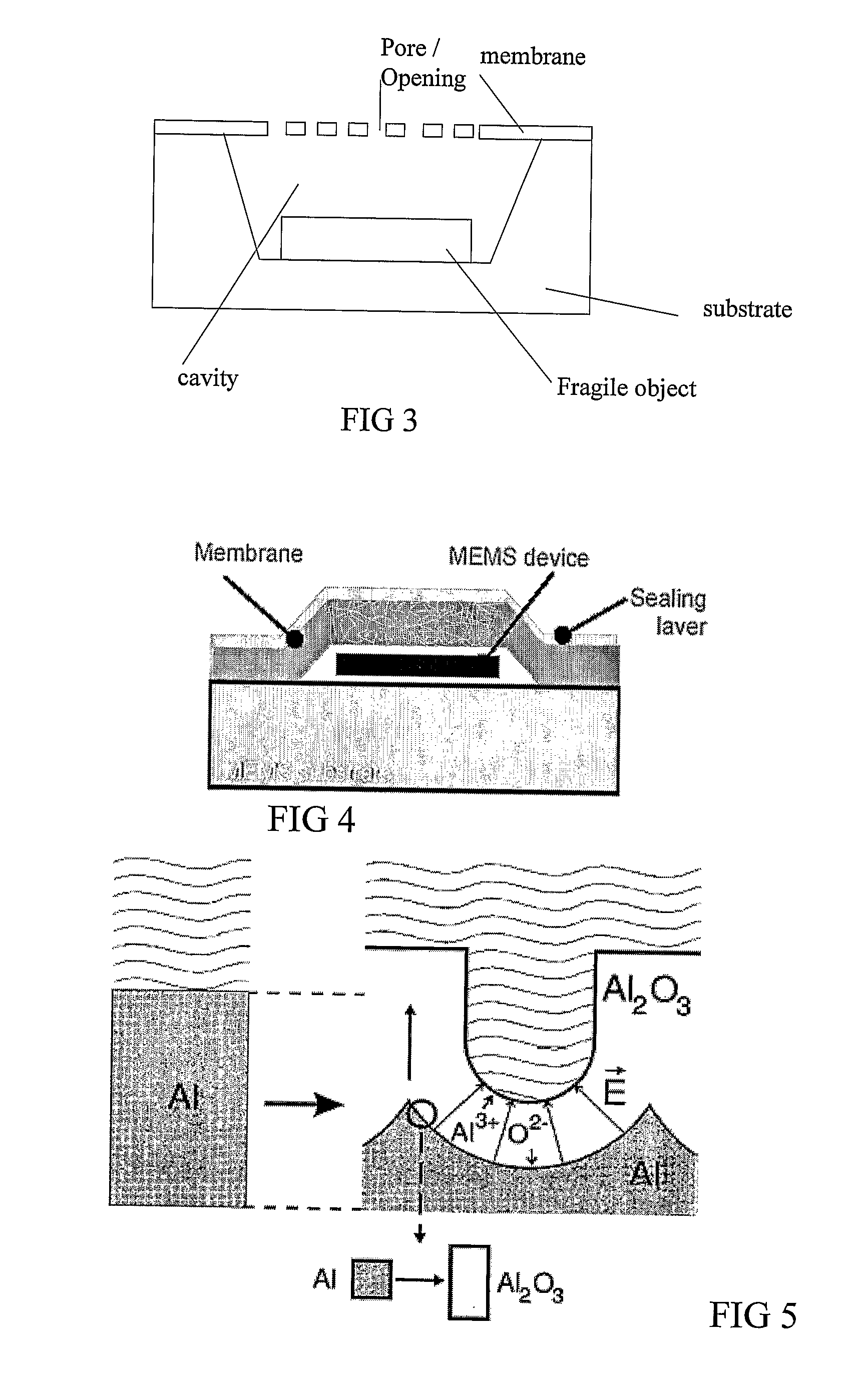

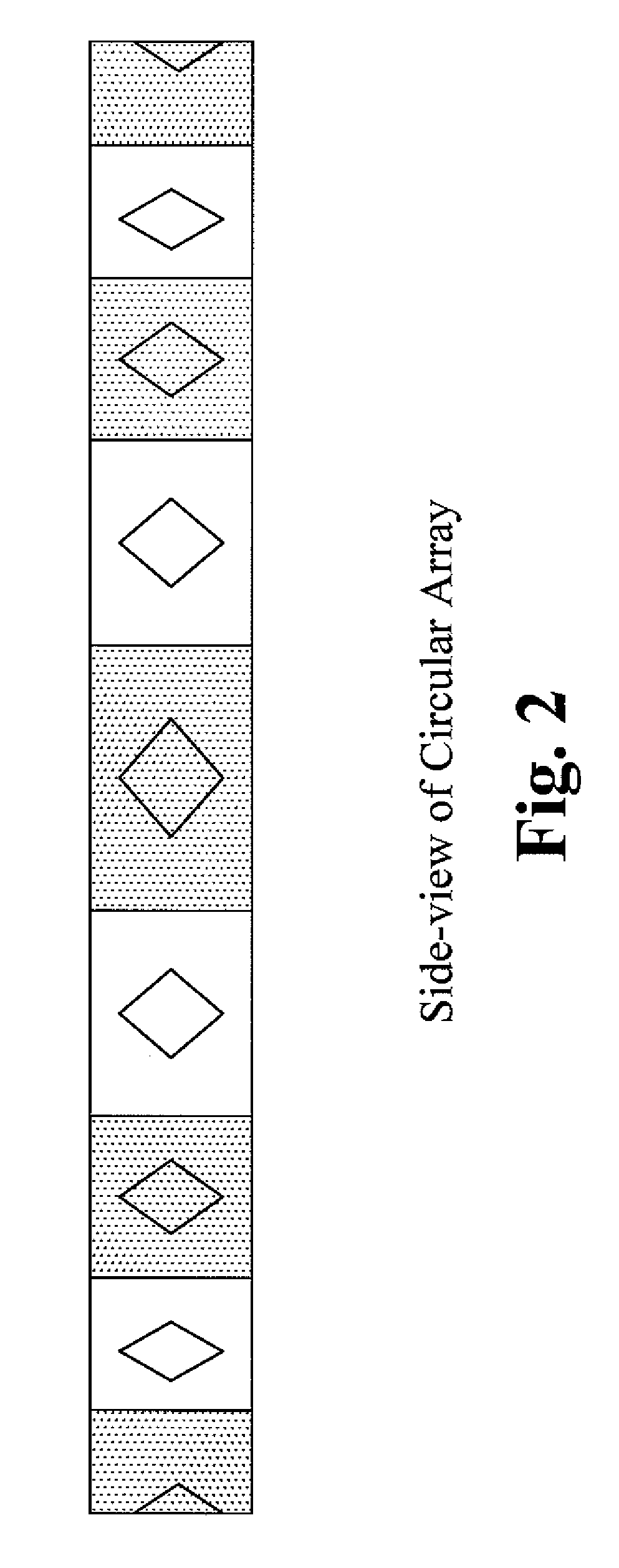

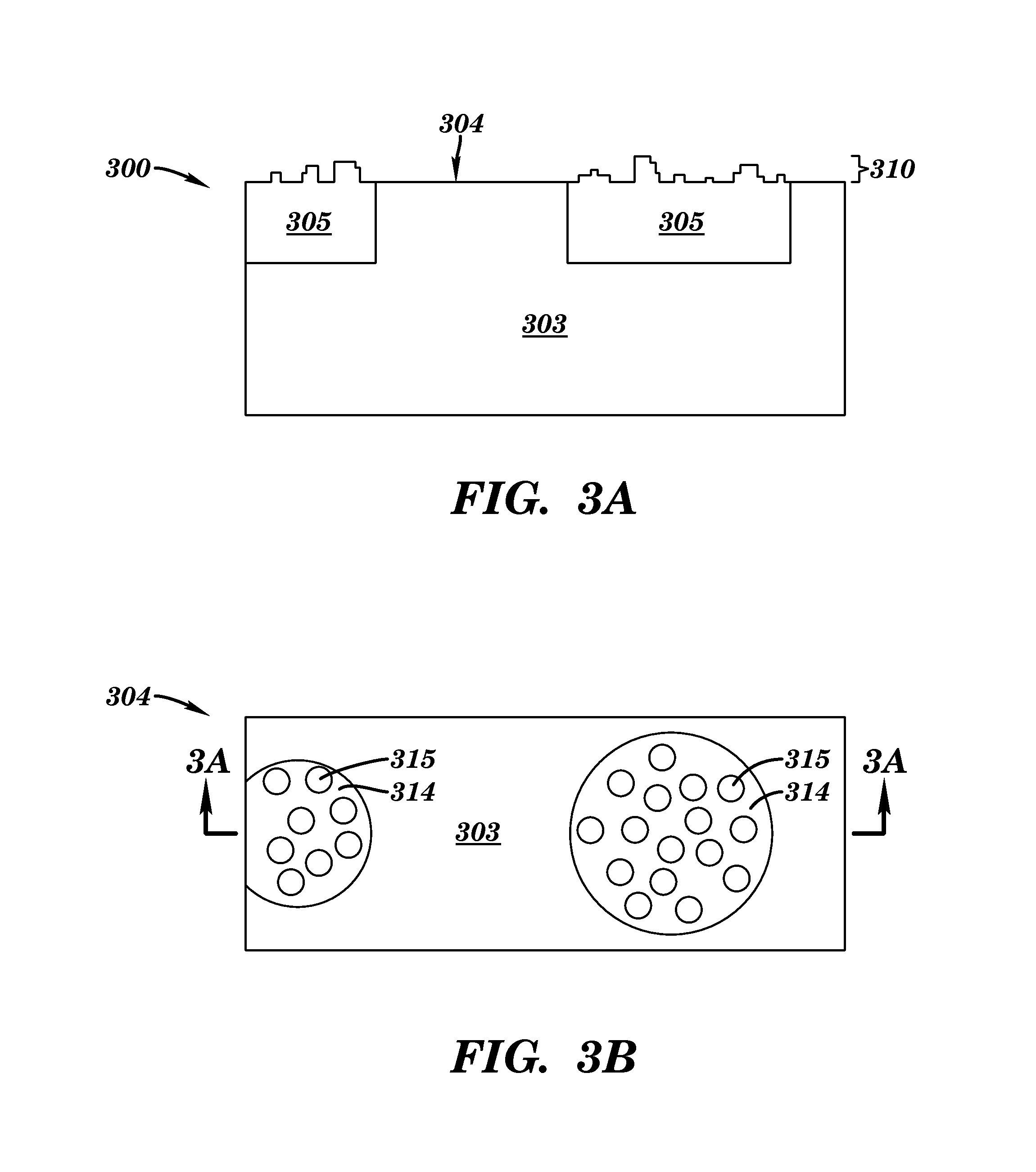

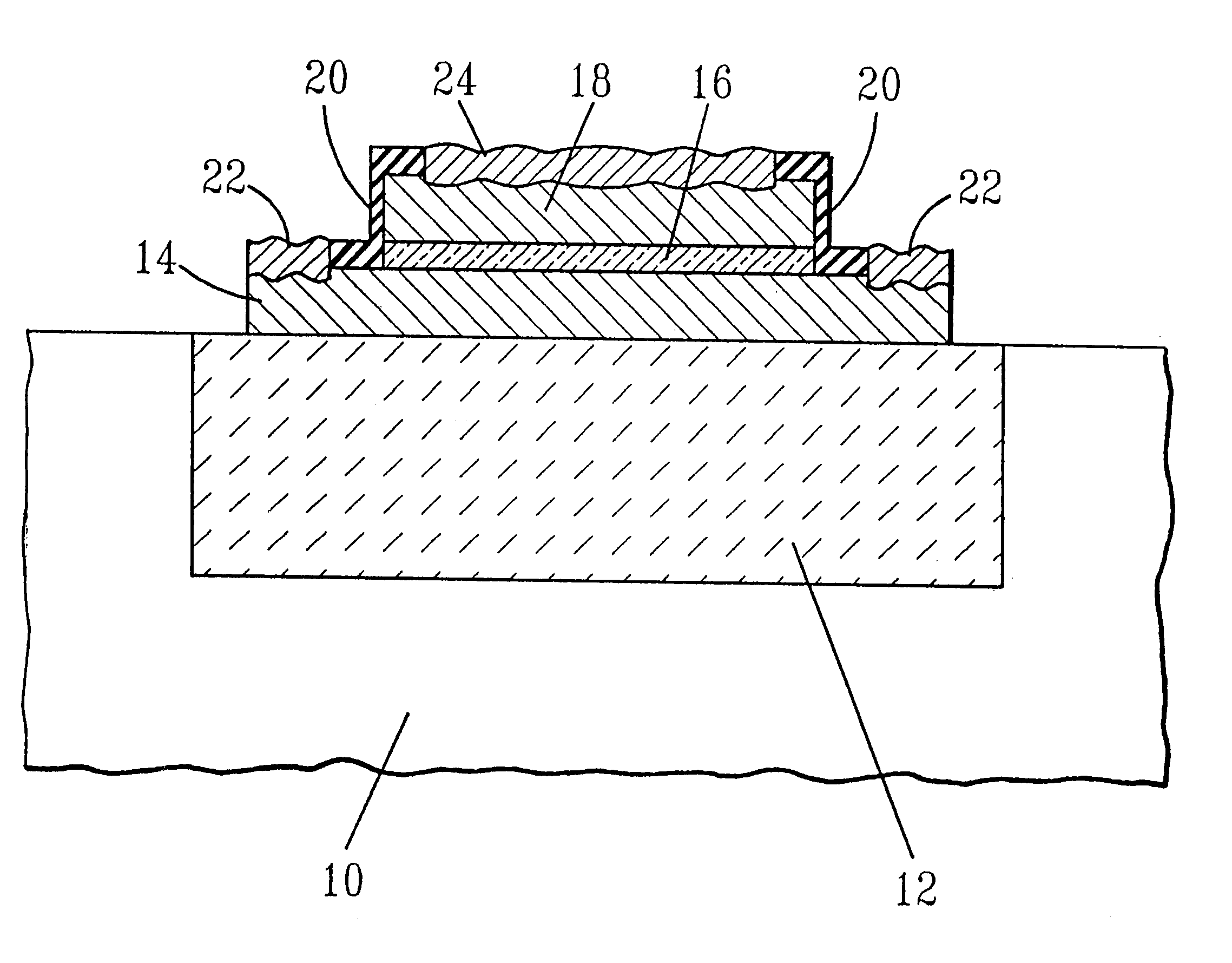

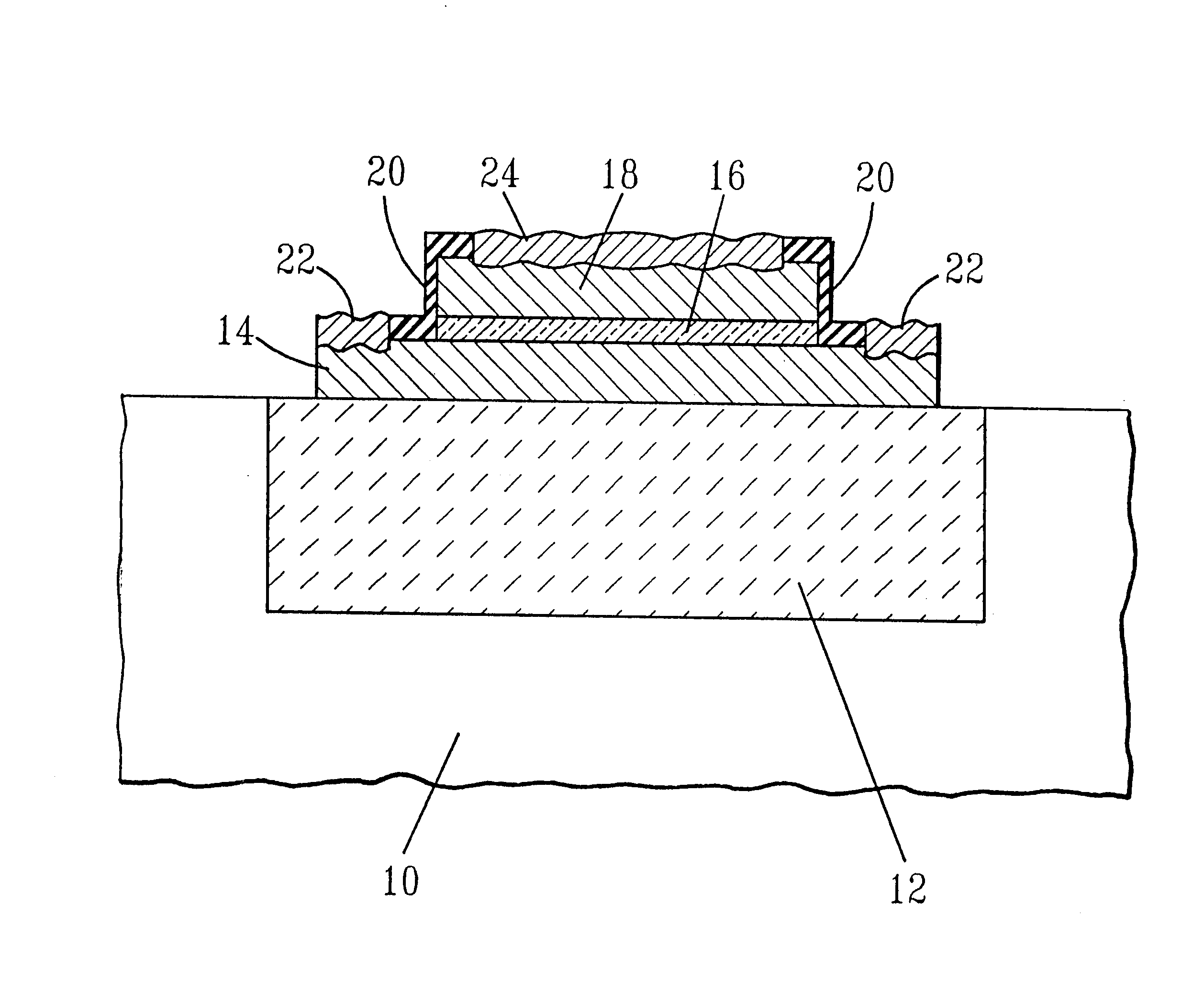

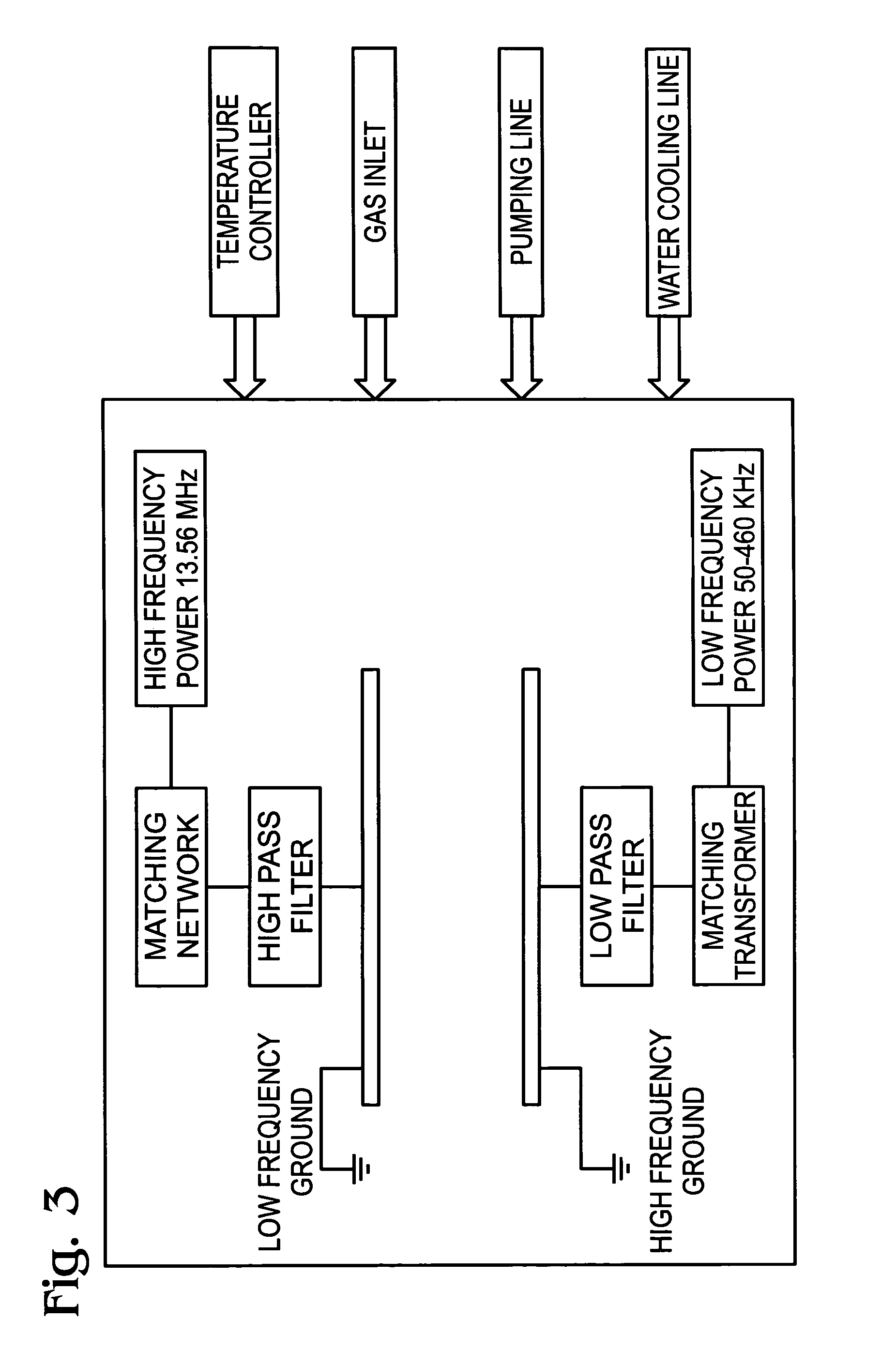

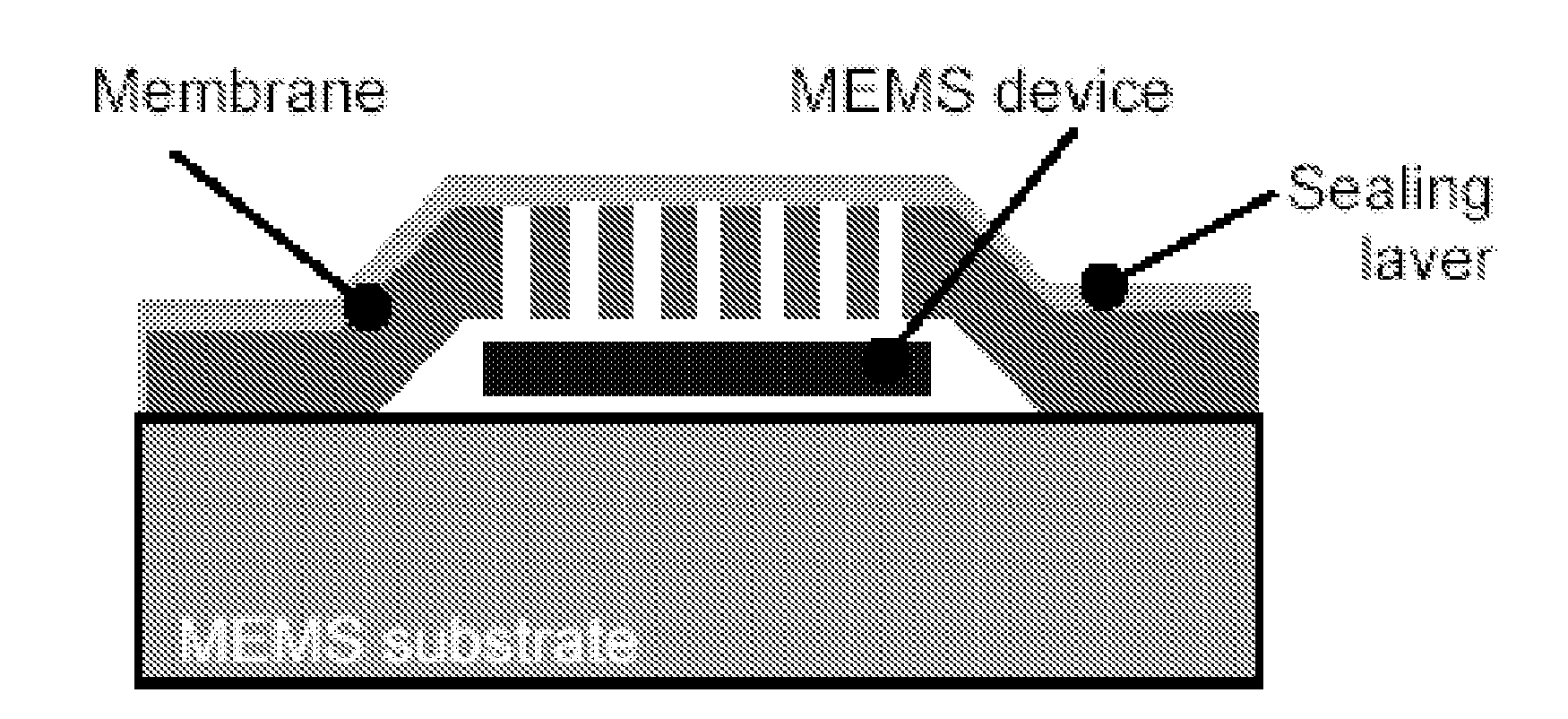

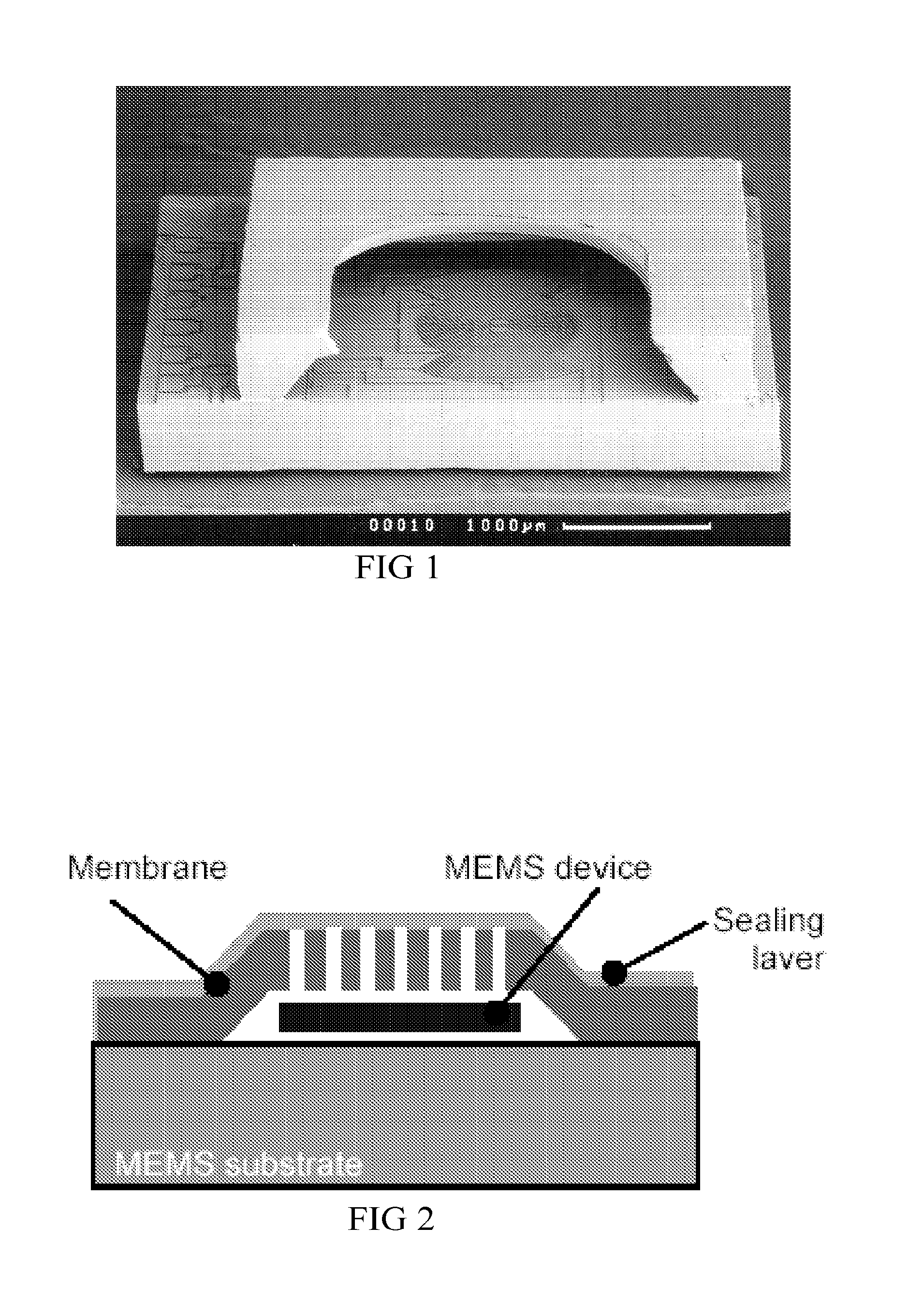

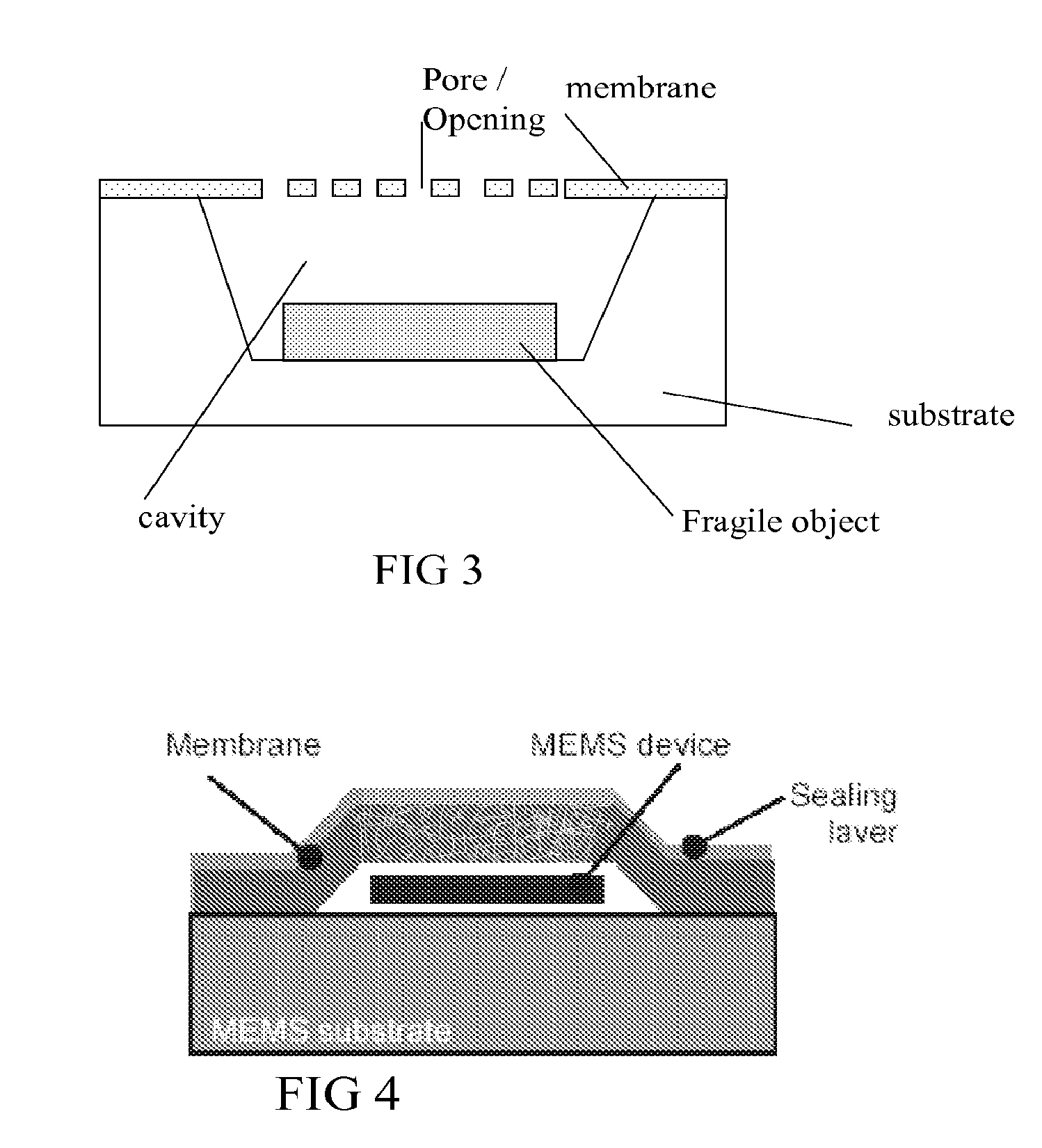

Method For Encapsulating A Device In A Microcavity

InactiveUS20080135998A1Low budgetReduce manufacturing complexitySemiconductor/solid-state device detailsSolid-state devicesPorous layerPorous membrane

Manufacturing a semiconductor device involves forming (200) a sacrificial layer where a micro cavity is to be located, forming (210) a metal layer of thickness greater than 1 micron over the sacrificial layer, forming (220) a porous layer from the metal layer, the porous layer having pores of length greater than ten times their breadth, and having a breadth in the range 10 nm-500 nanometers. The pores can be created by anodising, electrodeposition or dealloying. Then the sacrificial layer can be removed (230) through the porous layer, to form the micro cavity, and pores can be sealed (240). Encapsulating MEMS devices with a porous layer can reduce costs by avoiding using photolithography for shaping the access holes since the sacrificial layer is removed through the porous membrane.

Owner:KATHOLIEKE UNIV LEUVEN +1

Array structure for the application to wireless switch of WLAN and WMAN

InactiveUS7567213B2Improve efficiencyLow budgetIndoor communication adaptationIndividually energised antenna arraysArea networkWireless metropolitan area network

The present invention provides an antenna array structure which includes multiple array elements, and the antenna array structure is using for the application of the WLAN (wireless local area network) or WMAN (wireless metro area network.) Furthermore, the array elements of the present invention are phased arrays or attenuated arrays, and when configuration with different type of the array element is used, the corresponding BFN (beam forming network) can also be implemented in various possibilities. With all the configuration of the present invention, the manufacturers can have a stable array structure for their applications.

Owner:ACCTON TECHNOLOGY CORPORATION

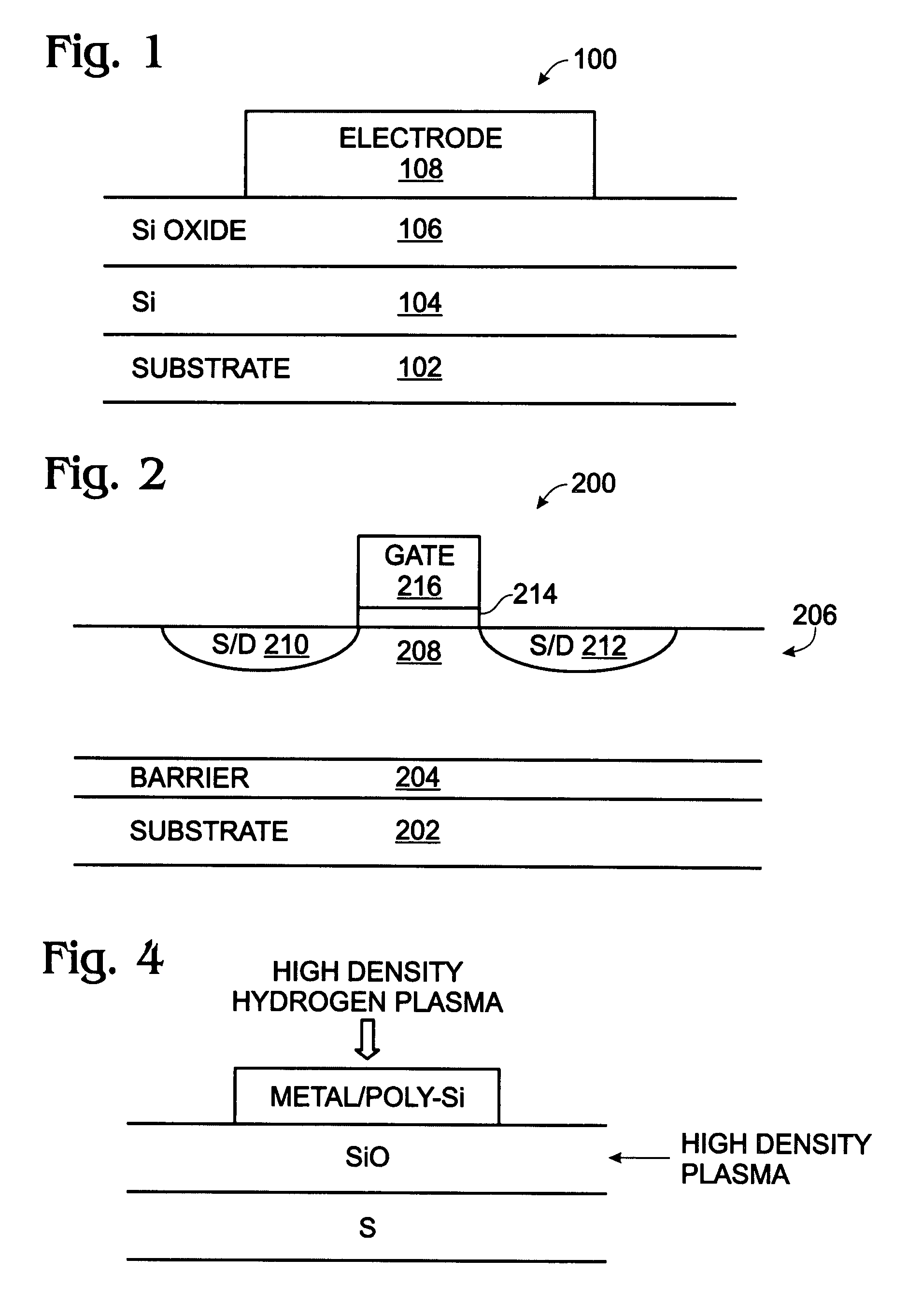

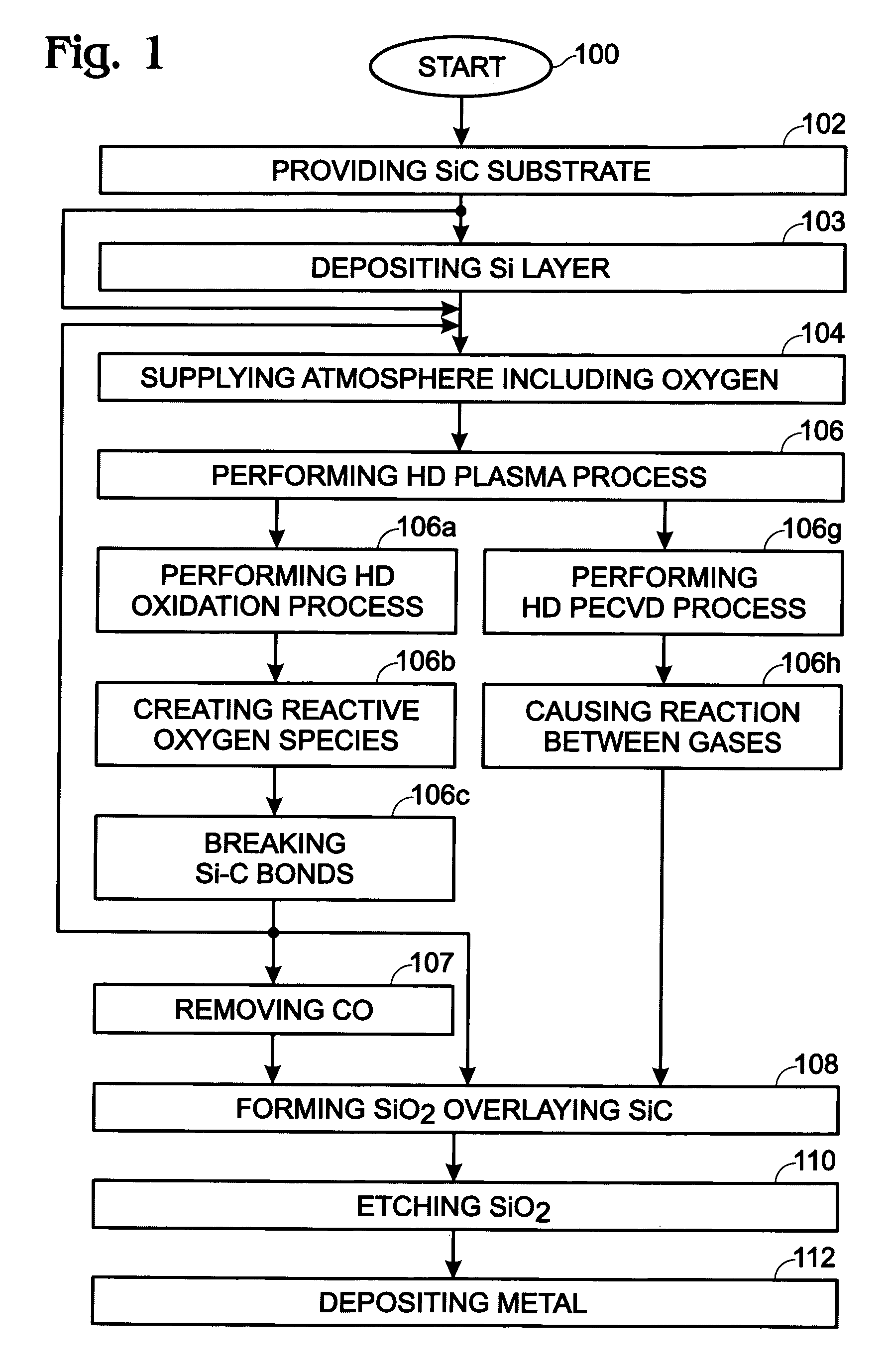

High-density plasma multilayer gate oxide

InactiveUS20060060859A1Improve bulk and interfacial qualityEfficient oxidationTransistorSolid-state devicesHigh densityGate insulator

A thin-film transistor (TFT) with a multilayer gate insulator is provided, along with a method for forming the same. The method comprises: forming a channel, first source / drain (S / D) region, and a second S / D region in a Silicon (Si) active layer; using a high-density plasma (HDP) source, growing a first layer of Silicon oxide (SiOx) from the Si active layer, to a first thickness, where x is less than, or equal to 2; depositing a second layer of SiOx having a second thickness, greater than the first thickness, overlying the first layer of SiOx; using the HDP source, additionally oxidizing the second layer of SiOx, wherein the first and second SiOx layers form a gate insulator; and, forming a gate electrode adjacent the gate insulator. In one aspect, the second Si oxide layer is deposited using a plasma-enhanced chemical vapor deposition (PECVD) process with tetraethylorthosilicate (TEOS) precursors.

Owner:SHARP KK

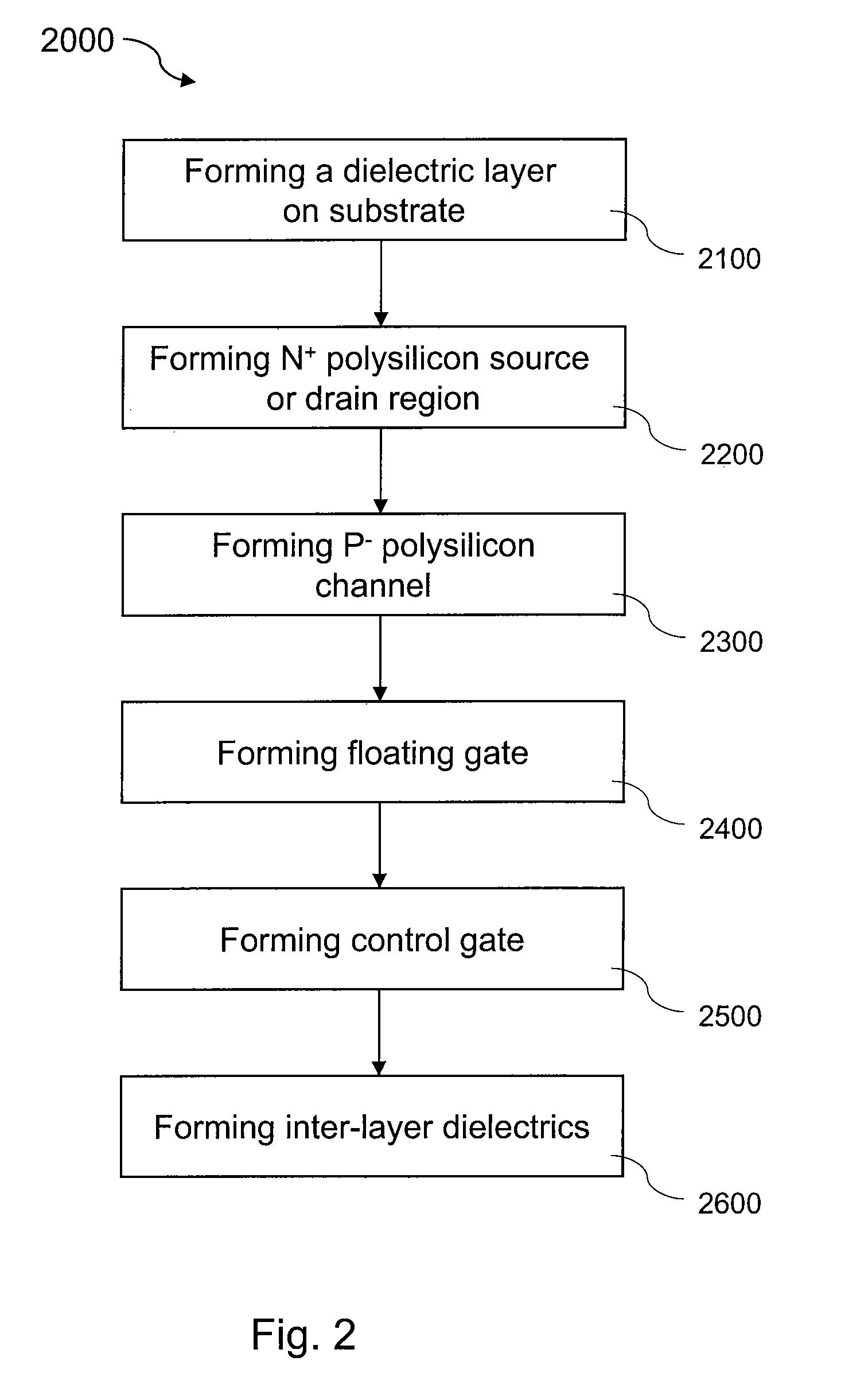

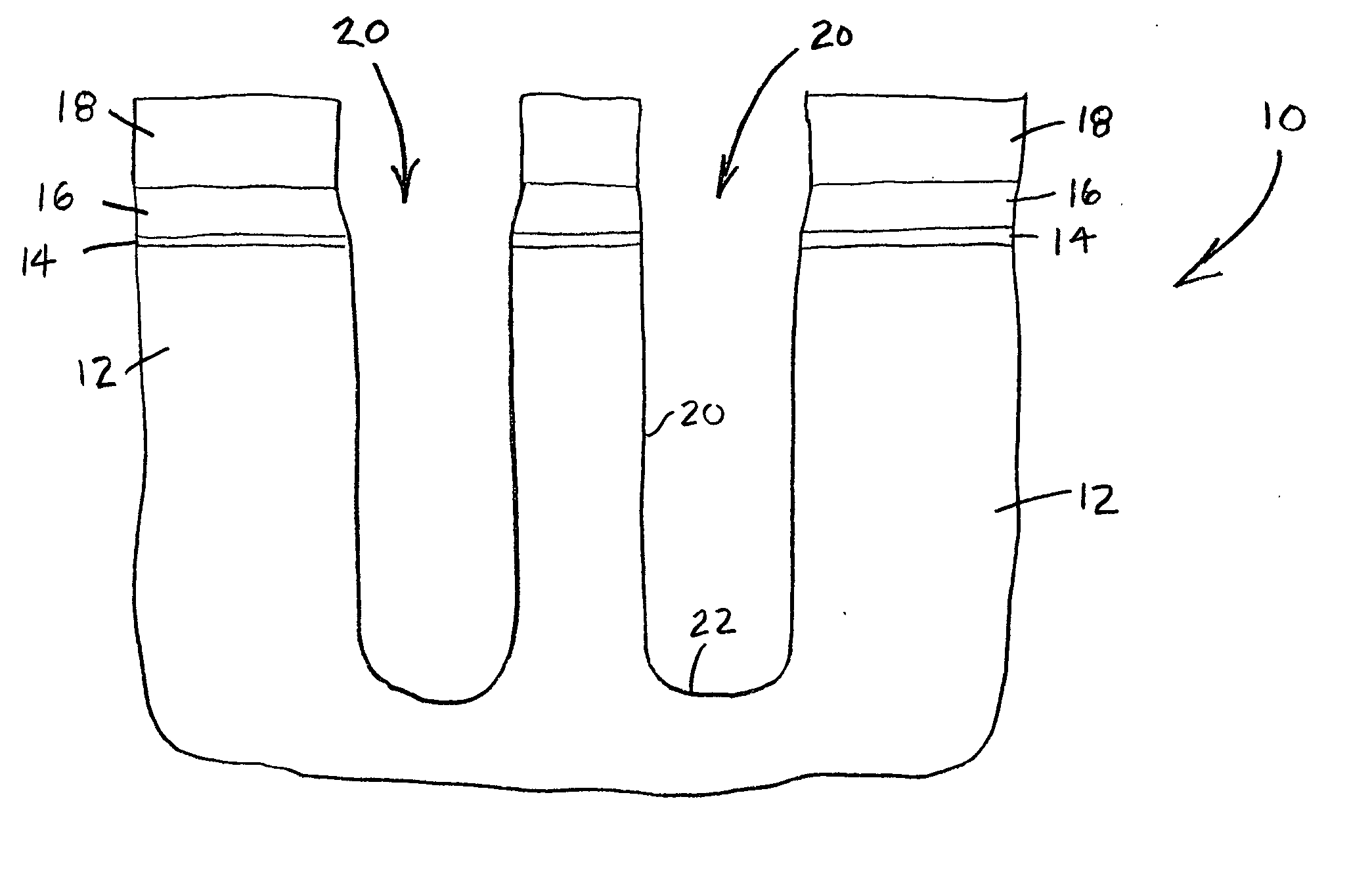

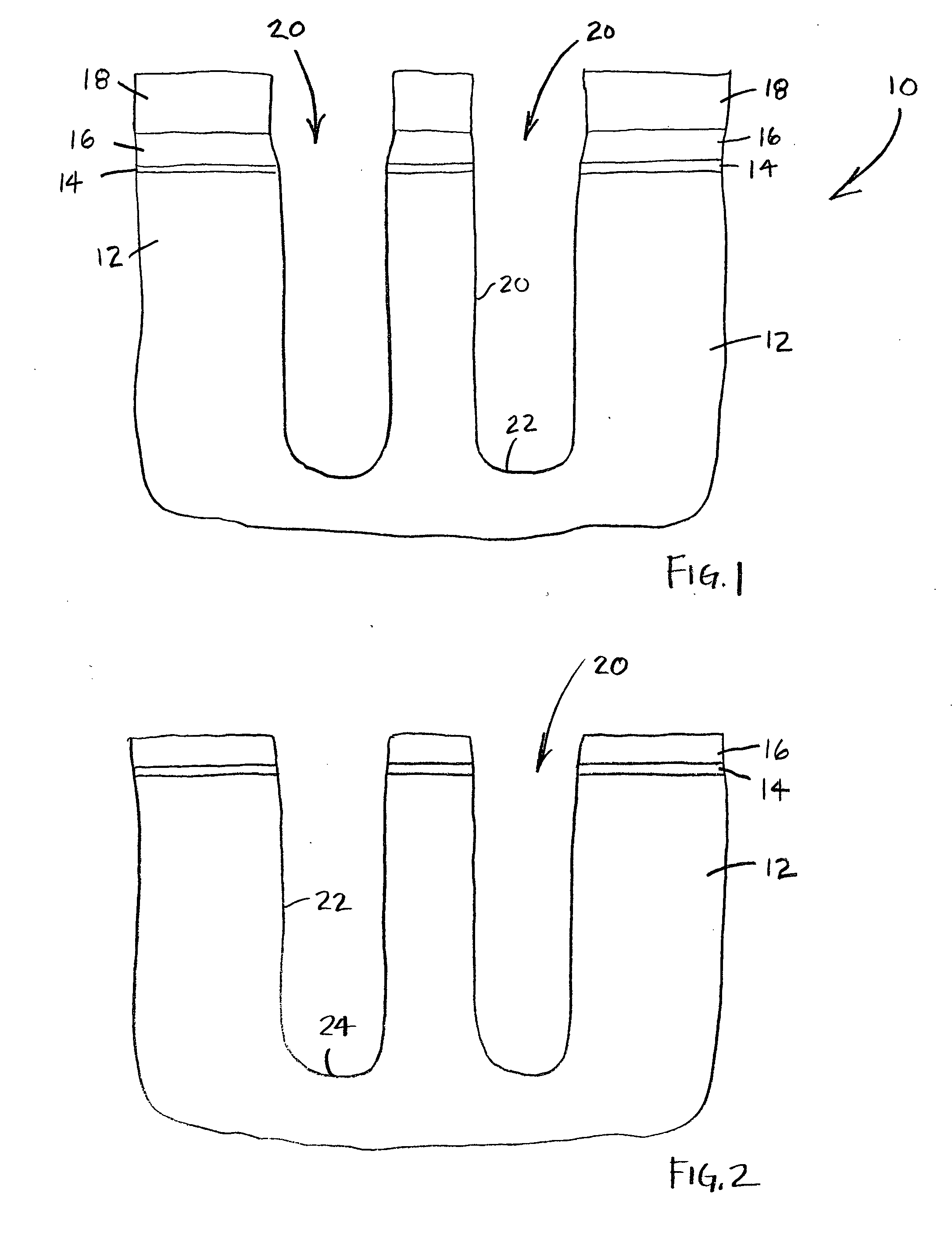

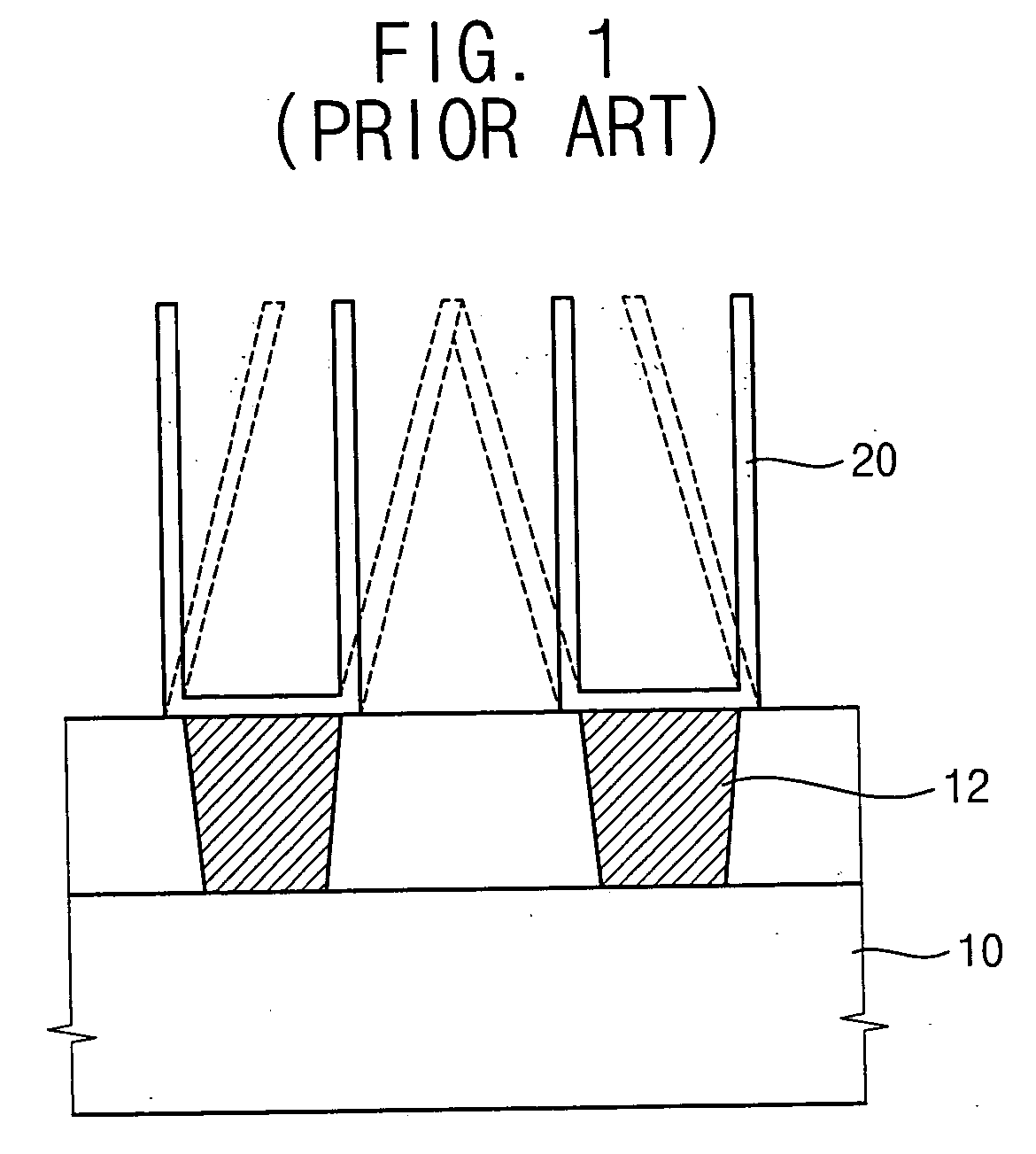

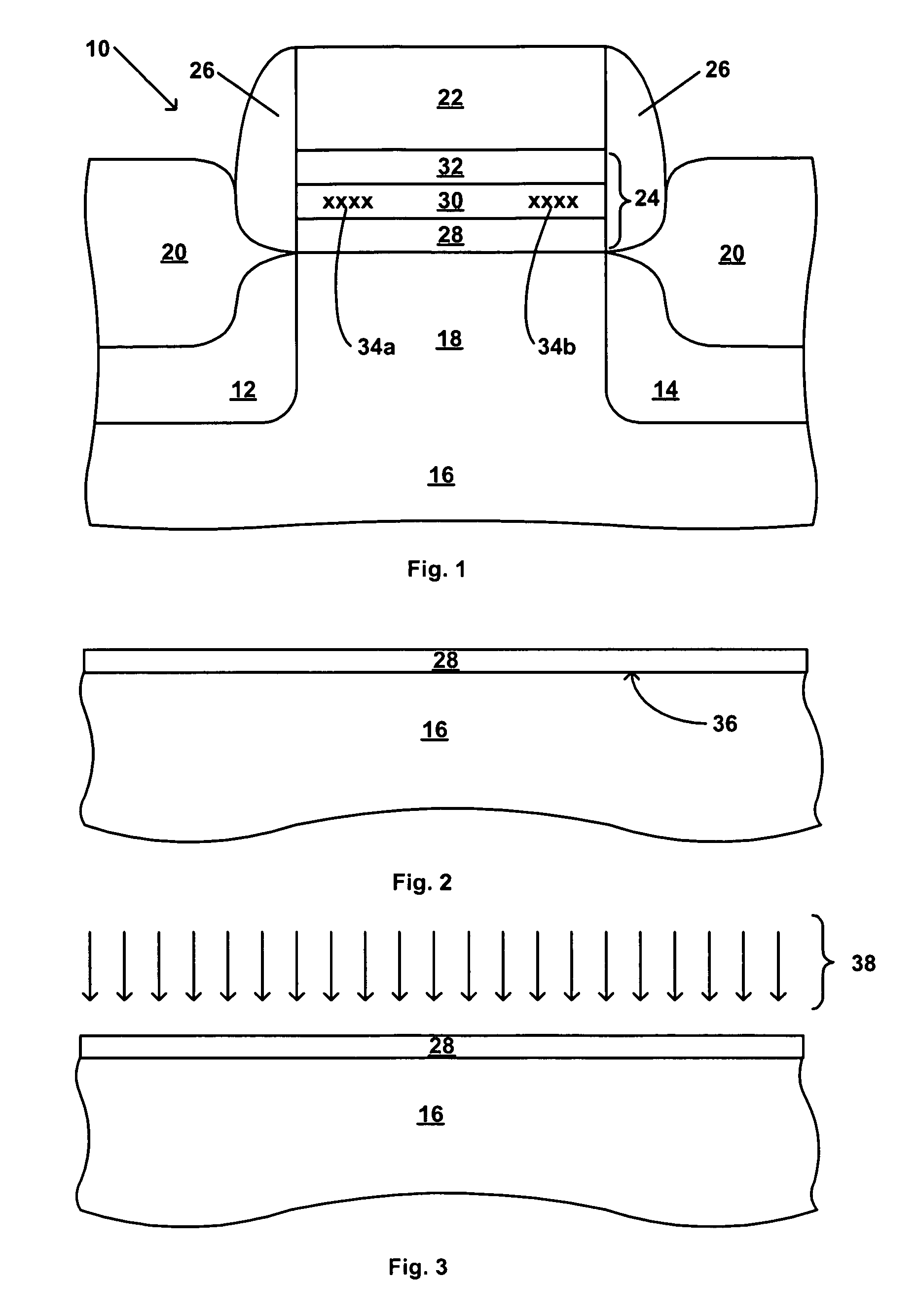

Method of forming a capacitor for a semiconductor device

InactiveUS20060046382A1Improve structural stabilityLow heat budgetSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

In an embodiment, a method of forming a capacitor for a semiconductor device of which structural stability is improved is shown. Cylindrical storage electrodes are formed in a matrix pattern on a substrate that includes an insulation interlayer having contacts therein so that a mold layer surrounds the cylindrical storage electrodes. Sacrificial plugs are formed with a cap within these electrodes. A stabilizing layer is formed on the etched mold layer and the cylindrical storage electrode by partially etching the mold layer. The stabilizing layer is etched until the sacrificial plug is exposed, thereby forming a spacer. While the sacrificial plug and the mold layer are fully removed, the spacer is partially removed, thereby forming a stabilizing member for supporting neighboring storage electrodes adjacent to each other. Accordingly, a structural stability of the capacitor is improved.

Owner:SAMSUNG ELECTRONICS CO LTD

ONO fabrication process for reducing oxygen vacancy content in bottom oxide layer in flash memory devices

InactiveUS6969886B1Reduce charge leakageIncrease oxygen contentSemiconductor/solid-state device manufacturingSemiconductor devicesOxygen vacancyOxygen content

A SONOS flash memory device, including a semiconductor substrate; an ONO structure formed on the semiconductor substrate, the ONO structure including a bottom oxide layer, a dielectric charge storage layer and a top oxide layer, the bottom oxide layer having a super-stoichiometric oxygen content and an oxygen vacancy content of about 1010 / cm2 or less, wherein the bottom oxide layer exhibits a reduced charge leakage relative to a bottom oxide layer having a stoichiometric or sub-stoichiometric oxygen content and a greater number of oxygen vacancies. In one embodiment, the bottom oxide layer has an oxygen vacancy content of substantially zero.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

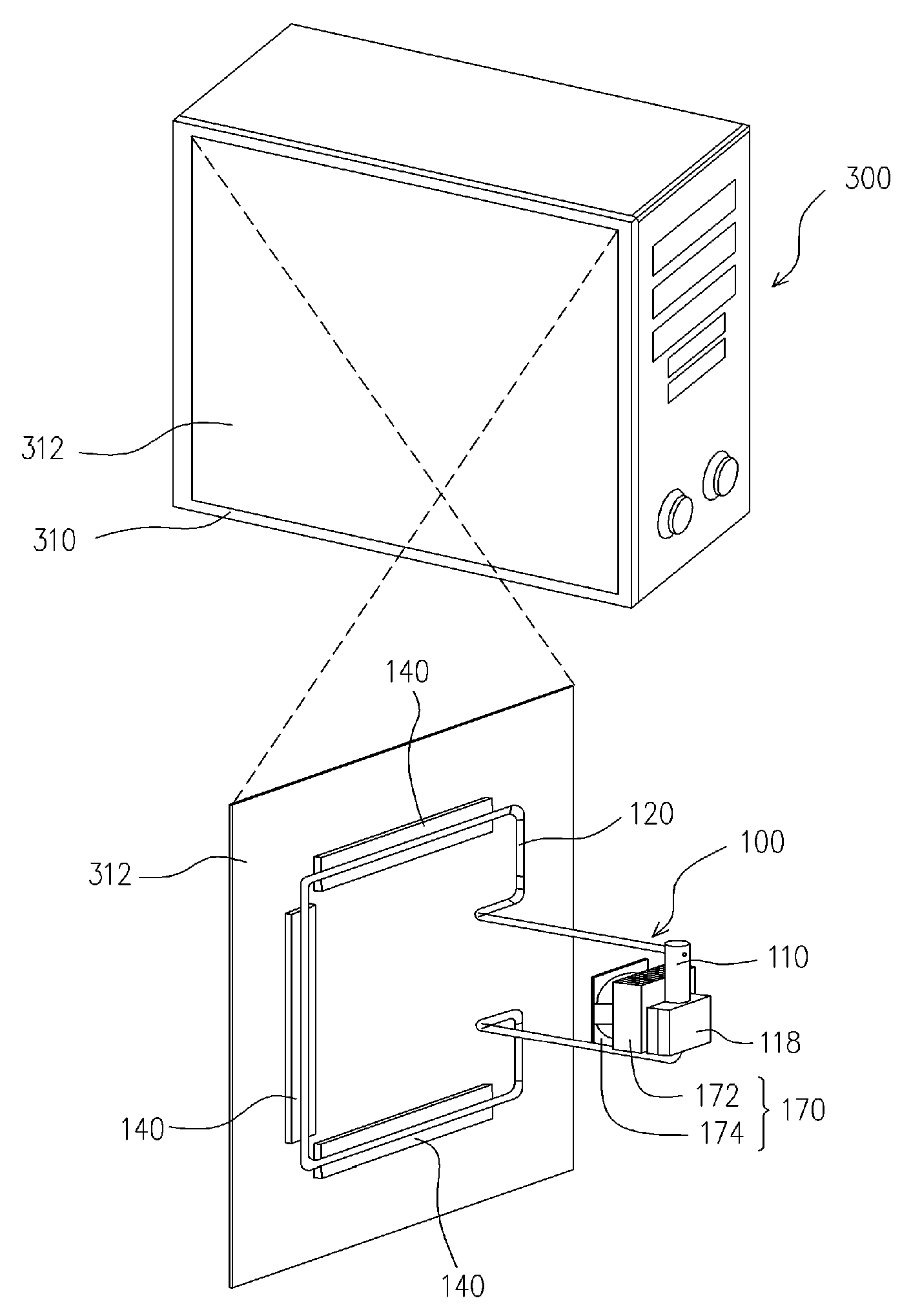

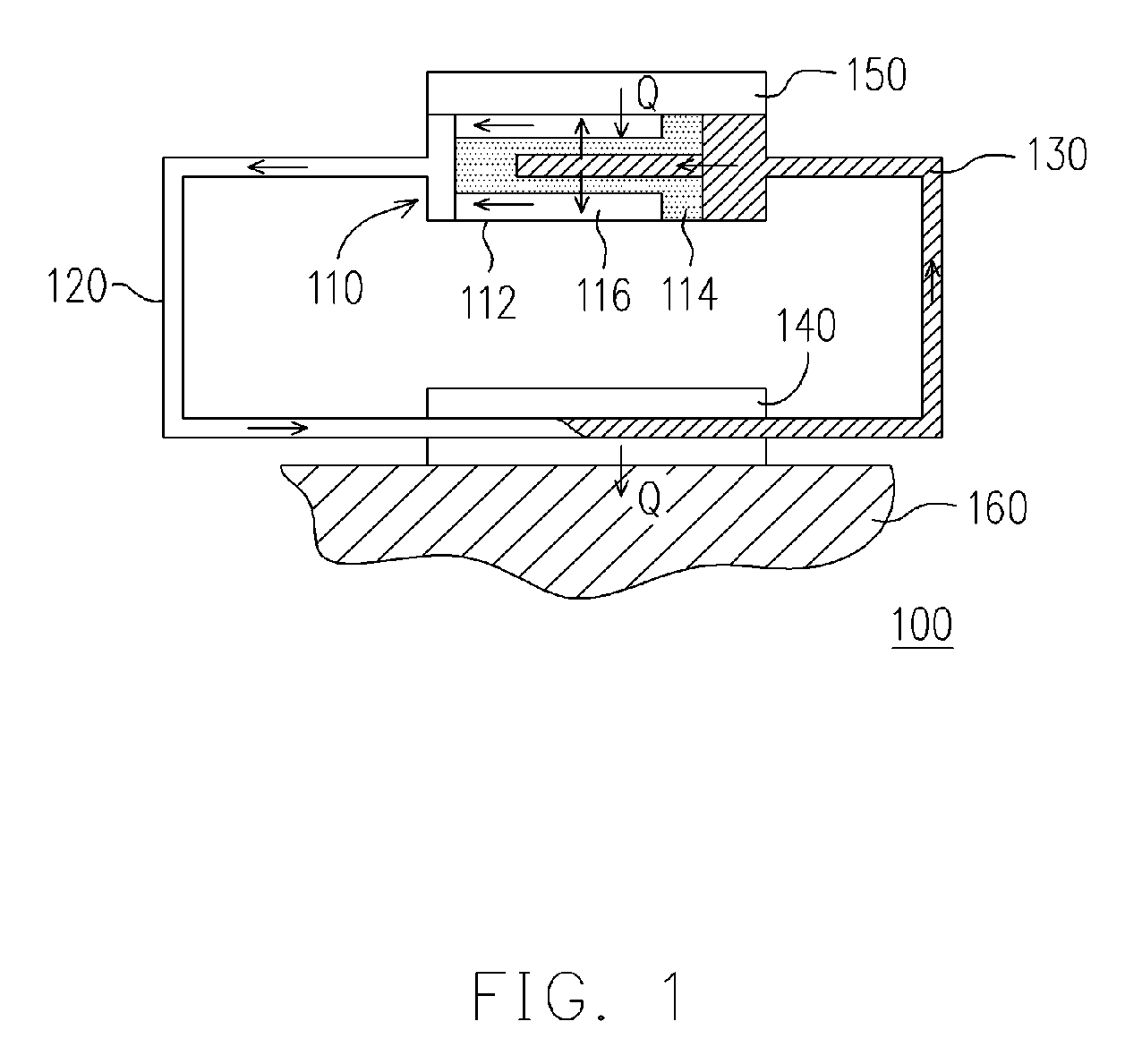

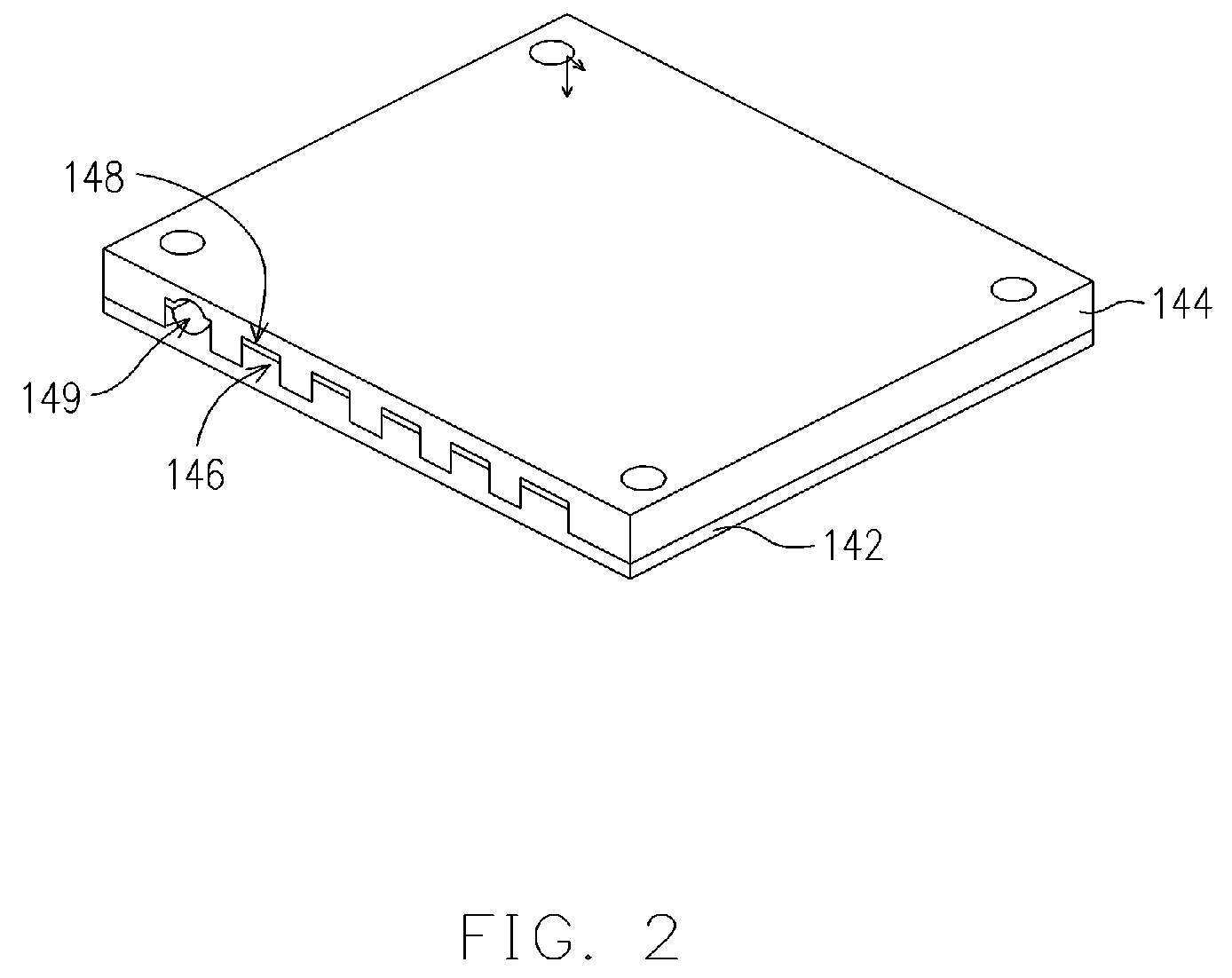

Heat pipe cooling system and thermal connector thereof

InactiveUS20060185827A1Low energy budgetLow budgetDigital data processing detailsSemiconductor/solid-state device detailsWorking fluidClosed loop

A heat pipe cooling system comprising an evaporator, a pipeline, a working fluid and a thermal connector is provided. The evaporator is connected to a heat-generating element, and the pipeline is connected to the evaporator. The working fluid is injected into a closed loop formed by the evaporator and the pipeline. The thermal connector comprises a first thermal conductive block and a second thermal conductive block. The first thermal conductive block has many first fitting parts and a contact surface. The contact surface is suitable for attaching to one of the surfaces of an object. The second thermal conductive block has many second fitting parts. The second fitting parts are suitable for meshing with the first fitting parts to form a piping channel inside the thermal connector. The piping channel is suitable for enclosing a section of the pipeline or directly serving as a part of the pipeline.

Owner:ADVANCED THERMAL DEVICES

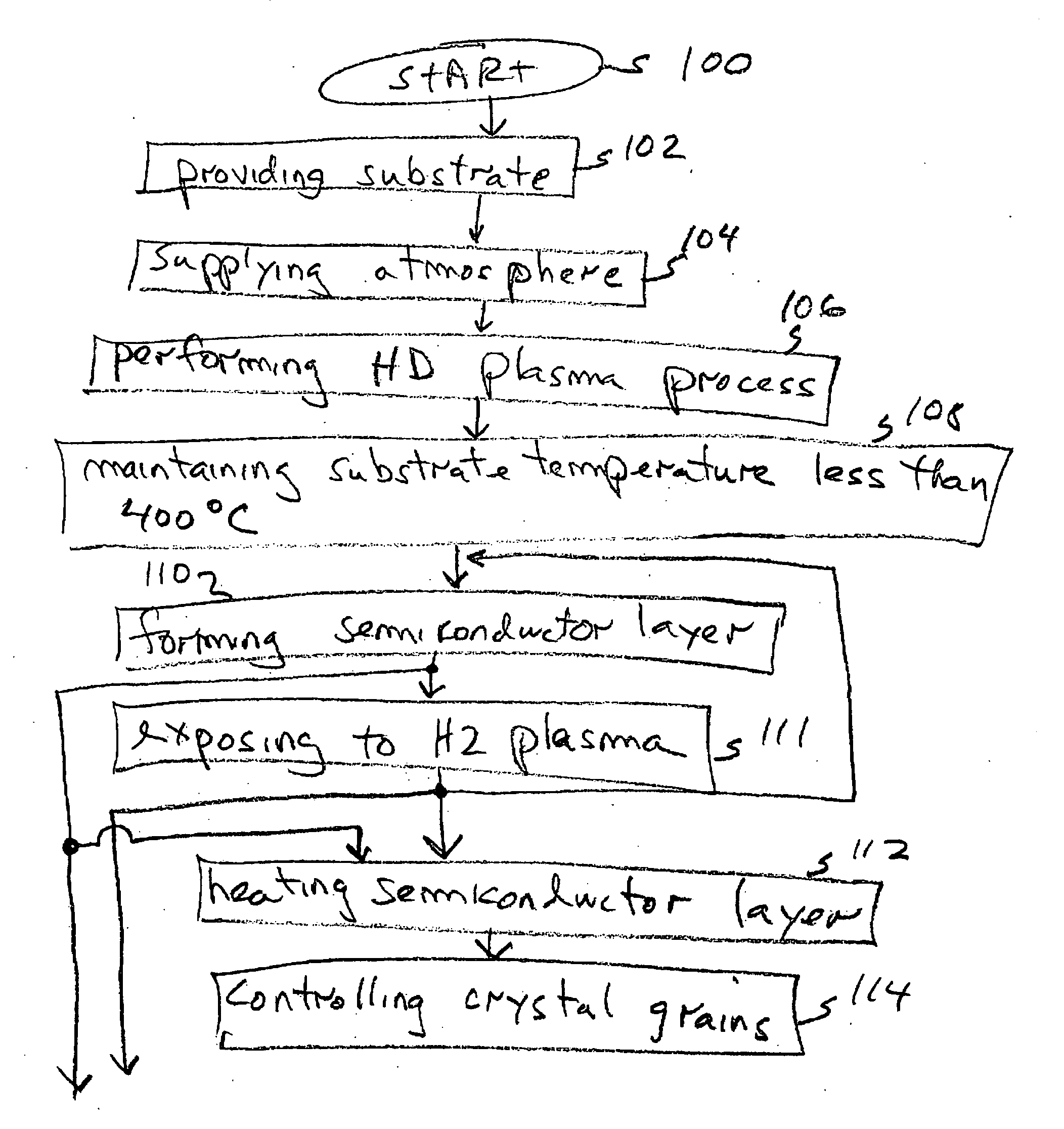

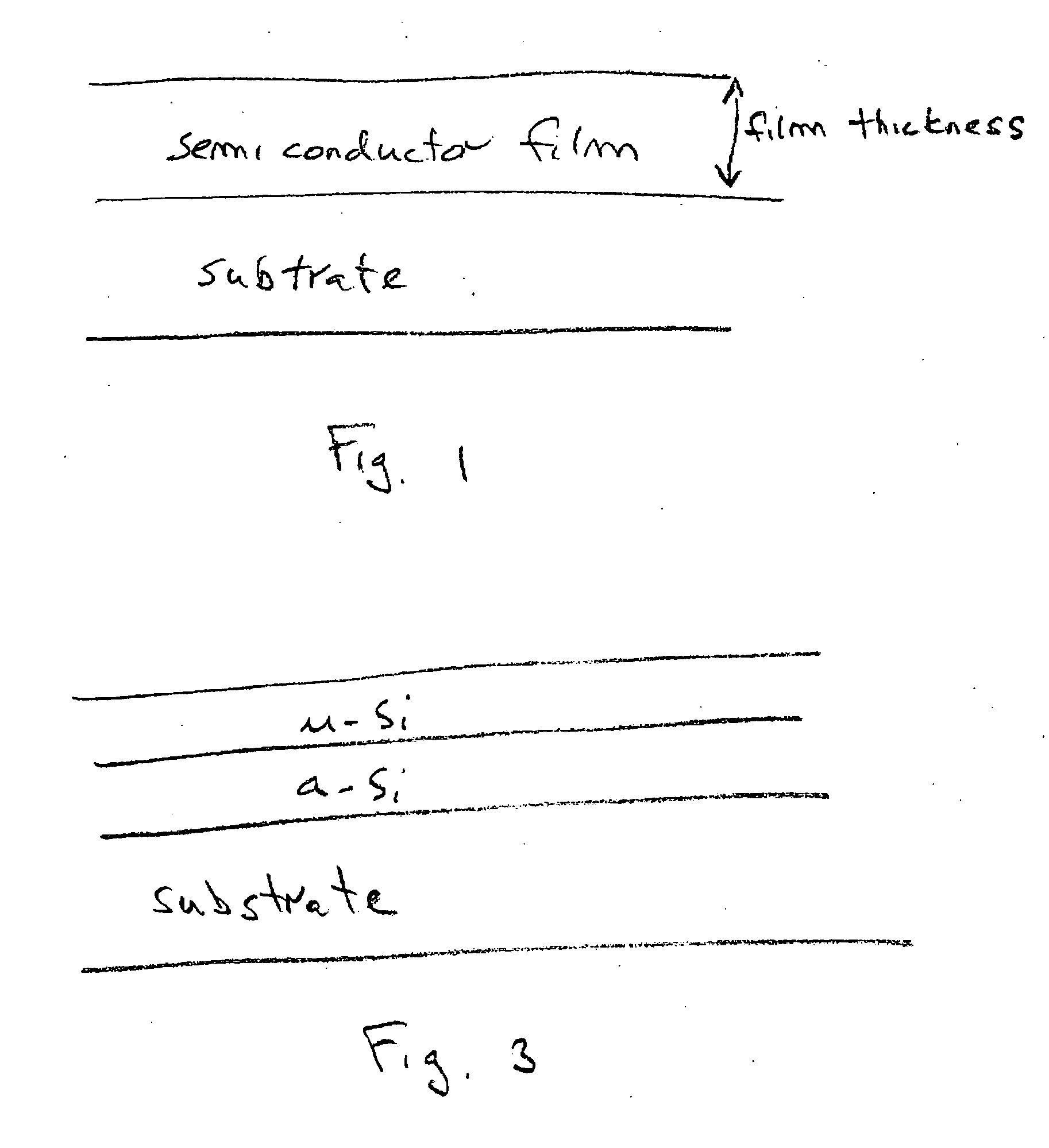

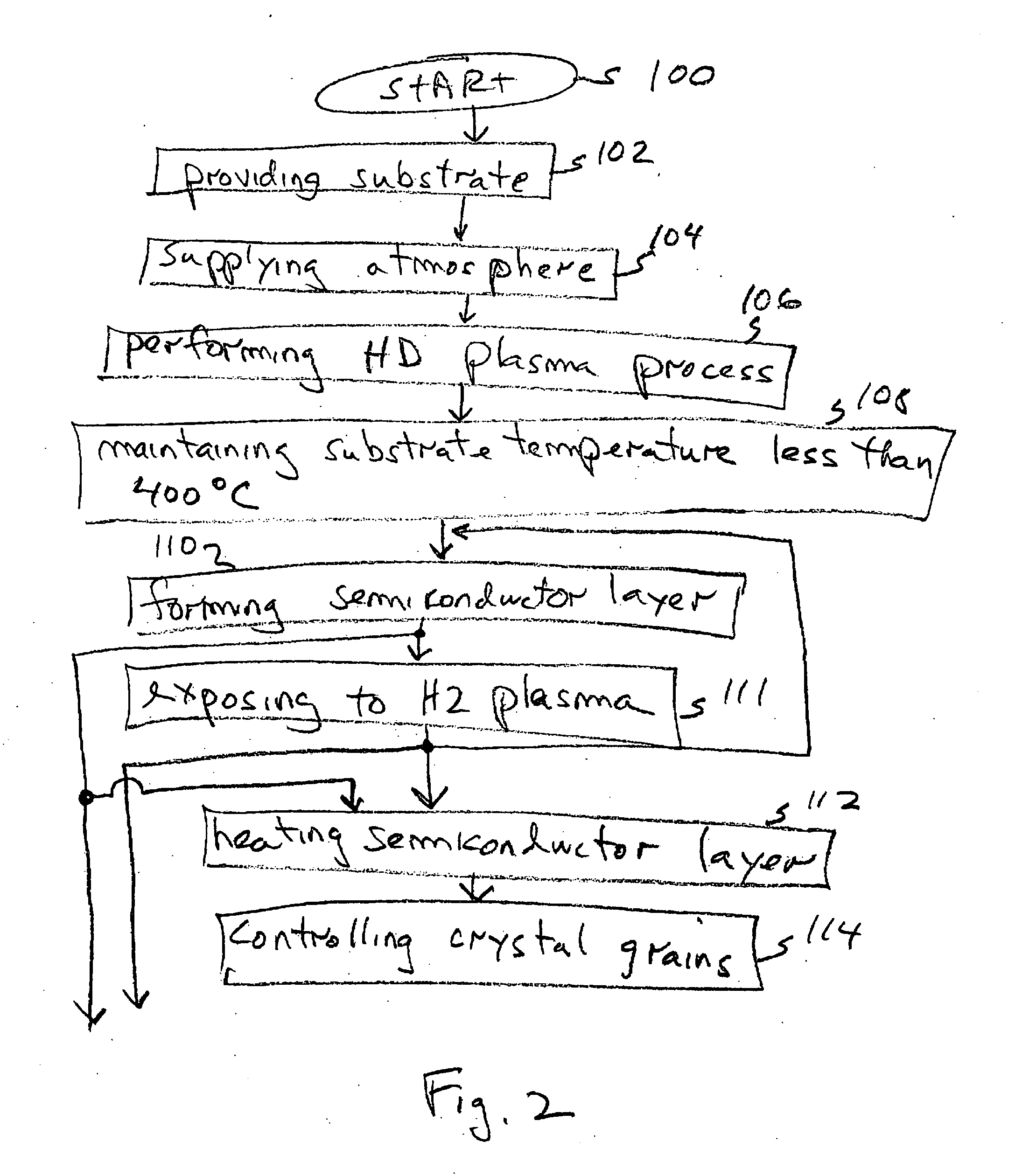

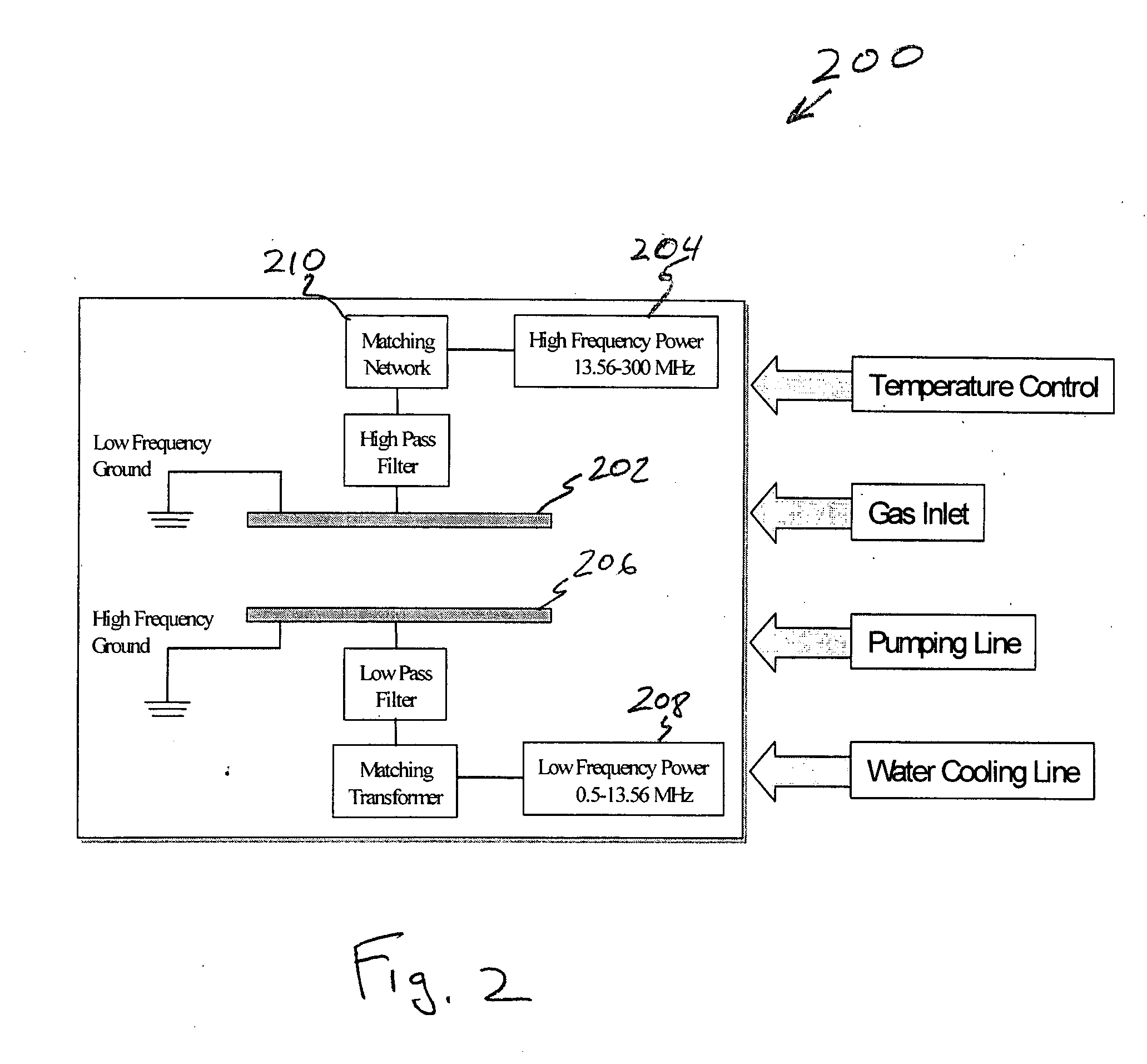

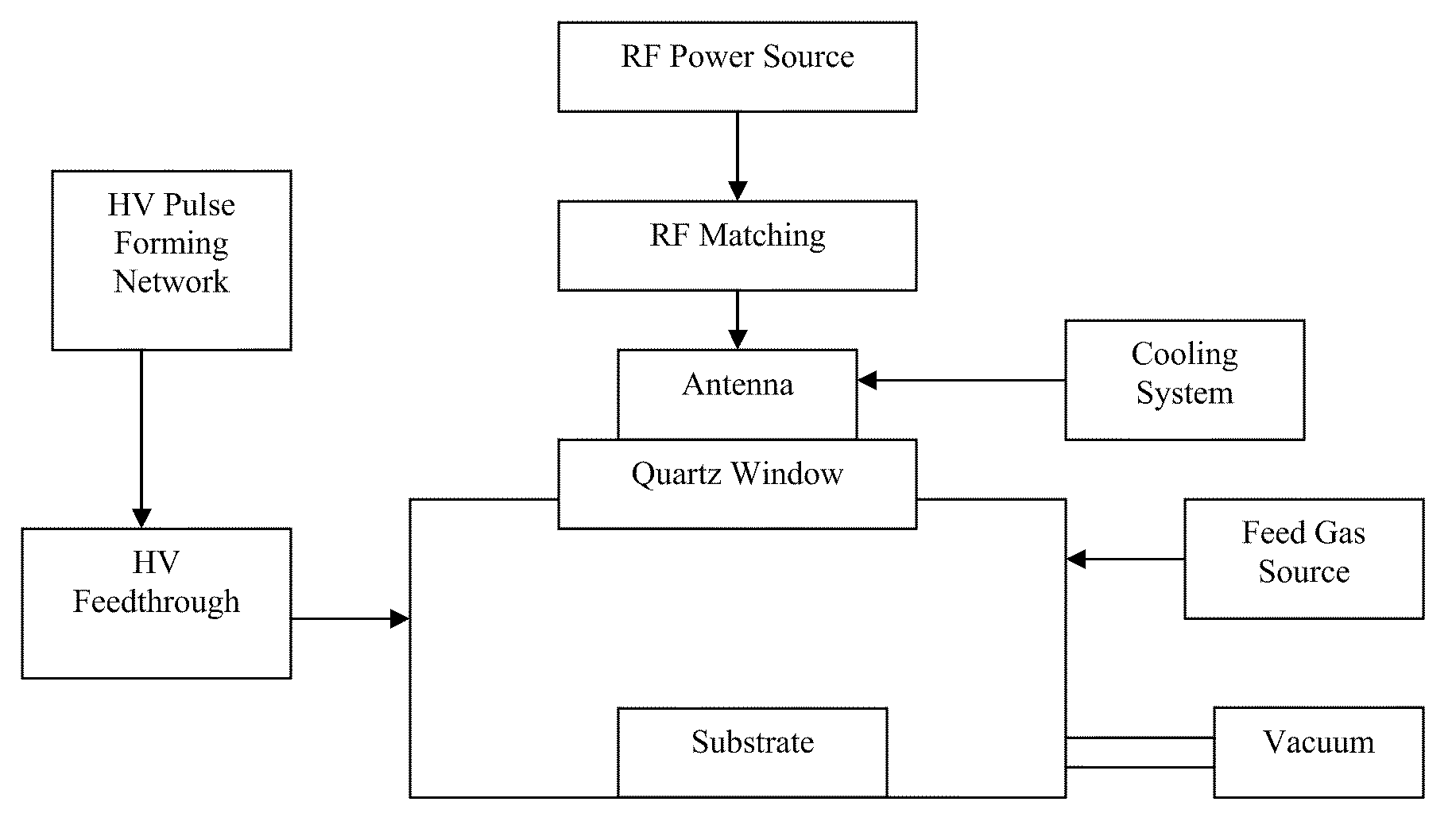

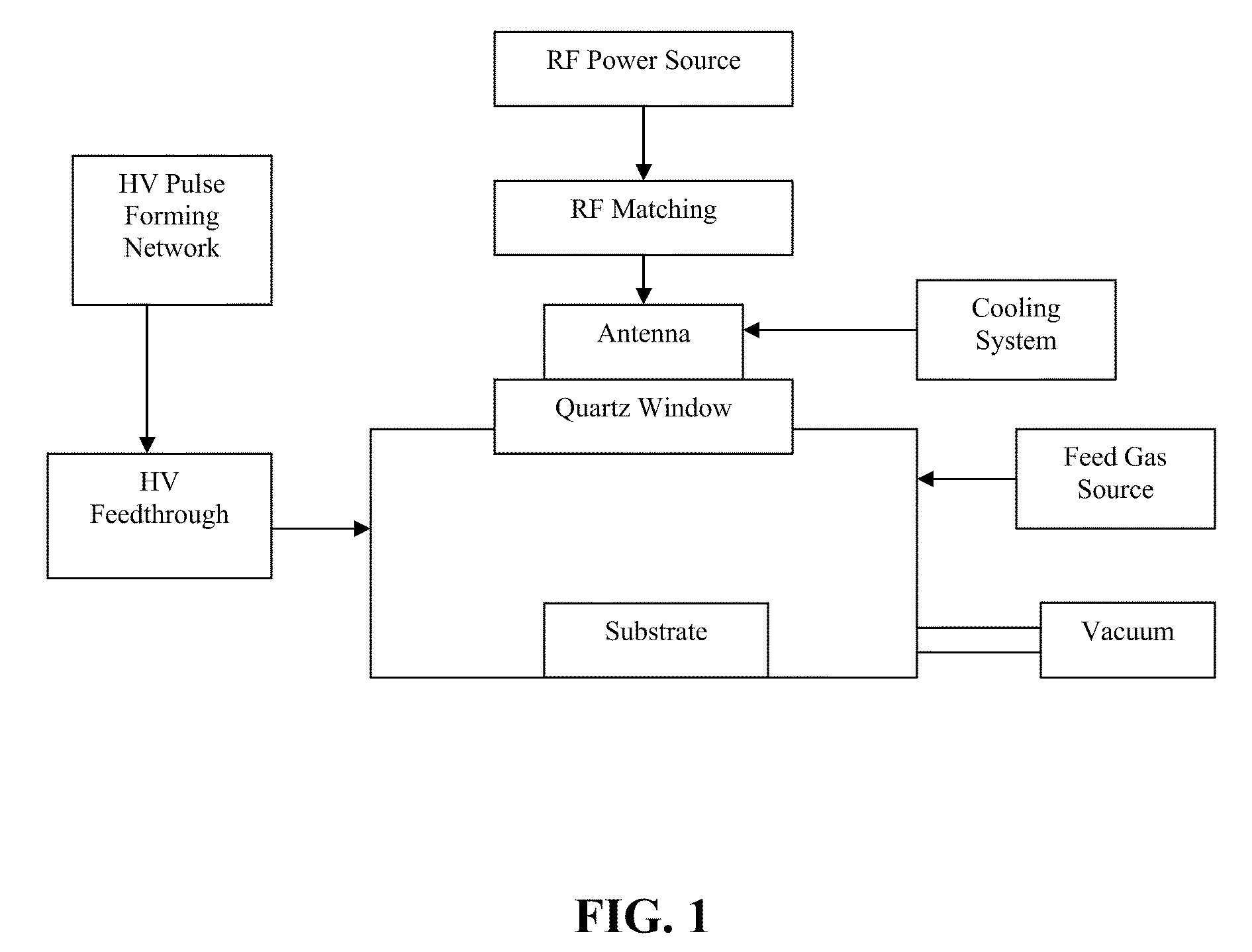

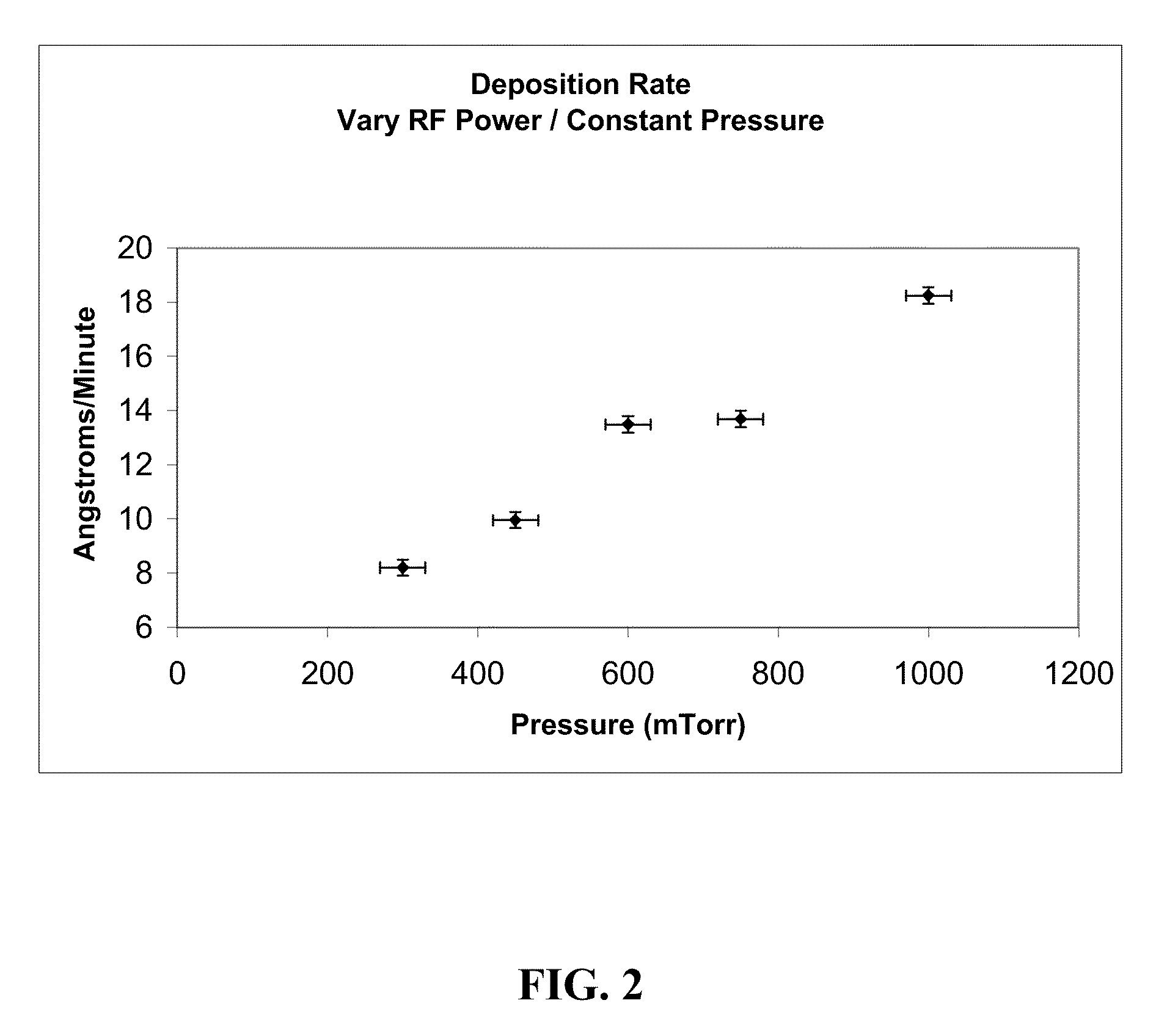

High density plasma process for silicon thin films

InactiveUS20050202653A1Increase depositionThermal budgetTransistorMolten spray coatingSilanesGermanium

A method is provided for forming a Si and Si—Ge thin films. The method comprises: providing a low temperature substrate material of plastic or glass; supplying an atmosphere; performing a high-density (HD) plasma process, such as an HD PECVD process using an inductively coupled plasma (ICP) source; maintaining a substrate temperature of 400 degrees C., or less; and, forming a semiconductor layer overlying the substrate that is made from Si or Si-germanium. The HD PECVD process is capable of depositing Si at a rate of greater than 100 Å per minute. The substrate temperature can be as low as 50 degrees C. Microcrystalline Si, a-Si, or a polycrystalline Si layer can be formed over the substrate. Further, the deposited Si can be either intrinsic or doped. Typically, the supplied atmosphere includes Si and H. For example, an atmosphere can be supplied including SiH4 and H2, or comprising H2 and Silane with H2 / Silane ratio in the range of 0-100.

Owner:SHARP KK

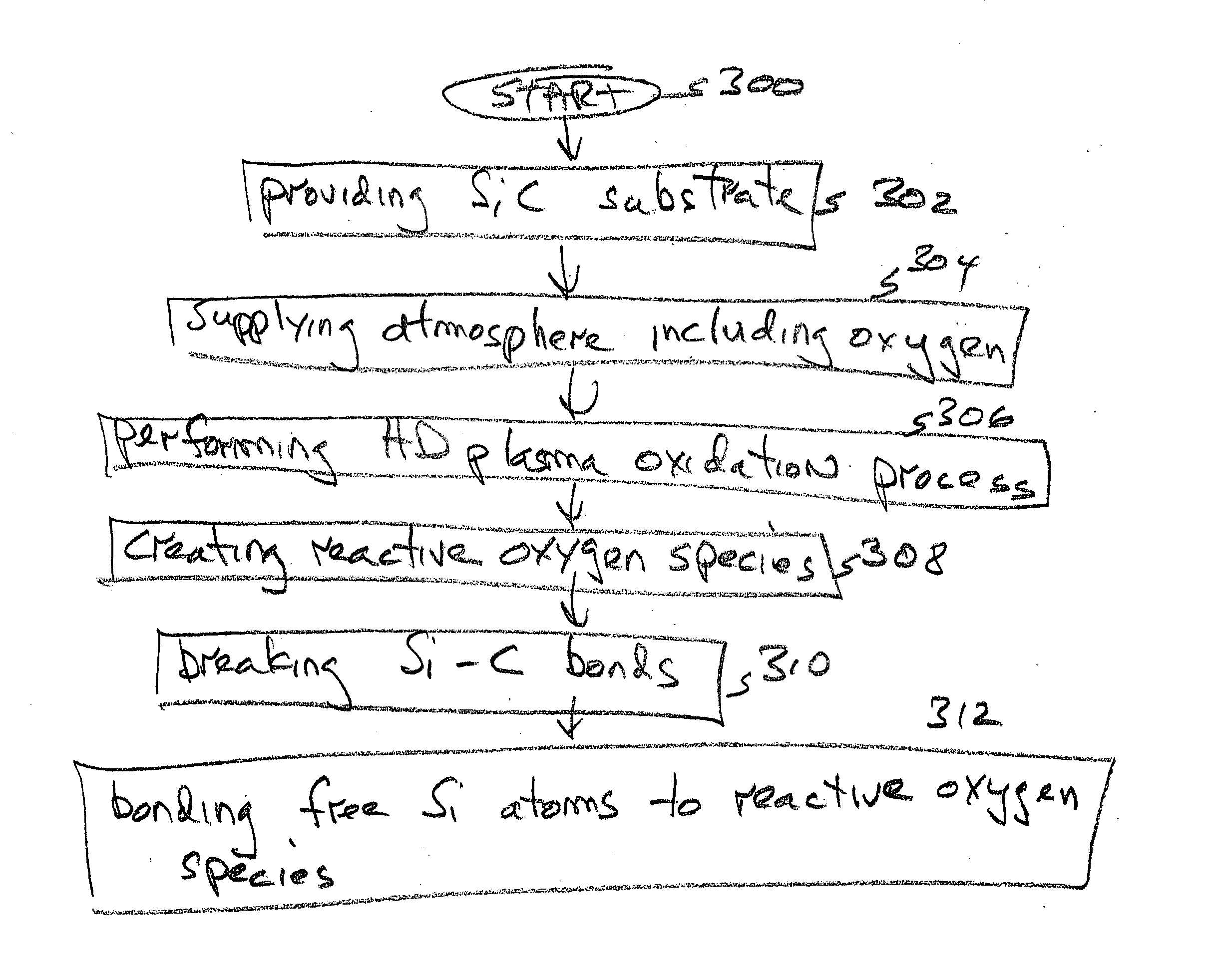

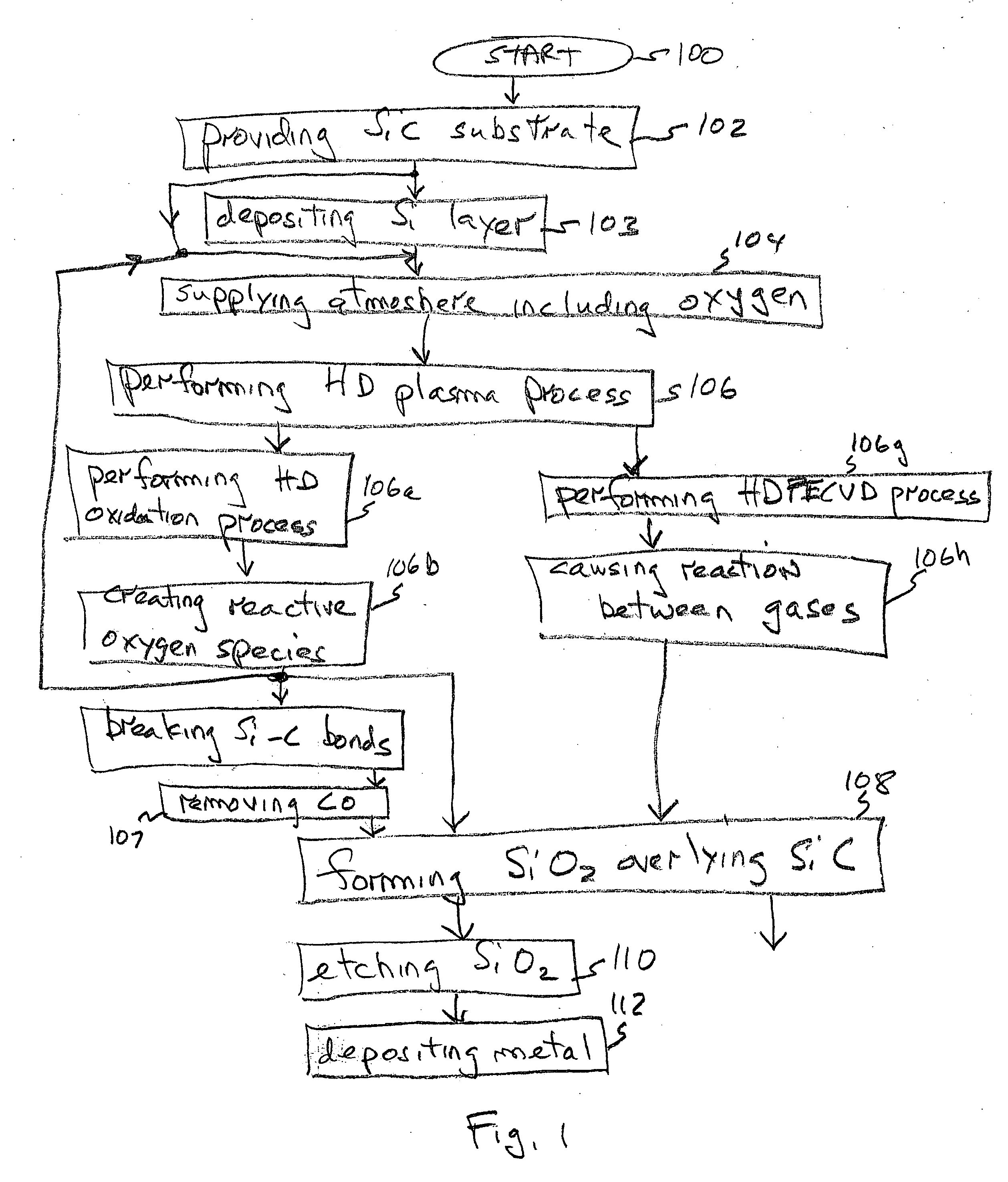

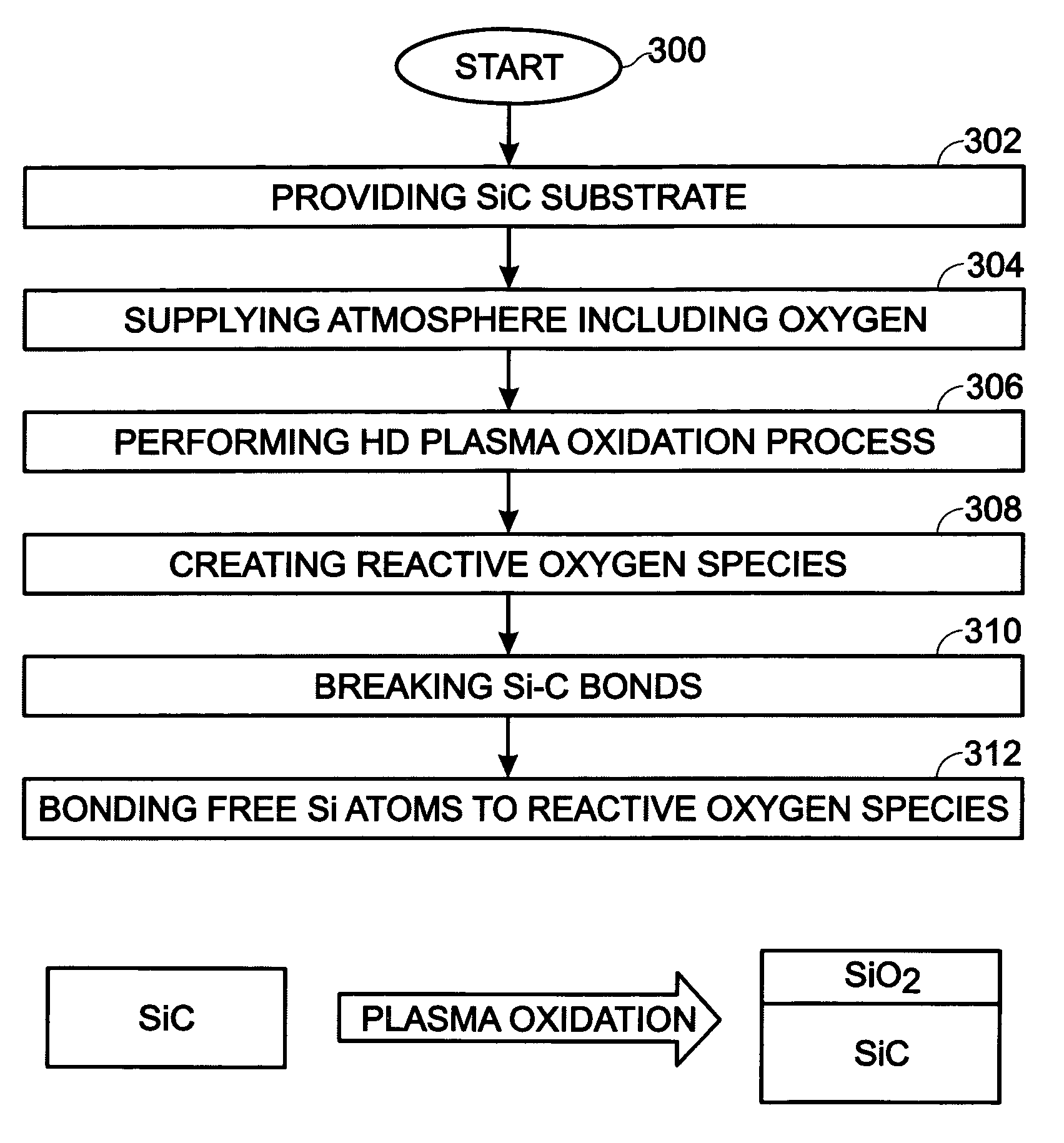

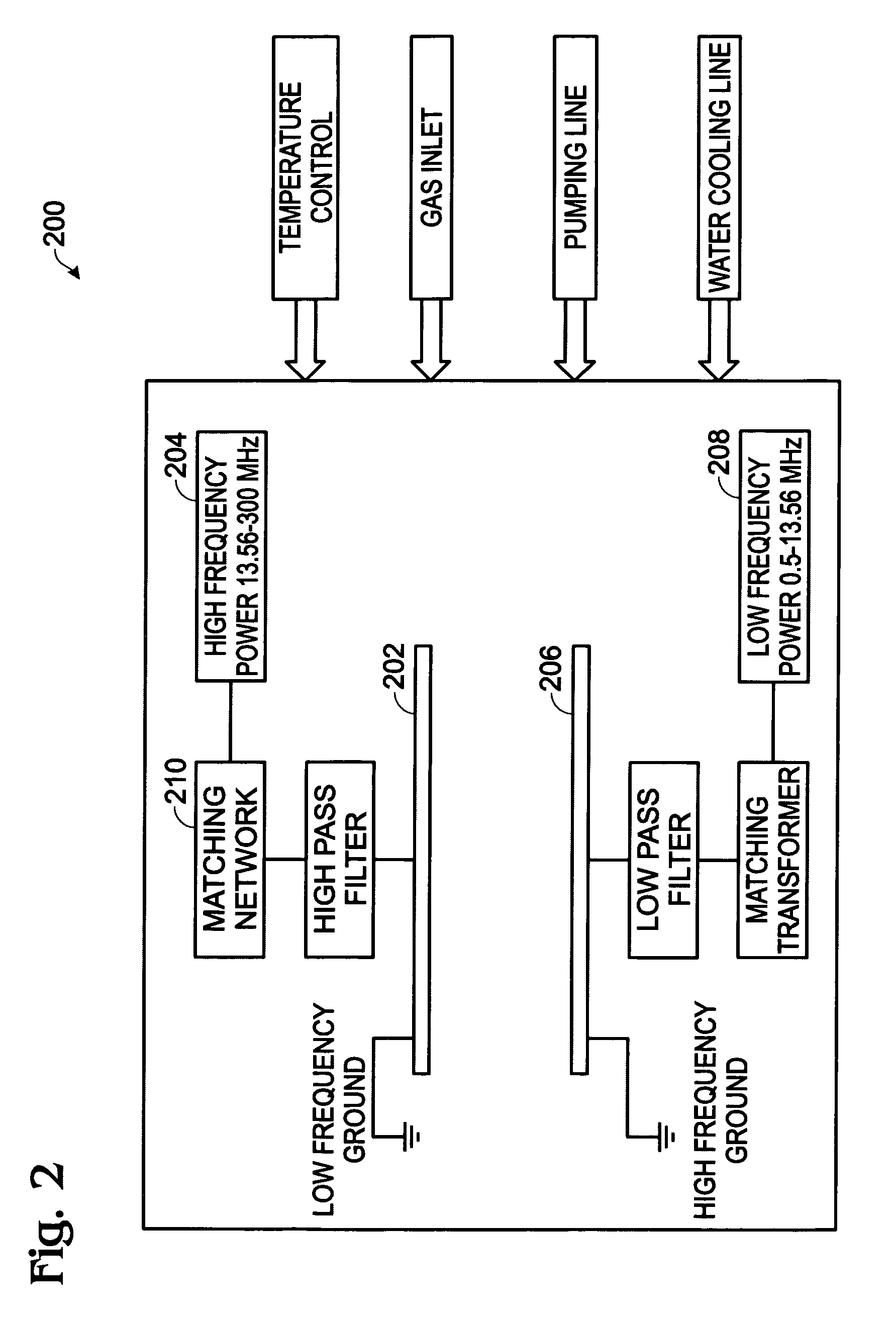

High density plasma process for the formation of silicon dioxide on silicon carbide substrates

ActiveUS20050215066A1Enhance growth/depositionThermal budgetFrom solid stateSemiconductor/solid-state device manufacturingHigh densityOxygen

Methods are provided for forming silicon dioxide (SiO2) on a silicon carbide (SiC) substrate. The method comprises: providing a SiC substrate; supplying an atmosphere including oxygen; performing a high-density (HD) plasma-based process; and, forming a SiO2 layer overlying the SiC substrate. Typically, performing the HD plasma-based process includes connecting a top electrode to an inductively coupled HD plasma source. In one aspect, SiO2 is grown on the SiC substrate. Then, an HD plasma oxidation process is performed that creates a reactive oxygen species and breaks the Si—C bonds in the SiC substrate, to form free Si and C atoms in the SiC substrate. The free Si atoms in the SiC substrate are bonded to the HD plasma-generated reactive oxygen species, and the SiO2 layer is grown.

Owner:SHARP KK

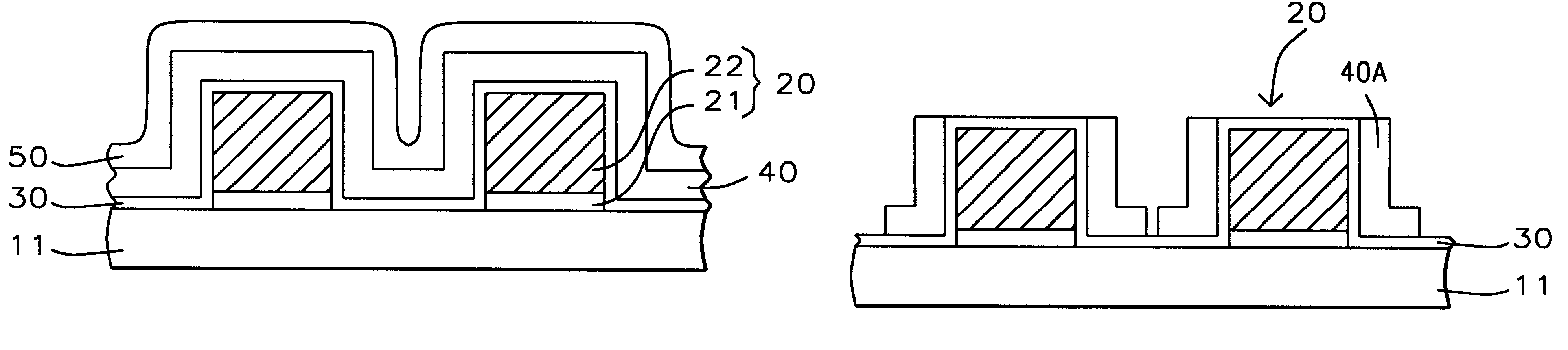

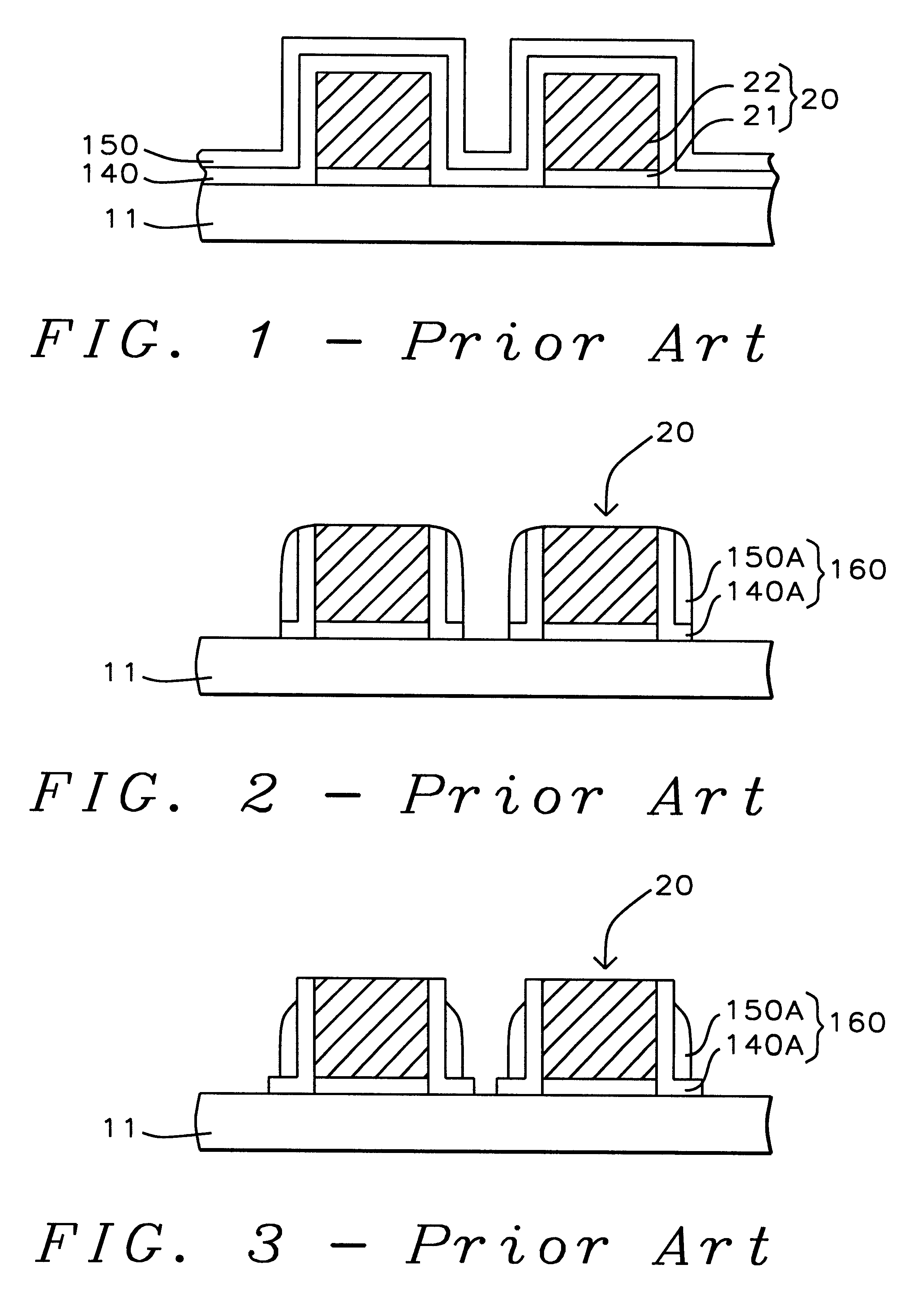

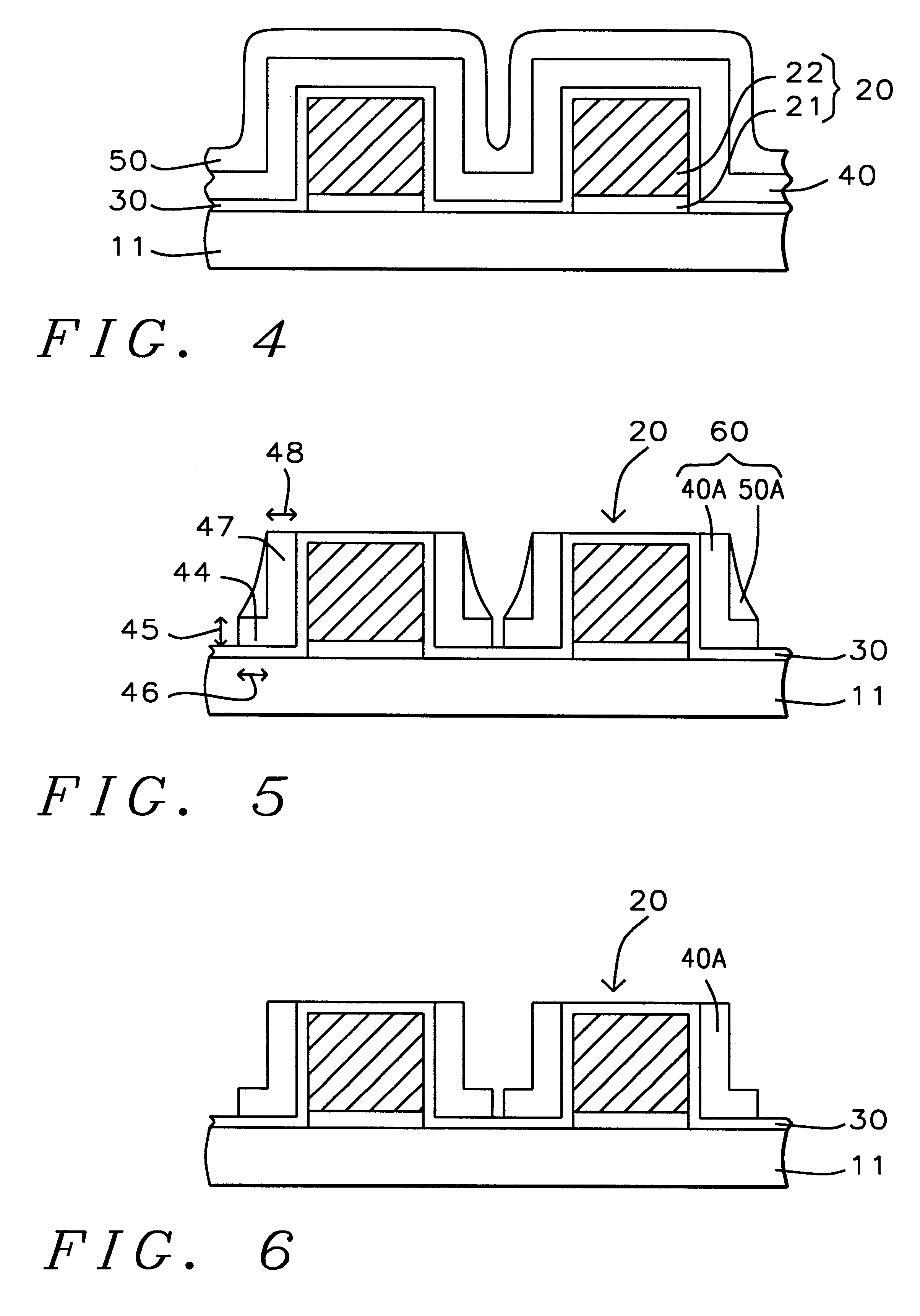

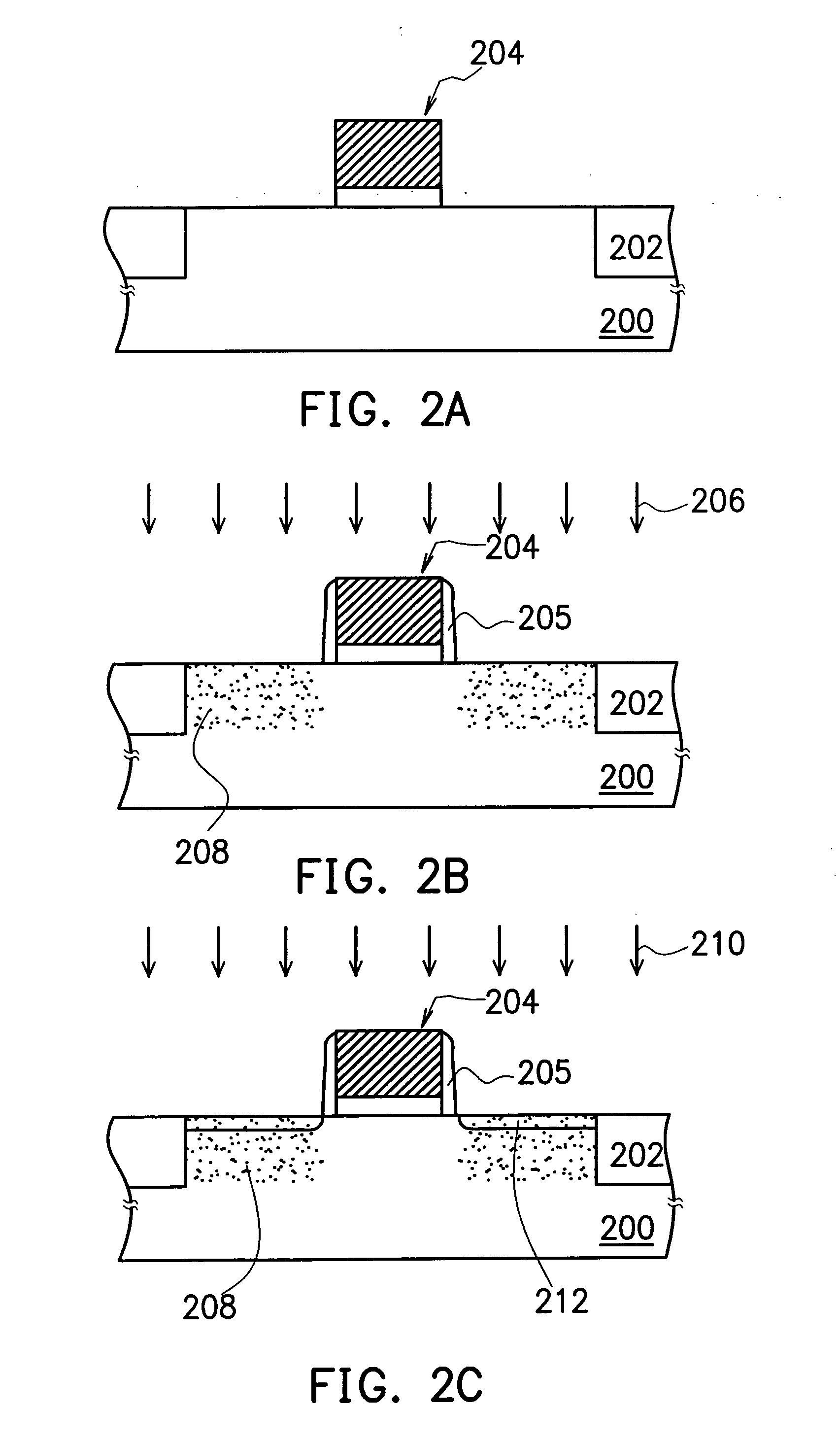

Method for forming an L-shaped spacer with a disposable organic top coating

InactiveUS6294480B1Reduce sensitivityExcellent gap fillingTransistorSemiconductor/solid-state device manufacturingOrganic structureDielectric

A method for forming an L-shaped spacer using a sacrificial organic top coating. A semiconductor structure is provided having a gate structure thereon. A liner oxide layer is formed on the gate structure. A dielectric spacer layer is formed on the liner oxide layer. In the preferred embodiment, the dielectric spacer layer comprises a silicon nitride layer or a silicon oxynitride layer. A sacrificial organic layer is formed on the dielectric spacer layer. The sacrificial organic layer and the dielectric spacer layer are anisotropically etched to form spacers comprising a triangle-shaped sacrificial organic structure and an L-shaped dielectric spacer. The triangle-shaped sacrificial organic structure is removed leaving an L-shaped dielectric spacer.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

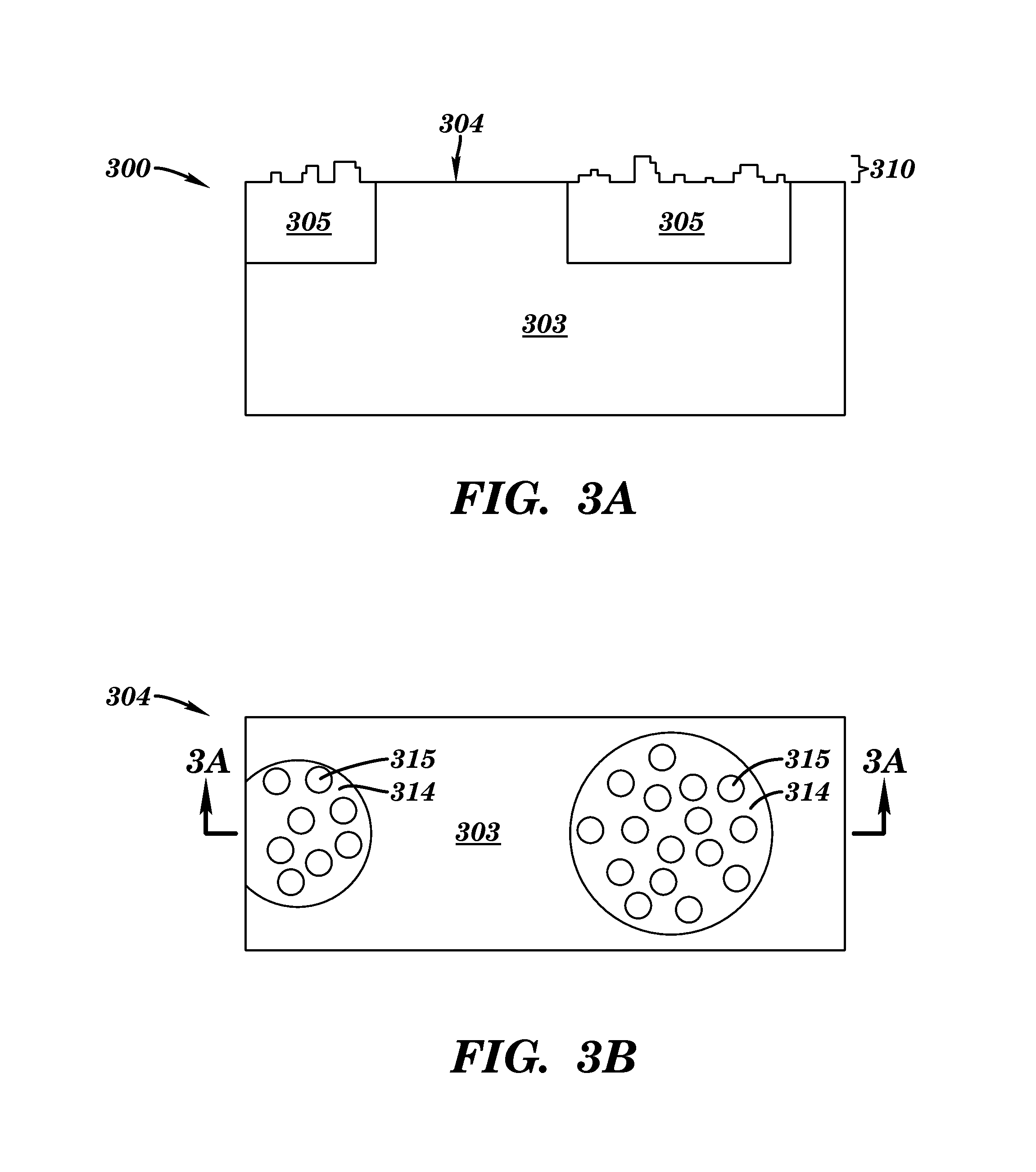

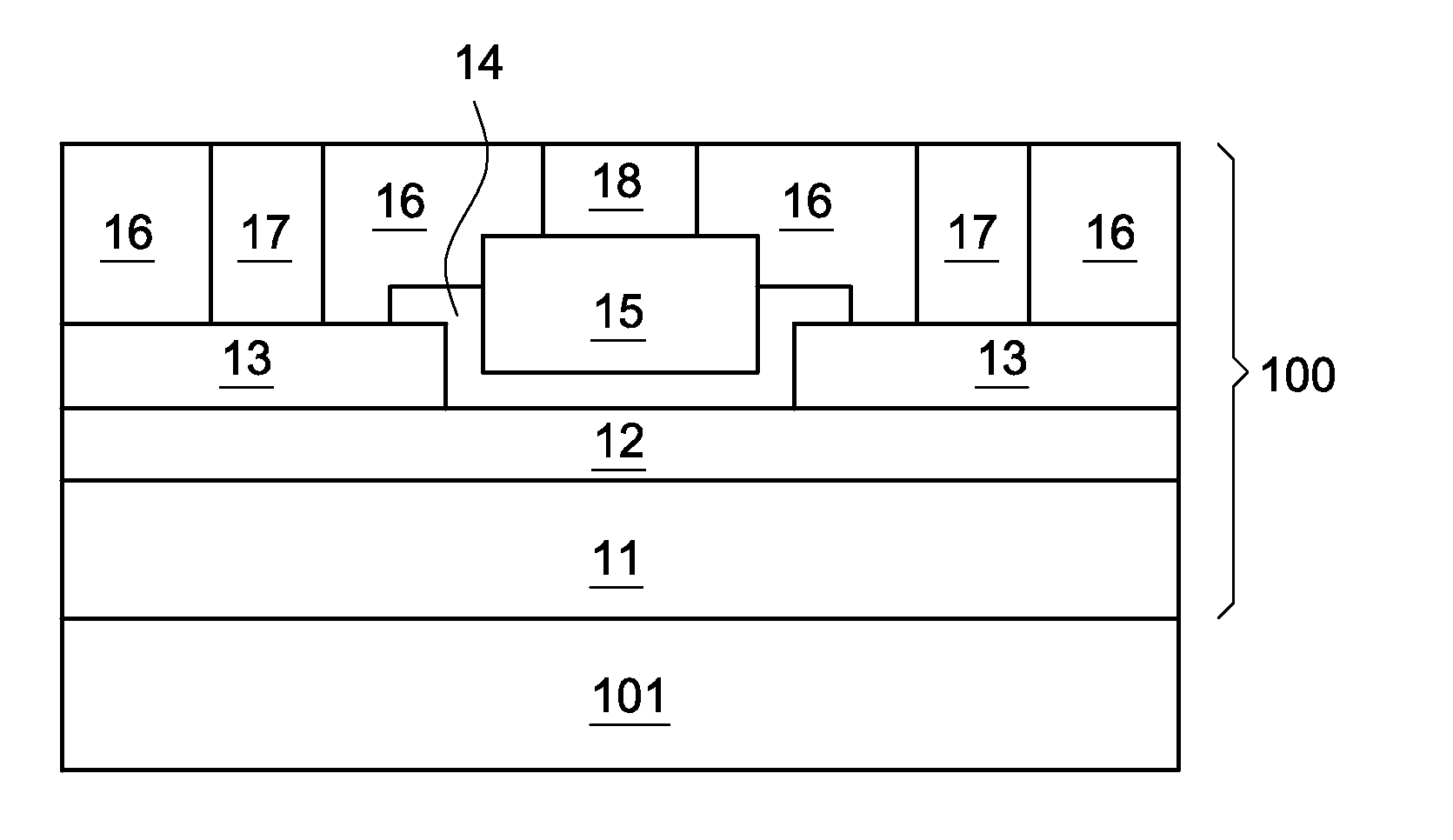

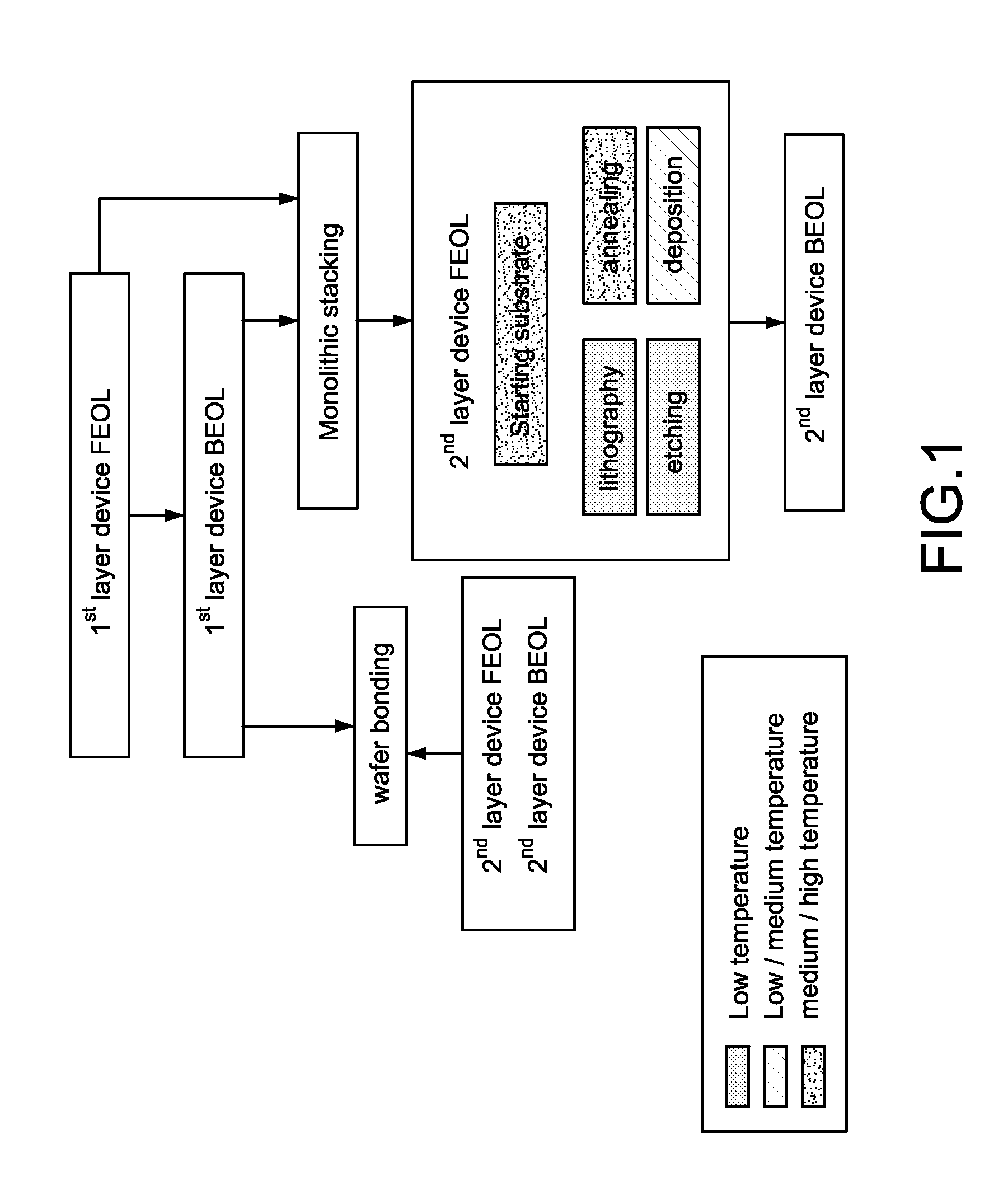

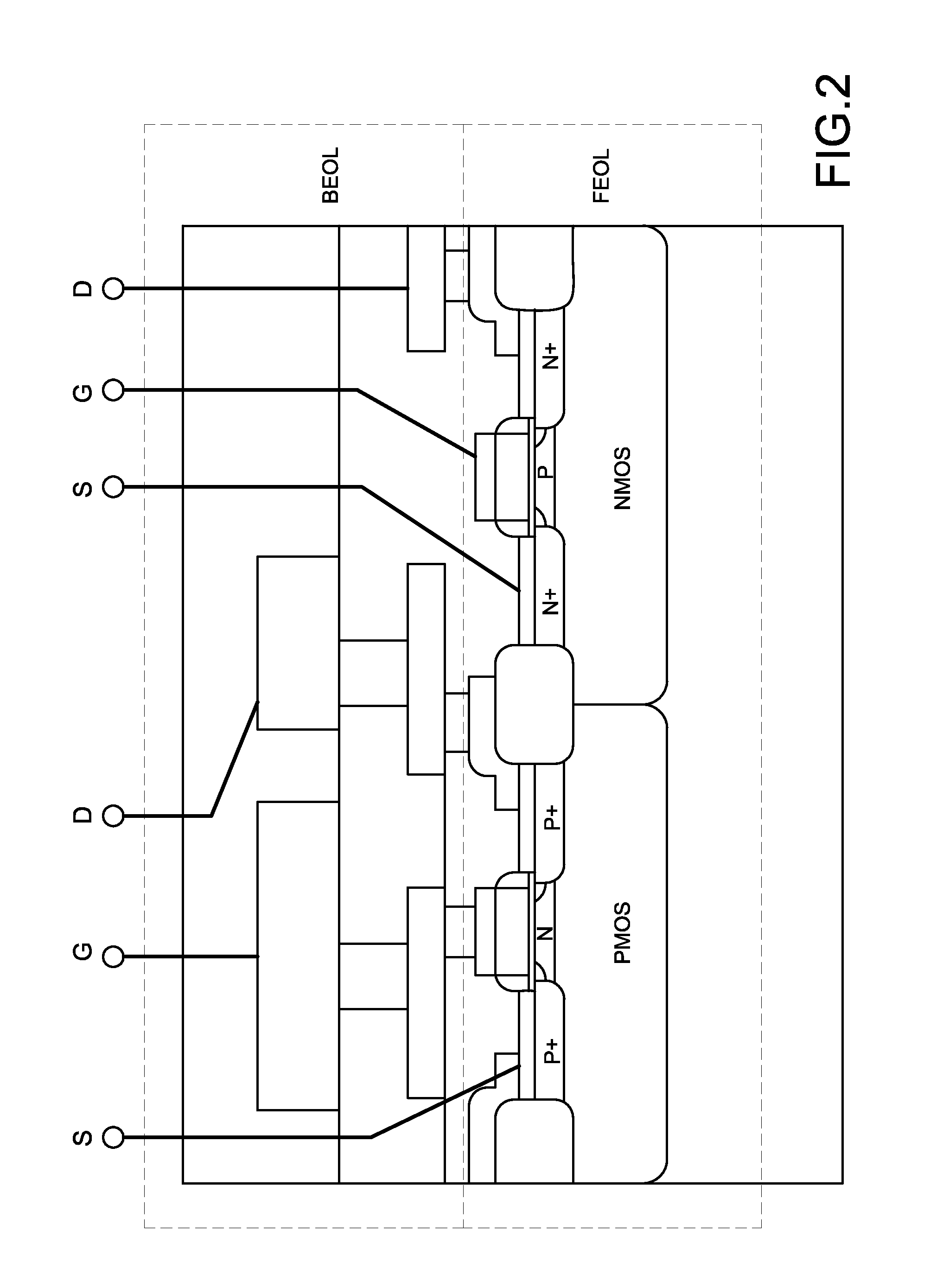

Electrical switch using gated resistor structures and three-dimensional integrated circuits using the same

ActiveUS20120056258A1Low thermal budgetImprove interconnect densityTransistorSolid-state devicesElectrical resistance and conductanceIsolation layer

An electrical switch using a gated resistor structure includes an isolation layer, a doped silicon layer arranged on the isolation layer and having a recessed portion with reduced thickness, the doped silicon layer having a predetermined doping type and a predetermined doping profile; a gate layer arranged corresponding to the recessed portion. The recessed portion in the doped silicon layer has such thickness that a channel defined under the gate can be fully depleted to form a high resistivity region. The recessed channel gated resistor structure can be advantageously used to achieve high interconnect density with low thermal budget for 3D integration.

Owner:CHEN SHU LU

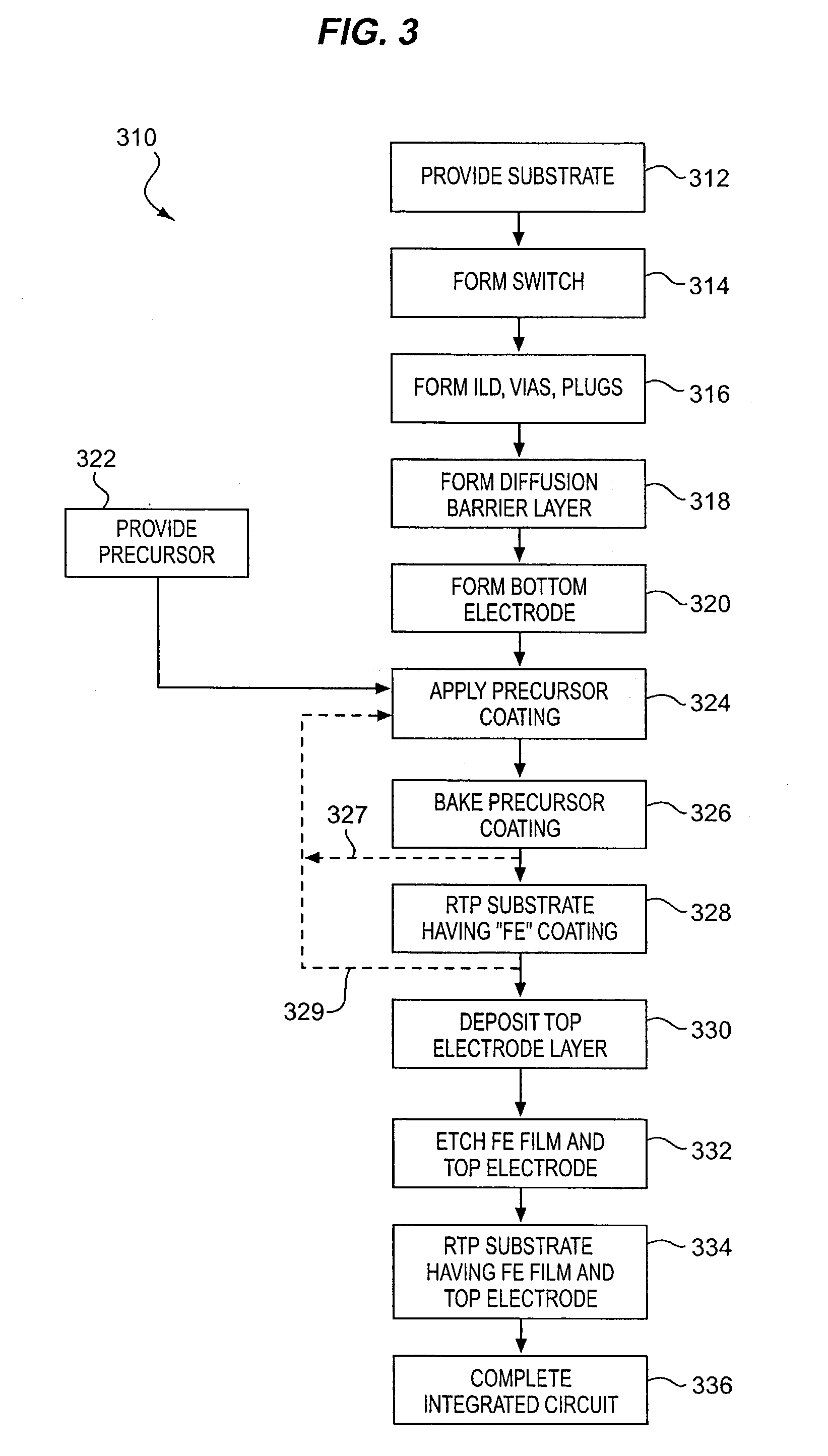

Low thermal budget fabrication of ferroelectric memory using RTP

InactiveUS20040101977A1Budget is reducedReduce the temperaturePolycrystalline material growthSemiconductor/solid-state device manufacturingOxygenHeat treated

A precursor for forming a thin film of layered superlattice material is applied to an integrated circuit substrate. The precursor coating is heated using rapid thermal processing (RTP) with a ramping rate of 100° C. / second at a hold temperature in a range of from 500° C. to 900° C. for a cumulative heating time not exceeding 30 minutes, and preferably less than 5 minutes. In fabricating a ferroelectric memory cell, the coating is heated in oxygen using RTP, then a top electrode layer is formed, and then the substrate including the coating is heated using RTP in oxygen or in nonreactive gas after forming the top electrode layer. The thin film of layered superlattice material preferably comprises strontium bismuth tantalate or strontium bismuth tantalum niobate, and preferably has a thickness in a range of from 25 nm to 120 nm. The process of fabricating a thin film of layered superlattice material typically has a thermal budget value not exceeding 960,000° C.-sec, preferably less than 50,000° C.-sec.

Owner:SYMETRIX

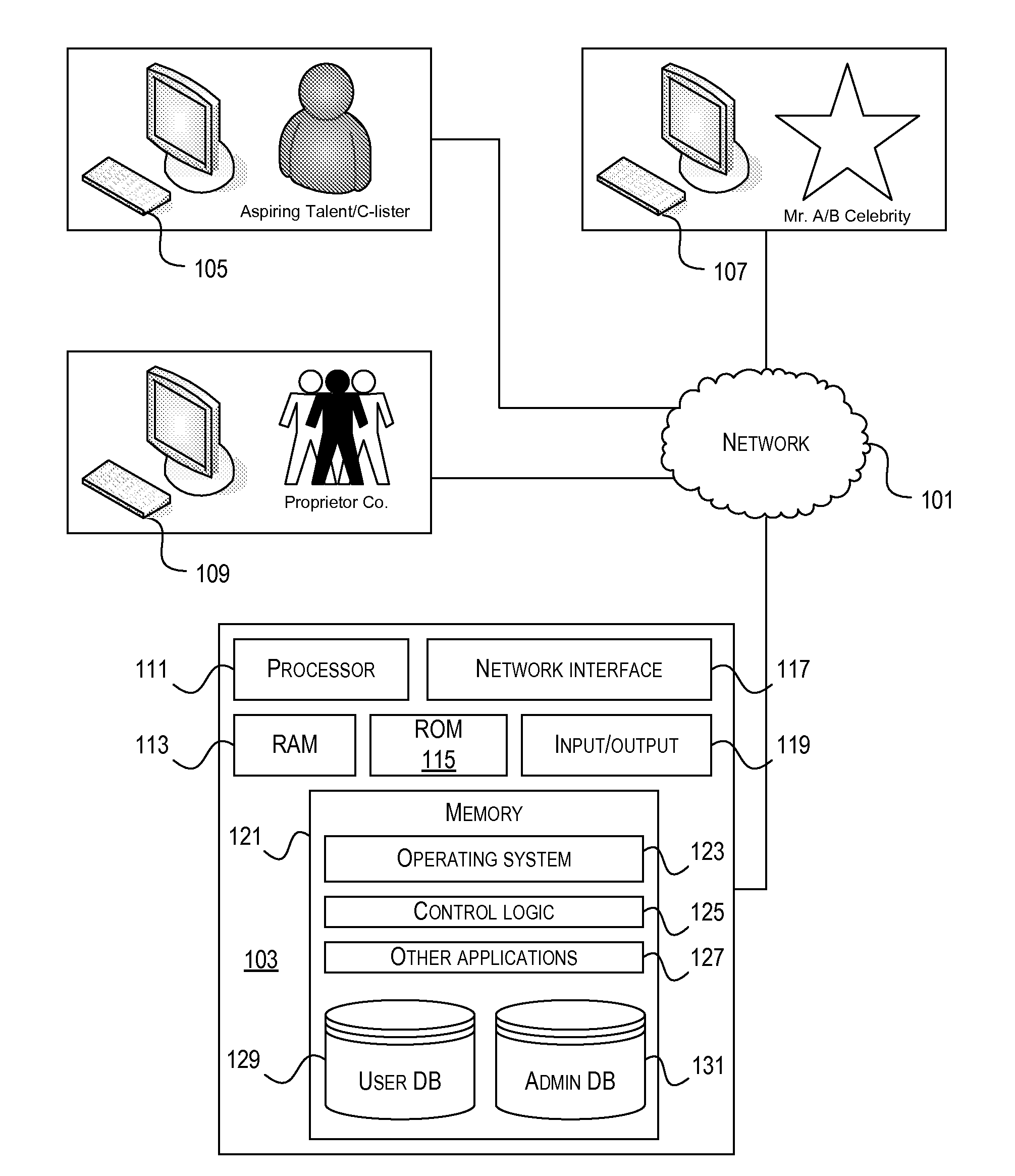

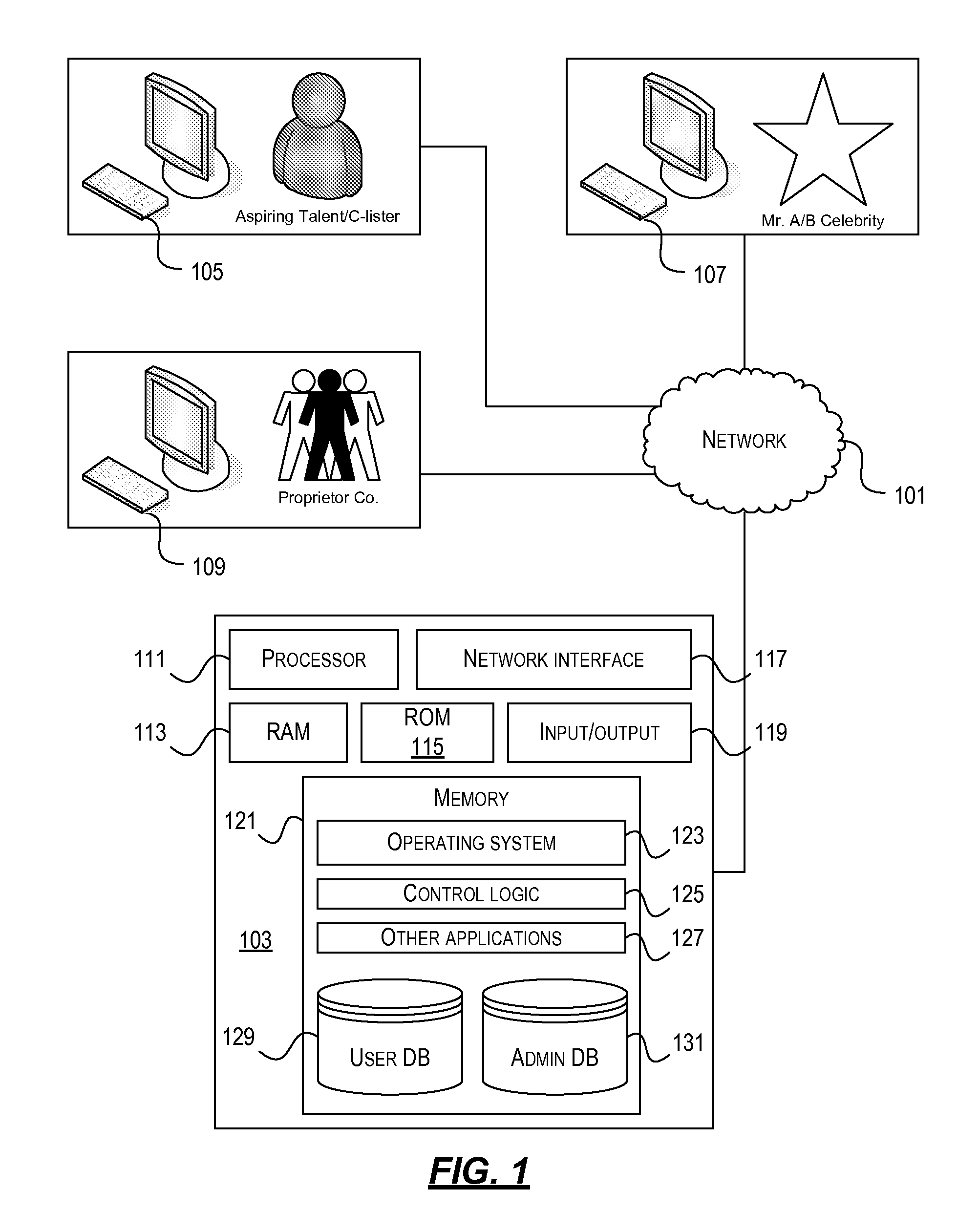

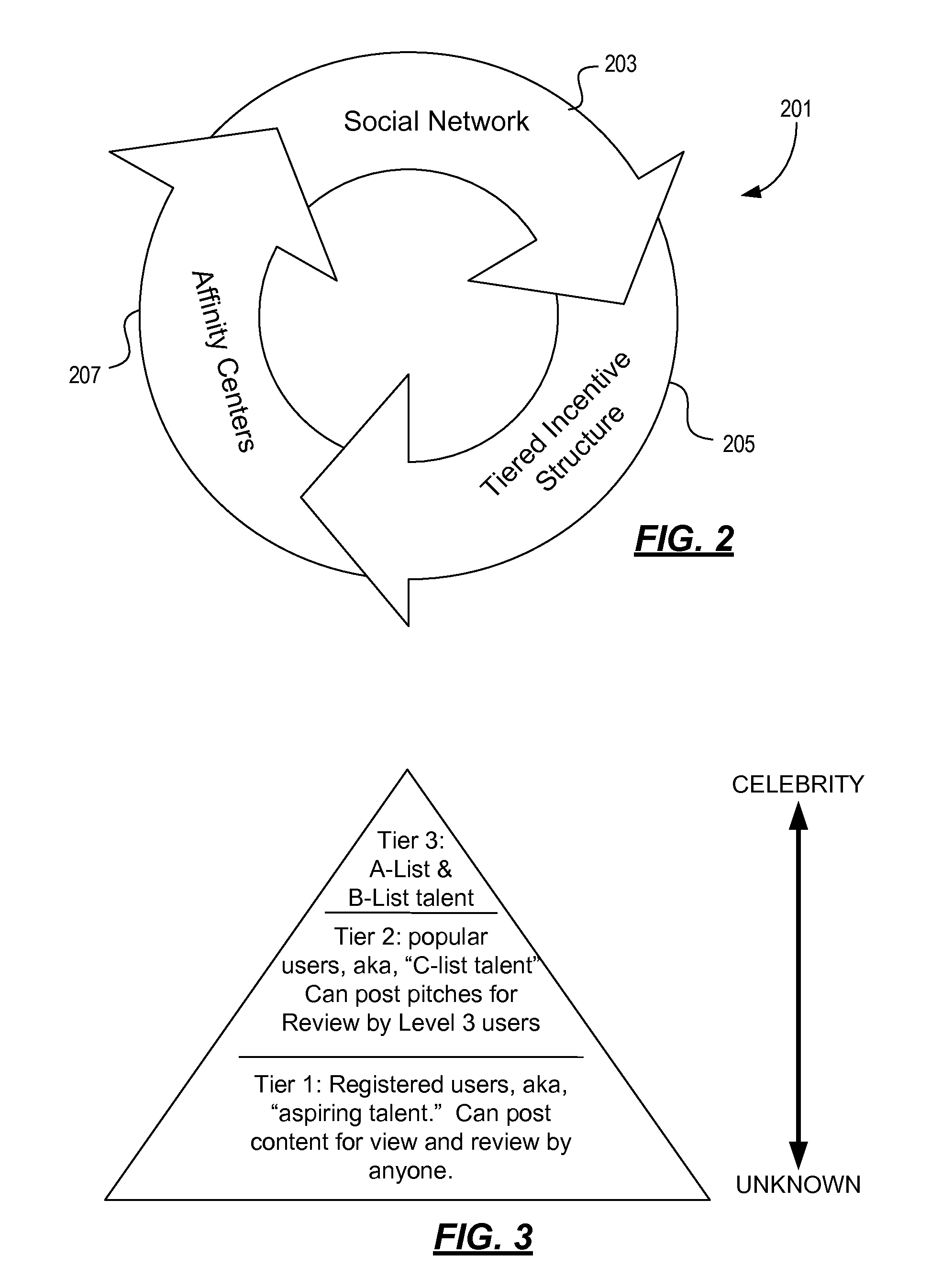

Media development network

Methods and systems for encouraging and identifying new talent, as well as an incentive structure for financing creative / media projects, are described. A social network web site allows users to post their own content, and filters users to the top who have achieved a given level of popularity. Popular users can then post media proposals to a private section of the web site, through which established stars and talent review the proposals. Users, in exchange for access to the private section, grant to a proprietor of the web site an option to make one or more future productions with that user at a reduced rate should that user reach stardom. Established stars and talent, in exchange for participating in a media proposal at a reduced rate, receive an interest in one or more productions by the user if / when the proprietor of the web site exercises an option to make a future production with the user.

Owner:CALAND PHILIPPE

Metal to metal bonding for stacked (3D) integrated circuits

ActiveUS20140191418A1Reduce the temperatureShorten the timeCooking-vessel materialsSemiconductor/solid-state device detailsMetal microstructureFine grain

The present invention provides a stabilized fine textured metal microstructure that constitutes a durable activated surface usable for bonding a 3D stacked chip. A fine-grain layer that resists self anneal enables metal to metal bonding at moderate time and temperature and wider process flexibility.

Owner:IBM CORP

HTO (high temperature oxide) deposition for capacitor dielectrics

InactiveUS6218315B1Improve reliabilityEtch rate reductionSolid-state devicesSemiconductor/solid-state device manufacturingDielectricGas phase

Reliable HTO (High Temperature Oxide) dielectrics are provide by a rapid thermal chemical vapor deposition (RTCVD) process in which a low pressure and a high ratio of reactants, e.g., oxygen-containing gas to silane-containing gas, is employed. Specifically, the reliable HTO is formed by a rapid thermal chemical vapor deposition at temperatures of from about 500° C. or above, said rapid thermal chemical vapor deposition process being carried out at a pressure of less than 80 Torr and in the presence of at least one oxygen-containing reactant and at least one silane-containing reactant, said reactants having a ratio of oxygen-containing to silane-containing of about 25:1 or greater. Semiconductor devices such as capacitors and transistors that include at least a layer of the high temperature oxide of the present invention used as a dielectric material are also provided.

Owner:IBM CORP

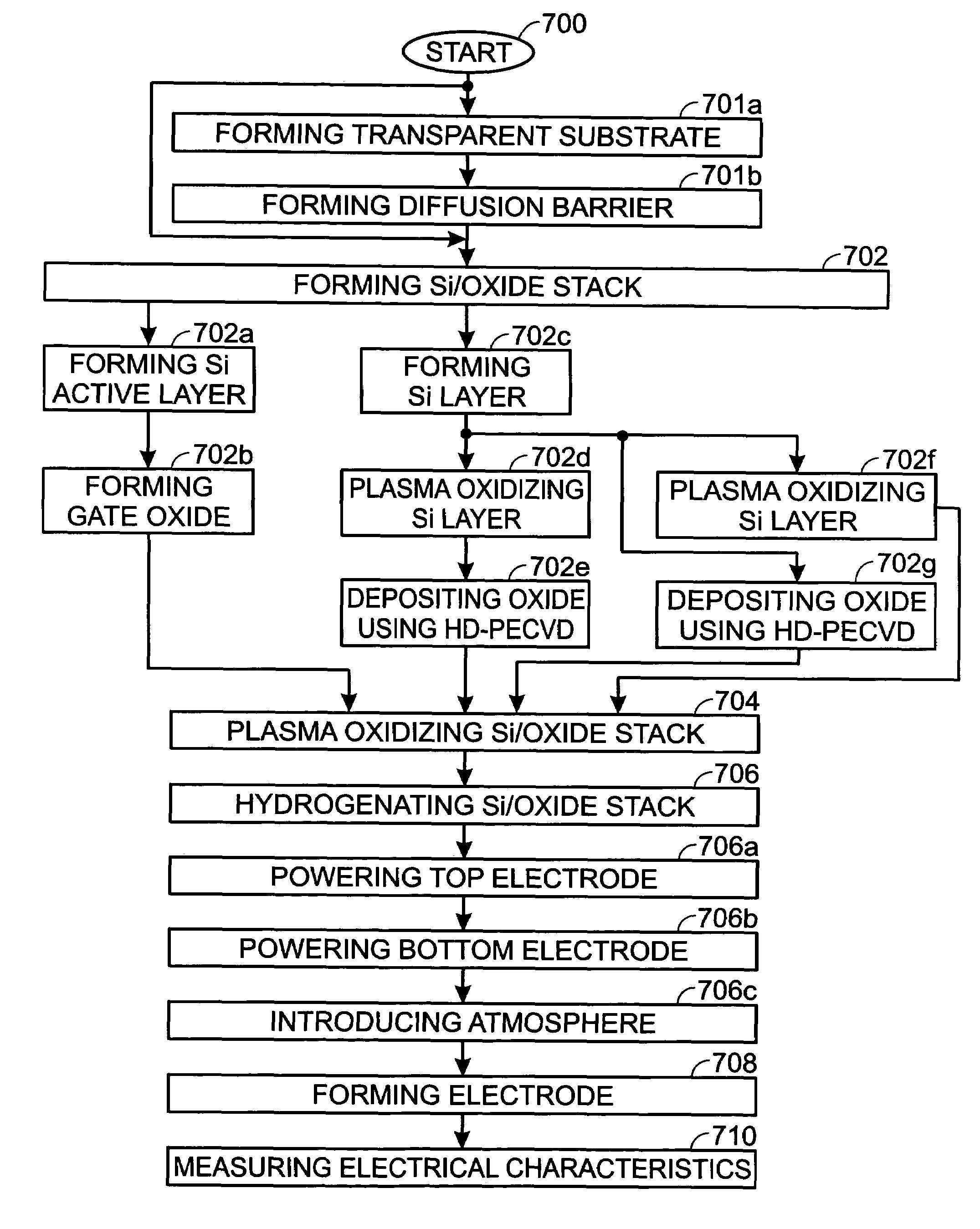

High-density plasma hydrogenation

InactiveUS7446023B2Enhancing concentration and stateLow budgetTransistorFrom solid stateHigh densitySystem pressure

A high-density plasma hydrogenation method is provided. Generally, the method comprises: forming a silicon (Si) / oxide stack layer; plasma oxidizing the Si / oxide stack at a temperature of less than 400° C., using a high density plasma source, such as an inductively coupled plasma (ICP) source; introducing an atmosphere including H2 at a system pressure up to 500 milliTorr; hydrogenating the stack at a temperature of less than 400 degrees C., using the high density plasma source; and forming an electrode overlying the oxide. The electrode may be formed either before or after the hydrogenation. The Si / oxide stack may be formed in a number of ways. In one aspect, a Si layer is formed, and the silicon layer is plasma oxidized at a temperature of less than 400 degrees C., using an ICP source. The oxide formation, additional oxidation, and hydrogenation steps can be conducted in-situ in a common chamber.

Owner:SHARP KK

Method for Encapsulating a Device in a Microcavity

InactiveUS20100210073A1Low budgetReduce manufacturing complexitySemiconductor/solid-state device manufacturingForming microstructural systemsPorous layerPorous membrane

Manufacturing a semiconductor device involves forming (200) a sacrificial layer where a micro cavity is to be located, forming (210) a metal layer of thickness greater than 1 micron over the sacrificial layer, forming (220) a porous layer from the metal layer, the porous layer having pores of length greater than ten times their breadth, and having a breadth in the range 10 nm-500 nanometers. The pores can be created by anodising, electrodeposition or dealloying. Then the sacrificial layer can be removed (230) through the porous layer, to form the micro cavity, and pores can be sealed (240). Encapsulating MEMS devices with a porous layer can reduce costs by avoiding using photolithography for shaping the access holes since the sacrificial layer is removed through the porous membrane.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

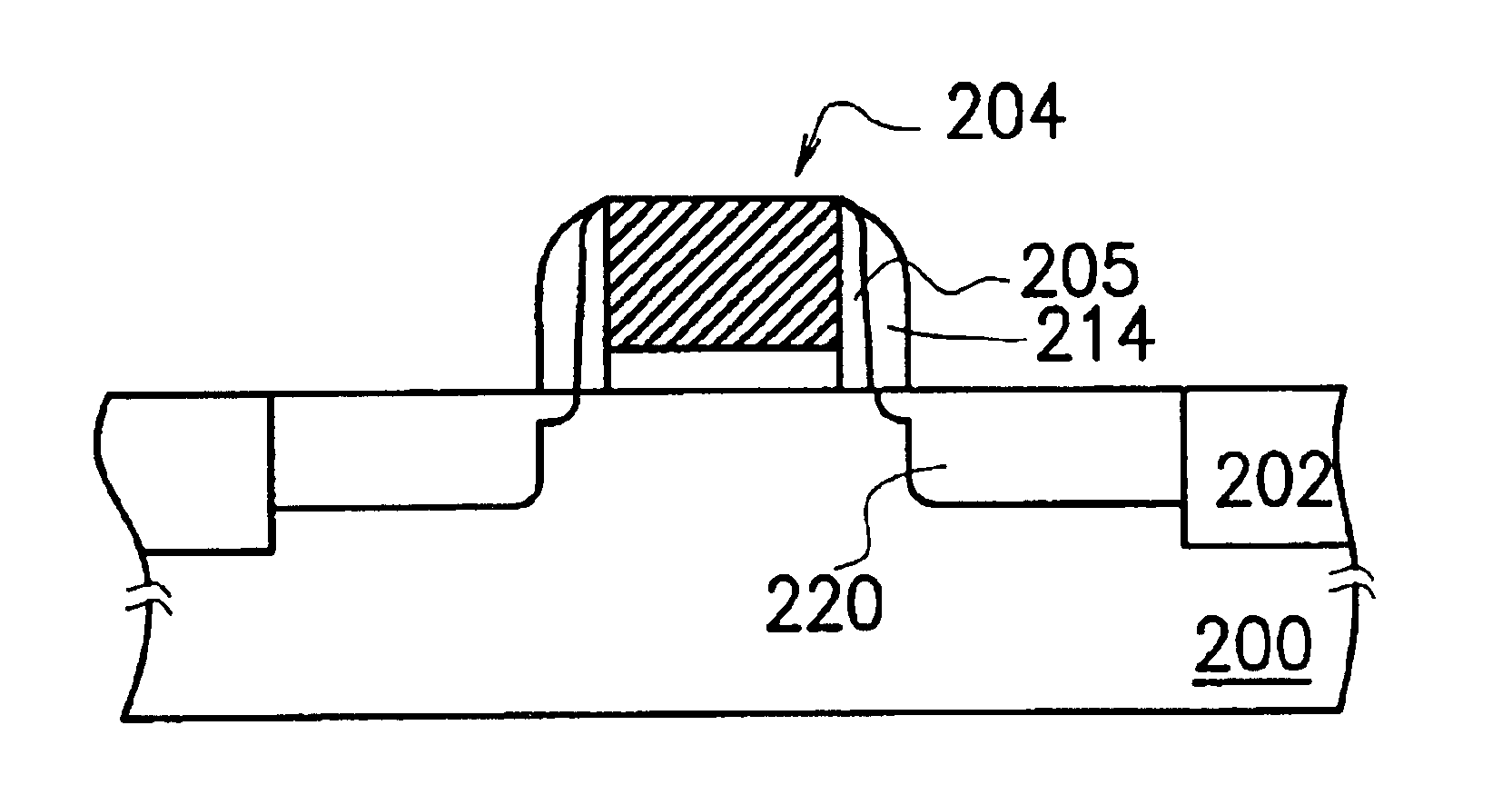

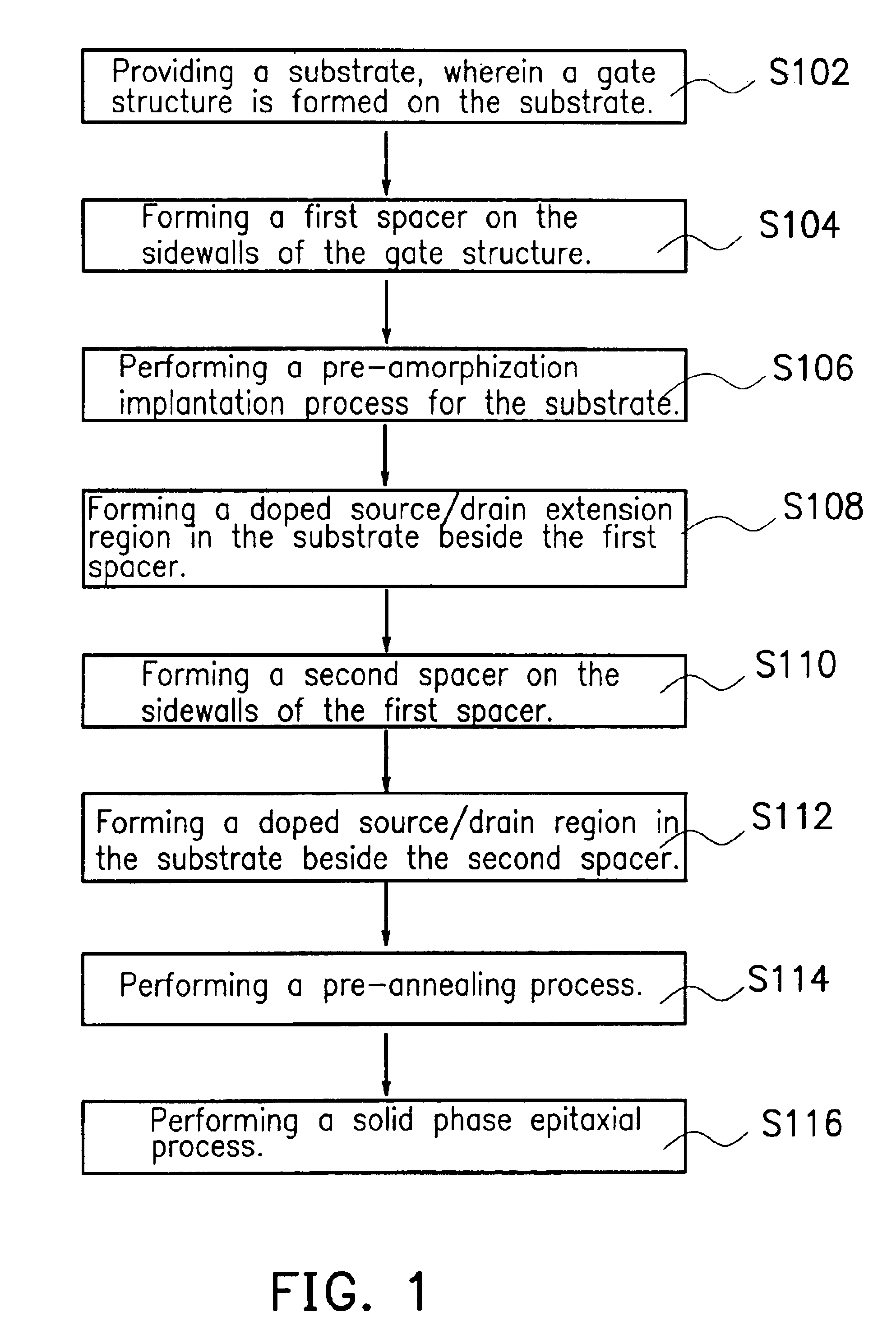

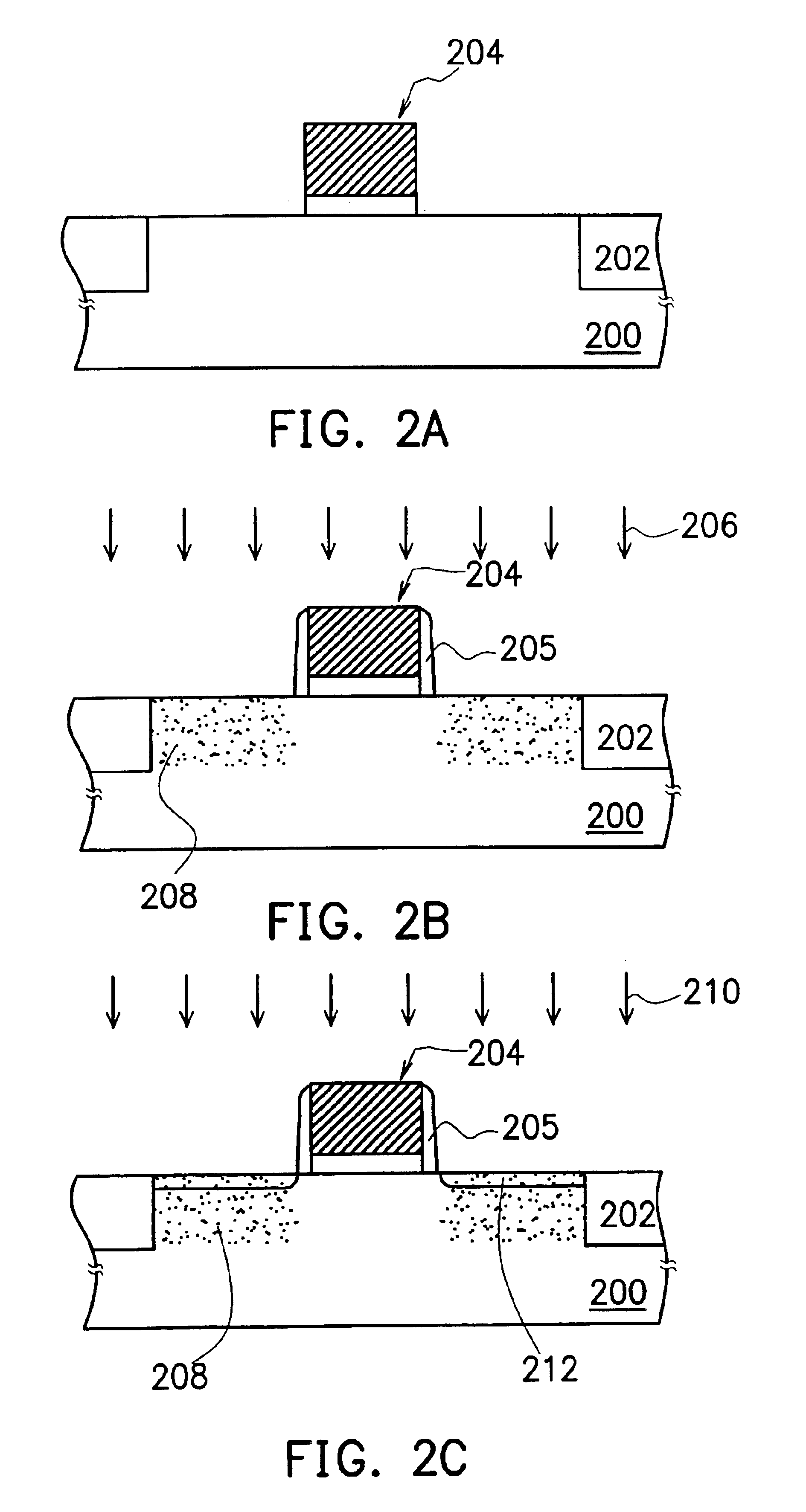

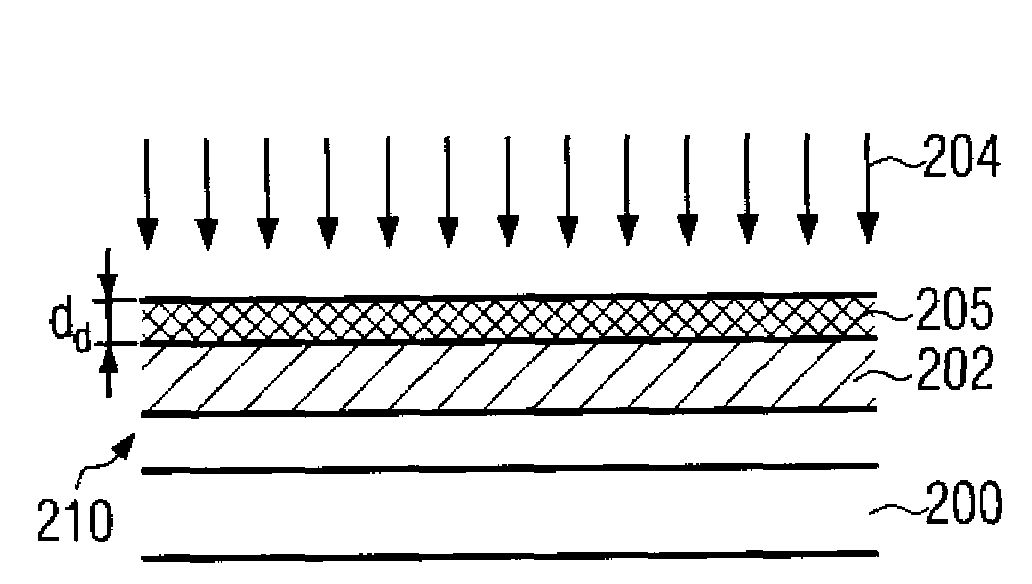

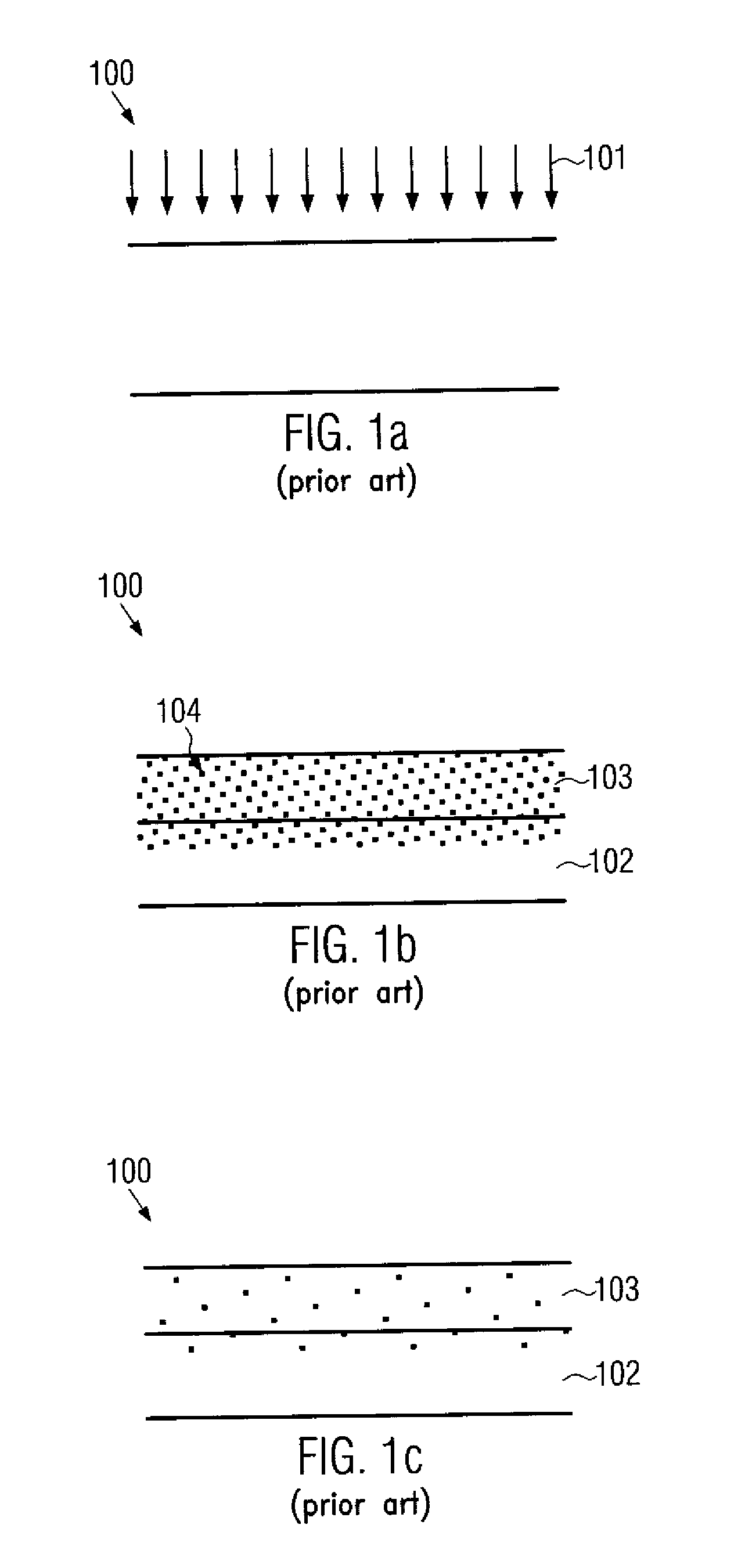

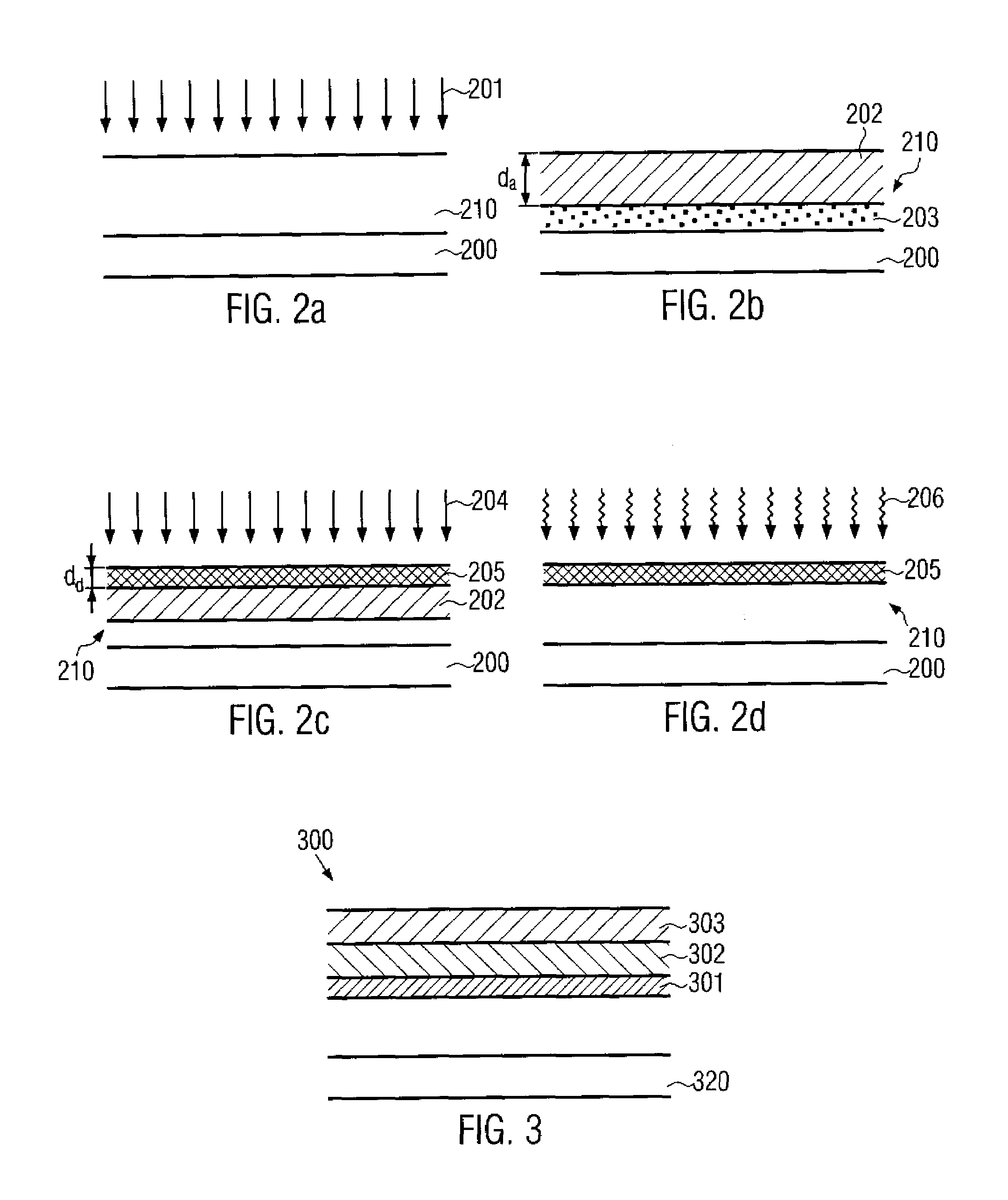

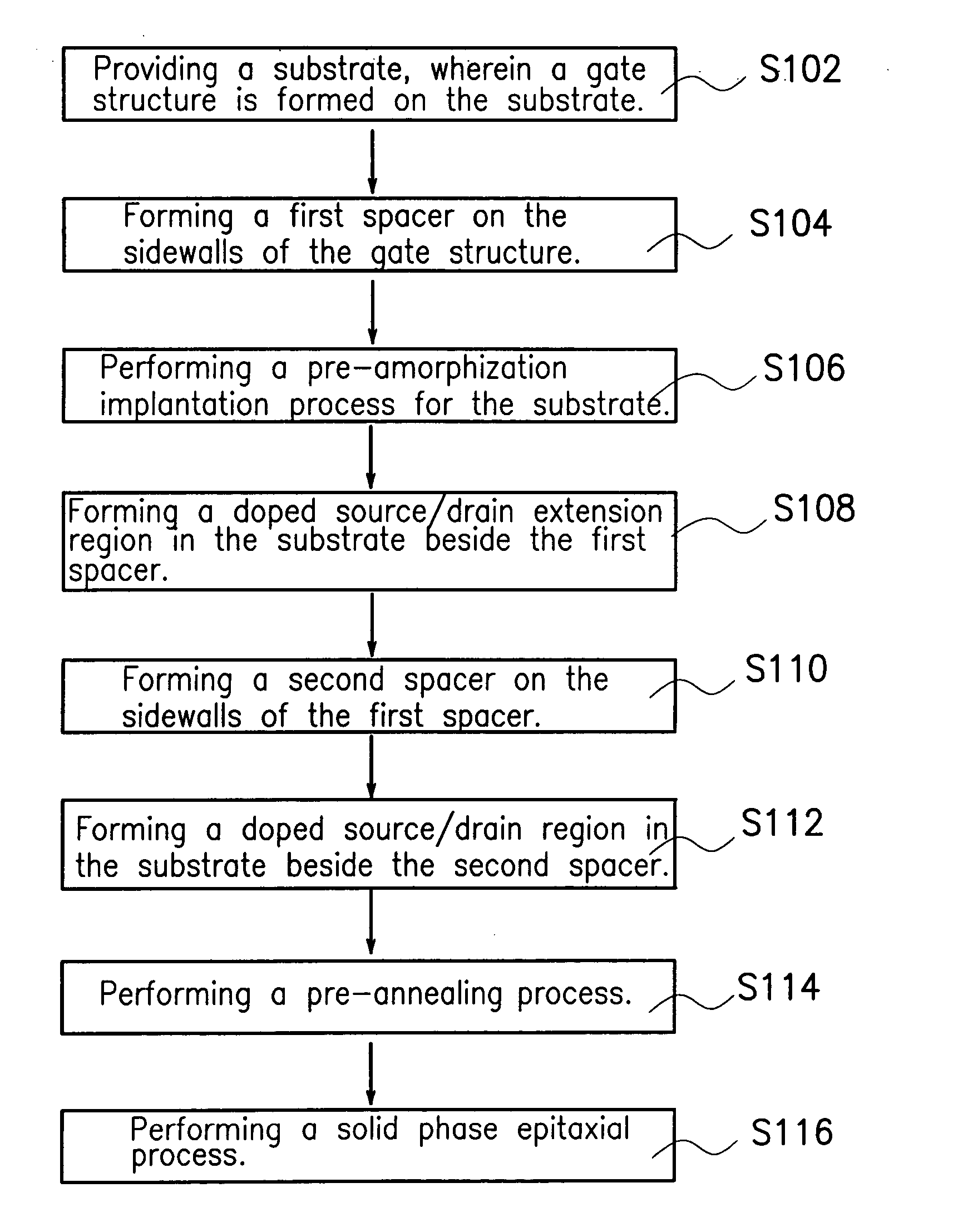

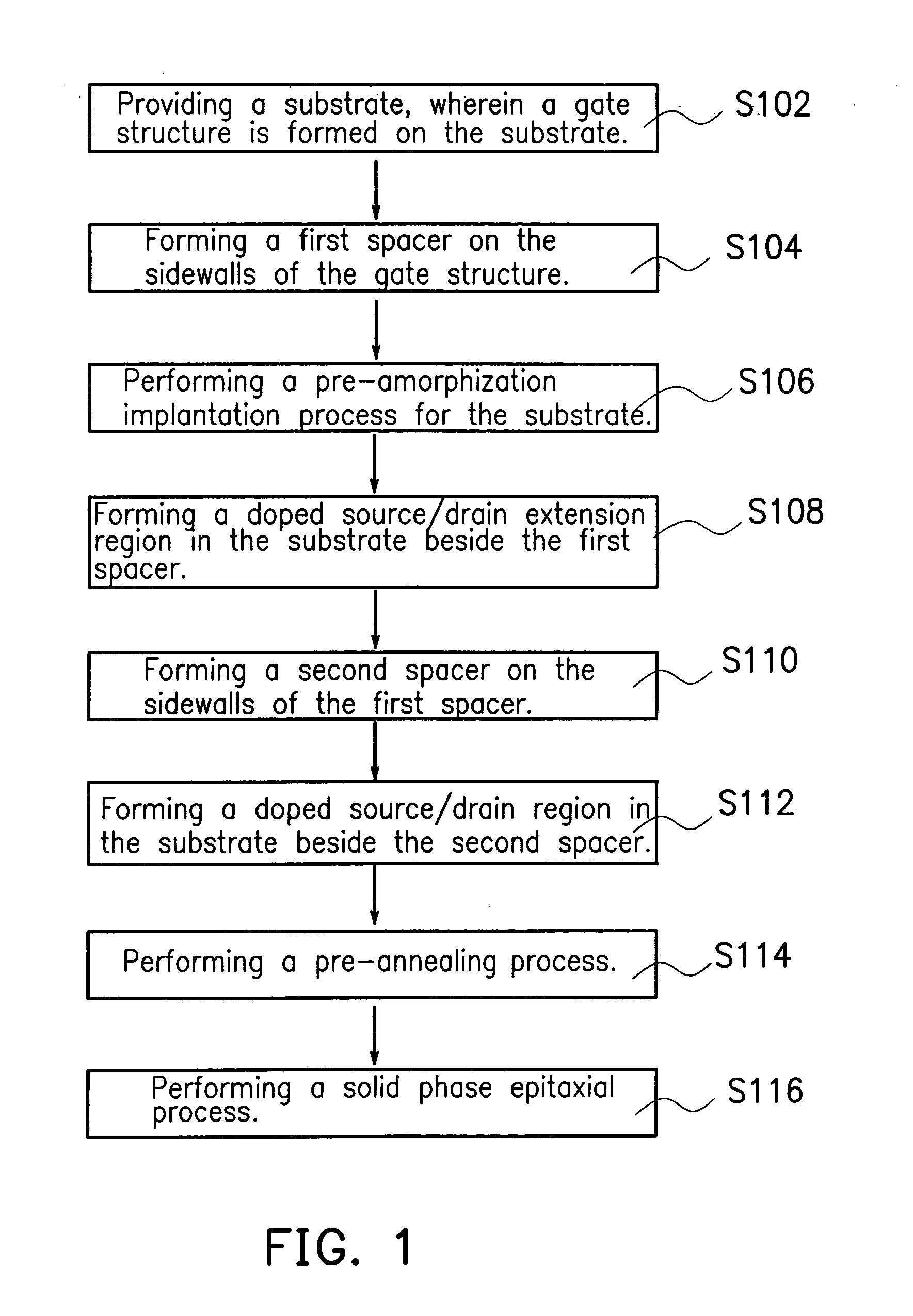

Method of manufacturing metal-oxide-semiconductor transistor

InactiveUS6943085B2Reduce sheet resistanceImprove electrical performanceTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of manufacturing a MOS transistor is provided. A substrate having a gate structure thereon is provided. A first spacer is formed on the sidewall of the gate structure. A pre-amorphization implantation is carried out to amorphize a portion of the substrate. A doped source / drain extension region is formed in the substrate on each side of the first spacer. A second spacer is formed on the sidewall of the first spacer. A doped source / drain region is formed in the substrate on each side of the second spacer and then a pre-annealing operation is performed. Thereafter, a solid phase epitaxial process is carried out to re-crystallize the amorphized portion of the substrate and activate the doped source / drain extension region and the doped source / drain region to form a source / drain terminal. Finally, a post-annealing operation is performed.

Owner:UNITED MICROELECTRONICS CORP

Method for forming ultra-shallow high quality junctions by a combination of solid phase epitaxy and laser annealing

InactiveUS20070232033A1High quality lattice structurePromote activationTransistorSemiconductor/solid-state device manufacturingDiffusionDopant

By using a combination of solid phase epitaxy re-growth and laser annealing, the present invention provides a low thermal budget method which allows the crystal lattice of a semiconductor surface to recover after the doping by ion implantation. The low thermal budget limits the out-diffusion of the dopants ions, thus avoiding the enlargement of the doped source / drain regions. Therefore, the method is suited, for instance, for the fabrication of ultra-shallow source / drain regions in MOS transistors elements. The method according to the present invention comprises a first pre-amorphization process in order to limit channeling effects, a doping process by ion implantation and a re-crystallization by solid phase epitaxy, followed by laser annealing.

Owner:GLOBALFOUNDRIES INC

Method of manufacturing metal-oxide-semiconductor transistor

InactiveUS20050054173A1Reduce sheet resistanceImprove electrical performanceTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A method of manufacturing a MOS transistor is provided. A substrate having a gate structure thereon is provided. A first spacer is formed on the sidewall of the gate structure. A pre-amorphization implantation is carried out to amorphize a portion of the substrate. A doped source / drain extension region is formed in the substrate on each side of the first spacer. A second spacer is formed on the sidewall of the first spacer. A doped source / drain region is formed in the substrate on each side of the second spacer and then a pre-annealing operation is performed. Thereafter, a solid phase epitaxial process is carried out to re-crystallize the amorphized portion of the substrate and activate the doped source / drain extension region and the doped source / drain region to form a source / drain terminal. Finally, a post-annealing operation is performed.

Owner:UNITED MICROELECTRONICS CORP

Silicon Oxynitride Coating Compositions

InactiveUS20090277782A1Low budgetReduce the temperatureVacuum evaporation coatingSputtering coatingNitrogen plasmaOptoelectronics

Silicon oxynitride compositions are described herein. These compositions are typically deposited onto substrates using a nitrogen plasma-based, reactive sputtering method. Depending on their composition, these coatings can be used for field emission suppression, dielectric applications, reflection control, and surface passivation.

Owner:COLLEGE OF WILLIAM & MARY

High density plasma process for the formation of silicon dioxide on silicon carbide substrates

ActiveUS7122488B2Enhance the growth/deposition of SiOImprove performanceFrom solid stateSemiconductor/solid-state device manufacturingHigh densityOxygen

Methods are provided for forming silicon dioxide (SiO2) on a silicon carbide (SiC) substrate. The method comprises: providing a SiC substrate; supplying an atmosphere including oxygen; performing a high-density (HD) plasma-based process; and, forming a SiO2 layer overlying the SiC substrate. Typically, performing the HD plasma-based process includes connecting a top electrode to an inductively coupled HD plasma source. In one aspect, SiO2 is grown on the SiC substrate. Then, an HD plasma oxidation process is performed that creates a reactive oxygen species and breaks the Si—C bonds in the SiC substrate, to form free Si and C atoms in the SiC substrate. The free Si atoms in the SiC substrate are bonded to the HD plasma-generated reactive oxygen species, and the SiO2 layer is grown.

Owner:SHARP KK