Patents

Literature

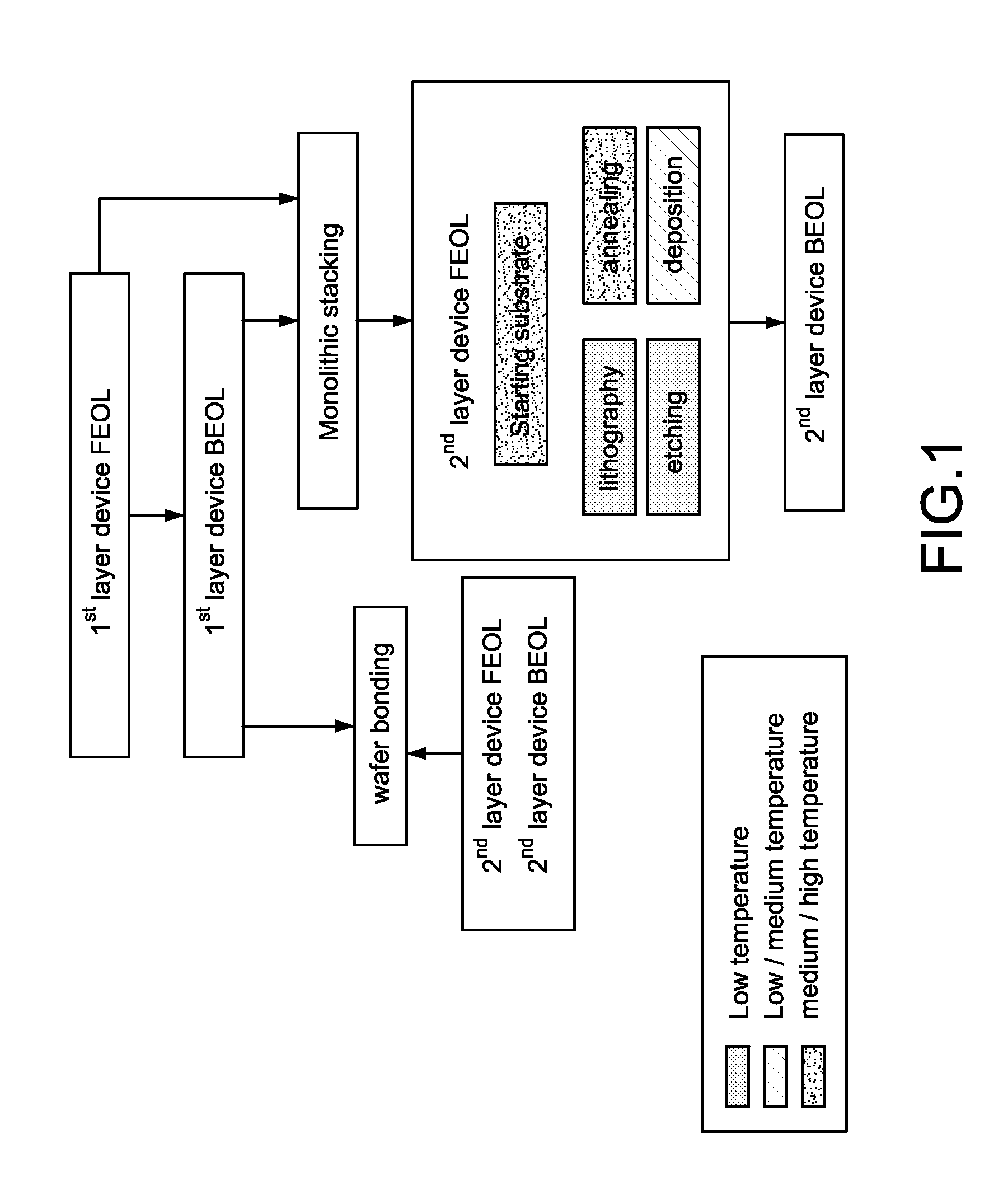

81results about How to "Improve interconnect density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

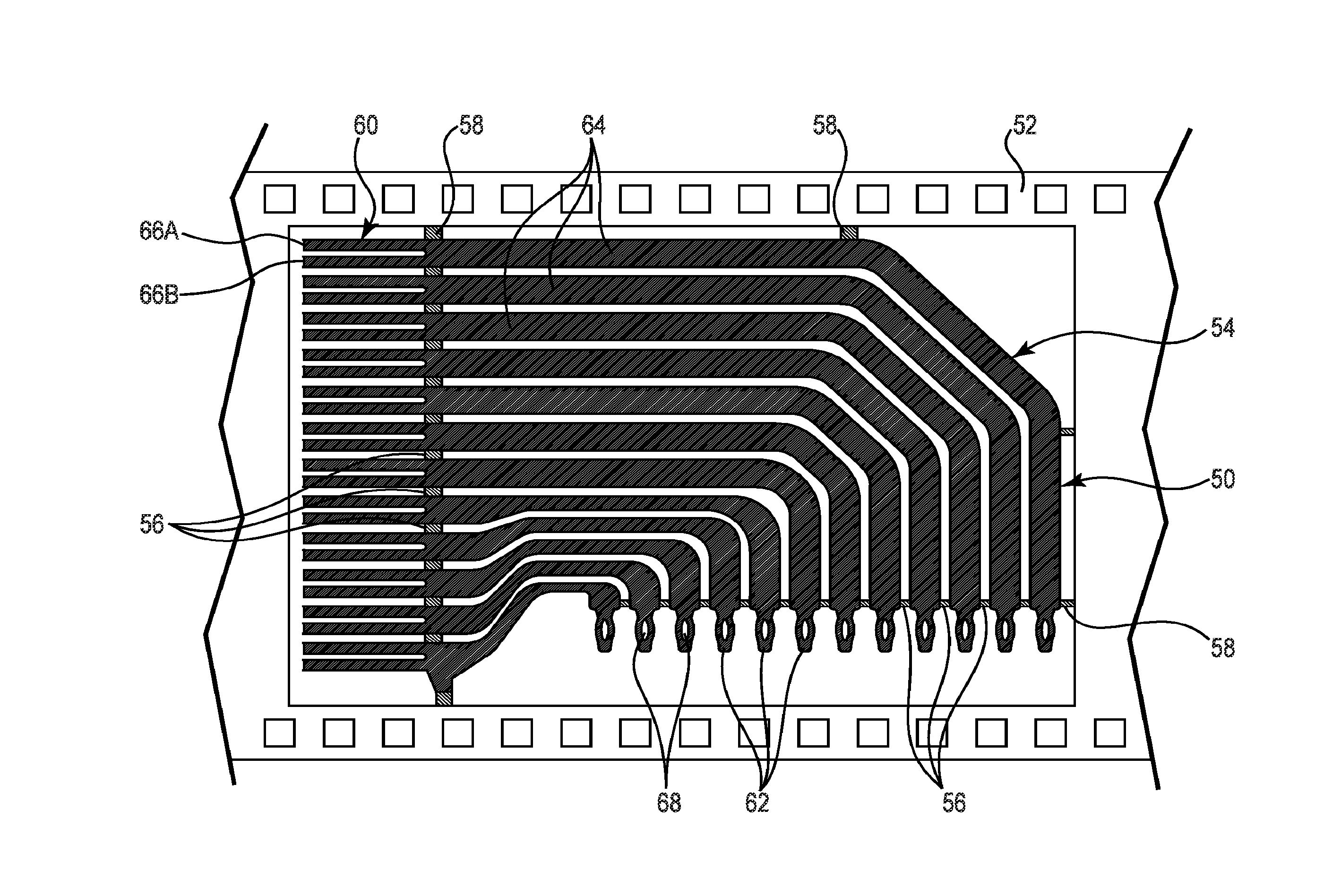

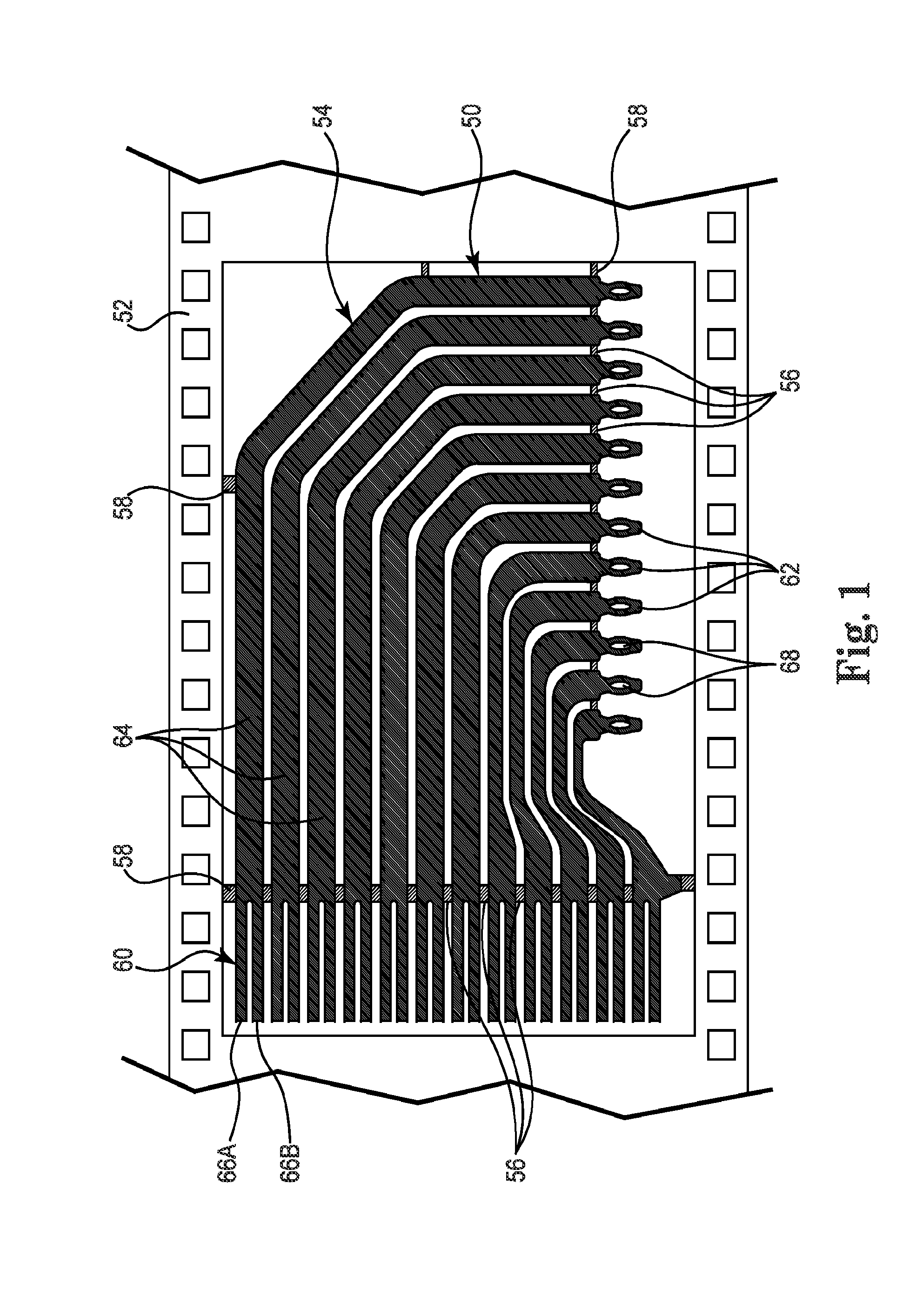

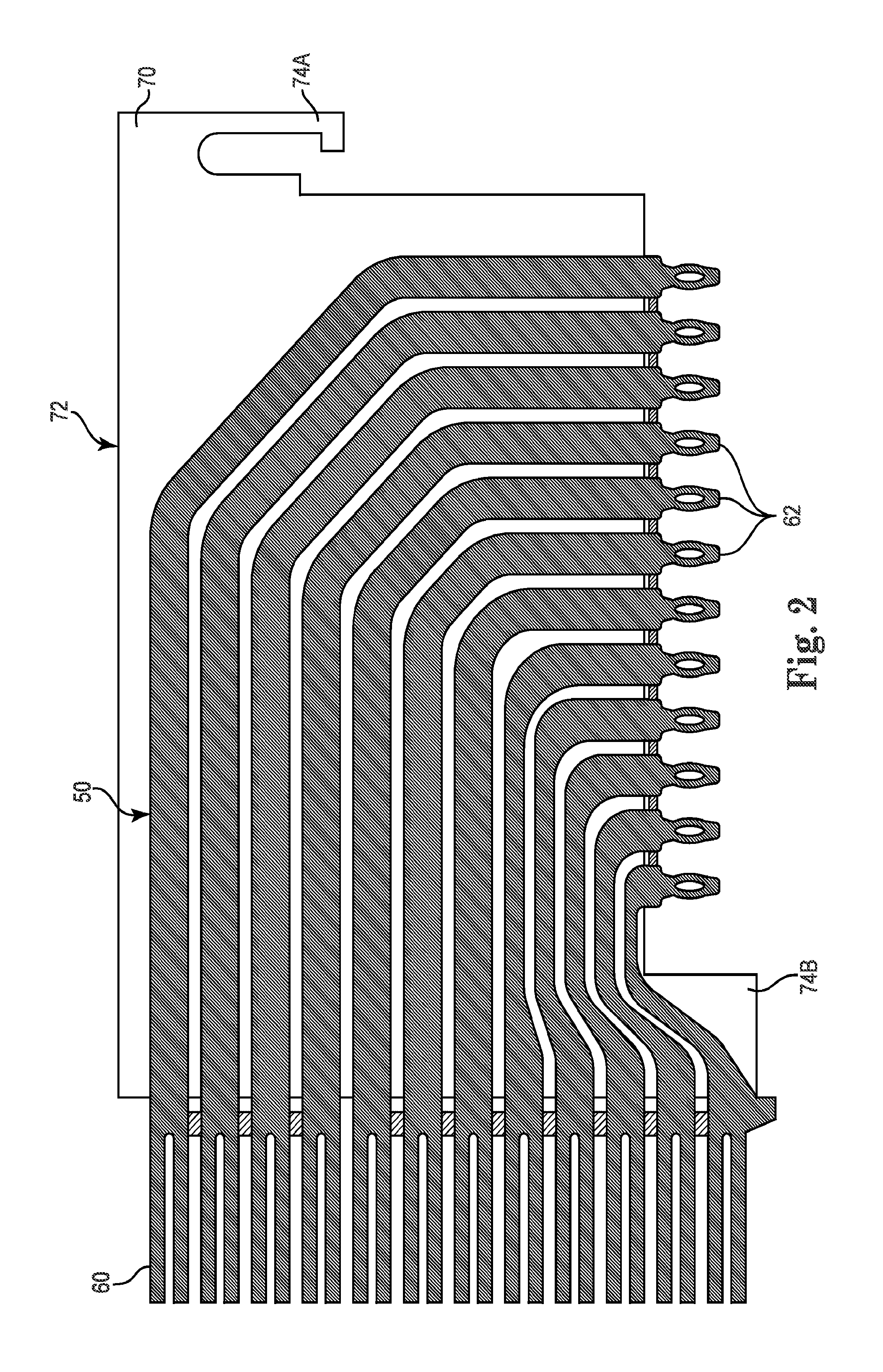

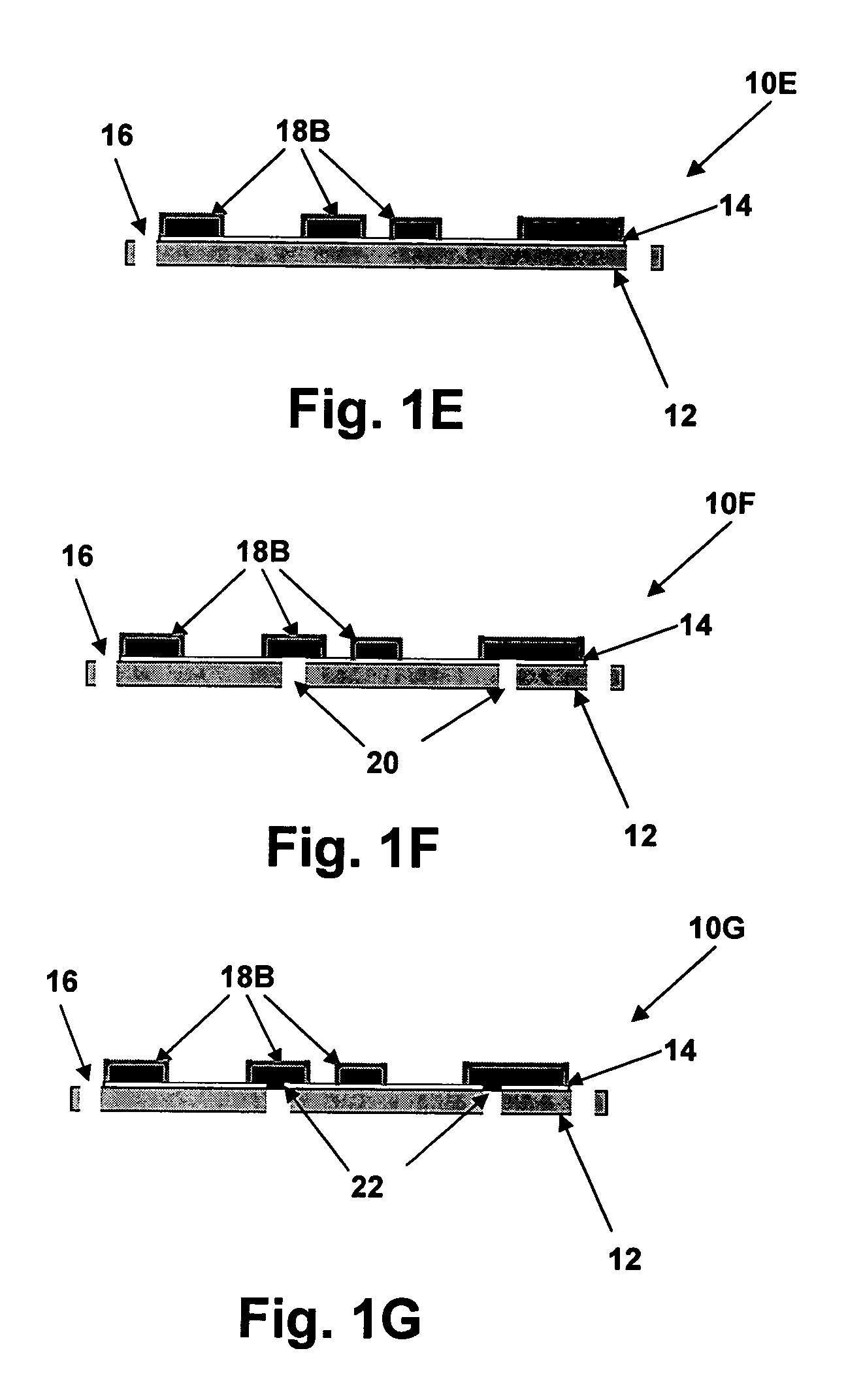

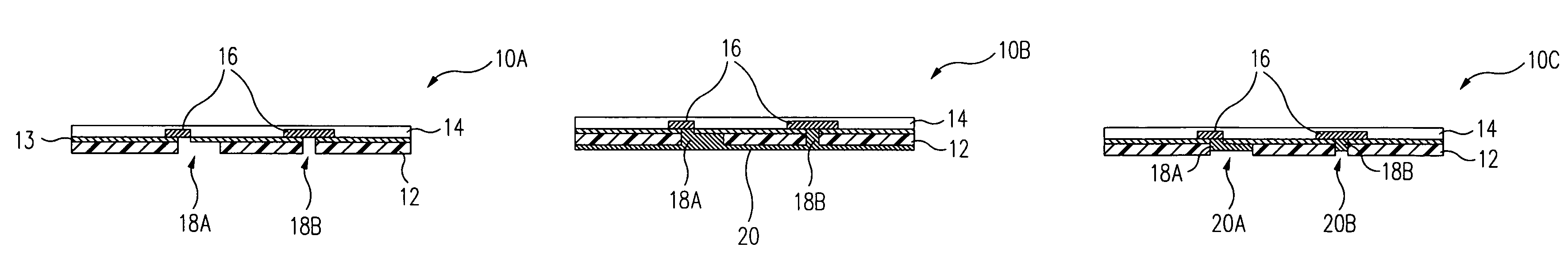

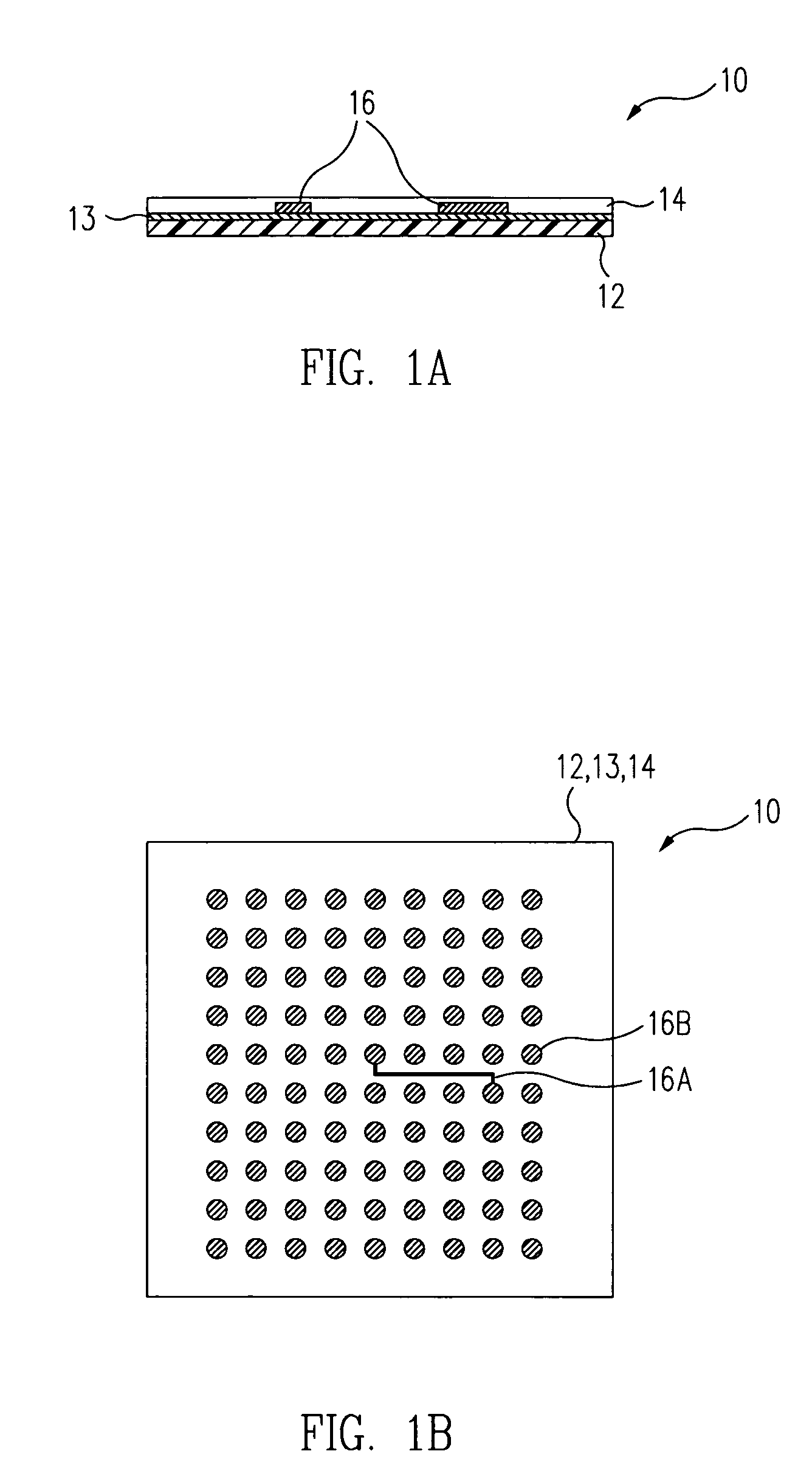

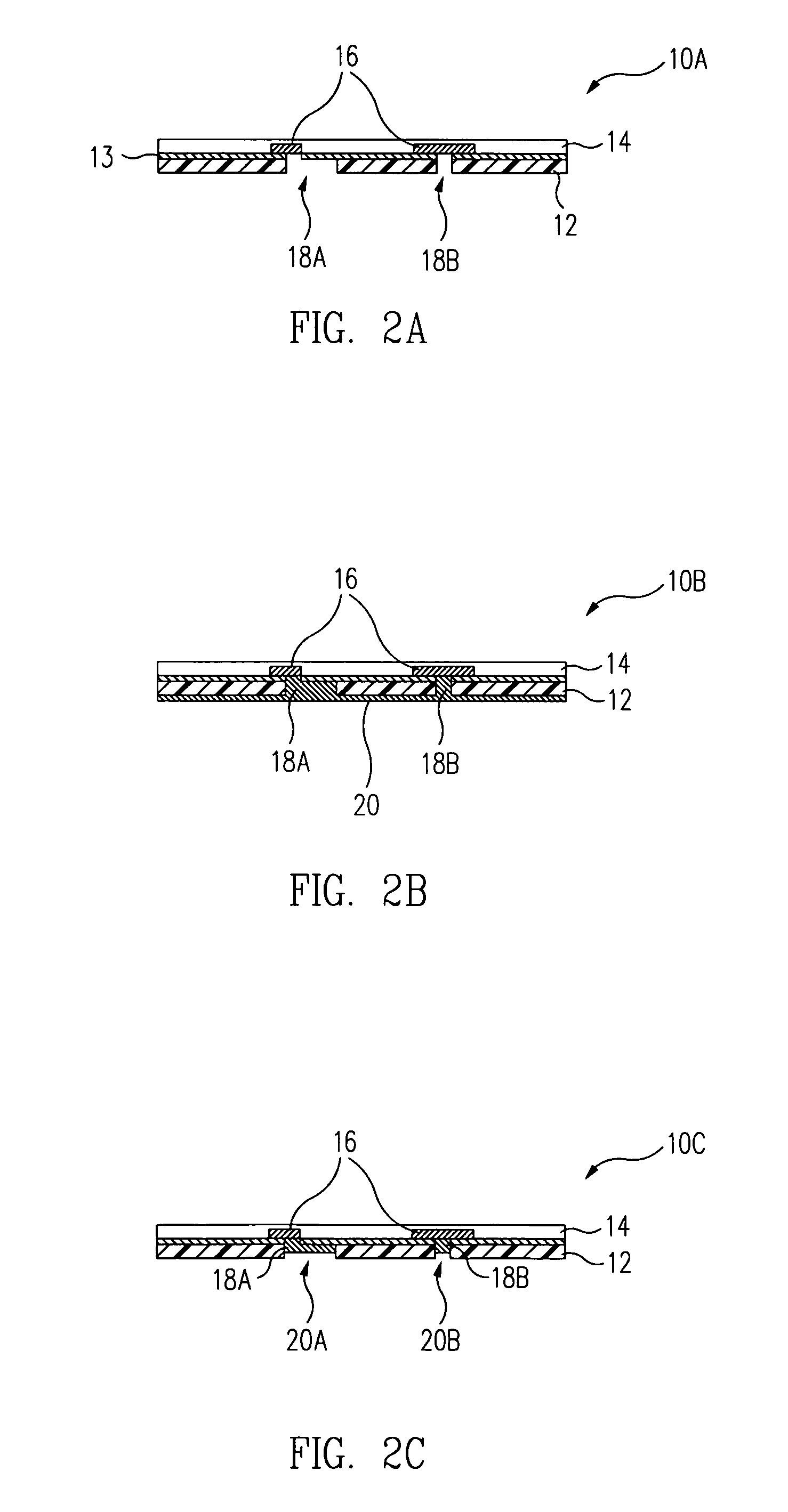

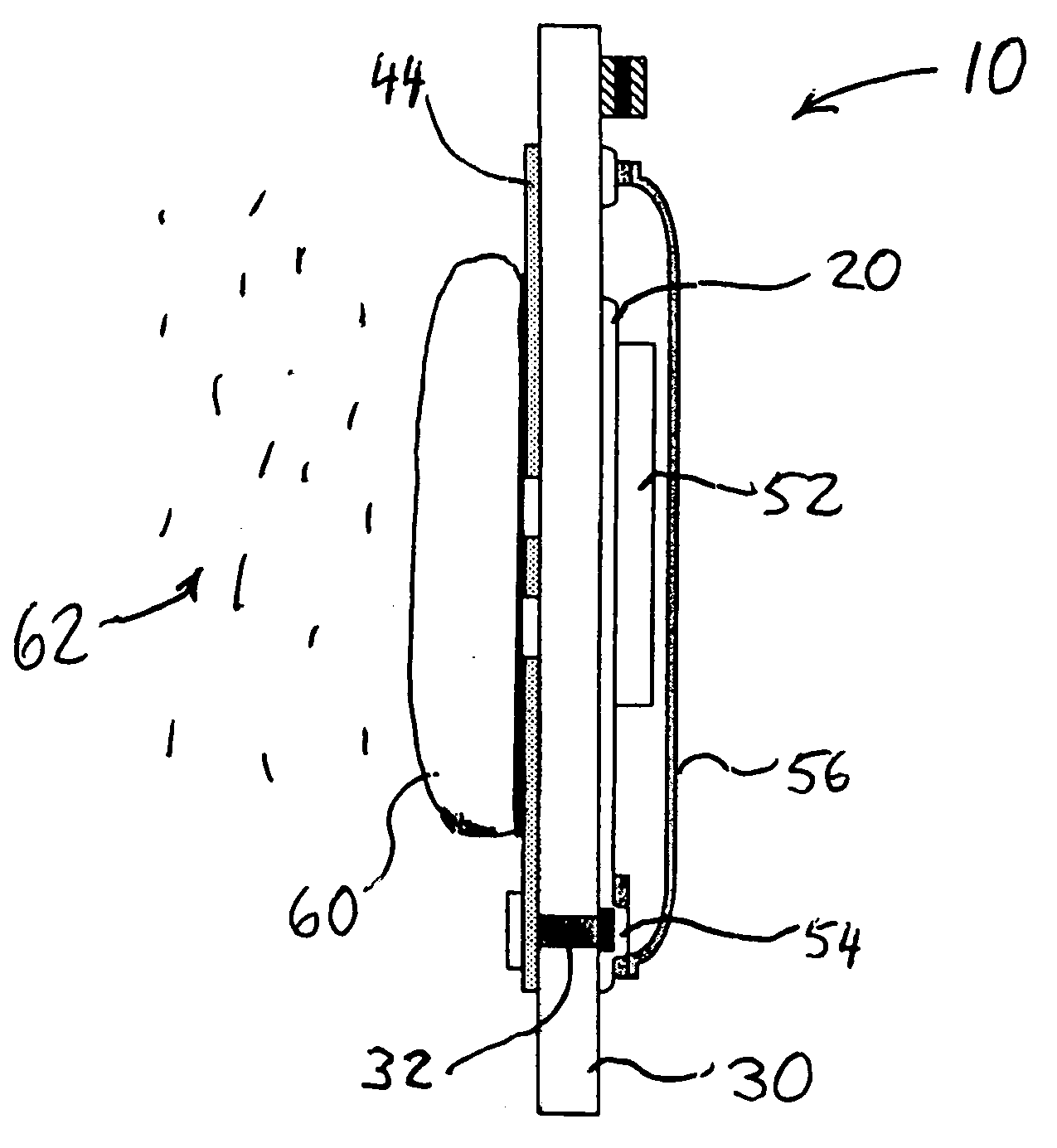

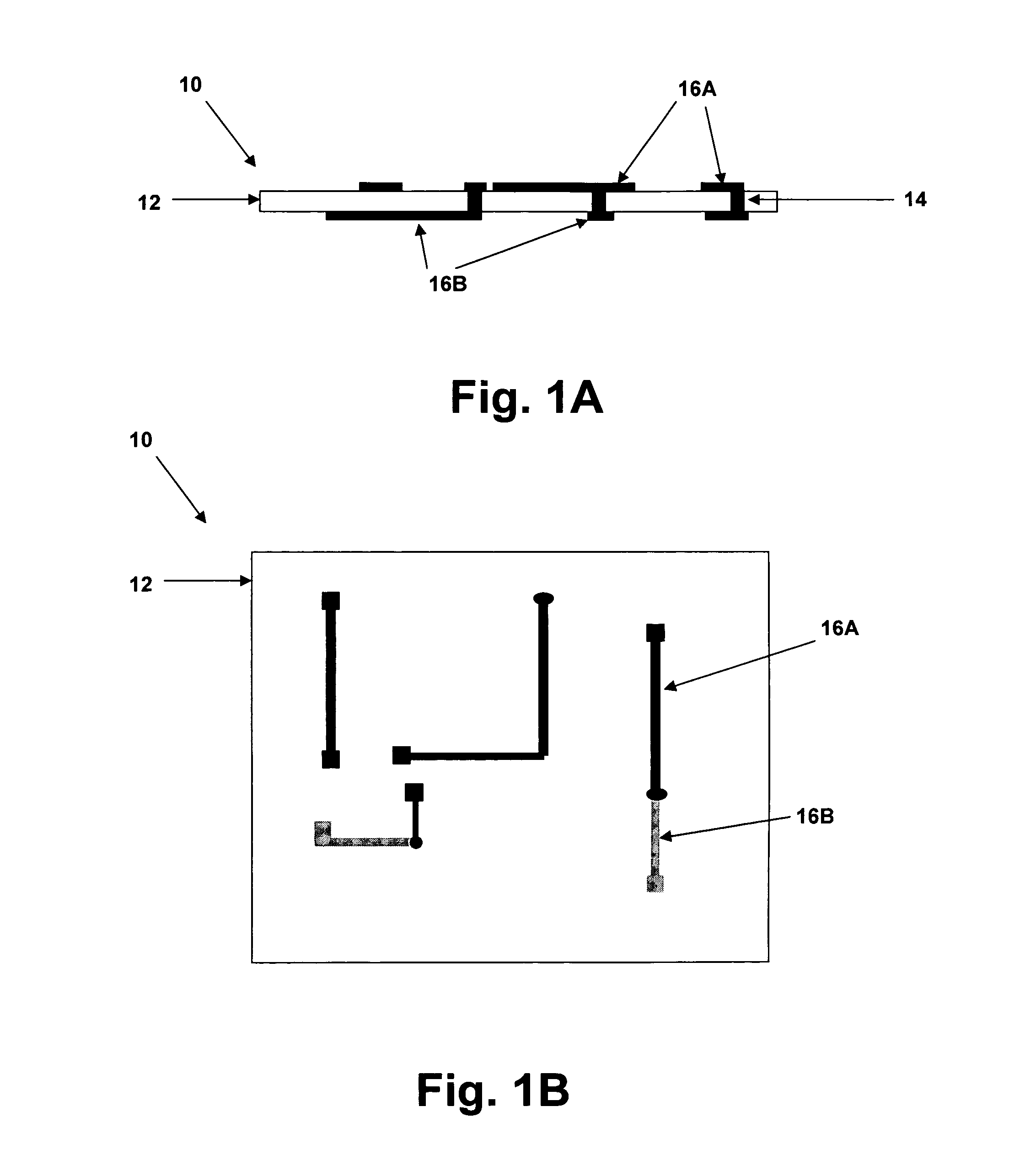

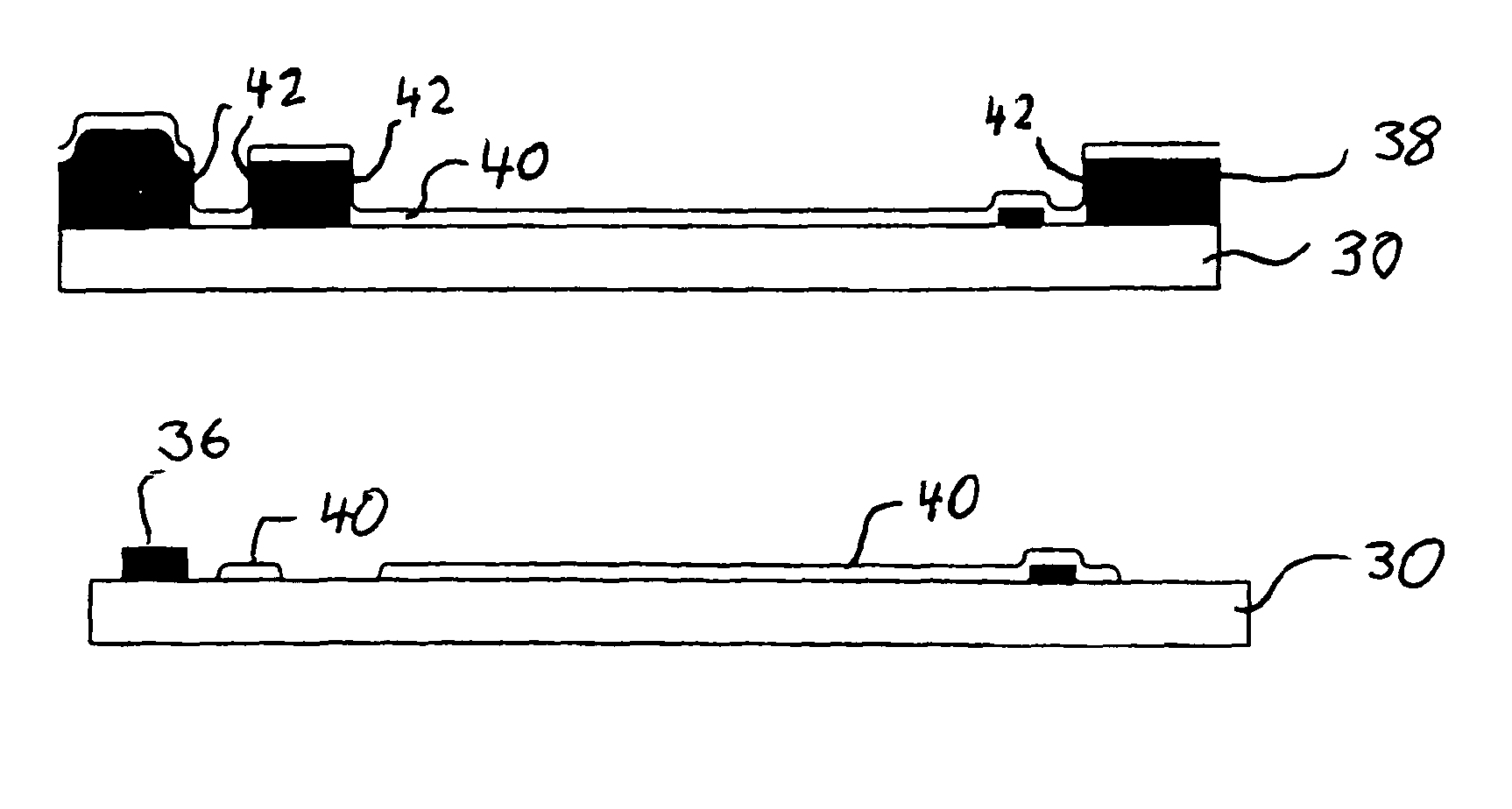

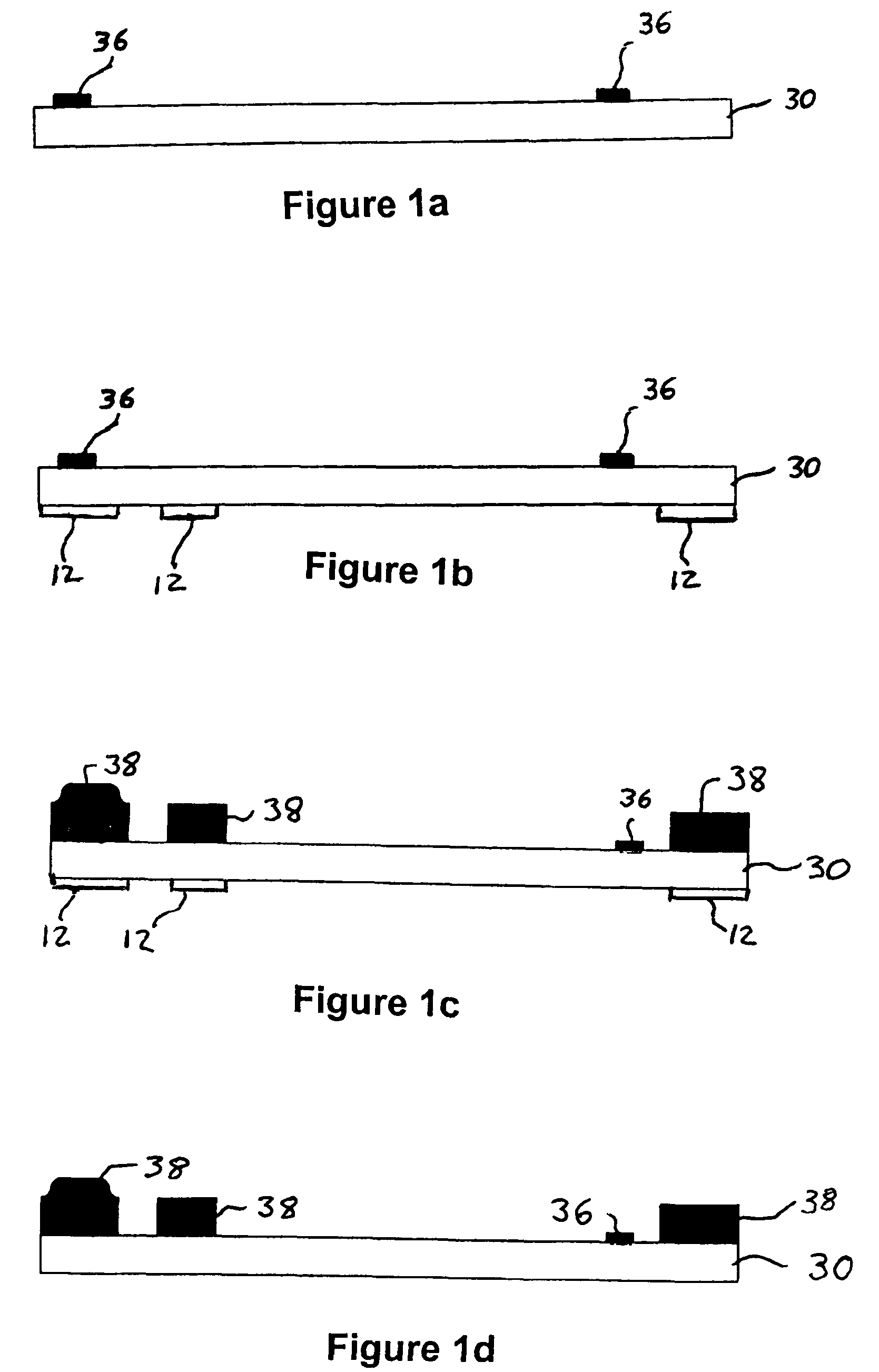

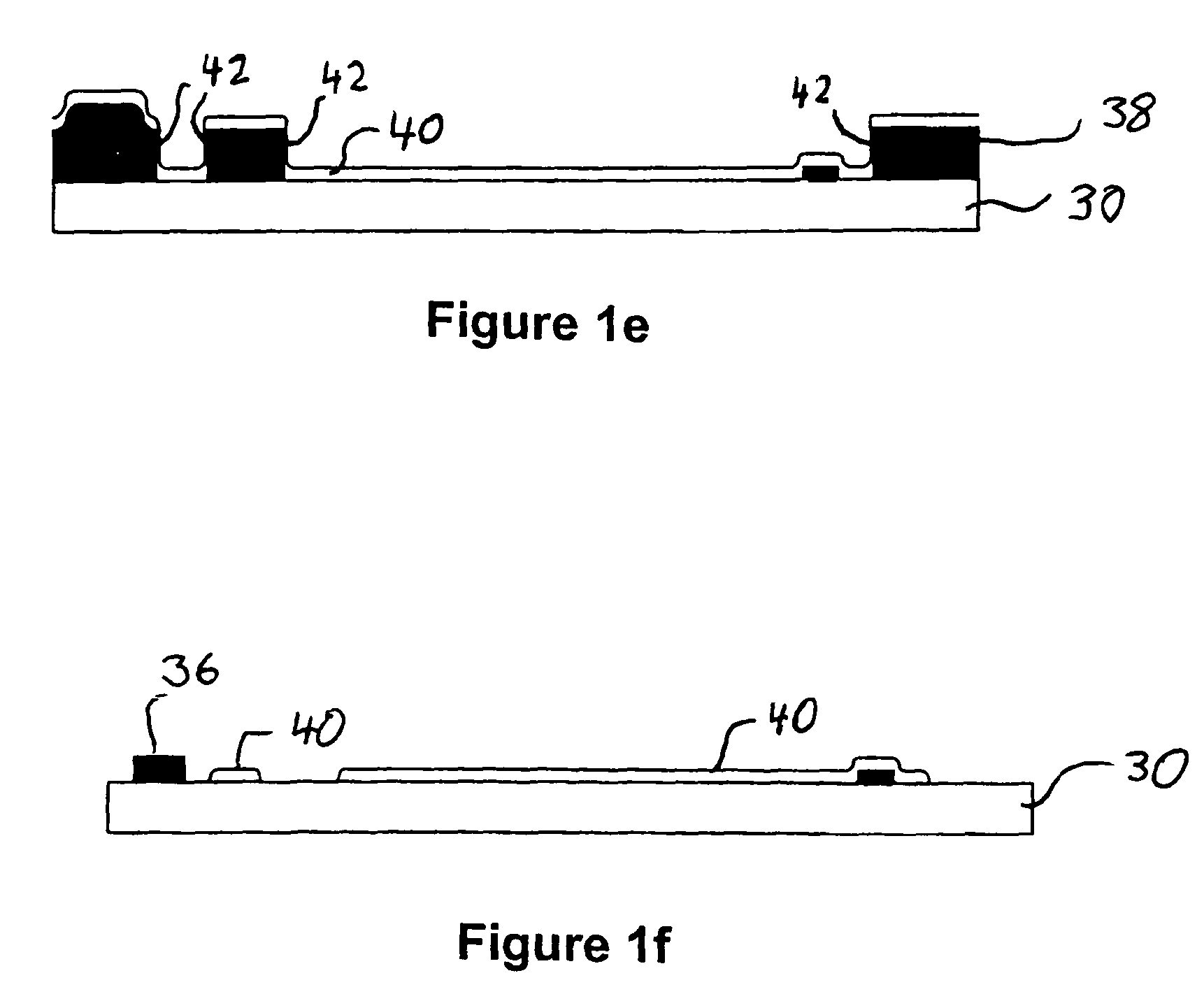

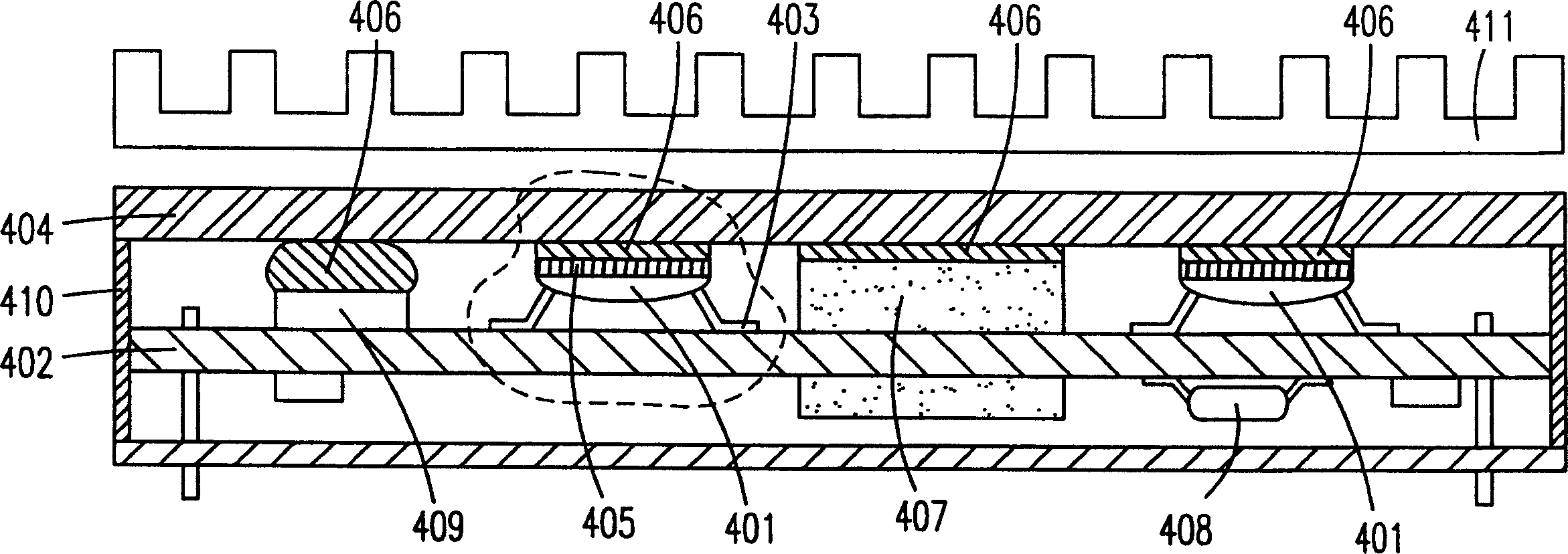

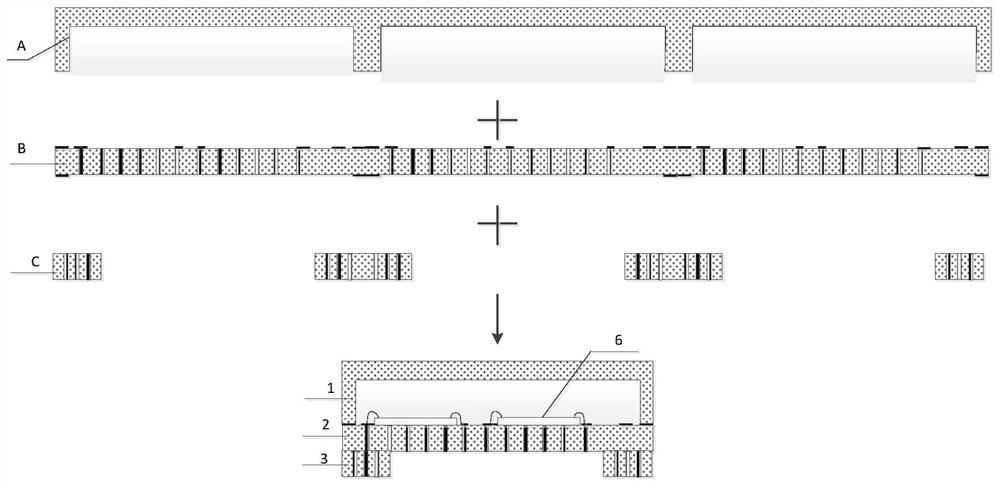

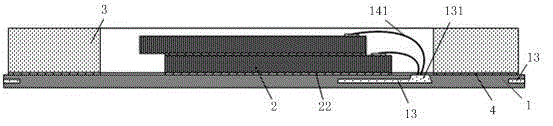

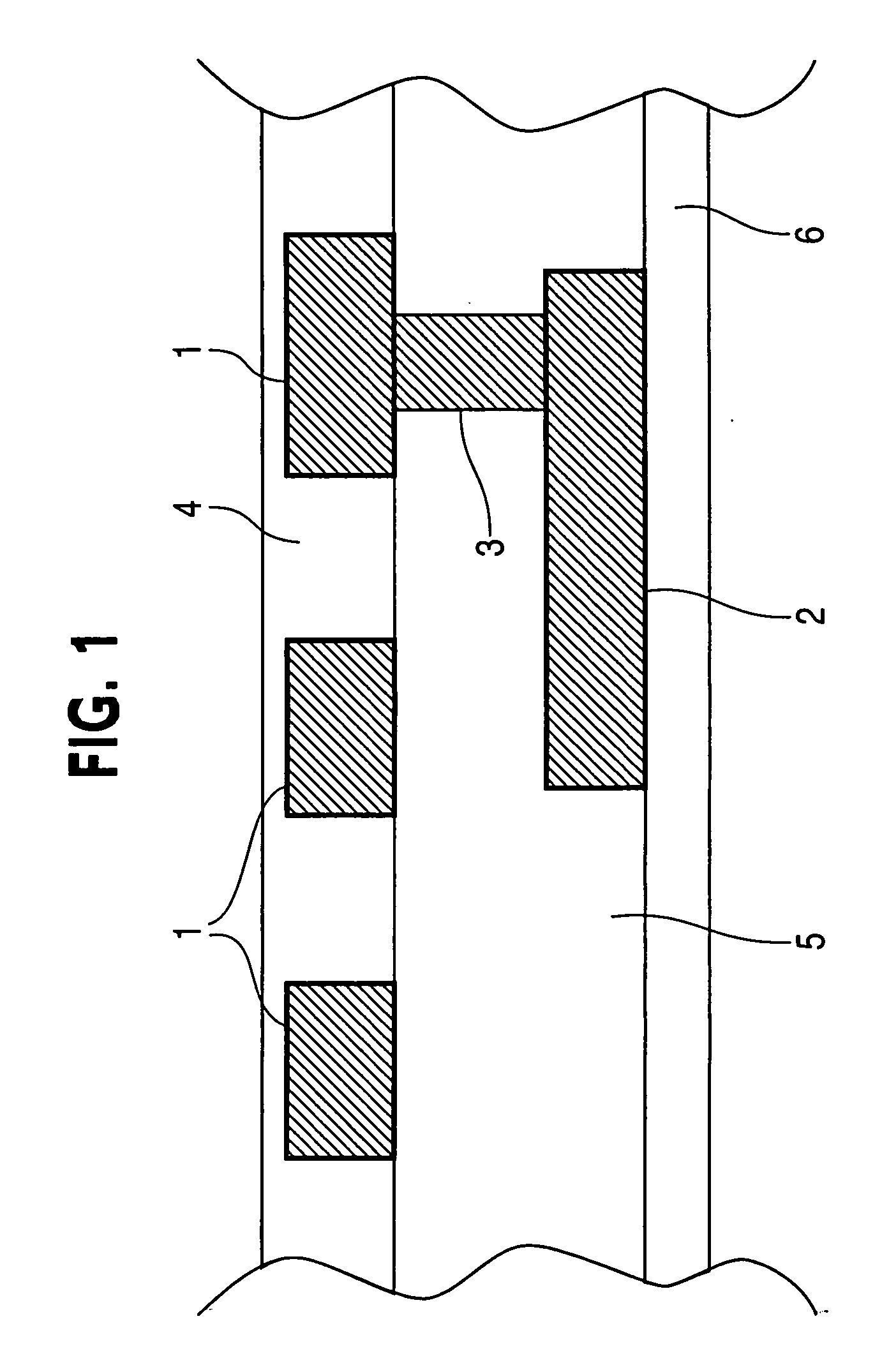

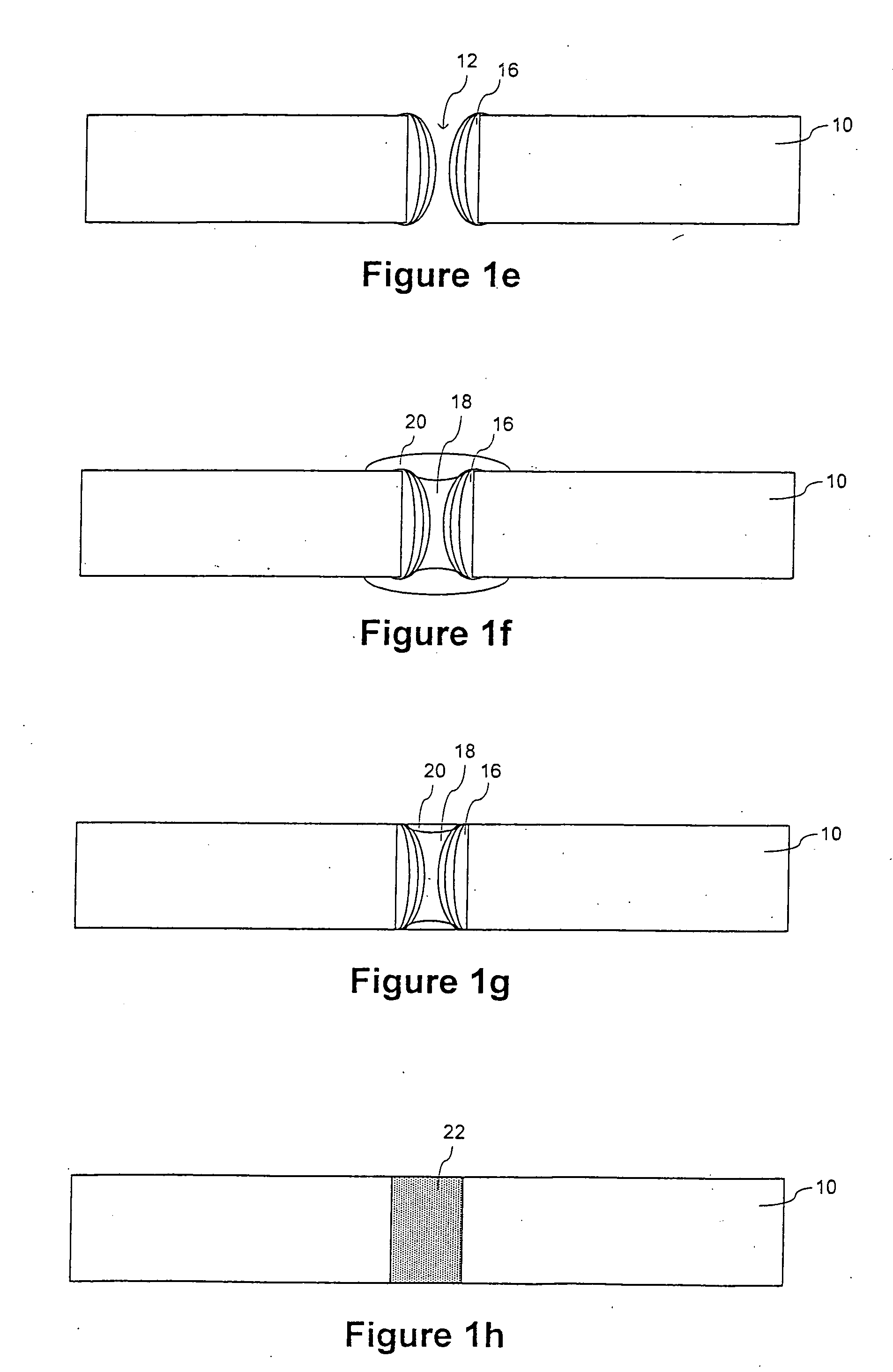

High speed backplane connector

InactiveUS20130203273A1Improve performanceLow costContact member assembly/disassemblyCoupling device detailsBackplane

A backplane connector including a substrate and a backplane connector set attached to the substrate. The backplane connector set includes a plurality of interconnect elements each having a conductive trace, a first contact member, and a second contact members matched to the first contact member. The first and second contact members extend beyond perimeter edges of the substrate. A plurality of conductive tie bars retain the interconnect elements in a fixed relationship prior to attachment to the substrate. Additive printing processes can be used to form the conductive traces.

Owner:HSIO TECH

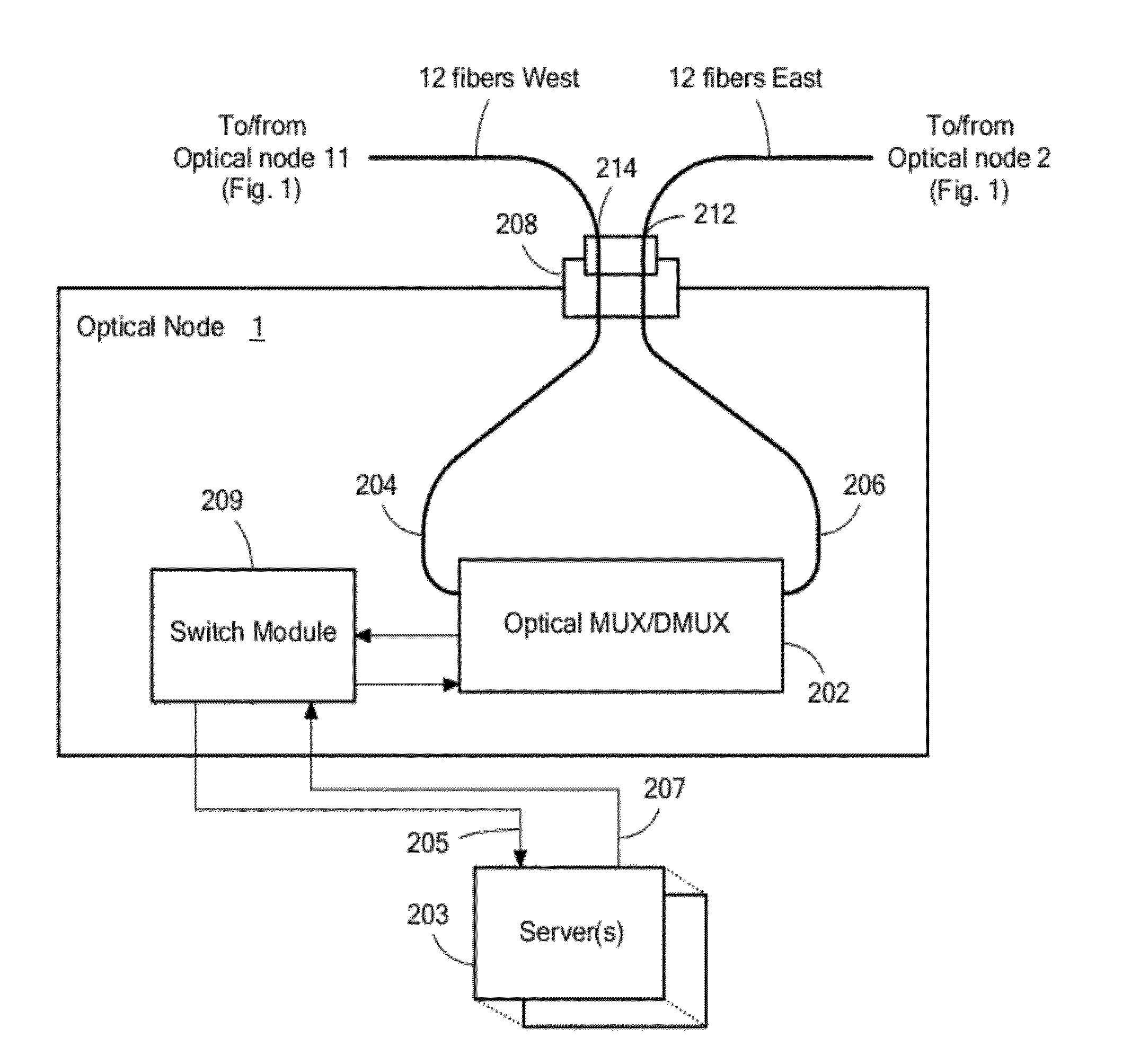

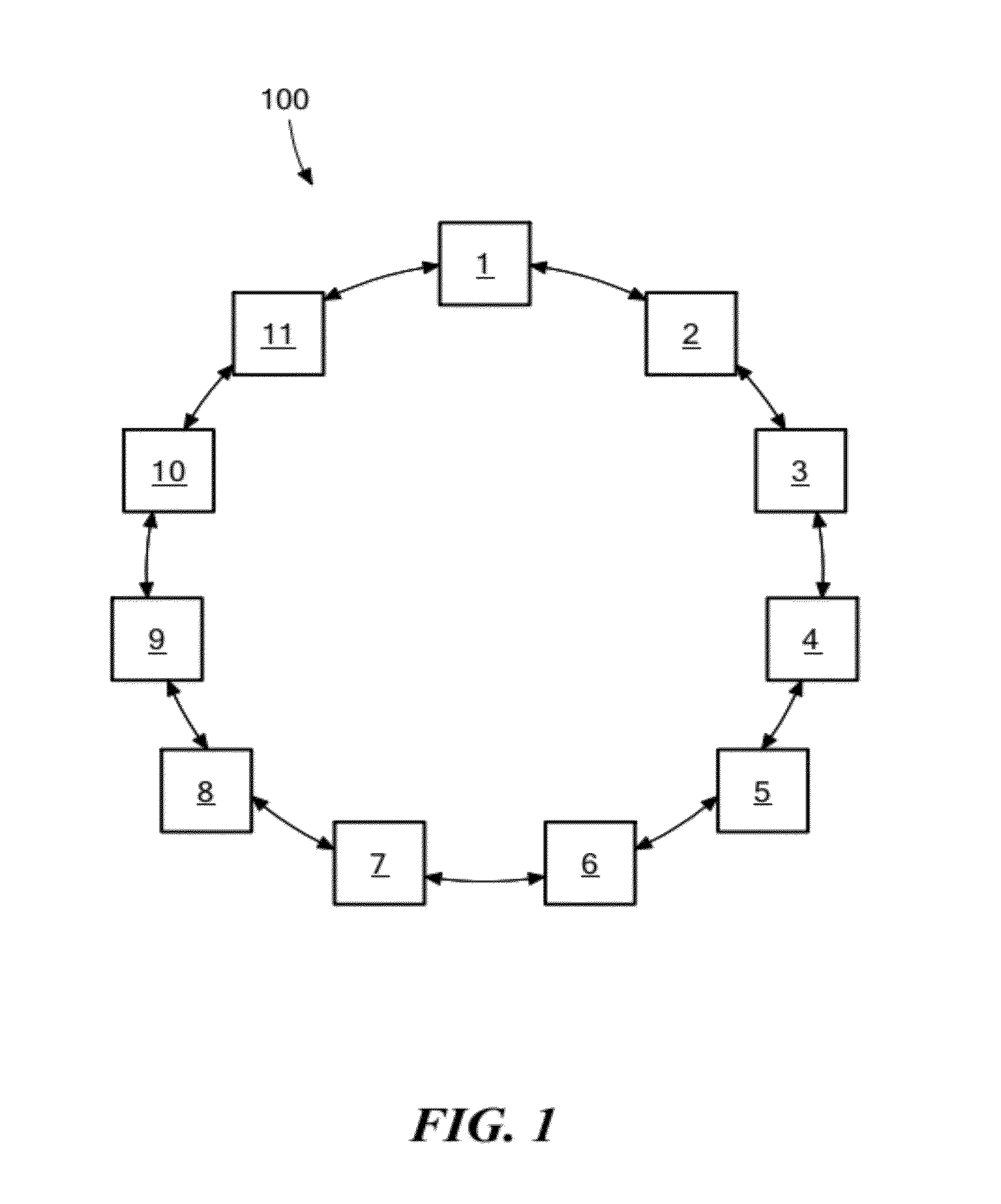

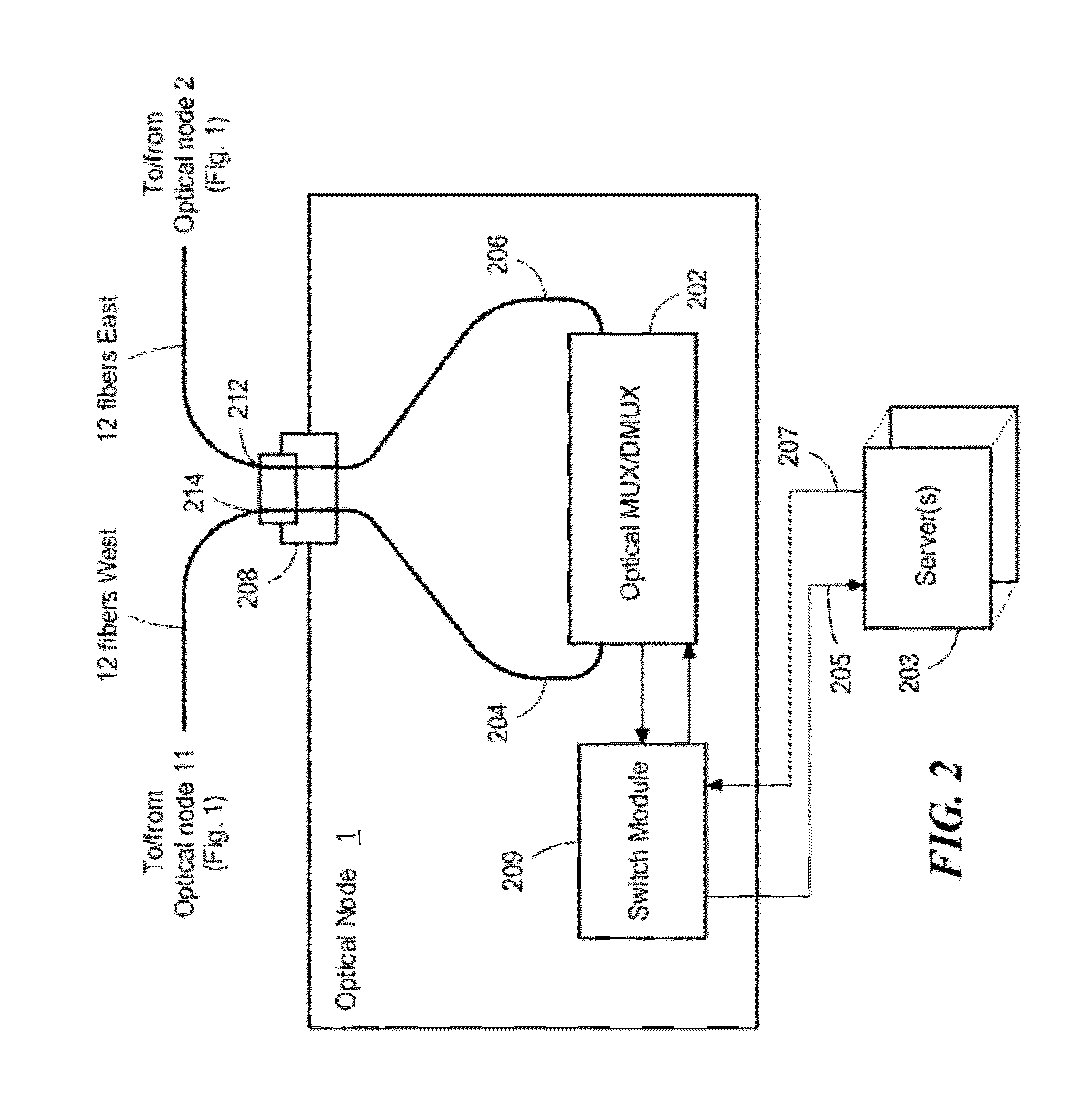

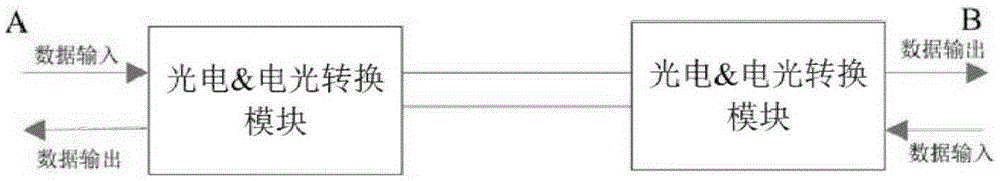

Optical architecture and channel plan employing multi-fiber configurations for data center network switching

ActiveUS20120321309A1Low latencyIncrease densitySpecial service provision for substationMultiplex system selection arrangementsMultiple dimensionFiber

Data center network architectures, systems, and methods that can reduce the cost and complexity of data center networks. Such data center network architectures, systems, and methods employ physical optical ring network and multi-dimensional network topologies and optical nodes to efficiently allocate bandwidth within the data center networks, while reducing the physical interconnectivity requirements of the data center networks. The respective optical nodes can be configured to provide various switching topologies, including, but not limited to, chordal ring switching topologies and multi-dimensional chordal ring switching topologies.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

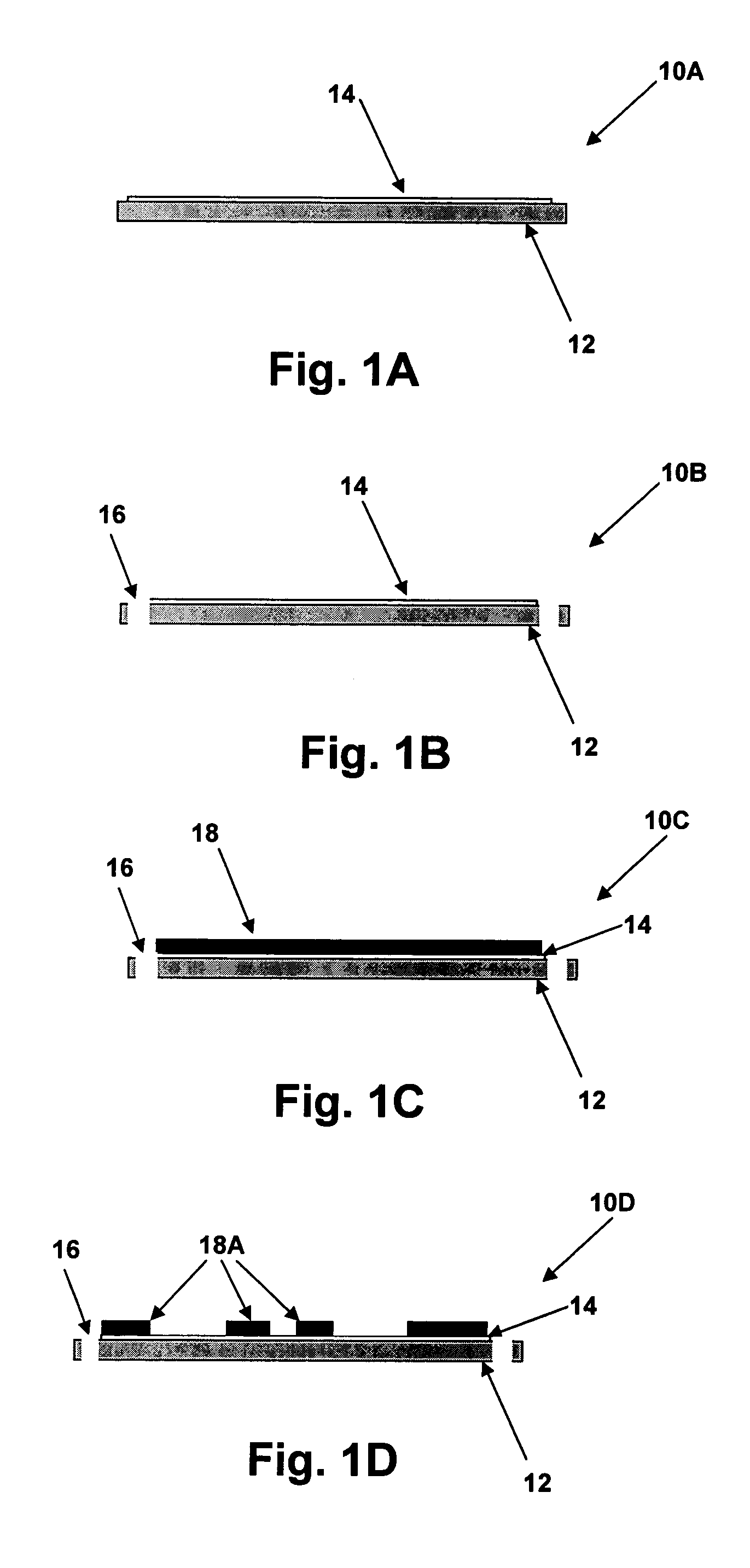

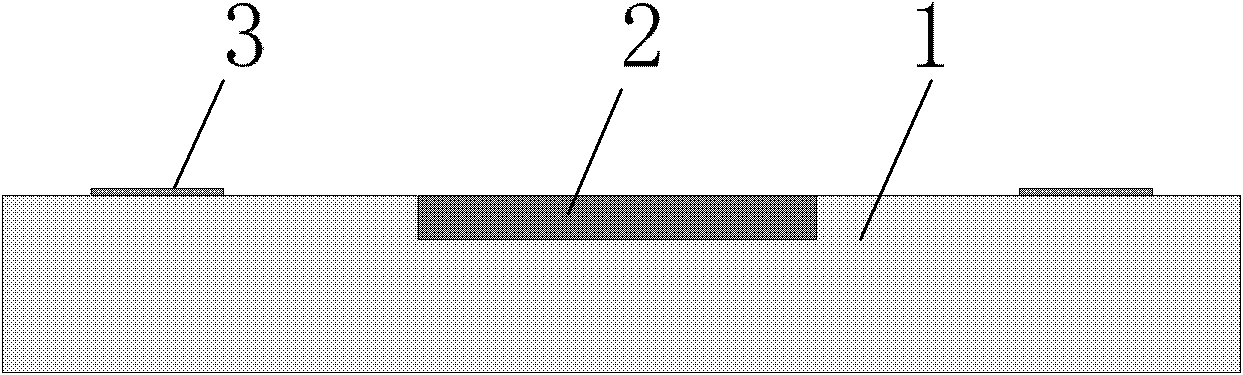

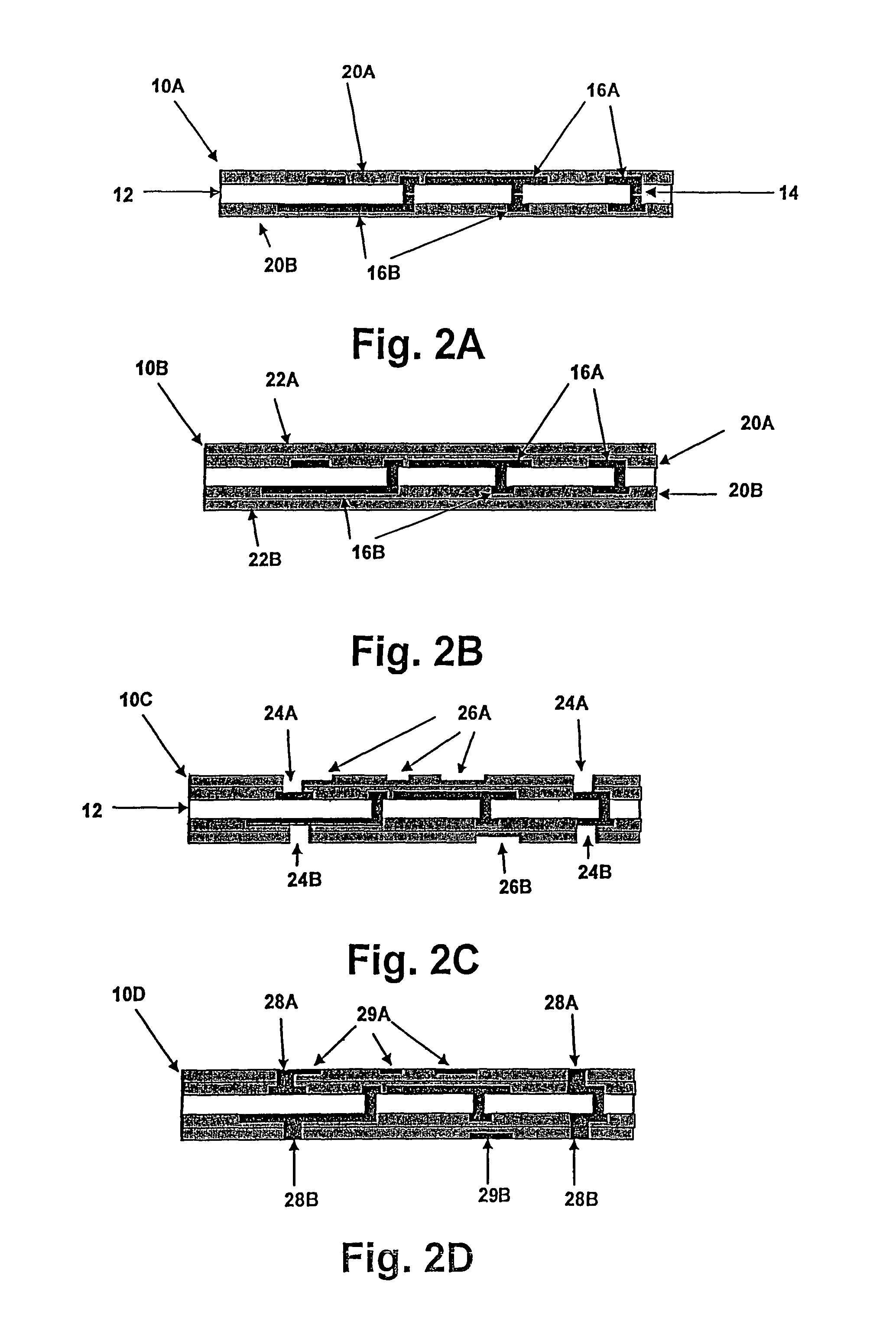

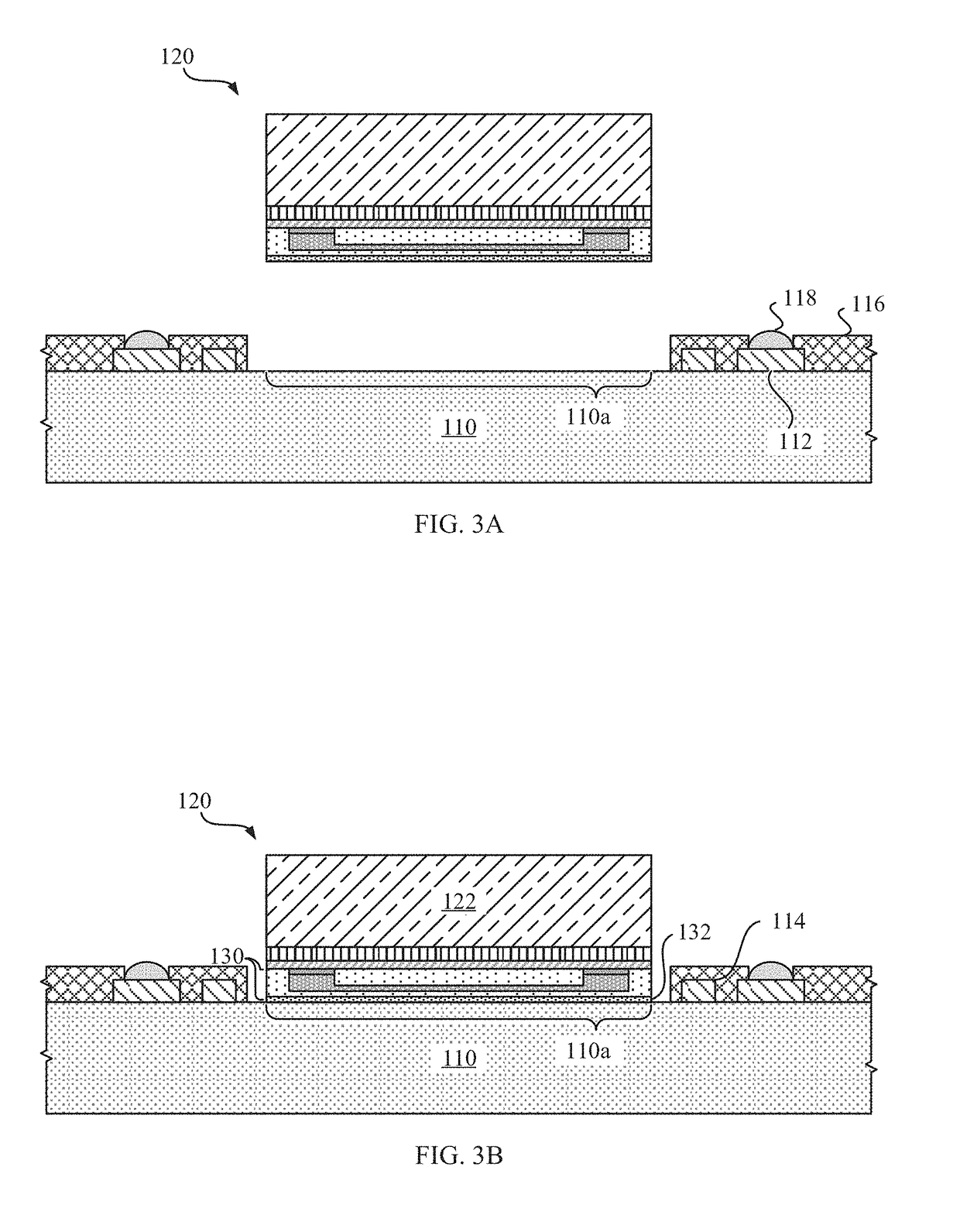

Integrated circuit substrate having laser-exposed terminals

InactiveUS7028400B1Improve interconnect densityLow manufacturing costPrinted circuit assemblingLine/current collector detailsIntegrated circuitElectroplating

An integrated circuit substrate having laser-exposed terminals provides a high-density and low cost mounting and interconnect structure for integrated circuits. The laser-exposed terminals can further provide a selective plating feature by using a dielectric layer of the substrate to prevent plating terminal conductors and subsequently exposing the terminals via laser ablation. A metal layer may be coated on one or both sides with a dielectric material, conductive material embedded within the dielectric to form conductive interconnects and then coating over the conductive material with a conformal protective coating. The protectant is then laser-ablated to expose the terminals. A dielectric film having a metal layer laminated on one side may be etched and plated. Terminals are then laser-exposed from the back side of the metal layer exposing unplated terminals.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

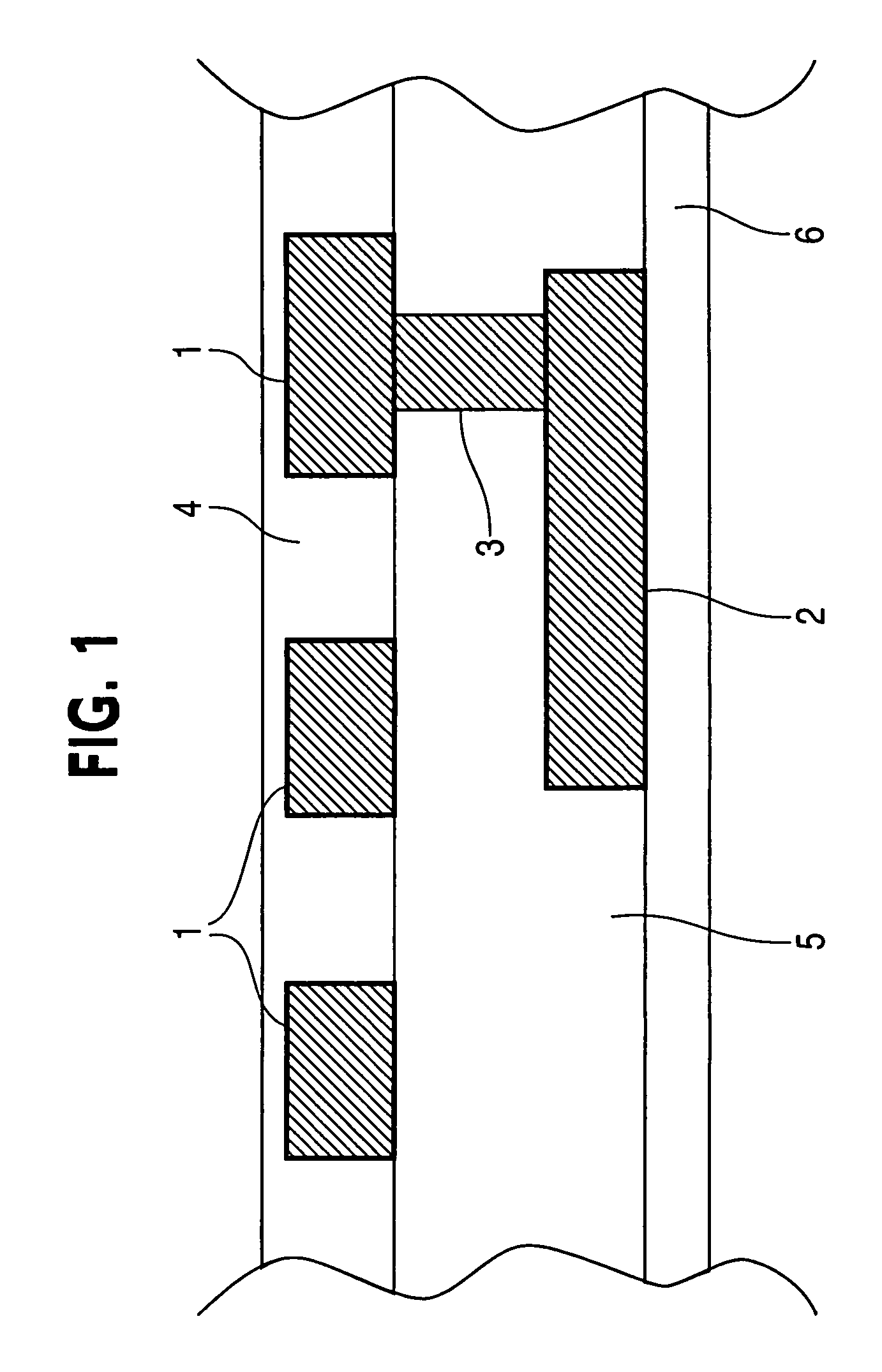

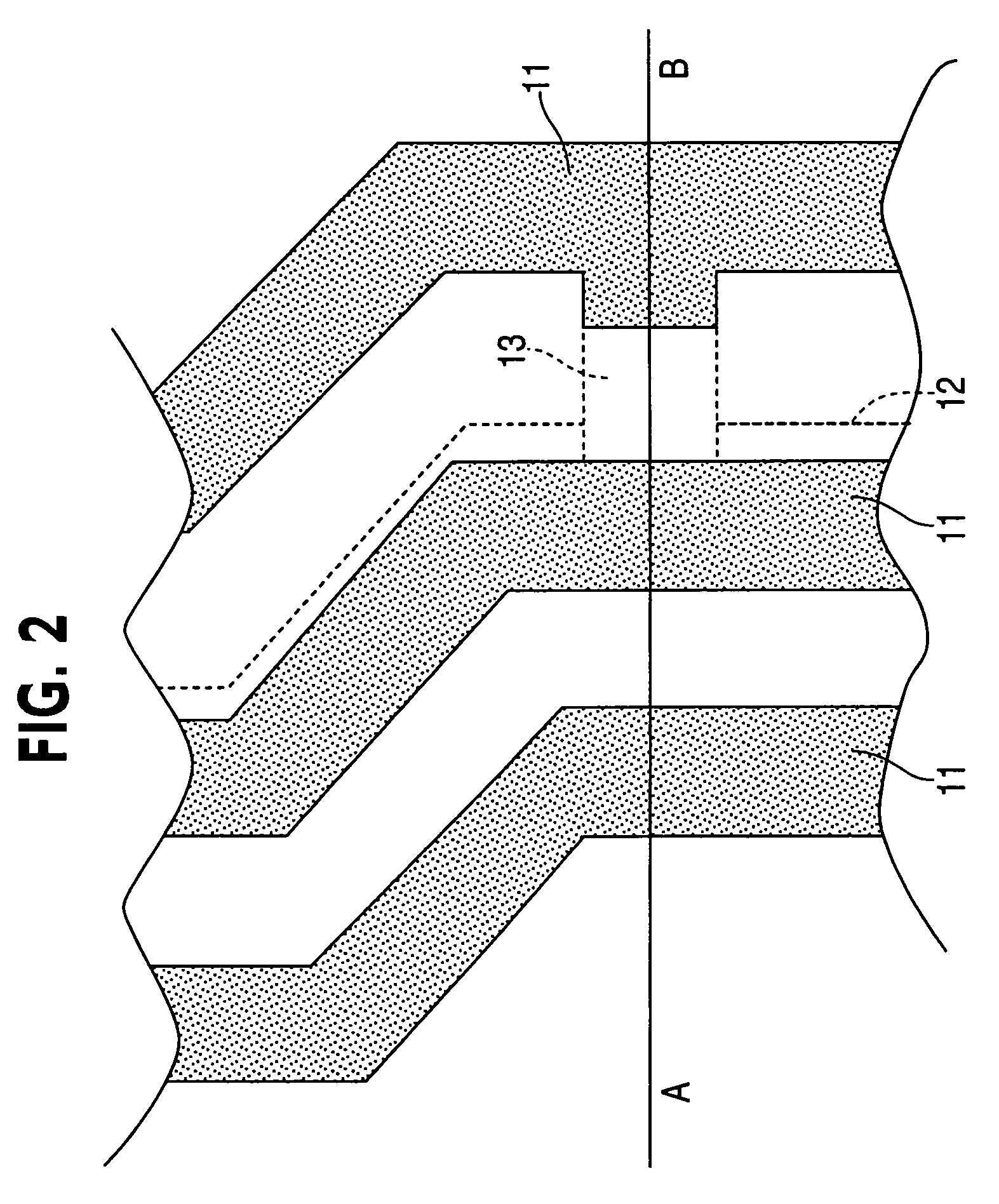

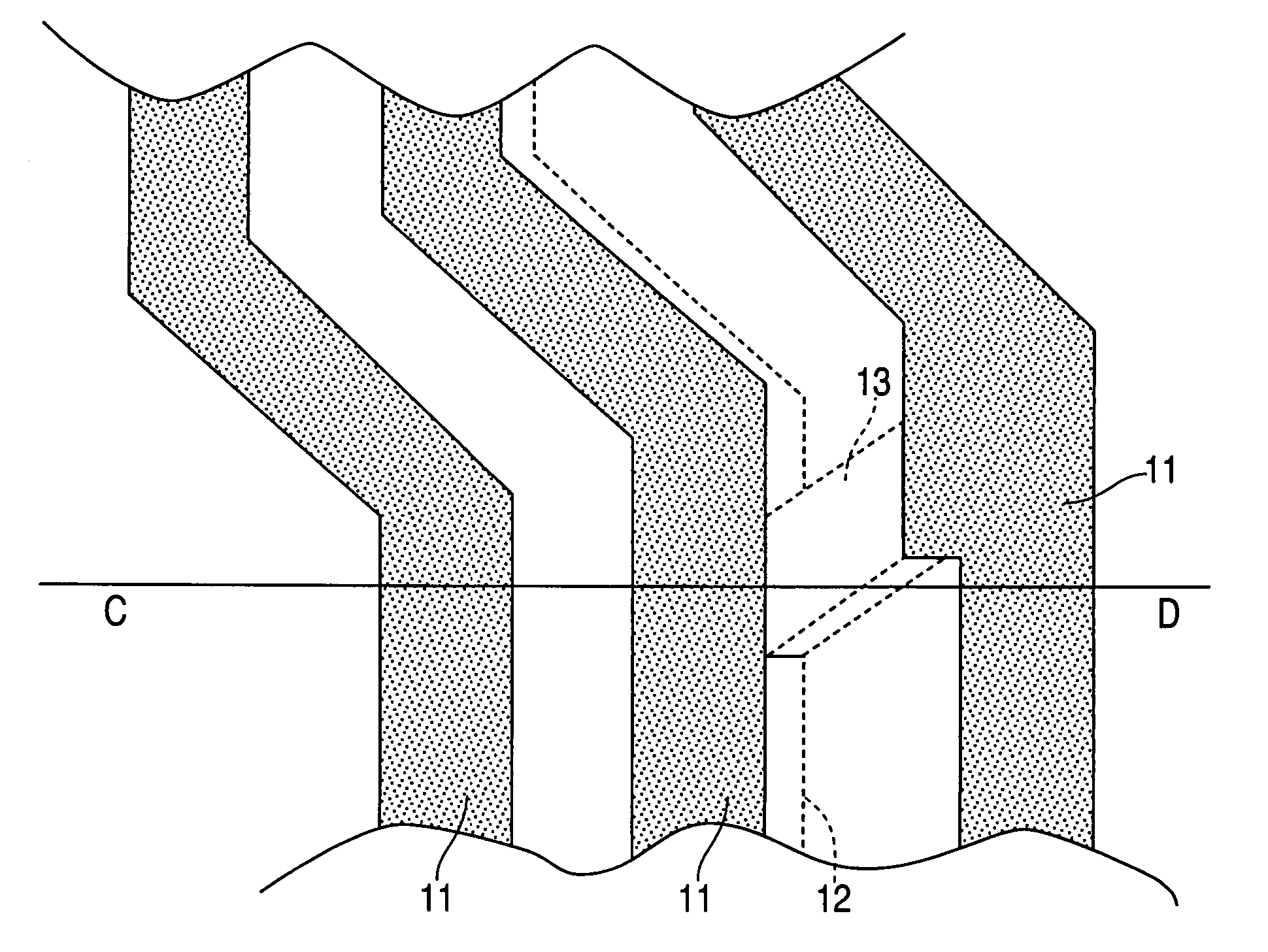

Multilayer interconnection structure and method for forming the same

InactiveUS7514355B2Decreasing interconnection resistance and interconnection capacityImprove interconnect densitySemiconductor/solid-state device detailsSolid-state devicesDiagonalConductive materials

Owner:FUJITSU SEMICON LTD

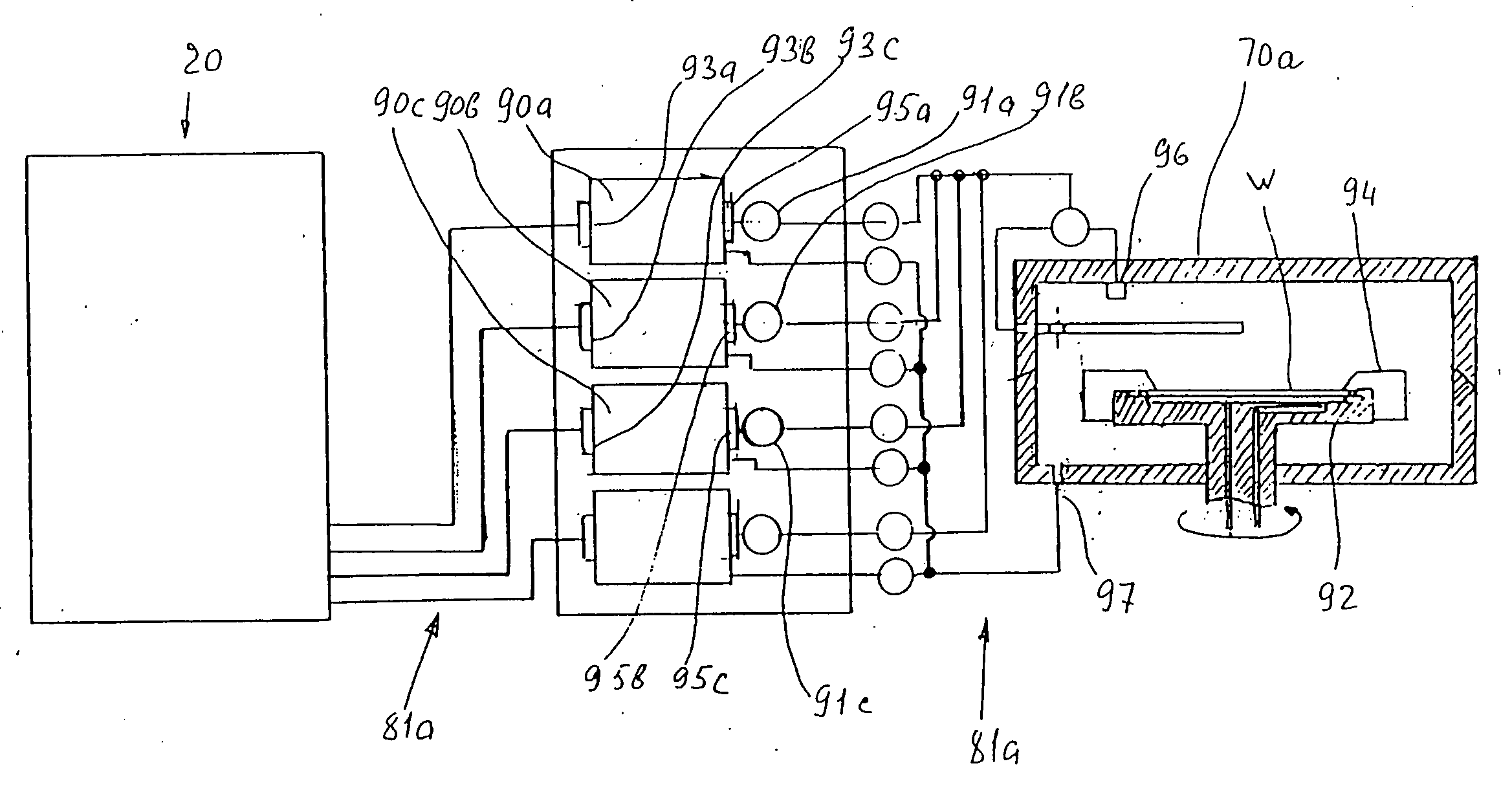

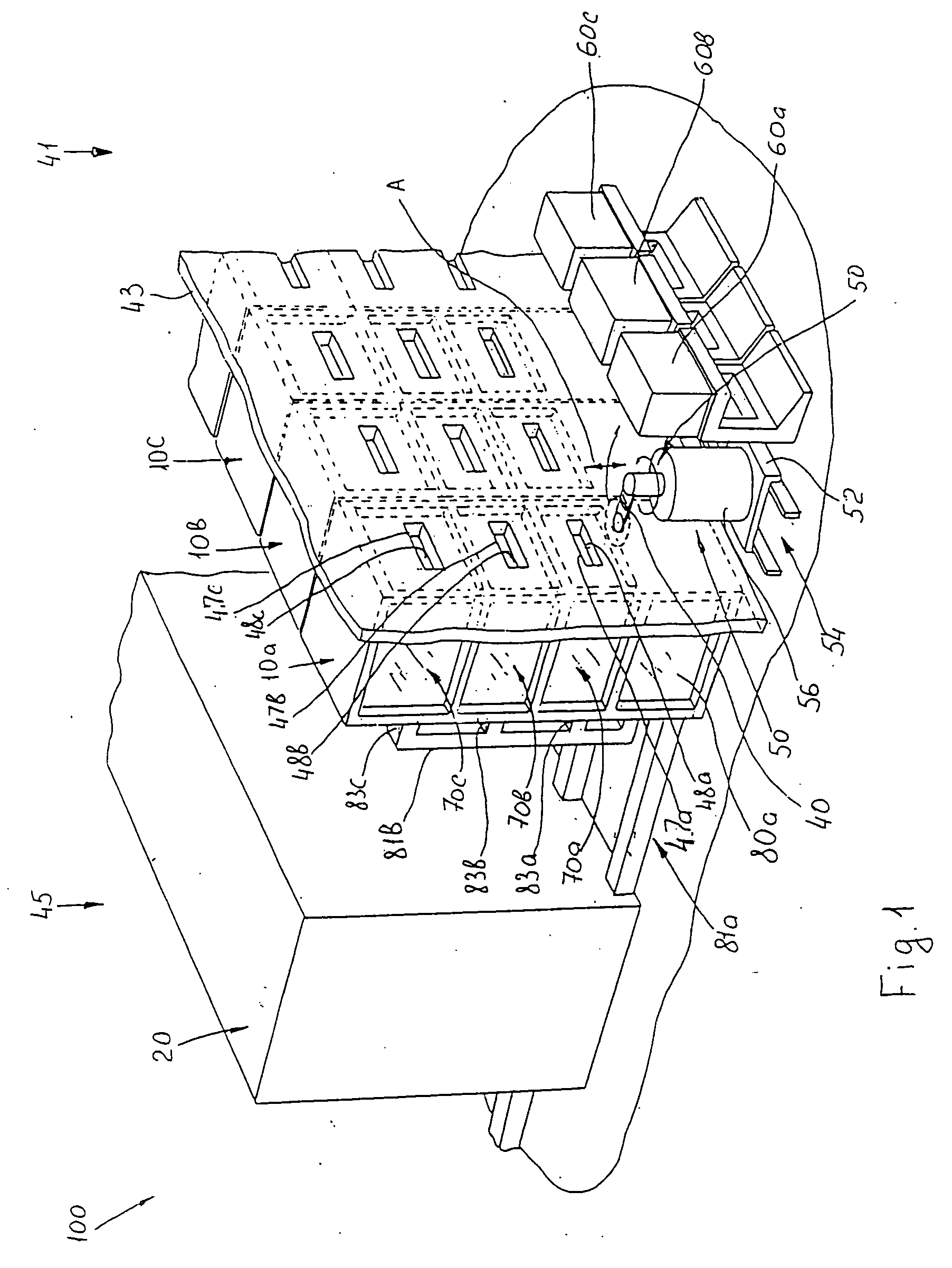

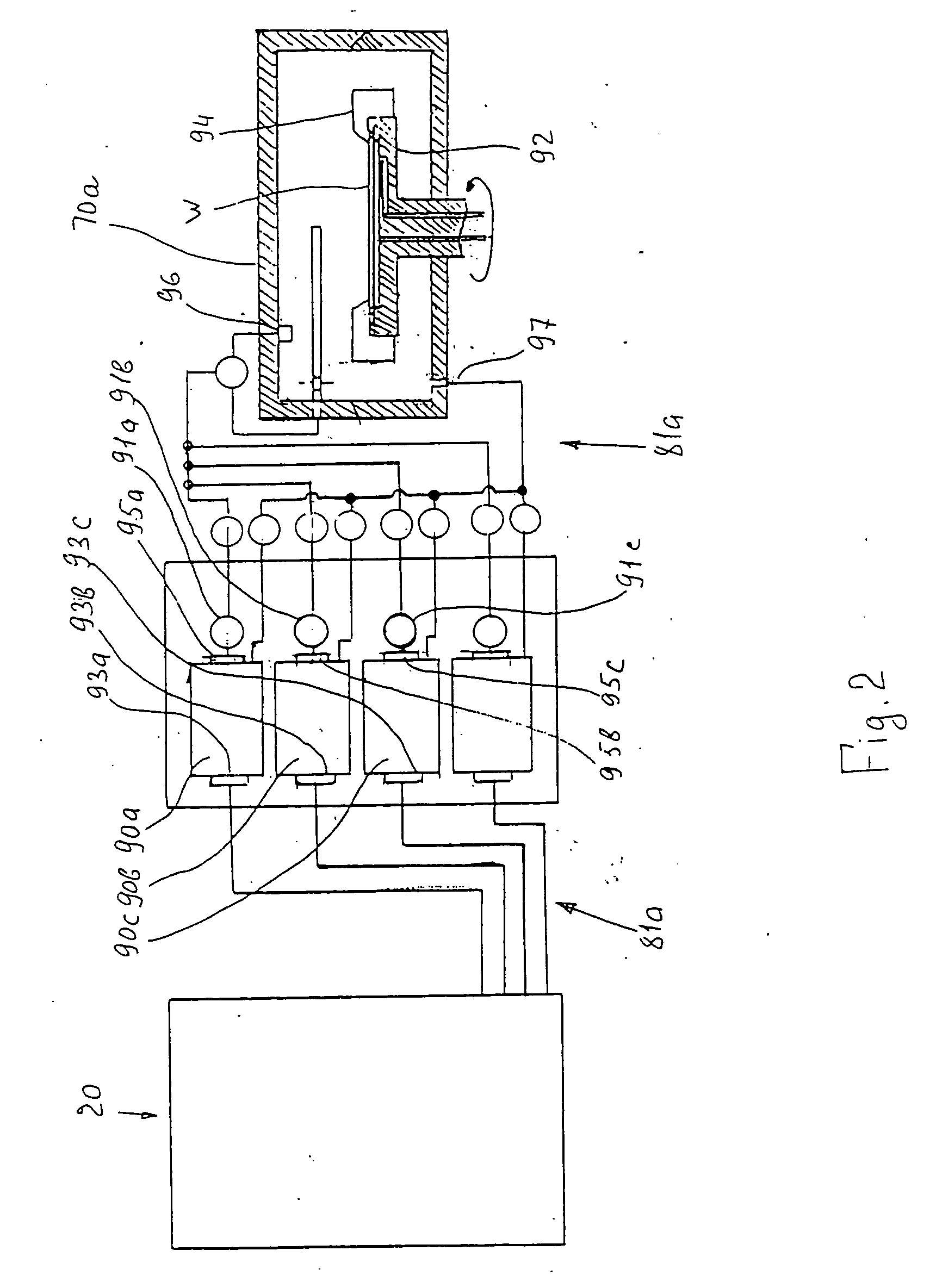

Spatially-arranged chemical processing station

InactiveUS20070051306A1Improve interconnect densityEfficient productionLiquid surface applicatorsMovable spraying apparatusChemical treatmentElectricity

The present invention discloses a station, e.g., for IC fabrication with a flexible configuration. It consists of an array of processing chambers, which are grouped into processing modules and arranged in a two-dimensional fashion, in vertical levels and horizontal rows, and is capable of operating independent of each other. Each processing chamber can perform electroless deposition and other related processing steps sequentially on a wafer with more than one processing fluid without having to remove it from the chamber. The system is served by a single common industrial robot, which may have a random to access to all the working chambers and cells of the storage unit for transporting wafers between the wafer cassettes and inlet / outlets ports of any of the chemical processing chambers. The station occupies a service-room floor space and a clean-room floor space. The processing modules and the main chemical management unit connected to the local chemical supply unit occupy a service-room floor space, while the robot and the wafer storage cassettes are located in a clean room. Thus, in distinction to the known cluster-tool machines, the station of the invention makes it possible to transfer part of the units from the expensive clean-room area to less-expensive service area.

Owner:LAM RES CORP

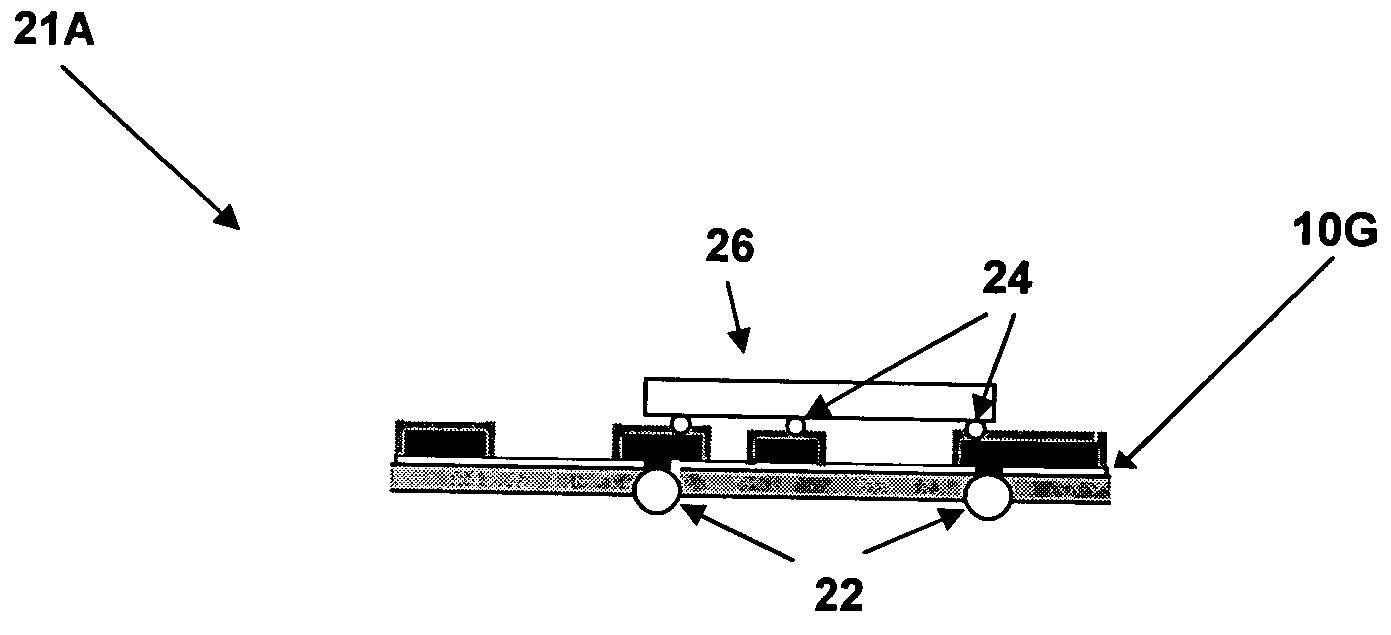

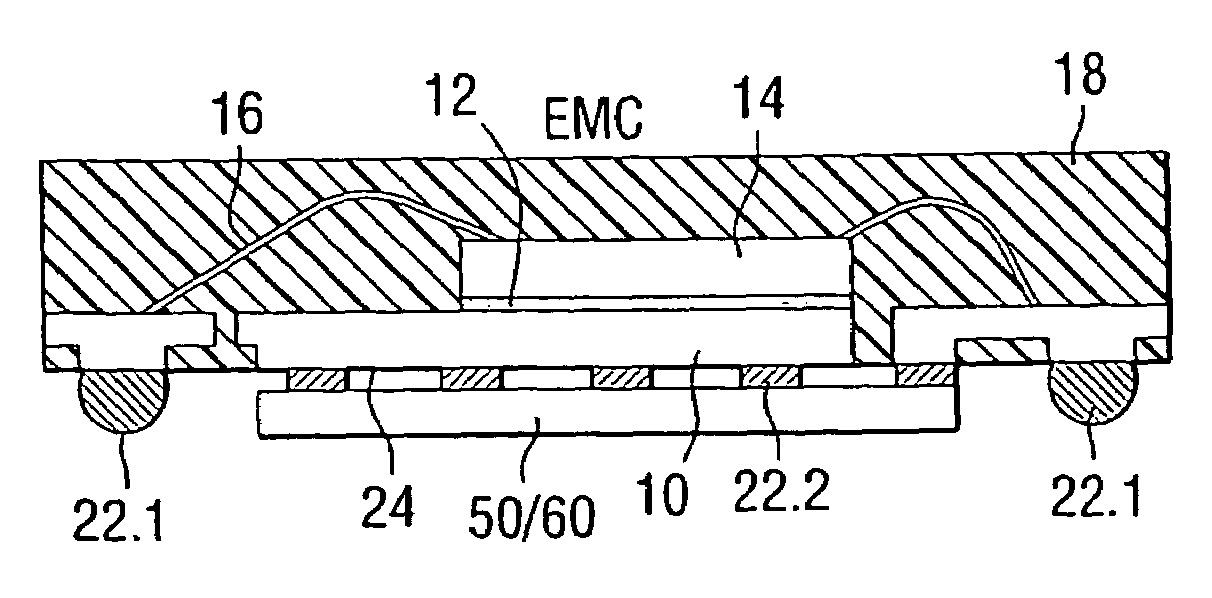

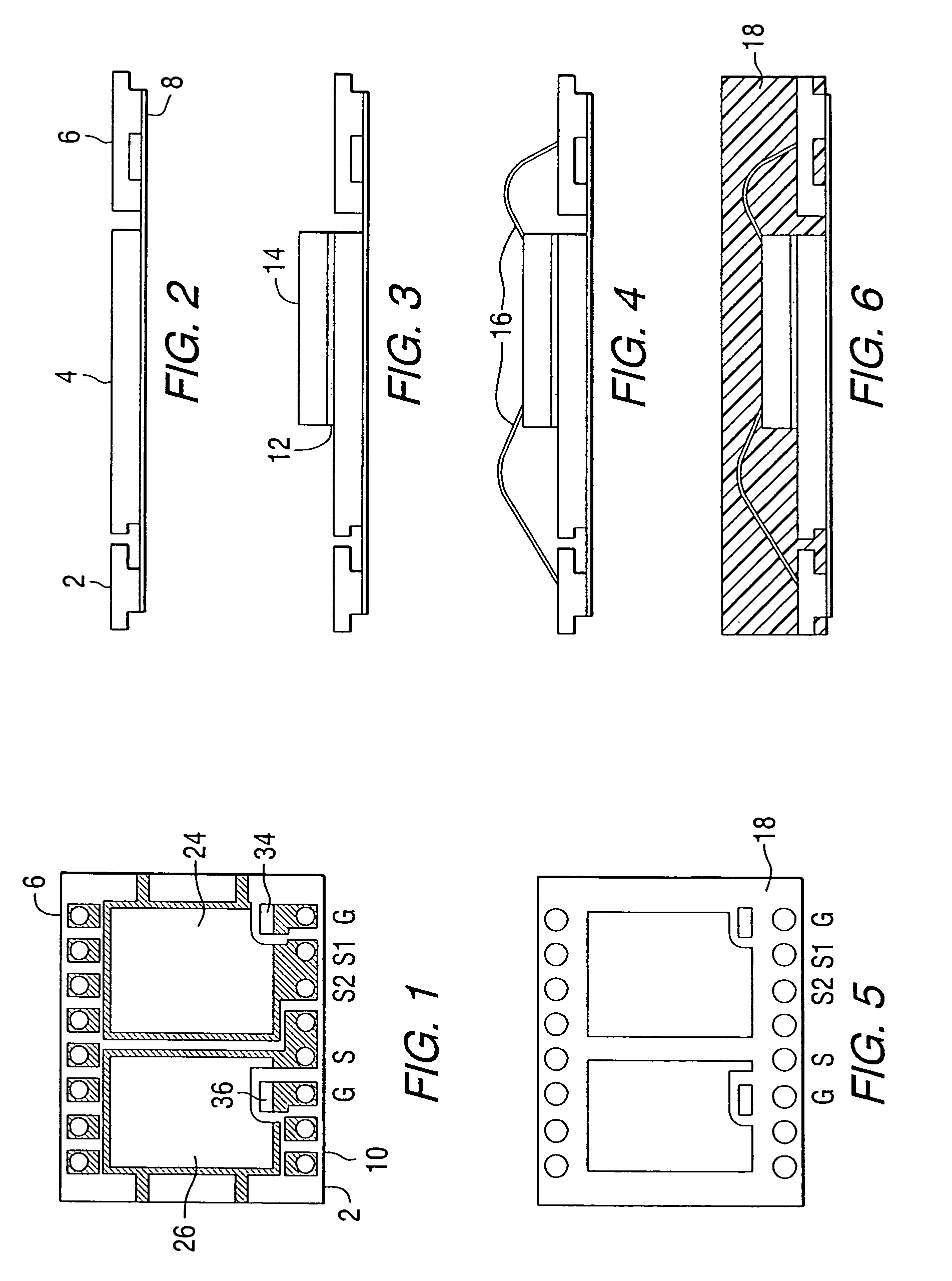

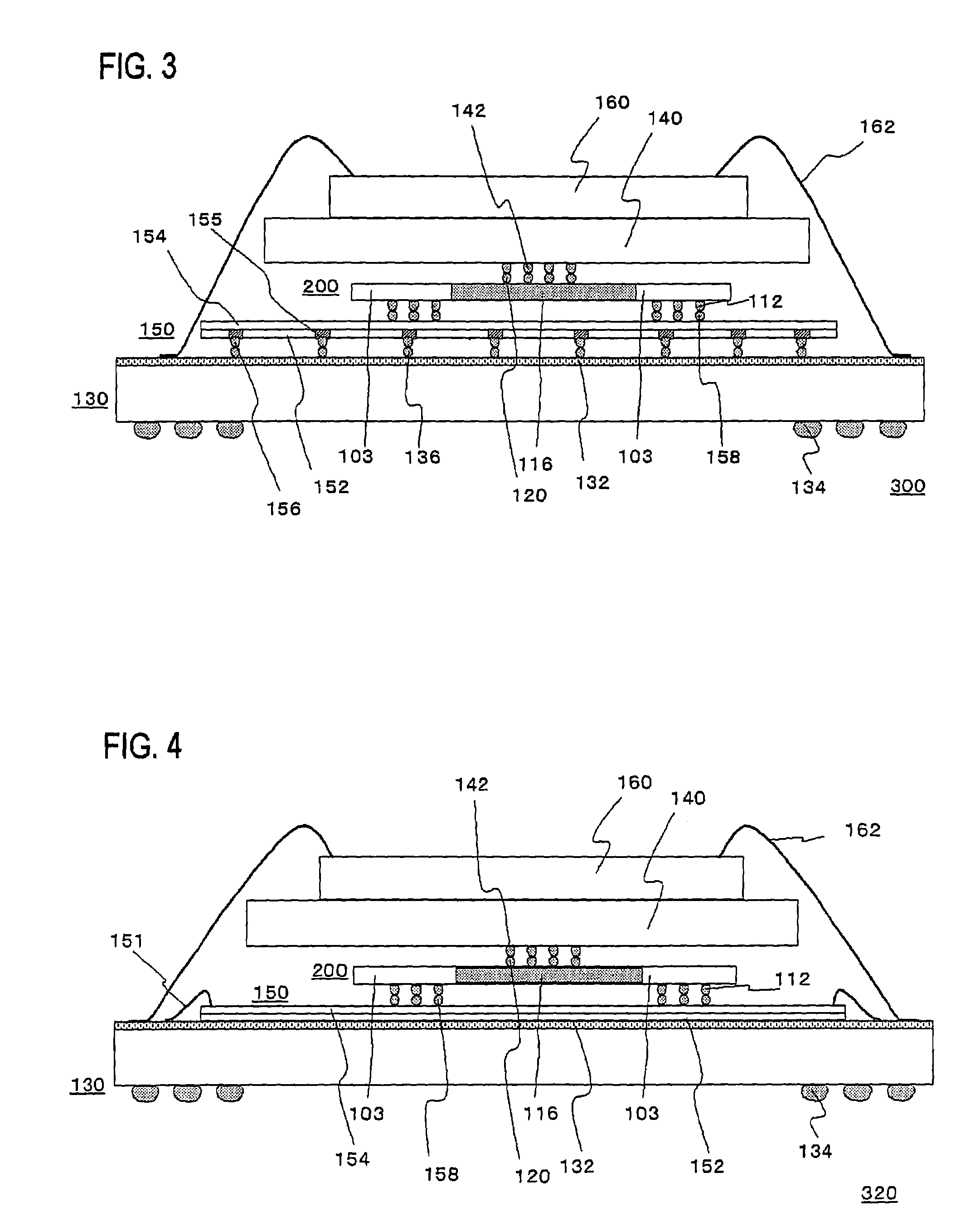

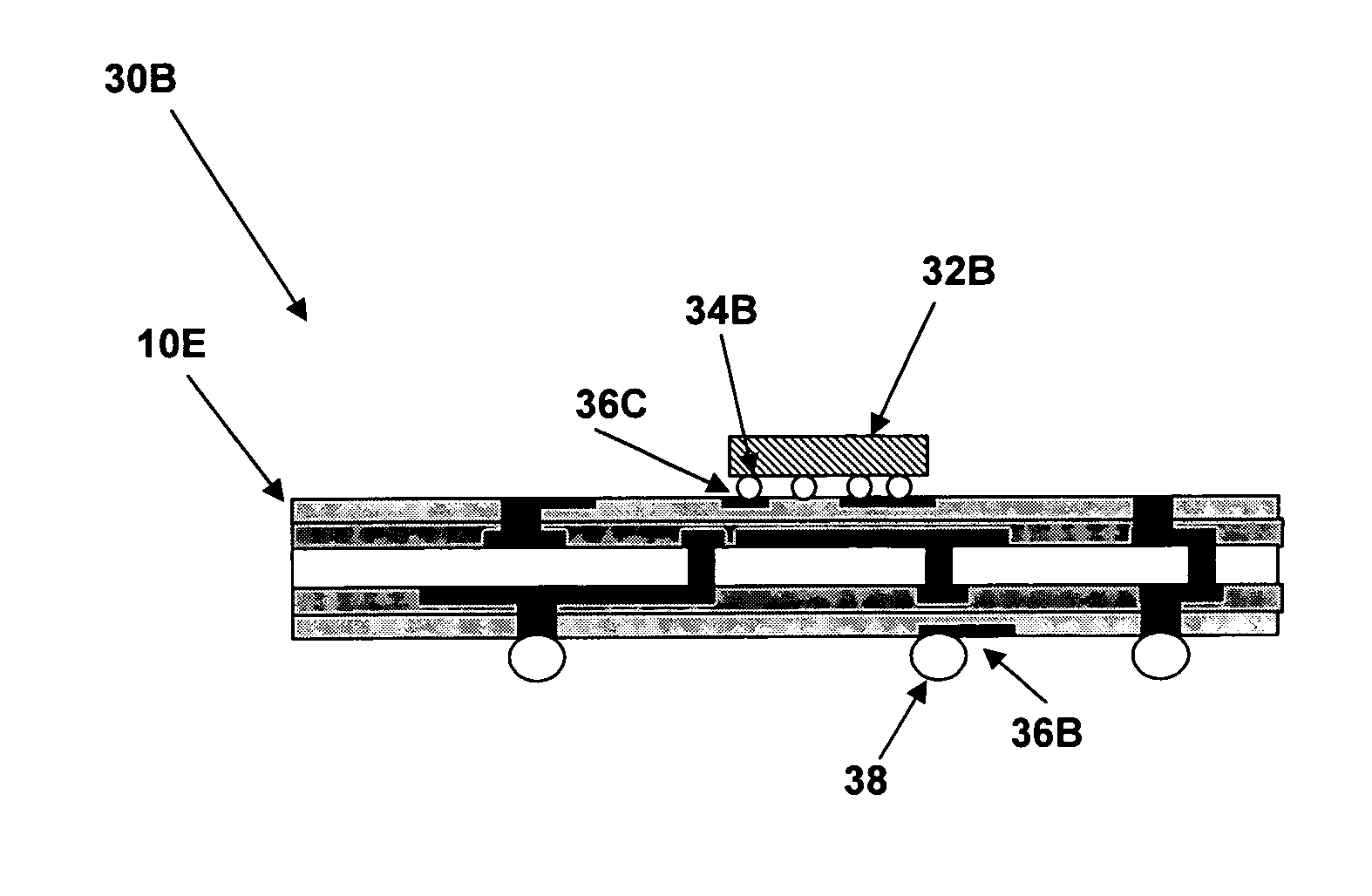

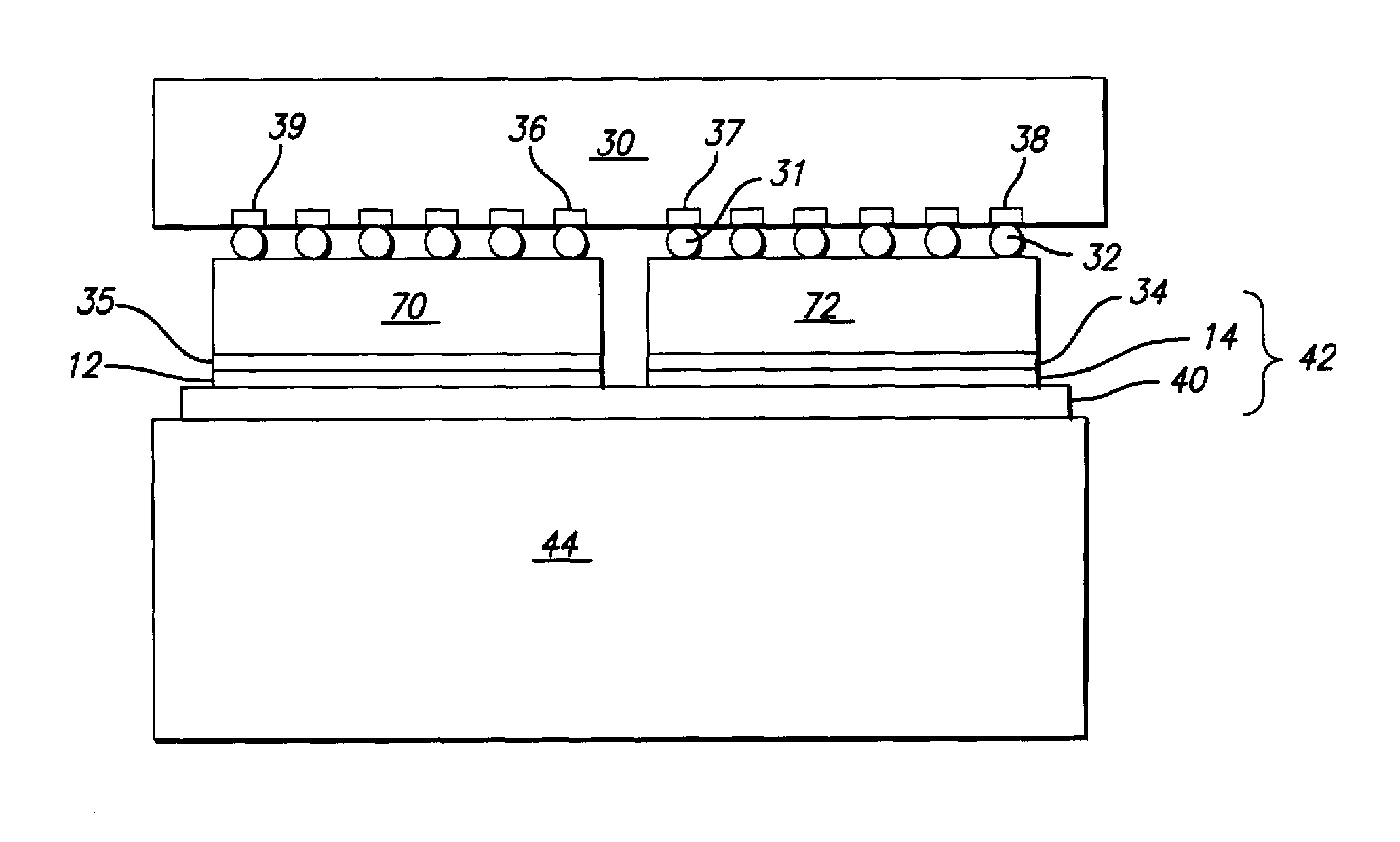

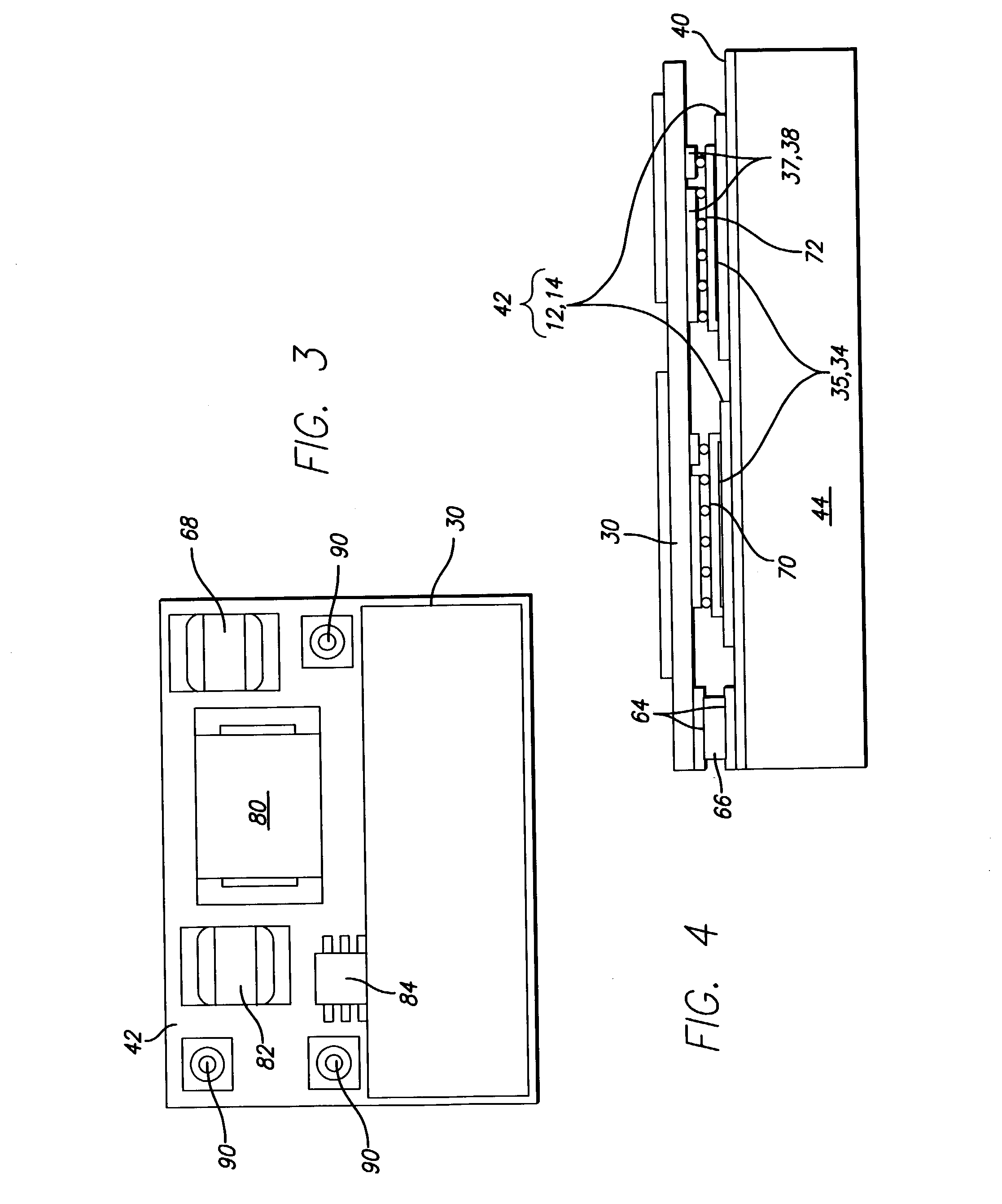

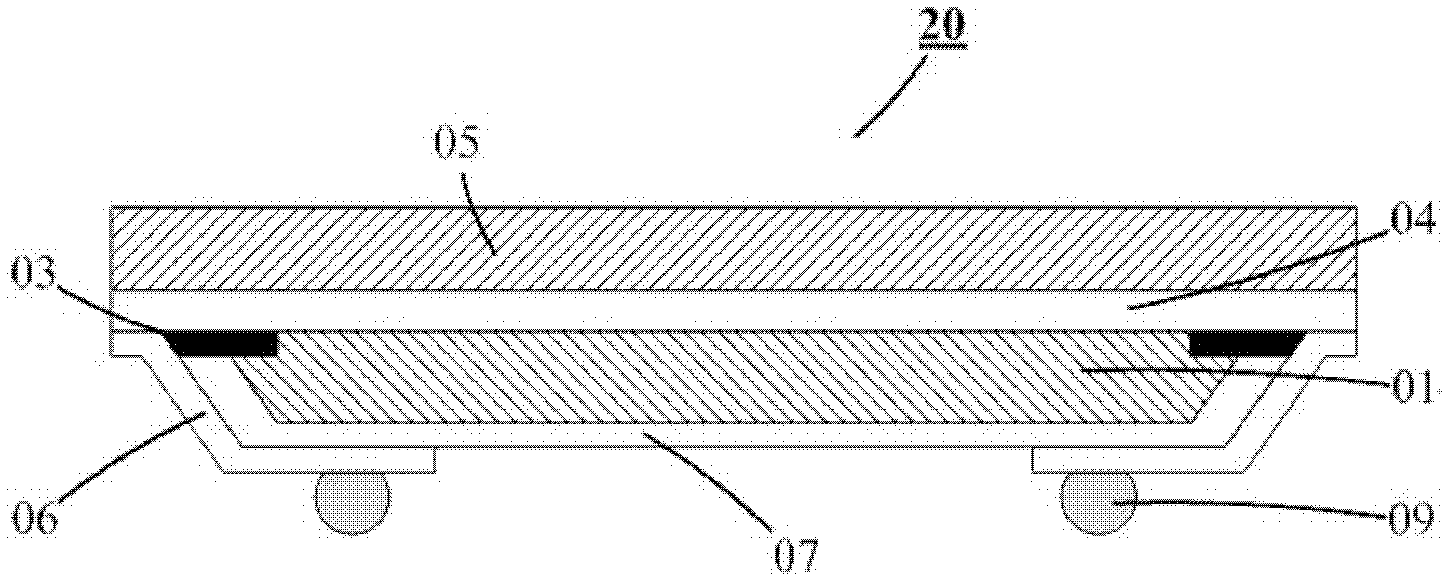

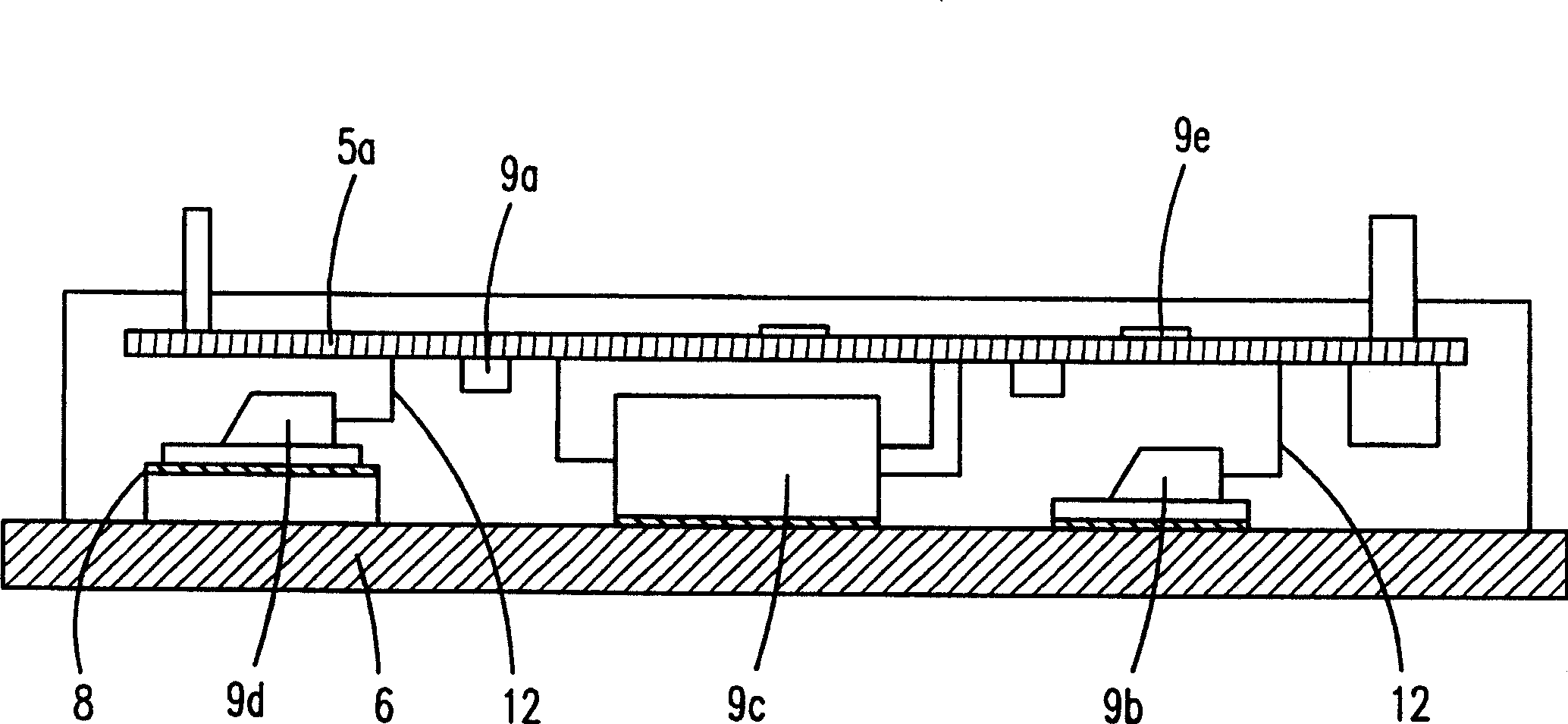

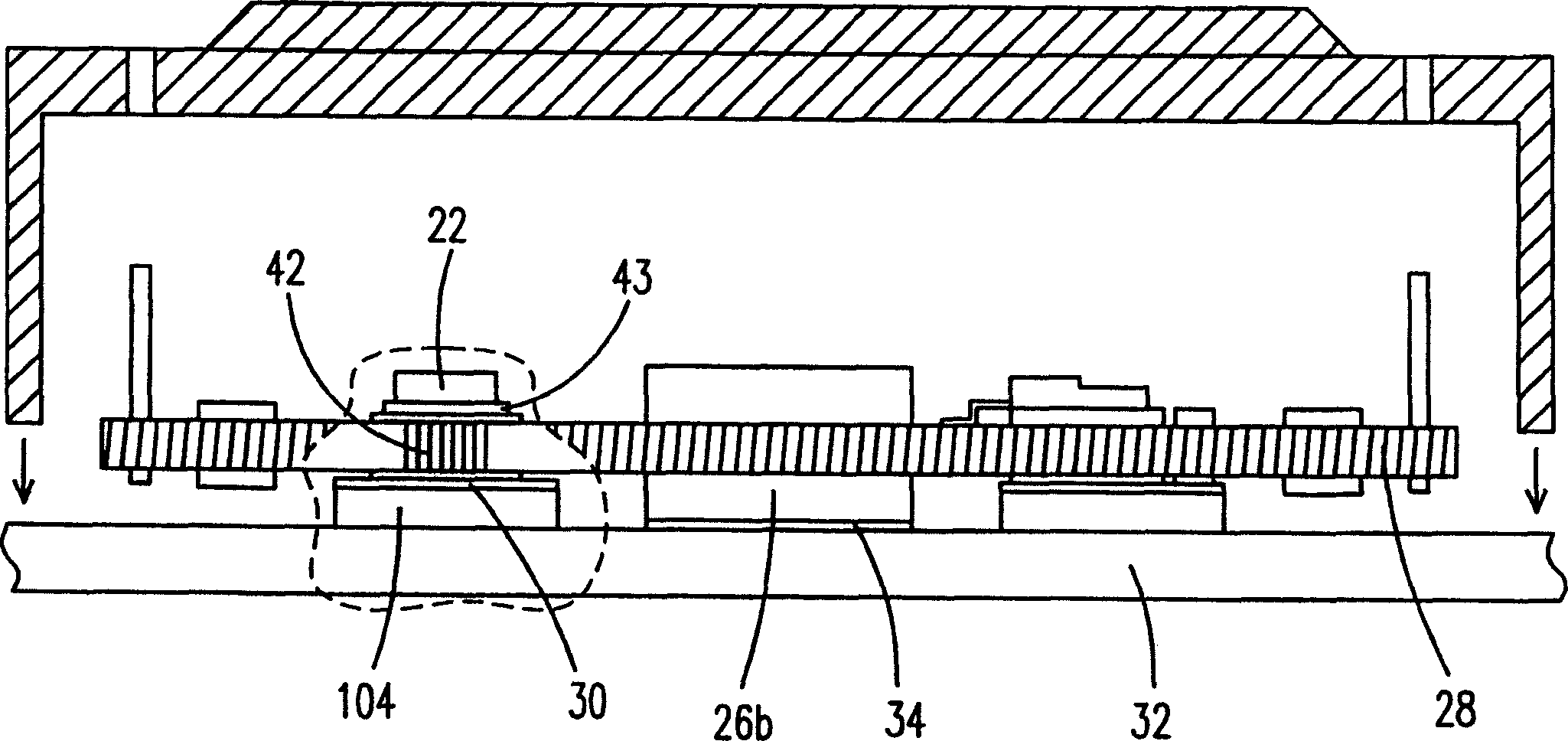

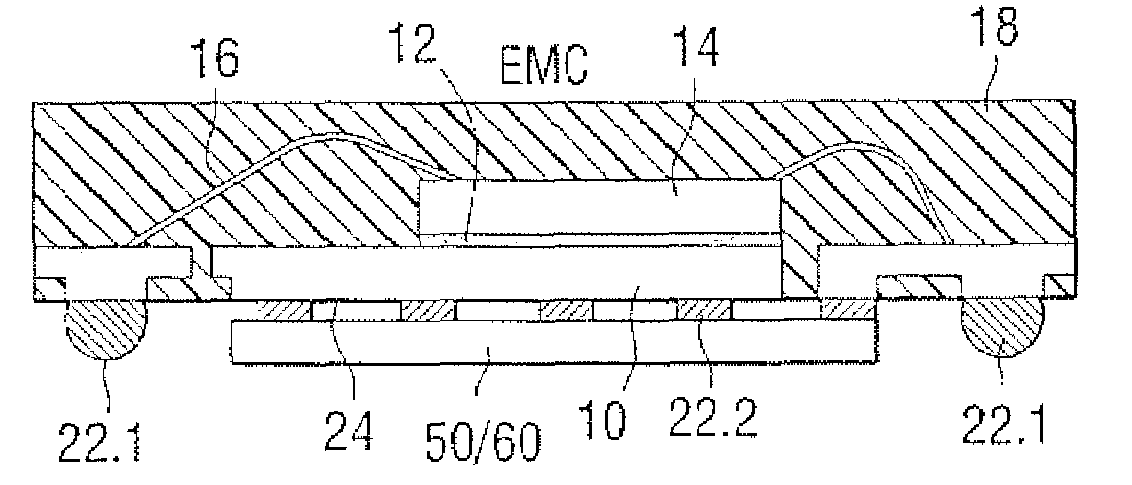

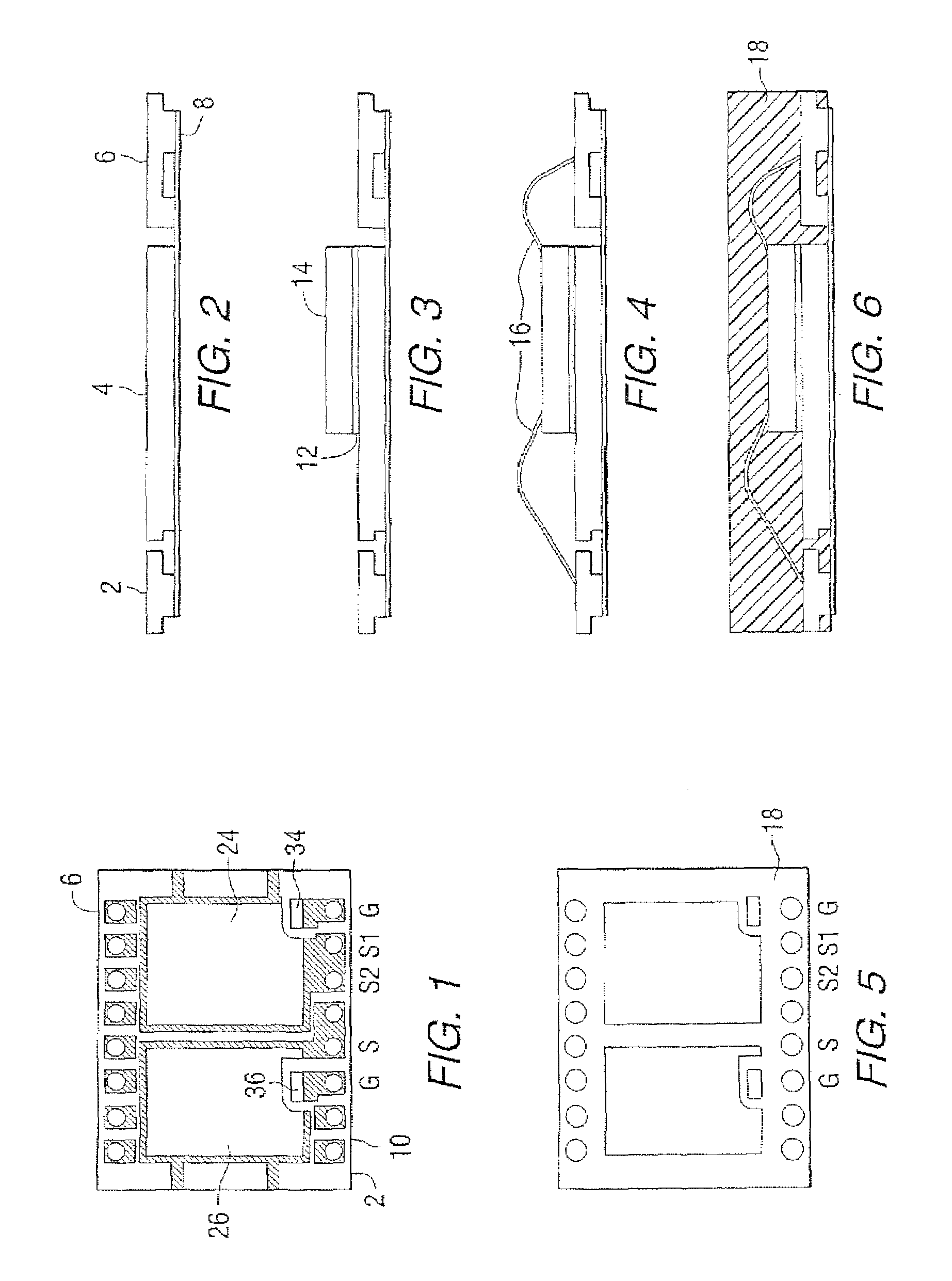

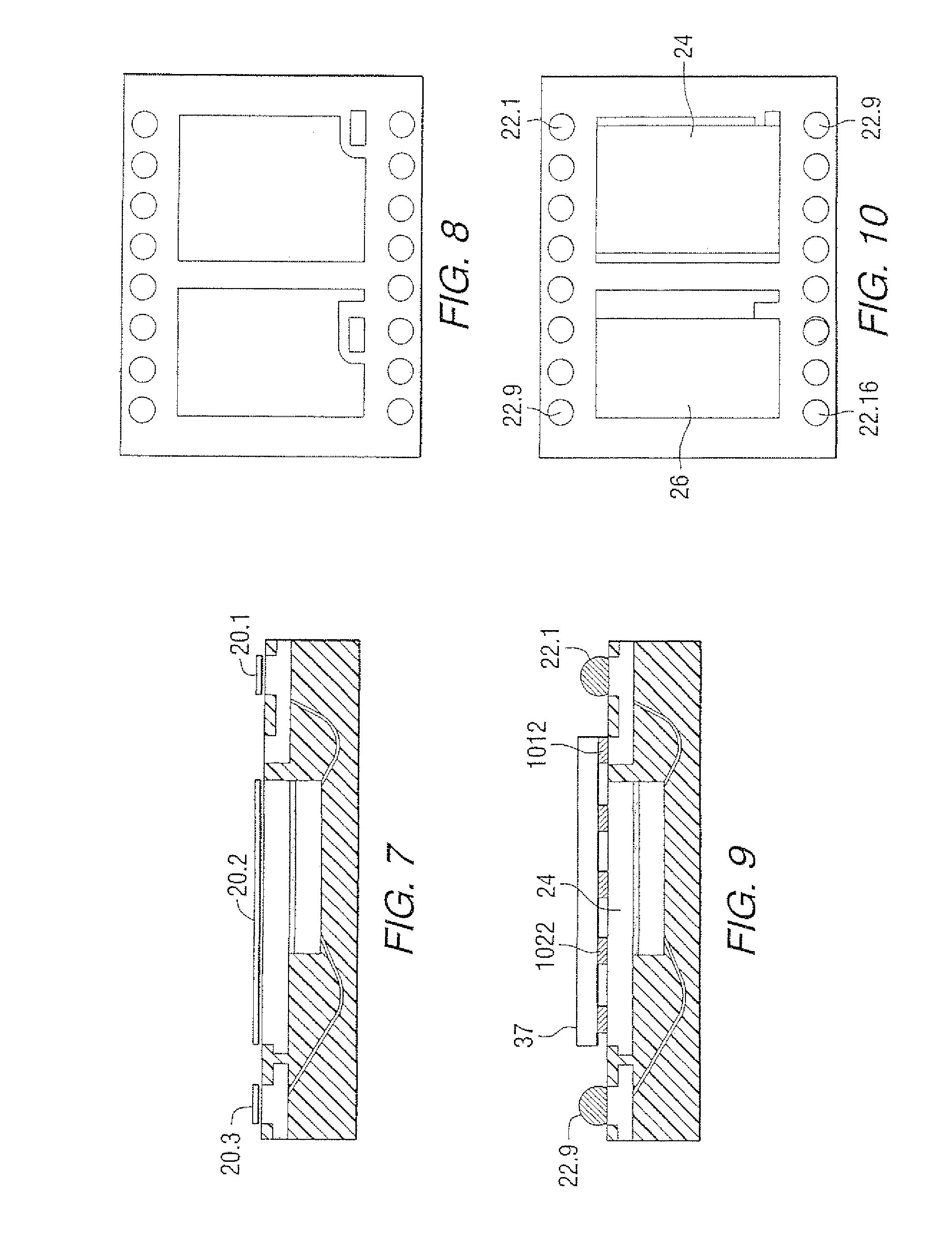

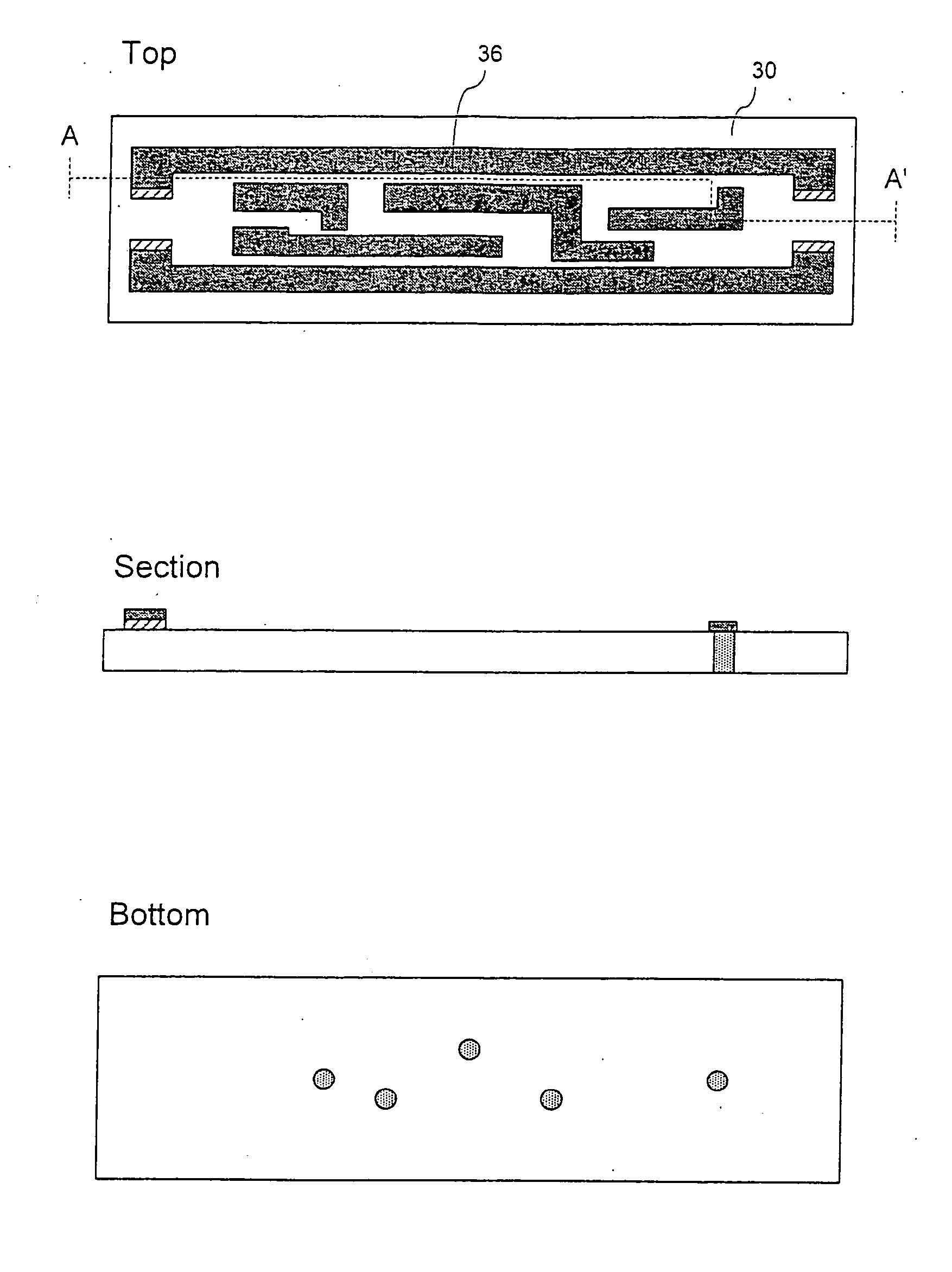

Multi-flip chip on lead frame on over molded IC package and method of assembly

InactiveUS7154186B2Improve signal integrityImprove interconnect densitySemiconductor/solid-state device detailsSolid-state devicesMOSFETIntegrated circuit

A multichip module package uses bond wire with plastic resin on one side of a lead frame to package an integrated circuit and flip chip techniques to attach one or more mosfets to the other side of the lead frame. The assembled multichip module 30 has an integrated circuit controller 14 on a central die pad. Wire bonds 16 extend from contact areas on the integrated circuit to outer leads 2.6 of the lead frame 10. On the opposite, lower side of the central die pad, the sources and gates of the mosfets 24, 26 are bump or stud attached to the half etched regions of the lead frame. The drains 36 of the mosfets and the ball contacts 22.1 on the outer leads are soldered to a printed circuit board.

Owner:SEMICON COMPONENTS IND LLC

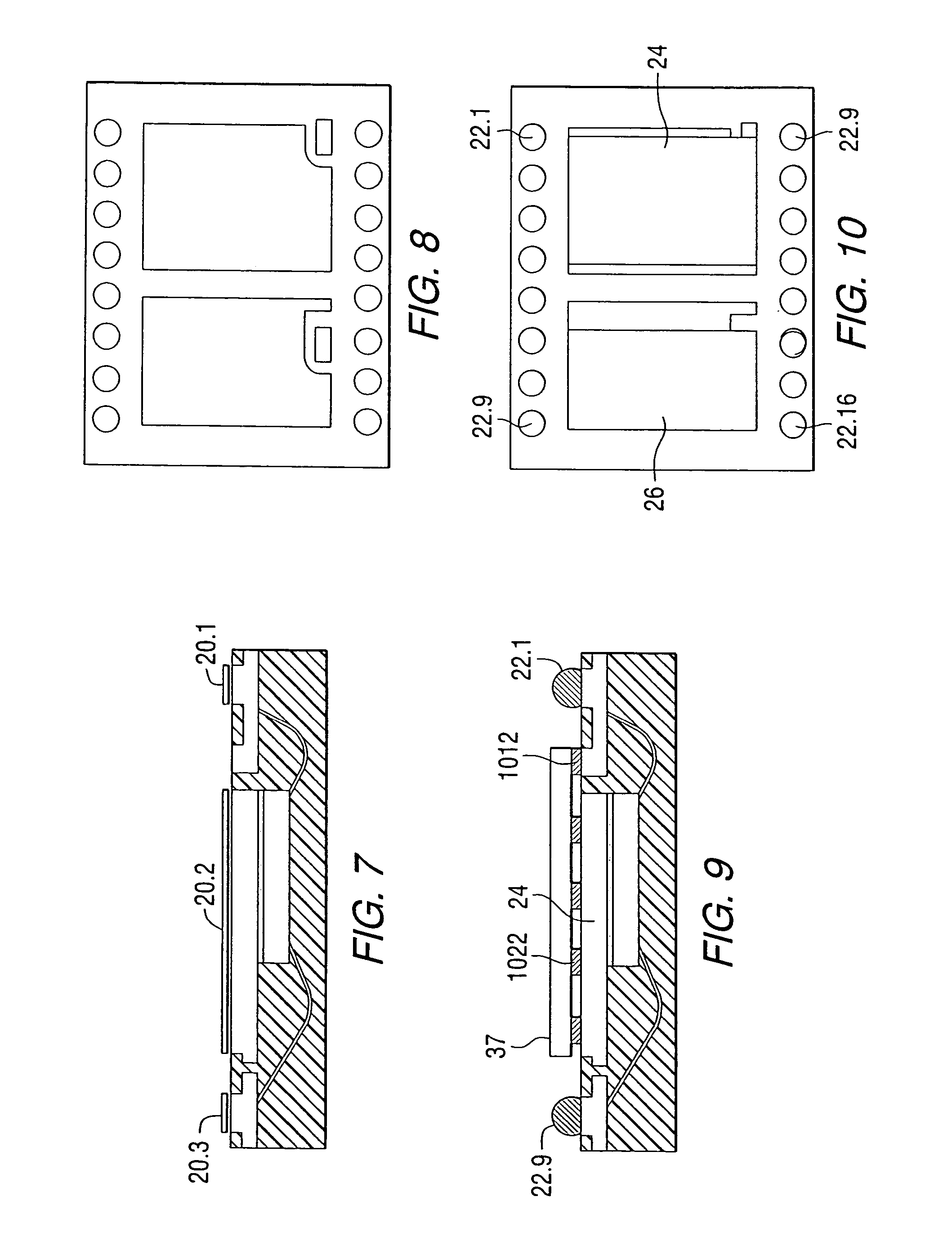

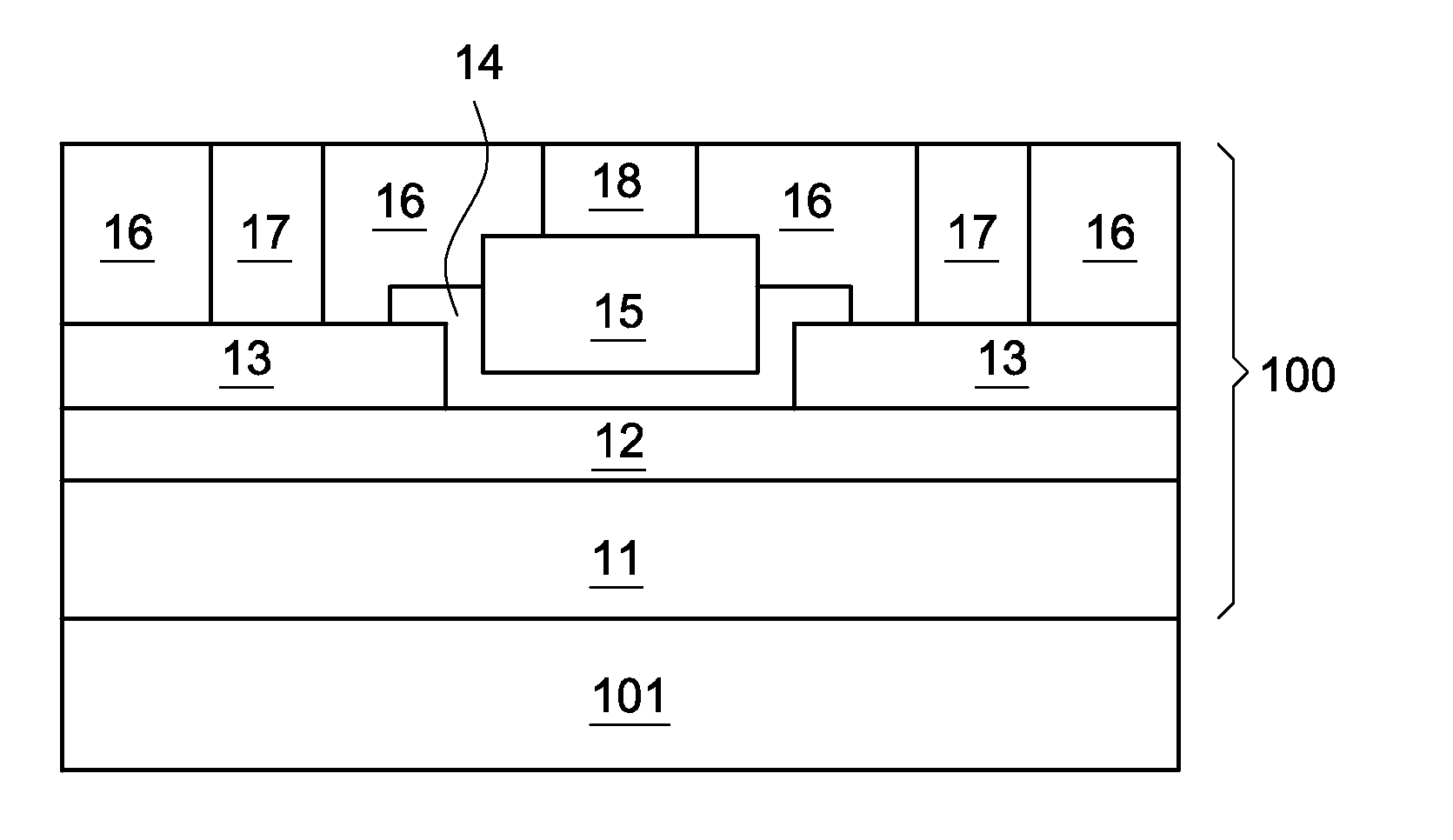

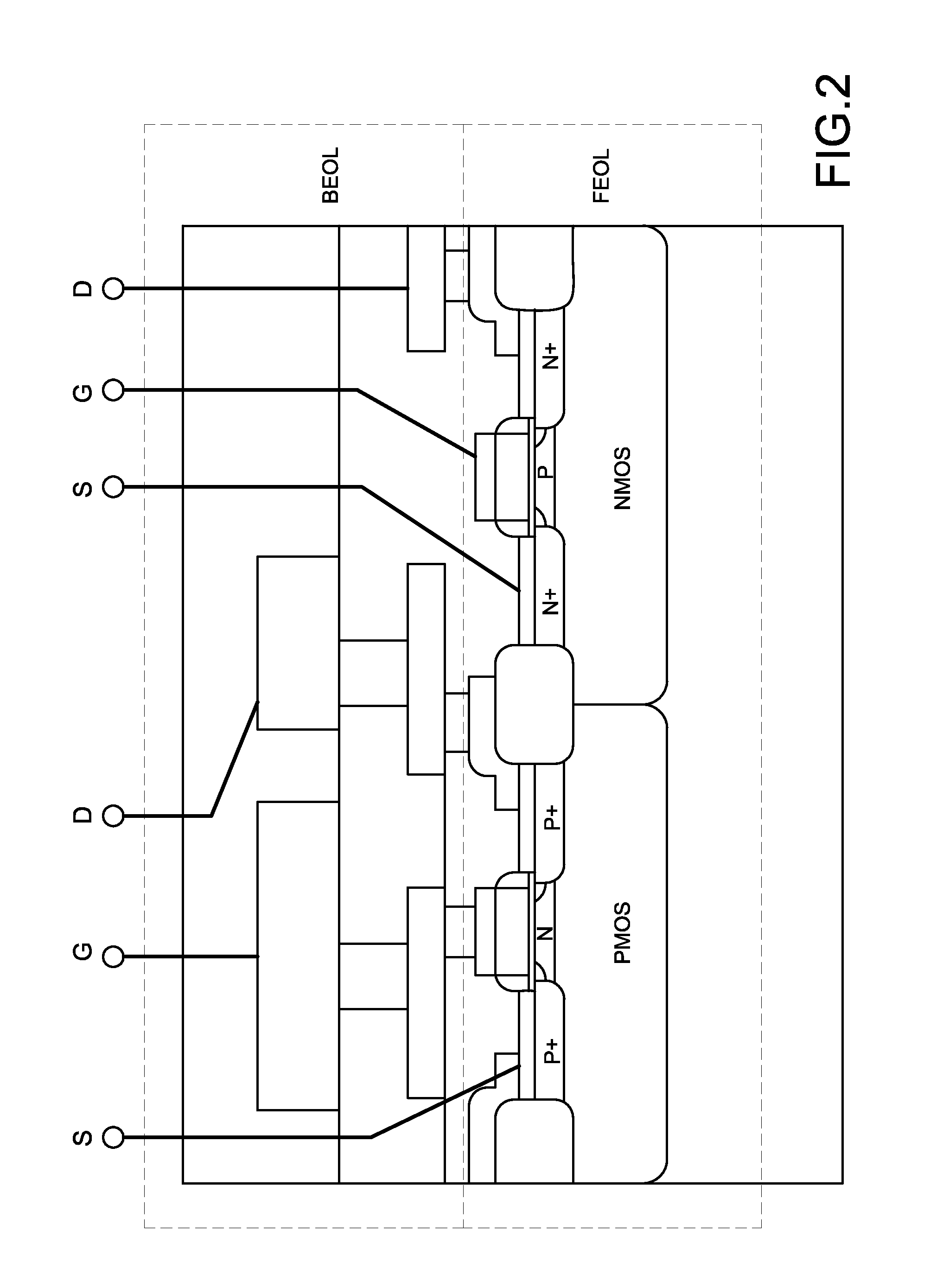

Electrical switch using gated resistor structures and three-dimensional integrated circuits using the same

ActiveUS20120056258A1Low thermal budgetImprove interconnect densityTransistorSolid-state devicesElectrical resistance and conductanceIsolation layer

An electrical switch using a gated resistor structure includes an isolation layer, a doped silicon layer arranged on the isolation layer and having a recessed portion with reduced thickness, the doped silicon layer having a predetermined doping type and a predetermined doping profile; a gate layer arranged corresponding to the recessed portion. The recessed portion in the doped silicon layer has such thickness that a channel defined under the gate can be fully depleted to form a high resistivity region. The recessed channel gated resistor structure can be advantageously used to achieve high interconnect density with low thermal budget for 3D integration.

Owner:CHEN SHU LU

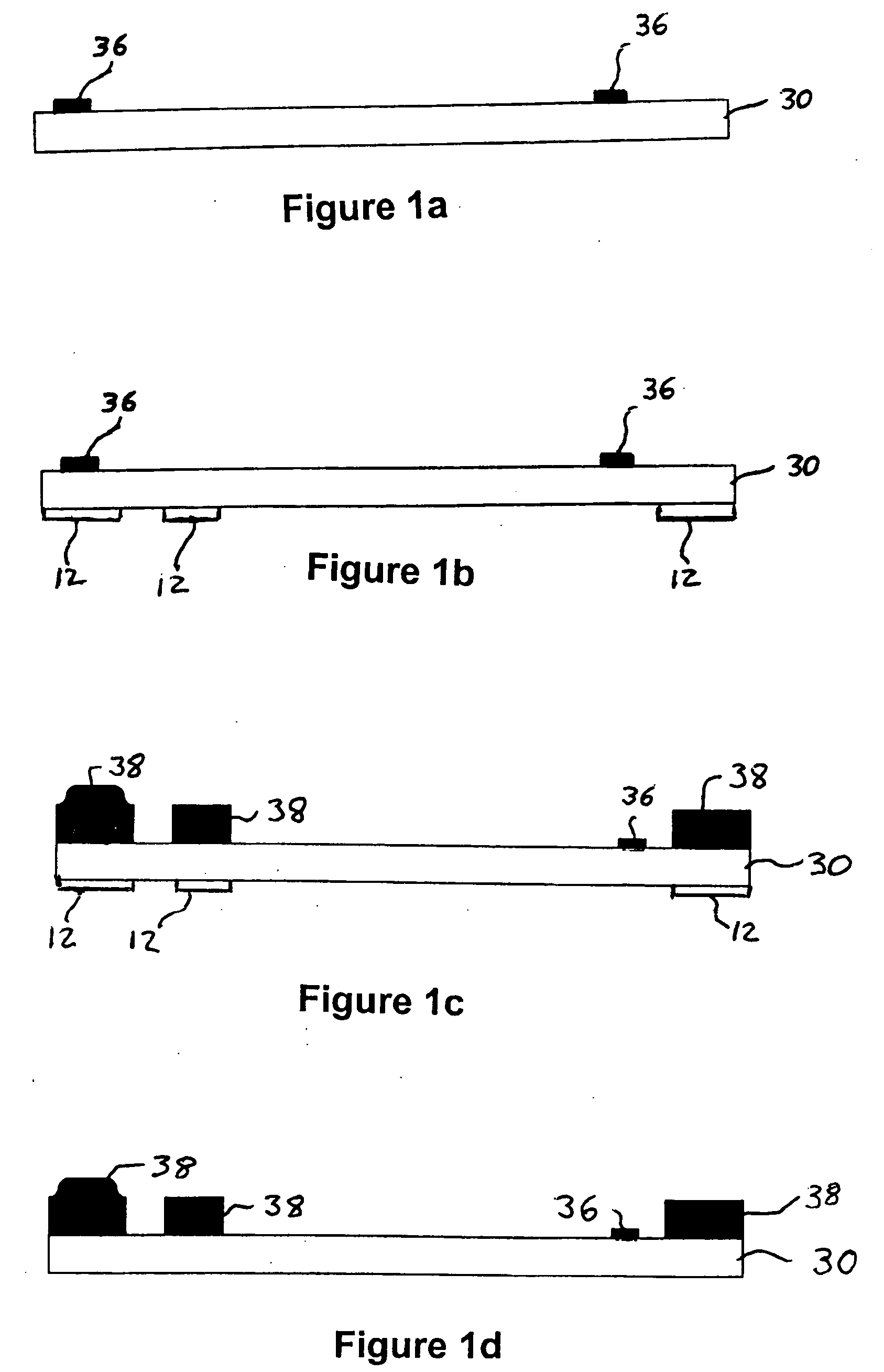

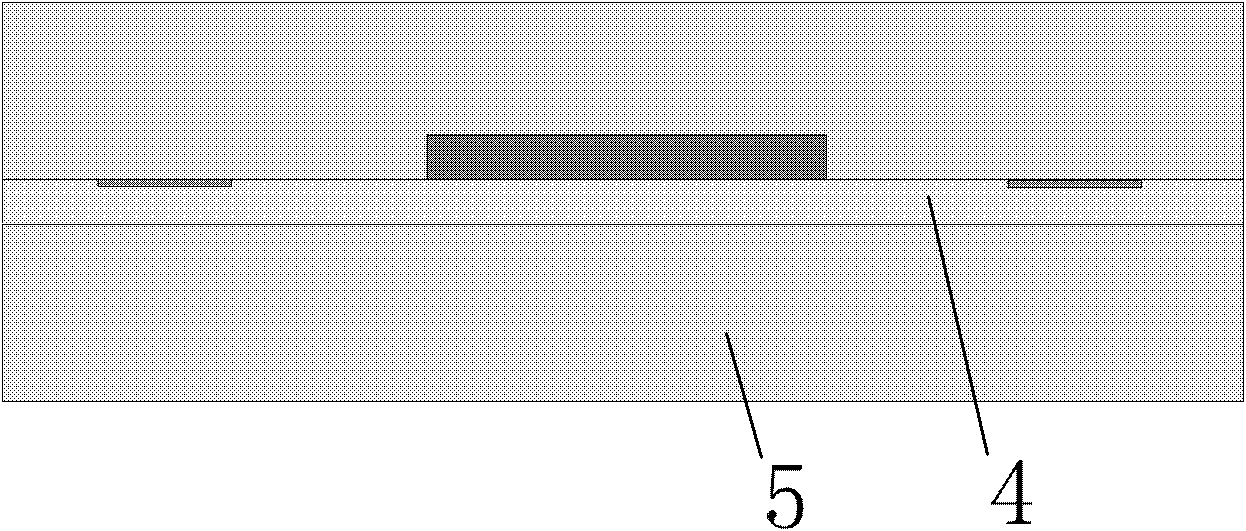

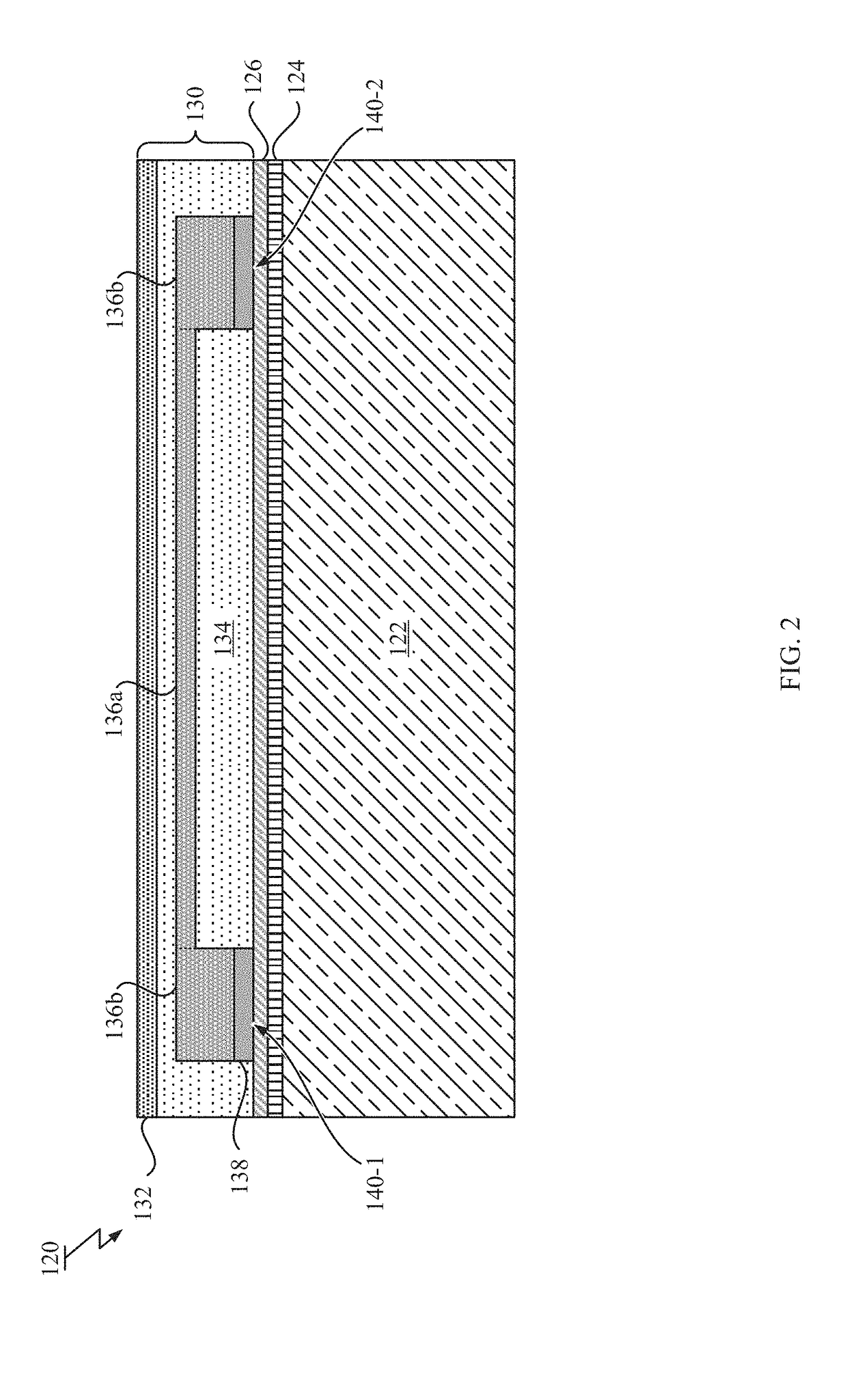

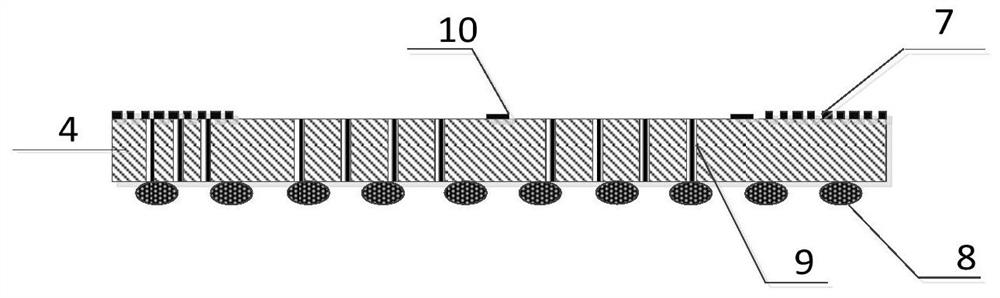

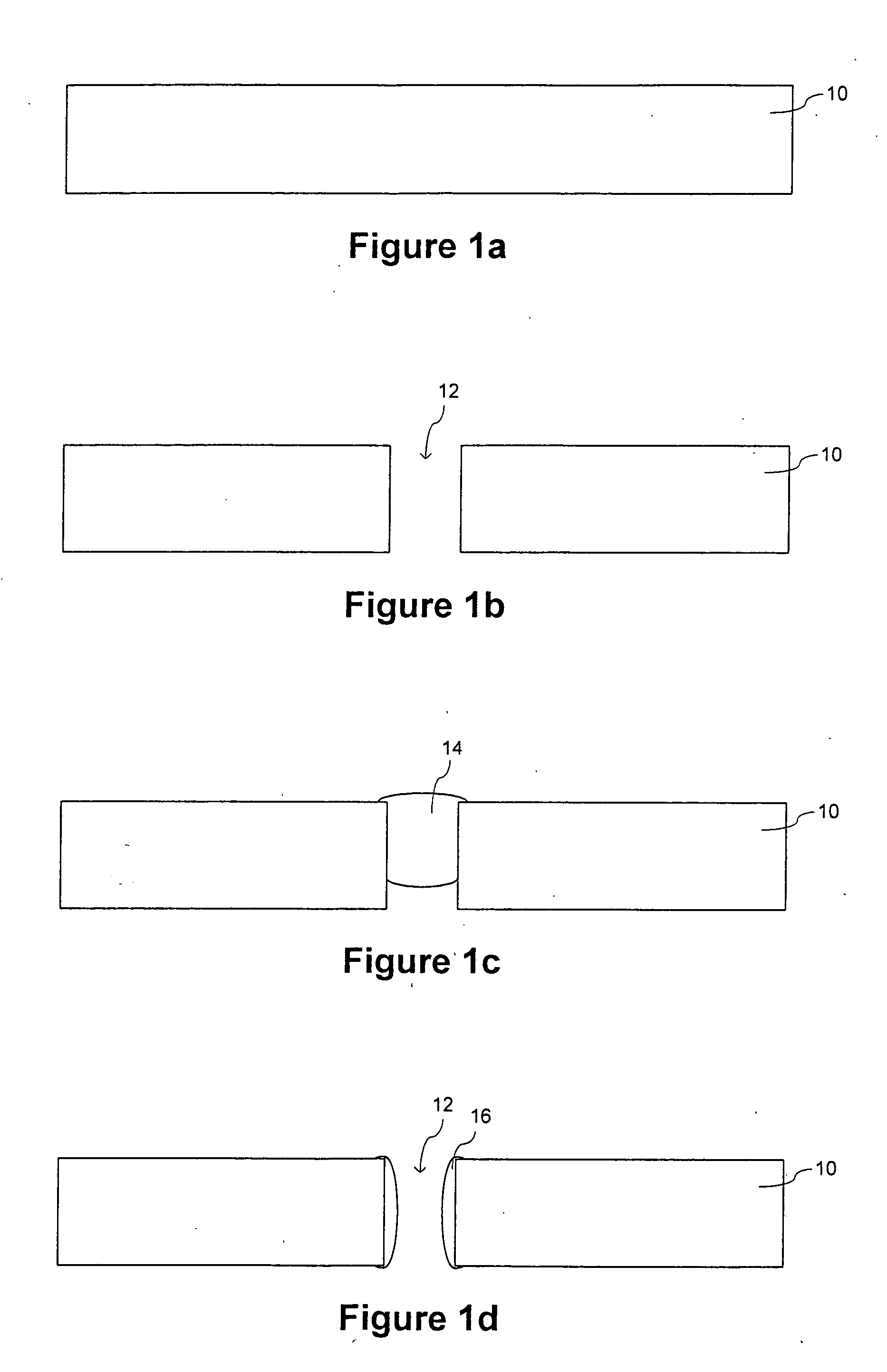

Method for making an integrated circuit substrate having embedded back-side access conductors and vias

InactiveUS7399661B2Improve interconnect densityReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesHigh densityElectrical conductor

A method for making an integrated circuit substrate having embedded back-side access conductors and vias provides a high-density mounting and interconnect structure for integrated circuits that is compatible with etched, plated or printed pre-manufactured substrate components. A circuit board or film having a pre-plated, etched or printed circuit, for example a rigid substrate having a Ball Grid Array (BGA) ball-attach pattern, is laser perforated to produce blind vias and / or conductive patterns that provide contact through to conductors of the prefabricated circuit board or film. Existing circuit board and substrate technology is thereby made compatible with laser-embedding technologies, providing the low-cost advantages of existing etching, plating and printing technologies along with a high conductor density associated with laser-embedded circuit technologies.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Multilayer circuit devices and manufacturing methods using electroplated sacrificial structures

InactiveUS20050161826A1Easy to produceHigh propertySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorMiniaturization

A multilayer circuit includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by electroplating techniques. Substrates formed in this manner enable significant increases in circuit pattern miniaturization, circuit pattern reliability, interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC

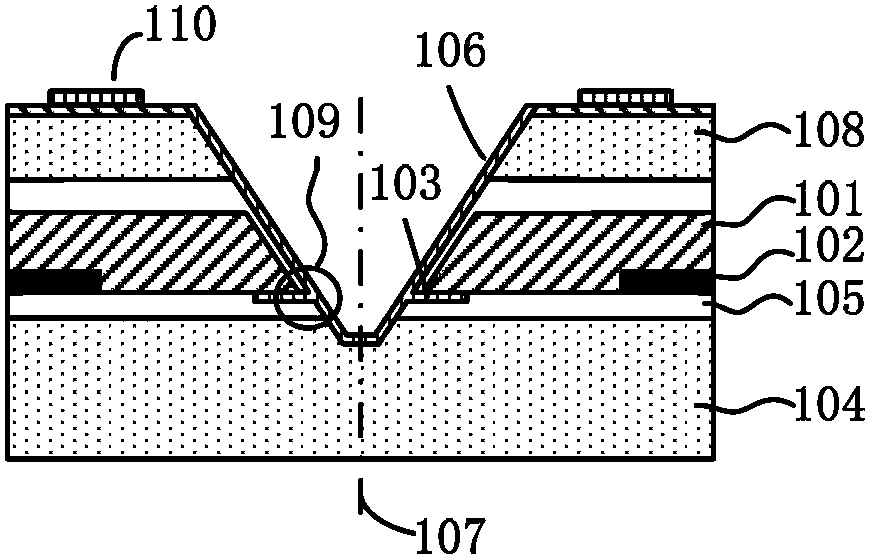

Method utilizing TSV (Through-Silicon-Via) to realize wafer level package of GaAs (gallium arsenide) image sensor

InactiveCN102544040AReduce volumeImprove package reliabilitySemiconductor/solid-state device manufacturingRadiation controlled devicesEtchingInterconnection density

The invention relates to a method utilizing TSV (Through-Silicon-Via) to realize wafer level package of a GaAs (gallium arsenide) image sensor. The method comprises the following steps: combining wet etching with mechanical machining to machine a groove; manufacturing a resin insulating layer in the groove; then manufacturing a through hole in resin by using a laser method; electroplating the inner part of the groove and the inner part of the through hole to realize the back extraction of the electrode of a front wafer surface; and making a passivating layer and solder bumps. The whole process is completed at a wafer level, and the interconnection density is high while the package cost is reduced. Meanwhile, a manufactured interconnection structure has high reliability.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

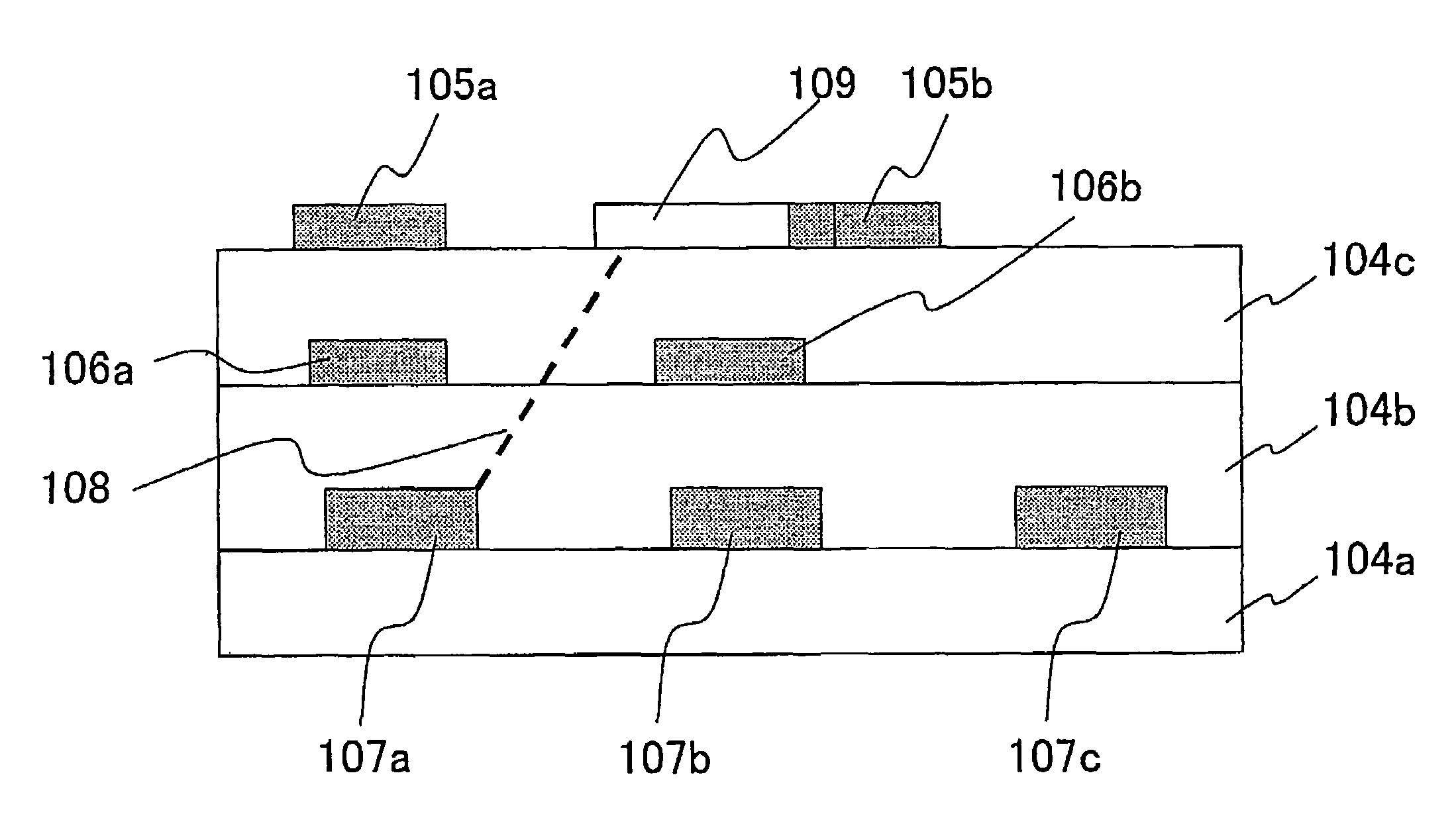

Semiconductor device

ActiveUS7247935B2Improves high speed operabilitySmall sizeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceInformation transmission

A semiconductor device, which is constituted in such a way that a pad portion of a logic chip is connected to an element region of a semiconductor chip with a bump bonding, is capable of achieving high speed operability of the elements, because delay of transmission of an electrical signal is suppressed a logic chip is directly connected to a DRAM, therefore, it is possible to suppress an increase of load capacitance caused by interconnects, and securing a wide bus width by a multiple pin connection. As a result, it becomes possible to enhance performance of the semiconductor device upon suppressing delay of information transmission from the logic chip to the DRAM.

Owner:RENESAS ELECTRONICS CORP

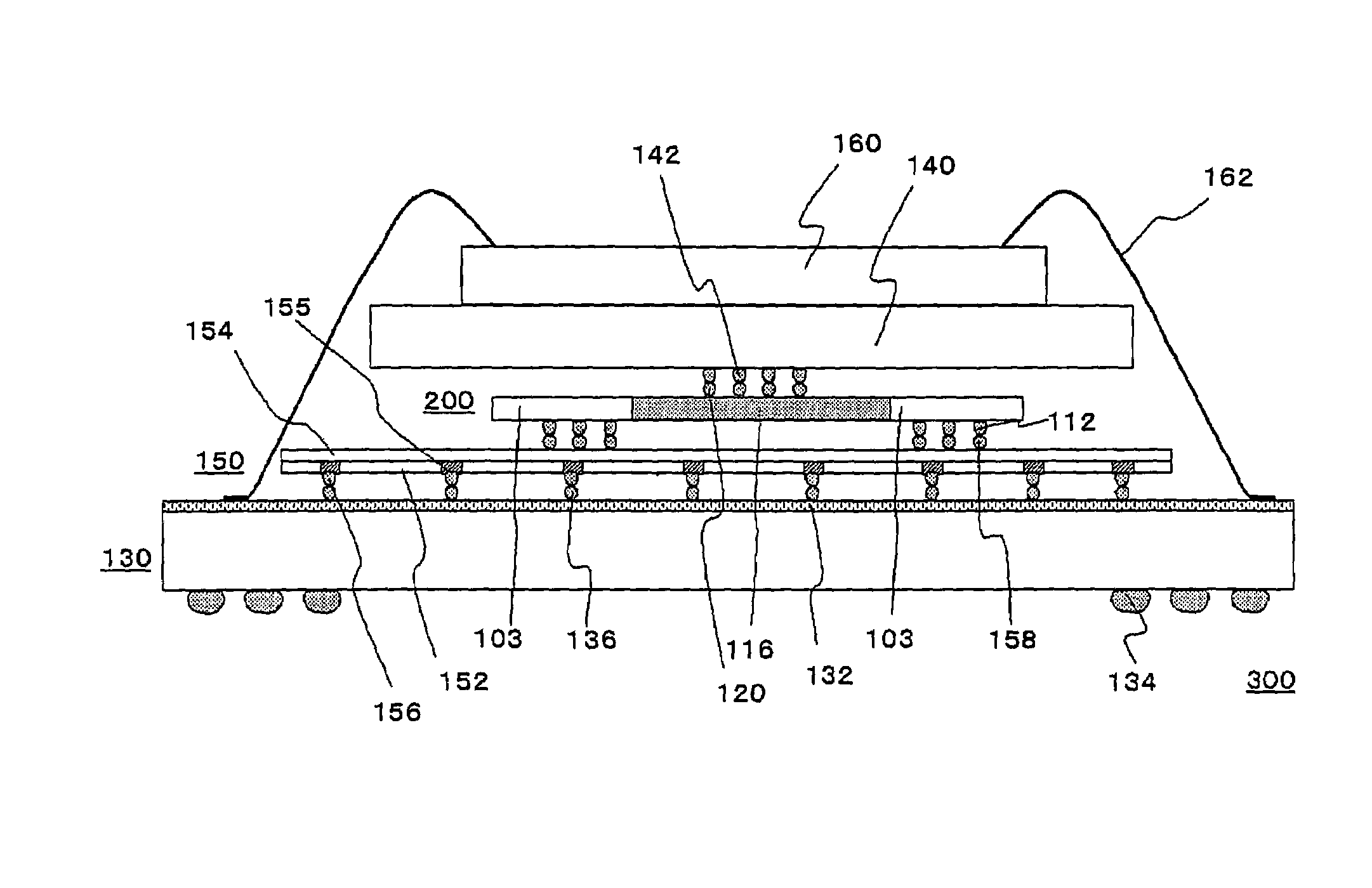

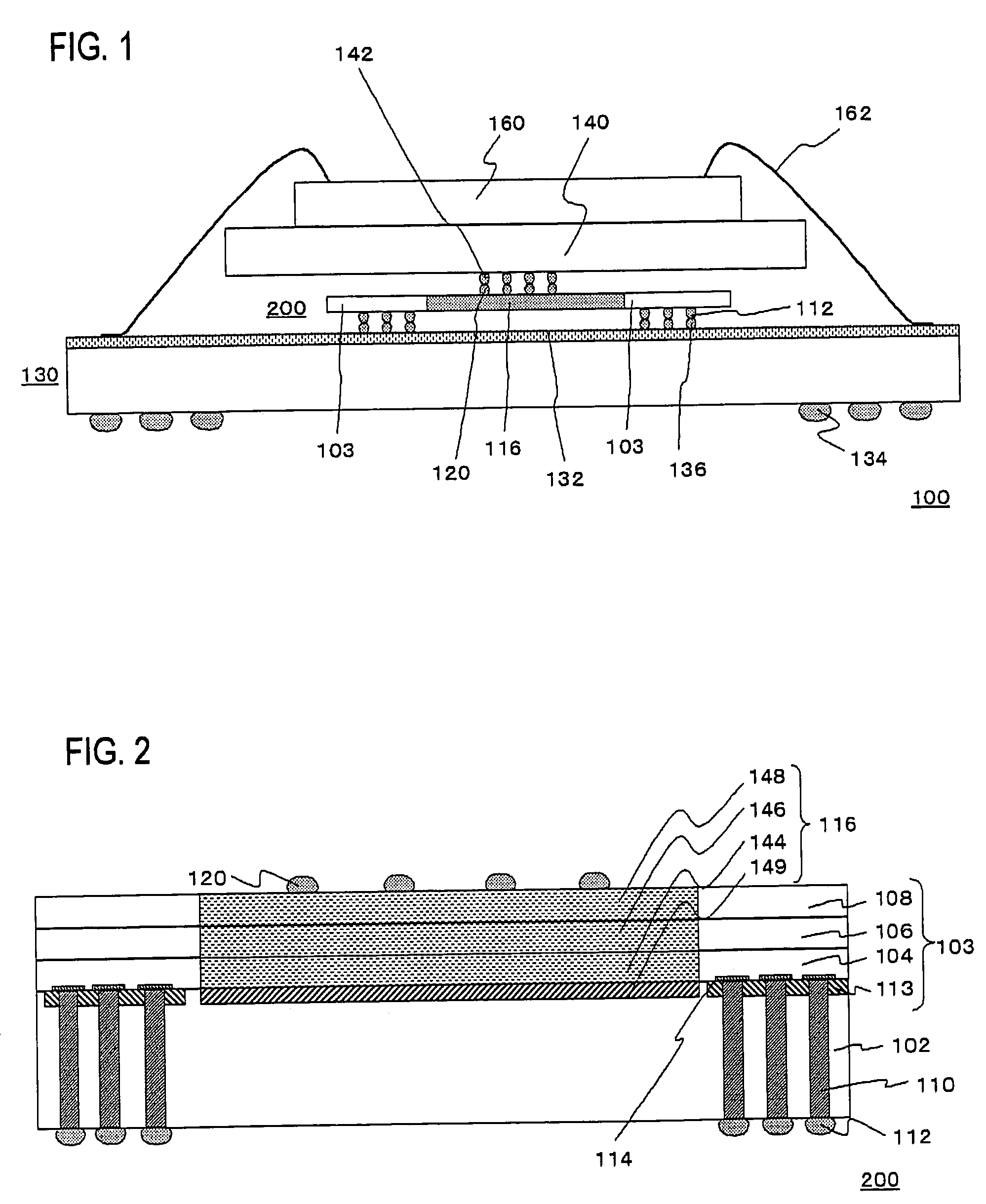

Method for making an integrated circuit substrate having laminated laser-embedded circuit layers

ActiveUS8826531B1Improve interconnect densityPrinted circuit assemblingLine/current collector detailsDielectricHigh density

A method for making an integrated circuit substrate having laminated laser-embedded circuit layers provides a multi-layer high-density mounting and interconnect structure for integrated circuits. A prepared substrate, which may be a rigid double-sided dielectric or film dielectric with conductive patterns plated, etched or printed on one or both sides is laminated with a thin-film dielectric on one or both sides. The thin-film is laser-ablated to form channels and via apertures and conductive material is plated or paste screened into the channels and apertures, forming a conductive interconnect pattern that is isolated by the channel sides and vias through to the conductive patterns on the prepared substrate. An integrated circuit die and external terminals can then be attached to the substrate, providing an integrated circuit having a high-density interconnect.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

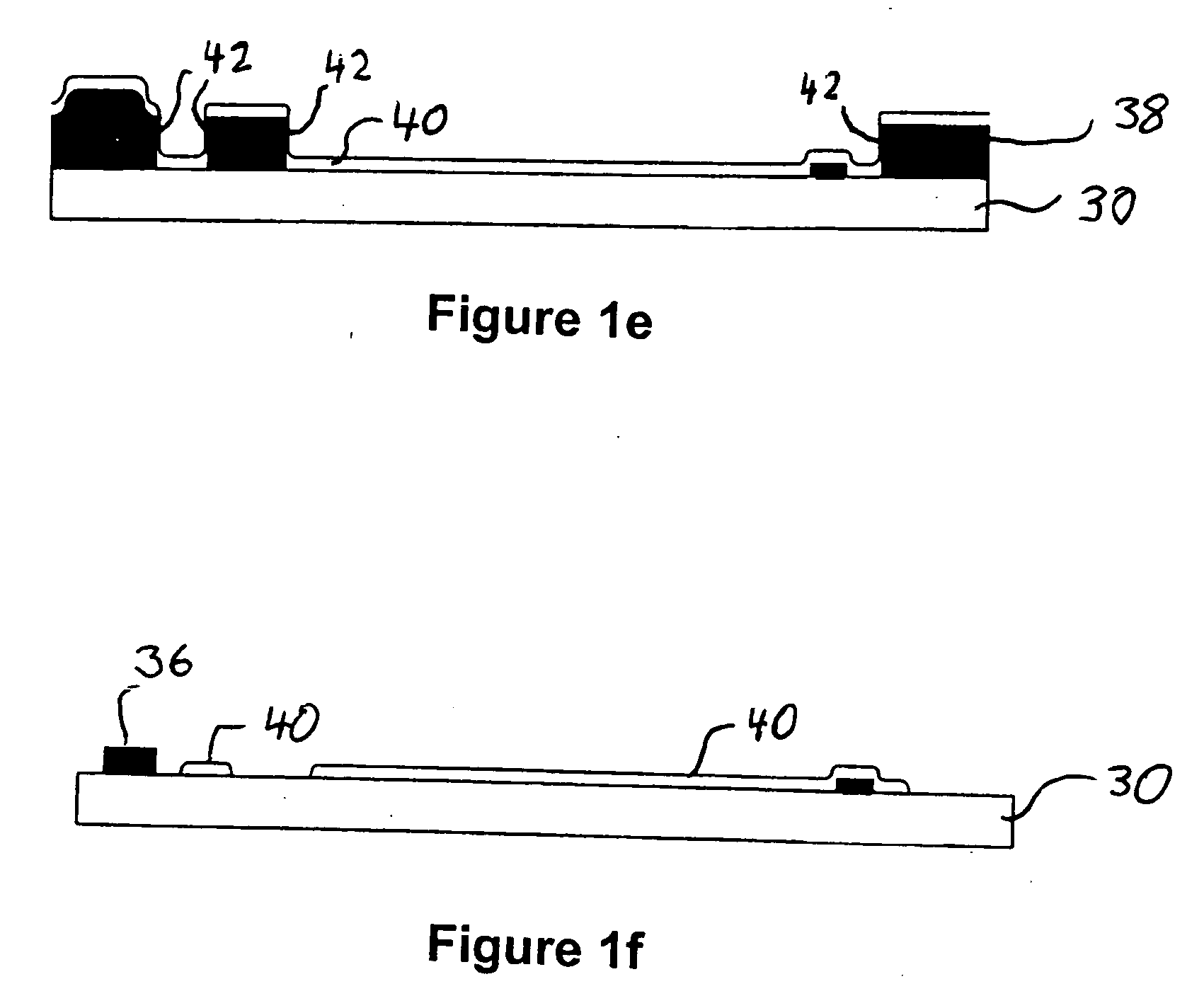

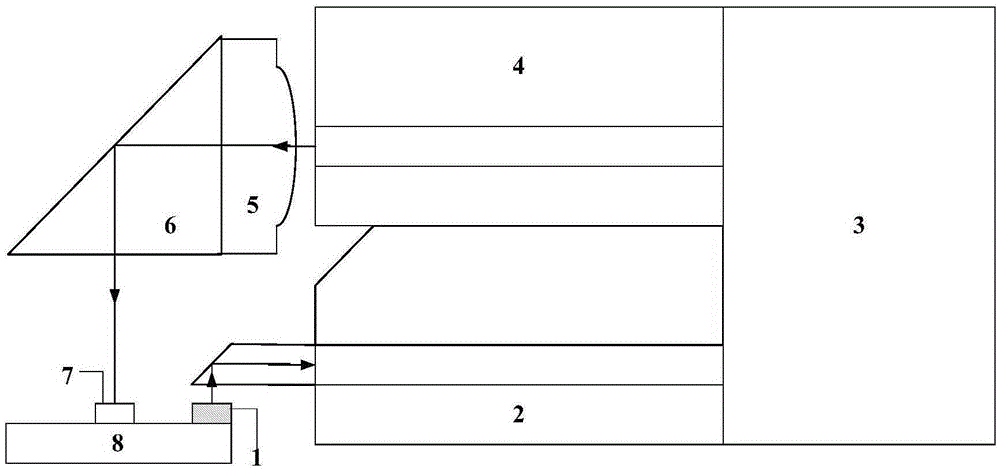

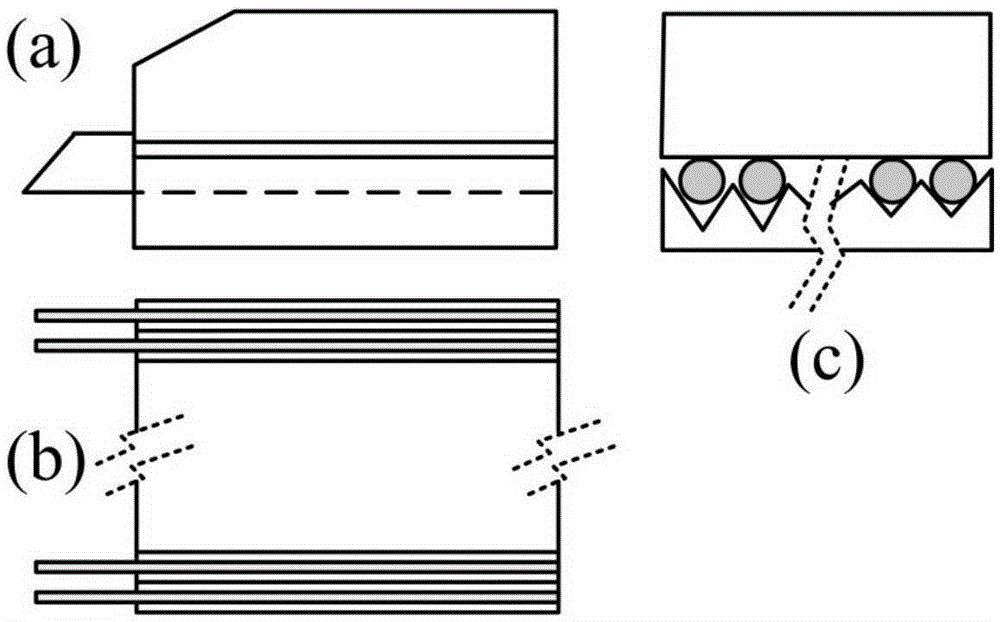

Optical fiber coupling module

InactiveCN105372770ACompact structureImprove interconnect densityCoupling light guidesHigh densityLaser array

The invention discloses an optical fiber coupling module and relates to an optical component in an active optical cable. An active optical cable in the prior art has defects such as large module size, a limited number of transmitting and receiving ports, complex process and the like. According to the optical fiber coupling module, a 45-degree oblique end surface optical fiber array is coupled to a laser array; a flat end surface optical fiber array is coupled to an optical detector through a right-angle prism and a micro lens array; and a transmitting assembly and a receiving assembly are integrated in one module. The optical fiber coupling module has the advantages of compact structure, high density interconnect and simple process.

Owner:HUAZHONG UNIV OF SCI & TECH

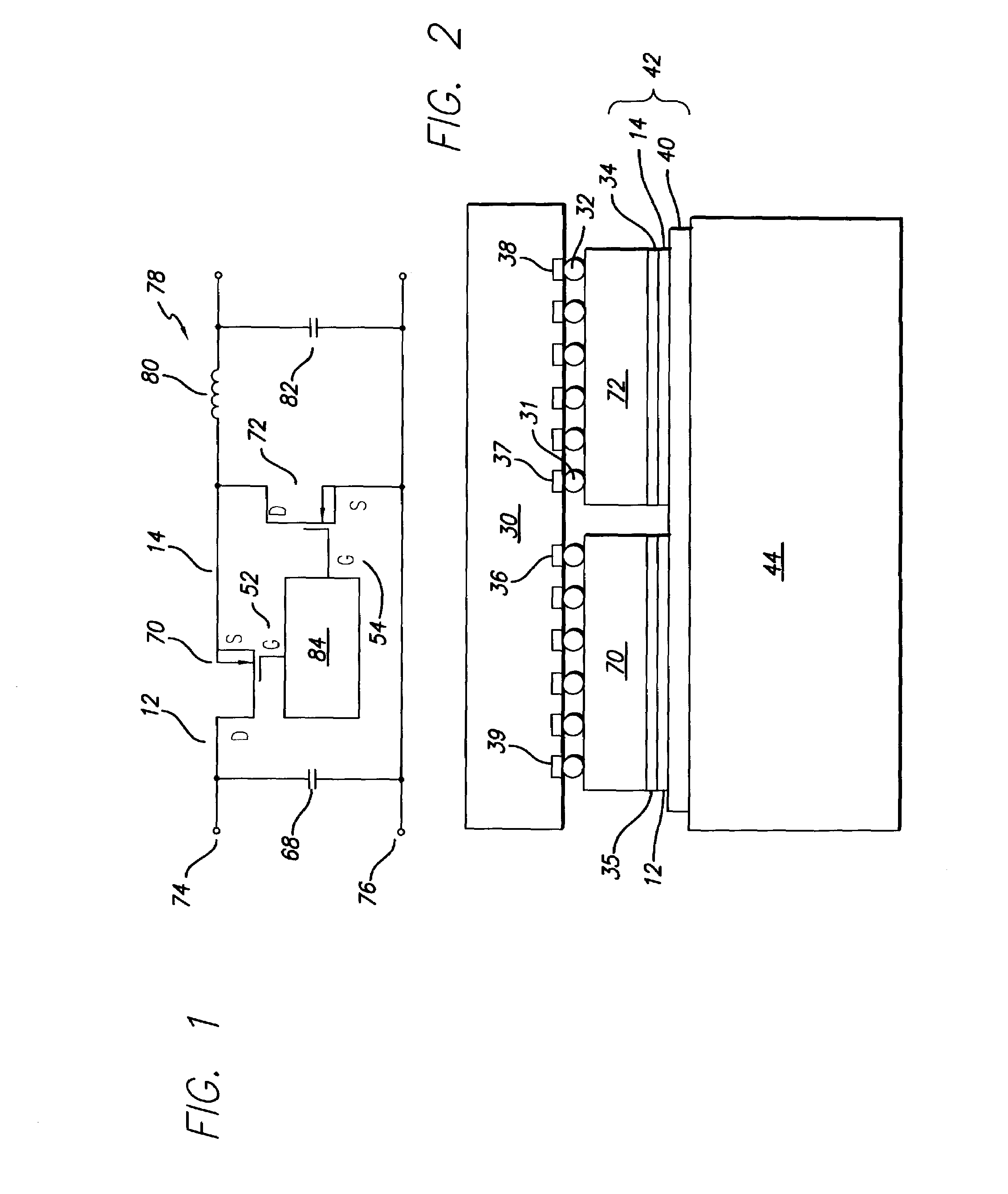

Power supply packaging system

InactiveUS7129577B2Solve the thickerLarge full package dimensionSemiconductor/solid-state device detailsPrinted circuit aspectsClose couplingLow voltage

A packaging system for a high current, low voltage power supply. The power supply uses bare die power FETs which are directly mounted to a thermally conductive substrate by a solder attachment made to the drain electrode metallization on the back side of the FETs. The source electrode and gate electrode of each FET are coupled to the circuitry on an overhanging printed circuit board, using CSP solder balls affixed to the front side of the FET die. The heat generated by the FETs is effectively dissipated by the close coupling of the FETs to the thermally conductive underlying substrate.

Owner:BEL POWER SOLUTIONS INC

Device interconnects

ActiveUS20090242260A1Reduce resistanceReduce capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical contacts

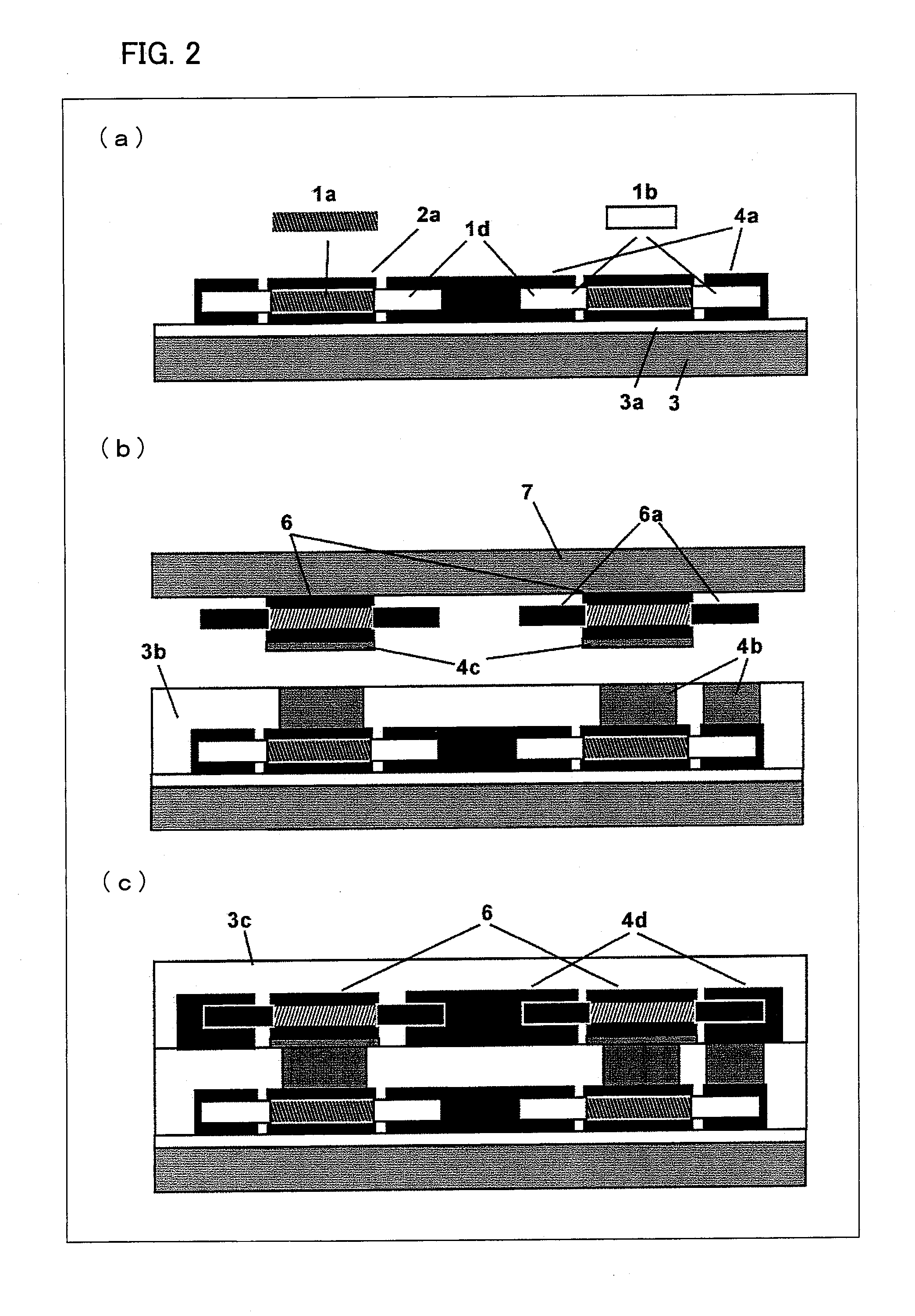

A method of fabricating a device structure, comprises: forming an insulating layer (3b) over a first set of devices disposed over a substrate (3); forming one or more vias in the insulating layer; disposing a second set of devices (6) over the insulating layer, wherein devices of the second set comprise respective electrical contacts (6a) and are disposed over the insulating layer (3b) such that a side on which a contact (6a) can be accessed faces the substrate (3); and forming one or more electrical contacts between the first set of devices and the second set of devices (6) through the via(s). The second set of devices and at least one via are positioned such that one or more of the vias lies at least partially within the footprint of two devices, each belonging to a different device layer.

Owner:SHARP KK

Compact optical fiber coupler

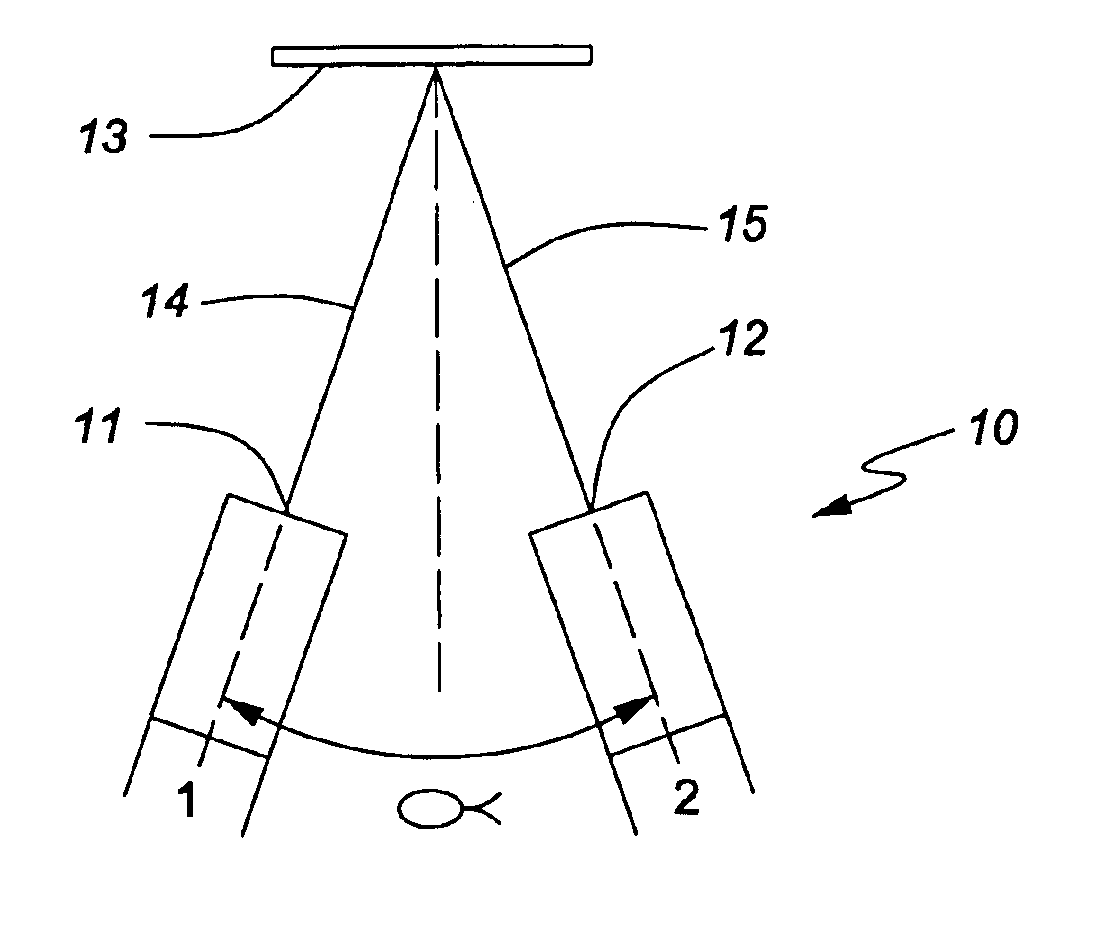

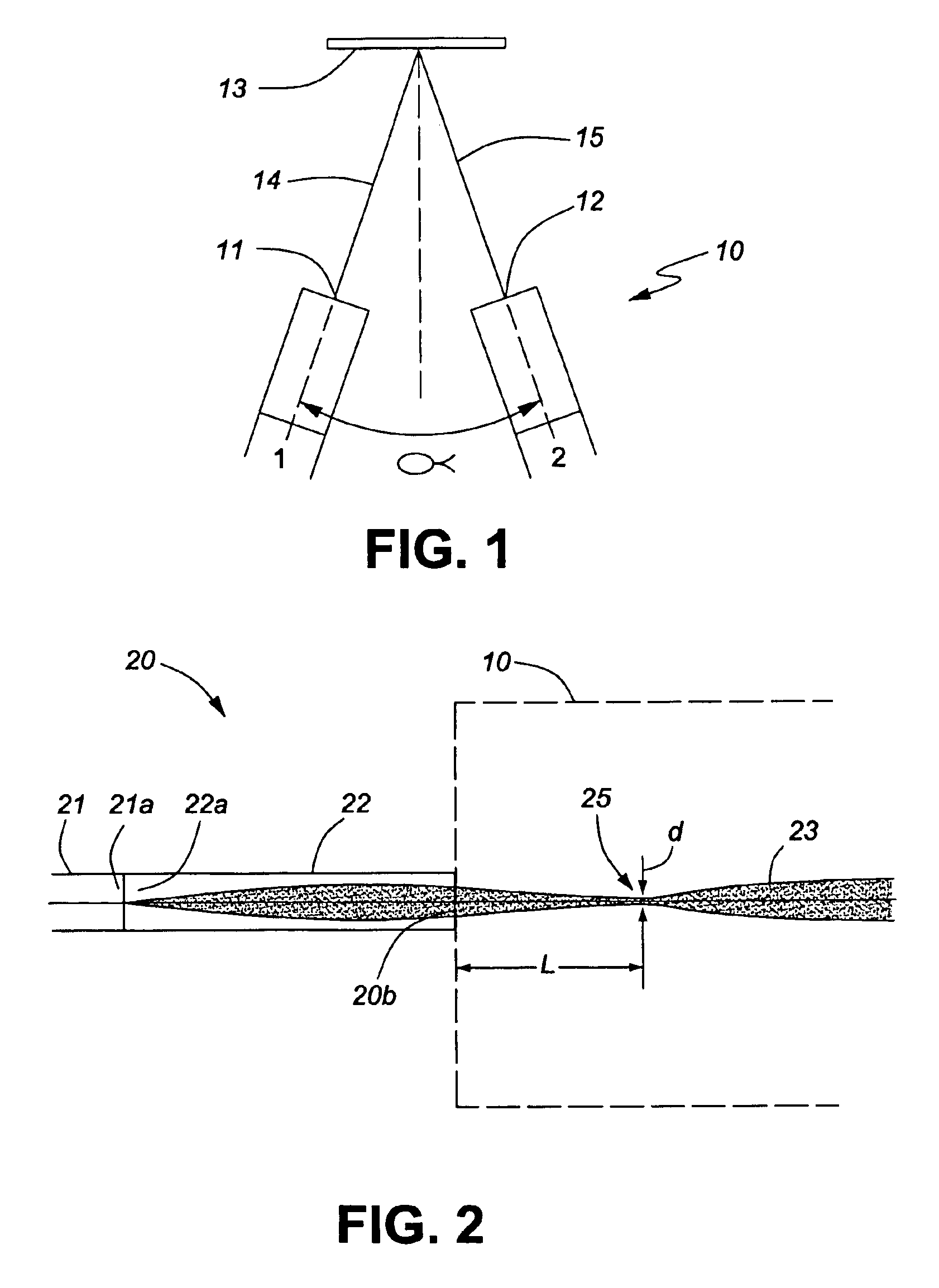

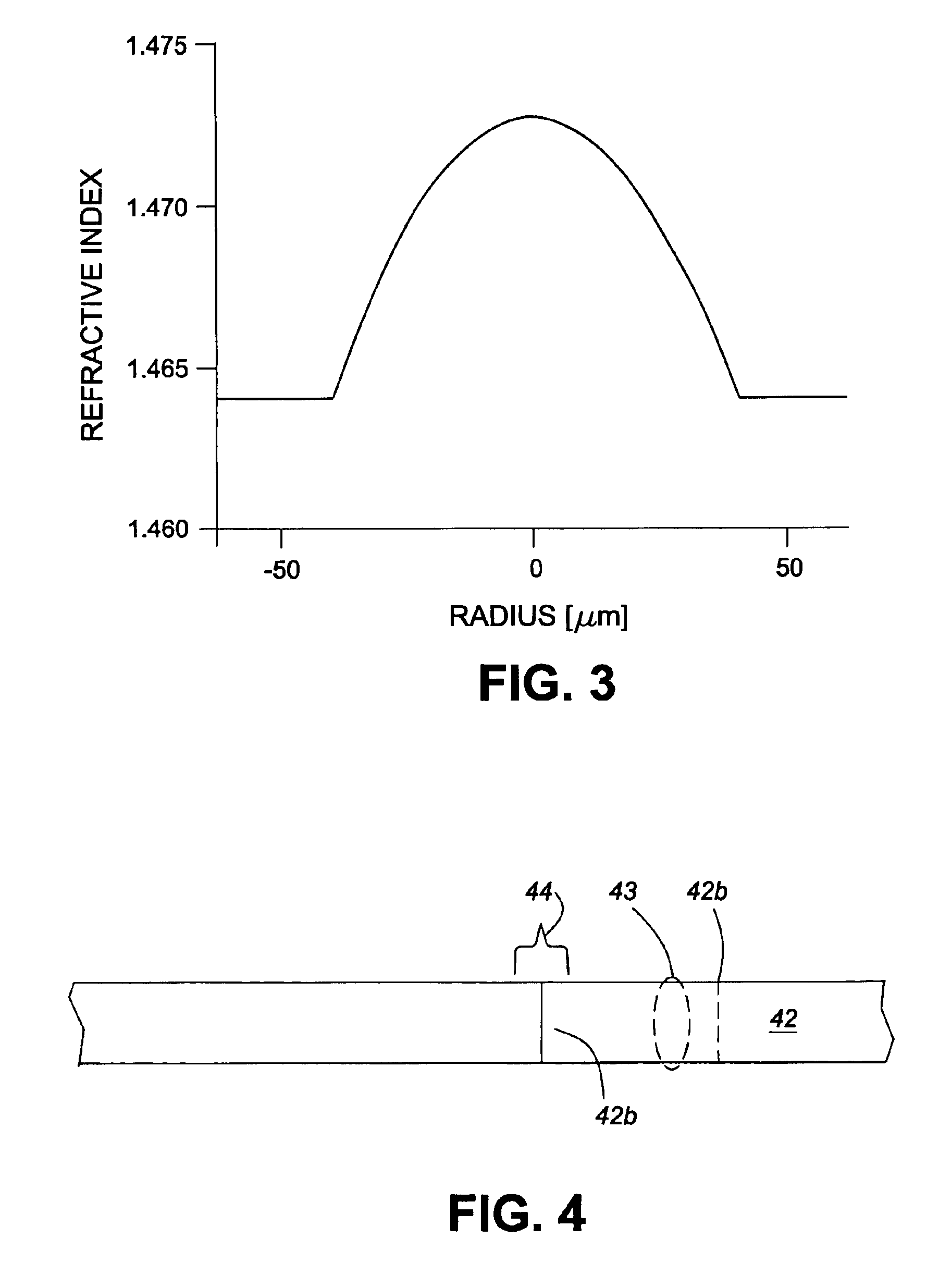

InactiveUS6873768B2Improve interconnect densityMinimize polarizationOptical fibre with graded refractive index core/claddingCoupling light guidesCouplingInterconnection density

The inventive coupling device enables a high interconnection density of single mode optical fiber in active and passive devises used in a fiber optic telecommunication system. The coupling device comprise a micro-lens formed by terminating a single mode optical fibers with an optimized gradient index fiber, thus avoiding a significant increase in fiber diameter. The gradient index is optimized to provide a long working distance to the minimum spot size so that efficient coupling can be achieved in a free space interconnection between either multiple single mode fibers or a single mode fiber to a transmitting or receiving device.

Owner:JDS UNIPHASE CORP

Multilayer circuit devices and manufacturing methods using electroplated sacrificial structures

InactiveUS8003513B2Improve interconnect densityNarrow dimensional toleranceSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorMiniaturization

A multilayer circuit includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by electroplating techniques. Substrates formed in this manner enable significant increases in circuit pattern miniaturization, circuit pattern reliability, interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC

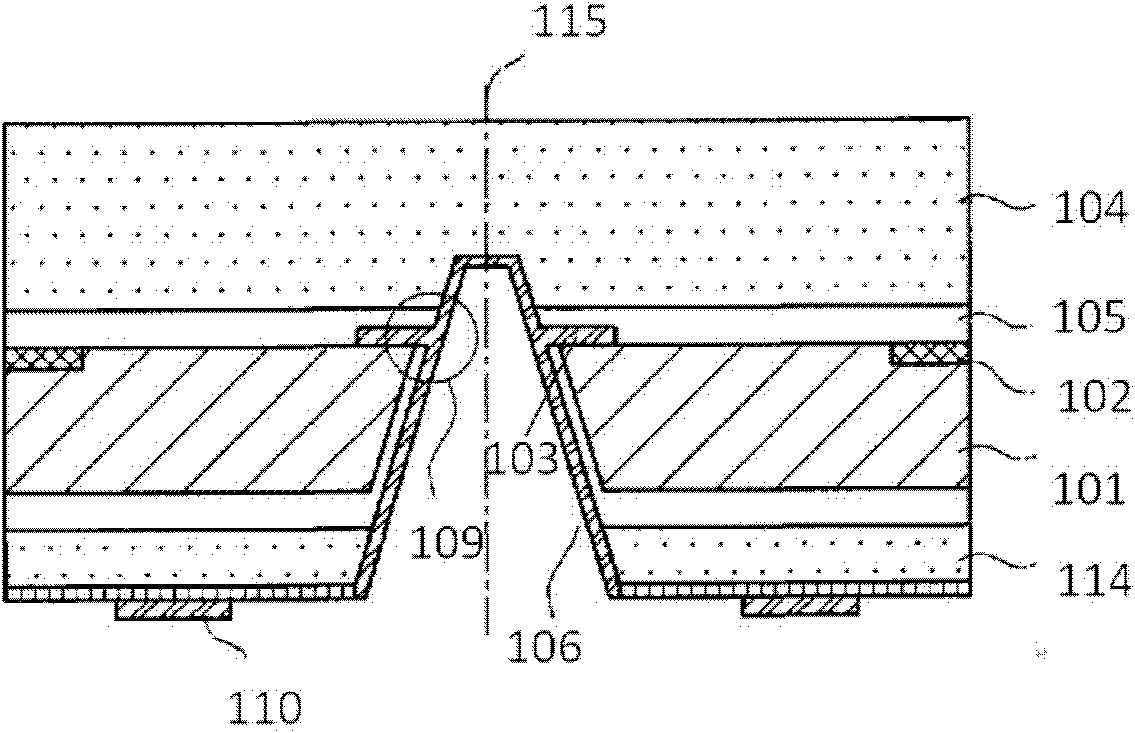

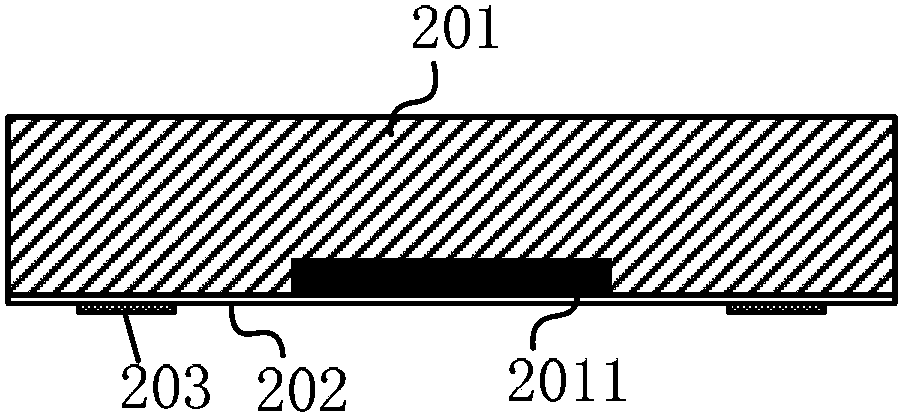

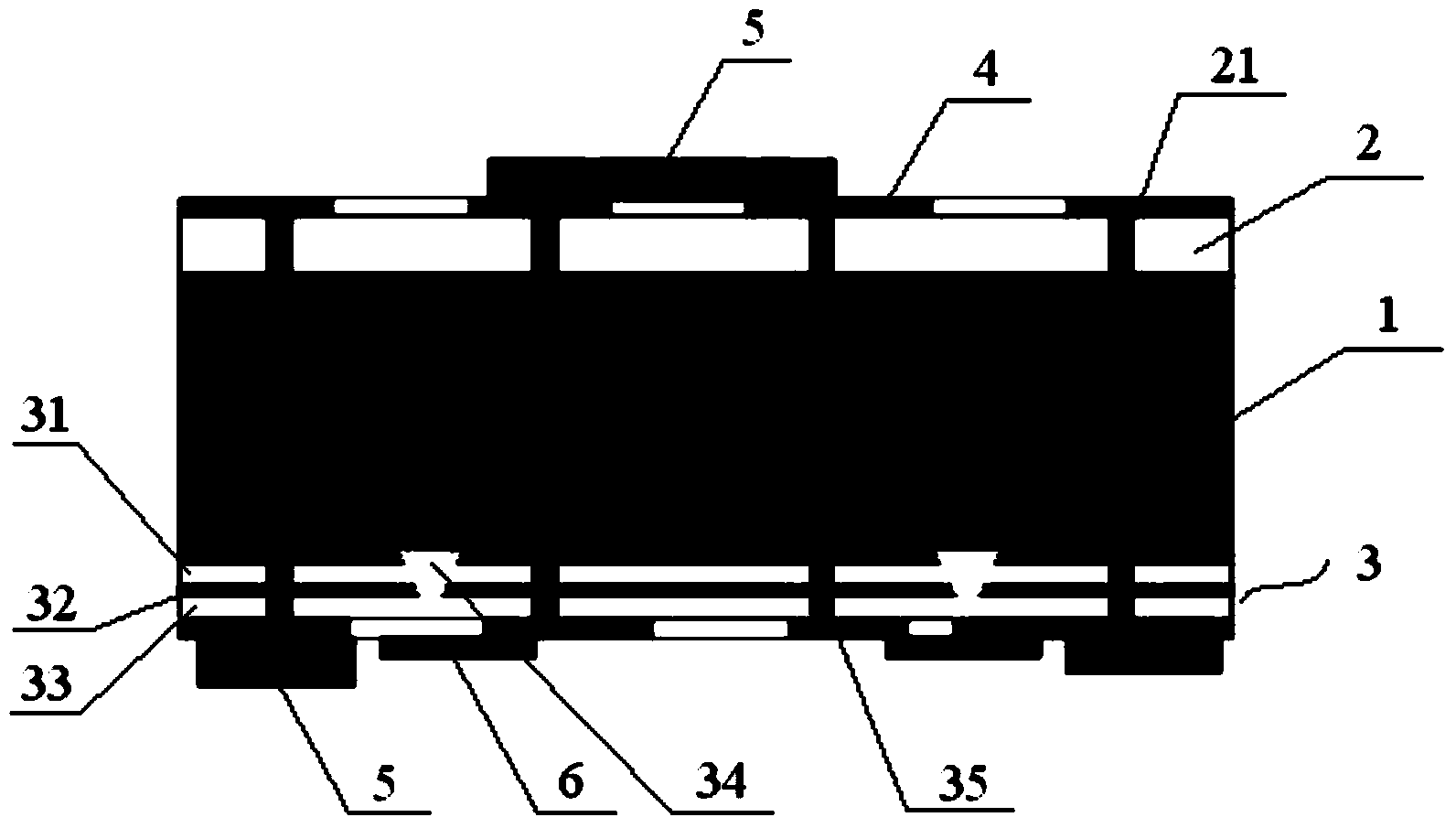

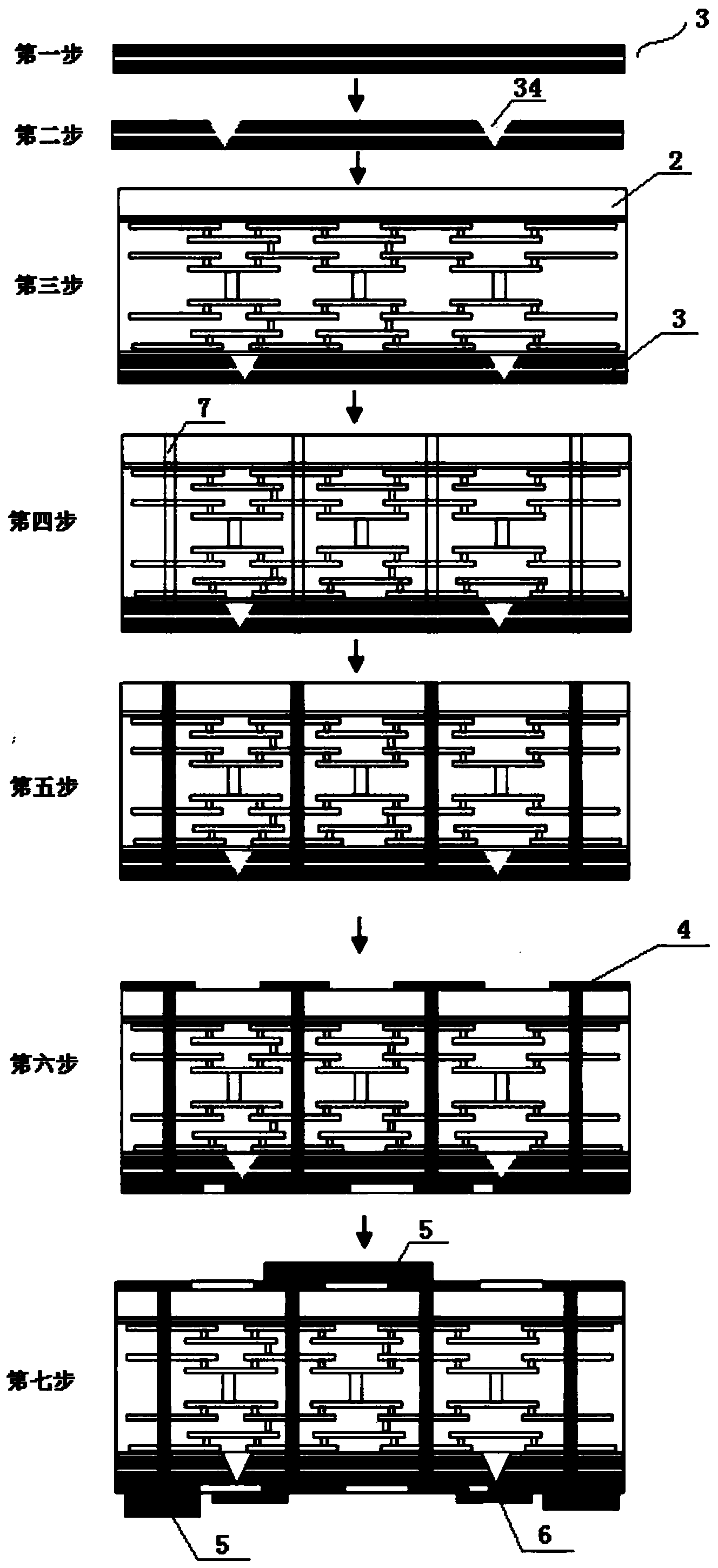

Wafer-level chip size encapsulation technology for GaAs (gallium arsenide) CCD (Charge Coupled Device) image sensor

ActiveCN102509718AImprove interconnect densityFirm packagingDecorative surface effectsSemiconductor/solid-state device manufacturingInterconnection densityCharge couple device

The invention relates to a wafer-level chip size encapsulation technology for a GaAs (gallium arsenide) CCD (Charge Coupled Device) image sensor. The technology is characterized by comprising the following steps of: (1) firstly bonding a glass wafer and a GaAs wafer through a resin adhesive so as to protect the active surface of a chip and improve the strength of a chip wafer; (2) manufacturing a trapezoidal-slot structure by a wet corrosion or physical method so as to reduce the lining thickness of a chip interconnection area; (3) manufacturing vertical interconnected through holes by a dry etching technology so as to expose a pad on the active surface of the chip; (4) sputtering seed-layer metal and electroplating, and manufacturing a hole metalizing and RDL layer to realize circuit interconnection from the active surface to the back surface of the chip; (5) manufacturing a passivation layer, a UBM layer and raised points; and (6) finally scribing to form an independent encapsulation chip. As the trapezoidal-slot structure on the back realizes thickness reduction only in the area with the pad, the cost is effectively lowered; and through the interconnection of the vertical through holes, the encapsulation interconnection density can be improved, and the signal transmission path is shortened.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

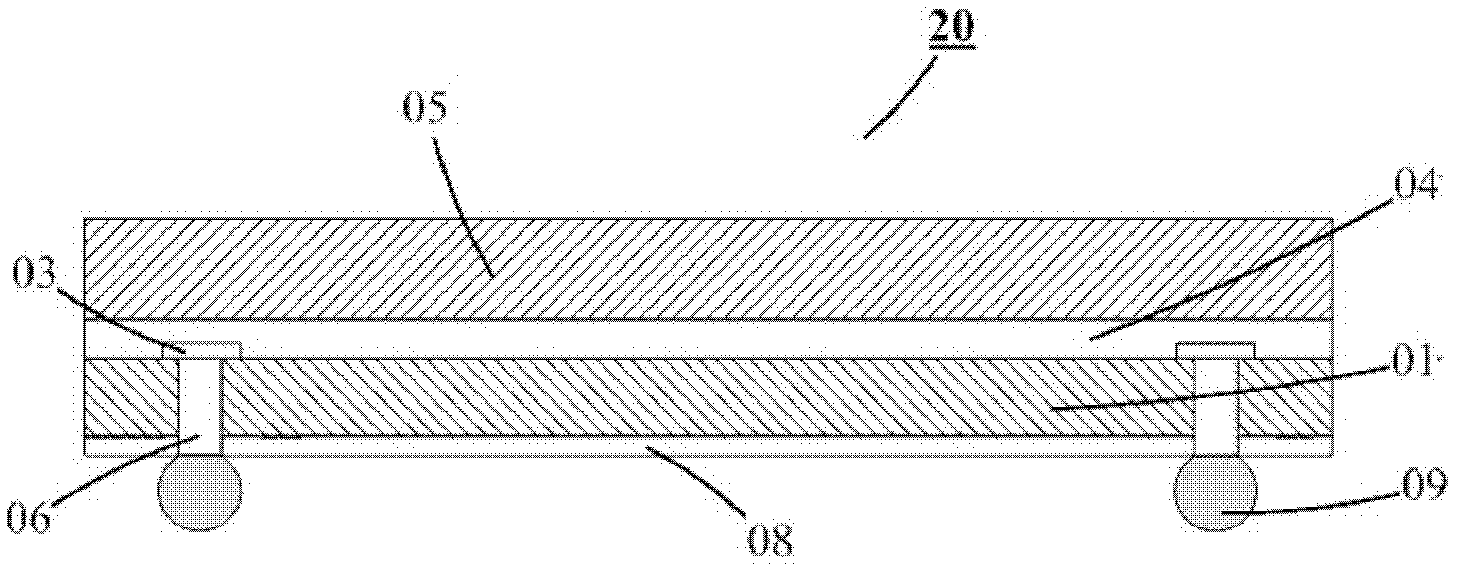

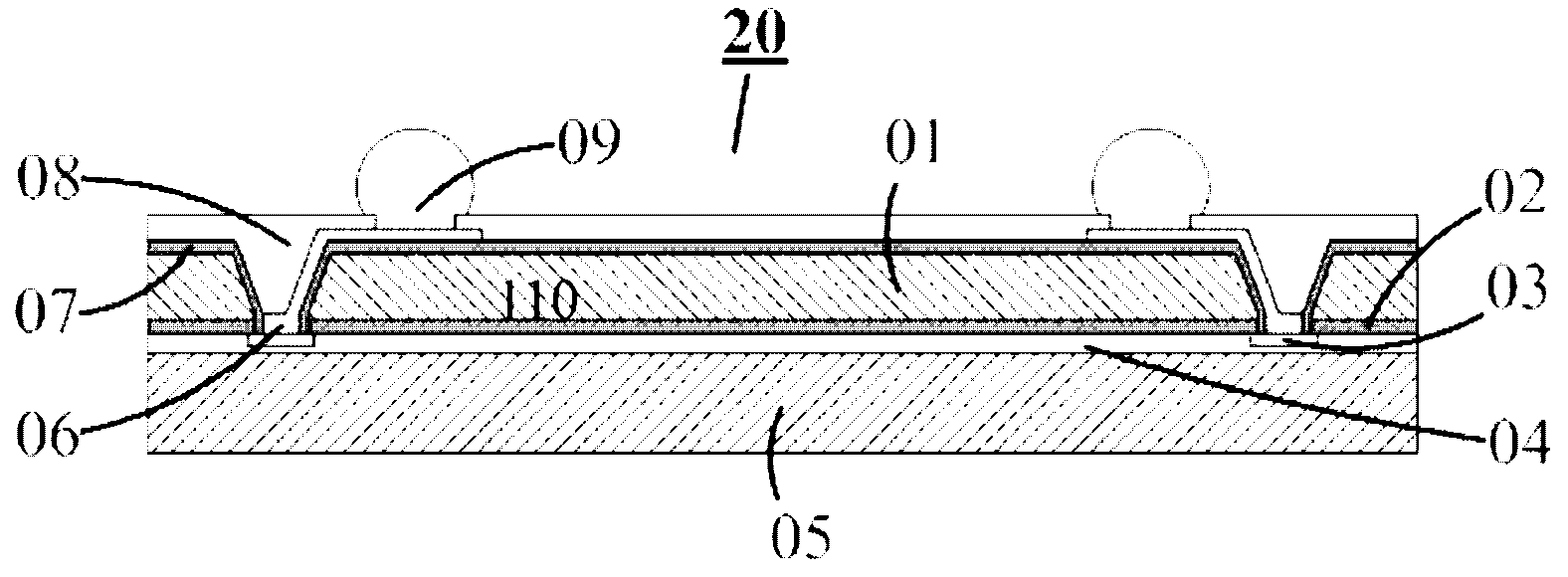

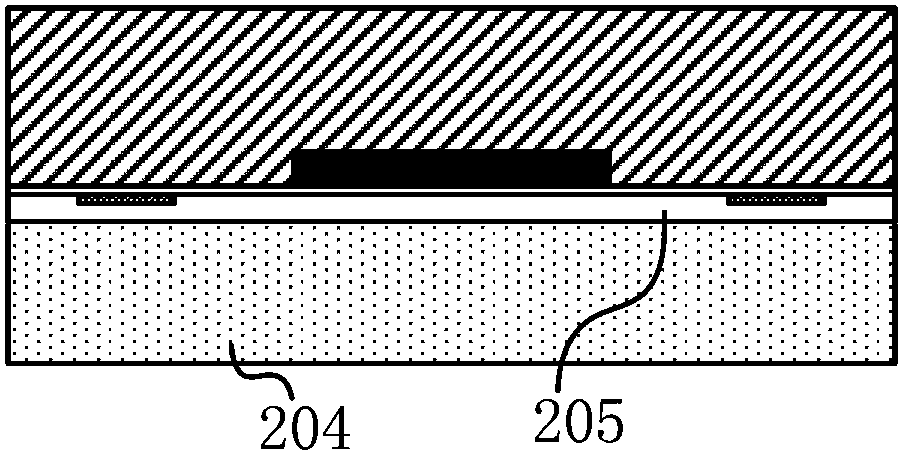

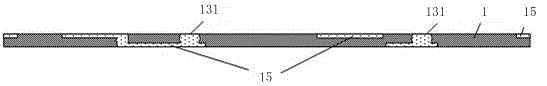

Wafer level packaging method and packaging structure for image sensor

InactiveCN103855173AOvercoming the problem of poor reliabilityOvercome costsRadiation controlled devicesMetal interconnectEngineering

The invention provides a wafer level packaging method and packaging structure for an image sensor. The packaging method comprises the steps that a first passivation layer is formed on the active face of a sensing wafer; at least one metal fan-out electrode is deposited on the first passivation layer; the active face of the sensing wafer and a transparent substrate are bonded; a second passivation layer is deposited on the back face of the sensing wafer, and a grooving mark is carved on the second passivation layer; grooves are formed in the grooving mark; a third passivation layer is manufactured on the back face of the sensing wafer; through holes penetrating through the metal fan-out electrodes are formed in the bottoms of the grooves; metal interconnecting wires are manufactured to guide the metal fan-out electrodes out to the back face of the third passivation layer through the through holes; a fourth passivation layer completely covering the metal interconnecting wires is manufactured; an opening is etched in the fourth passivation layer to expose one ends of the metal interconnecting wires; a UBM layer and soldering tin protrusions are manufactured on the fourth passivation layer. The wafer level packaging method and packaging structure are high in reliability, low in cost, small in signal delay and high in interconnecting density.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

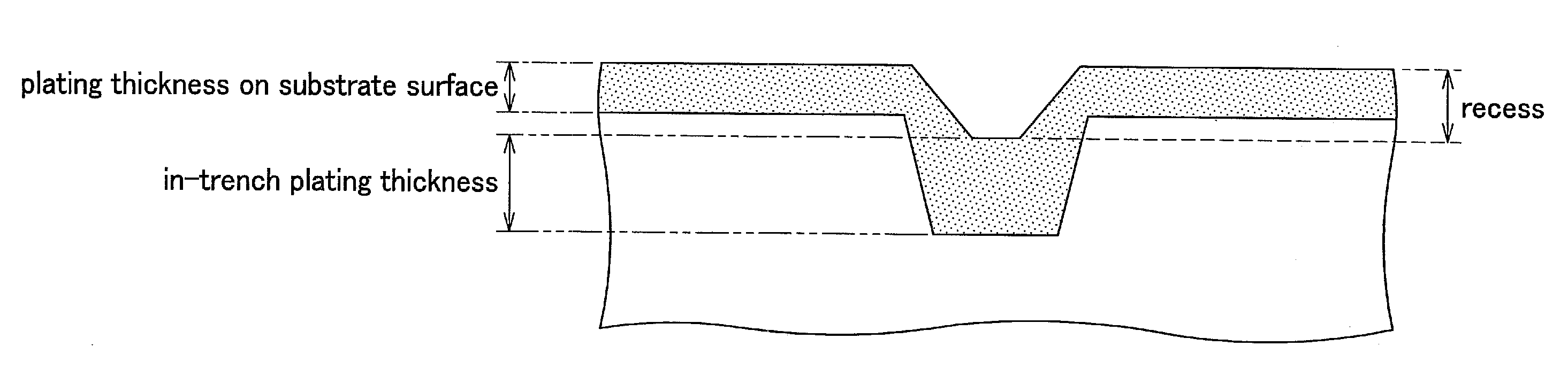

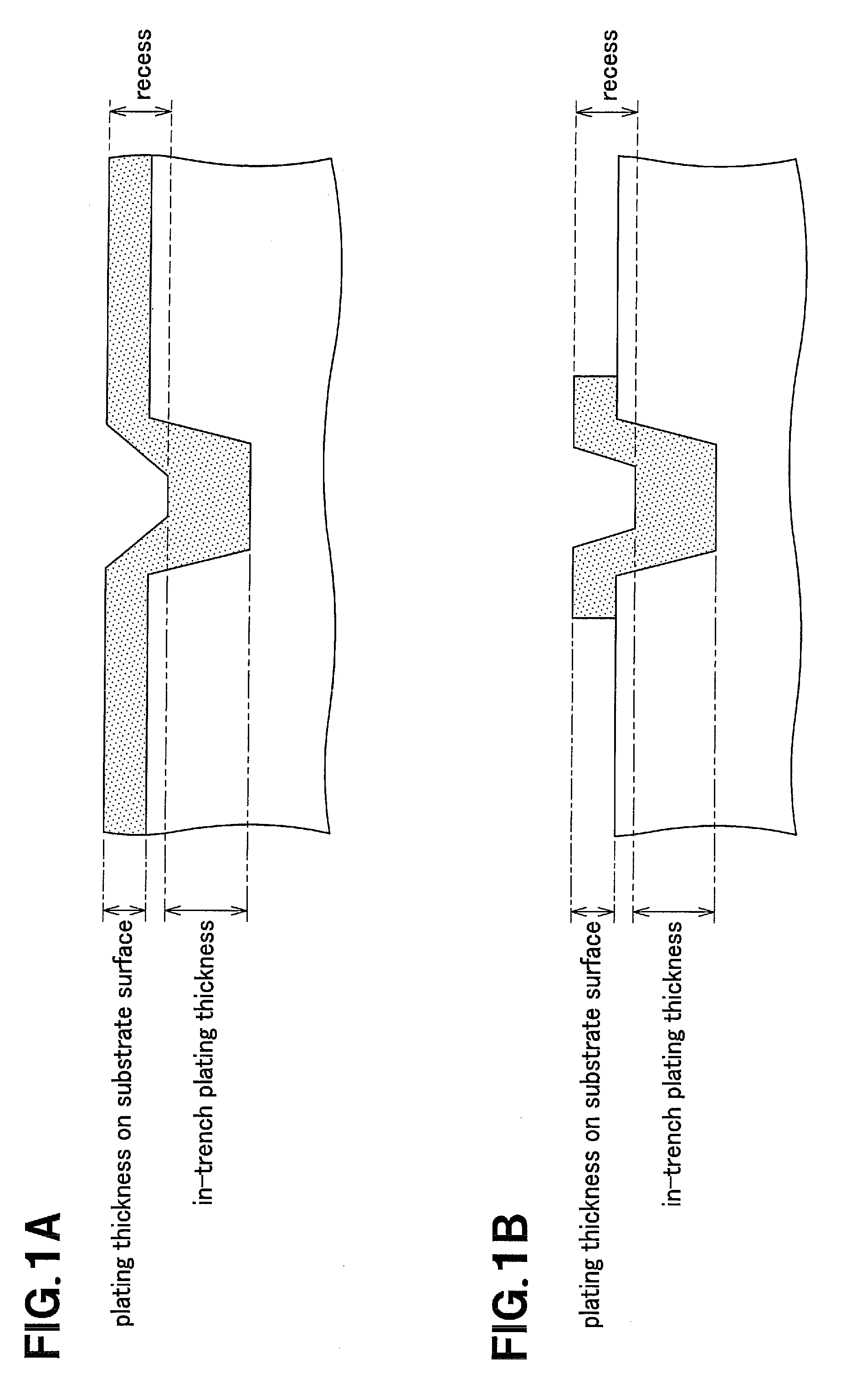

Electroless plating solution, method for electroless plating using the same and method for manufacturing circuit board

ActiveUS20100003399A1High interconnect densityImprove interconnect densityAnti-corrosive paintsLiquid/solution decomposition chemical coatingIonElectroless plating

Disclosed is an electroless plating solution exhibiting a good plating metal filling performance even for larger trenches or vias of several to one hundred and tens of μm, in a manner free from voids or seams, and allowing maintenance of stabilized performance for prolonged time.The electroless plating solution contains at least a water-soluble metal salt, a reducing agent for reducing metal ions derived from the water-soluble metal salt, and a chelating agent. In addition, the electroless plating solution contains a sulfur-based organic compound as a leveler having at least one aliphatic cyclic group or aromatic cyclic group to which may be linked at least one optional substituent. The aliphatic cyclic group or the aromatic cyclic group contains optional numbers of carbon atoms, oxygen atoms, phosphorus atoms, sulfur atoms and nitrogen atoms.

Owner:C UYEMURA & CO LTD

Solid-state hot-compression low-temperature bonding method using nickel micro needle cones

InactiveCN102543784AImprove interconnect densityImprove reliabilitySemiconductor/solid-state device manufacturingMetallic NickelHeat treating

The invention provides a solid-state hot-compression low-temperature bonding method using nickel micro needle cones. A layer of metallic nickel featured by being bestrewed with needle cones is manufactured on one side of a to-be-bonded welding spot, and welding flux is used on the other side of the to-be-bonded welding spot. A colligator is used for being aligned with the electrically interconnected welding spot, the welding spot is heated to a certain temperature not higher than the solder cap melting point, and a bonding pressing force is exerted and maintained for some time so that inlay bonding of needle cones and welding flux at the position of the interconnection point is achieved. A thin layer of precious metal is electroplated on the layer of nickel micro needle cones to prevent the surface from being oxidized prior to bonding. After bonding is finished, the welding spot is placed at a certain temperature for heat treatment for some time to achieve diffusion reaction and remove holes. The solid-state hot-compression low-temperature bonding method using nickel micro needle cones is capable of overcoming some defects in the prior art in novel encapsulation technology application, avoids thermal damage caused to components by reflow soldering process temperature, and resolves the problems of welding flux spreading in molten welding and solid-liquid phase fast reaction.

Owner:SHANGHAI JIAO TONG UNIV

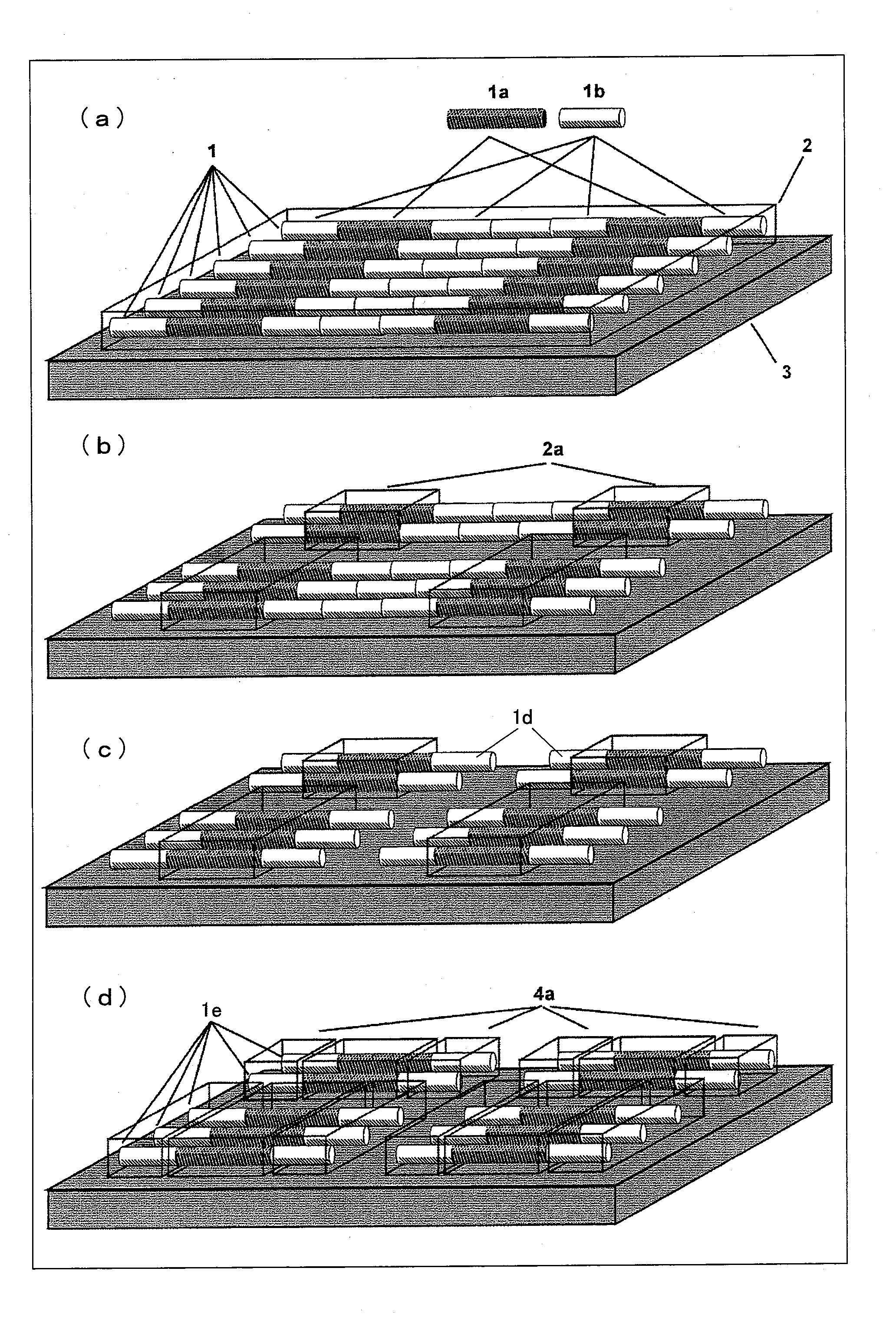

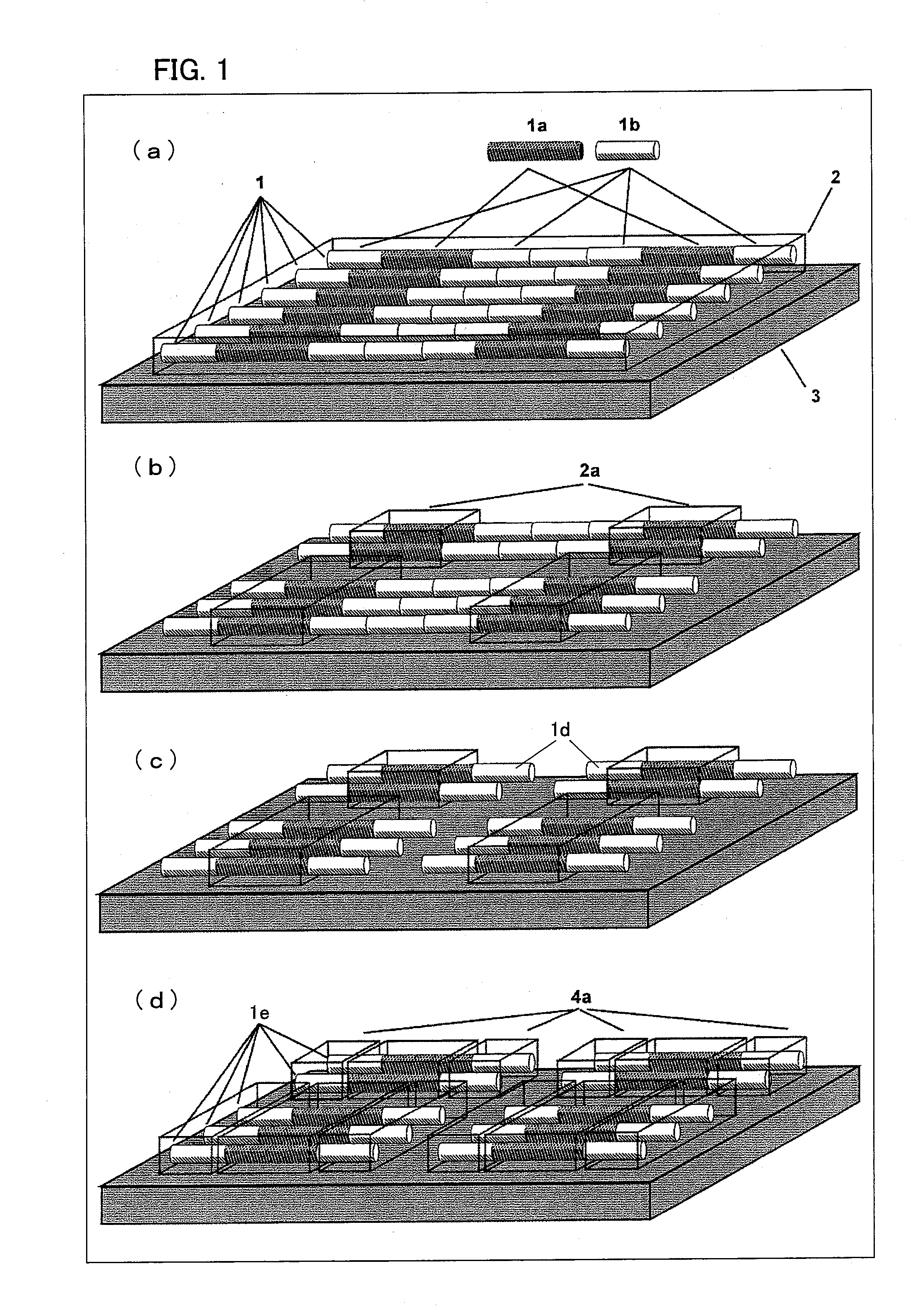

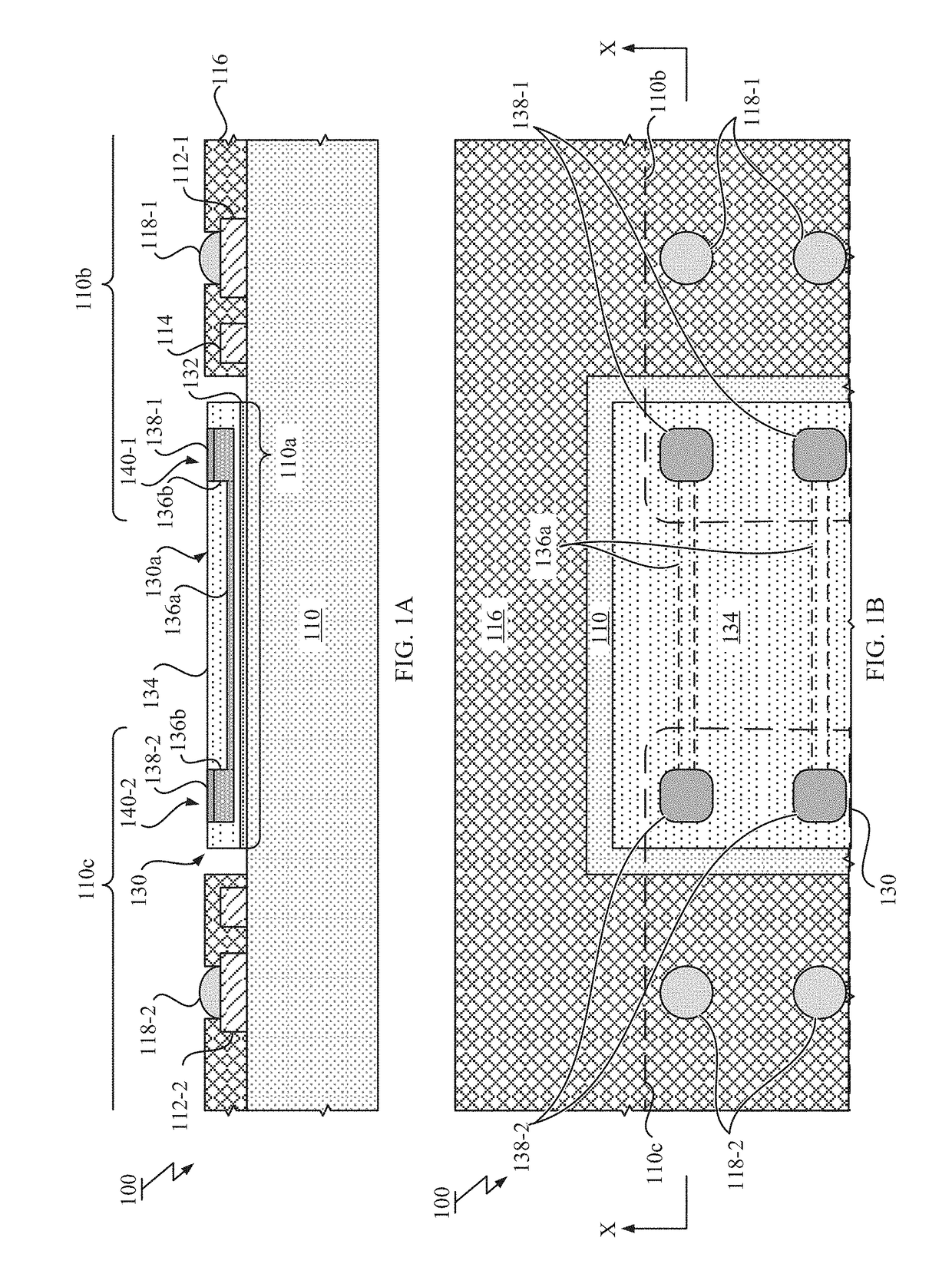

High-density interconnecting adhesive tape

ActiveUS20190051603A1Increase densityImprove production yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringHigh density

A technique for interconnecting chips by using an interconnection substrate is disclosed. The interconnection substrate includes a base substrate, a first group of electrodes on the base substrate for a first chip to be mounted, and a second group of electrodes on the base substrate for a second chip to be mounted. The interconnection substrate further includes an interconnection layer that includes a first set of pads for the first chip, a second set of pads for the second chip, traces and an organic insulating material. The interconnection layer is disposed on the base substrate and located within a defined area on the base substrate between the first group of electrodes and the second group of the electrodes.

Owner:IBM CORP

Power converter package with enhanced thermal management

ActiveCN1638114AImproved thermal managementImprove interconnect densityPrinted circuit assemblingSemiconductor/solid-state device detailsElectricityEngineering

The invention relates to a packaging technology of a power converter, in which all components are electrically connected to a multilayer circuit board. A subpackage having at least one power dissipating chip with an exposed upward facing top thermal block electrically connected to the board by a plurality of symmetrical pins. A heat spreading element is directly attached to the exposed top thermal block of the subpackage, the top surface of the planar magnetic part and other components with thermally conductive insulators. Heat dissipated by the subpackage is transferred from the exposed top thermal block to the attached heat spreader element and further to the ambient. This assembly features a compact and inexpensive power converter package with improved electrical performance and improved thermal management.

Owner:DELTA ELECTRONICS INC

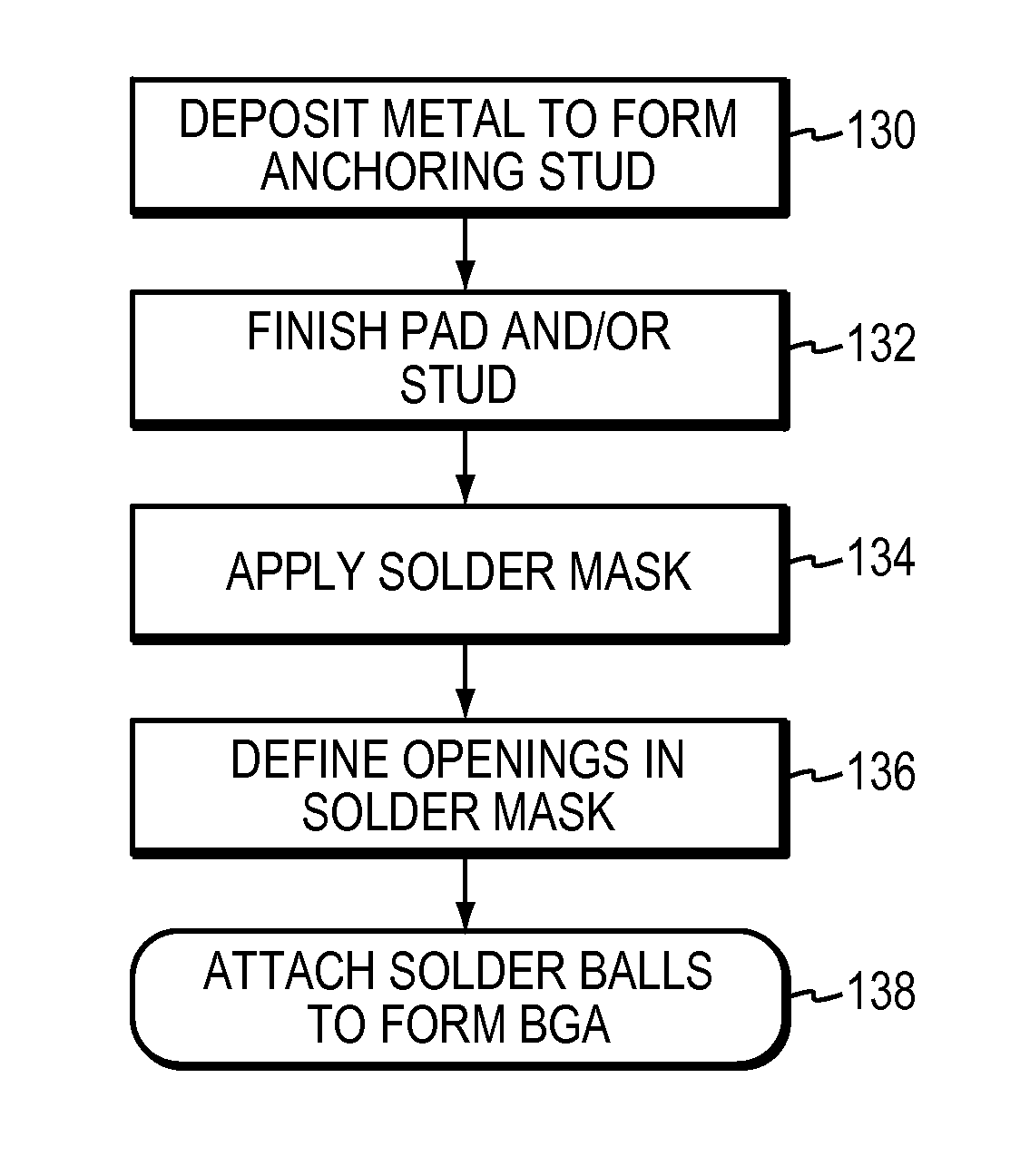

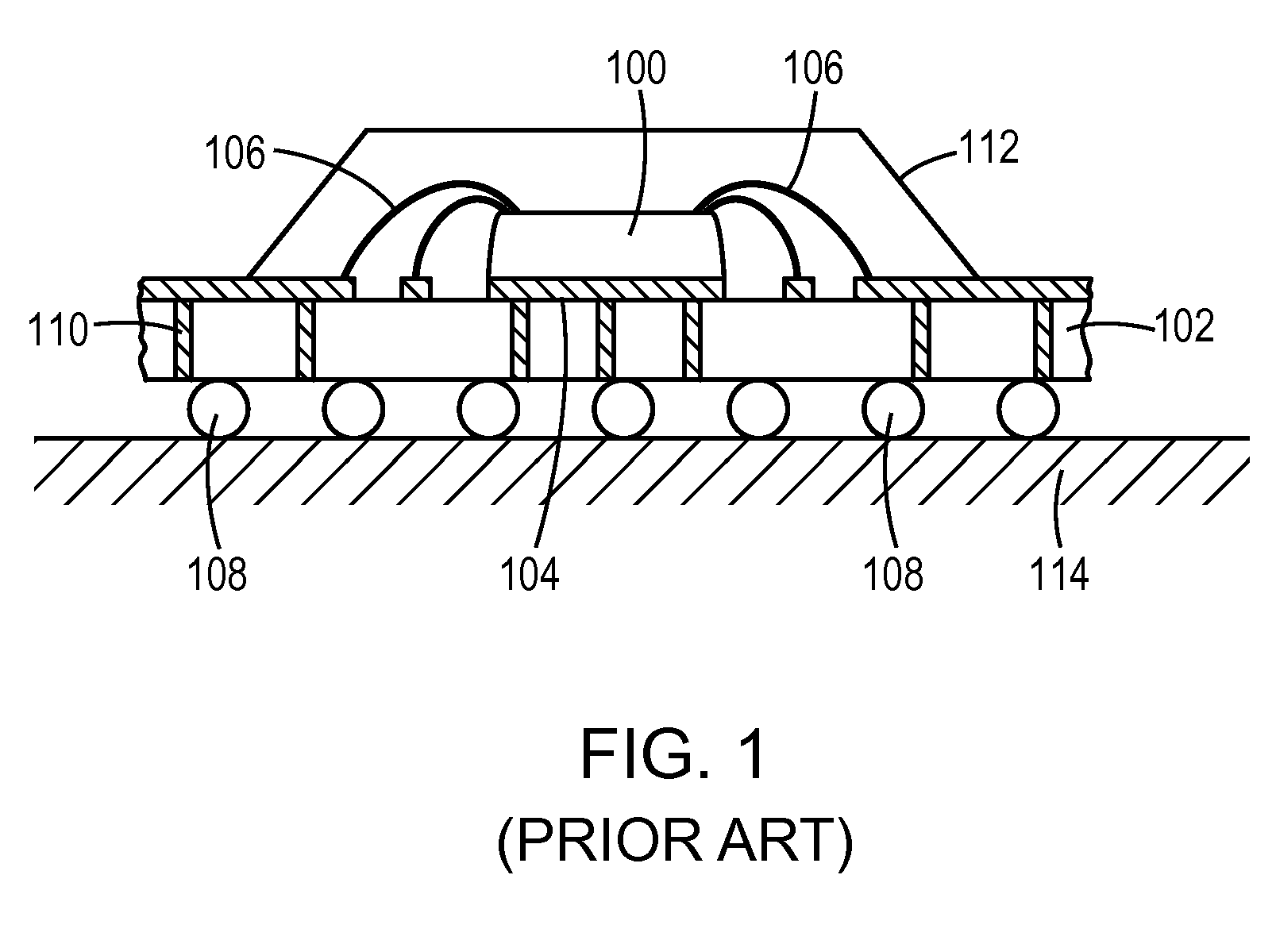

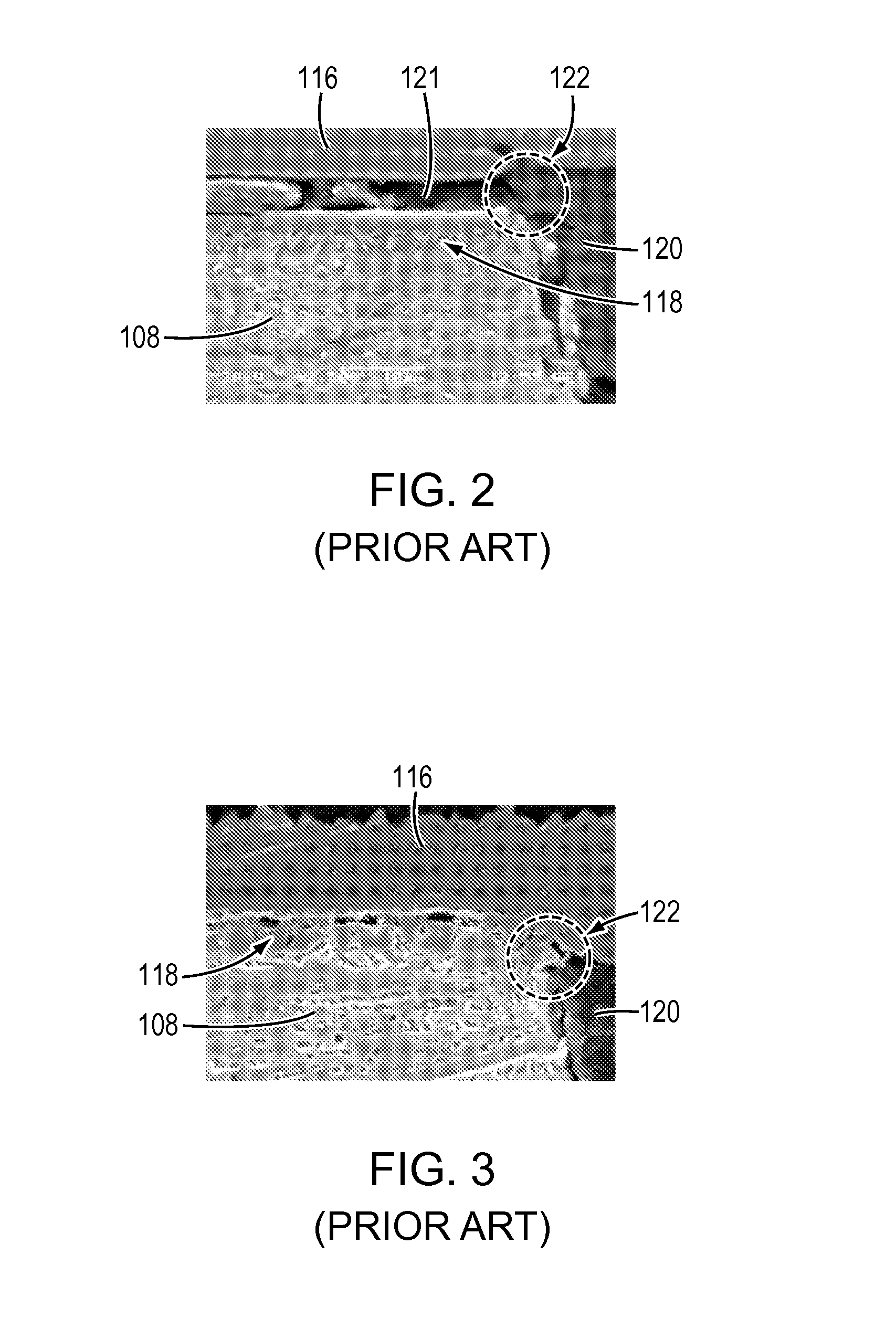

Surface mount package with enhanced strength solder joint

InactiveUS20090127695A1More feature and capabilityDecrease in package sizeSemiconductor/solid-state device detailsSolid-state devicesElectroplatingSurface mounting

A substrate pad in a semiconductor package having a geometry and structure that facilitates providing a solder joint to the pad that has enhanced structural integrity and resistance to mechanical impact. The pad may include a plated metal stud that anchors the solder to the pad interface, providing a more compliant solder joint, even when lead-free solder is used.

Owner:SKYWORKS SOLUTIONS INC

Method of assembly for multi-flip chip on lead frame on overmolded IC package

InactiveUS7335532B2Improve signal integrityReduce excess spaceSemiconductor/solid-state device detailsSolid-state devicesMOSFETEngineering

Owner:SEMICON COMPONENTS IND LLC

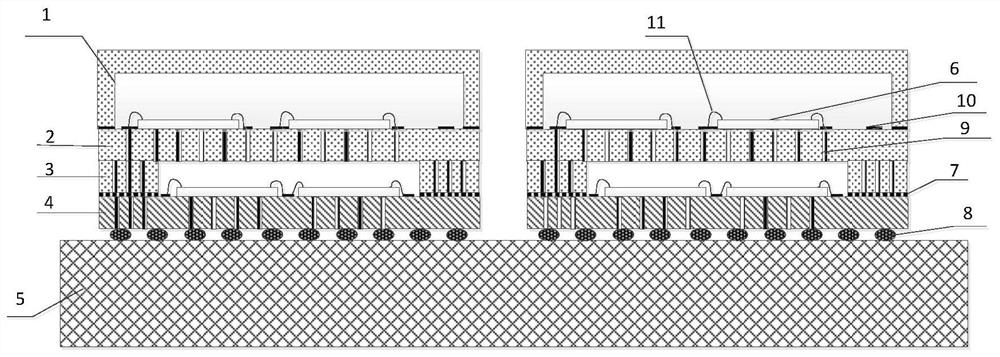

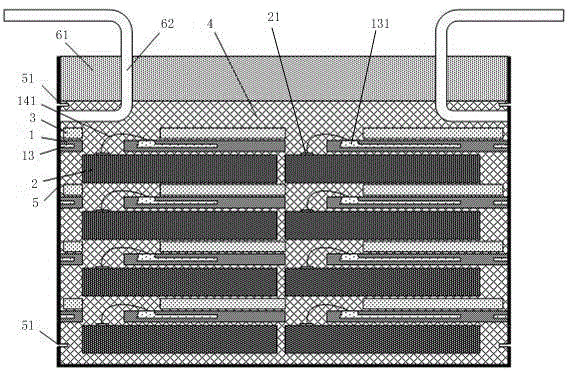

Radio frequency module three-dimensional stacking structure and manufacturing method thereof

ActiveCN112420679AHigh thermal conductivityImprove interconnect densitySemiconductor/solid-state device detailsSolid-state devicesHigh densityHemt circuits

The invention discloses a radio frequency module three-dimensional stacking structure and a manufacturing method thereof. The radio frequency module three-dimensional stacking structure comprises a glass cap layer, a glass carrier layer, a glass transfer frame layer, a silicon-based carrier layer, a ceramic packaging layer and radio frequency chips. The glass carrier layer, the glass transfer frame layer and the silicon-based carrier layer are all provided with through holes and interconnection lines; the glass cap layer, the glass carrier layer, the glass transfer frame layer, the silicon-based carrier layer and the ceramic packaging layer are stacked and interconnected in sequence from top to bottom; and the radio frequency chips are located on the upper surface of the silicon-based carrier layer and the upper surface of the glass carrier layer, and are connected with circuit bonding pads on the carrier layer through lead structures. Through combination and stacking of high-density substrates made of various materials, the radio frequency module is better in performance and higher in density, and the integration process is simple, flexible, better in reliability and the like.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

Aluminum-substrate-based three-dimensional lamination chip packaging structure and preparation method thereof

ActiveCN105023901AImprove packaging efficiencyReduce volumeSemiconductor/solid-state device detailsSolid-state devicesEpoxyAluminum substrate

The invention discloses an aluminum-substrate-based three-dimensional lamination chip packaging structure and a preparation method thereof. The structure comprises at least two layers of functionalized aluminum substrates, chips, aluminum-based dams, epoxy resin base bodies, a side metalized interconnection layer, and a signal leading-out layer. The functionalized aluminum substrates arranged in parallel have two opposite first surfaces and second surfaces. Chips are pasted on the second surfaces. The aluminum-based dams are pasted on the first surfaces. The epoxy resin base bodies are arranged between the functionalized aluminum substrates and the aluminum-based dams. The side metalized interconnection layer and the signal leading-out layer are arranged at the outer sides of the packaging structure in an encircling mode. The functionalized aluminum substrates contain aluminum-buried interconnection layers and through holes; and the chips and the aluminum-buried interconnection layers are electrically connected. Besides, the method includes the steps of preparation of functionalized aluminum substrates, preparation of through holes of the functionalized aluminum substrates, packaging of a multi-chip module, preparation of a signal leading-out layer; packaging of a three-dimensional lamination layer, and preparation of a side metalized interconnection layer. According to the invention, the packaging efficiency and interaction density are improved; and the size of the three-dimensional lamination chip packaging is effectively reduced.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

Multifunctional base plate based on PCB technology and manufacturing method thereof

ActiveCN103762205AImprove interconnect densityLarge interconnect transmission capacitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyInterconnection density

The invention discloses a multifunctional base plate based on the PCB technology and a manufacturing method thereof. The multifunctional base plate comprises a multilevel interconnection base plate, a glass base plate and an optical waveguide layer. An upper-layer graph is etched on the upper surface of the glass base plate, and a del-shaped reflector is arranged in the optical waveguide layer. A lower-layer graph is etched on the lower surface of the optical waveguide layer, and the upper-layer graph and the lower-layer graph are communicated with a transmission channel of the multilevel interconnection base plate through through holes vertically formed in the glass base plate, the multilevel interconnection base plate, and the optical waveguide layer in an embedded mode. The manufacturing method includes the steps of pressing the glass base plate and the optical waveguide layer, cutting the reflector, manufacturing the through holes, hole plating copper and face copper, etching the graphs and bonding pads and installing devices. The multifunctional base plate based on the PCB technology and the manufacturing method thereof can solve the problem of low losses of high-frequency transmission, so that the optical interconnection transmission capacity is high, the interconnection density is high, and the anti-electromagnetic interference capability is high; the multifunctional base plate based on the PCB technology and the manufacturing method thereof are suitable for millimeter wave interconnection, the manufacturing technology is simple, cost is low, and the multifunctional base plate based on the PCB technology and the manufacturing method thereof are also suitable for application with the sealing requirement.

Owner:NAT CENT FOR ADVANCED PACKAGING

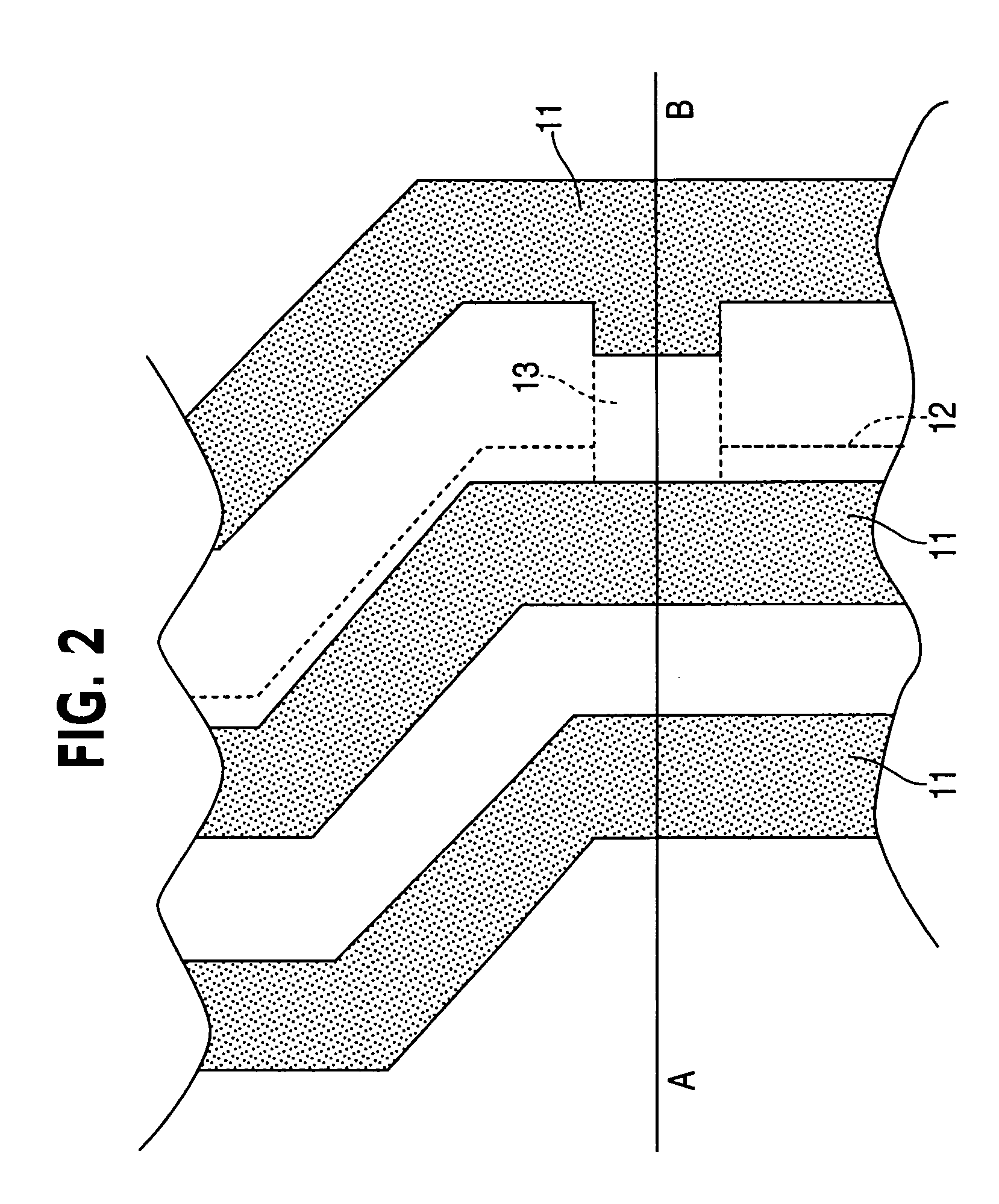

Multilayer interconnection structure and method for forming the same

InactiveUS20050287800A1Well formedDecreasing interconnection resistance and interconnection capacitySemiconductor/solid-state device detailsSolid-state devicesDiagonalInterconnection

A multilayer interconnection structure of the present invention includes first interconnection, second interconnection belonging to an interconnection layer different from an interconnection layer to which the first layer belongs, and third interconnection for connecting the first and second interconnections, the third interconnection belonging to a different interconnection layer and including interconnection along a body diagonal for connecting two points in different planes belong to different interconnection layers. A method for producing the multilayer interconnection structure includes a step of forming the third interconnection, the step including a step of forming a through hole along the body diagonal, and a step of filling the through hole with a conductive material.

Owner:FUJITSU SEMICON LTD

High reliability multilayer circuit substrates and methods for their formation

InactiveUS20050146039A1Easy to produceYield reduction due to misalignment is significantly reduced or eliminatedSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorOptoelectronics

A multilayer circuit substrate for multi-chip modules or hybrid circuits includes a dielectric base substrate, conductors formed on the base substrate and a vacuum deposited dielectric thin film formed over the conductors and the base substrate. The vacuum deposited dielectric thin film is patterned using sacrificial structures formed by shadow mask techniques. Substrates formed in this manner enable significant increases in interconnect density and significant reduction of over-all substrate thickness.

Owner:MEDTRONIC MIMIMED INC