Aluminum-substrate-based three-dimensional lamination chip packaging structure and preparation method thereof

A packaging structure, aluminum substrate technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of poor heat dissipation, large CTE mismatch, large line spacing, etc., to improve interconnection density, improve Packaging efficiency, the effect of increasing heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

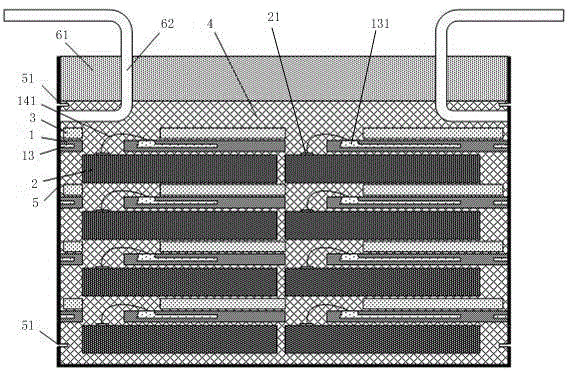

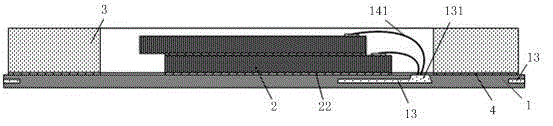

[0059] combine figure 1 , this embodiment describes in detail the schematic diagram of the packaging structure of the three-dimensional laminated chip based on the aluminum substrate of the present invention, which includes: at least two layers of functionalized aluminum substrates 1 arranged in parallel, chips 2, aluminum-based dams 3, epoxy resin The substrate 4, the side metallized interconnection layer 5 and the signal lead-out layer. In this embodiment, the functionalized aluminum substrate 1 arranged in parallel with three layers is taken as an example. The functionalized aluminum substrate 1 has two opposite surfaces, which are respectively the first surface 11 and the second surface. Two surfaces 12, the functionalized aluminum substrate 1 is provided with a buried aluminum interconnection layer 13 and a through hole 14; the buried aluminum interconnection layer 13 is embedded in the functionalized aluminum substrate 1; the through hole 14 penetrates the first surface o...

Embodiment 2

[0068] combine Figure 4 -5. This embodiment describes in detail the preparation method of the packaging structure of the three-dimensional laminated chip based on the aluminum substrate of the present invention, such as Figure 4 Shown is its flowchart, which includes the following steps:

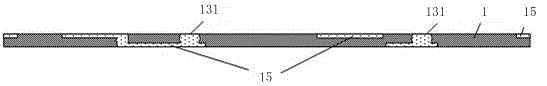

[0069] S11: Preparation of functionalized aluminum substrate: provide a double polished aluminum substrate, the aluminum substrate has two opposite first surfaces and second surfaces, carry out wiring design on the first surface and the second surface by photolithography process, and pass A buried aluminum interconnection layer embedded in the aluminum substrate is prepared on the aluminum substrate by anodic oxidation. One end of the buried aluminum interconnection layer exposes the first surface of the aluminum substrate, and the preparation of the functionalized aluminum substrate is completed. The corresponding functionalized aluminum substrate Schematic such as Figure 5a shown;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More