Patents

Literature

352results about How to "Improve package reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

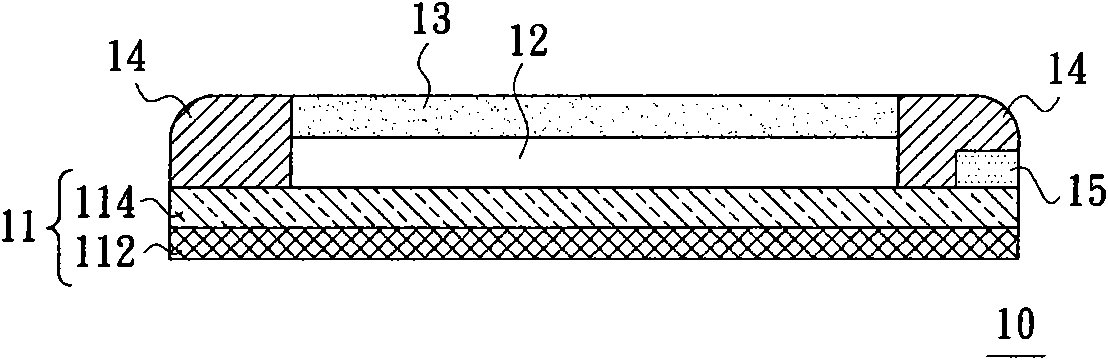

Semiconductor package structure and method for manufacturing the same

InactiveUS20060197216A1Improve packaging efficiencyImprove efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageActive surface

A semiconductor package structure comprises a chip, a plurality of via holes, a lid, an adhesive ring and a plurality of metal traces, wherein the chip has an optical component and a plurality of pads disposed on its active surfaces; the via holes penetrate the chip and are electrically connected to the pads; the lid is adhered onto the active surface of the chip by the adhesive ring such that the adhesive ring surrounds the optical component; and the plurality of metal traces is disposed on the back surface of the chip, electrically connected to the plurality of via holes, and used to define a plurality of solder pads thereon. The present invention also provides a method for manufacturing the semiconductor package structure.

Owner:ADVANCED SEMICON ENG INC

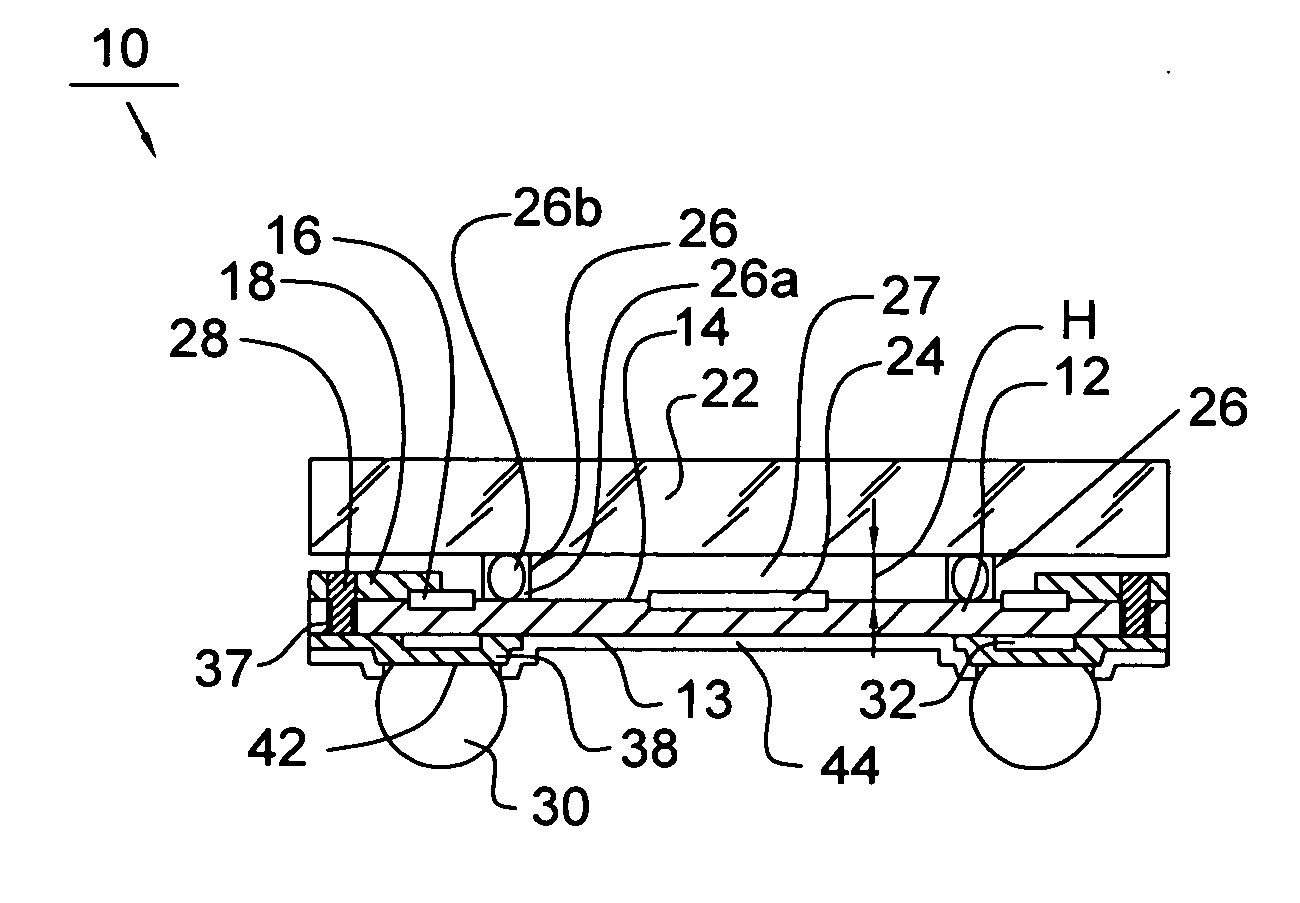

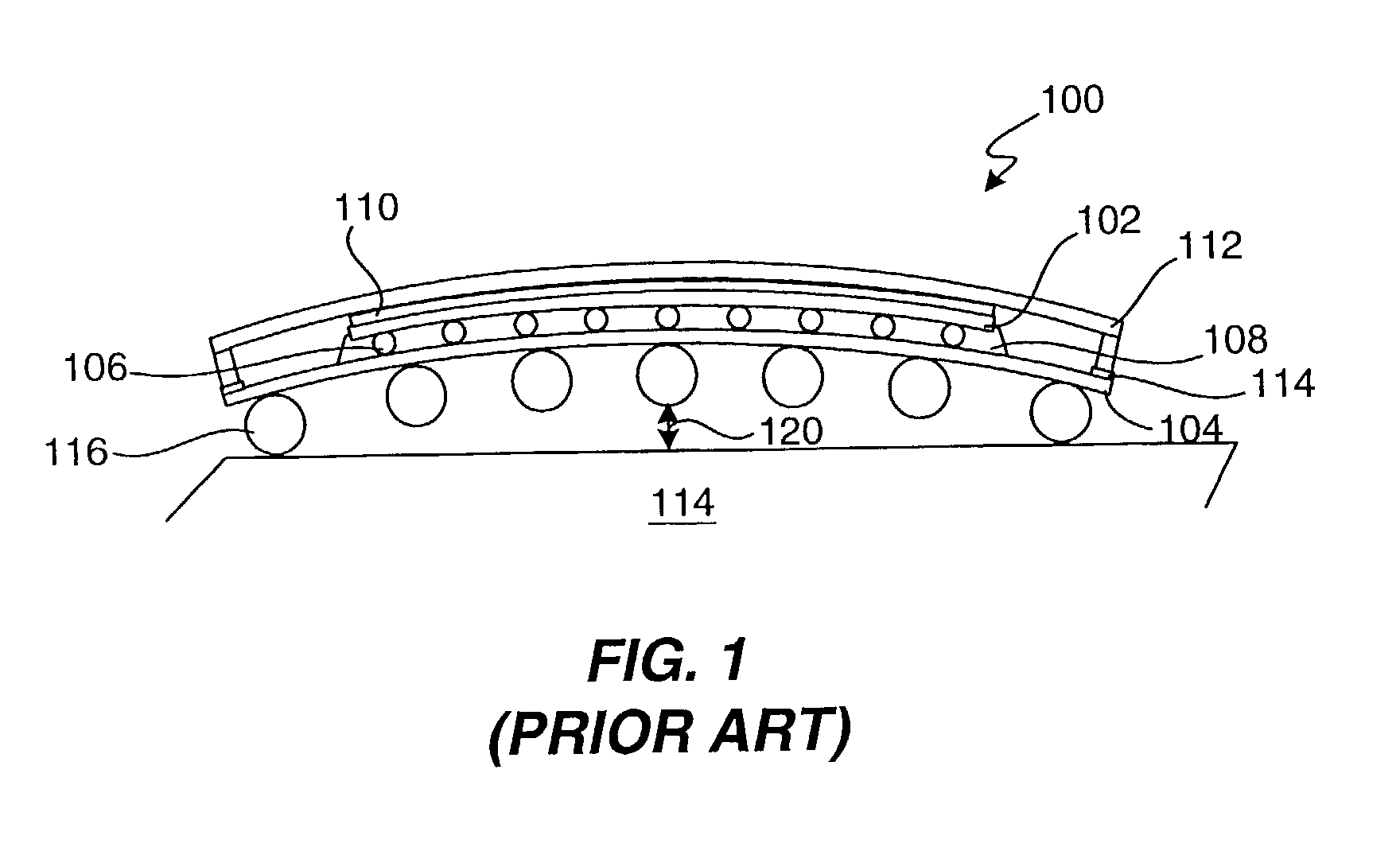

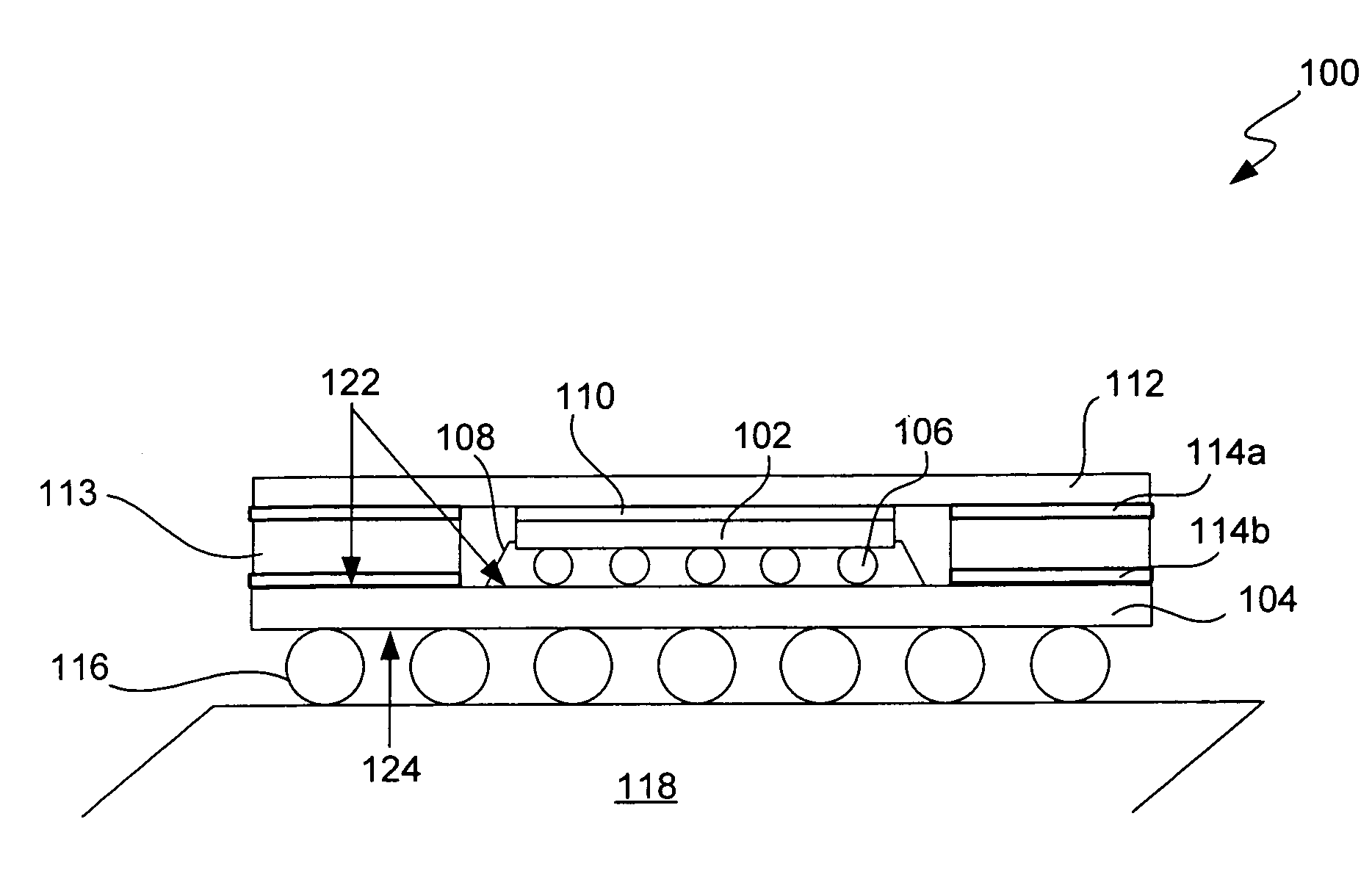

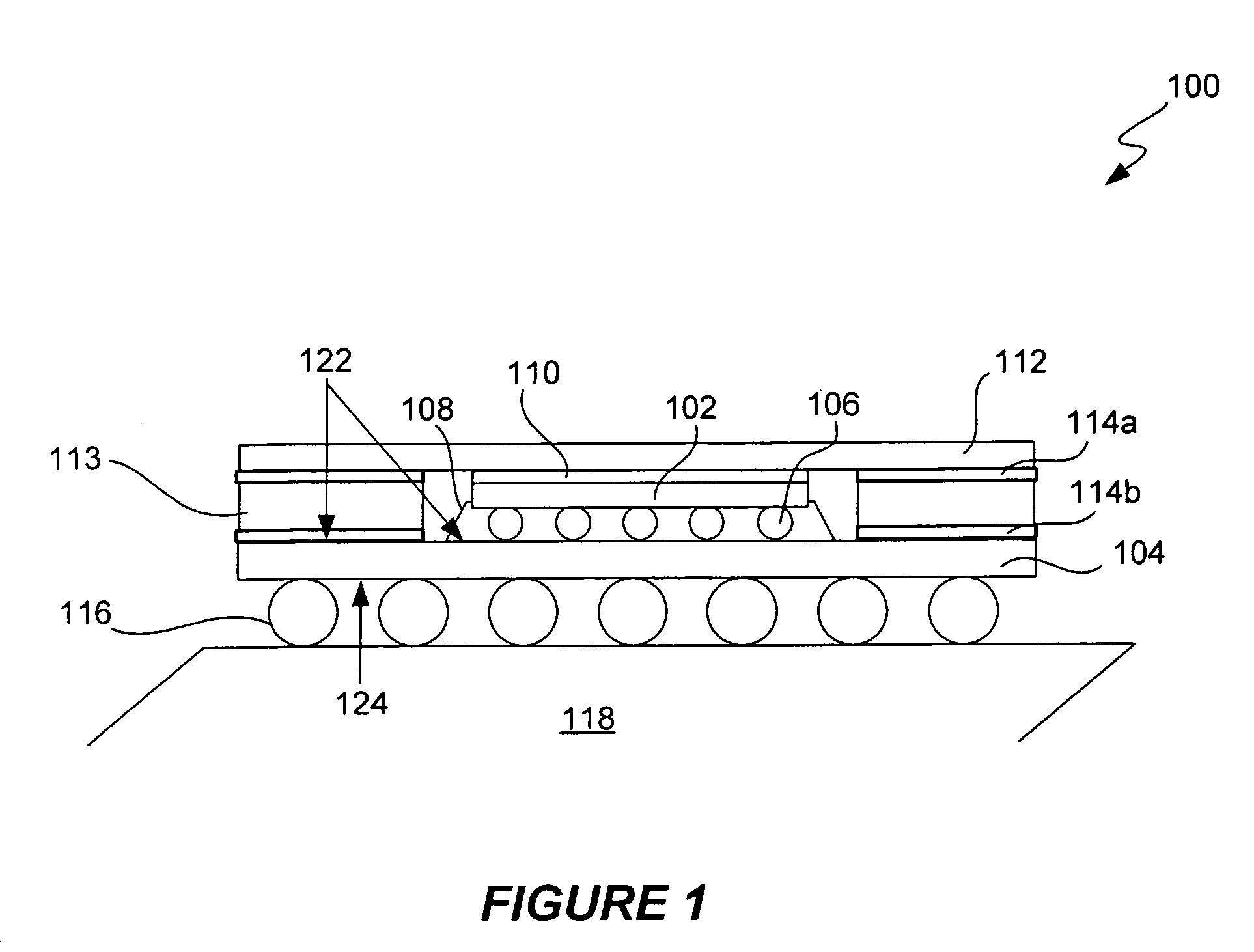

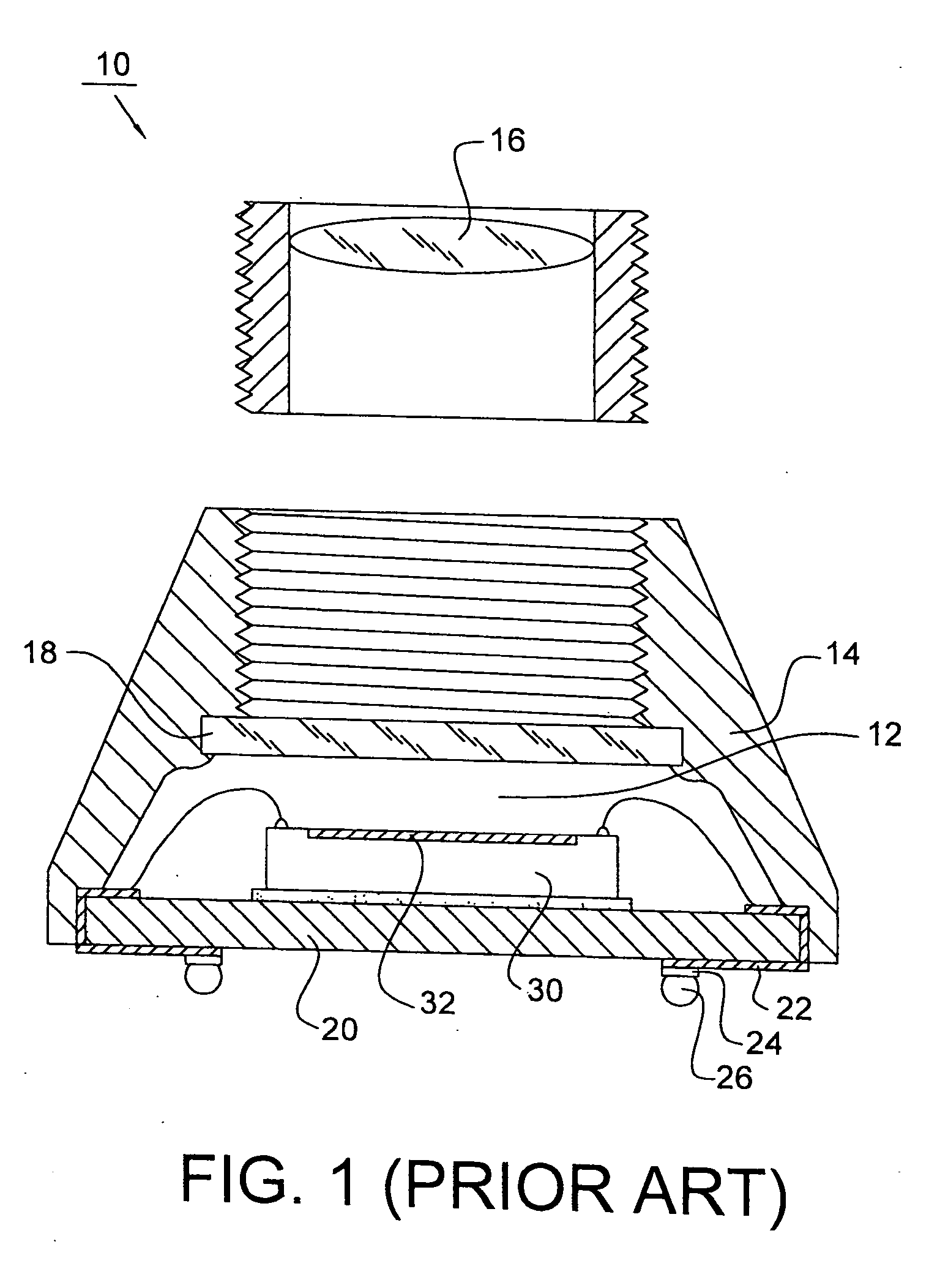

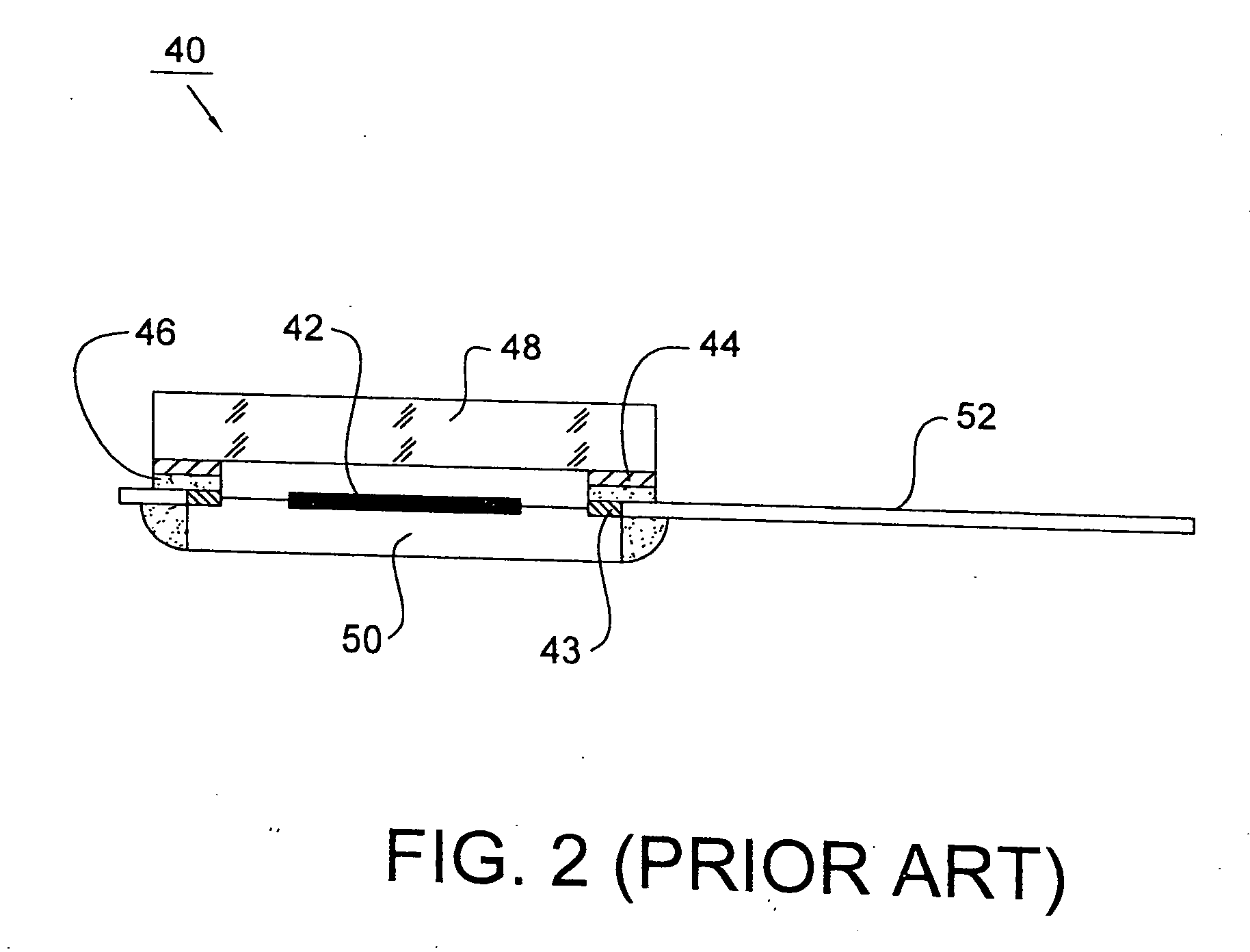

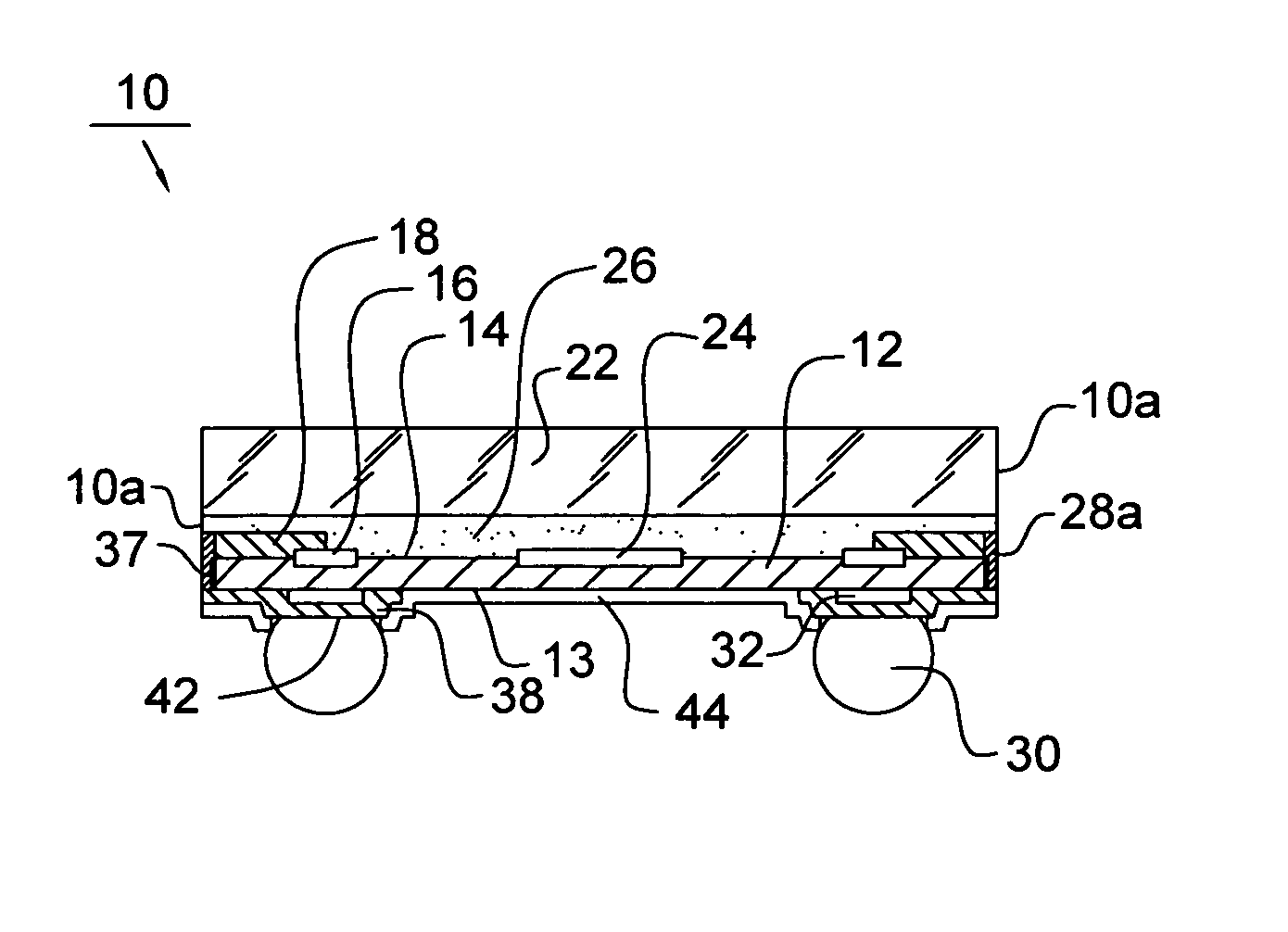

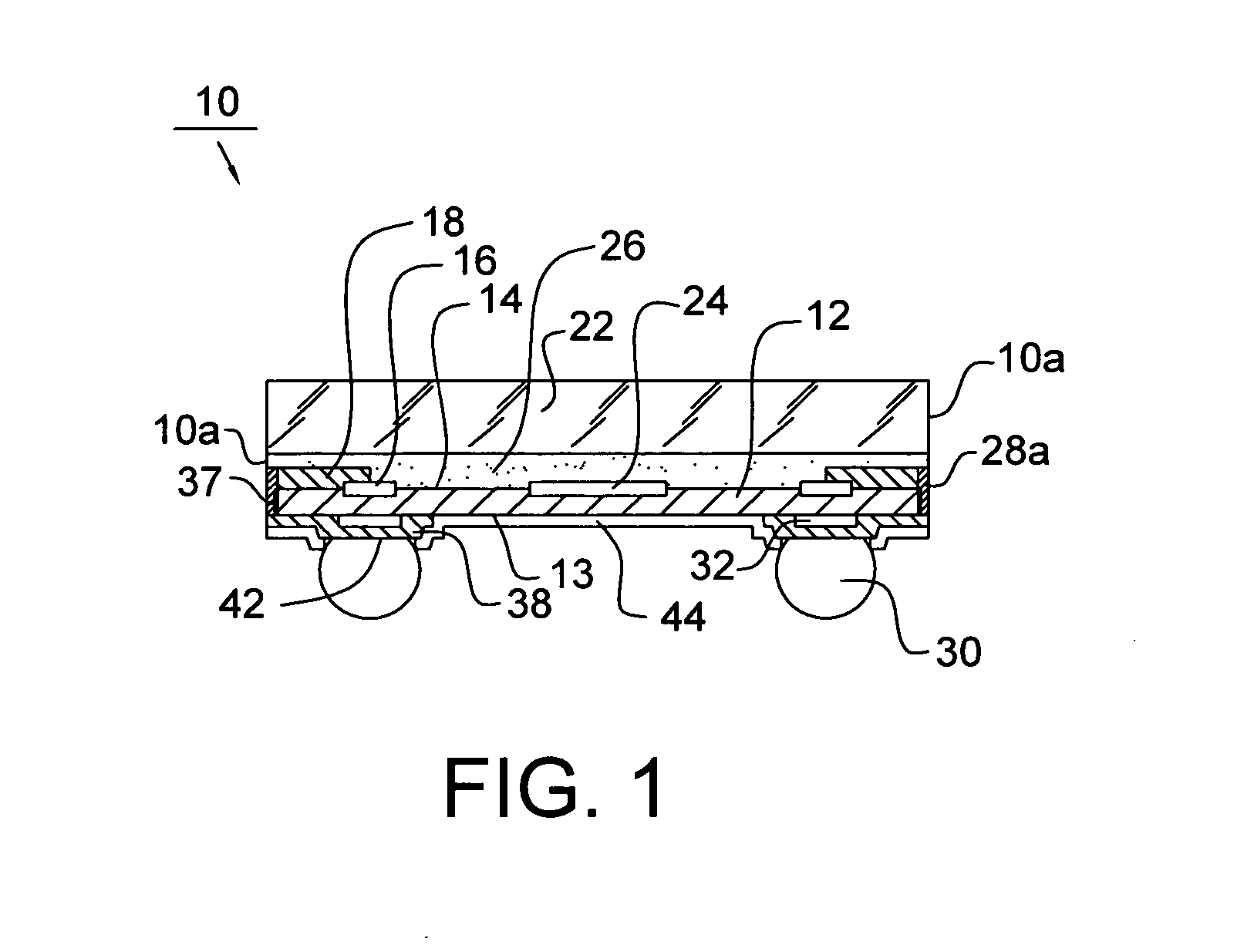

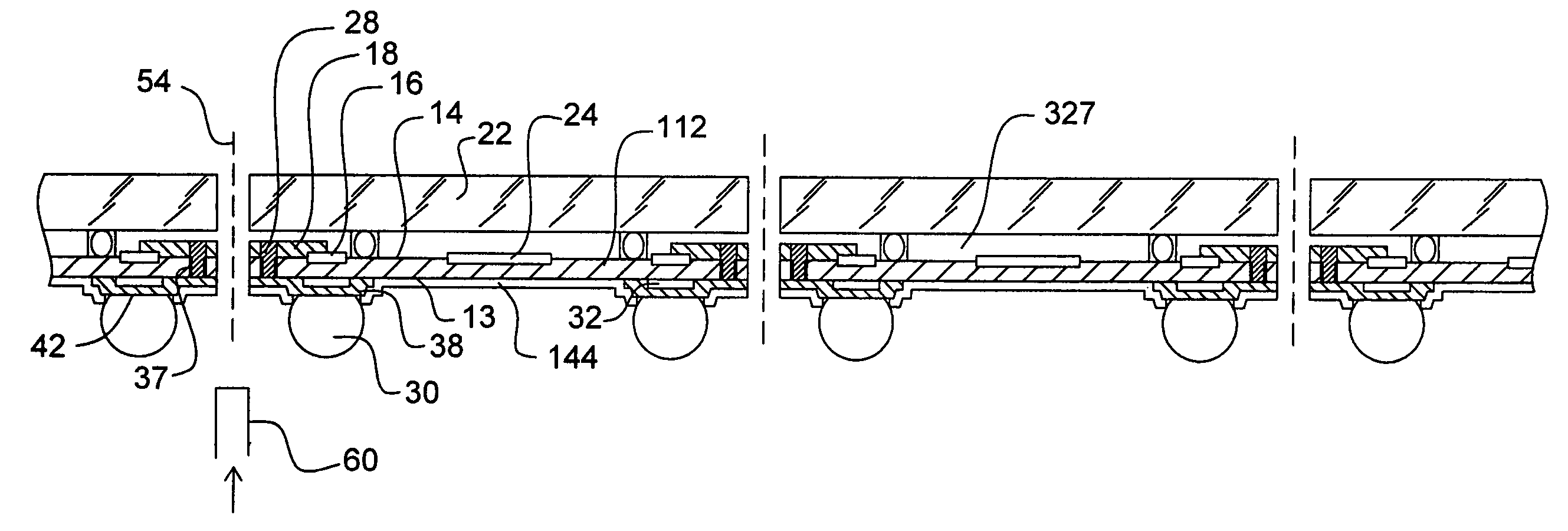

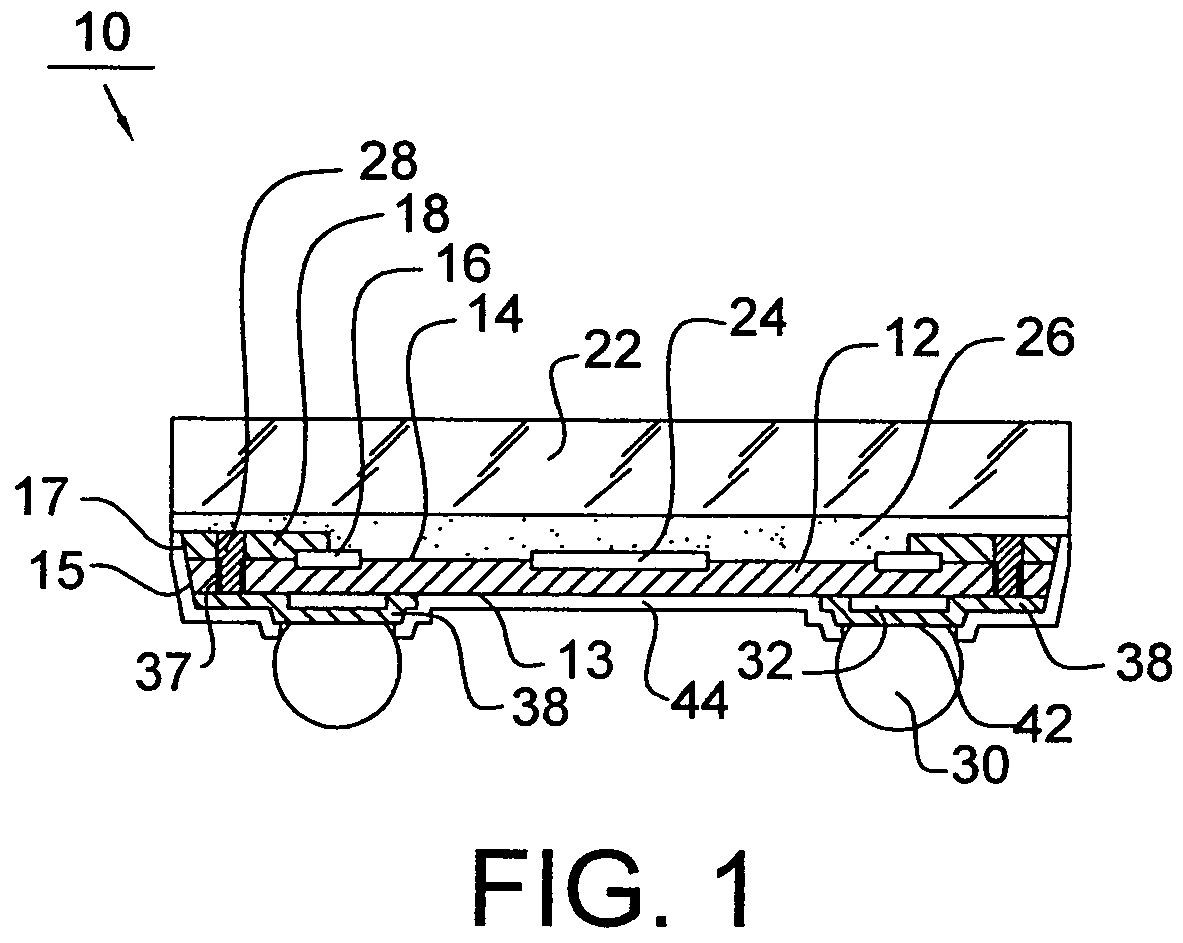

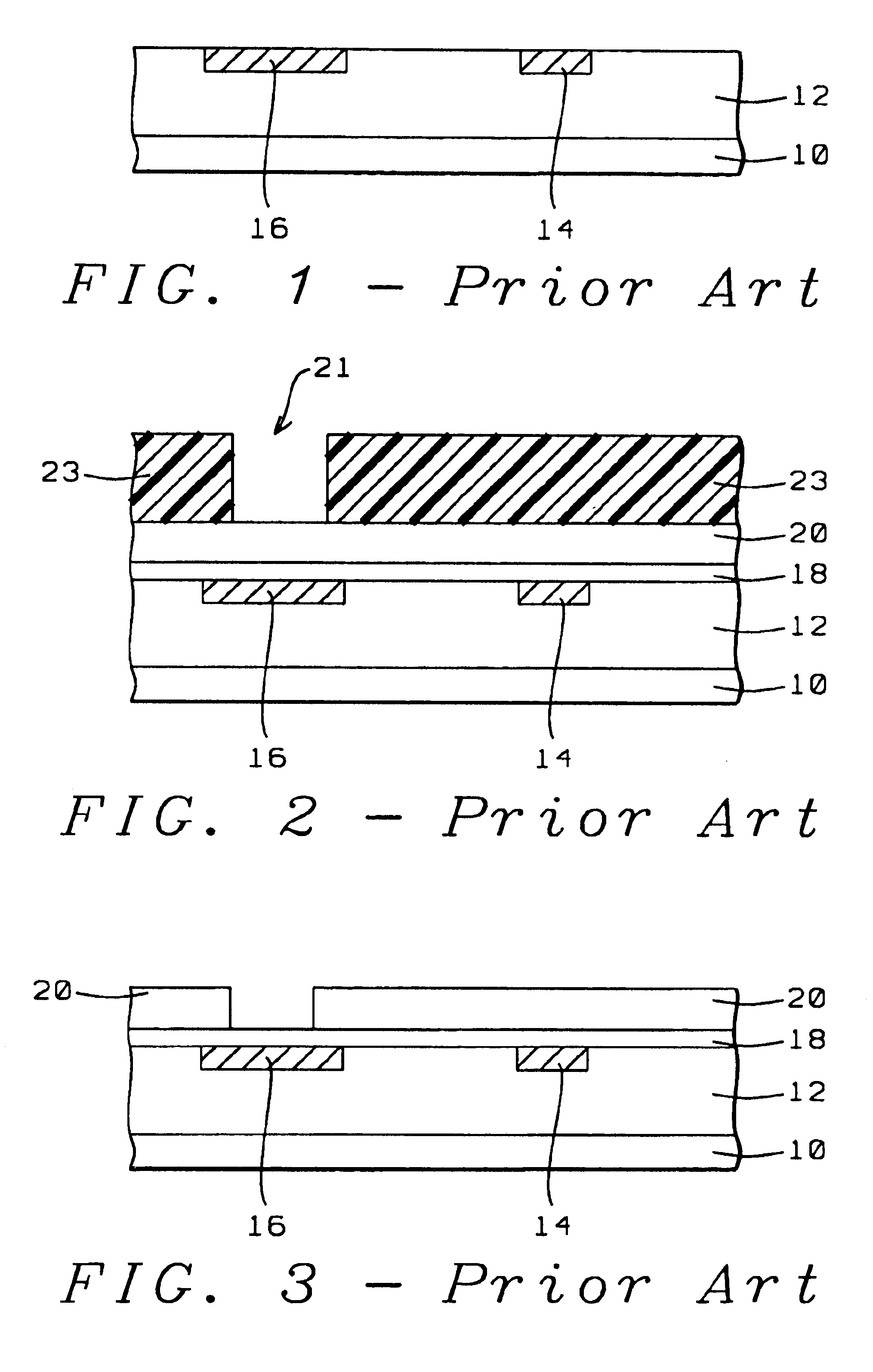

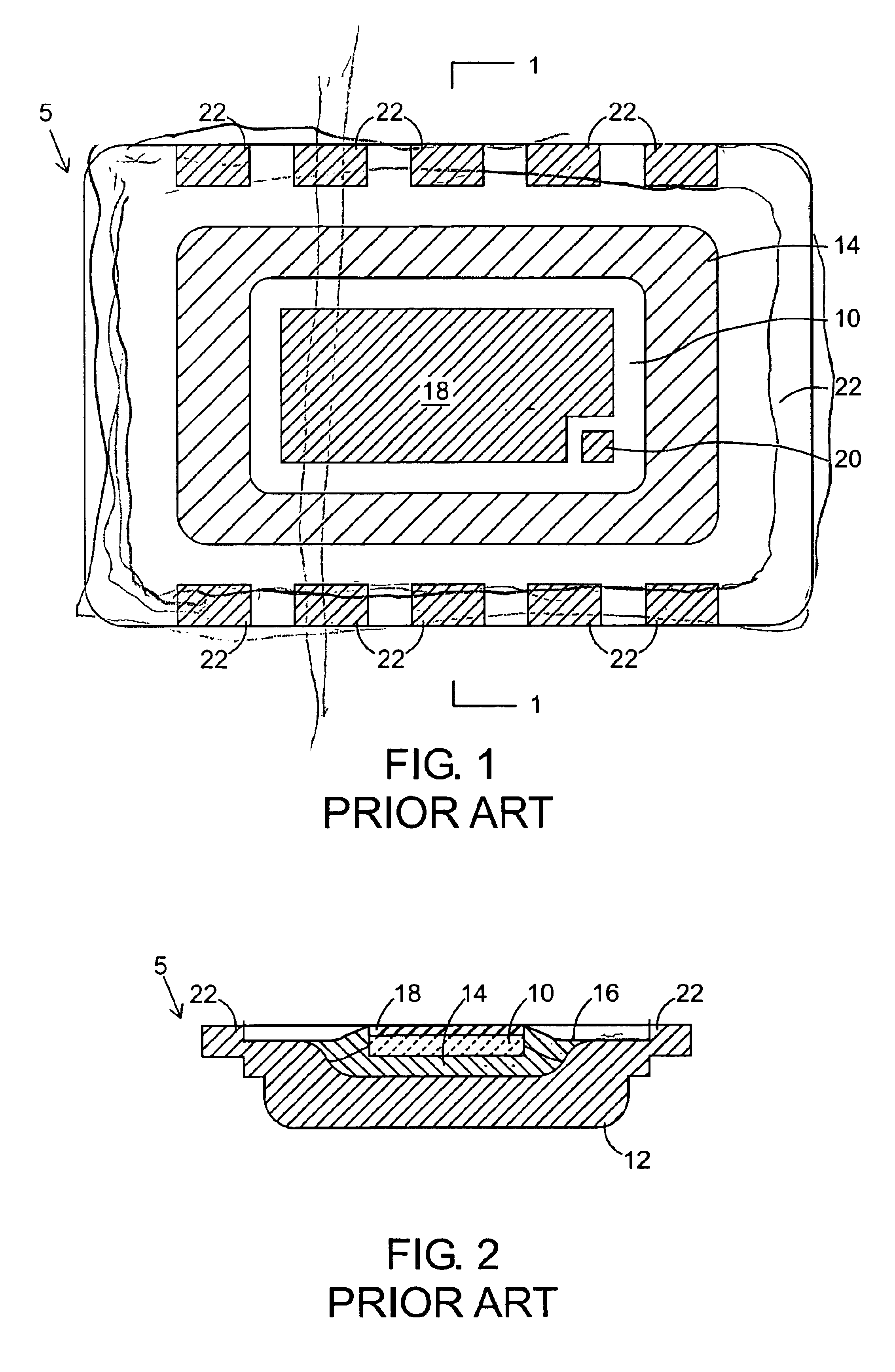

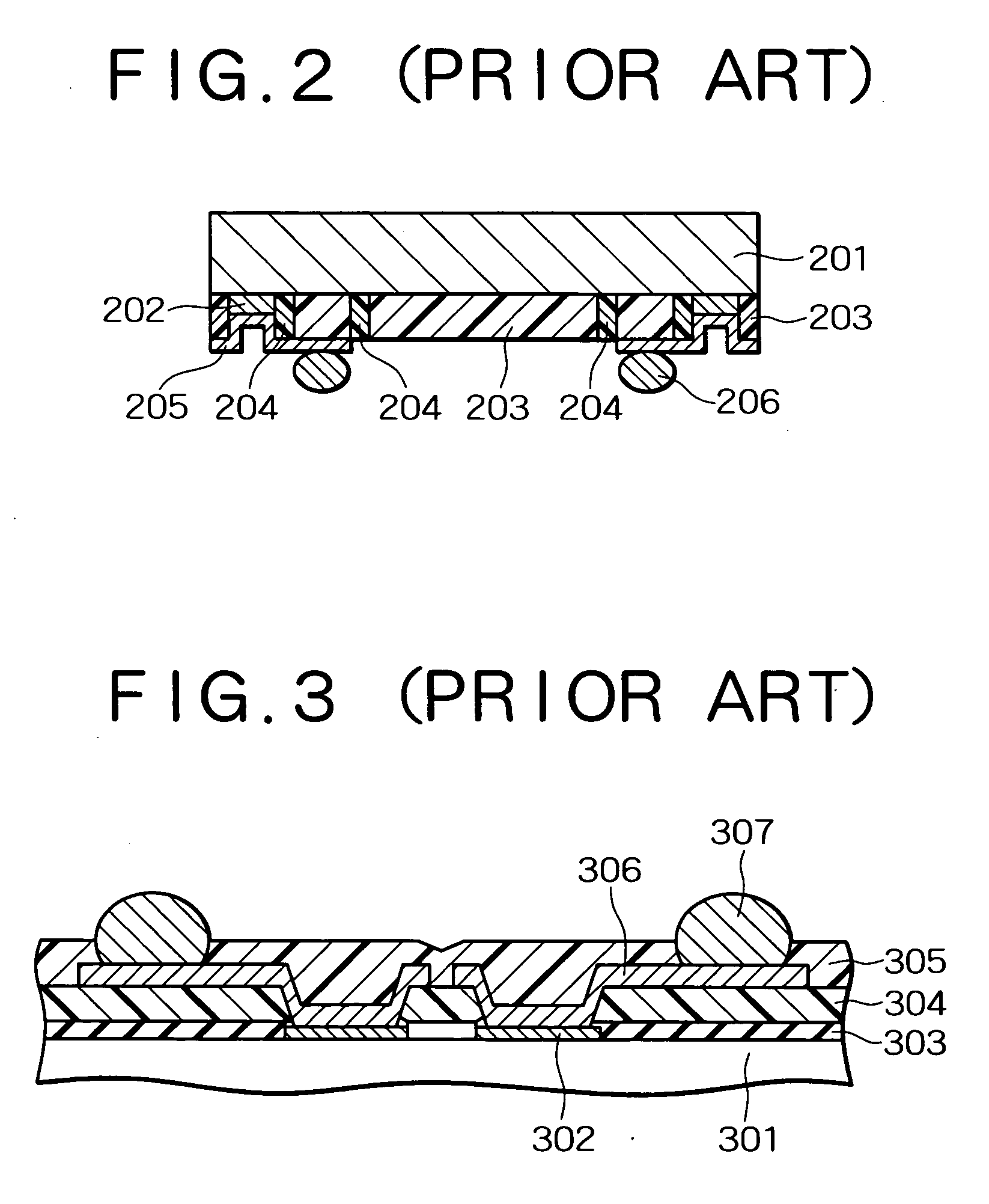

Flip chip package with warpage control

ActiveUS6949404B1Less bowEnhance reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat spreader

Provided are a semiconductor flip chip package with warpage control and fabrication methods for such packages. The packages of the present invention include heat spreader lids that are rigidly attached to the die or packaging substrate with a bond that can withstand the considerable bowing pressures caused by the CTE mismatch between the die and substrate. The result is a package with less bowing and so improved co-planarity (in compliance with industry specifications) with the PCB board to which it is ultimately bound. Package reliability is thereby also enhanced, particularly for large die sizes.

Owner:ALTERA CORP

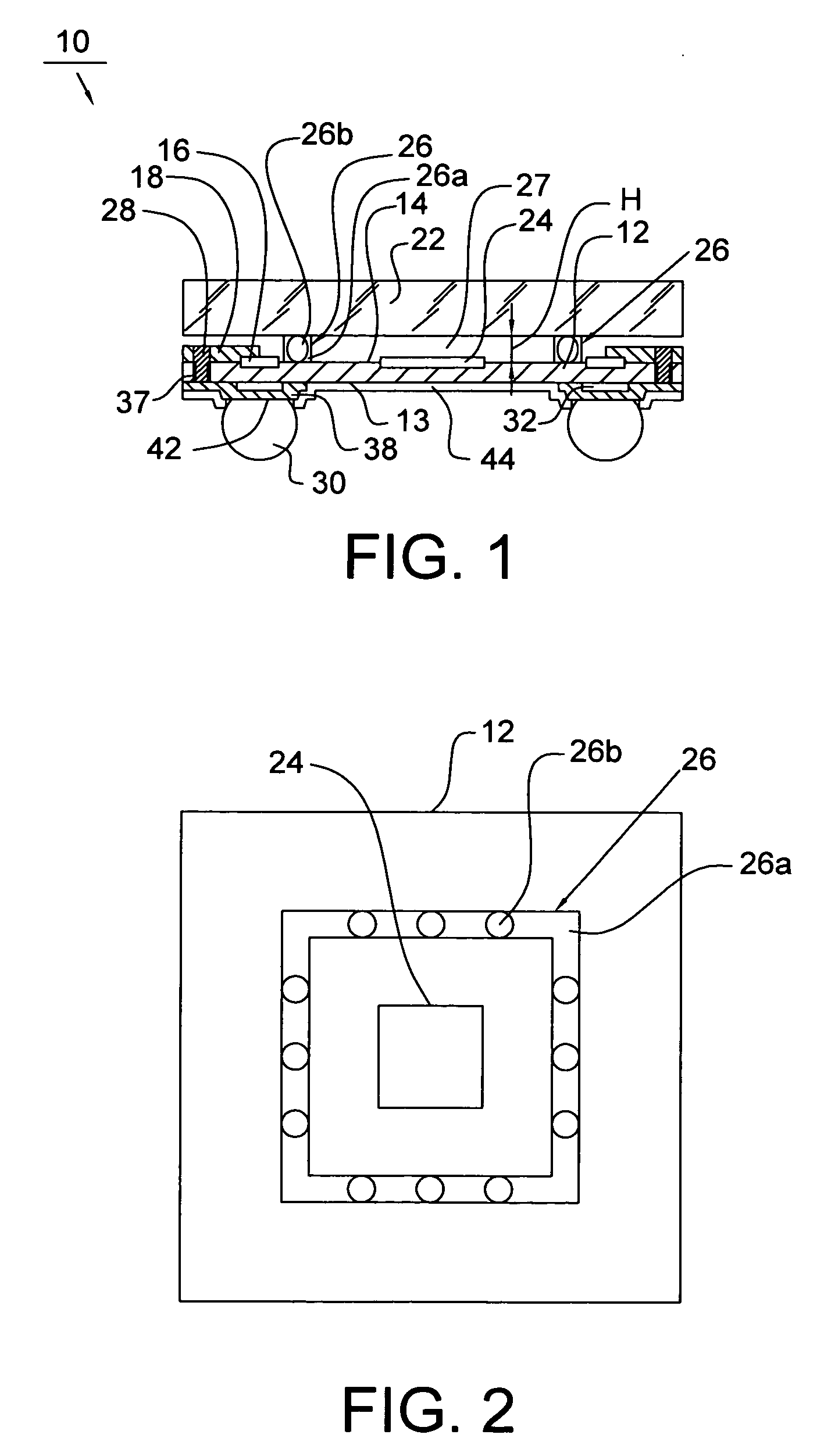

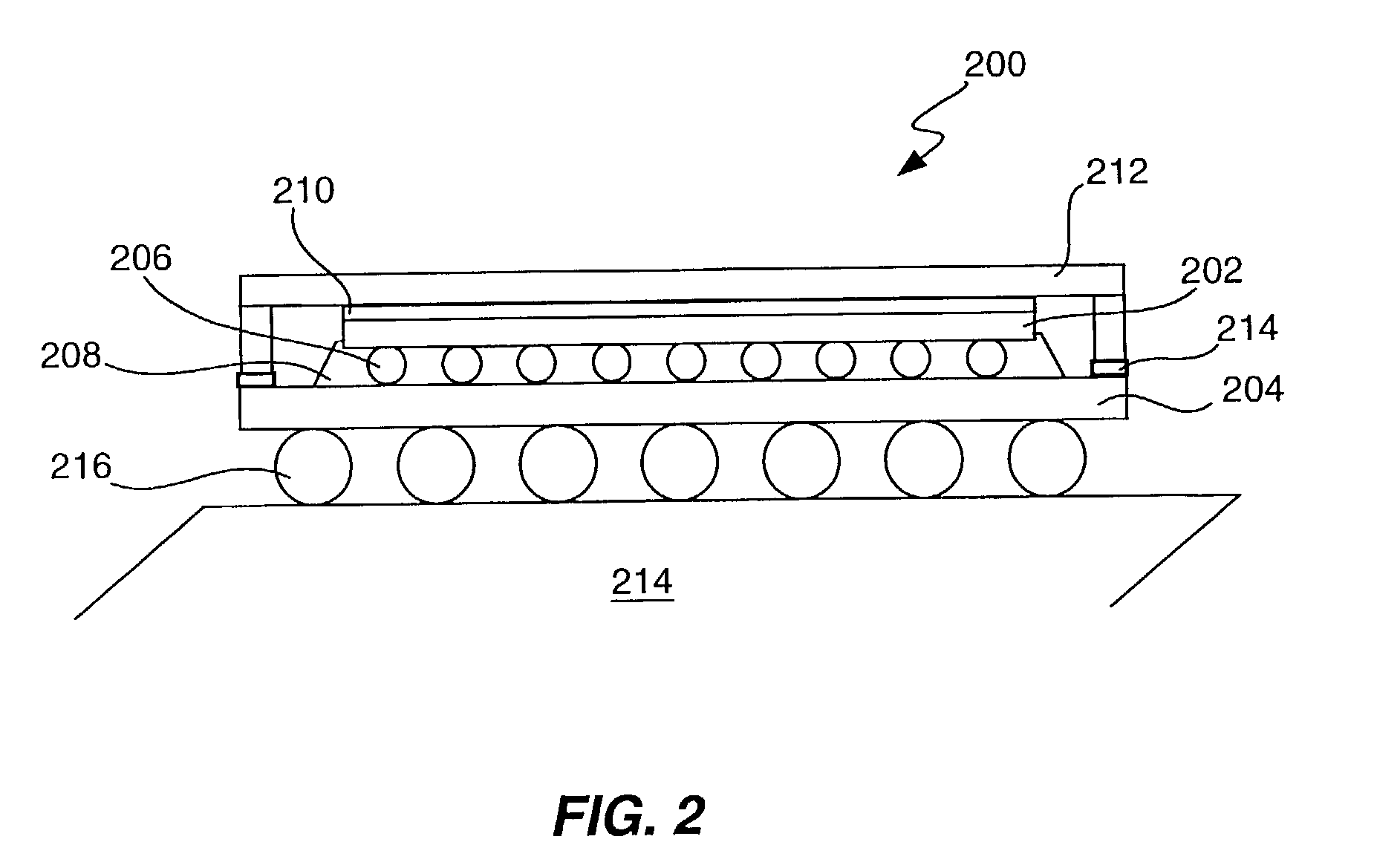

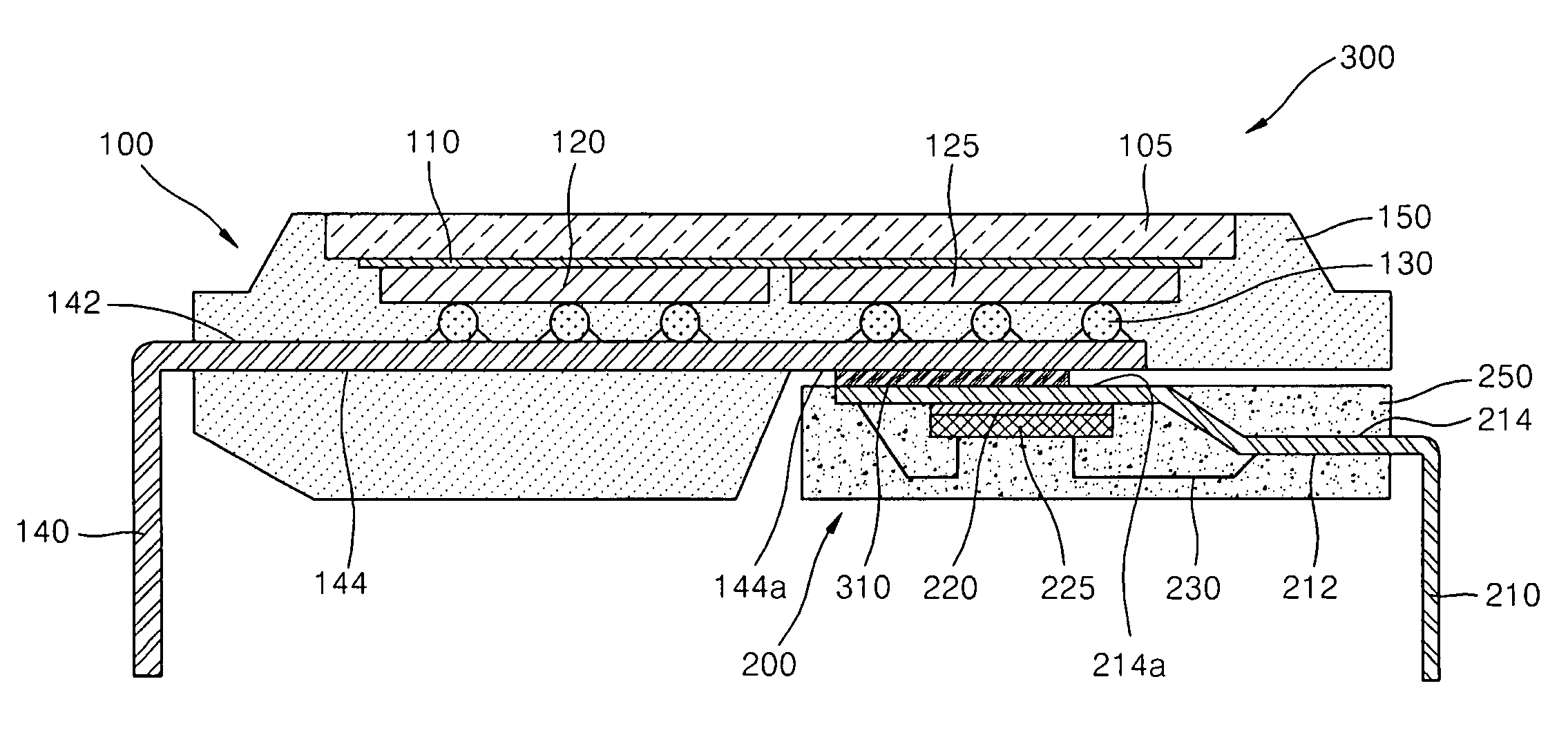

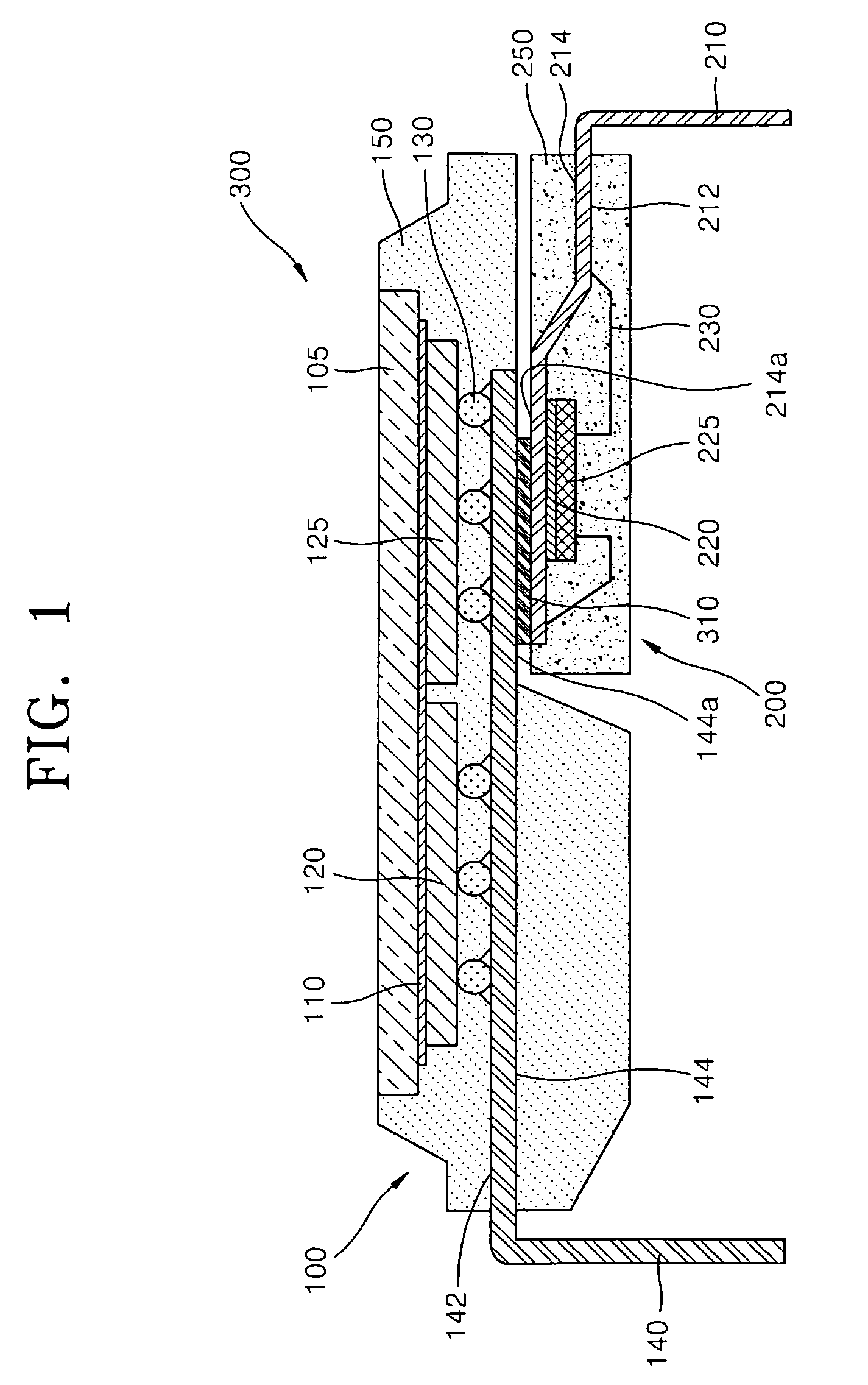

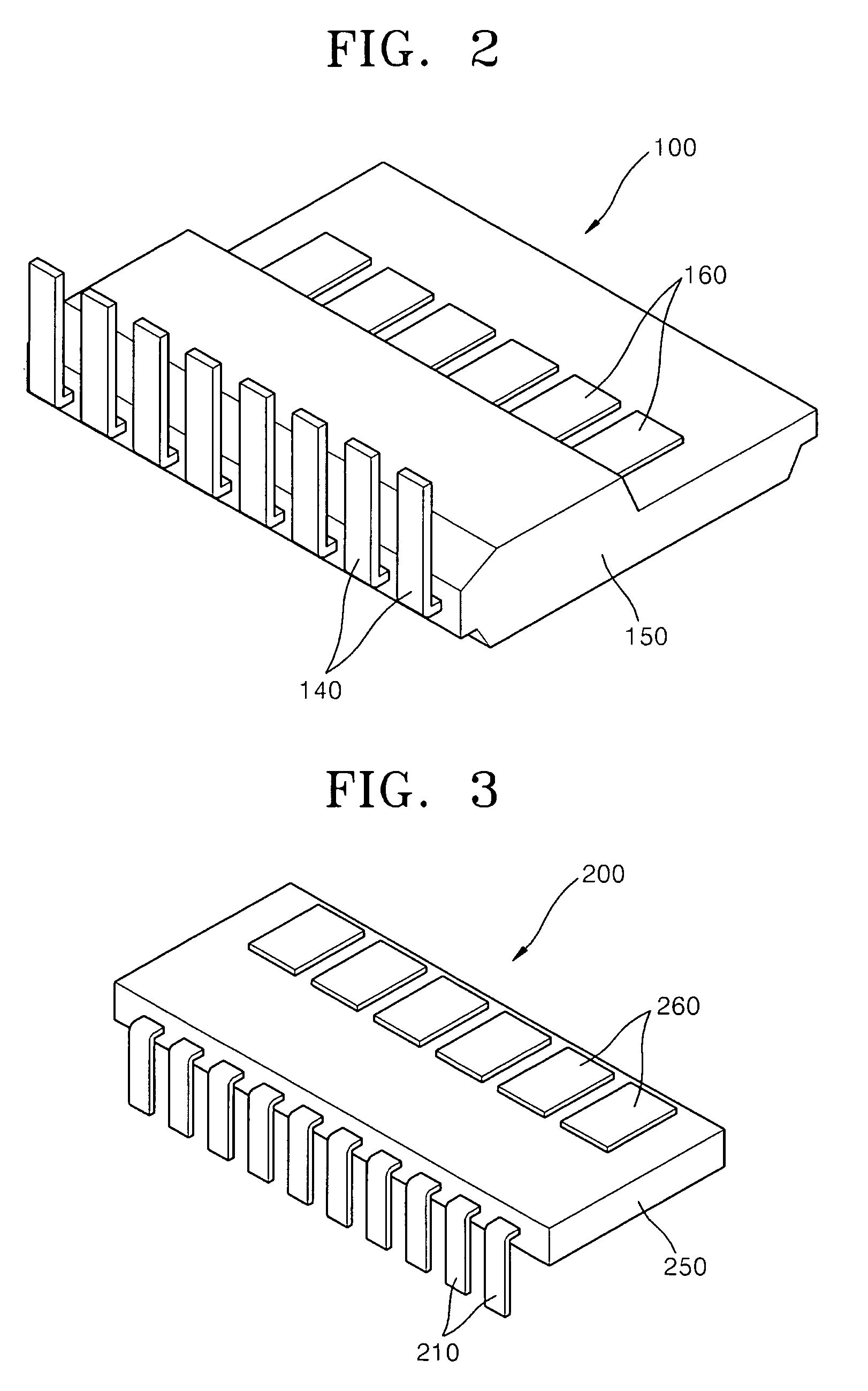

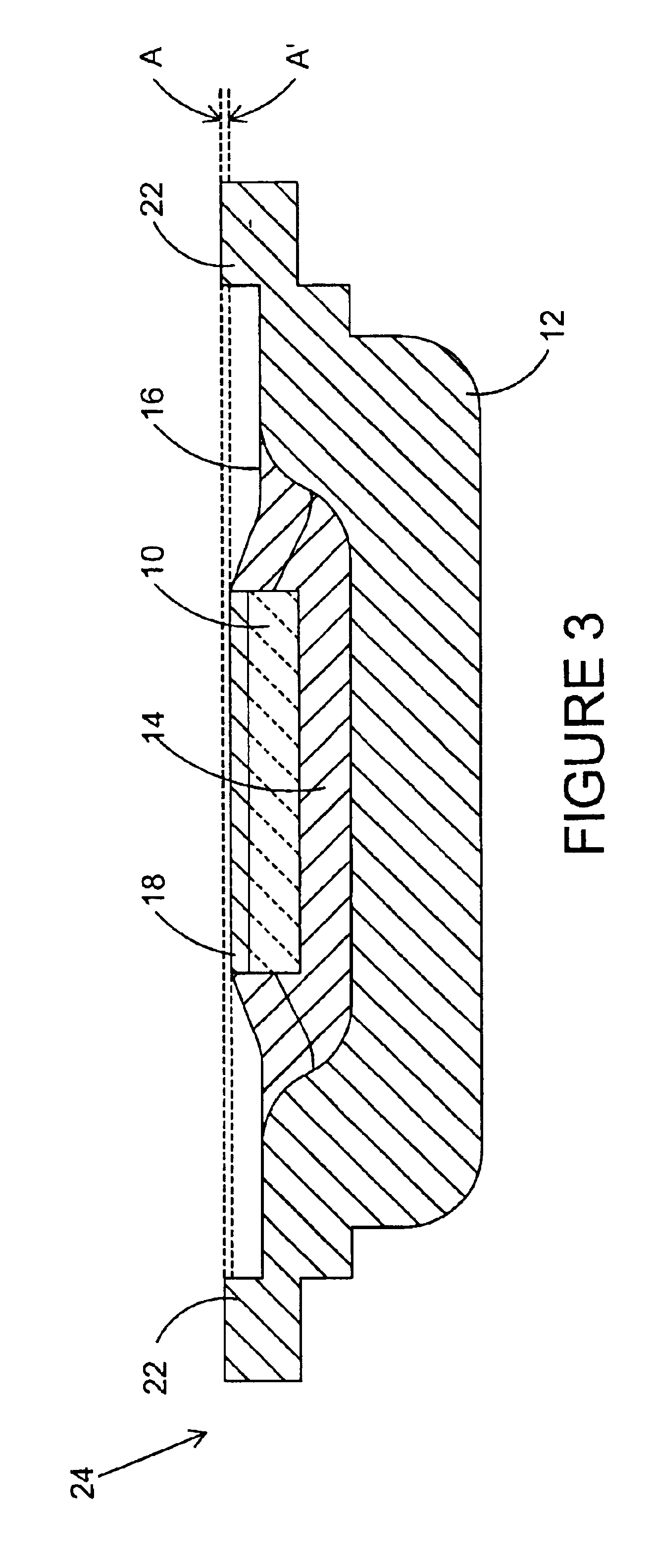

Stiffener for flip chip BGA package

ActiveUS7459782B1Improve package reliabilityLess bowingSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

Provided are semiconductor die flip chip packages with warpage control and fabrication methods for such packages. A package includes a heat spreader that is attached to a die and a stiffener, which are in turn attached to a package substrate. In general, the stiffener is made of a material that has a relatively low CTE value. For example, the stiffener material may have a CTE value less than 12 ppm / ° C. The material may also have a relatively low mass density value of less than 8.9 g / cm3. Such a material may include natural graphite or some composite form of it. The result is a package with less bowing and so improved co-planarity (e.g., in compliance with industry specifications) with the surface to which it is ultimately bound; thereby, improving the reliability of the package. Moreover, a package that is relatively lighter and more robust than conventional semiconductor die flip chip packages can be realized.

Owner:ALTERA CORP

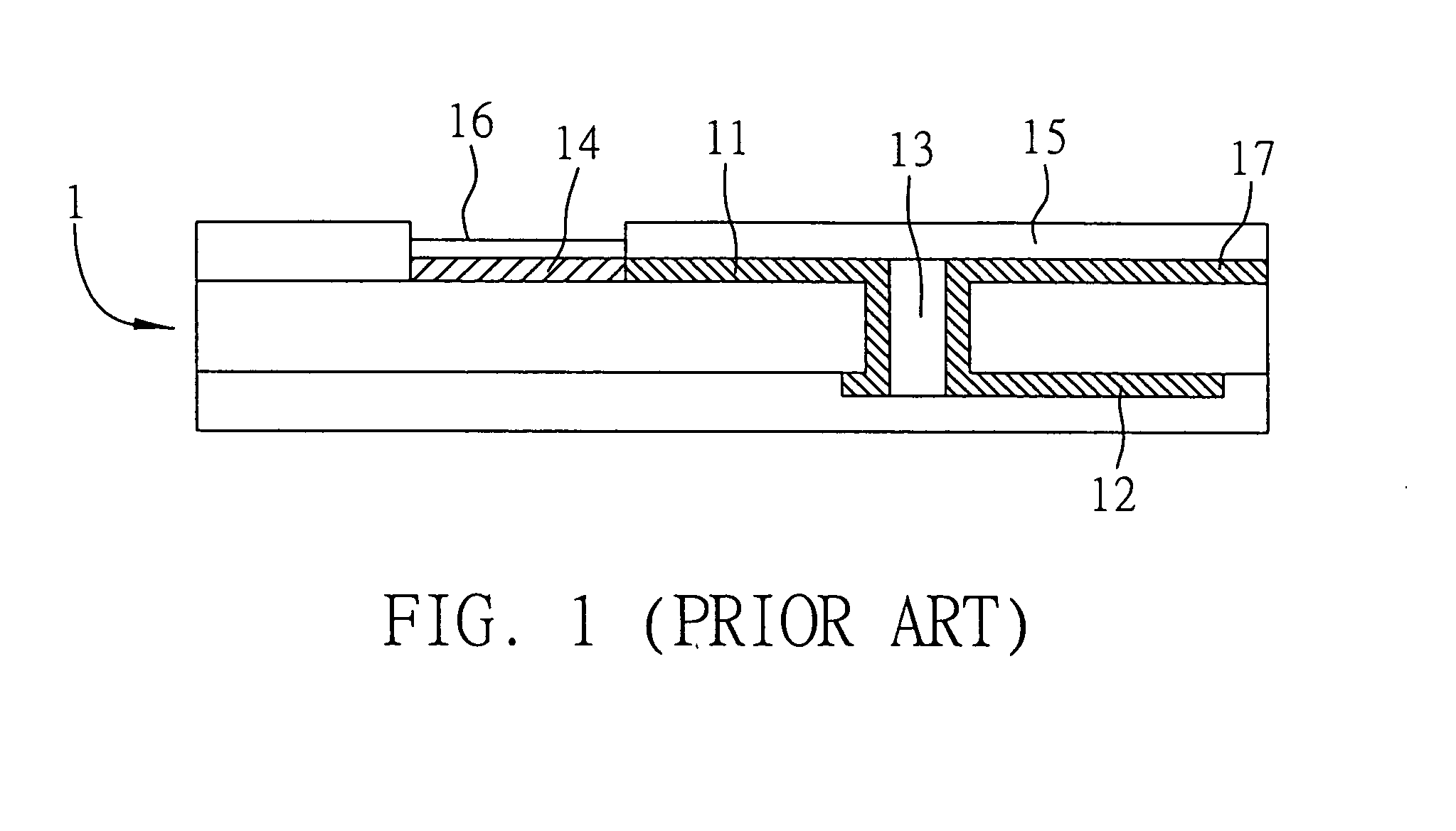

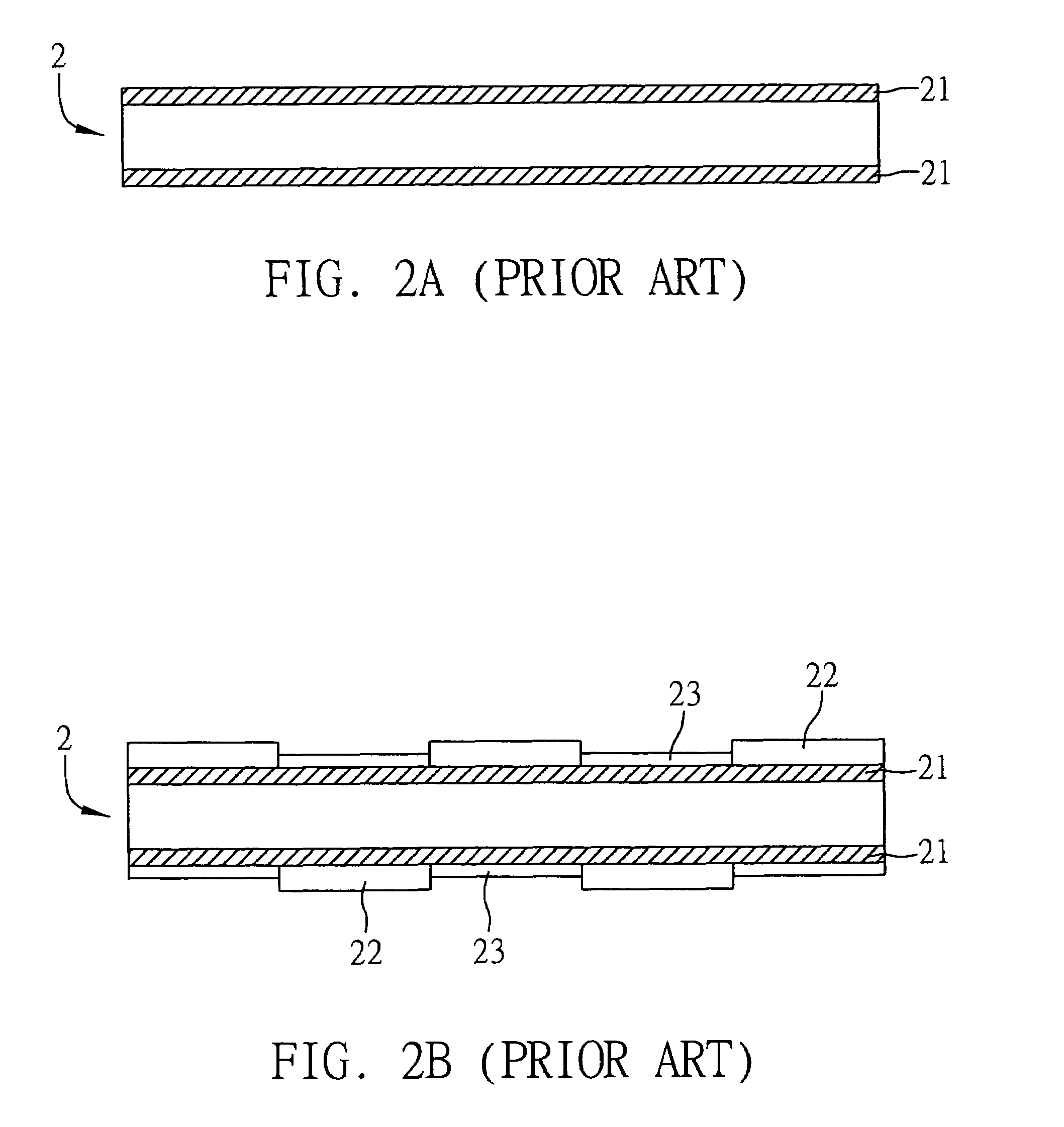

Sensor package

InactiveUS20060043555A1Maintaining gapInhibit swellingSemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

An image sensor package includes a bottom substrate, a transparent substrate, a plurality of spacers and adhesive. The bottom substrate includes a plurality of chips, which each includes an active surface and an image sensor disposed on the active surface. The transparent substrate includes a plurality of transparent substrate units which are respectively corresponding to the chips, wherein each transparent substrate unit is disposed above the active surface of the chip and covers the image sensor. The spacers are disposed between the transparent substrate unit and the chip for maintaining a predetermined gap between the transparent substrate unit and the image sensor. Each transparent substrate unit and chip are connected to each other by the adhesive.

Owner:HIMAX TECH LTD

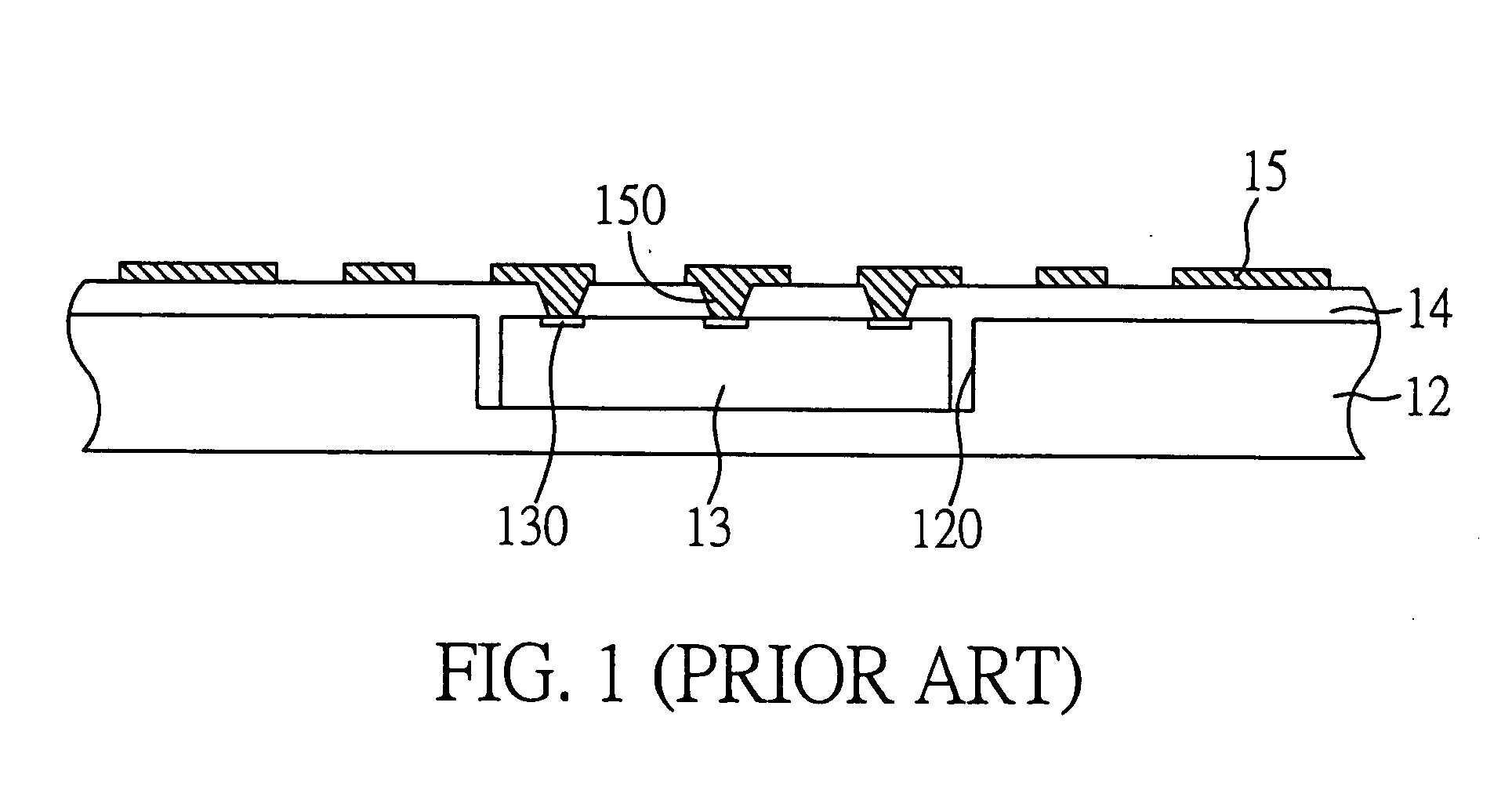

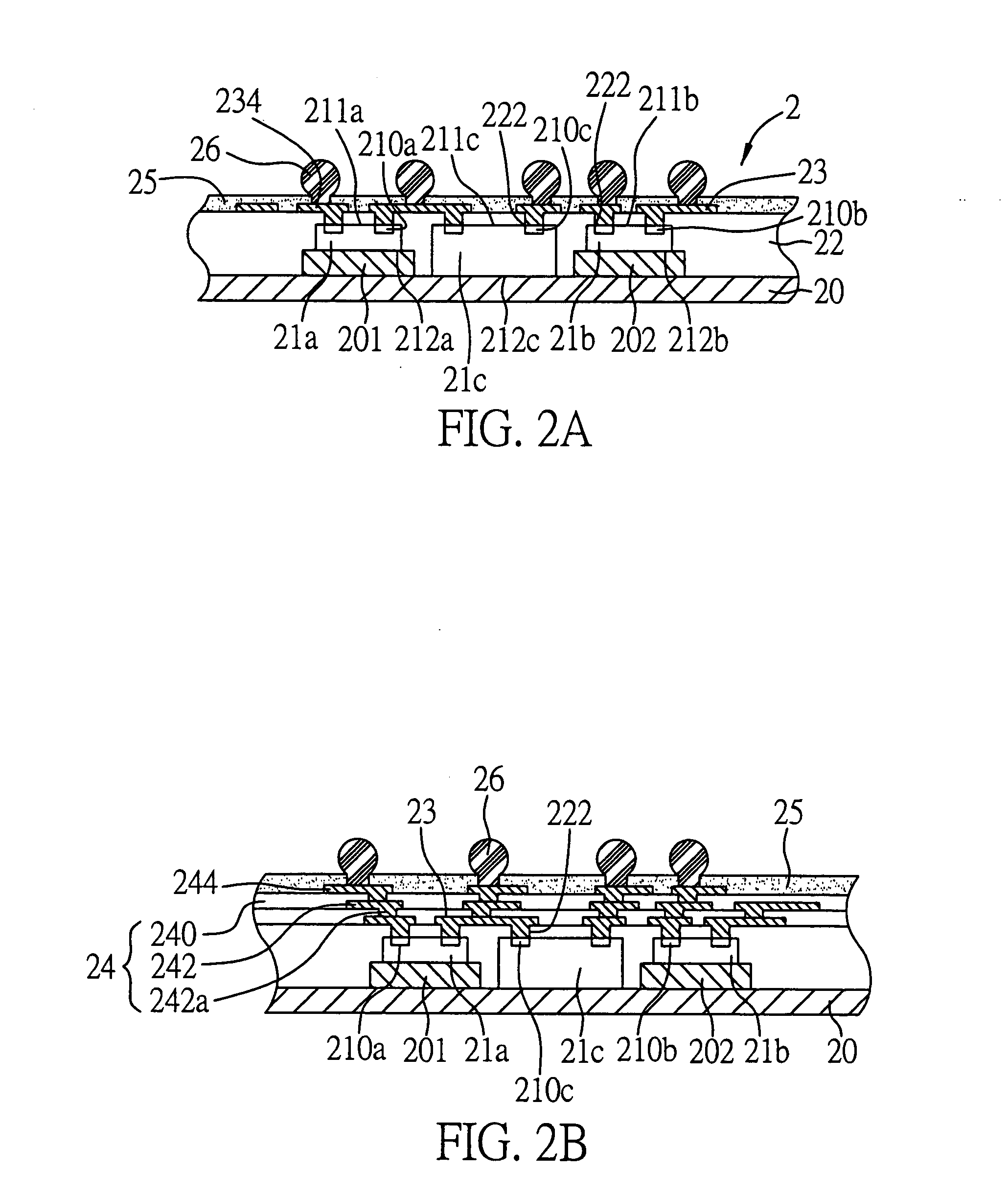

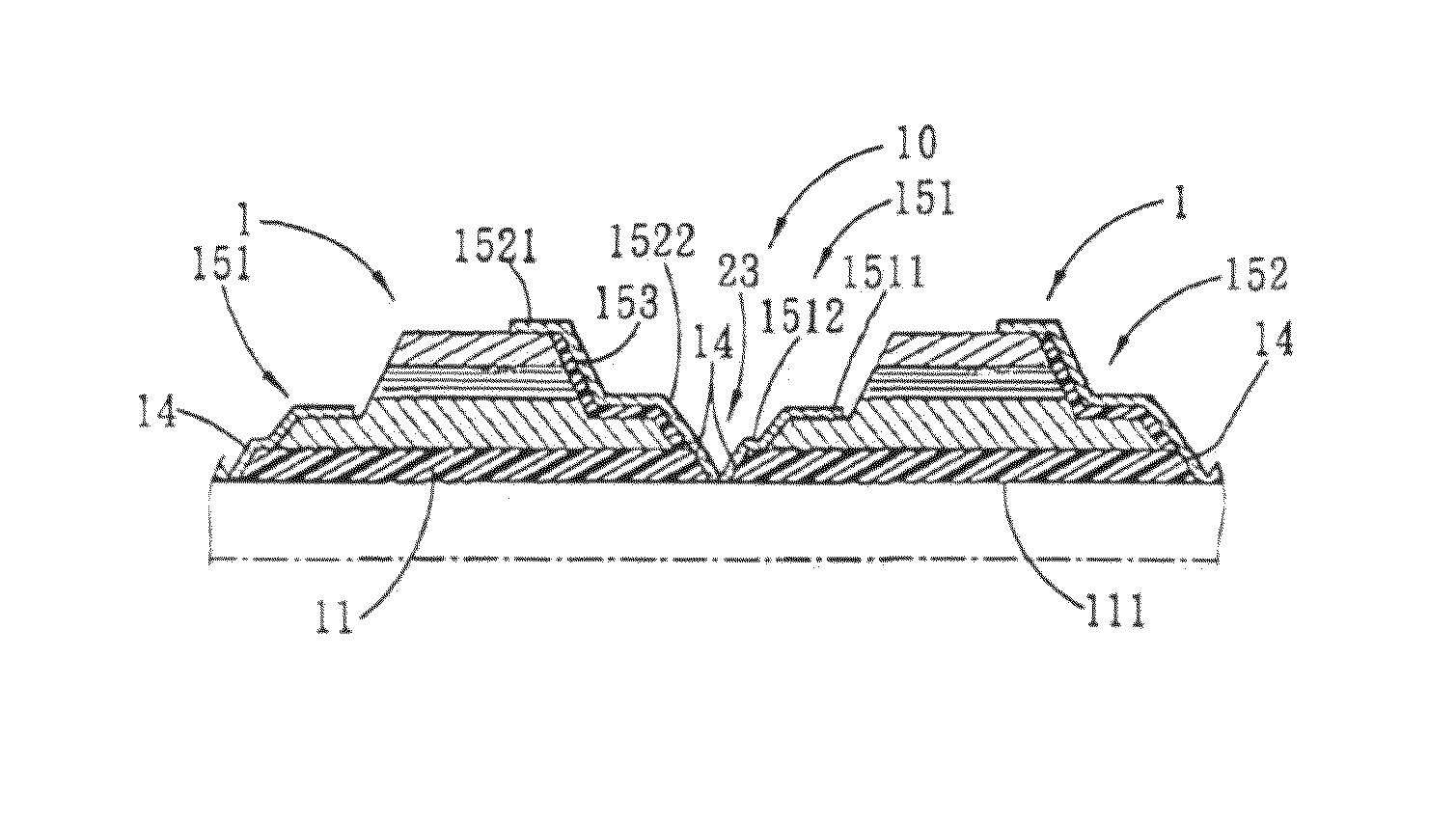

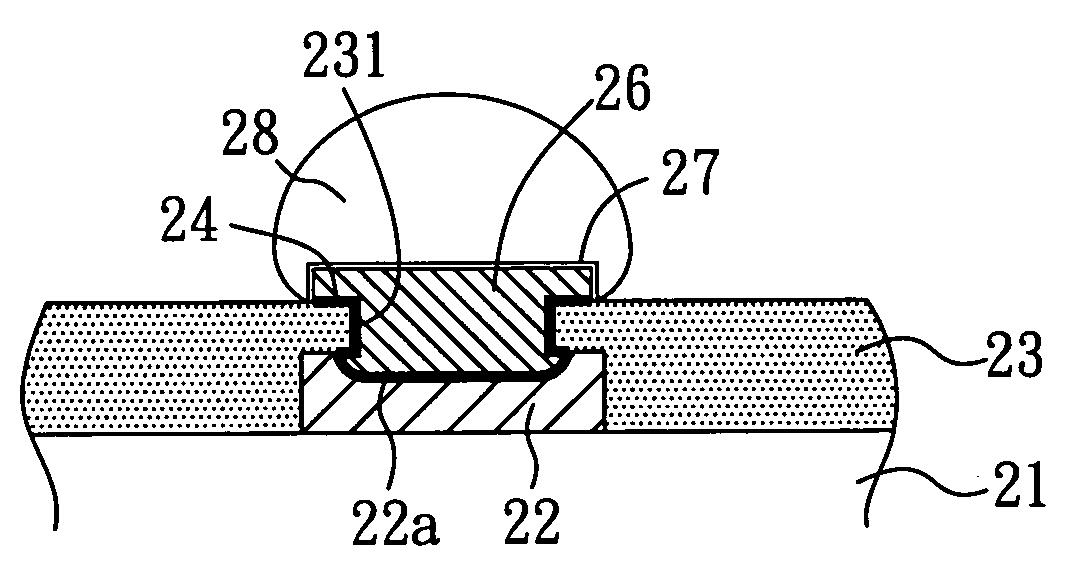

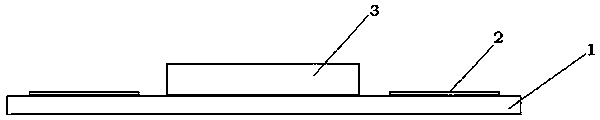

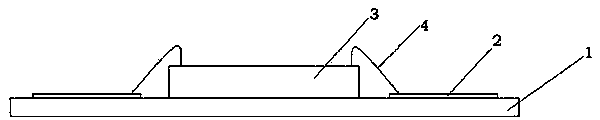

Embedded chip package structure

ActiveUS20070210423A1Avoid warpingReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

An embedded chip package structure is proposed. The embedded chip package structure includes a supporting board with a protruding section, a semiconductor chip formed on the protruding section of the supporting board, a dielectric layer formed on the supporting board and the semiconductor chip, and a circuit layer formed on the dielectric layer. The circuit layer is electrically connected to electrode pads of the semiconductor chip via a plurality of conducting structures formed inside the dielectric layer such that the semiconductor chip can be electrically connected to an external element through the circuit layer. By varying the thicknesses of the protruding section, the dielectric layer and the supporting board, warpage of the package structure resulted from temperature change during the fabrication process can be prevented.

Owner:UNIMICRON TECH CORP

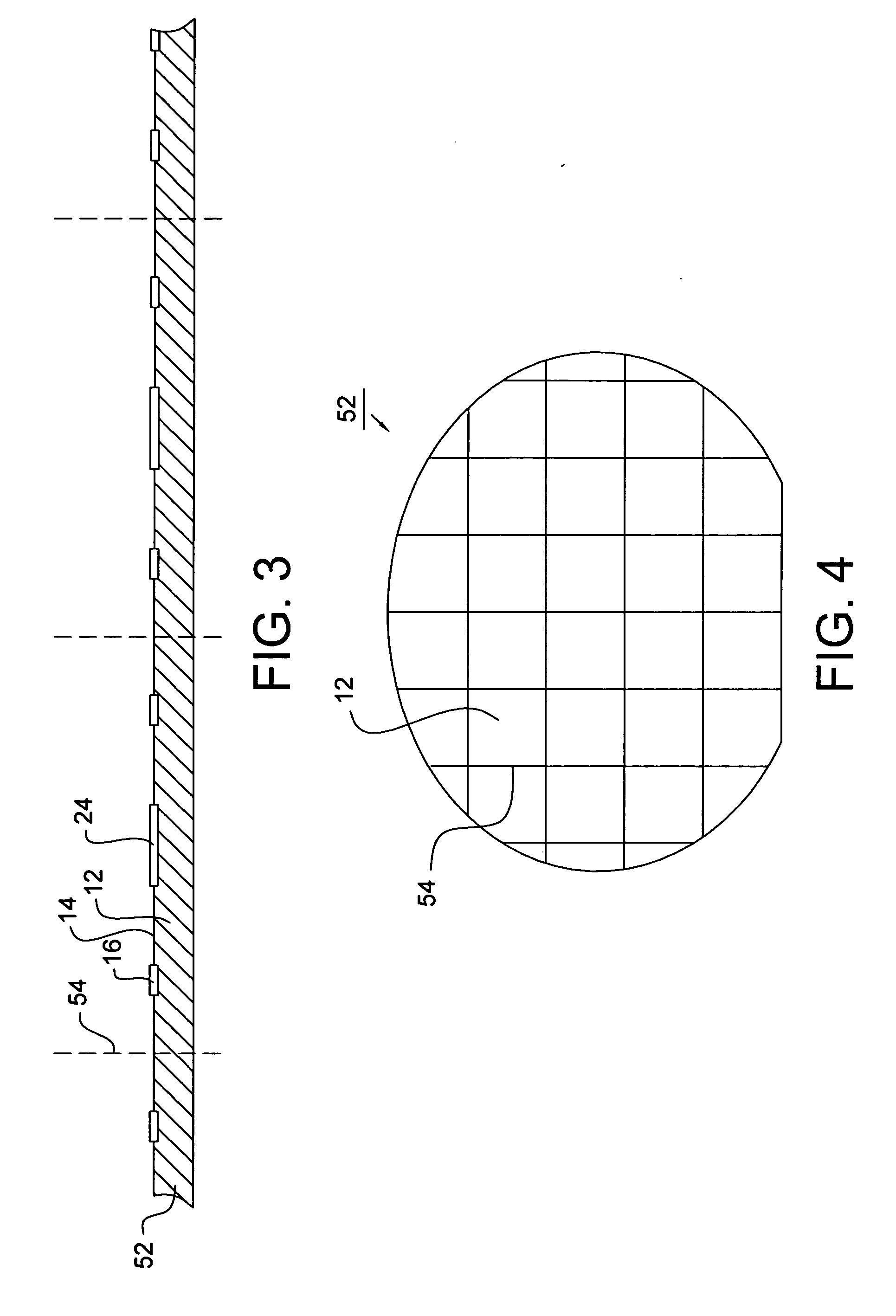

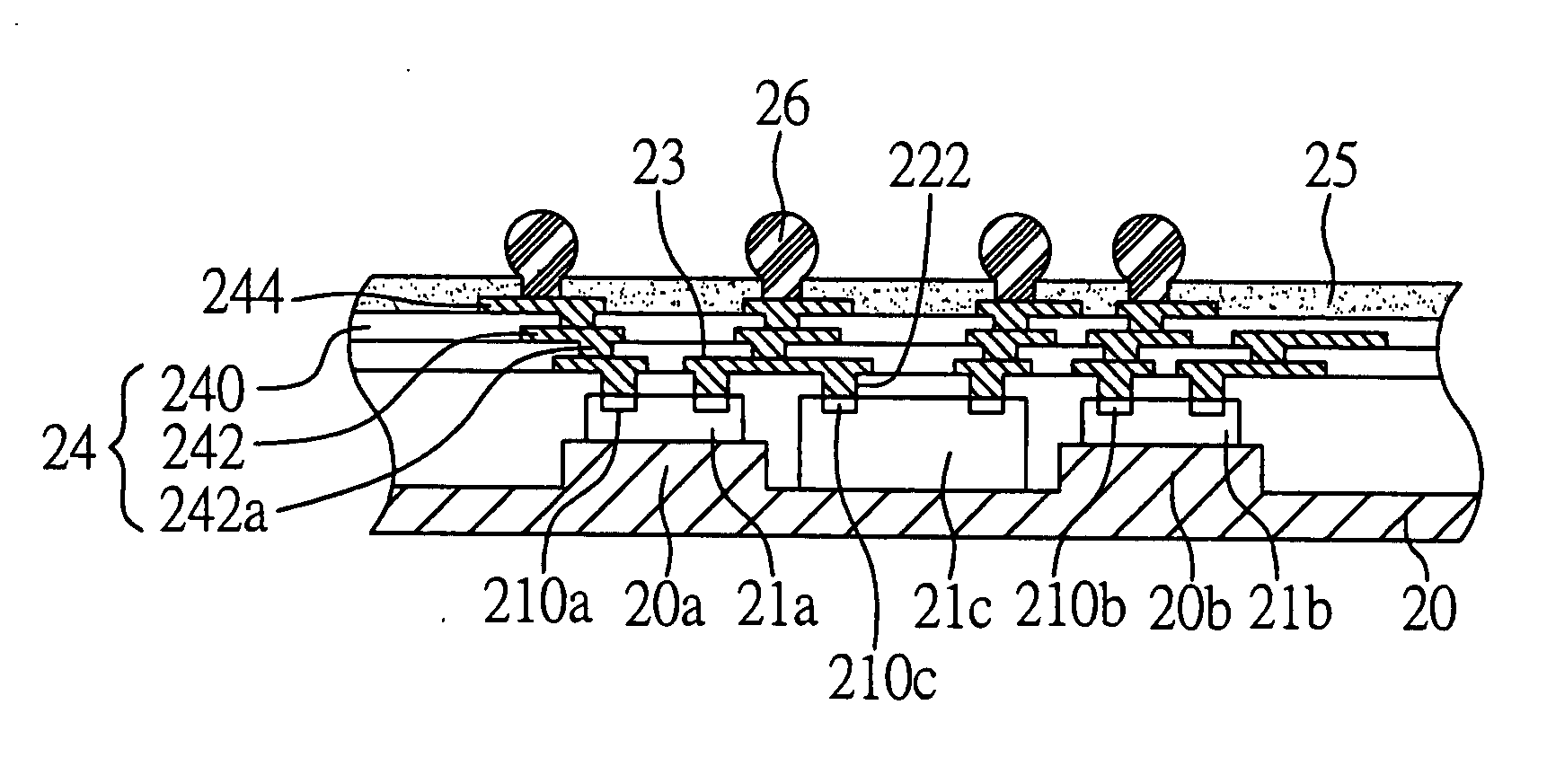

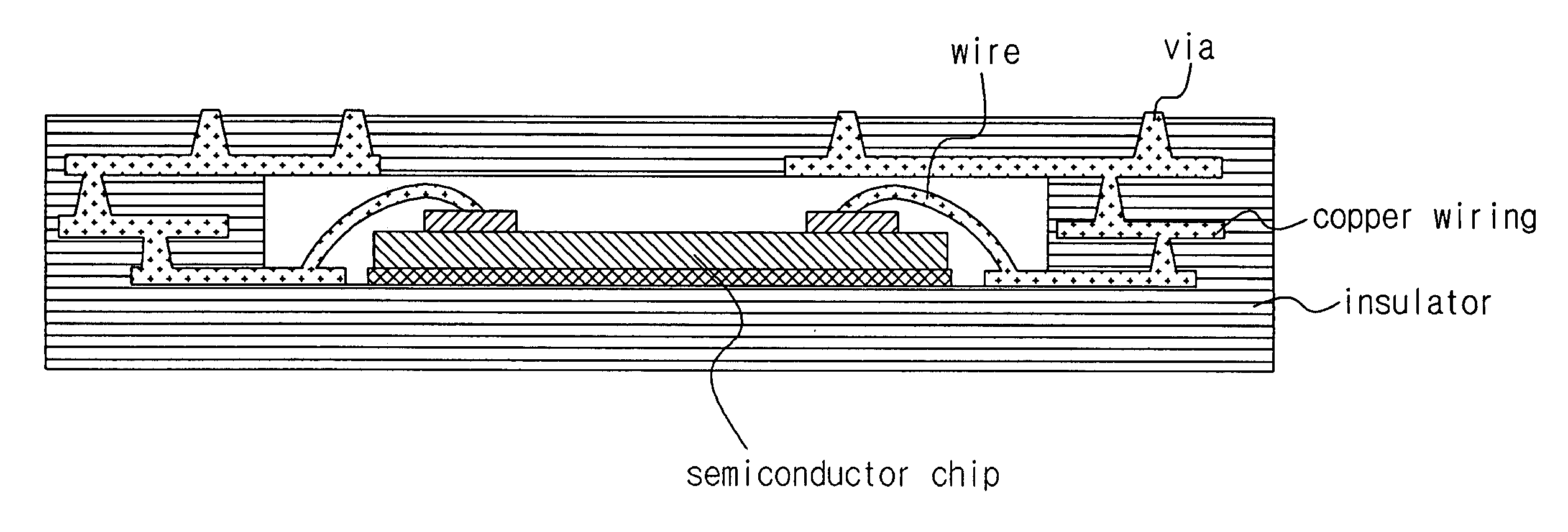

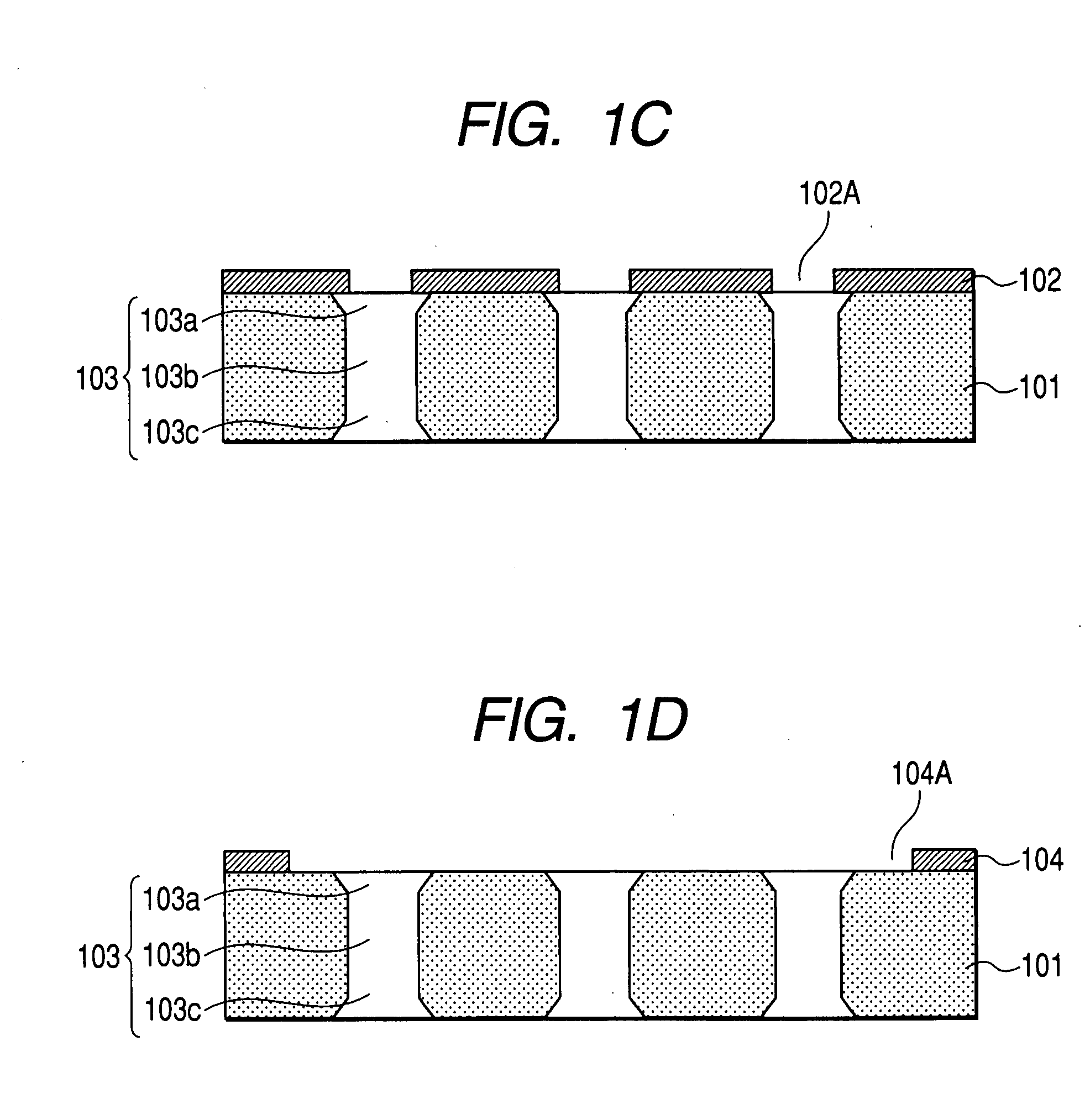

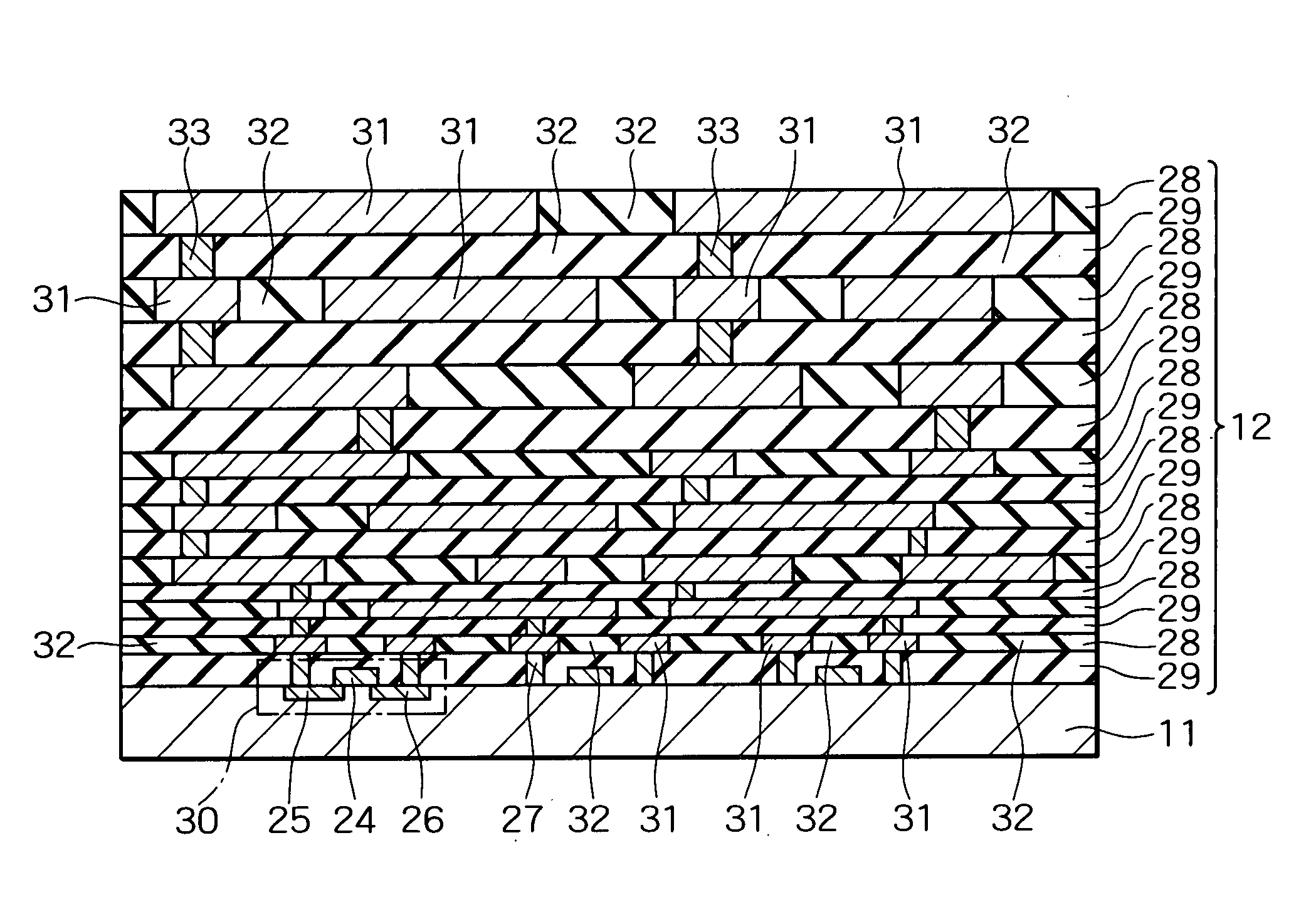

Fabrication method of an organic substrate having embedded active-chips

InactiveUS20090042336A1Large capacityImprove package reliabilitySemiconductor/solid-state device detailsSolid-state devicesFlip chip interconnectAdhesive

The fabrication method of an organic substrate having embedded active-chips such as semiconductor chips is disclosed. The present invention previously applies the conductive adhesives in a wafer state, makes them in a B-stage state, obtains individual semiconductor chips through dicing, and positions the individual semiconductor chips previously applied with the conductive adhesives in the cavities, making it possible to simultaneously obtain an electrical connection and a physical adhesion of the substrate and the semiconductor chips by means of a method of applying heat and pressure and stack the copper clad laminates on the upper portion of the substrate to which the semiconductor chips are connected. The present invention has advantages in processes such as a lead-free process, an environmental-friendly fluxless process, a low temperature process, ultra-fine pitch applications, etc., by mounting the active-chips through the flip chip interconnection using the non-solder bumps and the conductive adhesives.

Owner:KOREA ADVANCED INST OF SCI & TECH

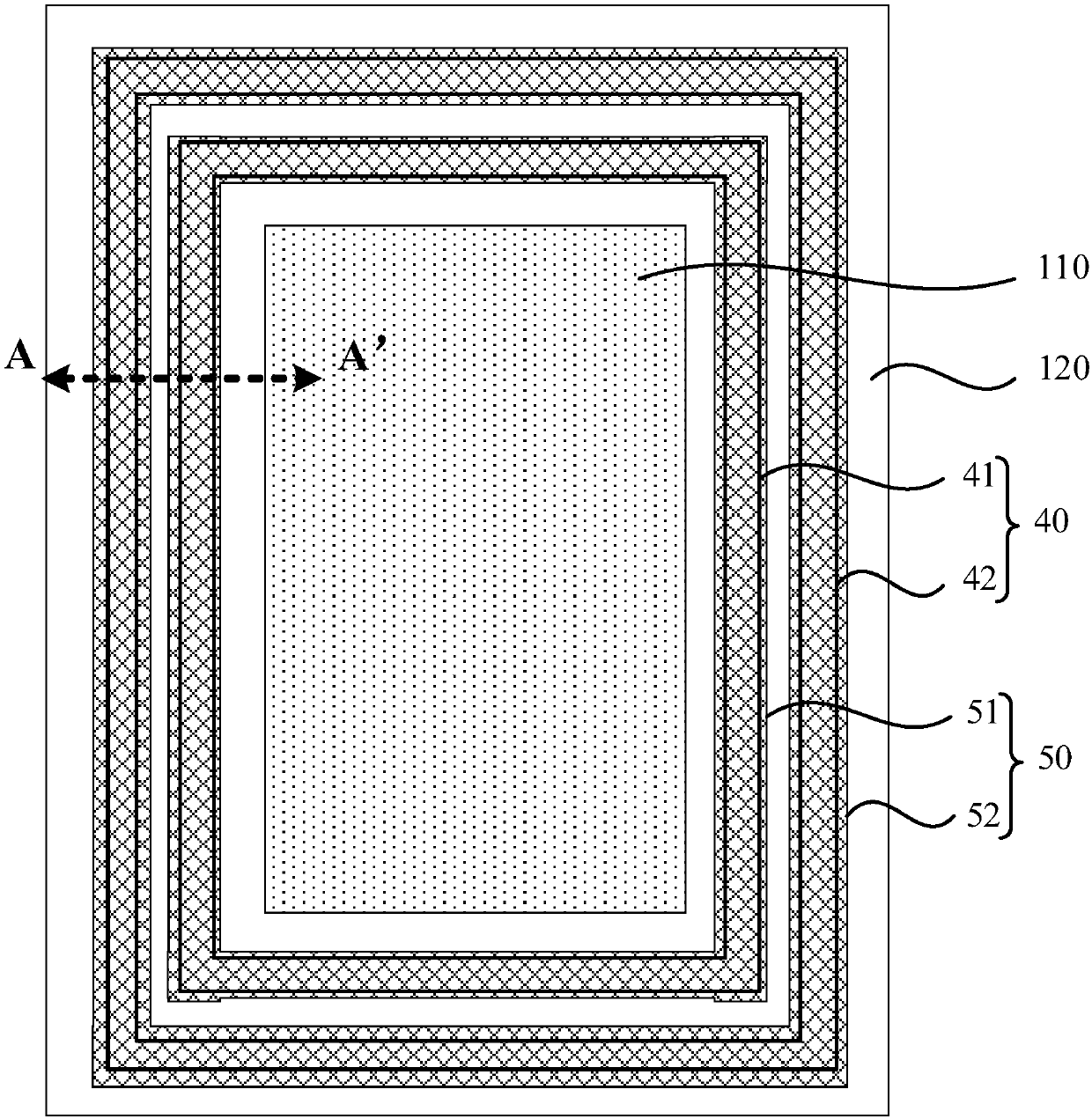

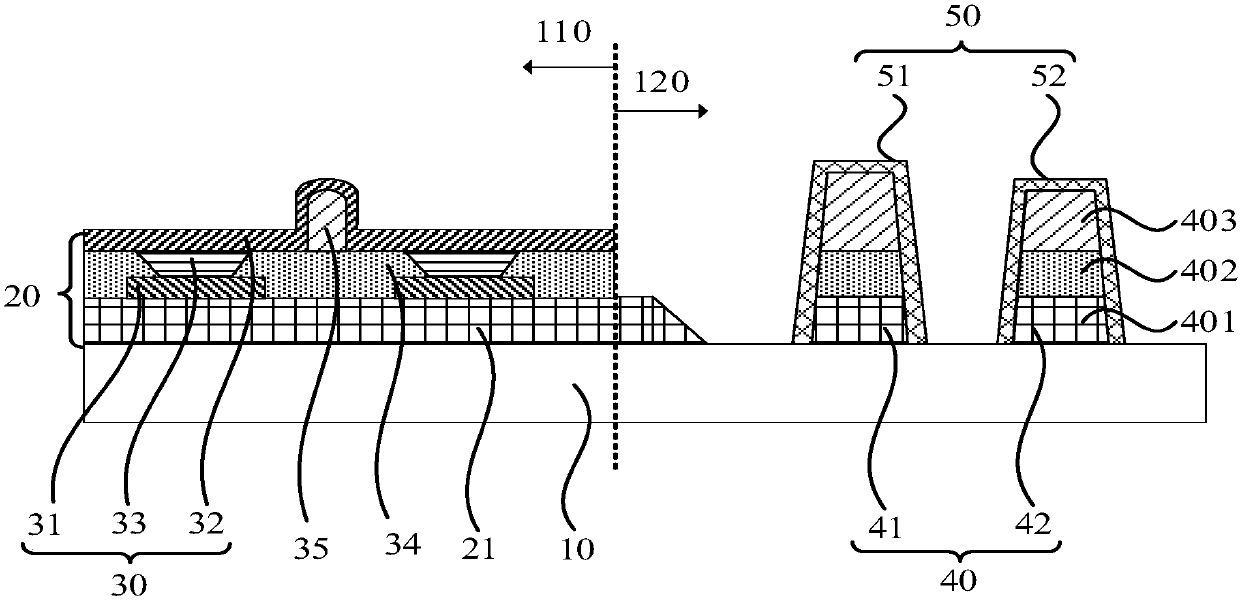

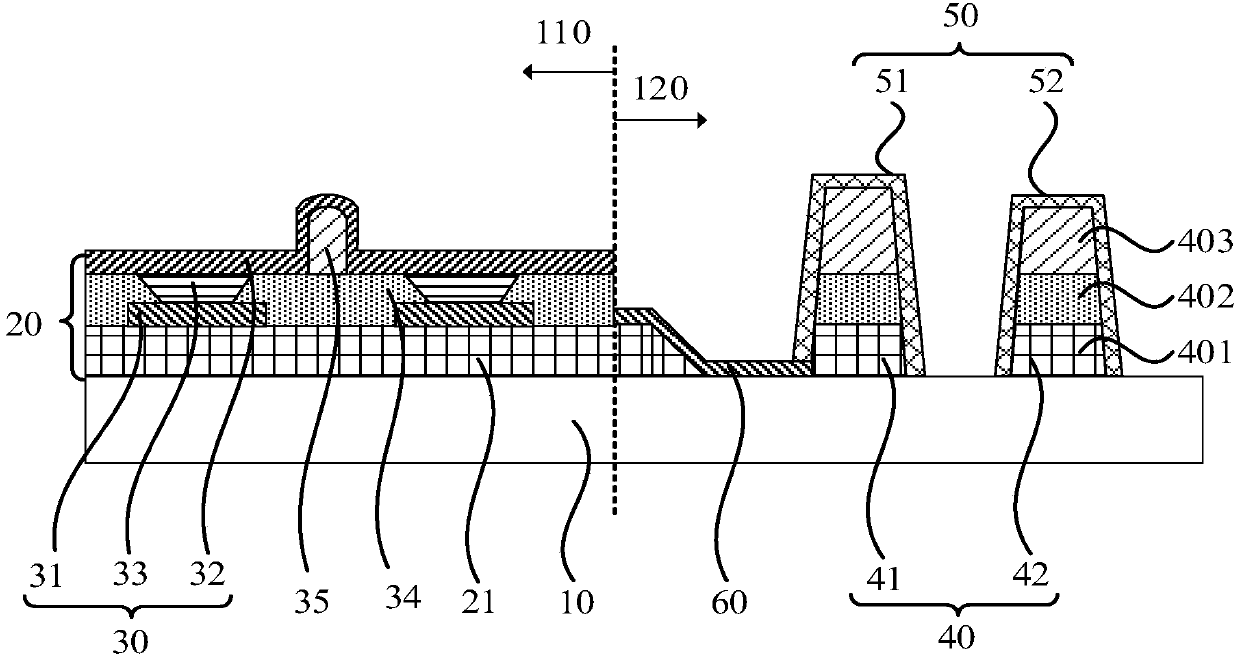

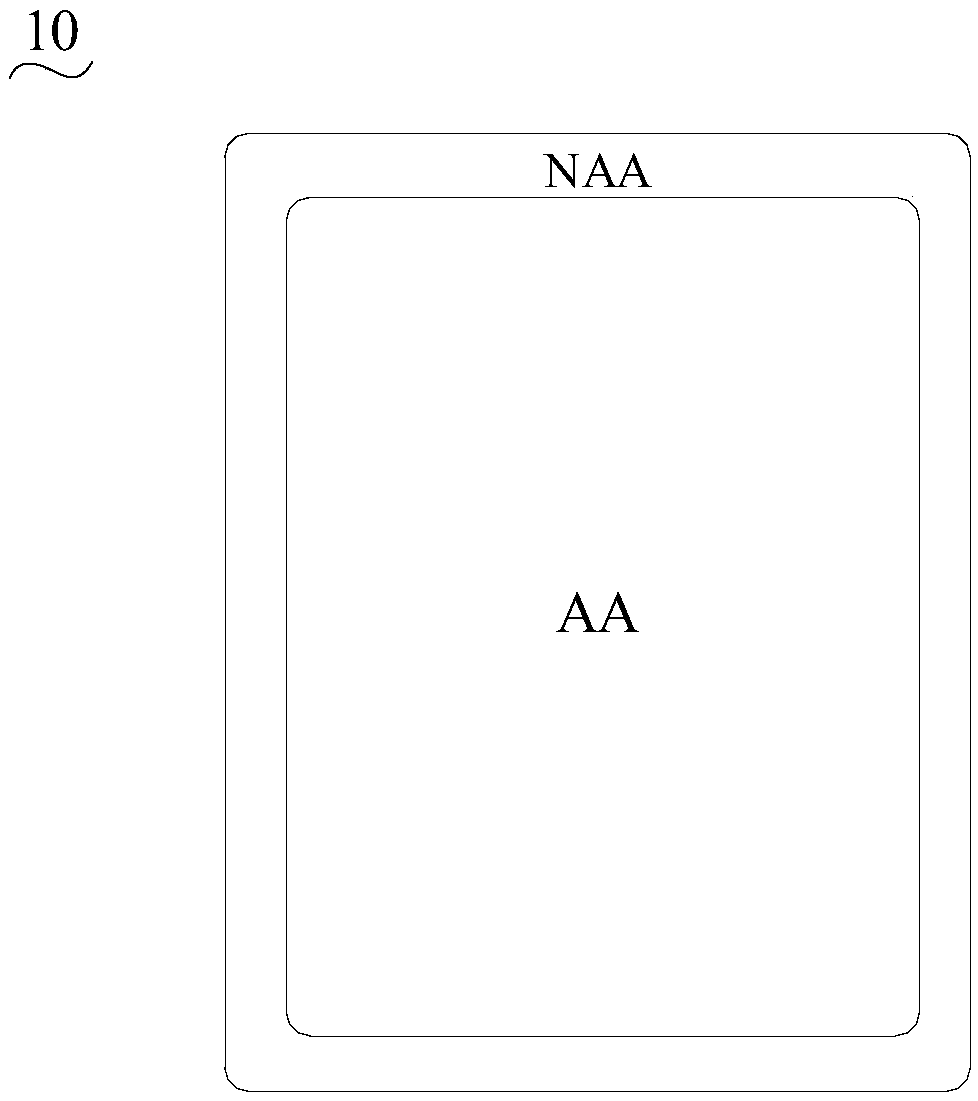

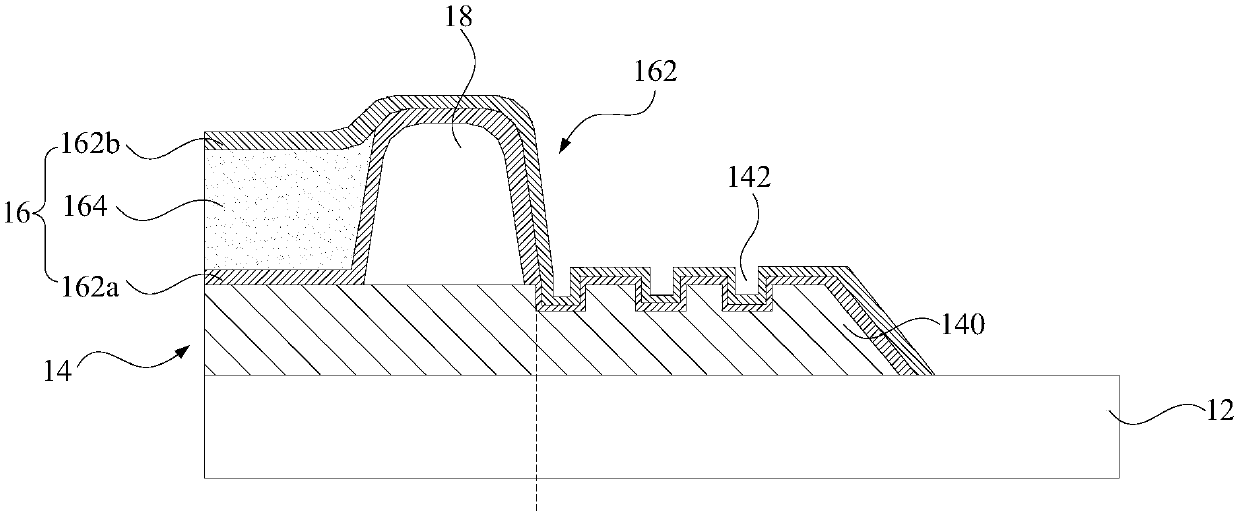

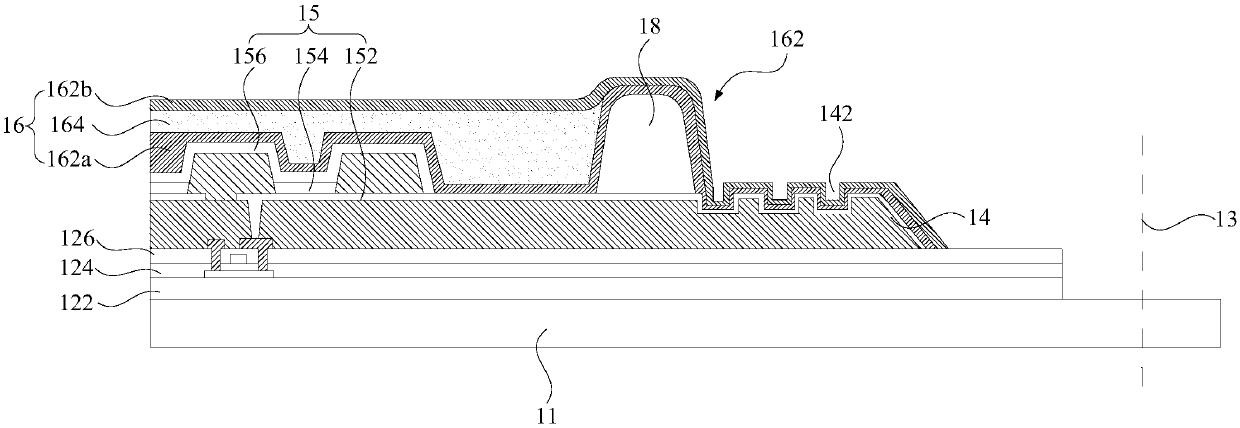

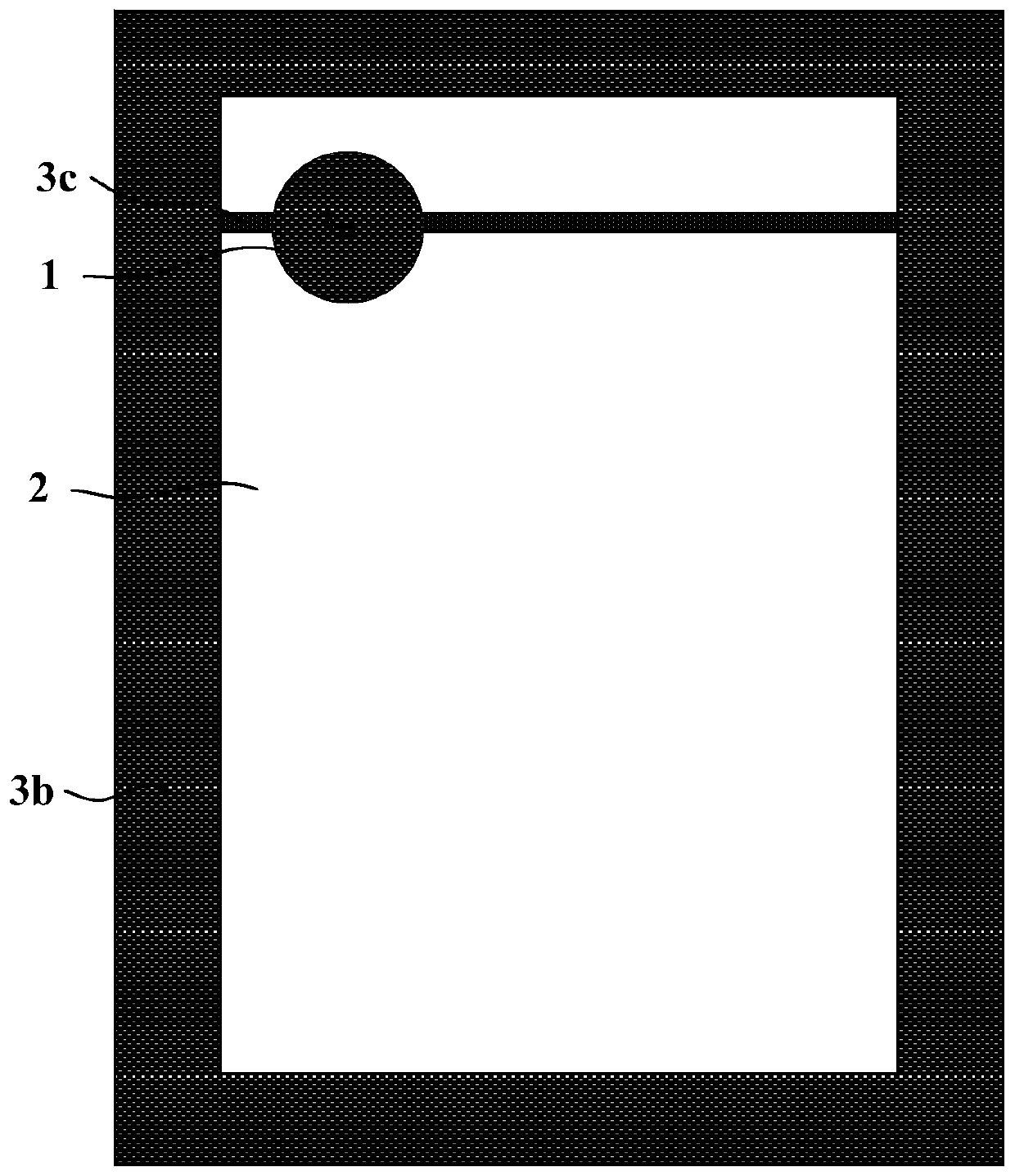

Organic light-emitting display panel, display device, and manufacturing method for organic light-emitting display panel

ActiveCN107845667AImprove package reliabilityCan not be damagedSolid-state devicesSemiconductor/solid-state device manufacturingForeign matterVertical projection

The invention provides an organic light-emitting display panel, a display device, and a manufacturing method for the organic light-emitting display panel. The organic light-emitting display panel comprises a substrate which comprises a display region and a non-display region, wherein the non-display region surrounds the display region; an organic light-emitting part which is located in the displayregion, and is disposed at a first side of the substrate; at least one retaining wall which is disposed in the non-display region and surrounds the organic light-emitting part; and at least one protection metal layer which is located in the non-display region and is located at one side, far from the substrate, of the retaining wall, wherein the vertical projection of the retaining wall on the substrate is located in the vertical projection of the protection metal layer on the substrate. The foreign matters formed in the organic light-emitting display panel are eliminated, and the packaging reliability of the organic light-emitting display panel is improved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

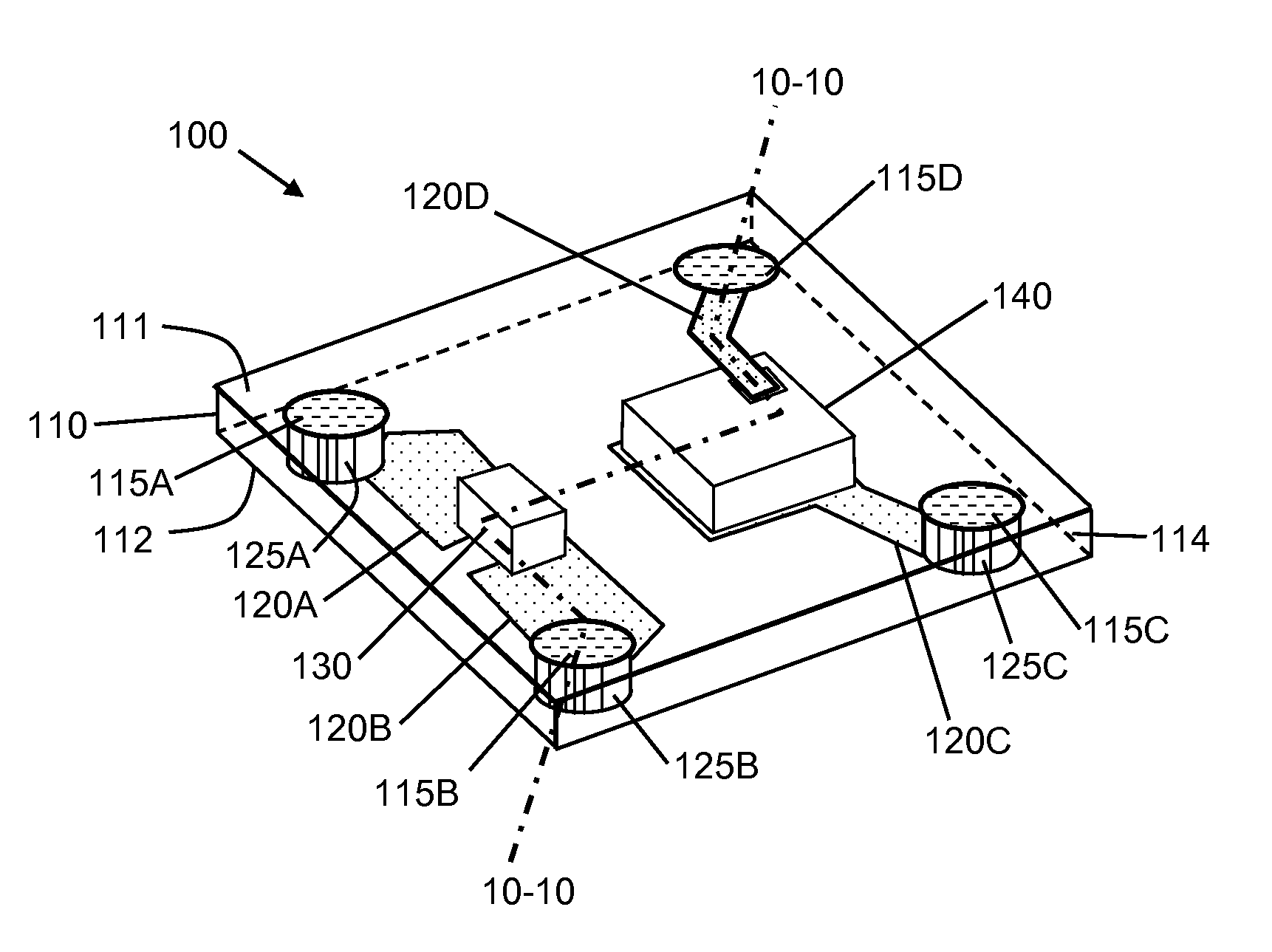

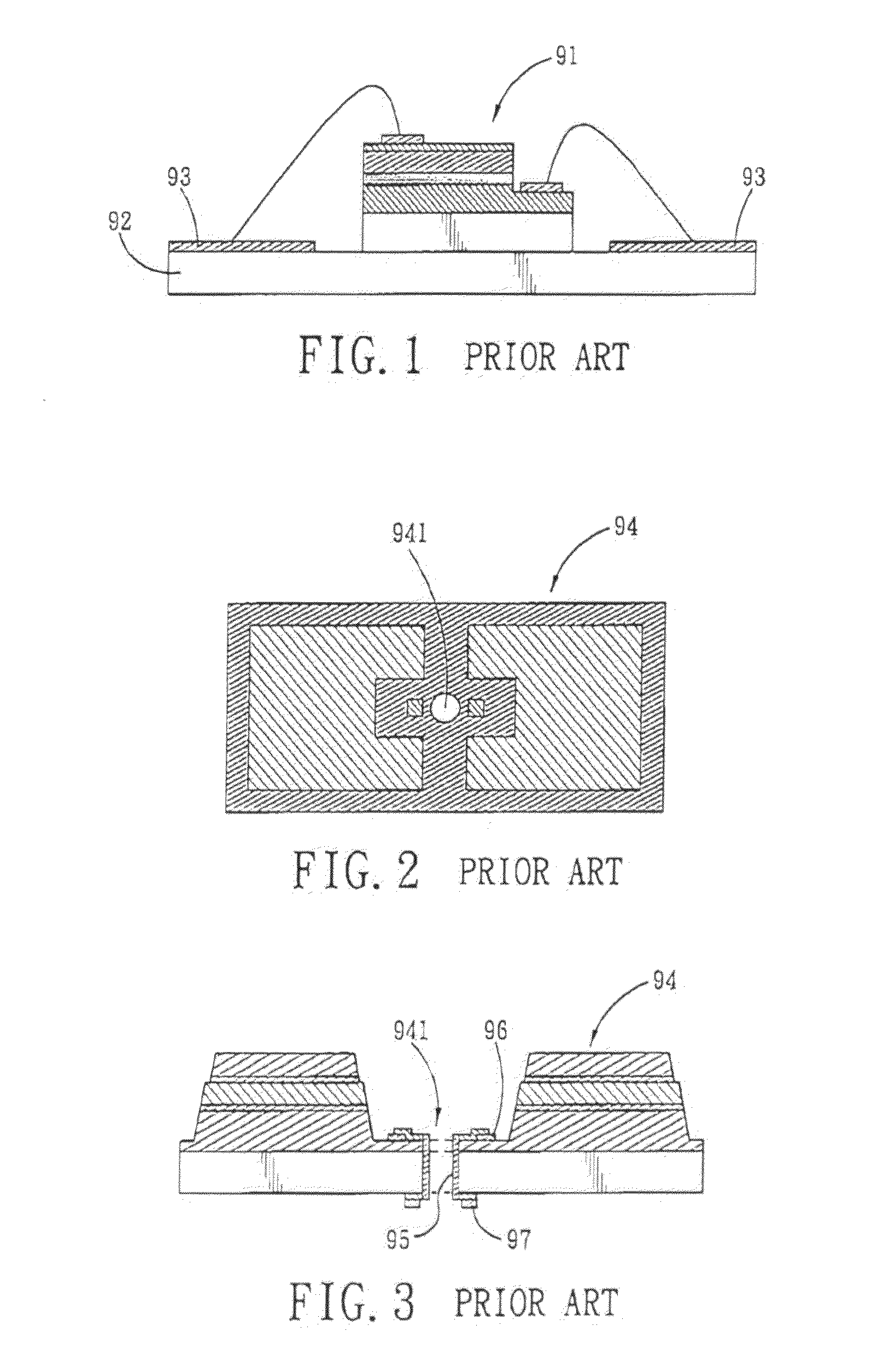

MEMS microphone module and method thereof

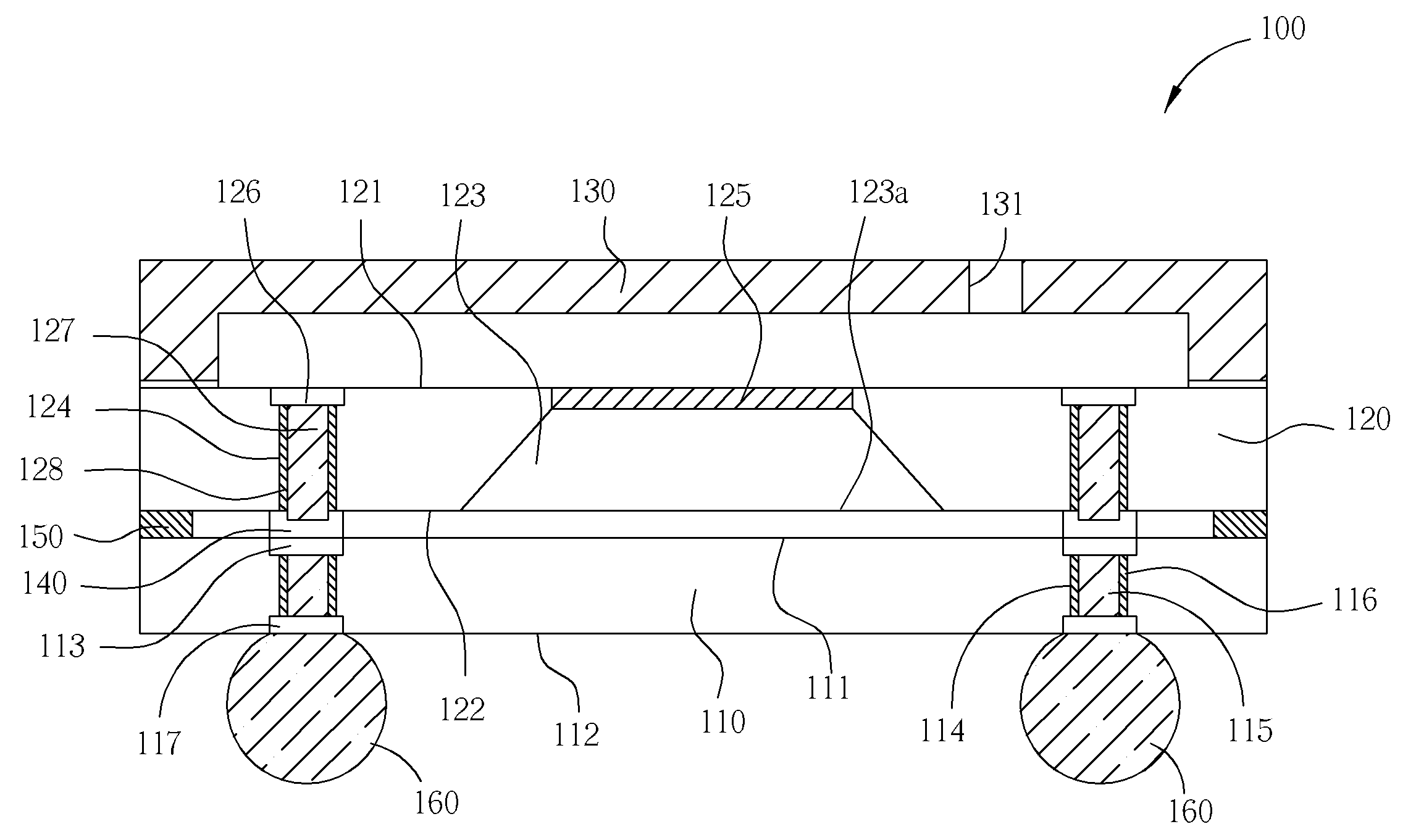

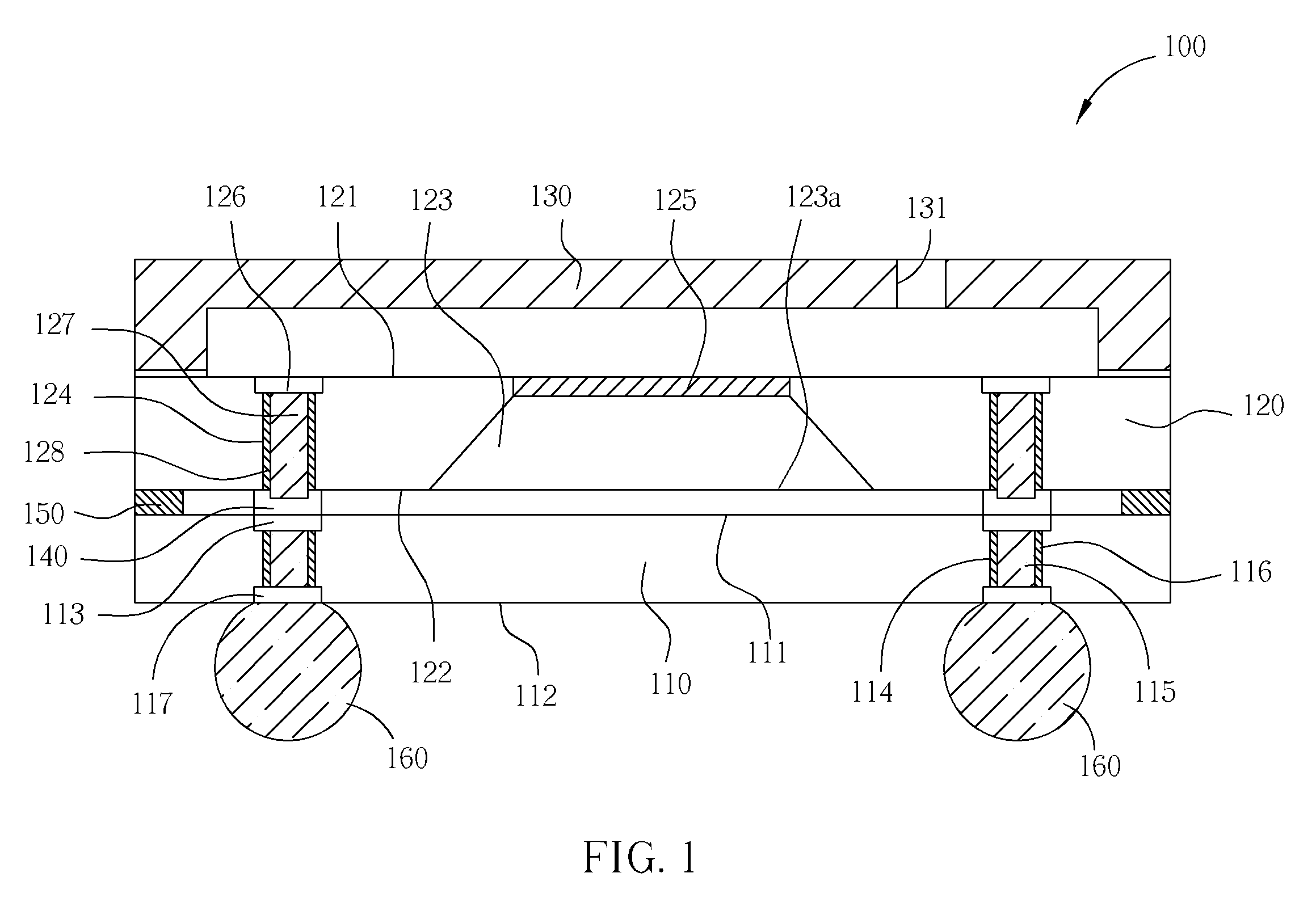

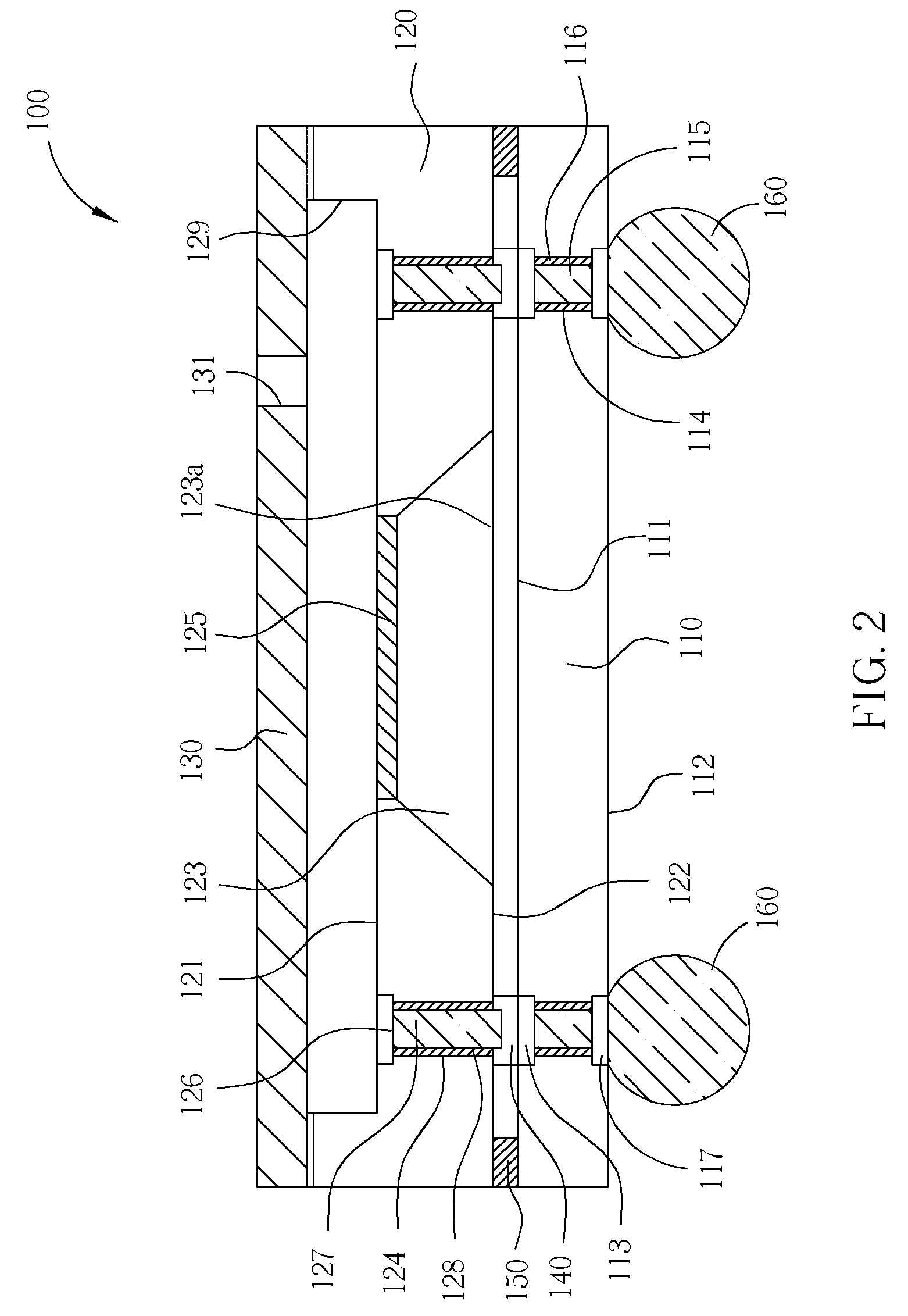

ActiveUS7808060B2Improve package reliabilityReduce package sizeSemiconductor/solid-state device detailsSolid-state devicesResonant cavityEngineering

A MEMS microphone module having an application specific IC and a microphone chip is disclosed. The application specific IC has a plurality of first vias and a plurality of first pads, and the first vias are connected to the first pads. The microphone chip has a resonant cavity, a plurality of second vias and a plurality of second pads, and the second vias are connected to the second pads. The microphone chip is disposed on a first surface of the application specific IC with an opening of the resonant cavity facing toward a first surface of the application specific IC. The second conductive vias of the microphone chip are also electrically connected to the first vias of the application specific IC. By placing the microphone chip on the first surface of the application specific IC, the present invention could reduce the package size and increase the reliability of the package.

Owner:ADVANCED SEMICON ENG INC

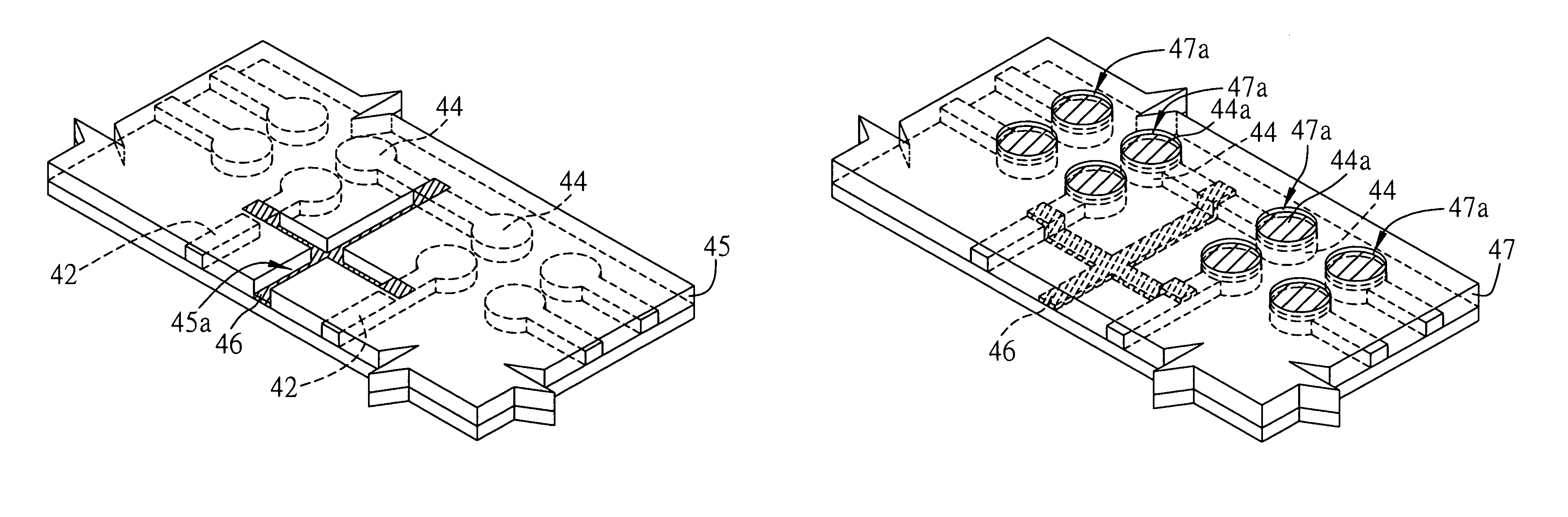

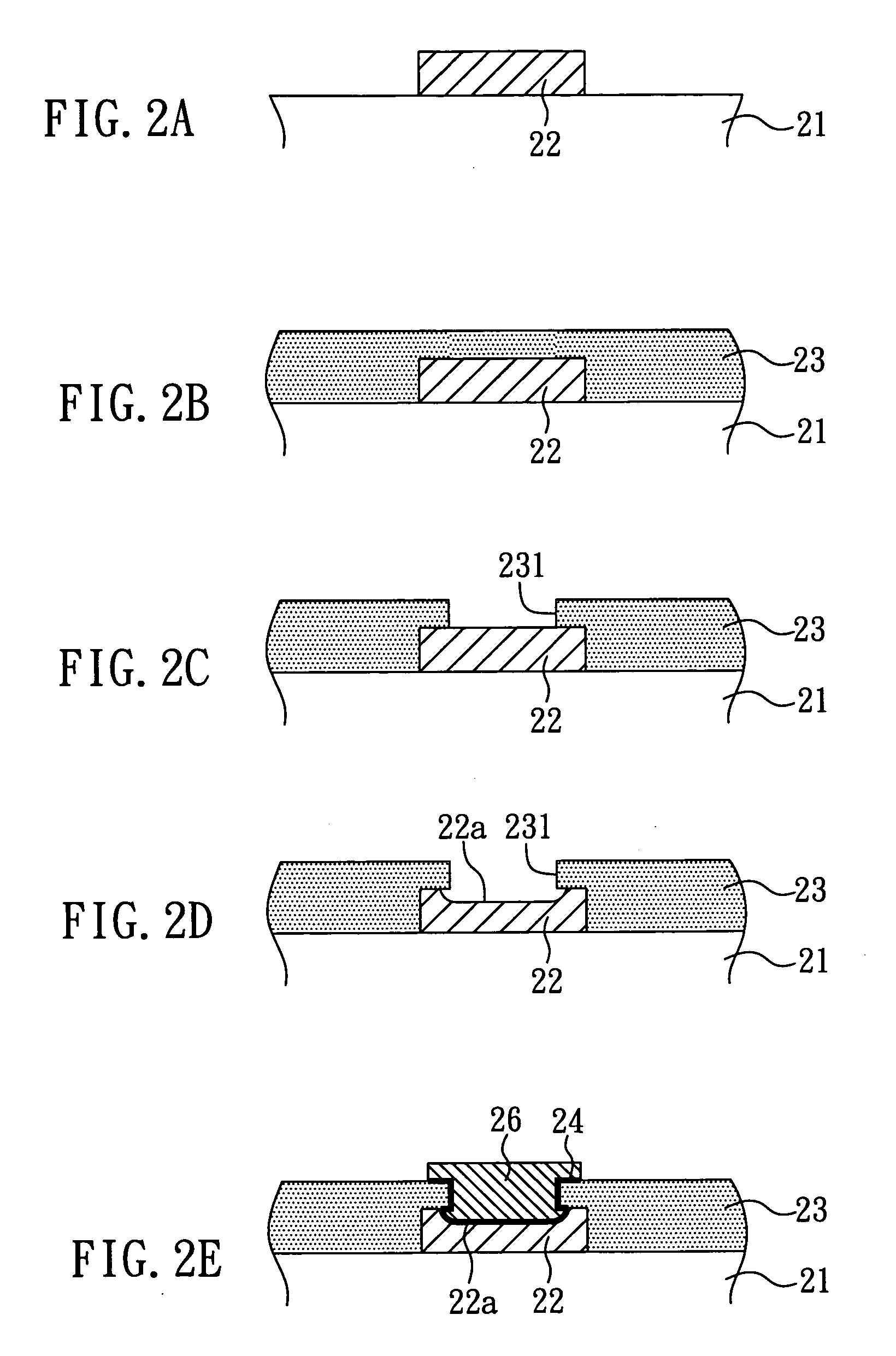

Method for fabricating semiconductor package substrate with plated metal layer over conductive pad

ActiveUS7041591B1Easy to oxidizeElectrical connectionElectrolysisSemiconductor/solid-state device detailsResistSolder mask

A method for fabricating a semiconductor package substrate having a plated metal layer on a conductive pad is proposed. First of all, a first resist layer is formed on a semiconductor package substrate having a plurality of traces and conductive pads on a surface thereof. The first resist layer is provided with at least an opening, such that the opening is able to contact the adjacent trace. Subsequently, a conductive film is formed in the opening, such that the conductive film can electrically connect the adjacent trace and conductive pad. After removing the first resist layer, a second resist layer having a plurality of openings is formed on the surface of the substrate to expose the conductive pad. Afterwards, an electroplating process is performed on the substrate, so that a metal layer is formed on an exposed surface of the conductive pad. The second resist layer and the conductive film are then removed from the substrate. A solder mask layer having a plurality of openings is also formed on the surface of the substrate to expose the conductive pad which has been covered by the metal layer using the electroplating process.

Owner:PHOENIX PRECISION TECH CORP

Semiconductor package structure and method for manufacturing the same

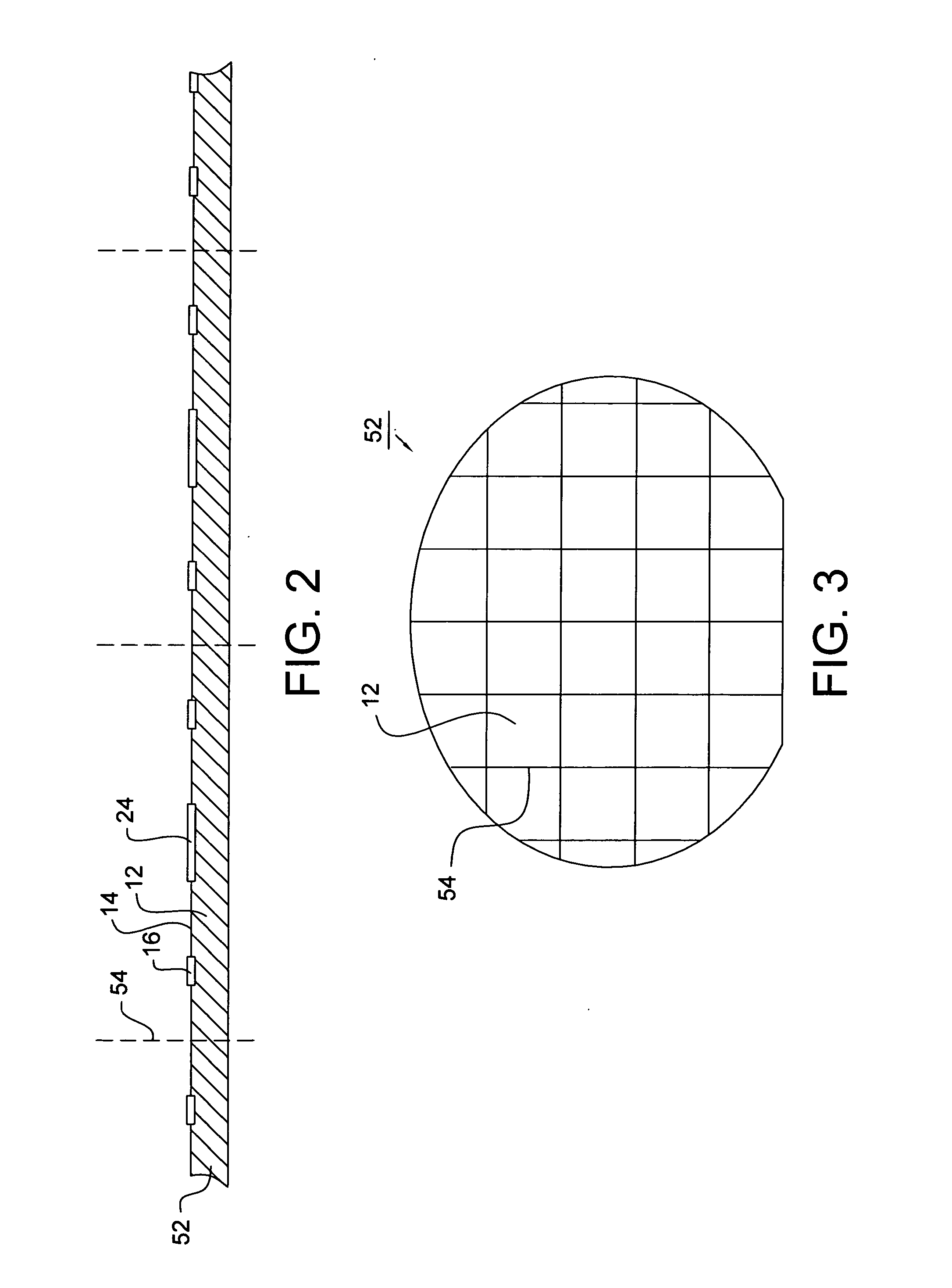

ActiveUS20060197217A1High package efficiencyImprove efficiencySemiconductor/solid-state device detailsSolid-state devicesEngineeringMetal

A semiconductor package structure comprises a chip, a plurality of pad extension traces, a plurality of via holes, a lid and a plurality of metal traces, wherein the chip has an optical component and a plurality of pads disposed on its active surface; pad extension traces are electrically connected to the pads; the via holes penetrate the chip and are electrically connected to the pad extension traces and exposed out of side surfaces of the semiconductor package structure; the lid is adhered onto the active surface of the chip; and the plurality of metal traces is disposed on the back surface of the chip, electrically connected to the plurality of via holes, and used to define a plurality of solder pads thereon. The present invention also provides a method for manufacturing the semiconductor package structure.

Owner:ADVANCED SEMICON ENG INC

Display panel and display device

ActiveCN109659444AImprove bending resistanceFlexibleSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The present invention relates to a display panel. The display panel comprises a substrate, a planarization layer, a light-emitting element and a package structure. The substrate has a display area anda non-display area; the planarization layer is disposed on the substrate to form a planarization surface; the light-emitting element is disposed on the planarization layer; the package structure is disposed on the light-emitting element and the planarization layer; the package structure includes a plurality of inorganic encapsulation film layers; the planarization layer includes a central portioncovering the display area and is extended to the peripheral portion of the non-display area; and the inorganic encapsulation film layers are configured to be in contact with the peripheral portion ofthe planarization layer at the non-display area. The planarization layer has a certain flexibility, can have an effect on releasing of stress and can facilitate reduction of the stress of the inorganic encapsulation film layers of the package structure at the package boundary so as to effectively prevent the inorganic encapsulation film layers from generating cracks, improve the package reliability of the package structure and improve the anti-bending performance of the display panel. The present invention further provides a display device.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

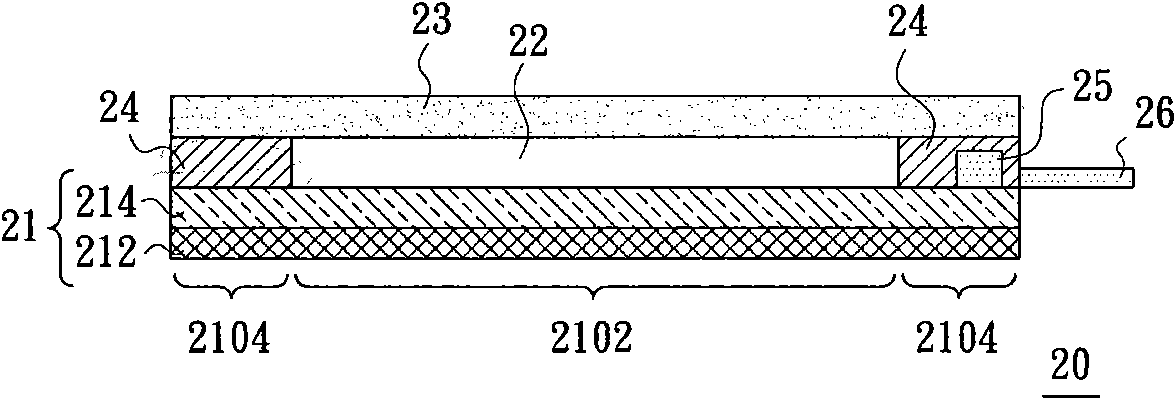

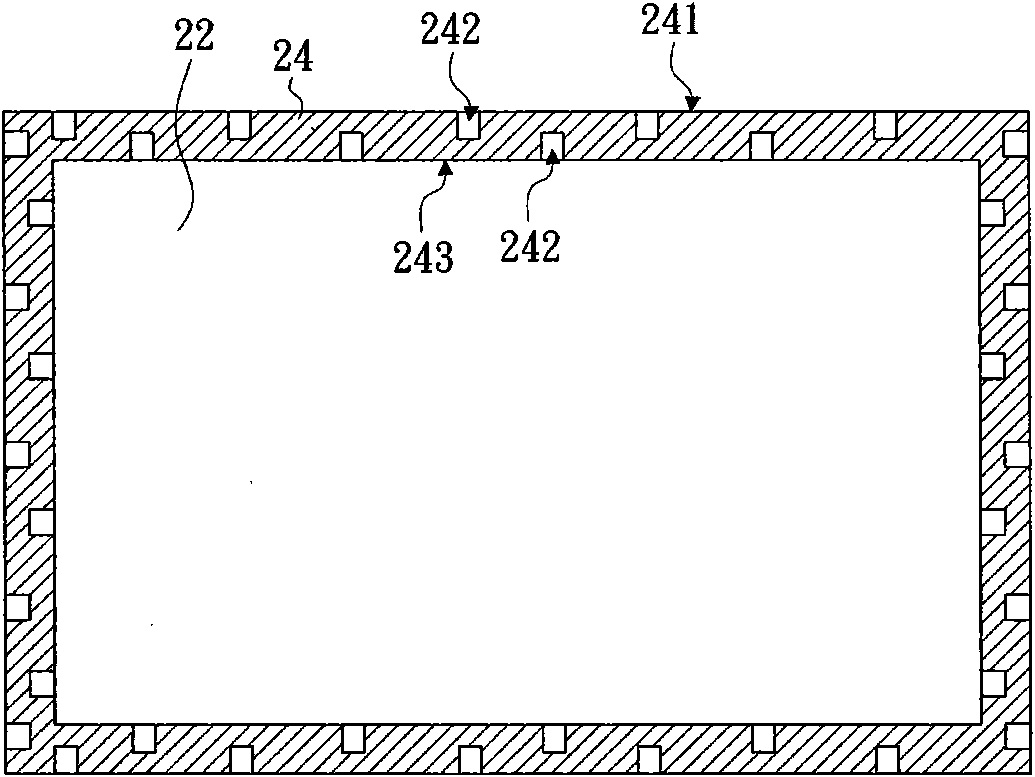

Flexible display Device

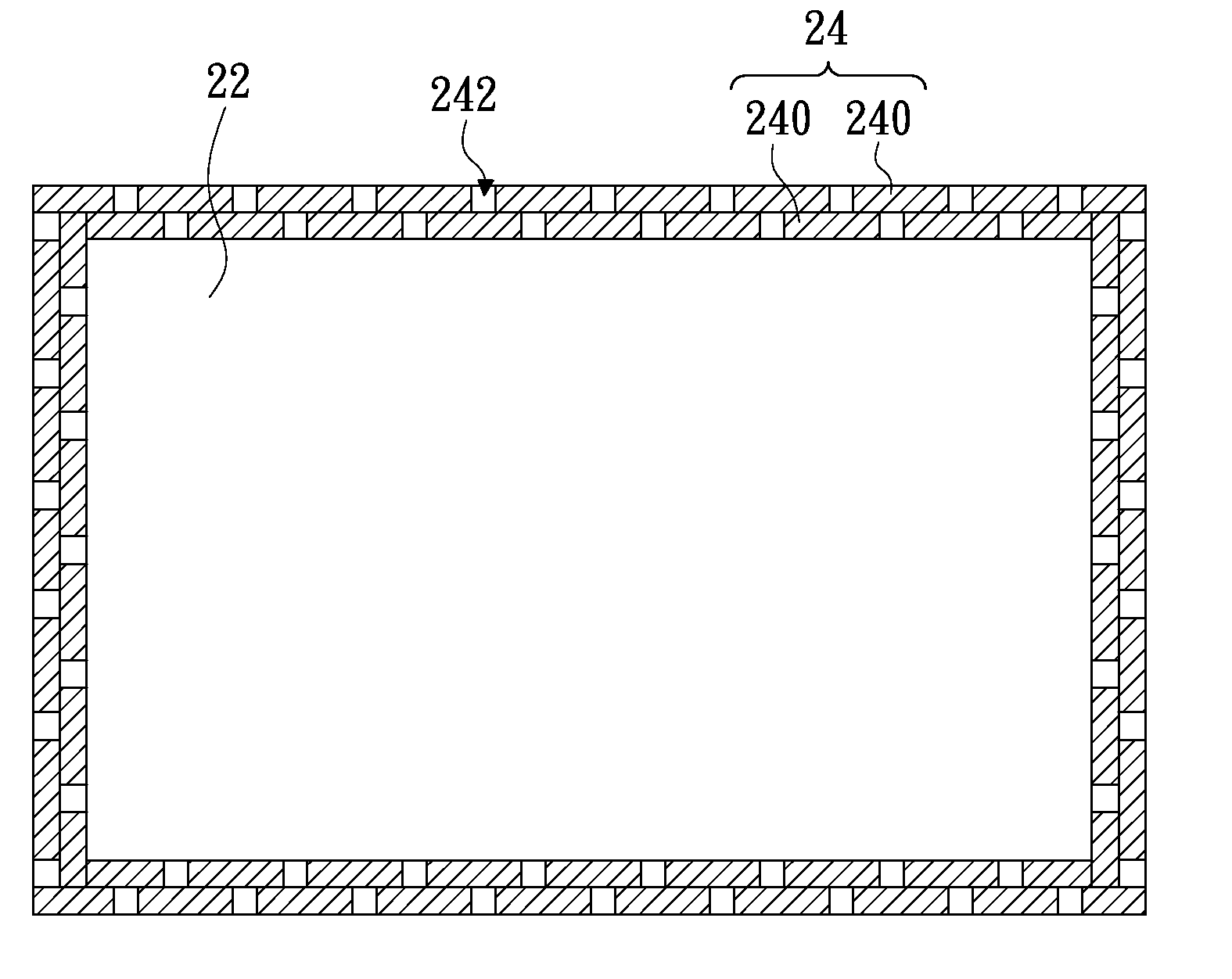

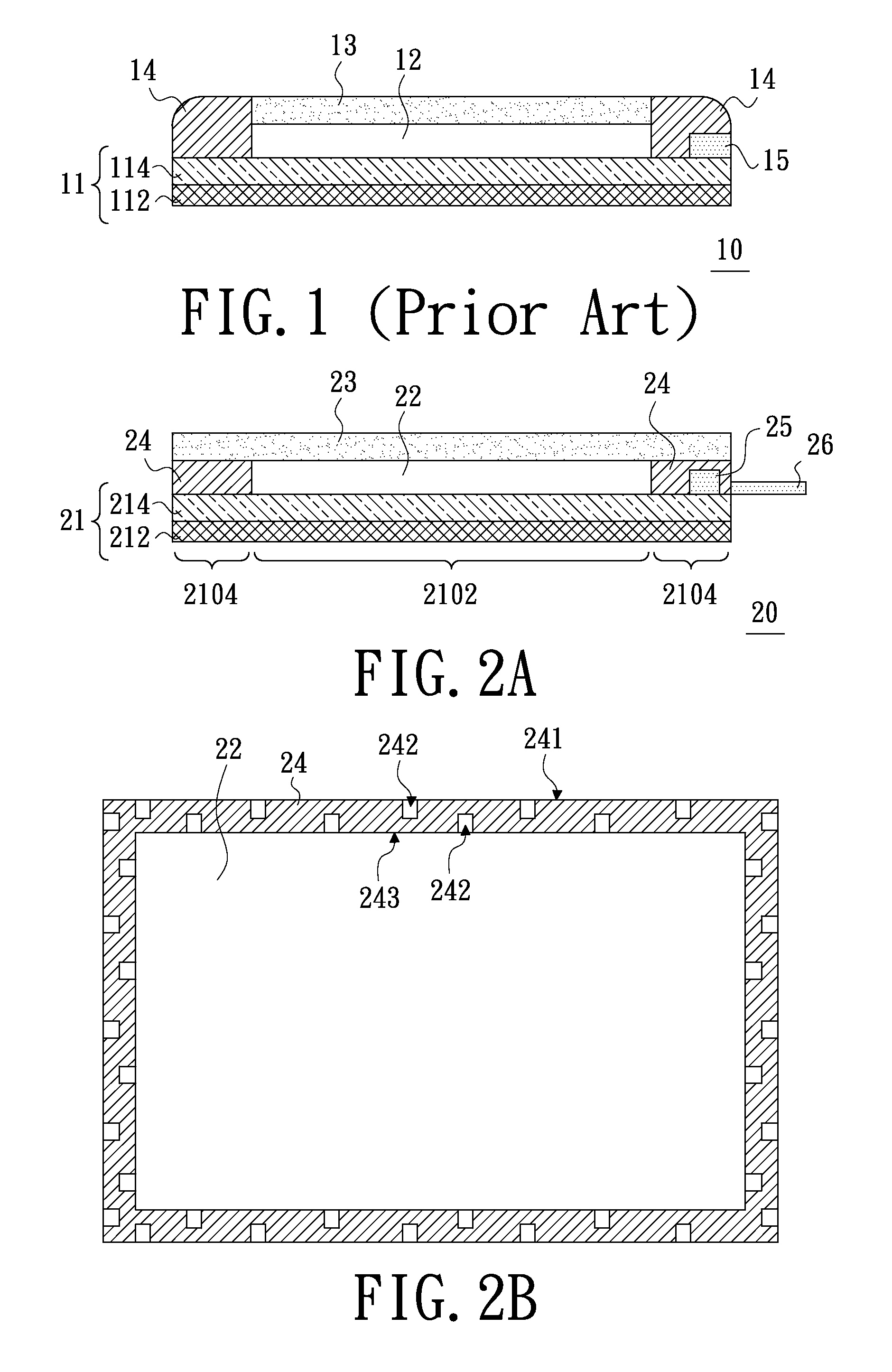

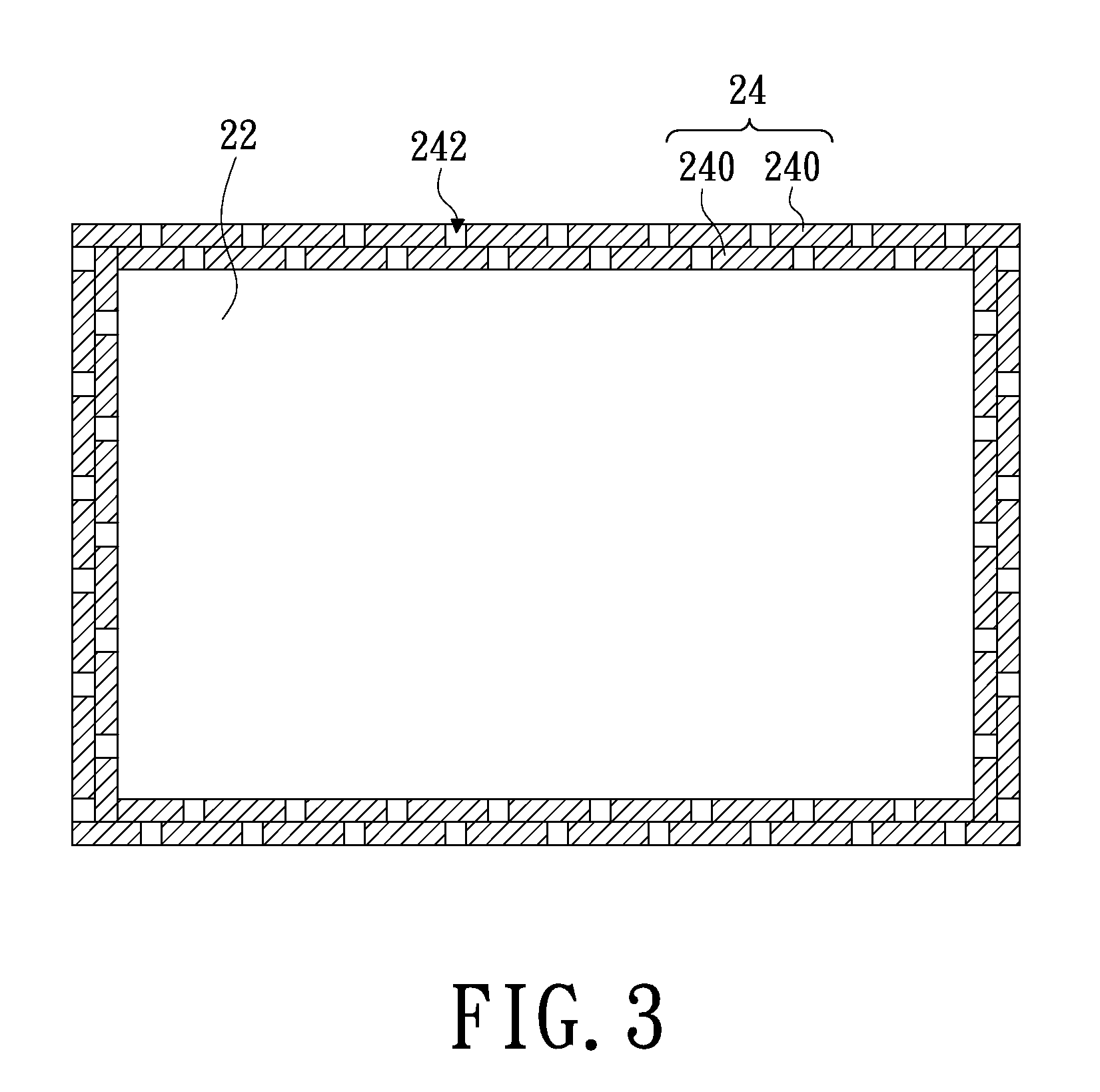

ActiveUS20100225875A1Improve package reliabilityPackaging reliability of the flexible display device may be enhancedPrinted circuit detailsNon-linear opticsEngineeringSealant

A flexible display device includes an array substrate, a display medium layer, a transparent substrate and a first sealant. The array substrate has a display region and a sealant spread region surrounding the display region. The display medium layer is disposed on the array substrate and located in the display region. The transparent substrate is disposed above the display medium layer. The first sealant is formed between the array substrate and the transparent substrate and located in the sealant spread region of the array substrate. The first sealant has a first sidewall and a second sidewall. One of the first sidewall and the second sidewall has a plurality of fillisters arranged at intervals. Since the first sealant of the flexible display device has the fillisters arranged at intervals, the stress imposed on the first sealant may be decreased. Therefore, the life of the first sealant may be prolonged and the sealing performance of the flexible display device can be improved.

Owner:E INK HLDG INC

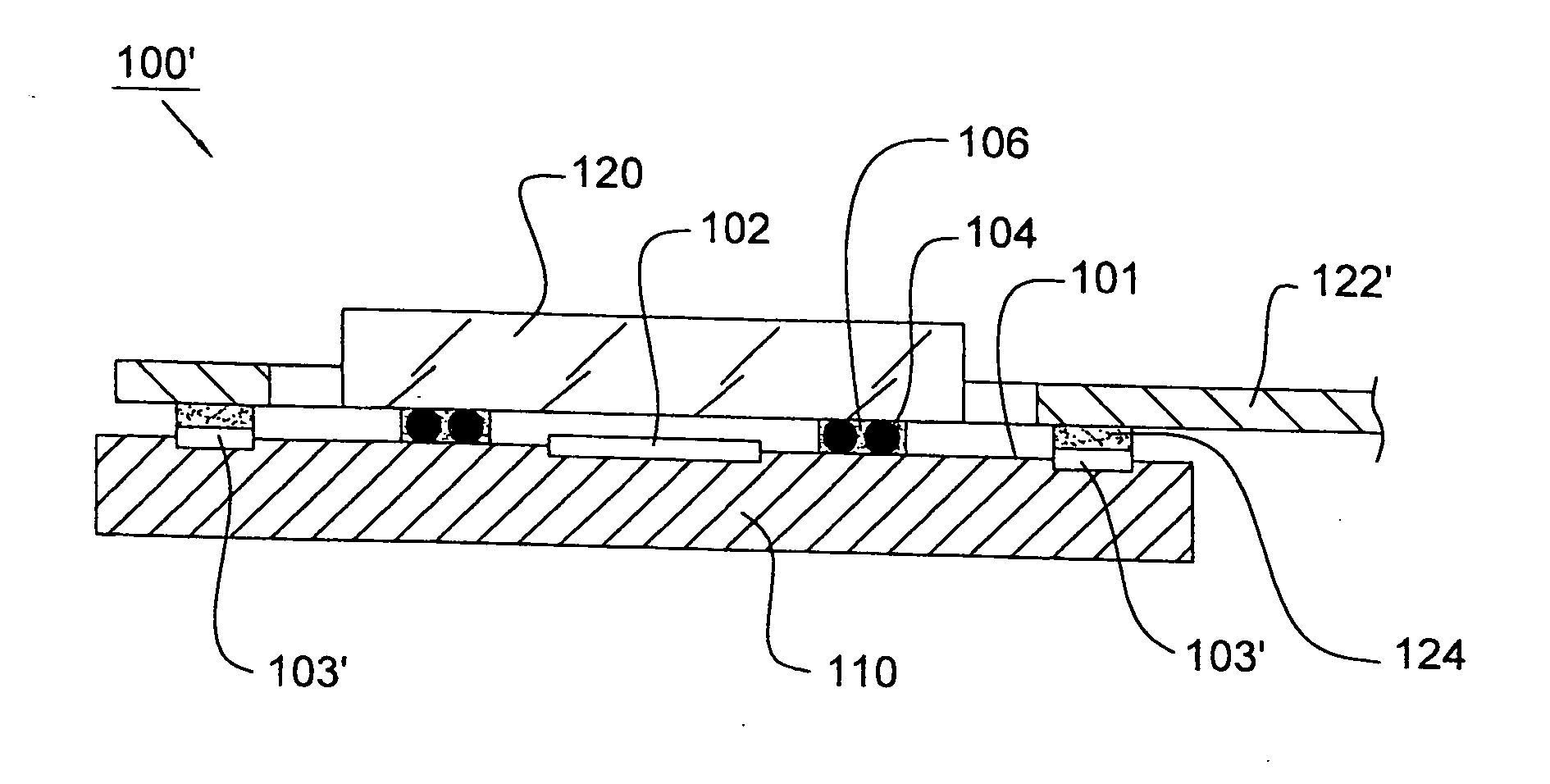

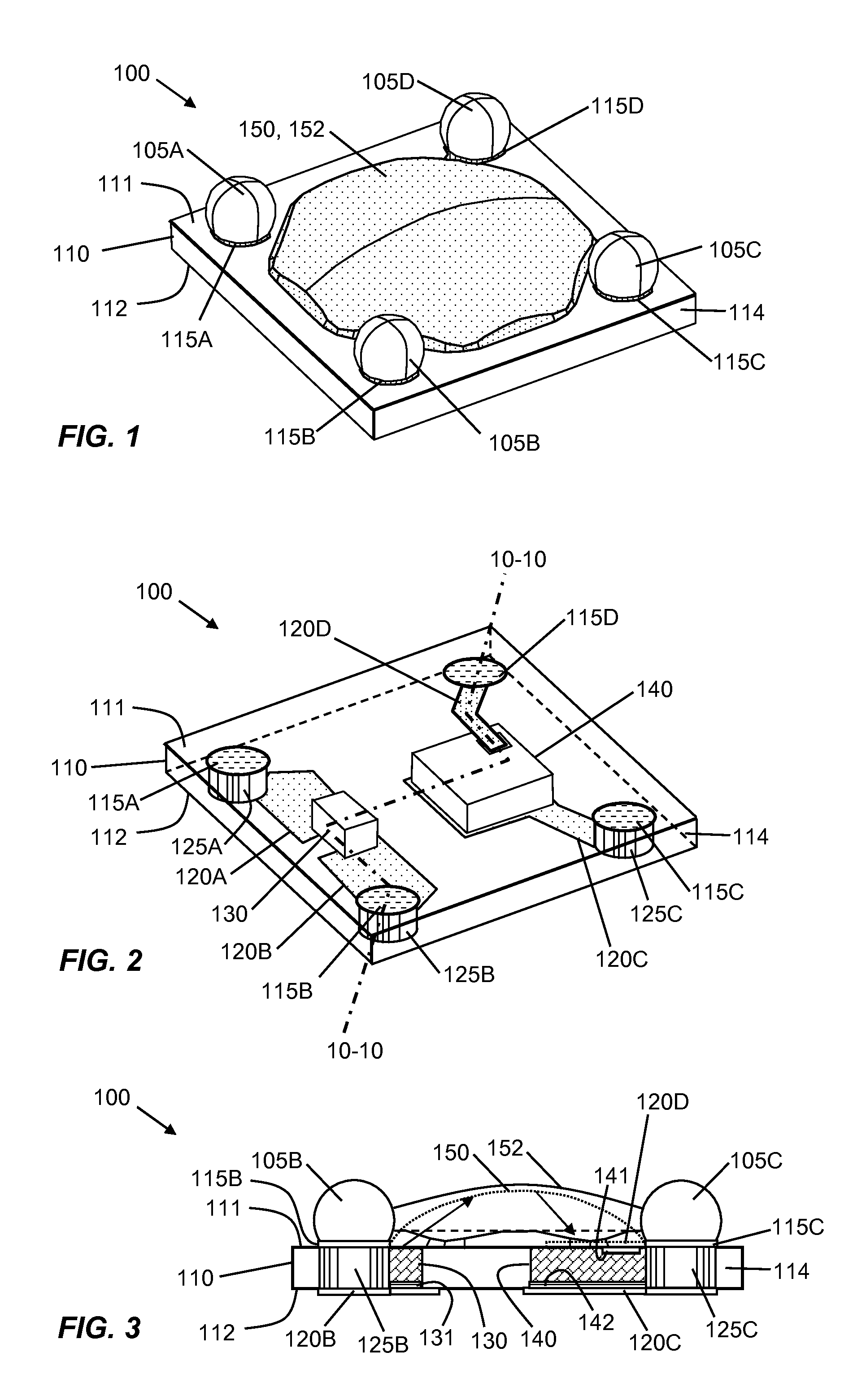

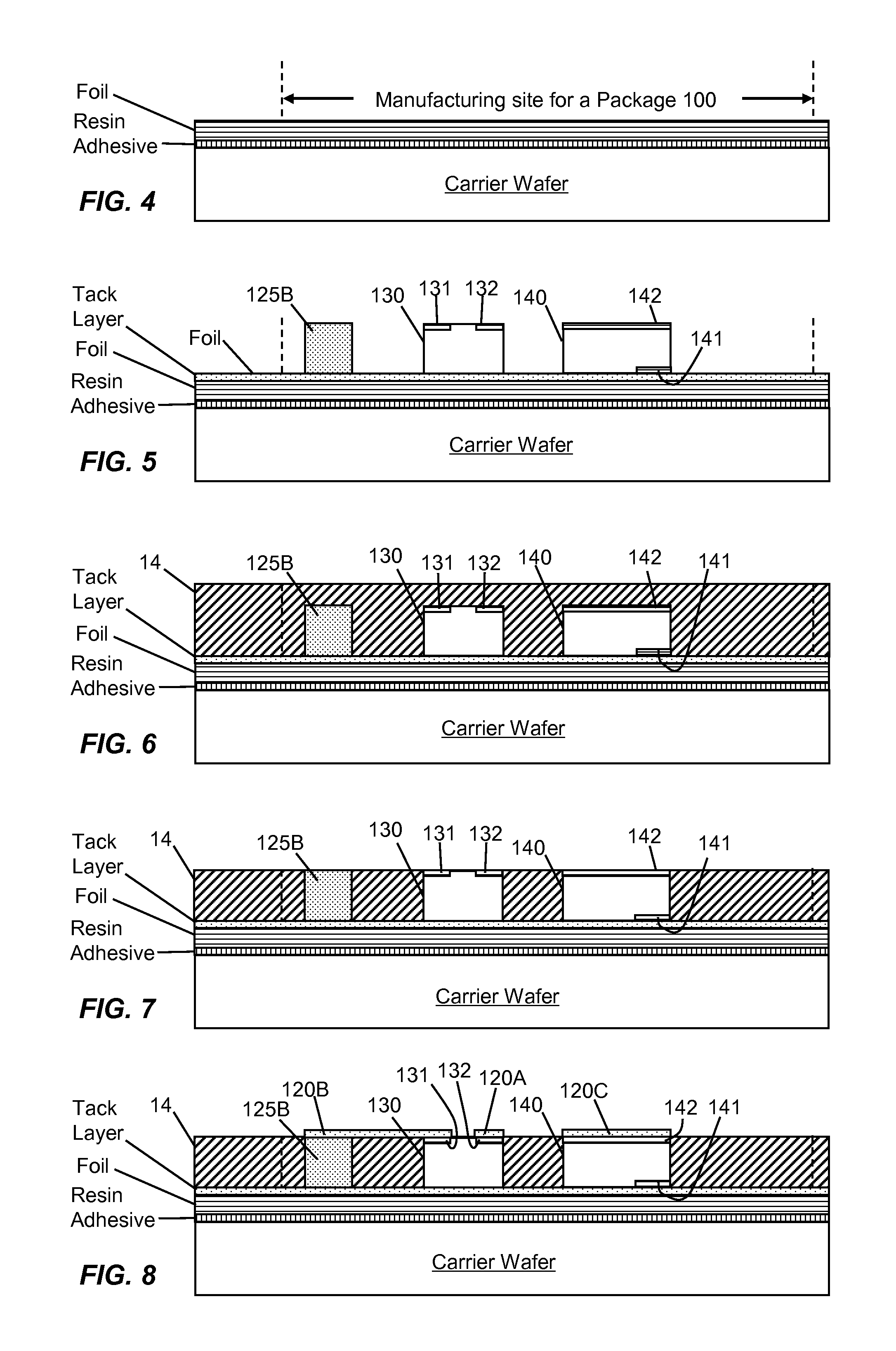

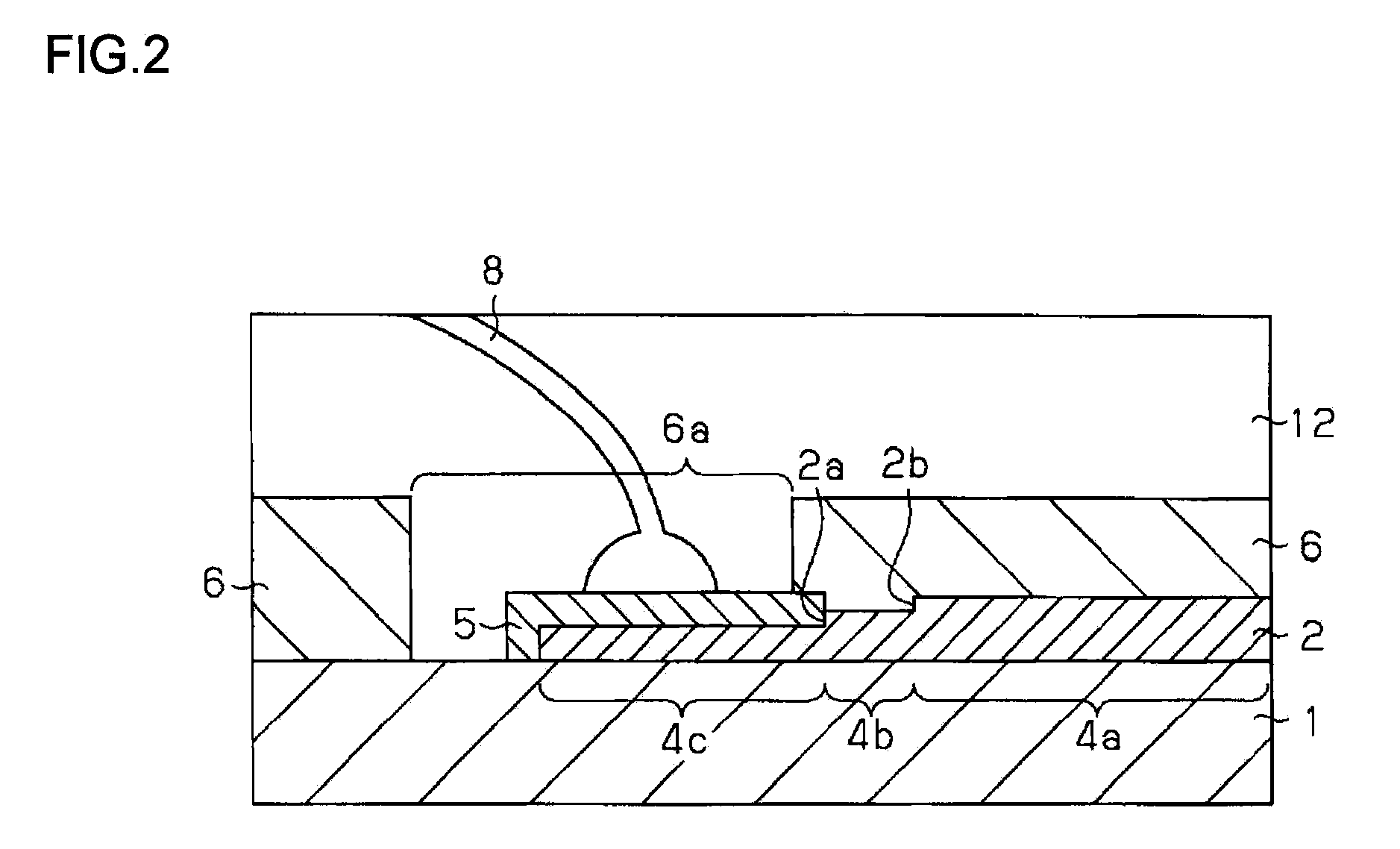

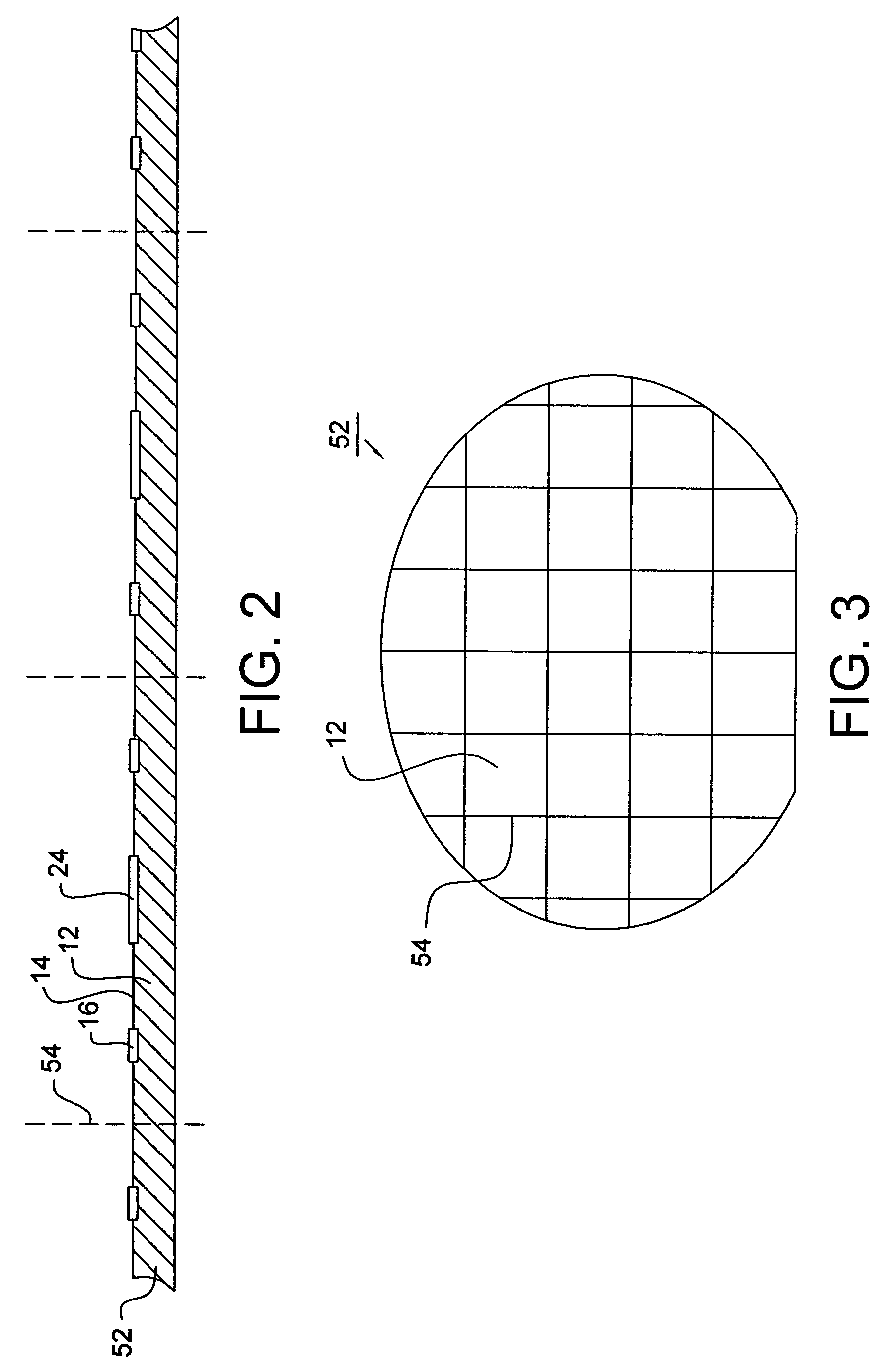

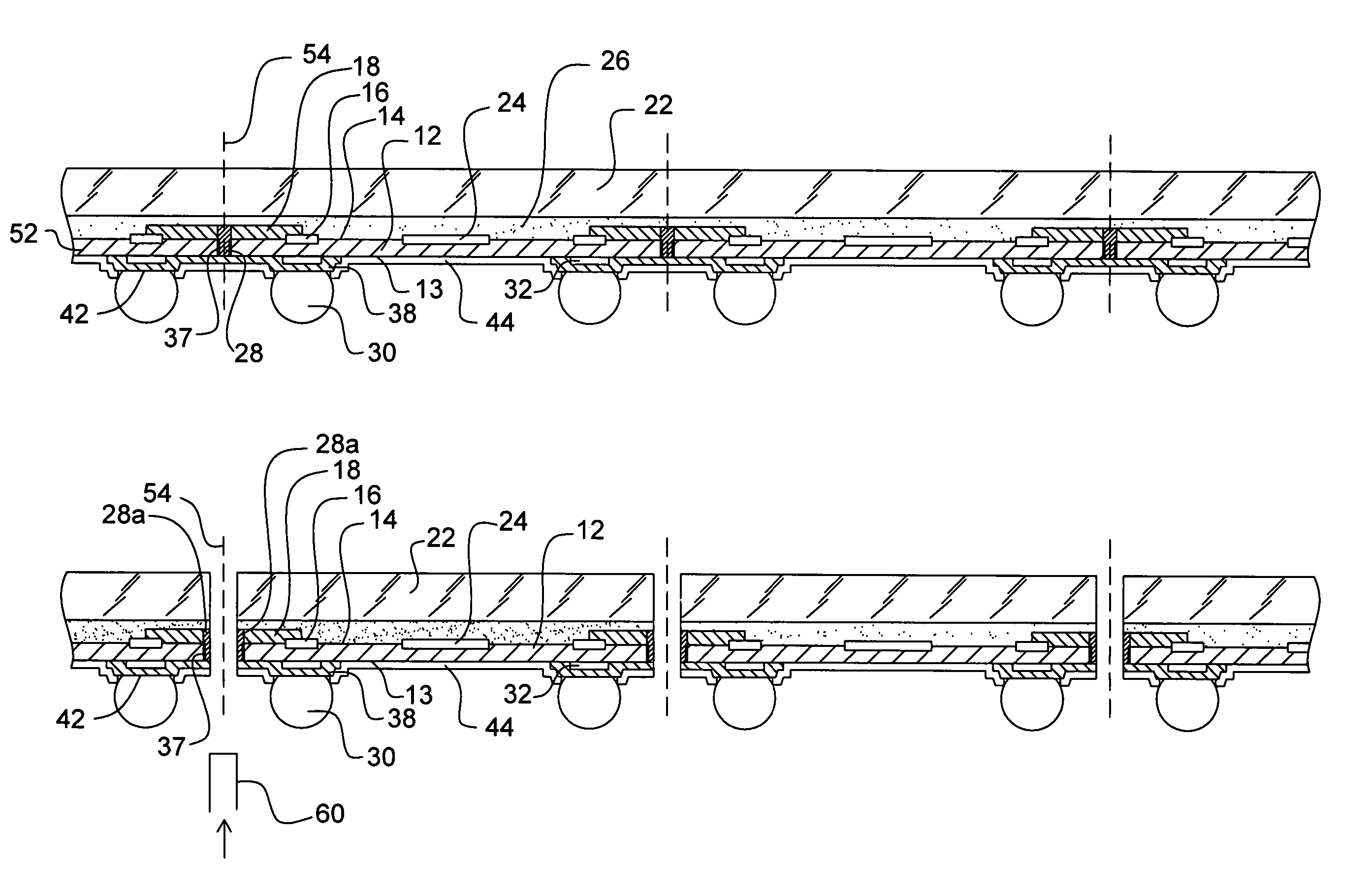

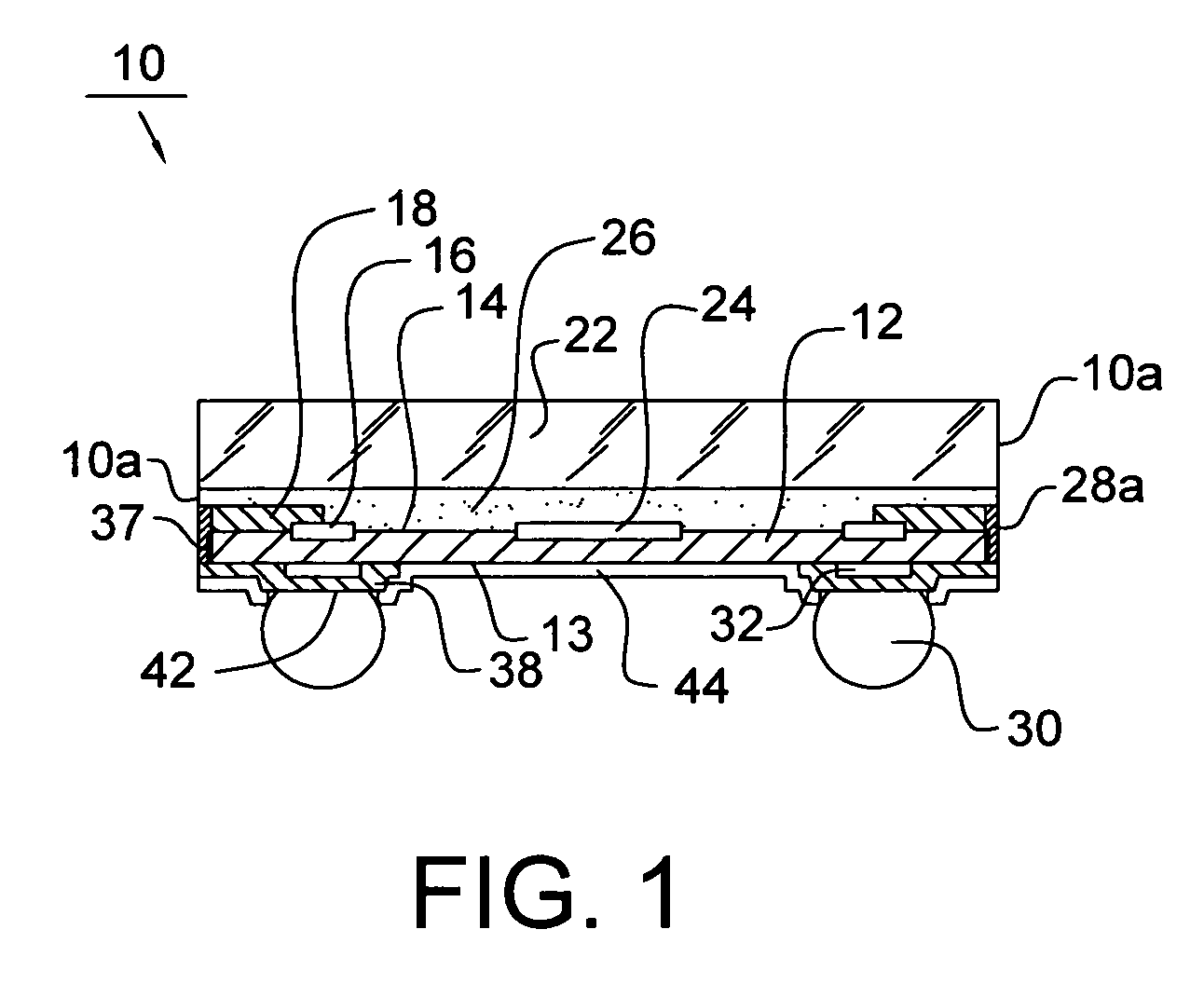

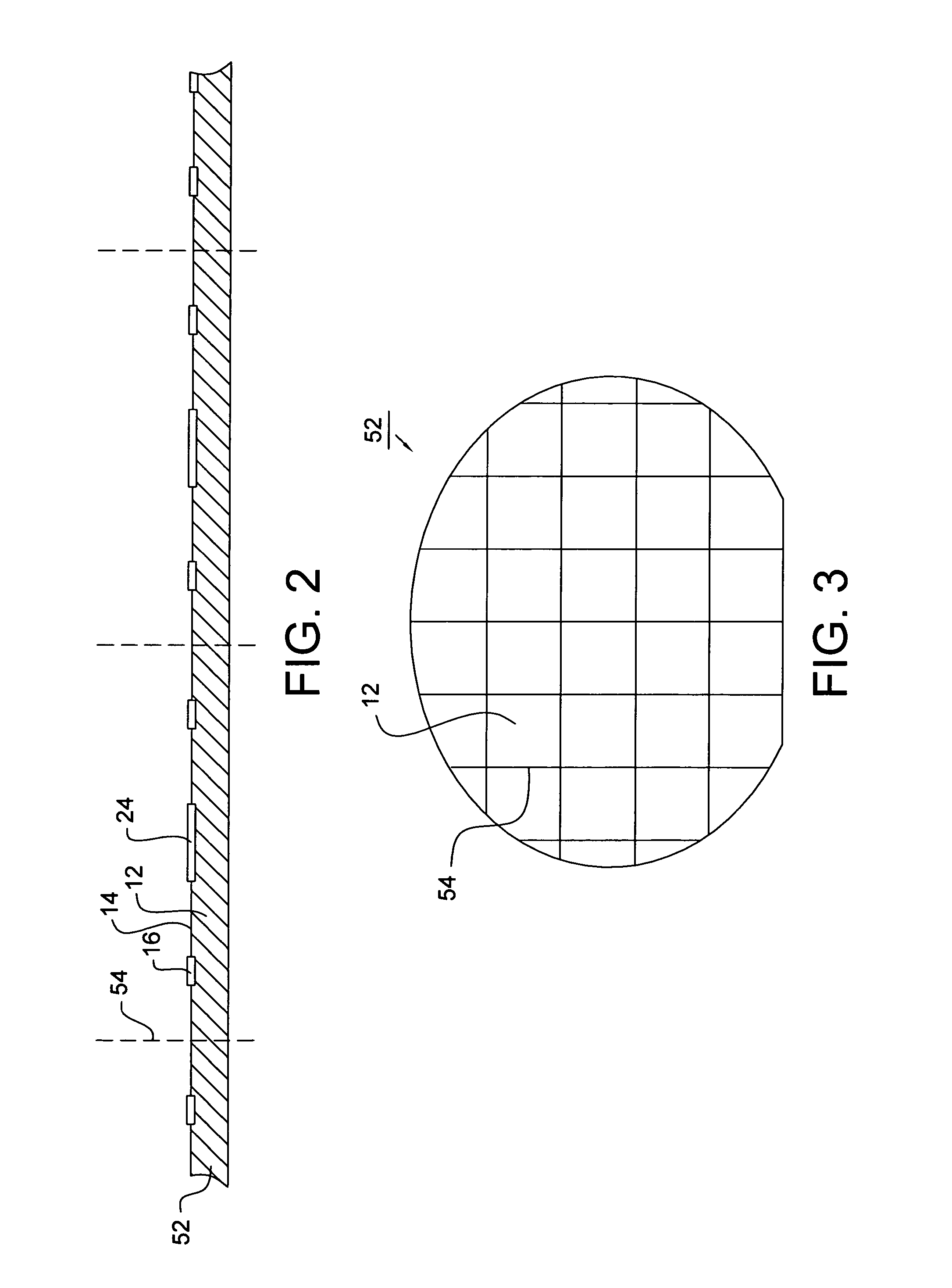

Wafer level molded opto-couplers

InactiveUS20120326170A1Small sizeReduce volumeSolid-state devicesSemiconductor/solid-state device manufacturingEngineering

Optocoupler packages and methods of making the same. An exemplary package comprises a substrate having a first surface, a second surface opposite the first surface, and a body of electrically insulating material disposed between the first and second surfaces; a first optoelectronic device embedded in the body of electrically insulating material of the substrate and disposed between the substrate's first and second surfaces, the first optoelectronic device having a first conductive region and a second conductive region; a second optoelectronic device embedded in the body of electrically insulating material of the substrate and disposed between the substrate's first and second surfaces and optically coupled to the first optoelectronic device, the second optoelectronic device having a first conductive region and a second conductive region; and a plurality of electrical traces disposed on one or both surfaces of the substrate and electrically coupled to the conductive regions of the optoelectronic devices.

Owner:SEMICON COMPONENTS IND LLC

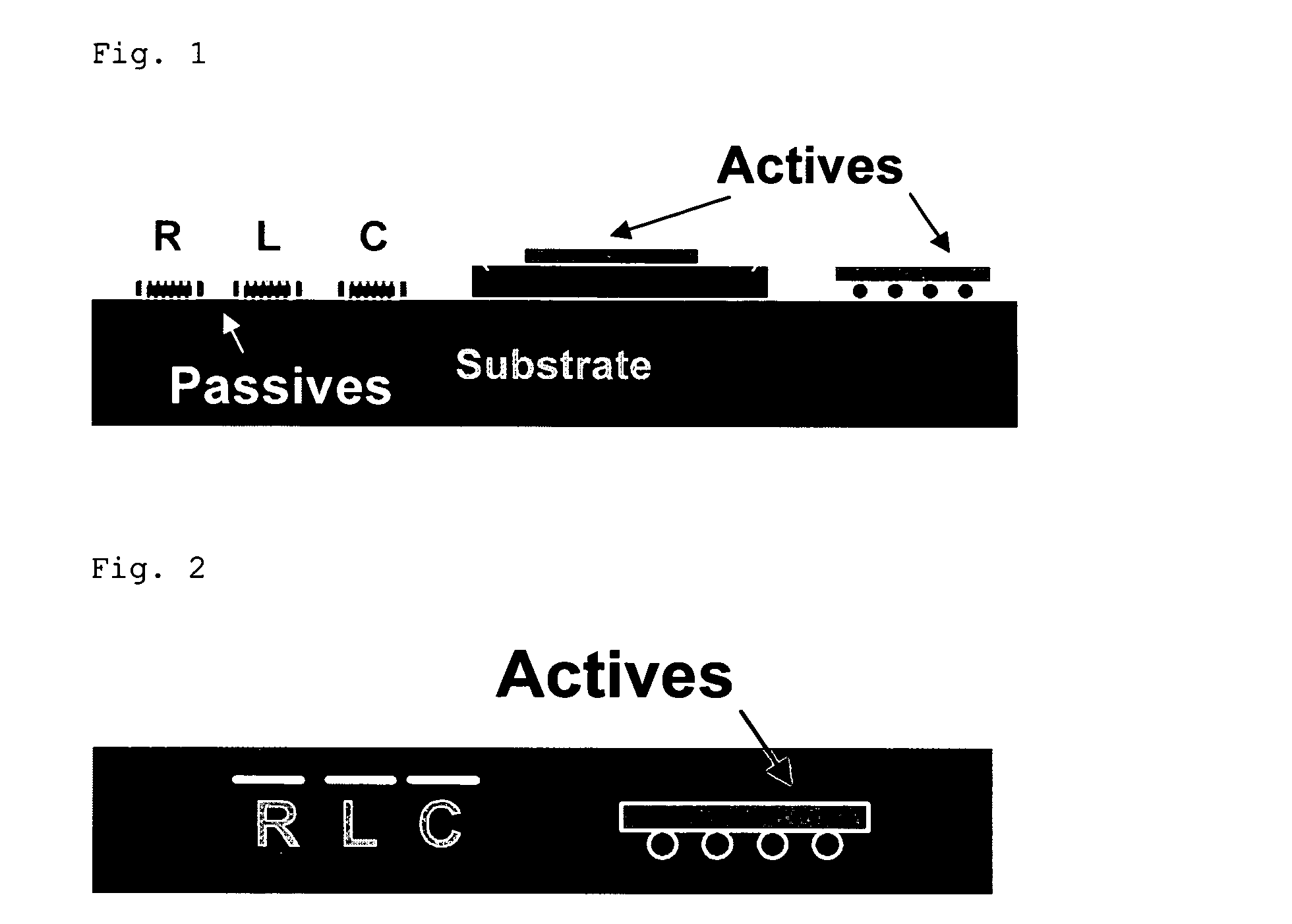

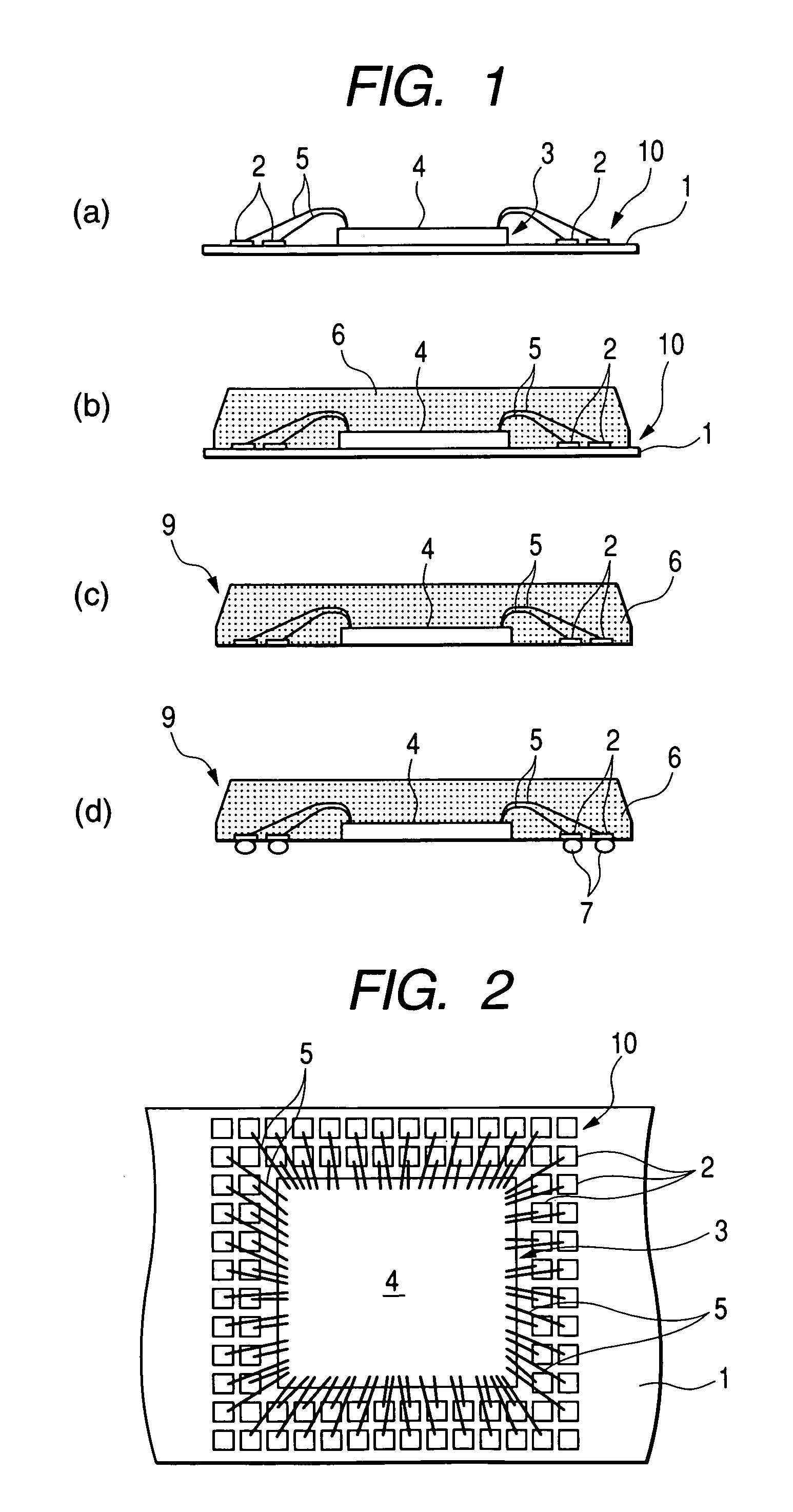

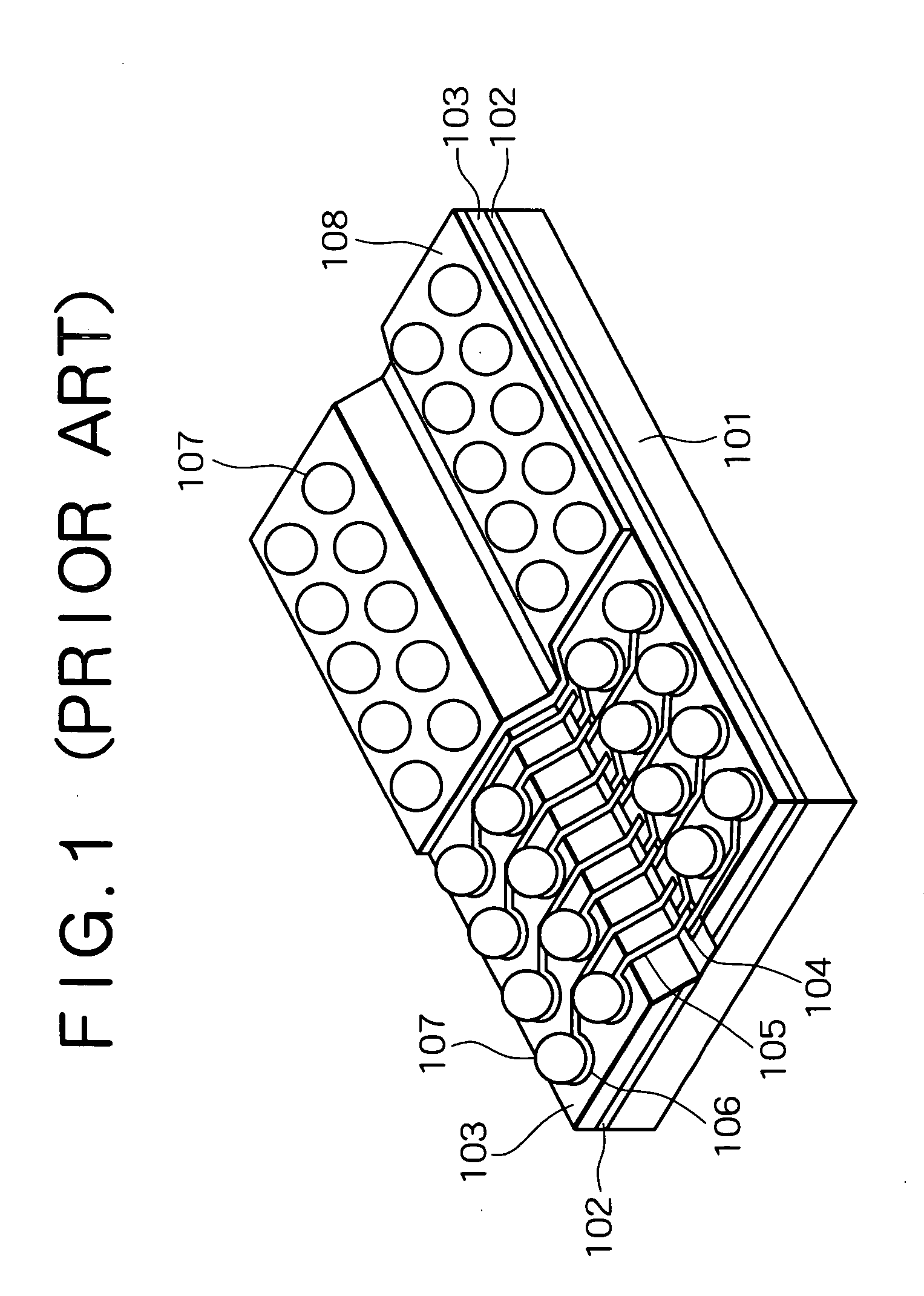

Packaging board and manufacturing method therefor, semiconductor module and mobile apparatus

ActiveUS7595553B2Improve package reliabilityLong distance of spreadingFinal product manufactureSemiconductor/solid-state device detailsResistComputer module

An advantage of the present invention is to suppress moisture infiltrating from a pad electrode portion from spreading over the surface of a wiring pattern and improve the reliability of a packaging board. The wiring pattern of the packaging board is formed on an insulating substrate and includes a wiring region, an electrode region (pad electrode) connected with a semiconductor device, and a boundary region provided between the wiring region and the electrode region. A gold plating layer is provided on the surface of the electrode region of the wiring pattern. The top surface of the boundary region of the wiring pattern is so formed as to be dented from the top surface of the wiring region of the wiring pattern, and there is provided a stepped portion in the boundary region. A solder resist is formed in such a manner as to cover part of the gold plating layer and the wiring pattern corresponding to the boundary region and the wiring region, and the solder resist has a predetermined opening through which to connect to the semiconductor device. A conductive member is connected to the gold plating layer in the electrode region, and a molded resin layer seals the entire semiconductor module.

Owner:III HLDG 12 LLC

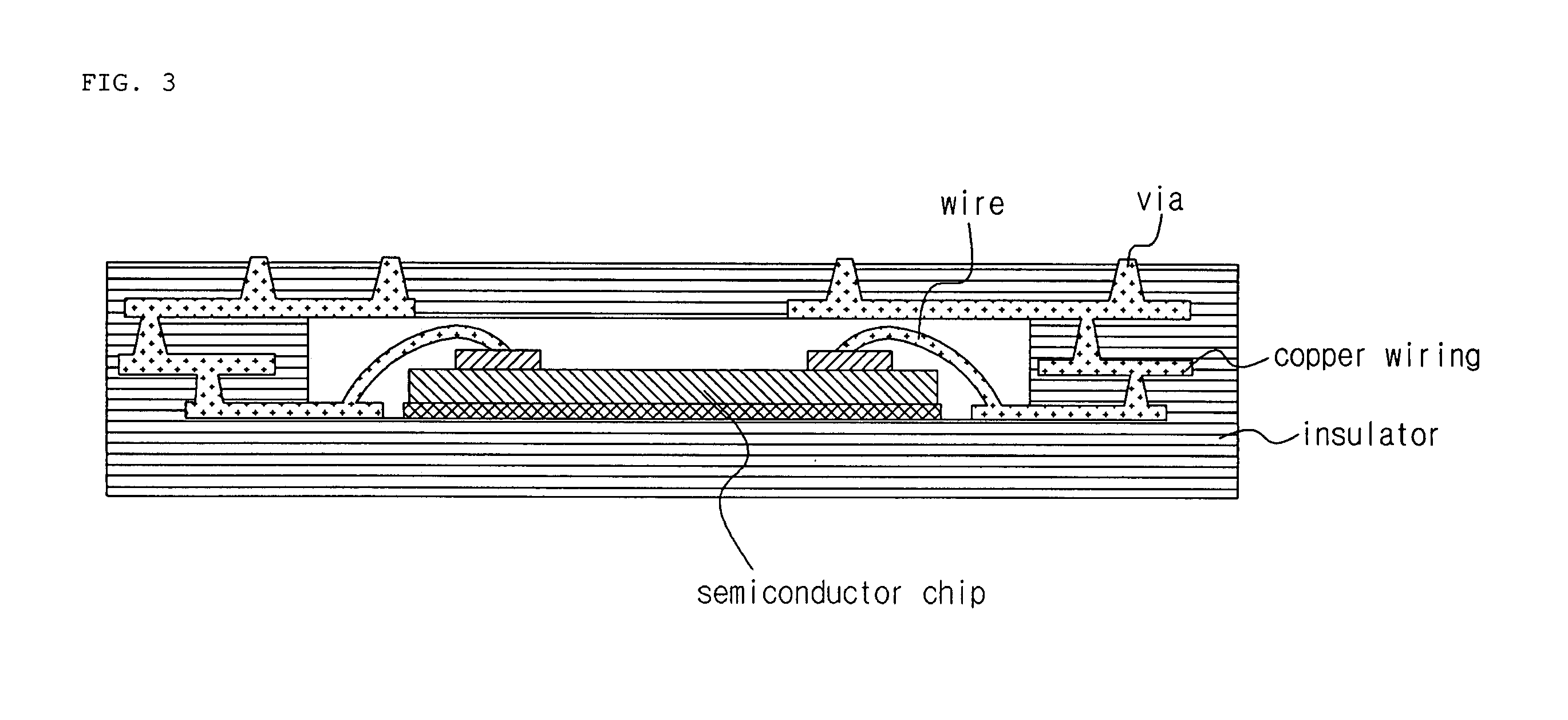

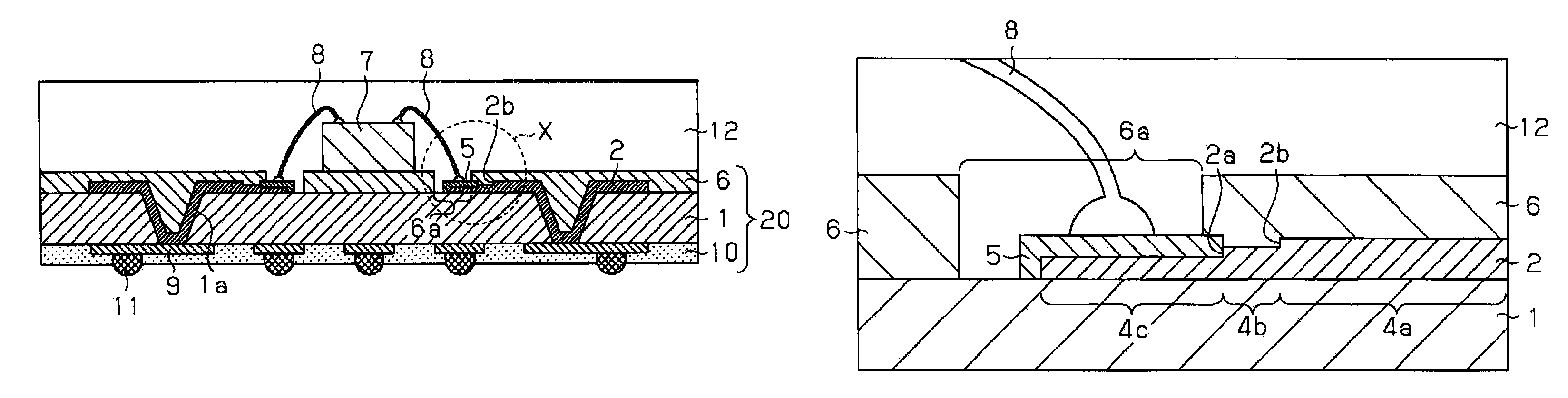

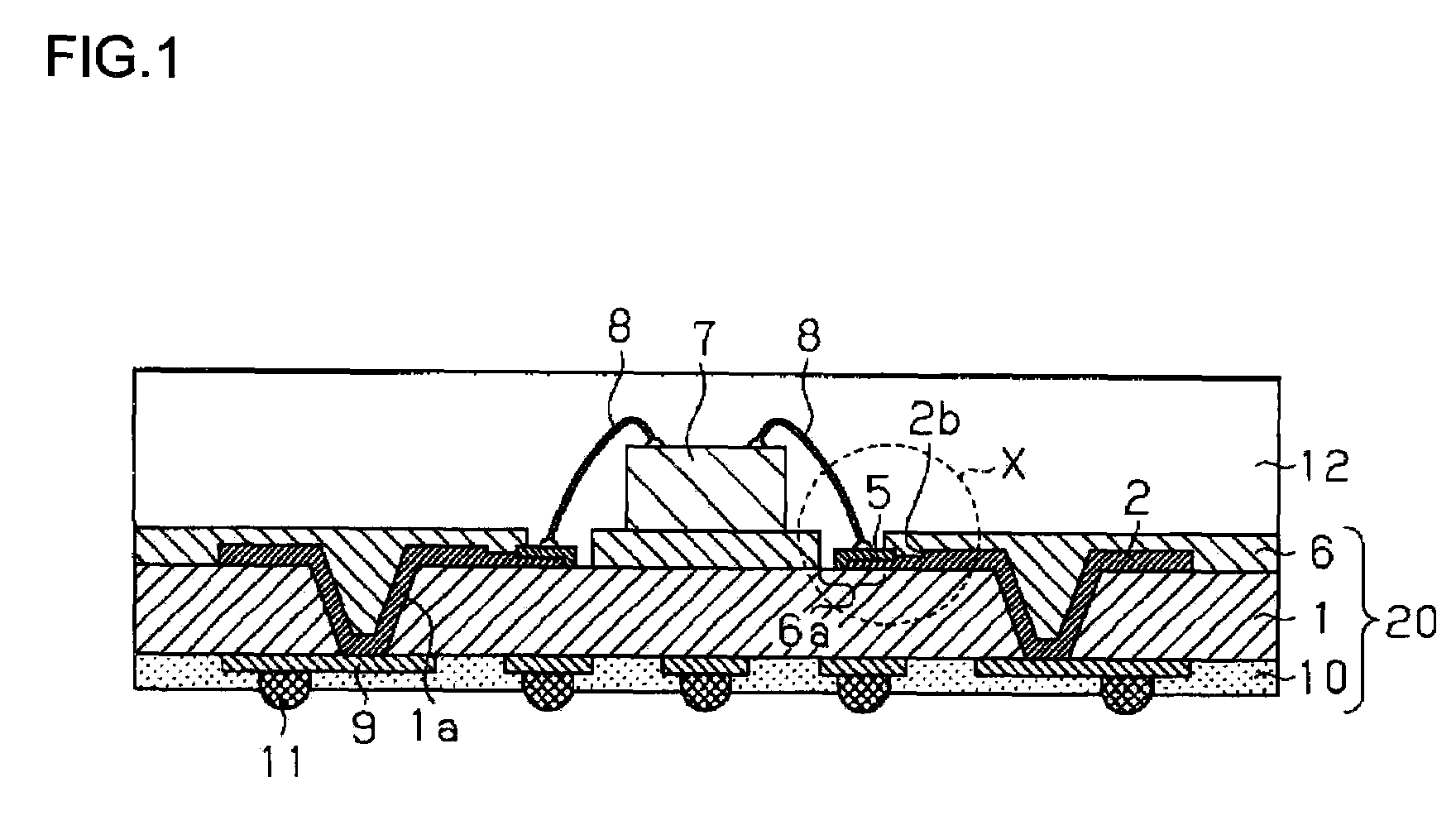

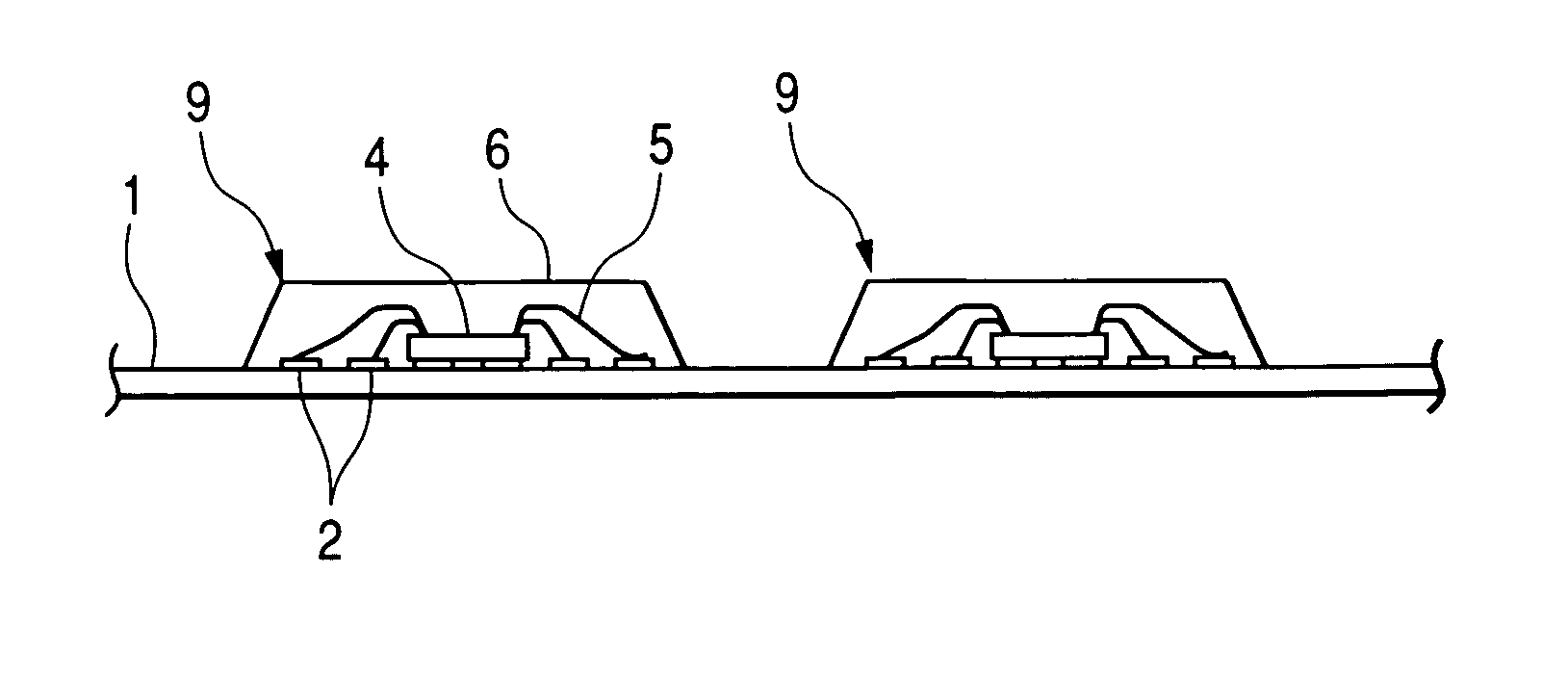

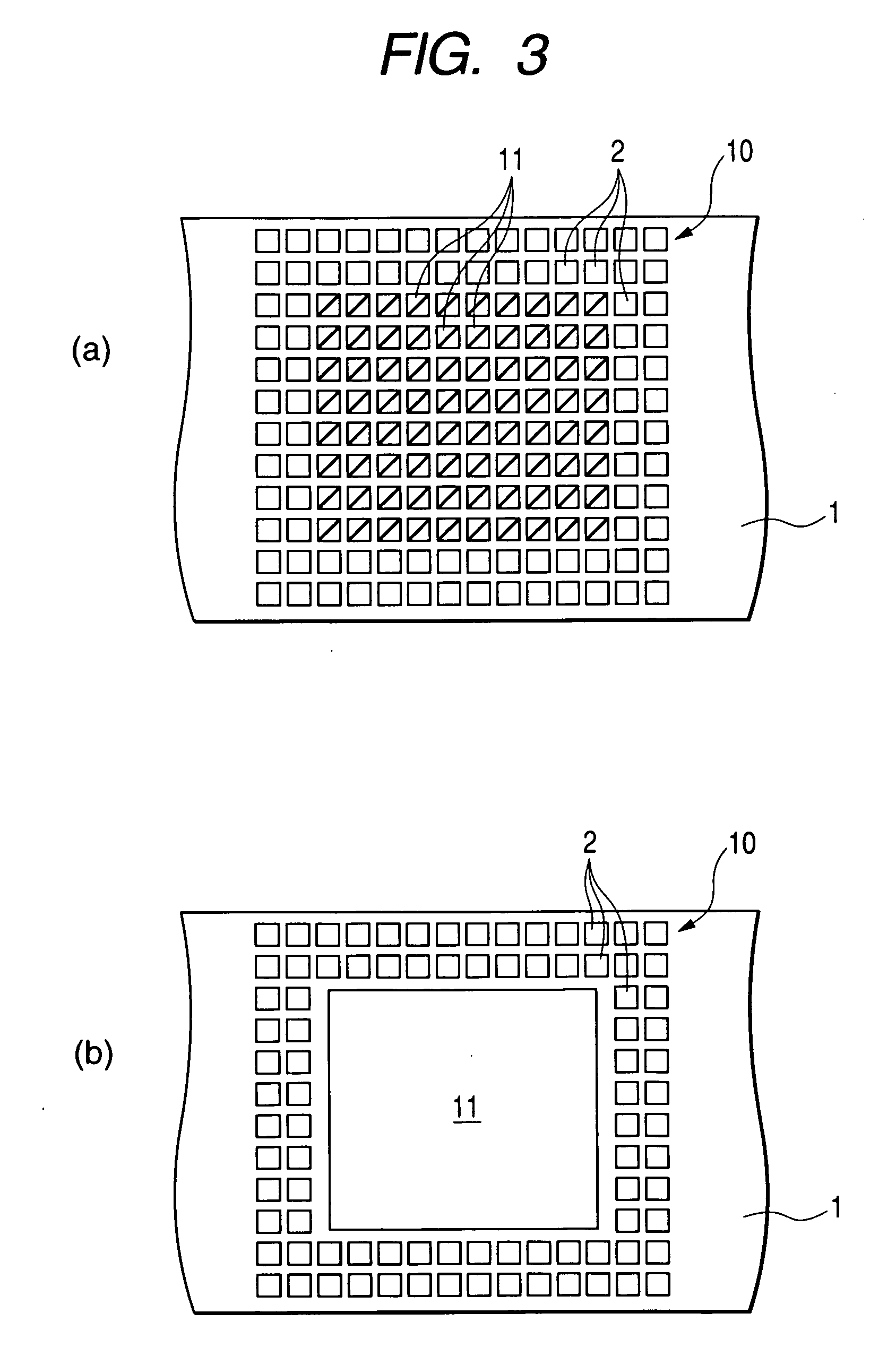

Semiconductor device and its manufacturing method

InactiveUS20050176171A1Small sizeReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesRough surfaceDevice material

A method of manufacturing a thin, small-sized, inexpensive, non-leaded, resin-sealed type semiconductor device is disclosed. A flexible tape having plural terminals peelably through a first adhesive in a product forming portion formed on a main surface of the tape is provided, a semiconductor element is fixed to the main surface of the tape peelably through a second adhesive, electrodes formed on the semiconductor element and the terminals are connected together through conductive wires, an insulating resin layer is formed in an area including the semiconductor element and the wires on the main surface of the tape to cover the semiconductor element and the wires, and the tape on a back surface of the insulating resin layer is peeled, allowing the terminals to be exposed to the back surface of the insulating resin layer. Exposed surfaces of the terminals are each formed by a gold layer. The terminals each comprise a main metal layer of copper foil and one or plural auxiliary metal layers formed on each of a main surface and a back surface of the main metal layer. The auxiliary metal layer(s) on the main surface of the main metal layer is (are) formed using a material which affords a rough surface, thereby roughening the main surface side of each terminal.

Owner:RENESAS ELECTRONICS CORP

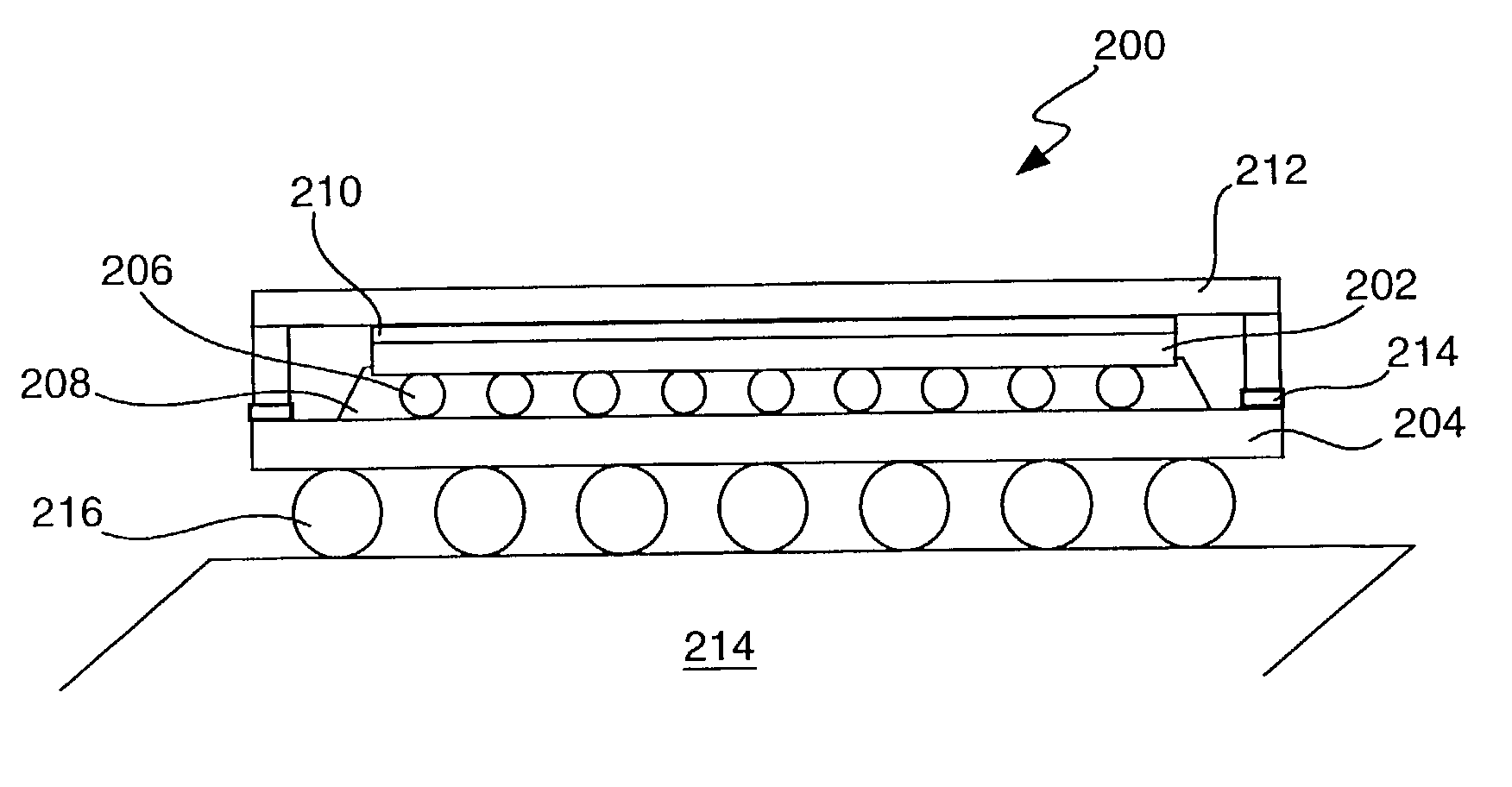

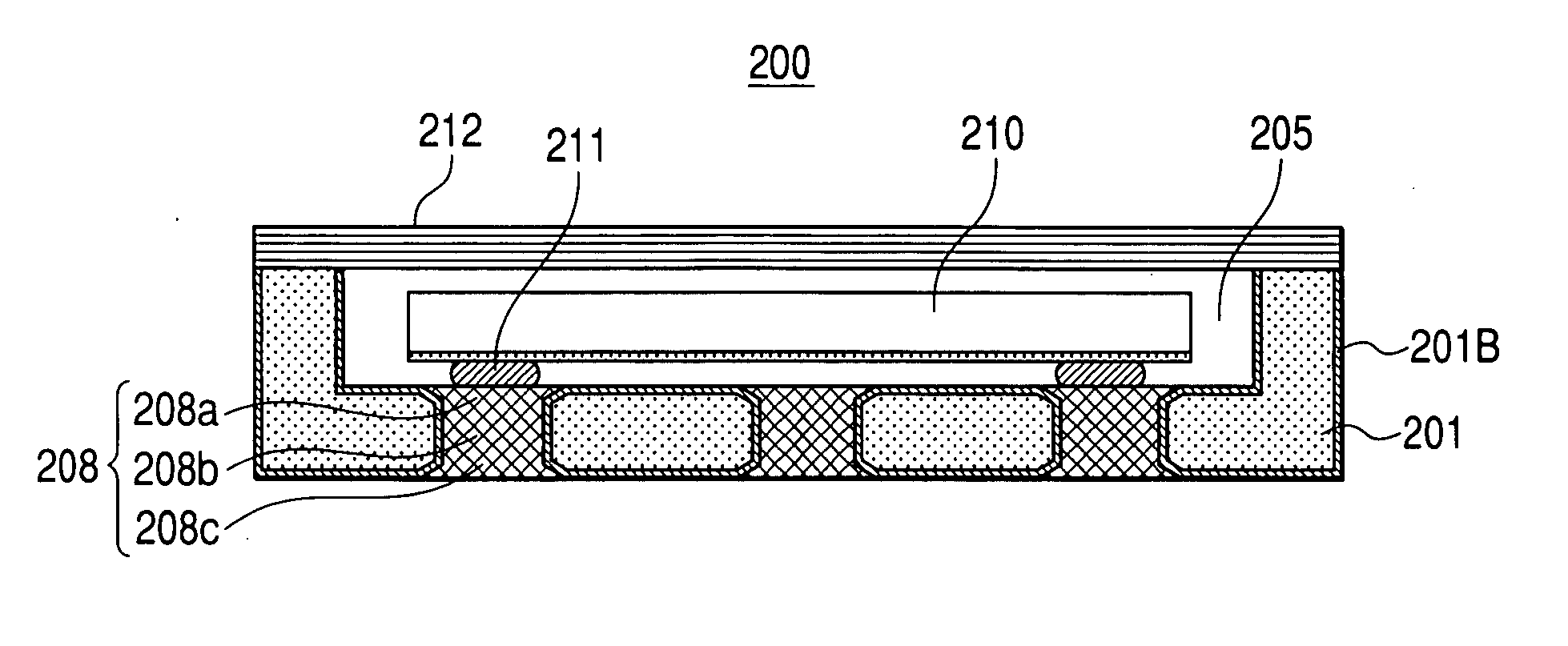

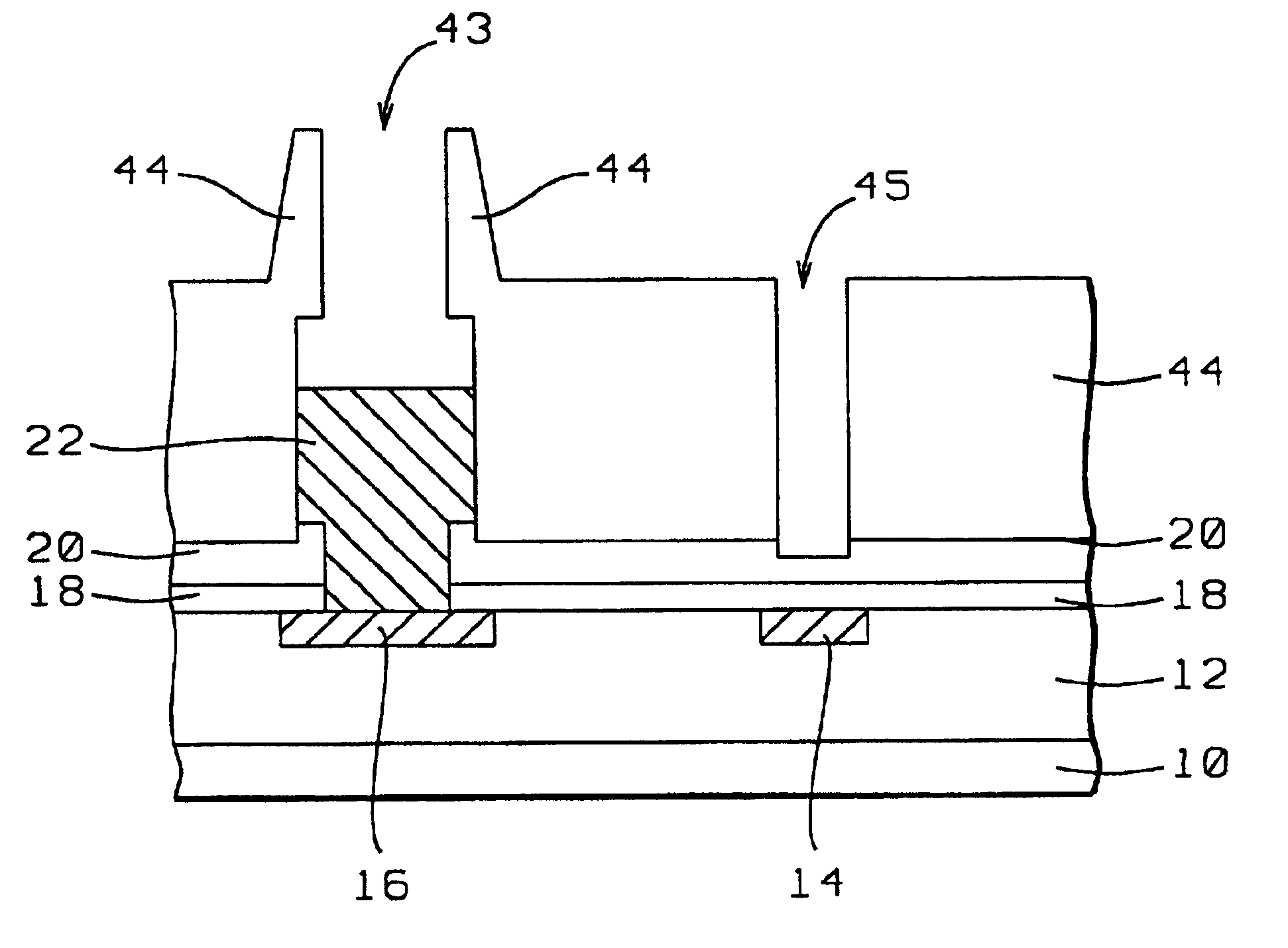

Semiconductor device package, semiconductor apparatus, and methods for manufacturing the same

ActiveUS20080054486A1Improve reliabilityImprove package reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSilicon

A method for manufacturing a package which includes: an etching step of etching a silicon substrate, and forming a via hole penetrating through the silicon substrate; and a step of embedding an electrically conductive material in the via hole, and forming a via plug, characterized in that the etching step includes a first etching step of forming the via hole in a straight shape, and a second etching step of forming the via hole in a taper shape.

Owner:SHINKO ELECTRIC IND CO LTD

Single-component high/low-temperature-resistant epoxy resin composition

ActiveCN102827566AImprove performanceSimple preparation processNon-macromolecular adhesive additivesMacromolecular adhesive additivesCross-linkEther

The invention provides a single-component high / low-temperature-resistant epoxy resin composition which comprises the following ingredients in parts by weight: 100 parts of rubber cross-linked modified epoxy resin, 0-20 parts of cardanol-type glycidol ether, 80-120 parts of alicyclic acid anhydride curing agent, 0.5-10 parts of latent curing accelerator, 10-40 parts of polyacrylate core-shell compound particle toughener, 2-20 parts of thixotropic agent and 50-100 parts of filler. The epoxy resin composition has the advantages of high toughness, high / low-temperature alternation resistance, simple preparation technique, low viscosity and favorable flowability, and can greatly enhance the packaging reliability and durability of electronic devices.

Owner:GUANGDONG TGPM AUTOMOTIVE IND GRP

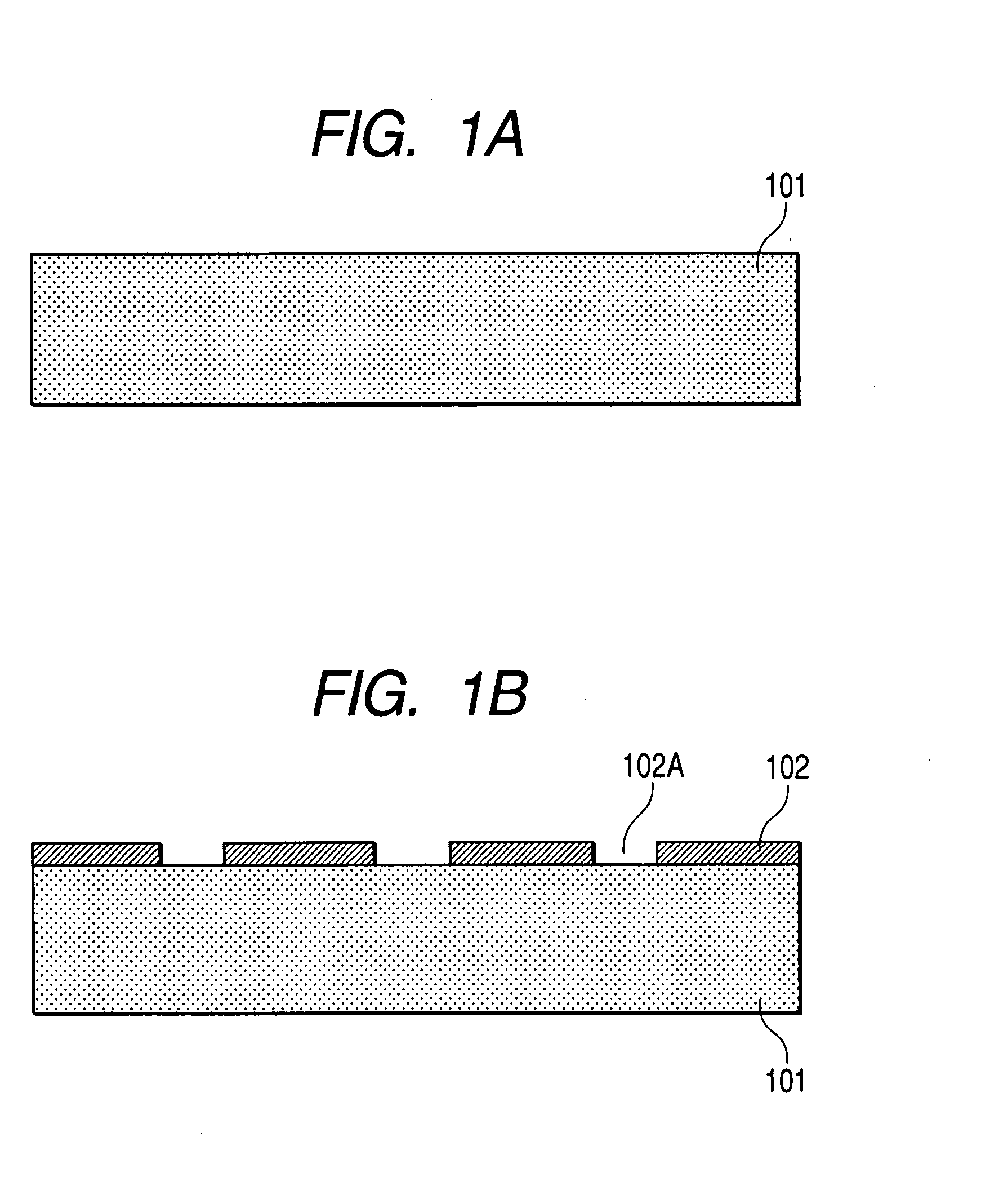

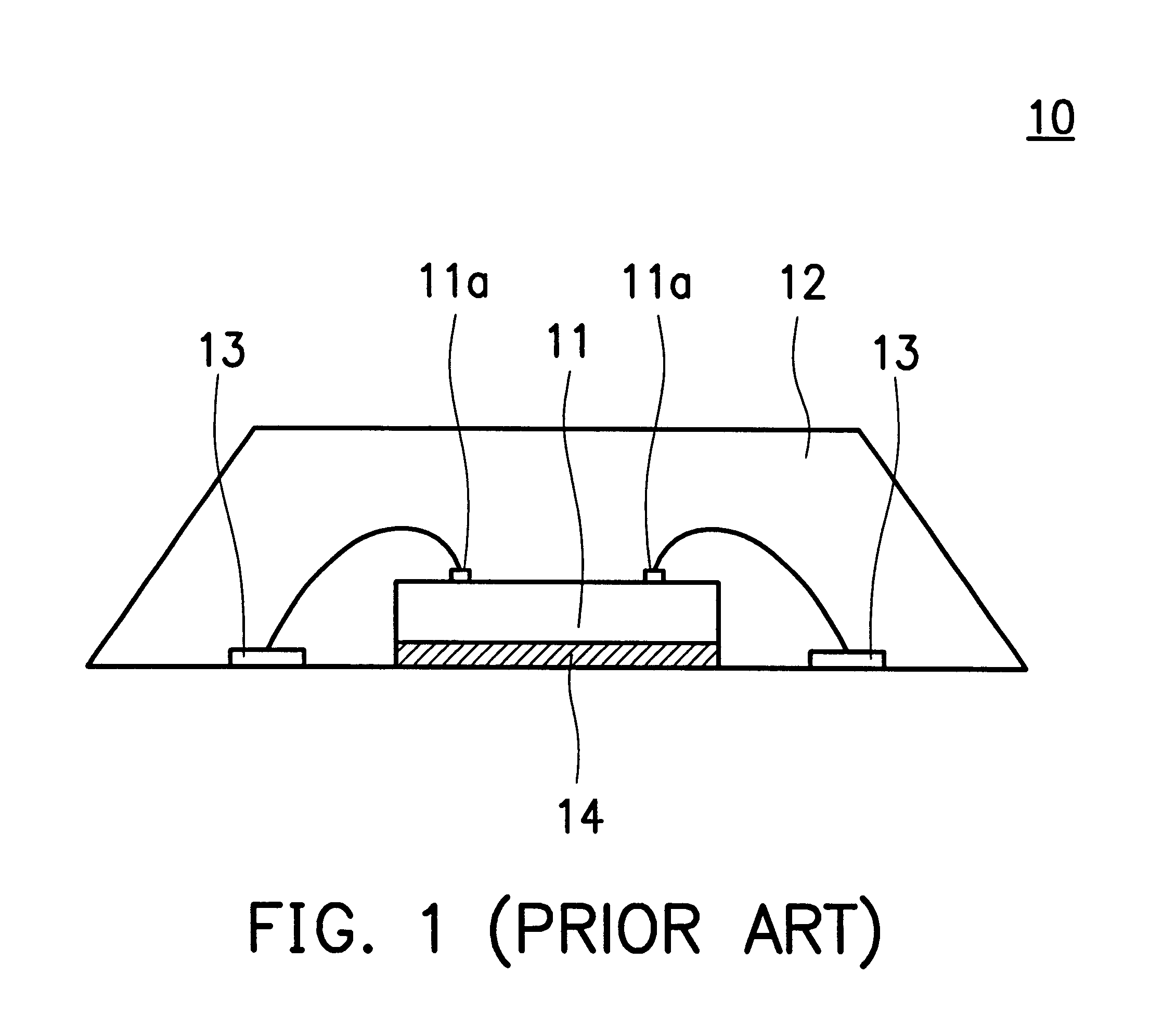

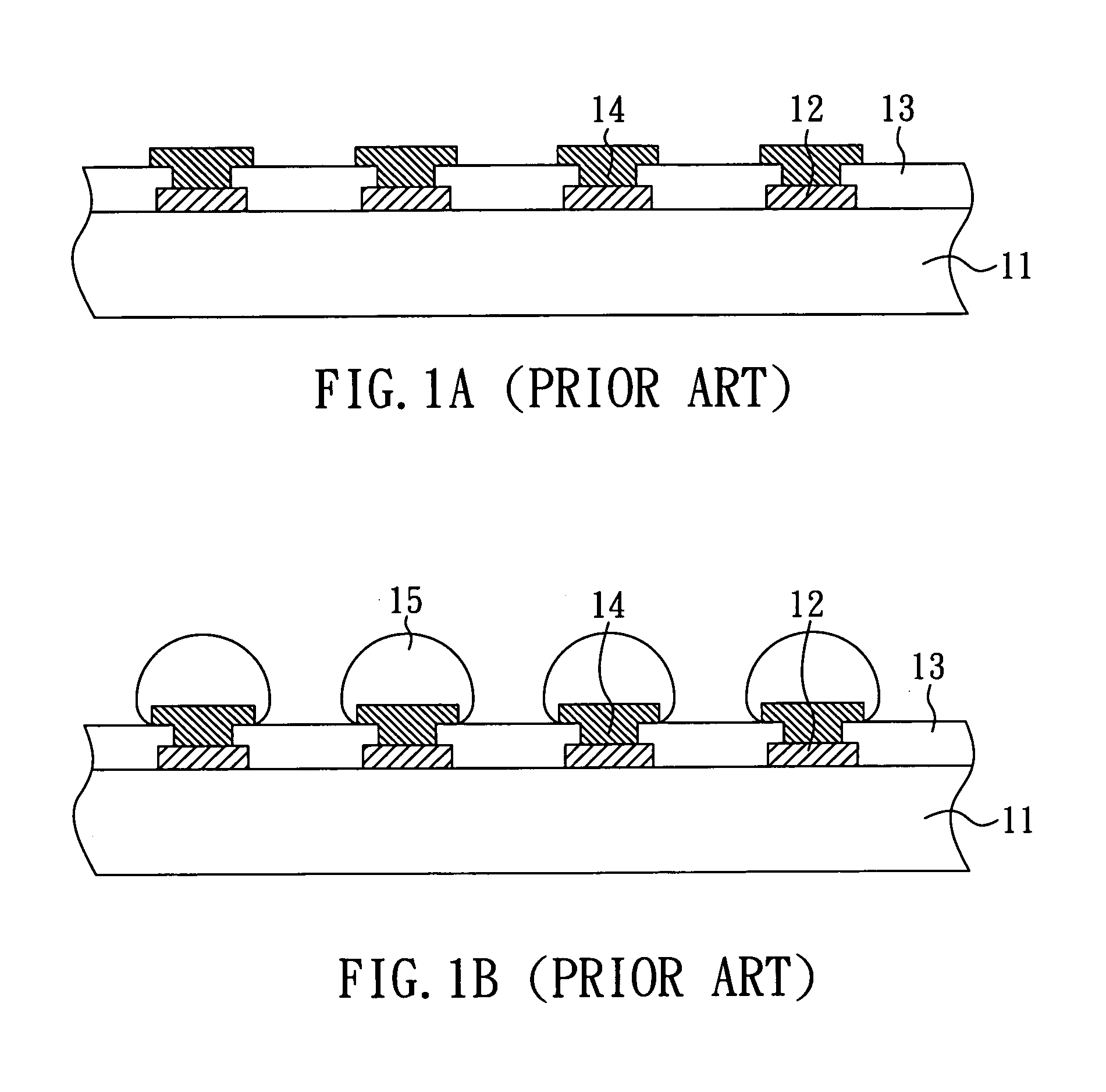

Method for packaging a semiconductor chip

InactiveUS6242284B1Cost savingGood interfaceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor chip

A method for packaging a semiconductor chip, generally comprising the following steps of: (a) forming a plurality of openings on the top surface of the conducting substrate, wherein the upper portions of the openings are formed larger than the lower portions of the openings; (b) forming insulating sections in the conducting substrate by filling an insulating material in the openings; (c) forming a plurality of leads insulated by the insulating sections by planarizing the bottom surface of the conducting substrate to expose and form planarized bottom surfaces of the insulating sections; (d) mounting a semiconductor chip on the bottom surface of the conducting substrate; (e) providing a plurality of conducting wires to electrically connect the semiconductor chip to the leads; and (f) encapsulating the semiconductor chip and the conducting wires. The package according to the present invention is characterized by upper portions of the leads that are purposedly formed larger than lower portions of the leads which prevents the leads from being easily detachable and the package from being destructed by water, the reliability of the package is thus increased.

Owner:ADVANCED SEMICON ENG INC

Semiconductor package and method for manufacturing the same

ActiveUS7285434B2Eliminate limitation and drawbackImprove efficiencySemiconductor/solid-state device detailsSolid-state devicesEffective surfaceSemiconductor package

A semiconductor package comprises a chip, a plurality of pad extension traces, a plurality of via holes, a lid and a plurality of metal traces, wherein the chip has an active surface, a back surface opposite to the active surface, an optical component disposed on the active surface, and a plurality of pads disposed on the active surface and electrically connected to the optical component; the pad extension traces are electrically connected to the pads; the via holes are formed through the chip and electrically connected to the pad extension traces; the lid is attached on the active surface of the chip; and the plurality of metal traces are disposed on the back surface of the chip, electrically connected to the plurality of via holes, and defines a plurality of solder pads thereon.

Owner:ADVANCED SEMICON ENG INC

Semiconductor package structure and method for manufacturing the same

ActiveUS7371602B2Improve efficiencyLow costSemiconductor/solid-state device detailsSolid-state devicesEffective surfaceSemiconductor package

Owner:ADVANCED SEMICON ENG INC

Power module and method of fabricating the same

ActiveUS7687903B2Easy to integrateSmall sizeSemiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

Owner:SEMICON COMPONENTS IND LLC

Integrated process for fuse opening and passivation process for CU/LOW-K IMD

InactiveUS6911386B1Reduce in quantityImprove bindingSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A new process flow is provided for the creation of a fuse contact and a bond pad. The invention starts with a semiconductor substrate over the surface of which is provided top level metal and fuse metal in the surface of a layer of insulation deposited over the surface of the substrate. A first etch stop layer is deposited over the surface of the layer of insulation over which a first passivation layer is deposited, an opening is created through these layers exposing the top level metal. A metal plug is created overlying the exposed surface of the top level metal. A stack of a patterned and etched hard mask layers, having been deposited at part of the creation of the metal plug and overlying a layer of metal plug material, remains in place over the surface of the created metal plug. A second layer of passivation material is deposited, the second layer of passivation is patterned and etched exposing the surface of the first layer of passivation overlying the fuse metal and exposing the surface of the stack of hard mask layers overlying the created metal plug. The stack of hard mask layers is then removed from the surface of the metal plug, exposing the surface of the metal plug to serve as a contact pad and further reducing the thickness of the first layer of passivation over the surface of the fuse metal, making the fuse more accessible for fuse blowing.

Owner:TAIWAN SEMICON MFG CO LTD

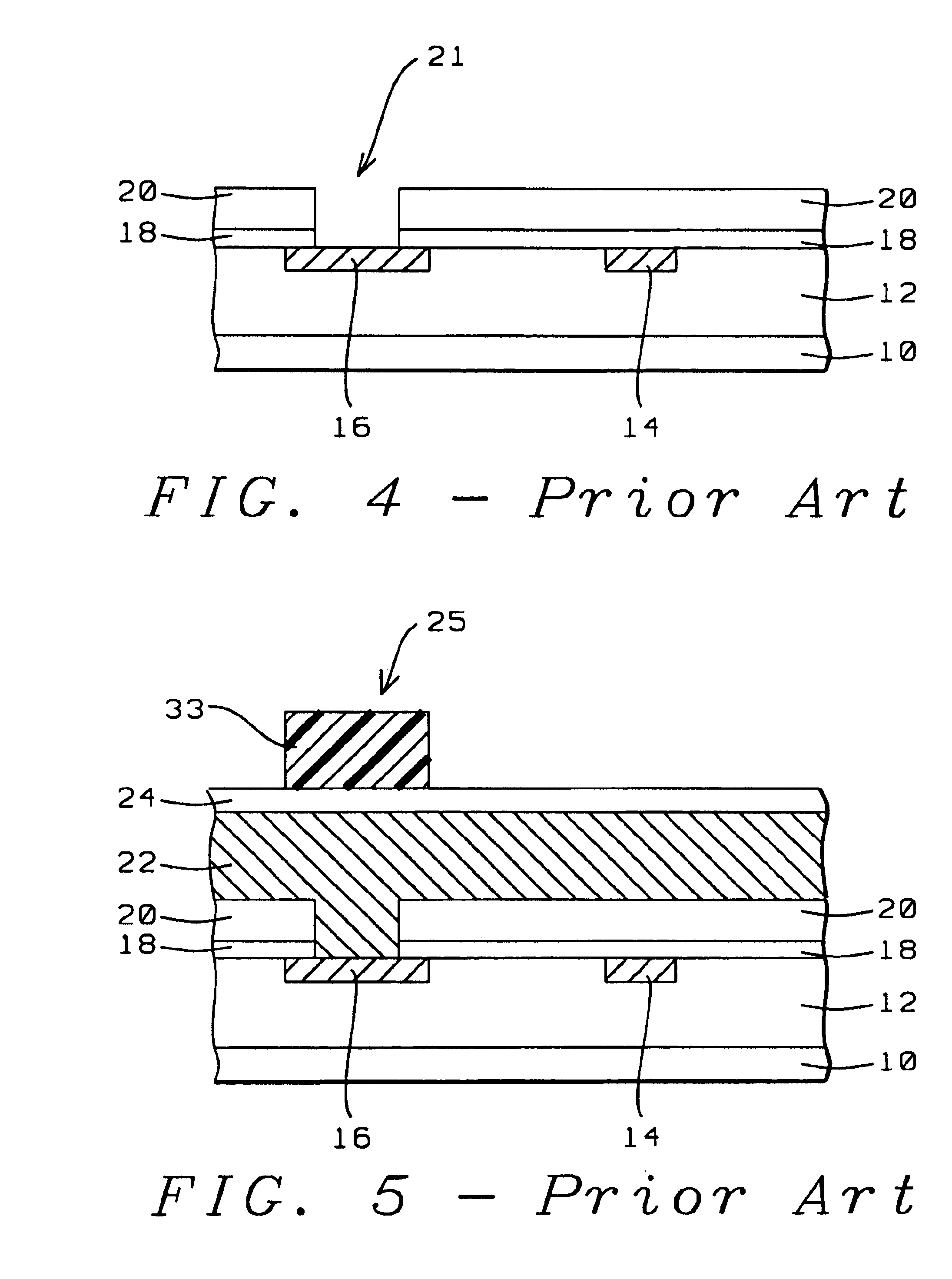

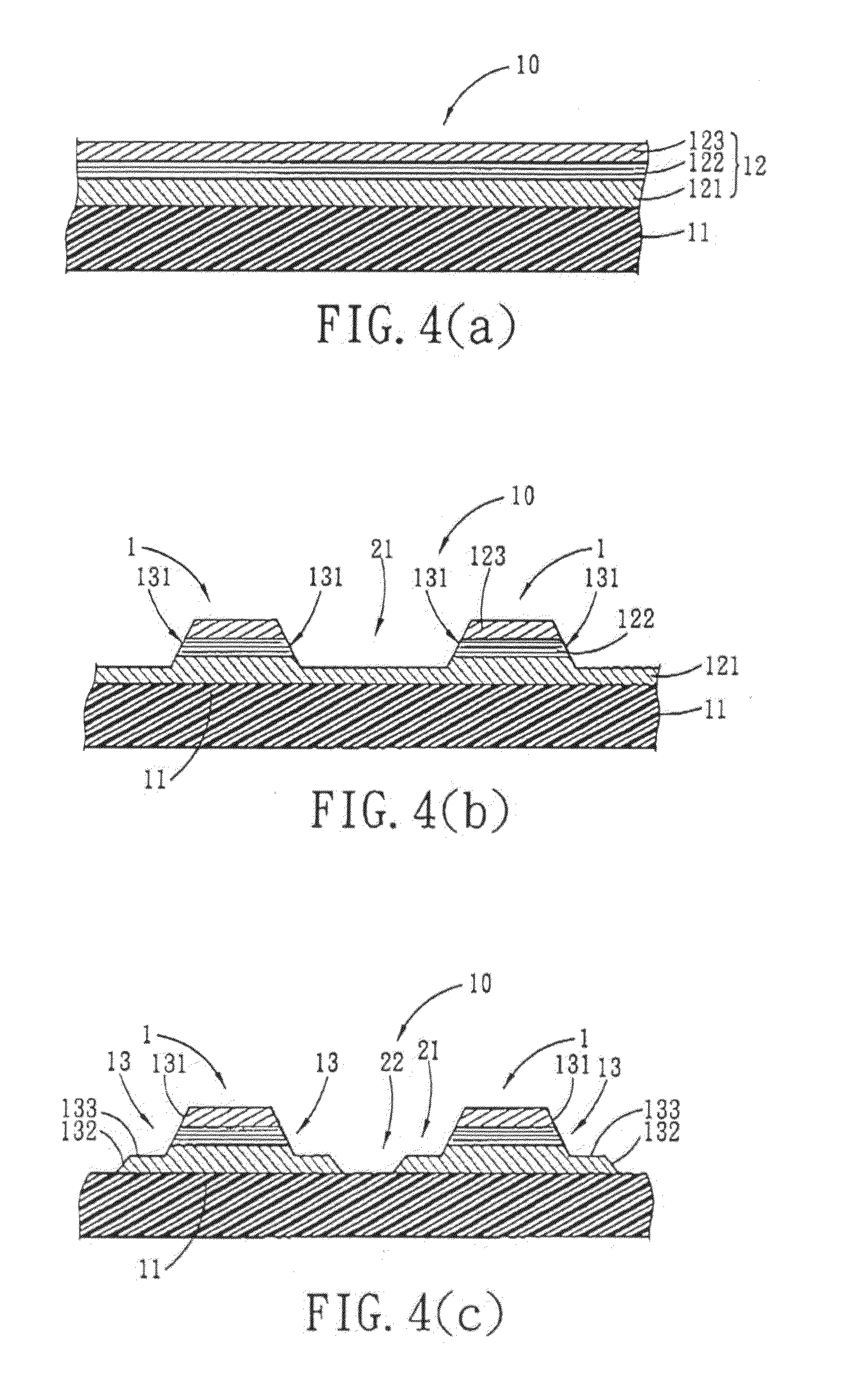

Light emitting diode chip, and methods for manufacturing and packaging the same

ActiveUS20100210046A1Reduce packaging volumeAvoid problemSolid-state devicesSemiconductor/solid-state device manufacturingDiodeLight-emitting diode

A light emitting diode chip includes a substrate, an epitaxial layer, two inclined plane units, and two electrode units. The substrate has top and bottom surfaces. The epitaxial layer is disposed on the top surface of the substrate. Each of the inclined plane units is inclined downwardly and outwardly from the epitaxial layer toward the bottom surface of the substrate, and includes an inclined sidewall formed on the epitaxial layer, and a substrate inclined wall formed on the substrate. Each of the electrode units includes an electrode disposed on the epitaxial layer, and a conductive portion extending from the electrode to the substrate inclined wall along corresponding one of the inclined plane units.

Owner:LITE ON TECH CORP +1

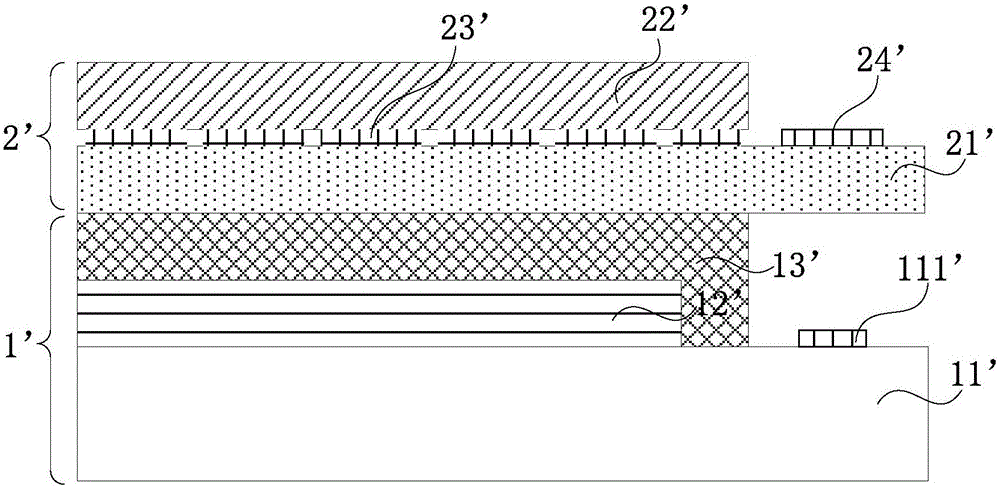

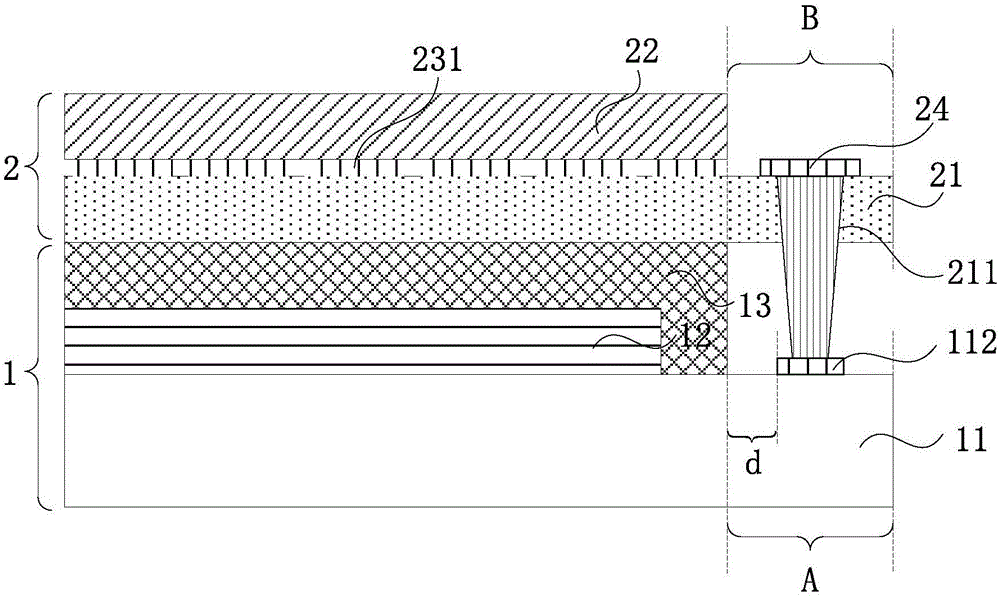

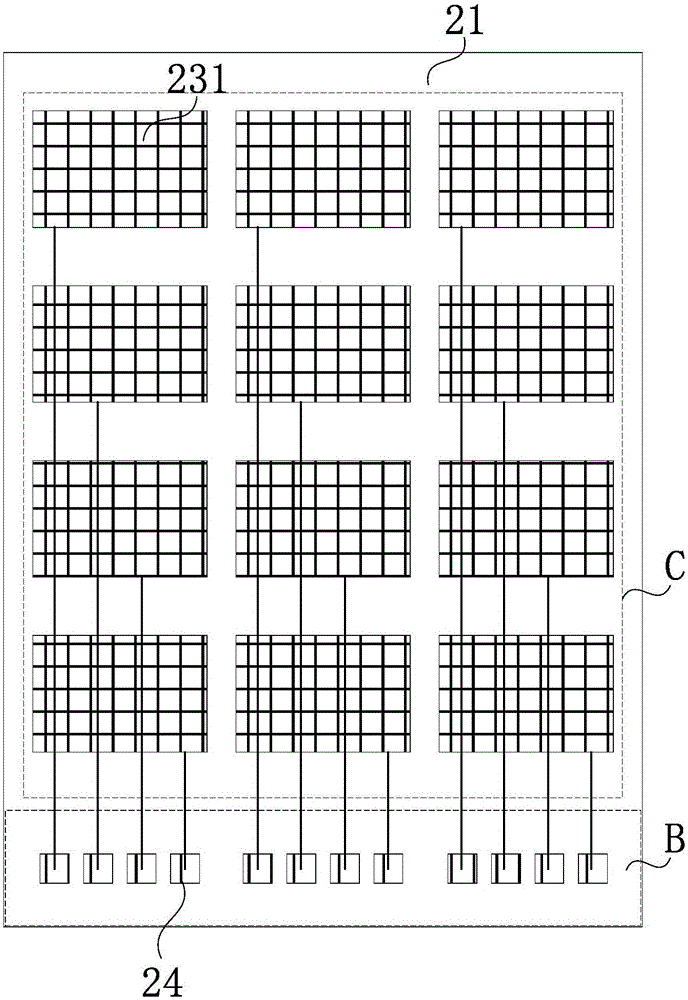

Display panel and manufacturing method thereof and flexible display device

ActiveCN106229332AReduce difficultySimple structureSolid-state devicesSemiconductor/solid-state device manufacturingOrganic light emitting deviceFlexible display

The invention provides a display panel and a manufacturing method thereof. The display panel comprises an organic light-emitting display screen and a touch layer set; the organic light-emitting display screen comprises an array substrate, an organic light-emitting device layer and a thin film encapsulation layer which are sequentially stacked; the touch layer set comprises a water-oxygen barrier layer located on the light-out side of the organic light-emitting display screen and a touch electrode layer, and the touch electrode layer is provided with multiple touch electrodes and multiple conducted pads which are electrically connected; the array substrate is provided with multiple first pads for conducting displaying and multiple second pads for conducting touching, and the conducted pads of the touch layer set are electrically connected to the second pads.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

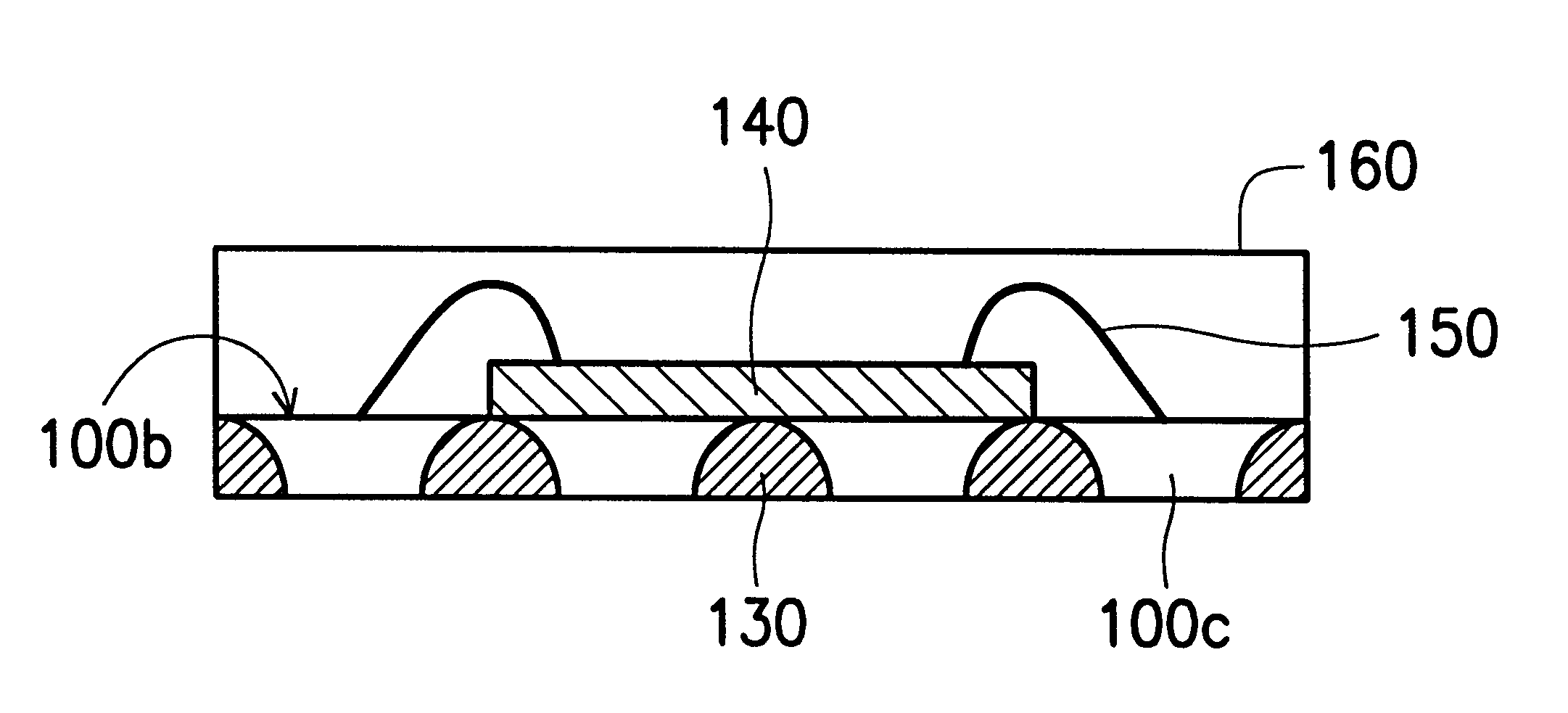

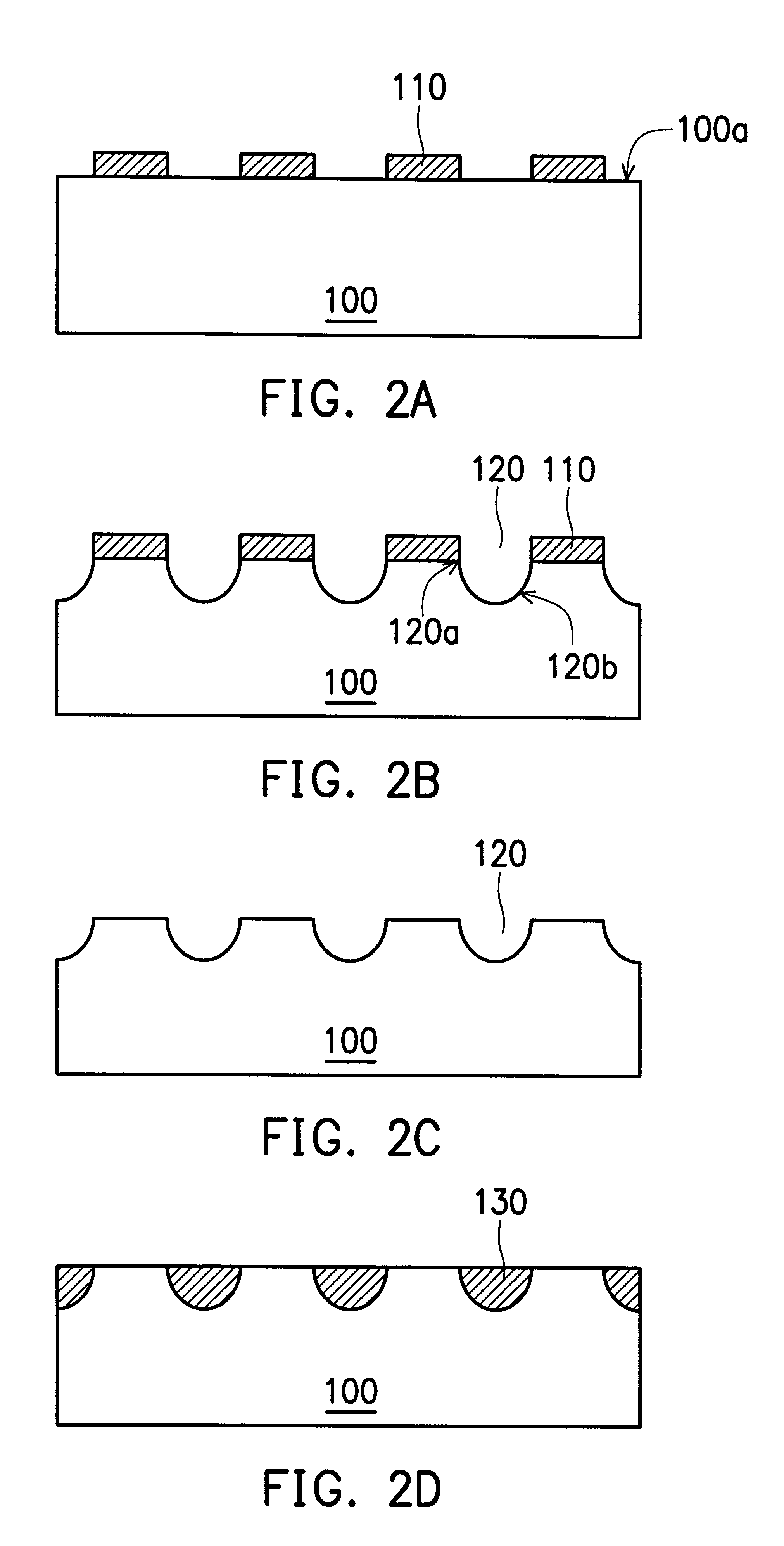

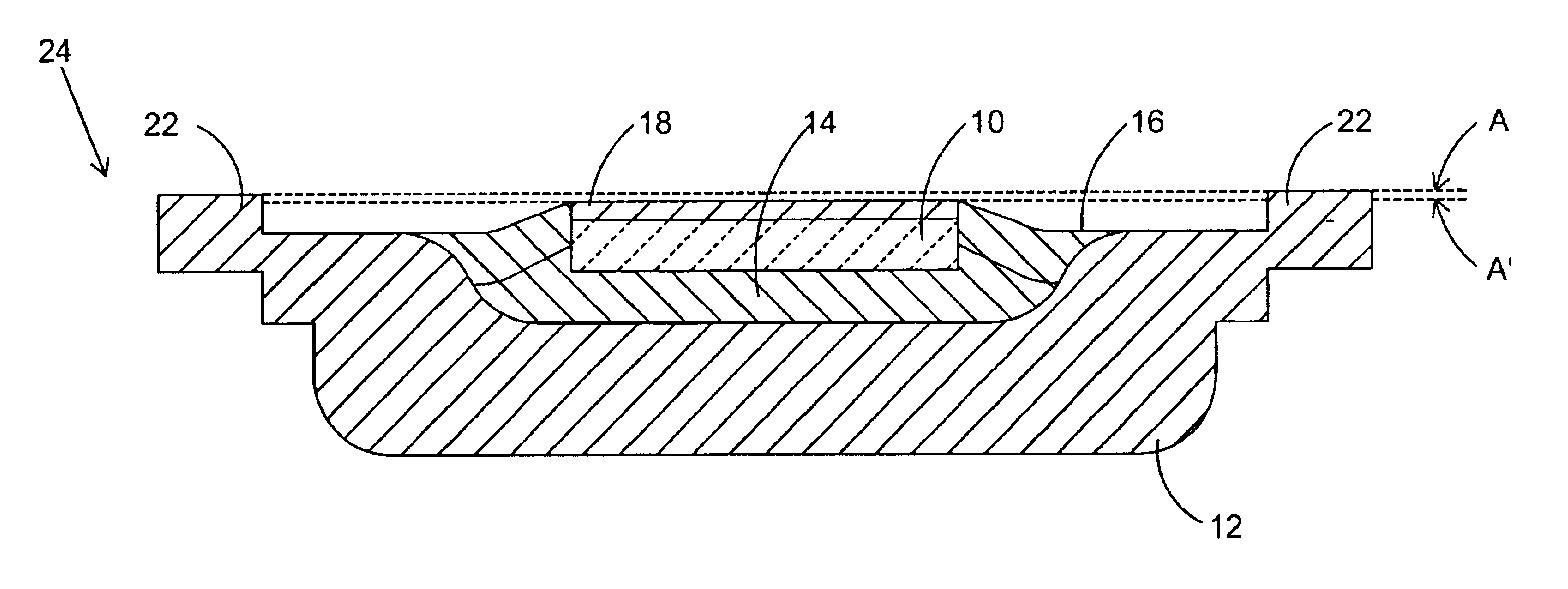

Packaging substrate and method for manufacturing the same

InactiveUS20080257595A1Increase joint surface areaAvoid joint crackingSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskEngineering

The present invention relates to a packaging substrate and a method for manufacturing the same. The packaging substrate includes: a substrate body, having a plurality of conductive pads on the surface thereof, wherein the top surfaces of the conductive pads have a concave each; a solder mask, disposed on the surface of the substrate body and having a plurality of openings to correspondingly expose the concaves of the conductive pads each; and a plurality of metal bumps, disposed correspondingly in the openings of the solder mask and over the concaves of the conductive pads. The present invention increases the joint surface area between the metal bumps and the conductive pads so as to inhibit the joint crack and improve the reliability of the conductive structure of the packaging substrate.

Owner:PHOENIX PRECISION TECH CORP

Surface mounted package with die bottom spaced from support board

InactiveUS6930397B2Reduce substrate failureReduce the number of failuresSemiconductor/solid-state device detailsSolid-state devicesMOSFETEpoxy

A semiconductor package according to the present invention includes a metal can which receives in its interior space a MOSFET. The MOSFET so received is oriented such that its drain electrode is facing the bottom of the can and is electrically connected to the same by a layer of conductive epoxy or a solder or the like. The edges of the MOSFET so placed are spaced from the walls of the can. The space between the edges of the MOSFET and the walls of the can is filled with an insulating layer. A surface of the MOSFET is sub-flush below the plane of a substrate by 0.001-0.005 inches to reduce temperature cycling failures.

Owner:INFINEON TECH AMERICAS CORP

Semiconductor device

ActiveUS20060012029A1Relieve pressureLarge driving currentSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A minute wiring structure portion including first wiring layers and first insulating layers, in which each of first wiring layers and each of first insulating layers are alternately laminated, is formed on a semiconductor substrate. A first huge wiring structure portion is formed on the minute wiring structure portion, and the first huge wiring structure portion is formed by successively forming on the minute wiring structure portion, in the following order, the first huge wiring portion including second wiring layers has a thickness of twice or more of the thickness of the first wiring layers and second insulating layers, in which each of second wiring layers and each of second wiring layers are alternately laminated, and a second huge wiring structure portion including third wiring layers has a thickness of twice or more of the thickness of the first wiring layer and a third insulating layer in which the elastic modulus at 25° C. is not more than that of the second insulating layers, each of the third wiring layers and each of the third insulating layers being alternately laminated.

Owner:RENESAS ELECTRONICS CORP

Copper-free flat packaging piece of AAQFN frame product and manufacturing process thereof

InactiveCN103474406AImprove package reliabilityLow costSemiconductor/solid-state device detailsSolid-state devicesHemt circuitsWafer thinning

Owner:HUATIAN TECH XIAN

Flexible display

ActiveCN101833902AImprove package reliabilityReduce stressStatic indicating devicesNon-linear opticsDisplay deviceEngineering

The invention discloses a flexible display, comprising a matrix base plate, a display dielectric layer, a transmitting base plate and a first sealant, wherein, the matrix base plate is provided with a display area and a sealant coating area which surrounds the display area; the display dielectric layer is configured on the matrix base plate and positioned in the display area; the transmitting base plate is configured above the display dielectric layer; and the first sealant is configured between the matrix base plate and the transmitting base plate, is positioned in the sealant coating area and surrounds the display area, and the first sealant is provided with a first side wall and a second side, wherein, at least one of the first side wall and the second side wall comprises a plurality of grooves arranged at intervals. The flexible display not only reduces bending stress that the sealant bears and prolongs the service life thereof, but also can improve the seal reliability of a display device because the sealant of the flexible display comprises a plurality of grooves arranged at intervals.

Owner:E INK HLDG INC

Display panel and manufacturing method thereof

ActiveCN110190104AImprove display performance and packaging reliabilityImprove the display effectSolid-state devicesSemiconductor/solid-state device manufacturingSurface plateDisplay device

The embodiment of the invention discloses a display panel and a manufacturing method thereof. The display device comprises a first substrate, a hollow area, a first non-display area, a display area and a second non-display area surrounding the display area; an array layer and a light-emitting device layer are stacked on the first substrate in order, the array layer comprises an array metal layer and an insulating layer which are arranged at intervals, the light-emitting device layer comprises a first electrode layer, a pixel defining layer, an organic layer and a second electrode layer which are sequentially arranged in a stacking mode, at least part of the insulating layer and the pixel defining layer are arranged in the first non-display area in a contact mode, the pixel defining layer comprises at least one first groove, at least part of the insulating layer comprises at least one second groove, the first groove and the second groove are located in the first non-display area, the first groove and the second groove are at least partially overlapped in an orthographic projection perpendicular to a plane where the first substrate is located, and the first groove and the second groove are arranged in a contact mode to form a groove structure. The embodiment of the invention improves the packaging reliability.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD