Patents

Literature

1293 results about "Wafer-level packaging" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Wafer-level packaging (WLP) is the technology of packaging an integrated circuit while still part of the wafer, in contrast to the more conventional method of slicing the wafer into individual circuits (dice) and then packaging them. WLP is essentially a true chip-scale package (CSP) technology, since the resulting package is practically of the same size as the die. Wafer-level packaging allows integration of wafer fab, packaging, test, and burn-in at wafer level in order to streamline the manufacturing process undergone by a device from silicon start to customer shipment.

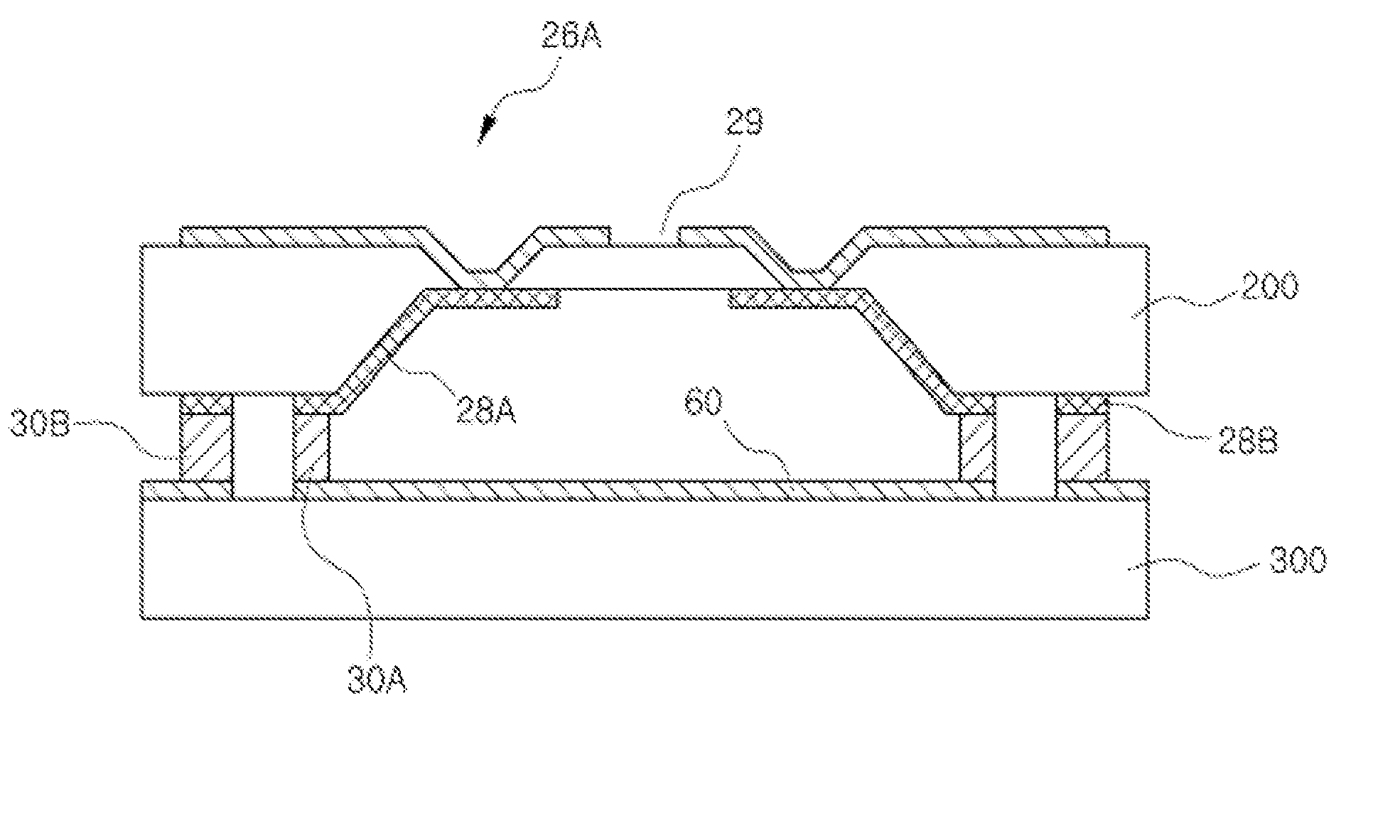

Wafer level package structure and fabrication methods

ActiveUS8759964B2Reduce harmSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A method of forming a package structure with reduced damage to semiconductor dies is provided. The method includes providing a die comprising bond pads on a top surface of the die; forming bumps on the bond pads of the die, wherein the bumps have top surfaces higher than the top surface of the die; mounting the die on a chip carrier, wherein the bumps are attached to the chip carrier; molding the die onto the chip carrier with a molding compound; de-mounting the chip carrier from the die; and forming redistribution traces over, and electrically connected to, the bumps of the die.

Owner:TAIWAN SEMICON MFG CO LTD

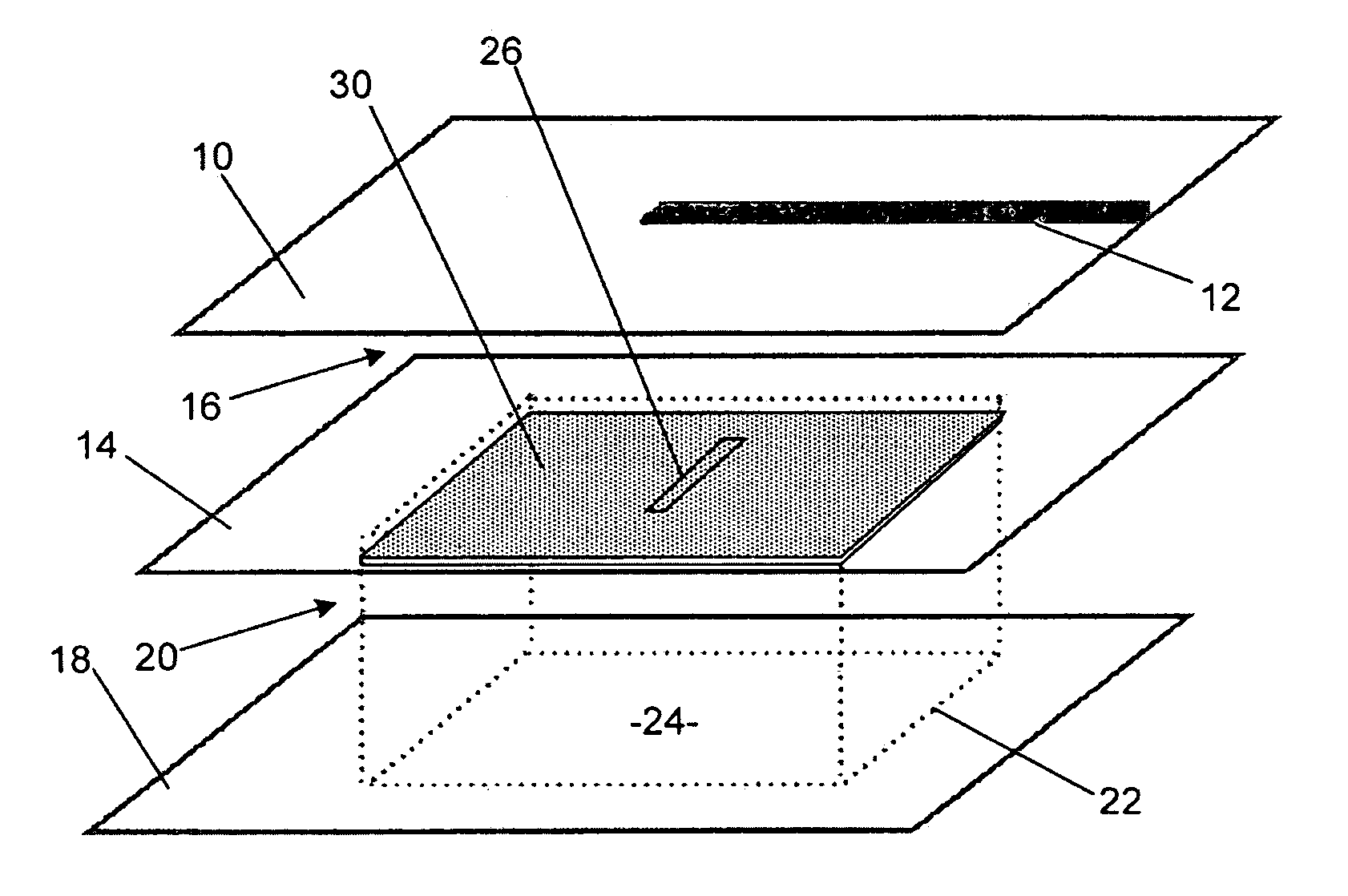

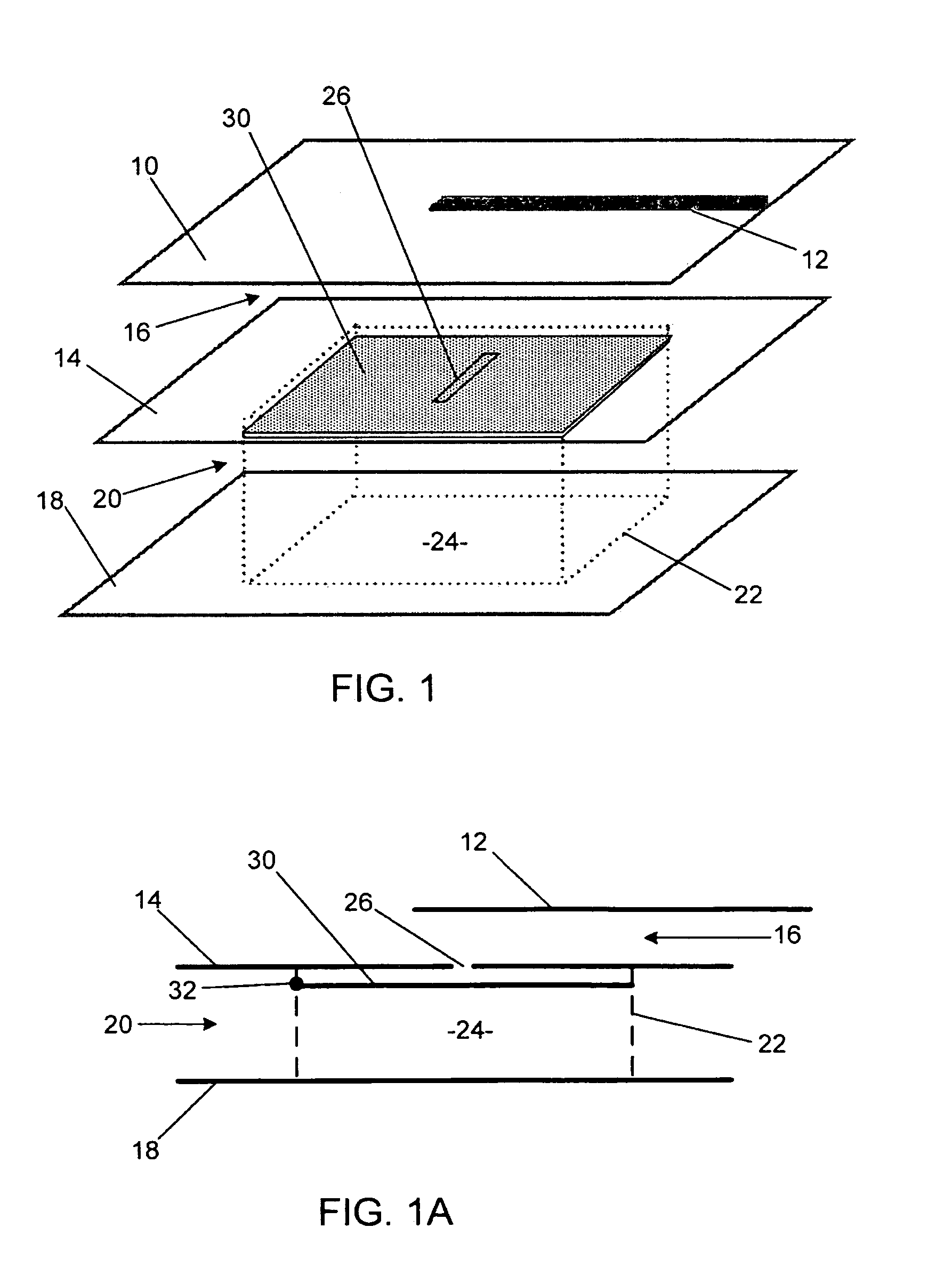

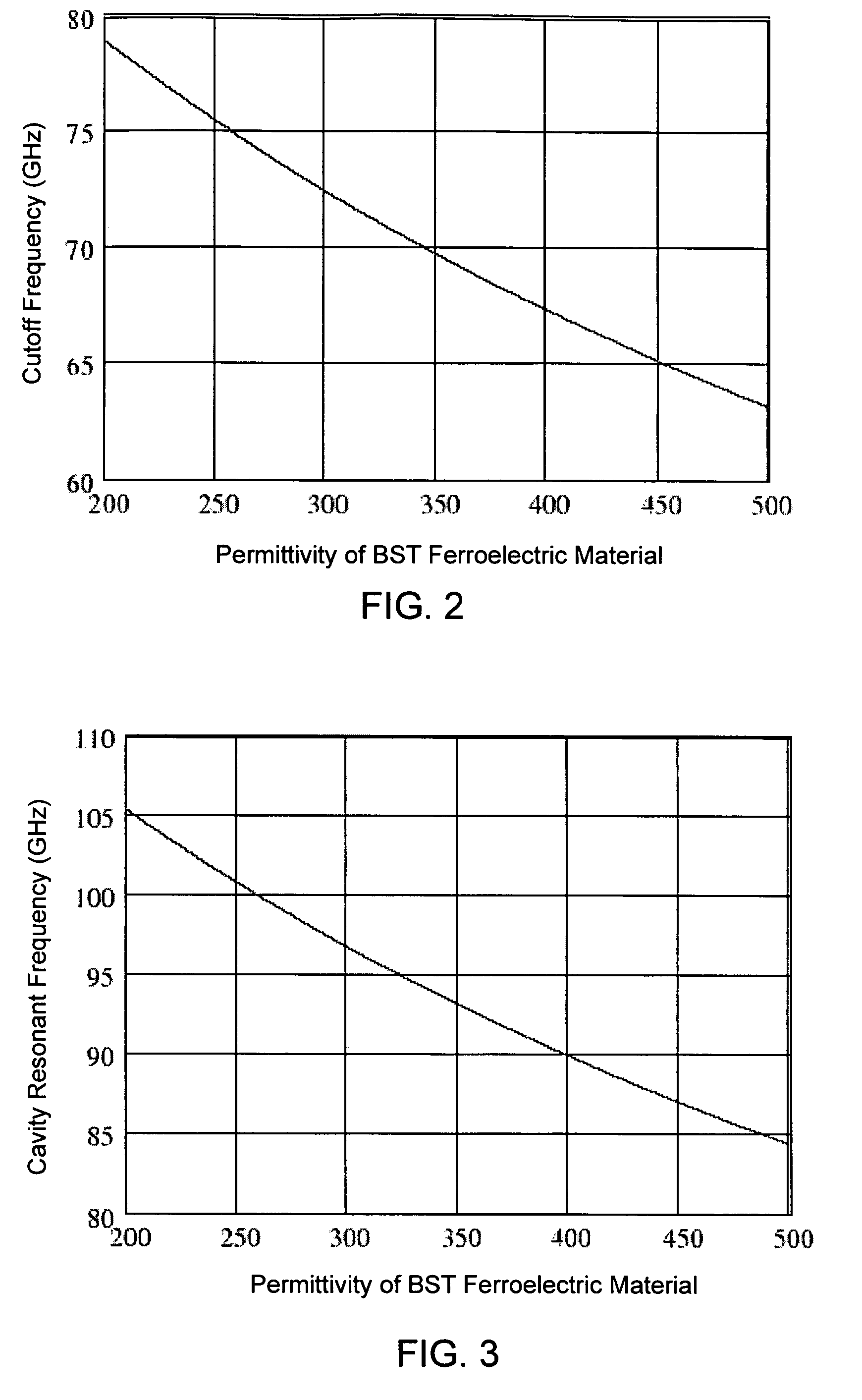

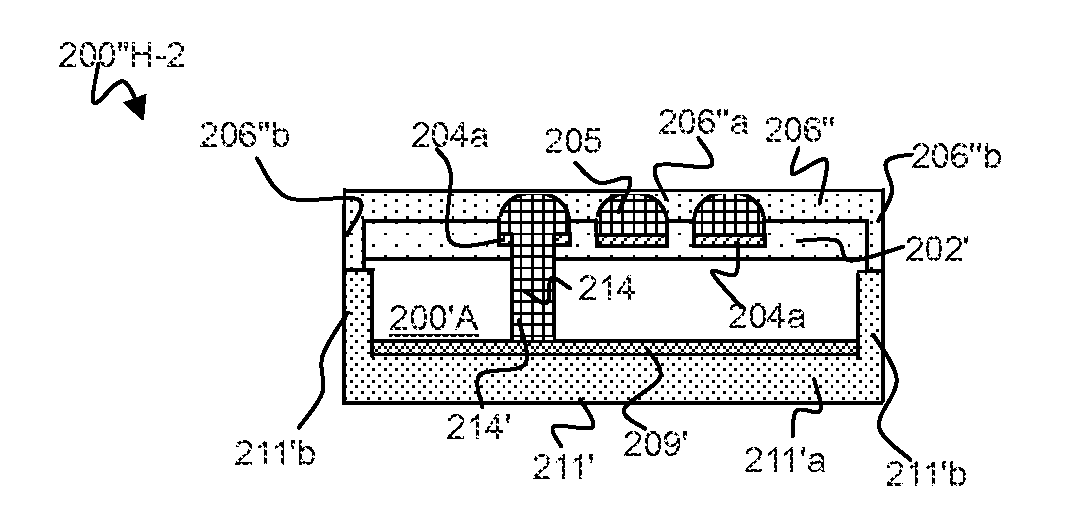

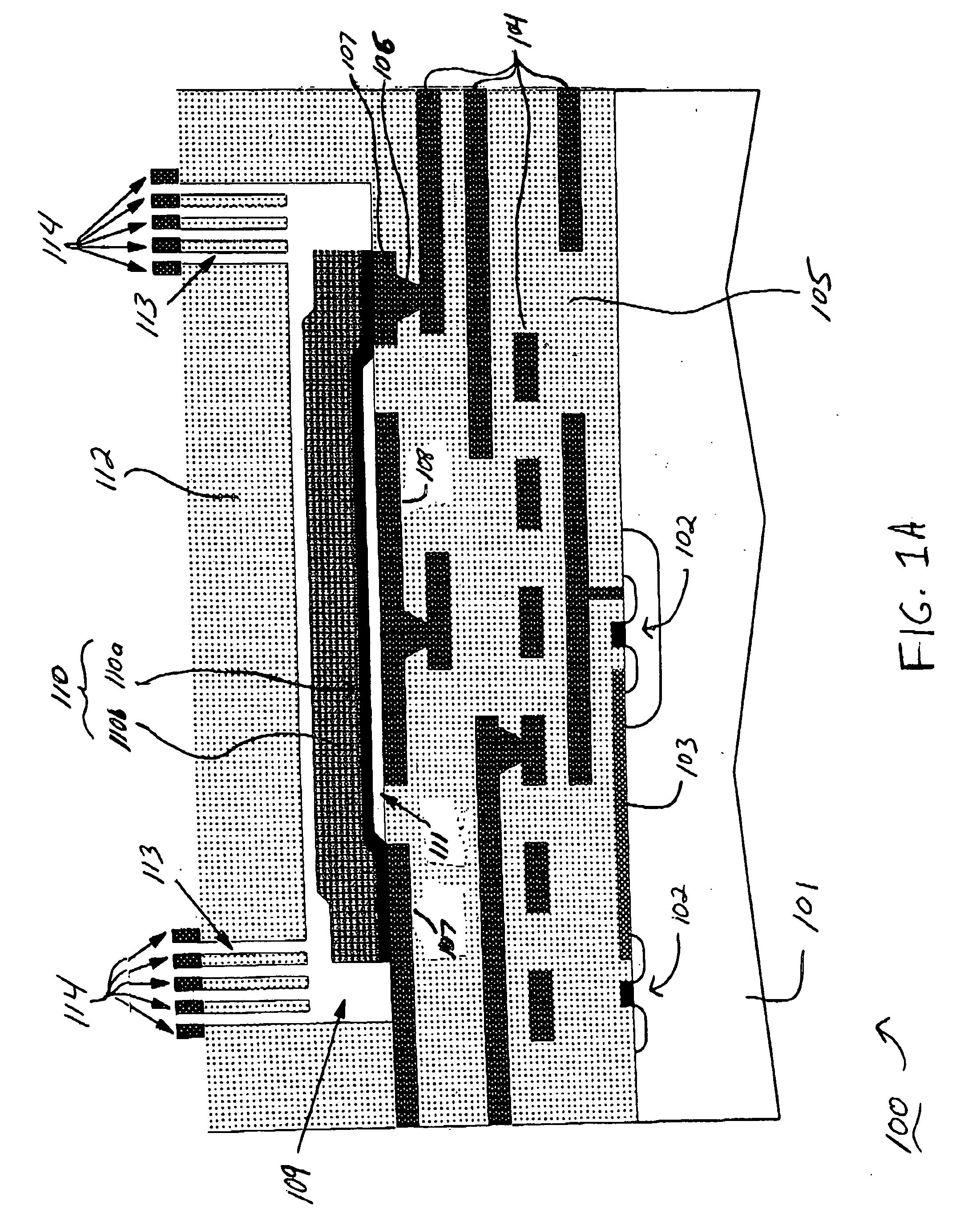

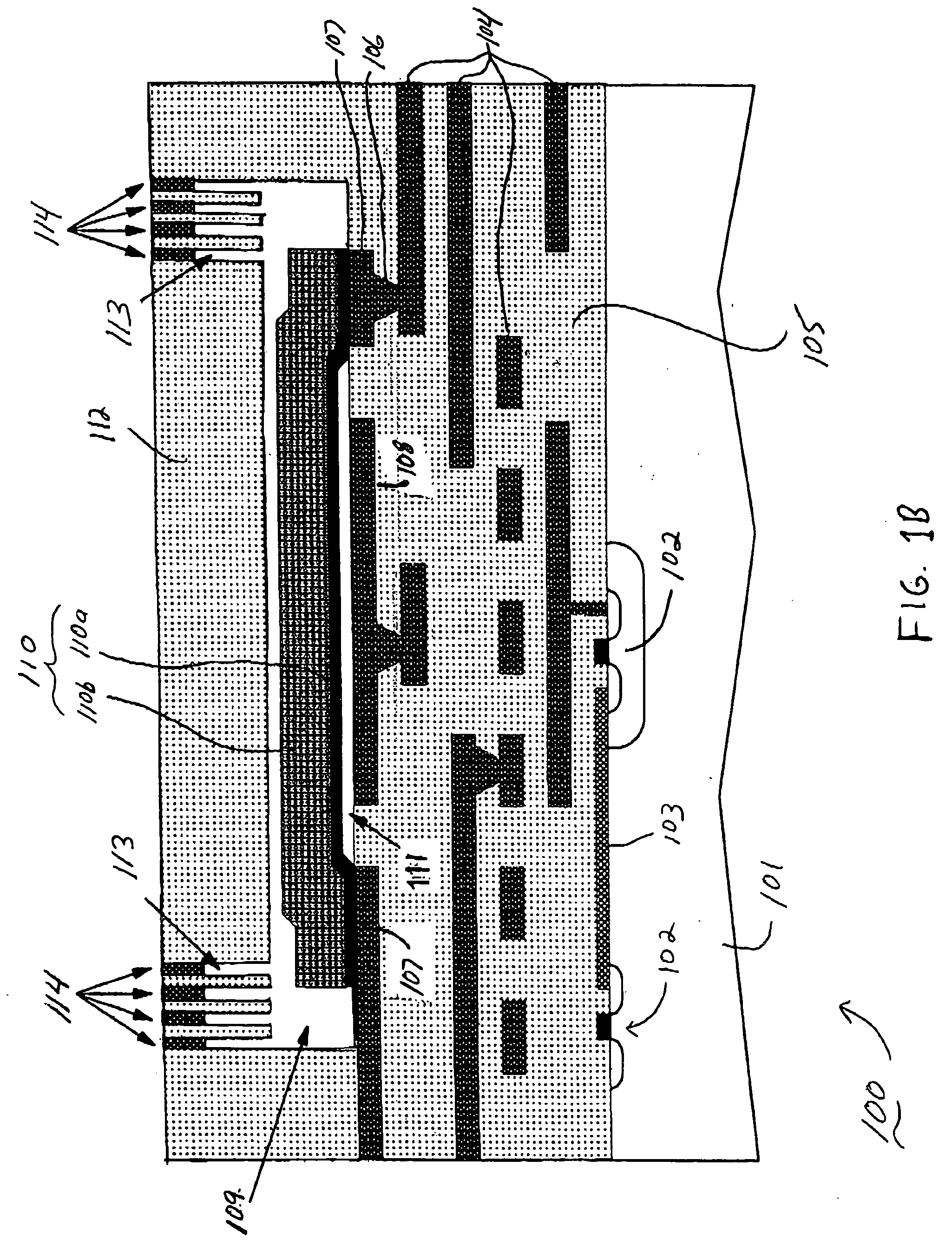

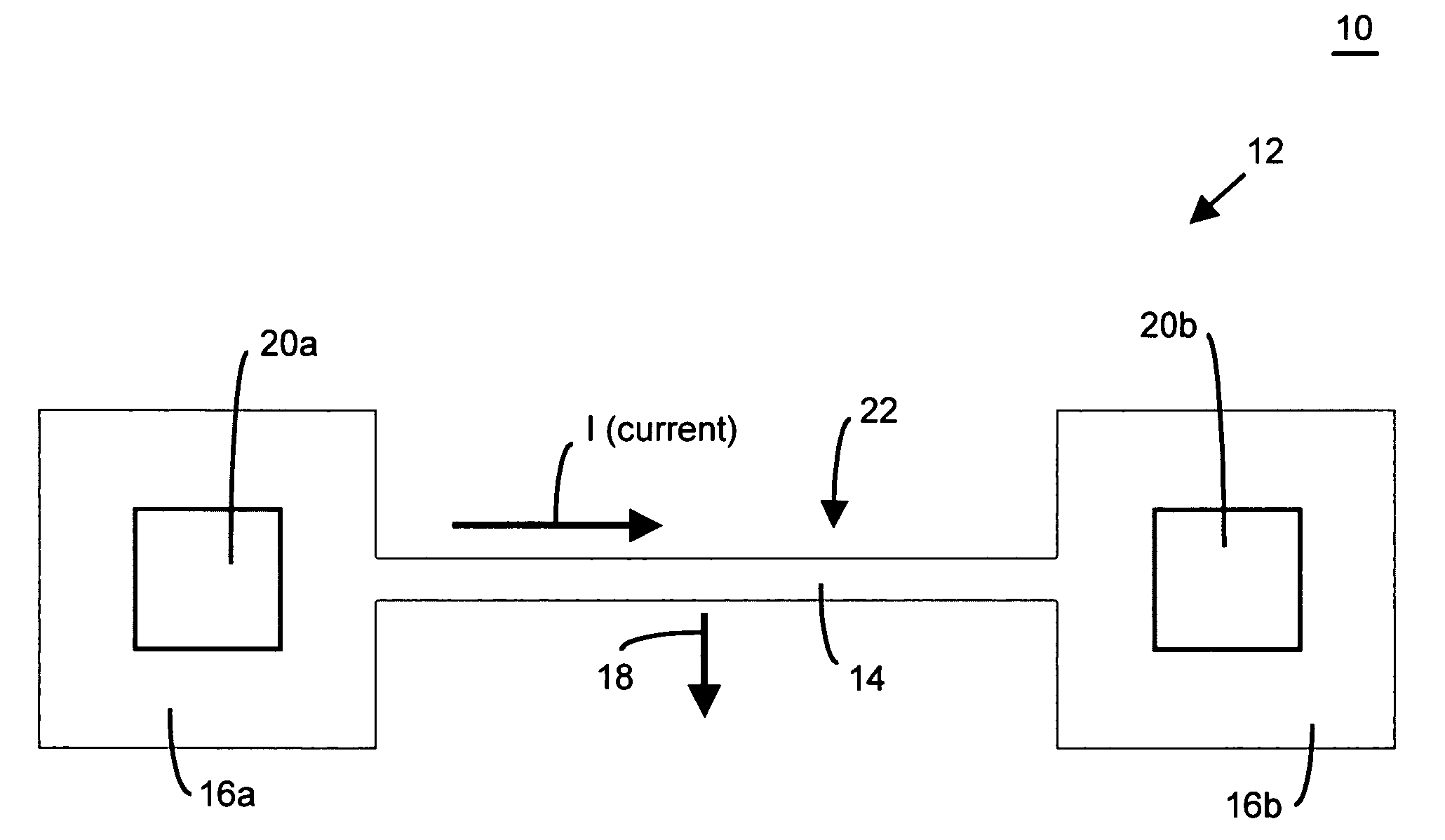

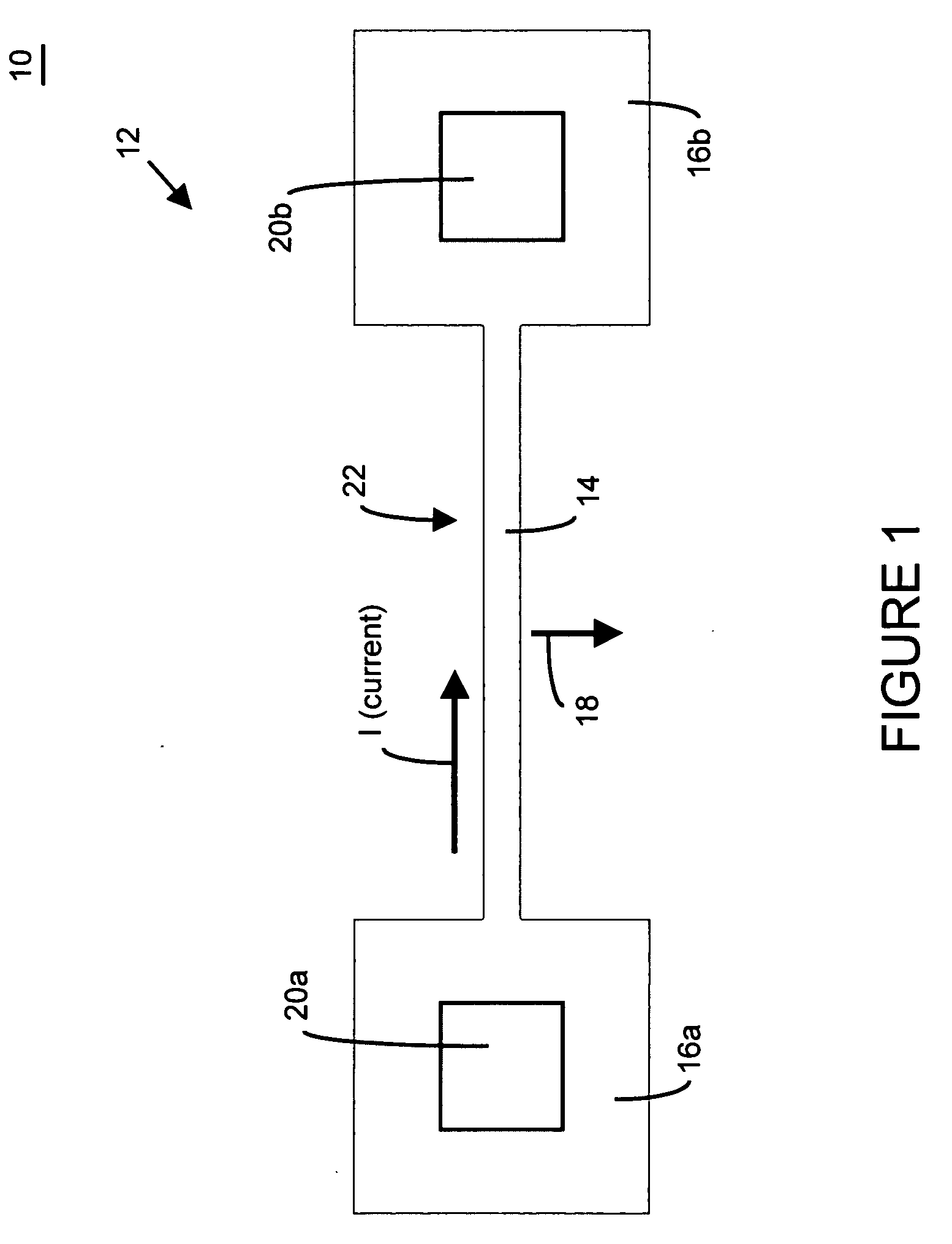

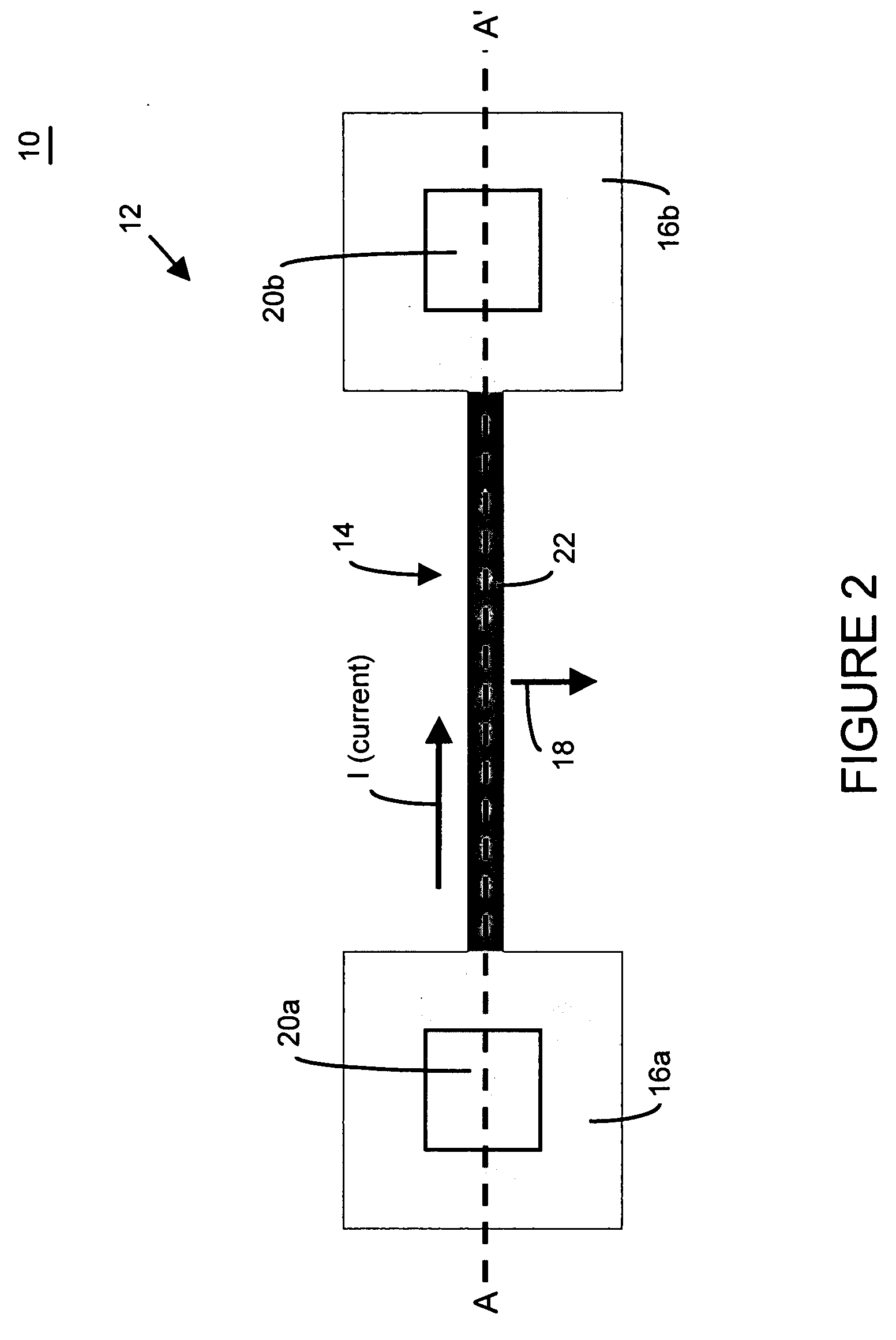

Monolithic microwave integrated circuit (MMIC) waveguide resonators having a tunable ferroelectric layer

ActiveUS7570137B2Improve scalabilityEasy to integrateResonatorsOscillations generatorsElectromagnetic couplingResonant cavity

A ferroelectric loaded waveguide resonator capable of operation at microwave, millimeter-wave and higher frequencies and suitable for integration into a three-dimensional monolithic microwave integrated circuit (3D MMIC) is disclosed. The resonator includes a resonator cavity, which, in one form of the invention, is formed by two parallel metal layers and a metallized wall structure extending between the metal layers. The cavity is filled with dielectric material and includes a layer of ferroelectric material, which is used to control the resonant frequency by varying a voltage bias applied to the ferroelectric layer. The cavity includes a slot in one of the metal layers and a coupling strip formed adjacent to the slot to provide electromagnetic coupling to other components, such as a voltage controlled oscillator (VCO). The invention can also be applied to other multi-metal semiconductor or wafer level packaging technologies.

Owner:NORTHROP GRUMMAN SYST CORP

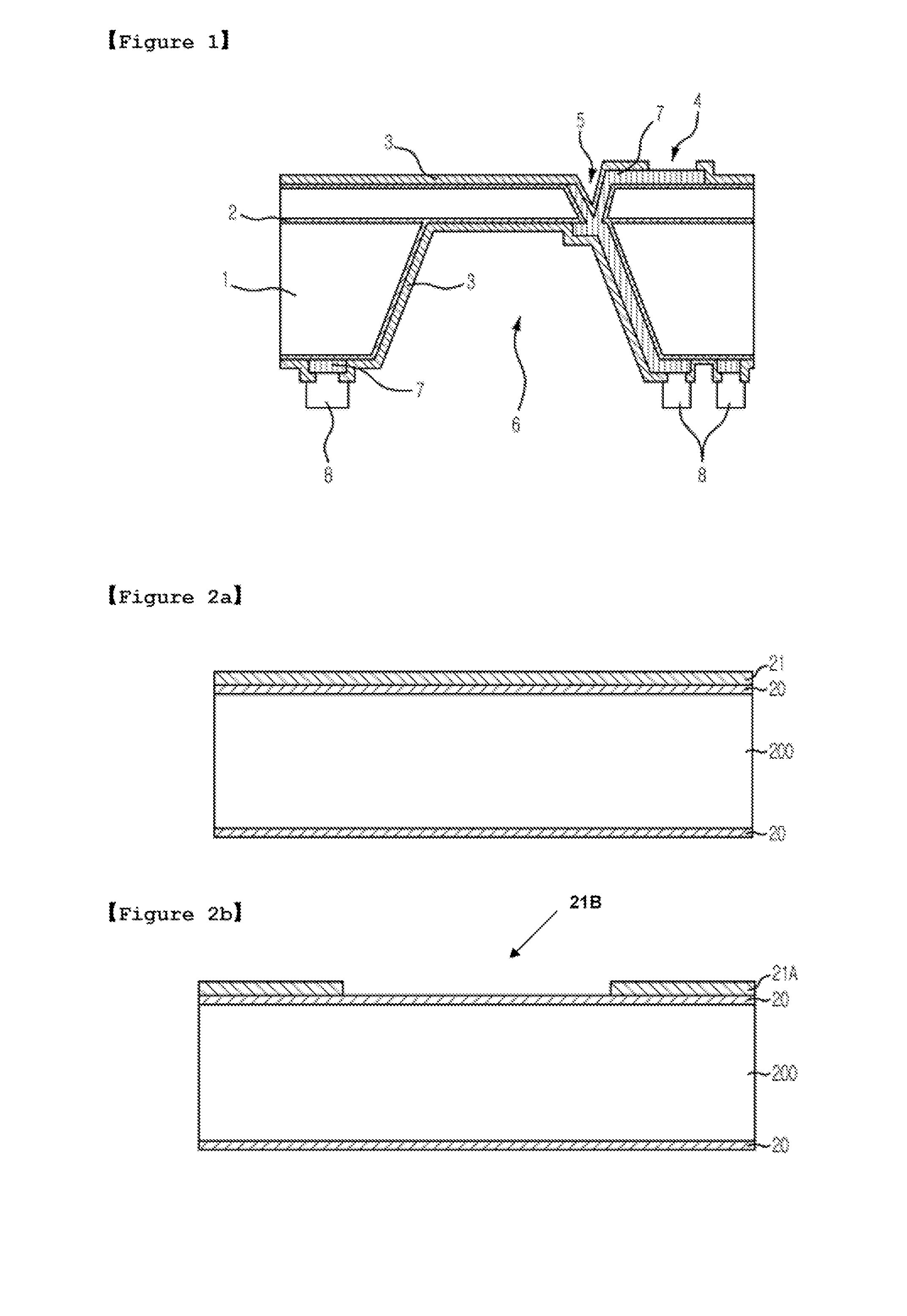

Cap Wafer for Wafer Bonded Packaging and Method for Manufacturing the Same

InactiveUS20080081398A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

The present invention relates to semiconductor device manufacturing techniques, and specifically to a field of device packaging techniques at wafer level. More specifically, it relates to a cap wafer for wafer bonding application that is bonded to top part of a device wafer. The method of the present invention excludes the use of deep reactive ion etching of silicon to form a through silicon via. The present invention provides a method for the preparation of cap wafer for wafer bonding application with a simple process of through silicon via interconnection and a wafer level packaging method using the same.

Owner:PHOCO

Through-wafer interconnects for photoimager and memory wafers

InactiveUS7300857B2High densityImprove functionalitySemiconductor/solid-state device detailsSolid-state devicesPath lengthLead bonding

A through-wafer interconnect for imager, memory and other integrated circuit applications is disclosed, thereby eliminating the need for wire bonding, making devices incorporating such interconnects stackable and enabling wafer level packaging for imager devices. Further, a smaller and more reliable die package is achieved and circuit parasitics (e.g., L and R) are reduced due to the reduced signal path lengths.

Owner:ROUND ROCK RES LLC

Wafer level package and multi-package stack

ActiveUS6982487B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip package includes a semiconductor chip having a through hole extending there through from an active first surface to an inactive second surface. A first conductive pad at least partially surrounds the through hole on the active first surface of the semiconductor chip. The package also includes a printed circuit board having a first surface attached to the inactive second surface of the semiconductor chip, and a second conductive pad aligned with the through hole of the semiconductor chip. A conductive material fills the through hole and contacts the first and second conductive pads.

Owner:SAMSUNG ELECTRONICS CO LTD

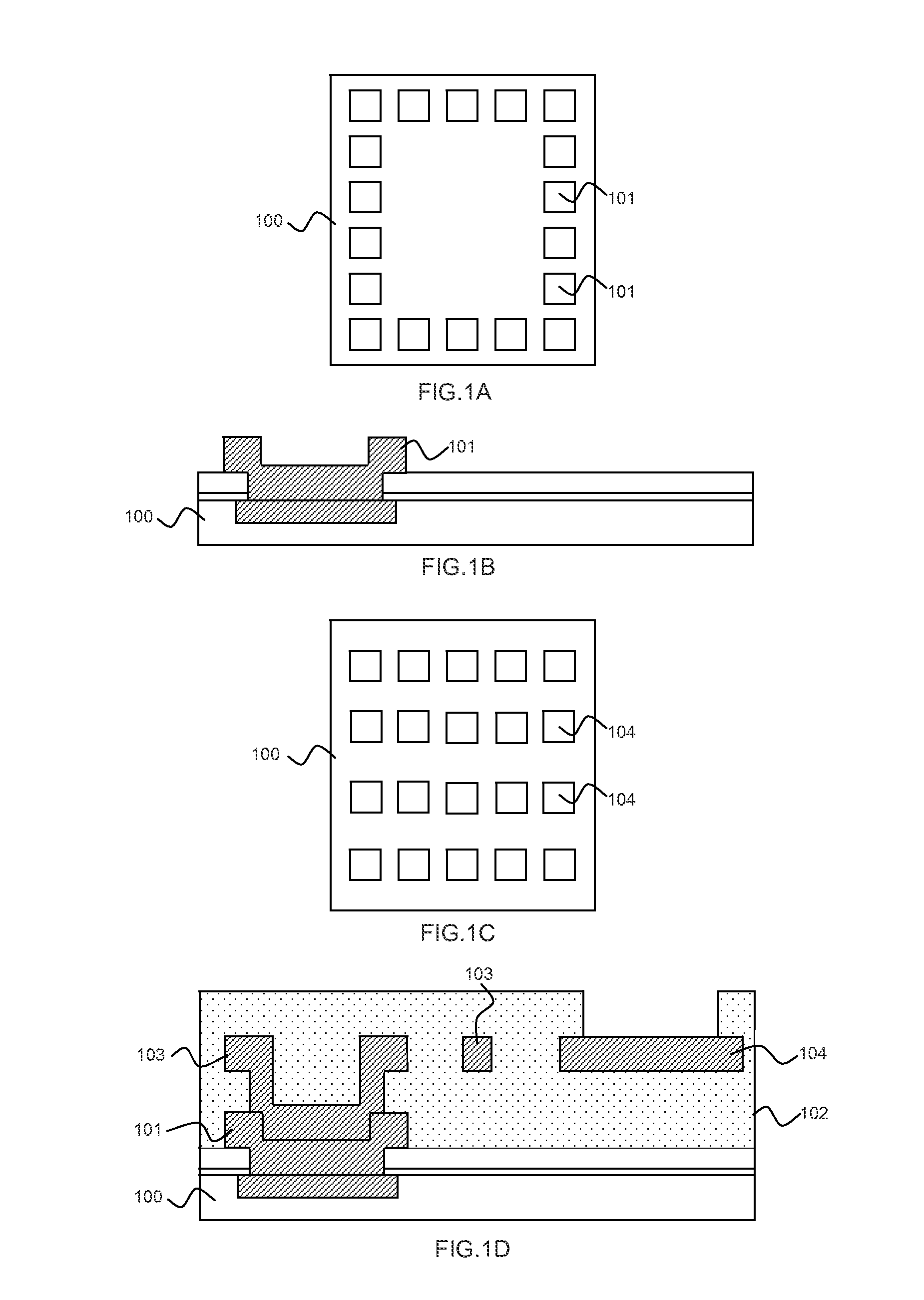

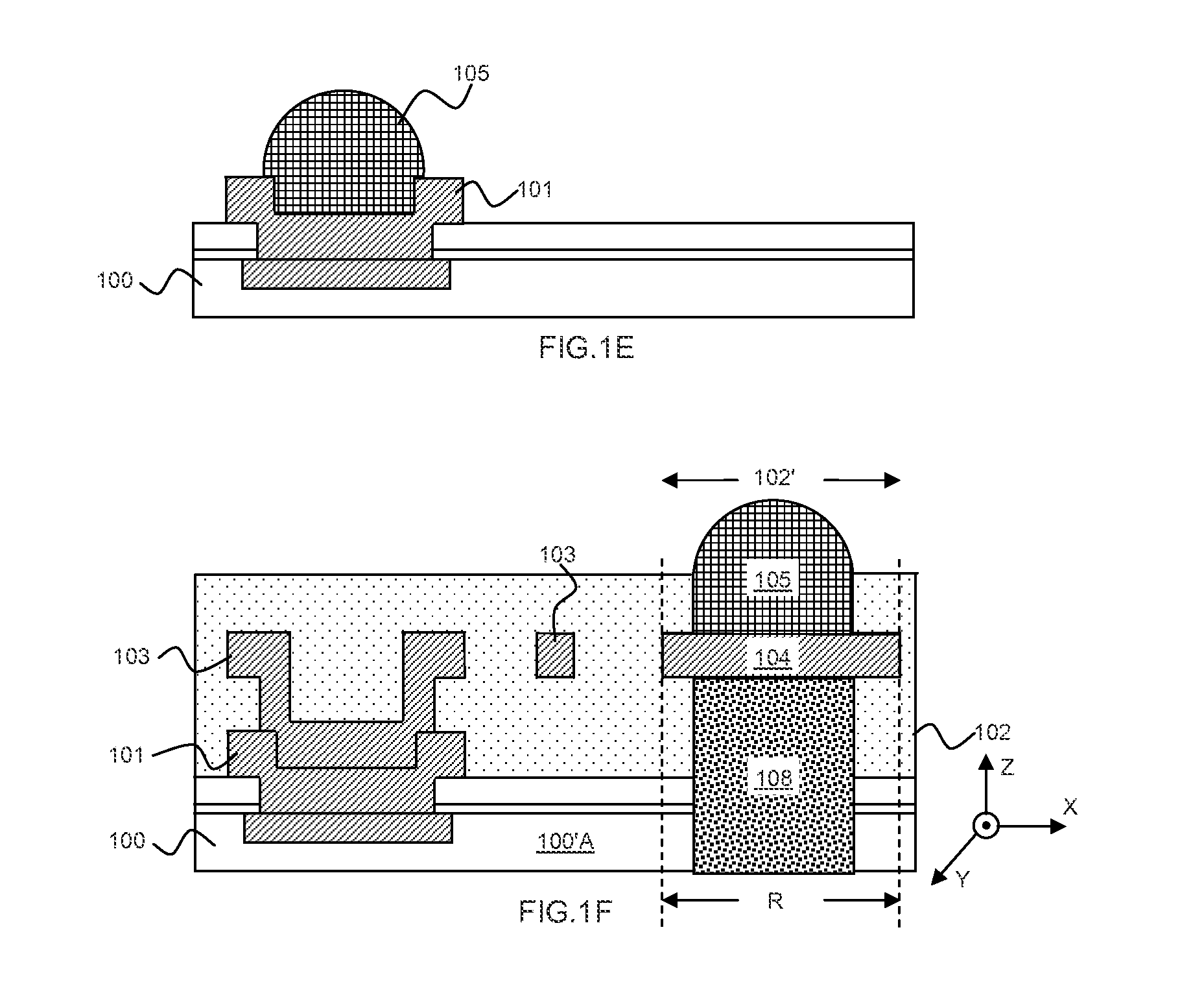

Methods and Apparatus of Wafer Level Package for Heterogeneous Integration Technology

ActiveUS20130264684A1Semiconductor/solid-state device detailsSolid-state devicesContact padElectrical and Electronics engineering

Methods and apparatus are disclosed to form a WLP device that comprises a first chip made of a first technology, and a second chip made of a second technology different from the first technology packaged together by a molding material encapsulating the first chip and the second chip. A post passivation interconnect (PPI) line may be formed on the molding material connected to a first contact pad of the first chip by a first connection, and connected to a second contact pad of the second chip by a second connection, wherein the first connection and the second connection may be a Cu ball, a Cu via, a Cu stud, or other kinds of connections.

Owner:TAIWAN SEMICON MFG CO LTD

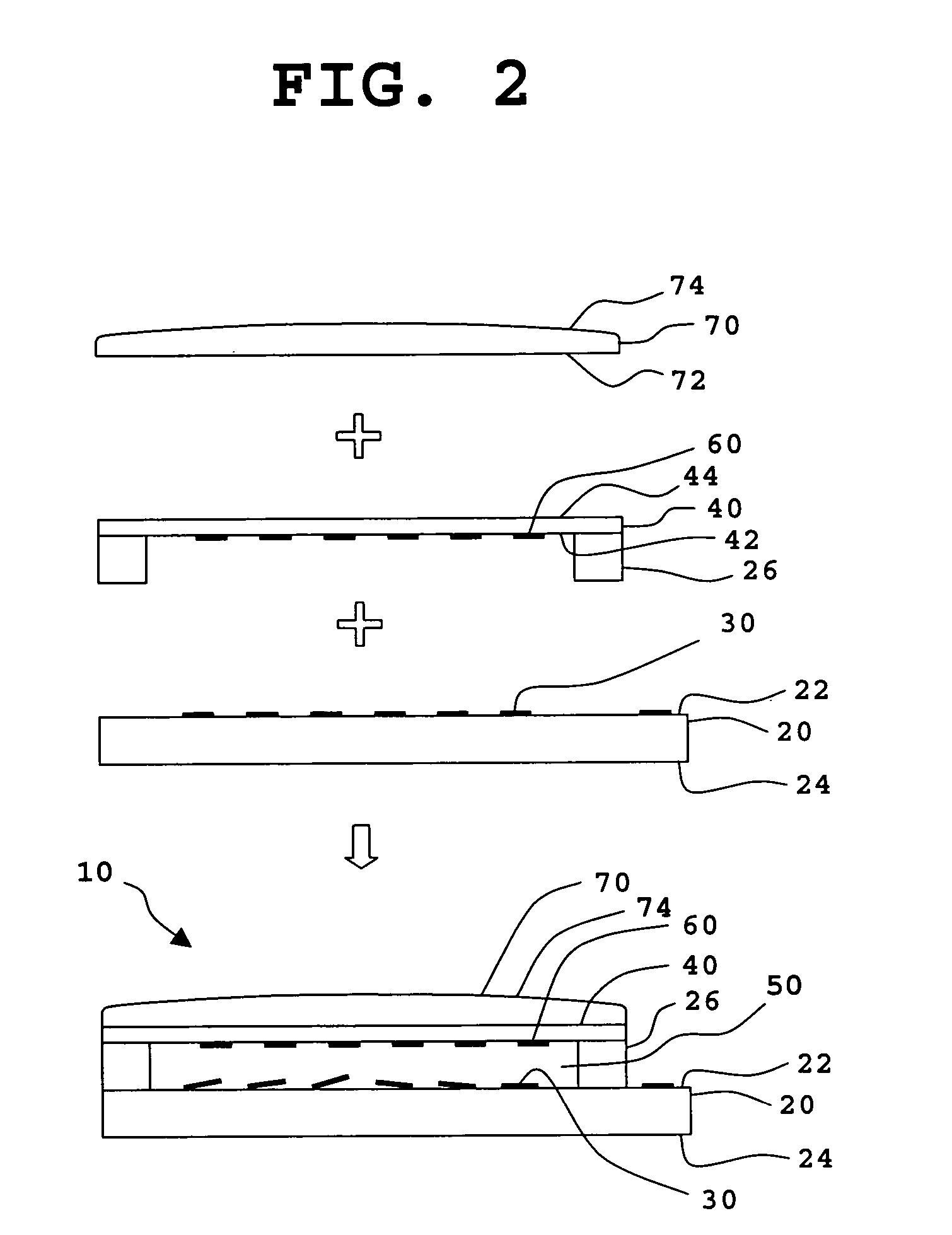

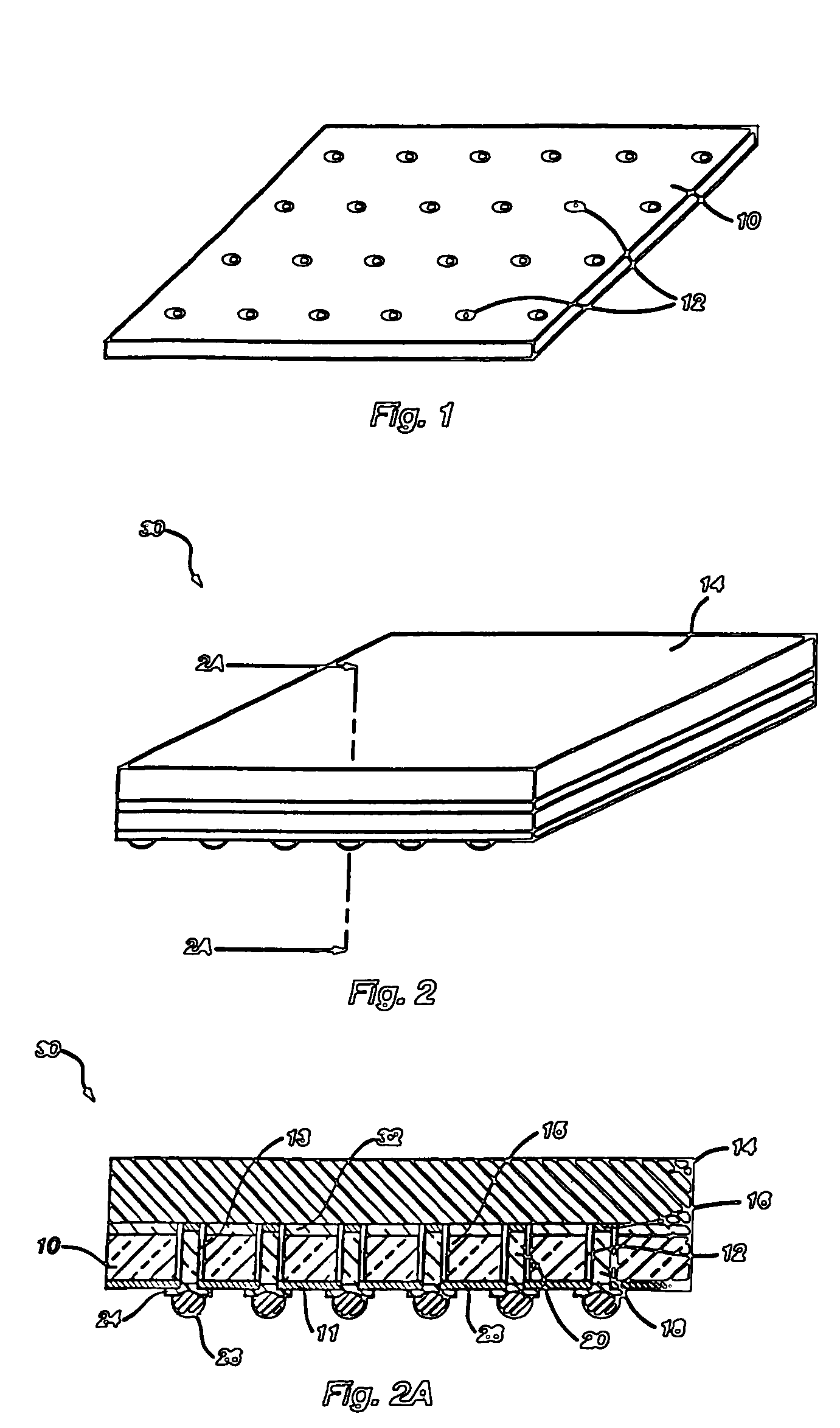

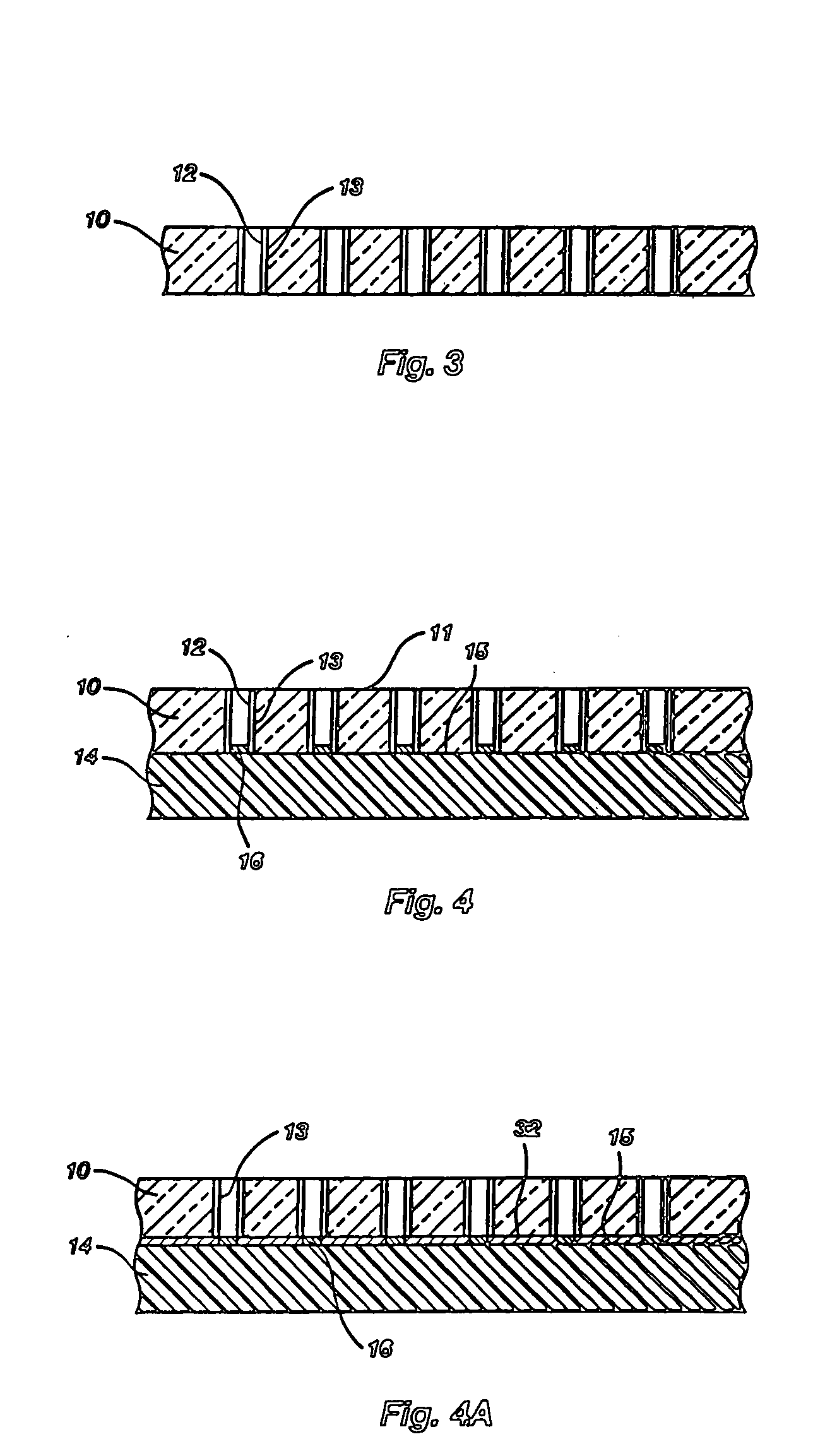

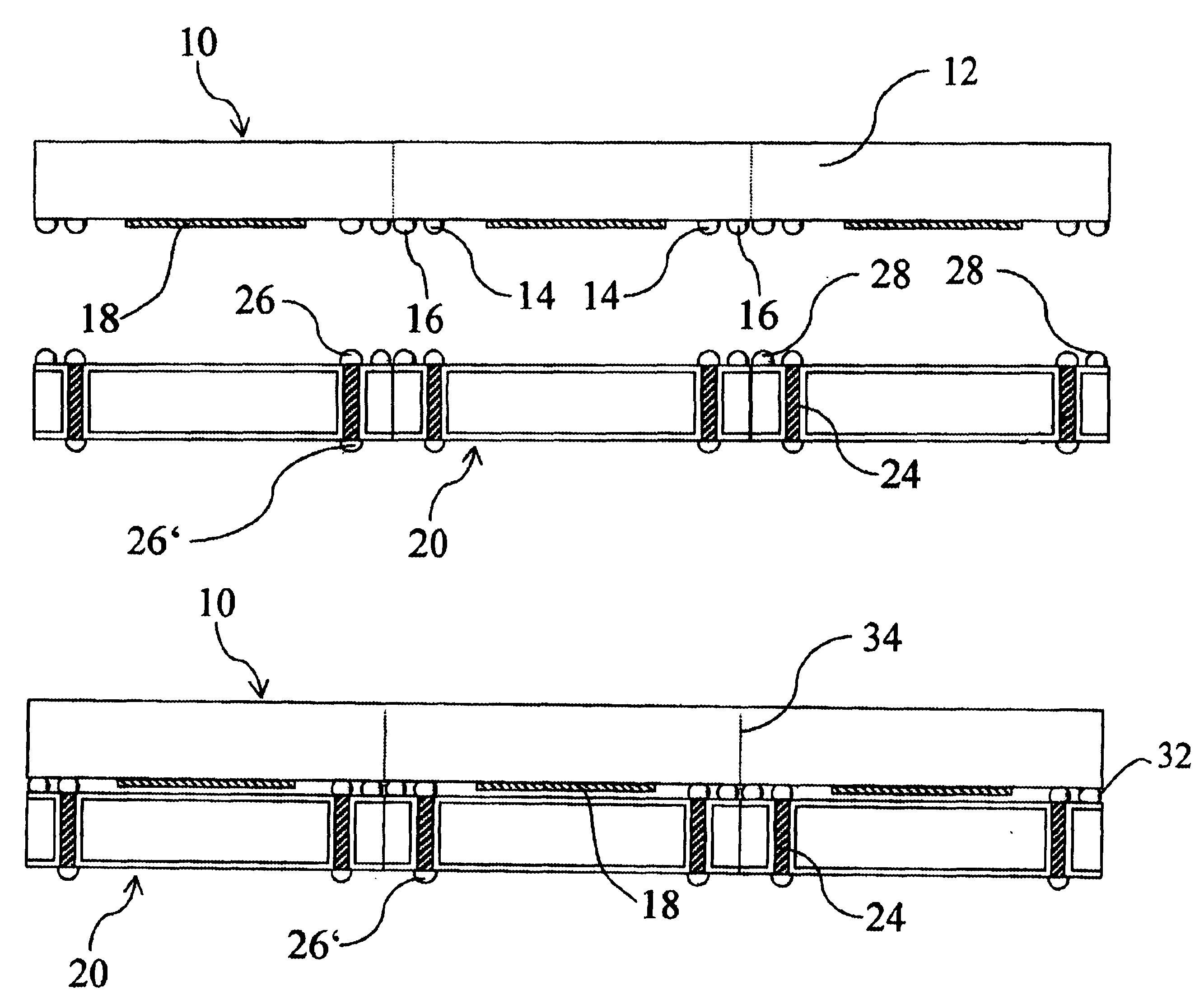

Wafer level package and fabrication method

InactiveUS7192807B1Maximize reliabilityMinimizes impedanceSemiconductor/solid-state device detailsSolid-state devicesSolder wettingConductive materials

A method of forming an electronic component package includes coupling a first surface of an electronic component to a first surface of a first dielectric strip, the electronic component comprising bond pads on the first surface; forming first via apertures through the first dielectric strip to expose the bond pads; and filling the first via apertures with an electrically conductive material to form first vias electrically coupled to the bond pads. The bond pads are directly connected to the corresponding first vias without the use of a solder and without the need to form a solder wetting layer on the bond pads.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Wafer level package and fabrication method

InactiveUS6905914B1Maximize reliabilityMinimizes impedanceSemiconductor/solid-state device detailsSolid-state devicesSolder wettingEngineering

A method of forming an electronic component package includes coupling a first surface of an electronic component to a first surface of a first dielectric strip, the electronic component comprising bond pads on the first surface; forming first via apertures through the first dielectric strip to expose the bond pads; and filling the first via apertures with an electrically conductive material to form first vias electrically coupled to the bond pads. The bond pads are directly connected to the corresponding first vias without the use of a solder and without the need to form a solder wetting layer on the bond pads.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Wafer level package for very small footprint and low profile white LED devices

ActiveUS20070202623A1Low costEmission of light is minimalSolid-state devicesSemiconductor/solid-state device manufacturingSurface mountingPhosphor

A surface mount LED package having a tight footprint and small vertical image size is fabricated by a method comprising: forming light emitting diode chips each having a substrate and a plurality of layers configured to emit electroluminescence responsive to electrical energizing; forming electrical vias in a sub mount, the electrical vias passing from a front side of the sub-mount to a back-side of the sub-mount; flip chip bonding the light emitting diode chips on the front-side of the sub mount such that each light emitting diode chip electrically contacts selected electrical vias; thinning or removing the substrates of the flip-chip bonded light emitting diode chips; and after the thinning, disposing a phosphor over the flip chip bonded light emitting diode chips.

Owner:GE LIGHTING SOLUTIONS LLC

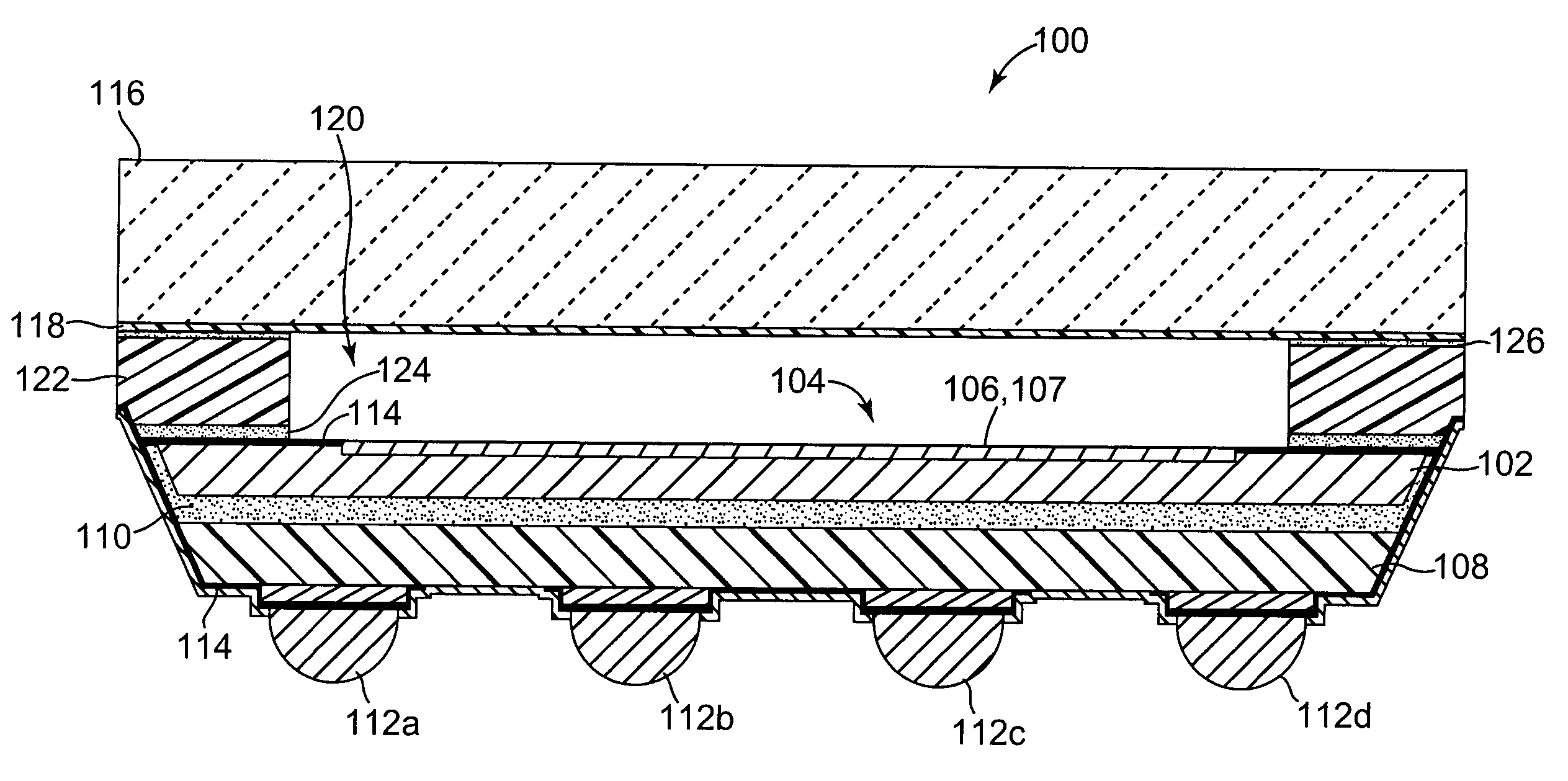

Integrally packaged imaging module

ActiveUS20050077458A1Television system detailsSemiconductor/solid-state device detailsDevice formEngineering

An integrally packaged imaging module includes an integrated circuit (IC), including an image sensing device formed on a semiconductor substrate, and wafer level packaging enclosing the IC. The wafer level packaging includes a transparent enclosure portion adapted to permit image acquisition of an image by the image sensing device over a desired range of wavelengths, and a first spacing structure providing a cavity between an inner surface of the transparent enclosure portion and the image sensing device. A depth of the cavity is configurable along an axis perpendicular to the semiconductor substrate to control a distance between an outer surface of the transparent enclosure portion and the image sensing device.

Owner:APTINA IMAGING CORP

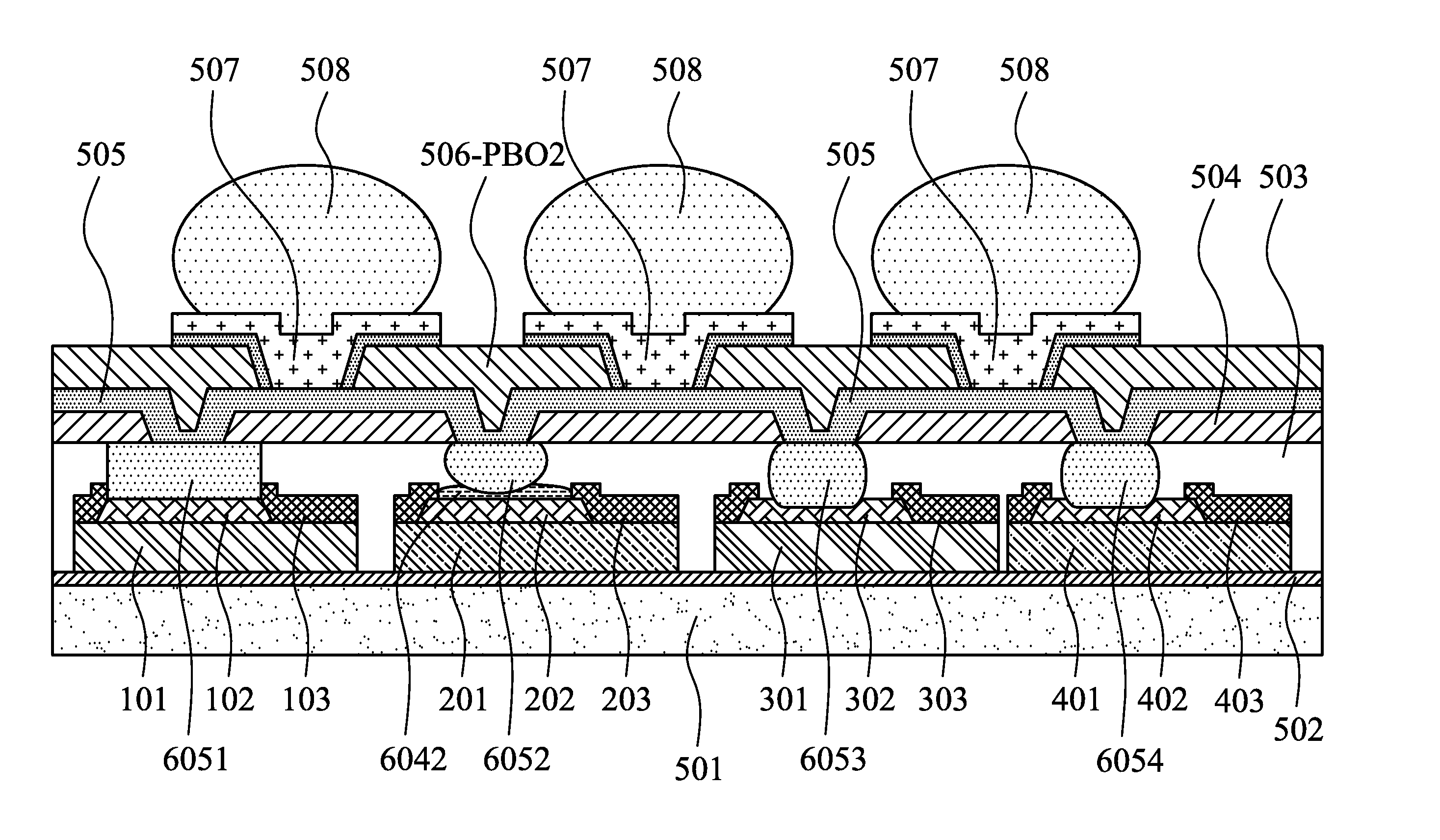

Image sensor module with a three-dimensional die-stacking structure

ActiveUS20080308928A1Image degradationShorten connection lengthSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionConductive materials

This invention provides an image sensor module with a three-dimensional die-stacking structure. By filling a conductive material into through silicon vias within at least one image sensor die, and into via holes within an insulating layer, vertical electrical connections are formed between the image sensor die and an image processor buried in the insulating layer. A plurality of solder bumps is formed on a backside of the image sensor module so that the module can be directly assembled onto a circuit board. The image sensor module of this invention is characterized by a wafer-level packaging architecture and a three-dimensional die-stacking structure, which reduces electrical connection lengths within the module and thus reduces an area and height of the whole packaged module.

Owner:IND TECH RES INST

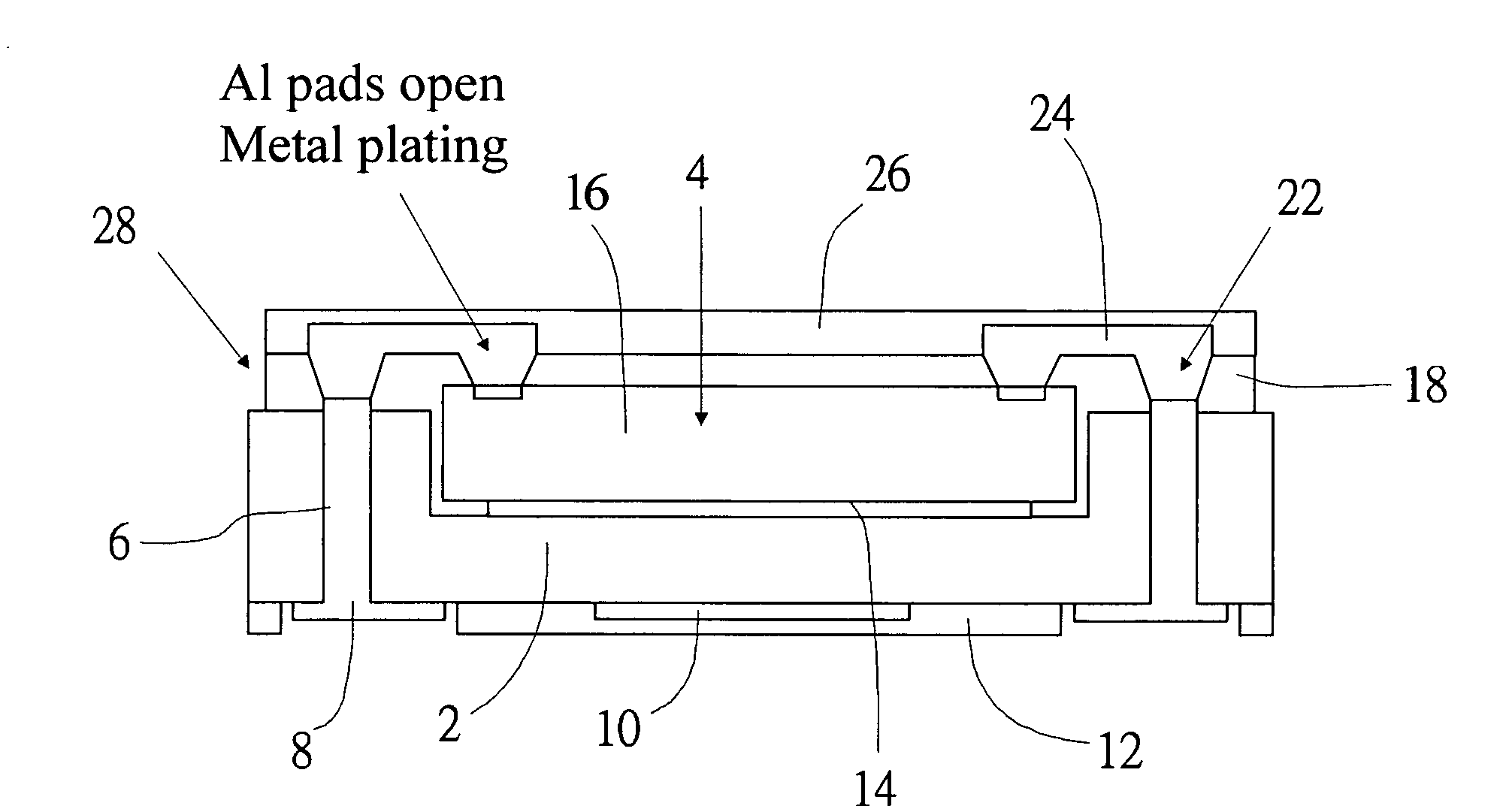

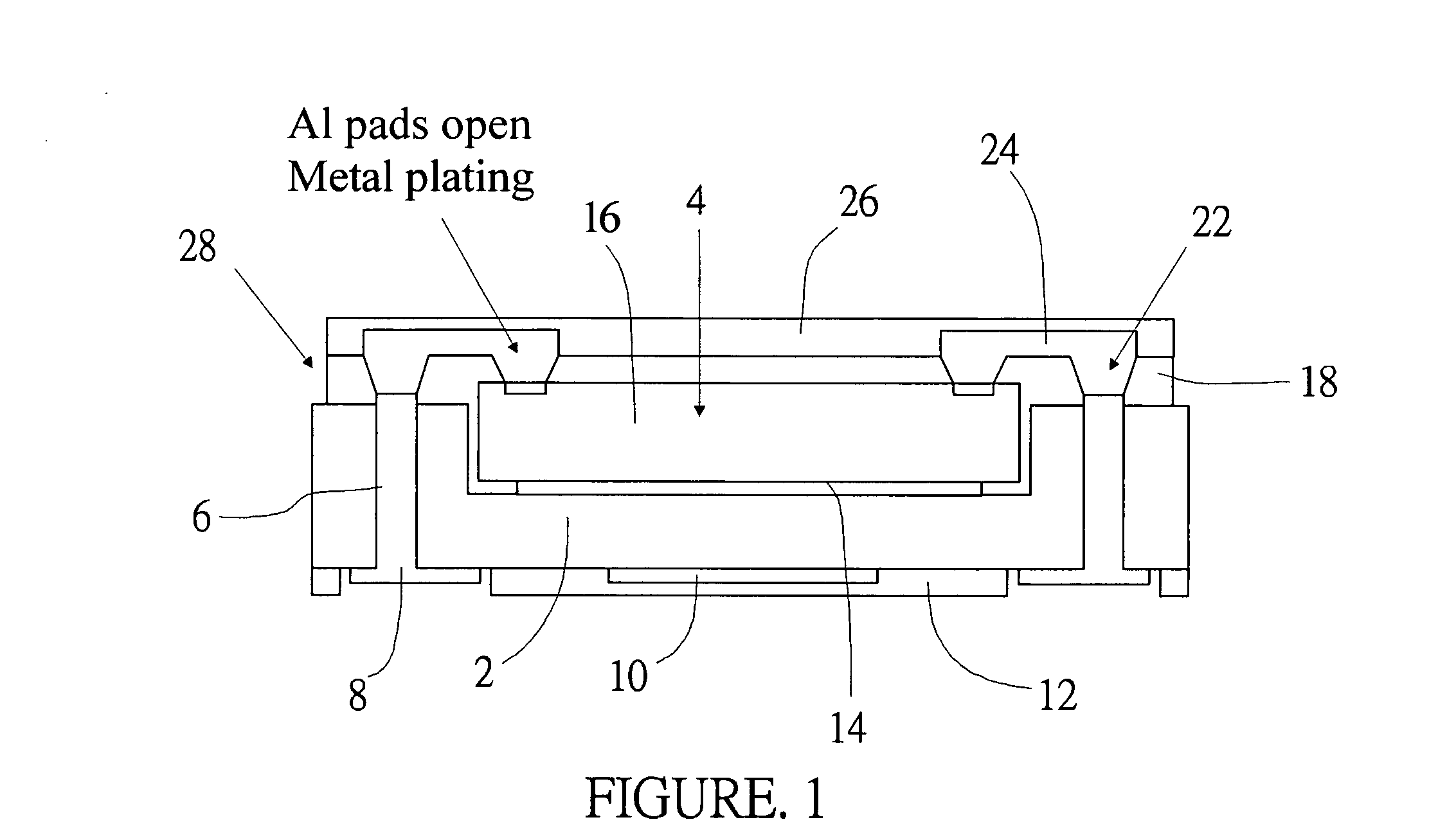

Structure for Electrostatic Discharge in Embedded Wafer Level Packages

ActiveUS20080265421A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A workpiece has at least two semiconductor chips, each semiconductor chip having a first main surface, which is at least partially exposed, and a second main surface. The workpiece also comprises an electrically conducting layer, arranged on the at least two semiconductor chips, the electrically conducting layer being arranged at least on regions of the second main surface, and a molding compound, arranged on the electrically conducting layer.

Owner:TAHOE RES LTD

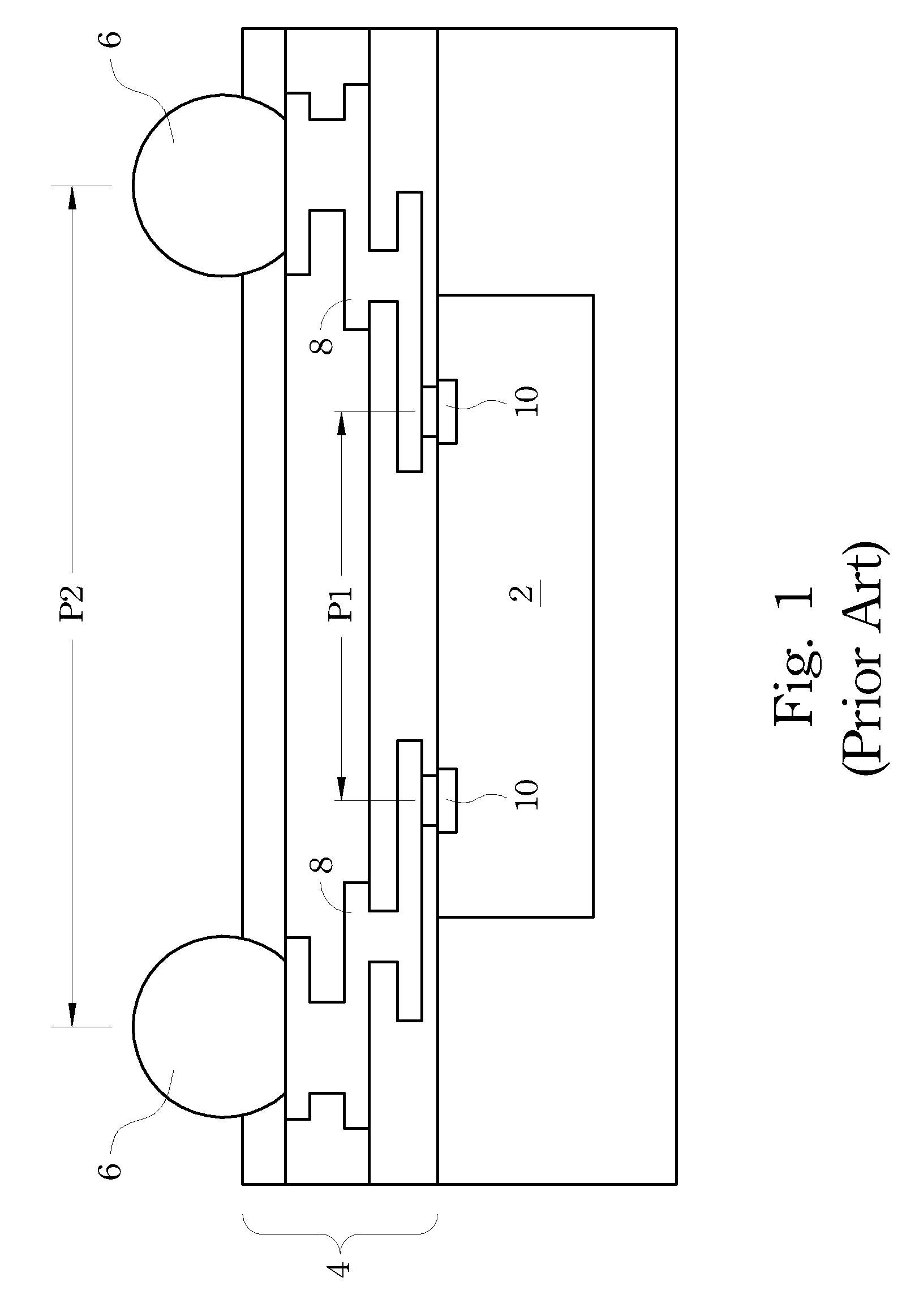

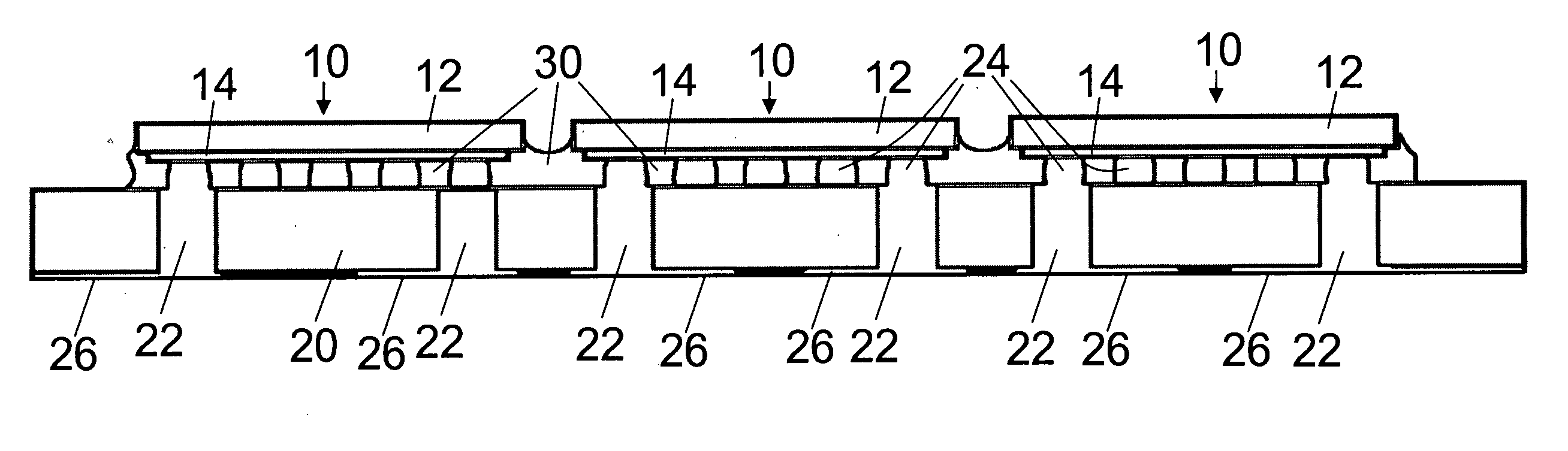

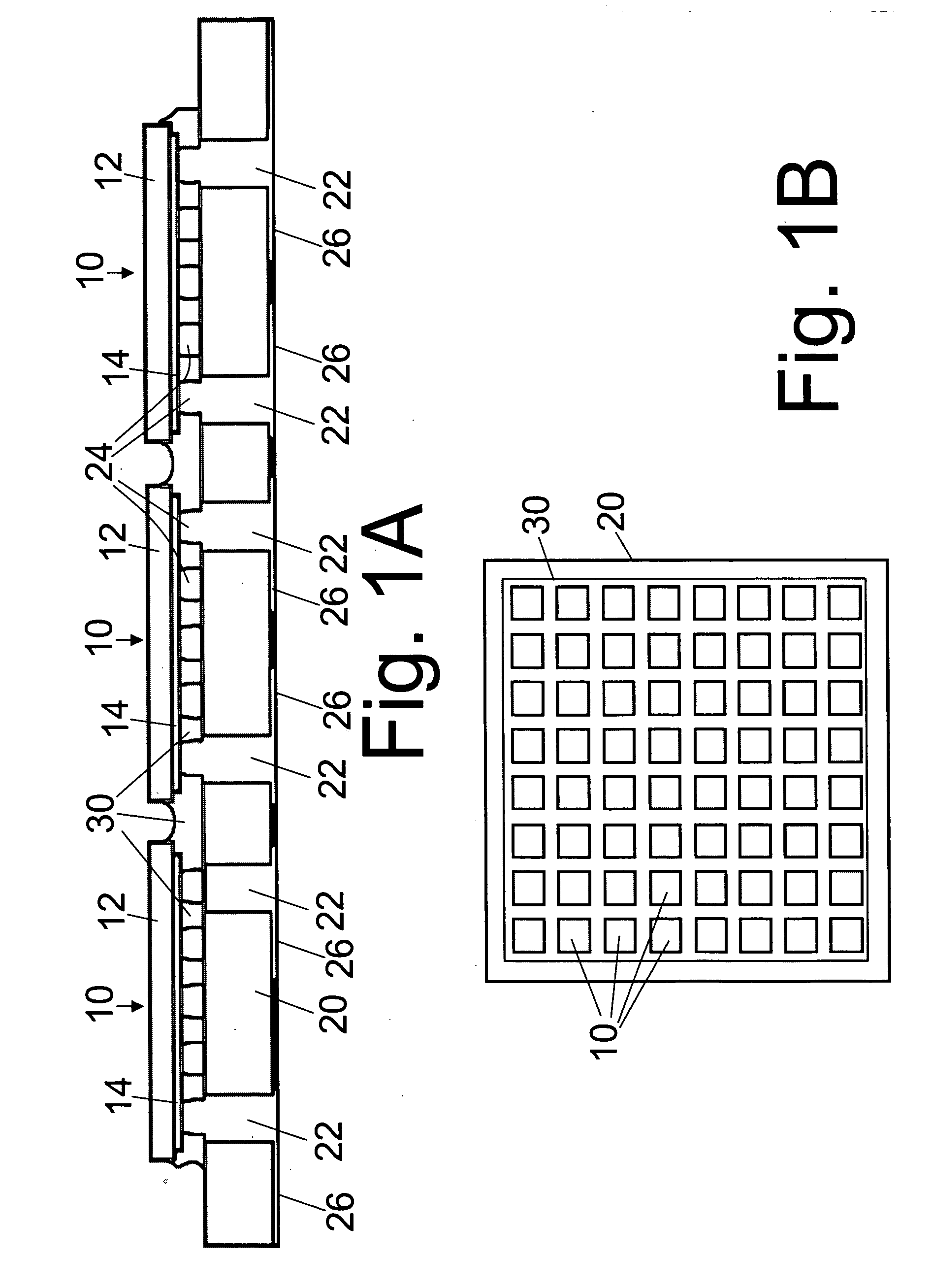

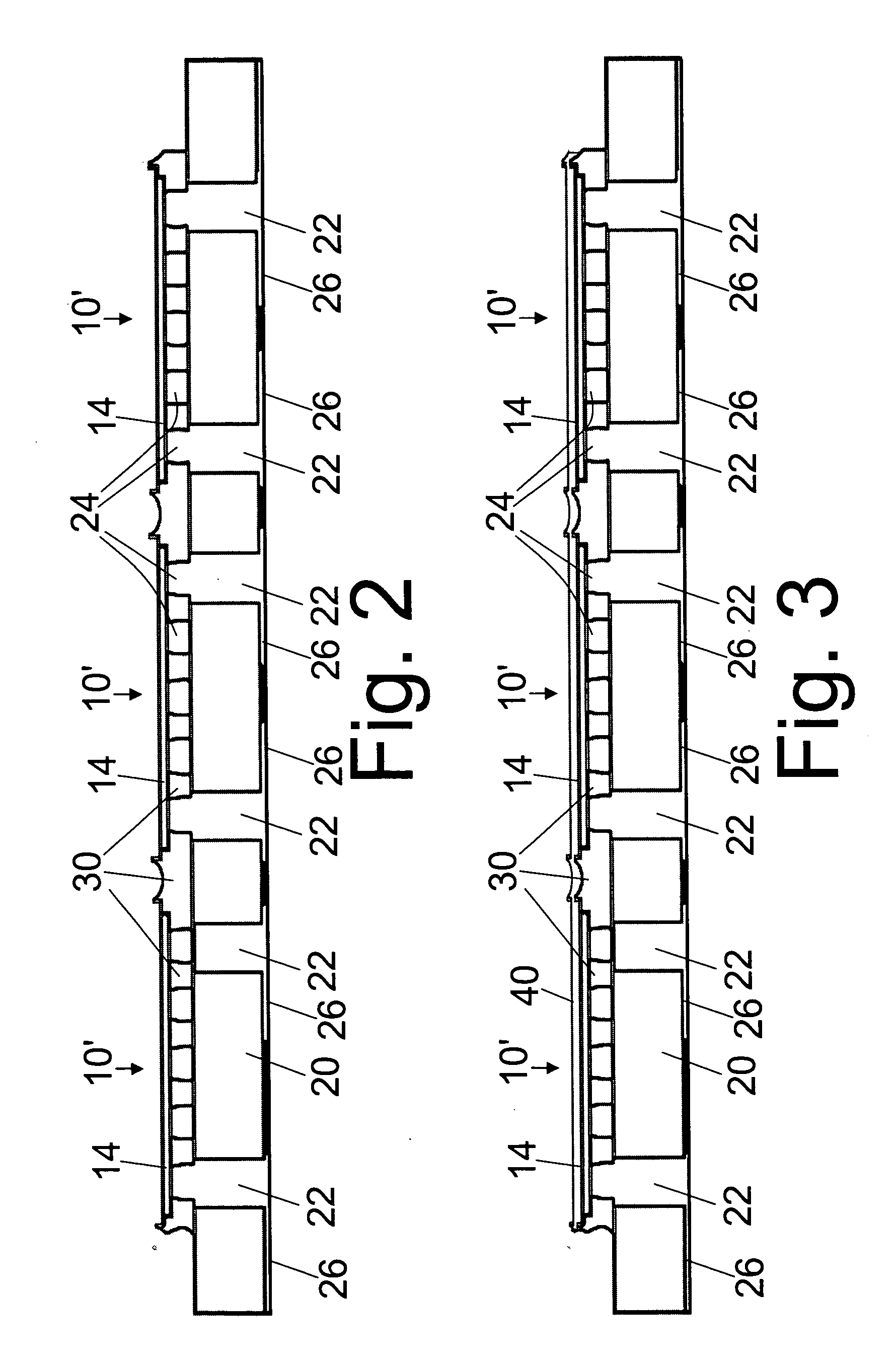

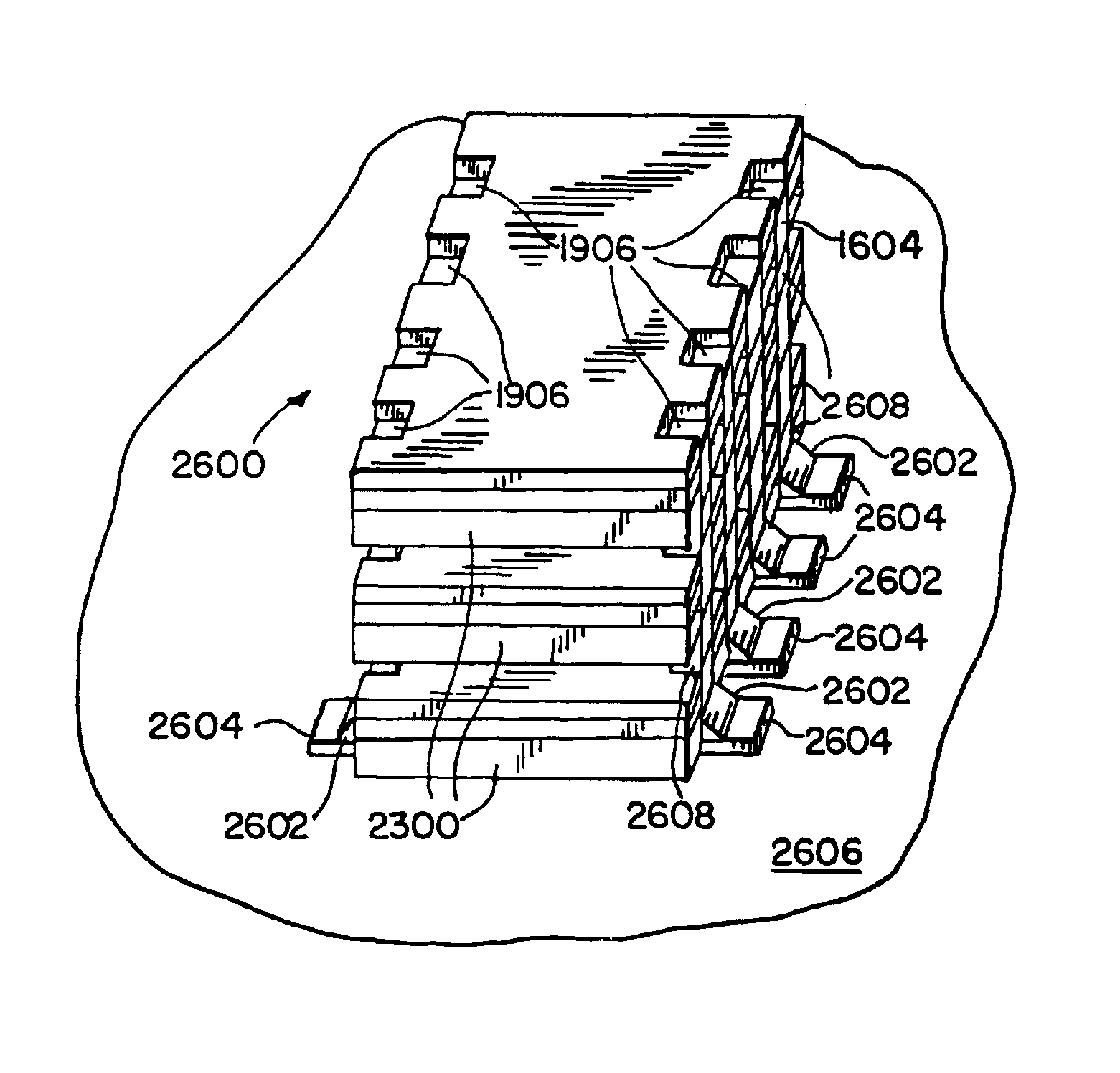

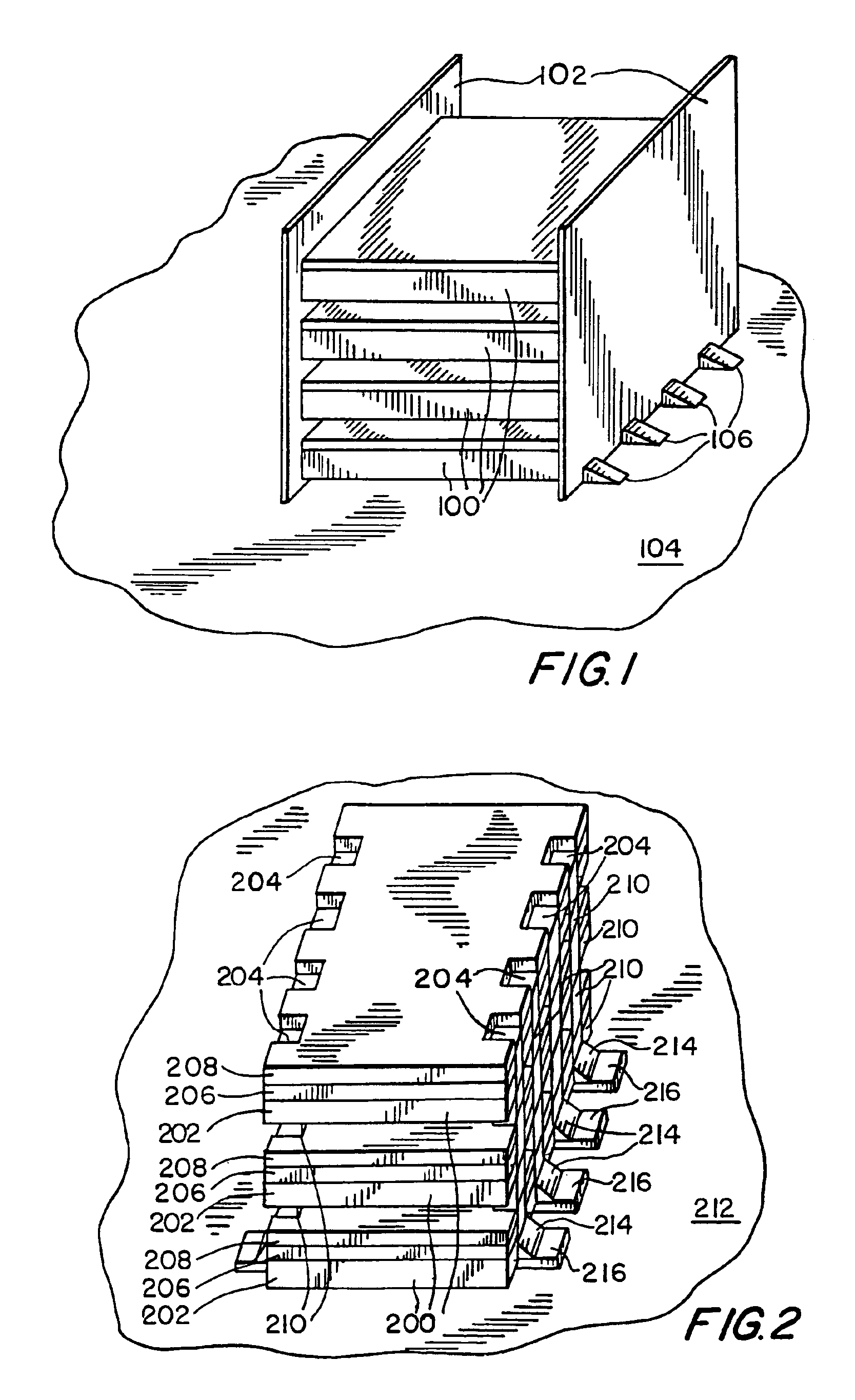

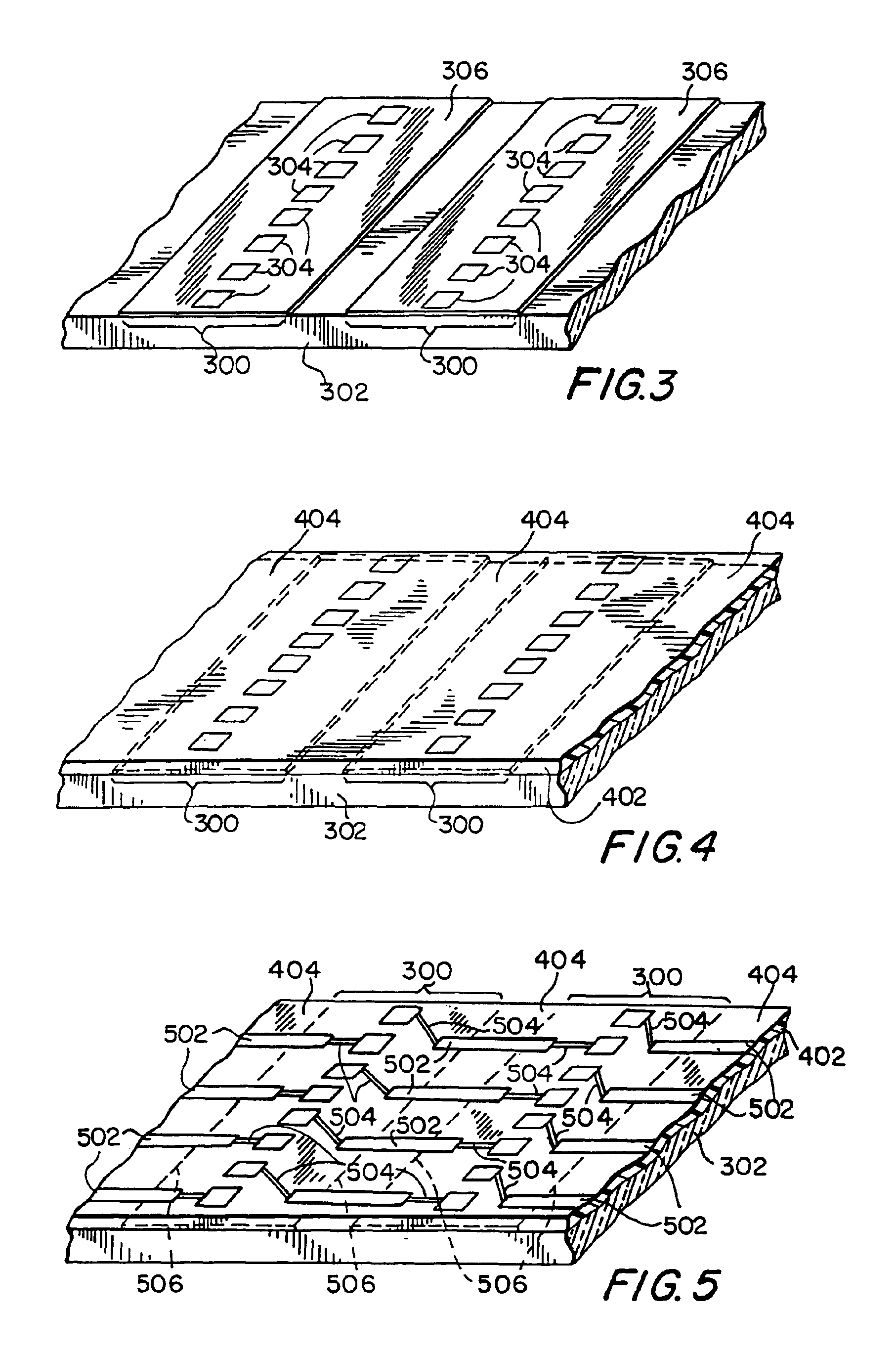

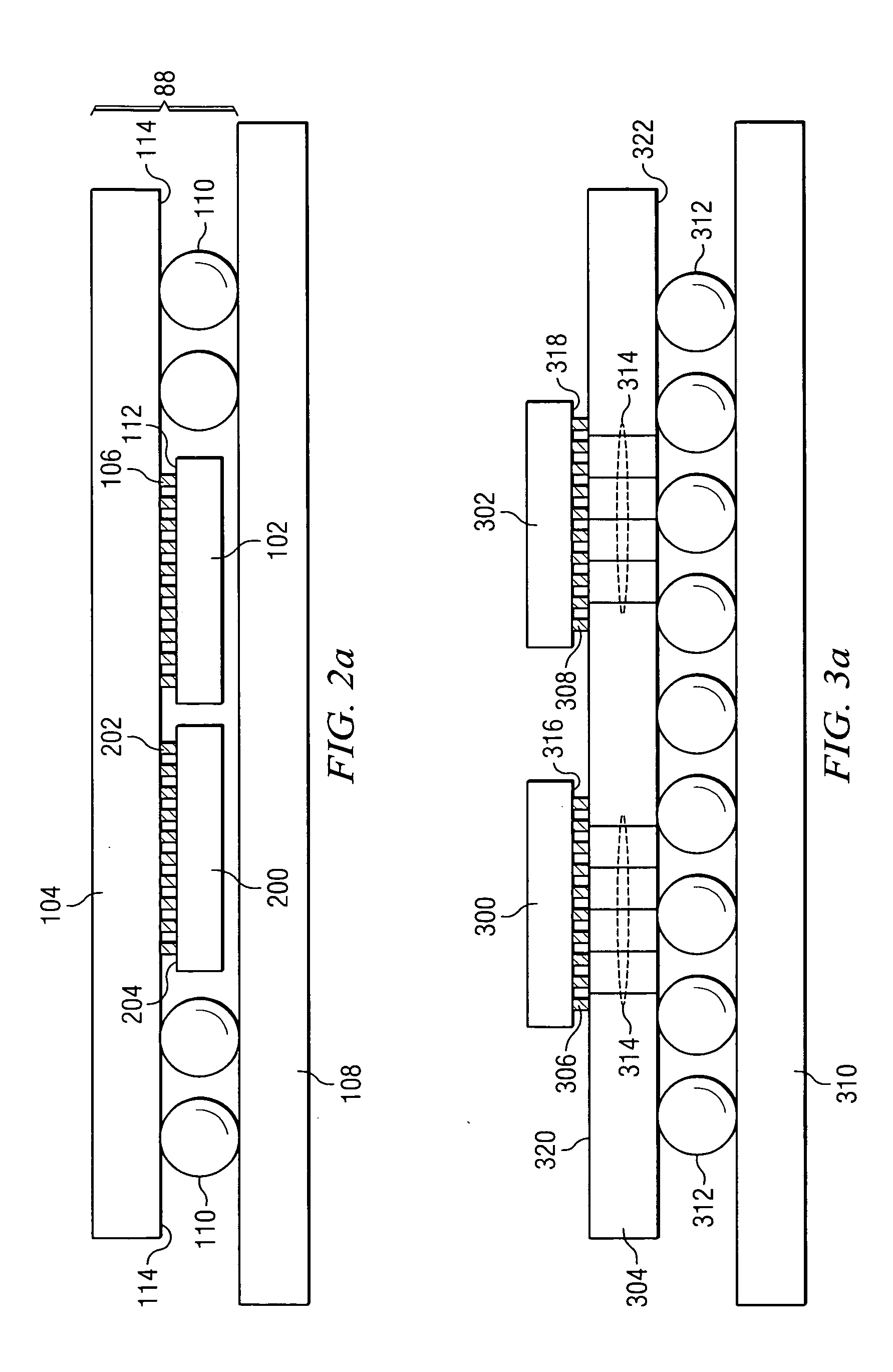

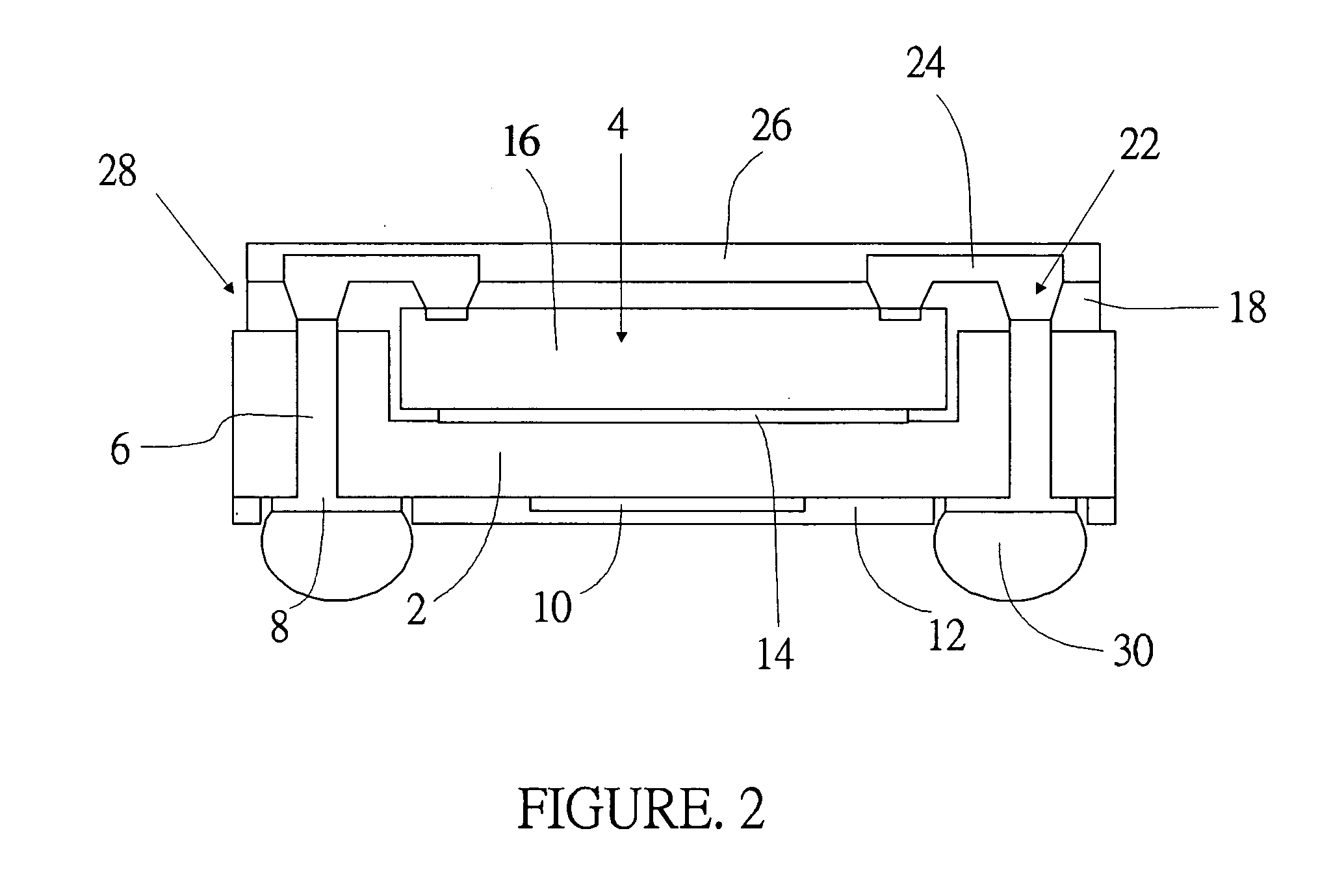

Castellation wafer level packaging of integrated circuit chips

InactiveUS6855572B2Characteristic is reliableEasy to produceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSealant

Systems and methods for packaging integrated circuit chips in castellation wafer level packaging are provided. The active circuit areas of the chips are coupled to castellation blocks and, depending on the embodiment, input / output pads. The castellation blocks and input / output pads are encapsulated and held in place by an encapsulant. When the devices are being fabricated, the castellation blocks and input / output pads are sawed through. If necessary, the wafer portion on which the devices are fabricated may be thinned. The packages may be used as a leadless chip carrier package or may be stacked on top of one another. When stacked, the respective contacts of the packages are preferably coupled. Data may be written to, and received from, packaged chips when a chip is activated. Chips may be activated by applying the appropriate signal or signals to the appropriate contact or contacts.

Owner:MICRON TECH INC

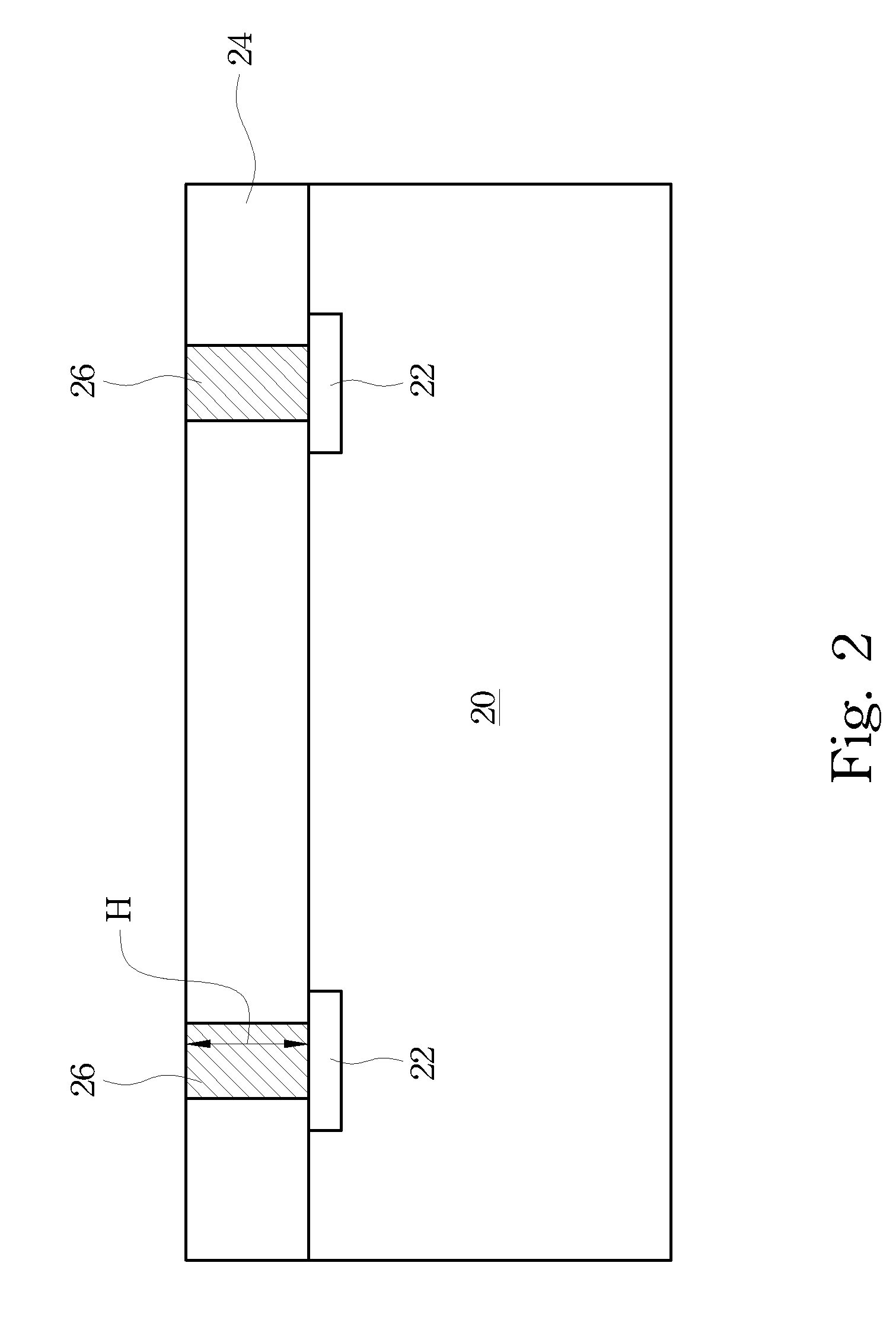

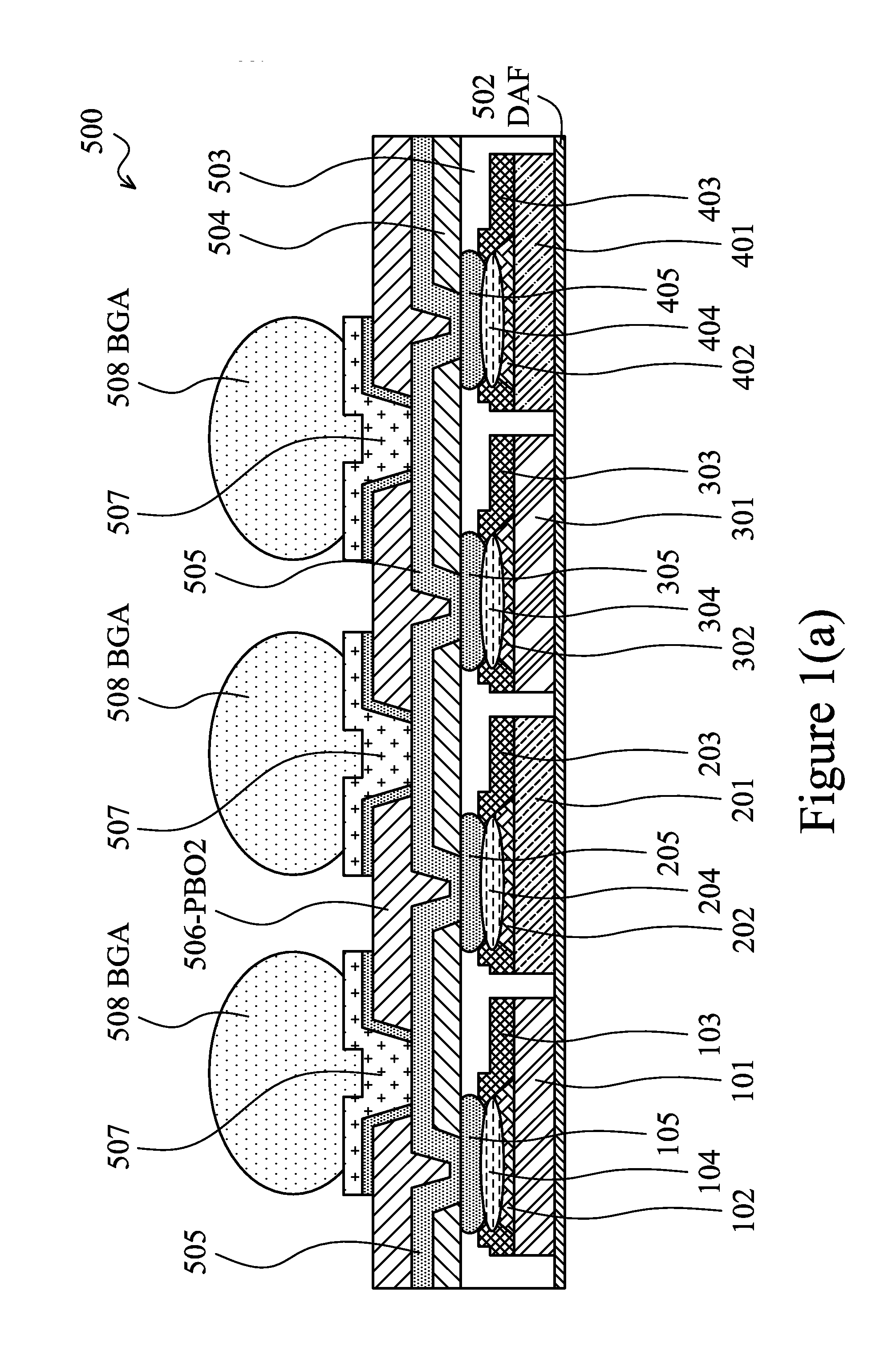

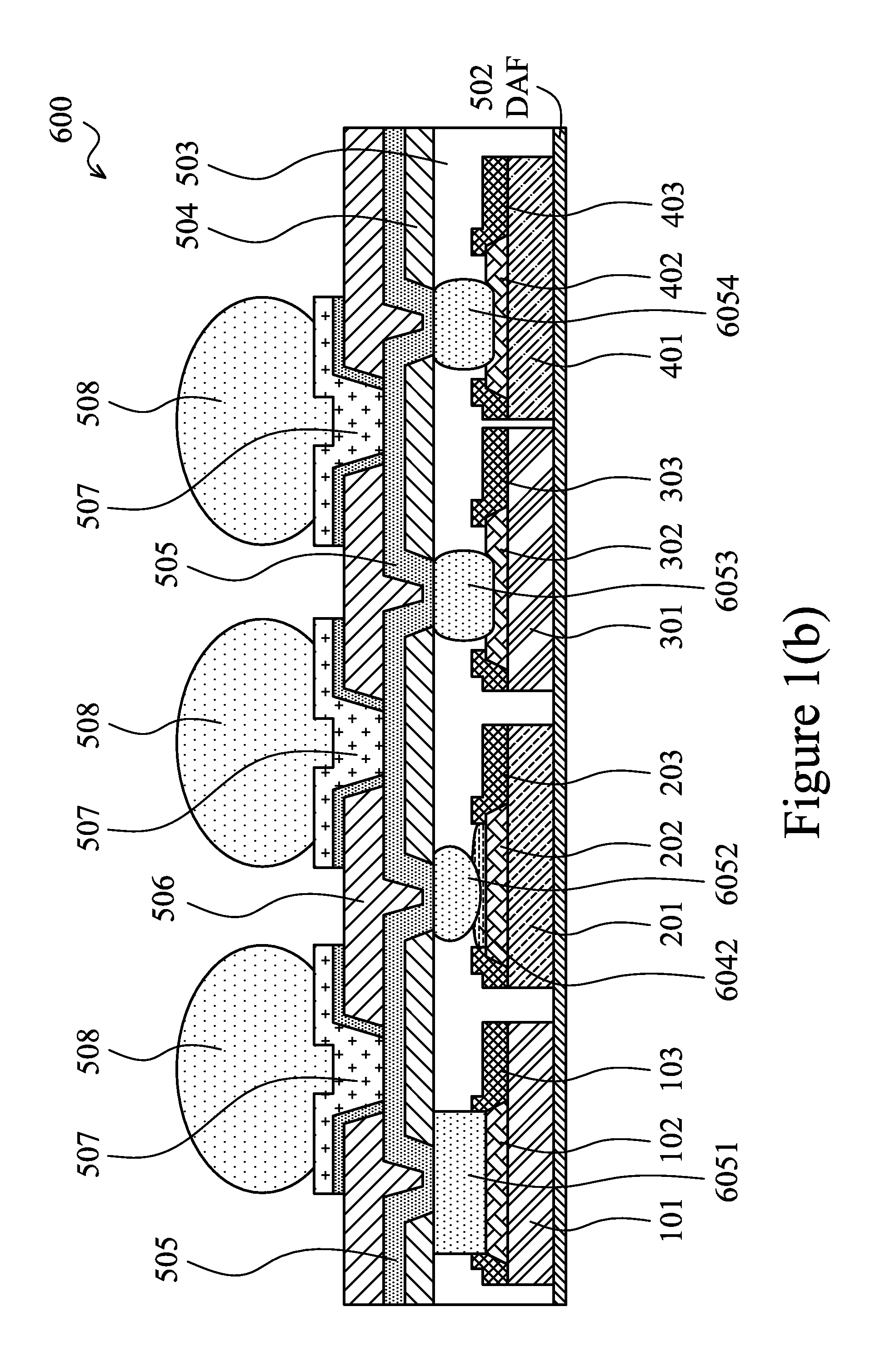

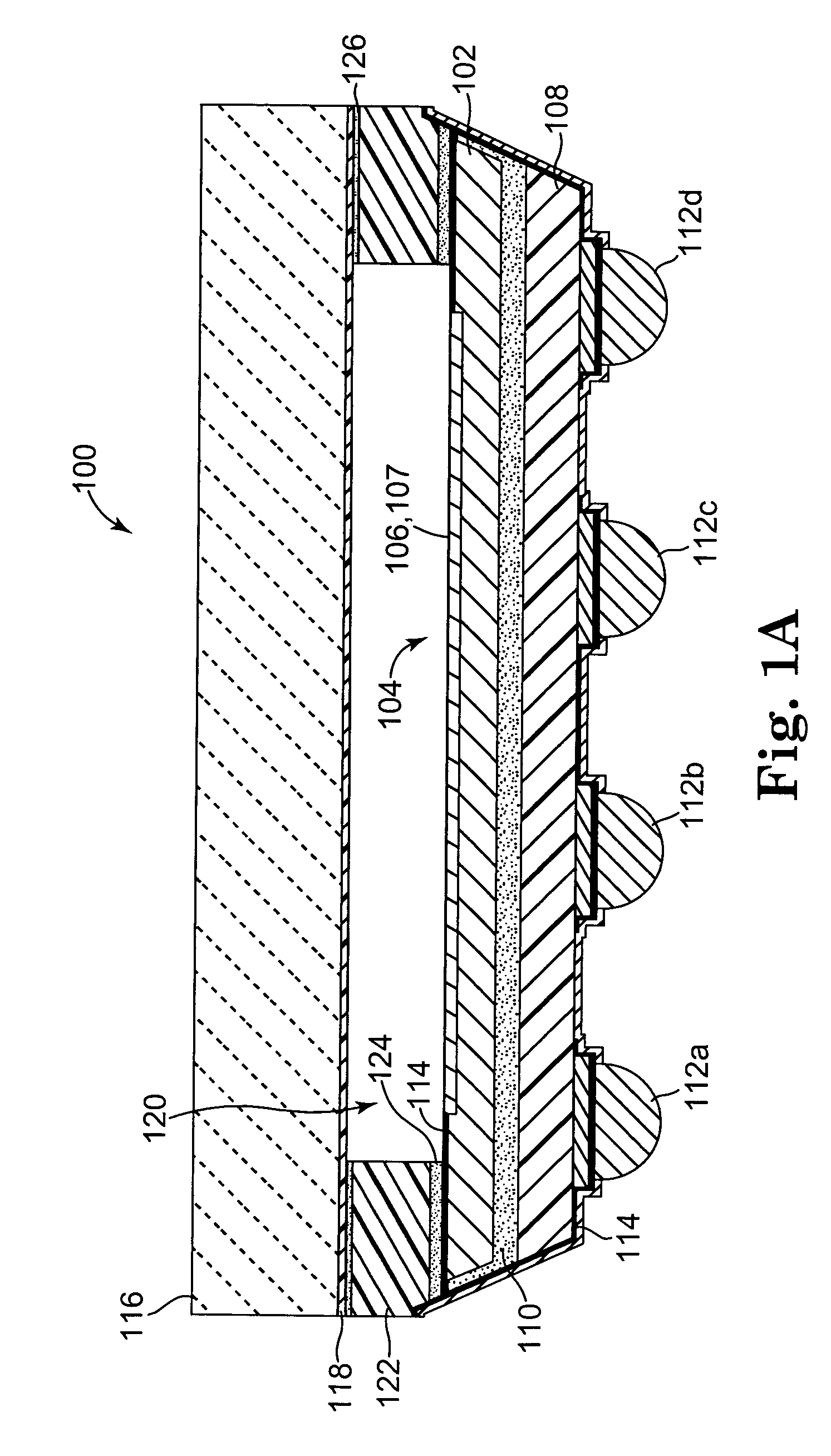

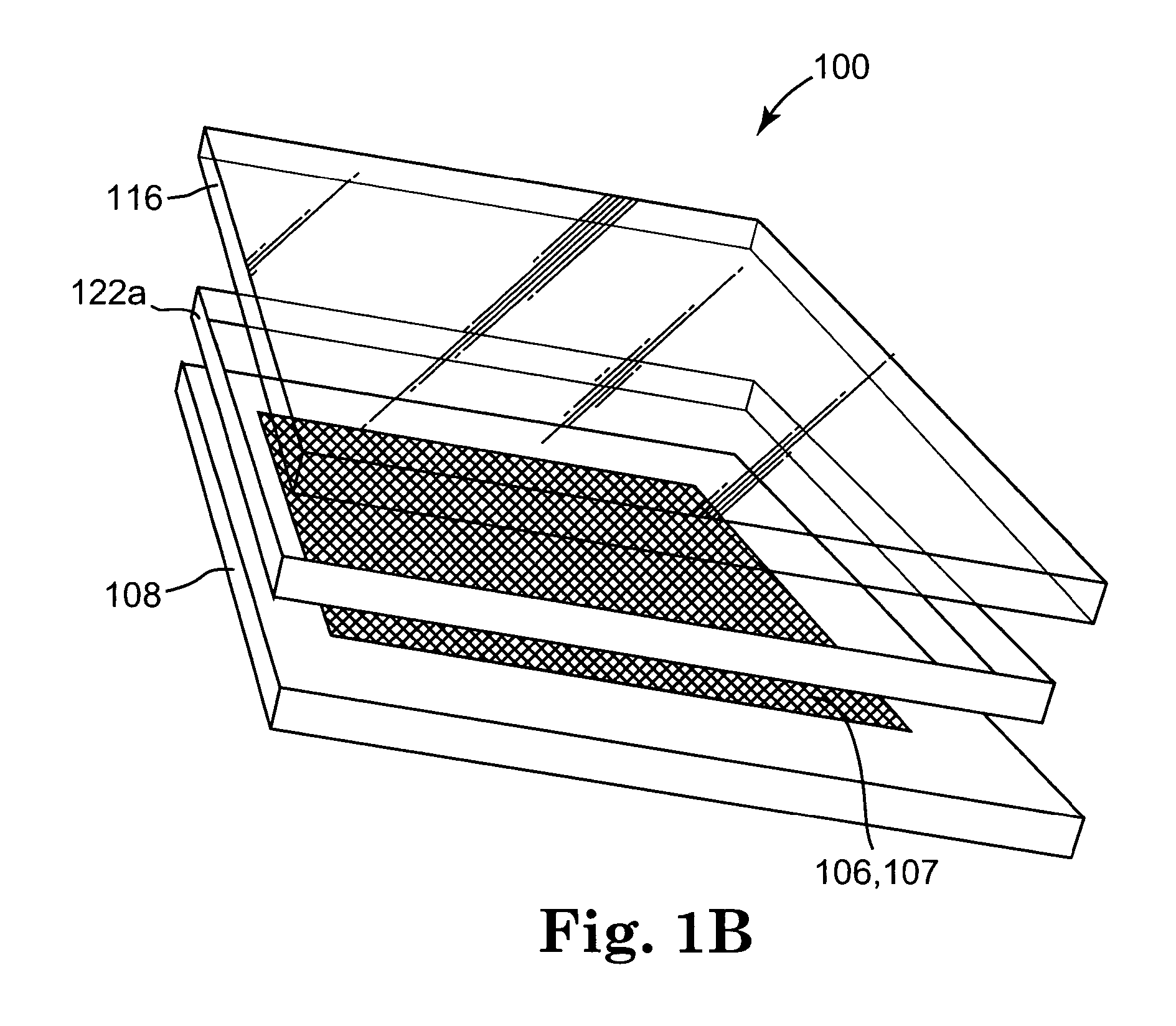

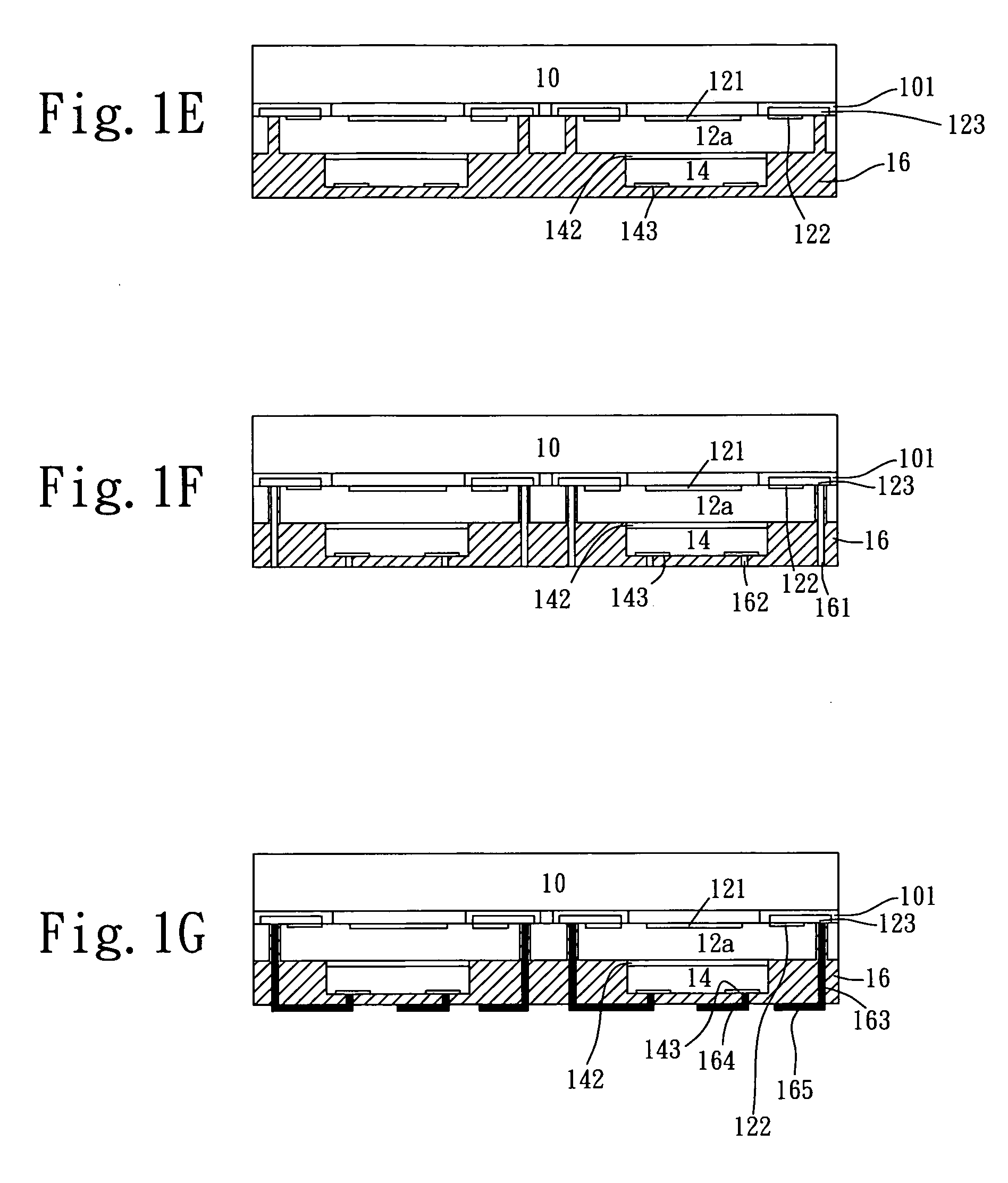

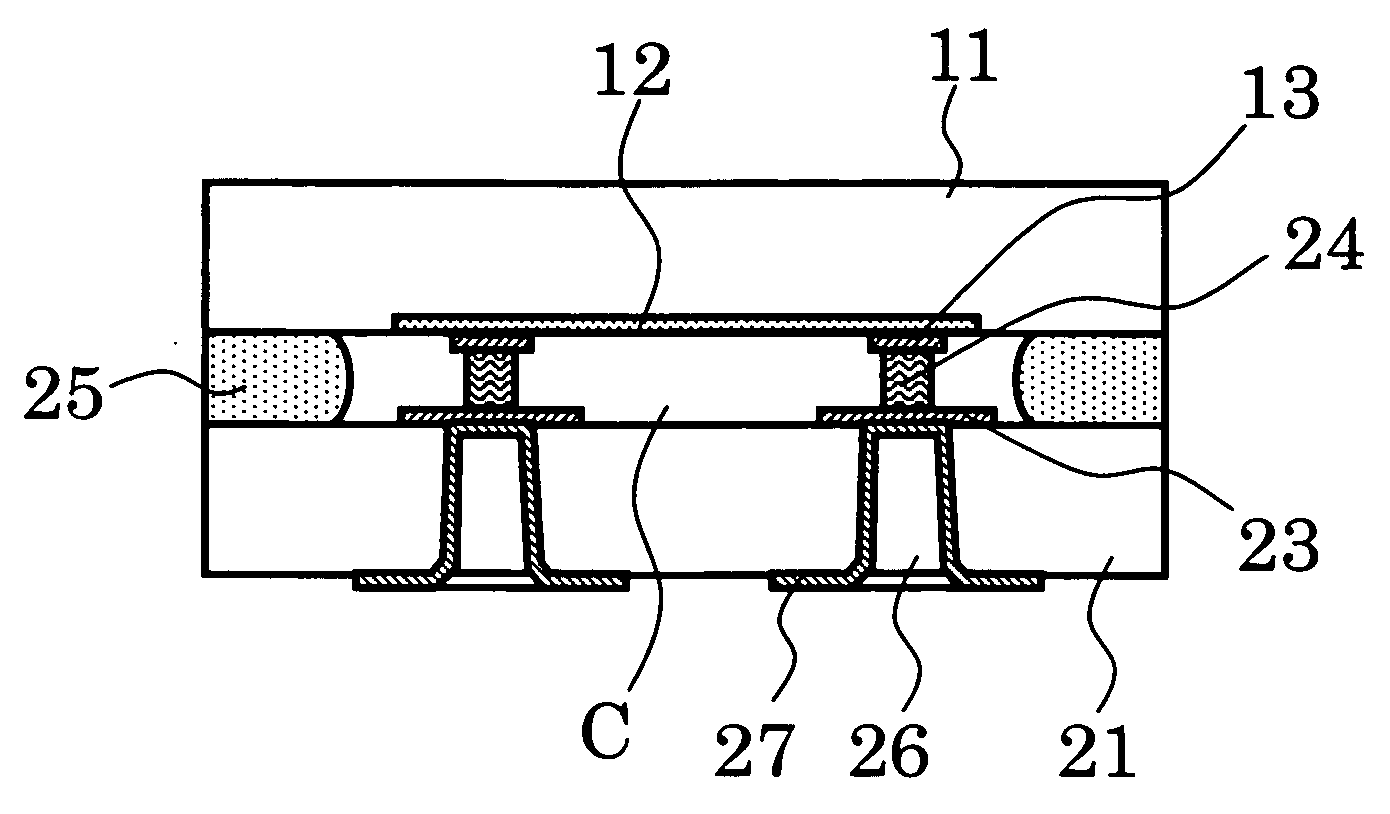

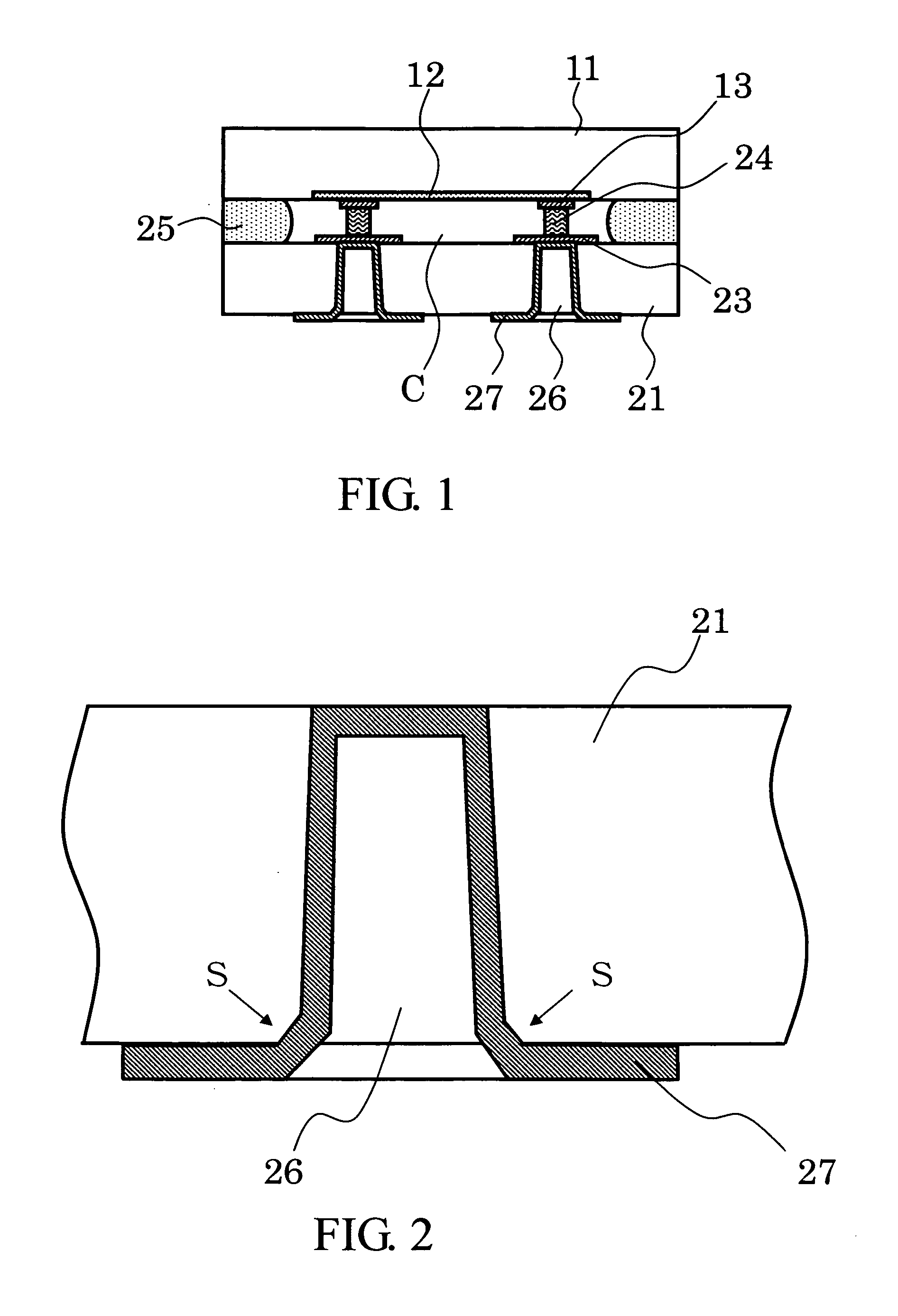

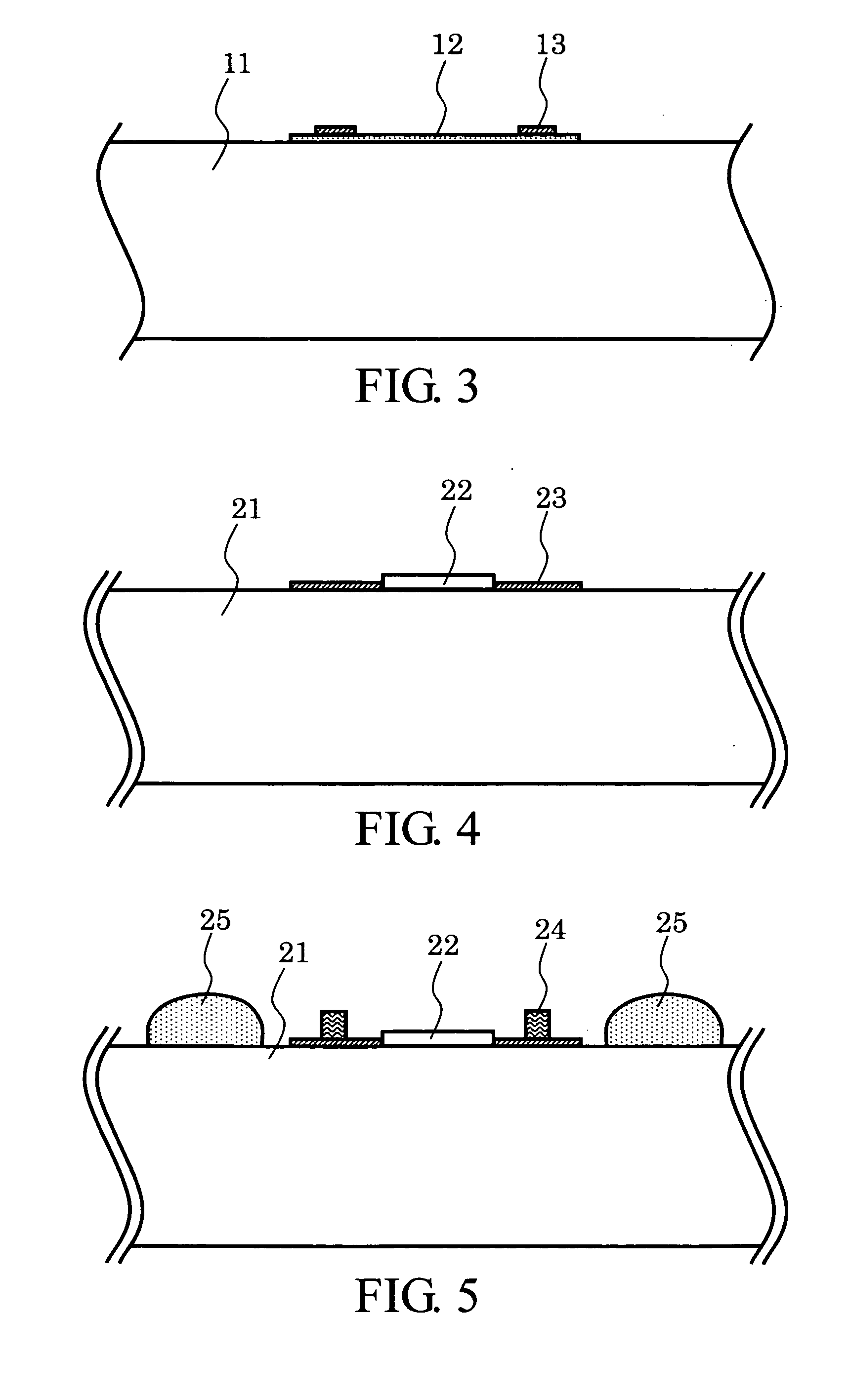

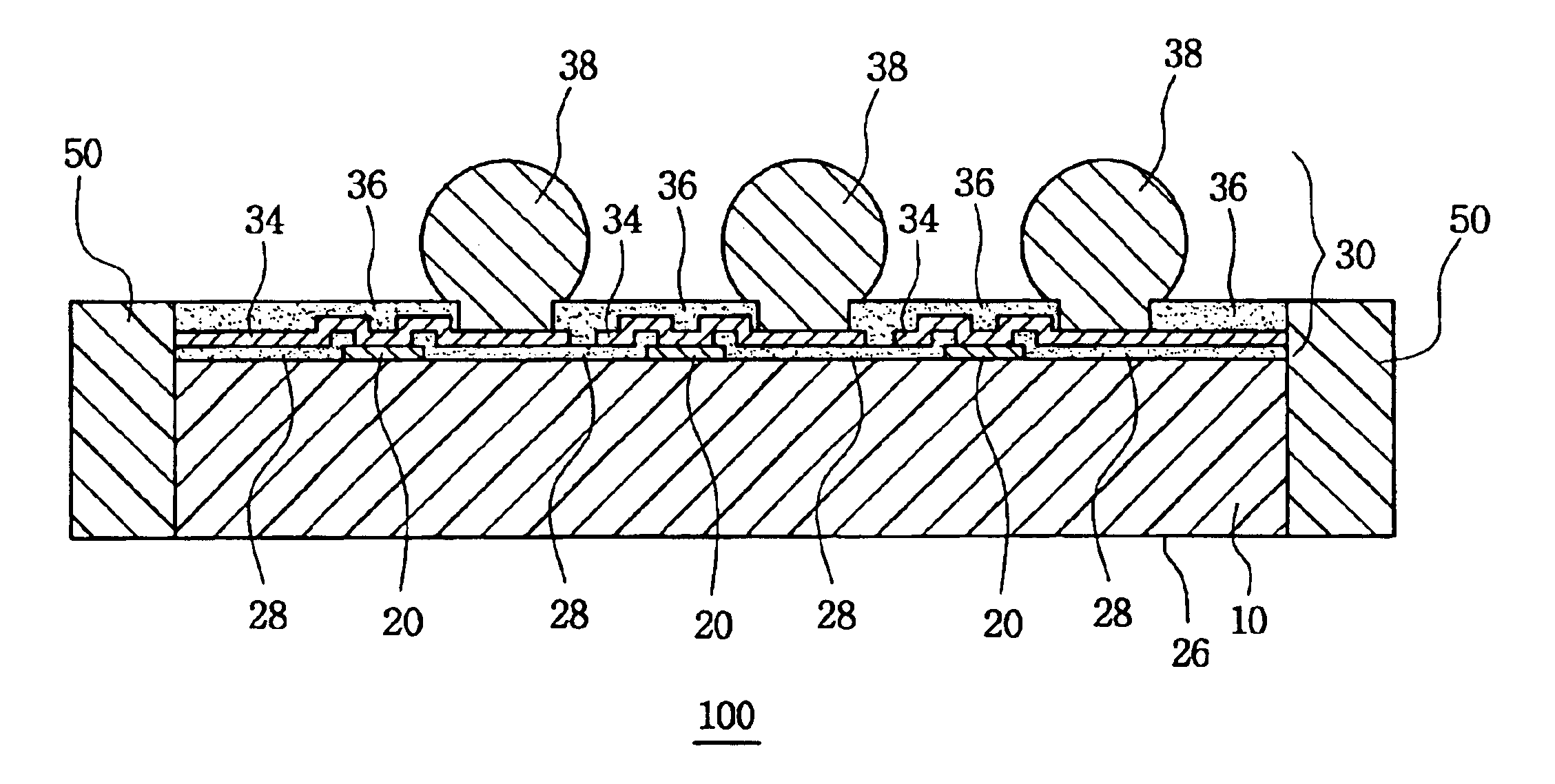

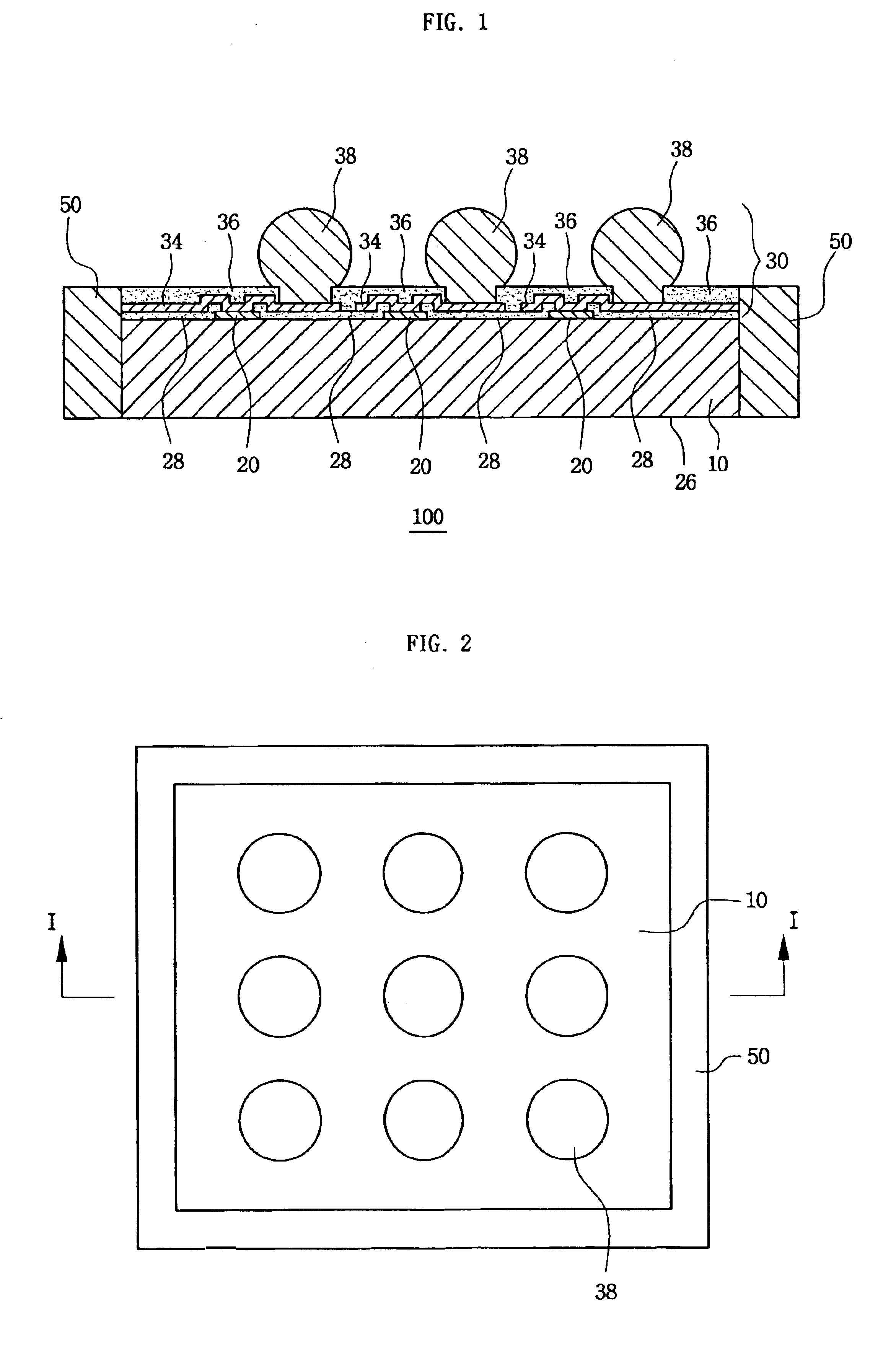

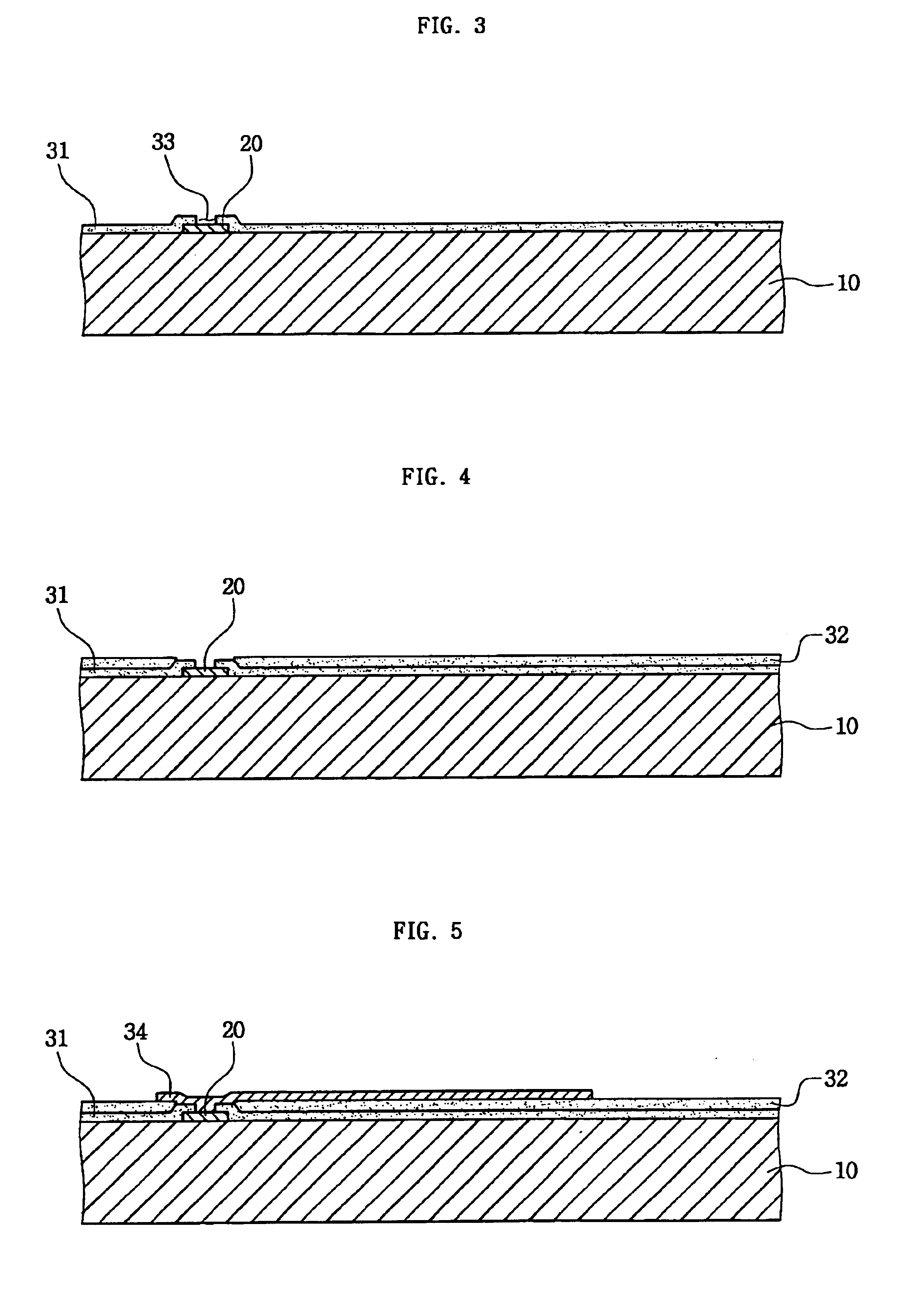

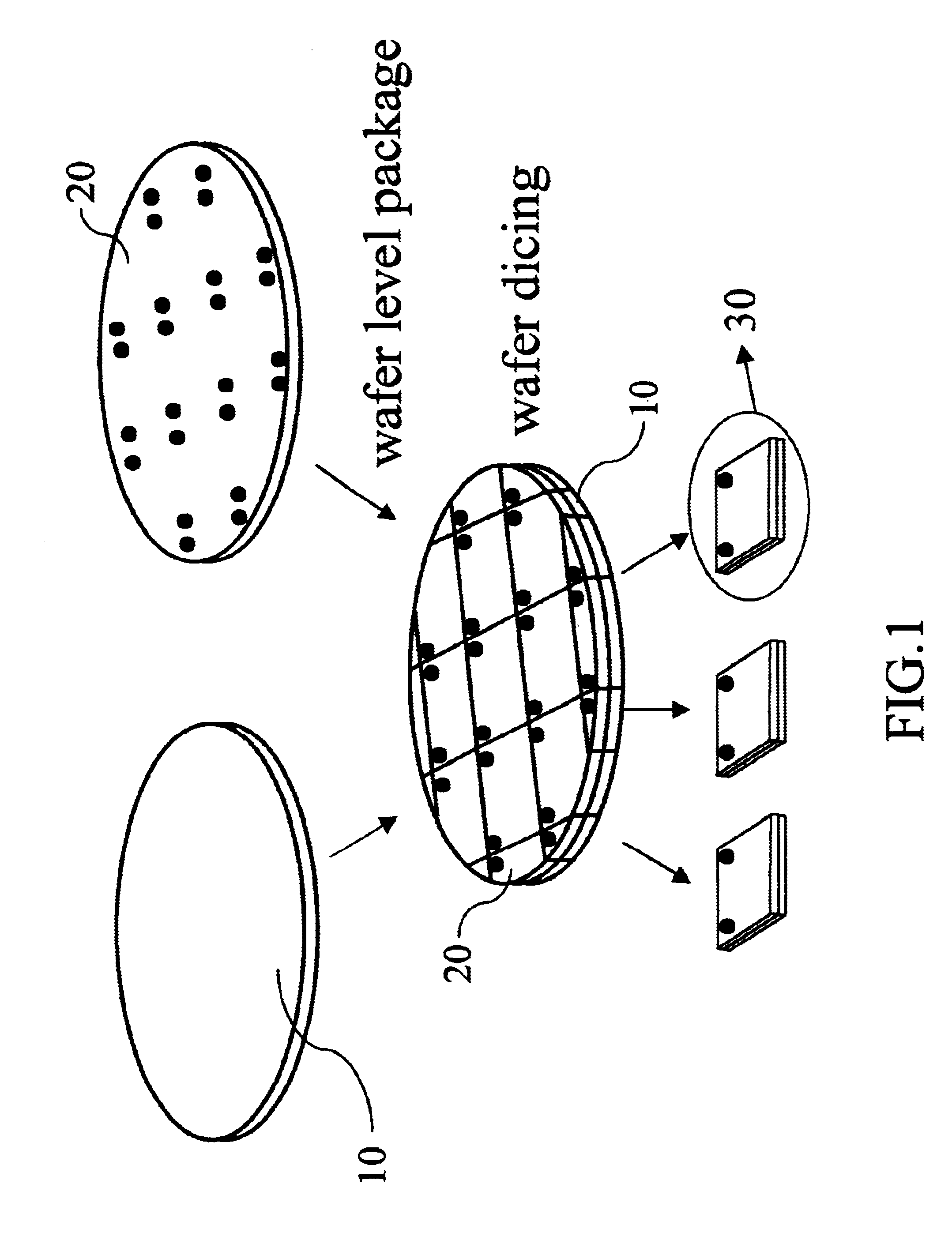

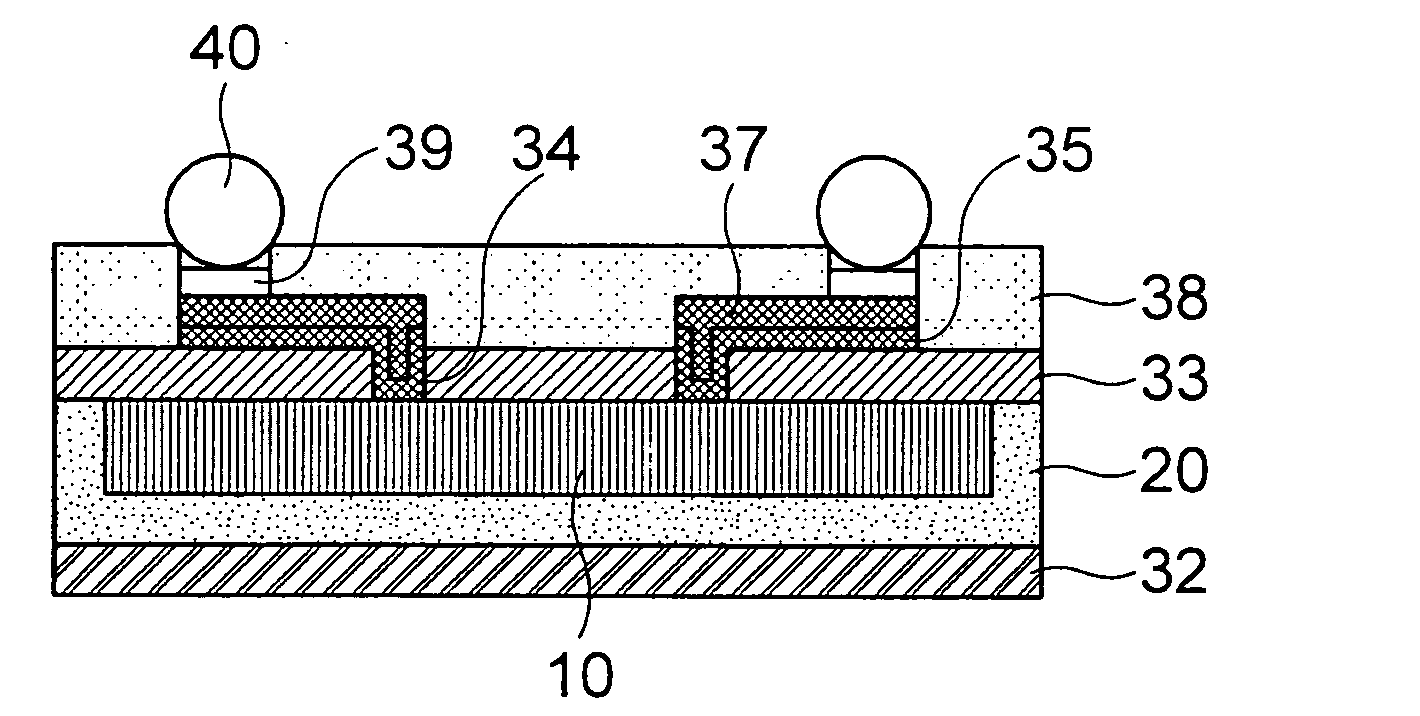

Wafer level package structure and the fabrication method thereof

ActiveUS20130037935A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipConductive materials

The present invention relates to a package for semiconductor device and the fabrication method for integrally encapsulating a whole semiconductor chip within a molding compound. In the semicondcutor device package, bonding pads distributed on the top of the chip are redistributed into an array of redistributed bonding pads located in an dielectric layer by utilizing the redistribution technique. The electrodes or signal terminals on the top of the semiconductor chip are connected to an electrode metal segment on the bottom of the chip by conductive materials filled in through holes formed in a silicon substrate of a semiconductor wafer. Furthermore, the top molding portion and the bottom molding portion seal the semiconductor chip completely, thus providing optimum mechanical and electrical protections.

Owner:ALPHA & OMEGA SEMICON INC

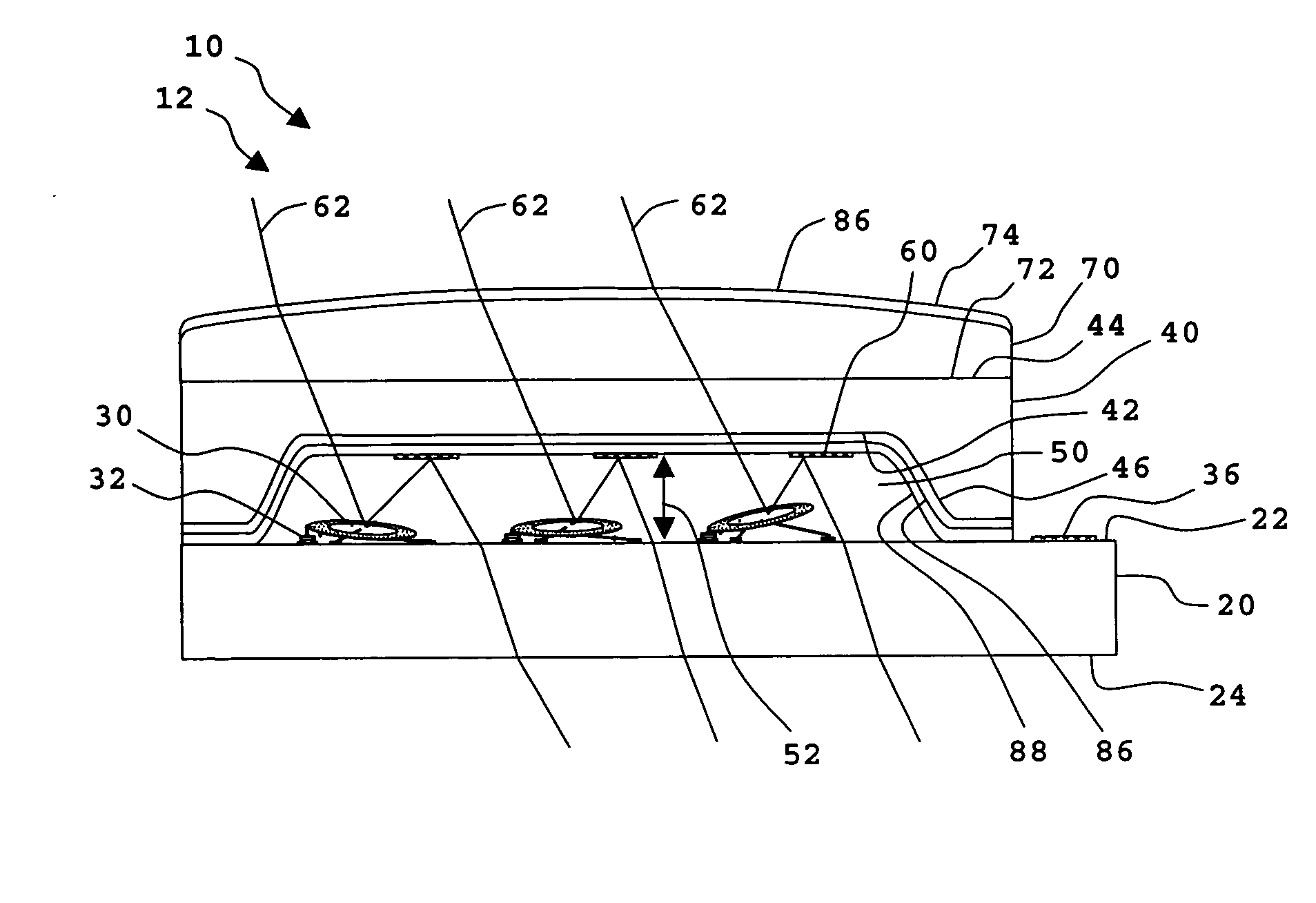

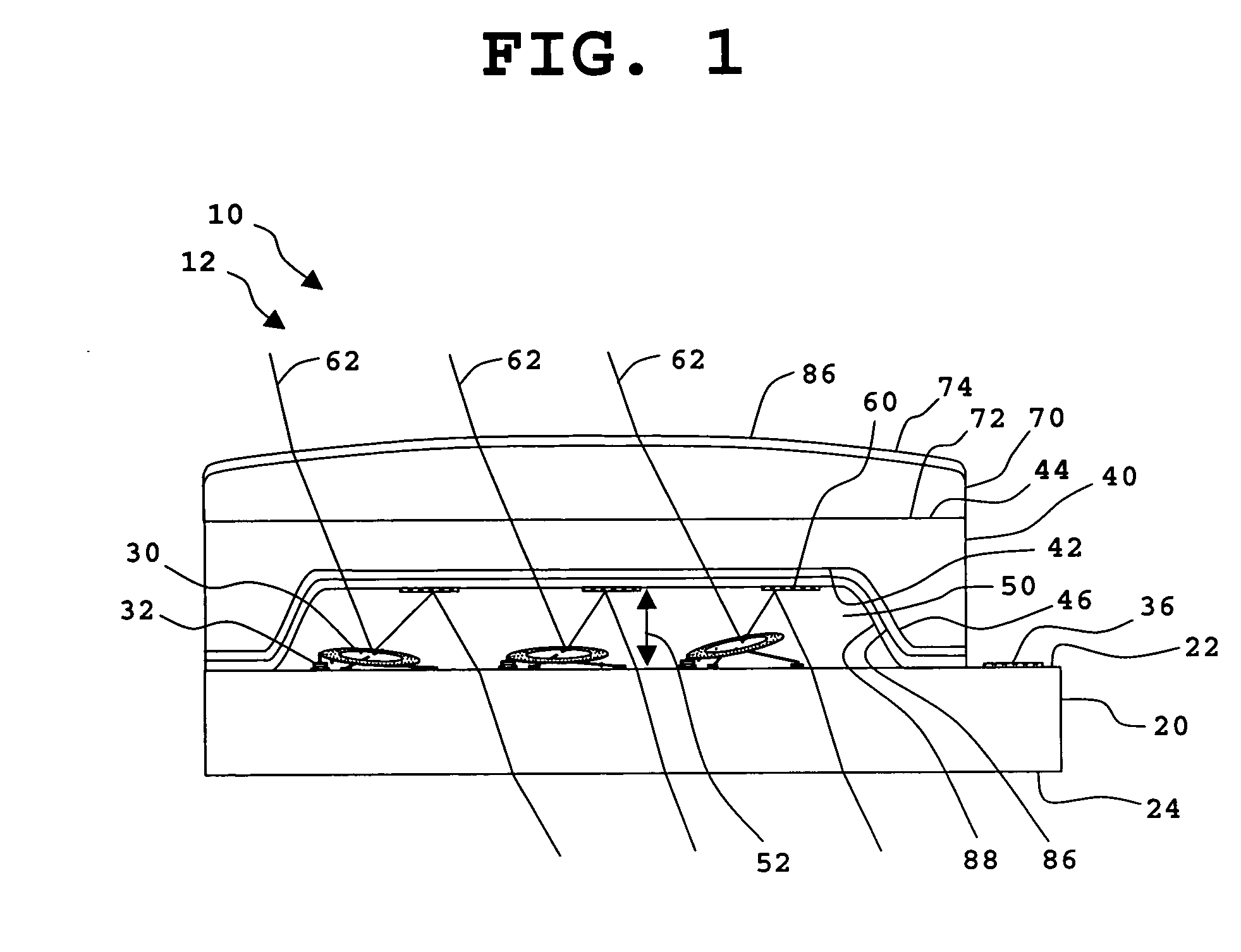

Large cavity wafer-level package for MEMS

InactiveUS20050184304A1Forming microstructural systemsMicrostructural device manufactureMicromirror arraySubstrate surface

The invention provides a wafer-level package for a micromirror array. The wafer-level package includes a substrate including a wafer having a substrate surface with a plurality of actuatable micromirrors coupled to the substrate surface. An optical window is attached to the substrate surface to form at least one sealed cavity between an inner surface of the optical window and the substrate surface. A beam of light transmitted through the optical window is redirected by at least one actuatable micromirror within the sealed cavity.

Owner:NANOGEAR

Apparatus and methods for encapsulating microelectromechanical (MEM) devices on a wafer scale

InactiveUS20060108675A1Reduce pressureSemiconductor/solid-state device detailsSolid-state devicesWaferingEngineering physics

Apparatus and methods are provided for enabling wafer-scale encapsulation of microelectromechanical (MEM) devices (e.g., resonators, filters) to protect the MEMs from the ambient and to provide either a controlled ambient or a reduced pressure. In particular, methods for wafer-scale encapsulation of MEM devices are provided, which enable encapsulation of MEM devices under desired ambient conditions that are not determined by the deposition conditions of a sealing process in which MEM release via holes are sealed or pinched-off, and which prevent sealing material from being inadvertently deposited on the MEM device during the sealing process.

Owner:IBM CORP

Wafer level packaging method

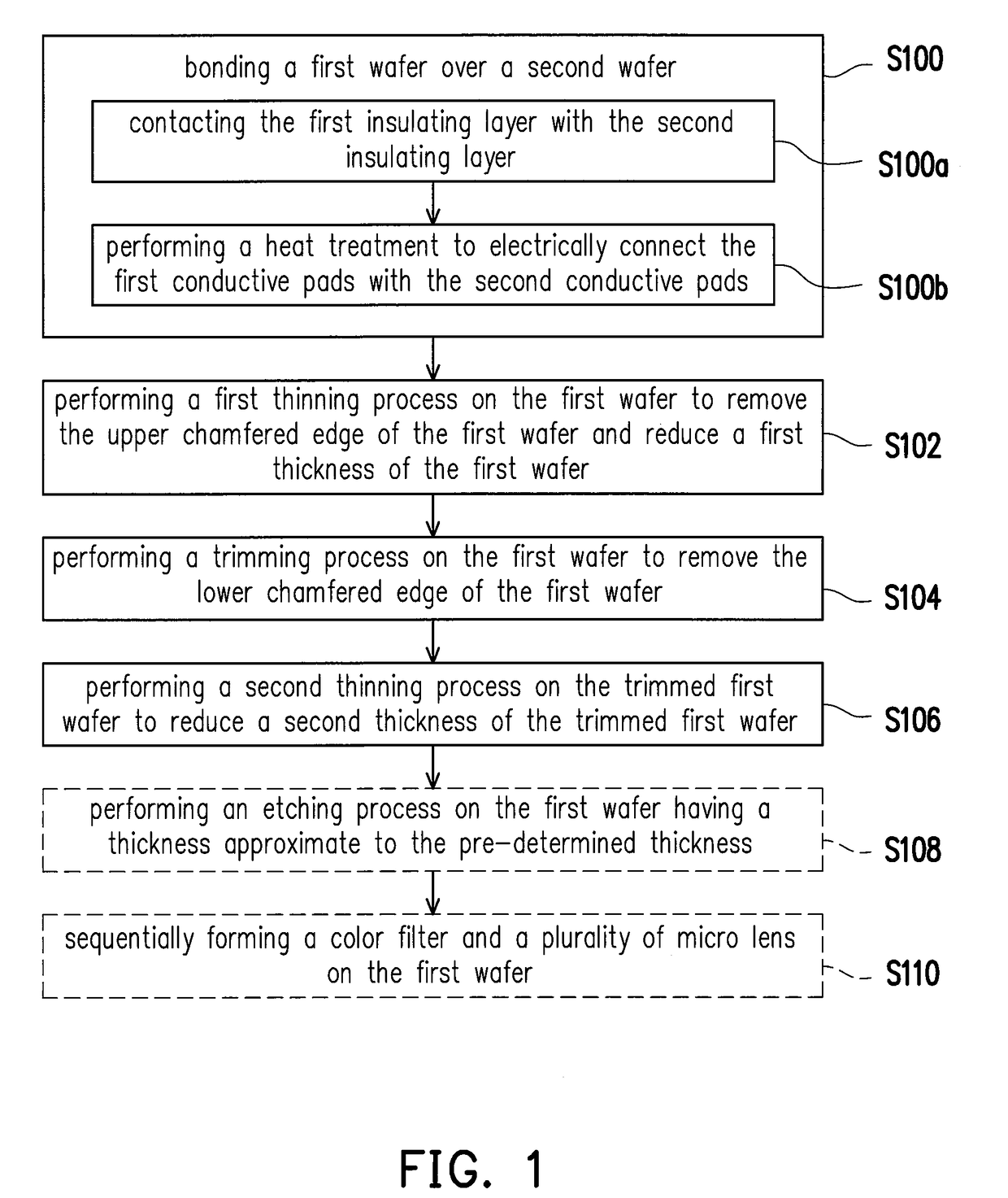

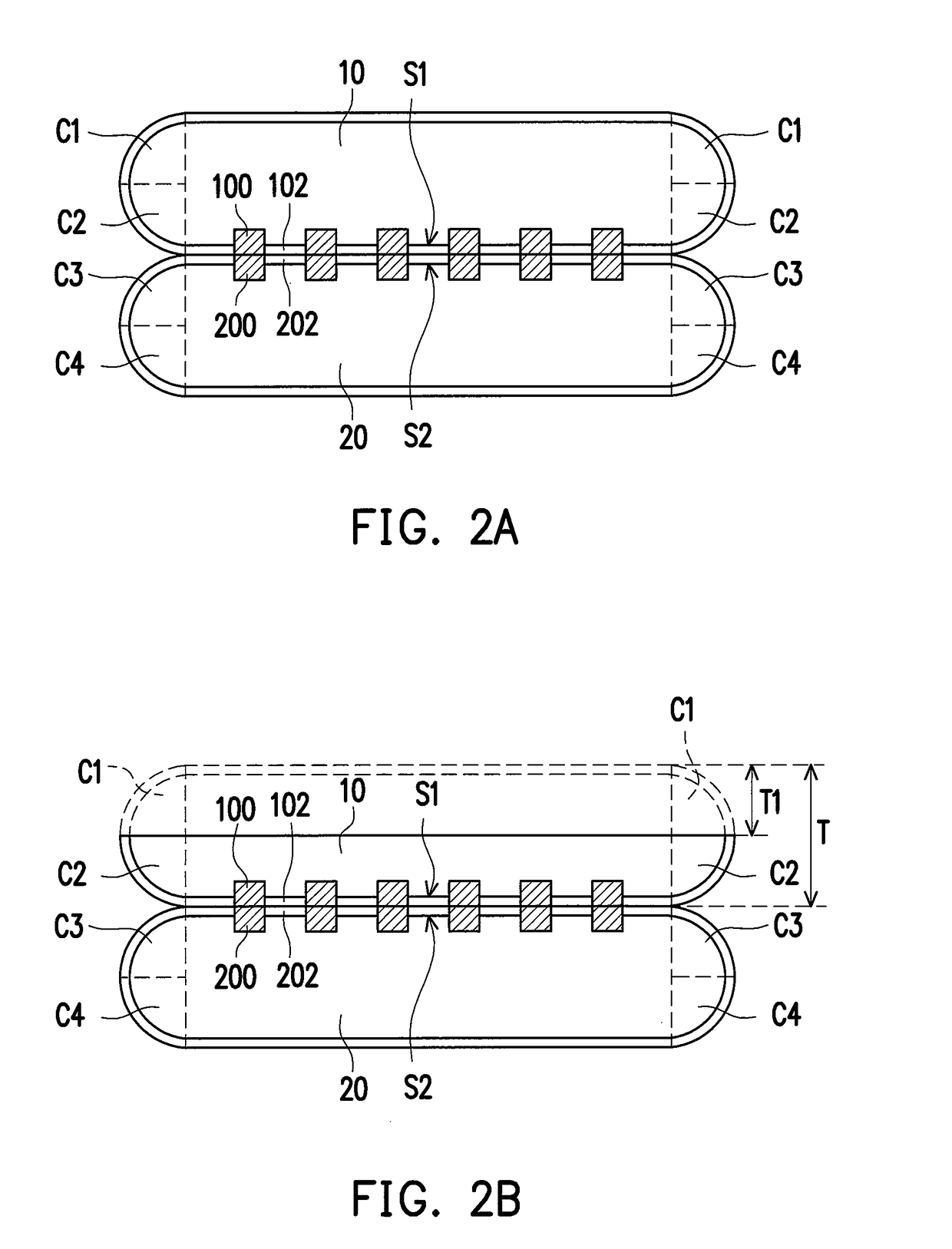

ActiveUS20180323227A1Improve Wafer YieldIncrease productionSemiconductor/solid-state device detailsSolid-state devicesEngineeringGrinding process

A wafer level packaging method includes the following steps. A first wafer is bonded over a second wafer. A first grinding process on the first wafer is performed, to remove an upper chamfered edge of the first wafer and reduce a thickness of the first wafer. A trimming process is performed on the first wafer, to remove a lower chamfered edge of the first wafer to form a trimmed first wafer. A second grinding process is performed on the trimmed first wafer, to reduce a thickness of the trimmed first wafer.

Owner:UNITED MICROELECTRONICS CORP

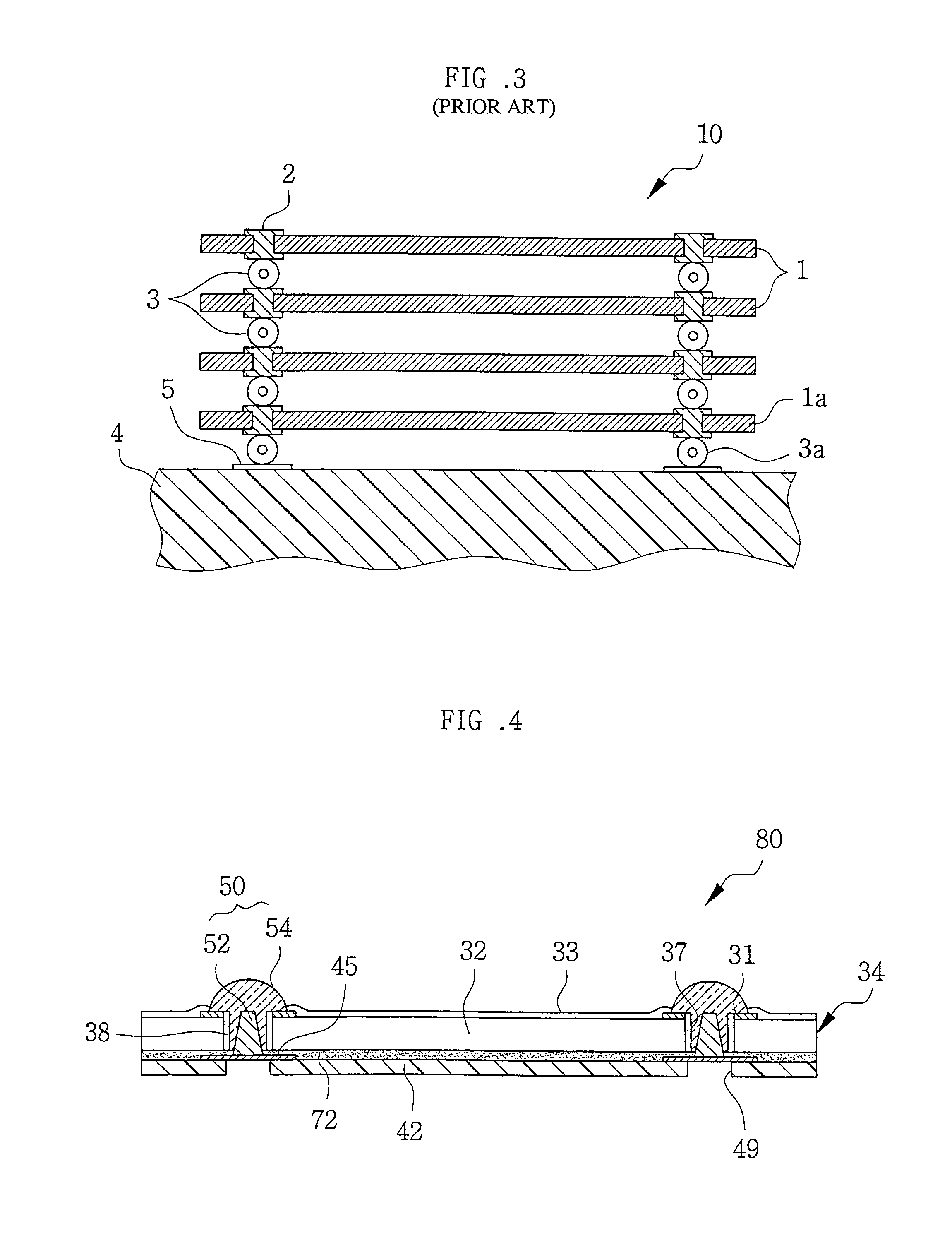

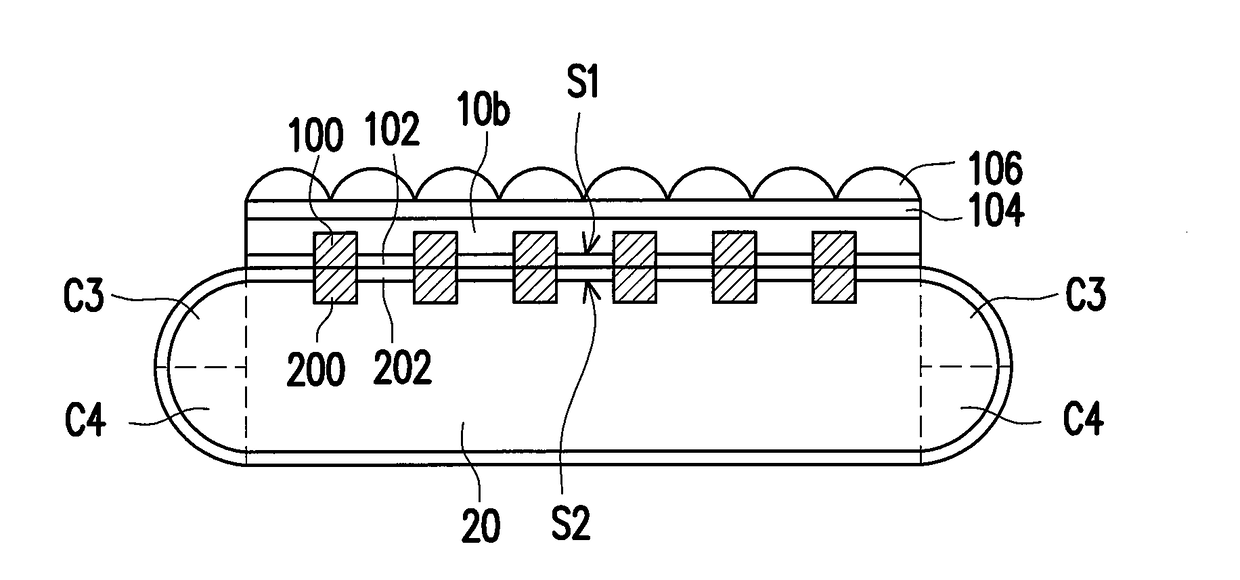

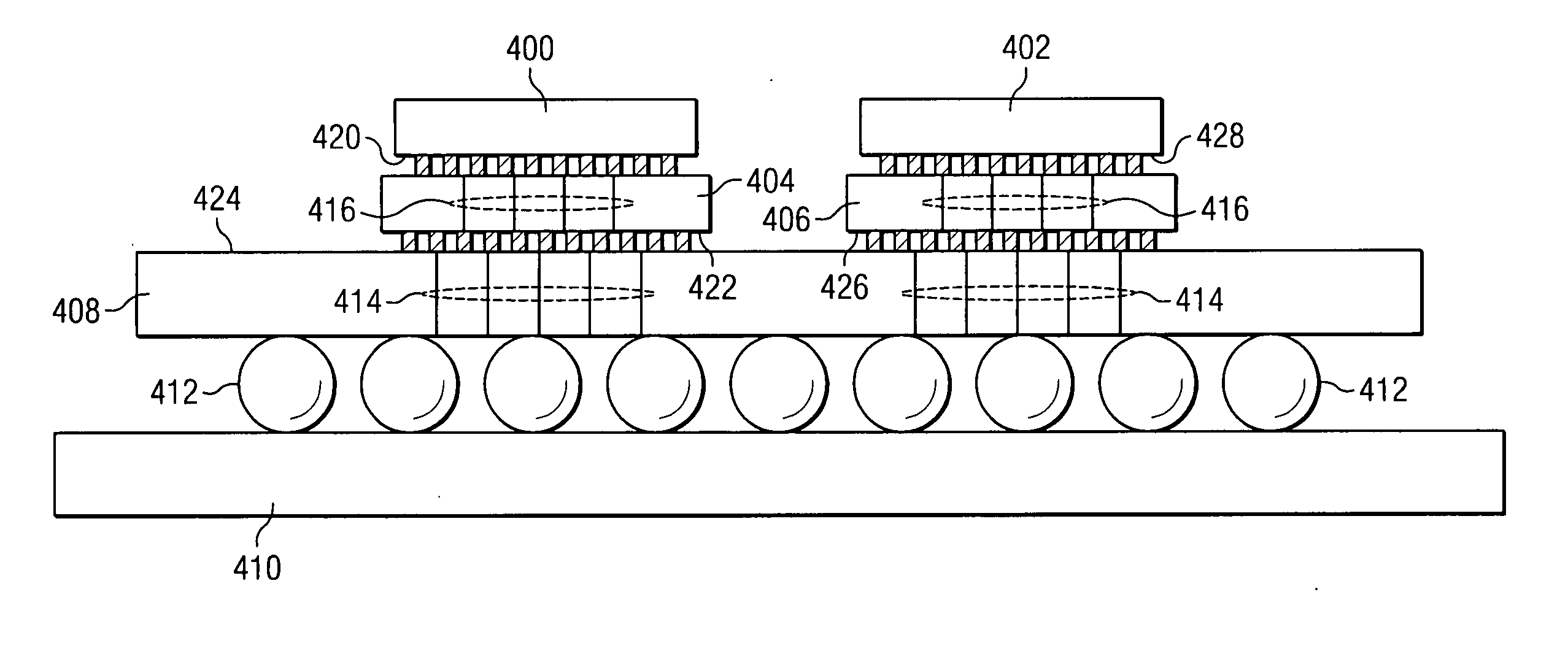

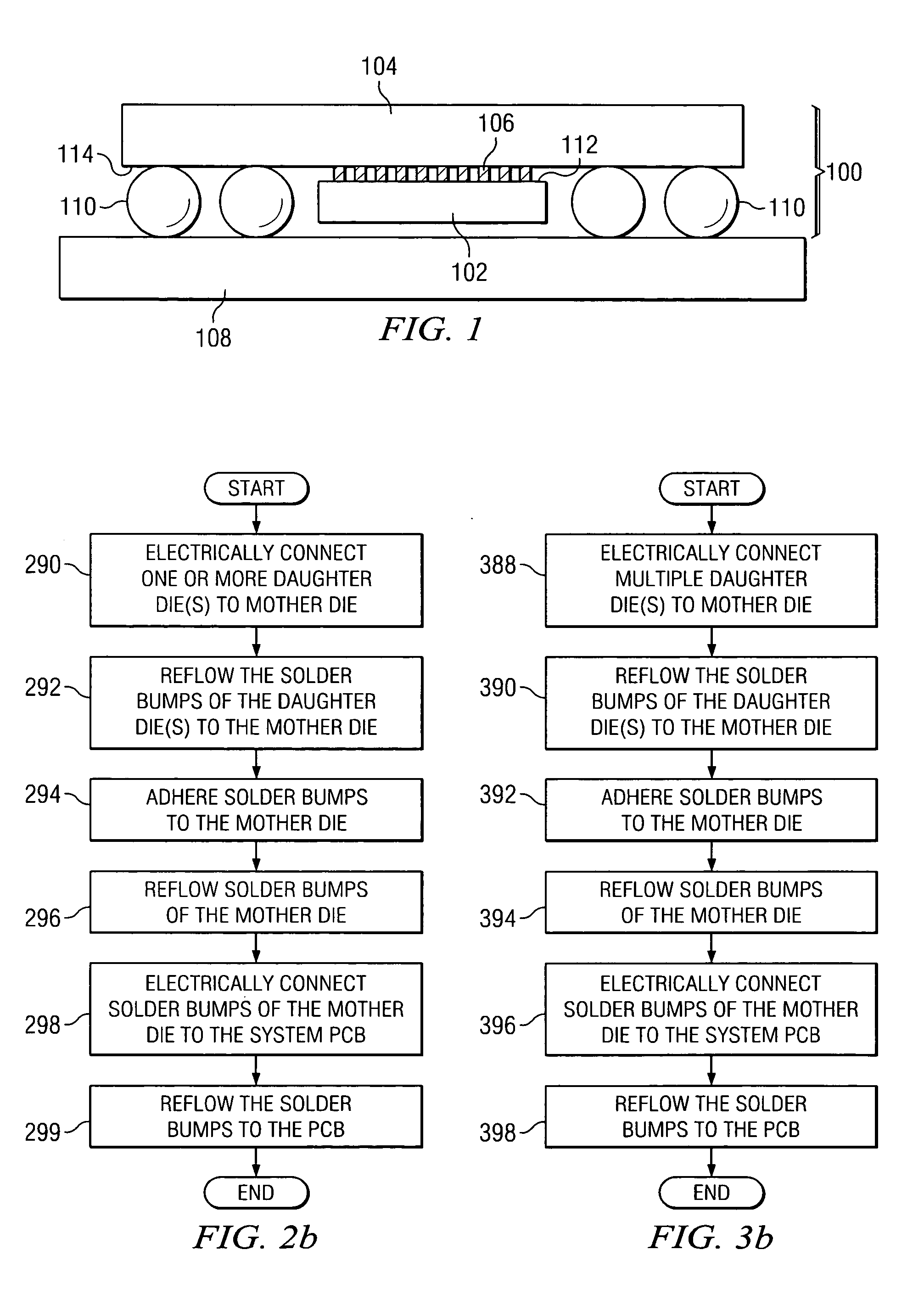

Stacked wafer scale package

InactiveUS20060038272A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringPrinted circuit board

A device comprising a first die enclosed in a wafer scale package, said first die adapted to mate with a printed circuit board (“PCB”) via solder bumps. The device further comprises a second die enclosed in a wafer scale package and electrically connected to a surface of the first die facing the PCB to form a die stack.

Owner:TEXAS INSTR INC

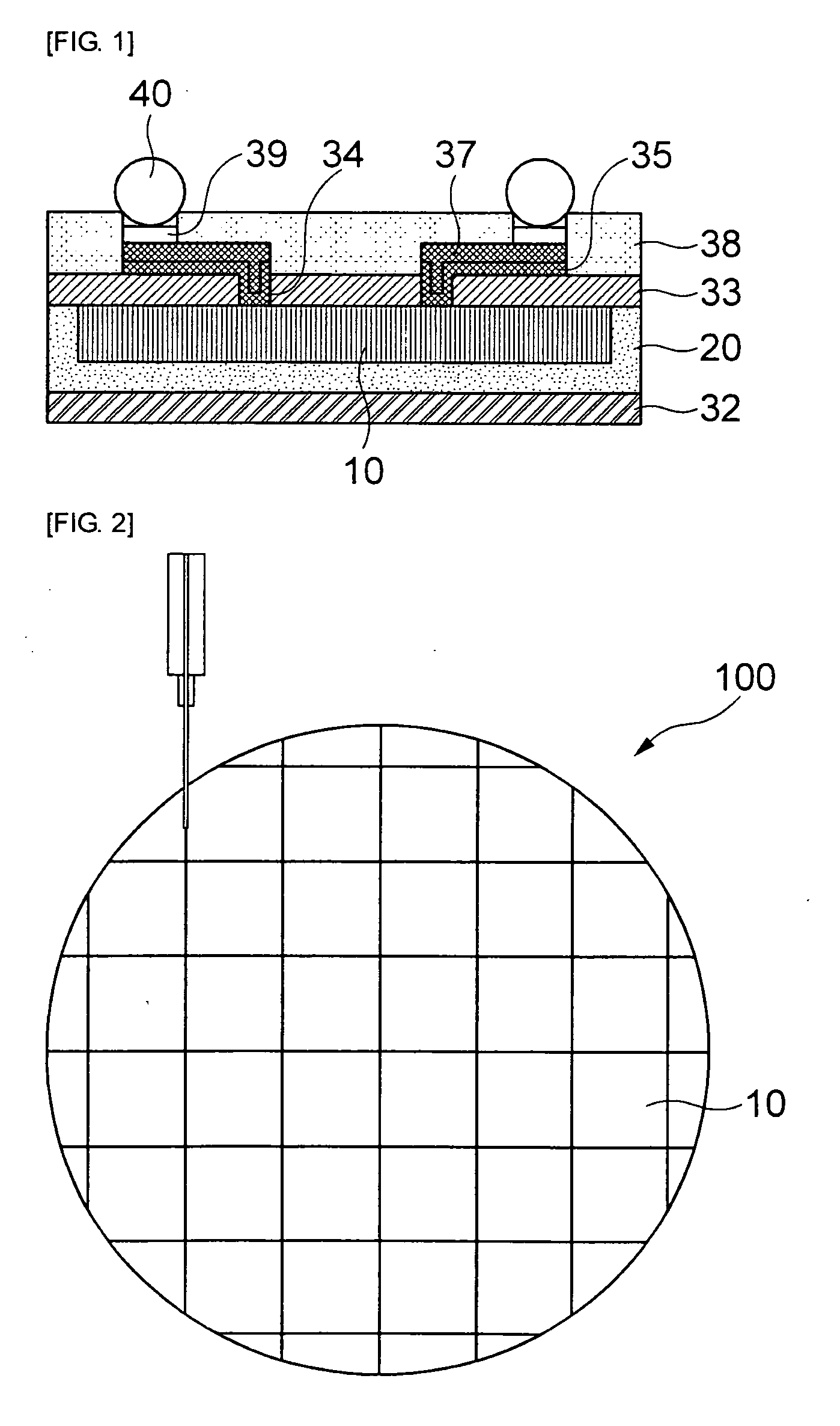

Wafer-level package and its manufacturing method

InactiveUS20050104204A1Impedence networksSemiconductor/solid-state device detailsEngineeringElectrical and Electronics engineering

A wafer-level package comprises: a first substrate; an electric element provided on the first substrate; a second substrate; an internal electrode pad; a well; and an external electrode pad. The second substrate is opposed to the first substrate with a predetermined gap therebetween. The electric element is provided between the first and second substrates. The internal electrode pad extends onto a first surface of one of the first and the second substrates. The inner electrode pad is connected to the electric element. The well penetrates the one of the first and the second substrates to the internal electrode. The external electrode pad is provided on a second surface of the one of the first and the second substrates and extends onto an inner wall of the well and being connected with the internal electrode pad.

Owner:KK TOSHIBA

Temperature controlled MEMS resonator and method for controlling resonator frequency

There are many inventions described and illustrated herein. In one aspect, the present invention is directed to a temperature compensated microelectromechanical resonator as well as fabricating, manufacturing, providing and / or controlling microelectromechanical resonators having mechanical structures that include integrated heating and / or temperature sensing elements. In another aspect, the present invention is directed to fabricate, manufacture, provide and / or control microelectromechanical resonators having mechanical structures that are encapsulated using thin film or wafer level encapsulation techniques in a chamber, and including heating and / or temperature sensing elements disposed in the chamber, on the chamber and / or integrated within the mechanical structures. Other aspects of the inventions will be apparent from the detailed description and claims herein.

Owner:ROBERT BOSCH GMBH

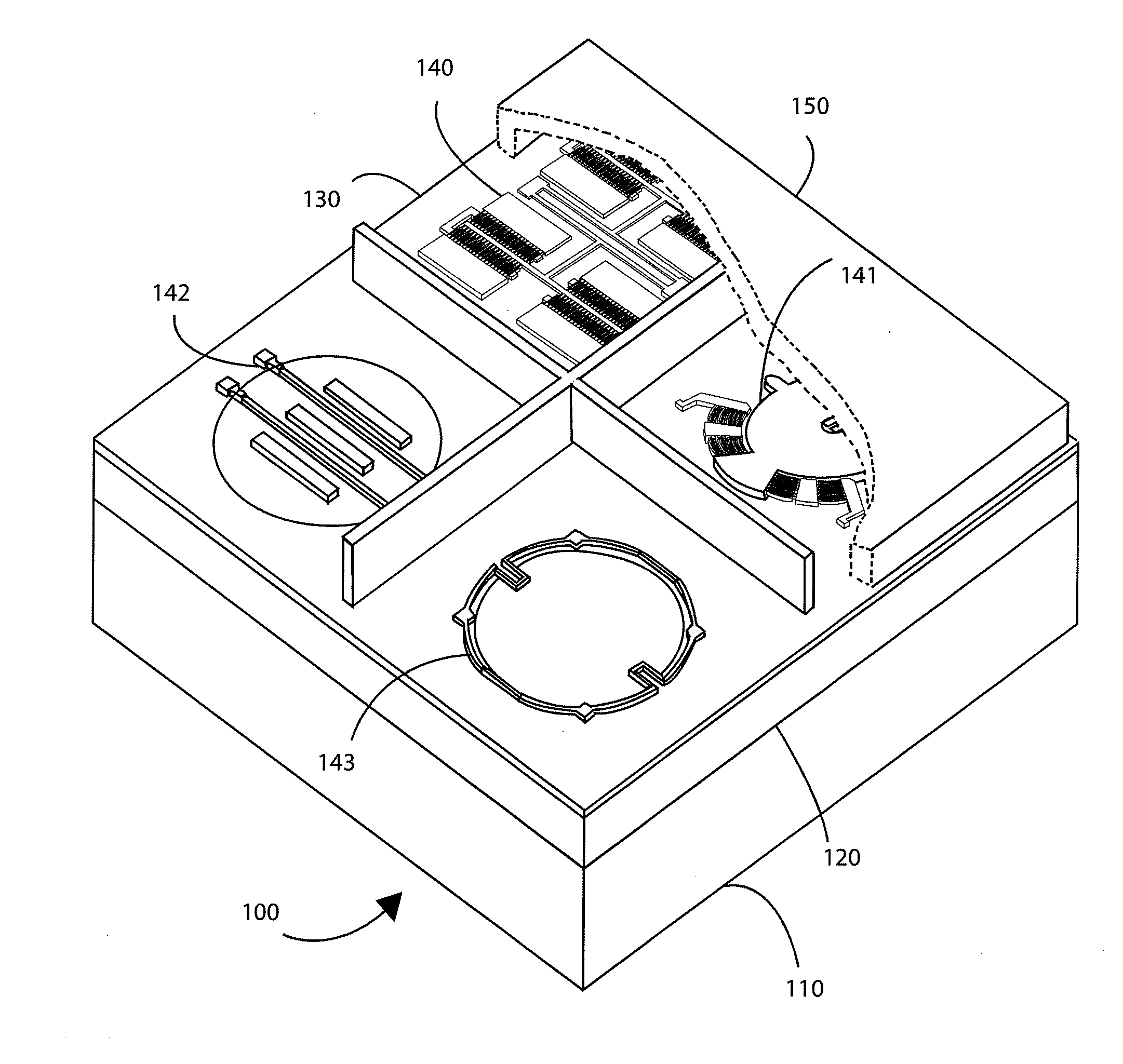

System on a Chip Using Integrated MEMS and CMOS Devices

ActiveUS20110265574A1Easy to useHigh device yieldVibration measurement in solidsMaterial analysis using sonic/ultrasonic/infrasonic wavesCmos memsSystem on a chip

An integrated MEMS system in which CMOS and MEMS devices are provided to form an integrated CMOS-MEMS system. The system can include a silicon substrate layer, a CMOS layer, MEMS and CMOS devices, and a wafer level packaging (WLP) layer. The CMOS layer can form an interface region, one which any number of CMOS MEMS devices can be configured.

Owner:MOVELLA INC

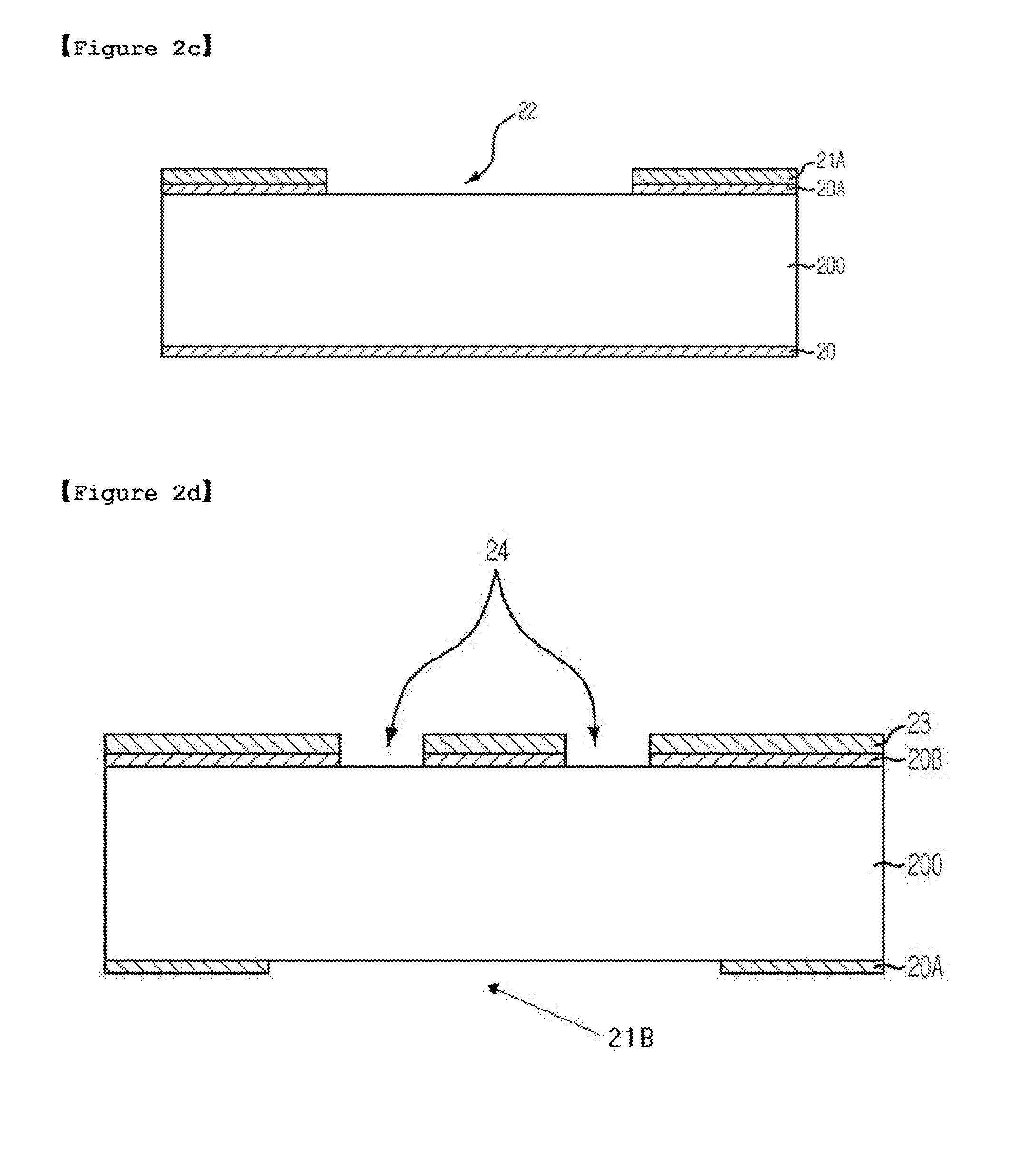

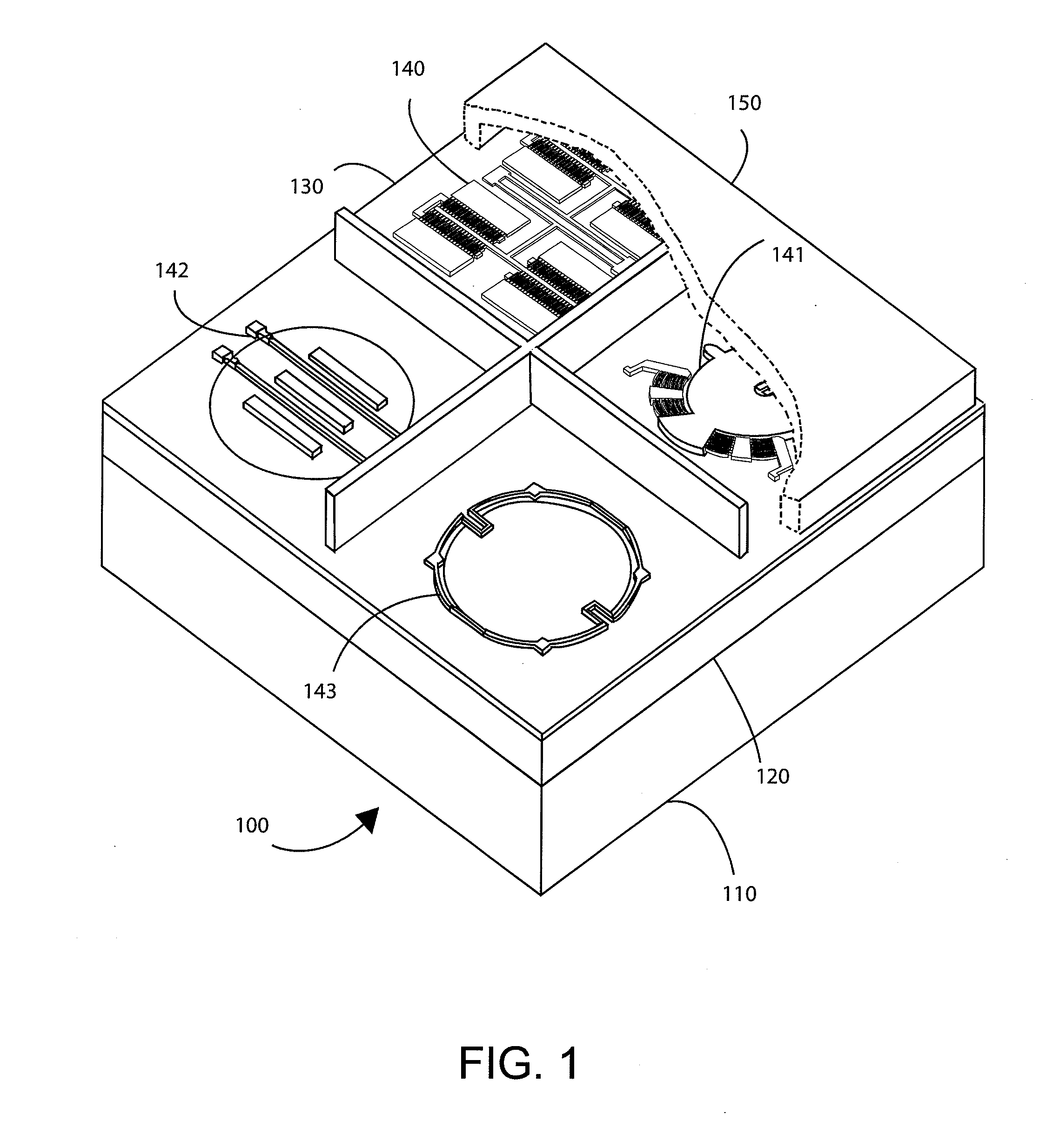

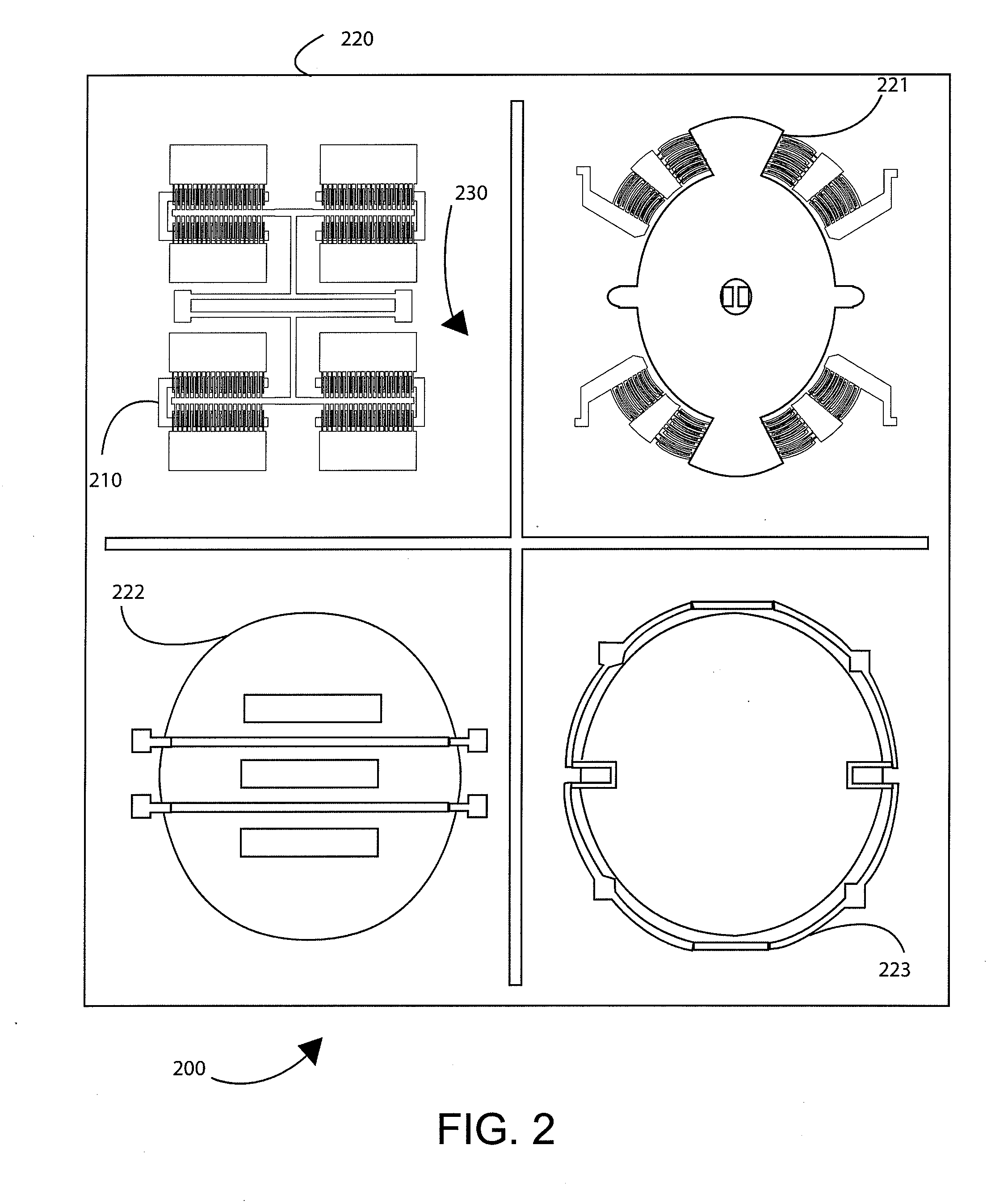

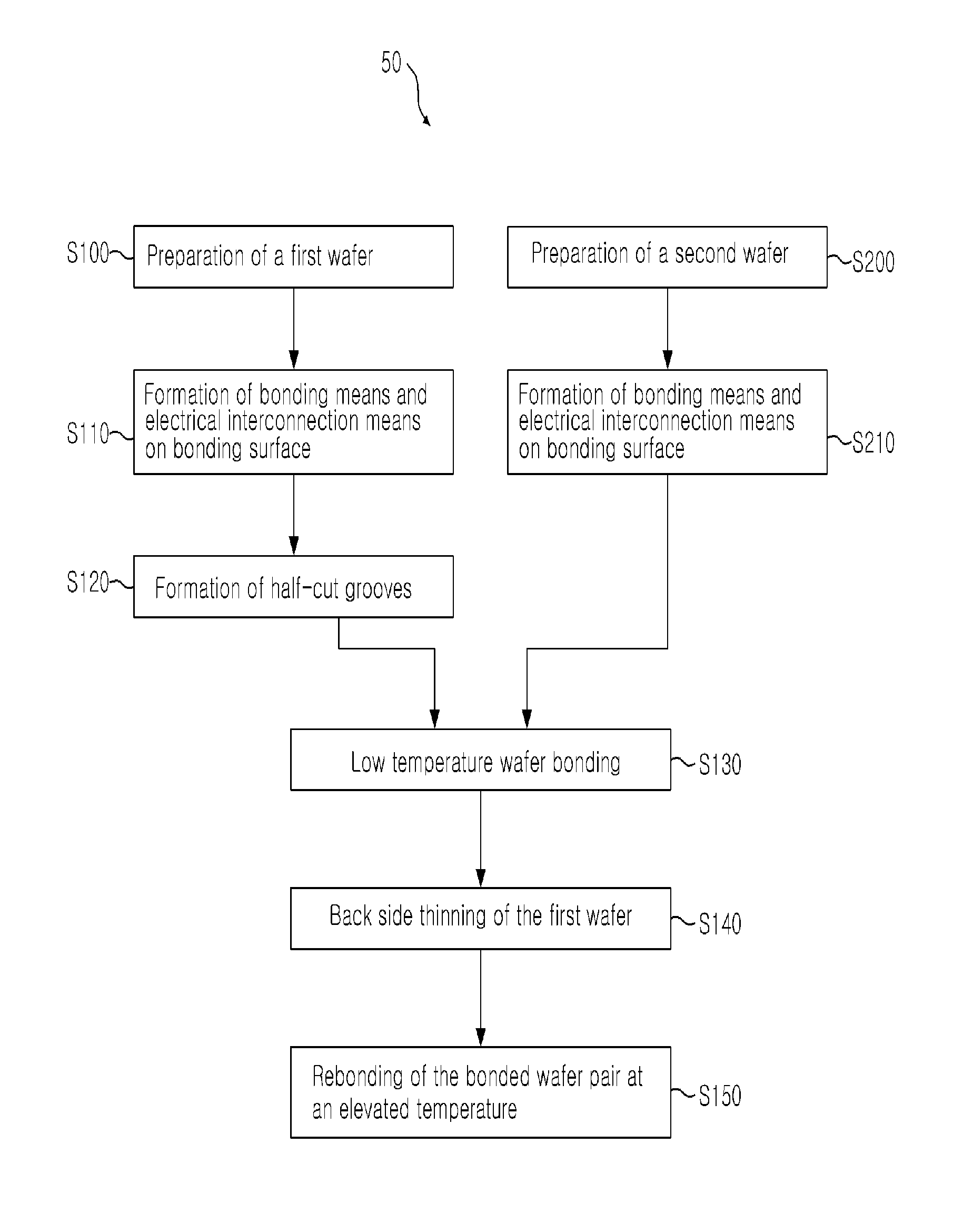

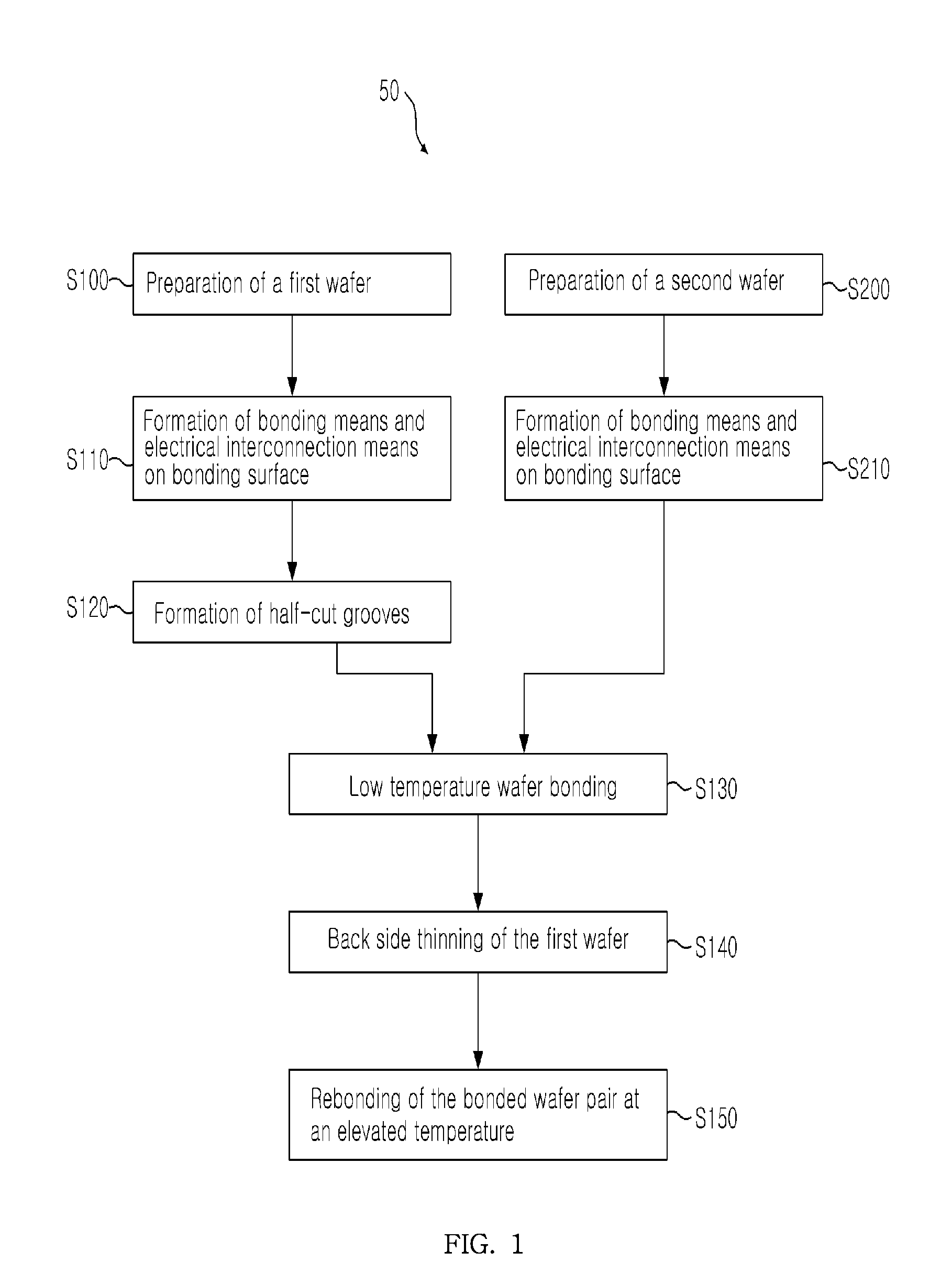

Method for manufacturing hetero-bonded wafer

InactiveUS8241961B2Low costGood adhesionSemiconductor/solid-state device detailsSolid-state devicesEngineeringThermal expansion

A method for manufacturing a hetero-bonded wafer having a large mismatch of thermal expansion coefficient comprises forming a wafer bonding means and an electrical interconnection means on at least one bonding surface of two wafers to be bonded with each other, forming grooves in the bonding surface of one wafer along dicing lines with an interval between the grooves being equal to or an even multiple of a die width, bonding the two wafers at a temperature less than 200° C., thinning a back side of the grooved wafer such that at least a portion of the grooves is exposed, and rebonding the bonded wafer pair at an elevated temperature higher than the first bonding temperature. The method for manufacturing a hetero-bonded wafer can avoid wafer level bow / warp and also reduce debonding and cracking in individual segments induced by thermal stress due to a mismatch of thermal expansion coefficient. Embodiments of the method are useful for wafer level packaging and the fabrication of hybrid devices by heterogeneous wafer bonding.

Owner:KIM YOUNG HAE

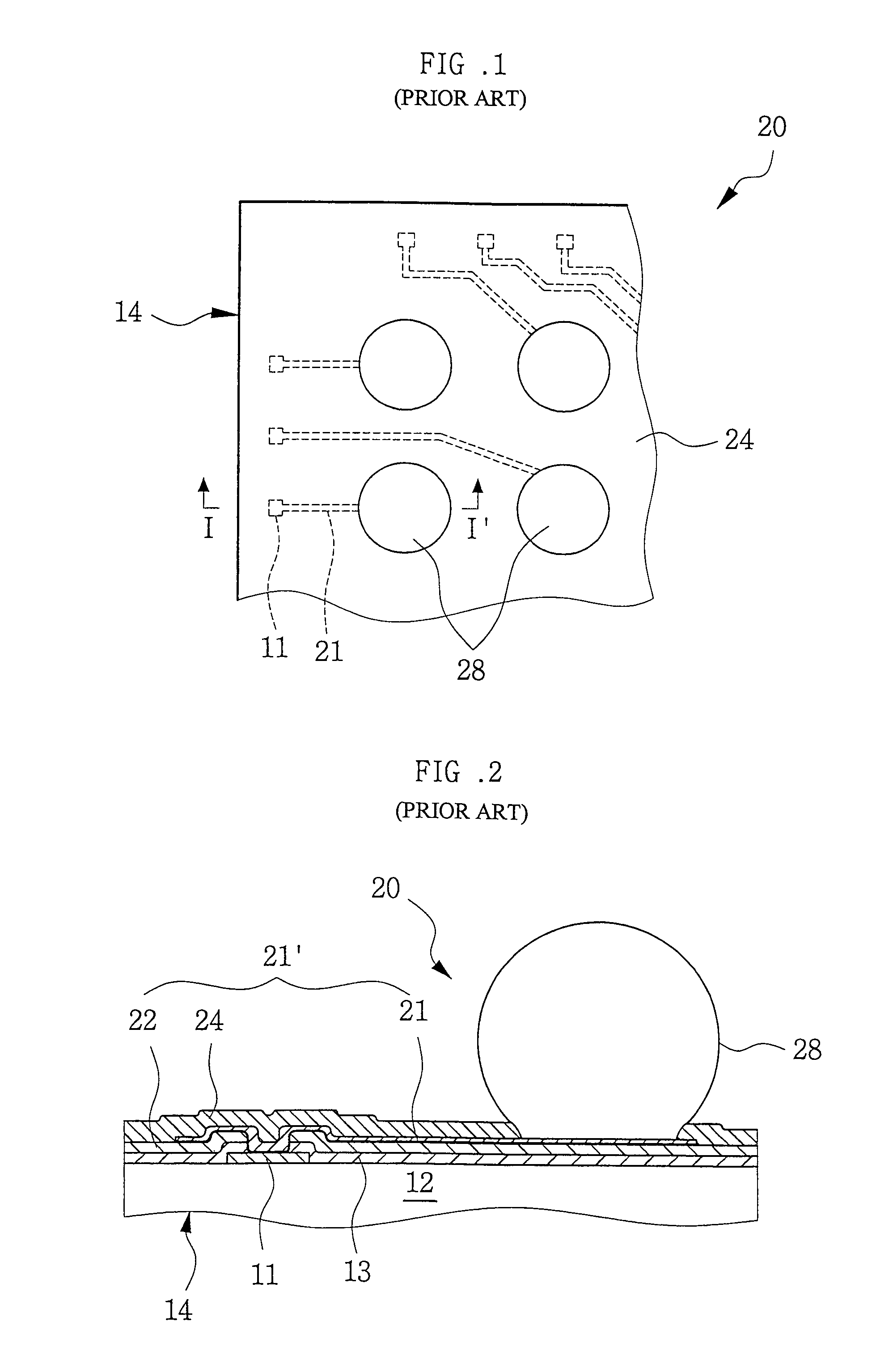

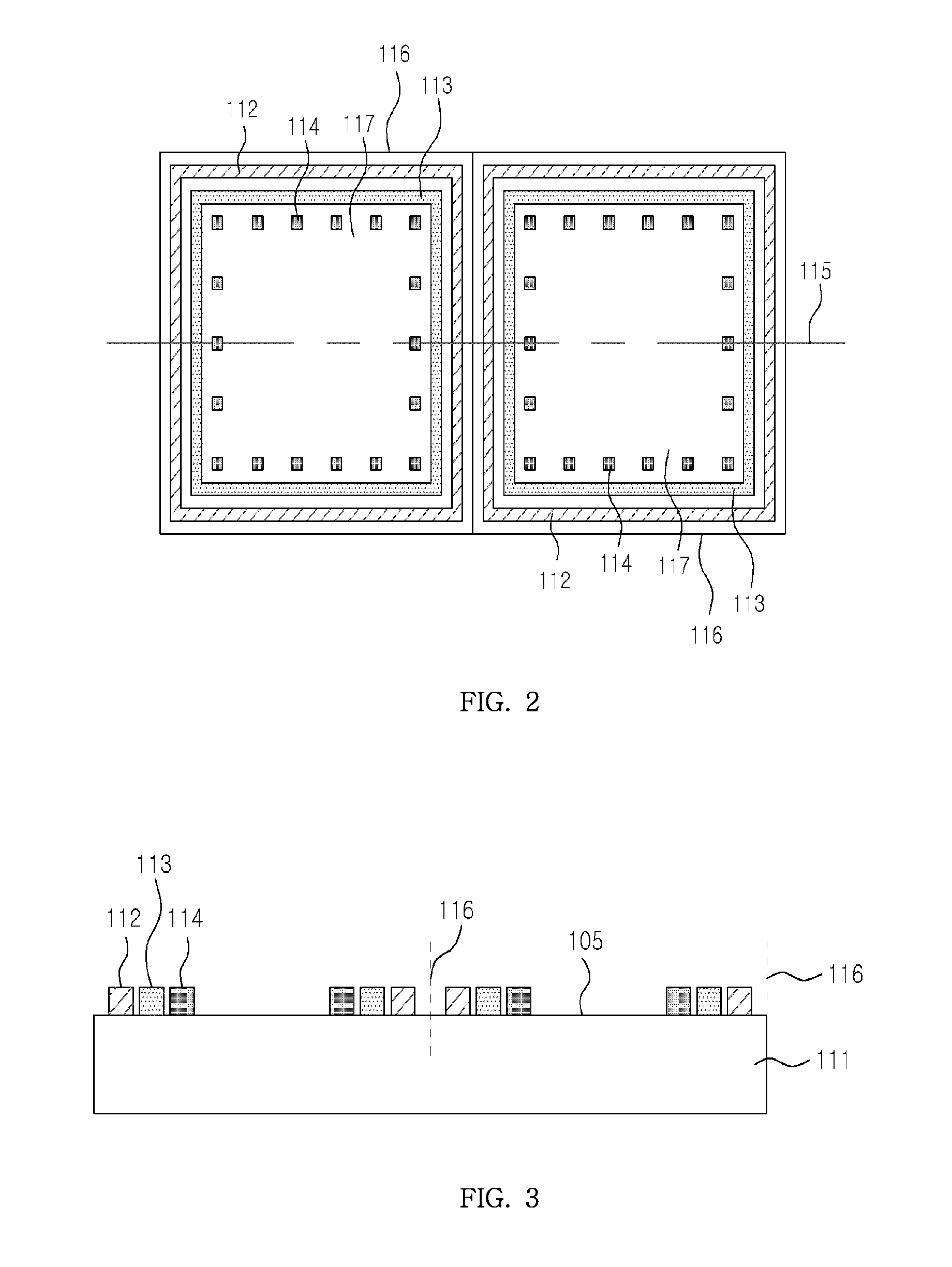

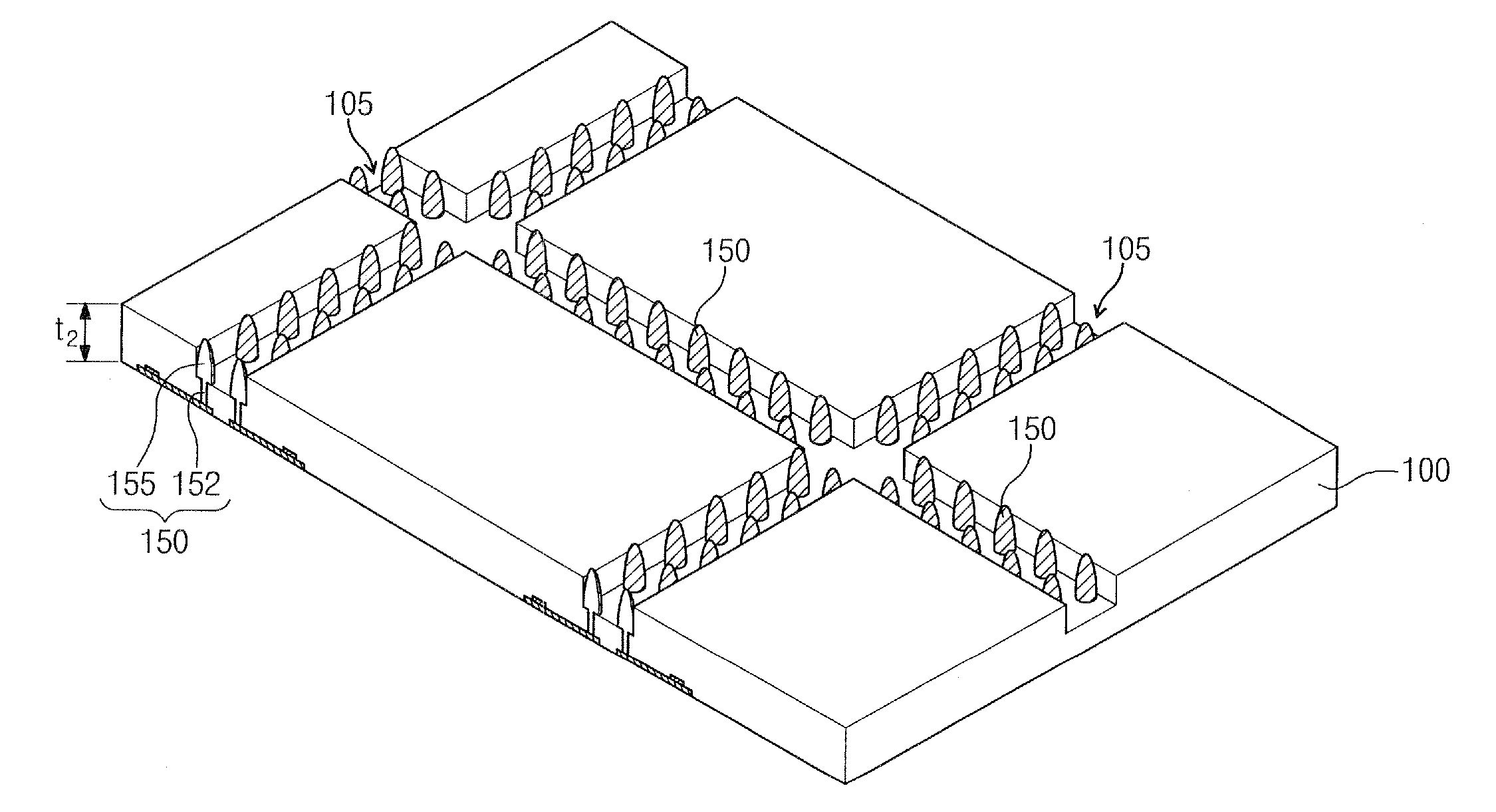

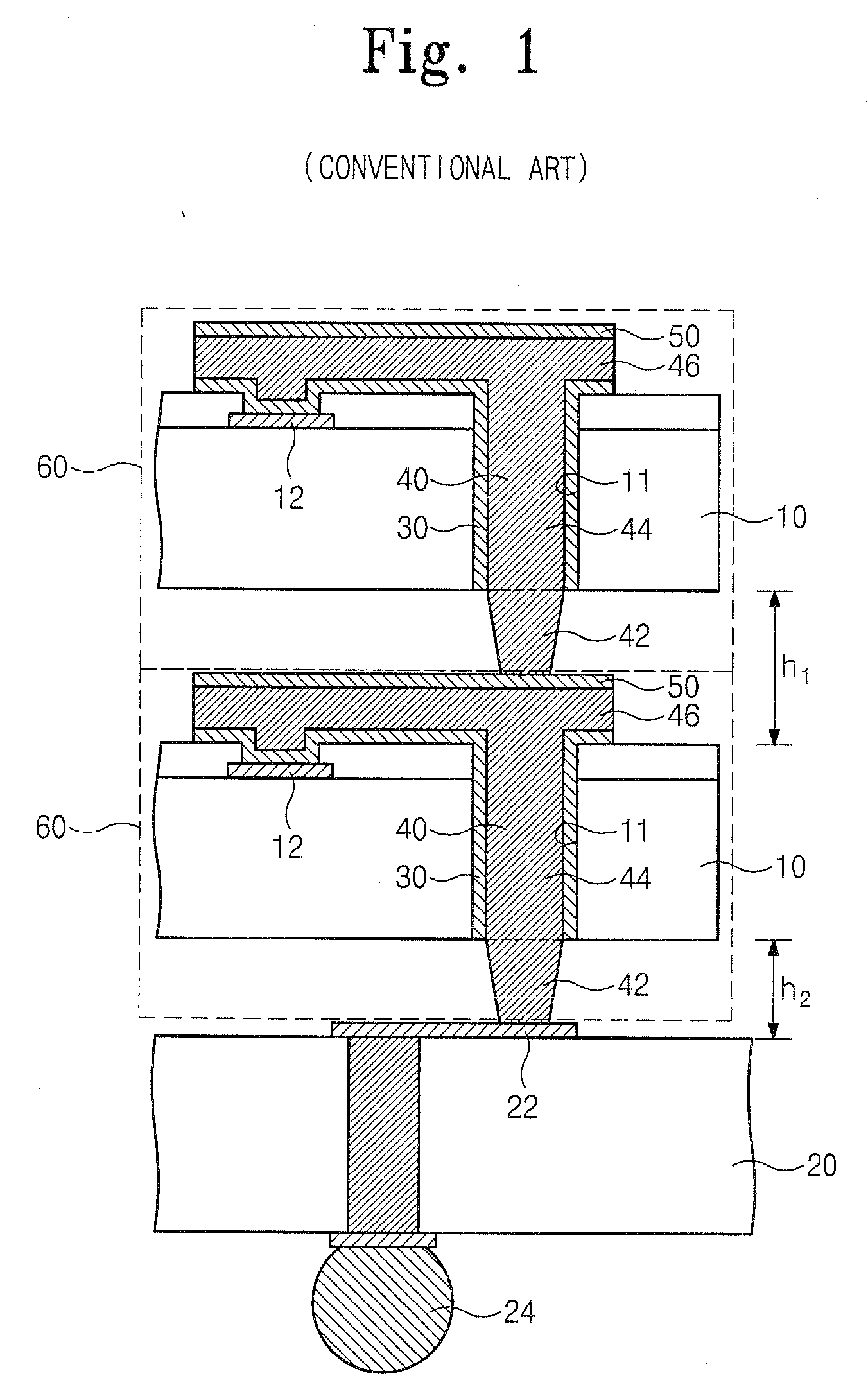

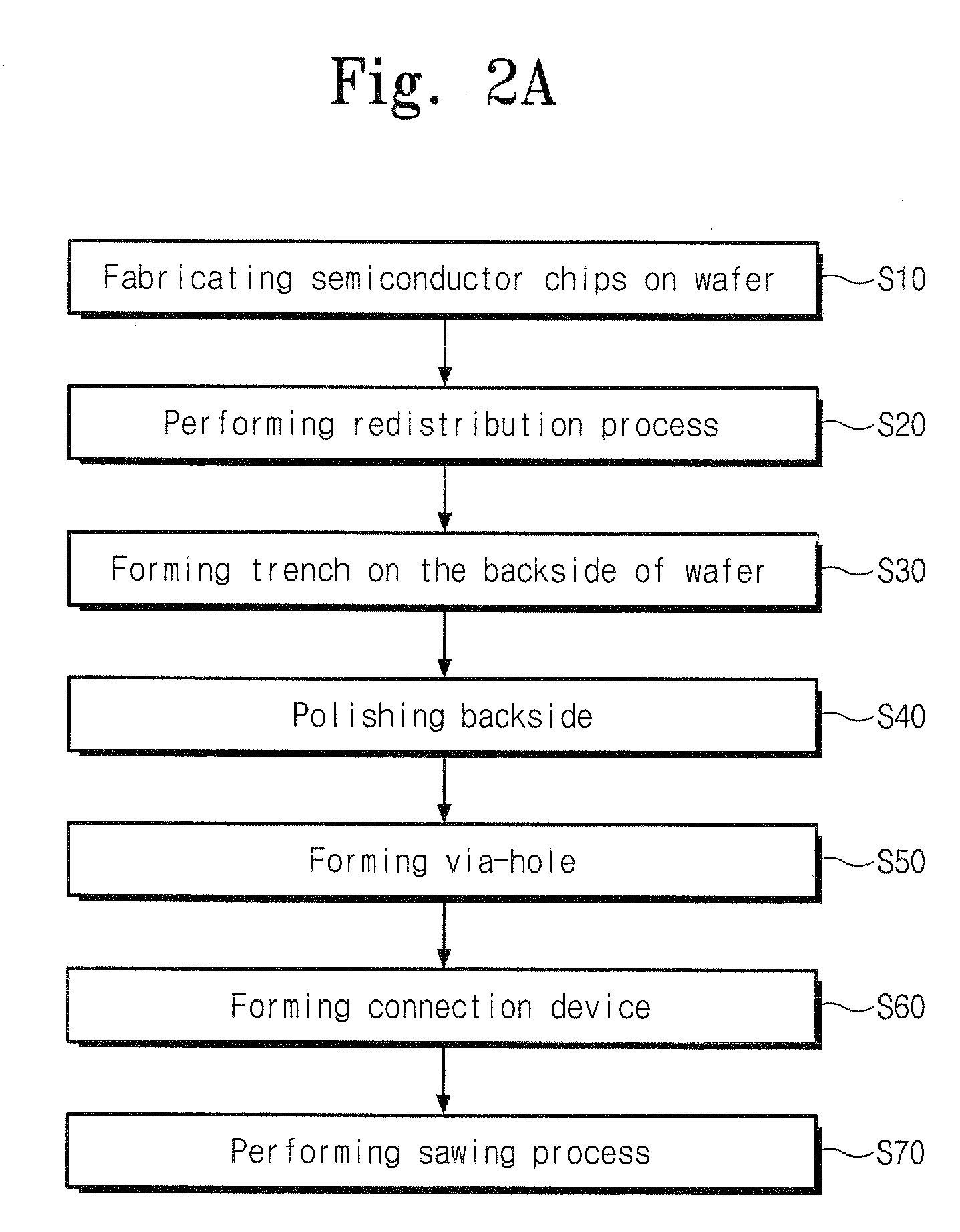

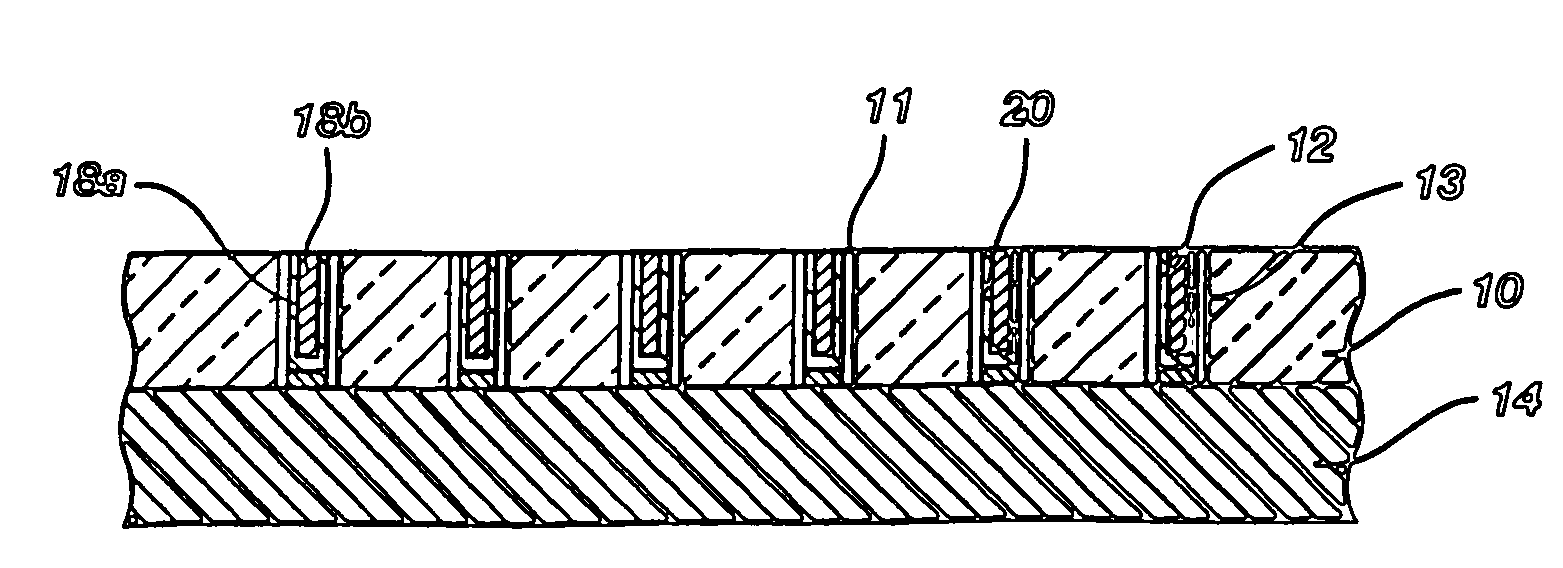

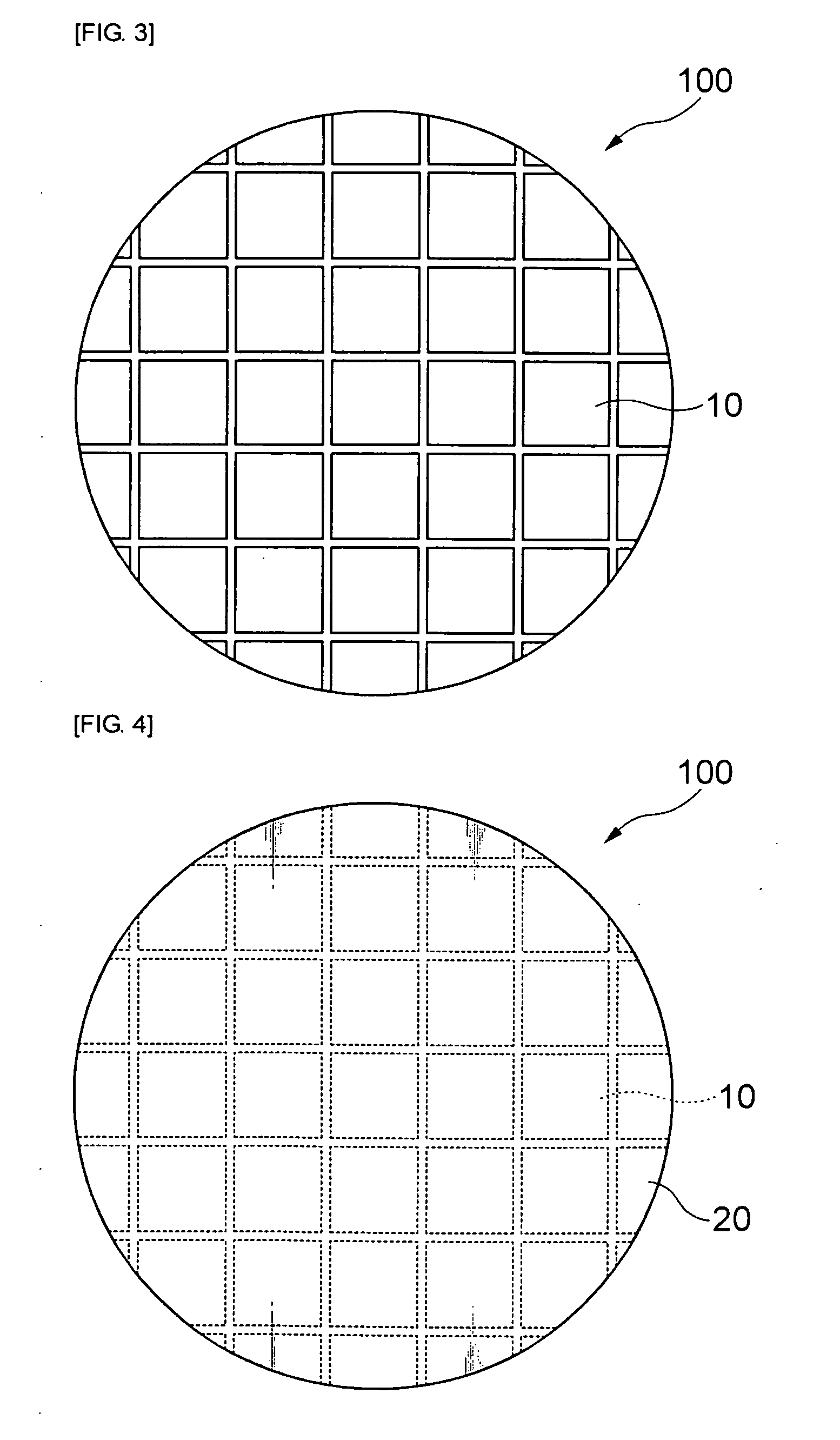

Wafer level package and method of fabricating the same

InactiveUS20070269931A1Reduce manufacturing costPackage thickness is lowSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipWafer-level packaging

Wafer level packages and methods of fabricating the same are provided. In one embodiment, one of the methods comprises forming semiconductor chips having a connection pad on a wafer, patterning a bottom surface of the wafer to form a trench under the connection pad, patterning a bottom surface of the trench to form a via hole exposing the bottom surface of the connection pad, and forming a connecting device connected to the connection pad through the via hole. The invention provides a wafer level package having reduced thickness, lower fabrication costs, and increased reliability compared to conventional packages.

Owner:SAMSUNG ELECTRONICS CO LTD

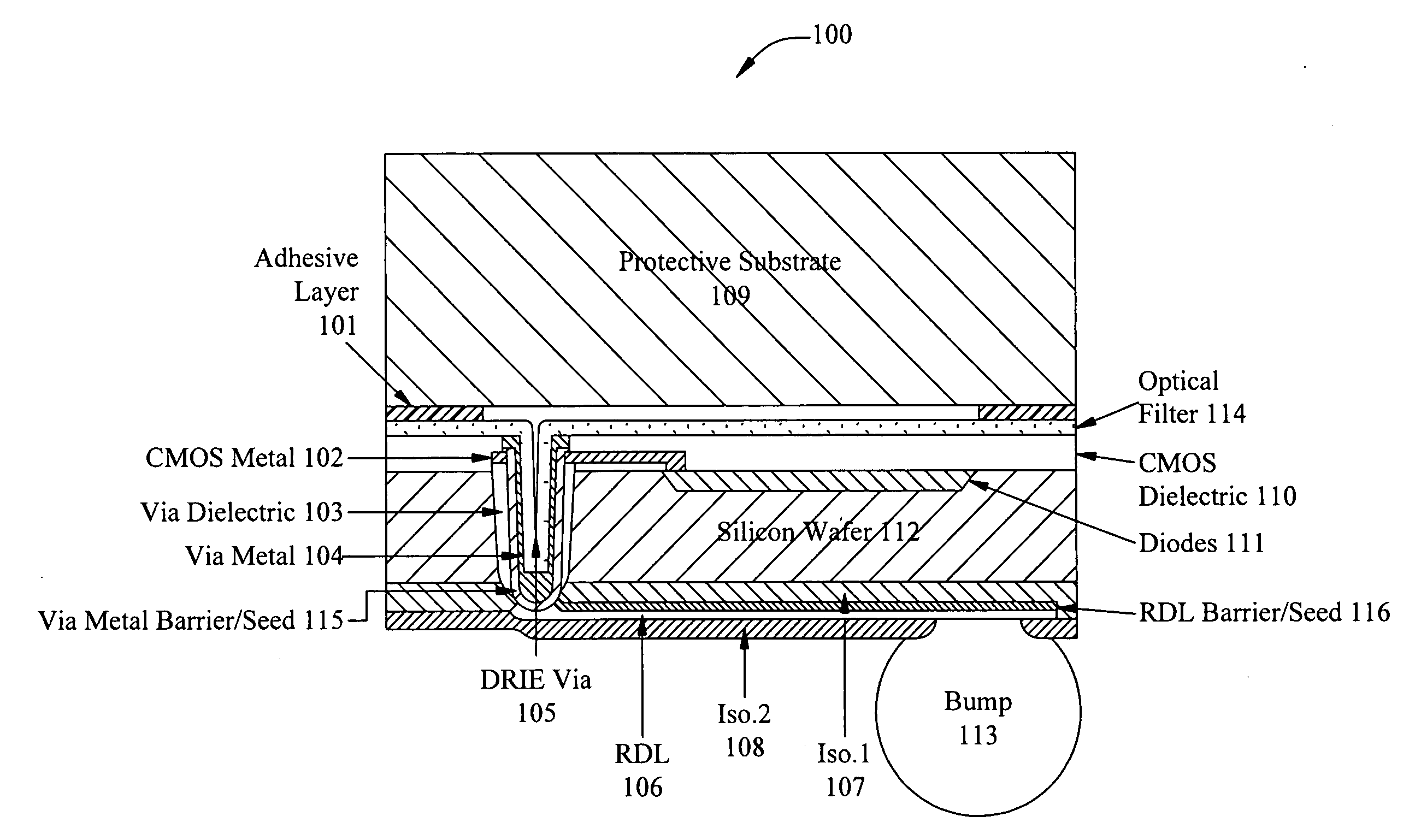

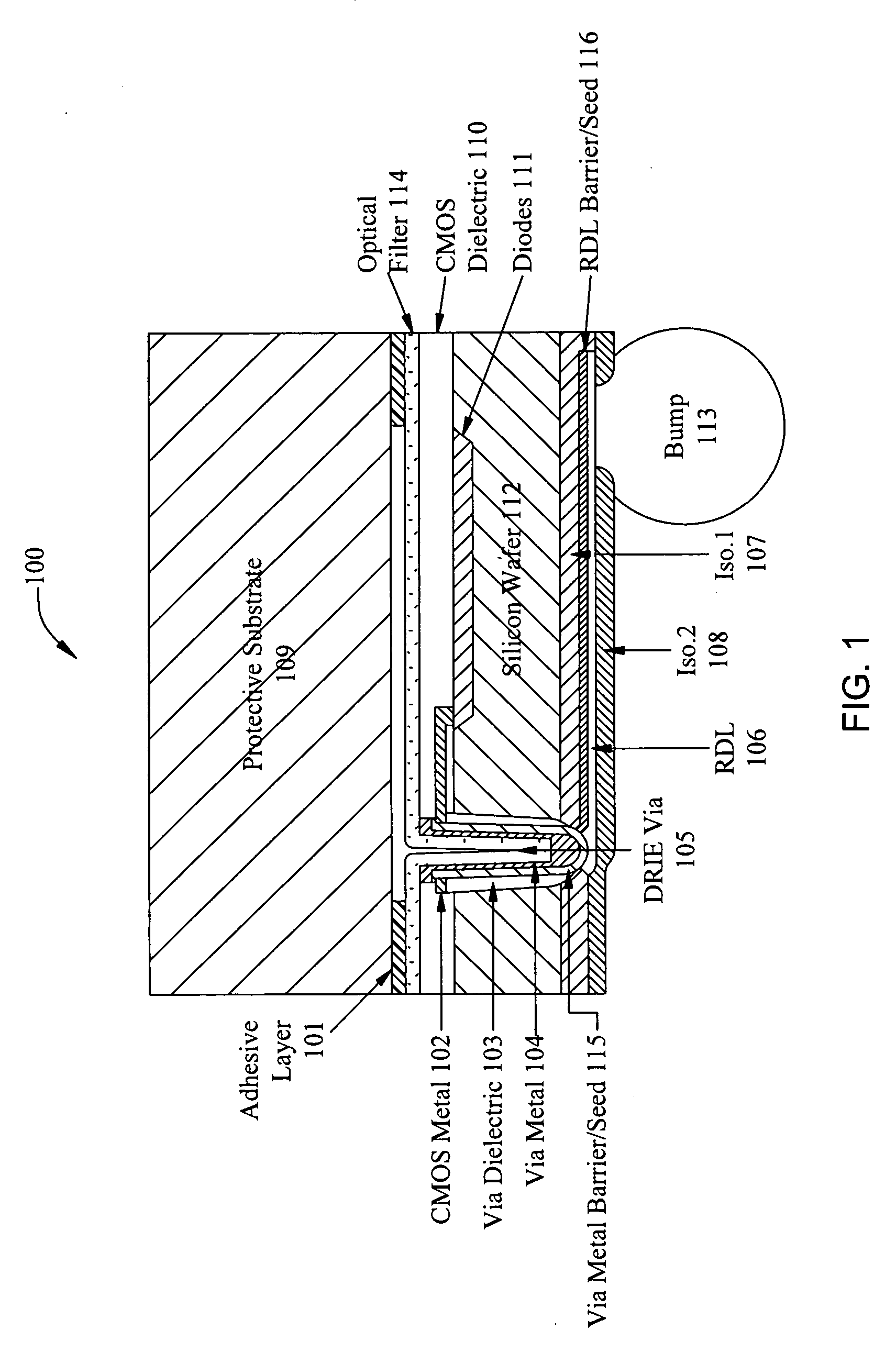

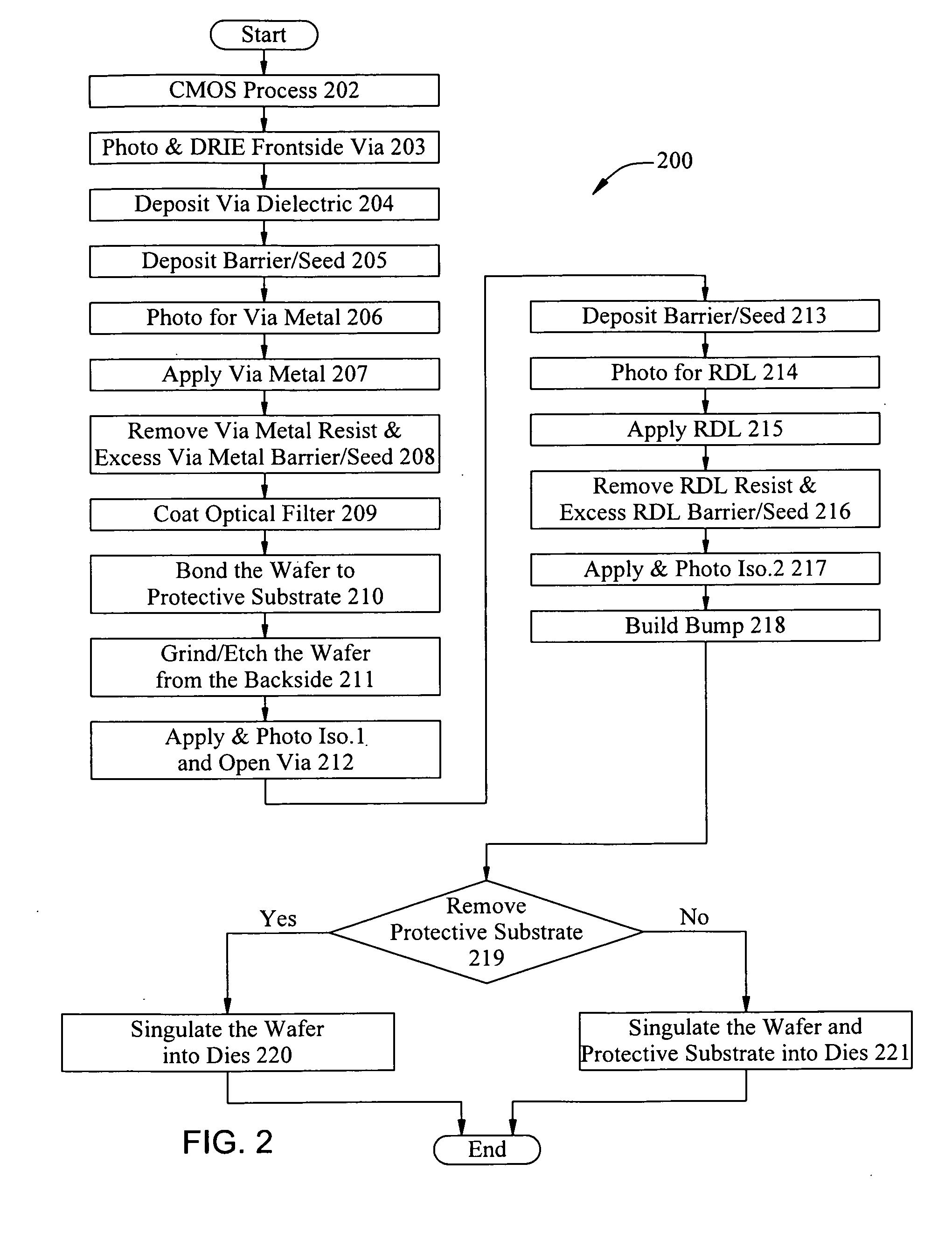

Light Sensor Using Wafer-Level Packaging

ActiveUS20100187557A1Cost-effective and reliable solutionEliminate needSemiconductor/solid-state device detailsSolid-state devicesEngineeringPrinted circuit board

The present invention provides systems, devices and methods for fabricating miniature low-power light sensors. With the present invention, a light sensitive component, such as a diode, is fabricated on the front side of a silicon wafer. Connectivity from the front side of the wafer to the back side of the wafer is provided by a through silicon via. Solder bumps are then placed on the back side of the wafer to provide coupling to a printed circuit board. The techniques described in the present invention may also be applied to other types of semiconductor devices, such as light-emitting diodes, image sensors, pressure sensors, and flow sensors.

Owner:MAXIM INTEGRATED PROD INC

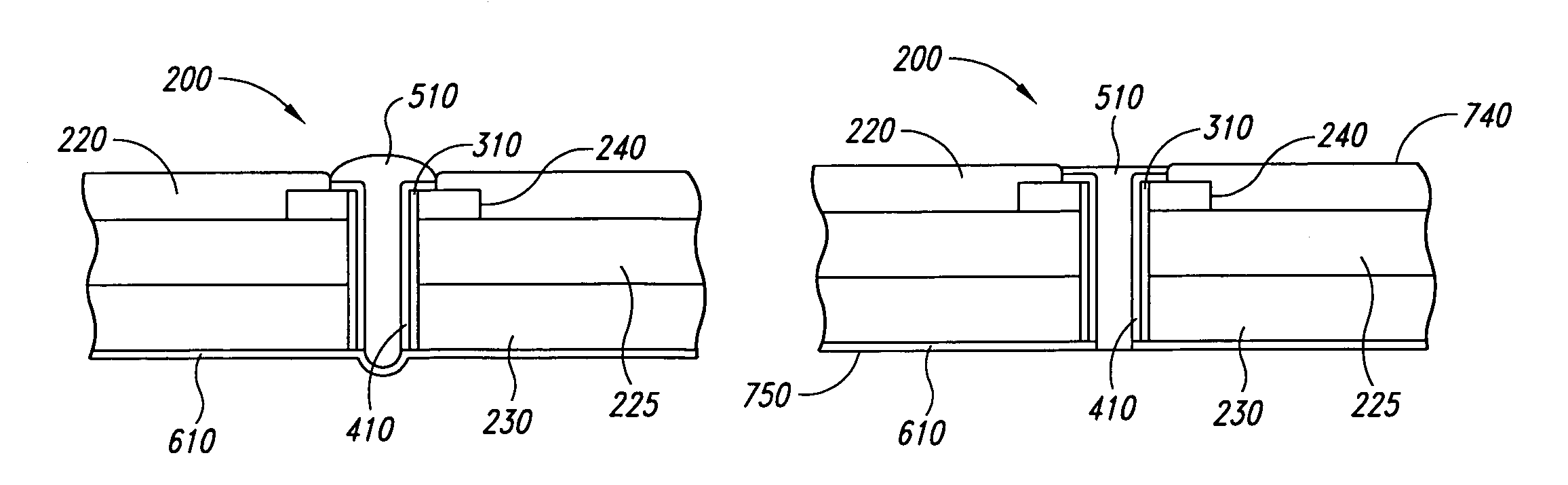

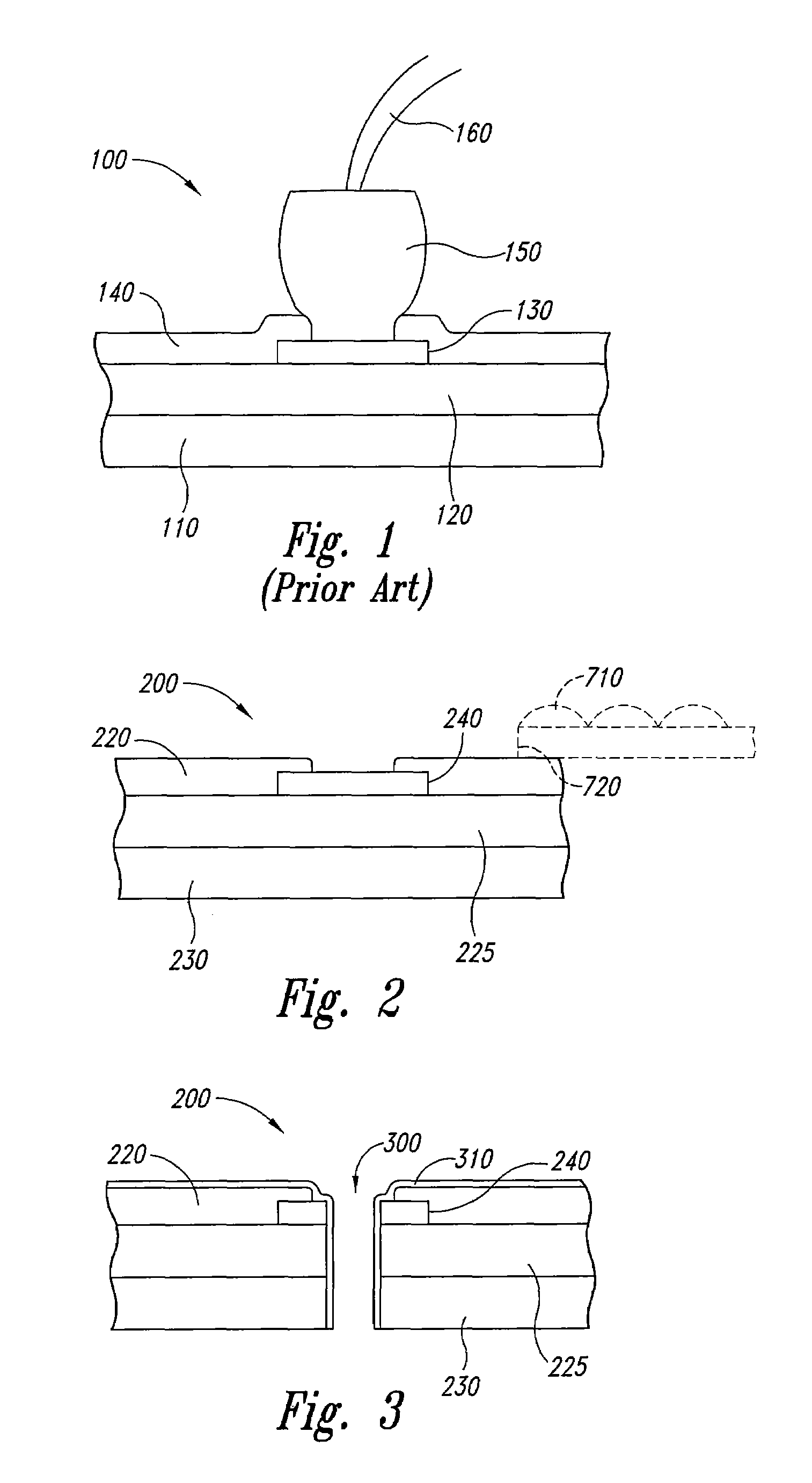

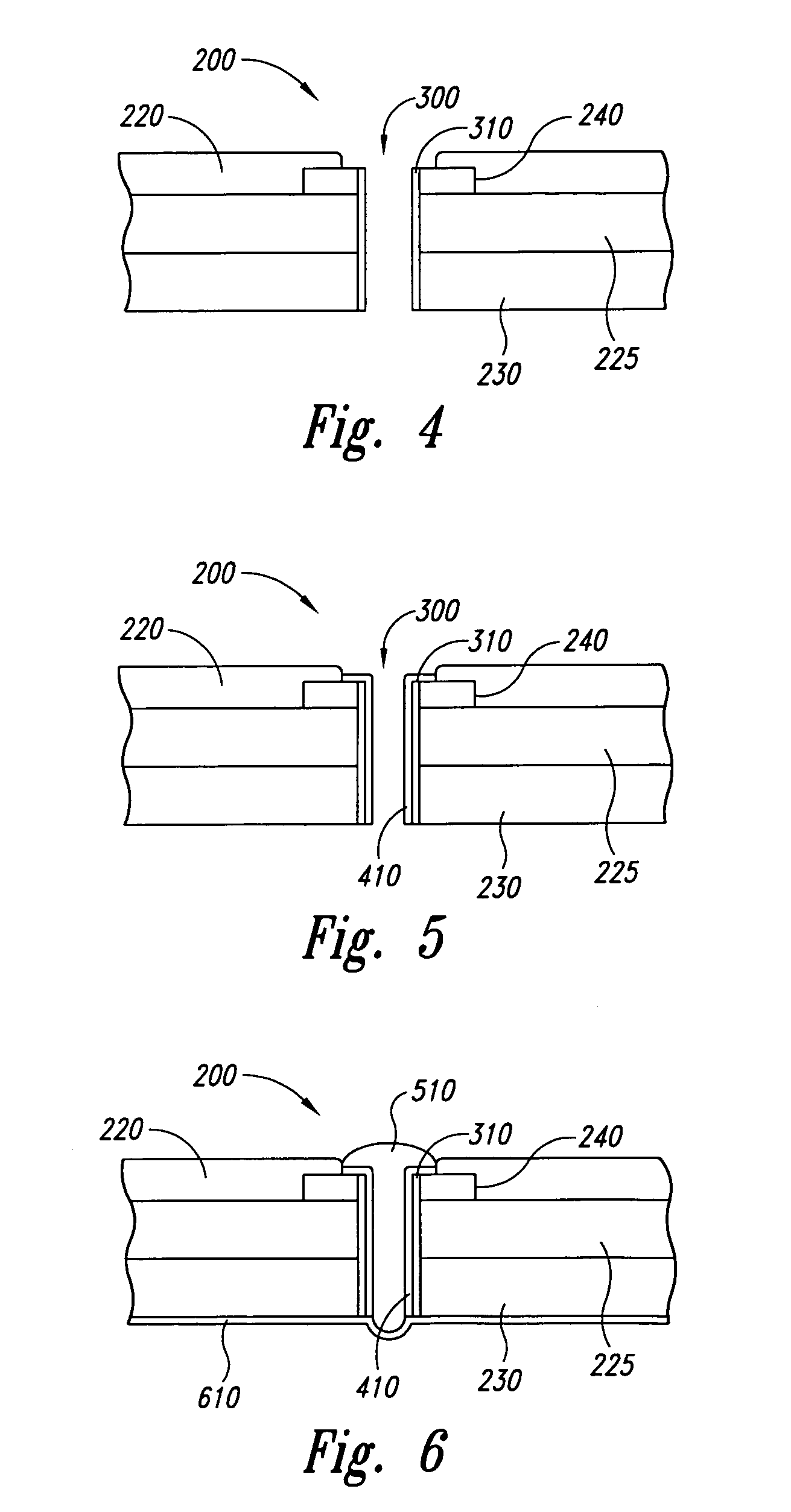

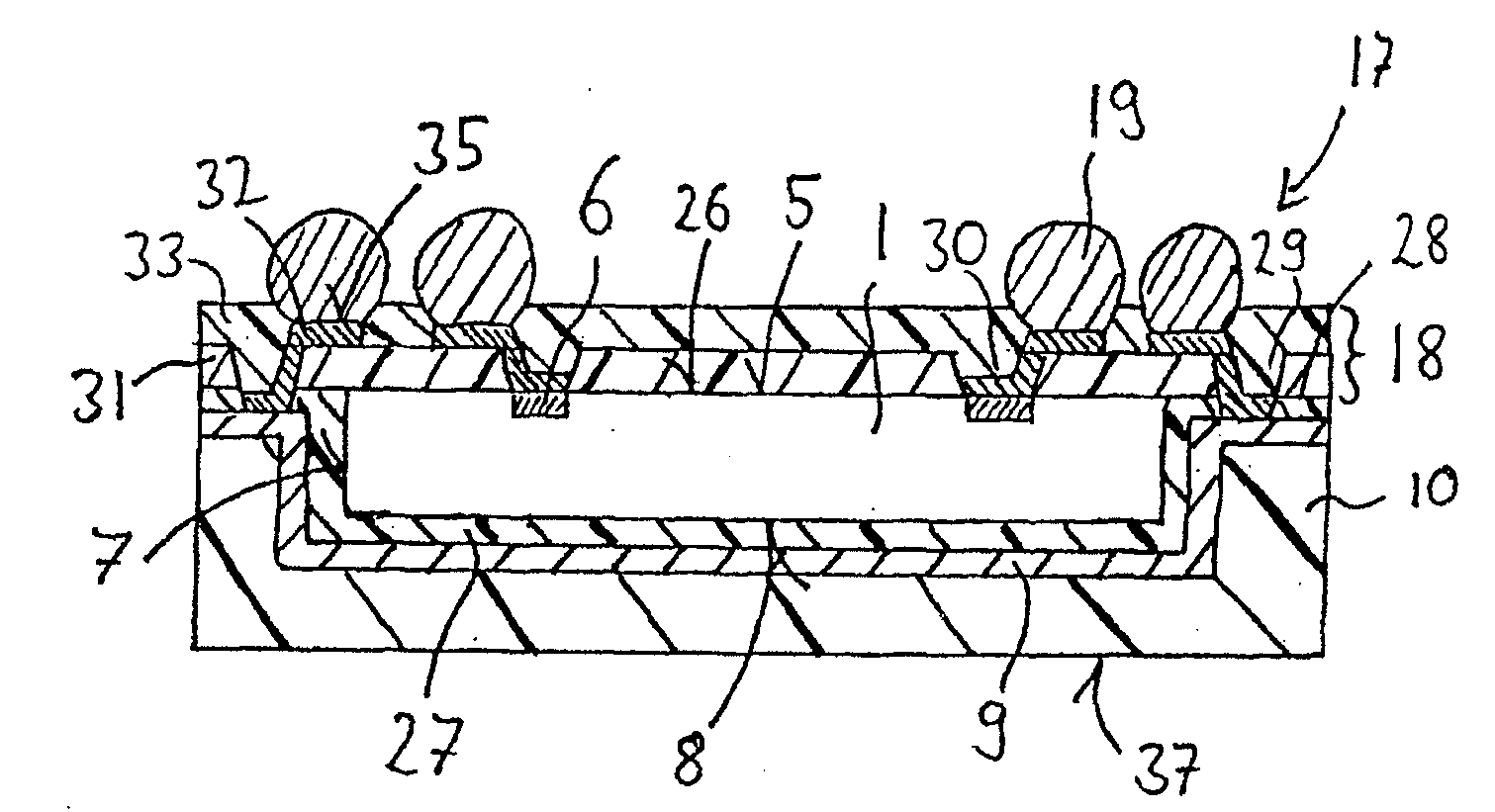

Carrier for wafer-scale package and wafer-scale package including the carrier

InactiveUS7271491B1Easy to reconfigureSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageConductive materials

A carrier for use in a chip-scale package, including a semiconductor substrate, such as a semiconductor wafer, with a plurality of apertures formed therethrough. The present invention also includes a chip-scale package including the carrier. When the carrier is employed in such a package, a semiconductor device or a wafer including a plurality of semiconductor devices thereon is invertedly aligned with and disposed over the carrier so that bond pads of the semiconductor device or semiconductor devices substantially align with apertures through the semiconductor substrate. The chip-scale package also includes conductive material disposed in each of the apertures of the semiconductor substrate to form vias through the semiconductor substrate. Conductive traces may extend substantially laterally from selected vias. The chip-scale package may also include a contact or conductive bump disposed in communication with each via. An intermediate layer may be disposed between the semiconductor device and the semiconductor substrate. The intermediate layer may secure the semiconductor device to the semiconductor substrate and insulate structures of the semiconductor device. An insulative layer may be disposed on the semiconductor substrate opposite the semiconductor device. If the chip-scale package includes an intermediate layer or an insulative layer, the electrically conductive vias that extend through the semiconductor substrate are preferably exposed through such layers. The present invention also includes methods of fabricating the semiconductor substrate and assembling a chip-scale package of the invention, including substantially simultaneously assembling semiconductor devices and carrier substrates on a wafer-scale and singulating individual chip-scale packages from the assembled wafers.

Owner:MICRON TECH INC

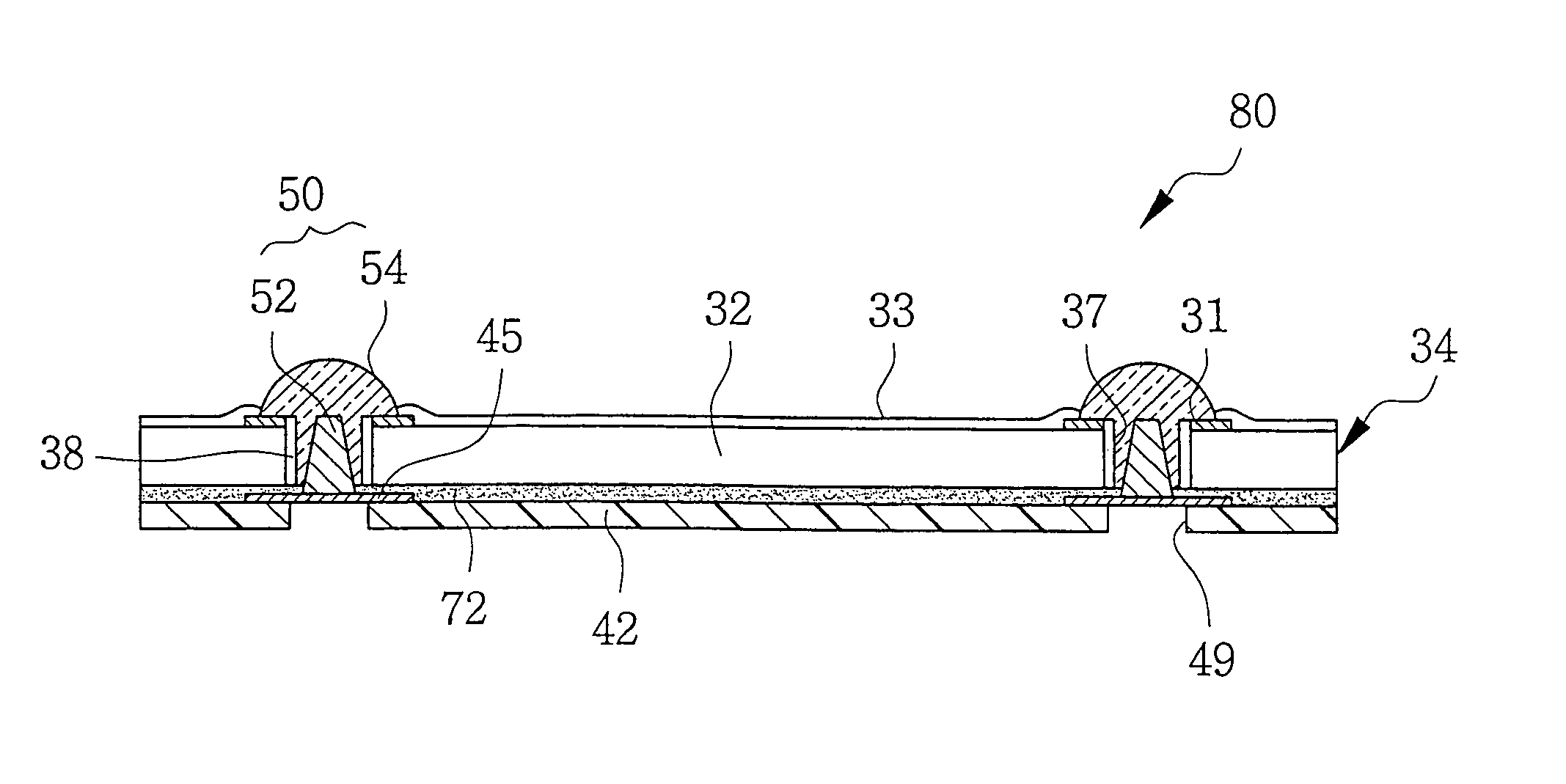

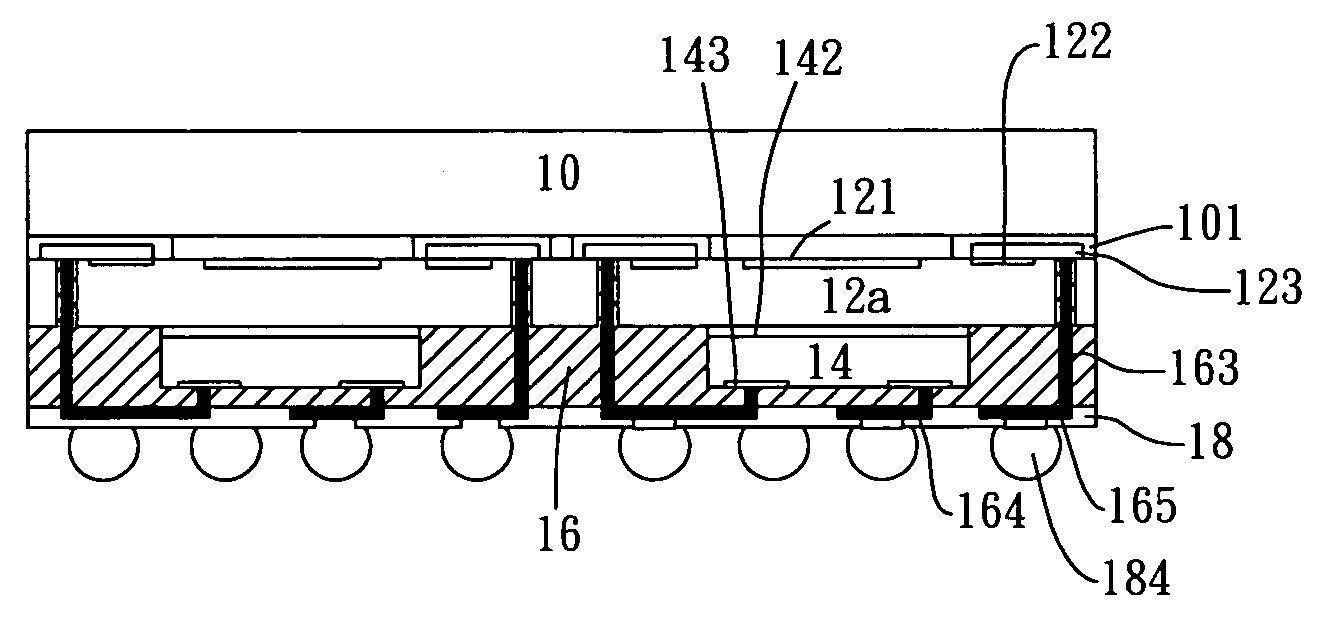

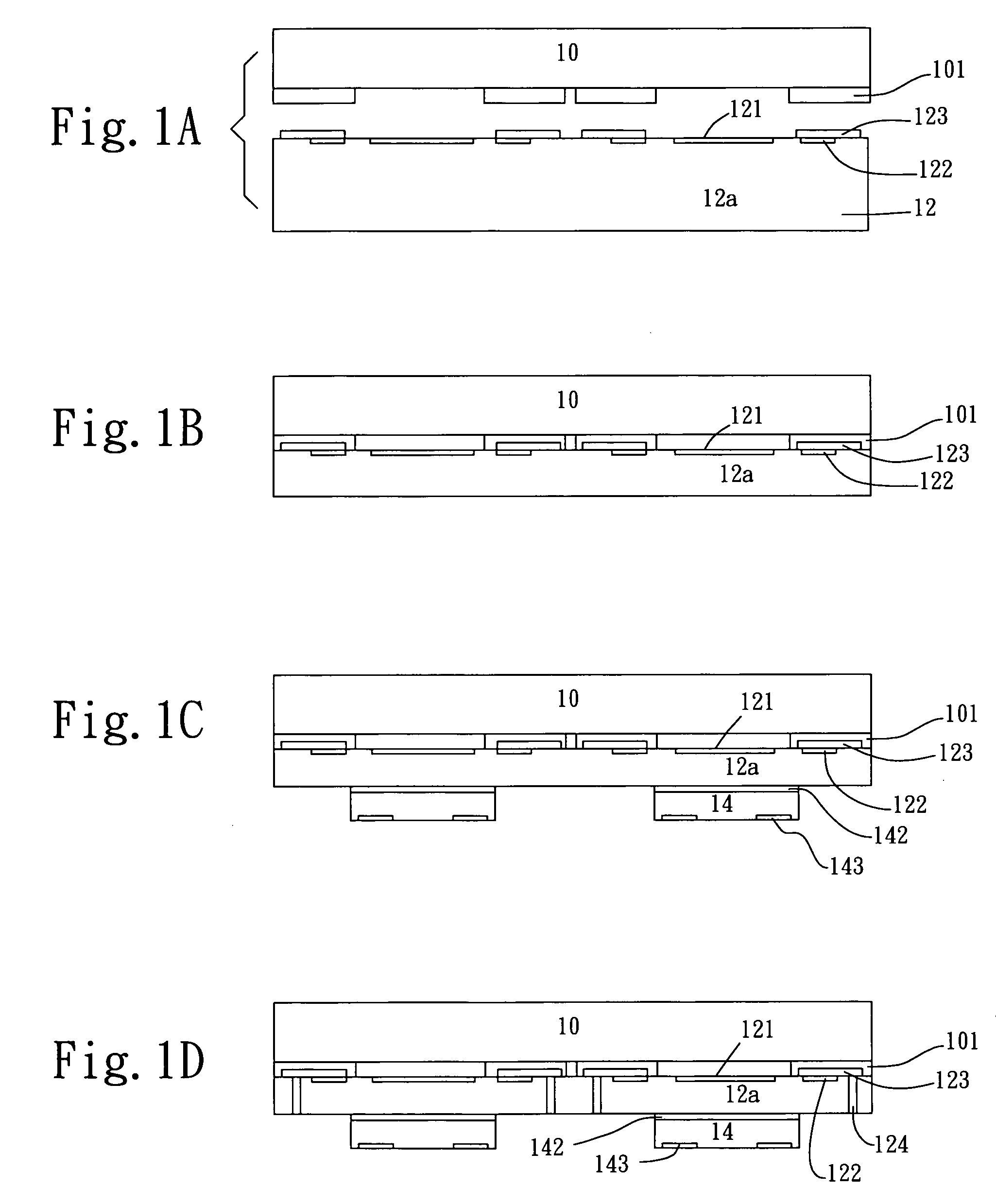

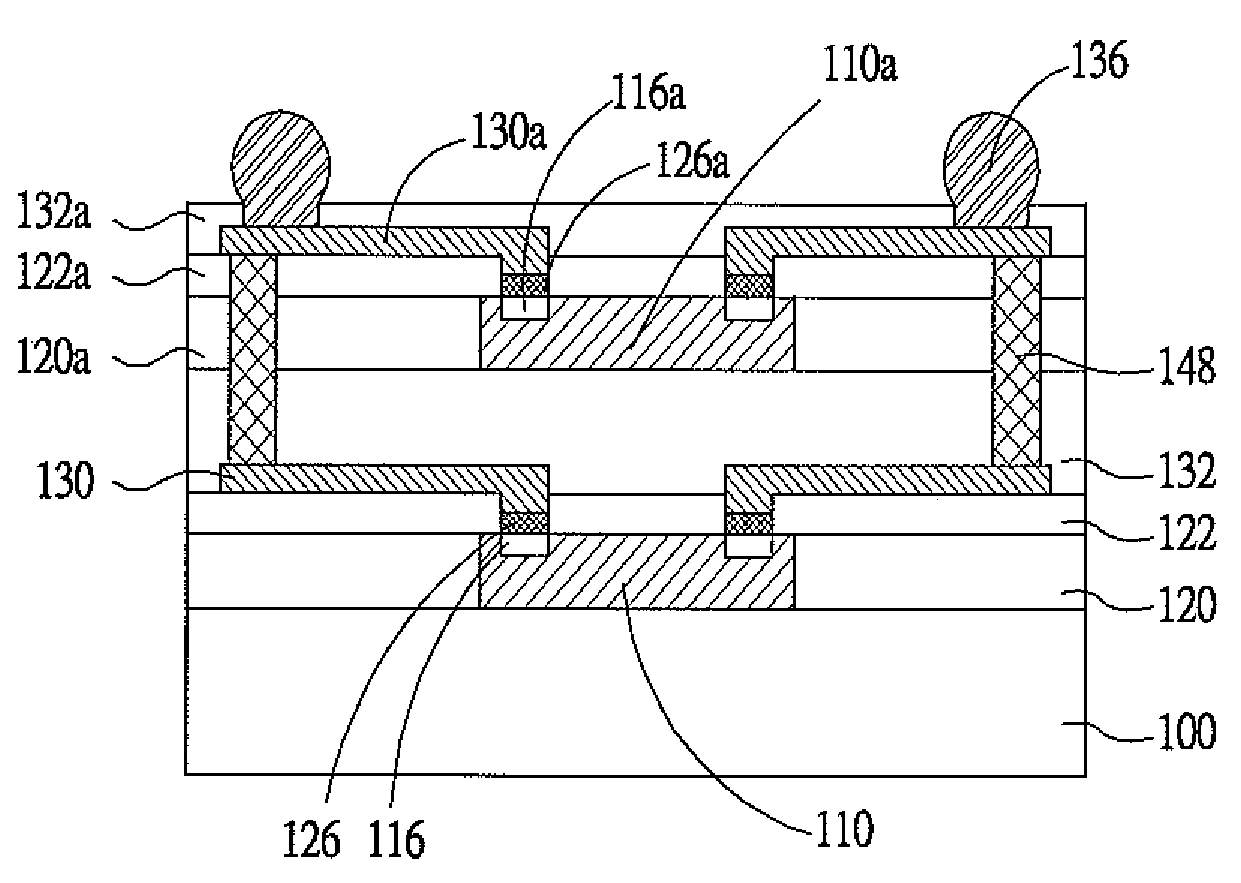

Wafer level package with die receiving cavity and method of the same

InactiveUS20080116564A1Board levelReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

The present invention provides a structure of package comprising a substrate with a die receiving cavity formed within an upper surface of the substrate and a through hole structure formed there through, wherein a terminal pad is formed under the through hole structure and the substrate includes a conductive trace formed on a lower surface of the substrate. A die is disposed within the die receiving cavity by adhesion and a dielectric layer formed on the die and the substrate. A re-distribution metal layer (RDL) is formed on the dielectric layer and coupled to the die and the through hole structure. Conductive bumps are coupled to the terminal pad.

Owner:ADVANCED CHIP ENG TECH

Wafer level package having a side package

InactiveUS6852607B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method of manufacturing a wafer level package includes forming a semiconductor wafer including semiconductor chips, and forming a package body on the sides of each semiconductor chip. The package body is formed by forming a space between each semiconductor chip and potting a package material in the space, which can be a mold resin. The wafer is then separated into separate semiconductor chips by cutting through the package body.

Owner:SAMSUNG ELECTRONICS CO LTD

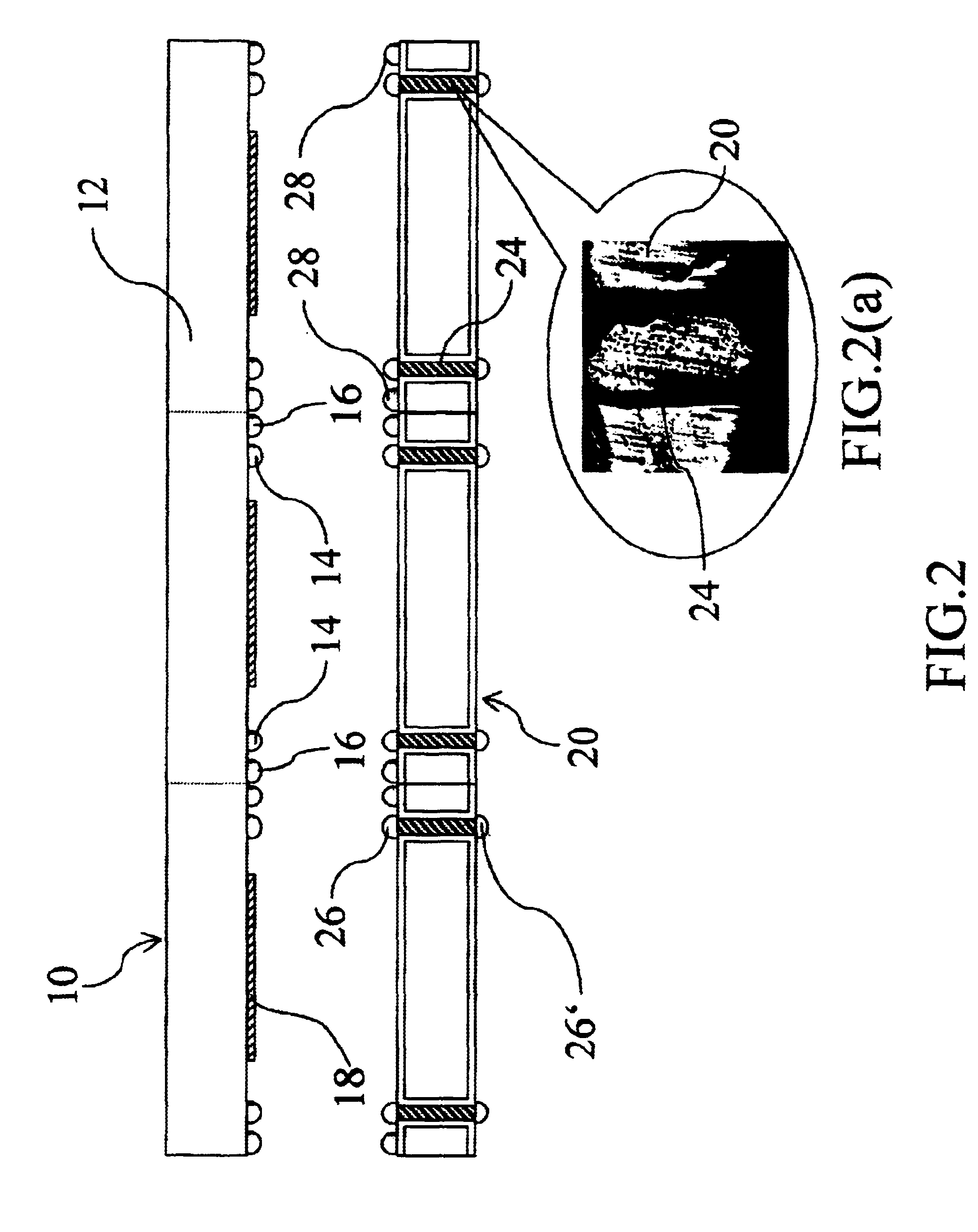

Wafer level packaging of micro electromechanical device

InactiveUS6710461B2Avoid damageImprove evennessDecorative surface effectsSemiconductor/solid-state device detailsElectrical conductorWafering

The present invention provides a wafer level package of micro electromechanical devices. The wafer level package of the present invention comprises a wafer having a plurality of micro electromechanical devices and a package wafer of the same size. A plurality of conductor plugs penetrate through the upper and lower surfaces of the package wafer. Solder bumps are formed on the conductor plugs to be adhered to predetermined solder bumps on the micro electromechanical device wafer so as to form a package device. The wafer level package of the present invention can prevent micro electromechanical devices from damage during the packaging procedure.

Owner:XIANGQUN SCI & TECH

Wafer level package and method of manufacturing the same and method of reusing chip

ActiveUS20100133680A1Improve production yieldReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesResistEngineering

The present invention relates to a wafer level package and a method of manufacturing the same and a method of reusing a chip and provides a wafer level package including a chip; a removable resin layer formed to surround side surfaces and a lower surface of the chip; a molding material formed on the lower surface of the removable resin layer; a dielectric layer formed over the removable resin layer including the chip and having via holes to expose portions of the chip; redistribution lines formed on the dielectric layer including insides of the via holes to be connected to the chip; and a solder resist layer formed on the dielectric layer to expose portions of the redistribution lines. Also, the present invention provides a method of manufacturing a wafer level package and a method of reusing a chip.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

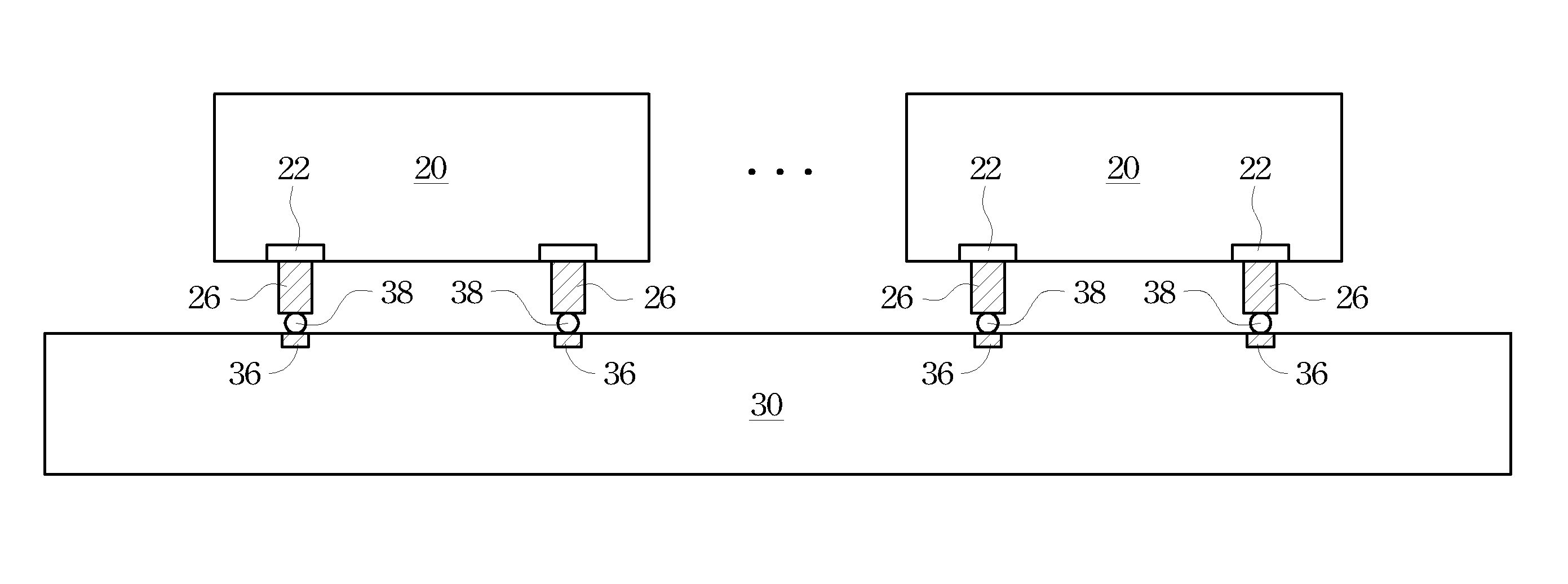

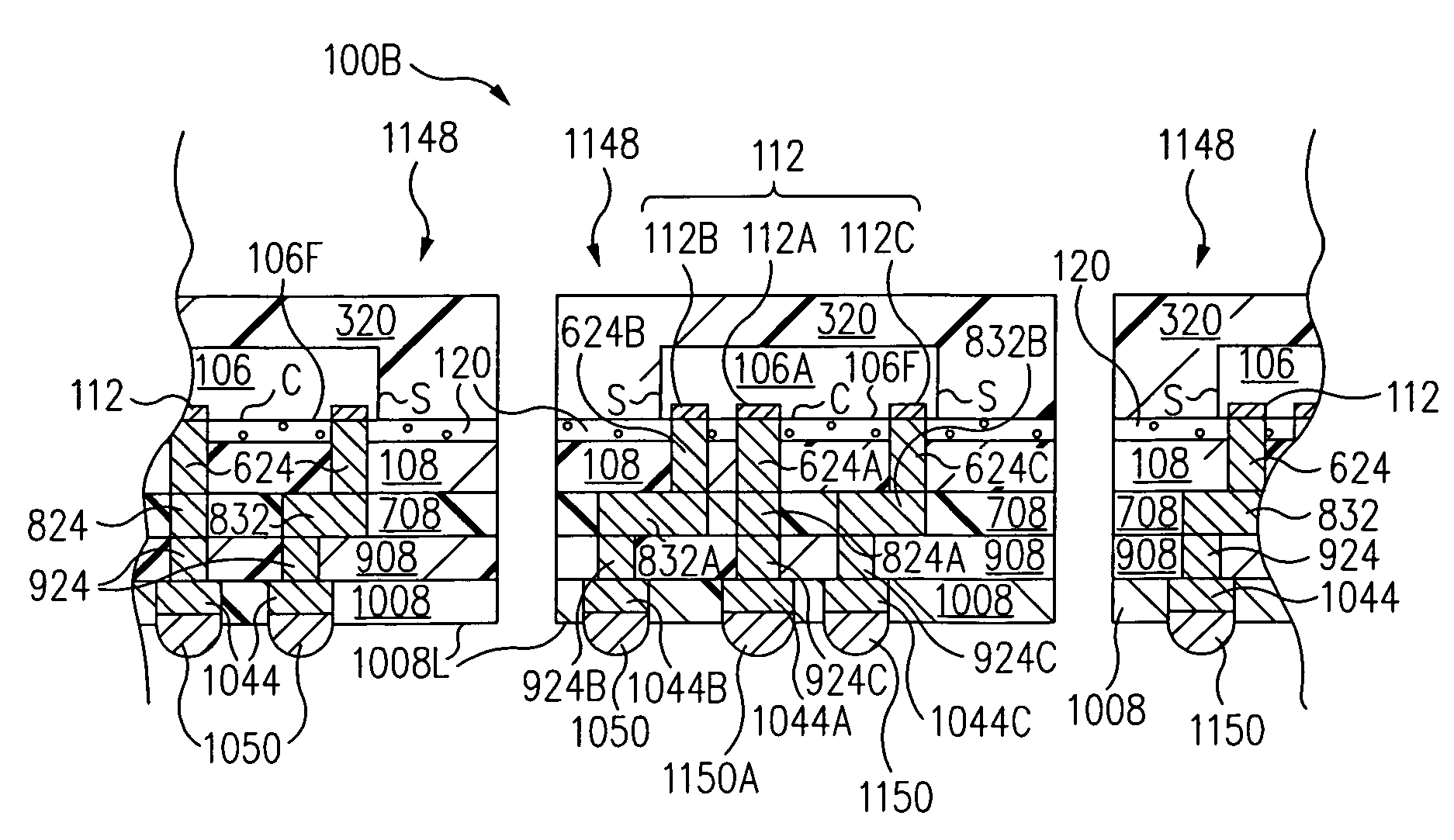

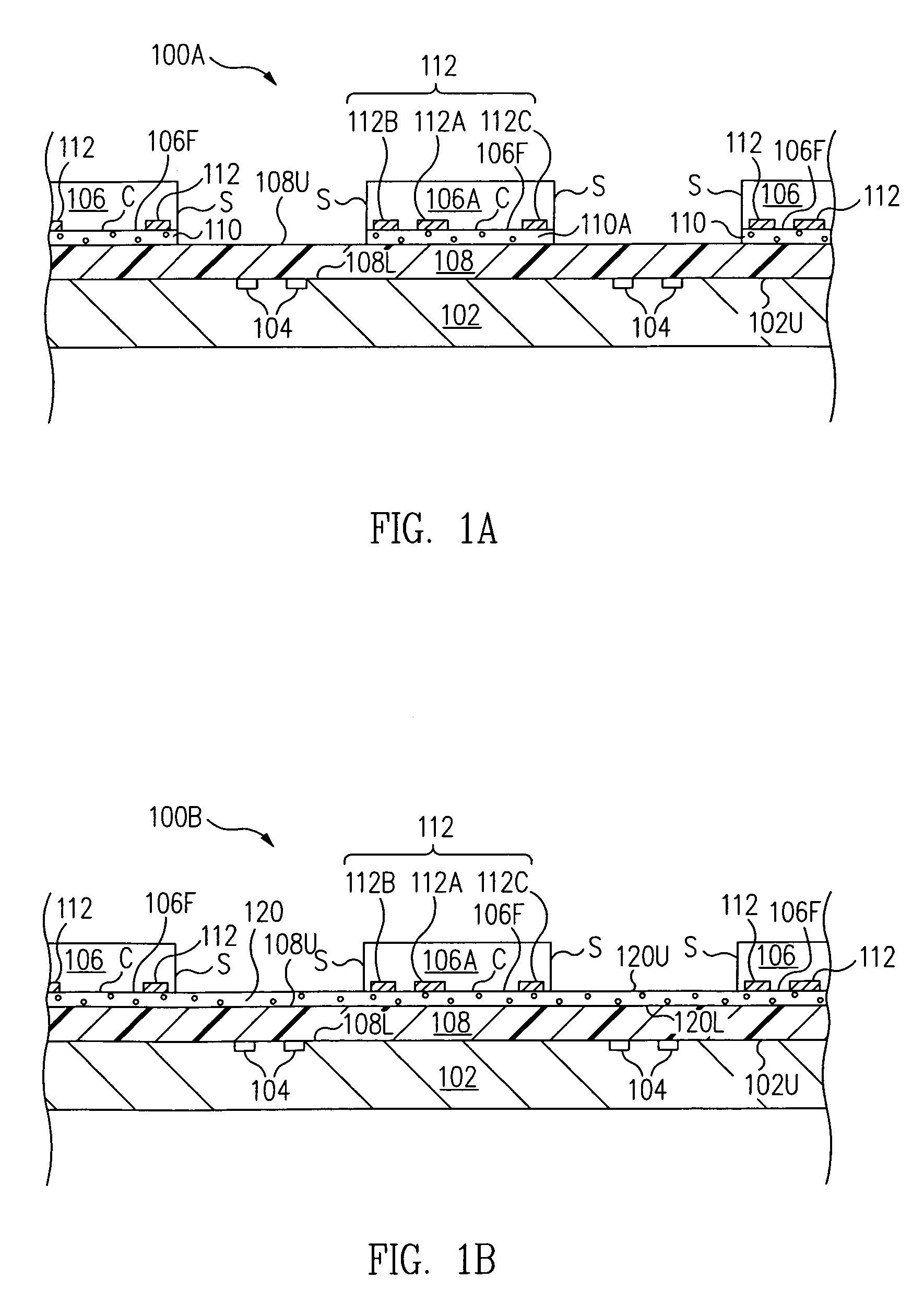

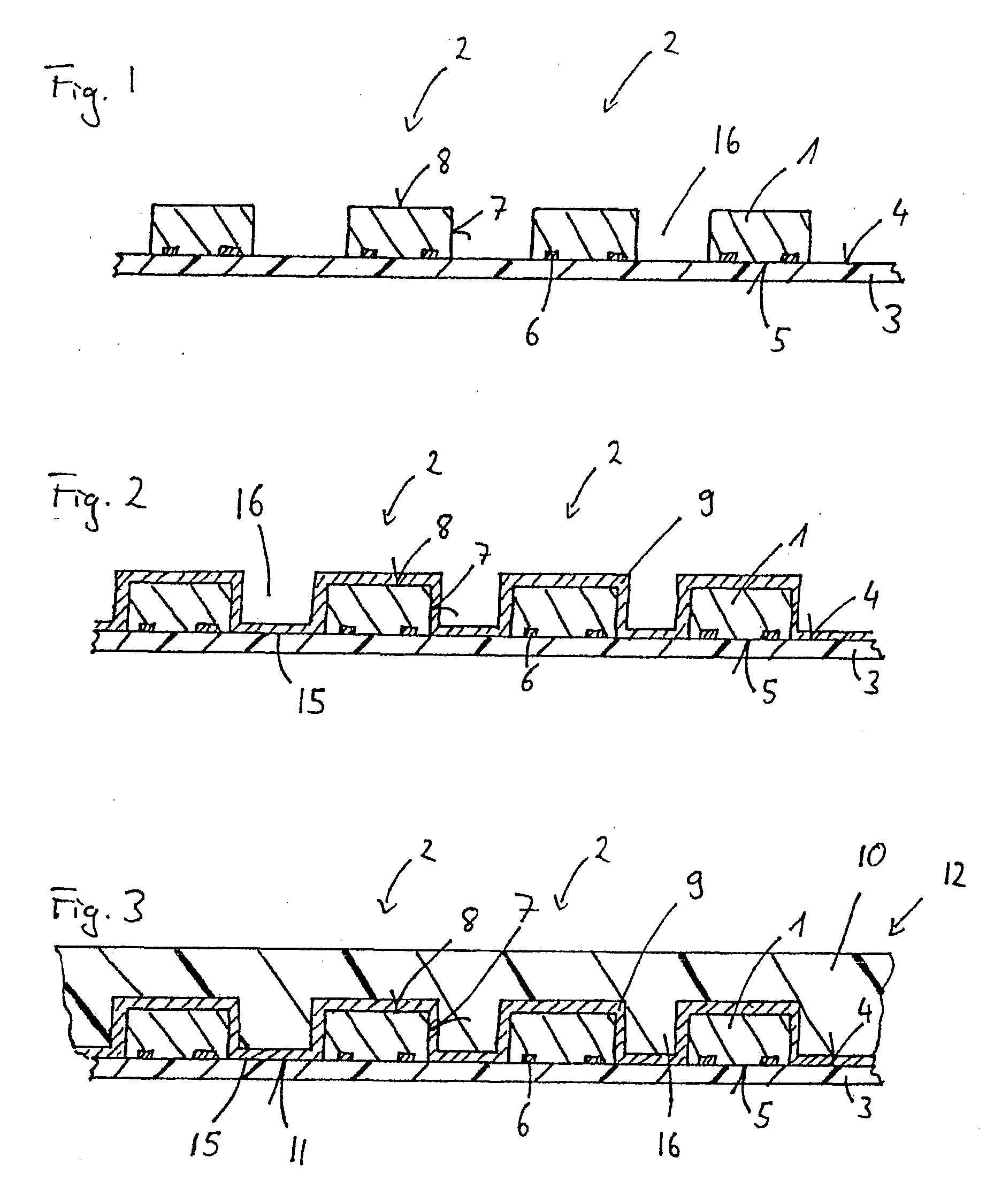

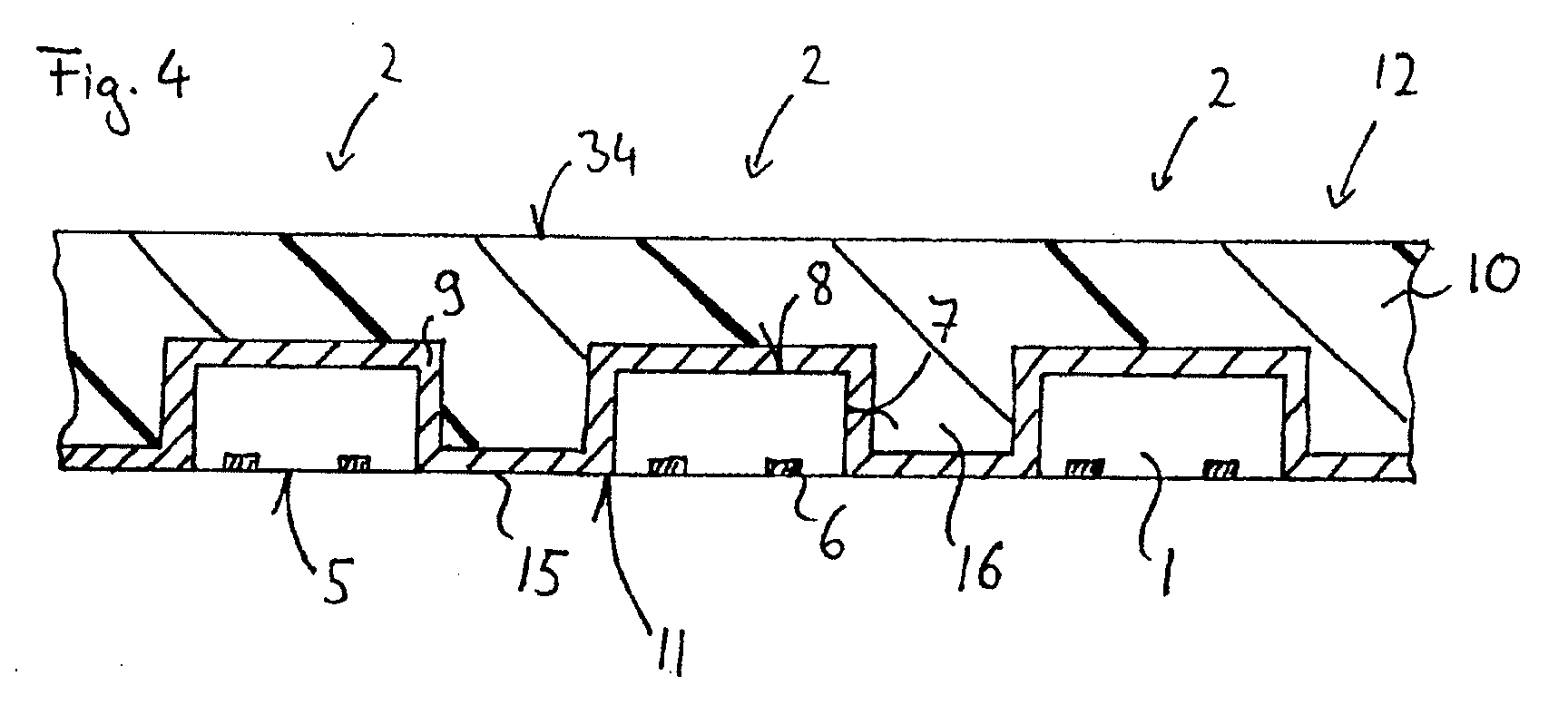

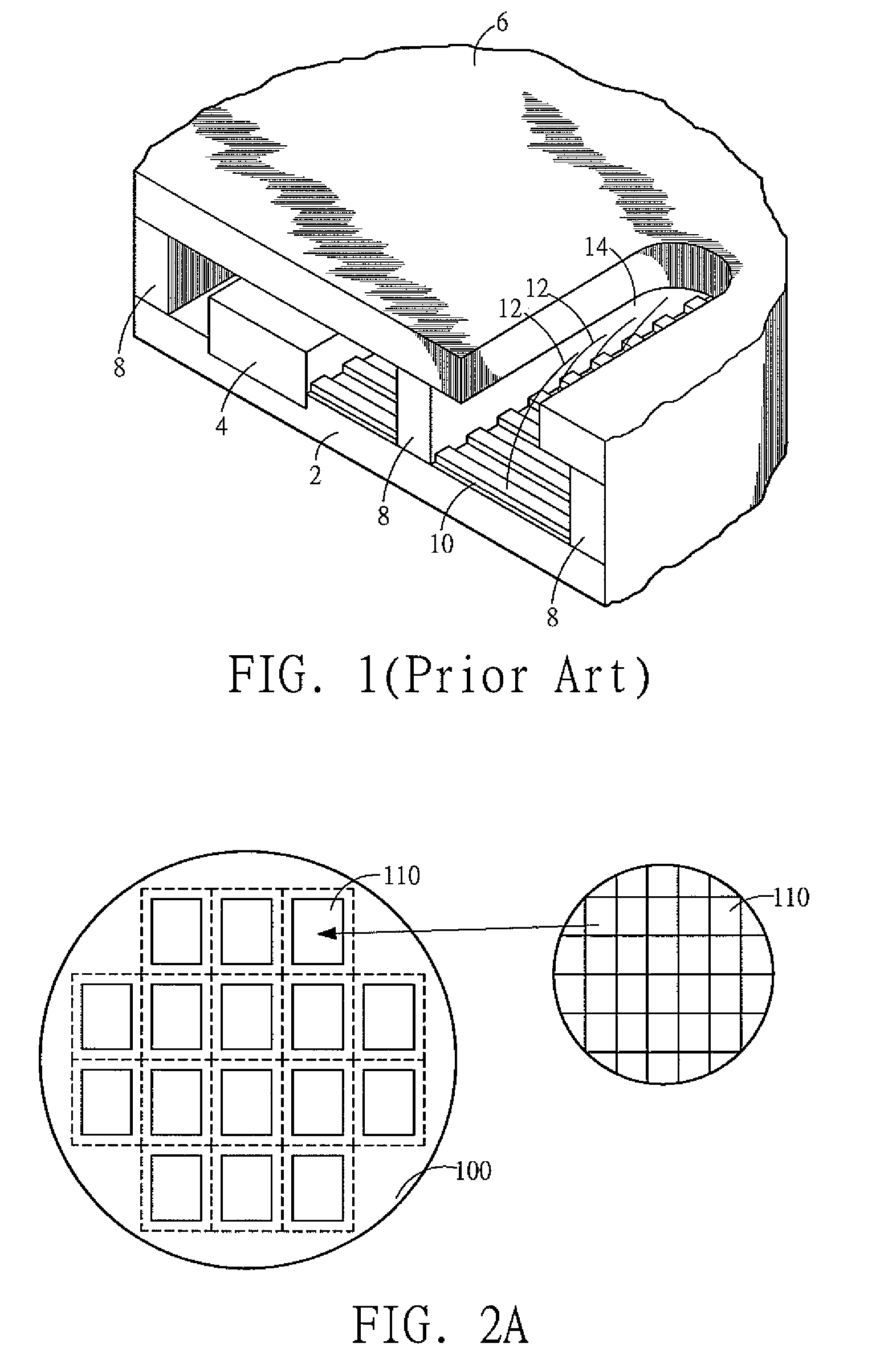

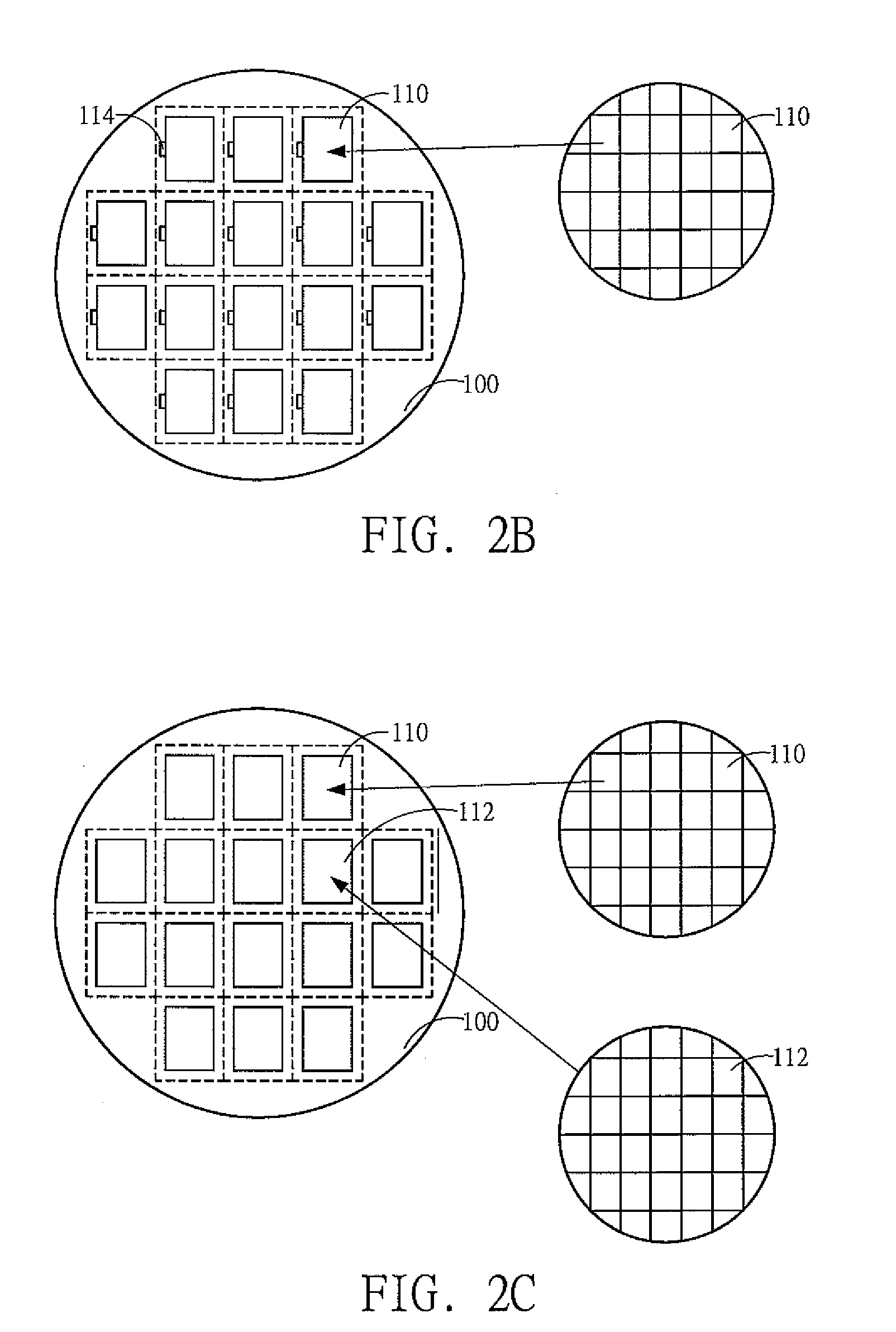

Fan out type wafer level package structure and method of the same

ActiveUS20060231958A1Avoid problemsLow costSemiconductor/solid-state device detailsSolid-state devicesEngineeringLarge size

To pick and place standard dice on a new base for obtaining an appropriate and wider distance between dice than the original distance of dice on a wafer. The package structure has a larger size of balls array than the size of the die by fan out type wafer level package. Moreover, the die may be packaged with passive components or other dice with a side by side structure or a stacking structure.

Owner:ADL ENERGY CORP