Patents

Literature

183results about How to "Reduce package thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

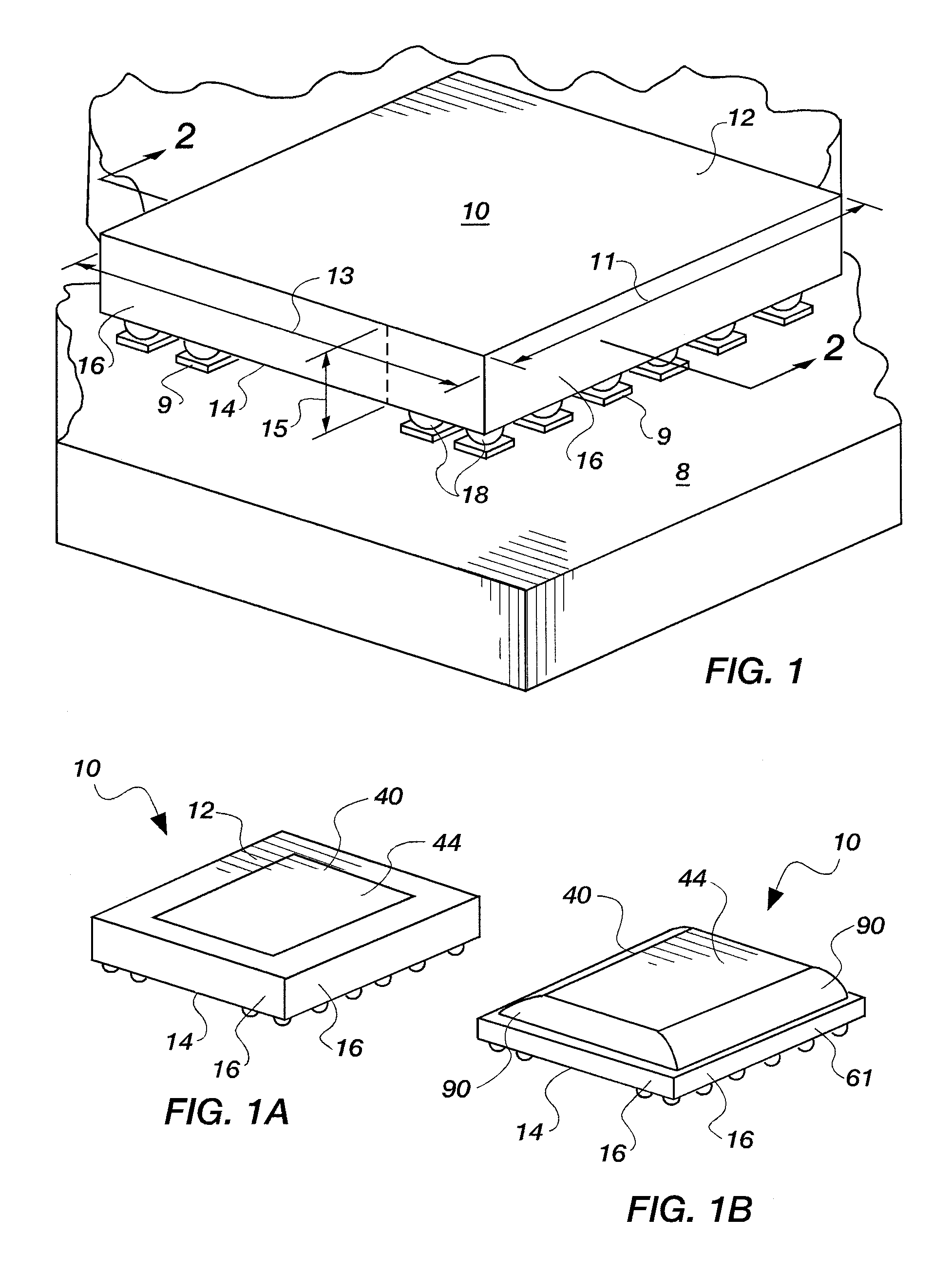

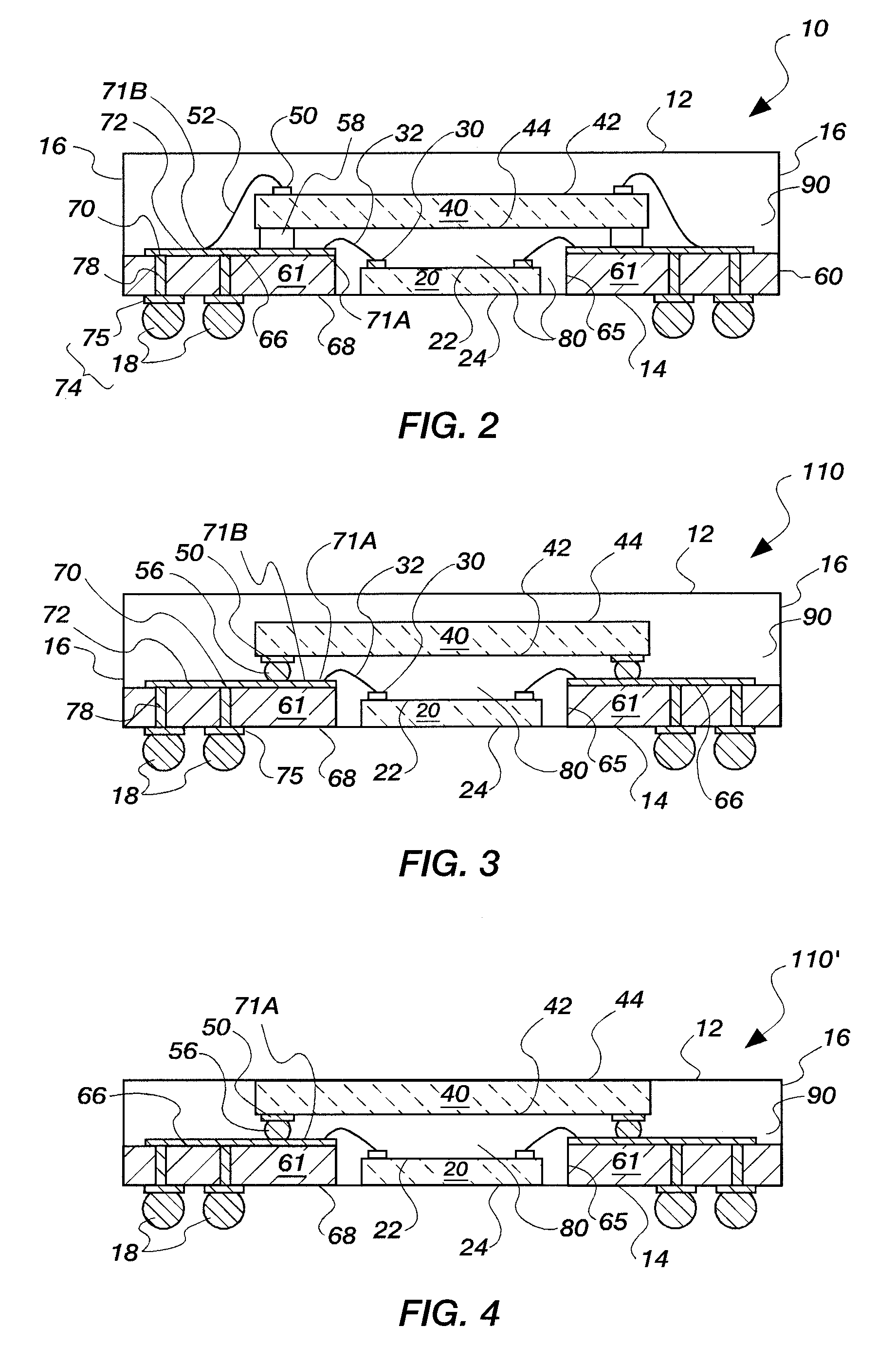

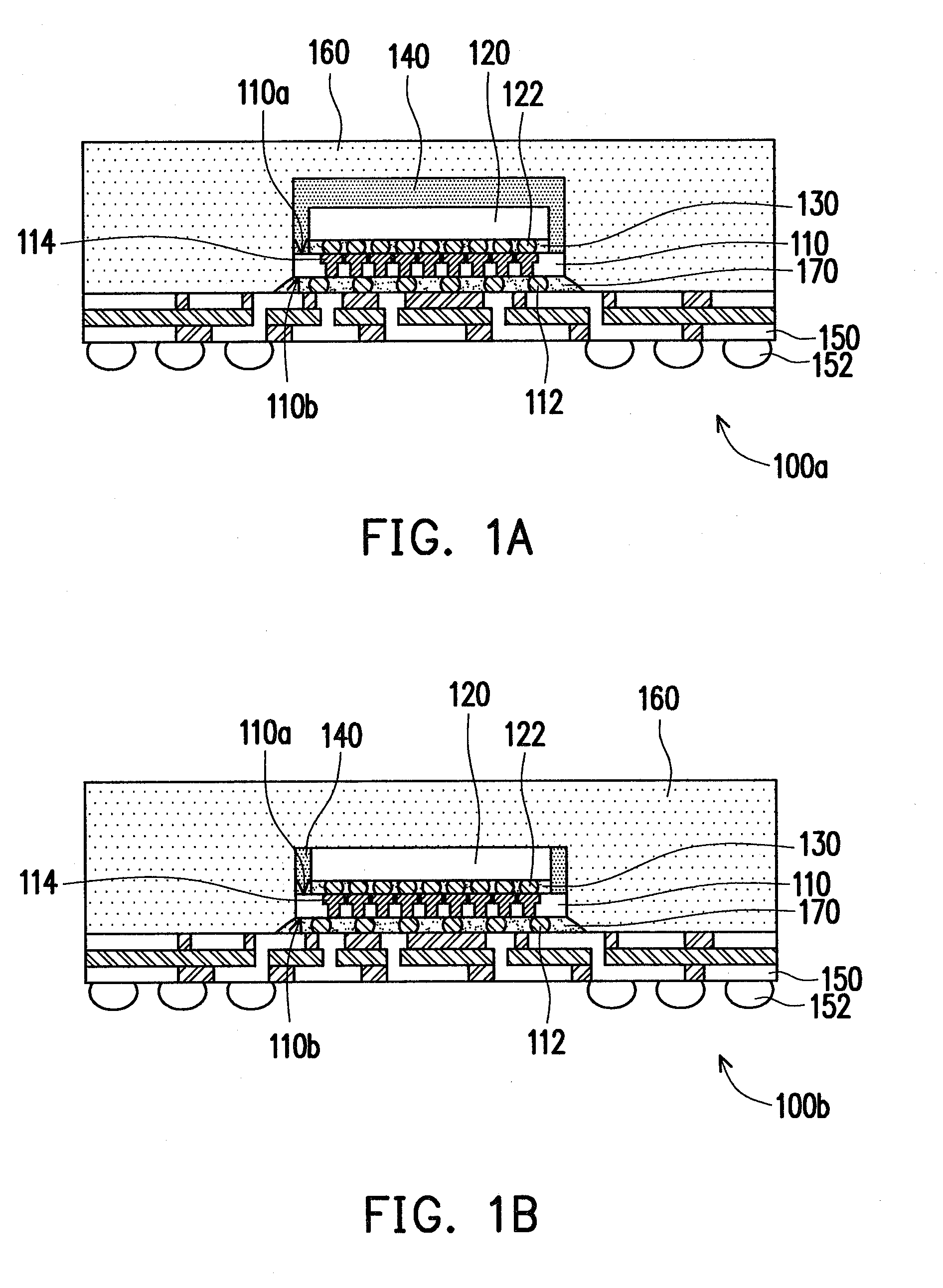

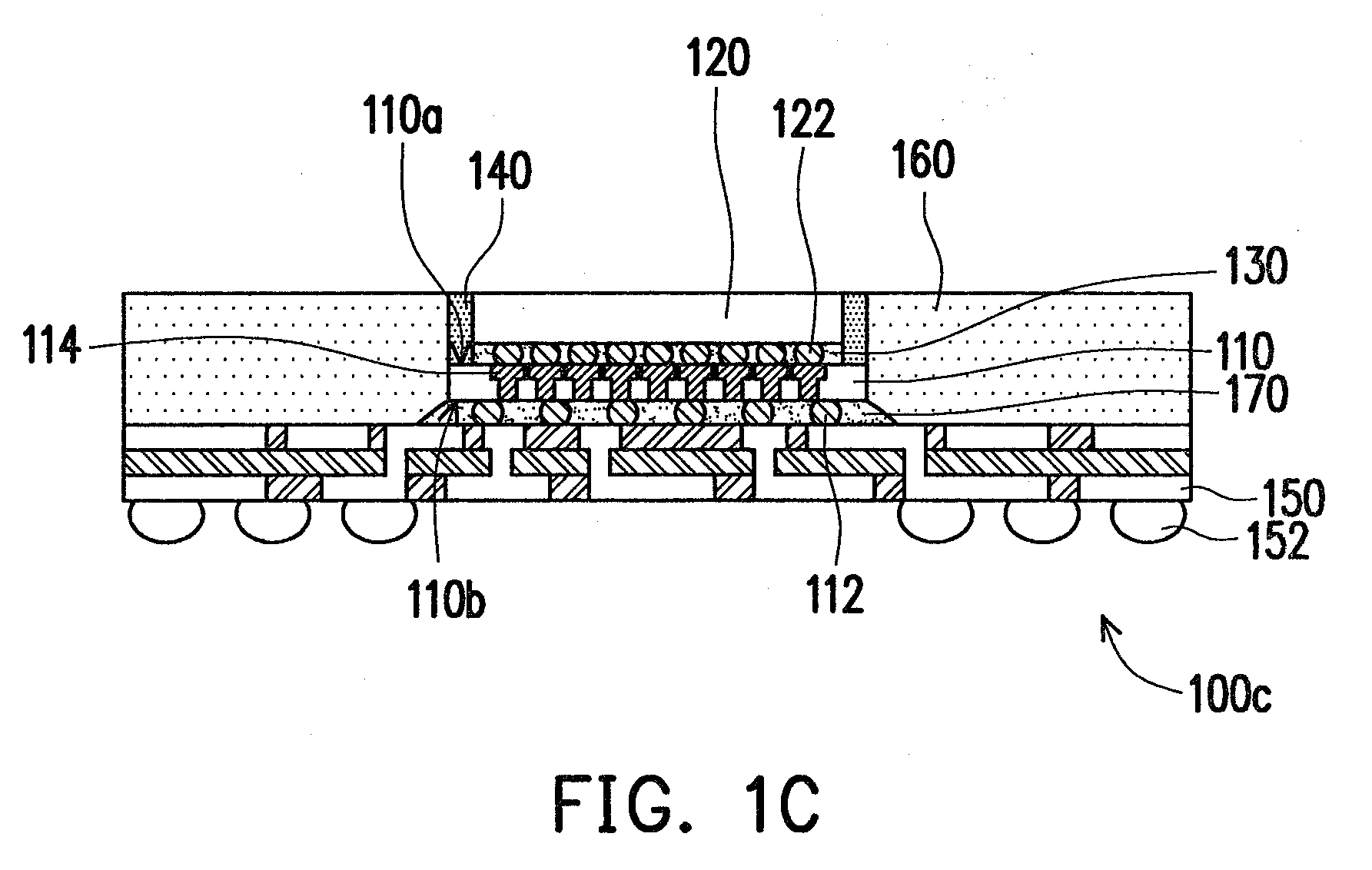

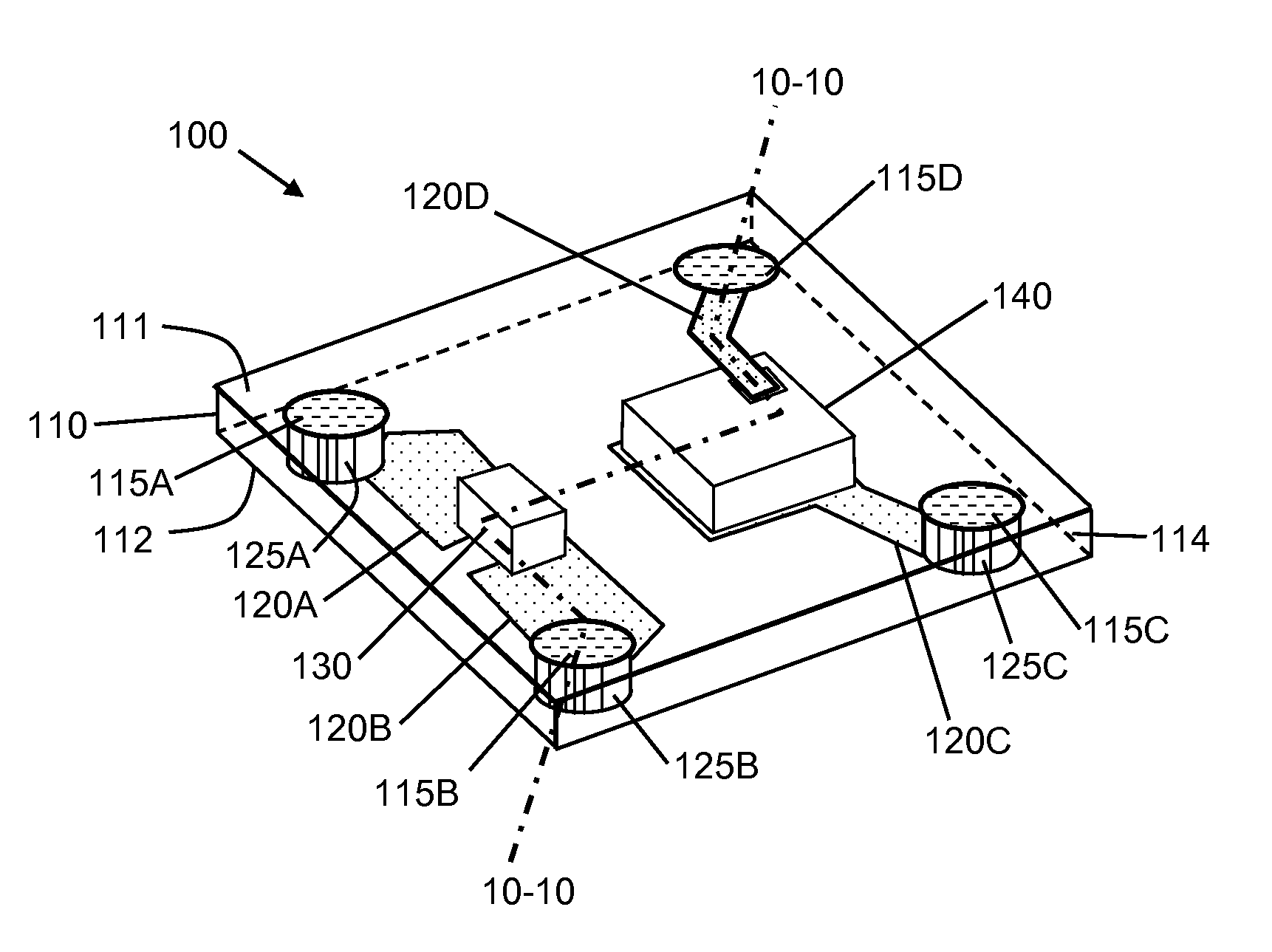

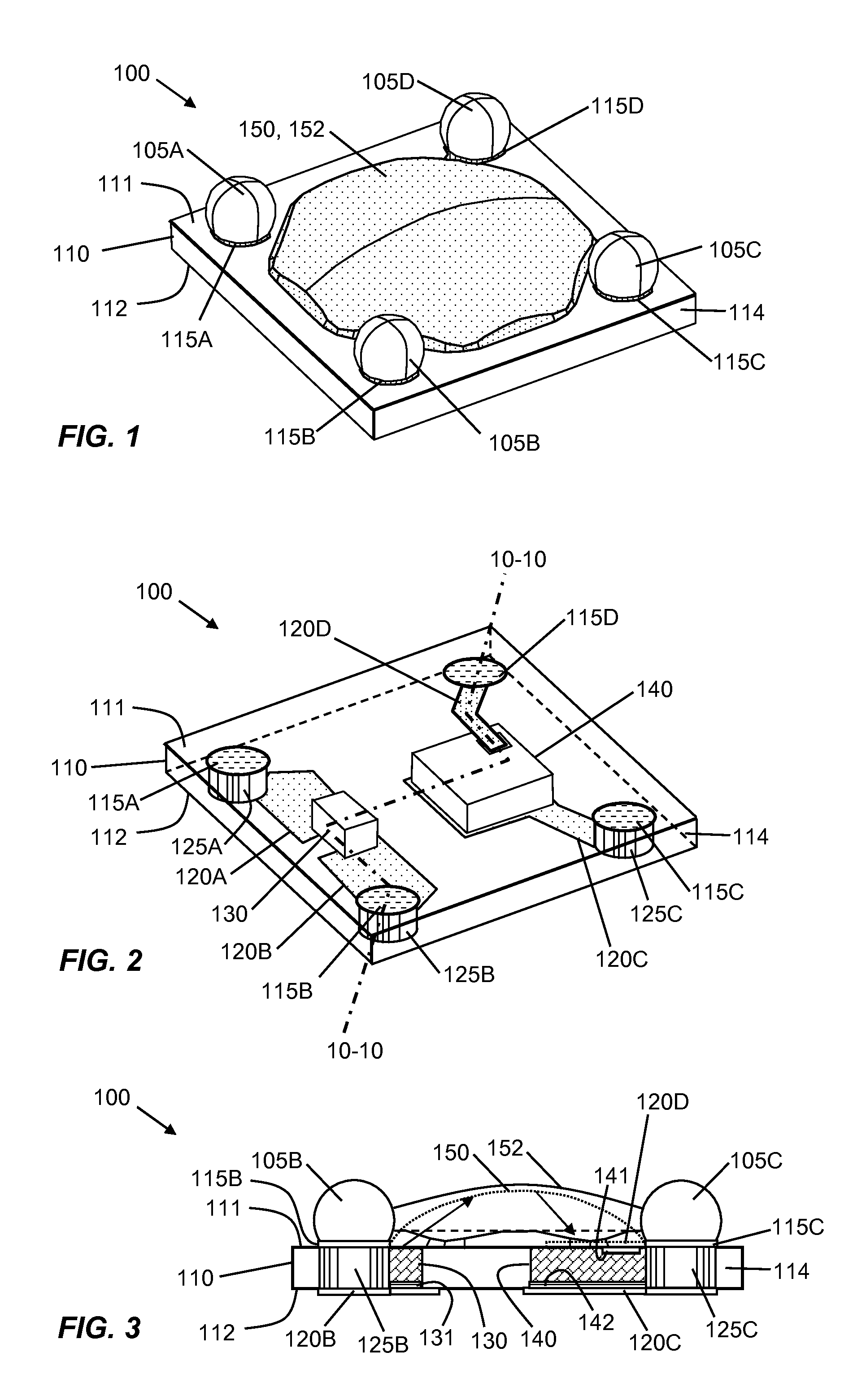

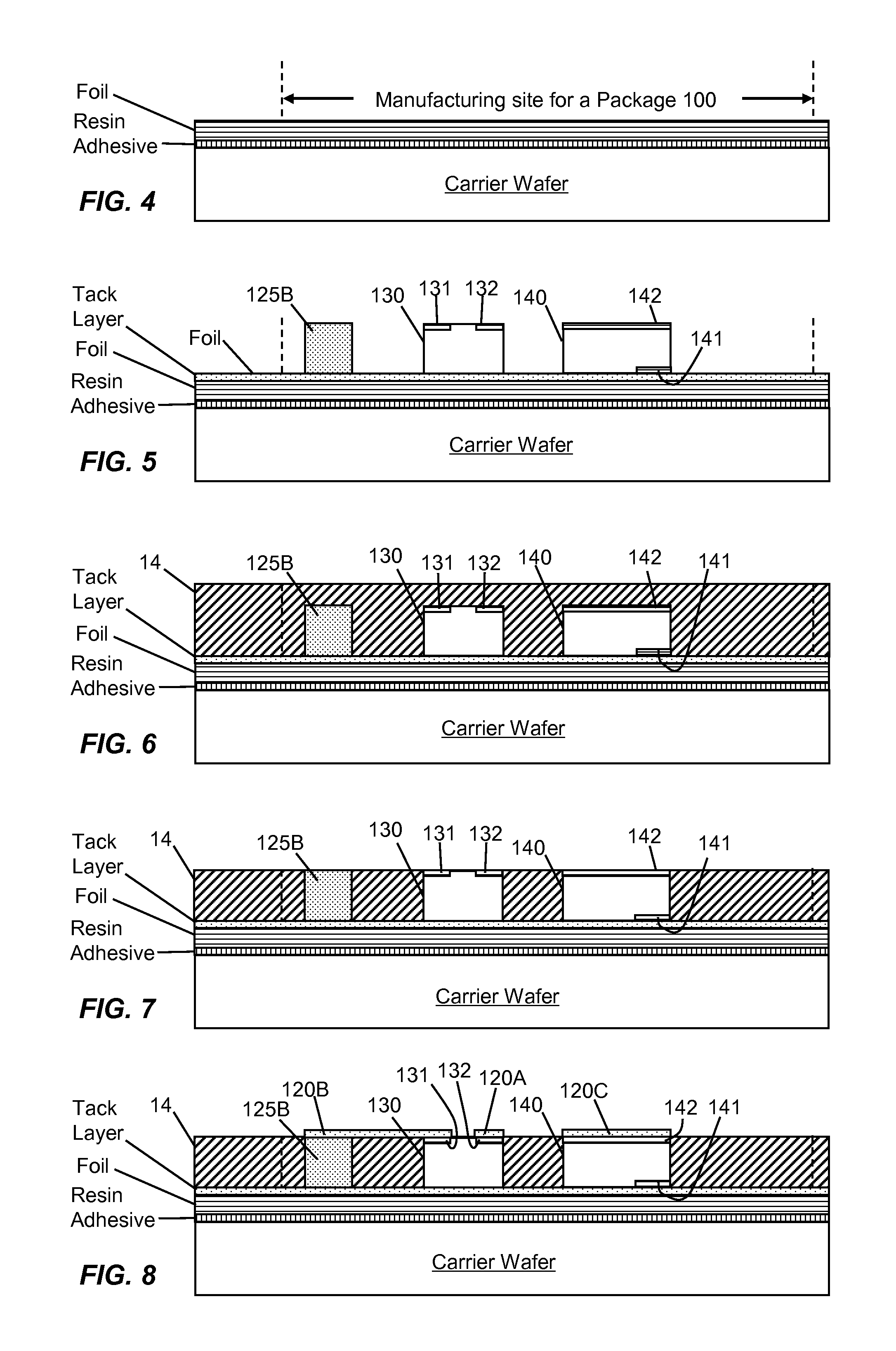

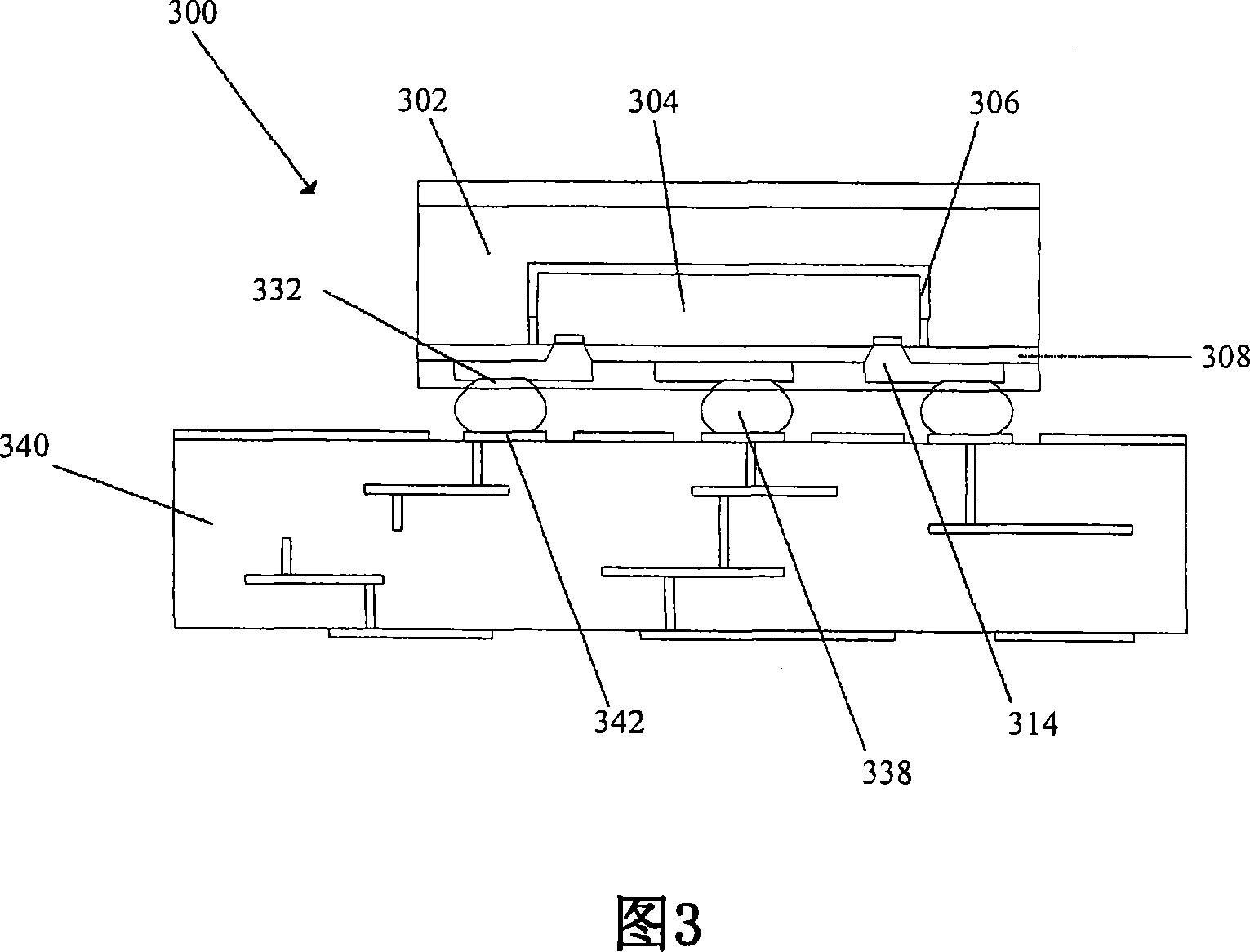

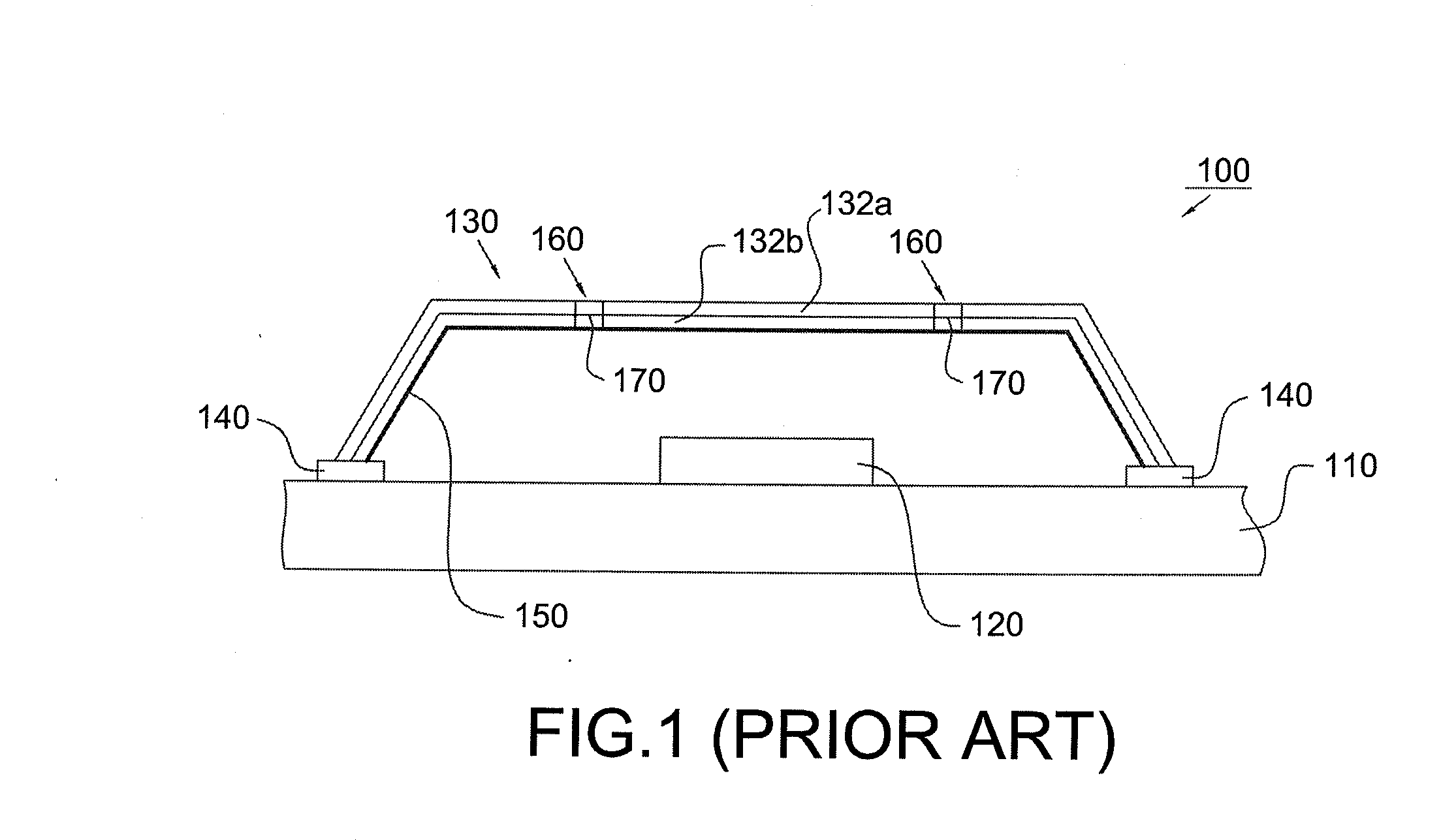

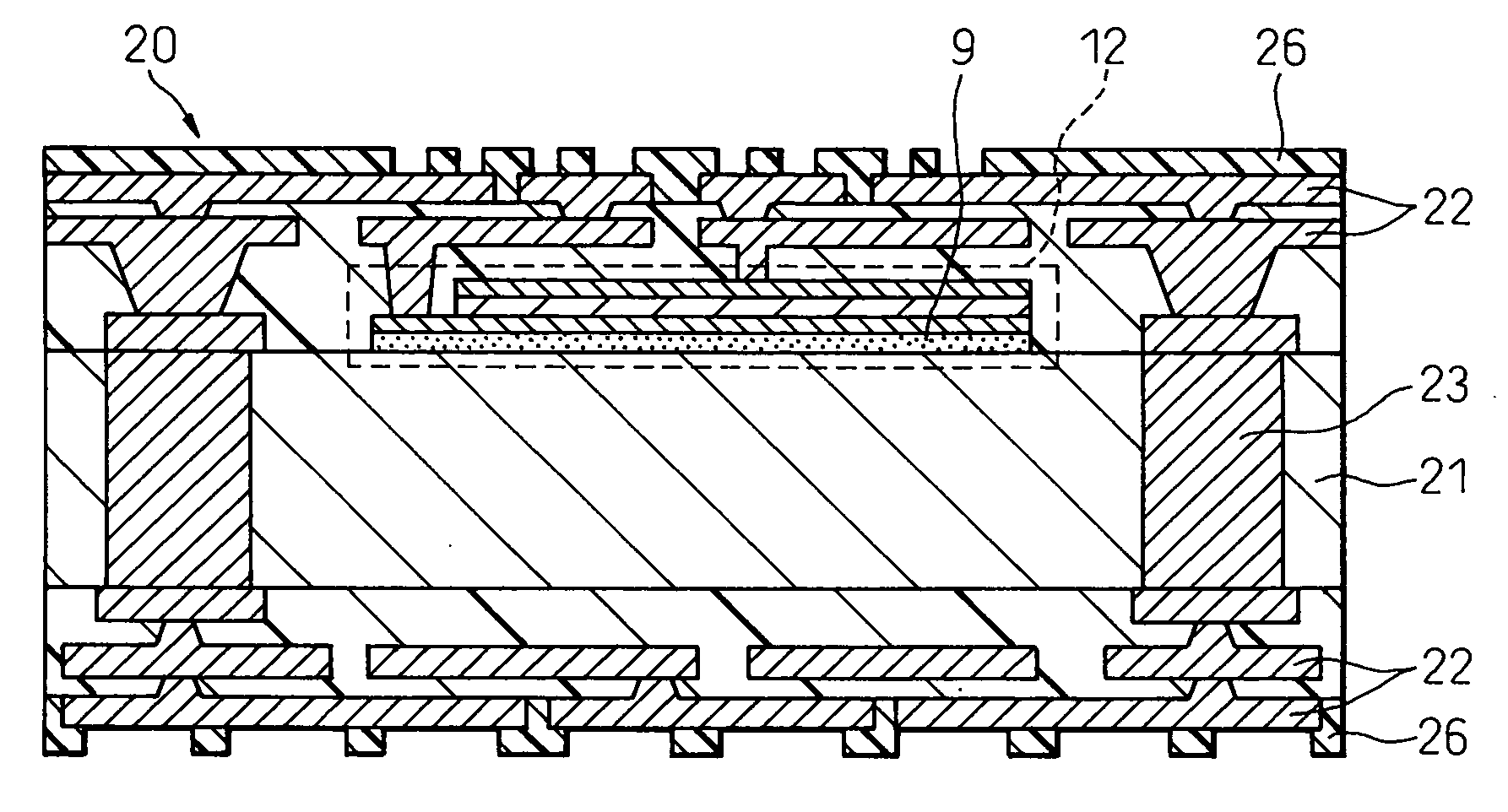

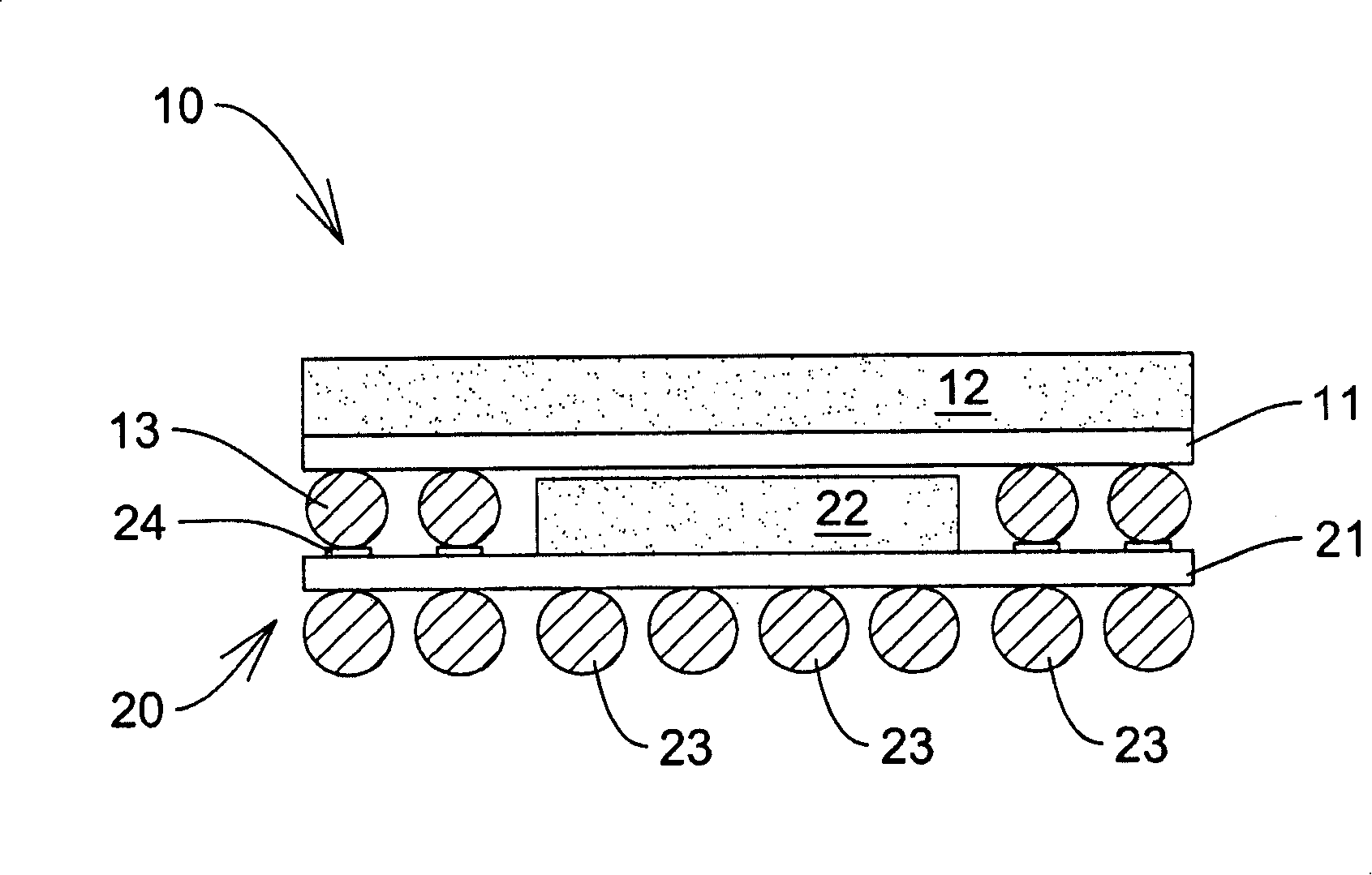

Methods for assembling multiple semiconductor devices

InactiveUS7198980B2Reduce area requirementsHelp positioningPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorElectrical connection

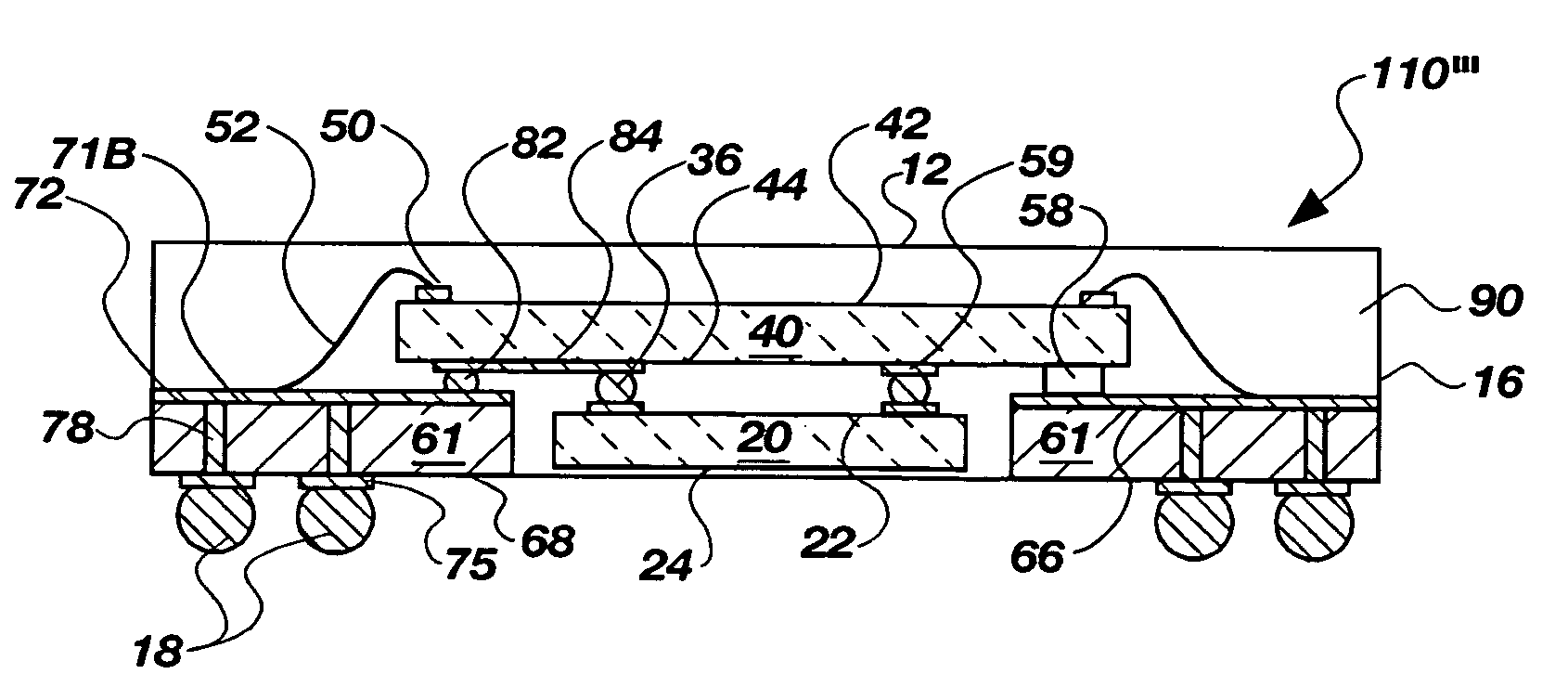

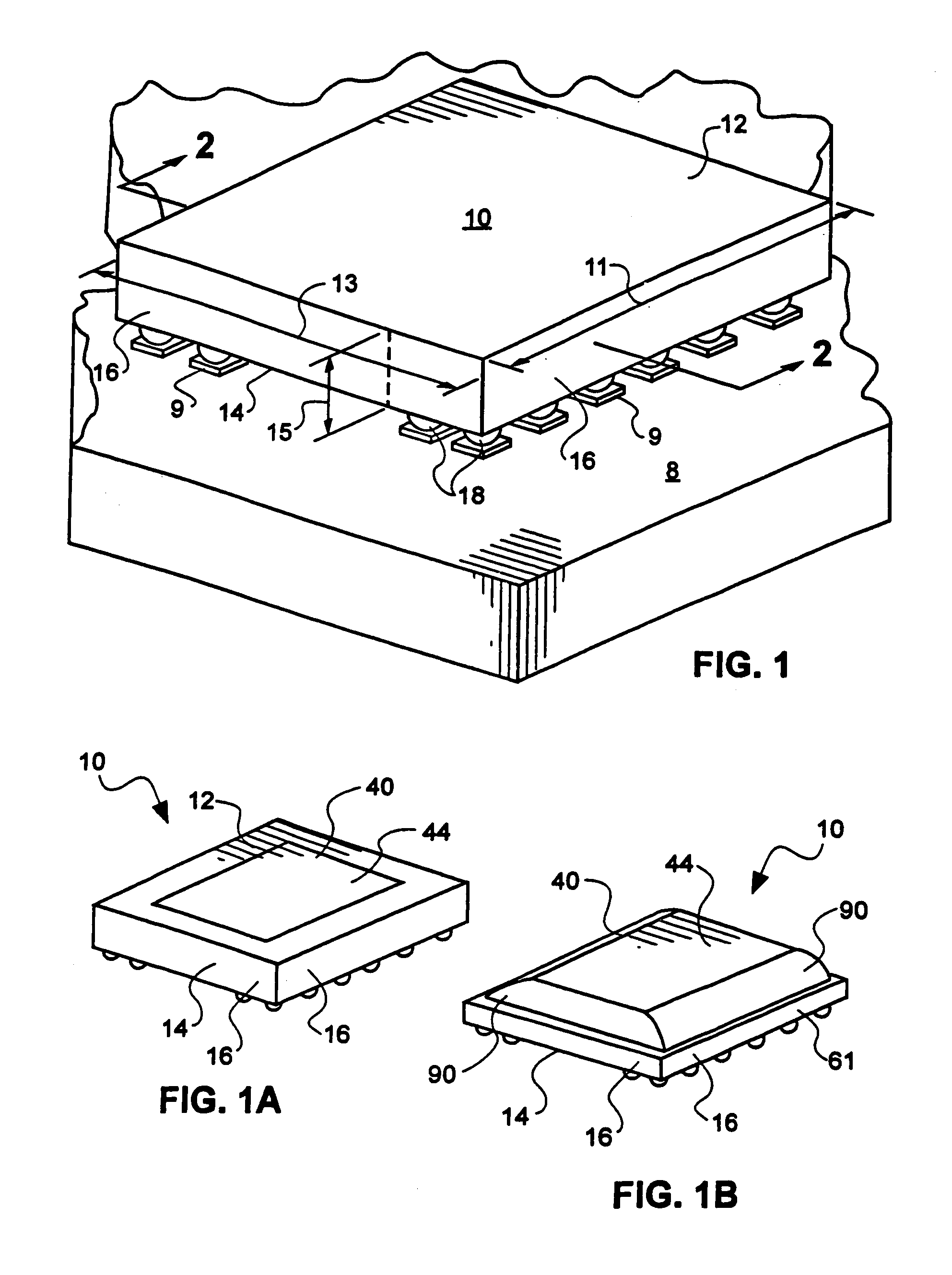

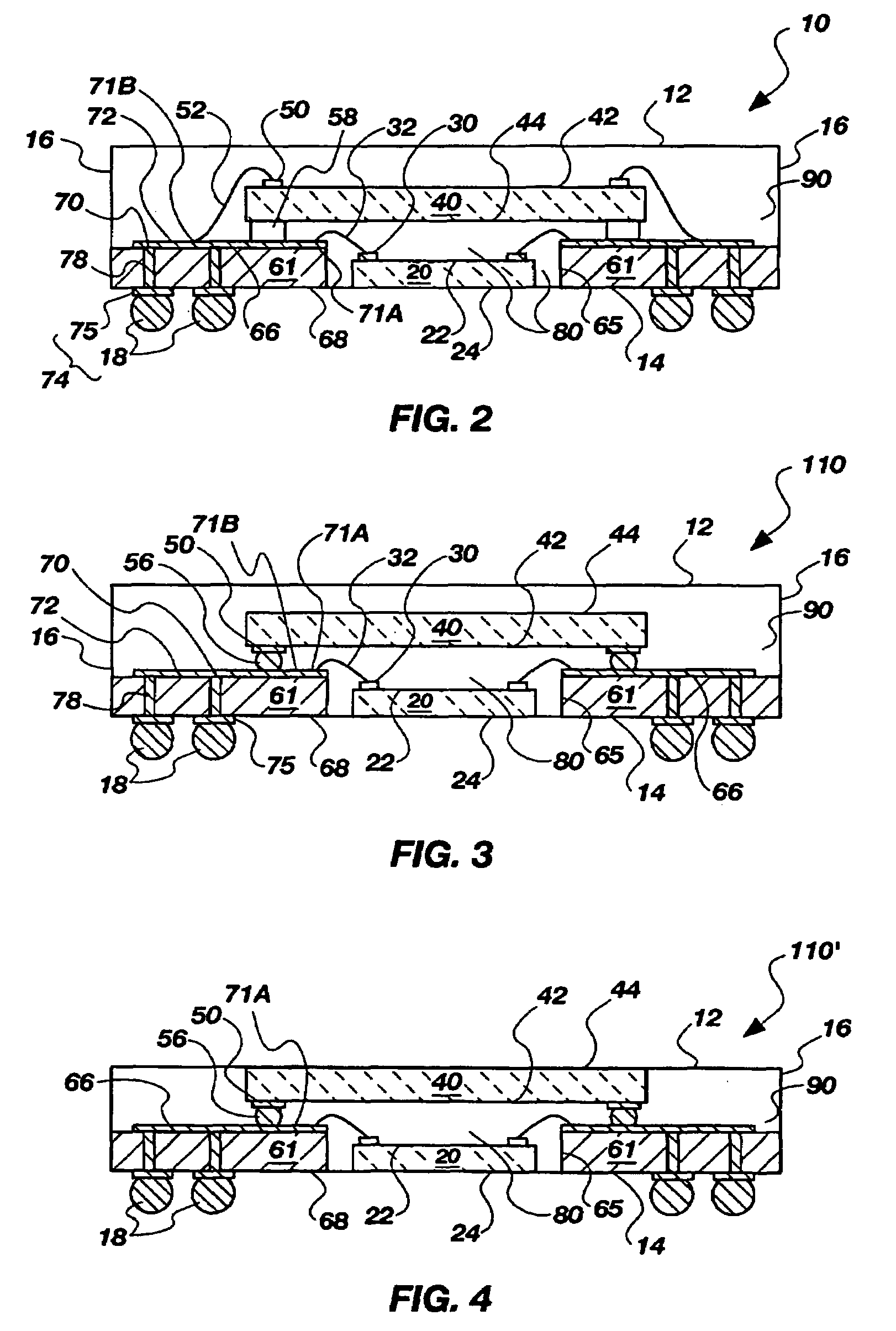

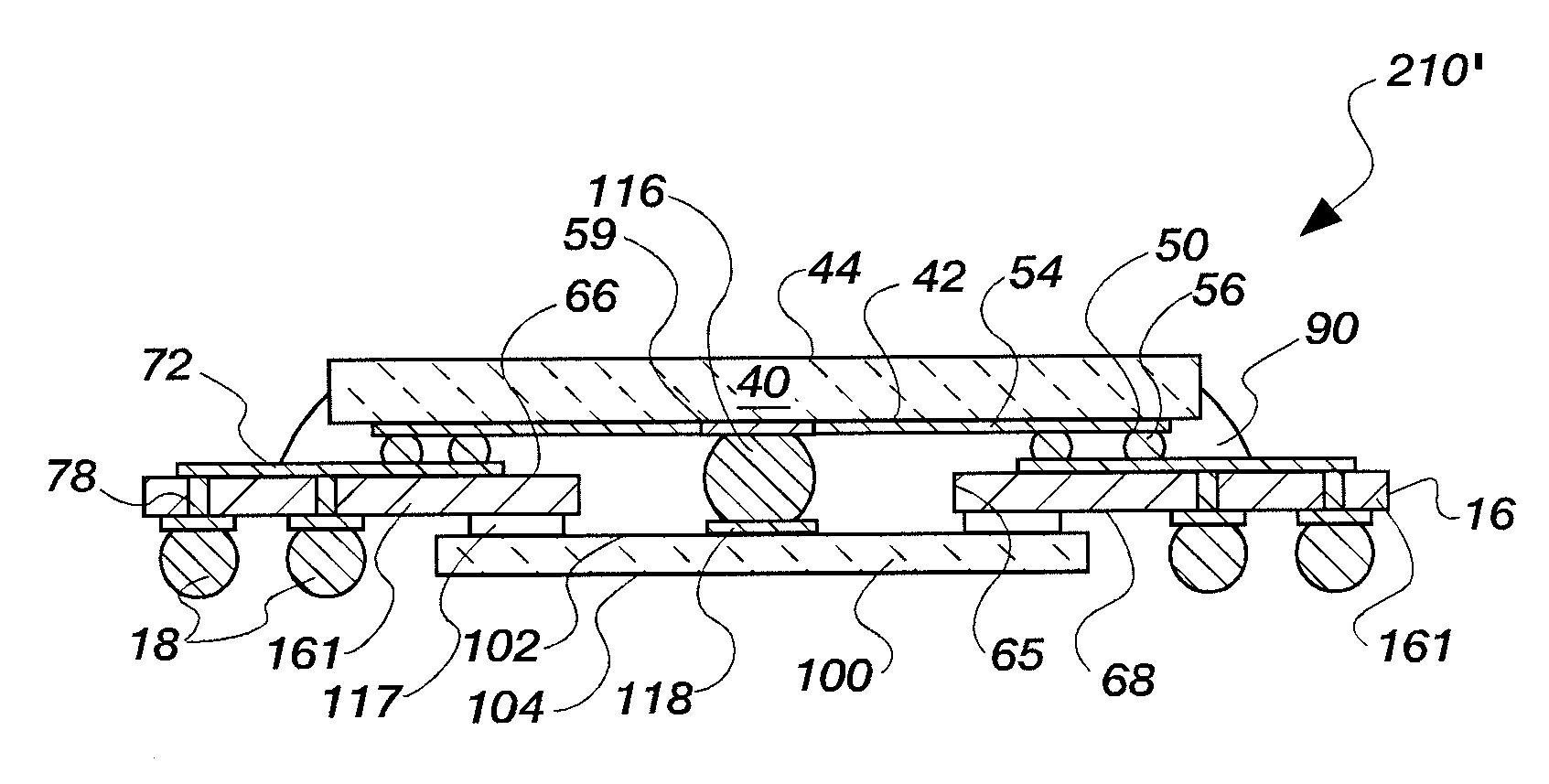

A multidie semiconductor device (MDSCD) package includes a generally planar interposer comprising a substrate with a central receptacle, upper surface conductors, and outer connectors on the lower surface of the interposer. Conductive vias connect upper surface conductors with outer connectors. One or more semiconductor devices may be mounted in the receptacle and one or more other semiconductor devices mounted above and / or below the interposer and attached thereto. The package may be configured to have a footprint not significantly larger than the footprint of the largest device and / or a thickness not significantly greater than the combined thickness of included devices. Methods for assembling and encapsulating packages from multidie wafers and multi-interposer sheets or strips are disclosed. Methods for combining a plurality of packages into a single stacked package are disclosed. The methods may include use of somewhat laterally extending intermediate conductive elements, flip-chip style electrical connection, or both within the same package.

Owner:MICRON TECH INC

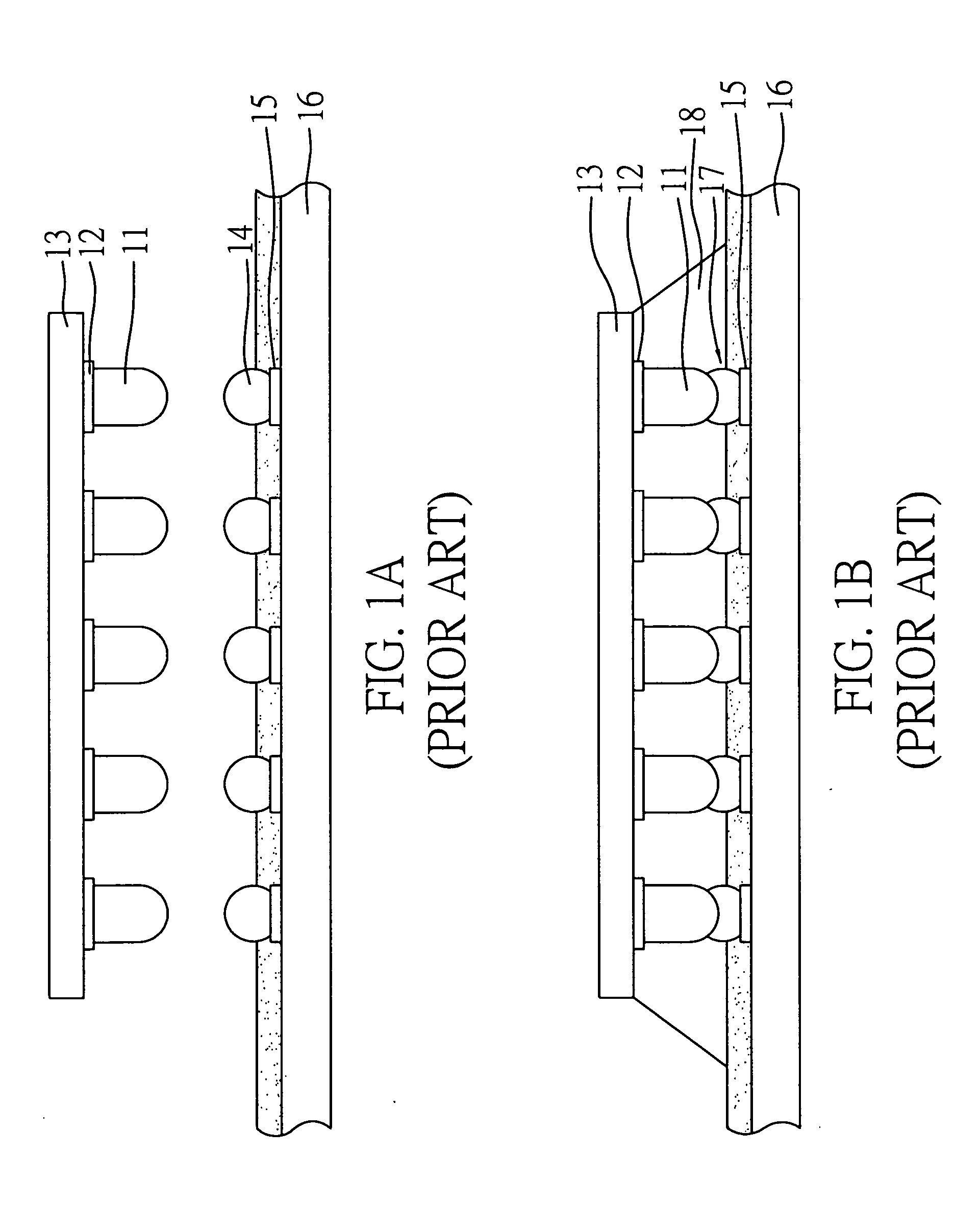

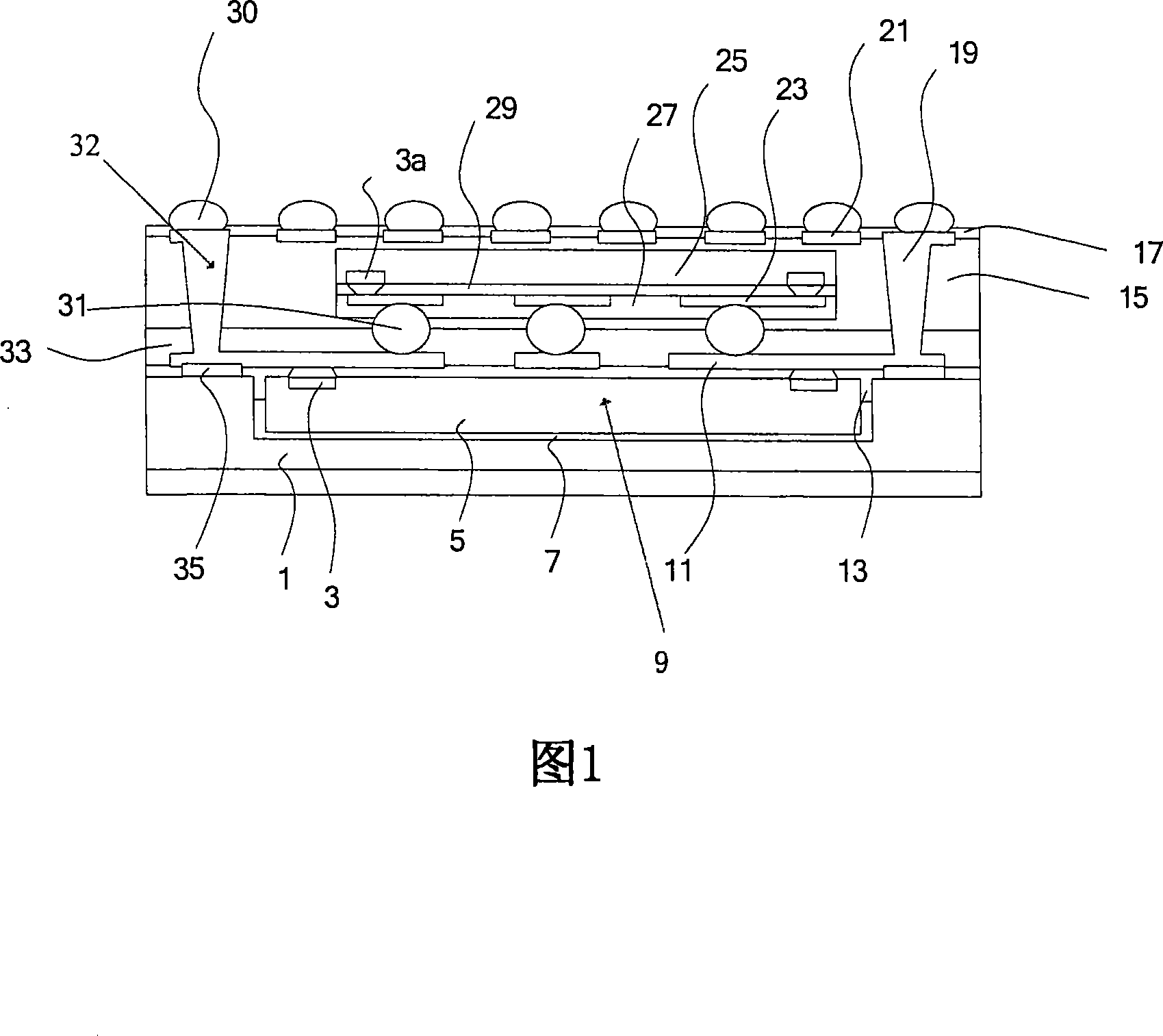

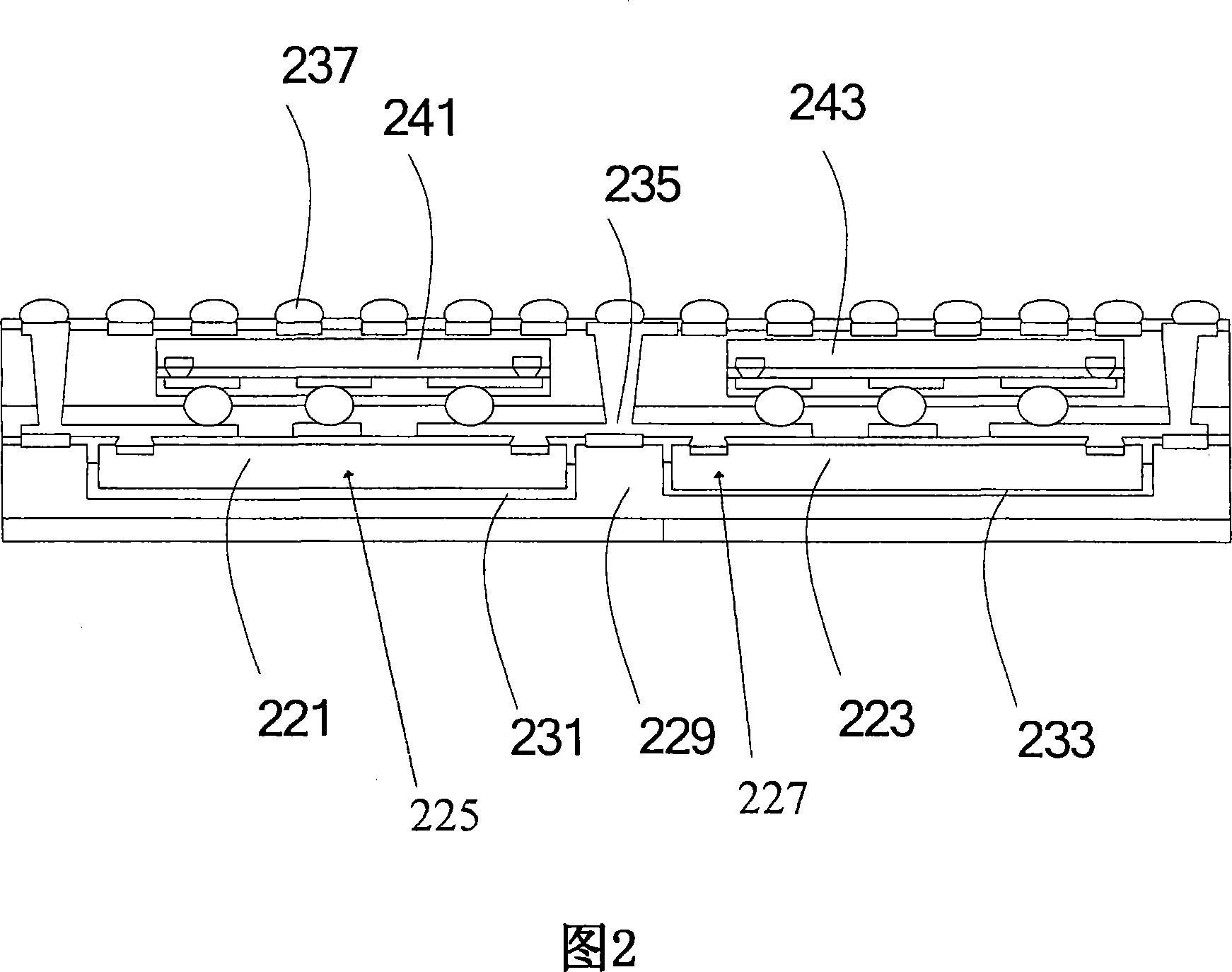

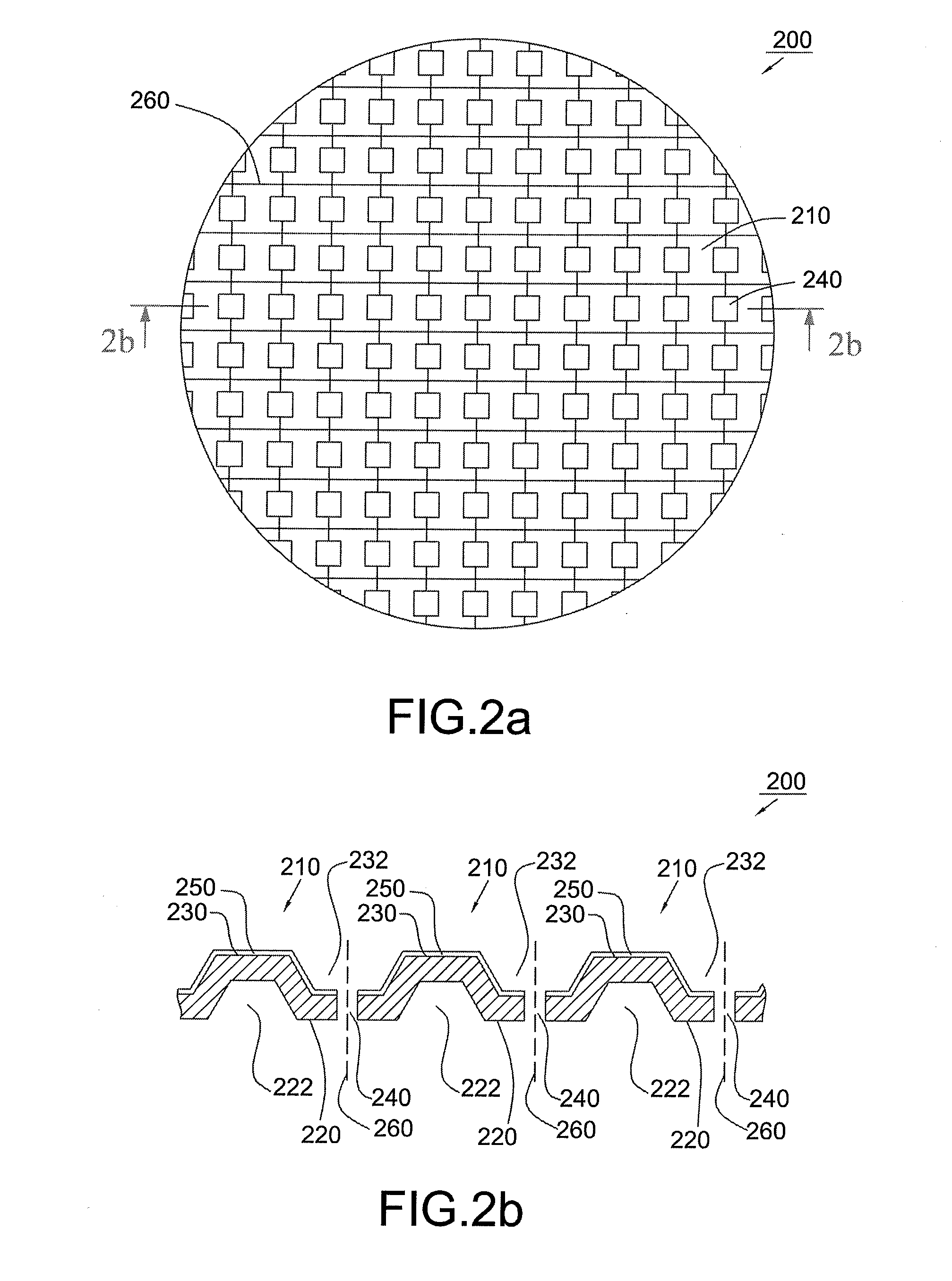

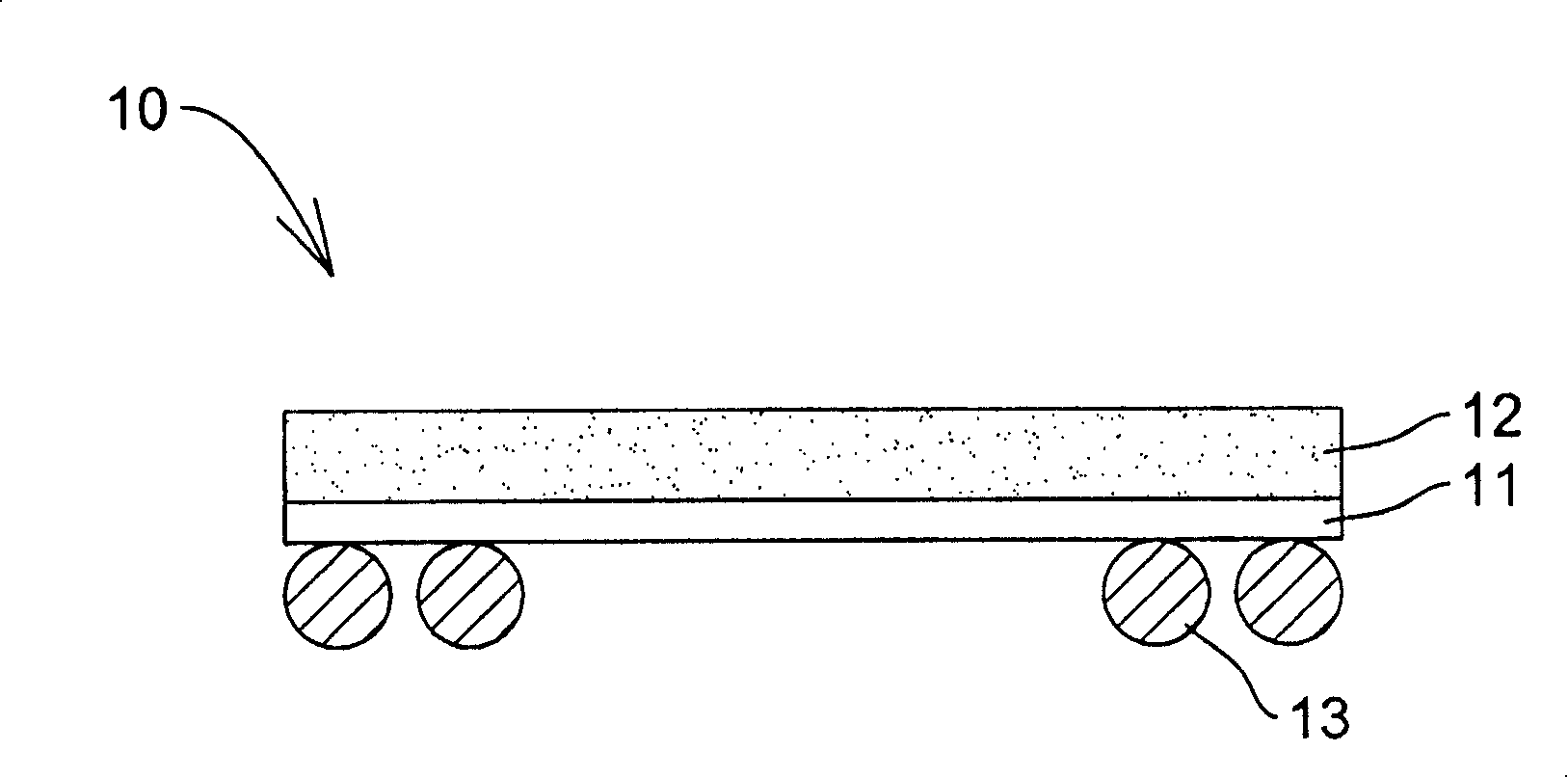

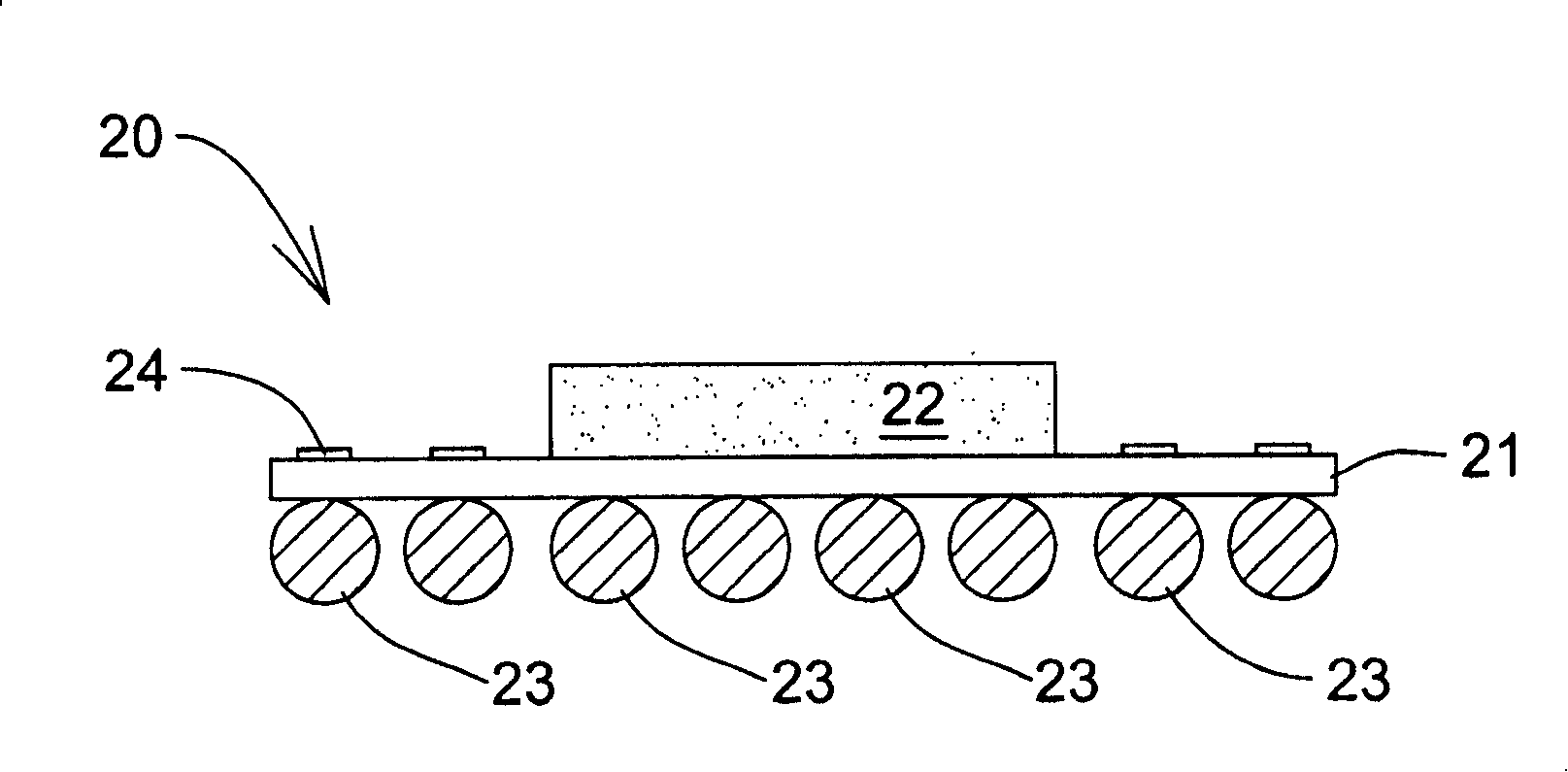

Semiconductor device assemblies and packages including multiple semiconductor device components

InactiveUS7573136B2Reduce area requirementsHelp positioningSemiconductor/solid-state device detailsSolid-state devicesContact padInterposer

A multidie semiconductor device assembly or package includes an interposer comprising a substrate with at least one receptacle therethrough. A plurality of semiconductor device components (e.g., semiconductor devices) may be assembled with the interposer. For example, at least one contact pad of a semiconductor device component adjacent to one surface of the interposer may be electrically connected to a corresponding contact pad of another semiconductor device component positioned adjacent to an opposite surface of the interposer. As another example, multiple semiconductor device components may be at least partially superimposed relative to one another and at least partially disposed within a receptacle of the interposer.

Owner:MICRON TECH INC

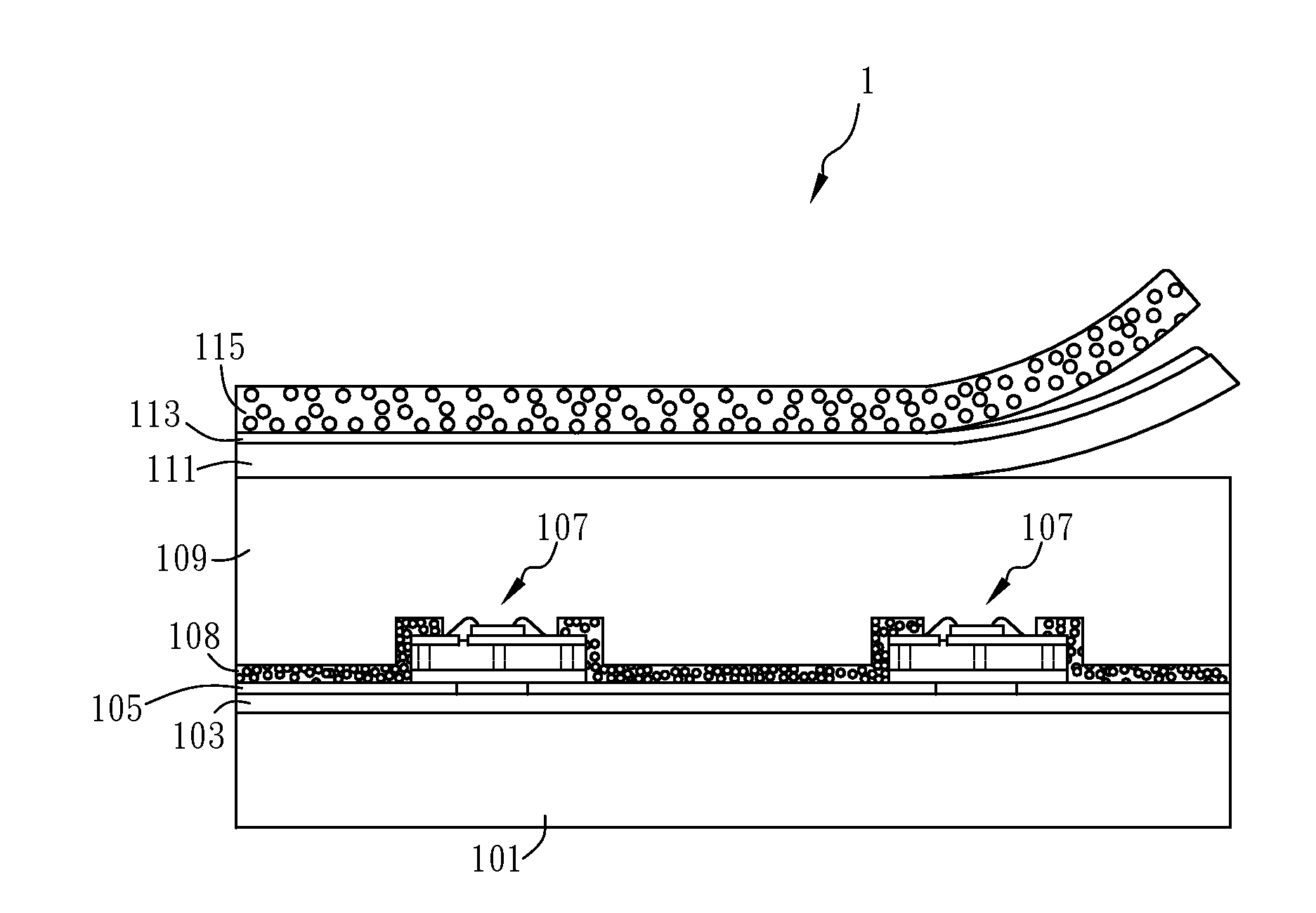

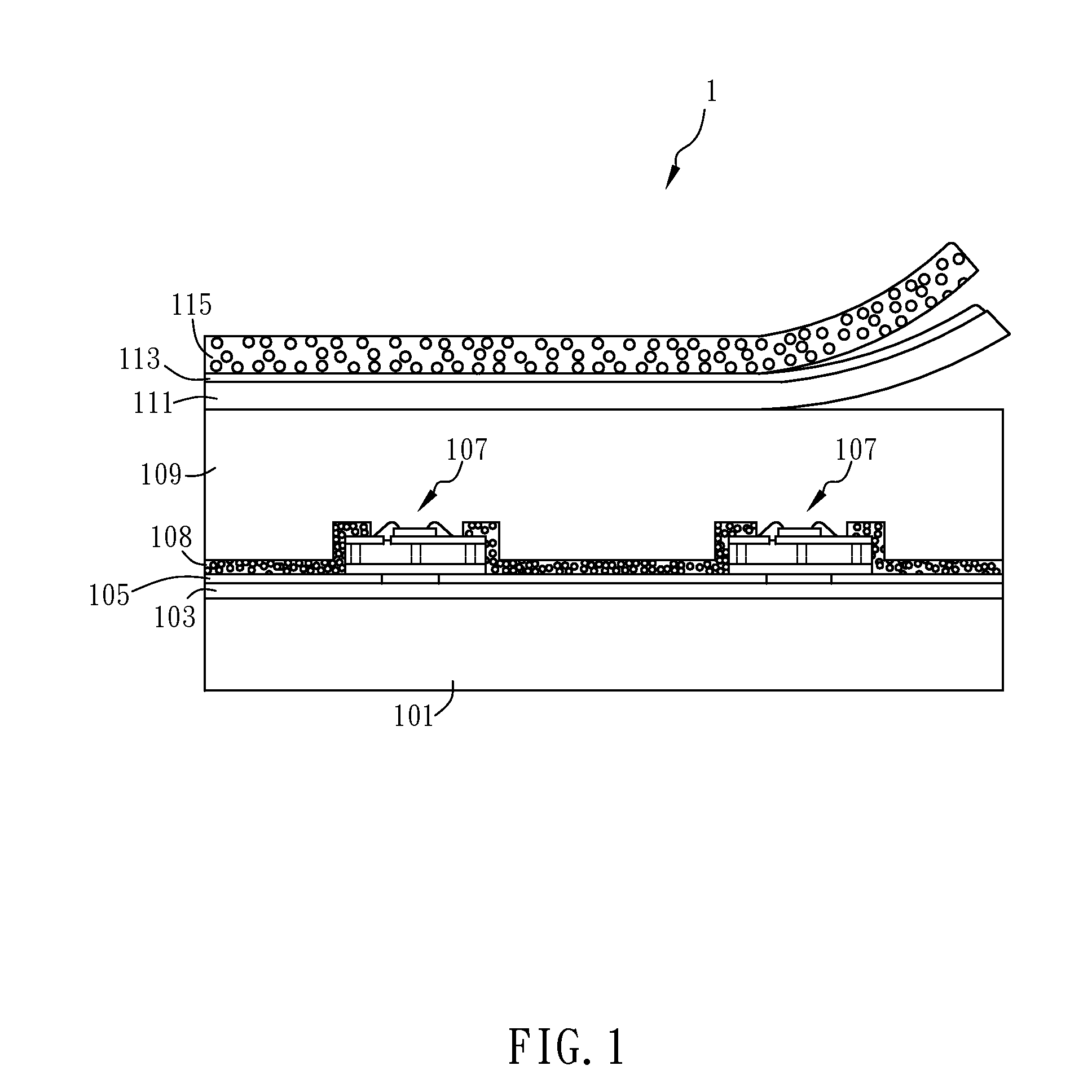

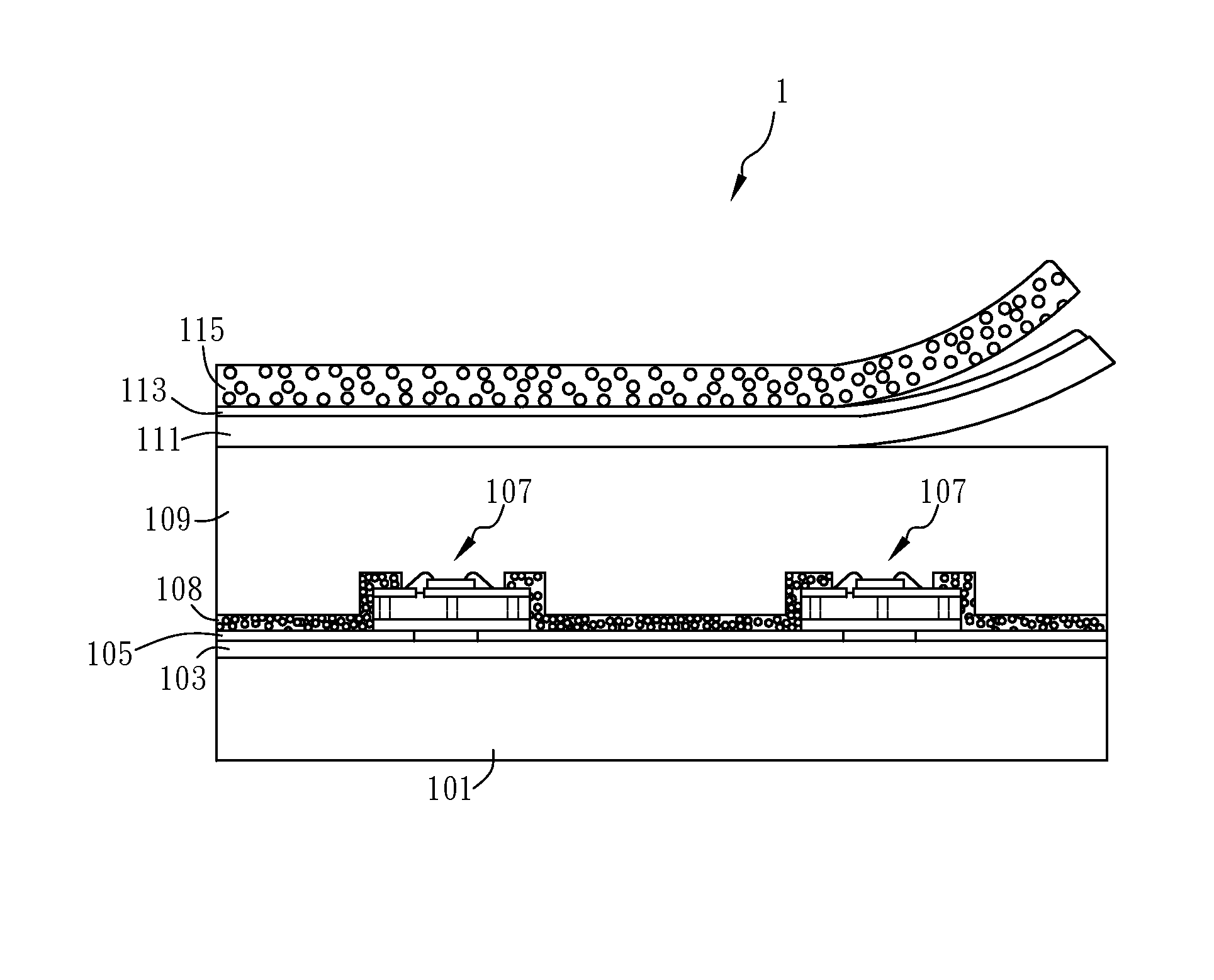

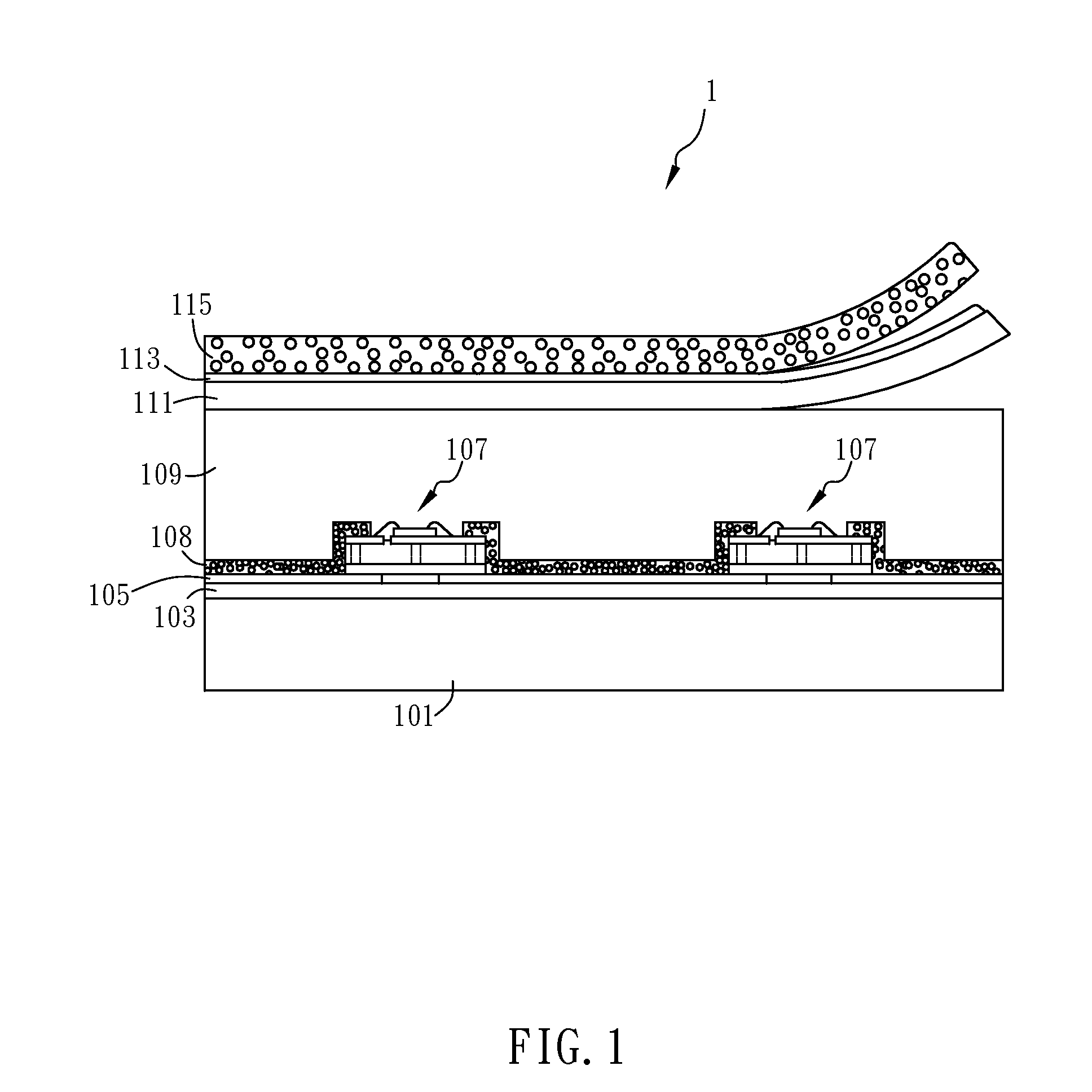

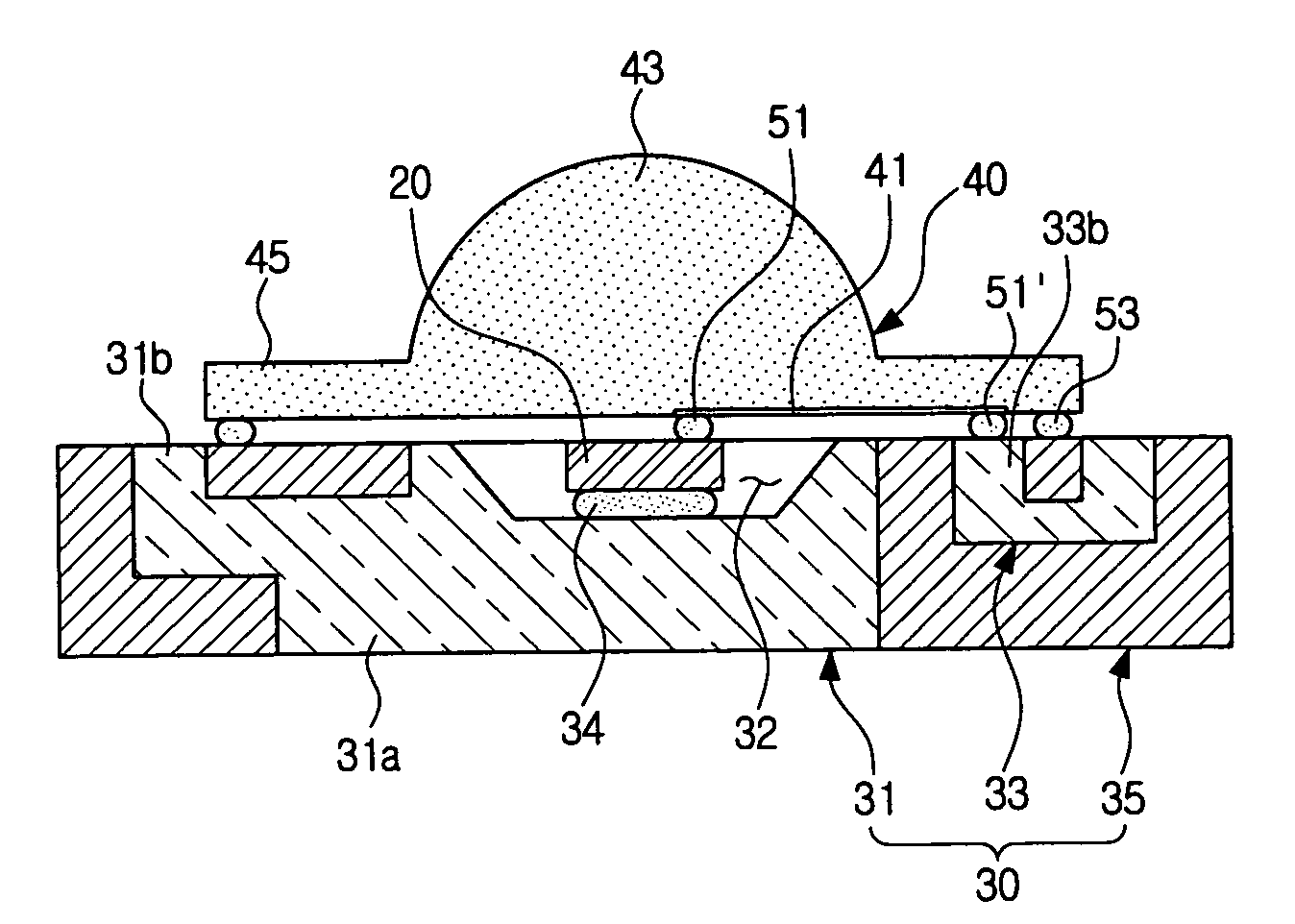

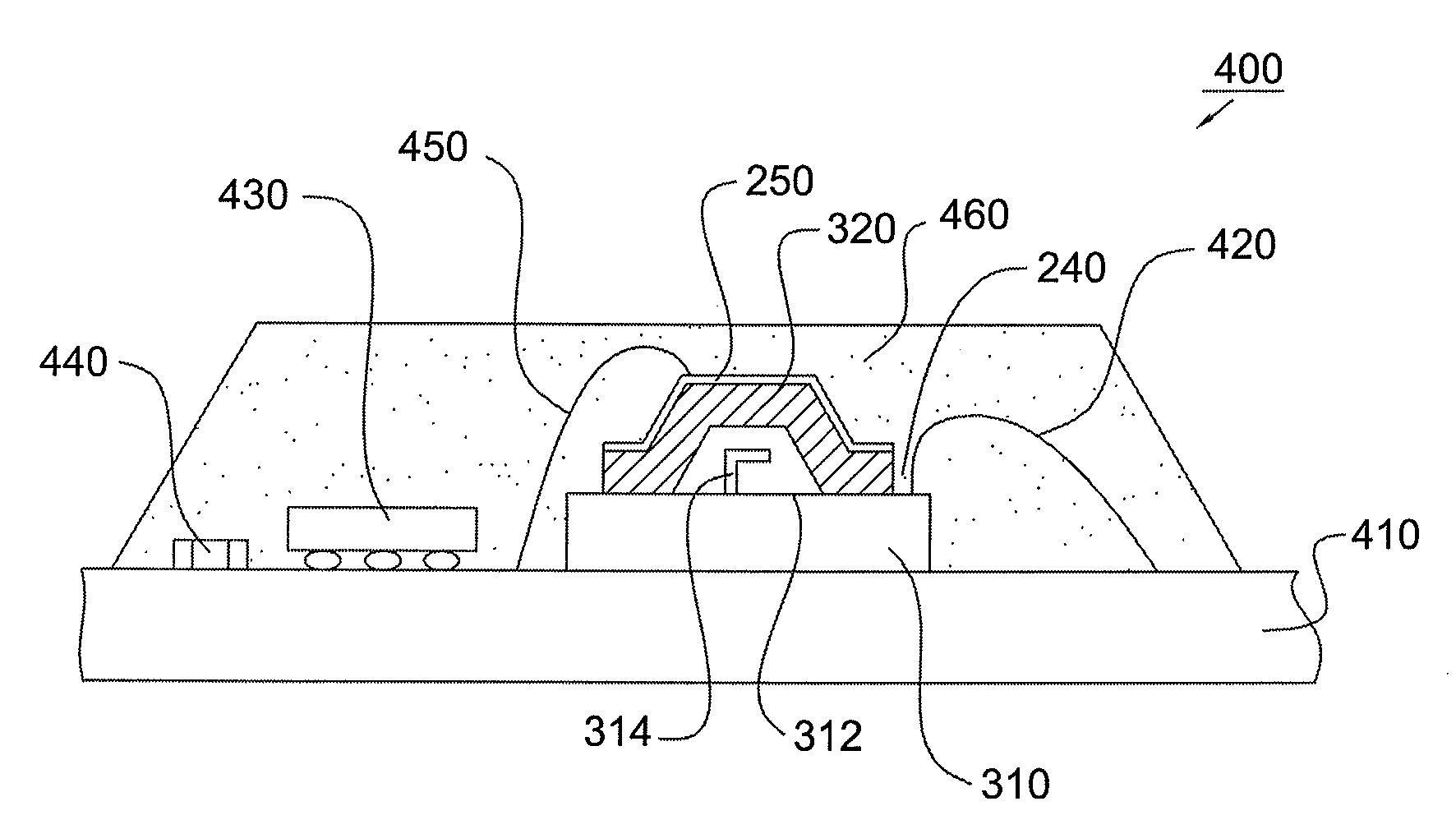

Lighting device, display, and method for manufacturing the same

InactiveUS20110006316A1Reduce thickness of packageReduce package thicknessSolid-state devicesSemiconductor/solid-state device manufacturingLight sourceWhite light

A display, a lighting device and a method for manufacturing the lighting device are provided. The lighting device comprises a substrate, an electrode layer, a plurality of light source units and a light scattering layer, which is covered by a transparent layer and a reflector layer to create a uniform surface light within an ultra thin format. A yellow phosphor layer is disposed above the reflector layer to create white light when a blue LED or UV LED is used. The lighting device also provides a unique electrode layout design which can be applied for local dimming control and can be easily applied for large size product applications.

Owner:LUXINGTEK

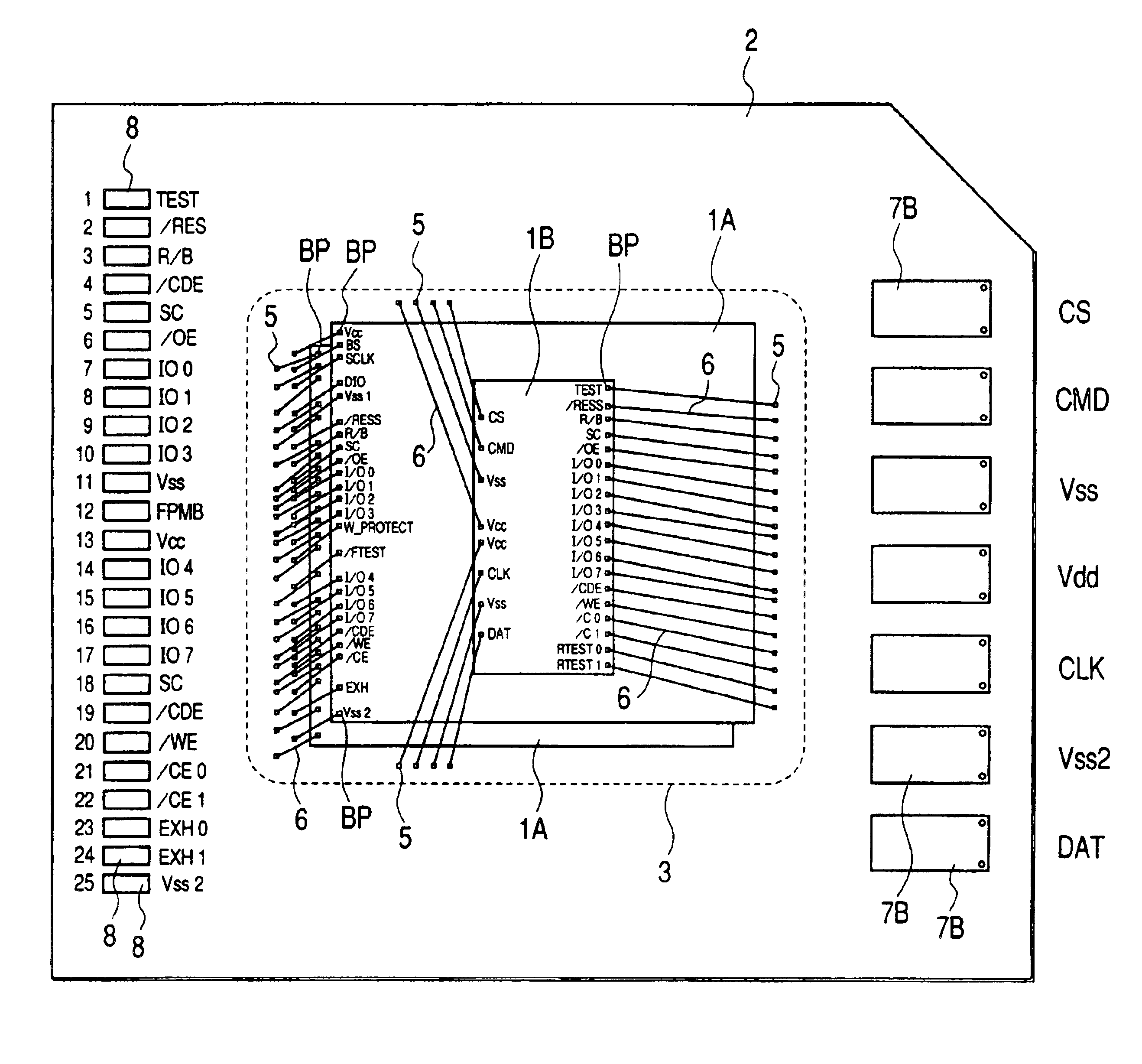

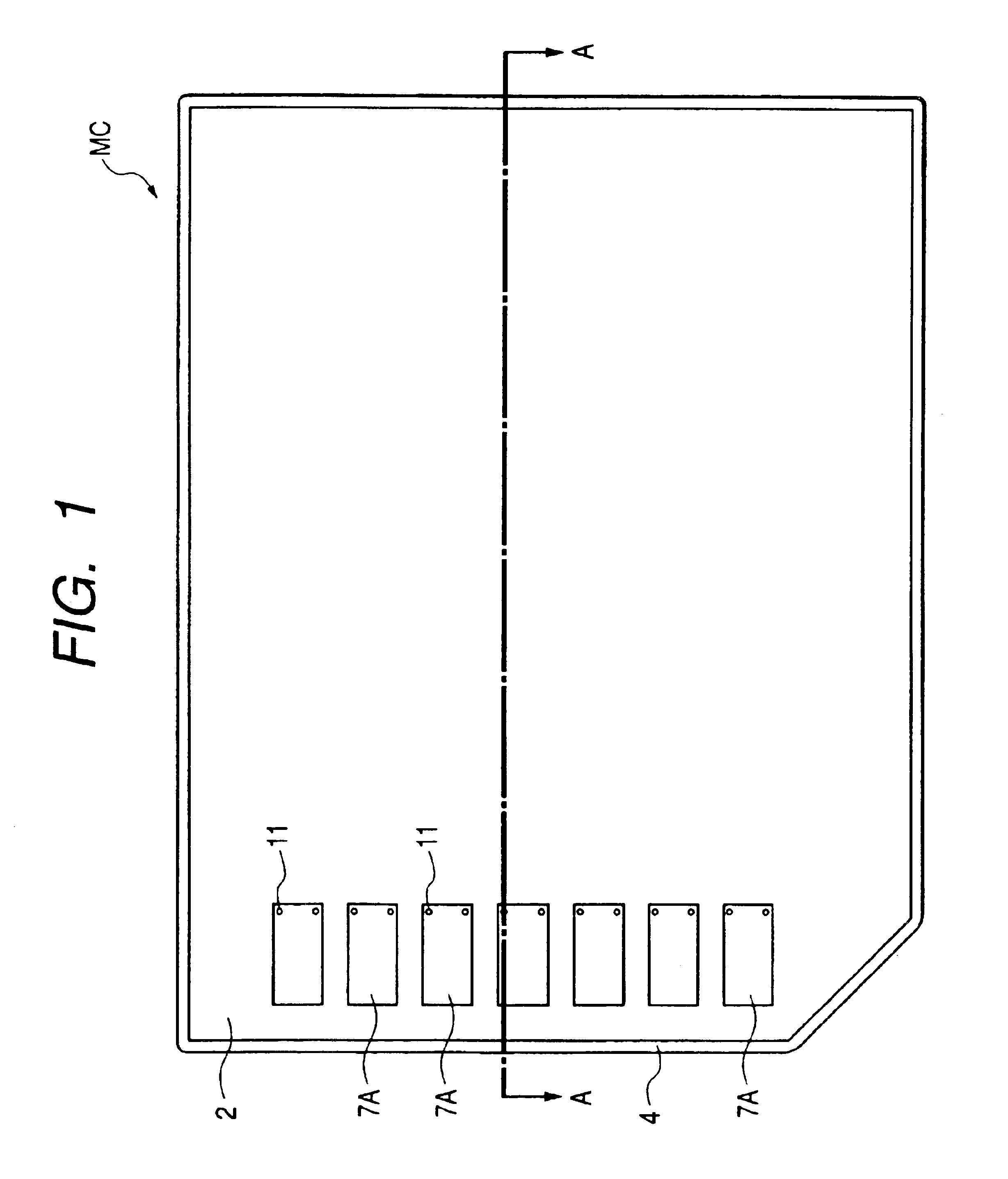

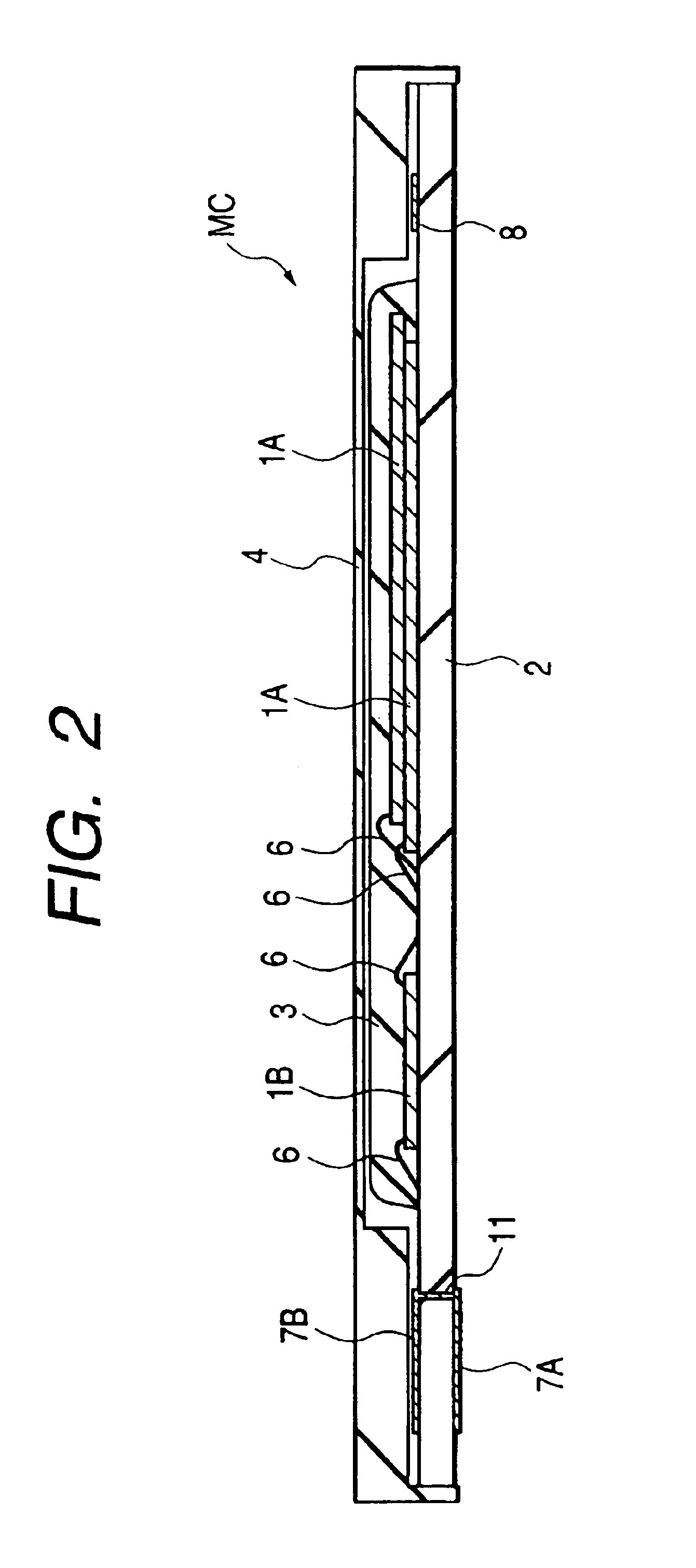

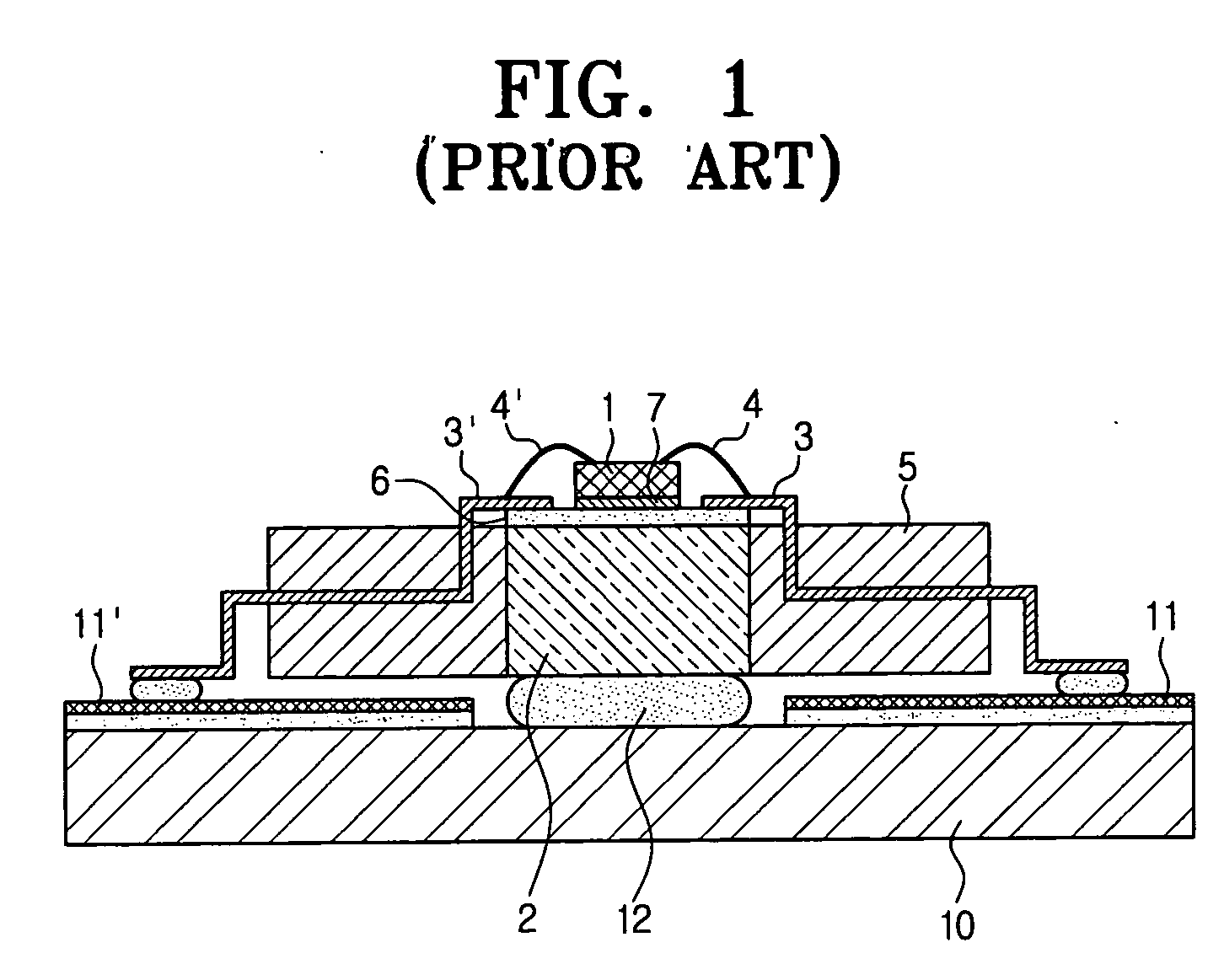

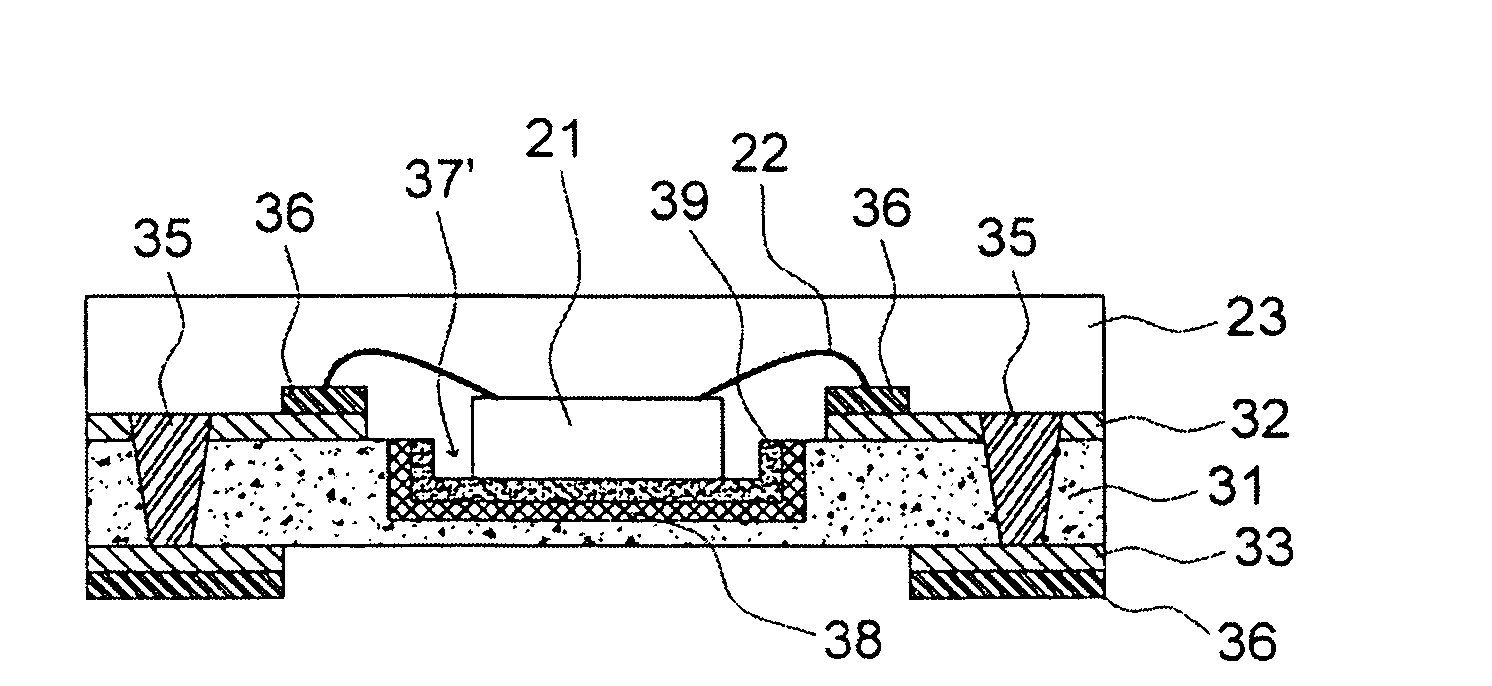

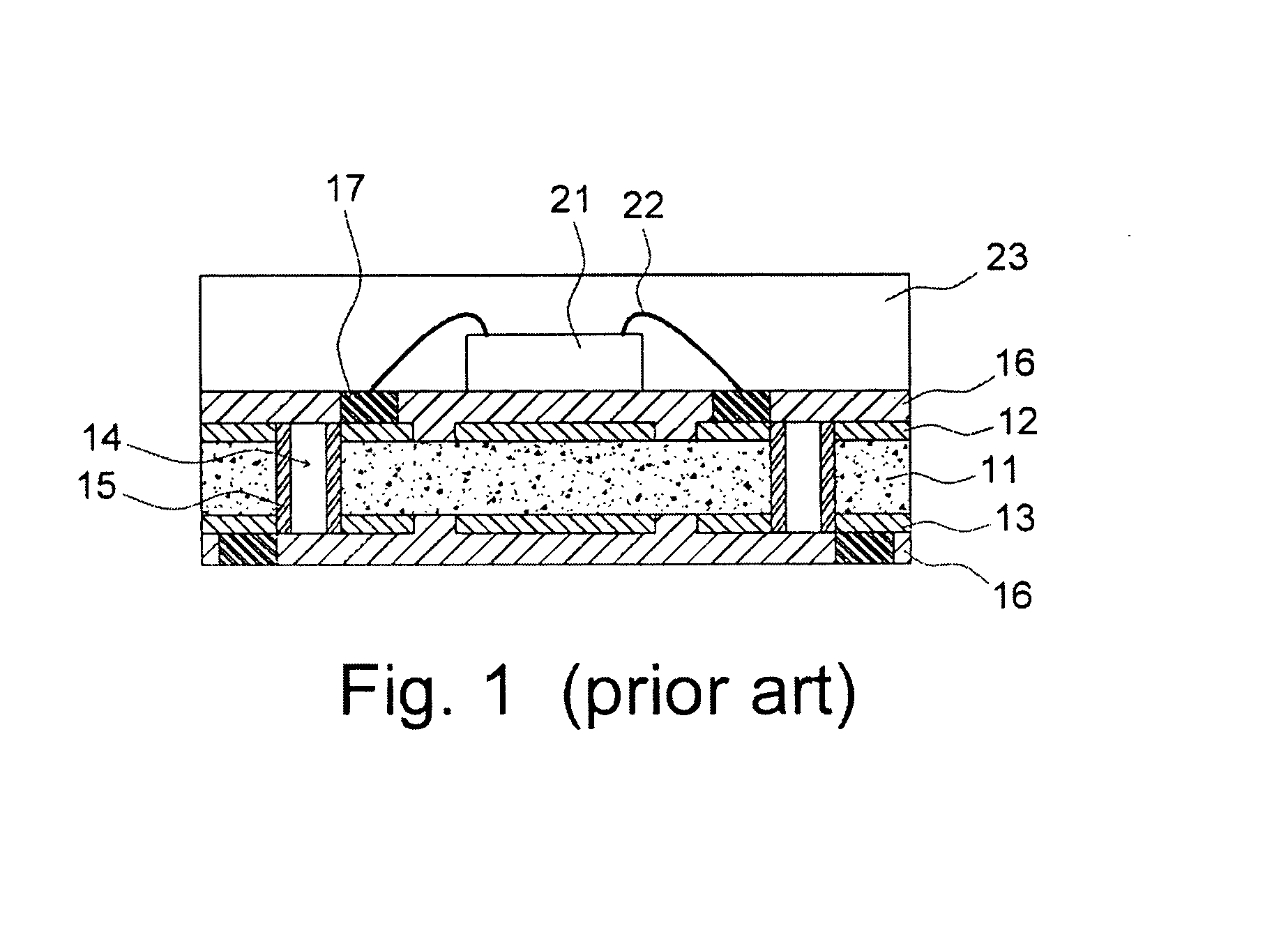

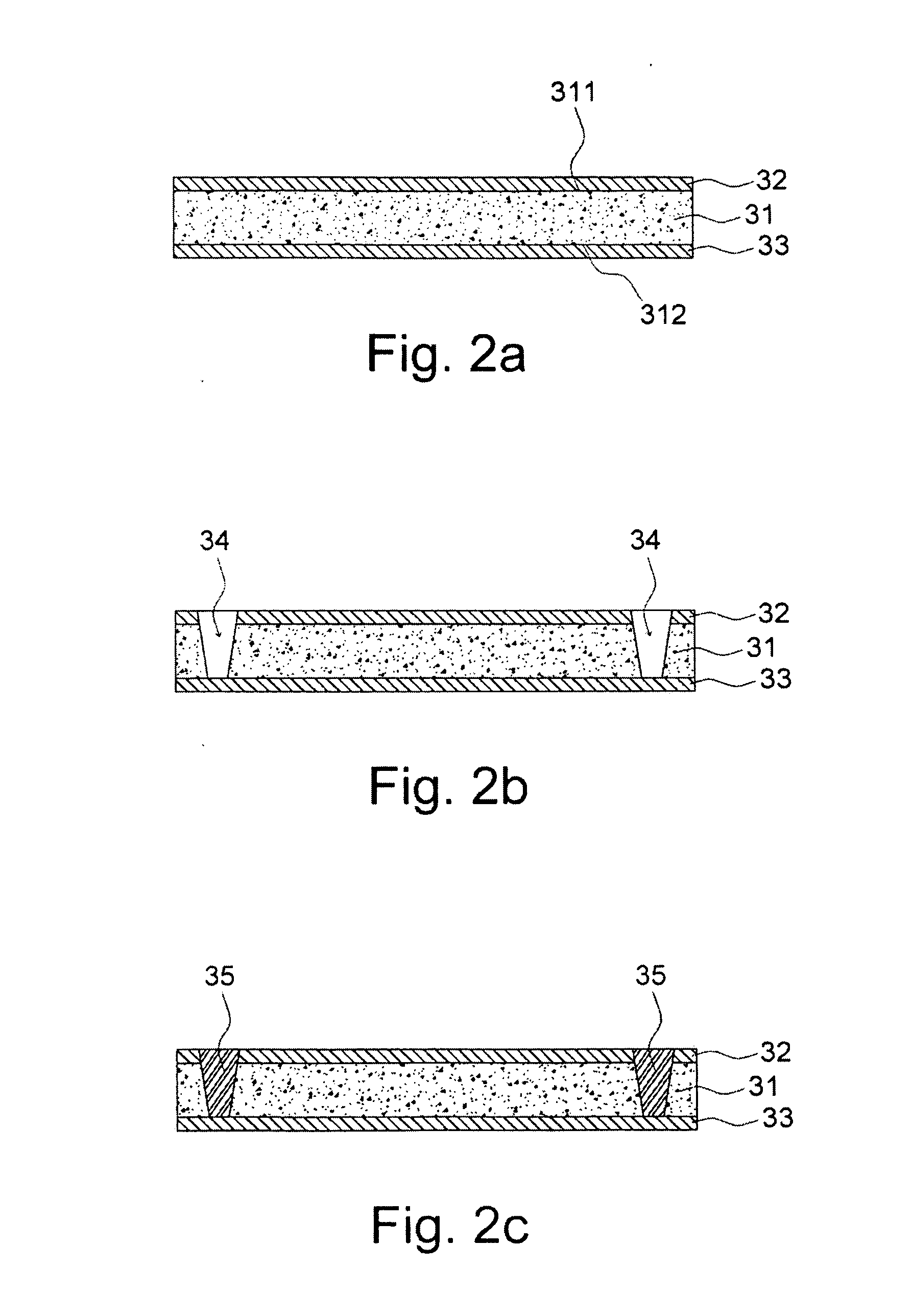

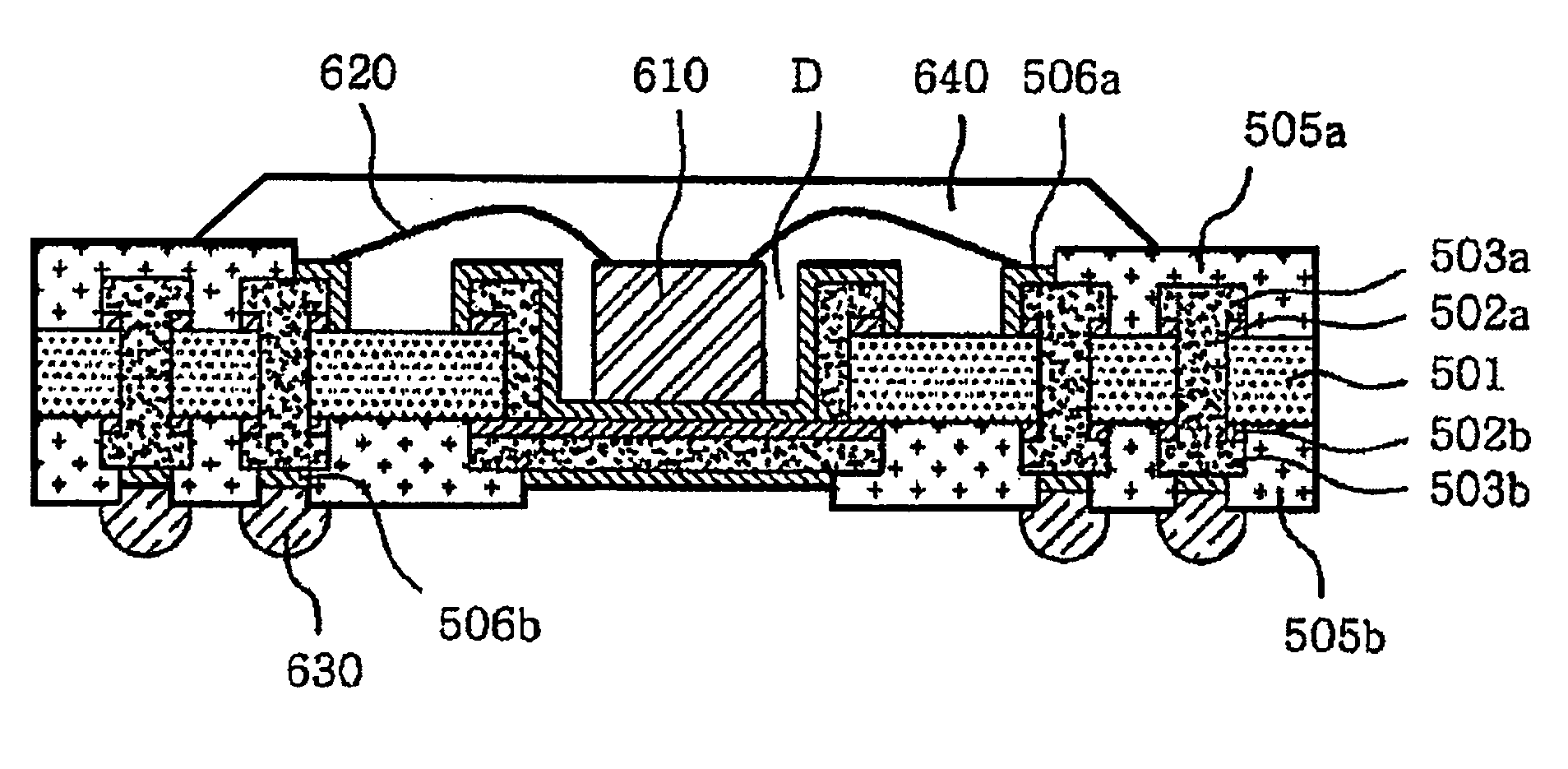

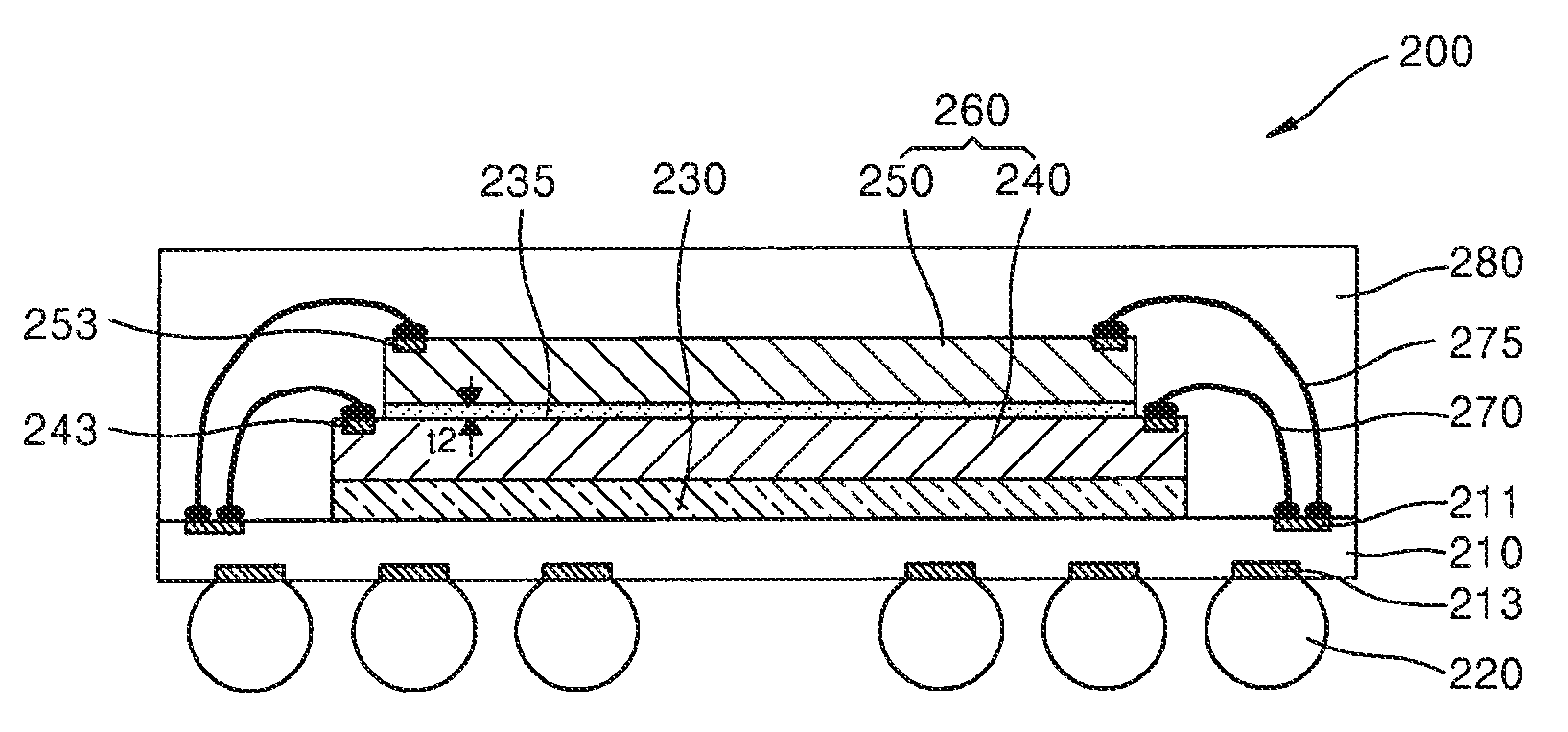

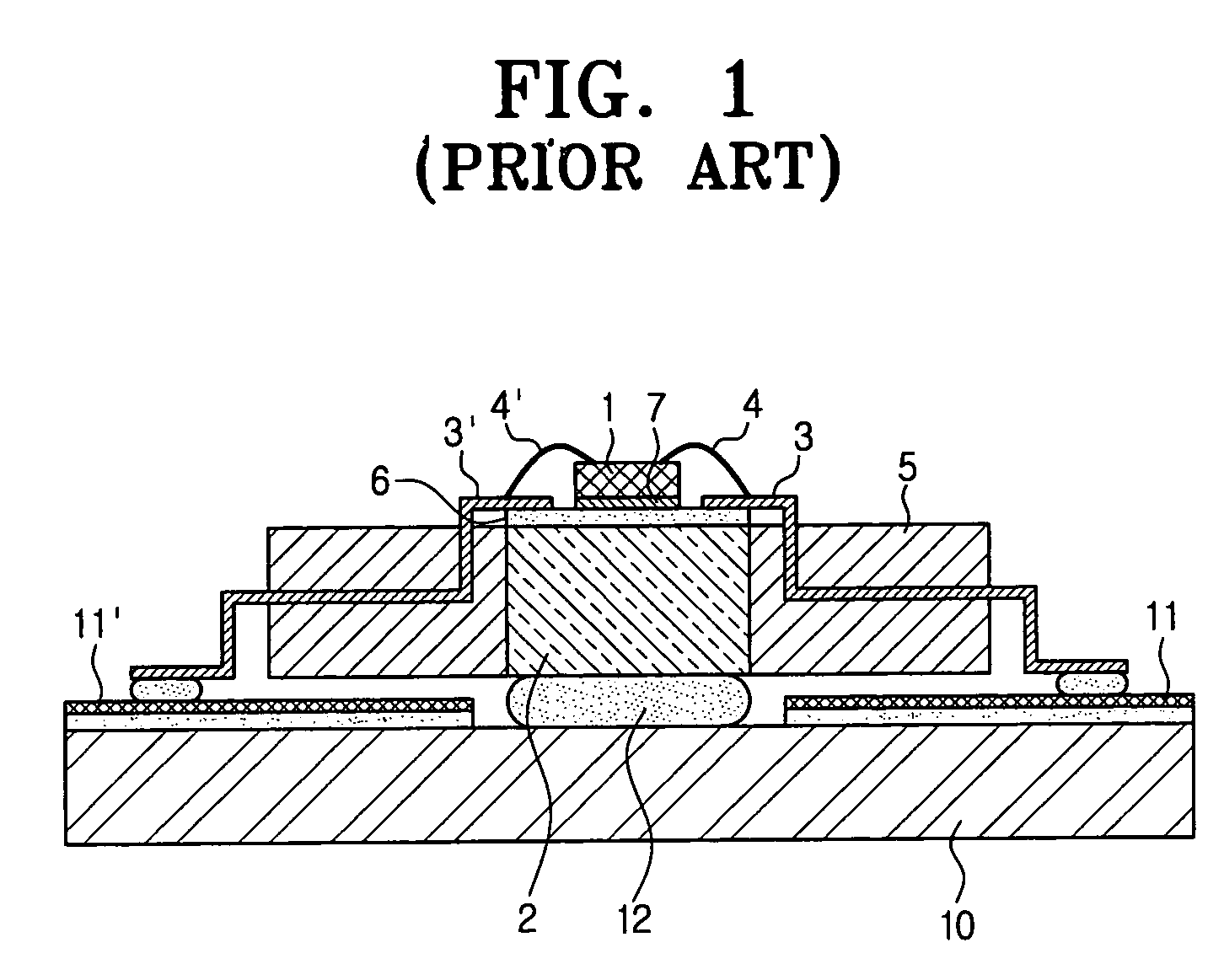

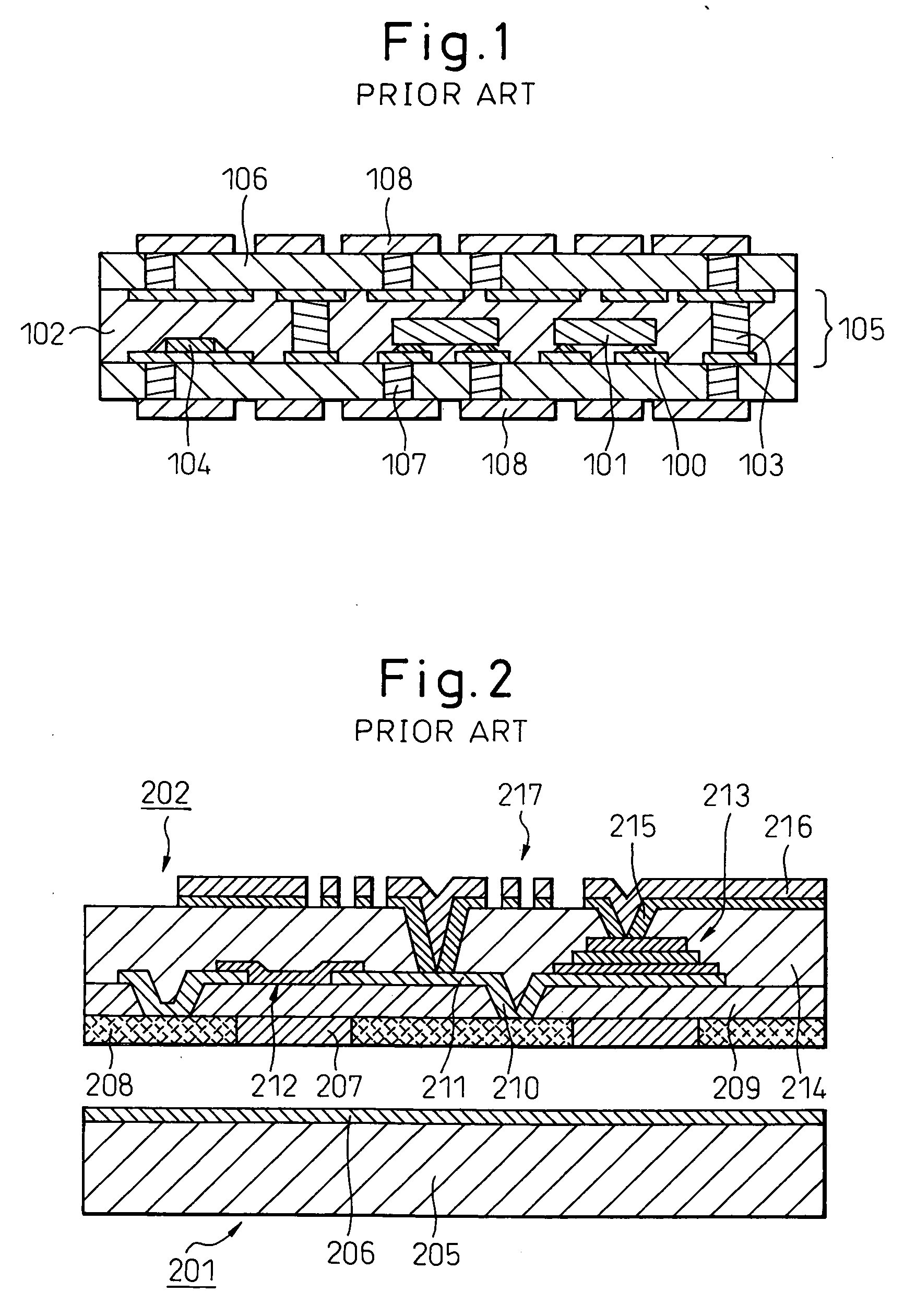

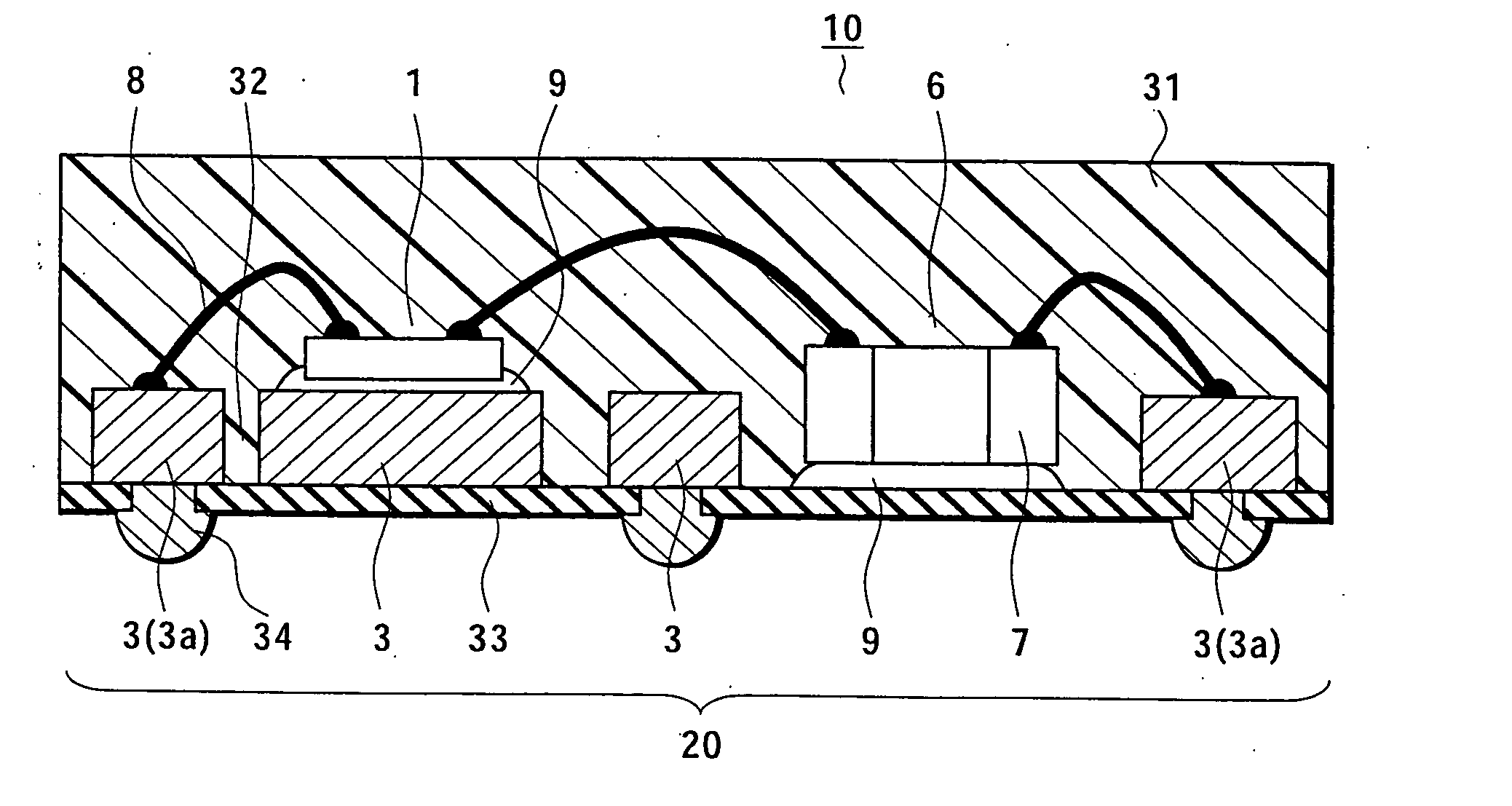

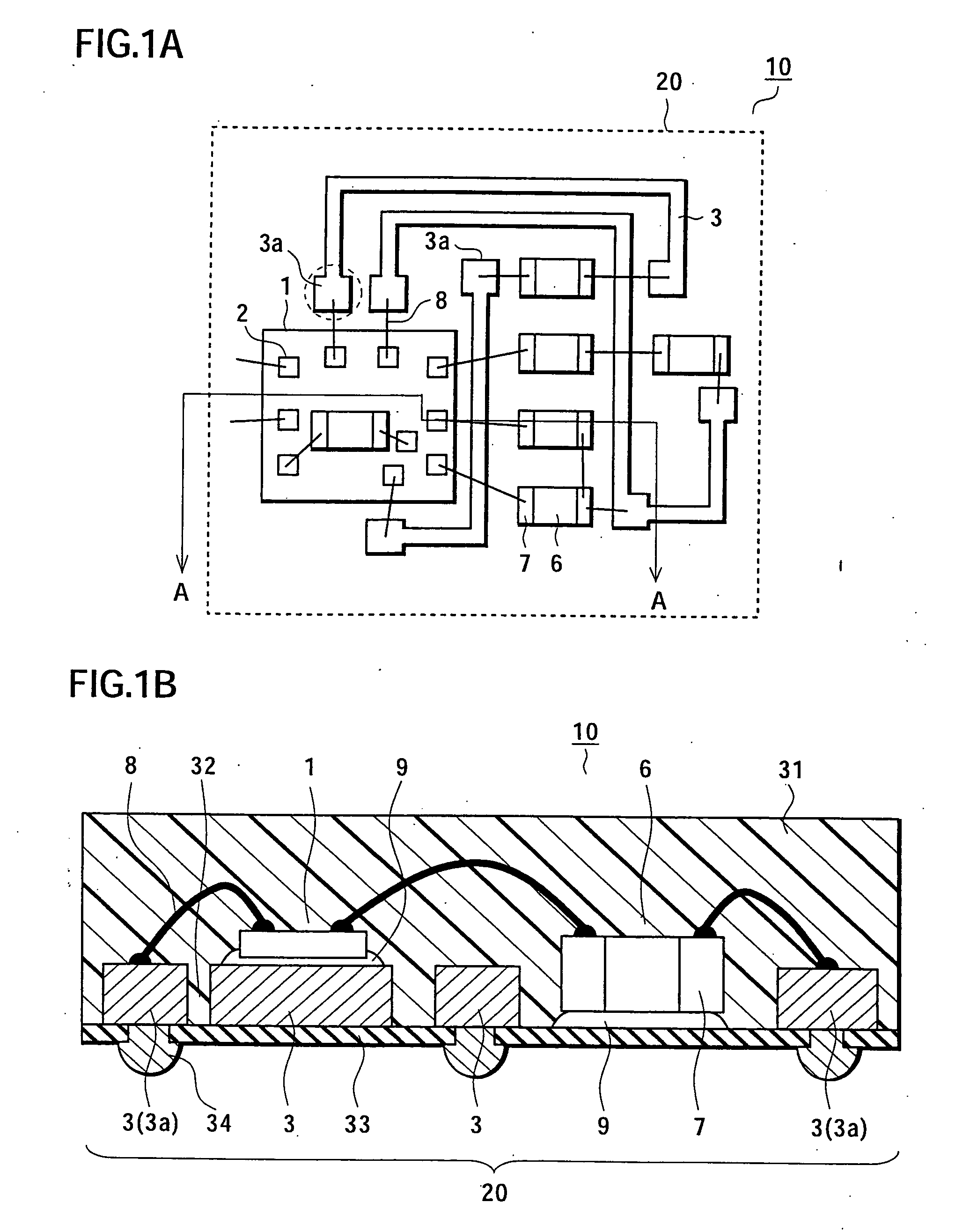

Semiconductor device and a method of manufacturing the same

InactiveUS7061105B2Reduce distanceIncrease in loop heightSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsMemory chipSemiconductor

Two memory chips mounted over a base substrate have the same external size and a flash memory of the same memory capacity formed thereon. These memory chips are mounted over the base substrate with one of them being overlapped with the upper portion of the other one, and they are stacked with their faces being turned in the same direction. The bonding pads BP of one of the memory chips are disposed in the vicinity of the bonding pads BP of the other memory chip. In addition, the upper memory chip is stacked over the lower memory chip in such a way that the upper memory chip is slid in a direction (X direction) parallel to the one side of the lower memory chip and in a direction (Y direction) perpendicular thereto in order to prevent partial overlapping of it with the bonding pads BP of the lower memory chip.

Owner:LONGITUDE LICENSING LTD

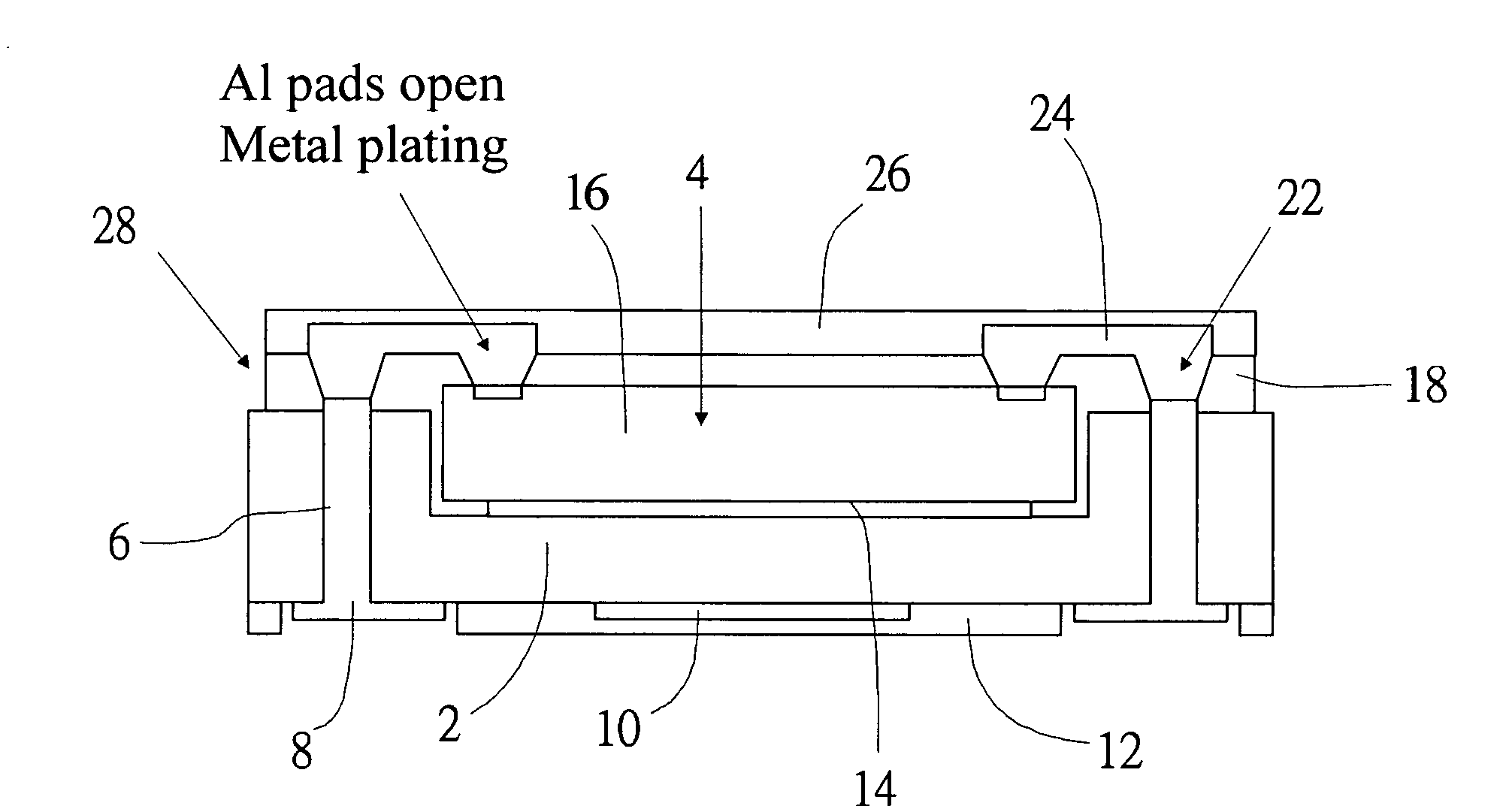

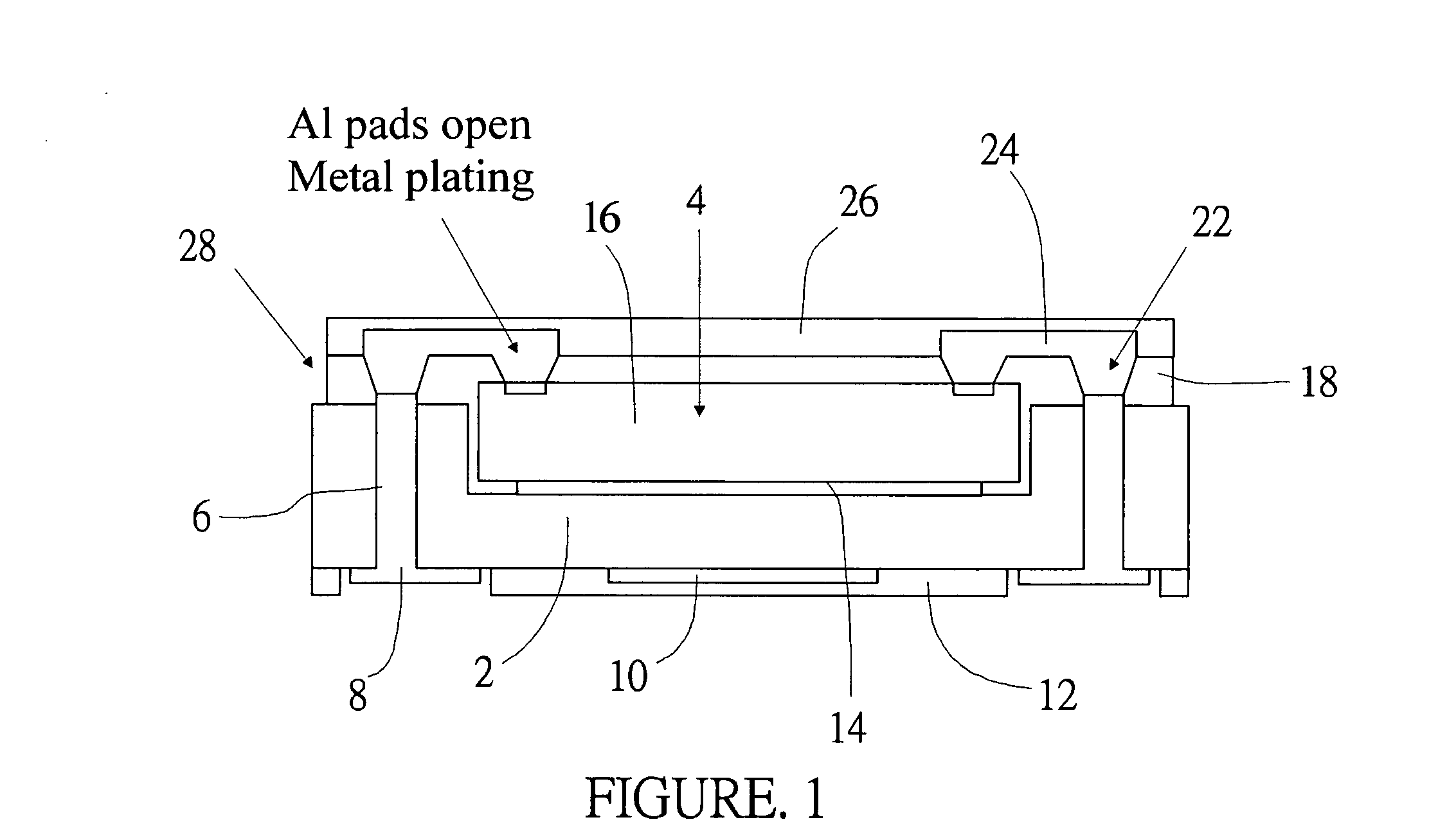

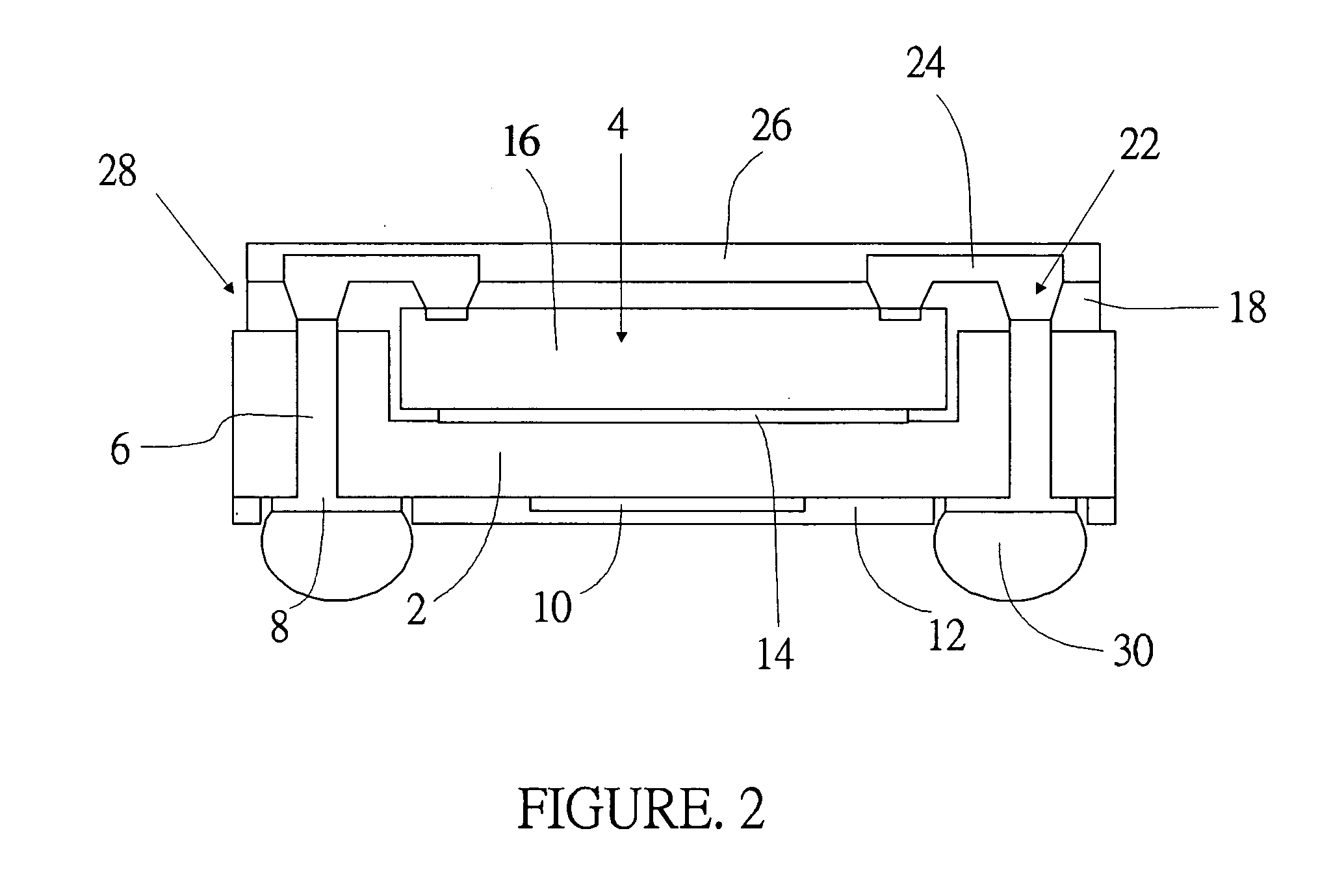

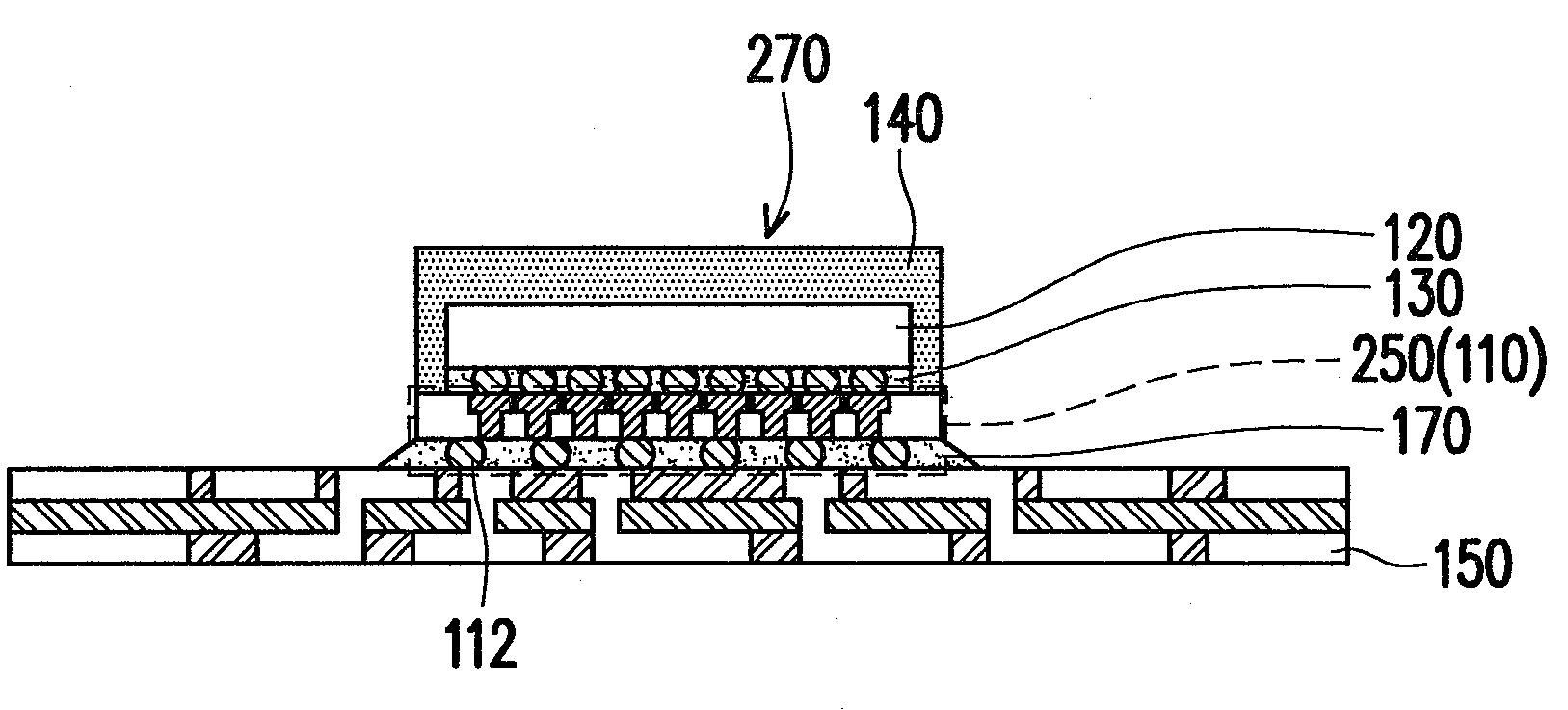

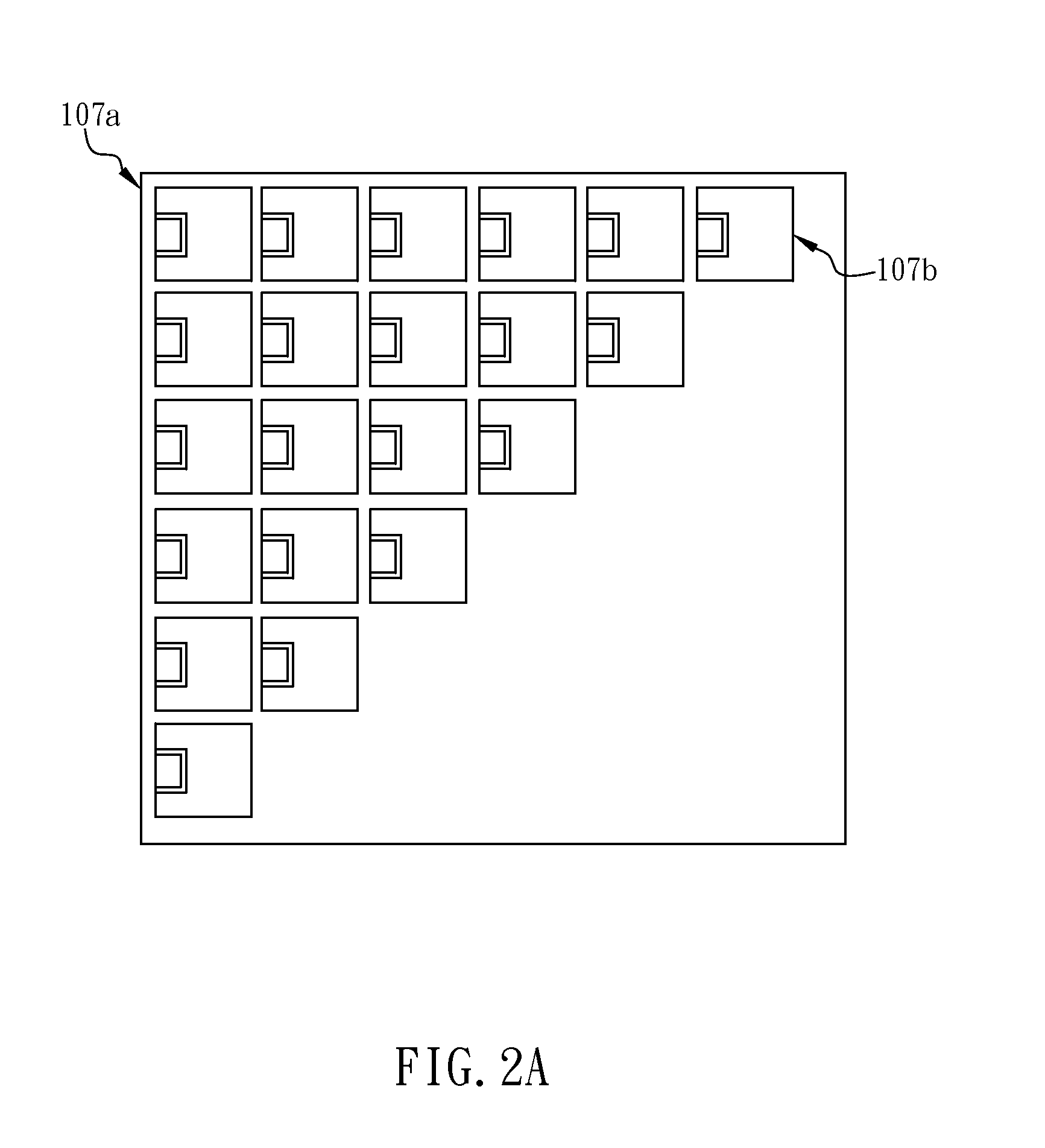

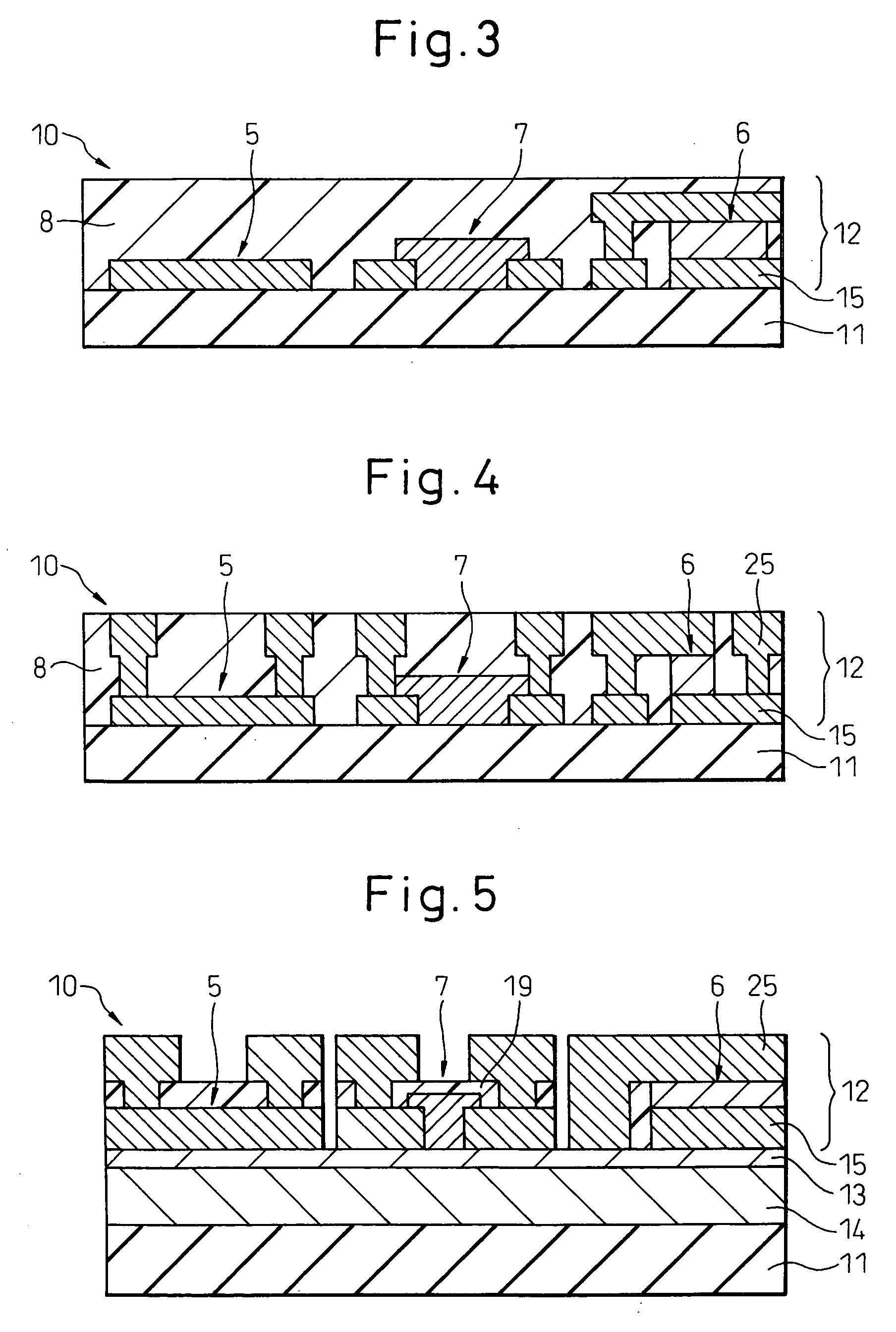

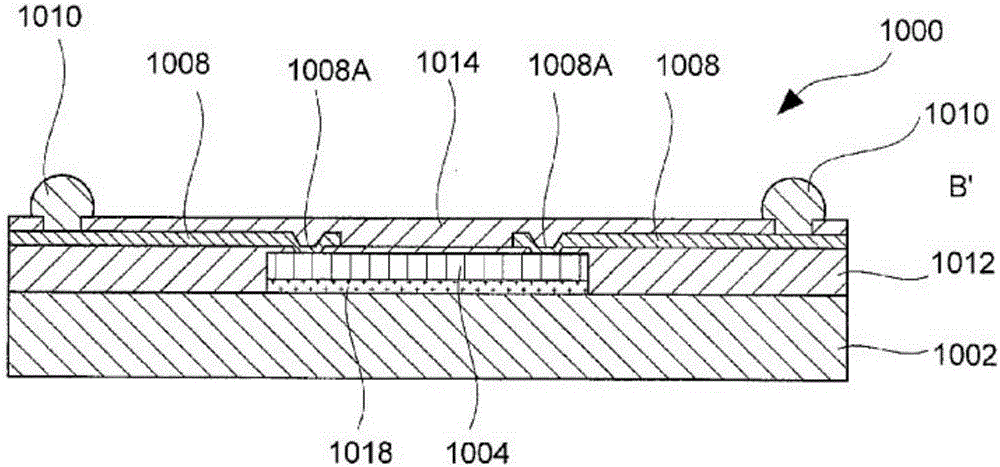

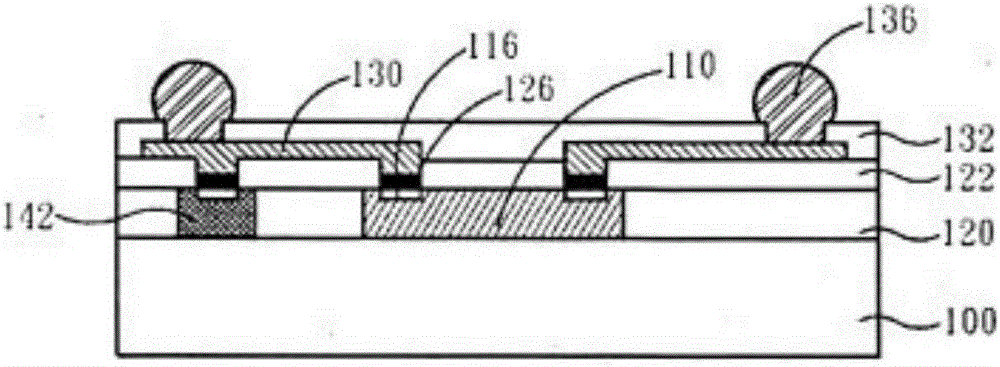

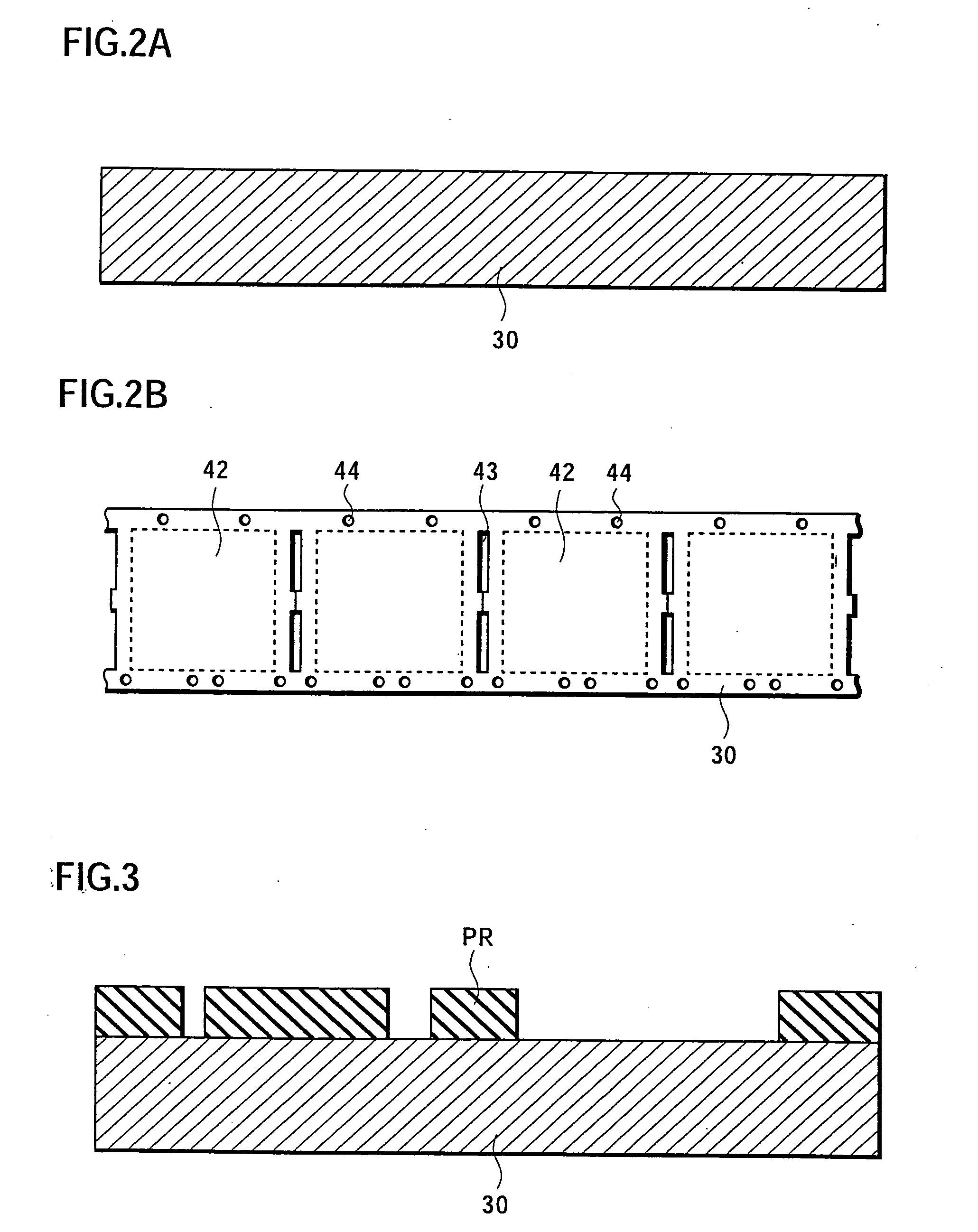

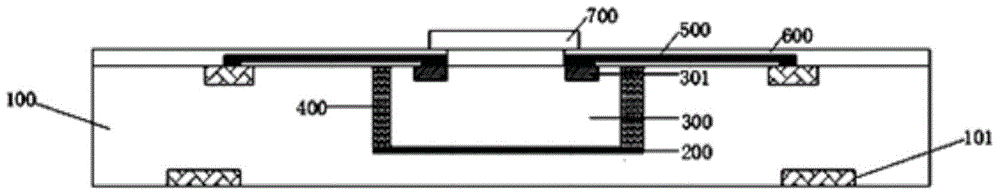

Wafer level package with die receiving cavity and method of the same

InactiveUS20080116564A1Board levelReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

The present invention provides a structure of package comprising a substrate with a die receiving cavity formed within an upper surface of the substrate and a through hole structure formed there through, wherein a terminal pad is formed under the through hole structure and the substrate includes a conductive trace formed on a lower surface of the substrate. A die is disposed within the die receiving cavity by adhesion and a dielectric layer formed on the die and the substrate. A re-distribution metal layer (RDL) is formed on the dielectric layer and coupled to the die and the through hole structure. Conductive bumps are coupled to the terminal pad.

Owner:ADVANCED CHIP ENG TECH

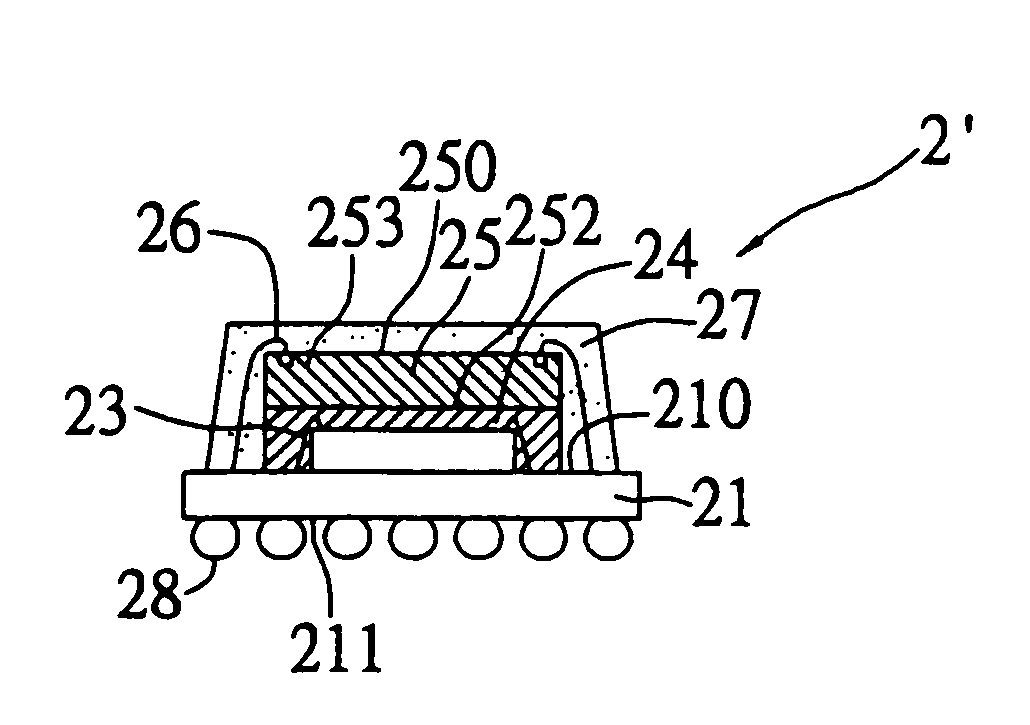

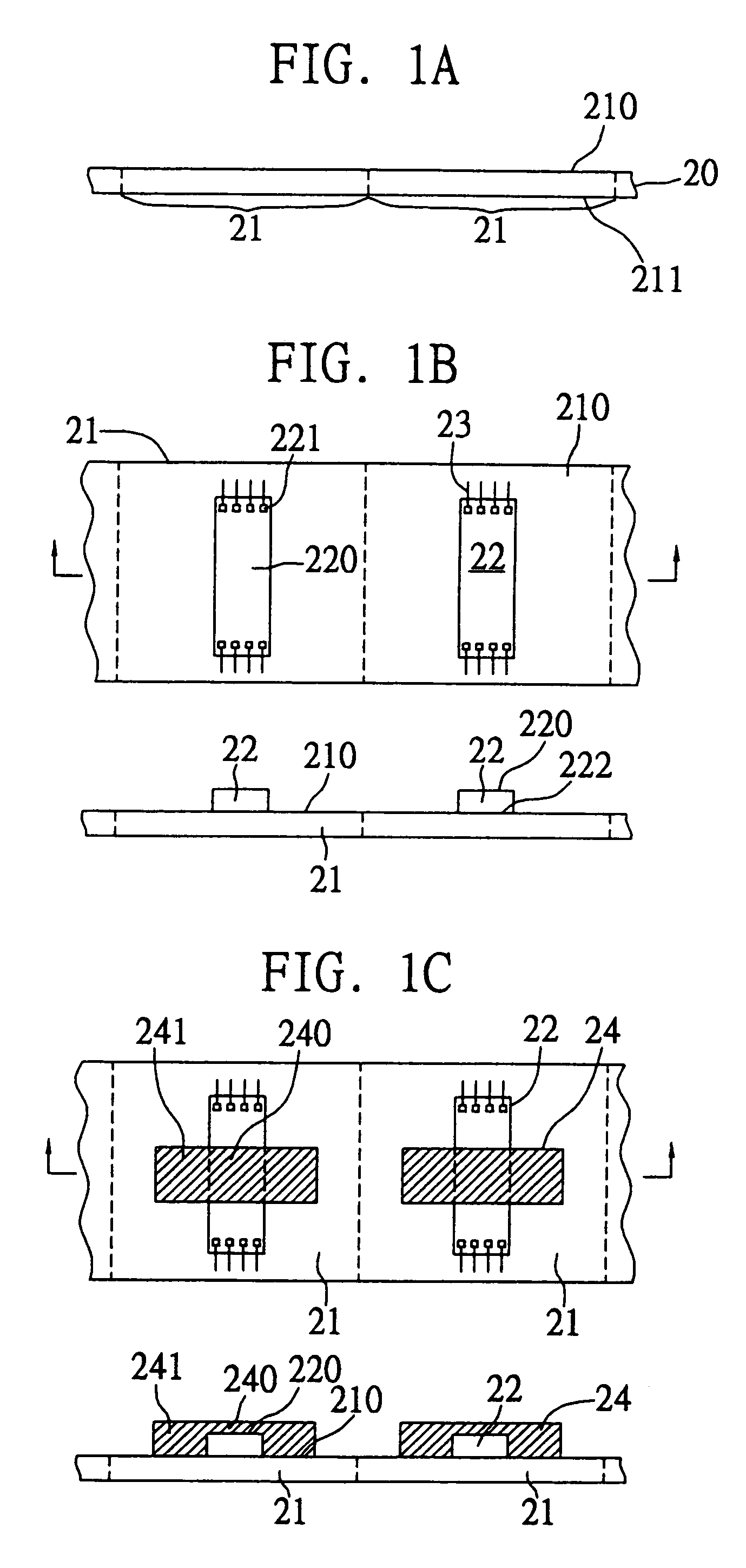

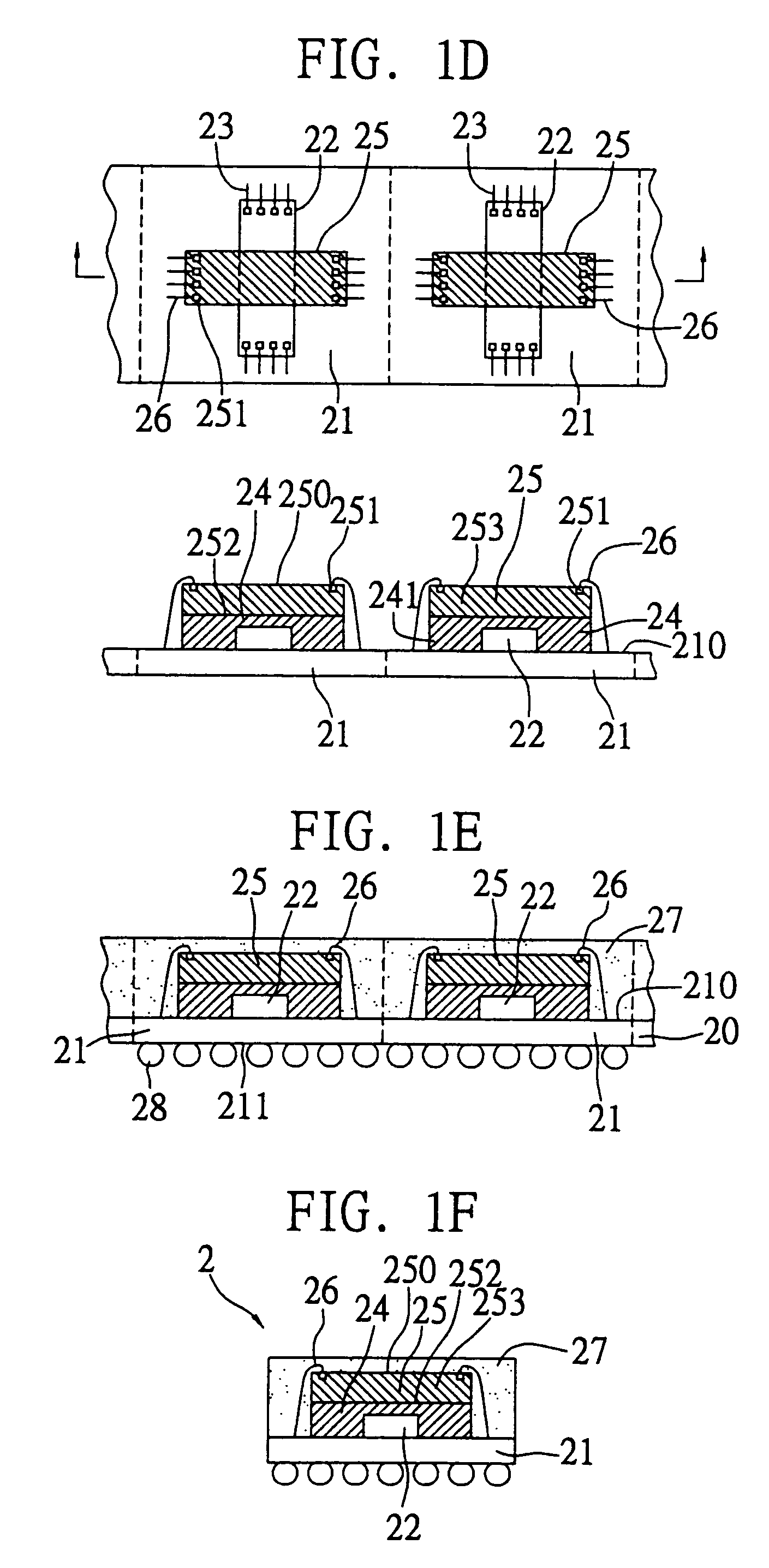

Micro-electronic package structure and method for fabricating the same

InactiveUS20060043549A1Simplify the manufacturing processImprove responseSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionSemiconductor chip

A micro-electronic package structure and a method for fabricating the same are proposed. A carrier is prepared and provided with a cavity for receiving at least one semiconductor chip having a plurality of electrical connection contacts. A dielectric layer is formed on the carrier, with the electrical connection contacts being exposed from the dielectric layer. A first circuit layer is formed on the dielectric layer and electrically connected to a portion of the electrical connection contacts of the chip. Another dielectric layer is formed on the first circuit layer and said dielectric layer, and a second circuit layer is formed on this dielectric layer and electrically connected to the rest of the electrical connection contacts of the chip and the first circuit layer by conductive vias, such that the chip is integrated into the carrier.

Owner:PHOENIX PRECISION TECH CORP

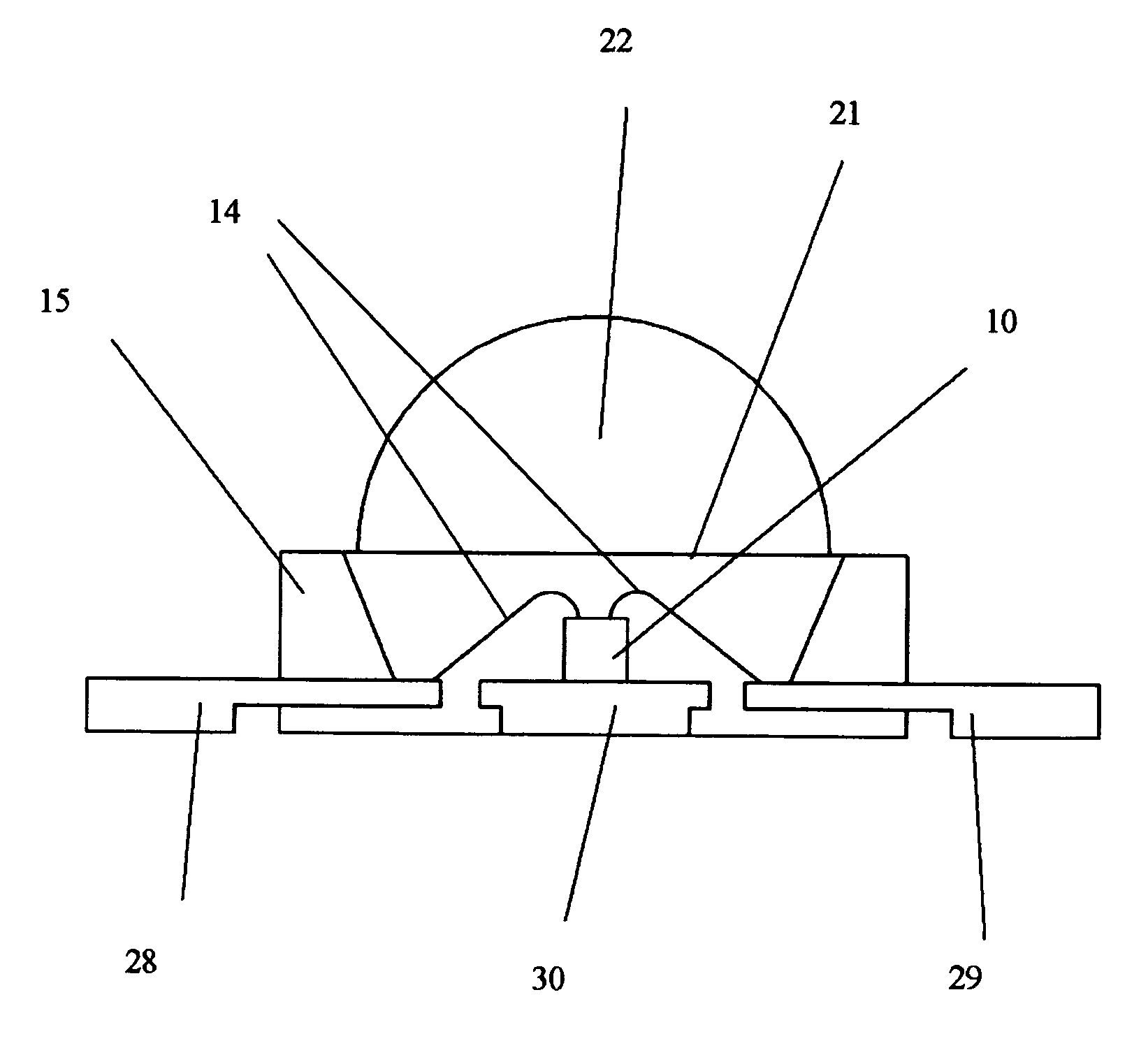

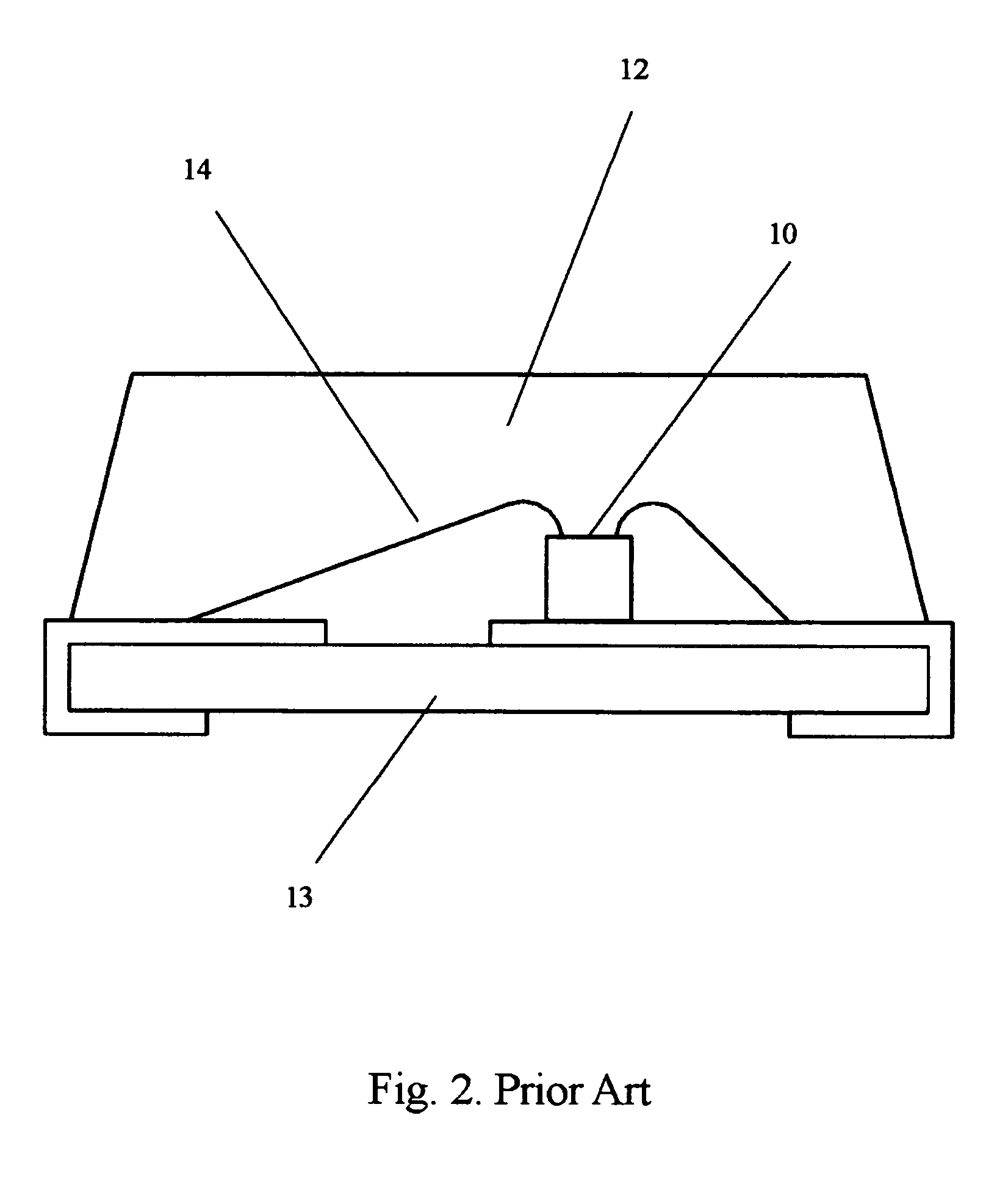

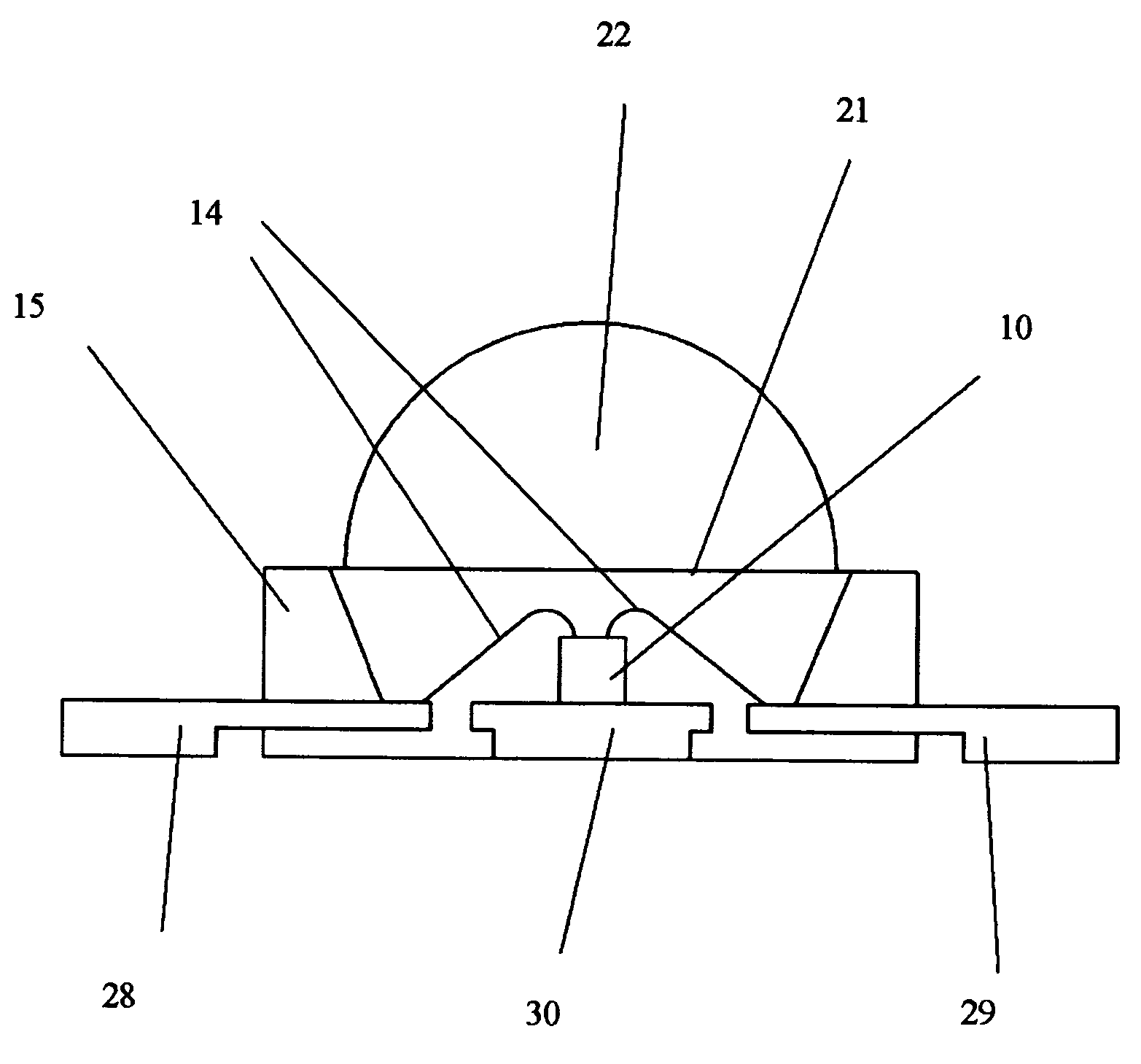

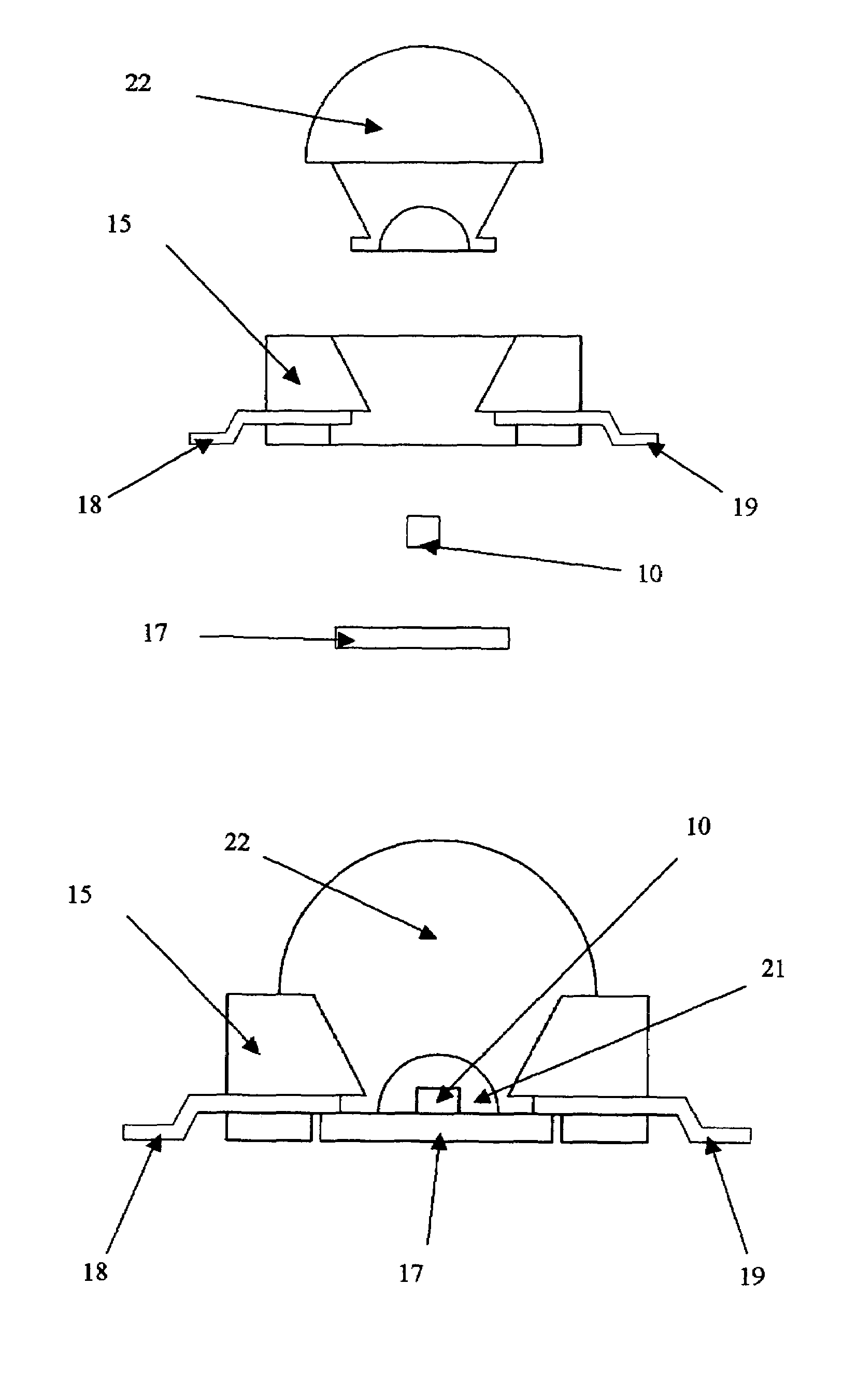

Low thermal resistance LED package

ActiveUS20060091410A1Reduce thermal resistanceProduction cost be reduceSolid-state devicesSemiconductor devicesEngineeringThin metal

A LED chip is bonded on a large submount serving as a heat sink. The submount is punched out from a thin metal sheet together with two other sections of lead frames for the LED and held together with insulating material. The planar structure makes the package thin. A transparent lens may be mounted over the submount. More than one LED of same or different color can be mounted on the submount.

Owner:PROLIGHT OPTO TECH +1

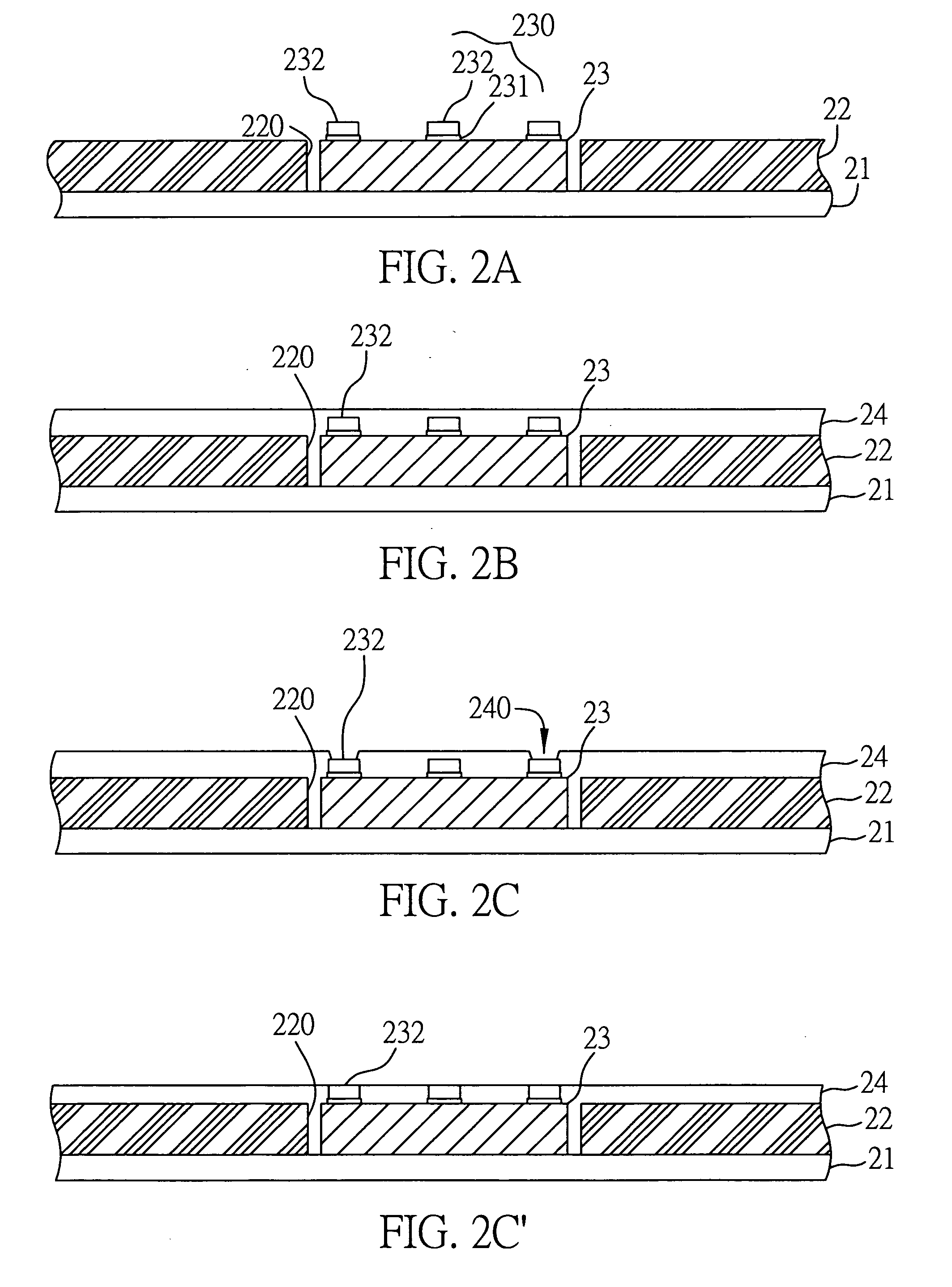

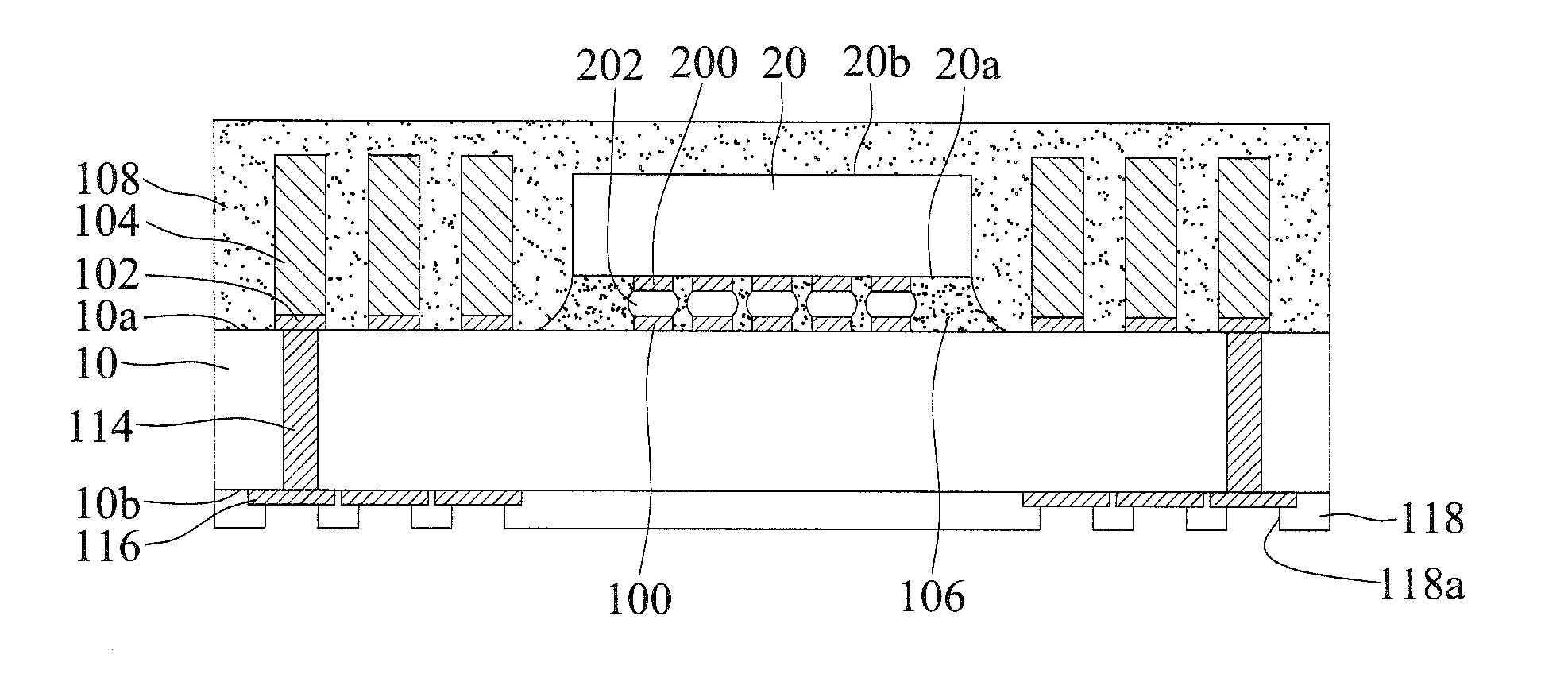

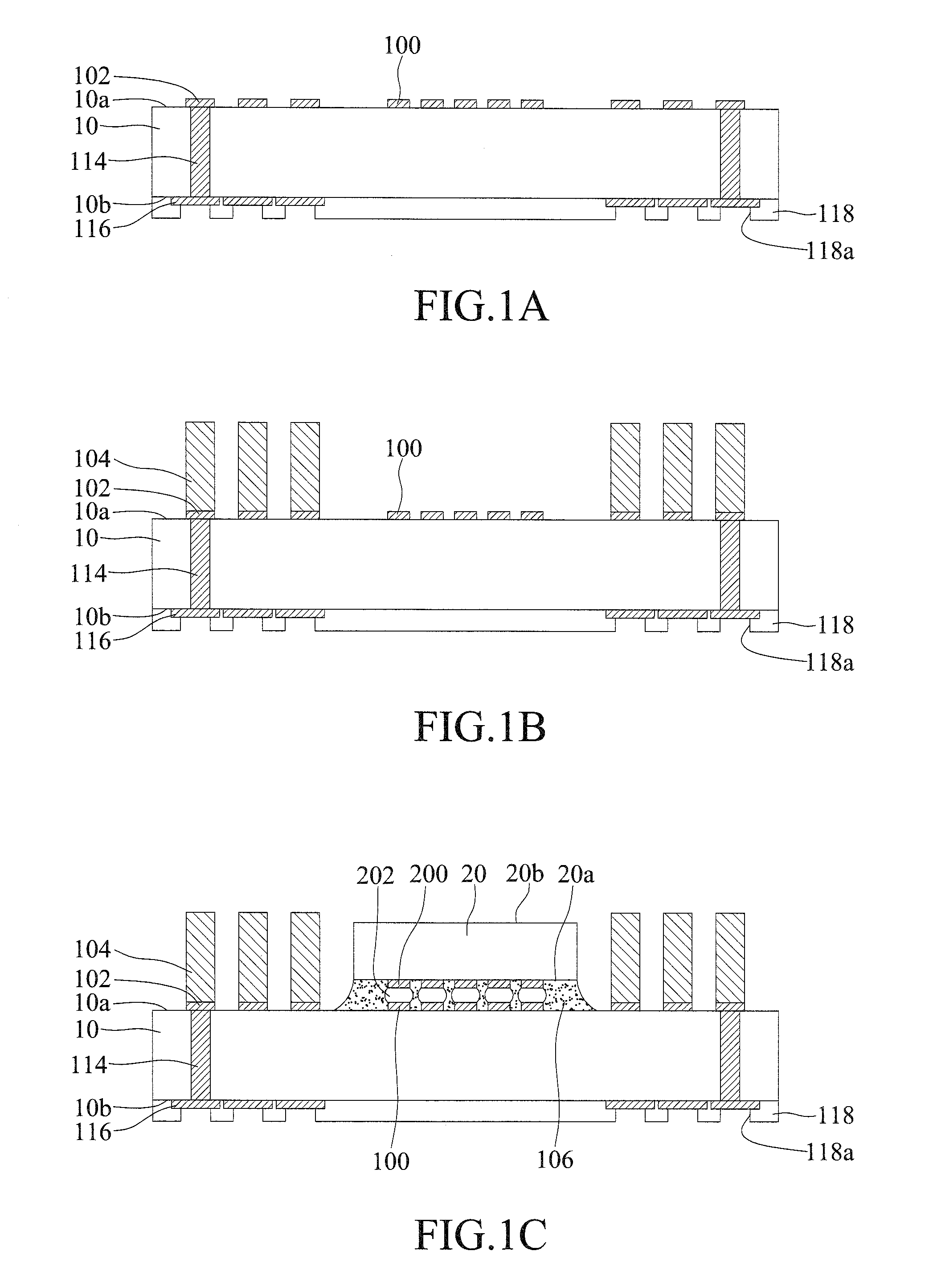

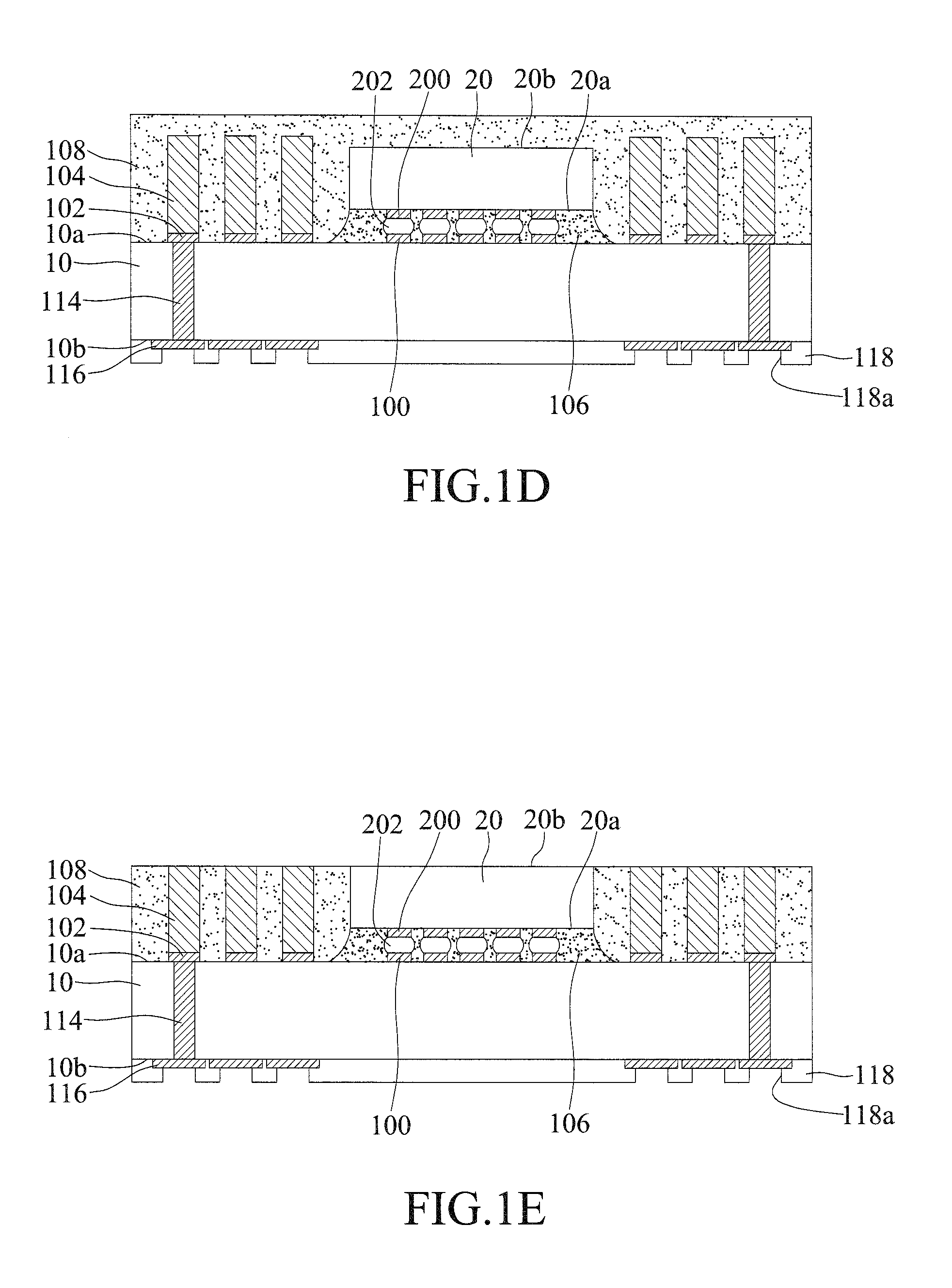

Package process and package structure

InactiveUS20100327465A1Reduce package thicknessAvoid fracturesFinal product manufactureSemiconductor/solid-state device detailsEngineeringSemiconductor

A package process is provided. First, a semiconductor substrate is disposed on a carrier, in which a surface of the carrier has an adhesive layer and the semiconductor substrate is bonded to the carrier by the adhesive layer. Next, a chip is bonded on the semiconductor substrate by flip chip technique and a first underfill is formed between the chip and the semiconductor substrate to encapsulate a plurality of first conductive bumps at the bottom of the chip. Then, a first molding compound is formed on the semiconductor substrate. The first molding compound at least encapsulates the side surface of the chip and the first underfill. Finally, the semiconductor substrate together with the chip and the first molding compound located thereon are separated from the adhesive layer of the carrier to form an array package structure.

Owner:ADVANCED SEMICON ENG INC

Low thermal resistance LED package

ActiveUS7381996B2Reduce thermal resistanceLow production costSemiconductor/solid-state device detailsSolid-state devicesThin metalEngineering

Owner:PROLIGHT OPTO TECH +1

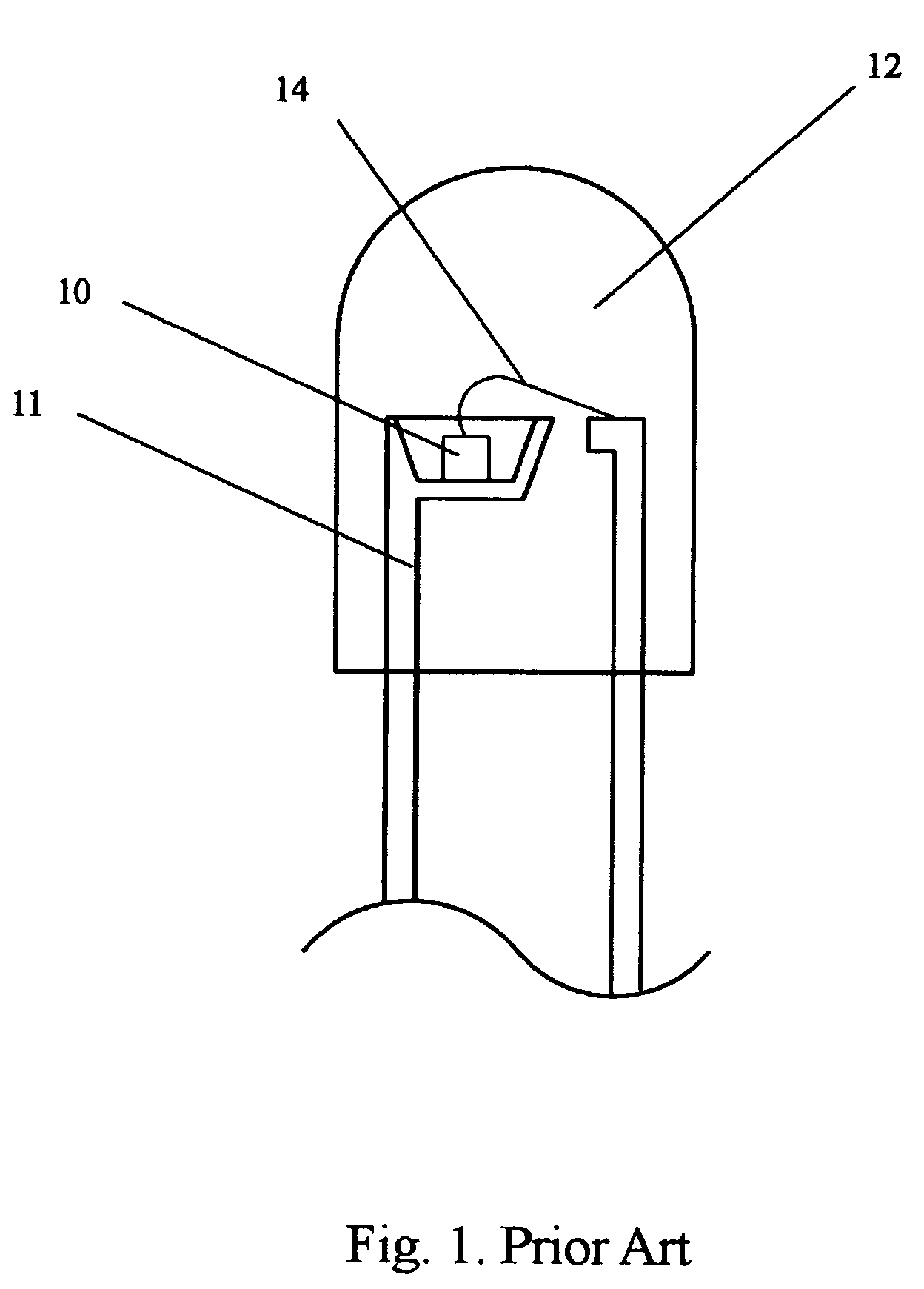

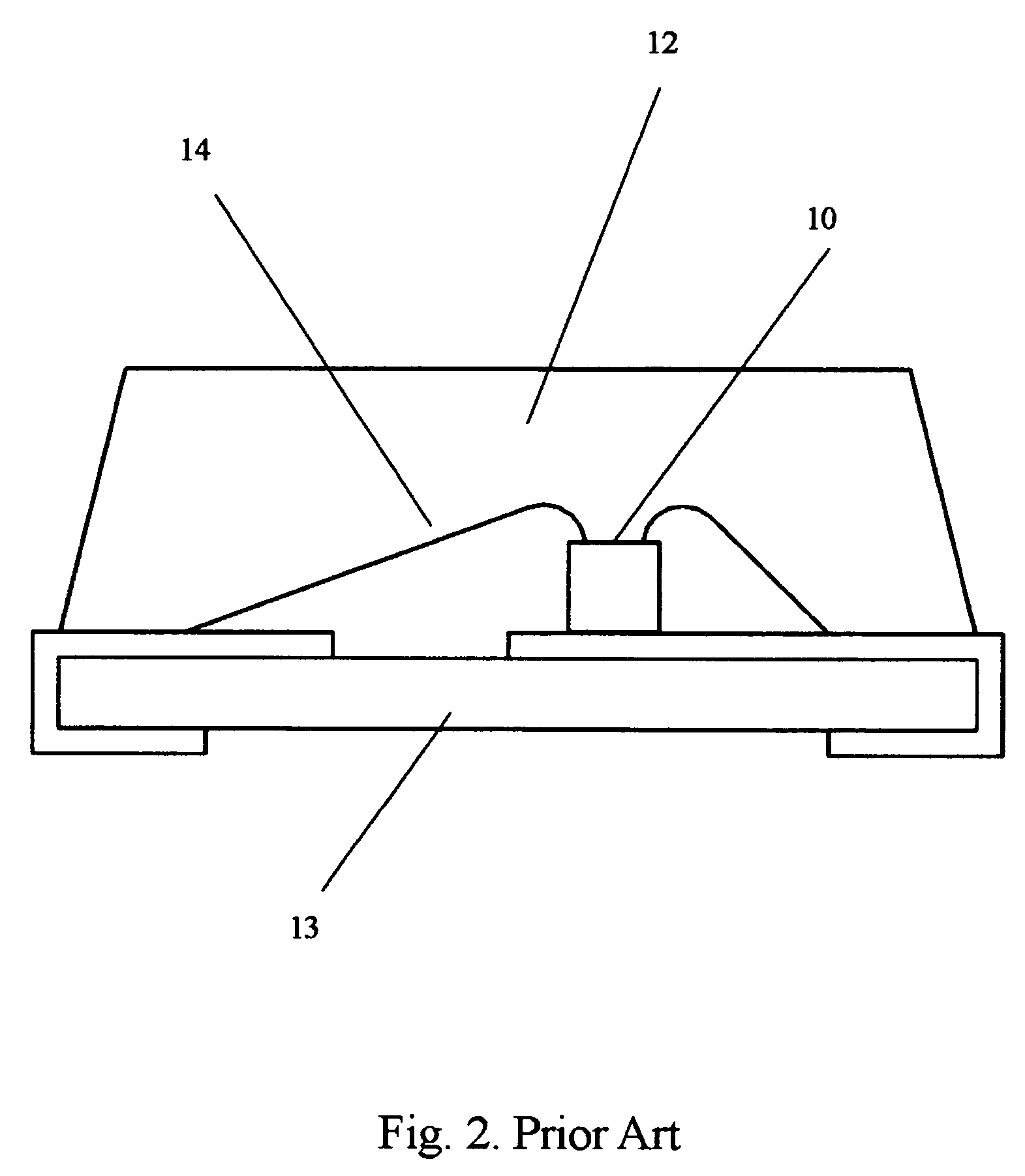

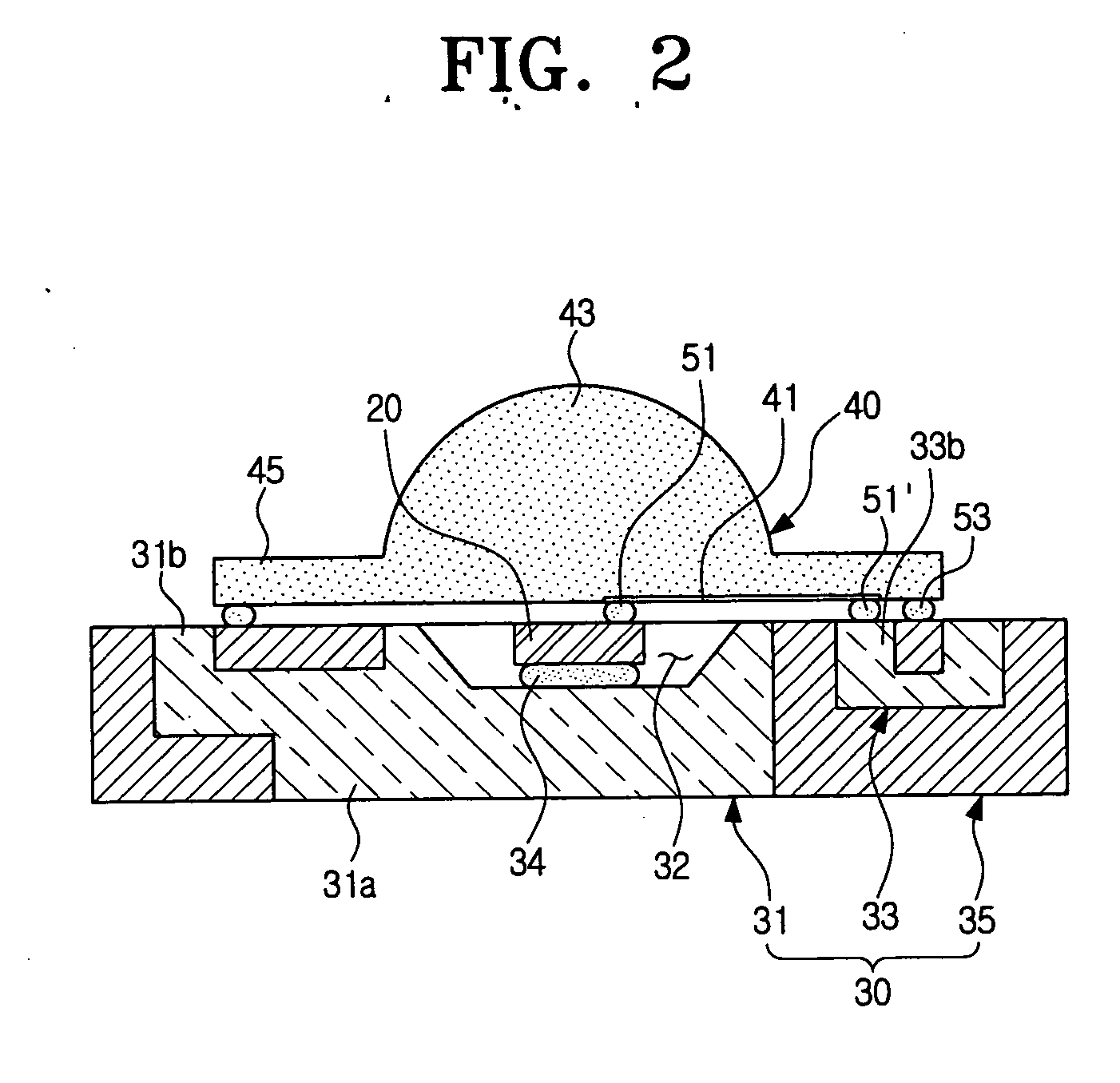

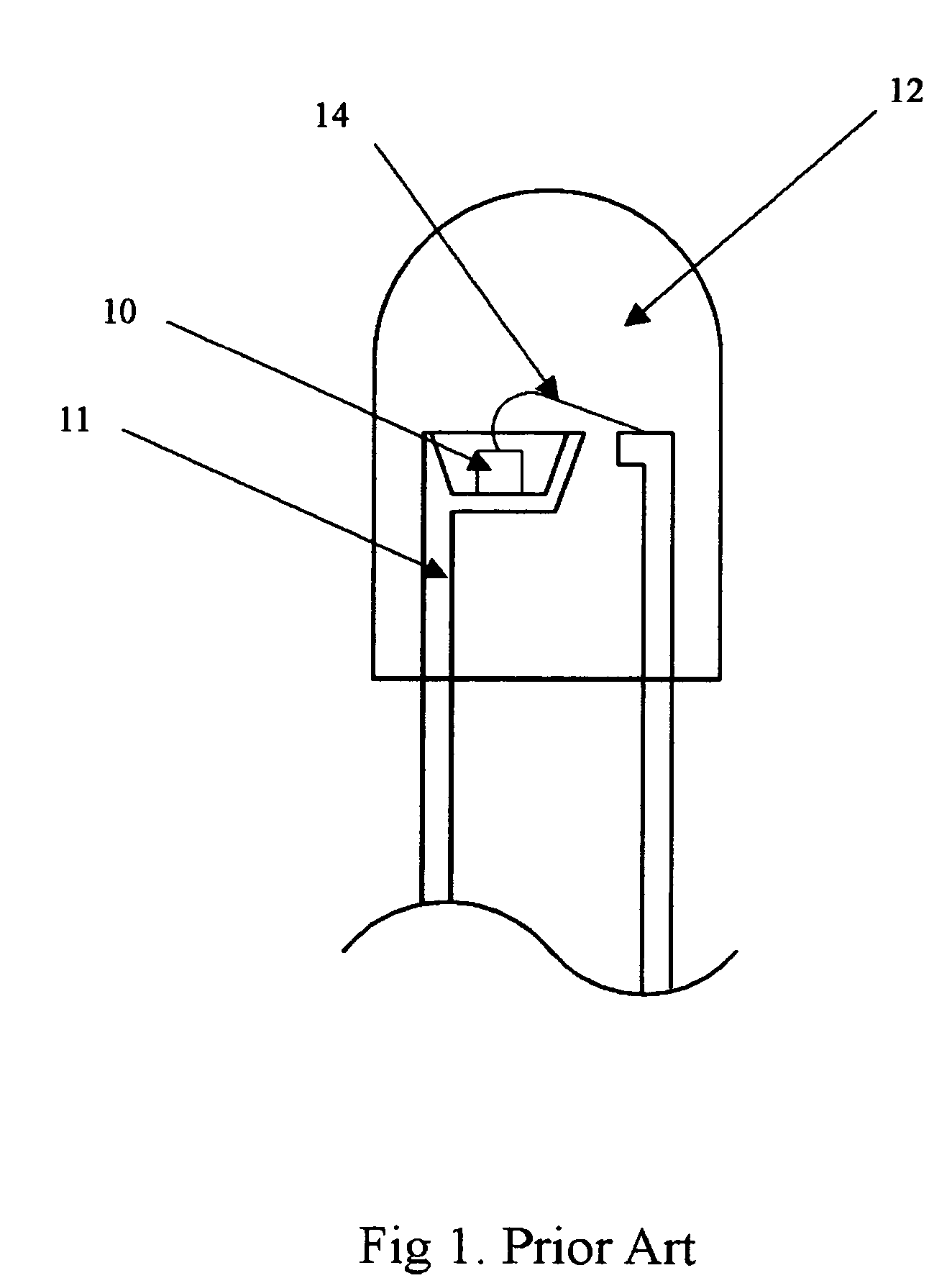

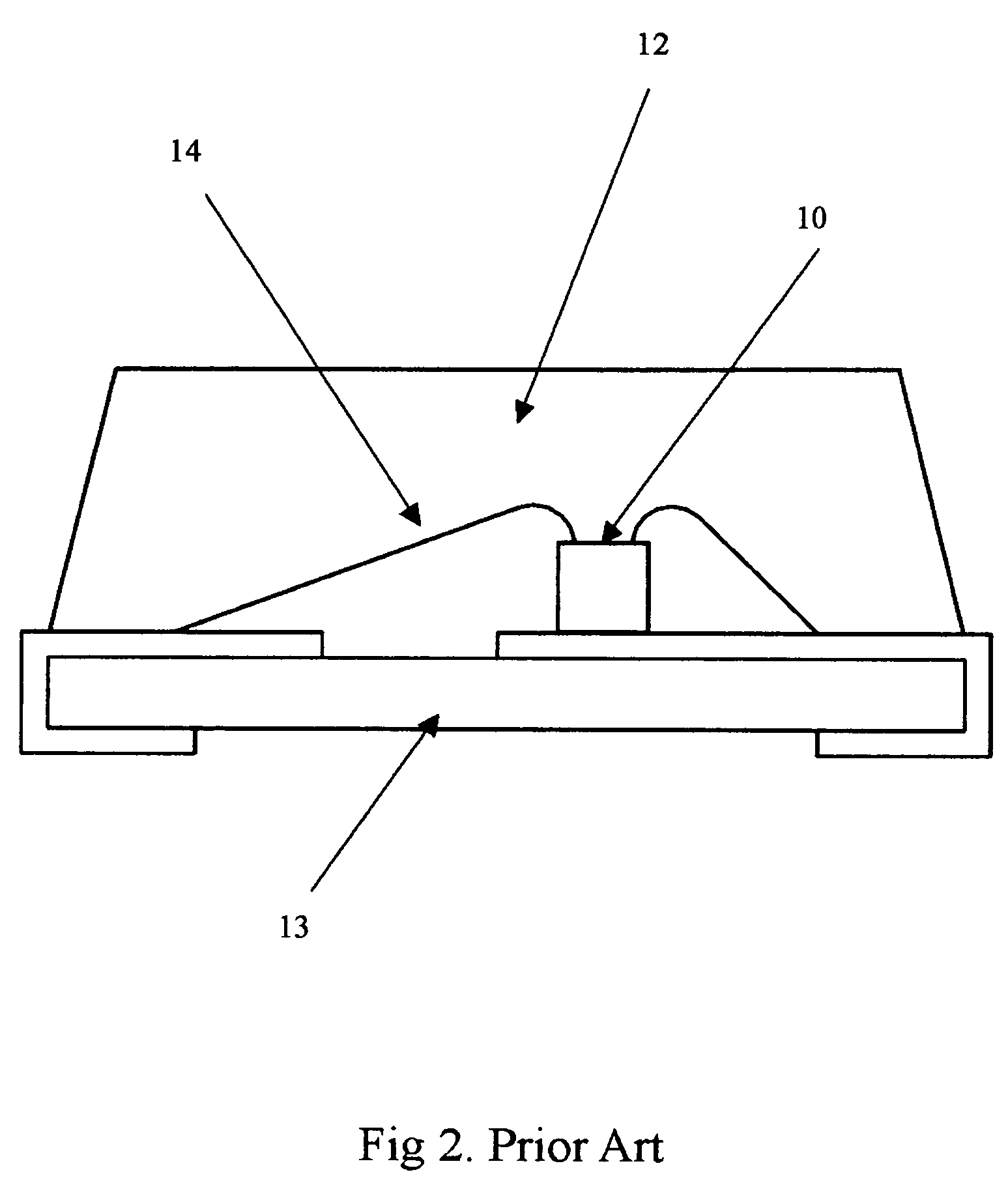

LED package, manufacturing method thereof, and LED array module using the same

InactiveUS20060279949A1Increase powerImprove cooling effectNon-electric lightingPoint-like light sourceElectrical conductorLed array

An LED package includes a substrate, an LED, and a cap. The substrate includes a first conductor unit, a second conductor unit, and a non-conductor unit which electrically insulates the first and second conductor unit. The LED is bonded to the first conductor unit. The cap is mounted on the substrate over the LED and comprises a conductive wire which connects the LED to the second conductor unit.

Owner:SAMSUNG ELECTRONICS CO LTD

Lighting device, display, and method for manufacturing the same

InactiveUS8110839B2Reduce package thicknessReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingLight equipmentPhosphor

A display, a lighting device and a method for manufacturing the lighting device are provided. The lighting device comprises a substrate, an electrode layer, a plurality of light source units and a light scattering layer, which is covered by a transparent layer and a reflector layer to create a uniform surface light within an ultra thin format. A yellow phosphor layer is disposed above the reflector layer to create white light when a blue LED or UV LED is used. The lighting device also provides a unique electrode layout design which can be applied for local dimming control and can be easily applied for large size product applications.

Owner:LUXINGTEK

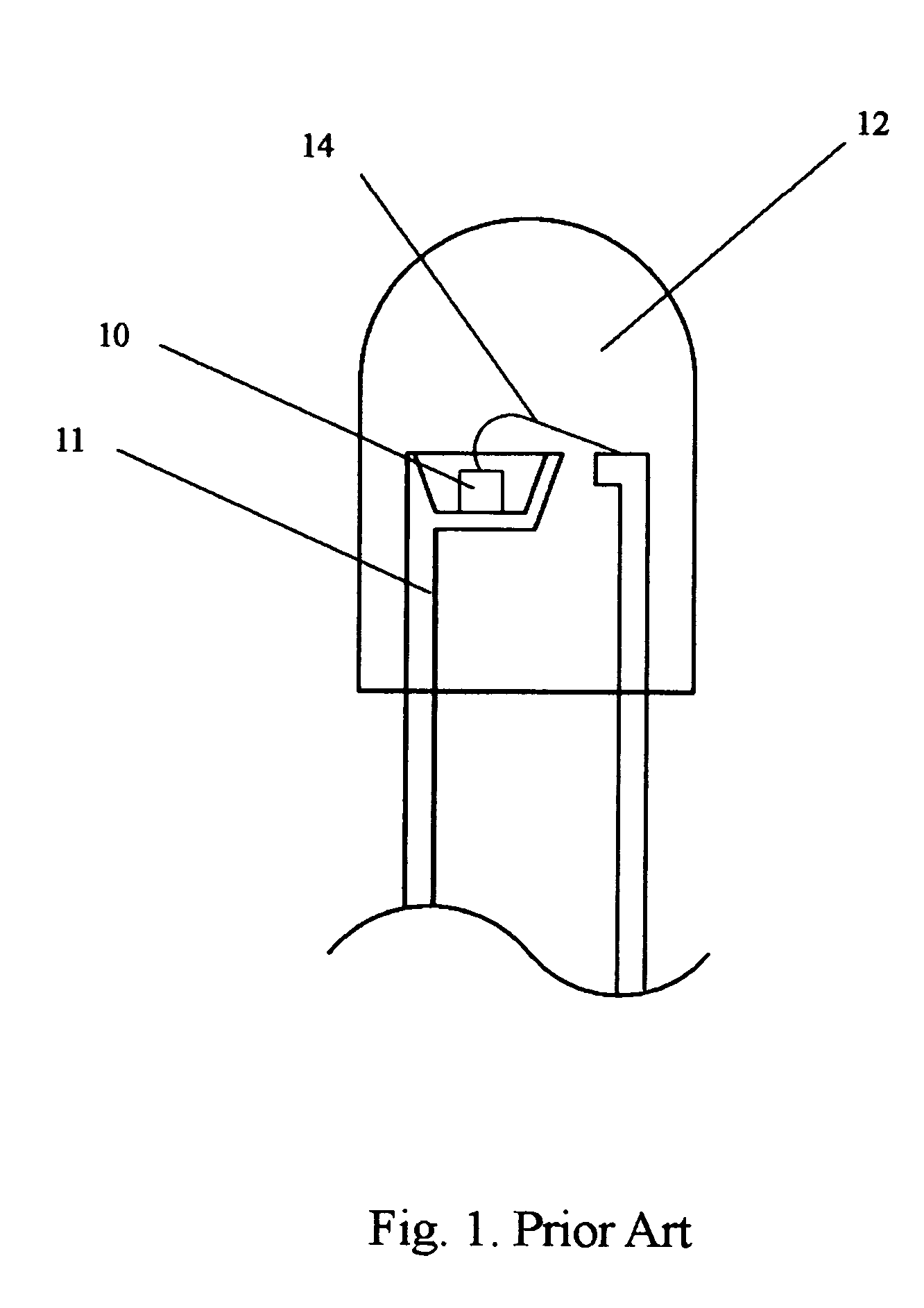

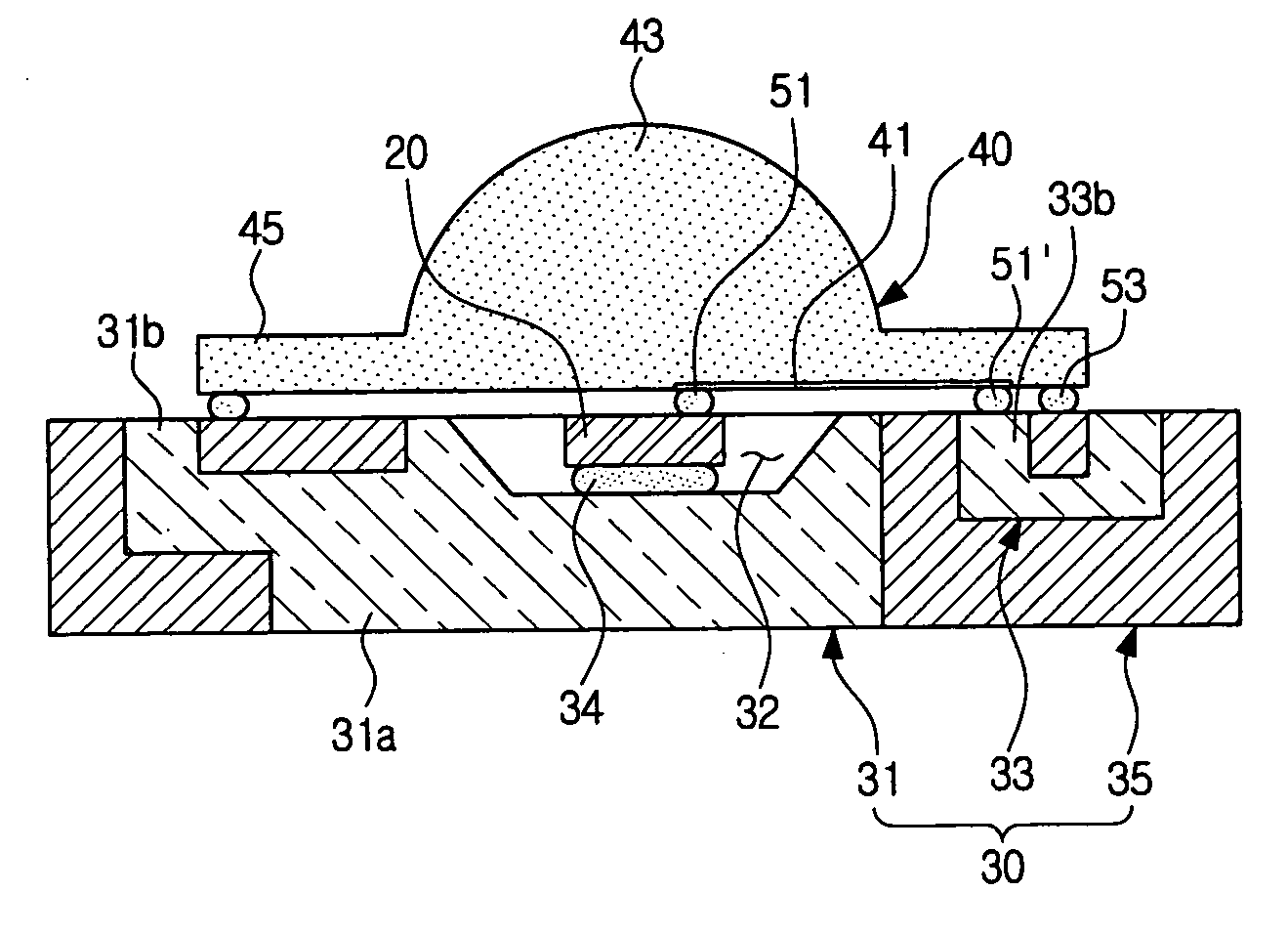

Low thermal resistance light emitting diode

ActiveUS7276739B2Reduce thermal resistanceLow production costSolid-state devicesSemiconductor devicesElectric power transmissionEngineering

A light emitting diode (LED) includes a LED chip, which can transfer electrical power to electric-magnetic wave. A set of lead frame is enclosed by electrical isolator material to form a cavity. An optics lens seats on top of the cavity and is bonded to said electrical isolator material. A submount to carry said LED chip is soldered or adhered to the lead frame and forms the electrical contact from said LED chip to lead frame. A high transparency material is utilized to enclosed the LED chip.

Owner:HSIN CHEN CHEN LUN +1

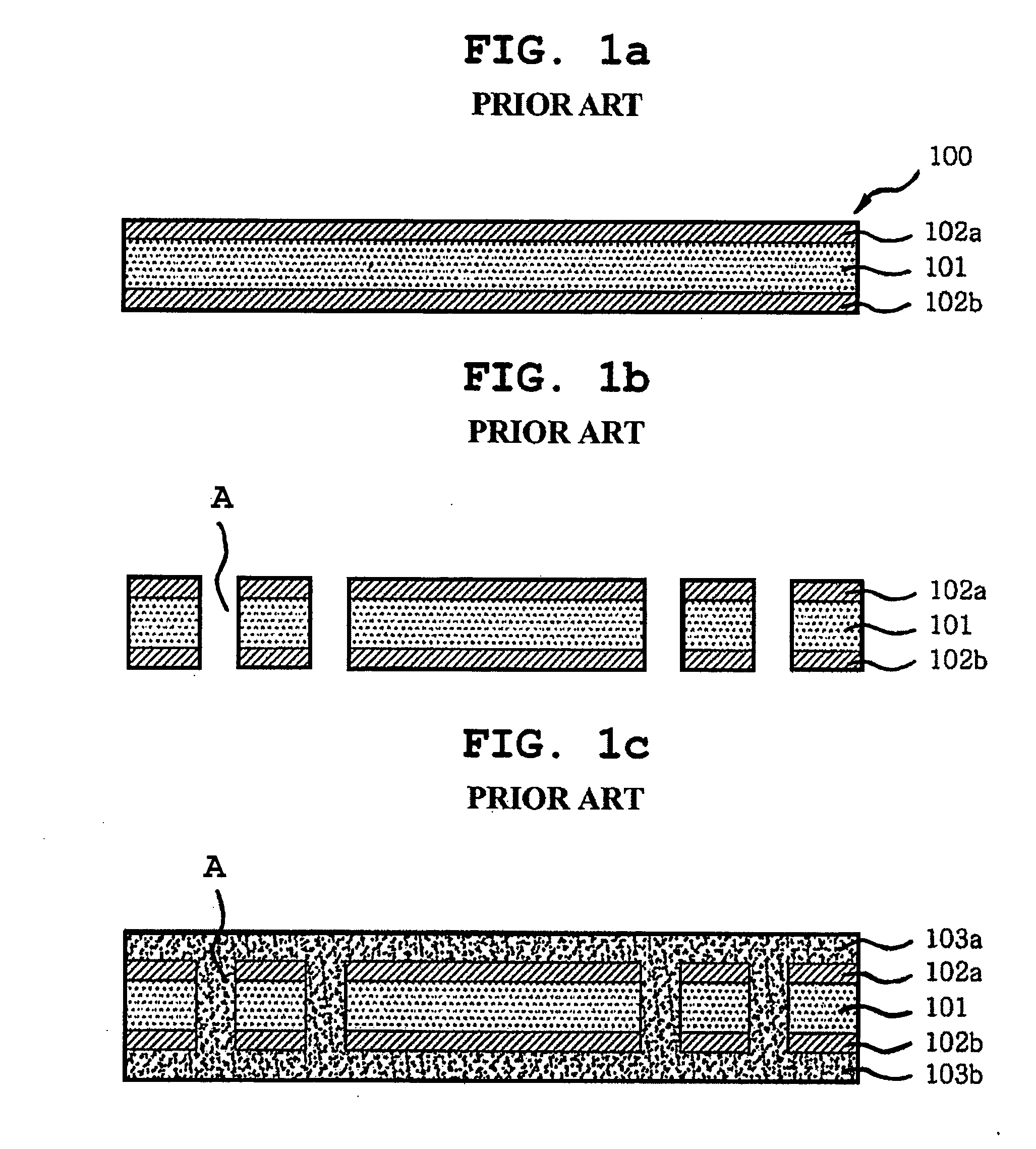

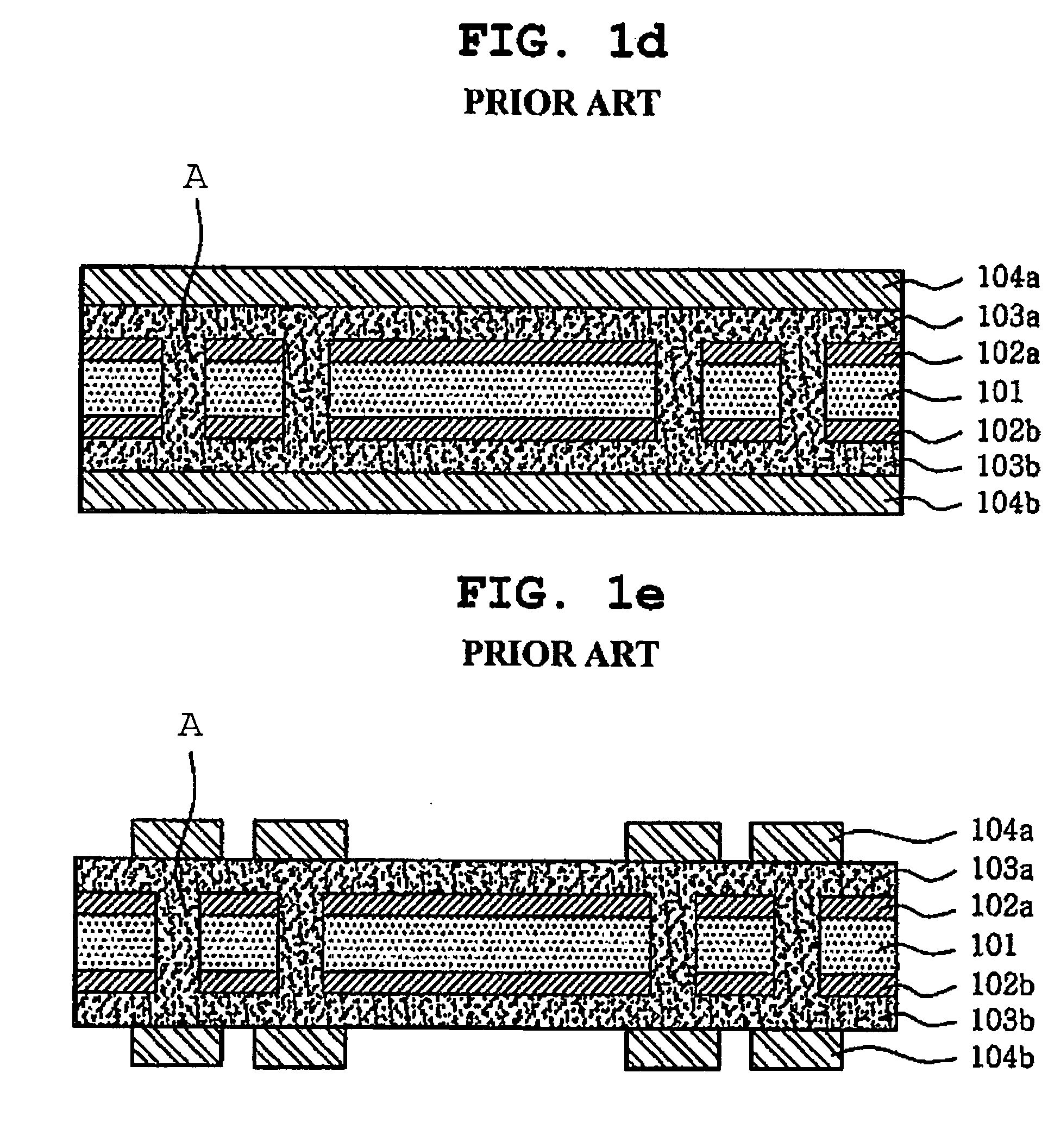

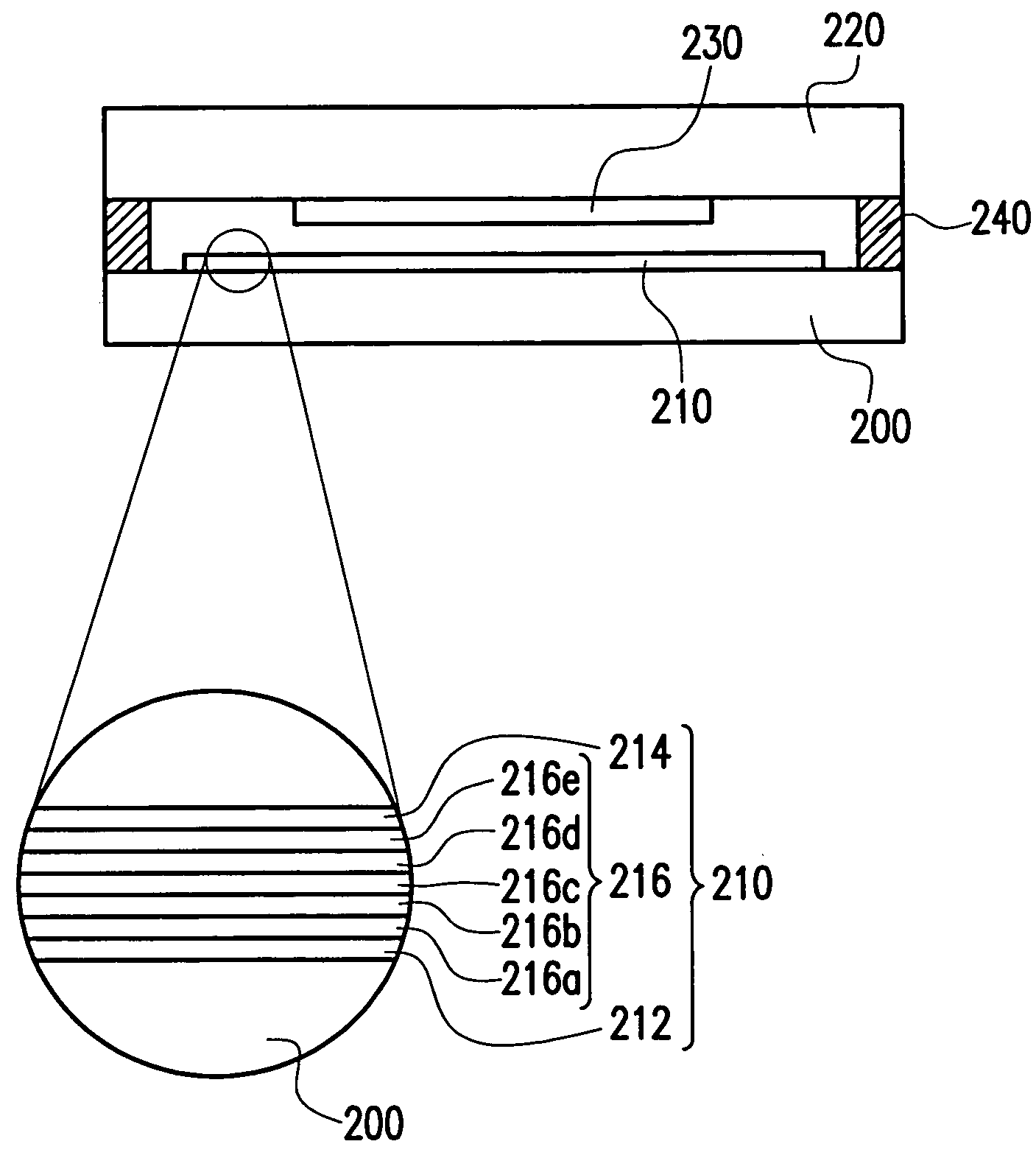

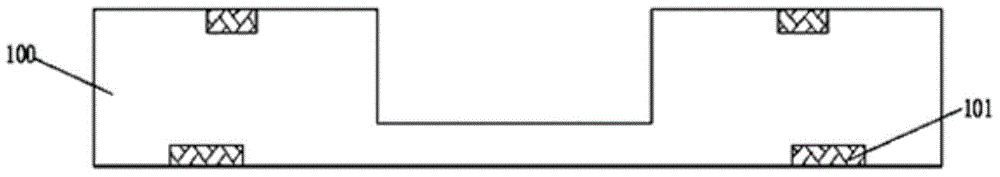

Thin double-sided package substrate and manufacture method thereof

InactiveUS20080315239A1Improve cooling effectReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesMetalElectrical and Electronics engineering

The present invention discloses a manufacture method for a thin double-sided package substrate, which includes steps: providing a carrier; respectively forming a first conductive layer and a second conductive layer on the upper and lower surfaces of the carrier; forming a through-hole penetrating the first conductive layer and the carrier but not penetrating the second conductive layer; setting a conductive element in the through-hole to electrically connect the first conductive layer with the second conductive layer; forming desired circuits on the first conductive layer and / or the second conductive layer; forming a first metal layer on the first conductive layer and / or the second conductive layer; and removing the carrier located in a predetermined region to form a chip receiving bay. The present invention also discloses a package substrate made by the abovementioned manufacture method, which can reduce the overall thickness of a chip package structure, increase the heat-dissipation effect of the chip and prevent the chip package structure from humidity penetration.

Owner:GIOTEK OPTOELECTRONICS +1

Wafer level molded opto-couplers

InactiveUS20120326170A1Small sizeReduce volumeSolid-state devicesSemiconductor/solid-state device manufacturingEngineering

Optocoupler packages and methods of making the same. An exemplary package comprises a substrate having a first surface, a second surface opposite the first surface, and a body of electrically insulating material disposed between the first and second surfaces; a first optoelectronic device embedded in the body of electrically insulating material of the substrate and disposed between the substrate's first and second surfaces, the first optoelectronic device having a first conductive region and a second conductive region; a second optoelectronic device embedded in the body of electrically insulating material of the substrate and disposed between the substrate's first and second surfaces and optically coupled to the first optoelectronic device, the second optoelectronic device having a first conductive region and a second conductive region; and a plurality of electrical traces disposed on one or both surfaces of the substrate and electrically coupled to the conductive regions of the optoelectronic devices.

Owner:SEMICON COMPONENTS IND LLC

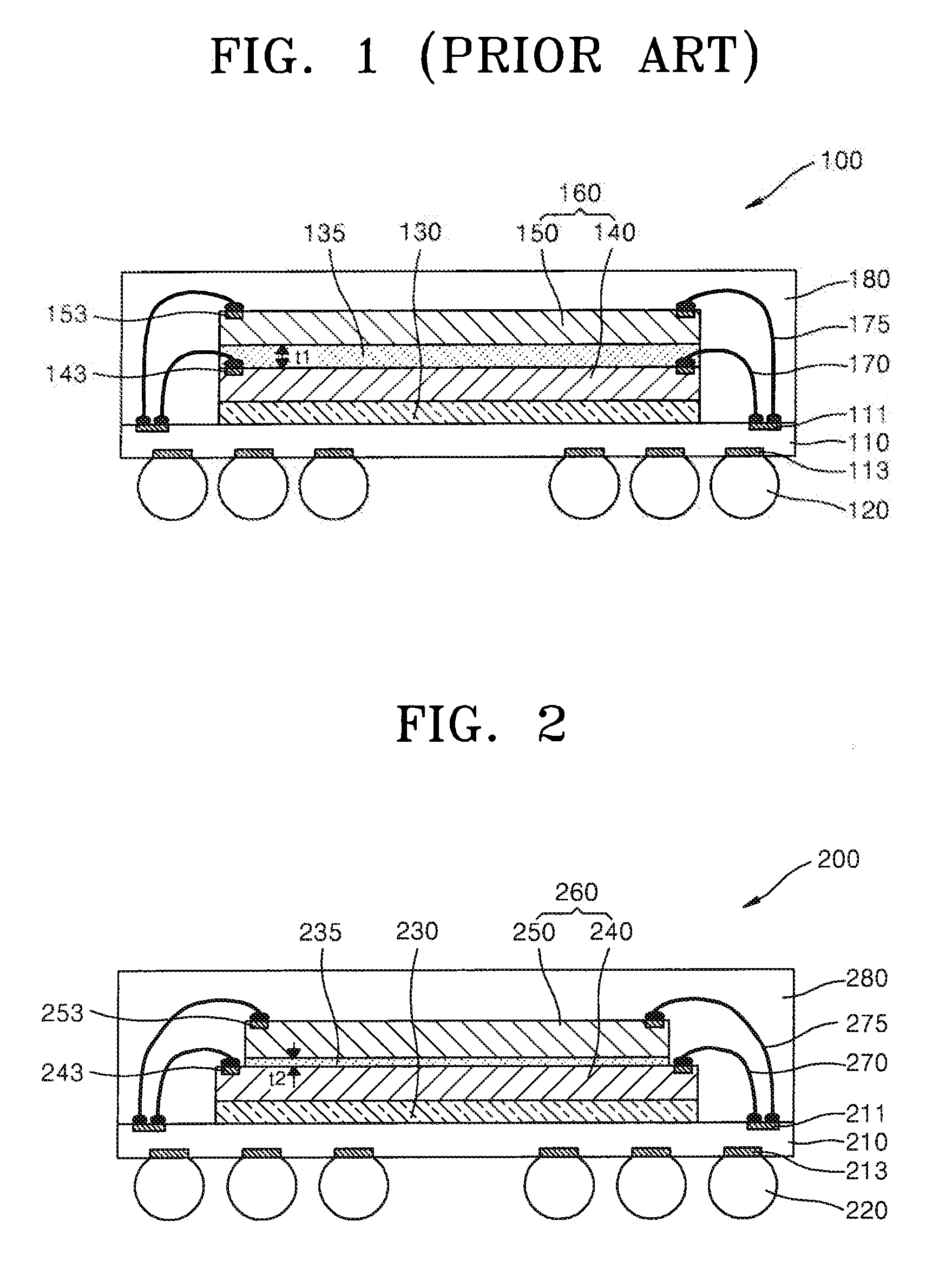

Ball grid array substrate having window and method of fabricating same

InactiveUS20060131729A1Reduce package thicknessSemiconductor/solid-state device detailsPrinted circuit aspectsChip sizeLead bonding

Disclosed is a ball grid array substrate having a window formed on a core material instead of a thin core material, and wherein a semiconductor chip is mounted thereon, thereby reducing the thickness of a package, and a method of fabricating the same. The ball grid array substrate comprises a first external layer which includes first circuit patterns, wire bonding pad patterns, and a window corresponding in size to a first chip mounted therein and wherein the chip is wire-bonded to the wire bonding pad patterns. A second external layer includes second circuit patterns, a portion corresponding in position to the window of the first external layer, and solder ball pad patterns. Second chips mounted on the solder ball pad patterns. An insulating layer interposed between the first and second external layers. The window is formed through the insulating layer at a position corresponding to the window of the first external layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

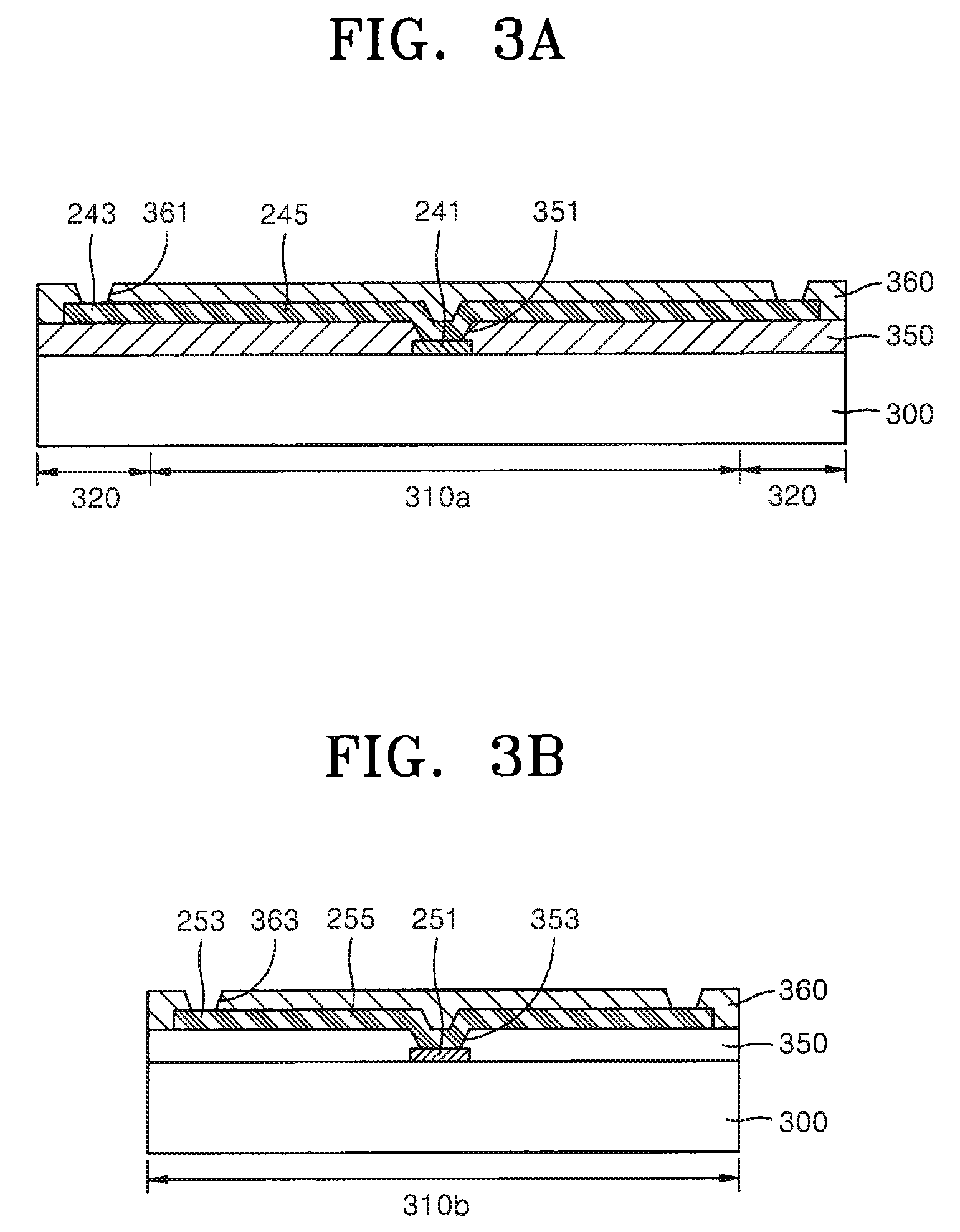

Chip stack package and method of fabricating the same

ActiveUS20080251939A1Reduce thicknessReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor chip

A chip stack package is provided, wherein semiconductor chips having different die sizes are stacked by arranging pads in a scribe region through a redistribution process, so that the thickness of the package can be reduced. A method of fabricating the chip stack package is also provided. In the chip stack package, a plurality of circuit patterns are arranged on one surface of a substrate, and a unit semiconductor chip is mounted thereon. The unit semiconductor chip includes a plurality of semiconductor chips sequentially stacked on the substrate. The semiconductor chips of the unit semiconductor chip have different die sizes. One of the semiconductor chips includes a plurality of first pads arranged in a first chip region, and the other semiconductor chips include second pads arranged in a scribe region at an outside of a second chip region defined by the scribe region.

Owner:SAMSUNG ELECTRONICS CO LTD

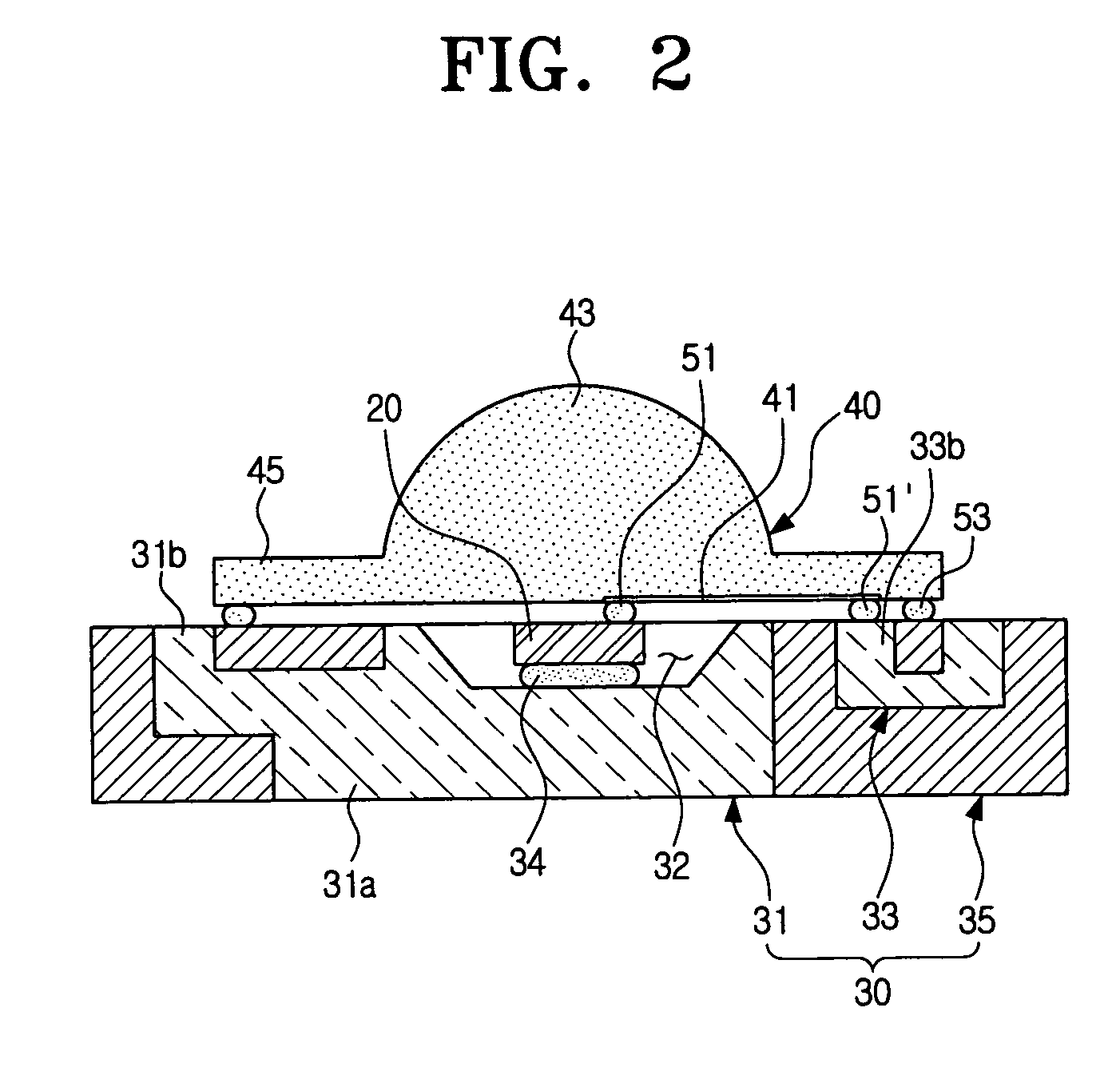

Multi-chip semiconductor package and fabrication method thereof

InactiveUS7091623B2Avoid crackingHigh mechanical strengthSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageConductive materials

A multi-chip semiconductor package and a fabrication method thereof are provided. A substrate having an upper surface and a lower surface is prepared. At least a first chip is mounted on the upper surface of the substrate. A non-conductive material is applied over predetermined area on the first chip and the upper surface of the substrate. At least a second chip is mounted on the non-conductive material, and formed with at least a suspending portion free of interference in position with the first chip, wherein the non-conductive material is dimensioned in surface area at least corresponding to the second chip, so as to allow the suspending portion to be supported on the non-conductive material. With the second chip being completely supported on the non-conductive material without causing a conventional chip-crack problem, structural intactness and reliability can be effectively assured for fabricated package products.

Owner:UTAC HEADQUARTERS PTE LTD

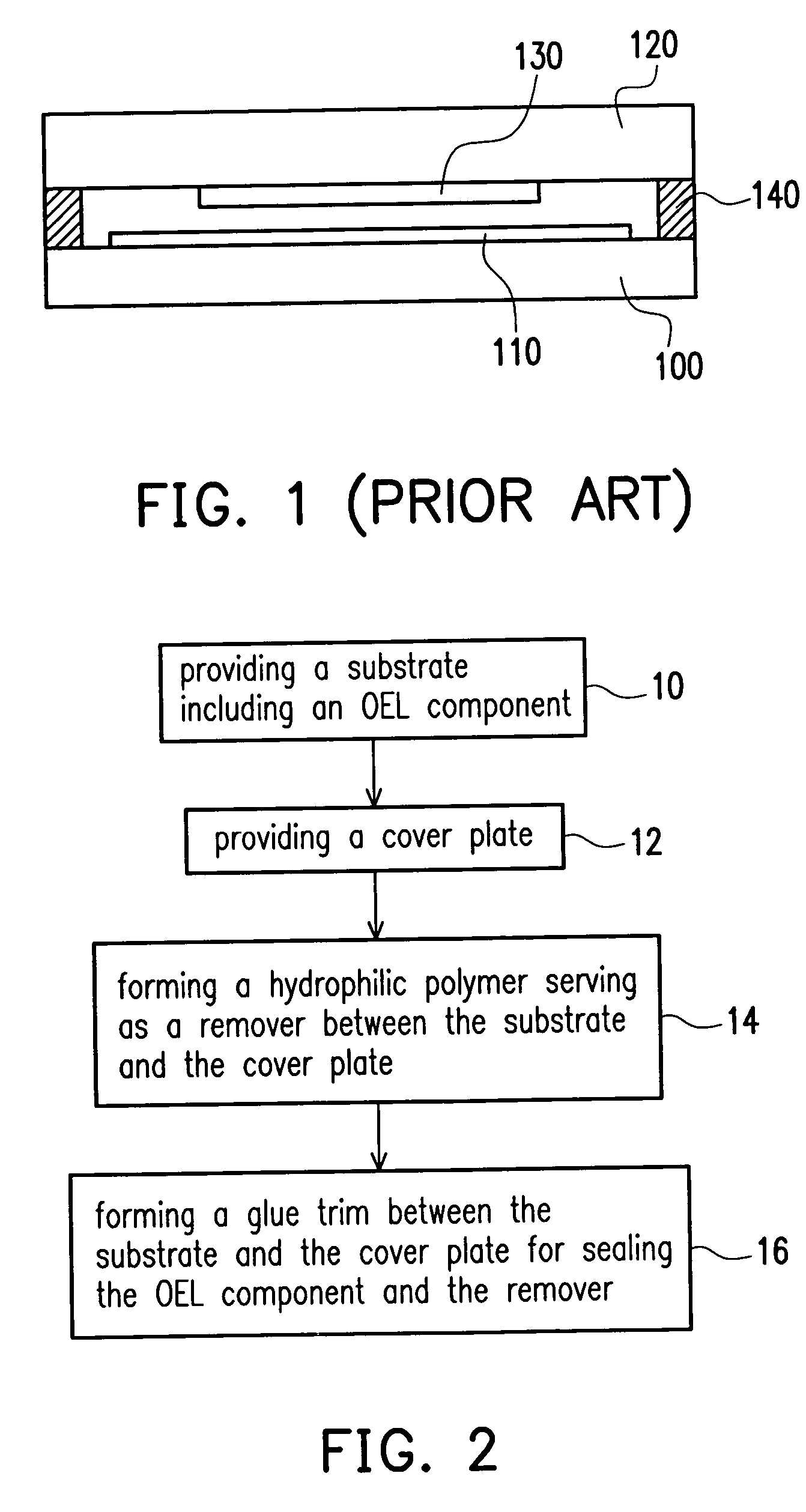

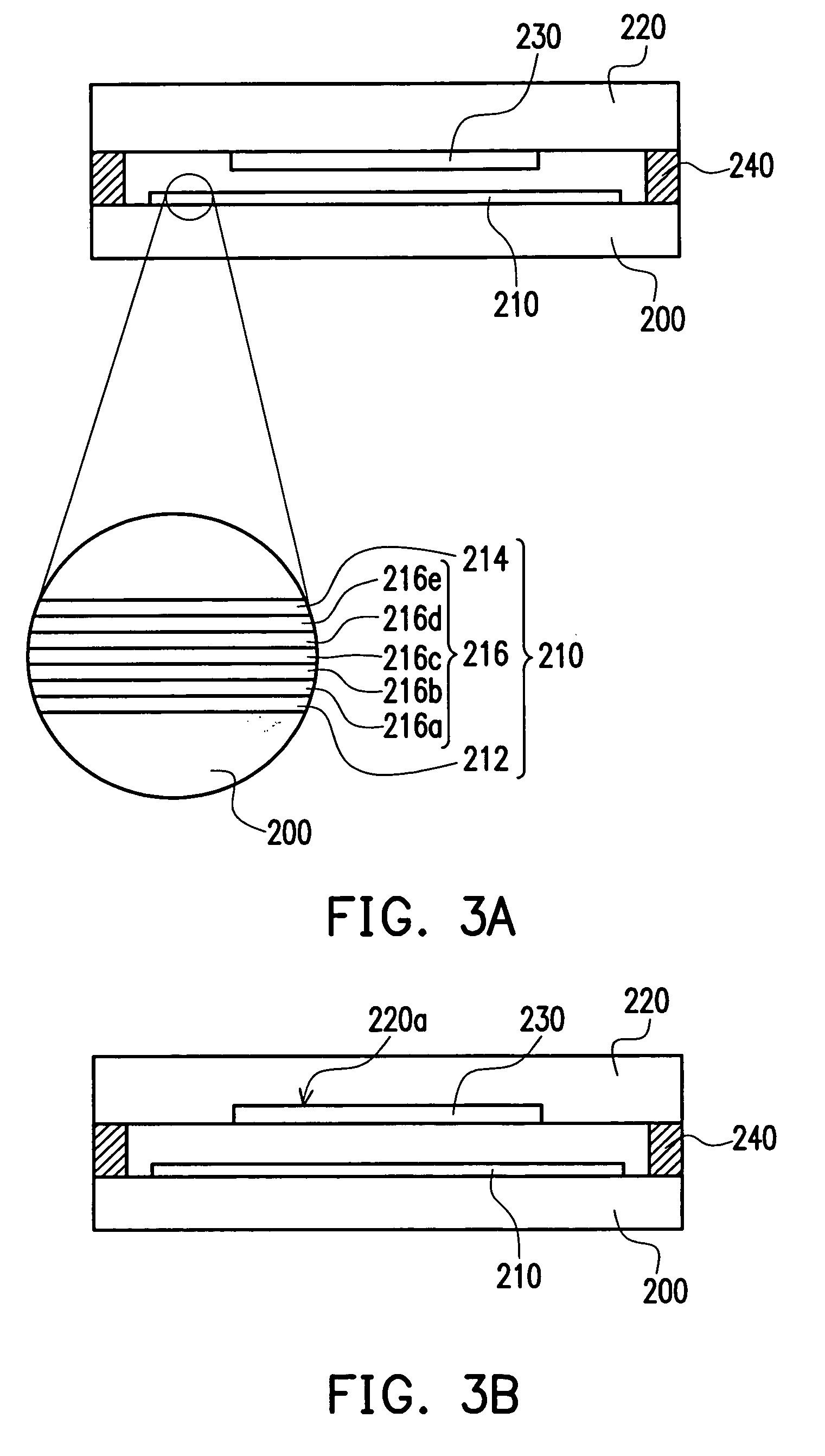

Package structure of organic electroluminescent device and package method thereof

InactiveUS20050276947A1Efficient removalGeneration of dark spot is reducedSolid-state devicesSemiconductor/solid-state device manufacturingHydrophilic polymersAdhesive

A package structure of an organic electroluminescent (OEL) device and a method of packaging thereof are provided. The package structure includes a substrate, an OEL component, a cover plate, a desiccant and an adhesive. The OEL component is disposed over the substrate. The cover plate is disposed over the substrate. The desiccant is disposed above the substrate or the cover plate. The desiccant includes, for example but not limited to, a hydrophilic polymer. The adhesive is disposed between the substrate and the cover plate, wherein the OEL component and the desiccant are sealed by the substrate, the cover plate and the adhesive. Therefore, moisture / oxygen in the package structure is absorbed and removed by the hydrophilic polymer.

Owner:RITDISPLAY

LED package, manufacturing method thereof, and LED array module using the same

InactiveUS7514718B2Increase powerImprove cooling effectNon-electric lightingWave amplification devicesElectrical conductorLed array

An LED package includes a substrate, an LED, and a cap. The substrate includes a first conductor unit, a second conductor unit, and a non-conductor unit which electrically insulates the first and second conductor unit. The LED is bonded to the first conductor unit. The cap is mounted on the substrate over the LED and comprises a conductive wire which connects the LED to the second conductor unit.

Owner:SAMSUNG ELECTRONICS CO LTD

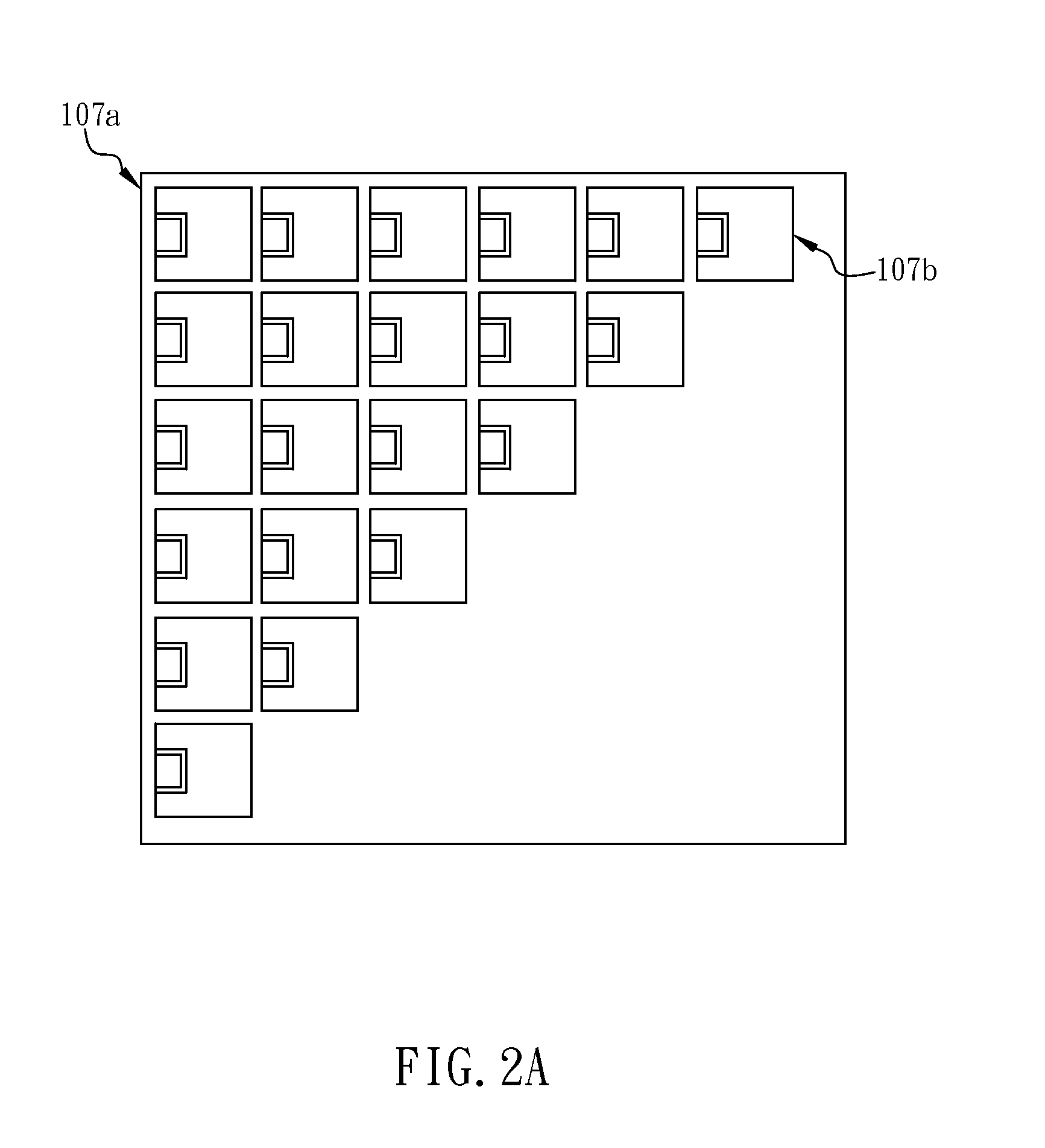

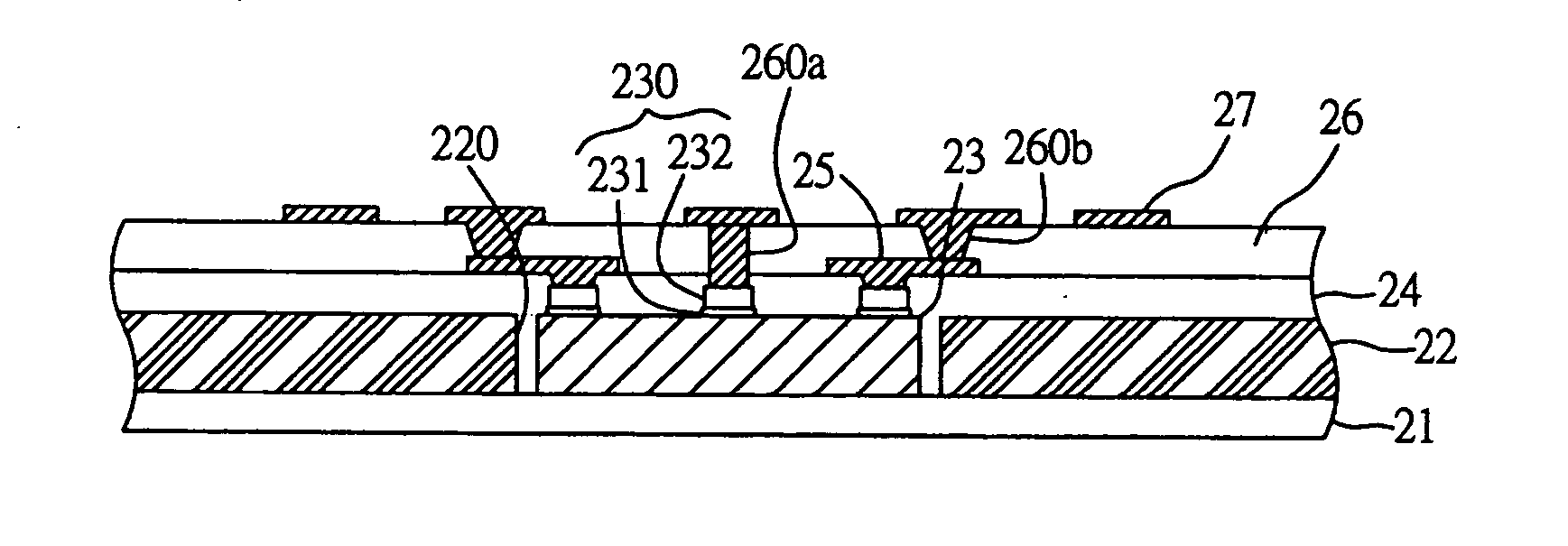

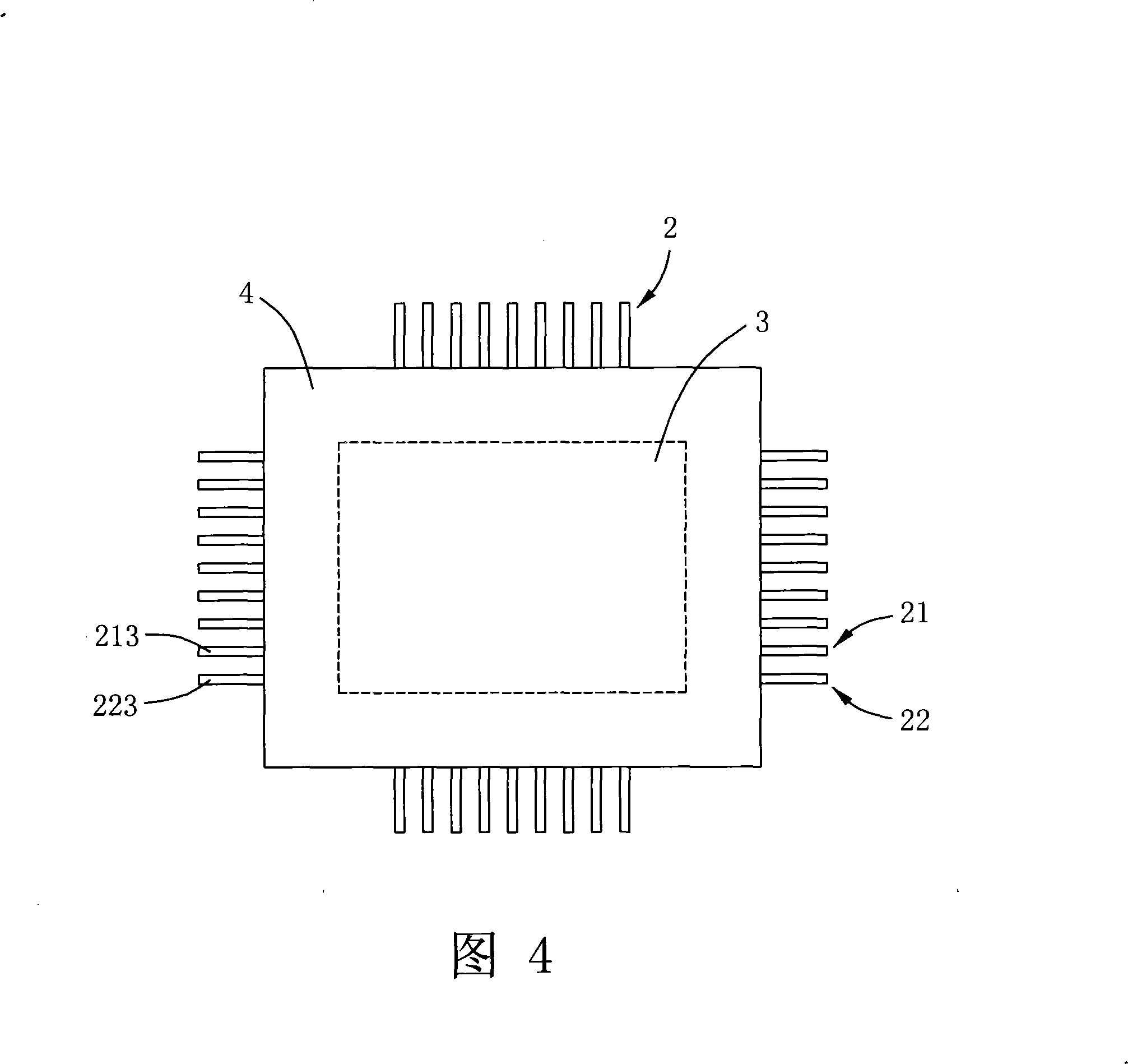

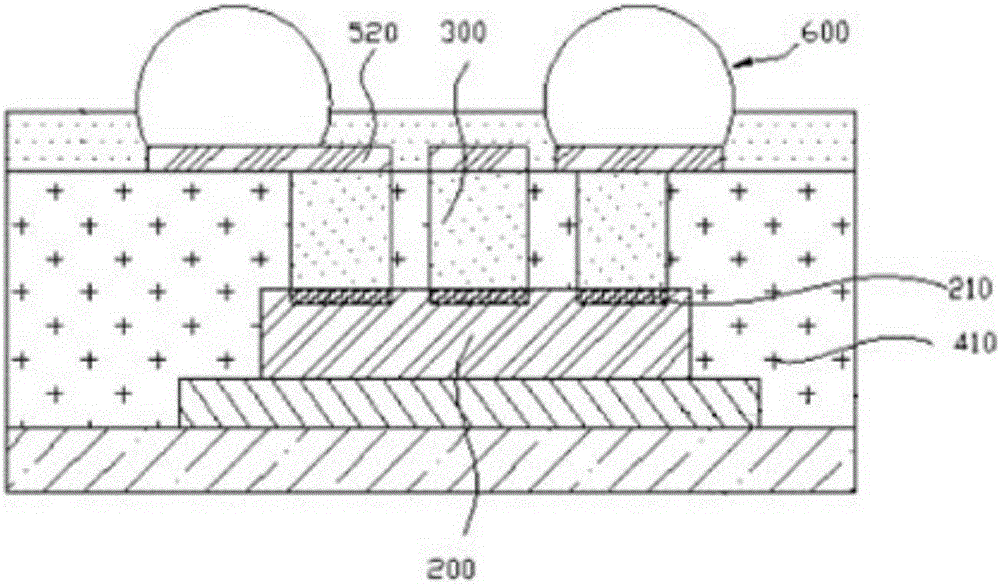

Multi-chips package with reduced structure and method for forming the same

InactiveCN101252125AReduce package thicknessImprove yieldSemiconductor/solid-state device detailsSolid-state devicesSystem in packageDielectric layer

The present invention provides a structure of multi-chips package and method of the same comprising a substrate with a pre-formed die receiving cavity formed within an upper surface of the substrate. A die is disposed within the die receiving cavity by adhesion and an elastic dielectric layer filled into a gap between the die and the substrate to absorb thermal mechanical stress; therefore the thickness of the package is reduced and the CTE mismatch of the structure is reduced. The present invention also provides a structure for SIP with higher reliability and lower manufacturing cost. the process is simpler and it is easy to form the multi-chips package than the traditional one. Therefore, the present invention discloses a fan-out WLP with reduced thickness and good CTE matching performance.

Owner:ADVANCED CHIP ENG TECH INC

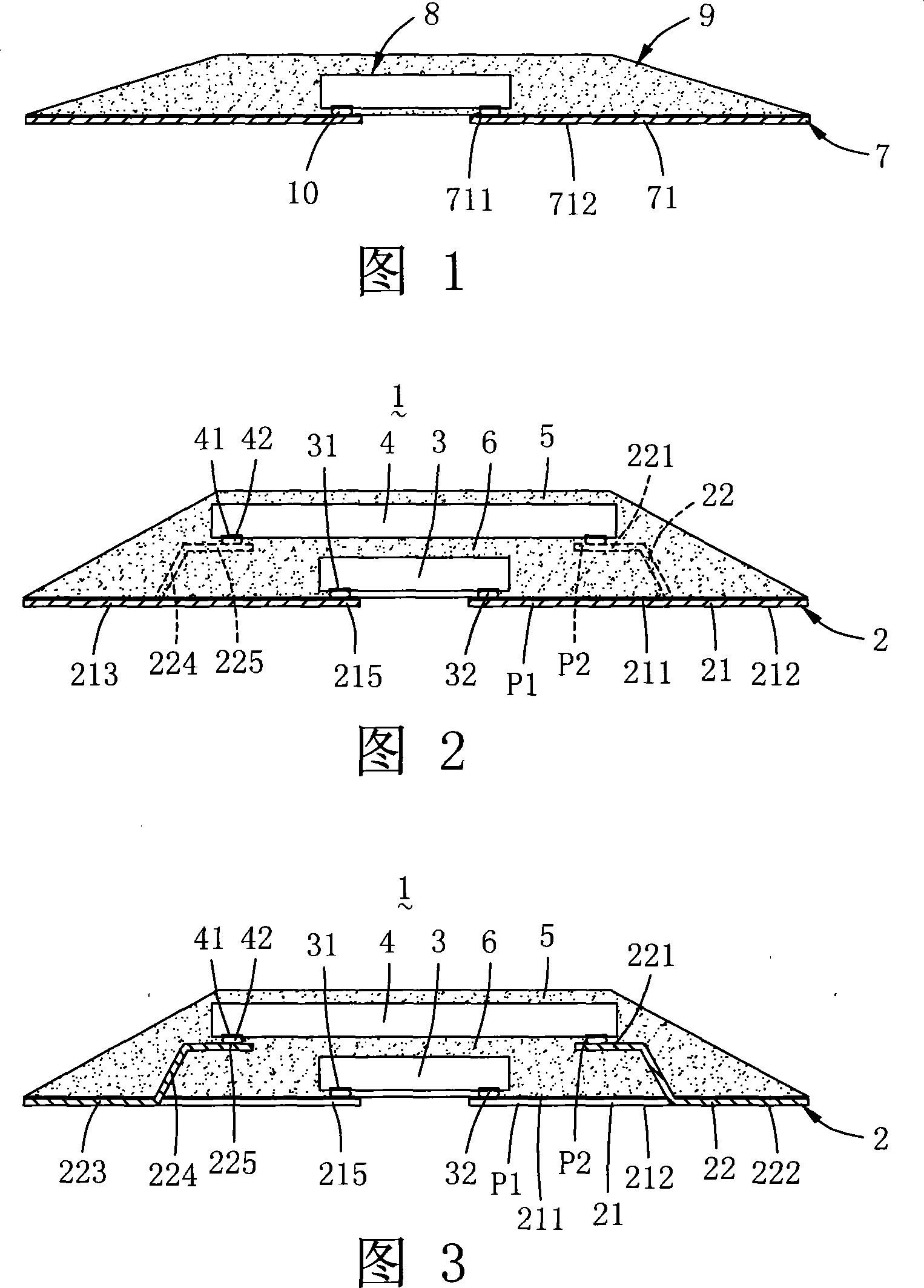

Square flat non-connection pin multi-chip encapsulation structure

InactiveCN101241904AImprove space utilizationReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesHeight differenceLead frame

The invention provides a low profile quad flat and no pin type multi-chip packaging structure comprising a lead frame, a first chip, a second chip and an adhesive body. The lead frame has a first pin and a second pin that are dislocating arranged. Each first pin includes a first external portion and a first finger portion. Each second pin includes a second external portion, a bending portion and a second finger portion, wherein the bending portion bends upward so that the second finger portion of the second pin forms a height difference with the first finger portion of the first pin. The first chip locates between these first pins and these the second pins, and the second chip locates above the first chip. The adhesive body covers the first chip, the second chip, the first pin and the second pin, and manifests the lower surface of the first pin and the second pin.

Owner:ADVANCED SEMICON ENG INC

Microelectromechanical system package and the method for manufacturing the same

ActiveUS20080185699A1Reduce package thicknessReduce thicknessMechanically variable capacitor detailsTransducer detailsMicroelectromechanical systemsSilicon

A method for manufacturing a microelectromechanical system package is provided. A plurality of cavities is first formed on the upper and lower surfaces of a silicon wafer. Next, the lower surface of the silicon wafer is bonded to the microelectromechanical system wafer in such a manner that the active areas of the chips on the microelectromechanical system wafer are received in the cavities on the lower surface of the silicon wafer, respectively. Finally, the structure assembly of the two wafers is singulated along the scribe streets to form individual microelectromechanical system chips whose active areas are covered by the cavities. These microelectromechanical system chips together with other components can be mounted to chip carriers to form microelectromechanical system packages.

Owner:ADVANCED SEMICON ENG INC

Electronic part-containing elements, electronic devices and production methods

InactiveUS20060017133A1Reduce thicknessSmall sizeSemiconductor/solid-state device detailsPrinted electric component incorporationElectrical and Electronics engineeringElectronic equipment

Owner:SHINKO ELECTRIC IND CO LTD

Packaging body capable of repeatedly stacking

InactiveCN101221945AReduce usageFast transmissionSemiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineeringFlip chip

The invention relates to a package which can be repeatedly piled, comprising a substrate which has a plurality of first welding pads; a chip which is arranged on the substrate and exposes an active surface which is in electric connection with the substrate; a plurality of second welding pads which are arranged on the active surface of the chip; and a package colloid which is arranged on the substrate for covering part of the chip, wherein, the package colloid forms a groove on the active surfaces and exposes second welding pads on the active surface; a plurality of conductive balls are arranged on the second welding pads for electrically connecting first welding pads of another package which can be repeatedly piled. Two packages are piled with the mode of flip chip, the periphery of the substrate is protected by the package colloid, thereby reducing the use of wire leads and improving the warping problem of the two piled packages.

Owner:POWERTECH TECHNOLOGY

Fan-out package structure and manufacturing method thereof

ActiveCN105206592AReduce package thicknessExpand the scope of applicationSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

The invention provides a fan-out package structure and a manufacturing method thereof. The structure comprises a chip having electrodes. The active surface of the chip is upward; the chip is circumferentially filled with a first insulating resin layer; the top portion of the first insulating resin layer is higher than the upper surface of the chip; the chip and the top portion of the first insulating resin layer are covered by a second insulating resin layer; the surface of the second insulating resin layer is provided with a re-wiring layer which is connected with the electrodes of the chip through openings of the second insulating resin layer; the second insulating resin layer and the re-wiring layer are covered by a third insulating resin layer; the third insulating resin layer is provided with openings for exposing bonding pads of the re-wiring layer; the bonding pads of the re-wiring layer are connected with conductive columns; the conductive columns are electrically connected with the electrodes on the active surface of the chip through the re-wiring layer; and the lower surface of the chip and the bottom of the first insulating resin layer are provided with a protection layer. The package structure does not have a bearing piece, thereby helping to reduce package thickness, and meanwhile, enlarging application range of the technology; and copper columns are not prepared on the chip, thereby facilitating to reduce the cost.

Owner:NAT CENT FOR ADVANCED PACKAGING

Circuit device and manufacturing method thereof

InactiveUS20050212107A1Shorten manufacture stepQuickly deliverFinal product manufactureResistor terminals/electrodesEngineeringSolder material

In the case of mounting a passive element in a circuit device, since an electrode part is tin-plated, the passive element is fixed to a mounting land part by use of a solder material, and wires cannot intersect with each other in a single layer. Accordingly, there are problems such as an increase in a mounting area, a restriction to a reflow temperature in mounting on a printed board, and deterioration of reliability due to solder crack after packaging. The electrode part of the passive element is gold-plated, and a bonding wire is directly fixed to the electrode part. Thus, a packaging density can be improved. Moreover, a package structure using no supporting substrate is adopted, and the passive element is bonded to an isolation trench. Thus, even in a structure having the bonding wire fixed therein, an increase in a package thickness is suppressed.

Owner:SANYO ELECTRIC CO LTD

Semiconductor package and fabrication method thereof

ActiveUS20150187722A1High bulk densityReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor package is provided, which includes: a packaging substrate having opposite first and second surfaces and a plurality of first and second conductive pads formed on the first surface; a chip having opposite active and inactive surfaces and disposed on the first conductive pads via the active surface thereof; a plurality of conductive posts formed on the second conductive pads, respectively; and a first encapsulant formed on the first surface of the packaging substrate for encapsulating the chip and the conductive posts and having a plurality of openings for exposing upper surfaces of the conductive posts, thereby increasing the package density and protecting the chip and the interconnection structure from being adversely affected by intrusion of moisture.

Owner:SILICONWARE PRECISION IND CO LTD

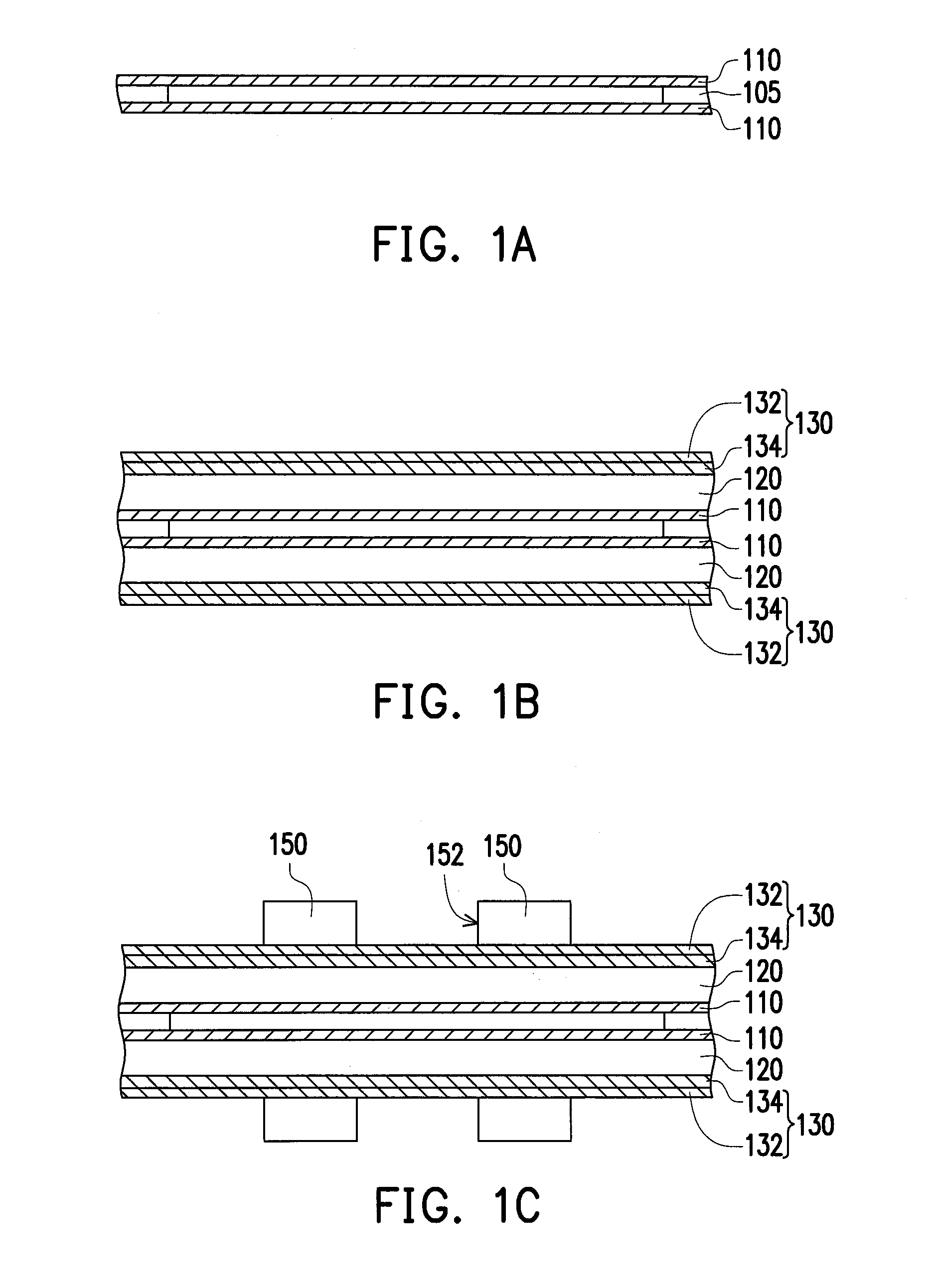

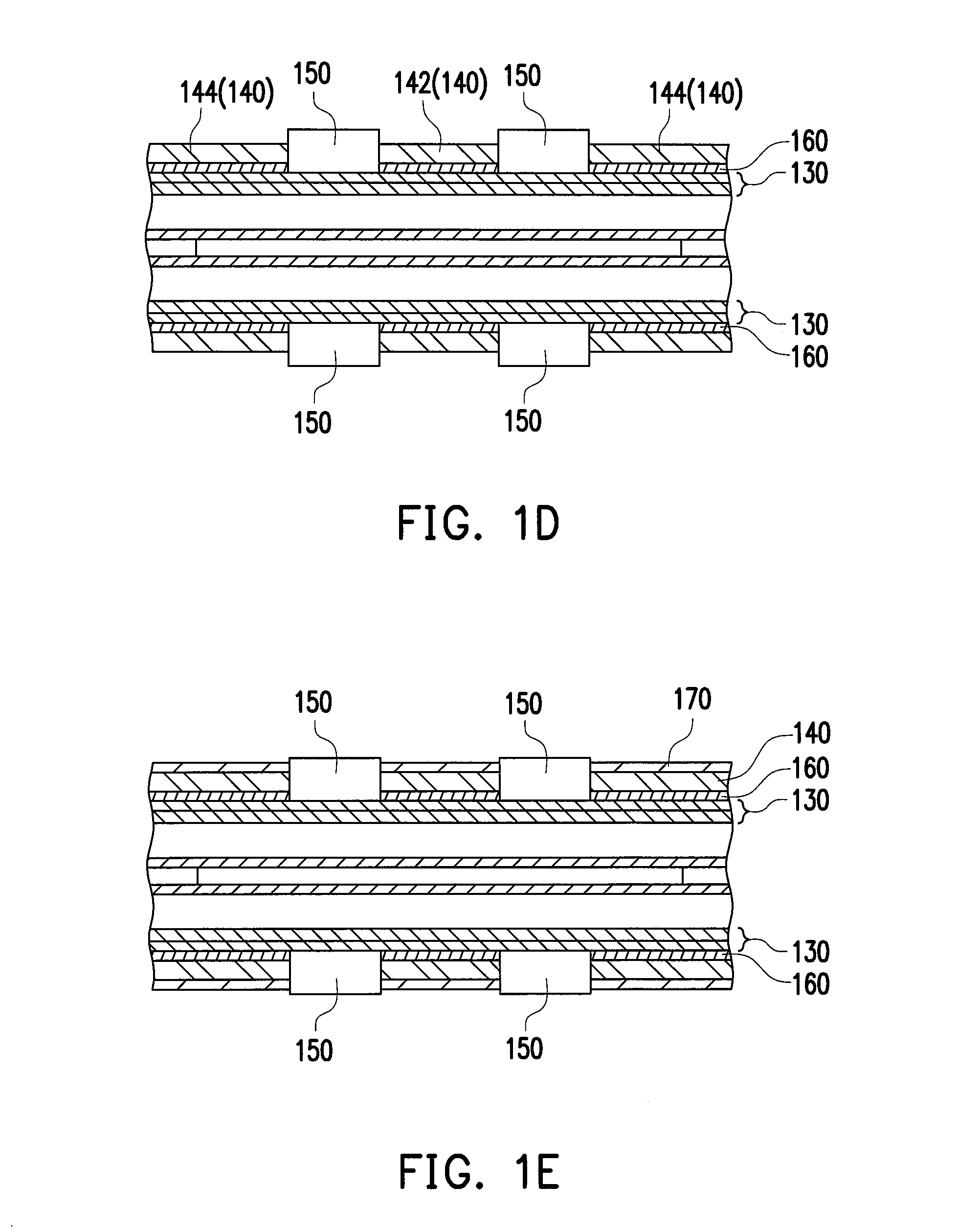

Package carrier and manufacturing method thereof

ActiveUS20150090481A1Reduce package thicknessReduce thicknessLamination ancillary operationsSemiconductor/solid-state device detailsMaterials scienceMetal

A manufacturing method of a package carrier includes the following steps. Firstly, two base metal layers are bonded together. Then, two supporting layers are laminated onto the base metal layers respectively. Next, two release metal films are disposed on the supporting layers respectively, wherein each of the release metal films includes a first metal film and a second metal film separable from each other. Next, two patterned metal layers are formed on the release metal films respectively, wherein each of the patterned metal layers is suitable for carrying and electrically connected to a chip. Then, the base metal layers are separated from each other to form two package carriers independent from each other. A package carrier formed by the manufacturing method described above is also provided.

Owner:SUBTRON TECH

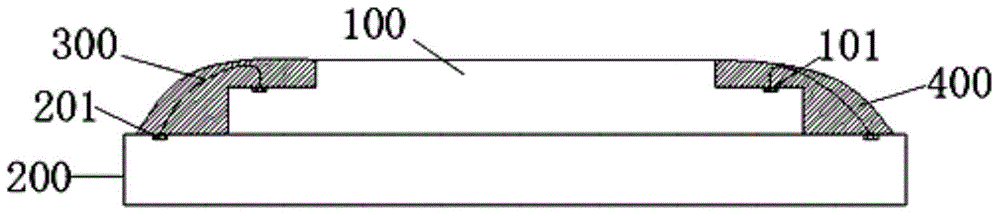

Fingerprint identification chip packaging structure and packaging method thereof

ActiveCN105990269ASimple connection and wiring processReduce package thicknessSemiconductor/solid-state device detailsSolid-state devicesFingerprintElectrical and Electronics engineering

The invention discloses a fingerprint recognition chip packaging structure, comprising: a substrate, the substrate is provided with a groove or a hollow part penetrating through the substrate; a chip for fingerprint recognition is embedded in the groove or the hollow part middle. Embedding the chip in the groove or hollow part processed on the substrate can effectively reduce the thickness of the package. Since the upper surface of the chip is basically flush with the upper surface of the substrate, the connection and wiring process between the electrodes is very simple. Therefore, the problems existing in the prior art can be well solved.

Owner:深圳明阳芯蕊半导体有限公司

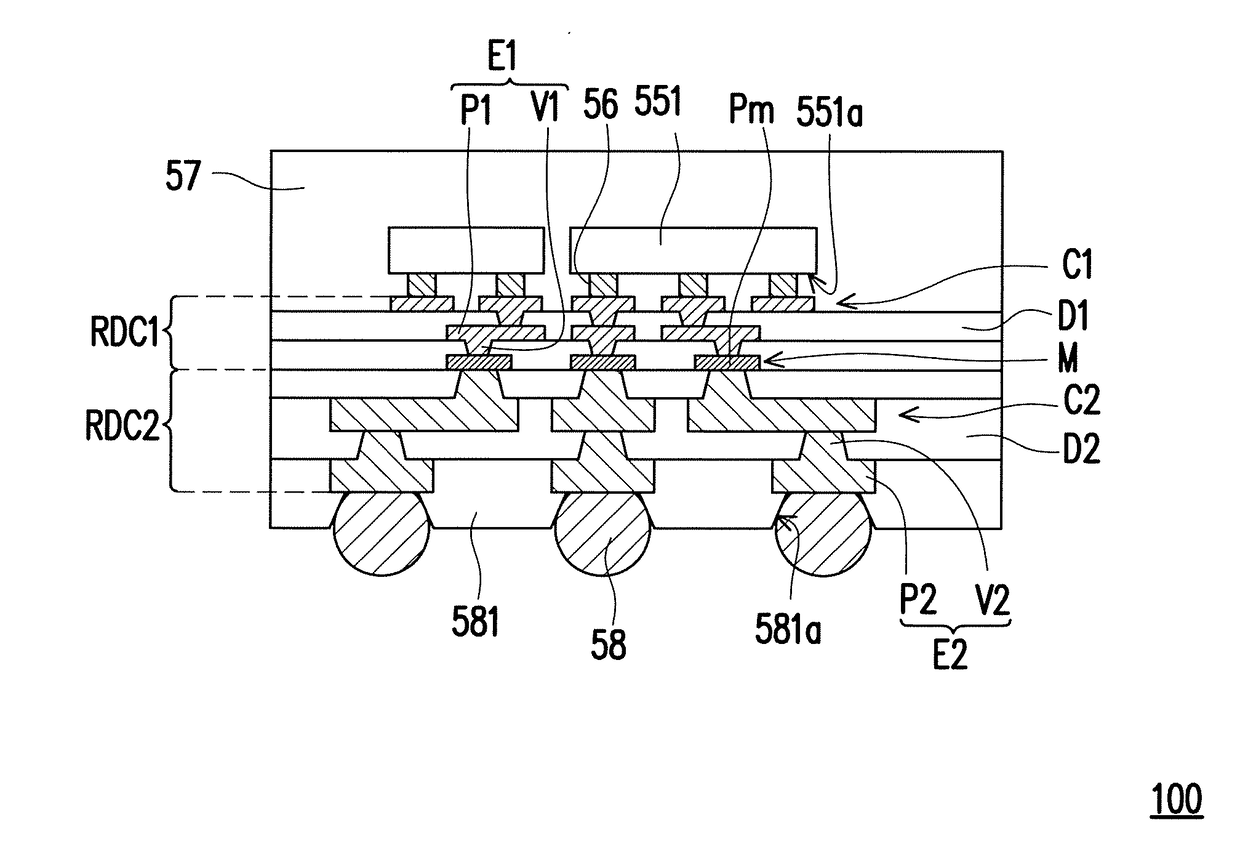

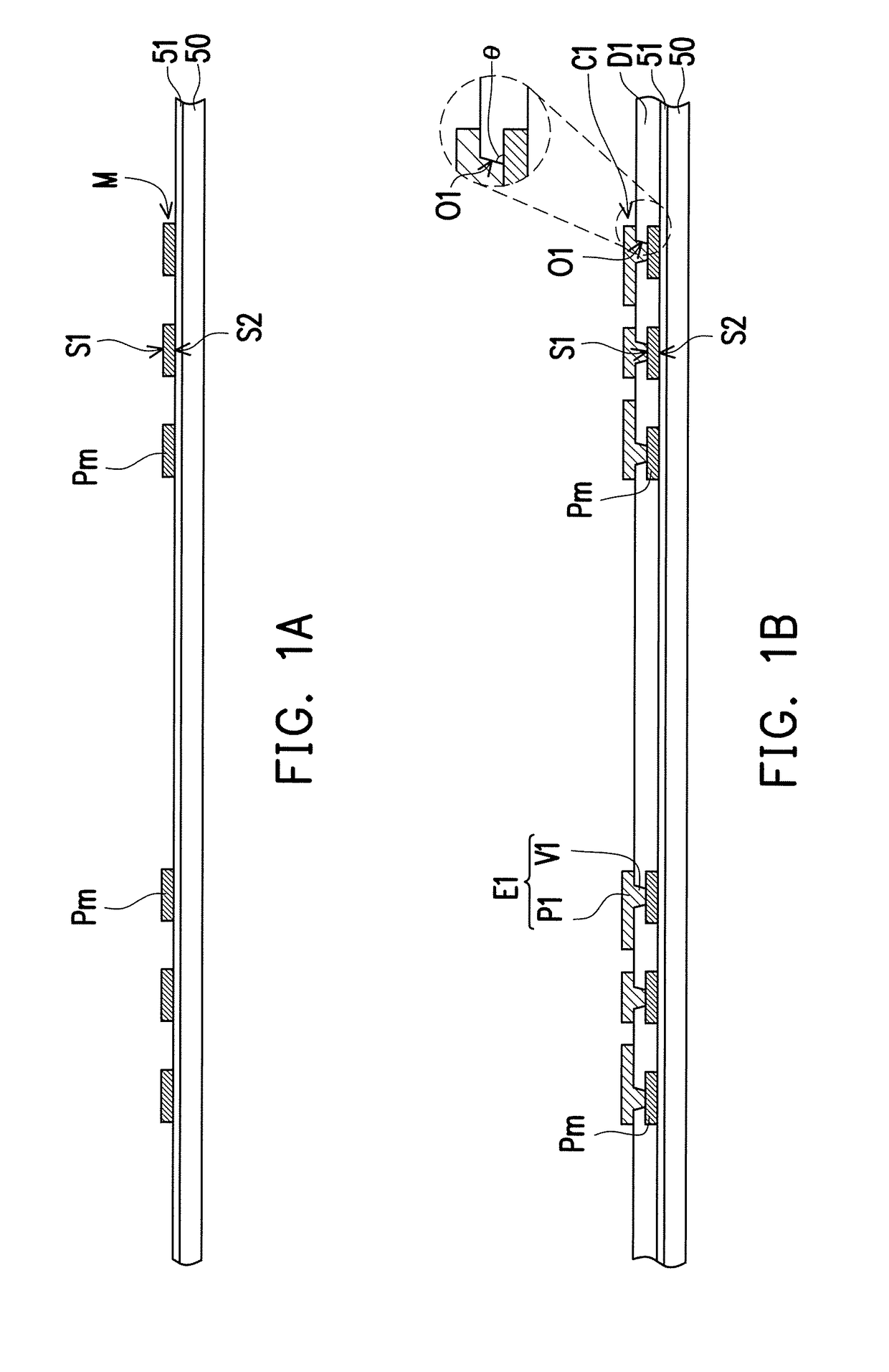

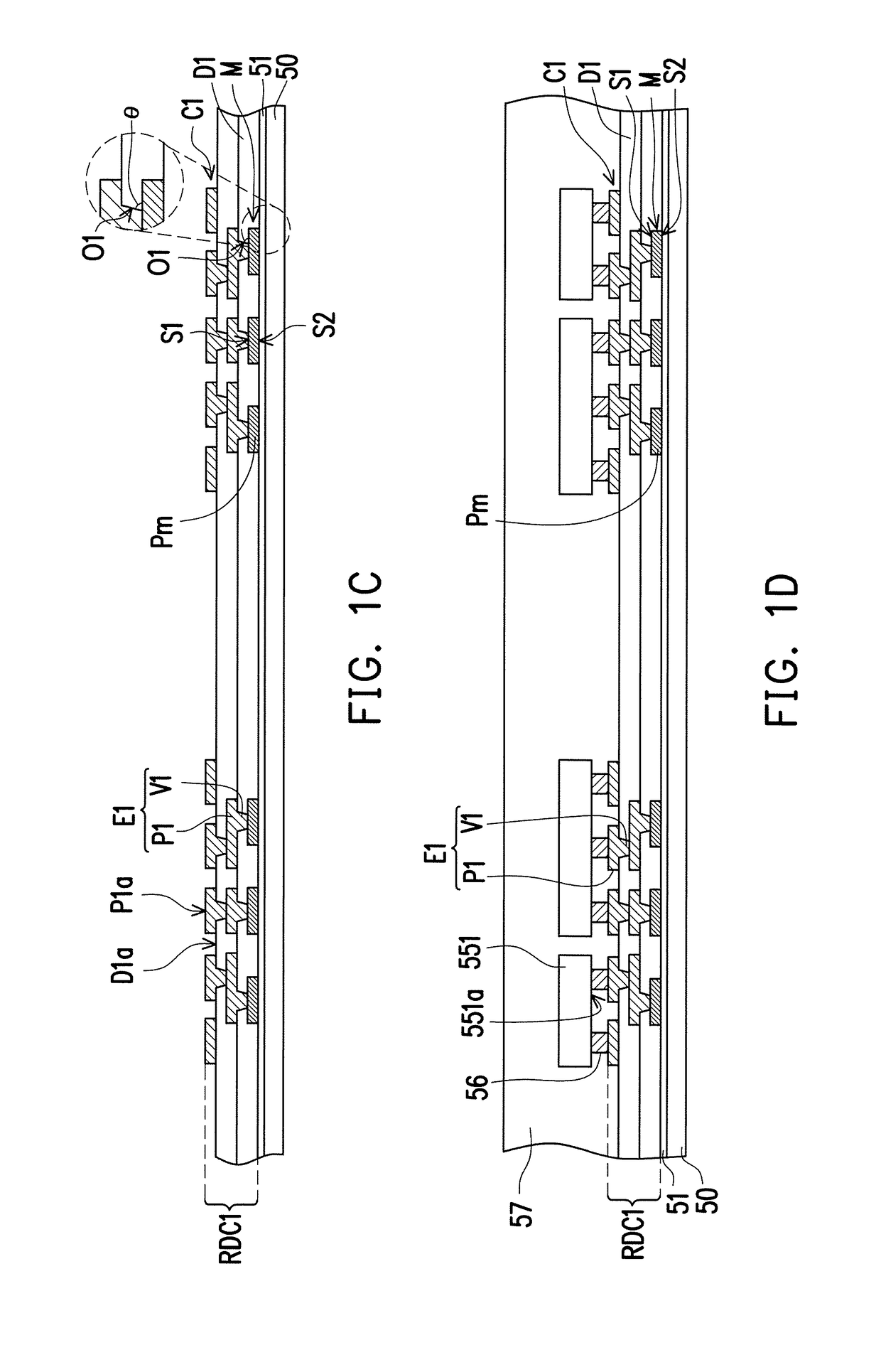

Electronic package and manufacturing method thereof

ActiveUS20180012774A1Small sizeSimple manufacturing processSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic packages

An electronic package including a middle patterned conductive layer, a first redistribution circuitry disposed on a first surface of the middle patterned conductive layer and a second redistribution circuitry disposed on a second surface of the middle patterned conductive layer is provided. The middle patterned conductive layer has a plurality of middle conductive pads. The first redistribution circuitry includes a first patterned conductive layer having a plurality of first conductive elements. Each of the first conductive elements has a first conductive pad and a first conductive via that form a T-shaped section. The second redistribution circuitry includes a second patterned conductive layer having a plurality of second conductive elements. Each of the second conductive elements has a second conductive pad and a second conductive via that form an inversed T-shaped section.

Owner:HU DYI CHUNG