Multi-chips package with reduced structure and method for forming the same

A technology of encapsulation structure and grain, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve problems such as complex cutting procedures, reliability problems, and sticky sand cores, and achieve low manufacturing costs, increased yields, and high reliability. sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The present invention will be described in detail below in conjunction with its preferred embodiments and accompanying drawings. It should be understood that all preferred embodiments in the present invention are for illustrative purposes only. Therefore, except for the preferred embodiments in the text, the present invention It can also be widely applied in other embodiments. And the present invention is not limited to any embodiment, but should be determined by the scope of the appended claims and their equivalent fields.

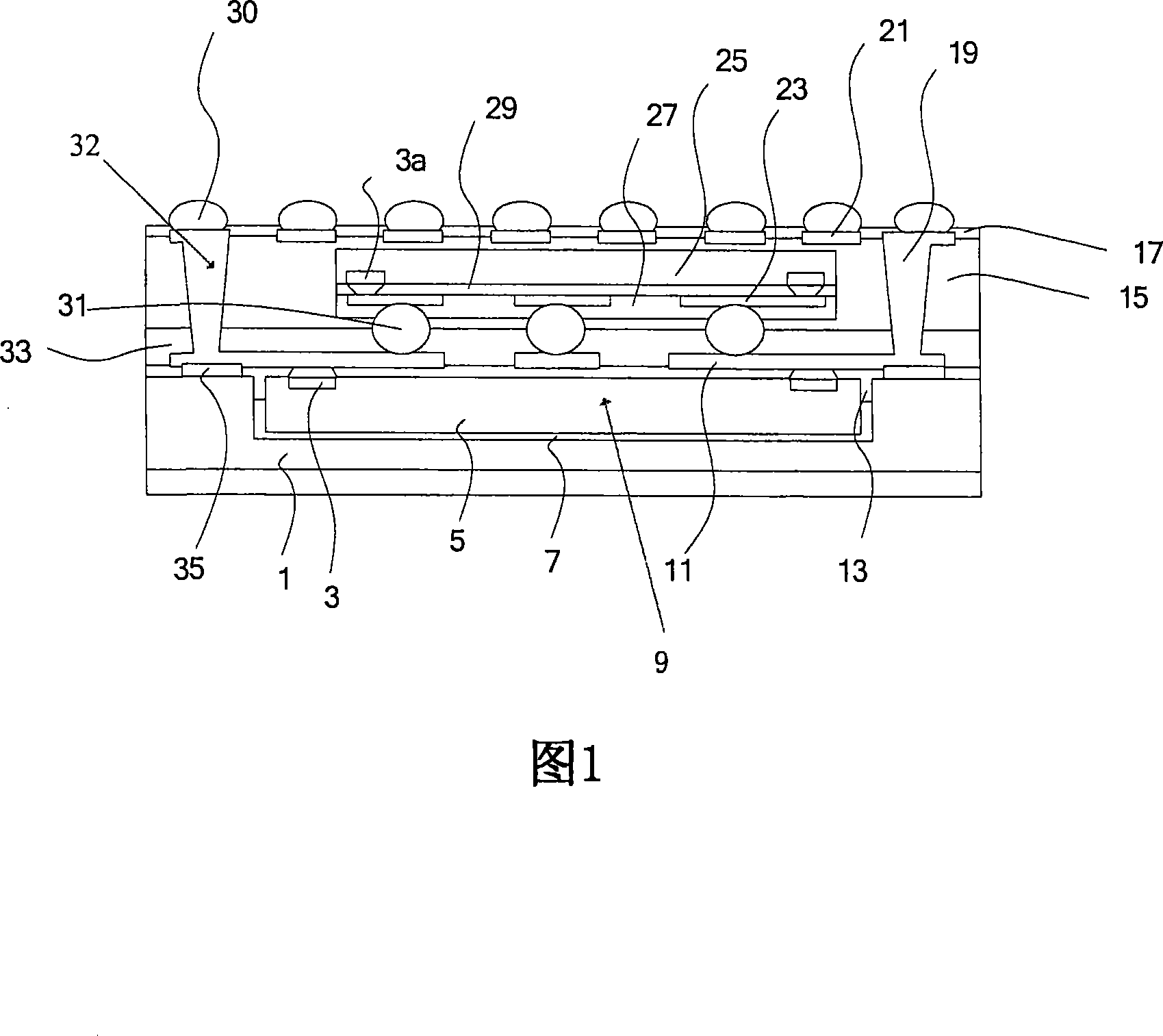

[0050] The invention discloses a fan-out wafer level packaging structure, which includes a substrate, wherein the substrate includes a pre-formed hole substrate and metal pads formed thereon. FIG. 1 shows a cross-sectional view of a board-level package (PSP) structure for a system-in-package (SIP) in an embodiment of the present invention. As shown in Figure 1, the system-in-package structure includes a substrate 1, and the substrate 1 includes a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More