Fan-out package structure and manufacturing method thereof

A manufacturing method and packaging structure technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of reduced overall chip thickness, cost, and increased process complexity, so as to reduce the thickness of the package and reduce the product cost. cost, the effect of expanding the scope of application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be further described below in conjunction with drawings and embodiments.

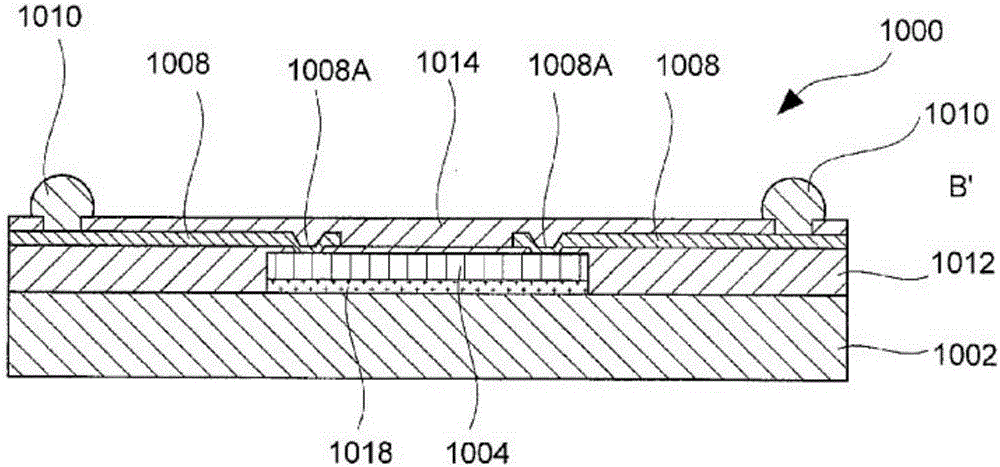

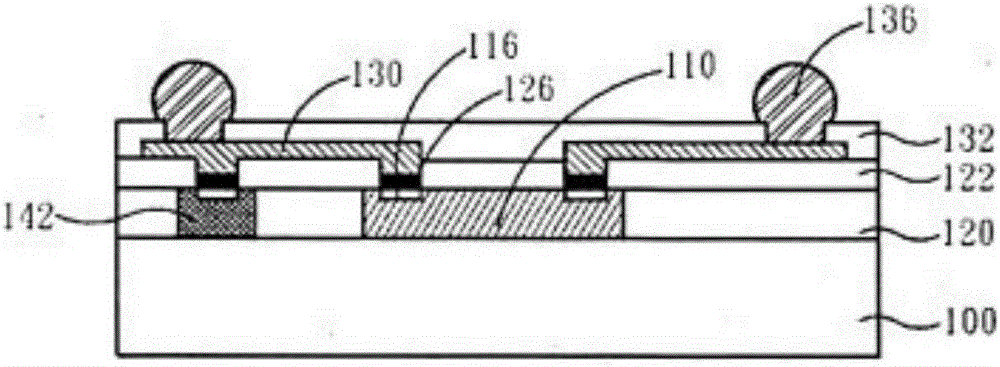

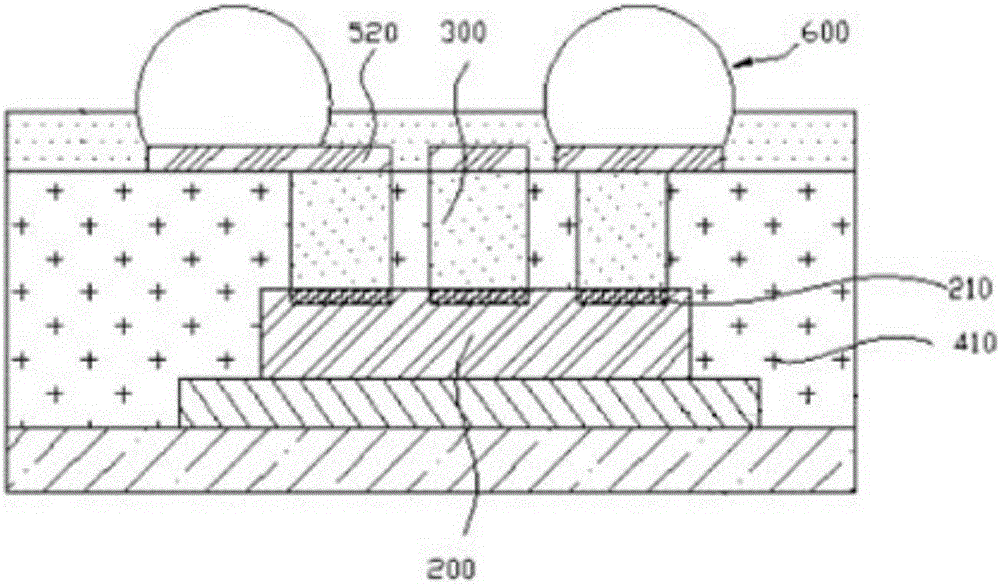

[0052] Such as Figure 4 As shown, the structure of the packaged product of the present invention includes a chip 102 with electrodes 105 on the front side of the chip 102 . The chip 102 may be a single chip or multiple chips, and may be an active chip or a passive chip.

[0053] The chip 102 actively faces upward, and the periphery of the chip 102 is filled with a first insulating resin layer 108. The top of the first insulating resin layer 108 is higher than the upper surface of the chip 102; the chip 102 and the top of the first insulating resin layer 108 are covered with a second insulating resin Layer 109, the surface of the second insulating resin layer 109 has a rewiring layer 112 connected to the electrode 105 of the chip through the opening of the second insulating resin layer 109, and the electrode 105 is drawn out through the rewiring layer 112. The redistr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More