Square flat non-connection pin multi-chip encapsulation structure

A multi-chip packaging, square flat technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of difficult manufacturing, high cost, and large overall thickness of the packaging structure, and achieve small packaging thickness, simple structure, and space improvement The effect of utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Relevant detailed description and technical contents of the present invention are as follows now in conjunction with the accompanying drawings:

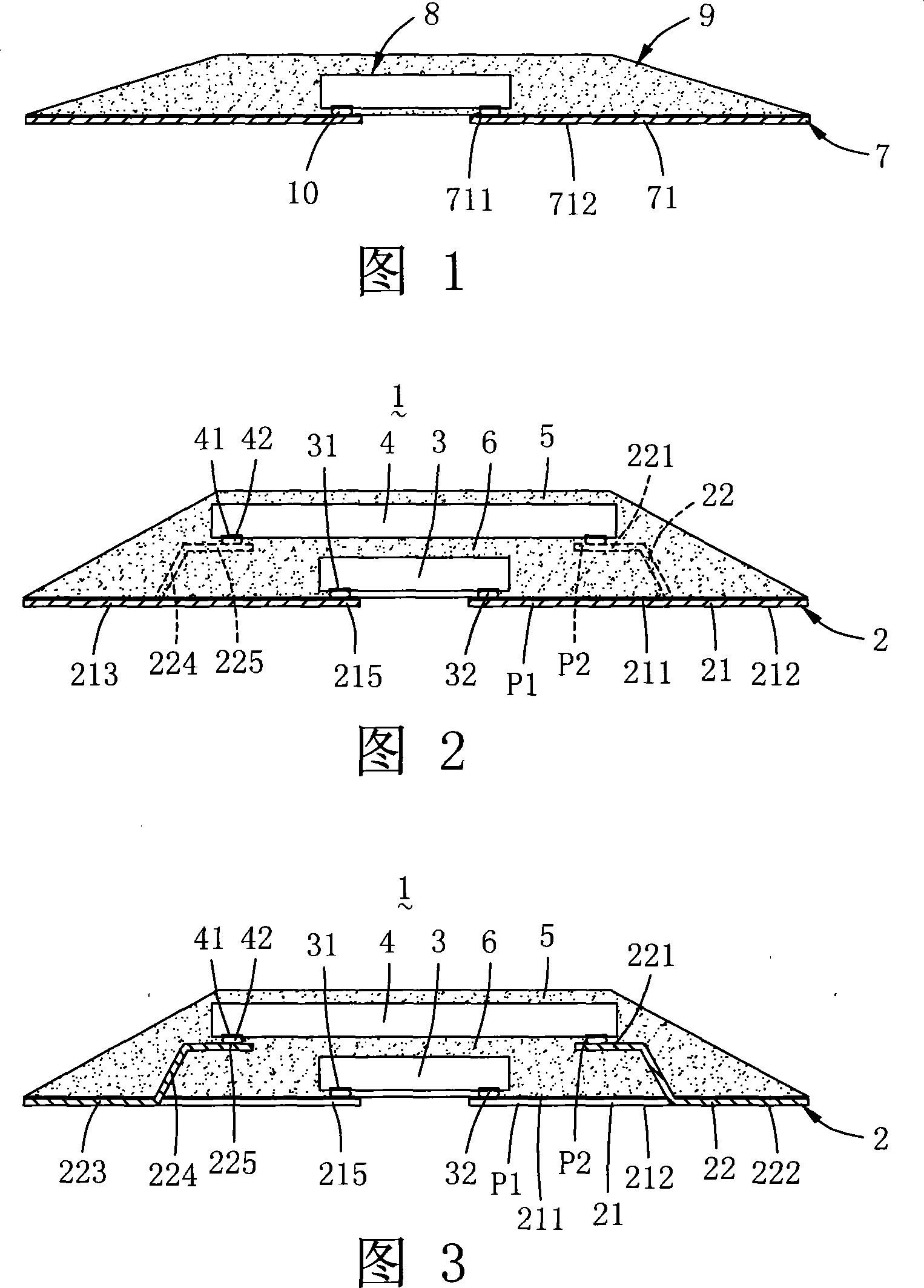

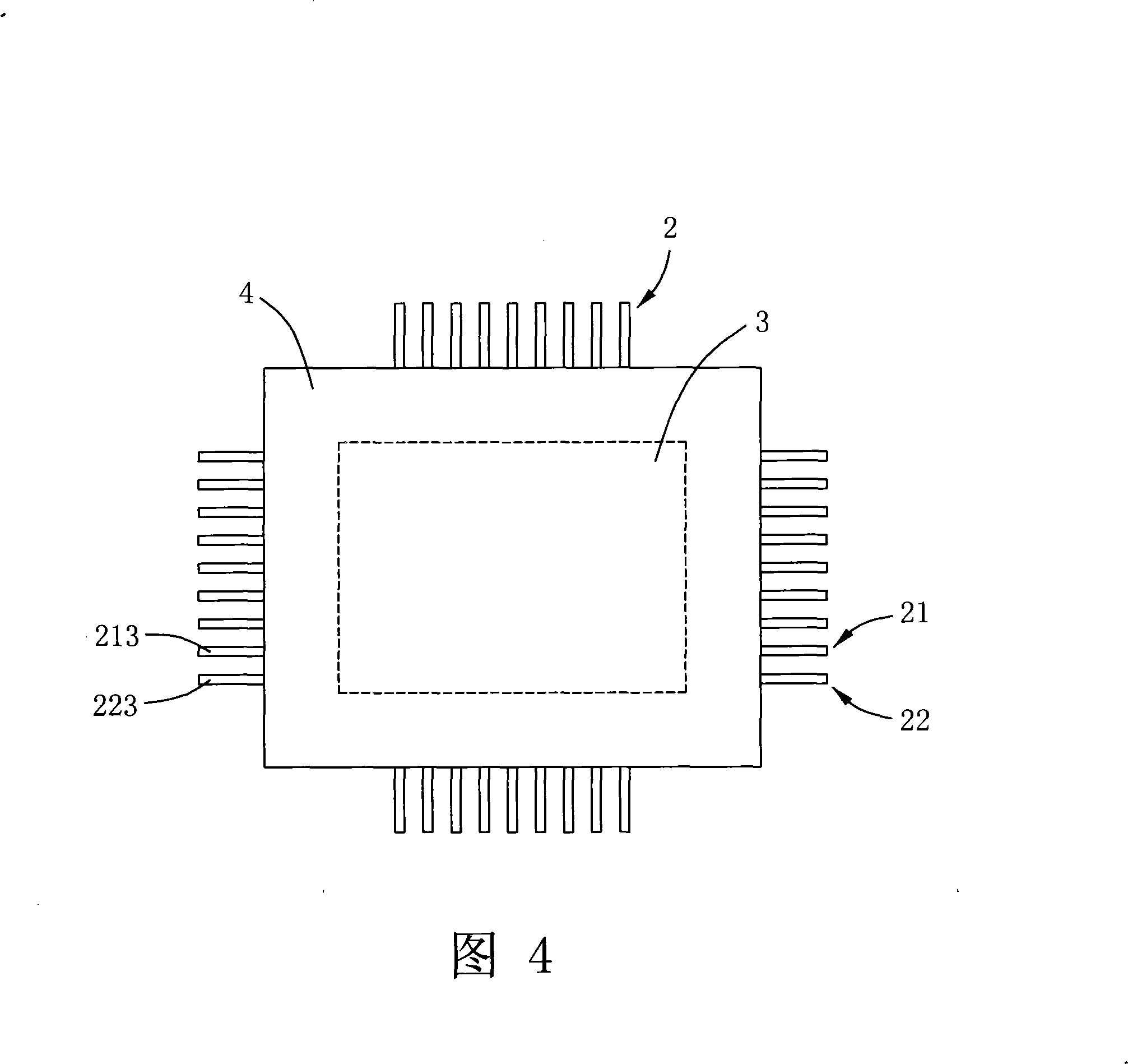

[0021] The invention discloses a quad flat no-pin (QFN) multi-chip packaging structure. Please refer to FIG. 2, FIG. 3 and FIG. 4, wherein FIG. 2 is a schematic cross-sectional view of a square flat non-pin multi-chip package structure according to a specific embodiment of the present invention, and FIG. FIG. 4 is a top view of the chip and lead frame stacking structure of the multi-chip packaging structure of the present invention. As shown in FIG. 2 and FIG. 3 , the quadrilateral flat leadless multi-chip package structure 1 of the present invention mainly includes a lead frame 2 , a first chip 3 , a second chip 4 and an encapsulant 5 .

[0022] The lead frame 2 has a plurality of first pins 21 and a plurality of second pins 22 extending on different planes, wherein each first pin 21 has a first upper surface 211 and a first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More