Patents

Literature

62 results about "Quad Flat Package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

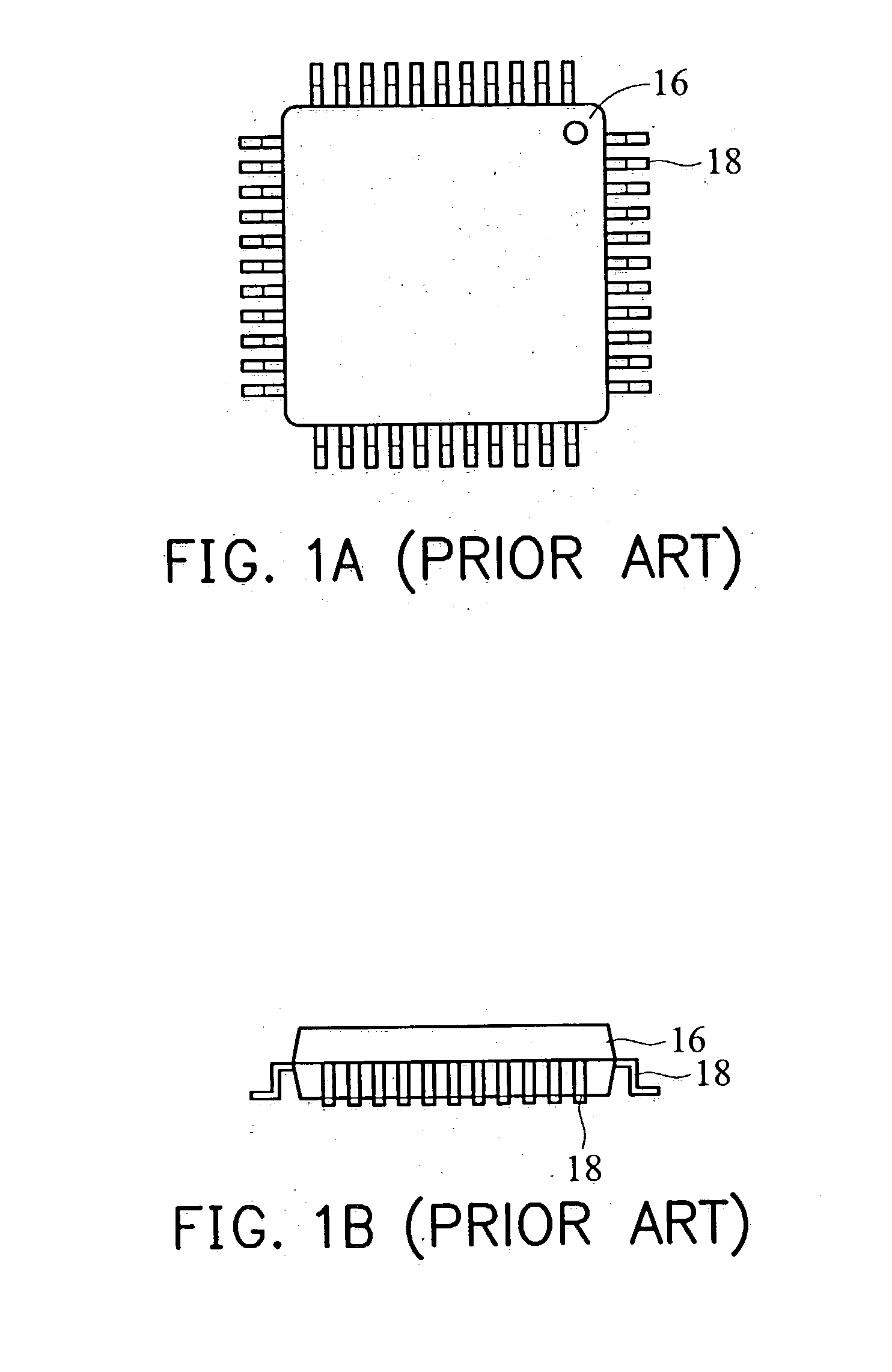

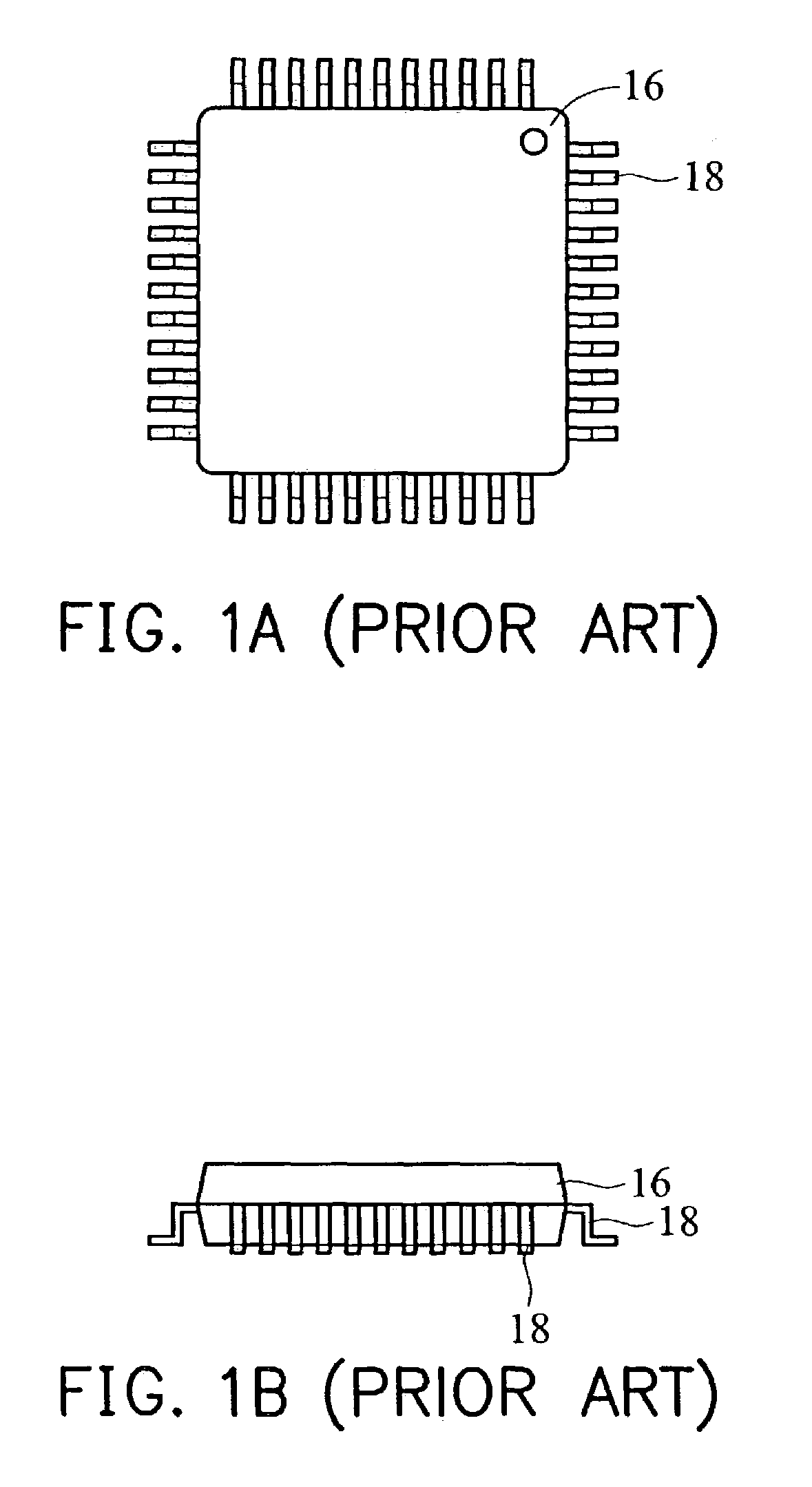

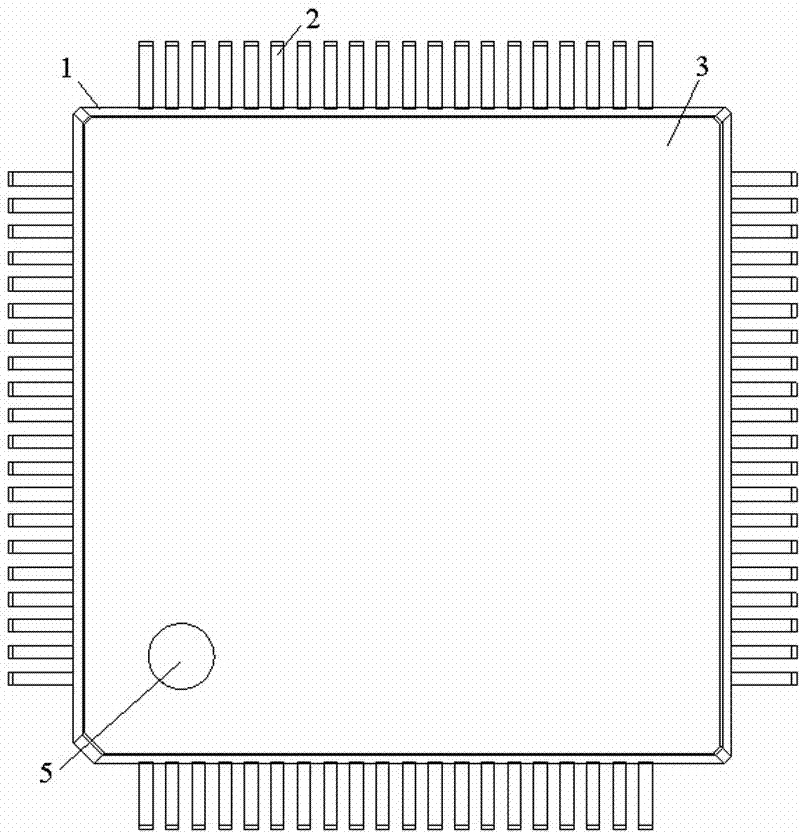

A QFP or Quad Flat Package is a surface-mounted integrated circuit package with "gull wing" leads extending from each of the four sides. Socketing such packages is rare and through-hole mounting is not possible. Versions ranging from 32 to 304 pins with a pitch ranging from 0.4 to 1.0 mm are common. Other special variants include low-profile QFP (LQFP) and thin QFP (TQFP).

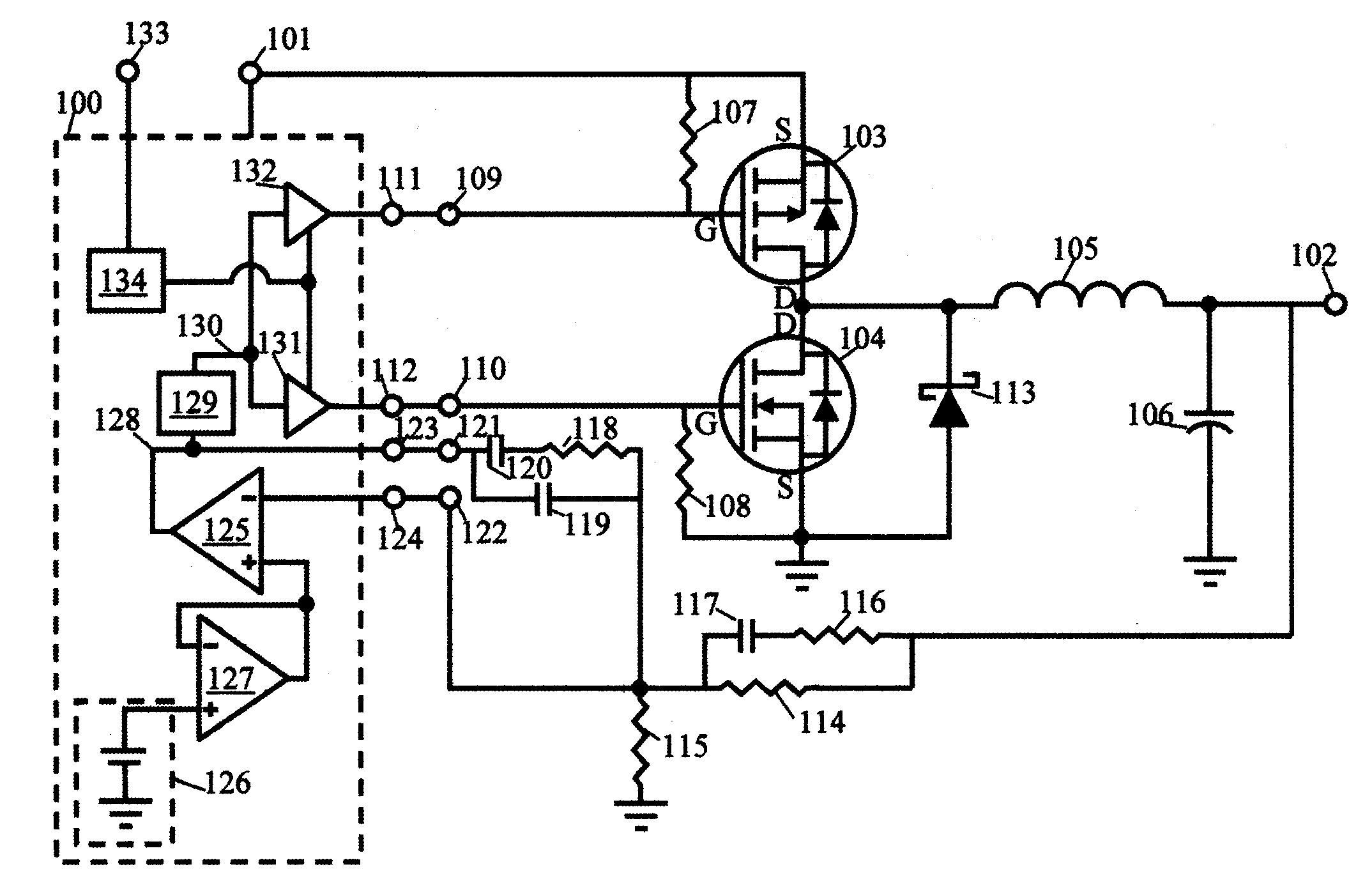

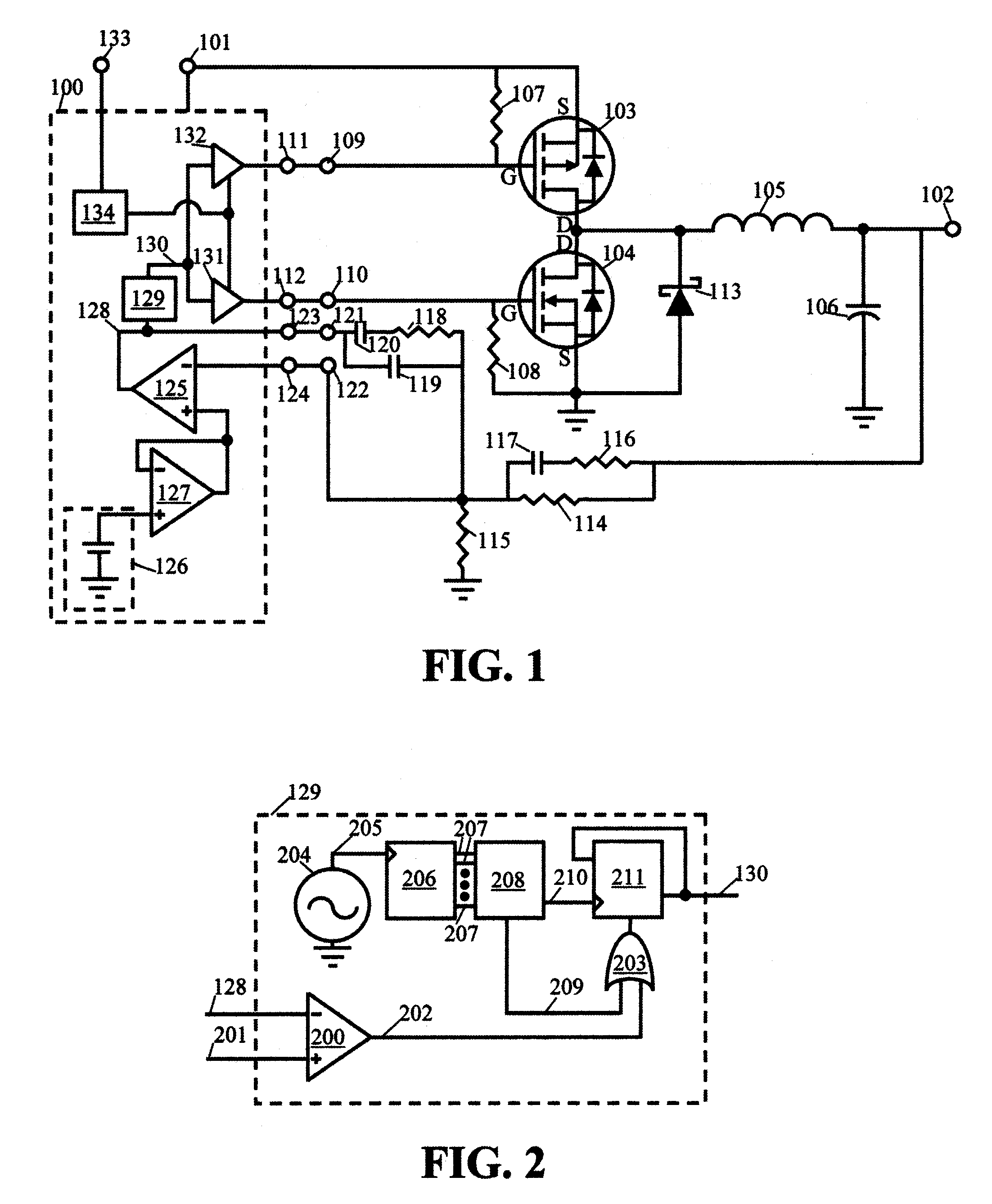

System and method for integrating a digital core with a switch mode power supply

InactiveUS20050024908A1Good power savingMinimal costDigital data processing detailsDc-dc conversionCapacitanceEngineering

A digital core embodied within a semiconductor die is situated within any of a variety of integrated circuit packaging technologies including but not limited to Ball Grid Array or Quad Flat Pack surface mount technology. Said semiconductor die is of the variety that requires plural separate power supply voltage domains such as a digital core supply of differing voltage than the input / output pad ring supply voltage. Within the integrated circuit package including said semiconductor die also exists a high efficiency DC-to-DC voltage converter of type commonly known as a chopper or a switch mode power supply. In the preferred embodiment this switch mode power supply would be of the highest efficiency, a synchronous step-down regulator, thus to enable powering the entire integrated circuit from one supply voltage. The components contained within the integrated circuit package along with the semiconductor die include the majority if not the totality of the components comprising the switch mode power supply, which could include the power switching transistors; an inductor core and windings; the output voltage fixing circuitry; the output capacitor; and the substrate for mounting said components when integrated within a packaging technology that does not already include a substrate such as within the periphery of a lead frame for leaded devices.

Owner:CUFER ASSET LTD LLC

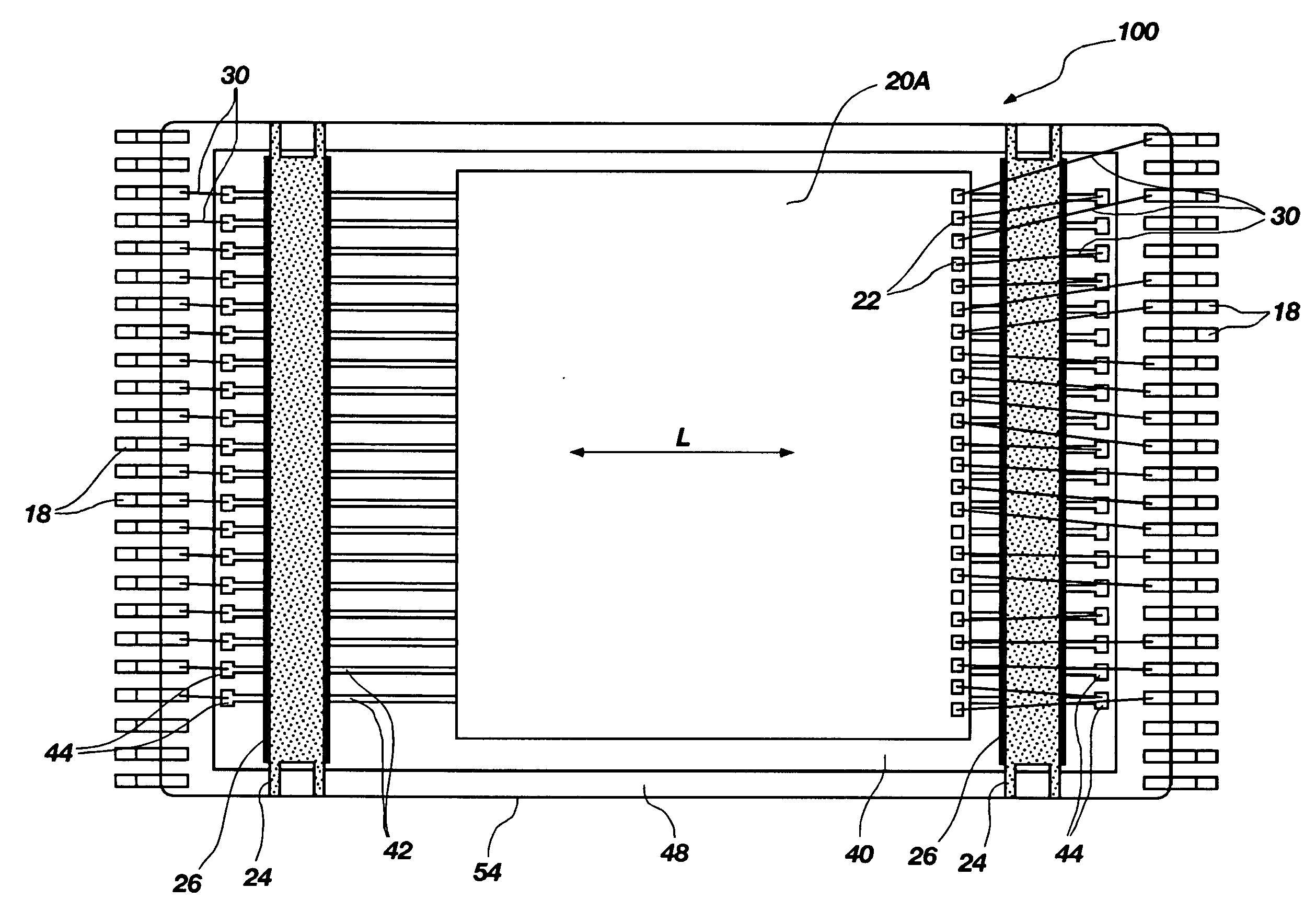

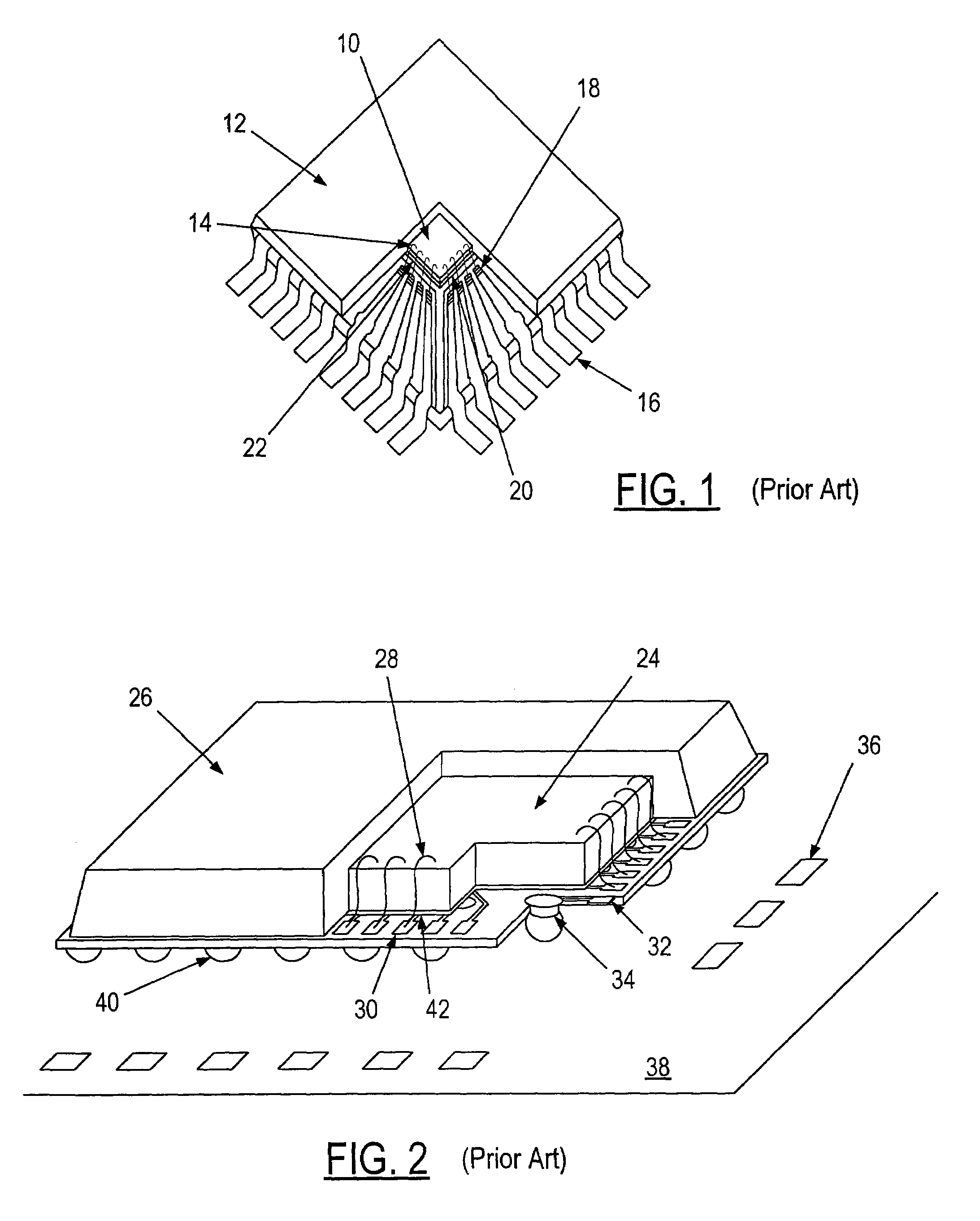

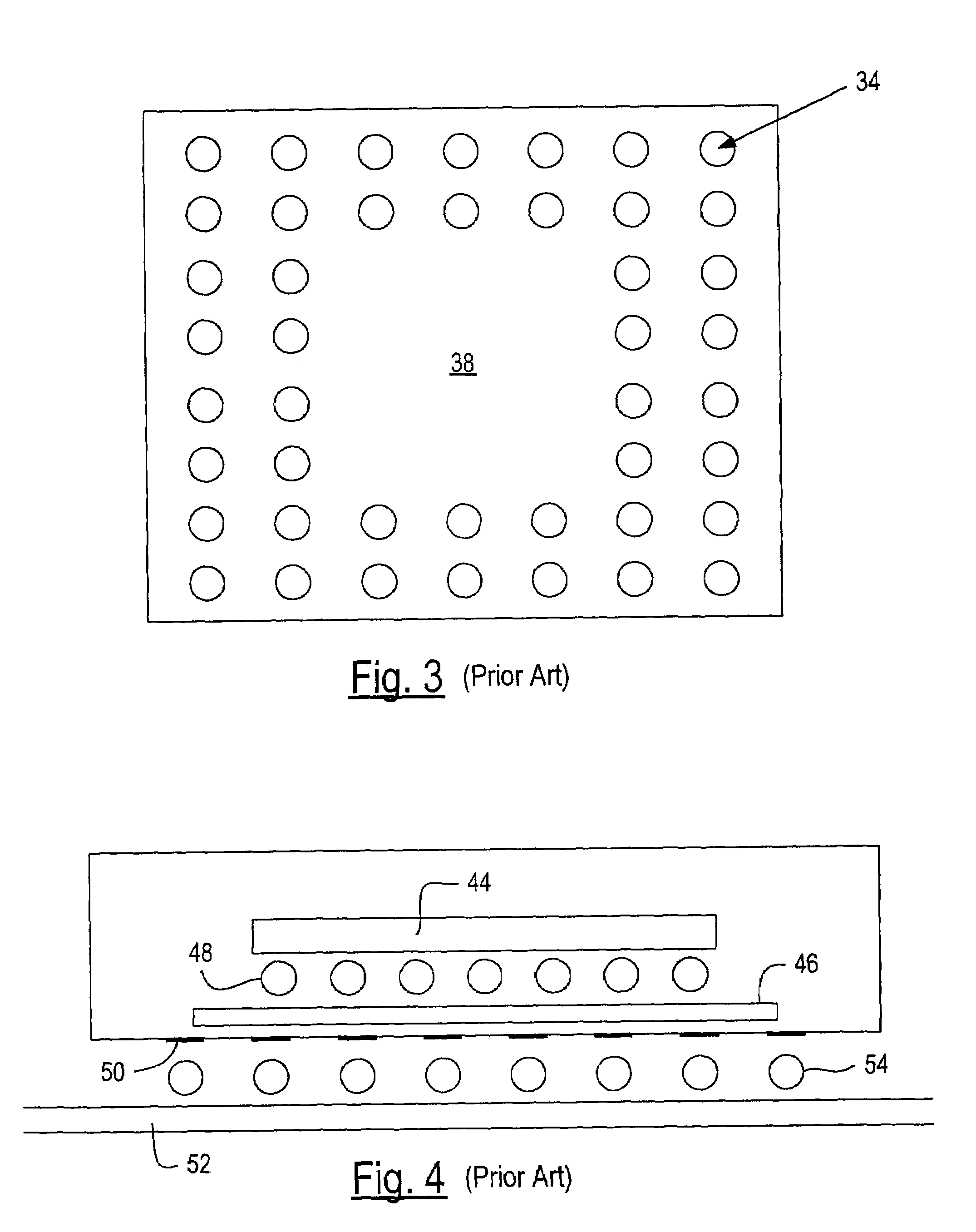

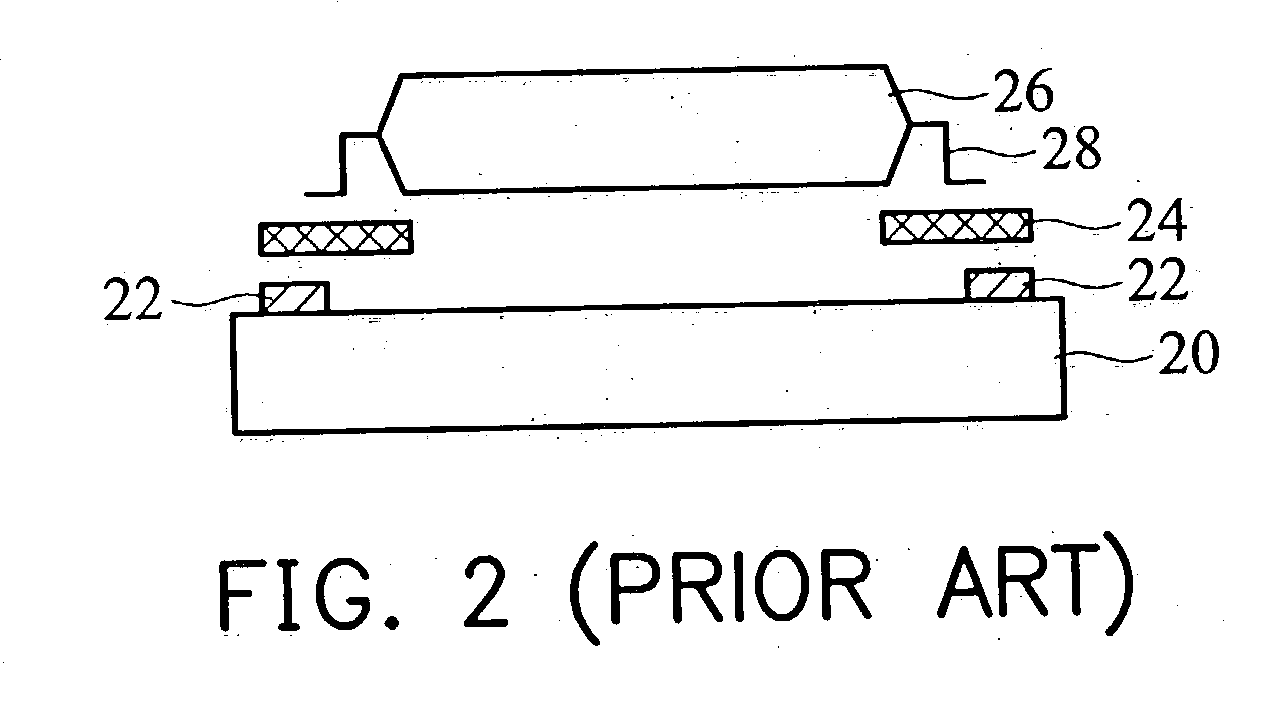

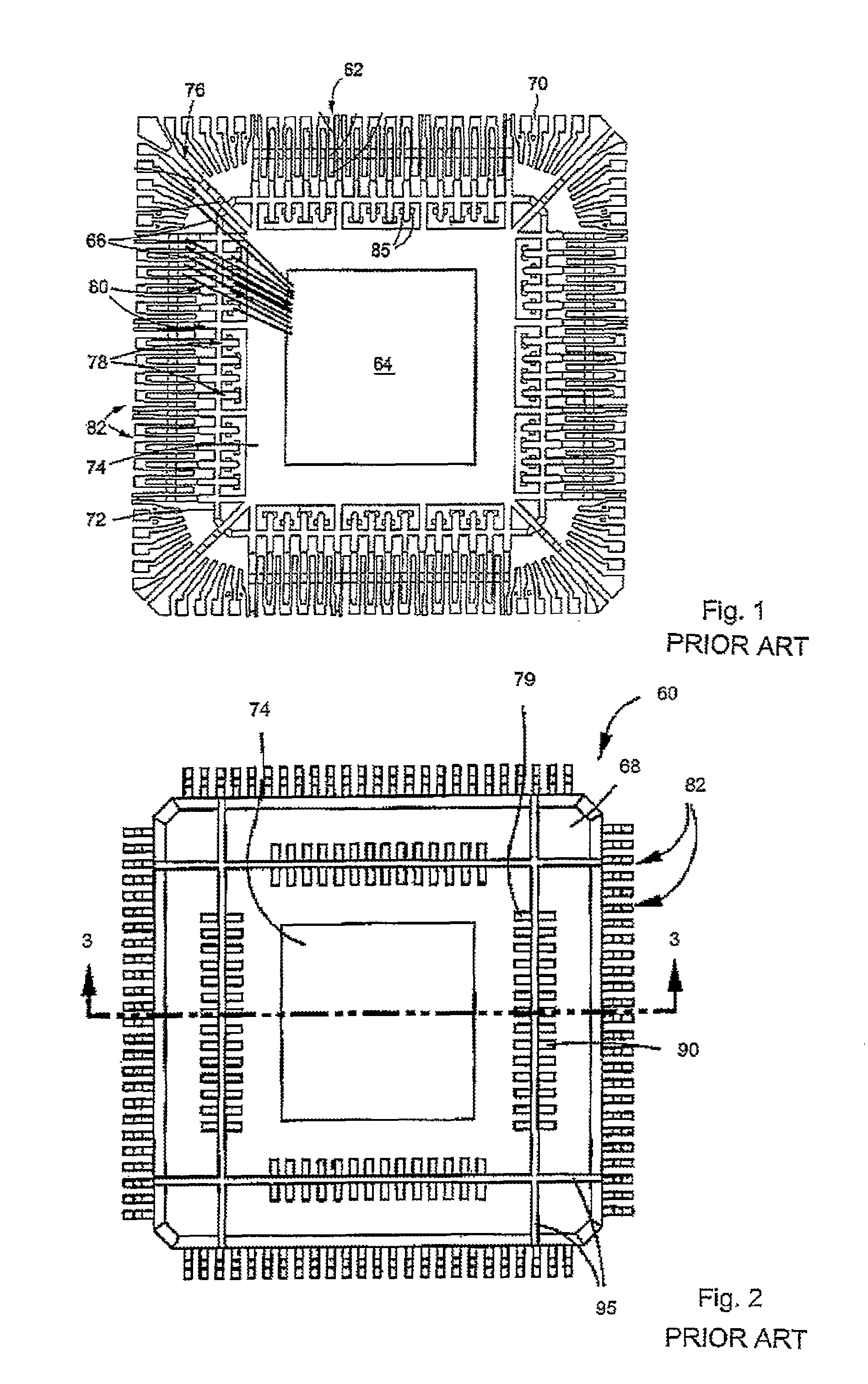

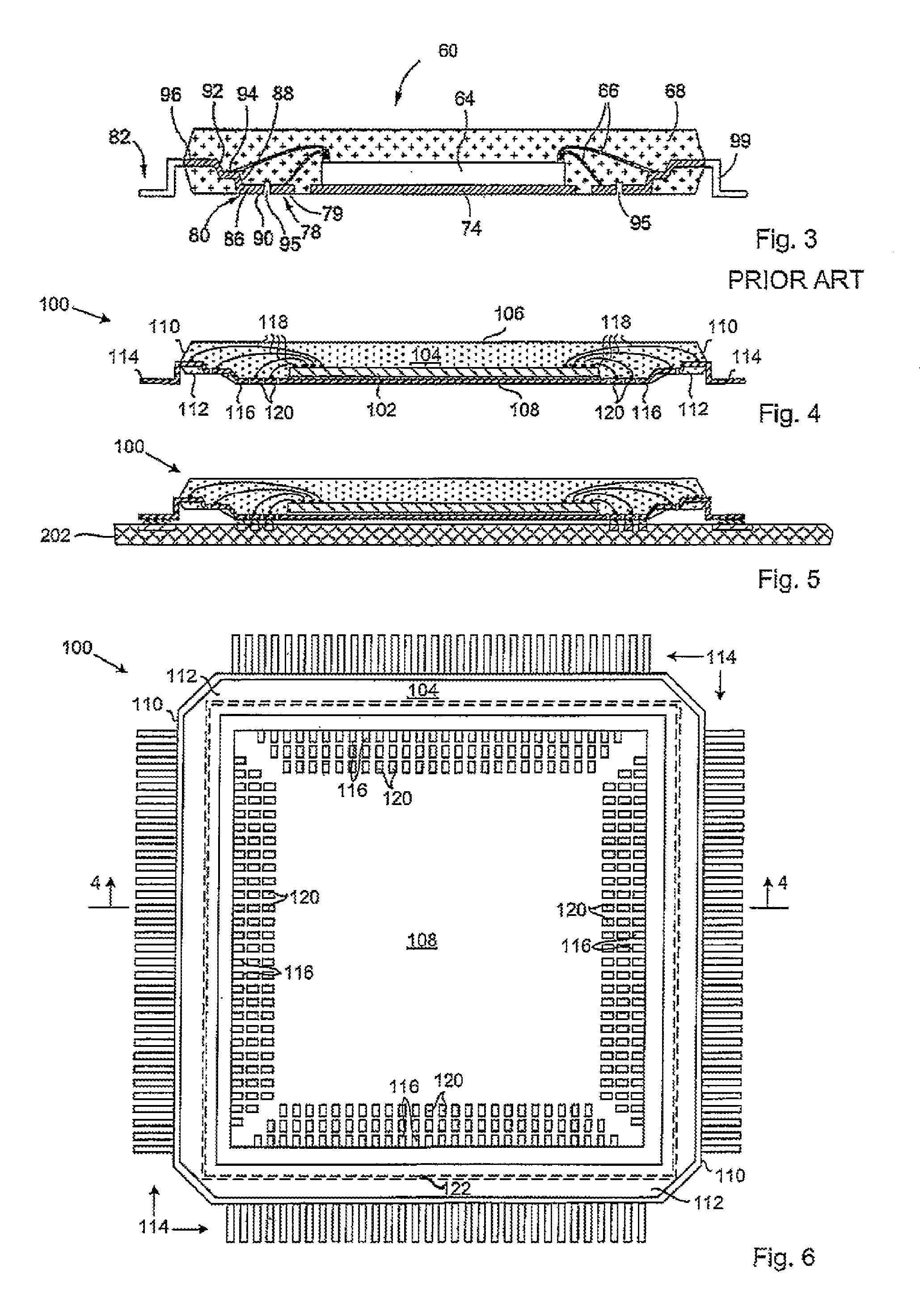

High density stacked die assemblies, structures incorporated therein and methods of fabricating the assemblies

ActiveUS20080054432A1Semiconductor/solid-state device detailsSolid-state devicesHigh densityQuad Flat Package

A stacked semiconductor die assembly includes at least two partially offset semiconductor dice with bond pads located adjacent at least one peripheral side thereof supported on a redistribution element formed of a material of substantially similar CTE to that of the dice, and a paddle-less lead frame secured to the redistribution element during fabrication, including encapsulation. The assembly is configured to be substantially vertically symmetrical with respect to inner ends of lead fingers of the lead frame to facilitate uniform encapsulant flow. The semiconductor die assembly may be configured in a package with leads extending from two sides thereof, such as a thin small outline package (TSOP), or four sides thereof, such as a quad flat pack (QFP).

Owner:MICRON TECH INC

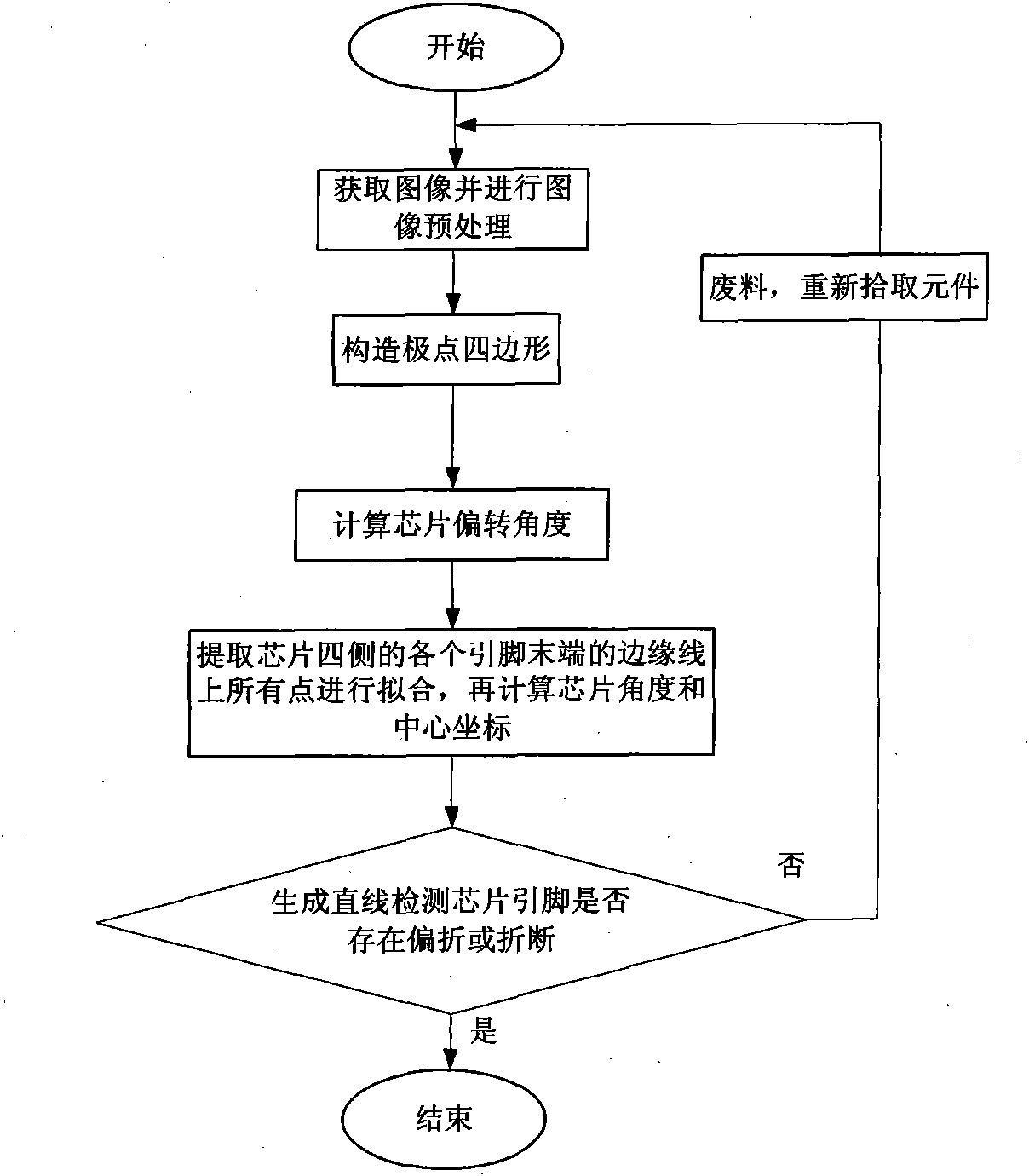

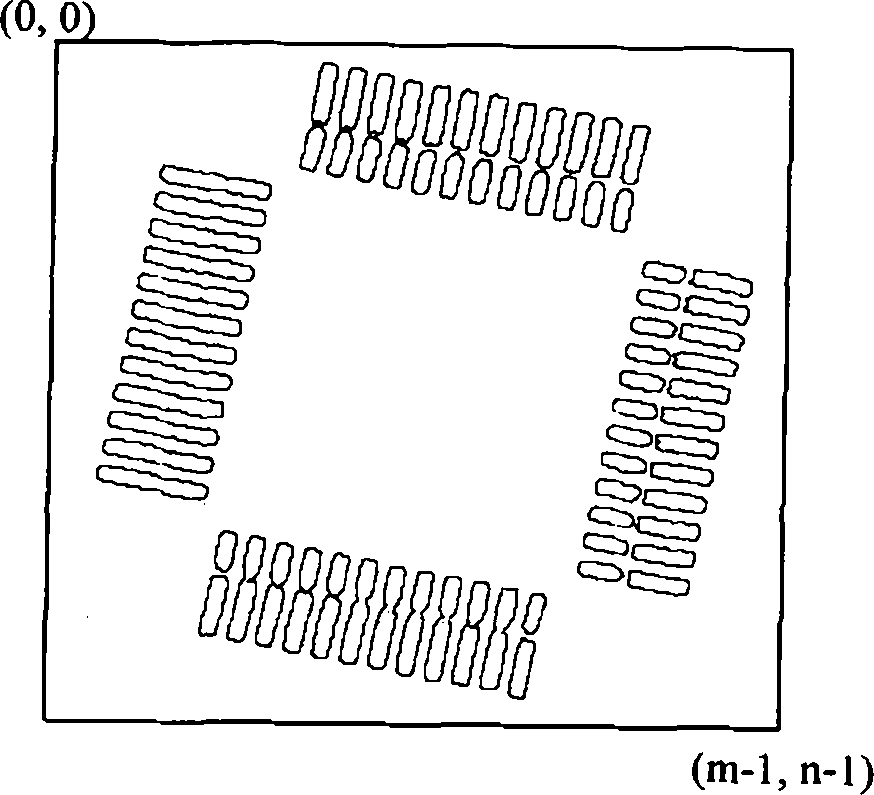

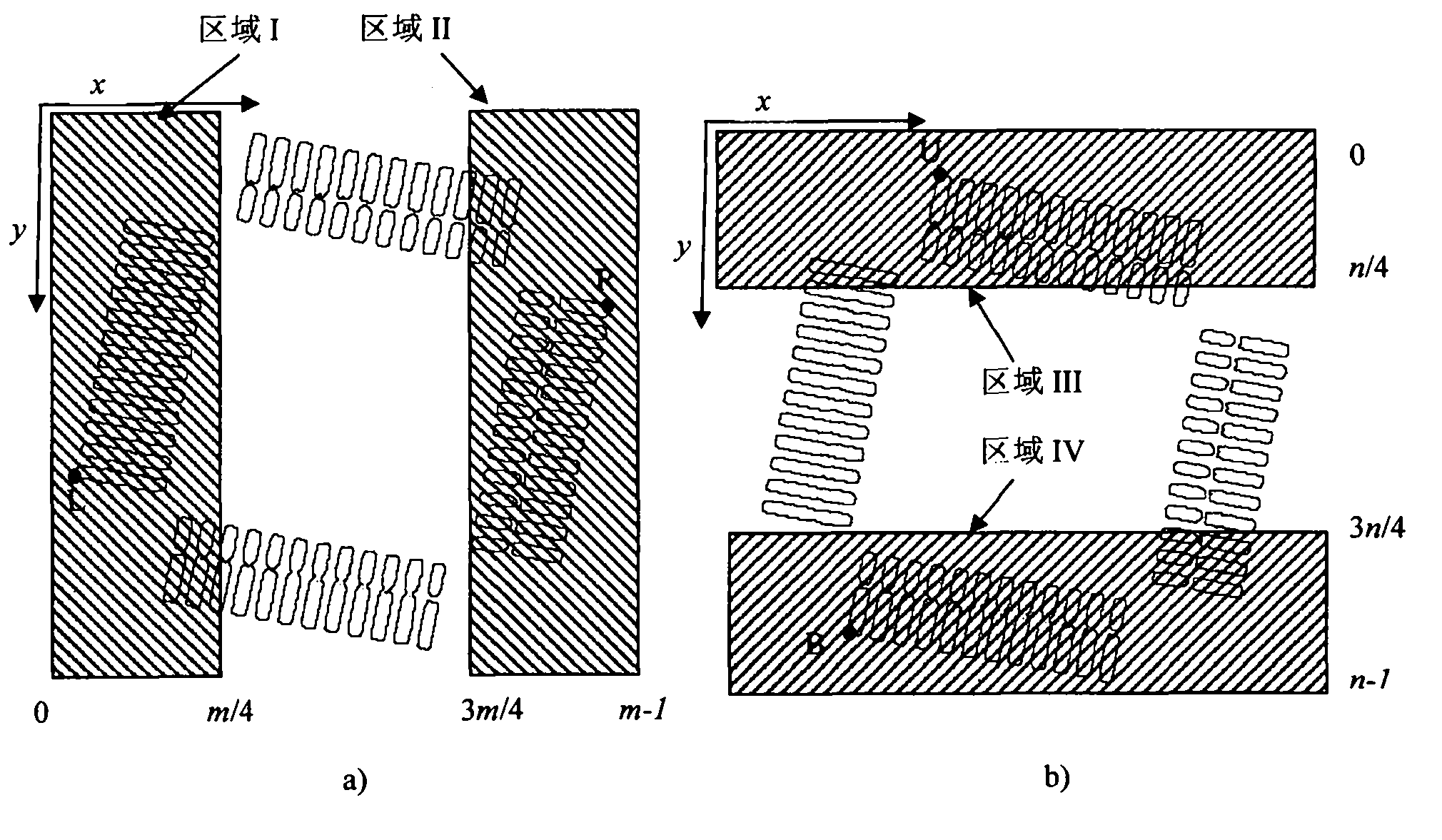

Method for positioning and detecting QFP (Quad Flat Package) chip

InactiveCN101936708AFast positioningRapid positioningUsing optical meansComputer hardwareEngineering

The invention relates to a method for positioning and detecting a QFP (Quad Flat Package) chip, comprising the following steps of: a collecting and pretreating an image of the QFP chip; b extracting four extreme points of coordinate axes x and y on the contour of the QFP chip to generate a extreme quadrangle; c calculating the coarse deflection angle of the QFP chip according to the extreme quadrangle on the contour of the QFP chip; and d determining four straight lines according to the coarse deflection angle and the four extreme points, fitting edge points into four straight lines by adopting a least square method after extracting the edge point of the tail end in the length direction of a pin at each side according to the set threshold value, and finally accurately calculating the deflection angle and the central coordinate of the QFP chip, thereby accomplishing the positioning and detection of the QFP chip. The invention improves the positioning and detecting precision and speed of the QFP chip and can accurately and efficiently accomplish the positioning and detection of the QFP chip on a high-speed chip mounter.

Owner:HOHAI UNIV CHANGZHOU

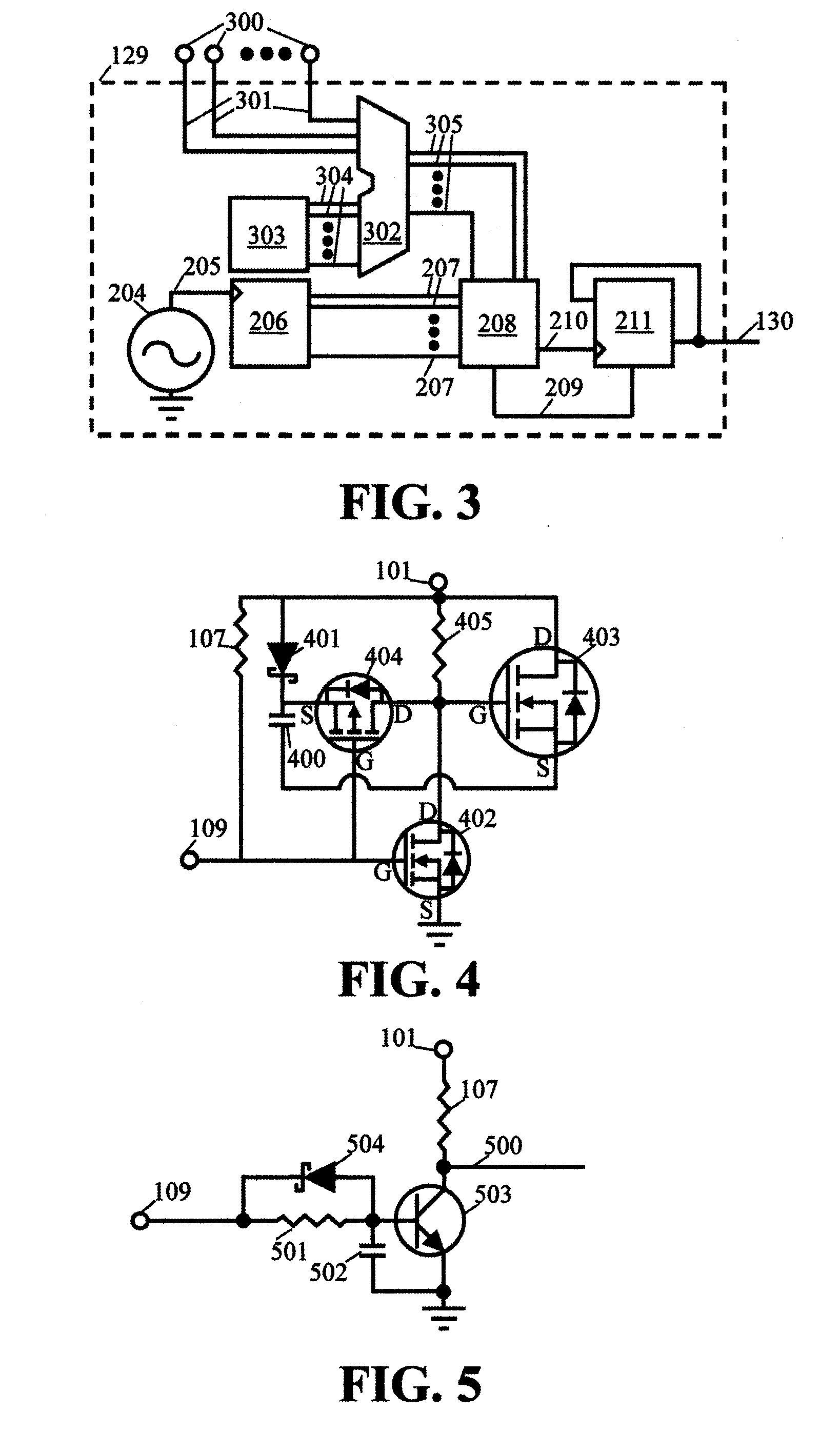

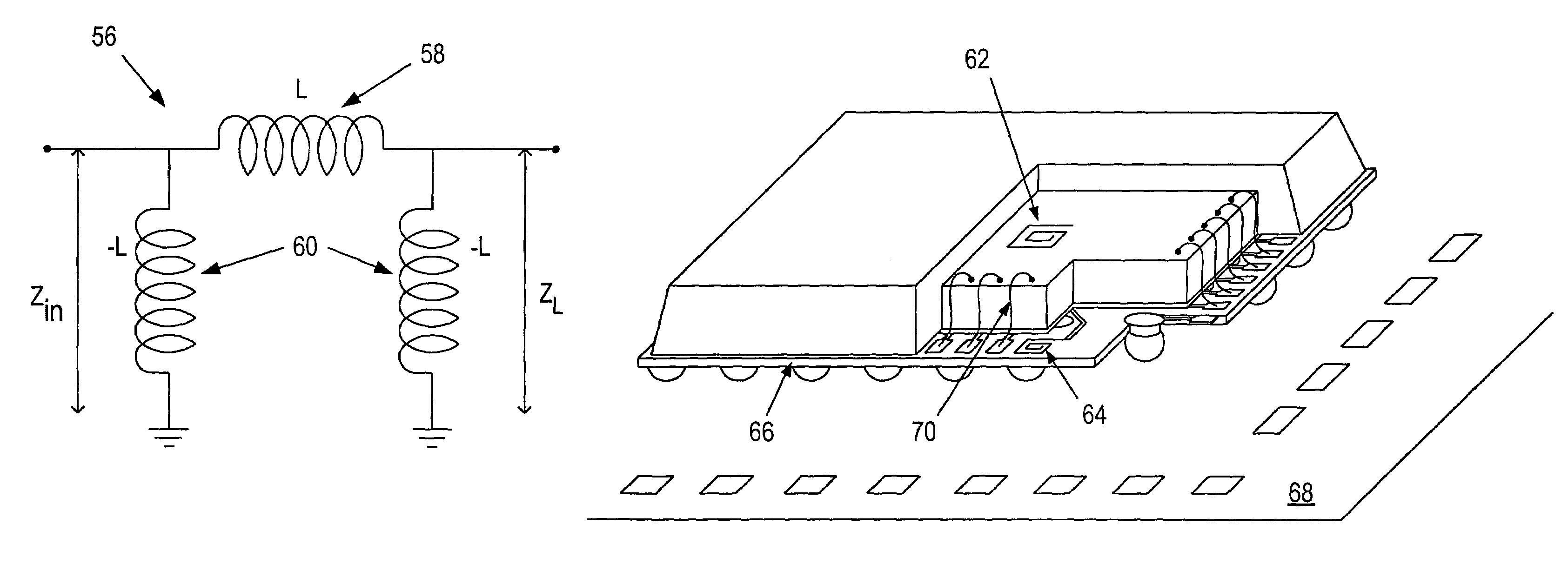

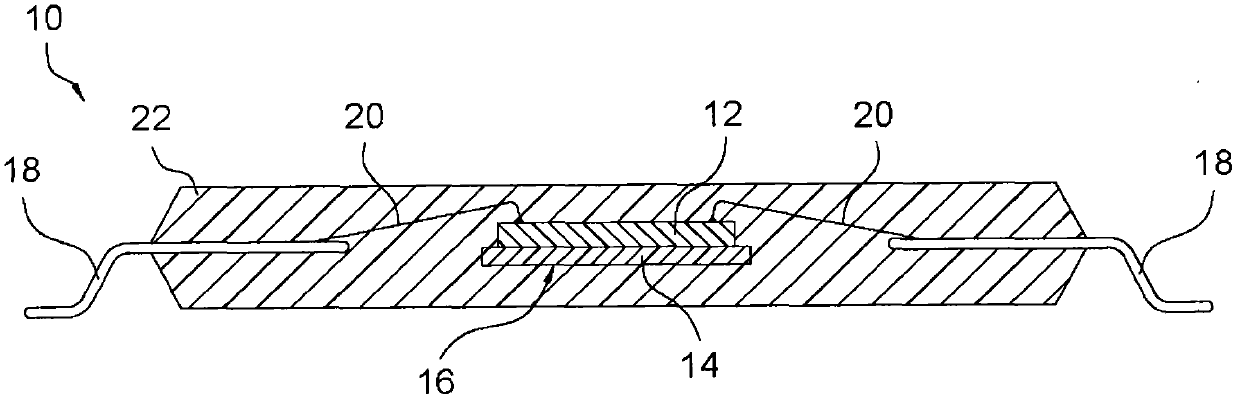

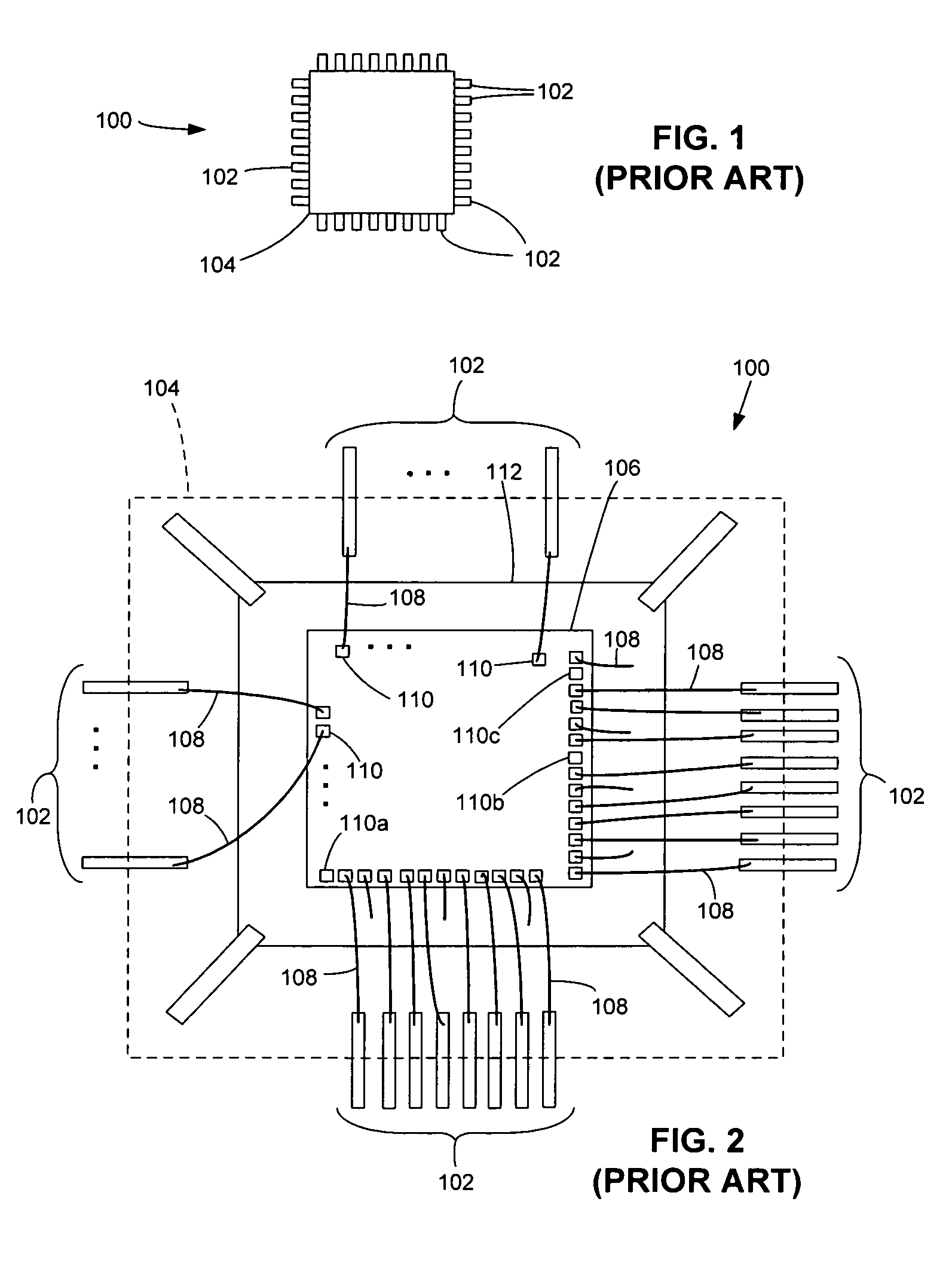

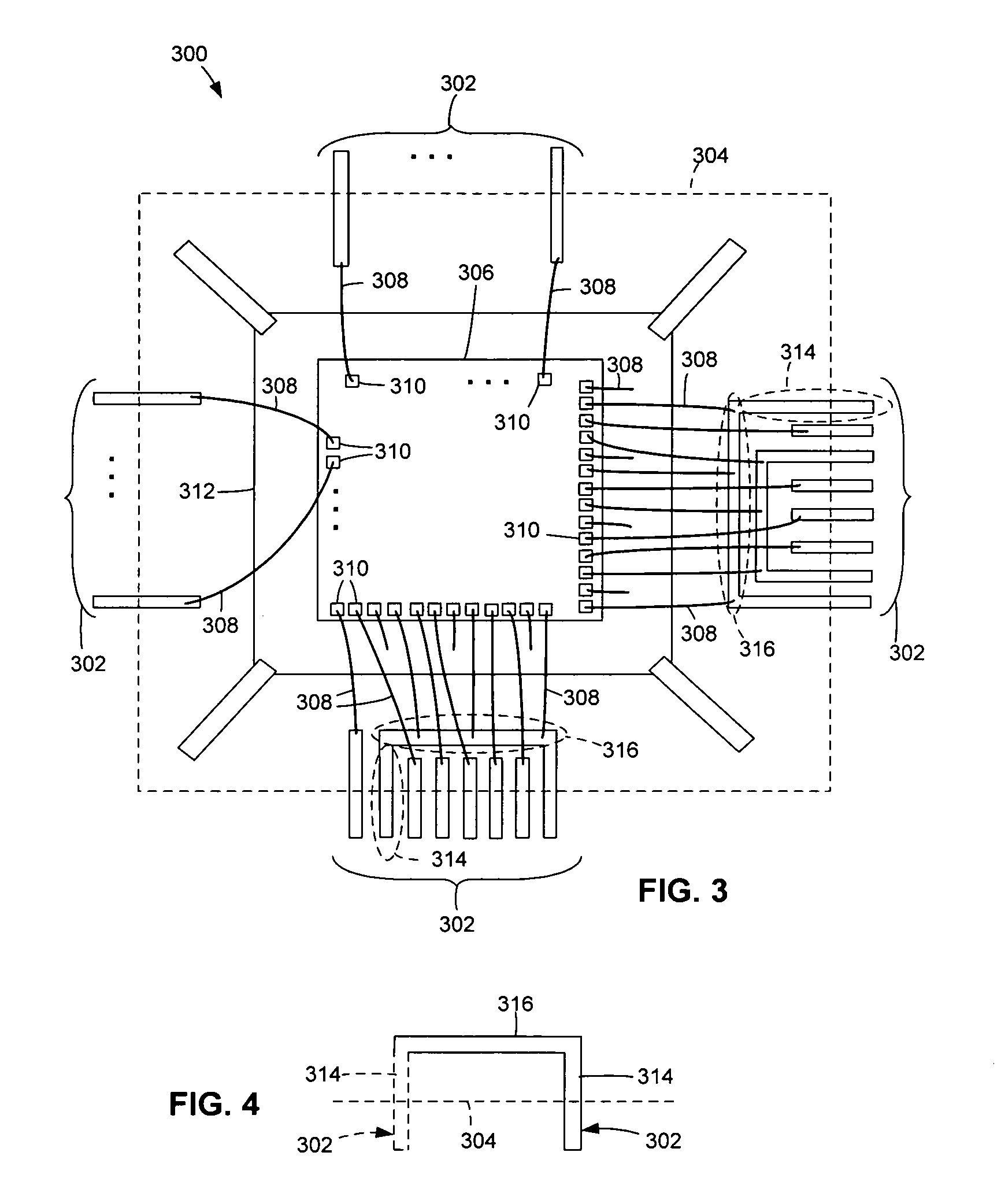

Integrated circuit incorporating wire bond inductance

InactiveUS7342300B2Semiconductor/solid-state device detailsSolid-state devicesLead bondingComputer module

The invention relates to the field of electronics, more particularly to the wire bonds incorporated into an integrated circuit package such as a quad flat pack, a ball grid array or hybrid style module. The present invention takes the normally undesirable wire bond inductance and uses it in an operational circuit where positive inductance is required. The circuit in which the wire bond inductance is used is located primarily in the integrated circuit die housed in the integrated circuit package, but may also include off-die components. In one example, a wire bond is used as the required series inductance in a discrete circuit impedance inverter which consists of two shunt-to-ground negative inductances and one series positive inductance. One of the negative inductances is located on-die, while the other is located off-die.

Owner:ZARBANA DIGITAL FUND

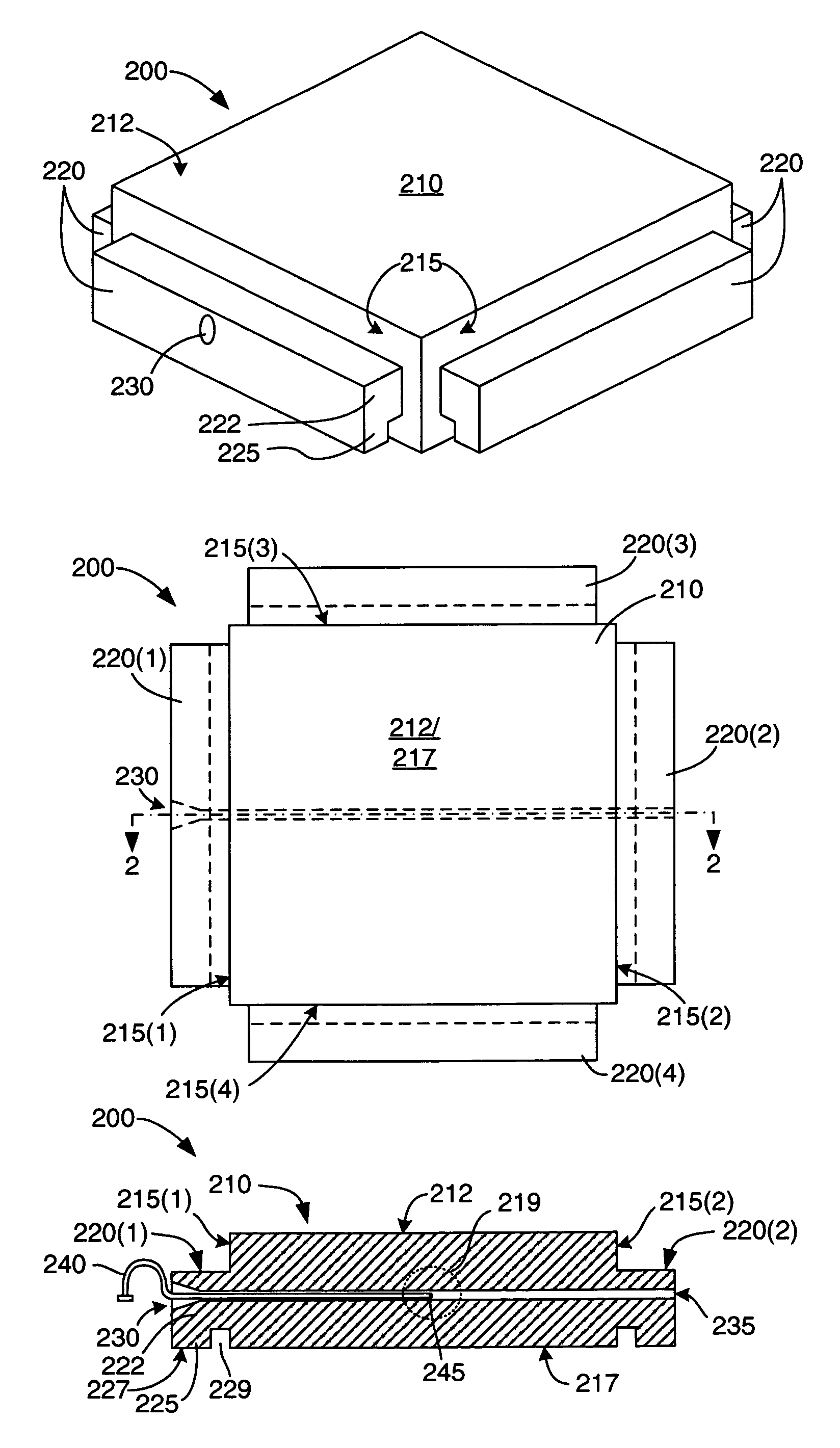

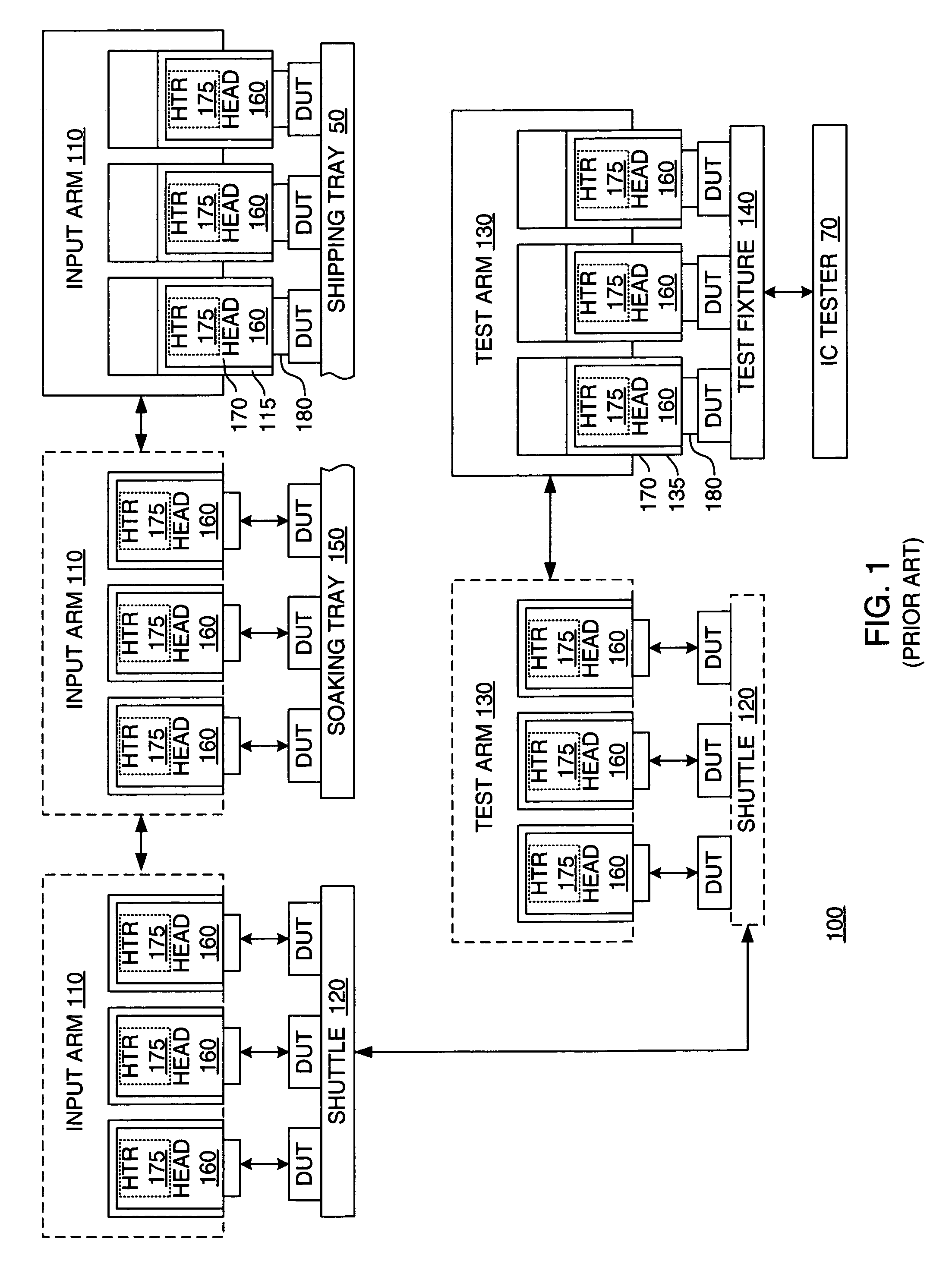

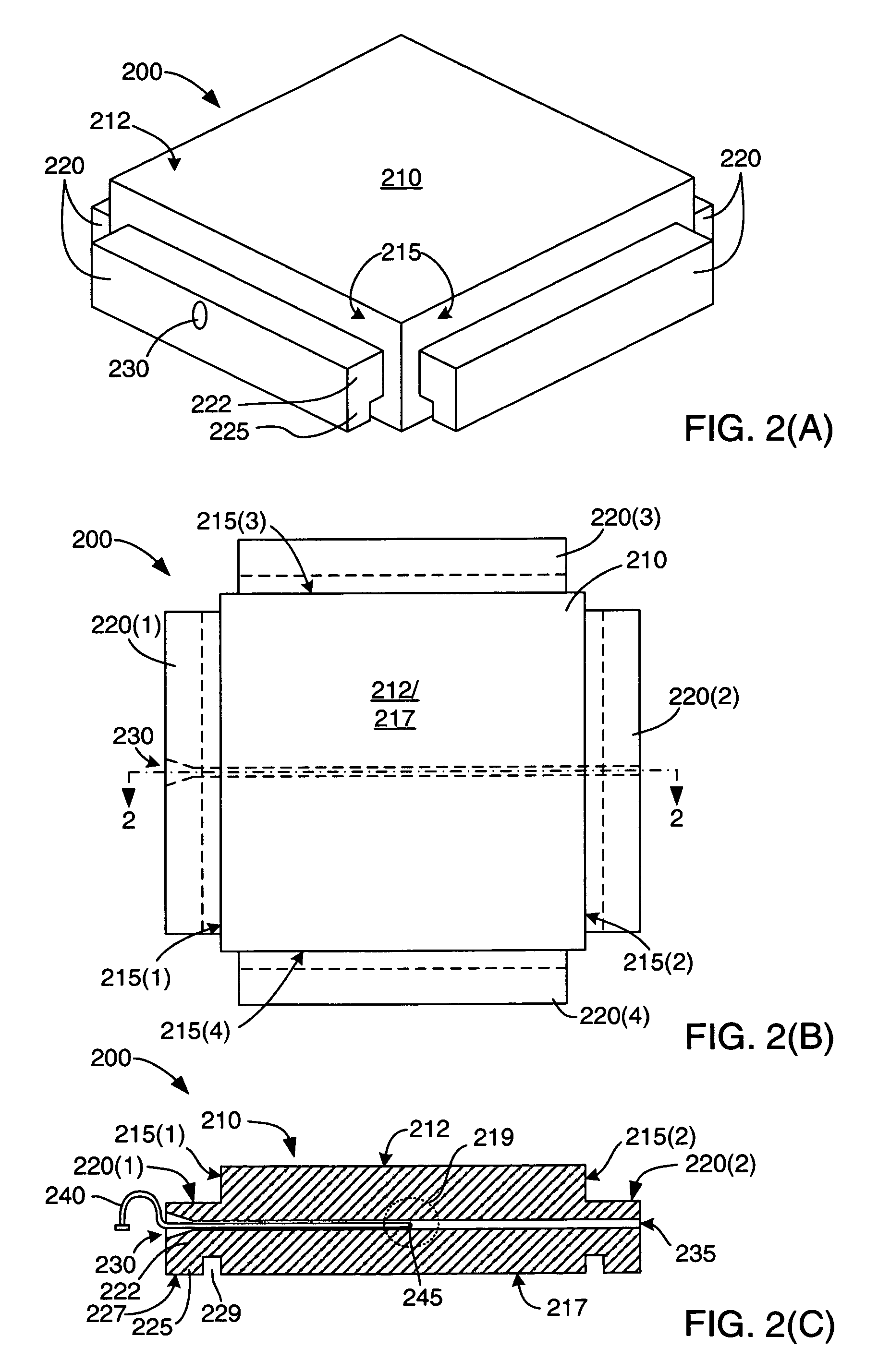

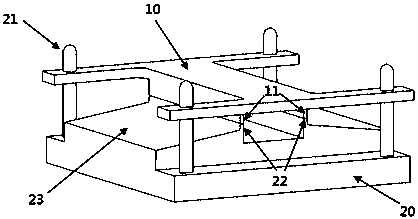

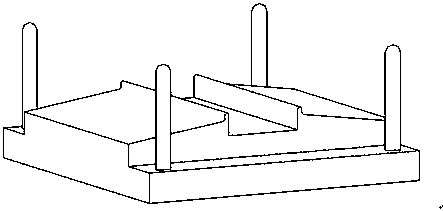

Method and apparatus for verifying temperature during integrated circuit thermal testing

ActiveUS6956390B1Accurate estimateAccurate predictionMeasurement instrument housingIndividual semiconductor device testingContact padConfirmation test

An test block includes a box-like body and four rails extending from side edges of the body. During thermal testing, the test block is mounted between a test head and a test socket such that the rails provide a thermal path between the test block body and contact pads formed on the test socket. In this manner the rails emulate the thermal path formed by the metal leads extending from a conventional Quad Flat Pack Integrated Circuit (QFP IC), thereby reliably duplicating the actual thermal path of the QFP IC. The test block is mounted on the test system and its temperature is measured before and after testing QFP IC devices. Confirming that the test block is within test temperature specifications before and after the QFP-IC test procedure provides a highly reliable verification that the QFP-IC's actual test temperature is within the test temperature specifications.

Owner:XILINX INC

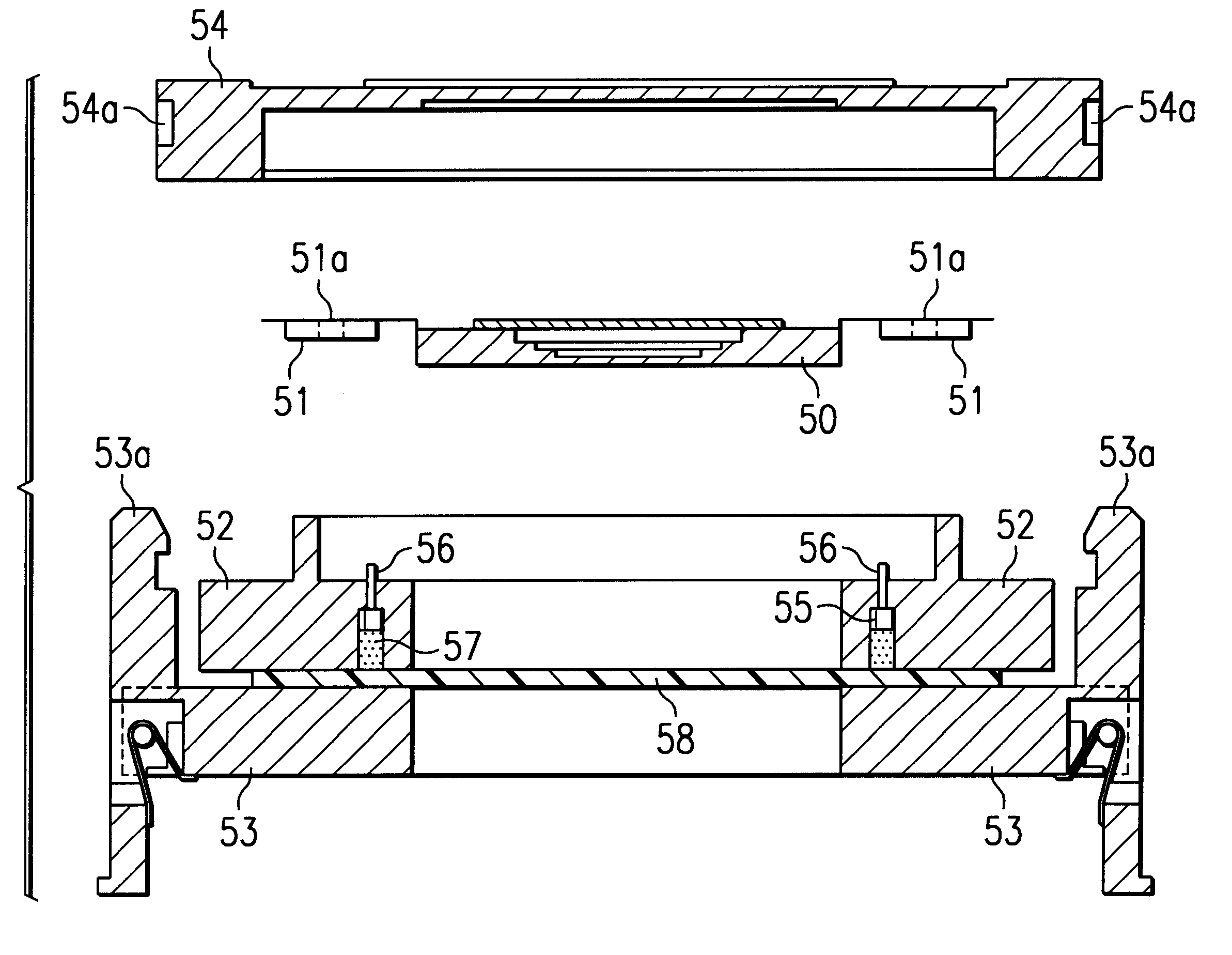

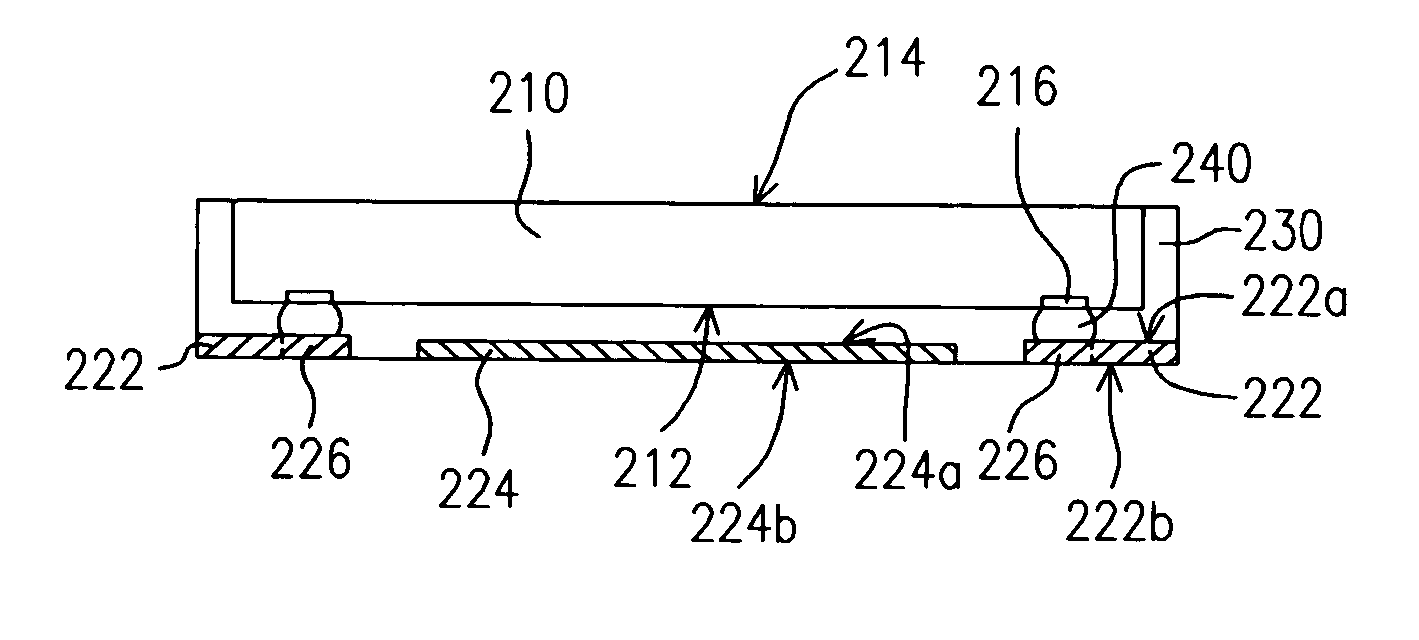

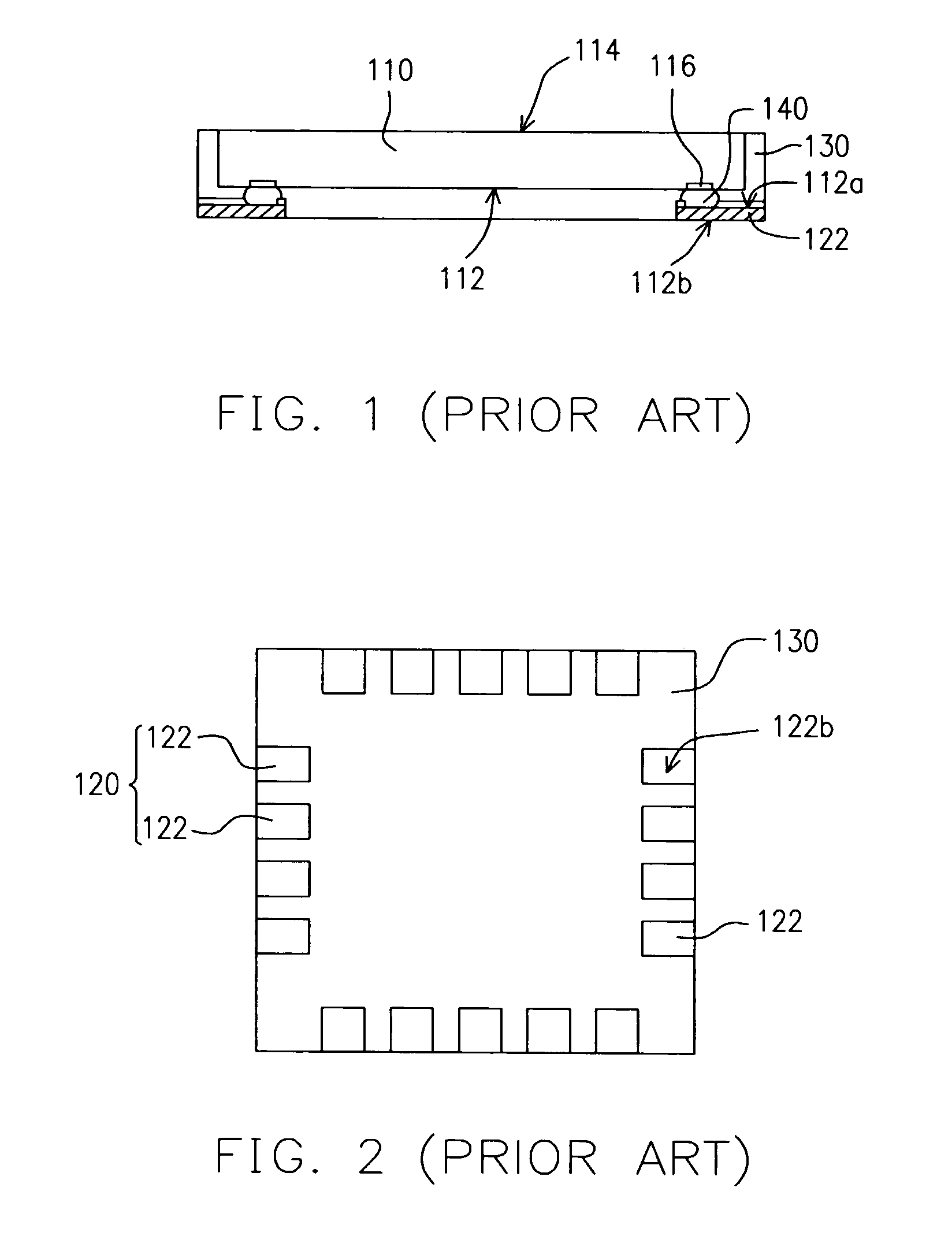

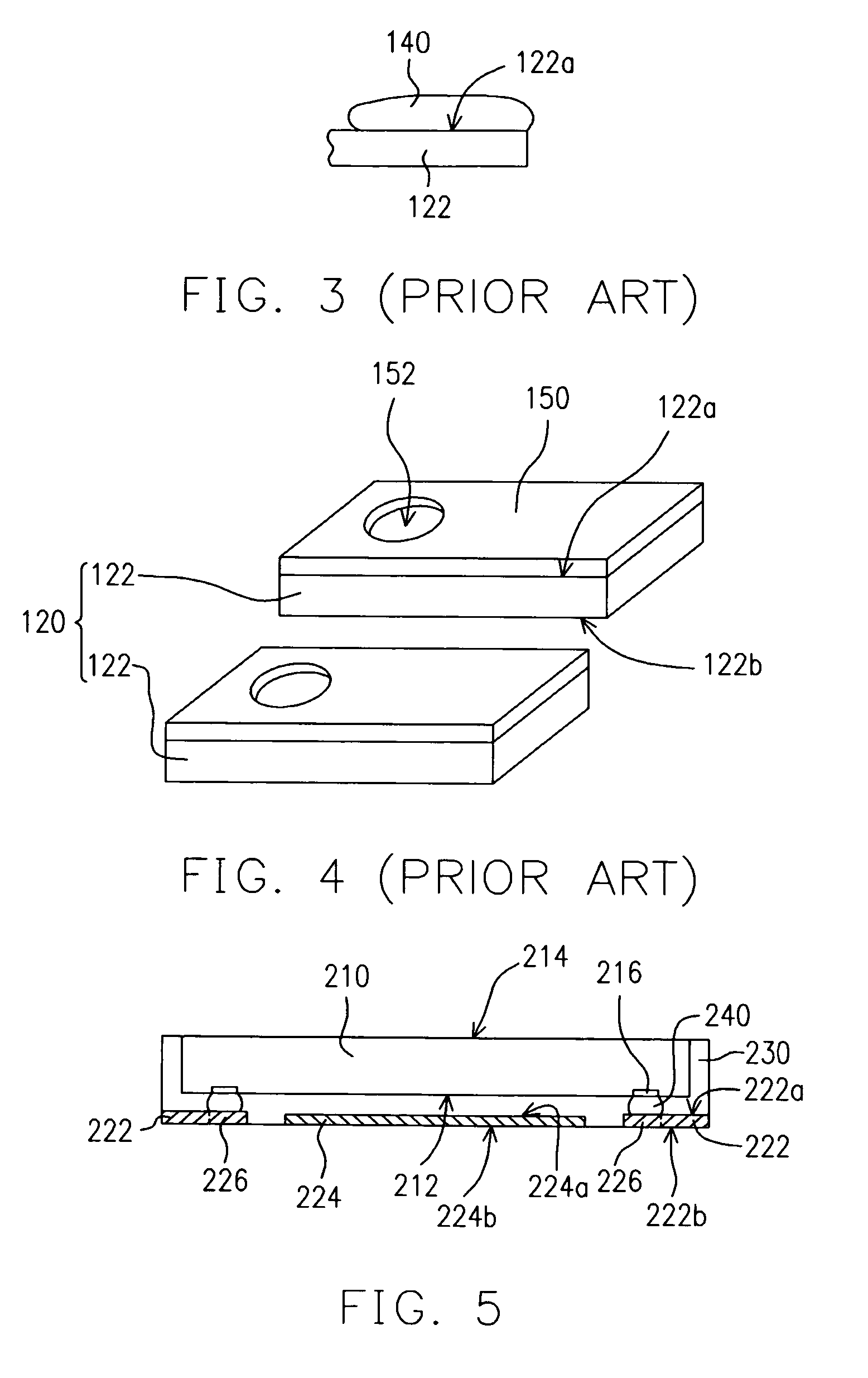

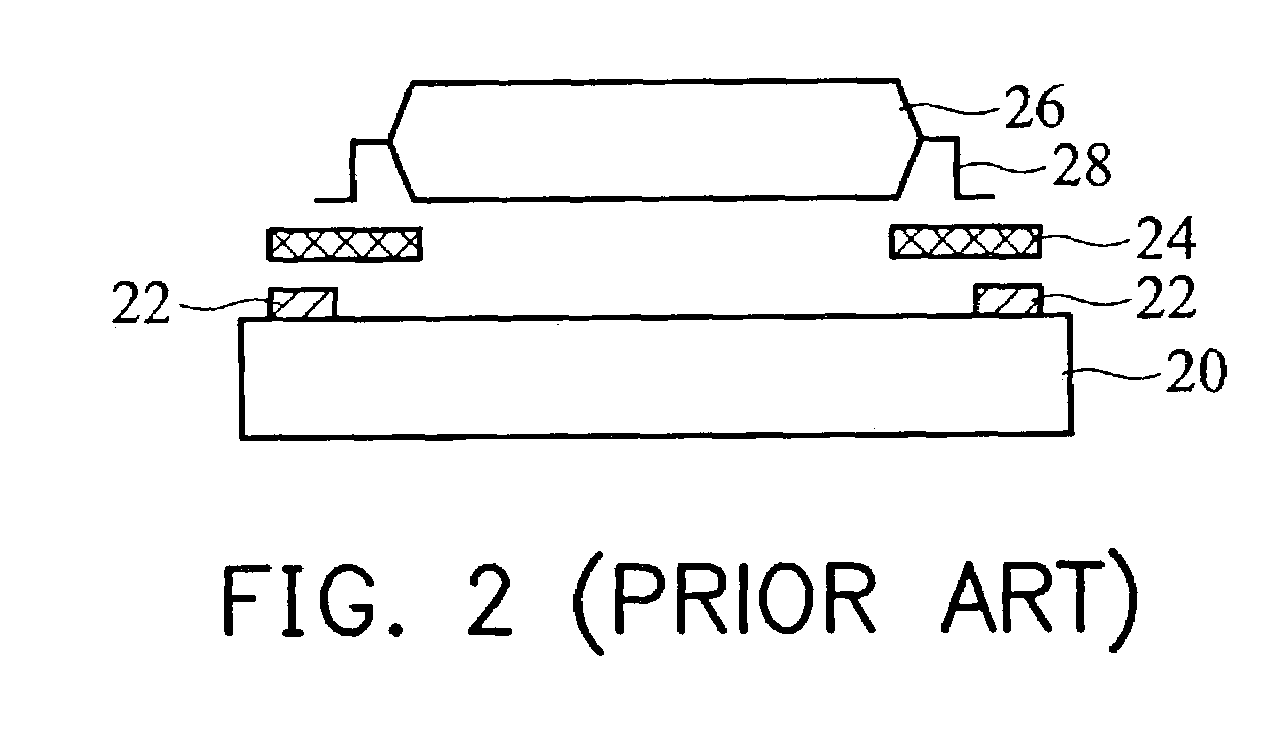

Expanded lead pitch for semiconductor package and method of electrical testing

InactiveUS6377061B1Efficient expansionEasy and precise testingMeasurement instrument housingIndividual semiconductor device testingElectricitySurface mounting

The invention relates to packages of semiconductor devices, specifically of the surface mount and Quad Flat Pack families, that can be used in current semiconductor device production, and to a method of automated testing. The packages have a plurality of insulating tie bars supporting a multitude of leads. The tie bars are designed so that they comprise celectrically conductive vias in a pattern expanding the effective lead pitch for more convenient testing, without introducing unwanted side effects. The full benefit of the expanded lead pitch can be exploited during the electrical testing of the device which utilizes a test apparatus simplified for an automated testing procedure. The base of the apparatus includes a multitude of electrically conductive and mechanically elastic passageways with surface contours adapted for contacting the metallic end connectors of the semiconductor device-to-be-tested, as well as the metallic connector to the tester.

Owner:TEXAS INSTR INC

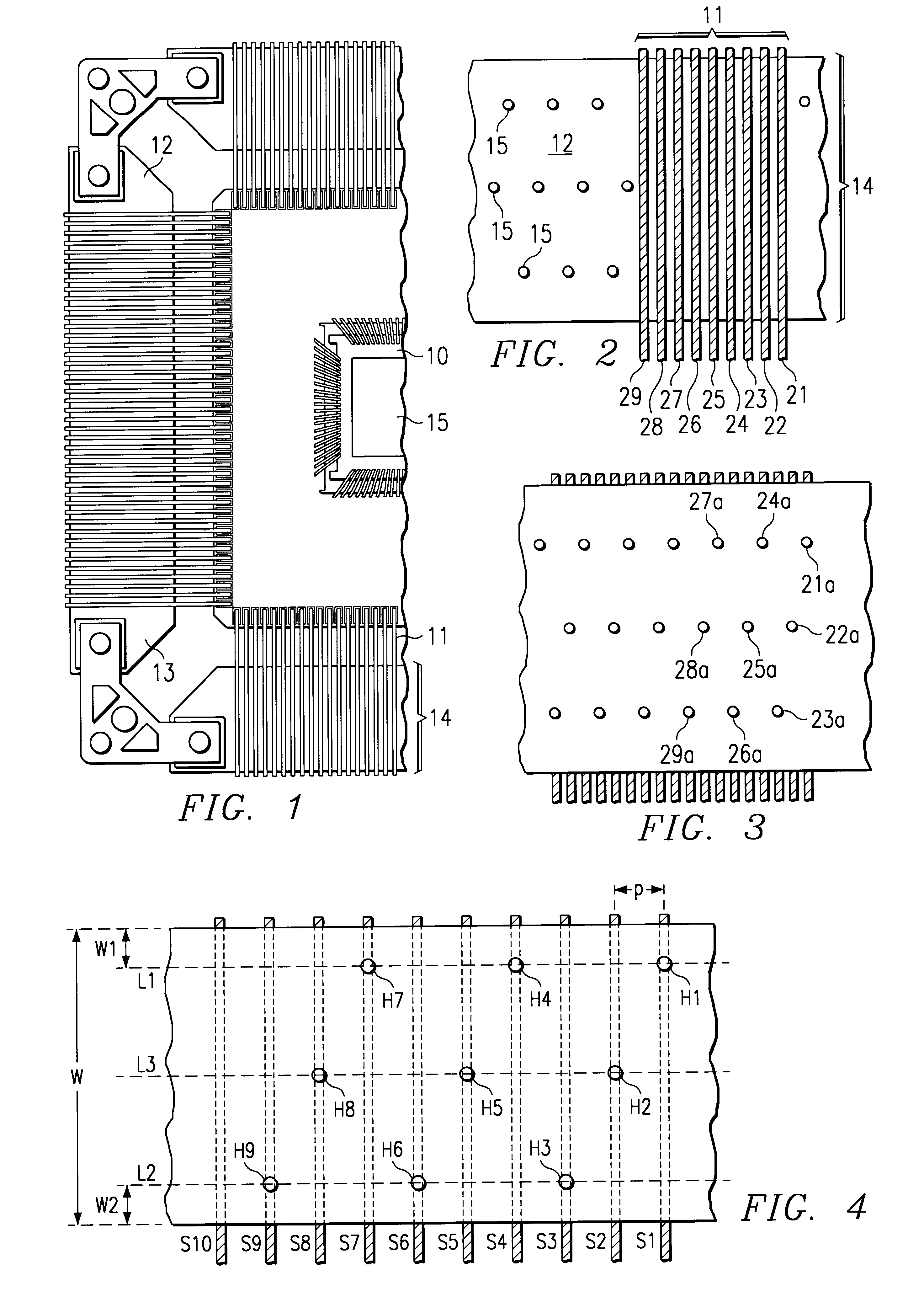

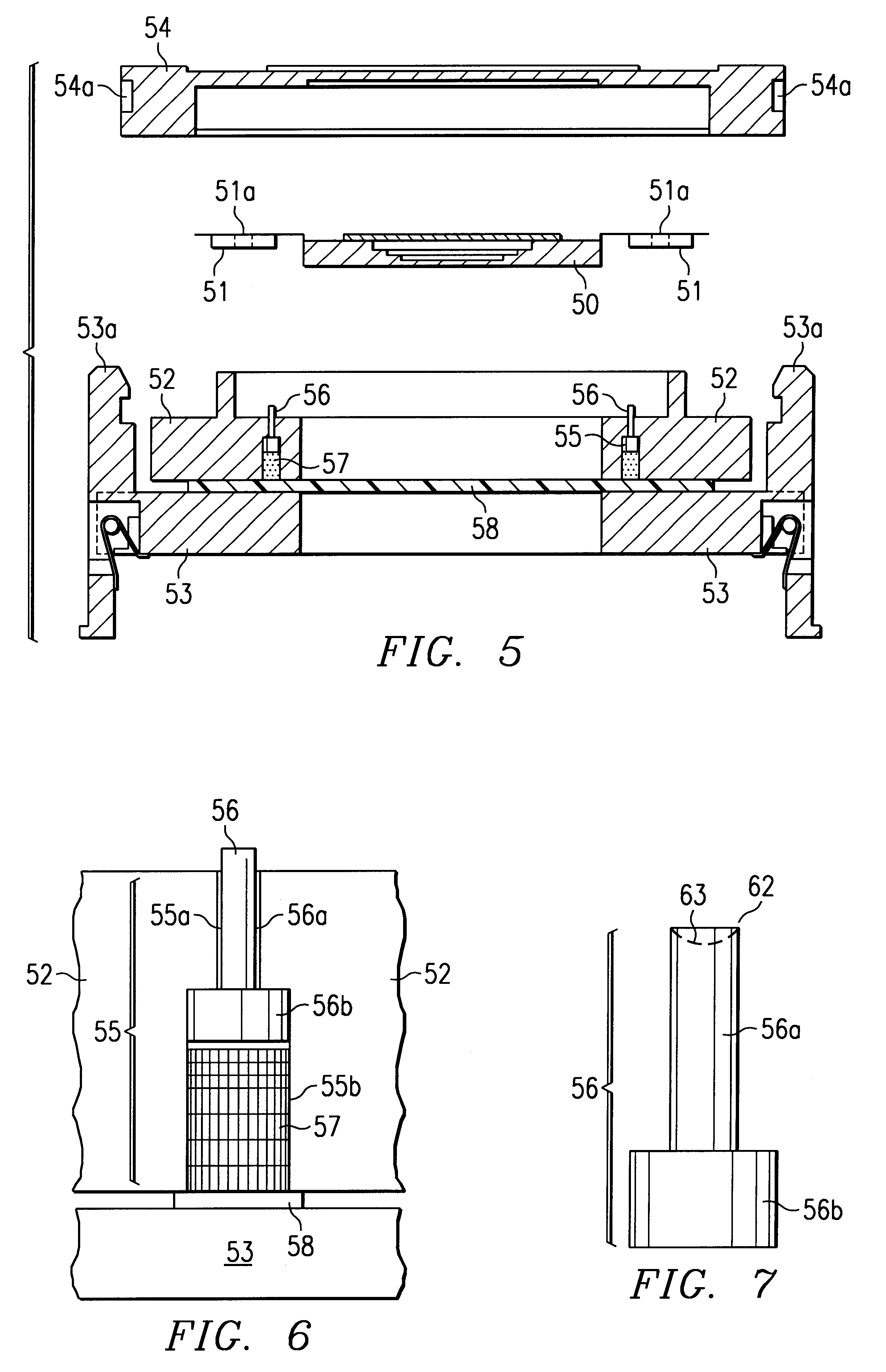

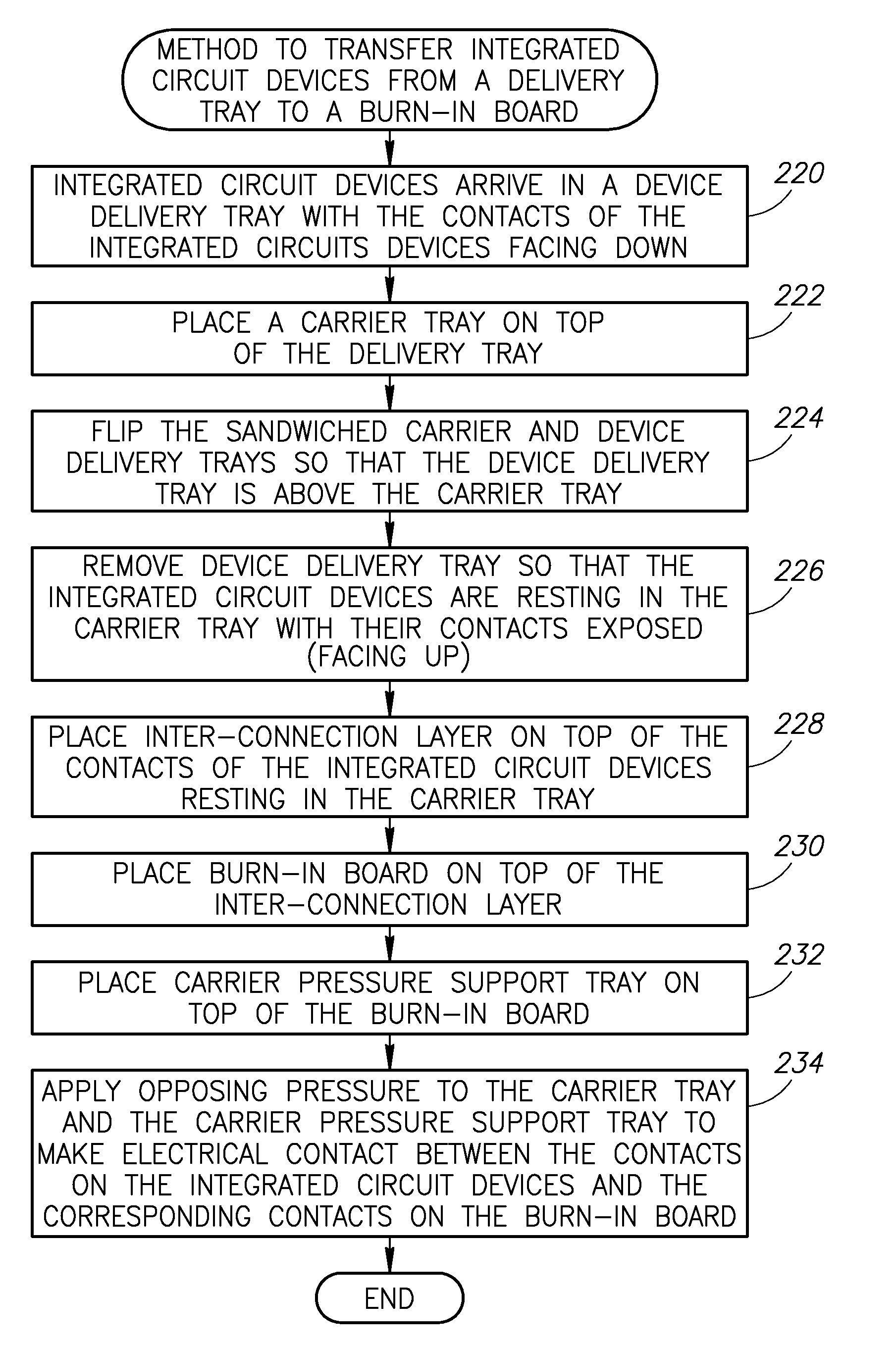

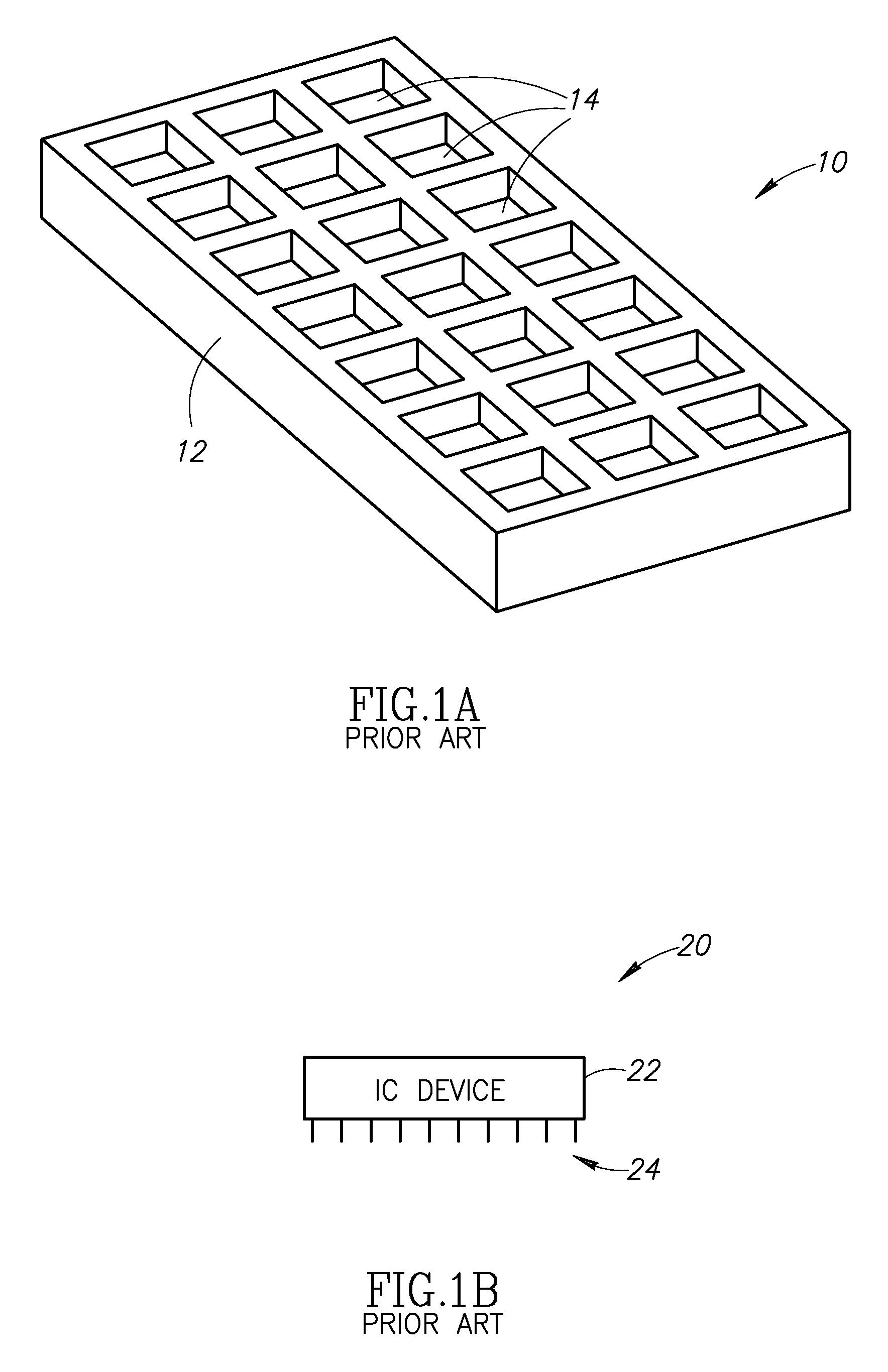

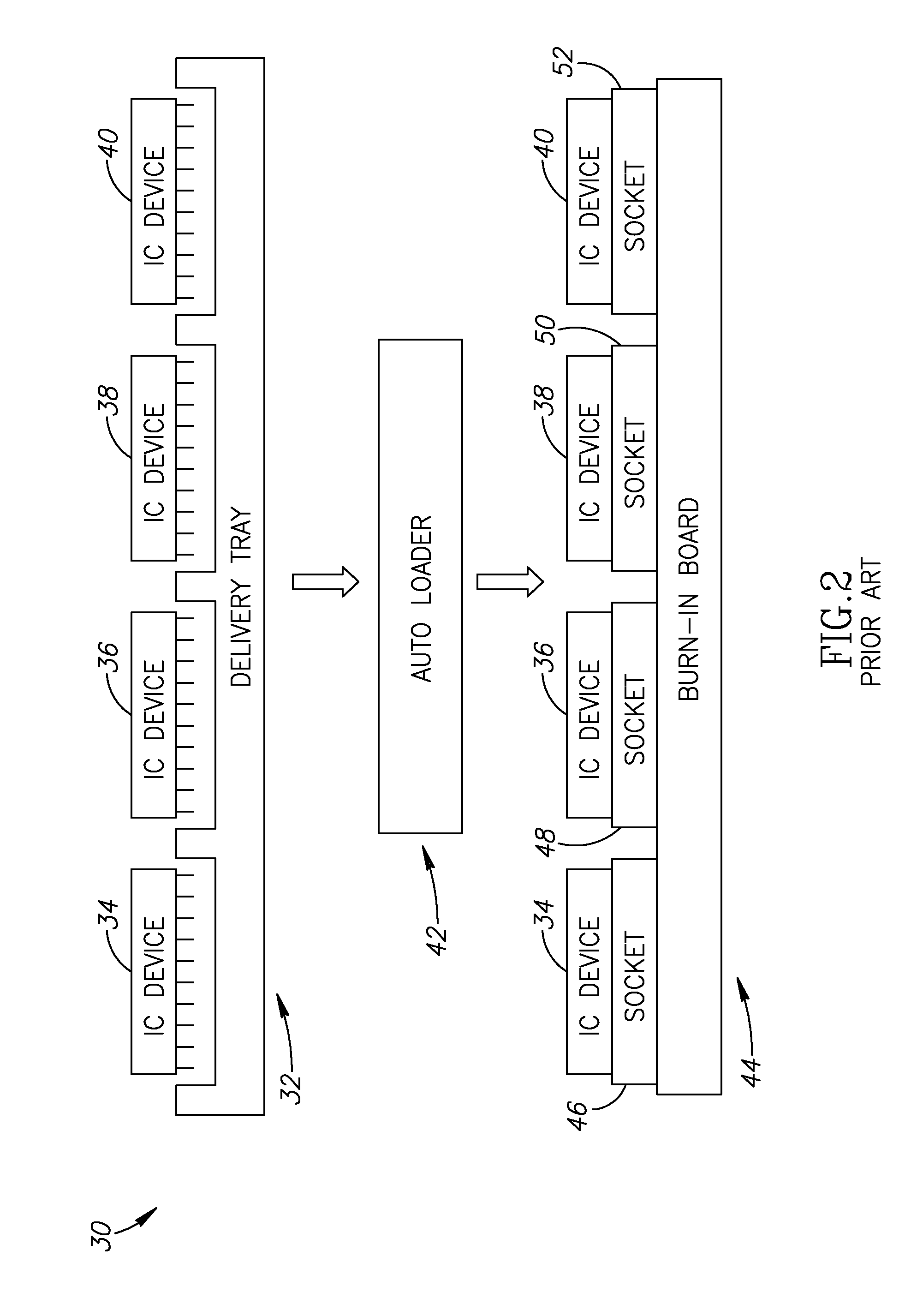

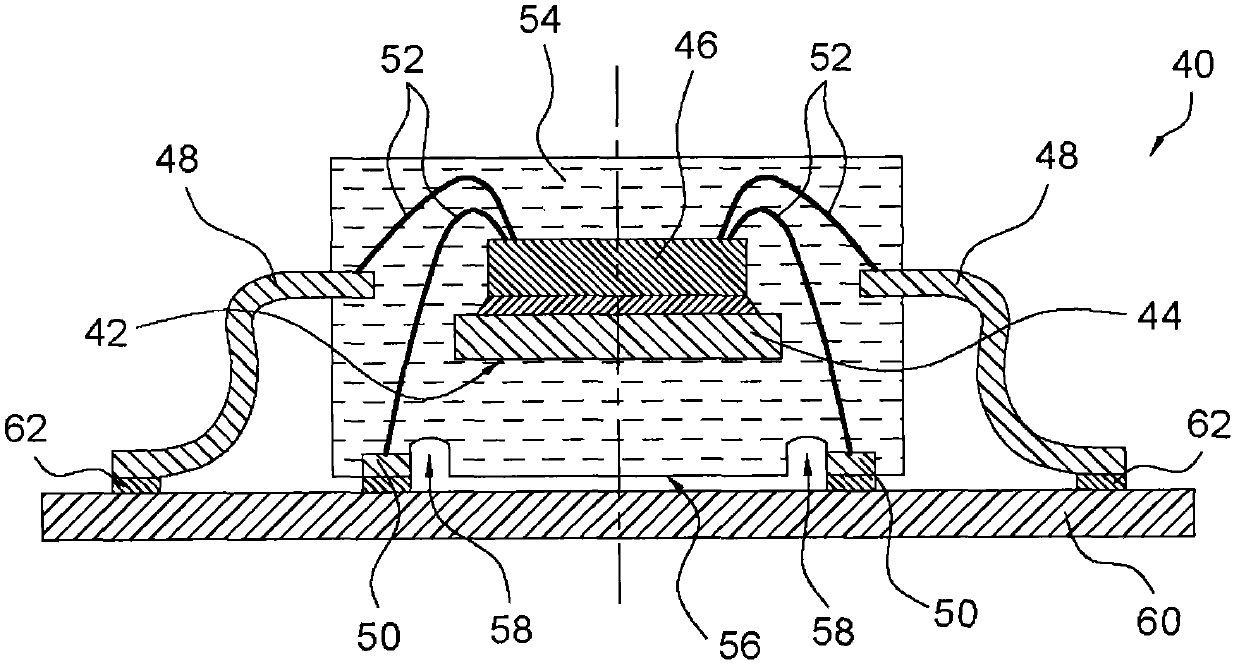

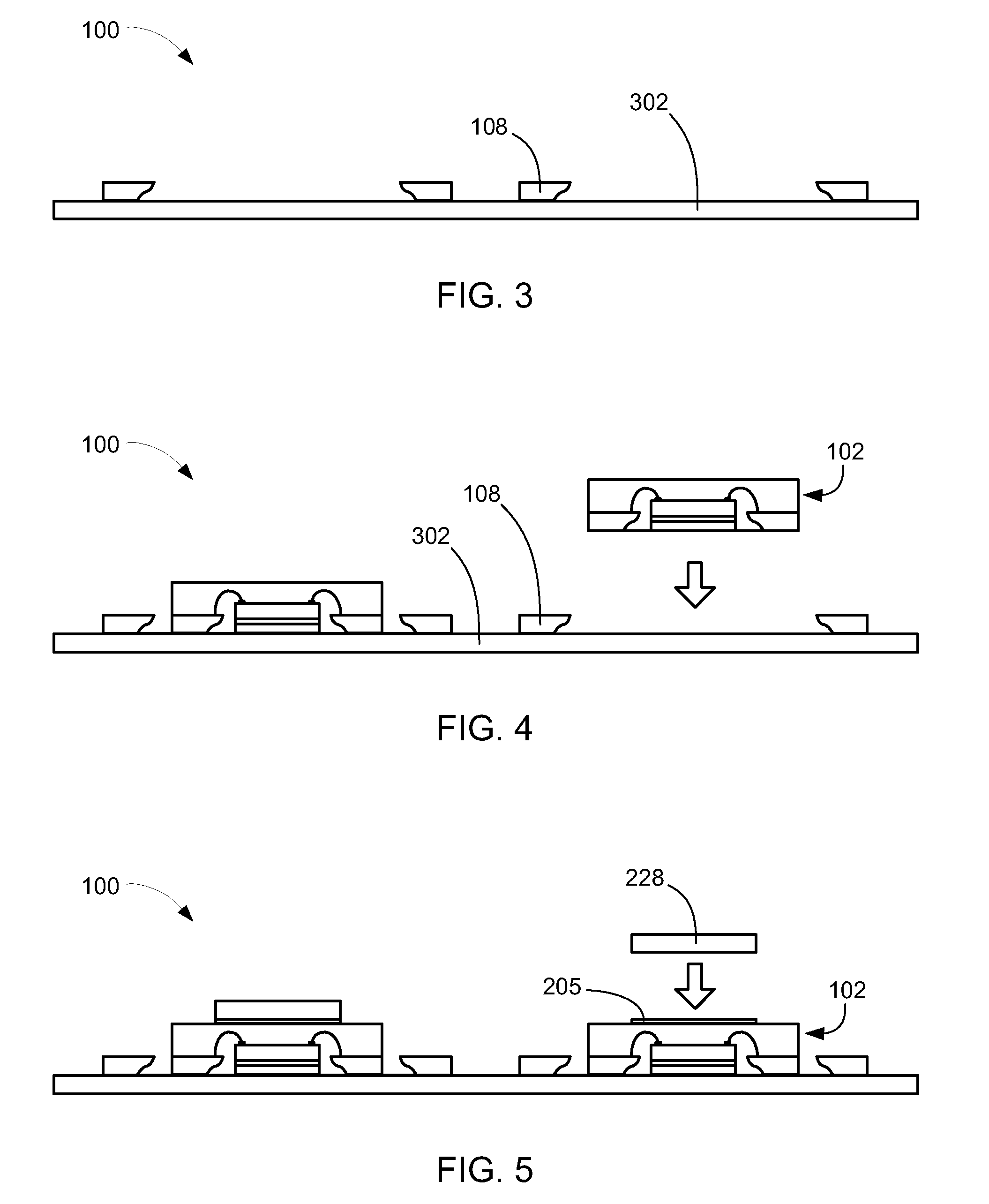

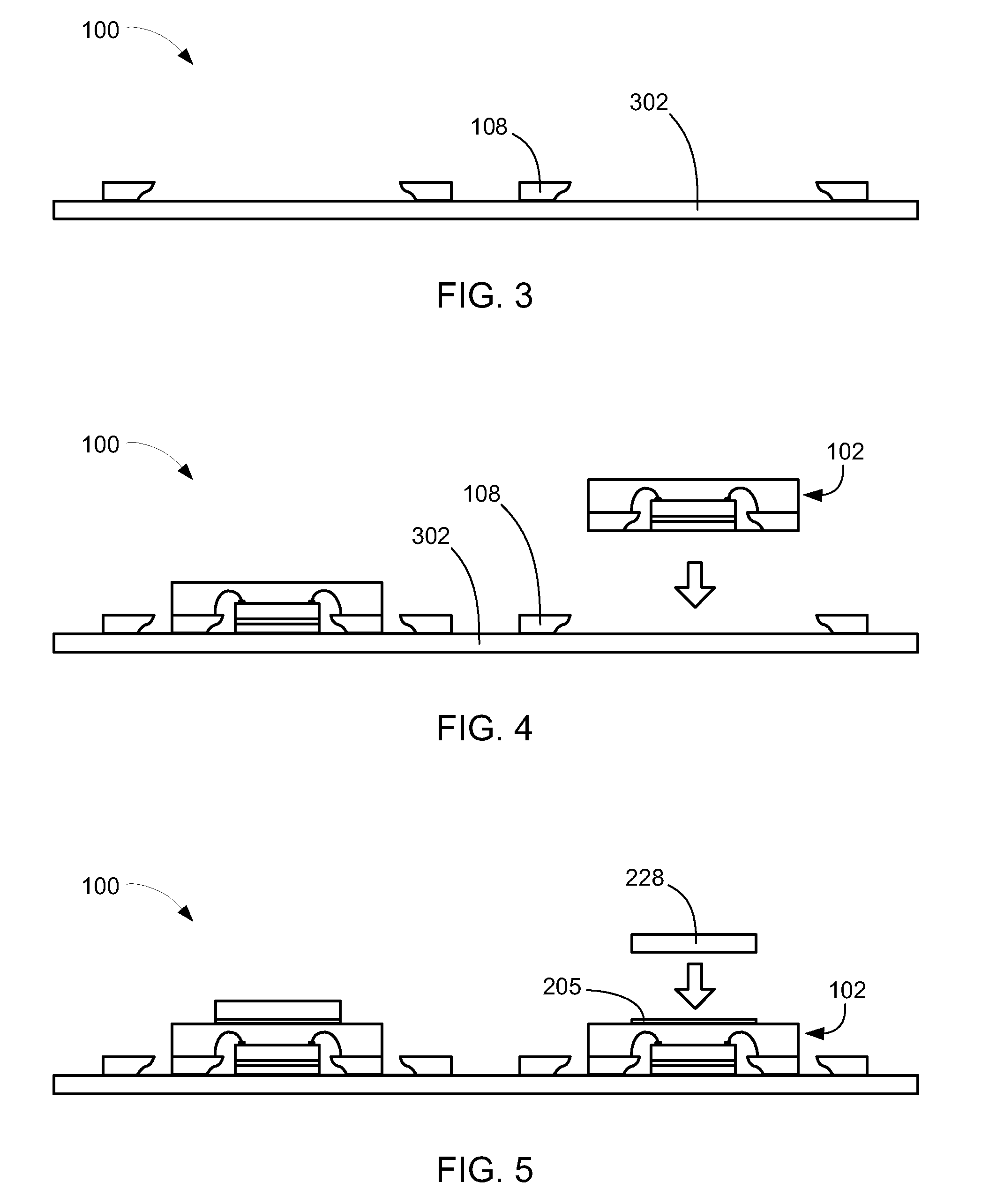

Burn-in-board architecture and integrated circuit device transfer method

ActiveUS20090174427A1Efficient transferReduces physical handlingIndividual semiconductor device testingContactless circuit testingSingle processQuad Flat Package

The present invention implements a mechanism using an inter-connection layer to couple a plurality of integrated circuit devices to a printed circuit board, thereby eliminating the need for sockets to hold the integrated circuit devices on the printed circuit board. The mechanism of the present invention is operative for integrated circuit devices packaged in a ball grid array, a quad flat pack or a leadless quad flat pack. The present invention also provides a mechanism to efficiently transfer a plurality of integrated circuit devices from an integrated circuit device delivery tray to a burn-in board in a single process without requiring an autoloader, resulting in increased transfer reliability and both cost and space savings.

Owner:TEXAS INSTR INC

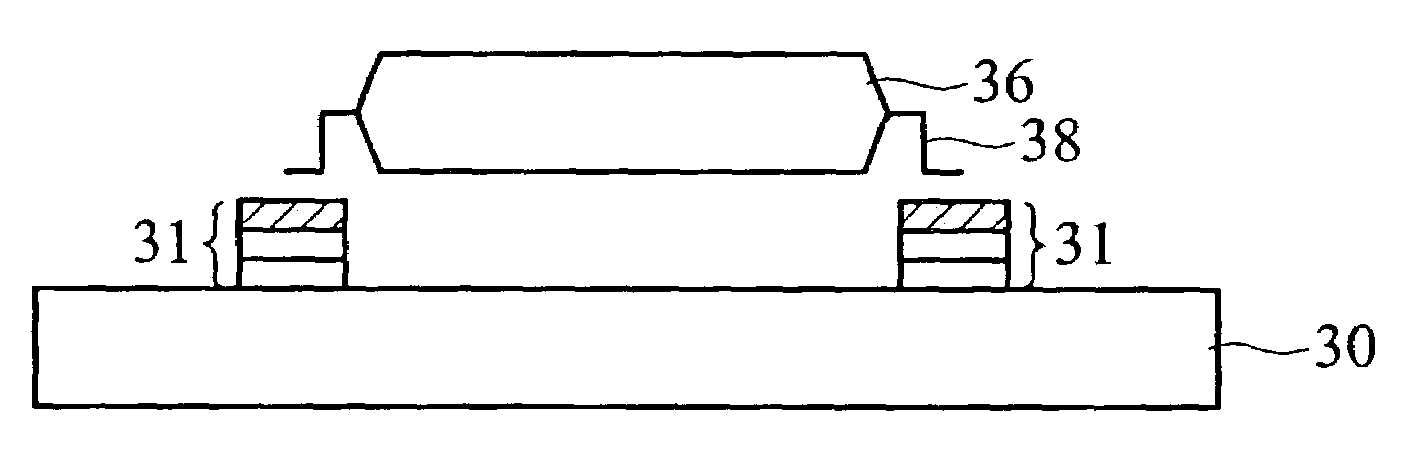

Flip-chip type quad flat package and leadframe

ActiveUS7067904B2Prevent crashLow production costSemiconductor/solid-state device detailsSolid-state devicesEngineeringQuad Flat Package

A flip-chip type quad flat package and a leadframe. The leadframe comprises a bump-connecting area and a non-connecting area. The maximum width of the bump-connecting area is larger than the width of the non-connecting area. A bump is limited to the bump-connecting area after performing a reflow process so that the bumps are prevented from collapsing, the manufacturing cost is reduced and the process is simplified.

Owner:ADVANCED SEMICON ENG INC

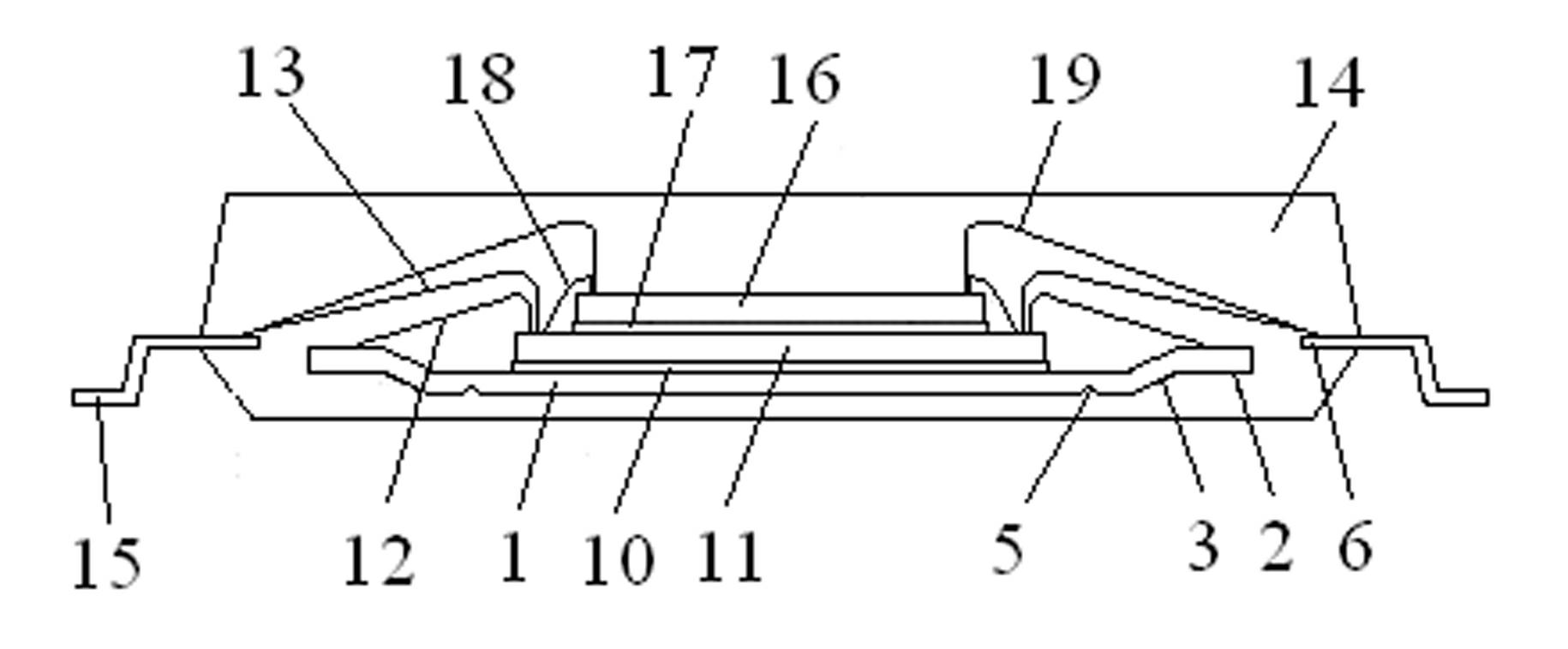

e/LQFP (low-profile quad flat package) planar packaging part with grounded ring and production method of e/LQFP planar packaging part with grounded ring

ActiveCN102522392ASimple structureImprove bindingSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingEngineering

The invention discloses an e / LQFP (low-profile quad flat package) planar package with a grounded ring, which comprises a carrier and the grounded ring, wherein one to two IC (integrated circuit) chips are adhered to the carrier. The IC chips are connected with an inner pin through bonding wires, the inner pin is connected with an outer pin, the lower end face of the grounded ring is higher than the upper end face of the carrier, and the carrier is connected with the grounded ring through a ribbed plate. The end face, without the IC chips, of the carrier is provided with an anti-overflow ring, the grounded ring, the bonding wires, the ribbed plate and the inner pin are packaged in a plastic packaging part which is fixedly packaged on the carrier, the outer pin is positioned outside the plastic packaging part, the outer pin and the plastic packaging part are coplanar, and the lower end face of the carrier is positioned outside the plastic packaging part or packaged inside the plastic packaging part. The e / LQFP planar package with the grounded ring is produced by procedures of wafer thinning, scribing, coring, bonding and the like. Layering or shedding of a ground wire caused by making the ground wire on the carrier can be avoided, the carrier is free of silver coating, and packaging reliability is improved.

Owner:TIANSHUI HUATIAN TECH +1

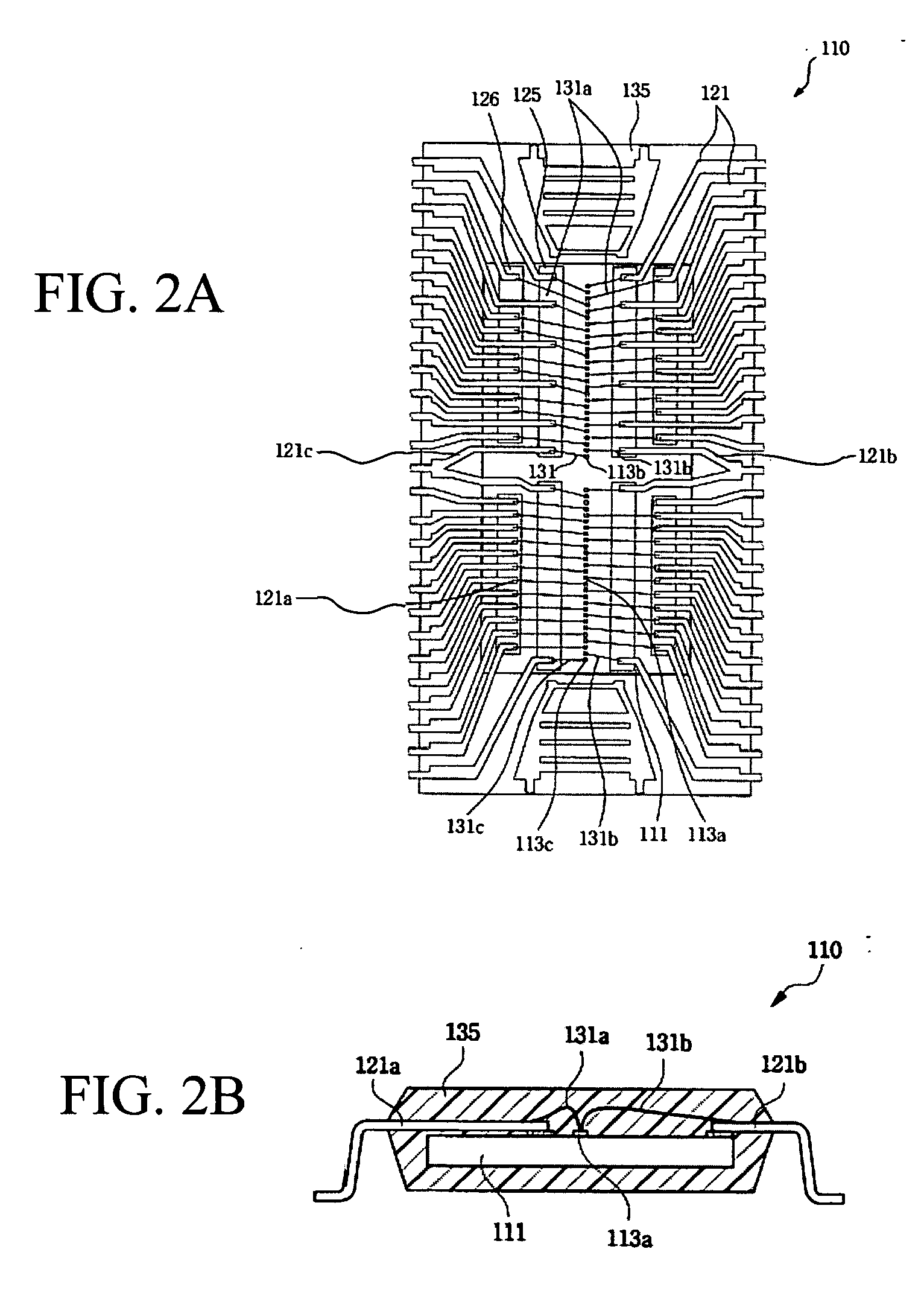

e/LQFP (low-profile quad flat package) stacked package with grounded ring and production method of e/LQFP stacked package with grounded ring

ActiveCN102522391ASimple structureImprove bindingSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingStructural engineering

The invention discloses an e / LQFP (low-profile quad flat package) stacked package with a grounded ring and a production method of the e / LQFP stacked package with the grounded ring. Two IC (integrated circuit) chips are adhered to a carrier in a stacked manner and connected with an inner pin through bonding wires, the inner pin is connected with an outer pin, the carrier is connected with the grounded ring through a ribbed plate, and the lower end face of the grounded ring is higher than the upper end face of the carrier. The lower end face of the carrier is provided with an anti-overflow ring, the grounded ring, the bonding wires, the ribbed plate and the inner pin are packaged in a plastic packaging part, the lower end face of the carrier is packaged in the plastic packaging part or positioned outside the plastic packaging parte. A wafer is thinned and scribed prior to being subjected to coring, bonding, plastic packaging and subsequent procedures to produce the e / LQFP stacked packaging part with the grounded ring. The carrier of the stacked packaging part is free of ground wire, layering caused by stress generated by making the ground wire and bonding failure of the ground wire can be avoided, and thereby reliability and testing yield of the package are improved.

Owner:TIANSHUI HUATIAN TECH +1

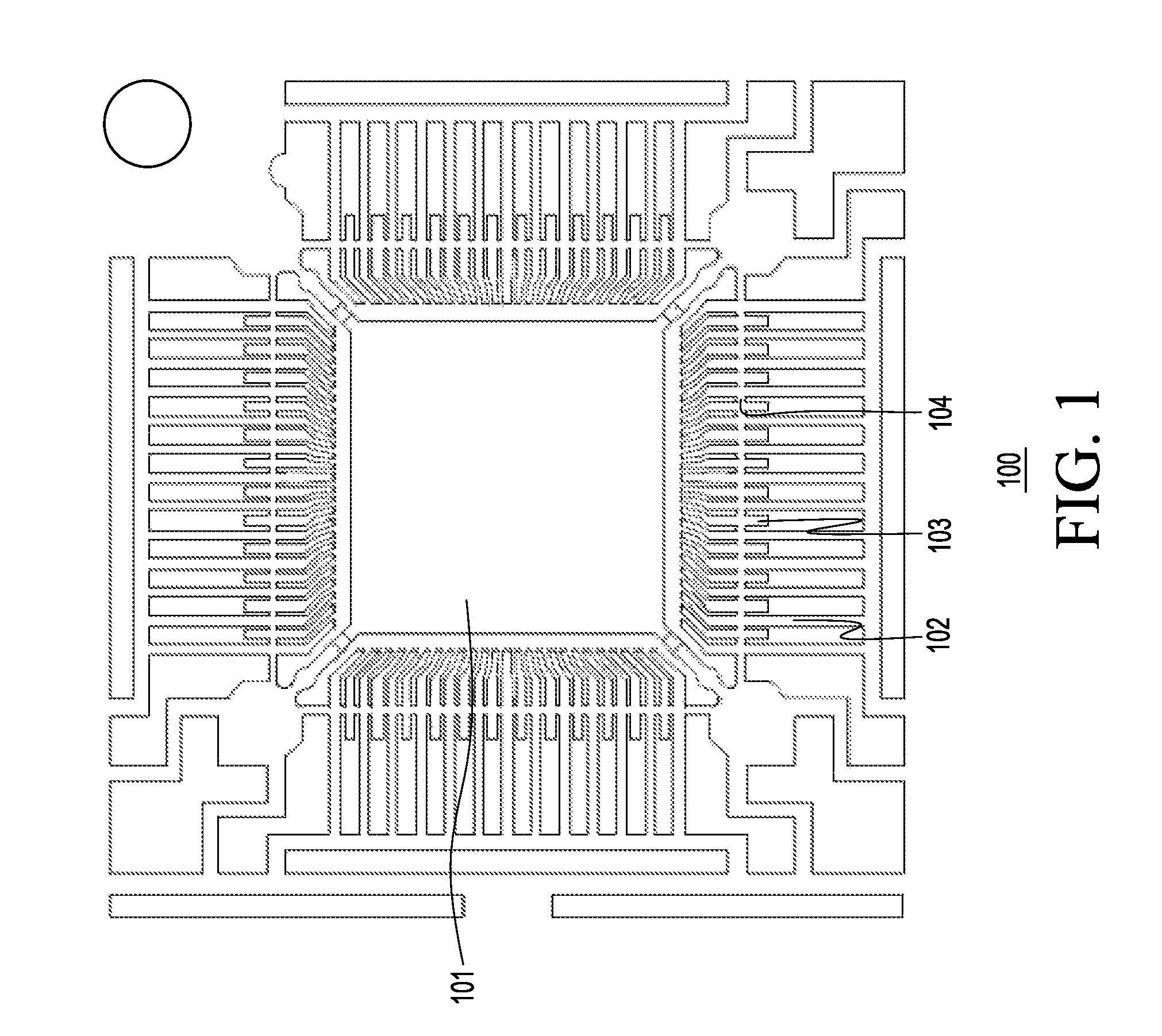

Semiconductor device with webbing between leads

ActiveUS20150206831A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialMetal particle

A quad flat package integrated circuit (IC) device has alternating inner and outer leads that protrude from a package body. The inner leads are j-shaped leads and the outer leads are gull-wing shaped leads. The package body is formed such that it includes plastic lead webbings between adjacent leads, which help prevent metal particles from getting lodged between the leads and causing electrical shorts. The webbings are made of the same molding compound as the package body and are formed together with the package body.

Owner:NXP USA INC

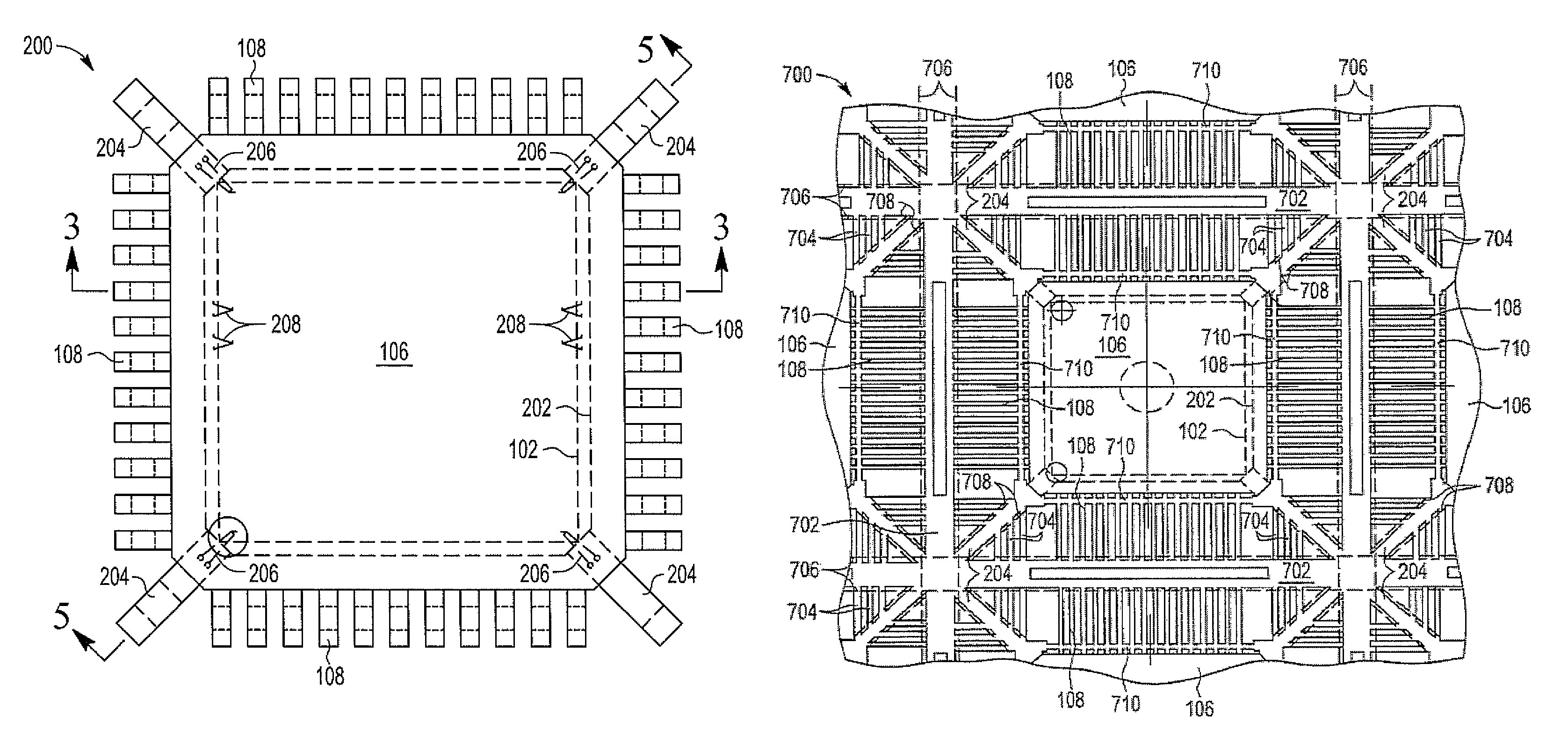

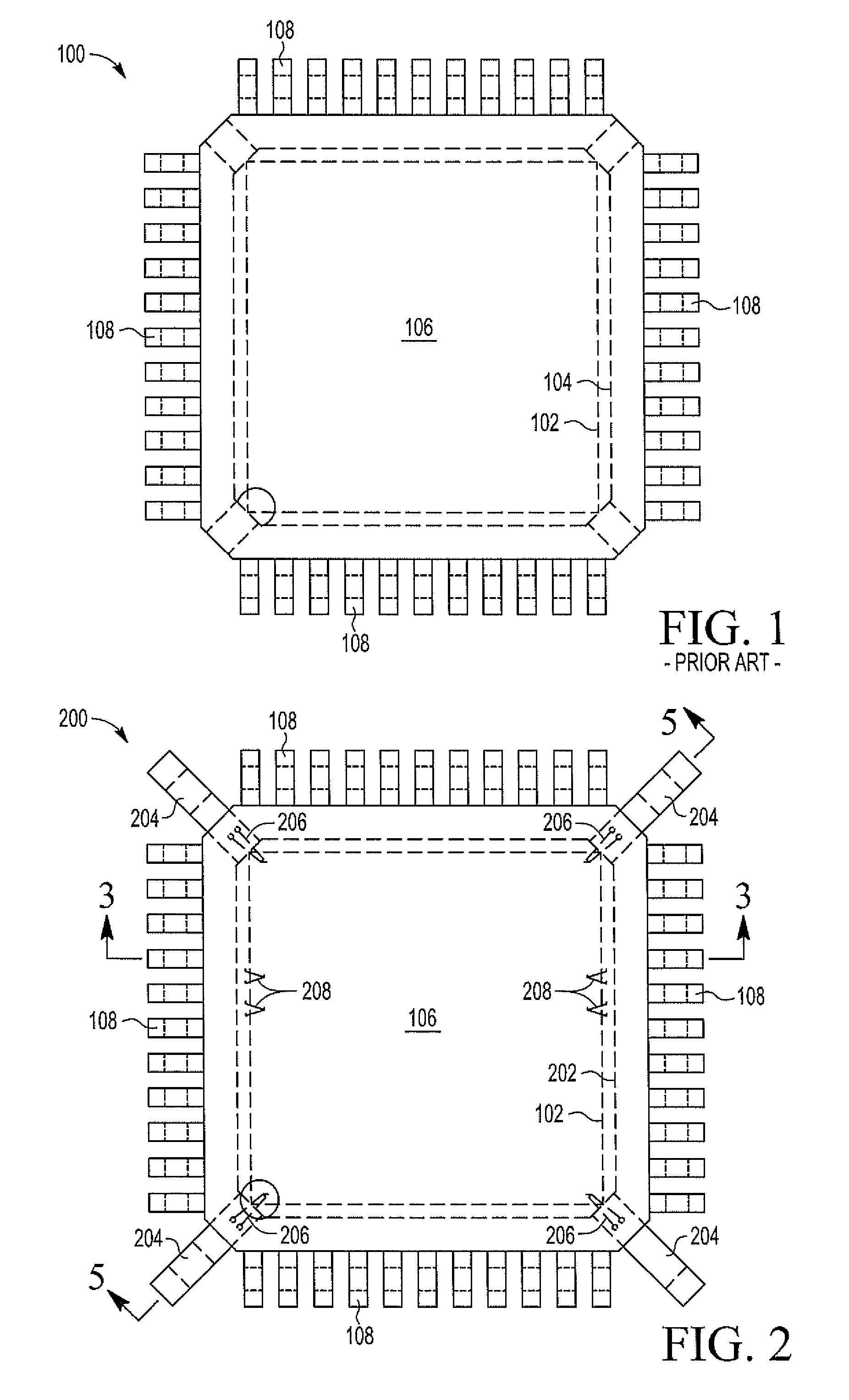

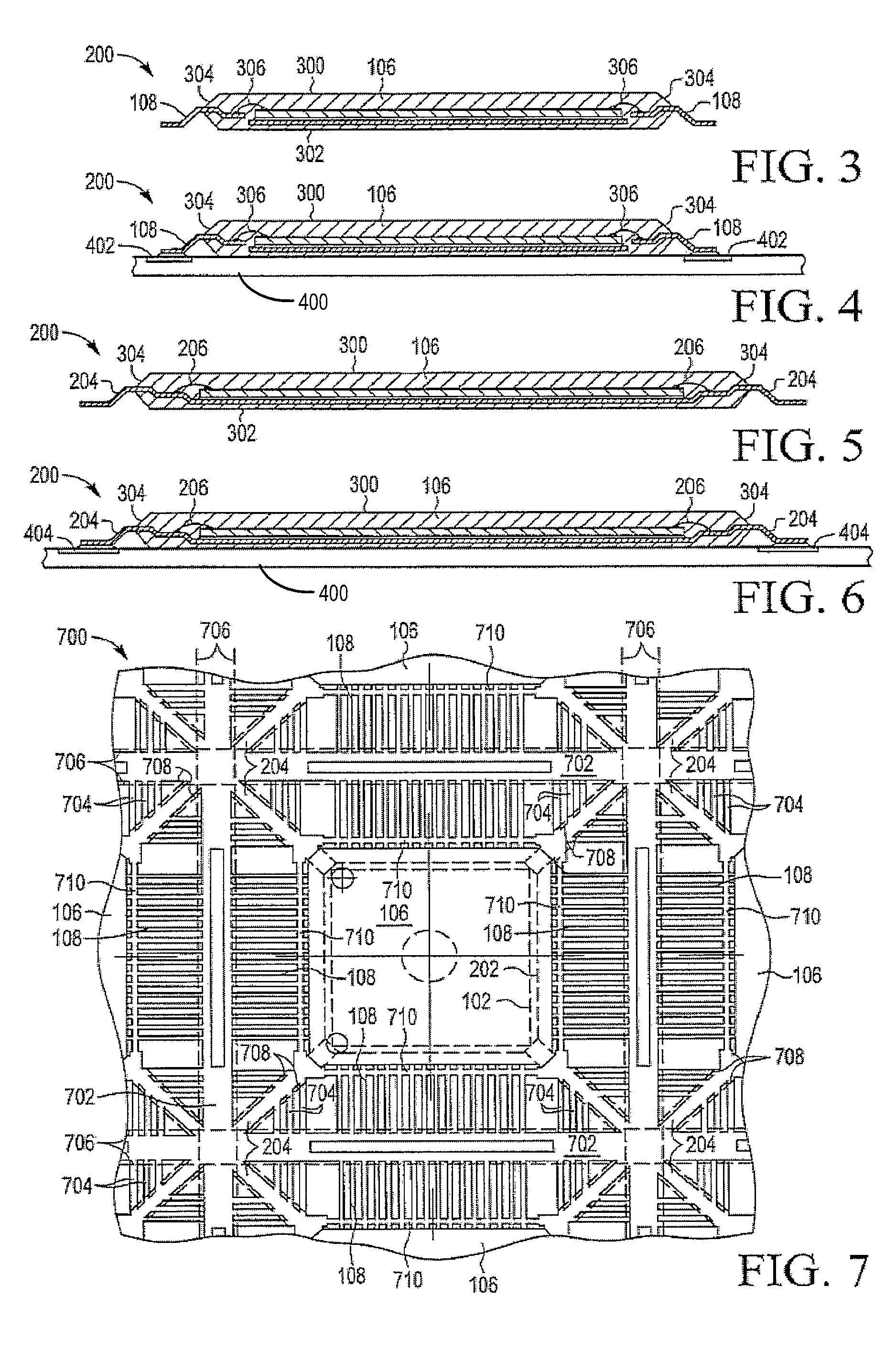

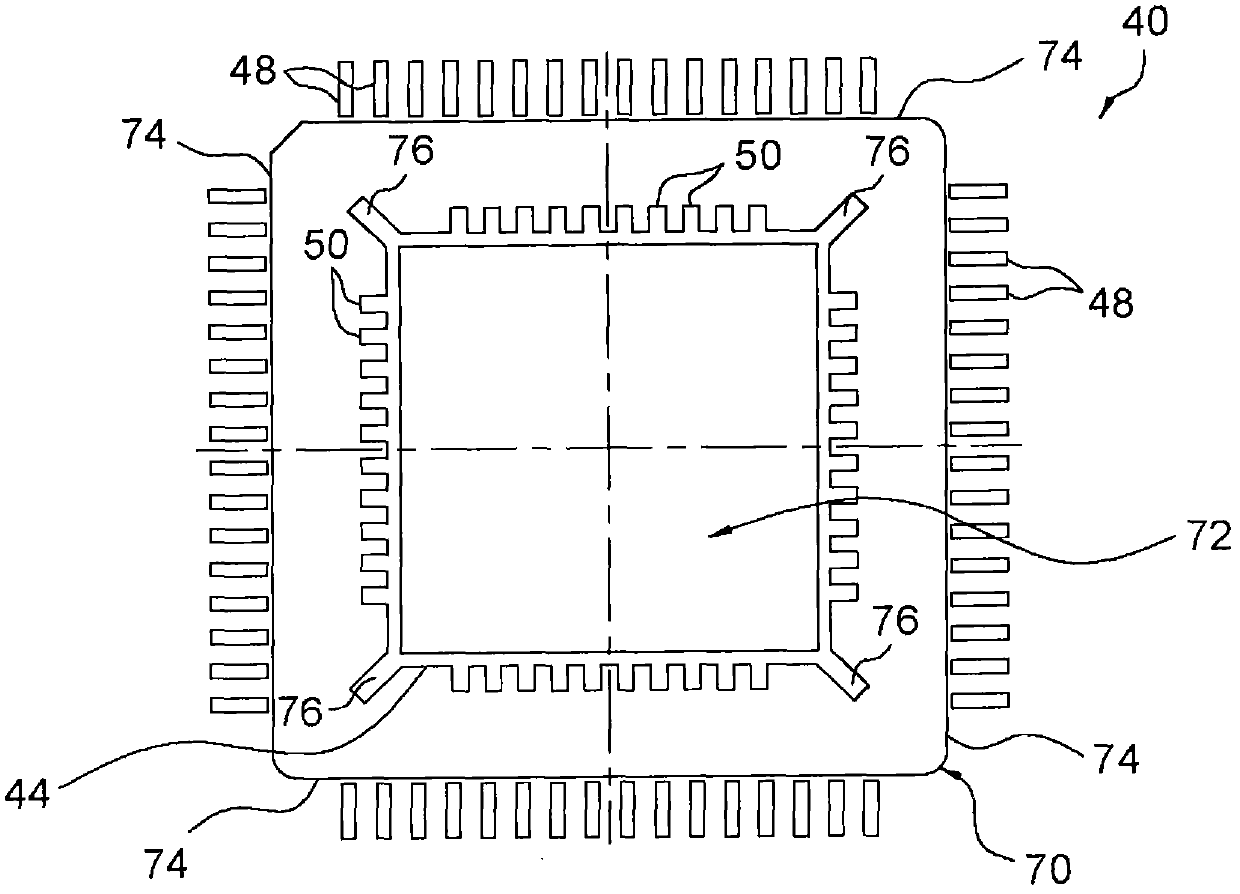

Semiconductor device with corner tie bars

ActiveUS9000570B2Semiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

A Quad Flat Pack (QFP) type semiconductor device includes four corner tie bars that, instead of being trimmed, are used for power and / or ground connections, and alternatively, to control mold flow during the encapsulation step of the assembly process.

Owner:NXP USA INC

Semiconductor device with webbing between leads

ActiveUS9190351B2Semiconductor/solid-state device detailsSolid-state devicesDevice materialMetal particle

A quad flat package integrated circuit (IC) device has alternating inner and outer leads that protrude from a package body. The inner leads are j-shaped leads and the outer leads are gull-wing shaped leads. The package body is formed such that it includes plastic lead webbings between adjacent leads, which help prevent metal particles from getting lodged between the leads and causing electrical shorts. The webbings are made of the same molding compound as the package body and are formed together with the package body.

Owner:NXP USA INC

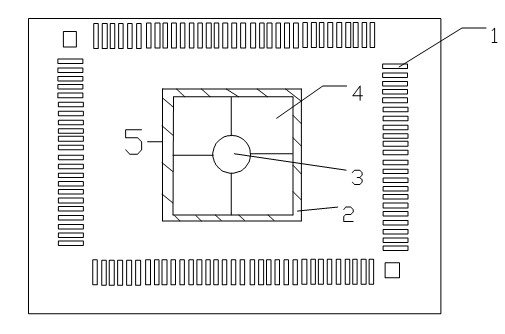

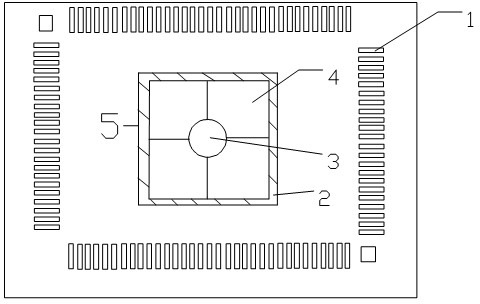

Quad flat package with exposed common electrode bars

ActiveUS20100207260A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringQuad Flat Package

An electronic package is provided. The electronic package comprises a die pad having a die attached thereon. A plurality of leads surrounds the die pad and spaced therefrom to define a ring gap therebetween. At least one first common electrode bar is in the ring gap and substantially coplanar to the die pad, in which at least one of the plurality of leads extends to the first common electrode bar. A molding compound partially encapsulates the die pad and the first common electrode bar, such that the bottom surfaces of the die pad and the first common electrode bar are exposed. A length of the first common electrode bar is substantially equal to a predetermined distance between two pads among a plurality of power or ground pads on a side of the die facing the first common electrode bar. An electronic device with the electronic package is also disclosed.

Owner:MEDIATEK INC

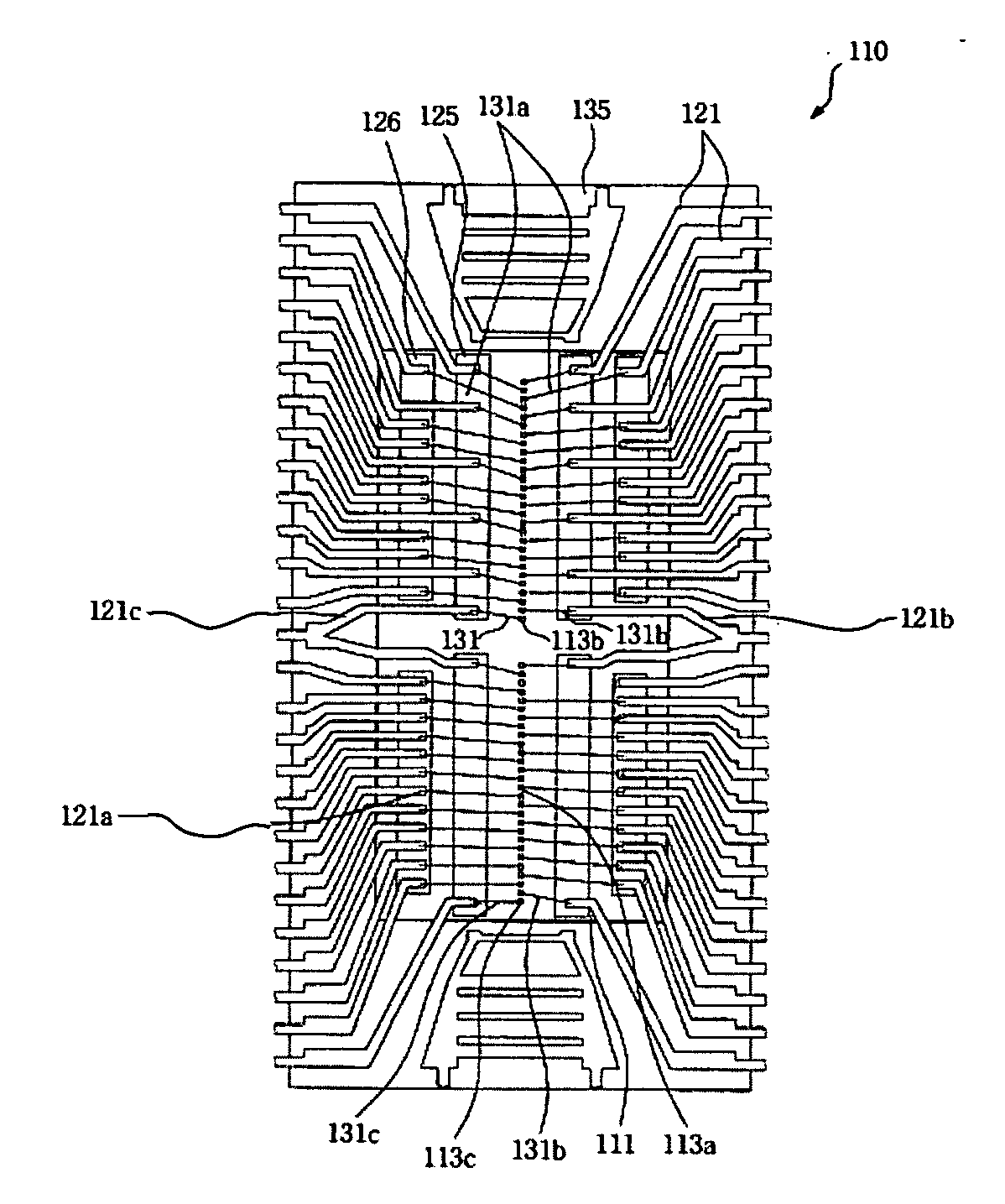

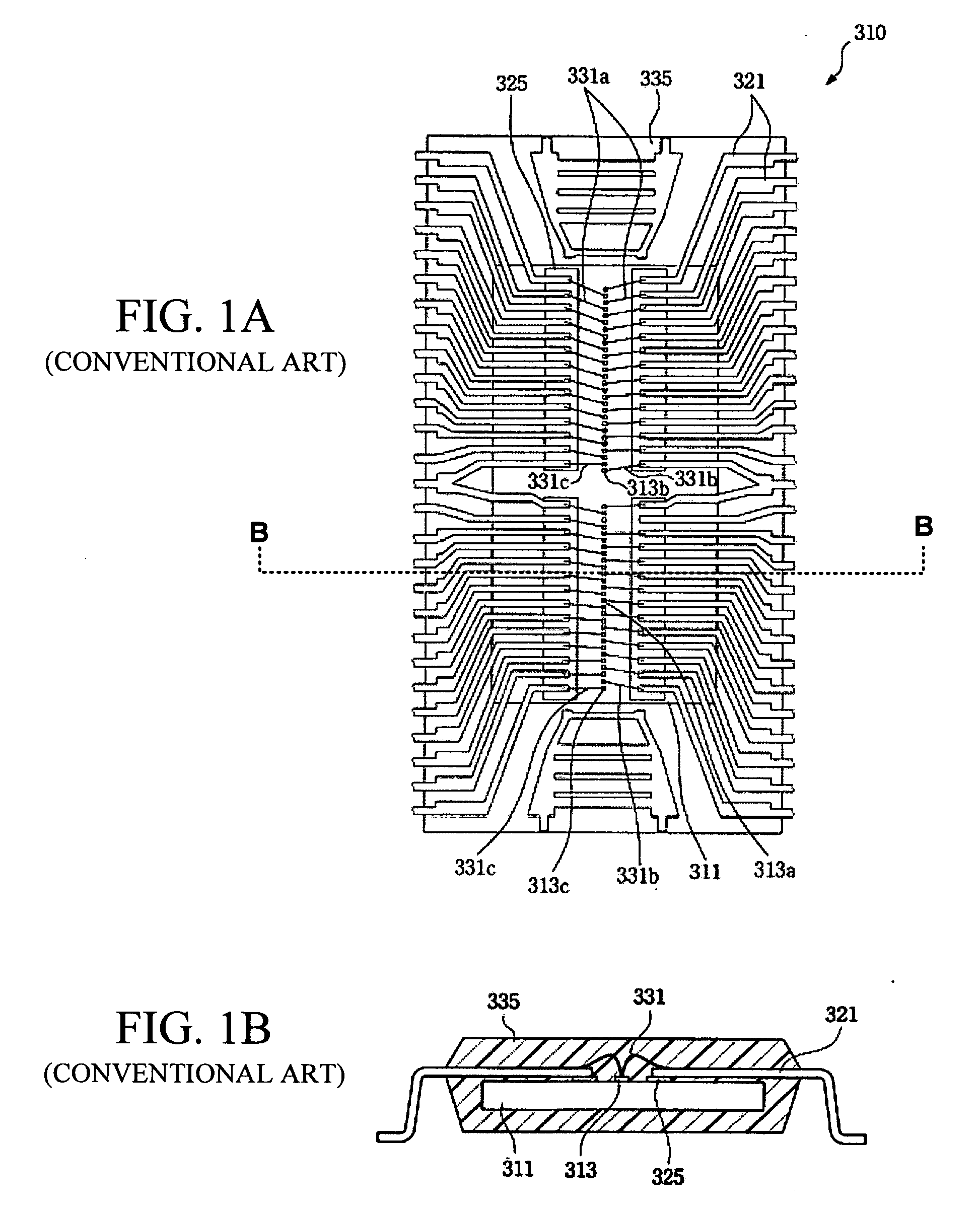

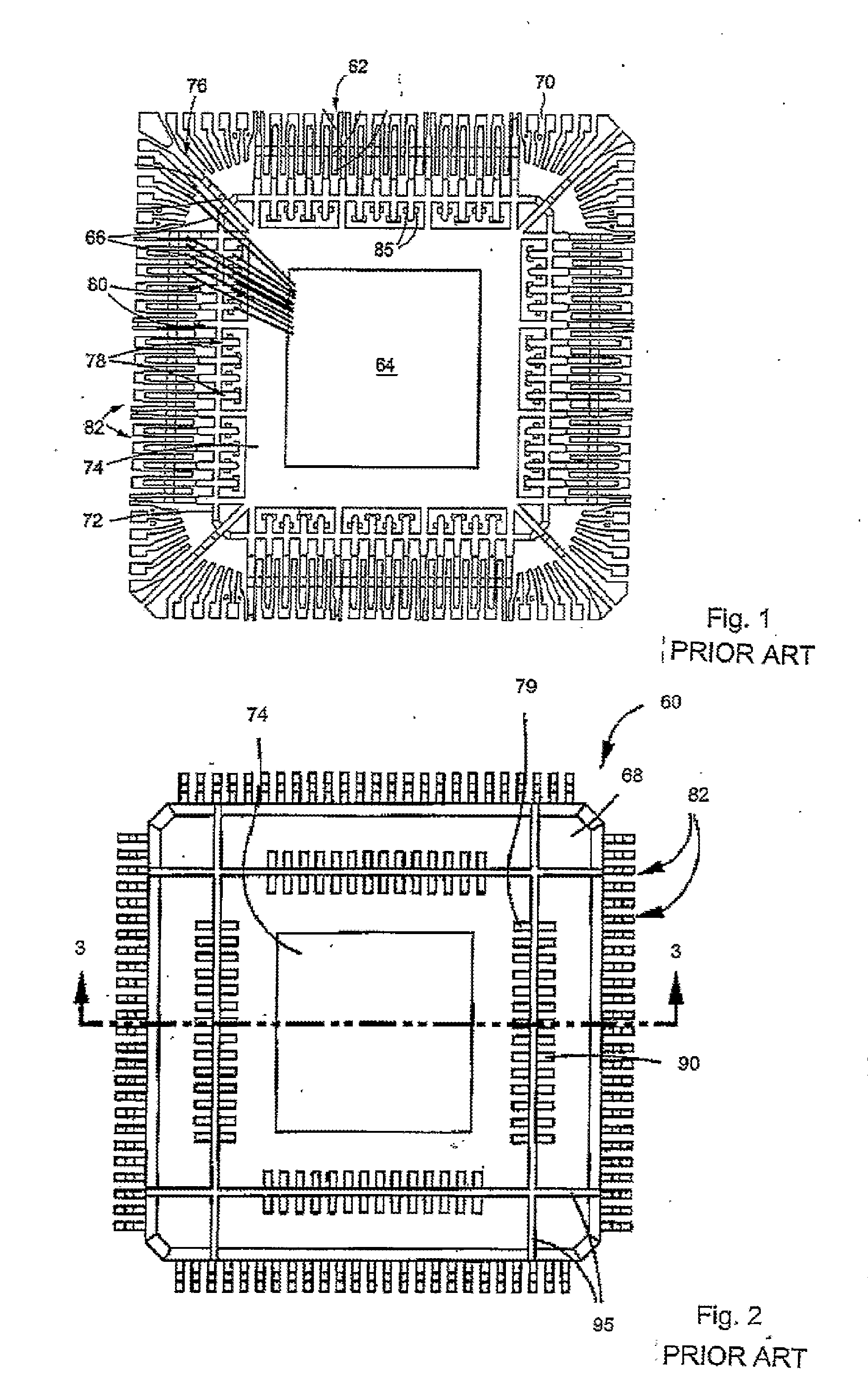

Semiconductor packages with asymmetric connection configurations

InactiveUS20060103002A1Improve performanceImprove stabilitySemiconductor/solid-state device detailsSolid-state devicesCapacitanceLead on chip

Provided are semiconductor devices and methods for configuring lead frames and / or device bonding pads to provide for the independent adjustment of the electrical characteristics of both fixed voltage lines, e.g., Vdd and Vss, and the signal lines, e.g., command, clock, data and address. In particular, the invention provides for adjusting the relative sizing of leads corresponding to fixed voltage lines and signal lines for increasing the relative capacitance on the fixed voltage lines to improve their stability will reducing the noise on the signal lines. The invention may be utilized with a variety of package configurations including lead-on-chip LOC configurations, more conventional quad flat pack QFP configurations in which the leads do not extend past the perimeter of the semiconductor chip or hybrid configurations in which some leads do extend past the perimeter of the semiconductor chip and across the active surface.

Owner:SAMSUNG ELECTRONICS CO LTD

Quad flat package with exposed common electrode bars

InactiveUS20090020859A1Semiconductor/solid-state device detailsSolid-state devicesQuad Flat PackageElectronic packages

An electronic package is provided. The electronic package comprises a die pad having a die attached thereon. A plurality of leads surrounds the die pad and spaced therefrom to define a ring gap therebetween. At least one first common electrode bar is in the ring gap and substantially coplanar to the die pad, in which at least one of the plurality of leads extends to the first common electrode bar. A molding compound partially encapsulates the die pad and the first common electrode bar, such that the bottom surfaces of the die pad and the first common electrode bar are exposed. An electronic device with the electronic package is also disclosed.

Owner:MEDIATEK INC

Load board

InactiveUS20050037638A1Printed circuit assemblingElectrically conductive connectionsEngineeringQuad Flat Package

A load board for packaged IC testing. The load board with predetermined testing circuit thereon has bonding pad areas on its surface. A plurality of bonding pads is formed on the bonding pad areas, each of which is disposed corresponding to a lead of a packaged IC for testing connection, such as a quad flat packaged IC (QFP), a dual inline packaged IC (DIP) or a small outline packaged IC (SOP). The bonding pads on the load board connect the leads of the testing IC directly during IC testing, thus the conventional test socket between a conventional load board and a packaged IC is omitted.

Owner:SILICON INTEGRATED SYSTEMS

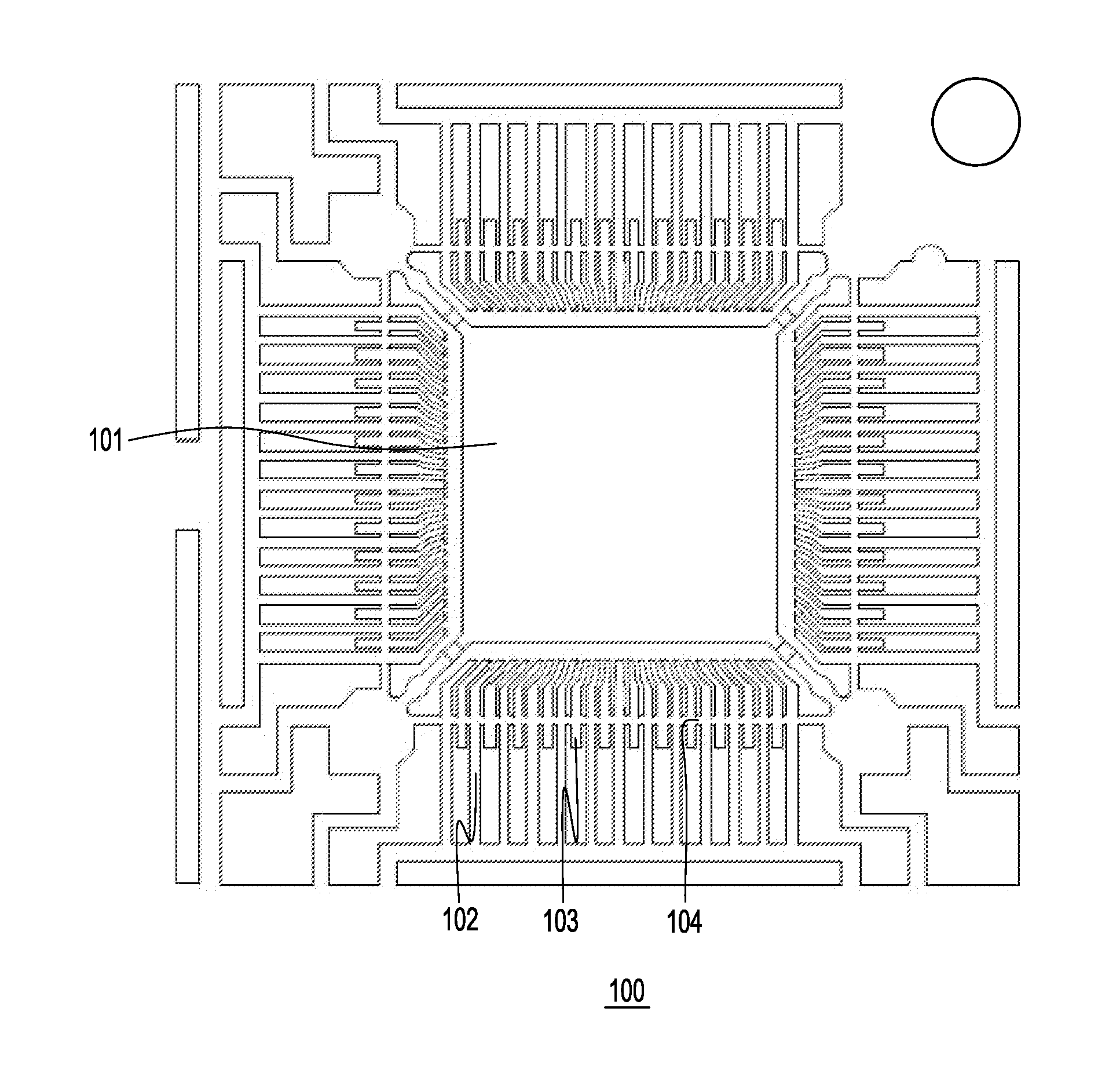

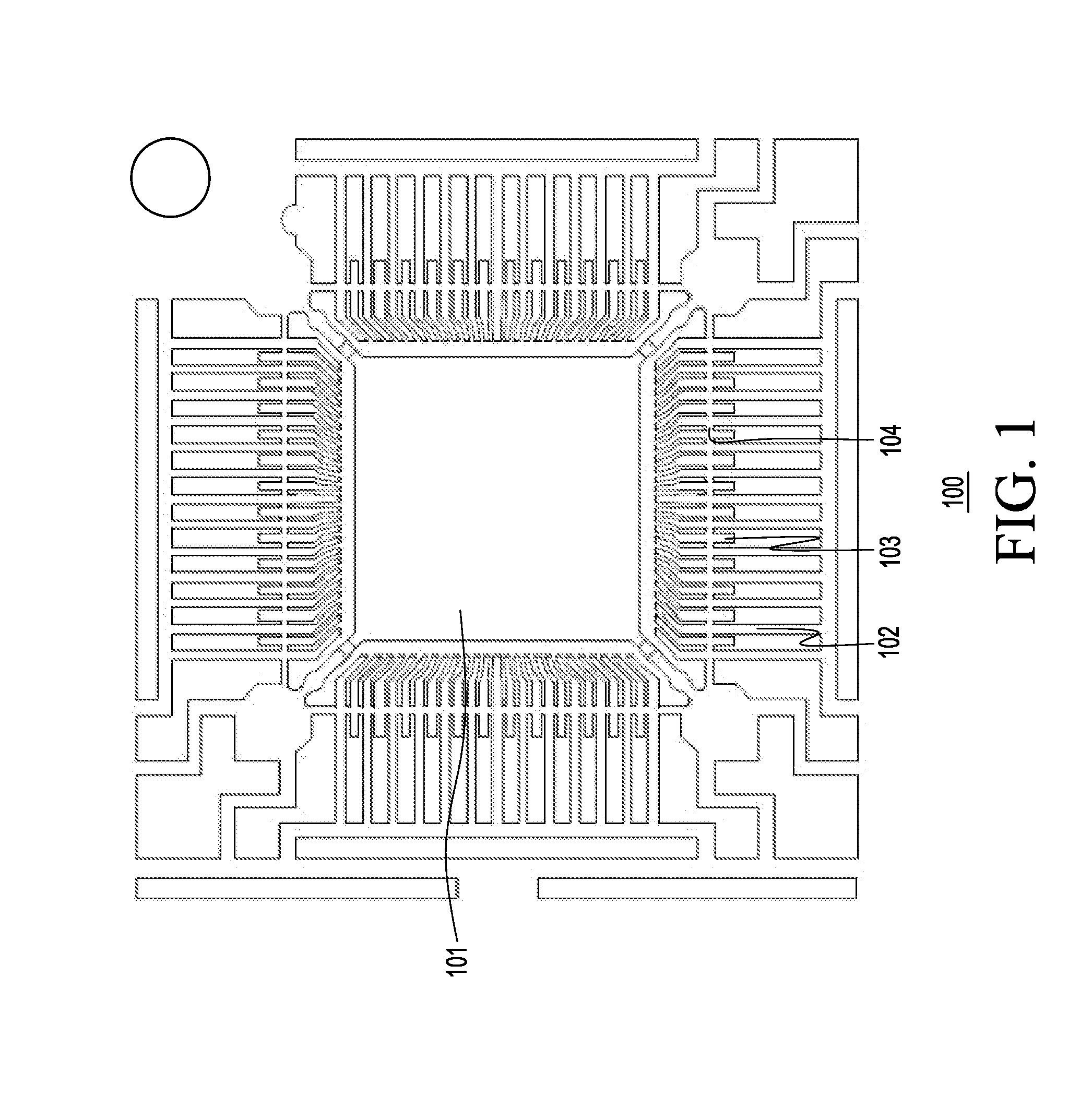

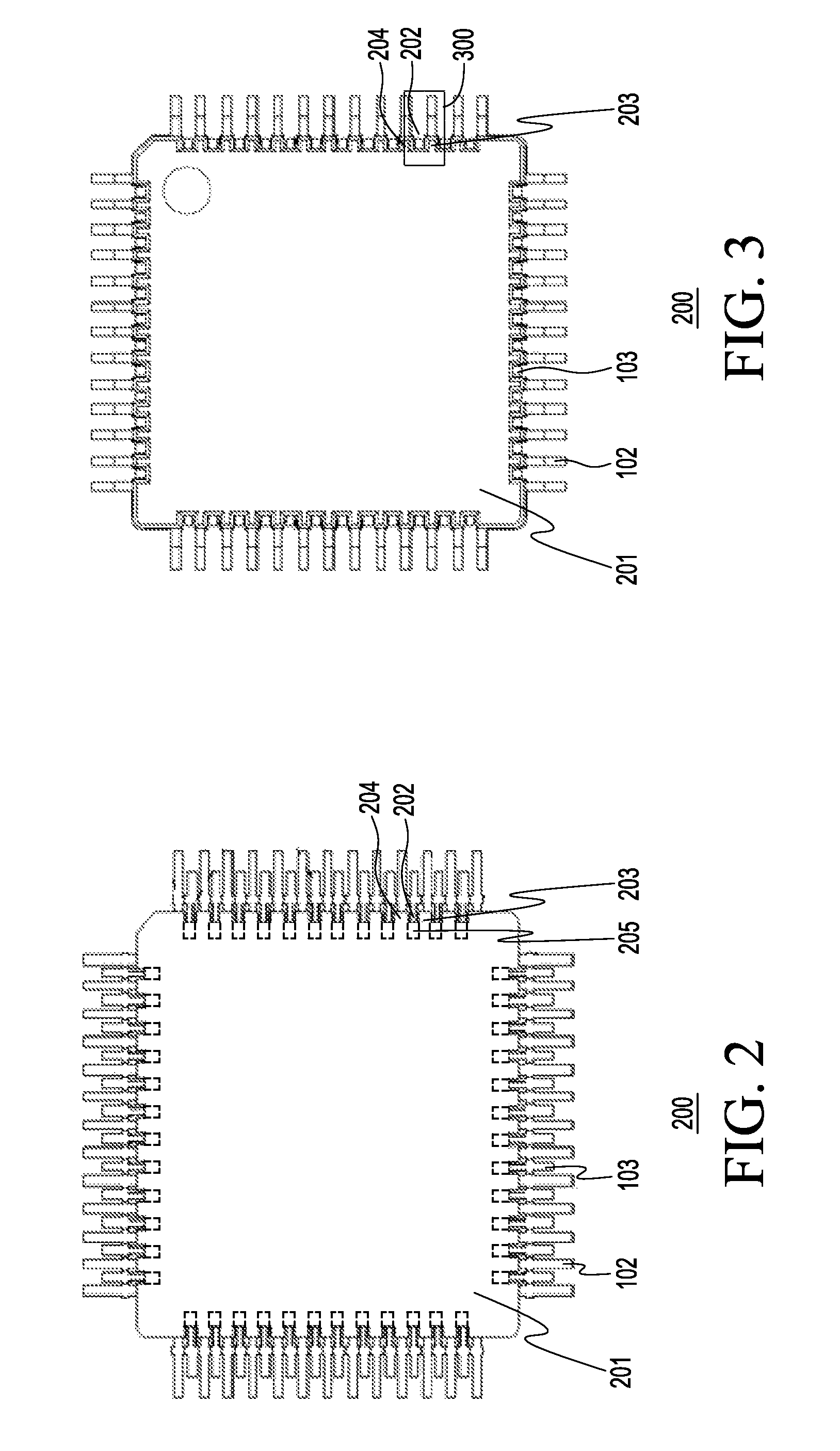

Quad flat semiconductor device with additional contacts

ActiveUS20150014833A1Semiconductor/solid-state device detailsSolid-state devicesQuad Flat PackageLead frame

A Quad Flat Package (QFP) semiconductor device has a multi-stepped lead frame for forming rows of external contacts. A semiconductor die is attached to a die pad of the lead frame and electrically connected to lead with bond wires. The die and bond wires are encapsulated with a mold compound and then multiple cuts are made to the lead frame to form the rows of external contacts.

Owner:NXP USA INC

Semiconductor device and packaging method thereof

InactiveCN102891090ASemiconductor/solid-state device detailsSolid-state devicesEngineeringQuad Flat Package

The invention provides a semiconductor device and a packaging method thereof. A quad flat packaging (QFP) device comprises a semiconductor tube core which is attached to a mark of a lead frame. A bonding pad of the tube core is electrically connected with internal and external leads of the lead frame by bonding wires. The tube core, a tube core mark, the bonding wires and the partial internal and external leads are covered by molding compounds, so that a packaging main body is defined. The external lead is similar to a gull wing-shaped lead of the traditional QFP device; and the internal lead forms a contact point on the bottom surface of the packaging main body. Cutting is performed on the internal side of the internal lead so as to separate the internal lead and the tube core pad.

Owner:FREESCALE SEMICON INC

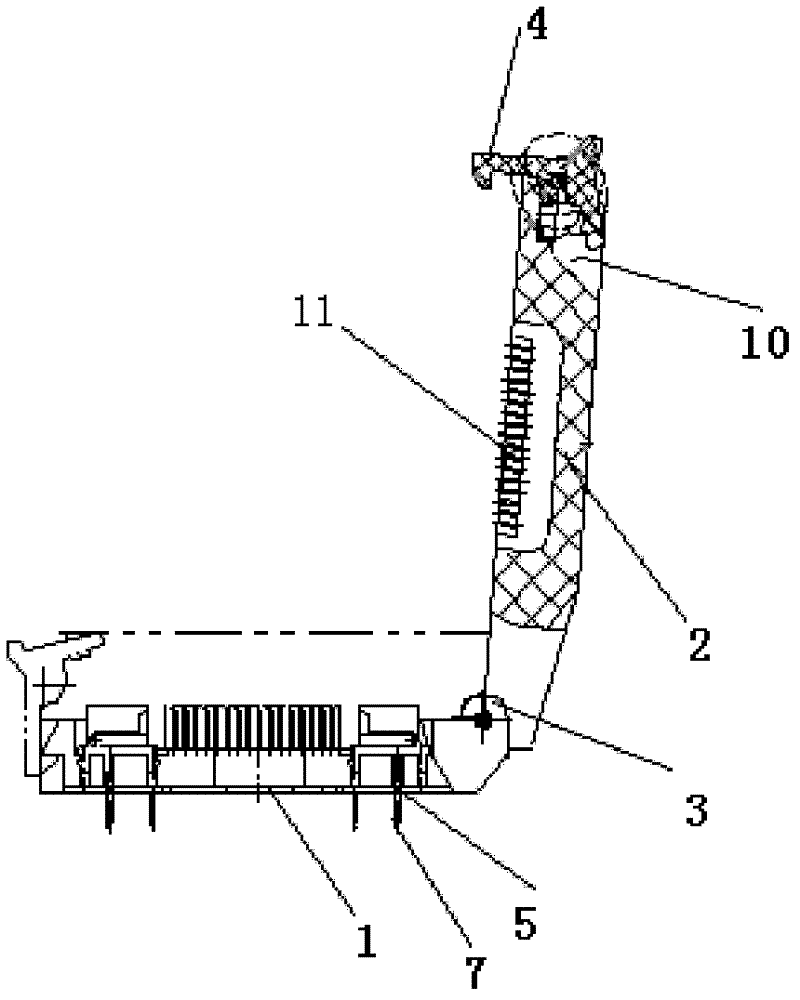

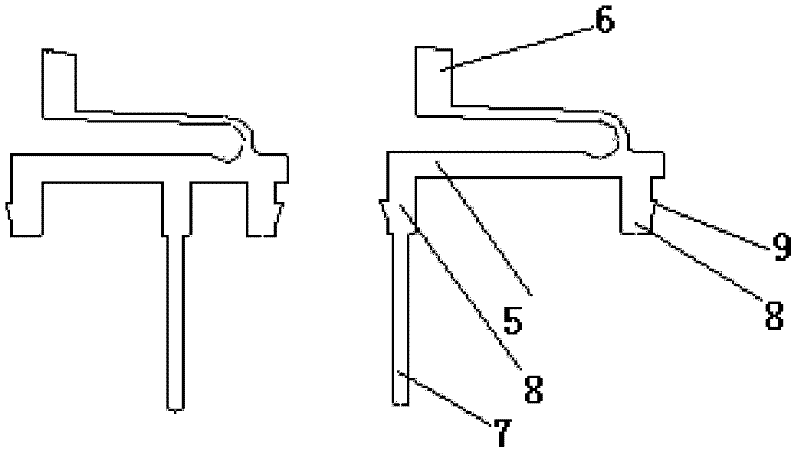

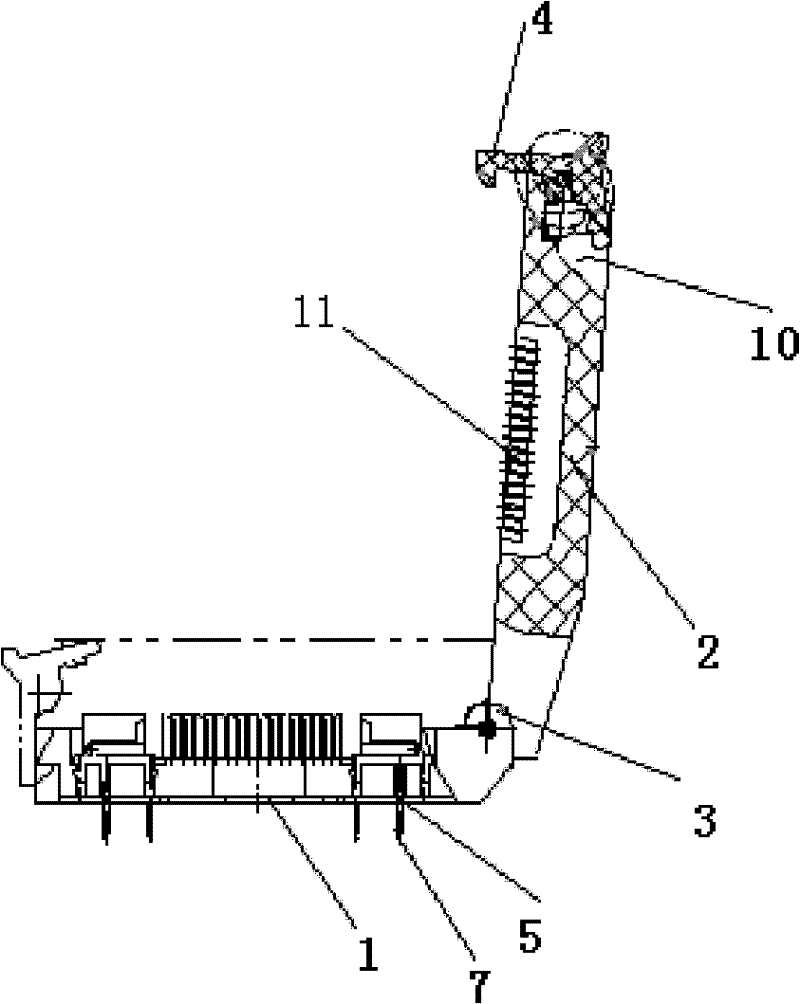

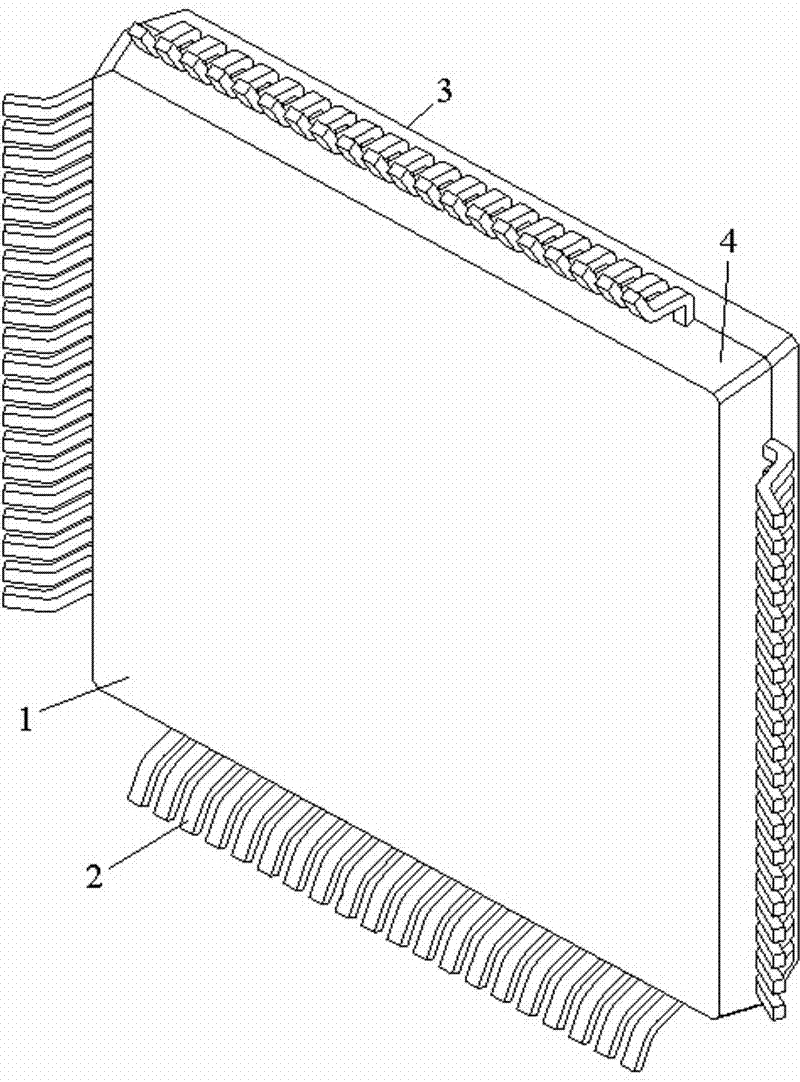

Ceramic quad flat package (CQFP) series aging test socket with pitch being no less than 0.8mm

InactiveCN102646889AEasy to placePrecise positioningElectrical testingCoupling contact membersEngineeringQuad Flat Package

The invention discloses a ceramic quad flat package (CQFP) series aging test socket with pitch being no less than 0.8mm. The CQFP series aging test socket comprises an installation plate and a cover plate which are movably hinged through a hinge shaft. The CQFP series aging test socket is characterized in that a torsion spring is sheathed on the hinge shaft, a clamping block which is in clamping fit with the installation plate is arranged at the end part of the cover plate, contact pieces with quantity being equal to the quantity of leads of a package are installed on the installation plate, the upper end of each contact piece is a contact end, the lower end of each contact piece is a welding end, the two sides of the middle part of each contact piece are respectively provided with a press fitting part and each press fitting part is provided with a barb. The back surface of the cover plate of the CQFP series aging test socket is provided with teeth, wherein the quantity of the teeth is equal to the quantity of the contact pieces and the width of the teeth is less than the slot width of the installation plate and is more than the width of the leads of the package. The teeth are used for providing enough pressure to the leads of the package through the contact pieces. The upper surface and the lower surface of the cover plate are provided with a plurality of process slots. The CQFP series aging test socket can be used for the aging test of the package both before forming and after forming, and is easy to machine and assemble. The structure of the CQFP series aging test socket is a novel structure which is designed according to the structural characteristics of the package, the package is convenient to place and position and the package can be well protected during testing.

Owner:中国电子科技集团公司第四十研究所

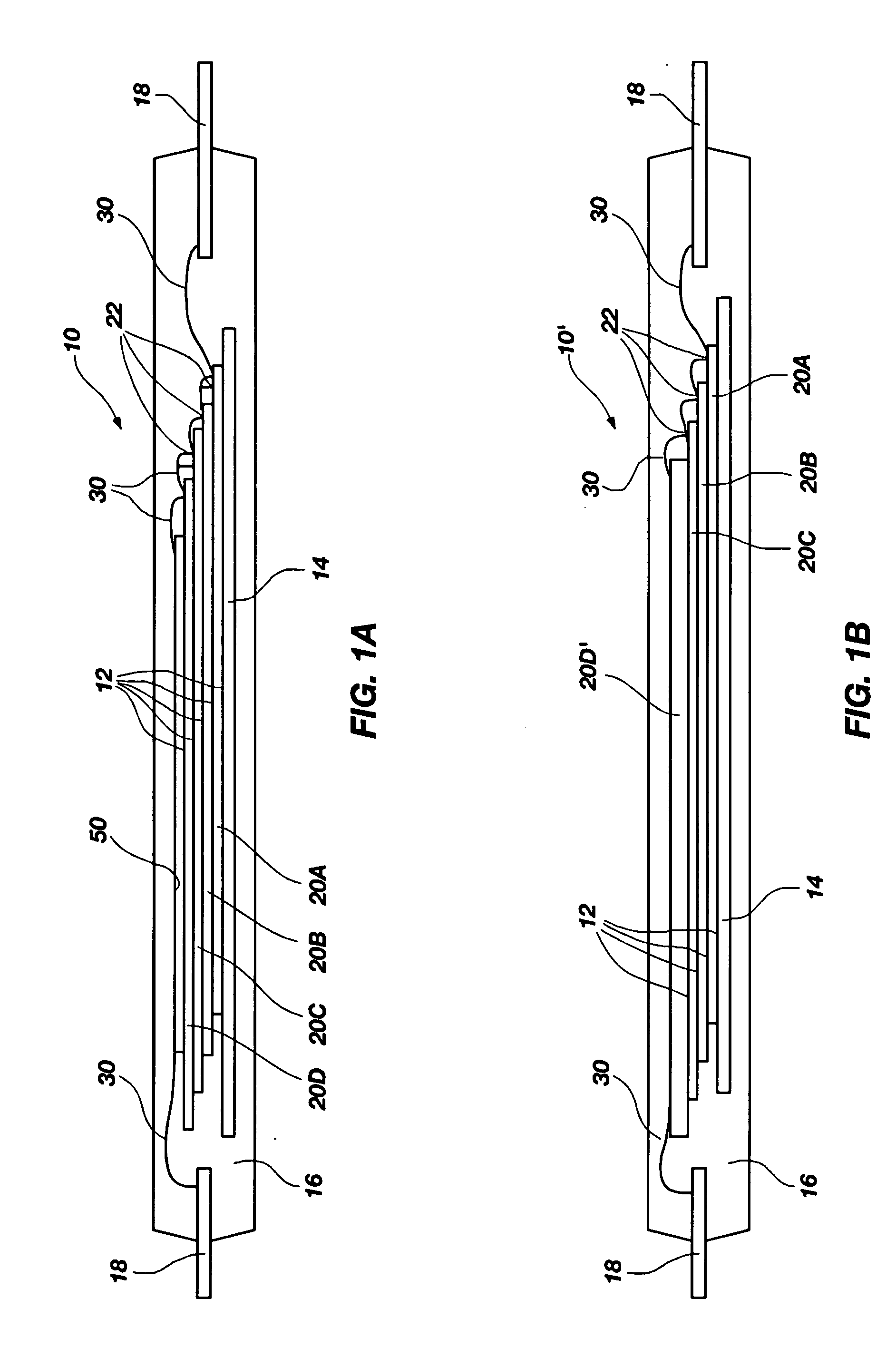

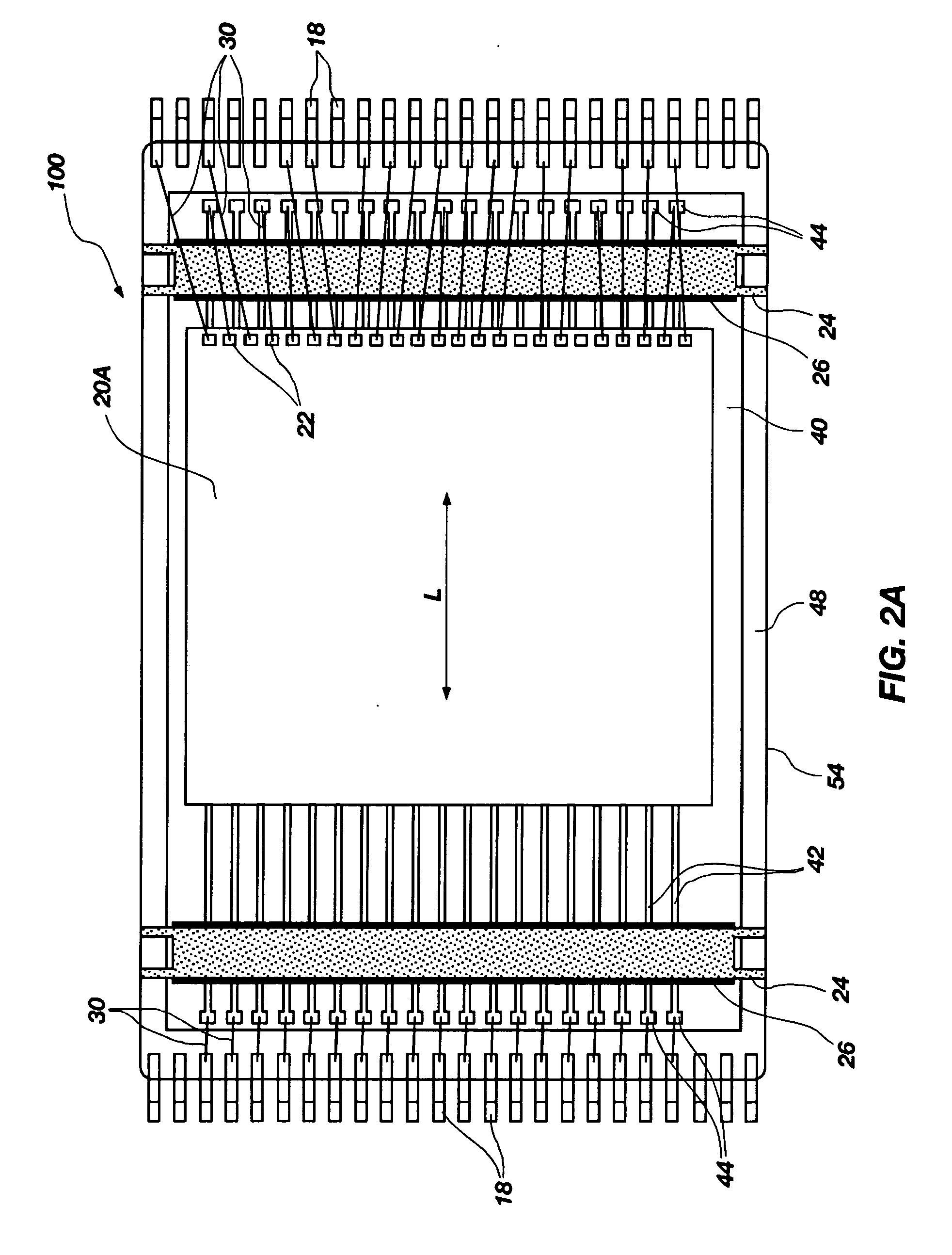

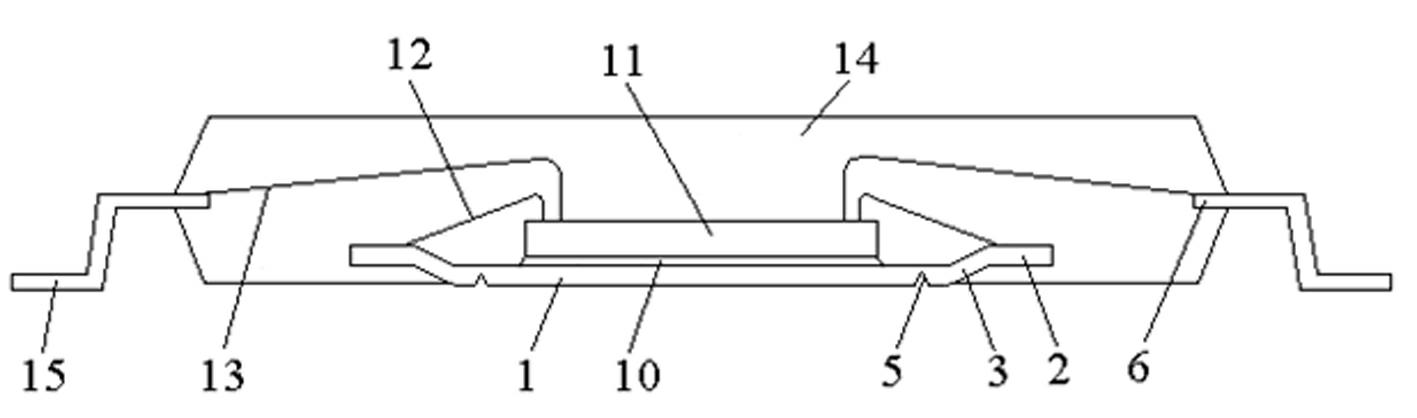

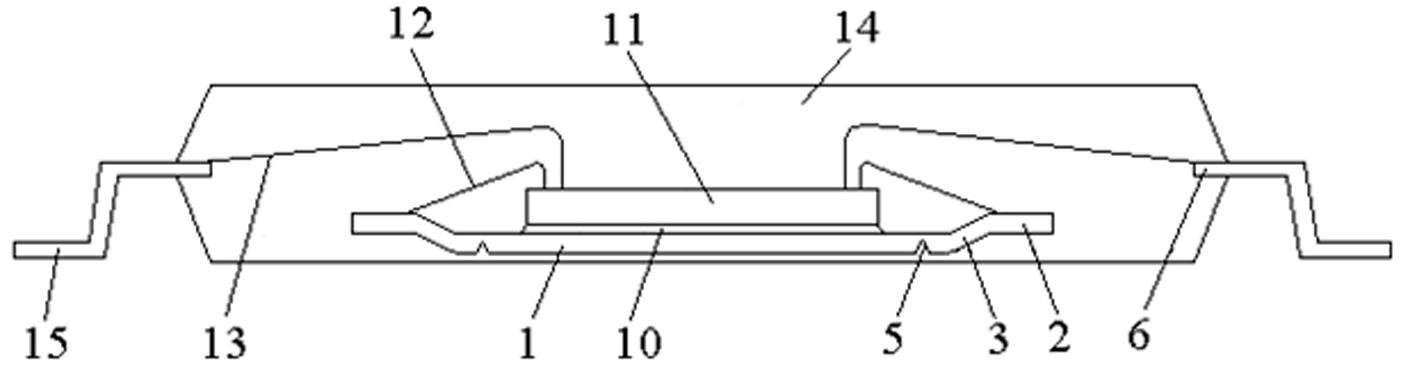

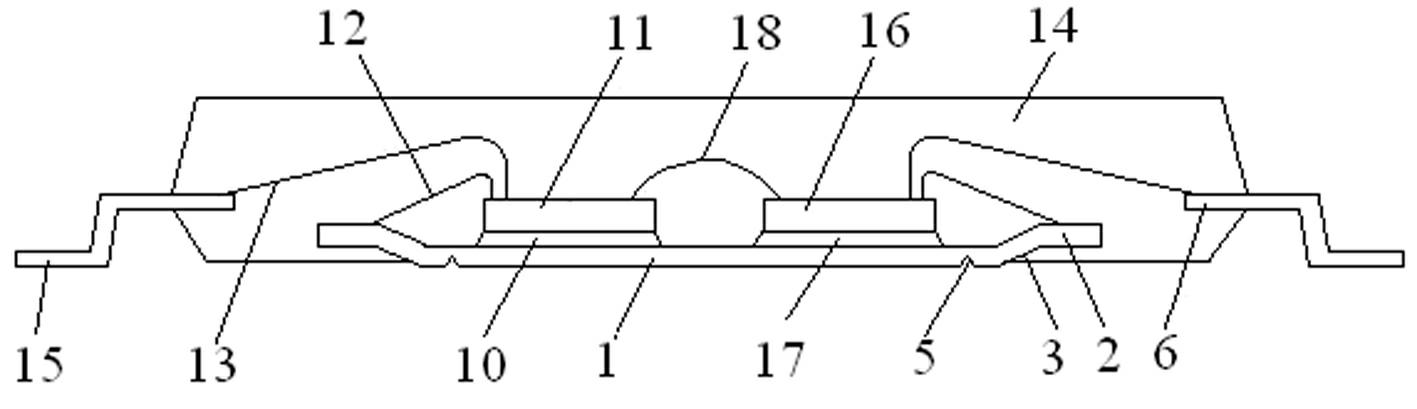

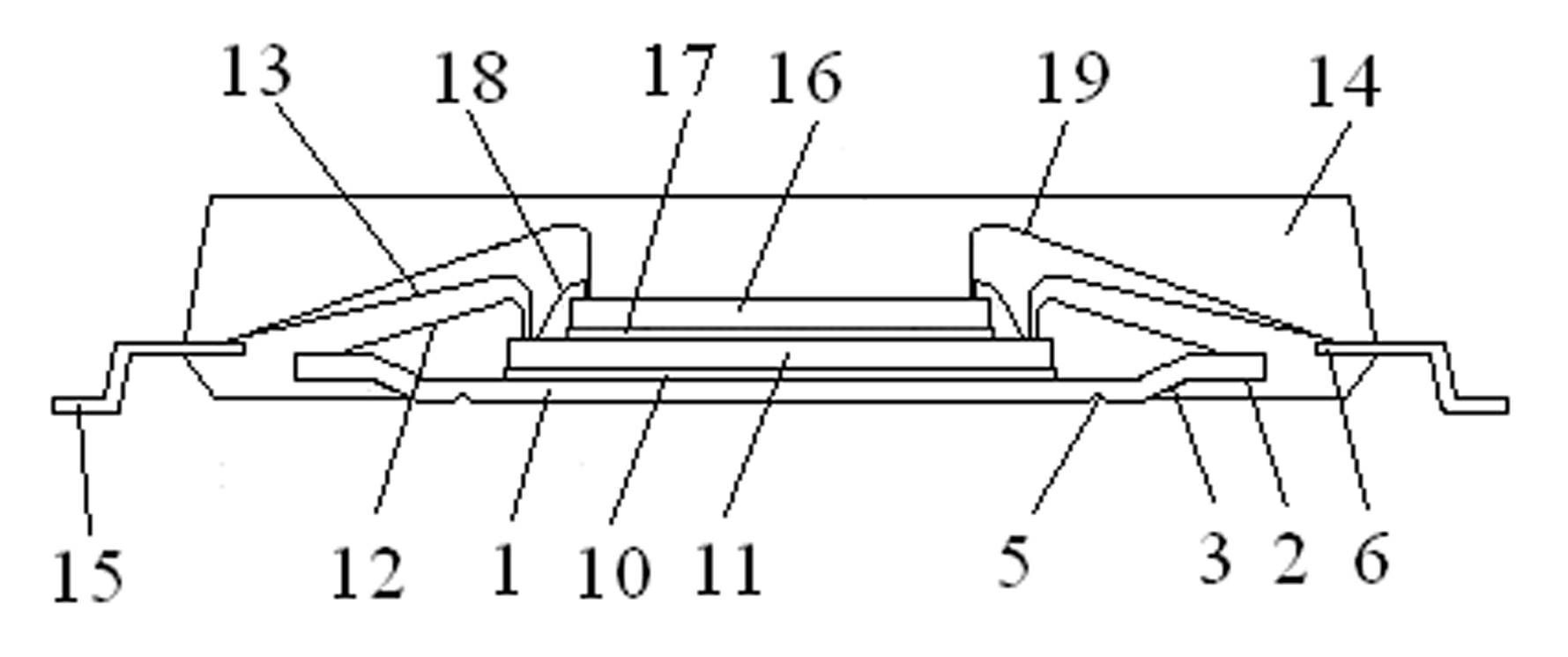

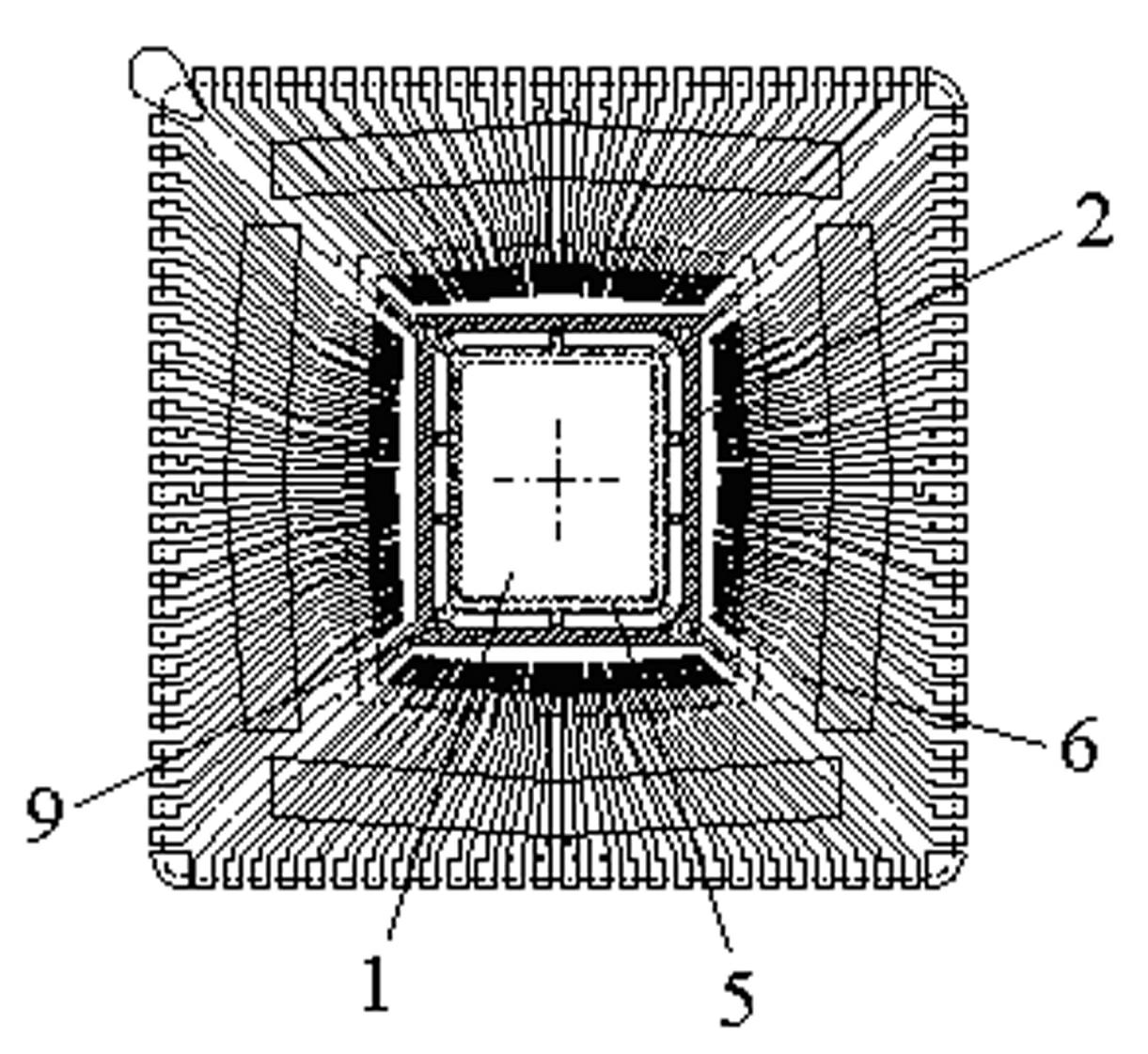

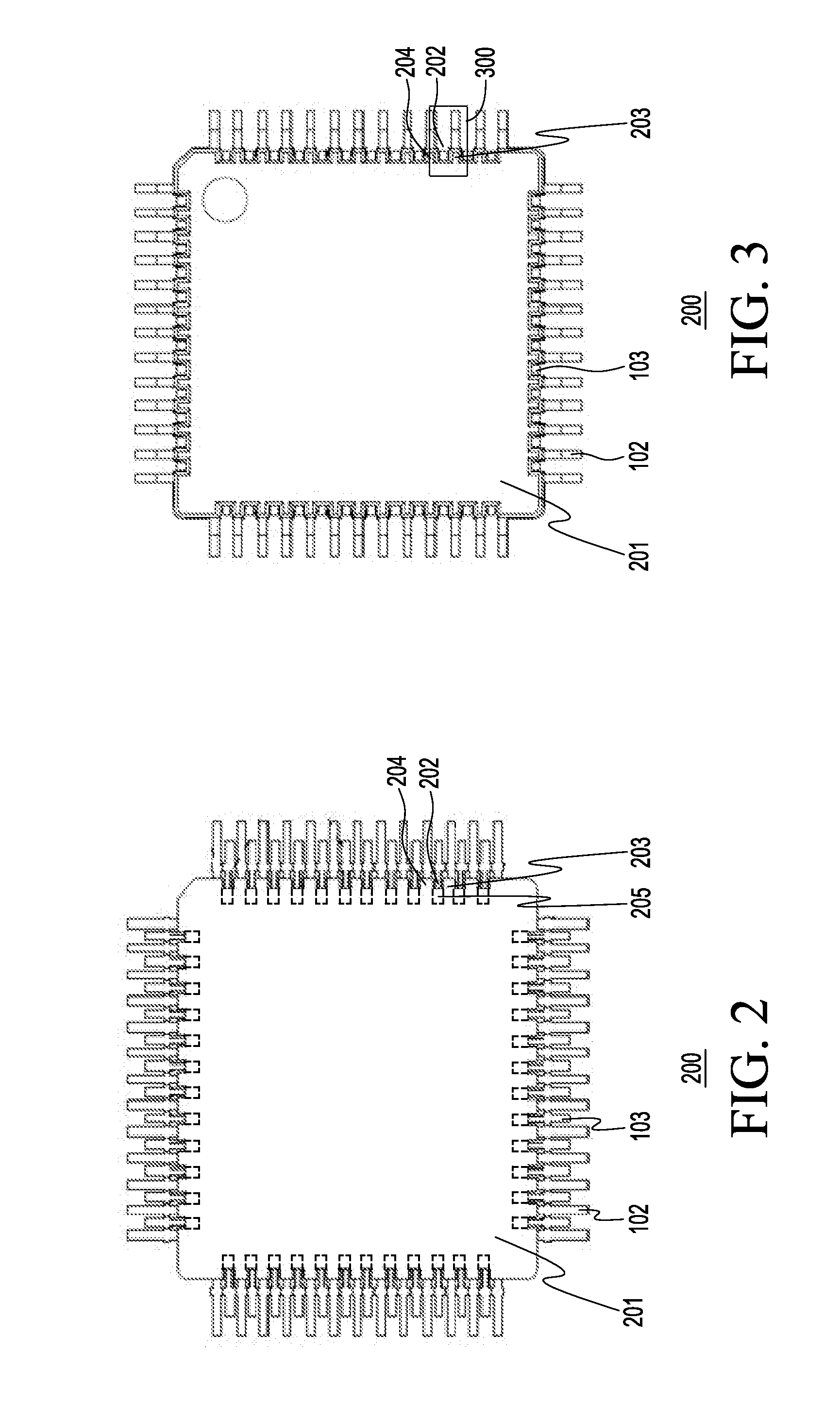

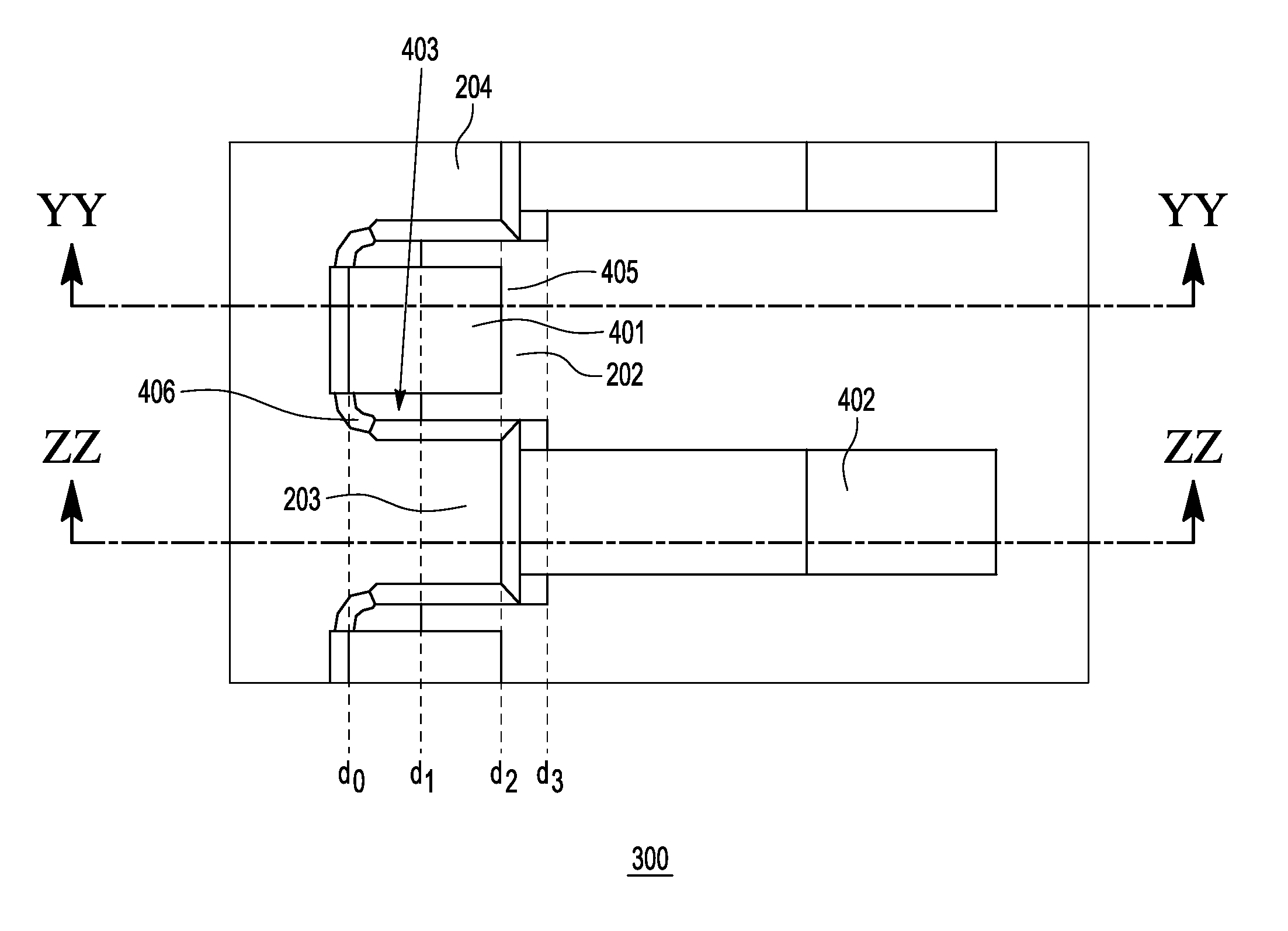

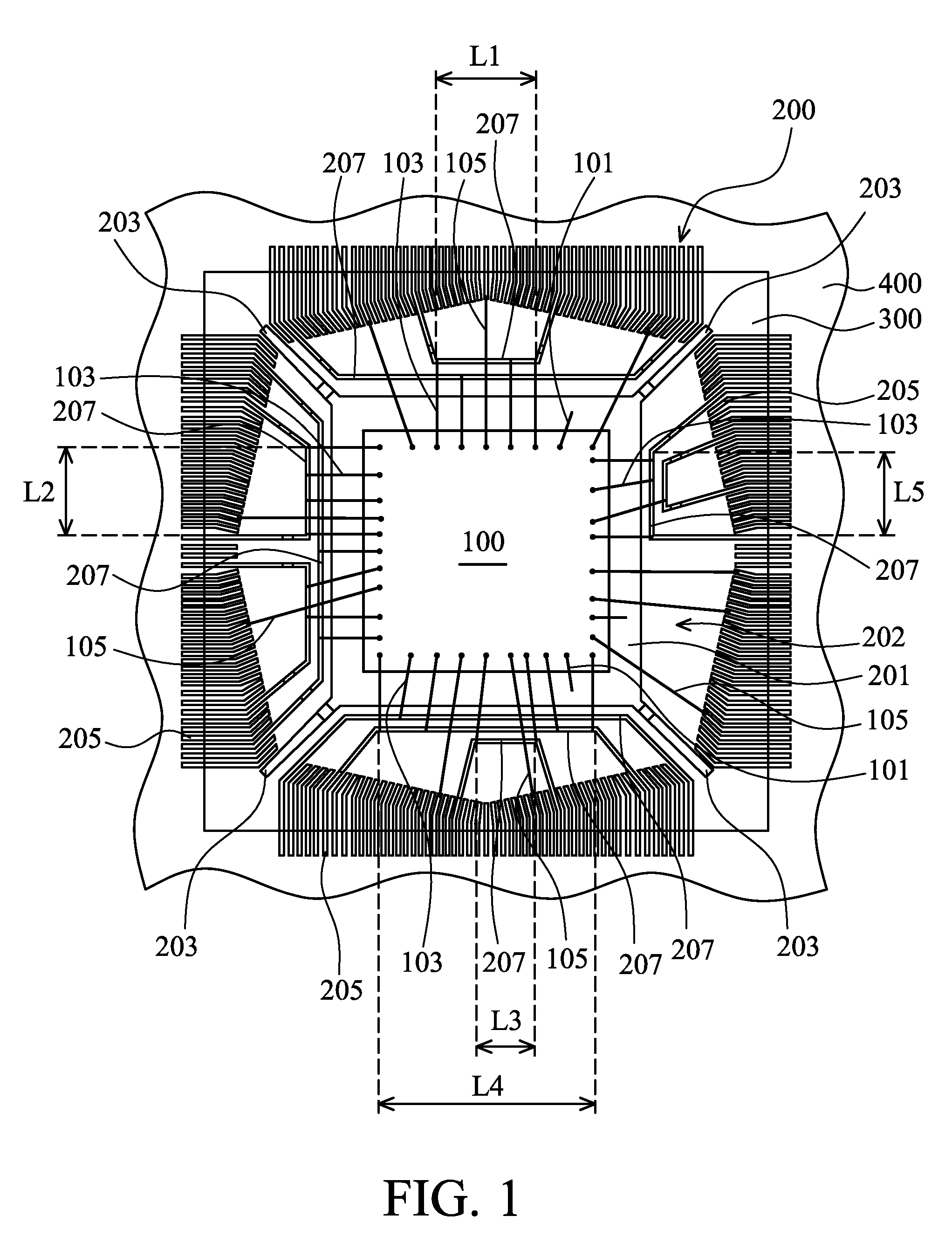

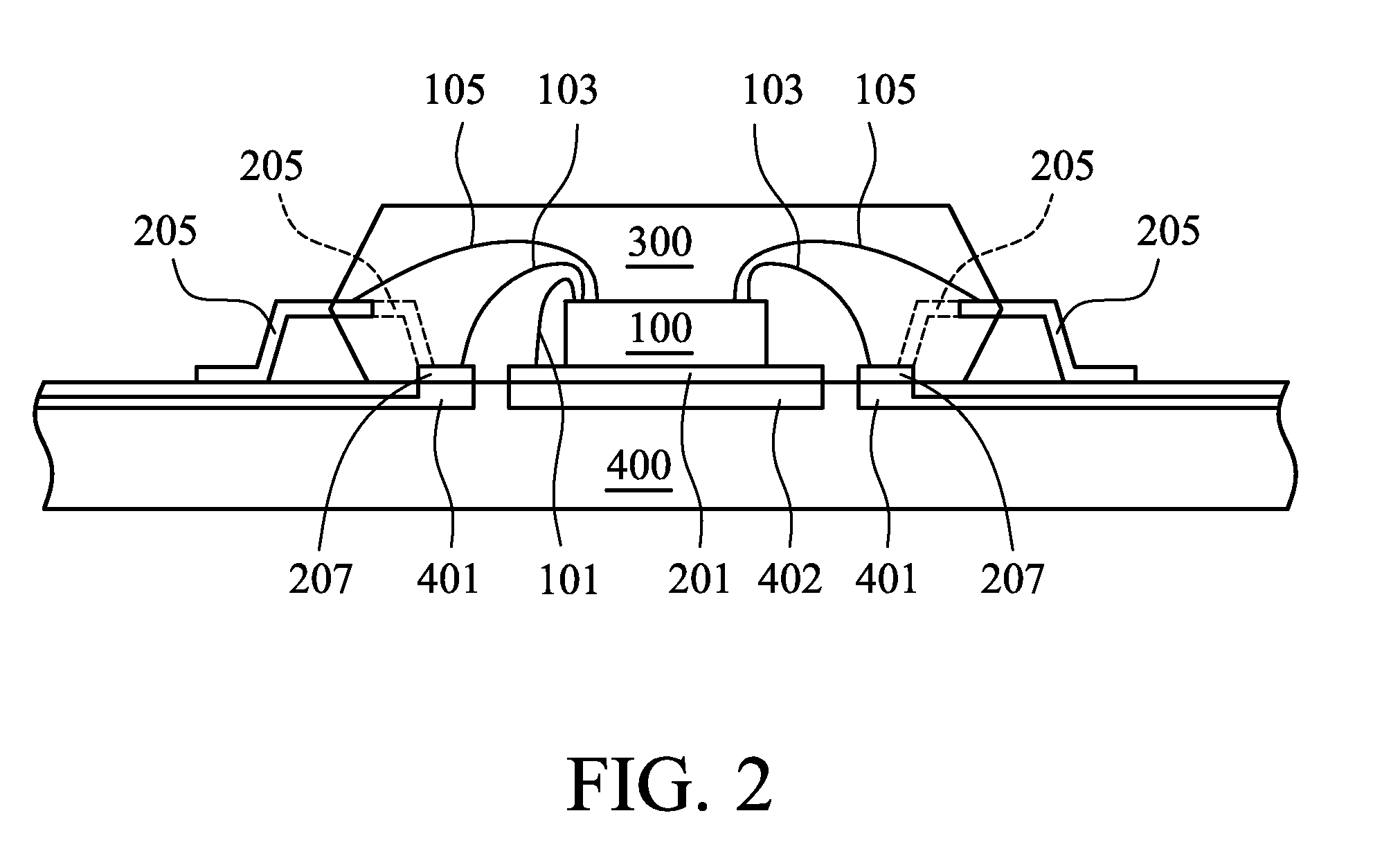

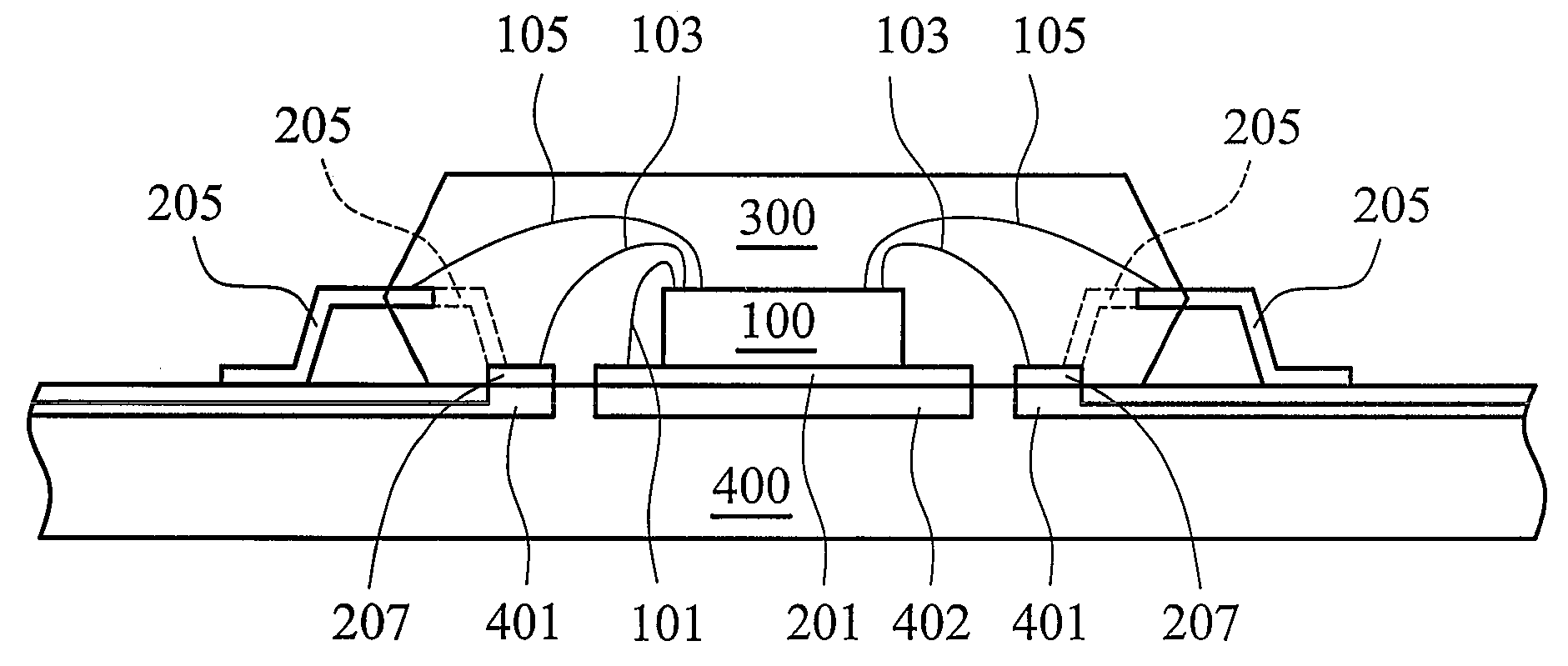

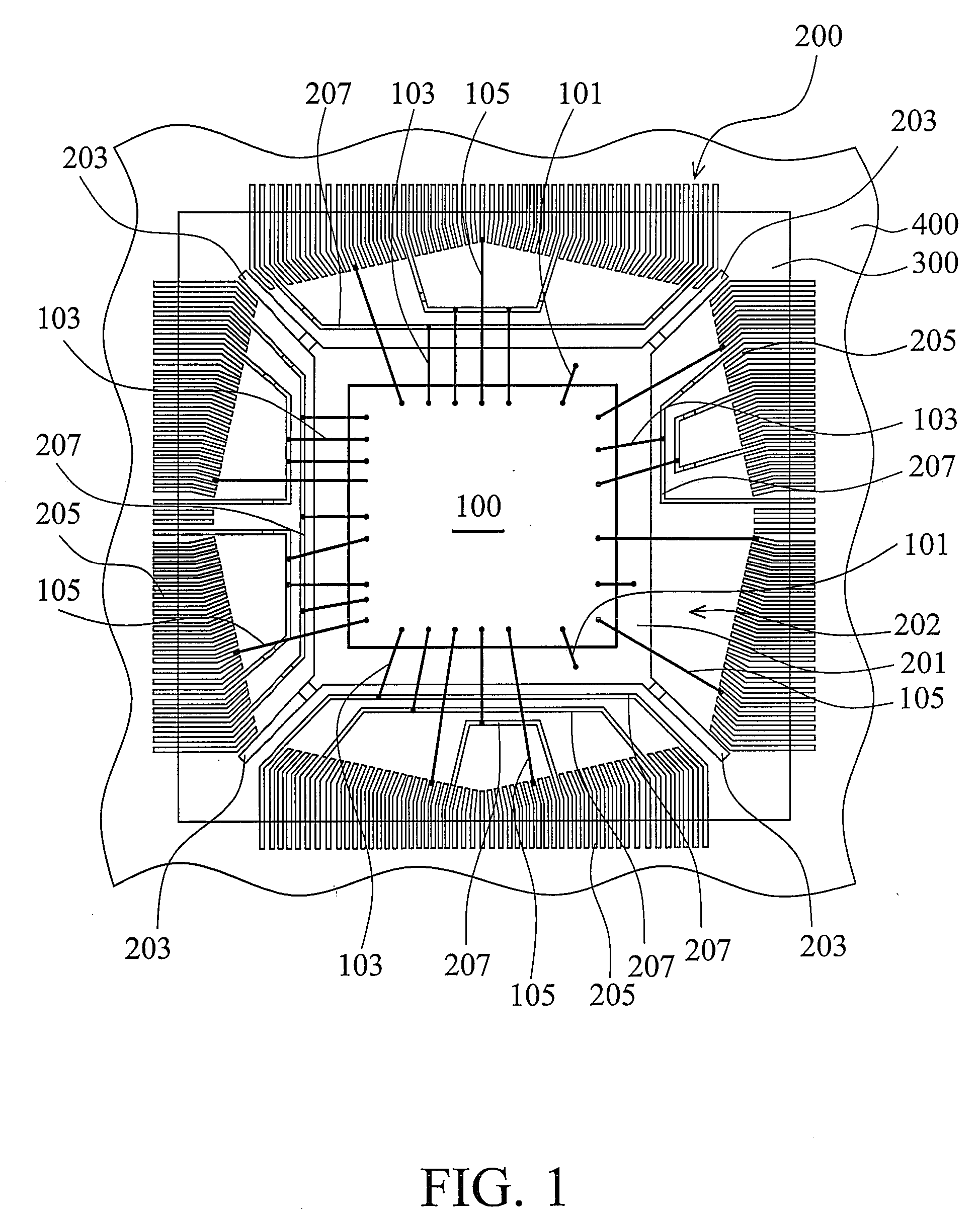

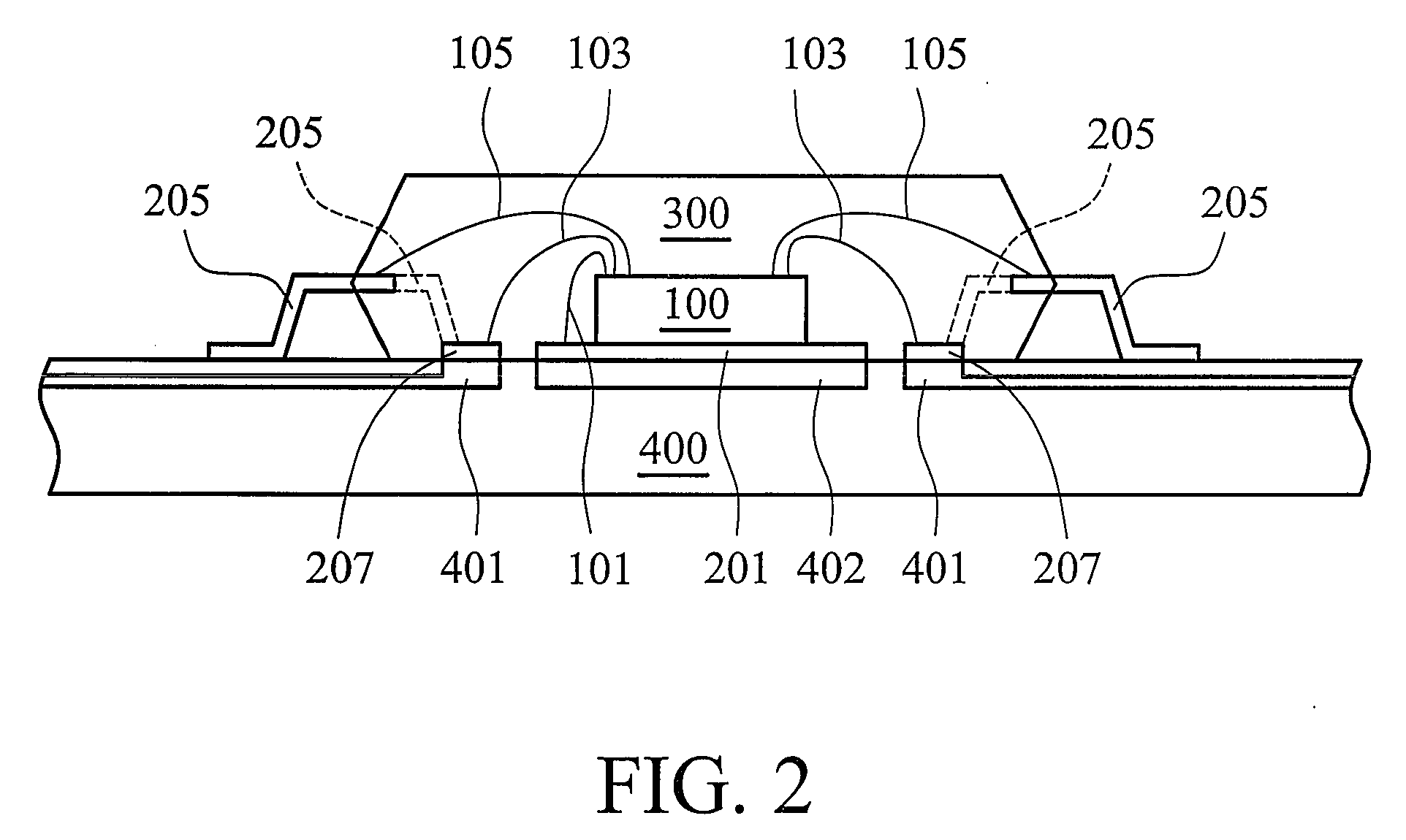

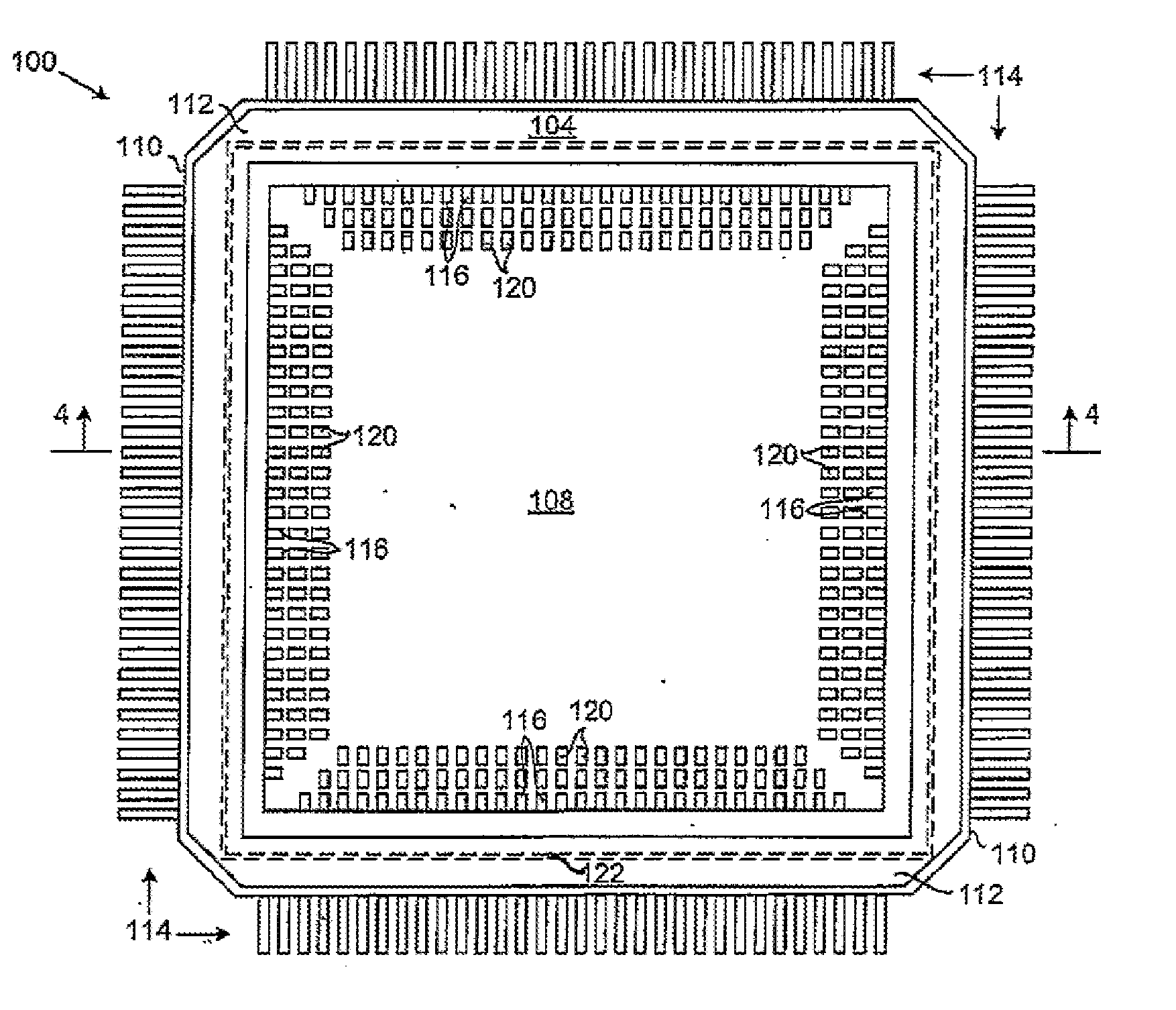

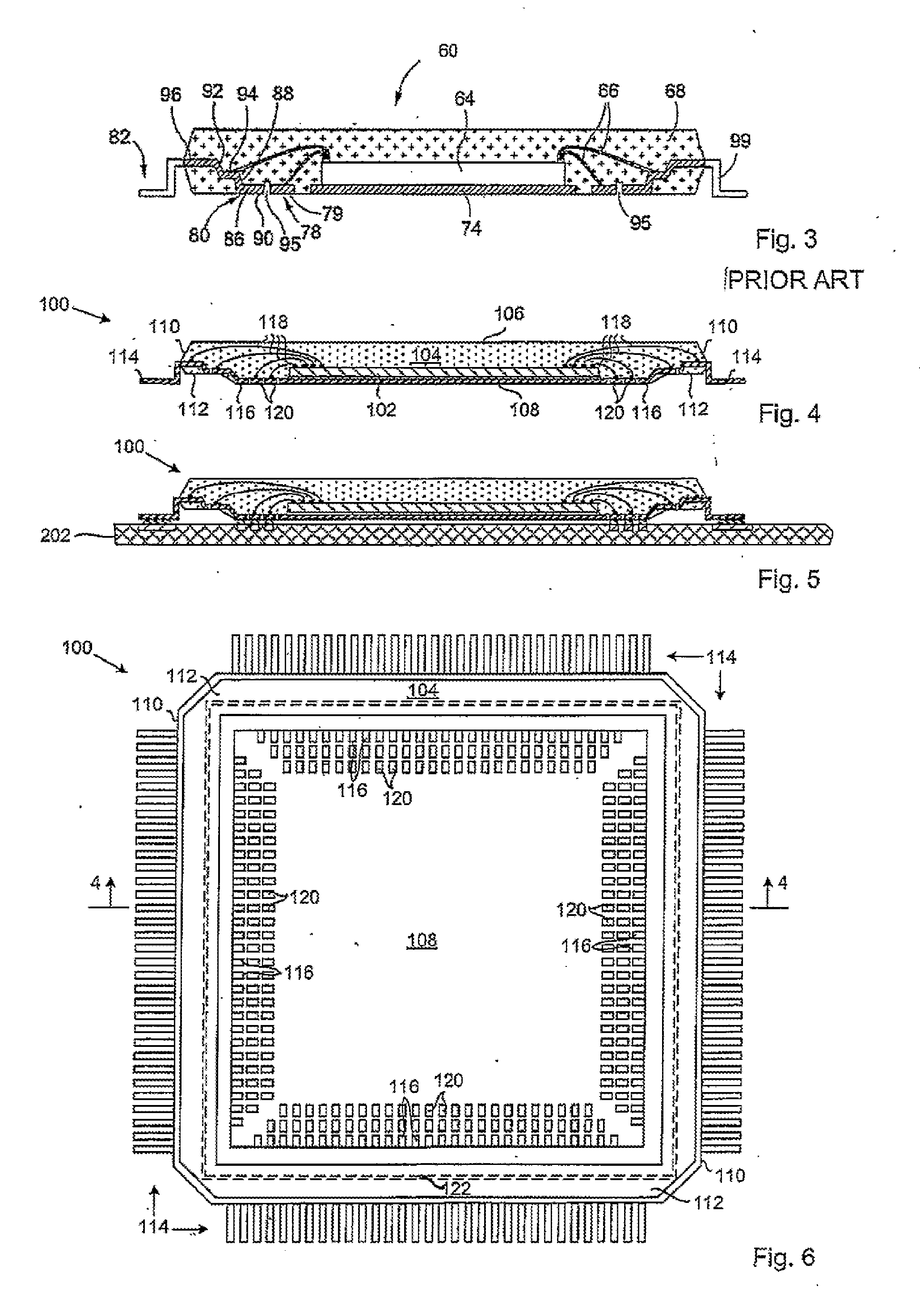

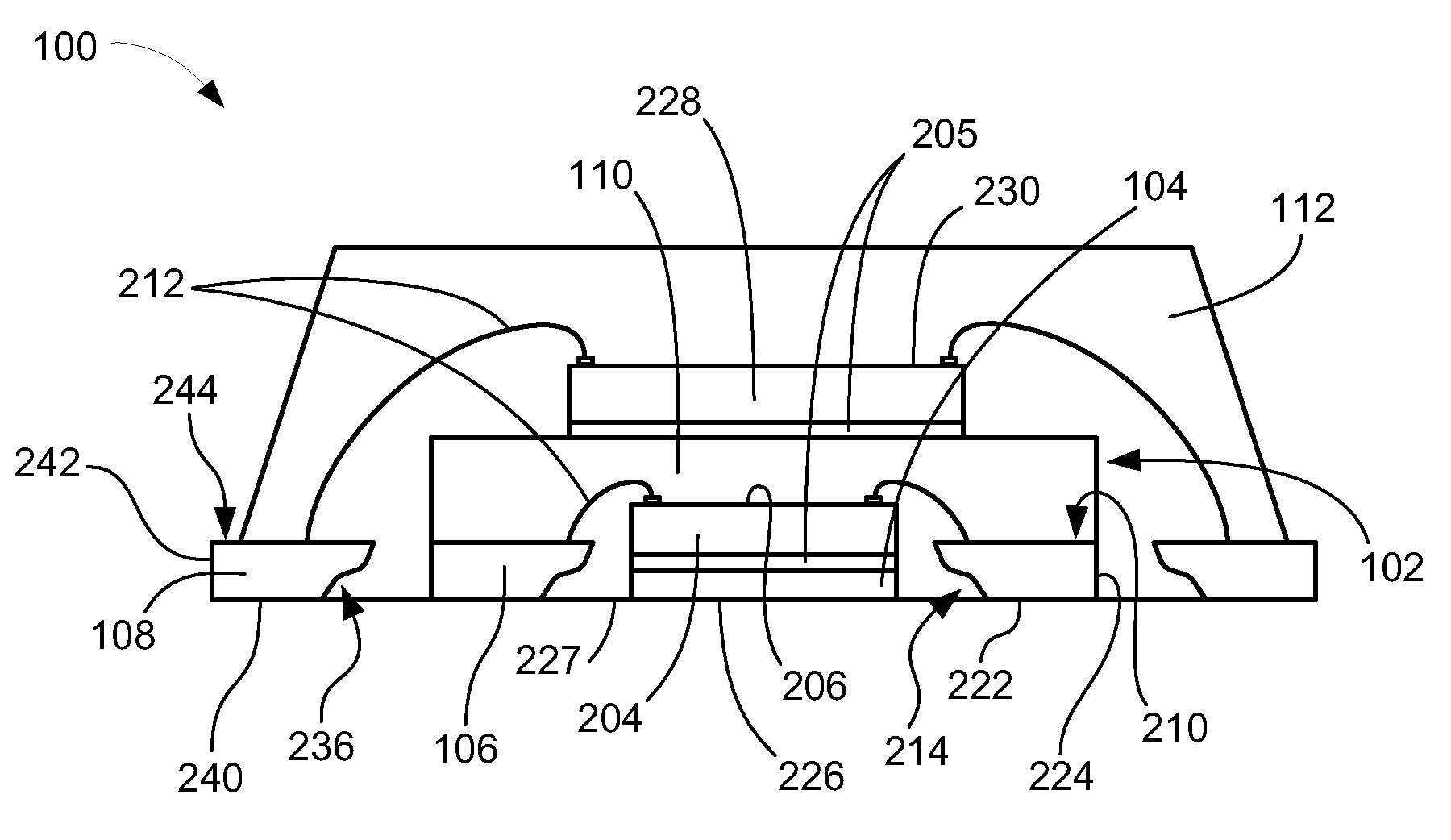

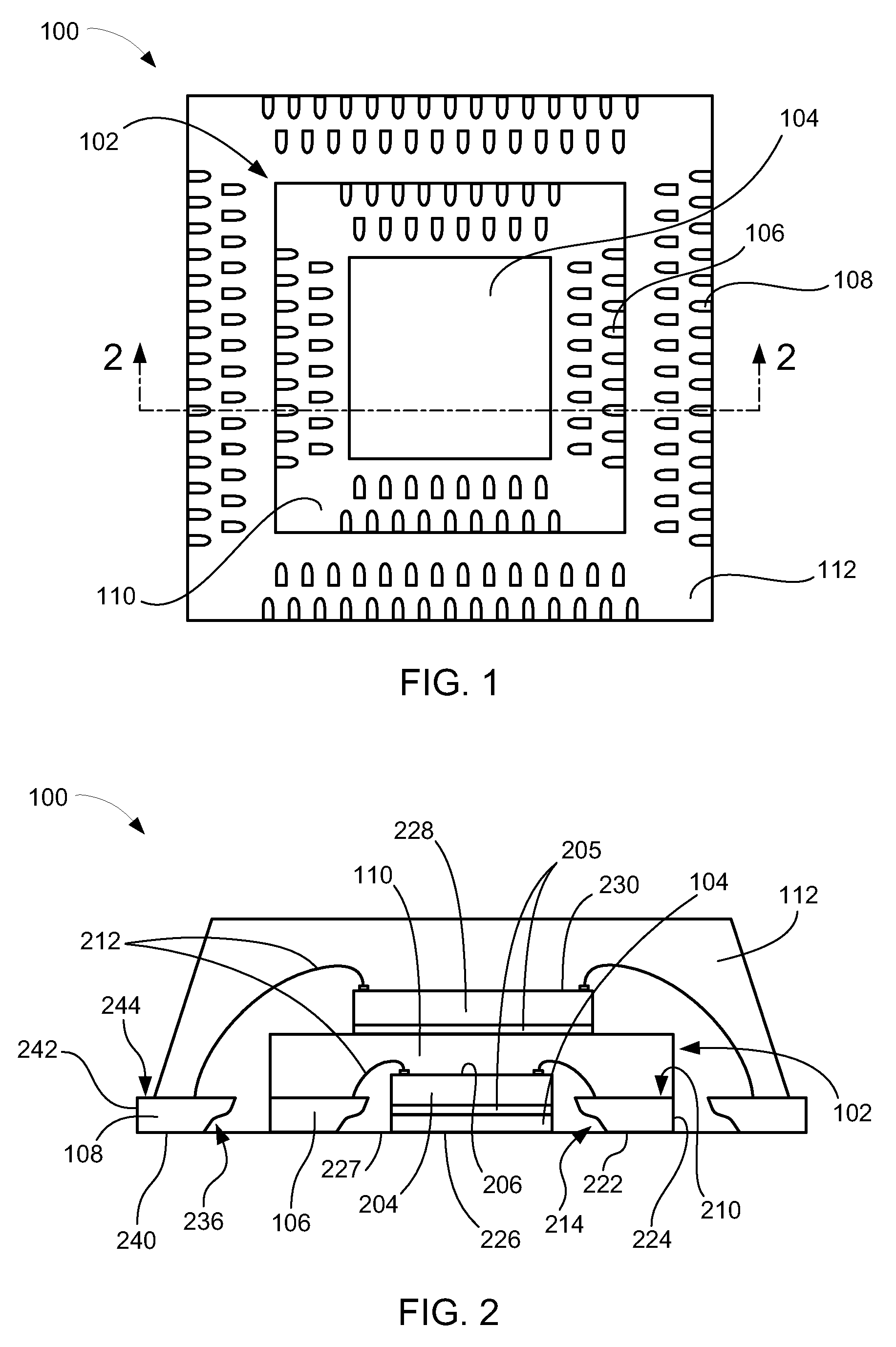

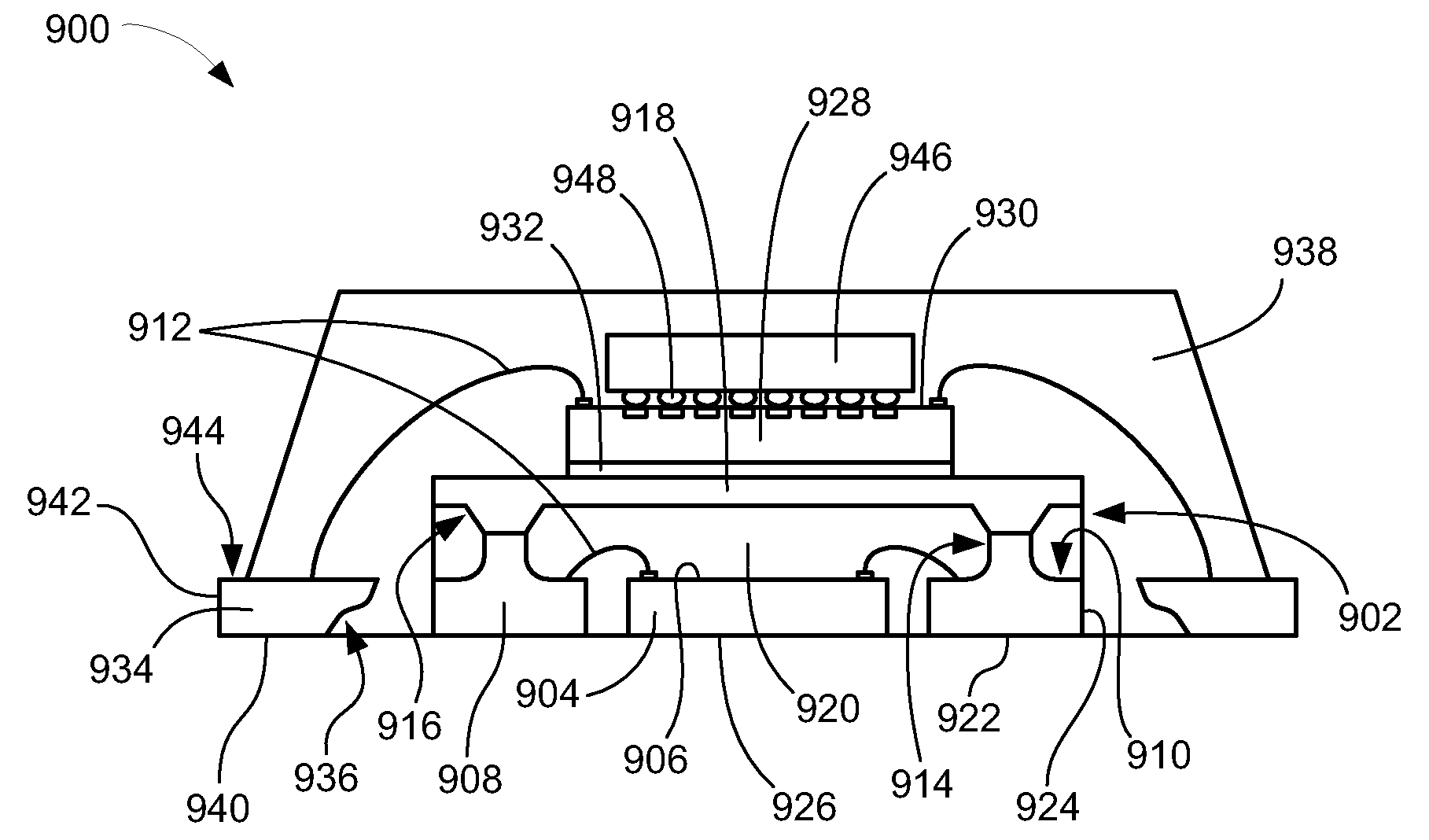

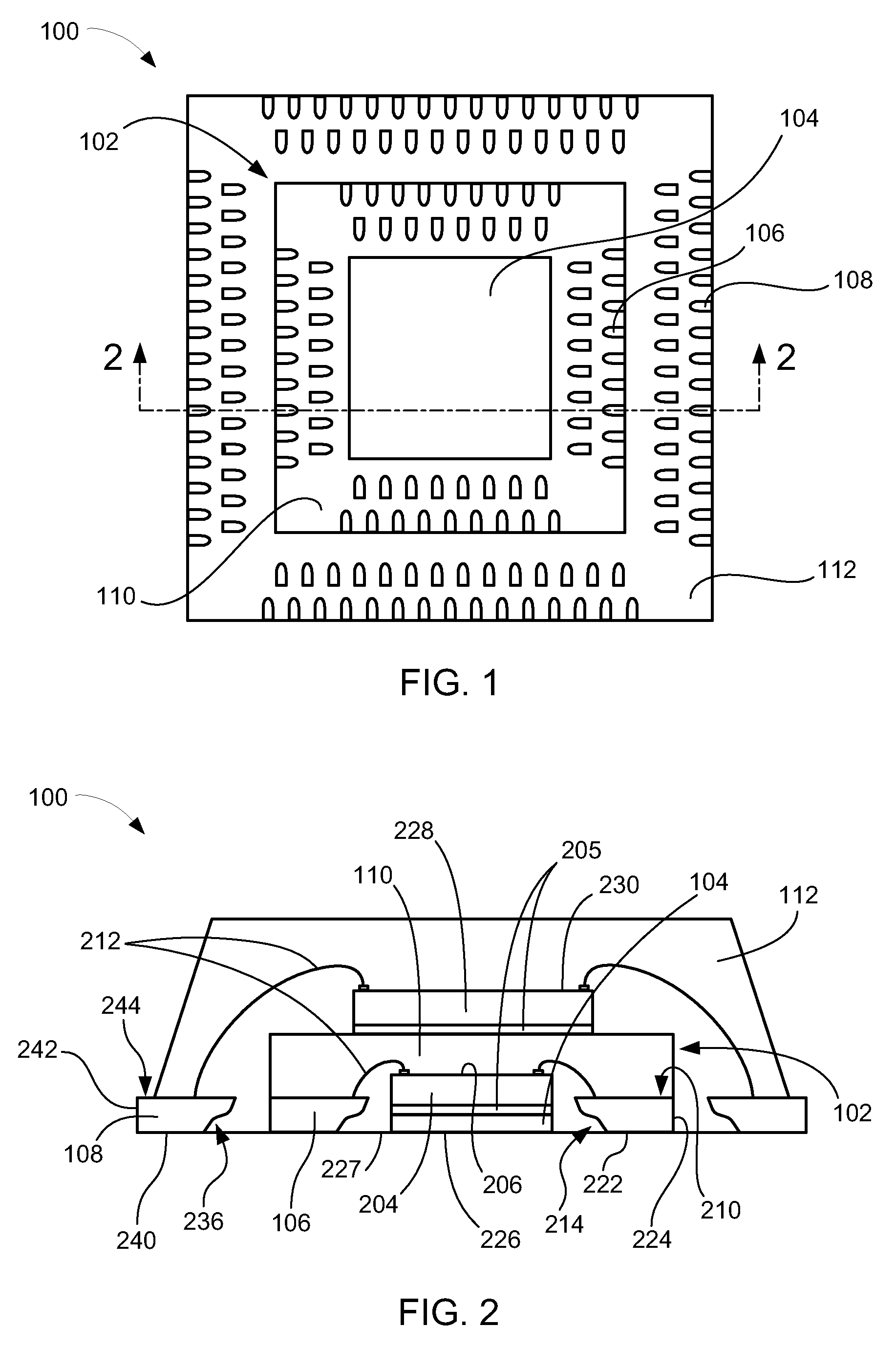

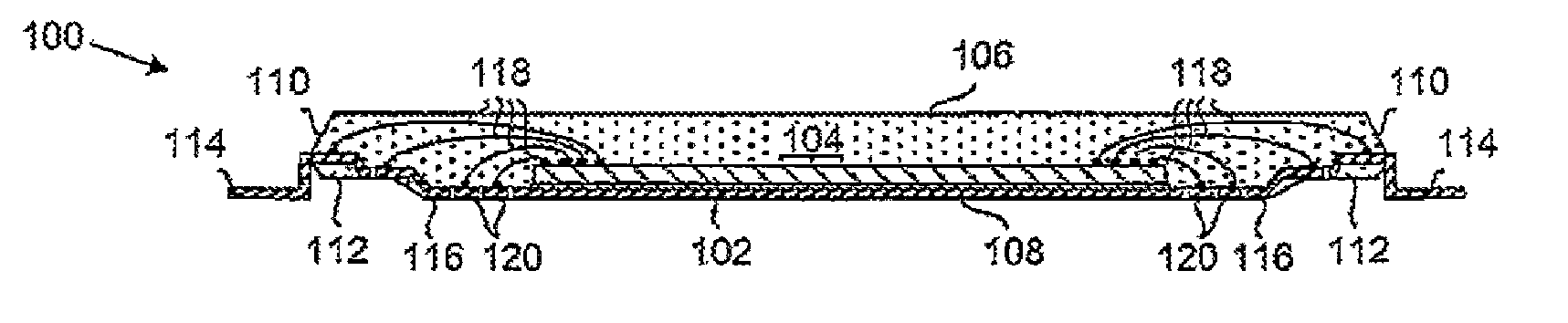

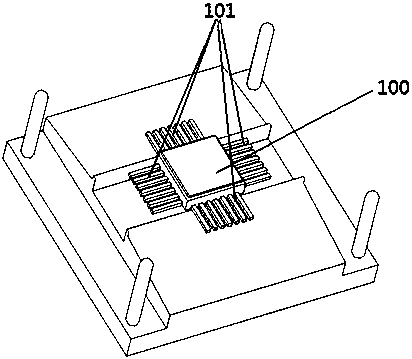

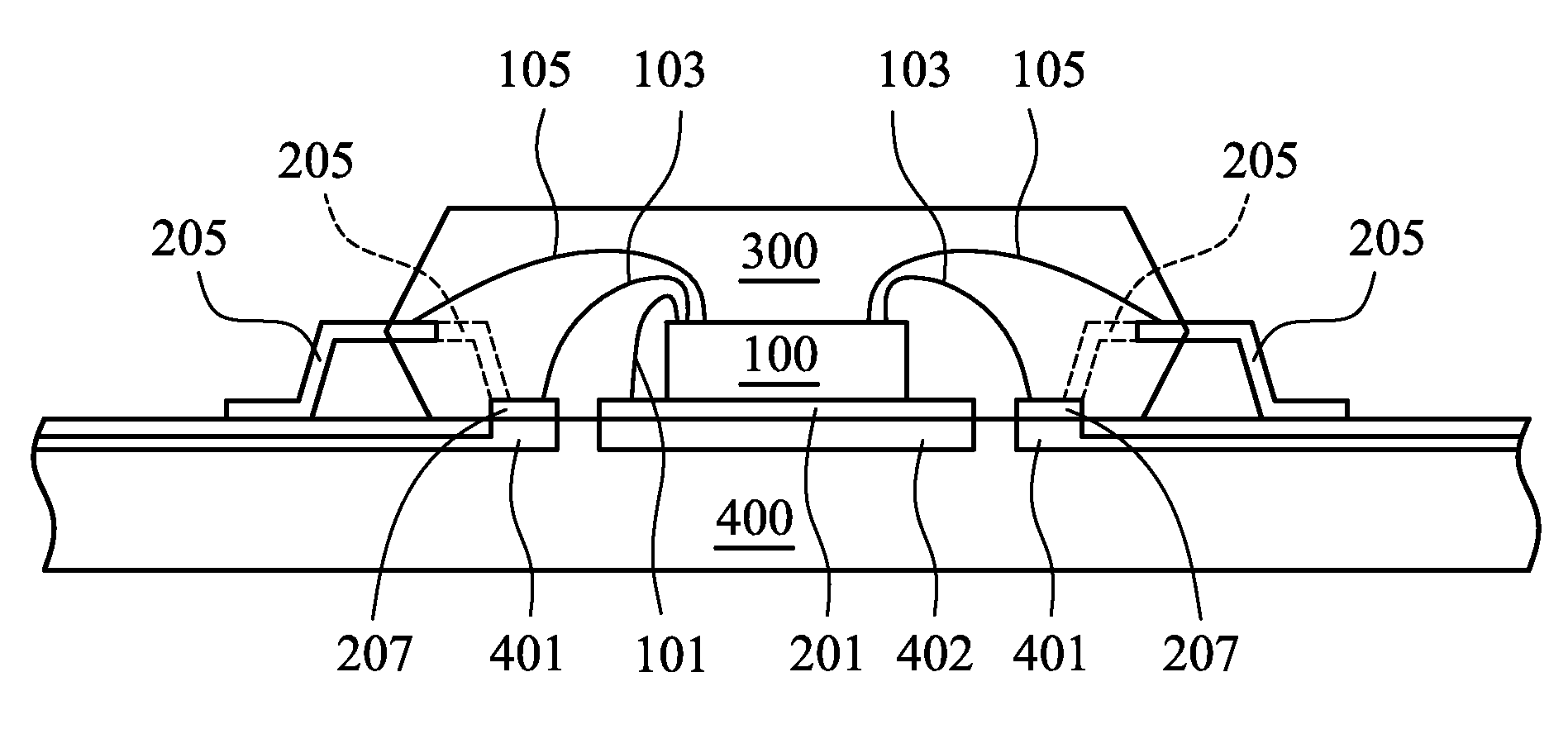

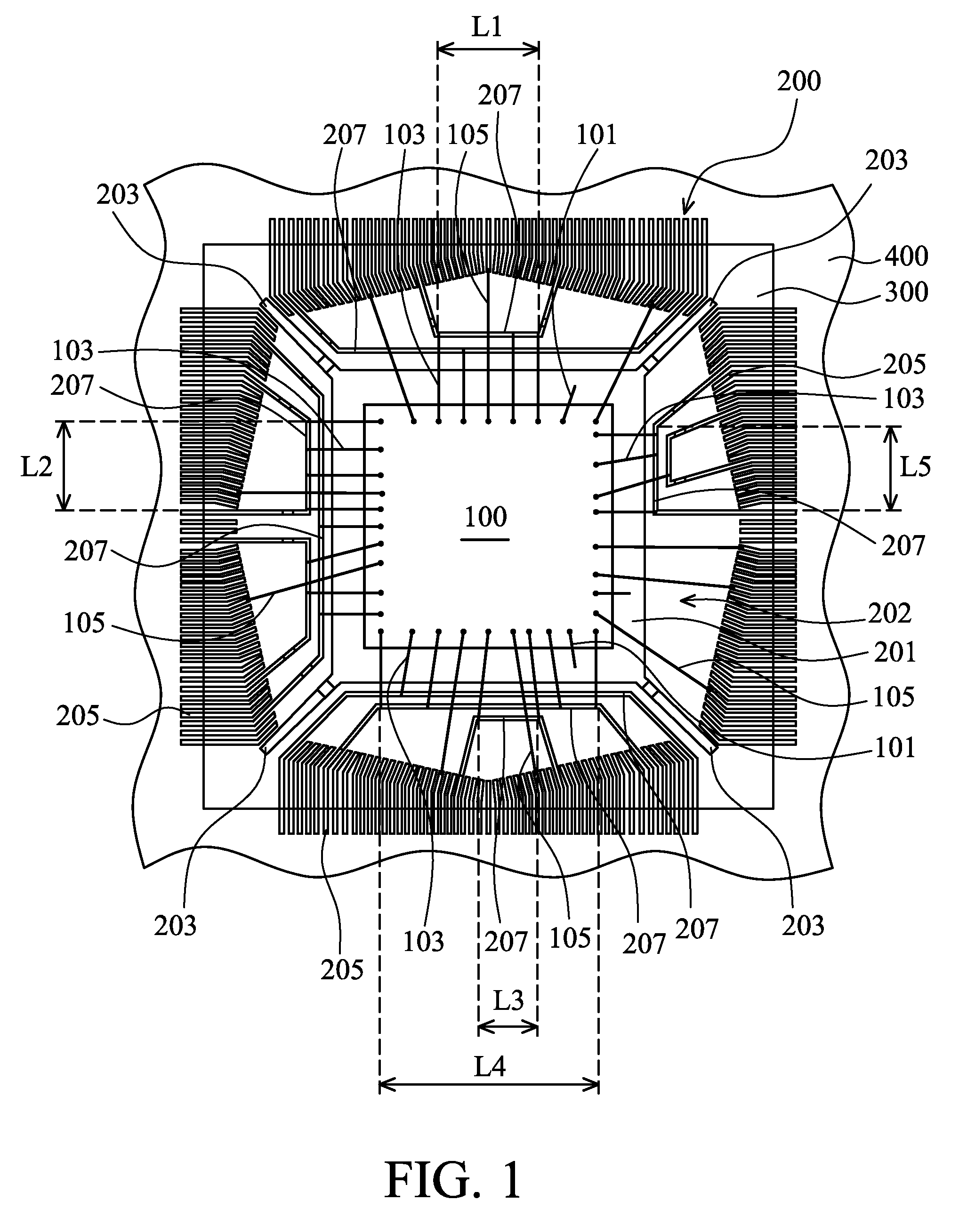

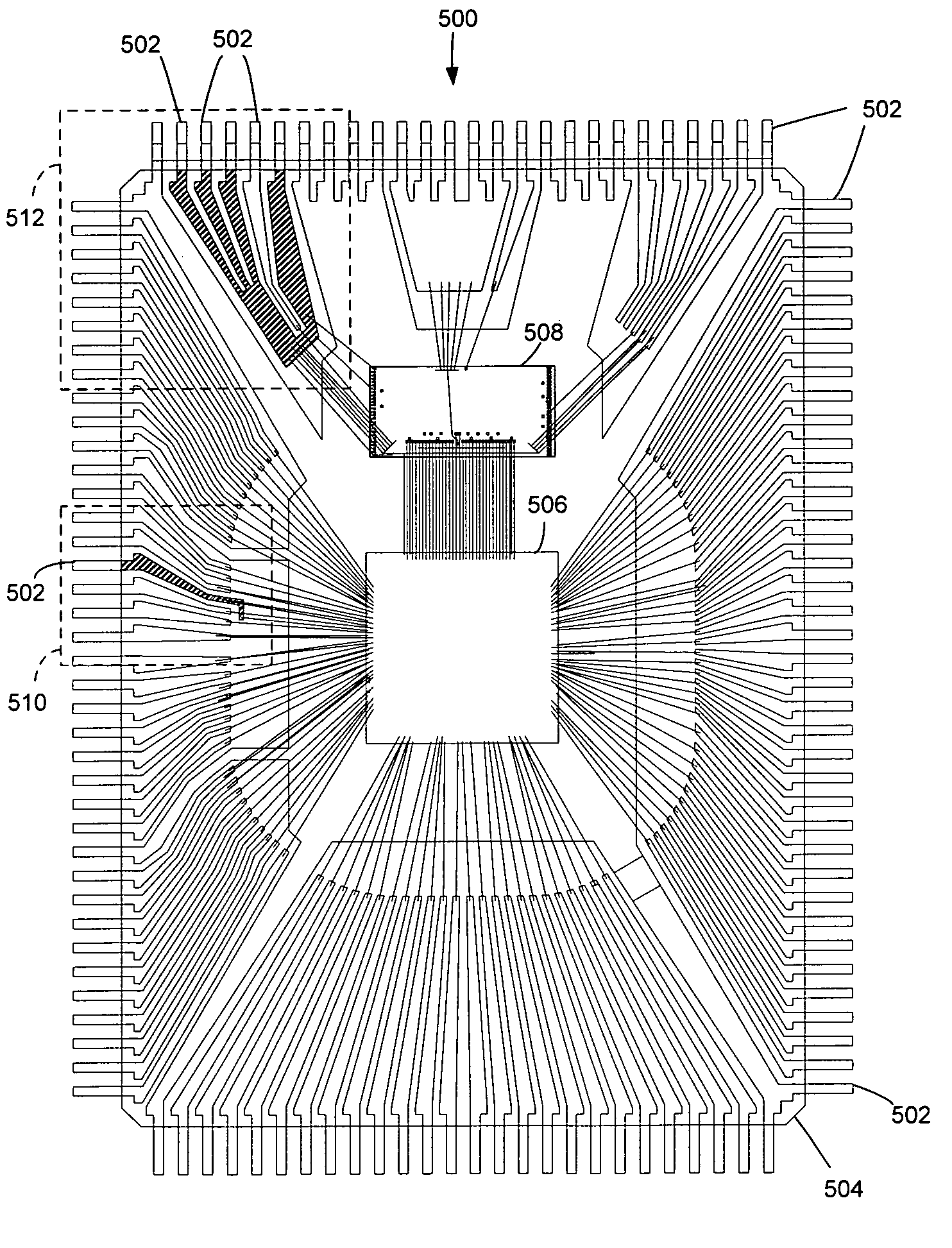

Quad flat pack in quad flat pack integrated circuit package system

ActiveUS20100072586A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringQuad Flat Package

An integrated circuit package system includes: providing a base package having a first integrated circuit with an inner lead on a periphery thereof and connected thereto with interconnects, and the inner lead partially encapsulated by an inner encapsulation; mounting an outer lead on the periphery of the base package; mounting a second integrated circuit above the base package and connected to the outer lead with the interconnects; and partially encapsulating, the base package and the outer leads with an outer encapsulation leaving a bottom surface of the inner lead and a bottom surface of the outer lead exposed.

Owner:STATS CHIPPAC LTD

Quad flat pack in quad flat pack integrated circuit package system

ActiveUS7777320B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringQuad Flat Package

An integrated circuit package system includes: providing a base package having a first integrated circuit with an inner lead on a periphery thereof and connected thereto with interconnects, and the inner lead partially encapsulated by an inner encapsulation; mounting an outer lead on the periphery of the base package; mounting a second integrated circuit above the base package and connected to the outer lead with the interconnects; and partially encapsulating, the base package and the outer leads with an outer encapsulation leaving a bottom surface of the inner lead and a bottom surface of the outer lead exposed.

Owner:STATS CHIPPAC LTD

Load board

InactiveUS7094068B2Printed circuit assemblingElectrically conductive connectionsEngineeringQuad Flat Package

A load board for packaged IC testing. The load board with predetermined testing circuit thereon has bonding pad areas on its surface. A plurality of bonding pads is formed on the bonding pad areas, each of which is disposed corresponding to a lead of a packaged IC for testing connection, such as a quad flat packaged IC (QFP), a dual inline packaged IC (DIP) or a small outline packaged IC (SOP). The bonding pads on the load board connect the leads of the testing IC directly during IC testing, thus the conventional test socket between a conventional load board and a packaged IC is omitted.

Owner:SILICON INTEGRATED SYSTEMS

Quad flat semiconductor device with additional contacts

ActiveUS8981541B2Semiconductor/solid-state device detailsSolid-state devicesQuad Flat PackageLead frame

A Quad Flat Package (QFP) semiconductor device has a multi-stepped lead frame for forming rows of external contacts. A semiconductor die is attached to a die pad of the lead frame and electrically connected to lead with bond wires. The die and bond wires are encapsulated with a mold compound and then multiple cuts are made to the lead frame to form the rows of external contacts.

Owner:NXP USA INC

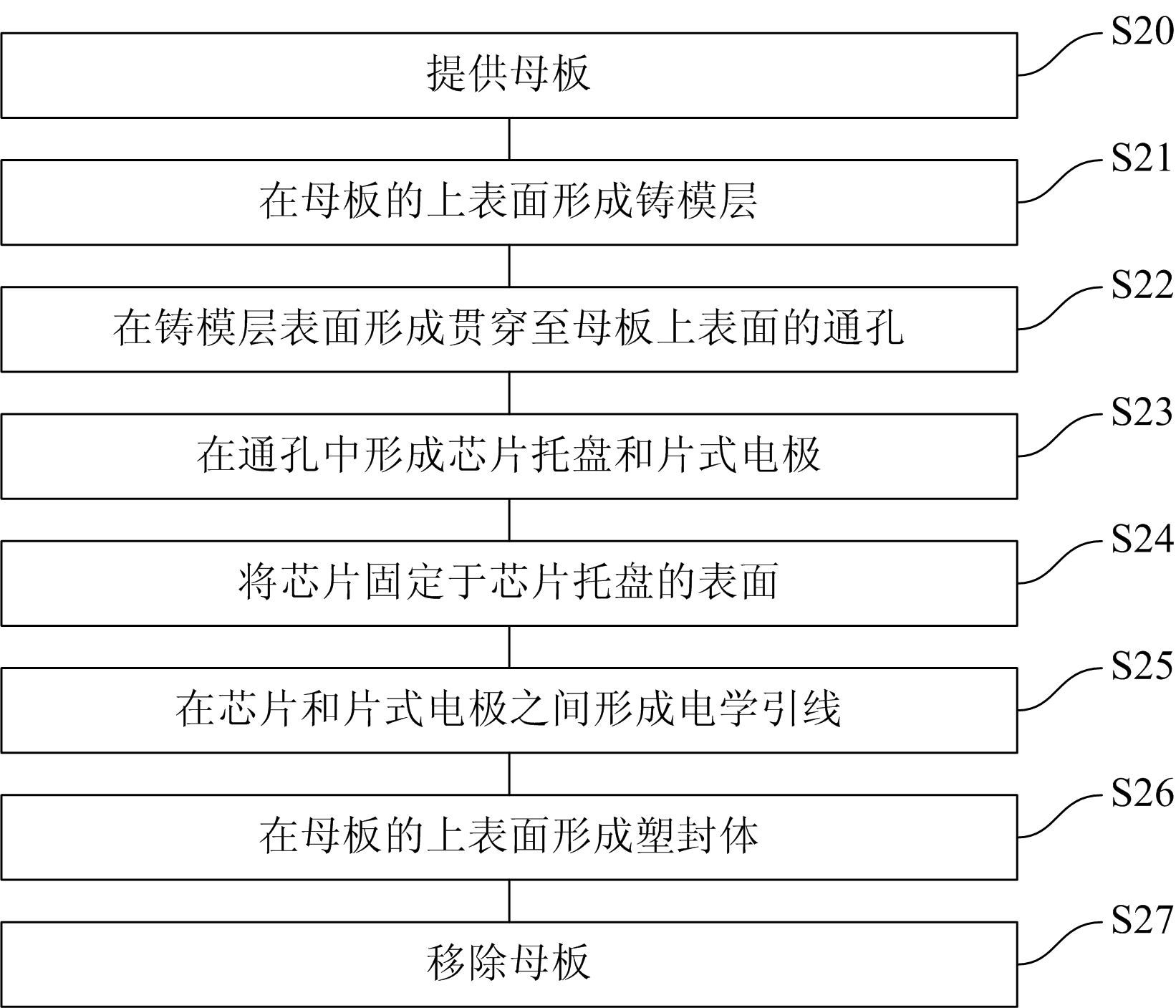

Quad flat no-lead package and manufacturing method thereof

InactiveCN102290358AEasy to fixReduce thermal stressSemiconductor/solid-state device detailsSolid-state devicesSurface layerCasting mold

The invention provides a method for manufacturing a quad flat no-lead package, comprising the following steps: providing a motherboard; forming a mold layer on the upper surface of the motherboard; forming a through hole penetrating to the upper surface of the motherboard on the surface of the mold layer, The opening area of the through hole close to the upper surface of the motherboard is smaller than the opening area of the other side; the chip tray and the chip electrode are formed in the through hole; the chip is fixed on the surface of the chip tray; between the chip and the chip electrode forming electrical leads between them; forming a plastic package on the upper surface of the motherboard; removing the motherboard to expose the chip tray and chip electrodes embedded in the plastic package.

Owner:SHANGHAI KAIHONG ELECTRONICS CO LTD +2

QFP (Quad Flat Package) grounding welding plate

InactiveCN102543929AApplicable thermal requirementsImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesSolder ballEngineering

The invention belongs to the QFP (Quad Flat Package) field and particularly relates to a QFP grounding welding plate. The QFP grounding welding plate comprises a heat radiating hole and a matrix arrangement hole, wherein the heat radiating hole is positioned in the middle of the grounding welding plate; and the matrix arrangement hole is positioned on the grounding welding plate and bypasses the heat radiating hole. The thickness of the periphery of the grounding welding plate is larger than that of the middle part of the grounding welding plate; solder paste is filled in the matrix arrangement hole; the thickness of the middle part of the grounding welding plate is 0.15-0.18 millimeter; the thickness of the periphery of the grounding welding plate is 0.3-0.4 millimeter; and the matrix arrangement hole is square or circular or triangular. The QFP grounding welding plate has the beneficial effects that as the heat radiating hole positioned in the middle of the grounding welding plate, the grounding welding plate has good heat radiation; and meanwhile, as the periphery of the grounding welding plate is thickened to 0.3-0.4 millimeter, a proper amount of solder paste is moistened and diffused to the whole grounding welding plate and does not generate solder balls, so that the grounding requirements are satisfied.

Owner:昆山美微电子科技有限公司

QFP (quad flat package) device pin molding fixture and using method thereof

PendingCN108580744ASimple structureEasy to processSemiconductor/solid-state device manufacturingQuad Flat PackageElectrical and Electronics engineering

The invention discloses a QFP (quad flat package) device pin molding fixture and a using method thereof. The pin molding fixture comprises a top cover, a base, a first clamping opening and a second clamping opening, wherein a plurality of fixed columns are arranged on the base; the top cover is arranged above the base through the plurality of fixed columns and can move up and down along the fixedcolumns; the first clamping opening is arranged at the bottom of the top cover and is formed by two platy objects which are perpendicular to the bottom surface of the top cover and are oppositely arranged; the second clamping opening is arranged on the top of the base and is formed by two platy objects which are perpendicular to the top surface of the base and are oppositely arranged; and the first clamping opening and the second clamping opening are aligned face to face to form a clamping part of a QFP device, so that the QFP device is located between the first clamping opening and the secondclamping opening, and pins to be machined and molded, of the QFP device are exposed out of the clamping part. The fixture provided by the invention is simple in structure and convenient to operate, can clamp a chip so as to prevent the chip from moving in the molding process of the chip, and then molds the chip by smearing along a molding surface; the chip is molded at a time; and the pins have consistent shapes and high accuracy.

Owner:SHANGHAI INST OF SPACE POWER SOURCES

Quad flat package with exposed common electrode bars

ActiveUS8283757B2Semiconductor/solid-state device detailsSolid-state devicesQuad Flat PackageElectron

An electronic package is provided. The electronic package comprises a die pad having a die attached thereon. A plurality of leads surrounds the die pad and spaced therefrom to define a ring gap therebetween. At least one first common electrode bar is in the ring gap and substantially coplanar to the die pad, in which at least one of the plurality of leads extends to the first common electrode bar. A molding compound partially encapsulates the die pad and the first common electrode bar, such that the bottom surfaces of the die pad and the first common electrode bar are exposed. A length of the first common electrode bar is substantially equal to a predetermined distance between two pads among a plurality of power or ground pads on a side of the die facing the first common electrode bar. An electronic device with the electronic package is also disclosed.

Owner:MEDIATEK INC

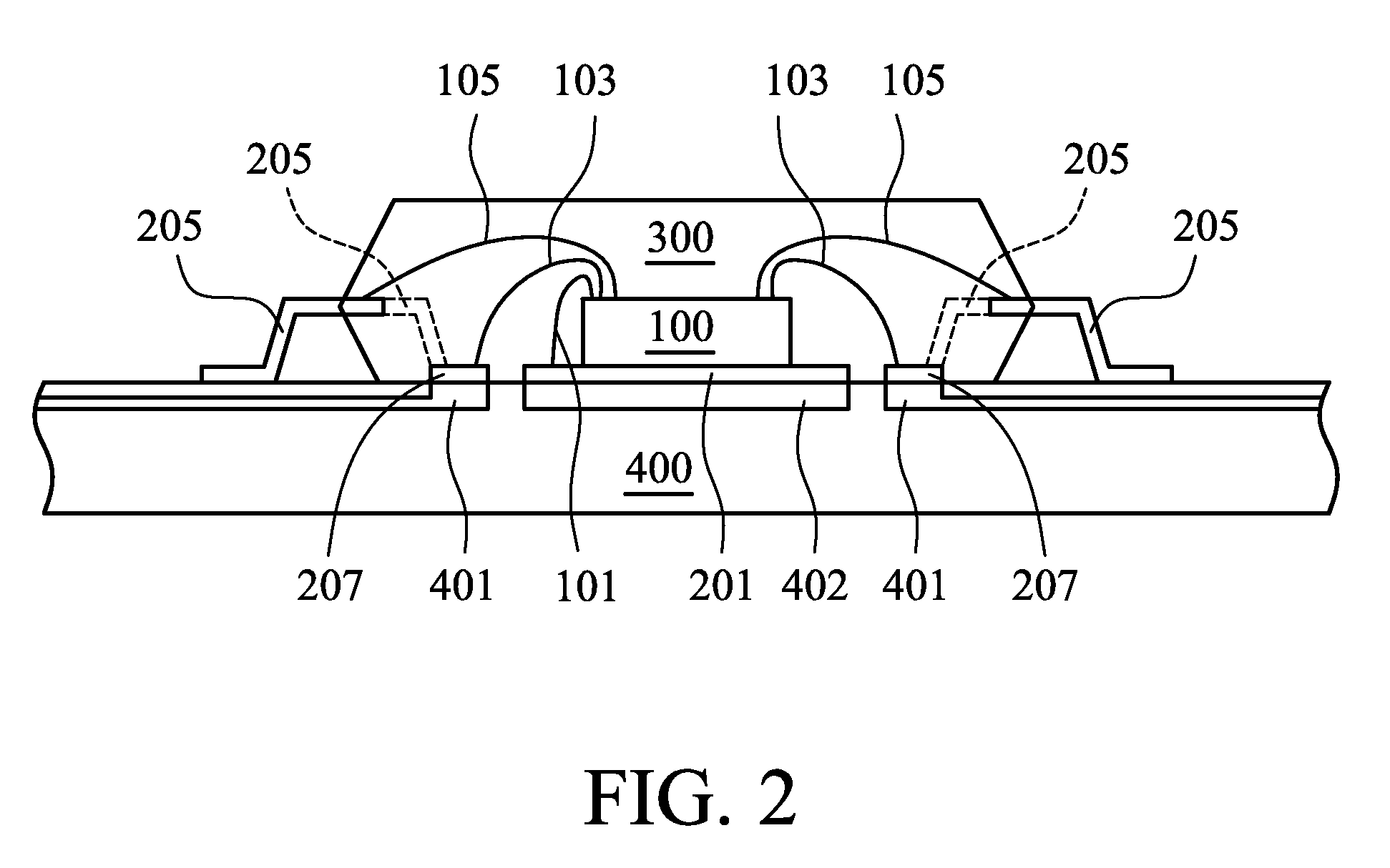

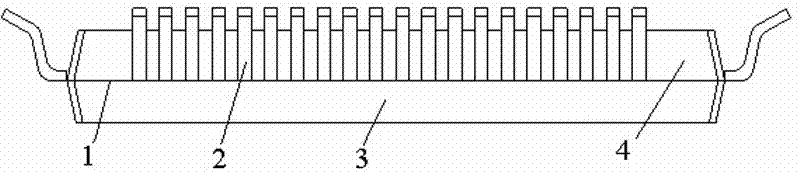

Tray for low-profile quad flat package (LQFP) integrated circuit

ActiveCN102244024ASimple structureEasy to manufactureSemiconductor/solid-state device manufacturingBiochemical engineeringQuad Flat Package

The invention discloses a tray for a low-profile quad flat package (LQFP) integrated circuit. The tray comprises a first frame and a flat plate, wherein the flat plate and the first frame form an upper frame body and a lower frame body; the upper frame body is internally provided with a plurality of first structural ribs and a plurality of second structural ribs; the first structural ribs and thesecond structural ribs are vertical to one another; the first structural ribs, the second structural ribs and the rim of the upper frame body encircle a plurality of storage containers; a base is arranged in each storage container, and a gap is reserved between the side face of the base and the inner wall of the corresponding storage container; the end faces of the bases are provided with segmental limiting ribs in a number the same as that of the side faces of the bases, and the segmental limiting ribs correspond to the side faces of the bases one to one; the segmental limiting ribs are shorter than the side edges of the bases; locators in a number the same as that of the bases are arranged in the lower frame body; and second limiting ribs are arranged on the end faces of spaced side walls of the locators respectively. The tray is simple in structure and easy to manufacture, and can prevent damage to the LQFP package integrated circuit during production and use and realize automatic operation.

Owner:天水华天集成电路包装材料有限公司

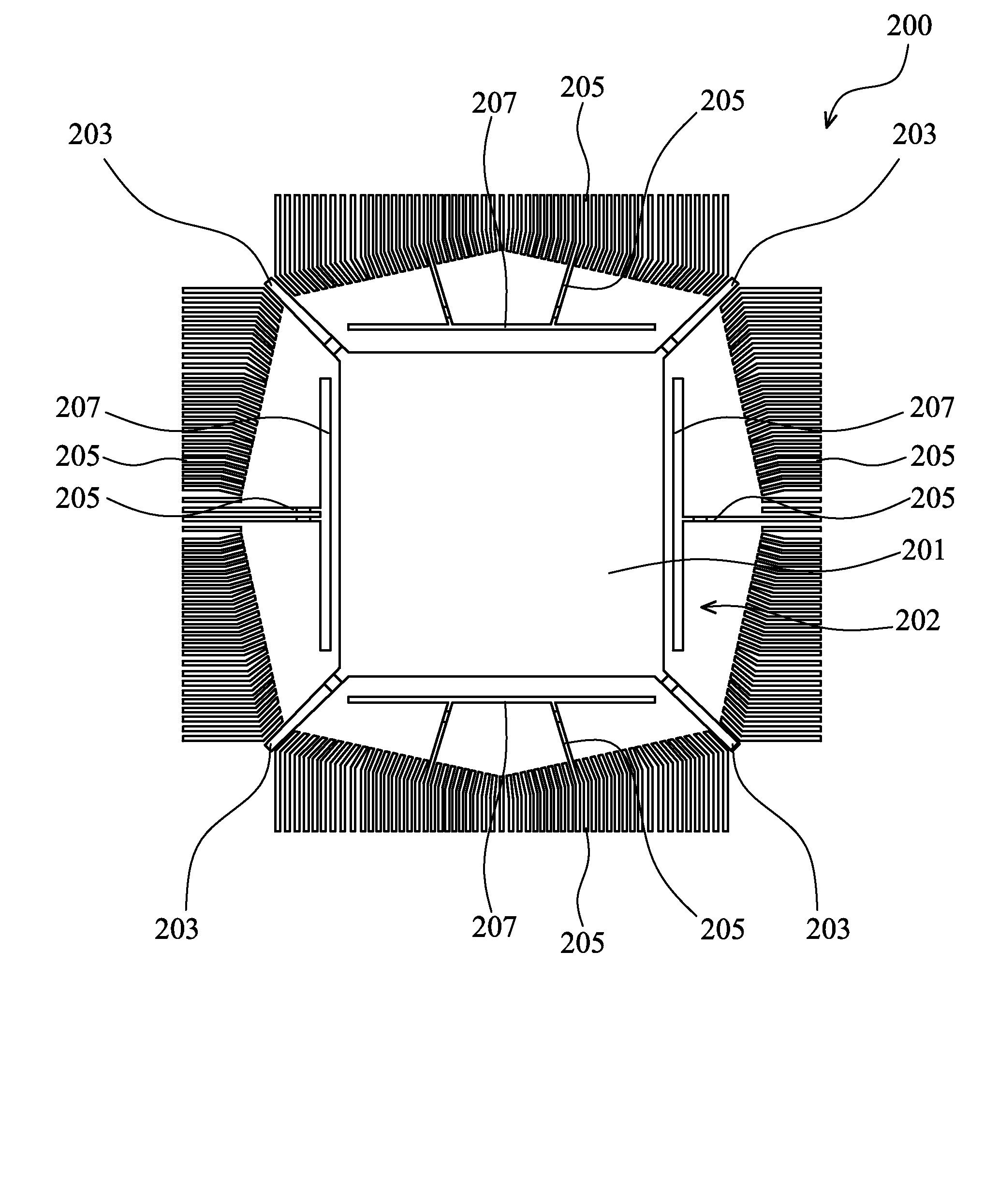

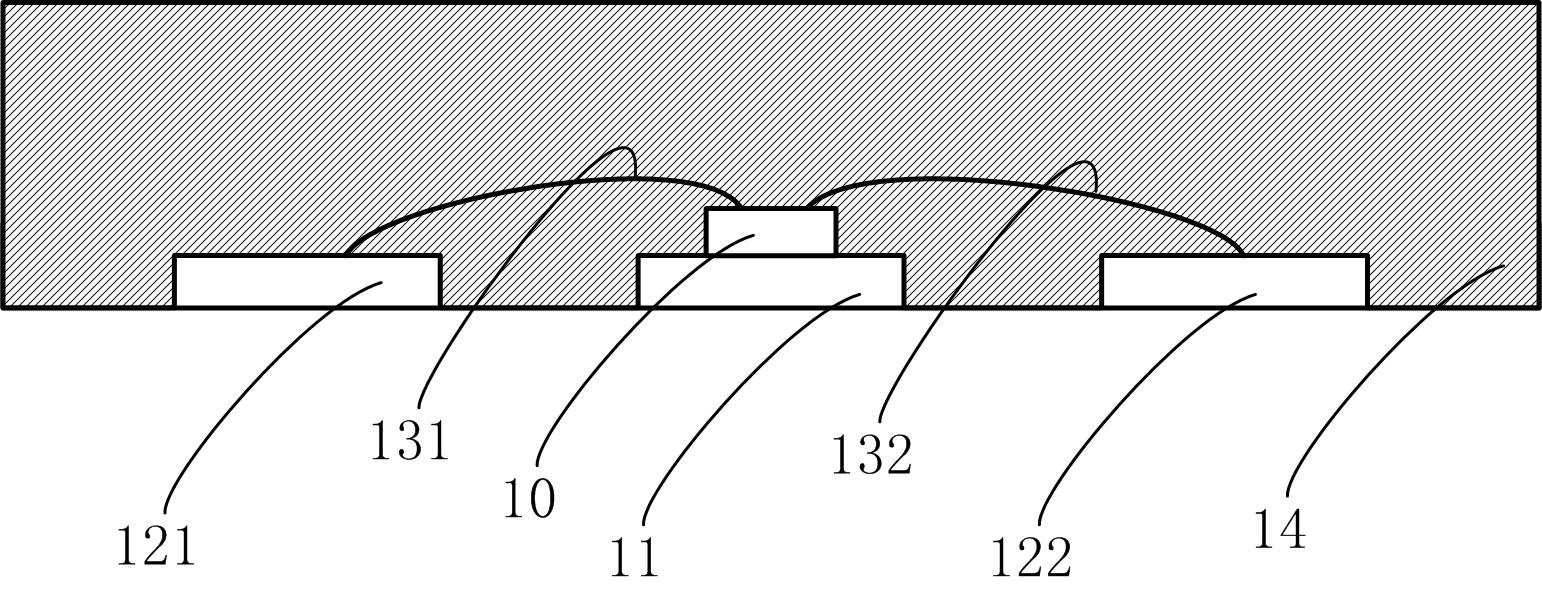

System and method for providing a power bus in a wirebond leadframe package

InactiveUS7495320B2Active connectionMaximizing numberSemiconductor/solid-state device detailsSolid-state devicesLead bondingQuad Flat Package

An integrated circuit (IC) package, such as a Quad Flat Pack (QFP), has at least one lead with a tip that extends substantially perpendicular to the ends of two or more bondwires, so that there is room for more than one bondwire to be attached to it along its length. Thus, bondwires leading from die bondpads that are not adjacent to one another can be efficiently connected to the same lead in a bus-like manner.

Owner:MARVELL INT TECH