Patents

Literature

33 results about "Lead on chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

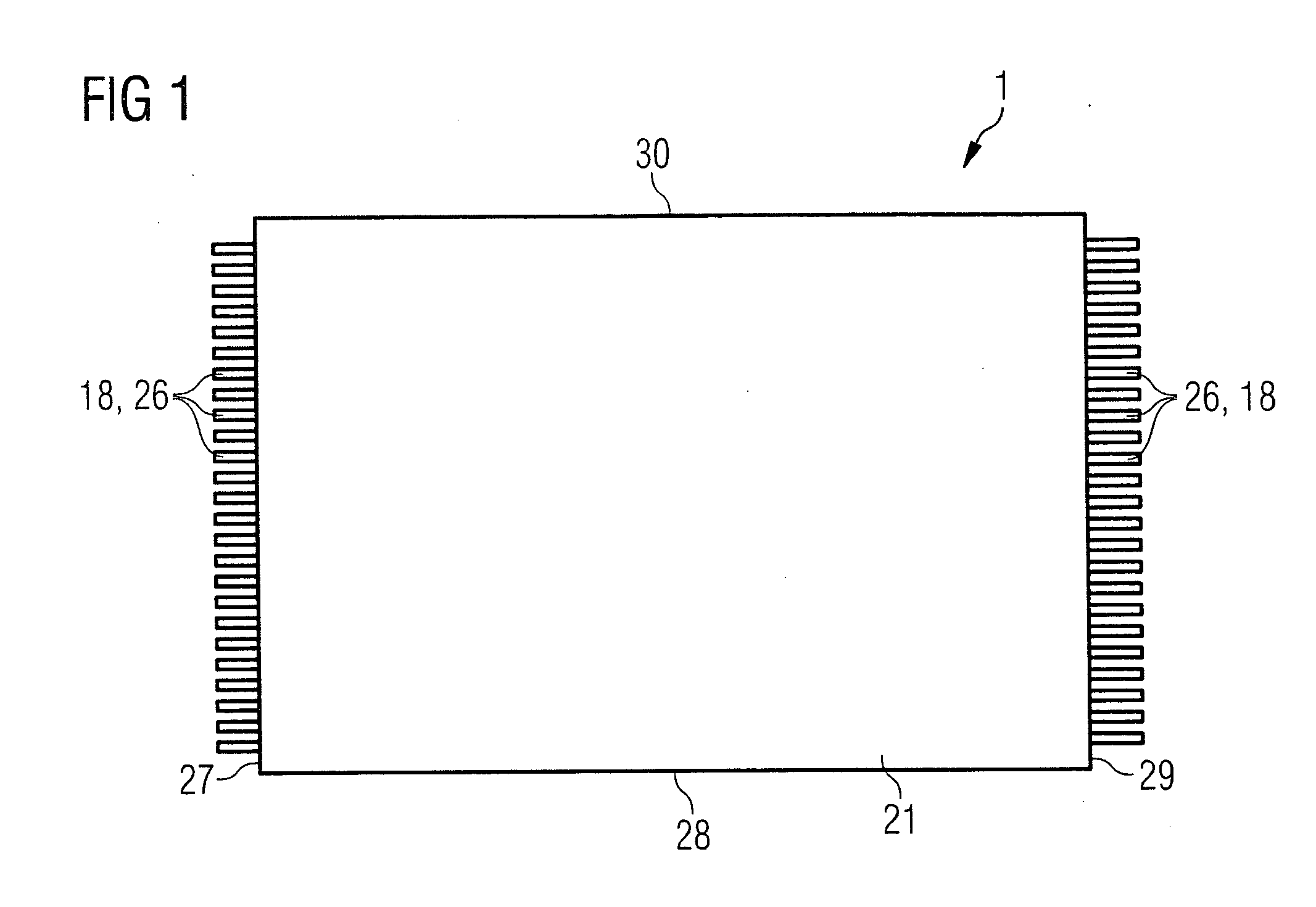

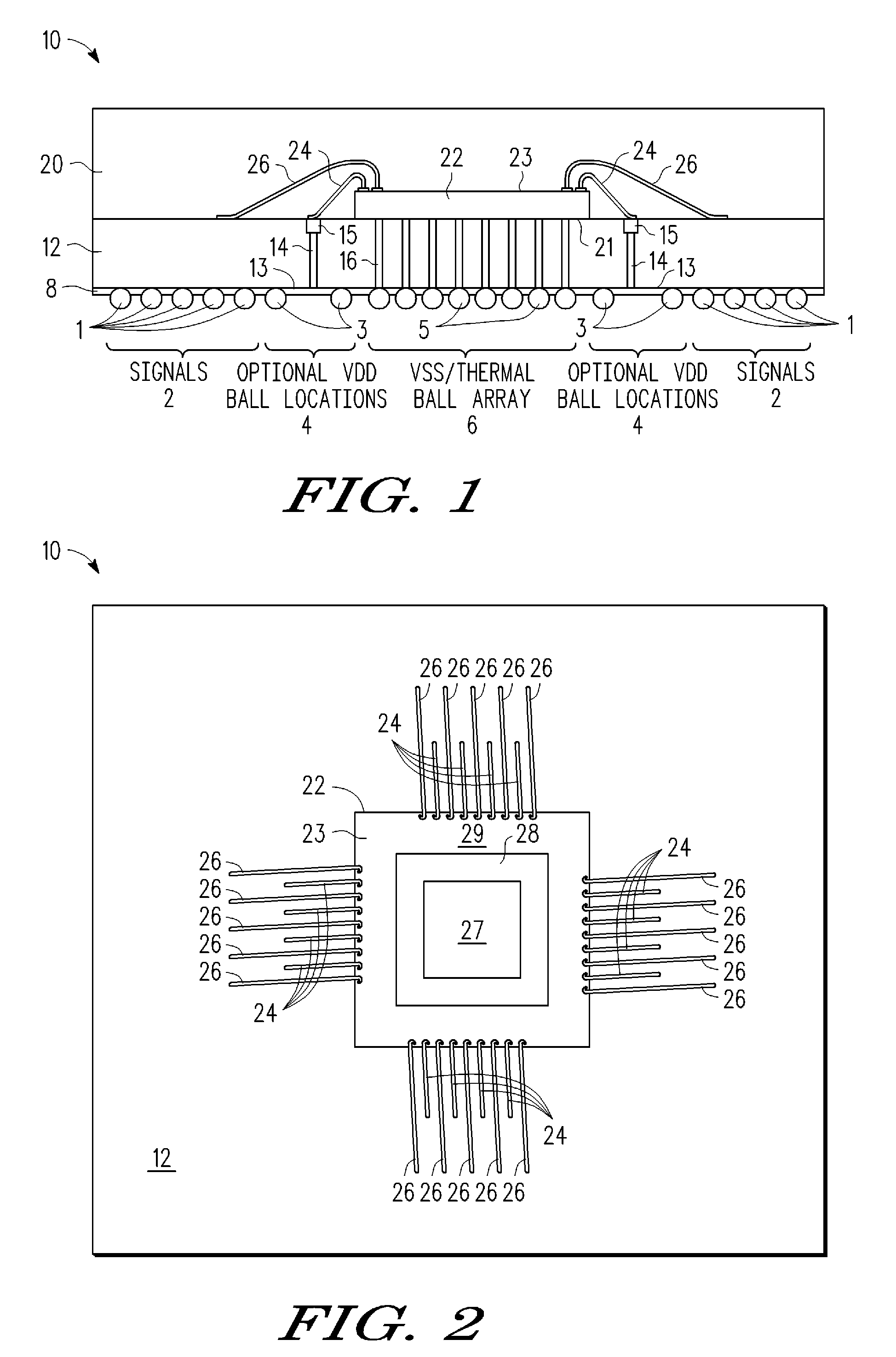

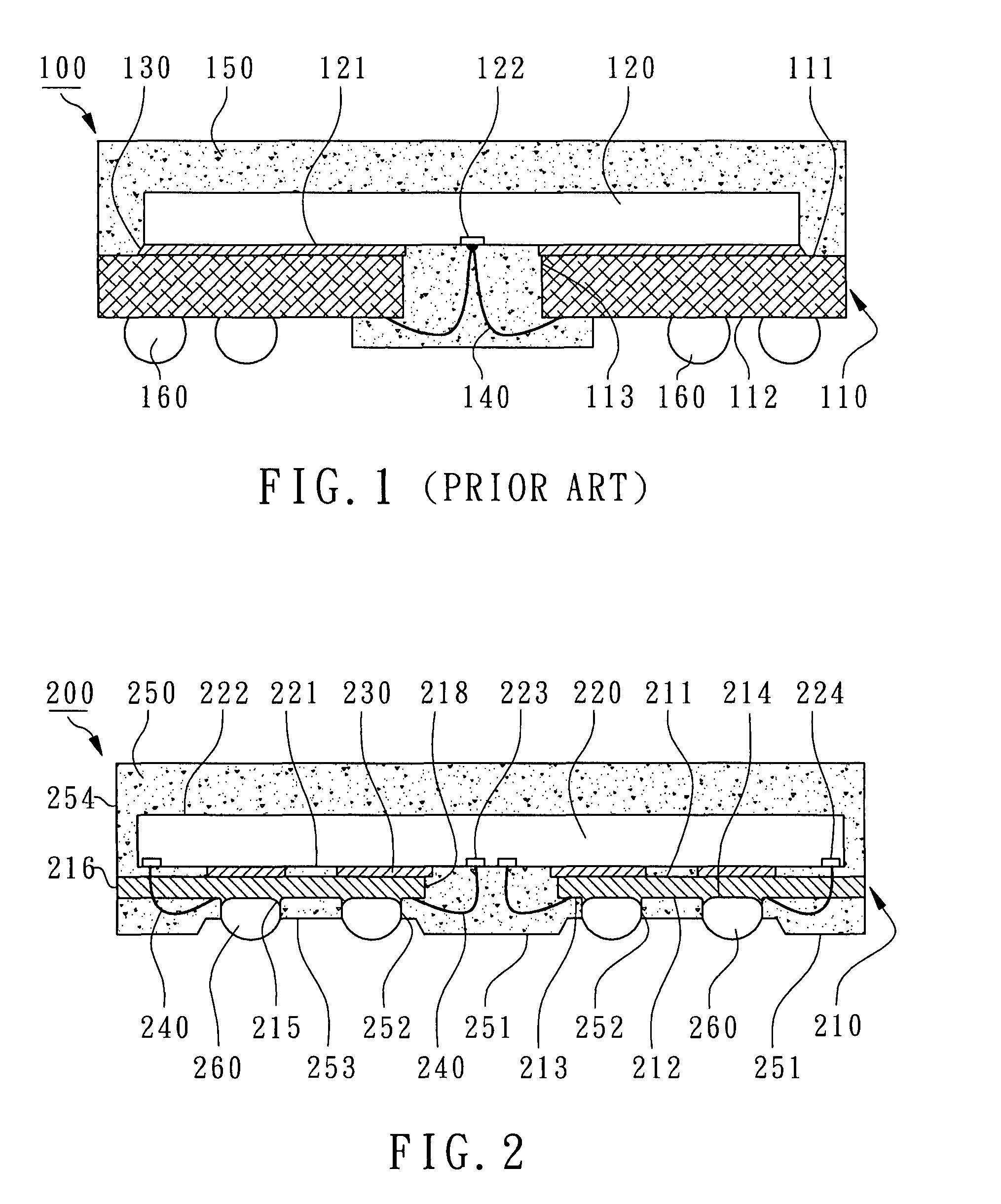

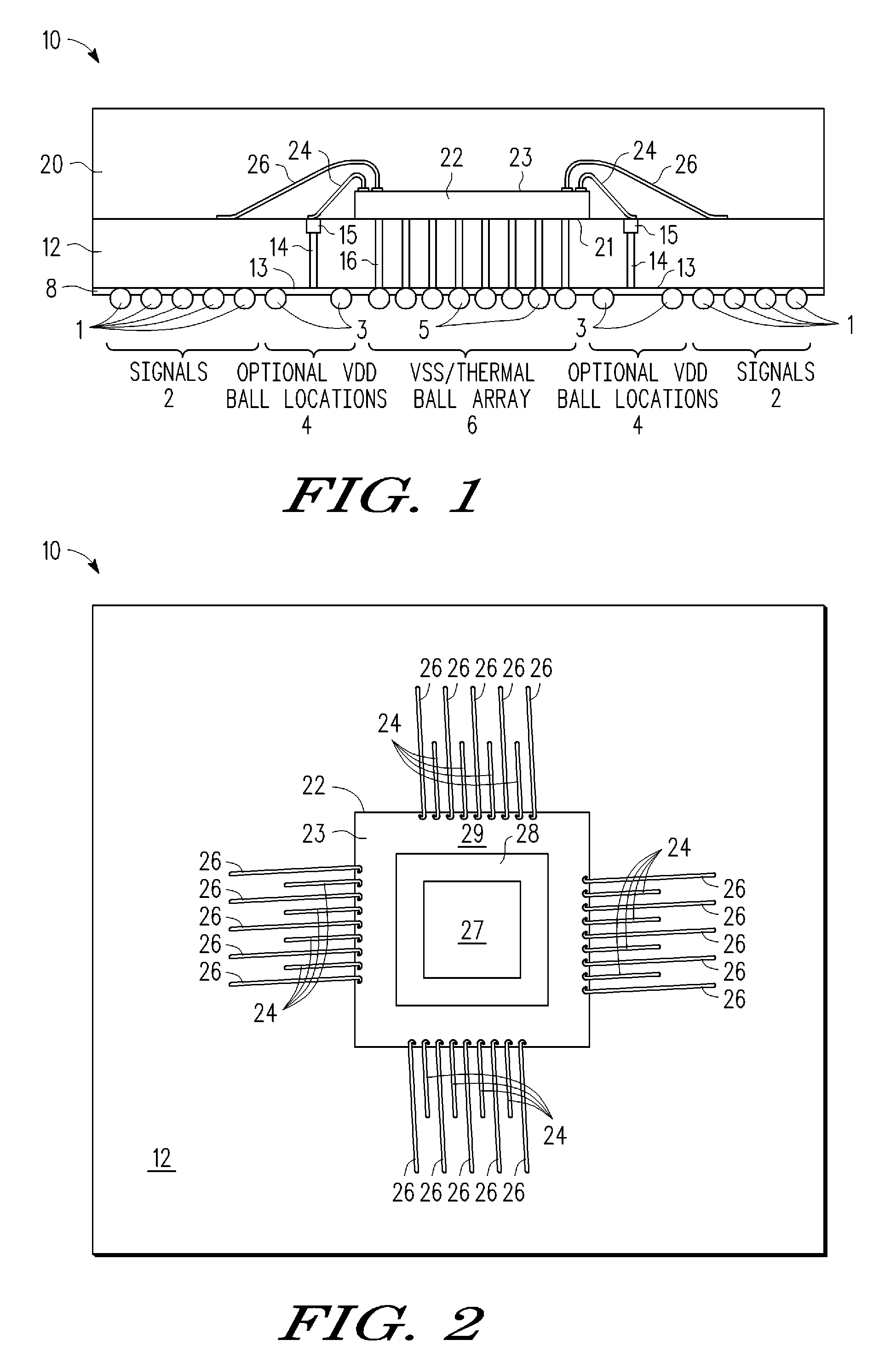

Thermally enhanced chip scale lead on chip semiconductor package and method of making same

InactiveUS6873032B1Enhanced thermalReliable electrical connectionSemiconductor/solid-state device detailsSolid-state devicesLead on chipElectrical connection

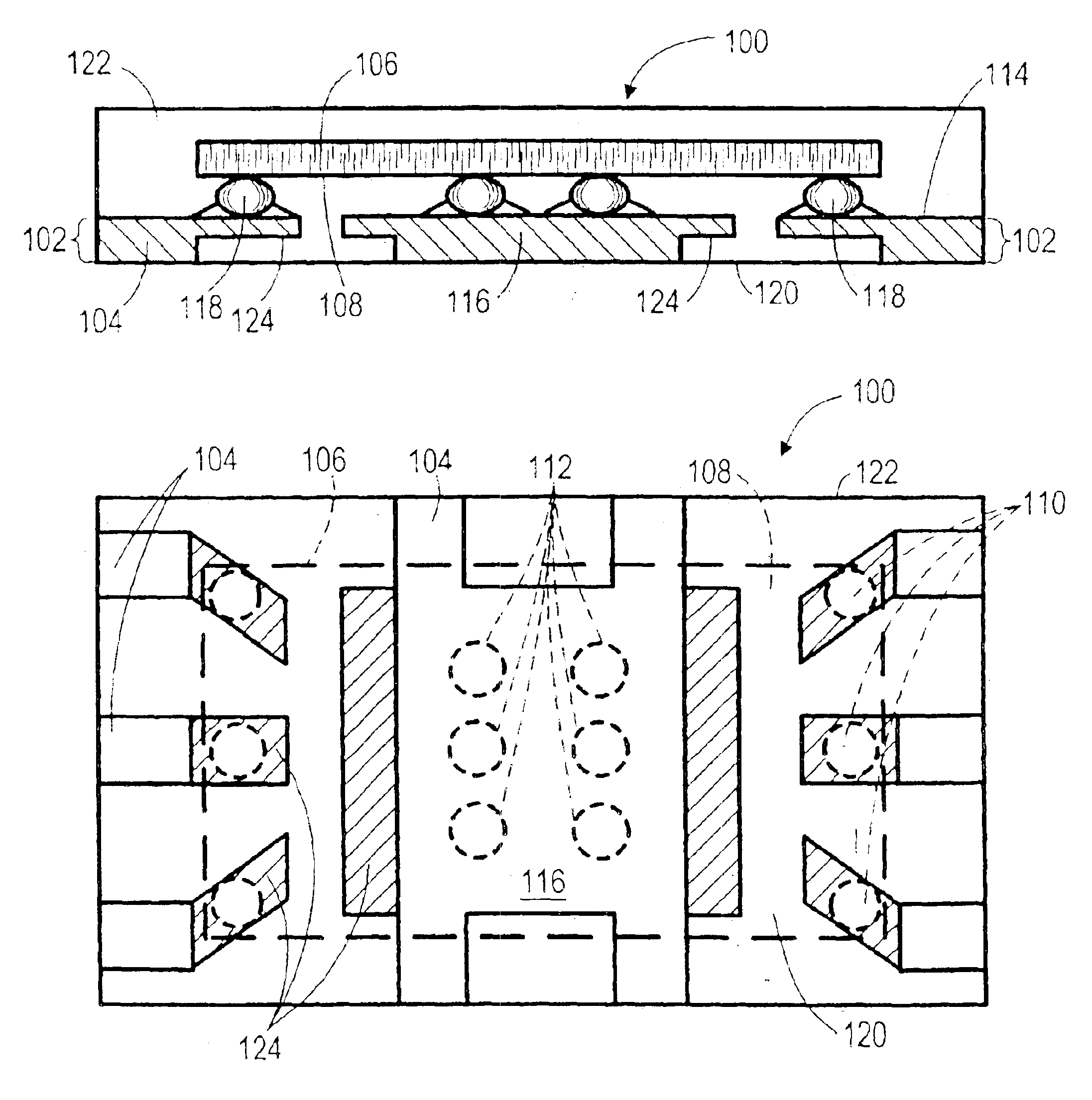

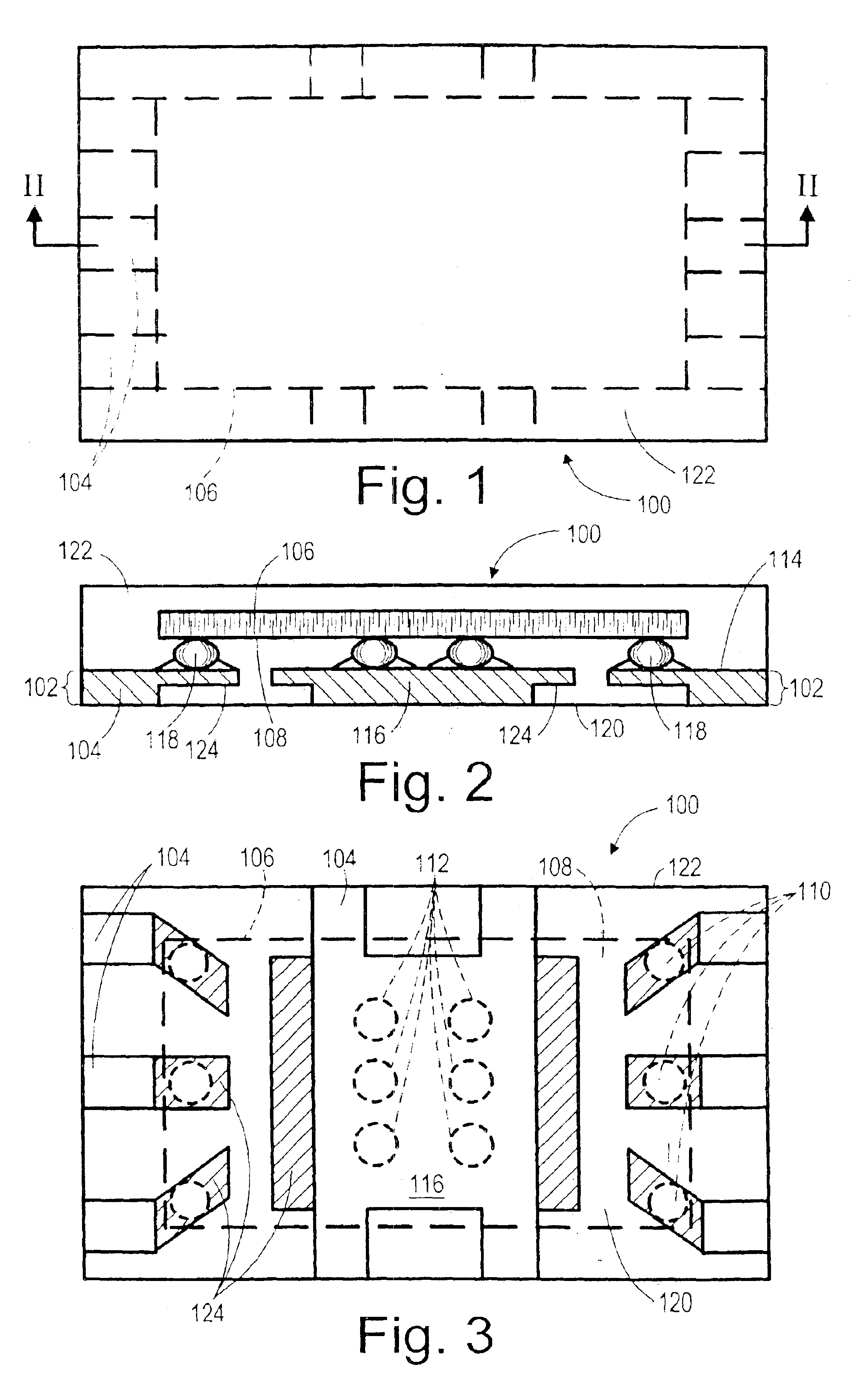

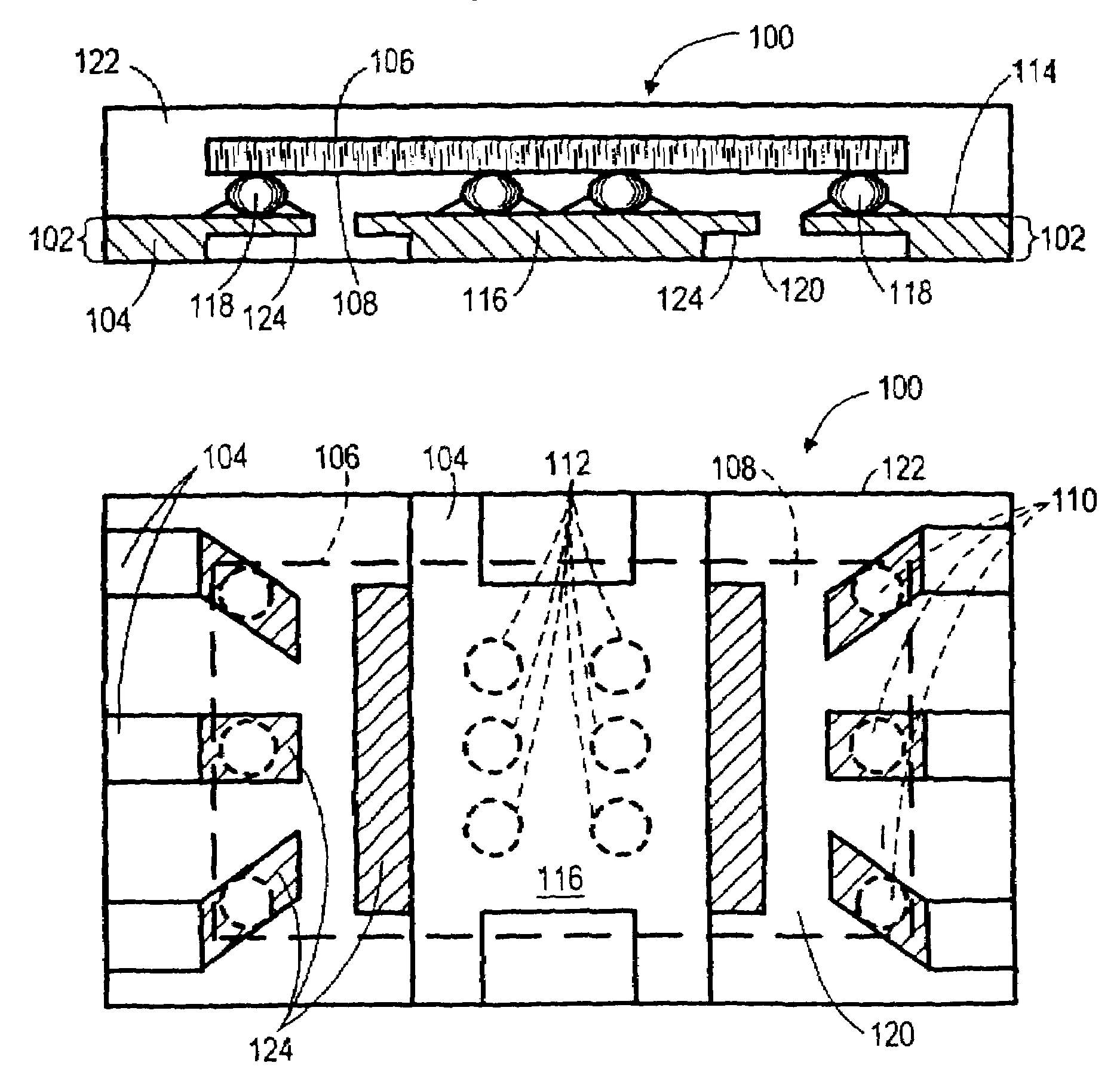

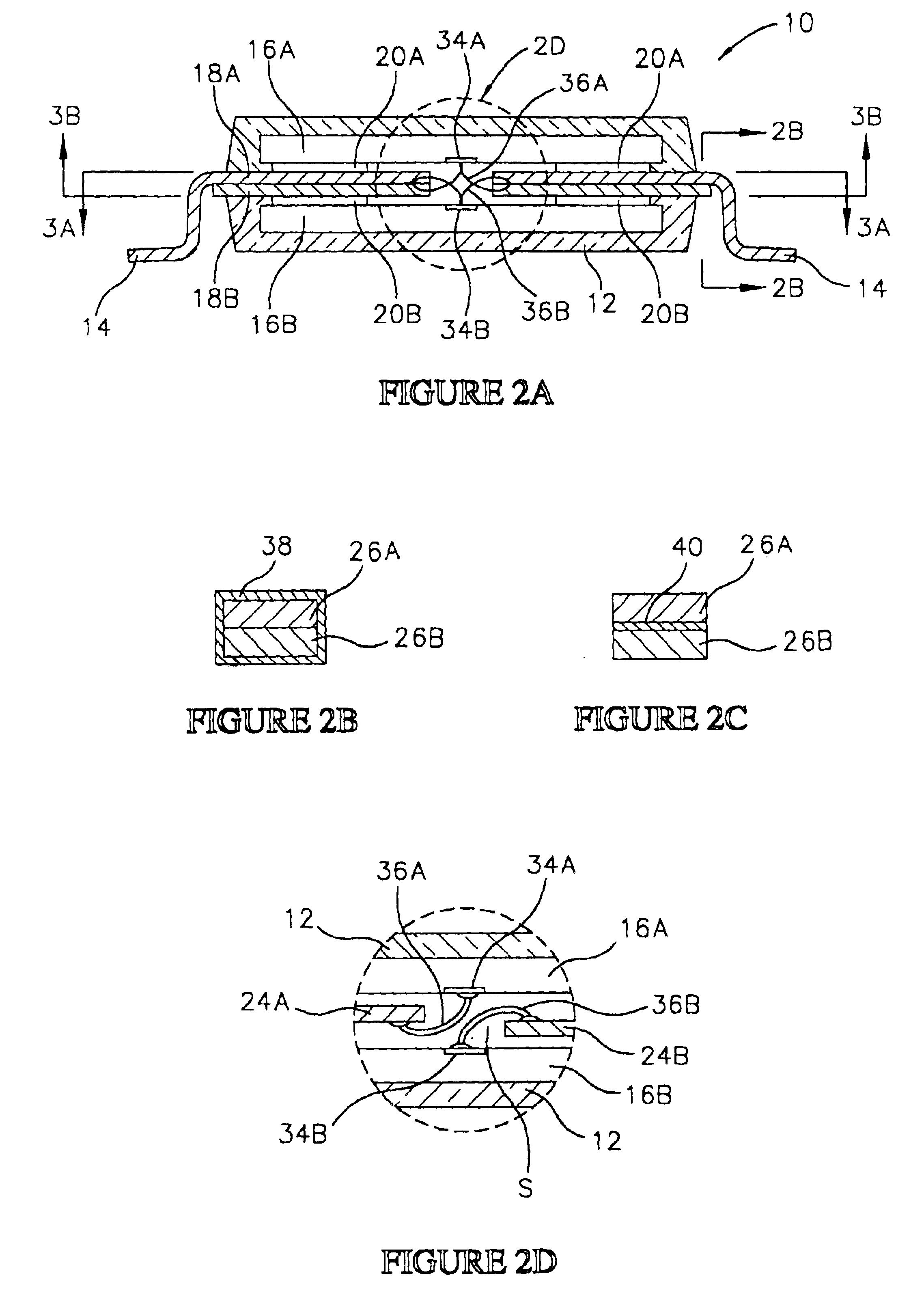

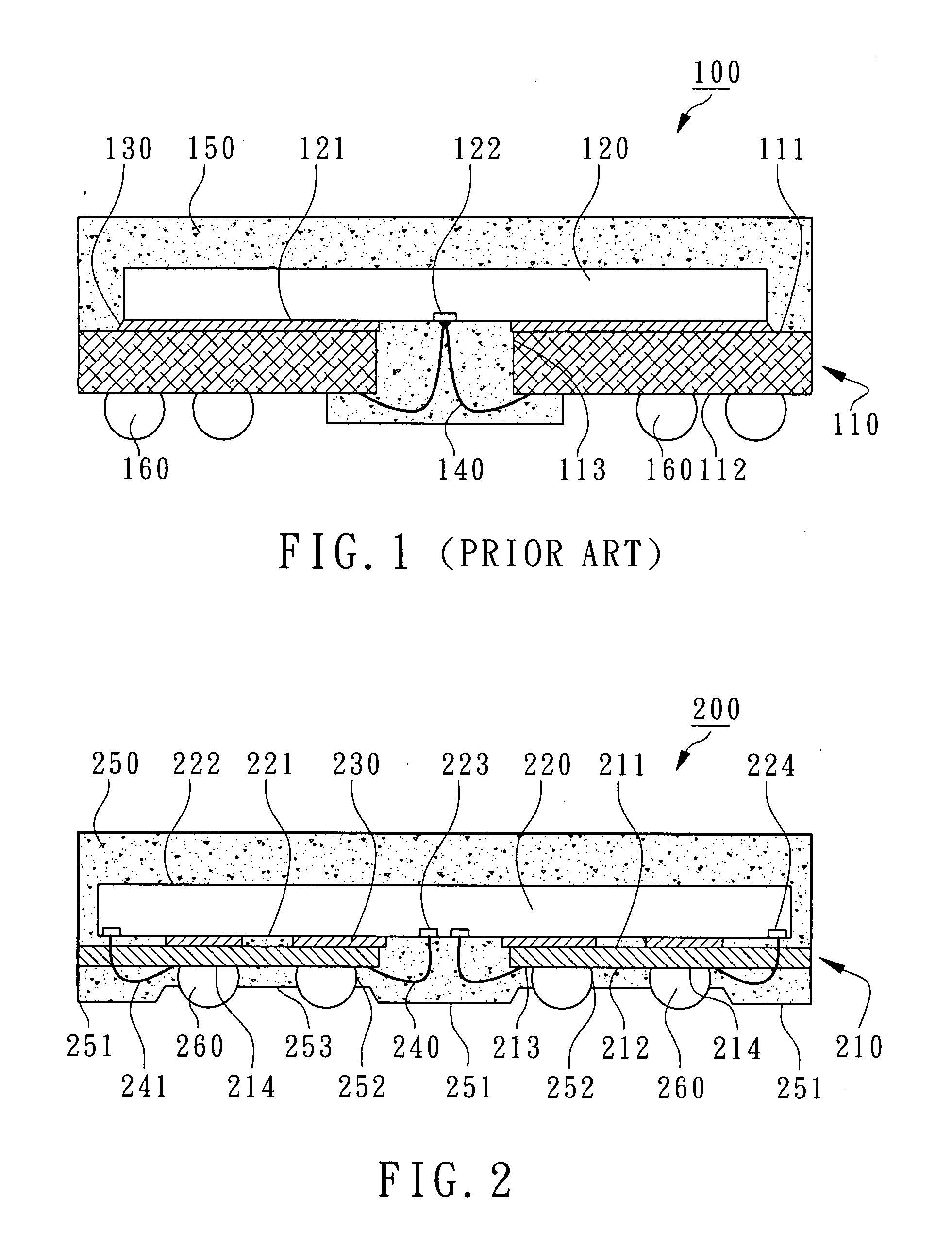

A thermally enhanced, chip-scale, Lead-on-Chip (“LOC”) semiconductor package includes a substrate having a plurality of metal lead fingers in it. A semiconductor chip having an active surface with a plurality of ground, power, and signal connection pads thereon is mounted on an upper surface of the substrate in a flip-chip electrical connection with the lead fingers. A plurality of the ground and / or the power connection pads on the chip are located in a central region thereof. Corresponding metal grounding and / or power lands are formed in the substrate at positions corresponding to the centrally located ground and / or power pads on the chip. The ground and power pads on the chip are connected to corresponding ones of the grounding and power lands in the substrate in a flip-chip connection, and a lower surface of the lands is exposed to the environment through a lower surface of the semiconductor package for connection to an external heat sink. The lands can be connected to selected ones of the lead fingers, and / or combined with one another for even greater thermal and electrical conductivity.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Thermally enhanced chip scale lead on chip semiconductor package and method of making same

InactiveUS7045883B1Enhanced thermalReliable electrical connectionSemiconductor/solid-state device detailsSolid-state devicesLead on chipElectrical connection

A thermally enhanced, chip-scale, Lead-on Chip (“LOC”) semiconductor packages includes a substrate having a plurality of metal lead fingers in it. A semiconductor chip having an active surface with a plurality of ground, power, and signal connection pads thereon is mounted on an upper surface of the substrate in a flip-chip electrical connection with the lead fingers. A plurality of the ground and / or the power connection pads on the chip are located in a central region thereof. Corresponding metal grounding and / or power lands are formed in the substrate at positions corresponding to the centrally located ground and / or power pads on the chip. The ground and power pads on the chip are connected to corresponding ones of the grounding and power lands in the substrate in a flip-chip connection, and a lower surface of the lands is exposed to the environment through a lower surface of the semiconductor package for connection to an external heat sink. The lands can be connected to selected ones of the lead fingers, and / or combined with one another for even greater thermal and electrical conductivity.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

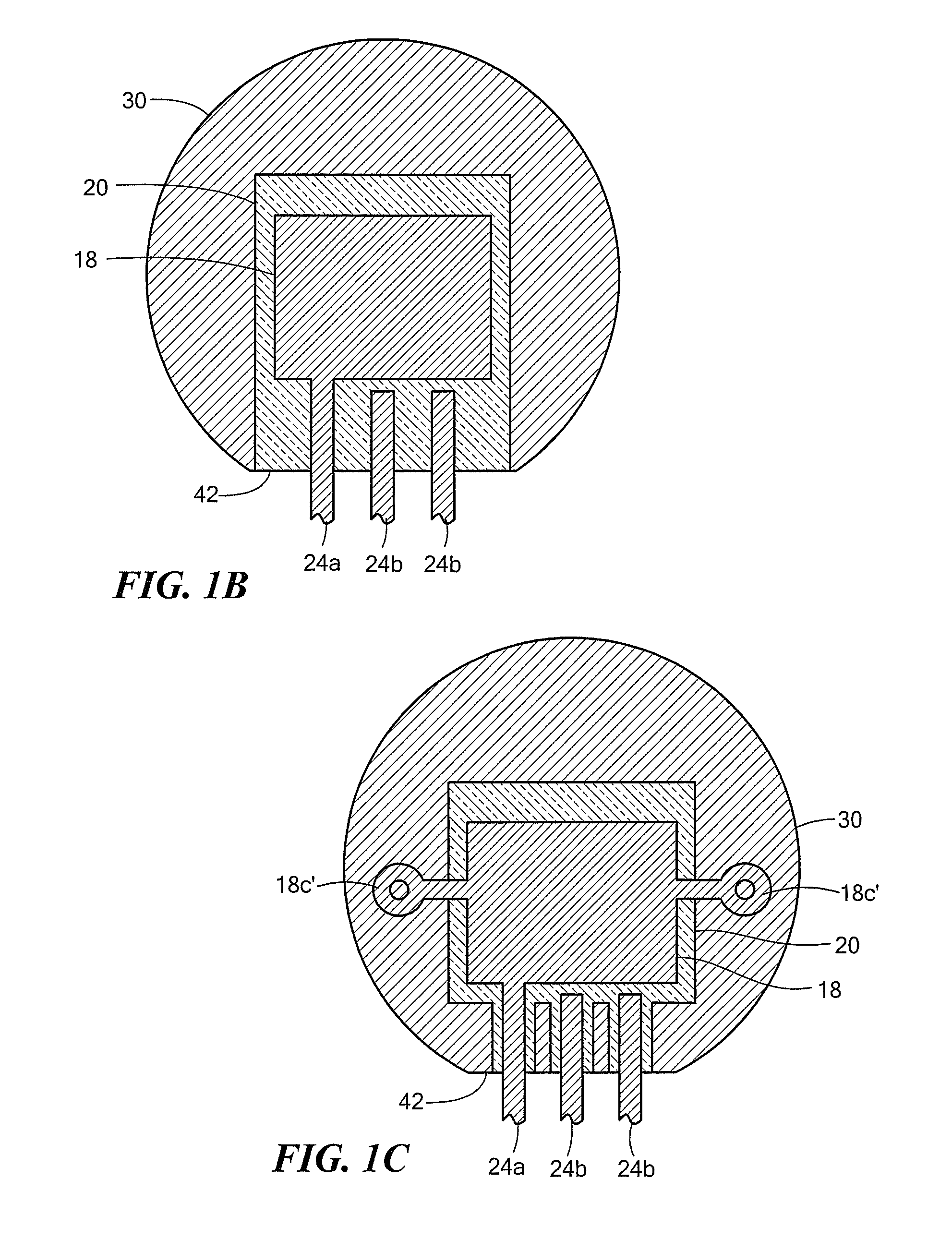

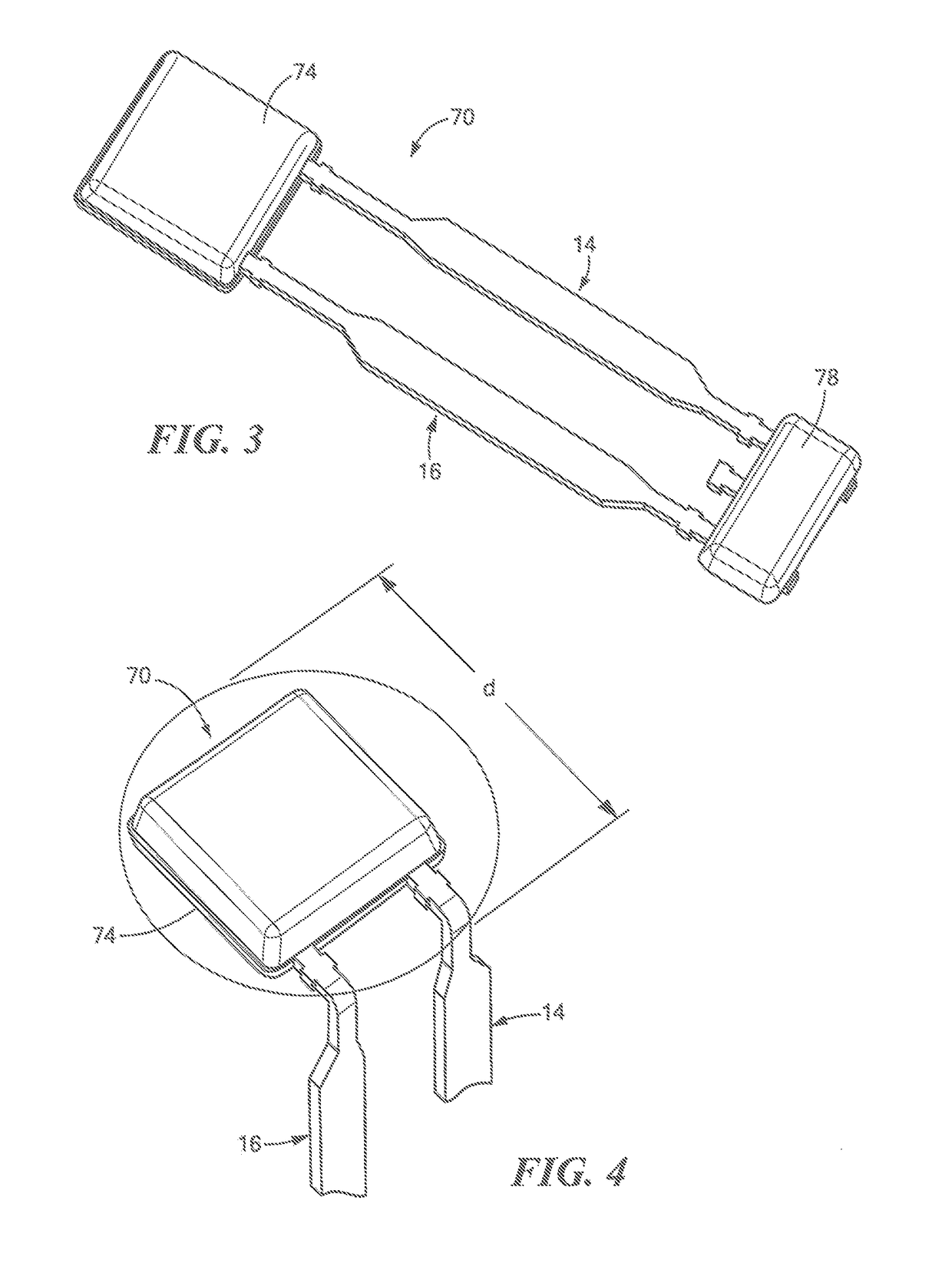

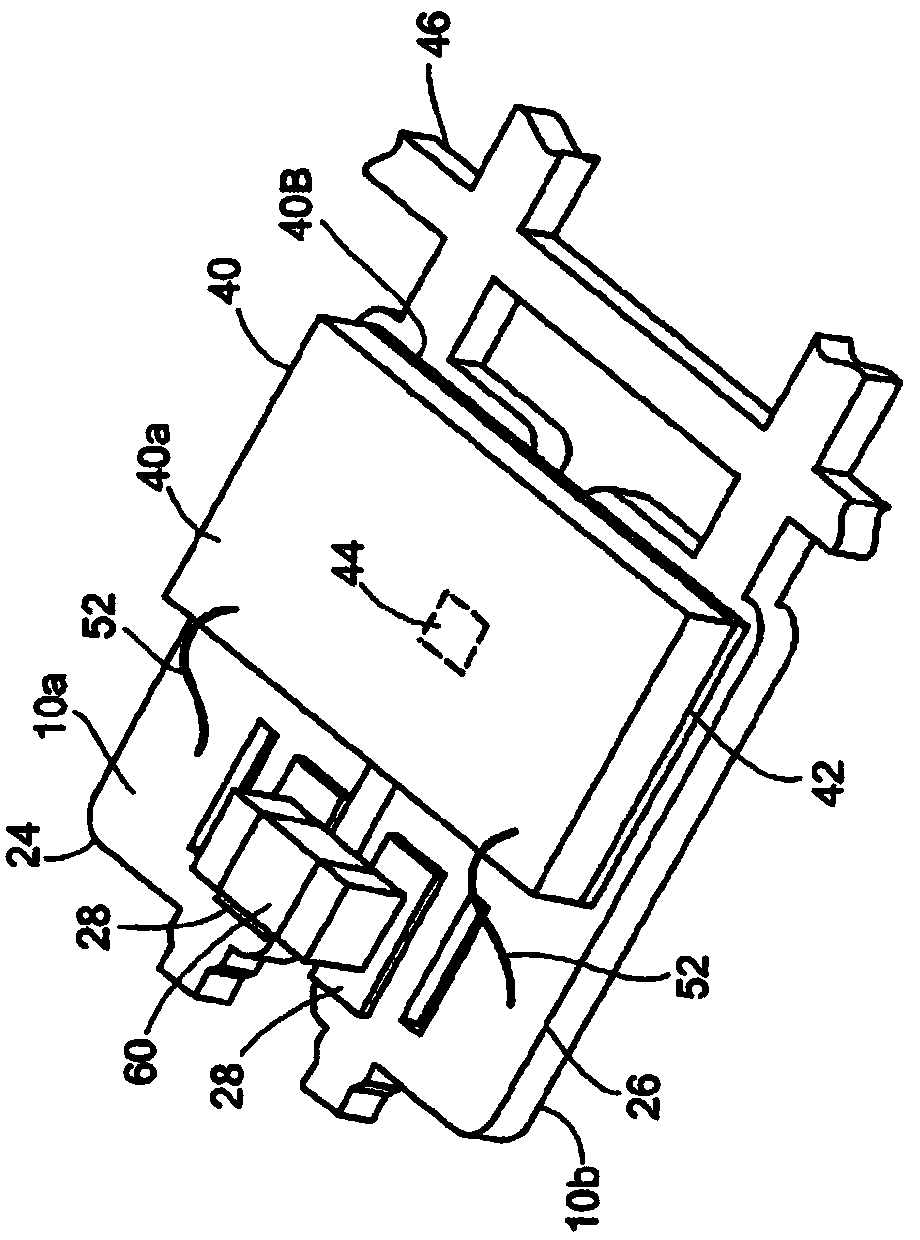

Magnetic Field Sensor Integrated Circuit with Integral Ferromagnetic Material

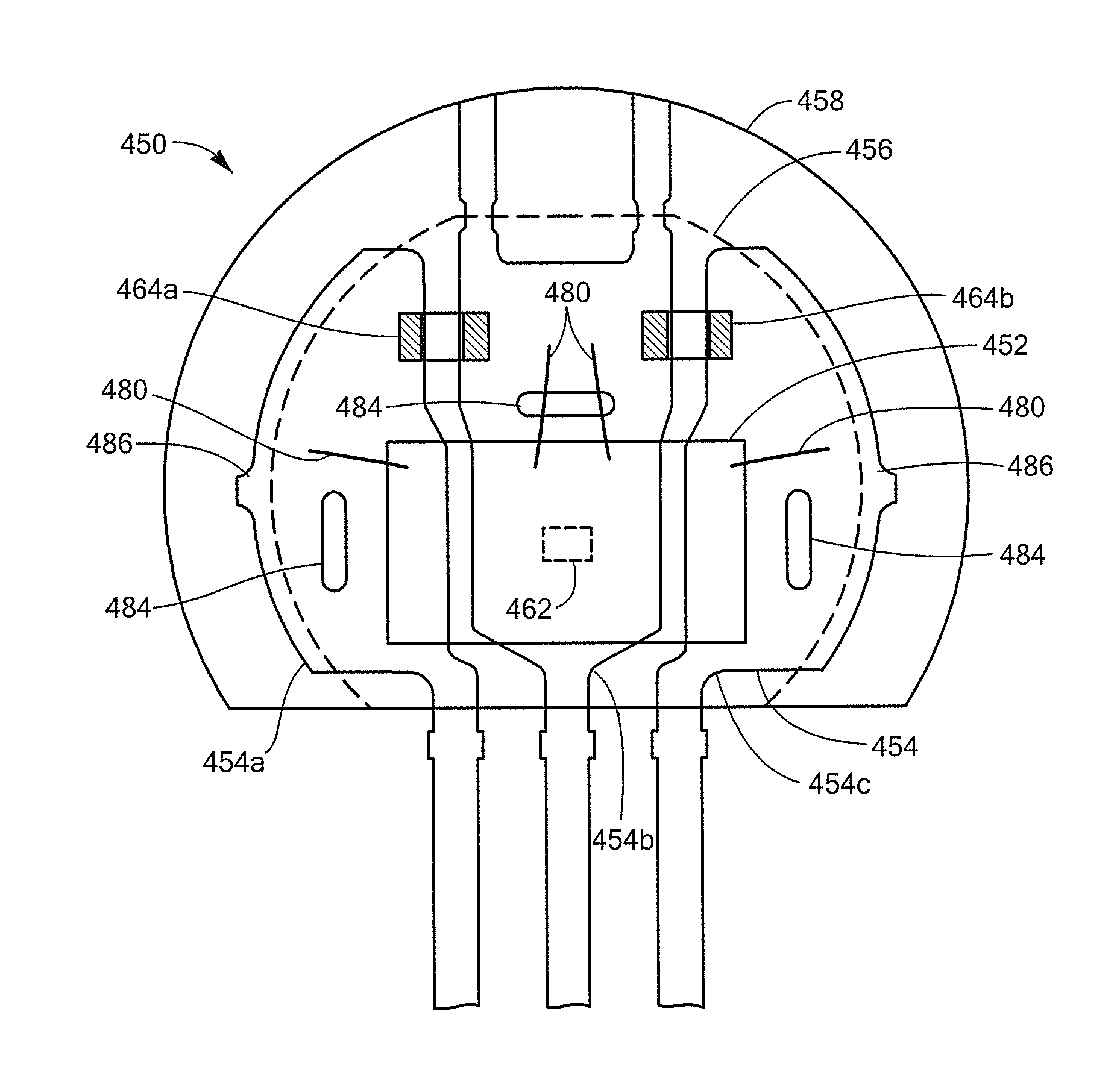

A magnetic field sensor includes a lead frame, a semiconductor die supporting a magnetic field sensing element, a non-conductive mold material enclosing the die and a portion of the lead frame, a ferromagnetic mold material secured to the non-conductive mold material and a securing mechanism to securely engage the mold materials. The ferromagnetic mold material may comprise a soft ferromagnetic material to form a concentrator or a hard ferromagnetic material to form a bias magnet. The ferromagnetic mold material may be tapered and includes a non-contiguous central region, as may be an aperture or may contain the non-conductive mold material or an overmold material. Further embodiments include die up, lead on chip, and flip-chip arrangements, wafer level techniques to form the concentrator or bias magnet, integrated components, such as capacitors, on the lead frame, and a bias magnet with one or more channels to facilitate overmolding.

Owner:ALLEGRO MICROSYSTEMS INC

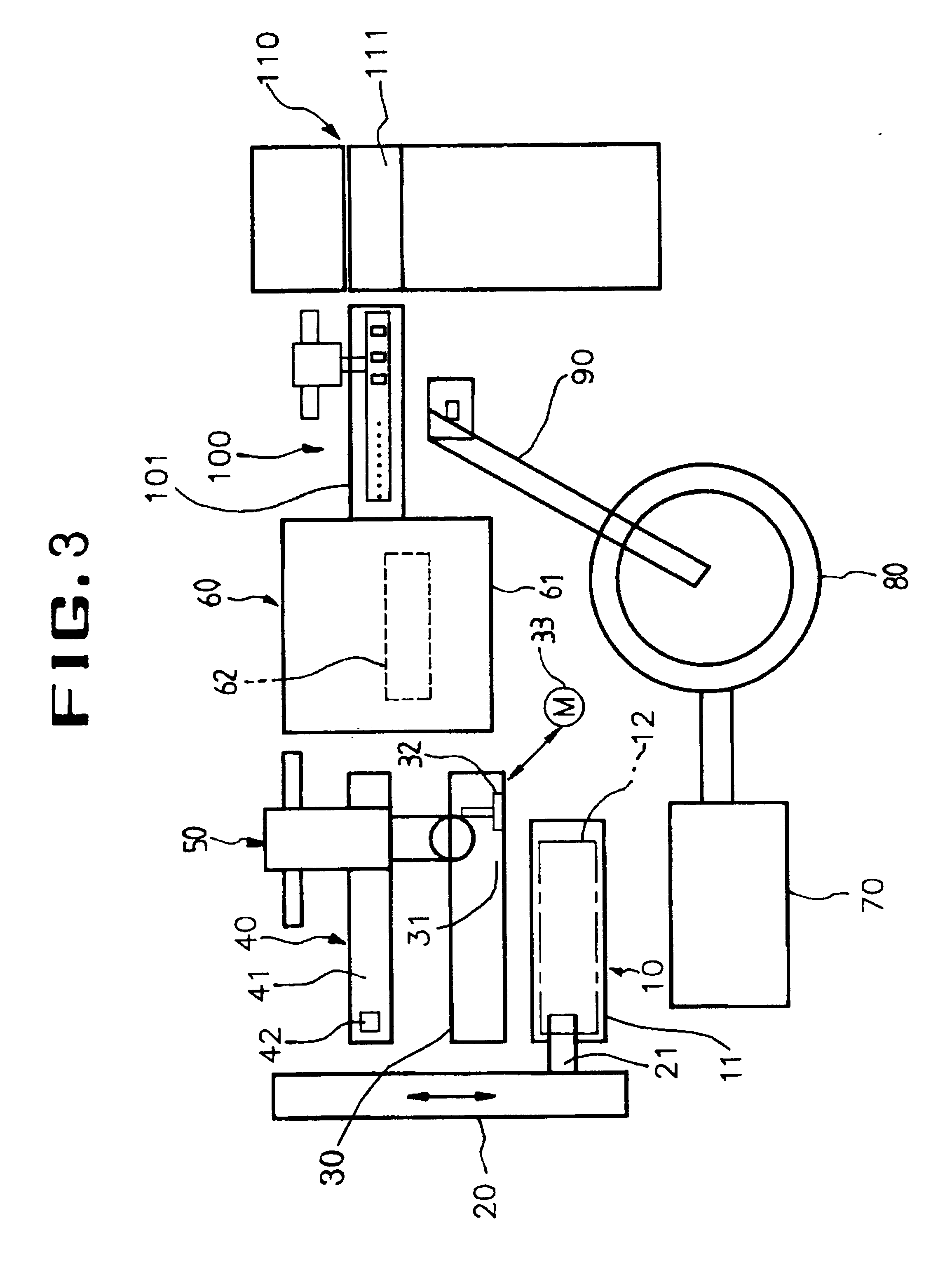

Die bonding apparatus

A die bonding apparatus includes: a lead frame supply station for accommodating a plurality of lead frames; a frame transferring device for picking up the lead frame and transferring it to an Ag epoxy application table or to a traveling rail; a frame fixing station for fixing the lead frame to the Ag epoxy application table by suction power of a vacuum pump or moving it back and forth through actuation of a motor; an Ag epoxy supply station for ejecting a predetermined amount of Ag epoxy through a nozzle to the top surface of the lead frame; a moving device for moving the lead frame forward on the traveling rail; a preheating station for receiving the lead frame into a magazine and preheating it; a wafer placement station for transferring wafers sequentially supplied from a wafer supply station to a predetermined location through rotation; a die transferring device for picking up a die and transferring it to a work site for die bonding; a die bonding station for precisely bonding the die to a site where a tape is stuck or Ag epoxy is applied in the lead frame according to lead on chip (LOC) or normal feature of the lead frame; and a stocker for accommodating the lead frame into an internal magazine.

Owner:SAMSUNG ELECTRONICS CO LTD

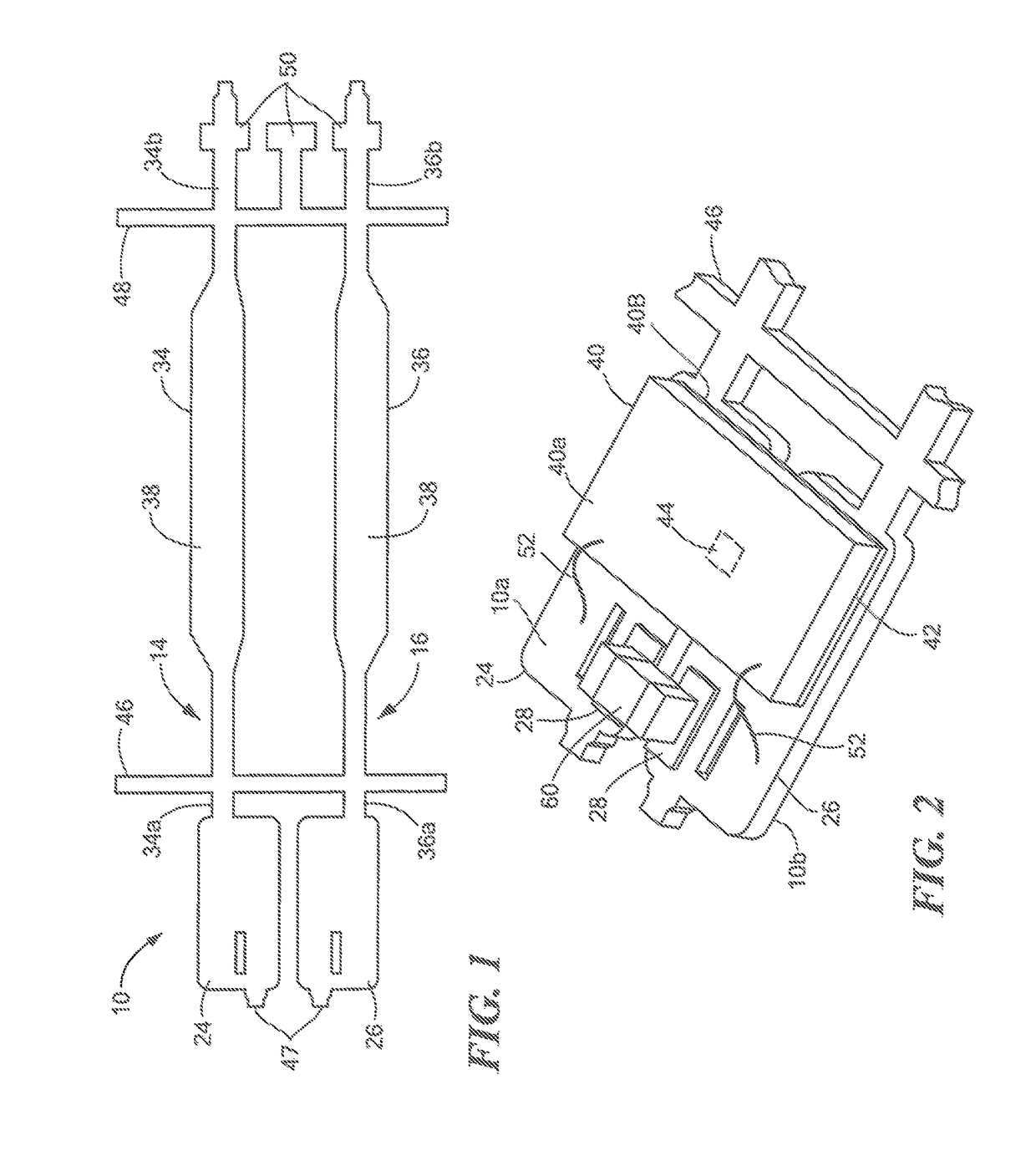

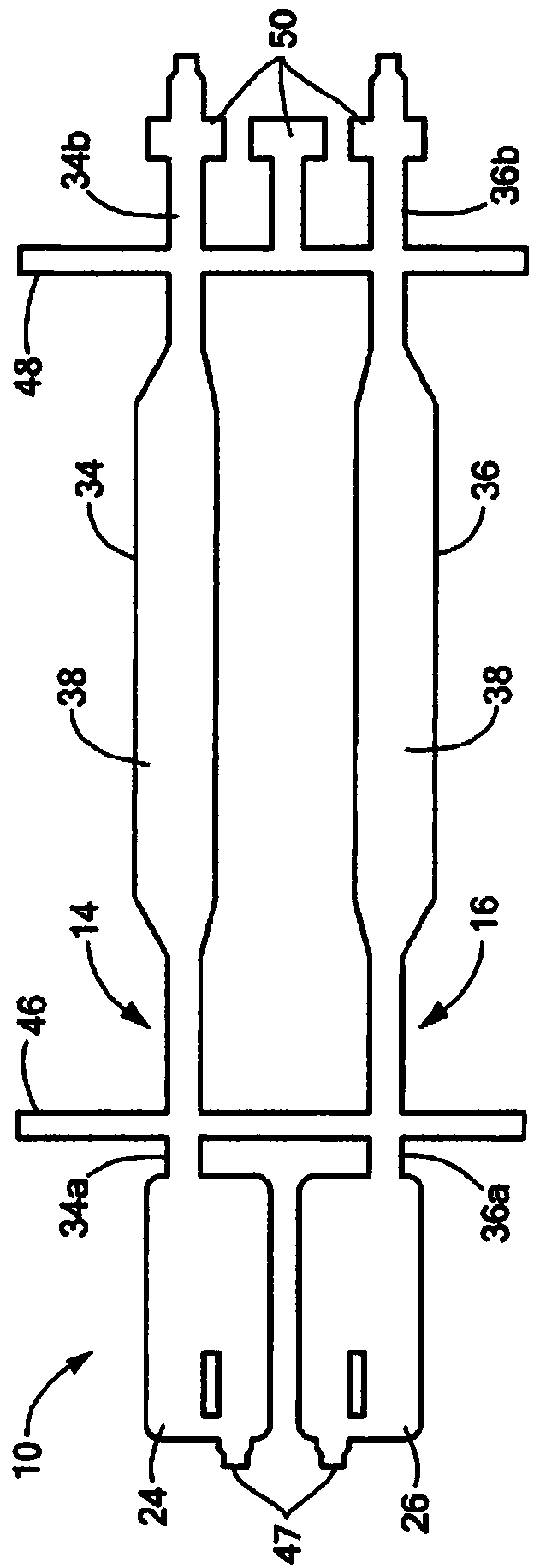

Integrated circuit package having a split lead frame

A magnetic field sensor includes a lead frame having a plurality of leads, at least two of which have a connection portion and a die attach portion. A semiconductor die is attached to the die attach portion of the at least two leads. The sensor further includes at least one wire bond coupled between the die and a first surface of the lead frame. The die is attached to a second, opposing surface of the lead frame in a lead on chip configuration. In some embodiments, at least one passive component is attached to the die attach portion of at least two leads.

Owner:ALLEGRO MICROSYSTEMS INC

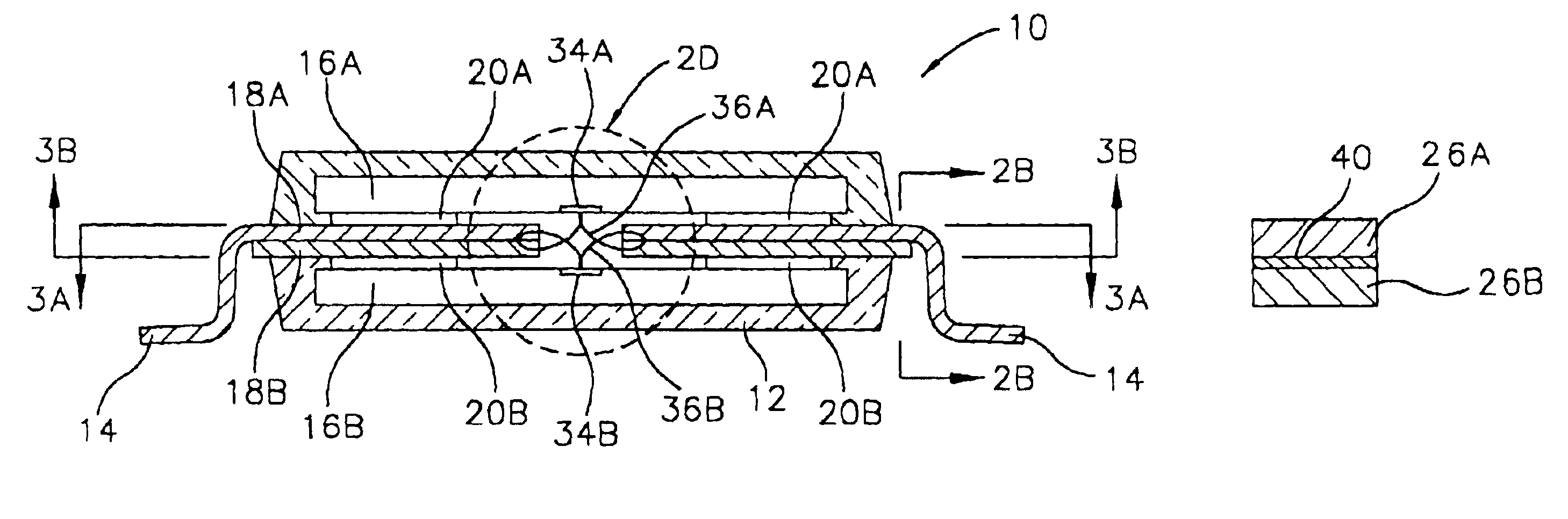

Method for fabricating semiconductor packages with stacked dice and leadframes

InactiveUS6858467B2Semiconductor/solid-state device detailsSolid-state devicesLead on chipSemiconductor package

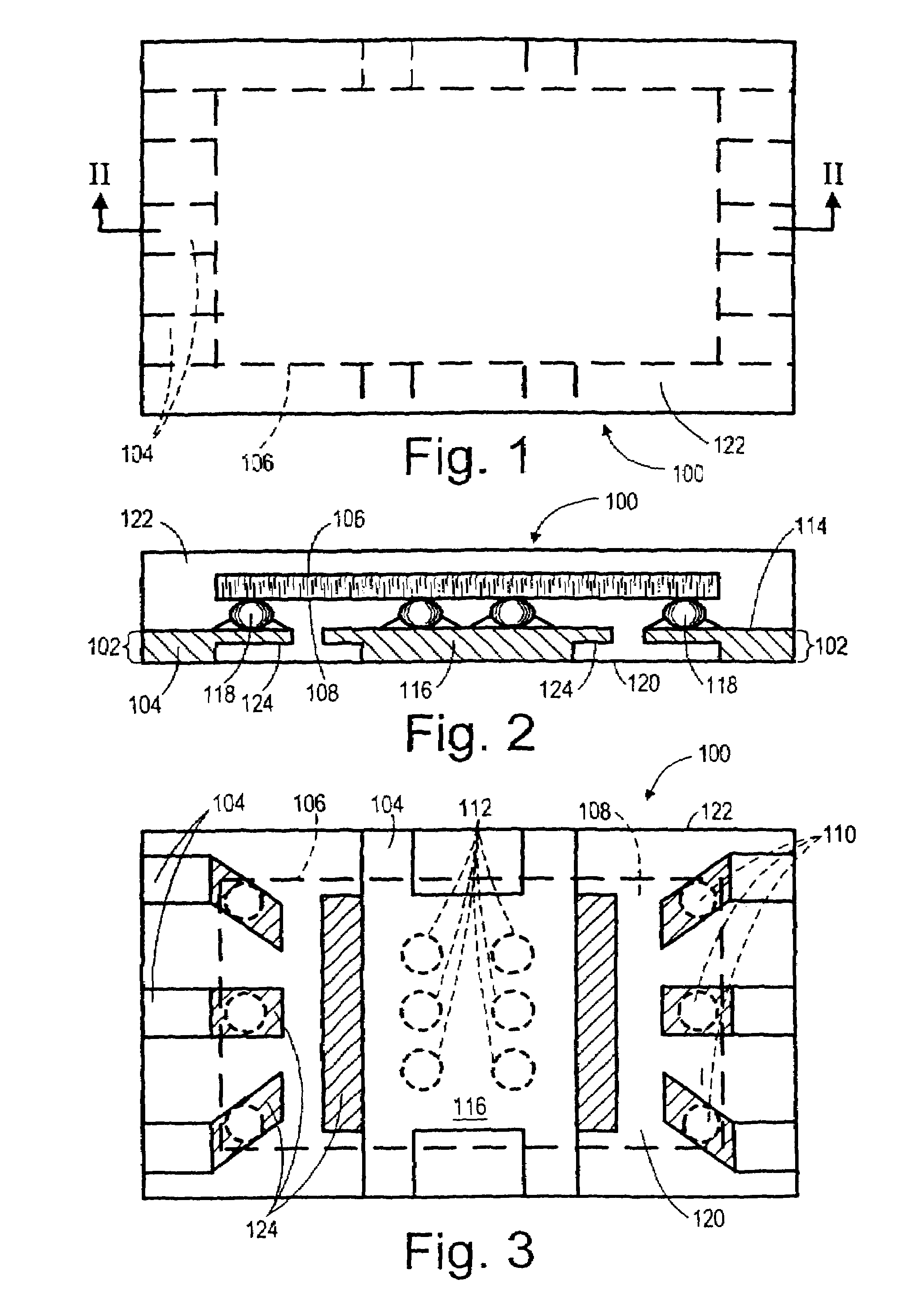

A semiconductor package, and a method for fabricating the package are provided. The package includes a plastic body, and a pair of stacked semiconductor dice encapsulated in the plastic body, and wire bonded to separate leadframe segments. A first leadframe segment includes lead fingers configured to support a first semiconductor die of the stacked pair, and to form terminal leads of the package. A second leadframe segment is attached to the first leadframe segment, and includes lead fingers that support a second semiconductor die of the stacked pair. The lead fingers of the second leadframe are in physical and electrical contact with the leadfingers of the first leadframe. In addition, tip portions of the lead fingers of the first leadframe segment are staggered relative to tip portions of the lead fingers of the second leadframe segment to provide space for bond wires. The lead fingers support the dice during encapsulation, and also provide a heat conductive path for transferring heat from the dice during operation. The package can be constructed using lead-on-chip leadframes and conventional semiconductor packaging equipment.

Owner:MICRON TECH INC

Thermally enhanced chip scale lead on chip semiconductor package and method of making same

InactiveUS7064009B1Enhanced thermalReliable electrical connectionSemiconductor/solid-state device detailsSolid-state devicesLead on chipElectrical connection

A thermally enhanced, chip-scale, Lead-on-Chip (“LOC”) semiconductor package includes a substrate having a plurality of metal lead fingers in it. A semiconductor chip having an active surface with a plurality of ground, power, and signal connection pads thereon is mounted on an upper surface of the substrate in a flip-chip electrical connection with the lead fingers. A plurality of the ground and / or the power connection pads on the chip are located in a central region thereof. Corresponding metal grounding and / or power lands are formed in the substrate at positions corresponding to the centrally located ground and / or power pads on the chip. The ground and power pads on the chip are connected to corresponding ones of the grounding and power lands in the substrate in a flip-chip connection, and a lower surface of the lands is exposed to the environment through a lower surface of the semiconductor package for connection to an external heat sink. The lands can be connected to selected ones of the lead fingers, and / or combined with one another for even greater thermal and electrical conductivity.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Packaged semiconductor grain

InactiveCN1921098AShorten the timeIncrease the number ofSemiconductor/solid-state device detailsSolid-state devicesLead on chipEngineering

A semiconductor die featuring vertical rows of bonding pad structures is disclosed. The rows of bonding pad structures are located vertically in the Y direction, or traversing the width of the semiconductor die. A vertical row of bonding pad structures is located on each side of the semiconductor die while a third vertical row of bonding pad structures is located in the center of the semiconductor die. A first set of wire bonds connect each bonding pad structure located on the sides of the semiconductor die to a conductive lead structure located on a ceramic package. A second set of wire bonds connect each bonding pad structure located in the center of the semiconductor die to a lead on chip (LOC) structure located on the semiconductor die. The configuration of only vertical rows of bonding pad structures allows optimized parallel testing of the completed semiconductor chip to be accomplished when compared to testing performed on a semiconductor chip featuring both vertical and horizontal rows of bonding pad structures located on all sides of the semiconductor chip.

Owner:ETRON TECH INC

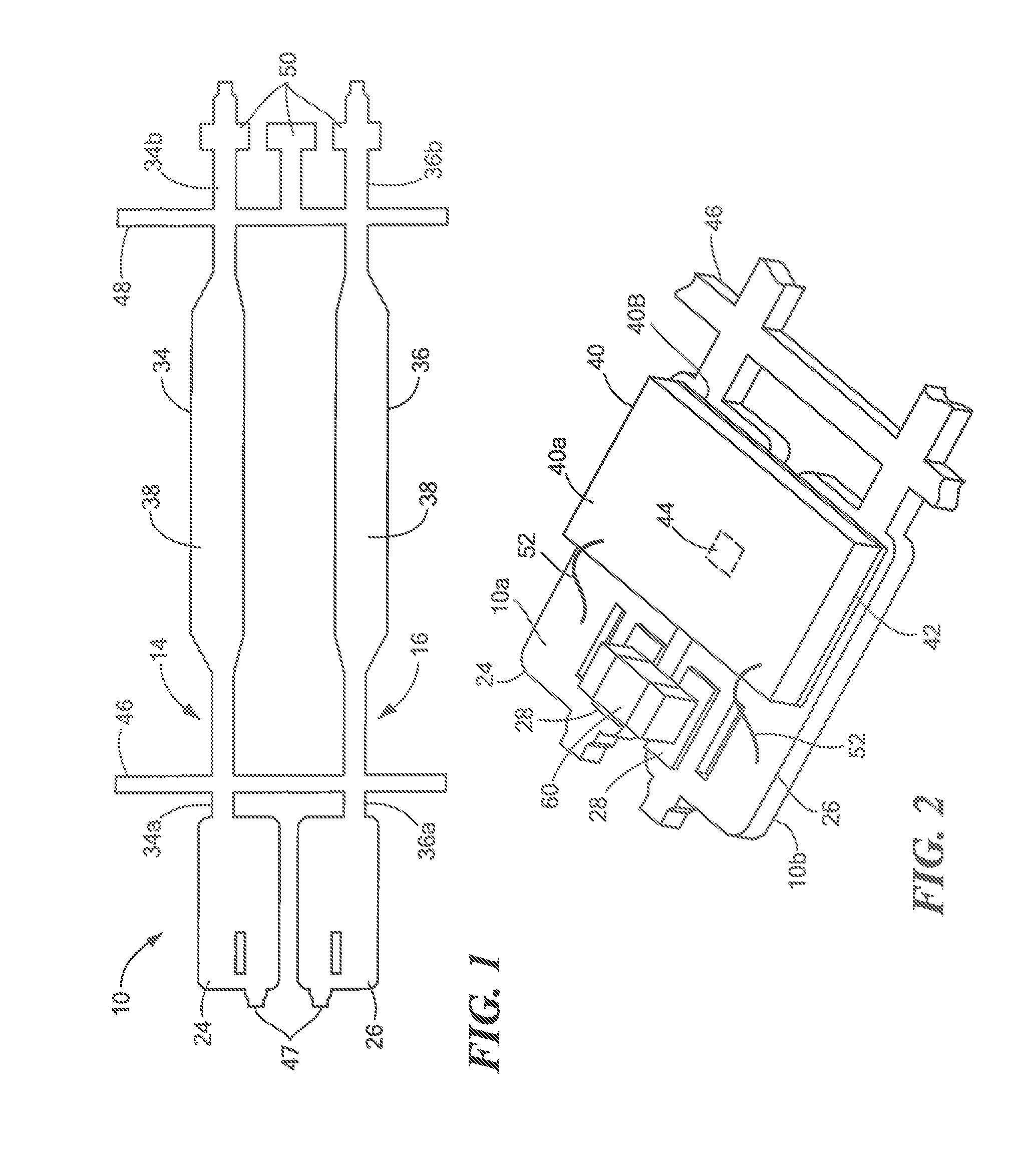

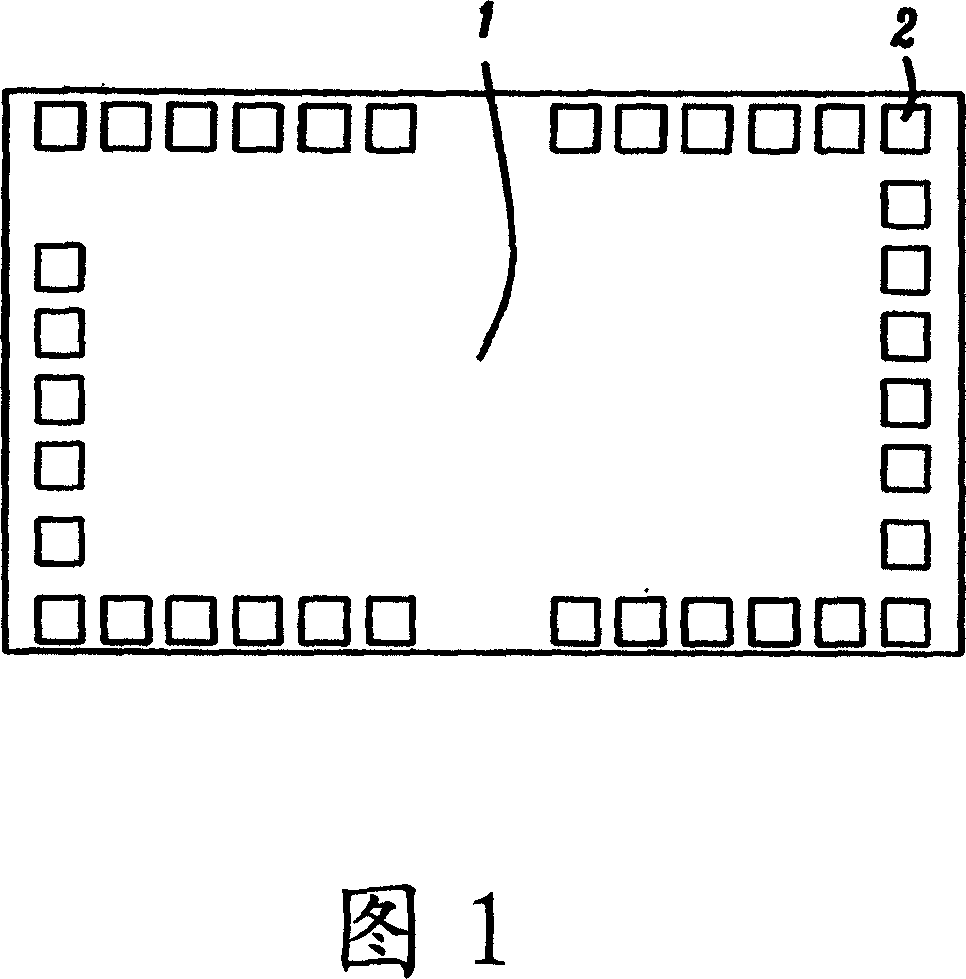

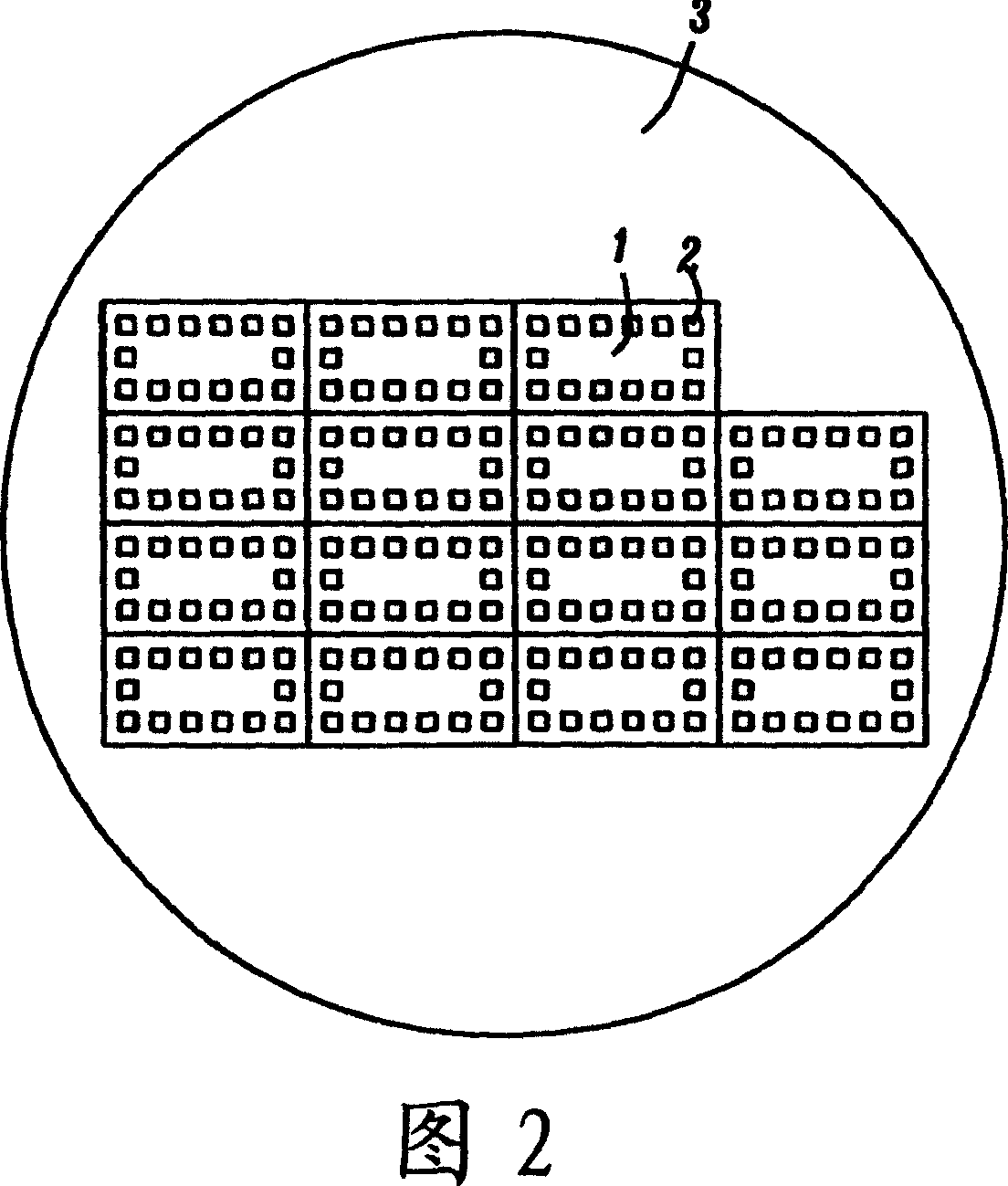

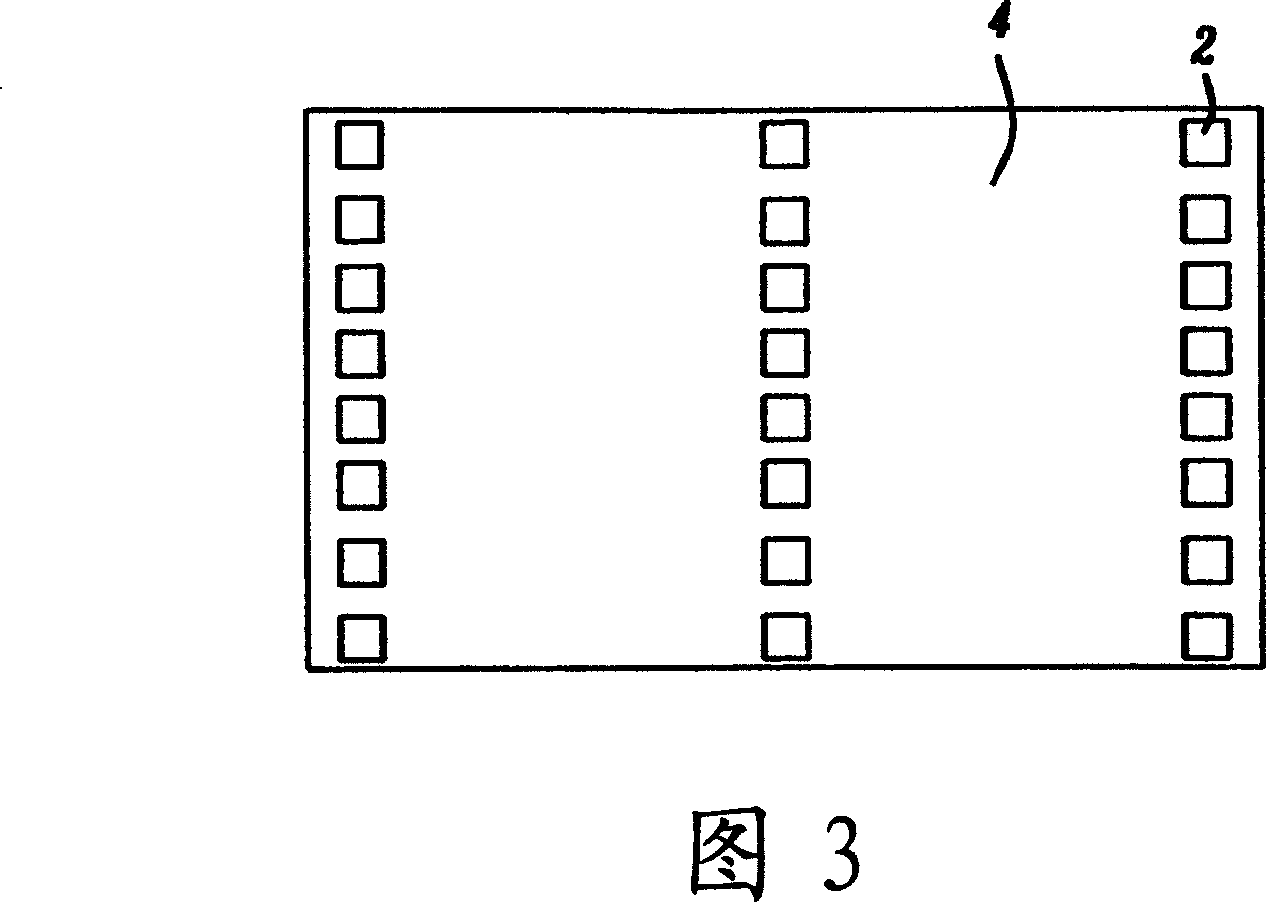

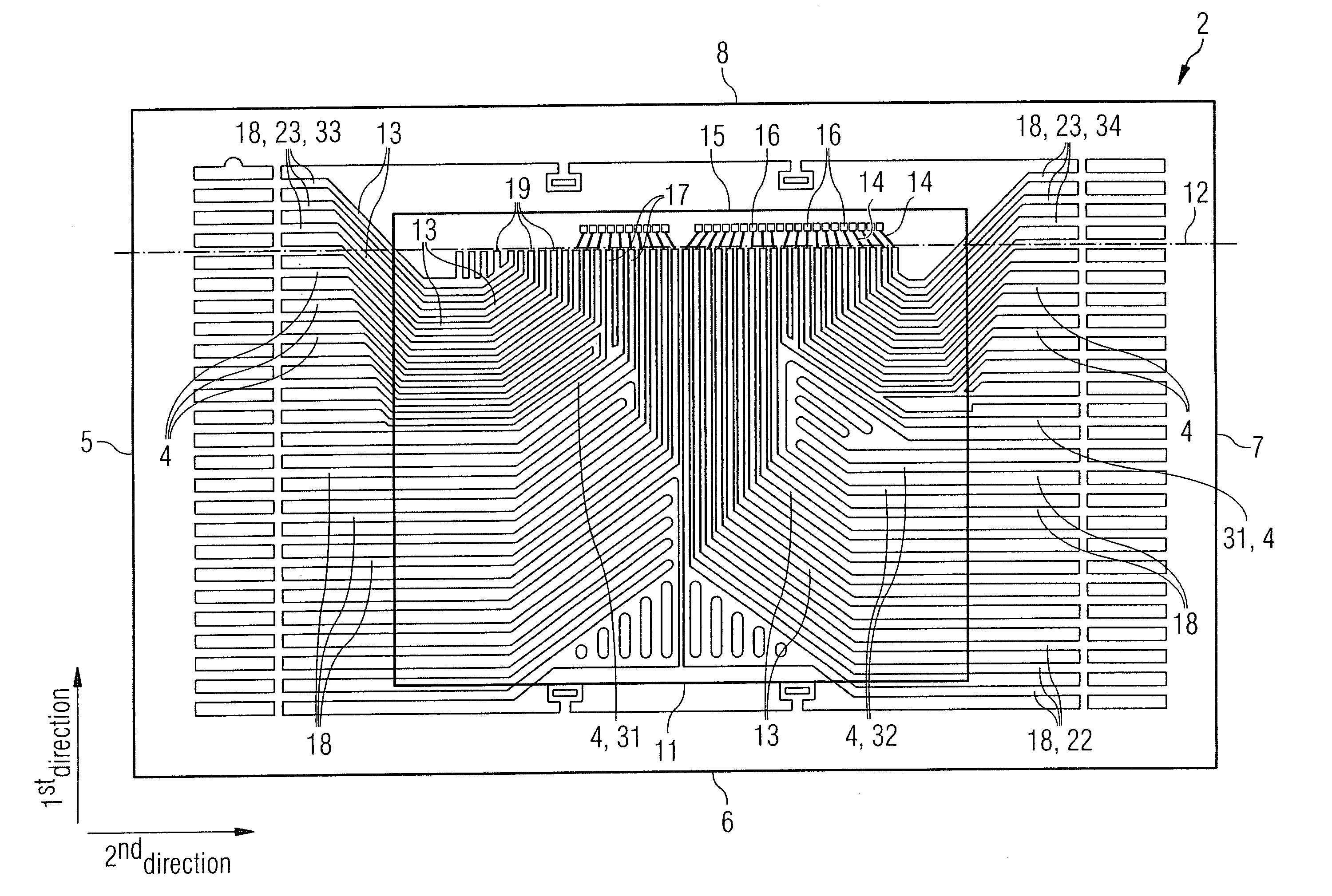

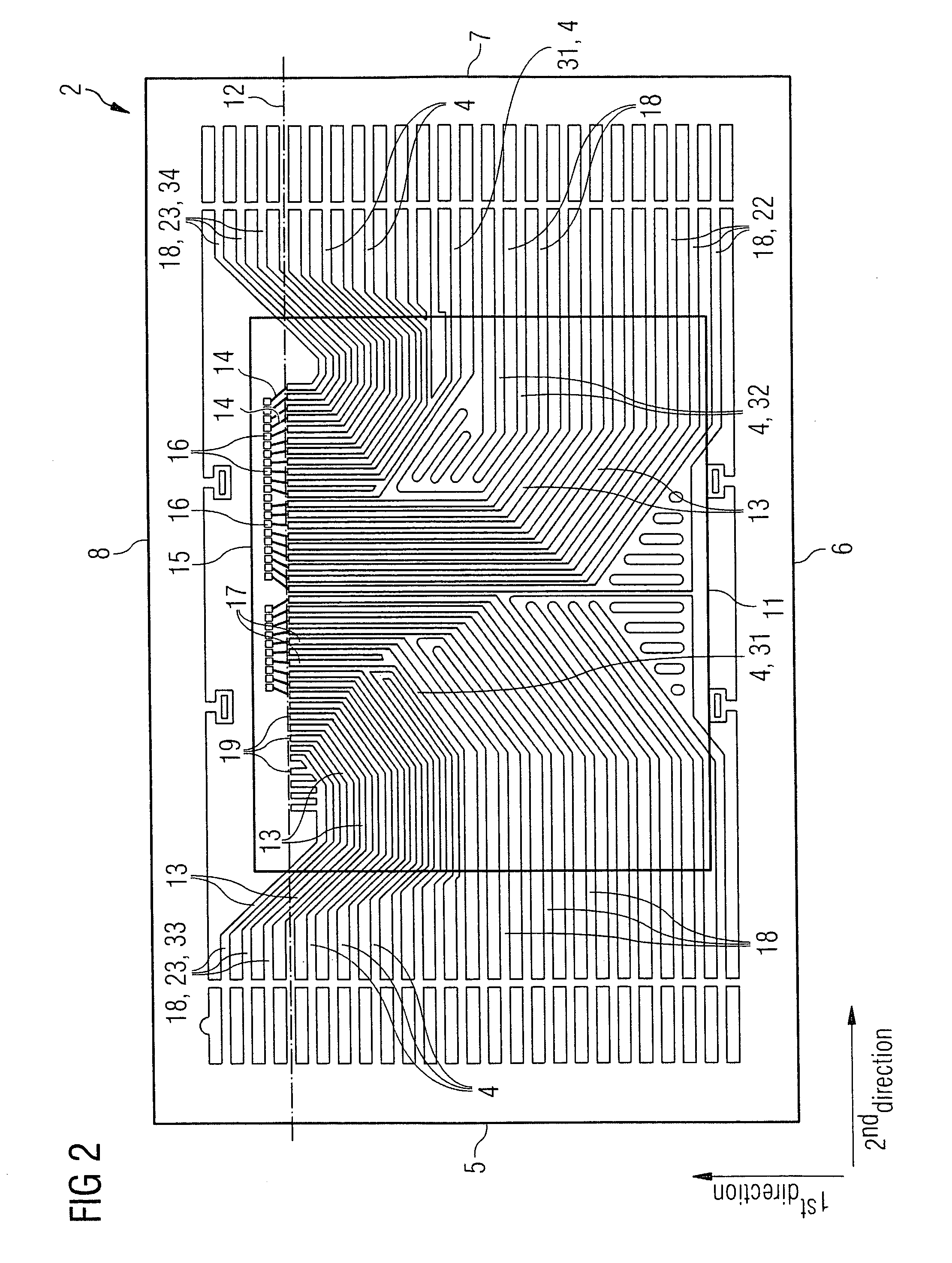

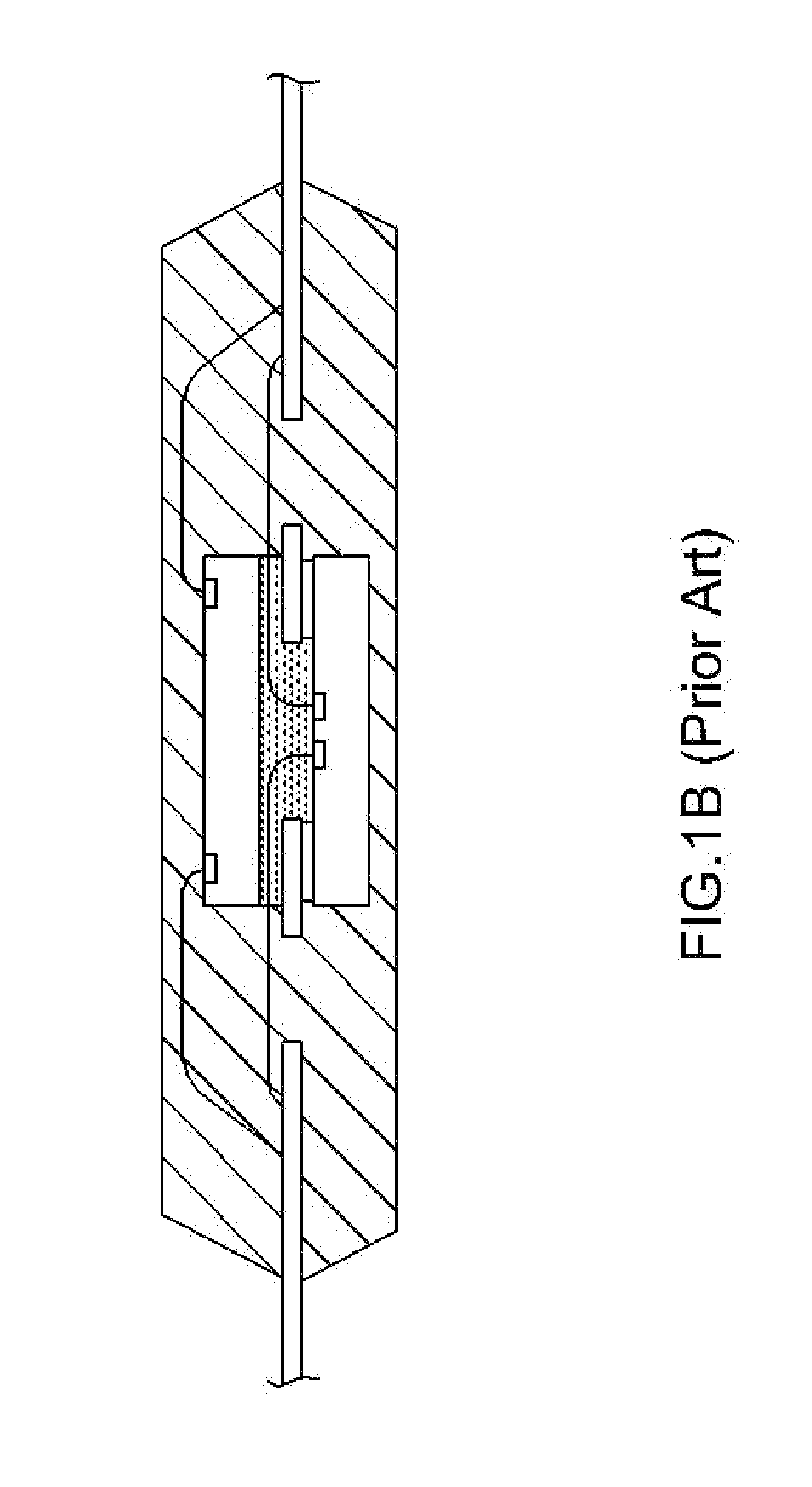

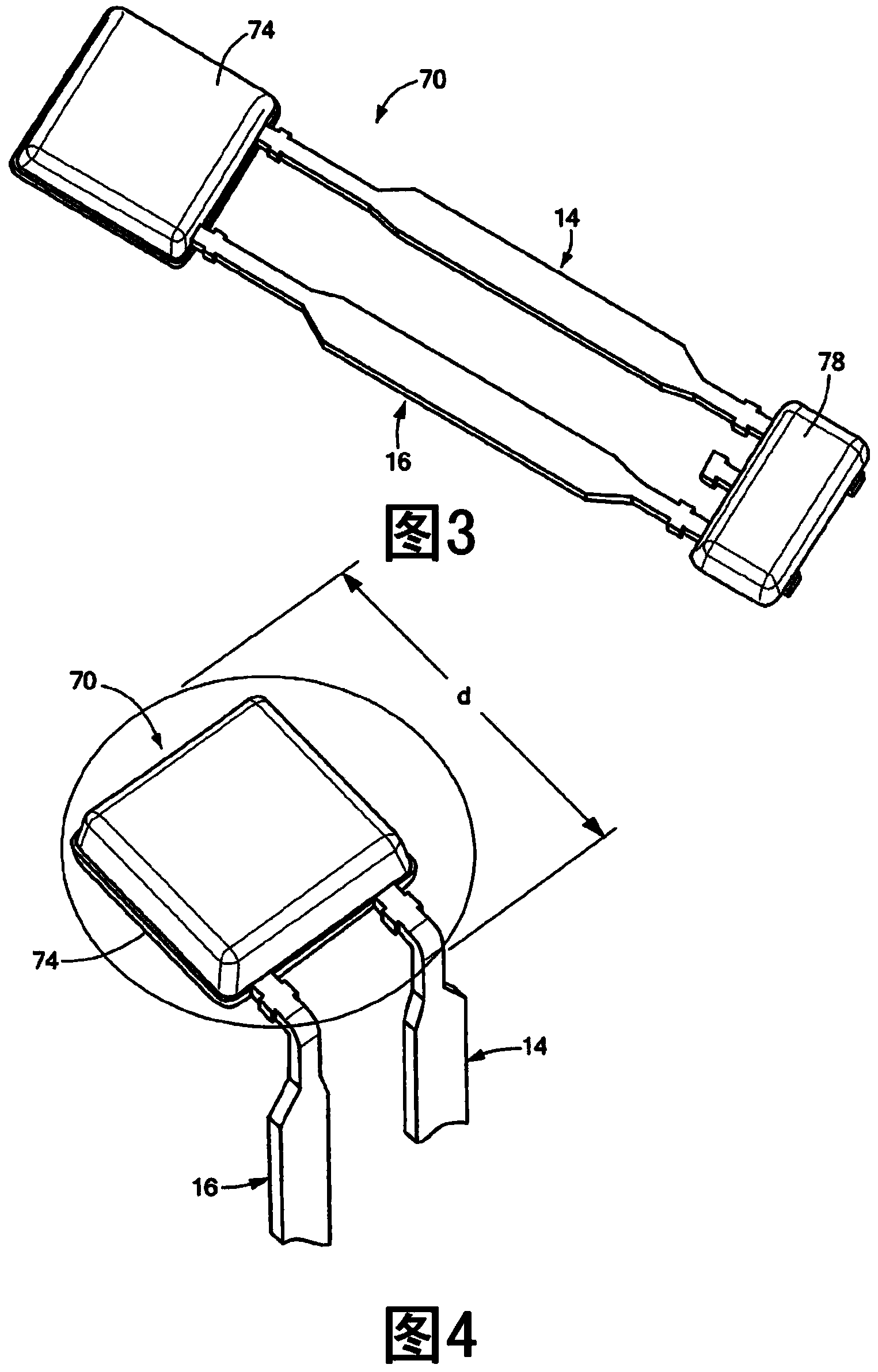

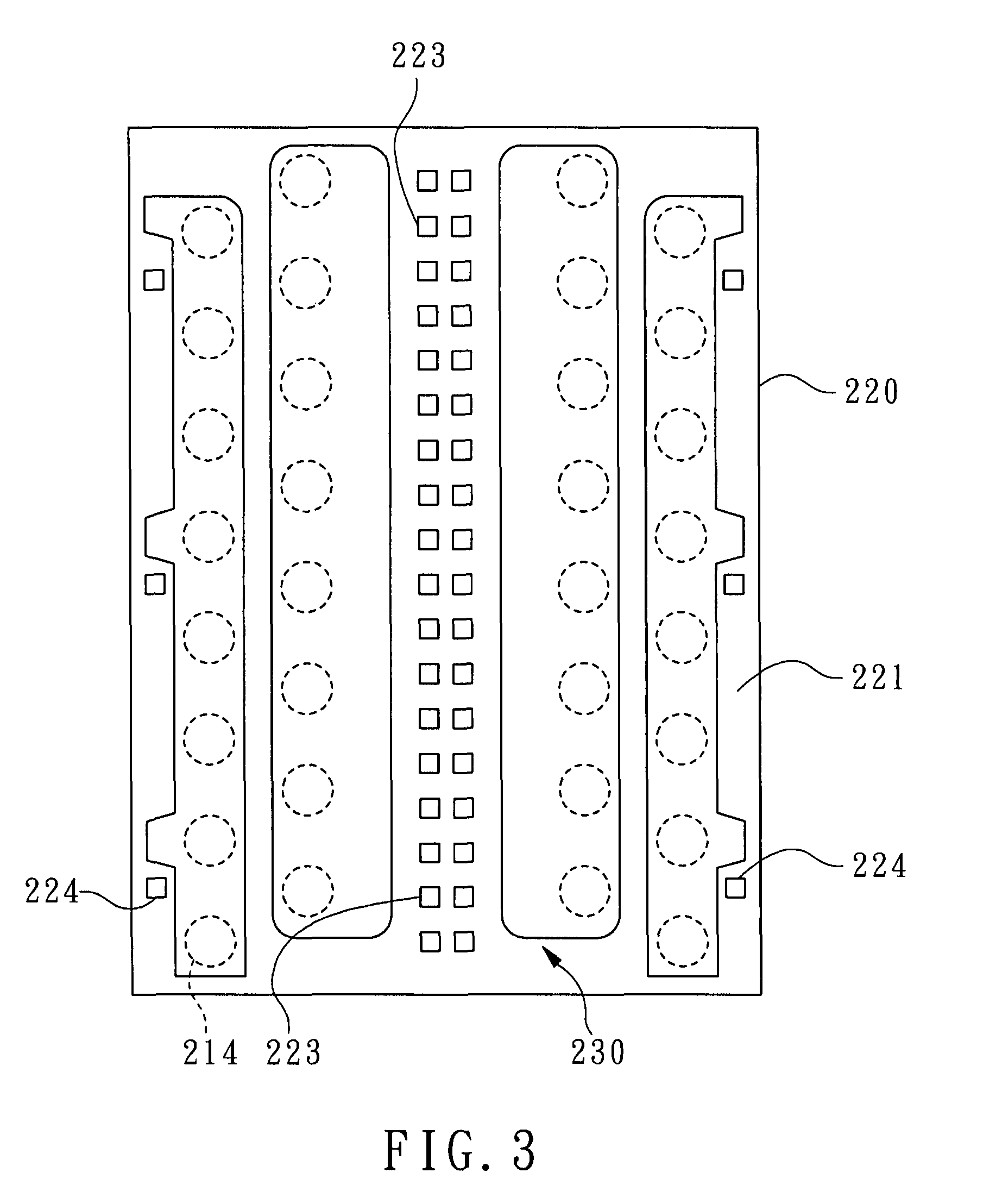

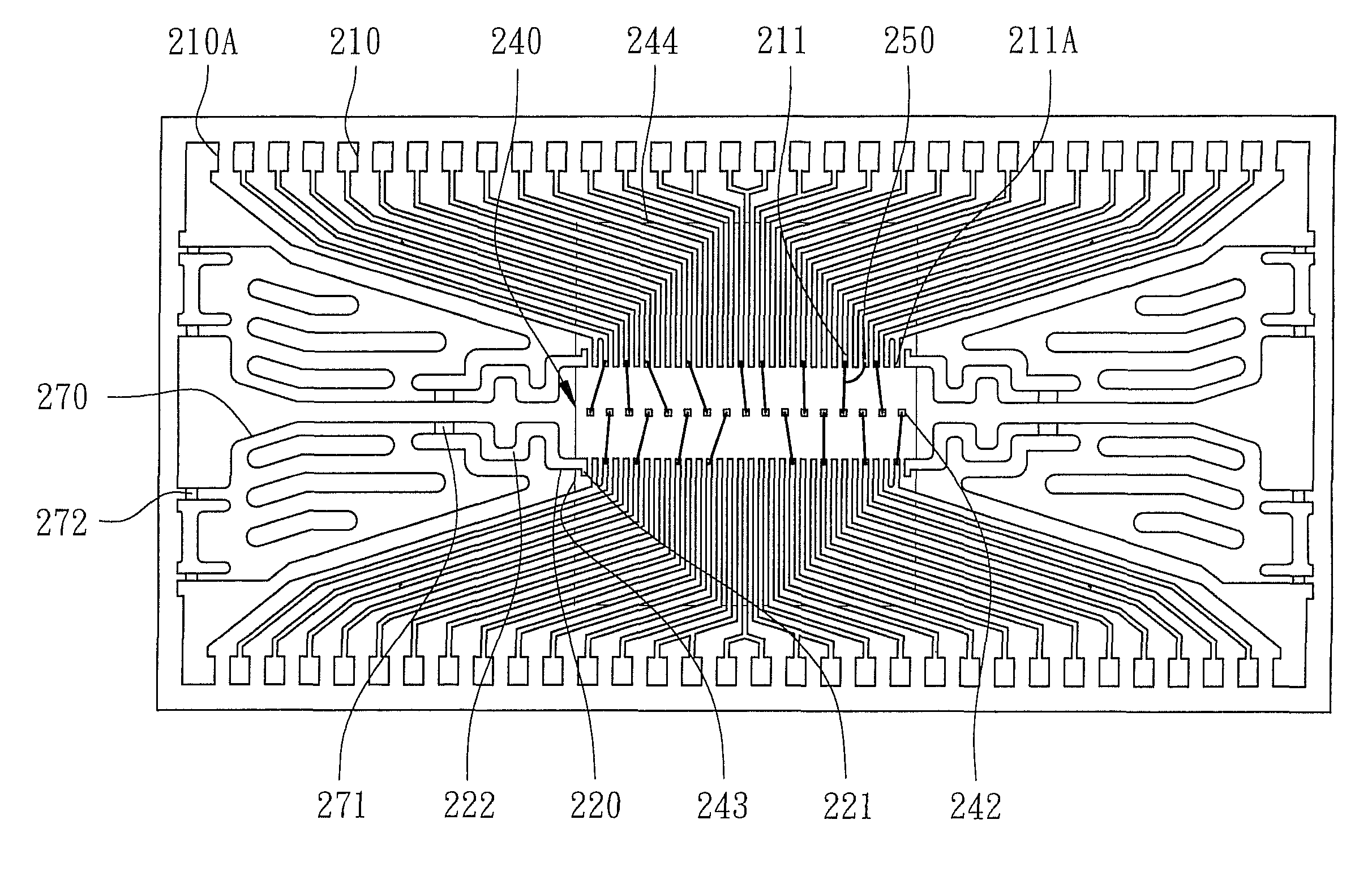

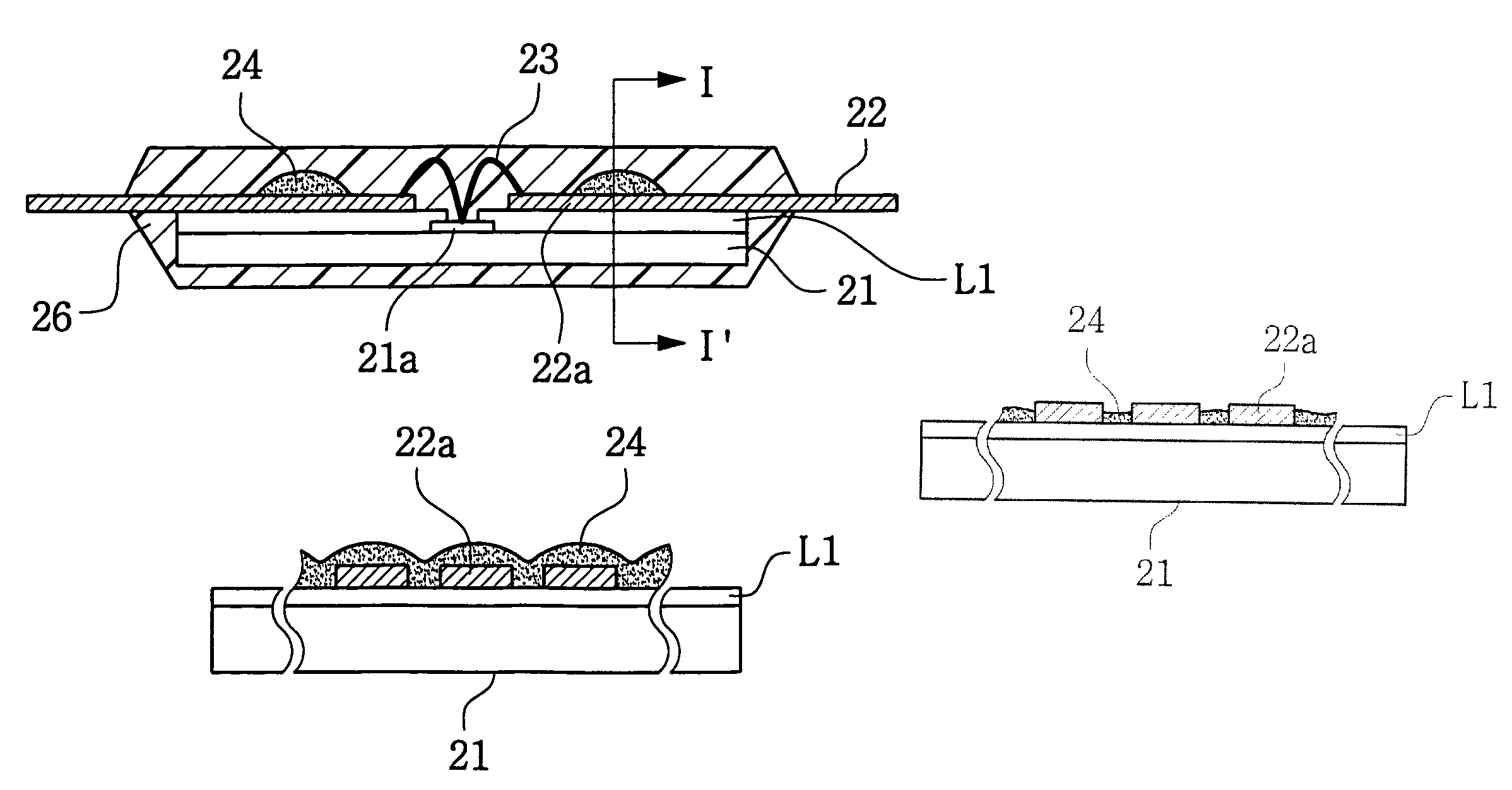

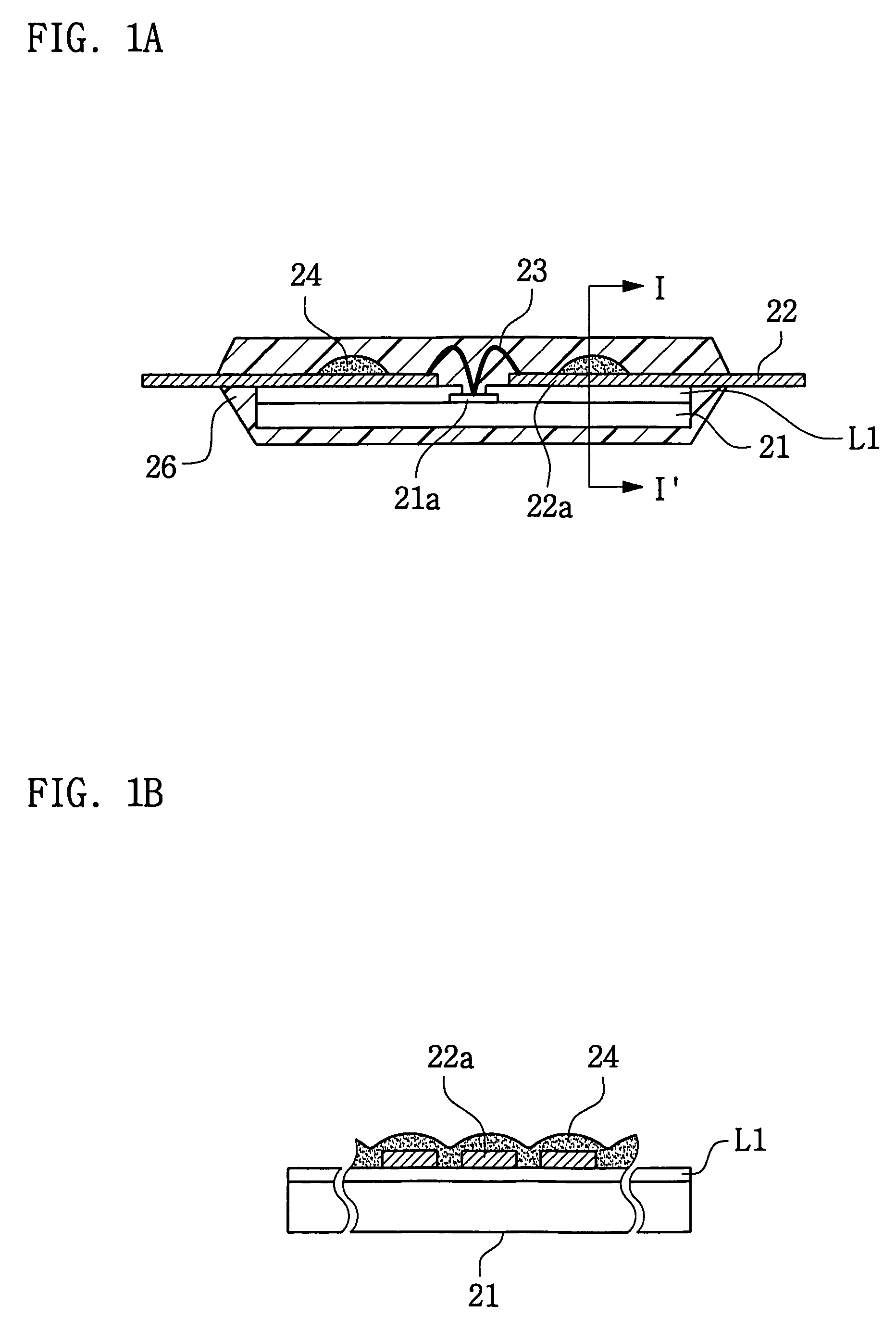

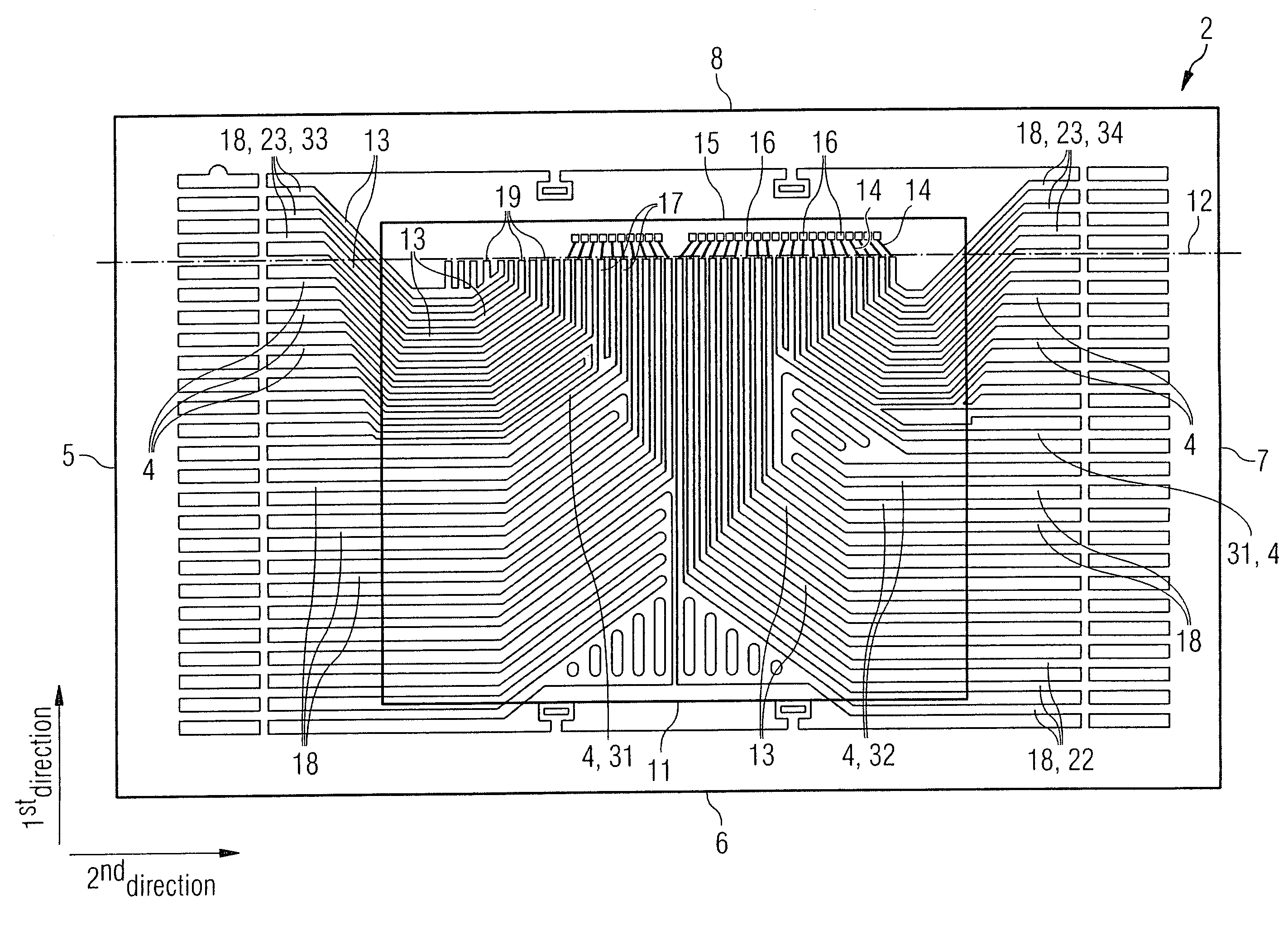

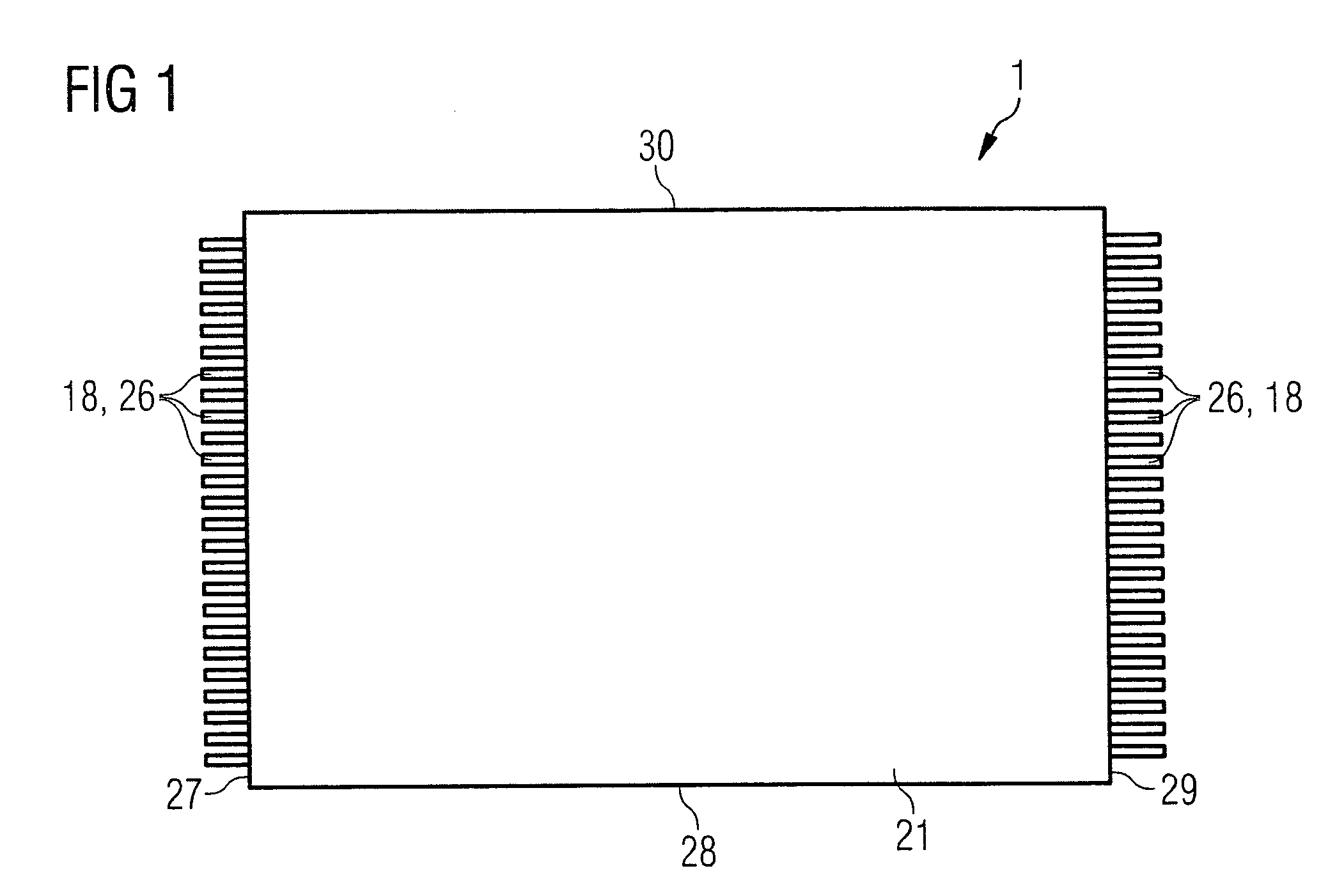

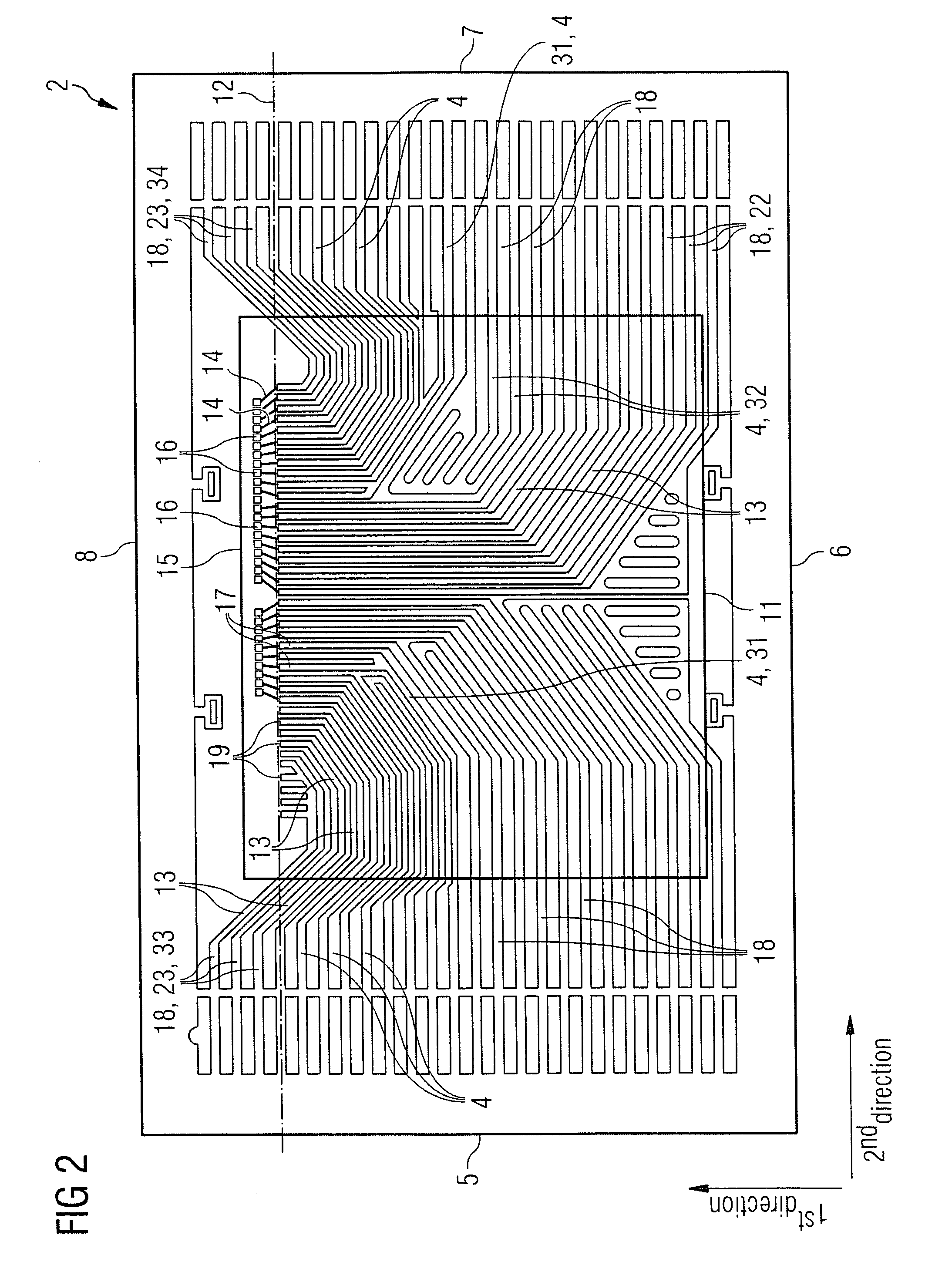

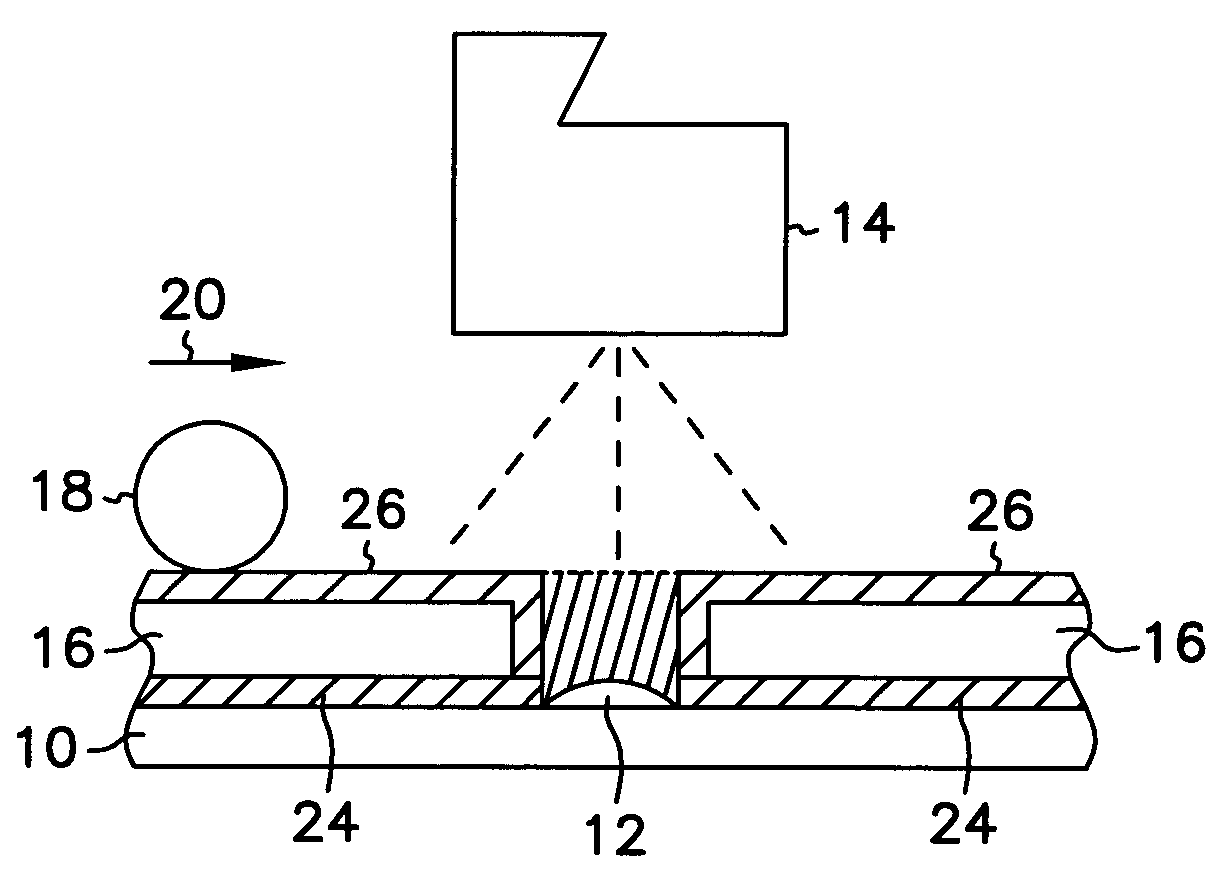

Semiconductor package based on lead-on-chip architecture, the fabrication thereof and a leadframe for implementing in a semiconductor package

InactiveUS20070023871A1Fast and low-cost processSemiconductor/solid-state device detailsSolid-state devicesLead on chipDevice material

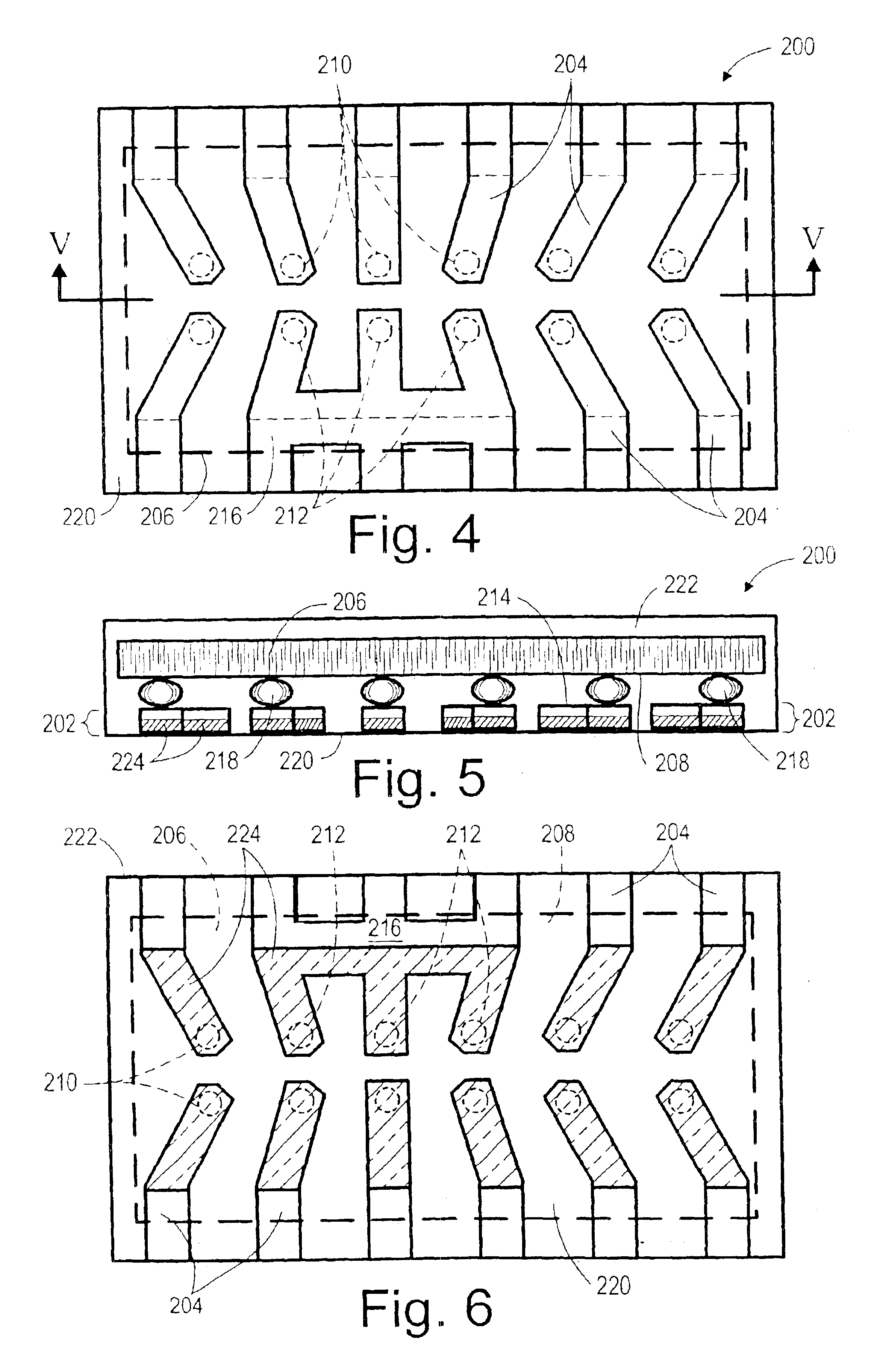

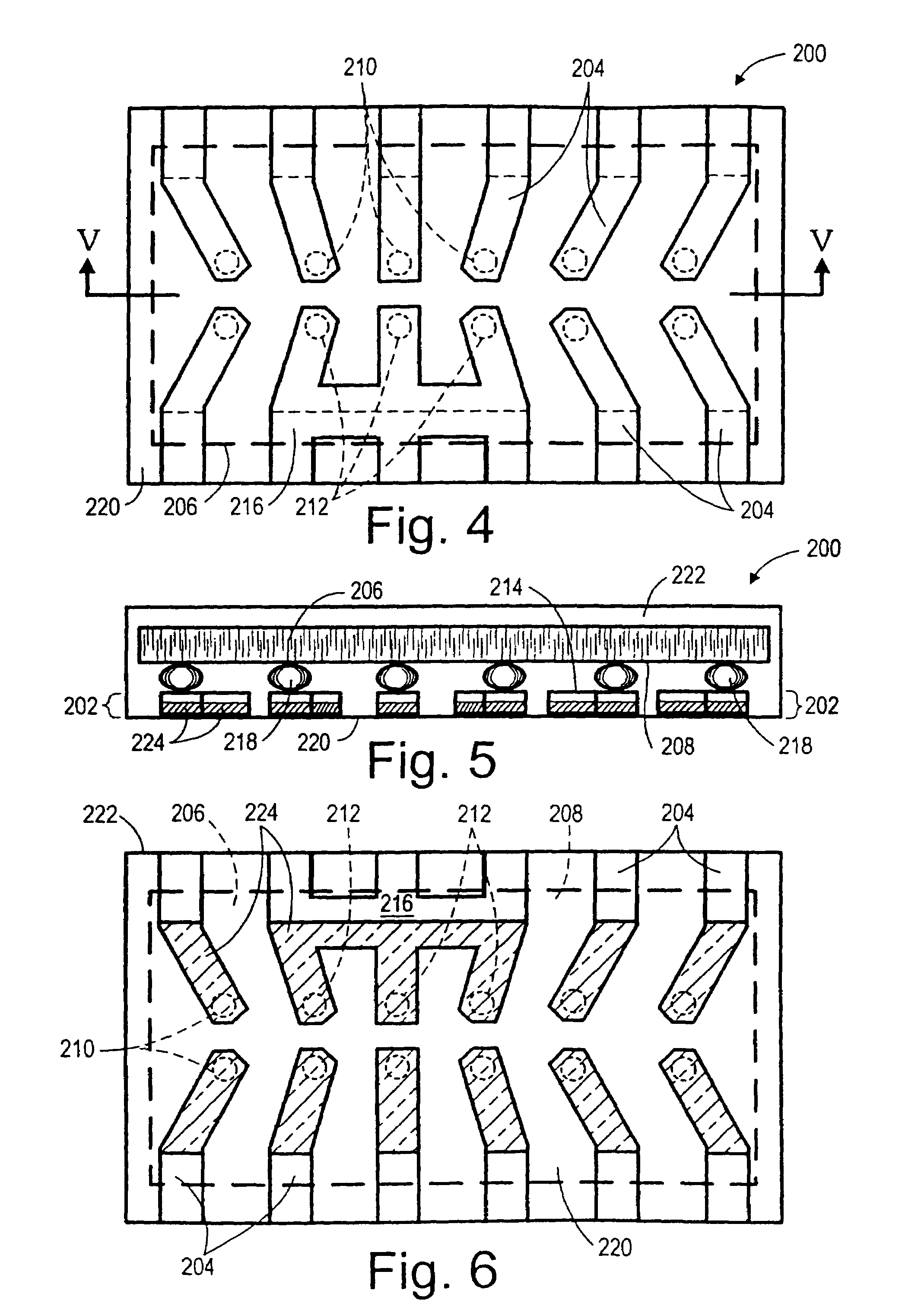

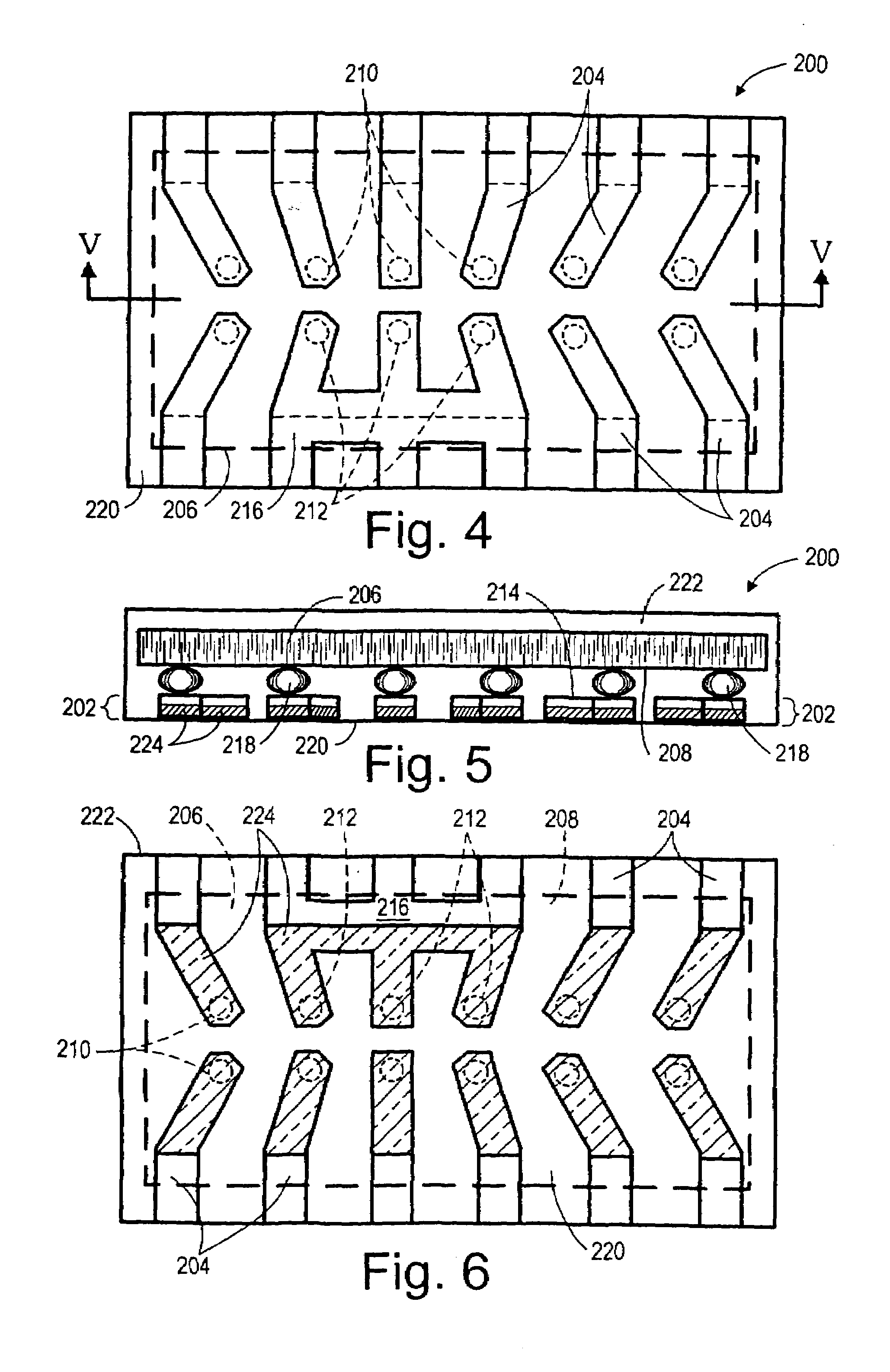

A leadframe includes a multiplicity of leads. The leads have a board level contact portion, an intermediate portion and a chip level contact portion. The intermediate portion is disposed between the board level contact portion and the chip level contact portion. The board level contact portions extend from one of the first side or the second side of the semiconductor device along a second direction. The chip level contact portions extend along the first direction. Ends of the chip level contact portions are aligned along a line extending along the second direction. This leadframe can be included with a semiconductor chip in a packaged integrated circuit.

Owner:POLARIS INNOVATIONS LTD

Integrated circuit package having a split lead frame

A magnetic field sensor includes a lead frame having a plurality of leads, at least two of which have a connection portion and a die attach portion. A semiconductor die is attached to the die attach portion of the at least two leads. The sensor further includes at least one wire bond coupled between the die and a first surface of the lead frame. The die is attached to a second, opposing surface of the lead frame in a lead on chip configuration. In some embodiments, at least one passive component is attached to the die attach portion of at least two leads.

Owner:ALLEGRO MICROSYSTEMS INC

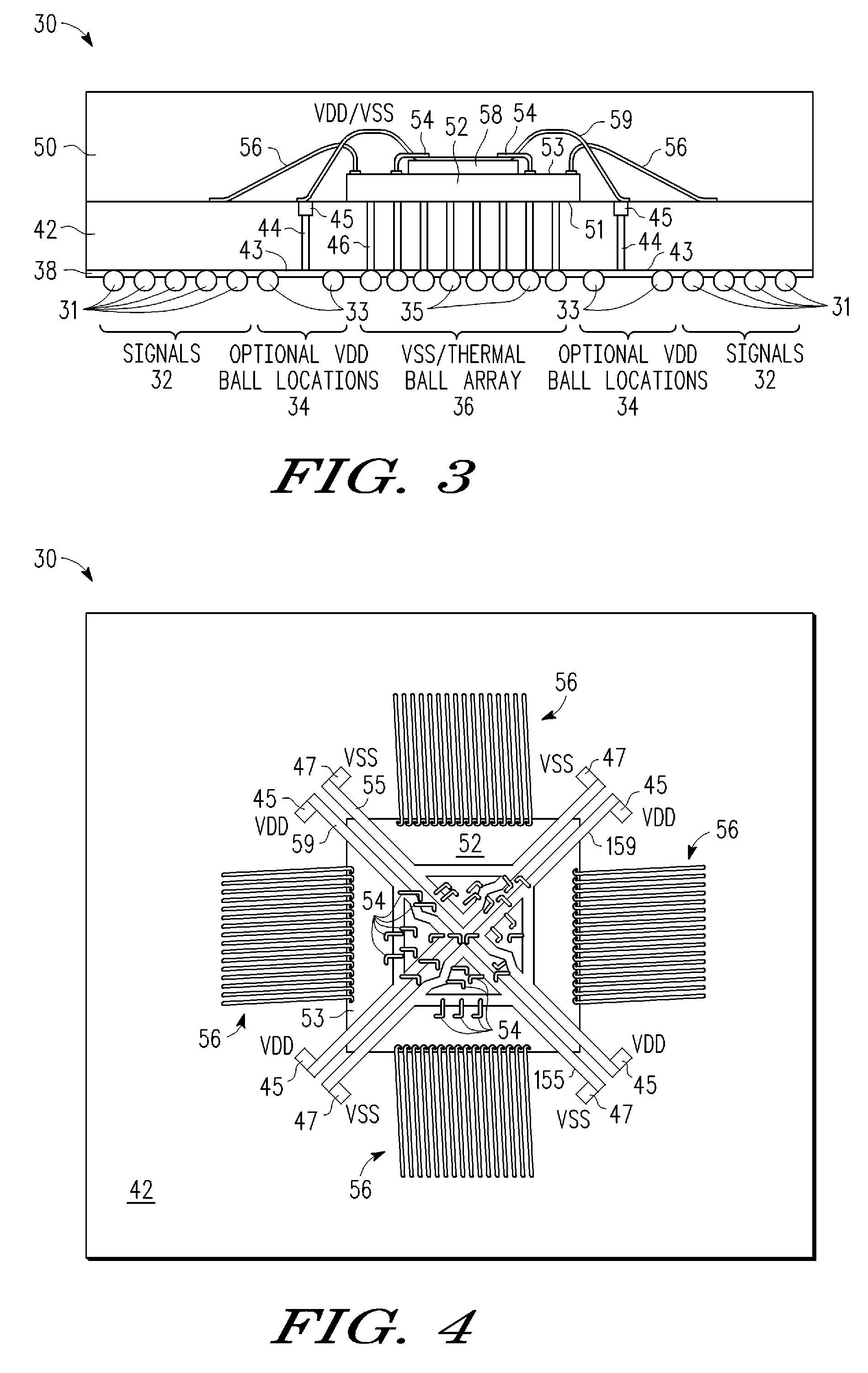

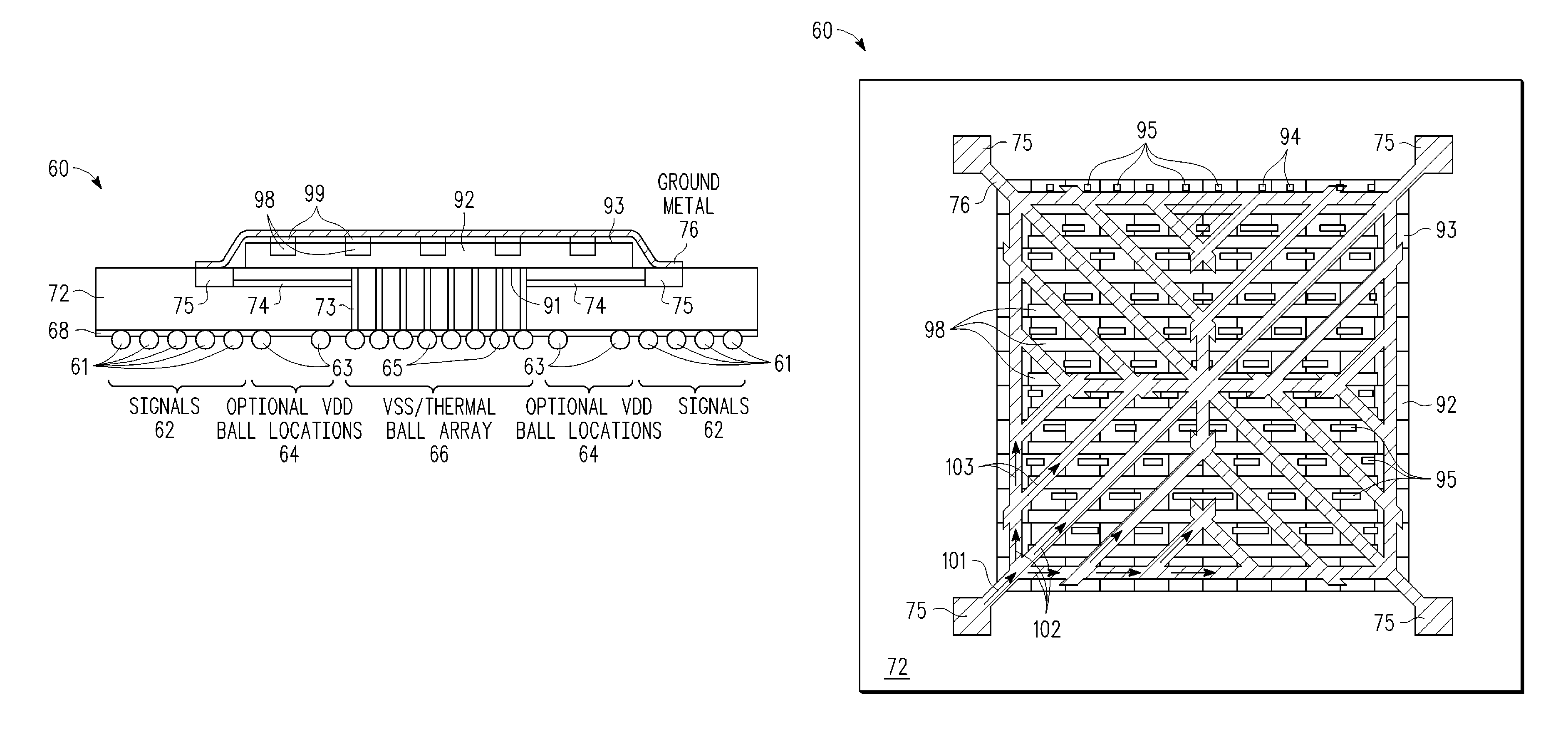

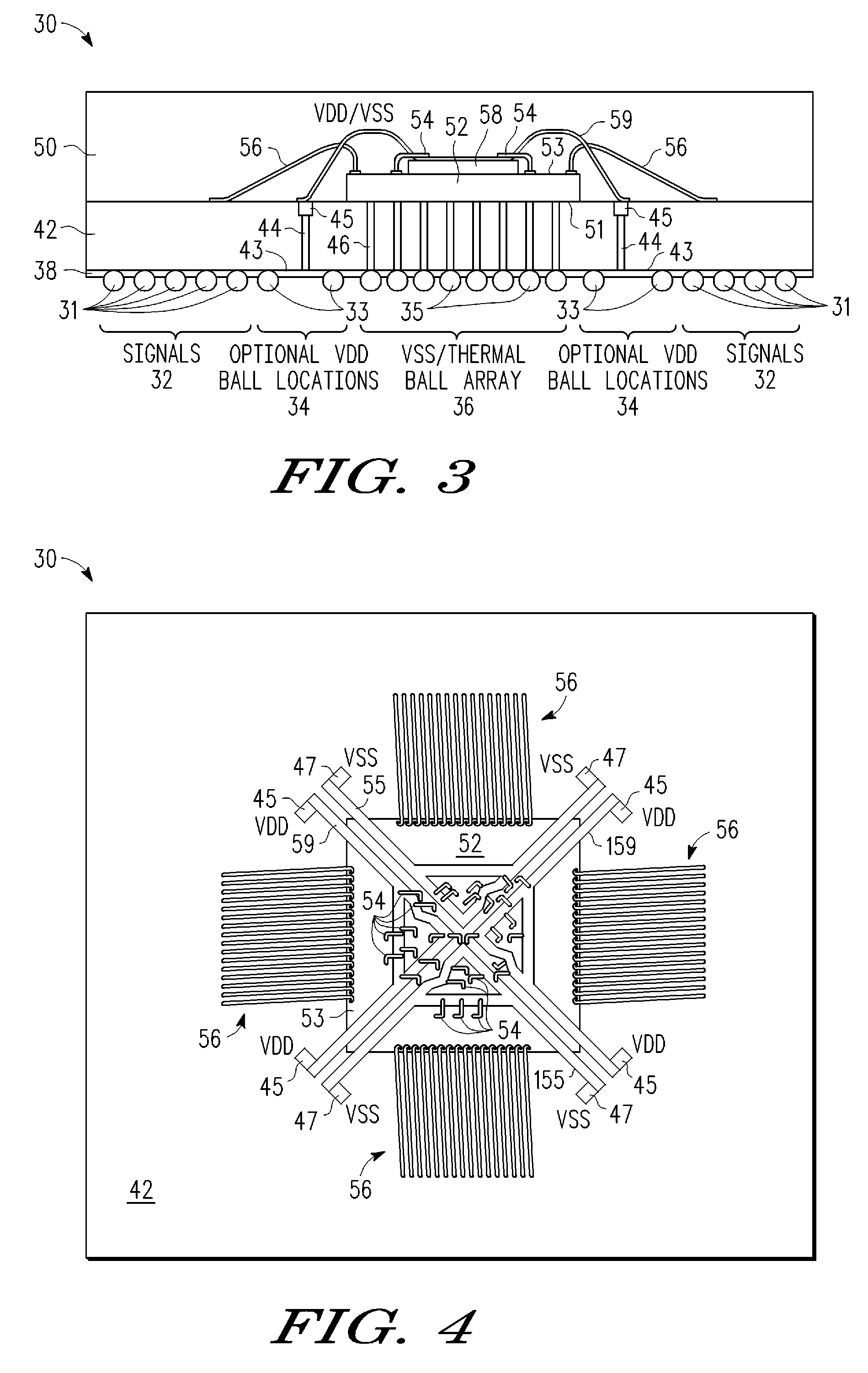

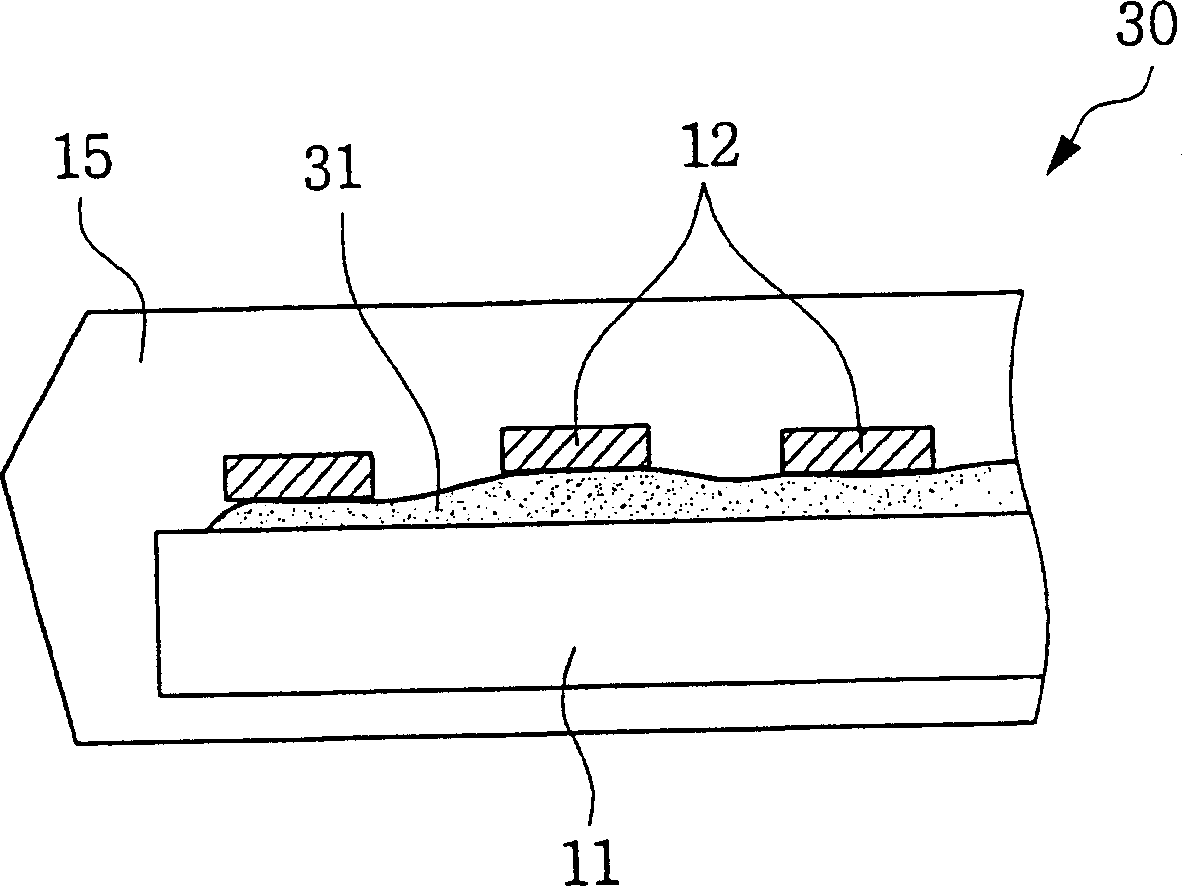

Power Lead-on-Chip Ball Grid Array Package

ActiveUS20100270663A1Semiconductor/solid-state device detailsSolid-state devicesLead on chipElectrical conductor

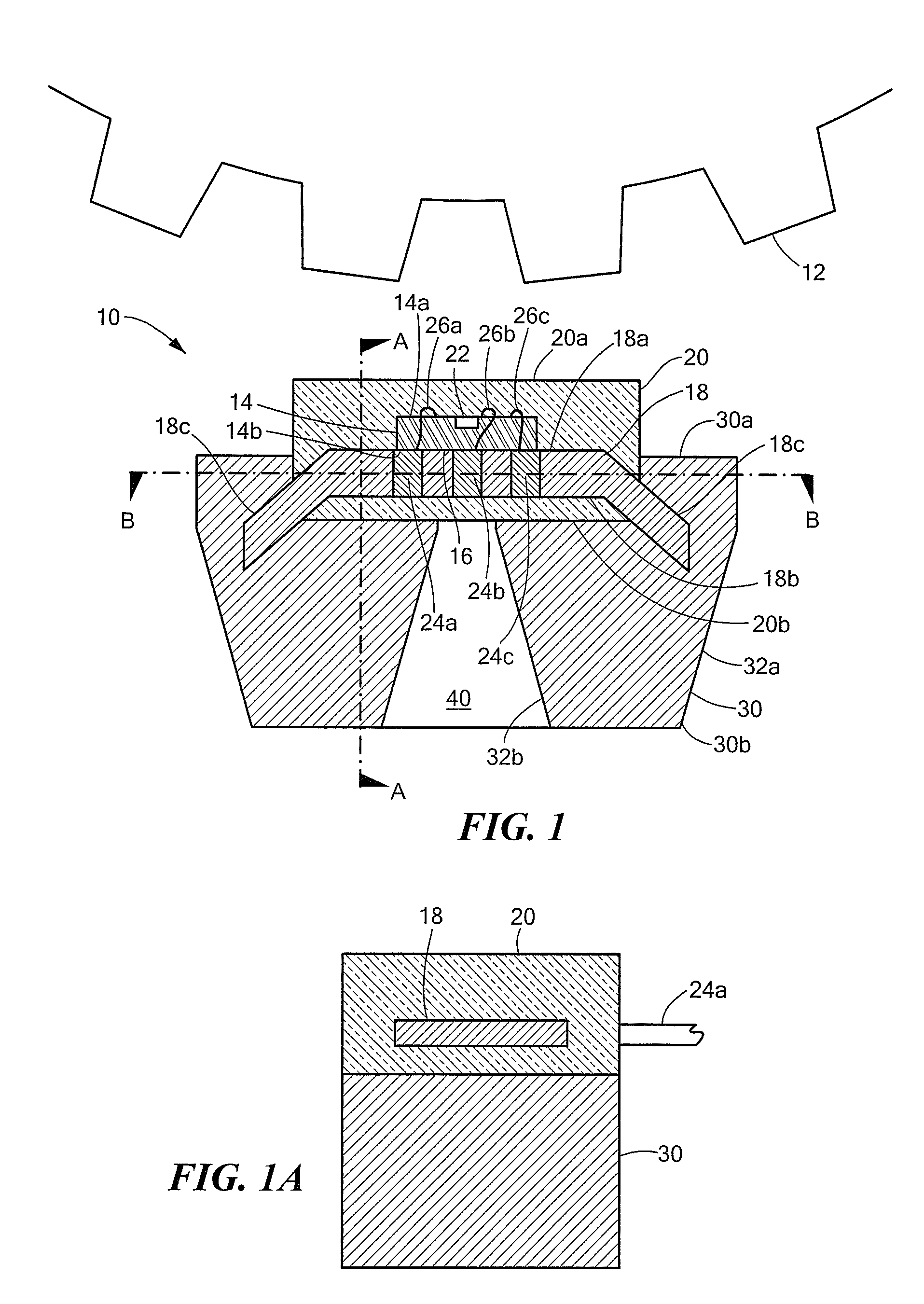

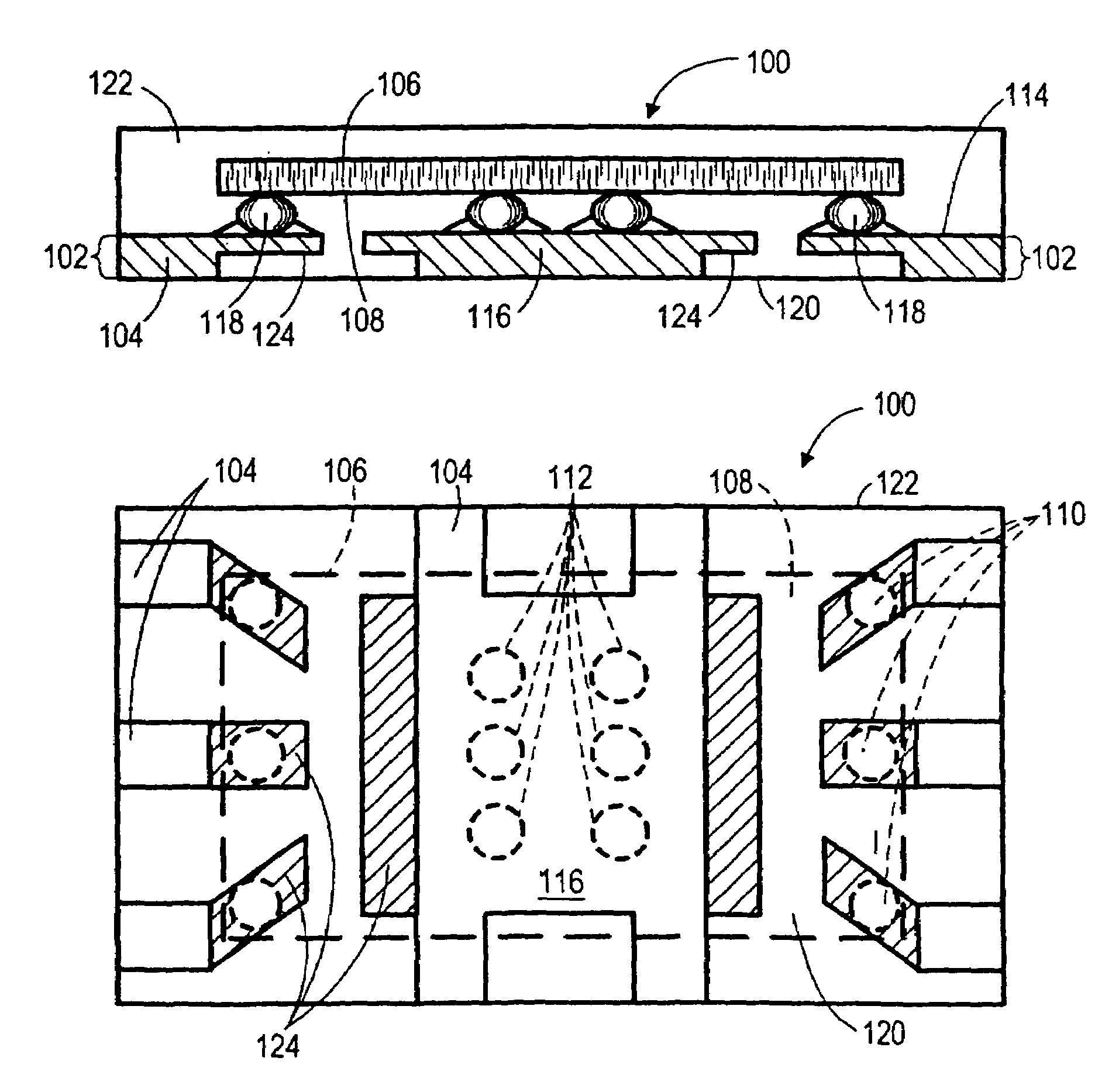

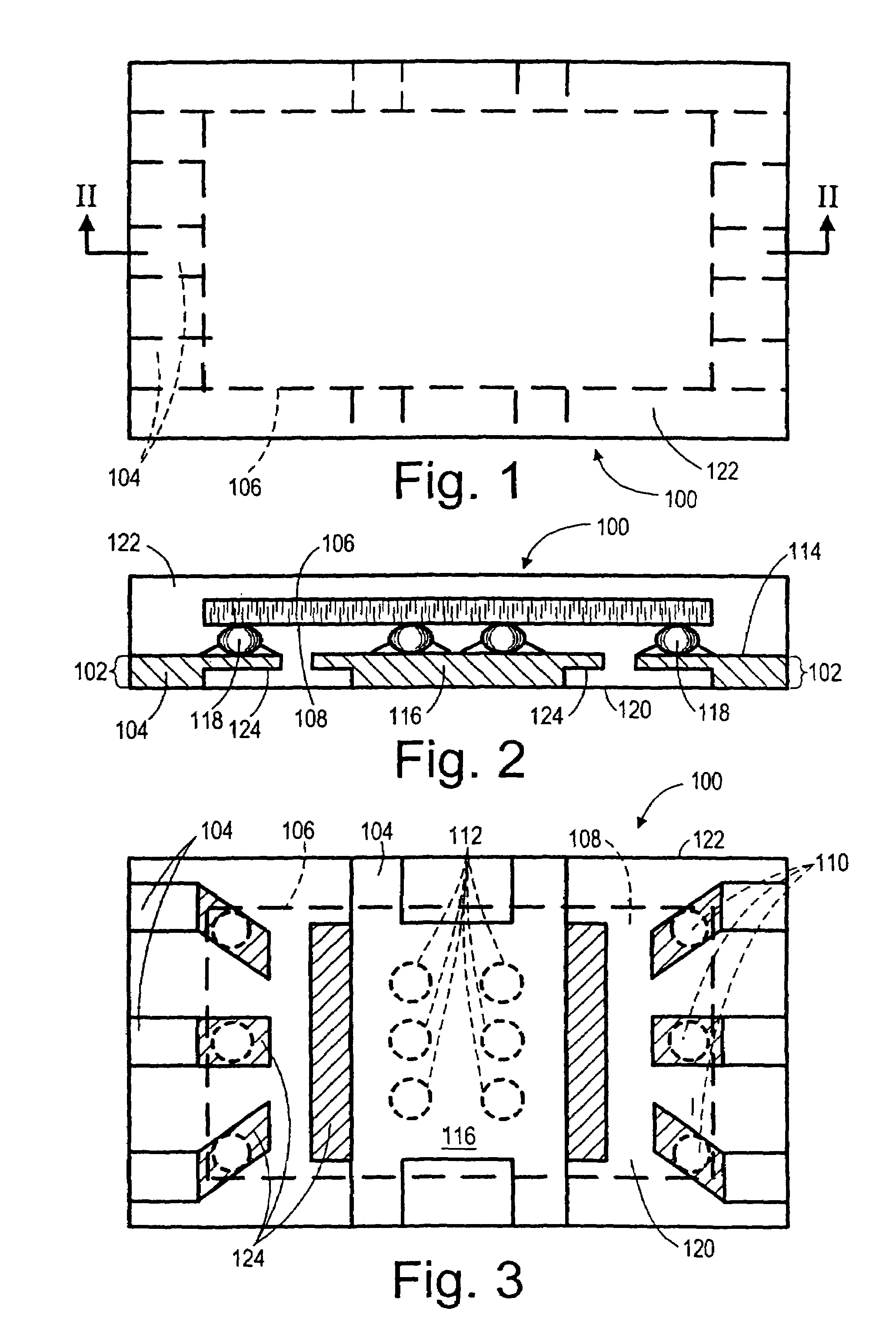

A packaging assembly (30), such as a ball grid array package, is formed which distributes power across an interior region of an integrated circuit die (52) by using an encapsulated patterned leadframe conductor (59) that is disposed over the die (52) and bonded to a plurality of bonding pads (45) formed in a BGA carrier substrate (42) and in the interior die region, thereby electrically coupling the interior die region to an externally provided reference voltage.

Owner:NXP USA INC

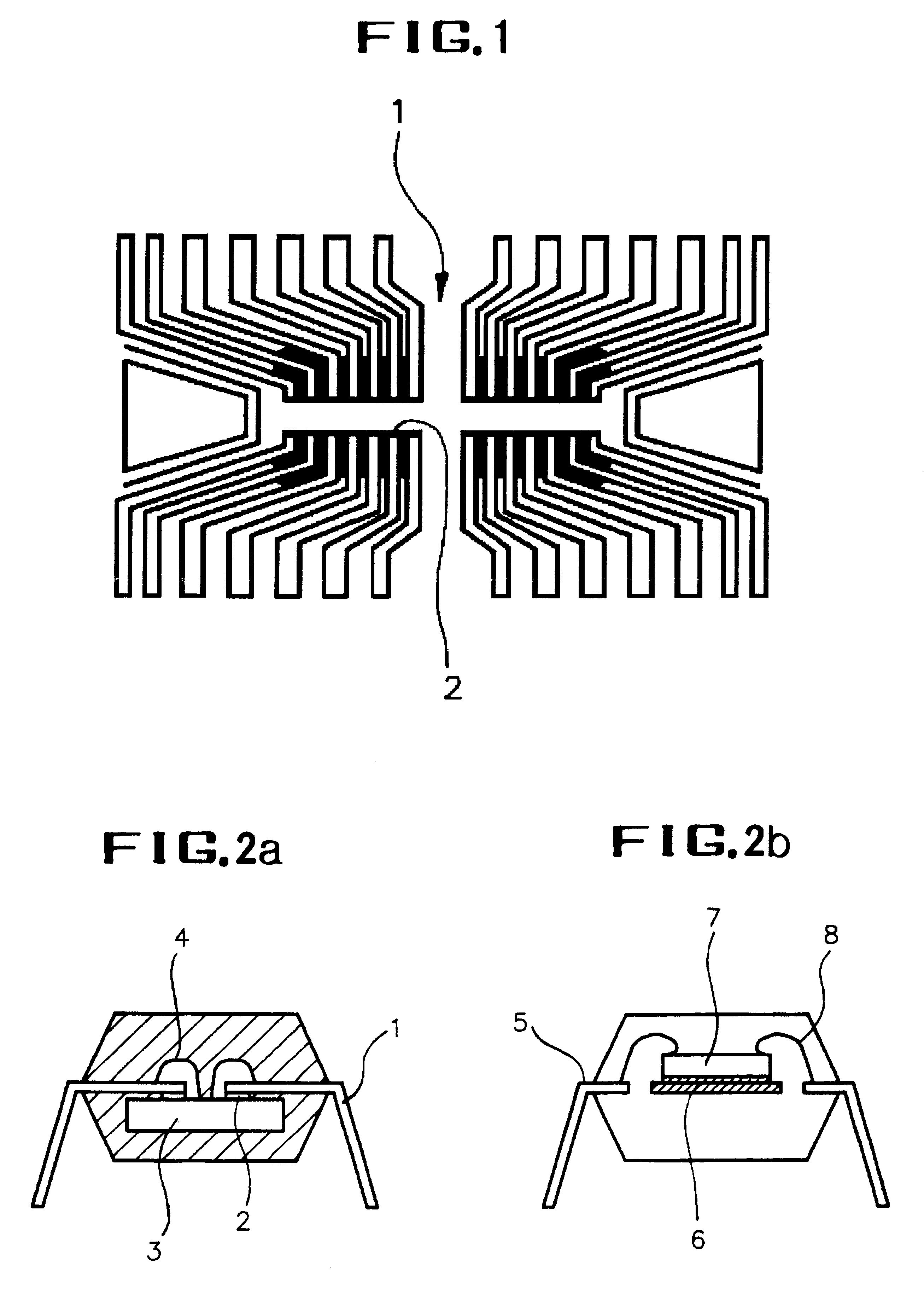

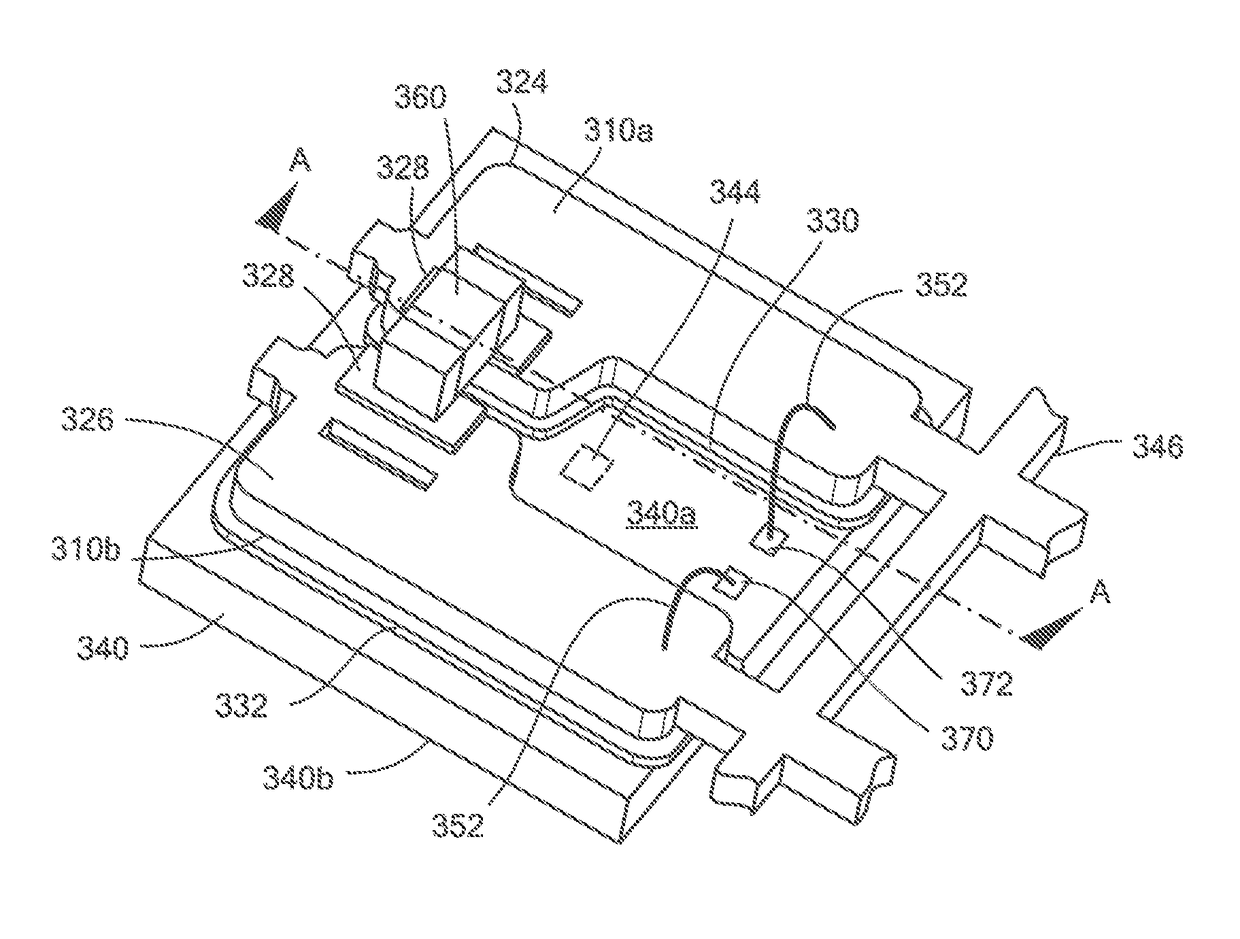

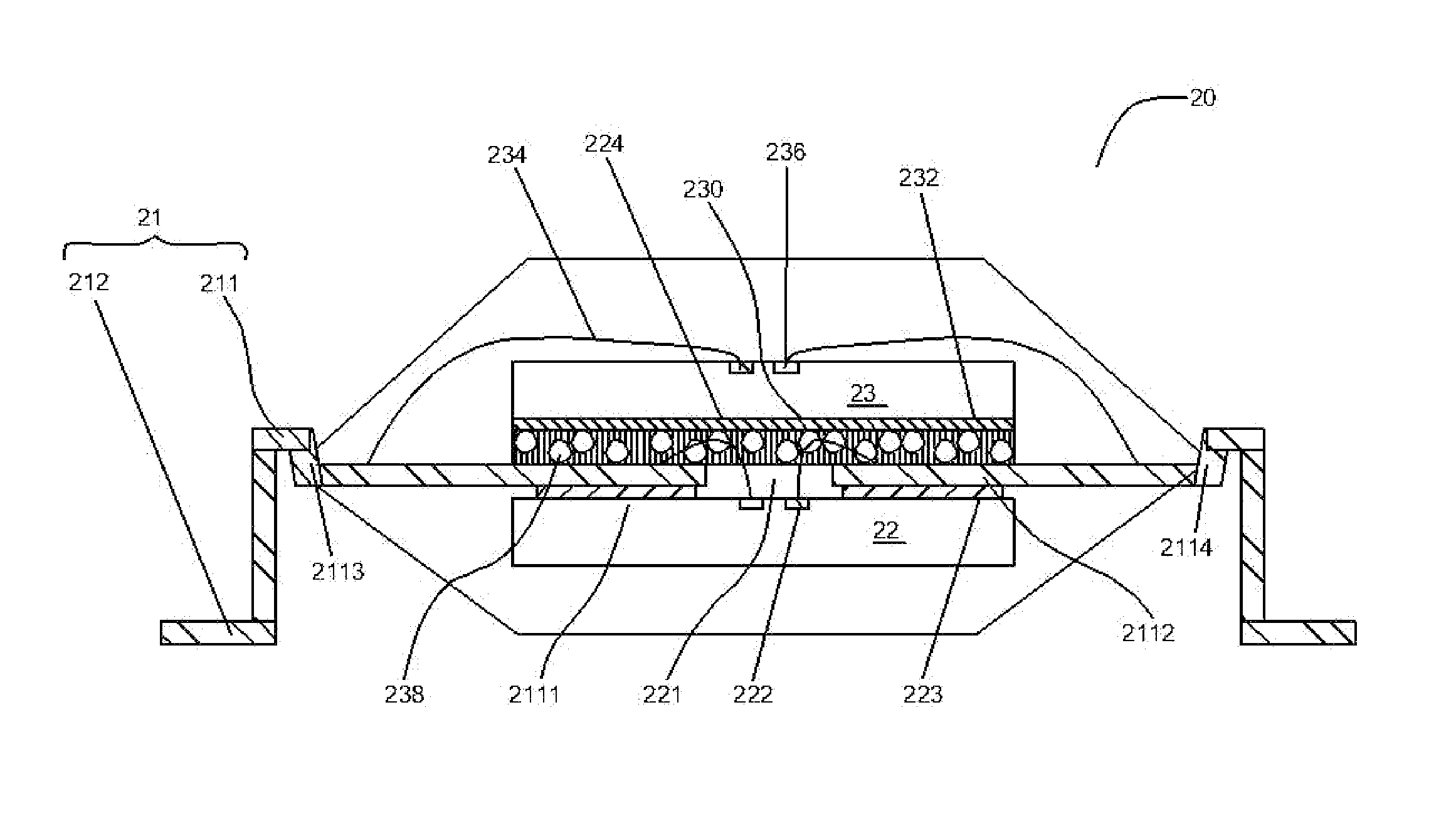

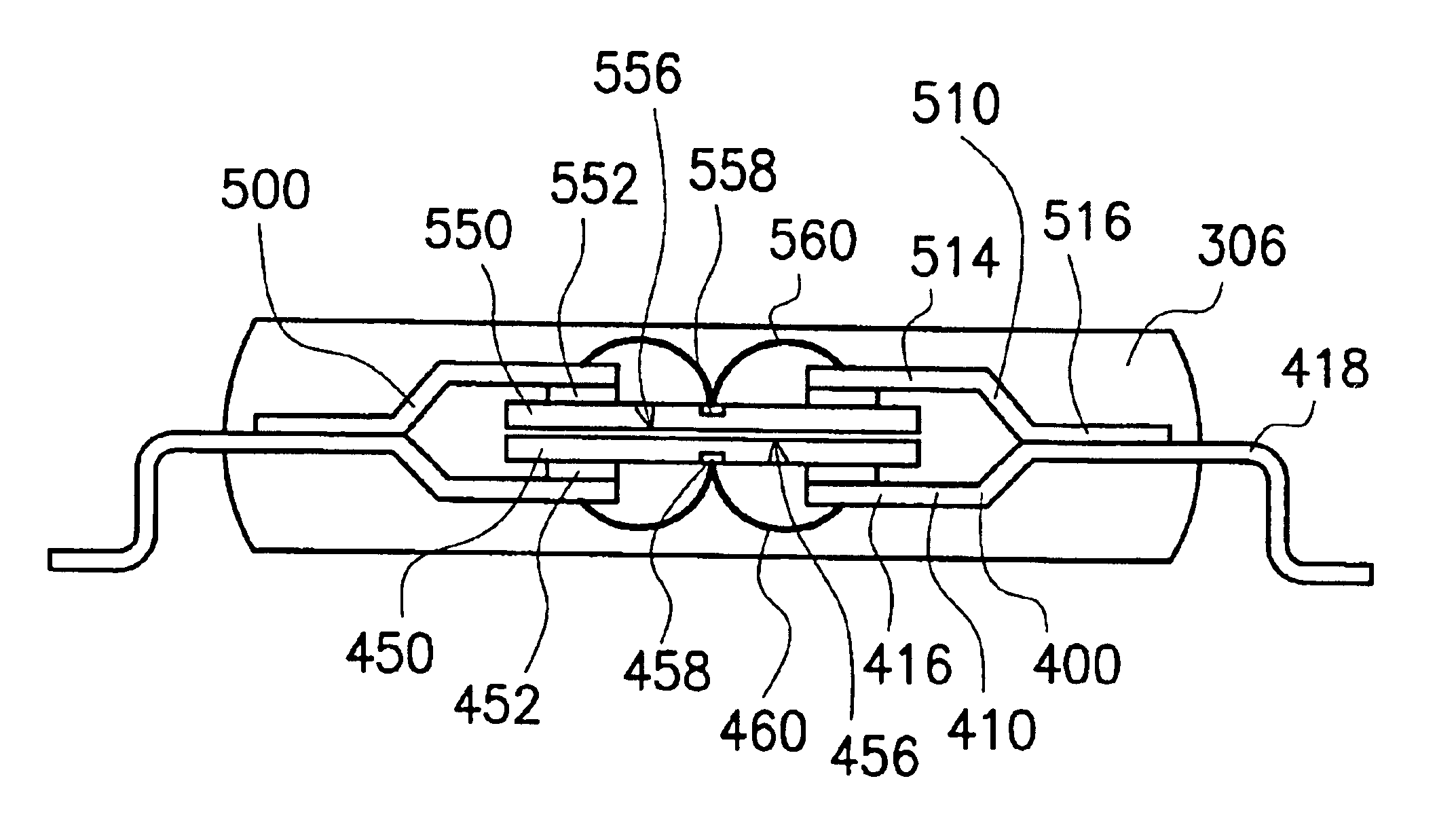

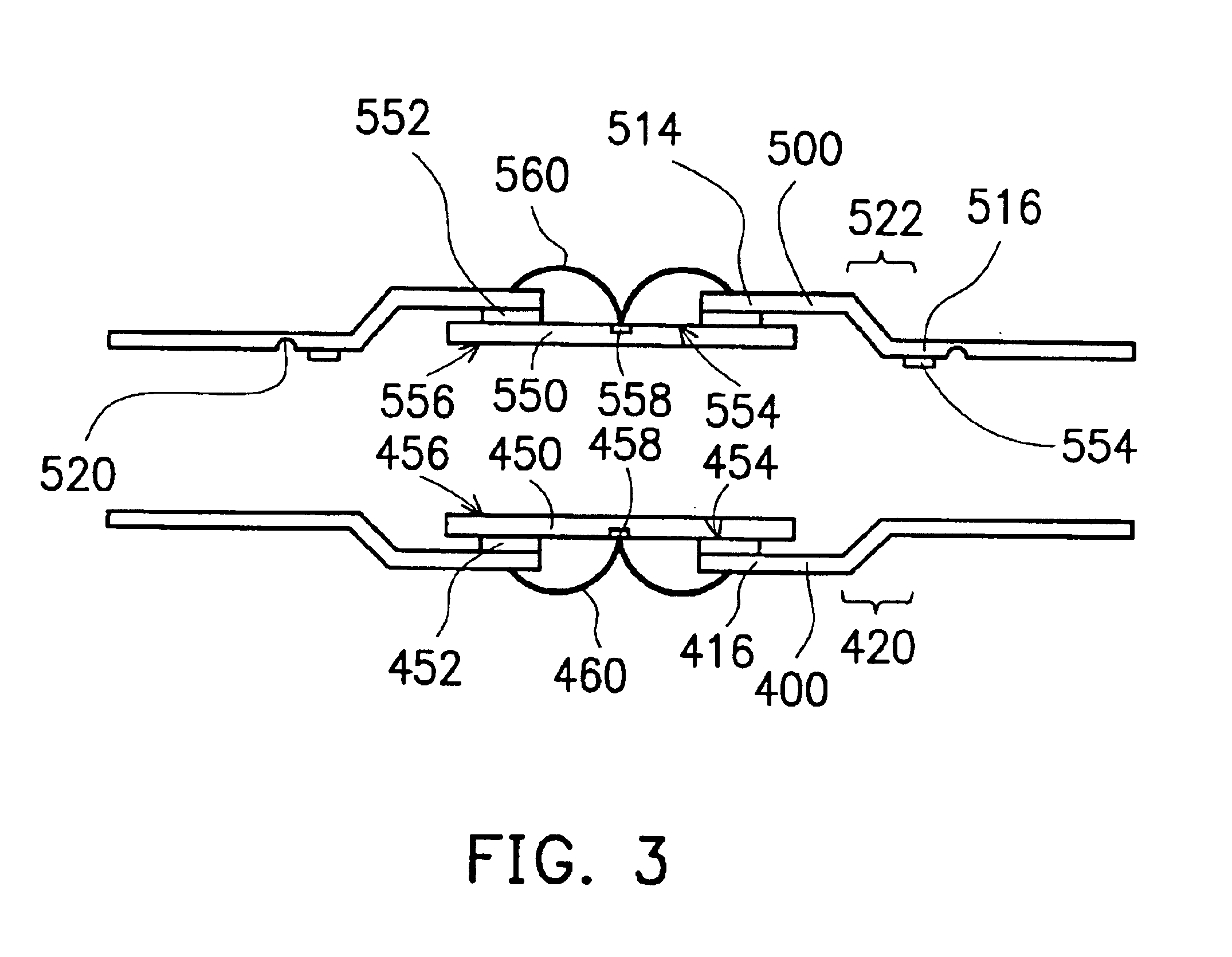

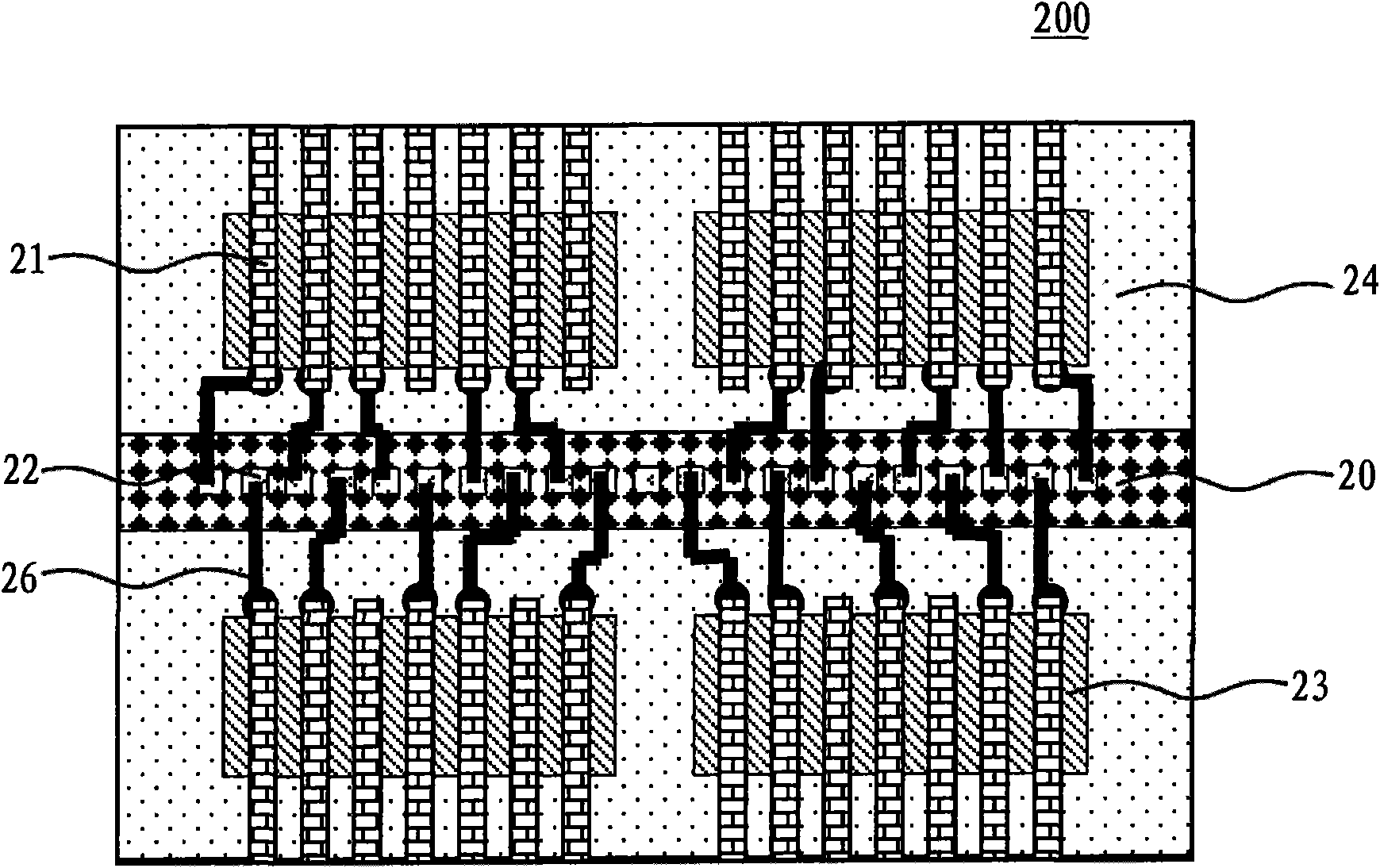

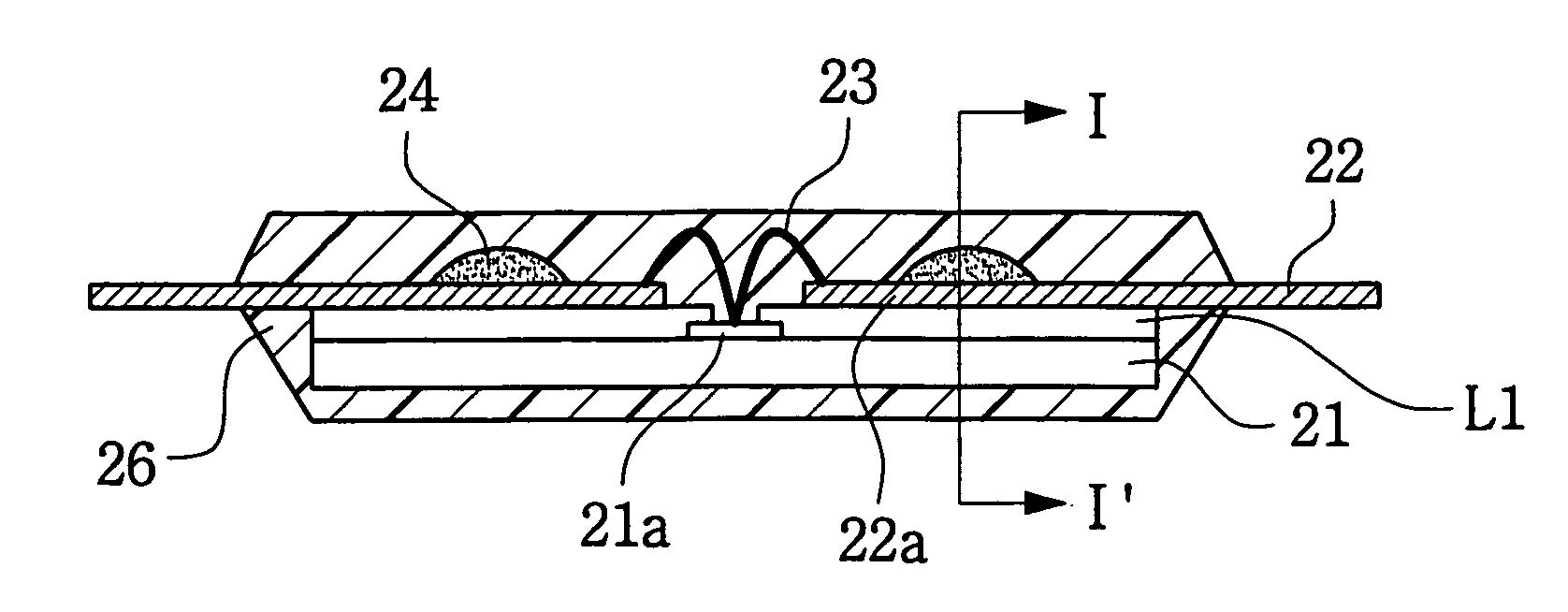

Chip-On-Lead and Lead-On-Chip Stacked Structure

InactiveUS20080283981A1Eliminates and reduces disadvantageEliminates and reduces and problemSemiconductor/solid-state device detailsSolid-state devicesLead on chipLead frame

A chip-stacked package structure comprises a lead frame, a first chip, and a second chip. The led frame is composed of a plurality of inner leads and a plurality of outer leads. The plurality of inner leads comprises a plurality of first inner leads in parallel and a plurality of second inner leads in parallel, wherein the ends of first inner leads and the ends of second inner leads are arranged in rows facing each other at a distance. The active surface of first chip is fixedly connected to the lower surface of first inner leads and second inner leads via a first adhesive layer. A plurality of metal pads is provided near the central area of the active surface of first chip and is exposed. A second adhesive layer is formed on the back surface of second chip for fixedly connecting the back surface of second chip and the upper surface of first inner leads and second inner leads. The gap formed by the thickness of second adhesive layer prevents the bonding wires connecting the first chip from contacting the back surface of second chip.

Owner:CHIPMOS TECH INC

Integrated circuit package having a split lead frame

A magnetic field sensor includes a lead frame having a plurality of leads, at least two of which have a connection portion and a die attach portion. A semiconductor die is attached to the die attach portion of the at least two leads. The sensor further includes at least one wire bond coupled between the die and a first surface of the lead frame. The die is attached to a second, opposing surface of the lead frame in a lead on chip configuration. In some embodiments, at least one passive component is attached to the die attach portion of at least two leads.

Owner:ALLEGRO MICROSYSTEMS LLC

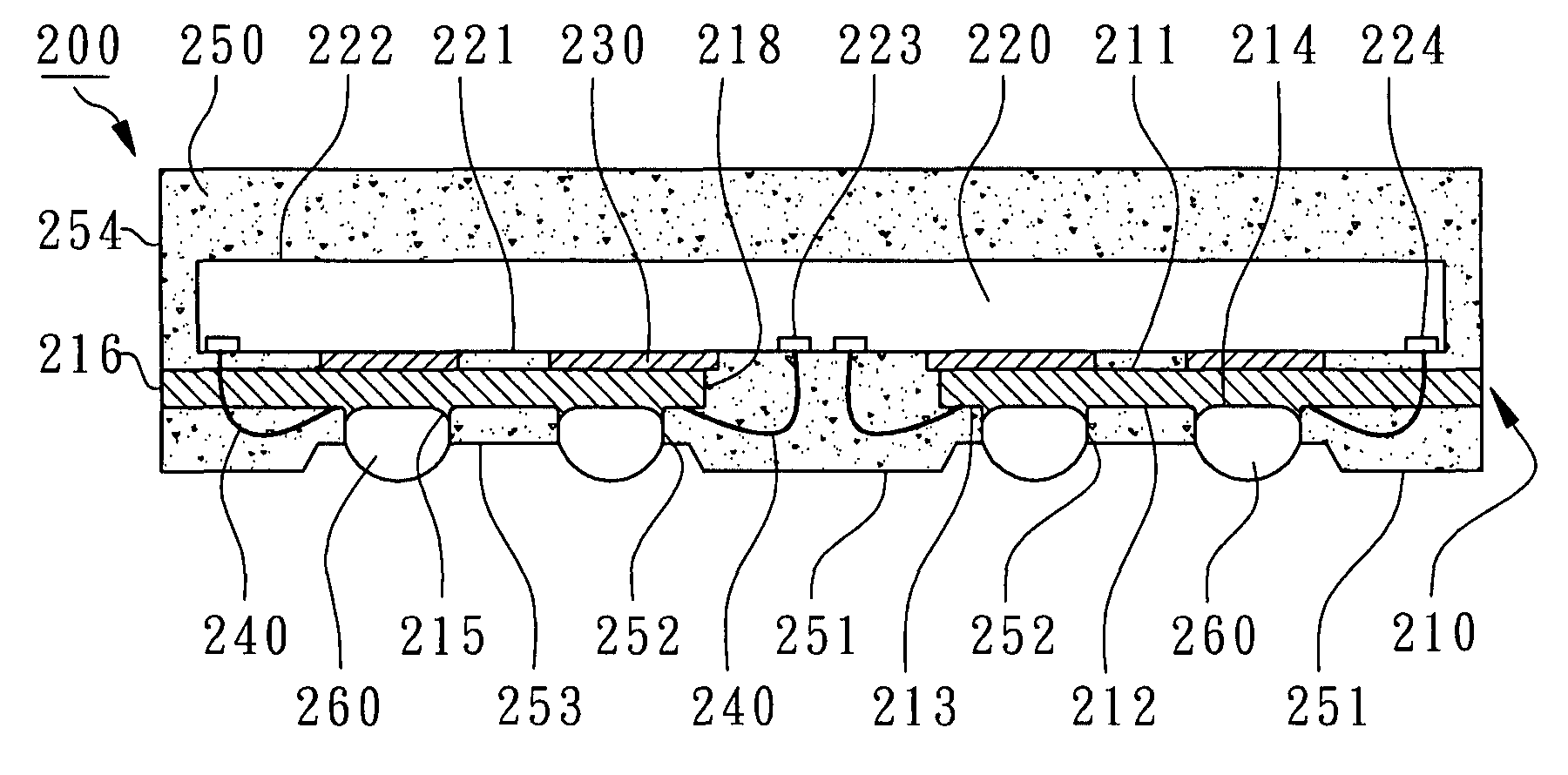

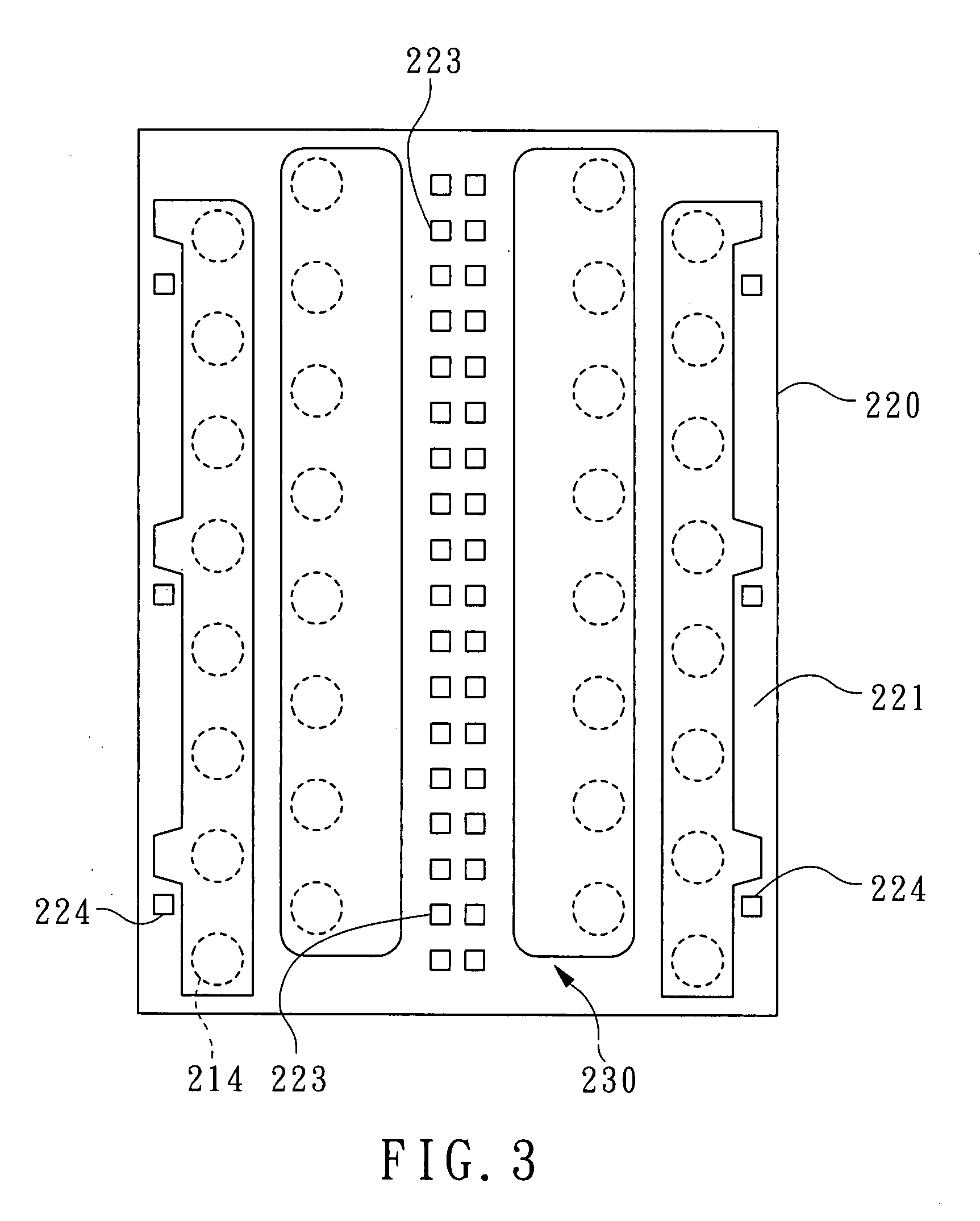

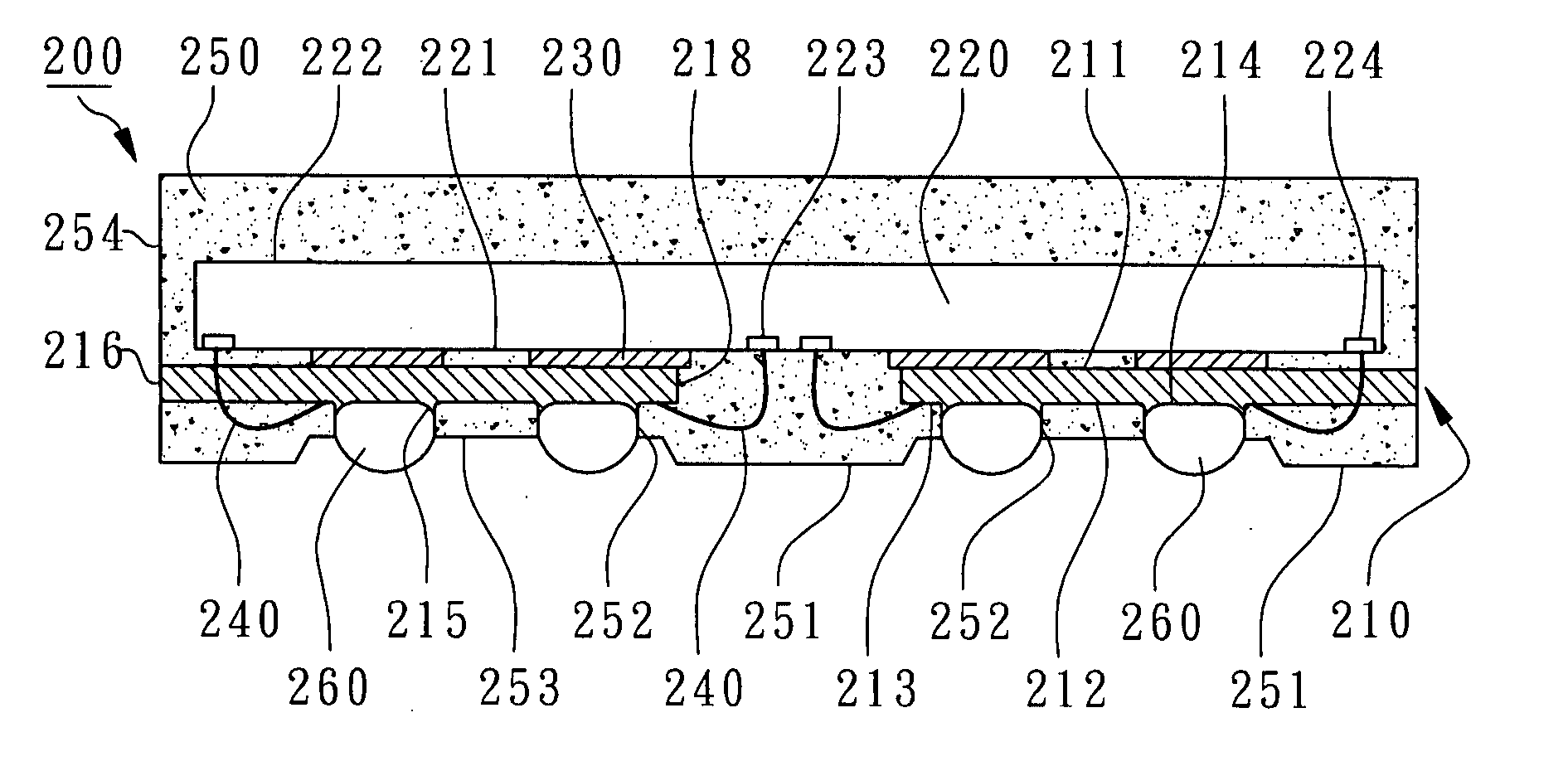

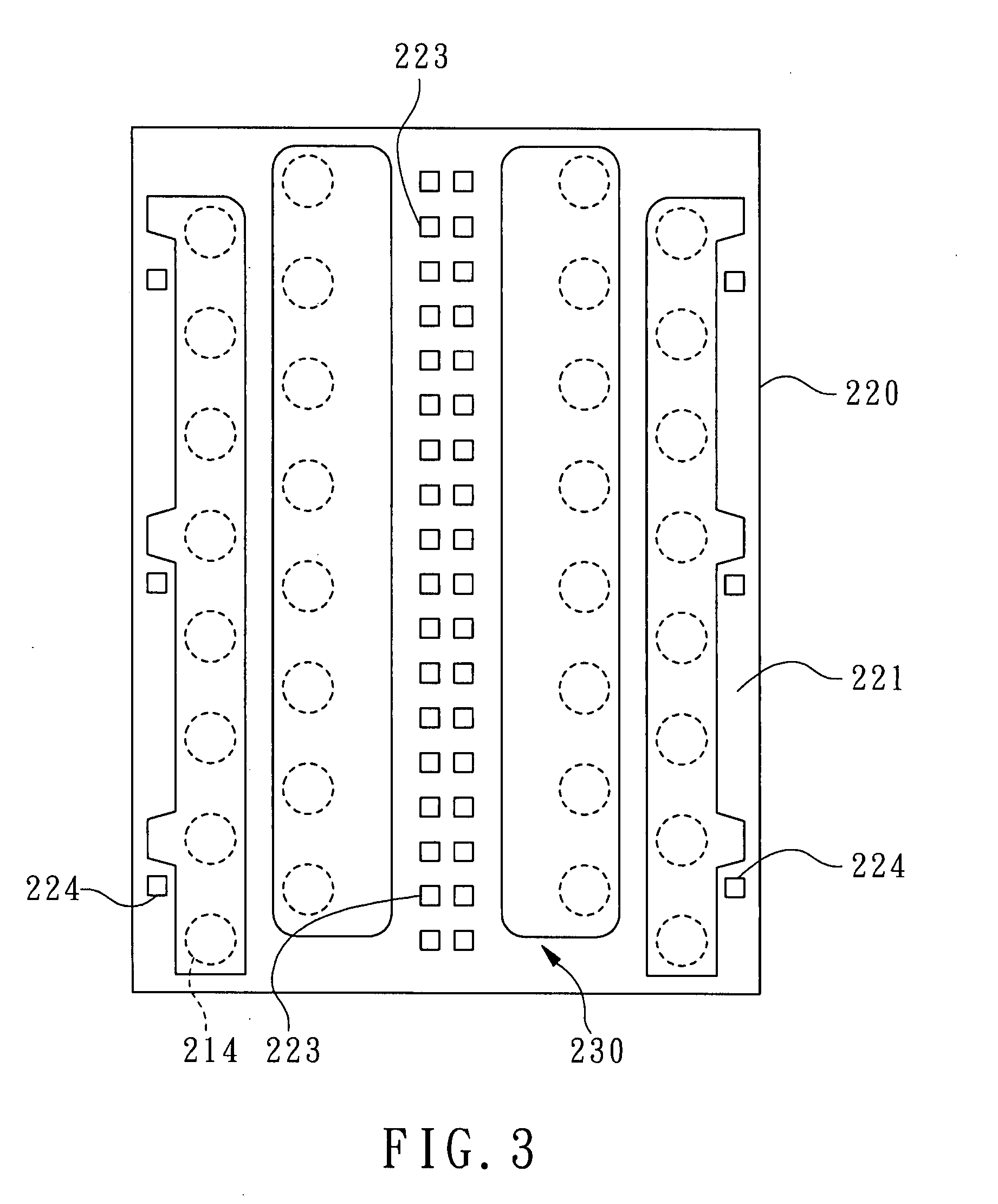

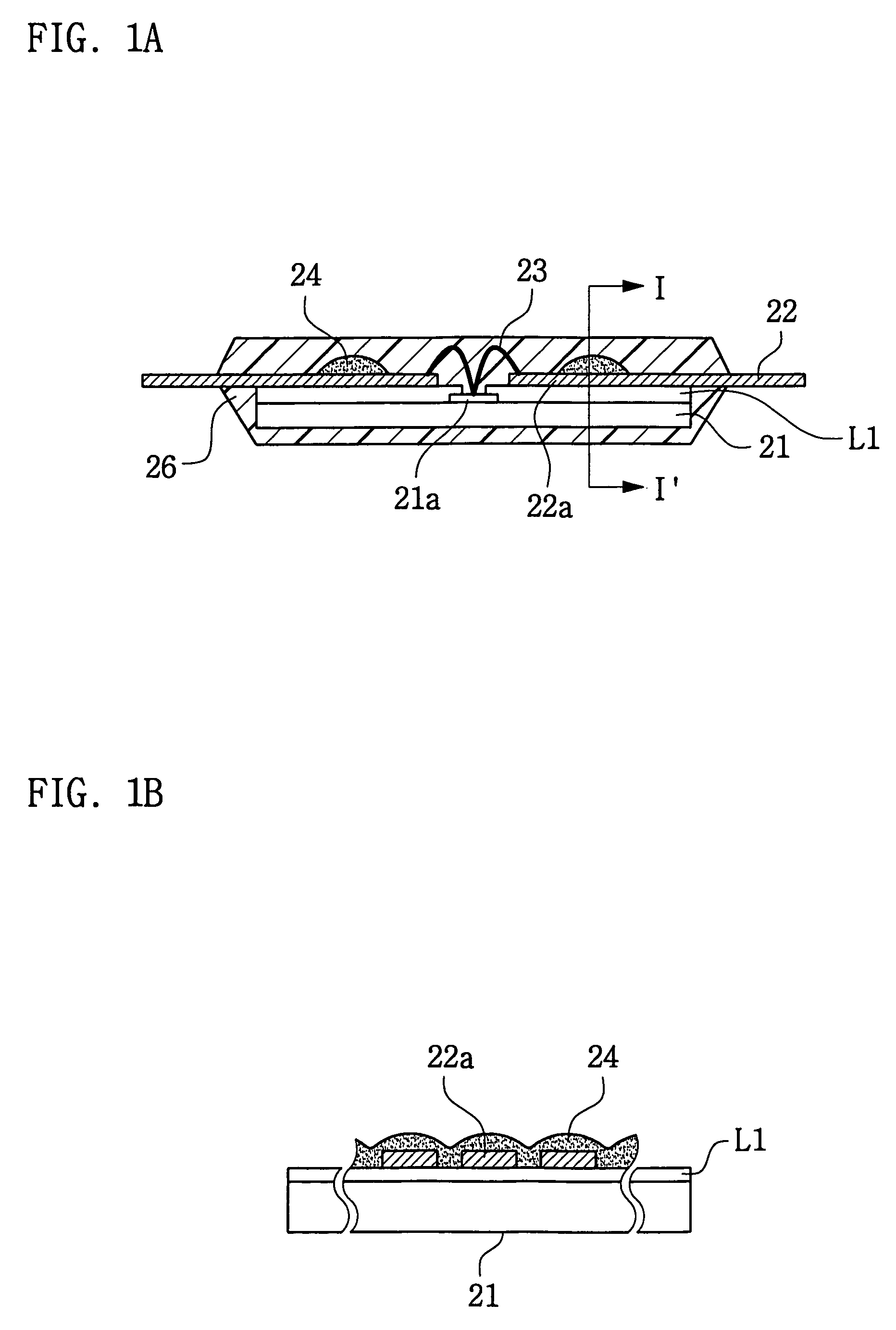

BGA package with leads on chip

ActiveUS7952198B2Increase the areaImprove welding strengthSemiconductor/solid-state device detailsSolid-state devicesLead on chipLead bonding

A BGA package primarily includes a leadless leadframe with a plurality of leads, a chip disposed on the leads, a die-attaching layer adhering to an active surface of the chip and the top surfaces of the leads, a plurality of bonding wires electrically connecting the chip to the leads, an encapsulant, and a plurality of solder balls. Each lead has a bottom surface including a wire-bonding area and a ball-placement area, moreover, a plurality of lips project from the bottom surfaces of the leads around the ball-placement areas. The encapsulant encapsulates the chip, the bonding wires, the die-attaching layer, and the top surfaces, the bottom surfaces except the ball-placement areas. The solder balls are disposed on the ball-placement areas.

Owner:CHIPMOS TECH INC

Multi-chip semiconductor package structure

InactiveUS6844616B2Reducing circuit spaceLow production costSemiconductor/solid-state device detailsSolid-state devicesLead on chipSemiconductor package

A multi-chip semiconductor package structure. The structure includes two chips and two lead frames. The leads on one of the lead frames have inner leads at one end and joint sections at the other end. The joint sections are connected with another lead frame. Both lead frames use a common set of external leads. The two chips and two lead frames are joined together forming a lead-on-chip structure with the two chips facing each other back-to-back. The assembly except the external leads is enclosed by packaging material.

Owner:VANGUARD INTERNATIONAL SEMICONDUCTOR CORPORATION

Semiconductor packages with asymmetric connection configurations

InactiveUS20060103002A1Improve performanceImprove stabilitySemiconductor/solid-state device detailsSolid-state devicesCapacitanceLead on chip

Provided are semiconductor devices and methods for configuring lead frames and / or device bonding pads to provide for the independent adjustment of the electrical characteristics of both fixed voltage lines, e.g., Vdd and Vss, and the signal lines, e.g., command, clock, data and address. In particular, the invention provides for adjusting the relative sizing of leads corresponding to fixed voltage lines and signal lines for increasing the relative capacitance on the fixed voltage lines to improve their stability will reducing the noise on the signal lines. The invention may be utilized with a variety of package configurations including lead-on-chip LOC configurations, more conventional quad flat pack QFP configurations in which the leads do not extend past the perimeter of the semiconductor chip or hybrid configurations in which some leads do extend past the perimeter of the semiconductor chip and across the active surface.

Owner:SAMSUNG ELECTRONICS CO LTD

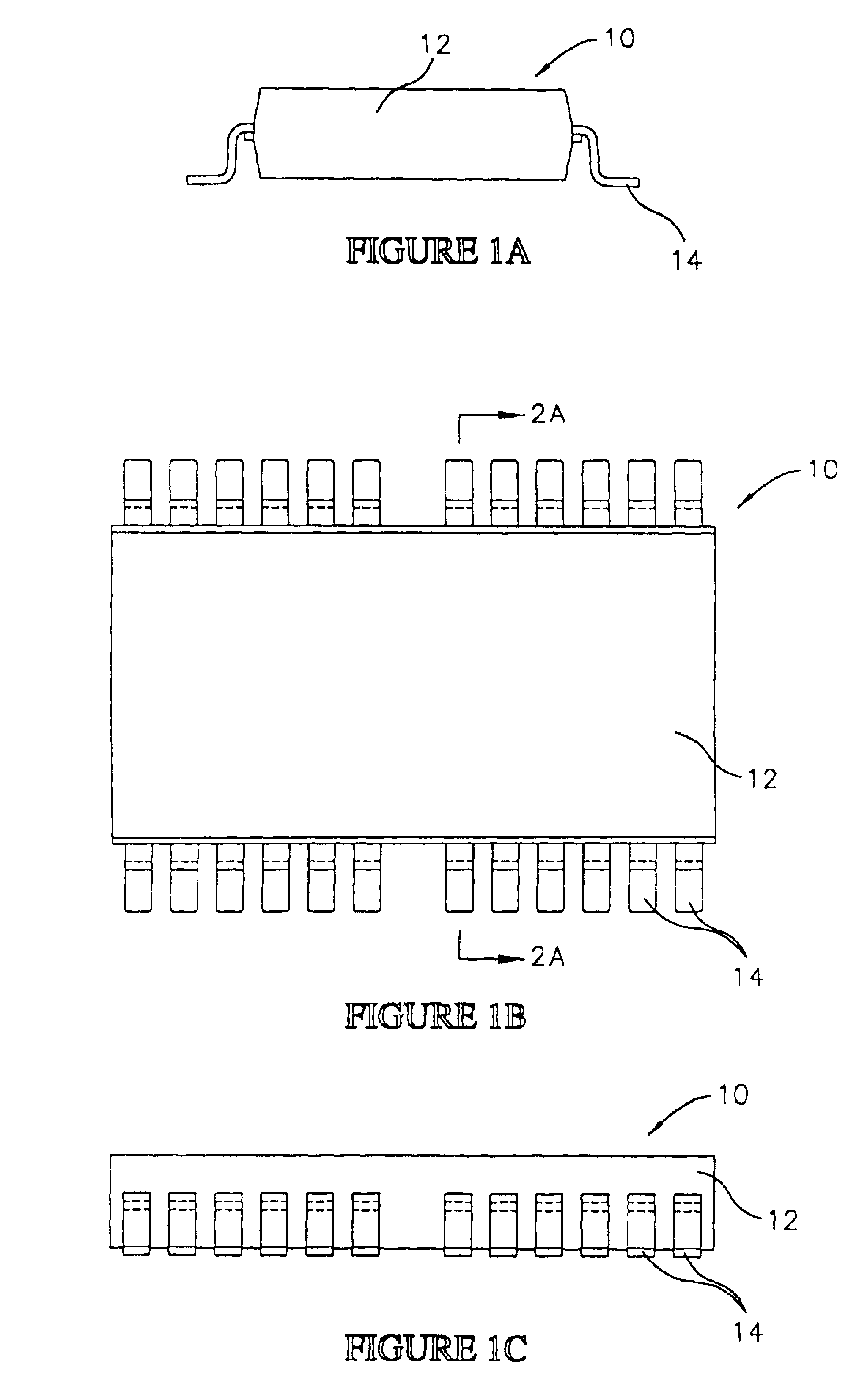

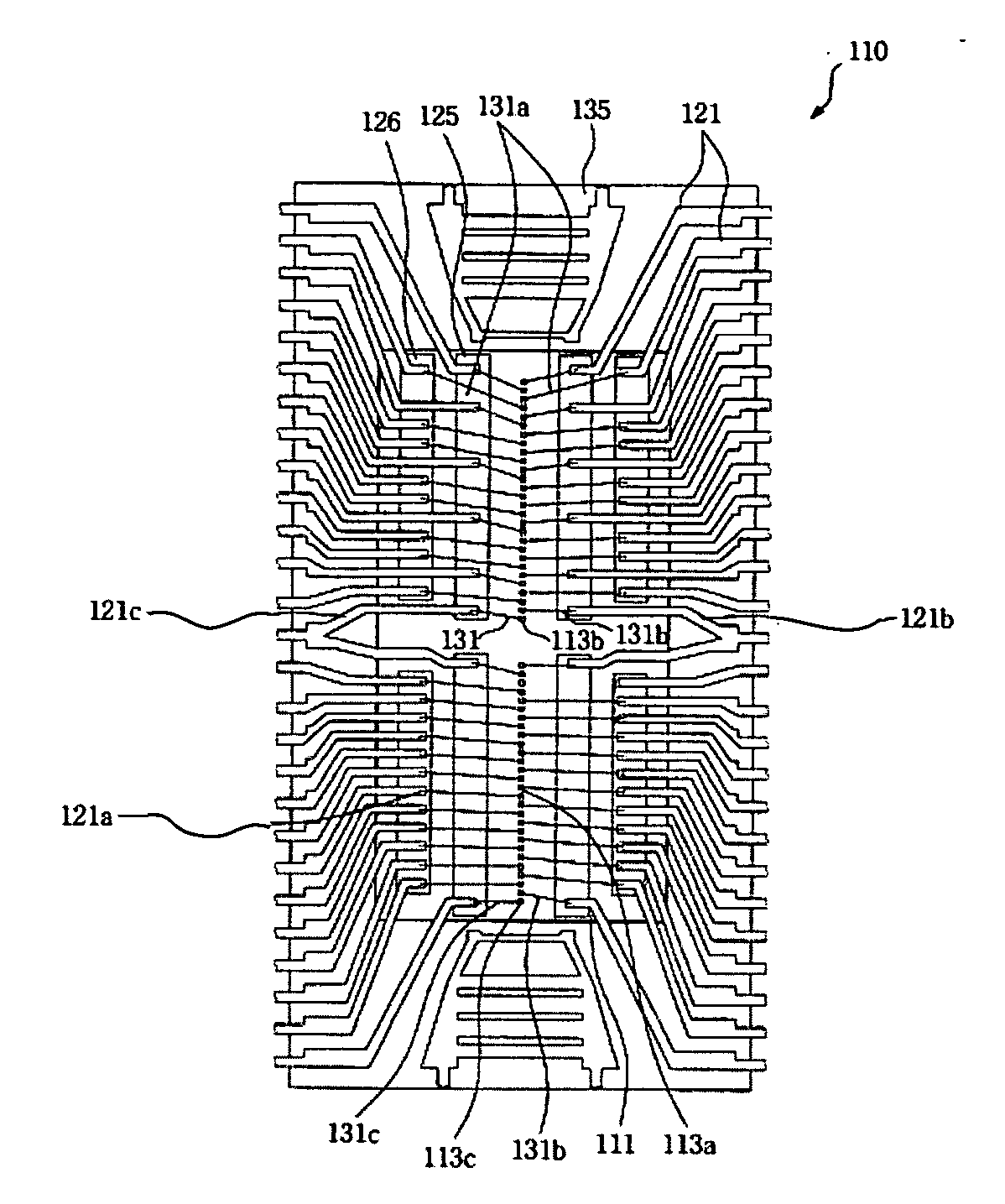

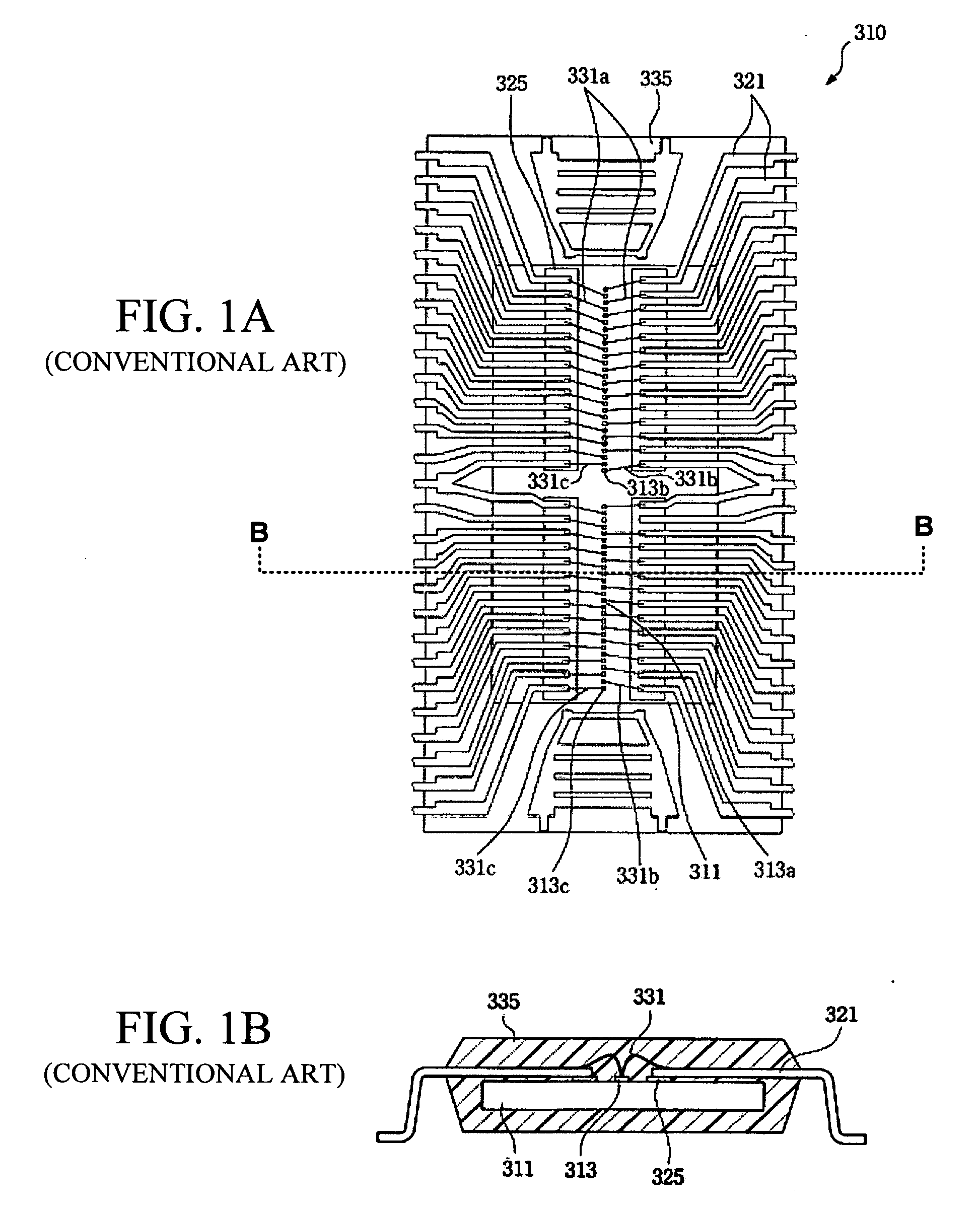

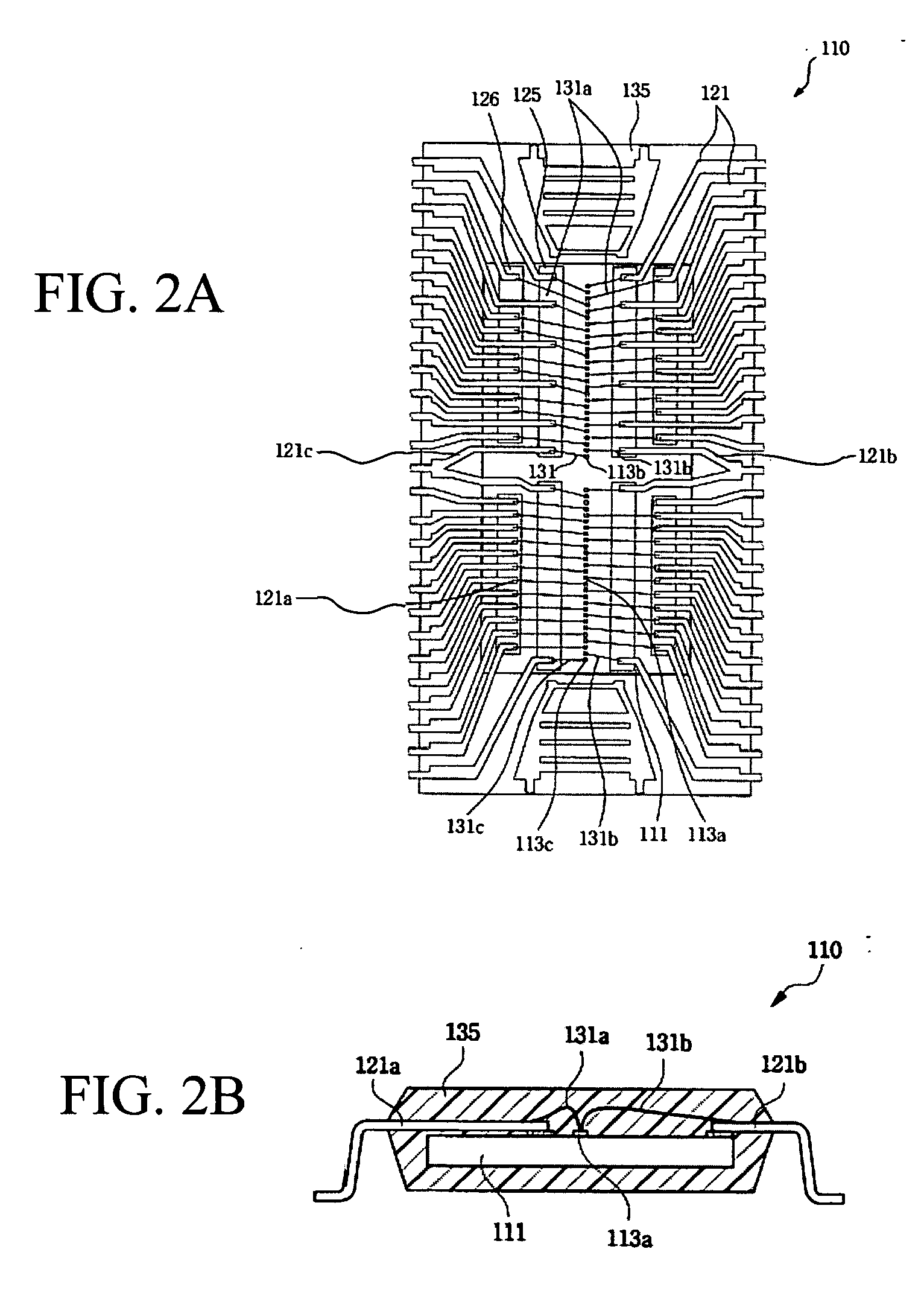

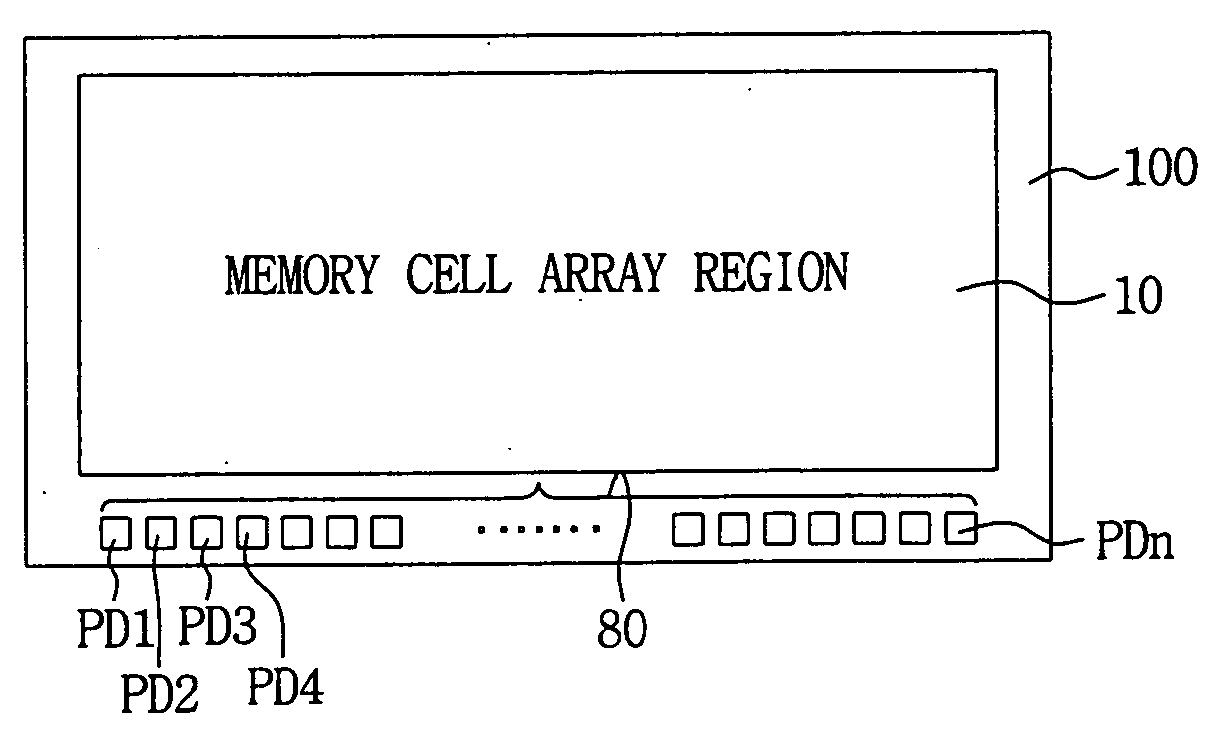

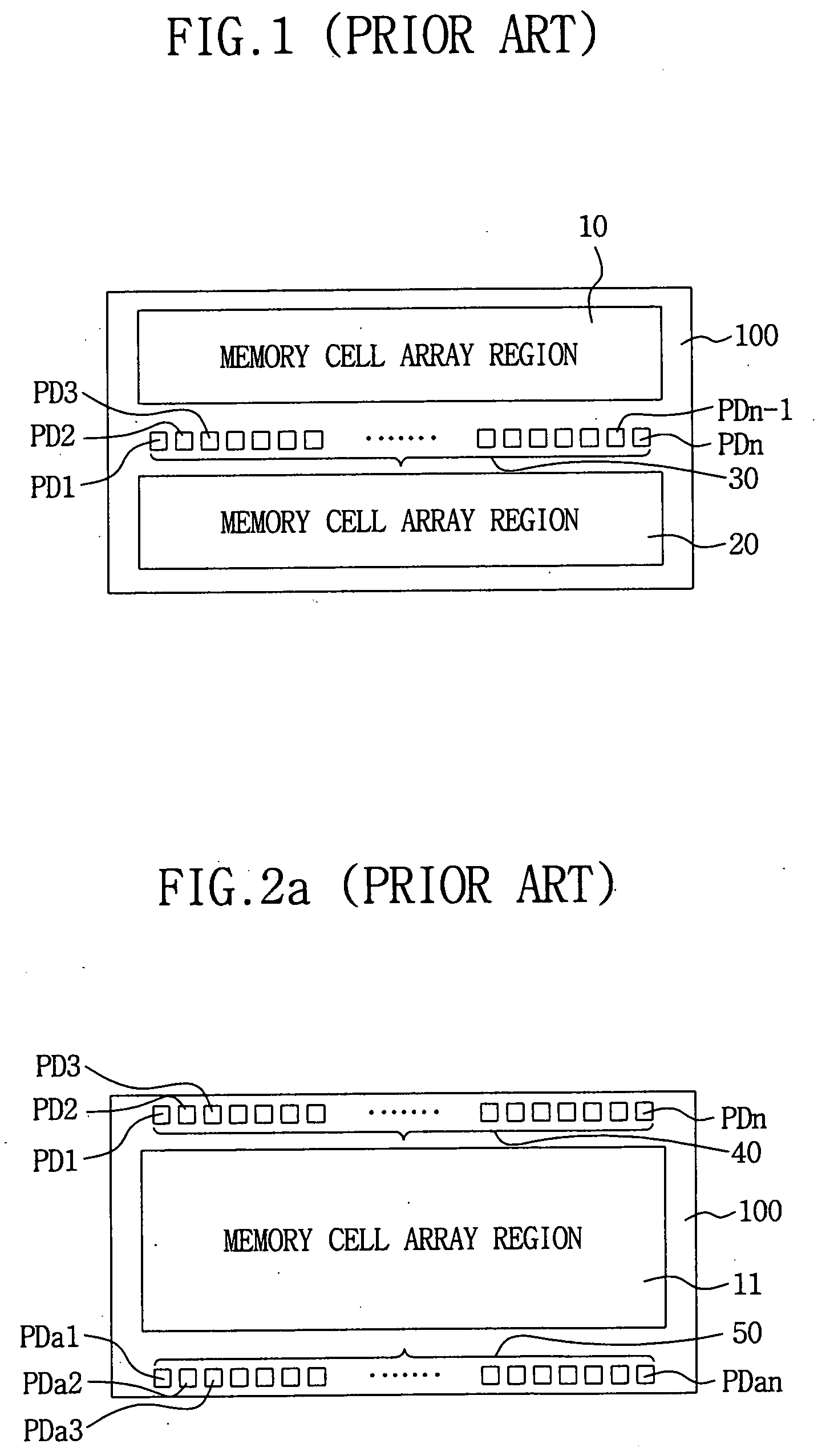

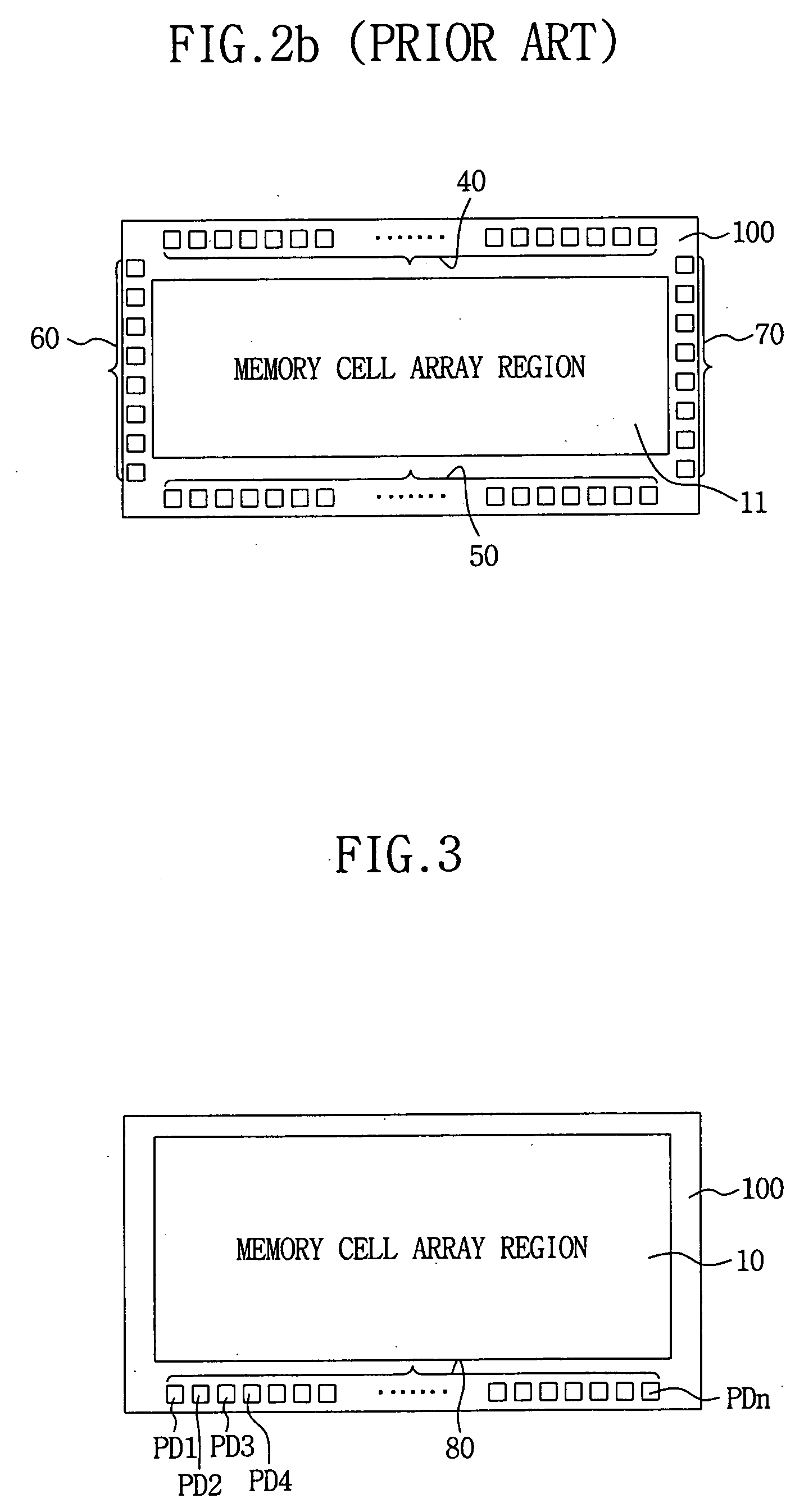

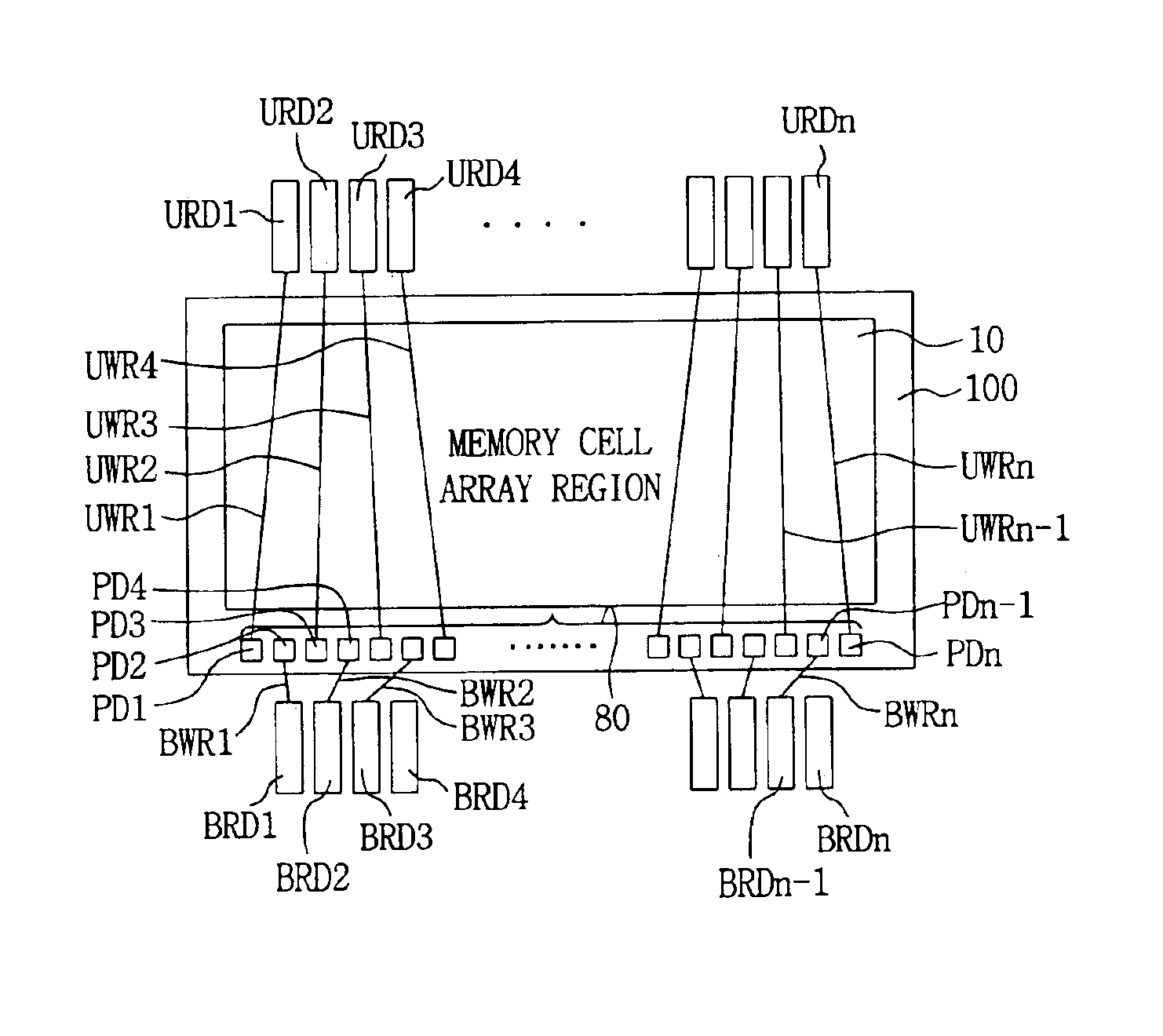

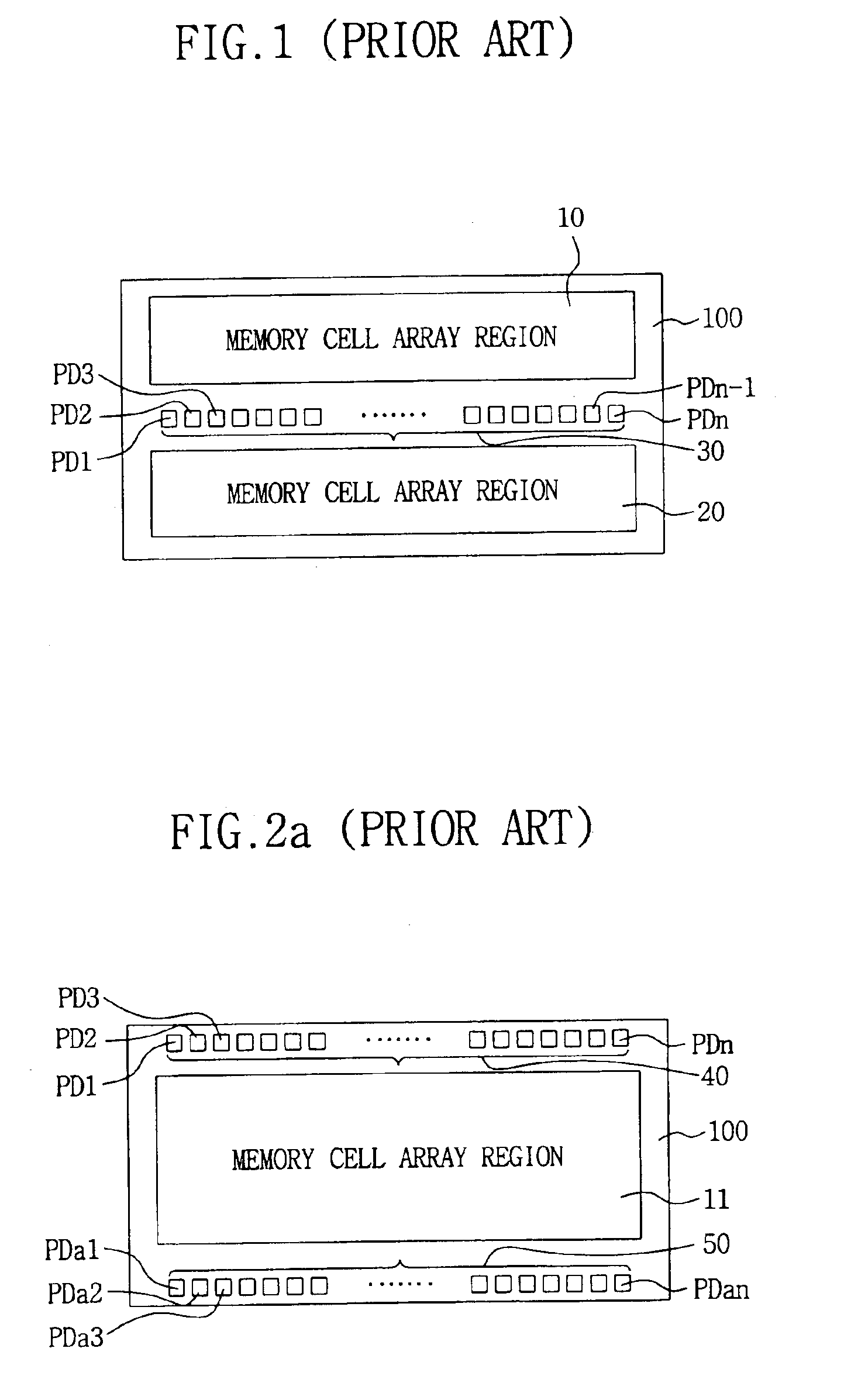

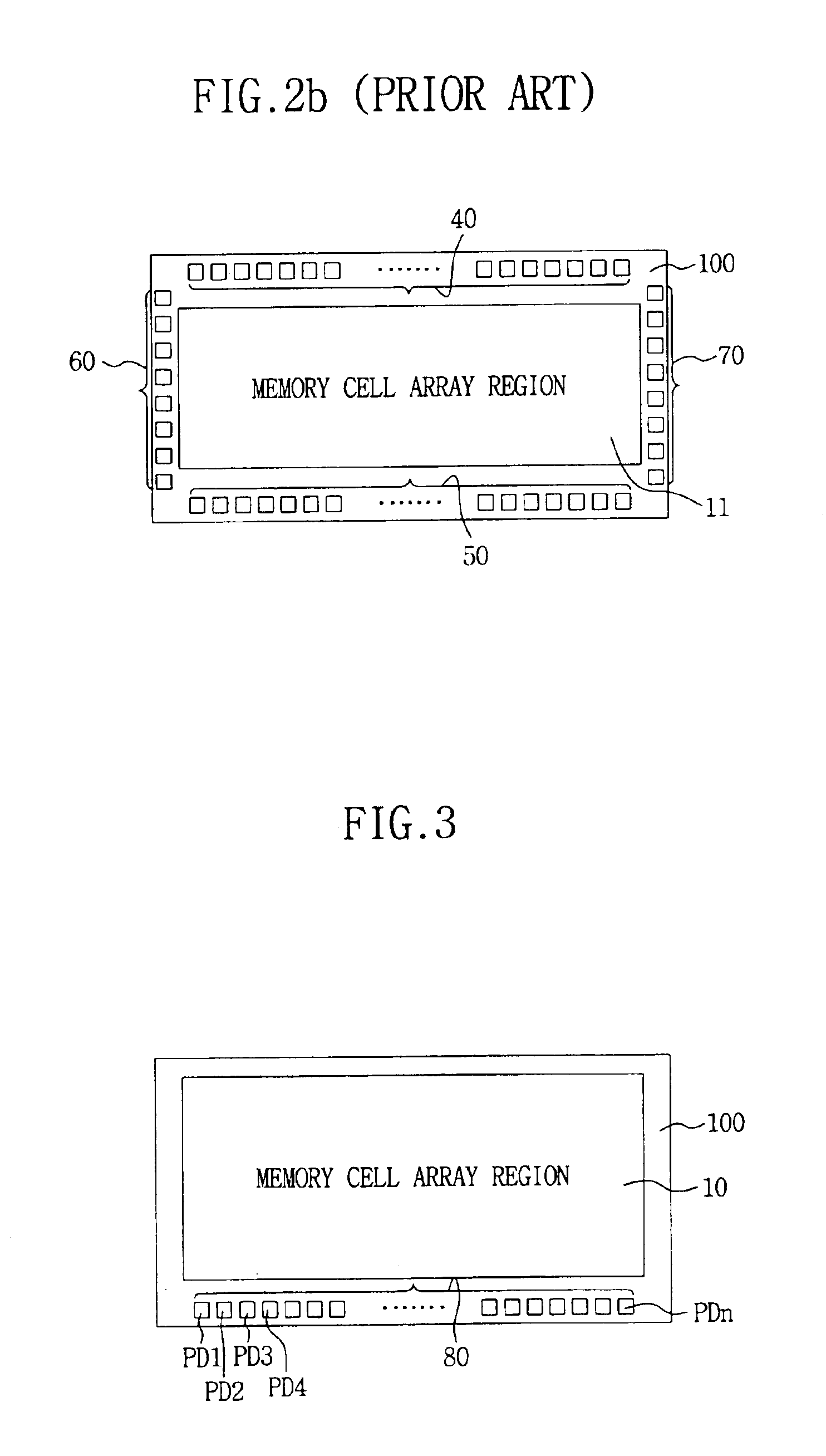

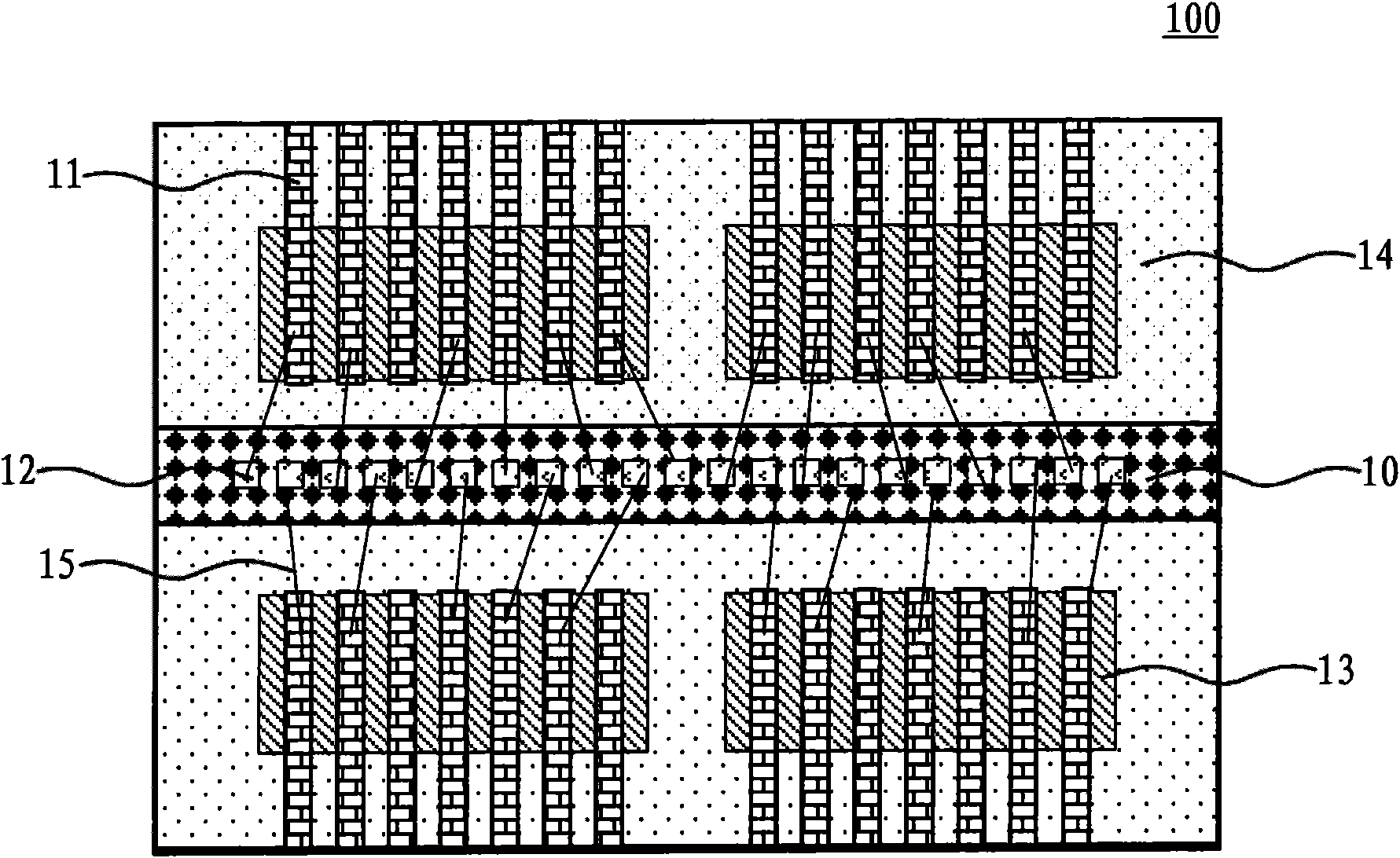

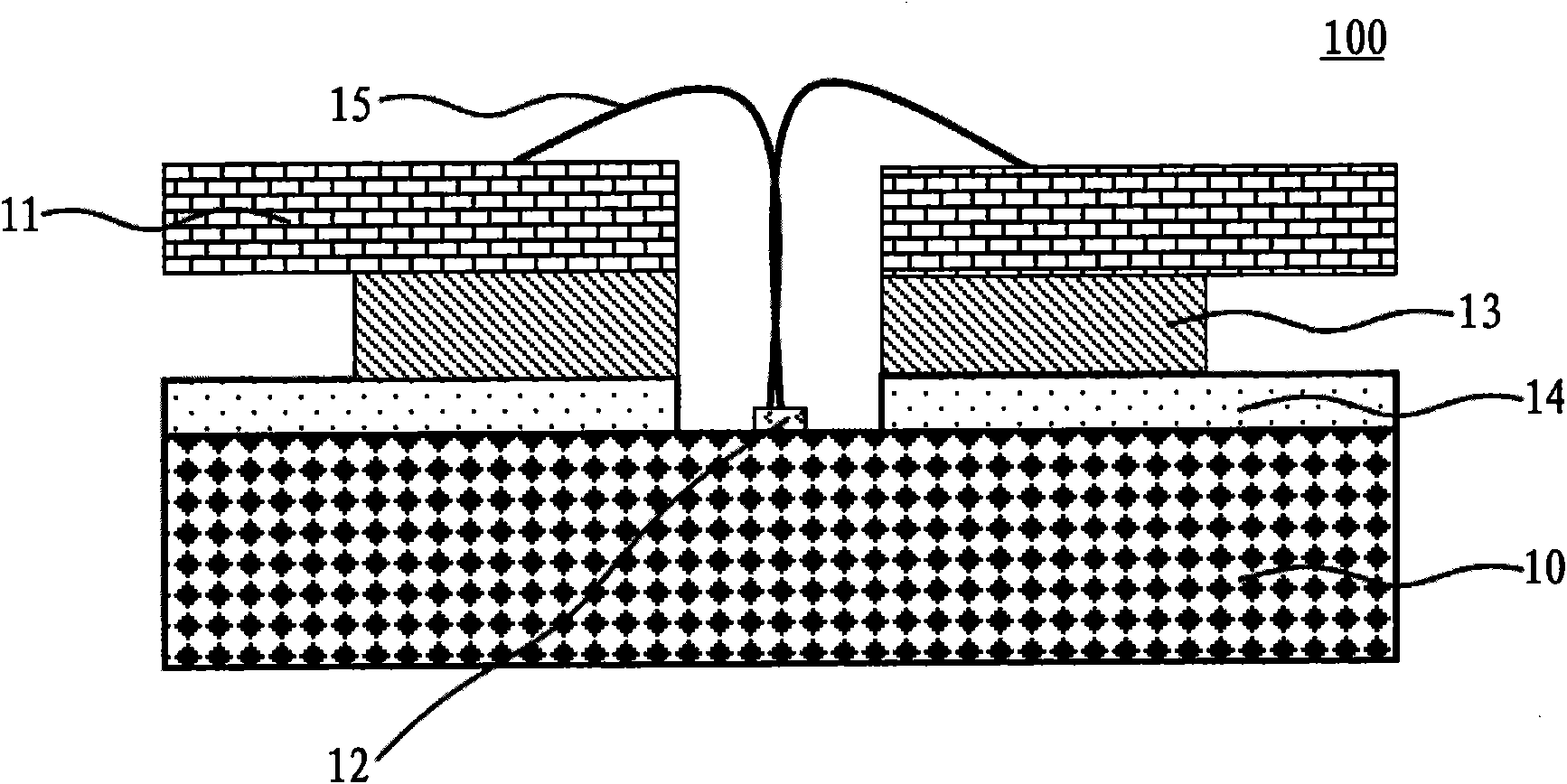

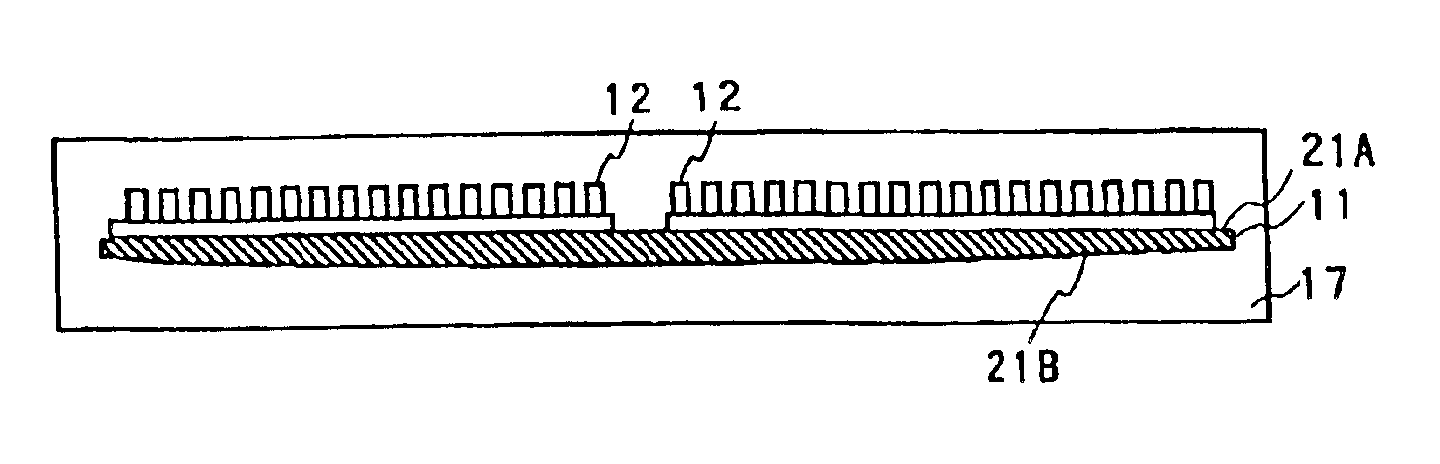

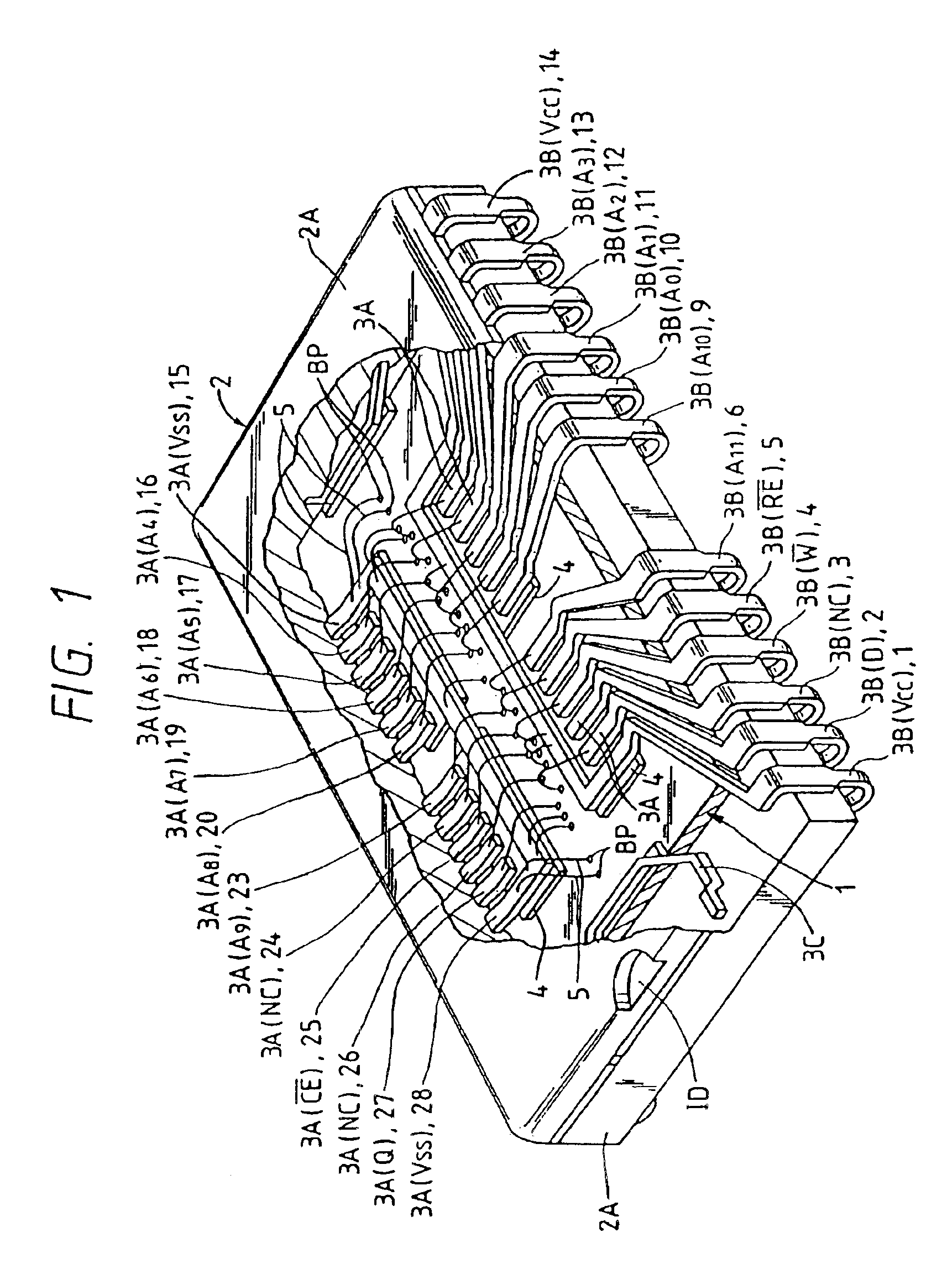

Semiconductor integrated circuit having pads layout for increasing signal integrity and reducing chip size

ActiveUS20040164422A1Semiconductor/solid-state device detailsSolid-state devicesLead on chipChip size

A semiconductor integrated circuit device includes a semiconductor chip having a memory cell array region surrounded with a peripheral circuit region and includes a plurality of bonding pads disposed at least in one row on only one side of the semiconductor chip. The circuit device may include first leads group disposed adjacent to the bonding pad side and a second leads group disposed opposite the first leads group. The second leads group may be formed over a portion of the semiconductor chip (lead-on-chip structure). A plurality of bonding wires connect the first and second leads group with the plurality of bonding pads respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

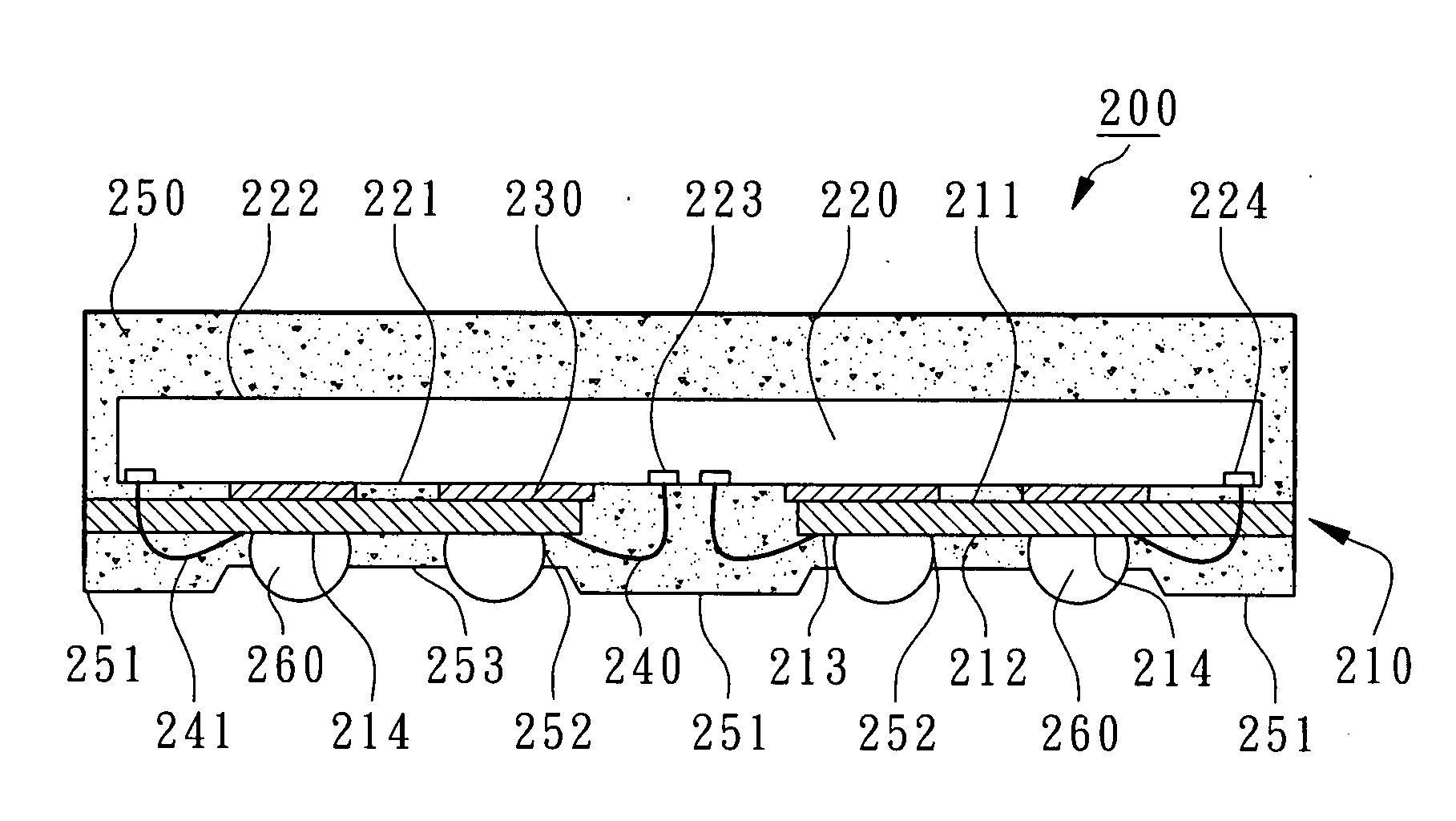

BGA package with leads on chip field of the invention

InactiveUS20080042277A1Improve stabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesLead on chipSolder ball

A BGA package primarily includes a plurality of leads from a leadless lead frame, a chip, and a die-attaching layer. The chip is electrically connected to the leads by a plurality of bonding wires. Solder balls are disposed at the ball placing regions of the leads. Encapsulant encapsulates the chip, the die-attaching layer, and the top surfaces, the bottom surfaces, and the sides of the leads so that the ball placing regions are embedded inside the encapsulant. A plurality of cavities are formed in the encapsulant to expose the corresponding ball placing regions to resolve the solderability of the solder balls and to enhance the stability and reliability of wire bonding and solder ball placing. In one embodiment, a die-attaching layer between the chip and the leads is patterned for elastically supporting the solder balls and for wire bonding.

Owner:CHIPMOS TECH INC

BGA package with leads on chip

ActiveUS20100200972A1Increase ball-joint areaReduce voidsSemiconductor/solid-state device detailsSolid-state devicesLead on chipSolder ball

A BGA package primarily includes a leadless leadframe with a plurality of leads, a chip disposed on the leads, a die-attaching layer adhering to an active surface of the chip and the top surfaces of the leads, a plurality of bonding wires electrically connecting the chip to the leads, an encapsulant, and a plurality of solder balls. Each lead has a bottom surface including a wire-bonding area and a ball-placement area, moreover, a plurality of lips project from the bottom surfaces of the leads around the ball-placement areas. The encapsulant encapsulates the chip, the bonding wires, the die-attaching layer, and the top surfaces, the bottom surfaces except the ball-placement areas, and the laterals of the leads between the top surfaces and the bottom surfaces. A plurality of cavities are formed in the bottom of the encapsulant to expose the corresponding and embedded ball-placement areas. The lips have a plurality of internal sides exposed inside the cavities. The solder balls are disposed on the ball-placement areas and on the internal sides of the cavities to make the solder balls partially embedded in the corresponding cavities to offer non-planar ball pads. It is effective to resolve the solderability of the solder balls and to enhance the reliability of wire bonding and the stability of solder ball placement.

Owner:CHIPMOS TECH INC

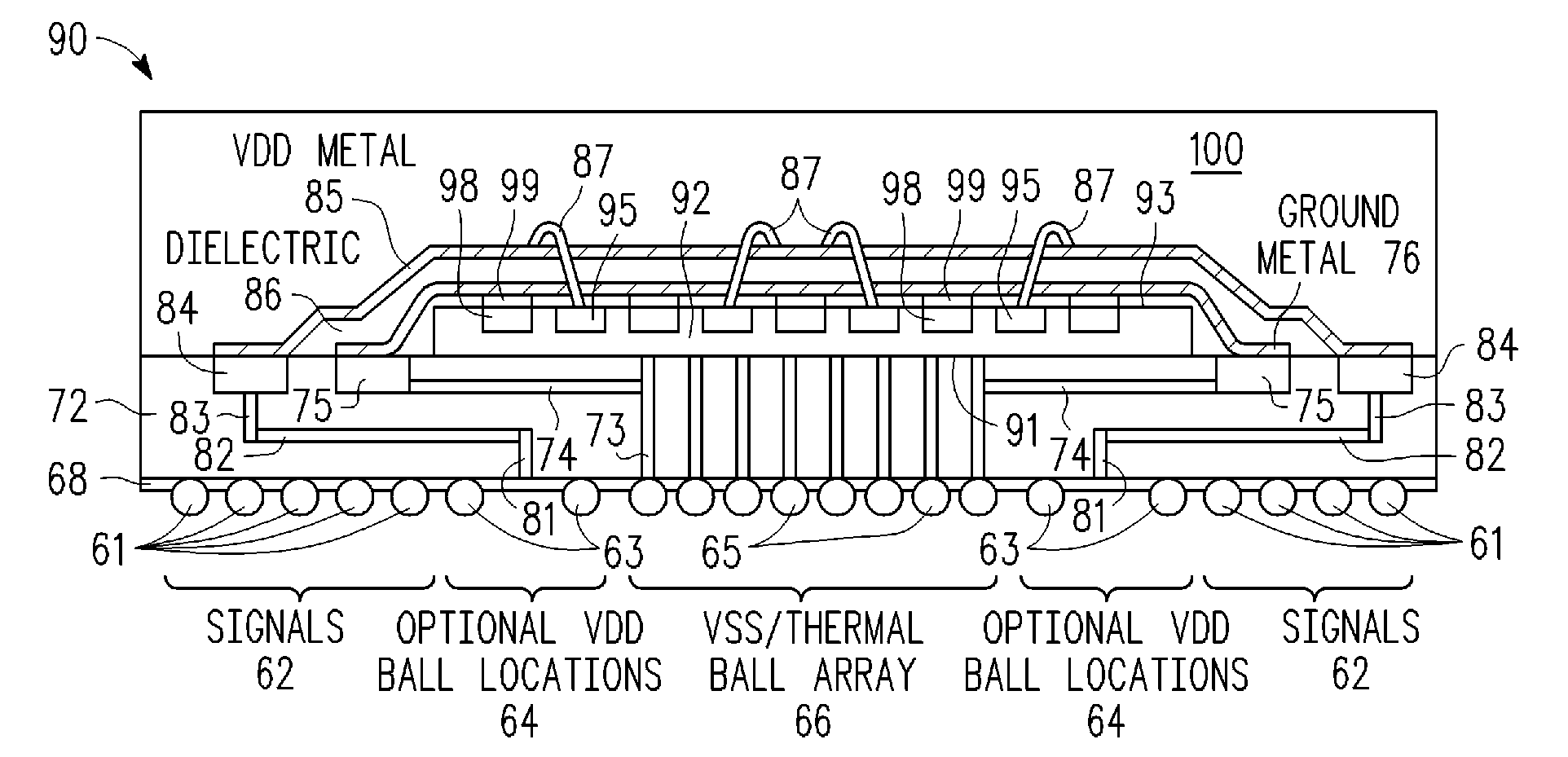

Power lead-on-chip ball grid array package

ActiveUS8129226B2Semiconductor/solid-state device detailsSolid-state devicesLead on chipElectrical conductor

A packaging assembly (30), such as a ball grid array package, is formed which distributes power across an interior region of an integrated circuit die (52) by using an encapsulated patterned leadframe conductor (59) that is disposed over the die (52) and bonded to a plurality of bonding pads (45) formed in a BGA carrier substrate (42) and in the interior die region, thereby electrically coupling the interior die region to an externally provided reference voltage.

Owner:NXP USA INC

Semiconductor integrated circuit having pads layout for increasing signal integrity and reducing chip size

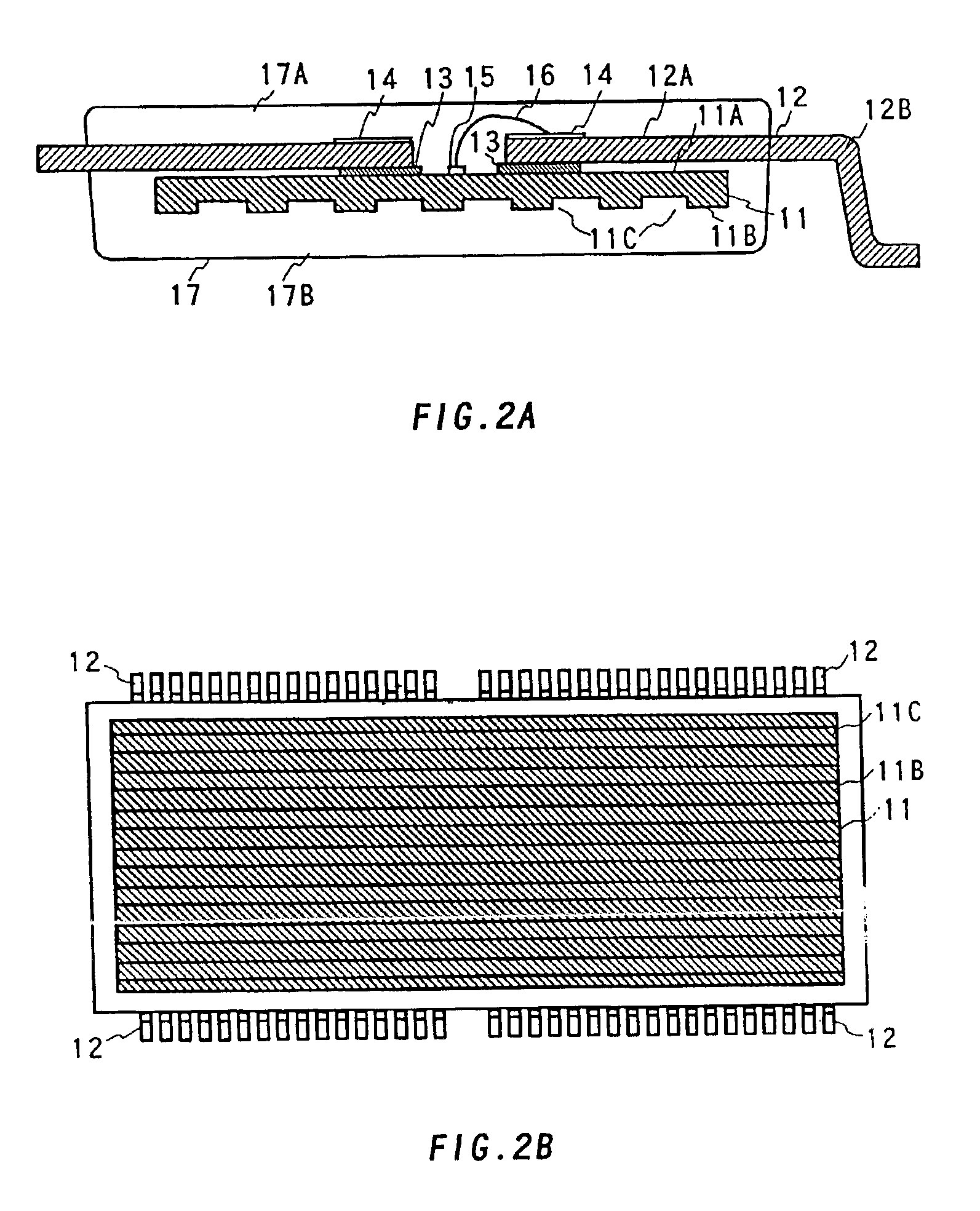

ActiveUS6975020B2Reduce chip sizeImprove signal integritySemiconductor/solid-state device detailsSolid-state devicesLead on chipChip size

A semiconductor integrated circuit device includes a semiconductor chip having a memory cell array region surrounded with a peripheral circuit region and includes a plurality of bonding pads disposed at least in one row on only one side of the semiconductor chip. The circuit device may include first leads group disposed adjacent to the bonding pad side and a second leads group disposed opposite the first leads group. The second leads group may be formed over a portion of the semiconductor chip (lead-on-chip structure). A plurality of bonding wires connect the first and second leads group with the plurality of bonding pads respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor package and manufacturing method thereof

InactiveCN102097407AReduce processing costsSemiconductor/solid-state device detailsSolid-state devicesLead on chipSemiconductor package

The invention discloses a semiconductor package and a manufacturing method thereof. The semiconductor package comprises a chip, chip surface protecting layers, chip bonding pads, lead on chip (LOC) tapes, pins, conducting components and resins, wherein the chip surface protecting layers are formed on the chip and cover the areas except the areas in which the chip bonding pads are about to form; the chip bonding pads are formed in the areas, which are not covered by the chip surface protecting layers, on the chip; the LOC tapes are formed on the chip surface protecting layers; the pins are formed on the LOC tapes which bond the pins and the chip surface protecting layers; the conducting components are formed on the chip bonding pads and part of the chip surface protecting layers and connect the chip bonding pads with the pins electrically; and the resins are used for packaging the components.

Owner:SAMSUNG SEMICON CHINA RES & DEV +1

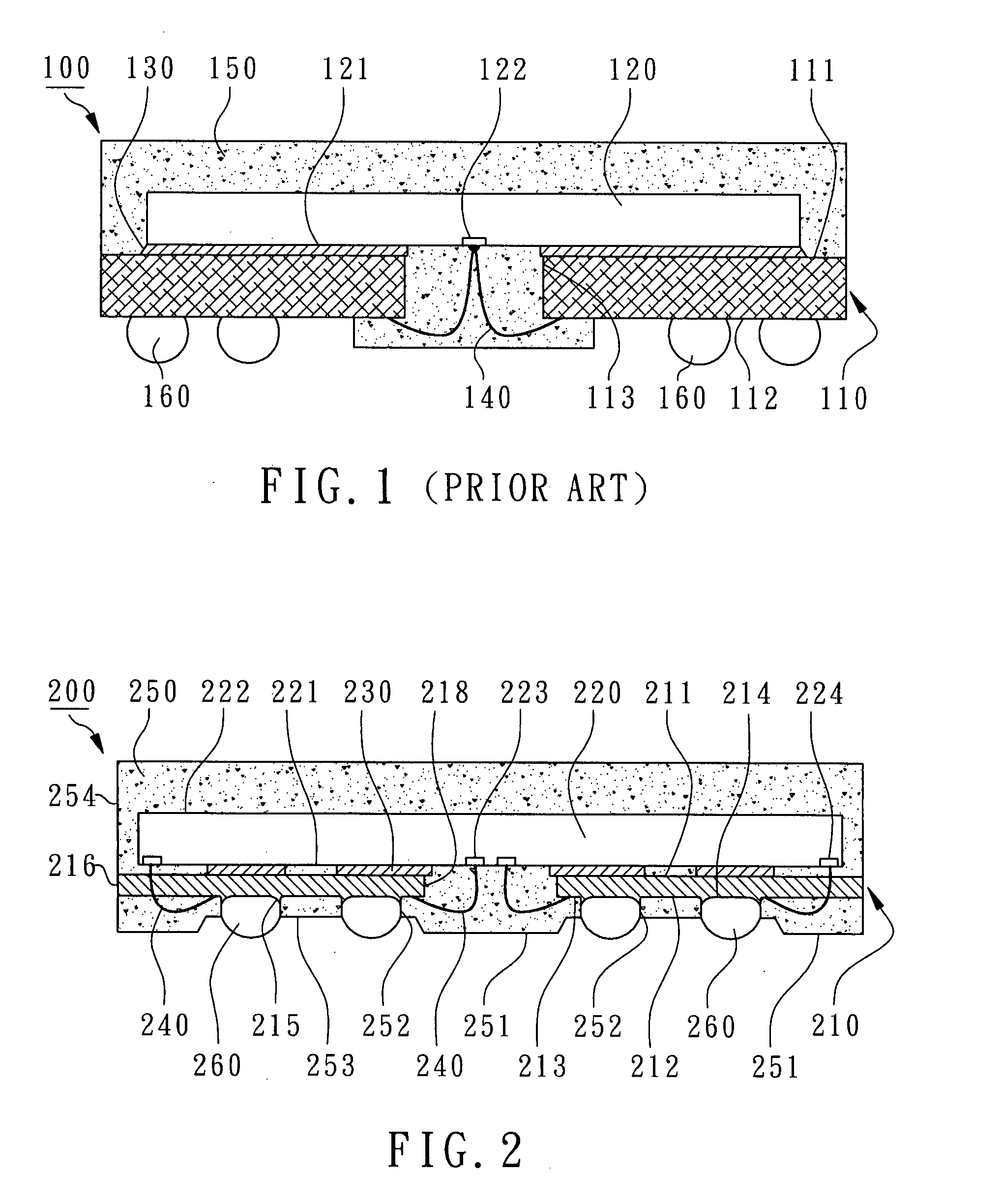

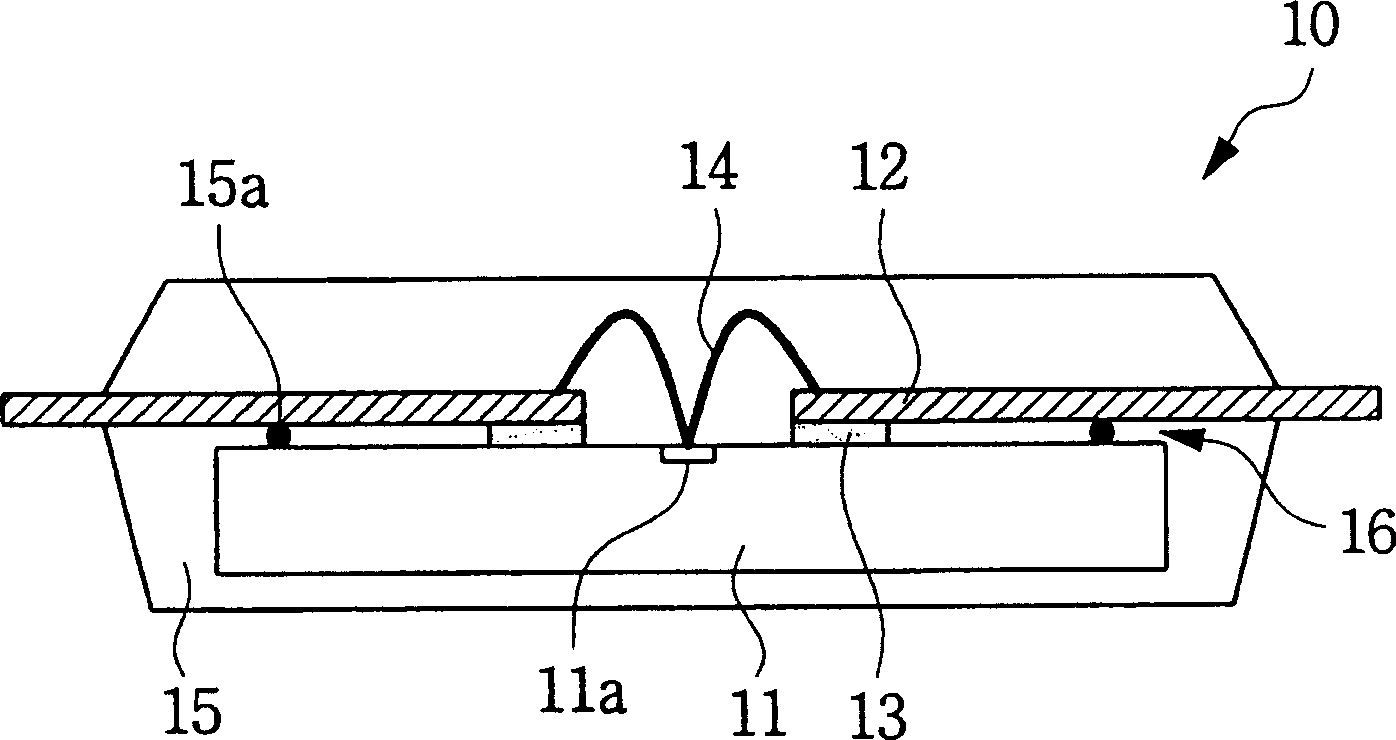

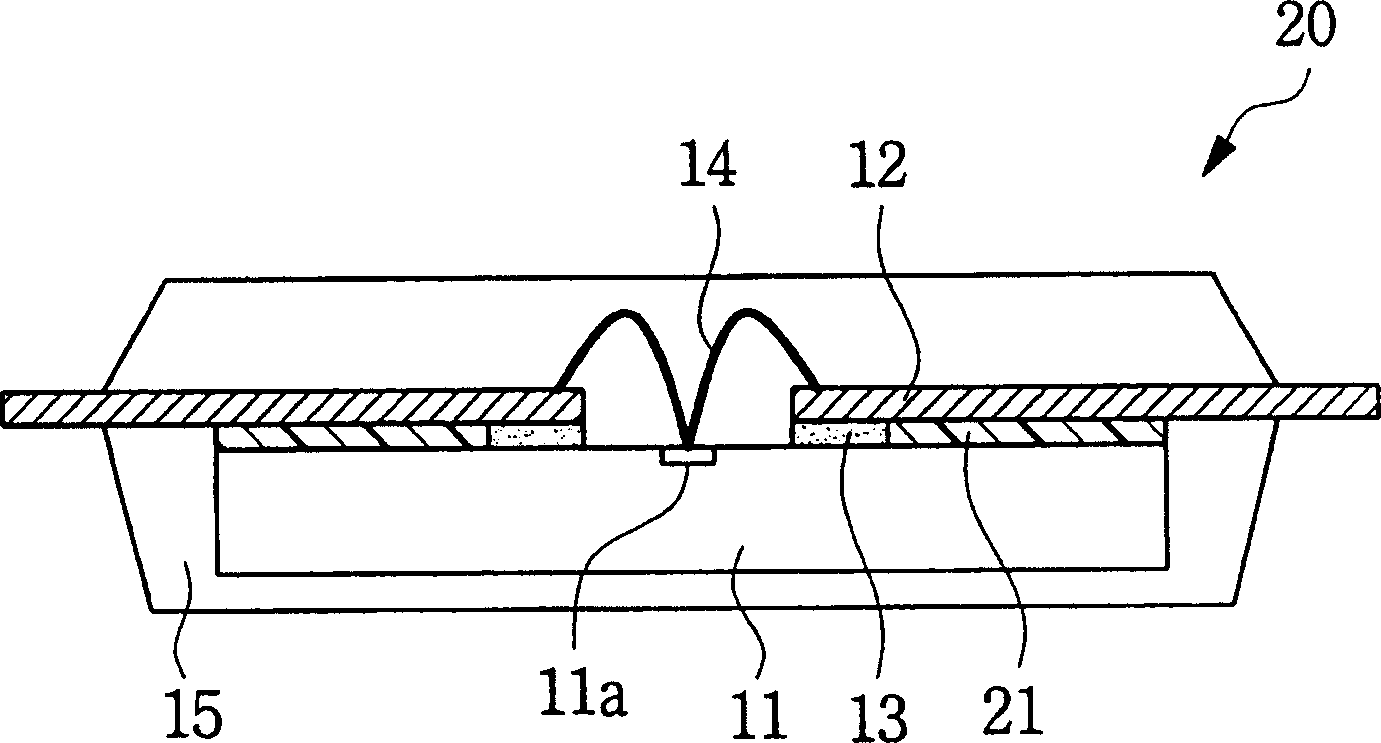

Lead on chip semiconductor package

InactiveUS20050212099A1Semiconductor/solid-state device detailsSolid-state devicesContact padLead on chip

The present invention provides an LOC package wherein the lead frame is in direct contact with the semiconductor device. The lead frame, which includes openings, is positioned directly on the semiconductor device. An adhesive material is applied in the opening in the lead frame. This adhesive material contacts both the lead frame and the semiconductor device. The lead frame is therefore securely held to the semiconductor device. Wires can then be bonded to contact pads on the semiconductor device and to the lead frame.

Owner:SAMSUNG ELECTRONICS CO LTD

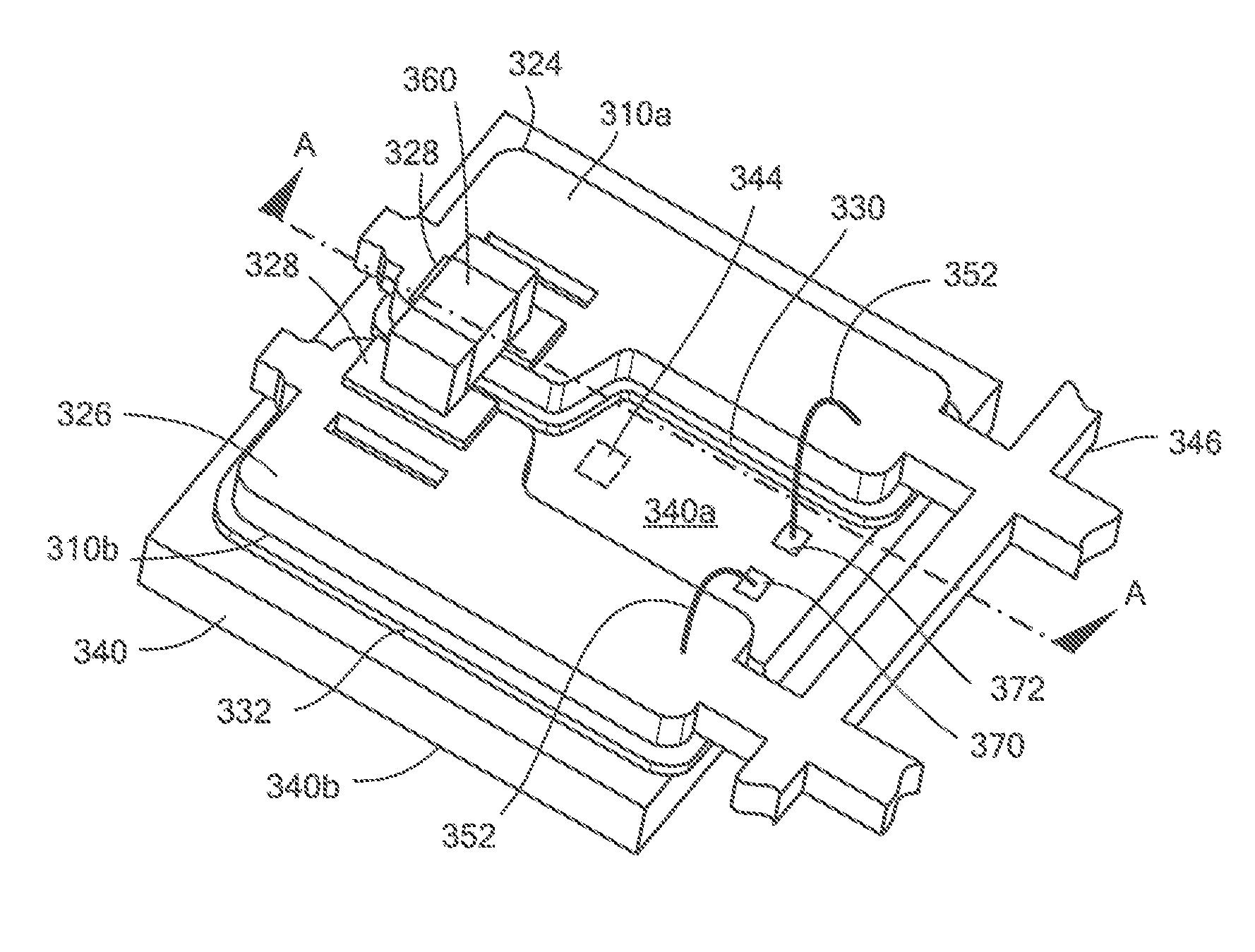

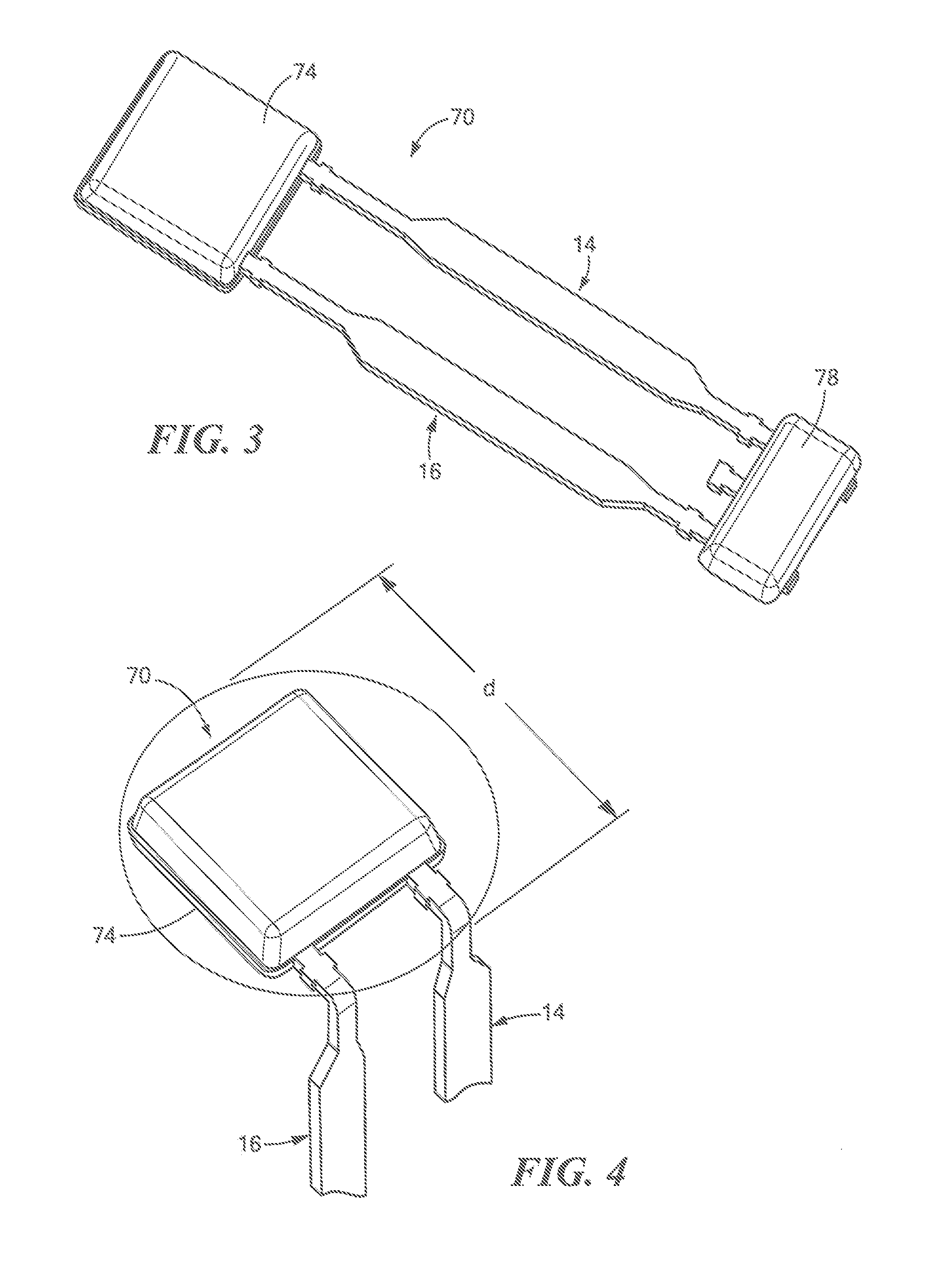

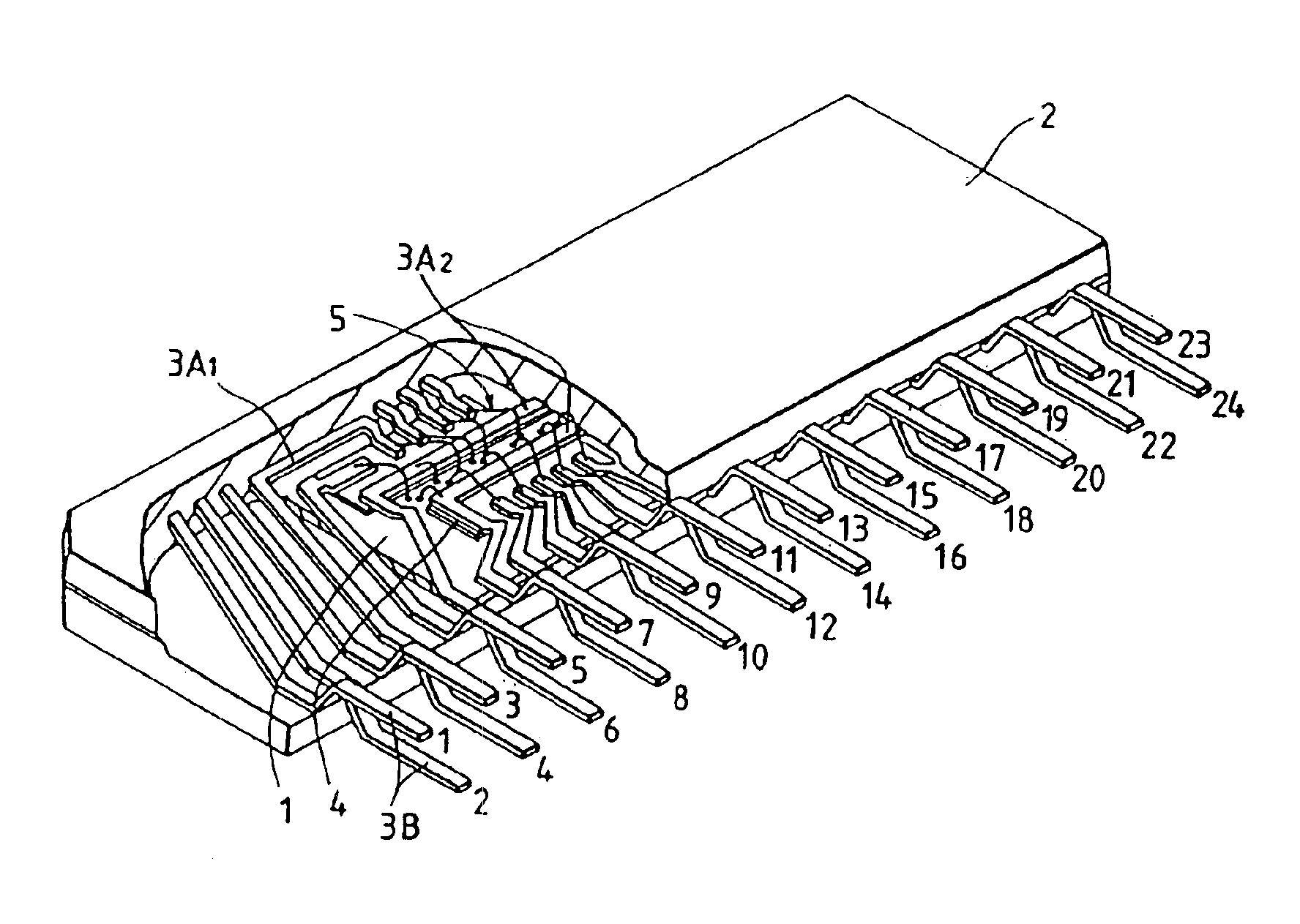

Lead-on-chip semiconductor package and leadframe for the package

InactiveUS7750444B2Reduce stress concentrationEliminate electricalSemiconductor/solid-state device detailsSolid-state devicesLead on chipSemiconductor package

A LOC semiconductor package with the leadframe for the package is revealed. The LOC semiconductor package primarily comprises a plurality of leadframe's leads, at least a tie bar, a chip, and an encapsulant encapsulating the components mentioned above. Each lead has a bonding finger. The tie bar has a dummy finger where the dummy finger is linearly disposed at one side of the disposition area of the bonding fingers. The chip has an active surface with the bonding fingers. When the dummy finger and the bonding fingers are disposed above the active surface by a die-attaching layer, the dummy finger is adjacent to one edge of the active surface. The bonding fingers are electrically connected with the bonding pads. The dummy finger will bear the concentrated stresses to avoid the bonding fingers on the active surface to delamination or break due to external stresses and to avoid the interference to the layout of the leads.

Owner:POWERTECH TECHNOLOGY INC

Method of making a lead-on-chip device

InactiveUS6913951B2Semiconductor/solid-state device detailsSolid-state devicesLead on chipEngineering

A semiconductor device which is sealed with a plastic sealing layer and whose thickness is regulated to be below a given value is known. Since the thickness of the device is small, and the thickness of the upper portion of the plastic sealing layer and the thickness of the lower portion thereof are different from each other, the plastic sealing layer becomes warped, thus causing a crack on the side of the semiconductor chip.To solve this problem, the semiconductor device according to the present invention comprises a semiconductor chip on which a plurality of grooves are defined. Consequently, the thickness of the lower portion of the plastic layer becomes greater, thereby preventing cracks from occurring on the semiconductor chip.

Owner:LAPIS SEMICON CO LTD

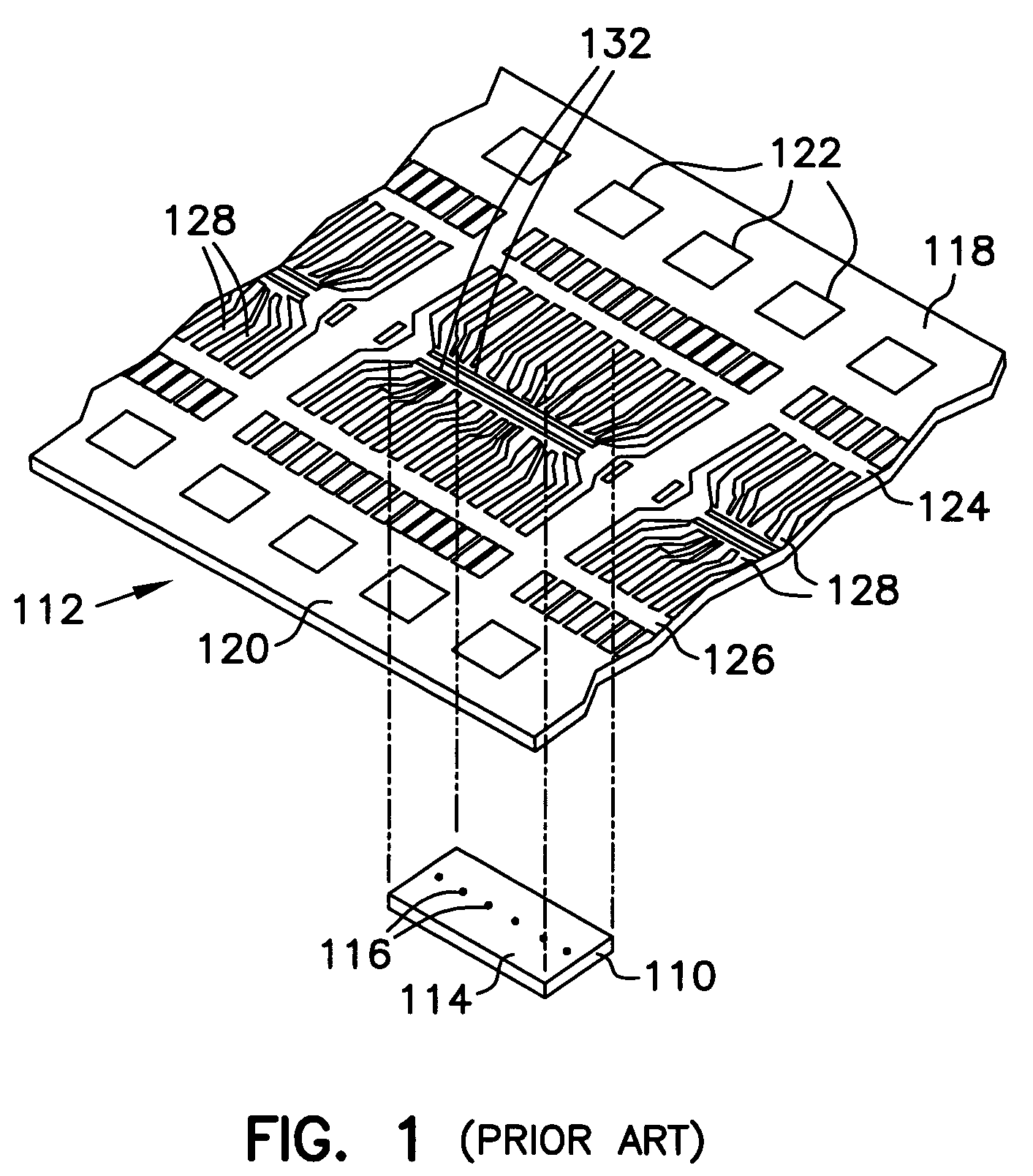

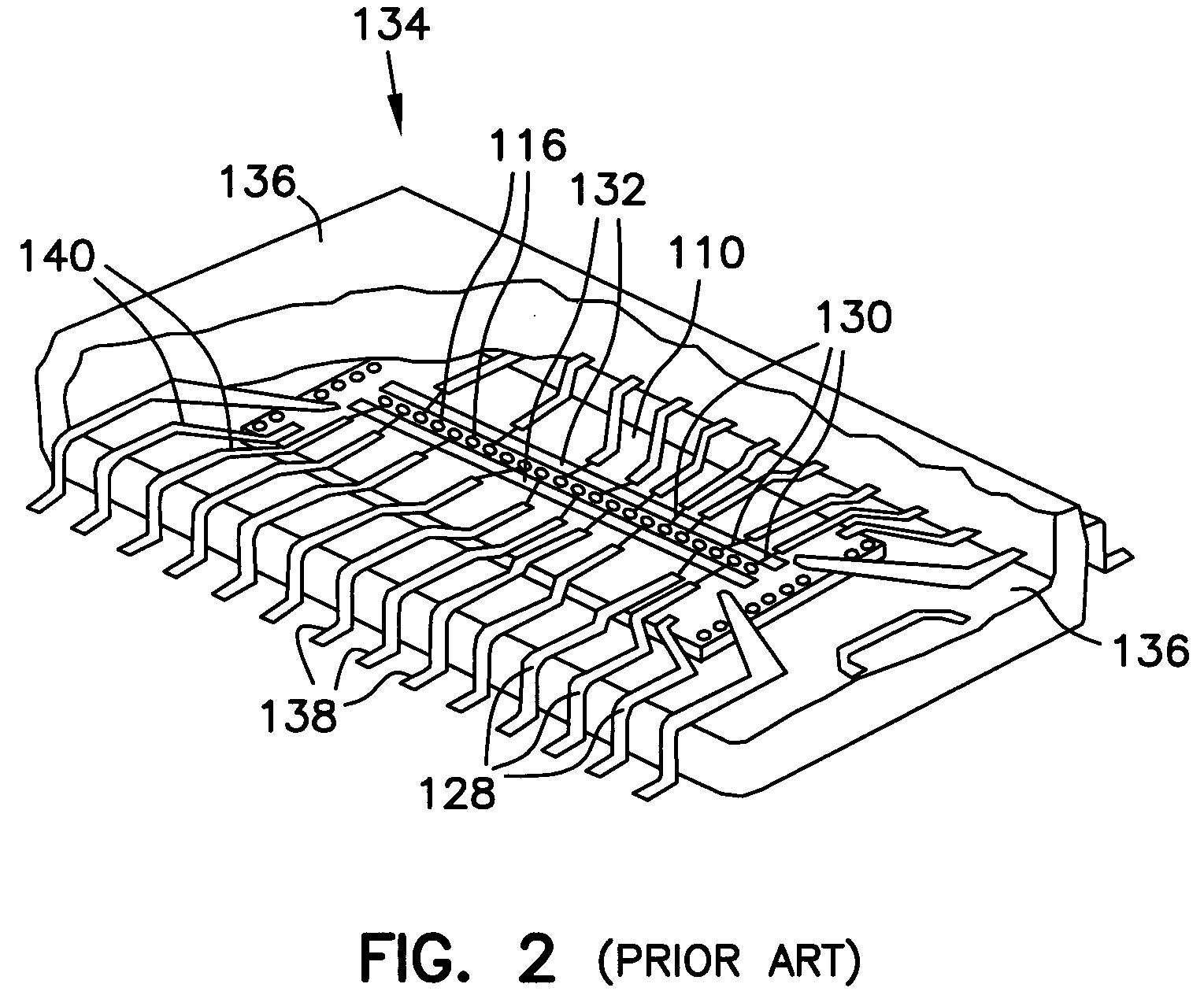

Lead on chip semiconductor package and producing method and equipment thereof

InactiveCN1674271ASemiconductor/solid-state device detailsSolid-state devicesLead on chipSemiconductor package

Used for semiconductor packing, an adhesive agent (130) is used on parts of a conductor framework (120) and on parts of a specific surface on an integrated switching circuit chip (ISCC) so as to hold the conductor framework on the ISCC. A majority of input / output contact points (112) are located on the top side of the ISCC. Independent claims are also included for the following: (A) A method for producing semiconductor packing; (B) and for a device for producing semiconductor packing.

Owner:SAMSUNG ELECTRONICS CO LTD

Lead on chip semiconductor package

InactiveUS7414303B2Semiconductor/solid-state device detailsSolid-state devicesContact padLead on chip

The present invention provides an LOC package wherein the lead frame is in direct contact with the semiconductor device. The lead frame, which includes openings, is positioned directly on the semiconductor device. An adhesive material is applied in the opening in the lead frame. This adhesive material contacts both the lead frame and the semiconductor device. The lead frame is therefore securely held to the semiconductor device. Wires can then be bonded to contact pads on the semiconductor device and to the lead frame.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor package based on lead-on-chip architecture, the fabrication thereof and a leadframe for implementing in a semiconductor package

InactiveUS7348660B2Fast and low-cost processSemiconductor/solid-state device detailsSolid-state devicesLead on chipSemiconductor package

A leadframe includes a multiplicity of leads. The leads have a board level contact portion, an intermediate portion and a chip level contact portion. The intermediate portion is disposed between the board level contact portion and the chip level contact portion. The board level contact portions extend from one of the first side or the second side of the semiconductor device along a second direction. The chip level contact portions extend along the first direction. Ends of the chip level contact portions are aligned along a line extending along the second direction. This leadframe can be included with a semiconductor chip in a packaged integrated circuit.

Owner:POLARIS INNOVATIONS LTD

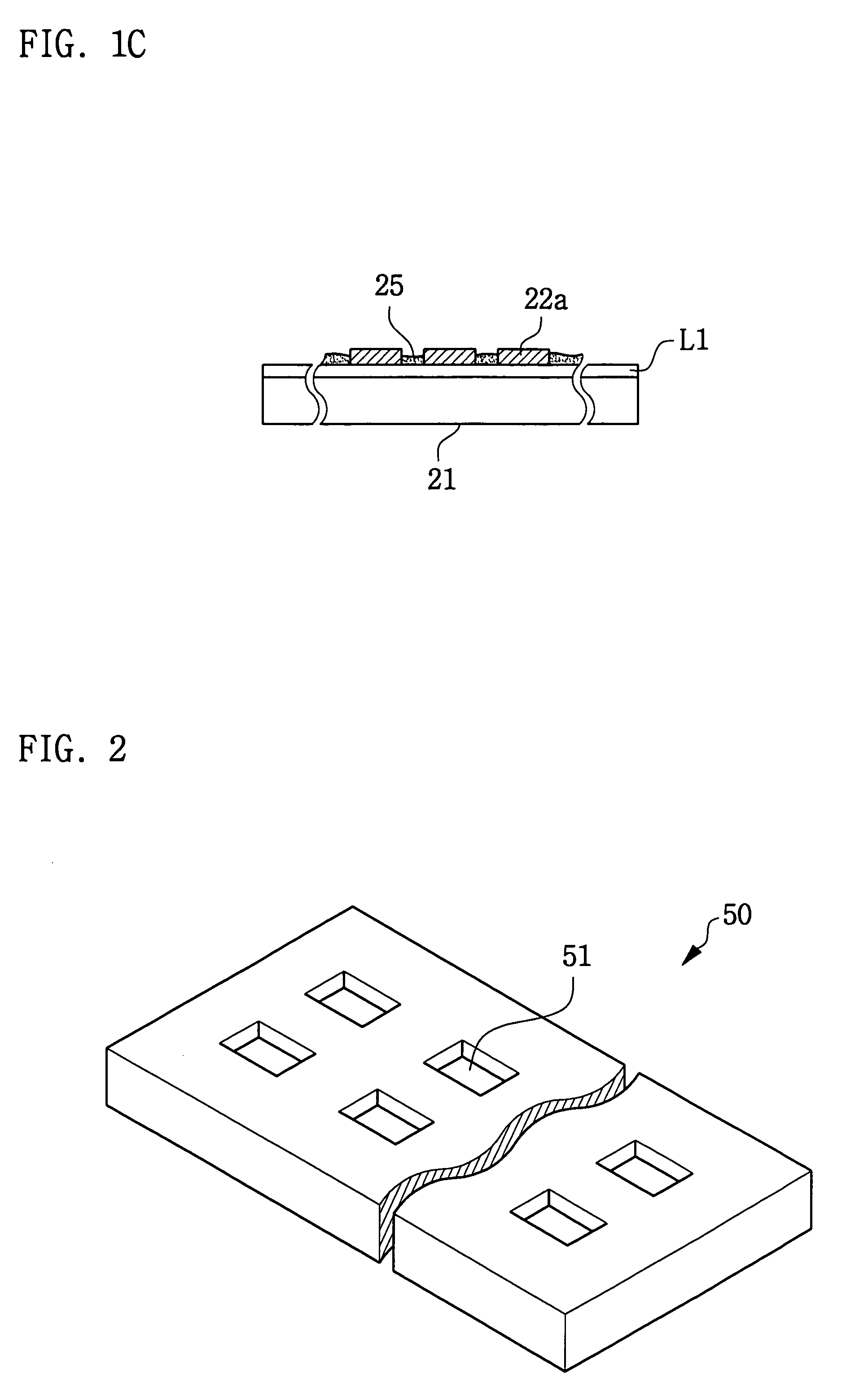

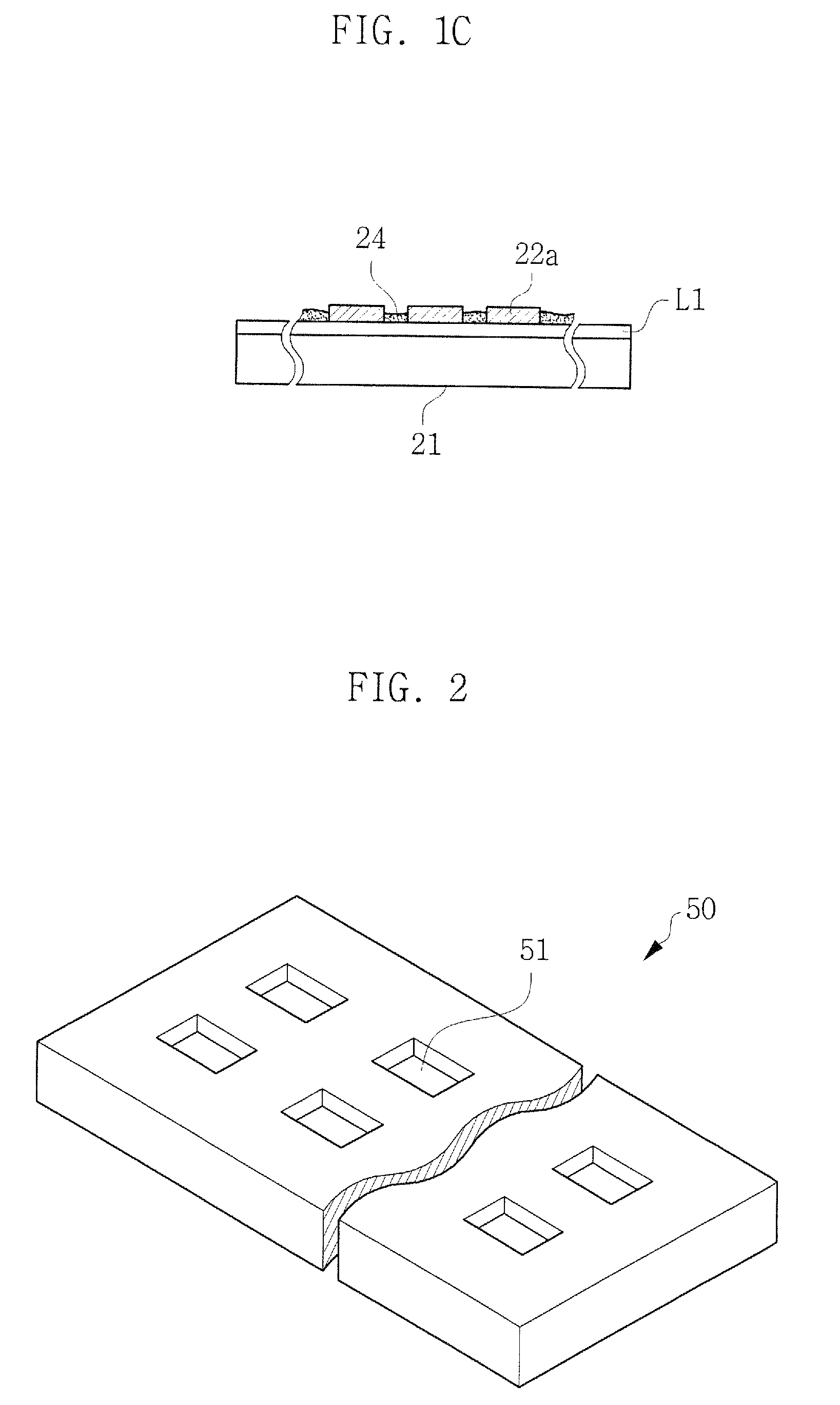

Apparatus for improving stencil/screen print quality

InactiveUS7476277B2Promote disseminationReduce surface tensionLiquid surface applicatorsSolid-state devicesScreen printingLead on chip

A method and apparatus for improved stencil / screen print quality is disclosed. The stencil or screen assists in application of a printable material onto a substrate, such as an adhesive to a semiconductor die of a semiconductor wafer during a lead-on-chip (LOC) packaging process. In one embodiment, the stencil includes a coating applied to at least one surface of a pattern of the stencil or screen to retard running of the printable material onto the surface. In another embodiment, the stencil or screen includes a second coating applied to at least one other surface of the pattern to promote spreading of the printable material onto the substrate.

Owner:MICRON TECH INC

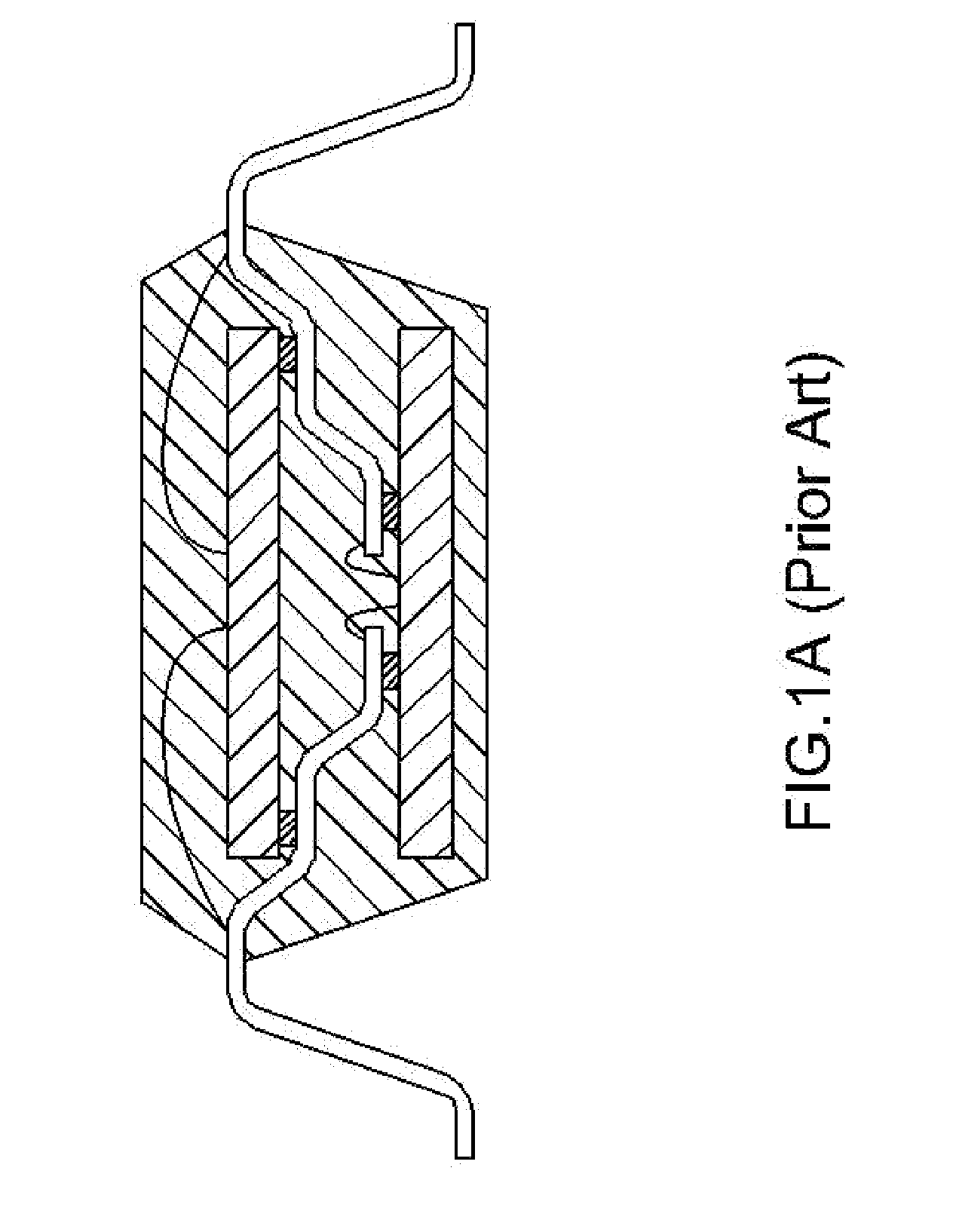

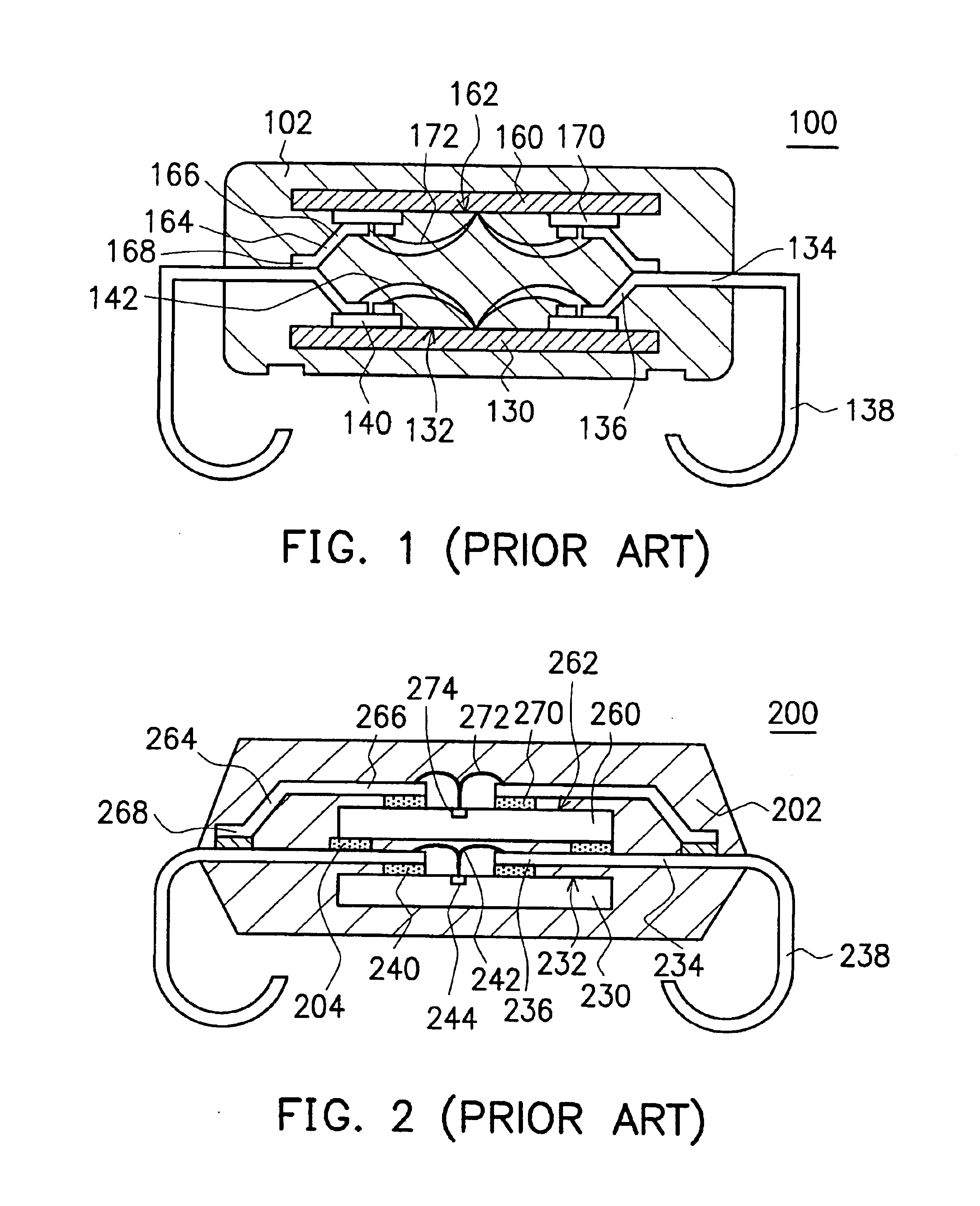

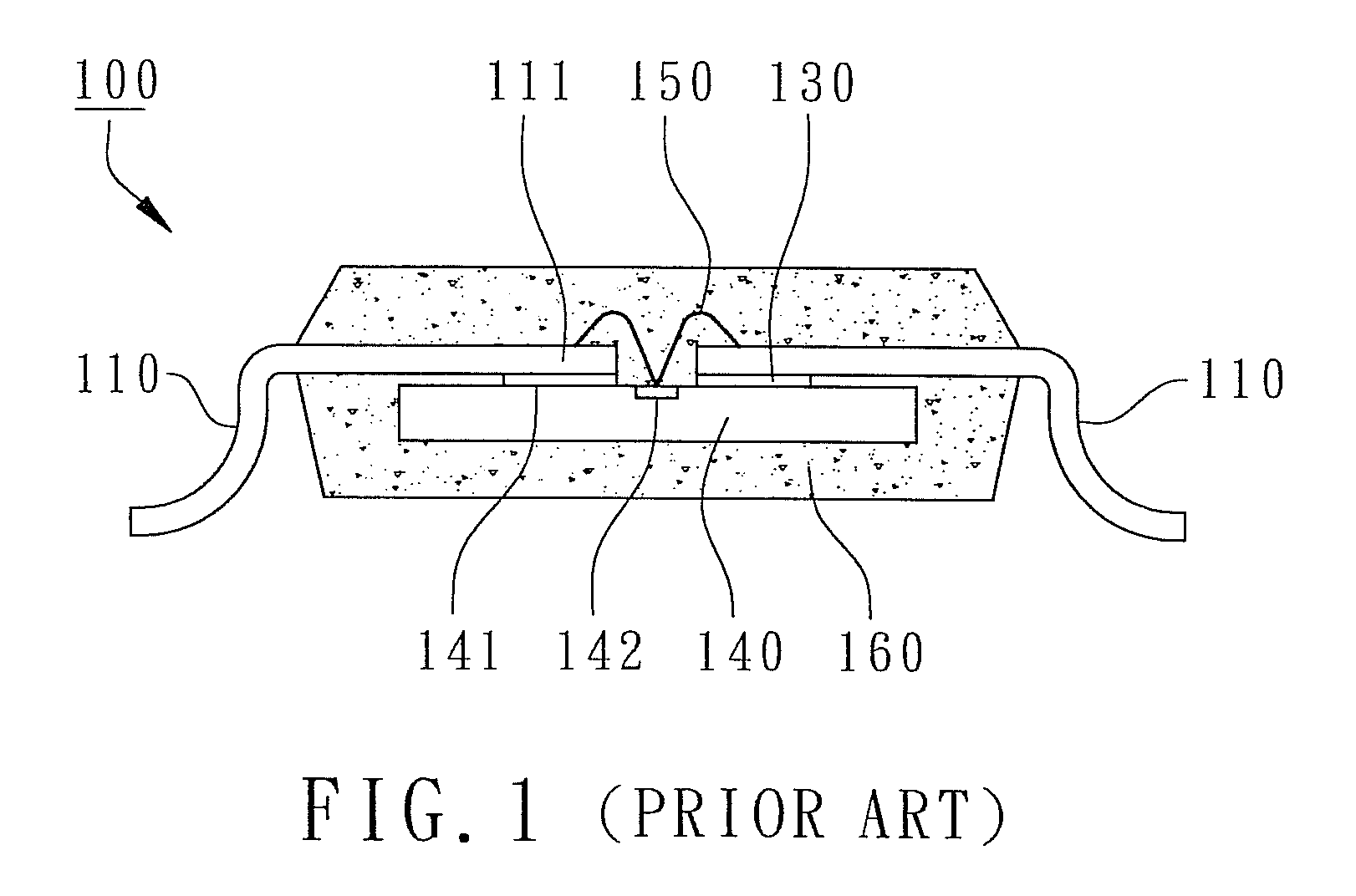

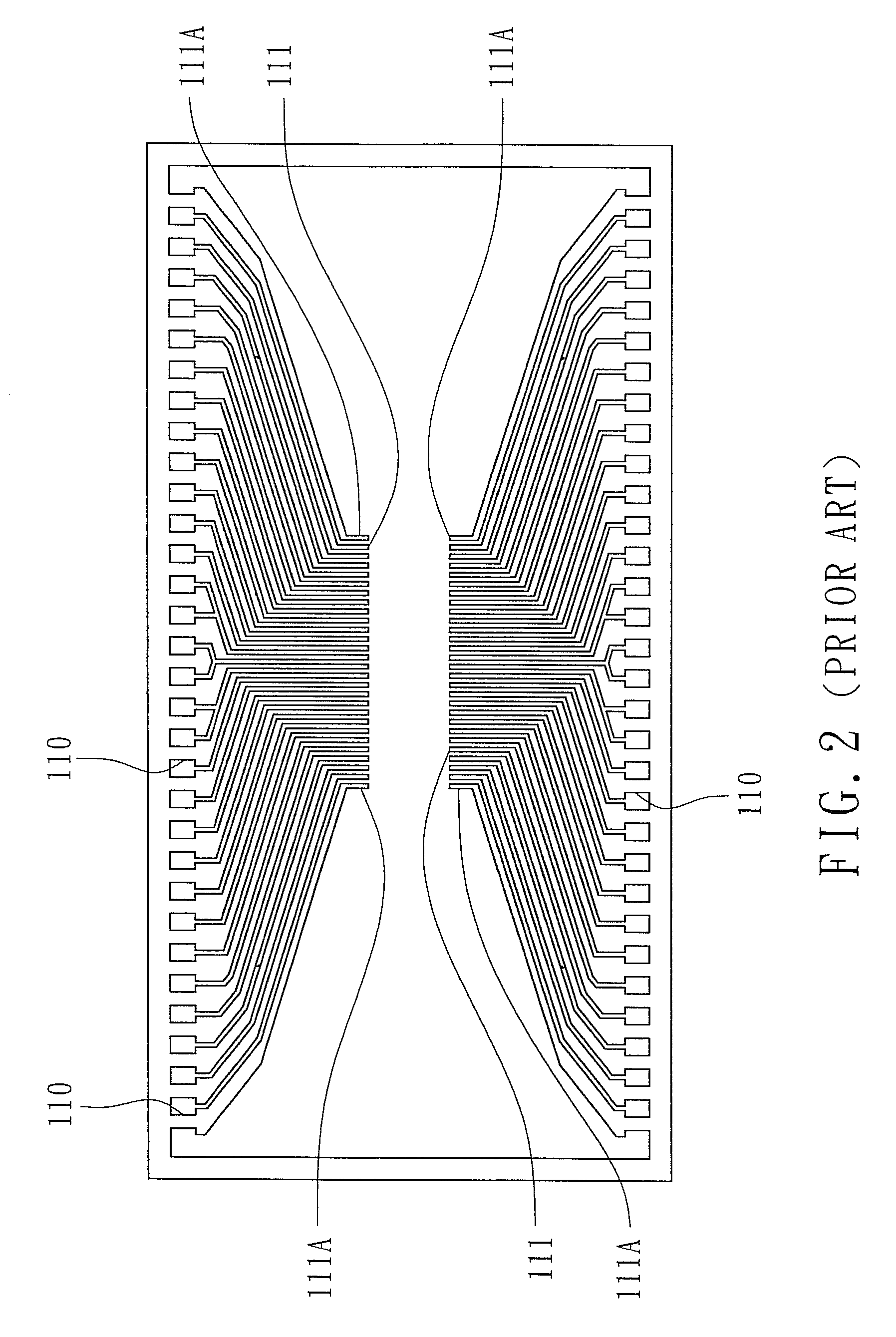

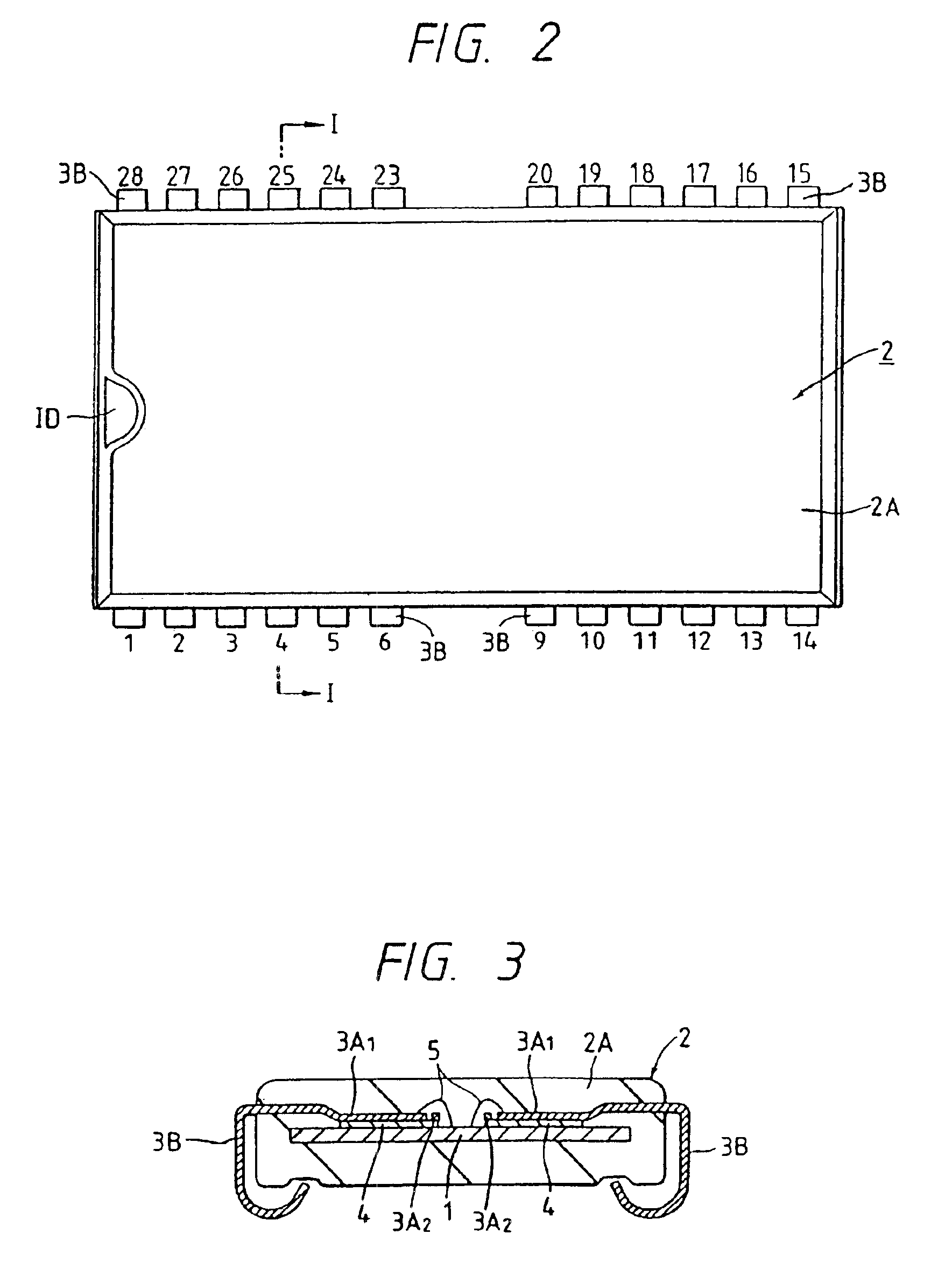

Semiconductor device

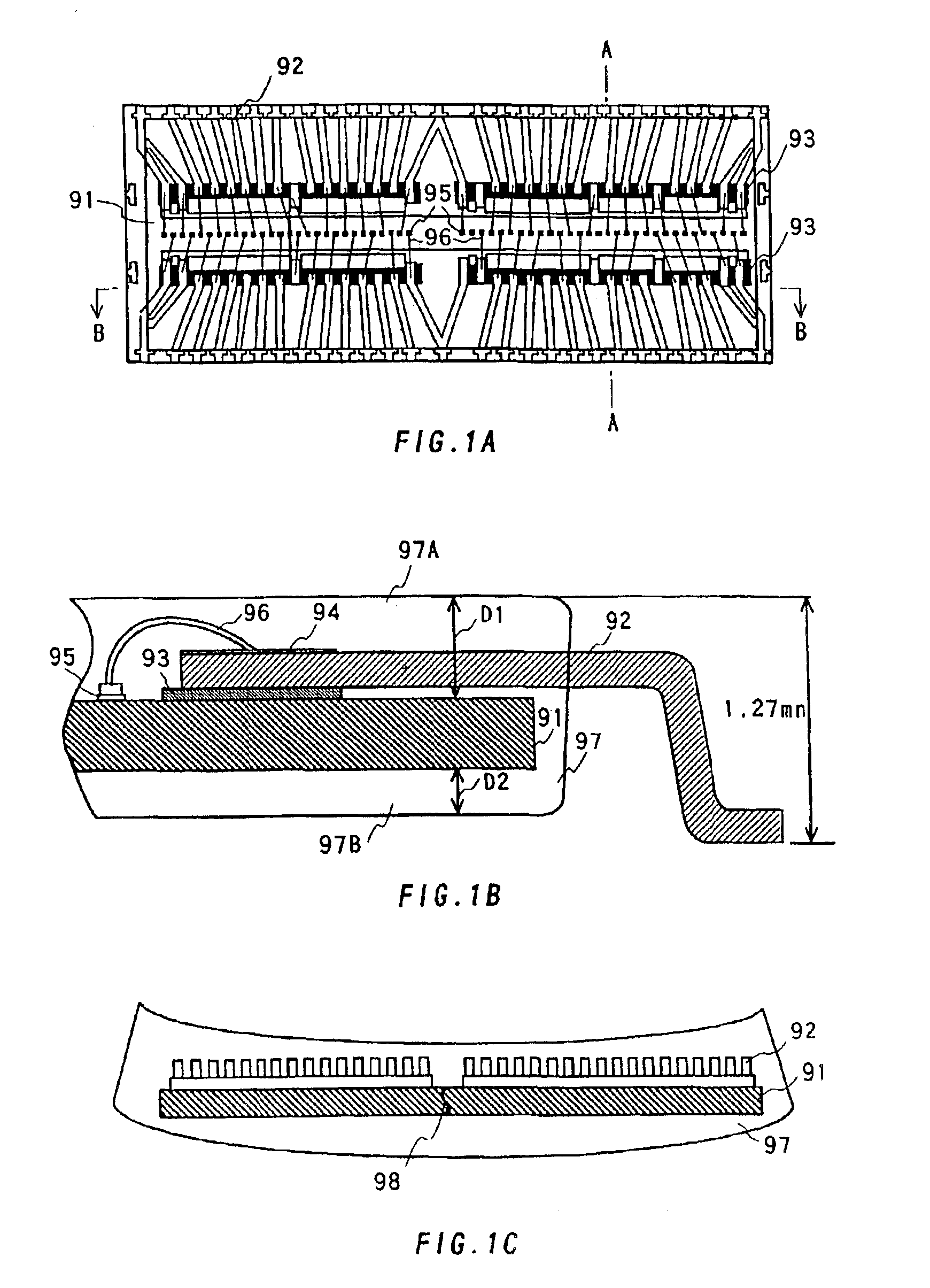

InactiveUS6919622B2Improve cooling effectReduced parasitic capacityPrinted circuit assemblingSemiconductor/solid-state device detailsLead on chipEngineering

As the semiconductor chip is large-sized, highly integrated and speeded up, it becomes difficult to pack the semiconductor chip together with leads in a package. In view of this difficulty, there has been adopted the package structure called the “Lead-On-Chip” or “Chip-On-Lead” structure in which the semiconductor and the leads are stacked and packed. In the package of this structure, according to the present invention, the gap between the leading end portions of the inner leads and the semiconductor chip is made wider than that between the inner lead portions except the leading end portions and the semiconductor chip thereby to reduce the stray capacity, to improve the signal transmission rate and to reduce the electrical noises.

Owner:RENESAS TECH CORP