Semiconductor package and manufacturing method thereof

A package and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of high-frequency chip interconnection limitations, poor heat dissipation performance of LOC packages, and high equipment costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

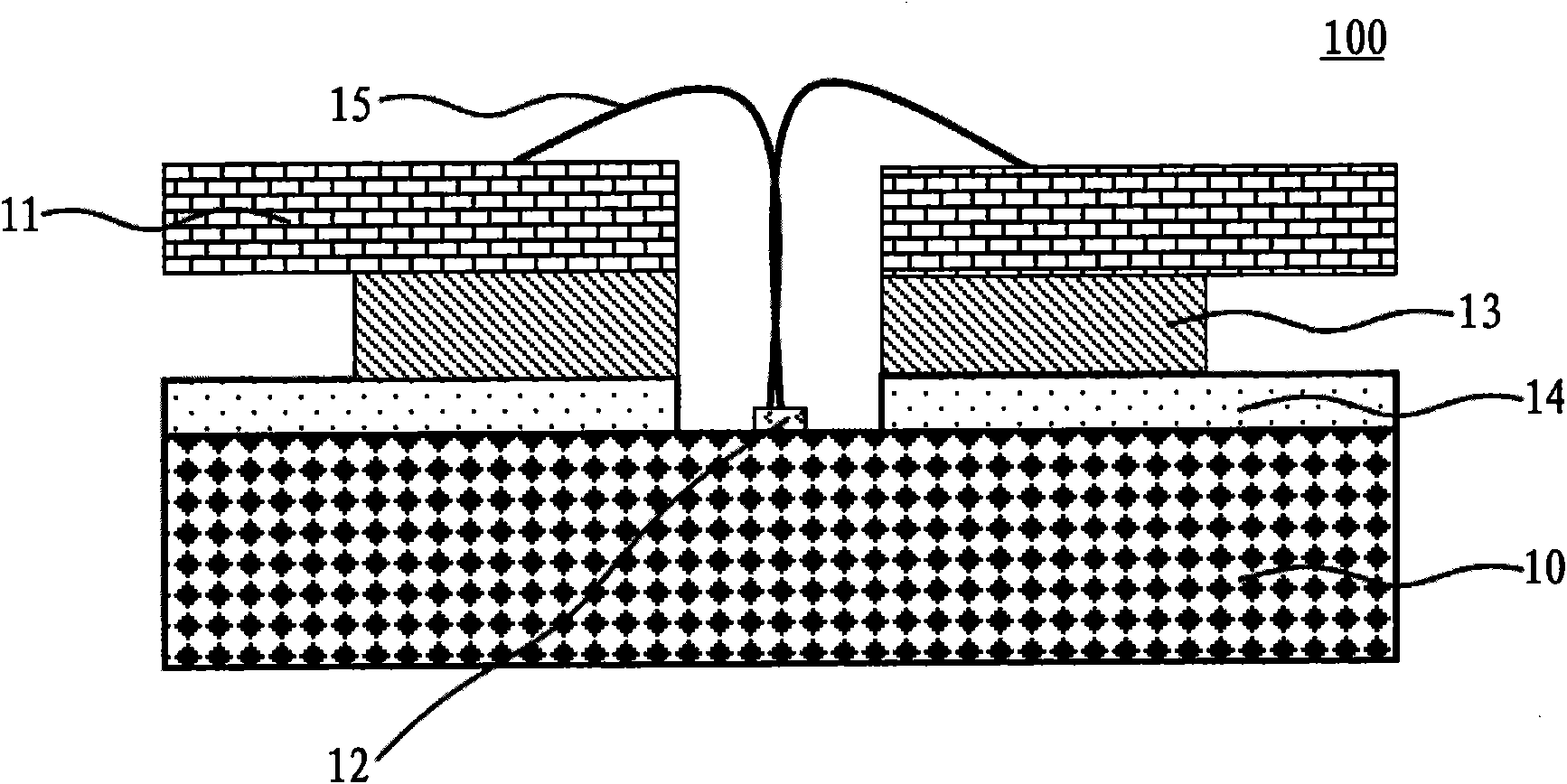

[0020] The semiconductor package and its manufacturing method according to the present invention use conductive elements instead of traditional gold wires to electrically connect the chip pads to the leads of the lead frame, thereby realizing the interconnection between the chip pads and the leads.

[0021] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings.

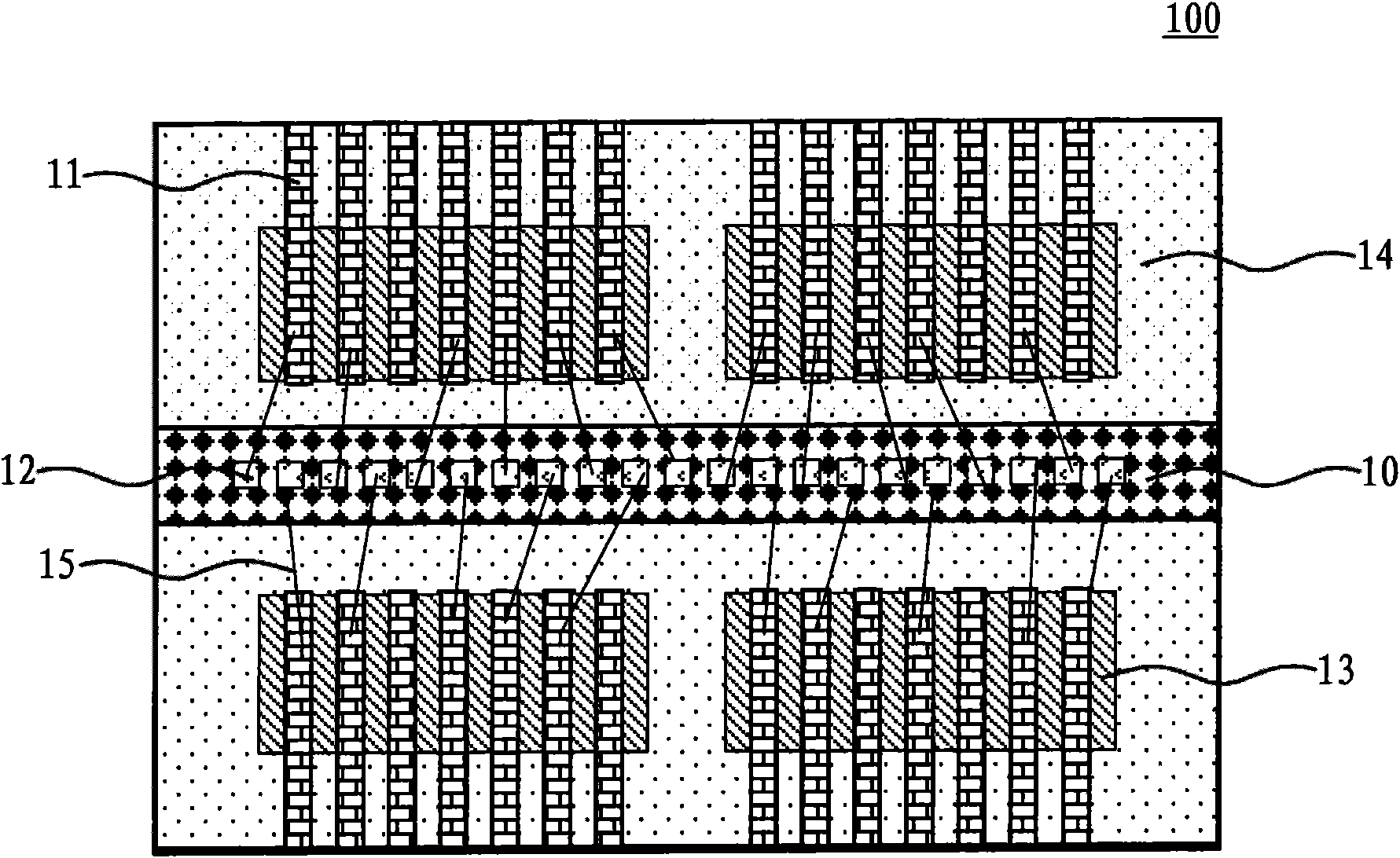

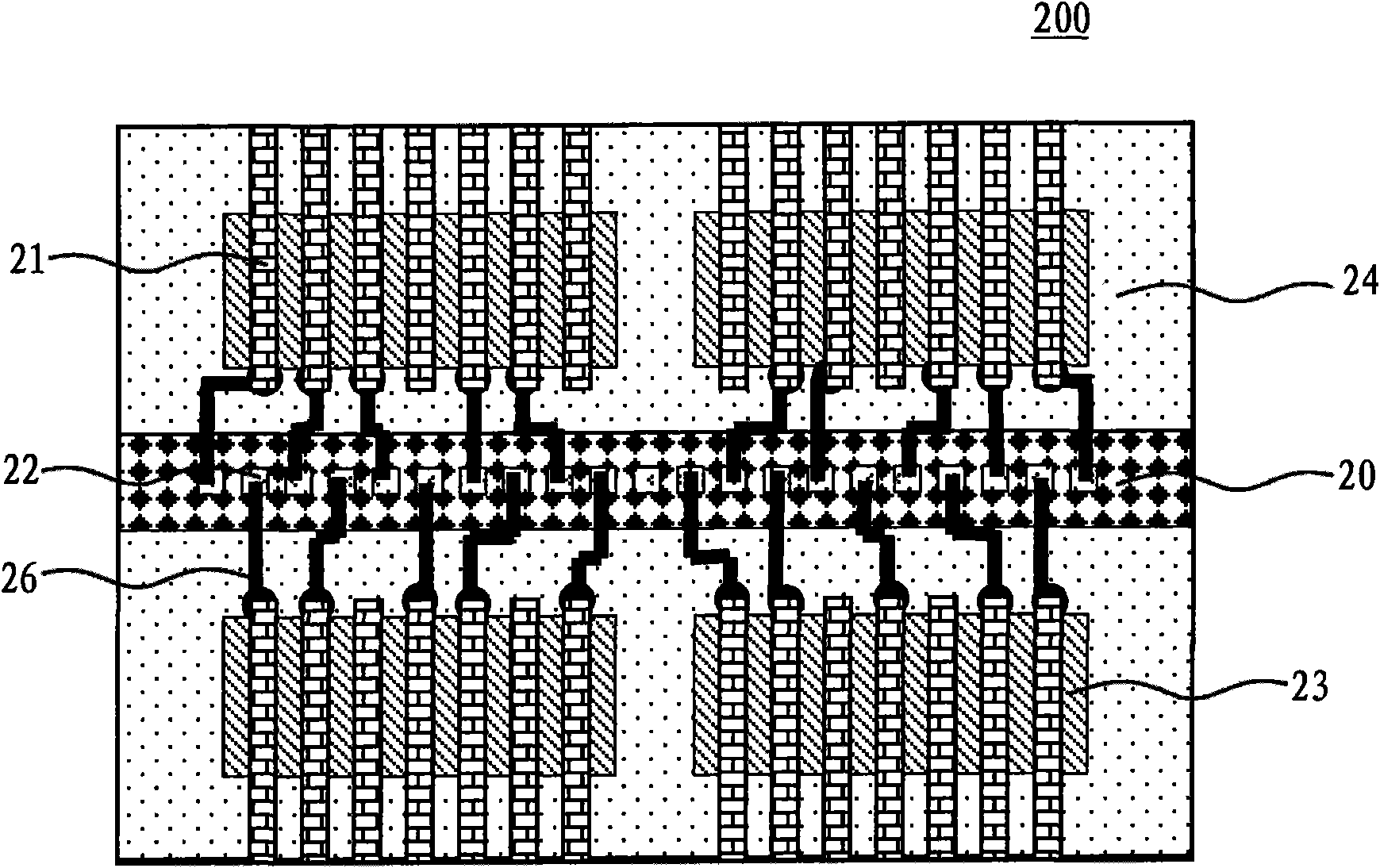

[0022] refer to image 3 and Figure 4 , the LOC package 200 according to the first exemplary embodiment of the present invention includes: a chip 20; a chip surface protection layer 24, formed above the chip 20, covering the area of the chip 20 except the area where the chip pad 22 will be formed; The chip pad 22 is formed on the area of the chip 20 that is not covered by the chip surface protection layer 24; the LOC tape 23 is formed on the chip surface protection layer 24; the pin 21 is formed on the LOC tape 23 and passed through the LOC tape...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More