Packaged semiconductor grain

A packaging structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve the problems of not mentioning testing and reducing cost chip pads, not mentioning new pad design and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

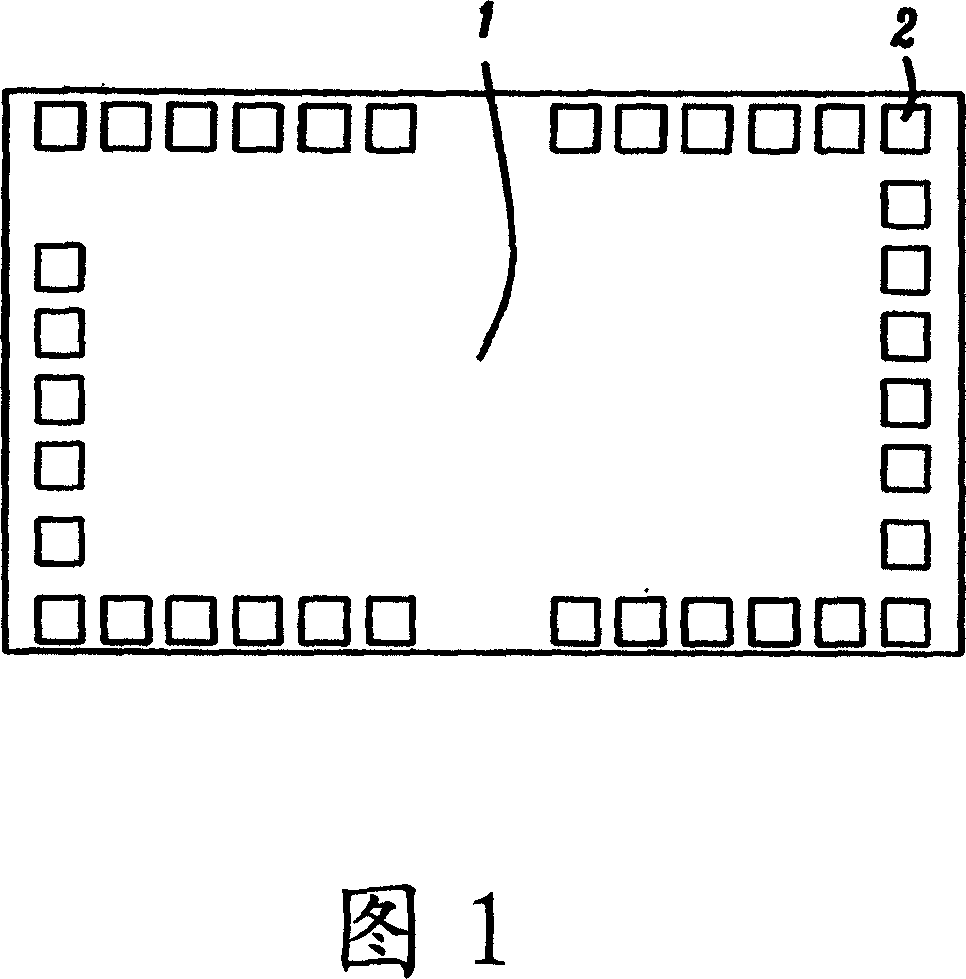

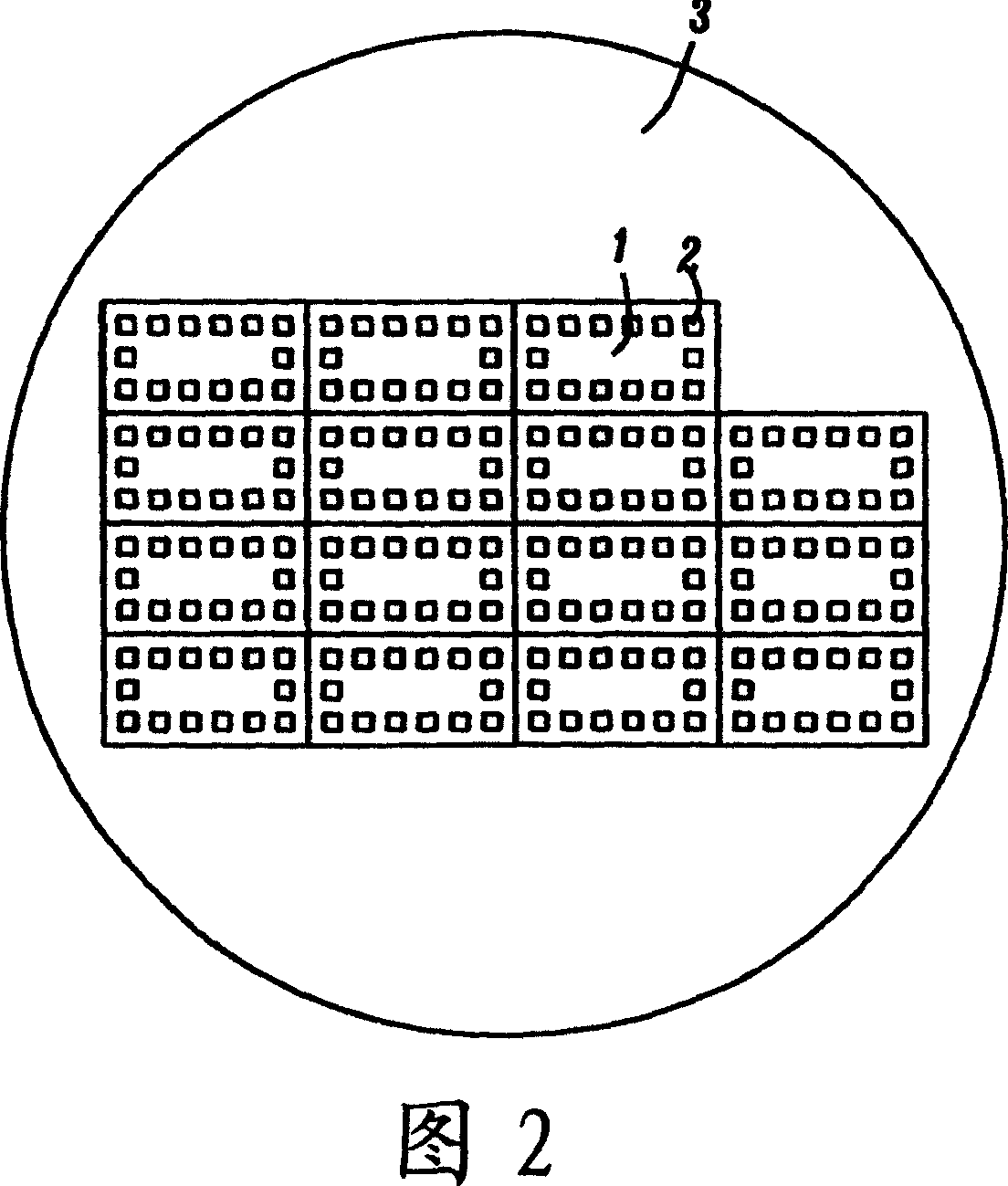

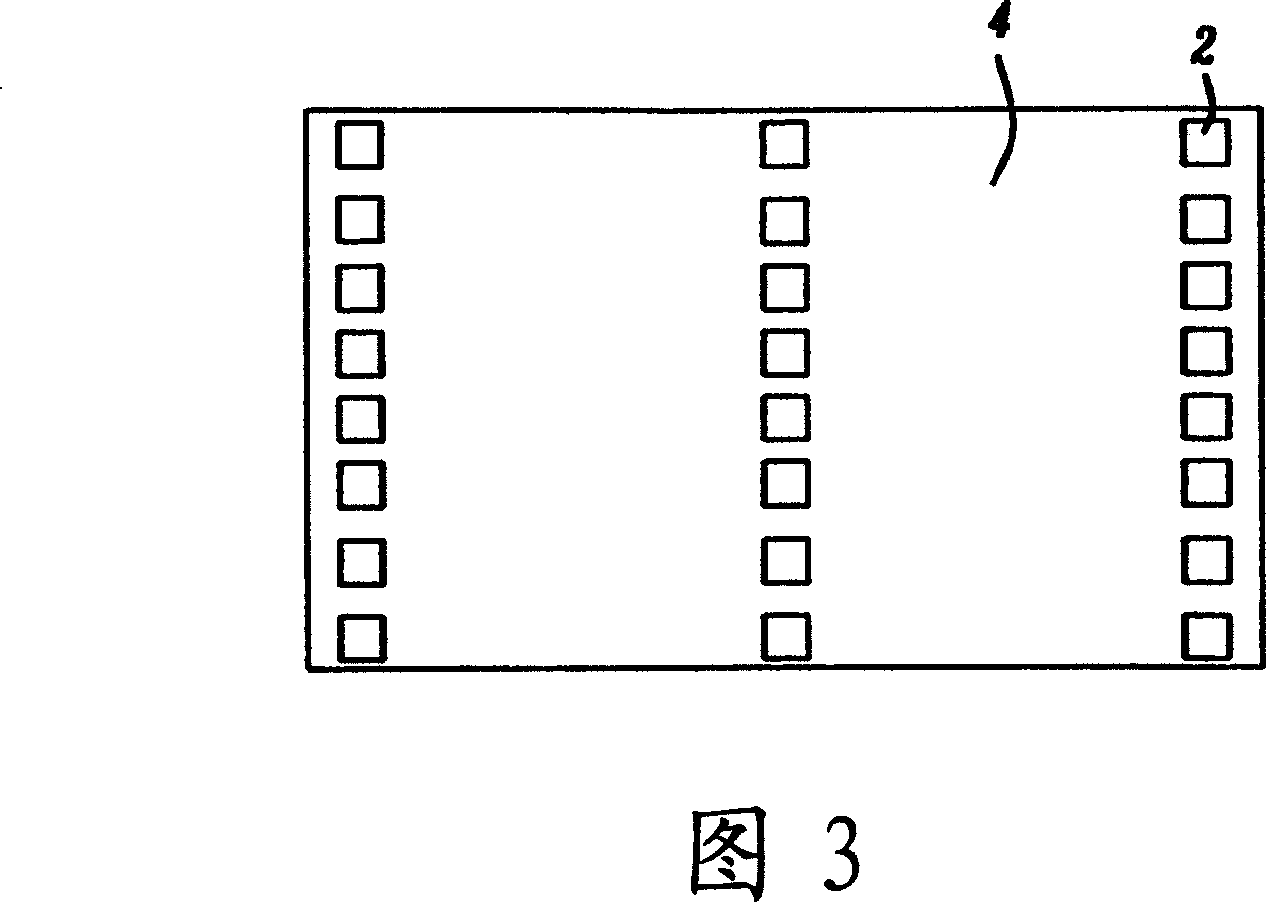

[0014] A semiconductor chip is obtained by forming a specific pattern or design of a circuit or device on a specific area of a semiconductor substrate or wafer, and replicating these specific patterns or device designs on the semiconductor wafer to produce more of the same Structure. Each semiconductor chip is composed of active components formed on a semiconductor wafer and an overlying conductive circuit connecting the active components to generate an array of components and circuits required by the designer. The covering conductive circuit includes a plurality of metal interconnect structures, and these metal interconnect structures are finally terminated near the topmost surface of the semiconductor chip, so as to connect the component circuit in the semiconductor substrate with the external package (package) Solder or connect. The characteristic of the semiconductor chip is that its surface has pad structures, and these pad structures are used as the interface between ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More